Manufacturing method for separated grid type flash memory embedded into logical circuit

A manufacturing method and a technology of separating gates, which are applied in circuits, semiconductor/solid-state device manufacturing, electrical components, etc., can solve problems such as memory operating speed signal transmission bandwidth limitations, and achieve the effect of simplifying the manufacturing process

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0034] The following describes the technical solutions of the present invention clearly and completely through specific embodiments in conjunction with the accompanying drawings. Obviously, the described embodiments are only a part of the implementation manners of the present invention, rather than all of them. According to these embodiments, all other implementation manners that can be obtained by a person of ordinary skill in the art without creative labor fall within the protection scope of the present invention.

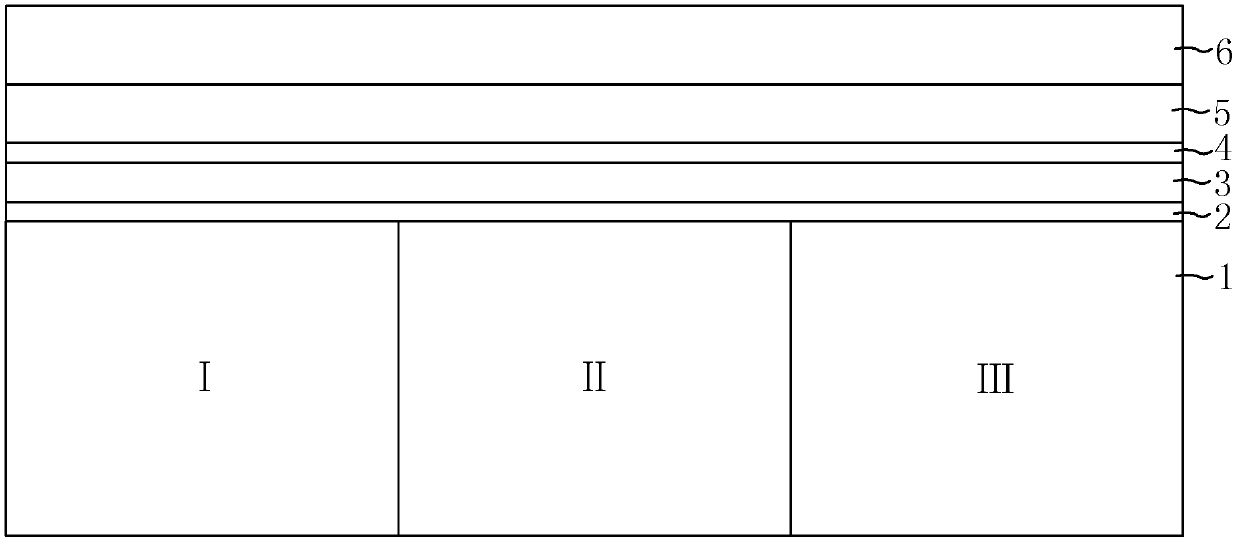

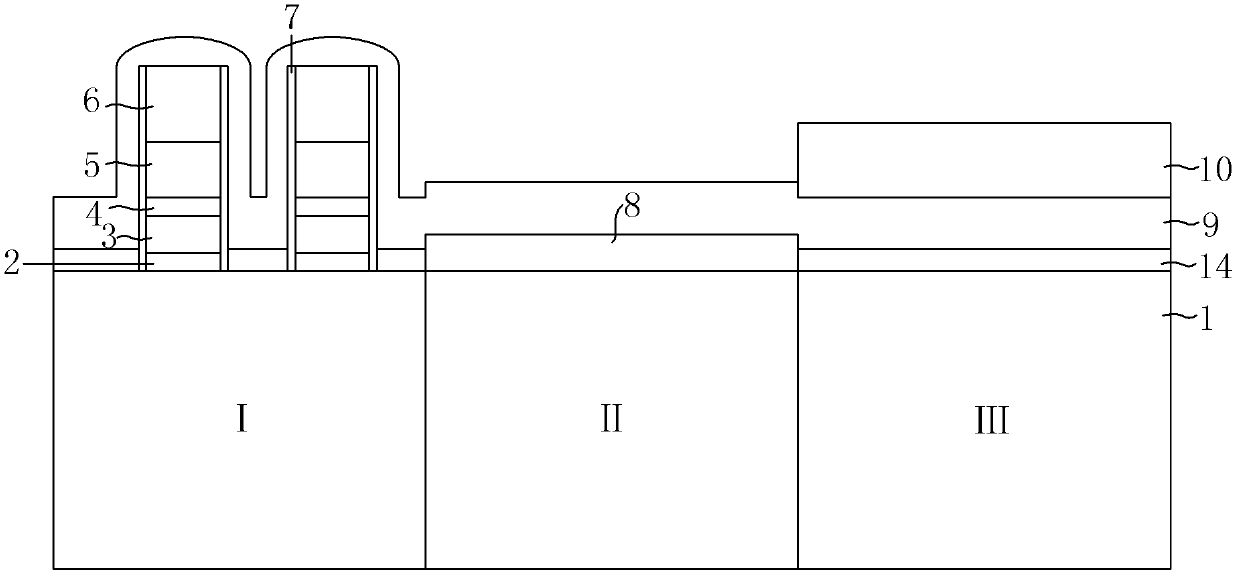

[0035] Figure 7 It is the manufacturing flow chart of the memory in the embodiment of the manufacturing method of the split-gate flash memory embedded in the logic circuit of the present invention, Figure 8 to Figure 19 Is in Figure 7 The schematic diagram of the structure of the split-gate flash memory embedded in the logic circuit during the manufacturing process is shown. The following will Figure 8 to Figure 19 versus Figure 7 The production method of the pr...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com