Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

137 results about "Parallel design" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

A parallel design, also called a parallel group study, compares two or more treatments. Participants are randomly assigned to either group, treatments are administered, and then the results are compared.

Parallel design method for movable vector forecasting flowing water based on AVS

InactiveCN101466036AReduce implementation complexityReduce complexityTelevision systemsDigital video signal modificationWater basedExternal storage

The invention discloses a pipelined parallel design method of motion vector prediction based on AVS video encoding standards. According to the characteristics of storing, extracting and accessing the externally-stored data, the AVS motion vector prediction can be designed into the following two parts: (1) the mode of a macro block is resolved and the specific calculating process of the motion vector prediction for each subblock by the macro block dividing mode which is corresponding to the macro block mode of each macro block is determined; (2) the motion vector prediction of the subblock is generated and the actual calculation of the motion vector prediction of each subblock is finished. The method has the advantages that: the separation of the external-storage reading operation from the external-storage writing operation is realized, thus carrying out the pipelined parallel processing on the motion vector prediction by taking the size of the subblock under the macro block dividing mode which is corresponding to the macro block encoding mode as the unit.

Owner:BEIJING CEC HUADA ELECTRONIC DESIGN CO LTD

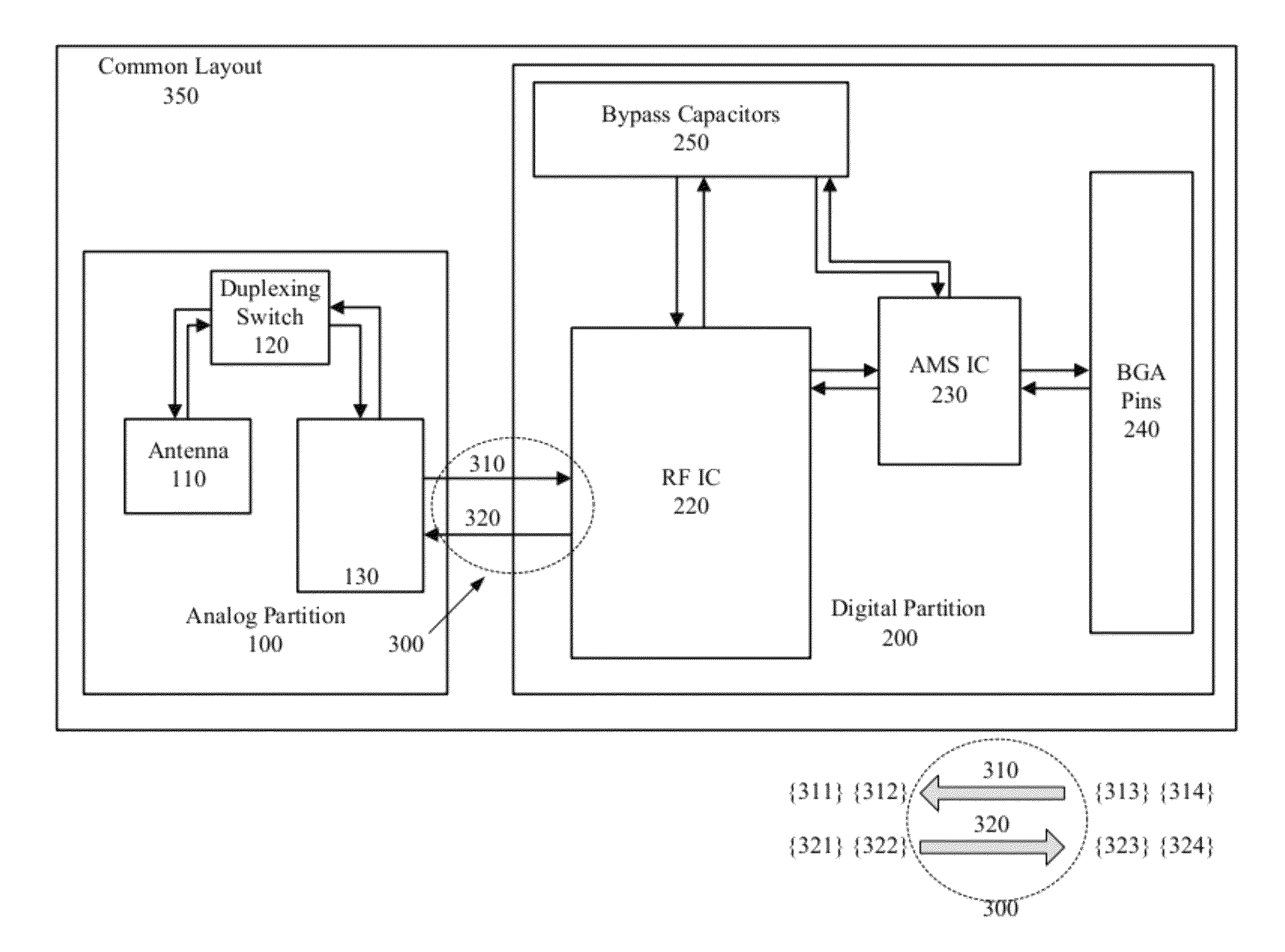

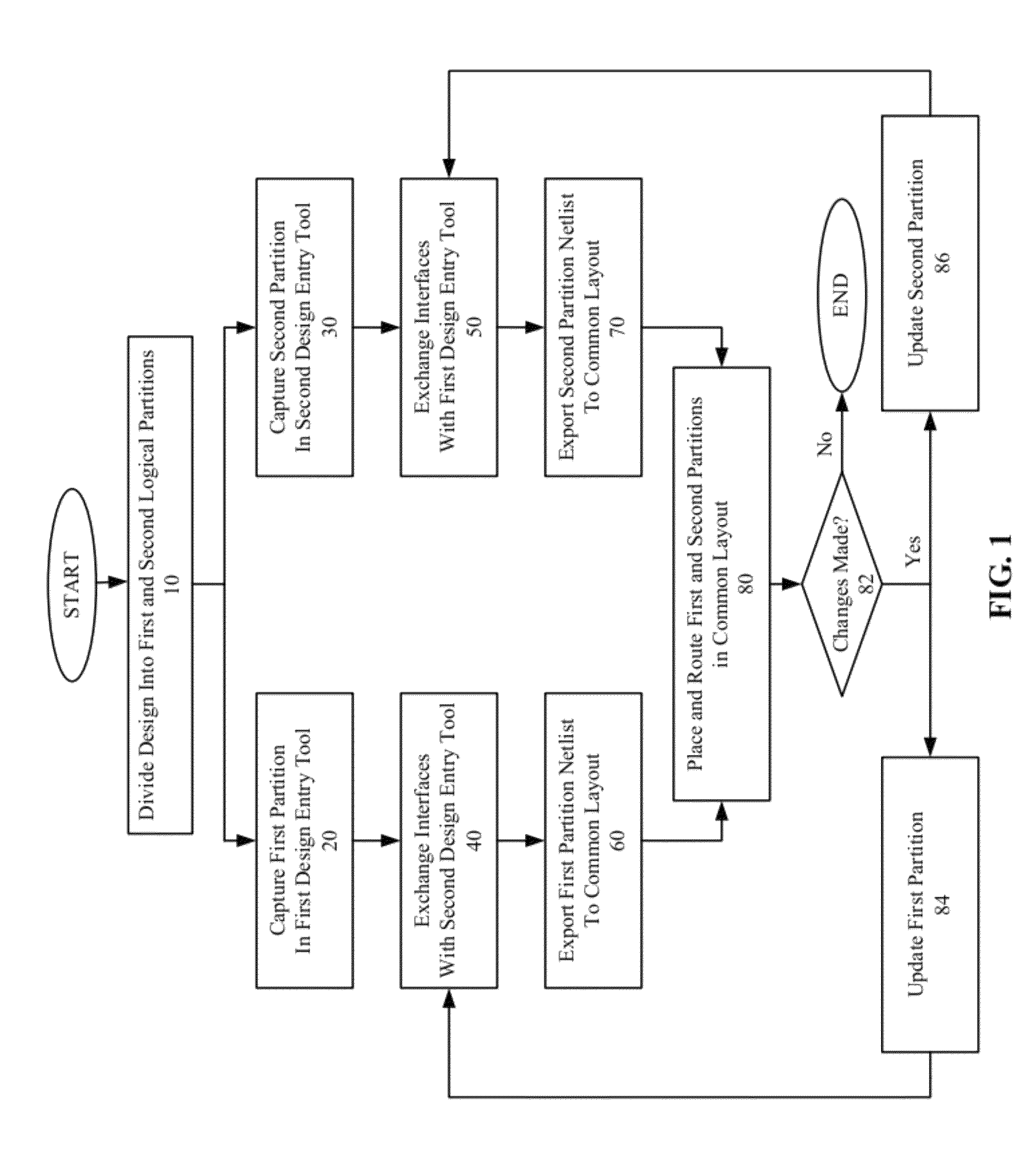

Method and apparatus for concurrent design of modules across different design entry tools targeted to a single layout

ActiveUS8316342B1Eliminate the problemDetecting faulty computer hardwareAnalogue computers for electric apparatusComputer moduleInterconnection

A method of interconnecting a first plurality of electronic components and a second plurality of electronic components to form an electronic circuit includes exporting a first netlist representing a first interconnection of the first electronic components in a first design entry tool, exporting a second netlist representing a second interconnection of the second electronic components in a second design entry tool, providing at least a first interface from the second plurality to the first plurality in the second design entry tool, populating the first interface through the first design entry tool, and exporting a third netlist representing the first interface from the second plurality to the first plurality from the second design entry tool, wherein the third netlist stitches the first netlist to the second netlist.

Owner:CADENCE DESIGN SYST INC

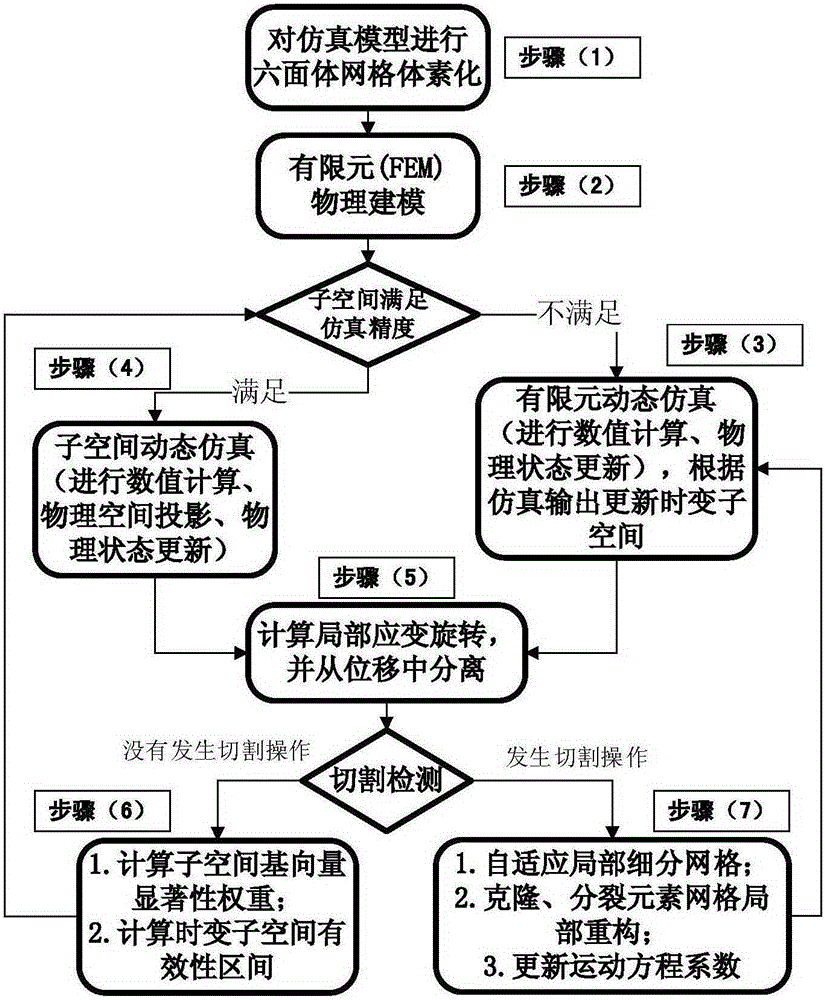

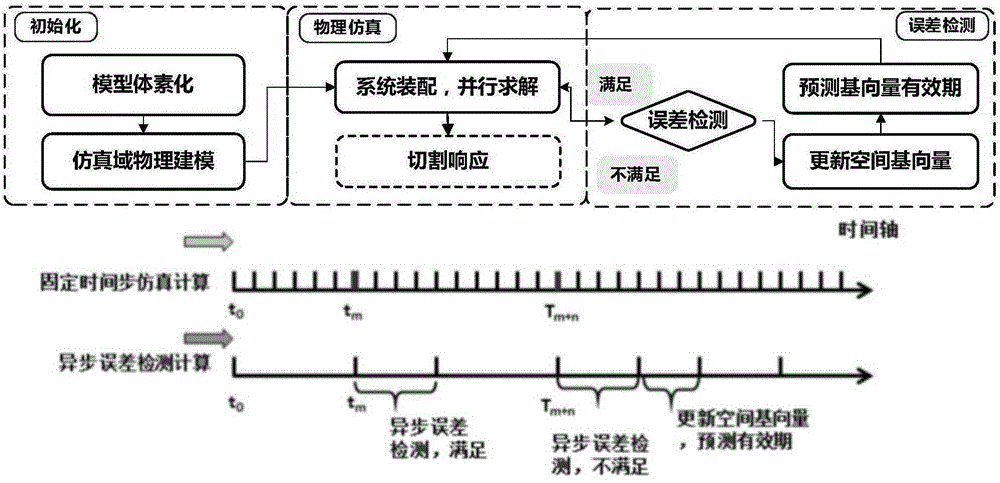

Real-time cutting simulation method of flexible object on the basis of finite element and time-variant modal analysis

ActiveCN105302974AQuick analysisBig errorSpecial data processing applicationsSoft tissue deformationSimulation

The invention relates to a real-time cutting simulation method of a flexible object on the basis of finite element and time-variant modal analysis. The real-time cutting simulation method carries out researches and is implemented mainly by aiming at a real-time interactive soft tissue deformation and cutting simulation algorithm of a virtual surgery. The method comprises the following steps: carrying out voxelization and finite element physical modeling on a simulation domain of a model, carrying out subspace construction on the basis of priori modal analysis, carrying out cutting operation response, carrying out significance analysis and screening on a subspace base vector, and carrying out subspace time-variant effectiveness estimation. The method carries out parallel design on the simulation algorithm and achieves real-time interactive efficiency by virtue of the powerful calculation capability of GPU (Graphics Processing Unit).

Owner:BEIHANG UNIV

Split ring metamaterial unit-based dual-frequency circularly polarized plane reflective array antenna

ActiveCN106532274AMeet application needsOverall small sizeRadiating elements structural formsPolarised antenna unit combinationsDielectric substrateMetamaterial

Owner:SHANGHAI RADIO EQUIP RES INST

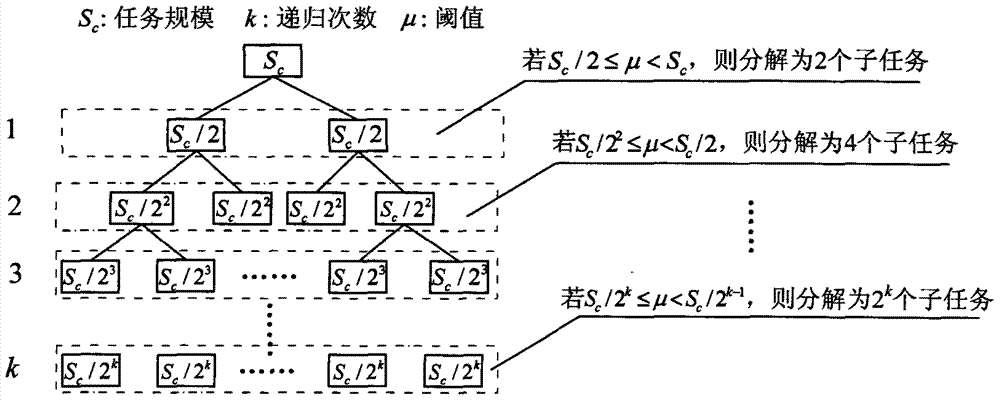

Cascade reservoir group optimized dispatching multi-core parallel computing design method based on Fork/Join framework

InactiveCN107015861AImprove computing efficiencyReduce computing timeResource allocationDesign optimisation/simulationDynamic planningParallel computing

The invention discloses a cascade reservoir group optimized dispatching multi-core parallel computing design method based on a Fork / Join framework. The method includes the following steps that 1, the Fork / Join parallel framework is established; 2, the Fork / Join parallel framework is achieved; 3, typical intelligent method parallel design in a coarse-grained mode is carried out; 4, typical dynamic planning method parallel design in a fine-grained mode is carried out. By means of PSCWAGA, PAHPSO, PDP and PDDDP method instance testing results, the Fork / Join multi-core parallel framework is adopted, the multi-core CPU parallel performance can be fully exerted, calculation time is greatly shortened, the calculation efficiency of the algorithm is remarkably improved, and the larger the calculation scale of the parallel method is, the shorter the calculation time is, and the more obvious the advantages of parallel calculation is. Along with gradual increase of the calculation scale, the speed-up ratio is gradually increased, the parallel efficiency is gradually improved, and the speed-up ratio is closer to an ideal speed-up ratio.

Owner:PEARL RIVER HYDRAULIC RES INST OF PEARL RIVER WATER RESOURCES COMMISSION

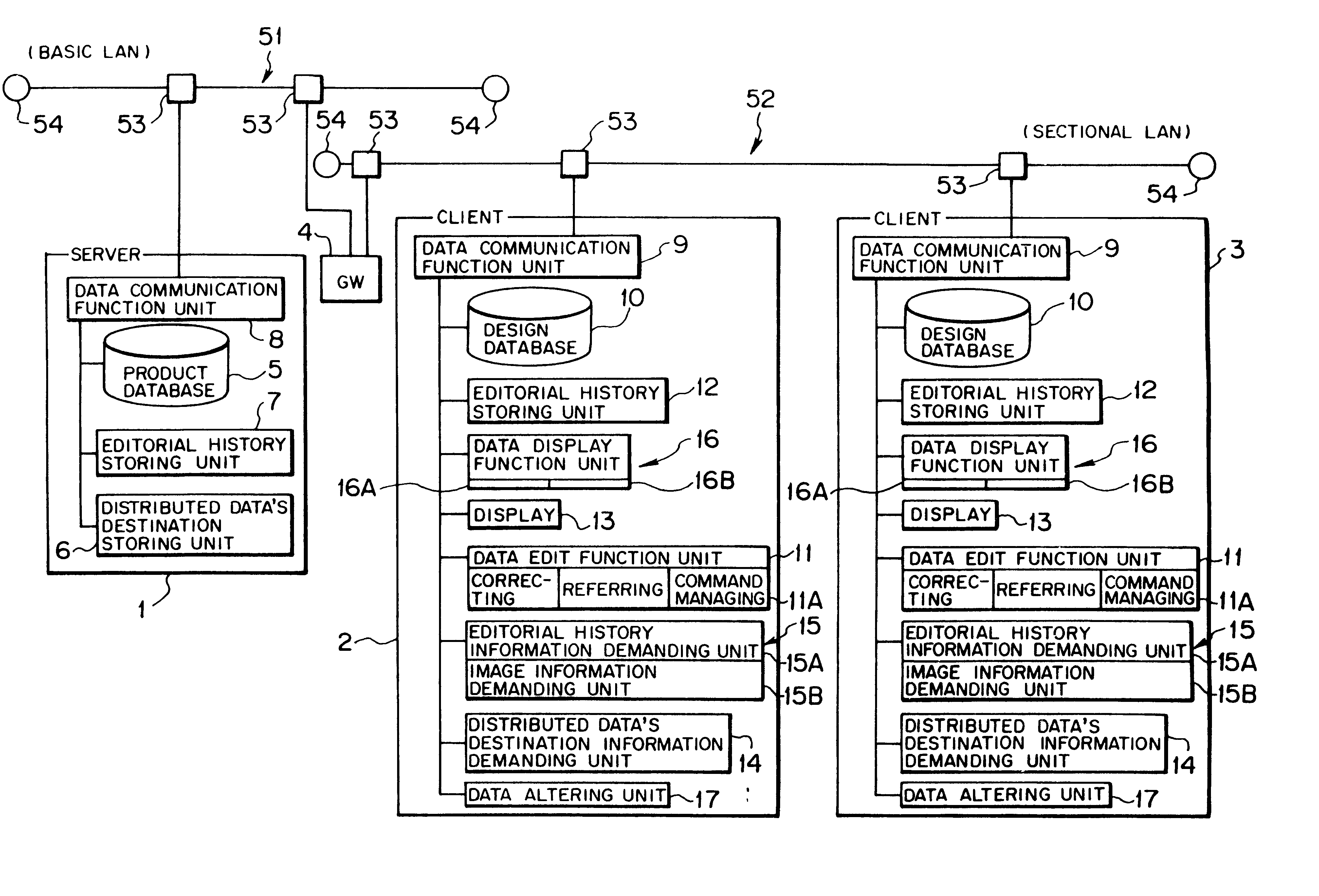

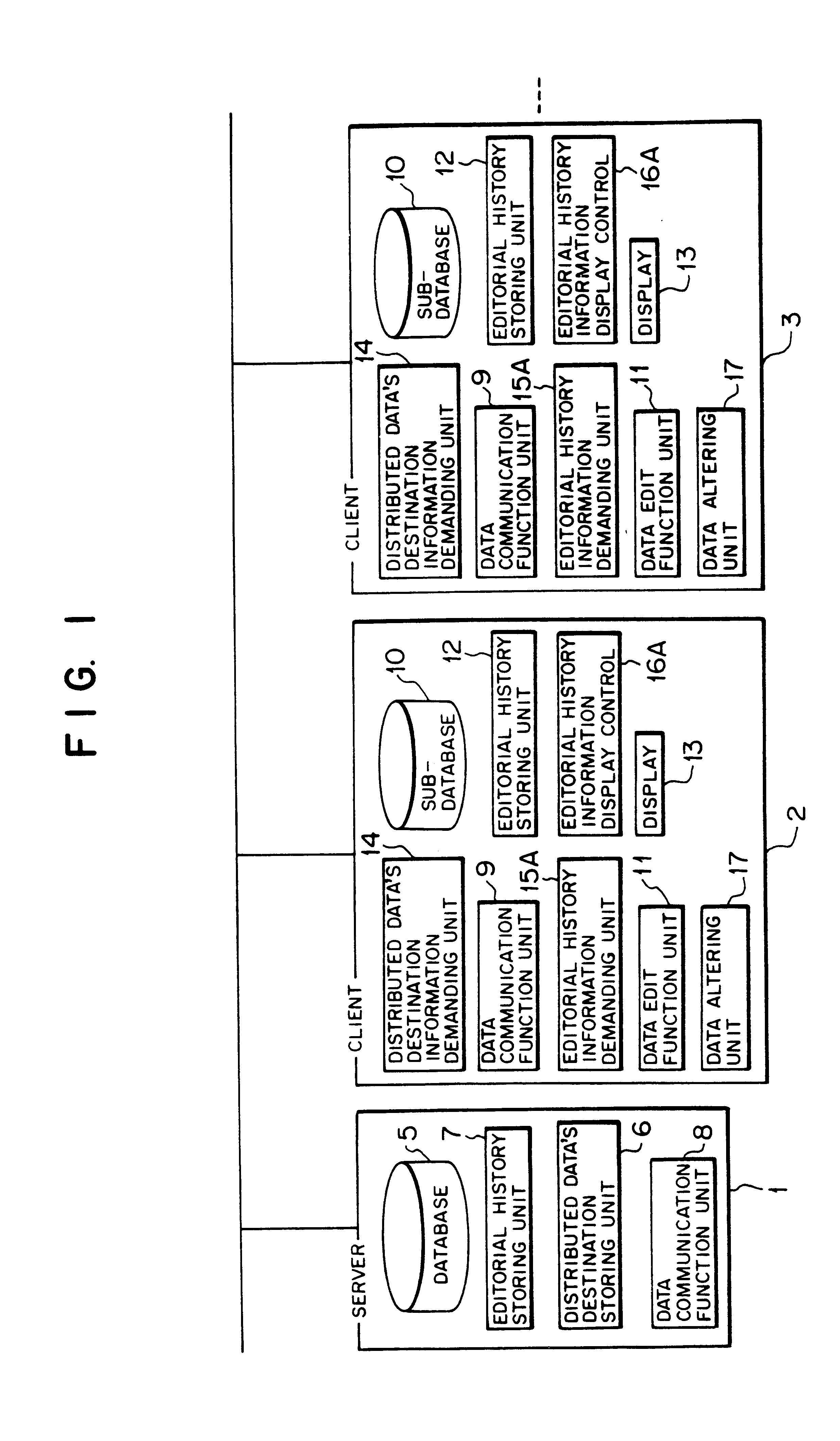

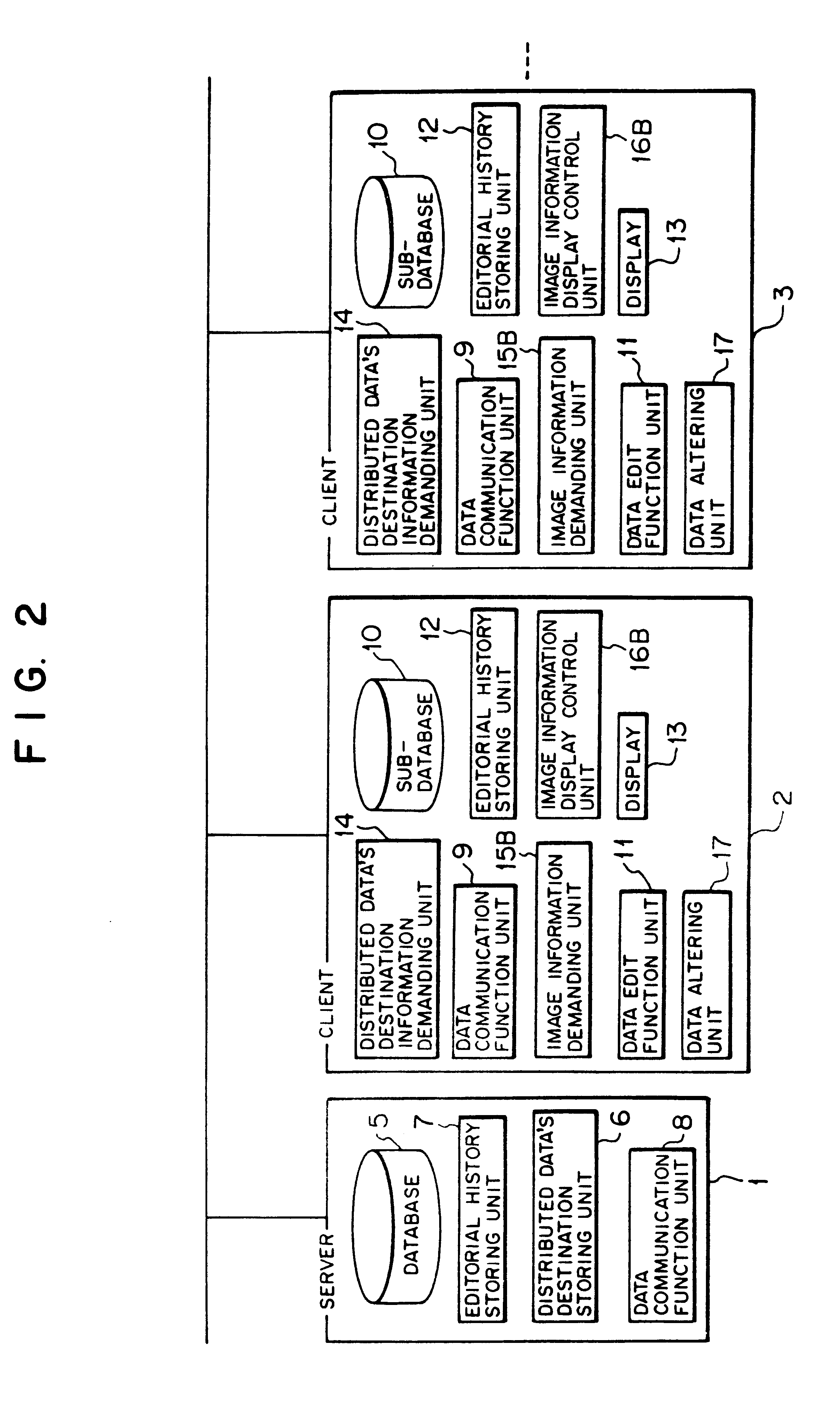

Method and apparatus for confirming matching of data in a distributed processing system

InactiveUS6182077B1Guaranteed to workEfficient executionData processing applicationsMultiple digital computer combinationsData matchingParallel design

A method and an apparatus for confirming matching of data in a distributed processing system aiming easy maintenance of the matching of the data and efficient parallel design work in a distributed processing system. In the distributed processing system having a server including a database and plural clients utilizing data in the database, said server and clients are connected to each other. The server stores information of destinations to which data in the database has been distributed and receives information of an editorial history of the data from a client that is a destination of the distributed data to store the editorial history information at the destination client on the side of the server. After that, matching of the data is confirmed on the side of another client on the basis of the distributed data's destination information or the editorial history information stored in the server.

Owner:FUJITSU LTD

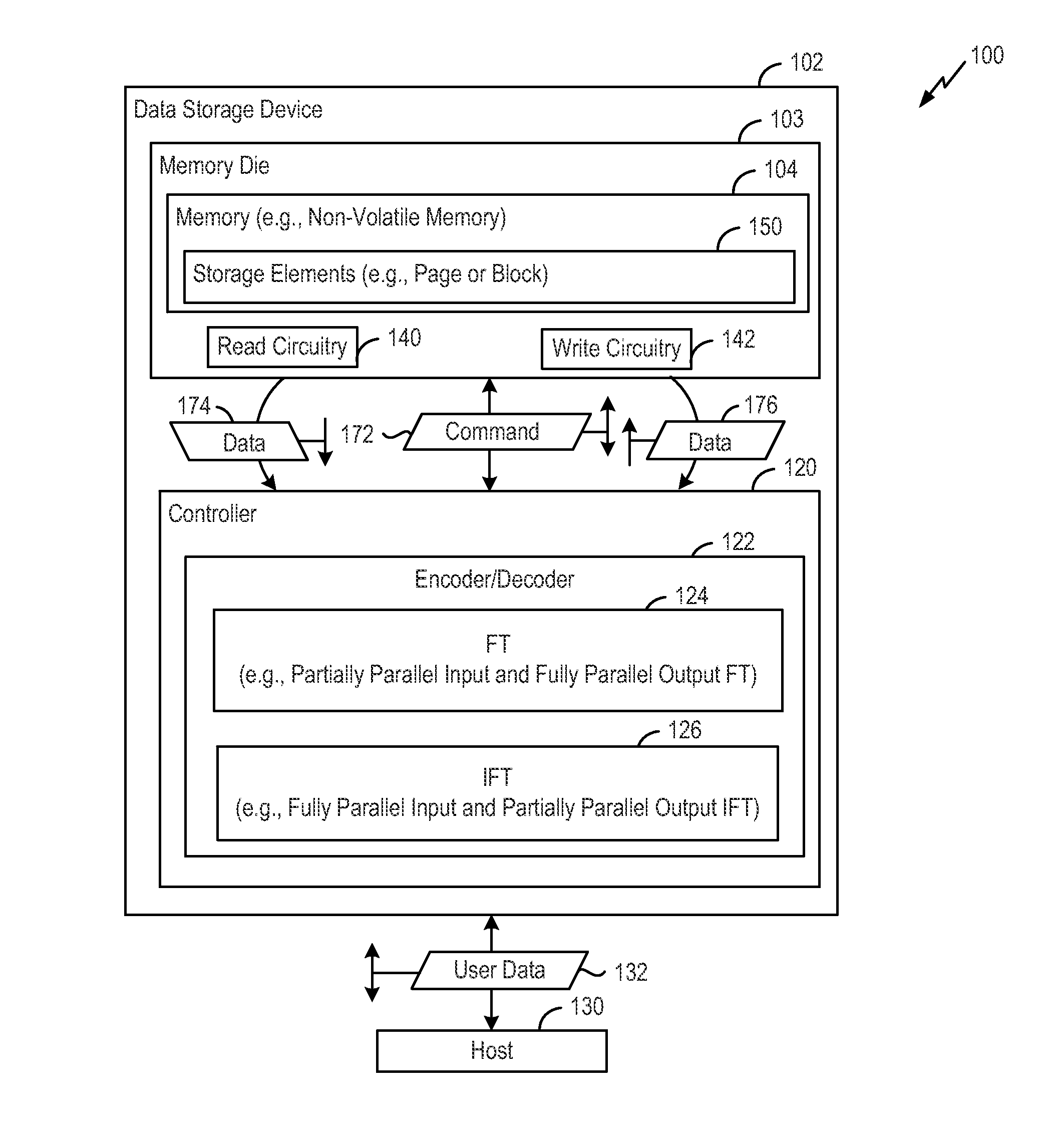

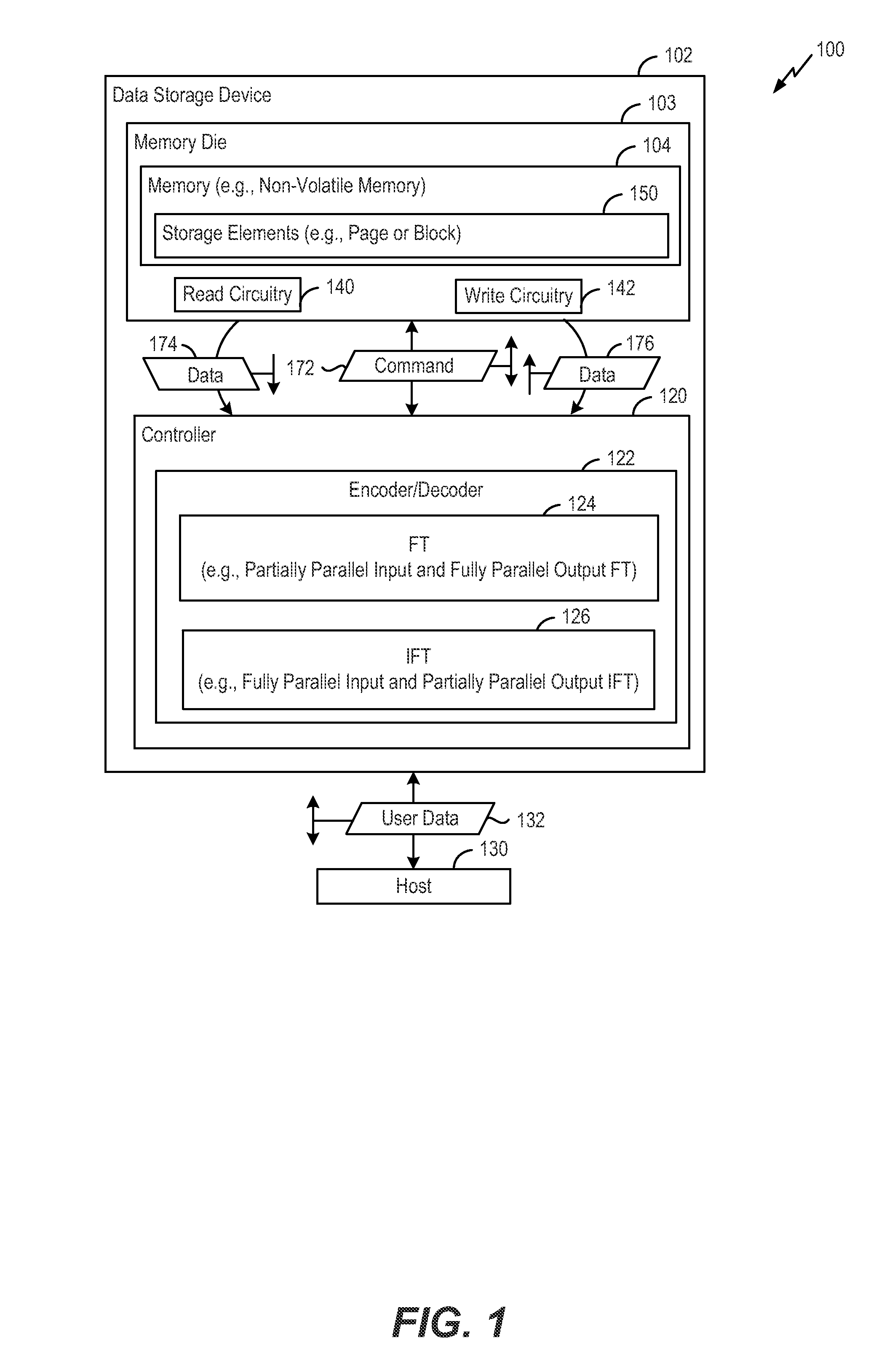

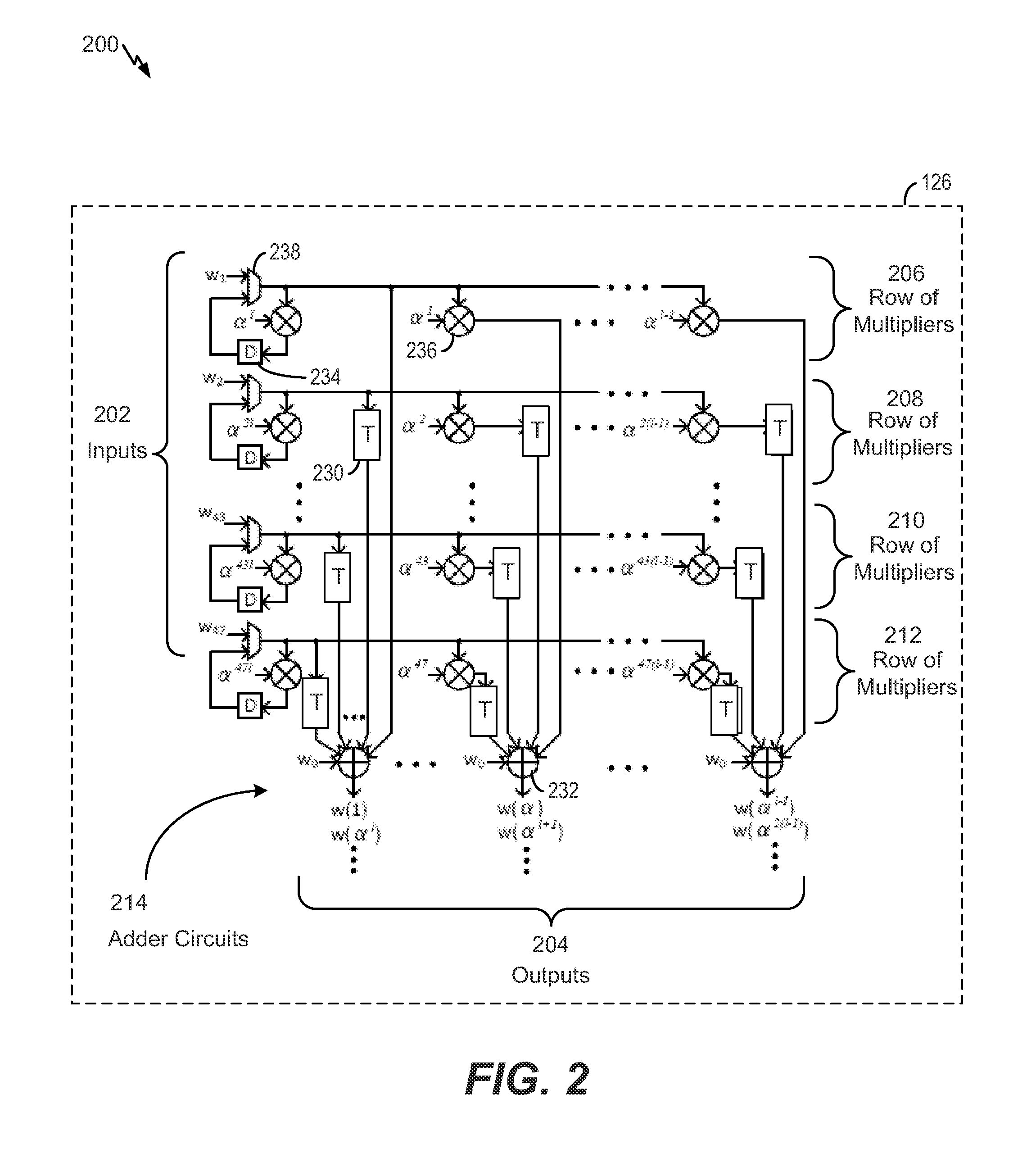

Low complexity partial parallel architectures for fourier transform and inverse fourier transform over subfields of a finite field

InactiveUS20150301985A1Wide applicationReduce complexityDigital computer detailsCode conversionFast Fourier transformFinite fourier transform

Low complexity partial parallel architectures for performing a Fourier transform and an inverse Fourier transform over subfields of a finite field are described. For example, circuits to perform the Fourier transforms and the inverse Fourier transform as described herein may have architectures that have simplified multipliers and / or computational units as compared to traditional Fourier transform circuits and traditional inverse Fourier transform circuits that have partial parallel designs. In a particular embodiment, a method includes, in a data storage device including a controller and a non-volatile memory, the controller includes an inverse Fourier transform circuit having a first number of inputs coupled to multipliers, receiving elements of an input vector and providing the elements to the multipliers. The multipliers are configured to perform calculations associated with an inverse Fourier transform operation. The first number is less than a number of inverse Fourier transform results corresponding to the inverse Fourier transform operation.

Owner:WODEN TECH INC

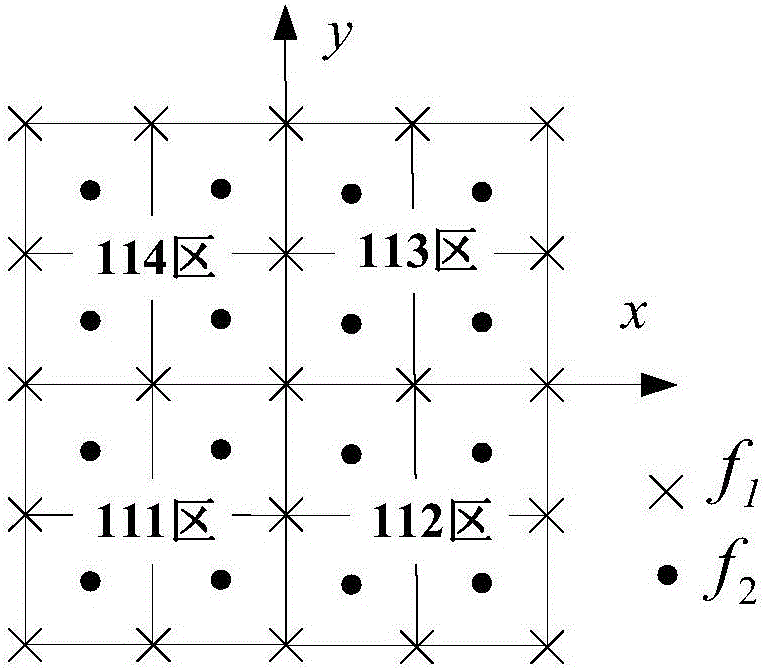

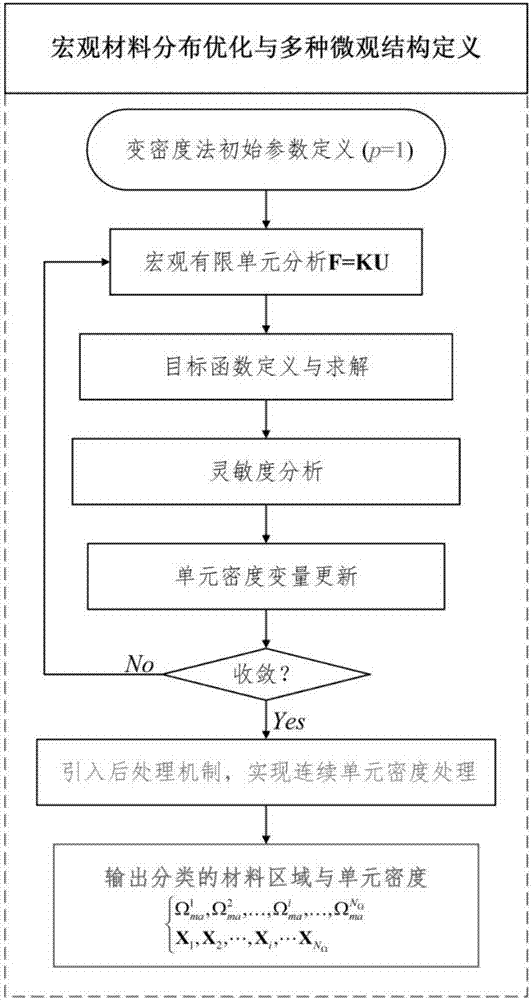

Multi-microstructure-oriented material structure integrated construction method

ActiveCN107391855ASimple designGuaranteed coupling effectGeometric CADSpecial data processing applicationsMacroscopic scaleTopology optimization

The invention belongs to the technical field of structural optimization and discloses a multi-microstructure-oriented material structure integrated construction method. According to continuously changing material distribution and unit density which are obtained through a traditional variable density method, a material area is divided and subjected to unit density grouping on the basis of a post-processing mechanism, definition and dividing of areas, with different material attributes, in a macrostructure are achieved, and various microstructures in the macrostructure are defined; a material structure integrated design model is established on the basis of a parameterized level set topological optimization method and the homogenization theory, that is, integrated design is carried out according to various defined microstructures and the macrostructure, the parallel design of the macroscopic structure and the microstructures is achieved, and under a given constraint condition, the performance of the overall structure is optimal.

Owner:HUAZHONG UNIV OF SCI & TECH

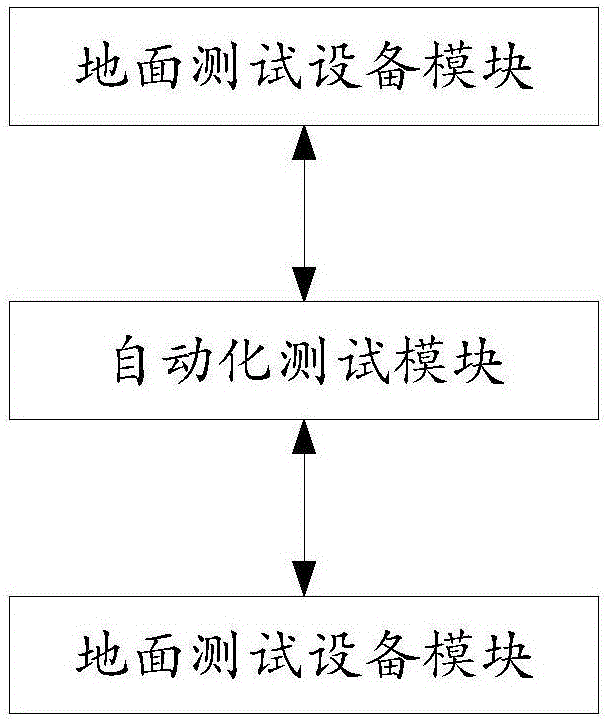

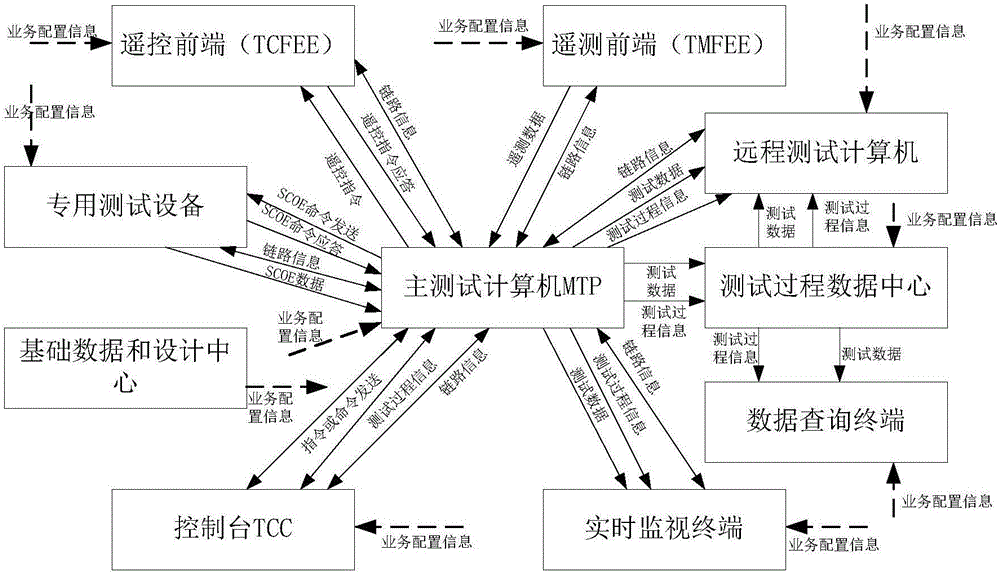

Parallel and automatic integrated testing system for satellites

ActiveCN106314825AImplement parallel designImplementAircraft components testingInformatizationCombined test

The invention relates to a parallel and automatic integrated testing system for satellites. The parallel and automatic integrated testing system comprises a ground testing equipment module, an automatic testing module and a data storage management module, wherein the data storage management module is connected with the automatic testing module through a data communication protocol for both-way communication, and the automatic testing module is connected with the ground testing equipment module through the data communication protocol for both-way communication. The parallel and automatic integrated testing system for the satellites realizes integration of integrated testing management, design, implementation and application for the satellites, improves the systematization, informatization and automation of satellite testing work, and can effectively increase the testing efficiency, effectively control quality risks in a testing process, increase the application analysis value of testing data and realize substantial saving of labor cost and management cost. The system is quite applicable to batch satellite testing, and parallel design and implementation on various layers of the integrated testing system for the satellites are realized.

Owner:AEROSPACE DONGFANGHONG DEV LTD

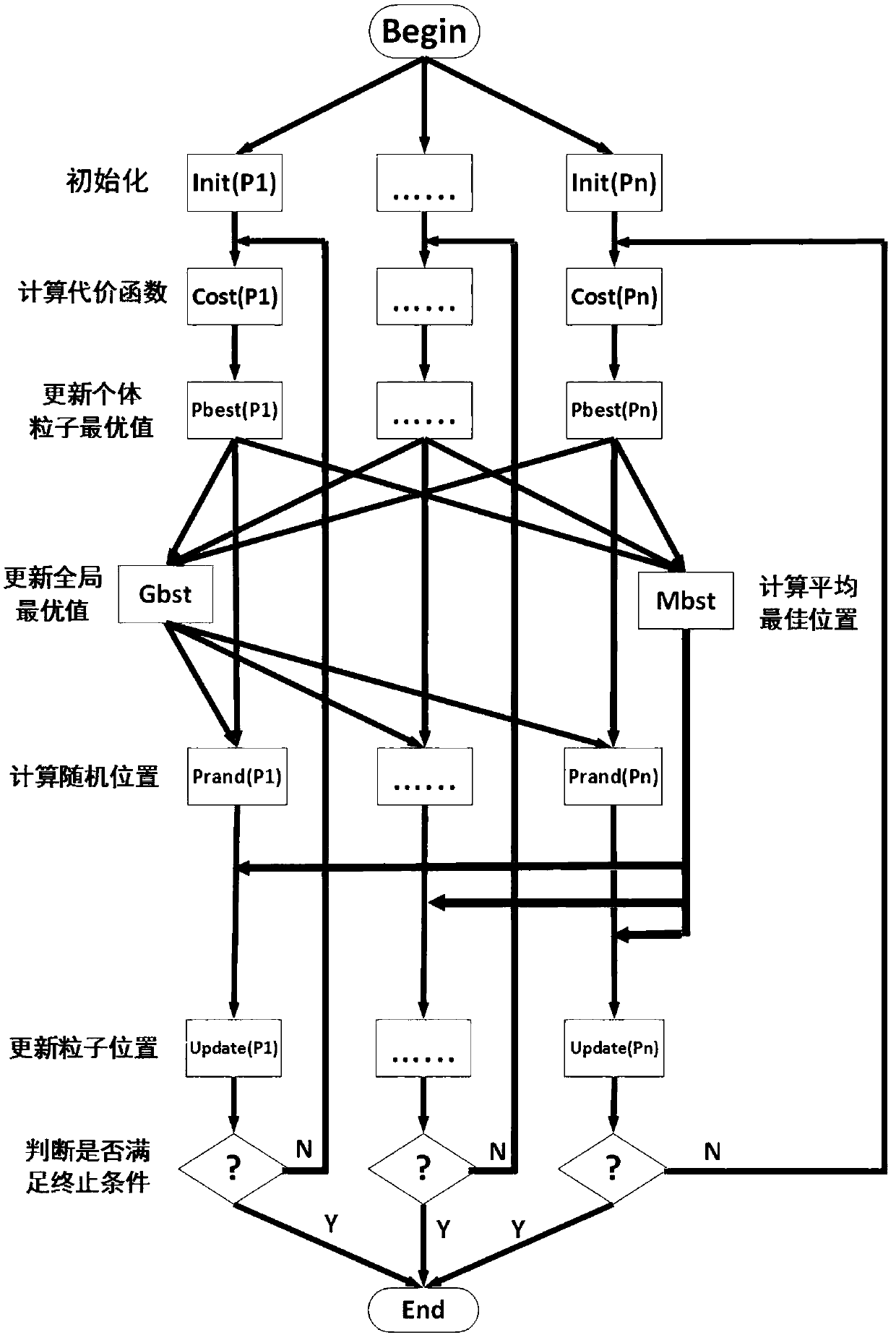

Non-linear model prediction control method based on quantum particle swarm optimization

ActiveCN108646734AFulfil requirementsGuaranteed comfortInternal combustion piston enginesPosition/course control in two dimensionsDiscretizationNon linear model predictive control

The invention relates to the field of unmanned vehicle control, and provides a parallel design scheme using quantum particle swarm optimization, to ensure that the control output meets the physical constraints of the vehicle and the comfort requirement for a human body so as to enable the vehicle to preferably adapt to the current road condition. The technical scheme of the parallel design schemeusing quantum particle swarm optimization includes the steps: establishing a kinetic model based on an unmanned vehicle, and performing discretization on the kinetic model; based on the above step, constructing a generalized cost function with a punishment item and an encouragement item by using a generalized Lagrangian multiplier so as to convert the constraint problem into a nonrestraint problem; and performing parallel design of quantum particle swarm optimization, performing optimized solution on the cost function of model prediction control by means of the parallel design to obtain a series of controlled variables, and finally acting the first component of the controlled variables on the vehicle. The parallel design scheme using quantum particle swarm optimization is mainly applied tothe unmanned vehicle control occasion.

Owner:TIANJIN UNIV

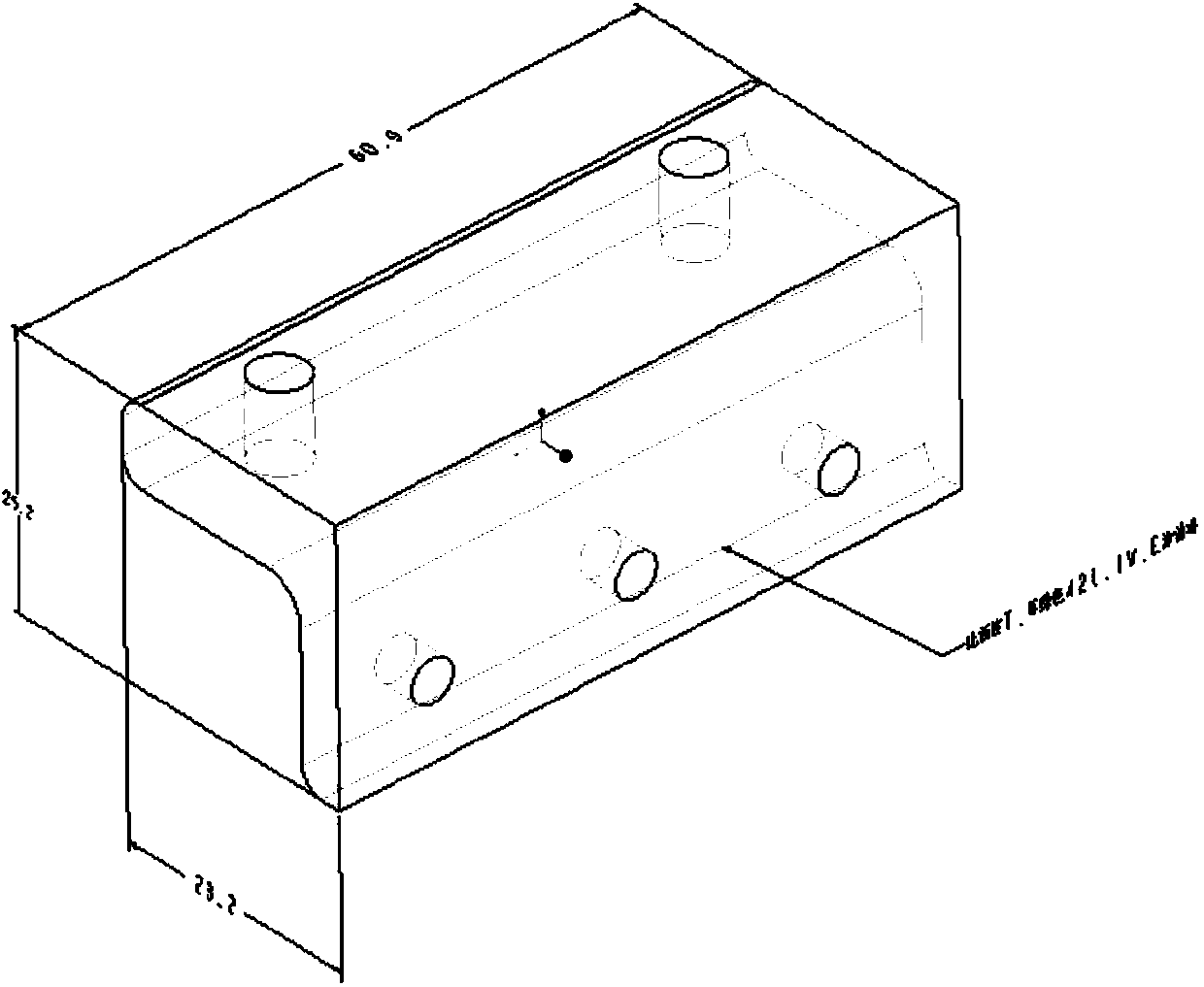

Dynamic odor measurement instrument

ActiveCN101470056ATest accurateInstrumentationPreparing sample for investigationEngineeringMass flux

The invention relates to a dynamic odor tester, comprising a shell and a test and control gas circuit mounted in the shell, wherein the test and control gas circuit is divided into three gas paths; the first gas path is a reference gas path; the second gas path is a mixed gas path; the third gas path is a tested gas path; the three gas paths are connected with a stop valve, a constant pressure valve, a rotor flux meter, a mass flux control meter, a venture mixing tube, a rotary mixing chamber, a reference gas outlet and a mixed gas outlet via pipelines and a gas source access port. The dynamic odor tester utilizes dynamic dilution and parallel design, and the negative pressure mixing mechanism in the venture mixing tube, and realizes dynamic gas distribution via the high speed rotary mixing tank. The dynamic odor tester has reliable performance, and can meet domestic three-point comparison odor bag method and European osmometer method. The dynamic odor tester can be used to test the strength and concentration of odor gas sample or the gas sample of peculiar smell in exhaust stack or environment gas, while the gas sample contains a sample containing one odor material and a composite odor sample containing at least two odor materials.

Owner:TIANJIN UNITED ENVIRONMENTAL ENG DESIGN

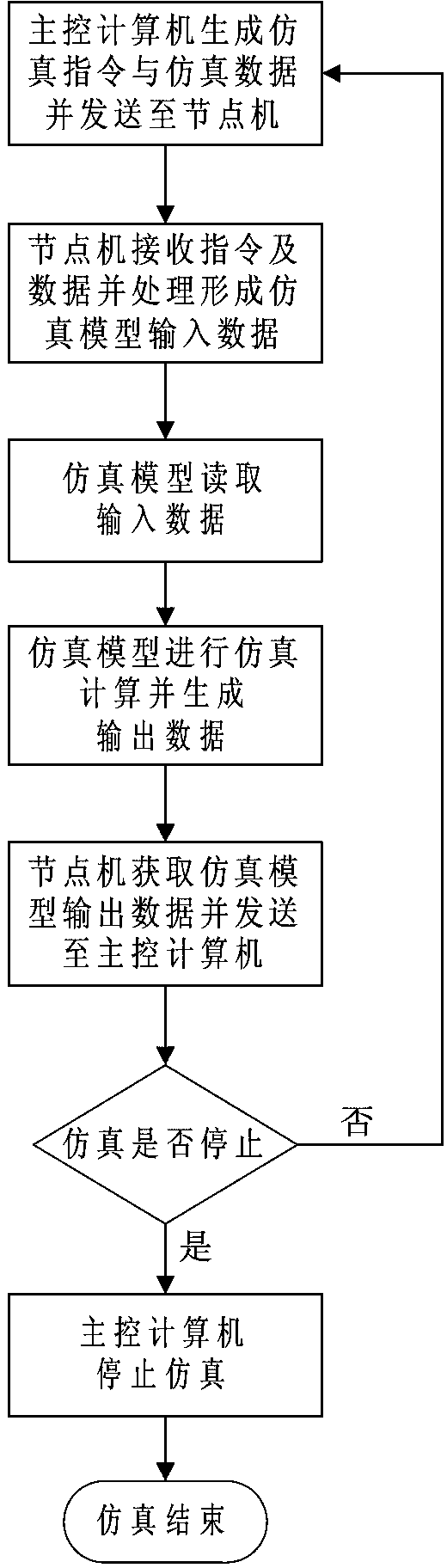

Method for dispatching distributed simulation models in aircraft simulation system

InactiveCN103279622AImprove design efficiencyPrecise deliverySpecial data processing applicationsSystems designData stream

The invention relates to a method for dispatching distributed simulation models in an aircraft simulation system and belongs to the technical field of aircraft system design. The dispatching method is based on a data flow dispatching idea, simulation progress is driven through a data flow, the simulation begins when the data flow is generated, and the simulation is finished when the data flow is terminated. The method for dispatching the distributed simulation models of the aircraft simulation system is achieved by formulating a data interaction protocol between the simulation models and a distributed simulation platform and designing a simulation model execution sequence algorithm. By means of the method, the concurrent design simulation of an aircraft can be achieved, the design efficiency of the aircraft is effectively improved, accurate transferring of simulation data is ensured, and correct execution of a simulation task is further guaranteed.

Owner:BEIJING INSTITUTE OF TECHNOLOGYGY

Basin rainfall monitoring wireless sensor network node optimization layout method

InactiveCN106257948AImprove efficiencyOptimized layout results are reasonableNetwork topologiesNetwork planningRegression analysisLongitude

The invention relates to a basin rainfall monitoring wireless sensor network node optimization layout method comprising the steps of correlation calculation; regression analysis; redundant site removing; additional arrangement of sites; additionally arranged site layout optimization calculation; and similarity calculation so that the optimal scheme of site layout can be obtained. The conventional site extraction method is improved, site network analysis is performed on existing rainfall site points based on the improved site extraction method, the redundant sites are removed, based on which the limitation of the road network on the feasibility of the site layout is directly considered, an optional area for additional arrangement of the sites is determined, the sites are additionally arranged in the optional area, a site layout optimization model is established with regression Kriging variance acting as a target function by comprehensively utilizing the correlation between the target variable rainfall and latitude and longitude, elevation, gradient, slope direction and other environmental variables, and the optimized layout of the rainfall monitoring sites is realized by solving the site layout optimization model in a high-performance way based on a parallel designed simulated annealing algorithm.

Owner:CHINA INST OF WATER RESOURCES & HYDROPOWER RES

Integrated modular unit including an analyte concentrator microreactor device connected to a cartridge-cassette

ActiveUS20150093304A1Large and small sample volumeSmall sample volumePreparing sample for investigationMaterial analysis by electric/magnetic meansMicroreactorModular unit

The integrated modular and interchangeable unit of the present invention comprises an analyte concentrator-microreactor (ACM) device having four entrance-exit ports identified as connection areas to a transport capillary for sample and buffer introduction, and to a separation capillary of a cartridge-cassette filled with an appropriate separation fluid for optimal separation of the analytes of interest. Affinity ligand groups are immobilized to microstructures contained within the main inner cavity or channel of the device or directly to the wall of the main inner channel for capturing one or more analytes. The inlet and outlet ends of the transport capillary are connected through a parallel design option to the analyte concentrator-microreactor (ACM) device to facilitate the path of sample and buffers through the inner cavity or channel of the analyte concentrator-microreactor (ACM) device.

Owner:GUZMAN NORBERTO

Method and apparatus for concurrent design of modules across different design entry tools targeted to single simulation

ActiveUS8521483B1Electronic circuit testingComputation using non-denominational number representationComputer architectureComputer module

A method of generating a representation of an electronic circuit across a plurality of design entry tools includes extracting a first partial circuit including a first plurality of first electronic components from a first partition, extracting a second partial circuit including a second plurality of second electronic components from a second partition, generating a simulation block in the first design entry tool including an interface between the first and second partitions, exporting a first netlist representing the interconnection of the first electronic components in the first partial circuit, populating the simulation block in the second design entry tool to include a second netlist representing the interconnection of the second electronic components in the second partial circuit and the interface between the first and second partitions, and exporting the second netlist to stitch the extracted first and second partial circuits using the interface between the first and second partitions.

Owner:CADENCE DESIGN SYST INC

Planarized side by side design of an inductive writer and single metallic magnetoresistive reader

InactiveUS6392840B1Reduce amountReduce in quantityConstruction of head windingsManufacturing heads with multiple gapsContact padMagnetic tape

In accordance with the present invention, an interleaved bi-directional magnetic tape head is provided in which the read element, write element, and servo element are formed on a common substrate. Each element has a contact pad area electrically associated withit, with each contact pad area located in a plane common to all contact pad areas. That is, the contact pad areas are planarized to each other. As a result of such planarization, two gold conduction layers, required in the prior art, are reduced to one layer. Further, the total number of mask layers is two less than the prior art, with a concomitant reduction in device fabrication time. Additionally, the unit cell size is reduced by about one-third.

Owner:IBM CORP

Satellite distributed type collaborative design method based on three-dimensional environment

ActiveCN106570301ARealize the establishmentImplement updateDesign optimisation/simulationSpecial data processing applicationsSimulationParallel design

The invention provides a satellite distributed type collaborative design method based on a three-dimensional environment. The satellite distributed type collaborative design method comprises the following steps of S1, establishing publish geometry of a mechanical interface of equipment and directly subordinated parts; S2, establishing publish geometry of a deck installing surface; S3, establishing publish geometry of a deck installing surface; S4, establishing a framework model and collecting interface information; S5, performing structural plate design according to framework-transferred pores; and S6, performing thermal control design according to framework-transferred footprint information. By adoption of the satellite distributed type collaborative design method, design intensions between disciplines can be transferred and driven through a three-dimensional model without artificial interpretation and conversion; and in addition, parallel design of the disciplines can be realized through a PDM (product data management) system, so that correctness and efficiency are greatly improved.

Owner:SHANGHAI SATELLITE ENG INST

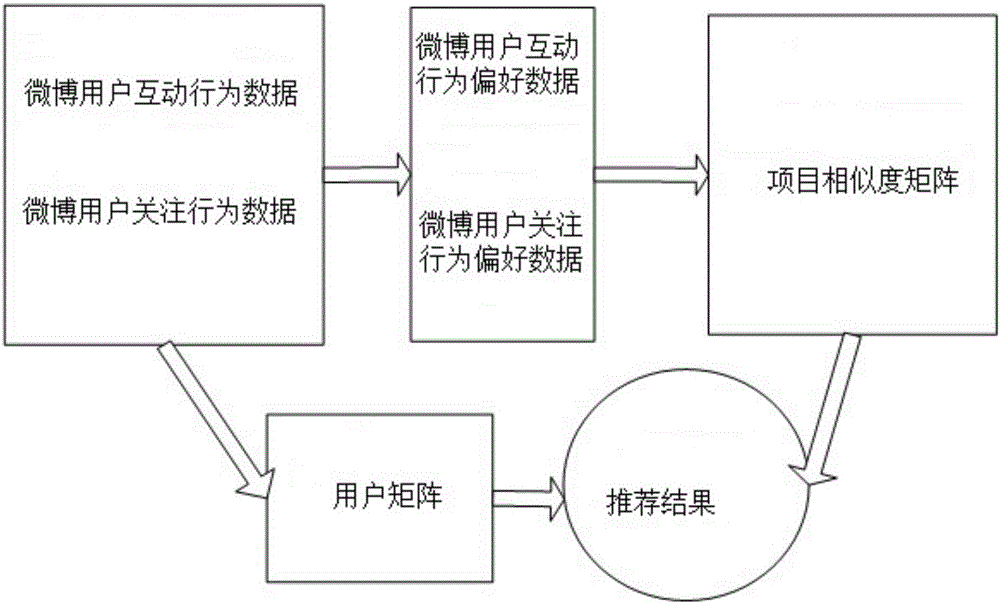

Microblog attention recommendation method based on parallel item-based collaborative filtering algorithm

ActiveCN105843860AImprove performanceImprove personalizationSpecial data processing applicationsPersonalizationMicroblogging

The invention discloses an microblog attention recommendation method based on a parallel item-based collaborative filtering algorithm. The method includes the steps of firstly, acquiring the microblog user interaction behavior data and microblog user attention behavior data; secondary, abstracting the microblog user interaction behavior preference data and microblog user attention behavior preference data from the above data and storing the data in an HDFS; then, adopting the MapReduce framework and the HDFS framework of the Hadoop to carry out the parallel design for the item-based collaborative filtering algorithm, and making mining analysis for the microblog user interaction behavior preference data and microblog user attention behavior preference data to find the item which is most similar with the item which is concerned by the user and filter the item which has been concerned by the user and recommending the item to a target user. The application of the item-based collaborative filtering algorithm under a non-traditional scene is realized, the displayed rating data is not depended on, and the recommendation individuation is improved.

Owner:SHANDONG UNIV

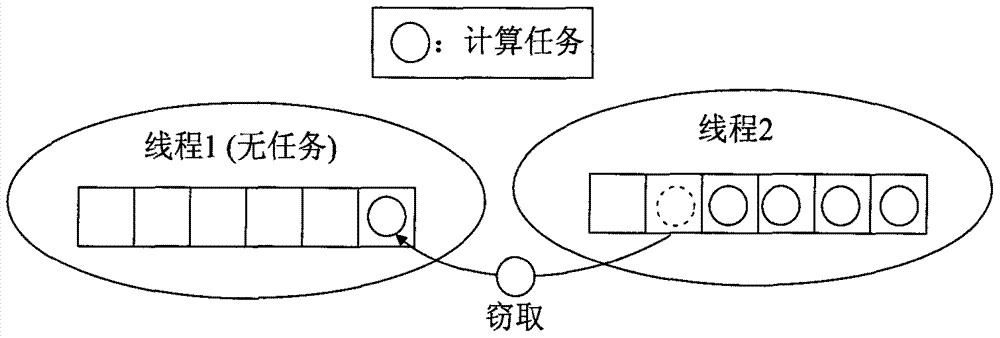

FFT-based large integer multiplication SSA algorithm multi-core parallel implementation method

ActiveCN104731563AGood time complexityRun fastConcurrent instruction executionComplex mathematical operationsGranularityComputation process

The invention discloses an FFT-based large integer multiplication SSA algorithm multi-core parallel implementation method. The method is used for carrying out multi-core parallel optimization on the large integer multiplication SSA algorithm from the point of fine granularity. The method is characterized in that the concurrent design is carried out on the four core computing processes which calculate the negative cyclic convolution based on the SSA algorithm respectively; in other words, the four computing processes comprising decomposition, FFT direct transformation, point multiplication and FFT inverse transformation are optimized respectively. The method sufficiently utilizes multi-core resources of hardware, increases the running speed and plays the quite important role in the actual application process.

Owner:INST OF SOFTWARE - CHINESE ACAD OF SCI

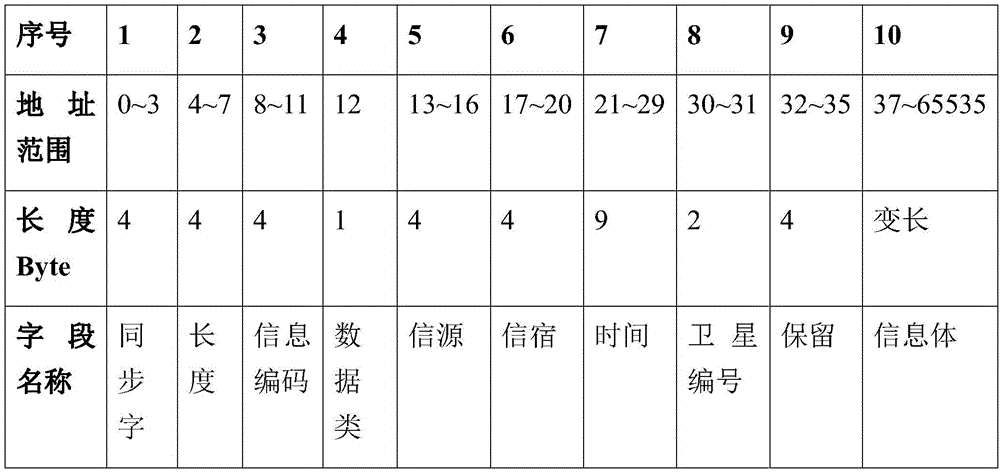

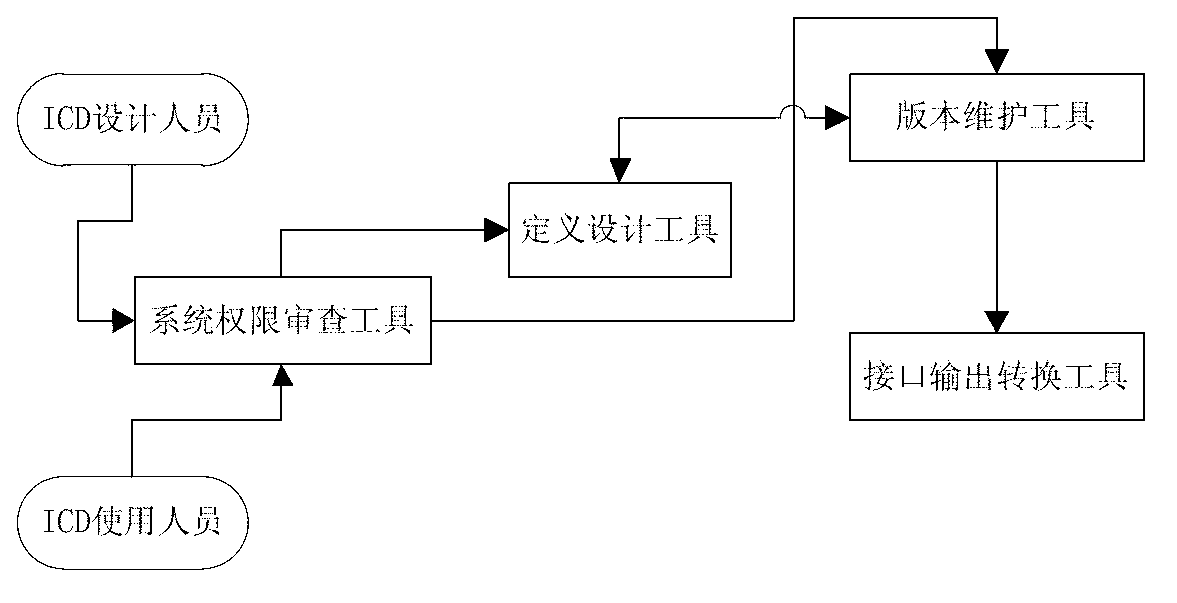

ICD (Interface Control Document) integrated management tool

ActiveCN102937800ADesign efficiencyCorrectly designedTotal factory controlProgramme total factory controlBit fieldManagement tool

The invention provides an ICD (Interface Control Document) integrated management tool. The ICD integrated management tool (namely an internal integrated design tool) consists of a definition design tool, a version maintenance tool, an interface output conversion tool and a system authority review tool, and is connected with a database management tool through a local area network, wherein the definition design tool is used for setting input and output of each module of a project management system and a bus management system in a grading manner in a visual design mode and an intuitive bytes and bit fields parallel design mode; the version maintenance tool forms a whole set of finished version specifications for ICD maintenance by virtue of different version repositories generated in an ICD; the interface output conversion tool is used for converting the ICD into an XML (Extensive Makeup Language) document describing the ICD by virtue of an XML document output system, and provides a whole set of complete conversion interface; and the system authority review tool guarantees the hierarchical authority and the confidential level of the ICD. By virtue of the ICD integrated management tool, the design of the ICD can be simpler, the management of the ICD can be more systemized, and the maintenance of the ICD can be more traceable.

Owner:10TH RES INST OF CETC

Spiral centrifugal fan and air treatment device

InactiveCN105626552AIncrease wind pressureReduce volumeEngine manufacturePump componentsAir volumeFresh air

The invention provides a spiral centrifugal fan. A centrifugal wind wheel of the centrifugal fan is located at the center position of a centrifugal wind wheel shell. One or more spiral air flues are arranged on the inner wall of the centrifugal wind wheel shell. The spiral air flues are located on the periphery of the centrifugal wind wheel, and air inlets of the spiral air flues are located in the radial outer side of the centrifugal wind wheel. Blades of the centrifugal wind wheel incline relative to the rotating axis of the centrifugal wind wheel. Air exhausted by the centrifugal wind wheel is forwards guided spirally through the spiral air flues. The spiral centrifugal fan has the beneficial effects of an axial flow fan and the beneficial effects of a centrifugal fan, axial air discharging can be achieved, and the beneficial effect of the high wind pressure of the centrifugal fan is achieved as well. Meanwhile, the noise of the spiral centrifugal fan is lower than that of the centrifugal fan, the size of the spiral centrifugal fan is smaller than that of the centrifugal fan, and the spiral centrifugal fan is noiseless, high in wind pressure, small in size and large in wind volume. The spiral centrifugal fan can serve as a ventilator, the spiral centrifugal fan can also serve as an air purifier when provided with a purification module, the spiral centrifugal fan can serve as a fan heater when provided with an electric heating module, and the spiral centrifugal fan can serve as a fresh air fan due to the parallel design. The wind direction is the axial direction, and after wind pipe connecting pieces are arranged, an inner wind pipeline and an outer wind pipeline are connected very conveniently.

Owner:柴俊麟

Virtual maintenance based maintainability analysis method for aircraft part

InactiveCN105045989AFind design flaws in timeMaintainability Design ImprovementsSpecial data processing applicationsStandardizationQualitative property

The invention discloses a virtual maintenance based maintainability analysis method for an aircraft part. Firstly, a maintenance attribute value of the to-be-analyzed aircraft part is quantitatively determined, wherein the maintenance attribute value comprises human factor engineering, reachability, simplified design, modularization, standardization and interchangeability, and testability; secondly, a natural language is quantitatively processed; thirdly, according to the obtained attribute value, performing weighted calculation on a comprehensive maintainability attribute value of the to-be-analyzed aircraft part; and finally, according to the comprehensive maintainability attribute value, calculating degree of membership, and obtaining comprehensive maintainability evaluation and partial evaluation of the to-be-analyzed aircraft part. According to the method, on the basis of determining maintainability influence attributes, each maintainability influence attribute is analyzed and inspected, an evaluation method for maintainability quantitative requirements is proposed, and parallel design-oriented maintainability qualitative analysis and evaluation are realized, so that design defects can be discovered in time and the improvement on maintainability design is facilitated.

Owner:NORTHWESTERN POLYTECHNICAL UNIV

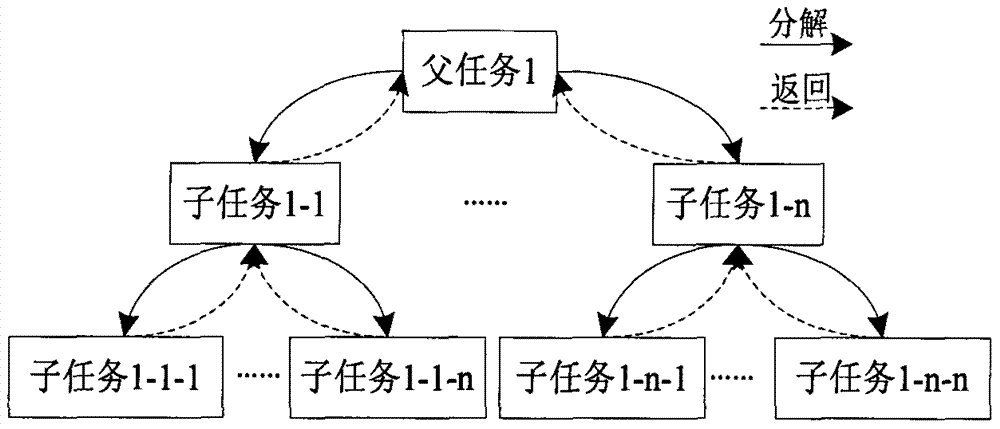

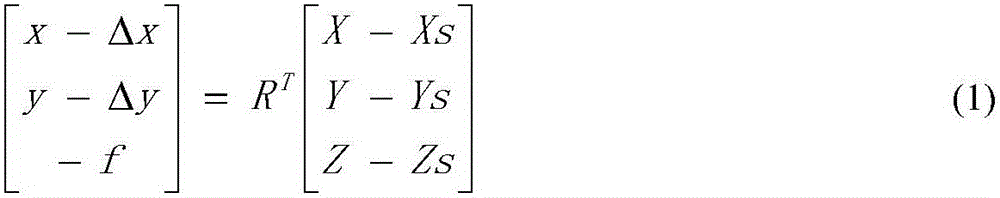

Precondition conjugate gradient block adjustment method based on GPU (Graphics Processing Unit) parallel acceleration

ActiveCN105808926ALow costEasy to handleSpecial data processing applicationsInformaticsParallel designParallel processing

The invention discloses a precondition conjugate gradient block adjustment method based on GPU (Graphics Processing Unit) parallel acceleration. In a traditional block adjustment flow, a precondition conjugate gradient method is imported to solve a large-scale normal equation, the storage and the direct inverse operation of the normal equation are avoided, a block adjustment flow is made to be suitable for a parallel design scheme, meanwhile, a GPU parallel computing framework is adopted to decompose the adjustment task of super-large scale testing region data into a plurality of subtasks, the subtasks are computed by different threads and are subjected to multi-thread collaborative parallel processing, and finally, summarization is carried out to obtain an integral block adjustment result. The precondition conjugate gradient block adjustment method is especially suitable for the block adjustment computation of a super-large scale testing region ( which contains more than 100 thousand of images, and the whole province, the whole nation or even the whole world is taken as a whole testing region).

Owner:北京中测智绘科技有限公司

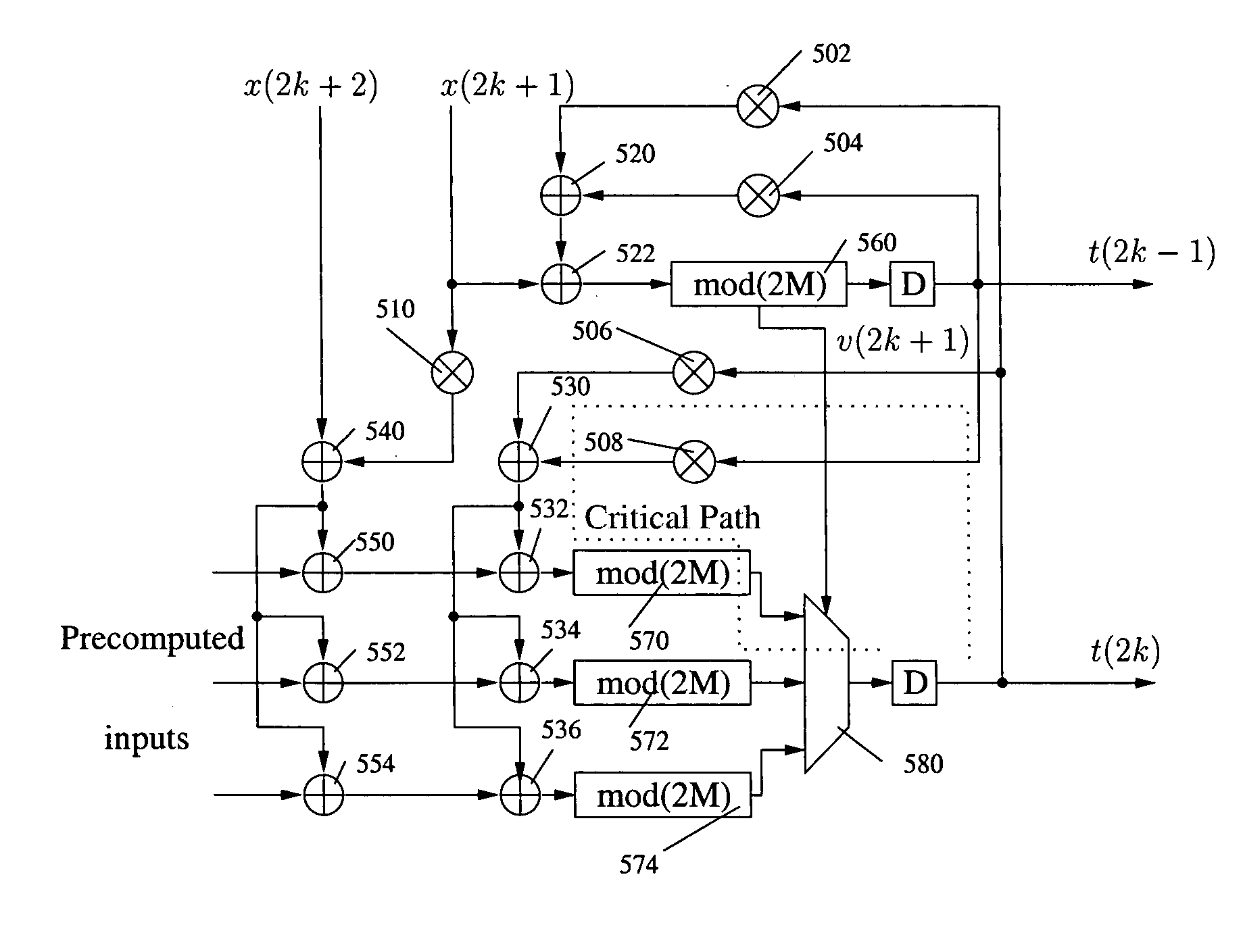

Parallel Tomlinson-Harashima precoders

A method to design parallel TH precoders and a circuit architecture to implement parallel TH precoders have been presented. The parallel design relies on the fact that a TH precoder can be viewed as an IIR filter with an input equal to the sum of the original input to the TH precoder and a compensation signal. The parallel design also relies on the fact that the compensation signal has finite levels. Therefore, precomputation techniques can be applied to calculate intermediate signal values for all possible values of the compensation signal.

Owner:PARHI KESHAB K

Product structure and process parallel design method based on model maturity

InactiveCN103631996AImprove the efficiency of research and developmentReduce error rateSpecial data processing applications3D modellingParallel designEngineering

The invention discloses a product structure and process parallel design method based on model maturity. The method includes the following steps that (1) maturity levels of product structure design models are defined; (2) the product structure design models at different maturity levels are distributed to corresponding process design staff in advance so as to enable product structure design and process design to be performed in parallel. Compared with the prior art, the method has the following advantages that the maturity of the product structure design models are divided, the product structure design models reaching certain maturity are distributed to the process design staff in advance, therefore, the effect that the product structure design and process design are performed in parallel is achieved, the product research and development efficiency is improved, the error rate is lowered, unnecessary time waste and unnecessary cost waste are avoided, the product research and development cycle is shortened, and the product research and development cost is reduced.

Owner:CHINA ELECTRONIC TECH GRP CORP NO 38 RES INST

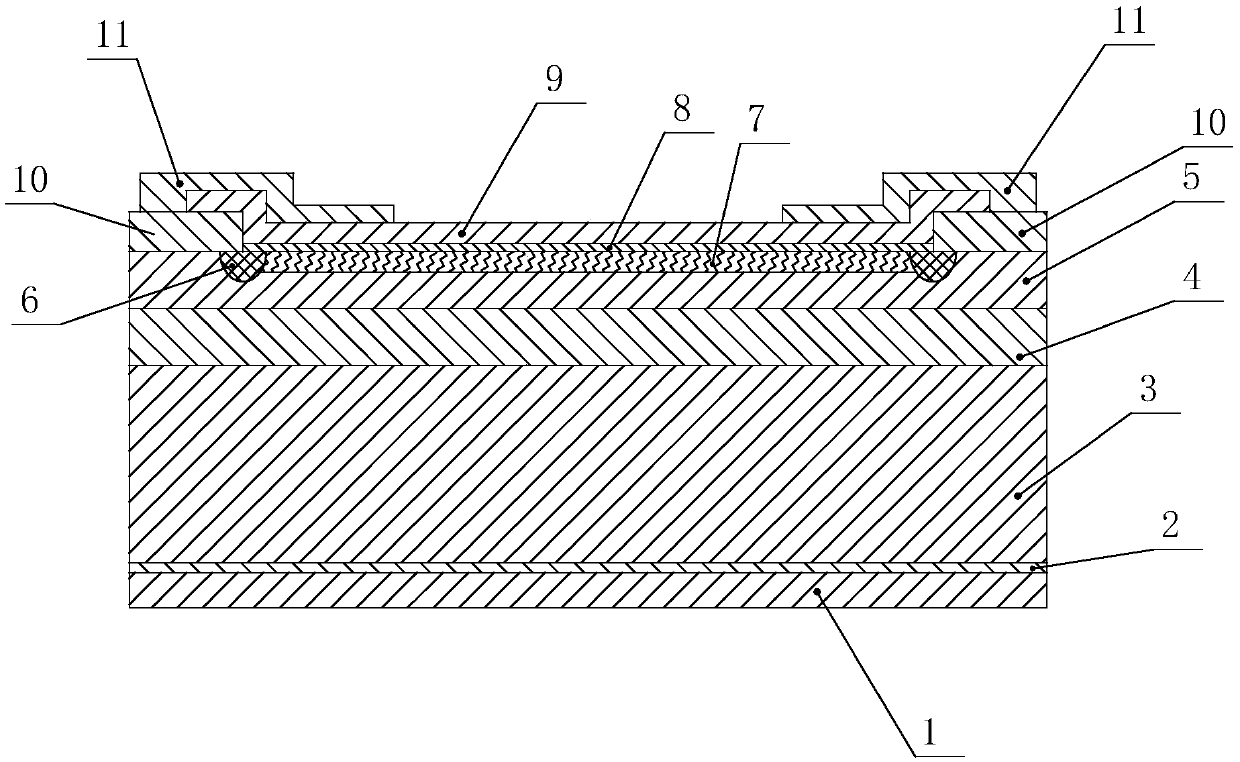

Large-current low-forward-voltage-drop silicon carbide Schottly diode chip and preparation method thereof

PendingCN108682695AForward voltage drop increasesOptimizing Forward Voltage DropSemiconductor/solid-state device manufacturingSemiconductor devicesP–n junctionPolyimide membrane

The invention provides a large-current low-forward-voltage-drop silicon carbide Schottly diode chip. The large-current low-forward-voltage-drop silicon carbide Schottly diode chip comprises a back laminated metal electrode, a front laminated metal electrode, an ohmic contact layer, a substrate, a first epitaxial layer, a second epitaxial layer, a P-type protecting ring, a N-type ion implanted layer, a Schottly metal Pt layer, an annular passivation layer and an annular polyimide film. The invention further provides a preparation method for the large-current low-forward-voltage-drop silicon carbide Schottly diode chip. The preparation method is capable of, through using a parallel design of a PN junction and a Schottly junction, double-layer epitaxial growth, and ion implantation and nitrogen ion doping, generating a large implantation effect in a large current by using a Schottly metal Pt, reducing the electrical resistivity of the epitaxial layer, realizing the manufacture for the large-current low-forward-voltage-drop silicon carbide Schottly diode, thereby overcoming the defects in the prior art that the forward voltage drop of a device is reduced as well as the reverse leakagecurrent of the device is increased while a low barrier metal is selected and a chip area is increased, a rate of finished products is reduced, and the manufacturing cost is increased.

Owner:JINAN JINGHENG ELECTRONICS

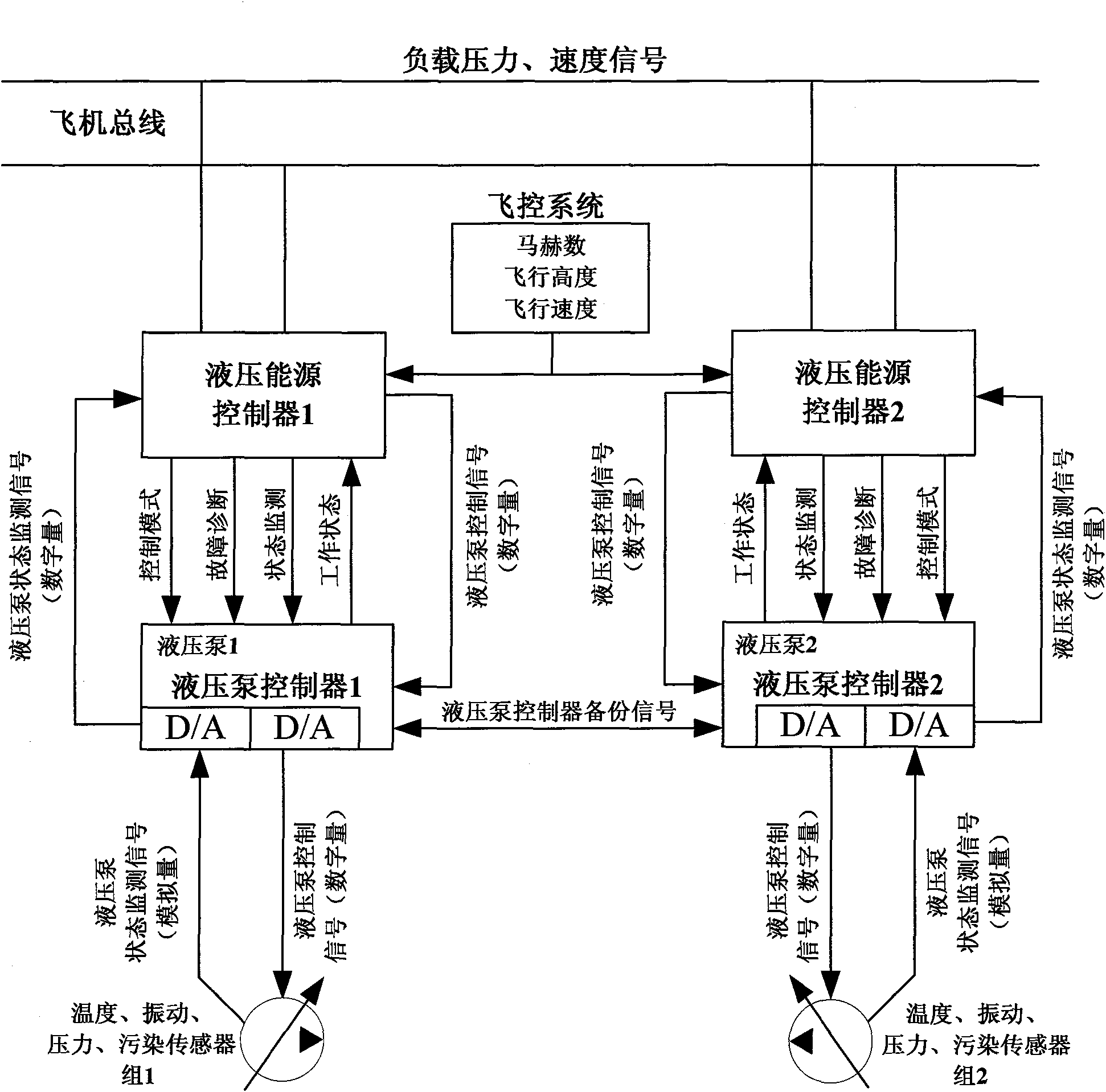

Method for implementing airborne variable pressure hydraulic energy system

InactiveCN101813110AImprove adaptabilityIncrease profitFluid-pressure actuator componentsHydraulic pumpEngineering

The invention discloses a method for implementing an airborne variable pressure hydraulic energy system. A hydraulic energy system is provided with a hydraulic pump, a hydraulic energy management control unit, and a vibration, temperature, pollution and pressure sensor group, wherein the management control unit consists of a hydraulic energy controller and a hydraulic pump controller; the hydraulic energy controller receives a plane bus signal and a flight state signal transmitted by a flight control system and sends a working state command to the hydraulic pump; the vibration, temperature, pollution and pressure sensor group senses the working state of the hydraulic pump and transmits monitored data to the hydraulic pump controller and performs fault diagnosis and fault isolation on the hydraulic pump; and the airborne variable pressure hydraulic energy system adopts a dual-pump parallel design mode. By using the method, the system can automatically regulate output flow and output pressure according to external load demand and can convert and work reliably in a plurality of working modes, thereby improving the energy utilization efficiency of a hydraulic system, reducing the thermal power loss of the system, and prolonging the service lives of the hydraulic system and accessories.

Owner:XIAN AIRCRAFT DESIGN INST OF AVIATION IND OF CHINA

Method for cooperatively computing and accelerating pre-stack time migration of earthquake by using CPU (Central Processing Unit)/MIC (Microphone)

ActiveCN103018776AImprove computing powerMeet processing needsSeismic signal processingScanning tunneling microscopeParallel computing

The invention provides a method for cooperatively computing and accelerating pre-stack time migration of an earthquake by using a CPU (Central Processing Unit) / MIC (Microphone), and relates to the field of high-property computing. According to the method, a CPU and MIC heterogeneous framework is used; a CPU is in charge of performing FFT (Fast Fourier Transform) computing, reading seismic channel data, performing process control and scheduling, and further participating in PSTM (Photon Scanning Tunneling Microscope) computing; the MIC is used for only performing the PSTM computing, and simultaneously performing CPU and MIC cooperative computation and common computation in an asynchronous parallel idea and dynamic load balance manner; and the integrated design comprises the following three aspects: parallel design of a PSTM computation partial serial algorithm, a PSTM integrated logic structural design and a CPU and MIC asynchronous computation design. The method provided by the invention has the beneficial effects that the PSTM properties can be improved by using the CPU / MIC cooperative computation; the building cost and management, operation and maintenance costs of a machine room can be reduced; and the simple realization and the low desired development cost can be realized.

Owner:LANGCHAO ELECTRONIC INFORMATION IND CO LTD

Spark framework-based parallelization method of text clustering model PW-LDA

ActiveCN109558482AIncreased complexityScale upText database clustering/classificationAlgorithmParallel design

The invention relates to the field of text topic clustering, in particular to a Spark framework-based parallelization method of a text clustering model PW-LDA. The method mainly comprises the steps ofdata loading, text data preprocessing, word vector training, Partion target segment extraction, LDA training, topic vector calculation, text clustering and the like. According to the method, a Sparkframework is used, the modules in the model are subjected to parallel design and implementation through the MapReduce technology and the GraphX technology, program operation is greatly accelerated, and therefore the feasibility of real-time operation is provided for the modules.

Owner:SUN YAT SEN UNIV

Concurrent design process

The present disclosure relates to a method for multi-user, at least partially concurrent, electronic circuit design. Embodiments may include receiving, at a client computing device, a user input corresponding to a change to an electronic circuit design, wherein the electronic circuit design is accessible by multiple users in an at least partially concurrent manner. Embodiments may also include implementing the change to the electronic circuit design at the client computing device without receiving authorization from a server computing device and transmitting the implemented change to the electronic circuit design to the server computing device.

Owner:CADENCE DESIGN SYST INC

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com