Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

247 results about "Electronic circuit design" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Electronic circuit design comprises the analysis and synthesis of electronic circuits.

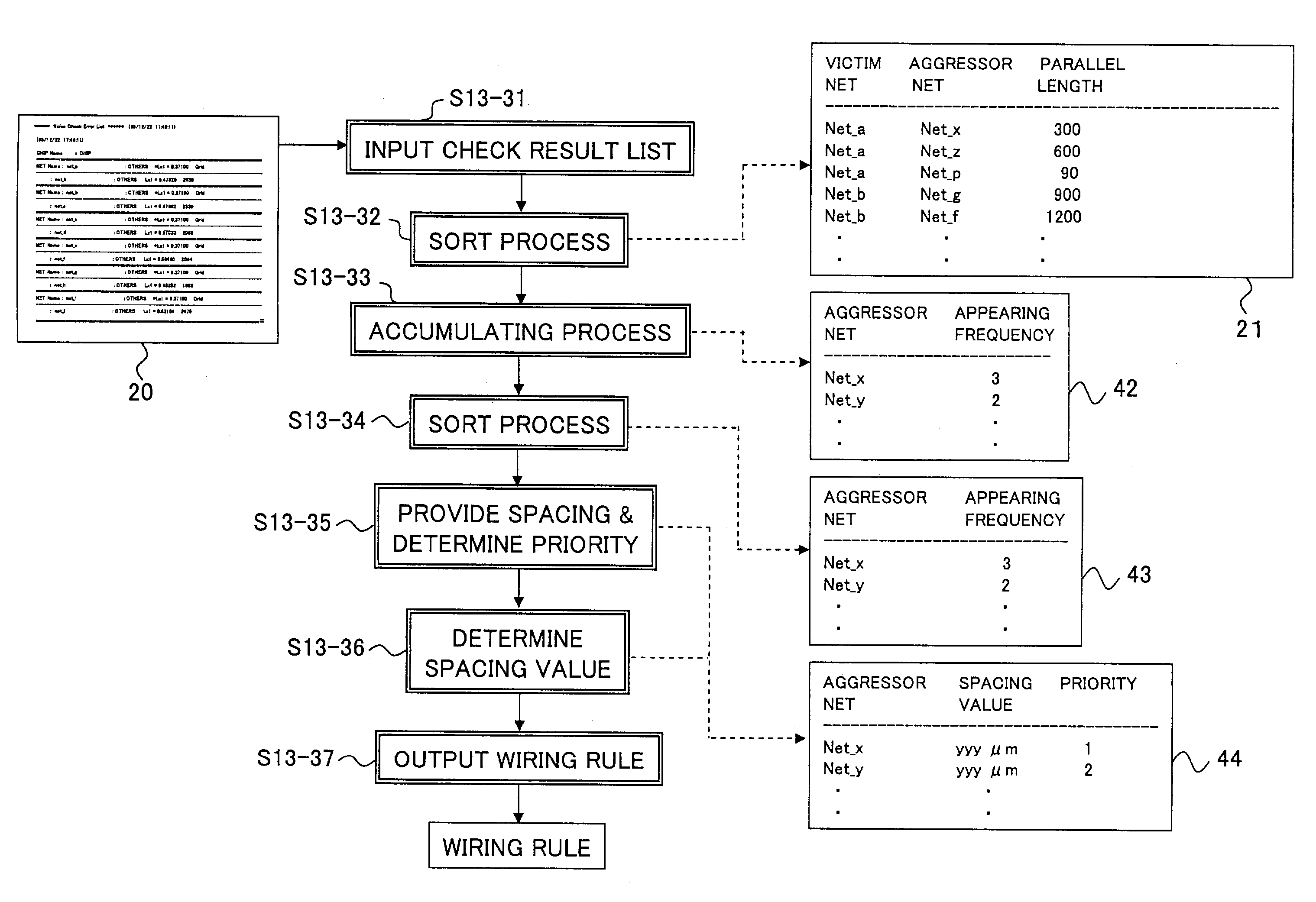

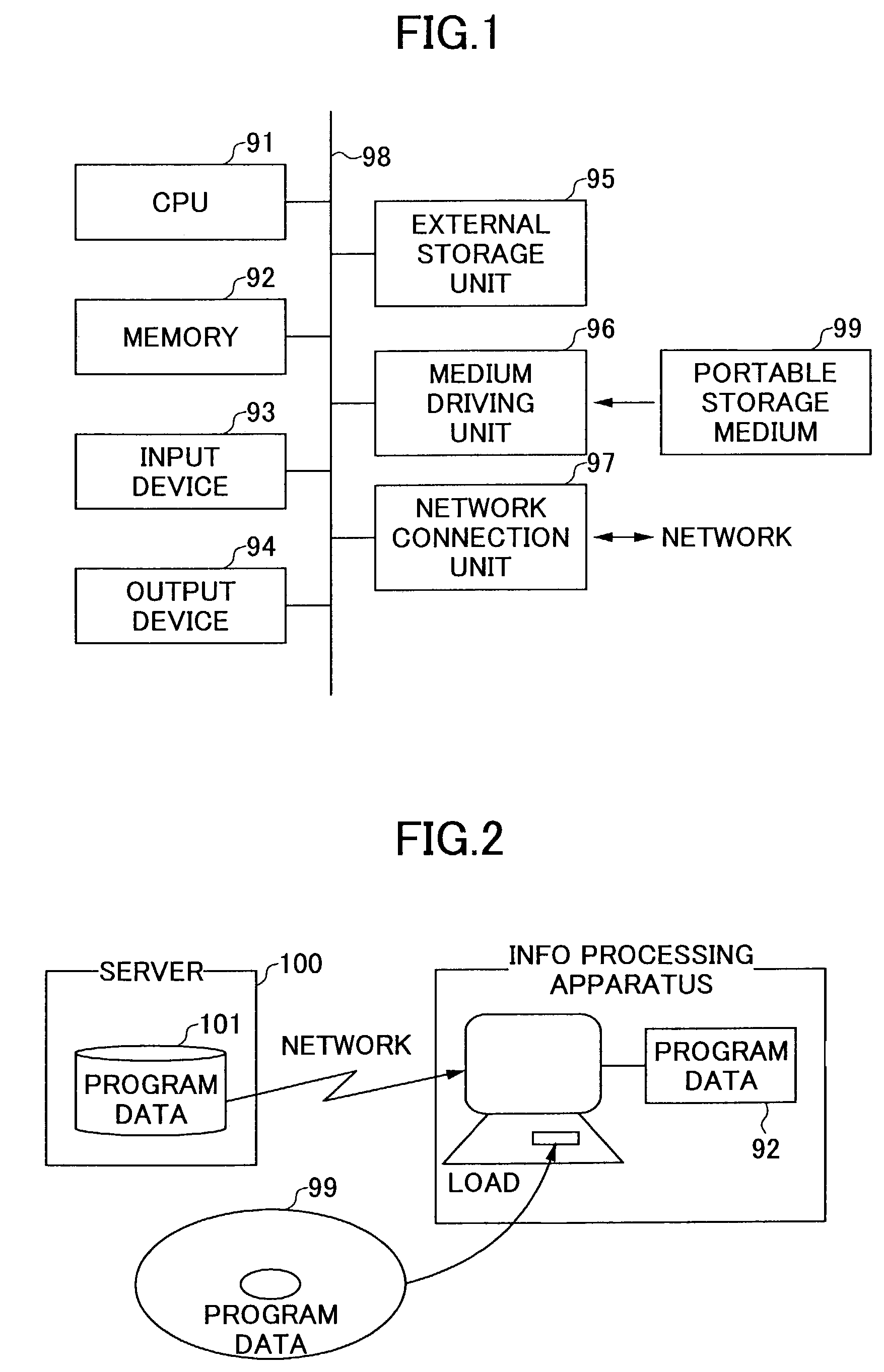

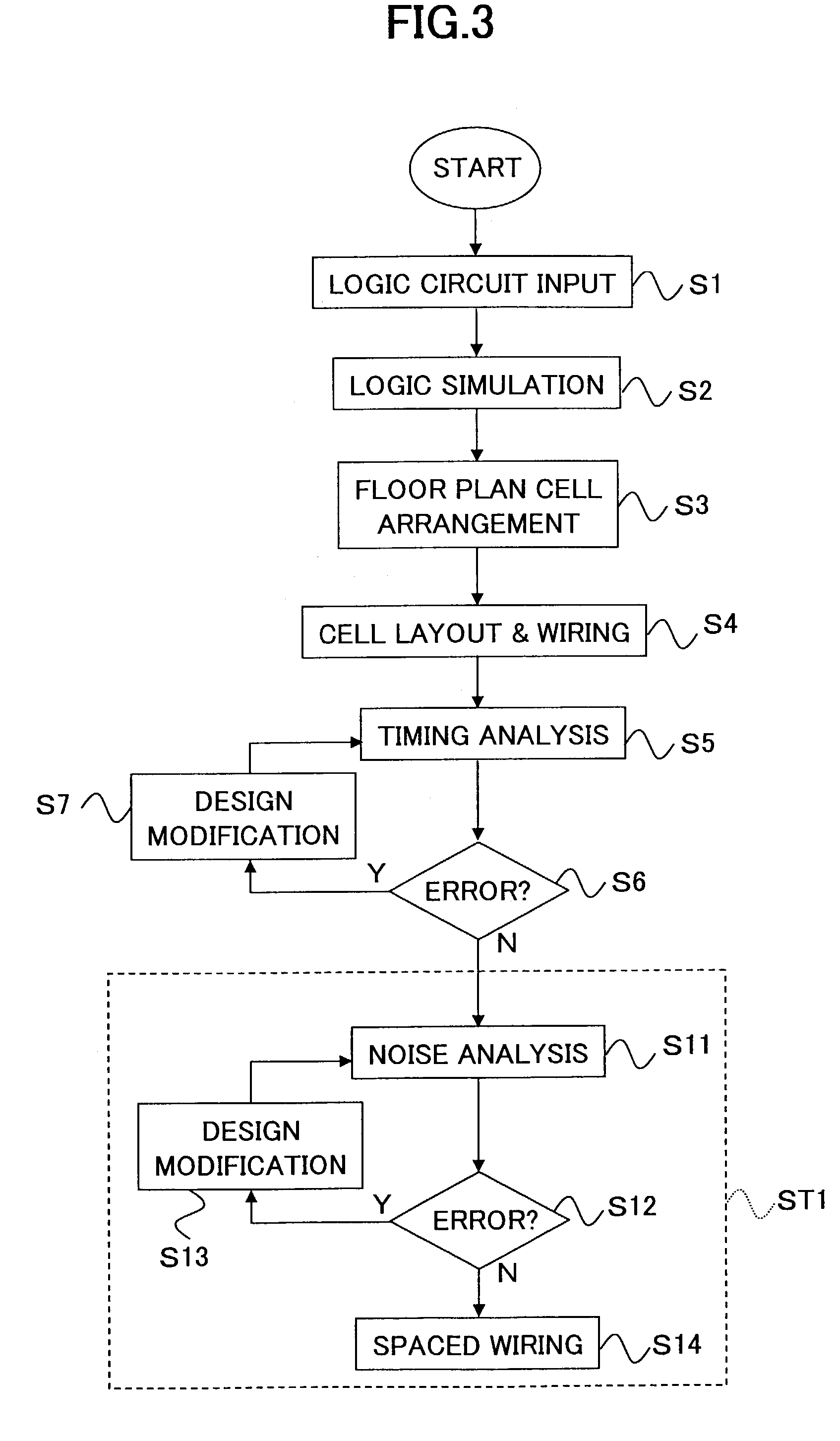

Electronic circuit design method, simulation apparatus and computer-readable storage medium

InactiveUS7086018B2Eliminate the problemReduce loadSemiconductor/solid-state device manufacturingComputer aided designEngineeringElectronic circuit design

An electronic circuit designing method analyzes noise with respect to a wiring pair, and automatically corrects the wiring pair by determining a spacing between wirings of the wiring pair so as to prevent generation of a noise error, if the noise error is detected based on the analysis of the noise.

Owner:FUJITSU LTD

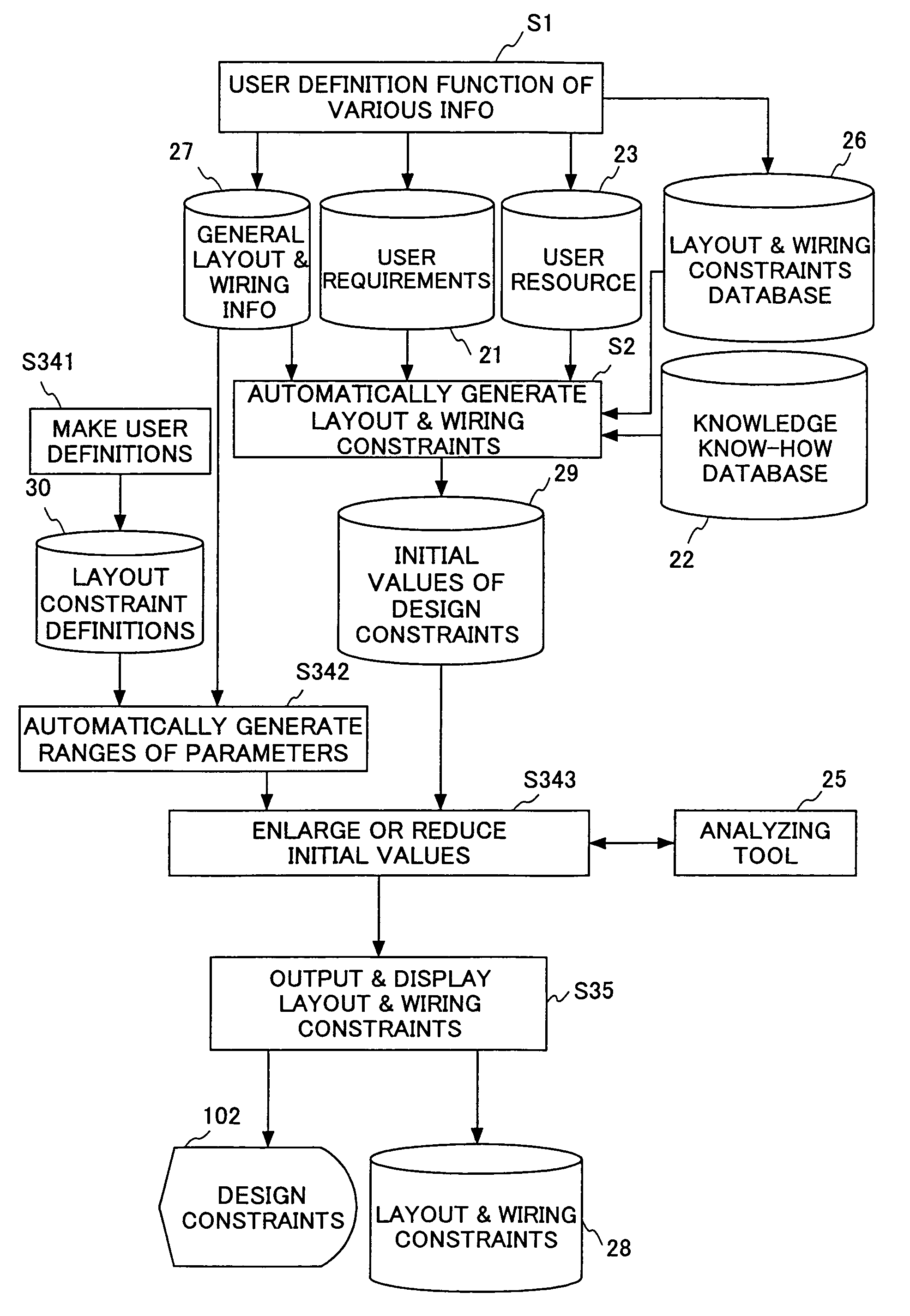

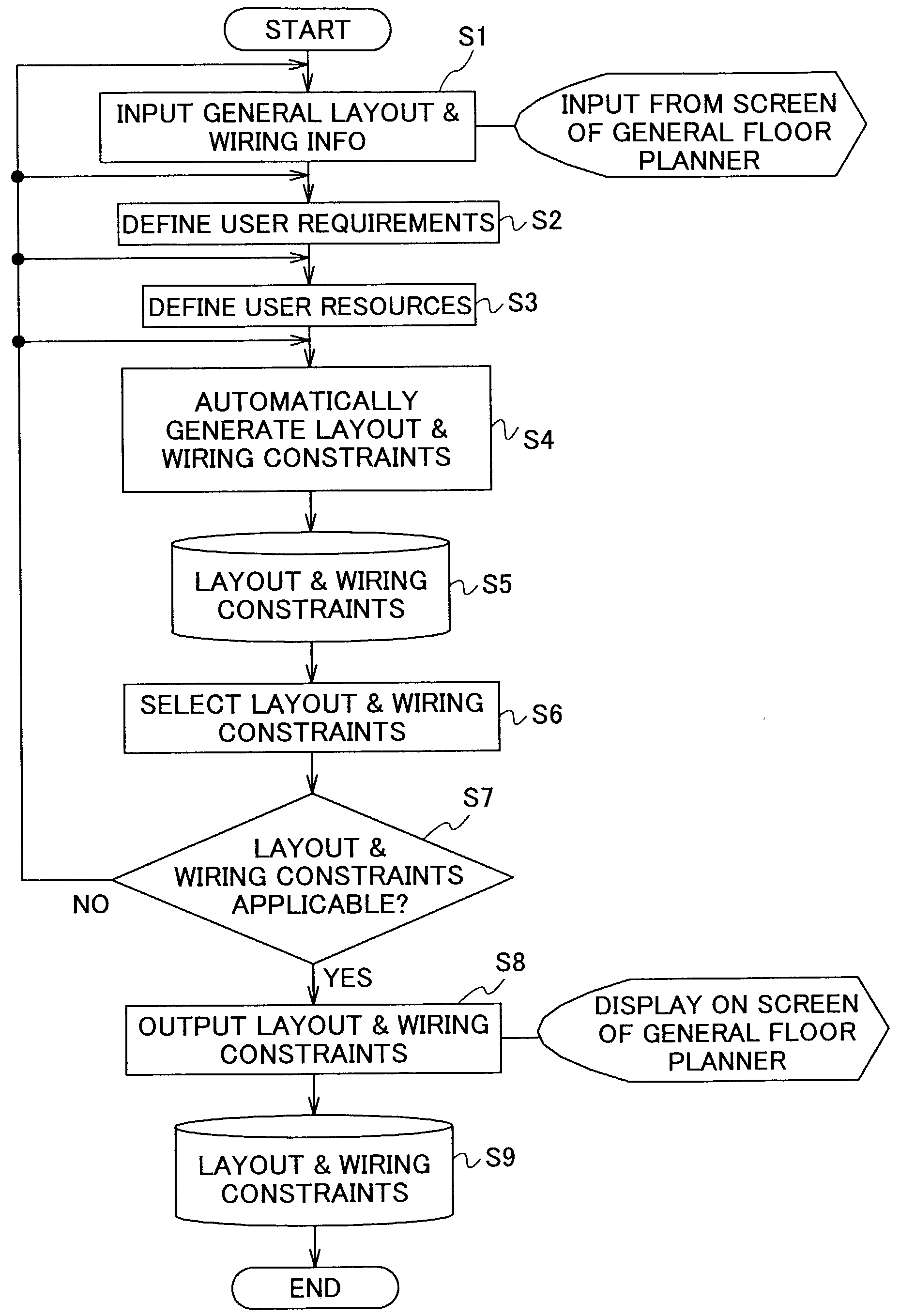

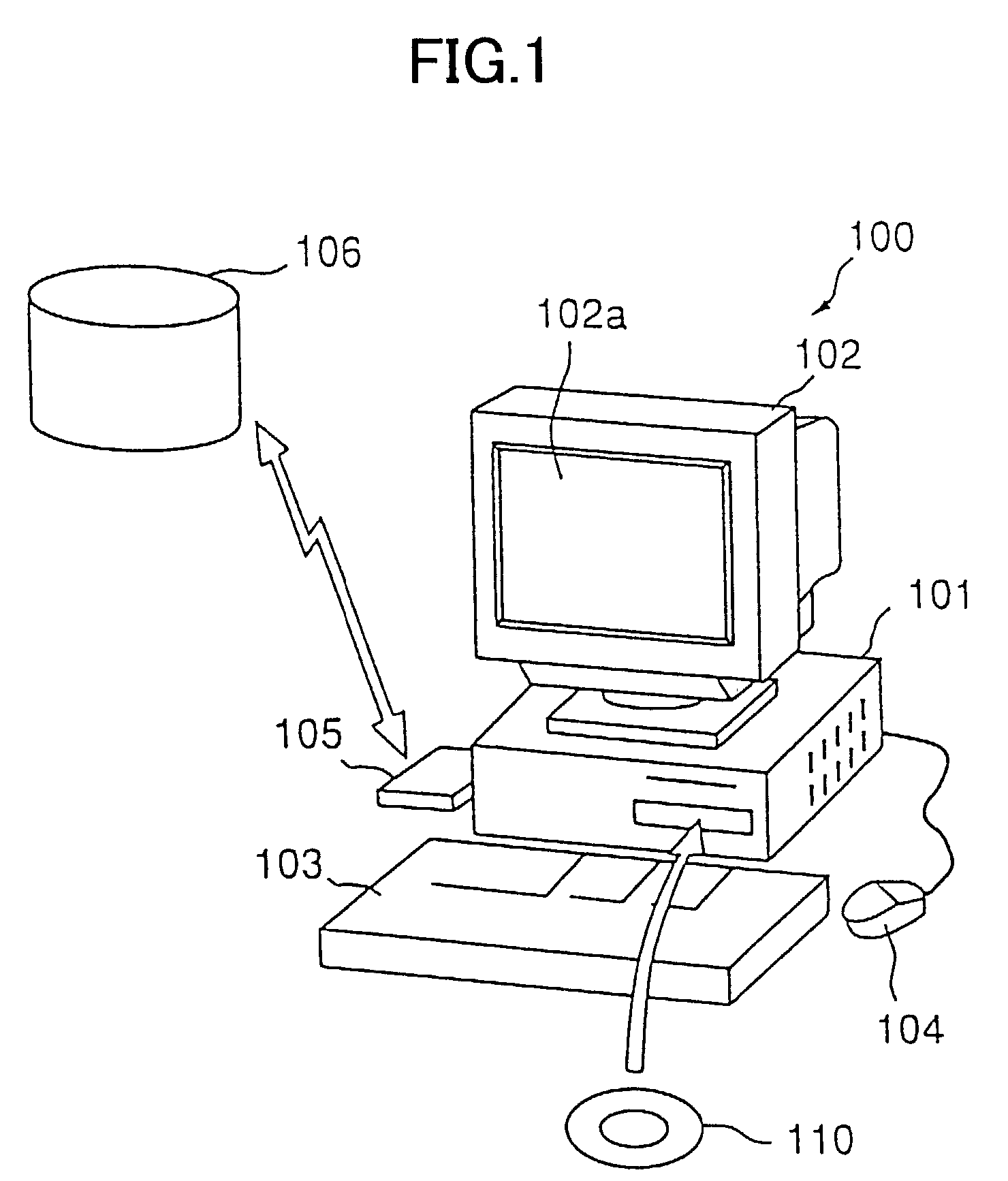

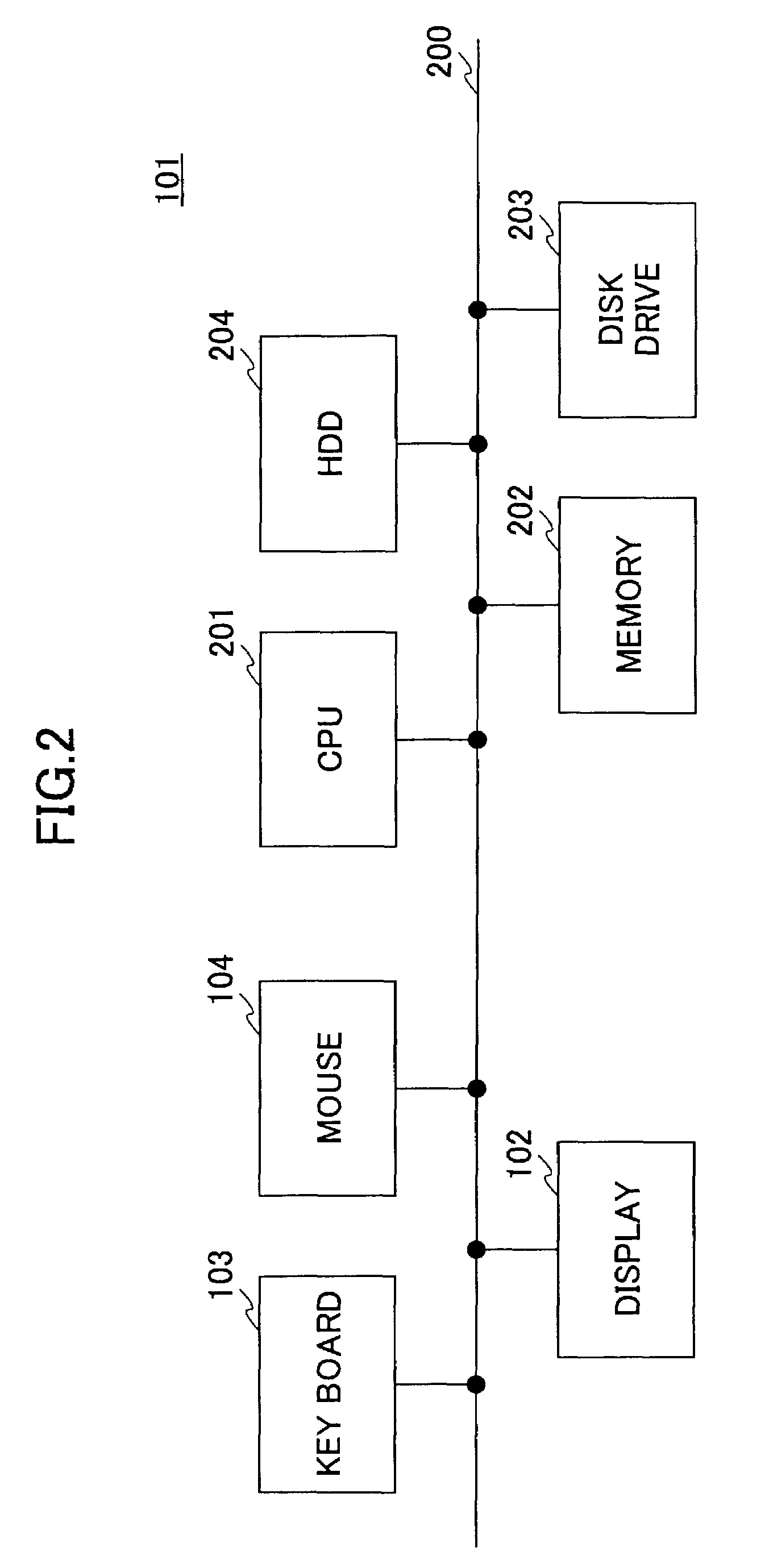

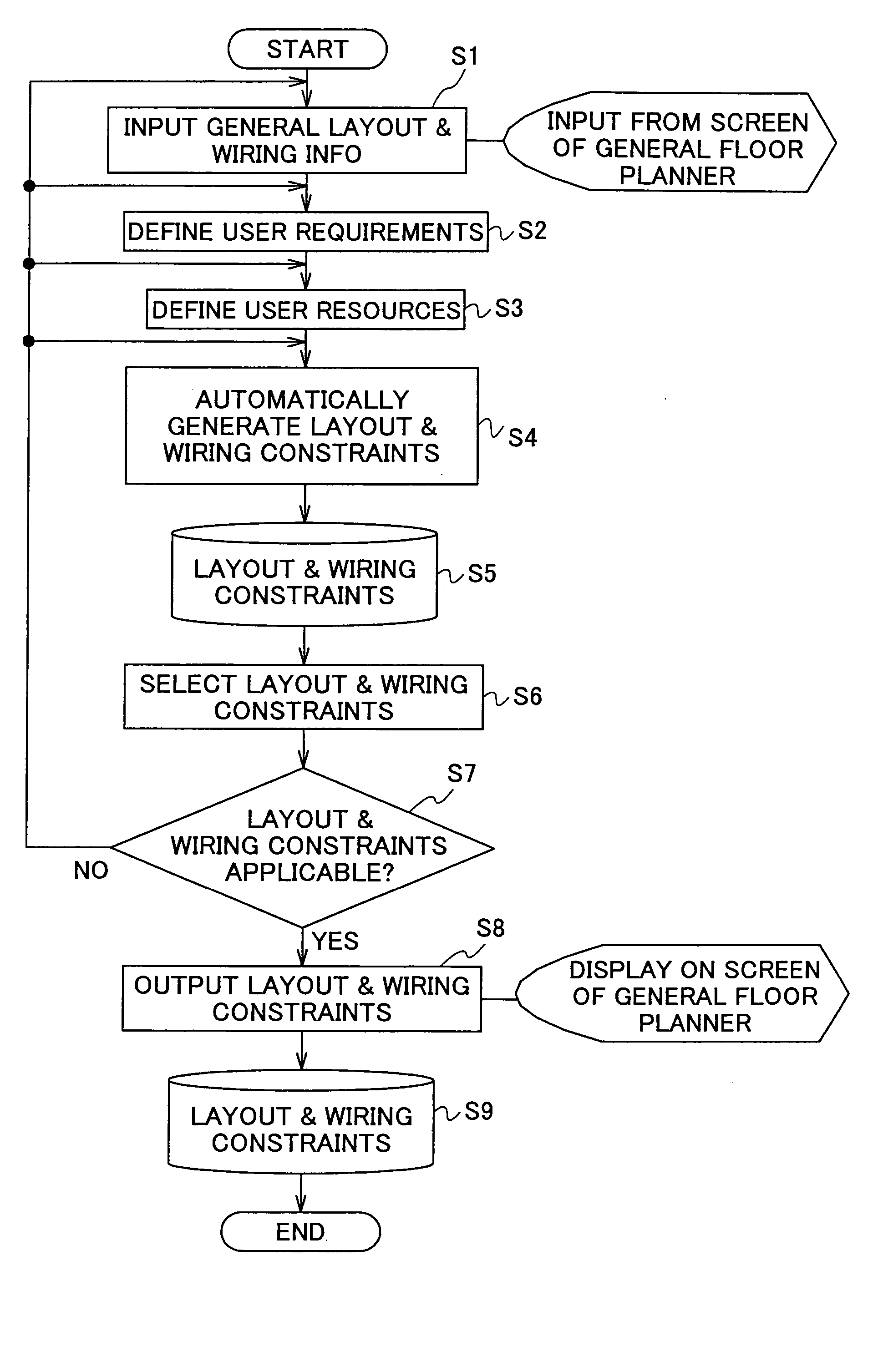

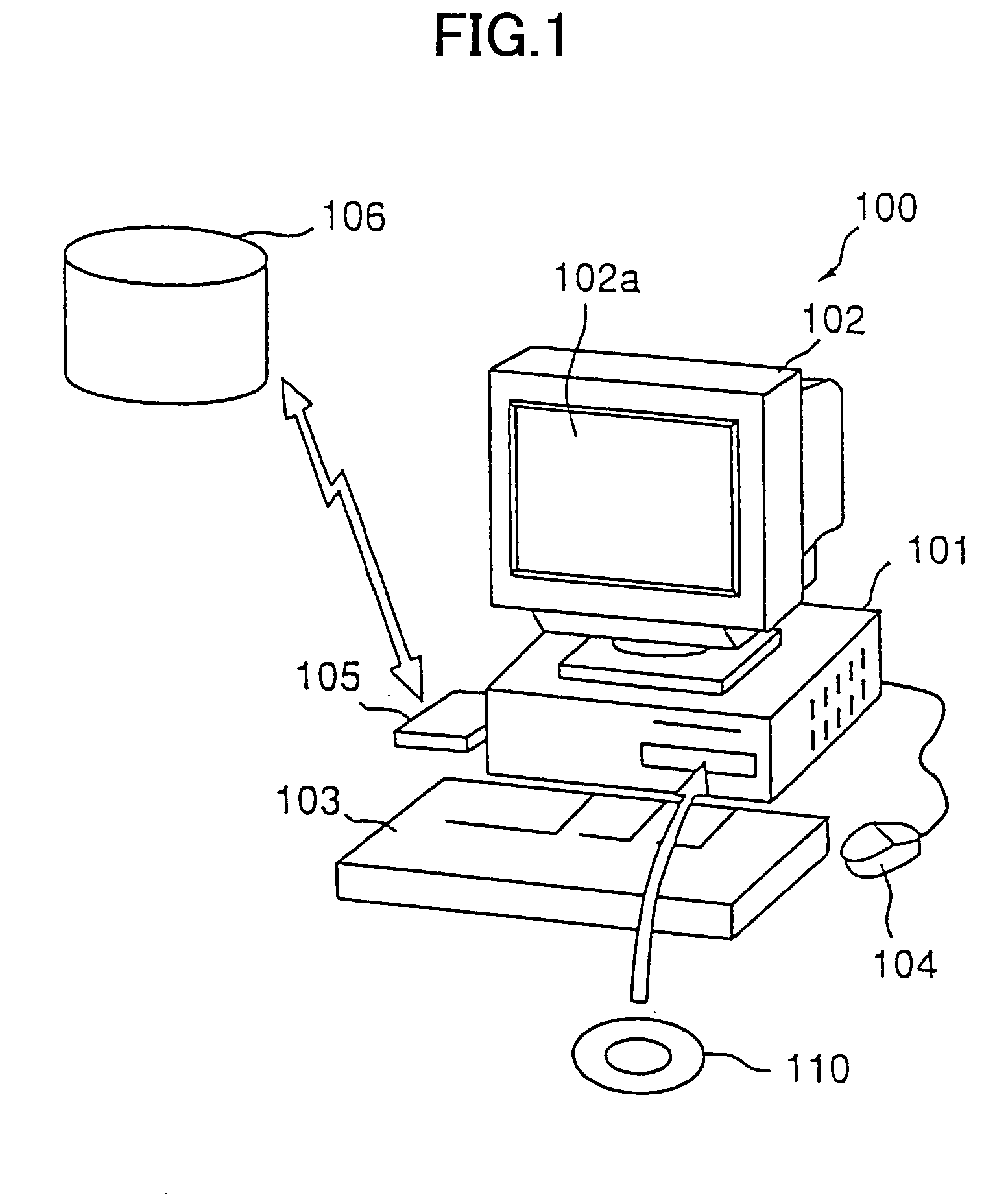

Electronic circuit designing method, apparatus for designing an electronic circuit, and storage medium for storing an electronic circuit designing method

InactiveUS7398497B2Semiconductor/solid-state device manufacturingComputer programmed simultaneously with data introductionEngineeringElectronic circuit design

An electronic circuit designing method and apparatus designs an electronic circuit by CAD, by generating design constraints with respect to the electronic circuit based on at least one of general layout and wiring information related to devices and wirings included in the electronic circuit, user requirements defined by a user, and user resources defined by the user, and urging an input to the user by displaying the design constraints.

Owner:FUJITSU LTD

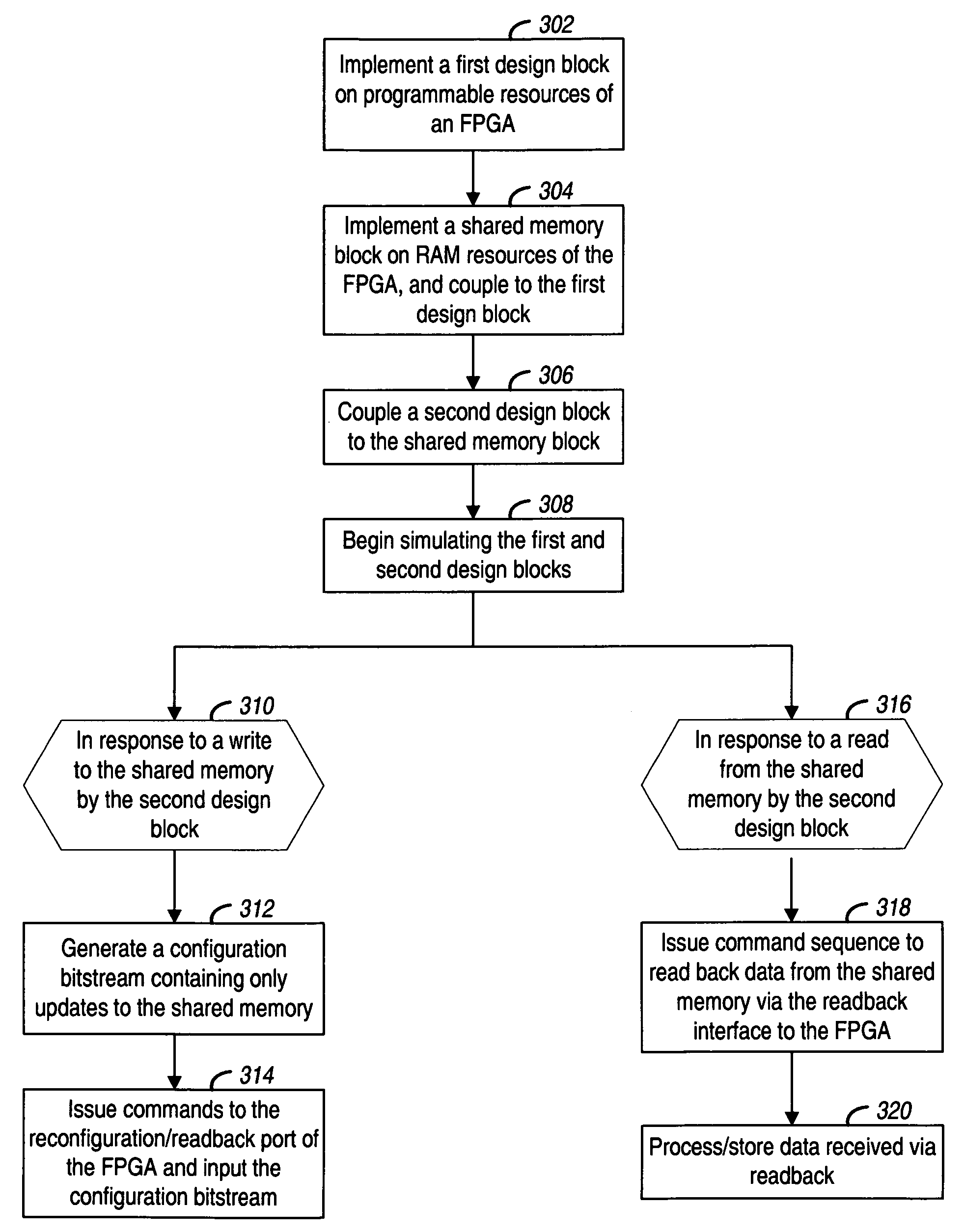

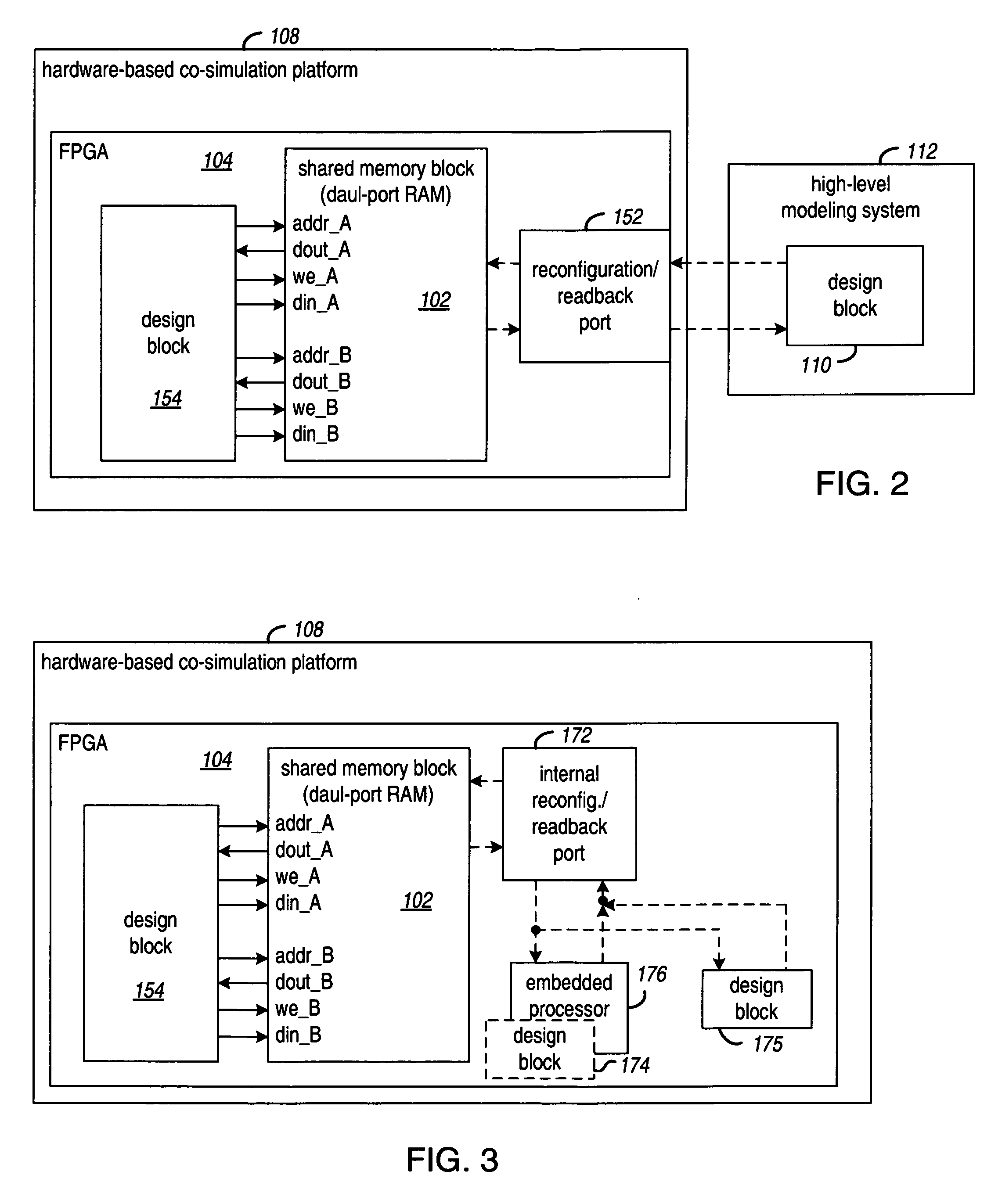

Shared memory interface in a programmable logic device using partial reconfiguration

ActiveUS7546572B1Electronic switchingSpecial data processing applicationsMemory addressMemory interface

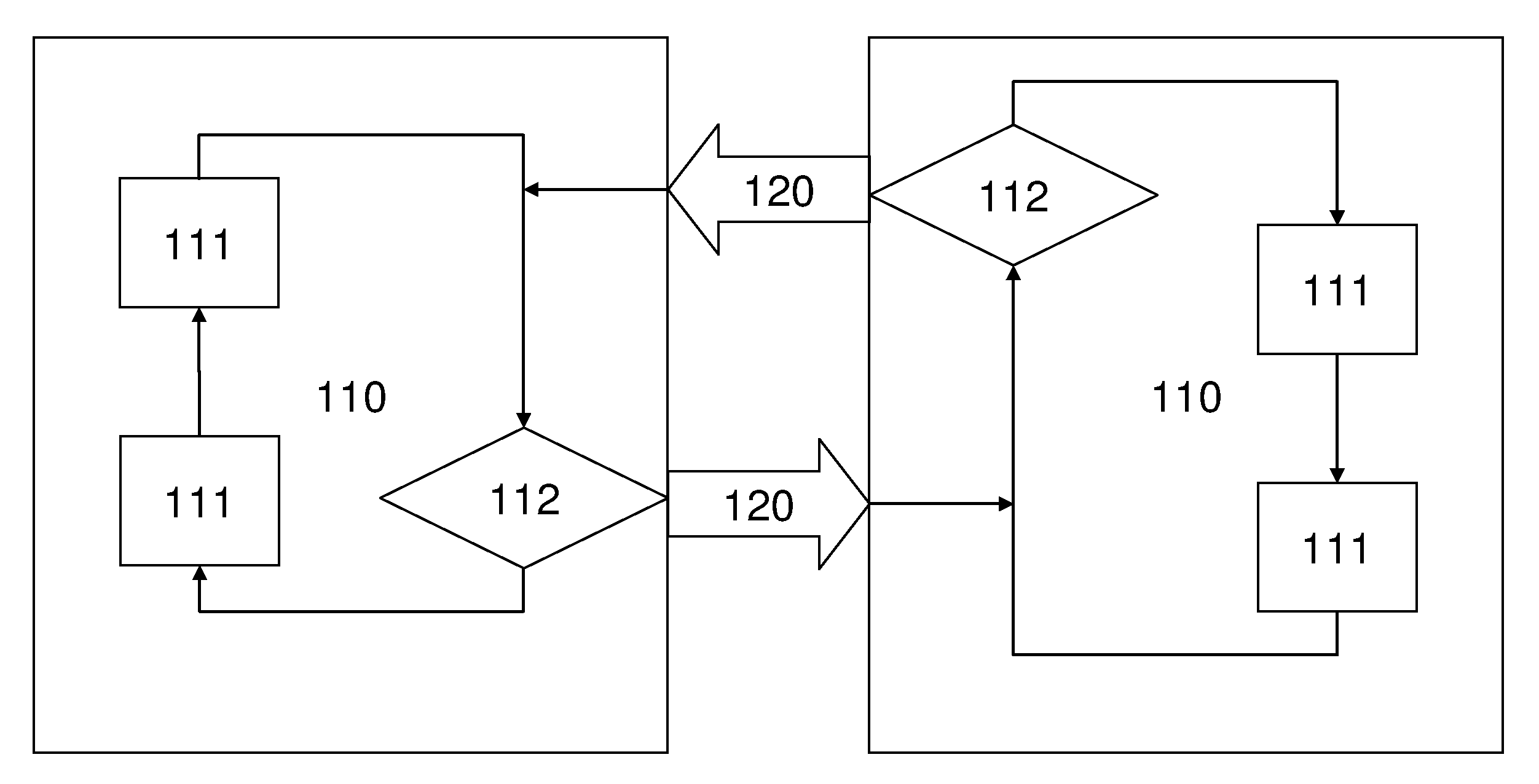

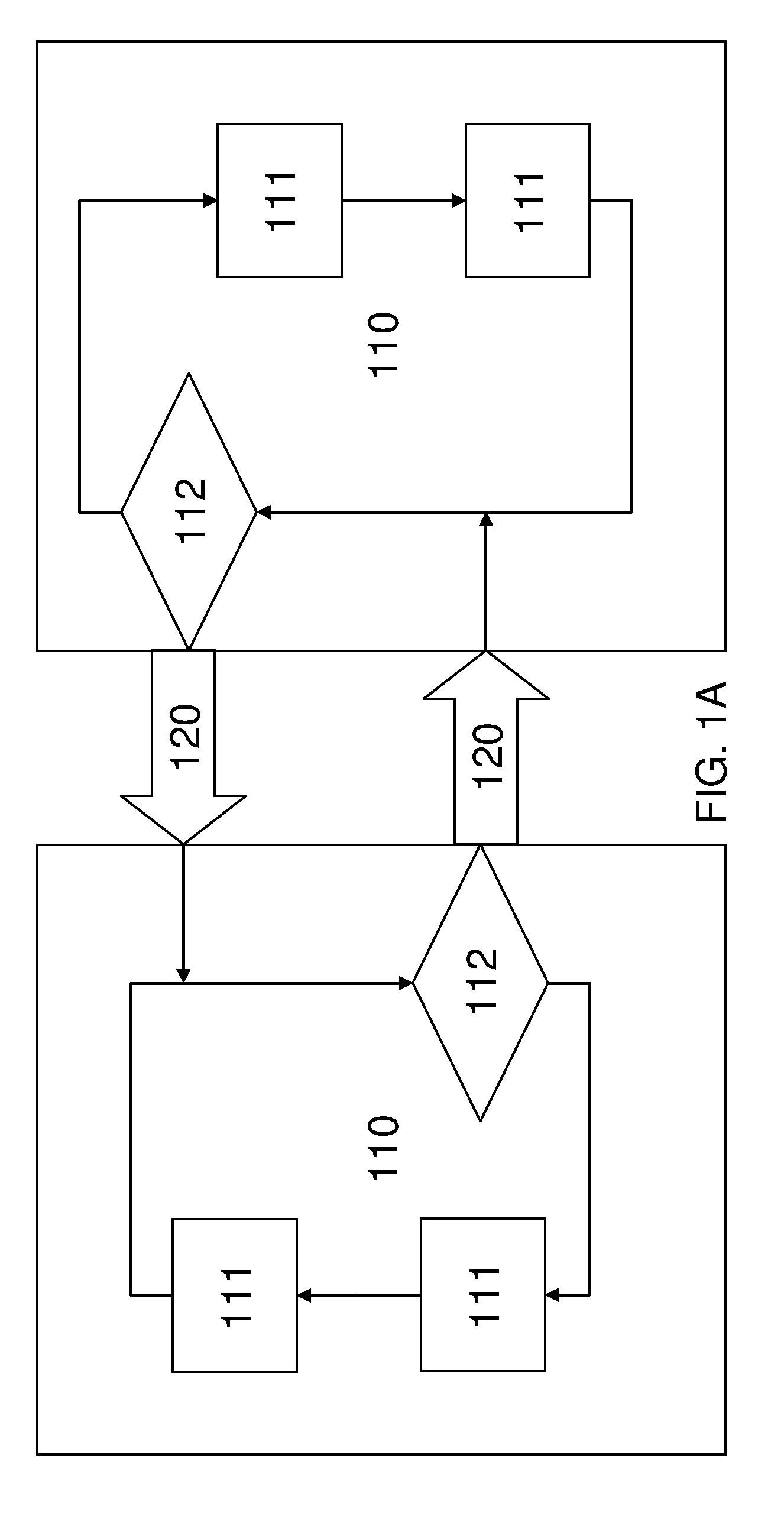

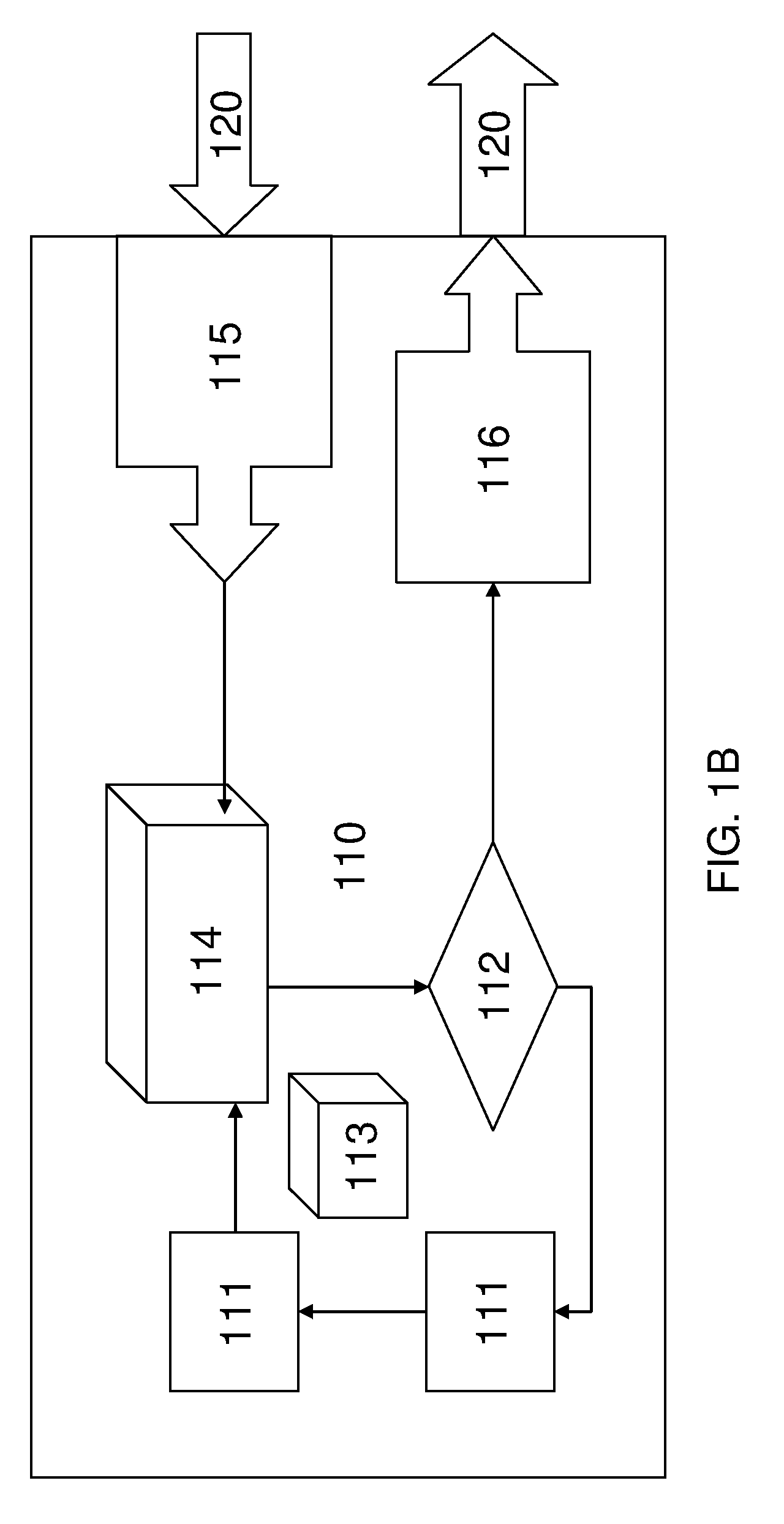

Partial reconfiguration of a programmable logic device is used in combination with a shared memory block for communicating between two blocks of an electronic circuit design. In one embodiment, a shared memory is implemented on RAM resources of a field programmable gate array (FPGA), and a first design block implemented in resources of the FPGA is coupled to the shared memory. A second design block is also coupled to the shared memory. In response to a write request by the second design block, a process determines the RAM resources of the FPGA that correspond to the shared memory address in the write request. A configuration bitstream is generated to include configuration data for partial reconfiguration of the FPGA with the data from the write request at the appropriate RAM resources. The FPGA is partially reconfigured with the configuration bitstream via a configuration port of the FPGA.

Owner:XILINX INC

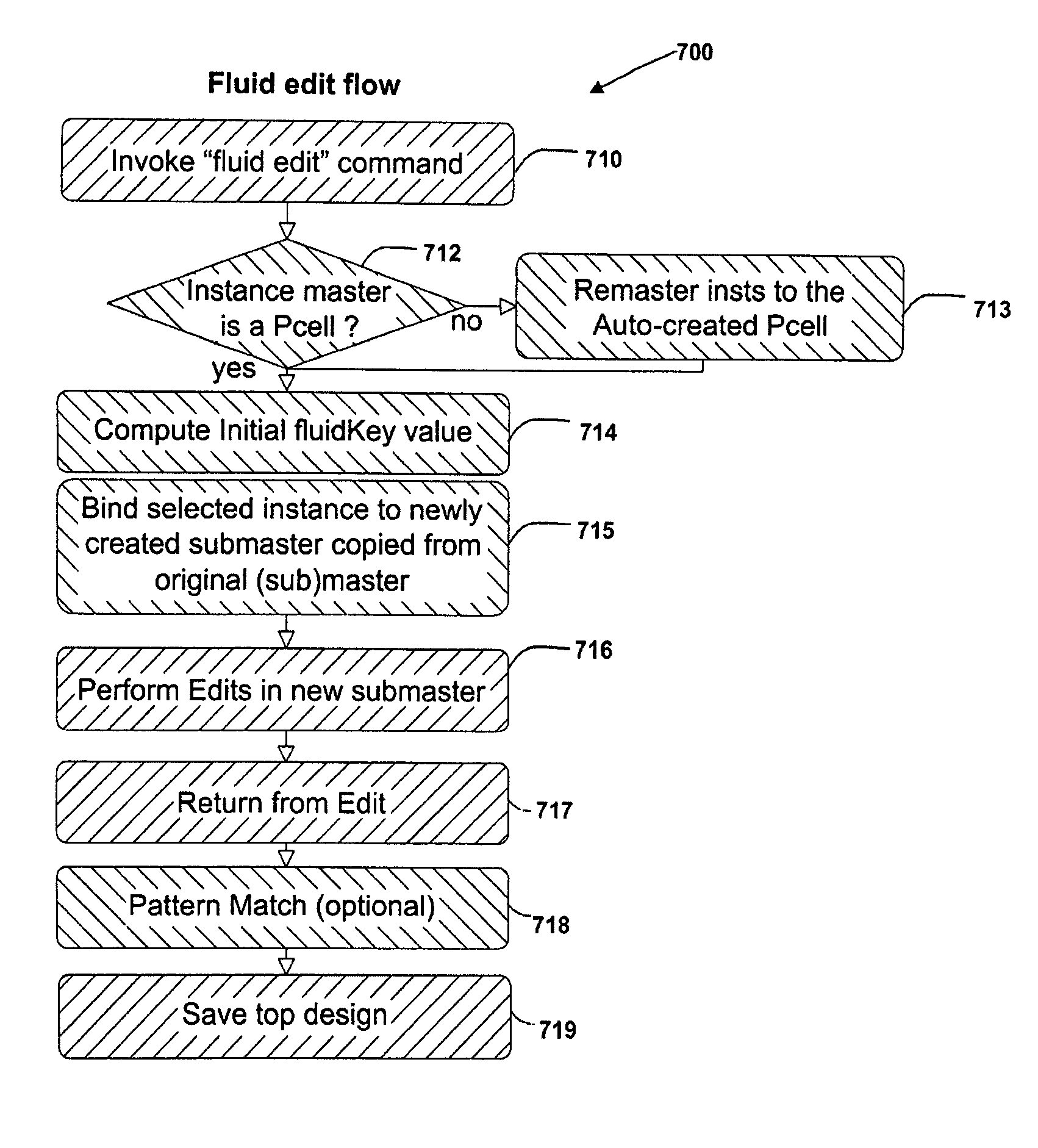

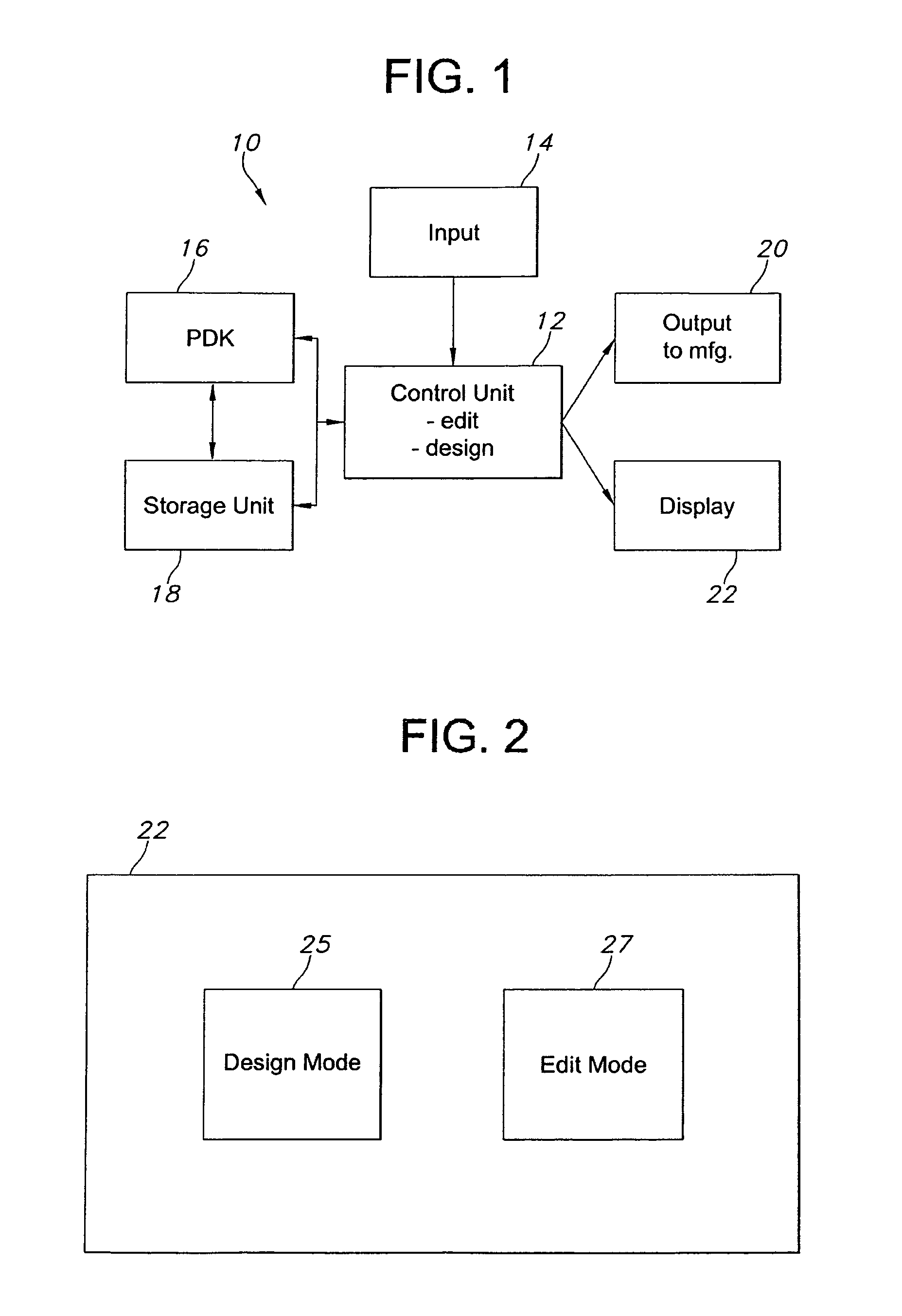

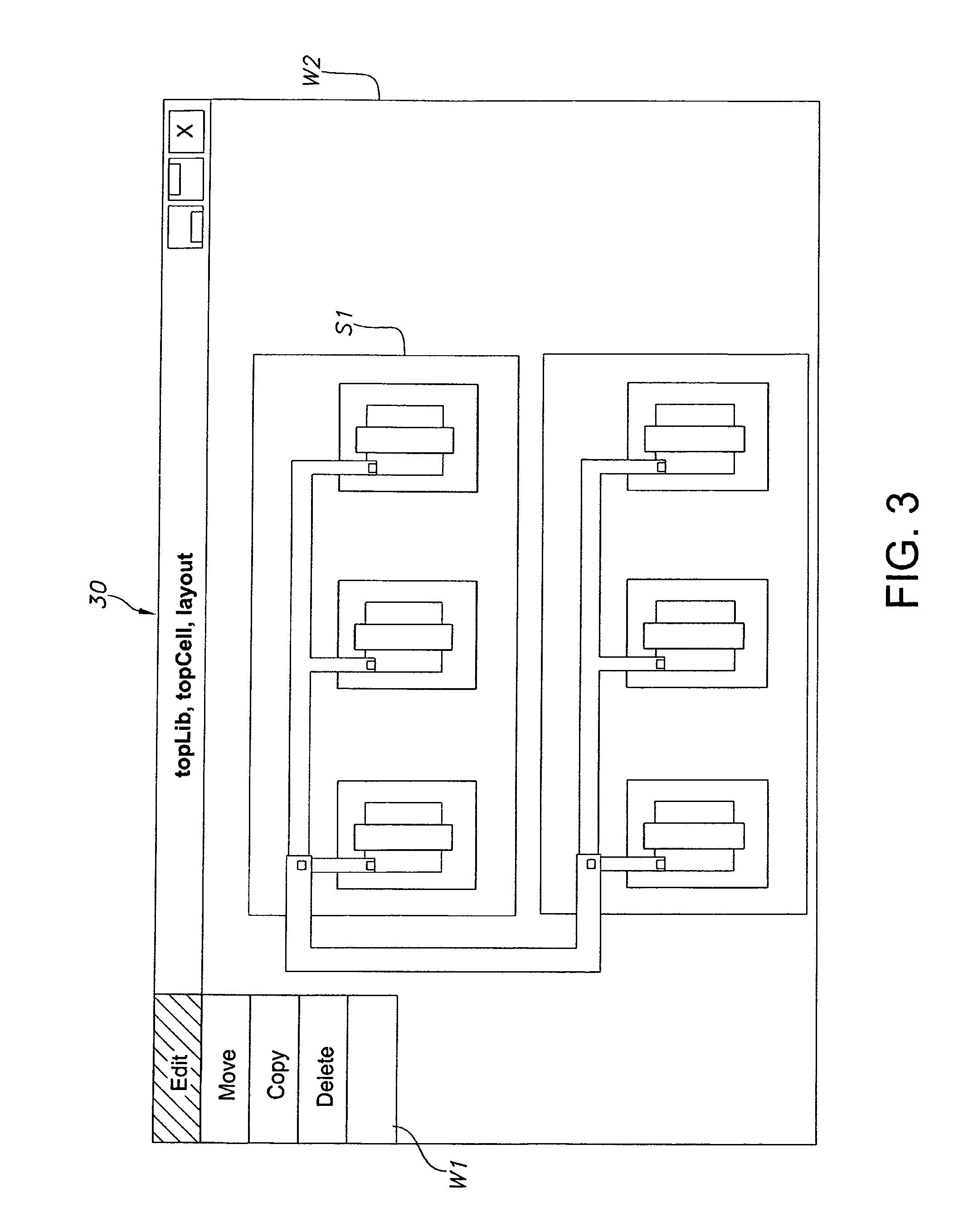

Systems and methods of editing cells of an electronic circuit design

InactiveUS8046730B1Computer programmed simultaneously with data introductionCAD circuit designComputer architectureElectronic circuit design

Systems and methods to enable a user to edit subMaster content of selected instances of an electronic layout design, including editing the contents of selected instances of an existing subMaster of an EDA design, generating a new subMaster to incorporate the modified contents of the selected instances, and binding the new subMaster to the selected instances without losing the design hierarchy of the layout design.

Owner:CADENCE DESIGN SYST INC

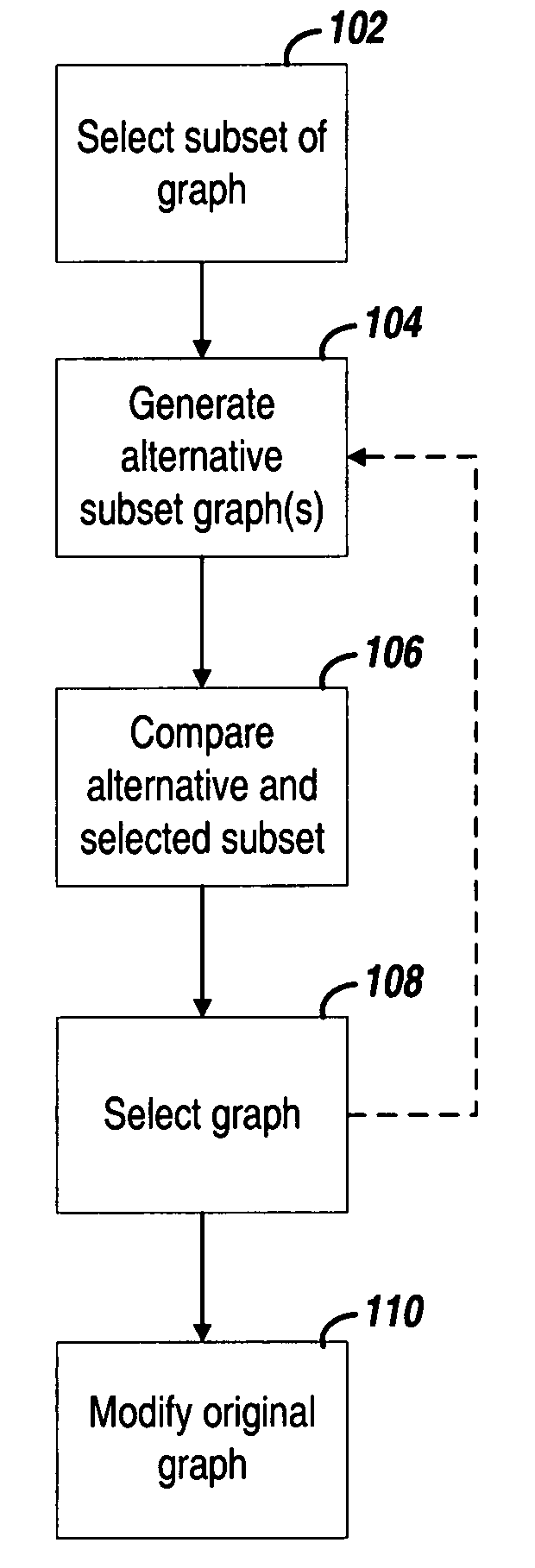

Efficient timing graph update for dynamic netlist changes

ActiveUS7657855B1Computer aided designSoftware simulation/interpretation/emulationAlgorithmElectronic circuit design

Various approaches for incrementally updating the timing of an implementation of an electronic circuit design are disclosed. In one approach, a subset timing graph is selected from a primary timing graph. Alternative subset timing graphs are generated that are functionally equivalent and structurally different with respect to the selected subset timing graph. For each of the alternative timing graphs, a respective timing metric is determined. The determined timing metrics and a timing metric for the selected subset timing graph are compared. An alternative timing graph is selected in response to the comparison. Structurally different portions of the selected one of the one or more alternative timing graphs are verified with regard to the design constraints. The structurally different portions are stored to the primary timing graph.

Owner:XILINX INC

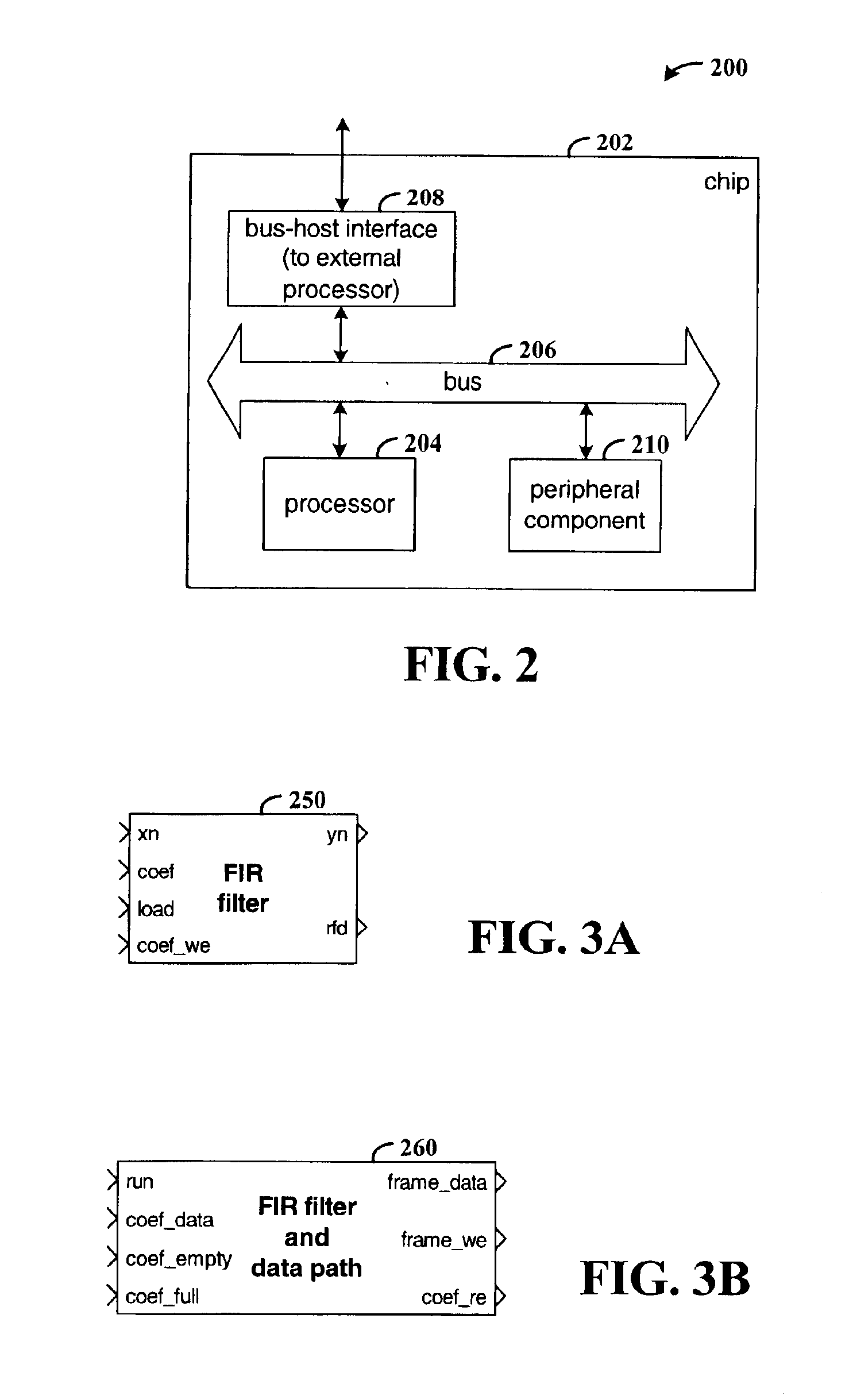

Method and system for generating a circuit design including a peripheral component connected to a bus

Method and system for generating an electronic circuit design. A first logic block is instantiated in the design in response to user input controls. The first logic block includes parameters that specify its interface requirements. Bus interface blocks, which are parameterizable to connect a logic block to a bus, are provided in a library. Bus interface blocks that connect the first logic block to the bus are instantiated in the design, and the bus interface blocks are parameterized in response to the requirements of, the first logic block. The bus interface blocks are connected to the first logic block in such a way that the first logic block is extended into a peripheral that can communicate with the bus.

Owner:XILINX INC

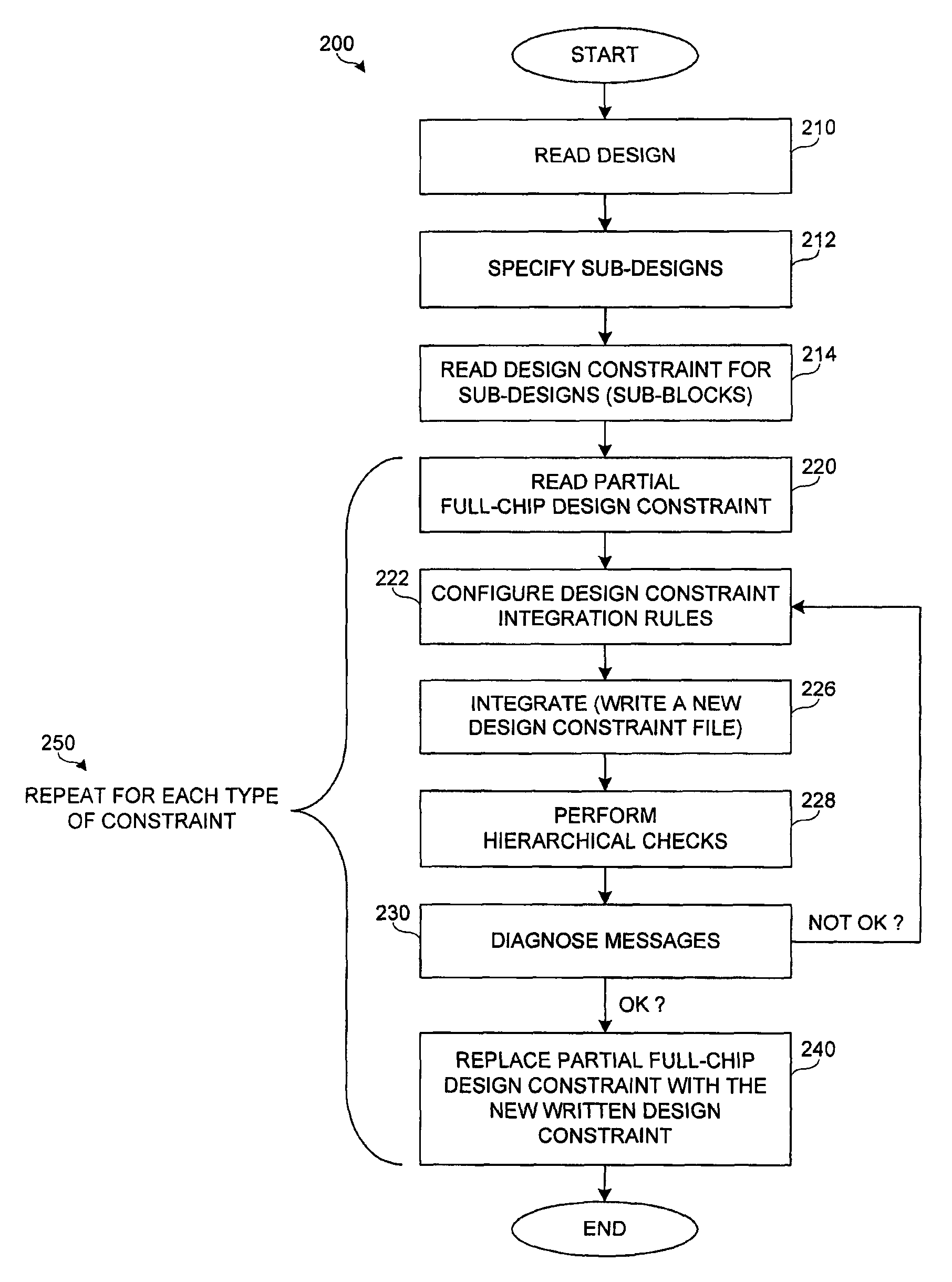

Method and system for generating design constraints

ActiveUS7962886B1Consistency issuesConstraint issuesDetecting faulty computer hardwareCAD circuit designConfiguration designIntegration rule

A method and system for generating design constraints for an electronic circuit design is disclosed. The method and system include reading a design description and an existing design constraint file, configuring design constraint integration rules, writing a new design constraint file, evaluating results of the new design constraint file, and replacing existing design constraint file with the new design constraint file.

Owner:CADENCE DESIGN SYST INC

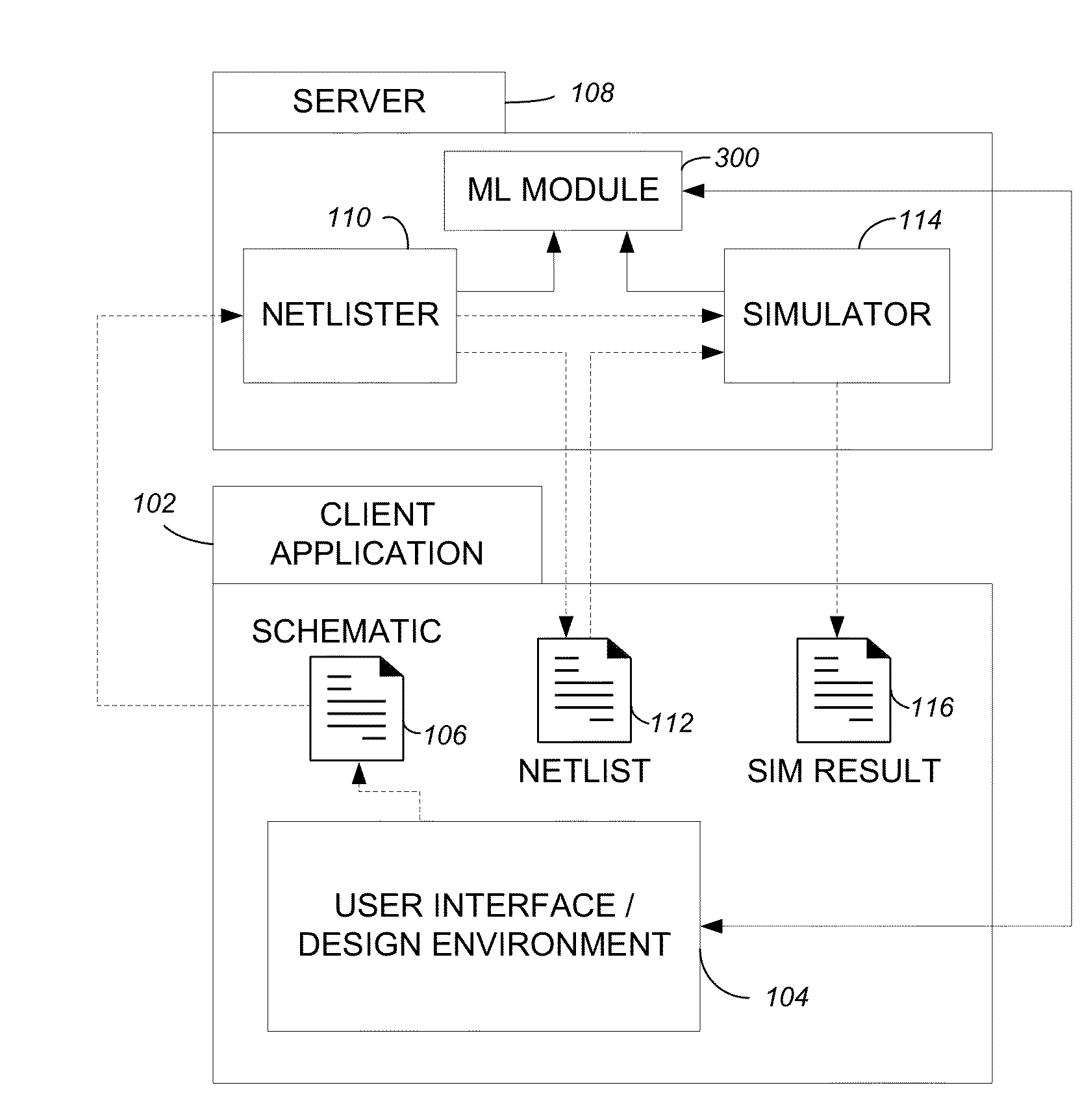

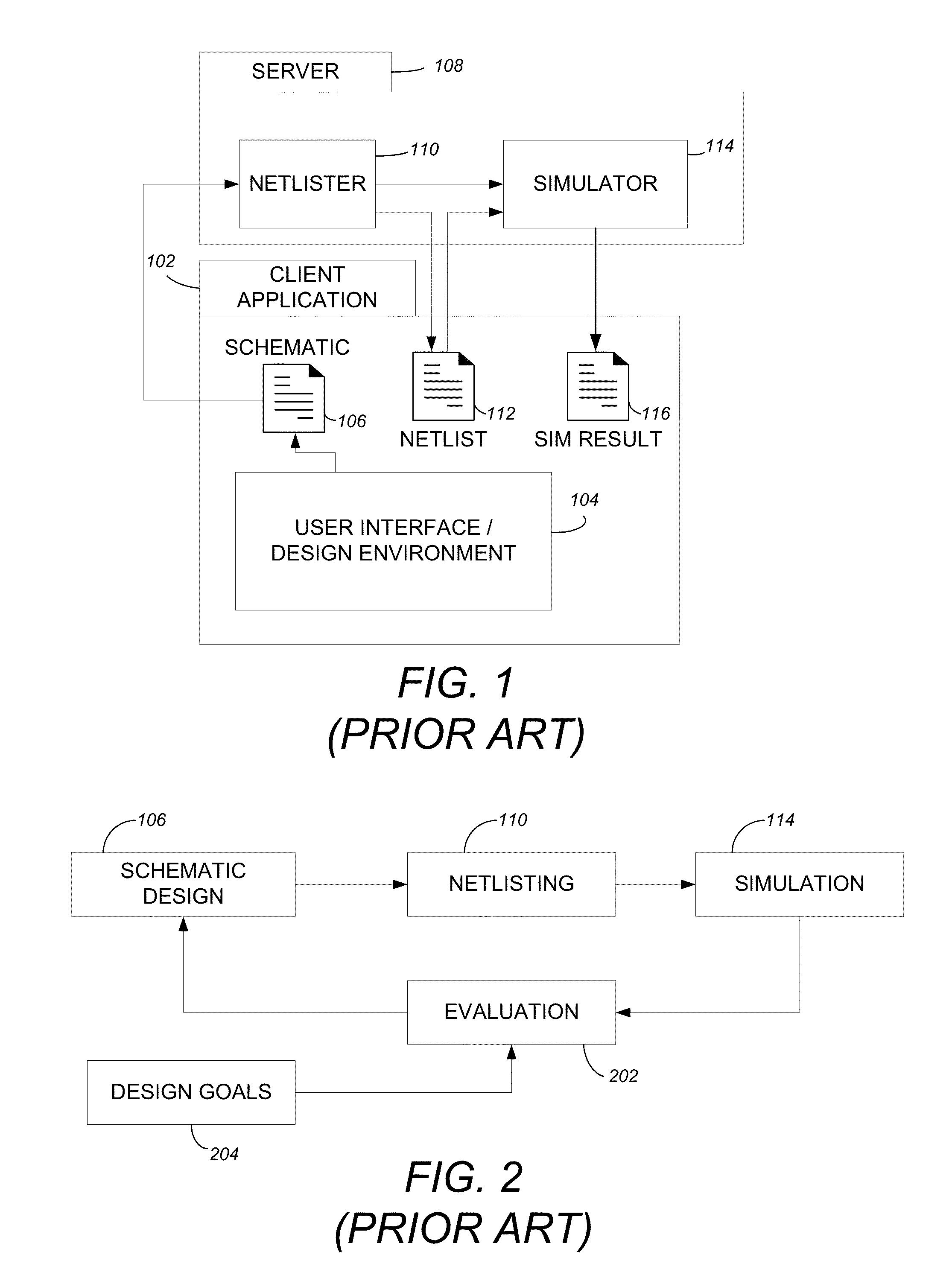

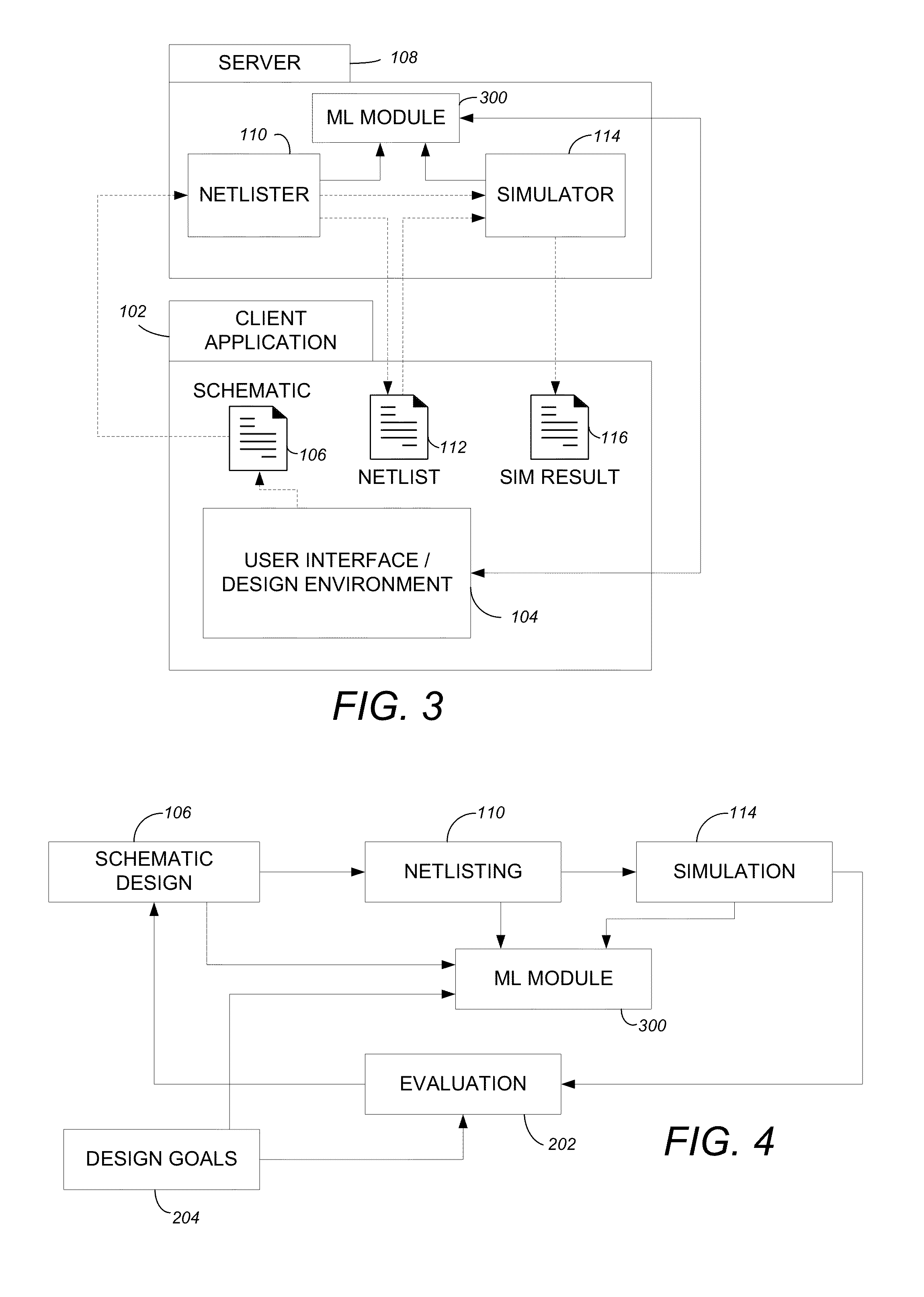

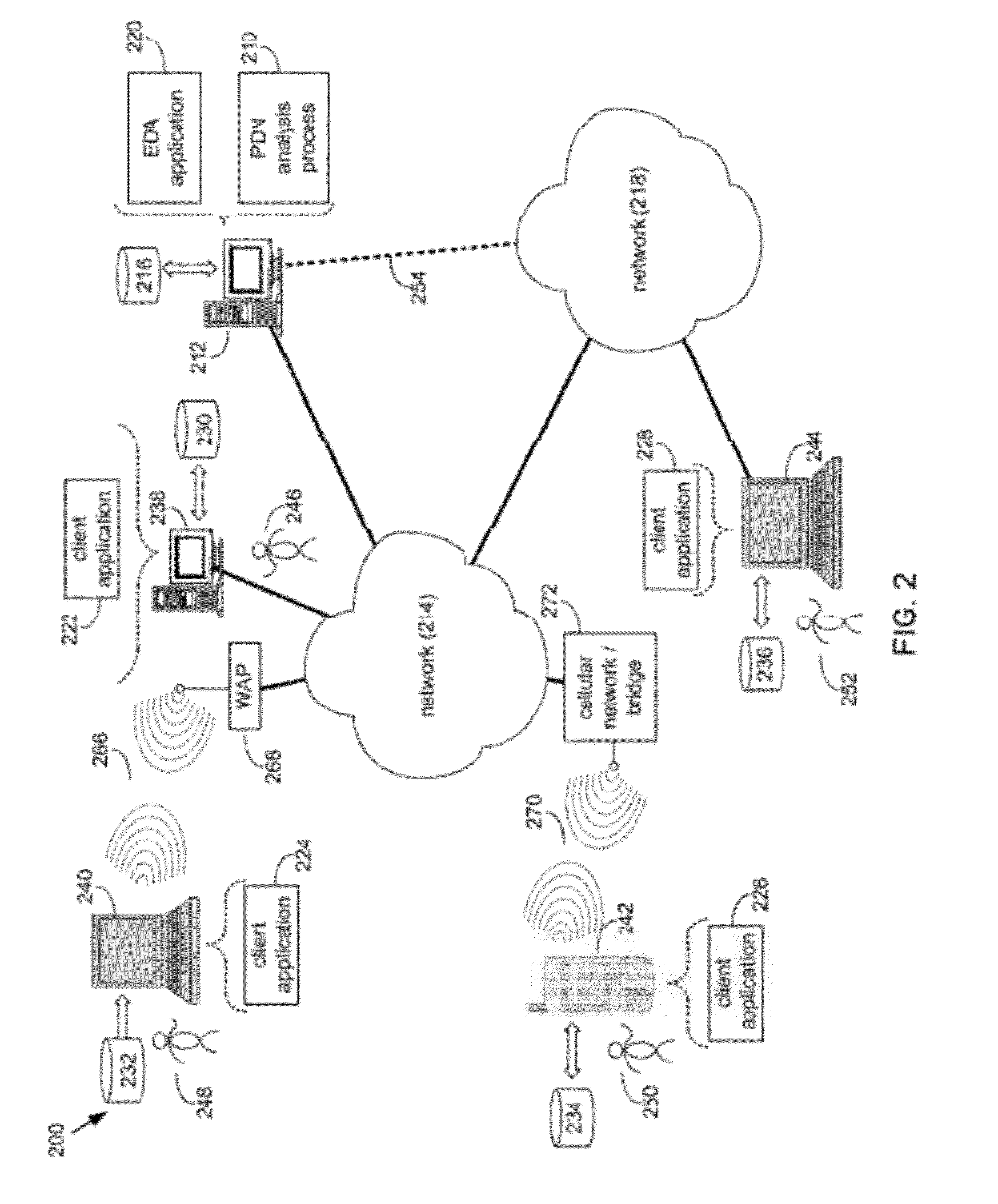

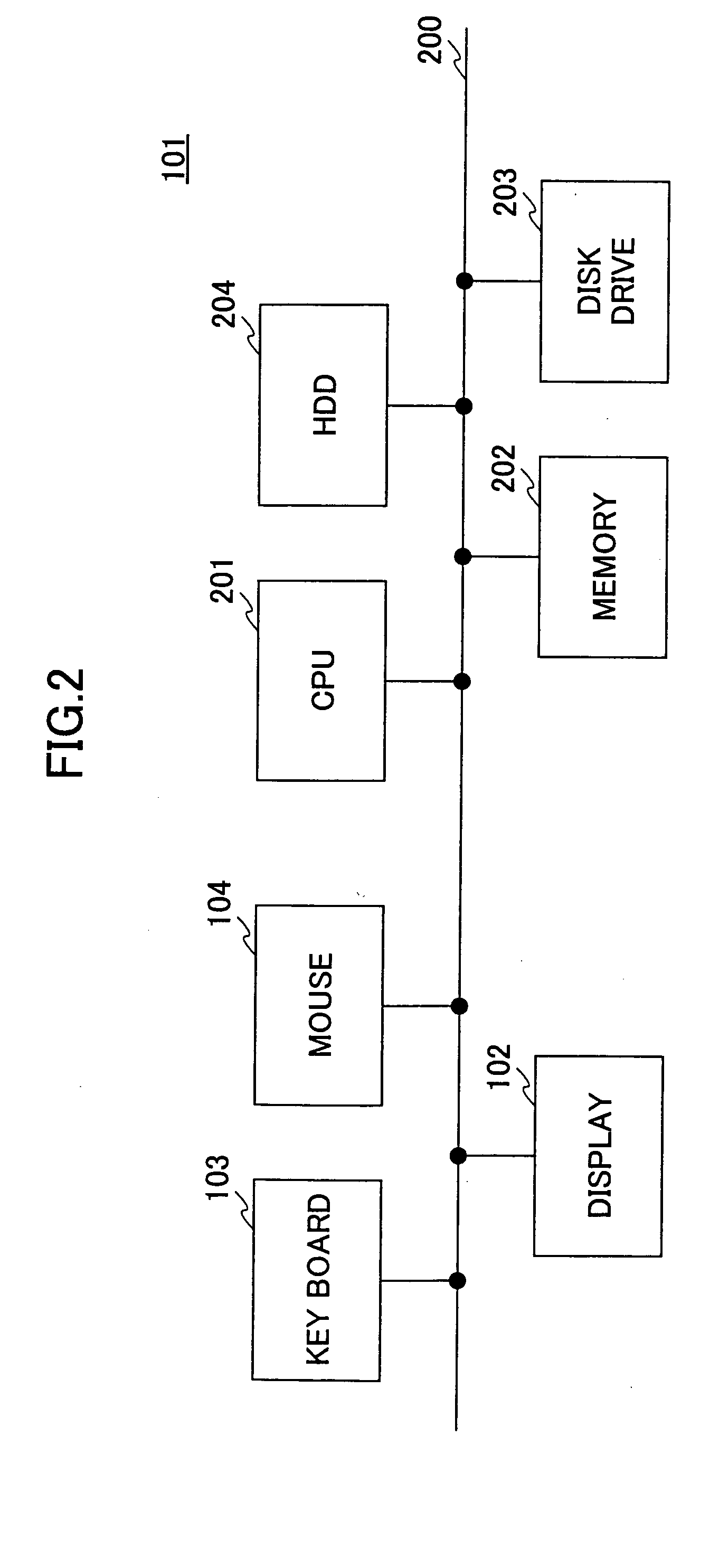

Predictive multi-user client-server electronic circuit design system utilizing machine learning techniques

ActiveUS20160253445A1Shorten design timeRapid designCAD circuit designSpecial data processing applicationsThe InternetTheoretical computer science

A predictive electronic circuit design system, method, and apparatus provide the ability to design an electronic circuit. An electronic computer aided design (CAD) environment server computing device is connected to the Internet and includes a machine learning module program. The machine learning module program has a netlist analyzer program, a database, and a classifier and predictor program. The netlist analyzer program receives a circuit netlist for a designed circuit from a user, characterizes the circuit netlist, and sends characterization data to the database. Characterization data from multiple users for multiple designed circuits are stored in the database. The classifier and predictor program uses design goal data, the characterization data for multiple designed circuits, and simulation results, to calculate and produce predictions and proposals for the user to make design changes to the designed circuit in order to better meet or exceed design goals.

Owner:AUTODESK INC

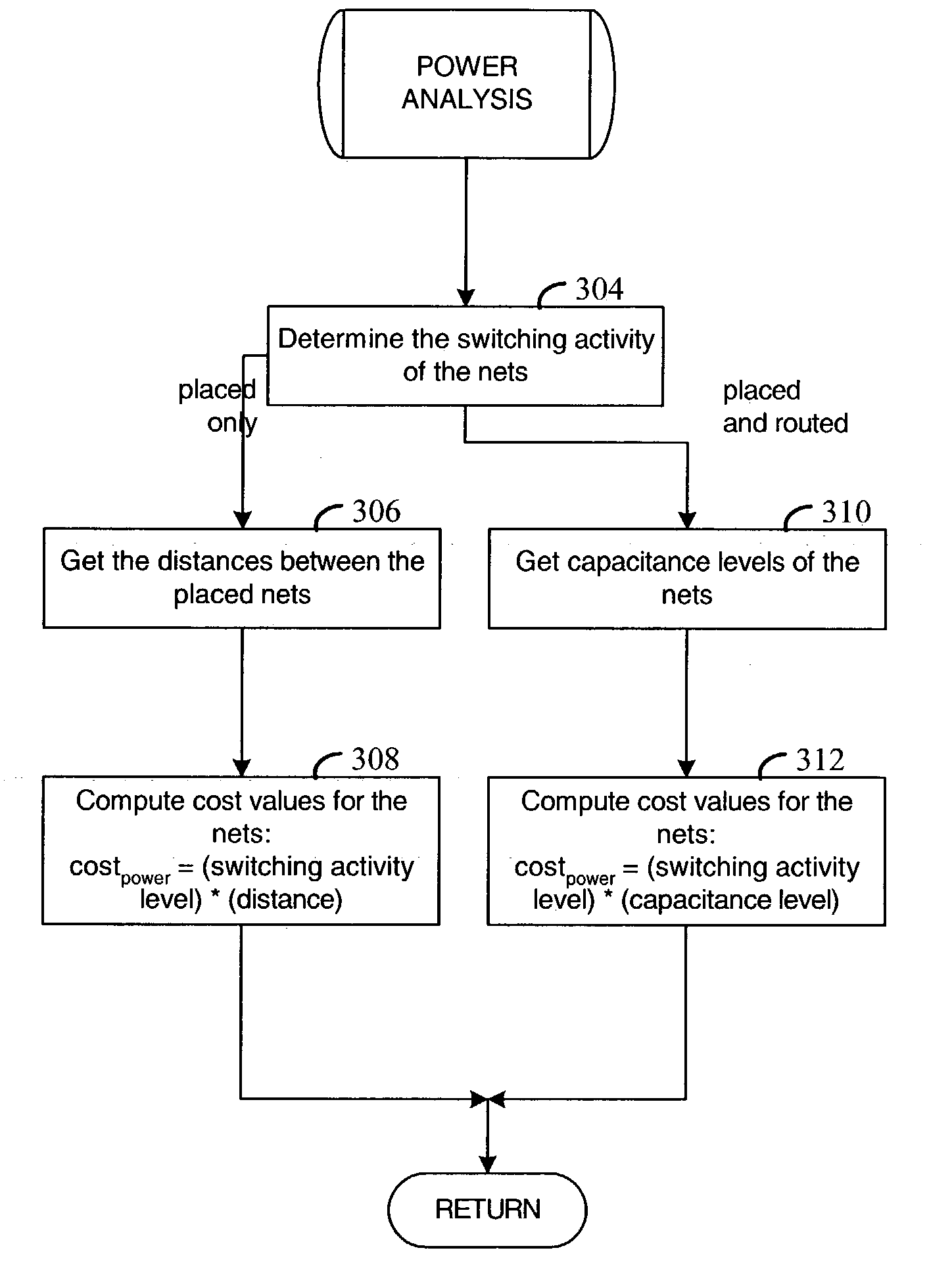

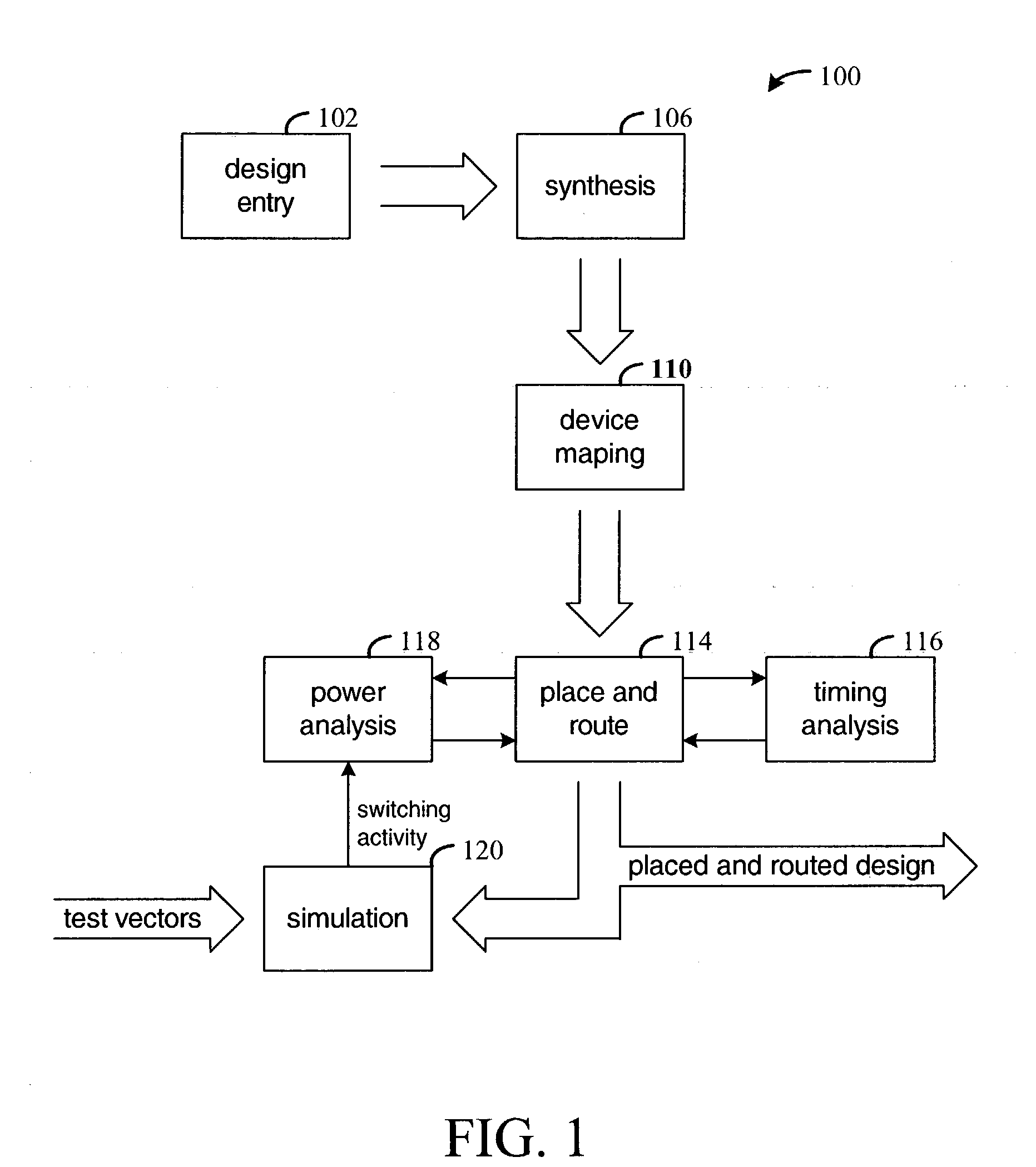

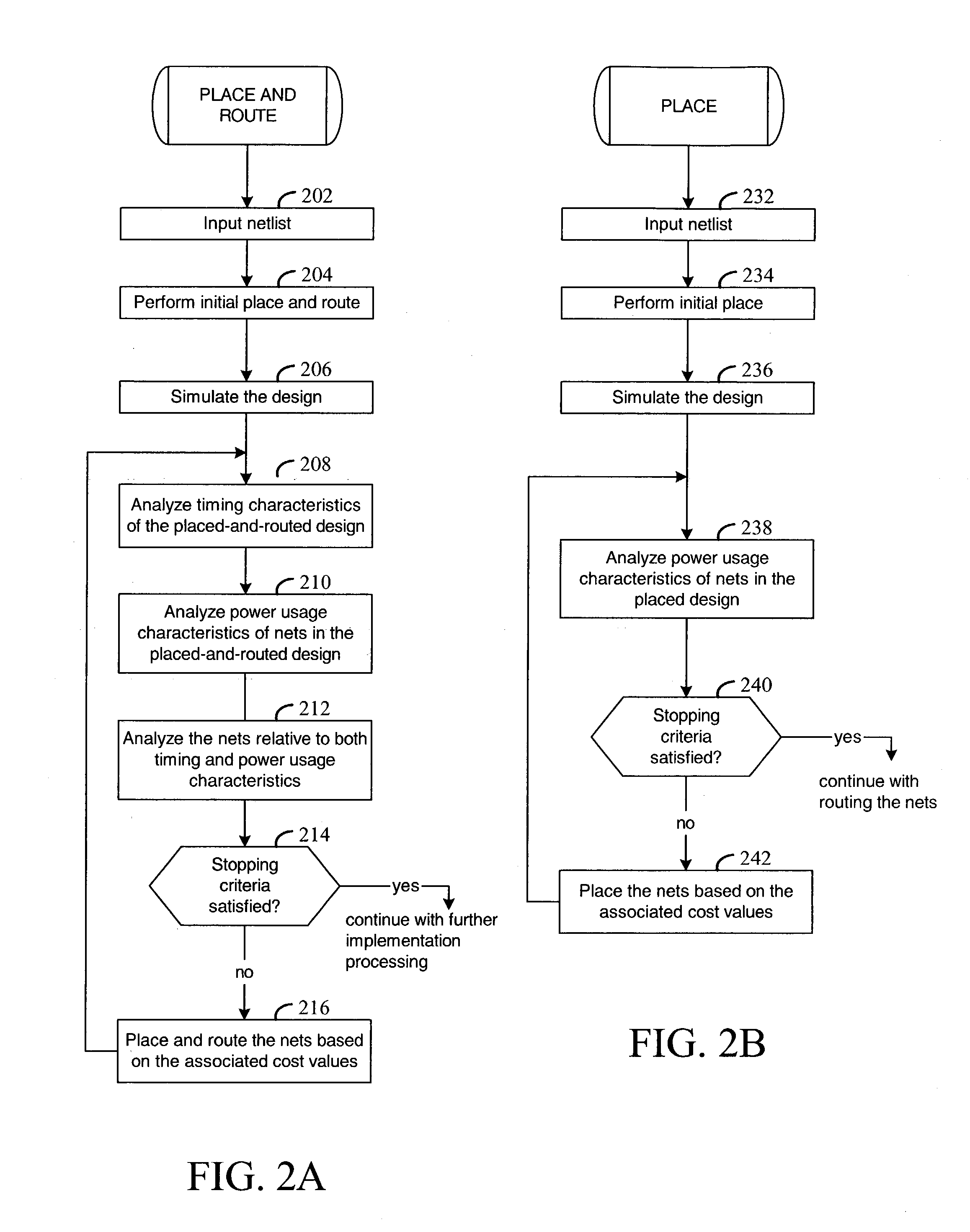

Place-and-route with power analysis

InactiveUS6950998B1Reduce power consumptionTime requiredComputer aided designSoftware simulation/interpretation/emulationPower analysisEngineering

Method and apparatus for placing and routing an electronic circuit design. Various embodiments are disclosed for analyzing placed and / or routed designs for power consumption characteristics and timing characteristics. New designs are iteratively generated in order to reduce power consumption and satisfy timing requirements of the design.

Owner:XILINX INC

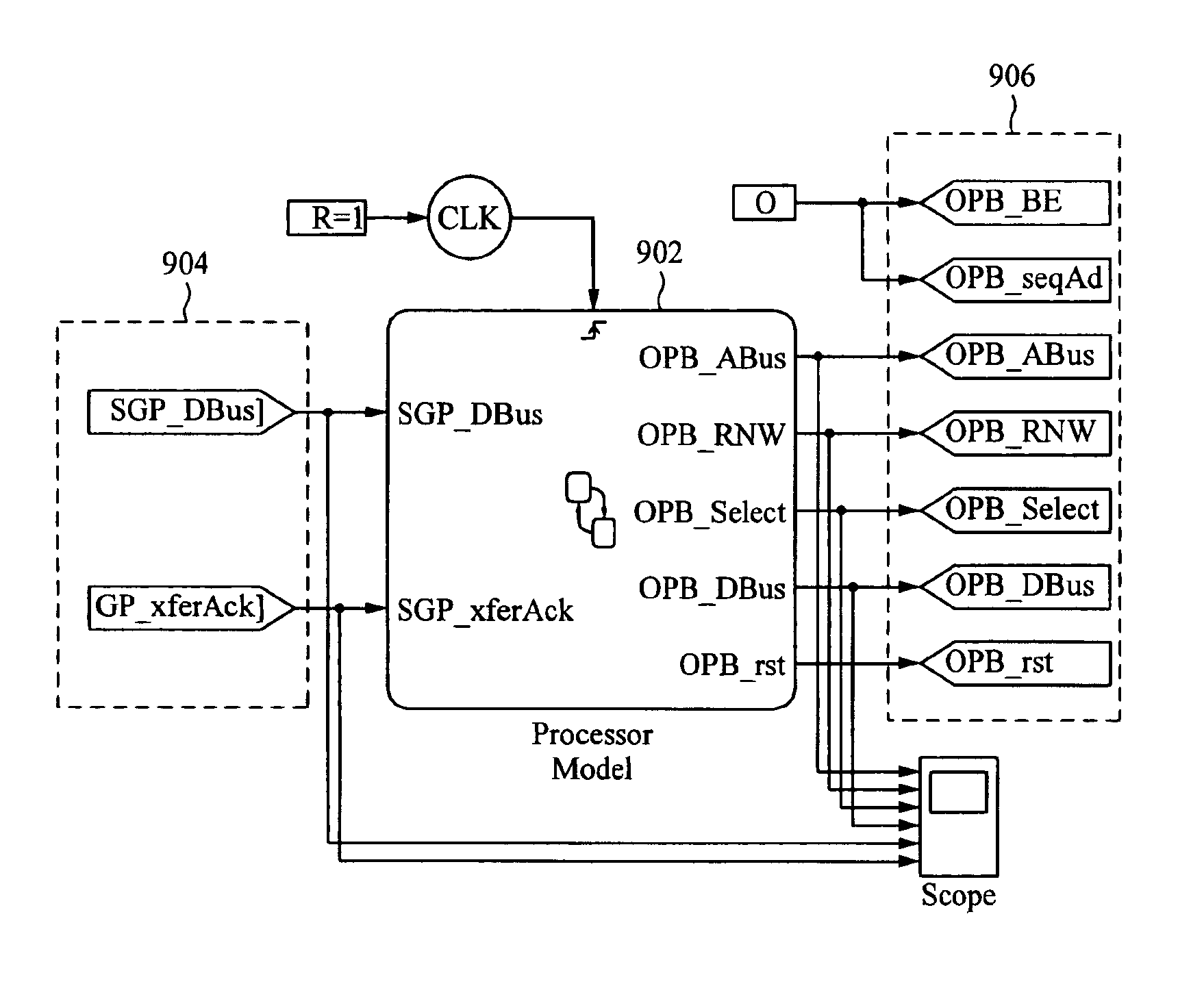

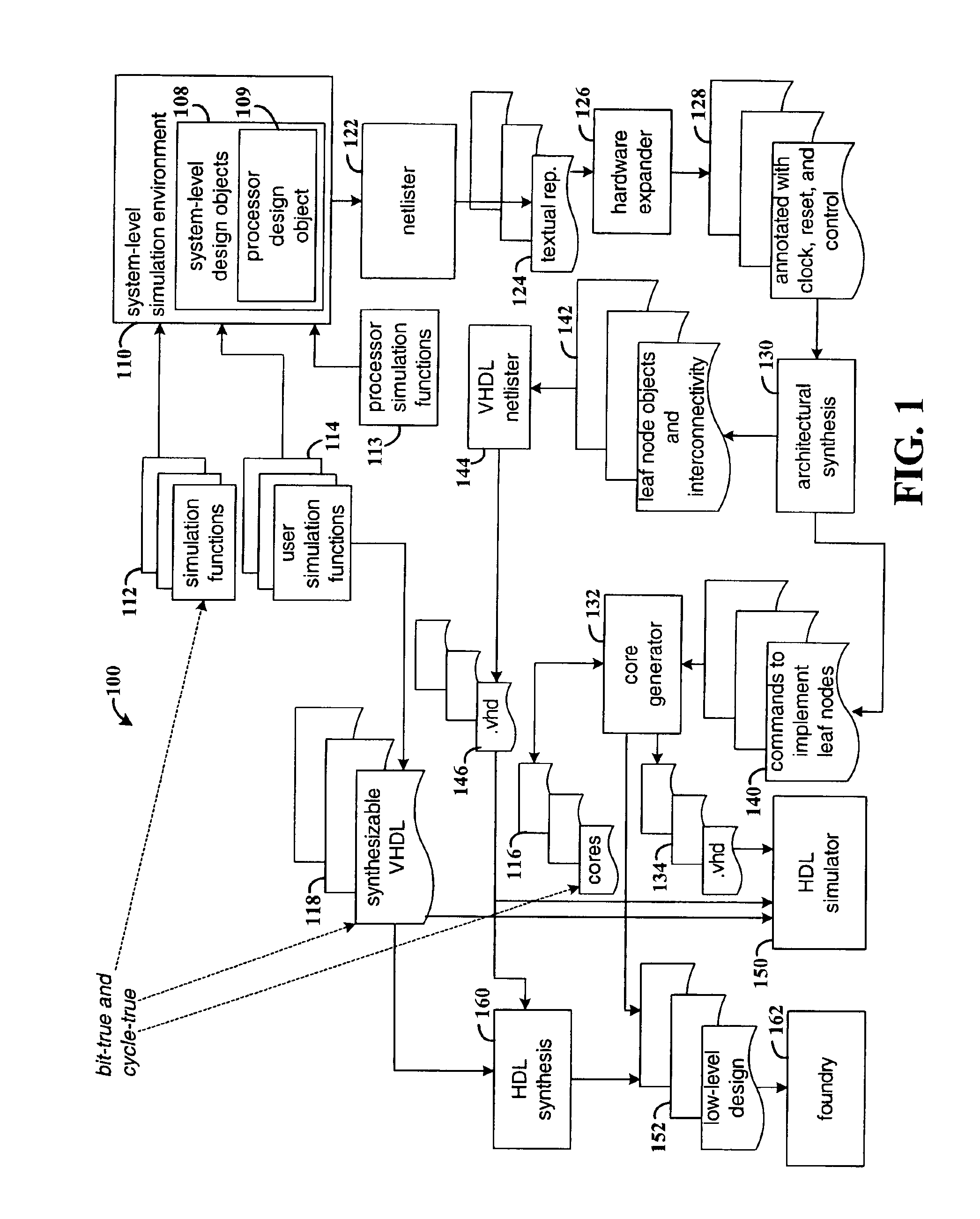

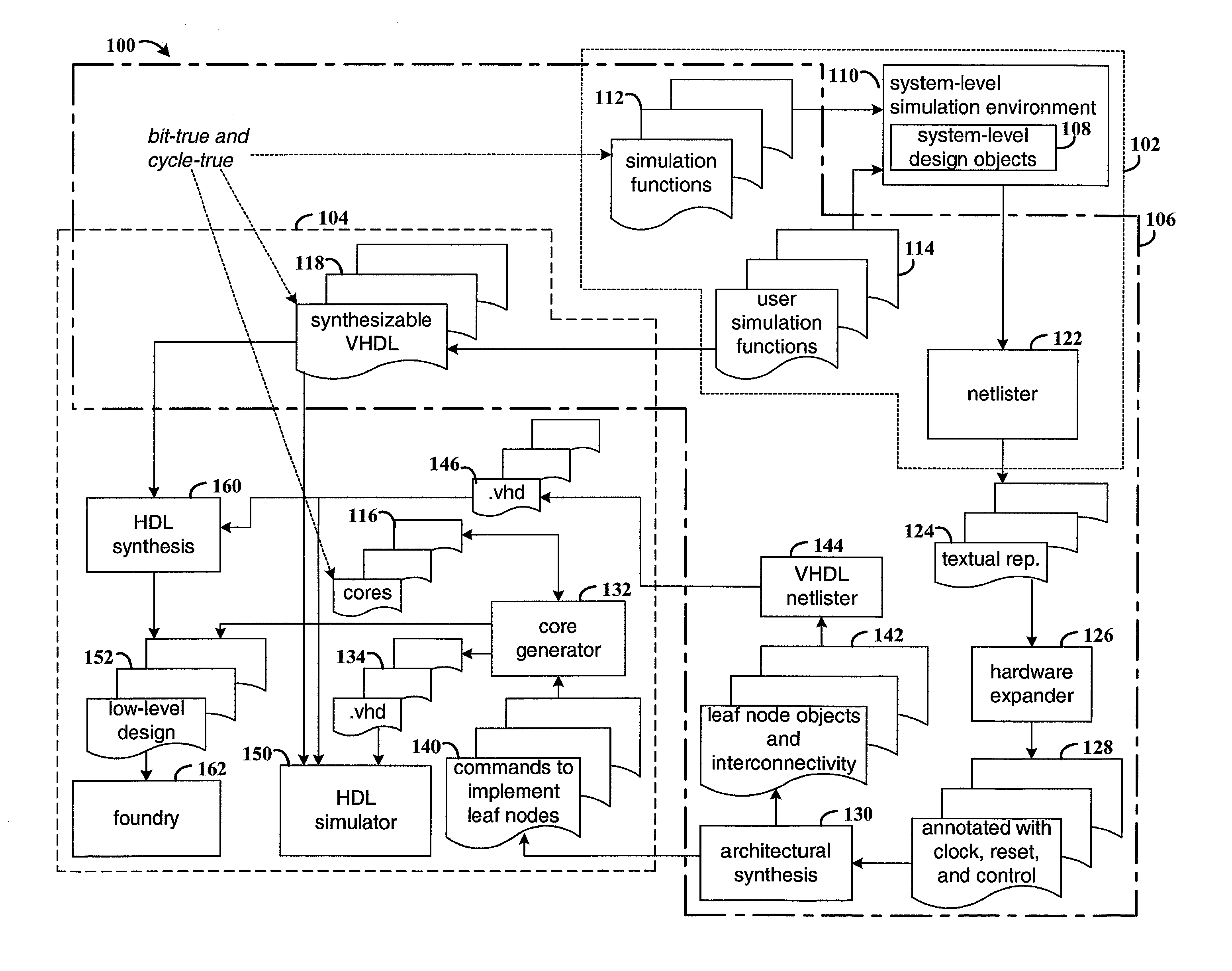

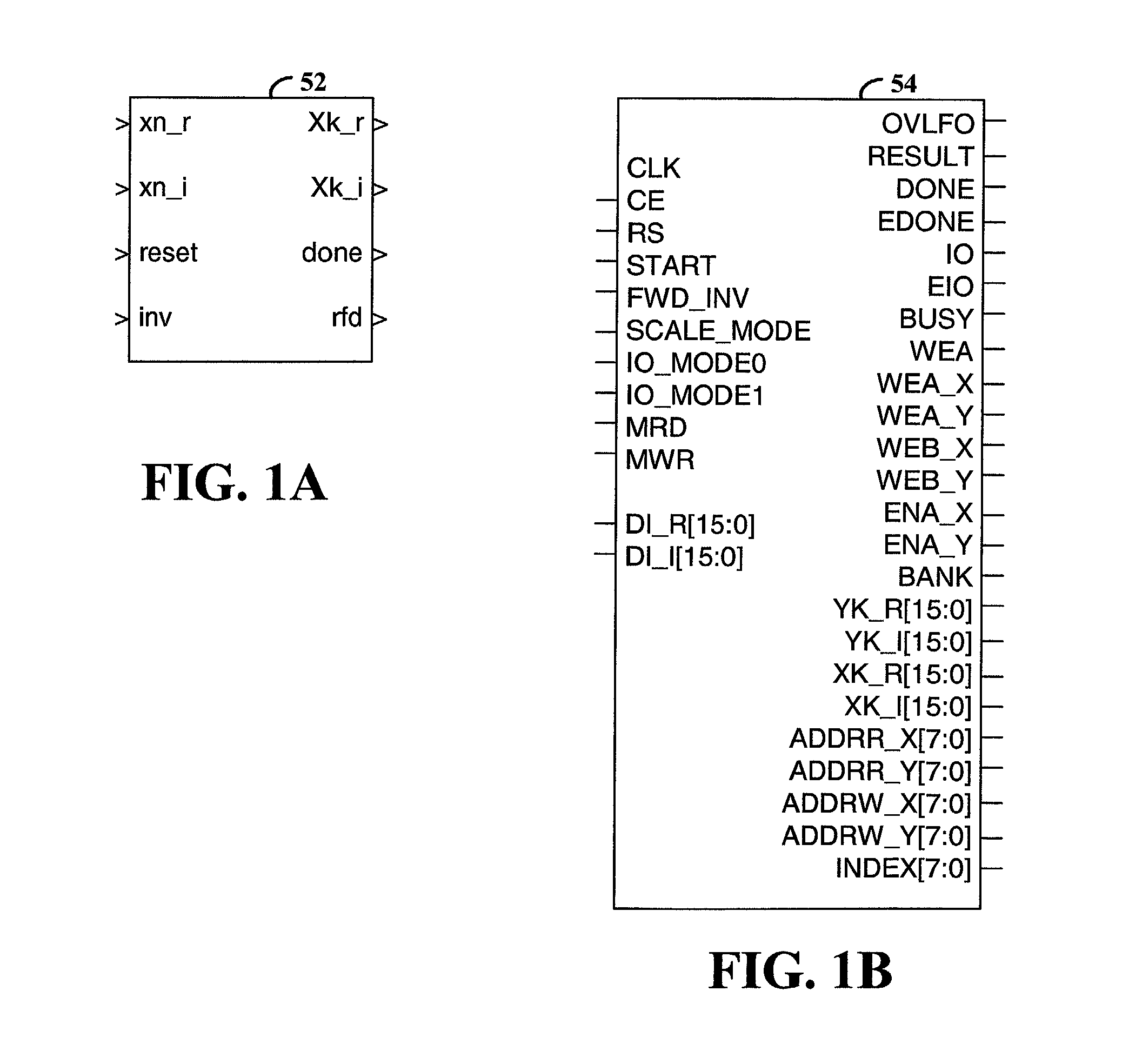

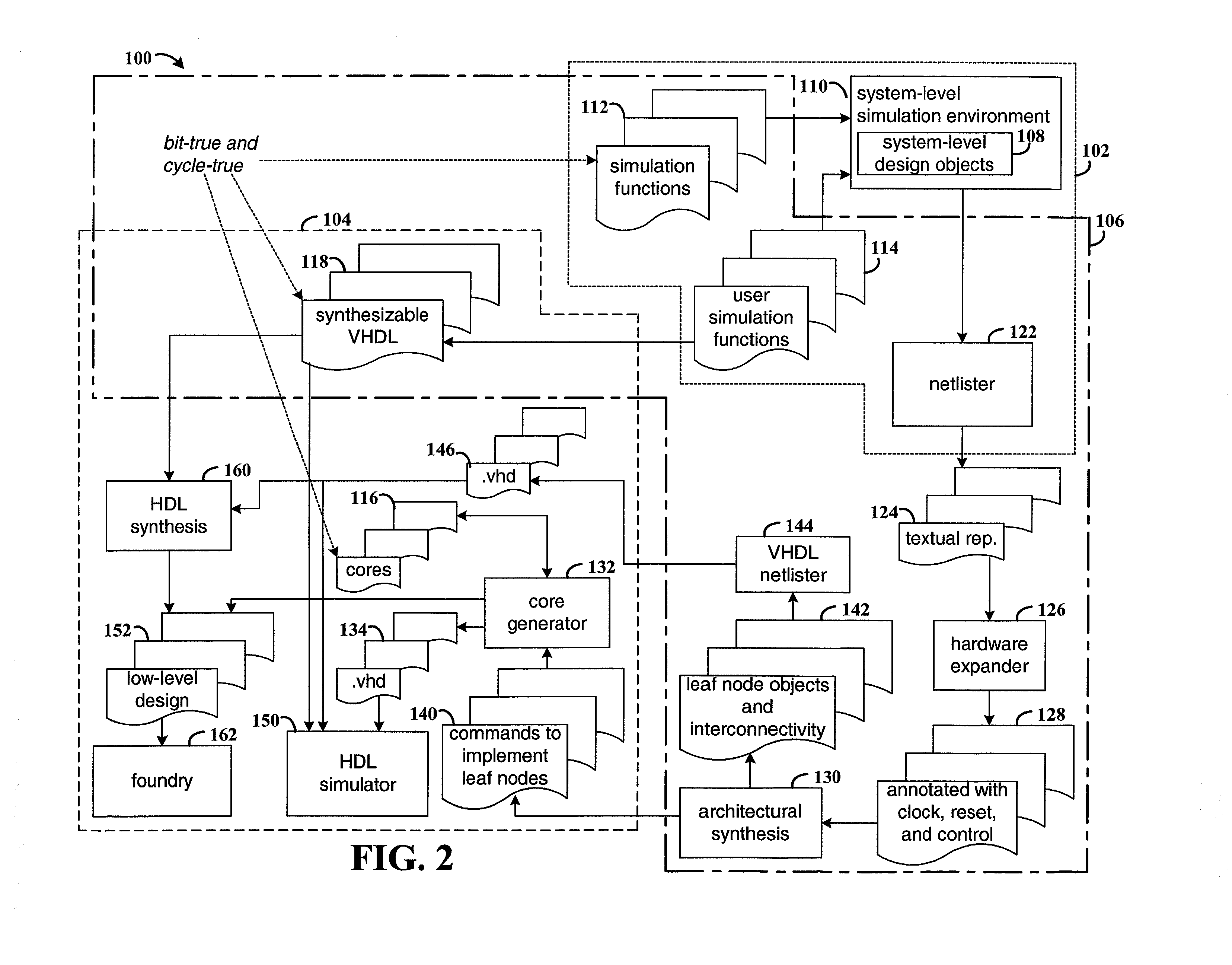

Method and system for modeling and automatically generating an electronic design from a system level environment

ActiveUS7110935B1CAD circuit designSoftware simulation/interpretation/emulationComputer architectureLevel design

Method and system for creating an electronic circuit design from a system-level environment. A plurality of user-selectable system-level design objects are provided in the system-level environment. Each system-level design object is defined by a system-level function and is selectable by a system-level designer. A plurality of hardware-level design objects are also provided. Each hardware-level design object is configured to generate a hardware definition of a hardware-level function. Each system-level design object maps to one or more hardware-level design objects. In response to selections made by the designer, a system-level design is instantiated in a system-level design file. The system-level design includes user-selected ones of the system-level design objects. The system simulates behavior of the system-level design consistent with both the system-level functions and behavior of a hardware definition from the hardware-level design objects that implement the user-selected ones of the system-level design objects.

Owner:XILINX INC

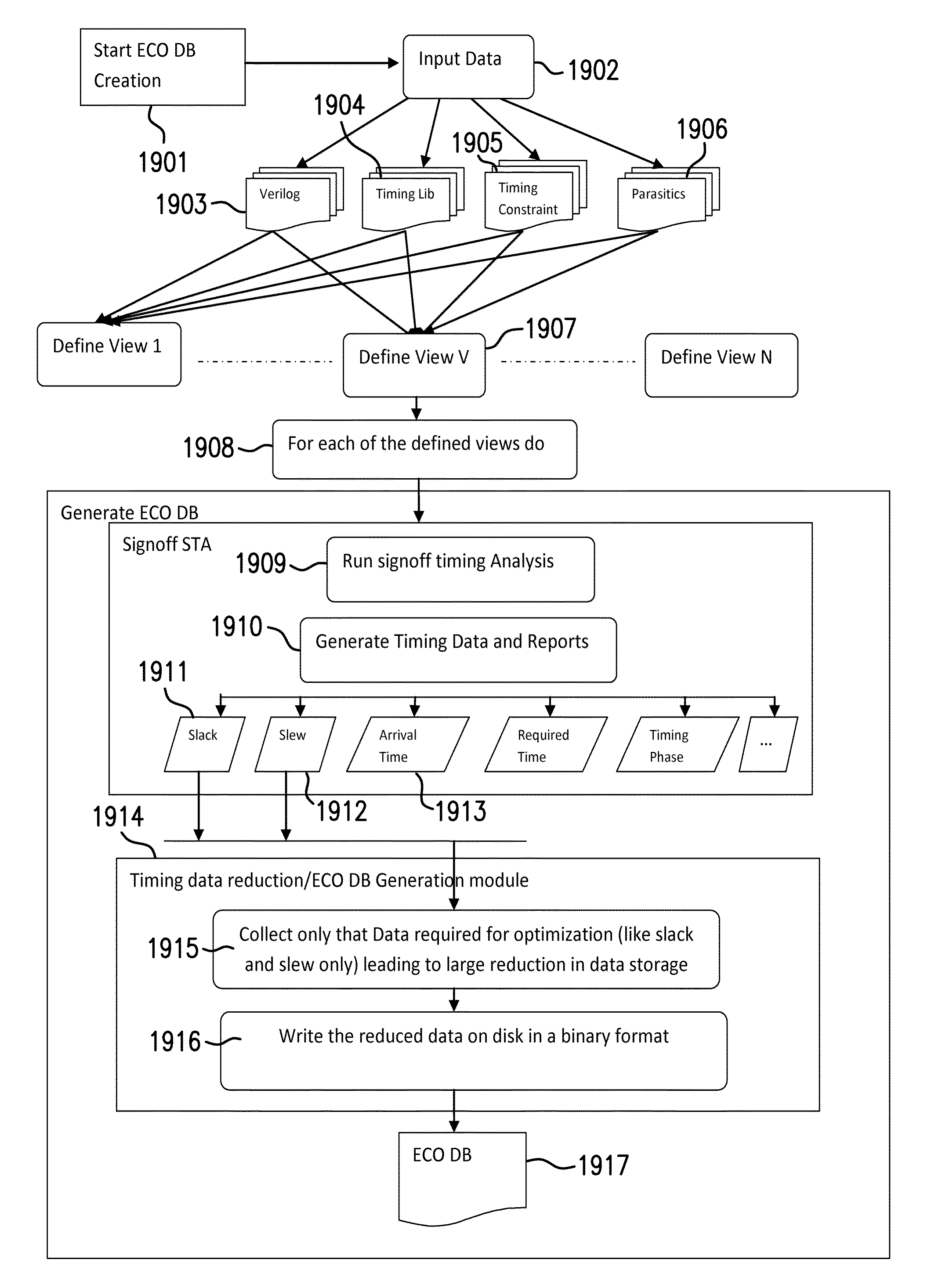

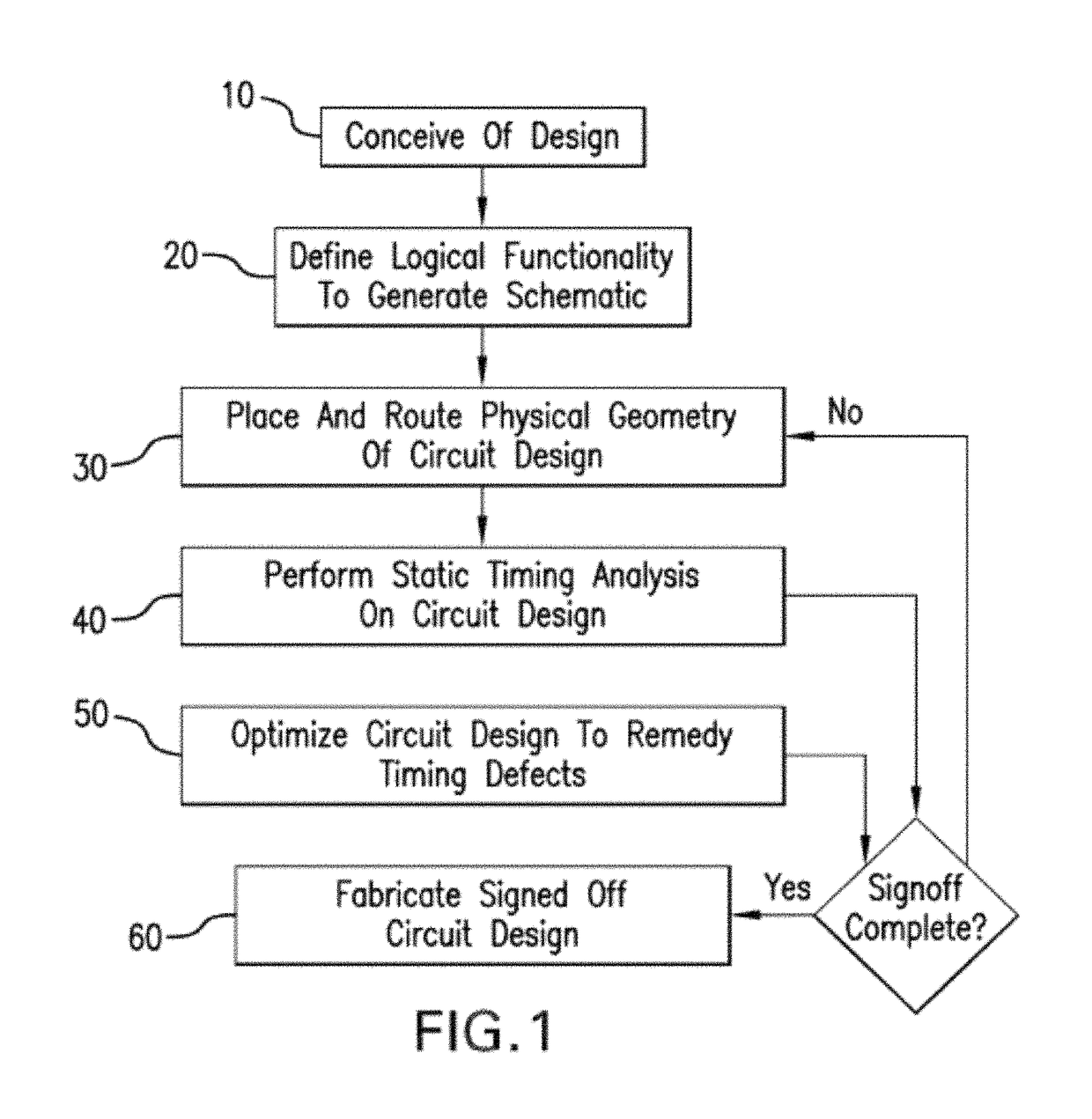

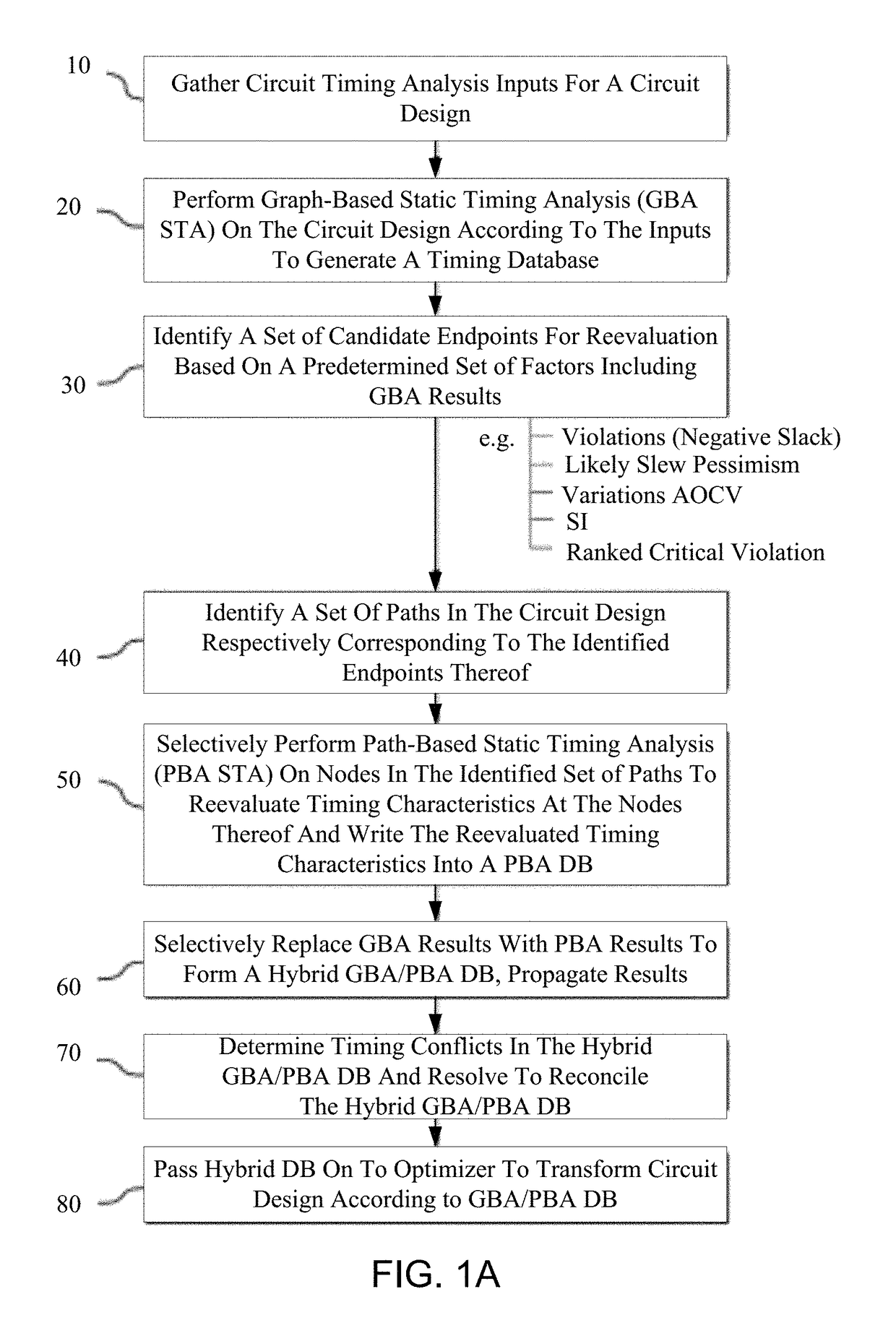

System and method for detecting and prescribing physical corrections for timing violations in pruned timing data for electronic circuit design defined by physical implementation data

ActiveUS8875082B1Good correlationReduce repeated iterationCAD circuit designSoftware simulation/interpretation/emulationElectronic circuit designComputer science

A system and method for expeditious operational timing signoff of a circuit design through a timing analysis and subsequent corrective or remedial optimization is performed with the goal of correlating timing between the physical implementation corrective optimizer module and the timing analysis module to reduce iterations therebetween. A physical optimizer in the correction module is imparted with knowledge of the physical implementation of the design to allow for legal, non-conflicting placement of corrective buffers or resizing of gates in accordance with the physical implementation data of the circuit design.

Owner:CADENCE DESIGN SYST INC

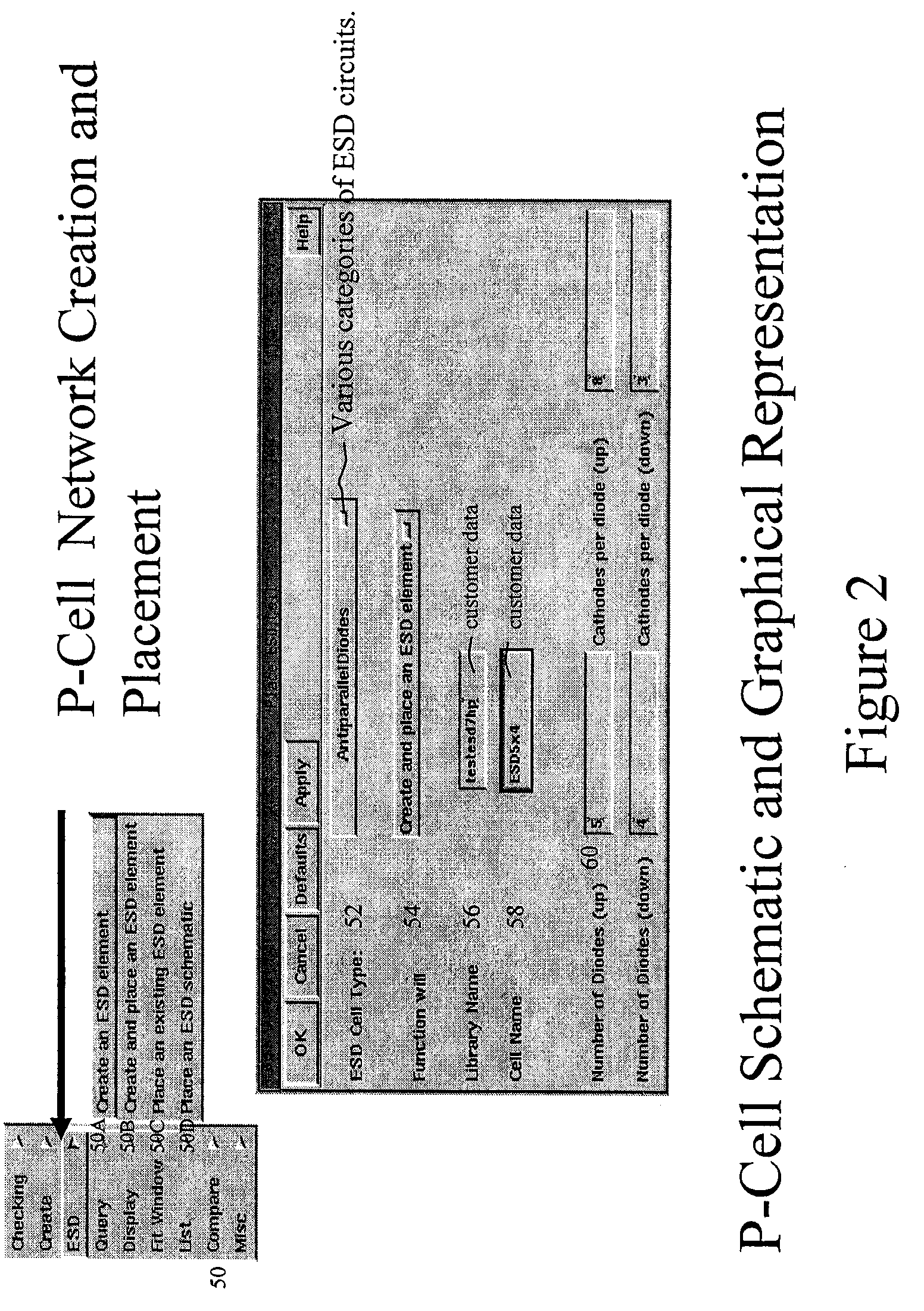

ESD design, verification and checking system and method of use

InactiveUS7134099B2Computer aided designSoftware simulation/interpretation/emulationDesign standardCell design

A computerized method and system for designing, verification and checking of the electrostatic discharge (ESD) protection circuits and their implementation in a integrated computer chip design where the computer chip comprises of electronic circuits designed in a parameterized cell design system, pads, interconnects and the ESD system uses a hierarchical system of parameterized cells (p-cells) which are constructed into higher level ESD networks. Lowest order p-cells pass user defined parameters to higher order p-cells to form an ESD protection circuit meeting design criteria. Ones of the p-cells are “grow-able” such that they can form repetition groups of the underlying p-cell element to accommodate the design parameters. Layout and circuit schematics are auto-generated with the user varying the number of elements in the circuit by adjusting the input parameters. The circuit topology automation allows for the customer to auto generate new ESD circuits and ESD power clamps without additional design work.

Owner:INT BUSINESS MASCH CORP

Electronic circuit designing method and apparatus, and storage medium

InactiveUS7322019B2Semiconductor/solid-state device manufacturingComputer programmed simultaneously with data introductionEngineeringElectronic circuit design

An electronic circuit designing method and apparatus designs an electronic circuit by CAD, by generating design constraints with respect to the electronic circuit based on at least one of general layout and wiring information related to devices and wirings included in the electronic circuit, user requirements defined by a user, and user resources defined by the user, and urging an input to the user by displaying the design constraints.

Owner:FUJITSU LTD

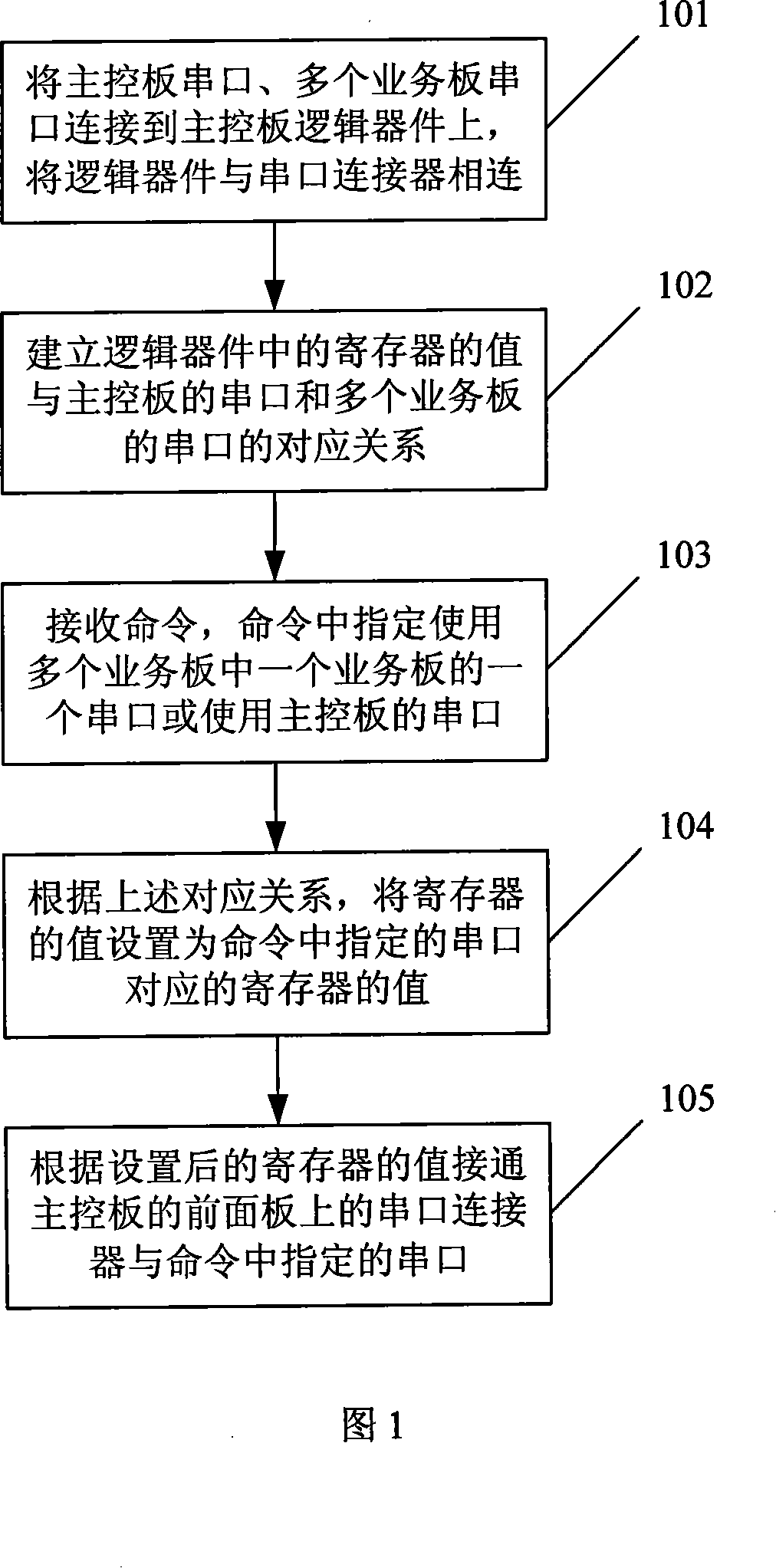

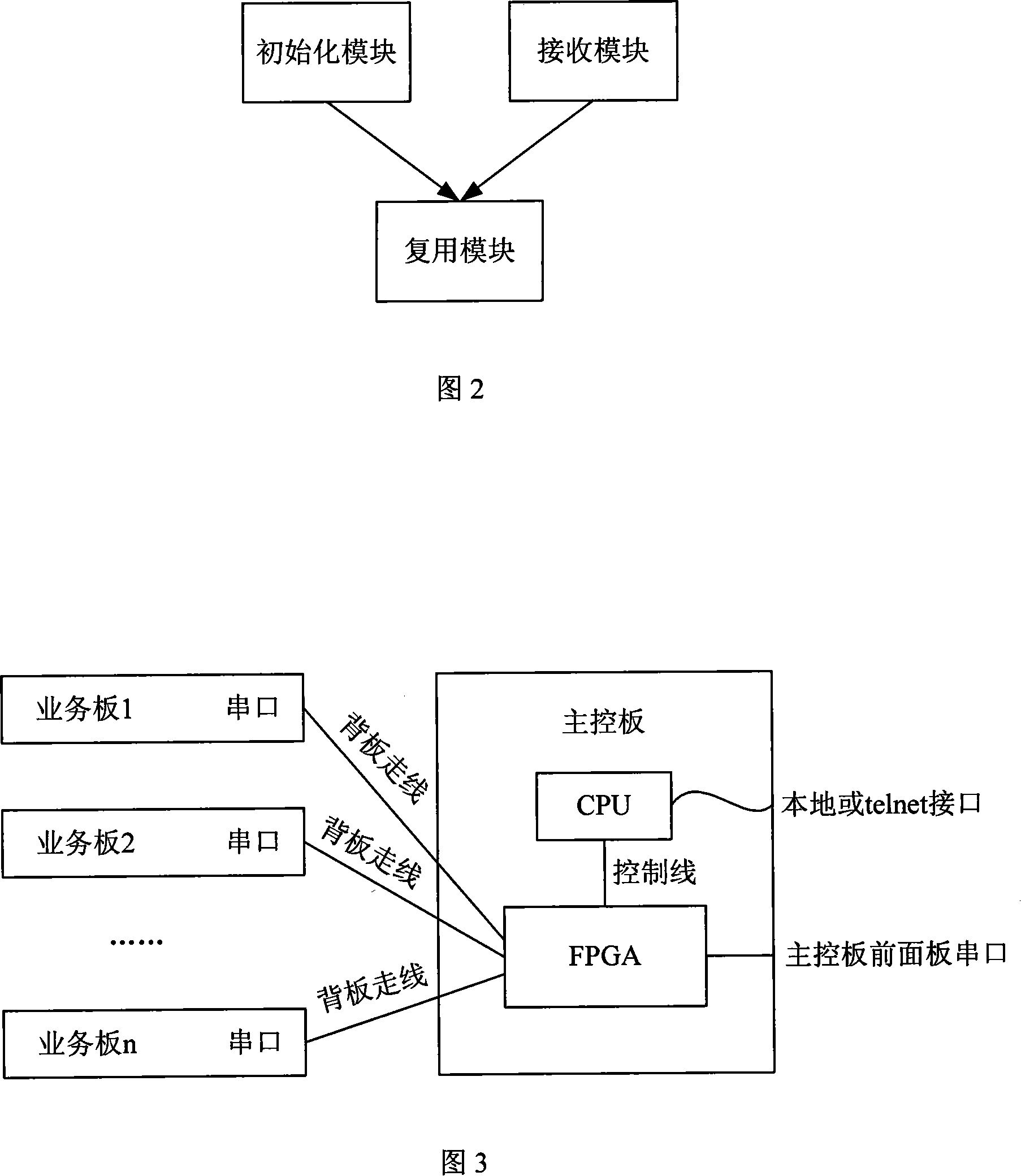

Serial port multiplexing method and device

InactiveCN101141402ARealize multiplexingLow costData switching networksMultiplexingProcessor register

The present invention discloses a method and a device for reusing a serial port, and belongs to the electronic circuit design field. The method comprises: the serial port of a master control board and the serial ports of a plurality of service boards are connected on the logic device of the master control board, and the logic device and the serial port connector on the front panel of the master control board are mutually connected; the corresponding relation between the register of the logic device and all the serial ports is established; an order is received, and one serial port of one service board or the serial port of the master control board is specified in the order; according to the corresponding relation, the value of the register is set as the value of the register corresponding to the serial port specified by the order; and the serial port connector and the specified serial port are connected according to the value of the register. In the device, the serial port of the master control board and the serial ports of the service board are connected with the serial port connector through the logic device, and the master control board comprises an initialization module, a receiving module and a reusing module. The present invention realizes the reusing of the serial port, and the communication with all the serial ports of the service board can be realized through the serial port connector, and the cost is reduced.

Owner:HUAWEI TECH CO LTD

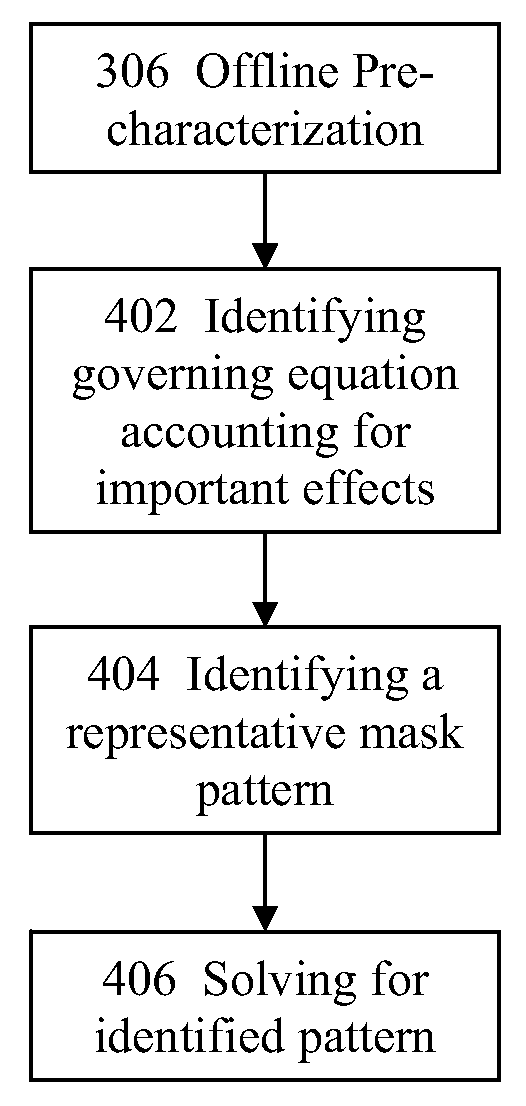

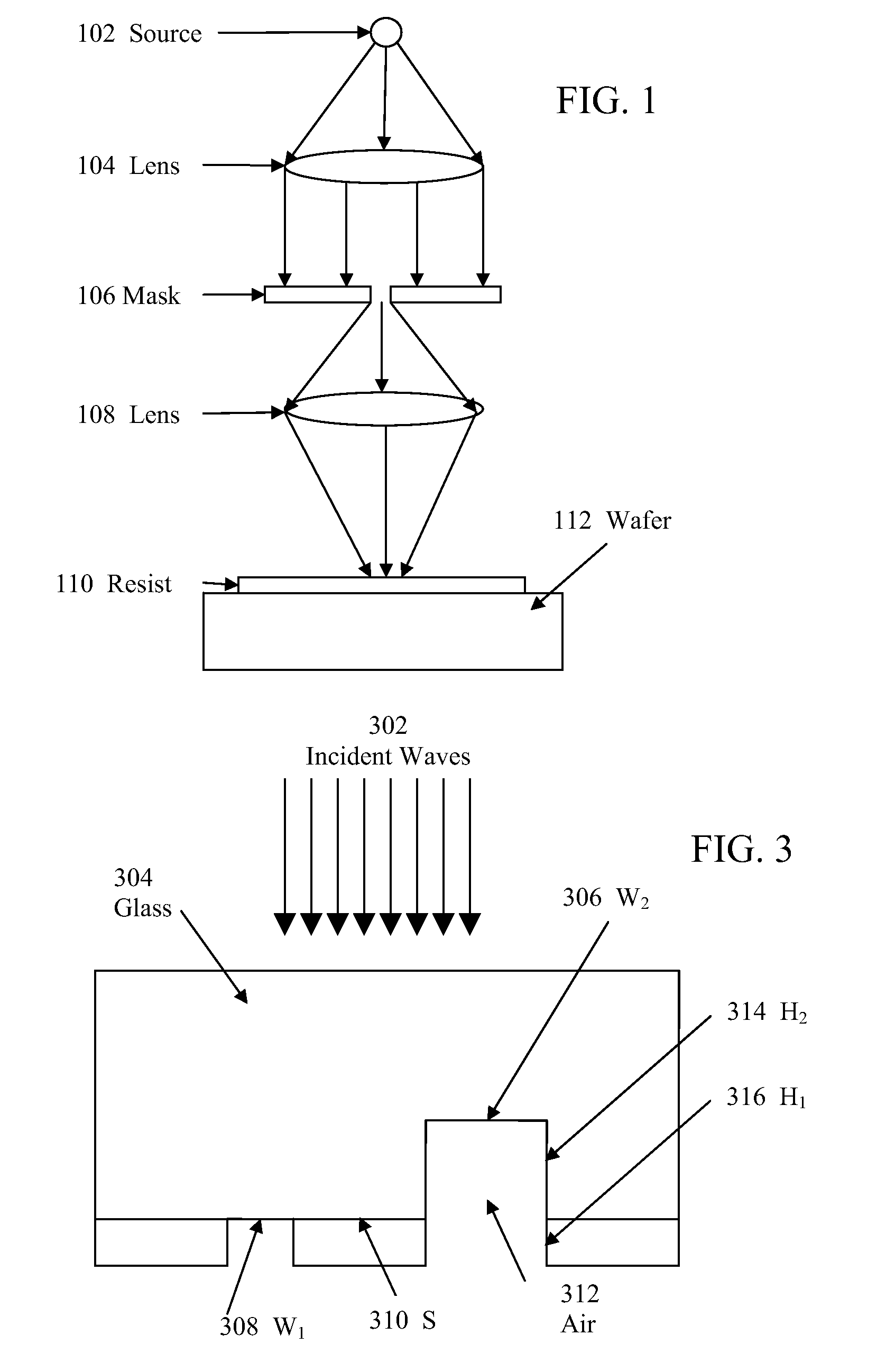

Method, system, and computer program prodcut for lithography simulation in electronic design automation

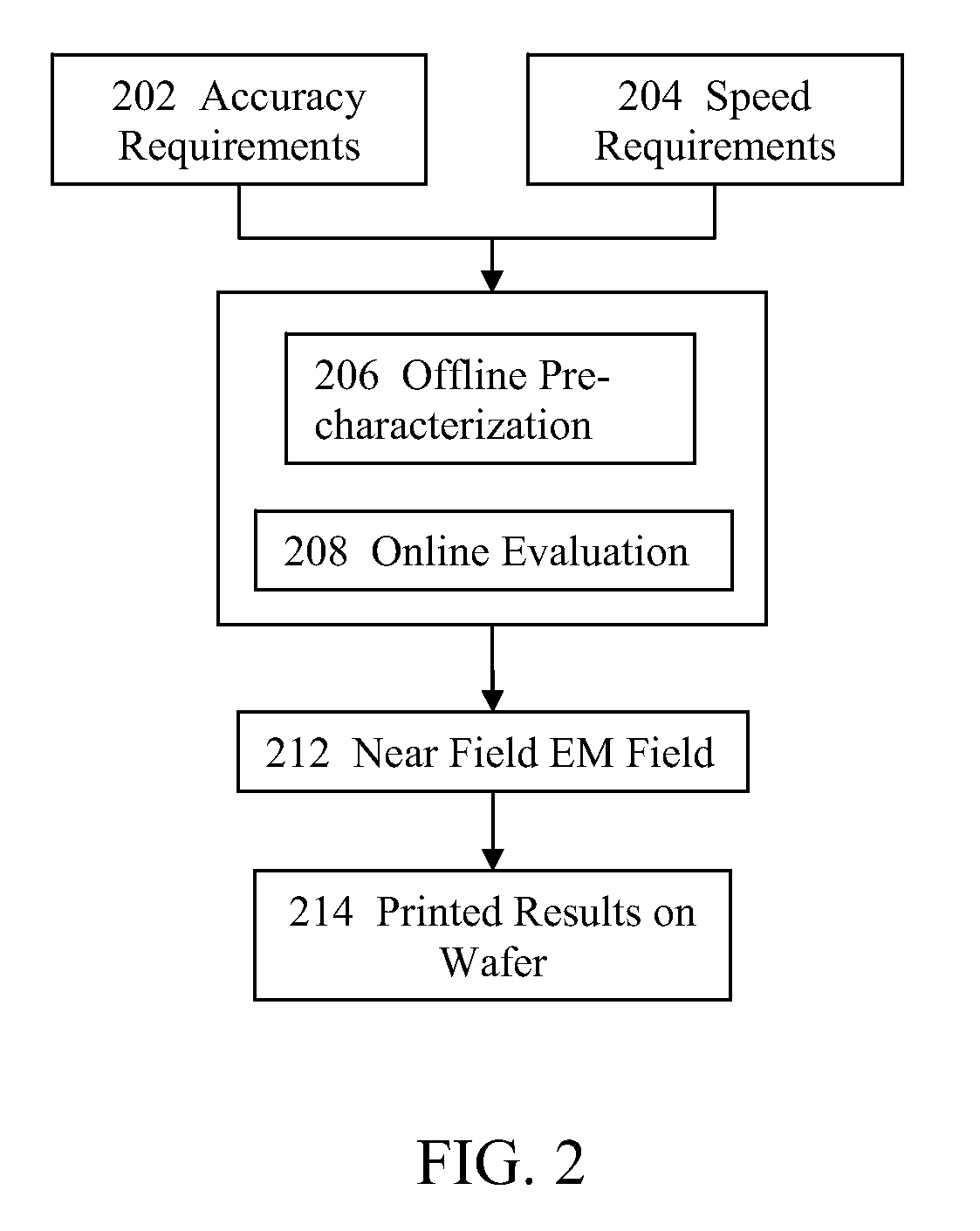

ActiveUS20100169060A1Improve performanceQuantity minimizationAnalogue computers for electric apparatusPhotomechanical apparatusElectromagnetic fieldElectronic circuit design

Disclosed are improved methods, systems, and computer program products for lithographic simulation of an electronic circuit design. Various embodiments of the present invention identifies a mask pattern, performs offline precharacterization for the mask pattern by solving an equation which models a solution for the mask pattern and an interaction between the mask pattern and one or more effects, performs online evaluation based at least upon a parameterized form of the equation, determines a field around the mask pattern based at least upon the act of performing the online evaluation, and stores a result of the act of determining an electromagnetic field around the mask pattern in a tangible computer readable or usable medium

Owner:CADENCE DESIGN SYST INC

Method and system for power delivery network analysis

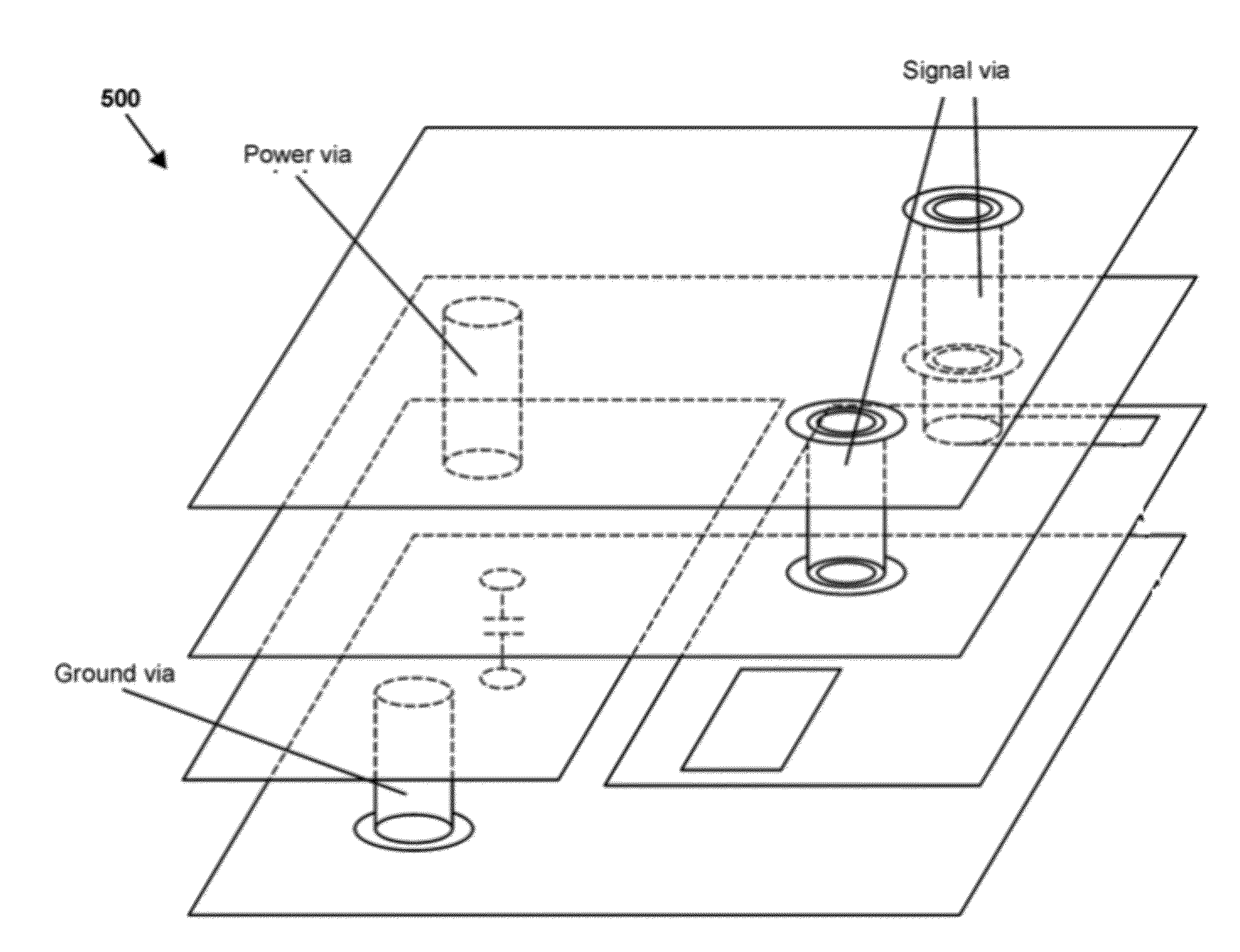

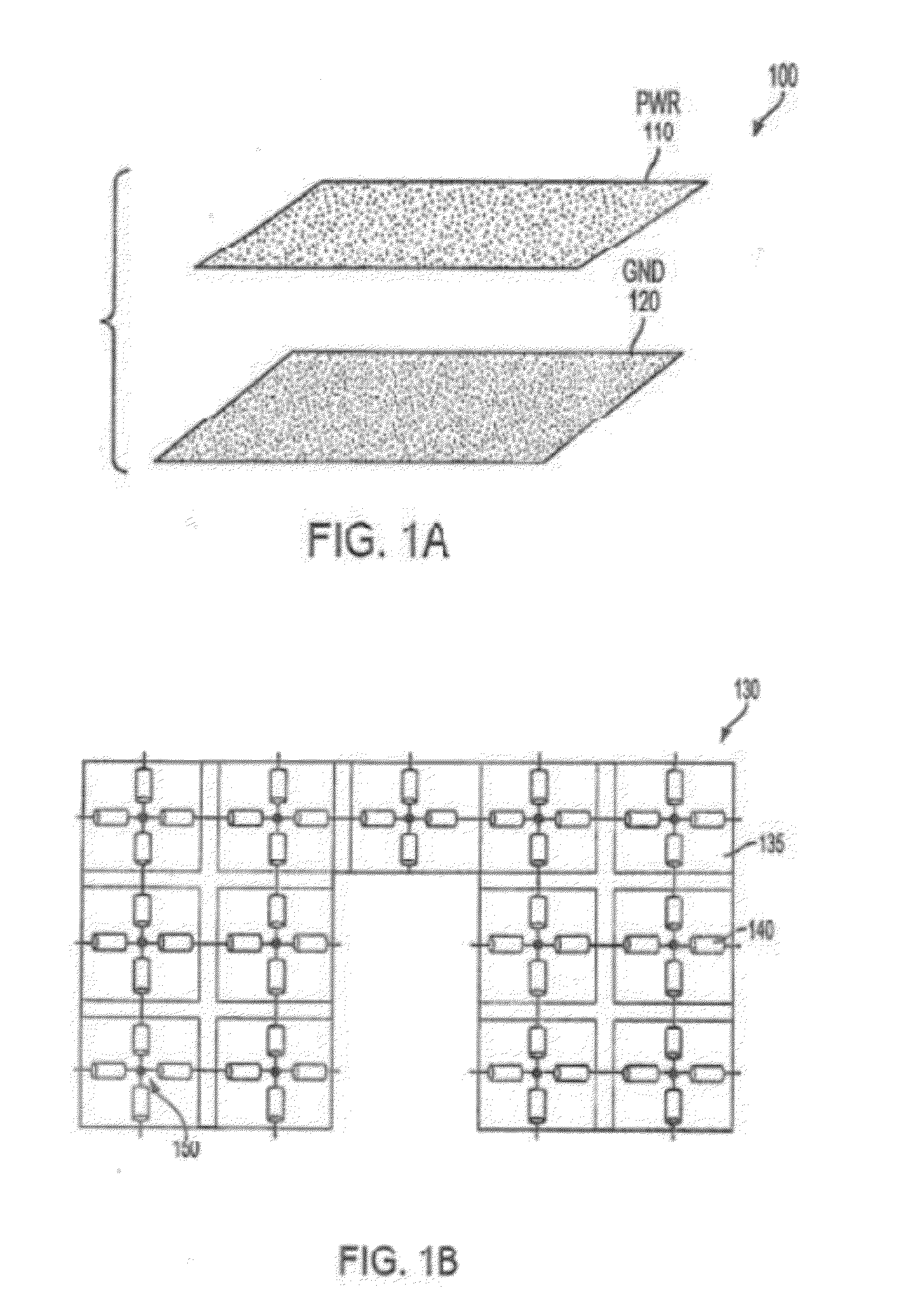

InactiveUS20120221990A1Geometric CADDesign optimisation/simulationElectricity deliveryStructure of Management Information

The subject application relates to a method and system for power delivery network analysis. The present disclosure is directed towards a computer-implemented method for displaying one or more results of a power delivery network (PDN) analysis associated with an electronic circuit design. The method may include extracting, using at least one processor, an electromagnetic (EM) model for each of one or more discontinuity structures associated with the electronic circuit design. The method may further include performing a power delivery network analysis of the electronic circuit design, the PDN analysis including a Method of Moments (MoM) calculation. The method may also include displaying a three dimensional image depicting one or more results of the PDN analysis. Numerous other features are also within the scope of the present disclosure.

Owner:CADENCE DESIGN SYST INC

Graphical user interface for prototyping early instance density

InactiveUS7810063B1Reduce iterative processComputer programmed simultaneously with data introductionCAD circuit designGraphicsGraphical user interface

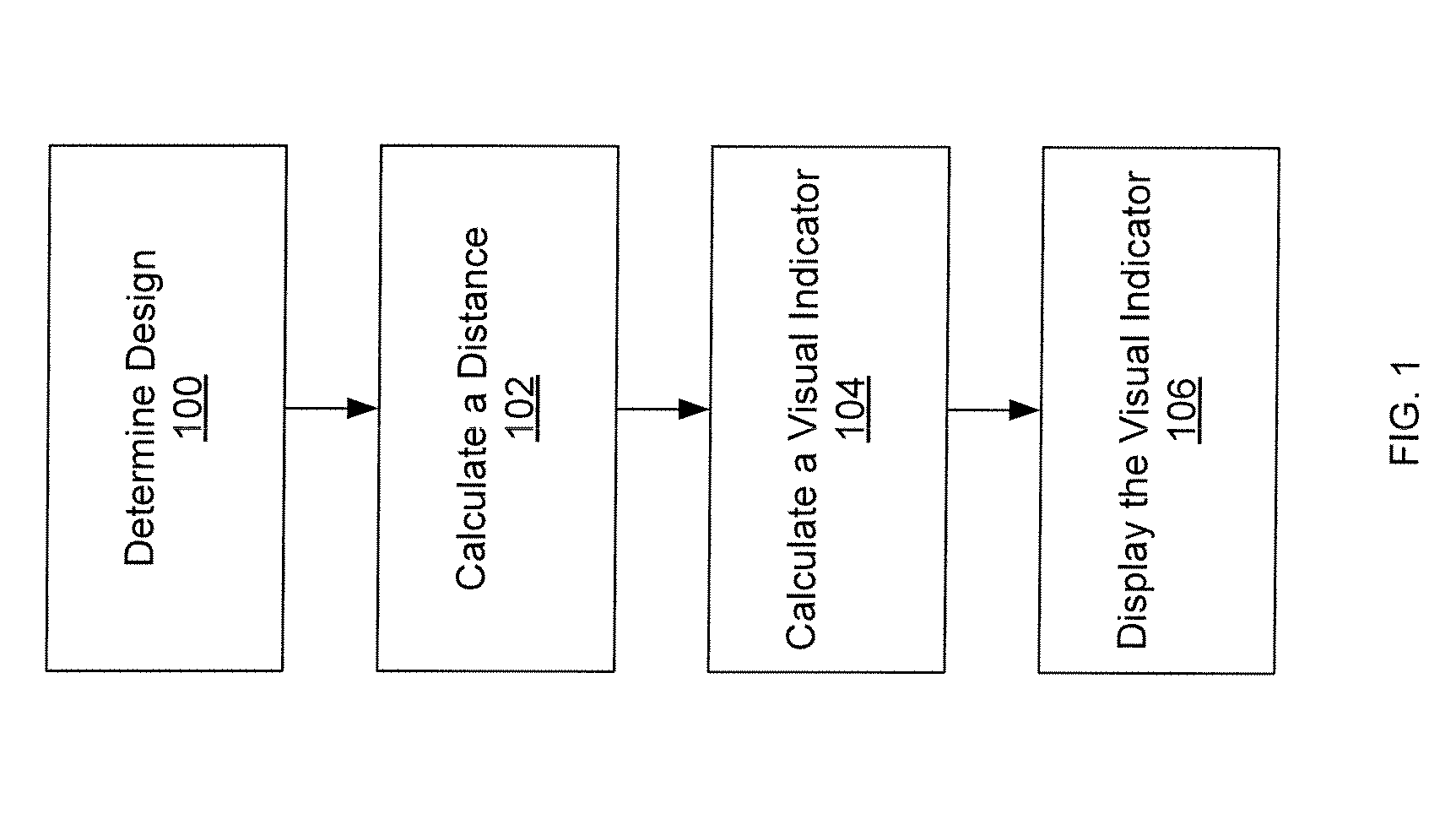

According to various embodiments of the invention electronic circuit design information can be presented to a designer by determining an electronic circuit comprising at least two gates and by determining a distance of one gate relative to another gate in a stage. A visual indicator for the stage can be calculated based on the distances between at least two gates in the stage. The visual indicator can then be displayed. The visual indicator can be a color and the relative distance can be indicated by brightness, hue or saturation, etc. Alternatively, the visual indicator can be a pattern and the relative distance between at least two gates can be indicated by darkness of the pattern.

Owner:CADENCE DESIGN SYST INC

System and method for automatically reconfiguring chain of abutted devices in electronic circuit design

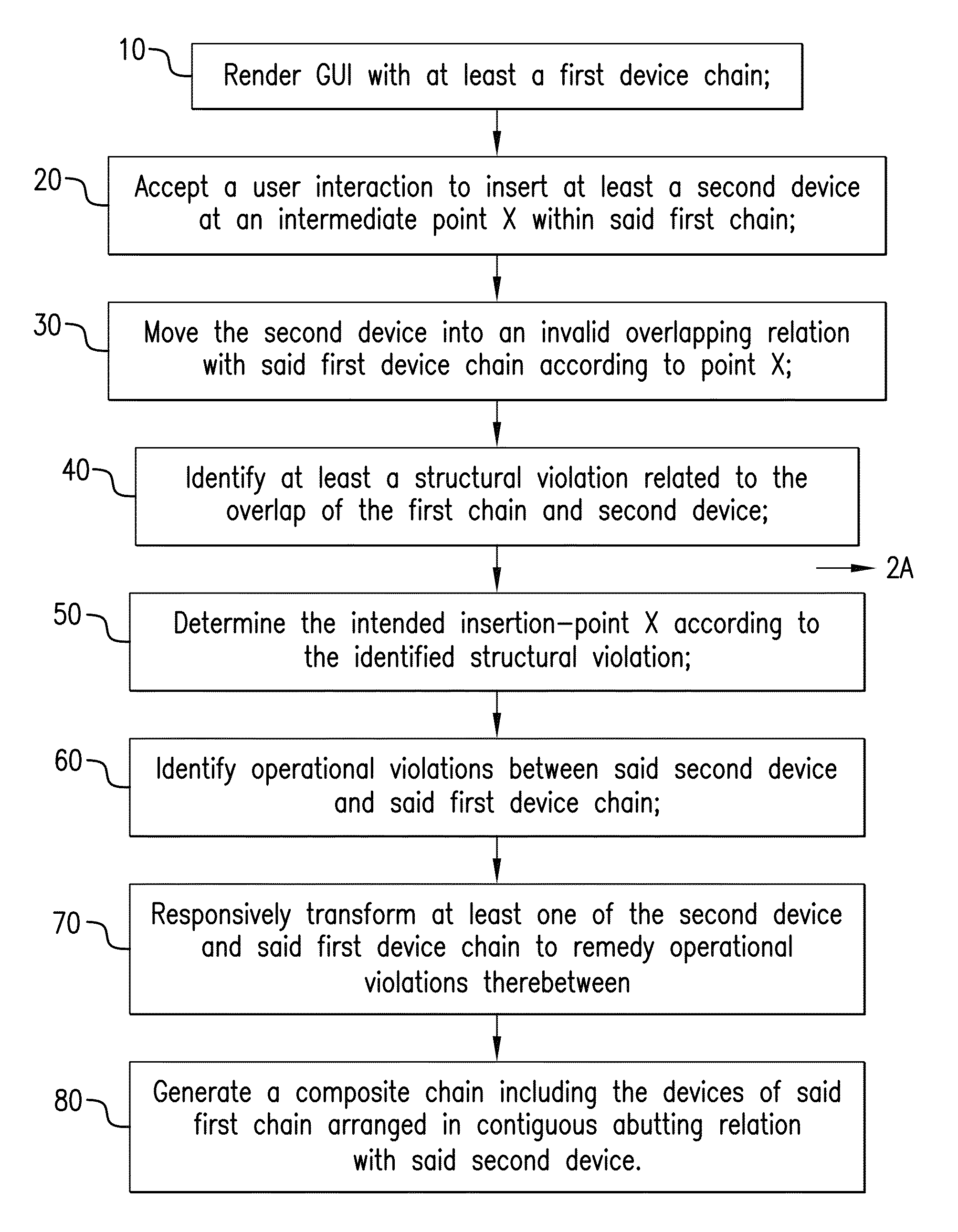

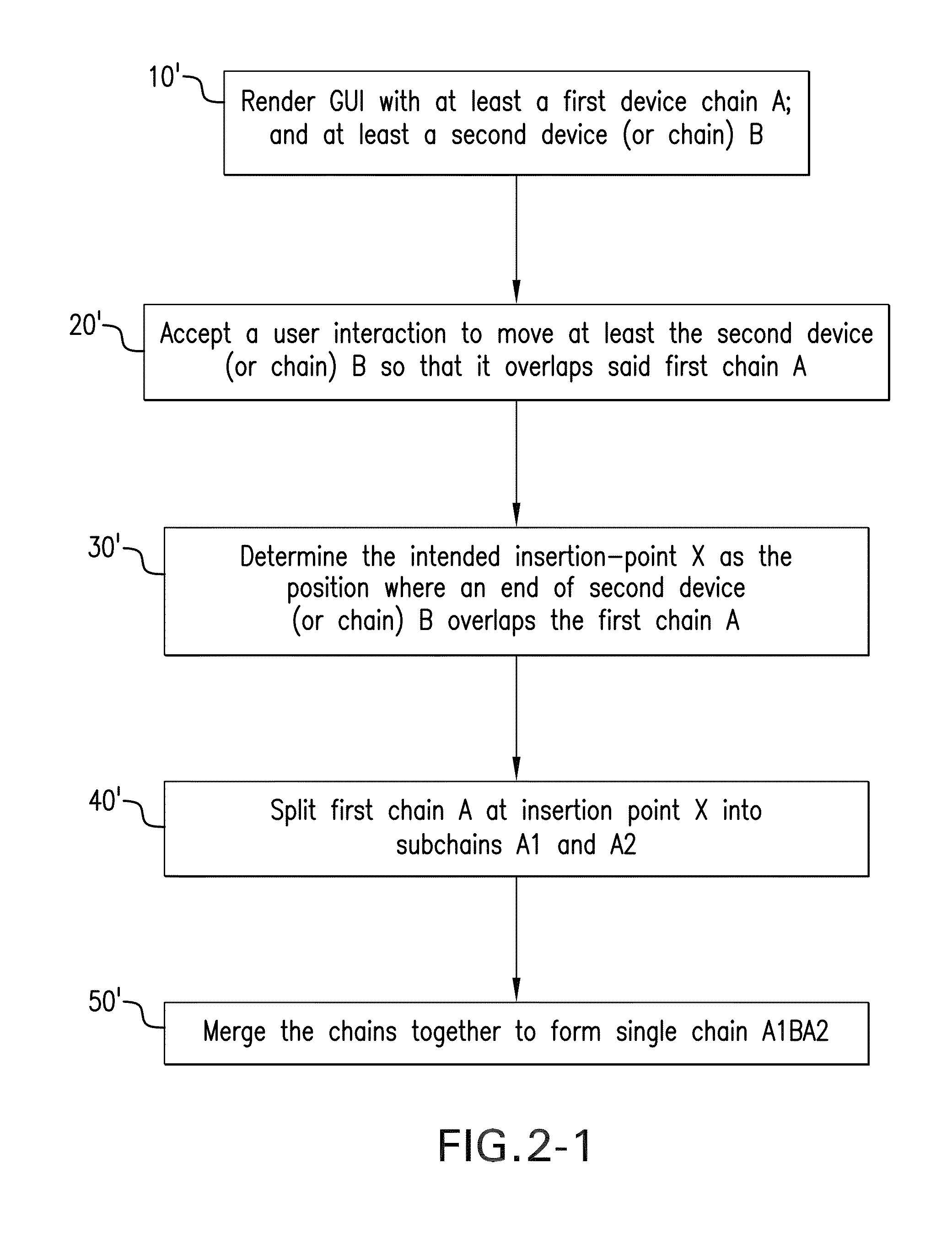

ActiveUS8910100B1Computer aided designSoftware simulation/interpretation/emulationComputer hardwareGraphics

The subject system and method are generally directed to the user-friendly insertion of at least one device, and optionally chains of devices, into at least one pre-existing chain of interconnected devices within a graphical representation of a circuit design such as a circuit layout, circuit mask, or a schematic. The system and method provide for discerning the intended insertion points and performing remedial transformations of the devices within the chains to ensure compliance with both structural and operational requirements of the circuit design.

Owner:CADENCE DESIGN SYST INC

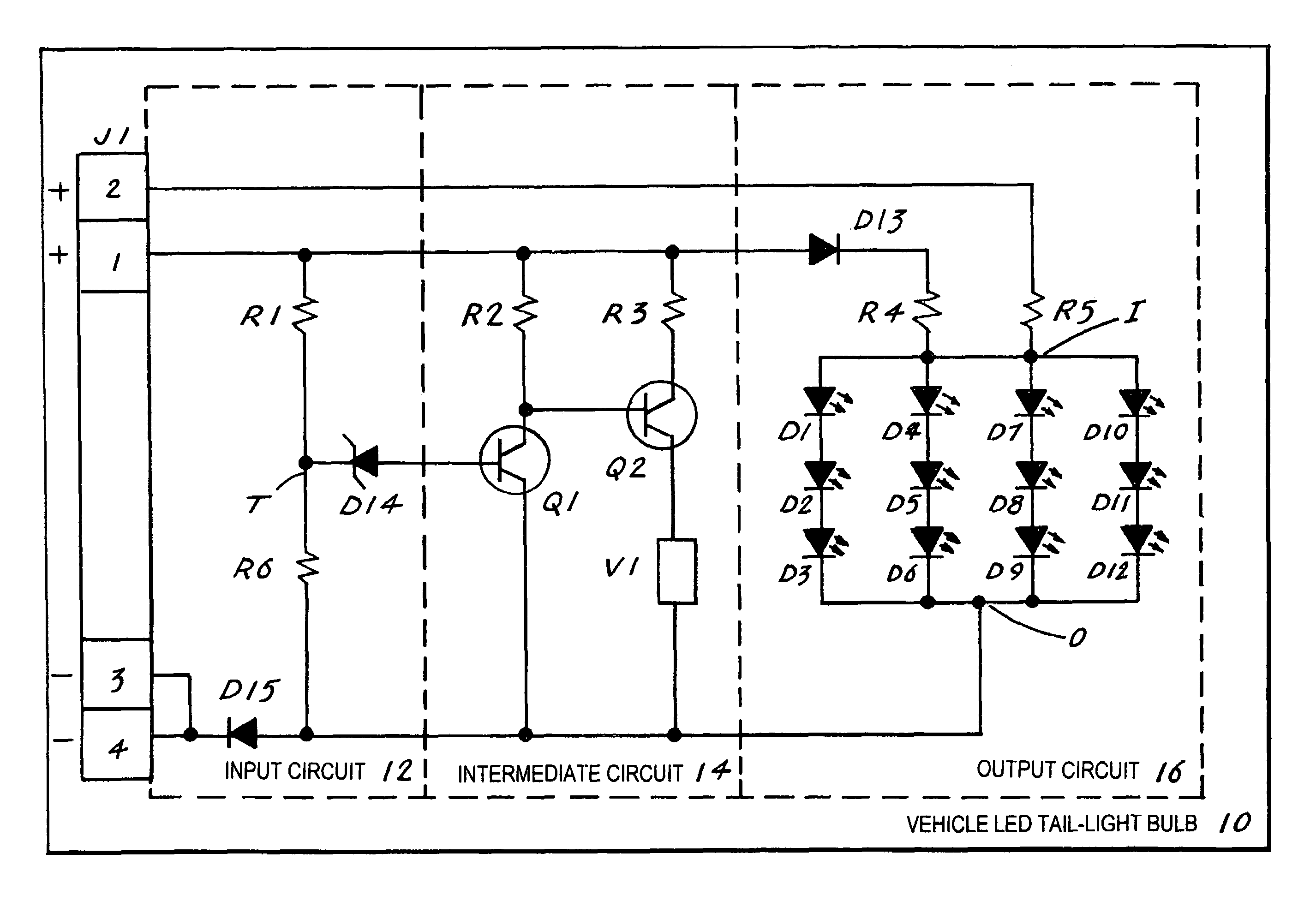

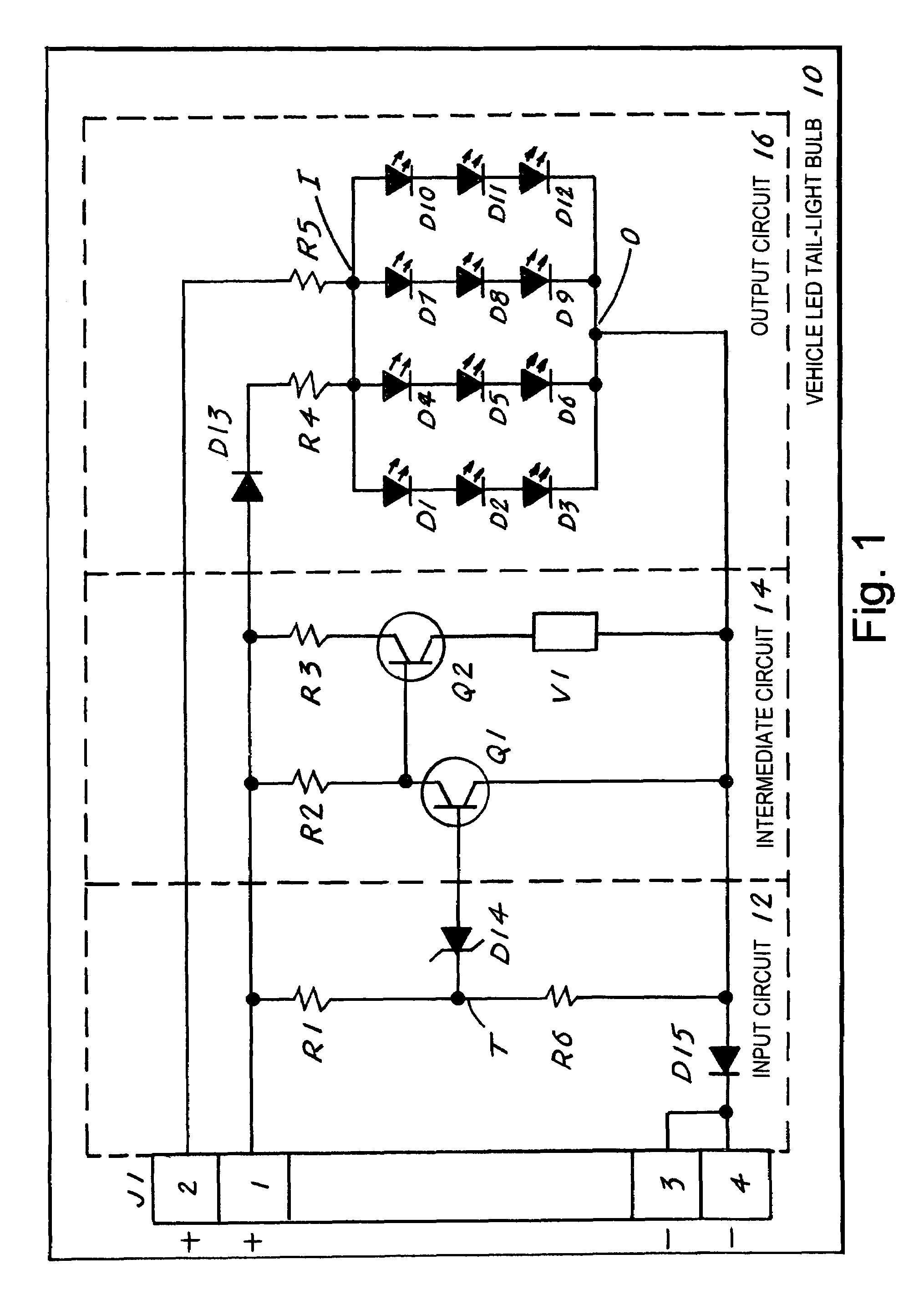

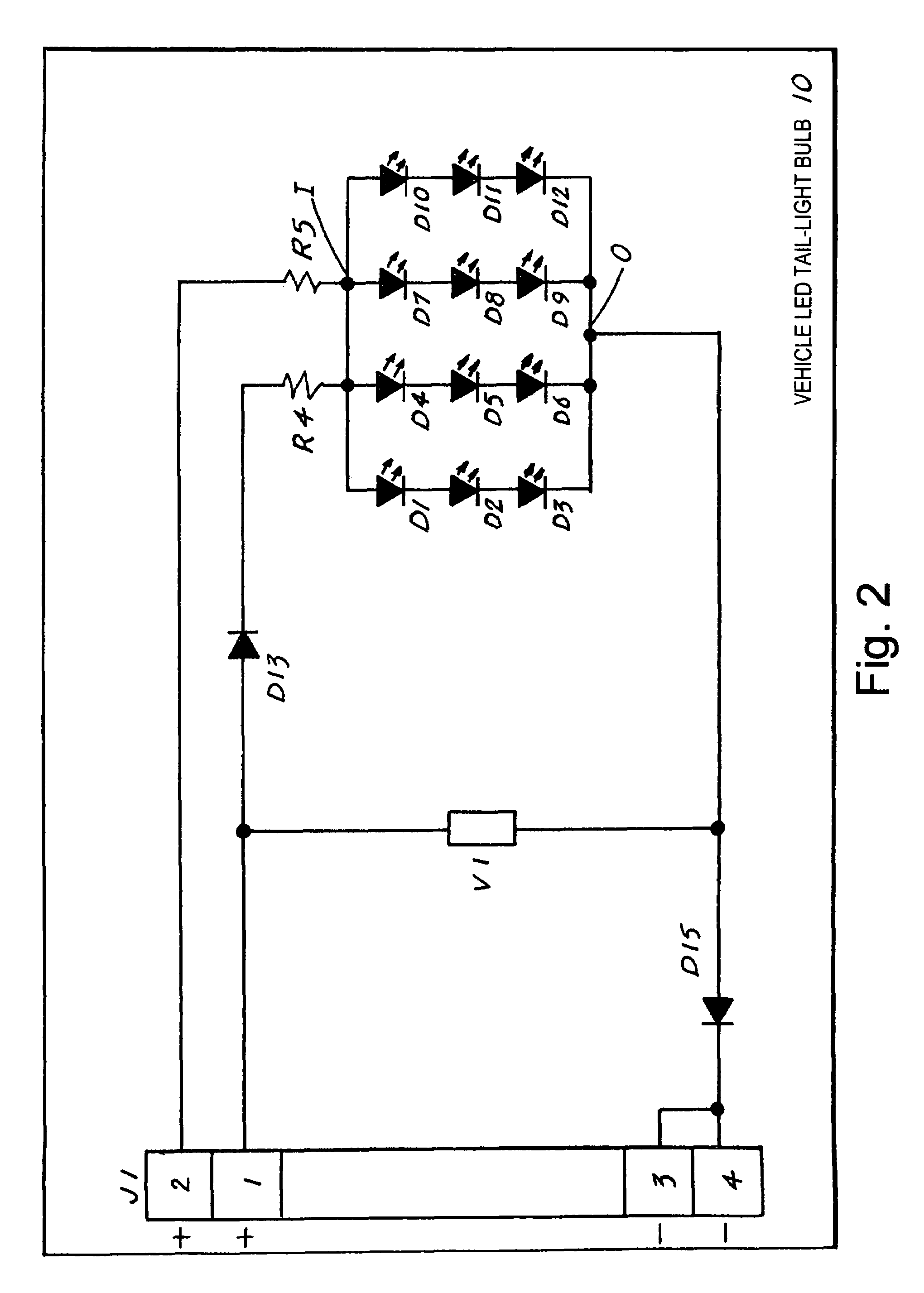

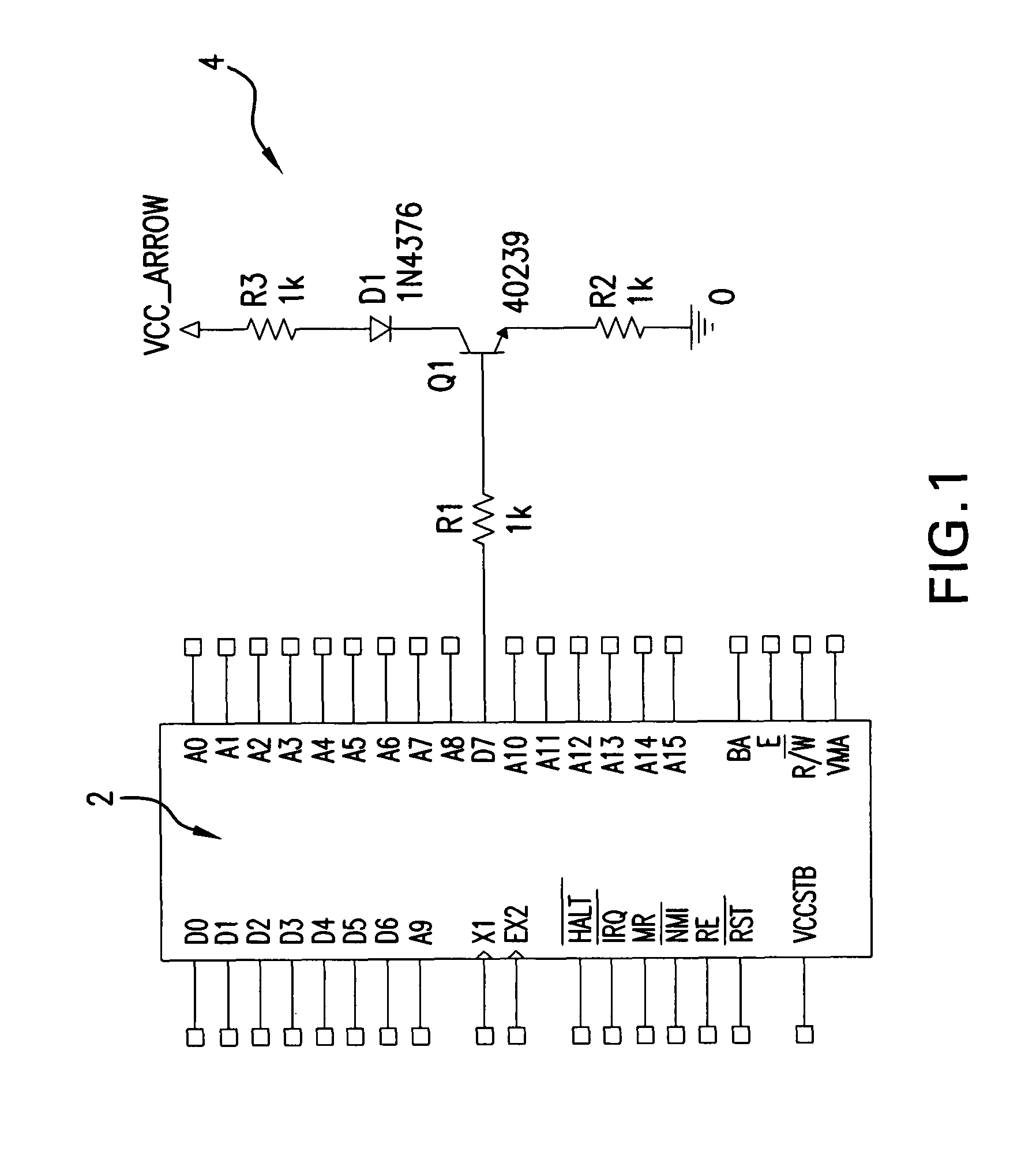

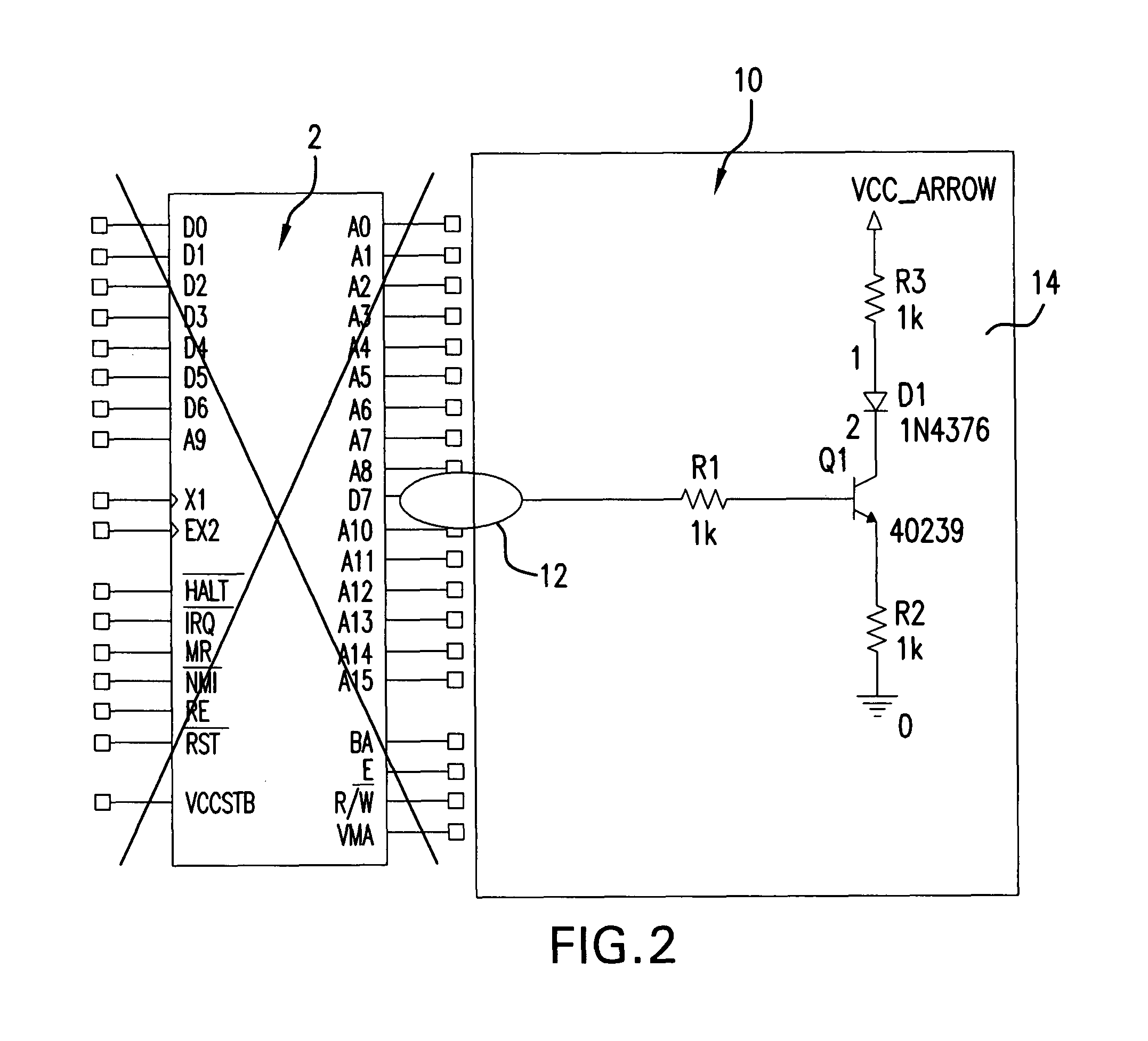

Vehicle LED tail-light bulb

A vehicle LED tail-light bulb (10) that is designed to replace an incandescent light bulb, to be inserted into a conventional right and left vehicle light socket and to function in combination with a vehicle battery that powers the bulb (10) and a flasher unit that is activated by a vehicle turn-signal arm. The LED tail-light bulb incorporates an electronics circuit consisting of an input circuit (12), an intermediate circuit (14) and an output circuit (16). The electronics circuit is designed to operate the left and right turn lights and in some cases an emergency light and to produce a current flow of sufficient magnitude to energize the vehicle flasher unit. The energized flasher unit then causes the bulb (10) to blink when the vehicle turn-signal arm is placed in either a right turn or a left turn position.

Owner:HUANG ZHEN QIU +1

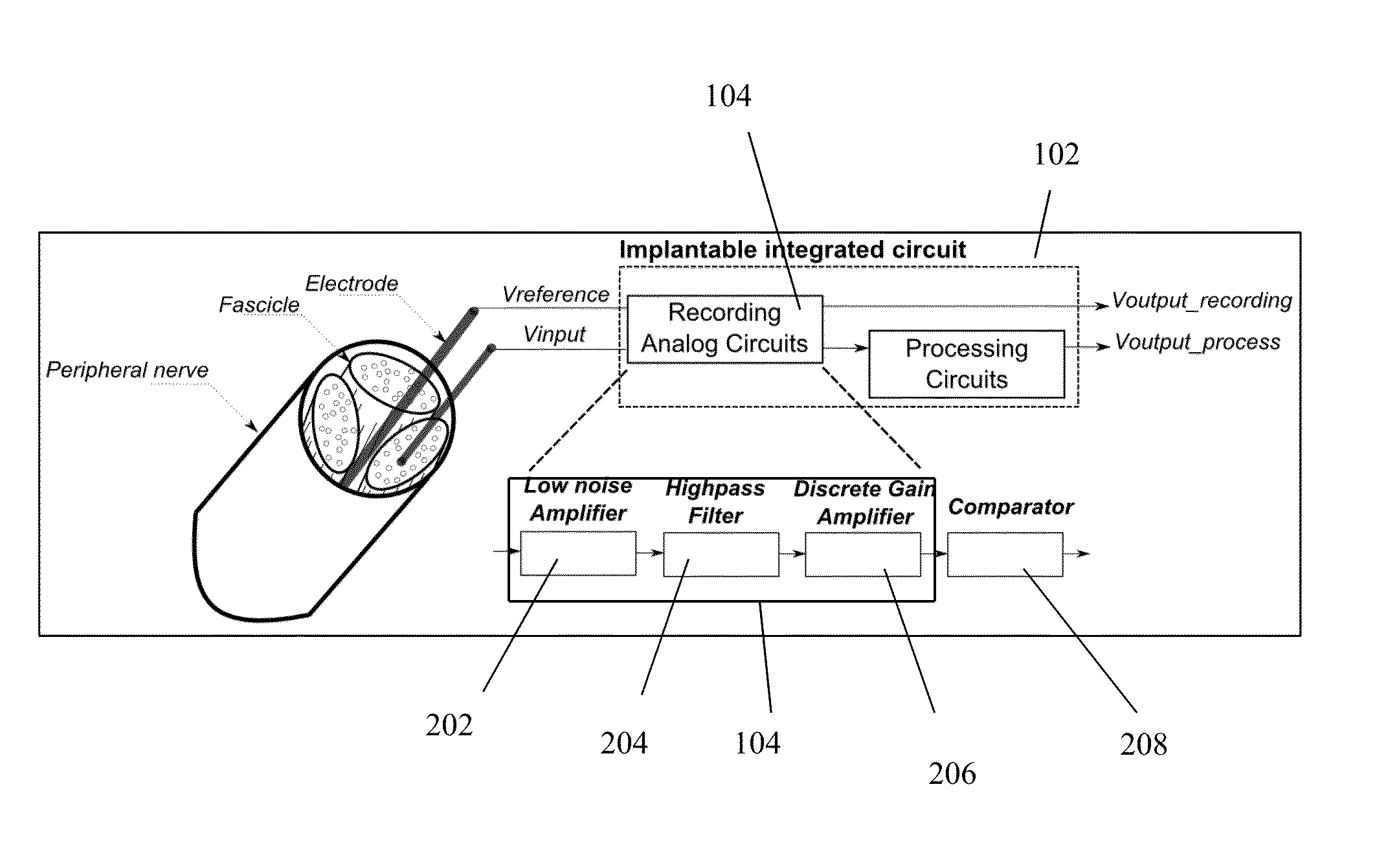

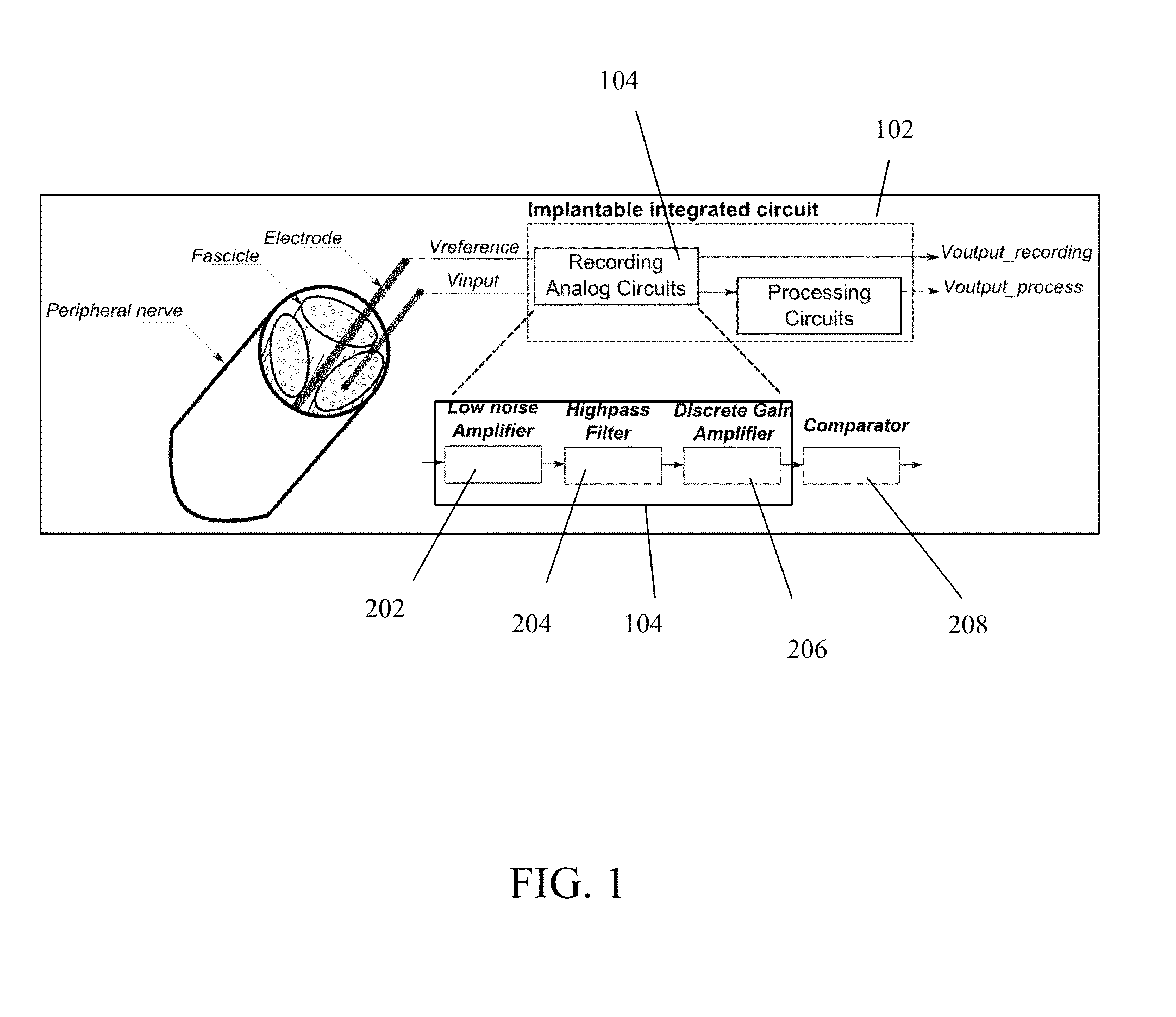

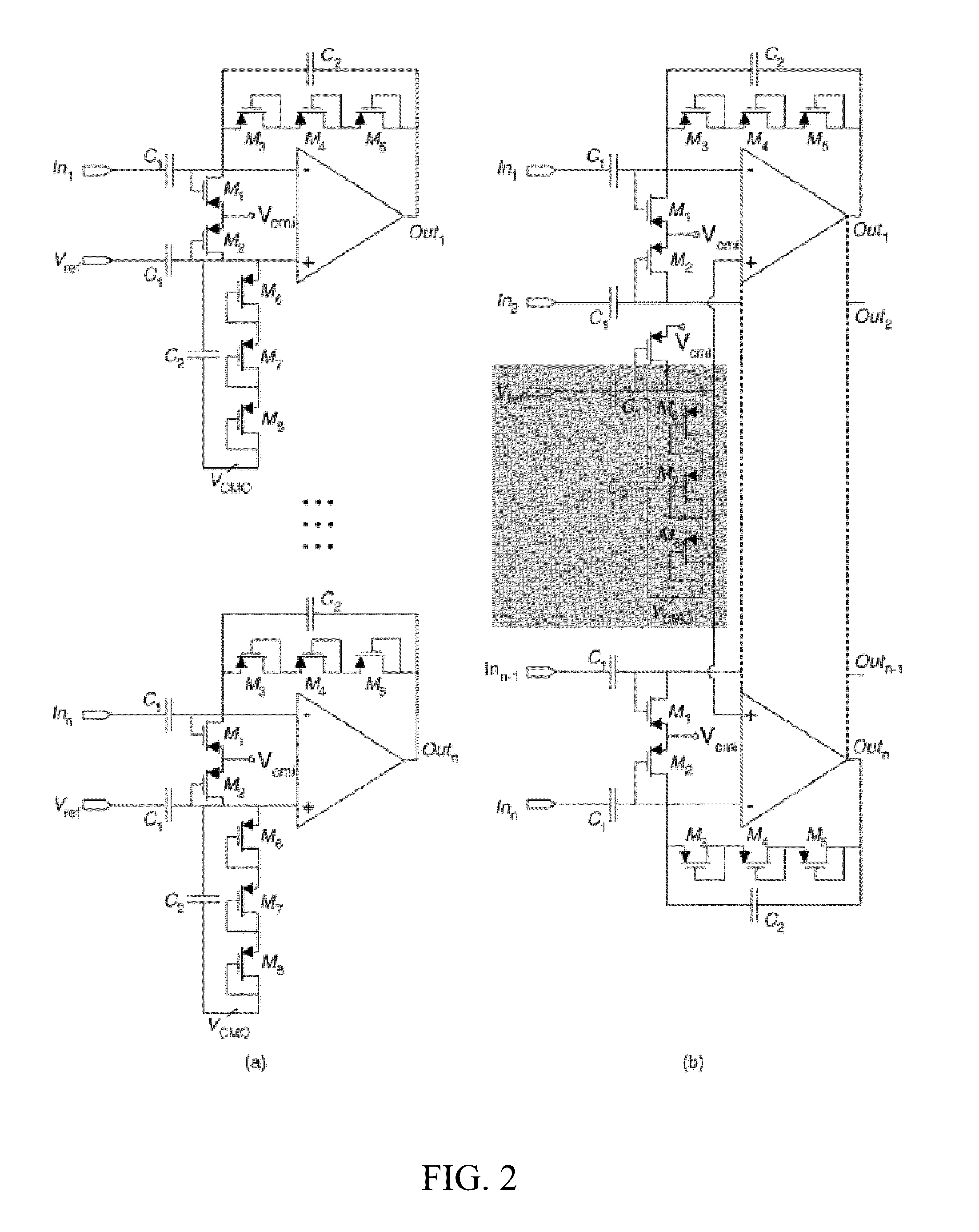

Low noise analog electronic circuit design for recording peripheral nerve activity

ActiveUS20140330102A1Improve noise characteristicsReduce power consumptionSensorsDifferential amplifiersLow noiseEngineering

Circuits and circuit systems to record activity (e.g., peripheral nerve activity) are provided. The circuits advantageously have good noise characteristics (e.g., low noise), as well as low power consumption and low area. A circuit can be implantable (e.g., in a human subject). Methods of designing, manufacturing, and using such circuits and circuit systems are also provided.

Owner:FLORIDA INTERNATIONAL UNIVERSITY

Electronic circuit designing method and apparatus, and storage medium

InactiveUS20050086626A1Semiconductor/solid-state device manufacturingComputer programmed simultaneously with data introductionElectronic circuit designUser defined

An electronic circuit designing method and apparatus designs an electronic circuit by CAD, by generating design constraints with respect to the electronic circuit based on at least one of general layout and wiring information related to devices and wirings included in the electronic circuit, user requirements defined by a user, and user resources defined by the user, and urging an input to the user by displaying the design constraints.

Owner:FUJITSU LTD

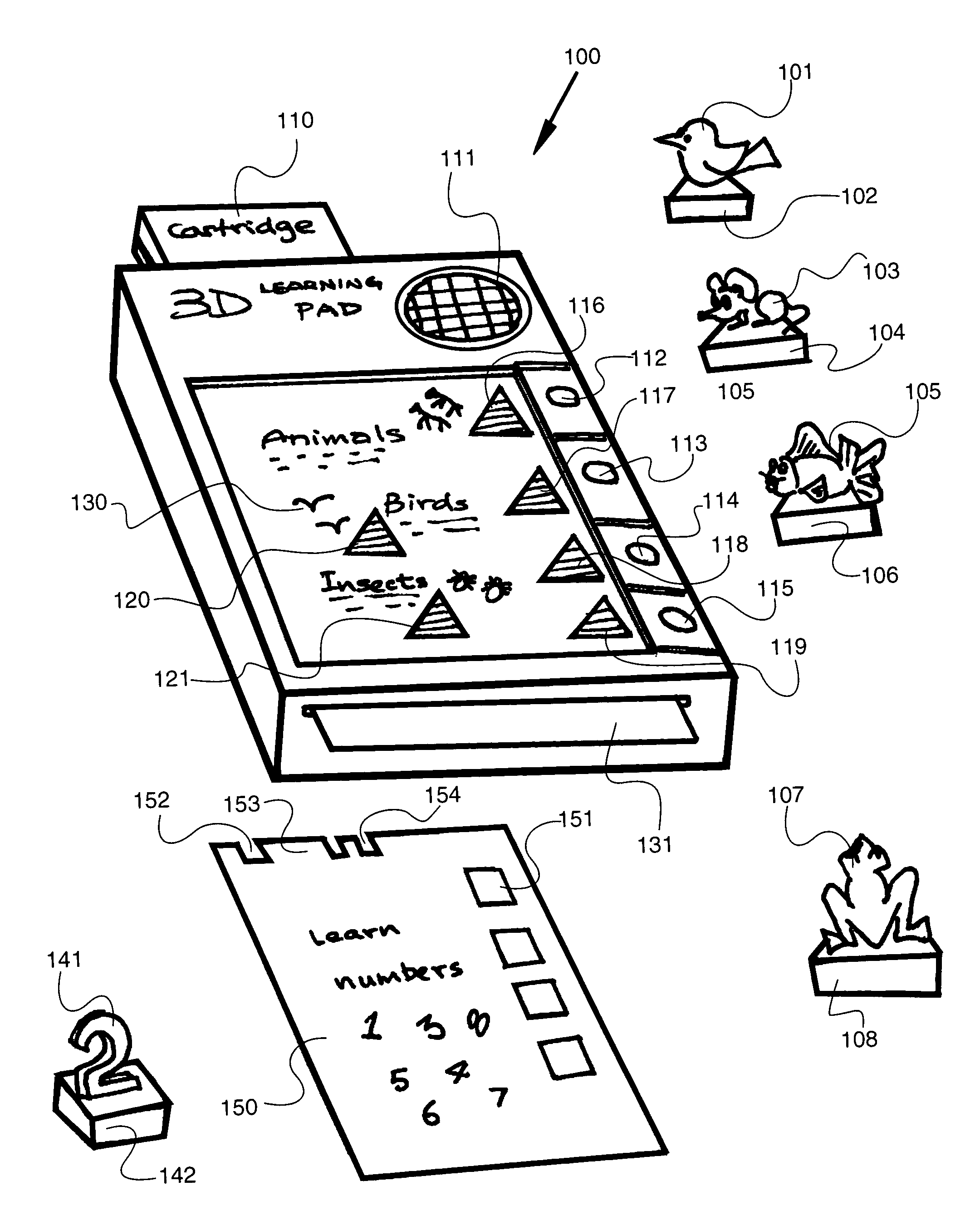

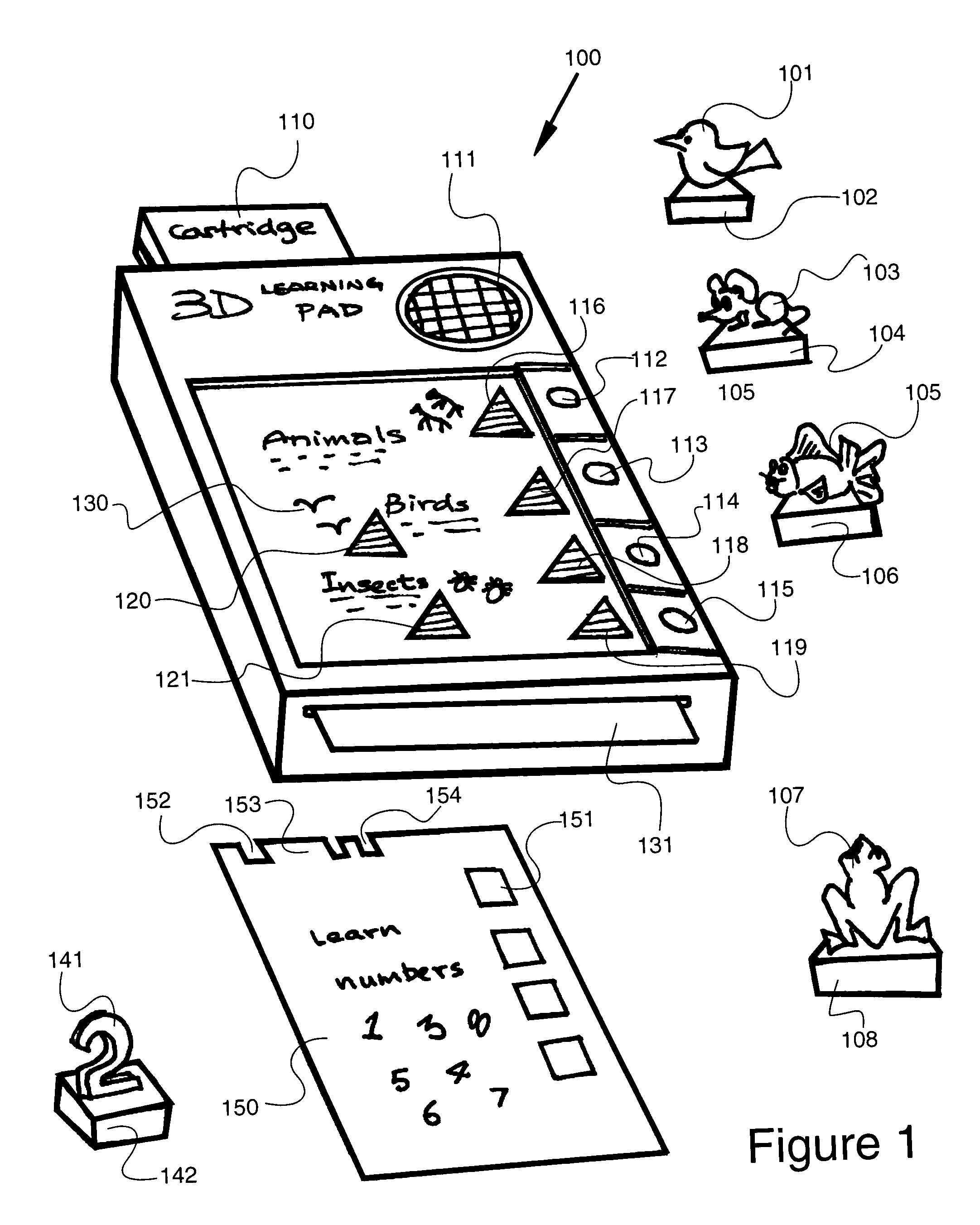

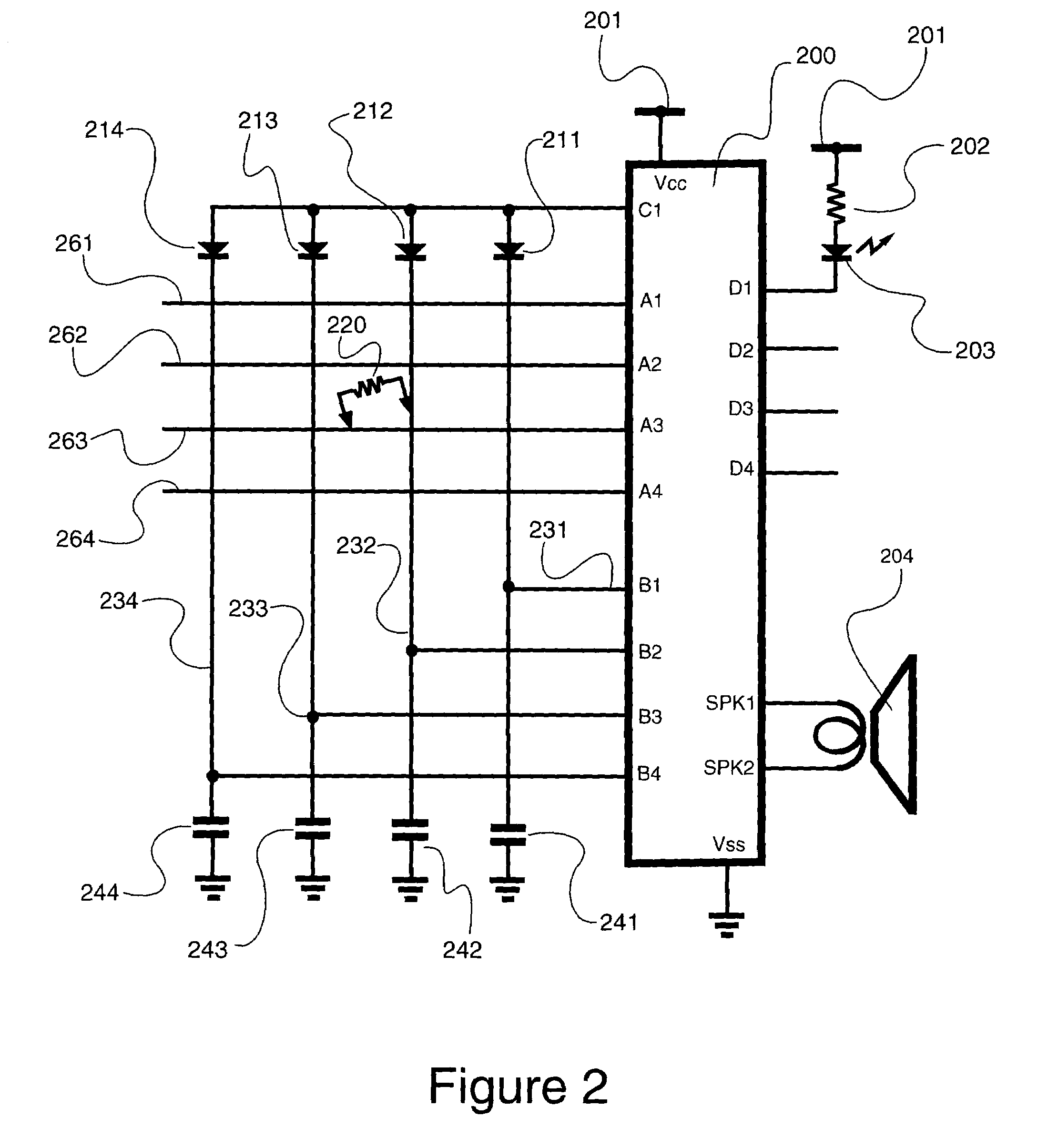

Receiver matrix configured to identify multiple external resistors

InactiveUS7392985B1Modified shapeEasy to trainBoard gamesElectrical resistance and conductanceElectronic circuit design

An electronics circuit designed for a matrix array of receivers configured to detect multiple external resistors of close values selected from the 100 ohm to 1 Mohm range, and to provide different responses according to the resistance of a resistor connected to a receiver.

Owner:PEOPLE INNOVATE FOR ECONOMY FOUND

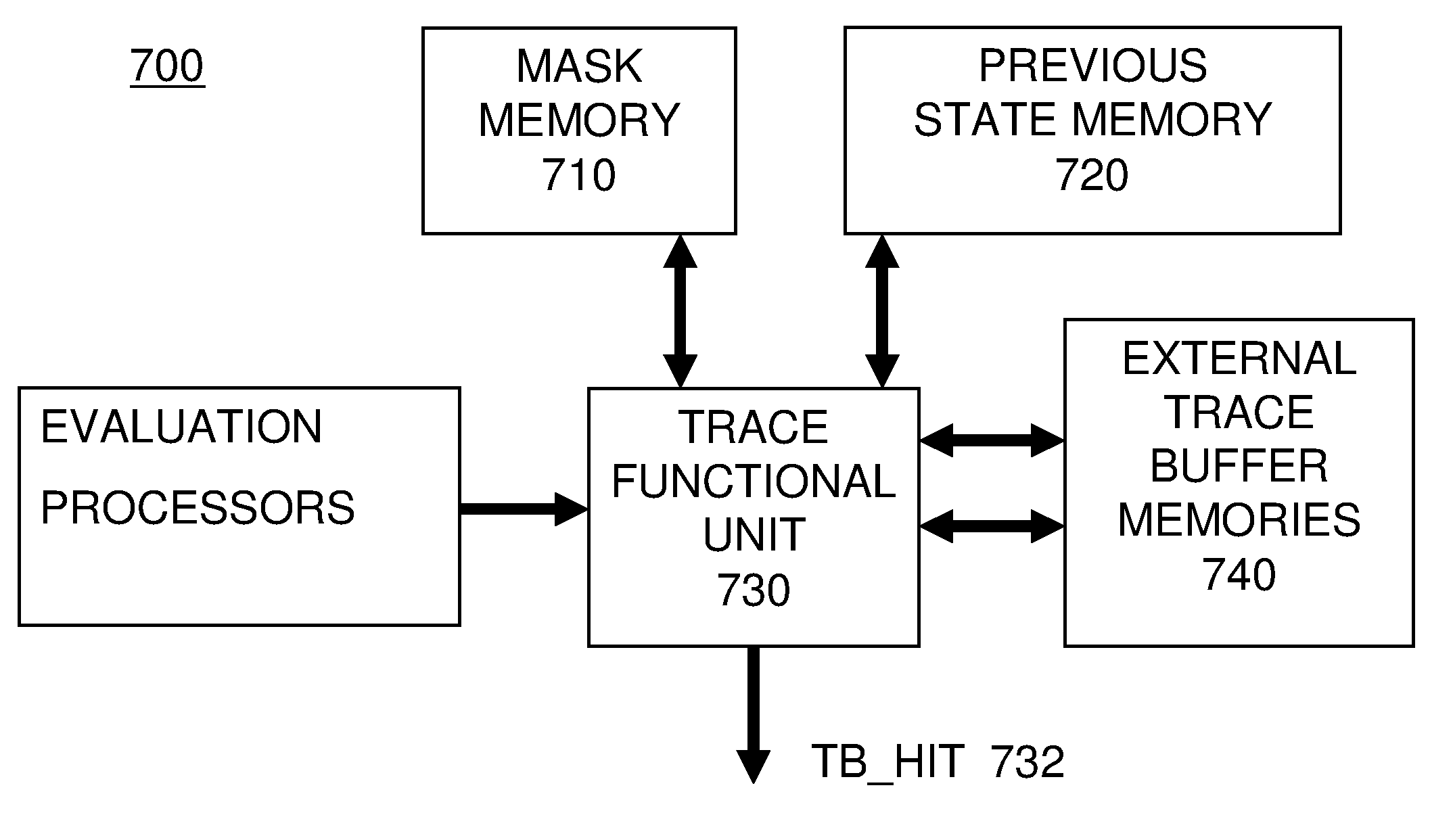

Scalable system for simulation and emulation of electronic circuits using asymmetrical evaluation and canvassing instruction processors

ActiveUS7548842B2Analogue computers for electric apparatusData switching by path configurationScalable systemParallel computing

Owner:EVE

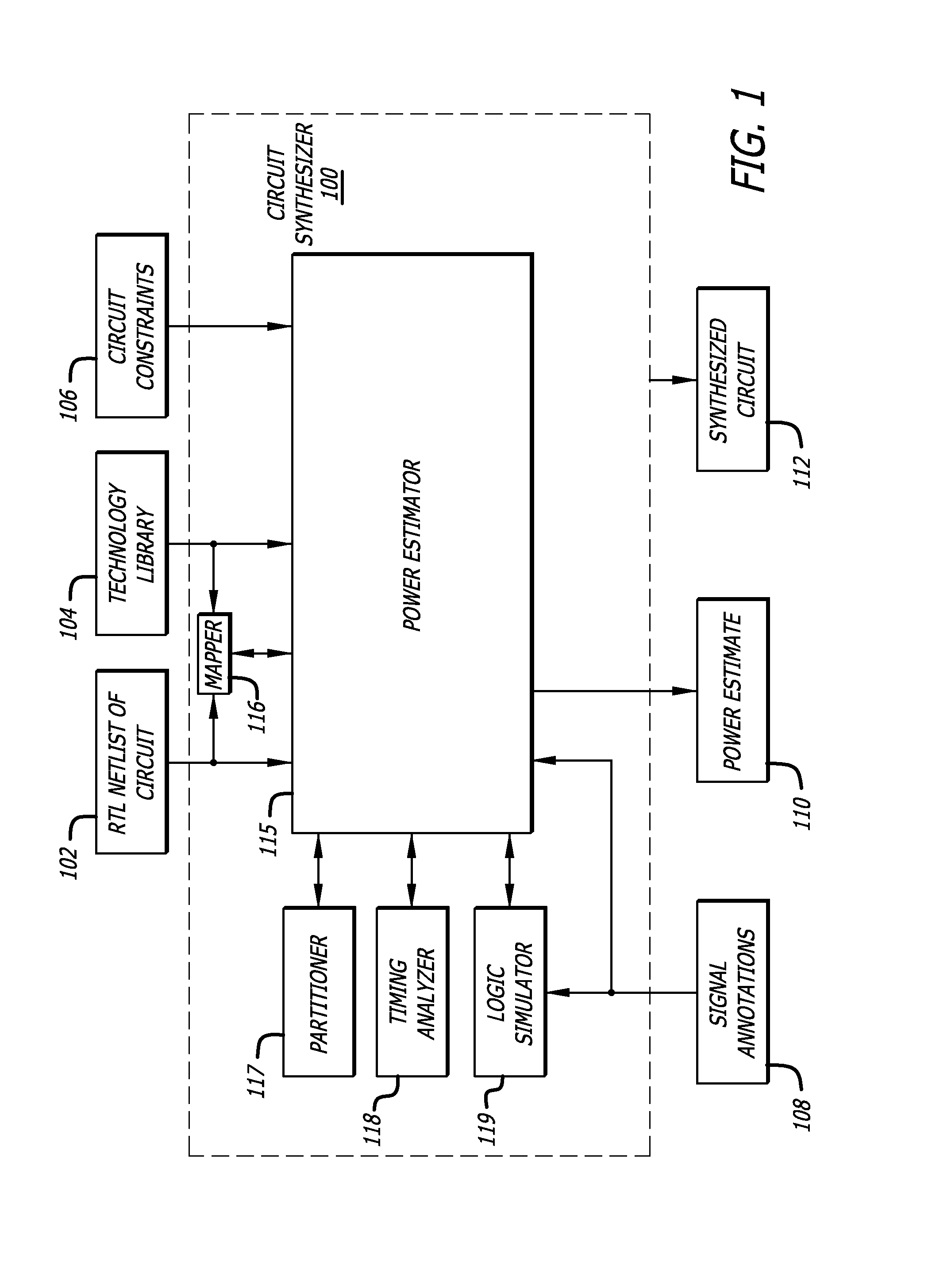

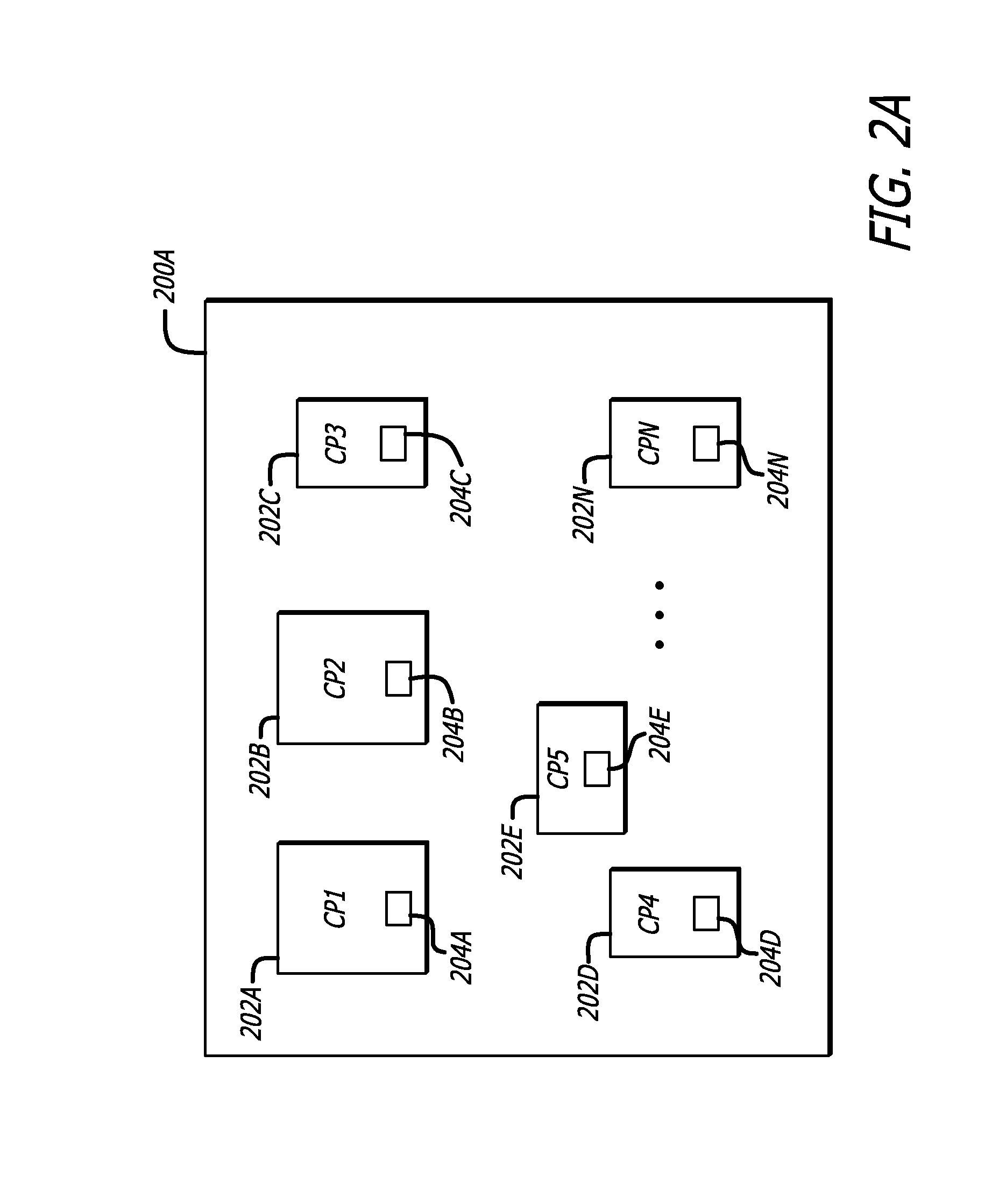

Early estimation of power consumption for electronic circuit designs

ActiveUS8201121B1CAD circuit designSoftware simulation/interpretation/emulationPower correctionElectronic circuit design

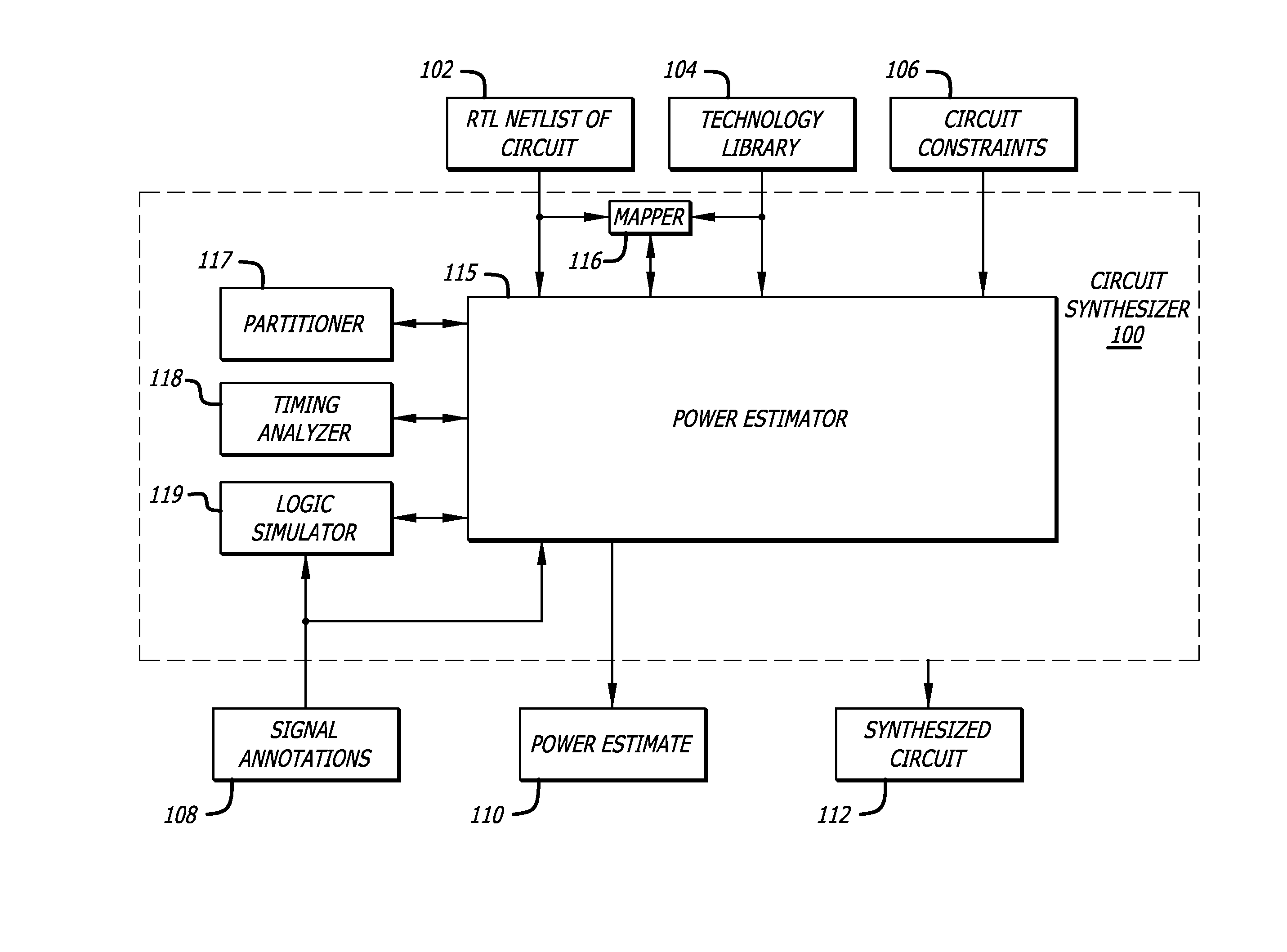

In one embodiment of the invention, a method of designing integrated circuits is disclosed. The method includes determining a power correction factor for a subset of partitions of circuits in an integrated circuit design; determining a gross power consumption estimate for all partitions of circuits in the integrated circuit design without synthesizing the entire integrated circuit design; and improving the accuracy of the gross power consumption estimate using the power correction factor to generate a reasonably accurate power consumption estimate for the entire integrated circuit design prior to substantially full circuit synthesis thereof.

Owner:CADENCE DESIGN SYST INC

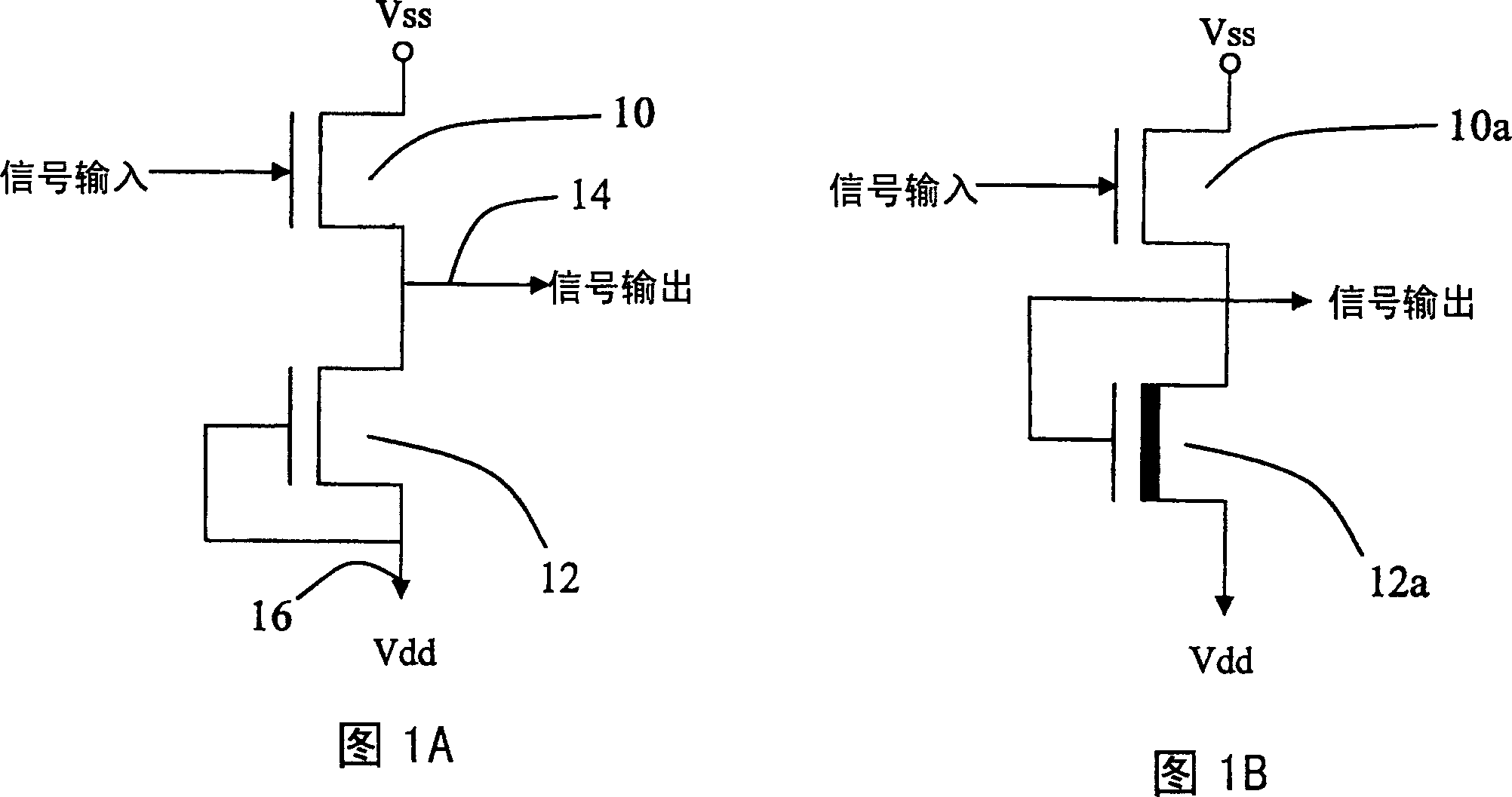

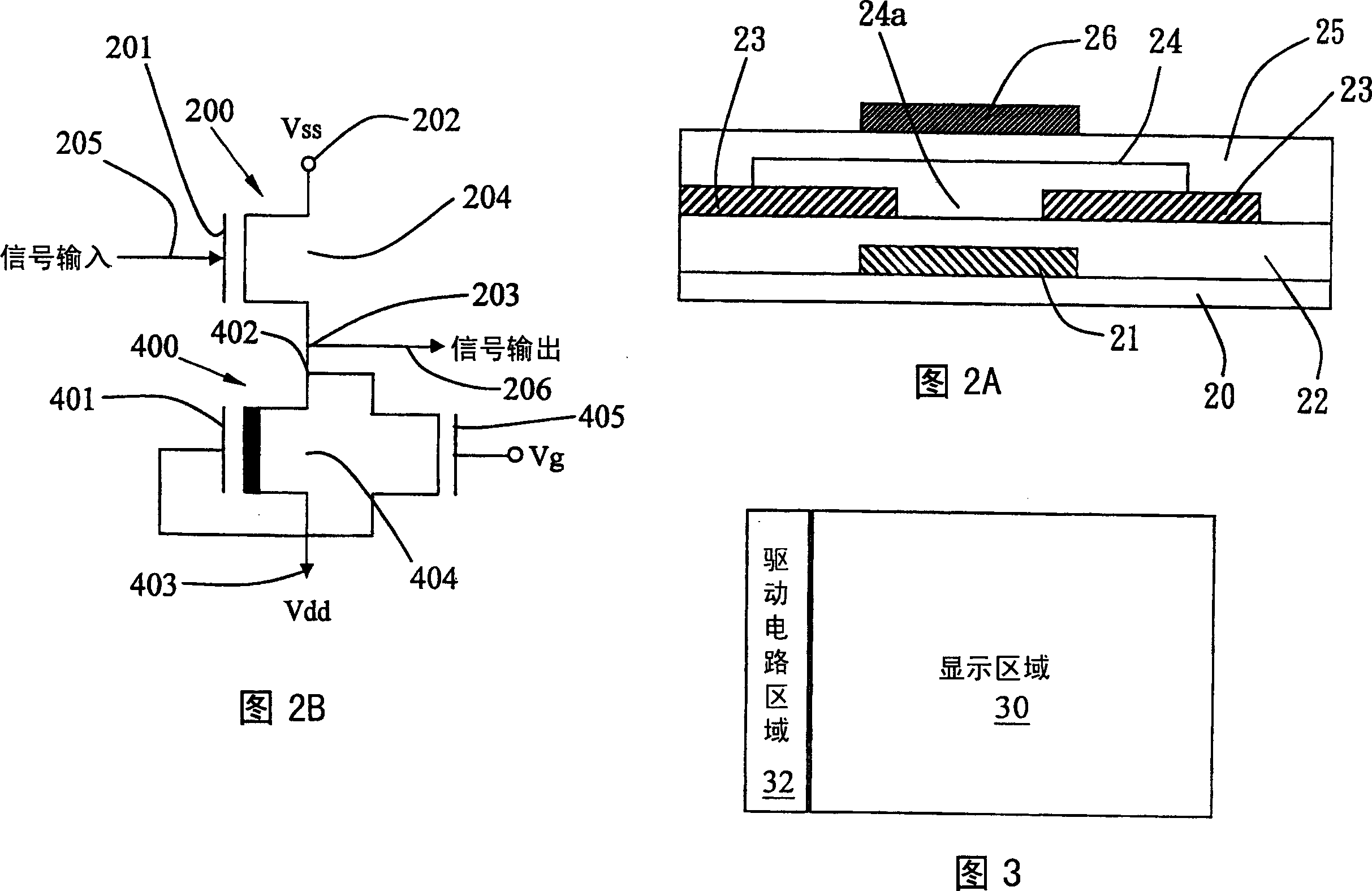

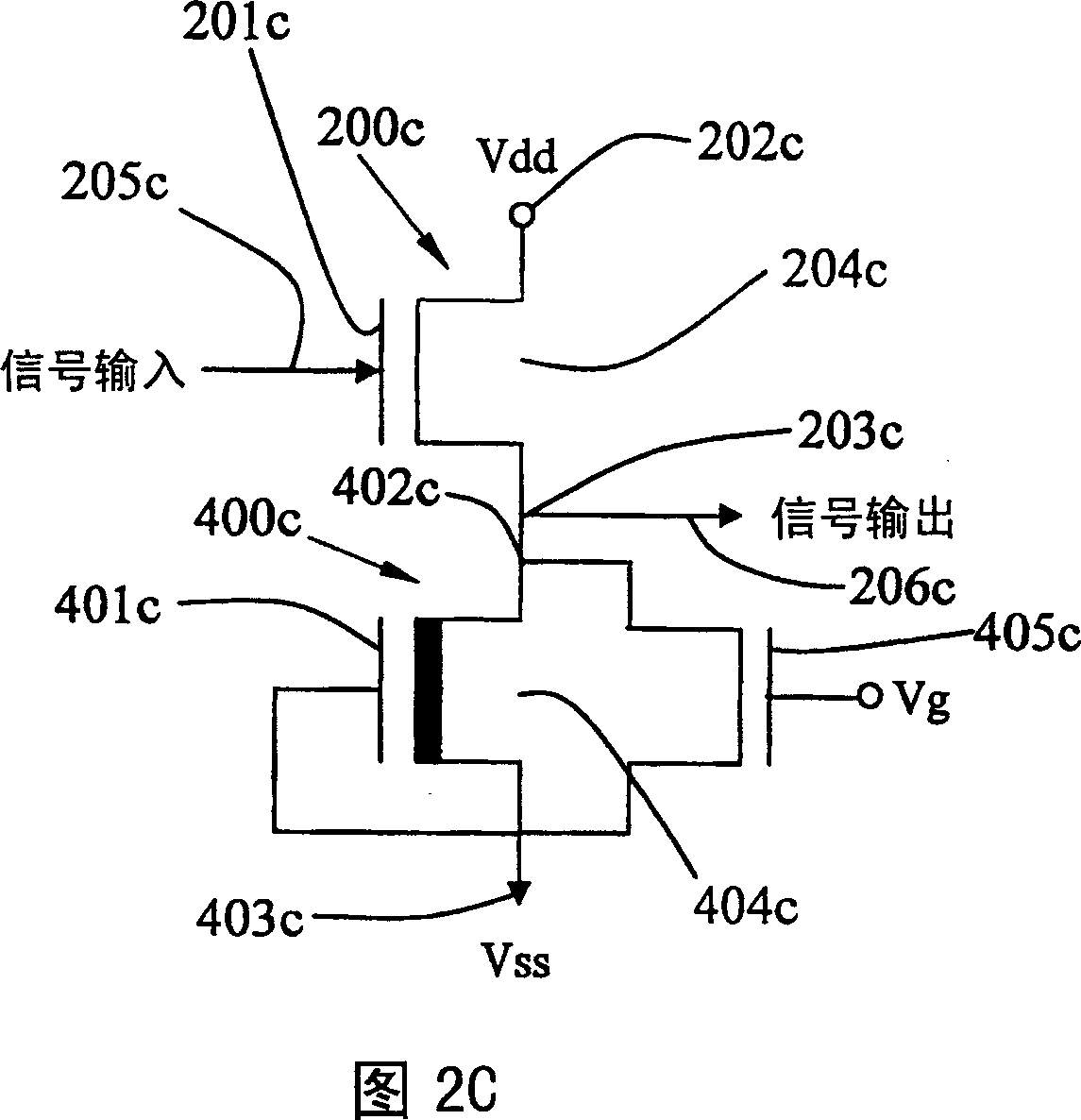

Circuit structure of organic thin film transistor with dual-gate and its use

ActiveCN101071845ASimple structureSimple and adjustableSolid-state devicesSemiconductor/solid-state device manufacturingBottom gateEngineering

The invention provides a circuit structure with double-gate organic TFT (thin film transistor) and its application. And the invention covers a protection layer on an organic TFT structure with a bottom gate to act as the other gate insulating layer and then locally forms a metal layer on the protection layer to act as the other gate and then completes a double-gate structure and applies it to electronic circuit design. Thus, it can regulate starting voltage of organic TFT corresponding to gate and benefit to change characteristic of the organic TFT to improve signal transmission accuracy.

Owner:IND TECH RES INST

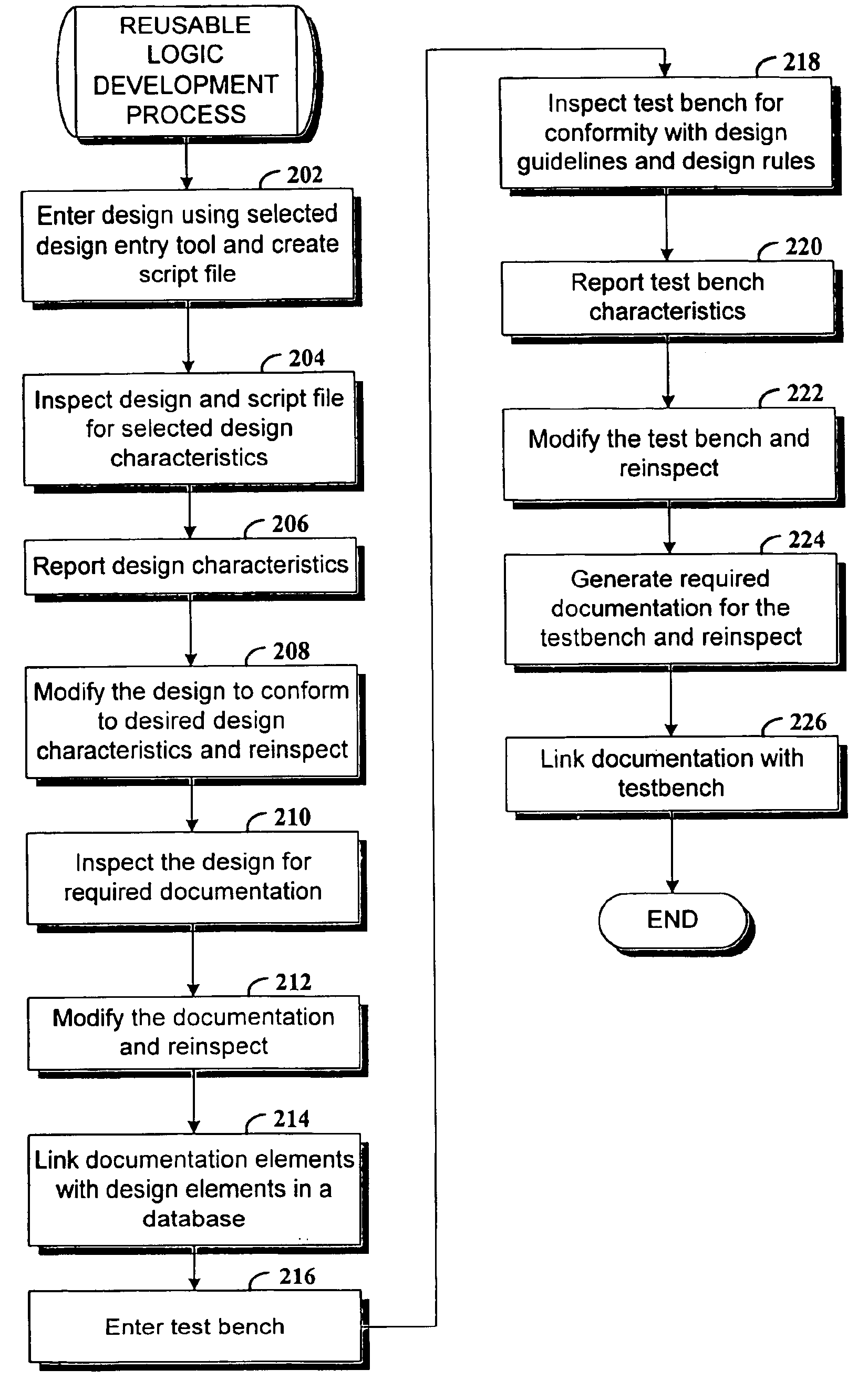

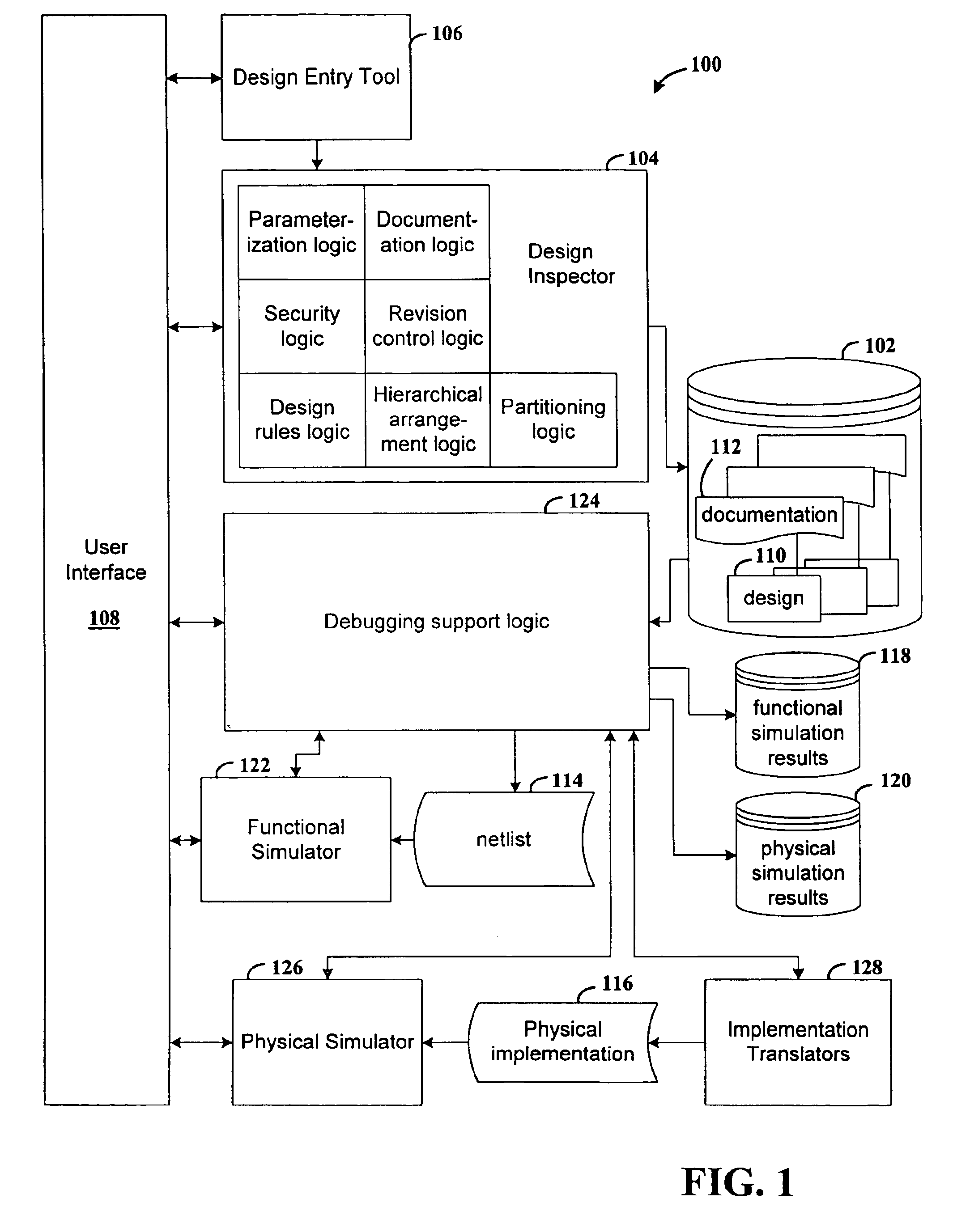

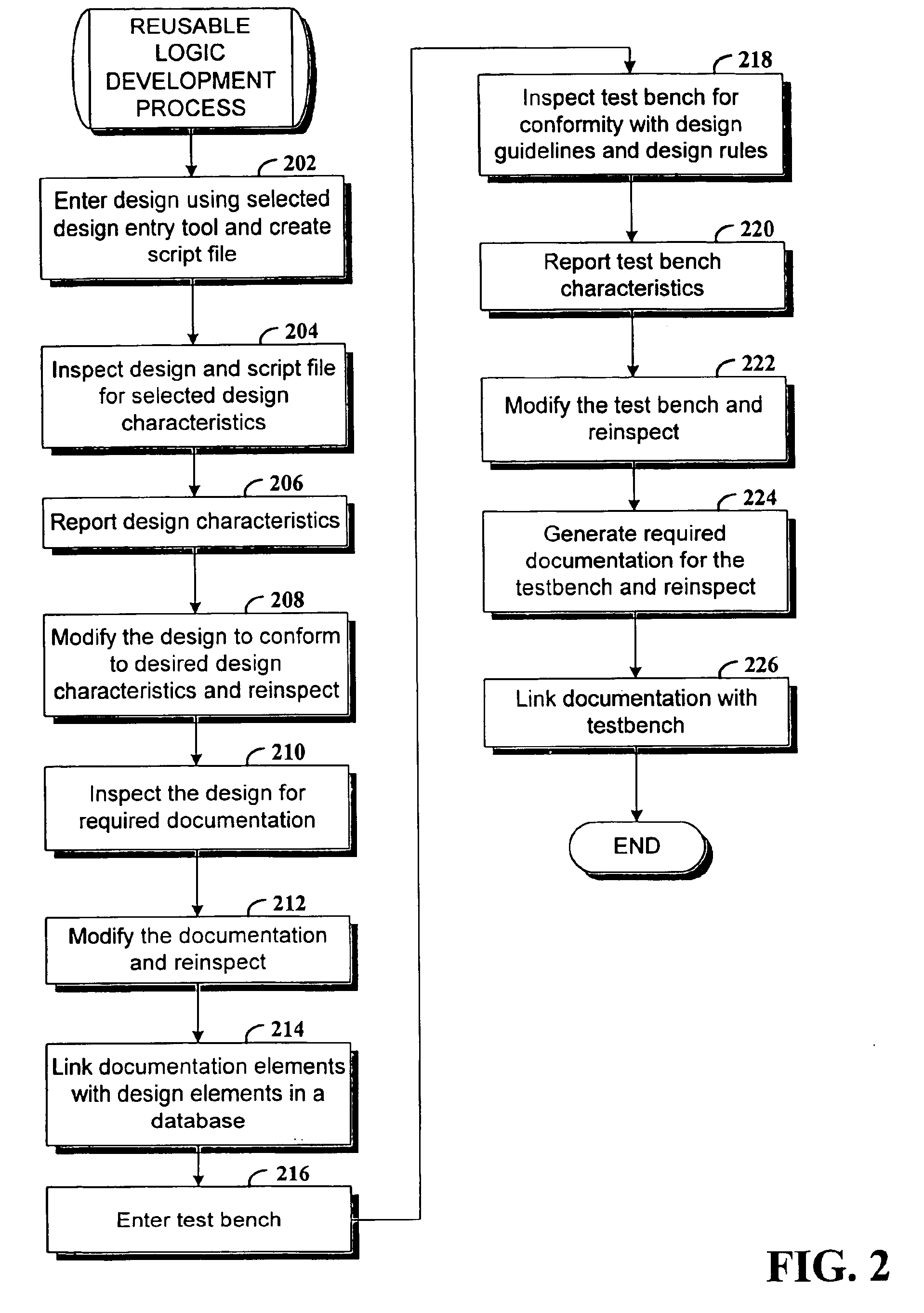

System and method for assisting in the development and integration of reusable circuit designs

InactiveUS6904397B1Well representedDetecting faulty computer hardwareElectrical testingDocumentation procedureEngineering

A system and method for developing a reusable electronic circuit design module are presented in various embodiments. In one embodiment, the functional design elements comprising a design module are entered into a database along with documentation elements that describe the design elements. The functional design elements are linked with selected ones of the documentation elements in the database. A testbench is simulated with the design module, and the generated results are stored in a database and linked with the functional design elements. By linking the simulation results, documentation, and design elements, the characteristics of the design module are easily ascertained by a designer who is reusing the design module.

Owner:XILINX INC

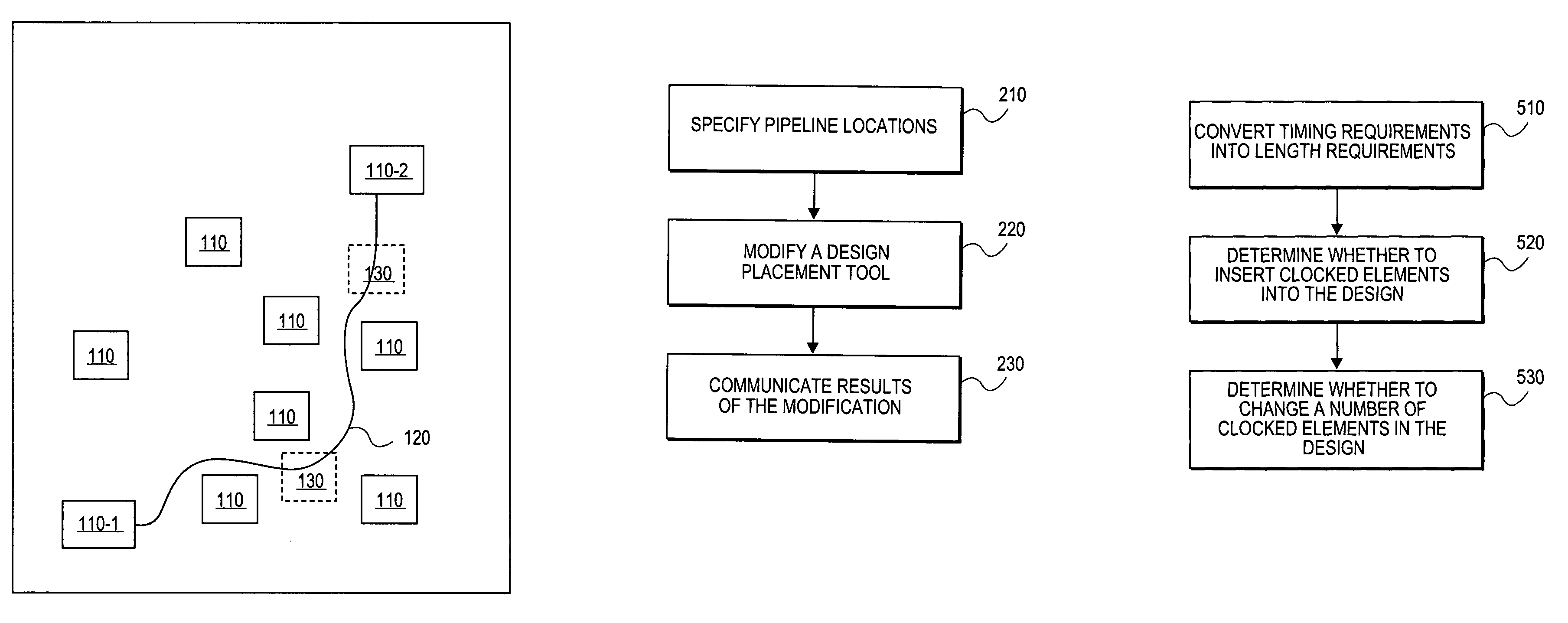

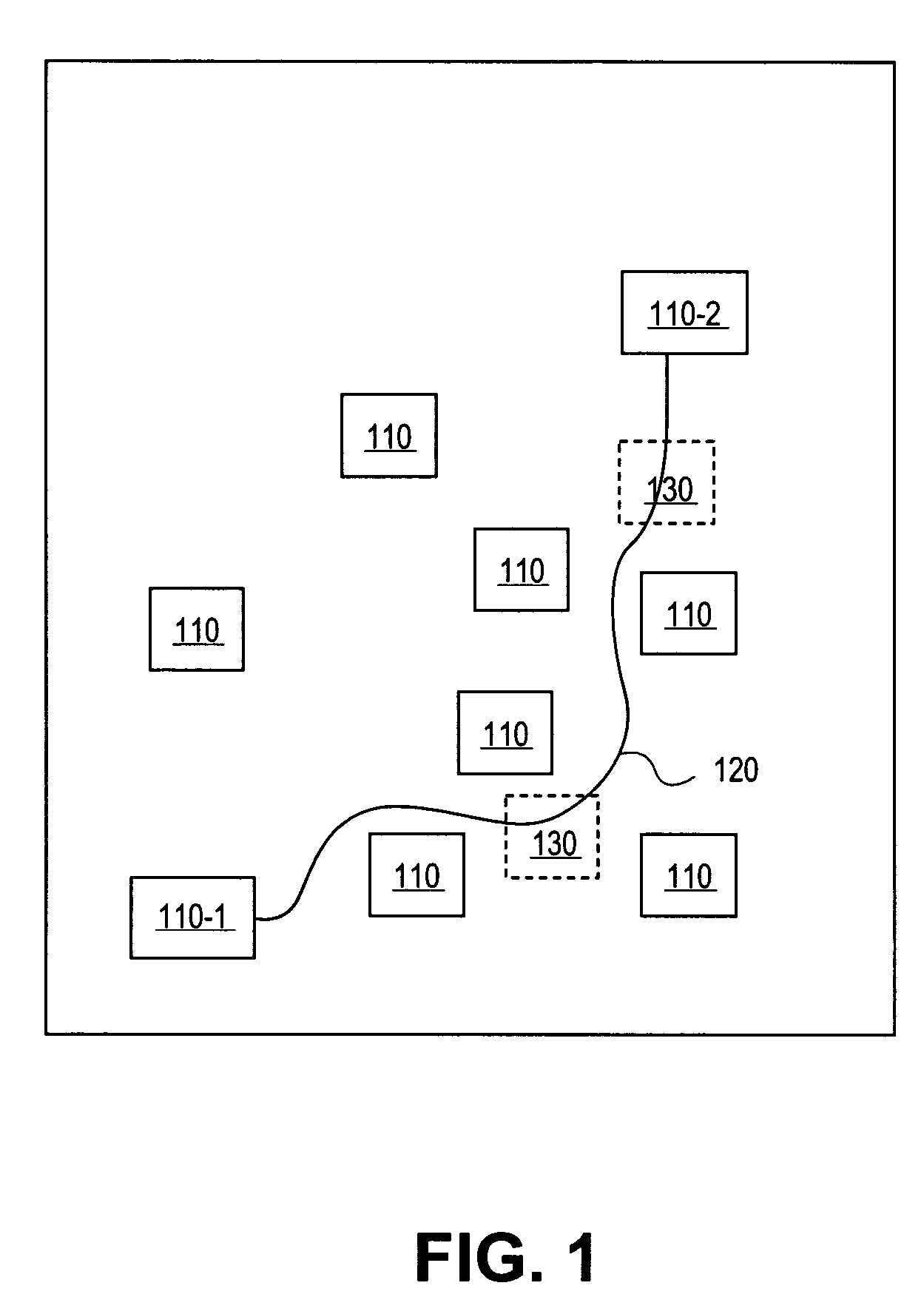

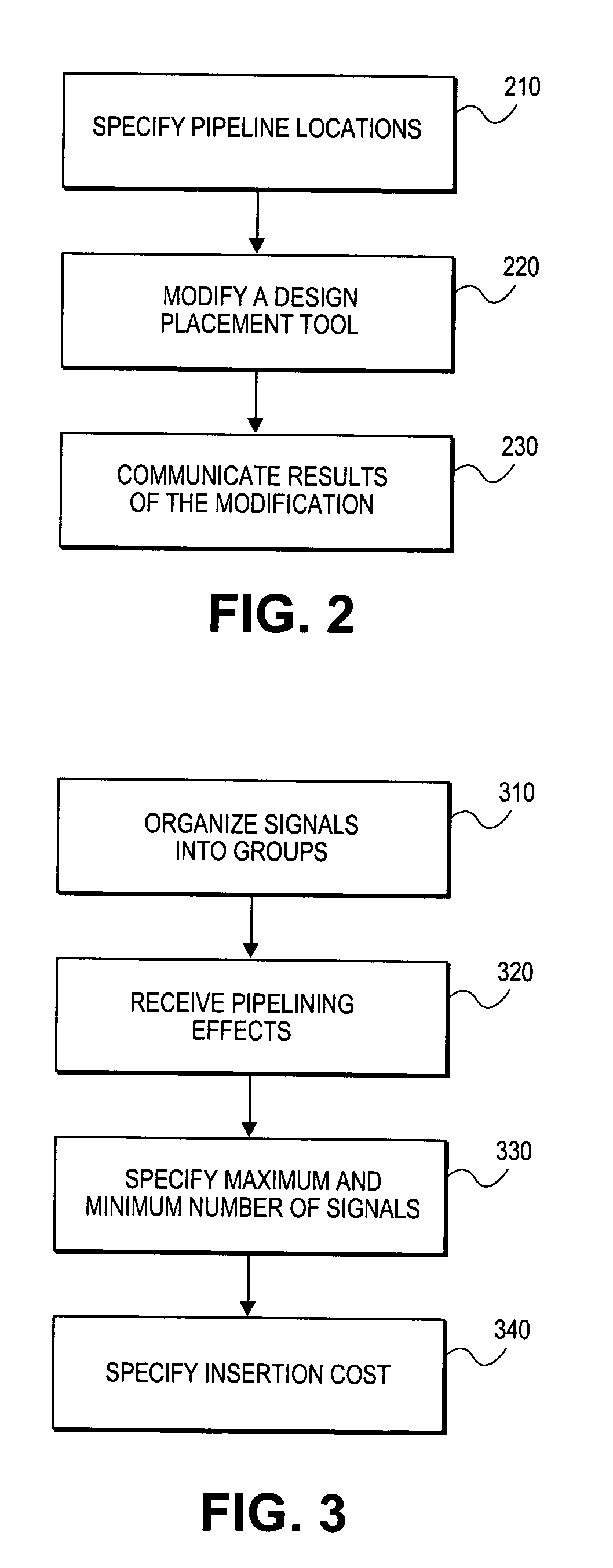

Automatic insertion of clocked elements into an electronic design to improve system performance

ActiveUS7207024B2Improve performanceImprove system performanceElectrical apparatusComputer programmed simultaneously with data introductionGenerative DesignEngineering

A method of improving a design of an electronic circuit includes generating the design, specifying one or more pipeline locations of the design, modifying the one or more pipeline locations of the design, and communicating the results to a user.

Owner:CADENCE DESIGN SYST INC

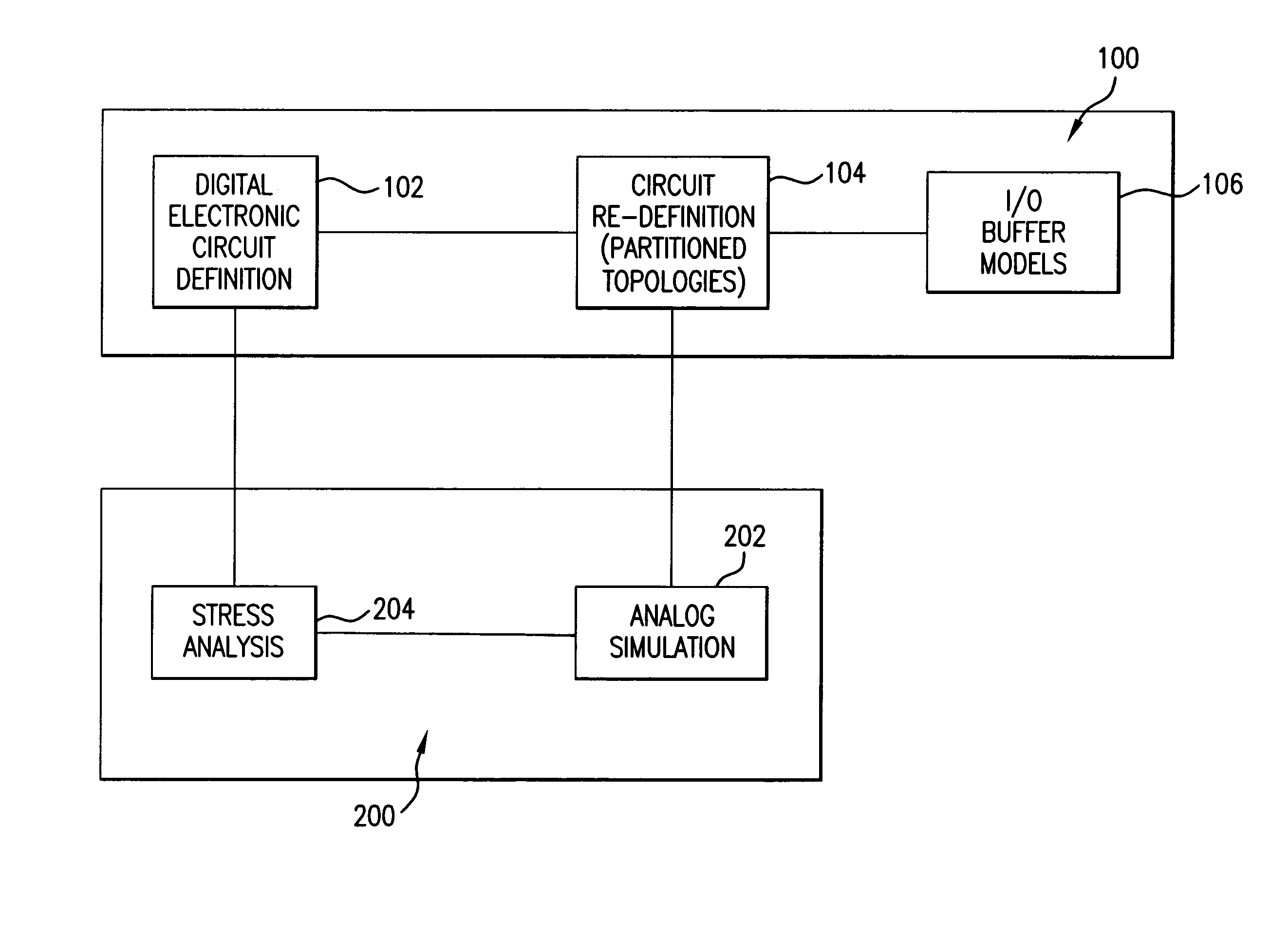

Method and system for automatic stress analysis of analog components in digital electronic circuit

ActiveUS8145458B1Accurate analysisAdapted simplyComputer aided designSpecial data processing applicationsStress measurementEngineering

An automated approach is provided for evaluating stress upon analog components embedded in a digital electronic circuit design. The approach includes establishing a computer readable circuit definition of the digital electronic circuit design. The circuit definition is then partitioned into a plurality of circuit portions, which are re-defined to form a plurality of analog topologies. The analog topologies are adapted for automatic analog simulation one independent of the other, with all digital components substituted by at least one subcircuit including instantiation of a corresponding input output (IO) buffer model. Automatic analog simulation is carried out upon the analog topologies to generate simulated results data, which are automatically postprocessed to generate worst-case stress measurement data for one or more critical components identified in the analog topologies.

Owner:CADENCE DESIGN SYST INC

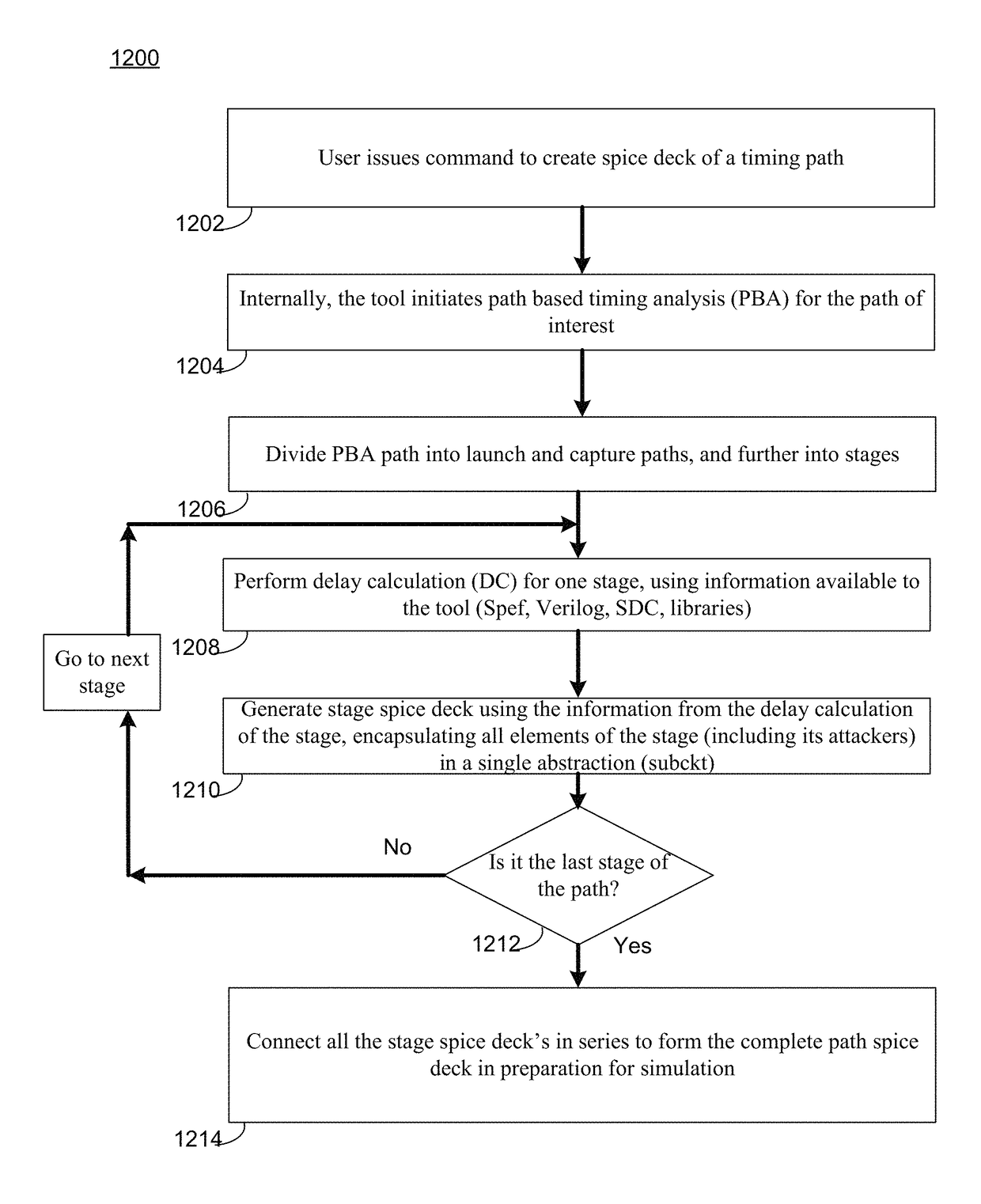

System and method for creating a spice deck for path-based analysis of an electronic circuit design using a stage-based technique

ActiveUS10031986B1Computer aided designSpecial data processing applicationsElectronic circuit designComputer science

The present disclosure relates to a system and method for performing Path-Based Analysis (PBA) of an electronic circuit design. Embodiments may include receiving a command to create a spice deck of a timing path associated with the electronic circuit design. In response to receiving the command, embodiments may further include initiating PBA for the timing path and identifying one or more stages within the timing path. Embodiments may also include performing a delay calculation for each of the one or more stages and generating a stage spice deck for each of the one or more stages based upon, at least in part, information from the delay calculation, wherein the stage spice deck encapsulates all elements of the stage. Embodiments may further include connecting the stage spice deck for each of the one or more stages in series to form a complete path spice deck.

Owner:CADENCE DESIGN SYST INC

A scalable system for simulation and emulation of electronic circuits using asymmetrical evaluation and canvassing instruction processors

ActiveUS20060277019A1Increased hardware resourcesMeet the limit requirementsAnalogue computers for electric apparatusData switching by path configurationScalable systemParallel computing

A scalable system for verifying electronic circuit designs in anticipation of fabrication by compiling a hardware description to instructions for canvassing processors and instructions for circuit evaluation processors which are scalably interconnected to provide simulation and emulation, having deterministically scheduled transfer of circuit signal values among the large number of circuit evaluation processors.

Owner:EVE

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com