Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

60results about How to "Reduce iterative process" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

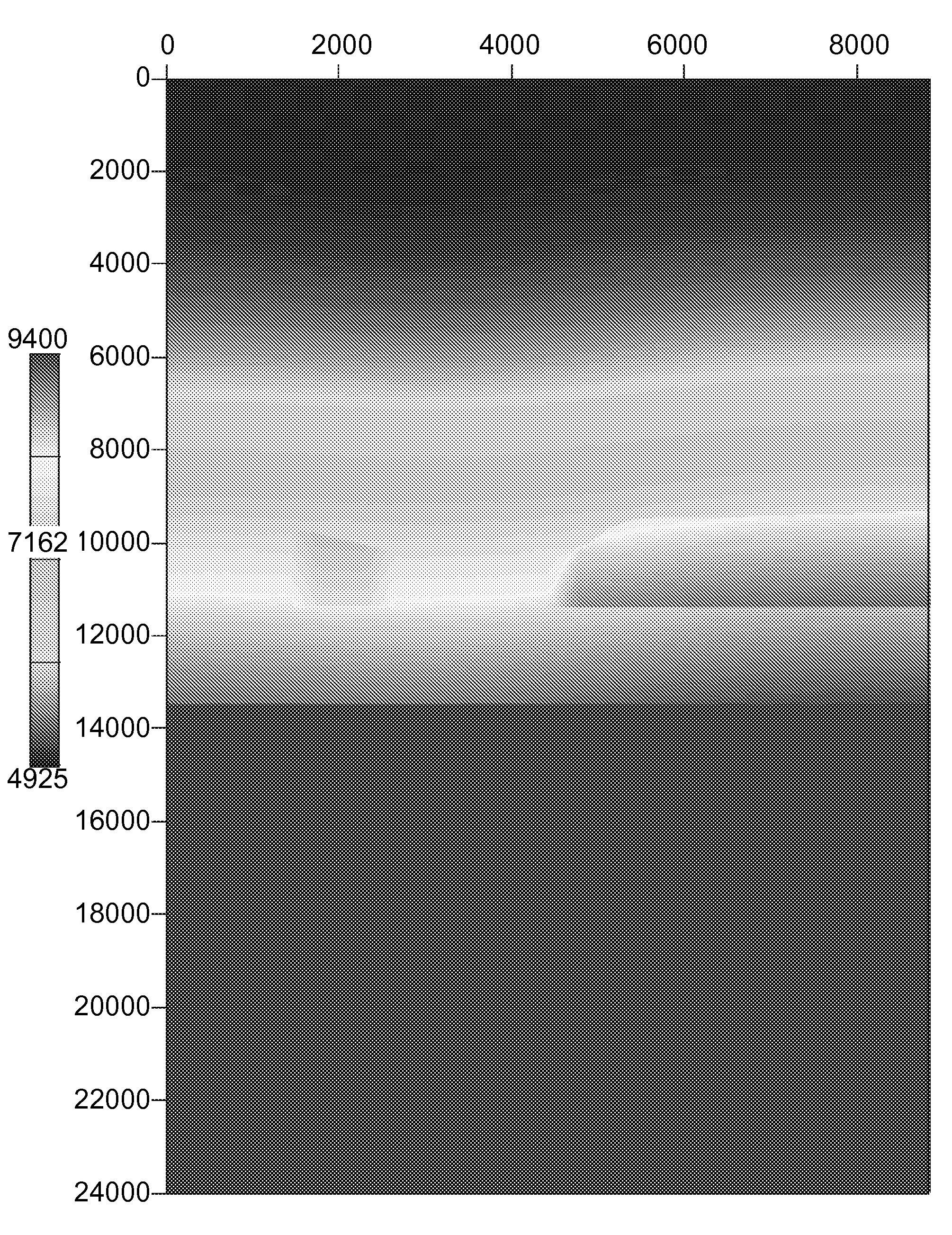

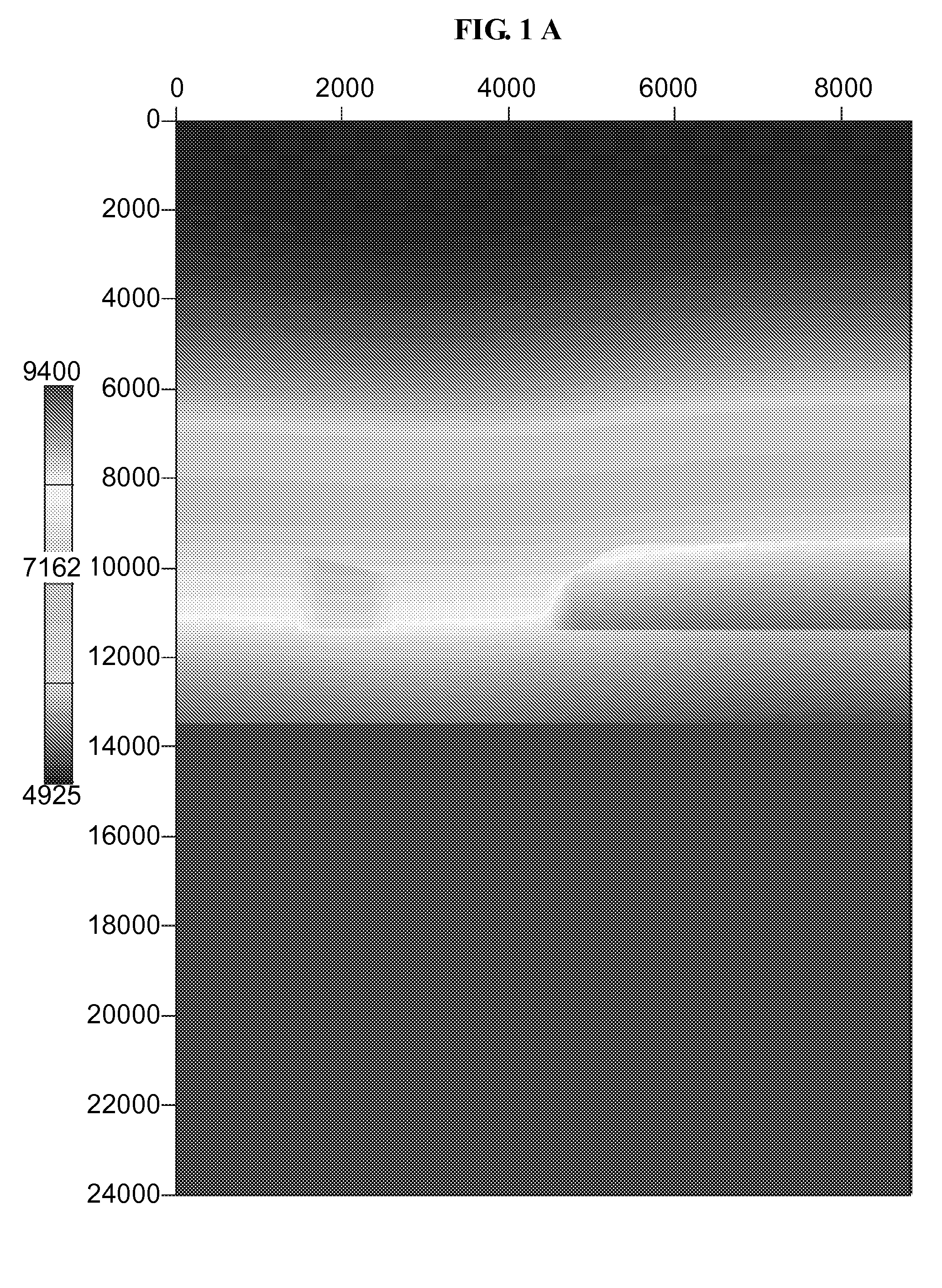

Dip guided full waveform inversion

InactiveUS20110131020A1Reduce difficultyLow costSeismologyComputation using non-denominational number representationImaging qualityFull waveform

A method of determining seismic data velocity models comprising dip-guided full waveform inversion that obtains a better velocity model with less computational requirements. DG-FWI quickly converges to provide a better image, obtains better amplitudes, and relies less on lower frequencies. Improved image quality allows detailed seismic analyses, accurate identification of lithological features, and imaging near artifacts and other anomalies.

Owner:CONOCOPHILLIPS CO

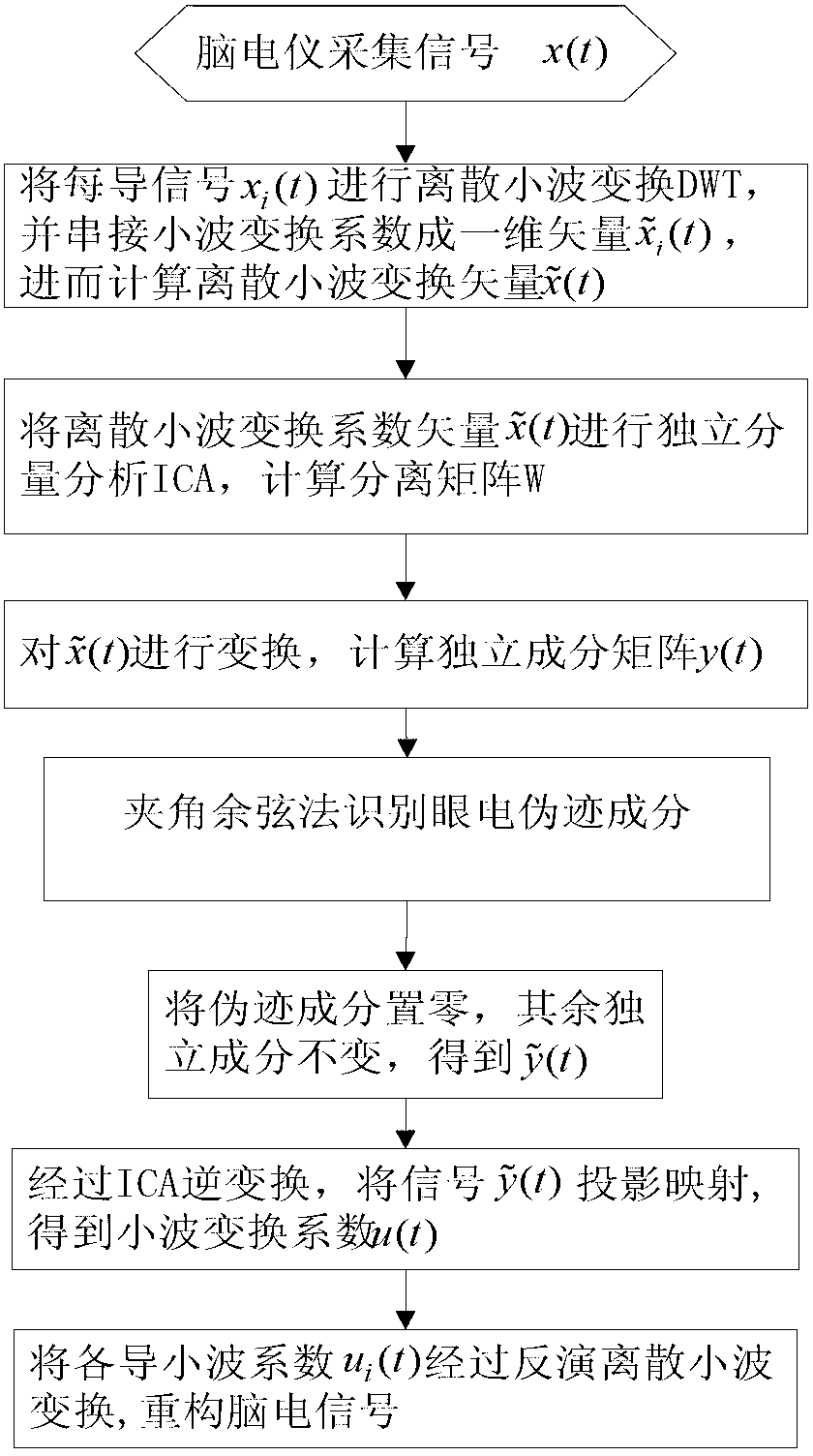

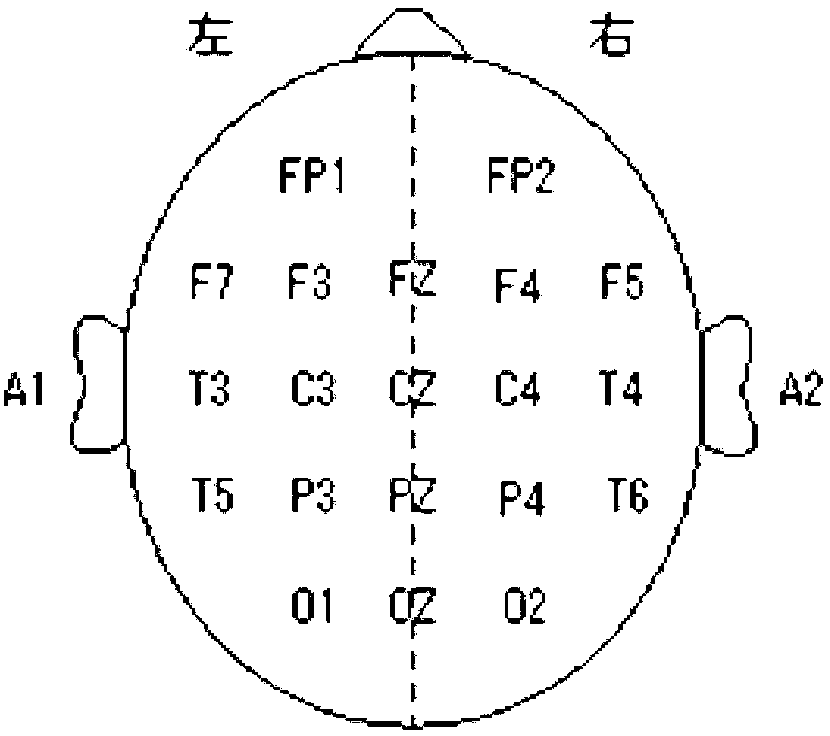

Method for rapidly and automatically identifying and removing ocular artifacts in electroencephalogram signal

InactiveCN102697493AImprove signal-to-noise ratioReduce iterative processDiagnostic recording/measuringSensorsElectro oculogramFastica algorithm

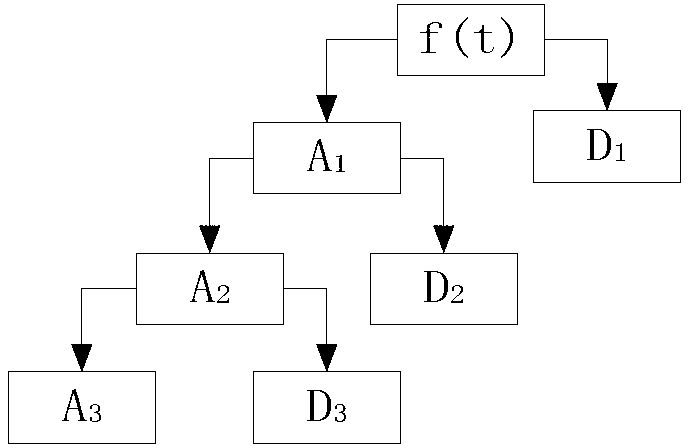

The invention provides a method for rapidly and automatically identifying and removing ocular artifacts in an electroencephalogram signal and belongs to the technical field of biological information and the method is mainly applied to a process of acquiring and preprocessing the electroencephalogram signal. The method comprises the following specific steps of: carrying out discrete wavelet transformation on an acquired multi-channel electroencephalogram signal and an electro-oculogram signal to obtain multi-scale wavelet coefficients; using the wavelet coefficients connected in series as an input for analyzing an independent component, and rapidly acquiring the independent component by using a negative entropy criterion-based Fast ICA (Independent Component Analysis) algorithm; identifying the ocular artifacts through a cosine method, performing zero resetting on the independent component, and projecting the other components through ICA inverse transformation and returning to all electrodes of an original signal; and finally obtaining the electroencephalogram signal for removing the ocular artifacts through inversion of the wavelet transformation. By utilizing the method for rapidly and automatically identifying and removing the ocular artifacts in the electroencephalogram signal, the problems that an ICA method is poor in discrete effect and low in convergence rate when beingapplied to noisy electroencephalogram signals are solved, and the function of rapidly and automatically identifying and removing the ocular artifacts in the electroencephalogram signal is realized.

Owner:BEIJING UNIV OF TECH

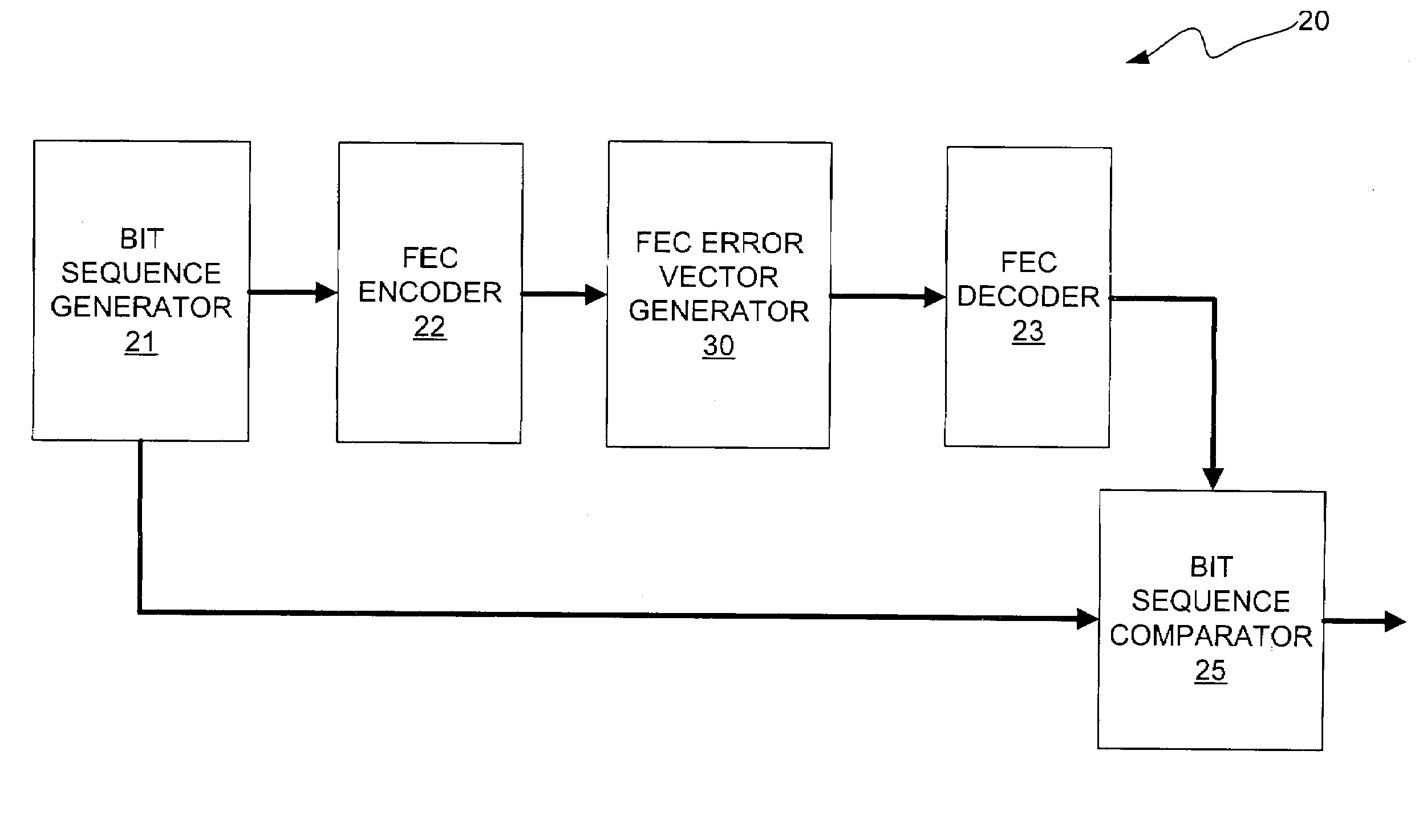

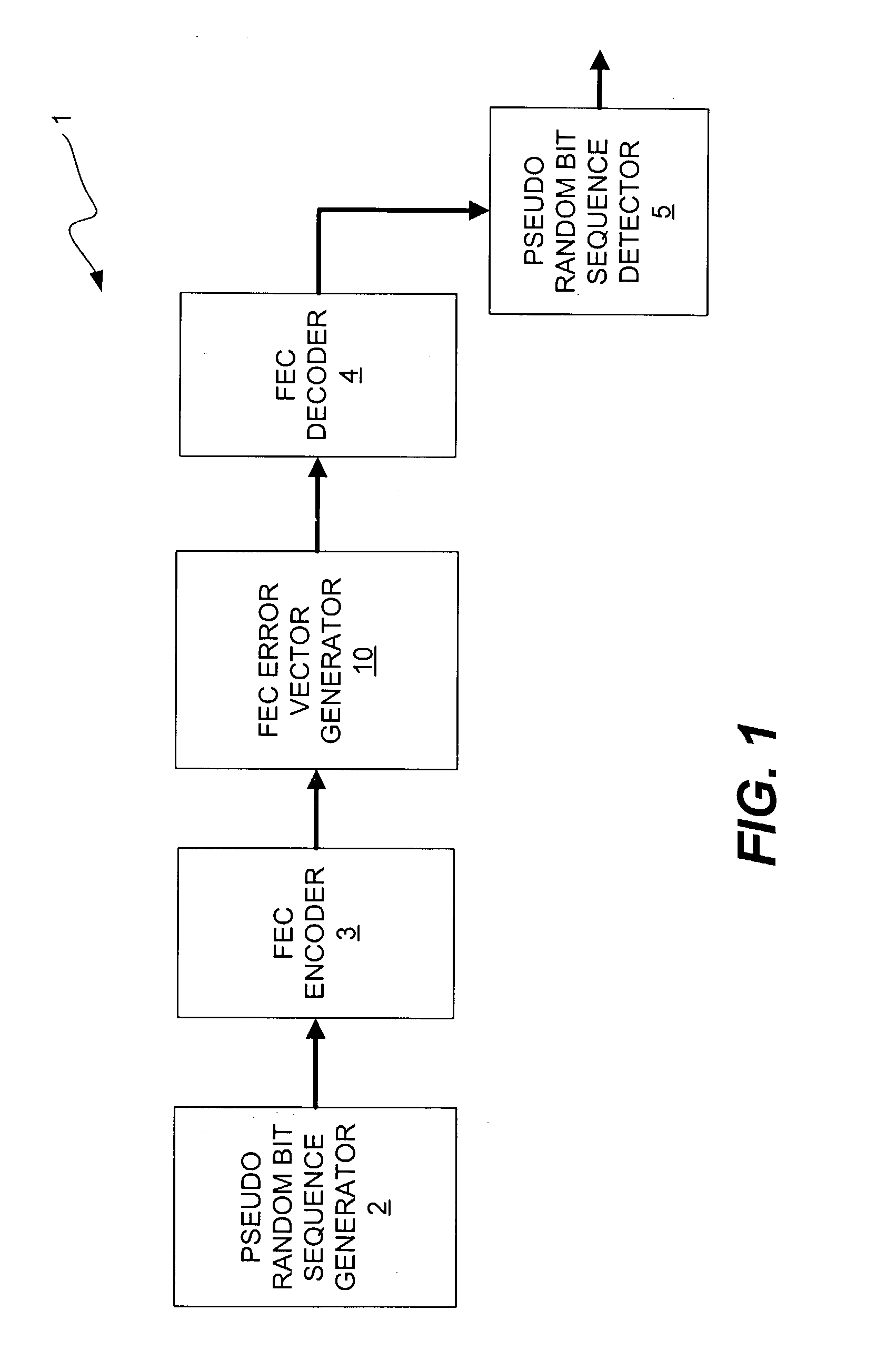

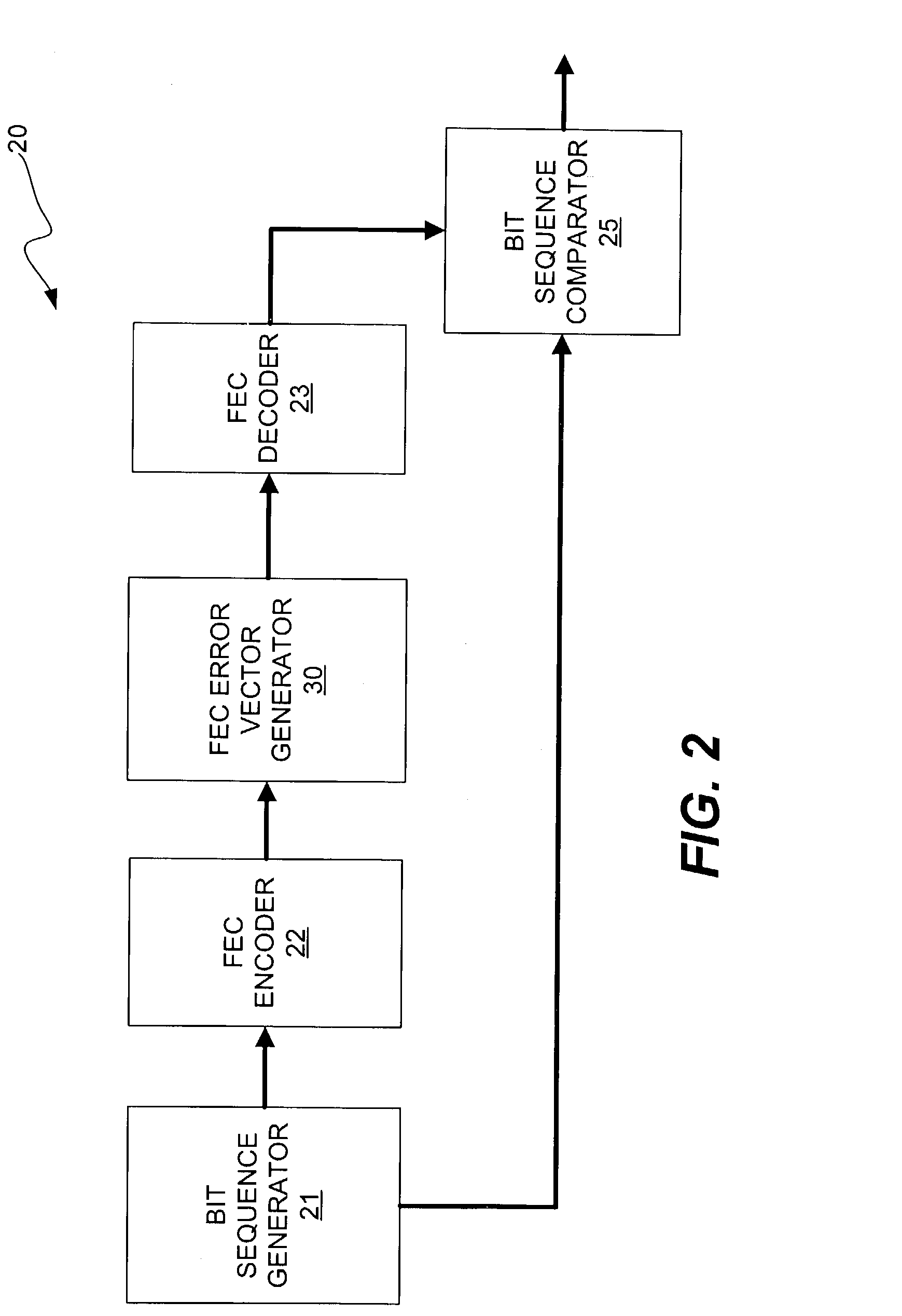

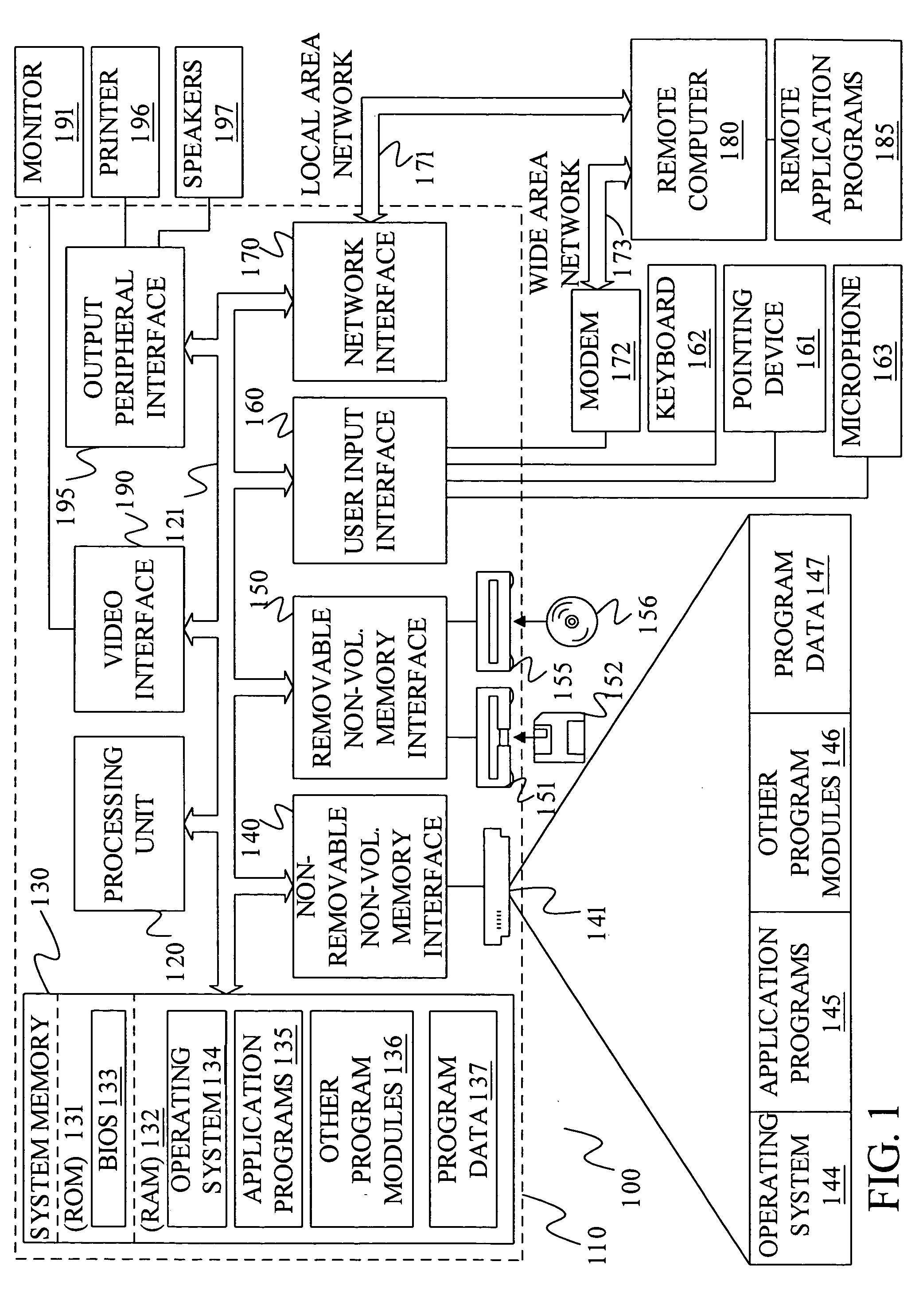

Method and apparatus for generating bit errors in a forward error correction (FEC) system to estimate power dissipation characteristics of the system

ActiveUS7073117B1Precision productionPower dissipationData representation error detection/correctionCode conversionFir systemForward error correction

A method and apparatus for generating and inserting bit errors in data words that have been encoded in a forward error correction (FEC) system in order to estimate power dissipation. In accordance with the present invention, it has been determined that a burst error generator that is capable of erroring the maximum number of correctable data bits in every FEC encoded frame, which allows the designer to accurately produce test vectors that are suitable for use in commercially available power estimation tools. In addition, after the IC is produced, the burst error generator of the present invention can be enabled to provide real-time FEC power dissipation data for use in system thermal modeling, thus obviating the need to use costly external devices that emulate a given error rate. Furthermore, the power dissipation data obtained in real-time may be used to refine the initial design power estimate, which will then allow the designer to develop a more accurate prediction of power consumption for future IC designs. Thus, the burst error generator of the present invention is capable of reducing iterations of IC designs by accurately estimating the worst-case power dissipation of FEC decoders.

Owner:CIENA

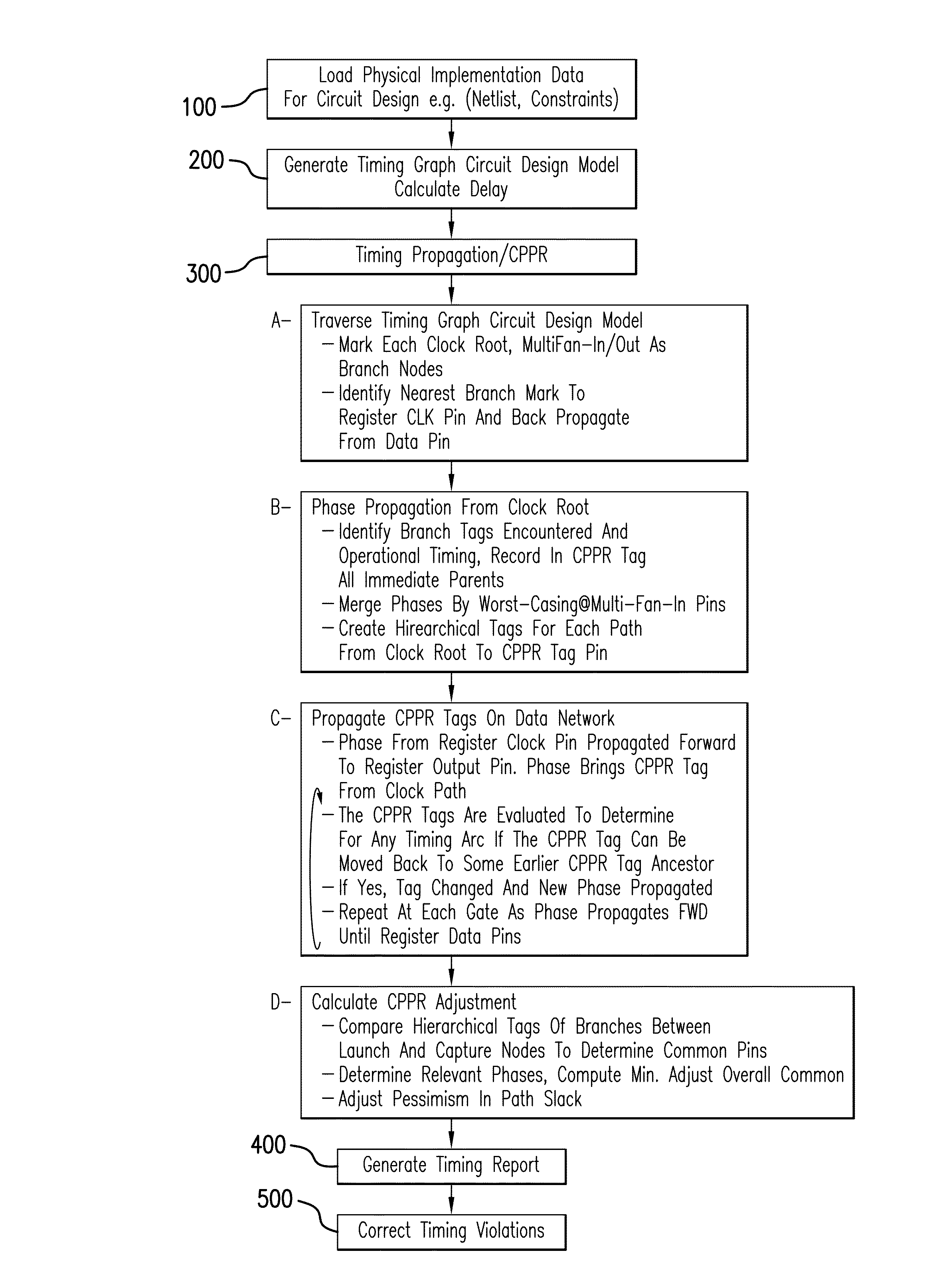

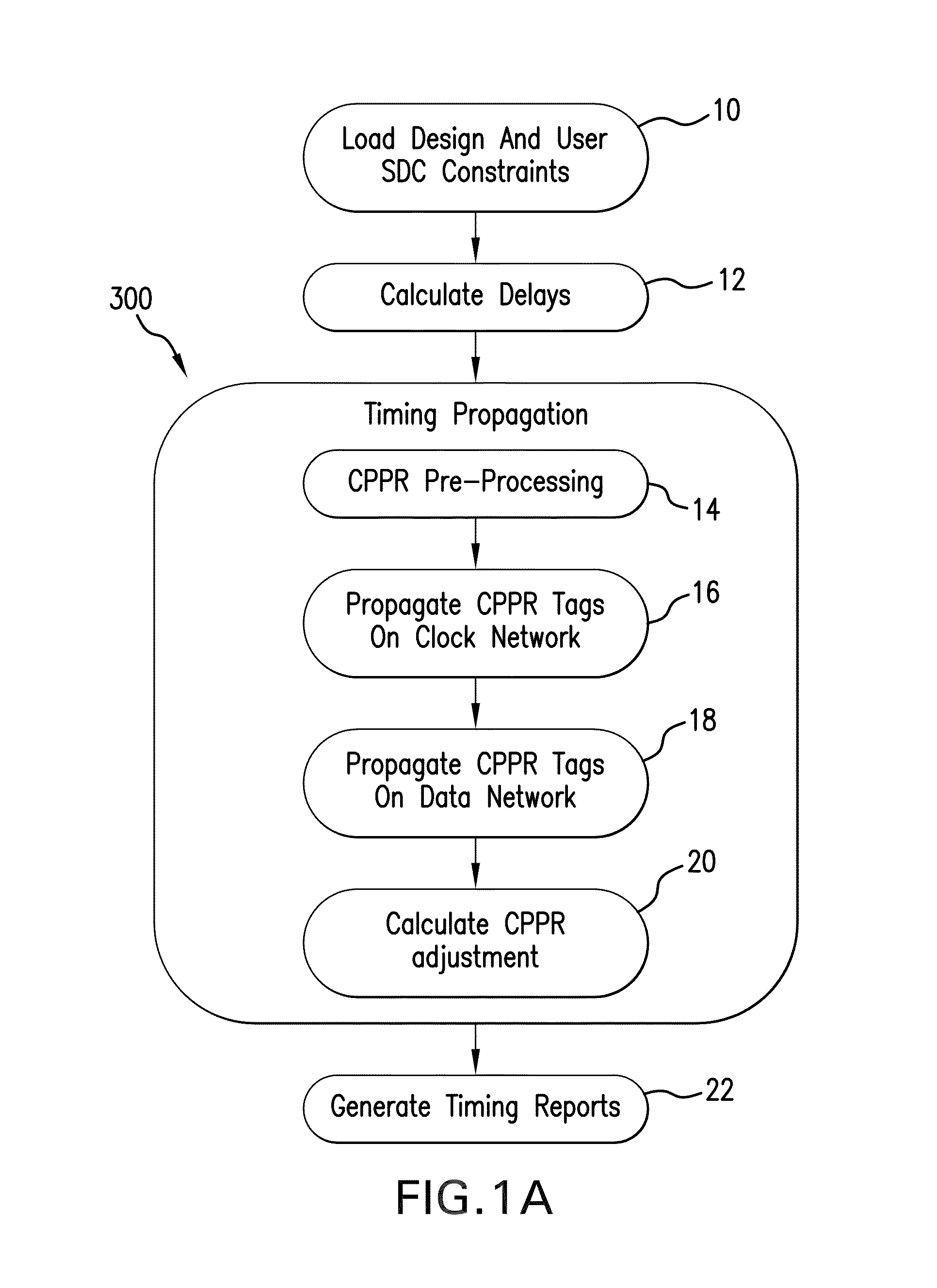

System and method for common path pessimism reduction in timing analysis to guide remedial transformations of a circuit design

ActiveUS8745561B1Reduce unnecessaryGood correlationDetecting faulty computer hardwareCAD circuit designSystems designMemory footprint

A system and method are provided for common path pessimism removal or reduction (CPPR) in a timing database provided to guide transformative physical optimization / correction of a circuit design for an IC product to remedy operational timing violations detected in the circuit design. Pessimism is reduced through generation of a common path pessimism removal (CPPR) tree structure of branching nodes, and operational timing characteristics of each node. The CPPR tree structure is used to avoid exponential phases propagating in an exploratory manner through the system design, as well as the resultant memory footprint thereof. Additionally, back-tracing node-by-node through the circuit design for each and every launch and capture flip flop pair end point through each possible path thereof is avoided.

Owner:CADENCE DESIGN SYST INC

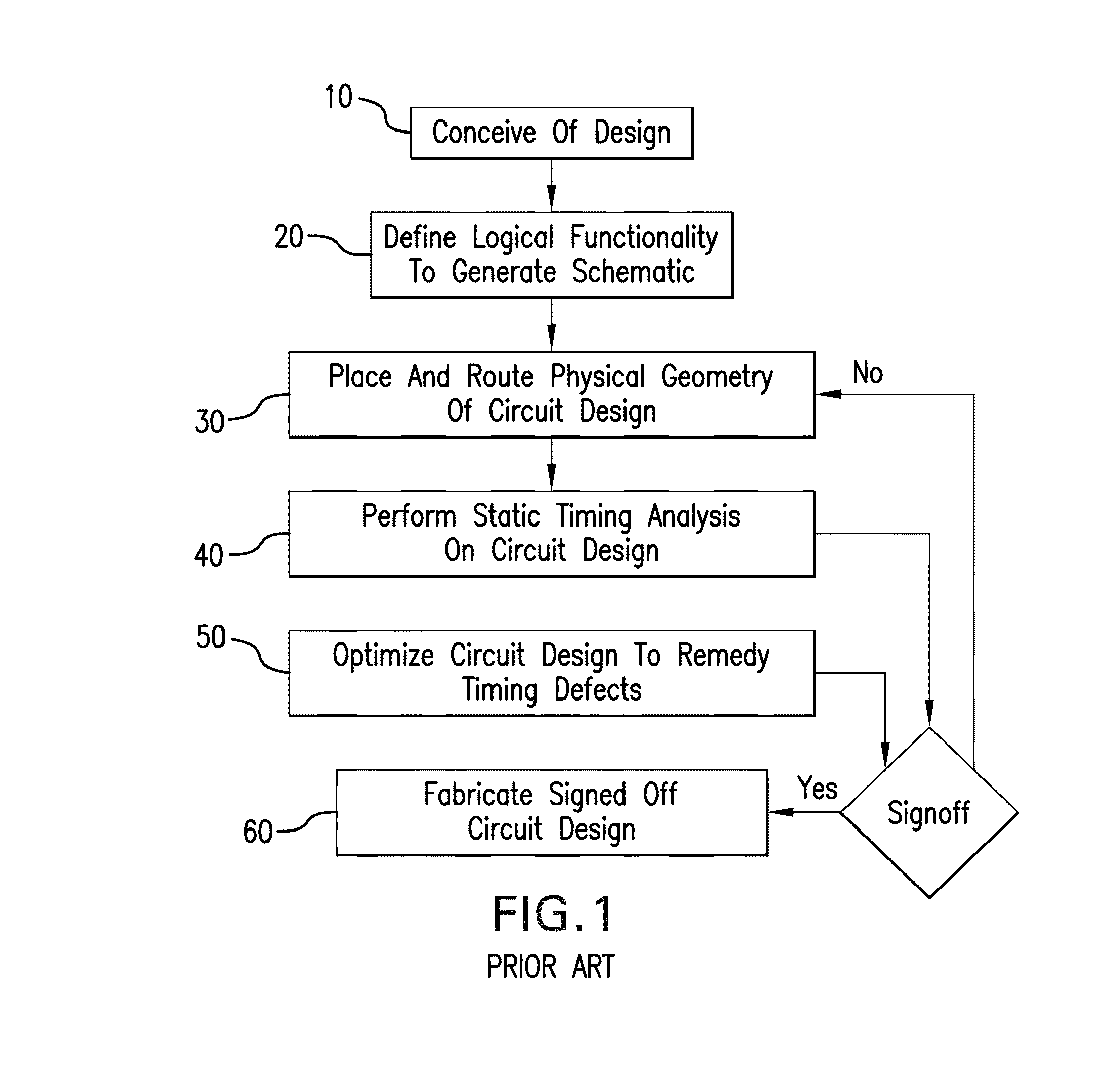

System and method for detecting and prescribing physical corrections for timing violations in pruned timing data for electronic circuit design defined by physical implementation data

ActiveUS8875082B1Good correlationReduce repeated iterationCAD circuit designSoftware simulation/interpretation/emulationElectronic circuit designComputer science

A system and method for expeditious operational timing signoff of a circuit design through a timing analysis and subsequent corrective or remedial optimization is performed with the goal of correlating timing between the physical implementation corrective optimizer module and the timing analysis module to reduce iterations therebetween. A physical optimizer in the correction module is imparted with knowledge of the physical implementation of the design to allow for legal, non-conflicting placement of corrective buffers or resizing of gates in accordance with the physical implementation data of the circuit design.

Owner:CADENCE DESIGN SYST INC

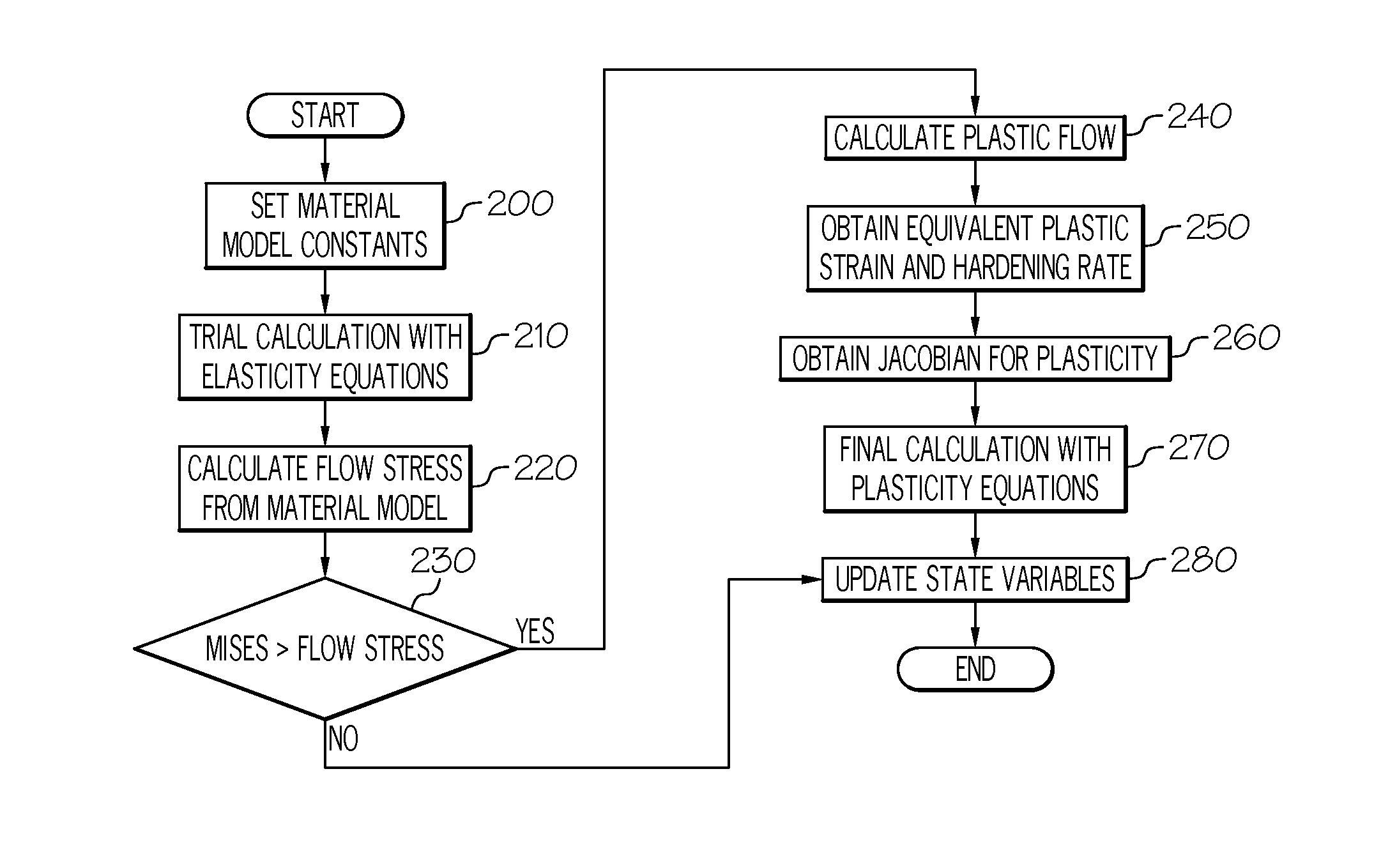

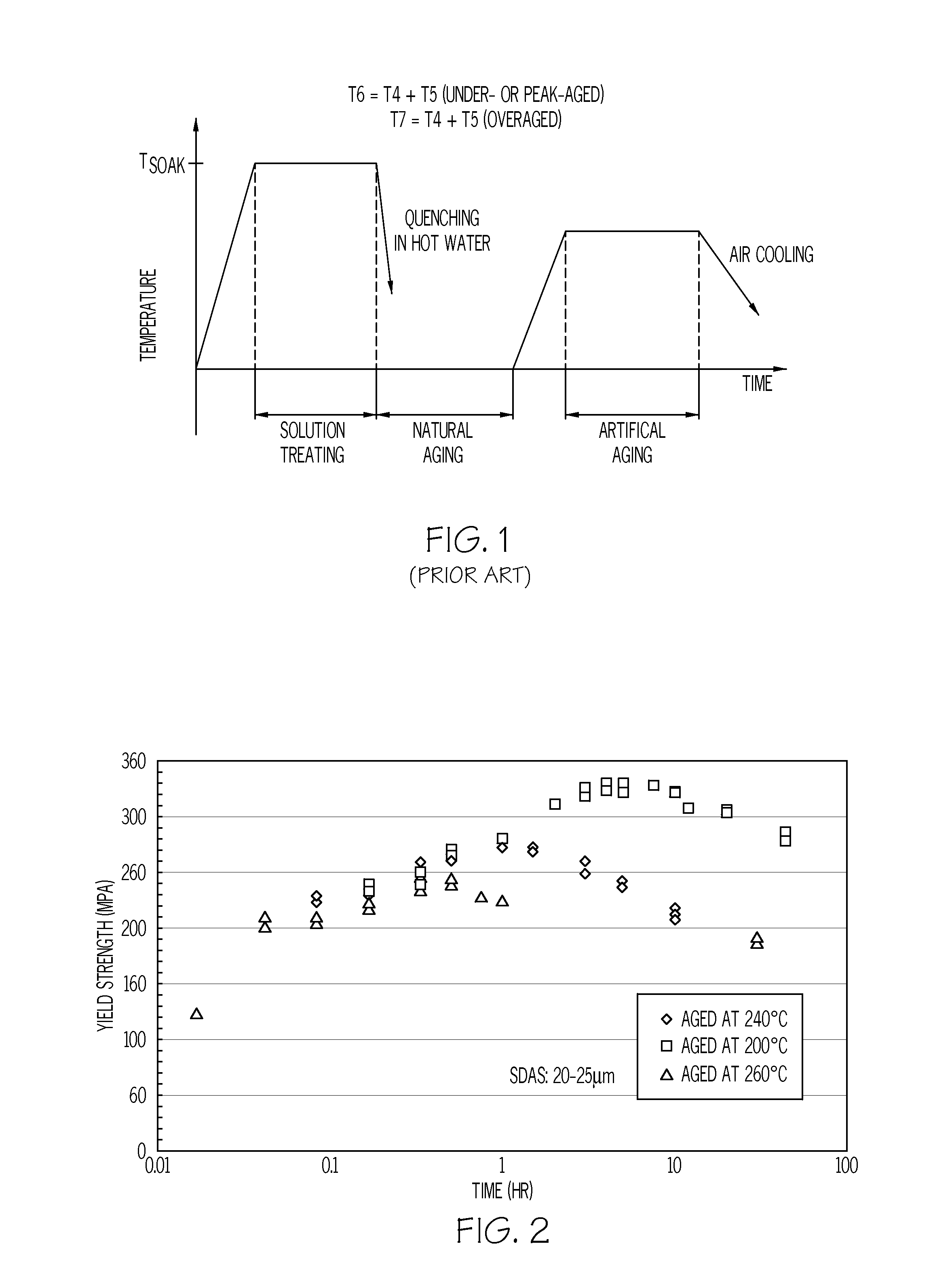

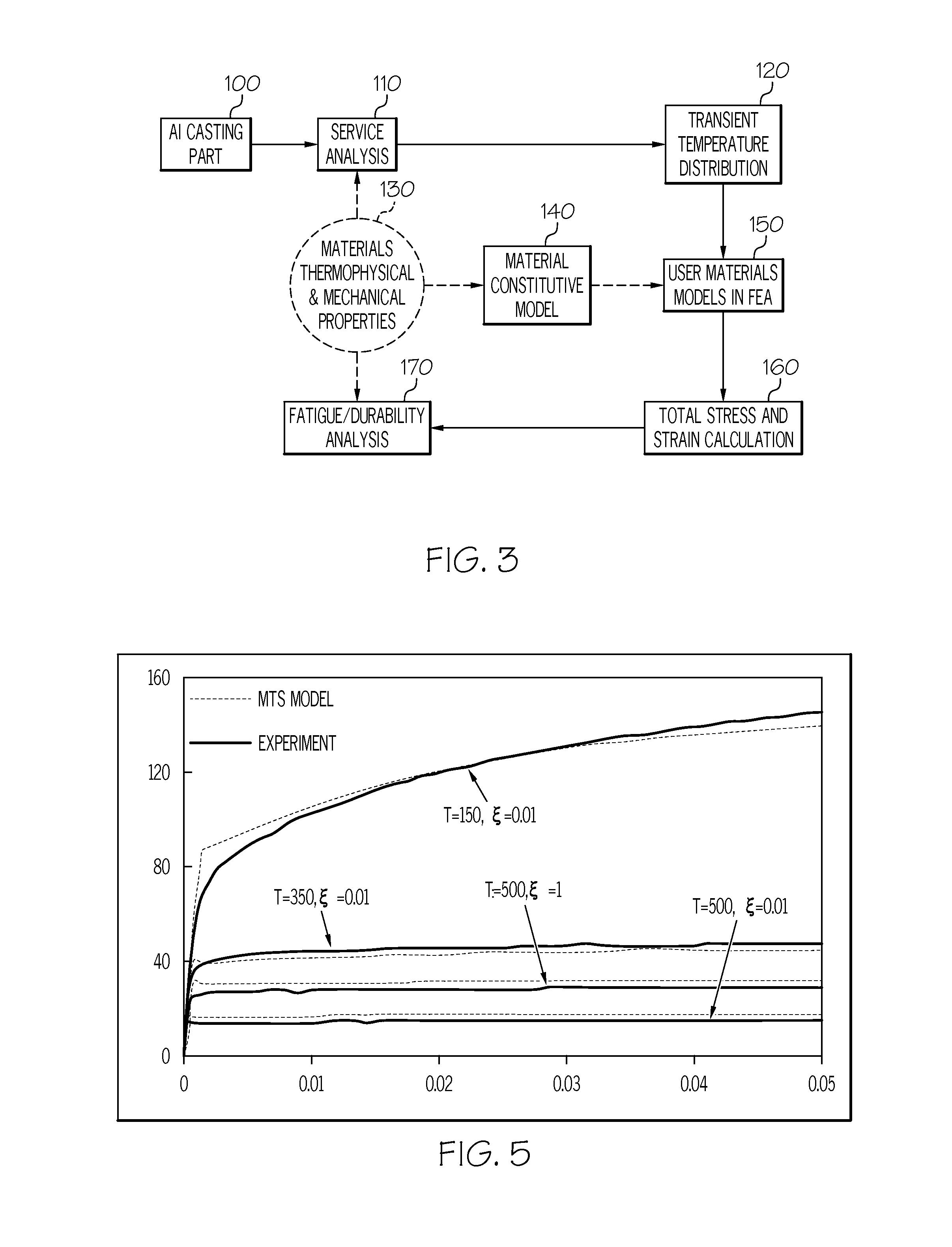

Product design reliability with consideration of material property changes during service

InactiveUS20150213164A1Accurate modelingImprove analysis accuracyComputation using non-denominational number representationDesign optimisation/simulationNODALDependability

A method of computationally determining material property changes for a cast aluminum alloy component. Accuracy of the determination is achieved by taking into consideration material property changes over the projected service life of the component. In one form, the method includes accepting time-dependent temperature data and using that data in conjunction with one or more constitutive relationships to quantify the impact of various temperature regimes or conditions on the properties of heat-treatable components and alloys. Finite element nodal analyses may be used as part of the method to map the calculated material properties on a nodal basis, while a viscoplastic model may be used to determine precipitation hardening and softening effects as a way to simulate the time and temperature dependencies of the material. The combined approach may be used to determine the material properties over the expected service life of a cast component made from such material.

Owner:GM GLOBAL TECH OPERATIONS LLC

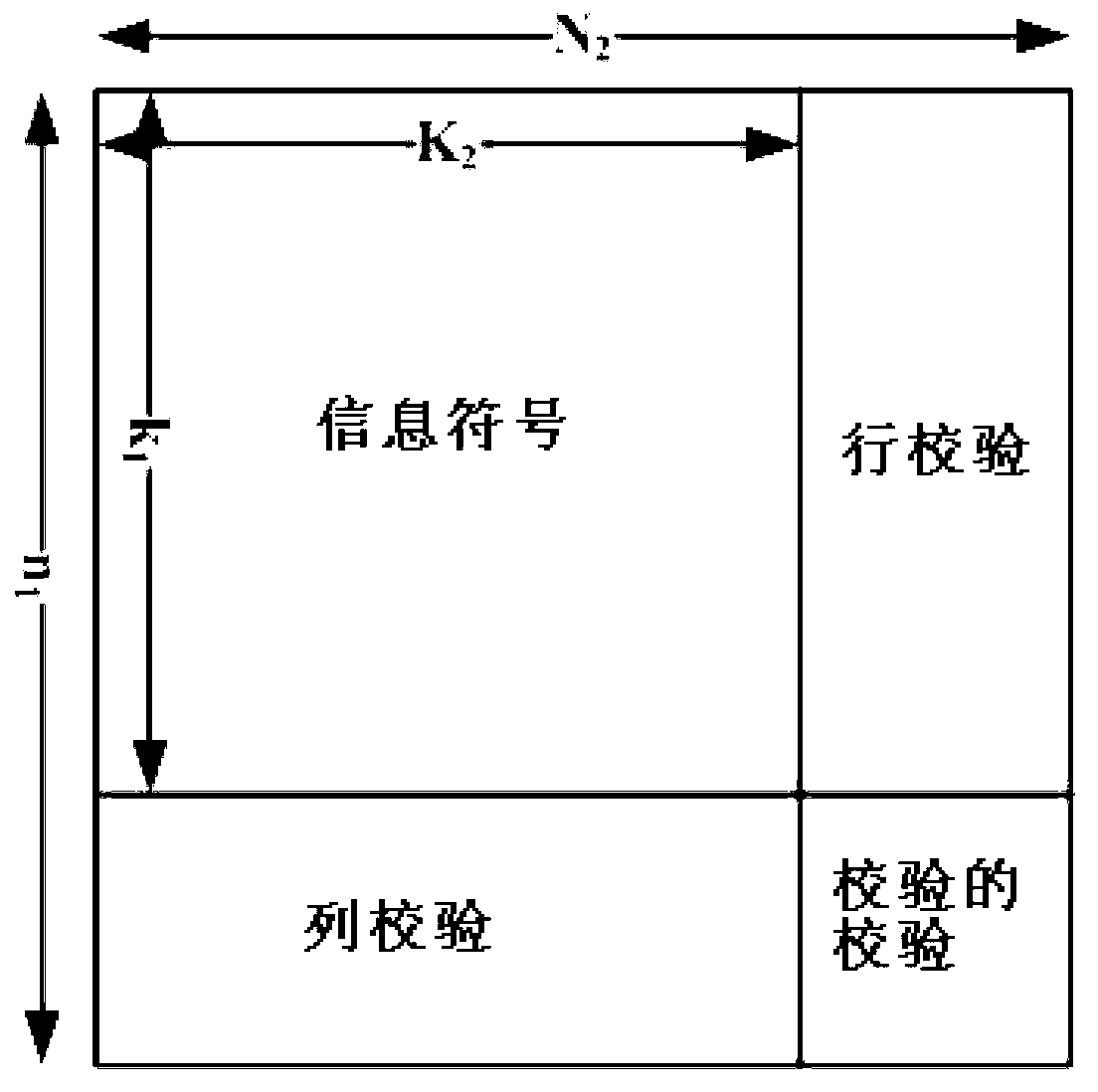

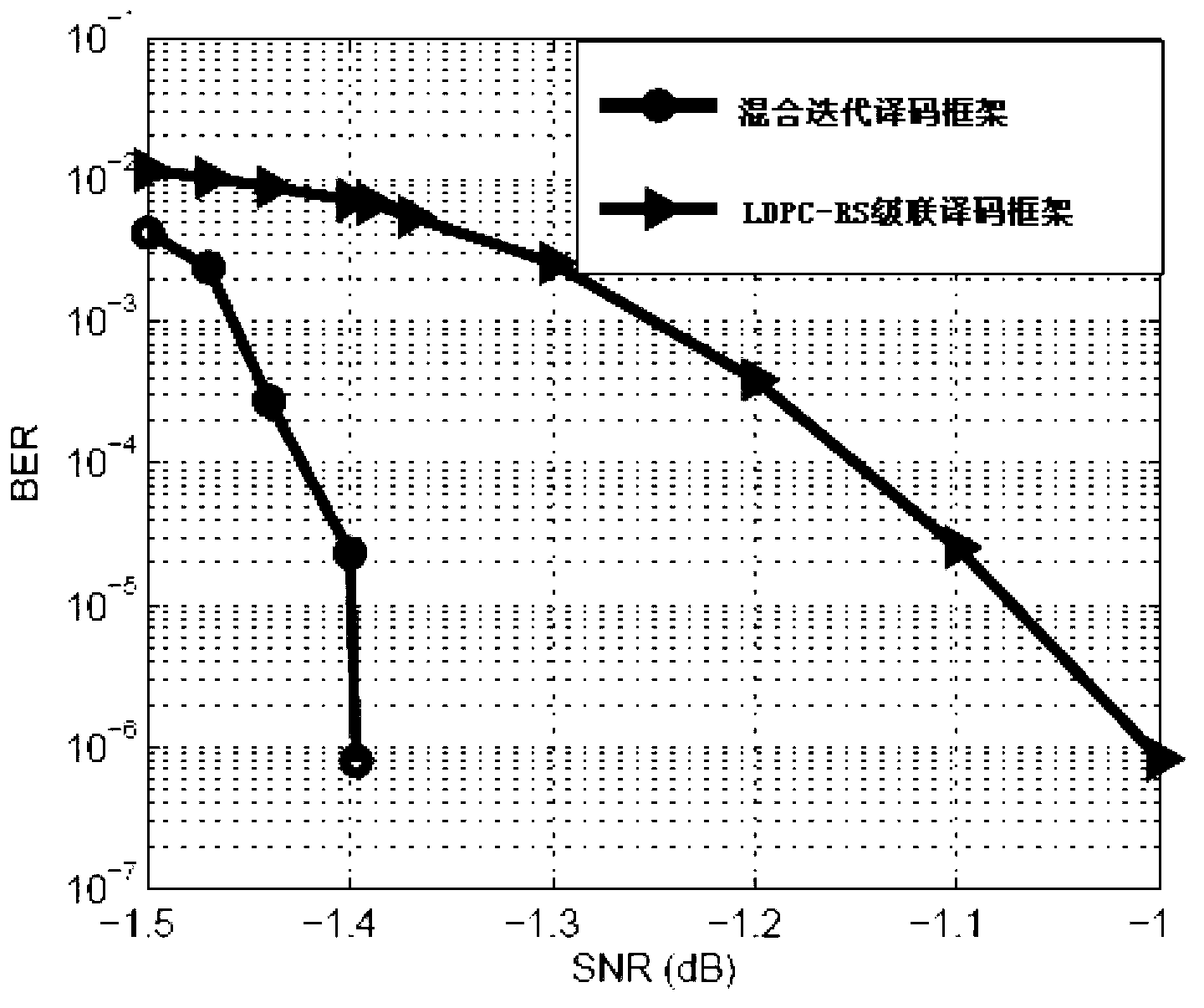

Mixed iterative decoding method for LDPC-RS two-dimensional product code

InactiveCN103269229AFast convergenceReduce iterative processError correction/detection using multiple parity bitsCoding blockCommunications system

The invention relates to a mixed iterative decoding method for an LDPC-RS two-dimensional product code in the technical field of communication system channel decoding. According to a received LDPC-RS product code block, log-SPA soft-decision decoding is conducted on LDPC codons of each row, bit soft value information after the decoding and soft value information corresponding to the edge of a bipartite graph are stored; improved WBF decoding is conducted on LDPC rows failed in the log-SPA soft-decision decoding and estimated bit error patterns of the rows failed in decoding can be returned through an improved WBF algorithm; when the estimated error patterns can be corrected by following RS, LDPC hard-decision decoding, RS+LDPC hard-decision decoding is converted; if all errors can not be corrected after one time of iteration is finished, bit soft values corresponding to the rows which is confirmed to be right after the hard-decision decoding are corrected and iteration of the next round is conducted. According to the mixed iterative decoding method for the LDPC-RS two-dimensional product code, the problem that when LDPC-RS is decoded through an SISO decoding structure, an RS soft-decision decoder is high in complexity. Meanwhile, compared with simple LDPC+RS cascading decoding, the mixed iterative decoding method for the LDPC-RS two-dimensional product code improves codon correction performance.

Owner:SHANGHAI JIAO TONG UNIV

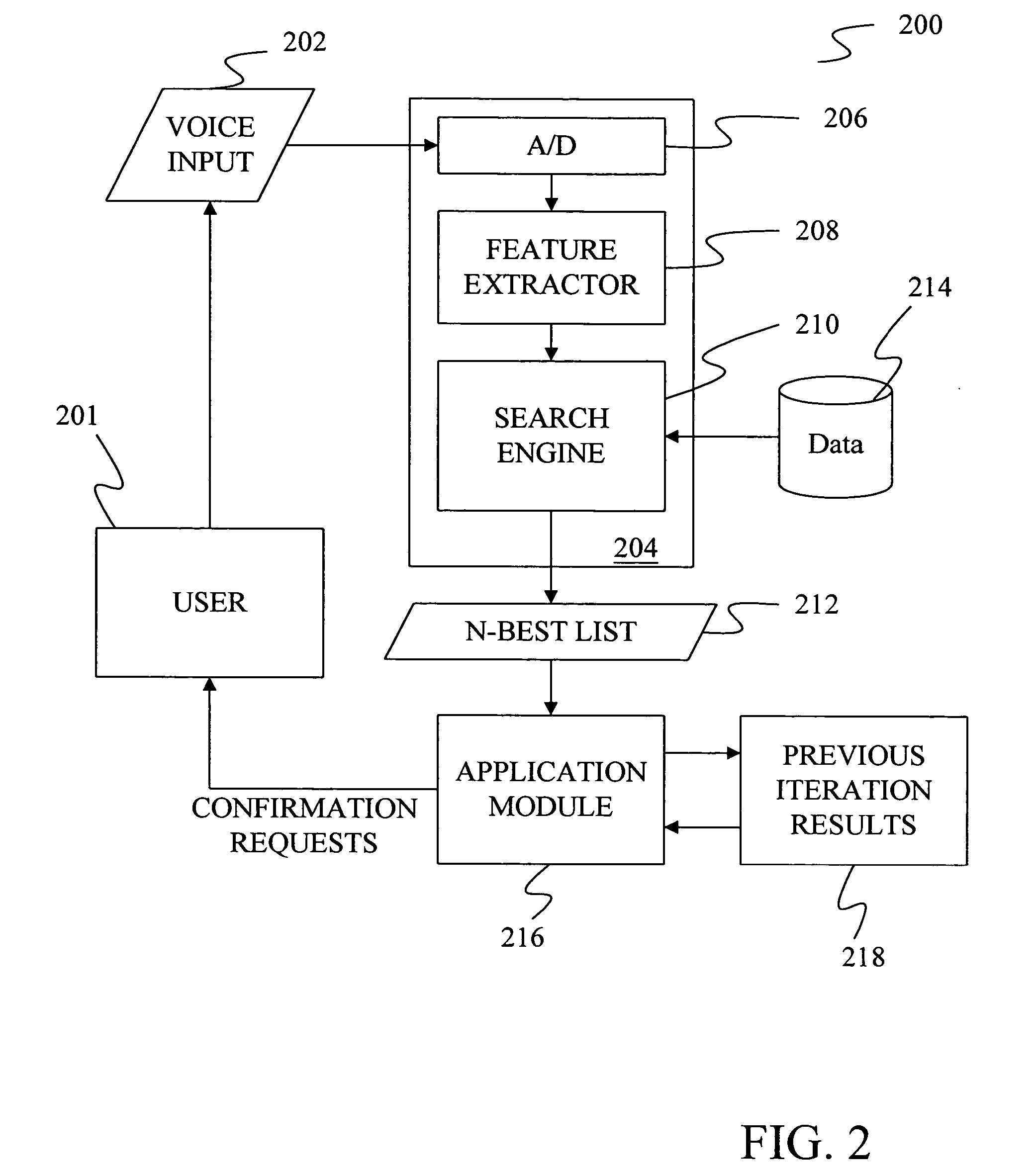

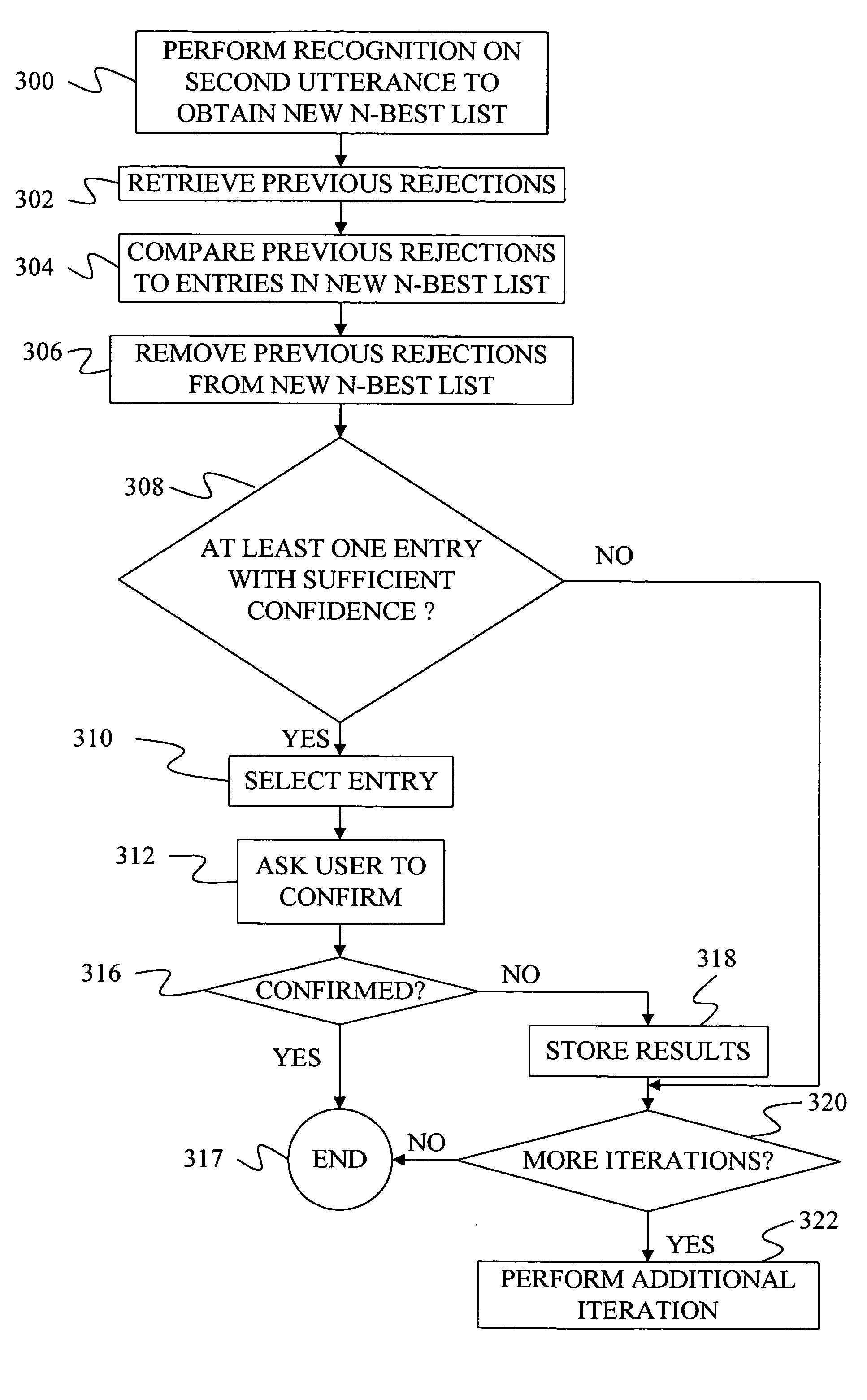

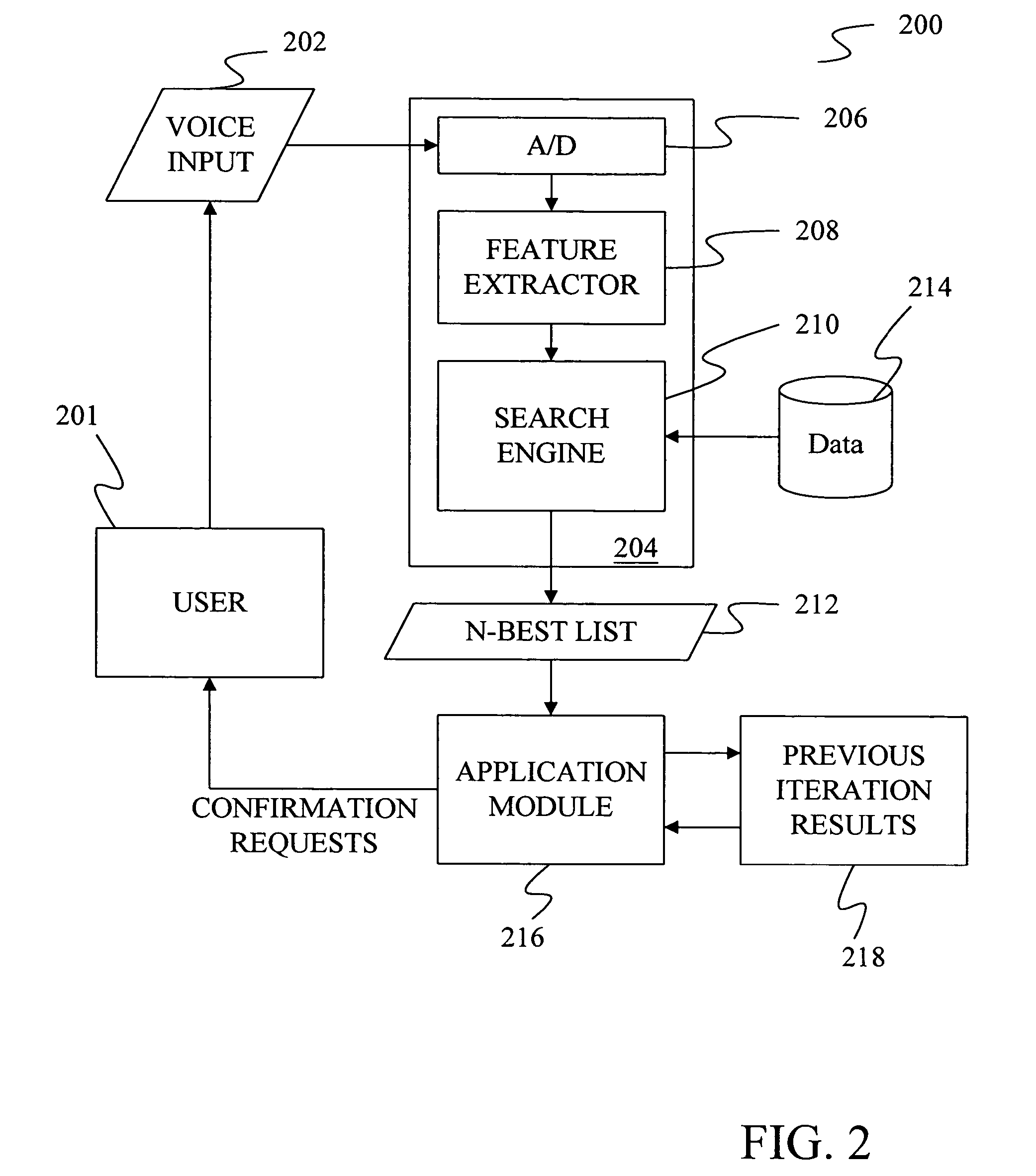

Speech recognition application or server using iterative recognition constraints

ActiveUS20060020464A1Reduce recognition iterationImprove the recognition success rateSpeech recognitionApplication moduleSpeech sound

A speech recognition application including a recognition module configured to receive input utterances and an application module configured to select a recognition from the speech recognition module using output from a first iteration to select a recognition result for a second iteration. In one embodiment, the application module eliminates a previous rejected recognition result or results from the N-Best list for recognition. In another embodiment, the application module rescores N-Best entries based upon N-Best lists or information from another iteration. In another illustrated embodiment, the application module uses a limited grammar from a current N-Best list for subsequent recognition, for example for rerecognition using a recorded input from a previous iteration.

Owner:MICROSOFT TECH LICENSING LLC

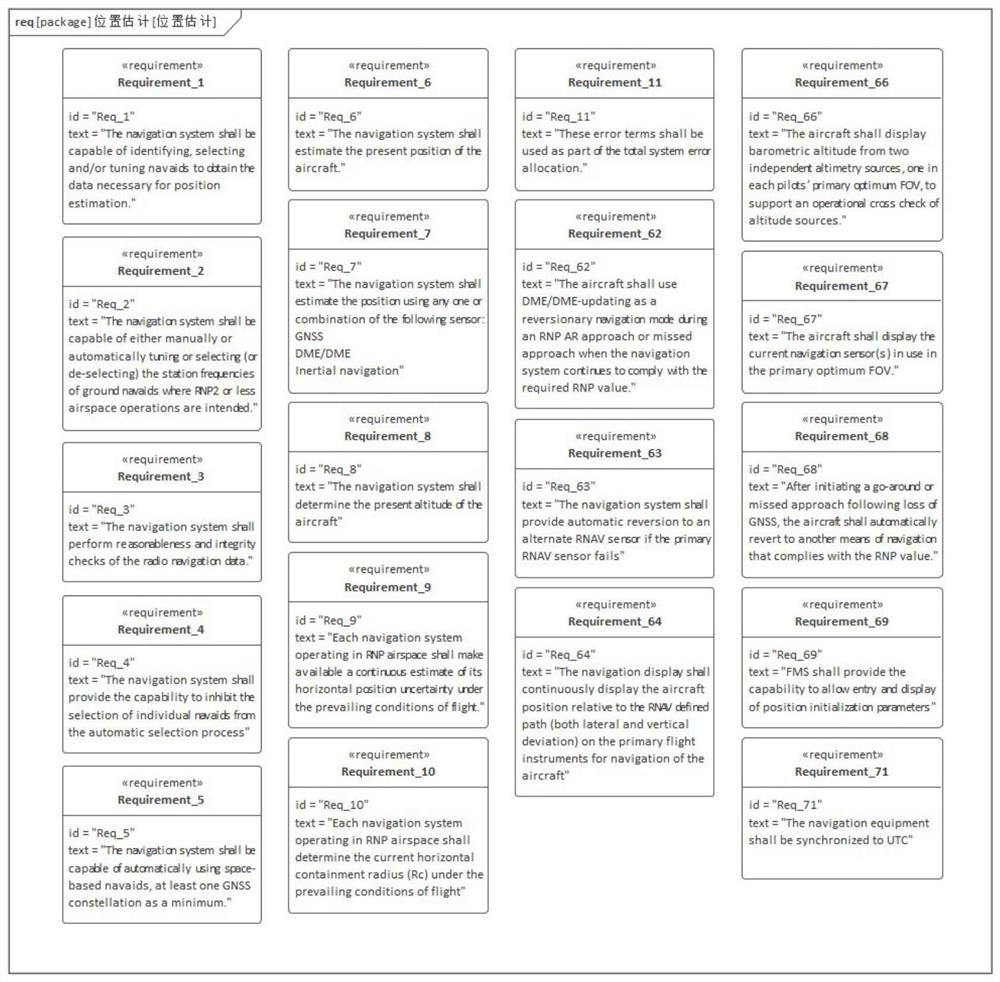

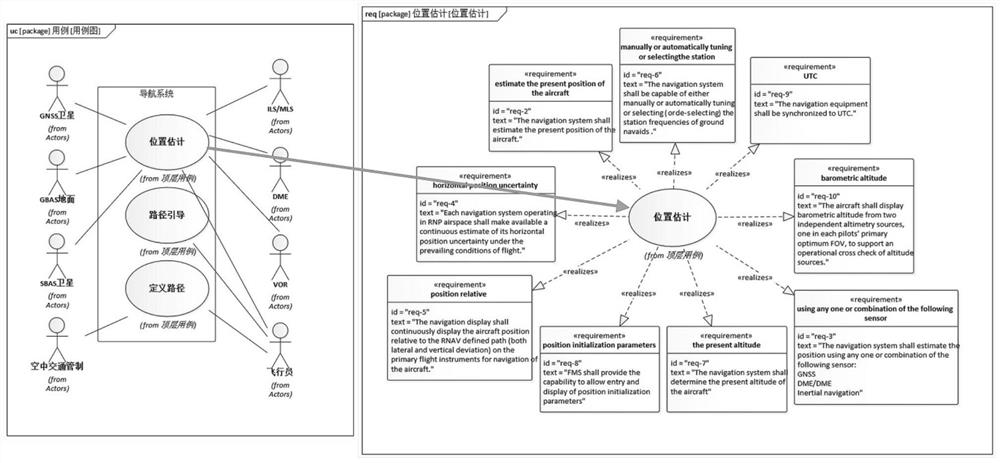

AMBSE method suitable for aircraft airborne system architecture design

PendingCN112380625AReduce iterative processAvoid Subversive ModificationsGeometric CADDesign optimisation/simulationSystems designSystem requirements

The invention discloses an aMBSE method suitable for aircraft airborne system architecture design, and the method comprises the steps: converting the demands of stakeholders into system demands, defining system cases, and carrying out the case planning; translating the confirmed use case into an executable black box model, and verifying the model and related system requirements through dynamic behavior simulation of the model; providing a series of alternative schemes meeting requirements for system requirements, and seeking an optimal architecture scheme; gradually expanding a system-level black box model for function analysis into a subsystem-level white box model, and integrating mutually independent subsystems into a complete system architecture in an incremental iteration mode. Smalliteration is added in the system development process, large iteration is reduced, the model is tested in the early stage of design, a reasonable architecture design thought is determined, problems inearly-stage design are prevented from being brought into the verification stage, the complexity of system design is reduced, and the problem of demand change in system engineering is effectively solved.

Owner:NANJING UNIV OF AERONAUTICS & ASTRONAUTICS

Speech recognition application or server using iterative recognition constraints

ActiveUS7809567B2Reduce iterative processIncrease successSpeech recognitionSpeech identificationRe identification

Owner:MICROSOFT TECH LICENSING LLC

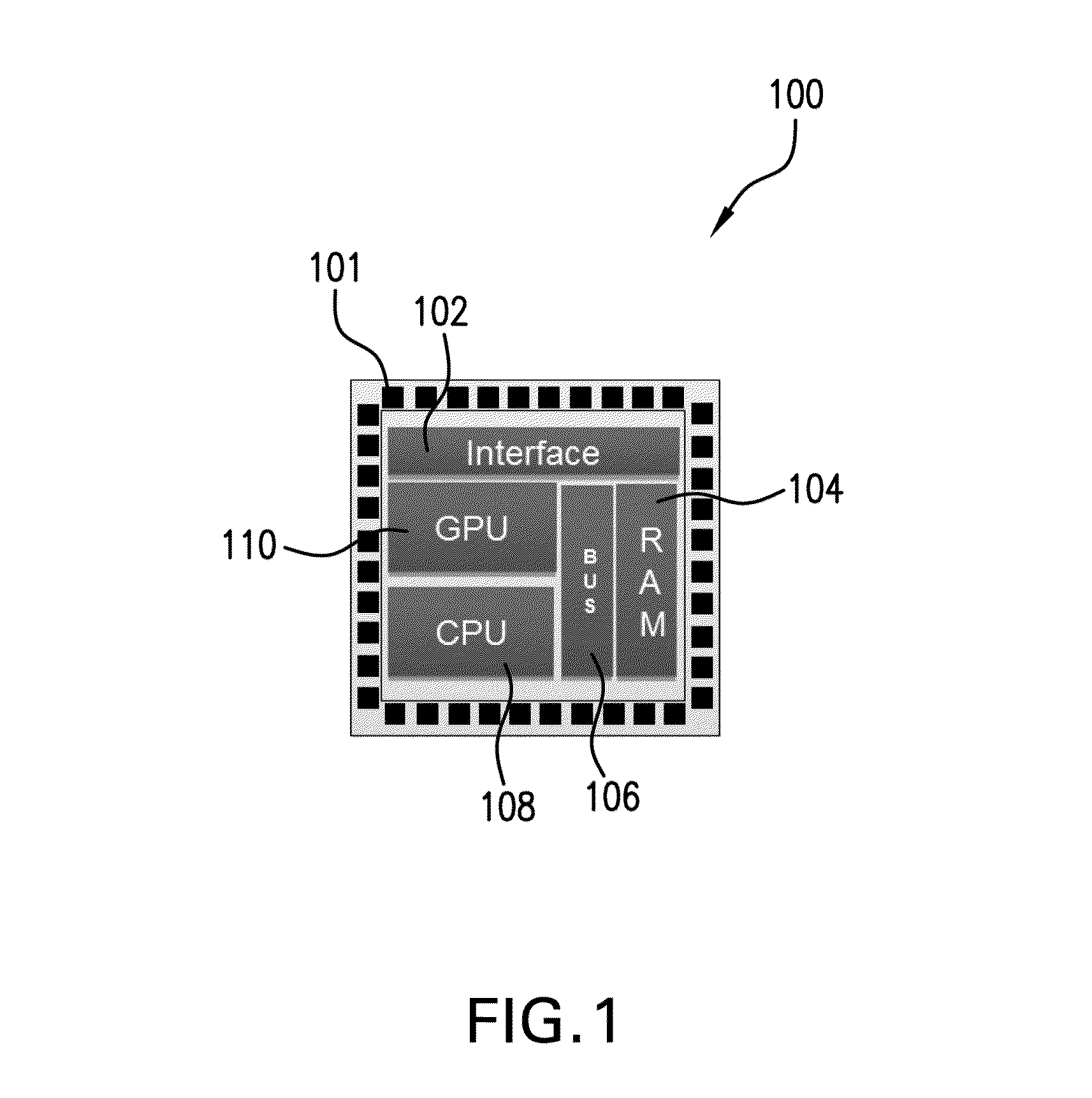

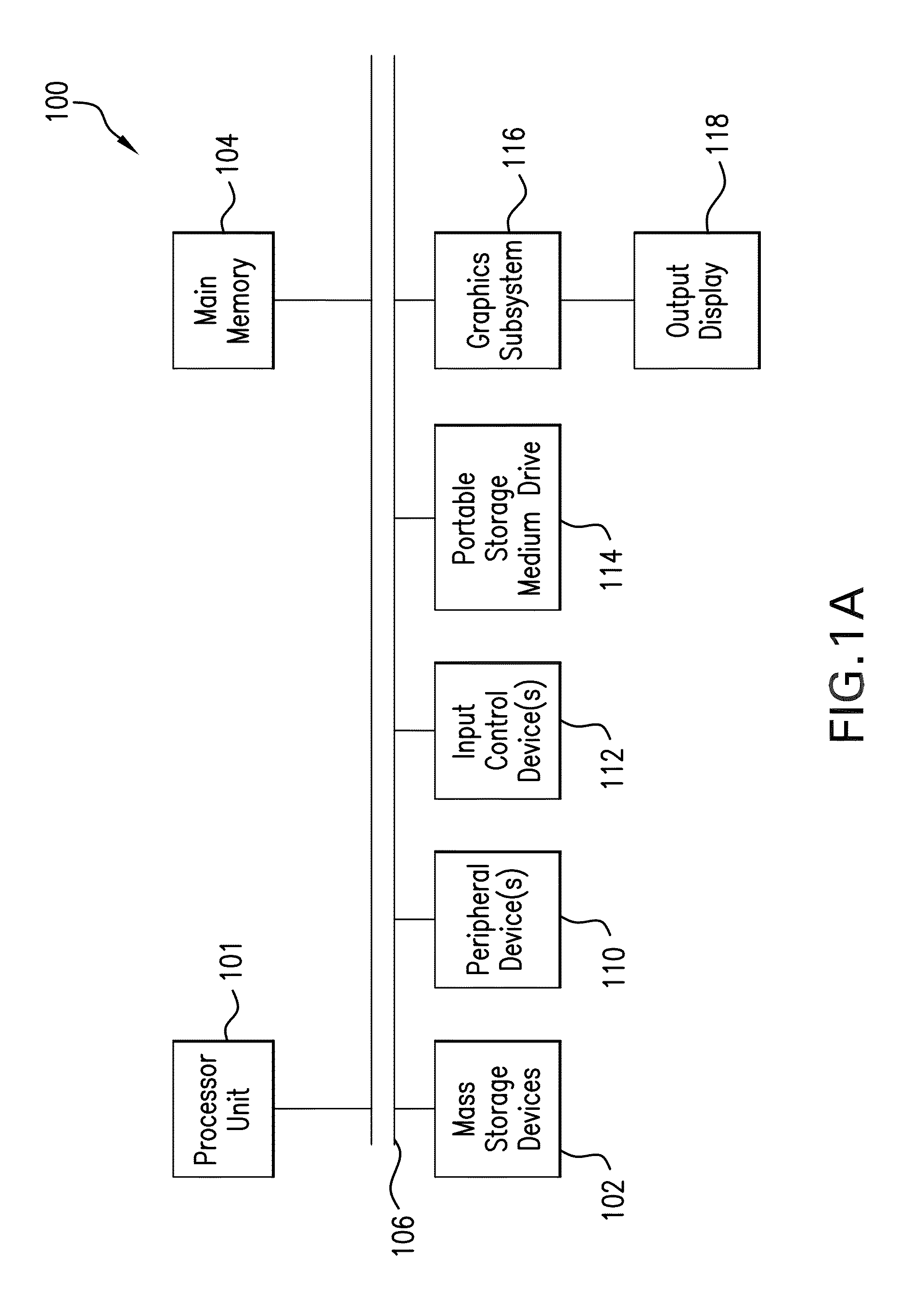

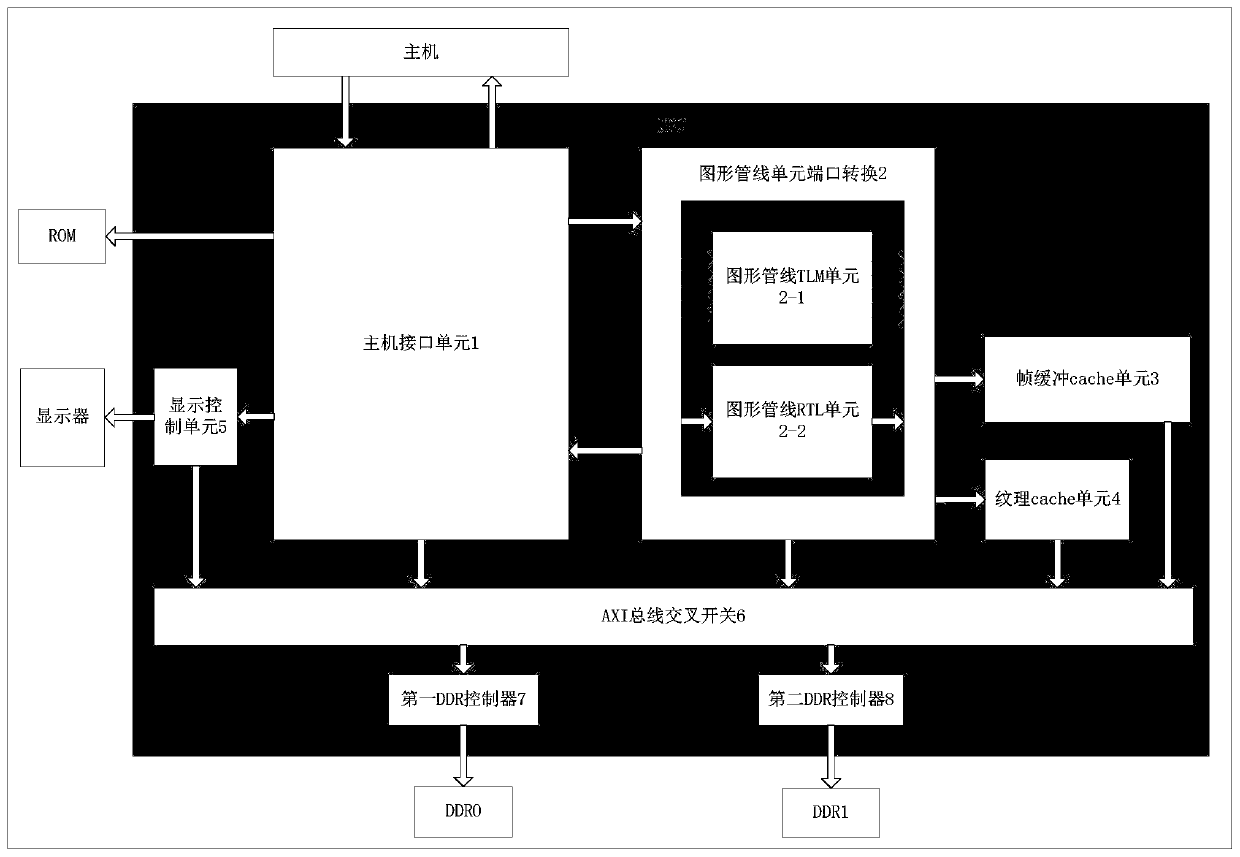

A GPU chip-oriented graphic pipeline unit function simulation method and platform

PendingCN109711003ASolve the problem that is not easy to buildConvenience to workSpecial data processing applicationsGraphicsSystemC

The invention relates to the technical field of computer hardware verification, in particular to a graphic pipeline unit function simulation method and platform for a graphic processing unit (GPU) chip. According to the method, a graphic processing unit (GPU) chip TLM virtual prototype platform based on SystemC is established (the virtual prototype verification platform comprises a host, an ROM, adisplay, DDR0, DDR1 and a GPU); a TLM transaction level port of a GPU graphic pipeline unit is converted into a hardware signal level port, an RTL code of the graphic pipeline unit is embedded into aTLM virtual prototype platform, and module level and system level function simulation is carried out on the RTL of the GPU. Therefore, the problem that the behaviors of the GPU module-level RTL simulation environment model and the GPU system-level RTL simulation environment model are not unified is solved through the TLM virtual prototype platform, the reusability of the simulation environment isimproved, and the development and verification work of the GPU chip RTL is accelerated.

Owner:XIAN AVIATION COMPUTING TECH RES INST OF AVIATION IND CORP OF CHINA

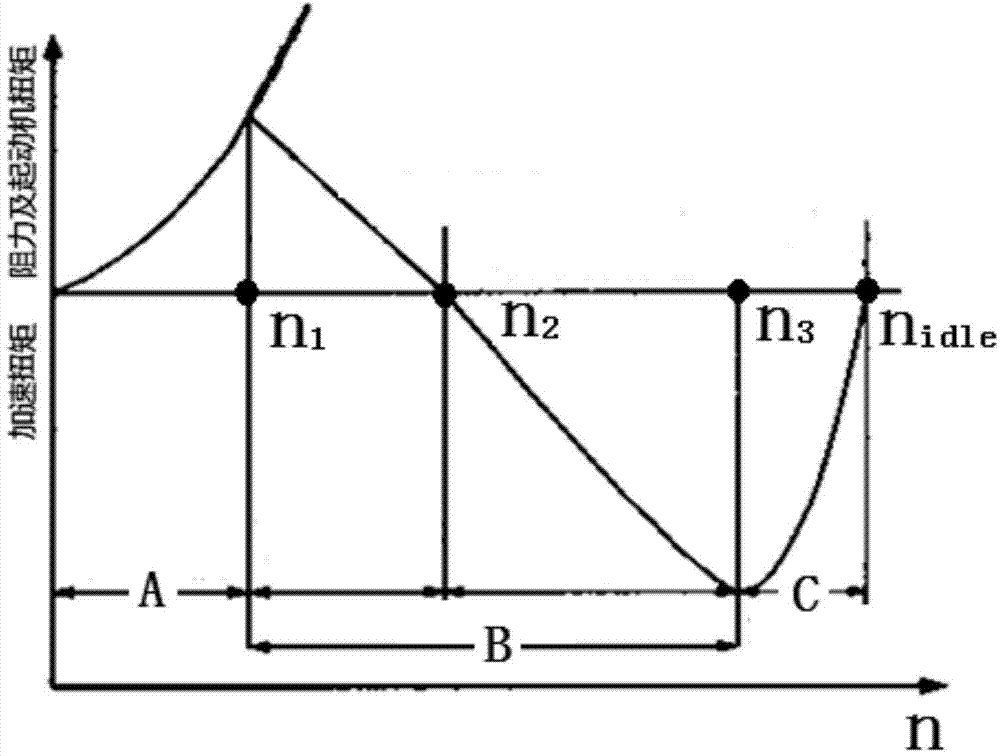

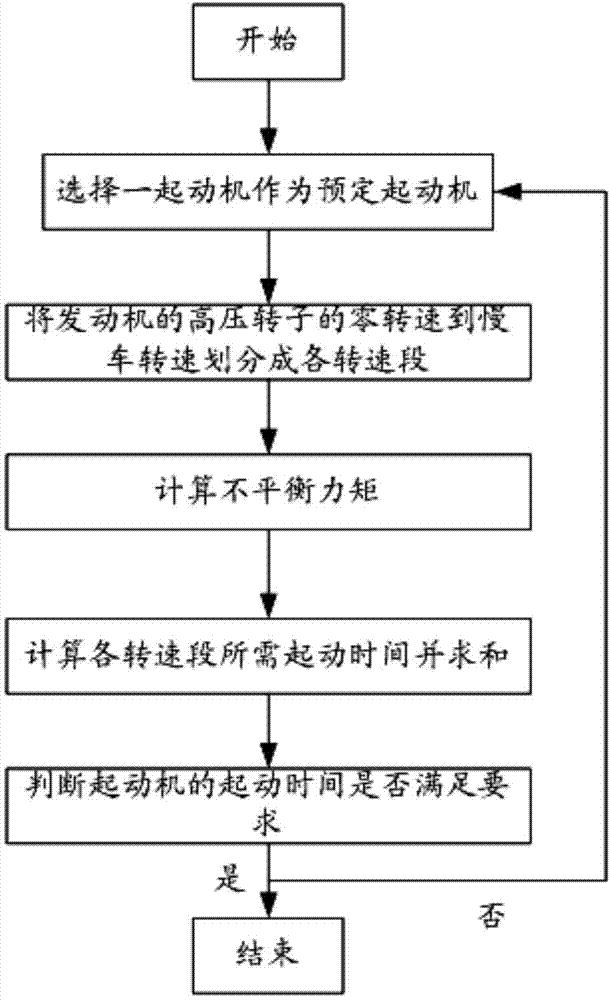

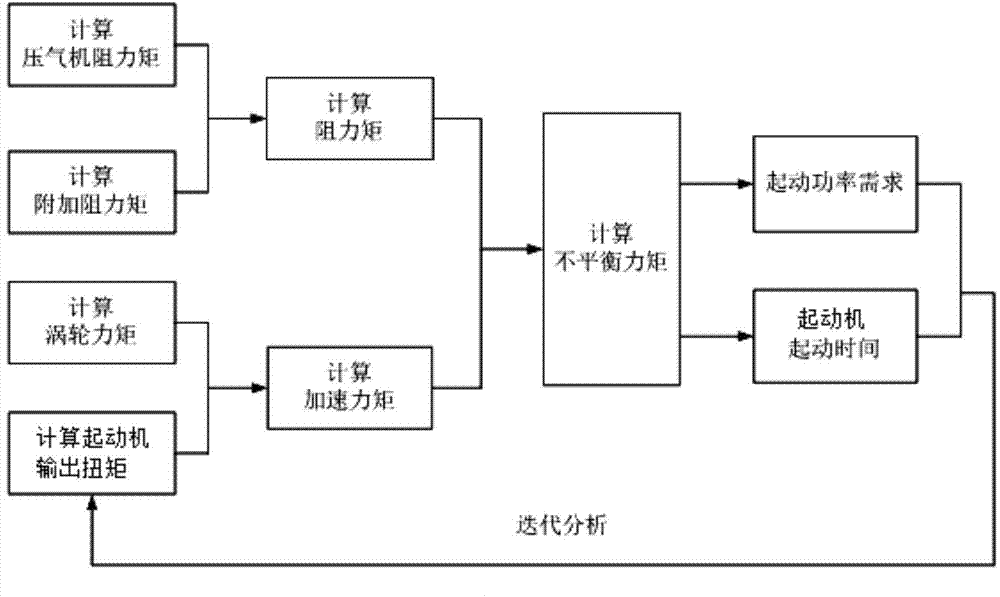

A type selecting method of a starter used for a turbofan engine

ActiveCN104747293AImprove design accuracyReduce iterative processTurbine/propulsion engine ignitionTurbine/propulsion engine startersTime rangeStart time

The invention relates to a type selecting method of a starter used for a turbofan engine. The method includes following steps: 10) selecting a starter as a preset starter; 20) dividing the revolving speed of a high-pressure rotor of the turbofan engine into a plurality of speed sections from zero to the idle speed, calculating unbalanced moments of two revolving speed nodes in each speed section, further calculating the average unbalanced moment and a starting time which are corresponding to each speed section, and adding the starting time of each speed section to obtain the starting time needed for the preset starter; and 30) comparing the starting time needed for the preset starter with a starting time range needed for the turbofan engine, wherein if the starting time needed for the preset starter is in the starting time range needed for the turbofan engine, starter type selecting is finished, and the maximum output power of the selected starter is outputted; and otherwise, a starter is selected again by combination of the maximum output power of the preset starter.

Owner:AECC COMML AIRCRAFT ENGINE CO LTD

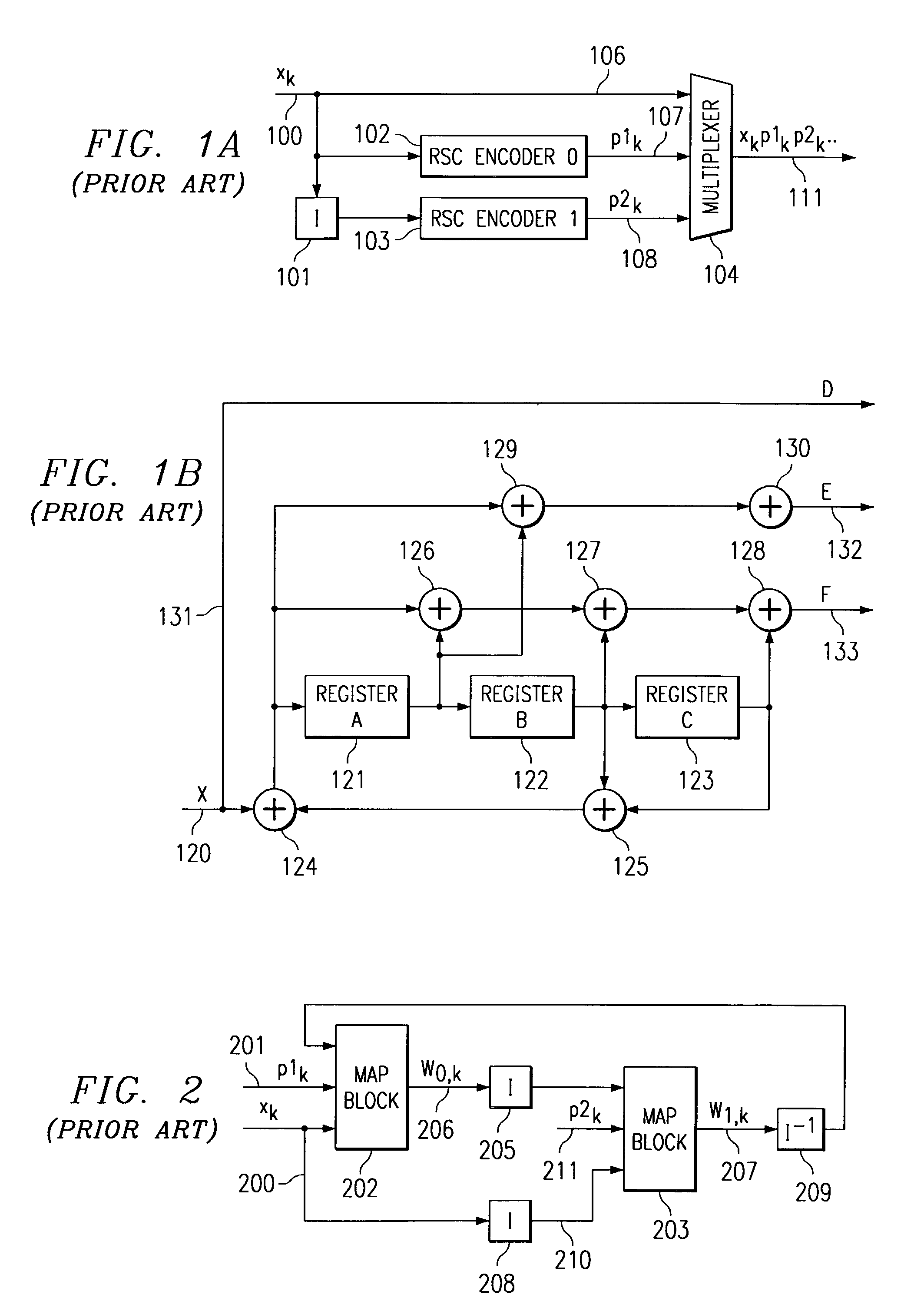

Turbo decoder prolog reduction

ActiveUS6996765B2Strong convergenceImprove performanceData representation error detection/correctionOther decoding techniquesSignal-to-noise ratio (imaging)Slide window

This invention describes implementation approaches for sliding window turbo decoders. Sliding windows are used for both the beta and alpha state metric calculations. Initialization of the beta / alpha prolog sections with data from a previous iteration is employed in conjunction with a reduced length prolog section. For subsequent sliding windows the trellis values of the prolog sections are dynamically initialized based upon data derived from the signal to noise ratio of the calculated extrinsic data or the difference between the two most probable trellis states.

Owner:TEXAS INSTR INC

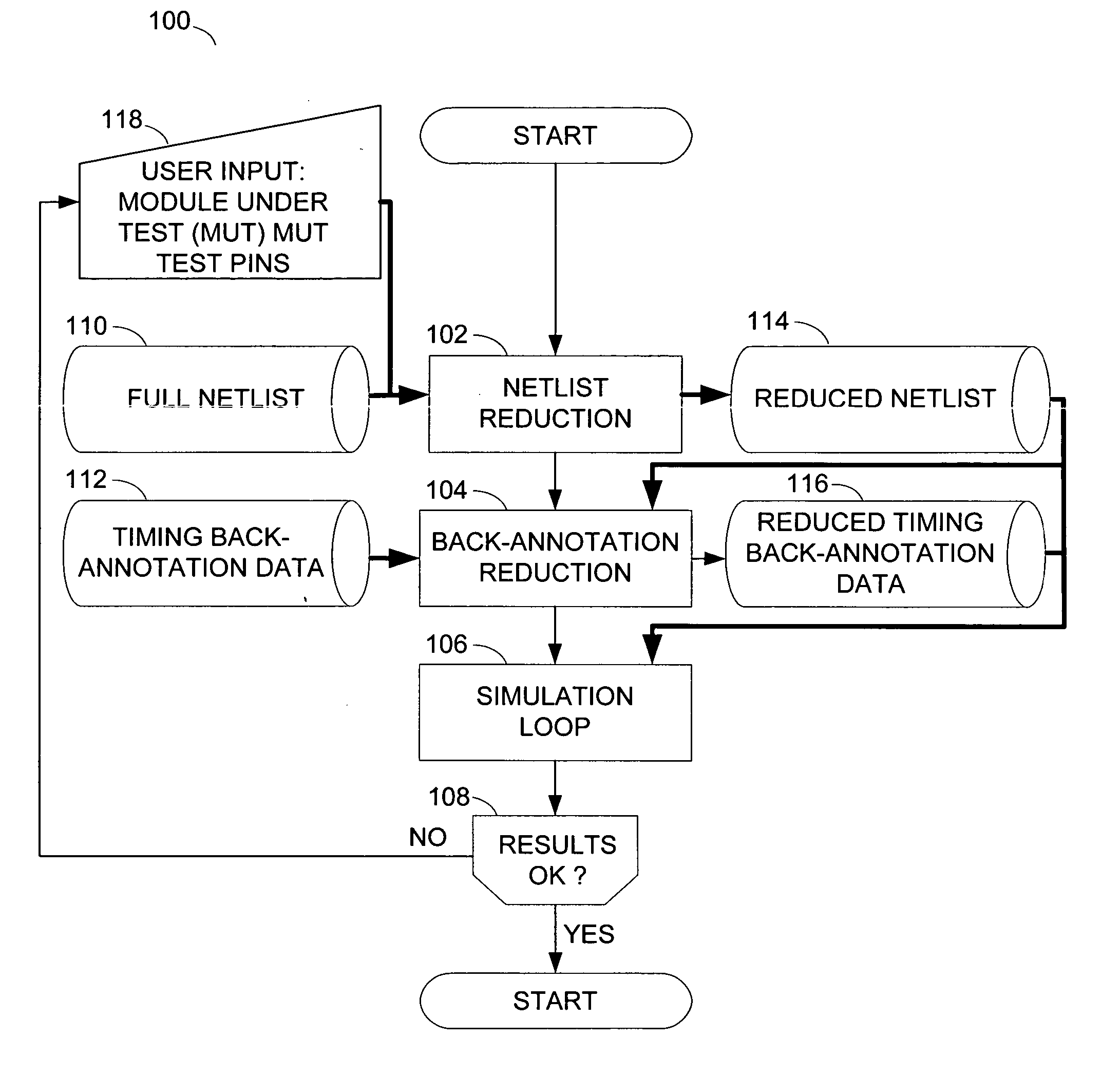

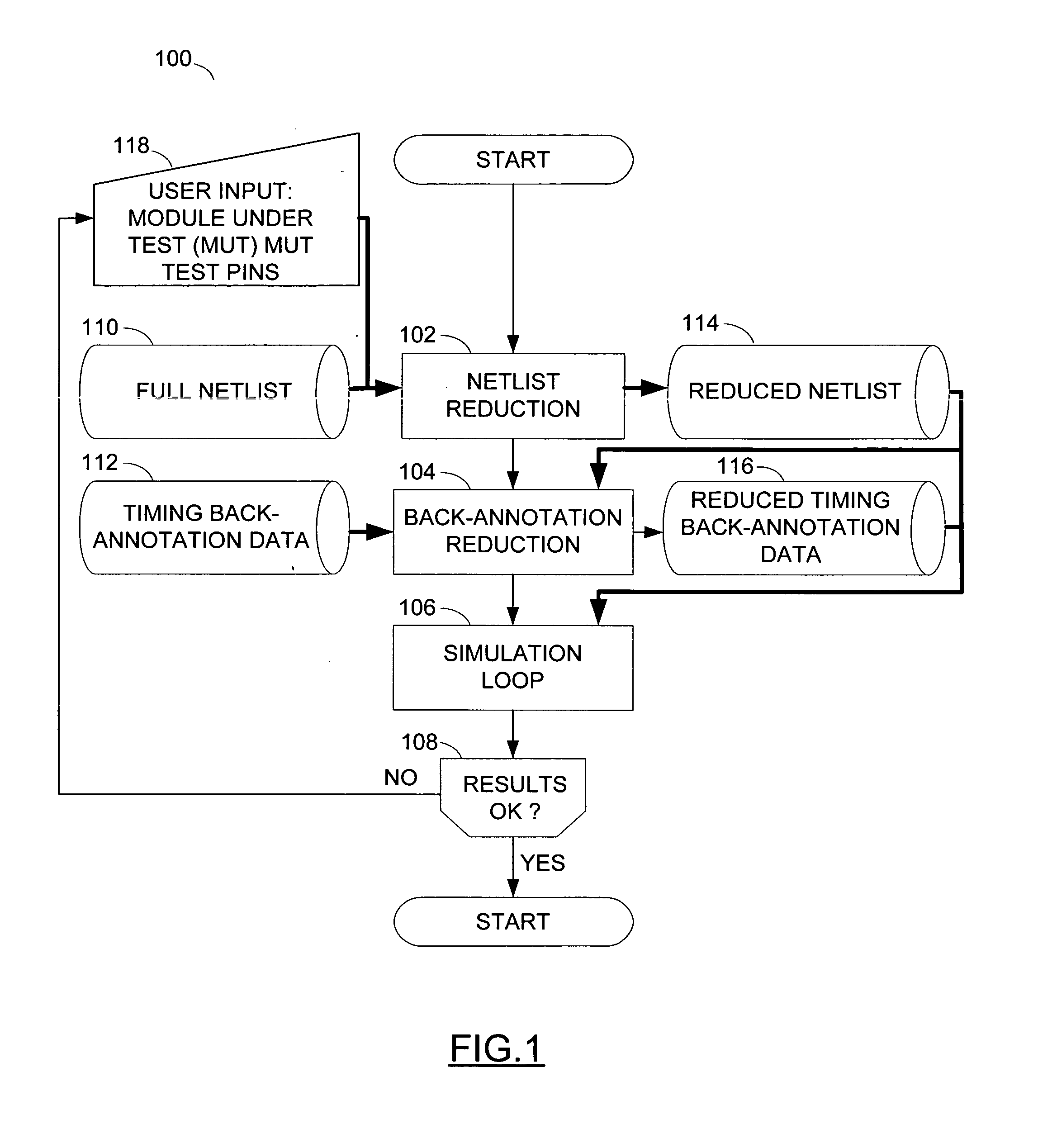

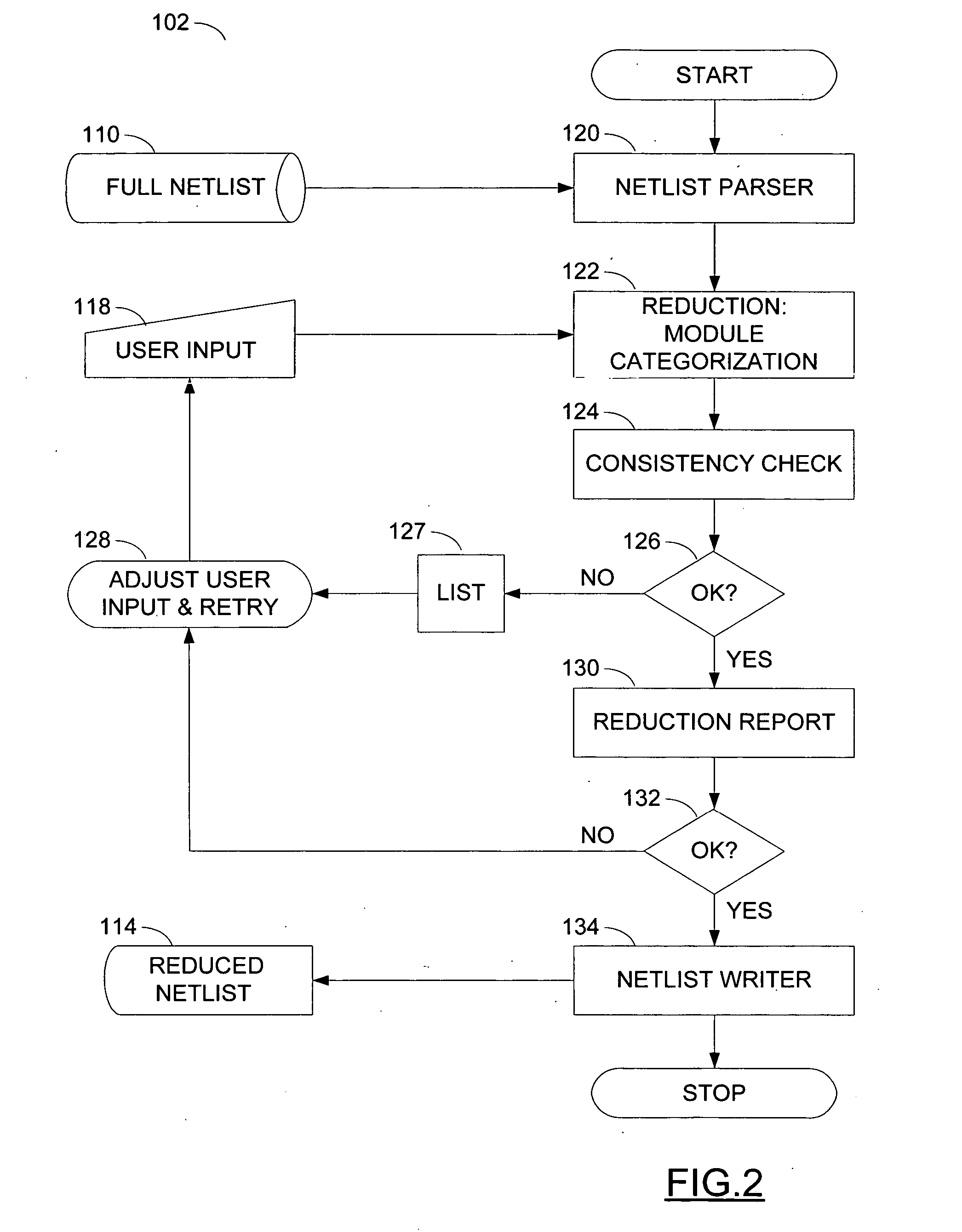

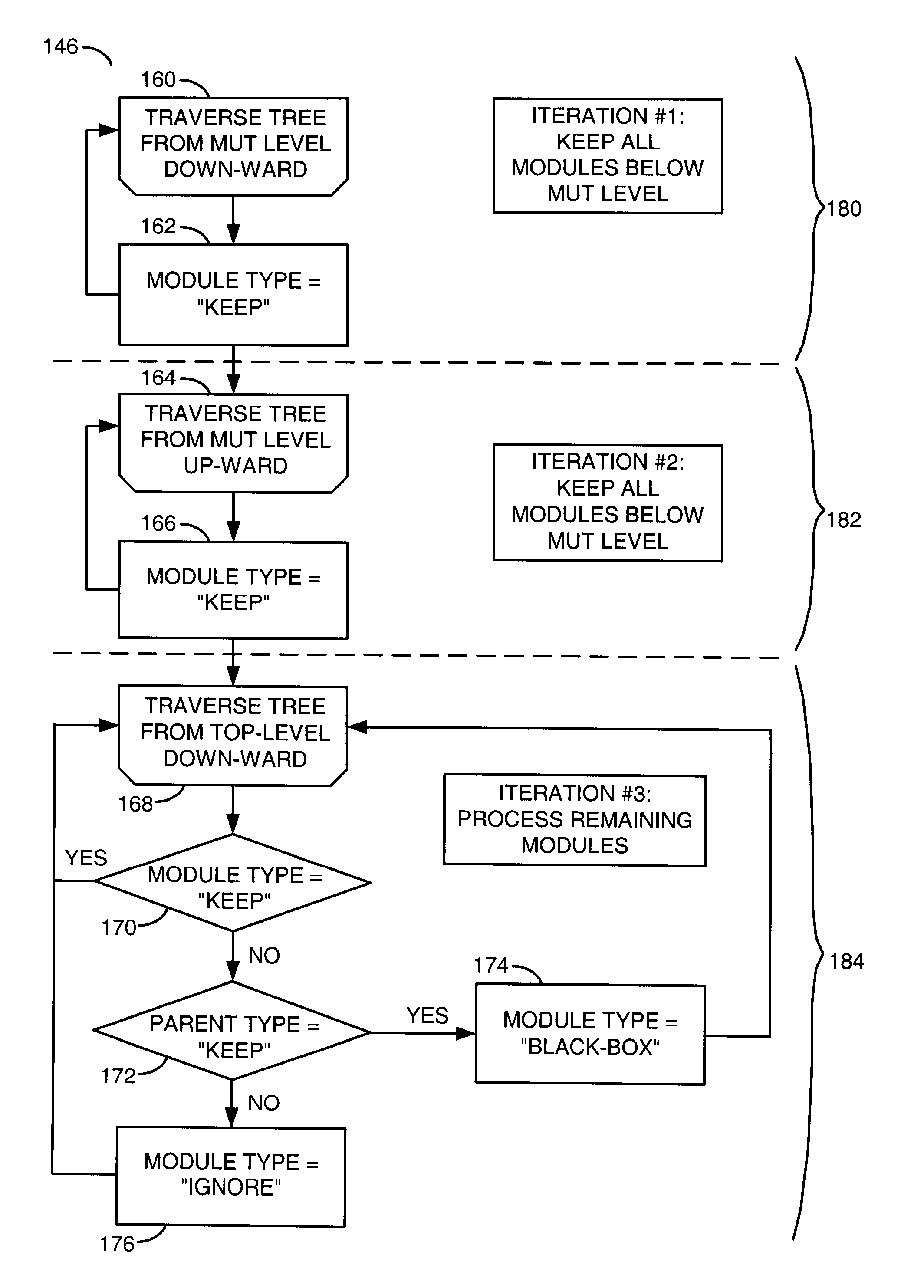

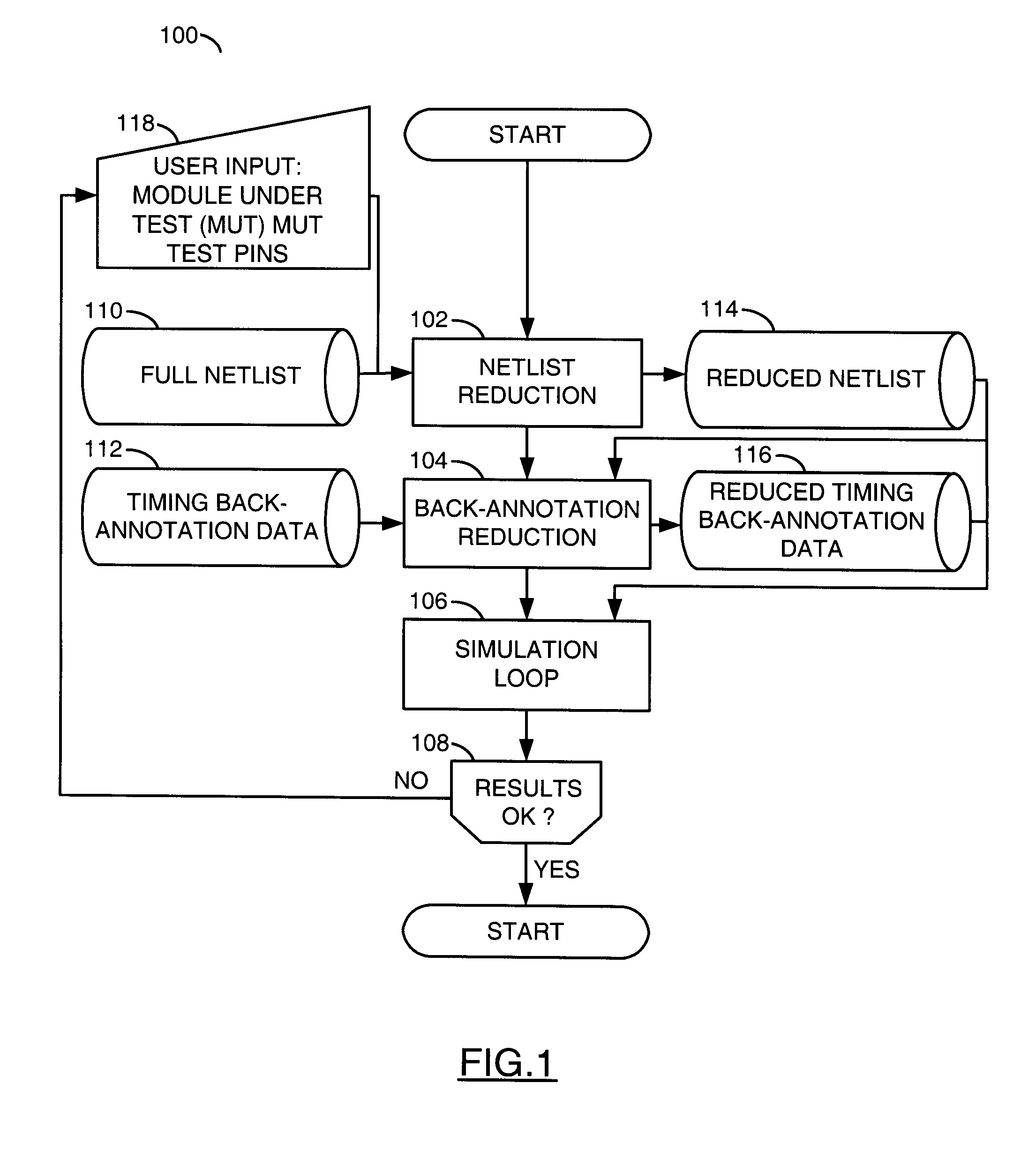

Gate-level netlist reduction for simulating target modules of a design

InactiveUS20050240387A1Improve design validation turnaround timeShorten the timeCAD circuit designProgram controlLevel structureEngineering

A method for analyzing a circuit design in preparation for a simulation. The method generally includes the steps of (A) marking each of a plurality of modules between a target module of the modules and a top module of the modules in a hierarchy of the circuit design as a first type by traversing upward through the hierarchy starting from the target module, (B) marking each of the modules as a second type where a parent module of the modules is marked as the first type by traversing downward through the hierarchy starting from the top module and (C) marking each of the modules as a third type where the parent module is not marked as the keep type by traversing downward through the hierarchy starting from the top module.

Owner:BELL SEMICON LLC

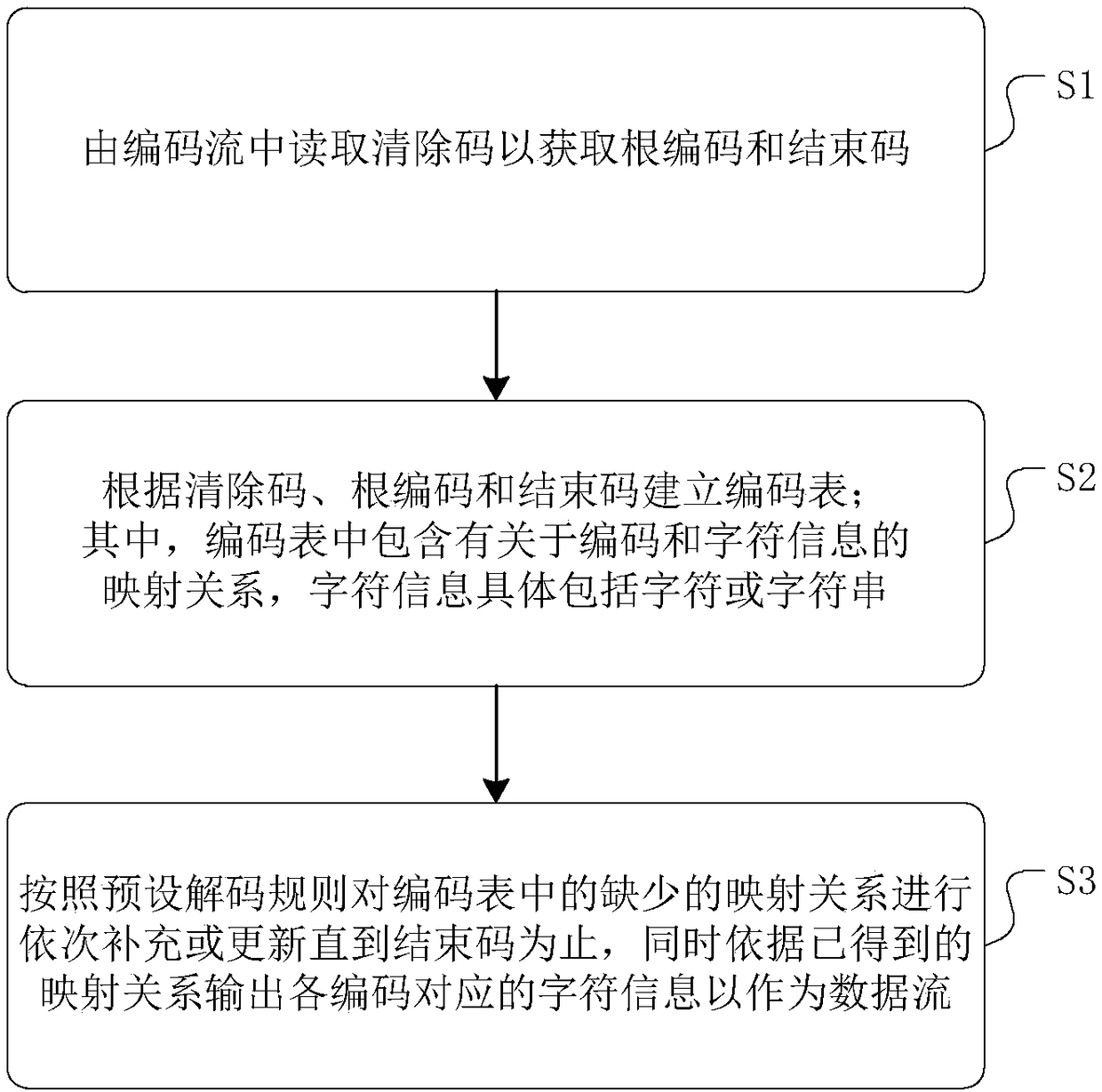

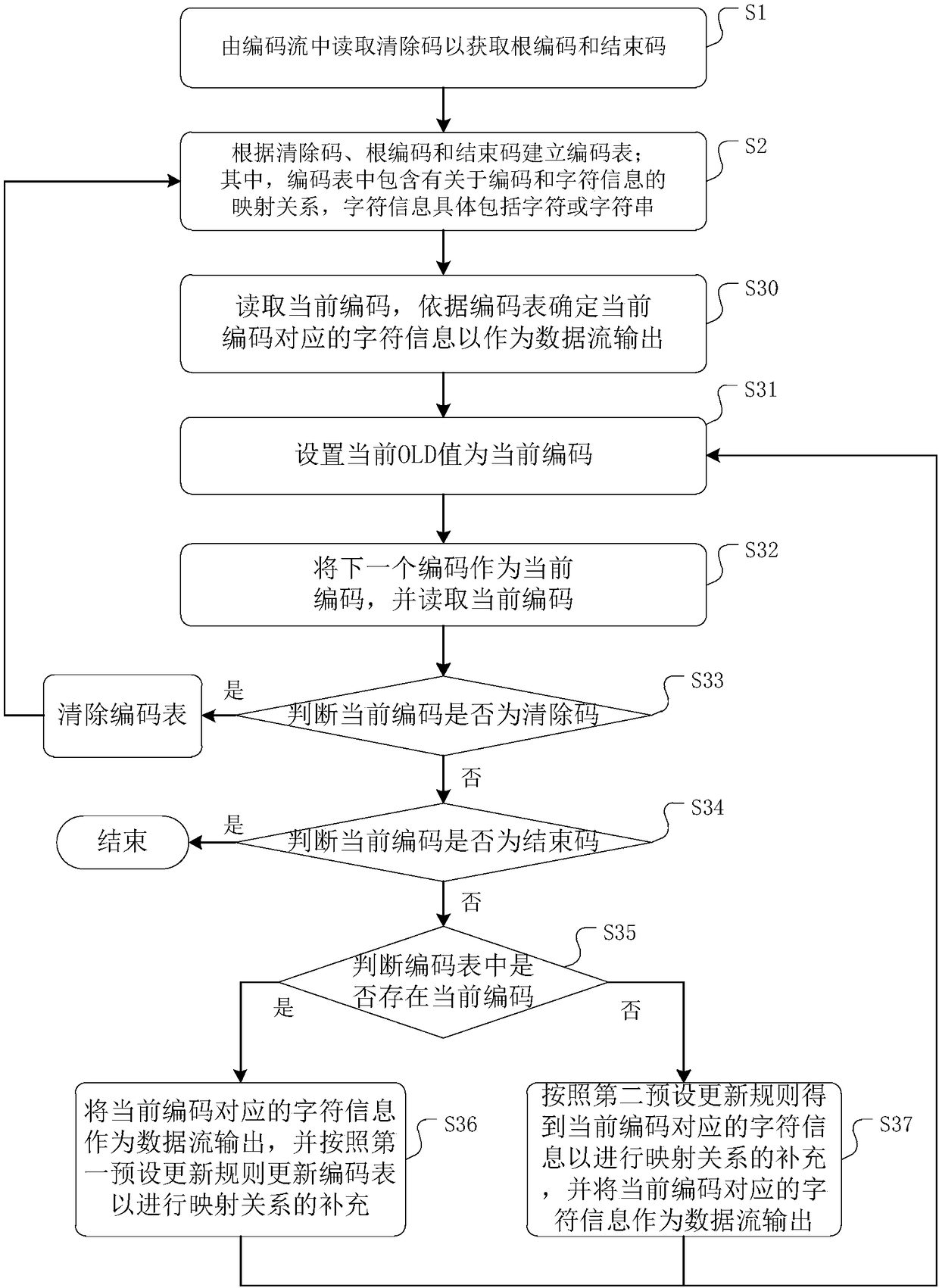

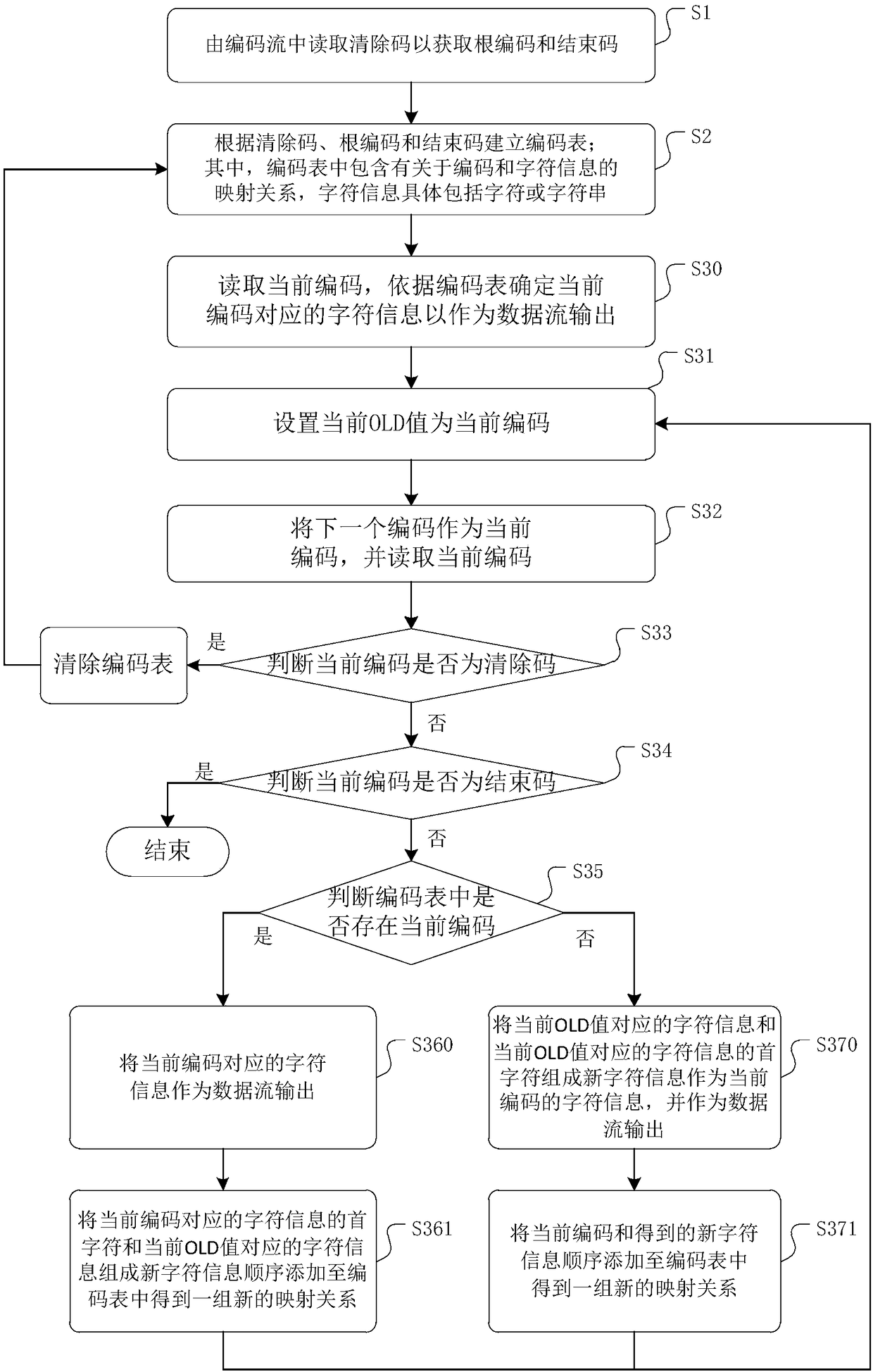

Data decoding method, device, and equipment based on LZW algorithm, and medium

InactiveCN108900196AImprove access efficiencyImprove decoding efficiencyCode conversionDecoding methodsComputer engineering

The invention discloses data decoding method, device, and equipment based on an LZW algorithm, and a medium. The data decoding method based on an LZW algorithm includes the steps: reading a clearing code from an encoding stream to obtain a root code and an end code; establishing a code table about the mapping relationship of code and character information, according to the clearing code, the rootcode, and the end code; and sequentially adding or updating the missing mapping relationship until the end code, and outputting the character information corresponding to each code as a data flow according to the obtained mapping relationship. The data decoding method maintains the mapping relationship from the codes to the character information through the code table, stores the code table in theform of a data table so as to effectively improve the access efficiency, and at the same time, because the mapping relationship is sequentially supplemented, as the number of reading encodings increases, the mapping relationship is also increased, so that the probability that the current code exists in the code table is greatly improved, and the corresponding character information is not requiredto be repeatedly calculated, thereby improving the decoding efficiency. The data decoding device and equipment based on the LZW algorithm, and the medium also have the above advantages.

Owner:ZHENGZHOU YUNHAI INFORMATION TECH CO LTD

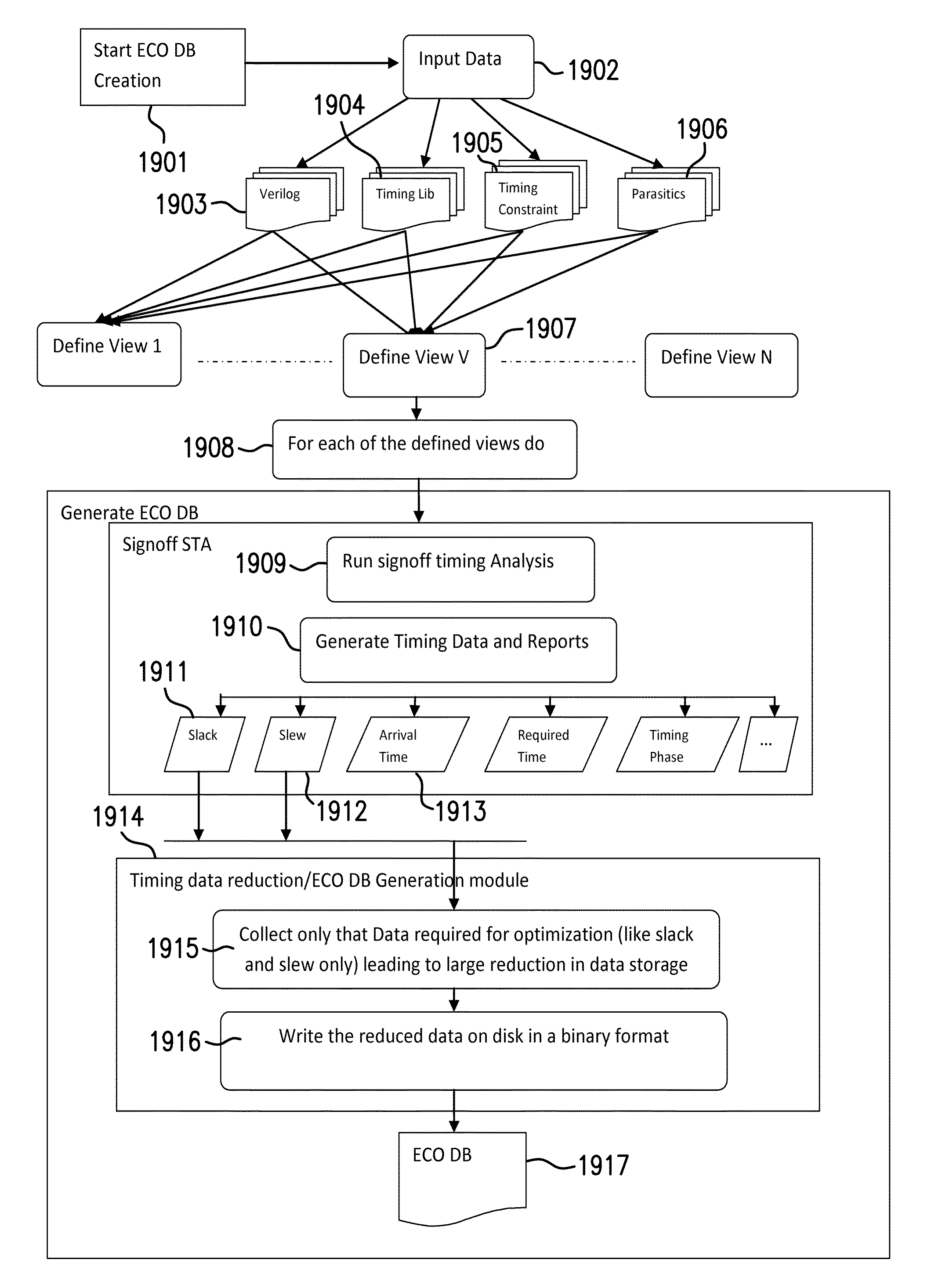

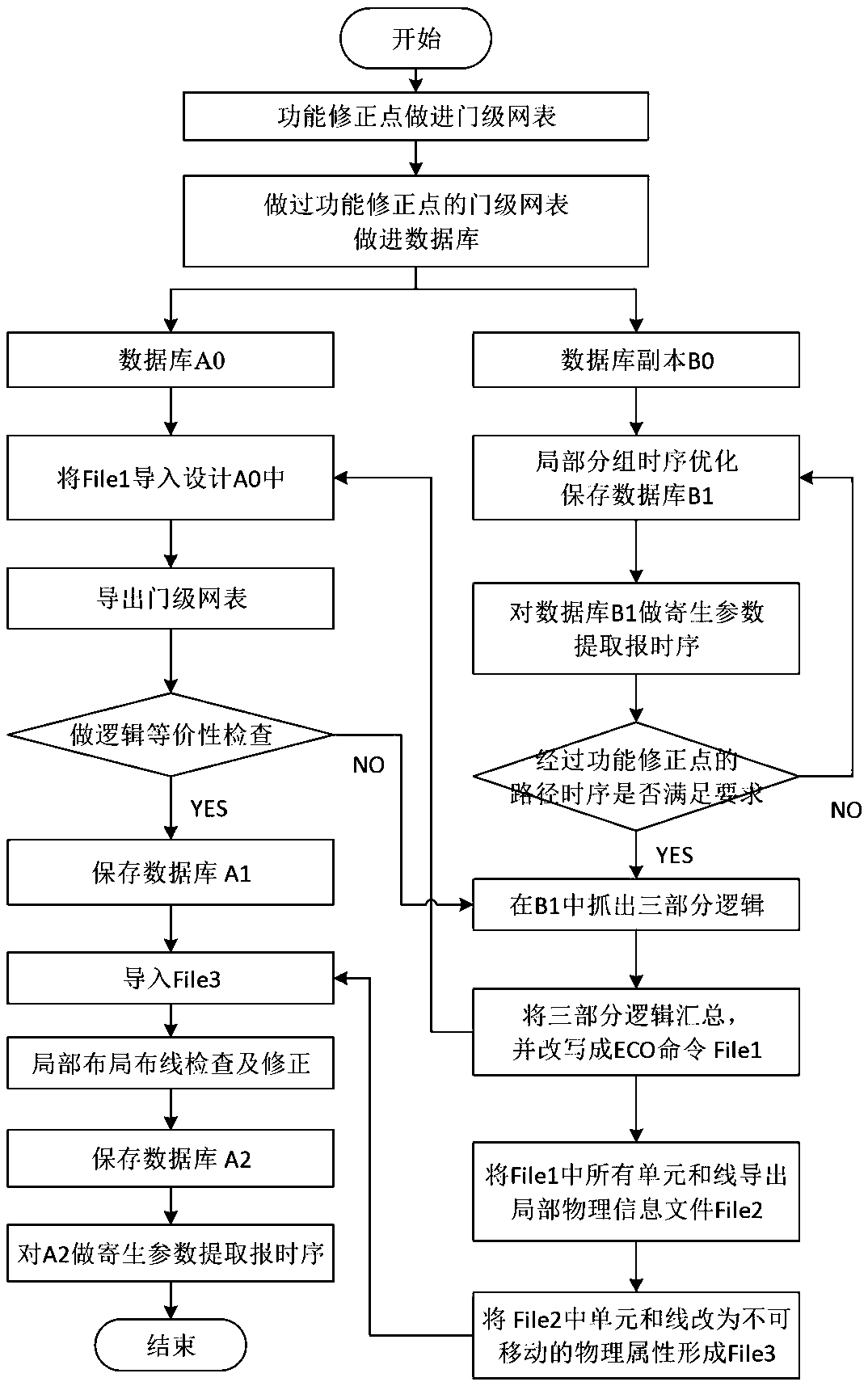

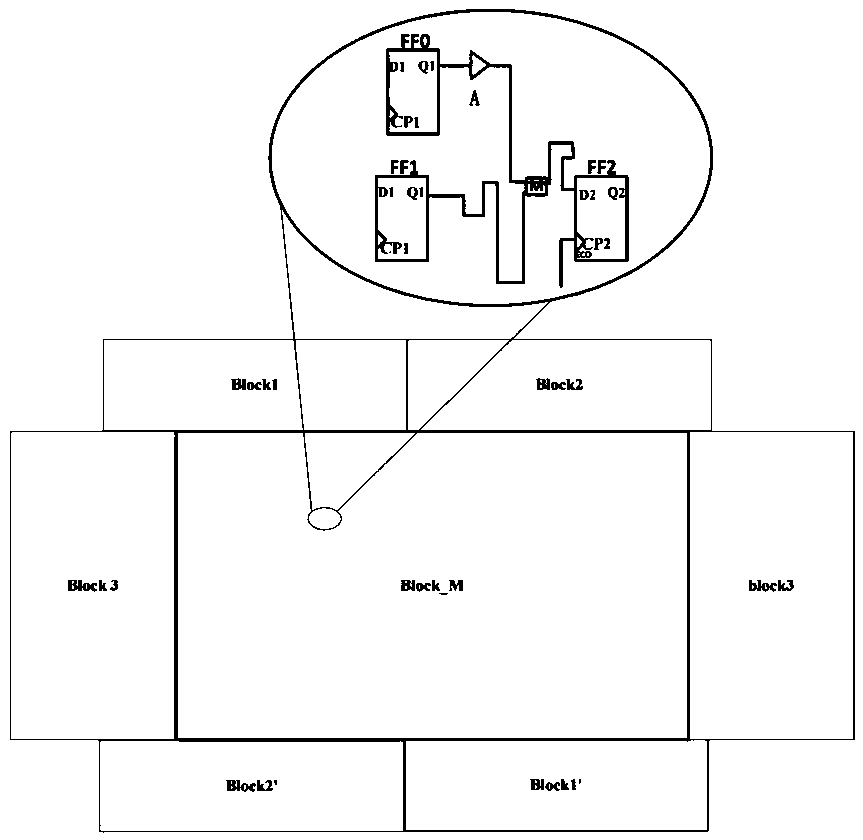

Method for quickly converging establishment time after gate-level netlist modification

ActiveCN110580393ADoes not affect interface timingReduce iterative processSpecial data processing applicationsComputer scienceDatabase

The invention discloses a method for quickly converging establishment time after gate-level netlist modification. The method comprises the following implementation steps: taking a function correctionpoint as a gate-level netlist and storing a database to obtain a database A0 and a copy B0; extracting function correction logic from the copy B0 after local time sequence optimization, and rewritingthe function correction logic into an ECO command File1; storing the database A0 into which the File1 is read as a database A1; exporting all units and lines in the File 1 to form a physical file File3; checking and correcting local layout wiring in the database A1 of the read-in file File3, storing the local layout wiring as a database A2, performing parasitic parameter extraction on the database A2, generating a time sequence analysis report according to a time sequence, and outputting the time sequence analysis report. According to the method, the problem of establishment time violation after sign-off front door level netlist function modification is efficiently solved in a short time with less iteration and small investment, a large amount of manpower and time investment is saved, andthe project design time is shortened.

Owner:PHYTIUM TECH CO LTD

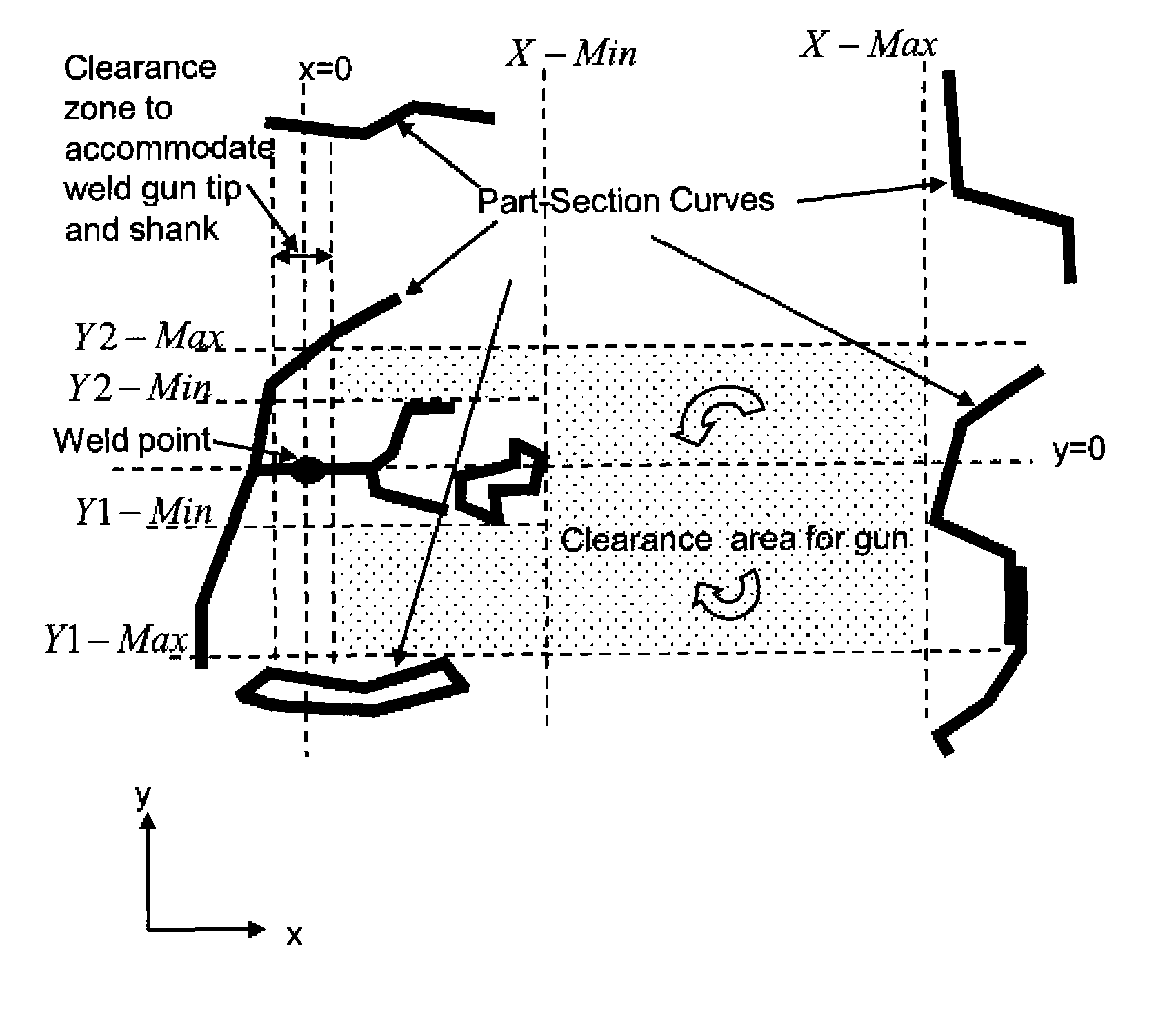

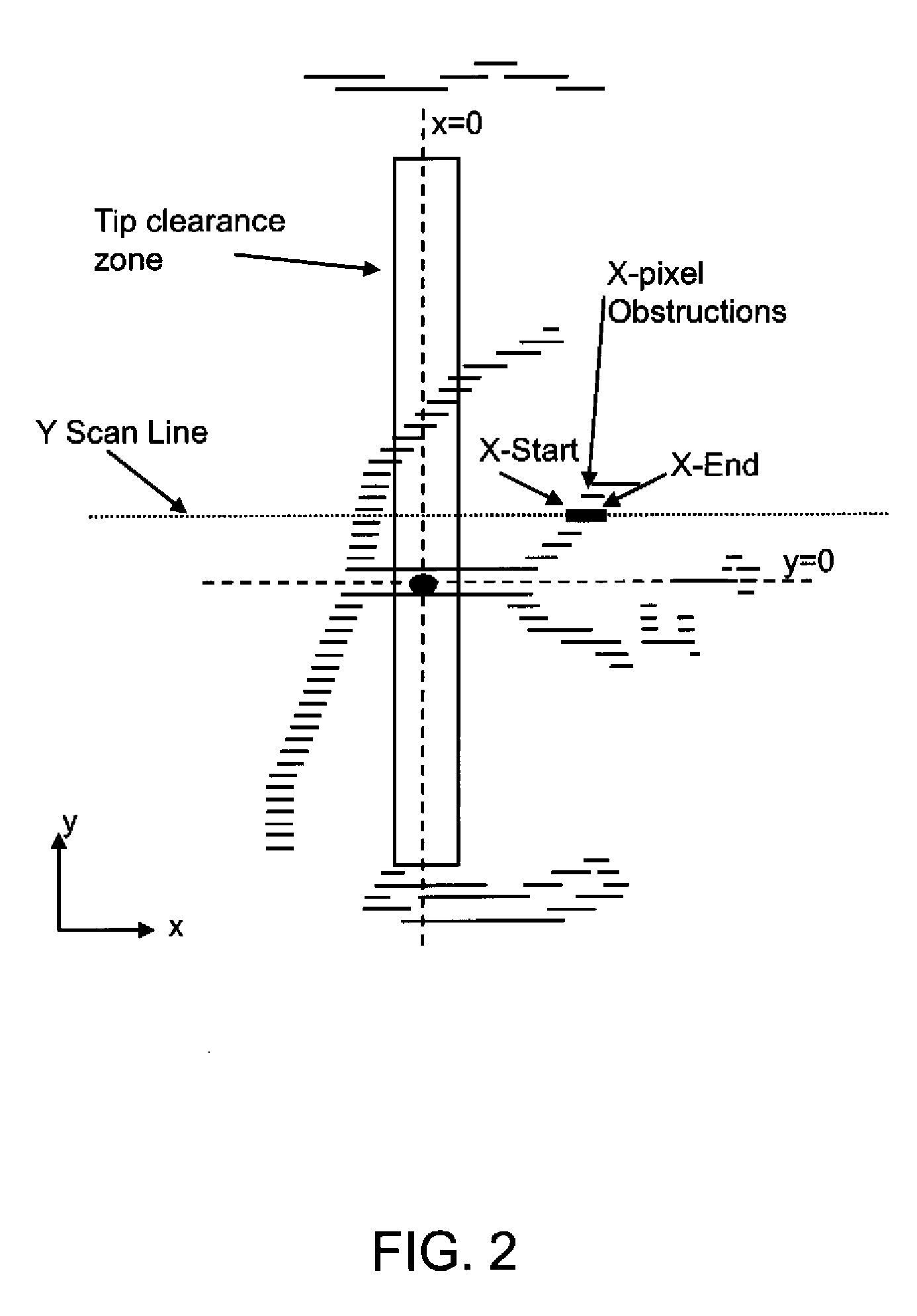

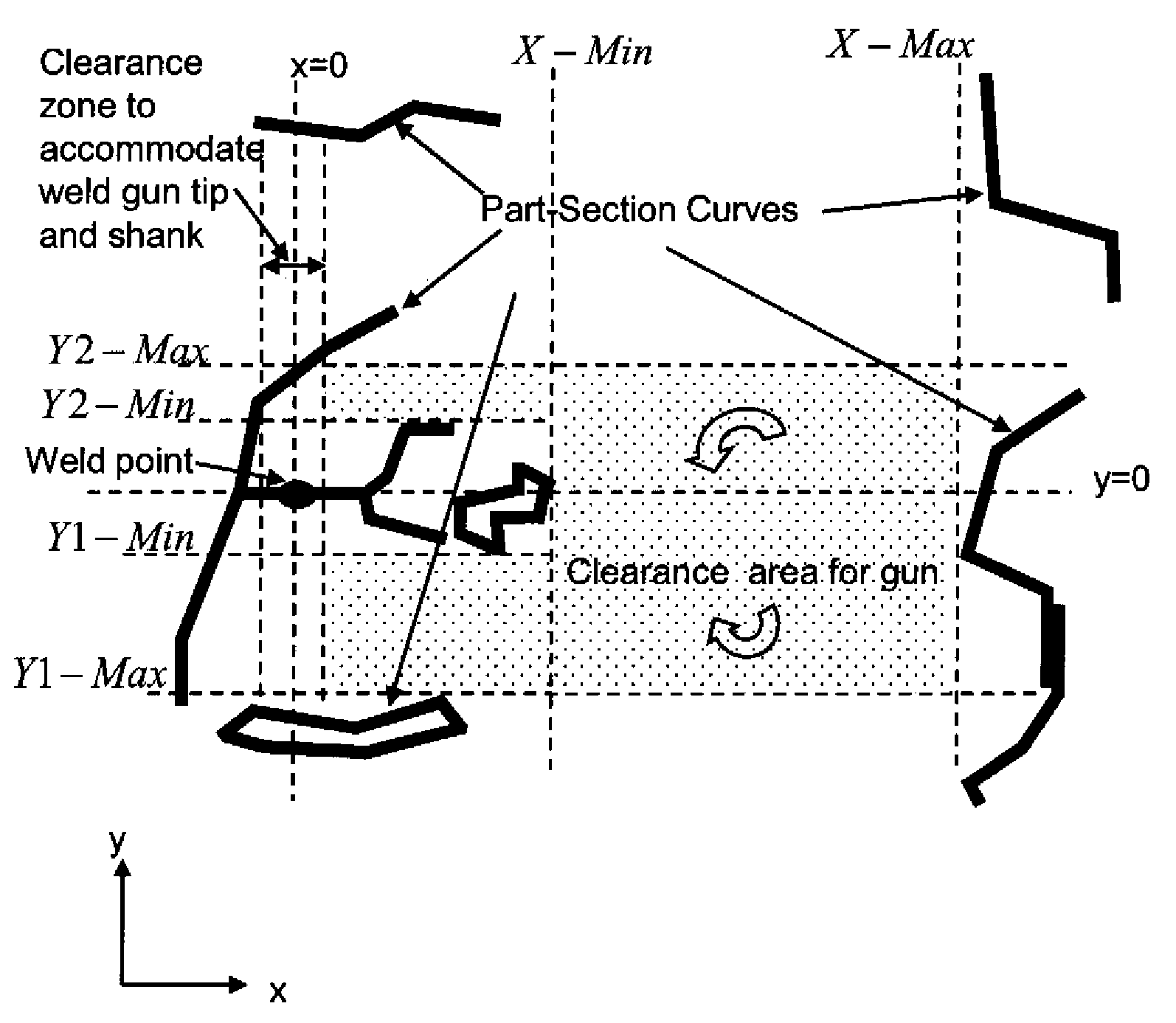

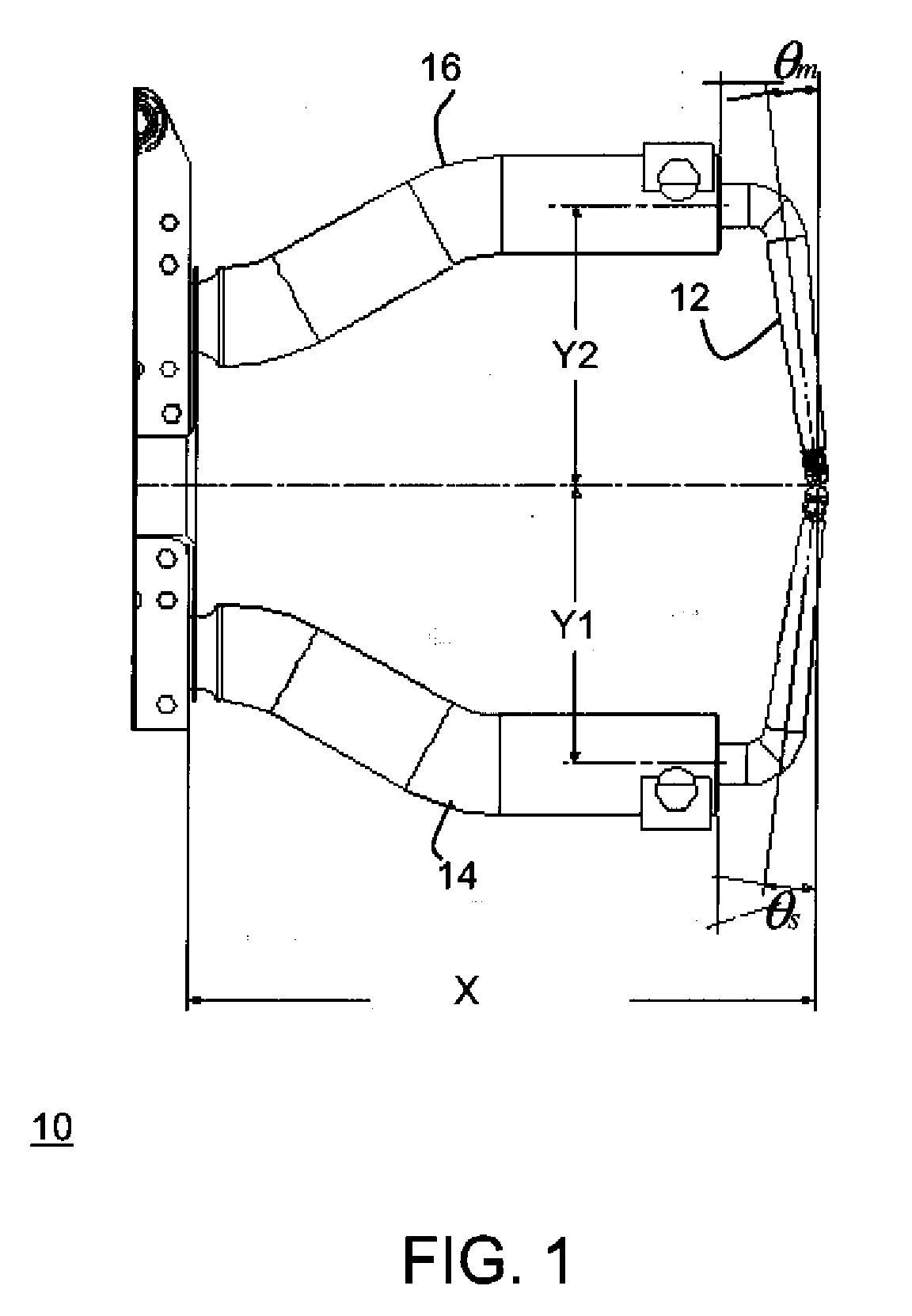

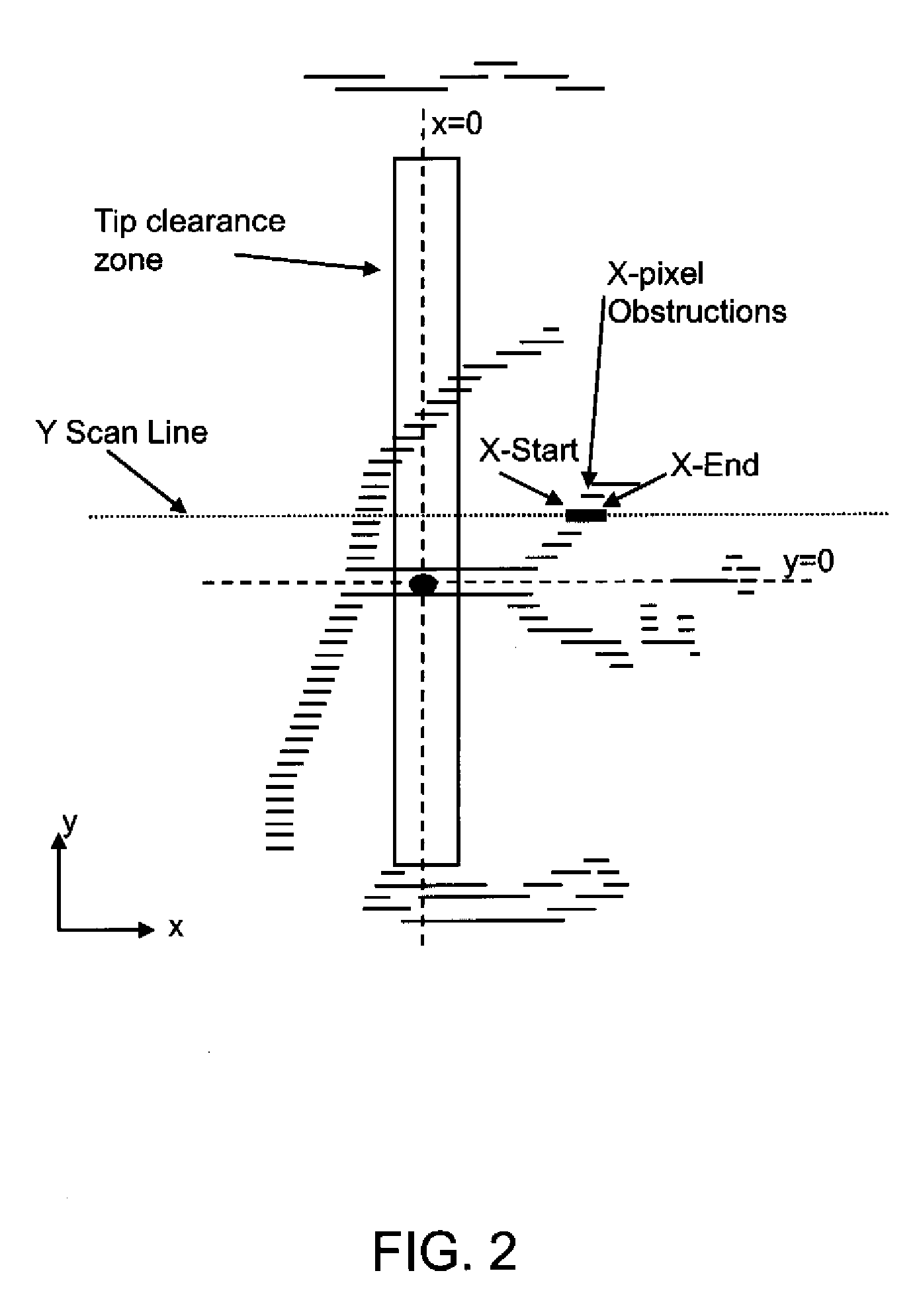

Automatic estimation of weldgun size using section geometry

InactiveUS7974733B2Reduce iterative processGood choiceElectrode supporting devicesComputation using non-denominational number representationSimulation

A method for estimating a plurality of geometrical parameters defining the size of a weld gun that has particular application for automatically selecting a weld gun for a welding operation. The method includes iteratively estimating a plurality of geometric parameters based on part section curves corresponding to a direction of approach of the weld gun to weld point of the plurality of weld points. Thereafter, a set of valid weld gun sizes are calculated based on the estimated plurality of geometric parameters. Similarly all the valid weld gun sizes are calculated corresponding to each of the weld gun approach direction. Further, each set of the valid gun sizes are estimated for each of the weld point for the welding operation. Finally, a weld gun for performing the welding operation is selected based on the set of weld gun sizes corresponding to the welding operation.

Owner:GM GLOBAL TECH OPERATIONS LLC

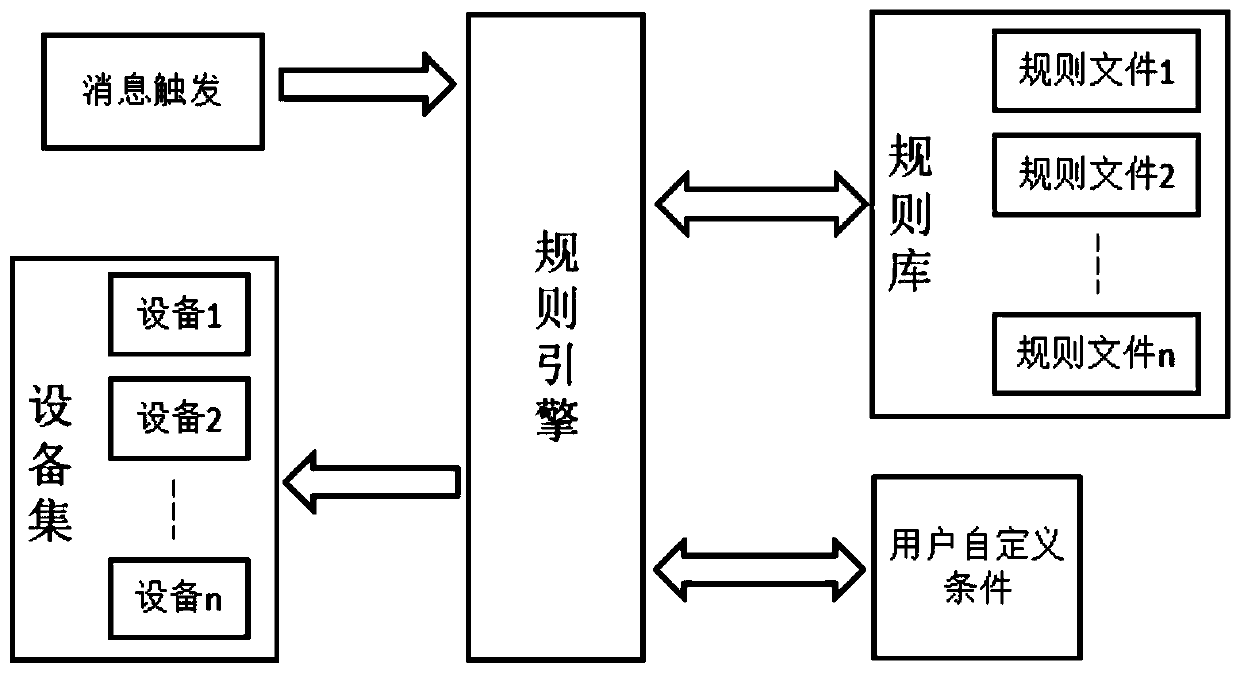

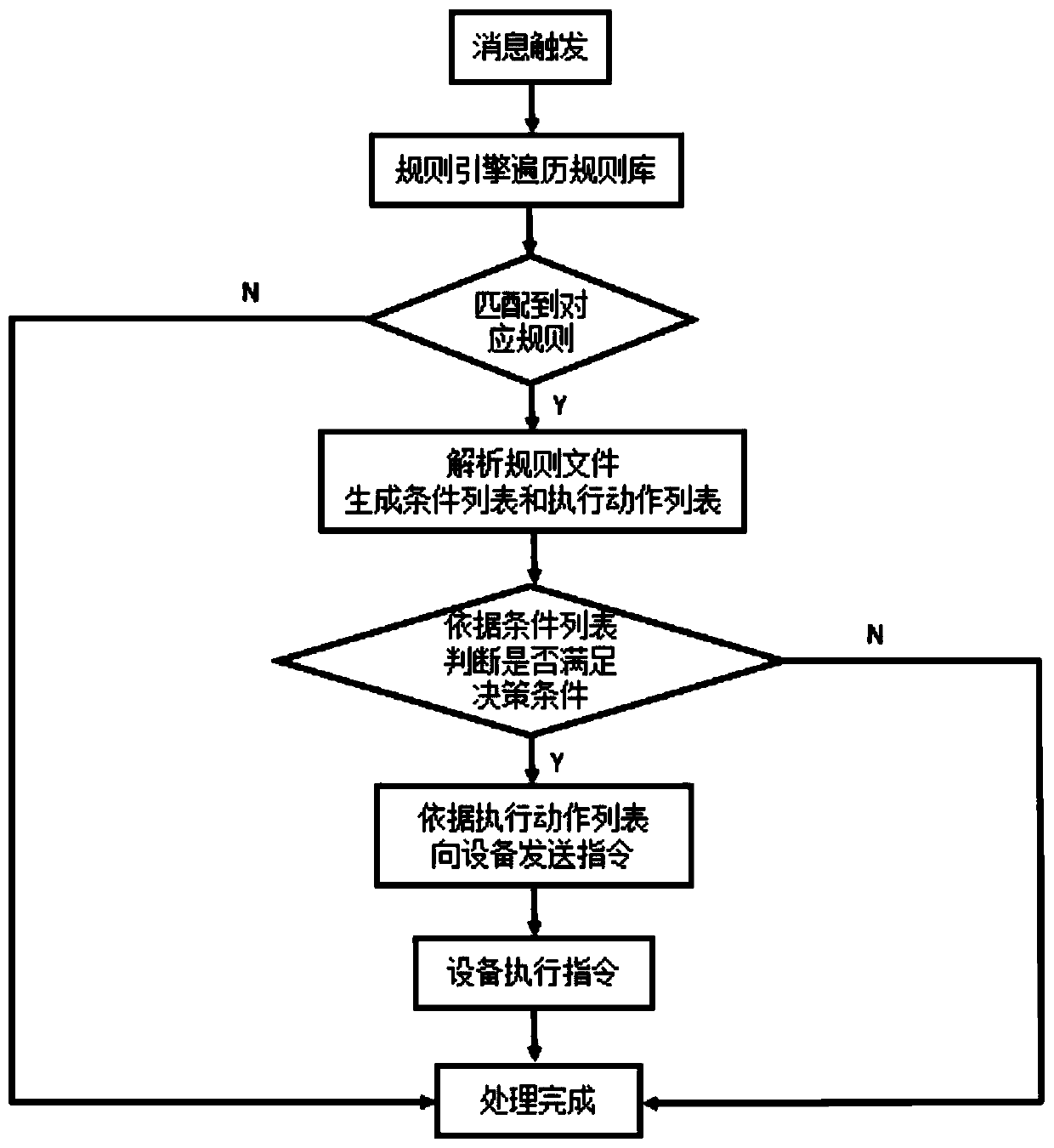

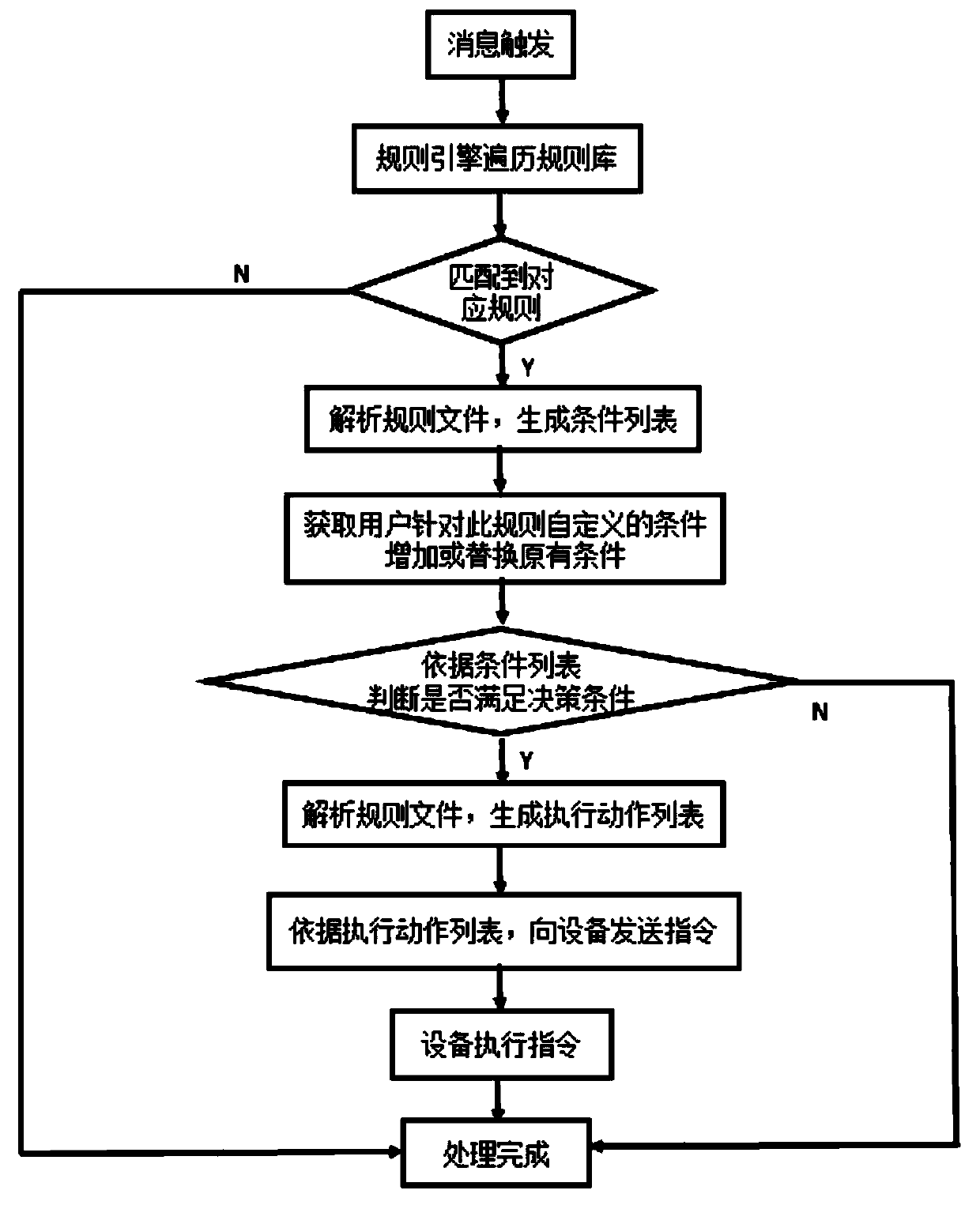

Equipment control system and method based on rule files

ActiveCN110737439AReduce iteration and maintenance costsPromote industrial development and applicationCode compilationInternet of ThingsOperating system

The invention relates to the technical field of Internet-of-things, and discloses an equipment control system and a method based on a rule file, which are used for solving the problems of applicationiteration and maintenance cost in the conventional equipment control system and the method. The system comprises a rule base, a message obtaining module and a rule engine. An application rule file isstored in the rule base; the rule engine matches a trigger message rule in a rule base according to the trigger message, and determines a rule file corresponding to the trigger message rule after successful matching; generating a condition list and an execution action list according to the rule file; and obtaining a parameter value of the parameter name according to the combination sequence in thecondition list, carrying out logical operation on the parameter value and the condition value according to an operator, judging whether a decision condition is met, and when the decision condition ismet, determining equipment for specifically executing the instruction according to the equipment class name contained in the execution action list, and sending the instruction to the corresponding equipment. The method is suitable for Internet-of-things equipment control.

Owner:SICHUAN CHANGHONG ELECTRIC CO LTD

Gate-level netlist reduction for simulating target modules of a design

InactiveUS7606692B2Increase turnaround timeShorten the timeCAD circuit designProgram controlComputer architectureEngineering

A method for analyzing a circuit design in preparation for a simulation. The method generally includes the steps of (A) marking each of a plurality of modules between a target module of the modules and a top module of the modules in a hierarchy of the circuit design as a first type by traversing upward through the hierarchy starting from the target module, (B) marking each of the modules as a second type where a parent module of the modules is marked as the first type by traversing downward through the hierarchy starting from the top module and (C) marking each of the modules as a third type where the parent module is not marked as the keep type by traversing downward through the hierarchy starting from the top module.

Owner:BELL SEMICON LLC

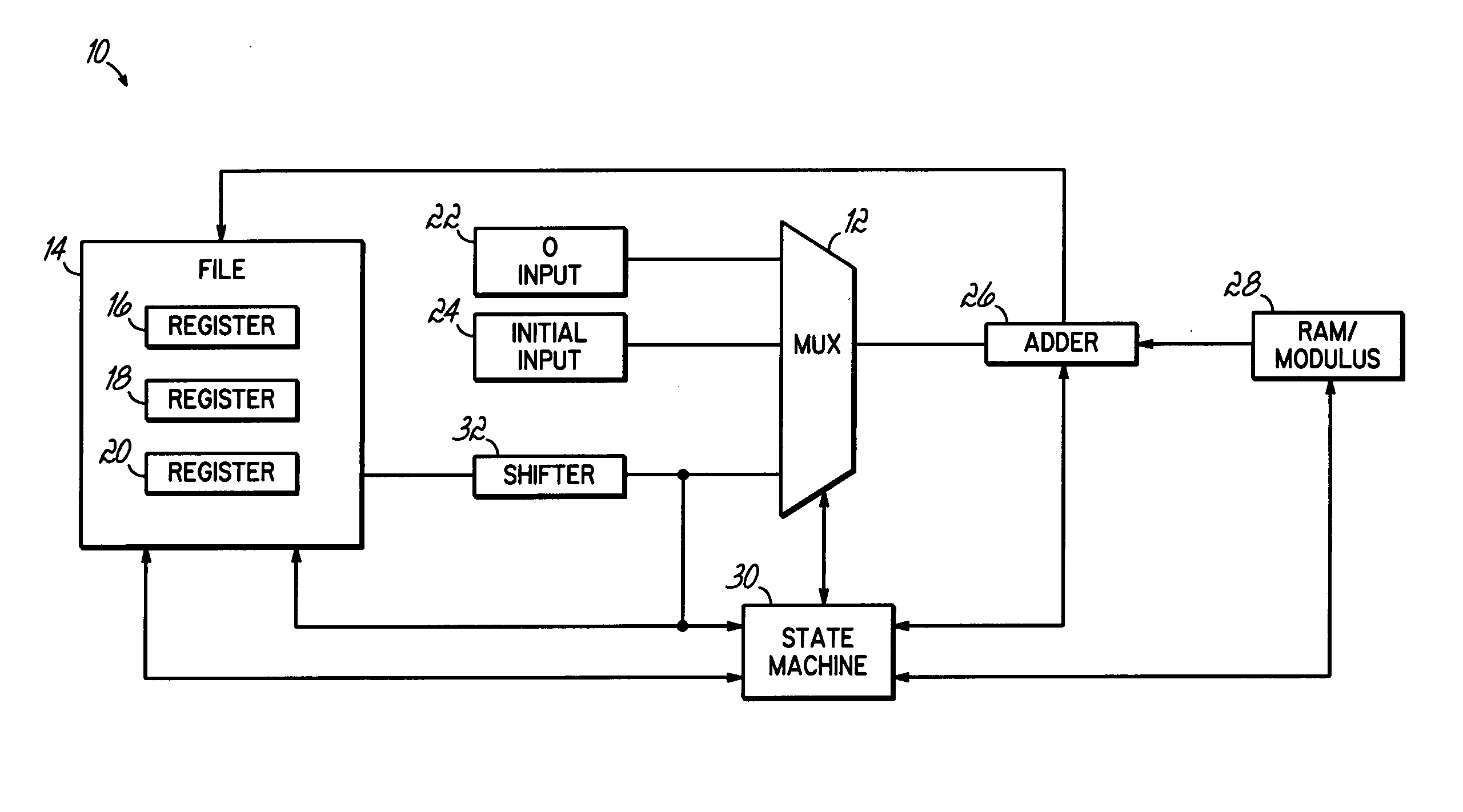

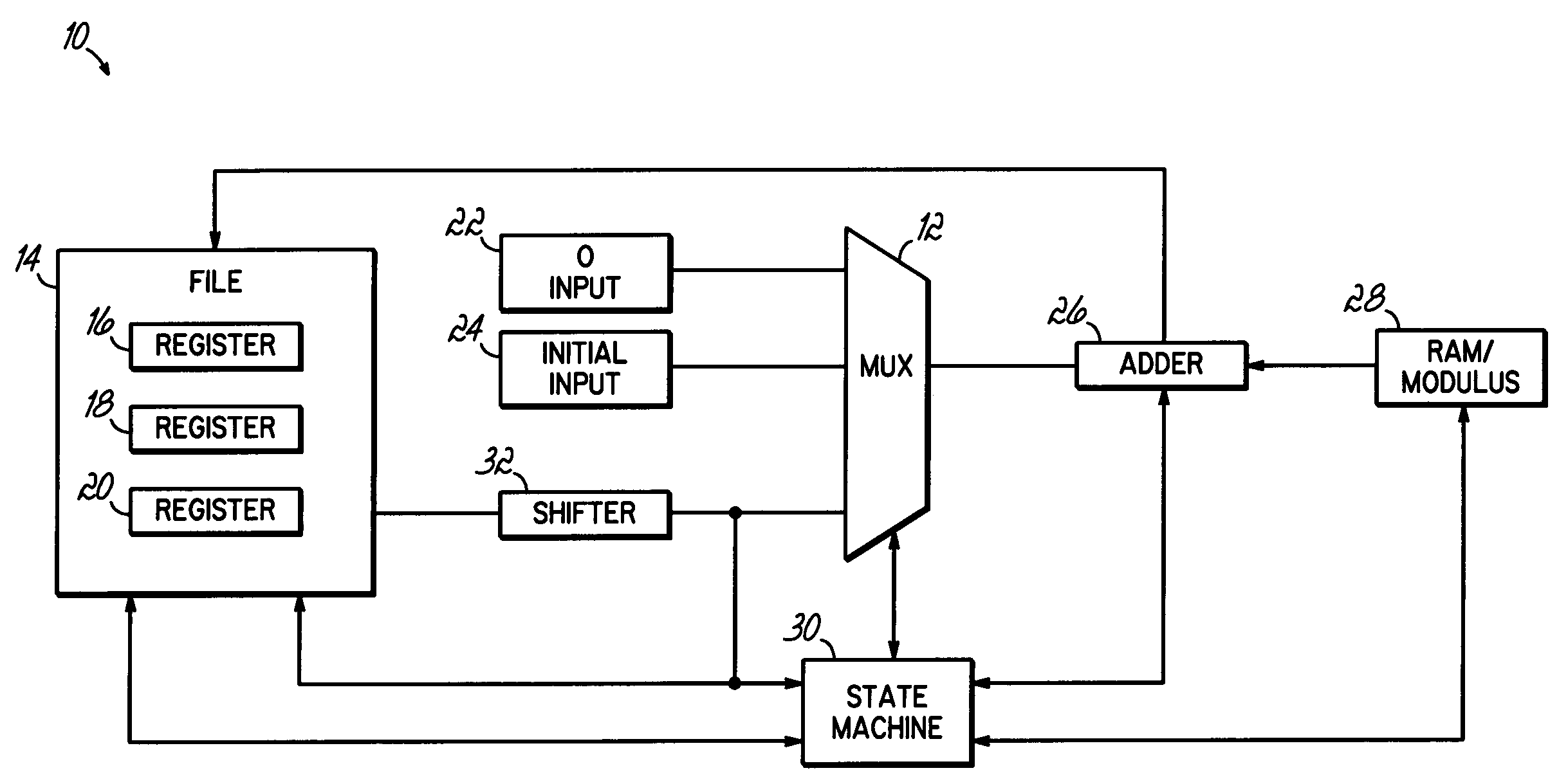

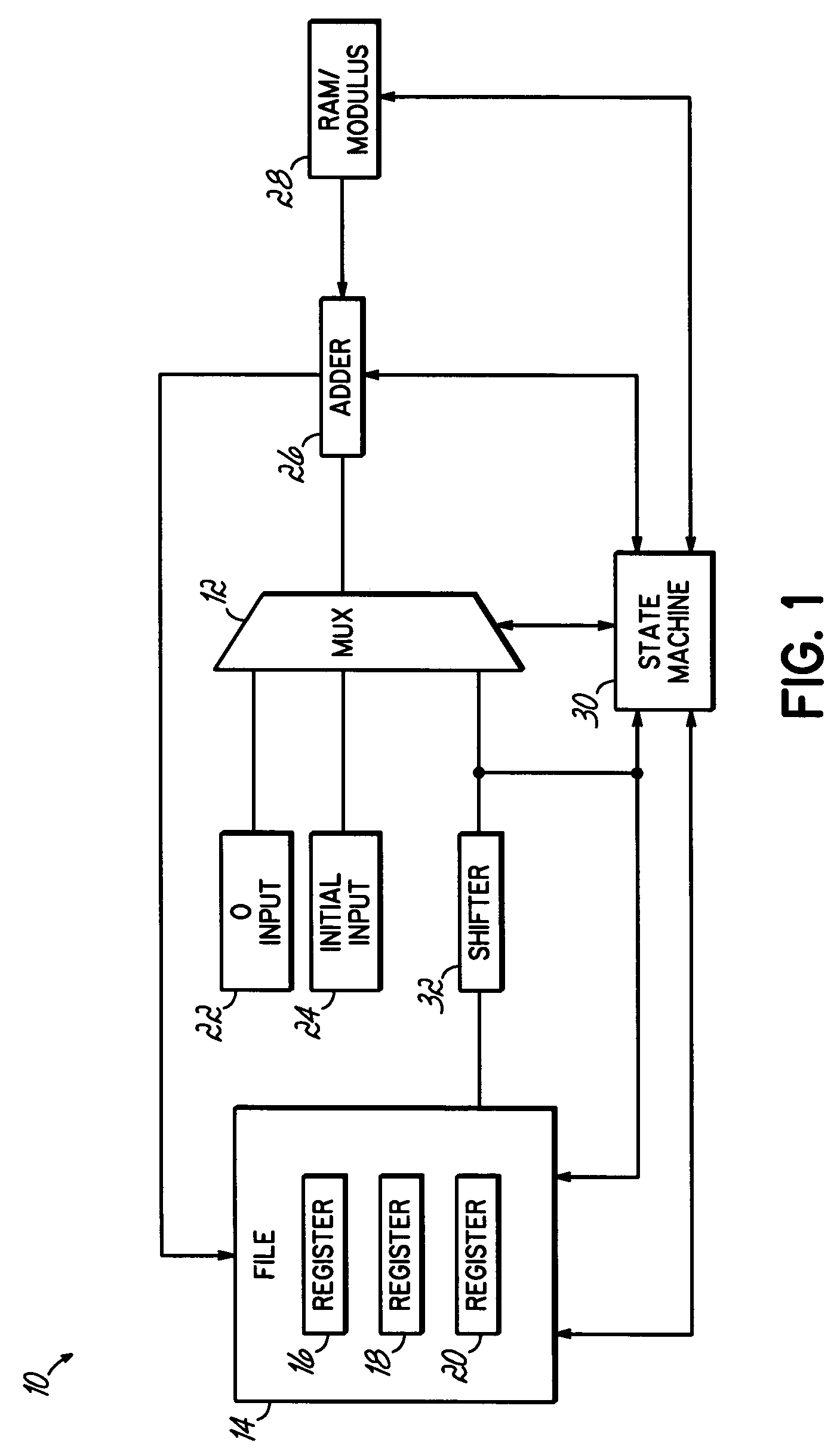

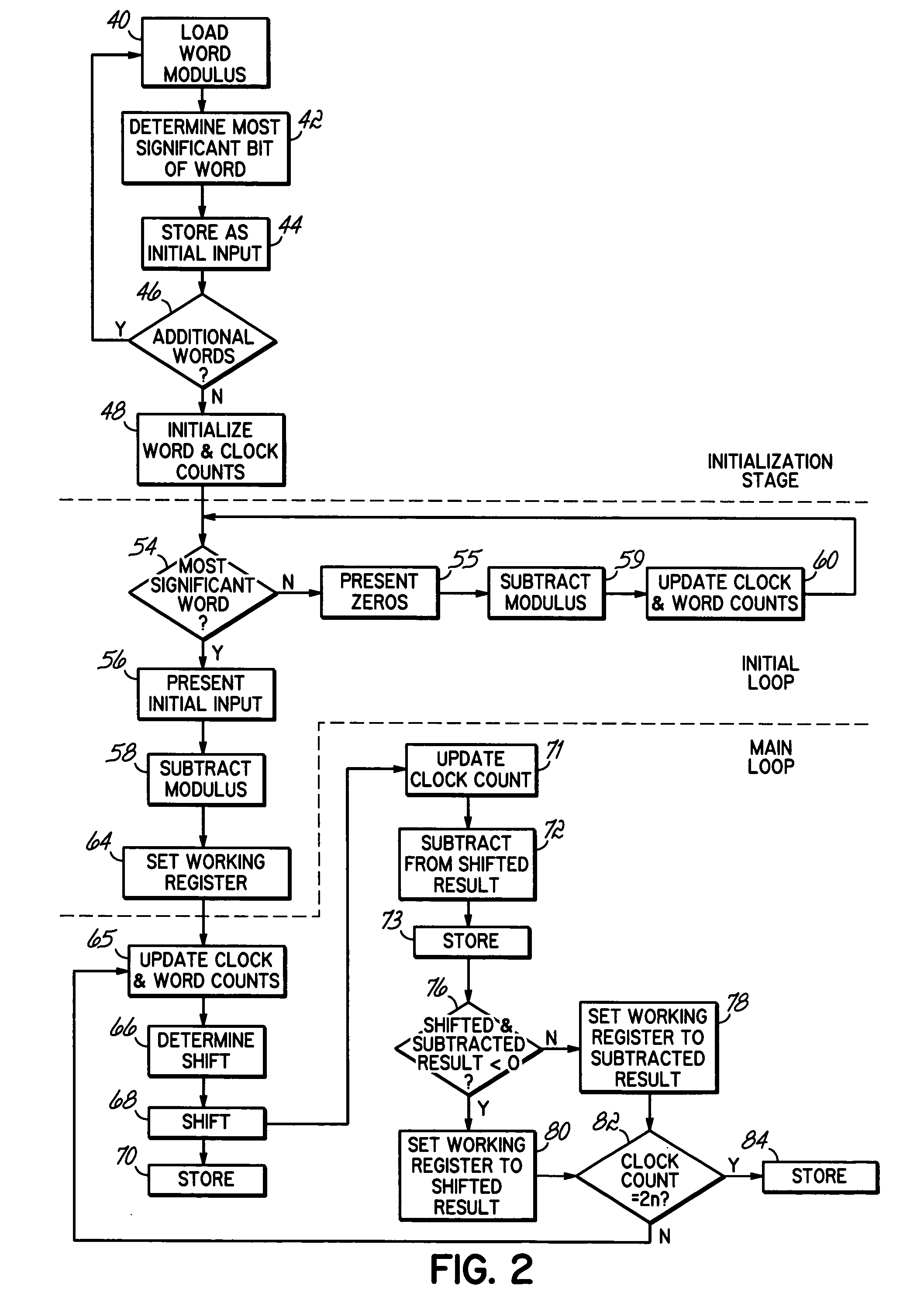

Correction parameter determination system

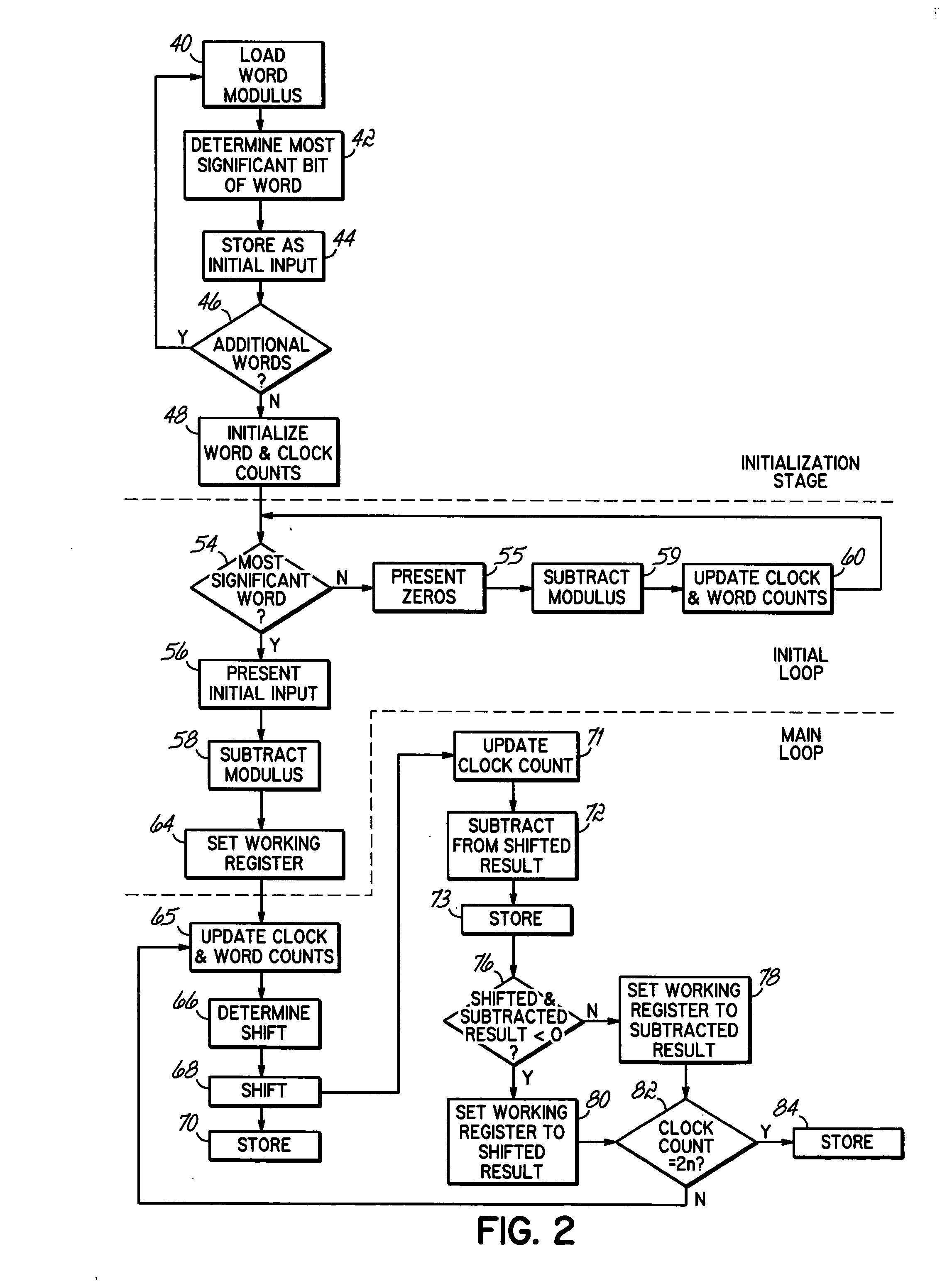

ActiveUS20050240836A1Reduce numberAccelerate determinationCode conversionDigital computer detailsSingle loopComputer science

An circuit arrangement and method for reducing the number of processing loops needed to generate an error correction parameter used in the Montgomery method. An initial input to a processing loop is set to a value equal to the modulus, left shifted one register position. Values of the working register are shifted multiple positions during a single loop iteration, and a shifted result is subtracted and compared to zero to determine subsequent contents of the working register.

Owner:III HLDG 6

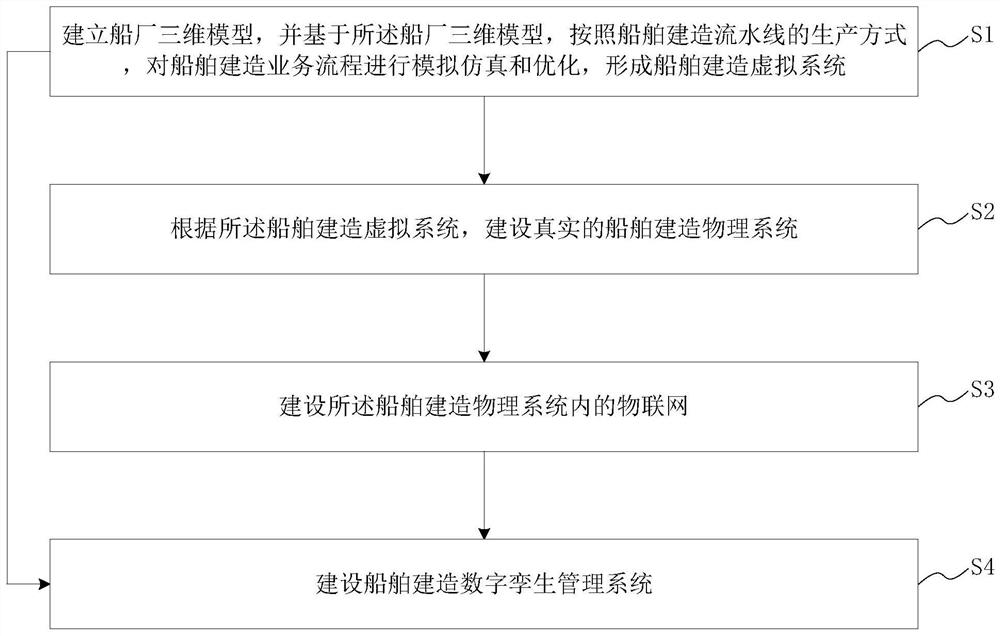

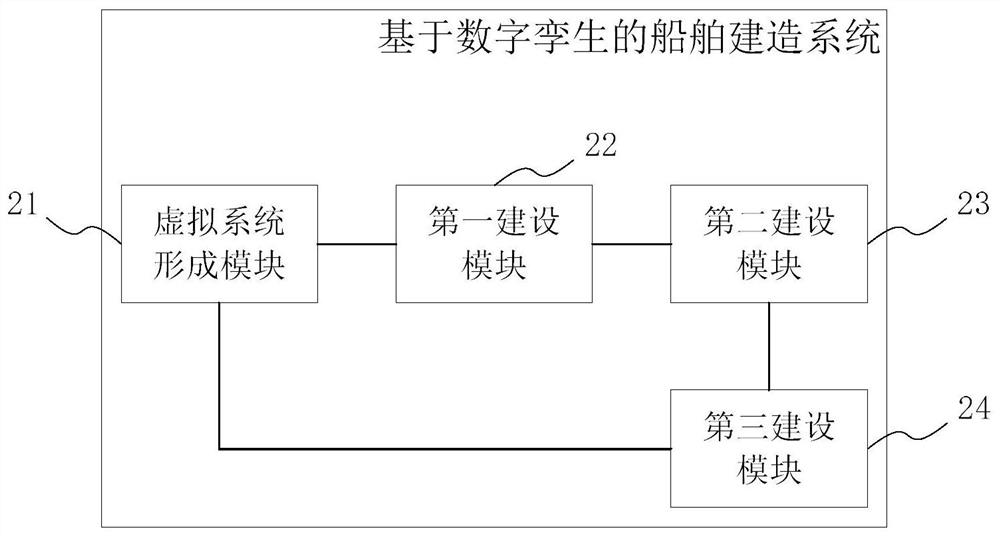

Shipbuilding method and system based on digital twinning, medium and terminal

PendingCN113268804AIncrease productionReduce quality defectsGeometric CADVirtual/augmented realityThree dimensional modelSystems engineering

The invention provides a shipbuilding method and system based on digital twinning, a medium and a terminal. The method comprises the following steps of establishing a shipyard three-dimensional model, and performing analog simulation and optimization on a shipbuilding business process according to a production mode of a shipbuilding assembly line based on the shipyard three-dimensional model to form a shipbuilding virtual system; establishing a real ship building physical system; establishing the Internet-of-things in the shipbuilding physical system; establishing a ship construction digital twinning management system; through data fusion between a ship construction virtual system and a physical system, various services such as intelligent production scheduling, collaborative process planning, product quality management, production process management and control, equipment health management, energy efficiency optimization analysis and the like are provided for ship construction; the method is used for solving the problems that in the actual ship building process, part machining and installation information is not clear, resource allocation is not reasonable, and equipment state information is not known, the ship building efficiency is improved, and the ship building cost is reduced.

Owner:JIANGNAN SHIPYARD GRP CO LTD

Automatic estimation of weldgun size using section geometry

ActiveUS20100198384A1Reduce iterative processGood choiceArc welding apparatusComputation using non-denominational number representationSimulationStructural engineering

A method for estimating a plurality of geometrical parameters defining the size of a weld gun that has particular application for automatically selecting a weld gun for a welding operation. The method includes iteratively estimating a plurality of geometric parameters based on part section curves corresponding to a direction of approach of the weld gun to weld point of the plurality of weld points. Thereafter, a set of valid weld gun sizes are calculated based on the estimated plurality of geometric parameters. Similarly all the valid weld gun sizes are calculated corresponding to each of the weld gun approach direction. Further, each set of the valid gun sizes are estimated for each of the weld point for the welding operation. Finally, a weld gun for performing the welding operation is selected based on the set of weld gun sizes corresponding to the welding operation.

Owner:GM GLOBAL TECH OPERATIONS LLC

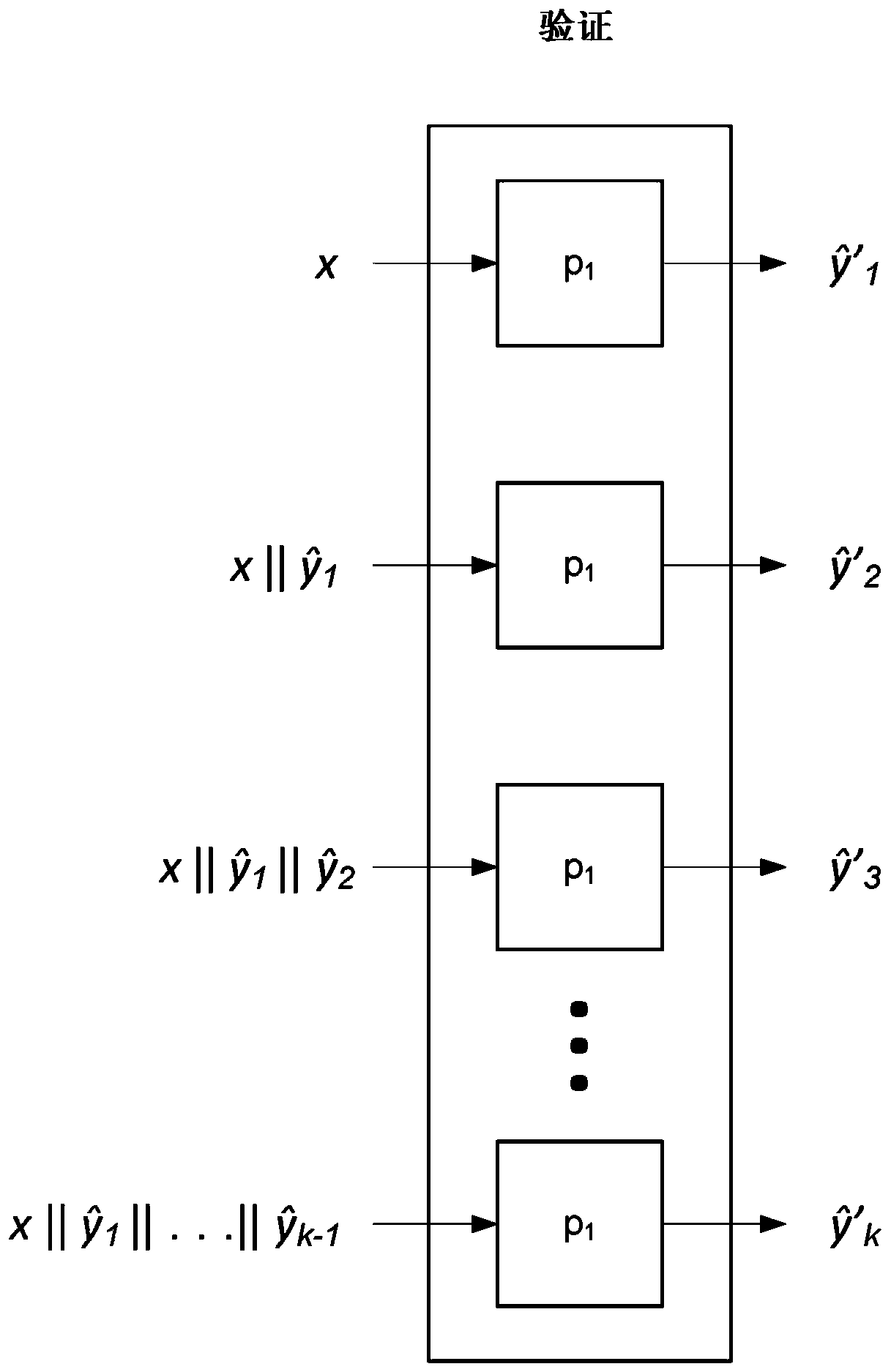

Parallel decoding using auto-regression machine learning model

PendingCN110245359AHigh speedImprove spawn speedNatural language translationMathematical modelsAlgorithmSequence model

The invention relates to parallel decoding using an auto-regression machine learning model, and provides a method, system, and device for generating output from auto-regression to a sequence model in a parallel mode, including computer program encoded in a computer storing medium. In one aspect, a block parallel decoding method uses a fact that some frameworks can score a sequence in sub-linear time. Prediction is generated for multiple time steps at a time, then the longest prefix verified by the scoring model is returned, and the method can improve the speed of greedy decoding on the premise that the performance is not influenced.

Owner:GOOGLE LLC

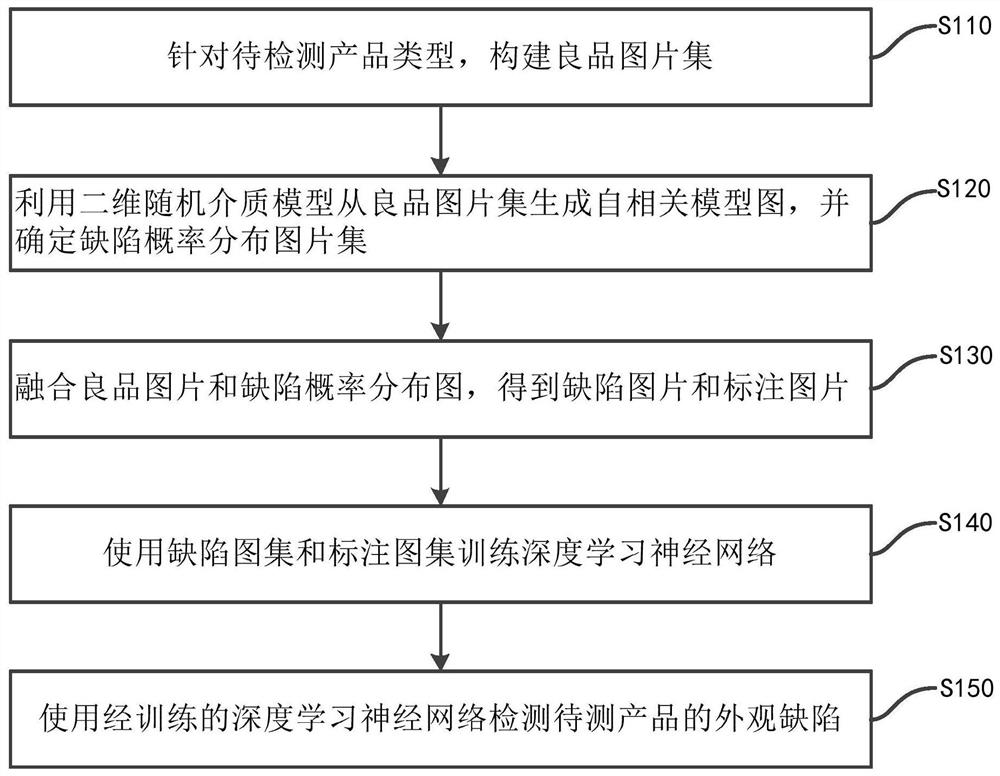

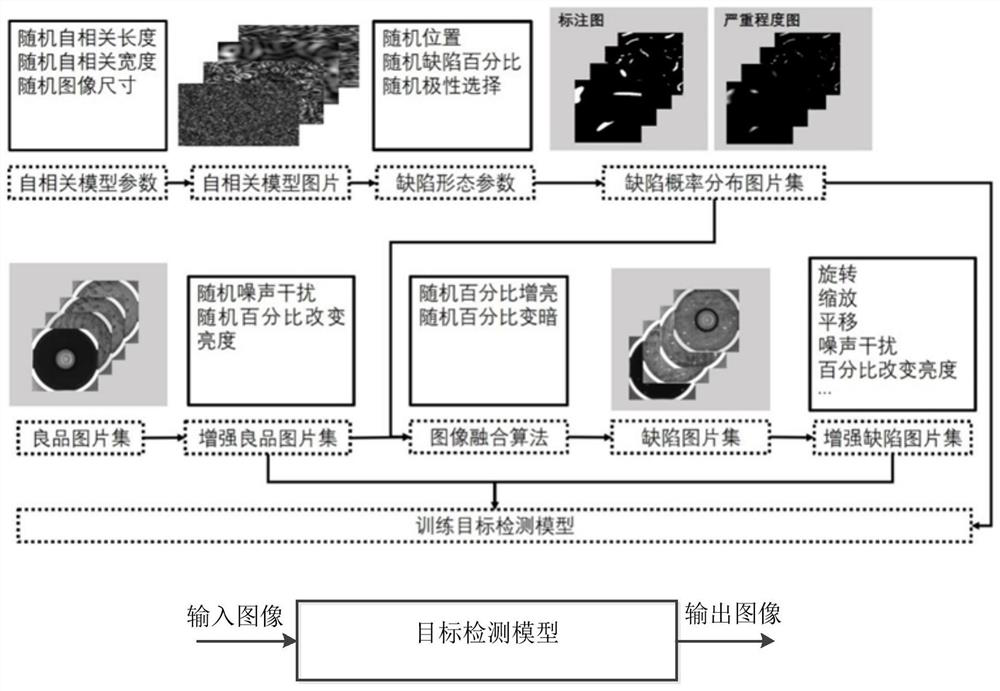

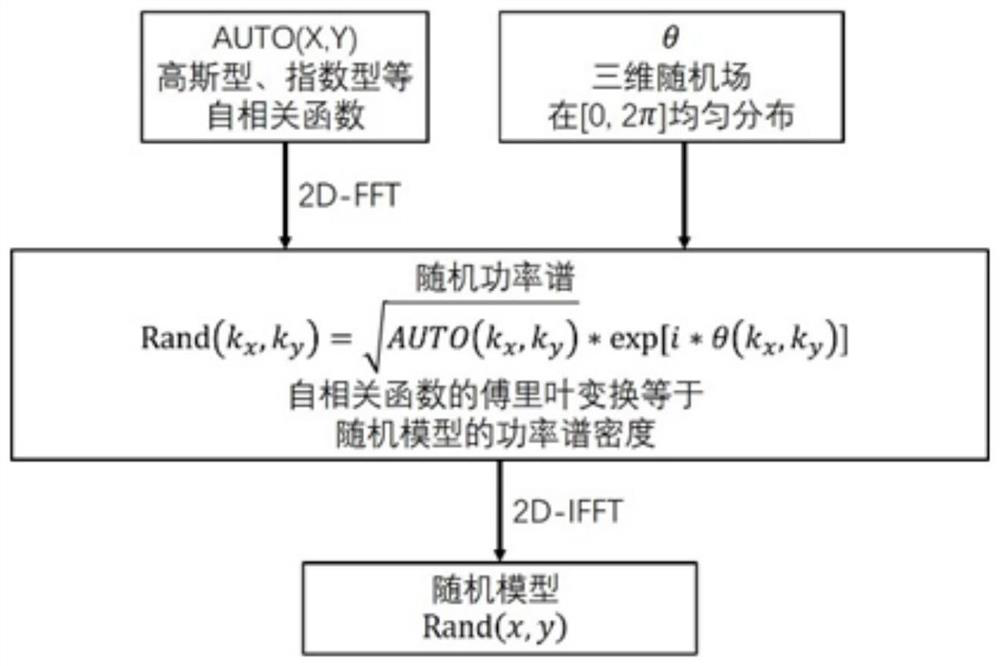

Product appearance defect detection method based on random defect model

PendingCN112907543AReduce iterative processImage enhancementImage analysisPattern recognitionAlgorithm

The invention discloses a product appearance defect detection method based on a random defect model. The method comprises the following steps: for a to-be-detected product, collecting good product pictures without appearance defects to form a good product picture set; based on the good product picture set, utilizing a two-dimensional random medium model to generate an autocorrelation model graph meeting set autocorrelation model parameters; generating a defect probability distribution picture set meeting set defect morphological parameters based on the self-correlation model graph; fusing the generated good product pictures and the defect probability distribution diagram to obtain a defect picture set and a corresponding marking picture set; training a deep learning neural network by using the defect picture set and the labeled picture set; and performing appearance defect detection on a to-be-detected product by using the trained deep learning neural network. According to the method, the defect picture set can be automatically generated for deep learning network training only by using the good product pictures, and the method can be applied to product quality detection of an industrial production line.

Owner:胡志雄

Correction parameter determination system

ActiveUS7278090B2Reduce in quantityImprove determinationDigital computer detailsCode conversionProcessor registerComputer science

An circuit arrangement and method for reducing the number of processing loops needed to generate an error correction parameter used in the Montgomery method. An initial input to a processing loop is set to a value equal to the modulus, left shifted one register position. Values of the working register are shifted multiple positions during a single loop iteration, and a shifted result is subtracted and compared to zero to determine subsequent contents of the working register.

Owner:III HLDG 6

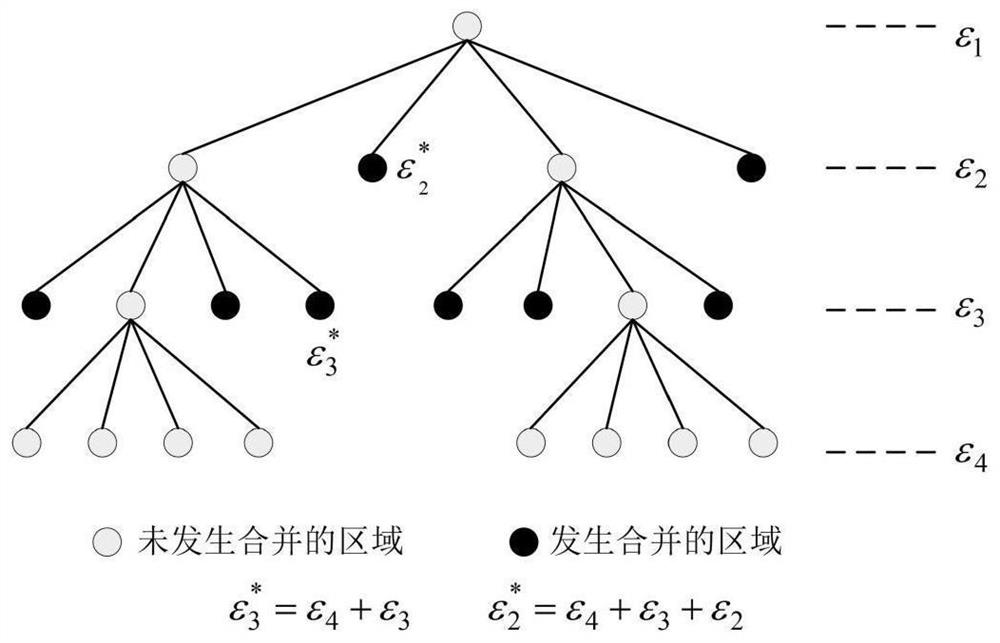

Position big data statistical publishing method and system

PendingCN113343279AImprove forecasting efficiencyReduce iterations and redundant operationsDigital data protectionSpacetimeMesh grid

The invention relates to a position big data statistical publishing method and system. The method comprises the following steps: dividing collected historical position big data into a plurality of first sets according to time units; dividing each first set into a plurality of second sets according to the release time interval; dividing the two-dimensional space region corresponding to each second set into a plurality of grids; recording whether the grids in the coverage area are merged or not according to a set grid area merging condition; taking a record whether to be merged as a division structure matrix; forming a three-dimensional space-time sequence by the division structure matrixes at the moment of the same release time, and training a deep learning model by taking the three-dimensional space-time sequence as input and taking the corresponding division structure matrixes as output; obtaining a prediction division structure according to the trained deep learning model; obtaining a noise adding release statistical value of each sub-region in the prediction division structure; and according to the publishing time sequence, publishing the noise adding publishing statistical value corresponding to each prediction division structure matrix. According to the invention, the execution efficiency of the release algorithm is improved.

Owner:LANZHOU UNIVERSITY OF TECHNOLOGY

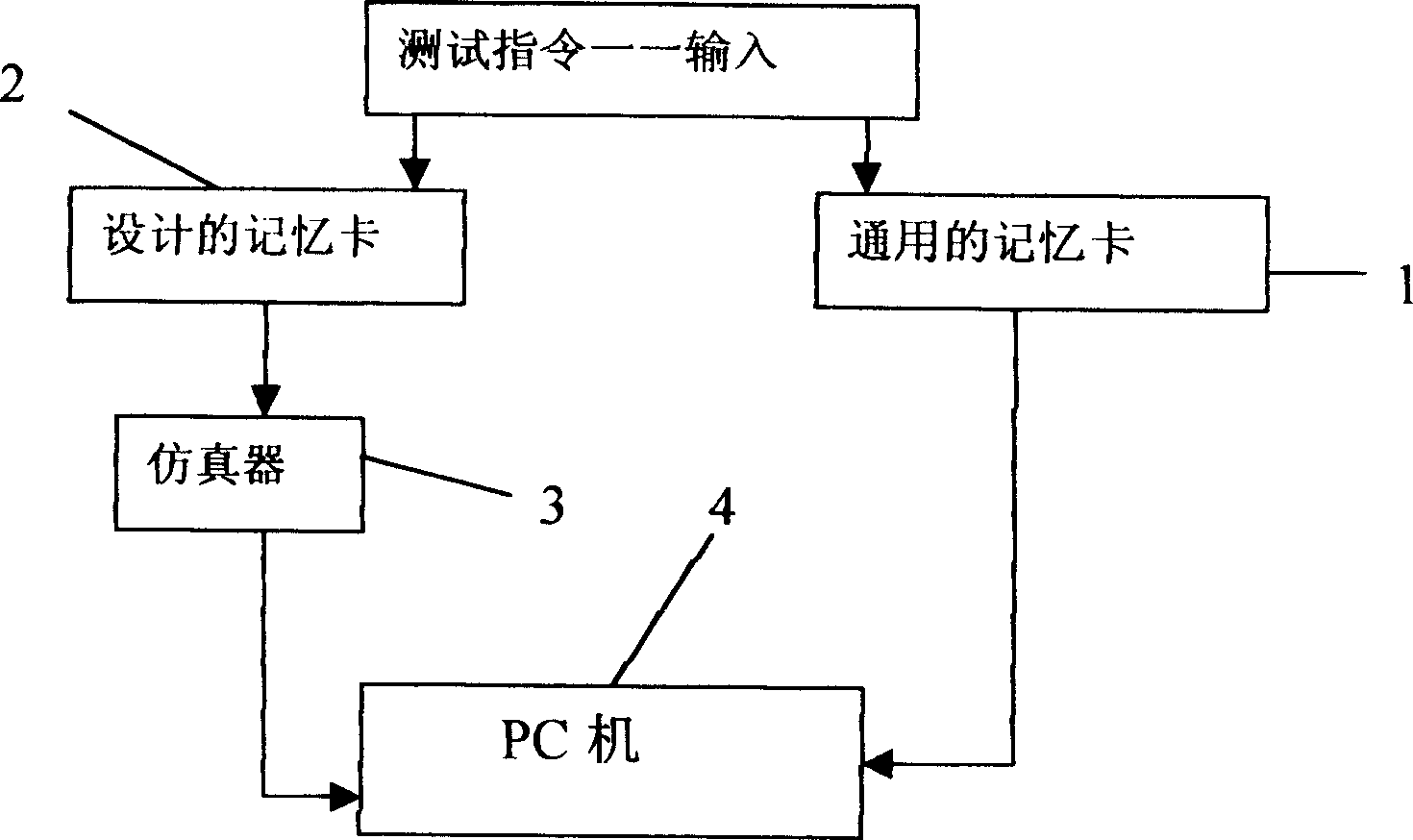

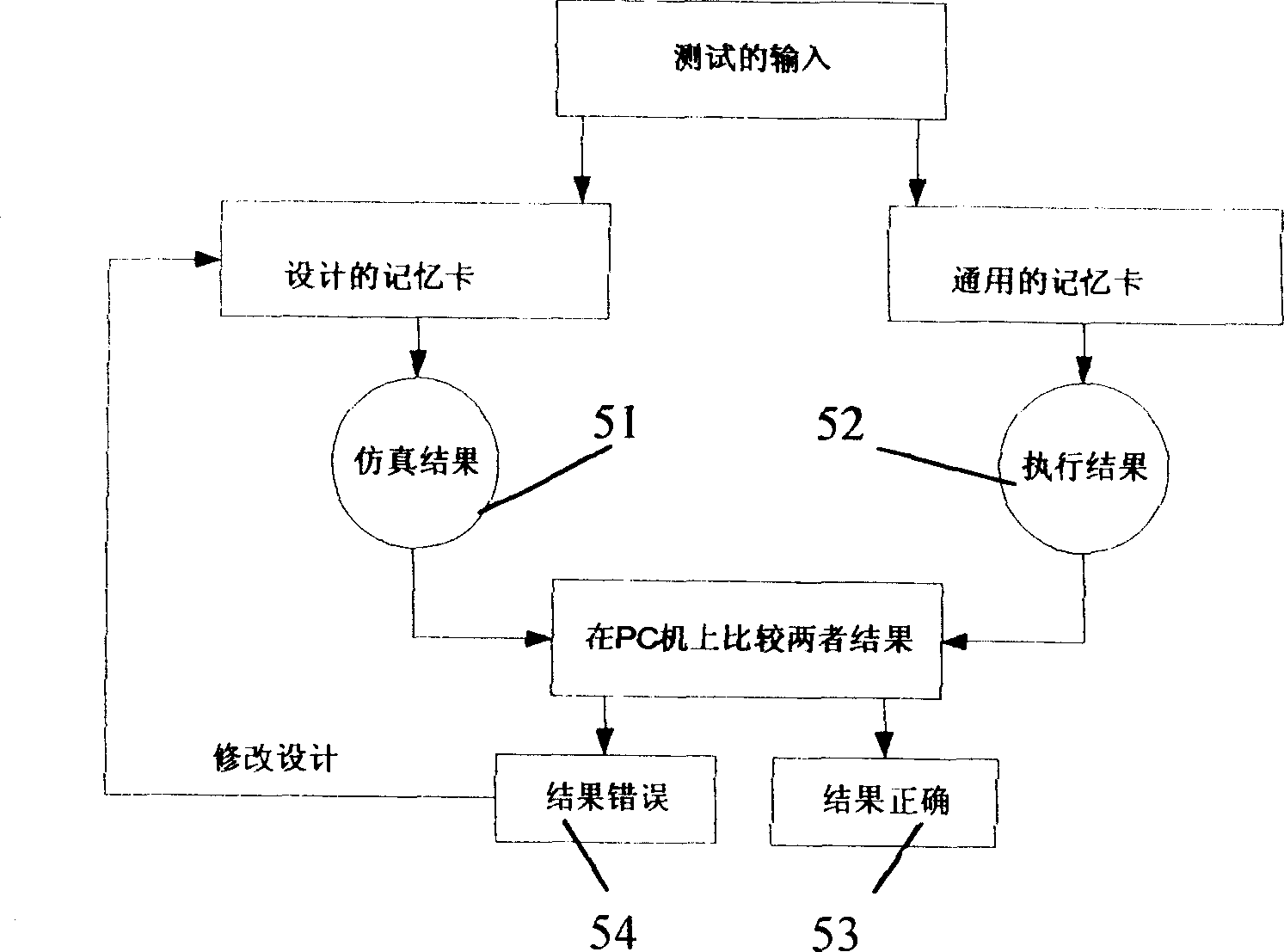

RTL level real-time hardware testing platform in memory card and test method thereof

InactiveCN1567556AReduce errorsReduce iterative processSemiconductor/solid-state device testing/measurementElectronic circuit testingTest platformMemory cards

The invention relates to a RTL-level real-time hardware testing platform in a memory card and its testing method, the platform including a universal memory card, a designed memory card, an emulator and a PC; inputting N testing instructions one by one in the universal memory card and inputting the corresponding result into the PC; similarly, inputting N testing instructions one by one into the designed memory card, using a Verilog HDL or VHDL emulator to obtain the test result and inputting the corresponding result into the PC; the N instructions mean the needed number of the testing instructions corresponding to a certain designed memory card; comparing the two results: if they are the same, it shows the hardware of the designed memory card exact or makes real-time modification of the hardware; the invention has the beneficial effects: because it uses existing standard for testing to reduce the artificial mistake factors in designing and the iterative process of designing and the testing efficiency is higher.

Owner:上海华园微电子技术有限公司

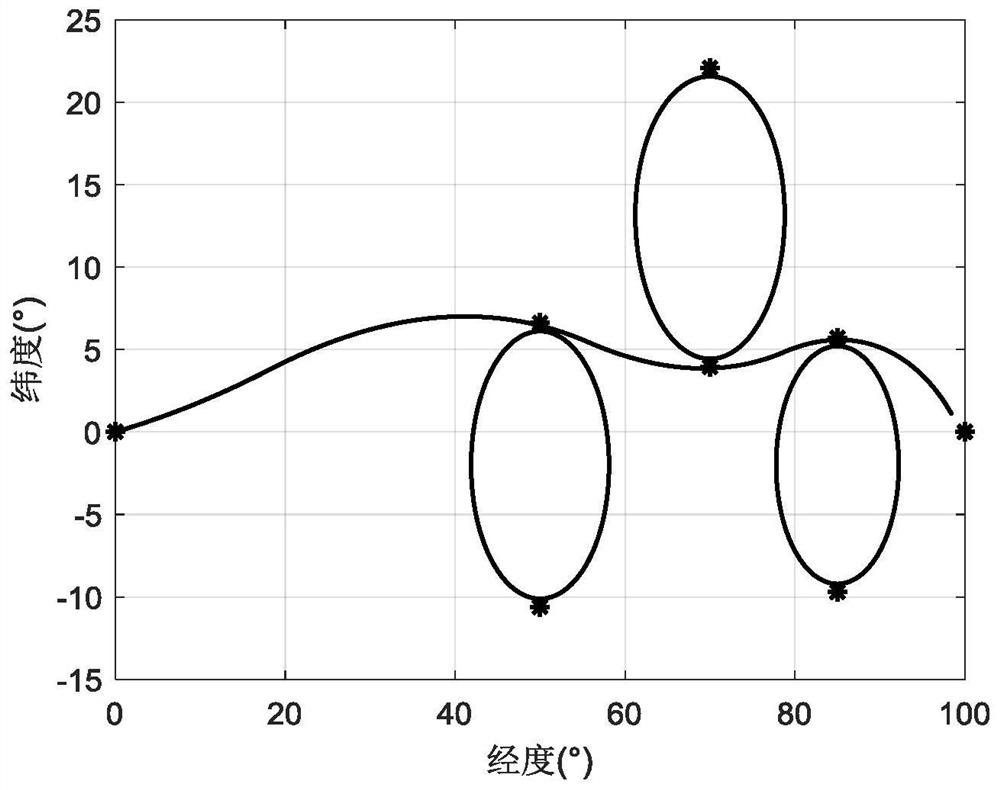

Aircraft no-fly zone avoidance trajectory planning method based on path point optimization

ActiveCN113093789AImprove efficiencyImprove global performanceAttitude controlPosition/course control in three dimensionsNo-fly zoneFlight vehicle

The invention provides an aircraft no-fly zone avoidance trajectory planning method based on path point optimization. The method comprises the following specific steps: 1, designing a path point optimization scheme; 2, designing transverse and longitudinal flight profiles; and 3, designing a profile tracking control law and guidance logic. Through the steps, path point selection and trajectory planning of a hypersonic flight vehicle can be realized at the same time, upper-layer task selection and lower-layer planning execution are integrally processed, iteration of a flight profile is reduced, trajectory planning efficiency and overall performance are improved, and good autonomy and universality are achieved; and the method disclosed by the invention is scientific and good in manufacturability, and has wide popularization and application values.

Owner:BEIHANG UNIV

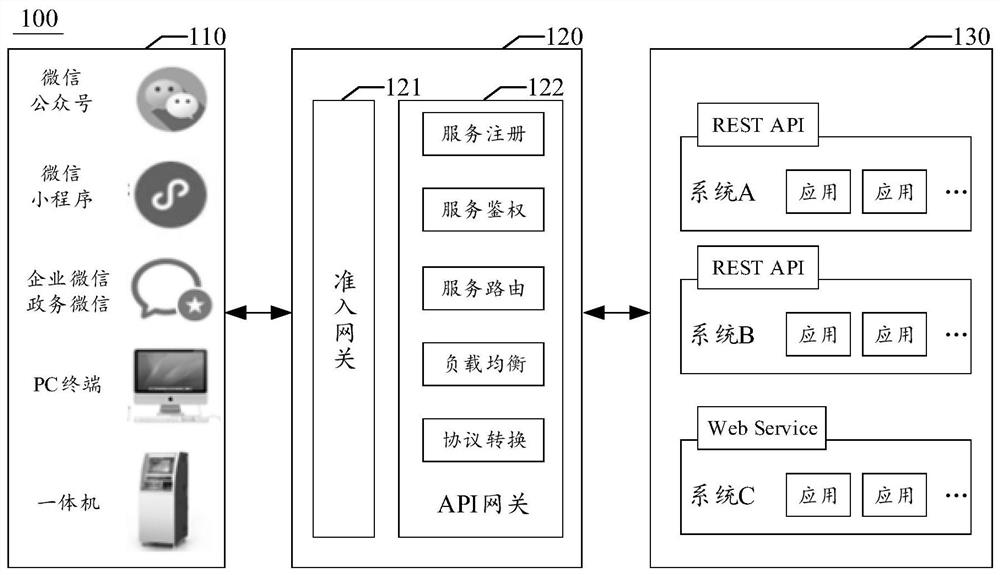

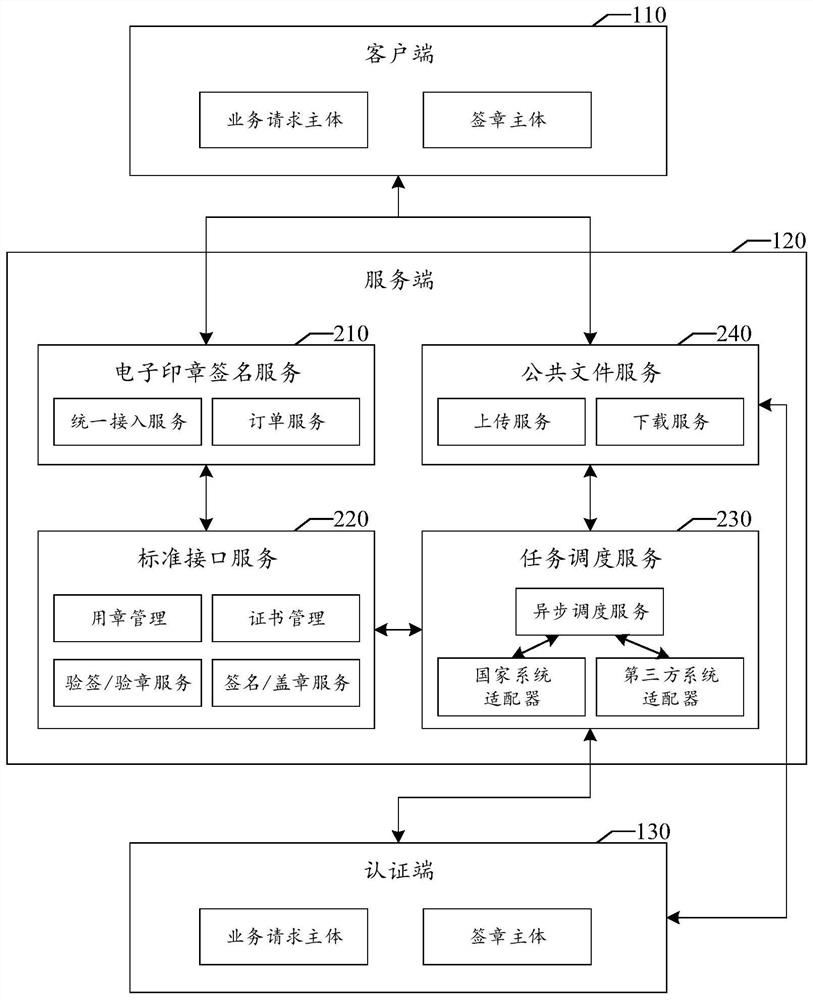

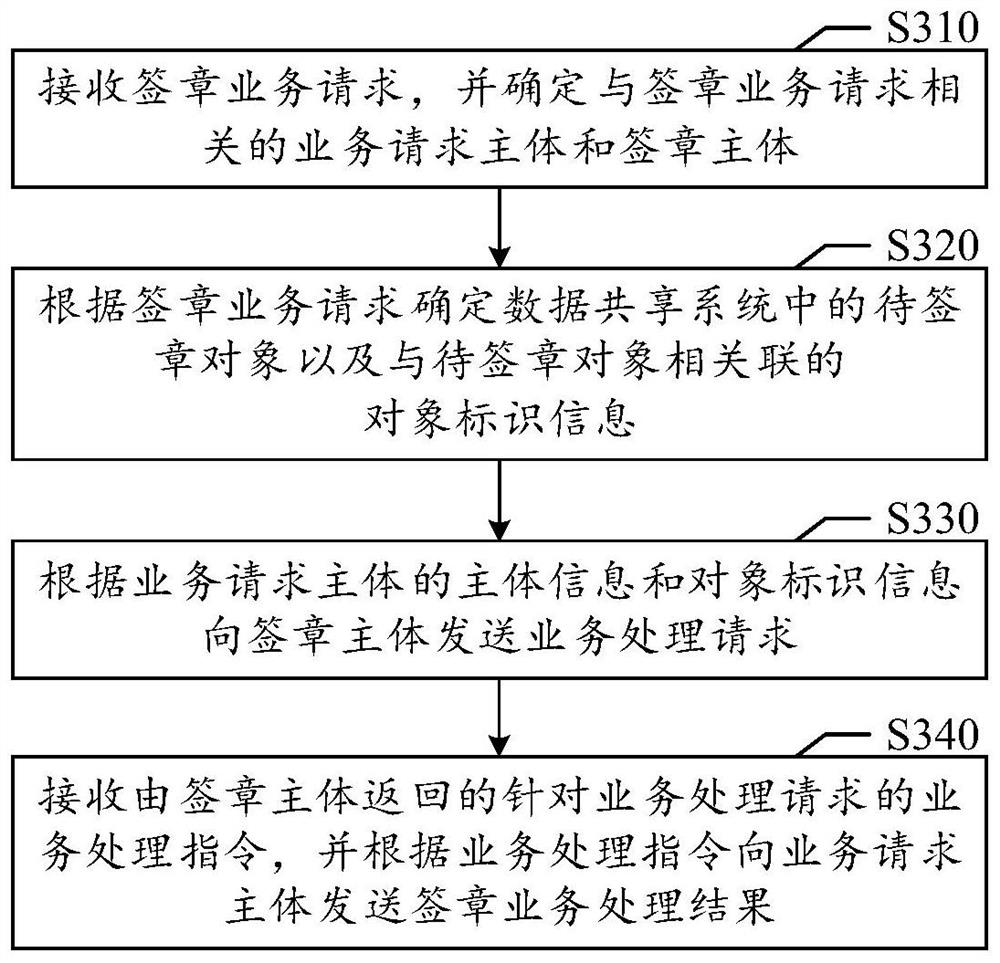

Signature business processing method, device, medium and electronic equipment

ActiveCN111182020BImprove efficiencyQuality improvementDigital data protectionTransmissionProcessing InstructionComputer network

The present disclosure relates to the field of computer technology, and provides a signature service processing method, a signature service processing device, a computer-readable medium, and electronic equipment. The method includes: receiving a seal service request, and determining the service request subject and the seal subject related to the seal service request; determining the object to be signed in the data sharing system and the object to be signed according to the seal service request The object identification information associated with the object to be signed; send a service processing request to the signature subject according to the subject information of the business request subject and the object identification information; receive the service request returned by the signature subject Processing the requested business processing instruction, and sending the signature business processing result to the business request subject according to the business processing instruction. The method improves the efficiency and quality of the electronic signature service, and reduces the consumption of manpower and material resource costs.

Owner:TENCENT TECH (SHENZHEN) CO LTD

Software architecture recovery method based on functional structure

ActiveCN112988216AEasy maintenanceHigh precisionReverse engineeringCOLA (software architecture)Algorithm

The invention relates to a software system structure recovery method based on a functional structure, belongs to the technical field of software system recovery, and solves the problem that a software system structure recovered by an existing mode is difficult to understand. The method comprises the following steps: constructing functional structure knowledge, wherein each function comprises a parent function and / or a child function and a function related class, and the lowest-layer function in the functions comprises function related classes; respectively mapping the parent function, the child function and the lowest layer function into a parent component, a child component and a leaf component, and dividing the function related class into the corresponding leaf component; removing classes included in the component from all classes to obtain unrecovered classes; calculating the correlation between each unrecovered class and each leaf component, and dividing the class with the correlation exceeding a correlation threshold value into the leaf component with the highest correlation; traversing all unrecovered classes repeatedly, and obtaining updated components; if all the classes are recovered, recovering the software system structure of the software based on the updated components.

Owner:BEIHANG UNIV

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com