Method for quickly converging establishment time after gate-level netlist modification

A gate-level netlist and fast convergence technology, applied in special data processing applications, instruments, electrical digital data processing, etc., can solve the problems of increasing project time cost and labor cost, long physical implementation cycle, and affecting chip design cycle, etc. Achieve the effect of shortening design time, saving manpower and time investment, and small investment

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

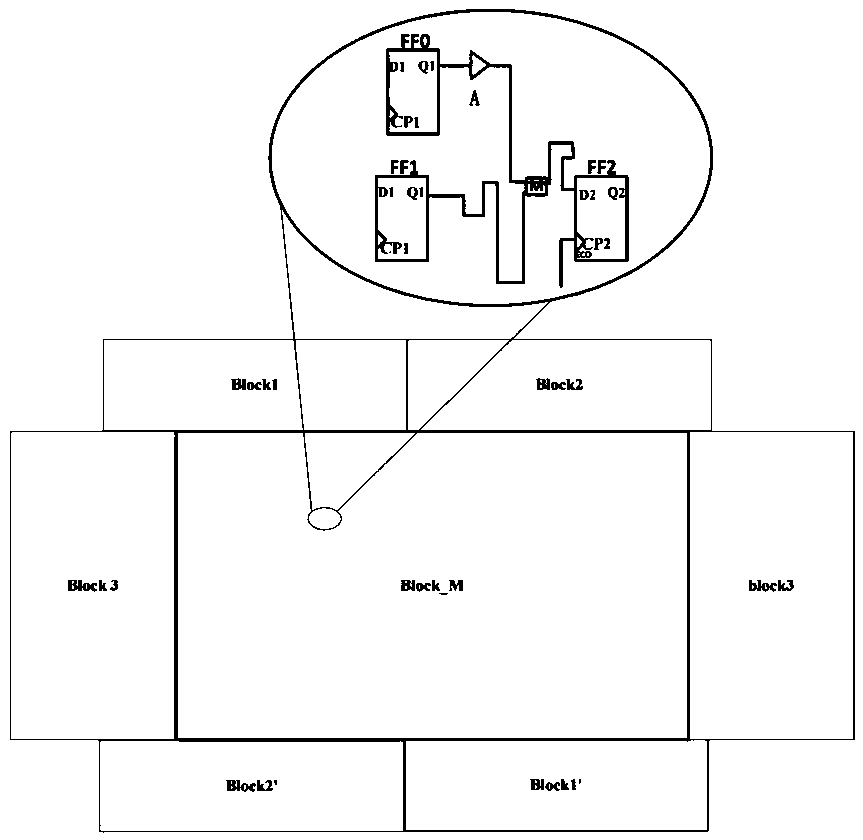

[0028] The following will take the design of a chip composed of 7 modules as an example, and further describe in detail the method for quickly converging and establishing time after the gate-level netlist is modified in the present invention.

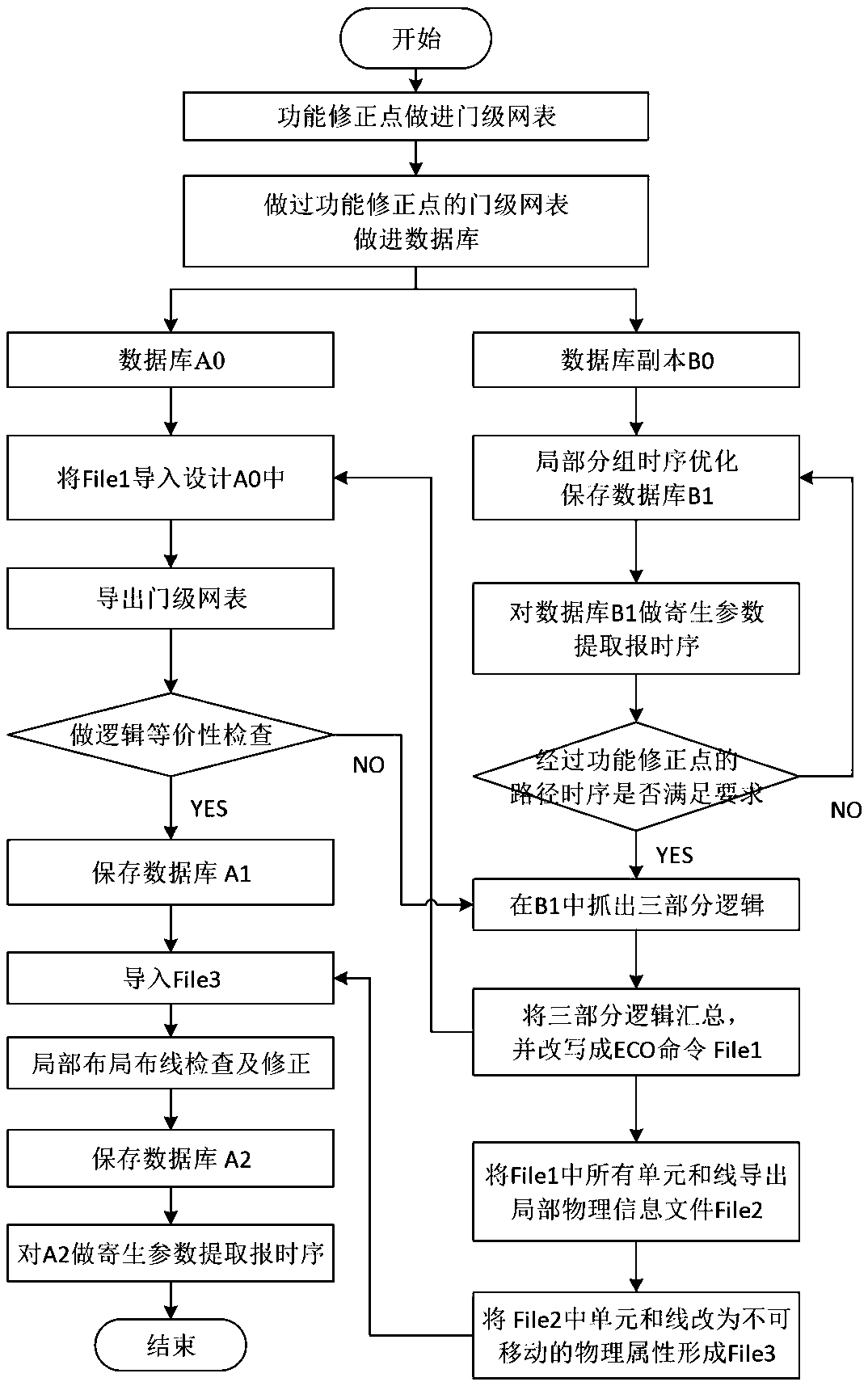

[0029] Such as figure 1 As shown, the implementation steps of the method for quickly converging the establishment time after the gate-level netlist is modified in this embodiment include:

[0030] 1) Put the function correction points into the gate-level netlist to obtain a new gate-level netlist, and put the new gate-level netlist into the database to obtain database A0 and generate a database copy B0;

[0031] 2) Extract function correction logic from database copy B0 after partial timing optimization and rewrite it into ECO command File1;

[0032] 3) Save the database A0 after reading the ECO command File1 as database A1; export all the units and lines in the ECO command File1 to the local physical information file File3;

[0033] ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com