Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

57 results about "Asynchronous computation" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Brief Introduction to Asynchronous Computation Expressions. Asynchronous operations, which use the Async<'a> type, are basically a way of writing Continuation Passing Style (CPS) programs.

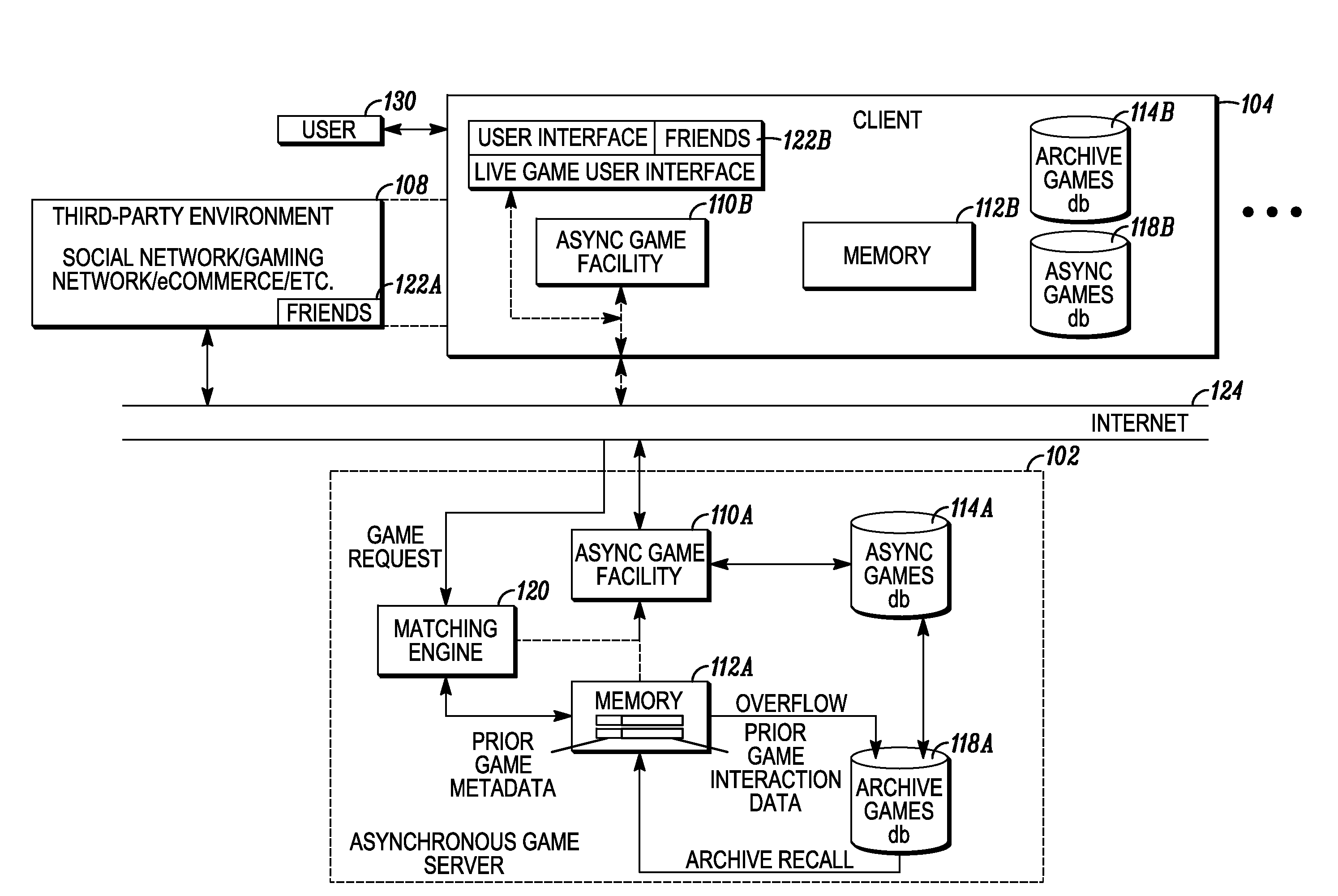

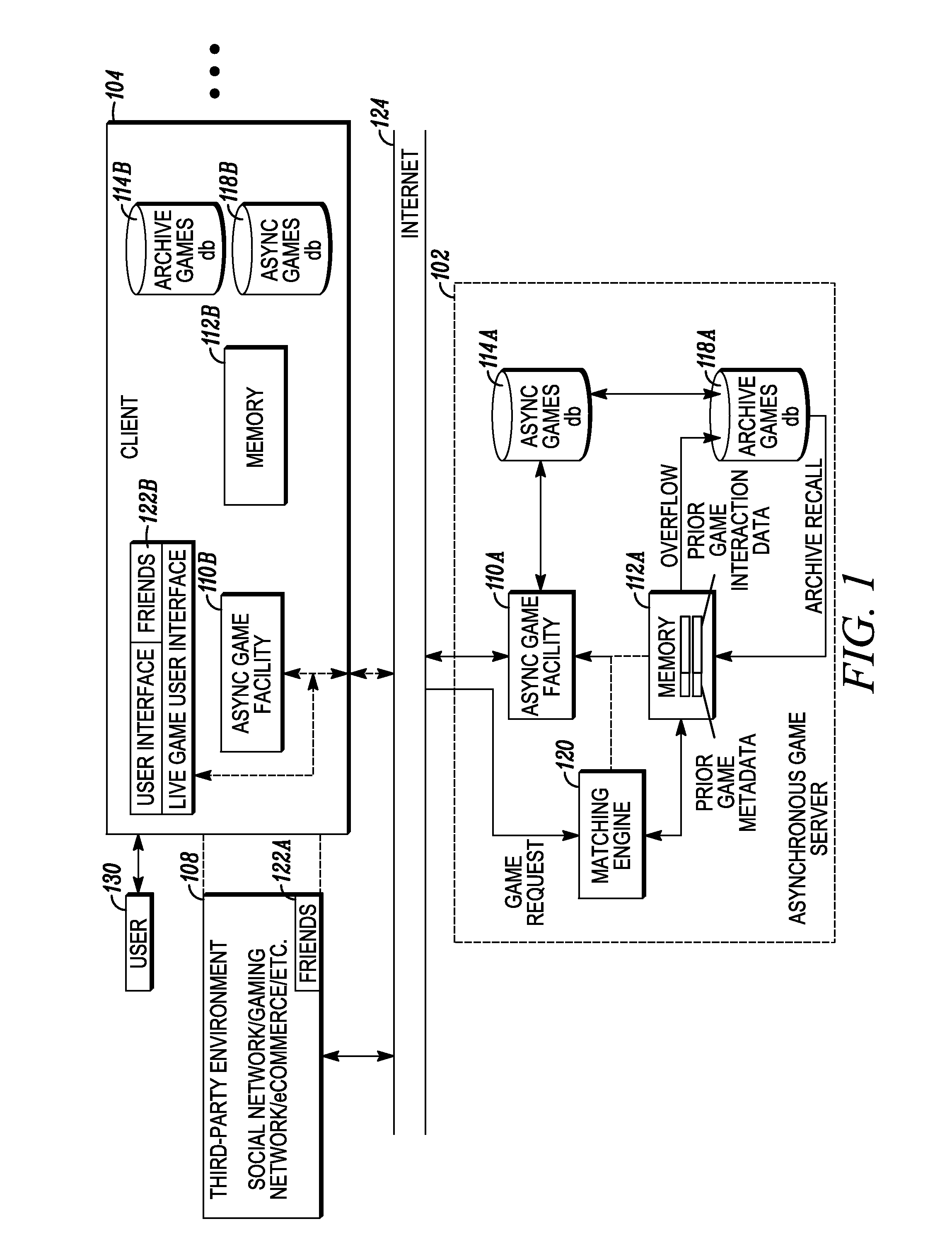

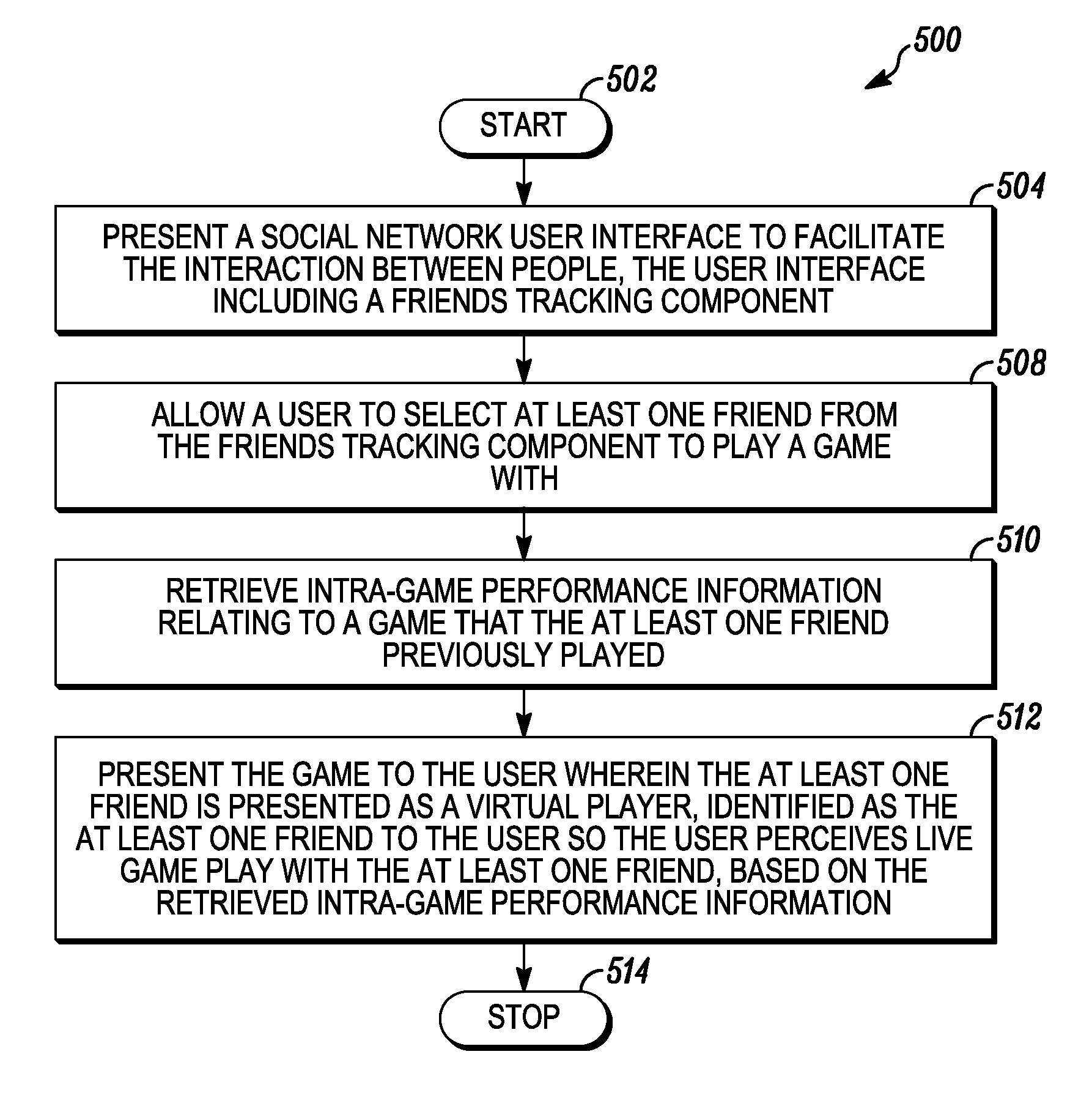

Interactive asynchronous computer game infrastructure

ActiveUS20100160038A1Video gamesSpecial data processing applicationsGame playAsynchronous computation

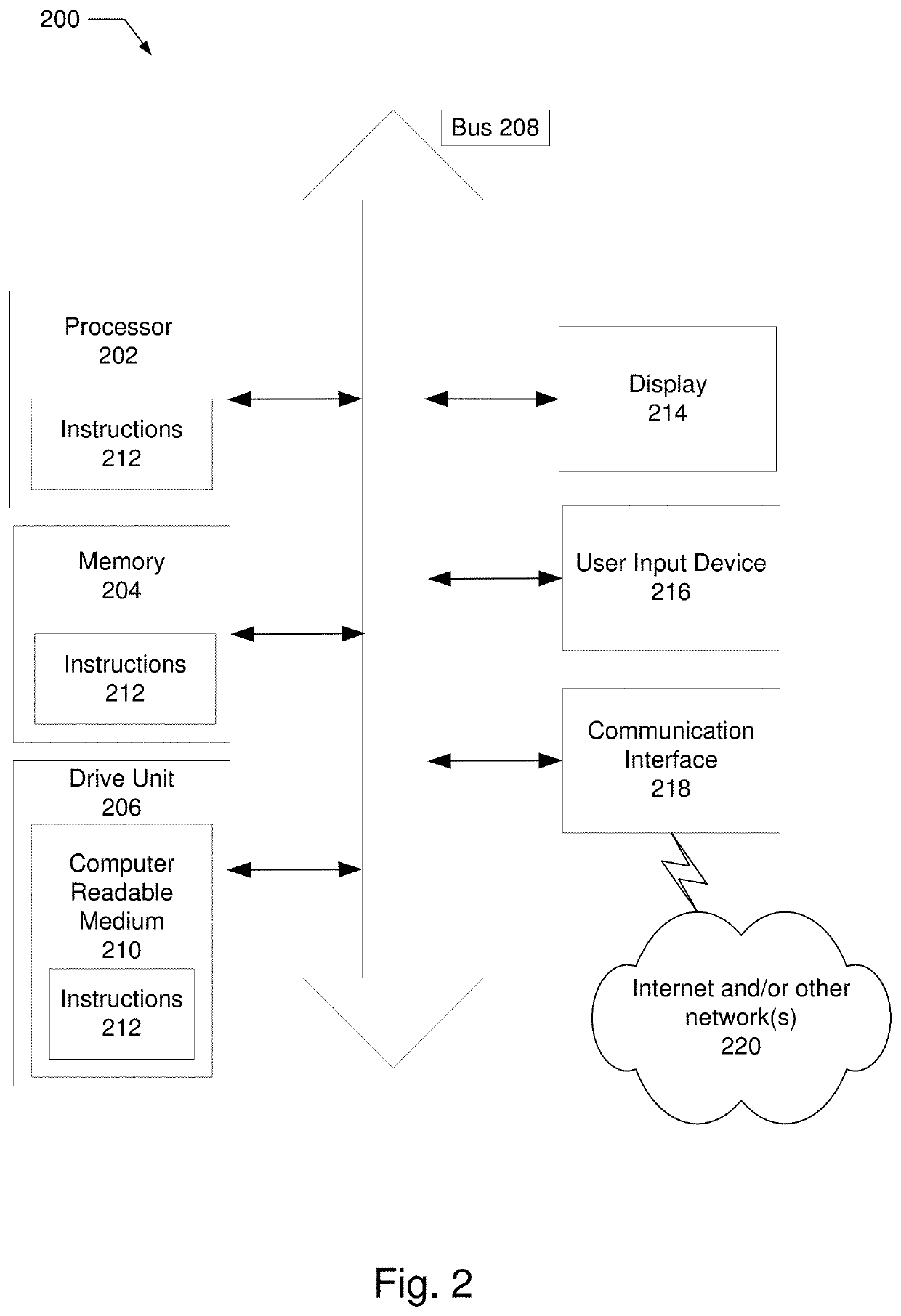

In embodiments of the present invention improved capabilities are described for a computer program product embodied in a computer readable medium that, when executing on one or more computers, receives a request for game play, and in response to the request, causing prior game play data to be retrieved, where the prior game play data was stored in response to prior game play of another user. Further, an asynchronous game play environment may be provided where an active participant, who made the request, is able to play against and interact with an apparently live participant based on the prior game play data.

Owner:TETRIS ONLINE INC

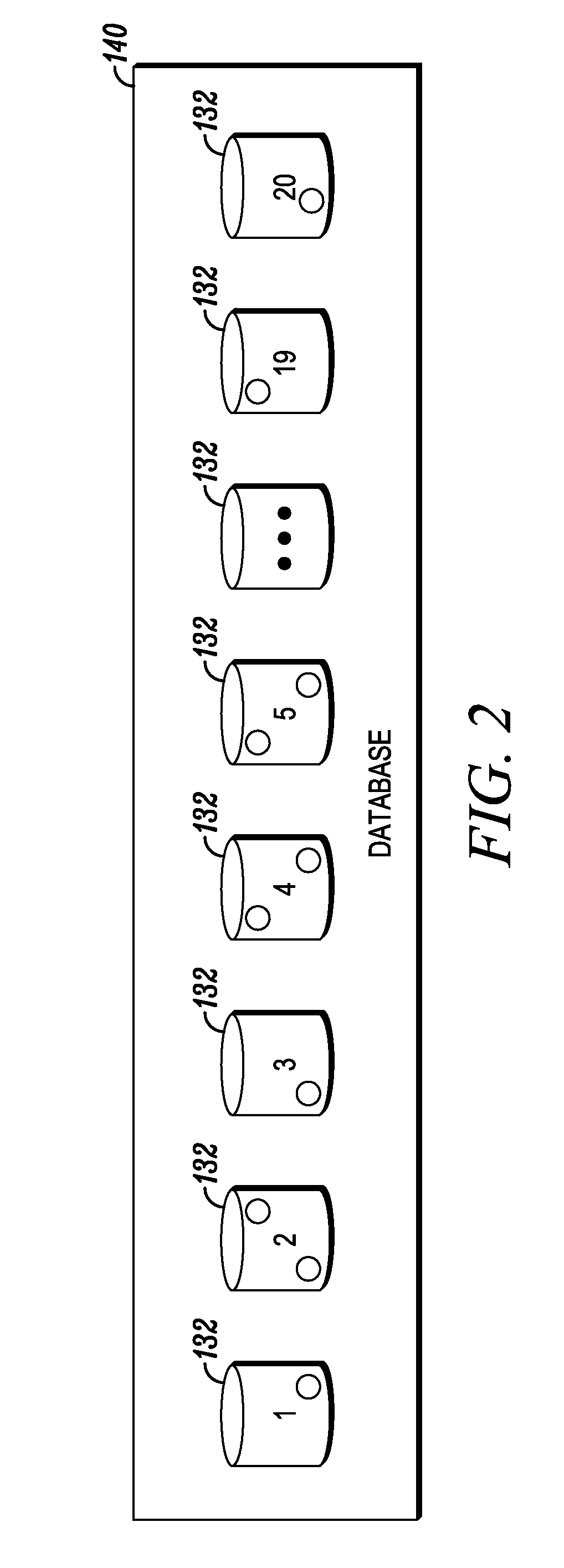

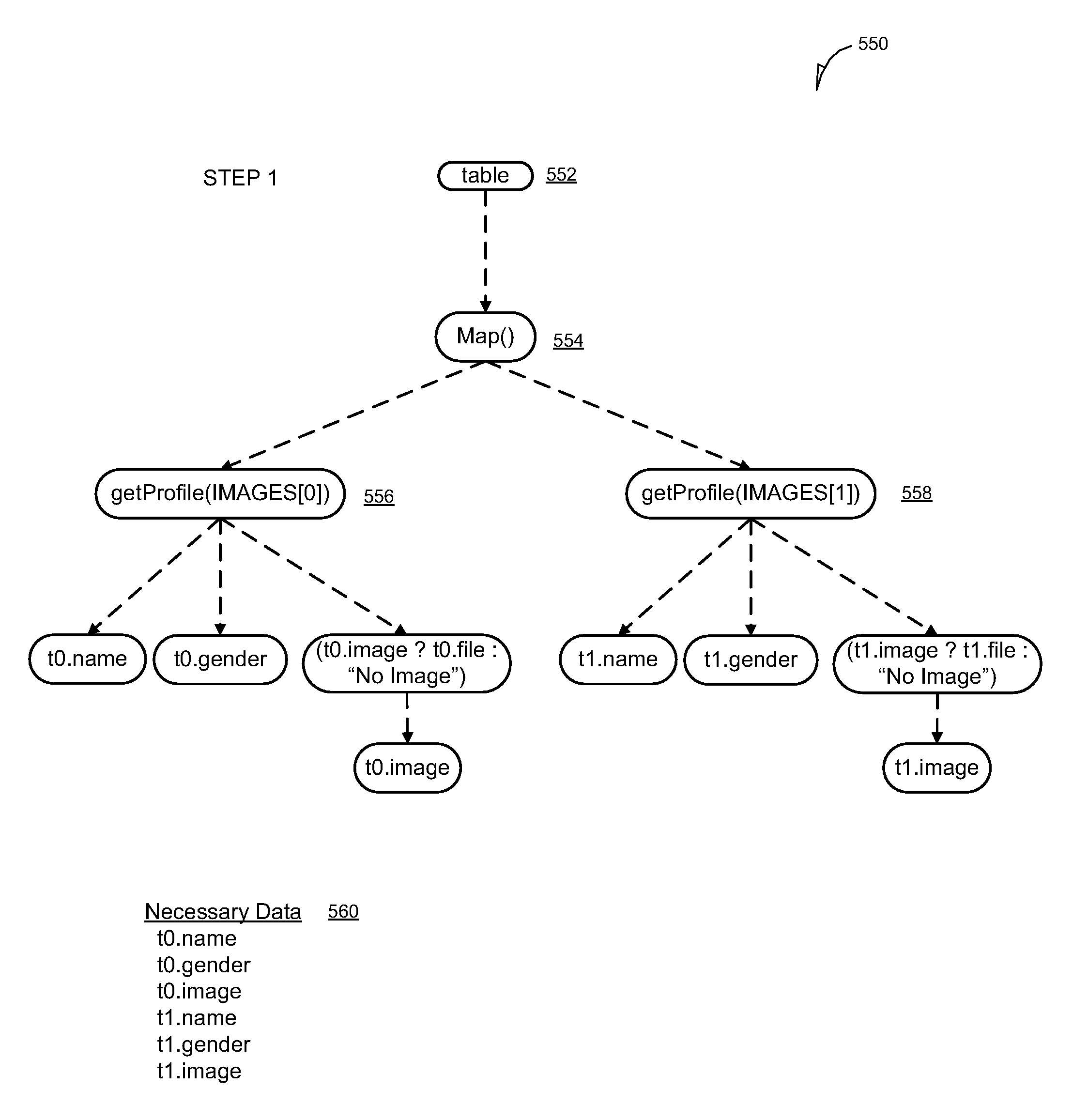

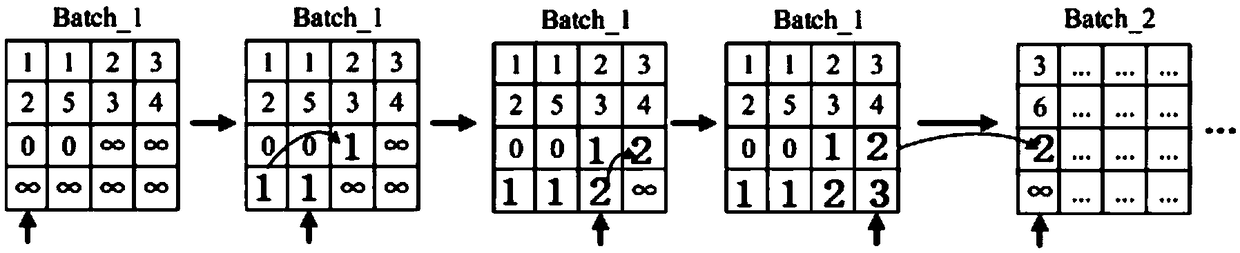

Asynchronous computation batching

ActiveUS9152668B1Digital data information retrievalSpecial data processing applicationsWeb applicationIndependent function

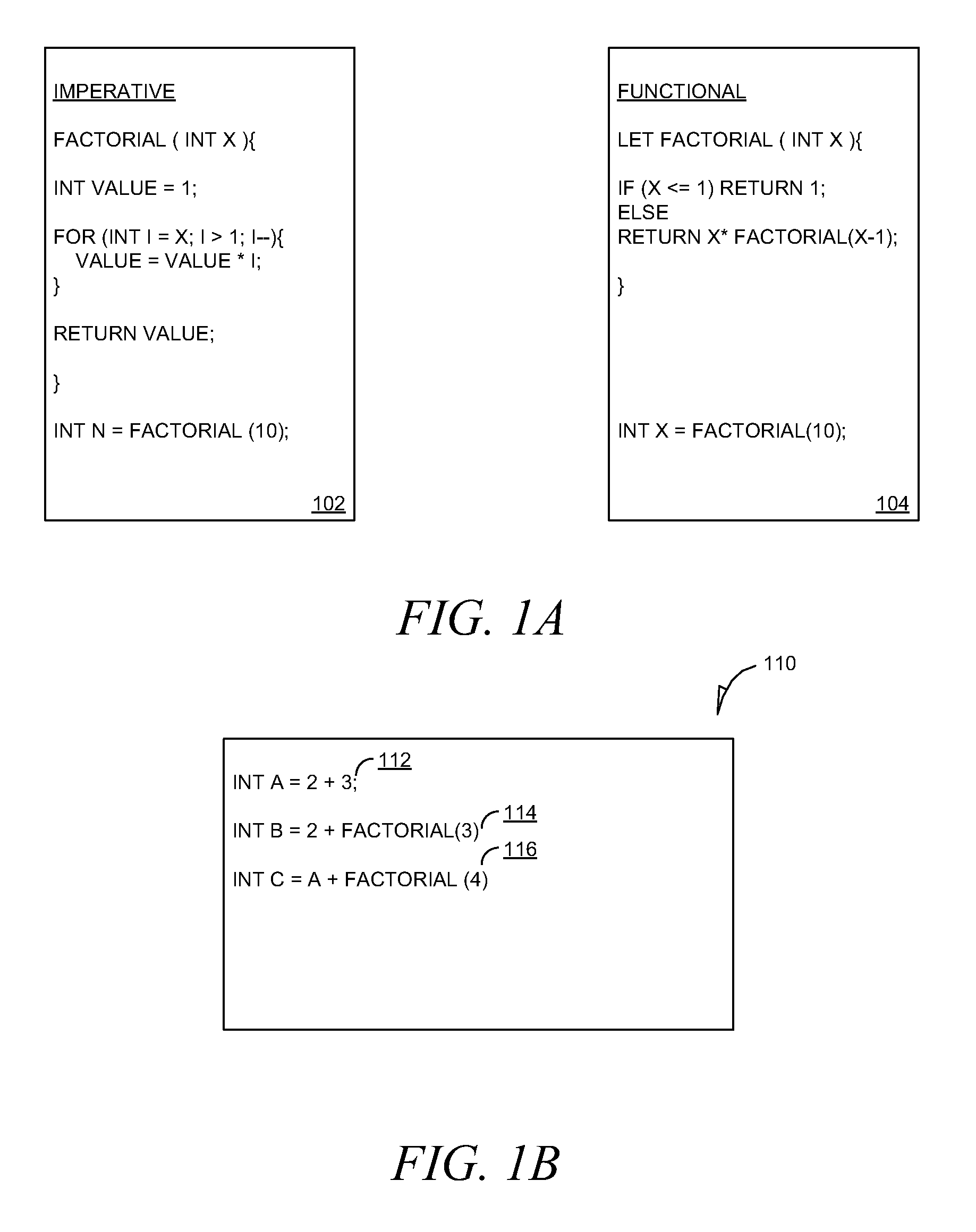

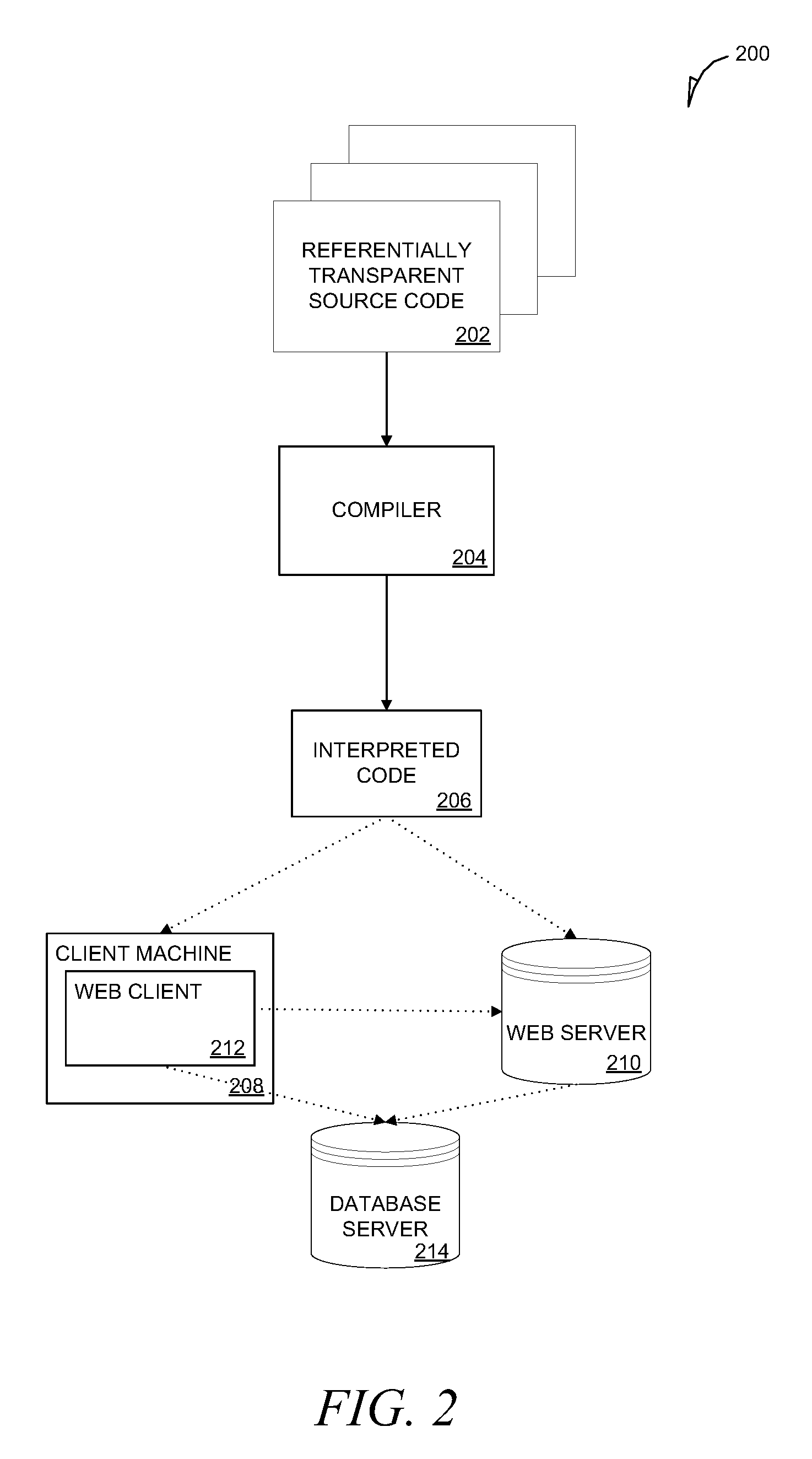

A method and a system implementing asynchronous computation batching. A web application written in a side-effect free manner possesses the quality of referential transparency. This property allows independent functions to be executed in any order or in parallel and enables necessary data for such functions to be gathered in a batch query. This property also extends to dependent functions and allows web applications to be written assuming random access to data on a database.

Owner:ASANA

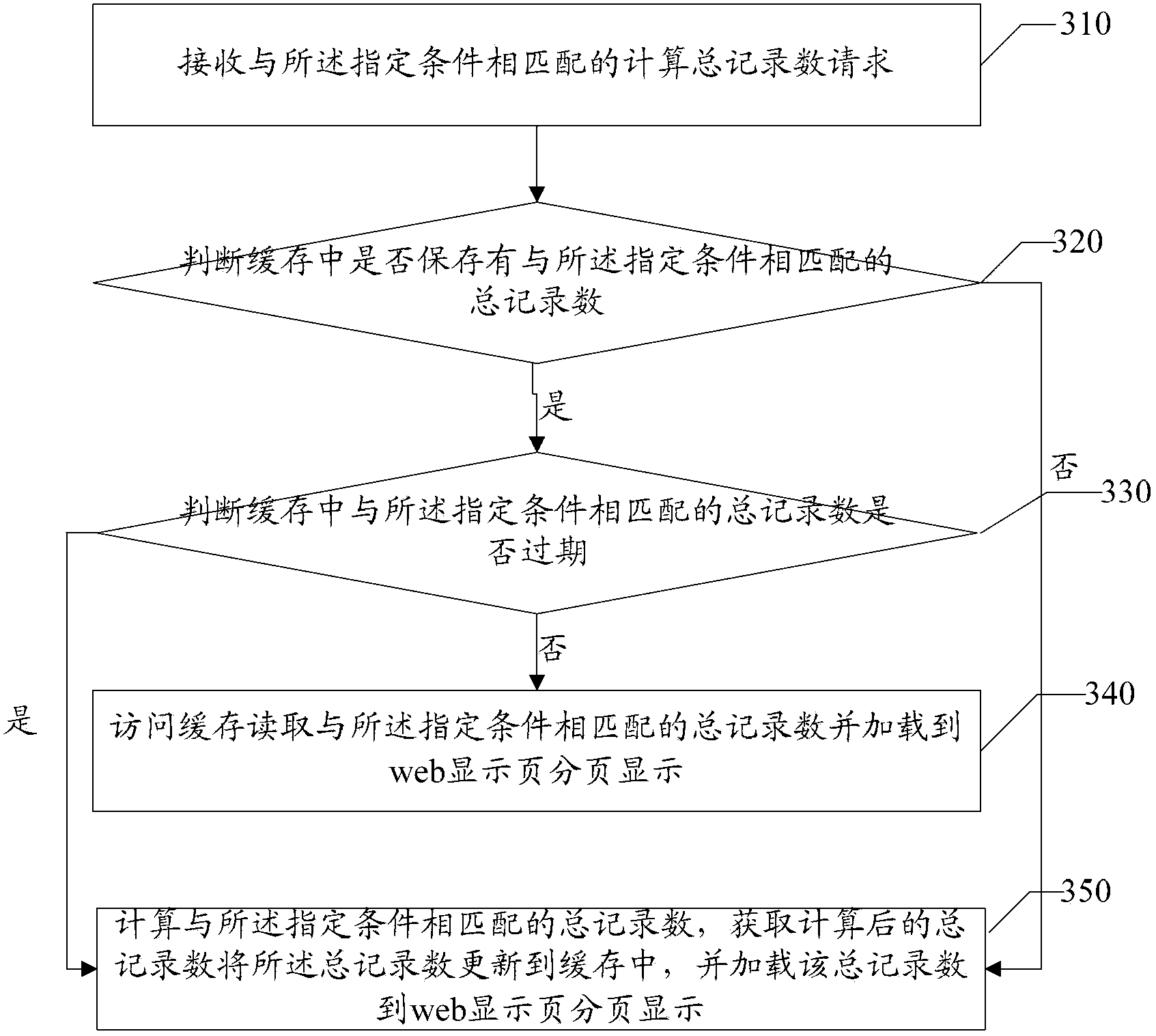

Optimized web paging query method and device

InactiveCN103425708AQuick responseReduce the number of timesSpecial data processing applicationsPagingWeb page

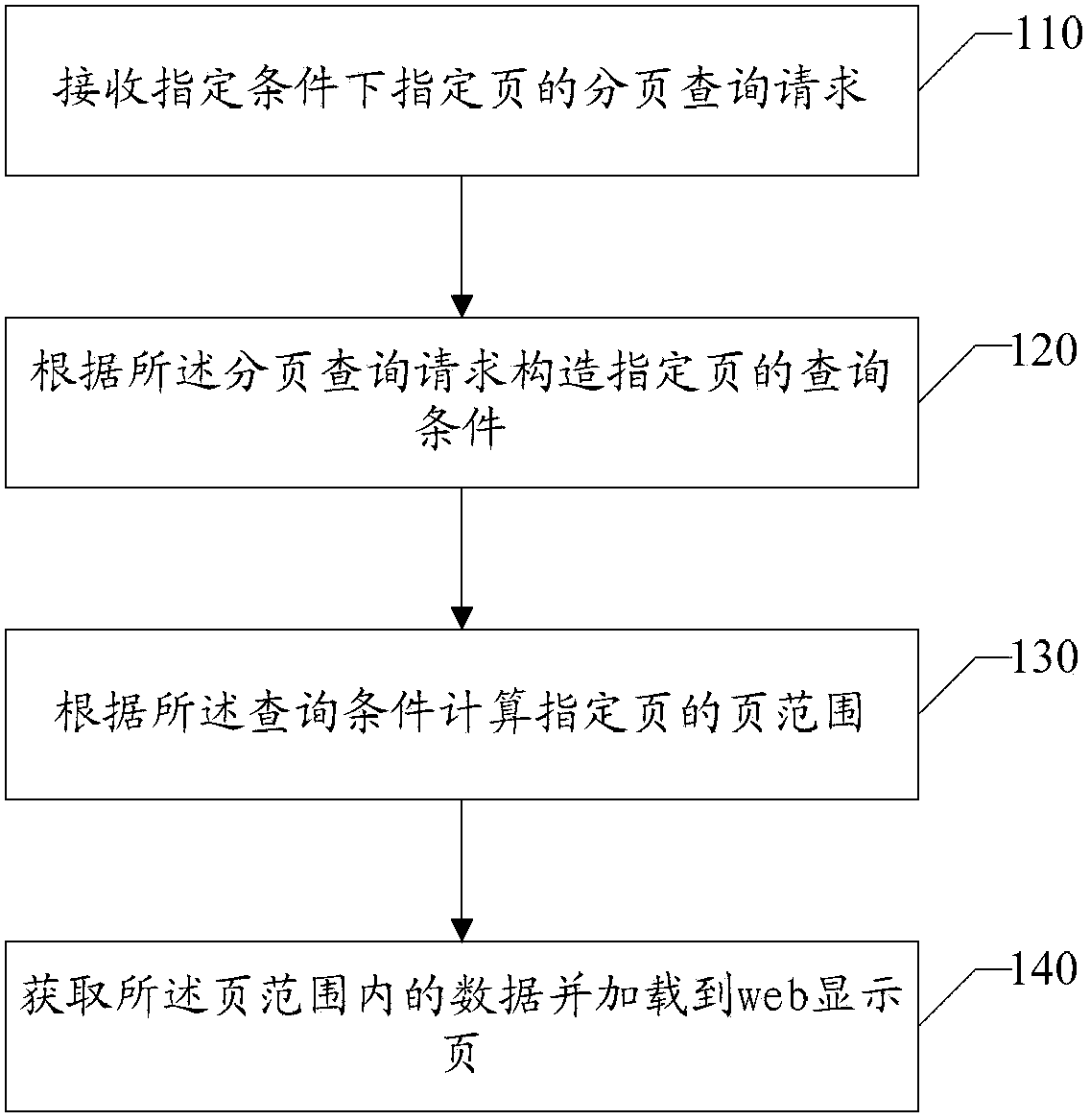

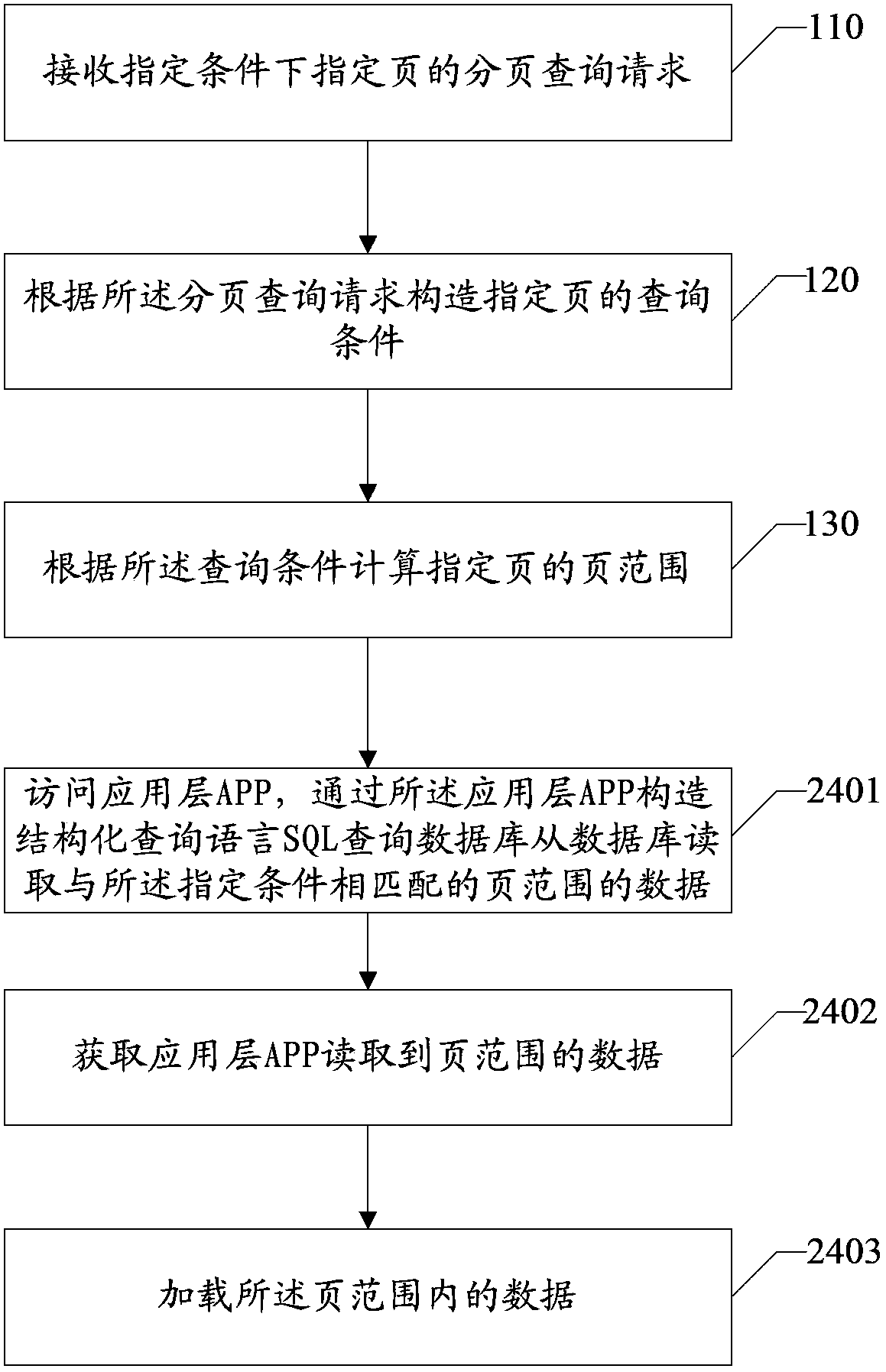

An embodiment of the invention discloses an optimized web paging query method and device. The optimized web paging query method includes asynchronously calculating a page range and a total record number: after a paging query request for an appointed page is received, firstly calculating the page range and then acquiring data loading display within the page range; and after a request for calculating the total record number is received, detecting whether a matched total record number is saved in a cache or not, if not, calculating the total record number and updating the same in the cache, and if so, reading the total record number from the cache directly. Through asynchronous calculation, the responding speed of web paging query is increased; by means of saving the total record number via the cache, the number of times for accessing to a database during web paging query is decreased, and loading efficiency is improved.

Owner:KINGDEE SOFTWARE(CHINA) CO LTD

Interactive asynchronous computer game infrastructure

In embodiments of the present invention improved capabilities are described for a computer program product embodied in a computer readable medium that, when executing on one or more computers, receives a request for game play, and in response to the request, causing prior game play data to be retrieved, where the prior game play data was stored in response to prior game play of another user. Further, an asynchronous game play environment may be provided where an active participant, who made the request, is able to play against and interact with an apparently live participant based on the prior game play data.

Owner:TETRIS ONLINE INC

Asynchronous computer communication

InactiveUS20070192504A1Improve computing processing speedImprove processing speedDigital data processing detailsGeneral purpose stored program computerData linesOperating system

A computer array (10) has a plurality of computers (12). The computers (12) communicate with each other asynchronously, and the computers (12) themselves operate in a generally asynchronous manner internally. When one computer (12) attempts to communicate with another it goes to sleep until the other computer (12) is ready to complete the transaction, thereby saving power and reducing heat production. A plurality of read lines (18), write lines (20) and data lines (22) interconnect the computers (12). When one computer (12) sets a read line (18) high and the other computer sets a corresponding write line (20) then data is transferred on the data lines (22). When both the read line (18) and corresponding write line (20) go low this allows both communicating computers (12) to know that the communication is completed. An acknowledge line (72) goes high to restart the computers (12).

Owner:ARRAY PORTFOLIO

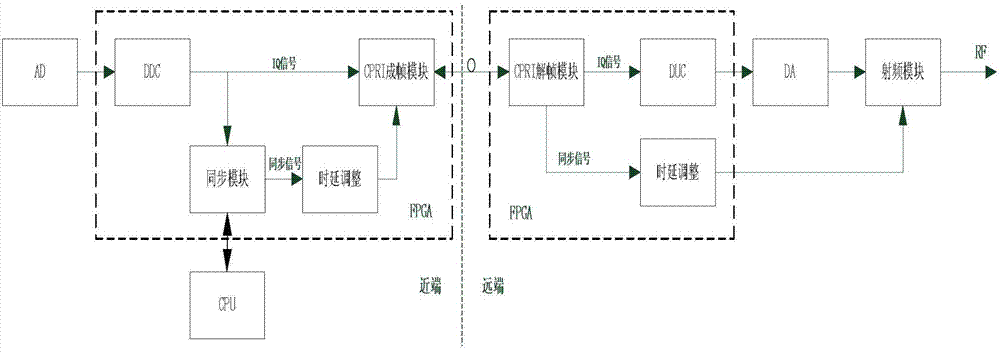

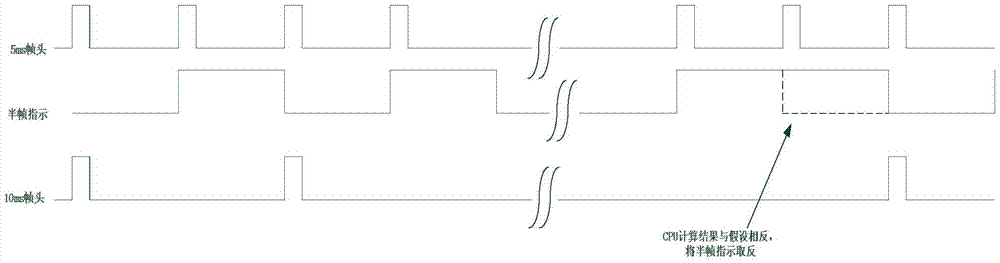

Synchronous detection method for TD-LTE (time division long term evolution) network optimized equipment

The invention provides a synchronous detection method for TD-LTE (time division long term evolution) network optimized equipment. The synchronizing with a base station is finished by fully using the hardware (mainly comprising an FPGA (field programmable gate array) and a CPU (central processing unit)) of the existing network optimized equipment. The method comprises the steps that a near end generates a synchronous switch signal according to an input signal and transmits the switch signal to each far end; each far end controls a radio frequency switch to realize uplink-downlink switching according to the switch signal. As the CPU is not a special signal processing chip, the CPU cannot realize real-time treatment under the condition of larger delay (time for calculating SSS once is at second level) and an LTE (long term evolution) semi-frame being 5ms long when massive data are processed. The method adopts an asynchronous calculation mode, so the demand on real-time property is reduced. The demand on the real-time property of the CPU is not high, a GPS (global positioning system) module and a modem do not need to be connected, the equipment cost is reduced, and the structure is more compact.

Owner:WUHAN HONGXIN TELECOMM TECH CO LTD

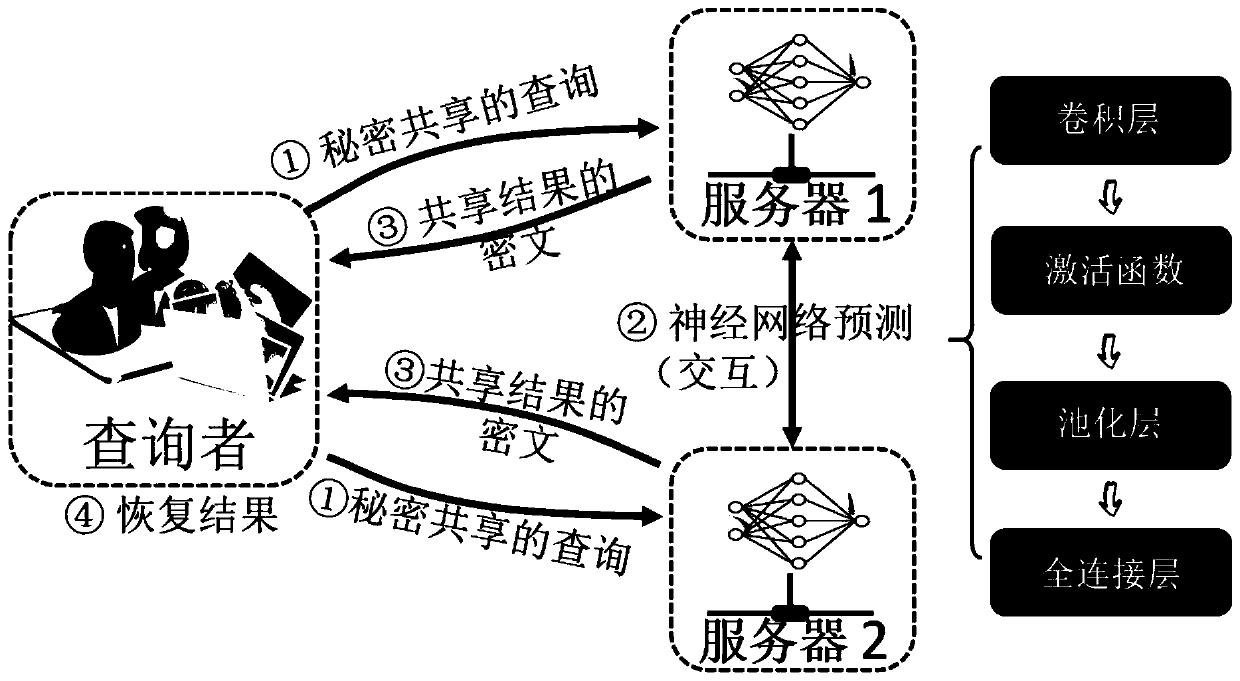

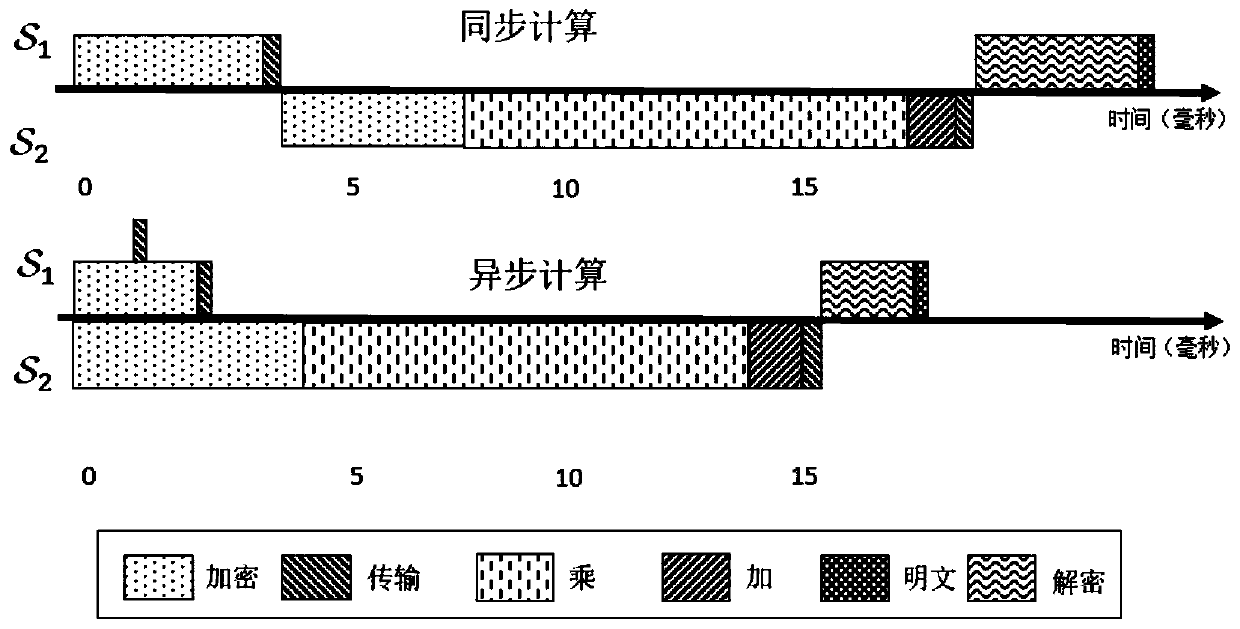

Outsourcing convolutional neural network privacy protection system based on secure two-party calculation

ActiveCN111324870AImprove accuracyCutting costsNeural architecturesProgram/content distribution protectionImaging processingAlgorithm

The invention discloses an outsourcing convolutional neural network privacy protection system based on secure two-party calculation, which randomly allocates a neural network and query data to two servers which are not communicated with each other, and realizes image processing through cooperative operation on the two servers. The two image components are input into two servers; information transmitted between servers is hidden in a convolution layer by using triples of random data. A confusion circuit is designed on an active layer to realize a ReLU function, then dimensionality reduction ofan image is carried out through average pooling, finally, two components of a prediction result are obtained through a full connection layer adopting triple hidden information, and the two componentsare returned to a user to be combined to obtain the obtained prediction result. In order to improve the calculation efficiency, an asynchronous calculation method and a parallel query method are adopted, independent calculations in the same query are carried out at the same time, and different parts of a plurality of queries are processed at the same time, so that the time of each query is greatlyreduced.

Owner:WUHAN UNIV

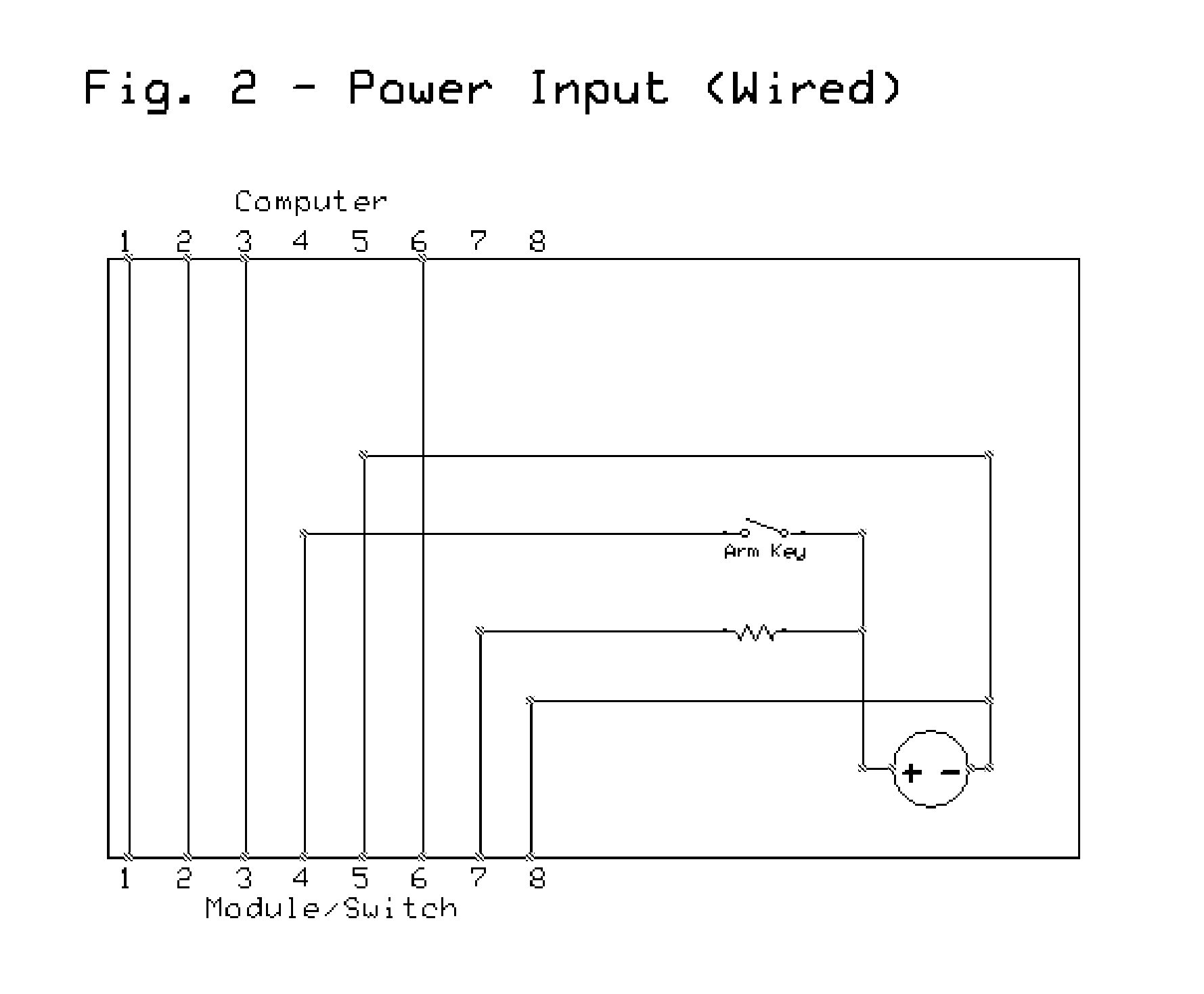

Computer system for the timed firing of pyrotechnic devices that uses a closed or open ethernet network.

InactiveUS20130192486A1Delay deploymentAccurate timingIncandescent ignitionElectric fuzesProprietary hardwareComputer module

Some of the most advanced fireworks displays incorporate music, video, lights, and other special effects. For the seamless operation of these displays, the presence of computerized firing systems on the market can be greatly appreciated. In addition to entertainment value, the abilities of initiating a fireworks display from a distance and being able to stop a display at any time has made shooting fireworks displays safer than ever. However, because of the expense of this hardware, these elaborate displays can be far out of reach for anyone who has a lower budget. The idea outlined in this patent will help solve that issue by suggesting an asynchronous computerized firing system. This system can be initiated using a personal computer without any proprietary hardware with the exception of low cost modules.

Owner:RUGGIERO BRIAN

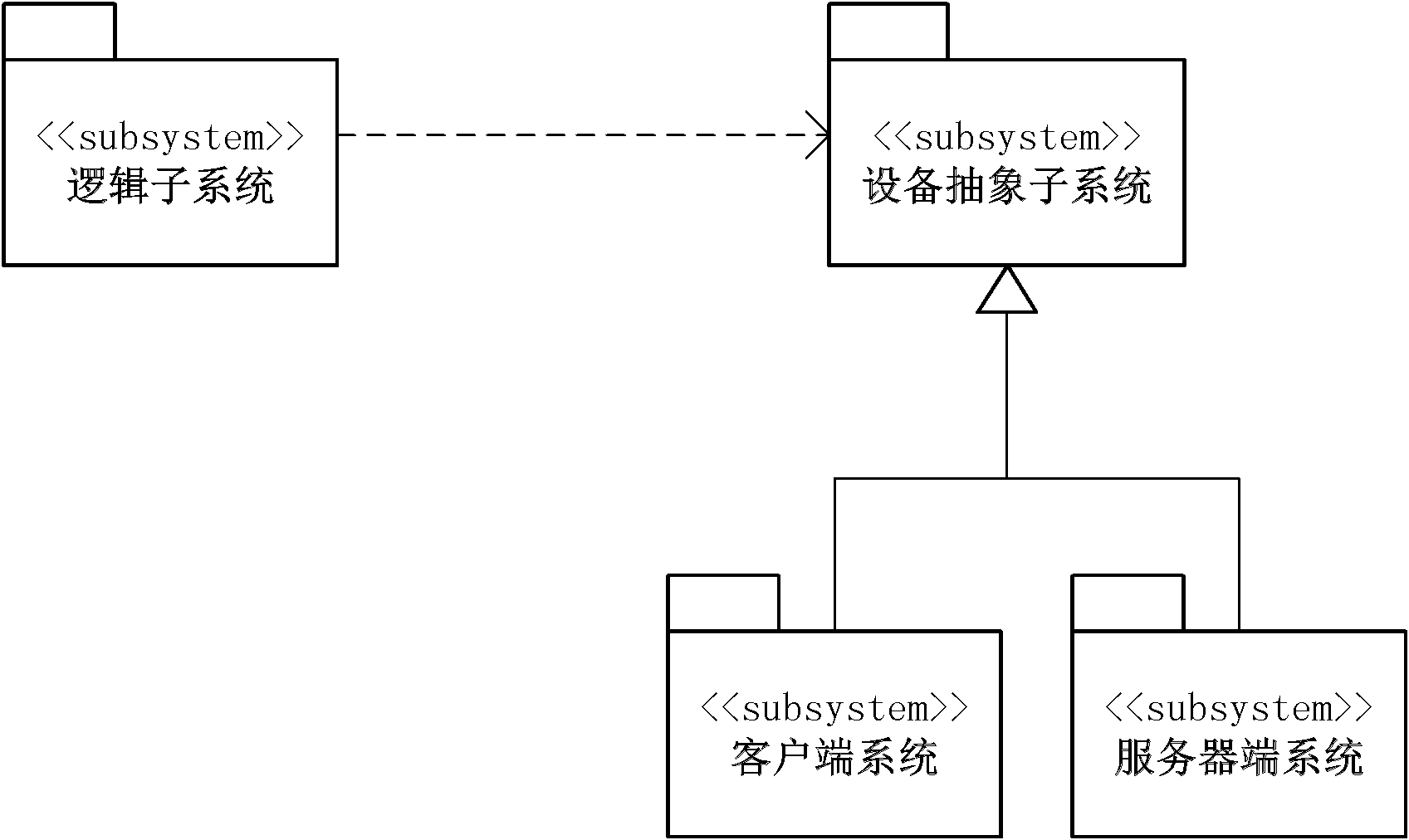

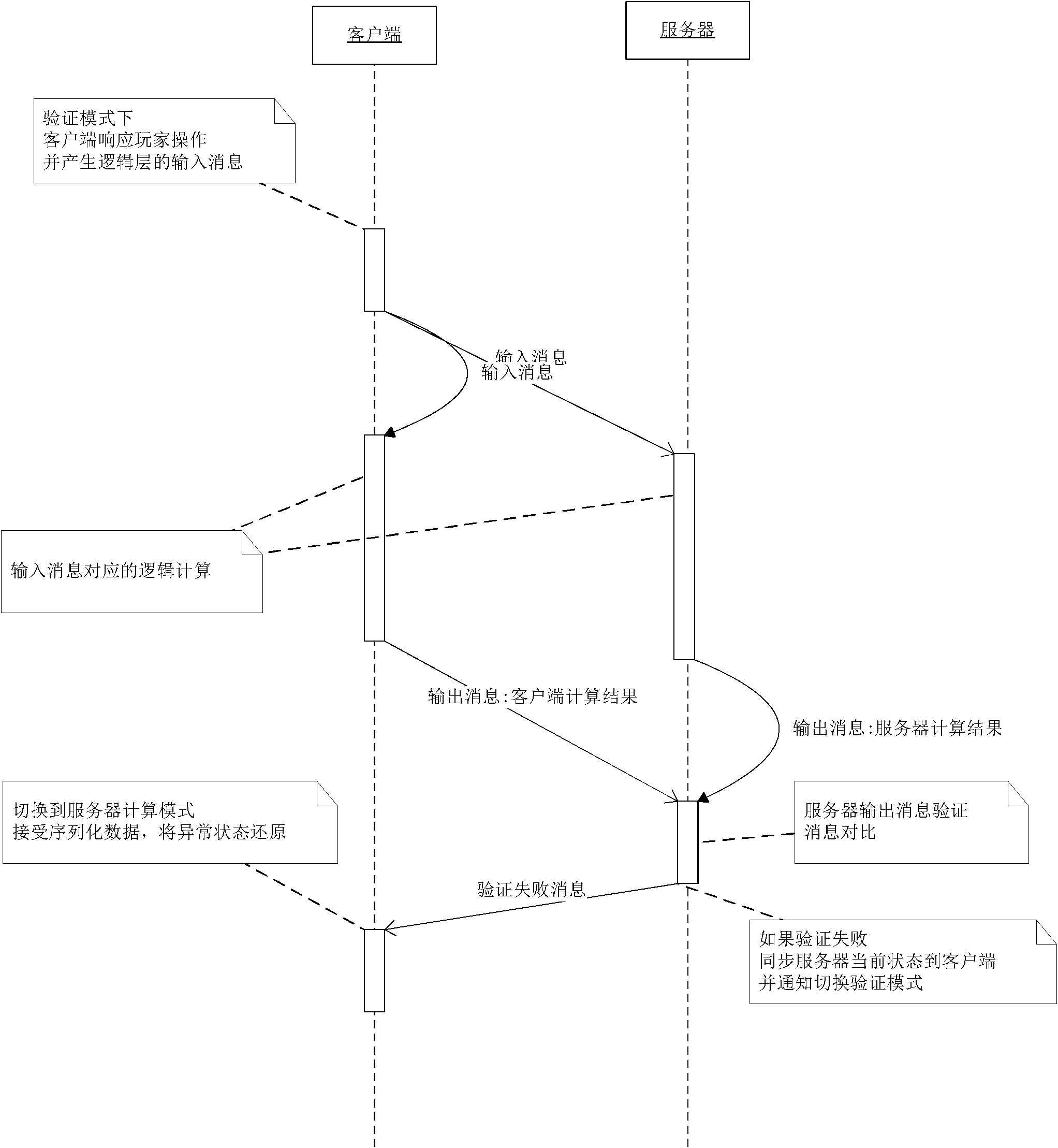

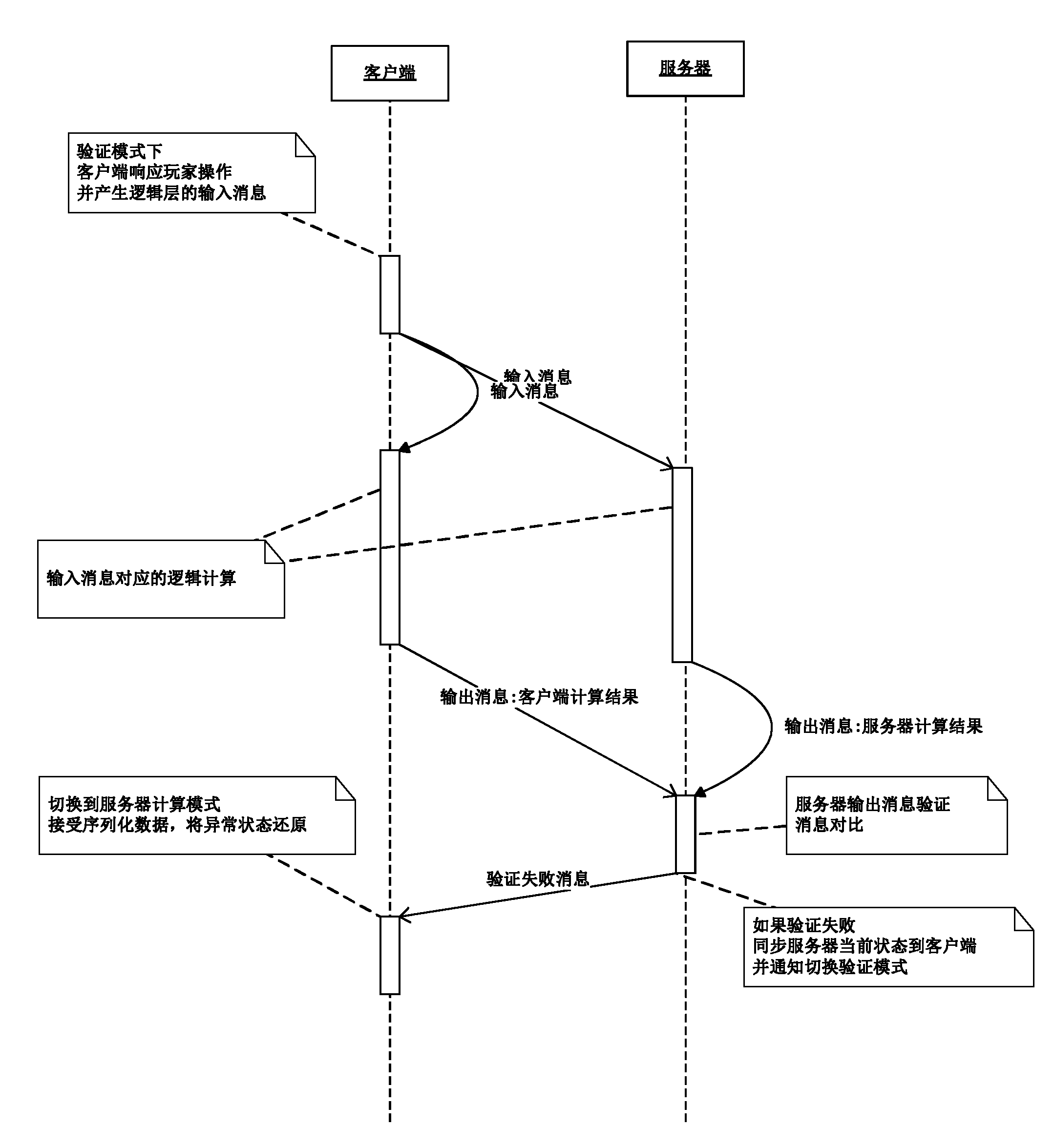

Asynchronous computation and synchronous backtracking method and system in delayed sensitive online game

The invention discloses an asynchronous computation and synchronous backtracking method and an asynchronous computation and synchronous backtracking system in a delayed sensitive online game. The method comprises the following steps that: logic computation modules of the game are arranged at a client and a server; the client synchronizes user input to the logic computation module at the client and transmits a computed result of the client which is generated through the logic computation module to the server; the server compares the accurate computed result generated by the server with the result which is transmitted by the client, if the results are inconsistent, the client is judged to be abnormal; and if a logically abnormal client is discovered, the server resynchronizes a state of the logically abnormal client on the current server to the client so as to cover the current abnormal state of the client through serialization. The asynchronous computation and synchronous backtracking method and the asynchronous computation and synchronous backtracking system in the delayed sensitive online game meet the requirements of timely responding to user operation and preventing the user from breaking a game rule simultaneously.

Owner:SHANGHAI WINGAME NETWORK TECH

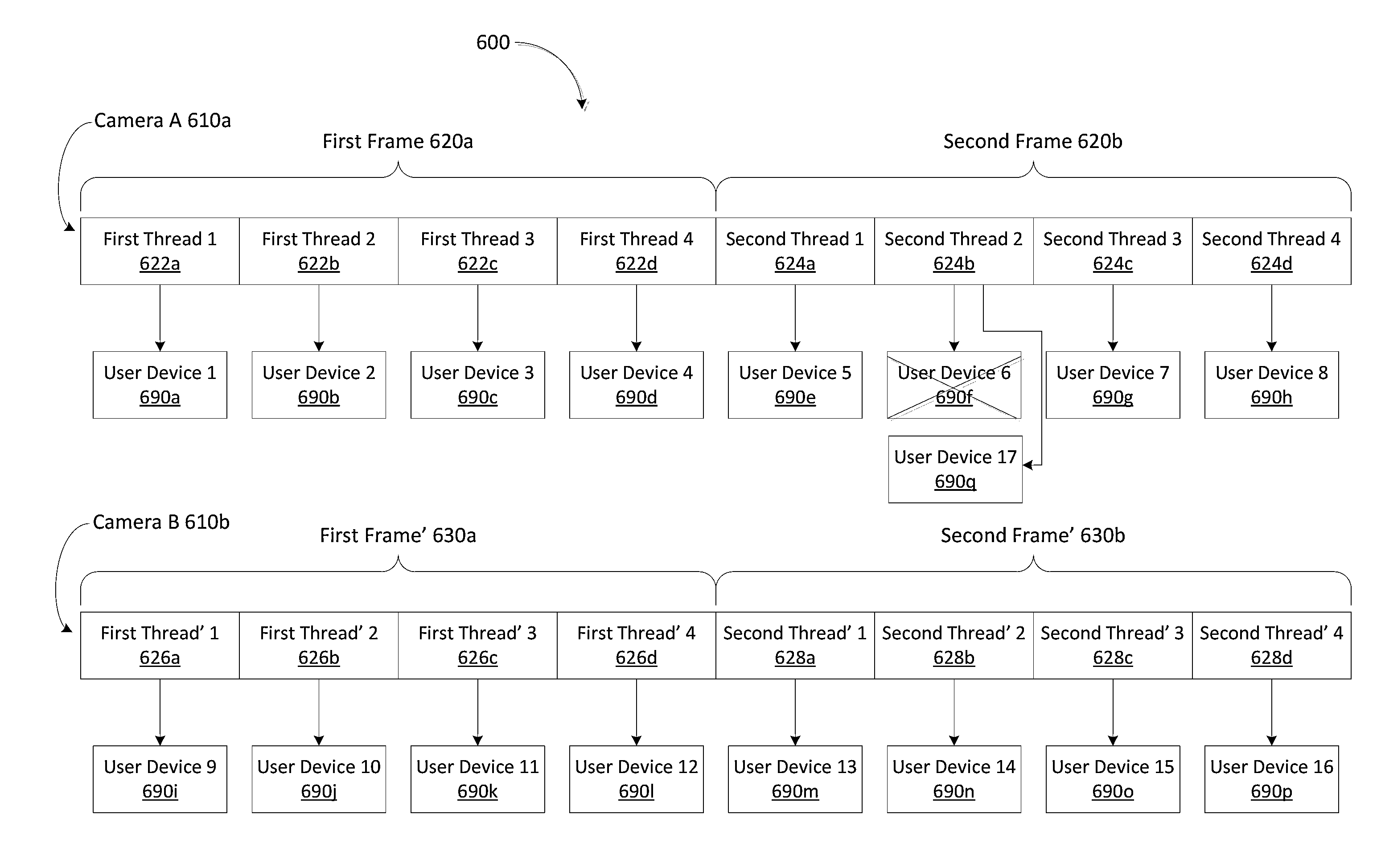

Systems and methods for scalable asynchronous computing framework

Systems and methods are described for a distributed data processing method, including, but not limited to: receiving, by a backend device, source data; partitioning, by the backend device, the source data into a plurality of data threads; sending, by the backend device, at least one of the plurality of data threads to each of a plurality of user devices; and determining, by the backend device, a job outcome for the source data based on a plurality of data thread results, each of the plurality of data thread results is determined by one of the plurality of user devices based on the at least one of the plurality of data threads.

Owner:LIVEPLANET

System and method for quickly determining reasonable alarm threshold of network

ActiveUS20180241611A1Improve efficiencyImprove data processing speedData switching networksTime segmentSimulation

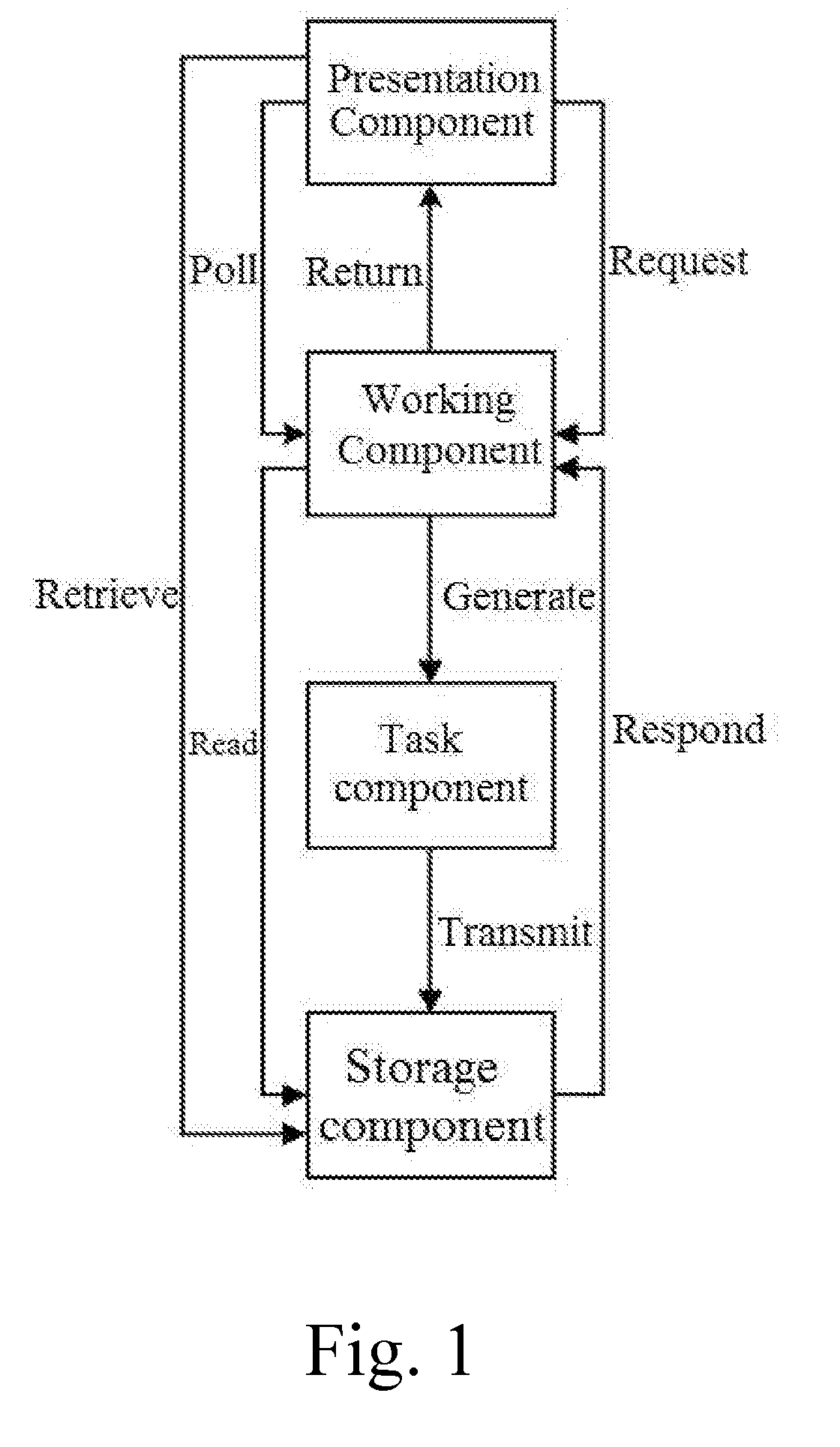

The present invention provides a system and method for quickly determining a reasonable alarm threshold of a network, including: a presentation component for setting the template type and template parameter of an alarm simulation template, a working component for generating an alarm simulation task according to the alarm simulation template, a task component for executing the alarm simulation task to generate a data result set, and a storage component for storing and providing the data result set for the presentation component. The present invention adopts the asynchronous calculation, and adopts fragment manner during data statistics; the time period is divided into time slices and processed in parallel, and then aggregated, to improve the data processing rate; the similar alarm points are merged, thereby accurately obtaining the actual number of alarms and presenting in an incremental mode.

Owner:SHANGHAI NETIS TECH

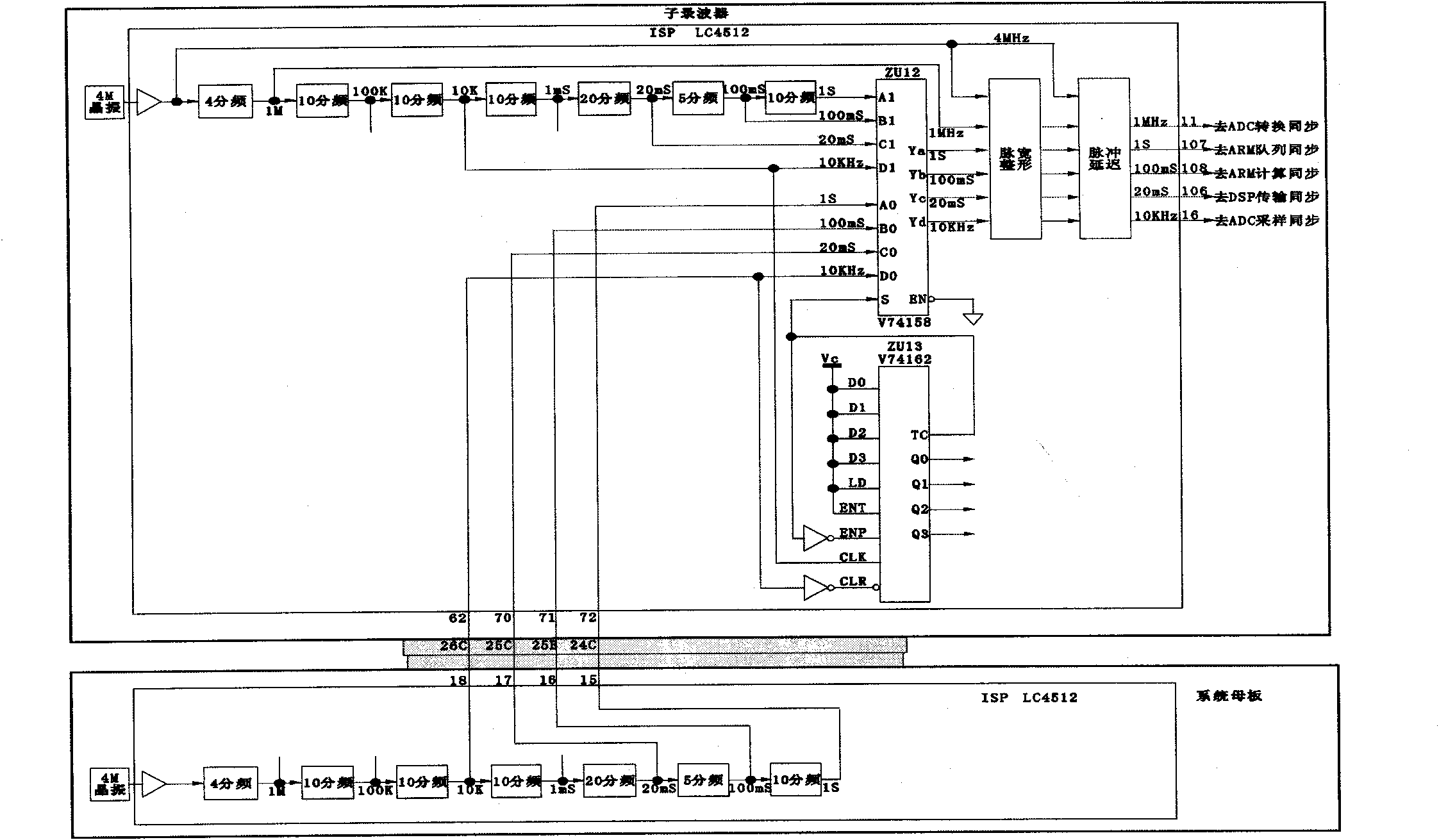

Synchronization method based on distributed-type integrated recorder parallel buses

InactiveCN101882989AGuaranteed strict synchronizationImprove reliabilityRecording measured valuesElectric digital data processingSynchronous controlControl line

The invention belongs to the category of high-speed large-capacity data measurement and recording. By adopting methods of synchronous parallel sampling, sectionally synchronous transmission, data queue synchronization, sectionally synchronous computing, parallel synchronous recording, on-line synchronous timing and accurate marking of absolute time of sampling data, and the like, the sectional computing synchronization and the accurate synchronization recording of a plurality of sub-recorders under an asynchronous computation process in a distributed-type integrated recorder are realized. A system clock provides the guarantee for synchronous parallel sampling and sectionally synchronous transmission. Parallel buses and control circuits which are integrated on the sub-recorders and a motherboard are taken as a synchronous hardware basis. The data queue synchronization and the computing and recording synchronization can be realized by matching a queue synchronization control line and a status line, a calculation synchronization control line and a status line as well as a recording, recorded value and definite value control line and a status line with a motherboard synchronization control circuit. The method conveniently and reliably ensures the strict synchronization of data recording of the distributed-type integrated recorder and the high-resolution time precise positioning of data mutation or scheduled events.

Owner:SICHUAN UNIV

Structural-dynamic-analysis explicit-different-step-length parallel computing method

ActiveCN108228970AImprove transfer efficiencySuitable for large scaleDesign optimisation/simulationSpecial data processing applicationsCyclic processNODAL

The invention provides a structural-dynamic-analysis explicit-different-step-length parallel computing method. The method includes the four steps that (1) data files required by parallel computing aregenerated with the partition multiple-node strategy; (2) time step lengths of all partitions are selected according to partition unit characteristics to be subjected to explicit prediction step computing; (3) in small-step-length partitions, partition-inside and boundary-node data is solved through step-by-step decreasing of the explicit sub-cycle process, and in large-step-length partitions, inside and boundary-node data is solved through the main time step length; (4) the boundary-node data required by paralleling is received by all the partitions, partition information is updated, strainsand stress are computed as required, and partition node data is output; if a main time step is ended, the program is stopped, and if a main time step is not ended, the step (2) is newly carried out. According to the structural-dynamic-analysis explicit-different-step-length parallel computing method, in the large-scale dynamic parallel analysis process, different time step lengths can be selectedaccording to the partition unit characteristics, partition different-step computing coupling is achieved with the multiple-node strategy, and parallel efficiency is effectively improved.

Owner:SHANGHAI JIAO TONG UNIV

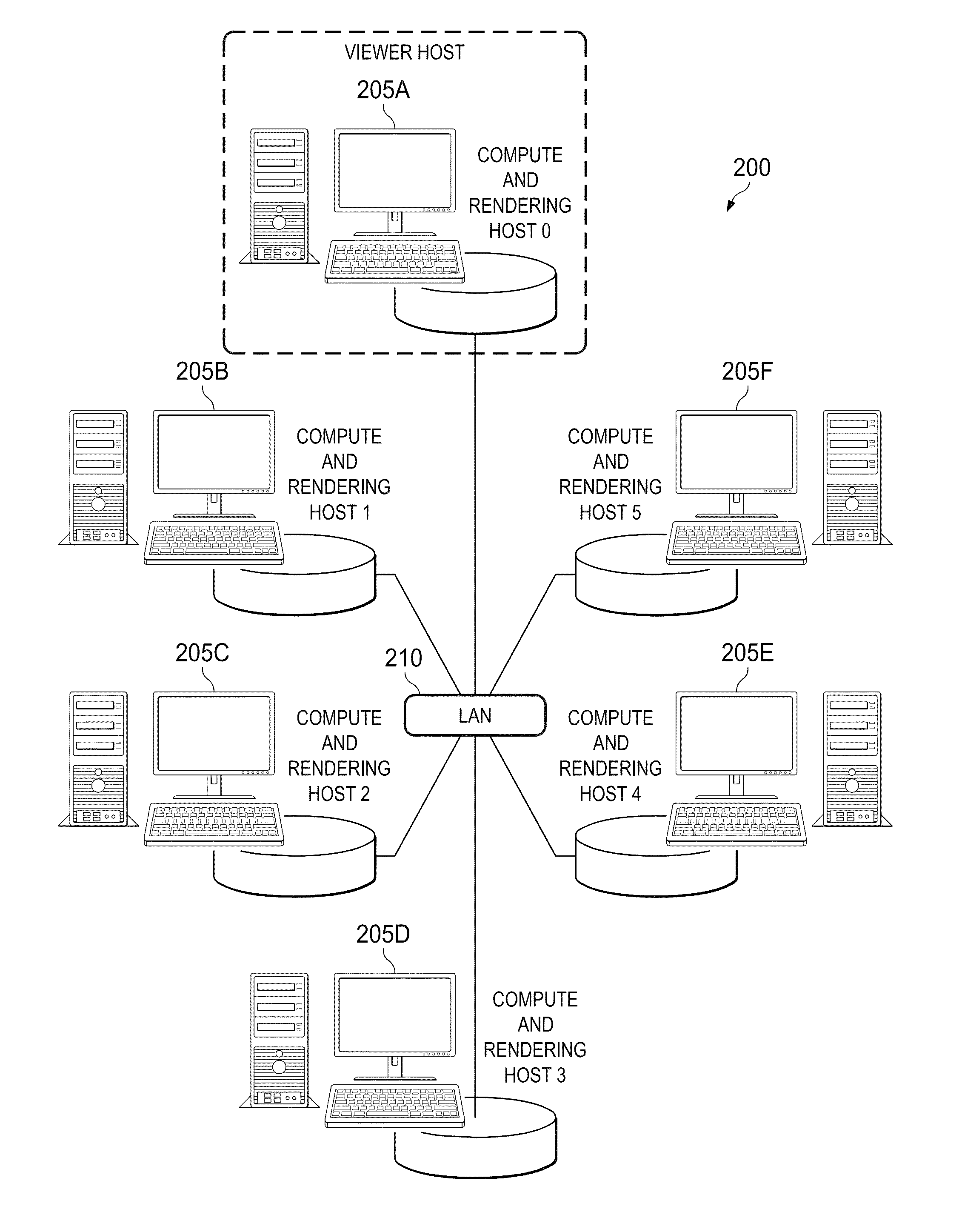

Asynchronous compute integrated into large-scale data rendering using dedicated, separate computing and rendering clusters

ActiveUS9117284B2Resource allocationProcessor architectures/configurationData setComputer graphics (images)

An asynchronous computing and rendering system includes a data storage unit that provides storage for processing a large-scale data set organized in accordance to data subregions and a computing cluster containing a parallel plurality of asynchronous computing machines that provide compute results based on the data subregions. The asynchronous computing and rendering system also includes a rendering cluster containing a parallel multiplicity of asynchronous rendering machines coupled to the asynchronous computing machines, wherein each rendering machine renders a subset of the data subregions. Additionally, the asynchronous computing and rendering system includes a data interpretation platform coupled to the asynchronous rendering machines that provides user interaction and rendered viewing capabilities for the large-scale data set. An asynchronous computing and rendering method is also provided.

Owner:NVIDIA CORP

Method for cooperatively computing and accelerating pre-stack time migration of earthquake by using CPU (Central Processing Unit)/MIC (Microphone)

ActiveCN103018776AImprove computing powerMeet processing needsSeismic signal processingScanning tunneling microscopeParallel computing

The invention provides a method for cooperatively computing and accelerating pre-stack time migration of an earthquake by using a CPU (Central Processing Unit) / MIC (Microphone), and relates to the field of high-property computing. According to the method, a CPU and MIC heterogeneous framework is used; a CPU is in charge of performing FFT (Fast Fourier Transform) computing, reading seismic channel data, performing process control and scheduling, and further participating in PSTM (Photon Scanning Tunneling Microscope) computing; the MIC is used for only performing the PSTM computing, and simultaneously performing CPU and MIC cooperative computation and common computation in an asynchronous parallel idea and dynamic load balance manner; and the integrated design comprises the following three aspects: parallel design of a PSTM computation partial serial algorithm, a PSTM integrated logic structural design and a CPU and MIC asynchronous computation design. The method provided by the invention has the beneficial effects that the PSTM properties can be improved by using the CPU / MIC cooperative computation; the building cost and management, operation and maintenance costs of a machine room can be reduced; and the simple realization and the low desired development cost can be realized.

Owner:LANGCHAO ELECTRONIC INFORMATION IND CO LTD

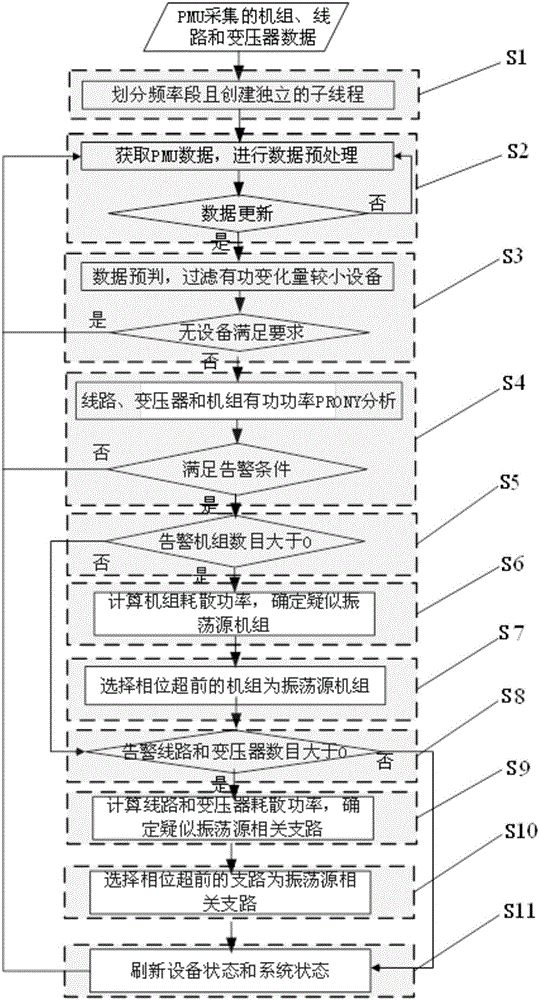

Forced oscillation disturbance source positioning method based on frequency band-dividing parallel computation

ActiveCN106571636AAvoid the problem of time-consuming analysis and calculationReduce the number of analysis data pointsFault location by conductor typesPower oscillations reduction/preventionTransformerSource element

The invention belongs to the technical field of power systems and automation thereof, and discloses a forced oscillation disturbance source positioning method based on frequency band-dividing parallel computation. A preset frequency range is divided into a plurality of frequency bands for parallel computation; as for each frequency band, through setting each data window length and each sampling frequency, analyzed data points are reduced; each frequency band adopts an asynchronous computation mode, other frequency bands do not need to be waited after one-round analysis computation, a result is refreshed and new data are obtained for next-round analysis, dissipation power of a unit, a transformer and a line is calculated, a suspected oscillation source related element is screened according to a threshold value, oscillation elements are grouped according to a dominant mode phase angle, and elements with advanced phases in the group of the suspected oscillation source elements are selected as the oscillation source unit, the related line and the transformer. The scheme is reasonably designed, and forced power oscillation warning and disturbance source positioning information timeliness can be ensured.

Owner:NARI TECH CO LTD +2

Message reminding method and system in support of asynchronous and synchronous computation

ActiveCN107967595AImprove performanceImprove acceleration performanceFinanceOffice automationExtensibilityBusiness management

The invention discloses a message reminding method and system in support of asynchronous and synchronous computation. The method comprises the following steps: in a business management system, asynchronous message reminding and synchronous message reminding are integrated, wherein the asynchronous message reminding adopts at least two asynchronous computation modes to obtain message data needed bythe message reminding, different reminding rules are configured according to characteristics of the message reminding, the synchronous message reminding adopts at least one synchronous computation mode to obtain message data needed by the message reminding, and finally, the message data needed by the message reminding through asynchronous computation and synchronous computation are aggregated asa collection of message data, and message reminding is carried out in a unified mode. The method and the system enhance the message reminding function performance and the extensibility through adopting technologies such as reading and writing separation, a timing task and an asynchronous computation task, and after a business operator logs in to the system (the business management system), unifiedmessage reminding can be acquired timely.

Owner:北京大数元科技发展有限公司

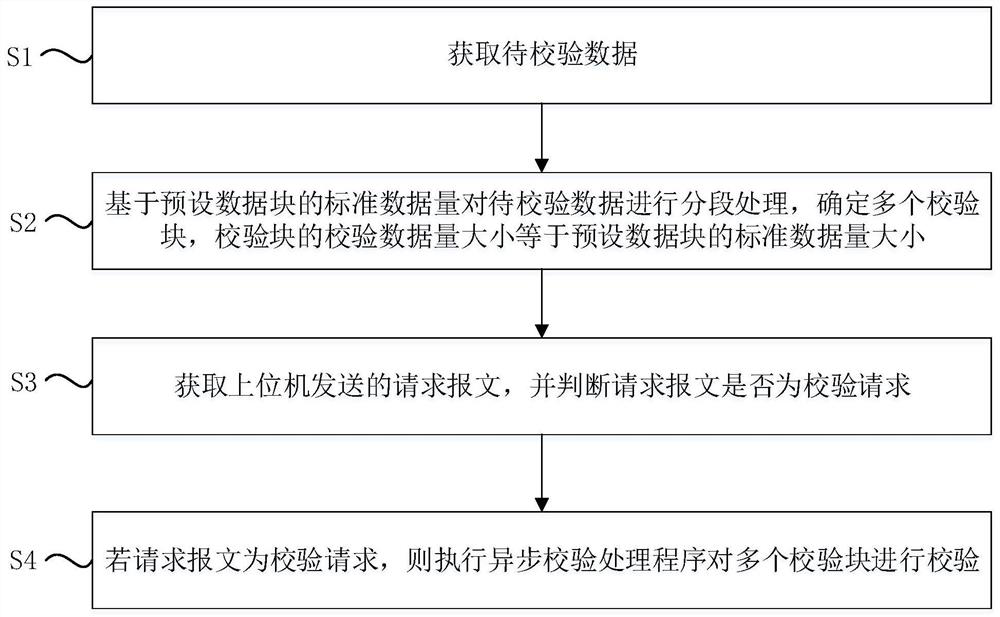

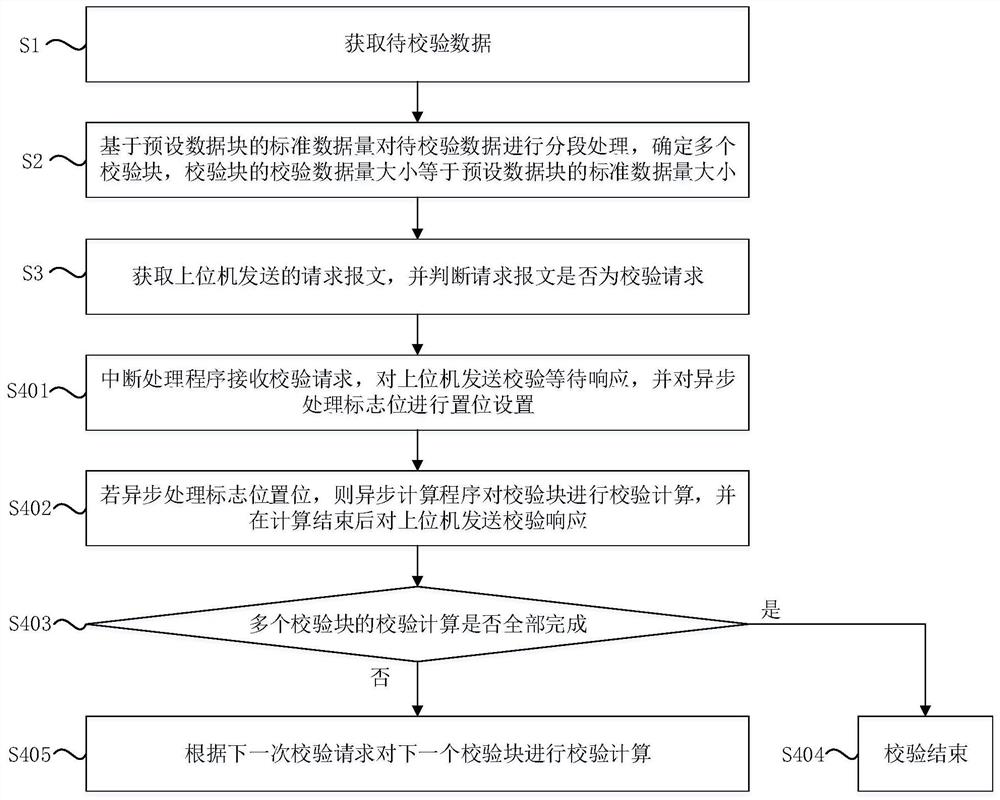

Data verification acceleration method and device, computer equipment and storage medium

ActiveCN112713964ASolve efficiency problemsTime-consuming to solveError detection/prevention using signal quality detectorForward error control useComputer hardwareSource Data Verification

The invention discloses a data verification acceleration method and device, computer equipment and a storage medium. The method comprises the steps of obtaining to-be-verified data; performing segmentation processing on the to-be-verified data based on the standard data size of the preset data block, and determining a plurality of verification blocks, the verification data size of the verification blocks being equal to the standard data size of the preset data block; obtaining a request message sent by an upper computer, and judging whether the request message is a verification request or not; if the request message is a verification request, executing an asynchronous verification processing program to verify the multiple verification blocks, wherein the asynchronous verification processing program comprises an interrupt processing program and an asynchronous calculation program, the interrupt processing program is used for sending a verification waiting response to the upper computer, and the asynchronous calculation program is used for calculating the verification blocks; and sending a verification response to the upper computer after the calculation is finished. According to the invention, the processing speed of data verification is improved by expanding the data size of the verification block for each verification processing and adopting an asynchronous calculation method to perform data verification.

Owner:WEICHAI POWER CO LTD

An asynchronous high energy efficiency map computational accelerator

ActiveCN109003222AFast convergenceReduce power consumptionImage memory managementProcessor architectures/configurationHigh energyOn board

The invention discloses an asynchronous high energy efficiency map computing accelerator, which includes sequentially connected data preprocessing module, data transmission module and data processingmodule, wherein: the data preprocessing module preprocesses a given example graph G in an initialization stage, partitions large-scale graph data, and further organizes the graph G into a sub-graph data Batch Row Vector with batch_size as a size; the data transfer module transfers the sub-graph data Batch Row Vector to the on-board DDR via PCIe DMA, and then to the on-chip accelerator via AXI DMA.The data processing module is an accelerator on-chip logic, comprising a memory module and a calculation module. The memory module comprises an on-chip cache, and the computing module comprises an on-chip computing module. The invention designs the asynchronous high energy efficiency map computational accelerator, adopts the asynchronous calculation mode to accelerate the convergence speed of themap algorithm, and customizes the accelerator based on the hardware platform to reduce the power consumption and the energy consumption of the system.

Owner:UNIV OF SCI & TECH OF CHINA

A multi-center biomedical data collaborative processing system and method without patient data sharing

ActiveCN110362586BSafe isolationPrivacy protectionDatabase updatingProgram initiation/switchingEngineeringPatient data

The invention discloses a multi-center biomedical data collaborative processing system and method without patient data sharing. The system includes a cloud server for coordinating model parameters and asynchronous calculations of each medical center and a local high-performance computing system for data. Medical center client; wherein the cloud server includes a parameter manager and a task scheduler; in the present invention, the parameter sharing mechanism and asynchronous communication mechanism are connected and managed through the parameter manager and task scheduler of the cloud server, and are jointly applied to multi-center medical data collaborative computing ;It can meet the security isolation of medical center data and cloud server, and fully protect the privacy of medical center patient data; at the same time, compared with direct synchronous exchange of data calculation results, it can effectively reduce calculation waiting time, and greatly improve the analysis efficiency and data processing of multi-center collaborative processing ability.

Owner:ZHEJIANG LAB

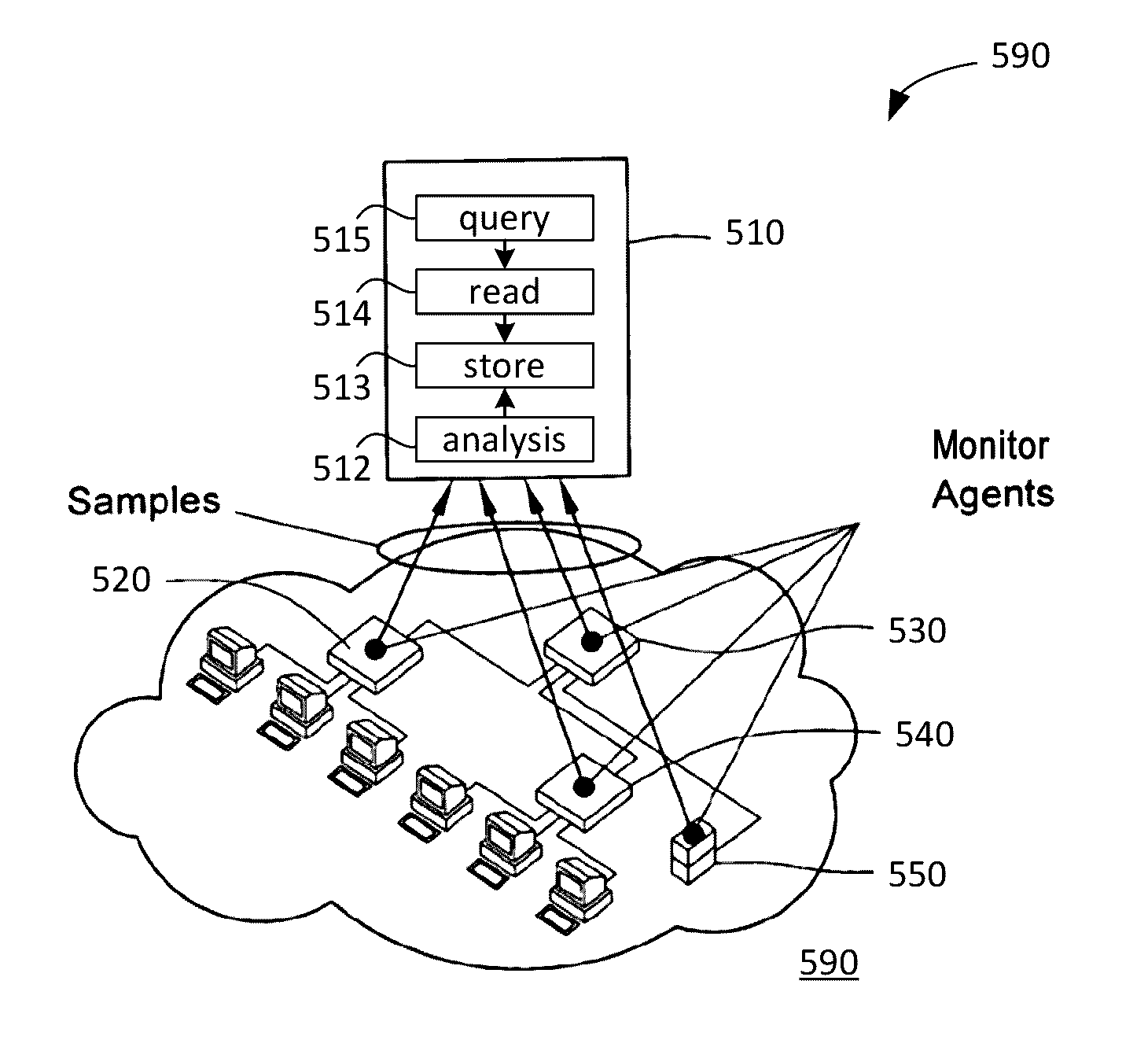

Method for asynchronous calculation of network traffic rates based on randomly sampled packets

A method for calculating rates based on random sampling includes updating at least one state variable when sampled information is received. The method further includes calculating a rate value based on the state variable and the elapsed time since the state variable was previously updated.

Owner:INMON

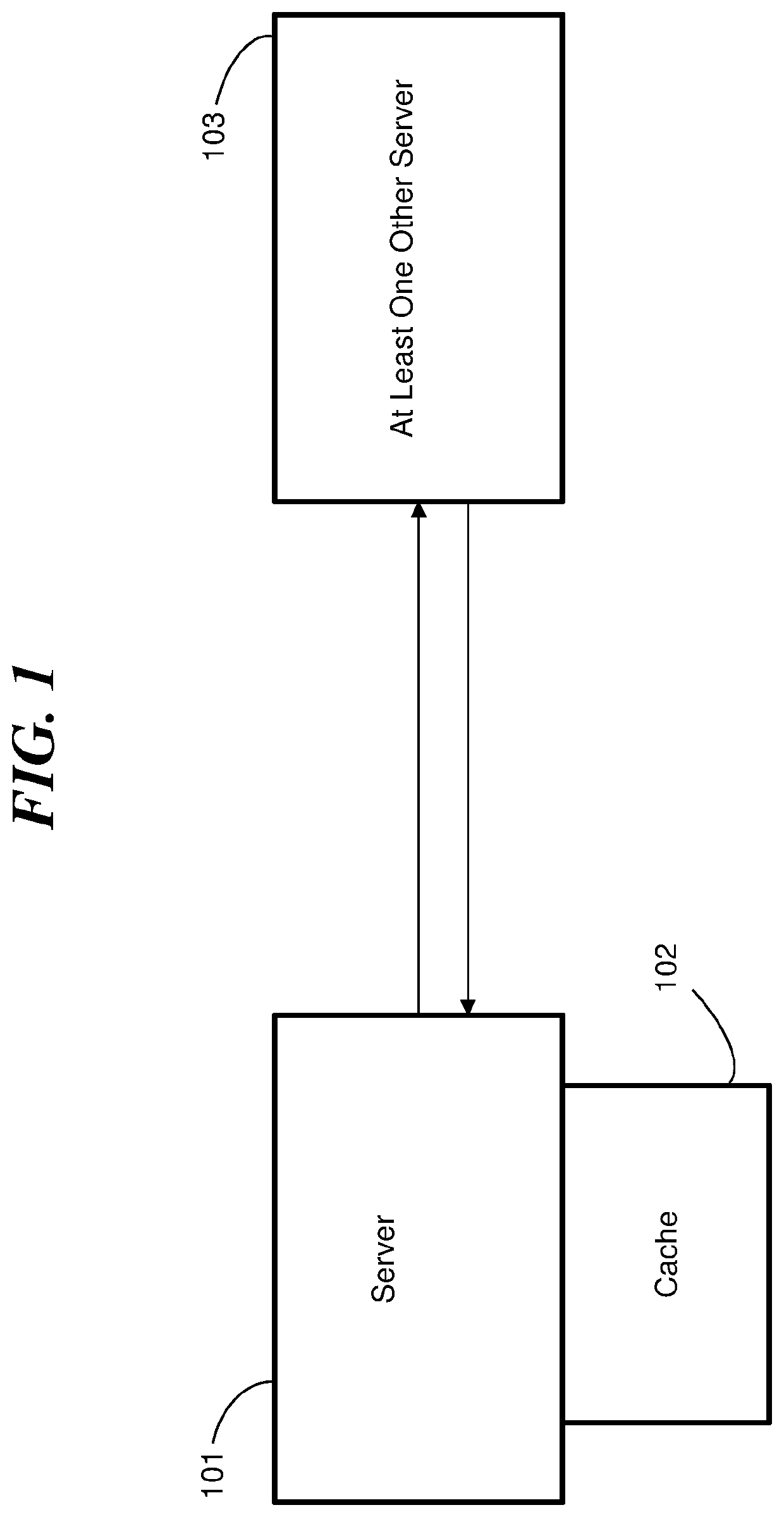

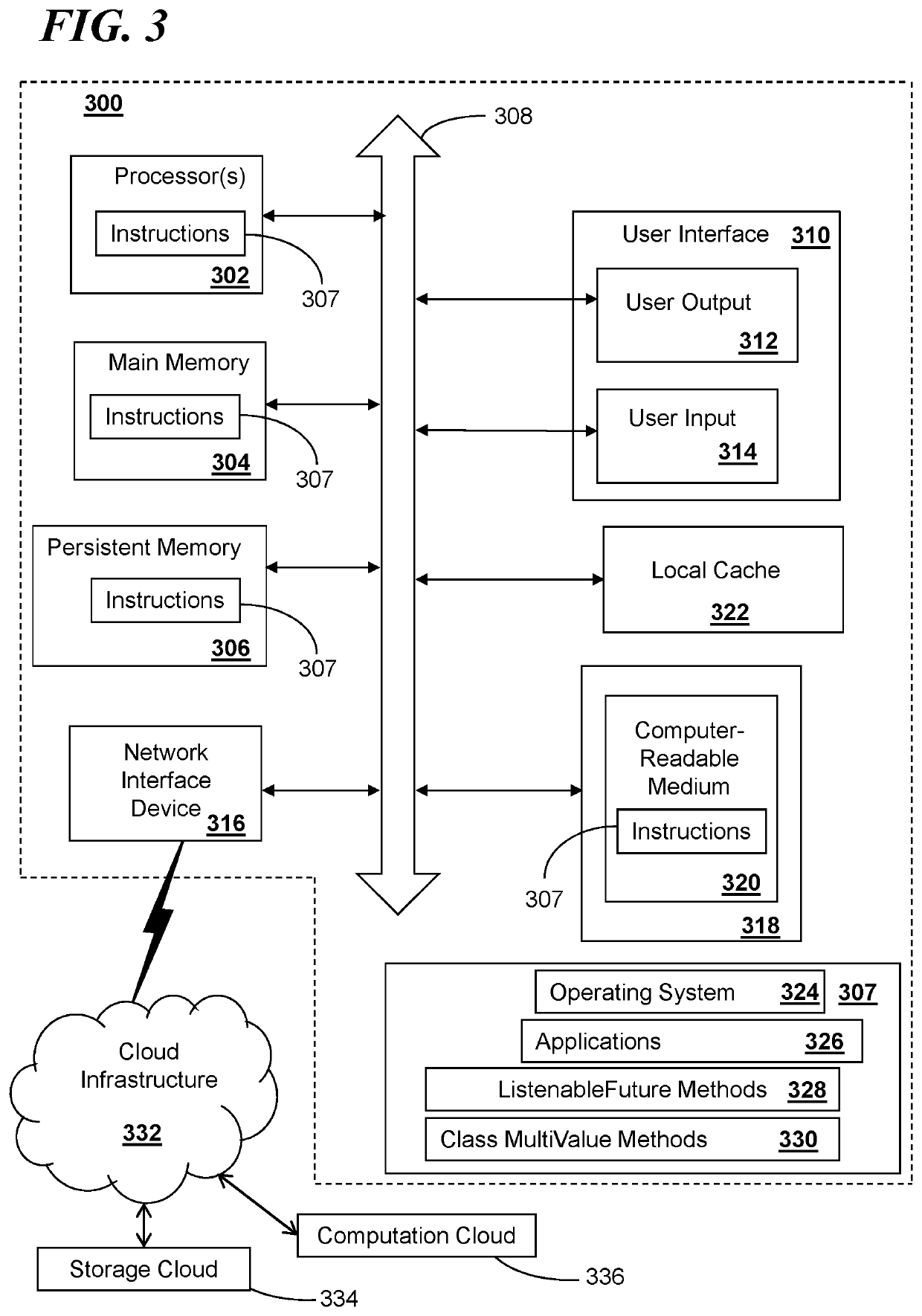

Asynchronous data store operations including selectively returning a value from cache or a value determined by an asynchronous computation

ActiveUS10540282B2Memory architecture accessing/allocationMemory systemsParallel computingHandling system

A processing system server and methods for performing asynchronous data store operations. The server includes a processor which maintains a cache of objects in communication with the server. The processor executes an asynchronous computation to determine the value of a first object. In response to a request for the first object occurring before the asynchronous computation has determined the value of the first object, a value of the first object is returned from the cache. In response to a request for the first object occurring after the asynchronous computation has determined the value of the first object, a value of the first object determined by the asynchronous computation is returned. The asynchronous computation may comprise at least one future, such as a ListenableFuture, or at least one process or thread. Execution of an asynchronous computation may occur with a frequency correlated with how frequently the object changes or how important it is to have a current value of the object. The asynchronous computation may receive different values from at least two servers and may determine the value of an object based on time stamps.

Owner:INT BUSINESS MASCH CORP

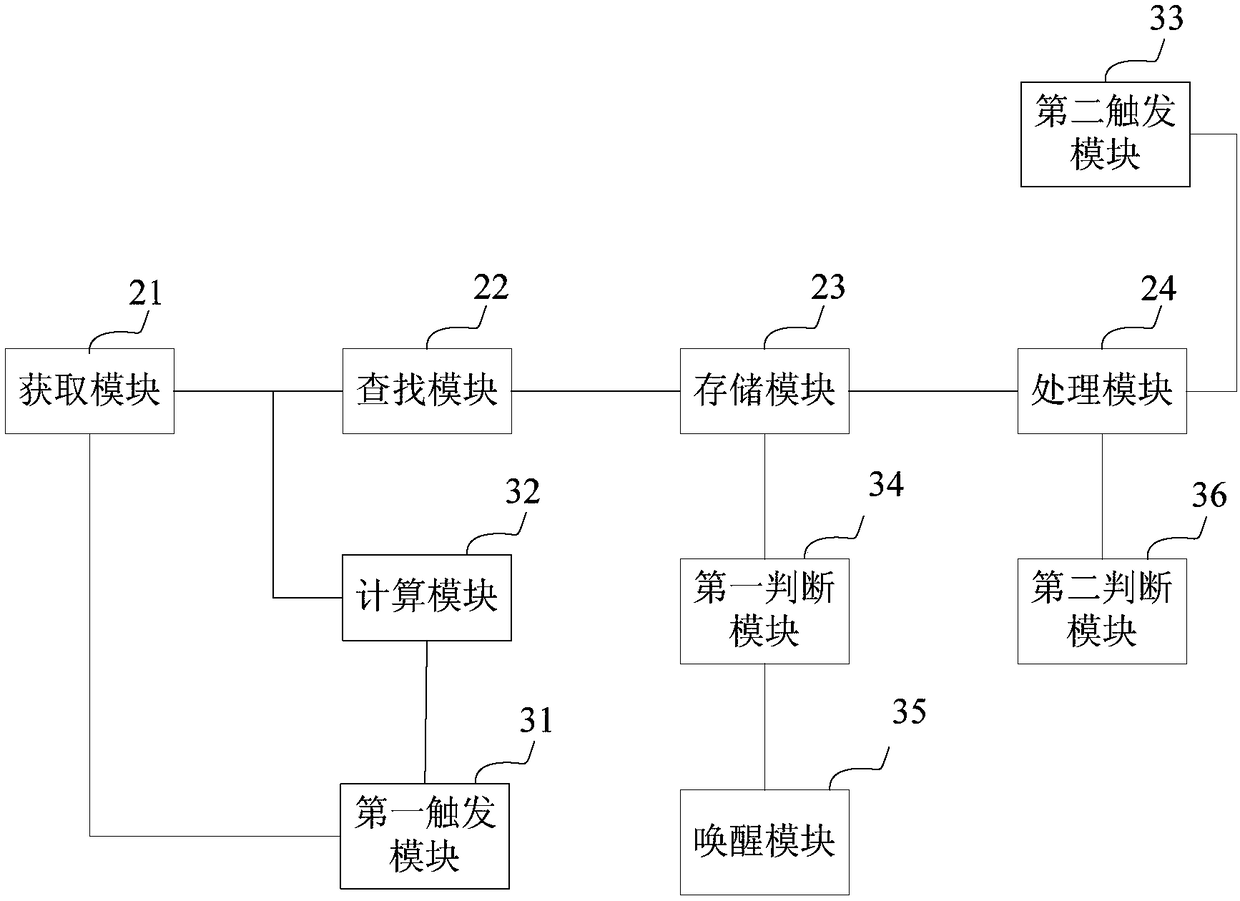

Asynchronous calculation method and device for network function in spreadsheet

ActiveCN108268564AImplement asynchronous computingShorten the timeSpecial data processing applicationsParallel computingCalculation methods

Owner:ZHUHAI KINGSOFT OFFICE SOFTWARE +2

Contract scheduling method and device for asynchronous trusted computing and electronic equipment

PendingCN113689296AImprove computing powerFinanceDigital data protectionProcessing InstructionTrusted Computing

The embodiment of the invention provides a contract scheduling method for asynchronous trusted computing, which comprises the following steps that a main chain cluster client initiates a first transaction request, pushes a submission contract engine and random processing to a first queue under a main chain cluster, stores a random processing result into a cache queue of each oracle machine, creates a computing engine by the oracle machine, a processing instruction for calculating the first transaction request is sent to the first node, a voting collection request is sent to the second node, the first node executes to obtain an in-chain execution result, if an out-of-chain request exists in the request, out-of-chain data is accessed for asynchronous calculation, and an out-chain calculation result is received, and the second node collects a voting result according to the out-of-chain calculation result received by the first node, generates proof information through the voting result in a zero-knowledge proof mode, and returns the proof information to the contract engine of the main chain for subsequent transaction processing. Through out-of-chain calculation, an out-of-chain result is obtained and is chained in a zero-knowledge proof mode, so that a contract engine can carry out credible complex calculation, and the calculation capability is improved.

Owner:北京泛融科技有限公司

A message reminder method and system supporting asynchronous and synchronous computing

ActiveCN107967595BImprove performanceImprove acceleration performanceFinanceOffice automationComputer networkBusiness management

The invention discloses a message reminder method and system supporting asynchronous and synchronous calculations. The method includes the following steps: in a business management system, integrating asynchronous message reminders and synchronous message reminders, wherein: the asynchronous message reminder adopts at least two One asynchronous calculation method to obtain the message data required for message reminders, and configure different reminder rules according to the characteristics of message reminders. Synchronous message reminders use at least one synchronous calculation method to obtain the message data required for message reminders. Finally, the asynchronous calculation And synchronously calculate the message data required for message reminders, summarize them into a message data collection, and perform message reminders in a unified manner. The method and system improve the performance and scalability of the message reminder function by adopting technologies such as read-write separation, timing tasks, and asynchronous computing tasks, so that business operators can obtain unified message reminders in time after logging into the system (business management system).

Owner:北京大数元科技发展有限公司

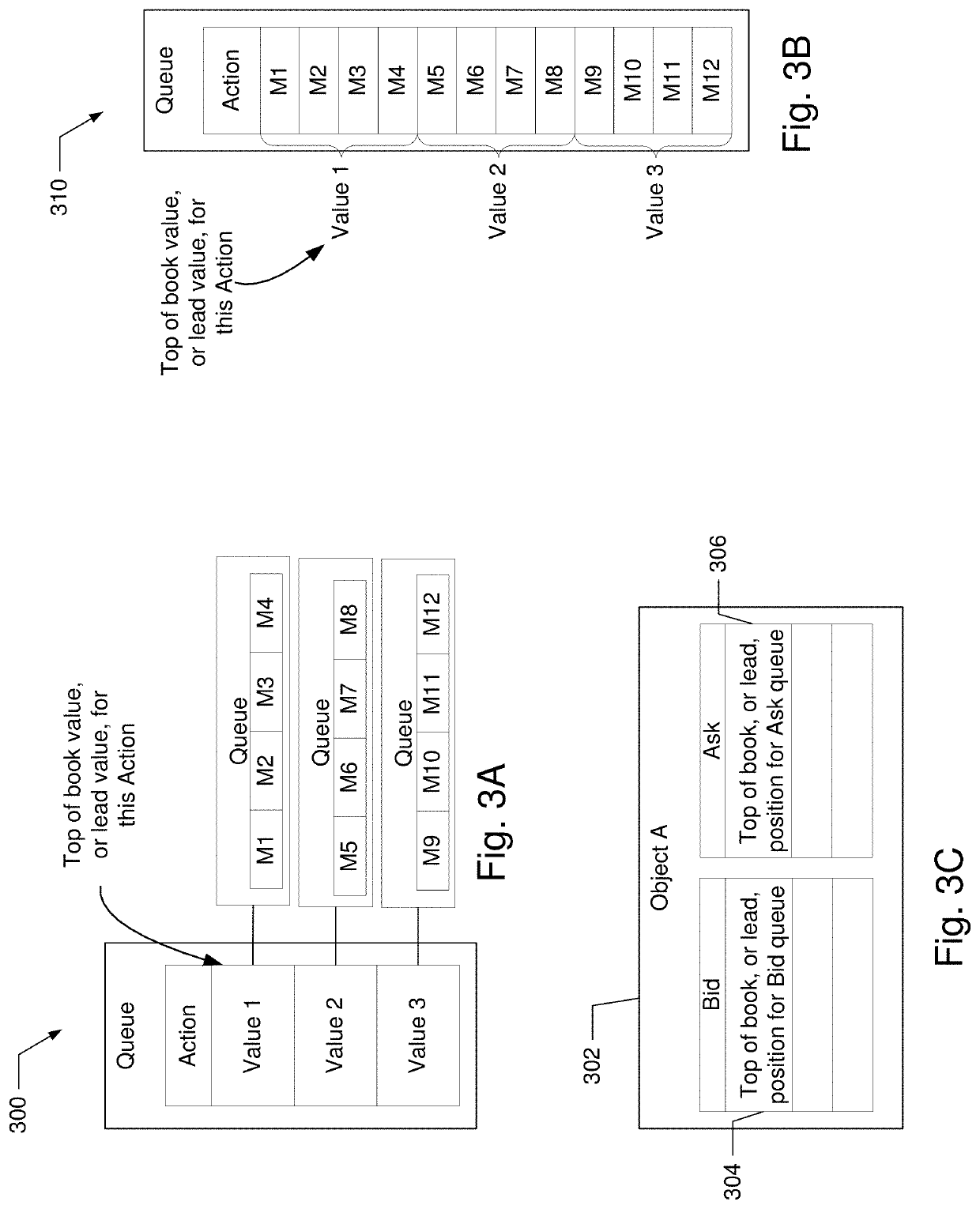

Asynchronous computational engine

A method includes retrieving a first dataset at a first frequency from a memory, the first dataset associated with a plurality of data objects; calculating at the first frequency and based on the first dataset, a first component for each of the data objects; retrieving a second dataset at a second frequency from the memory, the second dataset associated with the plurality of data objects; calculating at the second frequency and based on the second dataset, a second component for each of the data objects; weighting at one of the first or second frequencies, the first component by the second component for each of the data objects; calculating at one of the first or second frequencies, an asynchronous multi-component index based on the weighted first component; and generating at least one asynchronous multi-component index data object having a value that is determined from the calculated asynchronous multi-component index.

Owner:CHICAGO MERCANTILE EXCHANGE

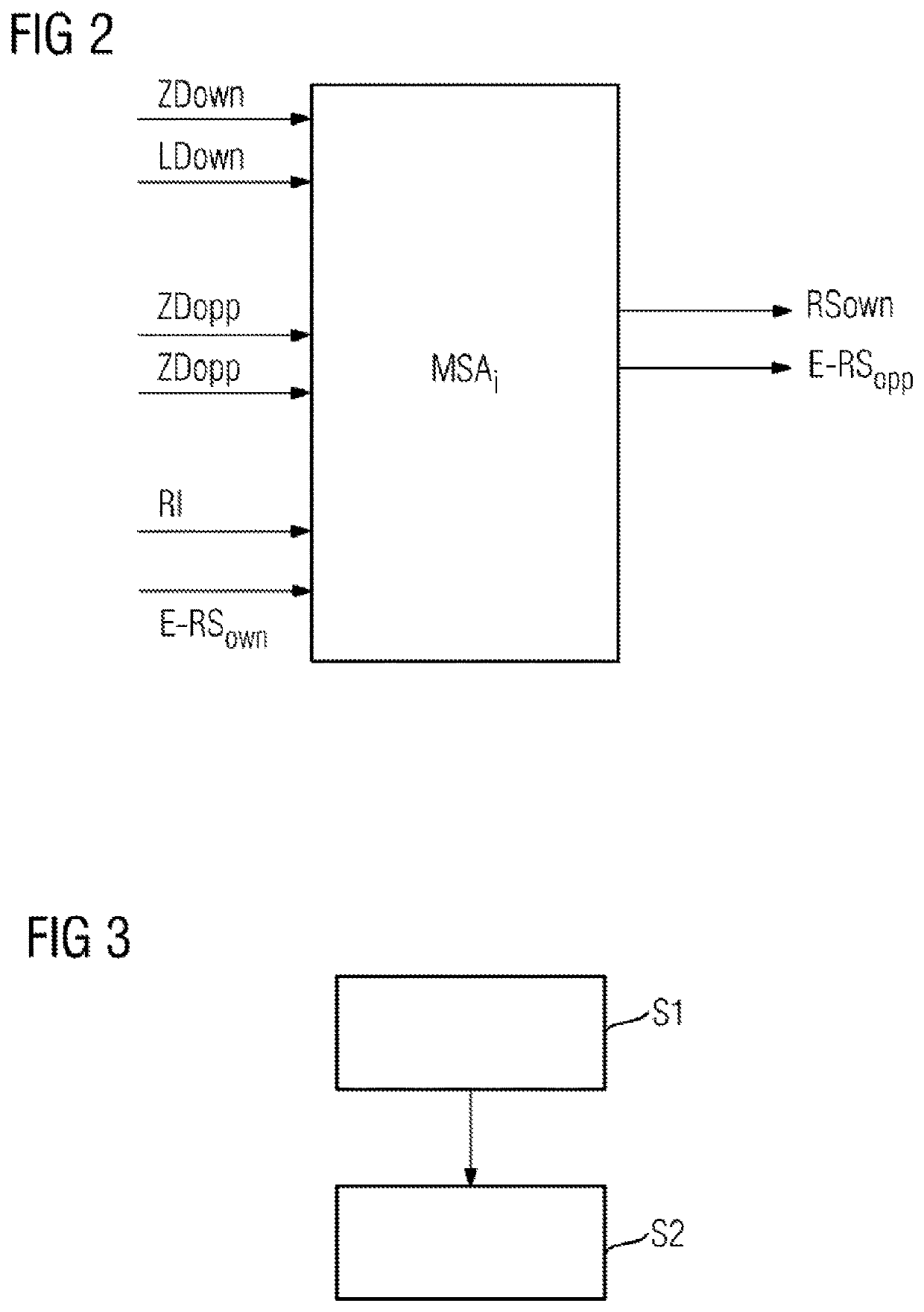

Assigning a control authorization to a computer

ActiveUS10613502B2Improve system stabilityOperational reliability is increasedProgramme controlComputer controlSoftware engineeringControl data

The invention relates to a system (1), comprising at least two asynchronous computers (2-i), on each of which at least one application (A) is executed, which provides control data (SD) for at least one actuation system (3), wherein the provided control data (SD) are transmitted by a control-authorized computer (2-i) that assumes a master computer status (M-RS) to the actuation system (3) for the control thereof, wherein the computers (2-i) of the system (1) cyclically exchange state data (ZD) and performance data (LD) with each other by means of a data interface in a data exchange (DAS), wherein the computers (2-i) each determine, on the basis of the state and performance data (ZDopp, LDopp) received from other computers (2-j) and on the basis of the computer's own state and performance data (ZDown, LDown, in a master / slave selection (MSA) performed on the computer (2-i), a computer status (RS) as a control-authorized or non-control-authorized computer (2-i) to be assumed by the particular computer (2-i) itself.

Owner:SIEMENS AG

Data processing method, device, system and equipment and storage medium

PendingCN114429111AImprove scalabilityNatural language data processingOffice automationComputer hardwareEngineering

The invention relates to a data processing method, device, system and equipment and a storage medium, is applied to a calculation processing server, and comprises the following steps: receiving a data calculation request which is sent by the data processing server and carries a data processing result of an editing cell; in response to the data calculation request, updating data in a target cell associated with the editing cell in the target table based on the data processing result to obtain a data updating result of the target cell; and sending the data updating result to the client. According to the method and the device, asynchronous calculation is carried out by the independent calculation processing server, so that calculation service with higher expandability is independent.

Owner:BEIJING DAJIA INTERNET INFORMATION TECH CO LTD

A Method of Accelerating Seismic Prestack Time Migration Using CPU/MIC Collaborative Computing

ActiveCN103018776BImprove computing powerMeet processing needsSeismic signal processingScanning tunneling microscopeParallel computing

The invention provides a method for cooperatively computing and accelerating pre-stack time migration of an earthquake by using a CPU (Central Processing Unit) / MIC (Microphone), and relates to the field of high-property computing. According to the method, a CPU and MIC heterogeneous framework is used; a CPU is in charge of performing FFT (Fast Fourier Transform) computing, reading seismic channel data, performing process control and scheduling, and further participating in PSTM (Photon Scanning Tunneling Microscope) computing; the MIC is used for only performing the PSTM computing, and simultaneously performing CPU and MIC cooperative computation and common computation in an asynchronous parallel idea and dynamic load balance manner; and the integrated design comprises the following three aspects: parallel design of a PSTM computation partial serial algorithm, a PSTM integrated logic structural design and a CPU and MIC asynchronous computation design. The method provided by the invention has the beneficial effects that the PSTM properties can be improved by using the CPU / MIC cooperative computation; the building cost and management, operation and maintenance costs of a machine room can be reduced; and the simple realization and the low desired development cost can be realized.

Owner:LANGCHAO ELECTRONIC INFORMATION IND CO LTD

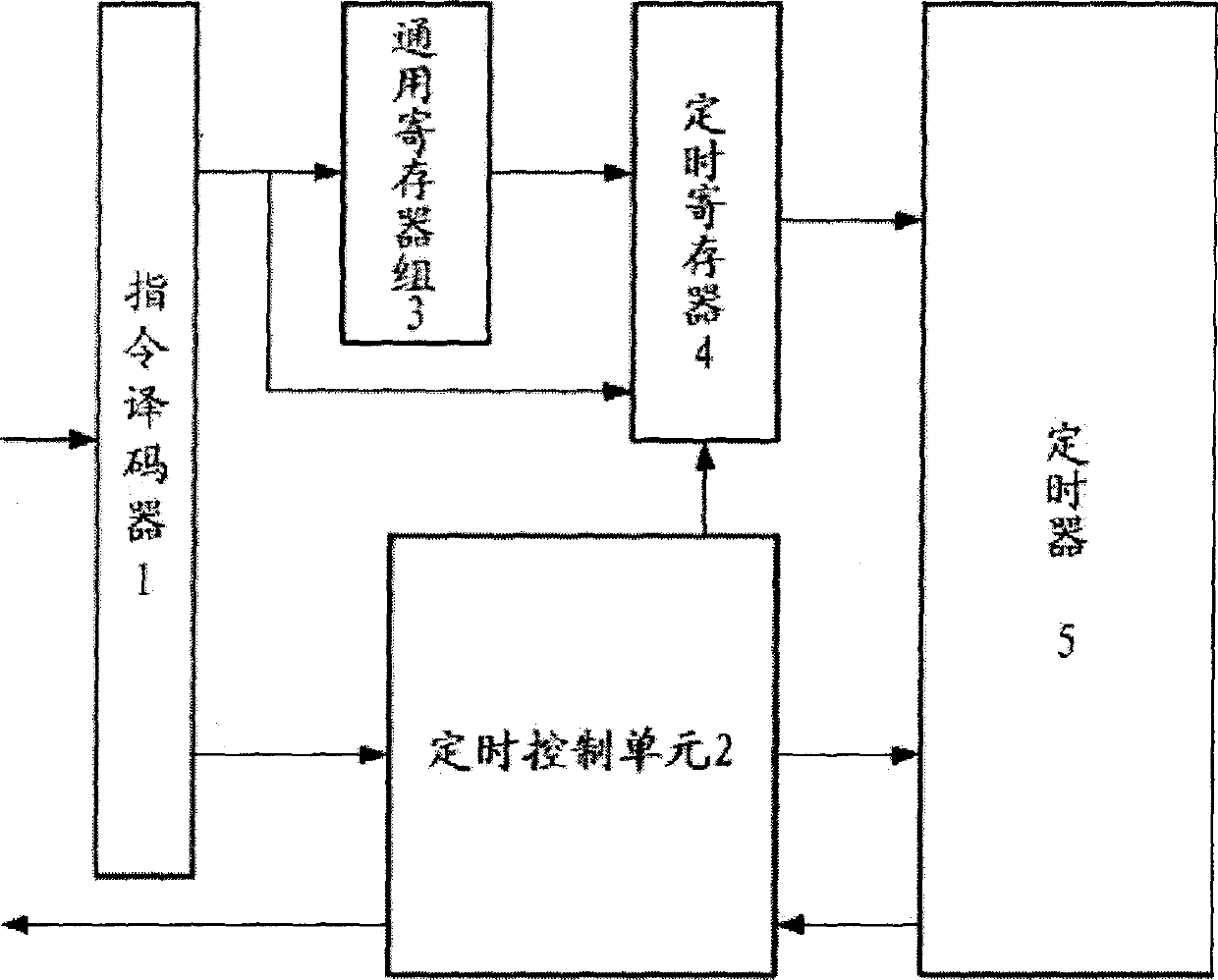

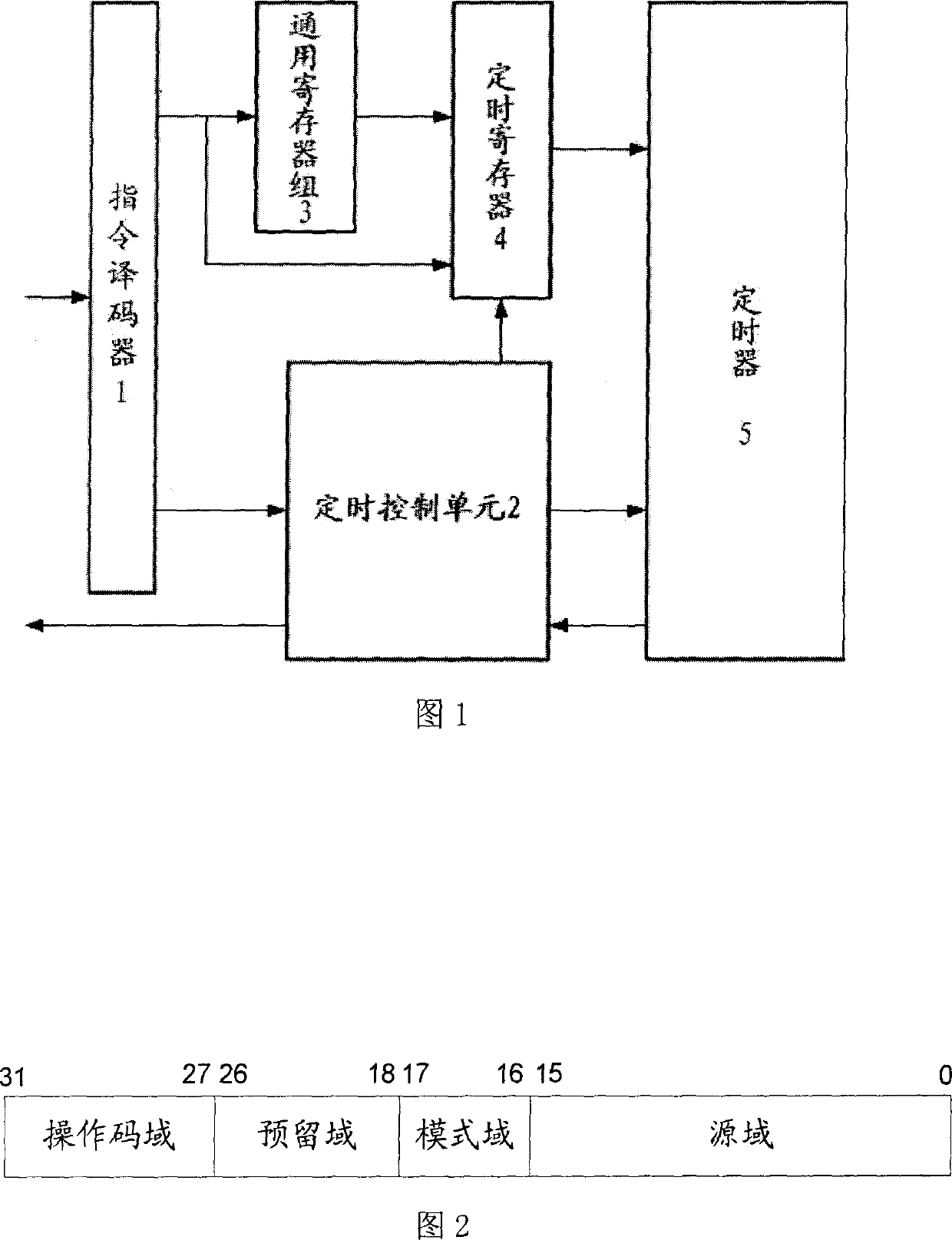

Method and device for asynchronously computing timing coutrol instruction for multi-address space

InactiveCN1776608AImplement Timing Control CommandsSimple structureMachine execution arrangementsTime controlTimer

The method includes steps: (1) obtaining the source and pattern codes by decoding instruction; (2) determining initial value of timer based on the source; (3) carrying out operations of starting, stopping and resetting timer based on pattern codes; (4) timing overflow of timer generates abnormal signal to report error. Embedding timing control unit to architecture of general processor without adding additional module, the method realizes instruction of timing control. Using one piece of instruction of timing control instead of timing operation implemented by multiple instructions usually, the invention solves issues of no response for error of asynchronous calculation as well as not ending for long time caused by error of transferring blocks with multiple addressing spaces. Features are simple structure and flexible application.

Owner:ZHEJIANG UNIV

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com