Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

57 results about "C-element" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

The Muller C-element (C-gate, hysteresis flip-flop, or sometimes coincident flip-flop, two-hand safety circuit) is a small digital block widely used in design of asynchronous circuits and systems. It has been specified formally in 1955 by David E. Muller and first used in ILLIAC II computer. In terms of the theory of lattices, the C-element is a semimodular distributive circuit, whose operation in time is described by a Hasse diagram. The C-element is closely related to the rendezvous and join elements, where an input is not allowed to change twice in succession. In some cases, when relations between delays are known, the C-element can be realized as a sum-of-product (SOP) circuit ,. Earlier techniques for implementing the C-element include Schmidt trigger, Eccles-Jordan flip-flop and last moving point flip-flop.

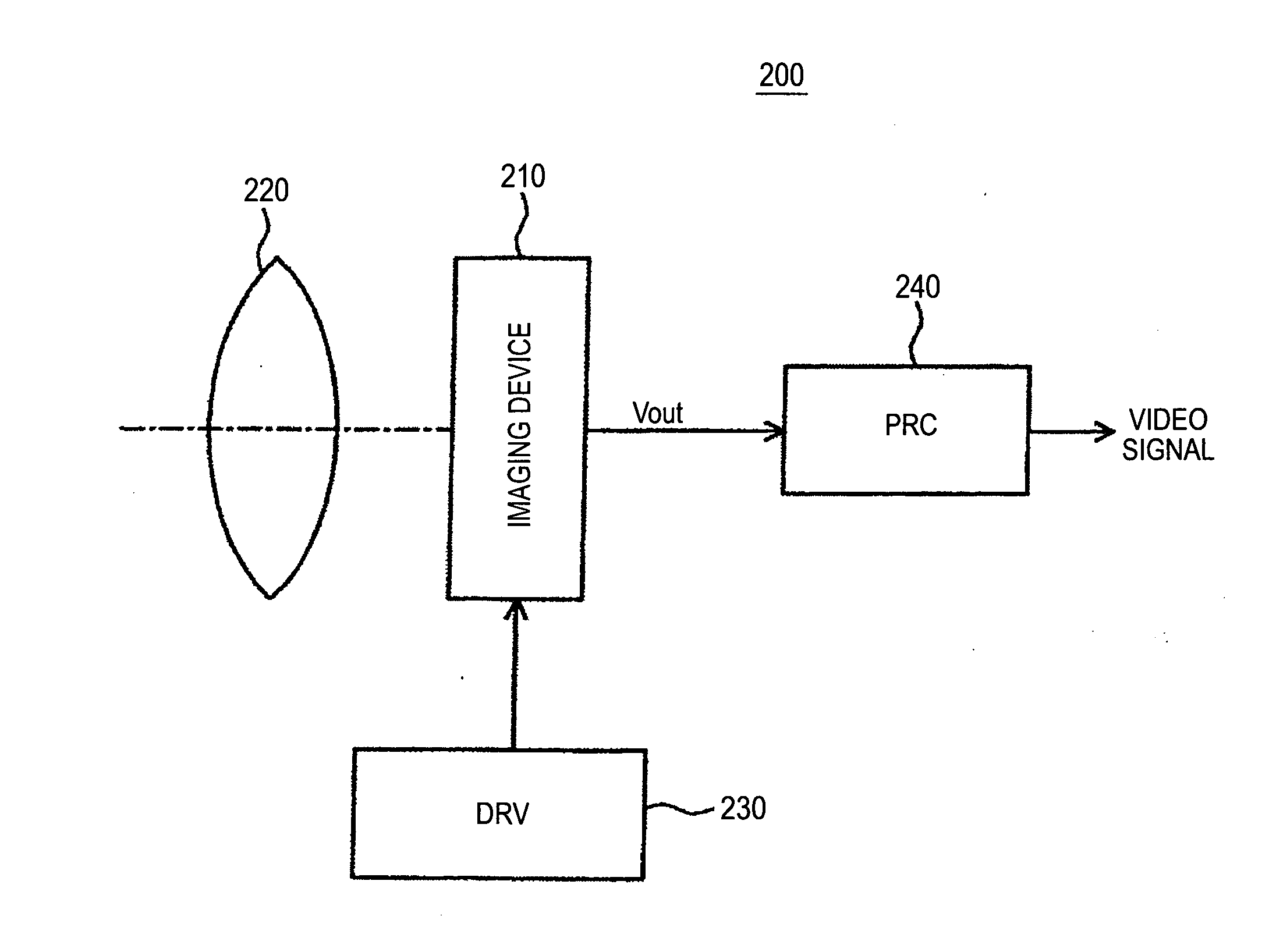

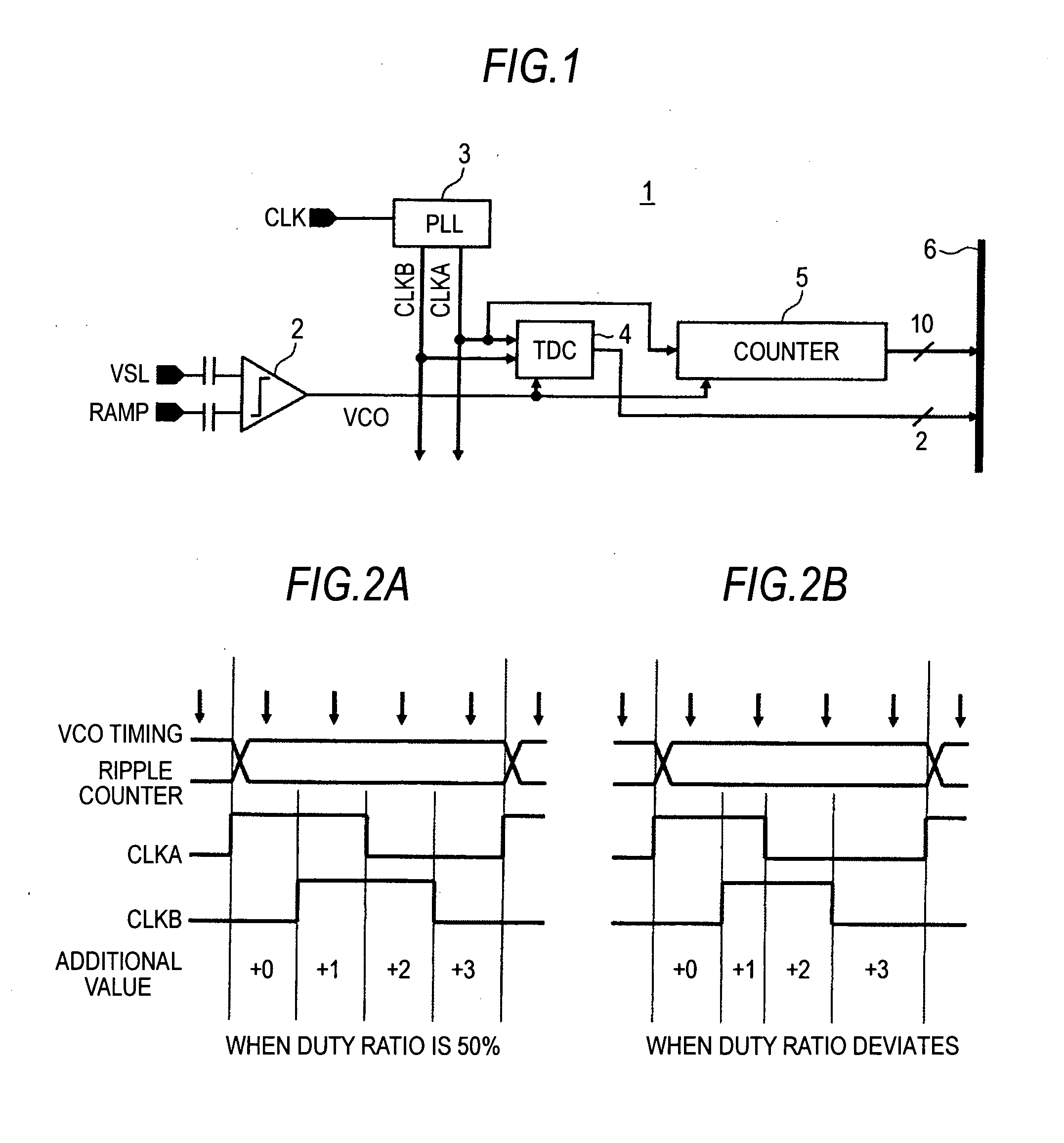

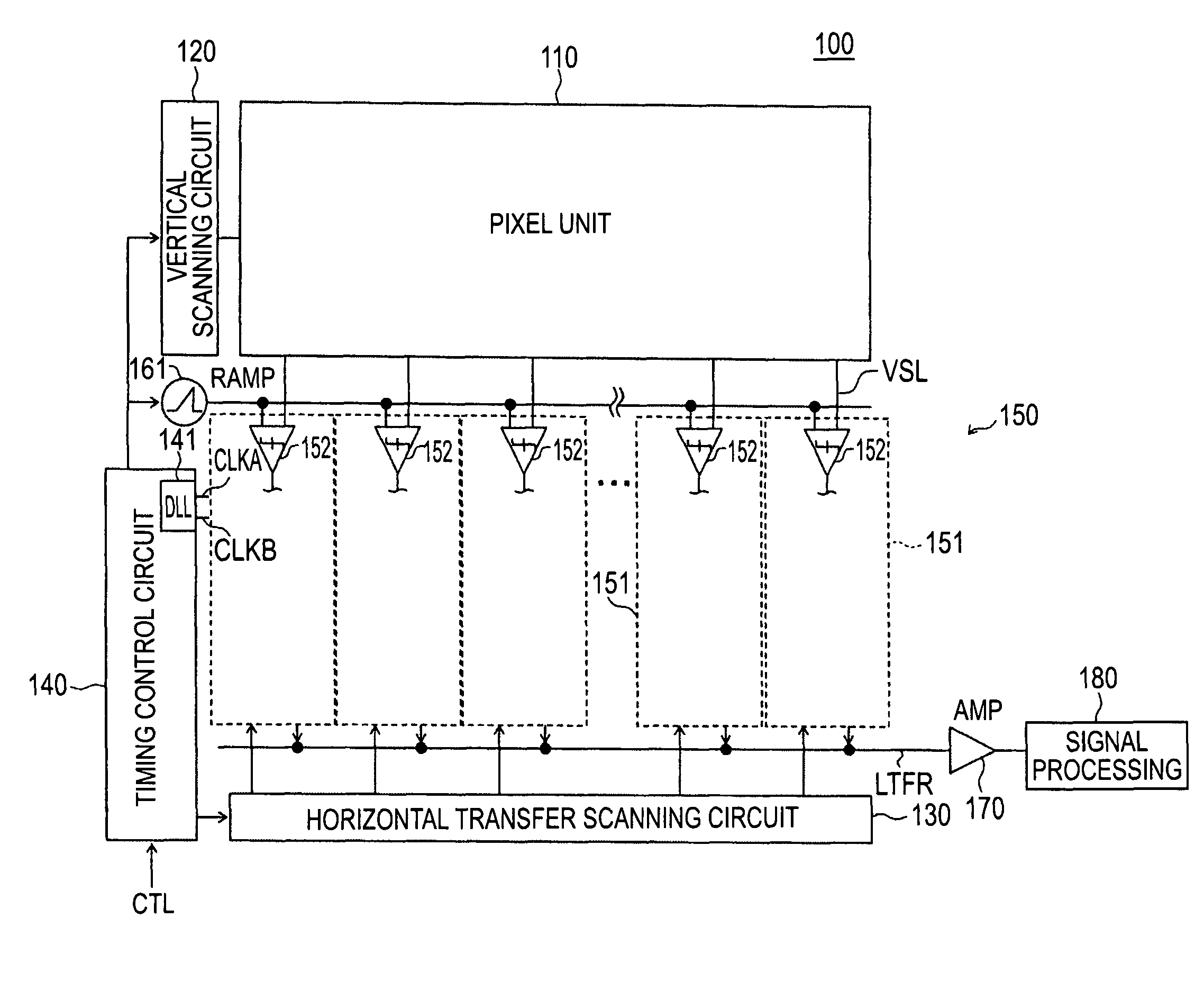

Duty correction circuit, delay locked loop circuit, column a/d converter, solid-state imaging device and camera system

ActiveUS20110187907A1Reduce in quantityReduce the number of timesAnalogue/digital conversionTelevision system detailsPhase differenceDelay-locked loop

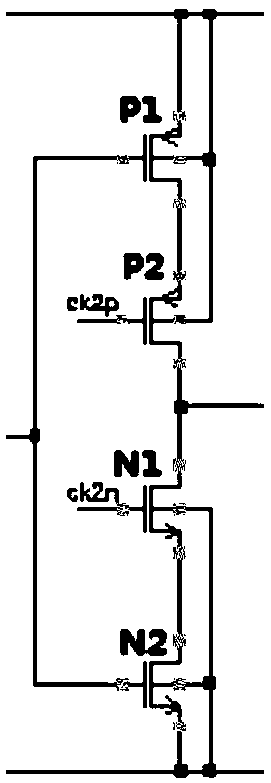

A duty correction circuit includes: a C-element including a first input and a second input; and an inverter connected to the second input of the C-element, wherein the C-element obtains an output of a logic “1” when both inputs are the logic “1”, obtains an output of a logic “0” when both inputs are the logic “0”, and maintains the output to a previous state in other conditions, and complementary clocks having a phase difference of an approximately half cycle are inputted to the first input of the C-element and the inverter respectively.

Owner:SONY CORP

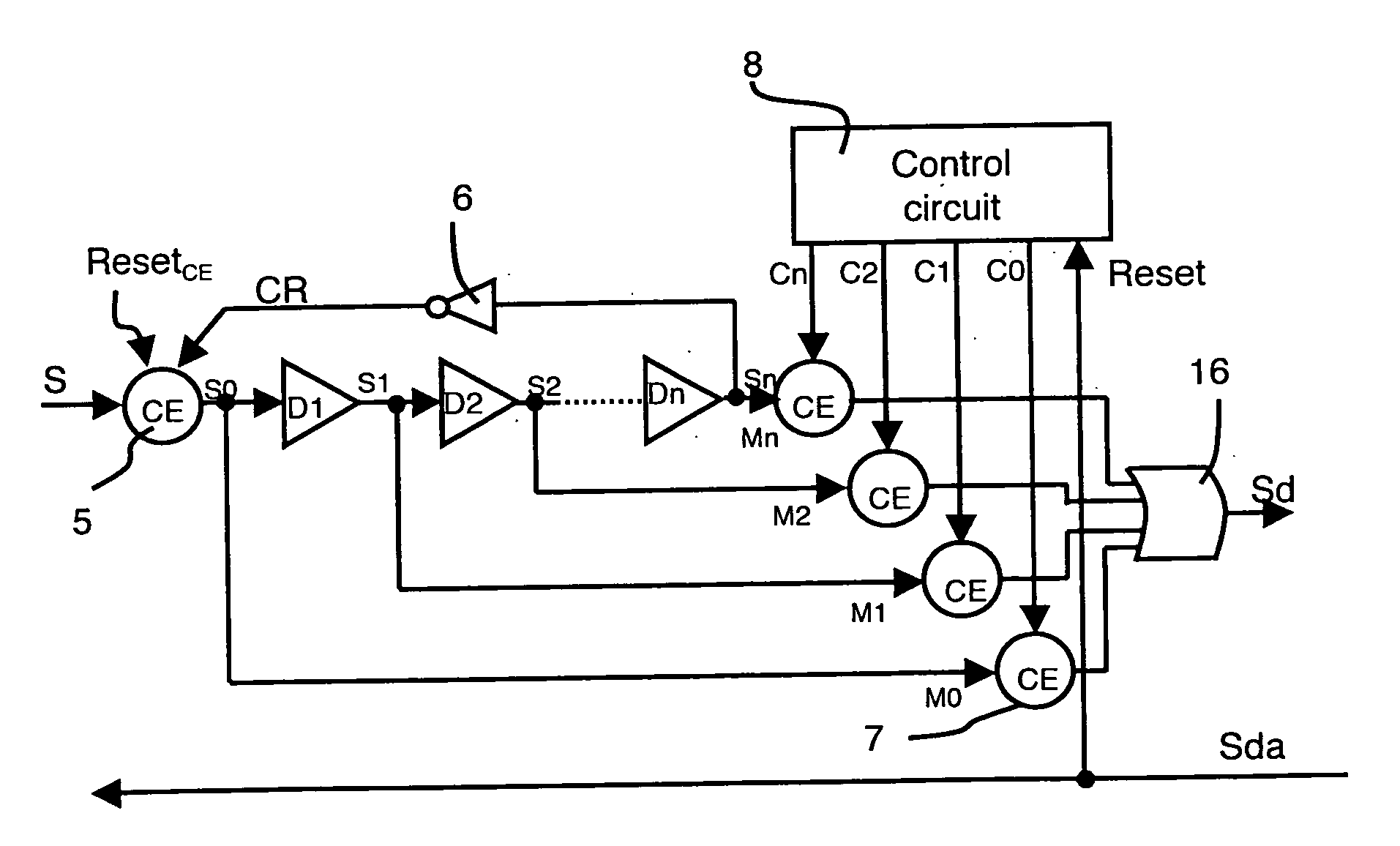

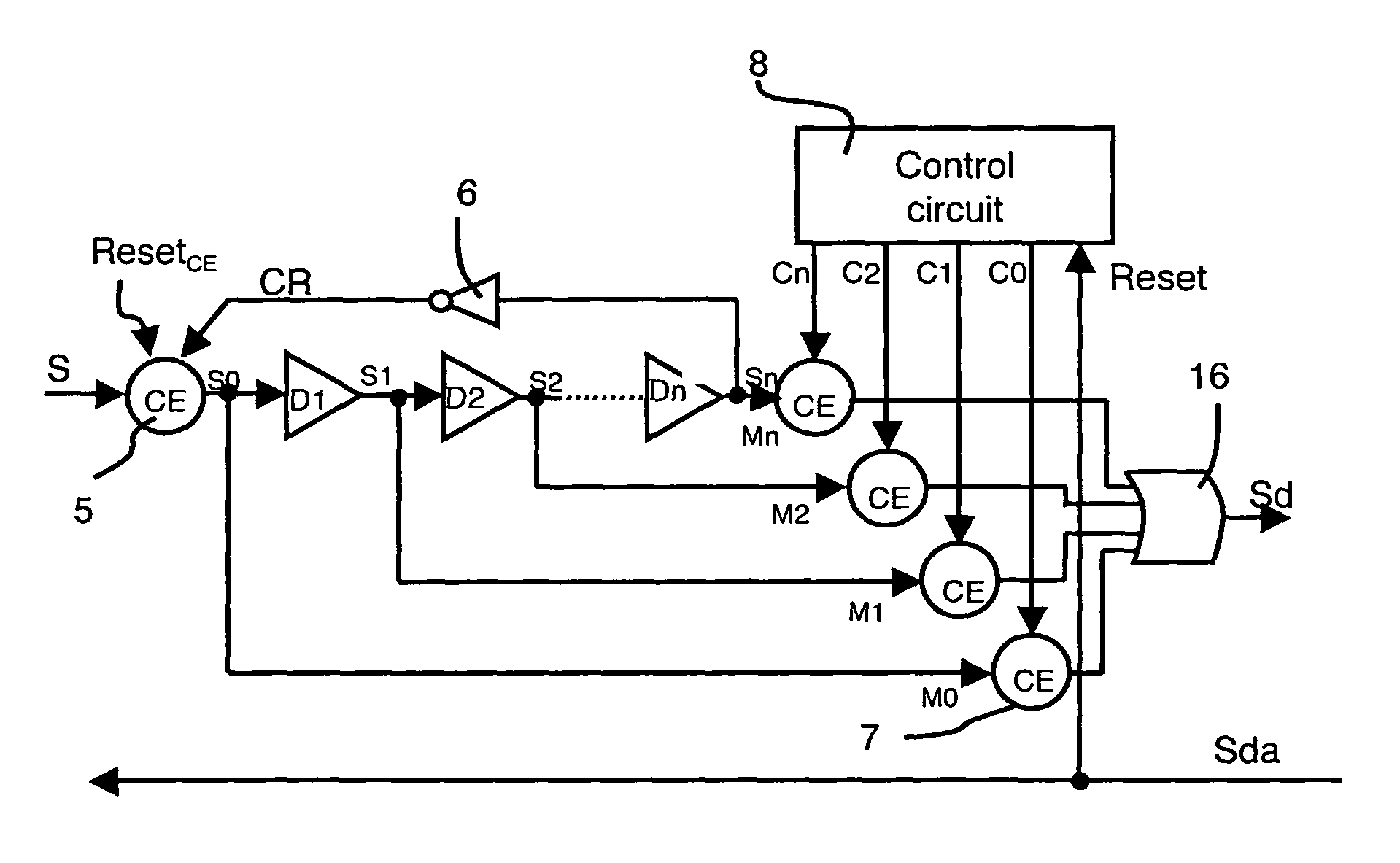

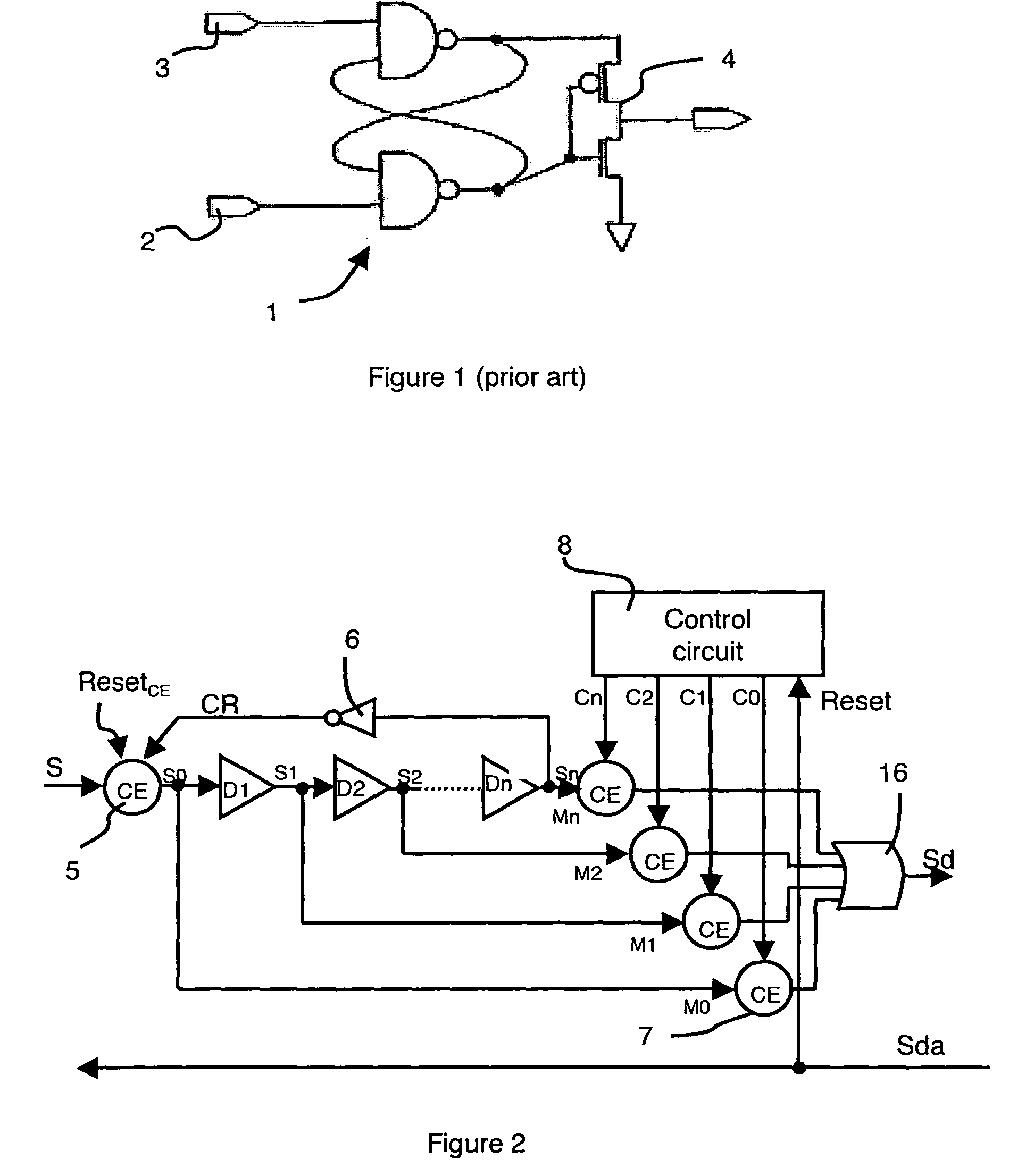

Asynchronous circuit insensitive to delays with time delay insertion circuit

The asynchronous circuit insensitive to delays comprises at least one time delay insertion circuit on the propagation path of a signal. The delay insertion circuit comprises, between an input and an output of the signal, a Muller C-element and a plurality of delay circuits connected in series to an output of the Muller C-element. The outputs of the delay circuits are connected to corresponding inputs of a multiplexing circuit having an output constituting the output of the delay insertion circuit. The Muller C-element comprises an input connected to the output of the last delay circuit via an inverter gate, and an input constituting the input of the signal to the delay insertion circuit. The multiplexing circuit control circuit preferably comprises a random generator.

Owner:TIEMPO

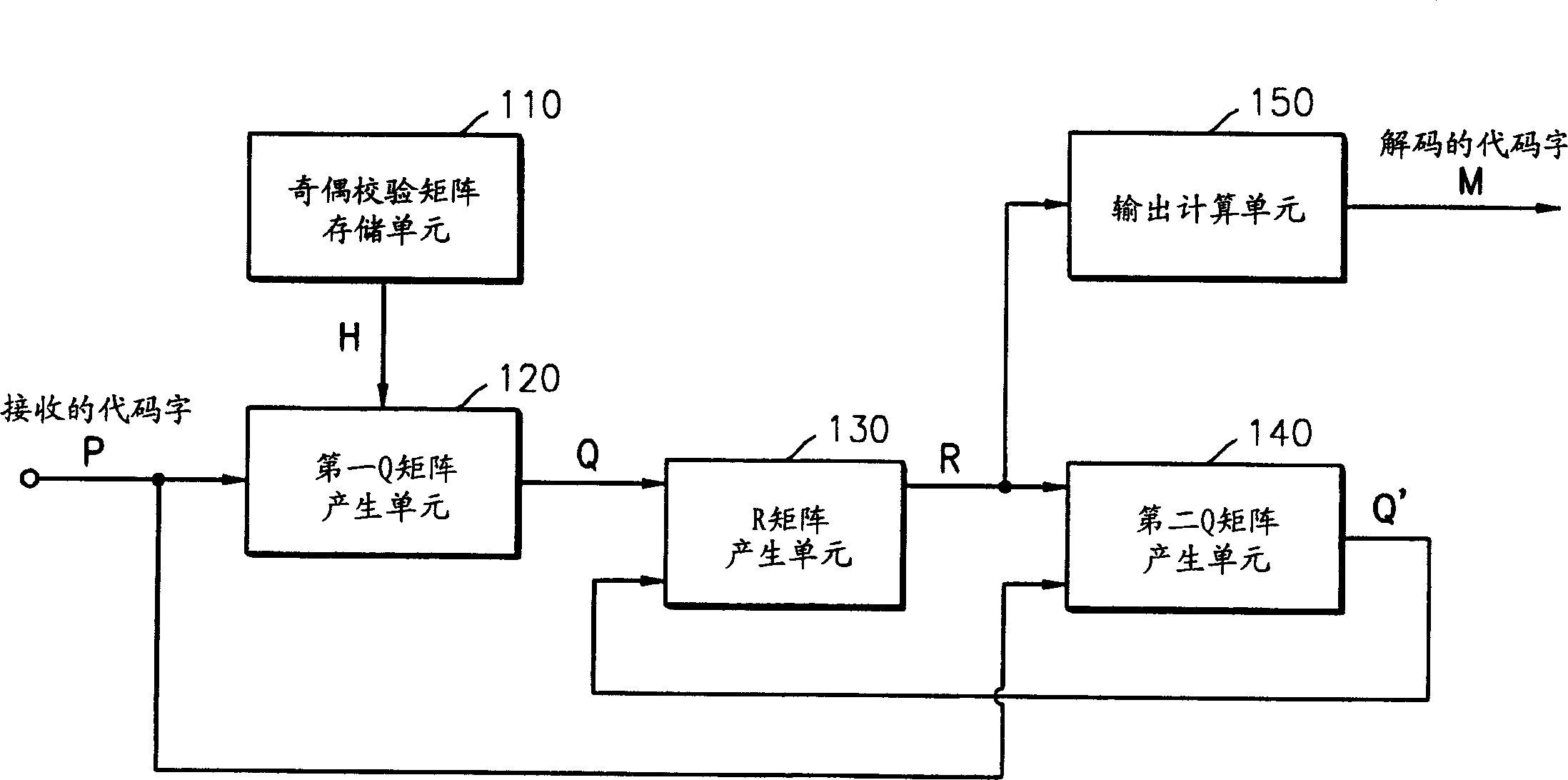

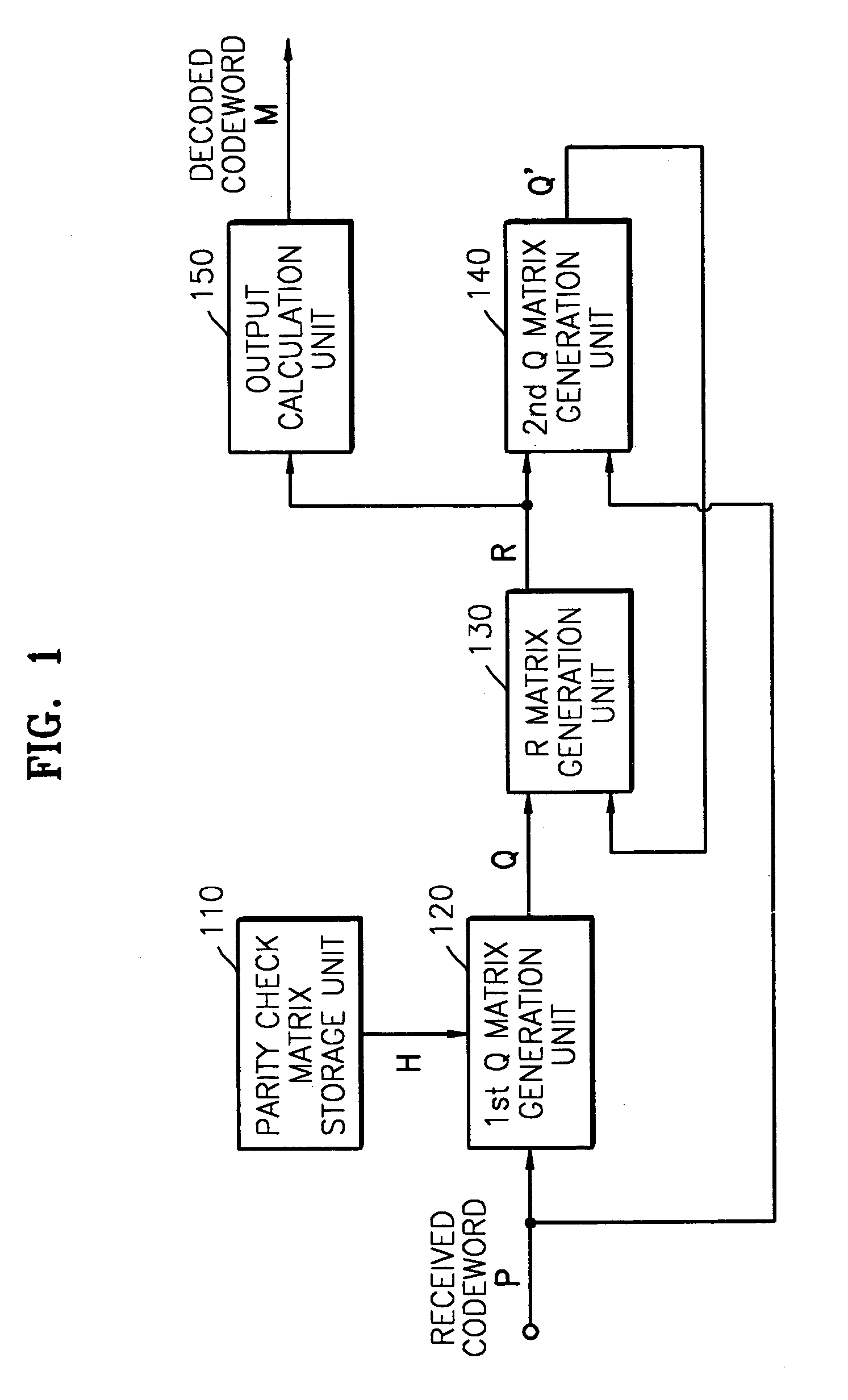

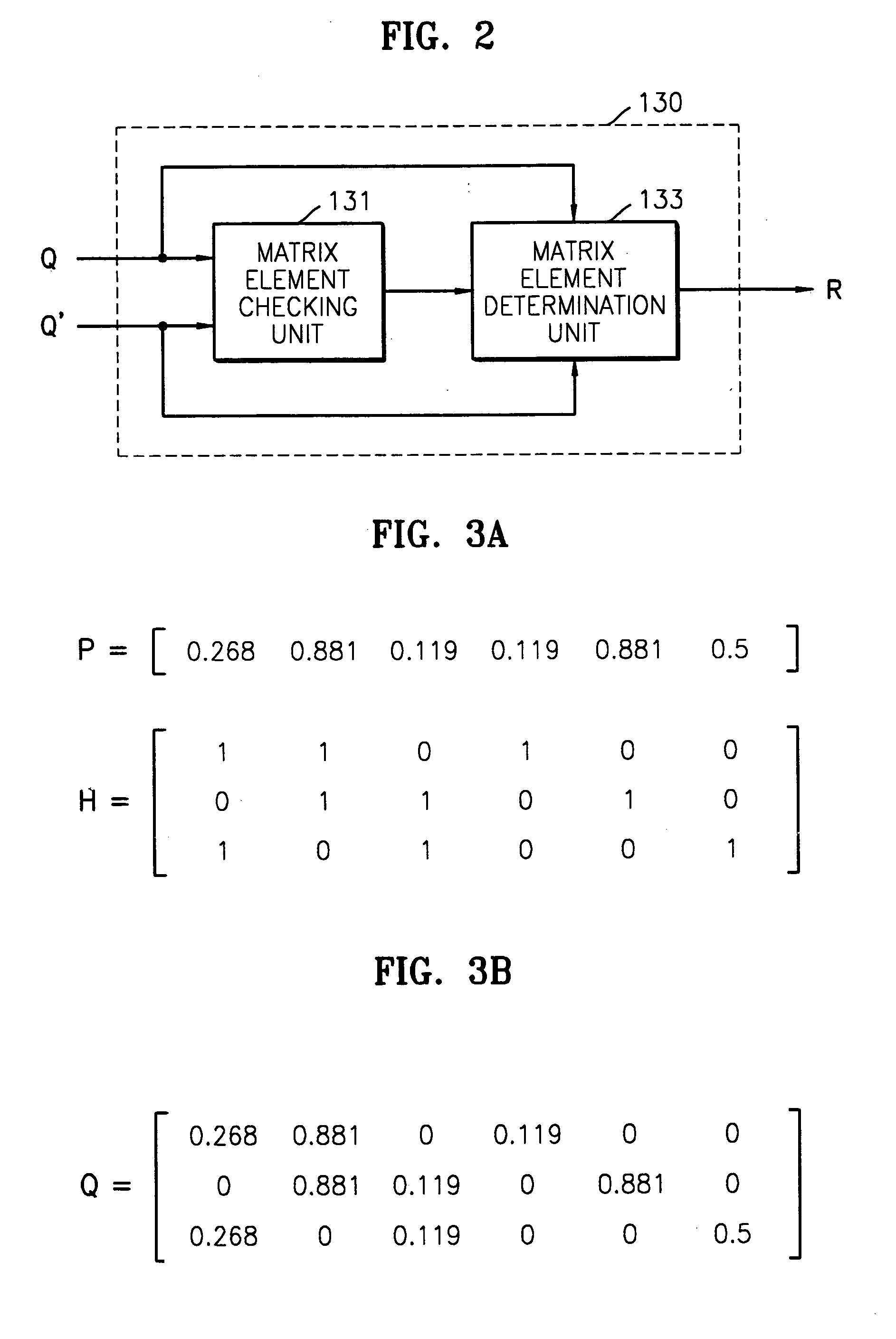

Low density parity check code decoder and method thereof

InactiveCN1499731AReduce complexityImprove decoding performanceError correction/detection using multiple parity bitsCode conversionParity-check matrixTheoretical computer science

An LDPC decoding method and apparatus of LDPC decoding a codeword formed by c code bits transmitted through a channel include receiving the codeword and a p x c parity check matrix formed of 0 and 1 values, comparing the codeword with each of p rows of the parity check matrix, the rows formed with c elements, generating an R matrix by obtaining a first minimum value that is a minimum value among elements that are not 0 in each row, a second minimum value that is a second smallest value in the same row, and a location of the first minimum value, and outputting a decoded codeword formed by c code bits by determining one code bit by adding elements of each column of the R matrix.

Owner:SAMSUNG ELECTRONICS CO LTD

Method and system for reducing power losses and state-overshoots in simulators for switched power electronic circuit

InactiveUS20160314230A1LimitLosses can be minimized/avoidedCAD circuit designSpecial data processing applicationsCapacitanceEngineering

A simulator for a switched electronic power converter circuit feeding a load / device uses a modified FAMNM solver. Provided is a method / system for reducing / eliminating spurious power losses and transients inherently caused by the FAMNM solver using an L / C element approach, wherein a switching device in the ‘on’ state is featured as an inductor L, and a switching device that is in the ‘off’ state is featured as either a capacitance C or series-connected resistance and capacitance R-C. The invention uses cross-initialization of the L / C switching elements to their final state of current and voltage when they change their conduction state. The correct cross-initialization is enabled from optional pre-stored tables of events and the system-states at the time of the cross-initialization. The inventive method is an enhancement over known Dommel and Pejovic type FAMNM solvers. The simulator applies to real-time or non-real time simulators and is suitable for all power converter topologies.

Owner:OPAL RT TECH INC

Silicon-containing alloys useful as electrodes for lithium-ion batteries

An electrode composition for a lithium ion battery has the formula SixSnqMyCz, where q, x, y, and z represent atomic percent values and (a) (q + x) > 2y + z; (b) q >= 0, (c) z >= 0; and (d) M is one or more metals selected from manganese, molybdenum, niobium, tungsten, tantalum, iron, copper, titanium, vanadium, chromium, nickel, cobalt, zirconium, yttrium, or a combination thereof. The Si, Sn, M, and C elements are arranged in the form of a multi-phase microstructure comprising: (a) an amorphous phase comprising silicon; (b) a nanocrystalline phase comprising a metal suicide; and (c) a phase comprising silicon carbide phase when z > 0; and (d) an amorphous phase comprising Sn when q > 0.

Owner:JOHNSON MATTHEY PLC

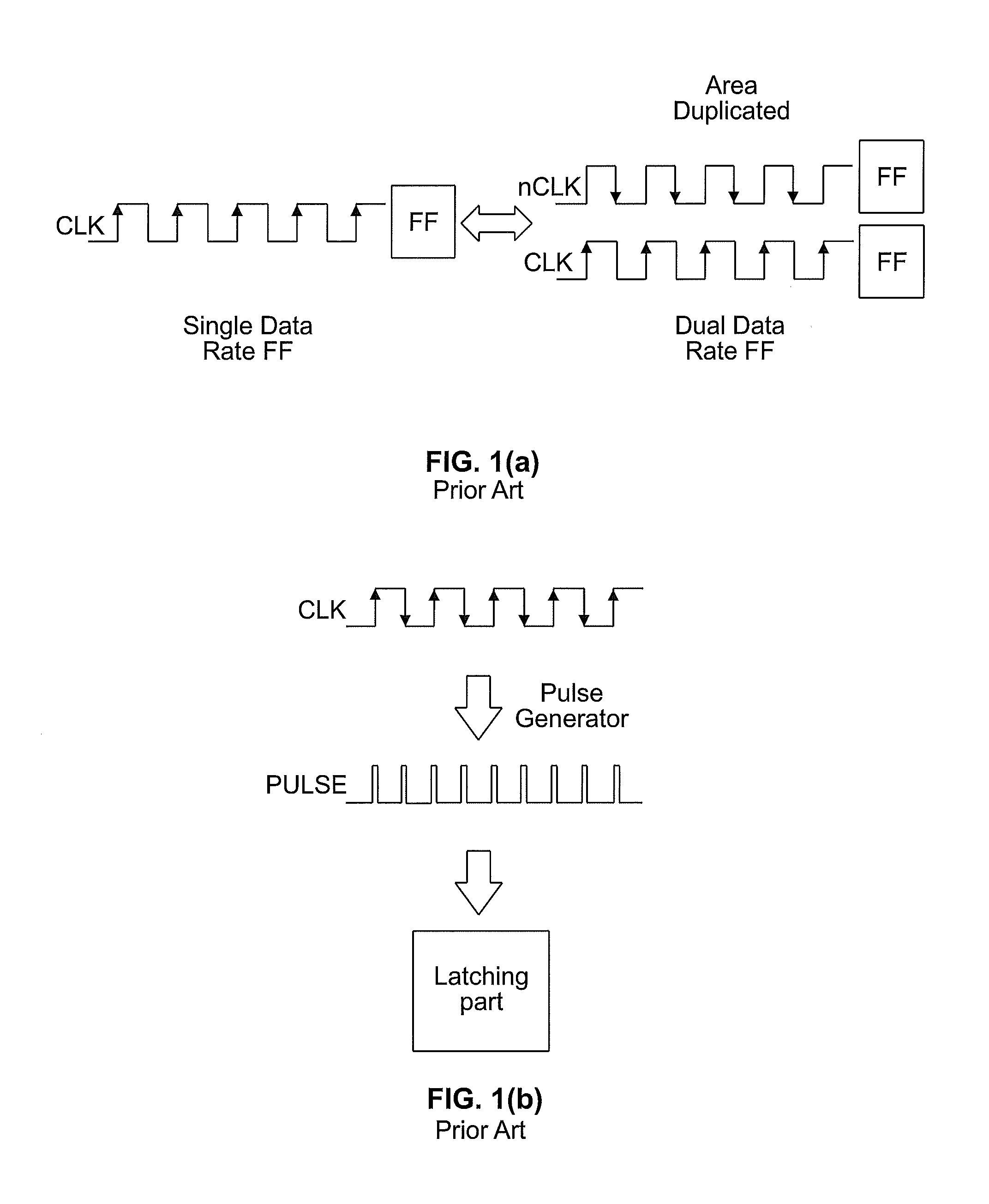

Dual data rate flip-flop circuit

A dual data rate flip-flop circuit for reducing single event upset errors in the flip-flop circuit including two or more latch circuits connected in parallel. The latch circuits each have a clock input, data input, and latch circuit output. The dual data rate flip-flop circuit also includes a C-element, which has a plurality of inputs and a C-element output. The outputs of the latch circuits are provided to inputs of the C-element, and a keeper circuit is connected to the C-element output. An output buffer inverter connects to the C-element output and has an output corresponding to the dual data rate flip-flop circuit output.

Owner:STC UNM

Asynchronous first-in first-out cell

ActiveUS20070097771A1Reduce circuit complexityReduce power consumptionDigital storageData conversionClock rateC-element

The present invention discloses an asynchronous first-in-first-out cell, wherein modified Muller C elements are used to reduce the complexity of the circuit of the asynchronous first-in-first-out cell; the asynchronous first-in-first-out cell of the present invention not only can be reusable, but also can apply to a single-supply-voltage system with a single clock frequency or multiple clock frequencies and a multiple-supply-voltage system with a single clock frequency or multiple clock frequencies. Further, when the asynchronous first-in-first-out cell of the present invention is applied to the interface circuit of a dual-supply-voltage 16-point radix-22 GALS-based FFT architecture, considerable power saving and latency reduction can be achieved.

Owner:NAT CHIAO TUNG UNIV

LDPC decoding apparatus and method

InactiveUS7120857B2Reduce complexityImprove decoding performanceError preventionTransmission systemsParity-check matrixTheoretical computer science

An LDPC decoding method and apparatus of LDPC decoding a codeword formed by c code bits transmitted through a channel include receiving the codeword and a p×c parity check matrix formed of 0 and 1 values, comparing the codeword with each of p rows of the parity check matrix, the rows formed with c elements, generating an R matrix by obtaining a first minimum value that is a minimum value among elements that are not 0 in each row, a second minimum value that is a second smallest value in the same row, and a location of the first minimum value, and outputting a decoded codeword formed by c code bits by determining one code bit by adding elements of each column of the R matrix.

Owner:SAMSUNG ELECTRONICS CO LTD

Data processor for controlling voltage supplied for processing

InactiveUS20050210305A1Reduce power consumptionExcess and shortage of voltage supply can be preventedEnergy efficient ICTVolume/mass flow measurementData transmissionC-element

In a data processor, each logic circuit receives data provided from the transfer control unit being connected, processes the data, and outputs the data to the transfer control unit in the next stage. The data processing speed is changed in accordance with the level of a voltage supplied to the logic circuit. Each transfer control unit includes a plurality of C elements receiving a request pulse for data transfer provided from the preceding stage and transferring the same to the next stage, a plurality of pipeline registers, and a plurality of P circuits. Each pipeline register, in response to every reception of the request pulse, receives, holds and outputs the data requested to be transferred. Each P circuit determines frequency of data supply to the logic circuit being connected, and controls the level of a voltage supplied to the logic circuit in accordance with the determined frequency.

Owner:SHARP KK

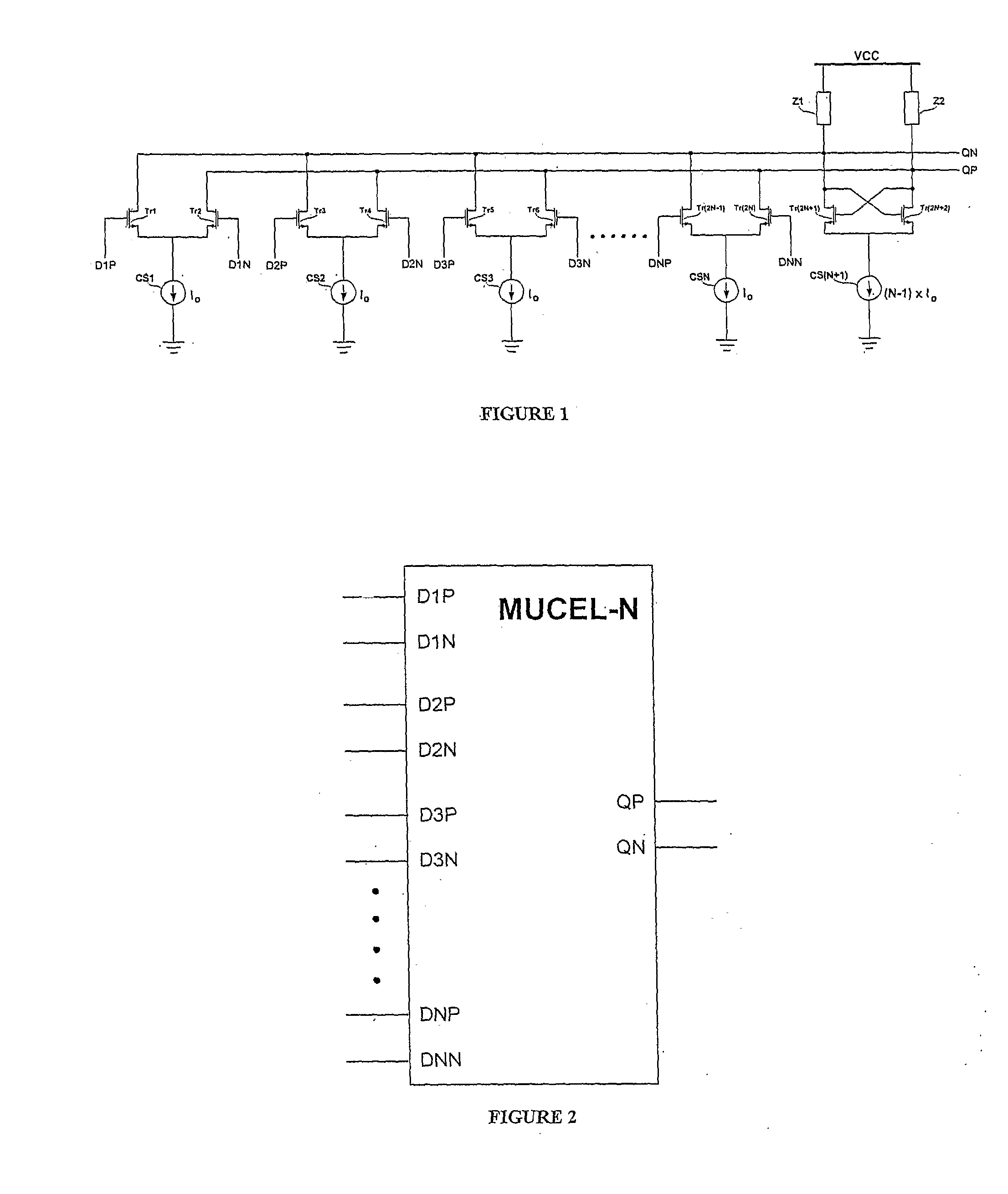

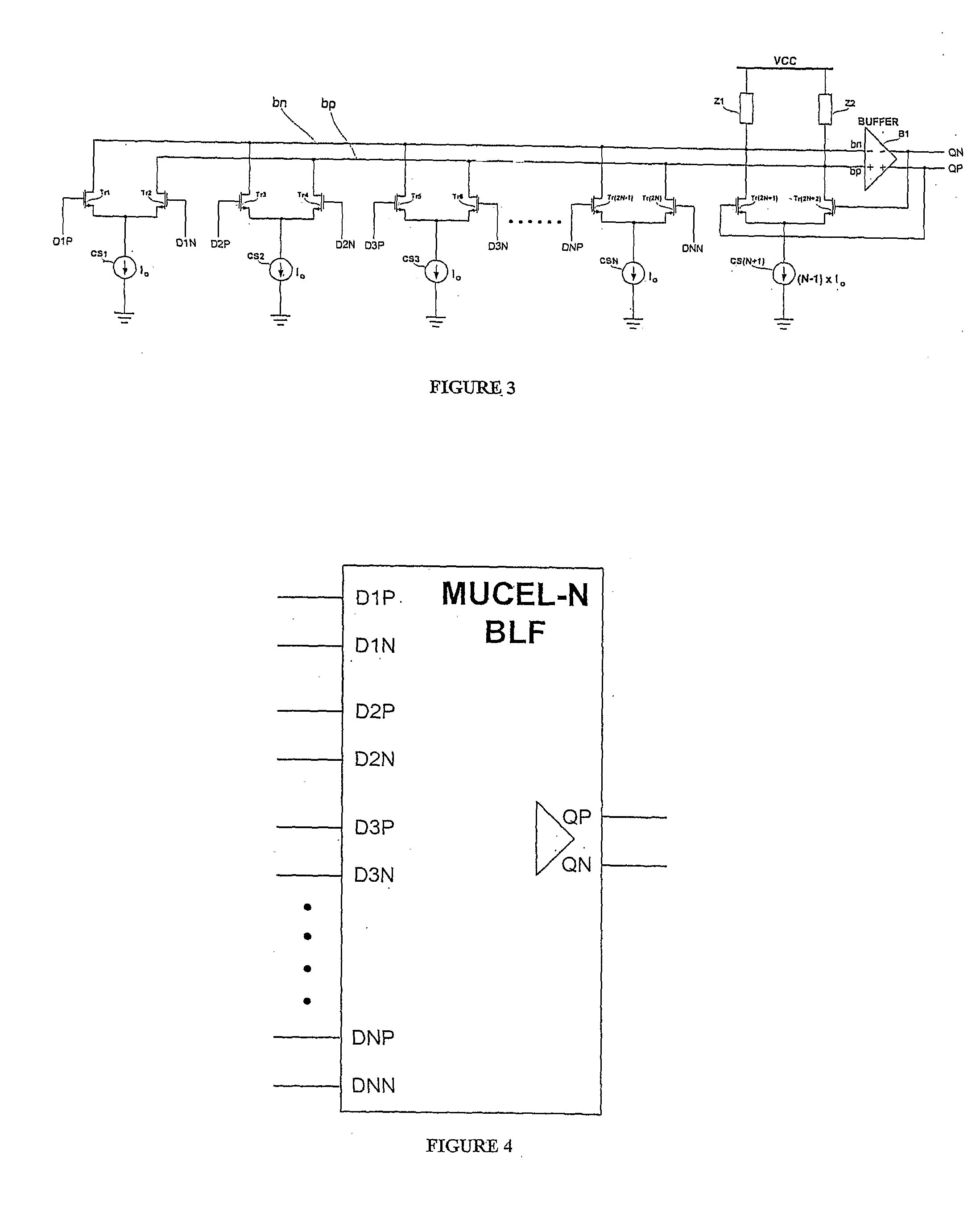

Muller-c element

InactiveCN101479942ASmall dampingEnlarged size to avoidSwitching accelaration modificationsLogic circuits characterised by logic functionDamping factorCapacitance

The invention relates to an electronic device that includes an MCML Muller-c element. The MCML Muller-c element has a first differential stage for operating in a trans- conductance state converting the differential input to a differential output current implementing the logical behavior of the MCML Muller-c element and a second stage operating as a trans-impedance stage being coupled to the first stage. Further, the MCML Muller-c element has peaking circuitry being coupled to the first stage, such that the peaking circuitry and the first stage provide a negative capacitance to the MCML Muller-c element for reducing the damping factor of the MCML Muller-c element.

Owner:NXP BV

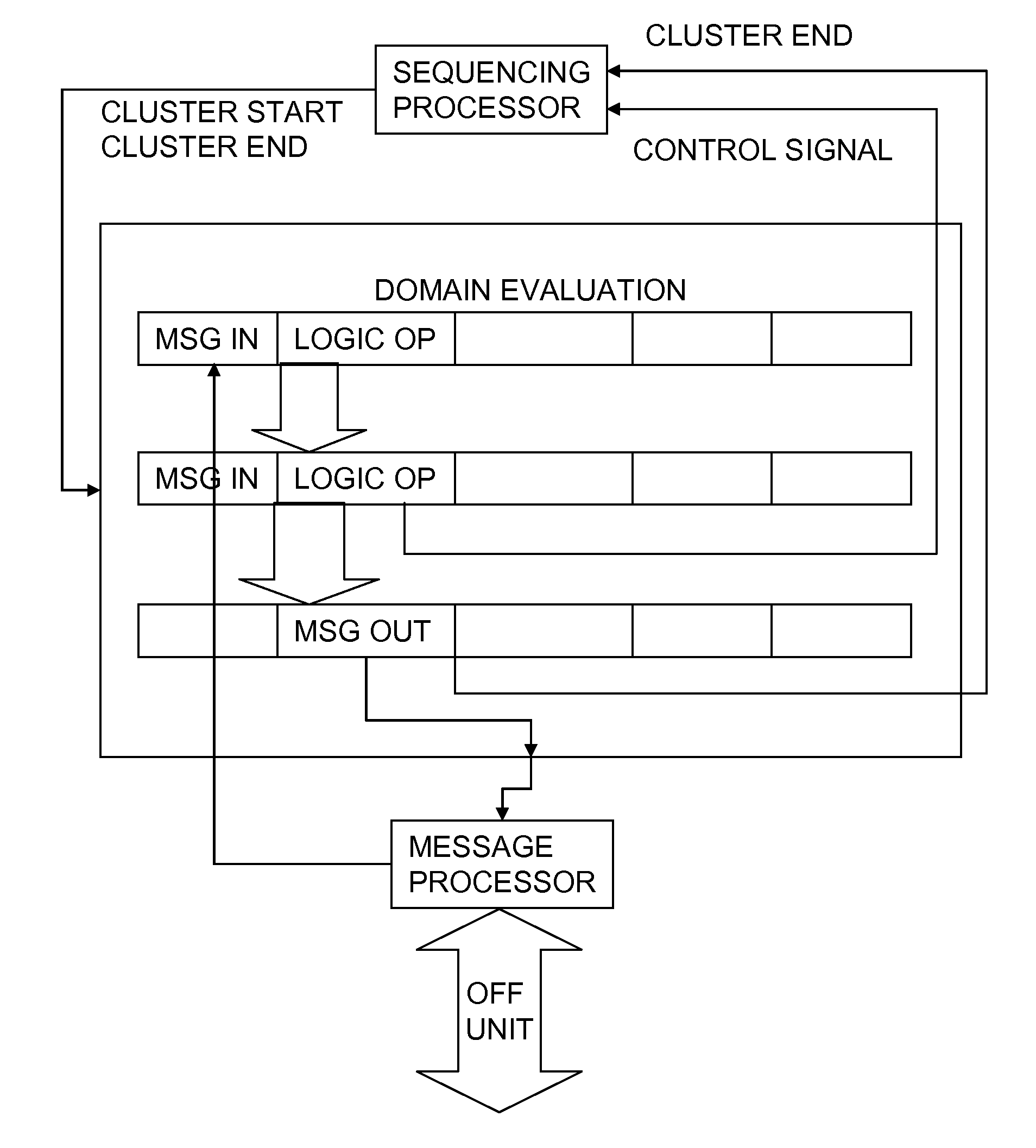

Method for delay immune and accelerated evaluation of digital circuits by compiling asynchronous completion handshaking means

ActiveUS8359186B2Low costImprove performanceAnalogue computers for electric apparatusData switching by path configurationOperandData-driven

An RTL hardware description language simulation accelerator and circuit emulator which operates on data driven asynchronous completion handshaking principles. Deploying Muller C elements to control latches, the system does not depend on externally provided clocks or internal timing circuits with delay logic or clock generators. Each levelized domain of logic signals a successor level to begin execution of instructions with a level complete message produced when all its input operands have produced a completion message. Each predecessor stage holds back data production until the successor stage is ready. Each levelized data-driven asynchronous domain evaluation processor is self-timed receiving completion messages from its predecessors, and sending completion messages to its successors.

Owner:EVE

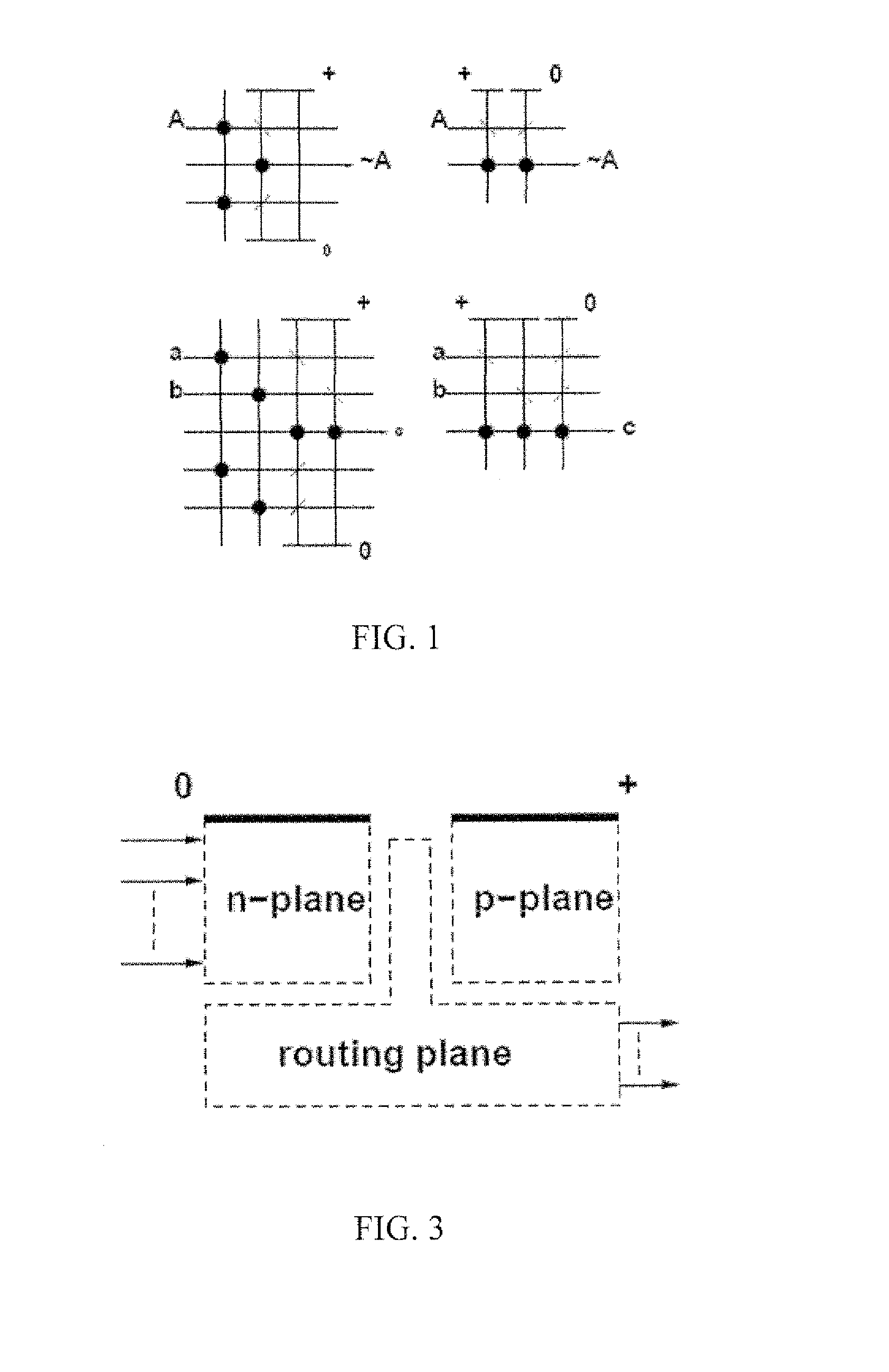

Internal Antenna for Handset and Design Method Thereof

InactiveUS20080258985A1Easily resonant frequencyImprove performanceSimultaneous aerial operationsBraking action transmissionCapacitanceEngineering

The present invention relates to an internal antenna for a handset and a design method thereof. The present invention provides an internal antenna for a handset and a design method thereof characterized in that a L / C element is attached to a slot line of an internal antenna, the attached L / C element is moved along the slot line, or the L / C element having a predetermined inductance / capacitance is attached and detached, thereby easily matching a resonant frequency.

Owner:E M W ANTENNA CO LTD

Light-emitting diode and manufacturing method thereof

InactiveCN104319332AReduce consumptionLow costSemiconductor devicesManufacturing technologyOhmic contact

The invention discloses a light-emitting diode, and belongs to the technical field of photoelectron manufacturing. The light-emitting diode comprises a substrate, a buffer layer, a distribution Prague reflection mirror, an n type limiting layer, an active layer, a p type limiting layer, a GaP window layer and a p type ohmic contact layer which are overlapped in sequence. An n type ohmic contact electrode is arranged on the face, opposite to the buffer layer, of the substrate. A p face bonding wire electrode is arranged on the face, opposite to the GaP window layer, of the p type ohmic contact layer. C element heavily-doped GaP layers overlap between the GaP window layer and the p type ohmic contact layer. The p type ohmic contact layer is an indium tin oxide film. The p face bonding wire electrode is an Al electrode. The p type ohmic contact layer is made of high-transmittance conducting film indium tin oxide instead of Au / AuBe / Au, the electrode mainly made of metal AL is adopted as the p face bonding wire electrode, and therefore the gold consumption in the chip manufacturing process can be greatly lowered, and cost can be effectively and greatly reduced.

Owner:HC SEMITEK SUZHOU

Method for delay immune and accelerated evaluation of digital circuits by compiling asynchronous completion handshaking means

ActiveUS20070294075A1Low costImprove performanceAnalogue computers for electric apparatusData switching by path configurationOperandData-driven

An RTL hardware description language simulation accelerator and circuit emulator which operates on data driven asynchronous completion handshaking principles. Deploying Muller C elements to control latches, the system does not depend on externally provided clocks or internal timing circuits with delay logic or clock generators. Each levelized domain of logic signals a successor level to begin execution of instructions with a level complete message produced when all its input operands have produced a completion message. Each predecessor stage holds back data production until the successor stage is ready. Each levelized data-driven asynchronous domain evaluation processor is self-timed receiving completion messages from its predecessors, and sending completion messages to its successors.

Owner:EVE

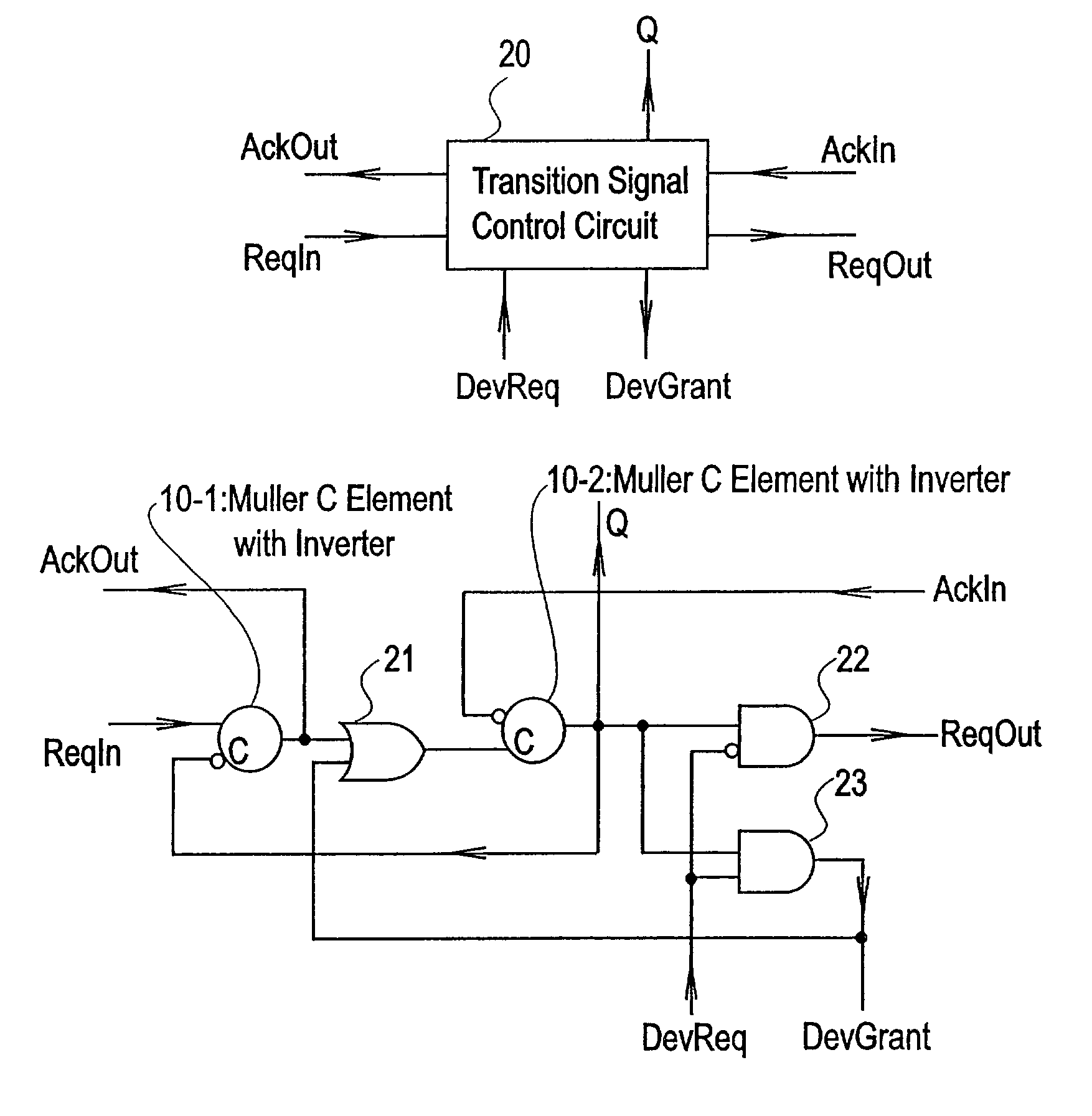

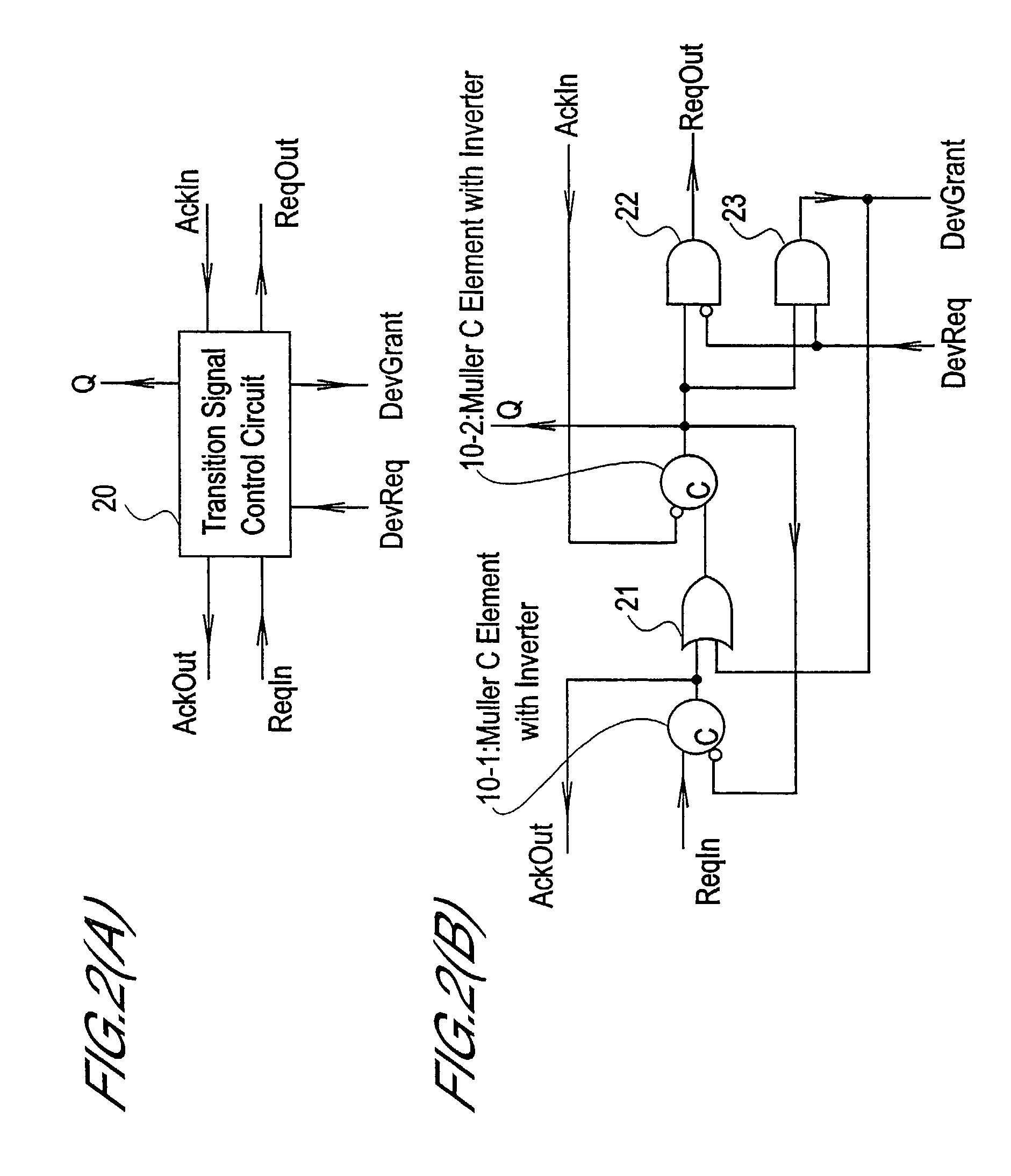

Transition signal control unit and DMA controller and transition signal control processor using transition signal control unit

InactiveUS7073087B2Easy to understandEasy to optimizeLogic circuits characterised by logic functionElectronic switchingEngineeringC-element

Transition signal control for creating asynchronous timing is provided using a transition signal control circuit, which includes Muller C elements each with an inverter. The control device is constituted by a machine ring including n-stages of transition signal control circuits, a state ring including k-stages of transition signal control circuits, and a synchronous circuit for synchronizing with the machine ring by receiving a vector which is output from the state ring. When the output vector of the state ring is received, the synchronous circuit outputs a vector to the machine ring. The output vector of the machine ring and the output vector of the state ring create timings for controlling the processor, for example, asynchronously, and these timings are input to the instruction decoder, for example.

Owner:LAPIS SEMICON CO LTD

Quadrature Divide-By-Three Frequency Divider and Low Voltage Muller C Element

ActiveUS20080260089A1Cost advantageEnsure effective implementationMajority/minority circuitsPulse counters with static storageLow voltageLocal oscillator

A low voltage, low power, wideband quadrature divide-by-three frequency divider using a wideband low voltage, low power differential Muller C element with multiple inputs operates on quadrature input and quadrature output signals. This frequency divider can be used in frequency synthesisers and as quadrature local oscillator generator.

Owner:TEXAS INSTR INC

Duty correction circuit, delay locked loop circuit, column A/D converter, solid-state imaging device and camera system

ActiveUS8284285B2Reduce in quantityReduce the number of timesAnalogue/digital conversionTelevision system detailsPhase differenceBuck converter

A duty correction circuit includes: a C-element including a first input and a second input; and an inverter connected to the second input of the C-element, wherein the C-element obtains an output of a logic “1” when both inputs are the logic “1”, obtains an output of a logic “0” when both inputs are the logic “0”, and maintains the output to a previous state in other conditions, and complementary clocks having a phase difference of an approximately half cycle are inputted to the first input of the C-element and the inverter respectively.

Owner:SONY CORP

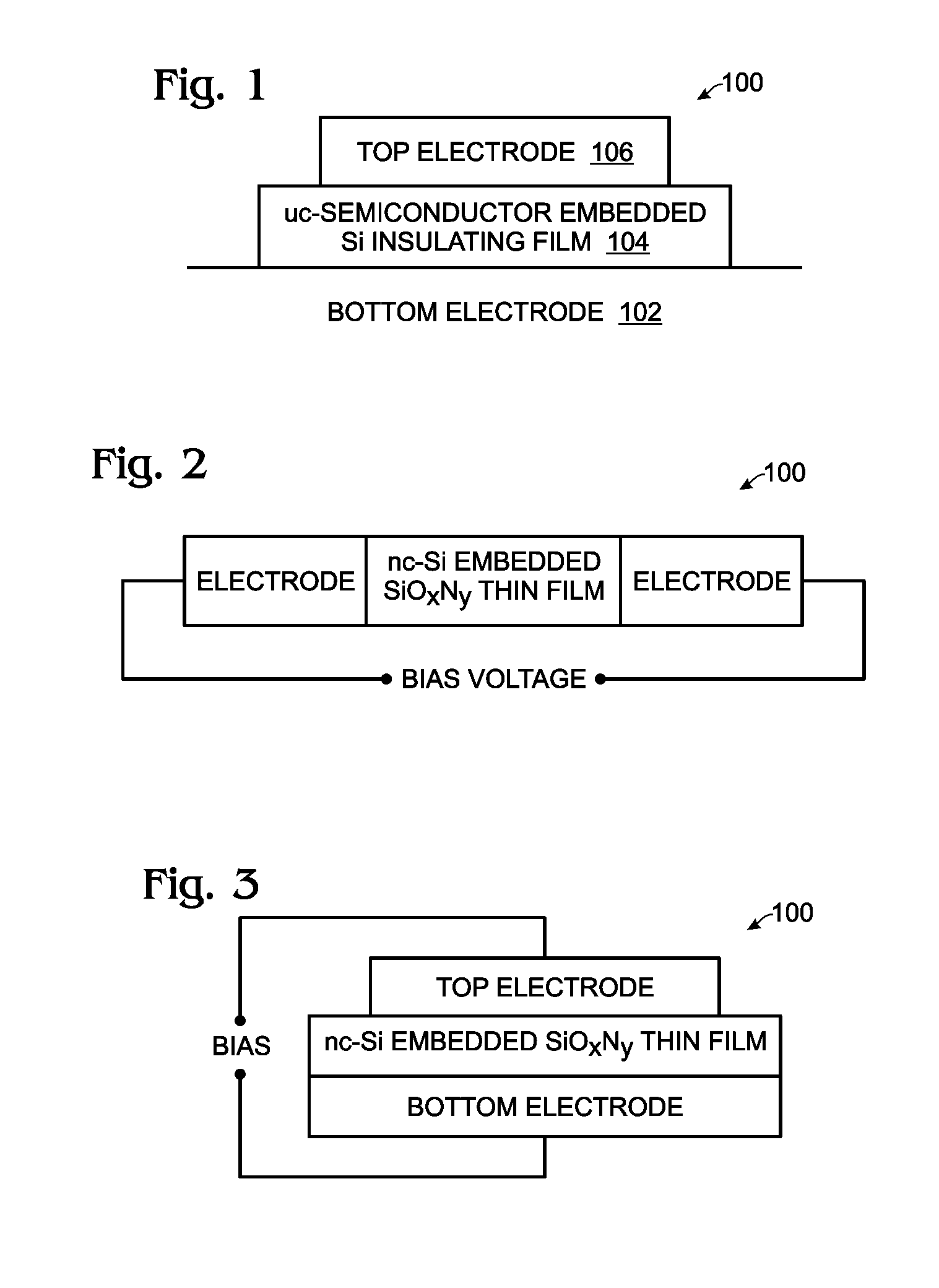

Silicon Nanoparticle Embedded Insulating Film Photodetector

InactiveUS20090294885A1Increase photocurrentEasy to integrateFinal product manufactureSemiconductor/solid-state device manufacturingHydrogenPhotovoltaic detectors

A photodetector is provided with a method for fabricating a semiconductor nanoparticle embedded Si insulating film for photo-detection applications. The method provides a bottom electrode and introduces a semiconductor precursor and hydrogen. A thin-film is deposited overlying the substrate, using a high density (HD) plasma-enhanced chemical vapor deposition (PECVD) process. As a result, a semiconductor nanoparticle embedded Si insulating film is formed, where the Si insulating film includes either N or C elements. For example, the Si insulating film may be a non-stoichiometric SiOXNY thin-film, where (X+Y<2 and Y>0), or SiCX, where X<1. The semiconductor nanoparticles are either Si or Ge. Following the formation of the semiconductor nanoparticle embedded Si insulating film, an annealing process is performed.

Owner:SHARP LAB OF AMERICA INC

Asynchronous circuit insensitive to delays with time delay insertion circuit

The asynchronous circuit insensitive to delays comprises at least one time delay insertion circuit on the propagation path of a signal. The delay insertion circuit comprises, between an input and an output of the signal, a Muller C-element and a plurality of delay circuits connected in series to an output of the Muller C-element. The outputs of the delay circuits are connected to corresponding inputs of a multiplexing circuit having an output constituting the output of the delay insertion circuit. The Muller C-element comprises an input connected to the output of the last delay circuit via an inverter gate, and an input constituting the input of the signal to the delay insertion circuit. The multiplexing circuit control circuit preferably comprises a random generator.

Owner:TIEMPO

Antenna module

InactiveUS20090040113A1Without complex adjusting processEnhanced radiationSimultaneous aerial operationsAntenna supports/mountingsElectrical conductorGround plane

An antenna module is provided. The antenna module comprises a first radiation conductor, a second radiation conductor, a short-circuit element (s / c element), a ground plane, a feed-in cable and a spurious radiation conductor. One terminal of the second radiation conductor is near the first radiation conductor with a gap. One terminal of the s / c element is connected to the second radiation conductor and the other side of the s / c element is connected to the ground plane. The feed-in cable comprises a centre conductor and an external conductor, wherein the centre conductor is connected to the first radiation conductor and the external conductor is connected to the ground plane. The spurious radiation conductor is connected to the second radiation conductor. The second radiation conductor comprises a spurious radiation plate, a first radiation piece and a second radiation piece within the two sides of the second radiation conductor. The first radiation piece and a second radiation piece are in parallel and a gap is conducted between the first radiation piece and the second radiation piece.

Owner:ADVANCED CONNECTEK INC

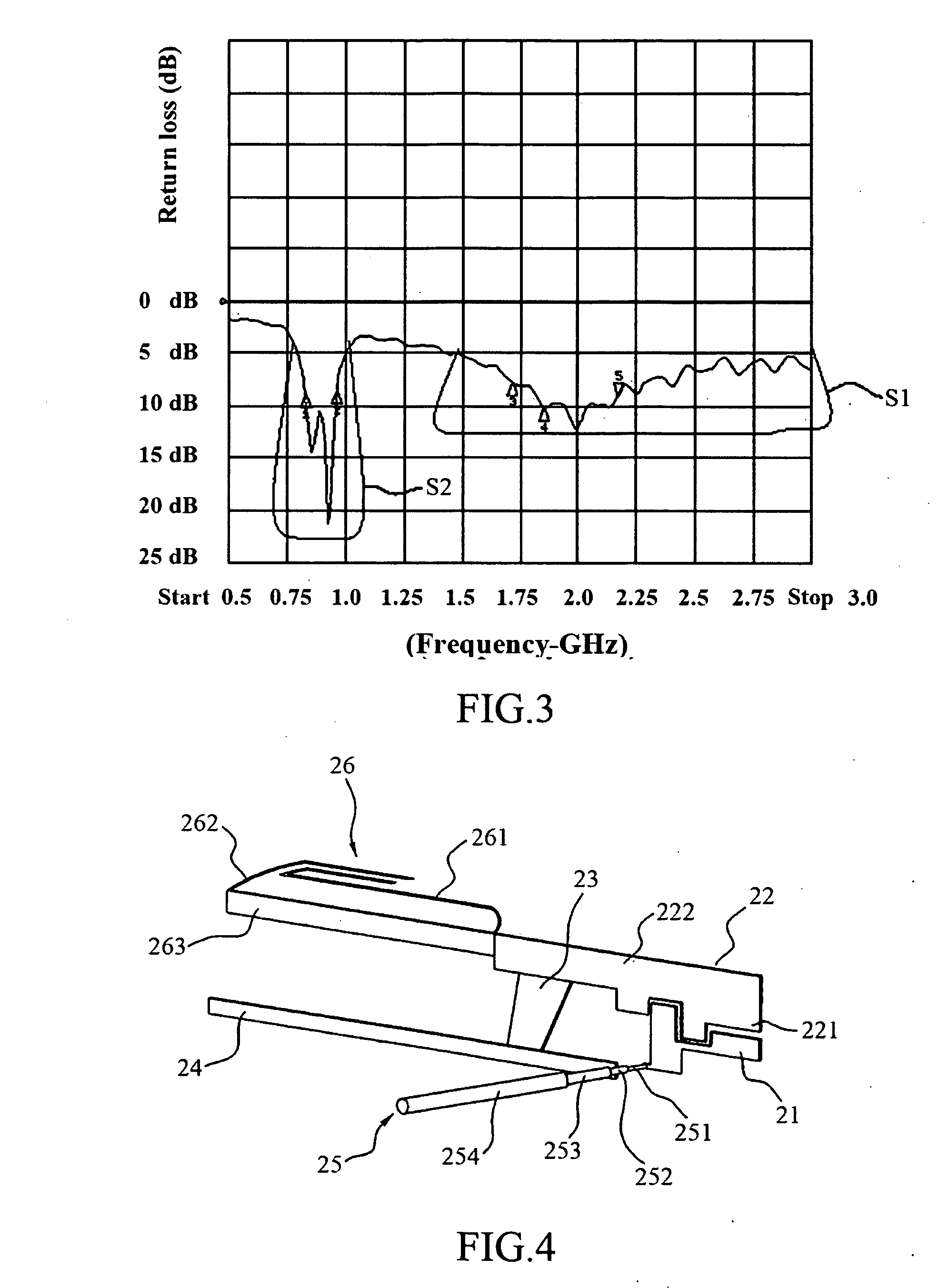

Asynchronous nano-electronics

InactiveUS7898284B2Reliability increasing modificationsNanoinformaticsNanoelectronic circuitsVoltage reference

Asynchronous nanoelectronic circuits that operate according to principles of quasi-delay insensitive design are described. Circuit or logic elements comprising n-type devices are fabricated in a first n-plane, p-type devices are fabricated in a p-plane, and connections are formed in a routing plane of a compute tile. A state-holding element comprising a selected one of a C-element, a precharge function-block, and a read-write register is described. The state-holding element can hold a value of an output of a logic element during a time when the output is disconnected from a reference voltage. Isochronic forks having an adversary path designed to make state transitions safe are explained.

Owner:CALIFORNIA INST OF TECH

Internal antenna for handset and design method thereof

InactiveCN1922757AGuaranteed performanceImprove matchSimultaneous aerial operationsBraking action transmissionCapacitanceEngineering

Owner:E M W ANTENNA CO LTD

Integral tester for electric vehicle

A integrated tested of electric motor car is featured as pre-reserving test ports of three lead out lines of Hall A, B and C elements; Hall element positive electrode power supply; low potential; speed control line of rotary handle; controller master power supply positive electrode; lamp circuit and controller master power supply negative electrode when electric motor car is assembled then inserting said ports into port of said integrated tester for carrying out test on electric motor car.

Owner:项青松

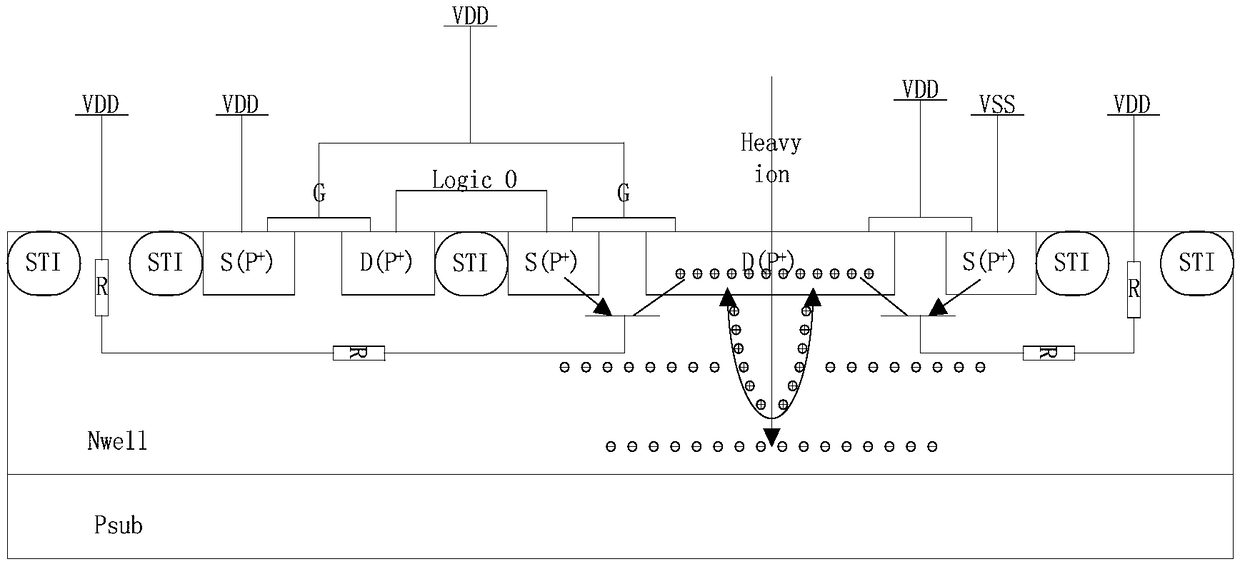

SEU and SET resisting DICE trigger design method based on SMIC 65nm commercial process

PendingCN109450407AImplement anti-SET hardened designKeep a safe distanceElectric pulse generatorEngineeringC-element

The invention discloses a SEU and SET resisting DICE trigger design method based on a SMIC 65nm commercial process. Firstly, an input circuit on a DICE trigger is replaced with a stack CMOS circuit soas to realize SET resisting reinforcement design of the input circuit; then, a primary latch and a secondary latch on the DICE trigger are processed so as to reduce an operating distance between SETpulse width and a charge sharing effect and realize SEU resisting reinforcement; finally, the output circuit on the DICE trigger is replaced with a C-element circuit so as to filter the SET in the latch broadcasted to an output end. The method in the invention uses the stack CMOS circuit and the C-element circuit in cooperation with a filling MOS tube and a source isolation MOS tube to realize thecircuit design of the DICE trigger, which is high in reliability, solves the problem of large timing sequence overhead brought by using a delay filtering circuit to realize SET reinforcement, effectively improves the capability of resisting SEU and SET of the DICE trigger, and achieves a prospective protection effect and low cost.

Owner:XIAN INSTITUE OF SPACE RADIO TECH

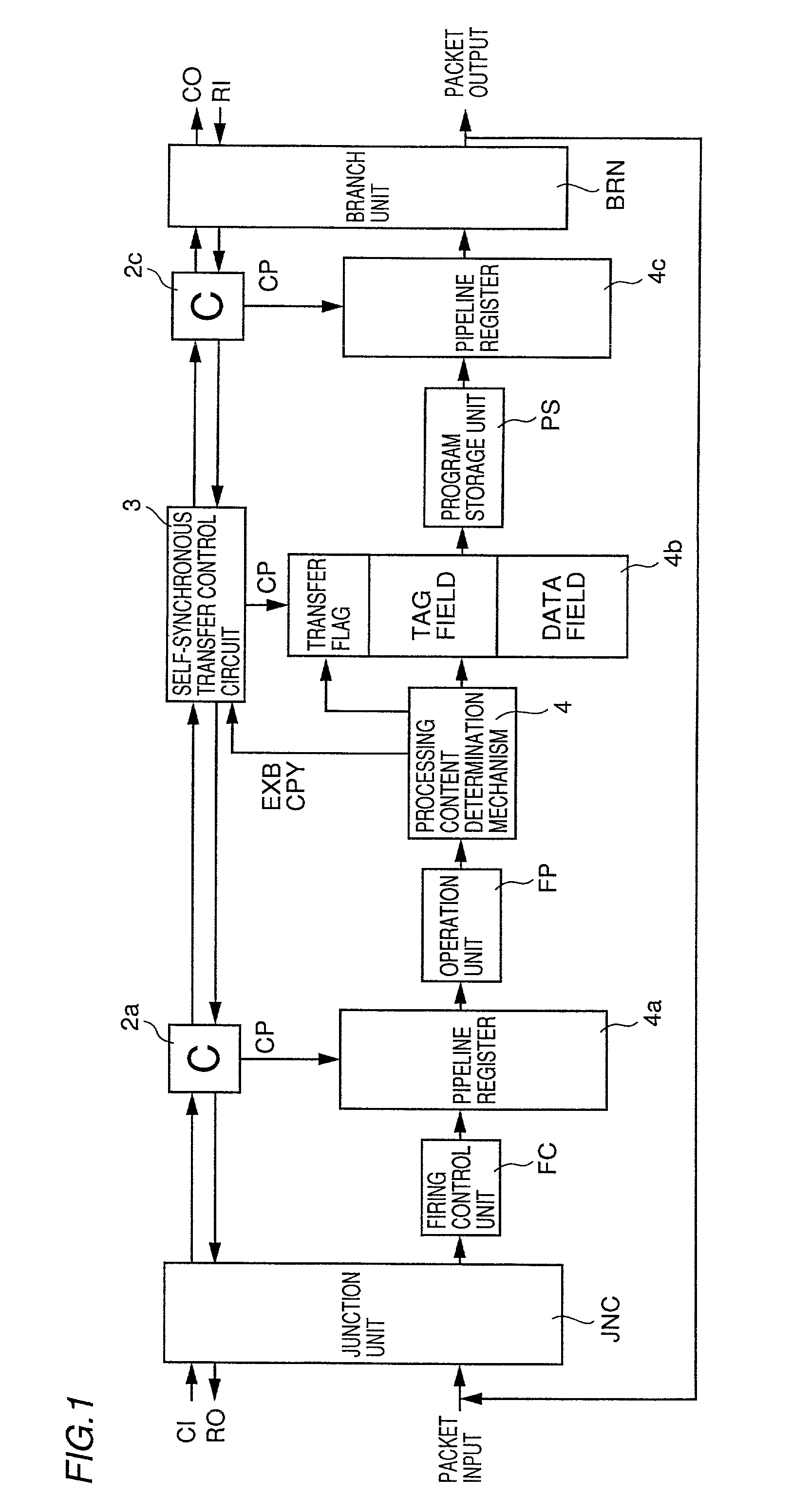

Data driven type information processing apparatus having deadlock breaking function

InactiveUS7082515B2Effective debugging functionEasy to getGeneral purpose stored program computerSpecific program execution arrangementsInformation processingProcessor register

A C element controls a pipeline register and successively transfers data packets. When a dead-lock state occurs, a data packet in the pipeline register is erased by a master reset signal, a host transfer flag operating circuit overwrites a data packet in the pipeline register so that it has a host transfer flag at the “H” level, and thereafter, when the host transfer flag is detected in the subsequent stage, the data packet is transferred to the host.

Owner:SHARP KK

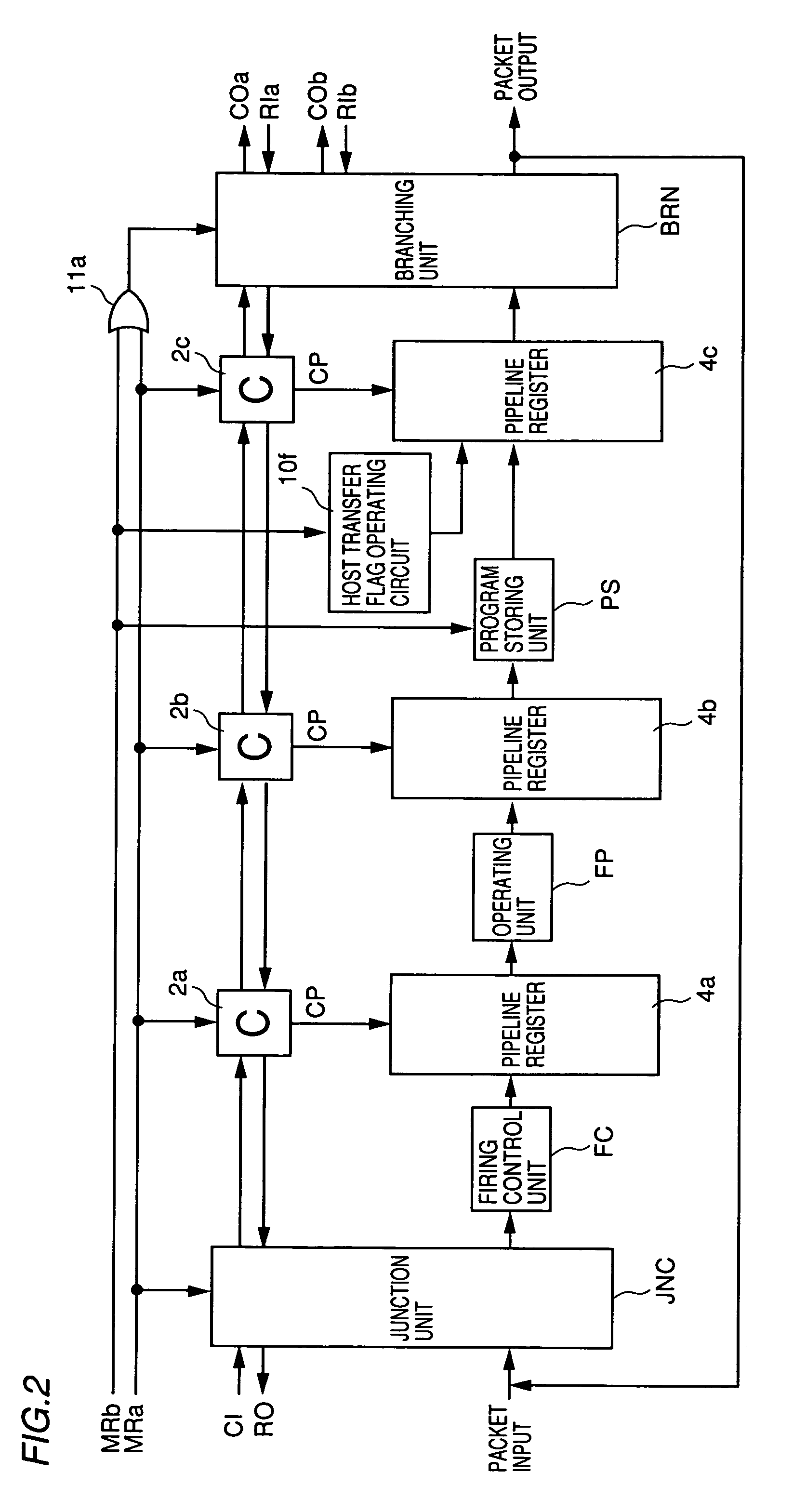

Data driven information processing apparatus

InactiveUS6959004B2Affecting reproducibilityAffecting speedError detection/correctionDigital data processing detailsInformation processingComputer hardware

A data packet, having a flag for determination of its processing content, a tag field and a data field, is sequentially transferred between pipeline registers according to pulses from C elements. A determination is made as to whether the tag field of the data packet includes information identical to that pre-stored in a tag field of a register within a processing content determination unit. Based on the determination result, the data packet is processed according to the information stored in a processing content determination field of the register.

Owner:SHARP KK

Asymmetric locking technique for asymmetric frequency locked loop

A system that generates a click signal includes a first digitally controlled oscillator (DCO) having a first fundamental frequency, and a second DCO having a second fundamental frequency. The system also includes a Muller C-element, which combines outputs of the first and second DCOs to produce the clock signal, which feeds back into the first and second DCOs. During a calibration operation, while the second DCO is set to a frequency larger than the target frequency, the system adjusts the first DCO with reference to a first feedback loop, which includes the first DCO, so that the clock signal matches the target frequency, and while the first DCO is set to the adjusted first fundamental frequency plus a frequency offset, the system adjusts the second DCO with reference to a second feedback loop, which includes the second DCO, so that the clock signal matches the target frequency.

Owner:ORACLE INT CORP

Antenna module

InactiveUS7786941B2Enhanced radiationImprove transmission bandwidthSimultaneous aerial operationsAntenna supports/mountingsElectrical conductorGround plane

An antenna module is provided. The antenna module comprises a first radiation conductor, a second radiation conductor, a short-circuit element (s / c element), a ground plane, a feed-in cable and a spurious radiation conductor. One terminal of the second radiation conductor is near the first radiation conductor with a gap. One terminal of the s / c element is connected to the second radiation conductor and the other side of the s / c element is connected to the ground plane. The feed-in cable comprises a centre conductor and an external conductor, wherein the centre conductor is connected to the first radiation conductor and the external conductor is connected to the ground plane. The spurious radiation conductor is connected to the second radiation conductor. The second radiation conductor comprises a spurious radiation plate, a first radiation piece and a second radiation piece within the two sides of the second radiation conductor. The first radiation piece and a second radiation piece are in parallel and a gap is conducted between the first radiation piece and the second radiation piece.

Owner:ADVANCED CONNECTEK INC

Asynchronous nano-electronics

InactiveUS20100283502A1Reliability increasing modificationsNanoinformaticsNanoelectronic circuitsProcessor register

Asynchronous nanoelectronic circuits that operate according to principles of quasi-delay insensitive design are described. Circuit or logic elements comprising n-type devices are fabricated in a first n-plane, p-type devices are fabricated in a p-plane, and connections are formed in a routing plane of a compute tile. A state-holding element comprising a selected one of a C-element, a precharge function-block, and a read-write register is described. The state-holding element can hold a value of an output of a logic element during a time when the output is disconnected from a reference voltage. Isochronic forks having an adversary path designed to make state transitions safe are explained.

Owner:CALIFORNIA INST OF TECH

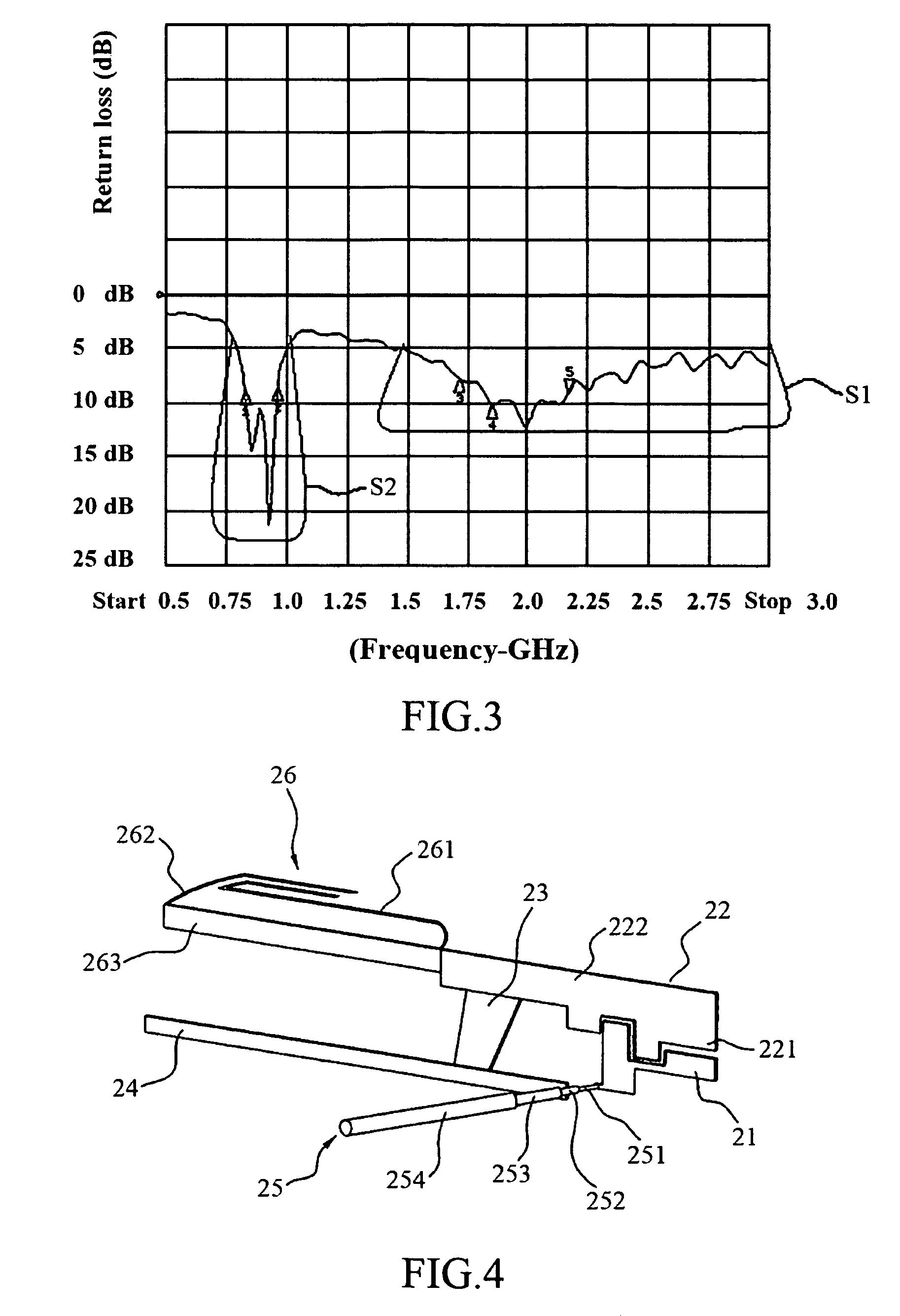

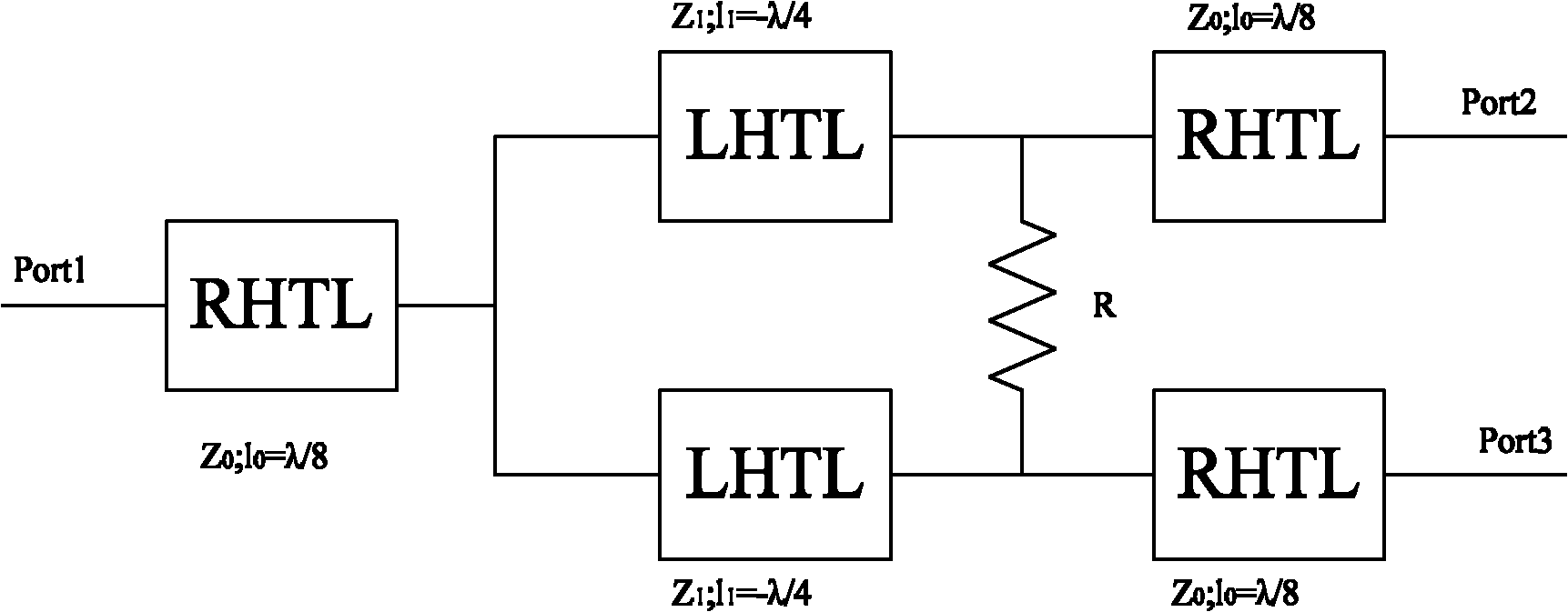

Wilkinson power divider based on left-handed microstrip line

The invention discloses a Wilkinson power divider based on a left-handed microstrip line. The Wilkinson power divider is characterized in that the input end and the output end are right-handed transmission lines in the length of lambda / 8; the Y-branch arm adopts a left-handed transmission line in the length of lambda / 4, wherein the lambda is the central operating wavelength; and the left-handed transmission line is realized by adopting a total set of L-C elements, i.e. the unit structure comprises a series capacitor CL and a parallel inductor LL. The invention has the advantages that the isolation bandwidth is added by approximate 50 percent to be 1.5 f0 and the size is smaller than that of a traditional power divider.

Owner:上海杰盛无线通讯设备有限公司

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com