SEU and SET resisting DICE trigger design method based on SMIC 65nm commercial process

A design method and trigger technology, applied in pulse generation, electrical components, generation of electrical pulses, etc., can solve the problems of single-event soft errors, the trigger is difficult to achieve the protective effect, and the anti-SET capability of the trigger is not improved, so as to improve the performance of the trigger. Reliability, improving the ability to resist SEU and SET, the effect of high reliability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

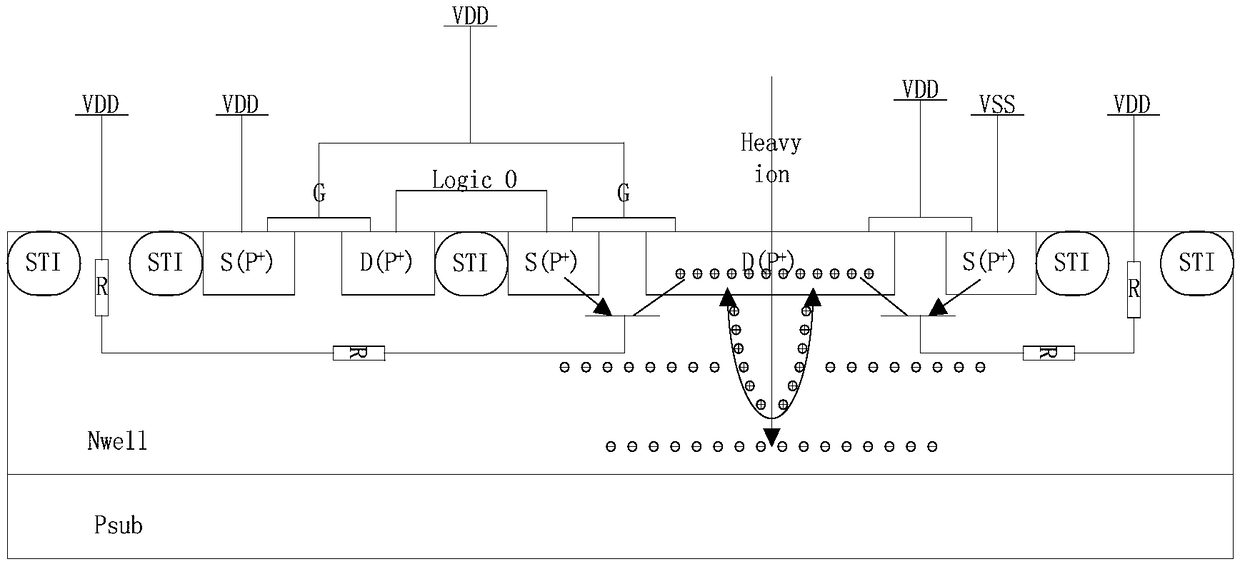

[0040] The present invention will be described in further detail below with reference to the accompanying drawings and embodiments.

[0041] In order to improve the anti-SEU / SET protection capability of the ASIC developed by using the 65nm anti-addition library and minimize the performance overhead, the present invention proposes a design method for anti-SEU and SET triggers based on the SMIC 65nm commercial process. Without affecting the chip design process, starting from the SEU and SET generation mechanism of 65nm commercial MOS devices, the circuit structure and physical layout of the flip-flop unit are reinforced against SEU / SET, achieving low cost and high reliability. .

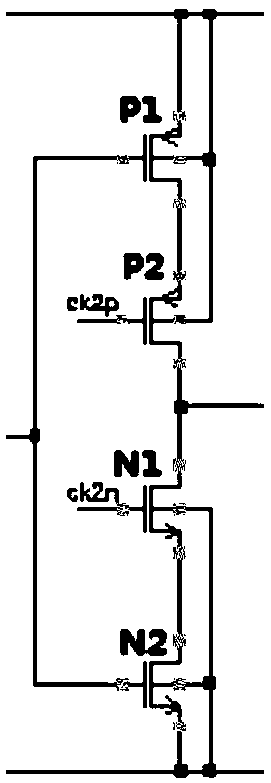

[0042] The DICE structure itself does not have the SET protection capability. The SET reinforcement of the traditional DICE trigger is realized through time redundancy. In order to achieve the ideal SET reinforcement effect, the time difference of the relevant input data is required to be very large, w...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com