Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

68results about How to "Test may pass" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

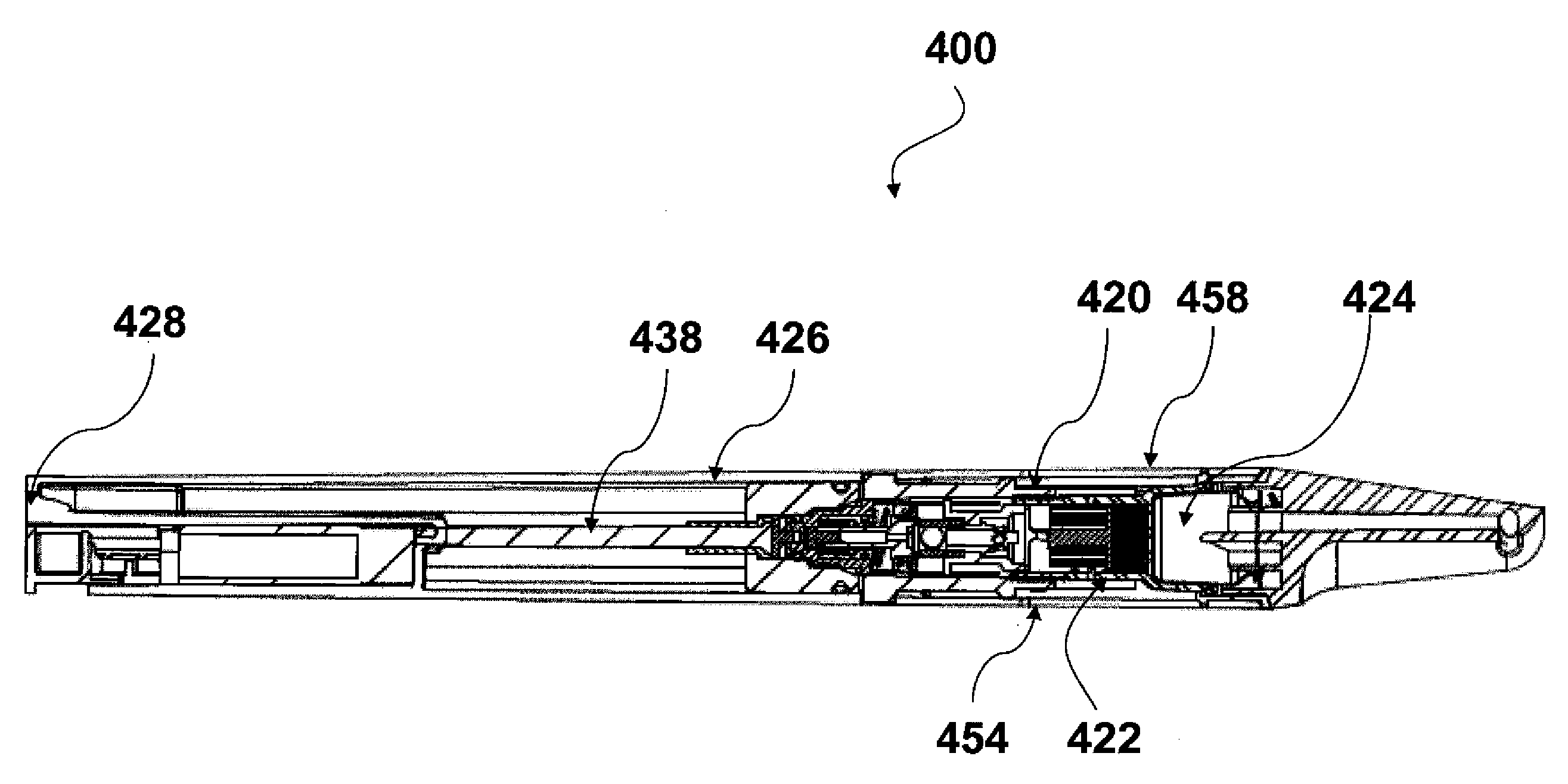

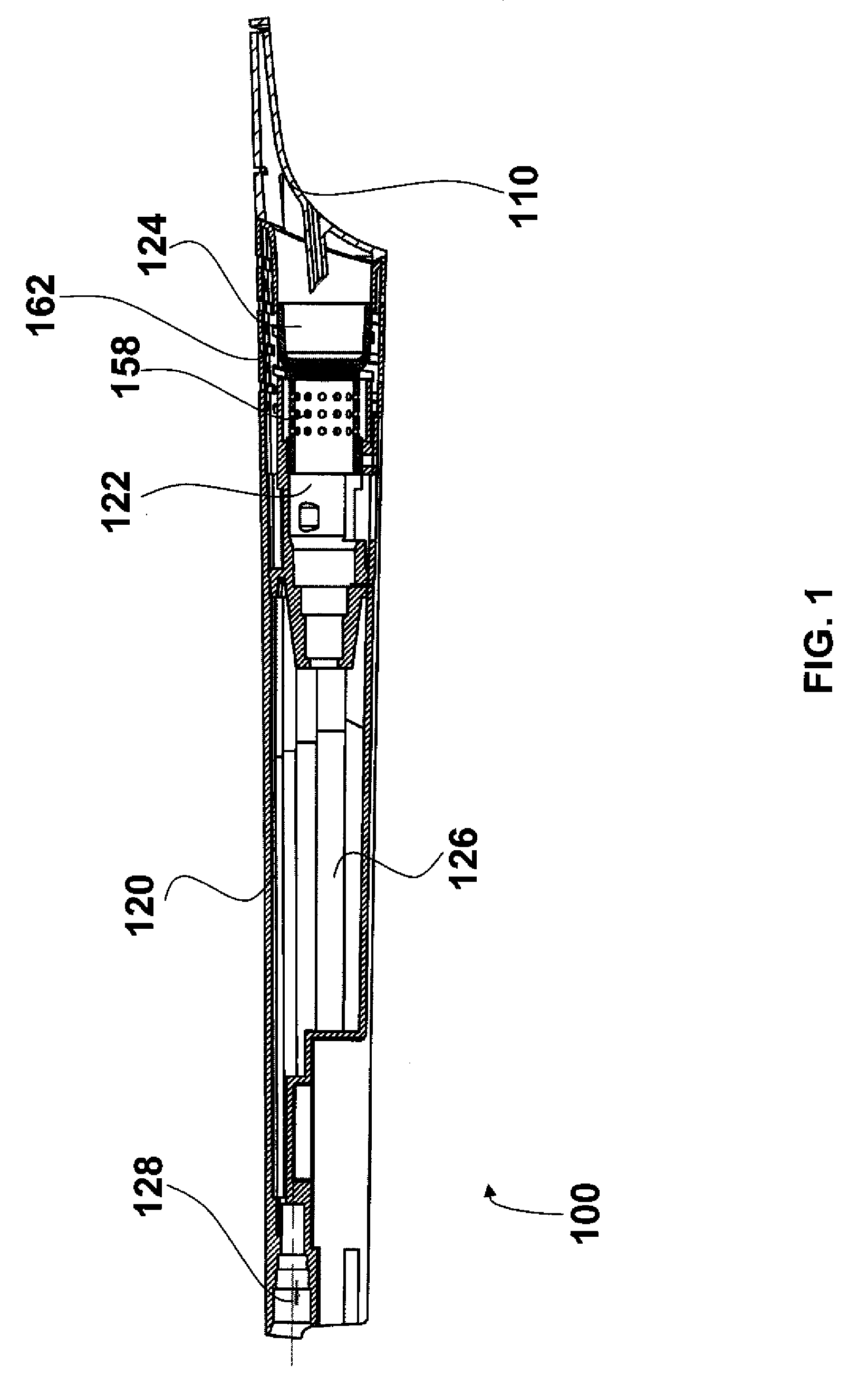

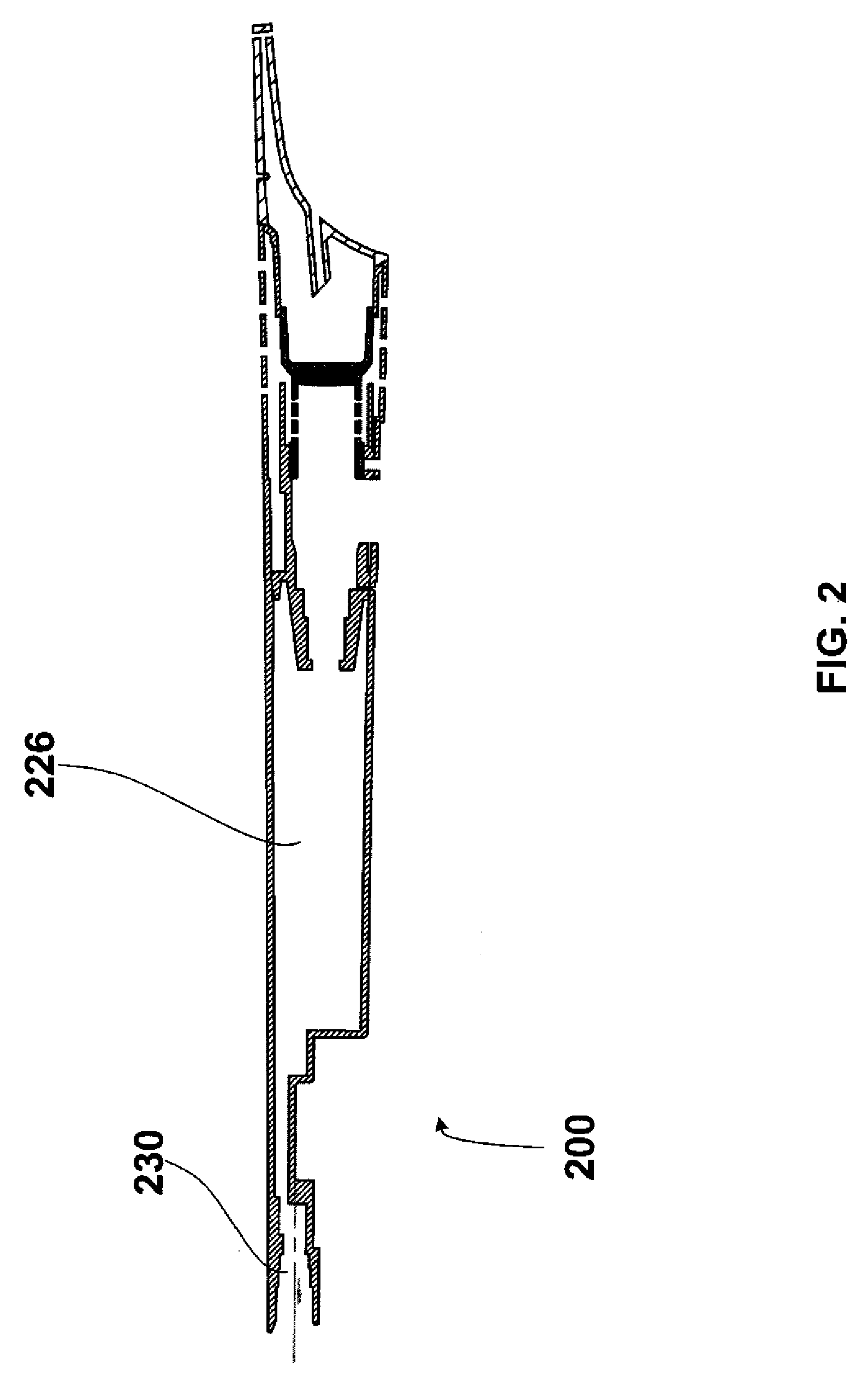

Aerosol devices and methods for inhaling a substance and uses thereof

ActiveUS20090151717A1Test may passRaise the gradeCigar manufactureSynthetic resin layered productsAnalyteChemical compound

Devices, cartridges, and method are described herein for emulating smoking wherein a device generates an aerosol for inhalation by a subject by heating a viscous material that can have a tactile response in the mouth or respiratory tract, while reducing Hoffman analytes and mutagenic compounds delivered to the user as compared to a common tobacco cigarette.

Owner:JLI NAT SETTLEMENT TRUST

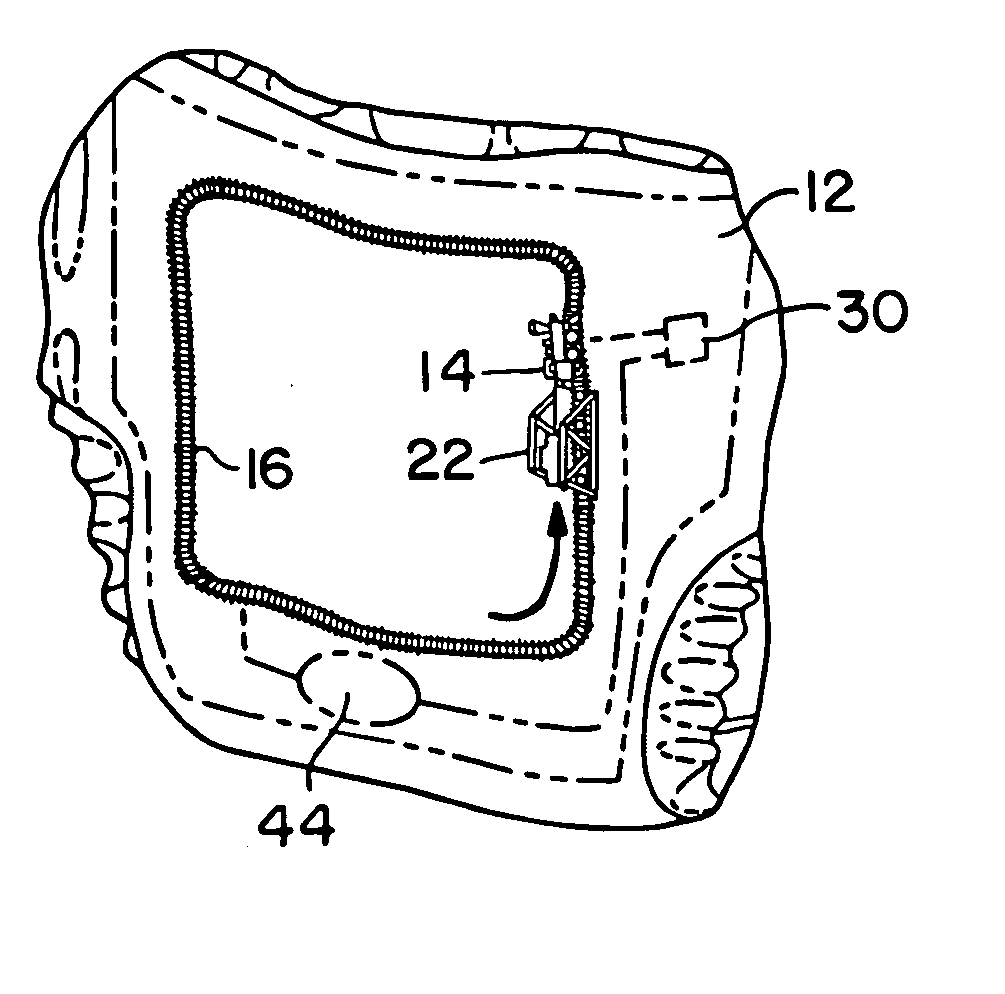

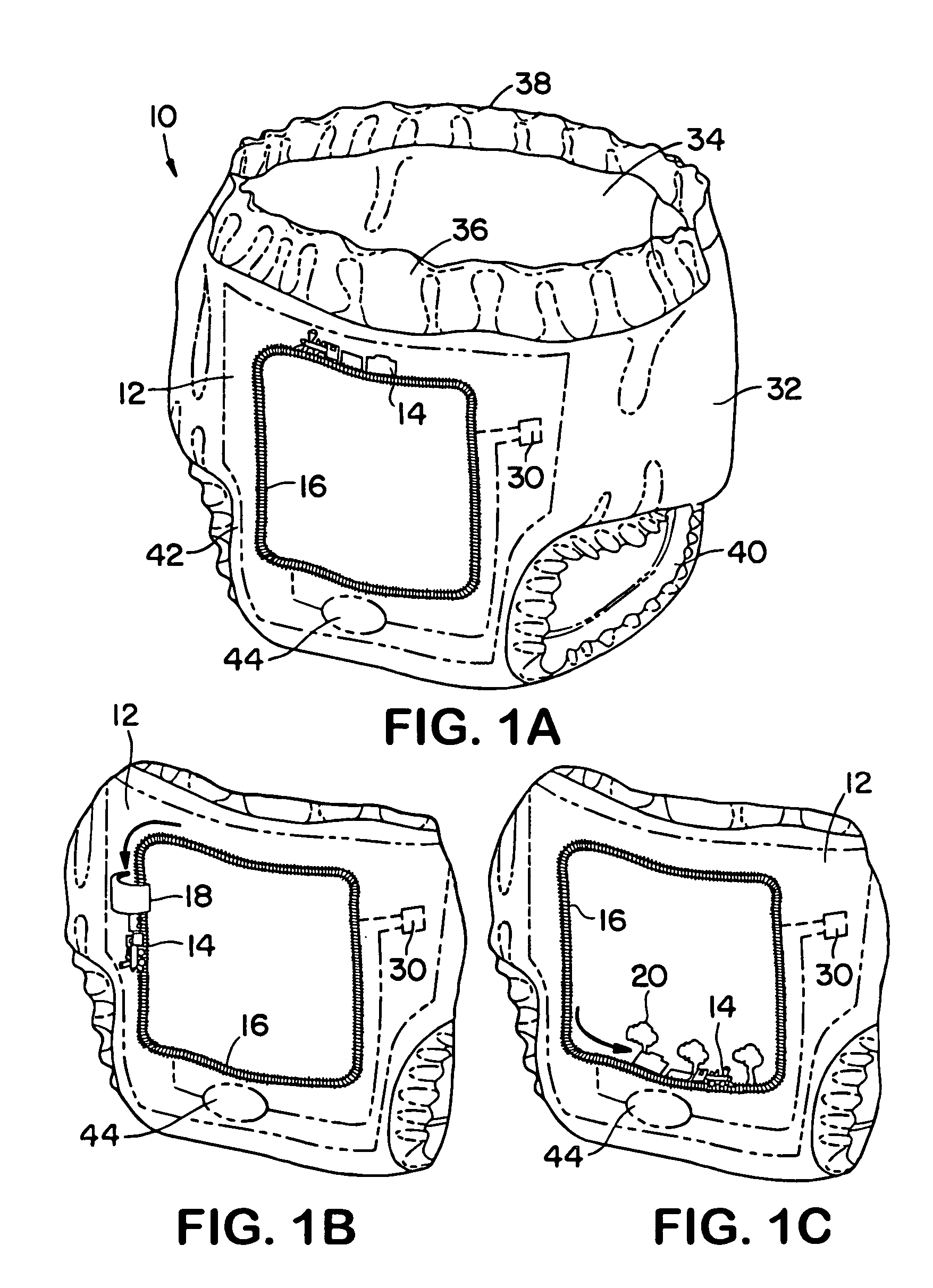

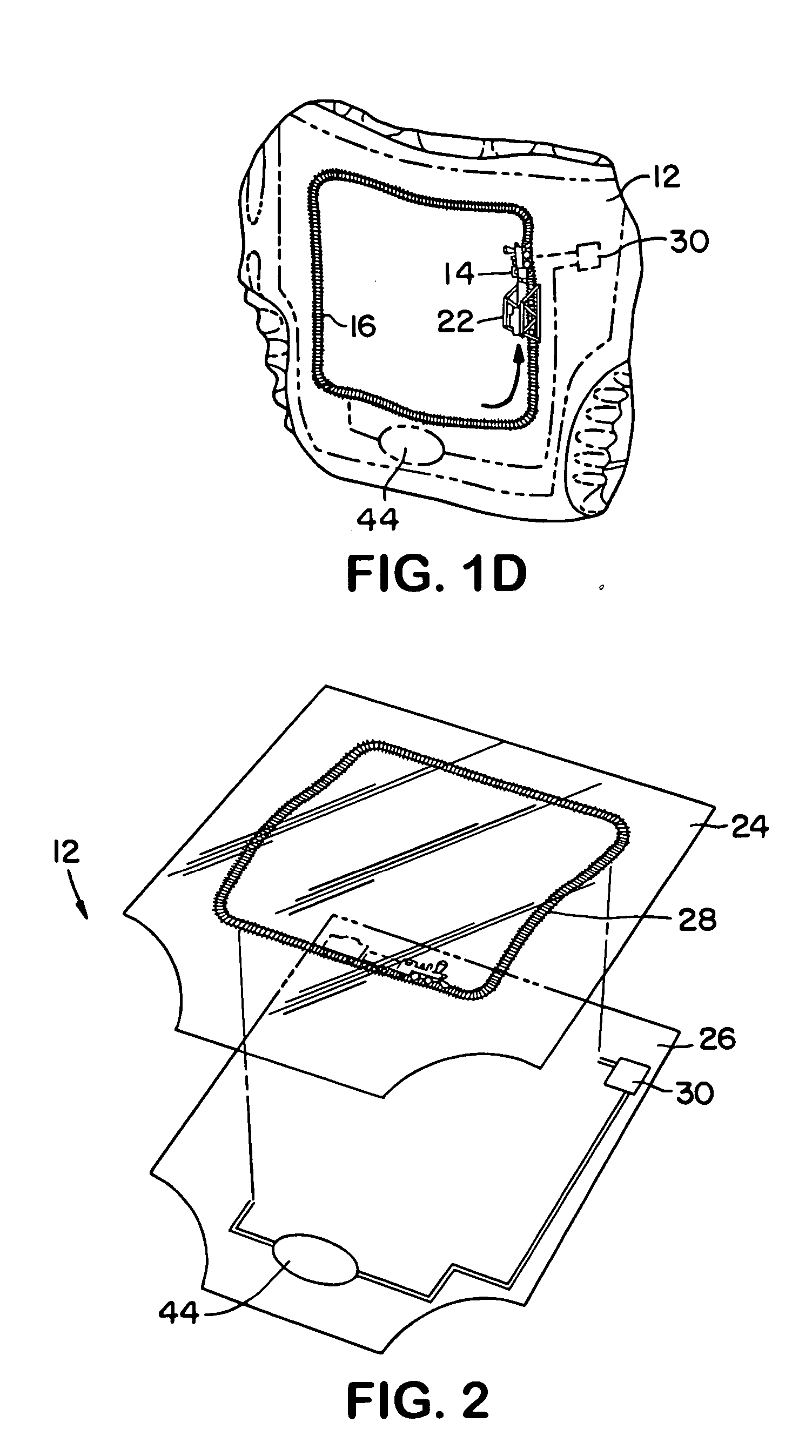

Live graphics on absorbent articles using electrochromic displays

An absorbent article is provided that includes an electroactive display. The electroactive display may include an electrochromic composition positioned between two electrodes. The electroactive display is configured to create and exhibit an image that contains active features such as moving graphics or color-changing objects. For instance, the electroactive display may display an animated cartoon character or a moving vehicle. The electroactive display may also create symbols or words. When combined with sensors, a power source, and the proper circuitry, the electroactive display may be used, for instance, as a wetness indicator or to indicate the presence of a particular substance. In other embodiments, the electroactive display may be used solely for aesthetic purposes.

Owner:KIMBERLY-CLARK WORLDWIDE INC

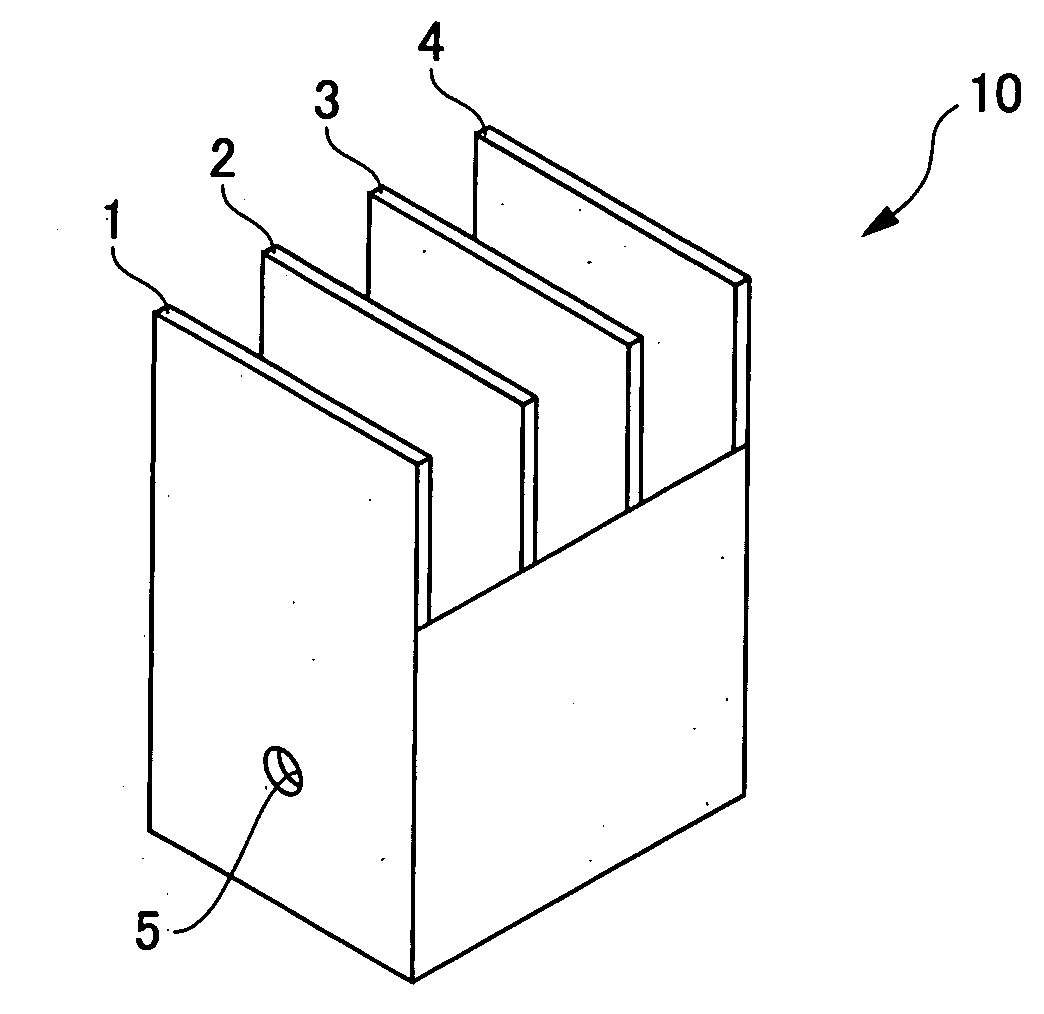

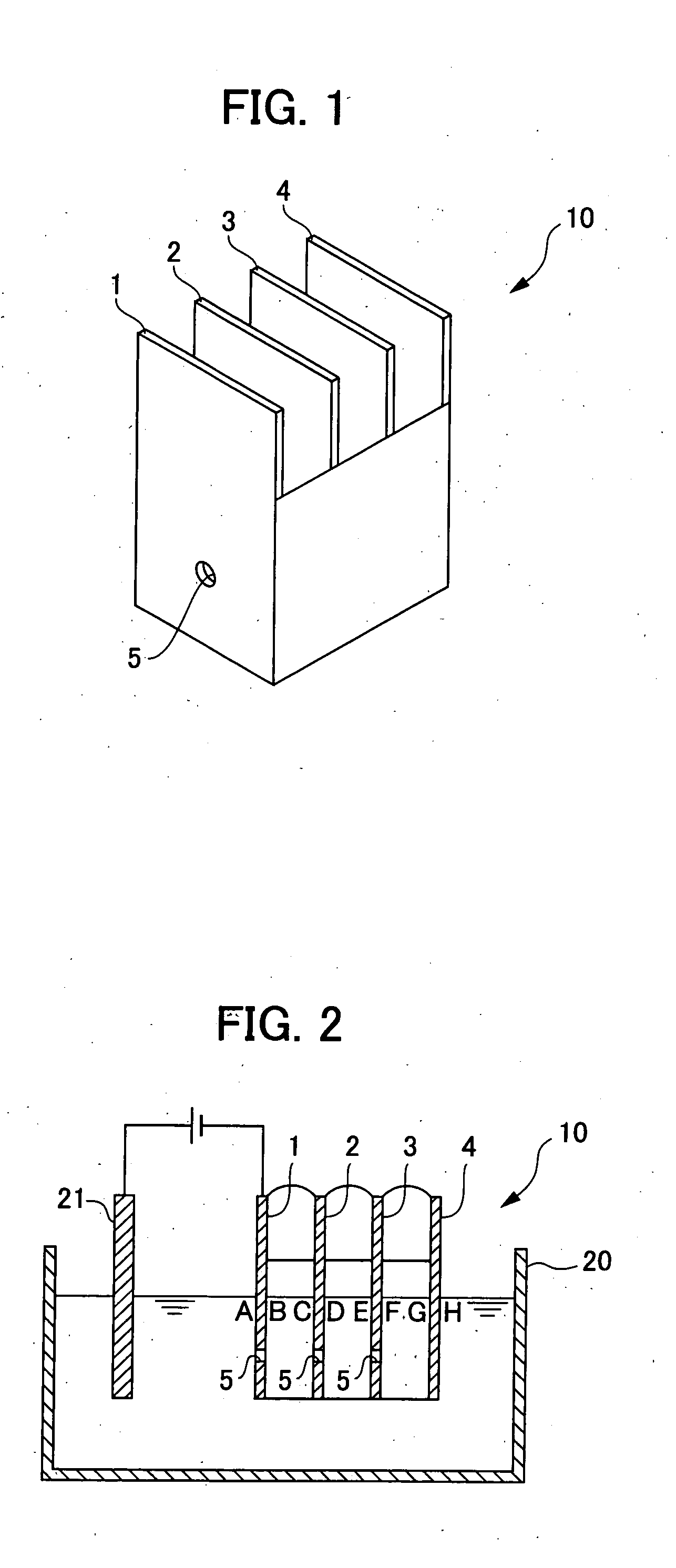

Metal surface treatment liquid for cation electrodeposition coating

ActiveUS20080230395A1Improve throwing powerPreventing copperElectrolysis componentsVolume/mass flow measurementAluminum IonIndium

A surface treatment with a zirconium ion that enables sufficient throwing power and superior anti-corrosion properties to be exhibited when thus surface treated metal base material is subjected to cation electrodeposition coating is provided. A metal surface treatment liquid thereof for cation electrodeposition coating includes zirconium ions, copper ions, and other metal ions, and having a pH of 1.5 to 6.5, in which: the other metal ions are at least one selected from the group consisting of tin ions, indium ions, aluminum ions, niobium ions, tantalum ions, yttrium ions and cerium ions; the concentration of zirconium ions is 10 to 10,000 ppm; the concentration ratio of the copper ions to the zirconium ions is 0.005 to 1 on a mass basis; and the concentration ratio of the other metal ions to the copper ions is 0.1 to 1,000 on a mass basis.

Owner:NIPPON PAINT SURF CHEM

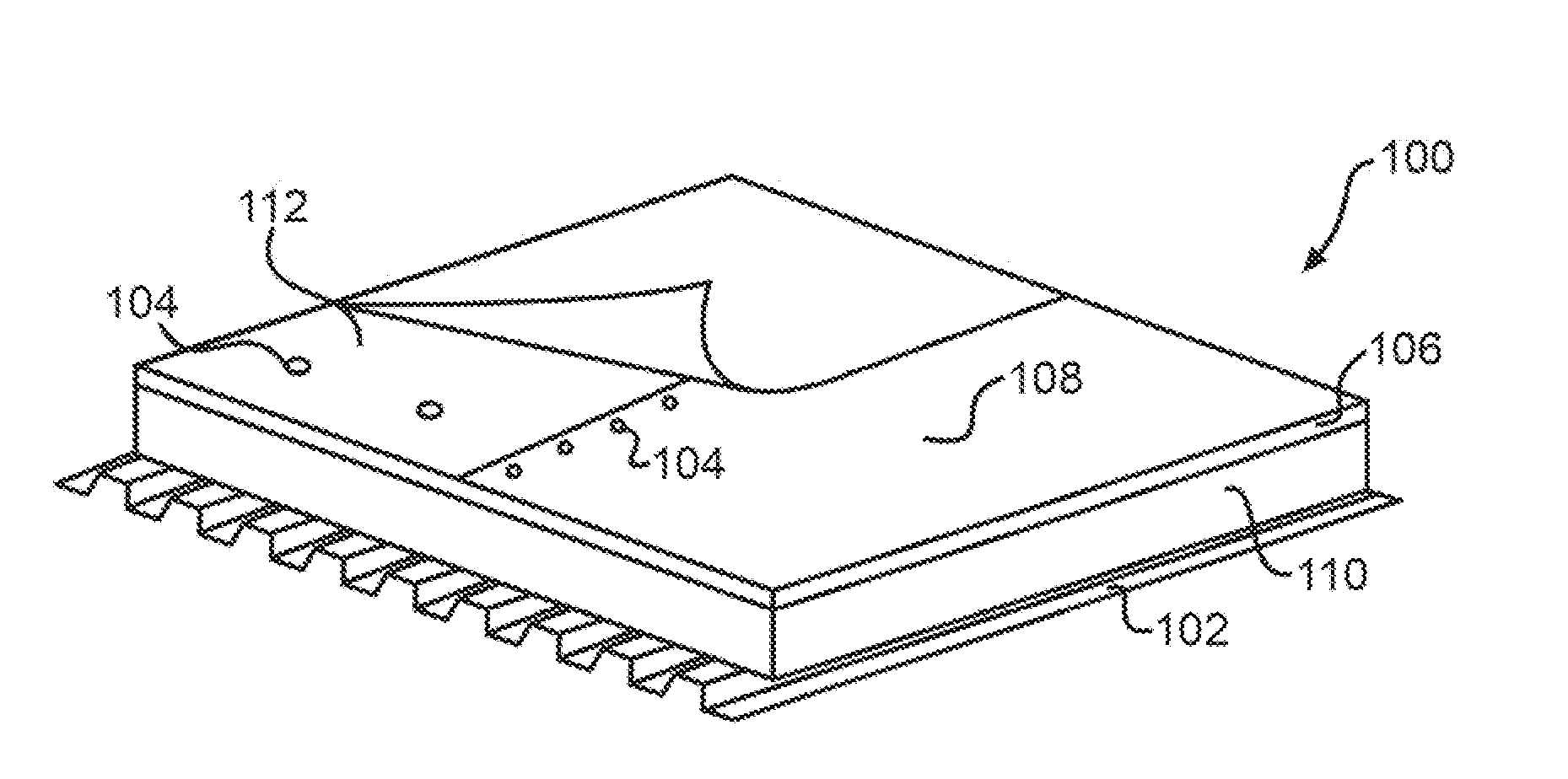

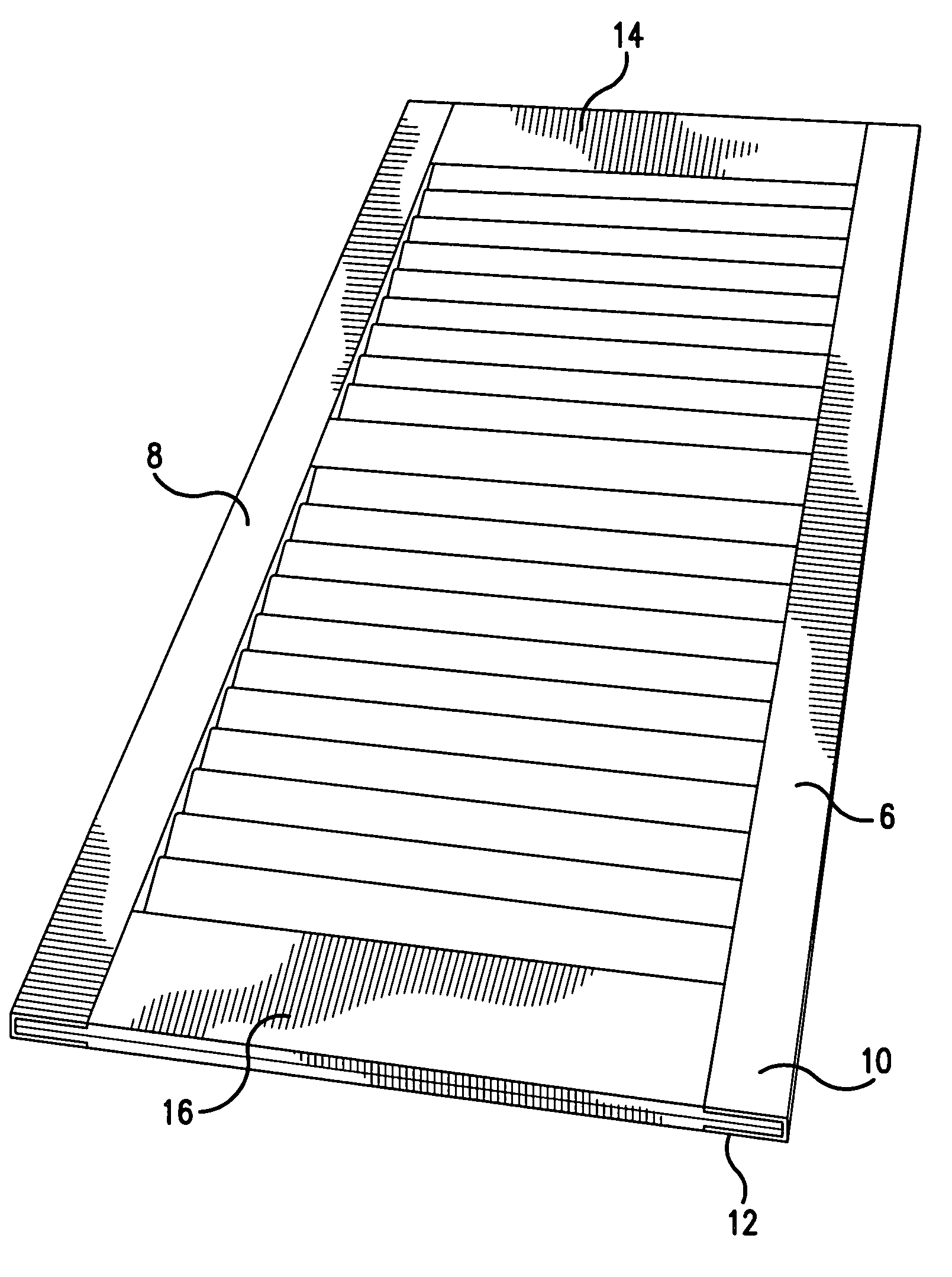

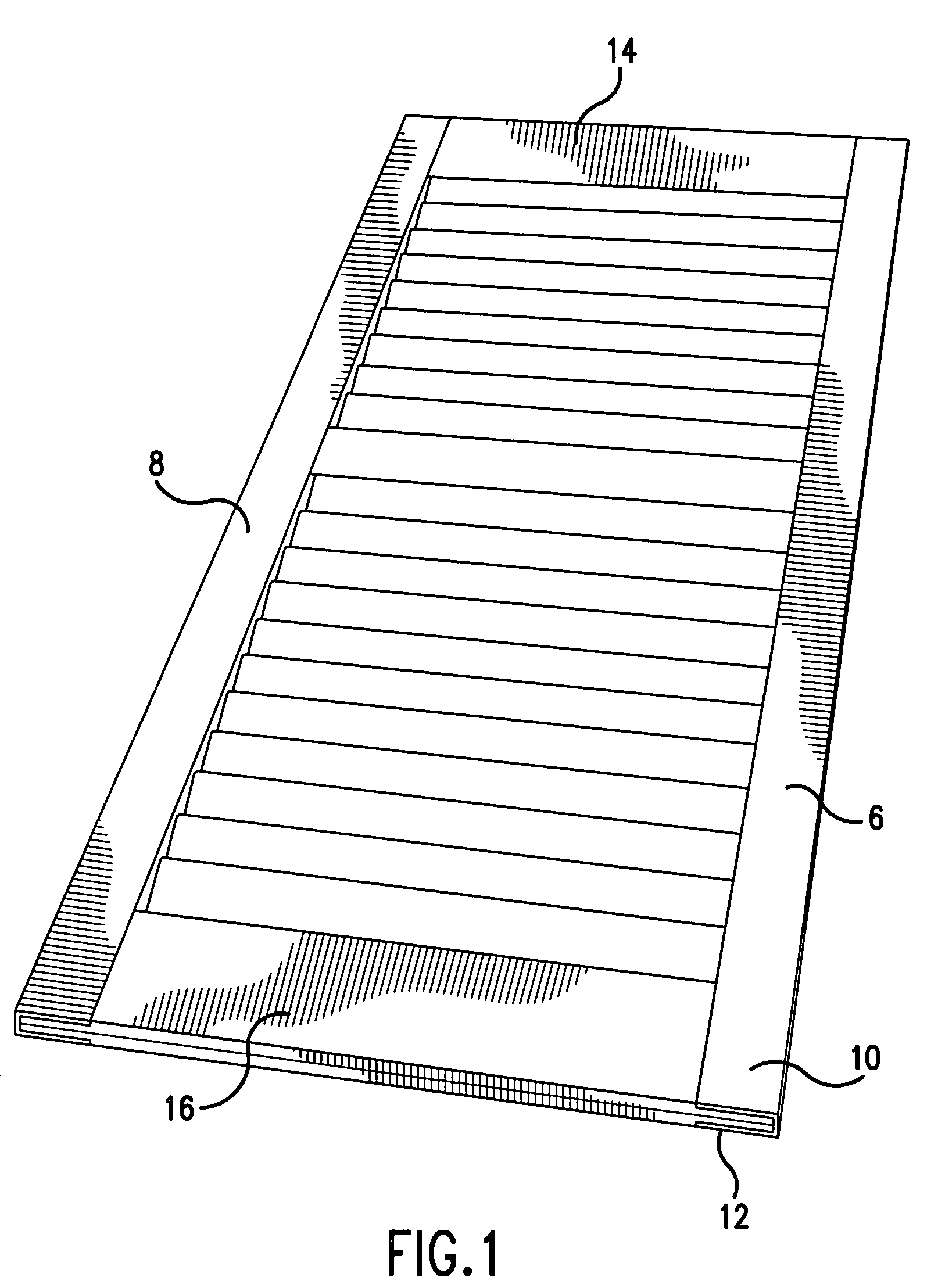

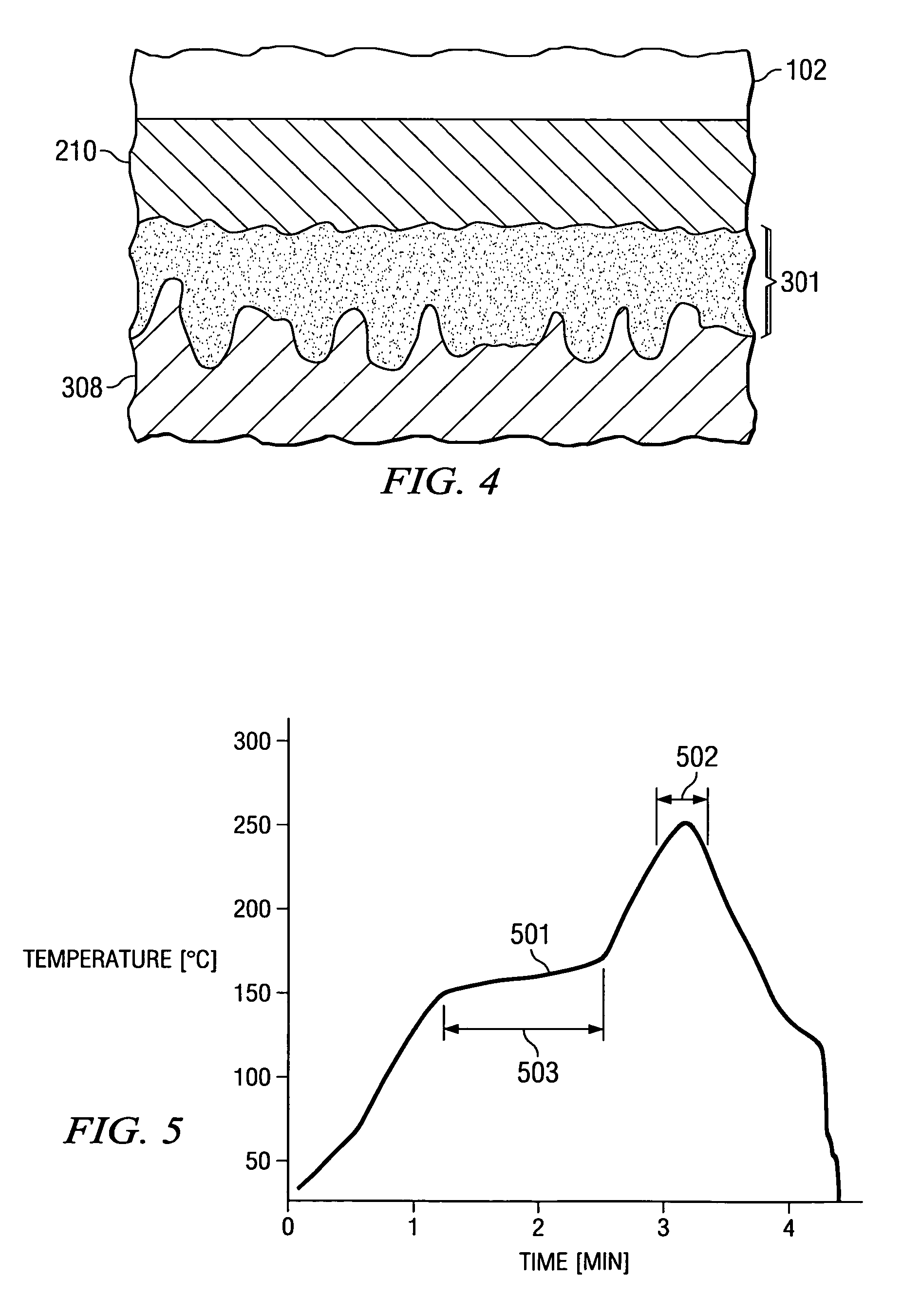

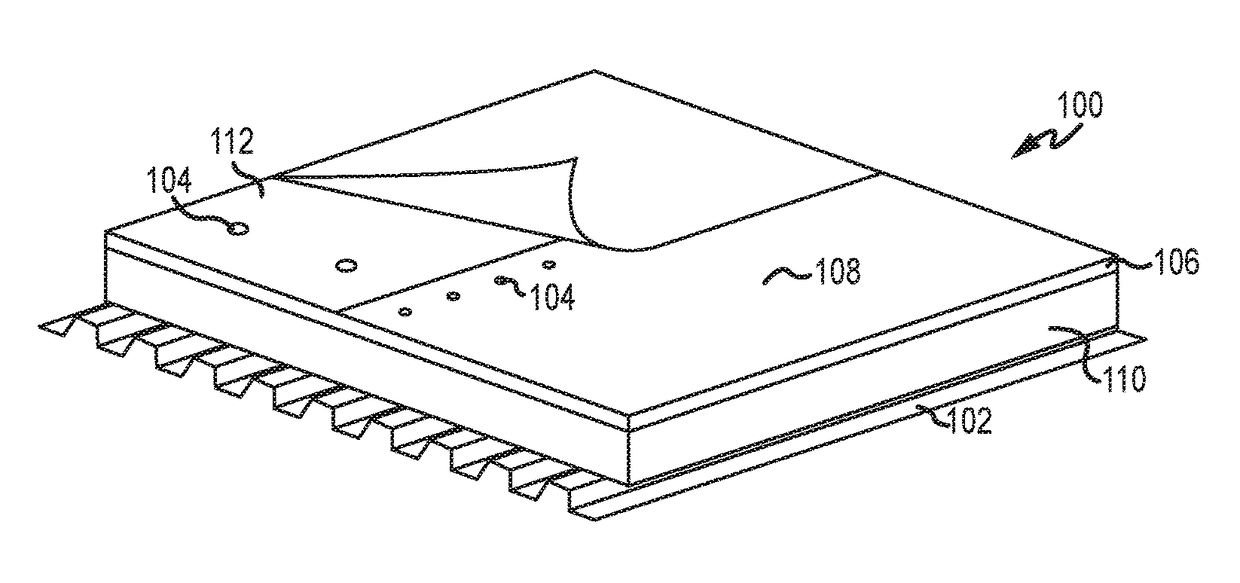

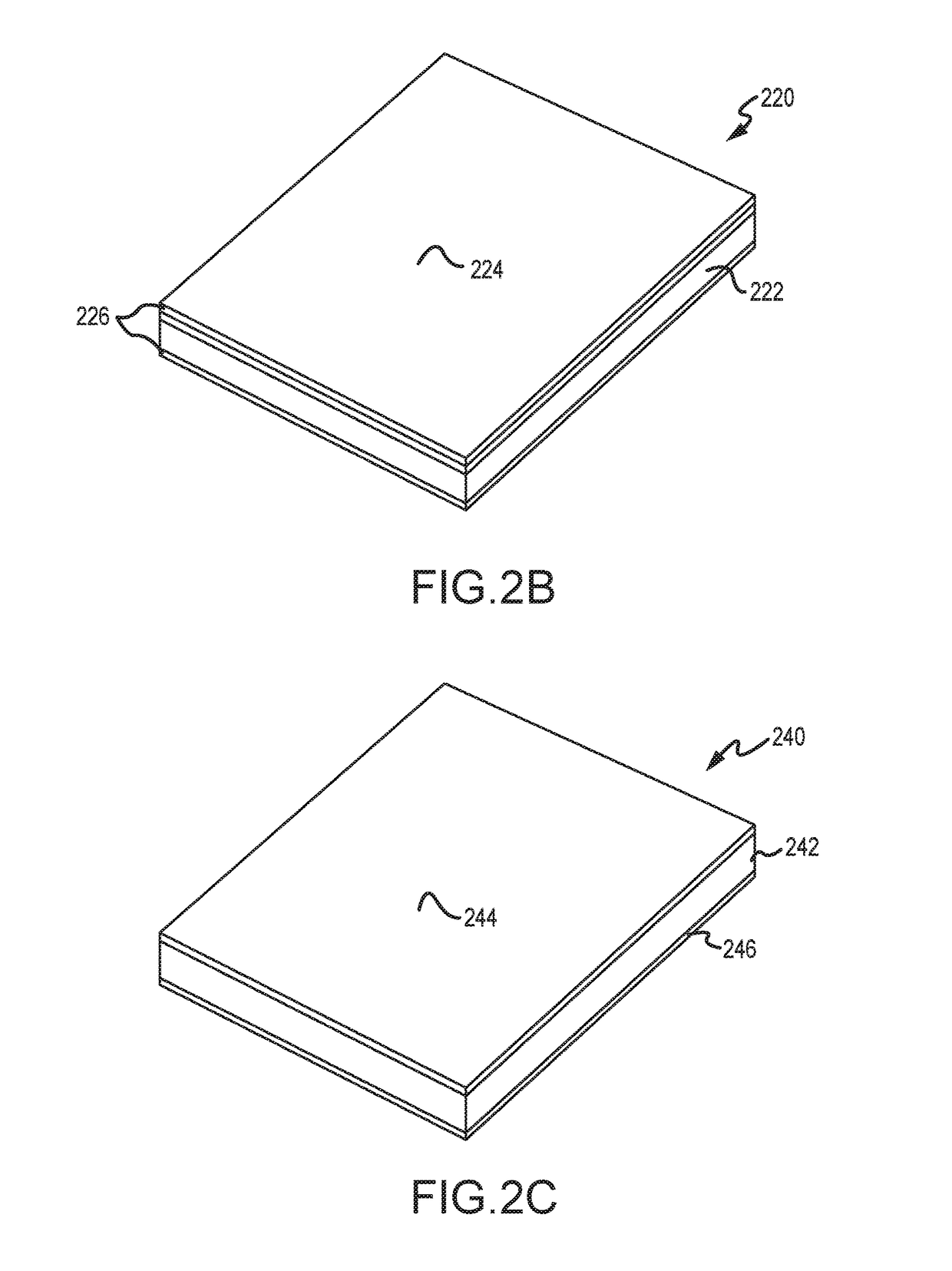

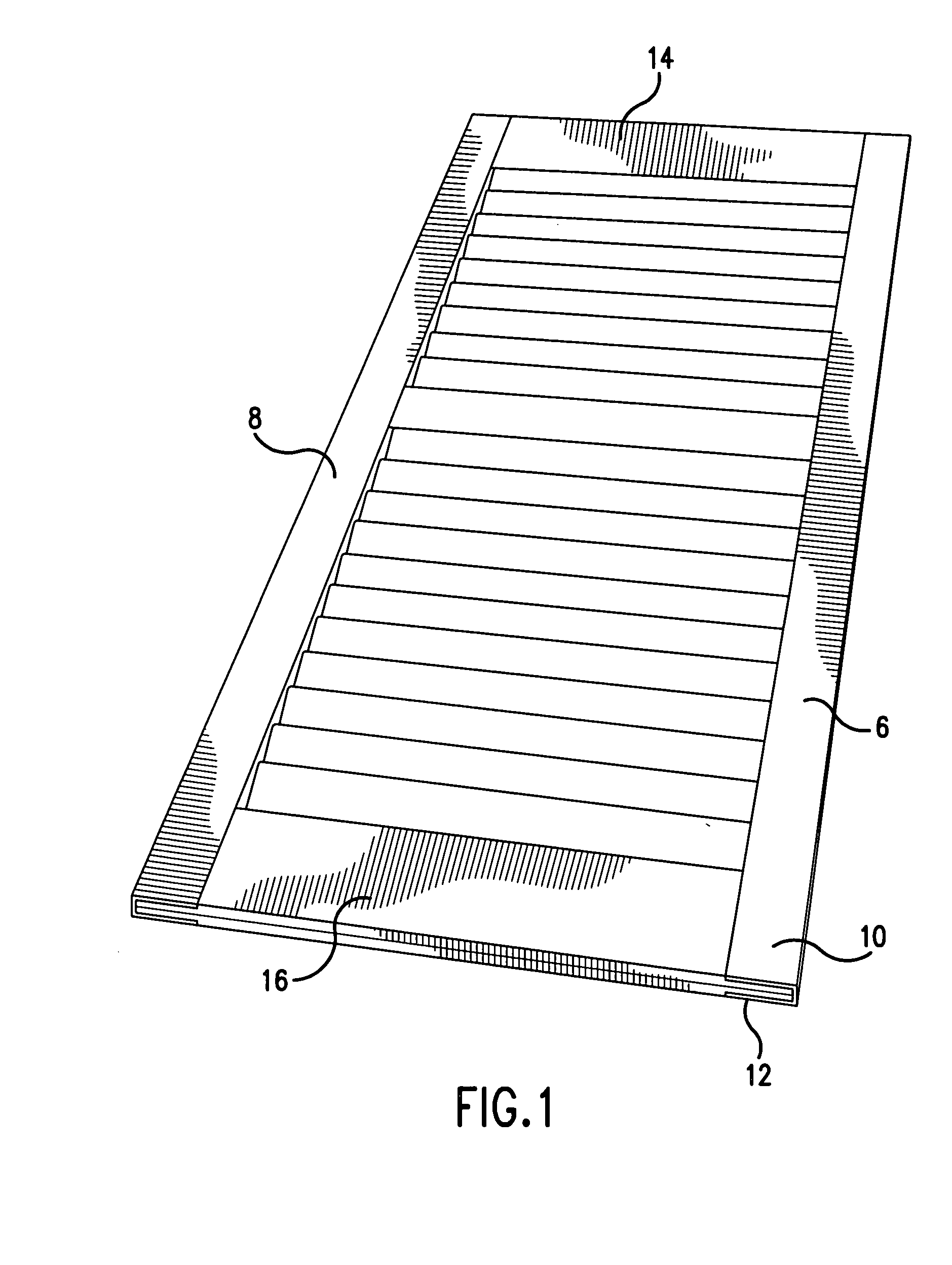

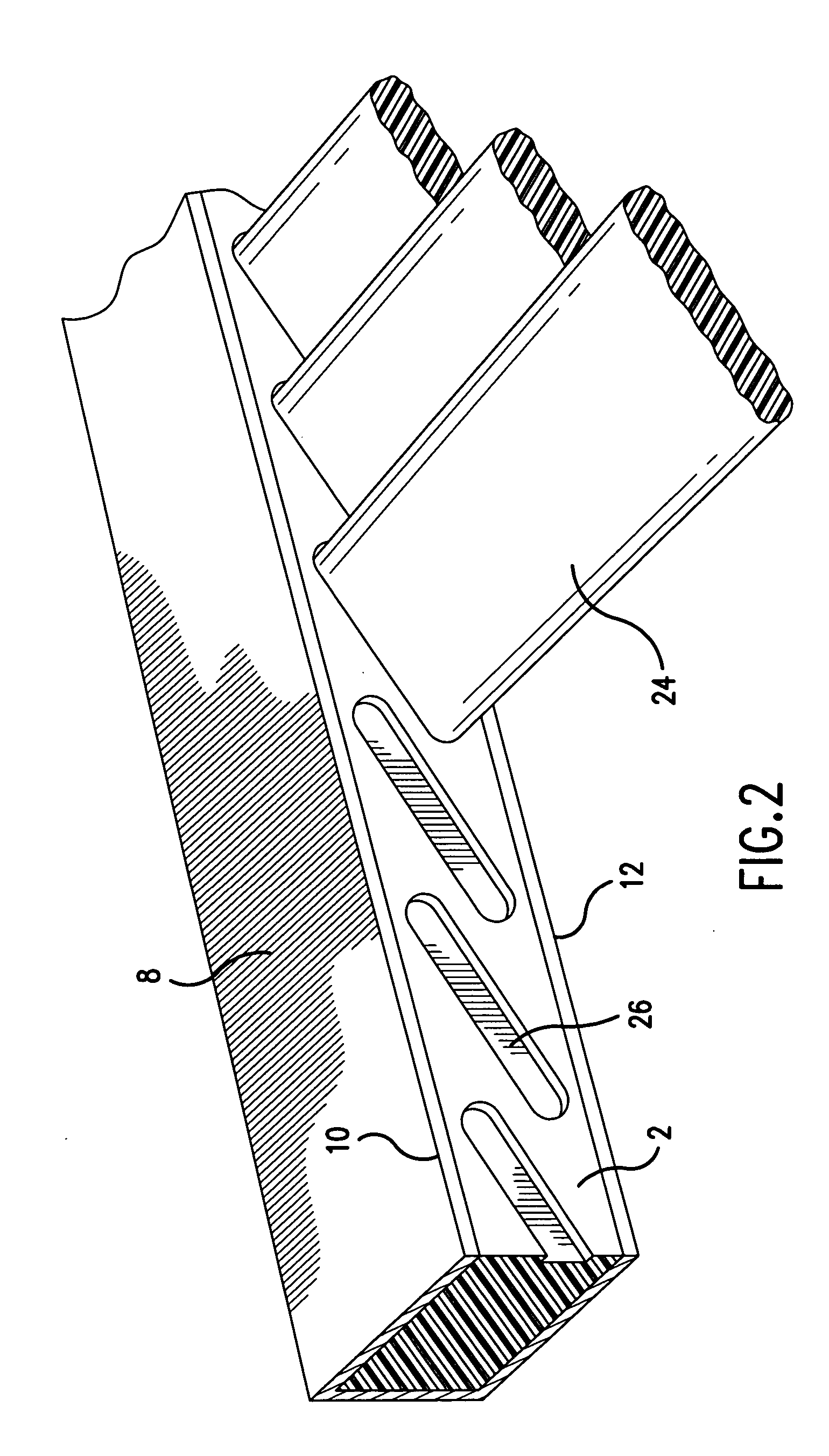

Fire resistant composite boards and methods

ActiveUS20140130435A1Improve fire resistancePrevent wind upliftBuilding roofsLiquid surface applicatorsFire resistanceCoating

Embodiments of the invention provide roofing boards and roofing systems having improved fire resistance properties and methods related to the same. According to one aspect, a roofing system is provided. The roofing system includes roofing panels positioned atop structural support members to form a roof deck. Roofing boards are positioned atop the roof deck and coupled thereto and a roofing membrane is positioned atop the roofing boards and coupled therewith. The roofing boards include a coating of a mineral based material applied to one or more surfaces in an amount between the range of about 0.10 lbs / ft2 and about 0.70 lbs / ft2. The mineral based material coating enables the roofing boards to pass the UL 790 class A tests, such as the burning brand test.

Owner:JOHNS MANVILLE CORP

Filled perfluoropolymer composition

InactiveUS20050187328A1Improve performanceGood physical propertiesSynthetic resin layered productsCellulosic plastic layered productsPlenum cablePolymer chemistry

The present invention relates to plenum cables jacketed with a composition comprising perfluoropolymer, inorganic char-forming agent, and hydrocarbon polymer, which passes the NFPA-255 burn test.

Owner:MEXICHEM AMANCO HLDG DE C V +1

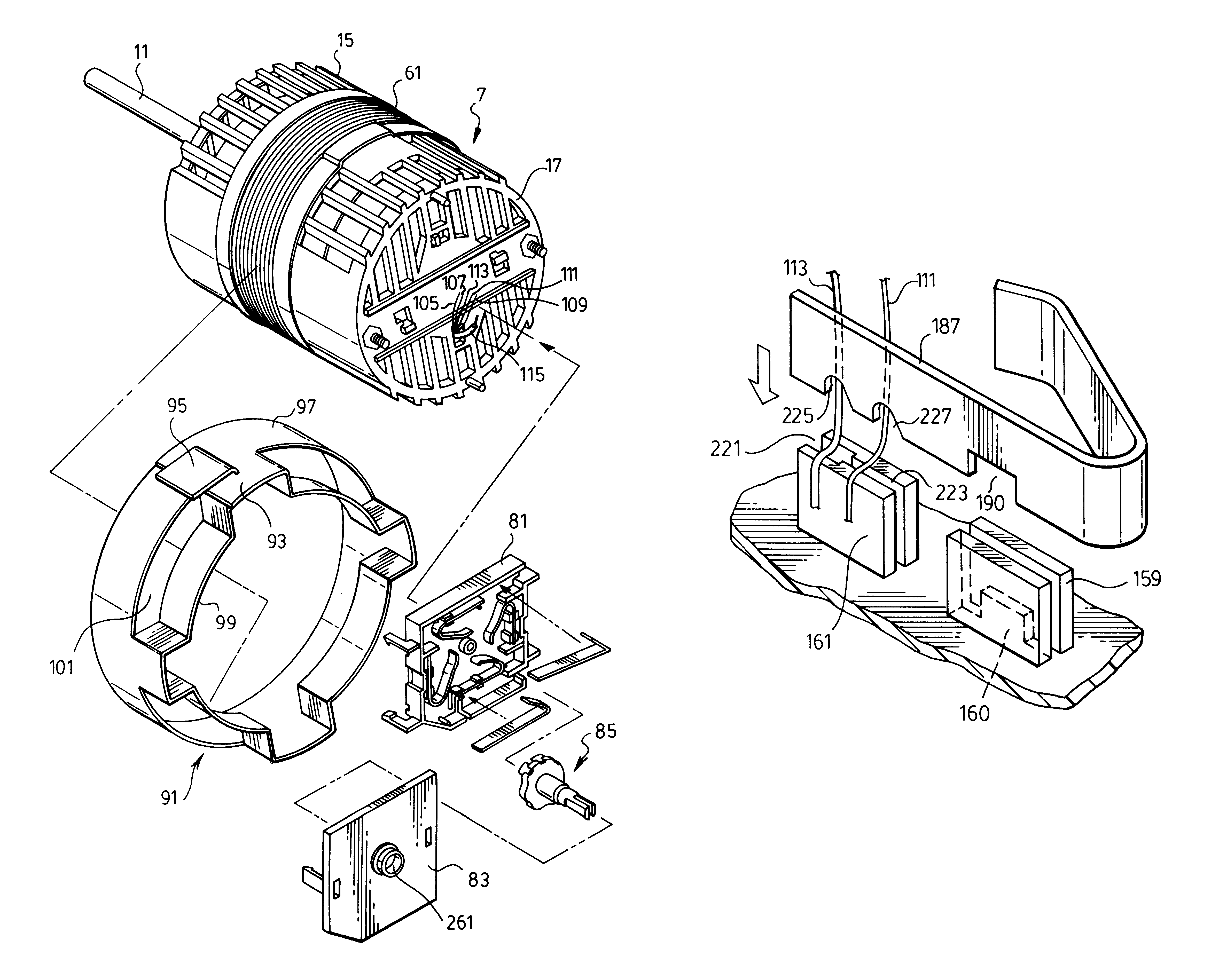

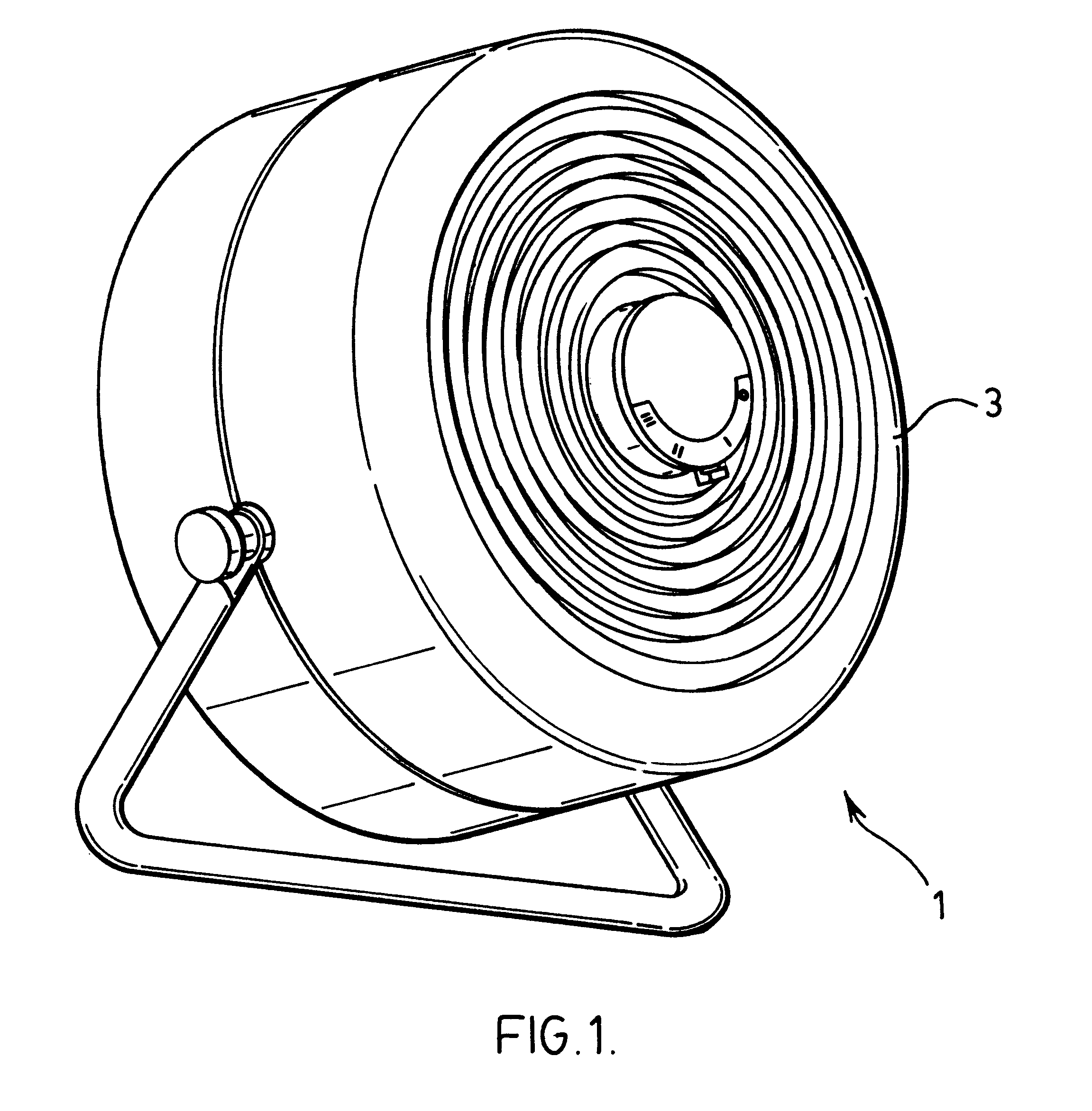

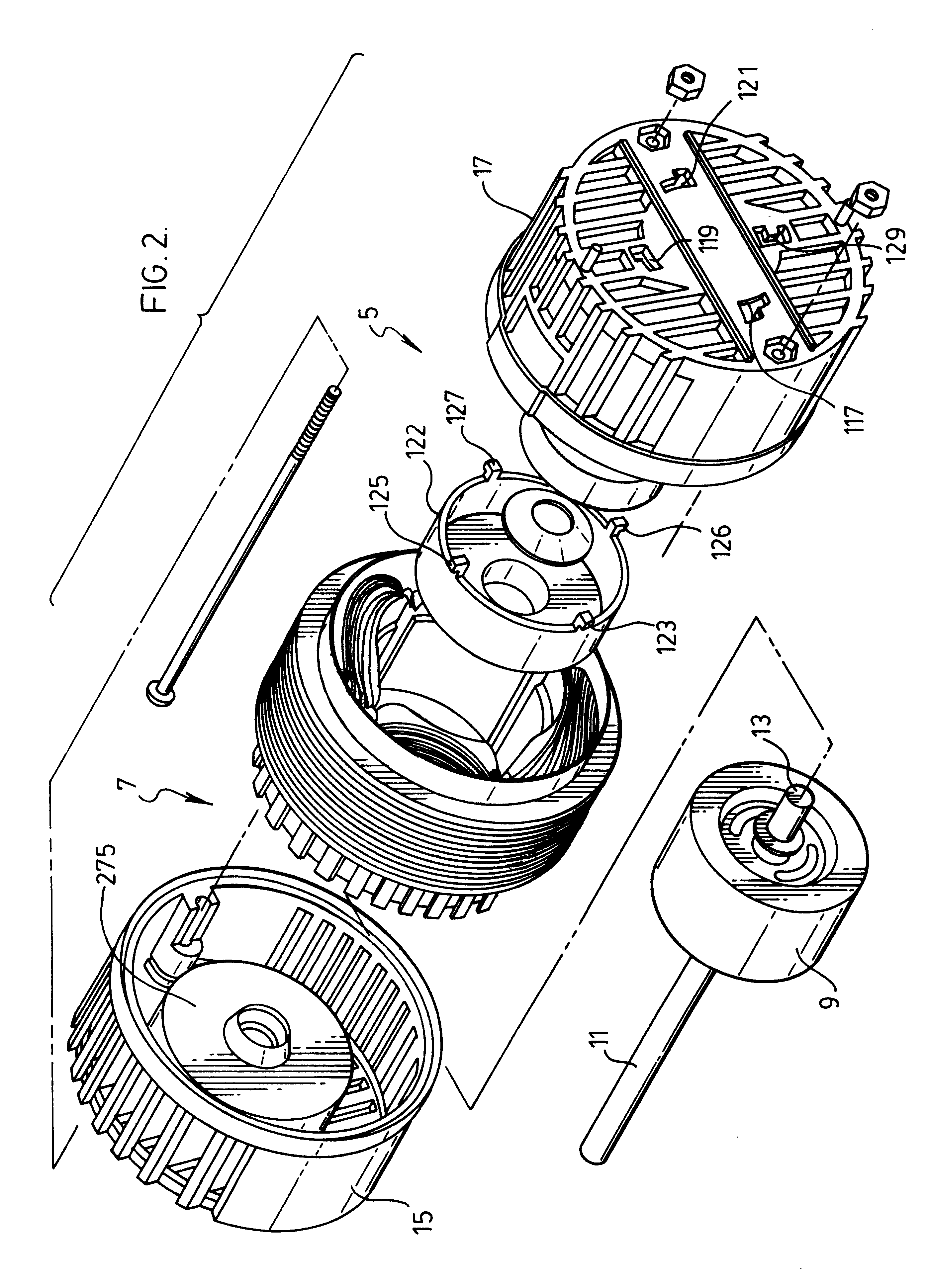

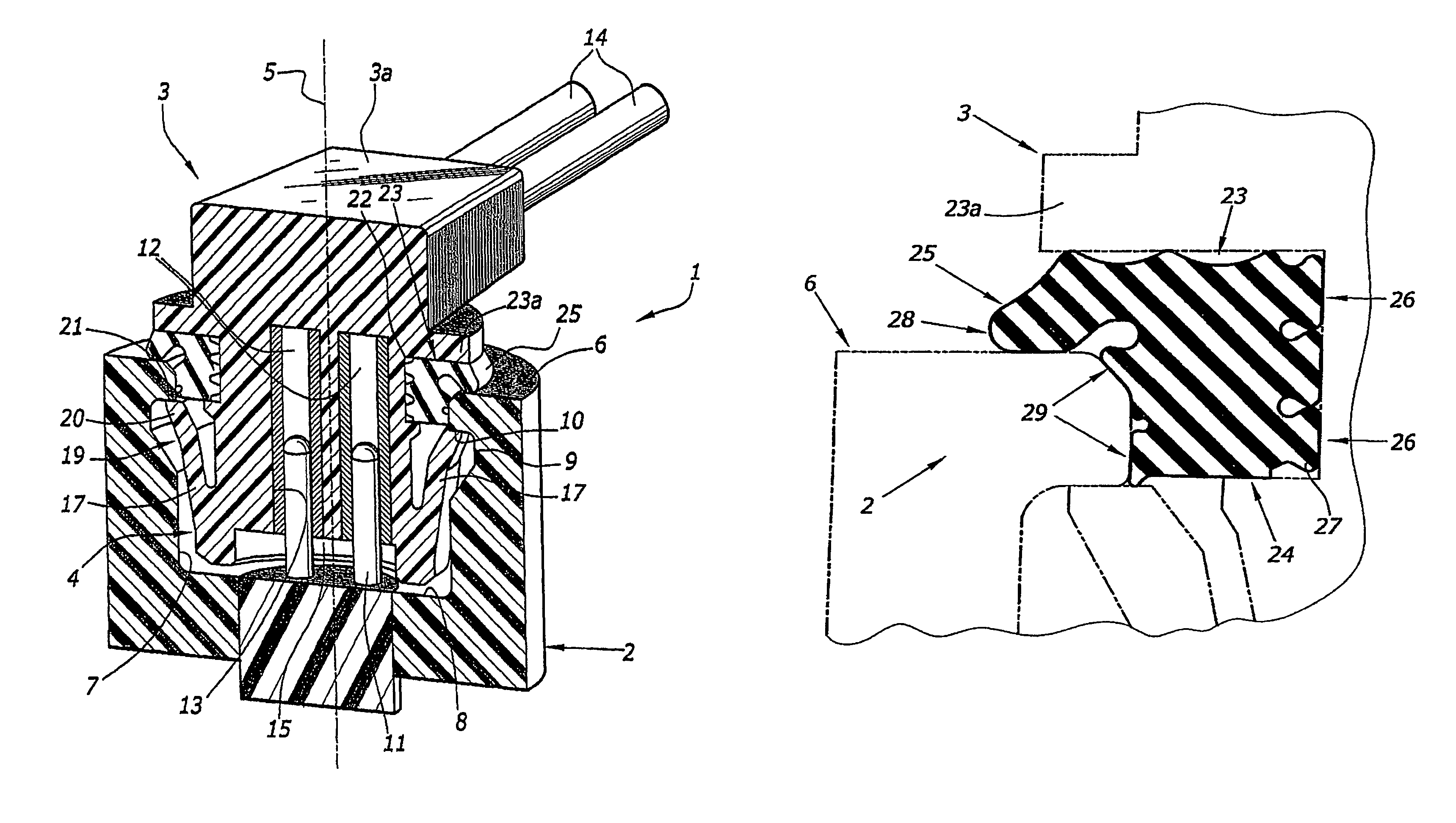

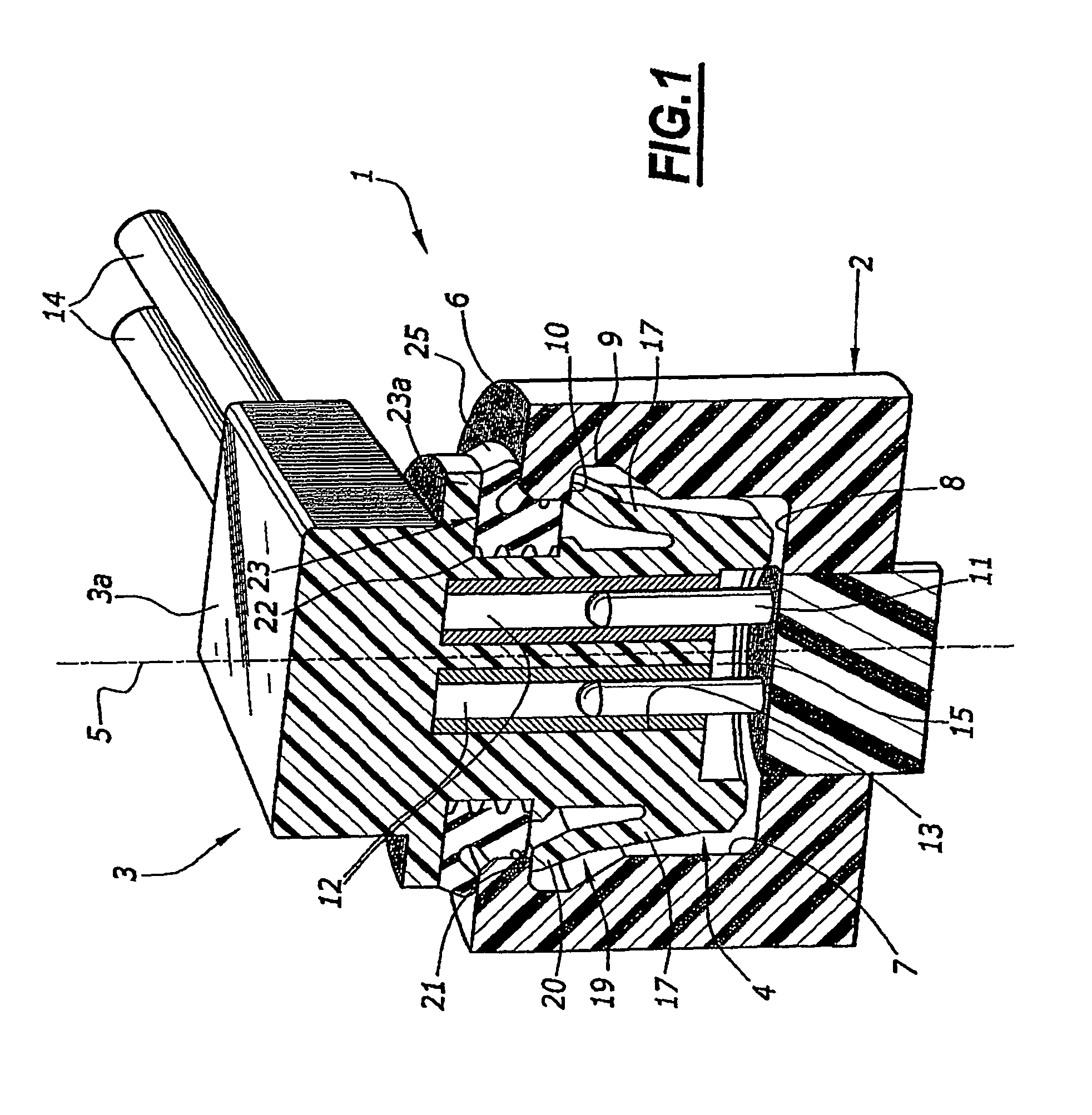

Motor mounted switch

InactiveUS6376947B1Avoid shortingPrecision injectionCoupling device connectionsWindingsMagnetic fluxElectric wire

An electrical appliance which operates at multiple speeds includes a motor construction having a stator and a rotor which rotates within the stator. The stator includes a plurality of magnetic flux inducing wires coiled on different poles of the stator. The stator and the rotor are contained within a motor housing with the appliance further including a switch housing mounted directly to the motor housing. The flux inducing wires have wire ends which extend out of the motor housing and into the switch housing which includes receptors to receive the ends of the flux inducing wires and which also receive electrical contact members which secure and electrically connect with the ends of the flux inducing wires within the receptors of the switch housing.

Owner:TATEISHI ART

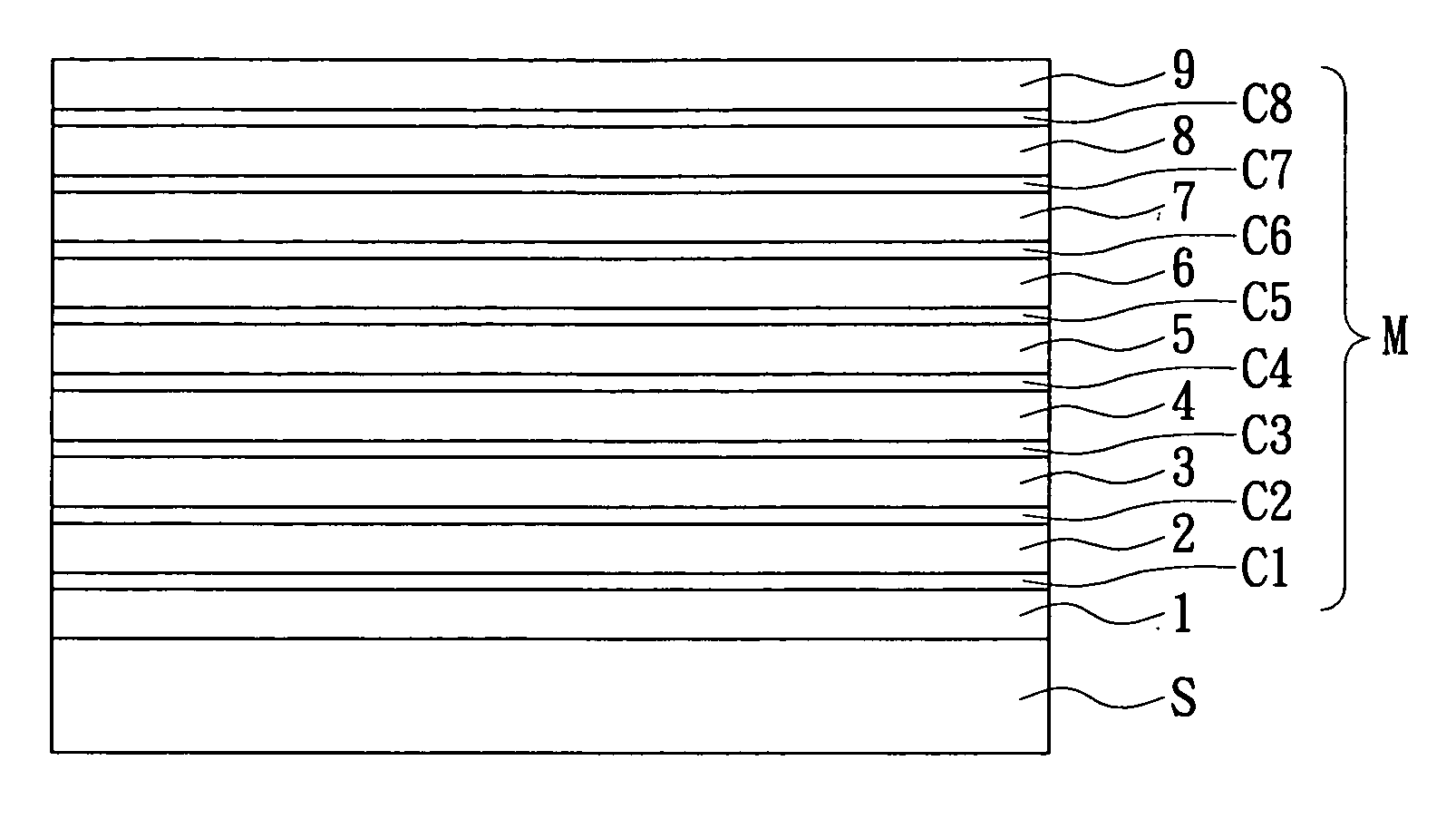

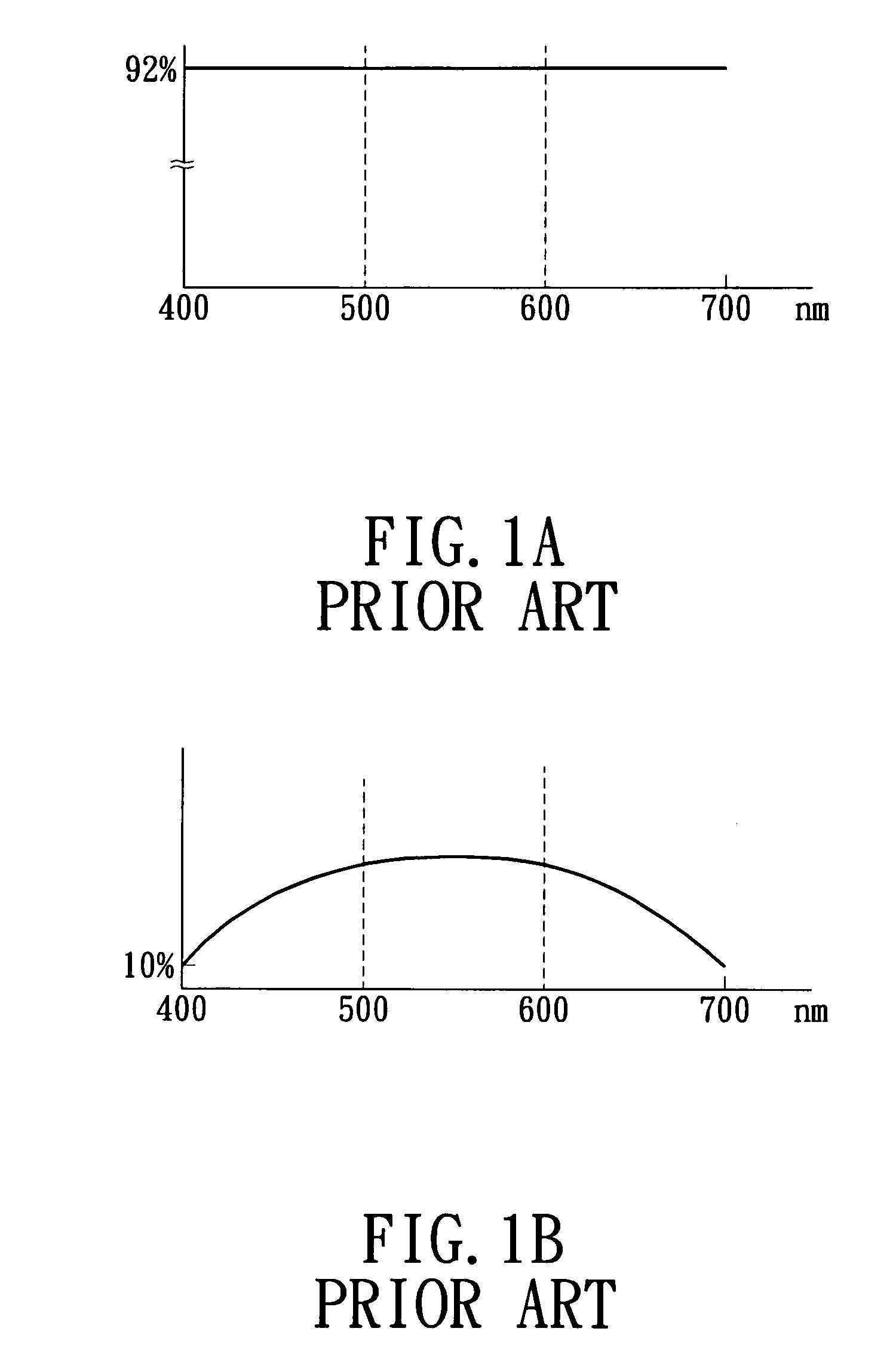

Extreme low resistivity light attenuation anti-reflection coating structure in order to increase transmittance of blue light and method for manufacturing the same

InactiveUS20090297877A1High light transmittanceLow resistivityRecord information storageMagnetic recordingMetal coatingTransmittance

An extreme low resistivity light attenuation anti-reflection coating structure in order to increase transmittance of blue light, includes a substrate and a coating module. The coating module is formed on a front surface of the substrate and composed of a plurality of silicon carbide compound coating layers, a plurality of Al-based oxide coating layers and a plurality of metal coating layers that are alternately stacked onto each other.

Owner:INNOVATION & INFINITY GLOBAL

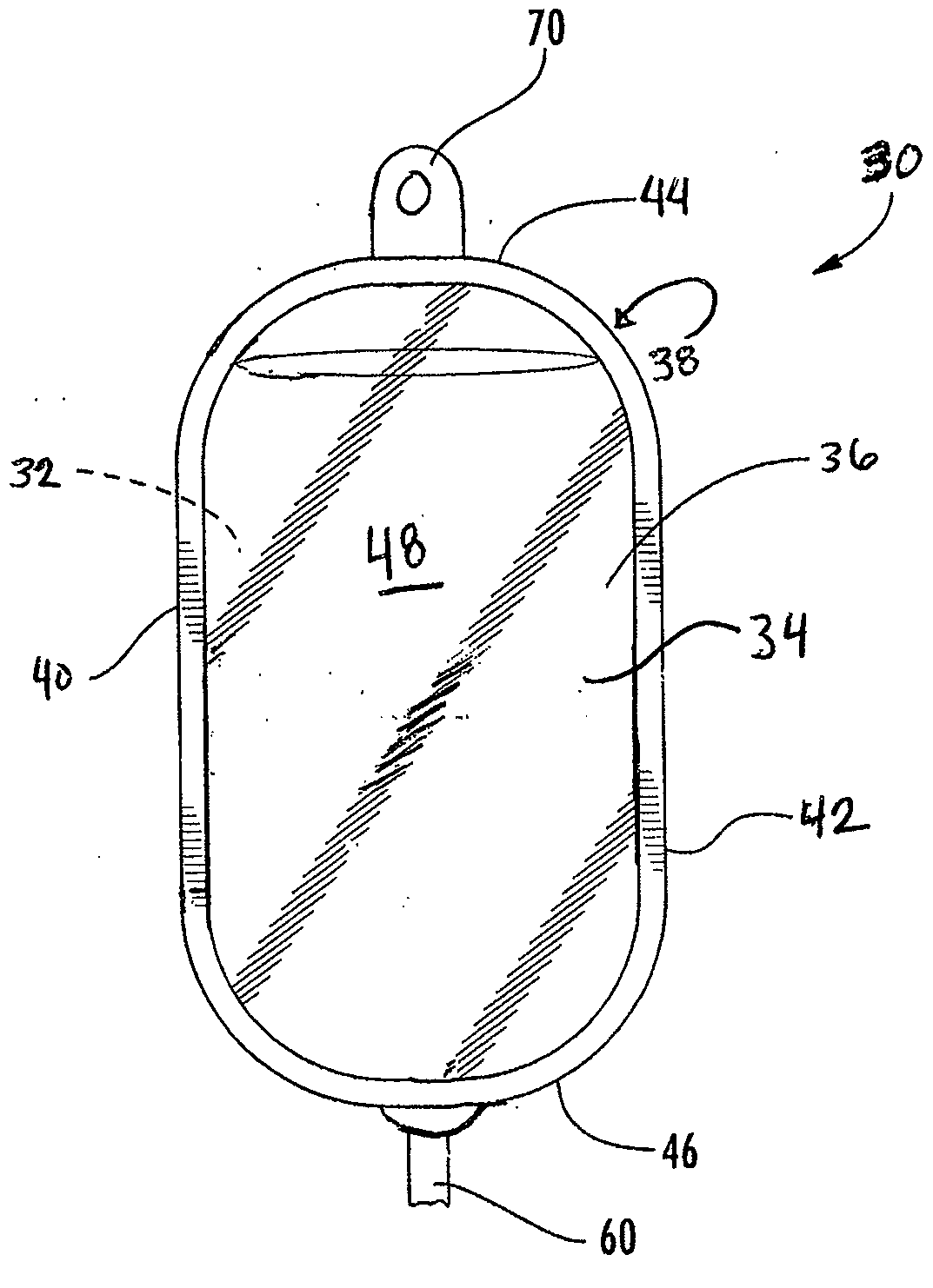

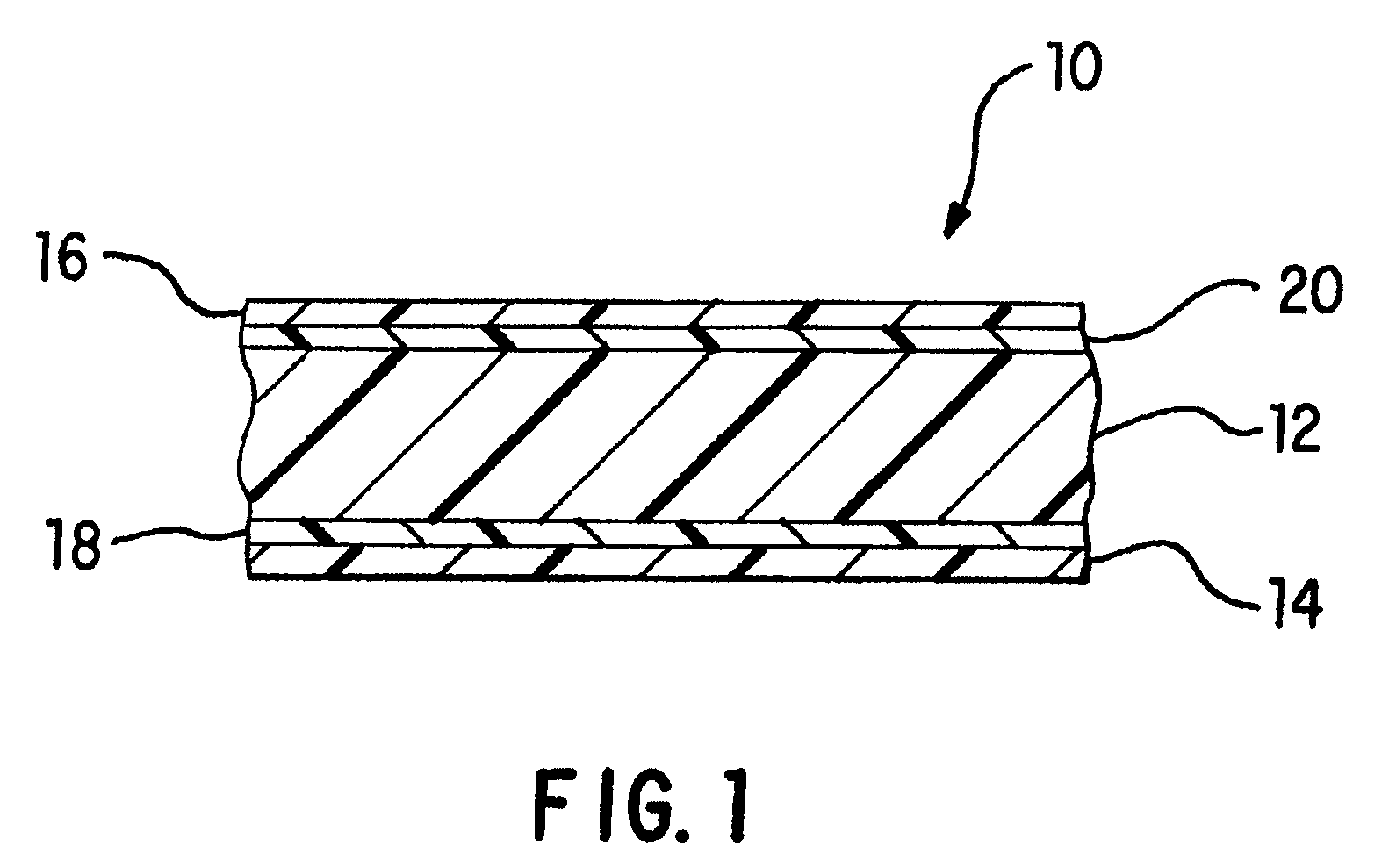

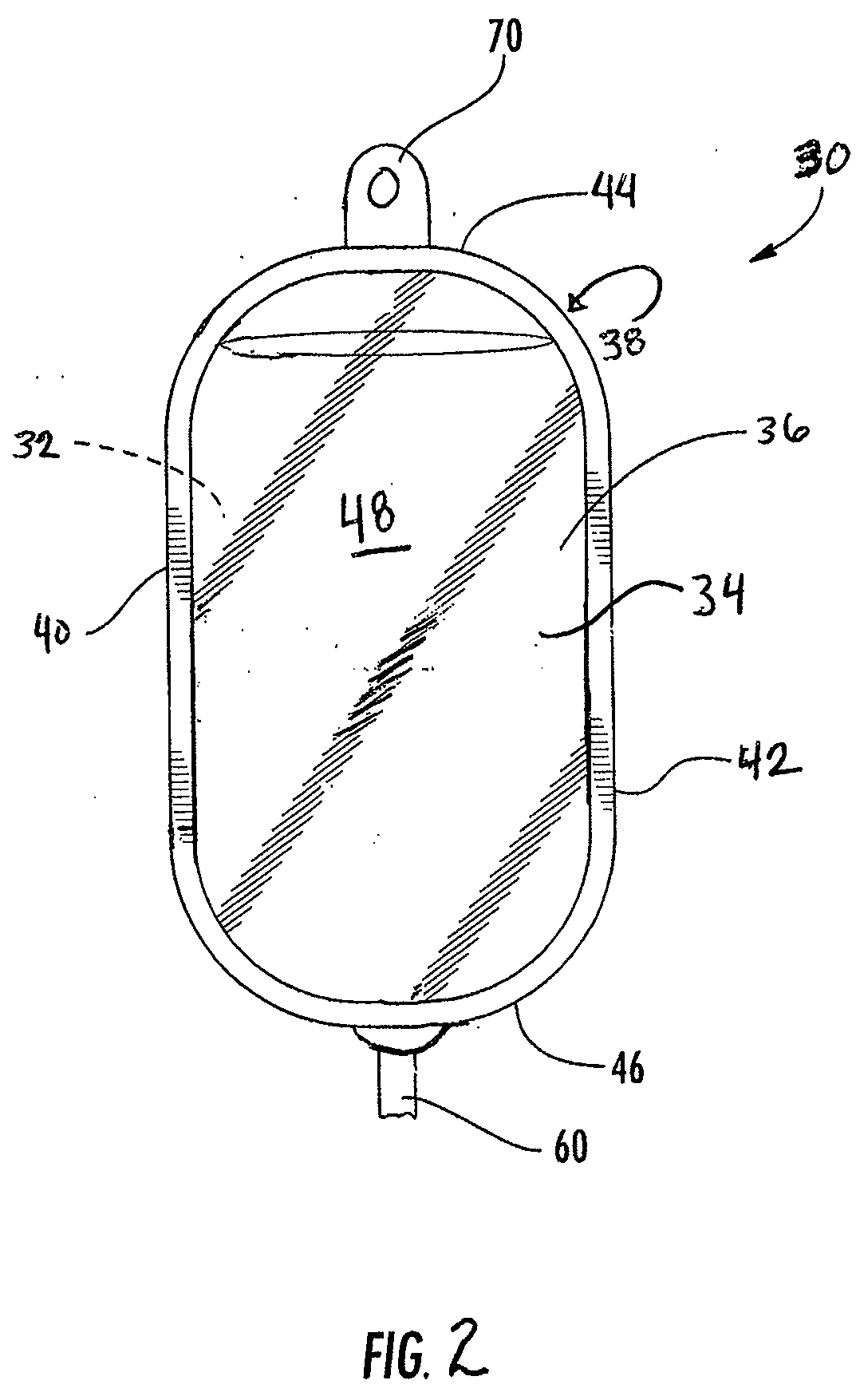

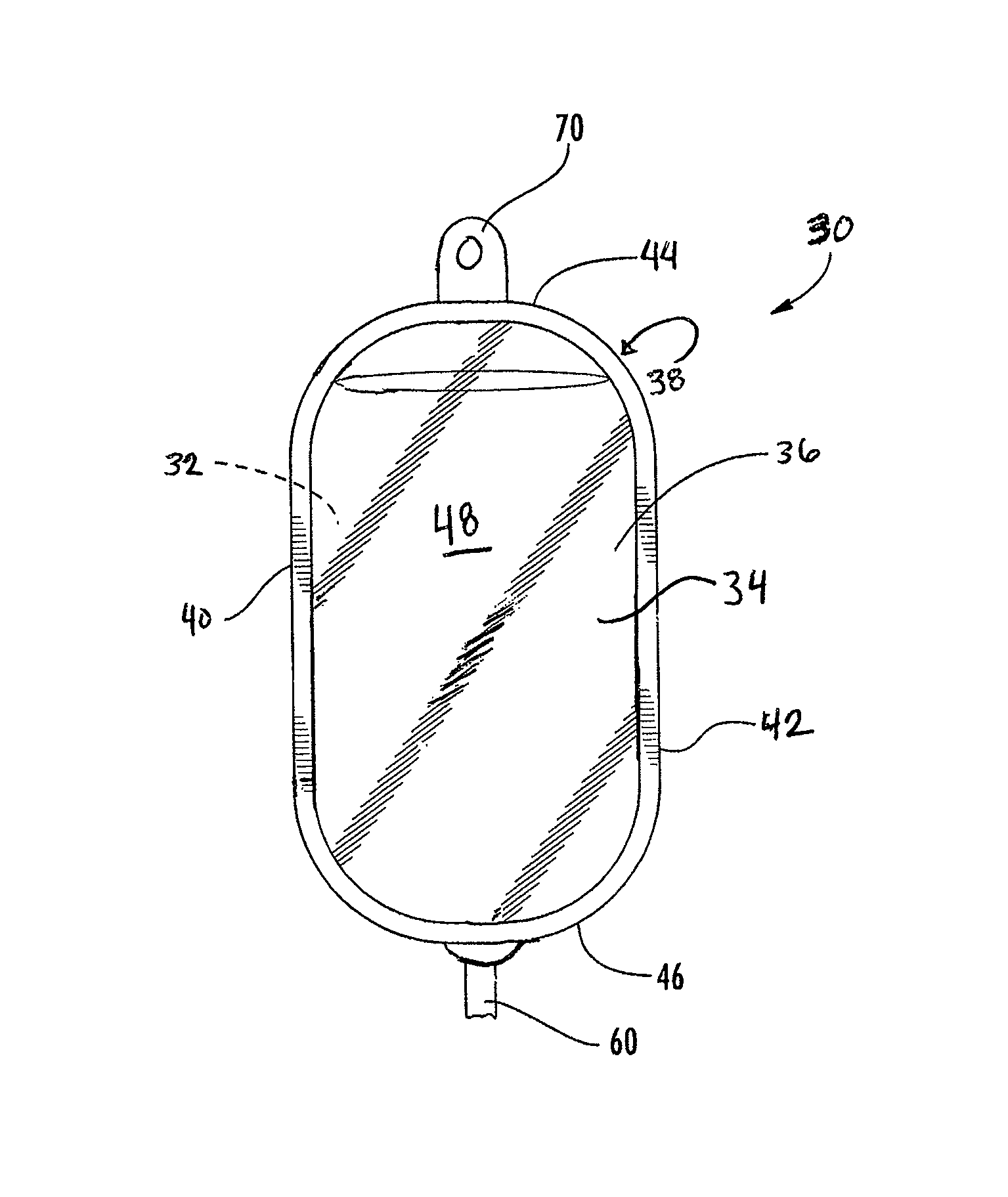

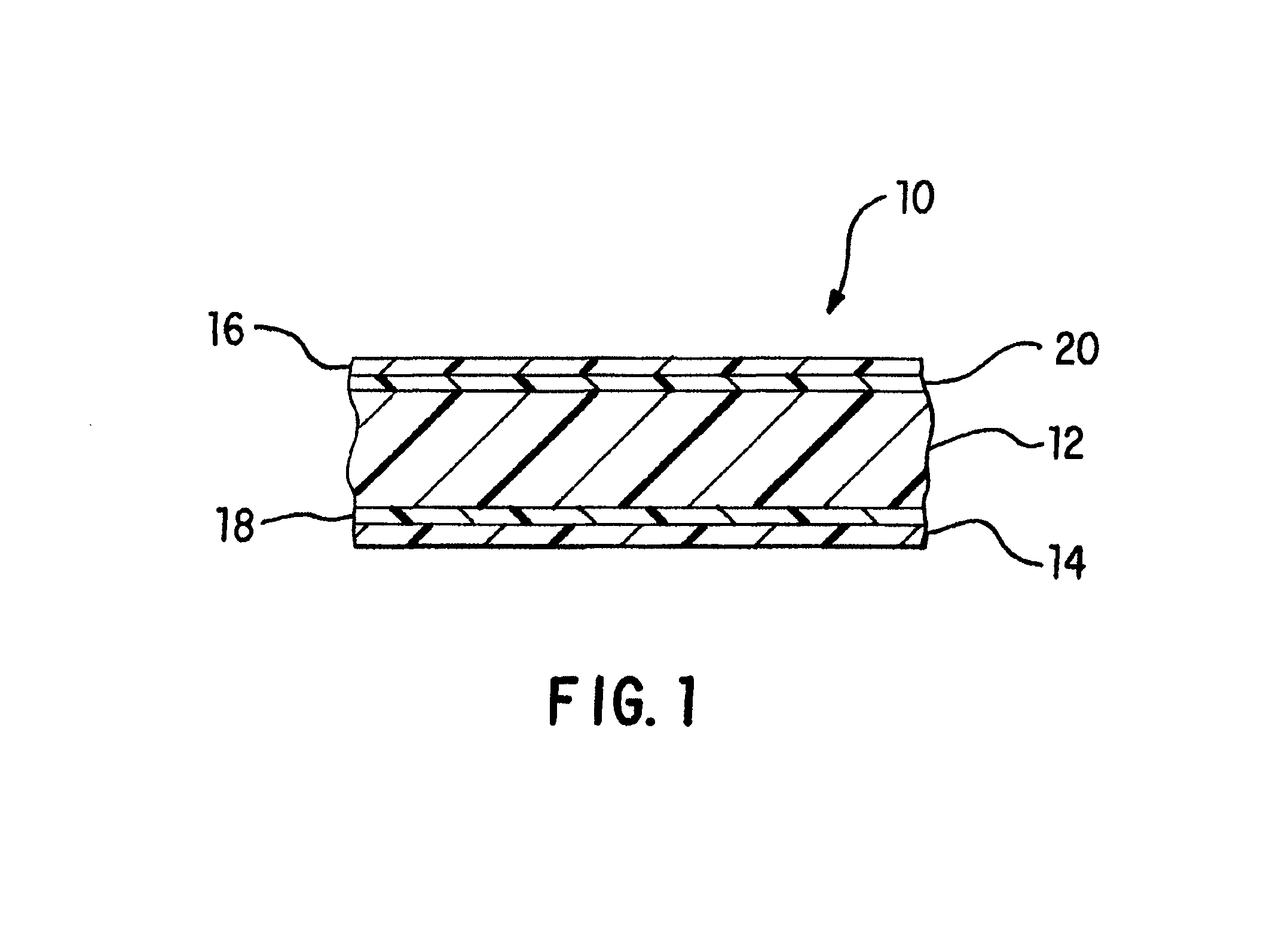

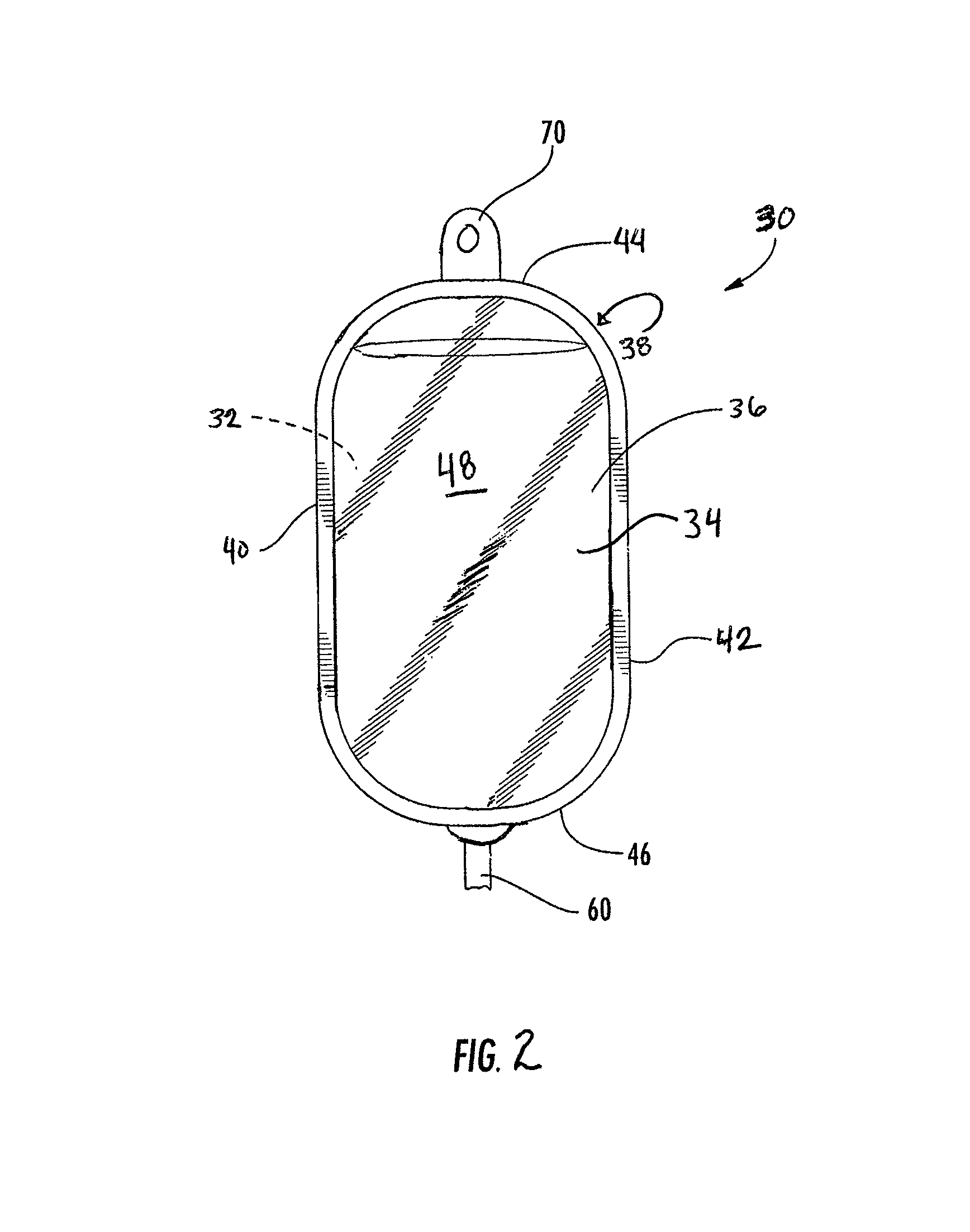

Multilayer Film for Medical Solution Pouches Having Reduced Proficiency for Forming Bubbles

ActiveUS20100256590A1Reducing and preventing presenceTest may passDiagnosticsSurgeryFoaming agentPolyamide

The present invention provides a multilayer film for forming medical solution pouches that help prevent or reduce the presence of bubbles or foam in the solution after heat sterilization. In particular, the present invention provides a multilayer film for forming medical solution pouches that are capable of passing the bubble test as set forth in the Chinese State Drug Package Container Material Standard No. YBB00112005. In particular, the present invention provides a multilayer film in which polyamide 612 or calcium stearate component has been incorporated as an anti-foaming agent. The presence of polyamide 612 or calcium stearate in one or more layers of the film helps prevent the formation of foam in the solution after heat sterilization.

Owner:CRYOVAC ILLC

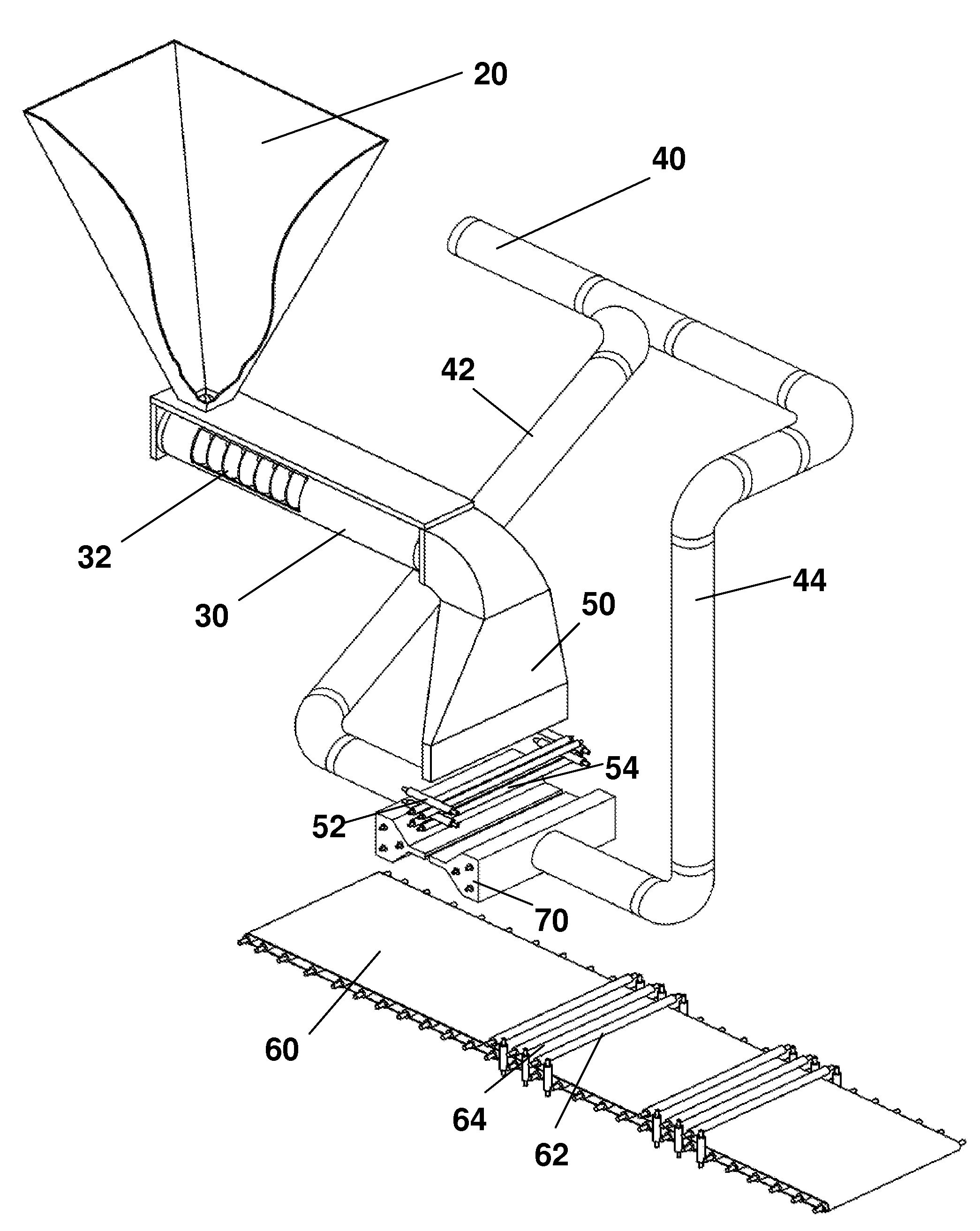

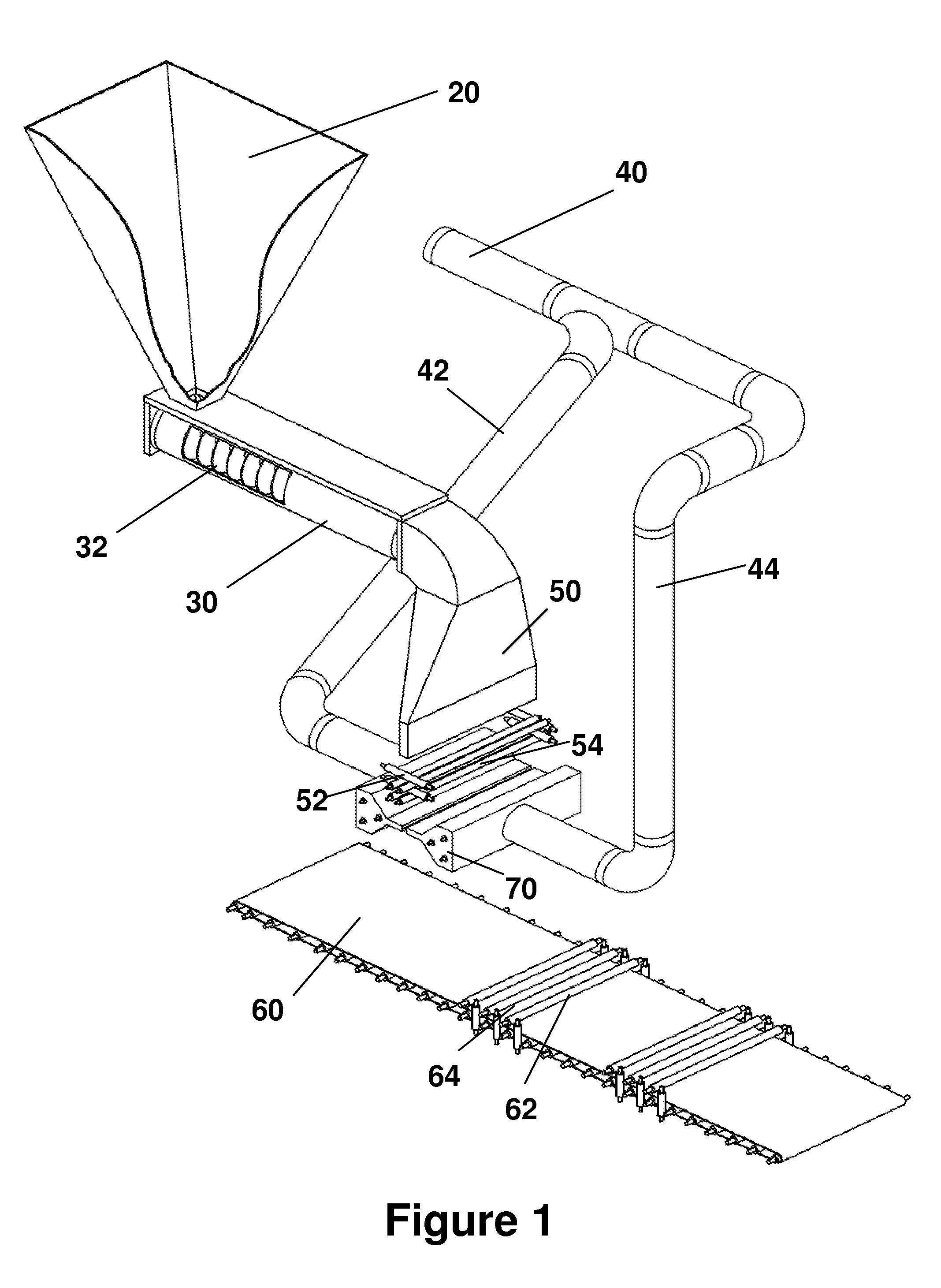

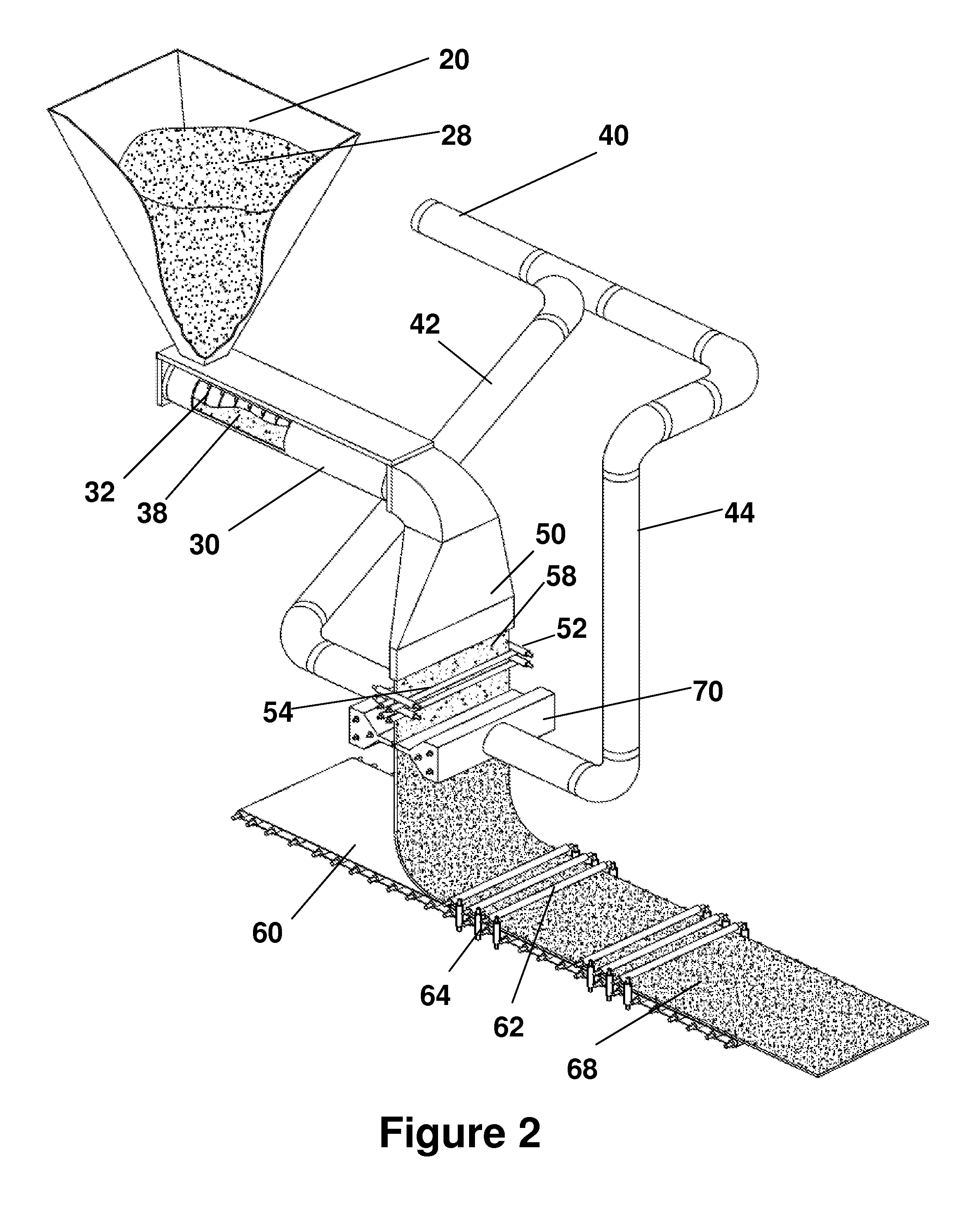

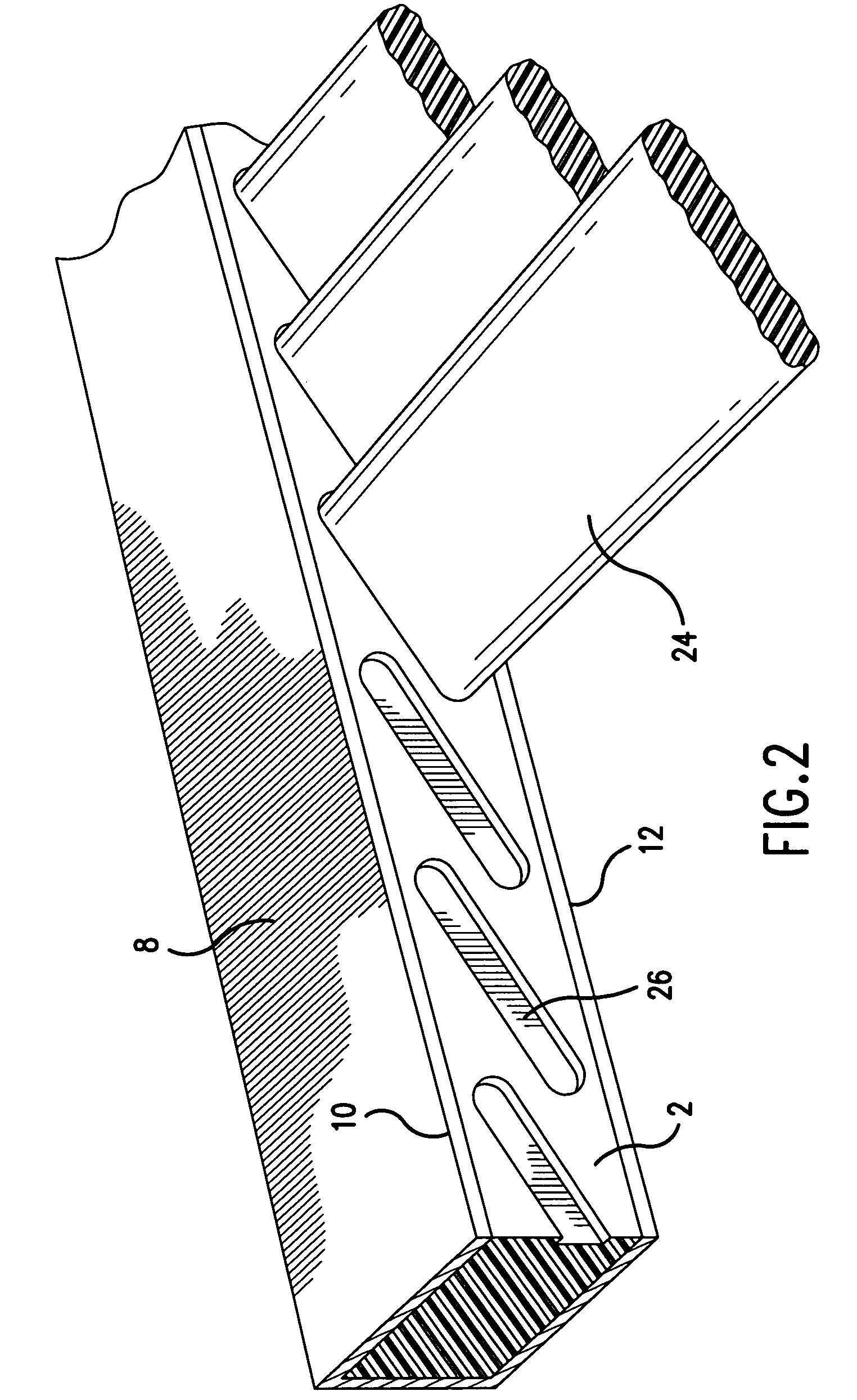

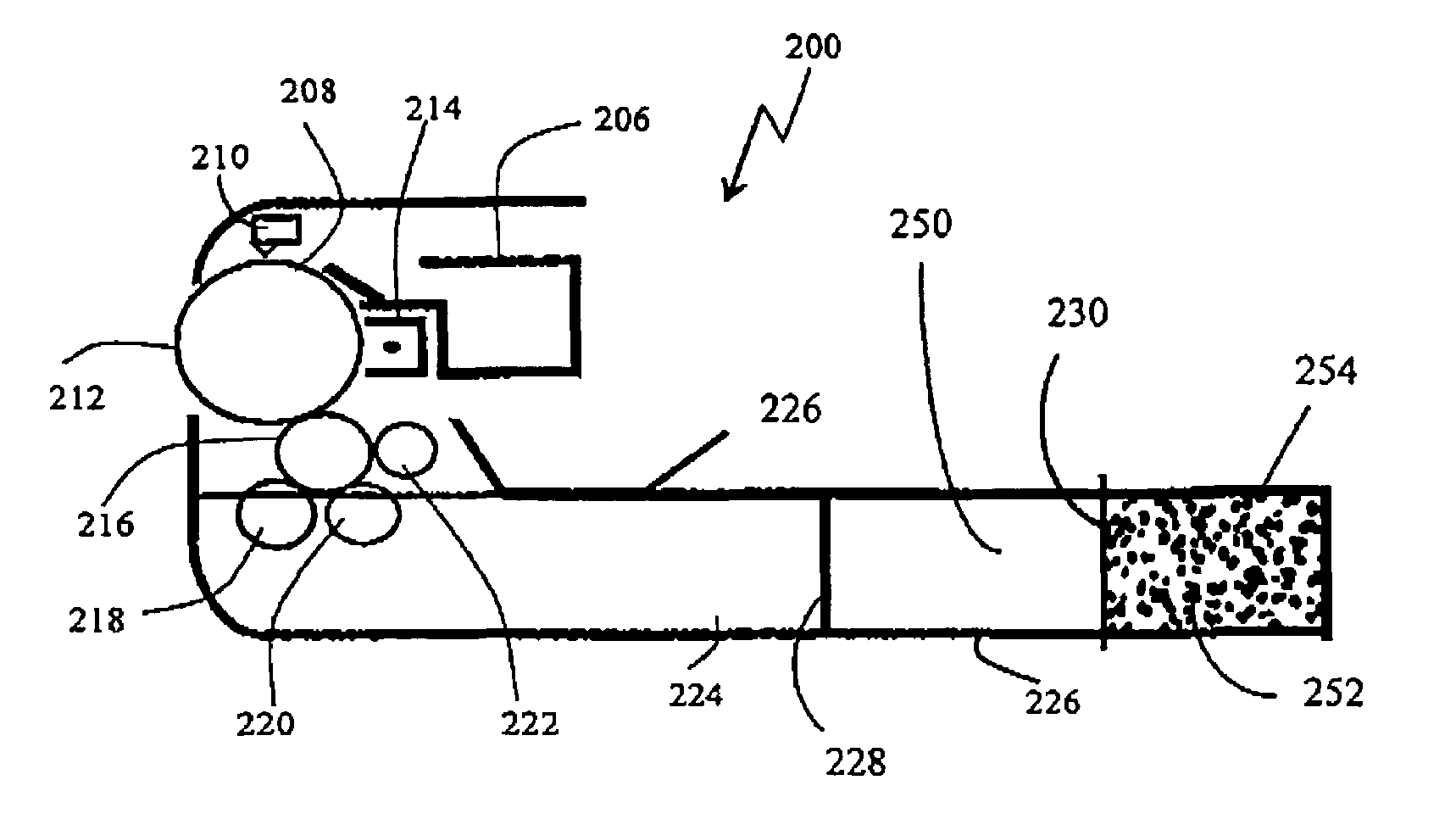

Extruded Cross-Banded Magnesium Oxide Construction Board and Method of Making Same

InactiveUS20100077939A1Fast preparationEasy to produceSolid waste managementShaping conveyorsSlurryChloride

Embodiments of the invention comprise a method of making a construction board (also known as wallboard) and a device for making same. The resulting construction board is formed by mixing of at least magnesium oxide, magnesium chloride, and a binding agent into a slurry, adding particulized solid material while funneling the slurry, and extruding the slurry comprising the particulized solid material.

Owner:TROUT KATHY

Self-preserved emulsions

InactiveUS20090298956A1Comfortable and non-irritating to eyeImpart propertyBiocideSenses disorderEmulsionPreservative

The use of multifunctional synthetic compounds to both stabilize and preserve therapeutic emulsions is described. The multifunctional synthetic compounds have unique molecular arrangement wherein a phosphate group is linked to one, two or three quaternary ammonium functionalities via a substituted propenyl group, and each quaternary ammonium functionality is further linked to at least one hydrocarbon chain. The pharmaceutical emulsions which include these multifunctional compounds may be prepared without heating or homogenization, and may not require the use of any additional stabilizing or preserving agents.

Owner:ALCON RES LTD

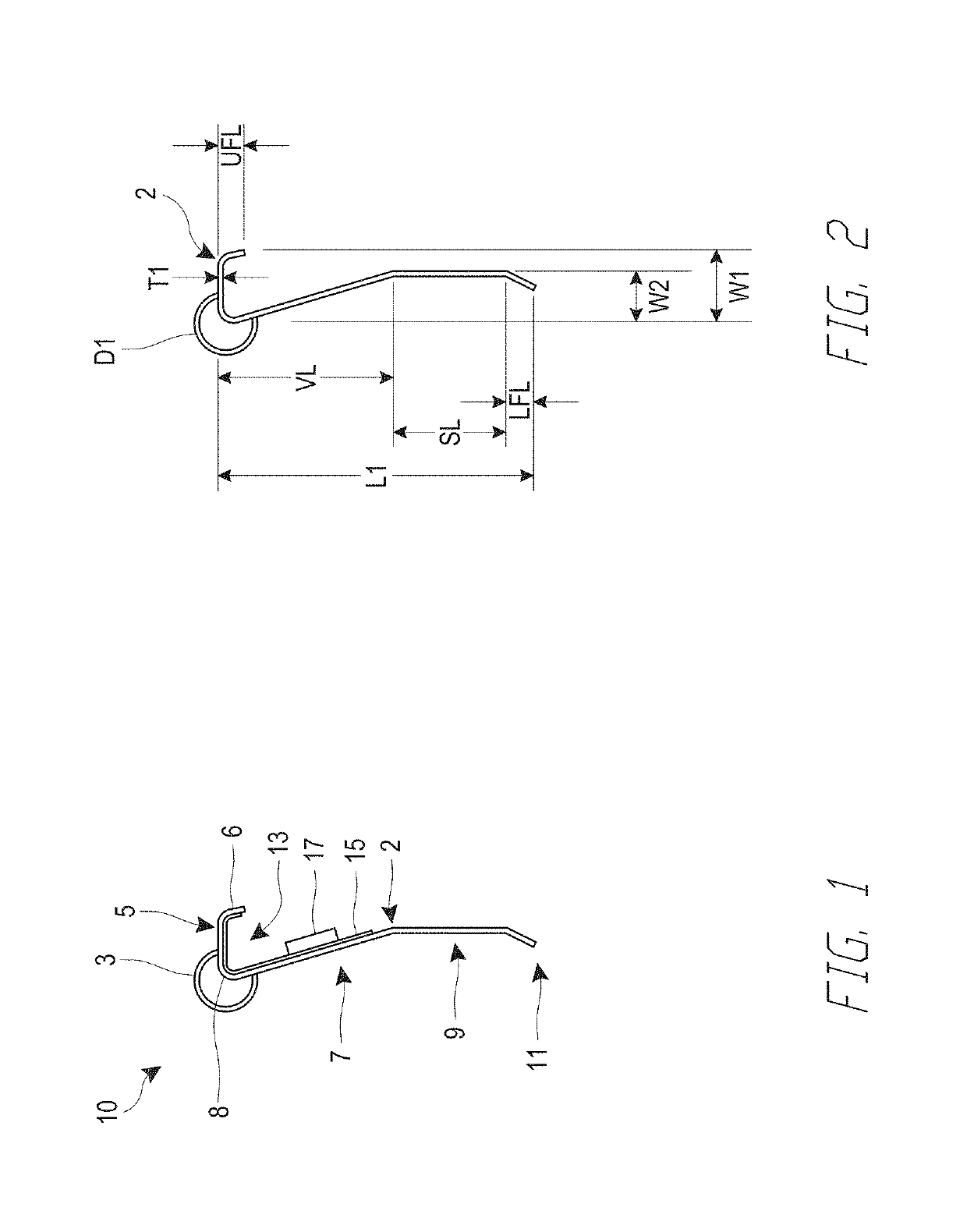

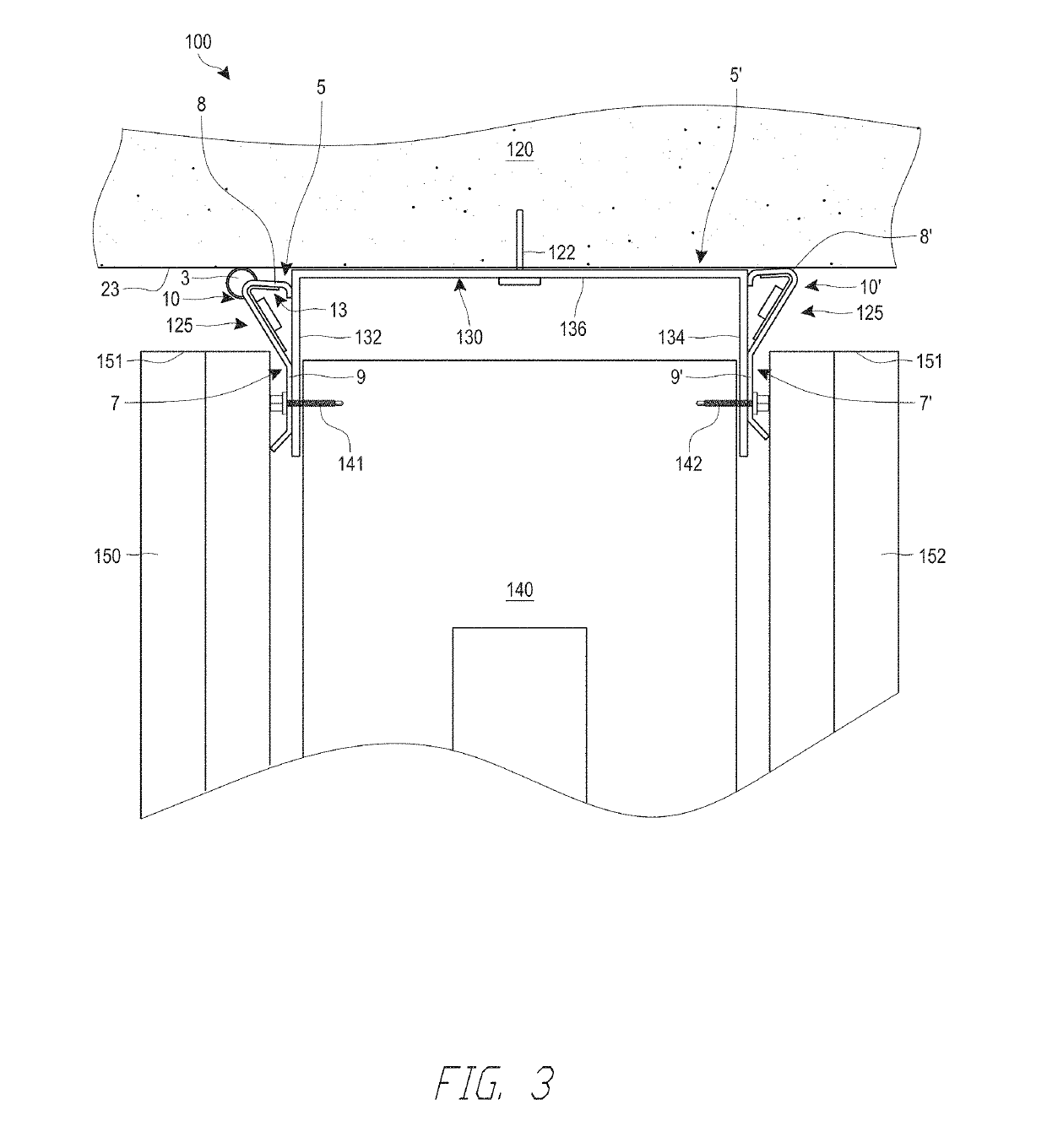

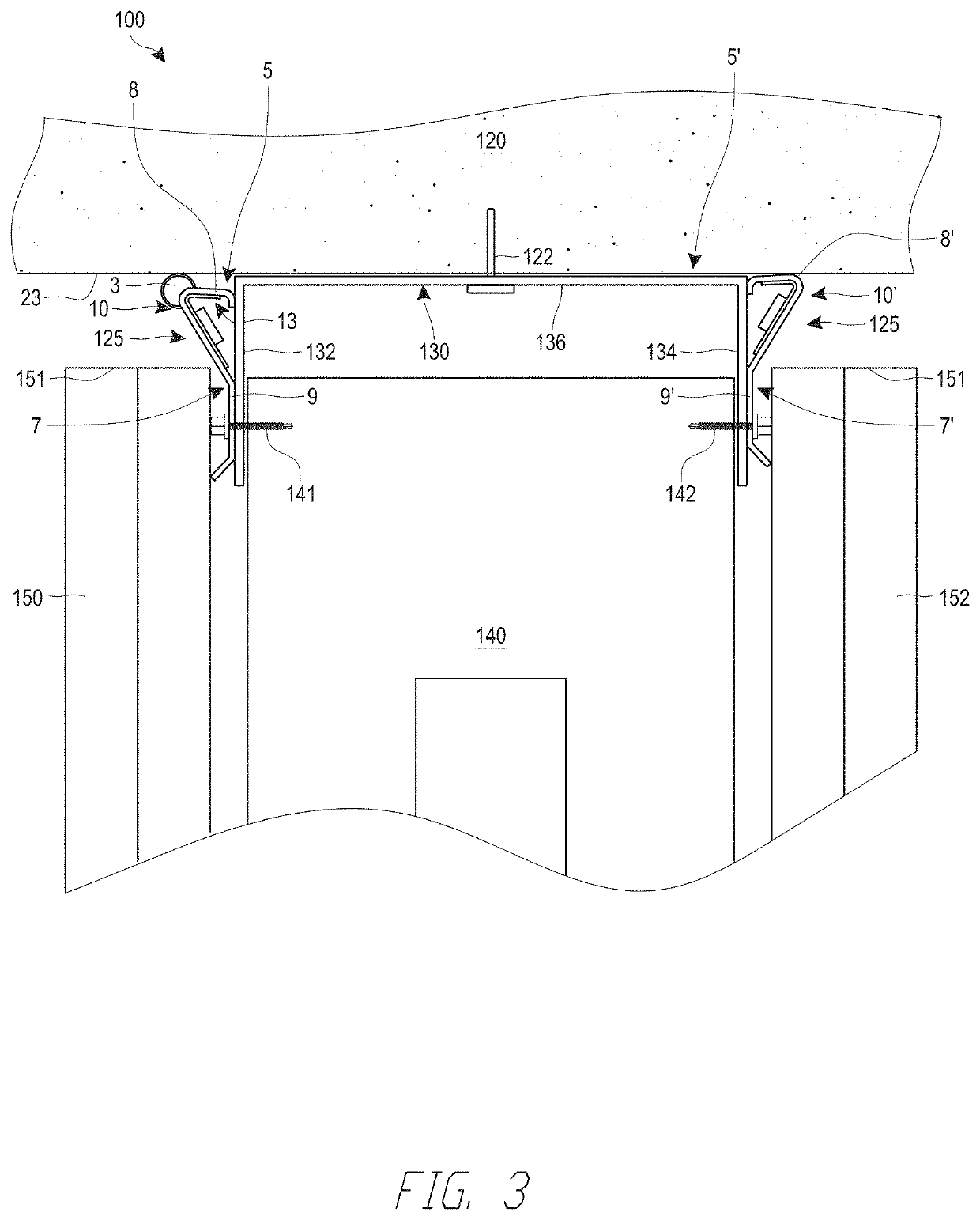

Multi-layer fire-rated joint component

ActiveUS20190284797A1Delayed expansionOpen the deflection gapWallsSynthetic resin layered productsJoint componentEngineering

An improved fire-blocking gasket profile for a fire-rated joint, such as a head-of-wall assembly. Fire-rated joints are aimed at inhibiting or preventing fire, heat, or smoke from leaving one portion of a building and entering another portion of a building. Fire-rated joints can also accommodate movement between adjacent building structures, such as between a ceiling and the top of a wall. The improved fire-blocking gasket profile includes a first layer formed of an intumescent material, a second layer formed of a foil lining and a third layer formed of the vinyl profile. The vinyl profile includes an air gap with the intumescent material positioned therein. A vertical portion of the vinyl profile is positioned between a header track and a wallboard in the fire-rated joint. A horizontal portion of the vinyl profile is positioned at least partially within a deflection gap and sealingly engages with the ceiling.

Owner:CEMCO LLC

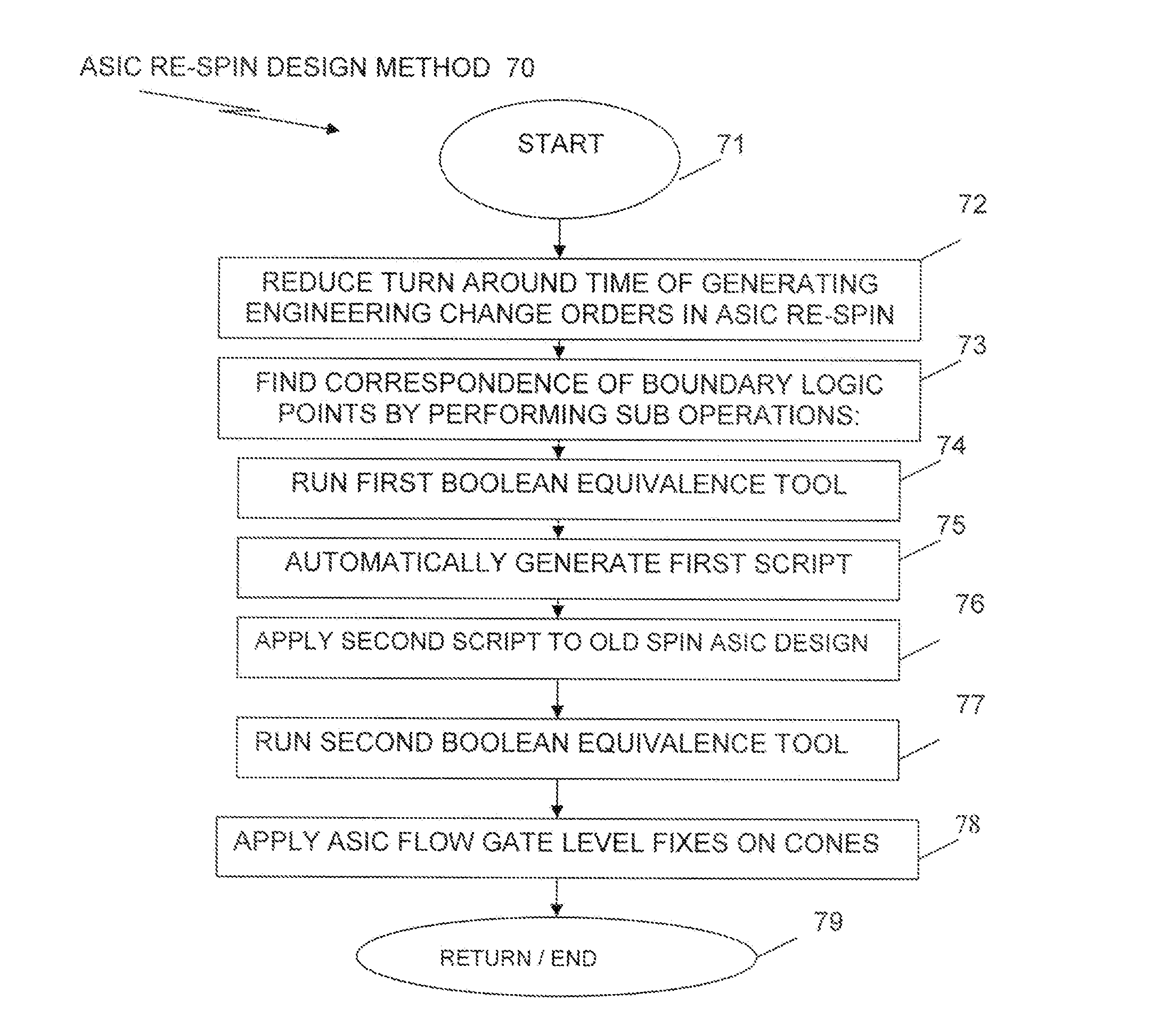

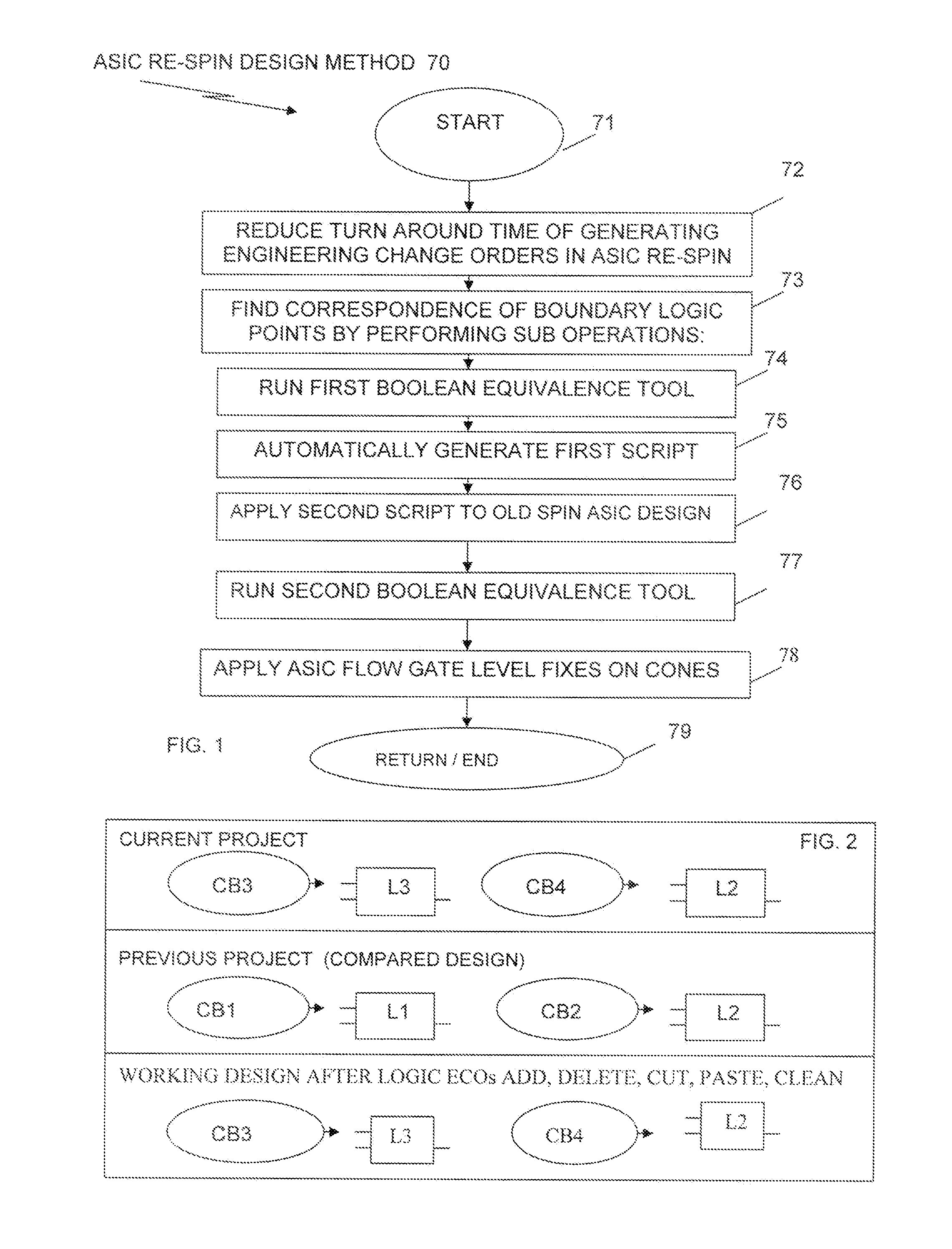

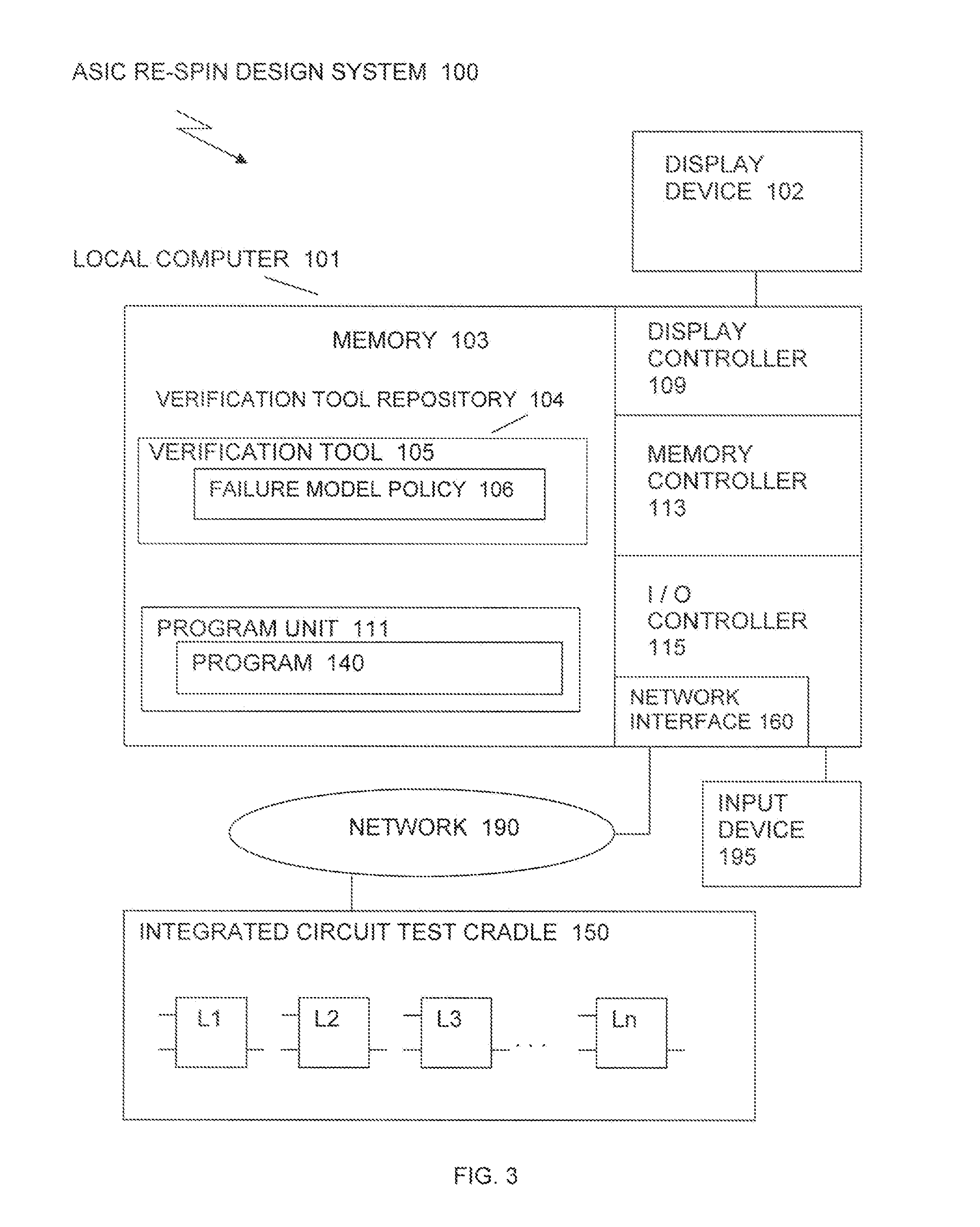

Method and system for reducing turn around time of complicated engineering change orders and asic design reutilization

InactiveUS20090178015A1Reduce turnaround timeTest may passCAD circuit designProgram controlEngineering change orderLogic gate

Reducing turn around time of engineering change orders in ASIC re-spin design includes finding, on the fly, all corresponding boundary points of storage gate elements indicated by engineering change orders to be either added, deleted or renamed. Boolean equivalence tools are used between an old spin ASIC design and a new ASIC design netlist, as well as between the new ASIC design netlist and a new re-spin ASIC design to obtain failing boundary storage gate elements and perform one or more of adding, deleting or modifying or renaming all failing boundary storage gate elements, so they pass correspondence tests. Engineering change order scripts are automatically generated to indicate which storage logic gate elements are to be added, deleted or modified and the scripts are applied to the old ASIC design to obtain the new re-spin ASIC design, after which ASIC flow gate level fixes are applied to synthesized storage gate elements.

Owner:GLOBALFOUNDRIES INC

Multilayer film for medical solution pouches having reduced proficiency for forming bubbles

ActiveUS8808595B2Reducing and preventing presenceTest may passFilament/thread formingDomestic containersFoaming agentPolyamide

The present invention provides a multilayer film for forming medical solution pouches that help prevent or reduce the presence of bubbles or foam in the solution after heat sterilization. In particular, the present invention provides a multilayer film for forming medical solution pouches that are capable of passing the bubble test as set forth in the Chinese State Drug Package Container Material Standard No. YBB00112005. In particular, the present invention provides a multilayer film in which polyamide 612 or calcium stearate component has been incorporated as an anti-foaming agent. The presence of polyamide 612 or calcium stearate in one or more layers of the film helps prevent the formation of foam in the solution after heat sterilization.

Owner:CRYOVAC ILLC

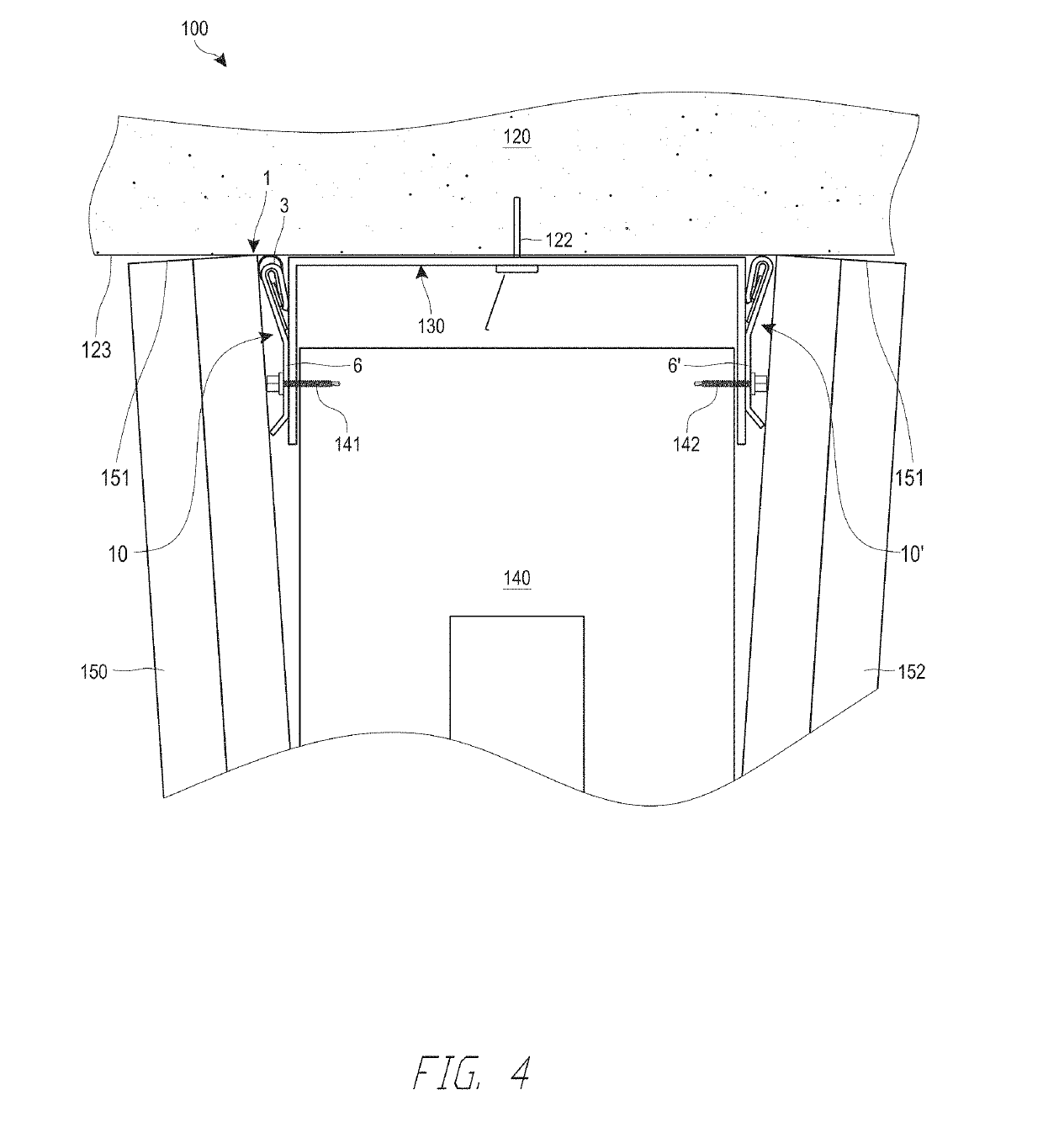

Corrosion resistant window shutter

InactiveUS7131241B2Test may passSignificant stressShutters/ movable grillesVentilation arrangementWindow shutterEngineering

Owner:BLACKWELL GROVER M +1

Multi-layer fire-rated joint component

ActiveUS10689842B2Open the deflection gapExcessive noiseWallsSynthetic resin layered productsSmoke EmissionJoint (building)

An improved fire-blocking gasket profile for a fire-rated joint, such as a head-of-wall assembly. Fire-rated joints are aimed at inhibiting or preventing fire, heat, or smoke from leaving one portion of a building and entering another portion of a building. Fire-rated joints can also accommodate movement between adjacent building structures, such as between a ceiling and the top of a wall. The improved fire-blocking gasket profile includes a first layer formed of an intumescent material, a second layer formed of a foil lining and a third layer formed of the vinyl profile. The vinyl profile includes an air gap with the intumescent material positioned therein. A vertical portion of the vinyl profile is positioned between a header track and a wallboard in the fire-rated joint. A horizontal portion of the vinyl profile is positioned at least partially within a deflection gap and sealingly engages with the ceiling.

Owner:CEMCO LLC

Method of making tough, flexible mats and tough, flexible mats

ActiveUS20050112978A1Promote recoveryHigh tensile strengthNatural cellulose pulp/paperSpecial paperGlass fiberFiber

Methods of making nonwoven mats having good strength after being scored and folded and particularly useful in making lightweight, compressible ceiling panels are disclosed. The mats also have excellent flame resistance. The mats include a blend comprising a major portion of glass fibers and a minor portion of man-made polymer fibers, the fibers being bound together with a cured binder containing a homopolymer or copolymer of polyacrylic acid and a polyol. The binder bonding the mat together can be cured to only a “B” stage to produce thermoformable mats or more fully cured to produce mats having the properties described above.

Owner:JOHNS MANVILLE INT INC

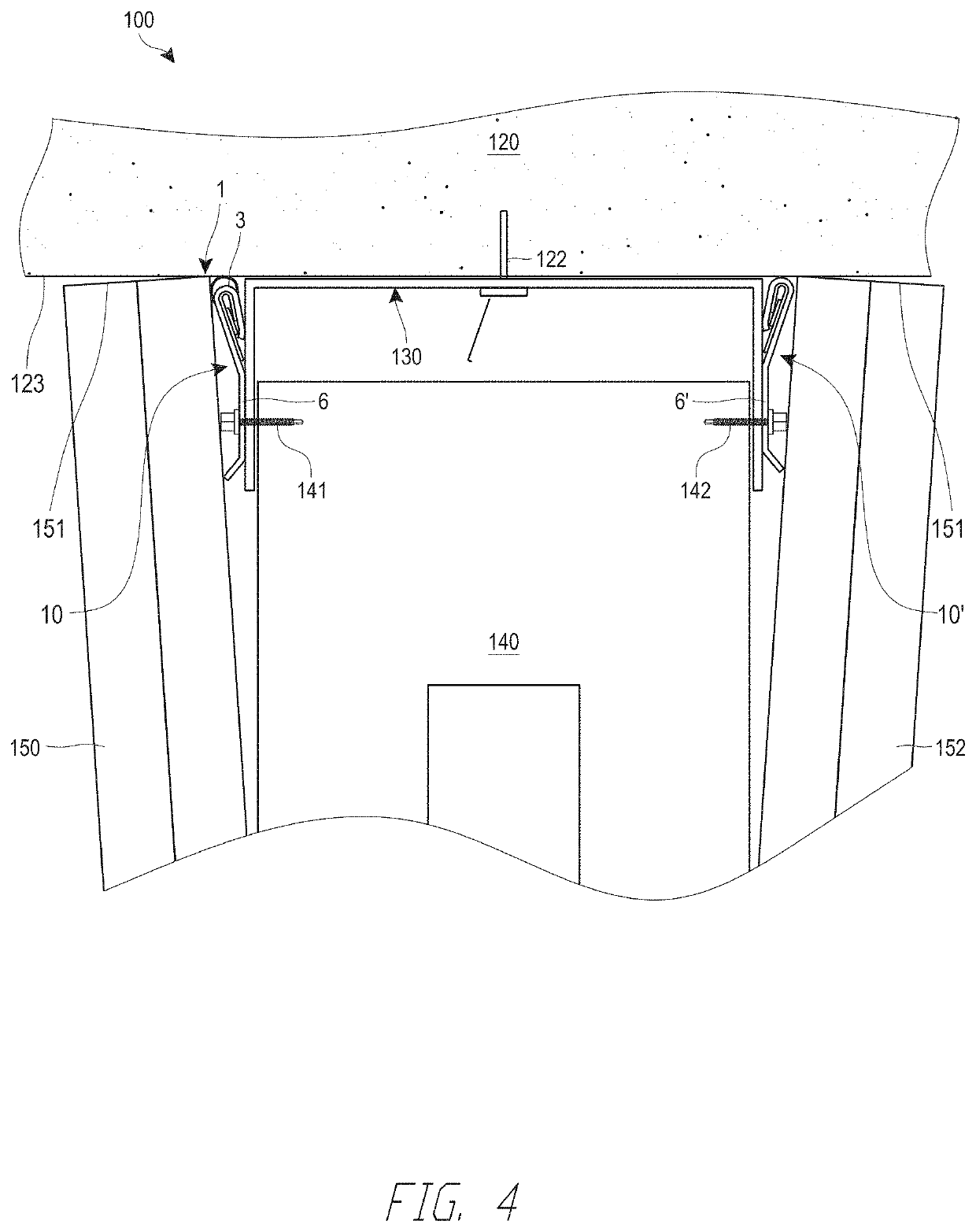

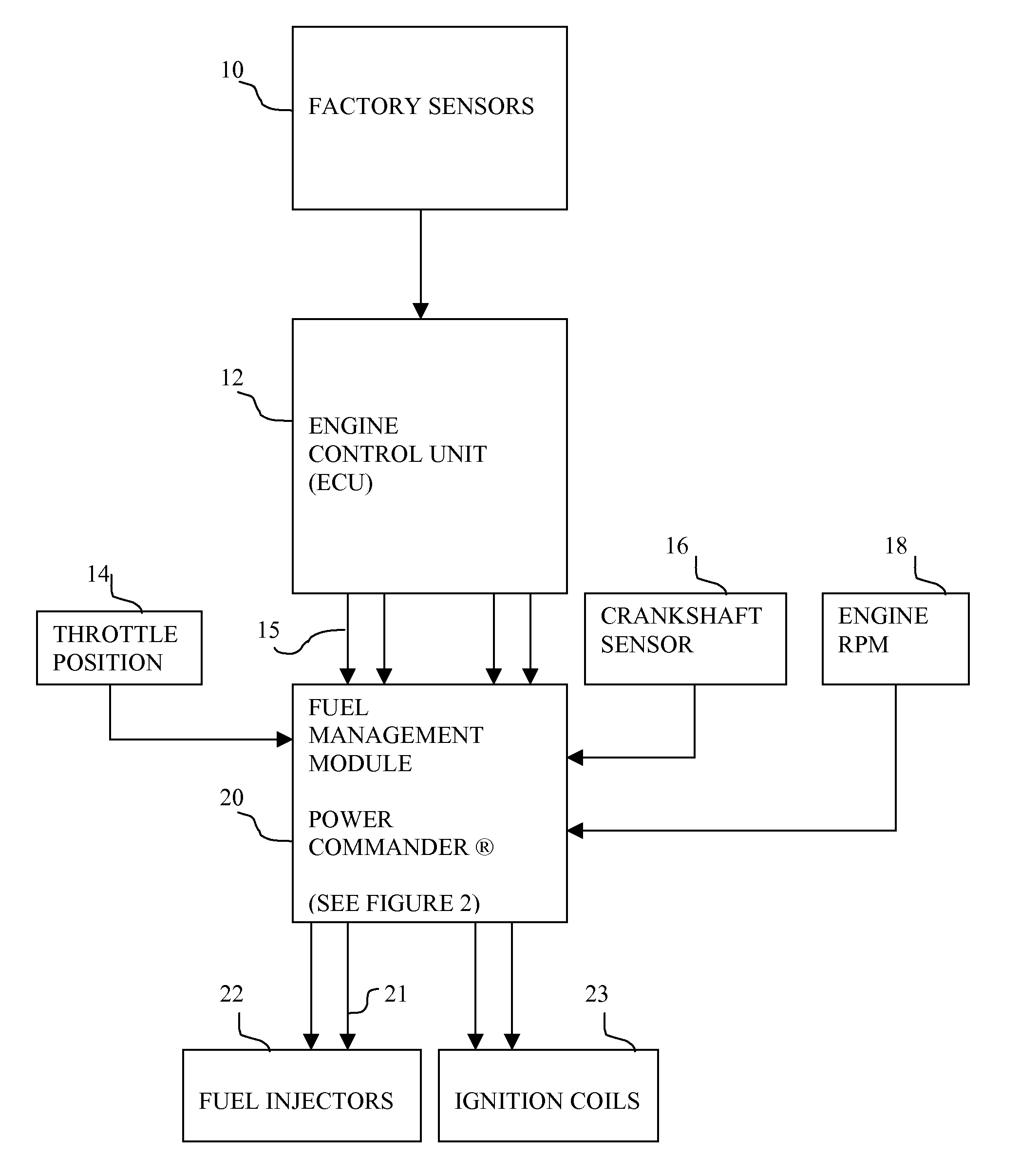

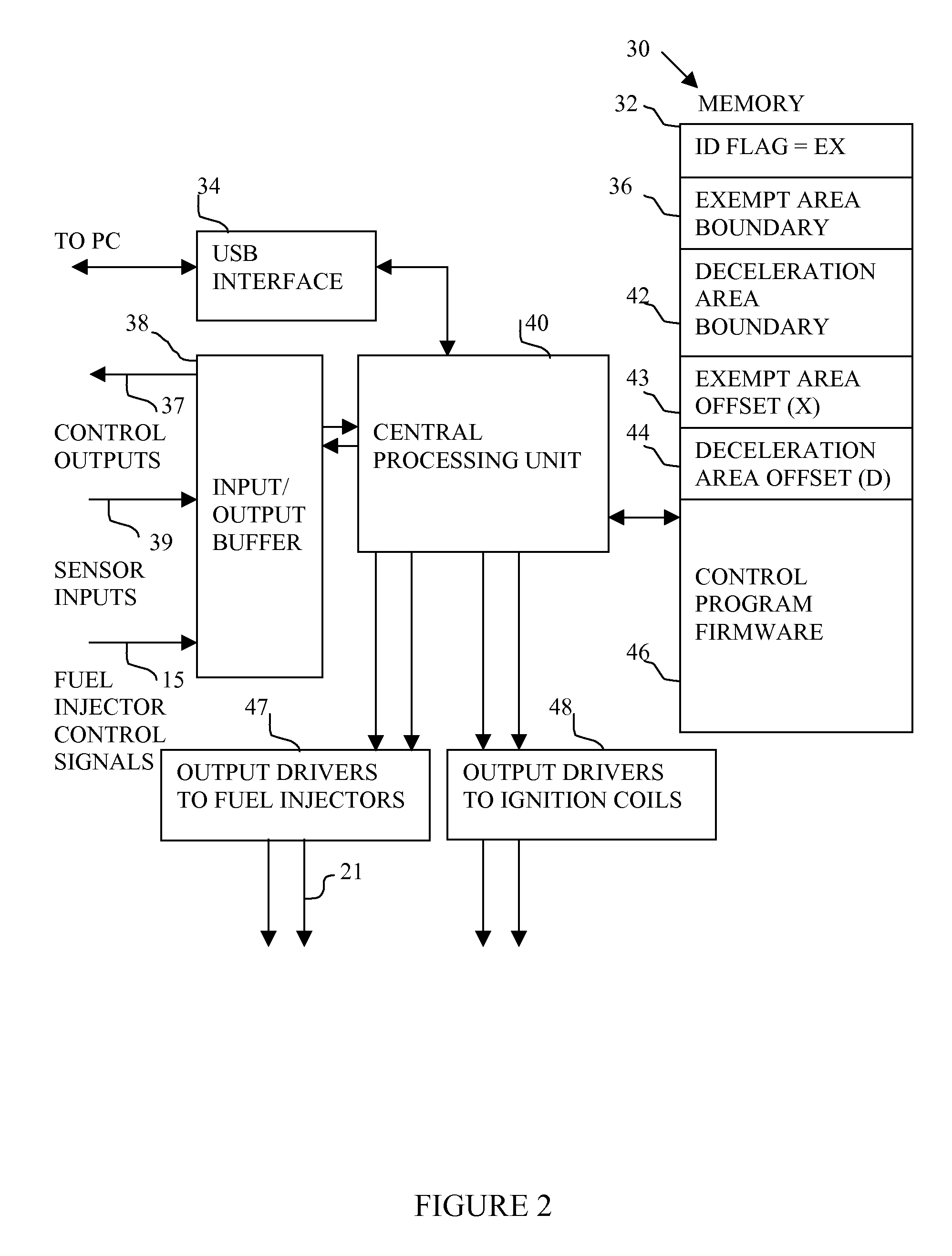

Fuel injection control system with exempt area of fuel map

InactiveUS20090093941A1Increase vehicle emissionAccelerate emissionsAnalogue computers for vehiclesElectrical controlControl systemManagement system

A fuel management system for fuel injected vehicles permits a user to modify vehicle performance without exceeding acceptable standards for vehicle emissions. A portion of the fuel management system fuel map is designated as an exempt area in which the user is not permitted to modify the fuel offset values.

Owner:DYNOJET RES

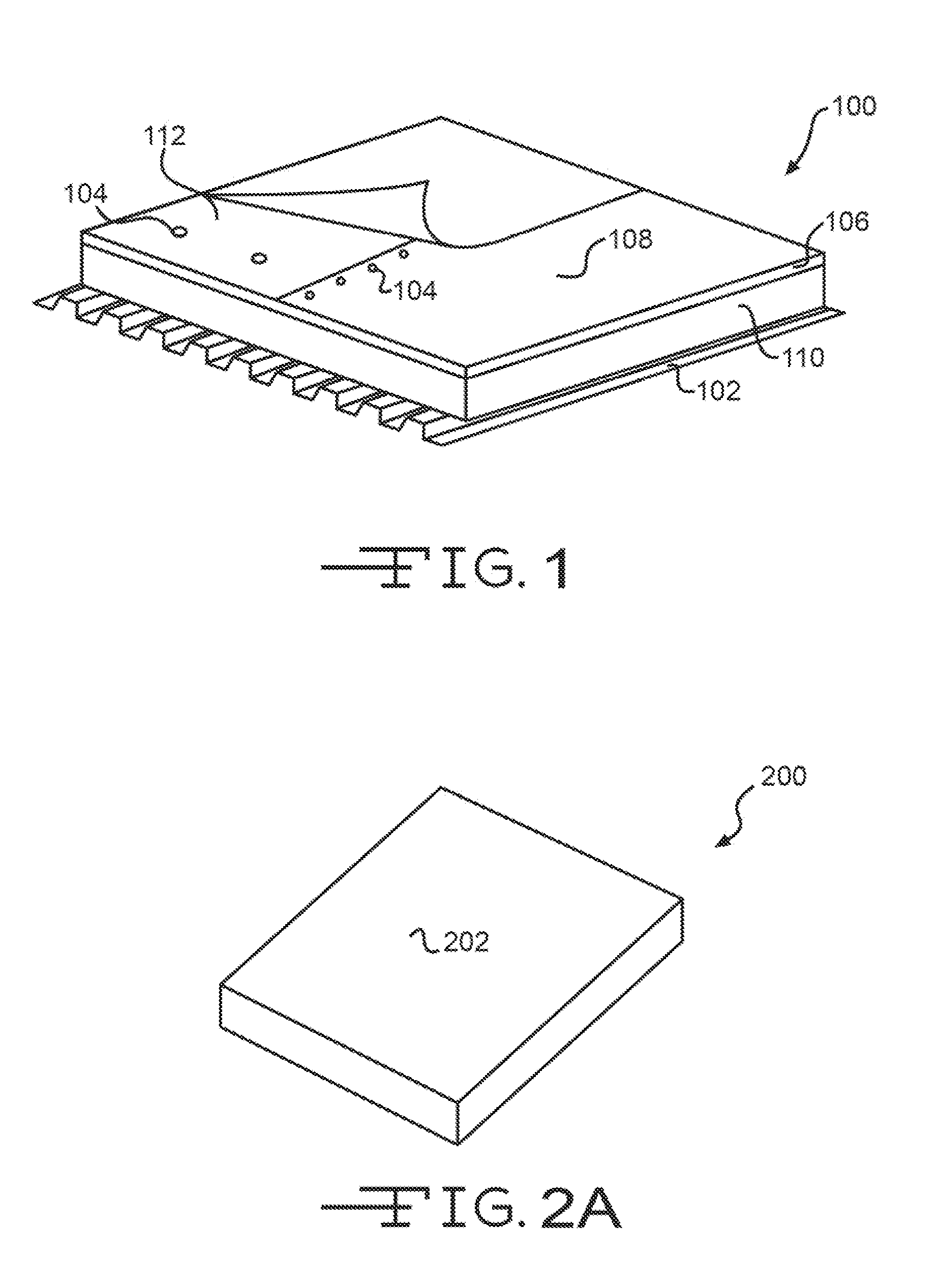

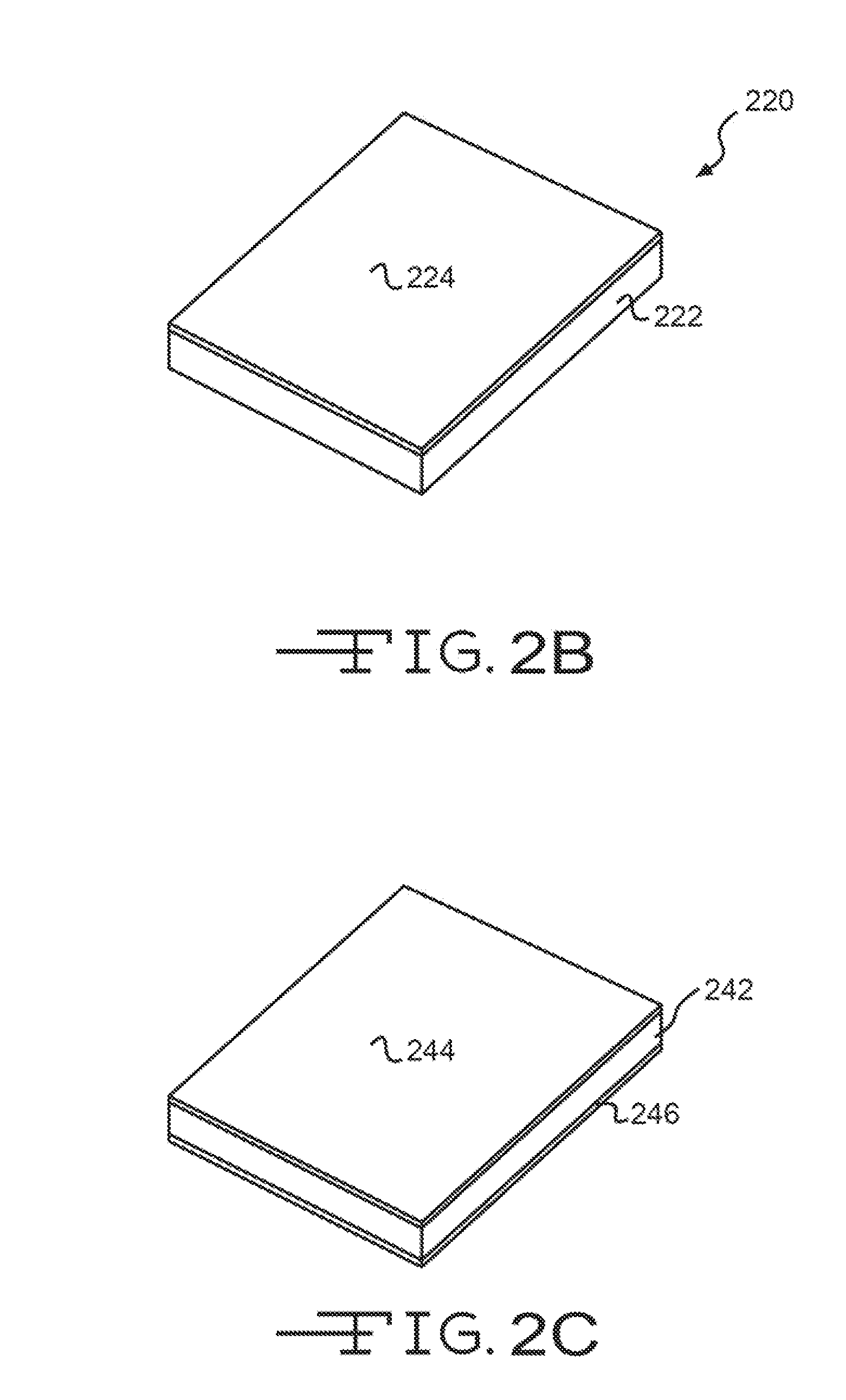

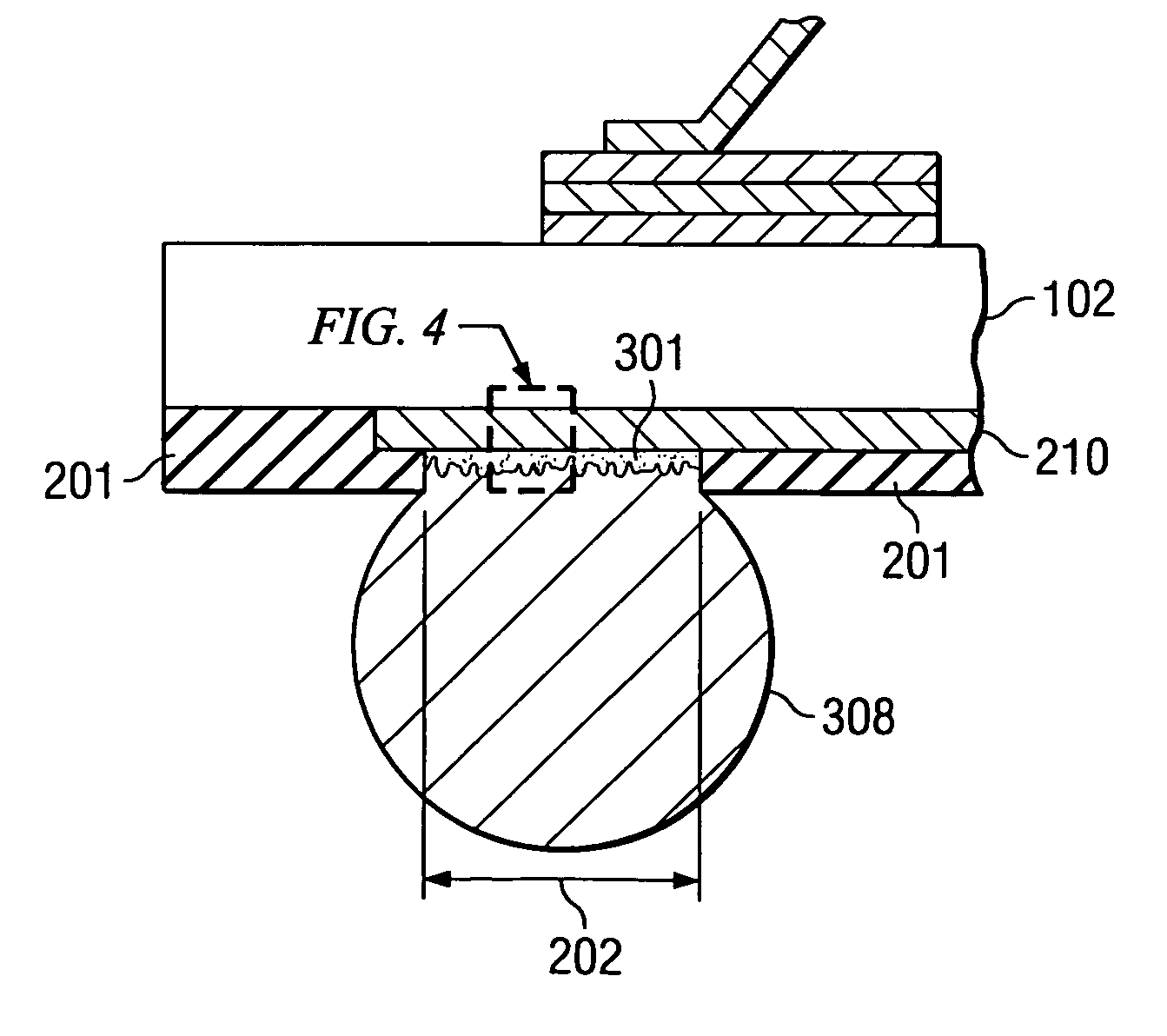

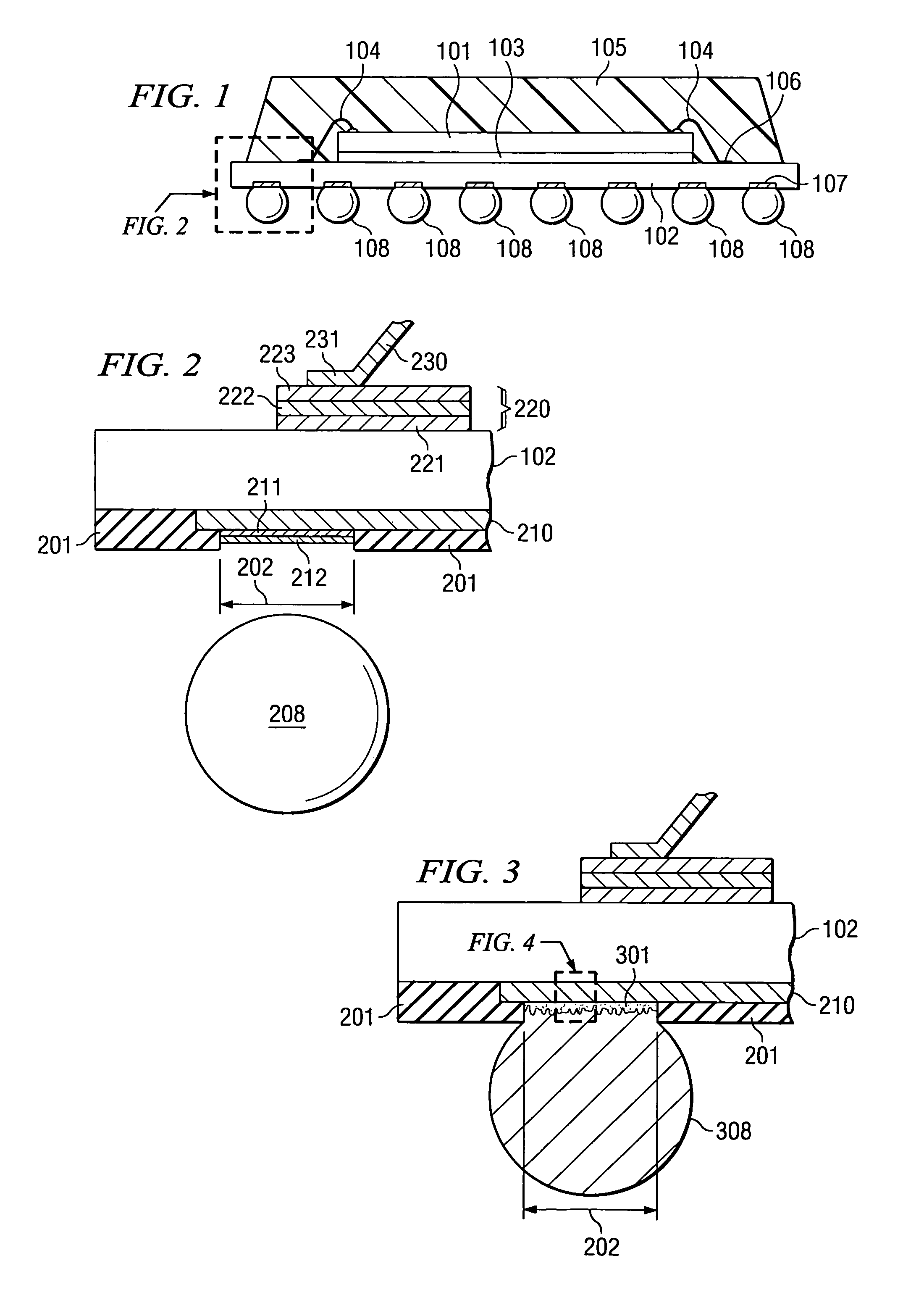

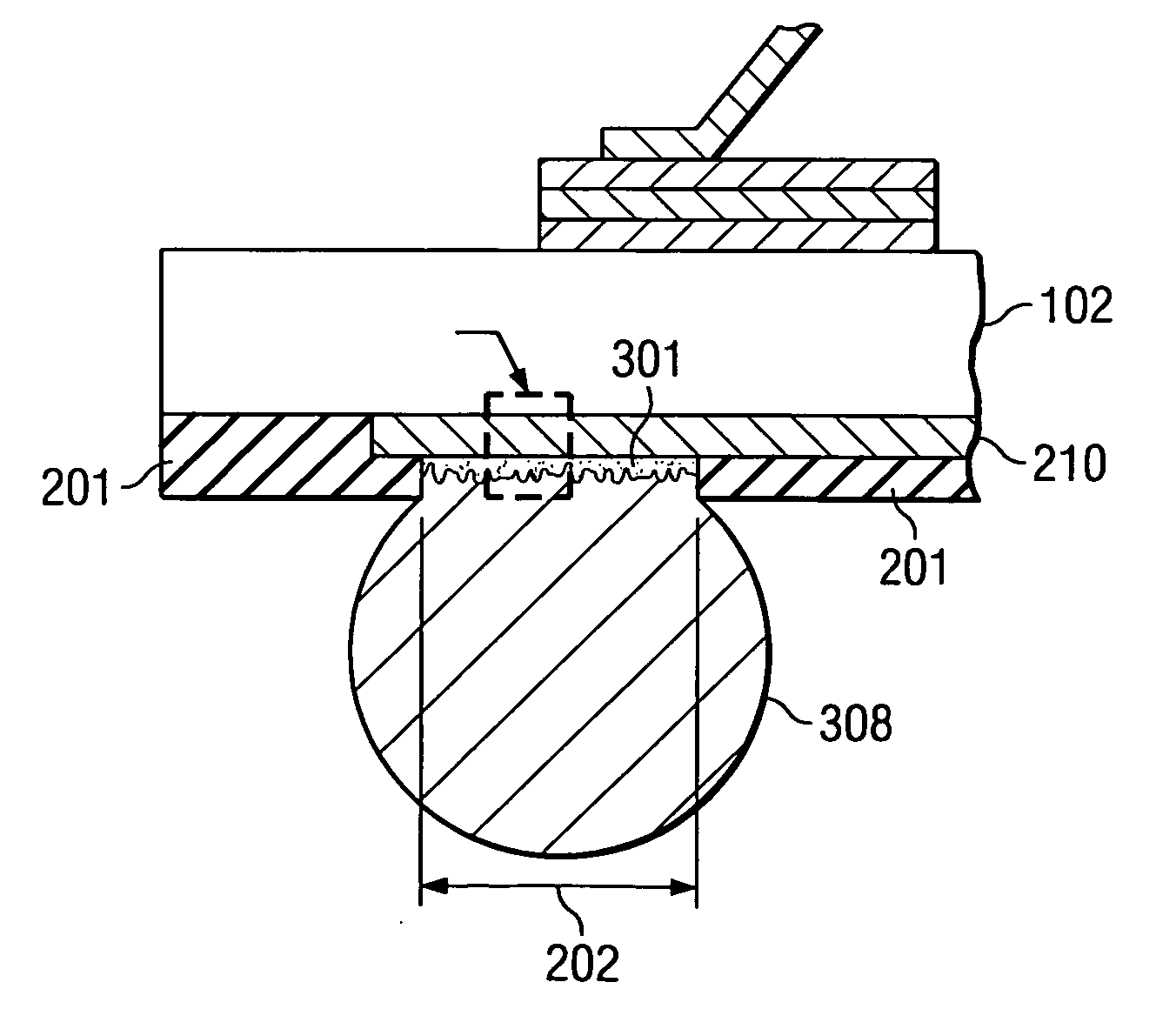

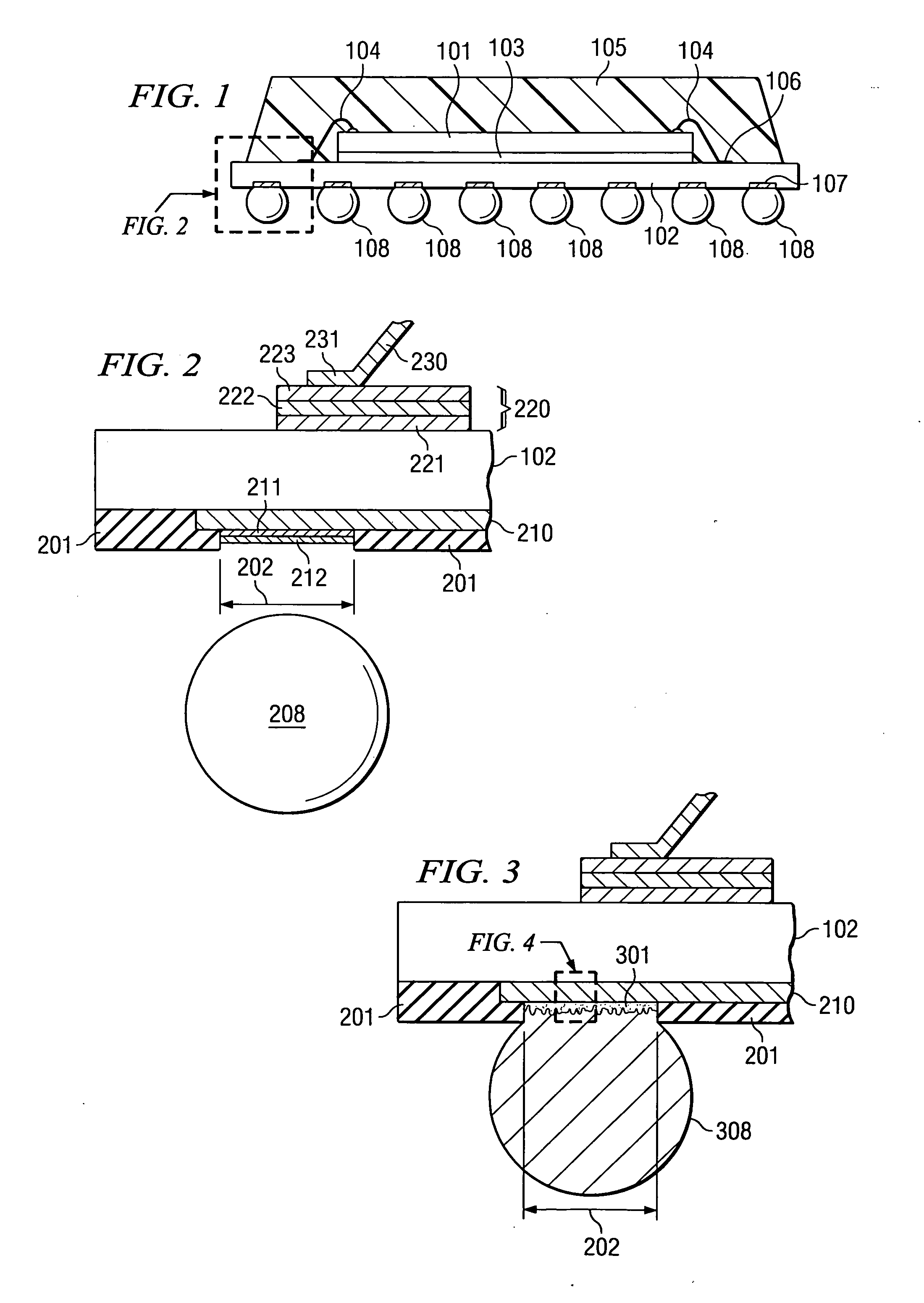

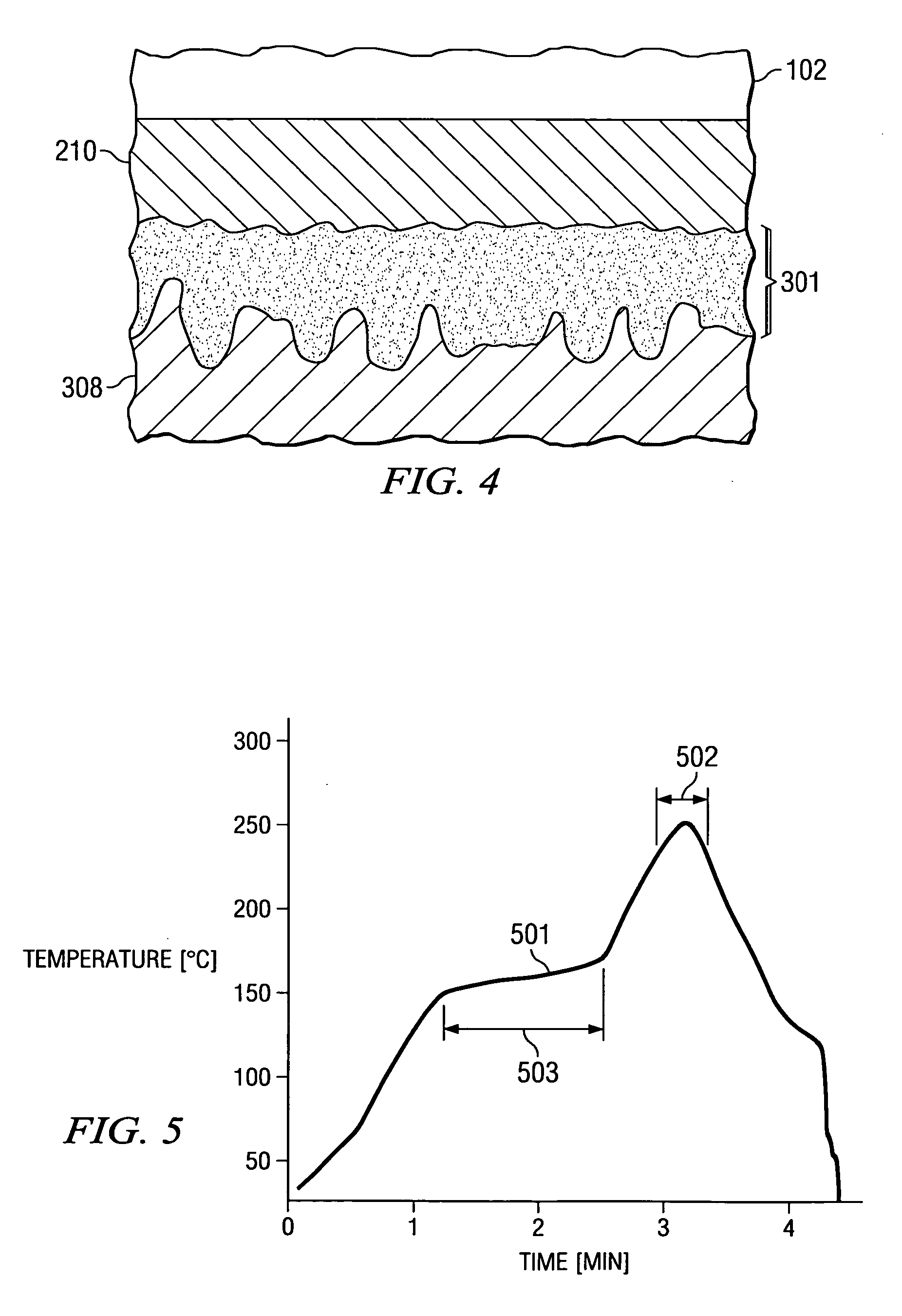

Semiconductor device with improved contacts

ActiveUS7233074B2Test may passImprove performanceSemiconductor/solid-state device detailsSolid-state devicesContact padAlloy

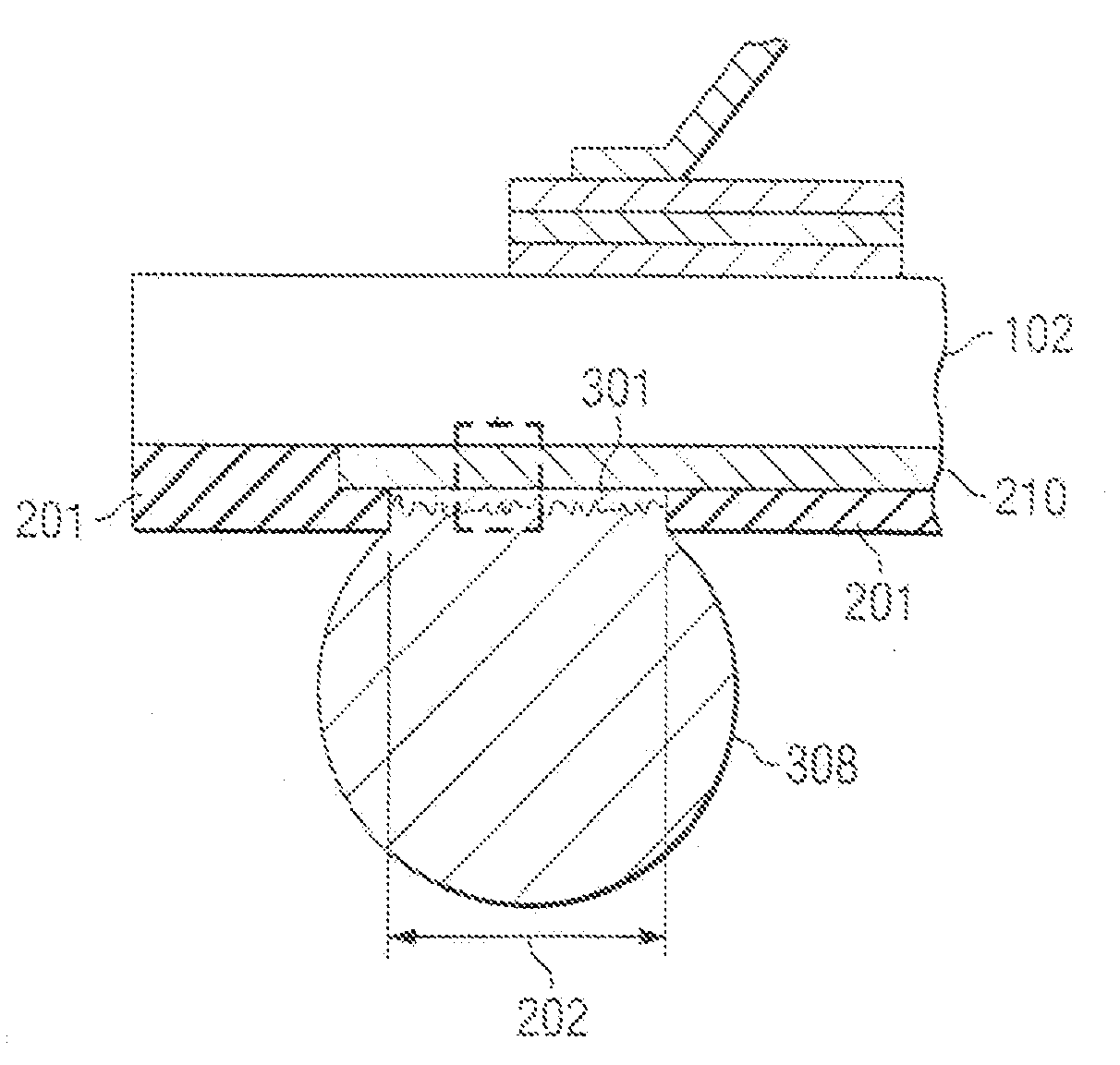

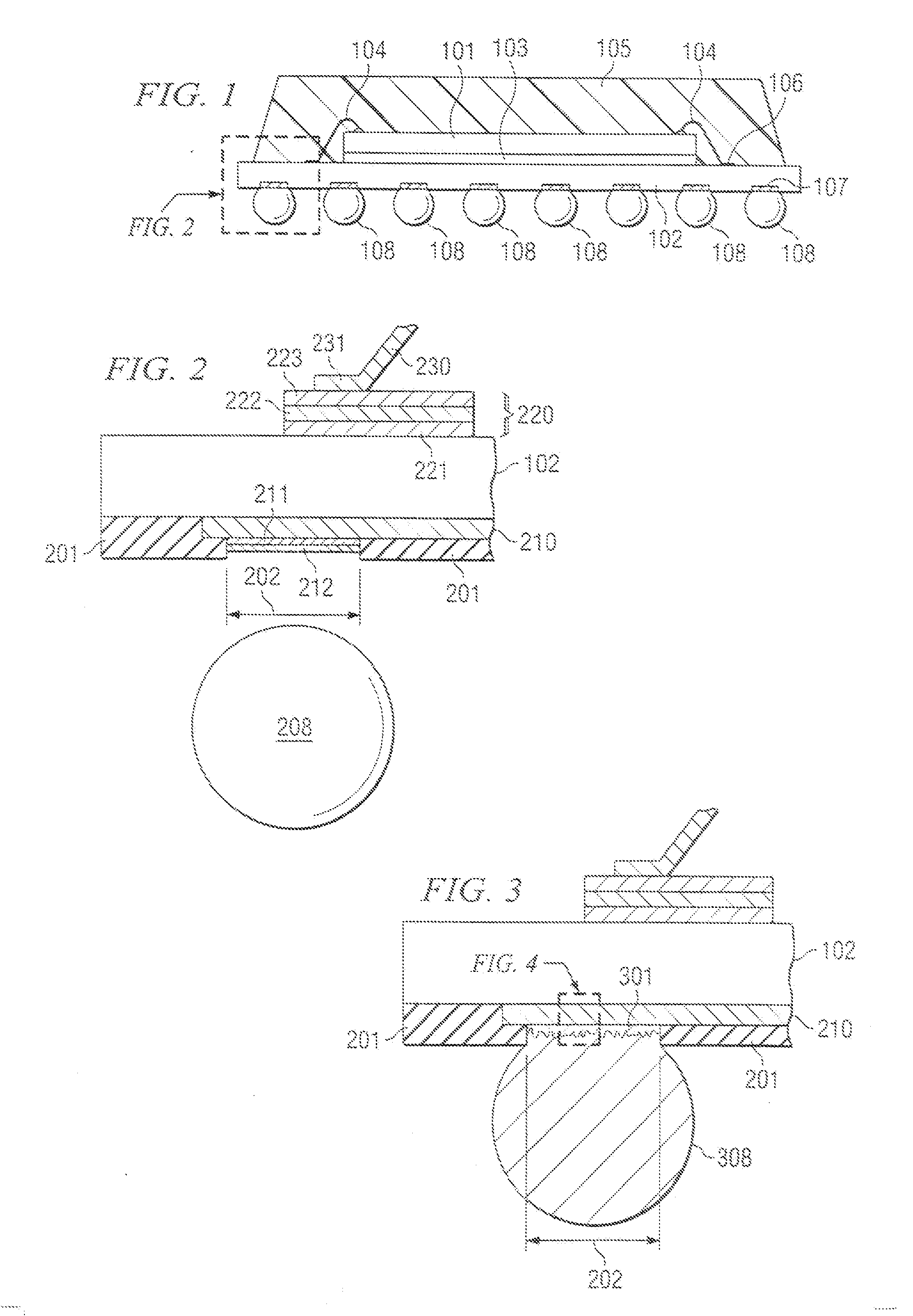

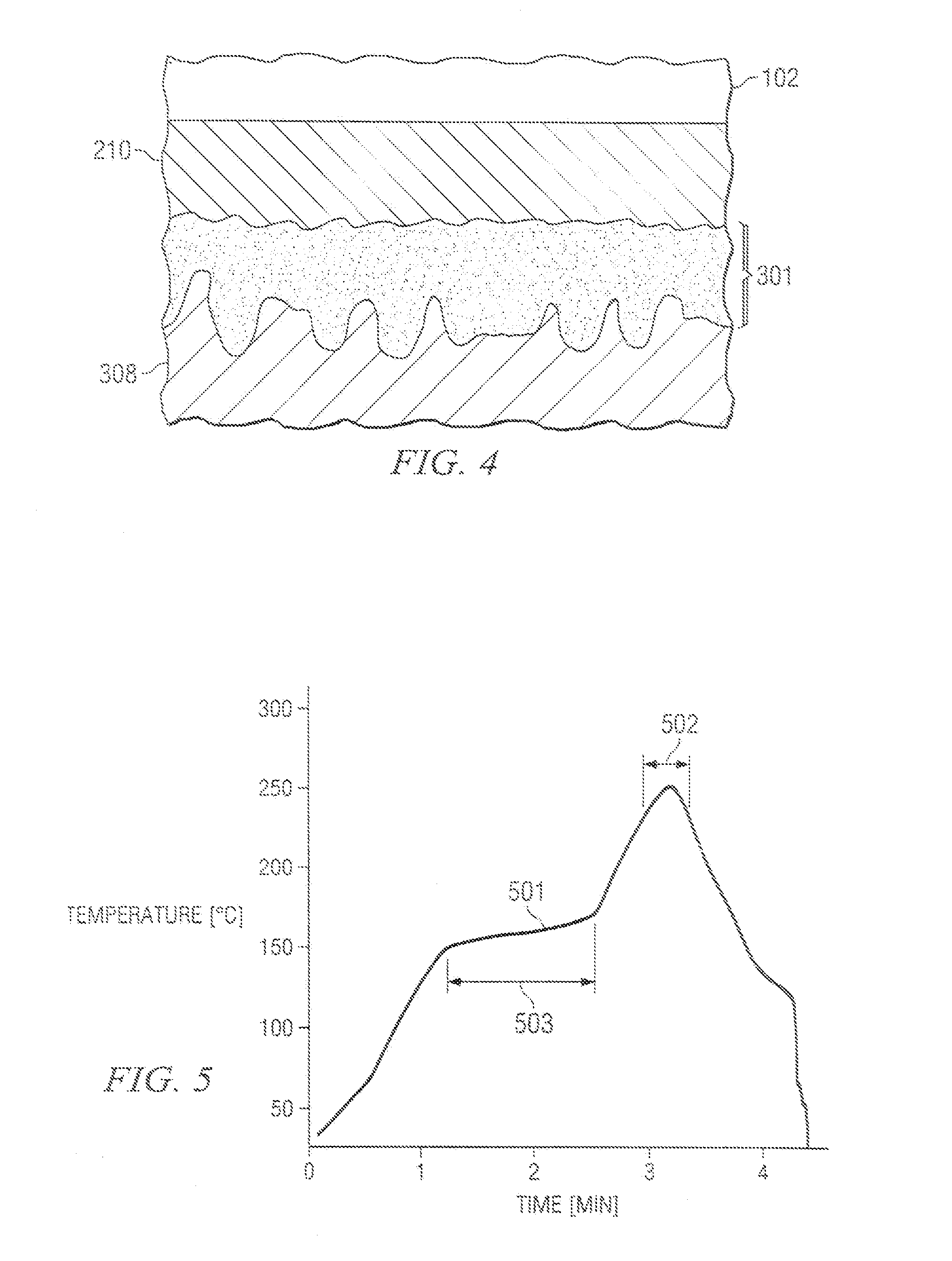

A device with a solder joint made of a copper contact pad (210) of certain area (202) and an alloy layer (301) metallurgically attached to the copper pad across the pad area. The alloy layer contains copper / tin alloys, which include Cu6Sn5 intermetallic compound, and nickel / copper / tin alloys, which include (Ni,Cu)6Sn5 intermetallic compound. A solder element (308) including tin is metallurgically attached to the alloy layer across the pad area. No fraction of the original thin nickel layer is left after the reflow process. Copper / tin alloys help to improve the drop test performance, nickel / copper / tin alloys help to improve the life test performance.

Owner:TEXAS INSTR INC

Fire resistant composite boards and methods

ActiveUS9605433B2Improve fire resistancePrevent wind upliftRoof covering using slabs/sheetsBuilding roofsFire resistanceCoating

Embodiments of the invention provide roofing boards and roofing systems having improved fire resistance properties and methods related to the same. According to one aspect, a roofing system is provided. The roofing system includes roofing panels positioned atop structural support members to form a roof deck. Roofing boards are positioned atop the roof deck and coupled thereto and a roofing membrane is positioned atop the roofing boards and coupled therewith. The roofing boards include a coating of a mineral based material applied to one or more surfaces in an amount between the range of about 0.10 lbs / ft2 and about 0.70 lbs / ft2. The mineral based material coating enables the roofing boards to pass the UL 790 class A tests, such as the burning brand test.

Owner:JOHNS MANVILLE CORP

Water-free, emulsifier-free, and preservative-free vehicle for active ingredients

A vehicle for carrying active ingredients, wherein the vehicle is water-free, emulsifier-free, and preservative free. Preferably, the vehicle is used to carry a skin care formulation for treating skin conditions that provides noticeable results within two weeks or less.

Owner:GALDERISI ALYSON

Over-current protection device

ActiveUS9997906B1Increase currentImprove efficiencyHeat-exchange elementsResistor manufactureFluoropolymerPolymer chemistry

An over-current protection device comprises first and second electrode layers and a PTC material layer laminated therebetween. The PTC material layer has a resistivity less than 0.05 Ω·cm and comprises a polymer matrix, a conductive ceramic filler and a carbon-containing conductive filler. The polymer matrix comprises a fluoropolymer having a melting point higher than 150° C. and comprises 50-60% by volume of the PTC material layer. The conductive ceramic filler having a resistivity less than 500μΩ·cm is dispersed in the polymer matrix and comprises 40-45% by volume of the PTC material layer. The carbon-containing conductive filler is dispersed in the polymer matrix and comprises 0.5-5% by volume of the PTC material layer. At 25° C., a ratio of a hold current to an area of the over-current protection device is 0.21-0.3 A / mm2, and a ratio of an endurable power to the area of the over-current protection device is 4.8-7.2 W / mm2.

Owner:POLYTRONICS TECH

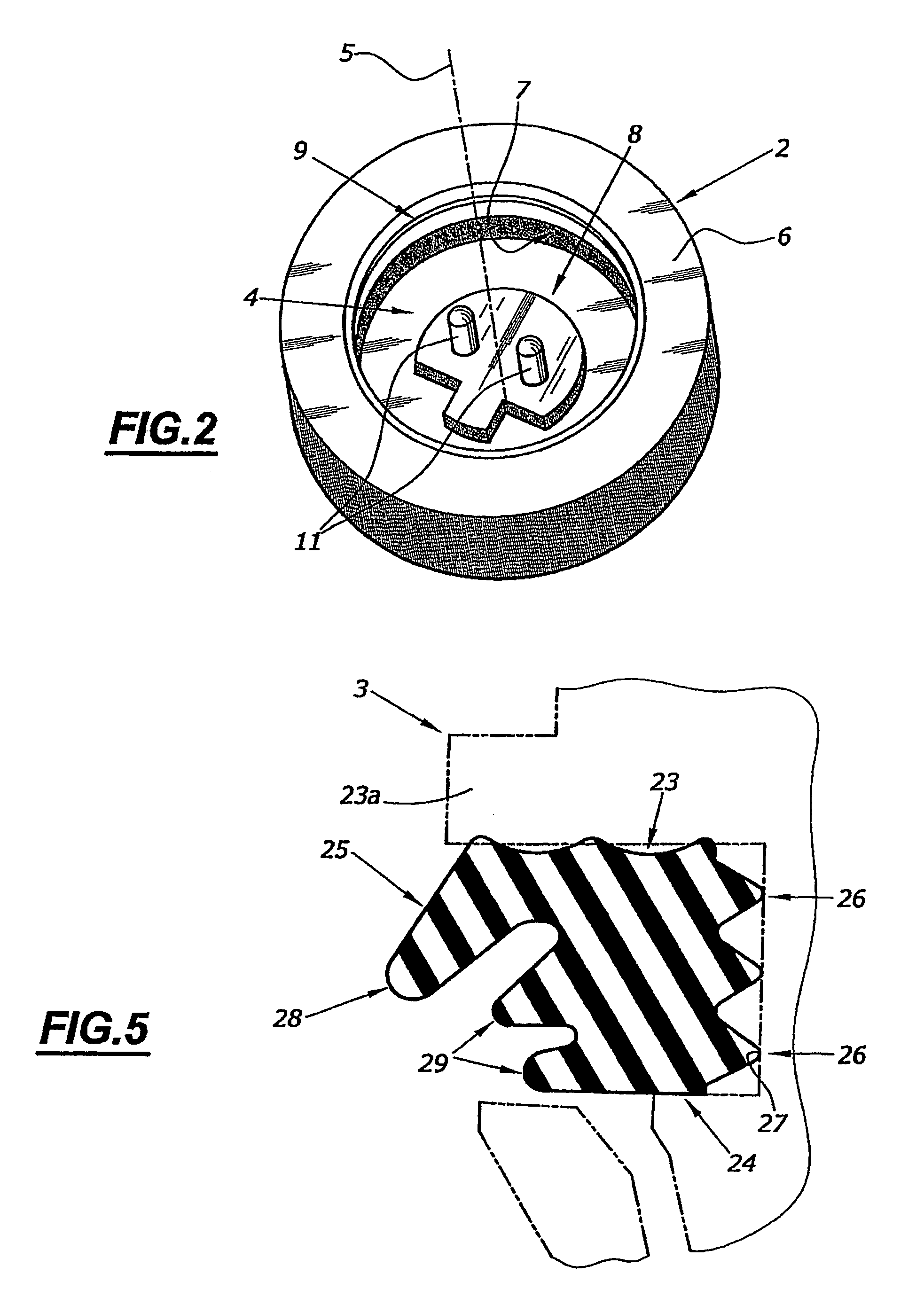

Electrical connector assembly for an airbag ignitor

ActiveUS7997940B2Prevent moistureTest may passVehicle connectorsCouplings bases/casesEngineeringAirbag

An electrical connector assembly for an airbag ignitor including a) a socket member having a mating aperture, an internal side wall portion having a locking slot, and a bottom wall portion having at least one pin contact extending therefrom; and b) a plug member adapted for mating with the socket member by insertion in the mating aperture and including a plug body and a plug nose, the plug nose including (i) at least one socket contact aperture for receiving a socket contact corresponding to a respective pin contact, and (ii) a resilient locking device adapted for engaging in the locking slot and locking the plug member in the socket member, wherein the plug member includes an annular gasket seal around the plug nose and under the plug body to seal the aperture between the socket member and the plug member when they mate.

Owner:APTIV TECH LTD

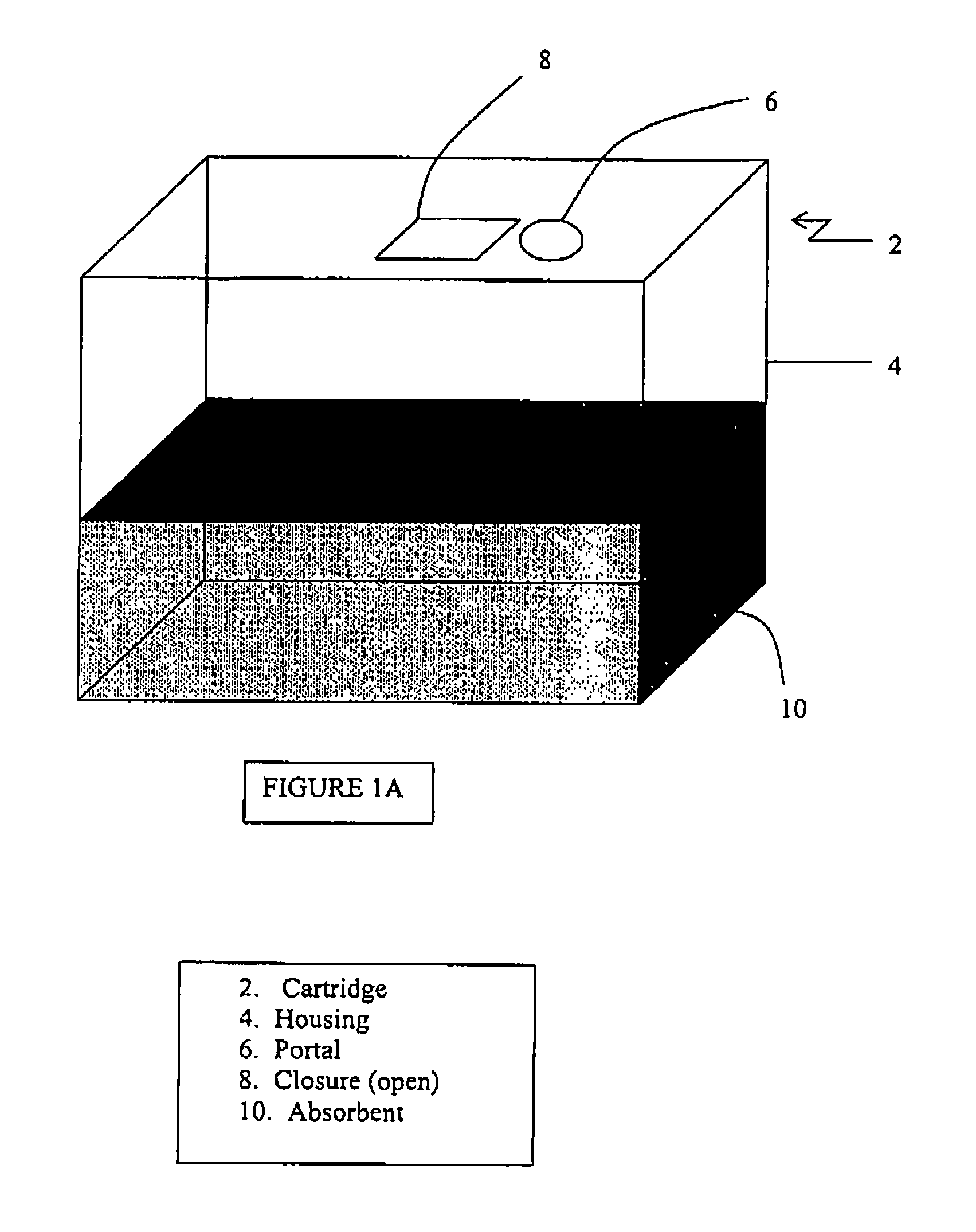

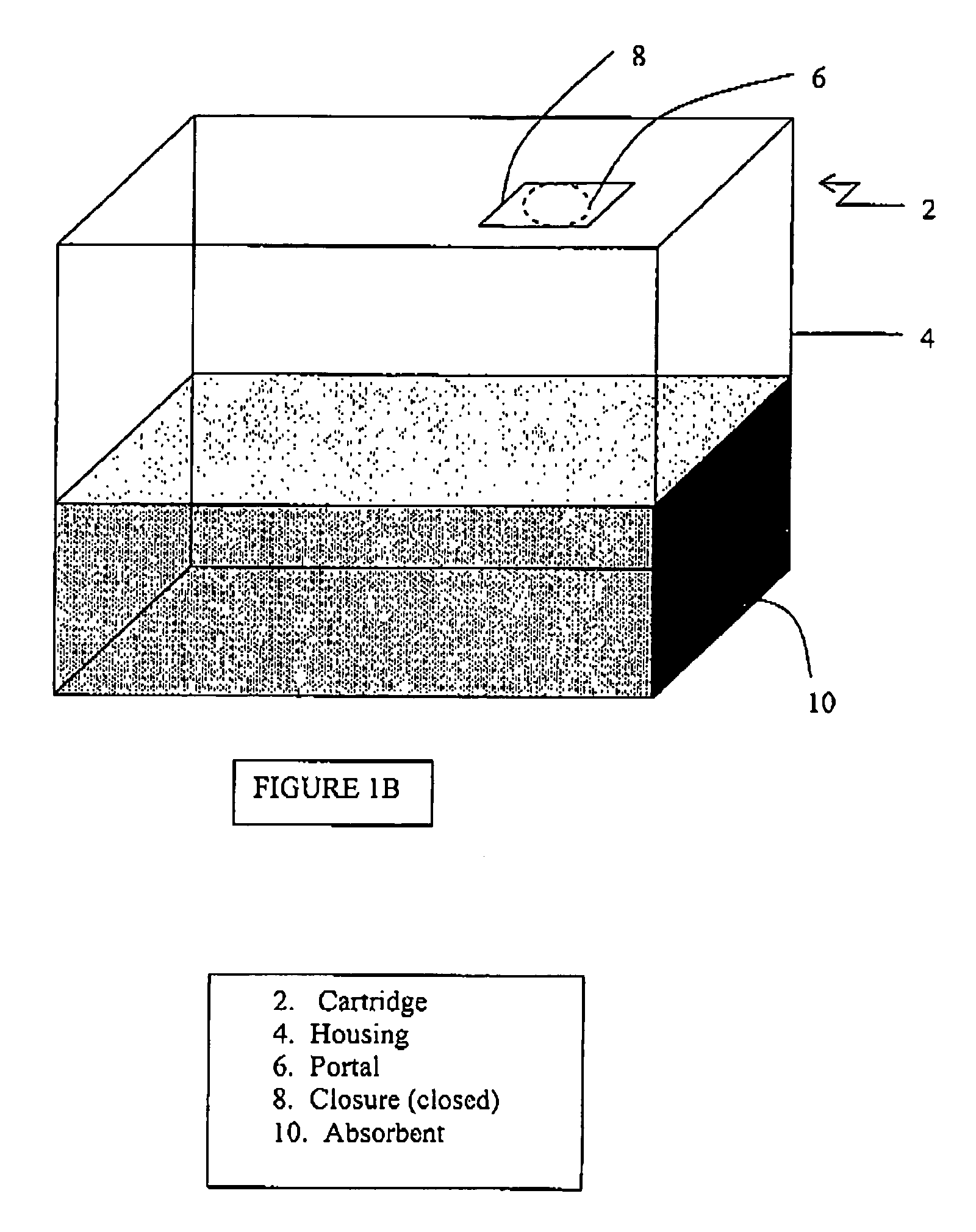

Ink disposal in cartridges

InactiveUS6999702B2Avoid environmentReduce flowElectrographic process apparatusDevelopersAbsorbent materialWaste management

An apparatus for assisting in the removal or waste or excess ink and a method for disposal of ink from electrophotographic printers comprises providing electrophotographic ink from a source, combining the ink with an absorbable material in a container to form a solid within the container, and closing the container so that the container with the solid inside may be disposed of without ink flowing from the container.

Owner:HEWLETT PACKARD DEV CO LP

Method of improving rust inhibition of a lubricating oil

ActiveUS20090042754A1Improve rust resistanceTest may passGroup 5/15 element organic compoundsAdditivesSolubilityAniline point

A method of improving the rust inhibition of a lubricating oil by incorporating a solubility improver having an aniline point less than 10° C. A method of improving the rust inhibition of a lubricating oil by incorporating a solubility improver to enable the lubricating oil to meet the requirements of the MIL-PRF-17331J specification. A method of improving the rust inhibition of a lubricating oil by incorporating a solubility improver, a mixture of mono and diacid amine phosphate salts, and a alkenyl succinic compound into the lubricating oil.

Owner:CHEVROU USA INC

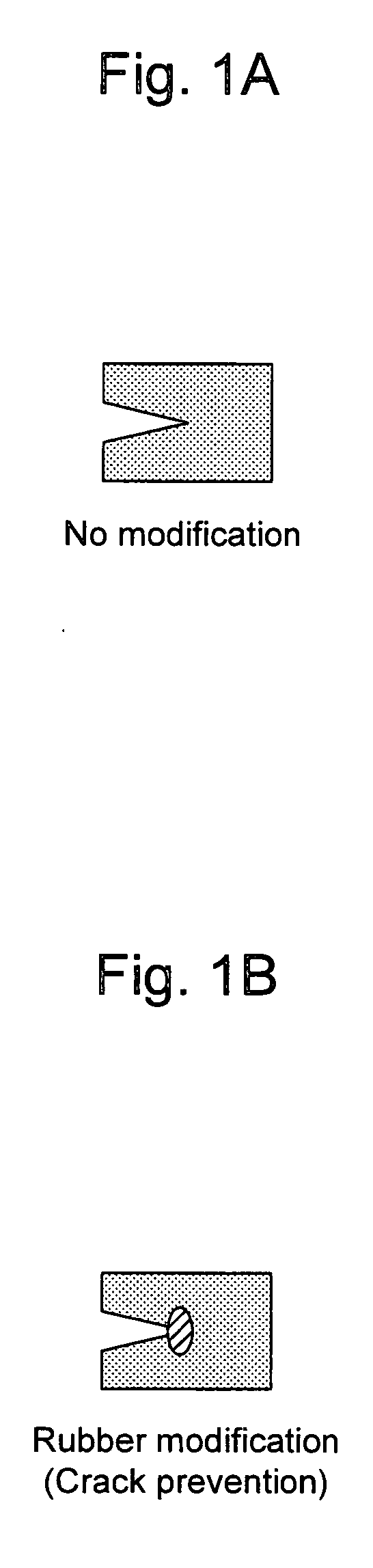

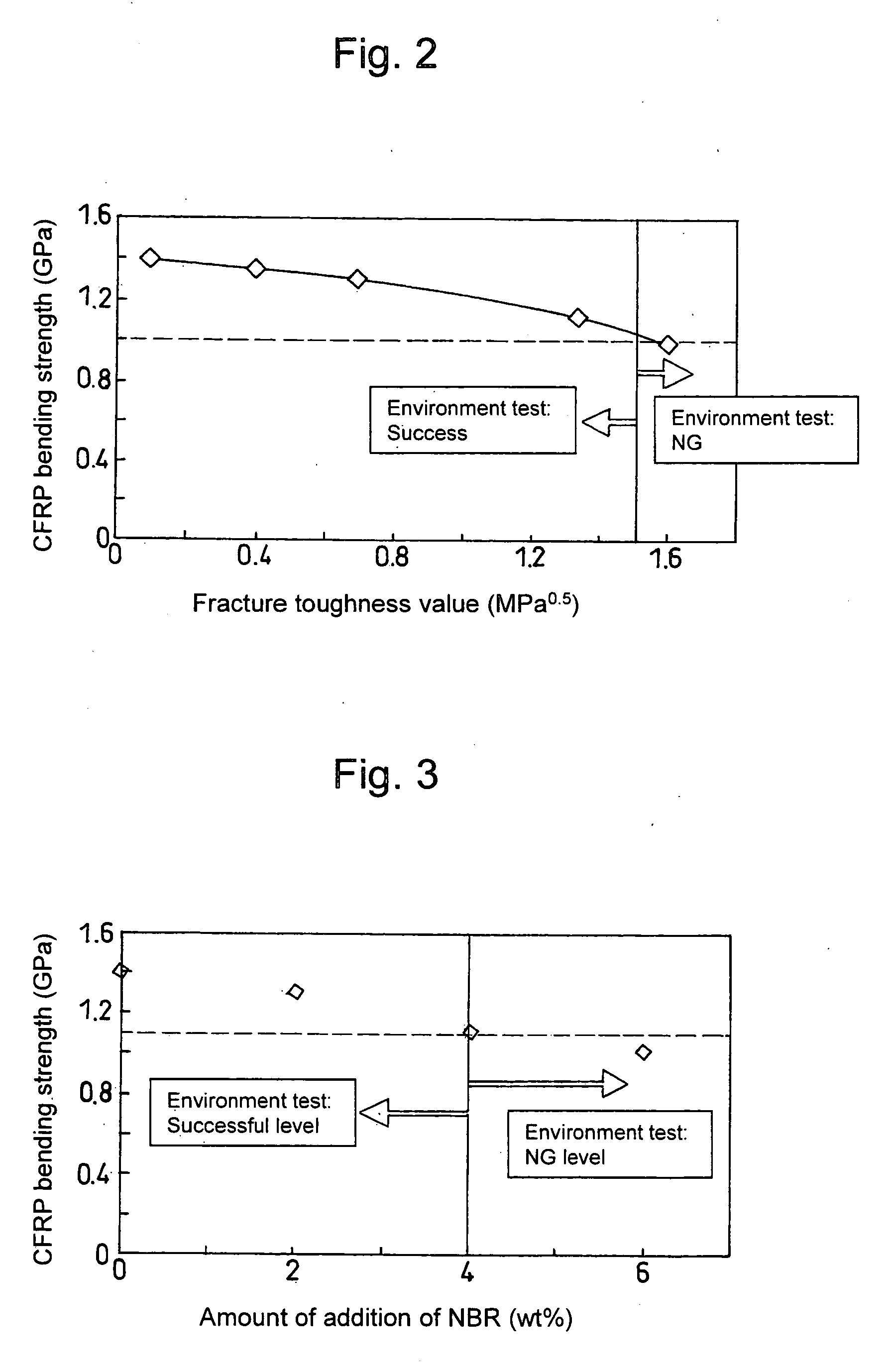

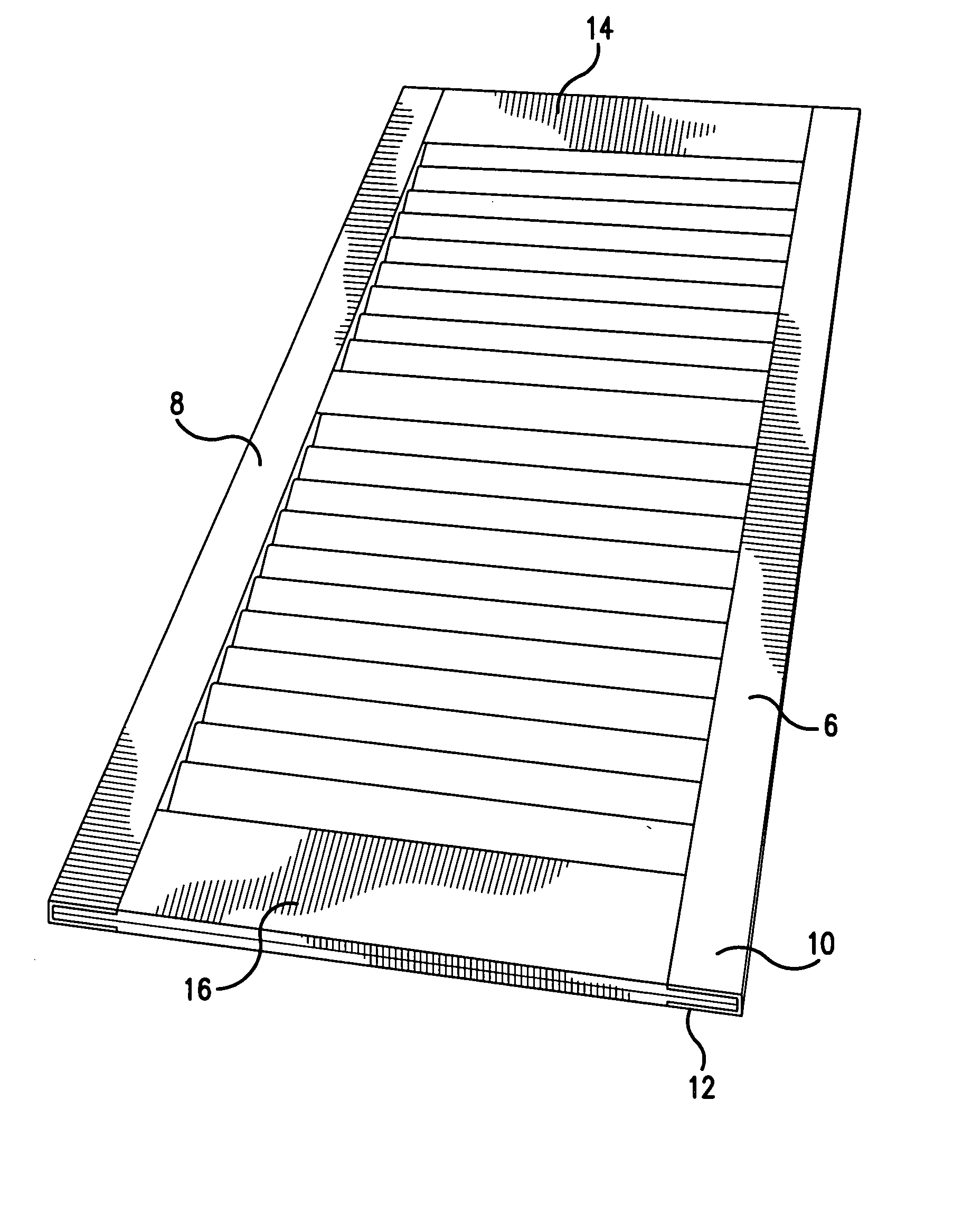

Gas Tank and Method for Producing the Same

ActiveUS20090255939A1Increase resistanceHigh strengthCeramic shaping apparatusThin material handlingElastomerFiber bundle

According to the present invention, a gas tank having a gas-barrier inner shell and an outer shell that is formed so as to cover the inner shell and is made of a pressure-resistant FRP, such outer shell comprising reinforcing fiber bundles (A), a thermosetting resin (B), and an elastomer particles and / or thermoplastic resin particles (C), provided that elastomer particles and / or thermoplastic resin particles (C) that have been dispersed in a thermosetting resin (B) exist in reinforcing fiber bundles (A), is provided. Such gas tank is excellent in strength and heat resistance and has suppressed gas permeability.

Owner:TOYOTA JIDOSHA KK +1

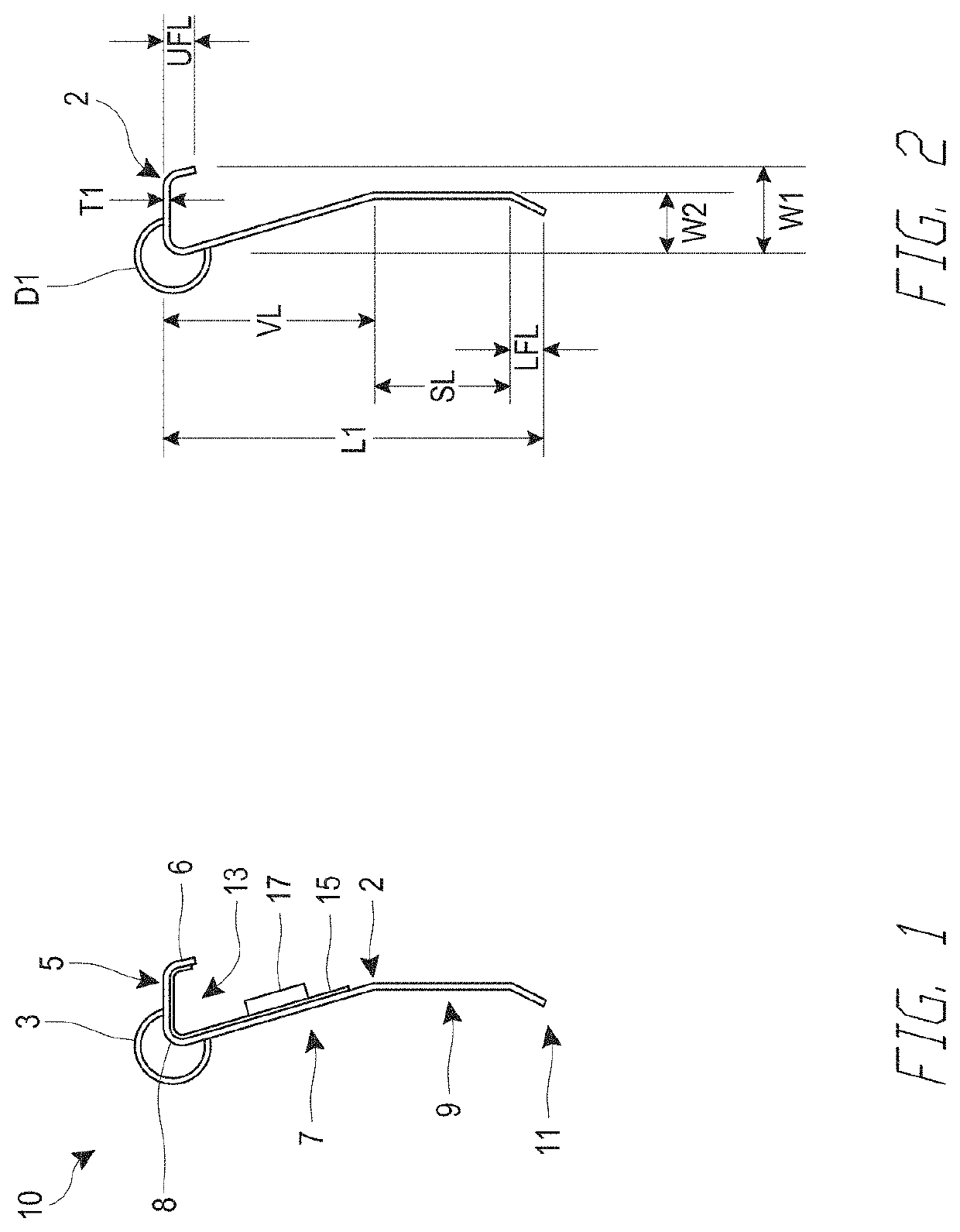

Corrosion resistant window shutter

InactiveUS20050022463A1Test may passSignificant stressBuilding roofsShutters/ movable grillesWindow shutterEngineering

A window shutter has corrosion resistant stiles with a non-metallic core and louvers, and non-metallic top and bottom rails. The shutter is resistant to the adverse effects of sunlight, humidity, rain and wind, and will retard flying objects, and will pass commonly used missile tests for building materials. The resulting shutter will also withstand substantial stresses from wind loads, so as to perform satisfactorily in wind load tests. The window covering of the invention is substantially maintenance free.

Owner:BLACKWELL GROVER M +1

Semiconductor device having improved mechanical and thermal reliability

ActiveUS20070035023A1Test may passImprove performanceSemiconductor/solid-state device detailsSolid-state devicesContact padDevice material

A device with a solder joint made of a copper contact pad (210) of certain area (202) and an alloy layer (301) metallurgically attached to the copper pad across the pad area. The alloy layer contains copper / tin alloys, which include Cu6Sn5 intermetallic compound, and nickel / copper / tin alloys, which include (Ni,Cu)6Sn5 intermetallic compound. A solder element (308) including tin is metallurgically attached to the alloy layer across the pad area. No fraction of the original thin nickel layer is left after the reflow process. Copper / tin alloys help to improve the drop test performance, nickel / copper / tin alloys help to improve the life test performance.

Owner:TEXAS INSTR INC

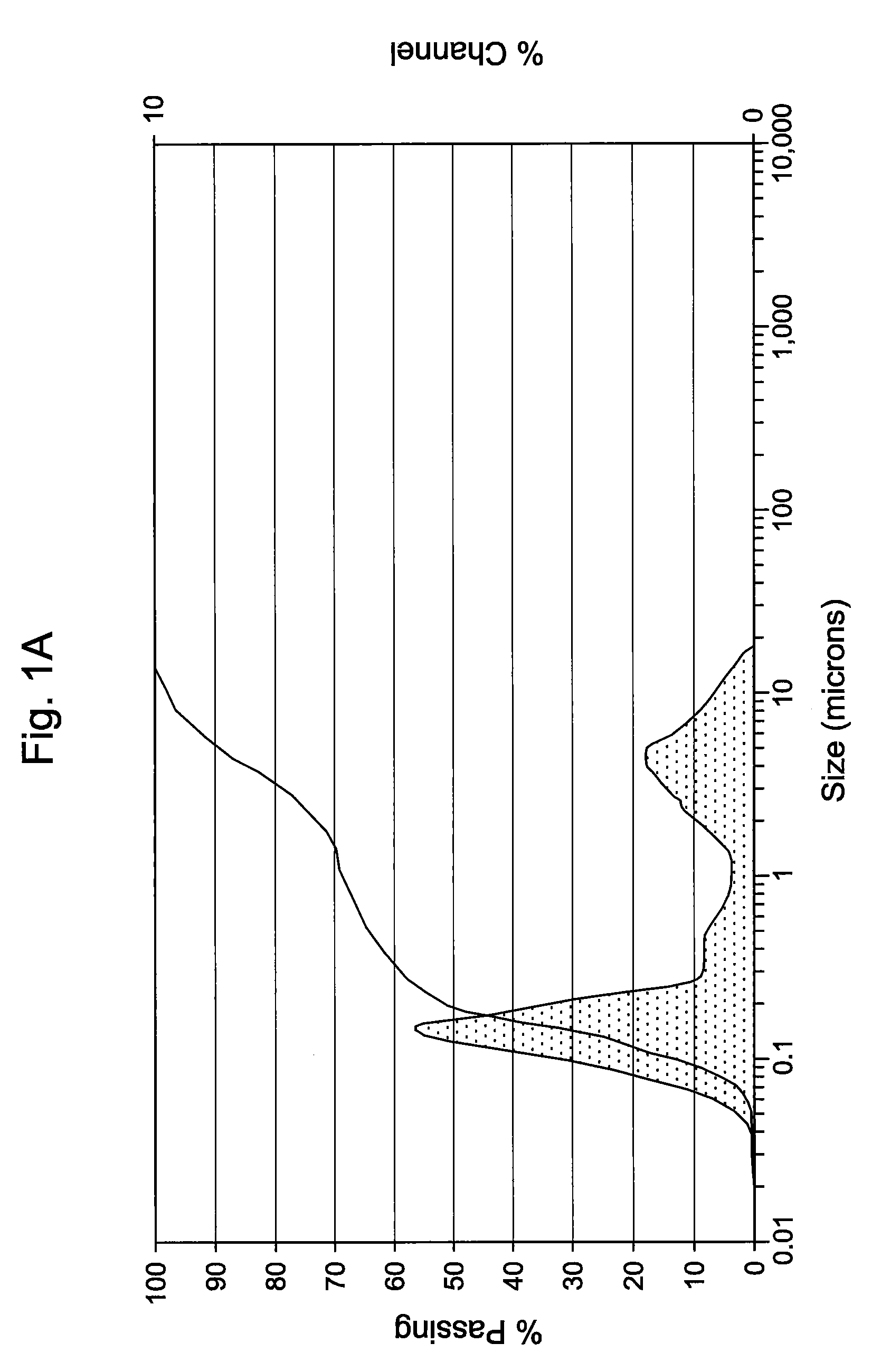

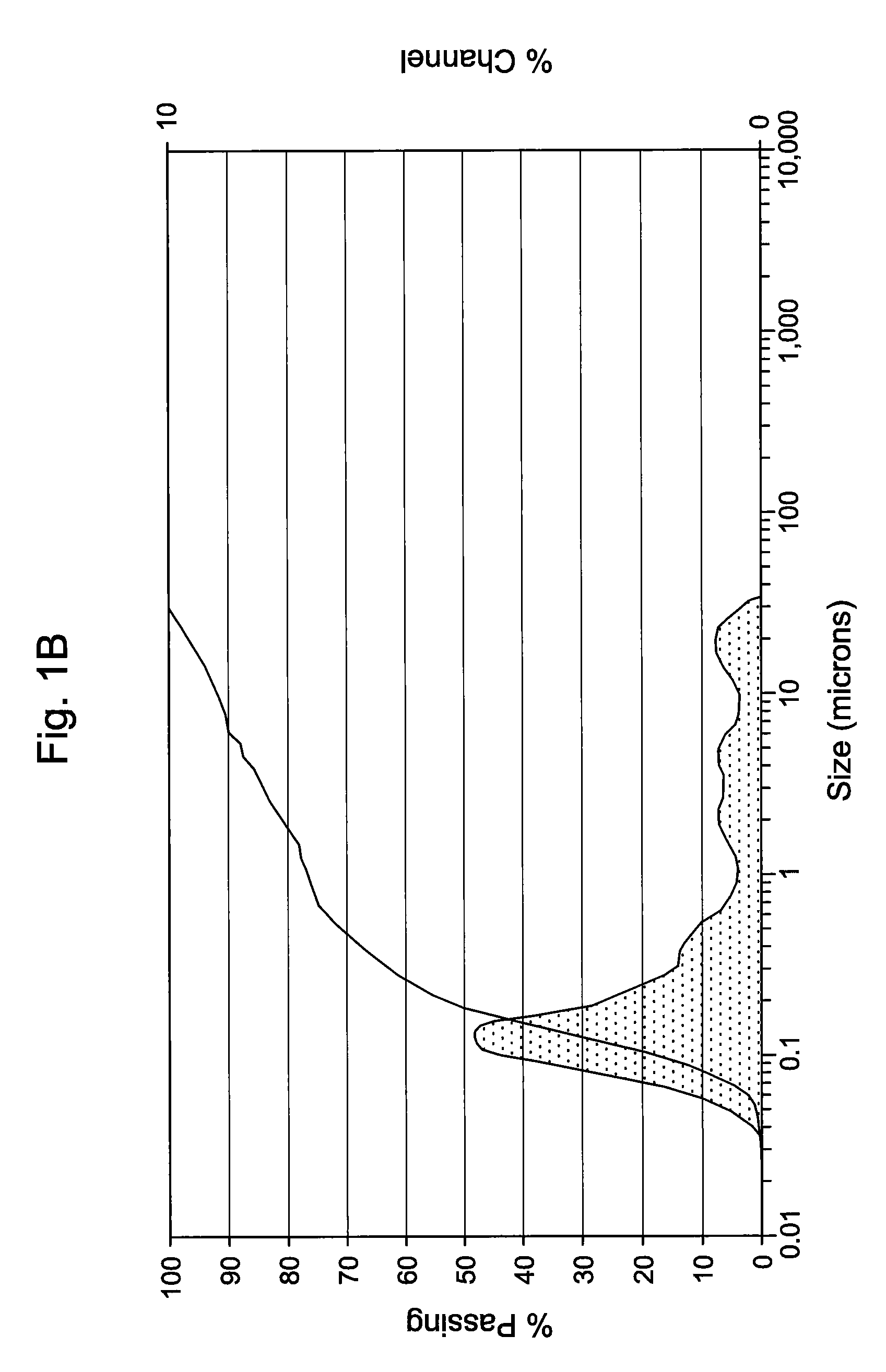

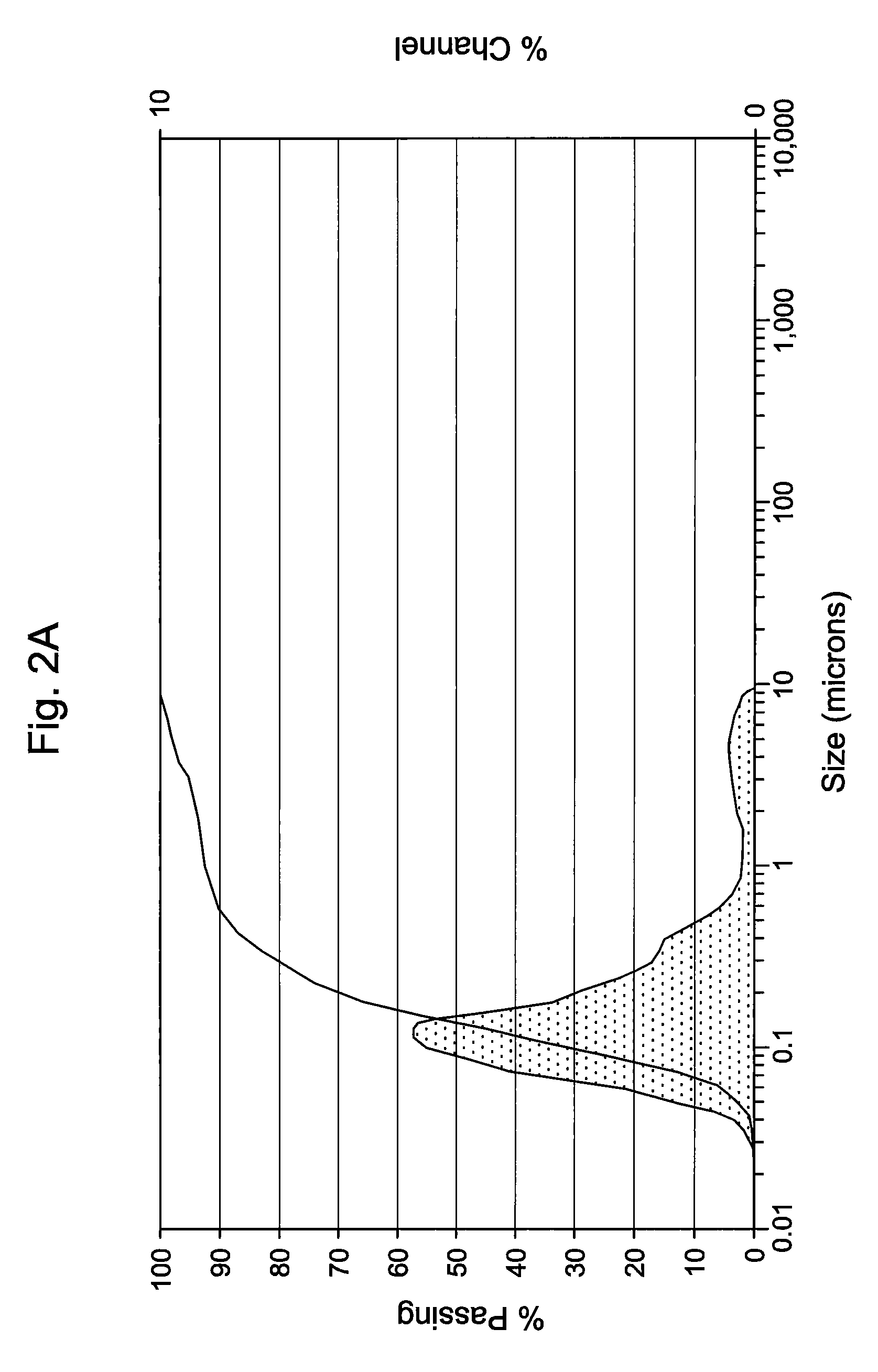

Non-Caking Mine Rock Dust

InactiveUS20140193642A1Effectively inertingEconomically viableSynthetic resin layered productsDust removalInorganic particleCoal dust

A composition for use as rock dust is disclosed. The composition may include a ground inorganic particulate material treated with at least one fatty acid, a salt thereof, or an ester thereof. Also disclosed is a composition including coal dust and mine rock dust, which may include a ground inorganic particulate material treated with at least one fatty acid, a salt thereof, or an ester thereof. The amount of mine rock dust may be sufficient to render the coal dust explosively inert. The composition may also include an untreated inorganic particulate material. The treated inorganic particulate material may be calcium carbonate. The untreated inorganic particulate material may be calcium carbonate. The fatty acid may be stearic acid.

Owner:IMERY PIGMENTS

Semiconductor Device with Improved Contacts

ActiveUS20070284740A1Test may passImprove performanceSemiconductor/solid-state device detailsSolid-state devicesContact padAlloy

A device with a solder joint made of a copper contact pad (210) of certain area (202) and an alloy layer (301) metallurgically attached to the copper pad across the pad area. The alloy layer contains copper / tin alloys, which include Cu6Sn5 intermetallic compound, and nickel / copper / tin alloys, which include (Ni,Cu)6Sn5 intermetallic compound. A solder element (308) including tin is metallurgically attached to the alloy layer across the pad area. No fraction of the original thin nickel layer is left after the reflow process. Copper / tin alloys help to improve the drop test performance, nickel / copper / tin alloys help to improve the life test performance.

Owner:TEXAS INSTR INC

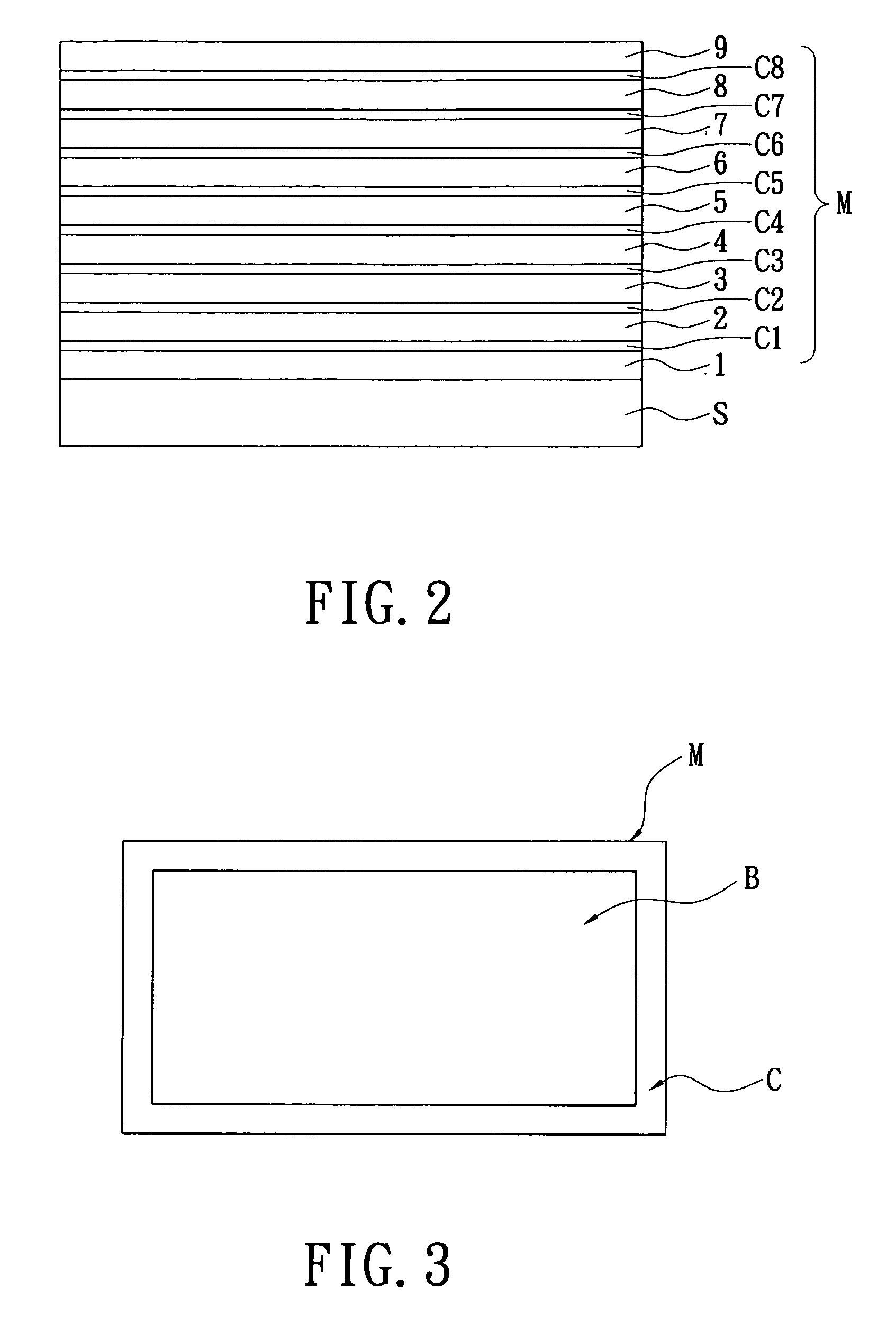

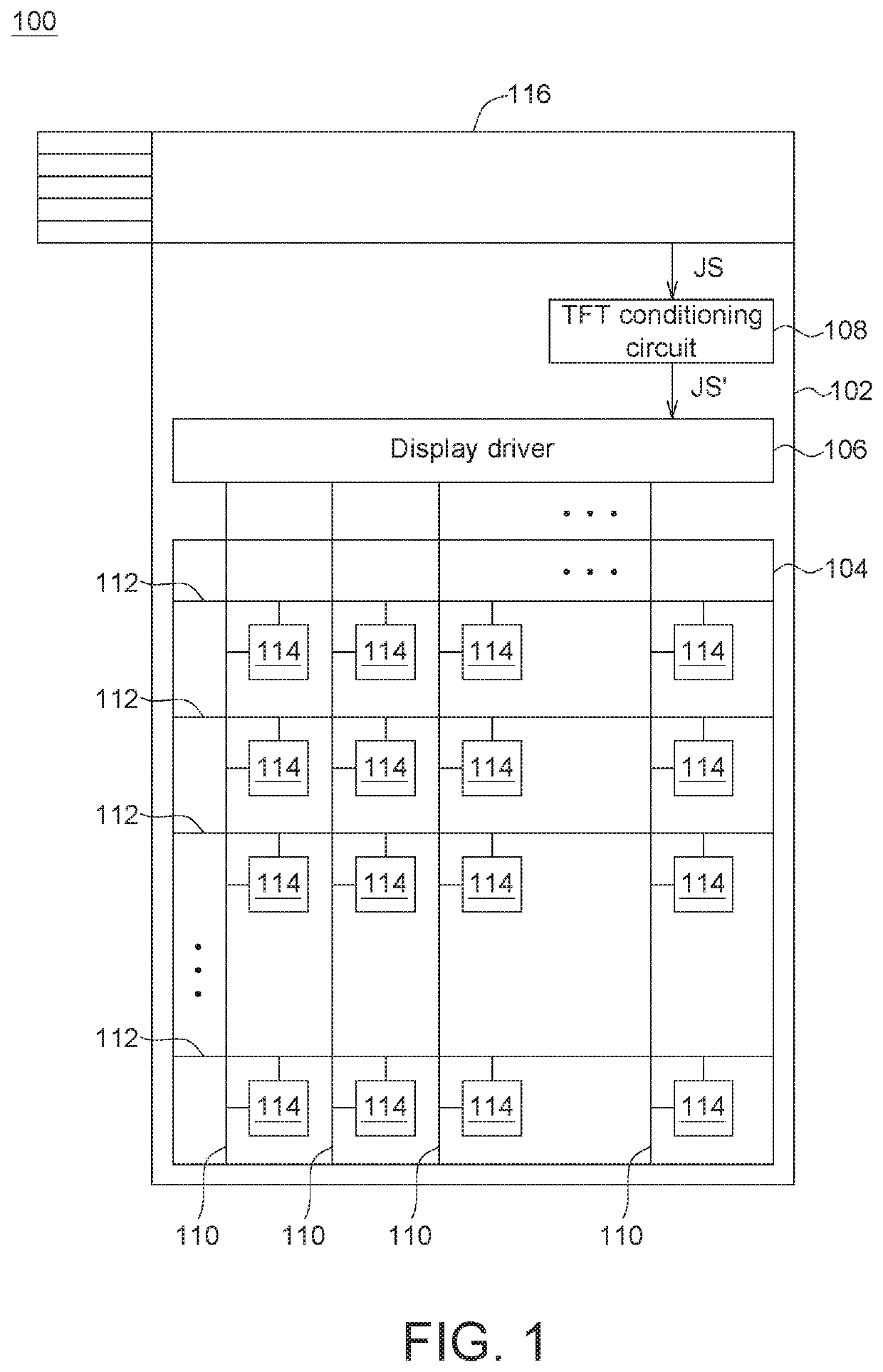

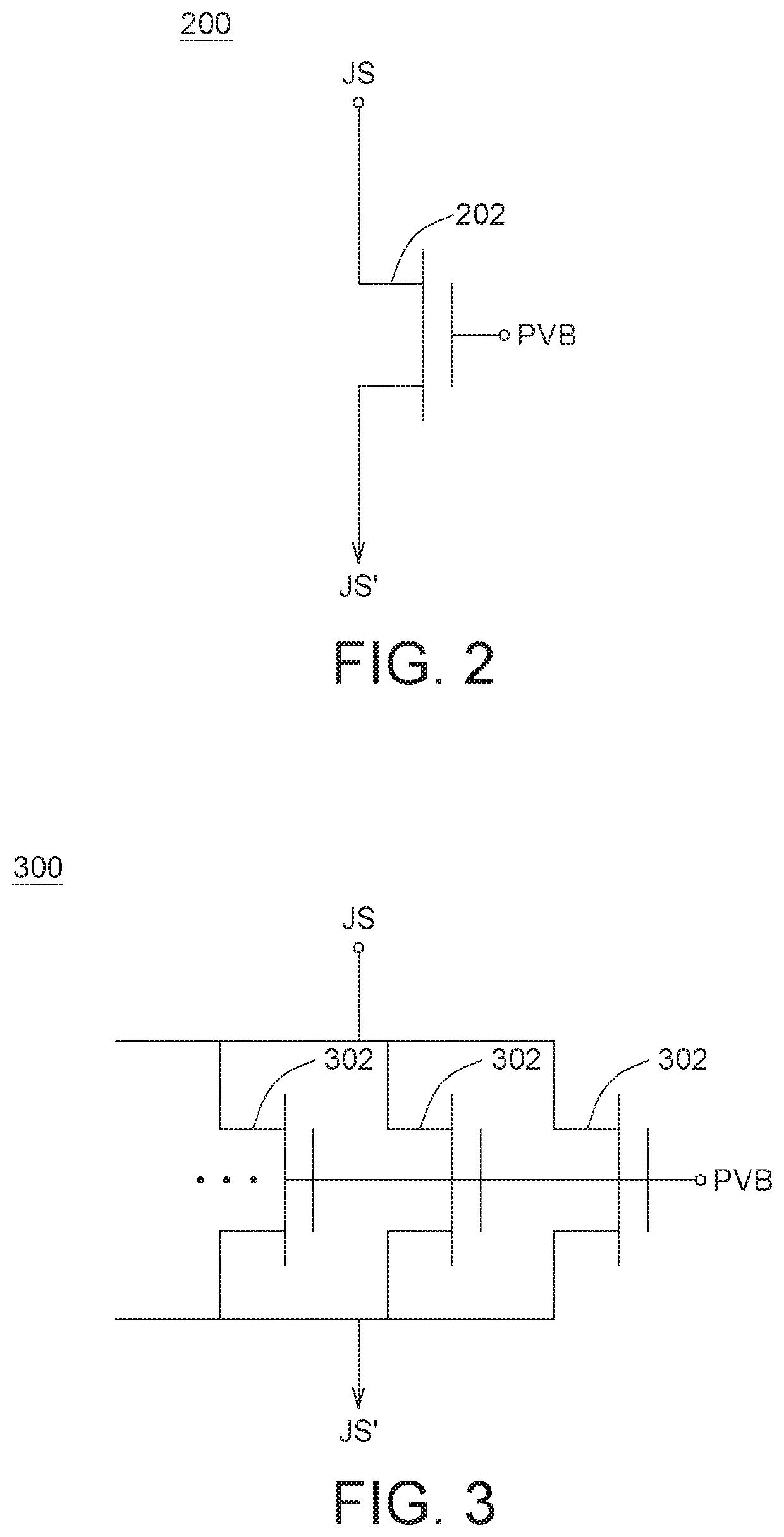

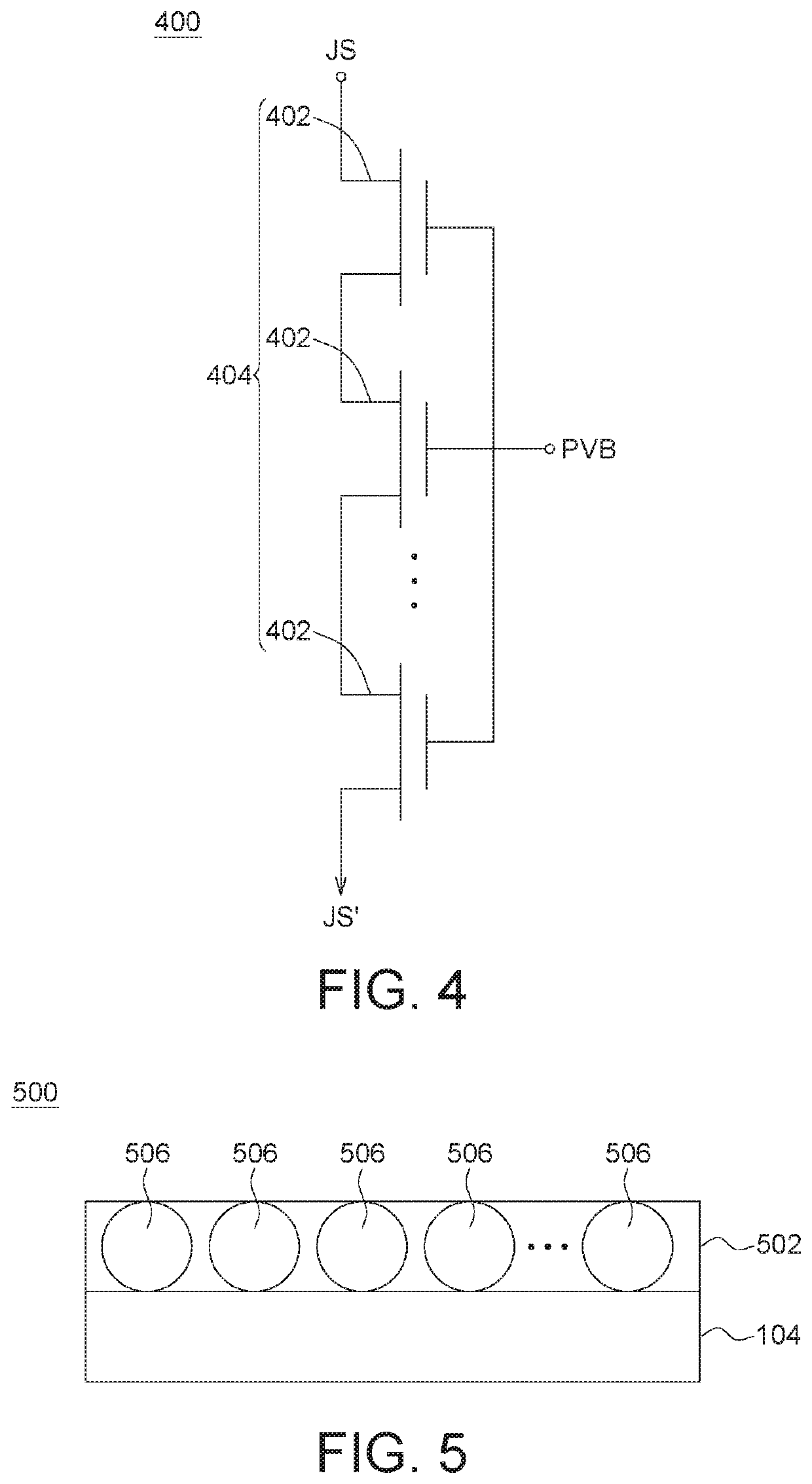

Display device and display driving circuit with electromagnetic interference suppression capability

ActiveUS20190362685A1Reduce electromagnetic interferenceTest may passStatic indicating devicesActive matrixElectromagnetic interference

A display device and a display driving circuit with electromagnetic interference suppression capability are provided. The display device includes a substrate, an active matrix, a display driver and a thin-film transistor (TFT) conditioning circuit. The active matrix disposed on the substrate includes multiple data lines, multiple gate lines and multiple pixels. The data lines intersect with the gate lines. The pixels are coupled to intersections of the data lines and the gate lines. The display driver disposed on the substrate generates signals for driving the data lines and / or the gate lines in response to a conditioned serial data clock. The TFT conditioning circuit disposed on the substrate is coupled to the display driver. The TFT conditioning circuit includes one or more TFTs, and attenuates an amplitude of a serial data clock in response to a predetermined gate bias to provide the conditioned serial data clock to the display driver.

Owner:E INK HLDG INC

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com