Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

286results about How to "Save logic resources" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Reed-Solomon code decoder

The invention discloses a Reed-Solomon code decoder (12), which comprises the following parts from input to output connected electrically: adjoint calculating mode, MEA algorism mode (22), money searching mode (23), Funi algorism mode (24) and correction output mode (25) and data buffer mode (26) between the output end and correction output mode, wherein the input is multi-byte bus input; the MEA algorism mode contains one or more paralleling 8-bit MEA algorism submode (41) between calculating mode and money searching mode, which divides time and processes respective 16-bit data through consolidating to halve each iterative time. The decoder saves resource because the broad bus band is more than 1 byte, which reduces the designing difficulty.

Owner:ZTE CORP

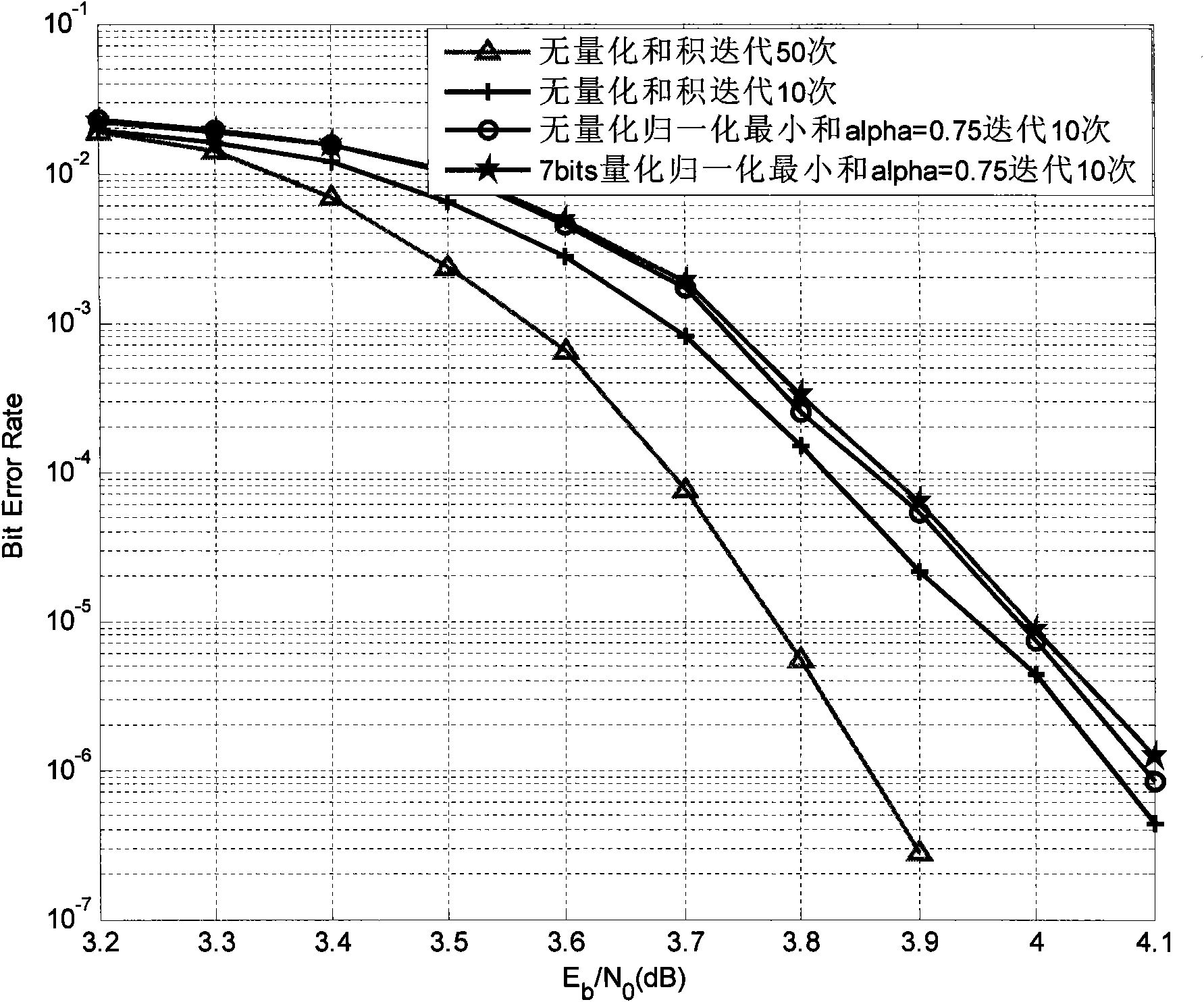

Encoding and decoding methods for shortening Turbo product code

InactiveCN101958720AImprove data throughputReduce encoding delayError correction/detection by combining multiple code structuresTest sequenceCoded element

The invention relates to encoding and decoding methods for shortening a Turbo product code. The encoding method comprises the following steps of: performing row or column encoding on an information sequence to be encoded; performing parallel encoding on code words of row or column component codes generated by the row or column encoding; and judging whether the encoding is finished. The decoding method comprises the following steps of: generating a hard decision sequence of a soft-input information sequence; selecting the least reliable bits in the soft-input information sequence; generating atest sequence according to the hard decision sequence and the least reliable bits; decoding the test sequence to generate candidate code words; calculating the measurement of the candidate code wordsand the soft-input information sequence; reducing the number of the candidate code words; determining decision code words according to the measurement of the candidate code words; and calculating external information of each code element in the decision code words. The encoding method has the advantages of improving data throughput and reducing encoding delay; and the decoding method has the advantages of saving a mass of logical resources and storage resources, particularly well balancing decoding complexity and data throughput under the condition of longer code length of component codes.

Owner:XIDIAN UNIV

Interrupt reporting method and network appliance

The present invention discloses an interrupting report method which includes: every service plate reports self terminal port status messages to master control board when self terminal port condition changes; the main control logical of master control board enquires the each service plate, judging whether or not the service plate has terminal port status messages reporting, if service plate has, then receiving the reporting terminal port status messages, and storing identification information of present service plate and received terminal port status messages in communion register of master control board, reporting middle break to CPU of master control board. The present invention also discloses a network appliance. Technical project of the invention can save logical resource of network appliance master control board when implementing middle break reporting function.

Owner:北京紫光通信科技集团有限公司

Pupil positioning device and method, and display driver of virtual reality device

ActiveCN107833251AAvoid cachingSolve the costInput/output for user-computer interactionImage enhancementTransfer procedurePupil

The embodiment of the invention provides a pupil positioning device and method, and a display driver of a virtual reality device. The pupil positioning device comprises a preprocessing circuit and a coordinate processing circuit, wherein the preprocessing circuit is used for preprocessing an eye image during an eye image transmission process, obtaining all boundary points of the eye image, and thecoordinate processing circuit is used for performing communication area processing on all boundary points, and determining the pupil center coordinates according to the maximum communication area. Aneye image is preprocessed in the data transmission process, the pupil center coordinates are determined by adopting a hardware communication region processing mode, and the large-data-quantity operation caused by delay is avoided. The processing speed is increased, the processing time is shortened, and the storage resources and the logic resources are saved. Hardware implementation is convenient,and the pupil positioning device is integrated in a display driver of a head-mounted virtual reality device.

Owner:BOE TECH GRP CO LTD

High grade encrypting criterion encrypter in Gbpassive optical network system and implementing method thereof

ActiveCN101114903AHigh encryption bandwidthSave logic resourcesMultiplex system selection arrangementsKey distribution for secure communicationSource dataData security

The invention discloses an advanced encryption standard (AES) encryption device of a gigabit passive optical network which comprises a data writing buffer module to save temporarily an encrypted source data, an encrypted information cache module to save temporarily a frame length encrypted with plaintext, an initial counter value and an initial key, an AES processing module to carry out data encryption, a data reading buffer module to save temporarily an encrypted data security data, an encrypted scheduling module to read and save temporarily a key and a frame length from the encrypted information cache module, to generate a counter value stream, to schedule the AES processing module, to input the processed counter value, security and source data into AES processing module and then transmit the encrypted data to the data reading buffer module. The invention further discloses a realizing method of the encryption device. The invention solves the problem that the prior art cannot adjust to higher needs of a bandwidth and a system frequency in a GPON high-speed system and satisfies the requirement of a fixed encryption delay in the GPON high-speed system at the same time.

Owner:SANECHIPS TECH CO LTD

Generation method of LTE (Long Term Evolution) system upstream reference signal q-step ZC (Zadoff-Chu) sequence system thereof

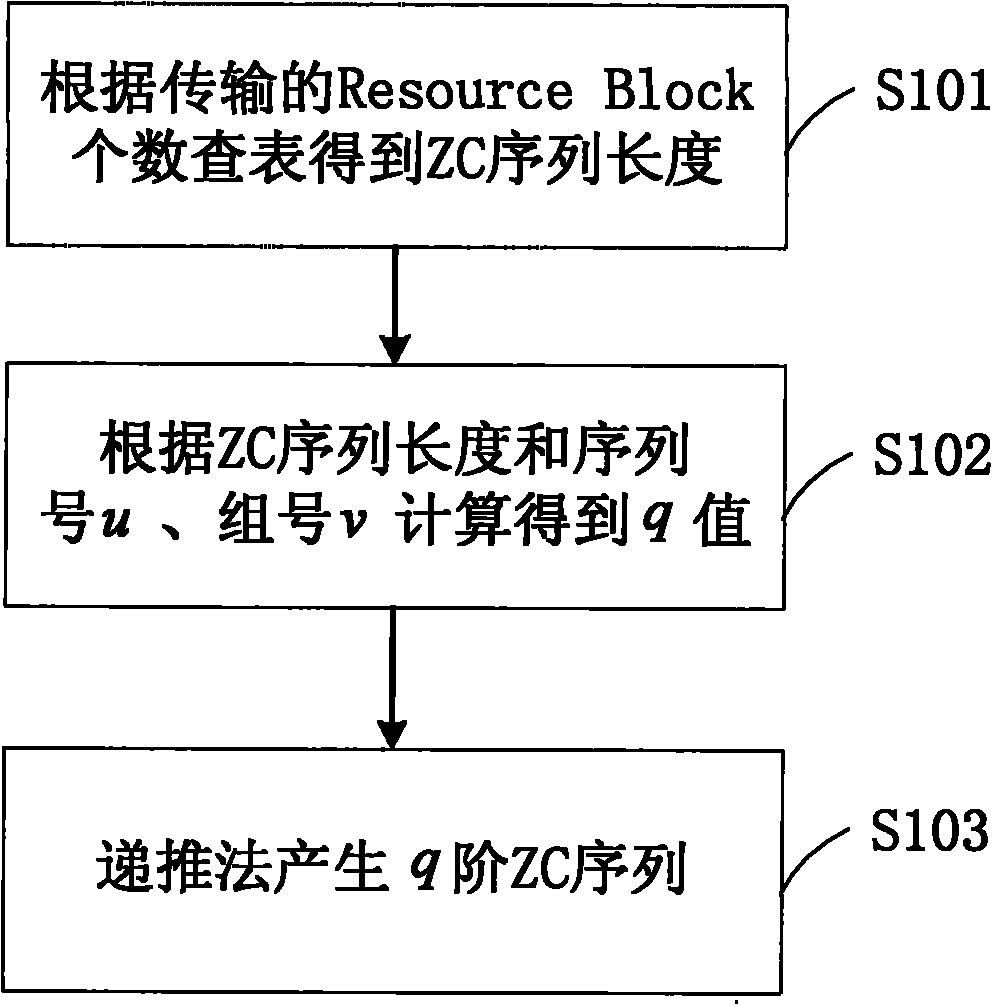

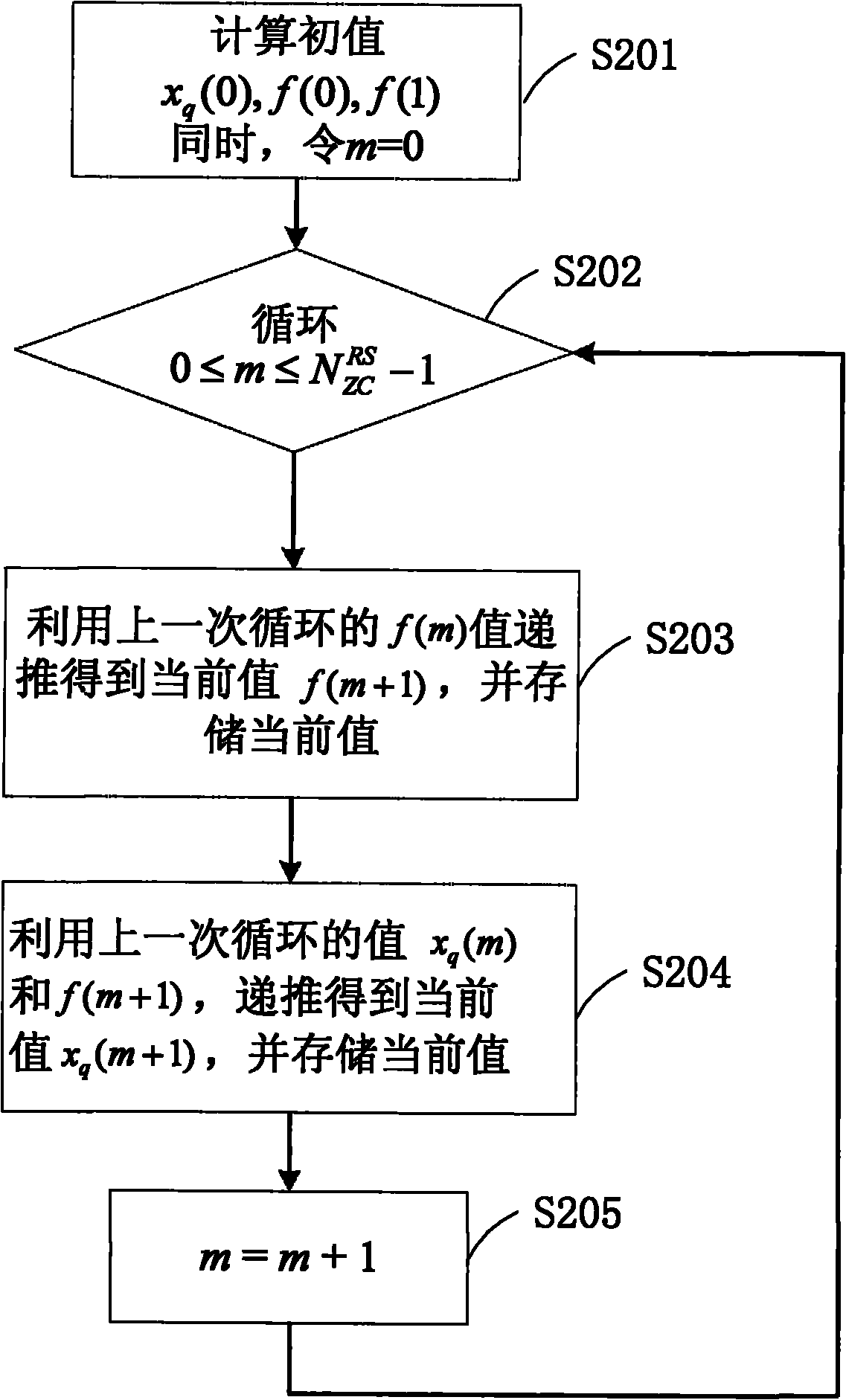

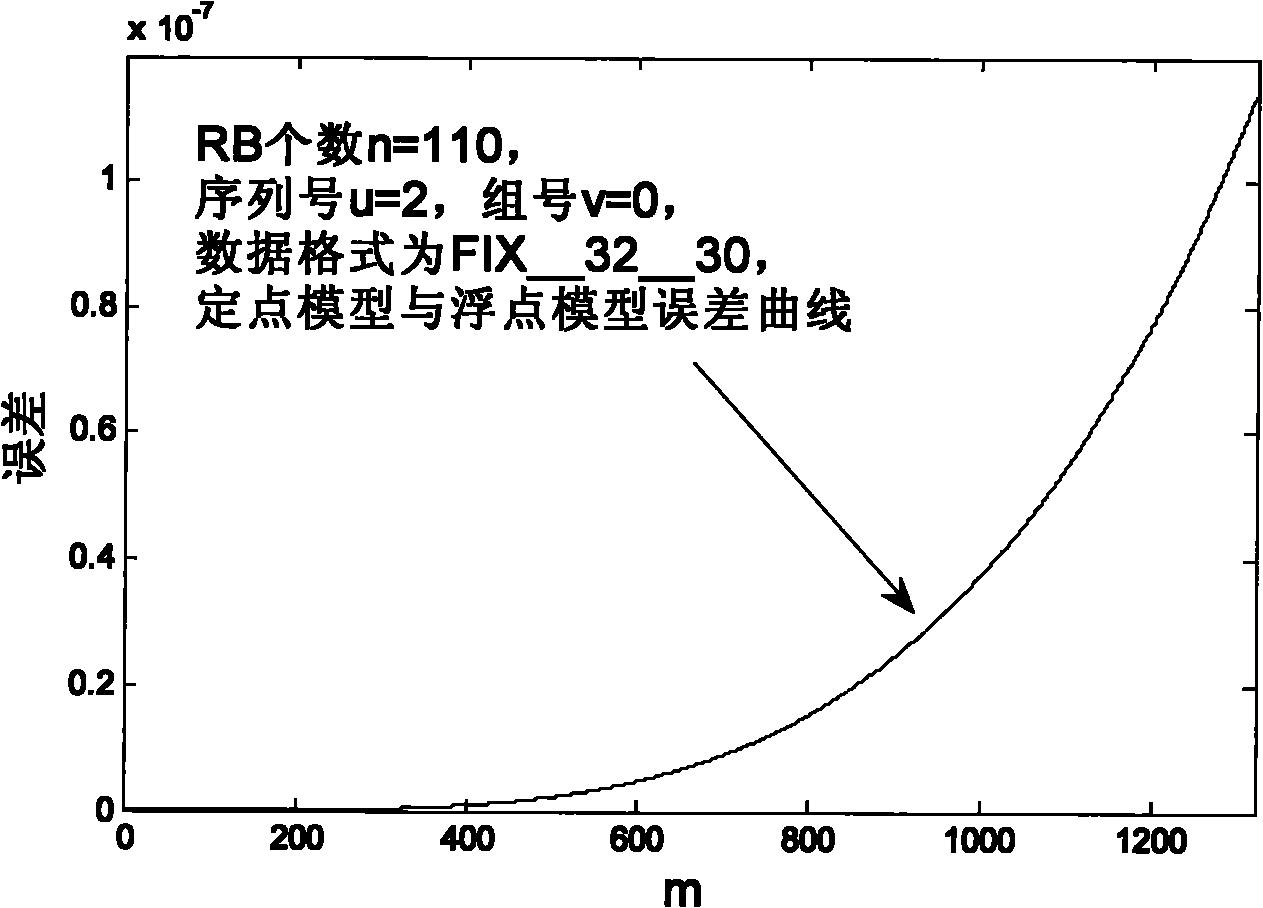

InactiveCN101917356AEasy to implementSave resourcesMulti-frequency code systemsTransmitter/receiver shaping networksProblem of timeResource block

The invention relates to a generation method of an LTE (Long Term Evolution) system upstream reference signal q-step ZC (Zadoff-Chu) sequence and a system thereof. The method comprises the steps of: firstly, acquiring the length of a ZC sequence according to the number of resource blocks; secondly, calculating a q value according to the length of the ZC sequence, a sequence number and a group number; and thirdly, generating the q-step ZC sequence by a recurrence method. In the invention, the problem of longer calculation time for calculating the maximum prime number is avoided by generating a ZC sequence length lookup table; since the ZC sequence is generated through recursion by skillfully using phase characteristics, the multiplication and division with large amplitude and poor precision during direct calculation of phases are avoided, and the invention has important meaning in practical realization of fixed points; the ZC sequence is generated by the recursion algorithm, and the problem of long calculation time caused by calculating trigonometric function many times during generating the ZC sequence directly by a formula is avoided.

Owner:INST OF COMPUTING TECH CHINESE ACAD OF SCI

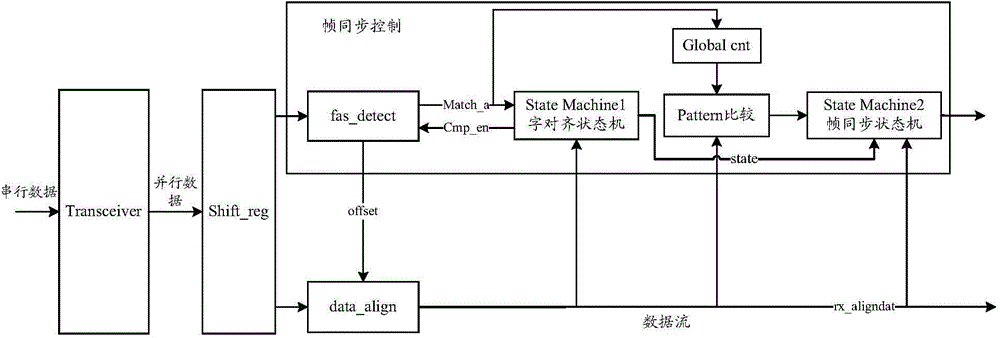

Frame synchronization method and device

ActiveCN104935393AImprove processing efficiencyReduce processing delayMultiplex system selection arrangementsTime-division multiplexSerial codeFrame synchronization

The embodiment of the invention discloses a frame synchronization method and device, and relates to the field of communication, wherein the method and device are used for improving the processing efficiency of frame synchronization. In the embodiment of the invention, the method comprises the steps: converting a received serial code stream and obtaining a parallel cod stream; employing a preset key field of a frame head corresponding to a data frame contained in the parallel code stream to match with each sub parallel code stream in the parallel code stream in a parallel manner; determining the offset of the frame head in a parallel code stream according to the position of the sub parallel code stream, which is successfully matched with the preset key field, in the parallel code stream; carrying out the pre-aligning processing of the parallel code stream according to the frame length corresponding to the data frame contained in the parallel code stream and the determined offset of the frame head; judging whether the pre-aligned frame head is a pseudo frame head or not, enabling the parallel code stream after pre-aligning to serve as a synchronized parallel code stream if the pre-aligned frame head is not the pseudo frame head, and outputting the parallel code stream, thereby solving the above problems.

Owner:RAISECOM TECH

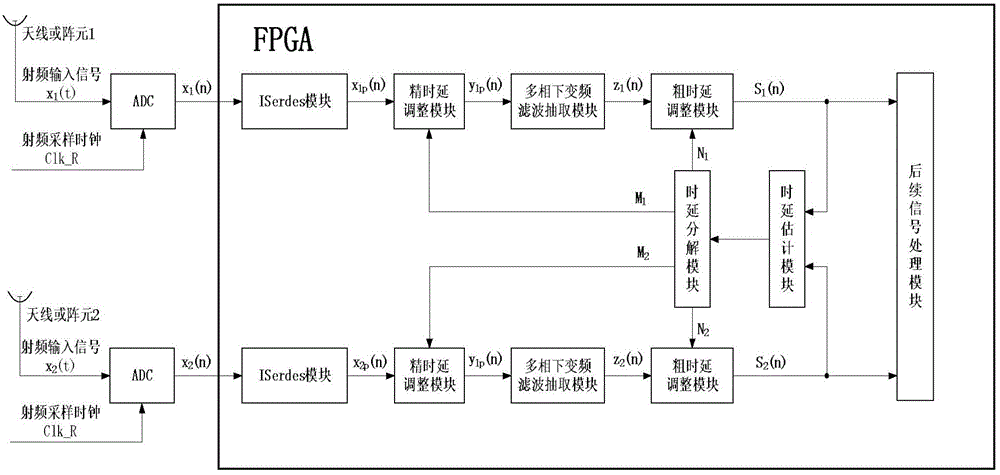

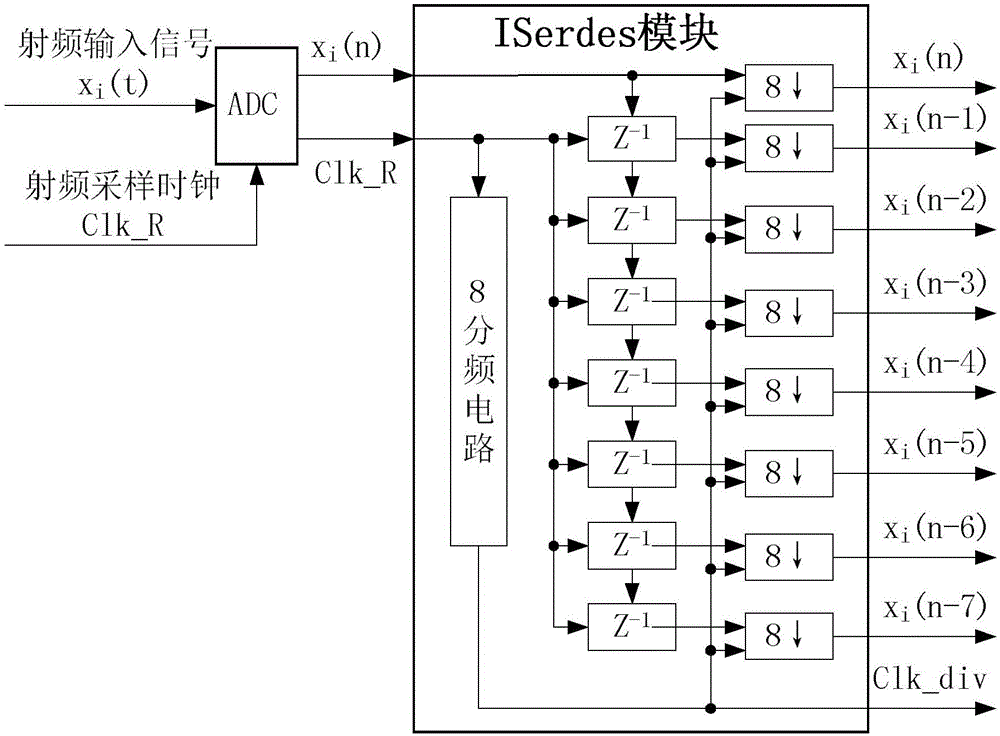

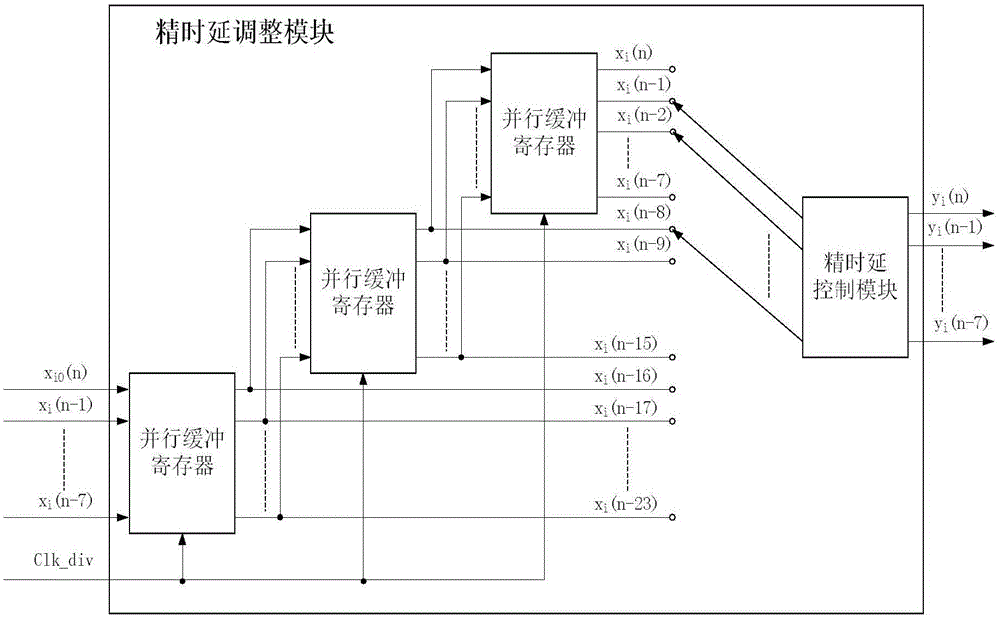

Method for adjusting time delays of multiple broadband receiving signals

ActiveCN105024745ASolve the high-precision time alignment problemRealize formationSpatial transmit diversityAntennasProblem of timeLow speed

The invention provides a method for adjusting the time delays of multiple broadband receiving signals. The method may solve a problem of time alignment of broadband signal baseband waveforms under to a large time-delay condition. The method is implemented by a technical scheme comprising: decomposing a time delay difference into a coarse grade and a fine grade and performing coarse-fine time delay difference adjustment on a baseband signal subjected to digital down-conversion and an AD sampling signal subjected to analog-to-digital conversion; sending a radiofrequency input signal and a radiofrequency sampling clock which are subjected to analog-to-digital conversion to a serial-parallel conversion ISerdes module to be converted into D parallel low-speed digital signals; obtaining 3*D pieces of data and D pieces of parallel data of a signal sequence by means of the delay of a fine time delay adjusting module; converting the data in to a digital signal by means of multiphase filtering summation of a multiphase down-conversion filtering extraction module; outputting a signal subjected to time delay adjustment of a first antenna, a second antenna, or an array element, decomposing the signal by a time delay decomposing module into the number of time delay periods controlling two coarse time delay adjusting modules and two fine time delay adjusting modules, adjusting the time delay difference of the broadband signals received by a compensation antenna or array element, and aligning the baseband waveforms of the multiple broadband receiving signals in a time domain.

Owner:10TH RES INST OF CETC

Rotating transformer conversion method and converter based on FPGA (field programmable gate array)

ActiveCN104796051AImplement decodingAccurate angle data to be measuredDynamo-electric machinesElectronic commutatorsResource consumptionField-programmable gate array

The invention relates to decoding algorithms of rotating transformers, aims at solving a series of problems like sensitive noise, delayed output and high resource consumption of conventional methods and realizing high-accuracy angle position output of the rotating transformers and good performance, and discloses a rotating transformer conversion method and a converter based on an FPGA (field programmable gate array). The rotating transformer conversion method includes the following steps: step 1, acquiring four sine and cosine signals different in phase; step 2, averagely dividing the whole period into eight parts according to symbol and amplitude of the signals; step 3, solving absolute value of the signals acquired in step 1; step 4, acquiring a preliminary estimation value of an angle theta. The rotating transformer conversion method and the converter are mainly applied to designing and manufacturing of the rotating transformers.

Owner:TIANJIN UNIV

Clock signal loss detecting circuit and clock signal loss detecting method

InactiveCN102497200ASave logic resourcesImprove overall performancePulse techniqueVIT signalsIntegrated circuit

The invention discloses a clock signal loss detecting circuit and a clock signal loss detecting method. The circuit comprises a frequency dividing module, a counting module, a displacing module, a comparing module and a detecting module. The method utilizes a low-frequency clock to detect a high-frequency and includes five steps to realize a process: dividing frequencies, counting, displacing, comparing and detecting. The clock signal loss detecting circuit and the clock signal loss detecting method have the advantages that by means of detecting whether clock signals lose or not, normal operation of an integrated circuit system can be guaranteed, logical resources are saved, and overall performance of the integrated circuit system is improved. Besides, a universal solution to the design of an application specific integrated circuit multiplexed by an IP (intellectual property) module is provided, so that time for developing products is shortened, and design cost is reduced.

Owner:SOUTHEAST UNIV

Method and device for processing multichannel data

ActiveCN101094176AReduce occupancyMore bandwidthData switching networksMessage queueReal-time computing

The method comprises: grouping the packet message queue in the management module; setting up a reading data module and a corresponding sending module for each group of packet message queue; wherein, if the amount of groups is less than the amount of packet message queues, said reading data module alternatively reads the packet information from each packet message queue in the group corresponding to itself; the read-out message is sent to a corresponding module; after receiving the message from the read data module, the send module sends out the received message via an outlet channel corresponding to the incoming channel.

Owner:XINHUASAN INFORMATION TECH CO LTD

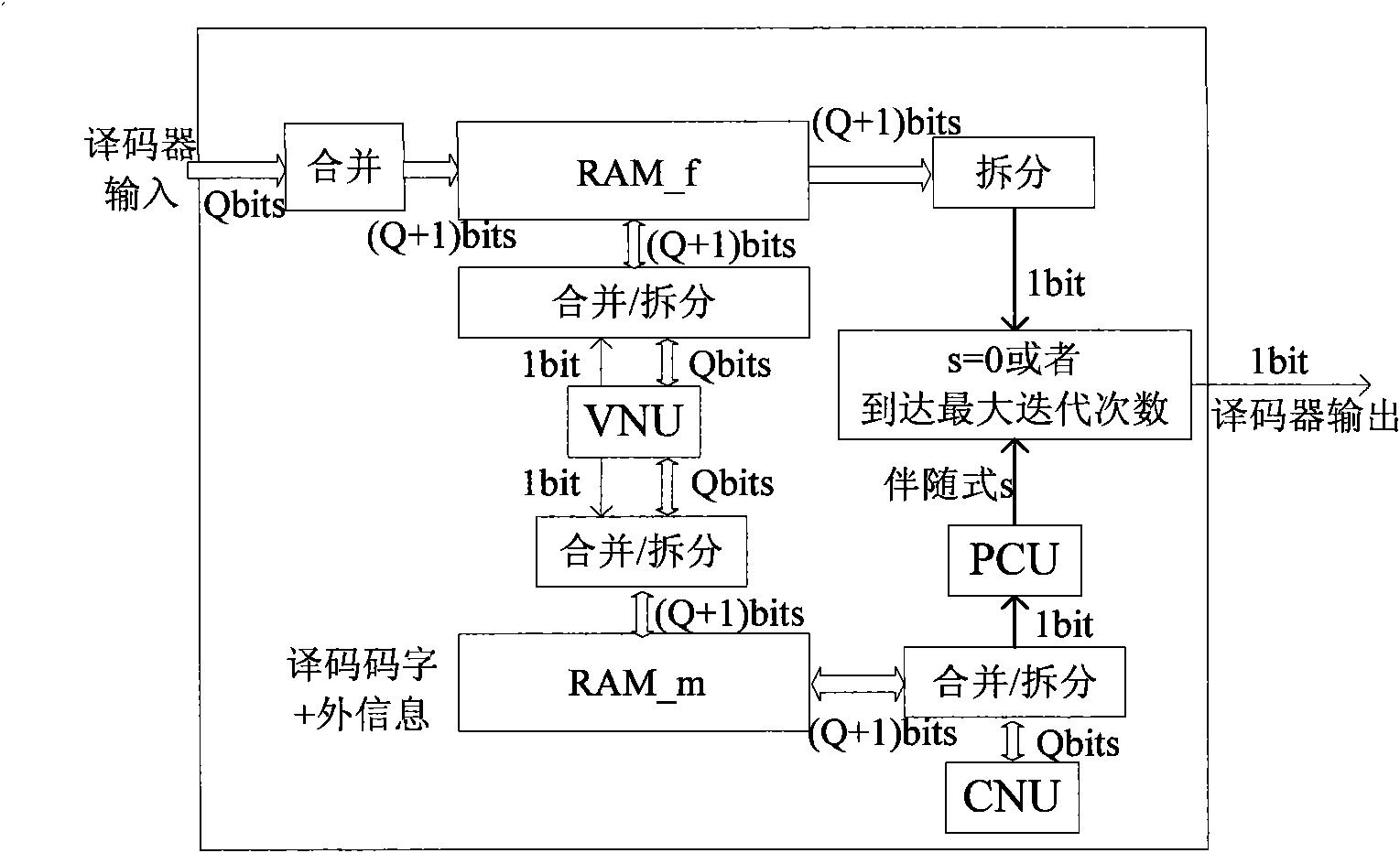

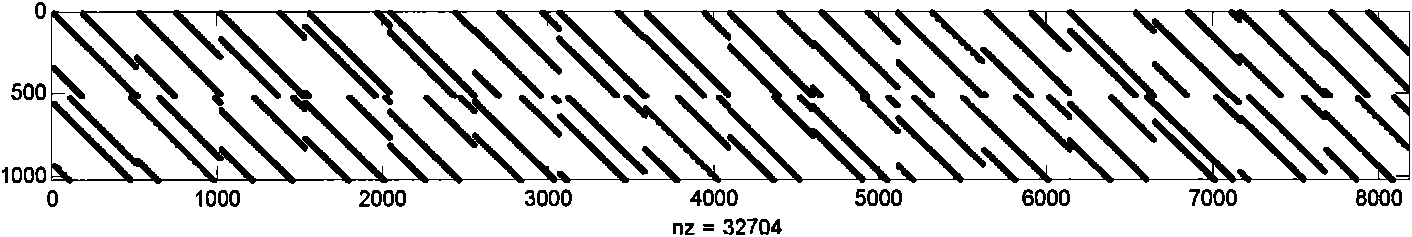

High efficiency storing method for coding digit of LDPC coder based on FPGA

ActiveCN101599302ASave logic resourcesReduce the quantity requiredData representation error detection/correctionRead-only memoriesProduction lineAddress generation unit

The invention discloses a high efficiency storing method for the coding digit of an LDPC coder based on an FPGA. In the method, the coding digit and external information (or channel information) share one storage block, thereby effectively reducing the requirement of the coder to the quantity of the storage resources; and the coding digit and the external information can be withdrawn when reading the storage block. Therefore, a check equation computational unit PCU and a check node update unit CNU can share one group of address information, and the PCU does not need additional address generation units; and finally, the design method of a step thinning production line is adopted to realize process units VNU, CNU and PCU, thereby effectively reducing the key path delay of the coder and providing a necessary safeguard to improve the throughput of the LDPC coder. When realizing the method with the FPGA, the invention not only can save a large number of the resources for respectively storing the digit and the logic resources for generating addresses which are needed by the PCU, but also can improve the throughput of the coders.

Owner:XIAN INSTITUE OF SPACE RADIO TECH

Data transmission method and device

ActiveCN107566925ASolve the defects of the mapping methodFix bugsTime-division multiplexTime-division multiplexing selectionData transmissionByte

The invention provides a data transmission method and device, and the method is used for a transmitting end of an OTN (optical transmission network). The method comprises the steps: converting a firstframe structure into a central frame structure, wherein the central frame structure is an irregular ODU frame, and at least a part of bytes of the irregular ODU frame in each clock period are effective bytes; converting the central frame structure into a second ODU frame, and transmitting the second ODU frame into a receiving end, wherein the rate of the second ODU frame is higher than the rate of the first frame structure. The second ODU frame is a regular ODU frame, and the bytes of the regular ODU frame in each clock period are effective bytes or ineffective bytes. The rate of the effective bytes of the central frame structure is equal to the rate of the second ODU frame. The method employs FMP mapping, and solves a problem that a GMP mapping mode has defects in the OTN business.

Owner:ZTE CORP

High-speed 8B/10B coder, decoder and processing method thereof for error input

InactiveCN101674089AHigh speedShorten the critical pathIndividual digits conversionPrecodingCritical path method

The invention provides a high-speed 8B / 10B coder, a decoder and a processing method thereof for error input. The coder comprises a data character precoding module, a RD calculating module and a data character precoding correction module, and the coder adopts a pipeline structure and a parallel processing method; the data character precoding module, the data character precoding correction module and the RD calculating module are respectively precoded and then post collected; the data character precoding module precodes input data in first-stage flow water, and calculates whether the current input code word can cause RD to turn by a RD_turn module; the RD calculating module calculates a RD value passing through the code word in second-stage flow water, and calculates the obtained RD value by using the former clock period to correct the precoded result of the current code word. The invention respectively adopts the pipeline structure and the parallel processing method when being applied in a high-speed serial interface, thus simplifying the circuit design, shortening the key path and improving speed.

Owner:INST OF ACOUSTICS CHINESE ACAD OF SCI

Low-power-dissipation FPGA self-adaption loading method and system

ActiveCN107450948AReduce power consumptionLow costPower supply for data processingProgram loading/initiatingLow power dissipationEmbedded system

The invention provides a low-power-dissipation FPGA self-adaption loading method and system. The low-power-dissipation FPGA self-adaption loading method and system are used for solving the technical problems existing in an existing loading method that an FPGA is high in power dissipation and a large number of internal resources are consumed. An external processing module packs multiple configuration files with different functions to obtain a total configuration file, and the total configuration file is written into a configuration information storage module; a target FPGA automatically loads a first configuration file from the configuration information storage module to achieve initial configuration; an FPGA function detection module detects the matching features of external input data and a current configuration file, and if the external input data is matched with the current configuration file, the target FPGA enters a normal work mode; if the external input data is not matched with the current configuration file, a self-adaption re-loading process is triggered, the next configuration file is loaded, and after the configuration is completed, the detection step is repeated. The low-power-dissipation FPGA self-adaption loading method and system can effectively lower the power dissipation of the FPGA and the consumption of the internal source of the FPGA.

Owner:XIDIAN UNIV

Digital down converter and digital upconverter

ActiveCN102098005AReduce complexitySave logic resourcesMulti-frequency-changing modulation transferenceFrequency changerDigital up converter

The invention provides a digital down converter and a digital upconverter. Intermediate-frequency signals are mixed by a first-level mixing module in the digital down converter; two paths of I / Q mixing signals are output in a two-carrier time division multiplexing mode; a first-level multi-rate conversion module and a second-level multi-rate conversion module synchronize clock frequency before extraction; and the received signals are subjected to multiple extraction and filtration in a multi-carrier time division multiplexing mode according to the synchronized clock frequency. The digital upconverter synchronizes the clock frequency before frequency interpolation; a third-level multi-rate conversion module, a fourth-level multi-rate conversion module, a second-level mixing module and a fifth-level multi-rate conversion module perform frequency interpolation and filtration on the received signals in the multi-carrier time division multiplexing mode according to the synchronized clock frequency and the received signal data rate. The converter reduces the complexity of a control signal and saves logical resources.

Owner:北京万海云科技有限公司

Transmission set of multiplexing multiplepath interface in physical layer

ActiveCN1728629AReduce processingSave logic resourcesTransmission path multiple useTransfer procedurePhysical layer

The transmission set includes interfaces in n bit wide of K routes of sending unit and in n bit wide of K routes of receiving unit, conversion unit for bit wide, distribution unit, merging unit, and reduction unit for bit wide. The conversion unit converts the sending signal in m bit wide to signal in K*n bit wide, which is transferred to distribution unit. The distribution unit sends signal in K*n bit wide through interface of K routes of sending unit respectively. The merging unit merges signals, which are received through interfaces of K routes of receiving unit, into signals in K*n bit wide, which are transferred to reduction unit for bit wide. The reduction unit converts signal in K*n bit wide to the received signal in m bit wide. The invention avoids using physical layer protocol for parsing sending signals and processes in twice by link layer in transport process, saving logic resources and reducing design difficulty.

Owner:NEW H3C TECH CO LTD

Implementation method of single-precision floating point trigonometric function covering full circumferential angle

InactiveCN103150137ASave logic resourcesIncrease working frequencyDigital data processing detailsDigital signal processingOriginal data

The invention discloses an implementation method of single-precision floating point trigonometric function covering full circumferential angle, and belongs to the field of processing of digital signal. The method comprises following steps: firstly, a preprocessing module CORDIC-PRE receives input single-precision floating point data, records the quadrant information of original data, converts the single-precision floating point data within a set angle range into high-precision floating point data, and inputs the high-precision floating point data to an iterative operation module CORDIC-CORE; secondly, the CORDIC-CORE finishes iterative operation of the CORDIC algorithm to the input data by adopting high-precision floating point operation; the result is input to a postprocessing module CORDIC-POST; thirdly, the CORDIC-POST performs quadrant recovery to sine and cosine functional values to be required to be calculated as per the quadrant information recorded in the CORDIC-PRE aiming to the input data; and the data after being recovered is converted into the precision floating point data and output. The implementation method is suitable for actual operation of CORDIC algorithm.

Owner:BEIJING INSTITUTE OF TECHNOLOGYGY

Image data Huffman decoding device and method

ActiveCN106341692ASolve the technical problem of low decoding efficiencyImprove decoding speedDigital video signal modificationHuffman decodingVideo image

The invention discloses an image data Huffman decoding device and method. The image data Huffman decoding device comprises a number of encoding stream inputting units Pi which are used for receiving encoding stream Li in multi-channel Huffman encoding stream representing image data, a Huffman decoding unit which is used for parallel-decoding multi-channel Huffman encoding stream to acquire multi-channel Huffman decoding stream and decoding the encoding stream Li to acquire decoding stream Mi, and a number of output units Qi which are used for outputting the decoding stream Mi. According to the invention, the Huffman decoding device is used to decode a number of Huffman codes or video images in parallel; the decoding speed and efficiency are greatly improved; less logic resources are occupied; the cost input is reduced; the decoding efficiency is improved; and the technical problem of the low efficiency of Huffman decoding in the prior art is solved.

Owner:HANGZHOU HIKVISION DIGITAL TECH

Ethernet and ATM tier joined data vonversion and correction device and method

InactiveCN1529476AReduce workloadImprove performancePulse automatic controlData switching by path configurationNetwork processorEthernet

The devices comprises sending module at same Ethernet from Ethernet to ATM layer, sending module for CRC generation, ATM sending module and ATM receiving module from ATM layer to Ethernet direction, receiving module for CRC checking, Ethernet receiving module as well as sending and receiving storage module at ATM side, and sending and storage module at Ethernet side. The said above devices implement conversion and verification of jointed data between Ethernet and ATM. The invention realizes bus conversion between Ethernet and ATM, and CRC calculation without need of resources of network processor. RAM look-up table is utilized in CRC calculation module so as to save lot of logic resources, and reduce system cost.

Owner:ZTE CORP

Filtering device and filtering method of cascaded integral comb filter

The invention relates to the communication field and particularly discloses a filtering device and a filtering method of a cascaded integral comb filter. In the invention, by the multiplexing of a cascaded integrator and a cascaded comb filter contained in a cascaded integral comb filter, the same cascaded integral comb filter can work as a cascaded integral comb extraction filter or as a cascaded integral comb interpolation filter so as to avoid arranging a cascaded integral comb filter in a receiving channel or a sending channel and favorably save logic resources and decrease the cost while reaching performance indexes.

Owner:钜泉科技(南京)有限公司

Coherent light BPSK/QPSK self-adaptive demodulation method and device

InactiveCN106100738AReduce complexity and costSave logic resourcesModulated-carrier systemsFibre transmissionClock recoveryVIT signals

The invention discloses a coherent light BPSK / QPSK self-adaptive demodulation method and device. The method comprises the following steps: (1) signal acquisition: performing analog-digital conversion on analog electric signals I and Q to obtain digital signals I and Q, performing serial-parallel processing to obtain a parallel signal; (2) format recognition: performing format recognition on the parallel signal; (3) clock recovery: performing the clock recovery on the parallel signal to obtain the parallel signal after the clock recovery; (4) frequency offset compensation; (5) phase noise compensation; (6) judging the acquired signal after the phase noise compensation in the step (5) according to a modulation format to obtain one bit of signal. The device comprises a first A / D conversion circuit and a second A / D conversion circuit, a FPGA chip, and a single chip; the first A / D conversion circuit and the second A / D conversion circuit are used for acquiring the first analog signal and the second analog signal, and converting the acquired analog signals into the first digital signal and the second digital signal to input to the FPGA chip. Through the adoption of the method and device disclosed by the invention, the coherent light BPSK / QPSK self-adaptive demodulation is realized.

Owner:HUAZHONG UNIV OF SCI & TECH

QC-LDPC (Quasi-Cyclic Low-Density Parity-Check) code decoder and implementation method thereof

ActiveCN101917249AOptimize routing resourcesReduce complexityError preventionError correction/detection using multiple parity bitsRound complexityControl unit

The invention provides a QC-LDPC code decoder and an implementation method thereof. The decoder comprises an HPU (Hydraulic Pumping Unit) array, a VPU (Visual Processing Unit) array, an ARAM-C array, a CARM-C array, a multiplexing unit and a control unit. The decoder and the implementation method thereof provided by the invention completely utilize characteristic of a QC-LDPC code semi-parallel decoder structure, develop optimizing potentials, carry out optimizing configuration on storage resources on the basis of reducing hardware implementation complexity by introducing a horizontal and a vertical multiplying multiplexing computing units, obviously improve the utilization efficiency of an RAM unit during hardware implementation, reduce quantity of required RAM units and reduce logic resources occupied by the multiplexing unit through RAM block combination, simultaneously optimize wiring resources required by hardware implementation effectively, and can flexibly exchange among logic resources, storage sources, wiring resources and throughput rates.

Owner:TSINGHUA UNIV

Infrared-thermometer self-adaption three platform histogram equalization system and method thereof

InactiveCN103353349AEasy to observeObservation inhibitionImage enhancementRadiation pyrometryResource consumptionDigital image

The invention discloses an infrared-thermometer self-adaption three platform histogram equalization system and a method thereof. The system is formed by an infrared digital image histogram statistics module, a self-adaption image three platform threshold calculating module, an image detail component determination module, a gray scale statistics correction module, a histogram accumulation module and a dynamic gray scale mapping function module. The infrared digital image histogram statistics module is connected with the self-adaption image three platform threshold calculating module. The self-adaption image three platform threshold calculating module is connected with the image detail component determination module and the gray scale statistics correction module respectively. The gray scale statistics correction module is connected with the histogram accumulation module. The image detail component determination module and the histogram accumulation module are connected with the dynamic gray scale mapping function module. Realization is simple. Resource consumption is small and a processing speed is fast. Problems that a contrast ratio is low in high and low temperature areas of an infrared image and a background noise is loud can be effectively solved.

Owner:NANJING UNIV OF SCI & TECH

Image remapping method and device based on programmable logic device

ActiveCN105528758ASave storage resourcesSave logic resourcesGeometric image transformationFpga implementationsProgrammable logic device

The invention relates to the technical field of TFT-LCD panel automatic optical inspection and specially relates to an image remapping method and device based on a programmable logic device. The method is characterized by dividing a target image into a plurality of image blocks; calculating an input line address and writing-back line address of each image block; carrying out remapping every time one image block is input according to the input line address of each image block, and writing back image data of the image blocks obtained after finishing remapping according to the corresponding writing-back line addresses; and inputting the next image block according to the input line address of the next image block and carrying out remapping until all of the image blocks of the target image finish remapping. The method is realized based on the FPGA, and is characterized by dividing the target image into the plurality of image blocks and inputting the image blocks one by one for processing, thereby saving storage and logic resources in the FPGA and facilitating integration of follow-up functions.

Owner:WUHAN JINGCE ELECTRONICS GRP CO LTD

Oscillograph with double-capture function

ActiveCN108776249ASave logic resourcesMeet diverse needsDigital variable displayDouble-timeSlow time

The invention discloses an oscillograph with a double-capture function. A user selects two time base gears by an upper computer; two different snap-shot coefficients are obtained by calculation and are simultaneously issued to corresponding modules; waveform data acquired and stored at a slow time base gear is used as main waveform data; waveform data obtained by carrying out acquisition and storage on the same data source at a rapid time base gear is used as capture waveform data; a main waveform and a capture waveform are simultaneously displayed by the upper computer. According to the invention, the same data source can be simultaneously captured by adopting different sampling rates according to double time base gears set by the user so as to meet the requirement of the user for diversification of the observation waveforms.

Owner:UNIV OF ELECTRONIC SCI & TECH OF CHINA

Method and apparatus for reporting information

InactiveCN101227689ASave logic resourcesDiversity/multi-antenna systemsRadio/inductive link selection arrangementsComputer scienceEmbedded system

The invention relates to an information reporting method and a device, wherein the method comprises setting a first-status zone bit of a first-in first-out memory according to a writing pointer of writing information and a reading pointer of reading information, when the first-status zone bit of the first-in first-out memory is not empty, sending interrupt request of request reading information, and reading information according to the interrupt information. The device comprises a first setting module which is used to set the first -status zone bit of the first-in first-out memory according to the writing pointer of writing information and the reading pointer of reading information, a sending module which is used to send interrupt request for reading information when the first-status zone bit of the first-in first-out memory is not empty and a reading module which is used to read information according to the interrupt request. The invention solves the shortcomings that the prior art which adopts request queue circuits to achieve information reporting occupies a large amount of logical resources.

Owner:HUAWEI TECH CO LTD

Power amplifier nonlinear self-adaptive simulation method based on sectioned polynomial and power amplifier nonlinear self-adaptive simulation system thereof

ActiveCN106125547AImprove simulation accuracyFast convergenceAdaptive controlLookup tableComputer science

The invention relates to a power amplifier nonlinear self-adaptive simulation method based on a sectioned polynomial. The power amplifier nonlinear self-adaptive simulation method comprises the steps that the amplitude of input signals is acquired according to the input digital baseband signals; power amplifier nonlinear characteristics are divided into three sections; the initial values of three sections of polynomial coefficients are stored in an ROM lookup table; the polynomial coefficient of the corresponding section is obtained through table look-up; the amplitude and the phase of output signals are acquired and the expected output signals are acquired through synthesis; and the expected output signals and partial feedback simulation output signals are compared so that error signals are acquired, the polynomial coefficients in the lookup table are continuously updated and finally the simulation output signals are enabled to approximate the expected output signals. The invention also discloses a power amplifier nonlinear self-adaptive simulation system based on the sectioned polynomial. With application of the simulation method based on the sectioned polynomial, the power amplifier nonlinear characteristics are described in the sectioned manner according to the amplitude of the input signals, and each section only uses one low-order polynomial for approximation so that the simulation precision can be enhanced and the computational complexity can be reduced.

Owner:CHINA ELECTRONIC TECH GRP CORP NO 38 RES INST

Service transmission method and apparatus

InactiveCN107040314AAvoid conversionReduce complexityTime-division multiplexElectromagnetic transmittersByteHardware implementations

The invention provides a service transmission method and apparatus. The service transmission method is applied to a sending end and comprises the following steps: dividing a payload part of a payload unit bearing a service layer frame of client service into a first predetermined number of logic channel units in advance, wherein each logic channel unit comprises a first storage part used for storing the cost of the client service and a second storage part used for storing the payload data of the client service; storing feature information of the client service in the first storage parts of the first predetermined number of logic channel units, and storing the payload data of the client service in the second storage parts of the first predetermined number of logic channel units; and sending the service layer frame to a receiving end. Therefore, all bytes processed within a clock cycle can belong to a certain logic channel unit, thereby avoiding the space division-time division- space division conversion process, saving logic resources, reducing the hardware implementation complexity, reducing the number of occupied bytes, preventing bandwidth waste and improving the bandwidth utilization rate.

Owner:ZTE CORP

Receiver card, data storage scheduling method and LED display control system

InactiveCN109215565AGuaranteed real-timeImprove bandwidth utilizationStatic indicating devicesData channelUpgrade

The invention discloses a receiving card, a data storage scheduling method and an LED display control system, comprising a control module, a receiving card memory and a receiving card microprocessor respectively connected with the control module, and a receiving card nonvolatile memory connected with the receiving card microprocessor. The control module is used for identifying and parsing the local data packet and executing the control instruction of the receiving card. The four Banks in the memory of the receiving card are divided into two Bank video streams, a correction coefficient channelcontaining one Bank and an online upgrade data channel containing one Bank , which are respectively used for storing the video data, the correction coefficient and the online upgrade data obtained byparsing. The receiver card microprocessor is used to realize the online upgrade of the system. The receiving card nonvolatile memory is used to cure the correction factor. The invention can realize video data processing, white balance correction, on-line upgrading and intelligent setting in the limited bandwidth, and improve the stability, flexibility and reliability of the display control.

Owner:HUAZHONG UNIV OF SCI & TECH

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com