Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

60results about How to "Reduce wiring density" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

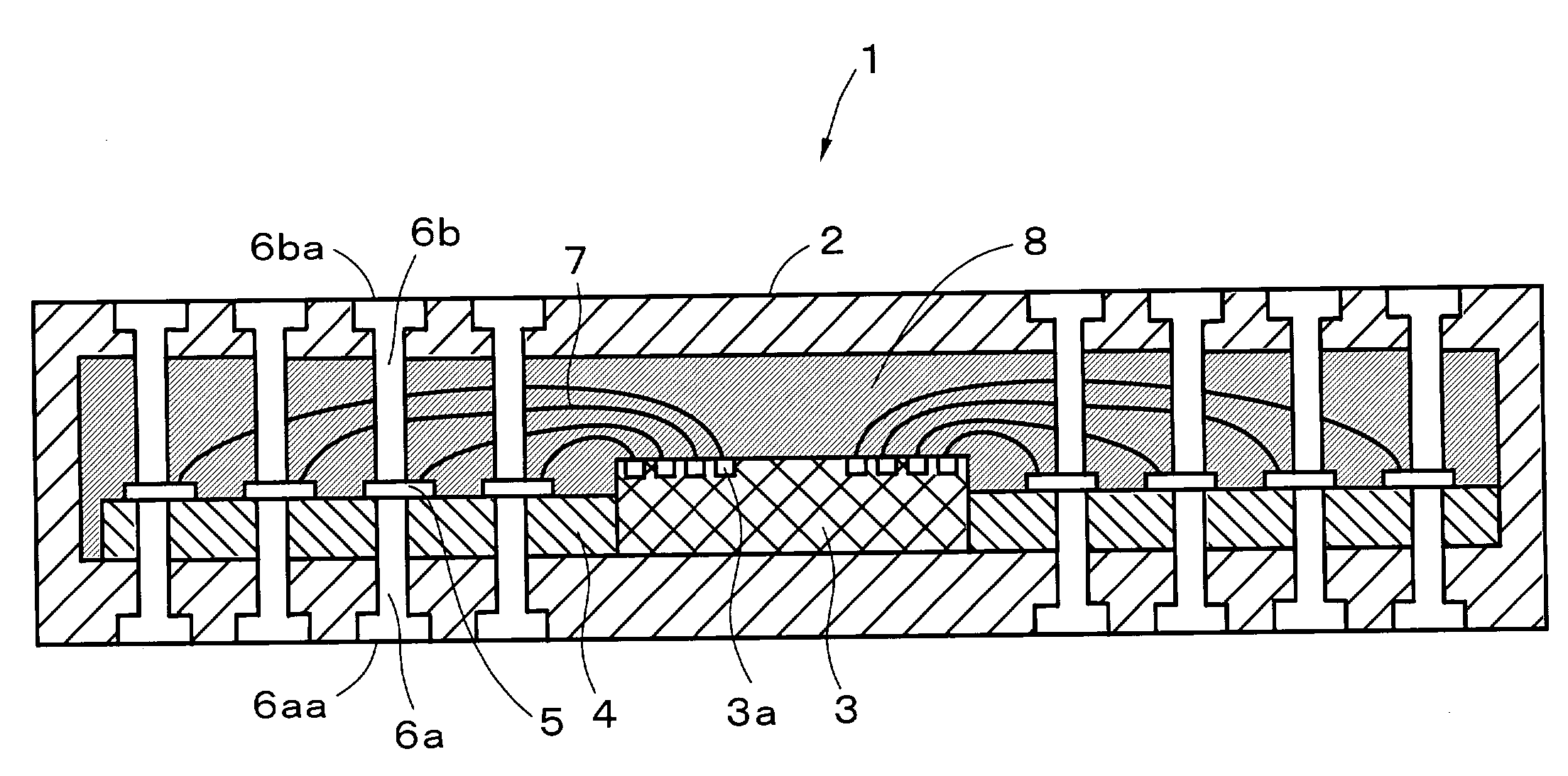

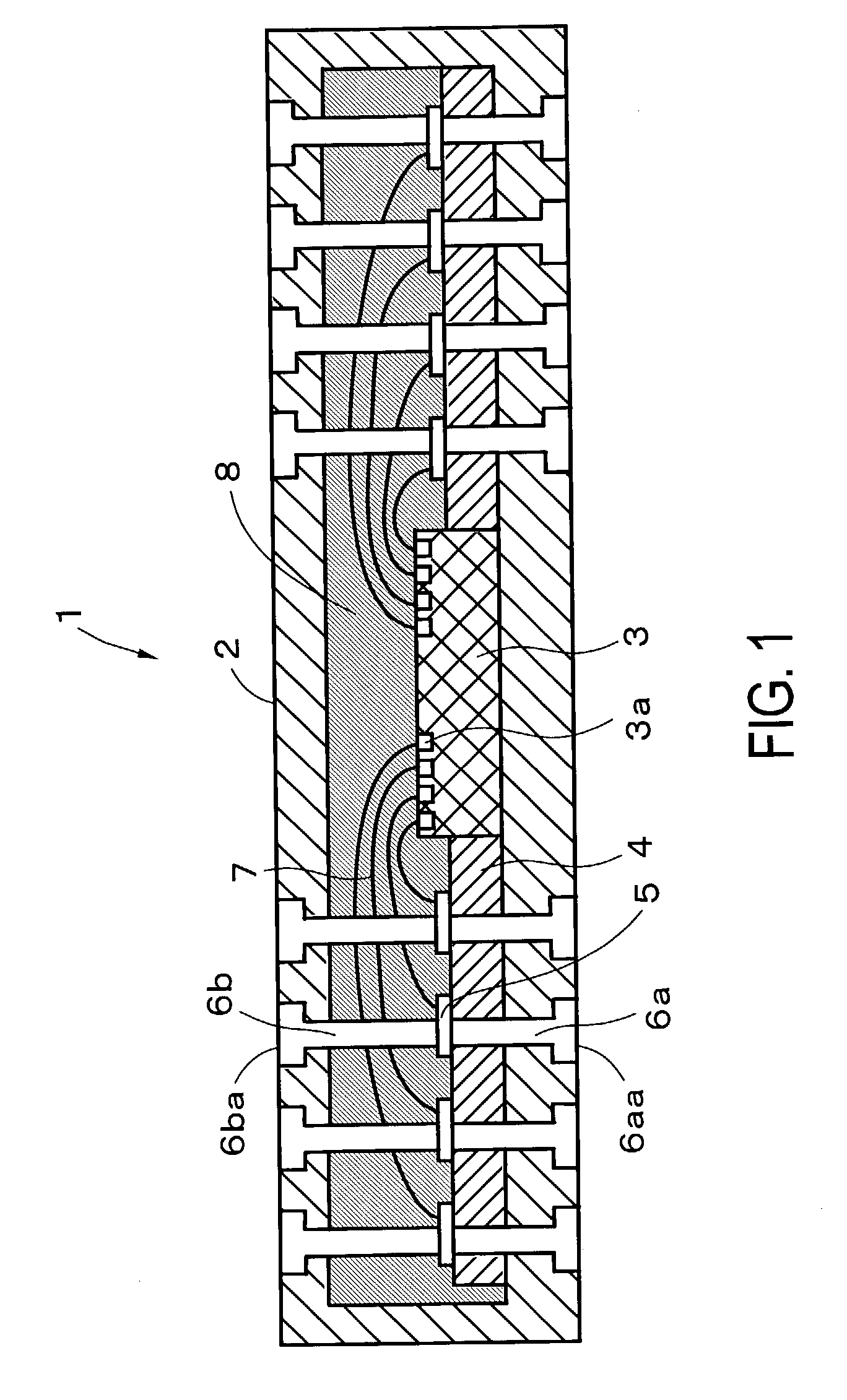

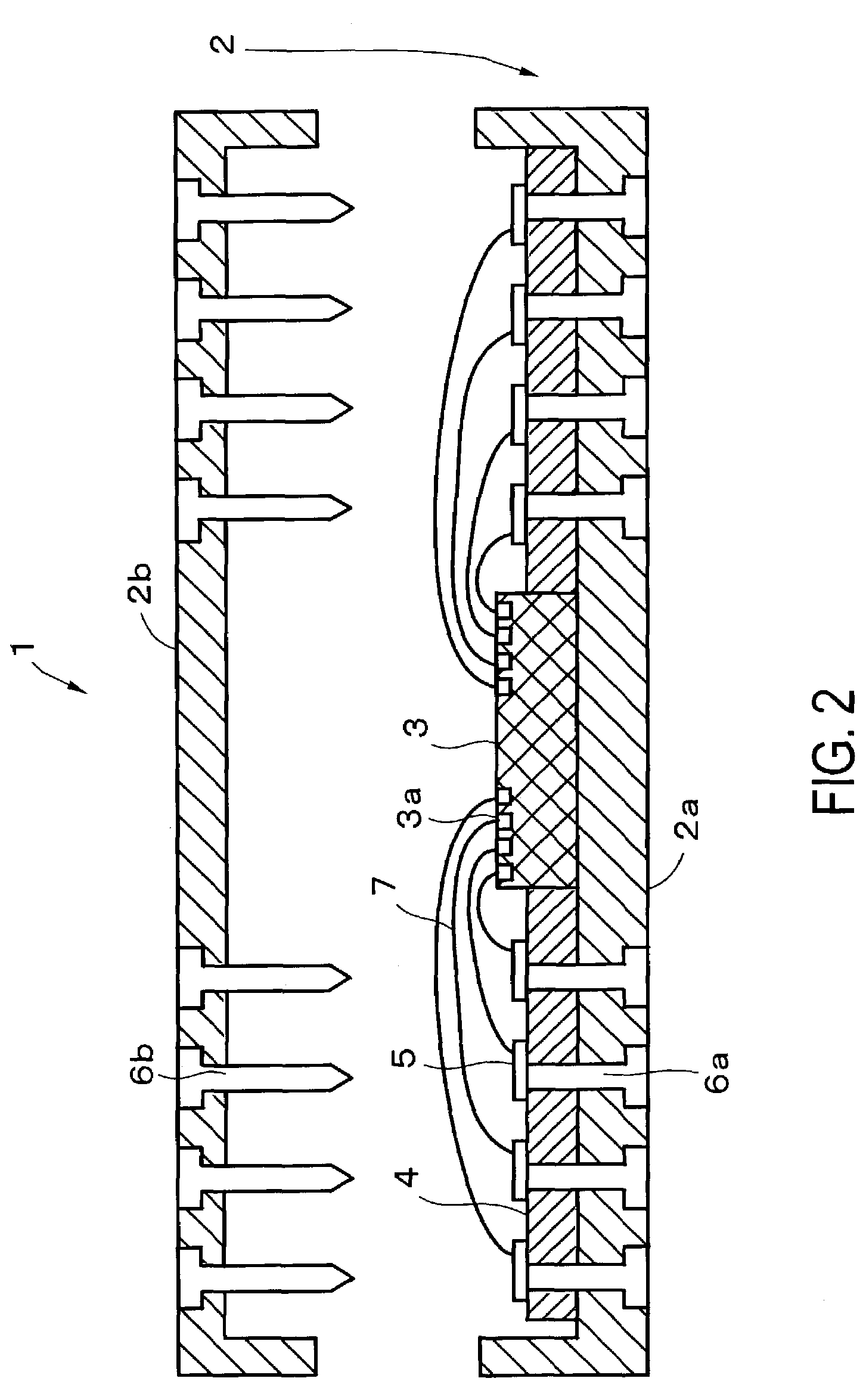

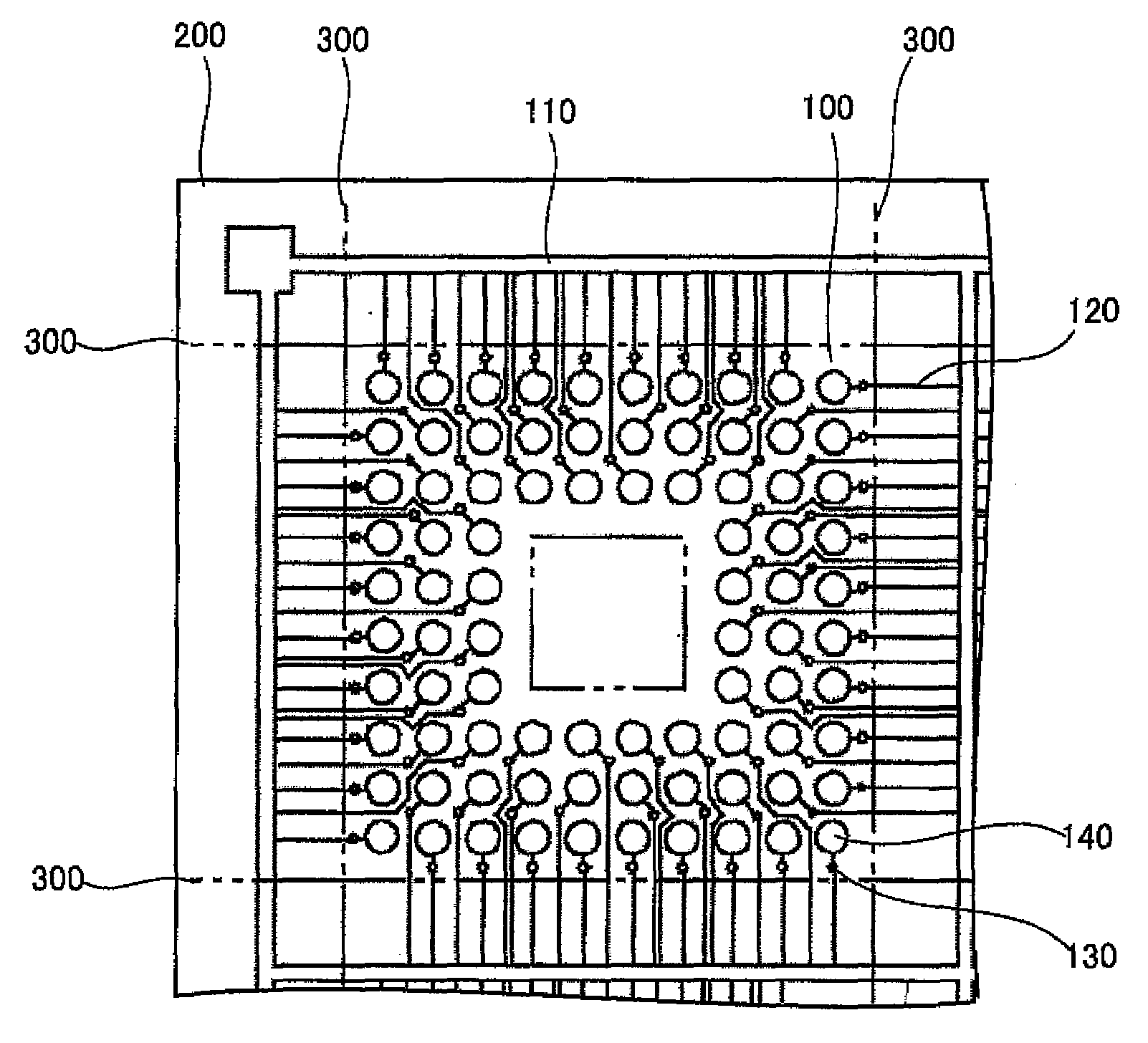

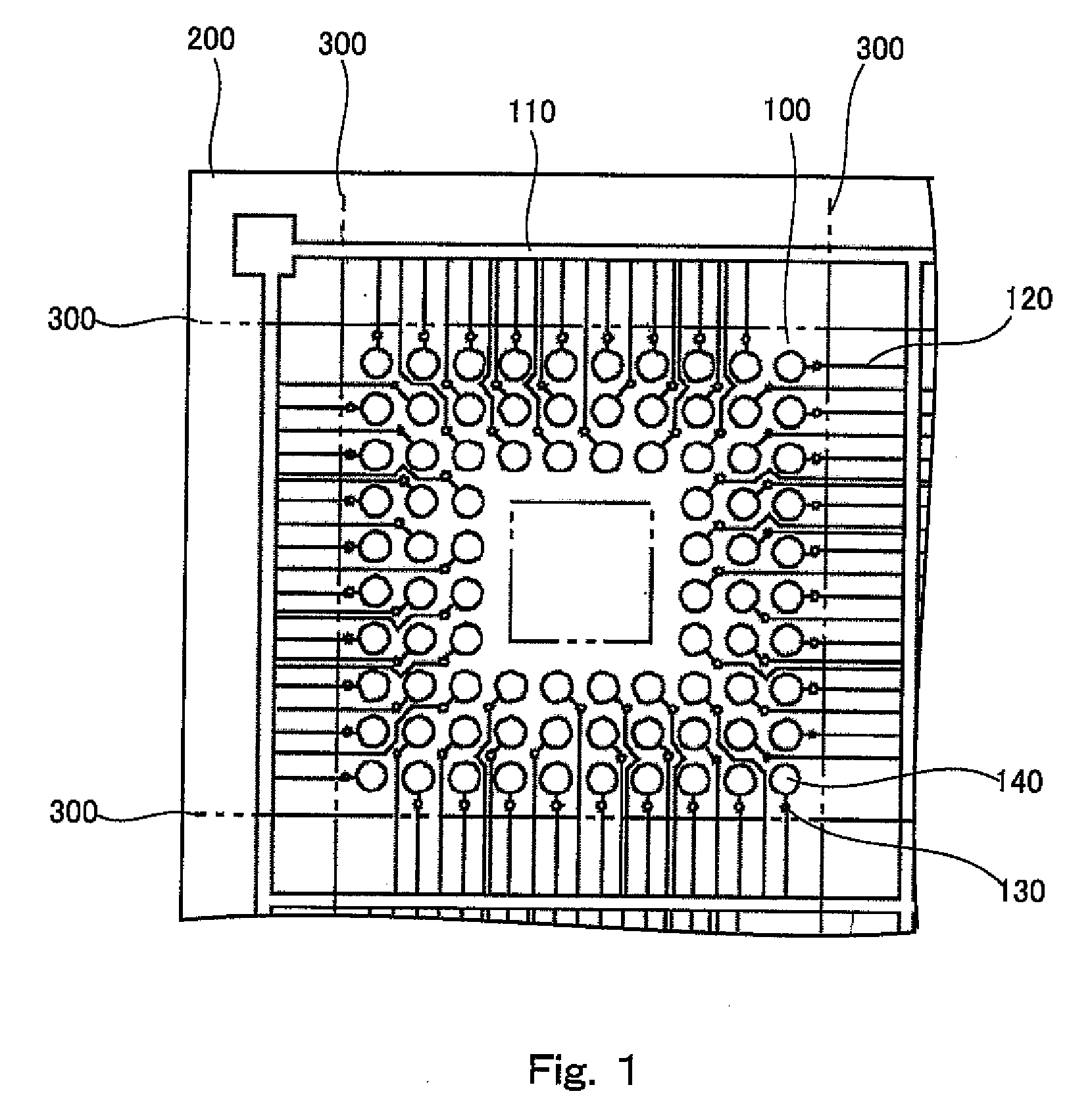

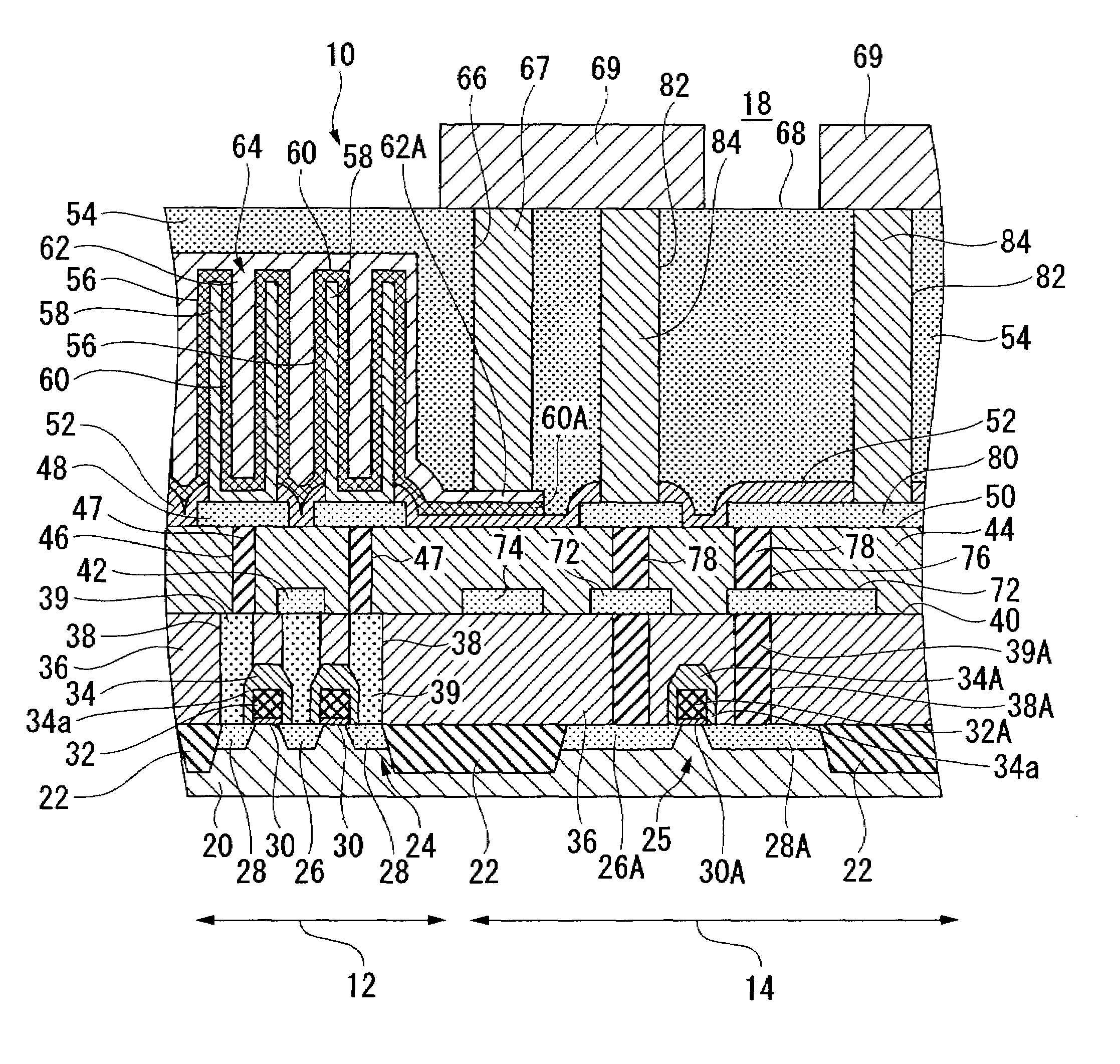

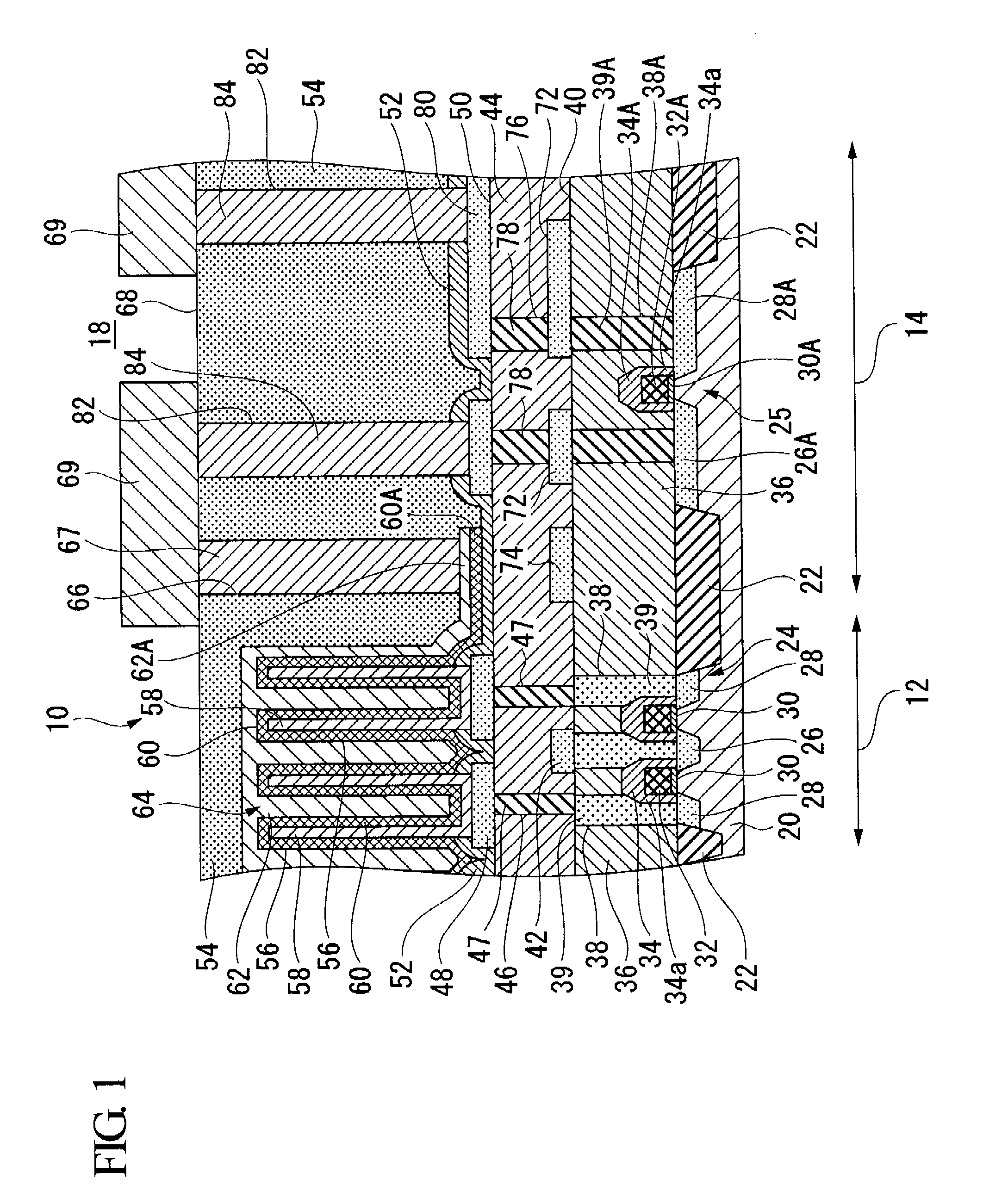

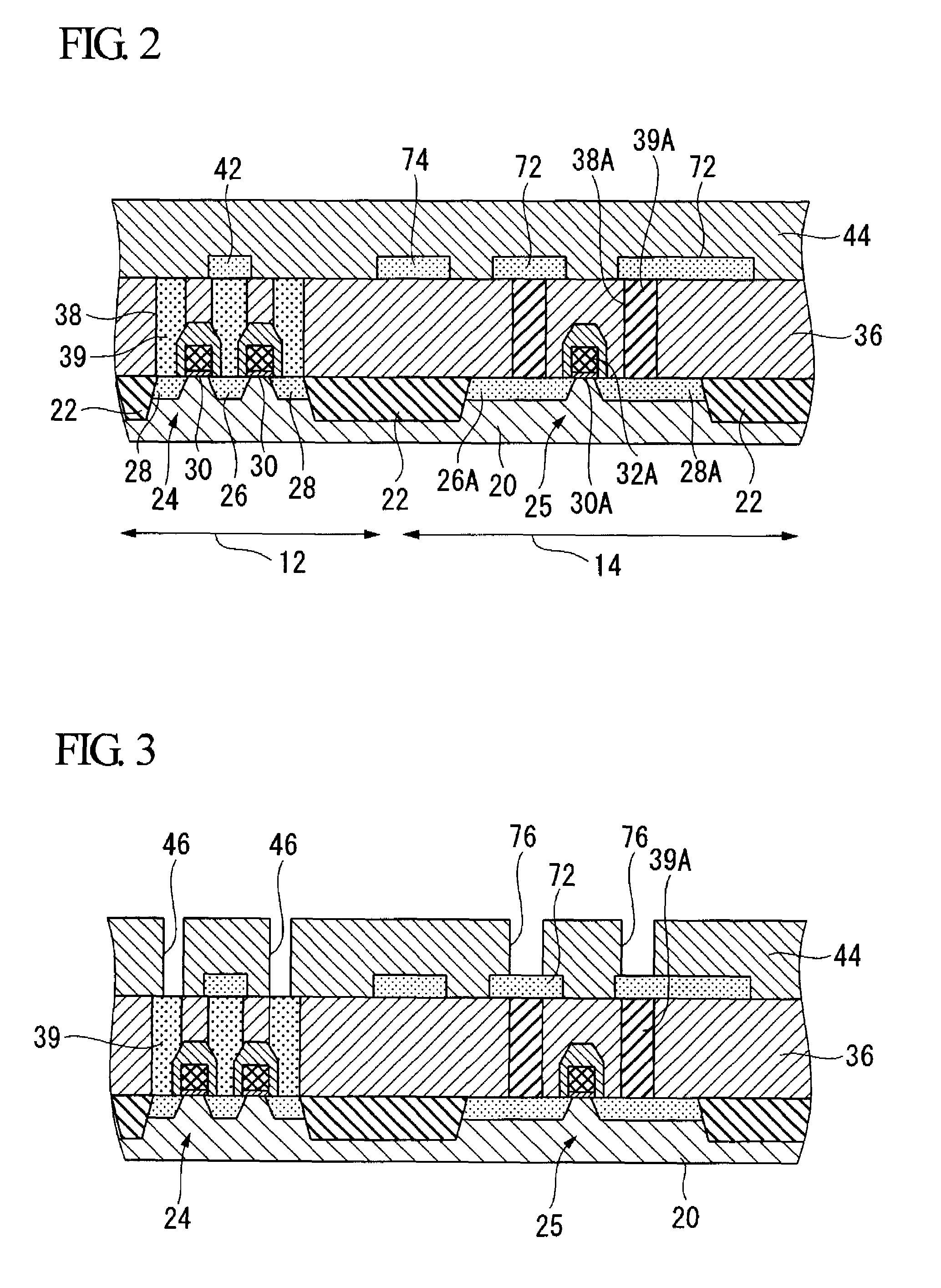

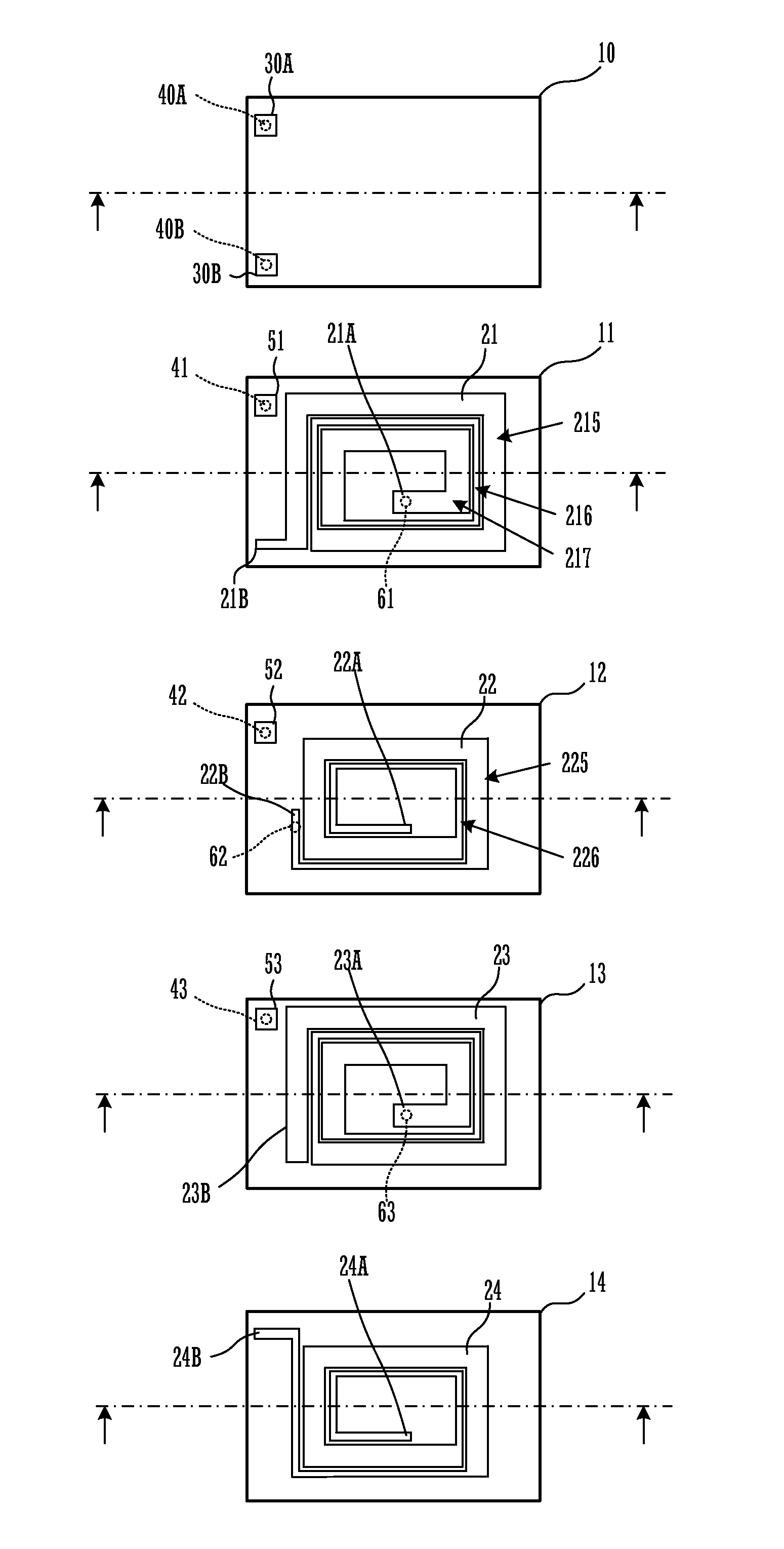

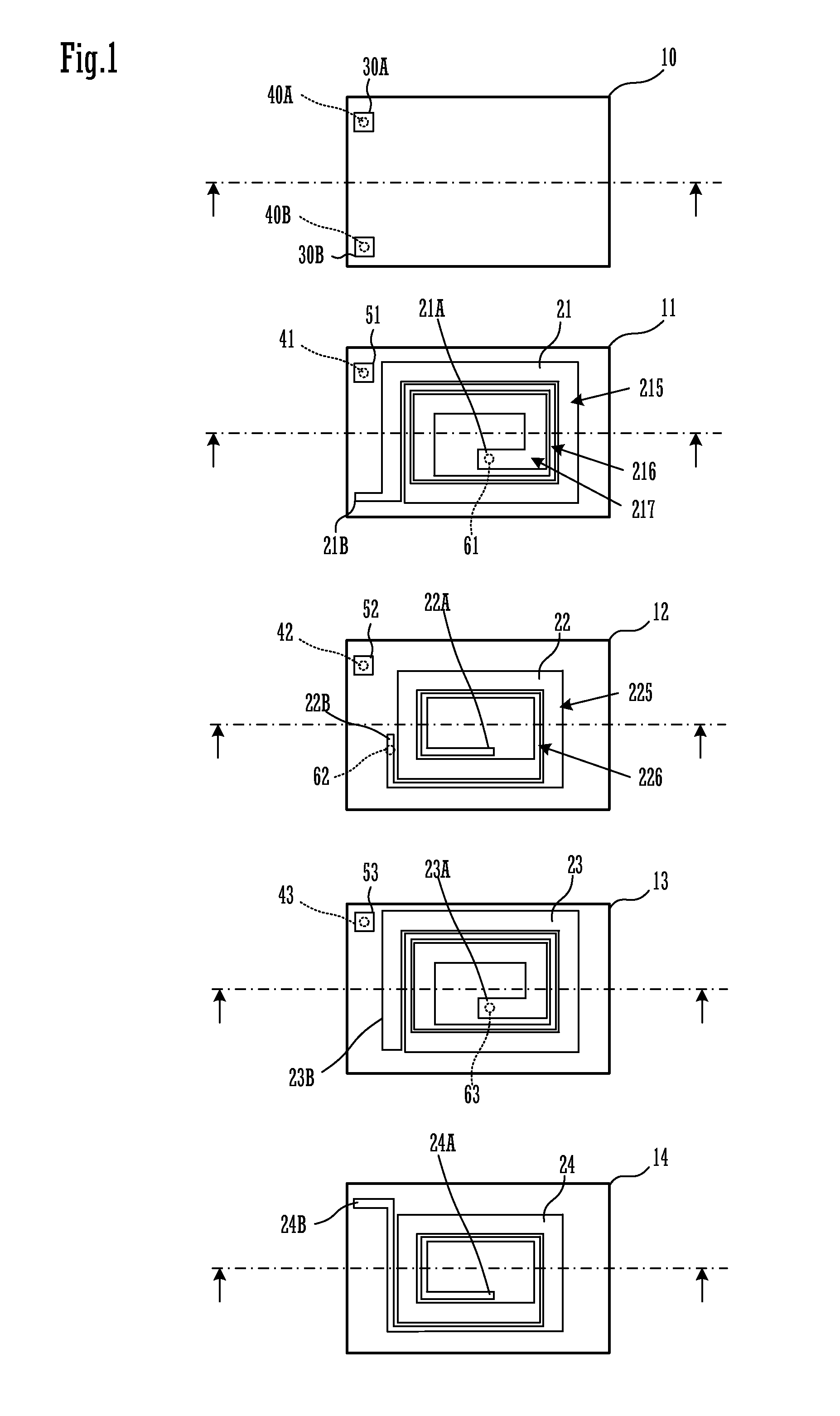

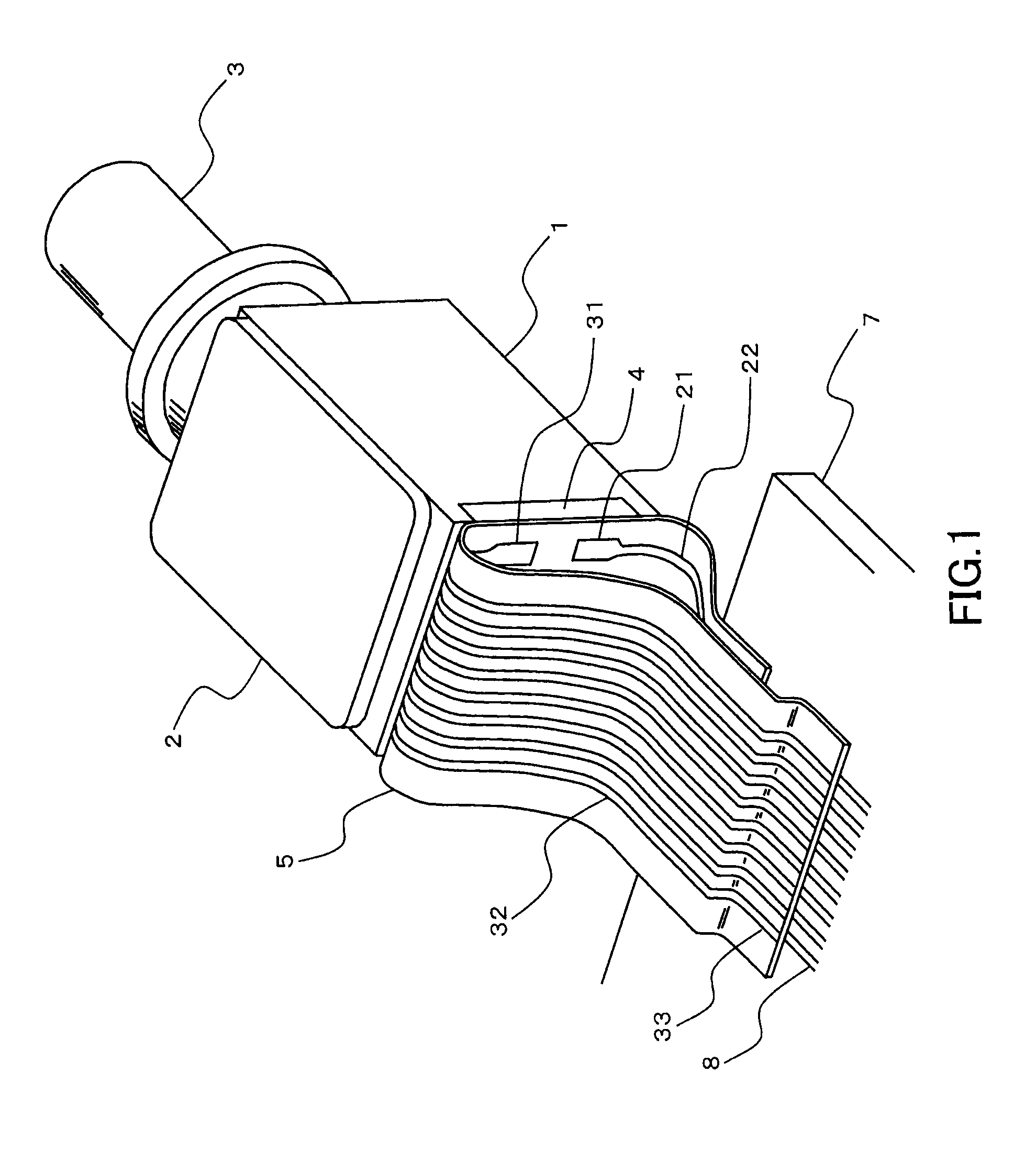

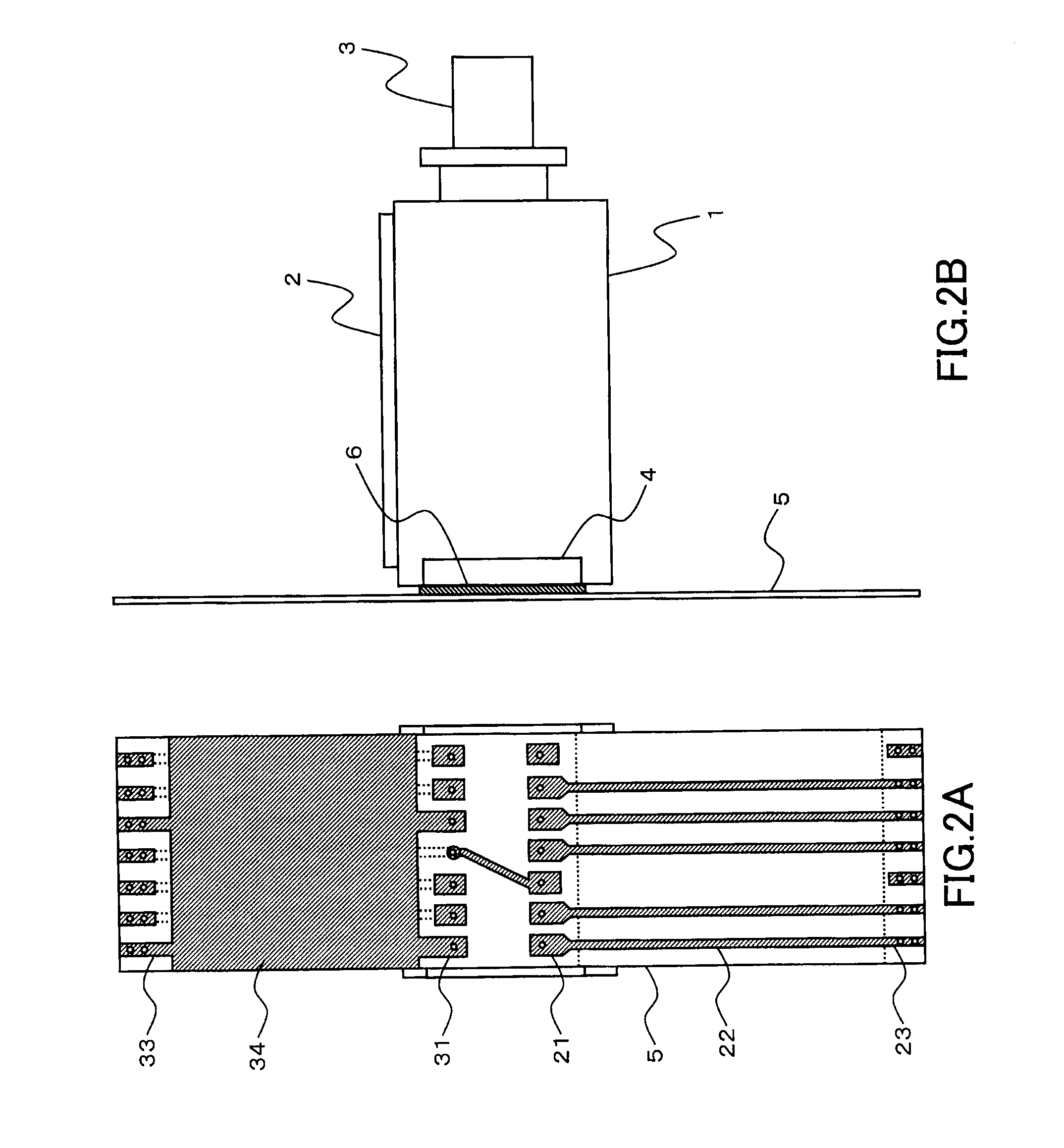

Semiconductor device and system having semiconductor device mounted thereon

InactiveUS7224054B2Reduce wiring densityEasy to routePrinted circuit assemblingSemiconductor/solid-state device detailsEngineeringBall grid array

A ball grid array packaged semiconductor device mounted on a mounting board and including pads formed within a package and are connected to signal lines of a bare chip by bonding wires. There are formed first vias extending from the respective pads to a bottom surface of a package, and second vias extending from the same respective pads to a top surface of the package to form continuous vias. This makes it possible to connect the mounting boards to the top and bottom surfaces of the package, thereby enabling reduction of the wiring density of wiring patterns on the mounting boards, and thereby facilitating routing of the wiring patterns on the mounting boards. The semiconductor device is capable of reducing wiring density of the wiring pattern on the mounting board.

Owner:SOCIONEXT INC

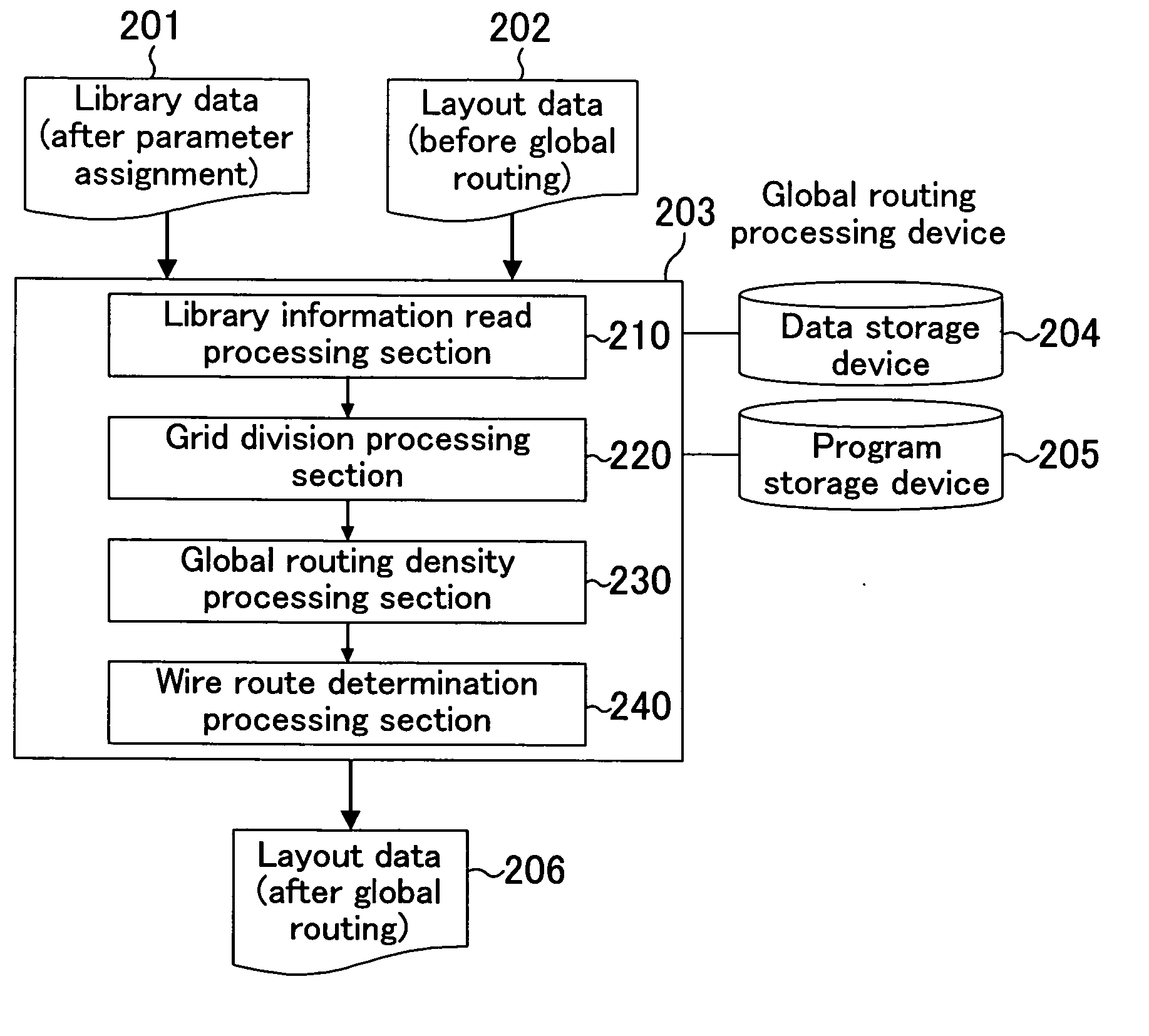

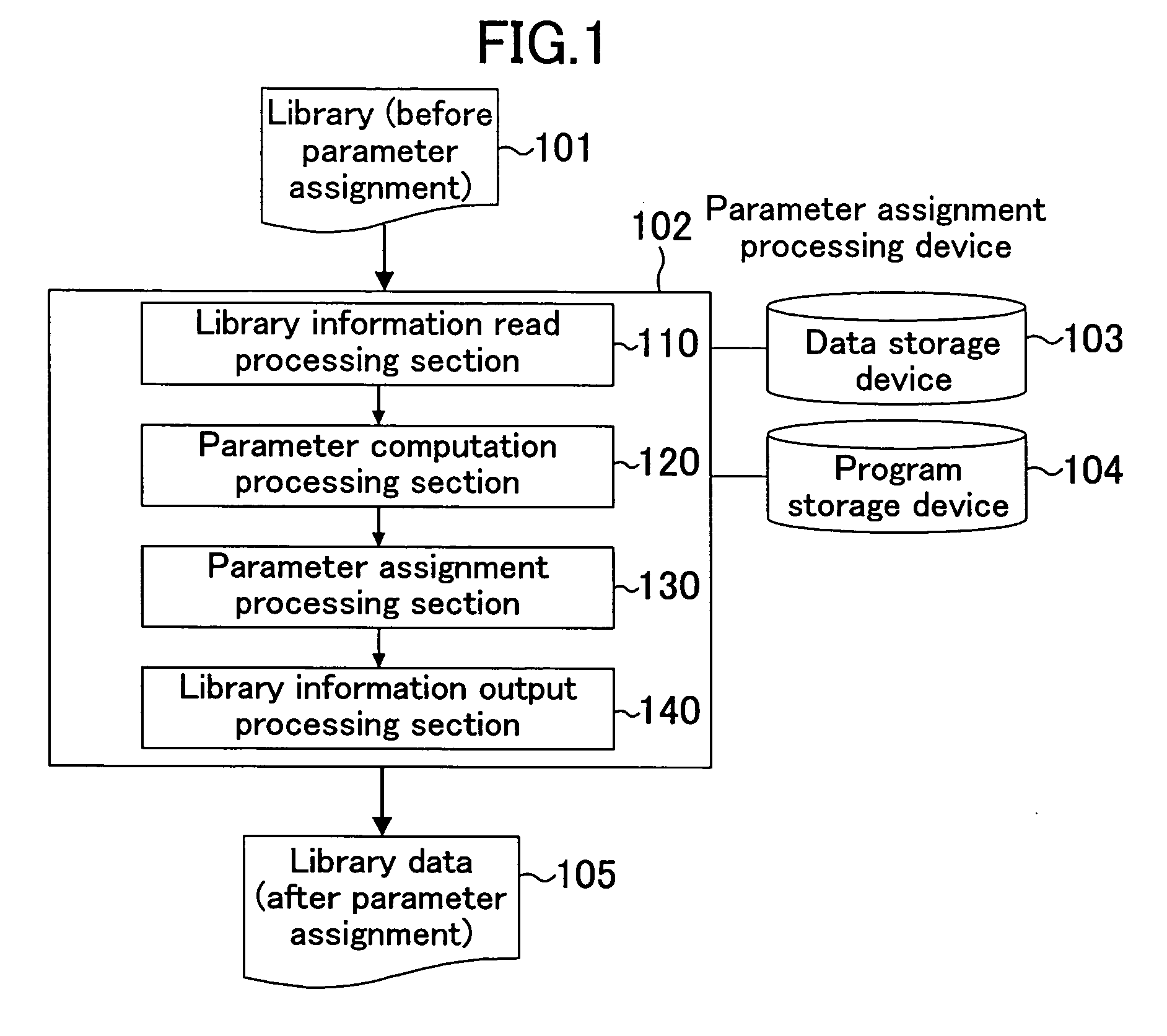

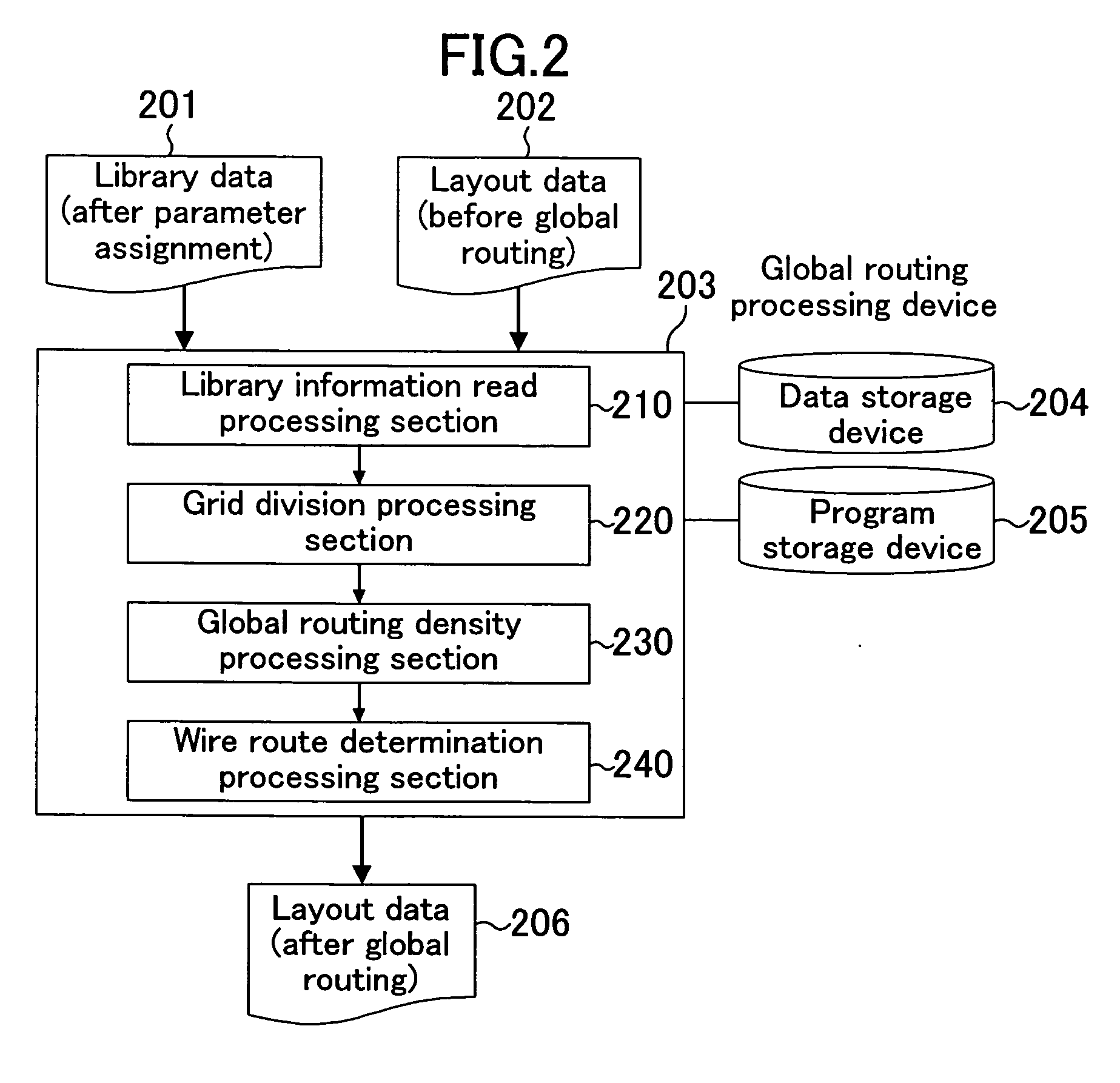

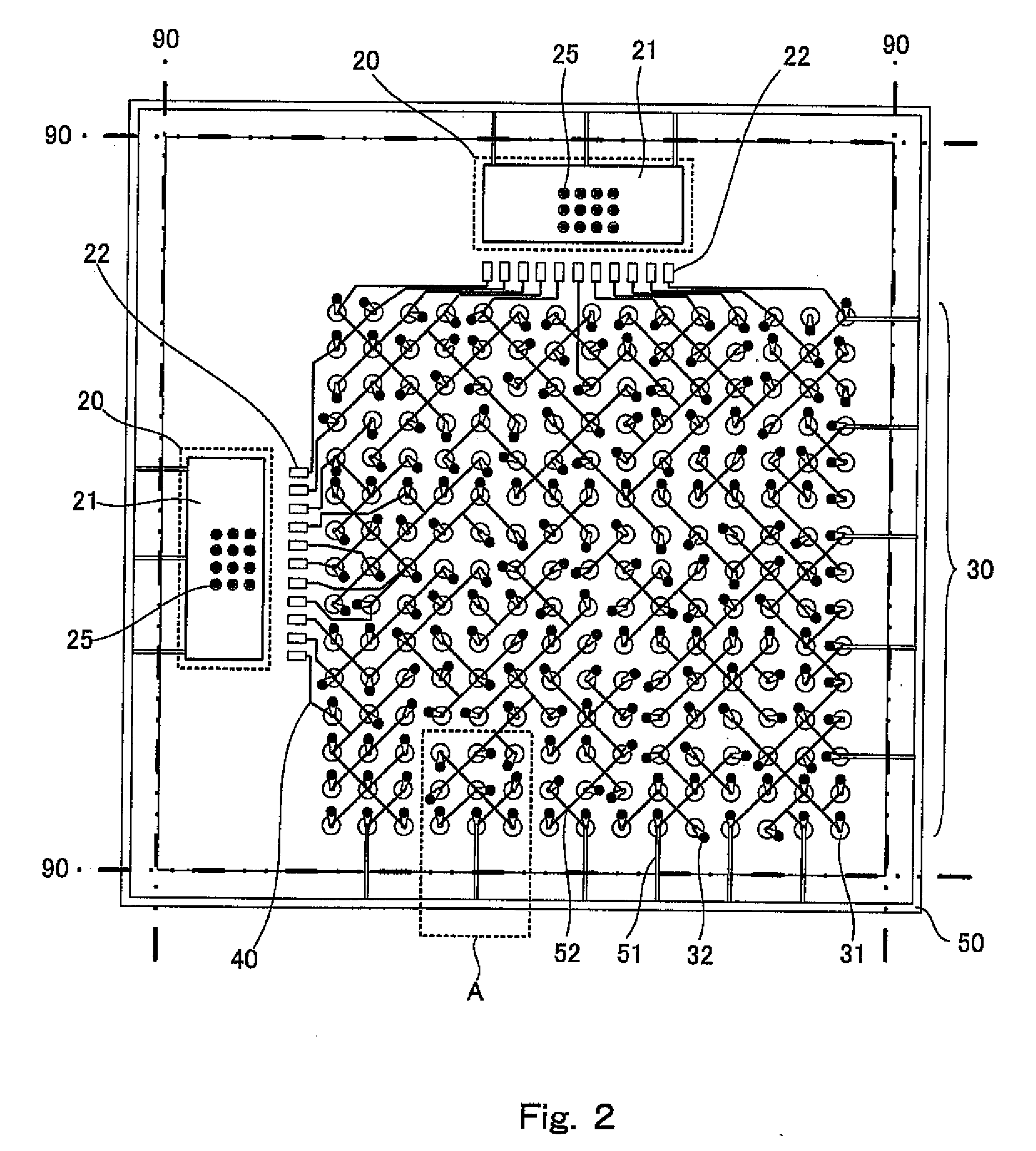

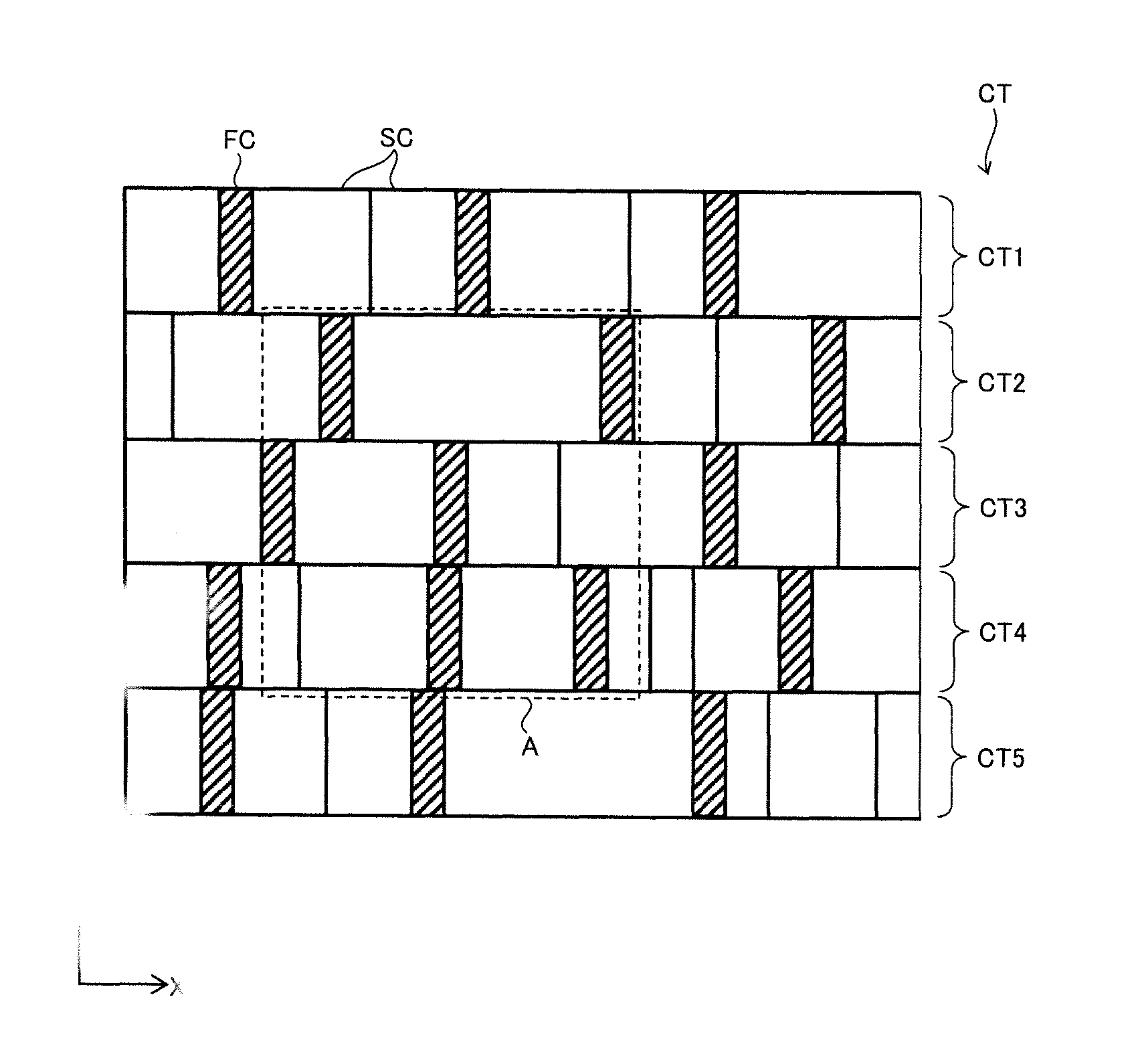

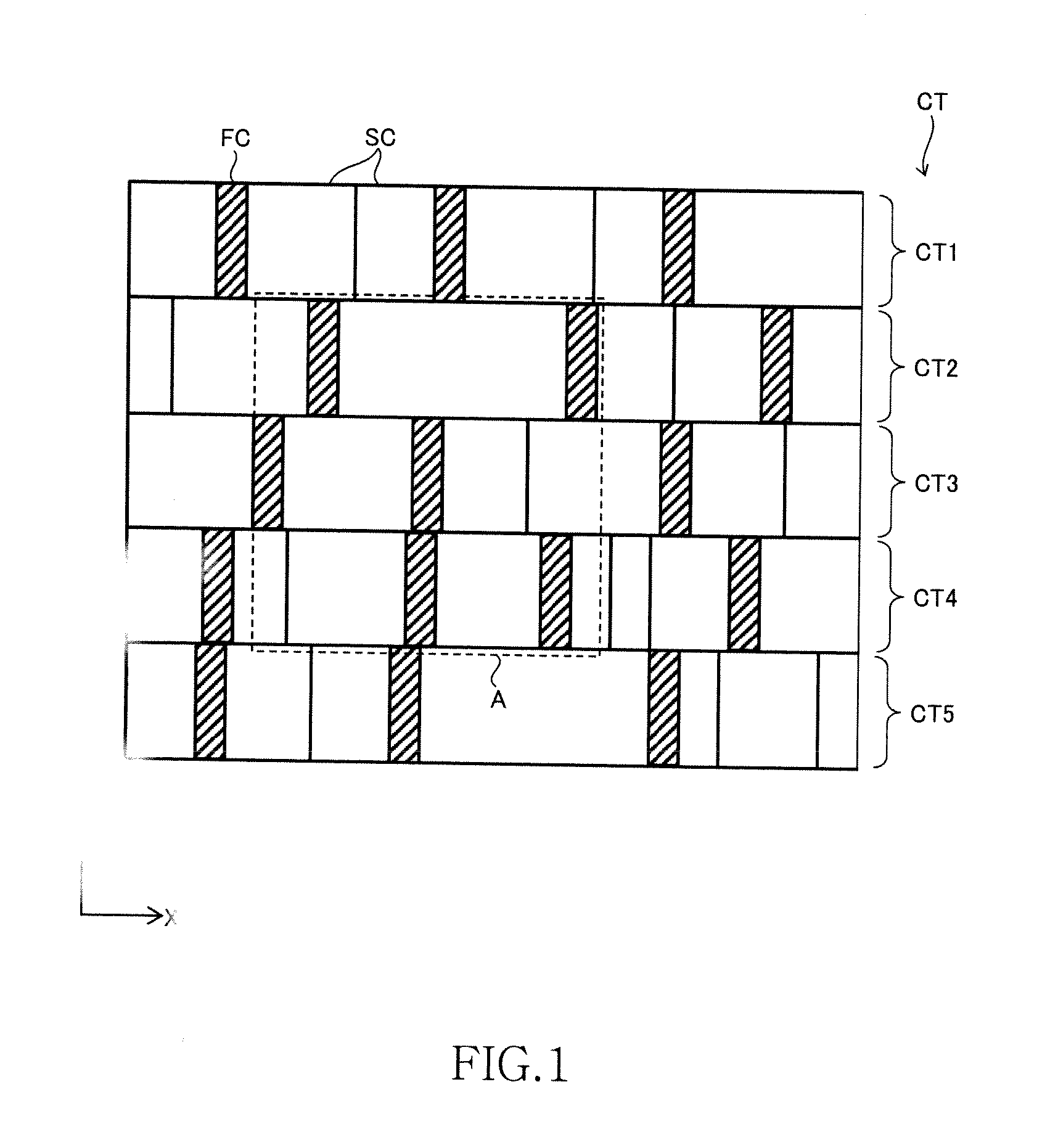

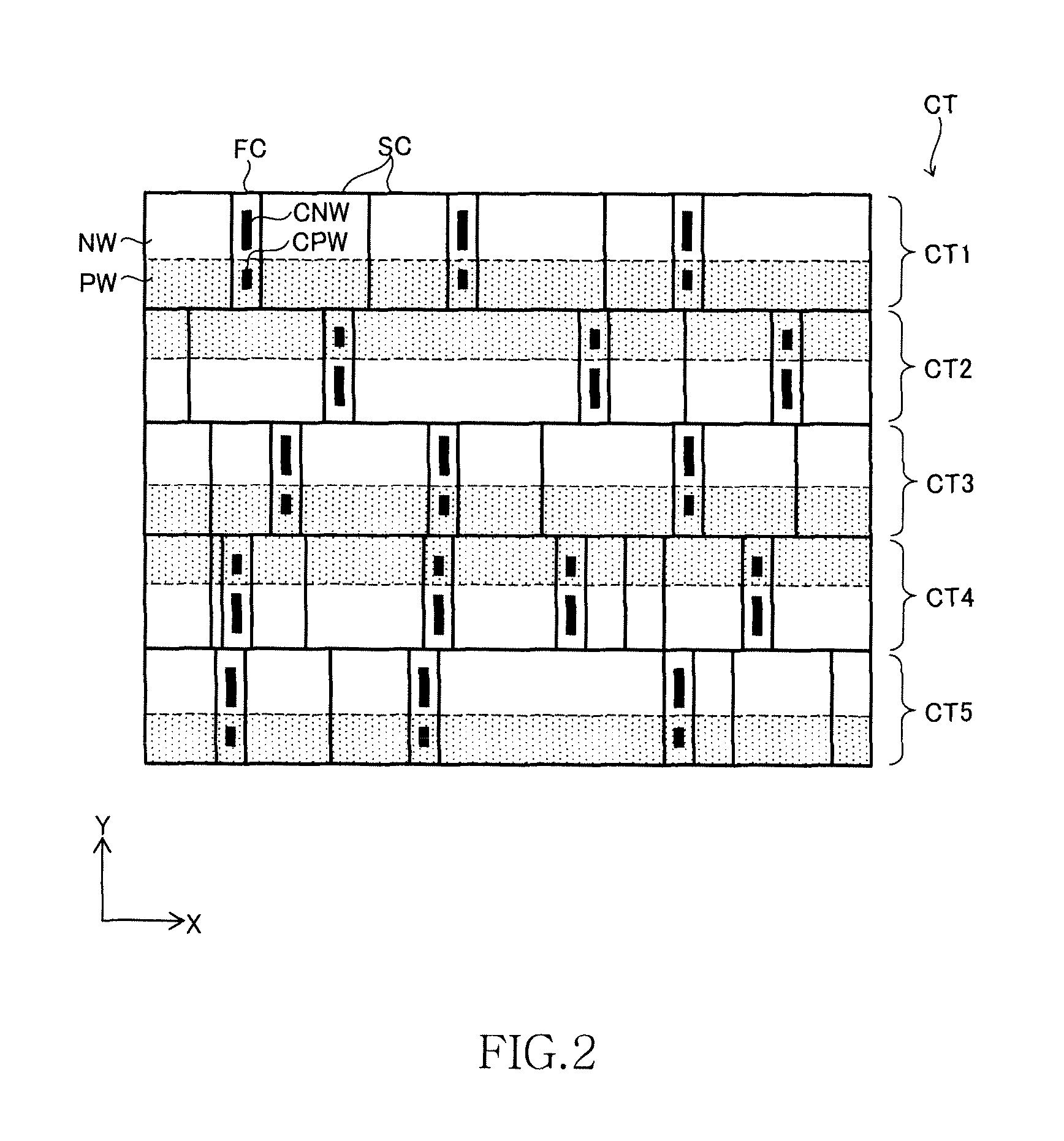

Method, program, and apparatus for designing layout of semiconductor integrated circuit

InactiveUS20070022400A1InhibitionReduce pointsCAD circuit designSoftware simulation/interpretation/emulationComputer architectureGrid pattern

In a method for designing a layout for an LSI, library data, which is information on a standard cell with an assigned parameter or parameters each indicating the probability of occurrence of violations of design rules at a pin connection point, is read into a library information read section in a global routing processing device. And in a global routing density processing section and a wire route determination processing section, the density of global routes that pass above a chip area divided into a plurality of portions in a grid pattern by a grid division processing section is set according to the parameters, so that the density of routes at pin connection points where the probability of occurrence of violations of design rules is high becomes low. Therefore, the global routing is carried out in such a manner that occurrence of violations of design rules at the pin connection points are prevented as much as possible.

Owner:PANASONIC CORP

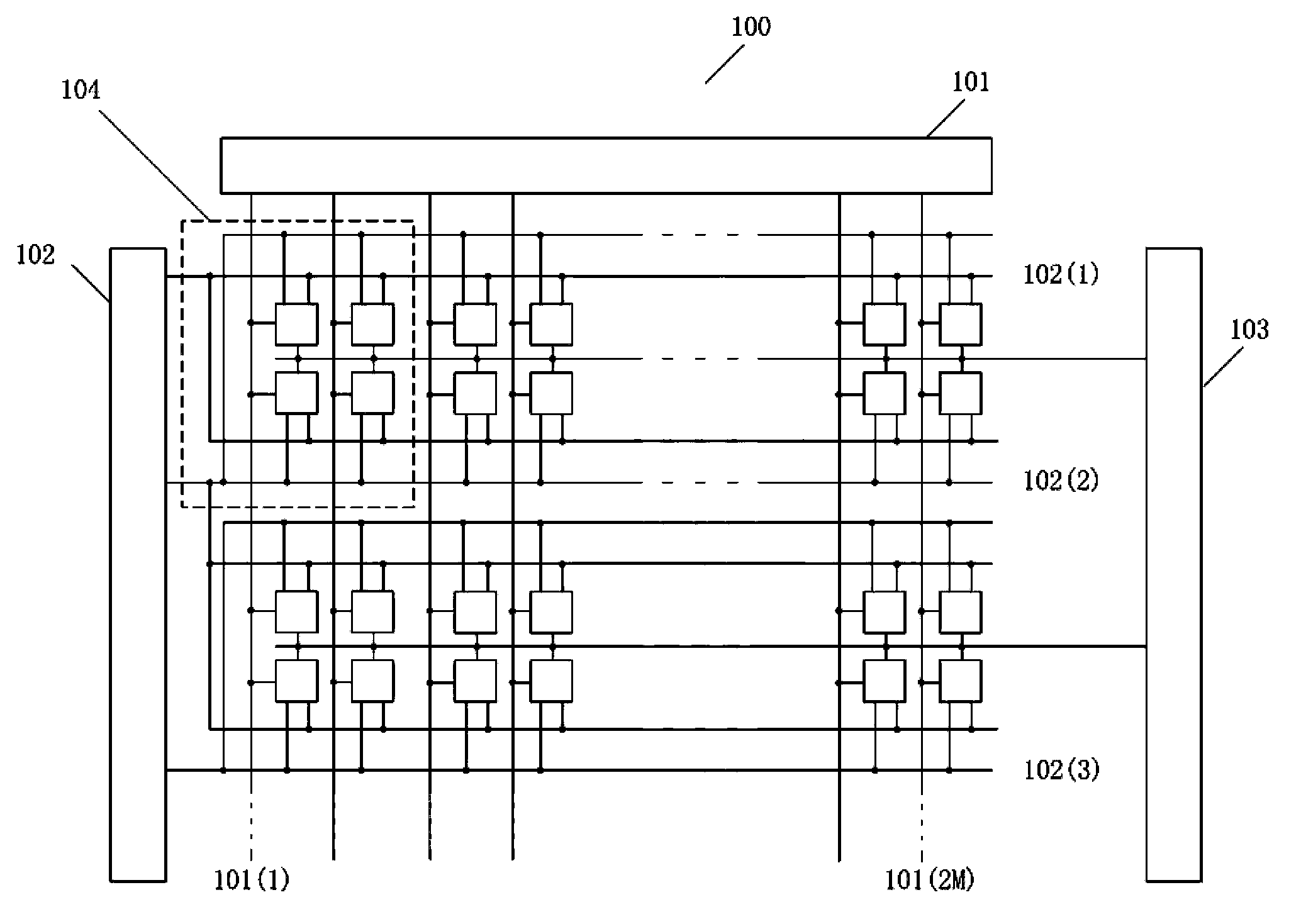

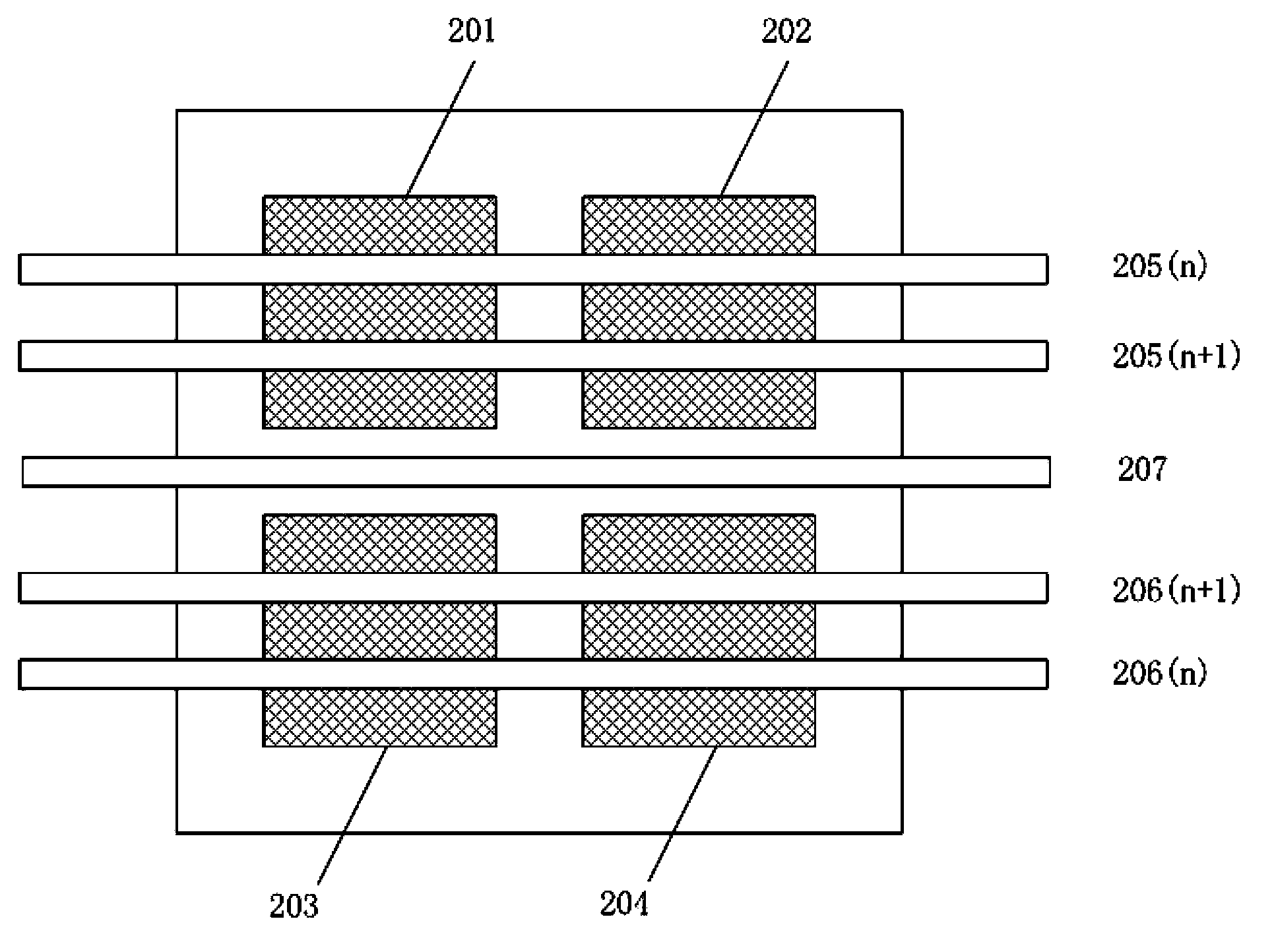

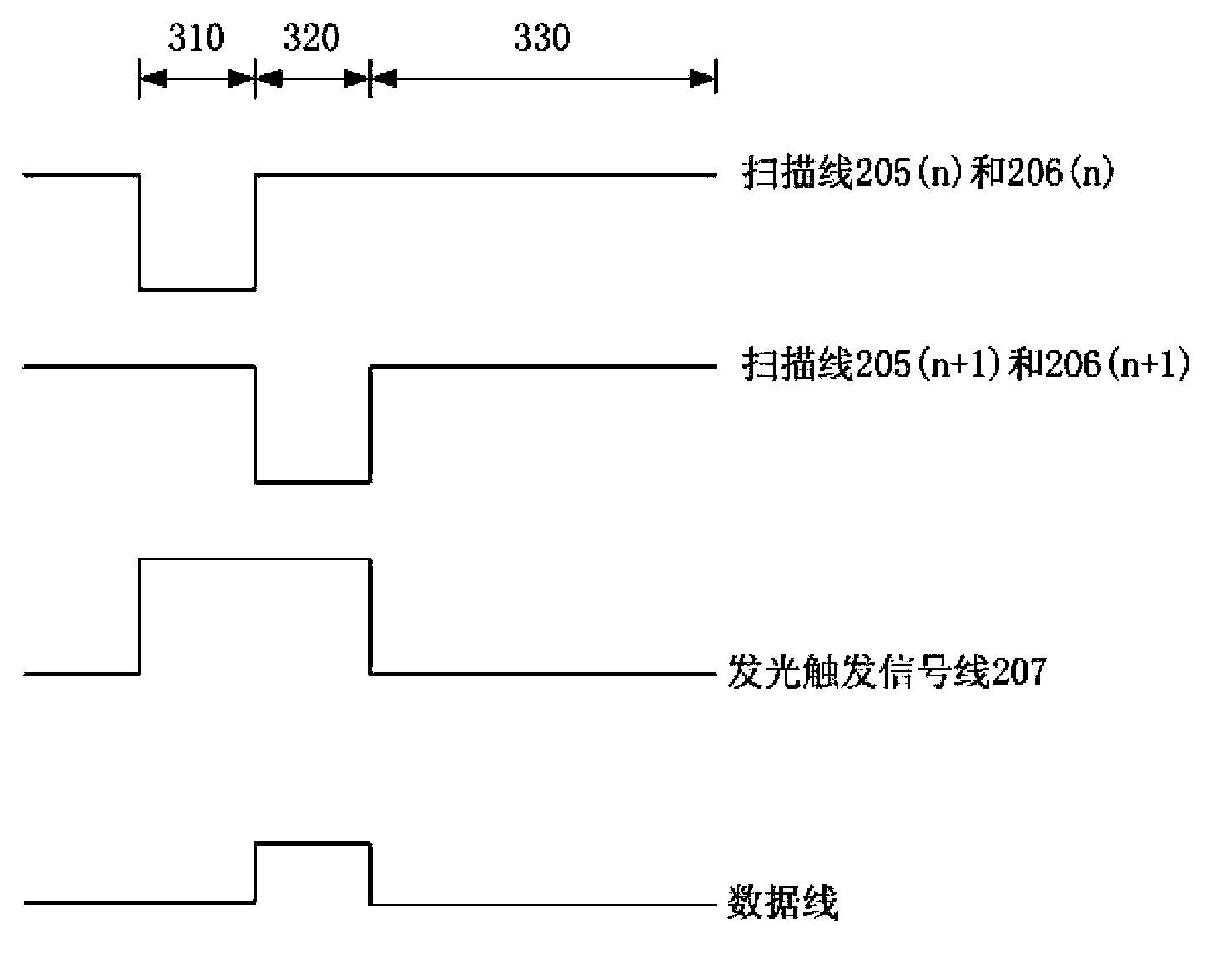

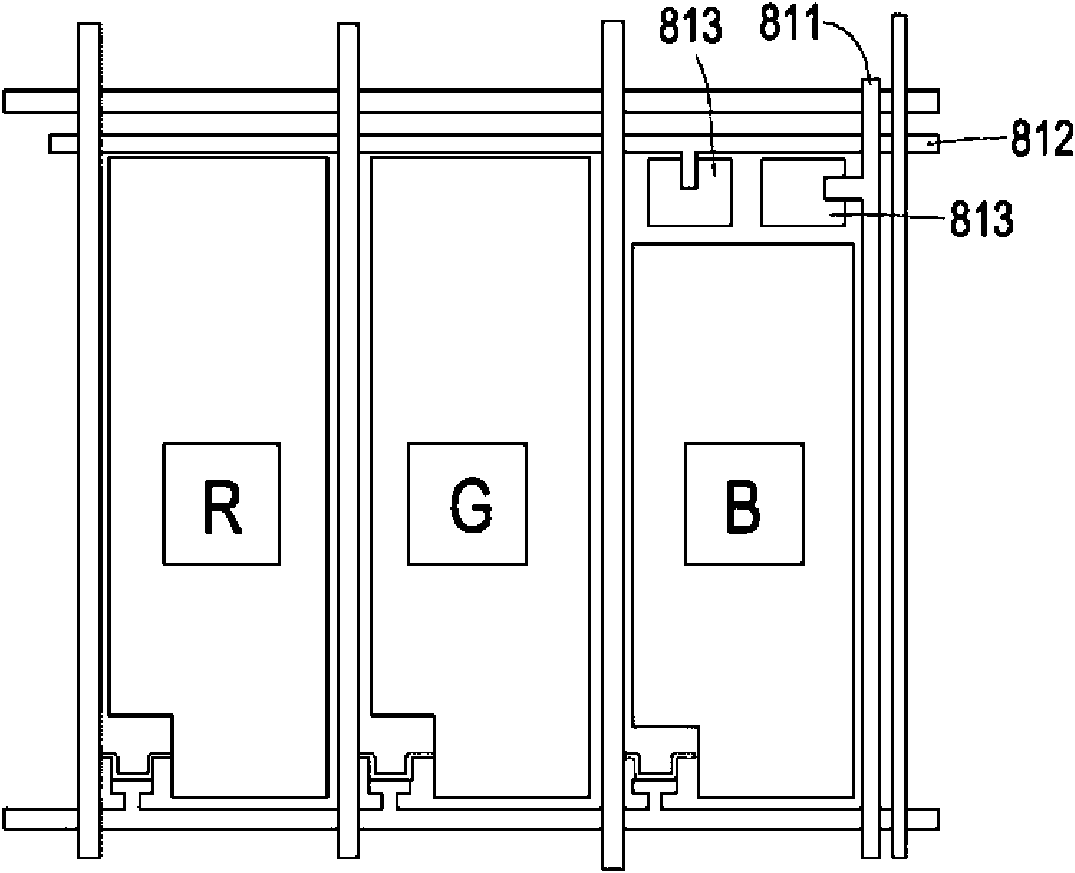

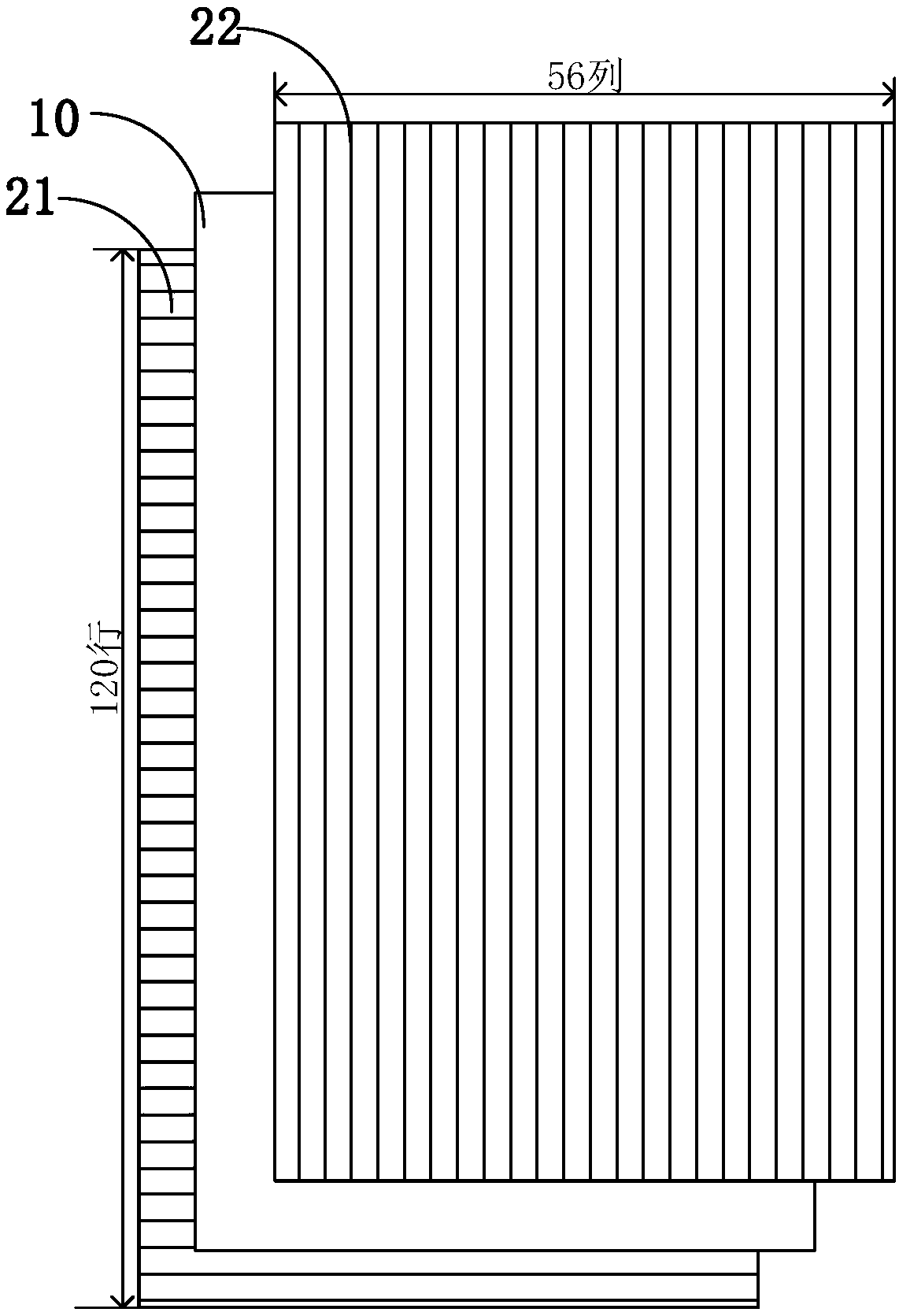

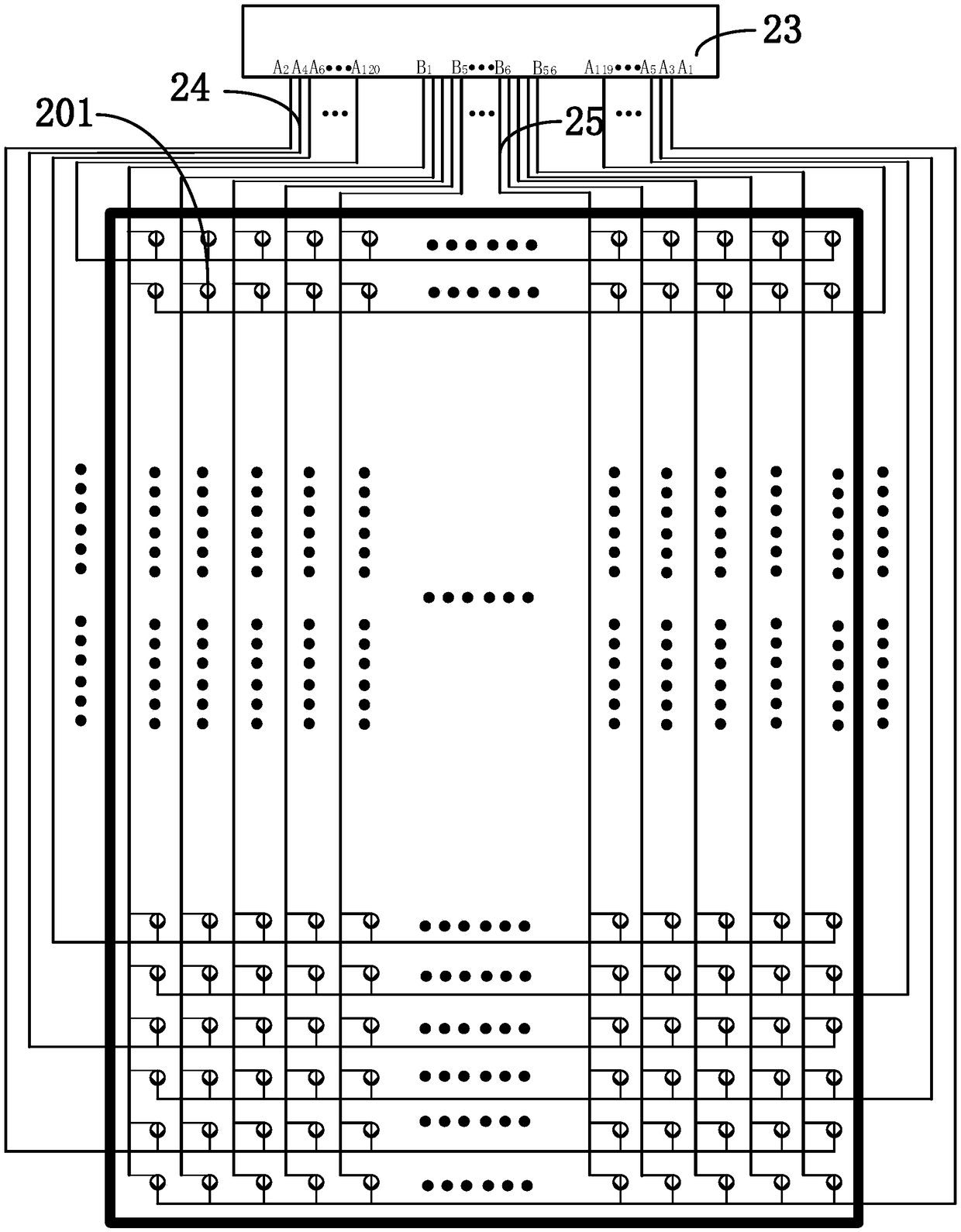

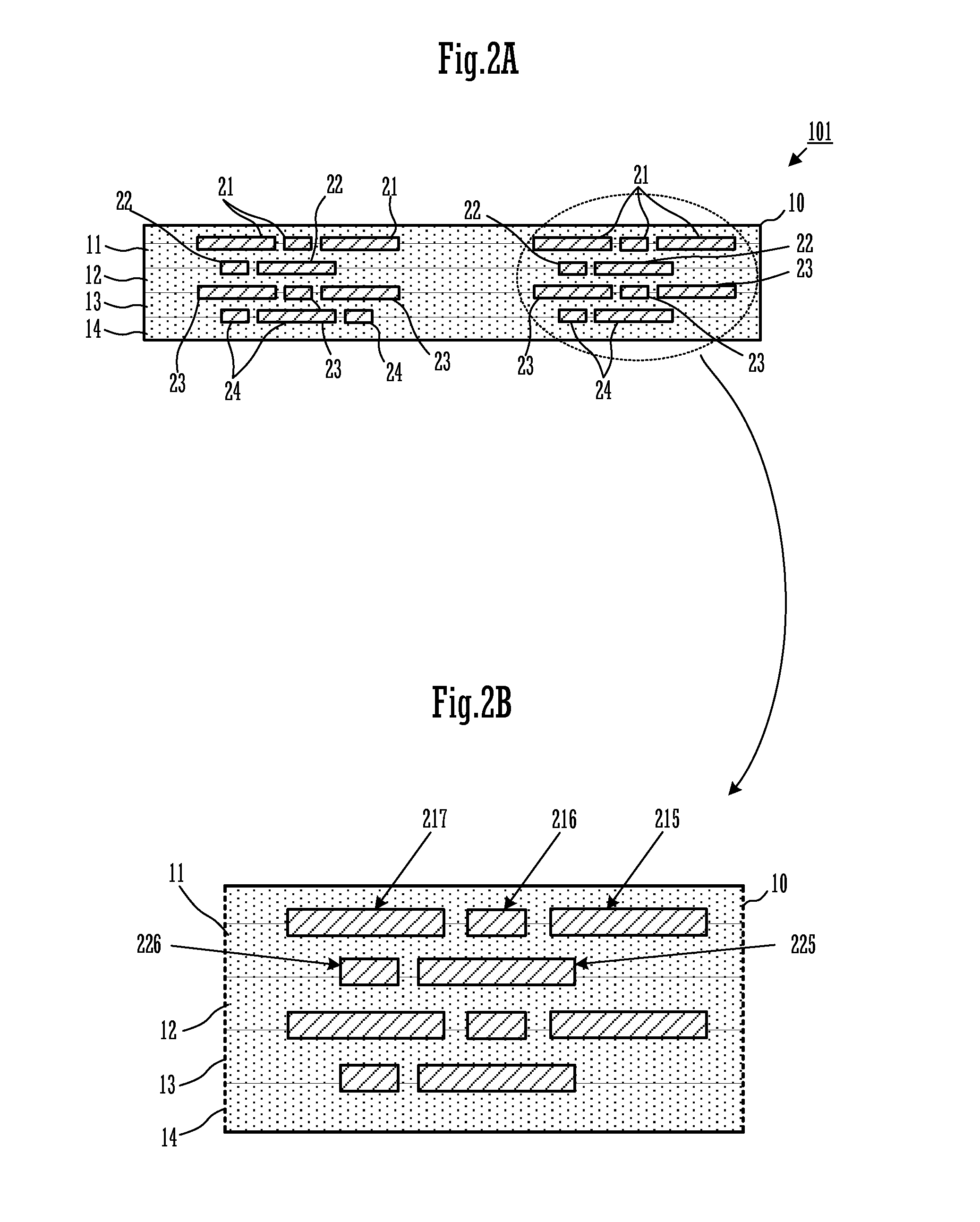

Organic light emitting diode display array

ActiveCN103886826AReduce wiringReduce wiring densityStatic indicating devicesLight-emitting diodeOLED

The invention discloses an organic light emitting diode display array. According to the organic light emitting diode display array, through changing the time sequence control relationship and circuit connection relationship of organic light emitting diode pixel units, organic light emitting diode sub pixels of adjacent lines can share signals of scanning lines arranged in the middle of the two. On the premise of not reducing the performances of a pixel compensation circuit, wiring of N-1 scanning lines can be reduced for N lines of sub pixel unit arrays, wiring density can be greatly reduced, and the wiring space is saved.

Owner:SHANGHAI TIANMA MICRO ELECTRONICS CO LTD

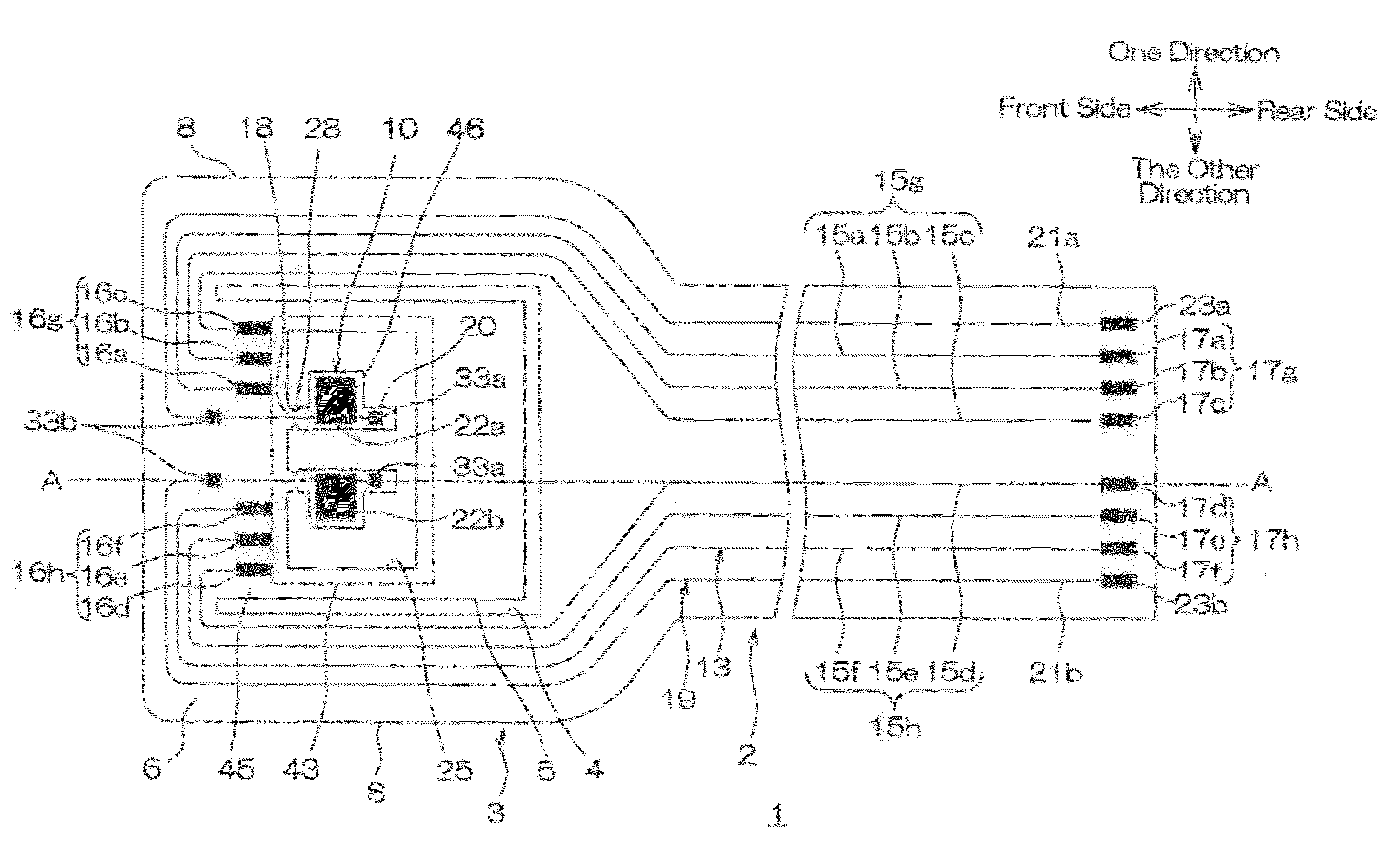

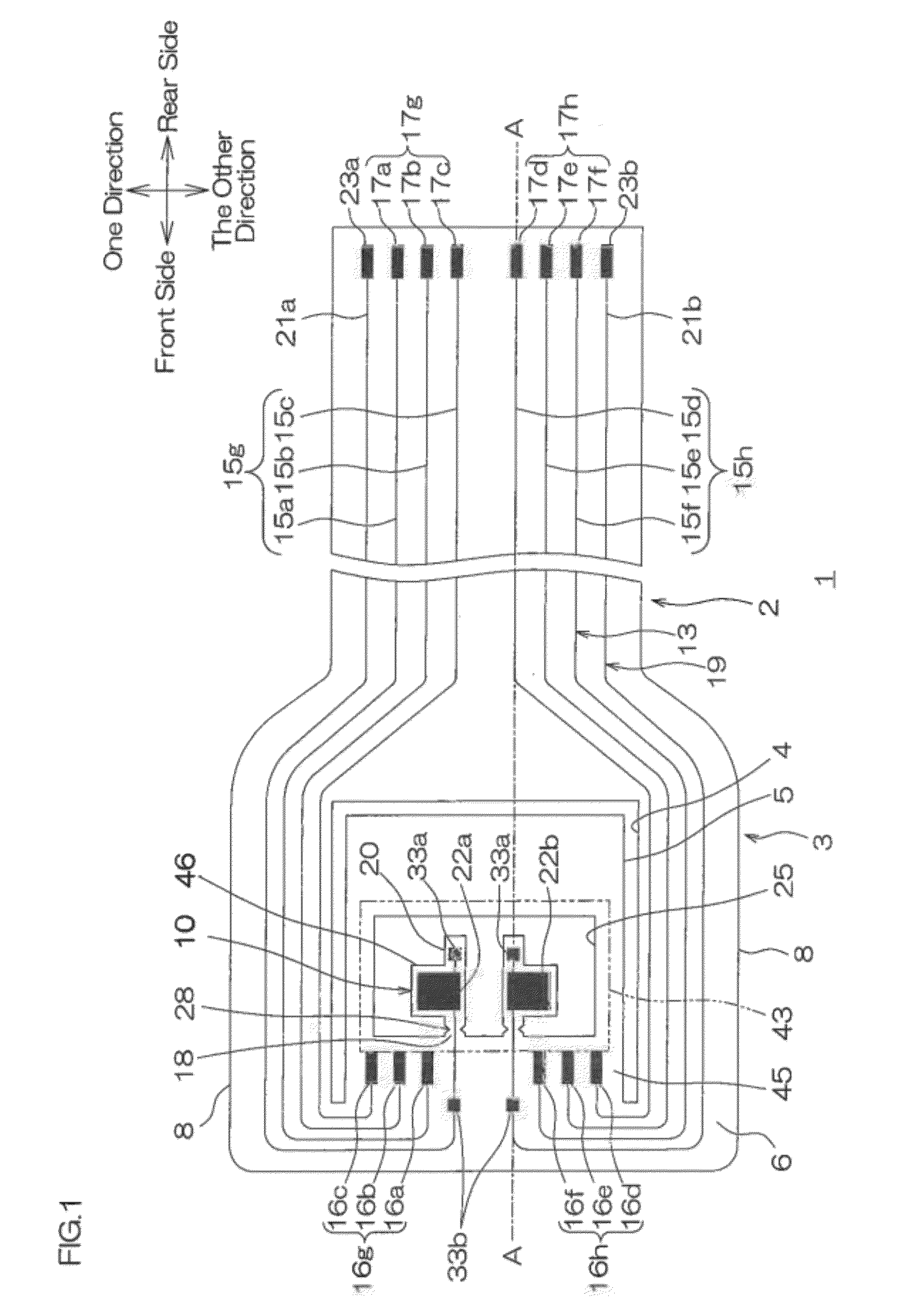

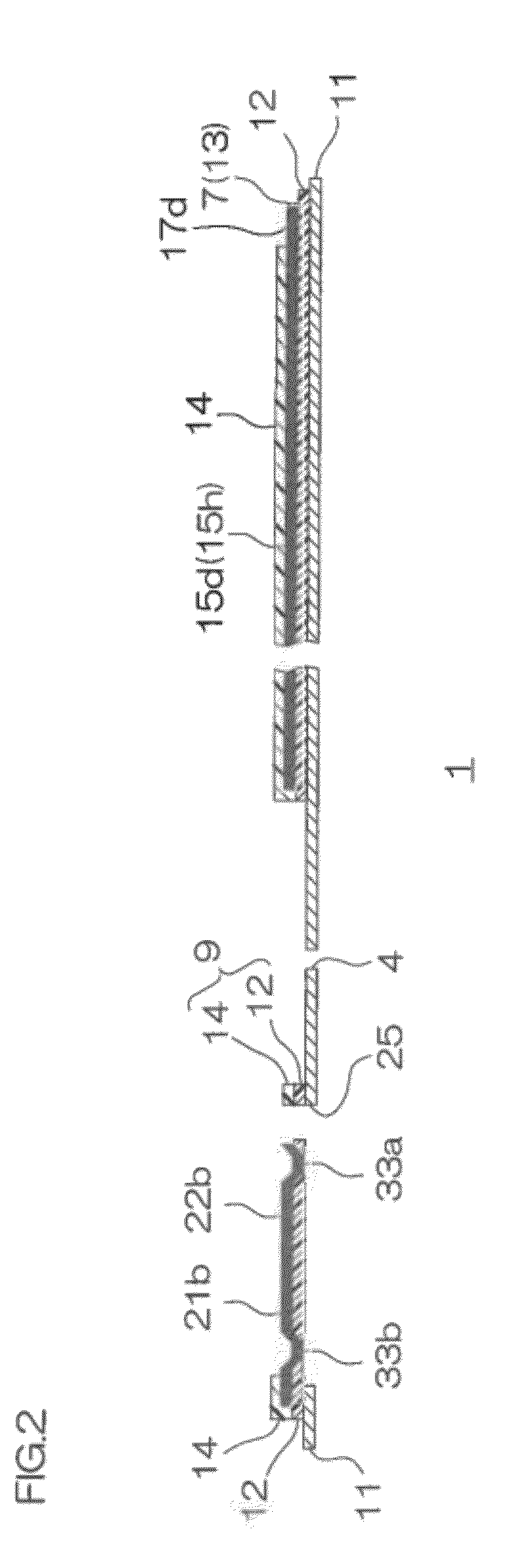

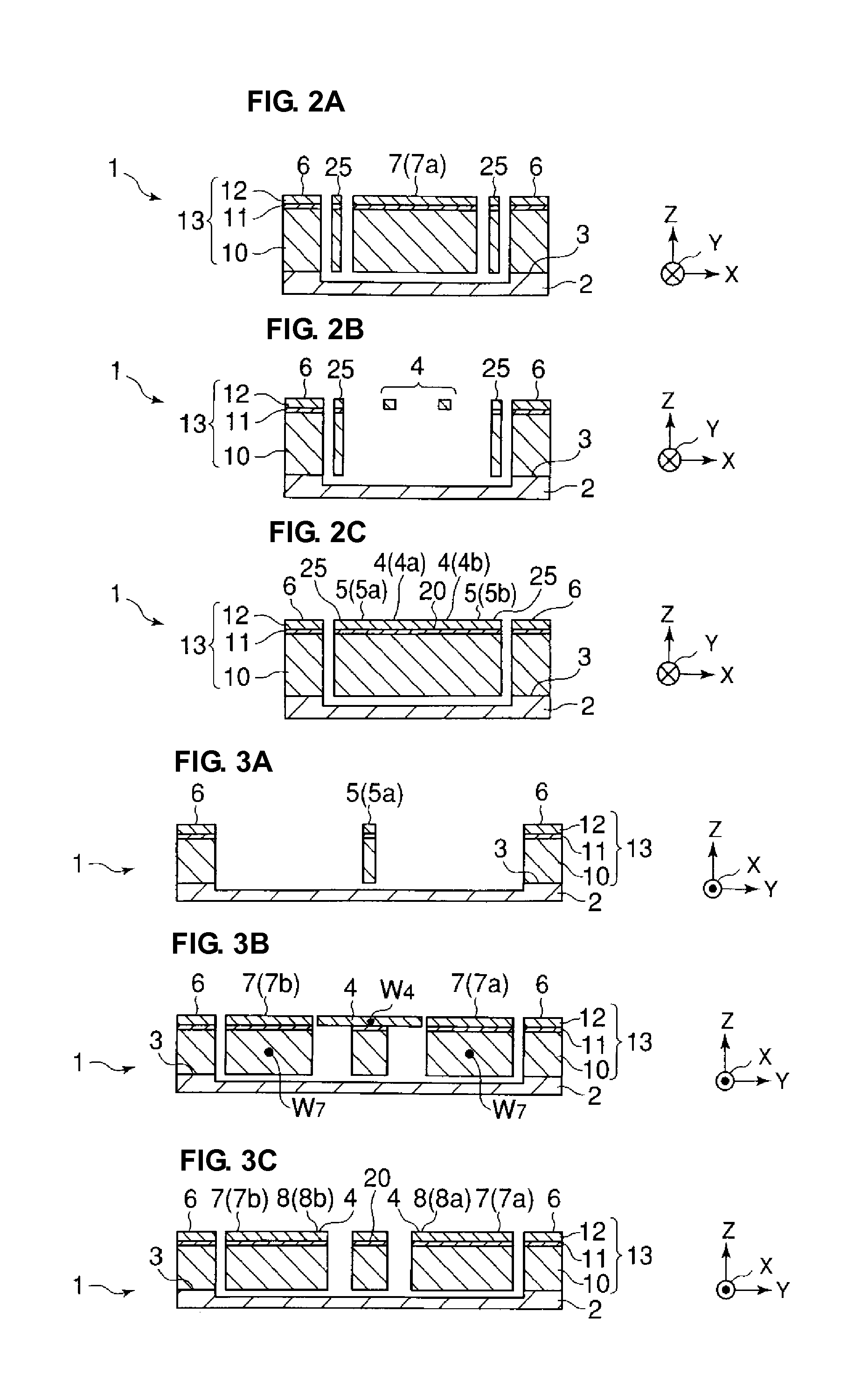

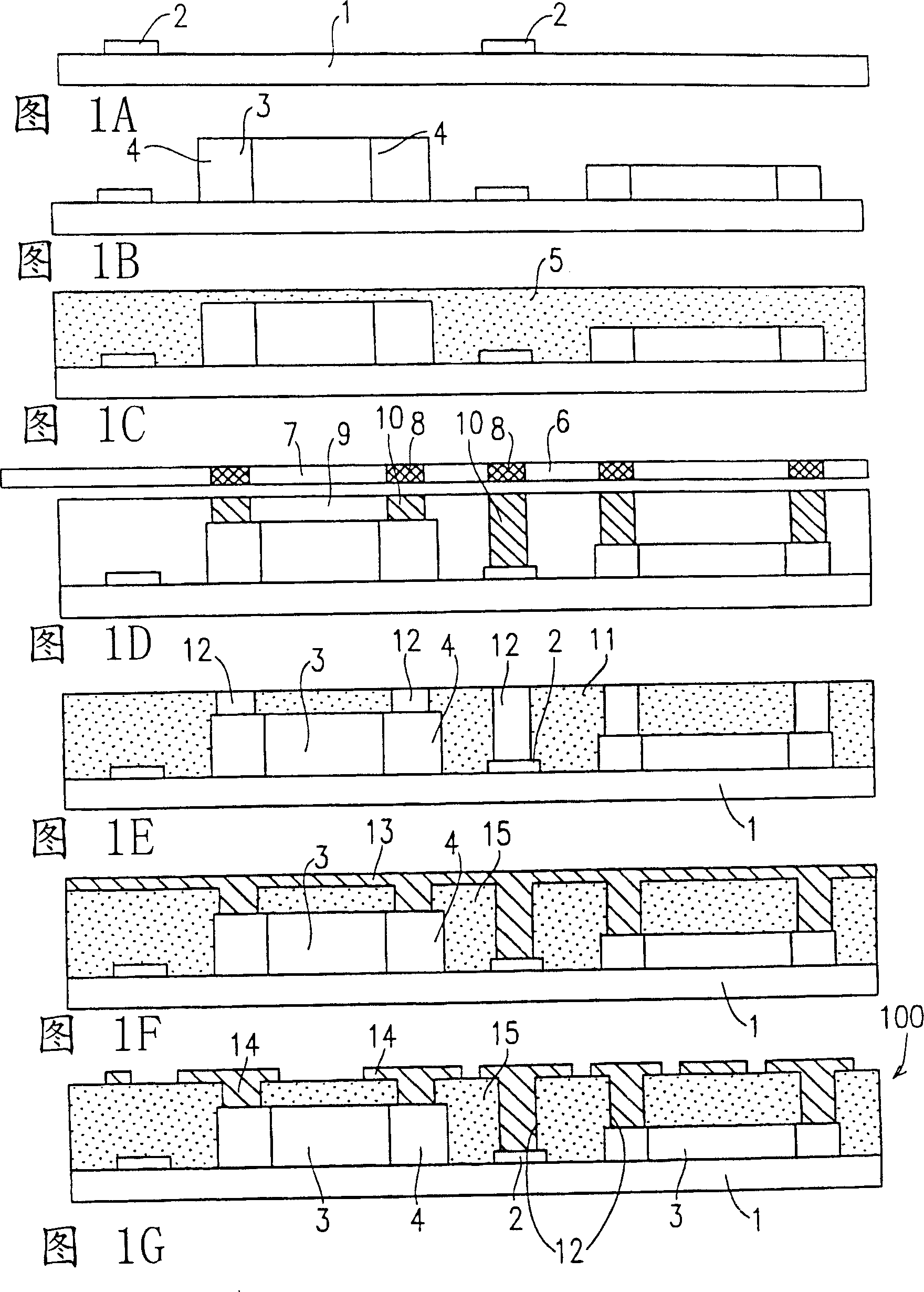

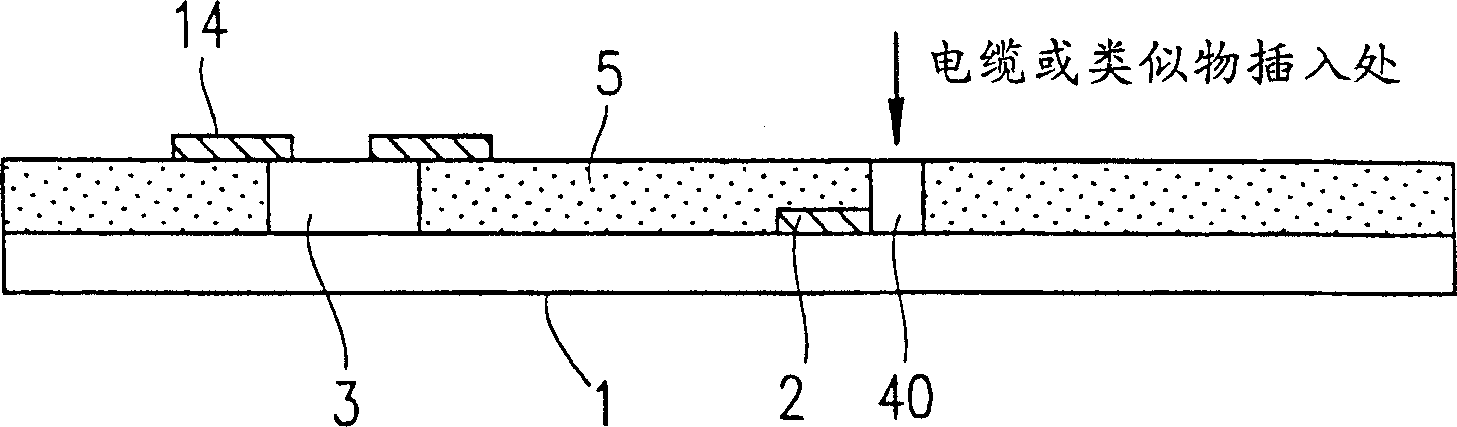

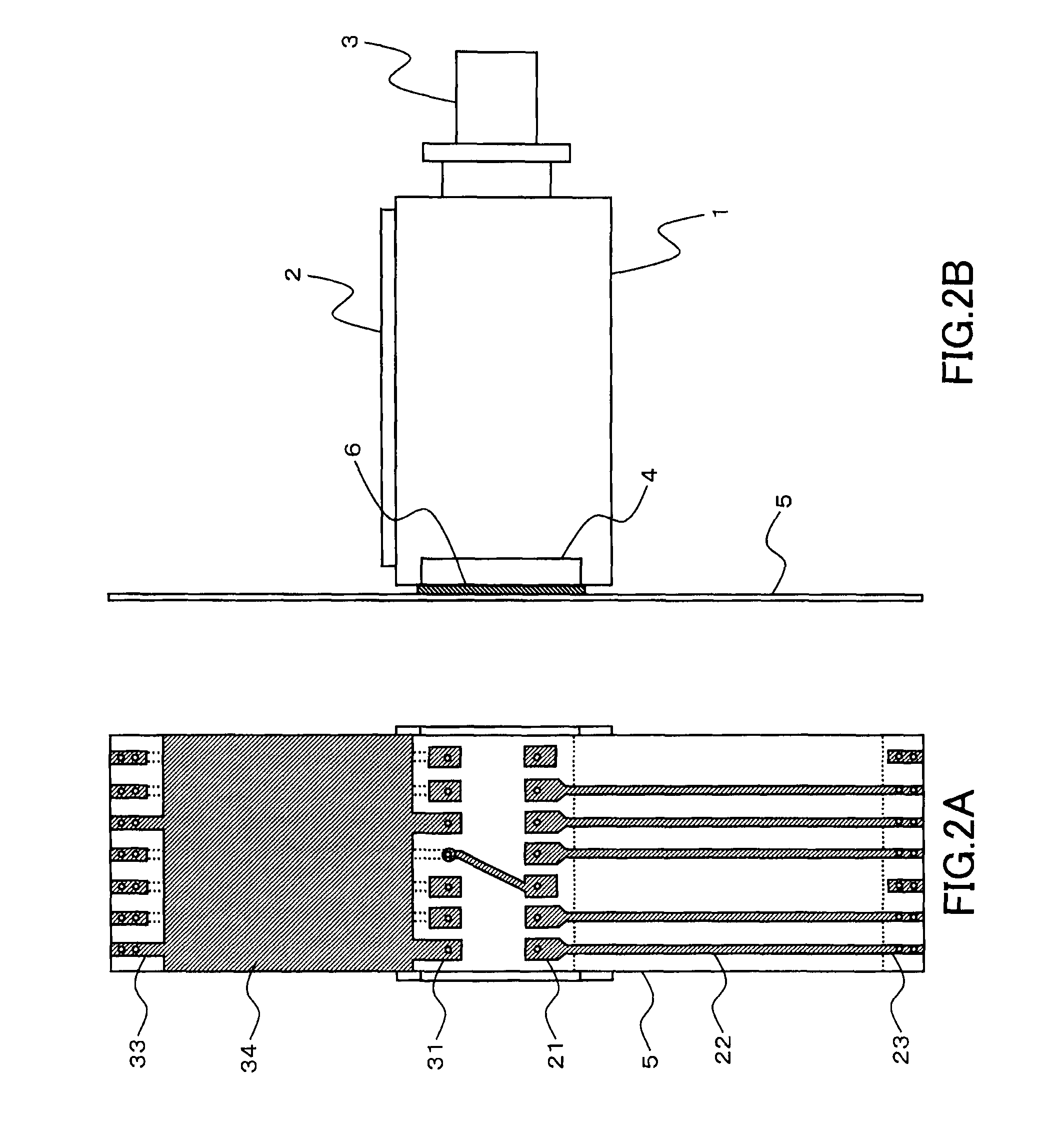

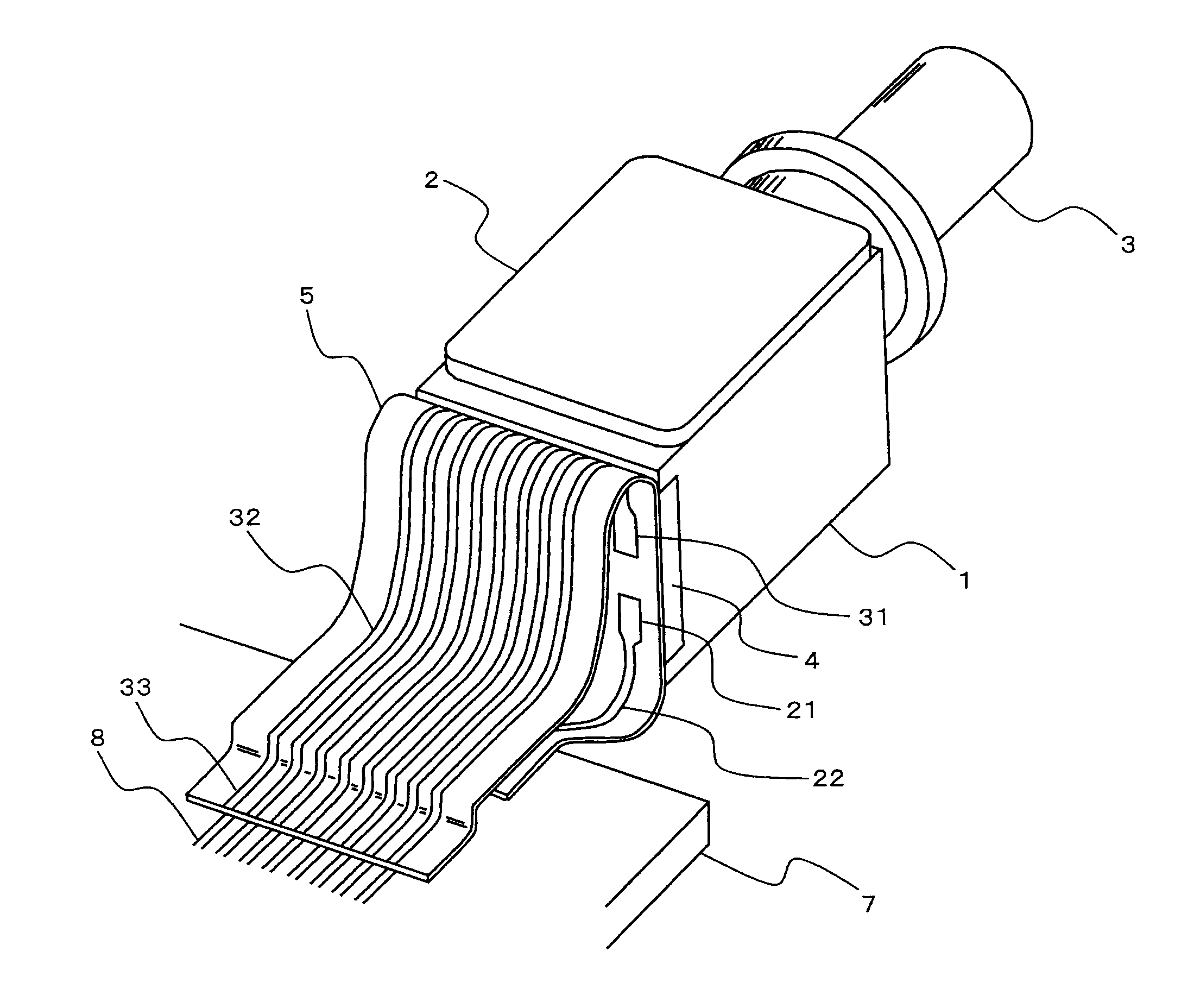

Suspension board with circuit

InactiveUS20120247824A1Reduce wiring densityEfficient productionArm with actuatorsRecord information storageElectrical and Electronics engineering

Owner:NITTO DENKO CORP

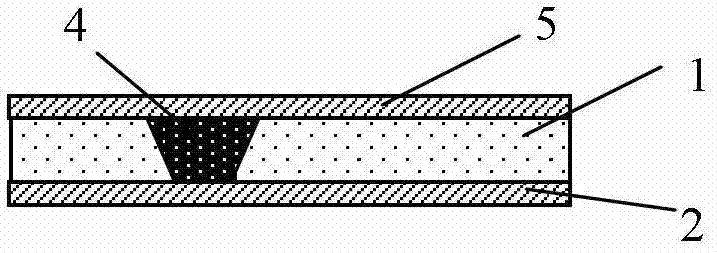

Manufacturing method for printed circuit board

ActiveCN103717013APlay a fixedPlay a supporting roleMultilayer circuit manufacturePrinted element electric connection formationHigh densityProcess engineering

The invention relates to a manufacturing method for a printed circuit board, wherein manufacturing of a multi-layer high-density interconnected printed circuit board can be realized by using the one-time compressing method. The method comprises the following steps that: first daughter boards and second daughter boards are manufactured; the plurality of first daughter boards and daughter boards are superposed together and heating and pressurizing are carried out, and thus the first daughter boards and the second daughter boards are bonded together to form a multi-layer and multi-stage printed circuit board; conventional processes like mechanical drilling, hole metallization, and electroplating and the like are carried out on the multi-layer printed circuit board so as to complete the manufacturing of the printed circuit board. According to the invention, expansion and shrinkage as well as deformation of materials during the manufacturing process can be effectively controlled, thereby effectively improving alignment precision between the holes and between the hole and the graph; and the safe distances between the holes and between the hole and the graph are reduced from 20 mil to 8mil, thereby effectively improving the wiring density of the printed circuit board. Moreover, under the circumstances that the investment of the PCB manufacturer equipment is not increased, the yield of the high-density interconnected printed circuit board can be substantially improved and the manufacturing period of the product can be shortened.

Owner:SHANGHAI MEADVILLE SCI & TECH +1

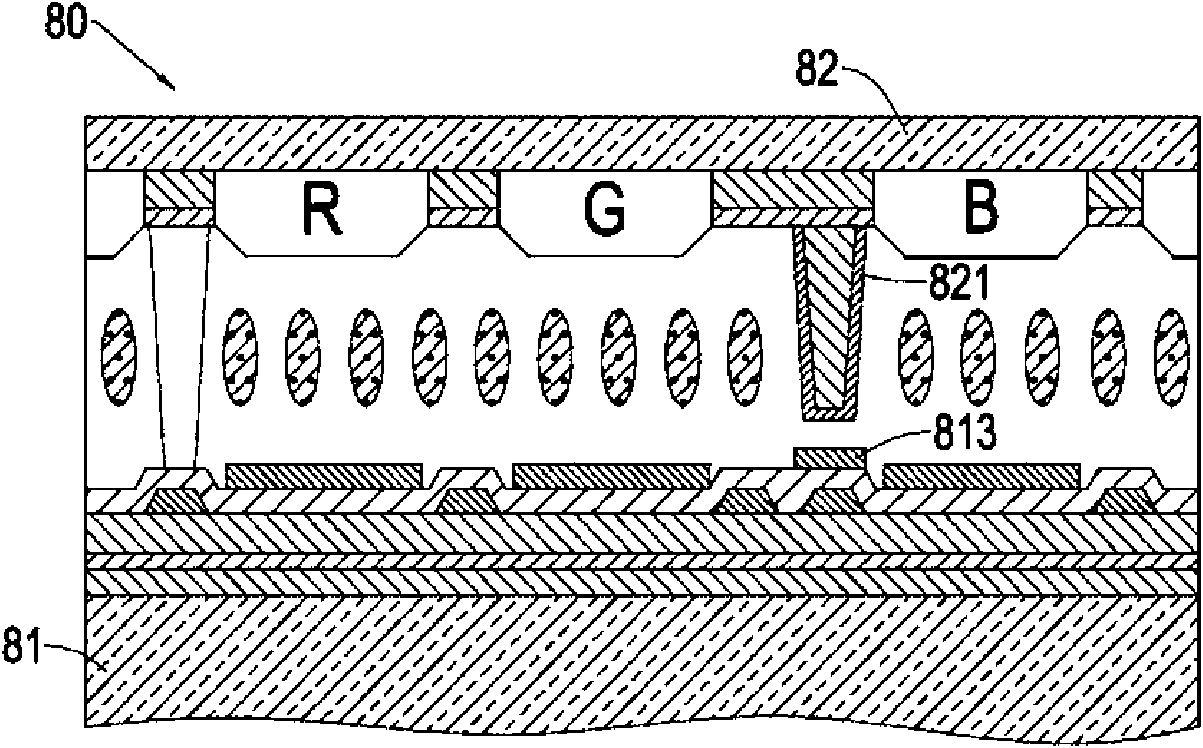

In-cell touch liquid crystal display (LCD)

InactiveCN102033347ALow costReduce wiring densityStatic indicating devicesNon-linear opticsLiquid-crystal displayTouch Senses

Owner:INNOCOM TECH (SHENZHEN) CO LTD +1

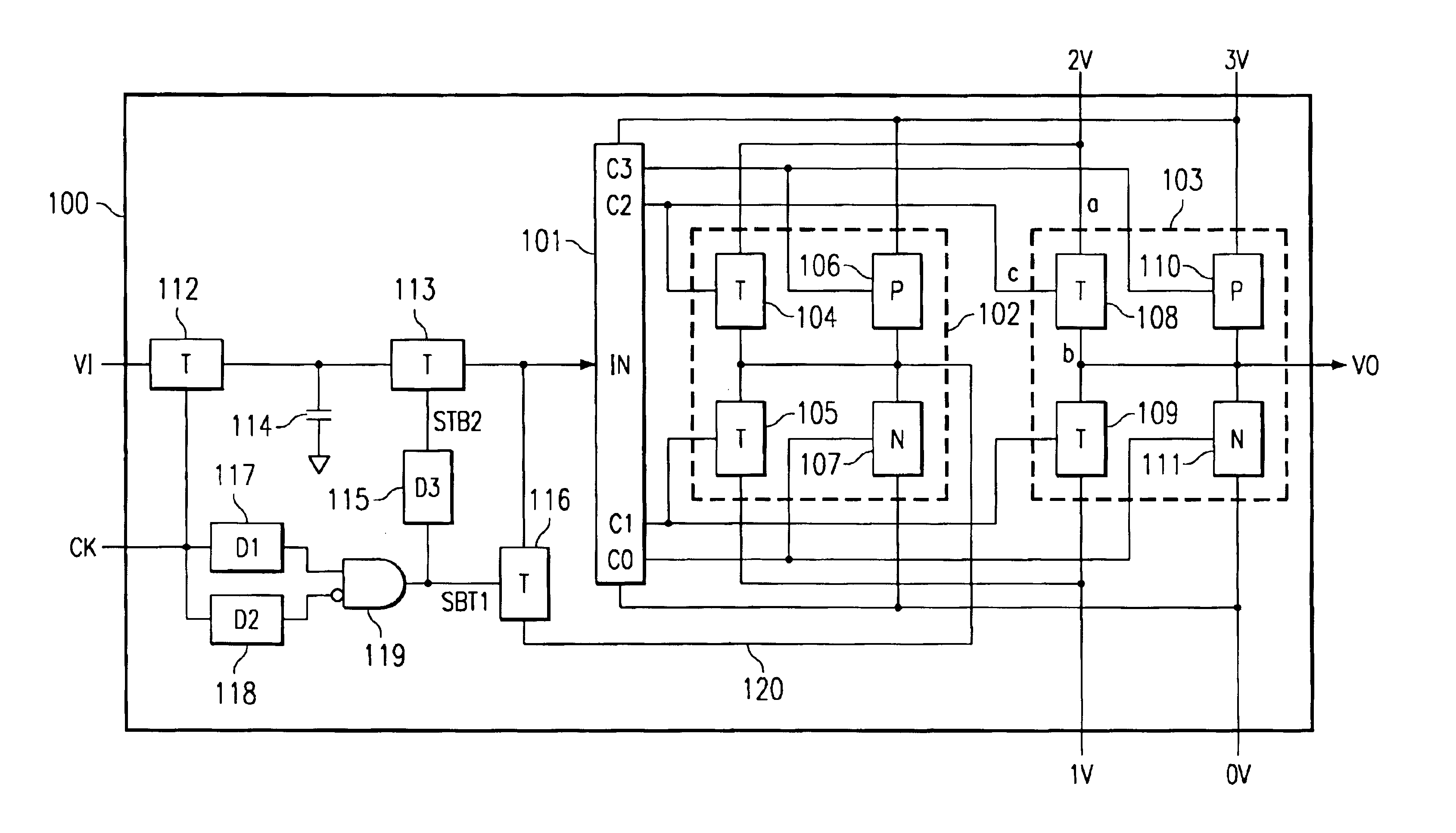

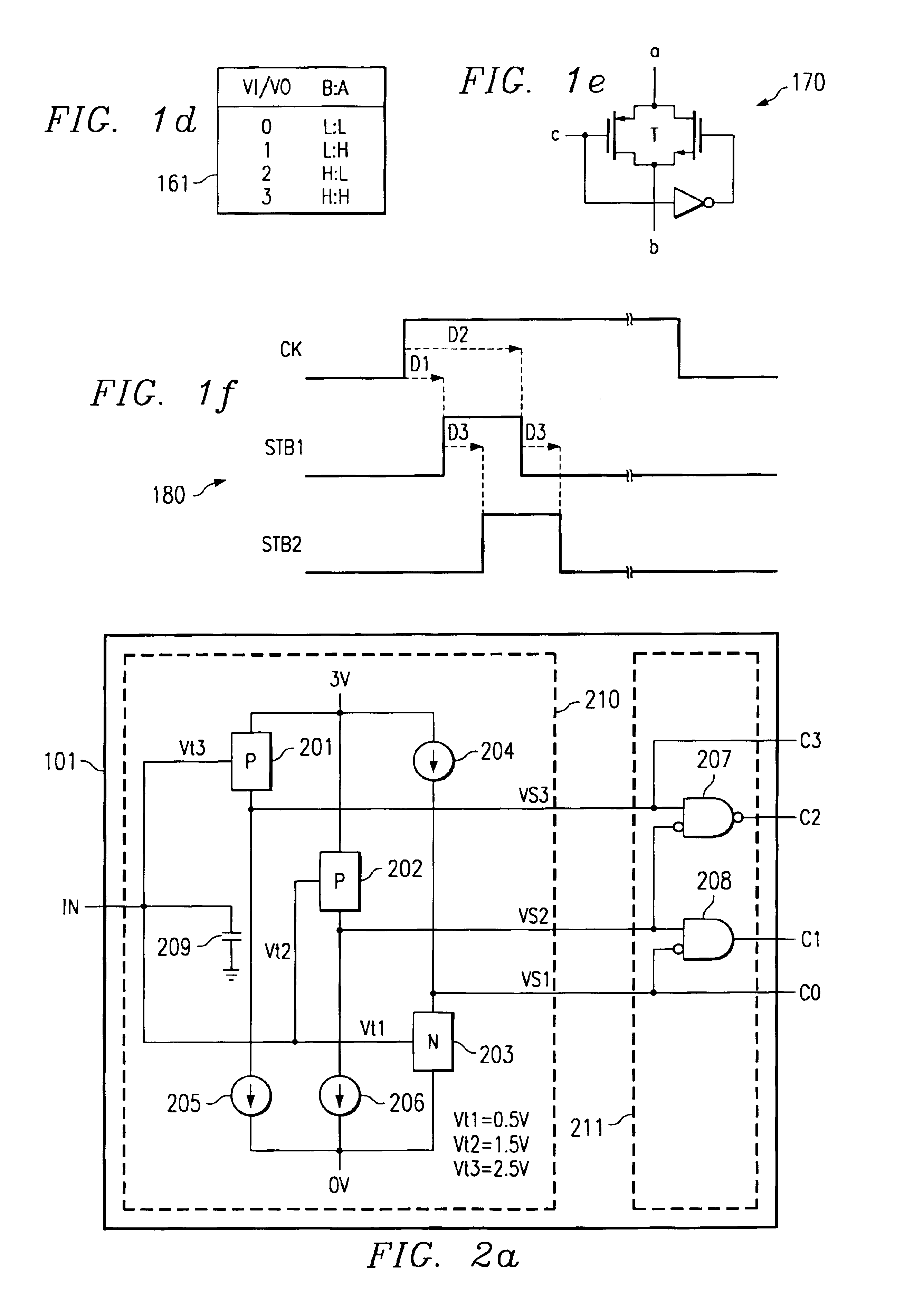

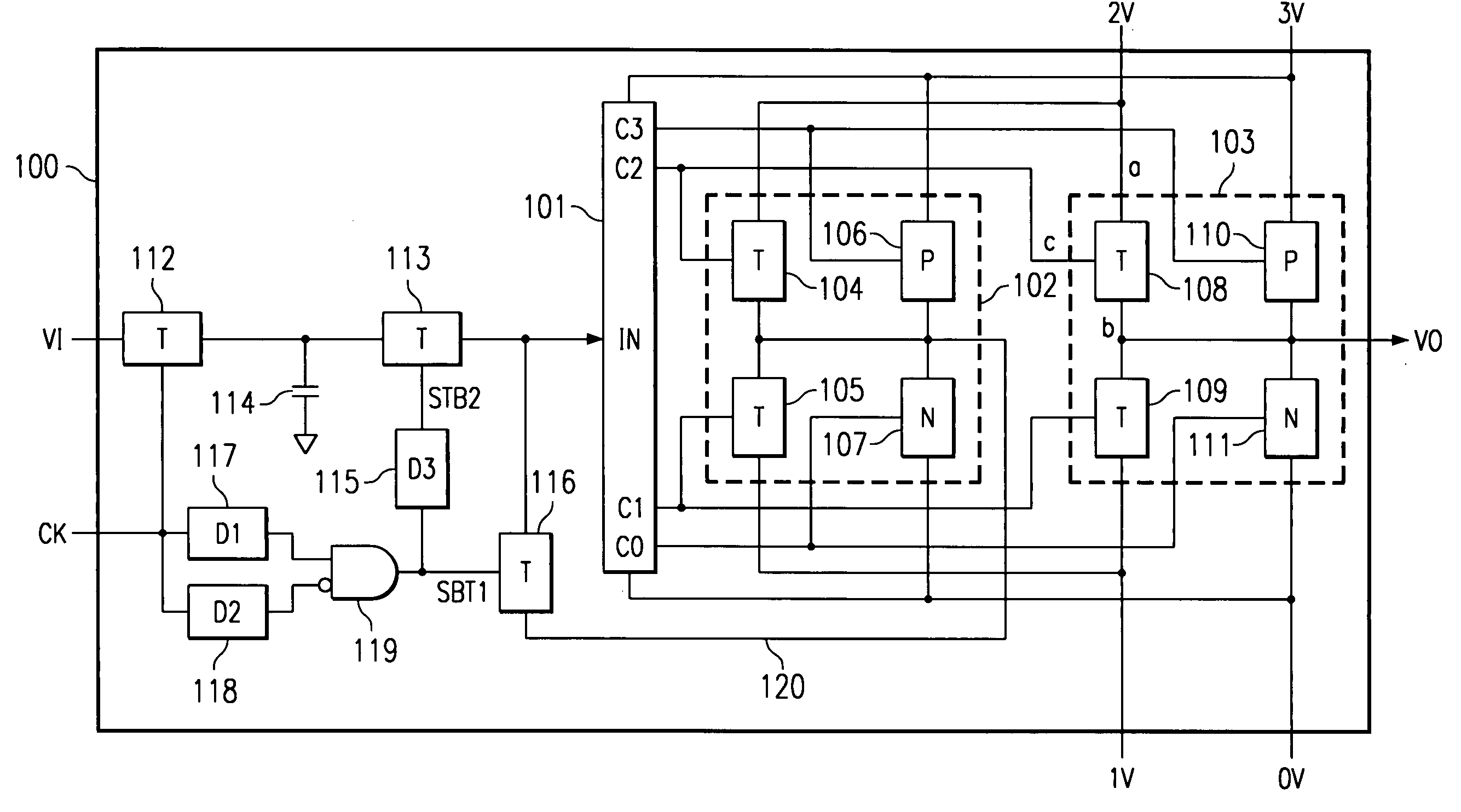

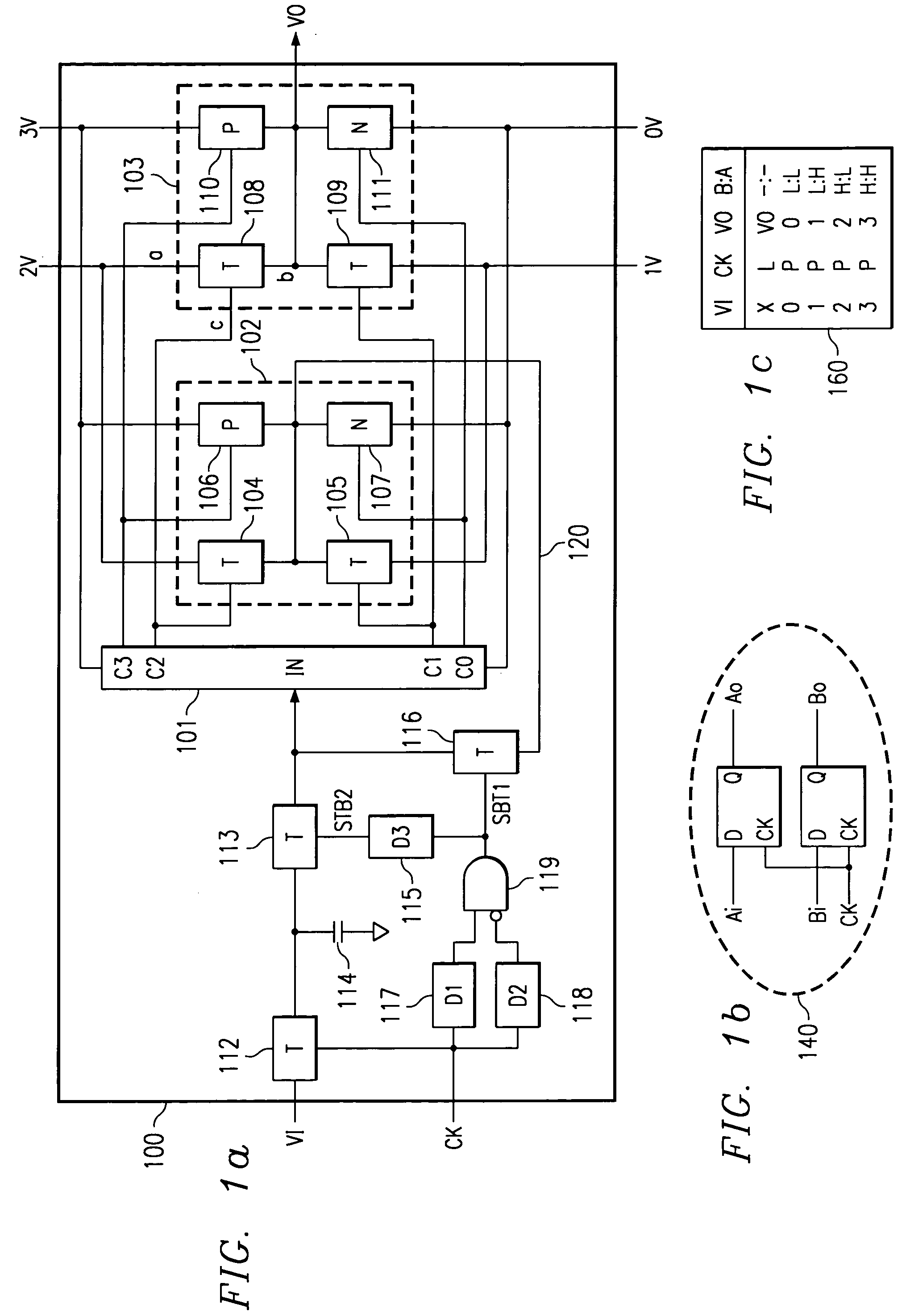

Quad state logic design methods, circuits, and systems

InactiveUS6963225B2Reduce wiring densityReduced wiring interconnectsLogic circuits characterised by logic functionMultistate logicHigh densityEngineering

Quad-state logic elements and quad-state memory elements are used to reduce the wiring density of integrated circuits. The resulting reduction in wiring interconnects between memories and logic elements results in higher speed, higher density, and lower power integrated circuit designs.

Owner:TEXAS INSTR INC

Circuit board structure and making method

InactiveCN1980540AShorten process timeReduce process costPrinted electric component incorporationMultilayer circuit manufactureElectric propertiesEngineering

Owner:PHOENIX PRECISION TECH CORP

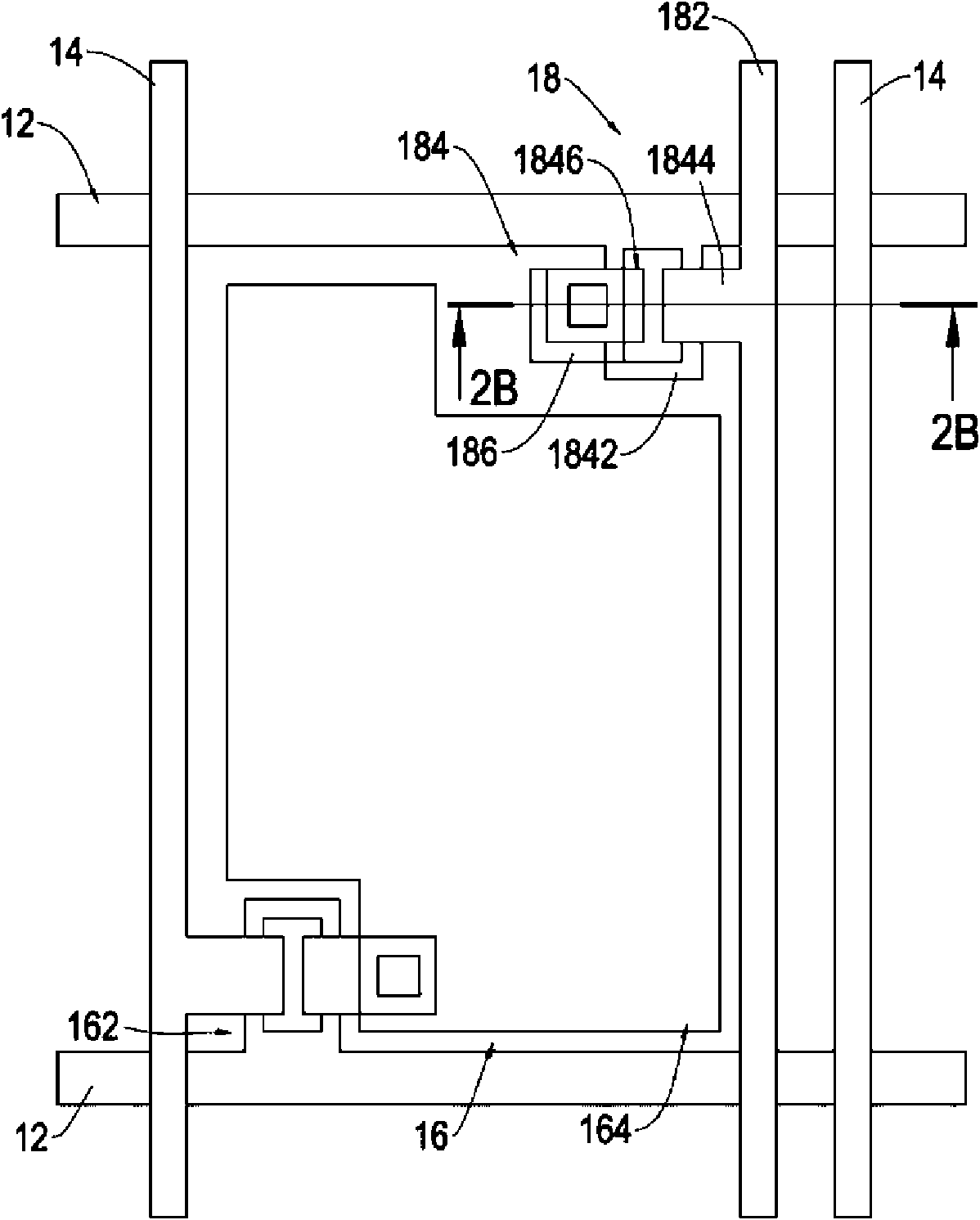

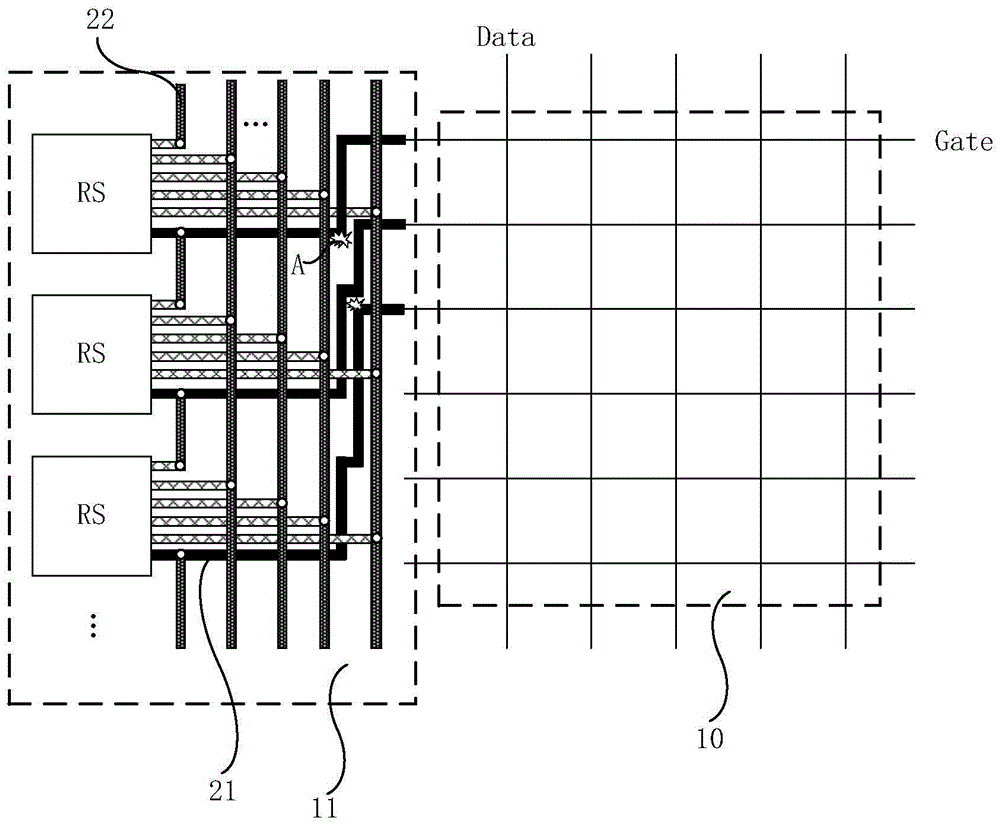

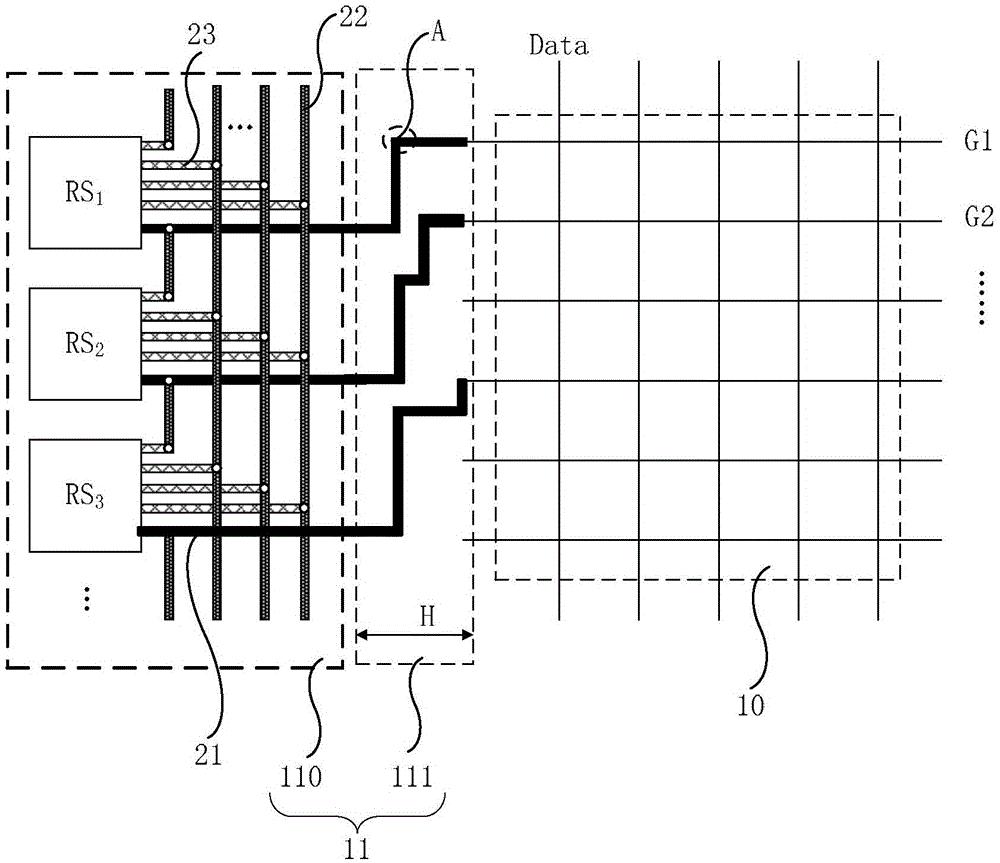

Array substrate, preparing method of array substrate and display device

ActiveCN105549288AReduce disconnectionReduce the chance of short circuitsSolid-state devicesNon-linear opticsShift registerDisplay device

The embodiment of the invention provides an array substrate, a preparing method of the array substrate and a display device and relates to the technical field of display. The wiring density of data leads in a densely-wired area can be reduced, and the probability of electrostatic discharge at a corner tip can be reduced. The array substrate comprises a display area and a peripheral area, wherein first data leads and at least two cascaded shifting register units are arranged in the peripheral area. The shifting register units are connected with grid lines in the display area through the first data leads. The minimum distance between every two adjacent first data leads is larger than or equal to a distance threshold value.

Owner:BOE TECH GRP CO LTD +1

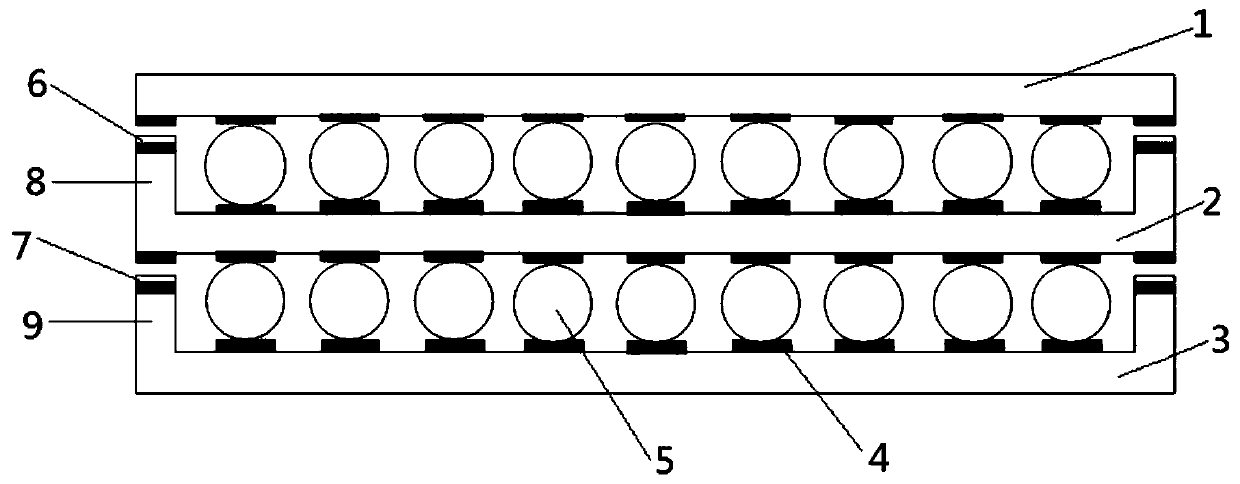

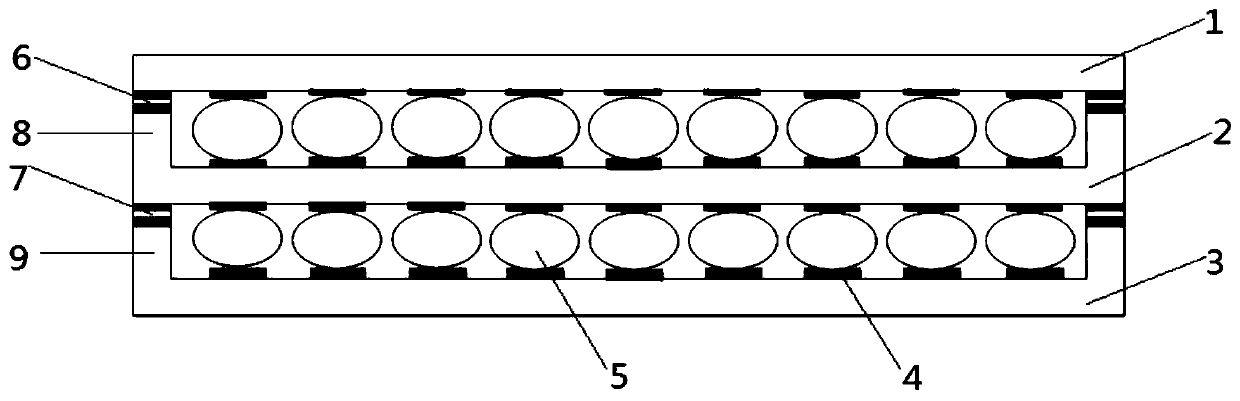

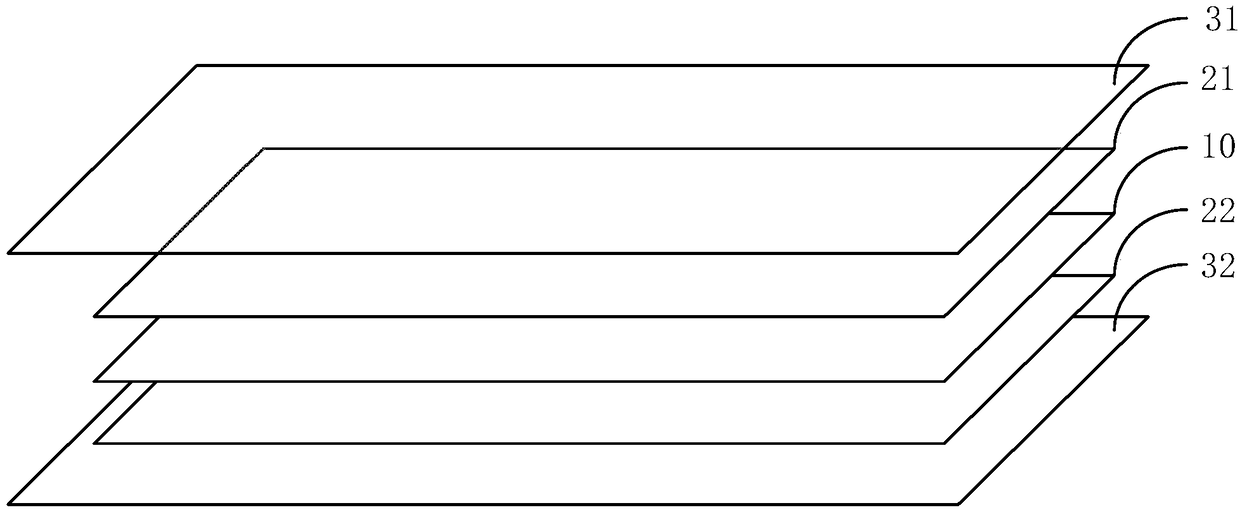

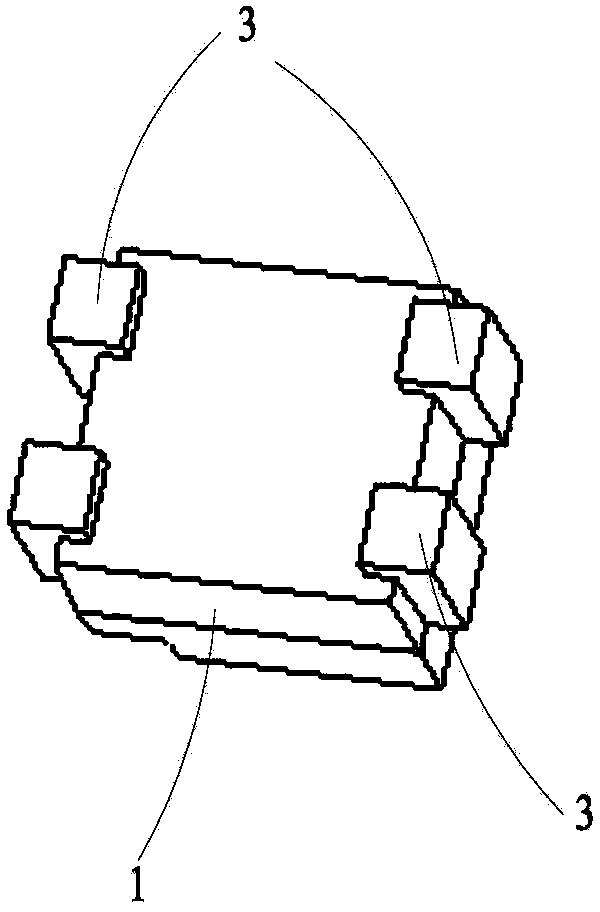

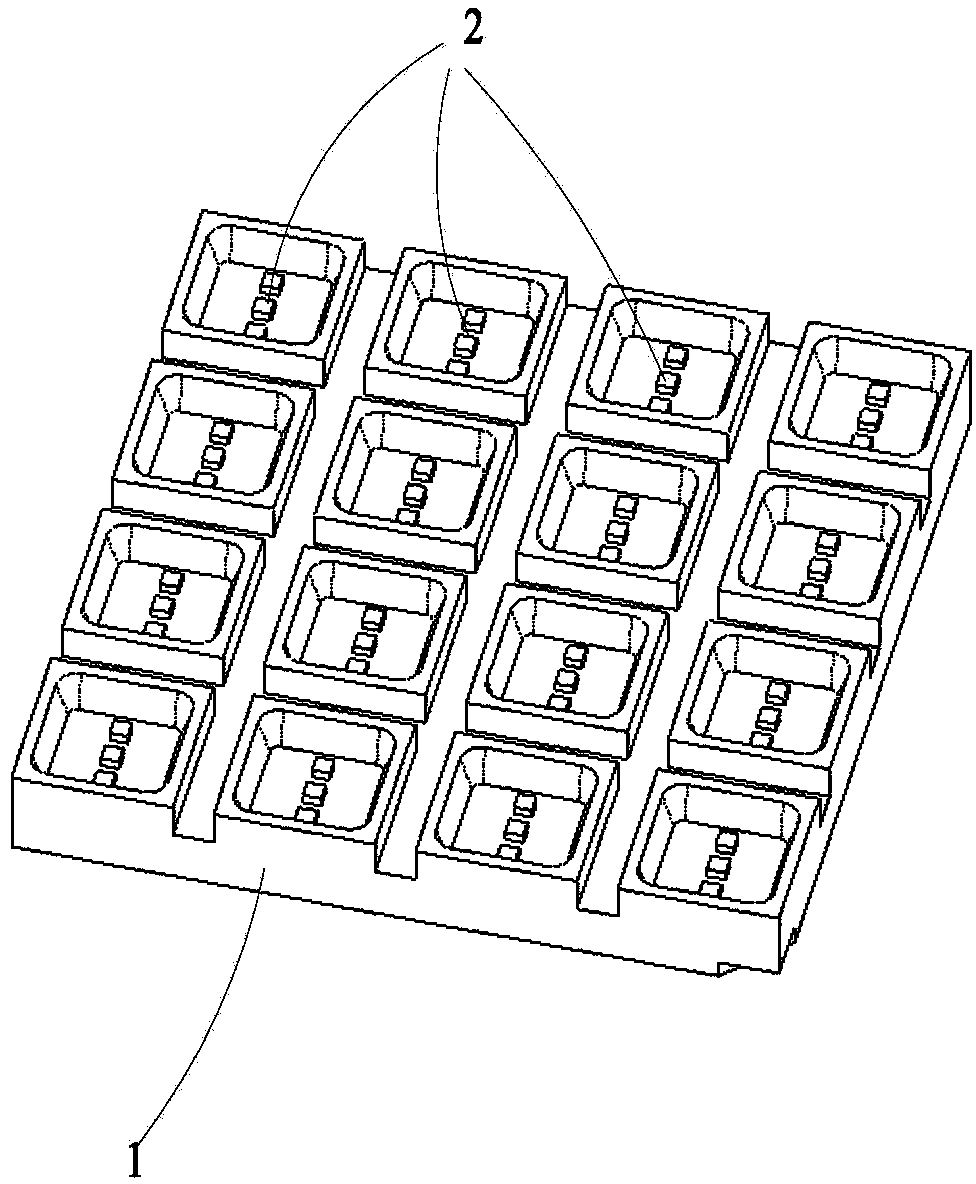

Self-alignment integrated package method of high-density three-dimensional lamination layer

PendingCN110211884AReduced Alignment DifficultyReduce failure rateSemiconductor/solid-state device detailsSolid-state devicesHigh densityInter layer

The invention discloses a self-alignment integrated package method of a high-density three-dimensional lamination layer, and aims to provides an integrated package method which employs a BGA welding ball as an interlayer mechanical support for multi-layer substrate self-alignment three-dimensional stack and also can be a signal interconnection passage among high-density layers. The self-alignmentintegrated package method is implemented according to the technical scheme that bonding pads are arranged on a lower surface of a top-layer substrate, an upper surface and a lower surface of an intermediate-layer substrate and an upper surface of a bottom-layer substrate and are used for welding micro BGA welding balls, the micro BGA welding balls are attached onto the upper surface of the intermediate-layer substrate and the upper surface of the bottom-layer substrate, the micro BGA welding balls on the upper surface of the intermediate-layer substrate are corresponding to the lower surface of the top-layer substrate, the micro BGA welding balls on the upper surface of the bottom-layer substrate are corresponding to the lower surface of the intermediate-layer substrate, vertical and interconnection rectangular array micro BGA ball welding is formed, a hollow square boss cavity box body is arranged at the peripheries outside an upper cavity surface of the intermediate-layer substrate 2and an upper cavity surface of the bottom-layer substrate 3, the cavity box body is stacked and placed in a backflow welding furnace by a tool, and self-alignment lamination layer welding is performed to form a package body.

Owner:10TH RES INST OF CETC

Array pressure sensor and pressure acquisition system

InactiveCN109443611AReduce design difficultyReduce the numberForce measurementDiagnostic recording/measuringImage resolutionPressure sense

The invention provides an array pressure sensor and pressure acquisition system for plantar pressure acquisition. The array pressure sensor and the pressure acquisition system are characterized in that the common row pressure sensing points of the array pressure sensor share the row lead wire, and the common column pressure sensing points share one column lead wire, and double surface wiring are performed on the row wire and the column wire, so as to enable the array pressure sensor to reduce the number and the wiring density of wire leads and reduce the design difficulty of the large-size array pressure sensor, thereby satisfying the increase of the pressure sensing area while ensuring the spatial resolution and sampling rate of the sampling. The invention also discloses a pressure acquisition system which is designed based on the array pressure sensor. The pressure acquisition system performs sampling on the array pressure sensor by means of the row sharing, column sharing and time sharing sampling method, so as to realize acquisition of the plantar pressure data in the natural walking state and guarantee accuracy and stability of the pressure acquisition system.

Owner:PEKING UNIV SHENZHEN GRADUATE SCHOOL

Method for manufacturing printed-circuit board

ActiveUS20090321266A1Reduce in quantityImprove routing densityPrinted circuit aspectsSolid-state devicesPrinted circuit boardElectrically conductive

There is provided a method for manufacturing a printed circuit board having an insulative board and a plurality of electroconductive pads arranged in a grid shape on the insulative board, the method comprising: a step for forming an electroconductive film on the insulative board; a step for forming a pattern on the electroconductive film so as to form the electroconductive pads, a lead wire connected to at least one of the electroconductive pads, and inter-pad wiring for electrically connecting each of the electroconductive pads not connected to the lead wire to any of the electroconductive pads connected to the lead wire, the inter-pad wiring being disposed between mutually adjacent electroconductive pads; a step for plating each of the electroconductive pads by immersing the insulative board in a plating bath and energizing each of the electroconductive pads through the lead wire; and a step for removing the inter-pad wiring.

Owner:LAPIS SEMICON CO LTD

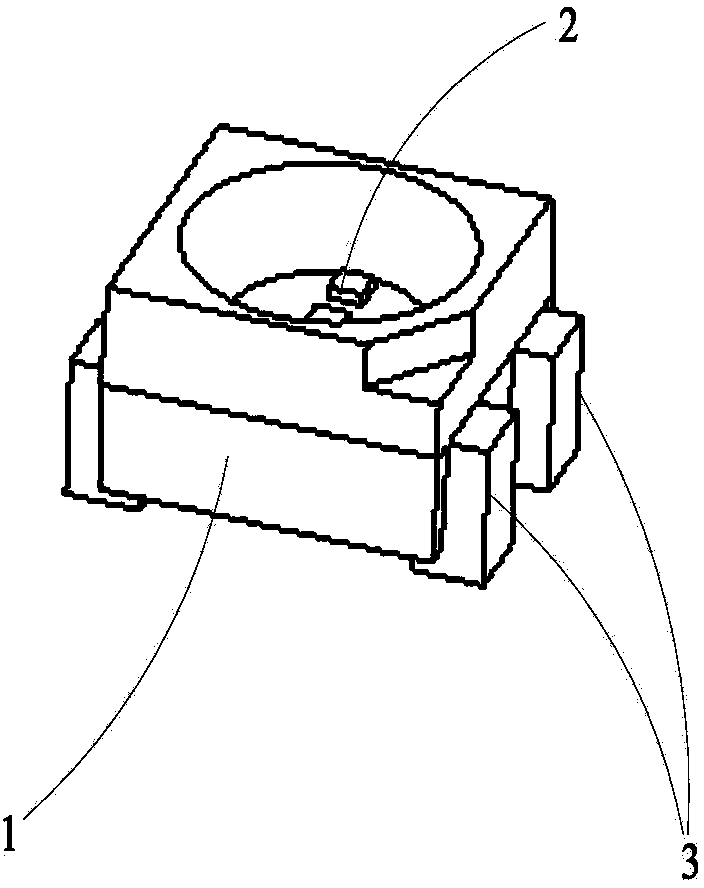

Acceleration sensor

InactiveUS20090071251A1Avoid distortionSmall sizeAcceleration measurement using interia forcesDevices characerised by mechanical meansShaped beamEngineering

An acceleration sensor includes a frame-shaped beam portion disposed above an XY substrate surface of a base in a floating state and a beam-portion supporting / fixing unit arranged to attach the beam portion to the base with support portions so as to be supported on two sides. The acceleration sensor also includes weight portions disposed above the XY substrate surface of the base in a floating state and connecting portions for attaching the weight portions to the beam portion in a cantilever state. The weight portions are movable in three axial directions including an X-axis direction, a Y-axis direction, and a Z-axis direction when the beam portion is deflected. The beam portion is provided with an X-axis-direction acceleration detection unit arranged to detect an acceleration in the X-axis direction, a Y-axis-direction acceleration detection unit arranged to detect an acceleration in the Y-axis direction, and a Z-axis-direction acceleration detection unit arranged to detect an acceleration in the Z-axis direction. The Z-axis-direction acceleration detection unit is disposed near proximal ends of Y-axis-direction extending portions of the beam portion, and the Y-axis-direction acceleration detection unit is disposed near distal ends of the Y-axis-direction extending portions.

Owner:MURATA MFG CO LTD

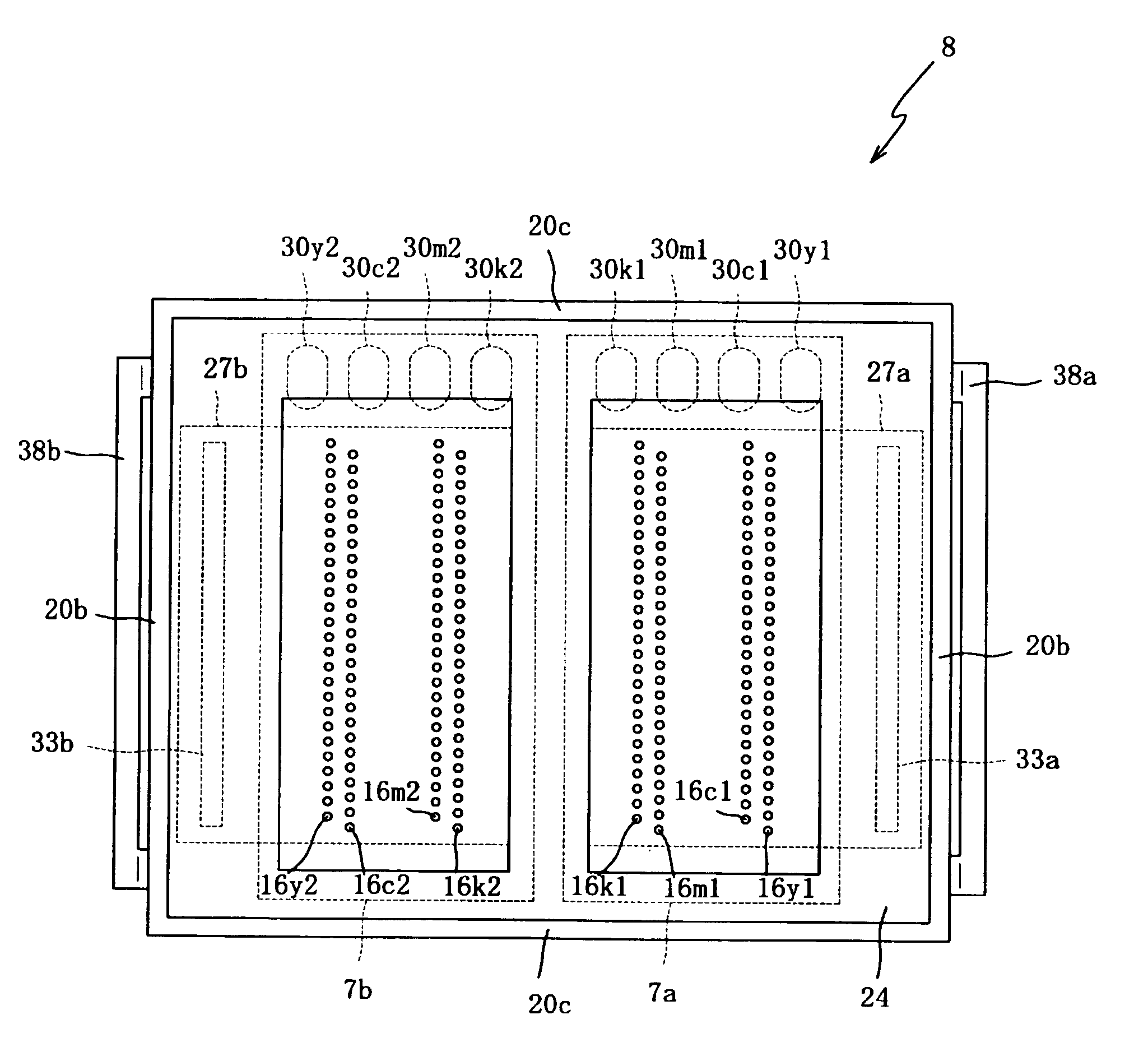

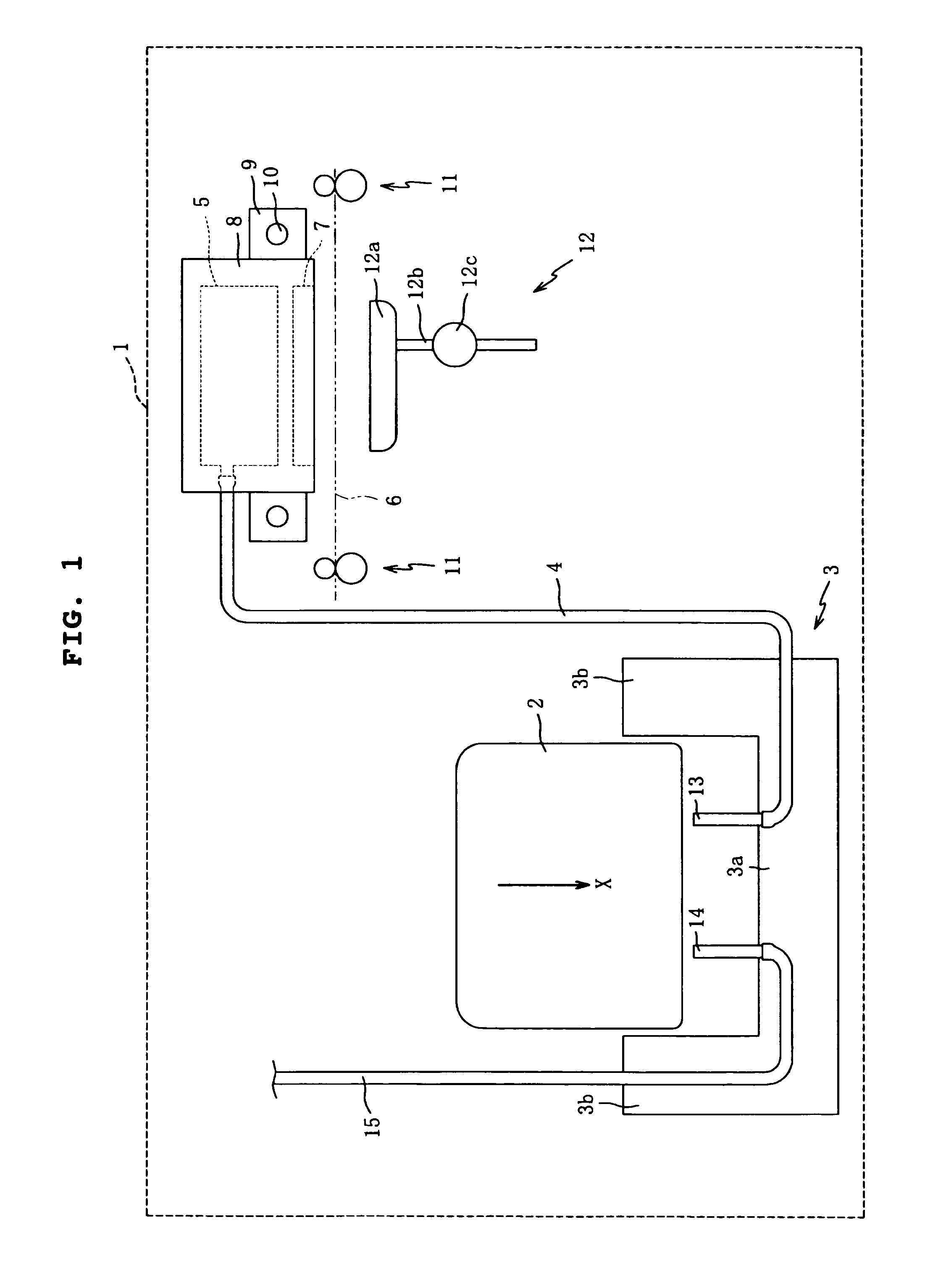

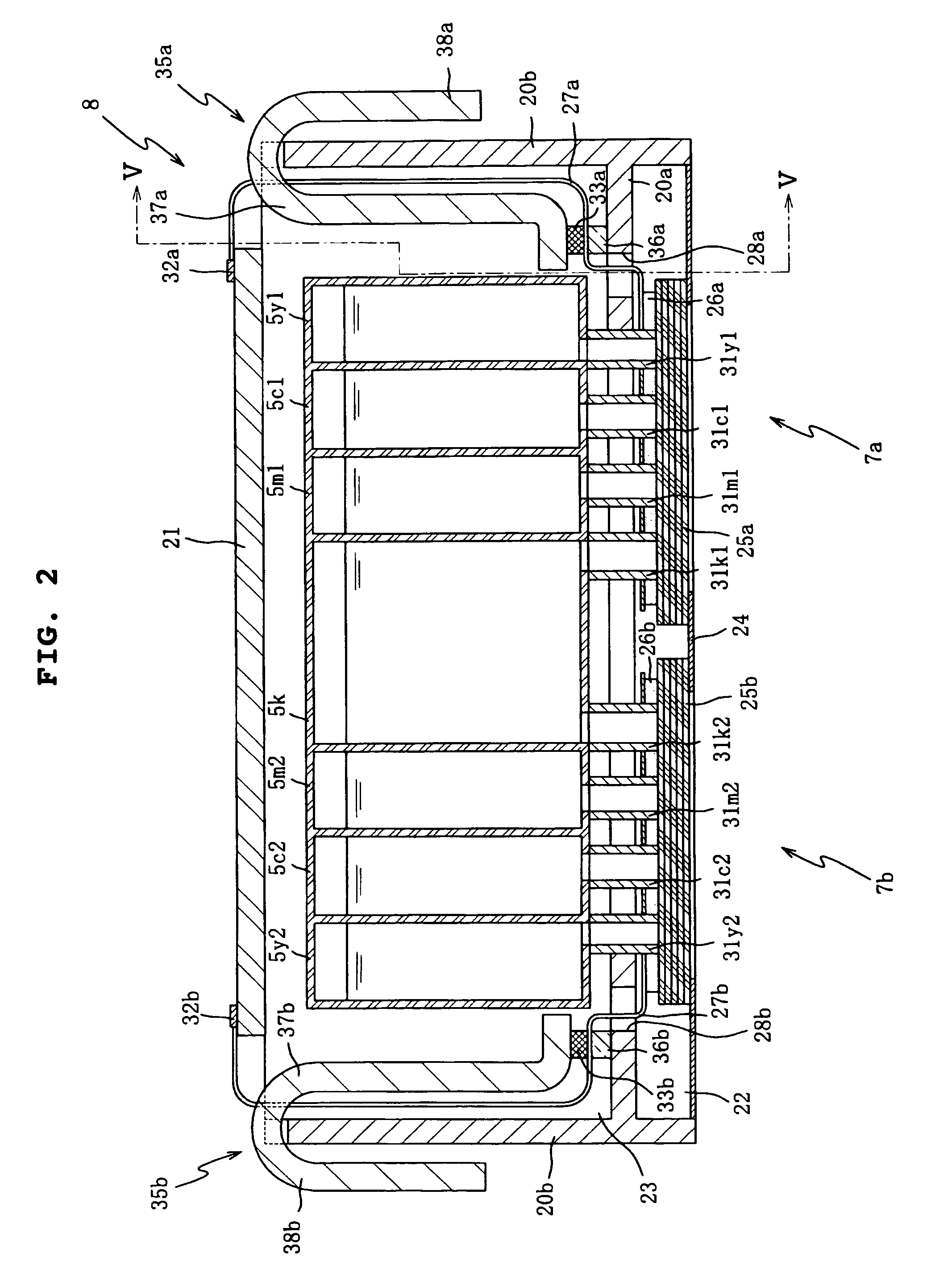

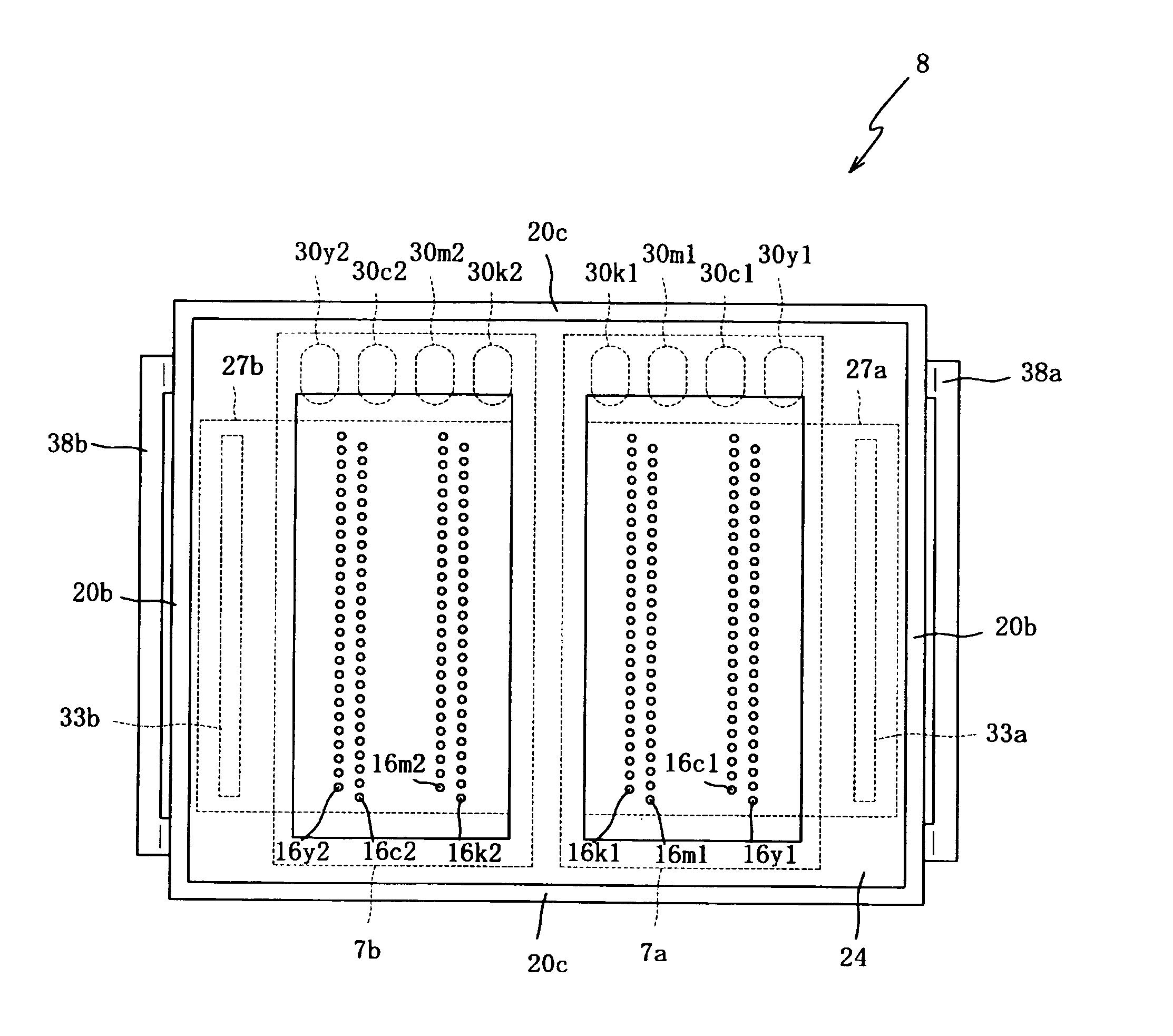

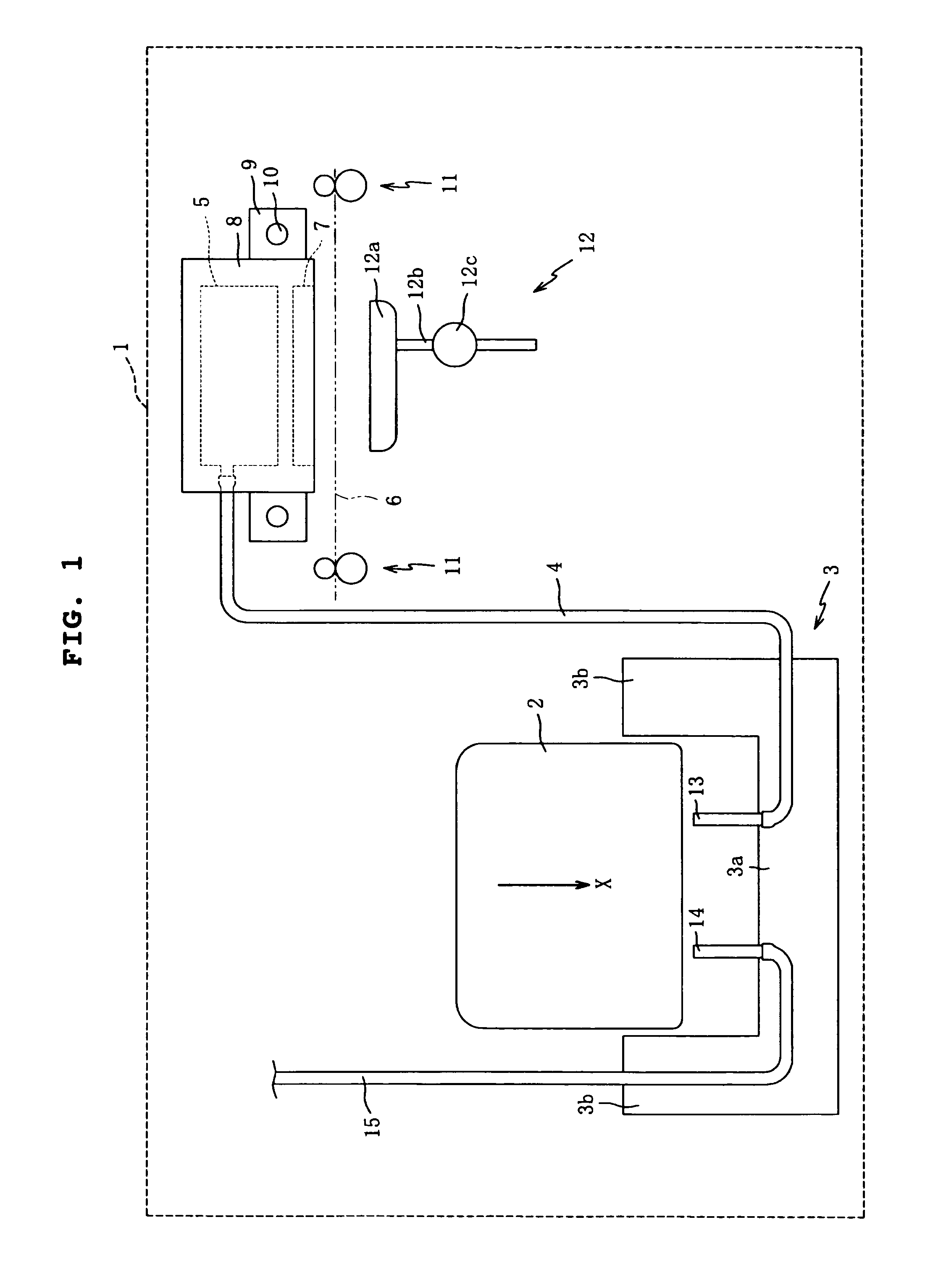

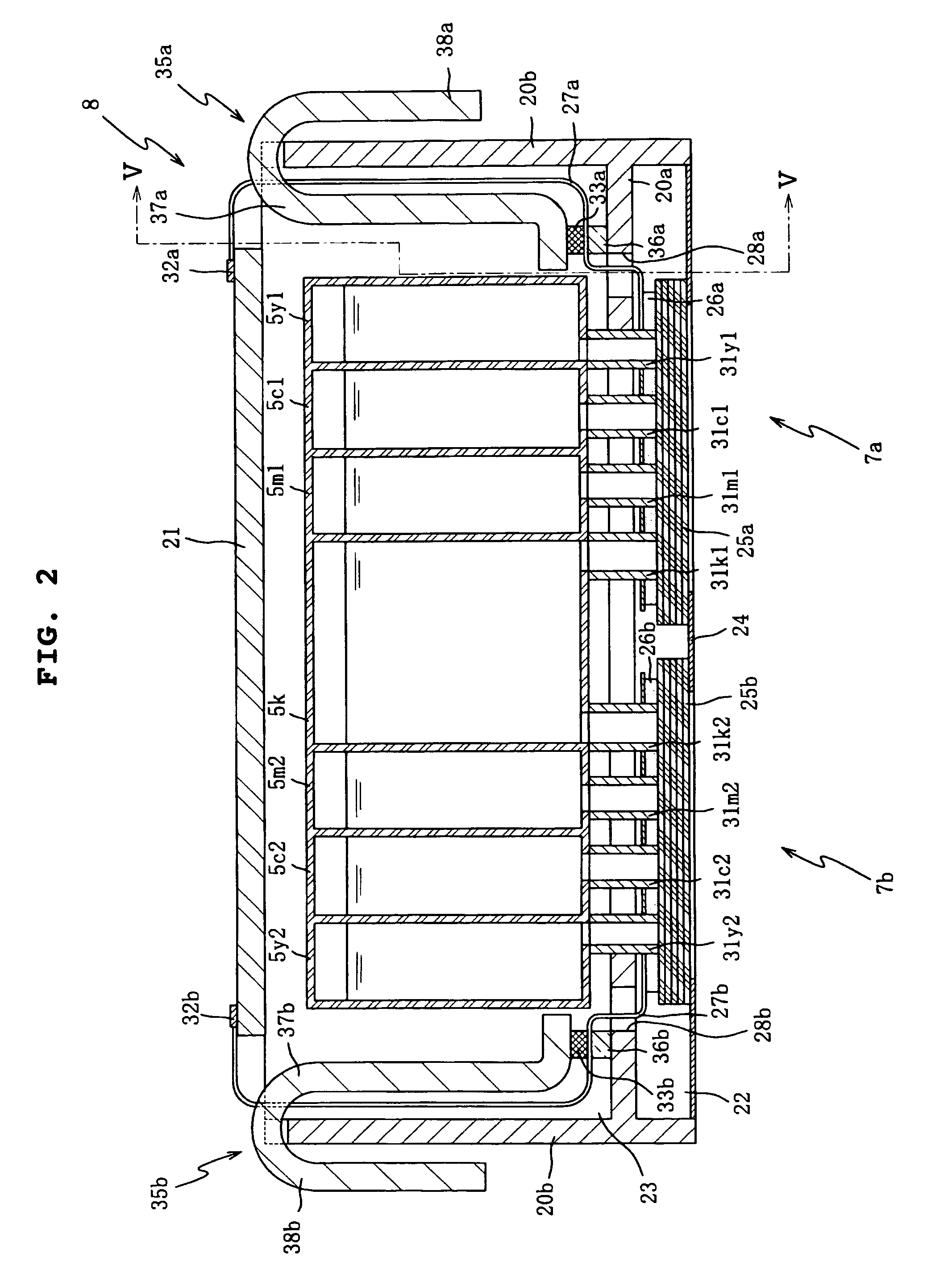

Ink-jet recording apparatus

An ink-jet recording apparatus includes a recording head which jets inks, and a cable which is connected to the recording head and which is provided with a driving circuit for applying a driving voltage of the recording head. The recording head is formed with nozzle arrays for jetting an ink of a dark color and an ink of a light color respectively. The nozzle array, which jets the ink of the dark color, is disposed farther from the driving circuit than the nozzle array which jets the ink of the light color. The nozzle array, which jets the ink of the dark color, is hardly affected by the heat from the driving circuit. Therefore, the deterioration of the recording quality, which would be otherwise caused by the disturbance of ink discharge from nozzles, is suppressed.

Owner:BROTHER KOGYO KK

Semiconductor device and manufacturing method thereof

InactiveUS7656693B2Reduce wiring densityIncrease flexibilityTransistorSolid-state devicesInter layerHemt circuits

In a memory cell area of a semiconductor device, first, second, and third inter-layer insulating films respectively cover a cell transistor, a bit wiring line, and a capacitor which are connected to each other. In an adjacent peripheral circuit area, a peripheral-circuit transistor is covered with the first inter-layer insulating film, a first-layer wiring line connected to the peripheral-circuit transistor is provided on the first inter-layer insulating film and covered with the second inter-layer insulating film, and a second-layer wiring line is provided on the third inter-layer insulating film. In the memory cell area, a landing pad is provided on the second inter-layer insulating film and between the capacitor and a contact plug for connecting the capacitor to the cell transistor. An assist wiring line connected to the first-layer wiring line is provided on the main surface of the second inter-layer insulating film, on which the landing pad is provided.

Owner:LONGITUDE SEMICON S A R L

Quad state logic design methods, circuits, and systems

InactiveUS20050179462A1Reduce wiring densityReduced wiring interconnectsMultistate logicDigital storageHigh densityEngineering

Quad-state logic elements and quad-state memory elements are used to reduce the wiring density of integrated circuits. The resulting reduction in wiring interconnects between memories and logic elements results in higher speed, higher density, and lower power integrated circuit designs.

Owner:TEXAS INSTR INC

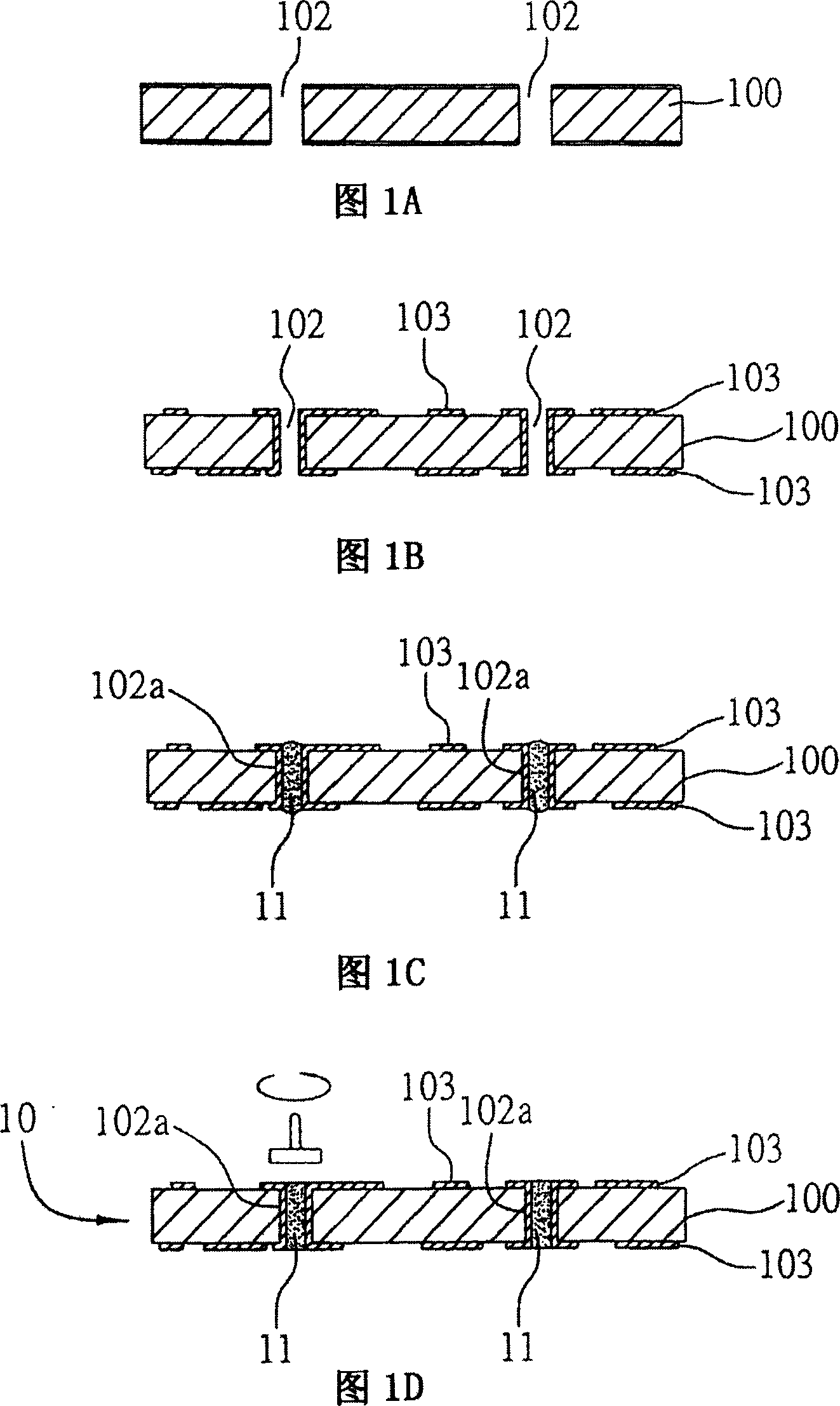

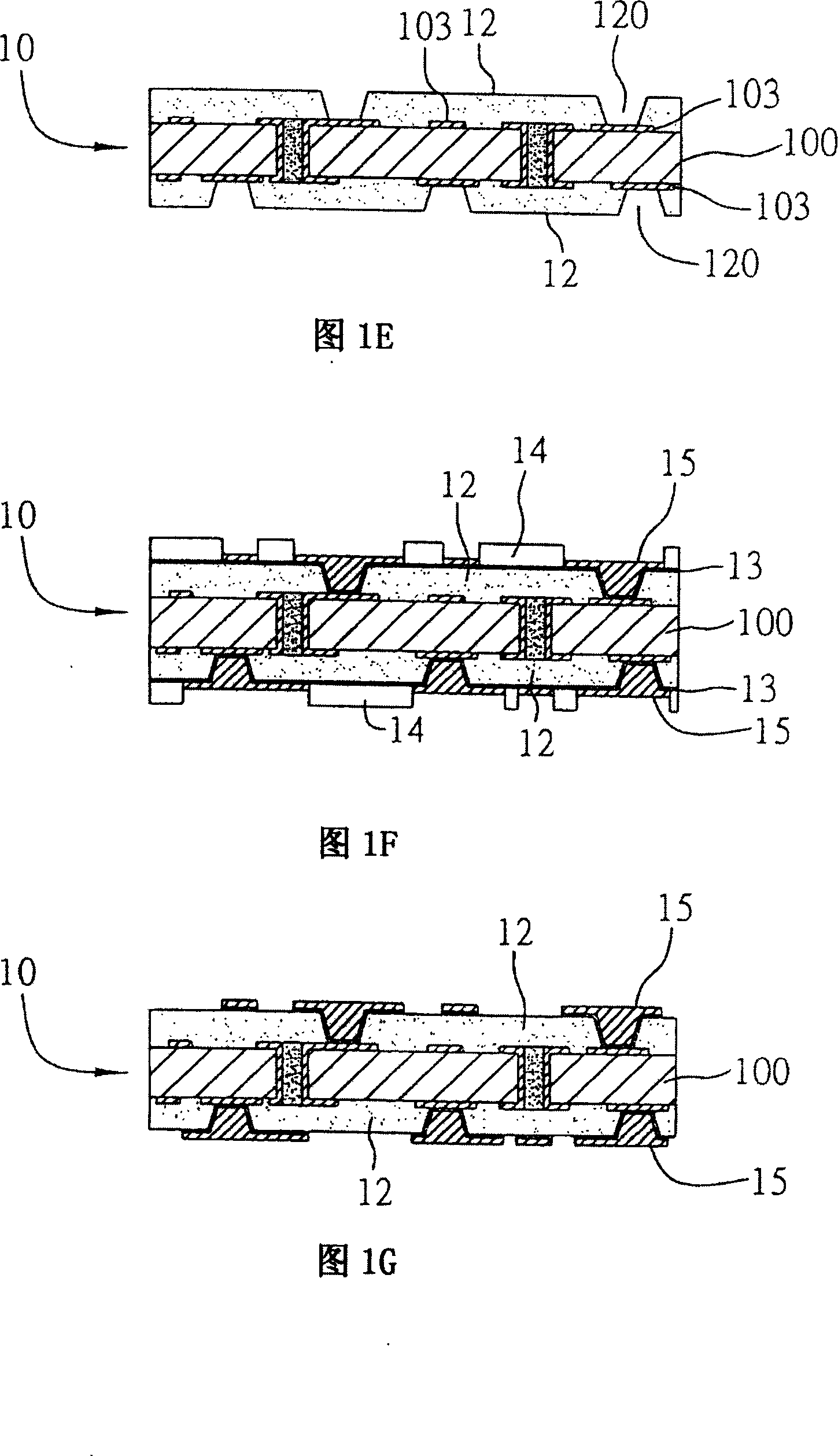

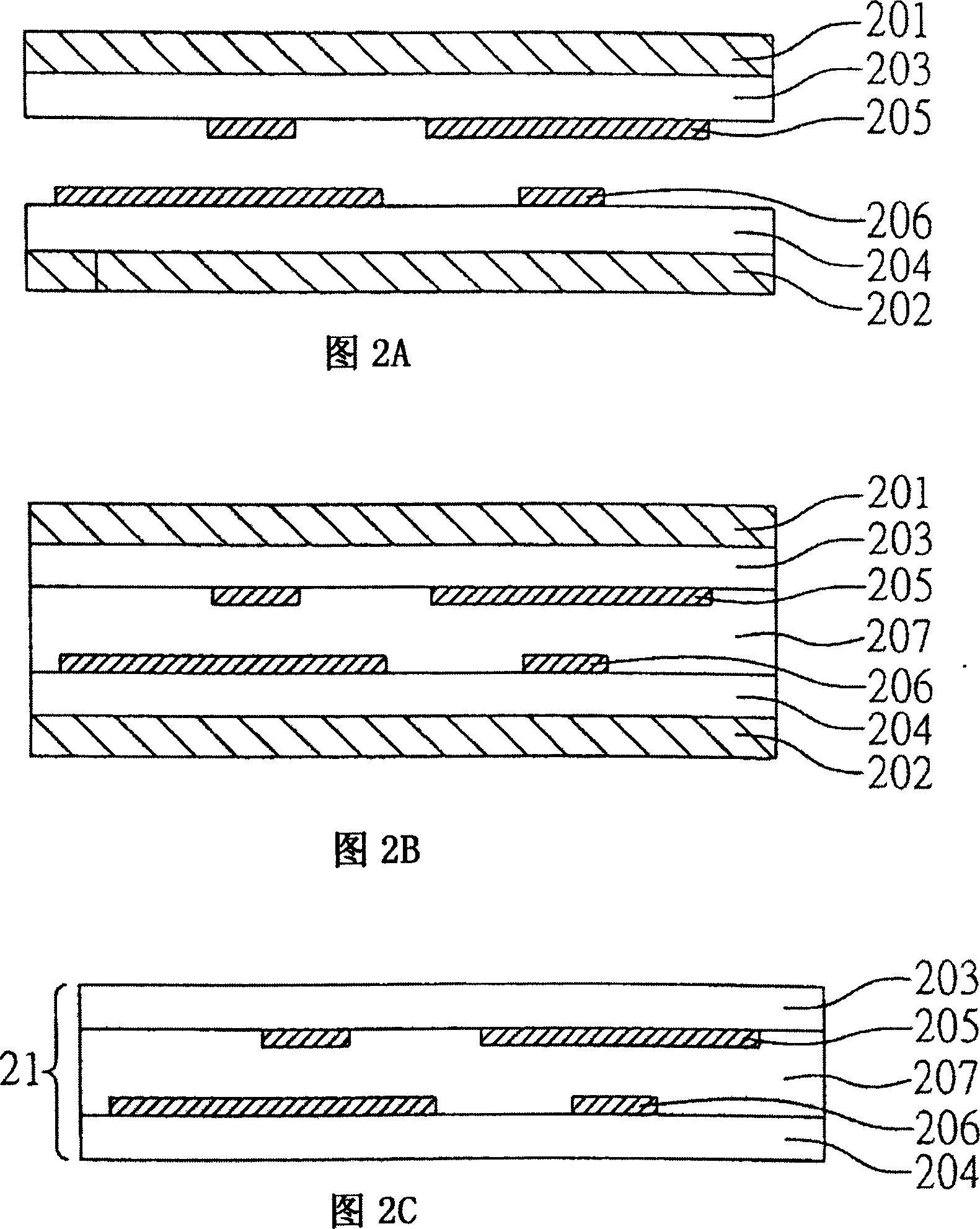

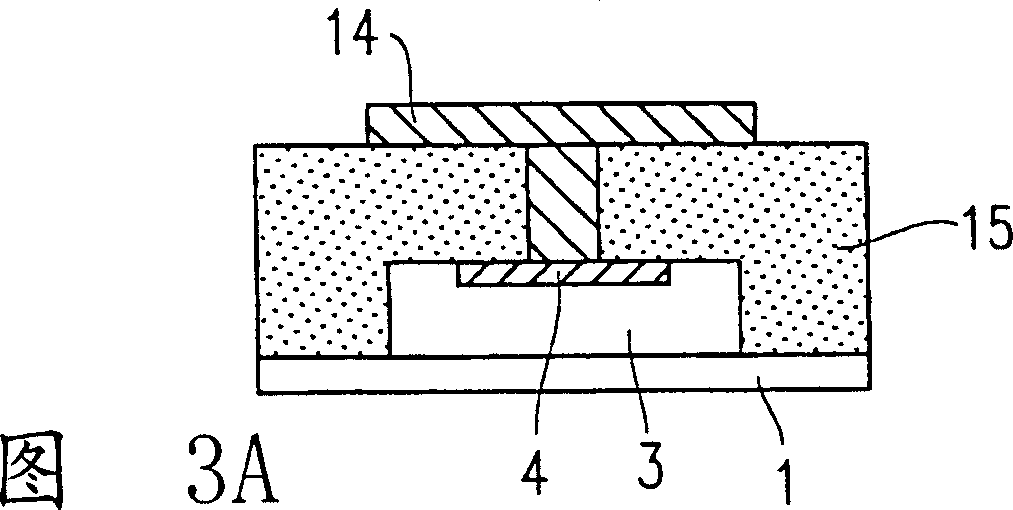

Circuit-board having internal electronic element and making method thereof

InactiveCN1438833AEasy and stable interconnectionReduce wiring densityPrinted circuit assemblingSemiconductor/solid-state device detailsEngineeringElectronic component

A built-in electronic component-mounted wiring board includes an electronic component having a connecting terminal and being mounted on a support; an insulating layer provided on the support so as to cover at least a portion of the electronic component; an opening provided in the insulating layer so as to expose the connecting terminal of the electronic component; and a connecting portion provided in the opening.

Owner:SHARP KK

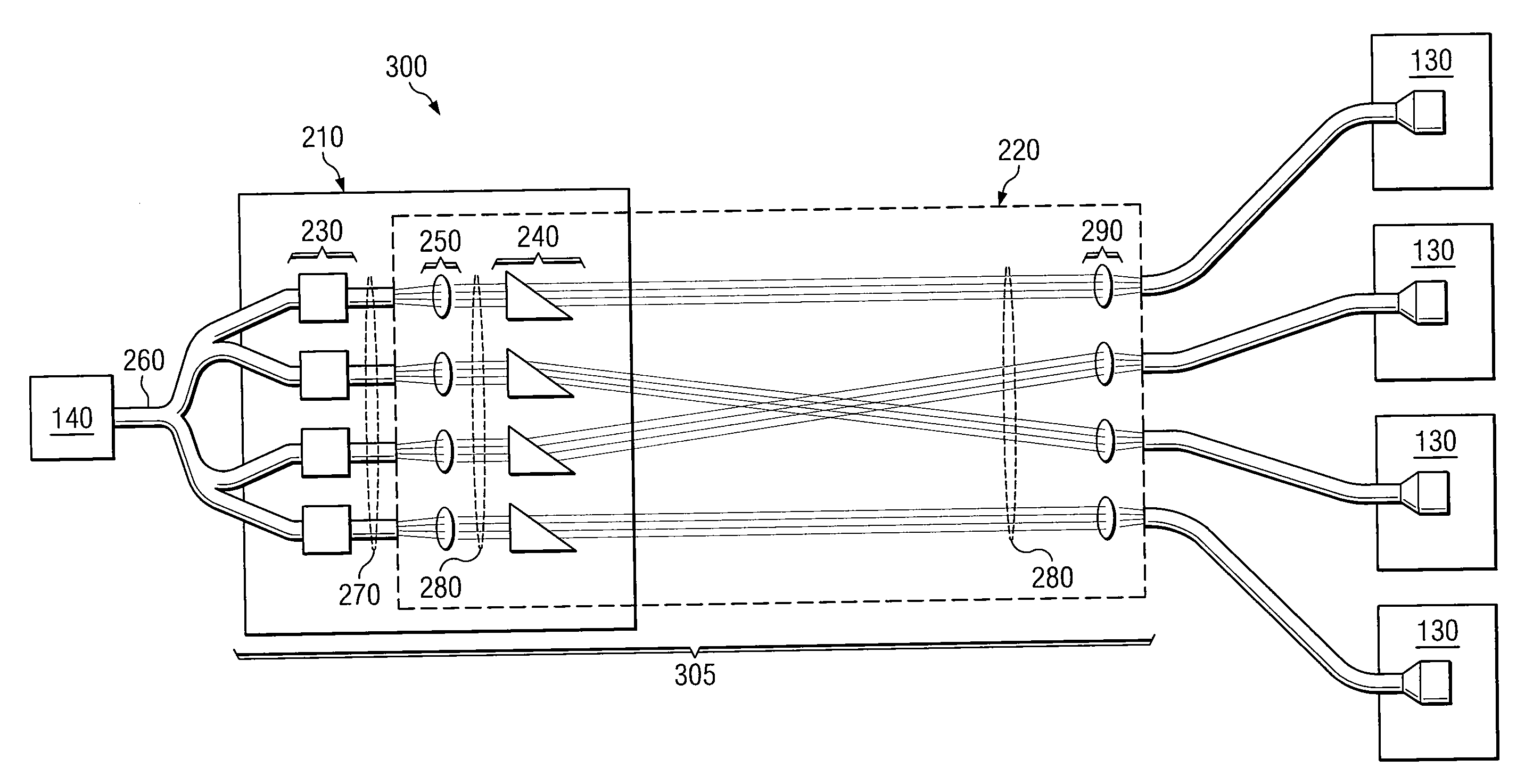

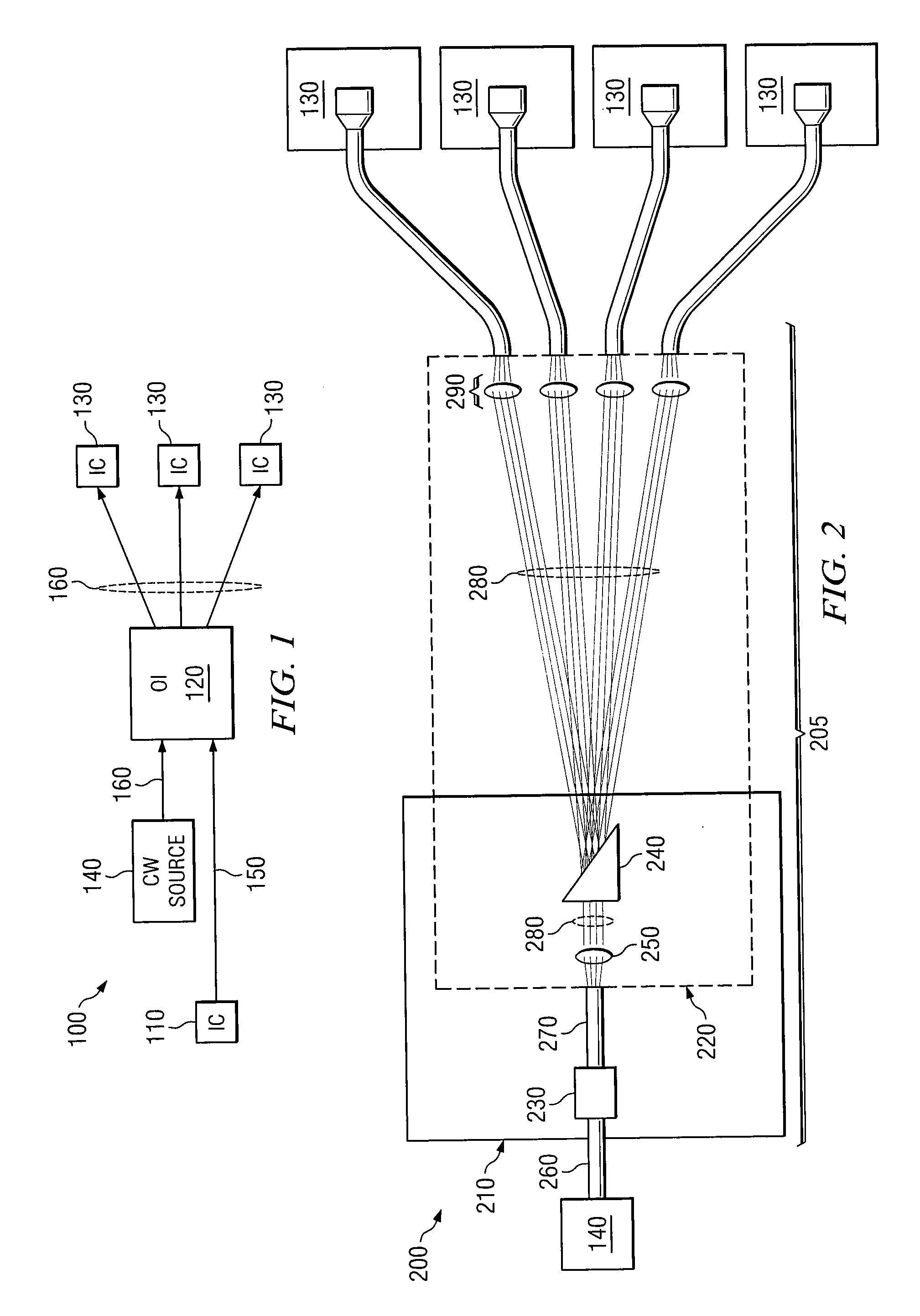

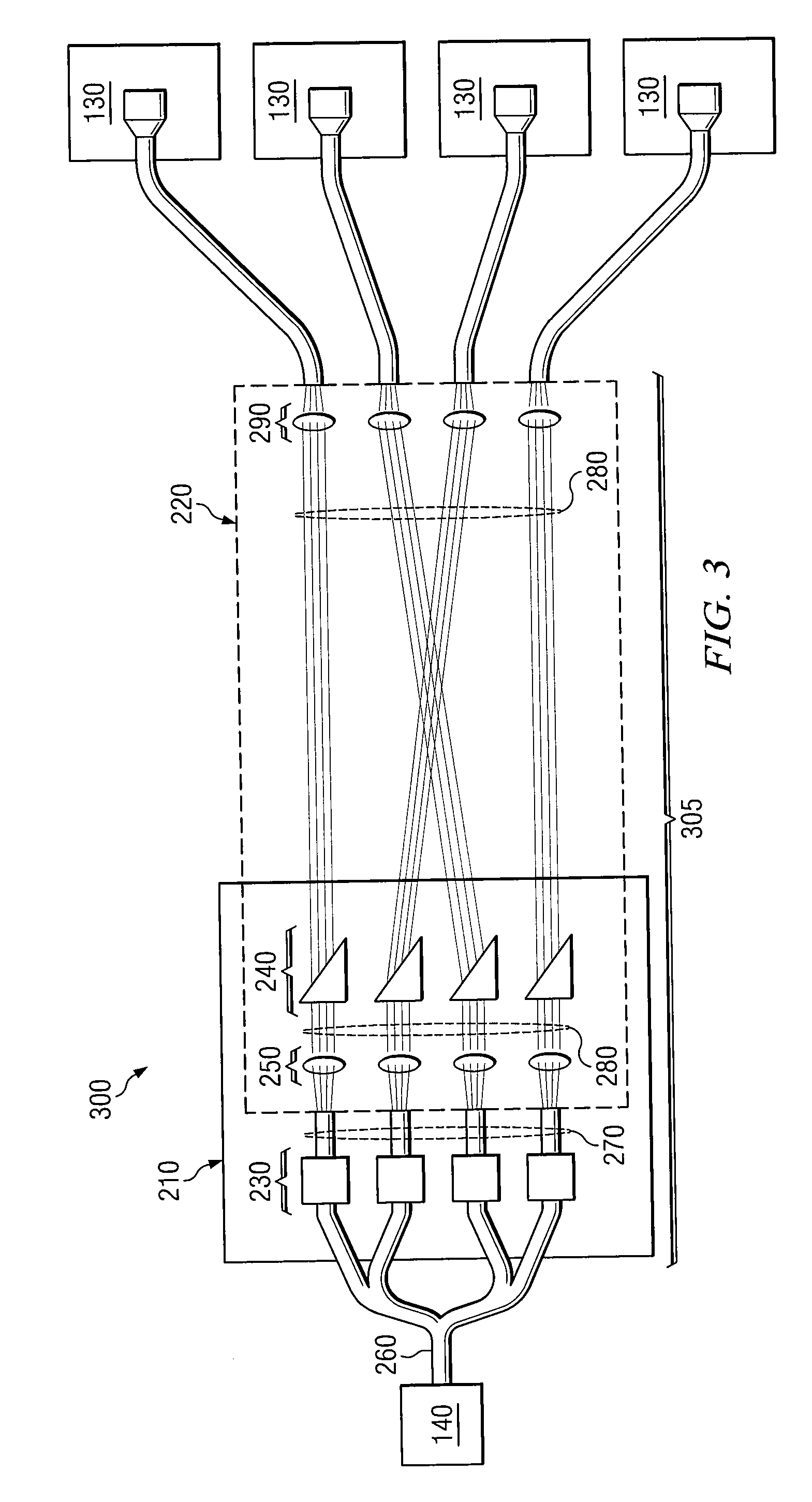

Dynamic Reconfigurable Optical Interconnect System

InactiveUS20100054655A1Eliminates and reducesReduce wiring densityMultiplex system selection arrangementsWavelength-division multiplex systemsLight beamPrism

An optical interconnect system includes an integrated circuit, at least one optical modulator, and a slab waveguide. The optical modulator is coupled to the integrated circuit and receives an input light beam from a light source and data from a source device and generates a modulated output light beam. The slab waveguide is coupled to the optical modulator and includes at least one input waveguide microlens, a plurality of output waveguide microlenses, and at least one deflector prism. The input waveguide microlens focuses the modulated output light beam from the modulator into a collimated light beam. The deflector prism is coupled to the integrated circuit, receives the collimated light beam from the input waveguide microlens, and deflects the collimated light beam toward one of the output waveguide microlenses according to an input voltage.

Owner:FUJITSU LTD

Method of manufacturing multilayer board, multilayer board, and electromagnet

ActiveUS20160027578A1Reduces and prevents tiltingAvoid tiltingPrinted circuit manufacturePrinted inductor incorporationLine widthEngineering

In a linear conductor forming step, a wide portion having a relatively large line width and a narrow portion having a relatively small line width are formed in each of a plurality of linear conductors. In addition, in a multilayer board, in base material layers adjacent to each other in a stacking direction, the wide portion overlaps the narrow portion on the adjacent base material layer, and end portions of the wide portions at both sides of the narrow portion in a line width direction, in a planar view. The wide portions are disposed such that the end portions thereof overlap each other in the stacking direction and resistance of a fluid thermoplastic resin increases. The narrow portion is located between the wide portions in the stacking direction.

Owner:MURATA MFG CO LTD

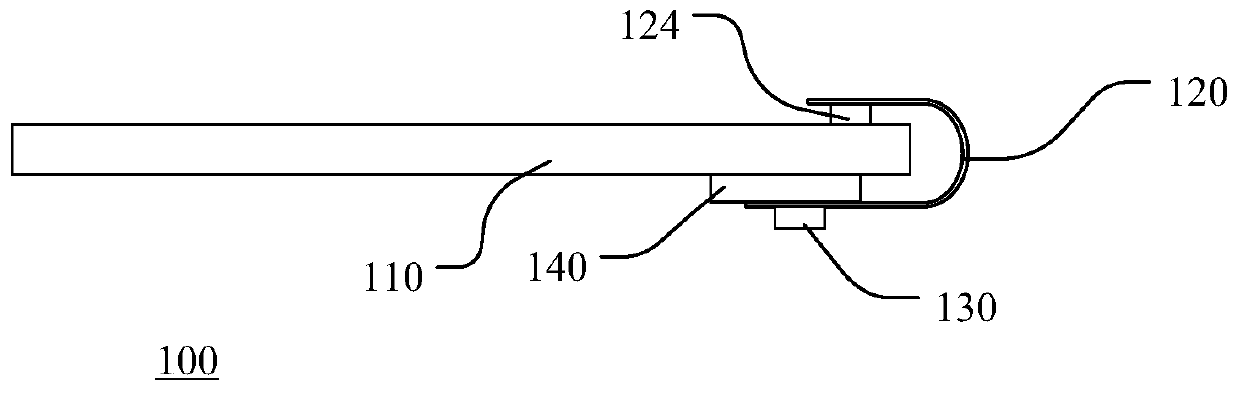

Display device, display system and manufacturing method

PendingCN110133883AReduced risk of short circuitsReduce the risk of electric leakageStatic indicating devicesNon-linear opticsChip on filmCapacitance

The invention discloses a display device, display system and manufacturing method. The display device comprises a display panel and a chip on film, wherein the chip on film comprises a driving chip, afirst electrode array, a second electrode array and a plurality of leads, the driving chip is provided with a plurality of chip pins; a plurality of chip pins are respectively led out by electrodes in the first electrode array; a second electrode array is used for providing a plurality of signal channels between the driving chip and the display panel; and the plurality of leads are respectively used for connecting the effective pins in the plurality of chip pins to the corresponding signal channels, so that the effective pins are electrically connected with the corresponding driving terminalson the display panel, when the plurality of chip pins comprise at least one idle pin and at least one effective pin, the leads, the effective pins and the driving terminals are the same in number. The chip of the display device comprises at least one idle pin, and the wiring density of the lead is reduced, so that the short circuit and electric leakage risks of the display device caused by overlarge wiring density are reduced, and the problem of increased coupling capacitance is avoided.

Owner:CHIPONE TECH BEIJINGCO LTD

Semiconductor device having plural standard cells

ActiveUS20130228877A1Reduce wiring densityTransistorSolid-state devicesField-effect transistorSemiconductor

Disclosed herein is a device that includes: a plurality of first standard cells arranged on a semiconductor substrate in a first direction, each of the first standard cells including at least one field-effect transistor; and a first power supply wiring extending in the first direction along one end of the first standard cells in a second direction. The field-effect transistor including a gate electrode formed on a gate wiring layer. The first power supply wiring being formed on the gate wiring layer.

Owner:LONGITUDE LICENSING LTD

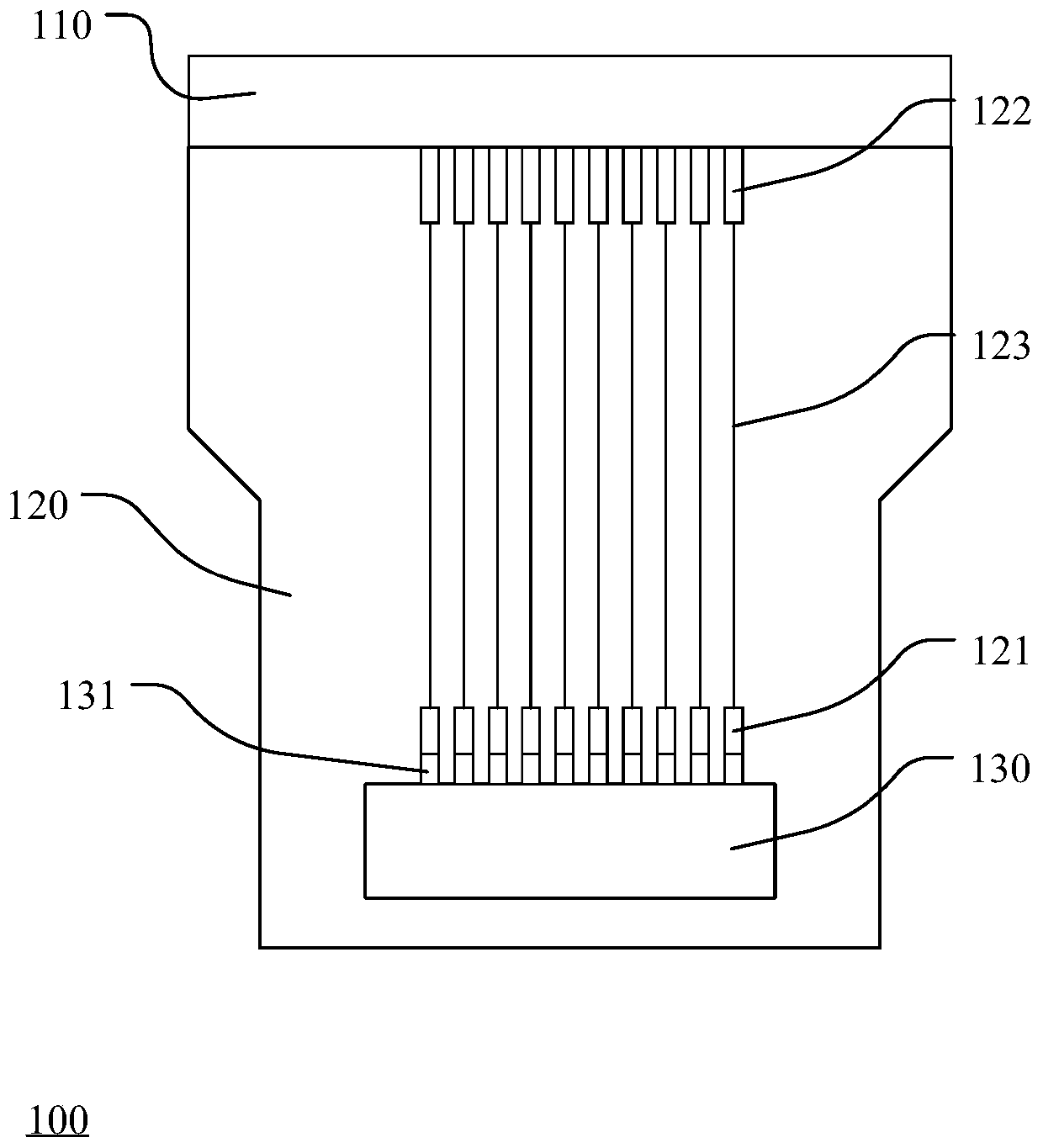

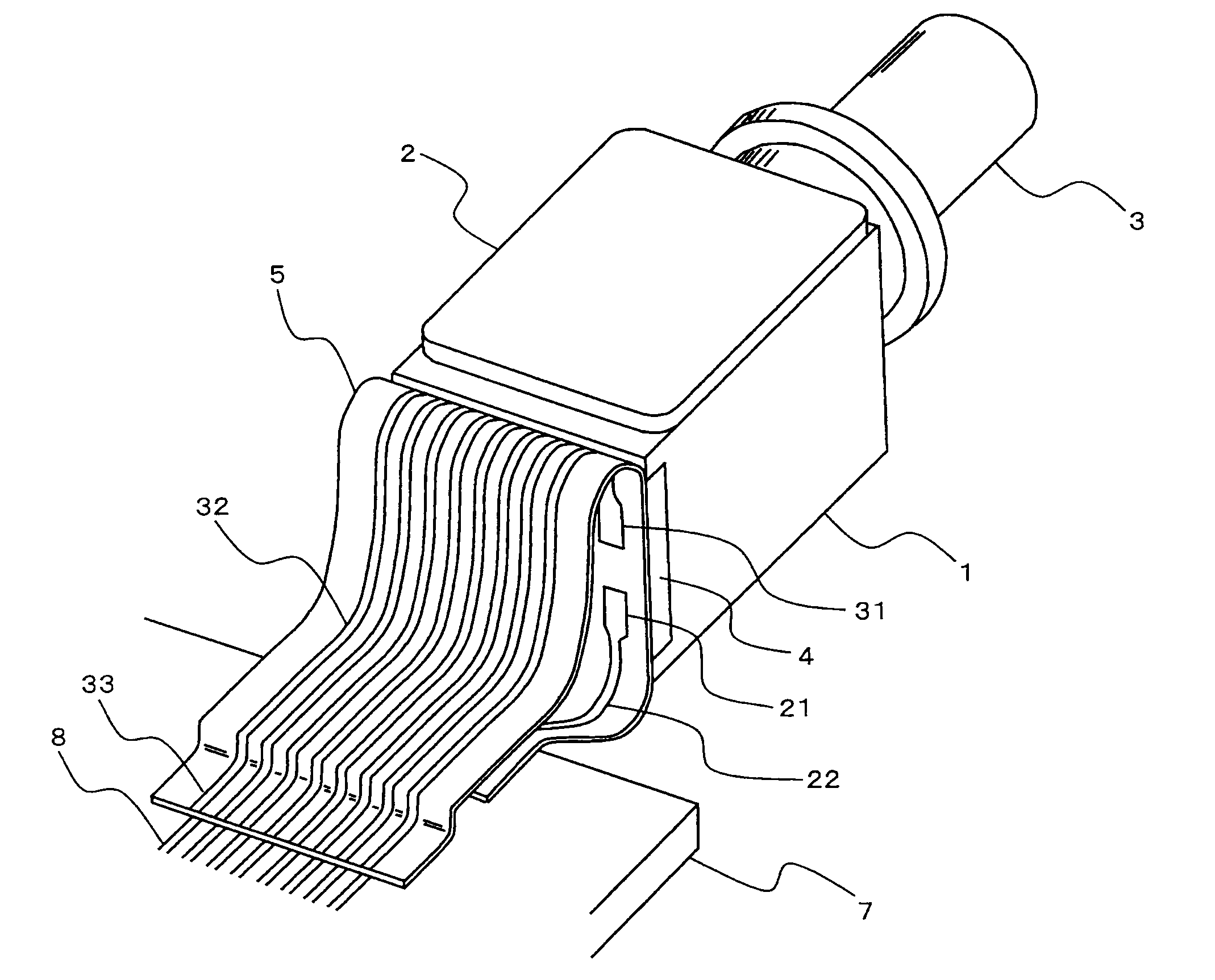

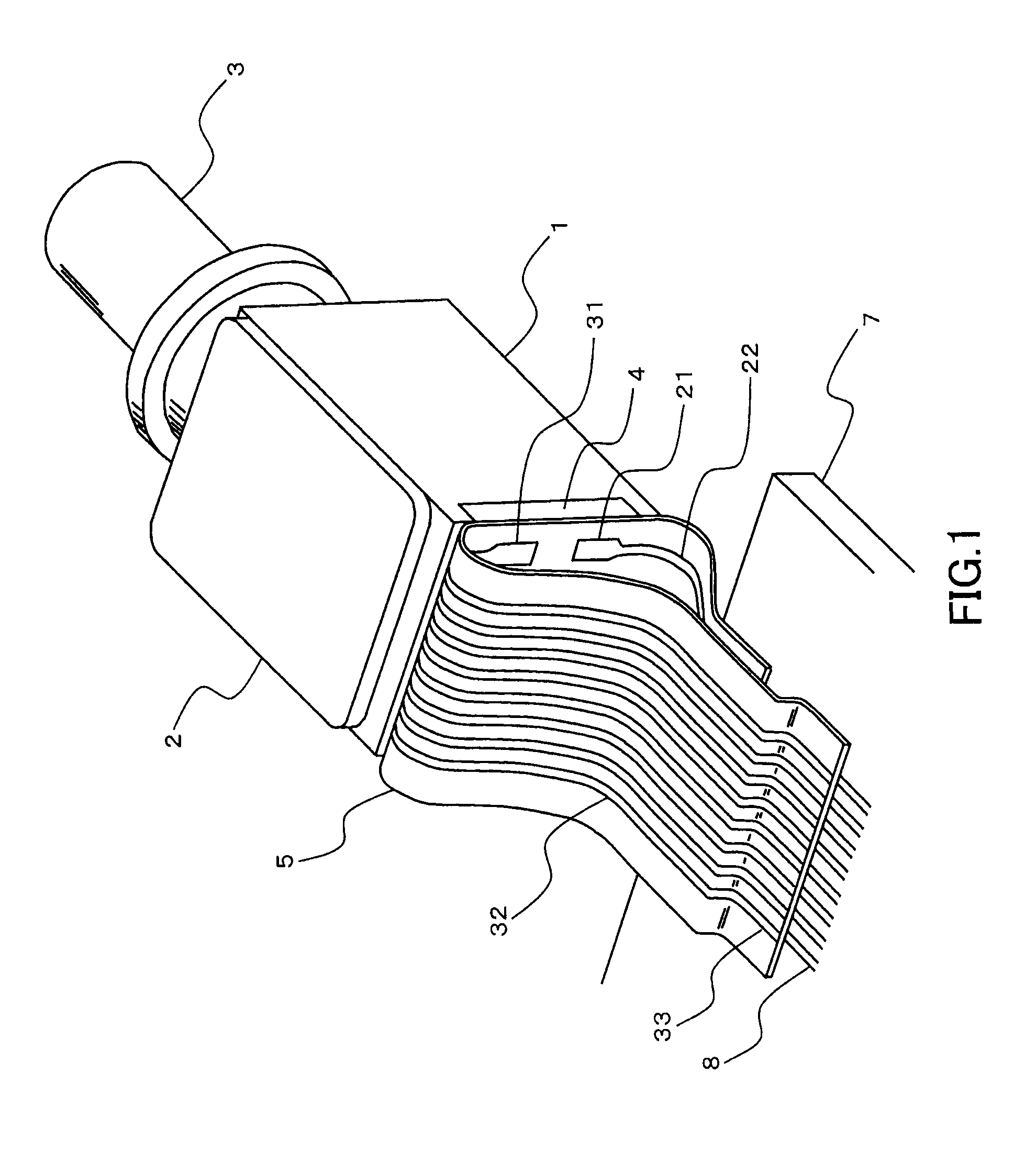

Optical module

ActiveUS8611094B2Reduce crosstalkReduce wiring densityCross-talk/noise/interference reductionPrinted circuit aspectsOptical ModuleComputer module

Provided is an optical module in which wiring density may be reduced to ensure isolation between lines to reduce crosstalk. A flexible printed circuit includes: dielectric layers; a first pattern facing portion including a first ground conductor pattern and a first wiring pattern electrically connected to an electric terminal, which are facing each other through the dielectric layer; and a second pattern facing portion including a second ground conductor pattern and a second wiring pattern electrically connected to the electric terminal, which are facing each other through the dielectric layer, the second pattern facing portion facing the first pattern facing portion, in which when the dielectric layer is bent along a portion between the first pattern facing portion and the second pattern facing portion, at least one of the first ground conductor pattern and the second ground conductor pattern is located between the first wiring pattern and the second wiring pattern.

Owner:MITSUBISHI ELECTRIC CORP

Optical module

ActiveUS20120008289A1Reduce wiring densityReduce crosstalkCross-talk/noise/interference reductionPrinted circuit aspectsOptical ModuleEngineering

Provided is an optical module in which wiring density may be reduced to ensure isolation between lines to reduce crosstalk. A flexible printed circuit includes: dielectric layers; a first pattern facing portion including a first ground conductor pattern and a first wiring pattern electrically connected to an electric terminal, which are facing each other through the dielectric layer; and a second pattern facing portion including a second ground conductor pattern and a second wiring pattern electrically connected to the electric terminal, which are facing each other through the dielectric layer, the second pattern facing portion facing the first pattern facing portion, in which when the dielectric layer is bent along a portion between the first pattern facing portion and the second pattern facing portion, at least one of the first ground conductor pattern and the second ground conductor pattern is located between the first wiring pattern and the second wiring pattern.

Owner:MITSUBISHI ELECTRIC CORP

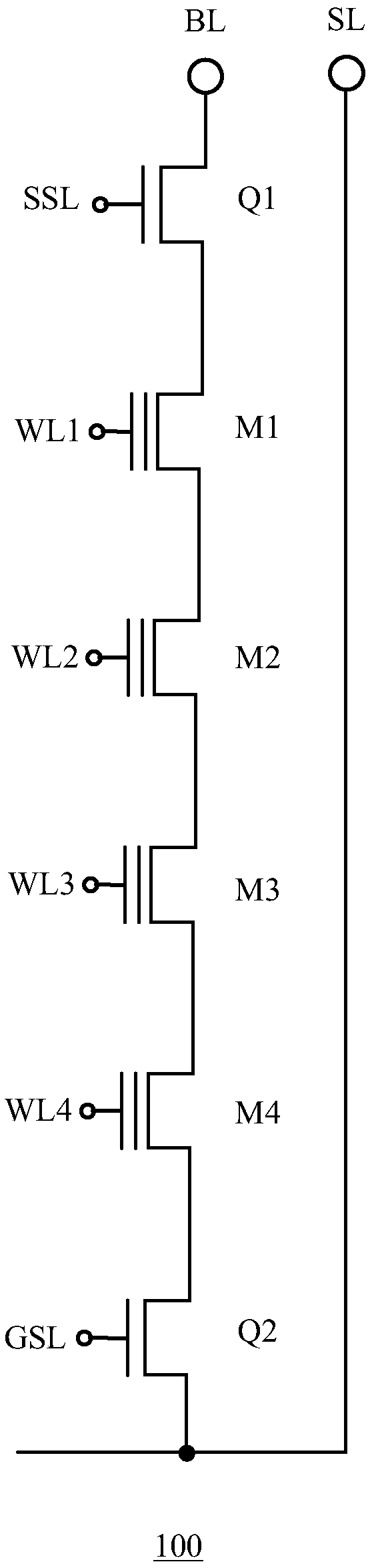

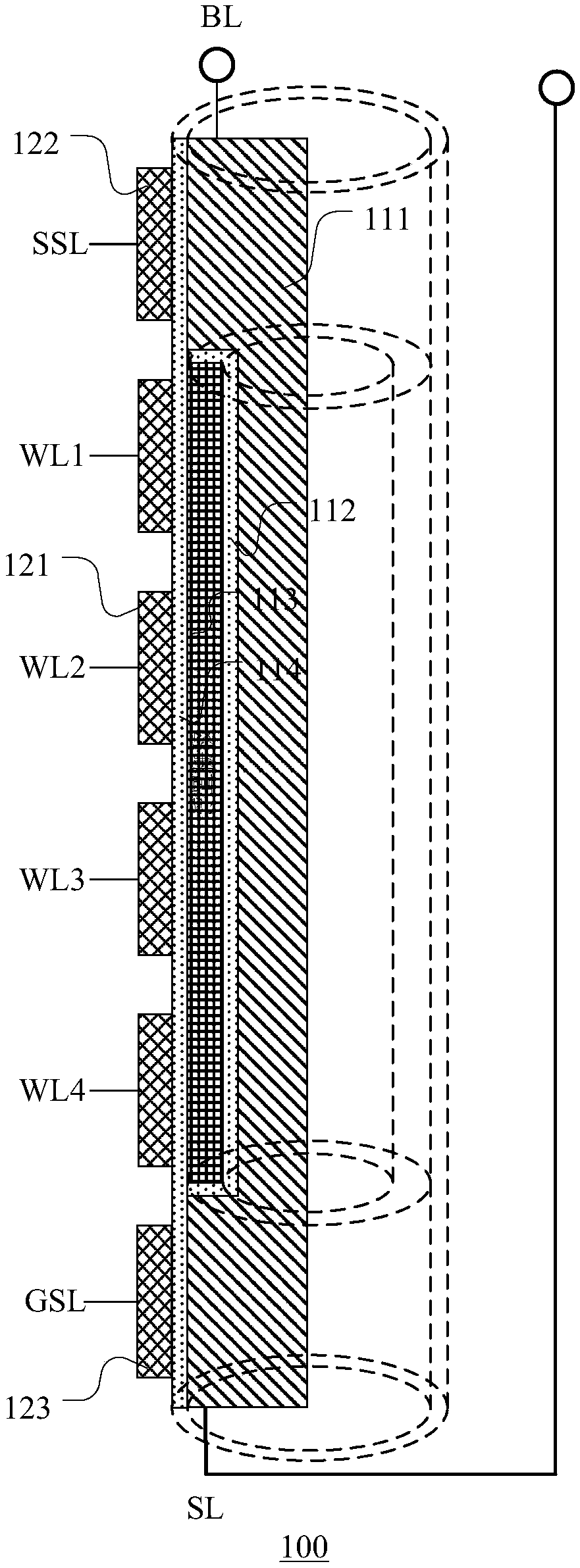

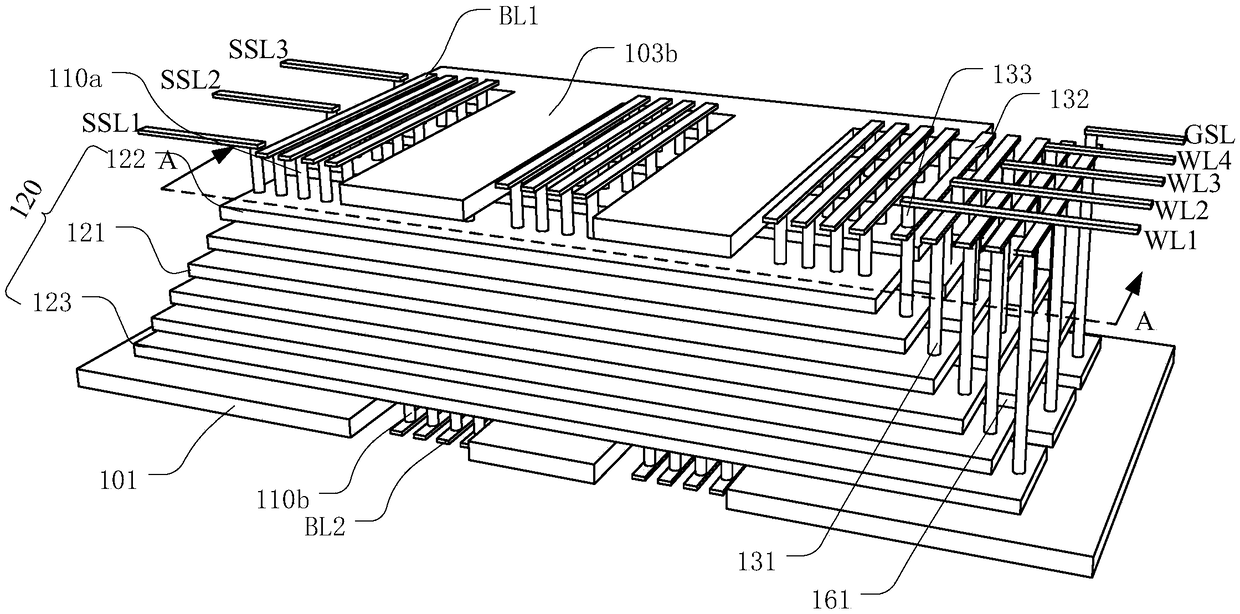

3D memory device and manufacture method thereof

ActiveCN109273457AImprove yieldImprove reliabilitySolid-state devicesSemiconductor devicesElectrical resistance and conductanceElectrical conductor

A 3D memory device and a method of manufacture that same are disclosed. The 3D memory device includes a laminated structure including a plurality of stacked gate conductors and a plurality of interlayer insulating layers; A plurality of channel columns penetrating the laminated structure; A plurality of bit lines and a common source line located on a surface of the laminated structure, one end ofthe channel post being connected to a corresponding bit line of the plurality of bit lines and the other end being connected to the common source line in common; Wherein the plurality of bit lines andthe common source lines are staggered on a surface of the laminated structure. The 3D memory device adopts common source lines and bit lines interleaved on the surface of the 3D memory device stack structure, and the interleaved wiring can use the common source lines between the bit lines to isolate the common source lines and the bit lines, thereby reducing parasitic capacitance and parasitic resistance, improving storage density and access speed, and improving yield and reliability of the 3D memory device.

Owner:YANGTZE MEMORY TECH CO LTD

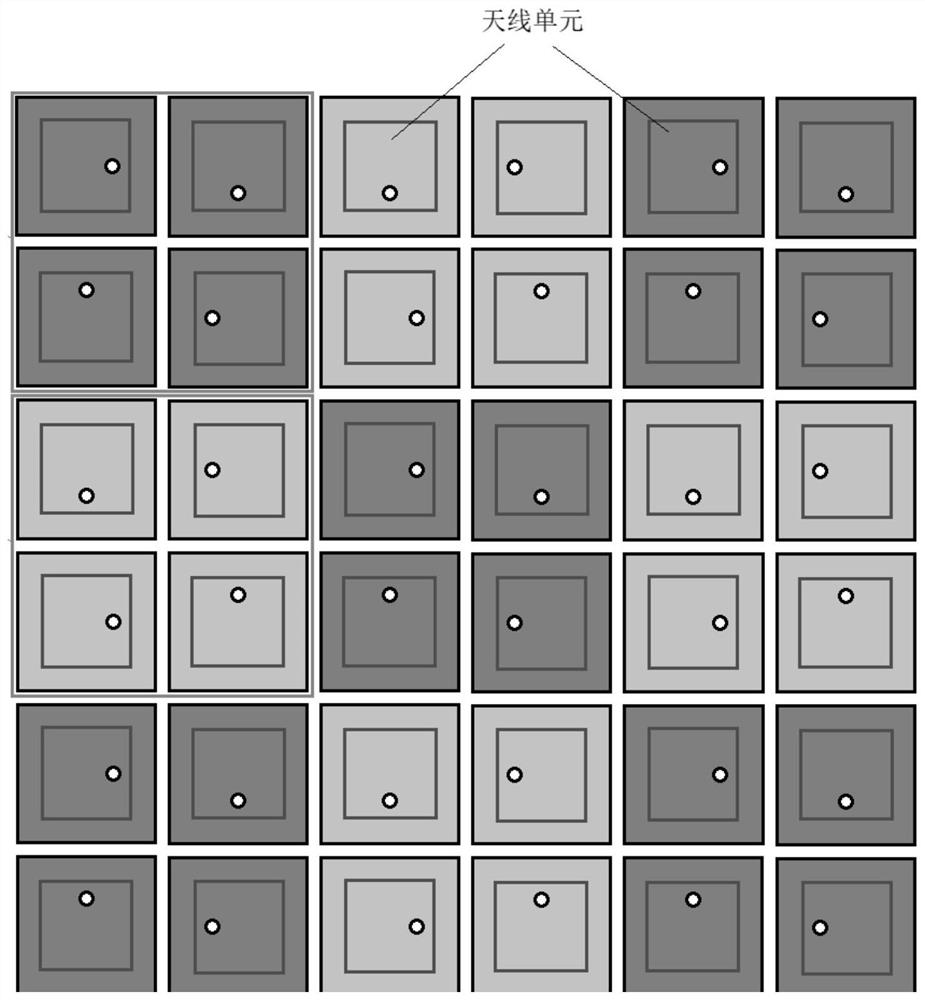

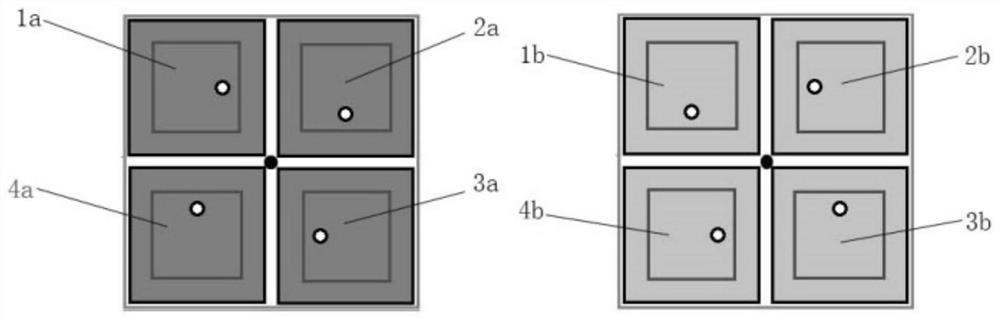

Single-feed-point array combined phased-array antenna

ActiveCN111883938AReduce mutual couplingReduce active standing wavesParticular array feeding systemsIndividually energised antenna arraysCircularly polarized antennaEngineering

The invention relates to the field of phased-array antennas, in particular to a single-feed-point array combined circularly polarized phased-array antenna. The antenna comprises a first array combination and a second array combination, wherein the first array combination consists of 2*2 single-feed-point circularly polarized antenna units, and the 2*2 single-feed-point circularly polarized antennaunits rotate clockwise or anticlockwise around the center of the first array combination for 0 degree, 90 degrees, 180 degrees and 270 degrees orderly; the second array combination is composed of 2*2single-feed-point circularly polarized antenna units, and the second array combination is obtained by translating each antenna unit of the first array combination clockwise or anticlockwise by 90 degrees around the center of the first array combination. The phased-array antenna is formed by arranging a plurality of first array combinations and a plurality of second array combinations in a staggered mode in the transverse direction and the longitudinal direction. The single-feed-point array combined circular polarization phased array antenna of the present invention is used for solving the problems of narrow axial ratio bandwidth, large cross polarization radiation and the like in single-feed-point circular polarization design.

Owner:GUANGZHOU STARWAY COMM TECH

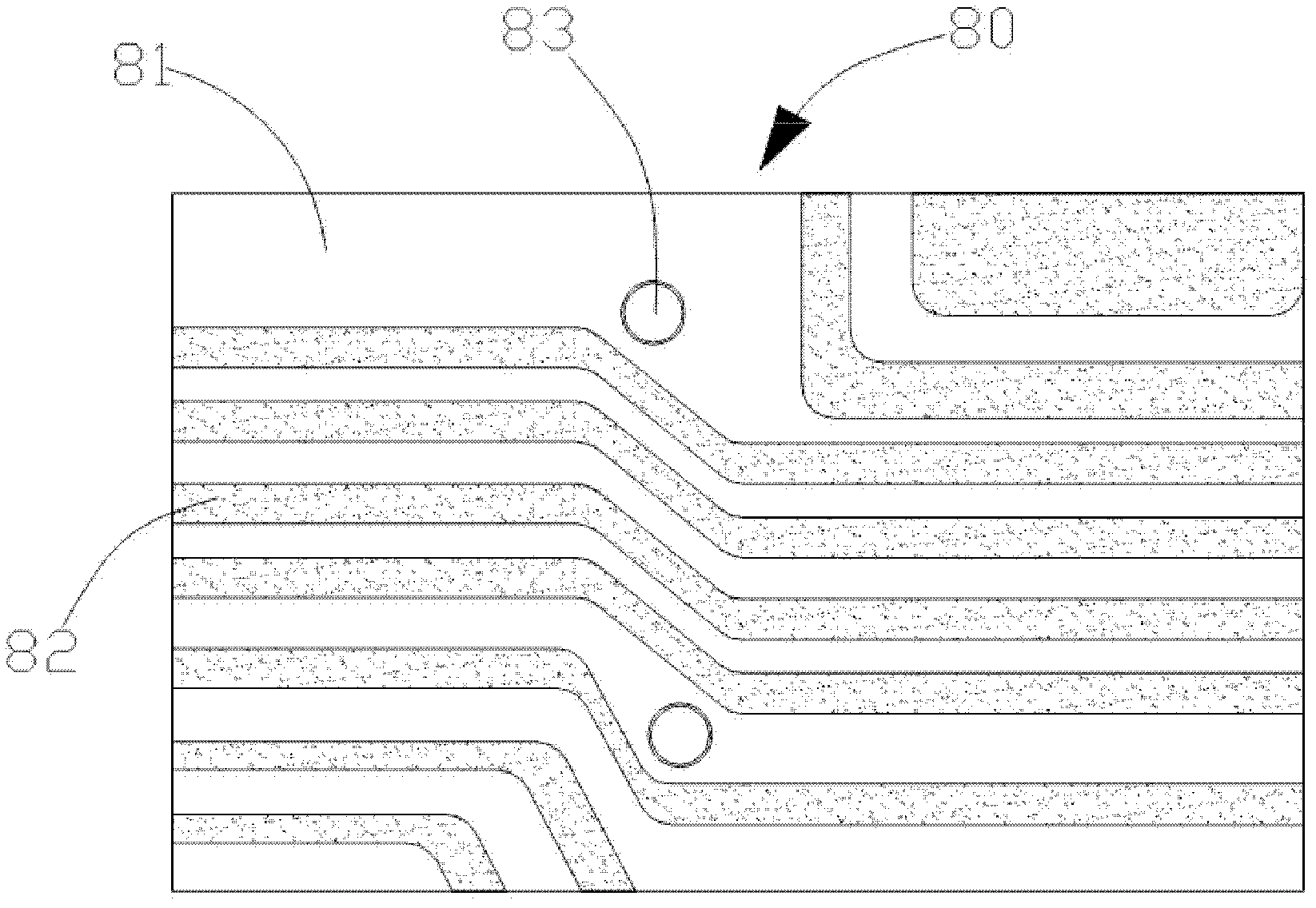

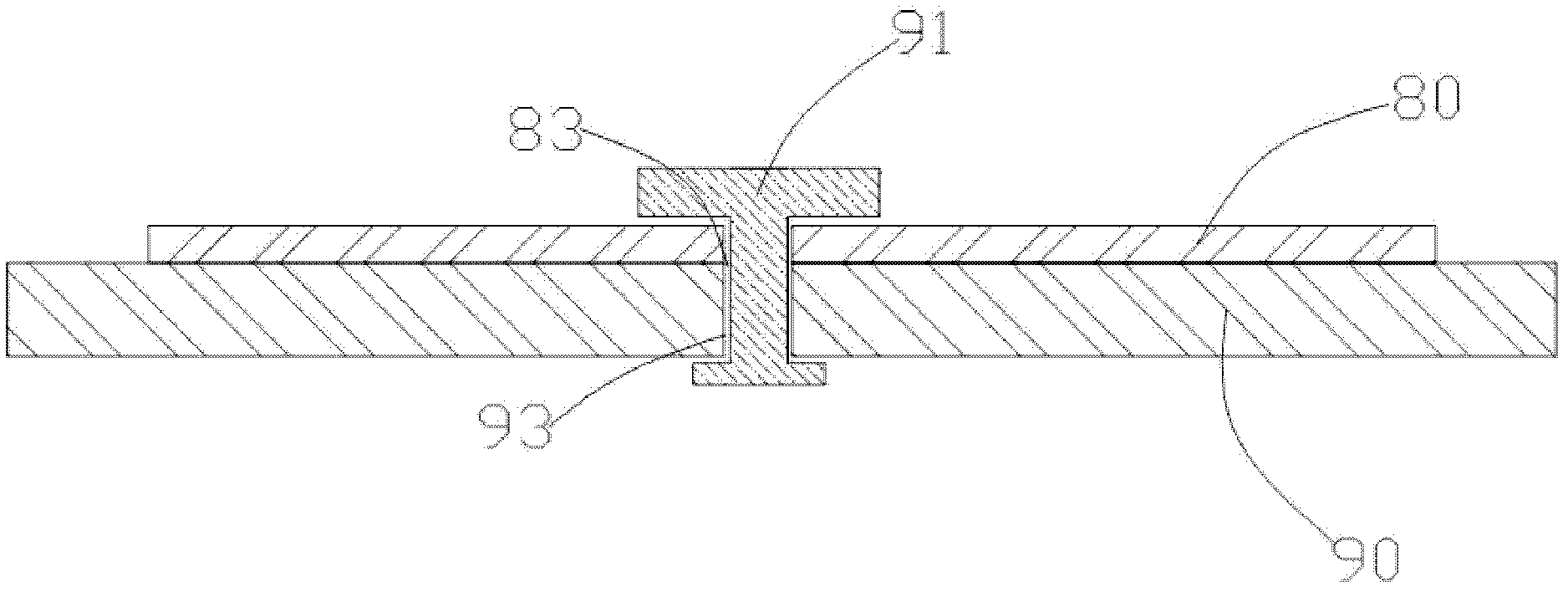

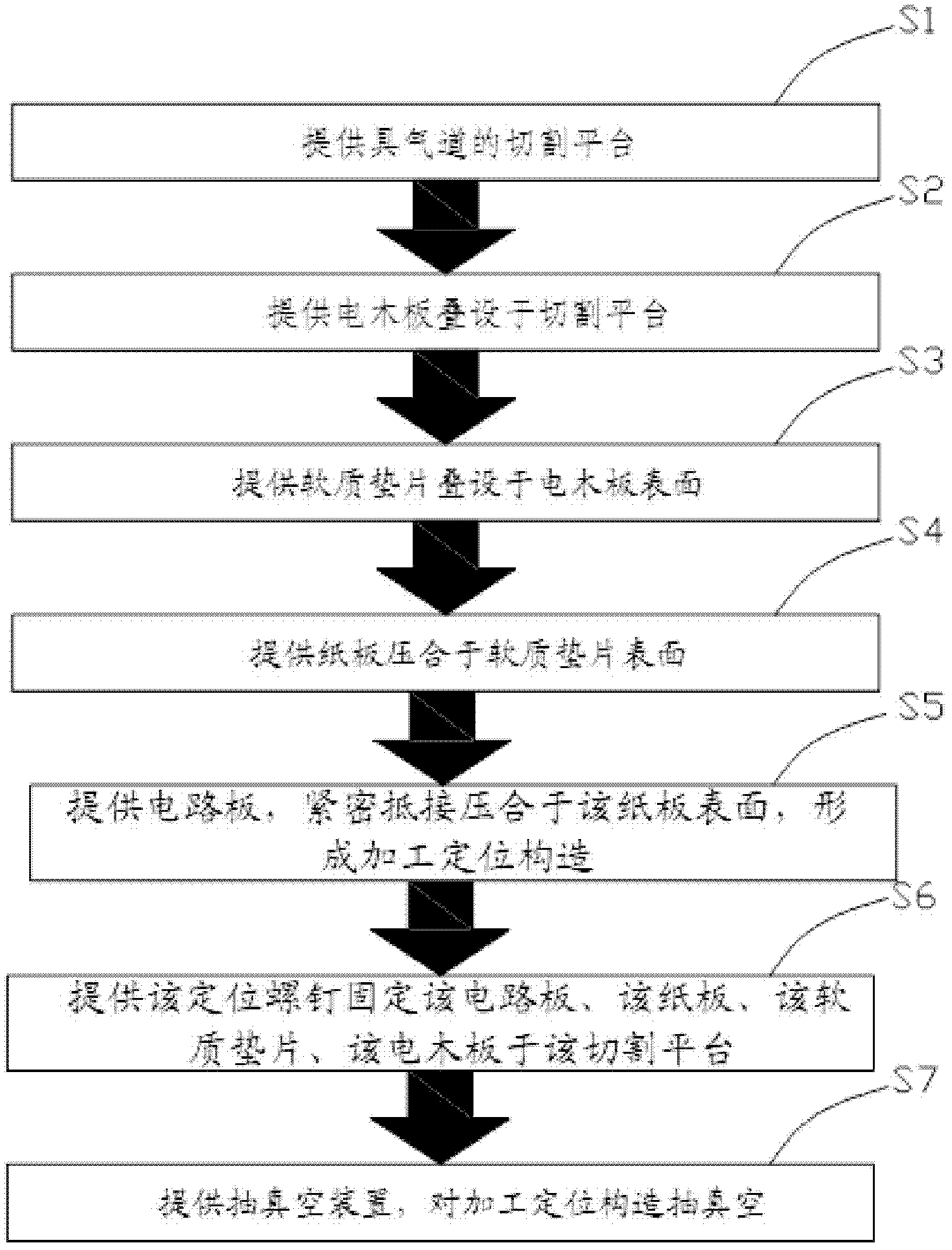

Circuit board processing method

The invention relates to a circuit board processing method, which comprises the following steps of: providing a cutting platform with a gas path, providing medium layers, overlapping the medium layers on the surface of the cutting platform, providing a circuit board, pressing the circuit board on the medium layer, providing a vacuumizing device, vacuumizing gas among the cutting platform and the medium layers so that a vacuum environment is formed from the cutting platform to the circuit board, and realizing adsorption and fixation among the circuit board and various medium layers. According to the method disclosed by the invention, the circuit board is fixed in a vacuum adsorption manner; a locating hole is not used; the problems of high cost, poor cutting effect and complex circuit design resulted from the arrangement of the locating hole can be effectively solved; and the locating effect is increased.

Owner:SHENZHEN WUZHU TECH +1

Ink-jet recording apparatus

Owner:BROTHER KOGYO KK

Super-small-point-interval SMD (surface mounted device) composited LED lamp

The invention discloses a super-small-point-interval SMD (surface mounted device) composited LED lamp. Multiple groups of LED pixel lamps are arrayed on the upper surface of a lamp body, multiple pins are arranged on the lower surface of the lamp body, the super-small-point-interval SMD composited LED lamp further comprises a driving unit, and the pins are electrically connected with the driving unit which is further electrically connected with each group of the LED pixel lamps. The super-small-point-interval SMD composited LED lamp is self-provided with the driving unit, so that the total number of the pins on an LED lamp board can be reduced, wiring difficulty and wiring density can be lowered, smaller point interval can be realized, higher definition and better display effect can be realized.

Owner:SHENZHEN AOTO ELECTRONICS

A method of manufacturing a printed circuit board

ActiveCN103717013BControl swelling and shrinking problemsReduce distortionMultilayer circuit manufacturePrinted element electric connection formationHigh densityEngineering

The invention relates to a manufacturing method for a printed circuit board, wherein manufacturing of a multi-layer high-density interconnected printed circuit board can be realized by using the one-time compressing method. The method comprises the following steps that: first daughter boards and second daughter boards are manufactured; the plurality of first daughter boards and daughter boards are superposed together and heating and pressurizing are carried out, and thus the first daughter boards and the second daughter boards are bonded together to form a multi-layer and multi-stage printed circuit board; conventional processes like mechanical drilling, hole metallization, and electroplating and the like are carried out on the multi-layer printed circuit board so as to complete the manufacturing of the printed circuit board. According to the invention, expansion and shrinkage as well as deformation of materials during the manufacturing process can be effectively controlled, thereby effectively improving alignment precision between the holes and between the hole and the graph; and the safe distances between the holes and between the hole and the graph are reduced from 20 mil to 8mil, thereby effectively improving the wiring density of the printed circuit board. Moreover, under the circumstances that the investment of the PCB manufacturer equipment is not increased, the yield of the high-density interconnected printed circuit board can be substantially improved and the manufacturing period of the product can be shortened.

Owner:SHANGHAI MEADVILLE SCI & TECH +1

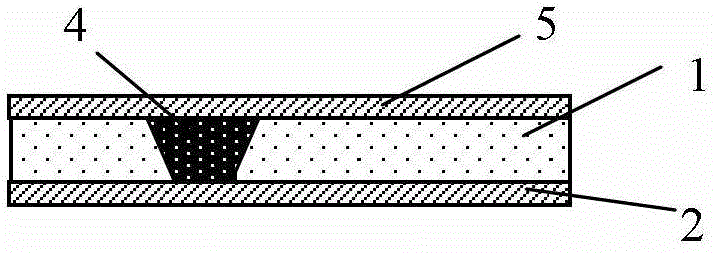

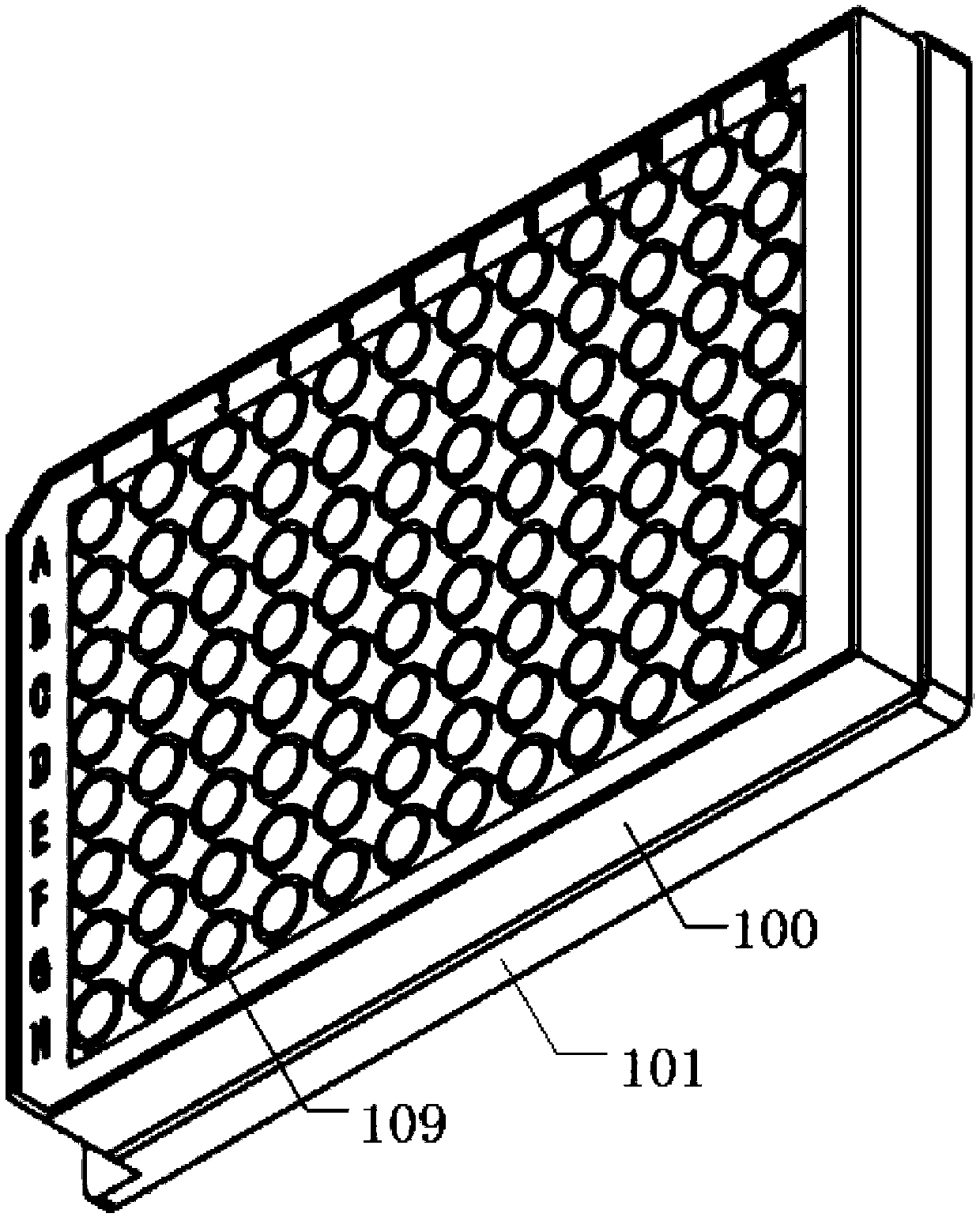

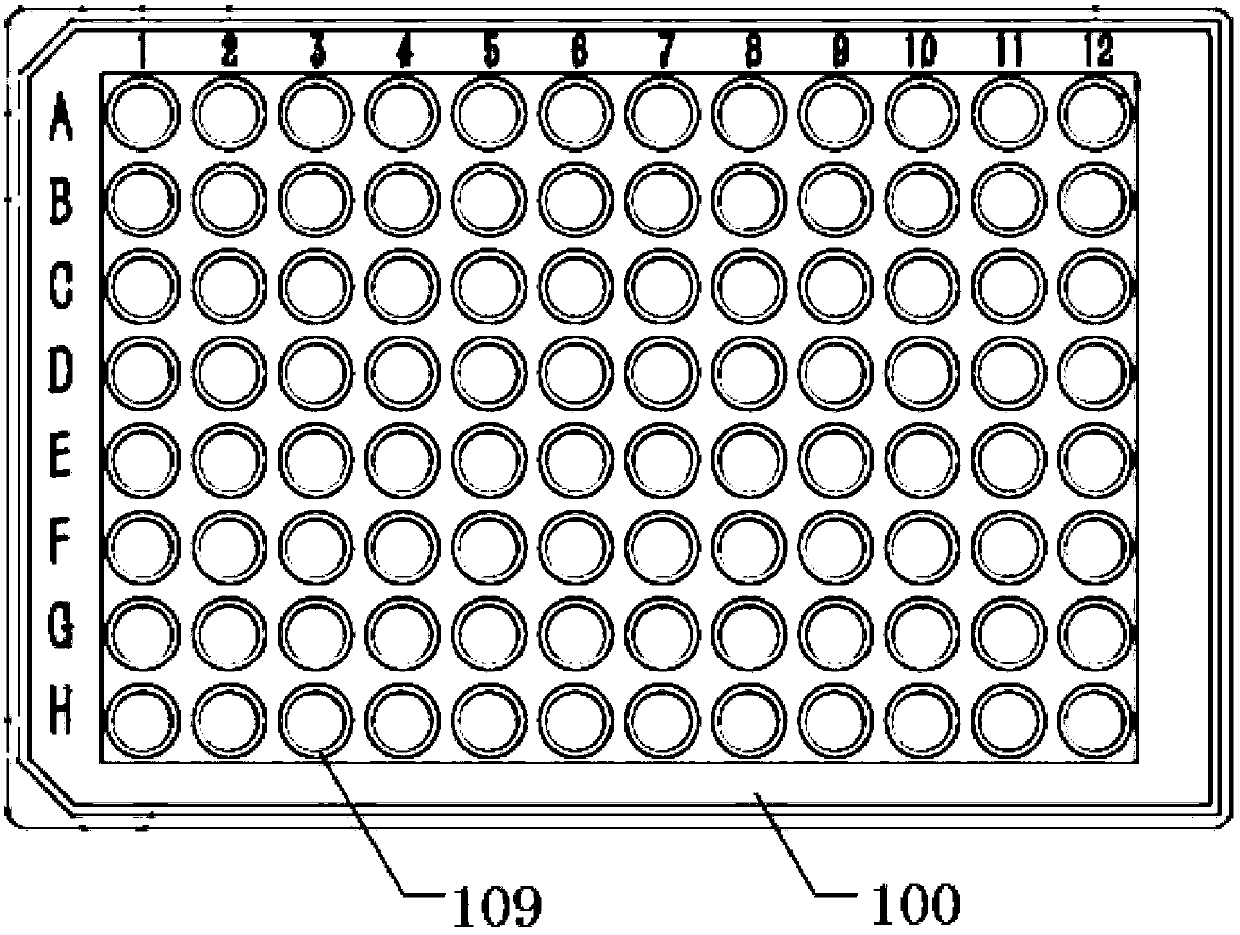

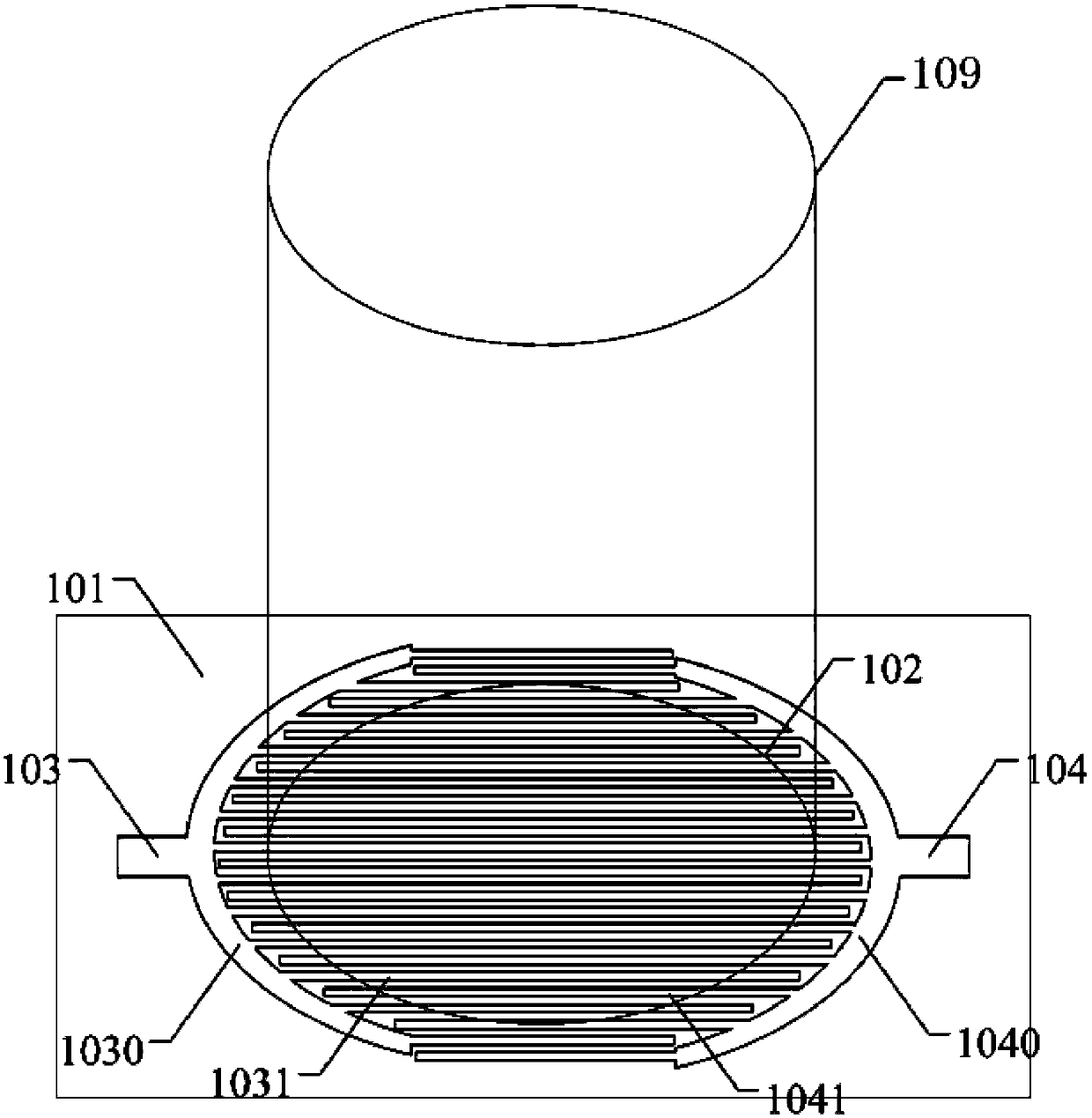

Wiring structure of sample detection pore plate, and sample detection pore plate

PendingCN110118811AReduce the number of partsReduce volumeMaterial analysis by electric/magnetic meansEngineeringVoltage

The invention provides a wiring structure of a sample detection pore plate, and the sample detection pore plate. The sample detection pore plate is provided with a substrate, a plurality of detectionelectrodes are disposed on the surface side of the substrate, each of the plurality of detection electrodes comprises a working electrode to which a voltage is applied and an opposite electrode for detecting and outputting a detection signal, the wiring structure comprises a power supply wiring for supplying power to the working electrode and a signal wiring for outputting the detection signal ofthe opposite electrode, and each of the power supply wiring and the signal wiring comprises a surface wiring portion disposed on the surface of the substrate, a back surface wiring portion disposed onthe back surface of the substrate, and a wiring penetrating portion for penetrating through the substrate and connecting the surface wiring portion with the back surface wiring portion. The wiring structure provided by the invention can reduce the wiring length on the surface side of the substrate, reduce the wiring density and improve the degree of freedom in the wiring design on the surface side and the back surface side of the substrate.

Owner:北京易活生物科技有限公司

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com