Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

51results about How to "No additional process steps" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

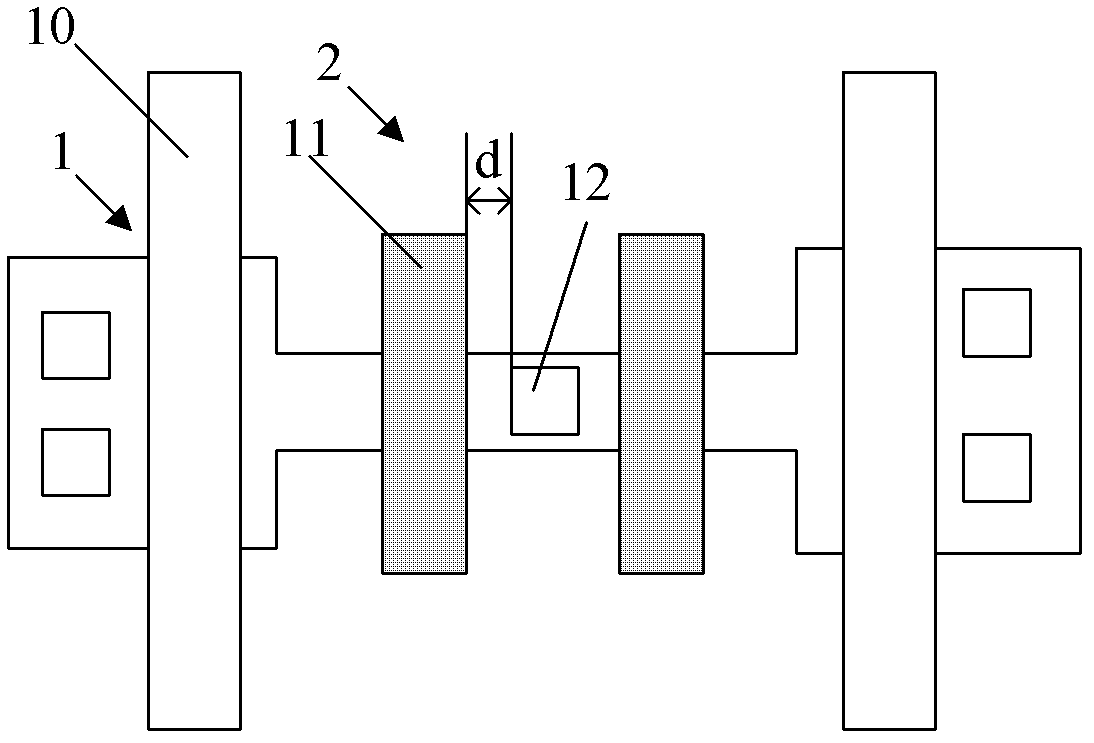

Electrostatic discharge protection circuit, display panel and display device

ActiveCN103268876AAdd release pathImprove anti-static performanceSolid-state devicesEmergency protective arrangements for limiting excess voltage/currentDisplay deviceBottom gate

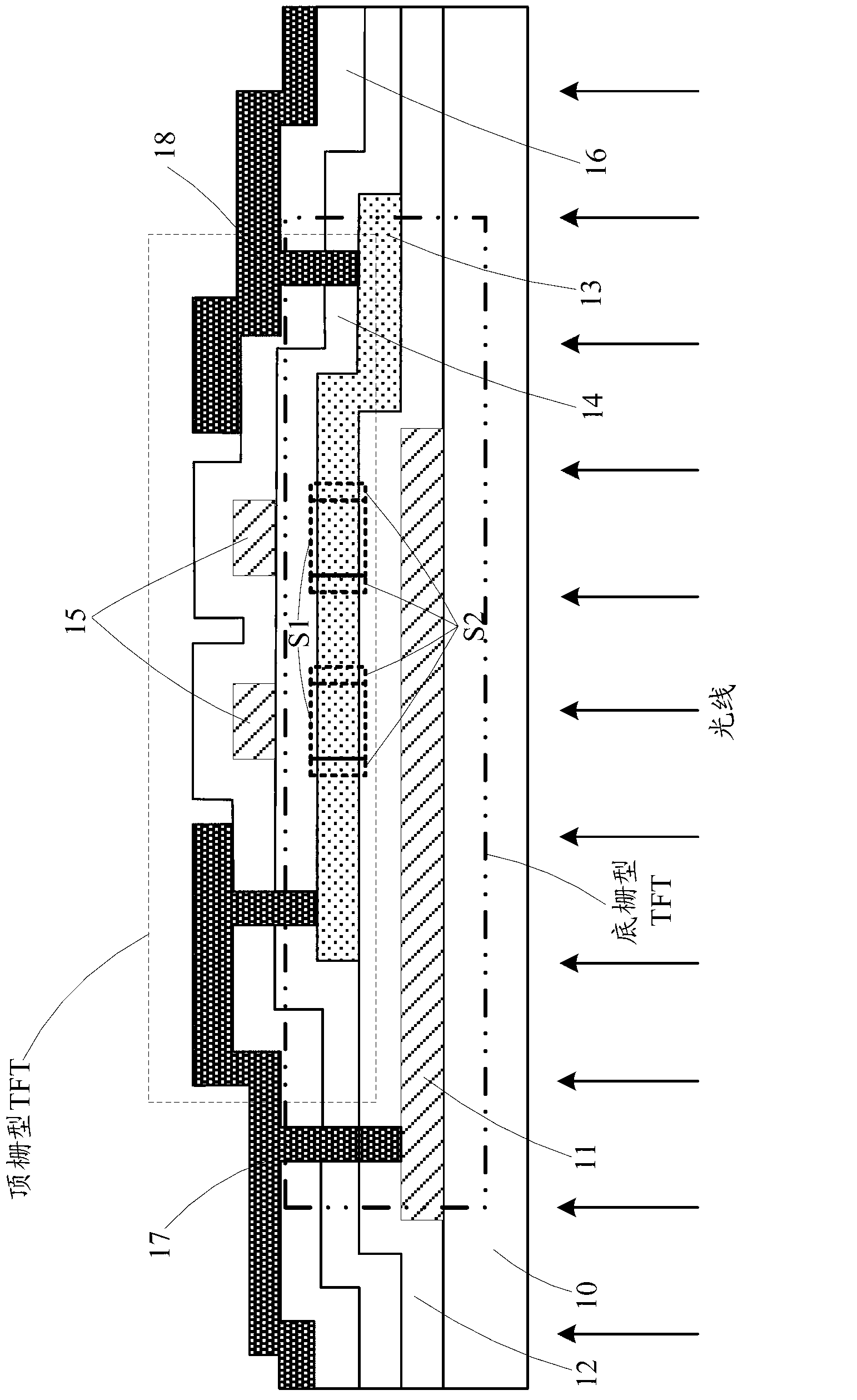

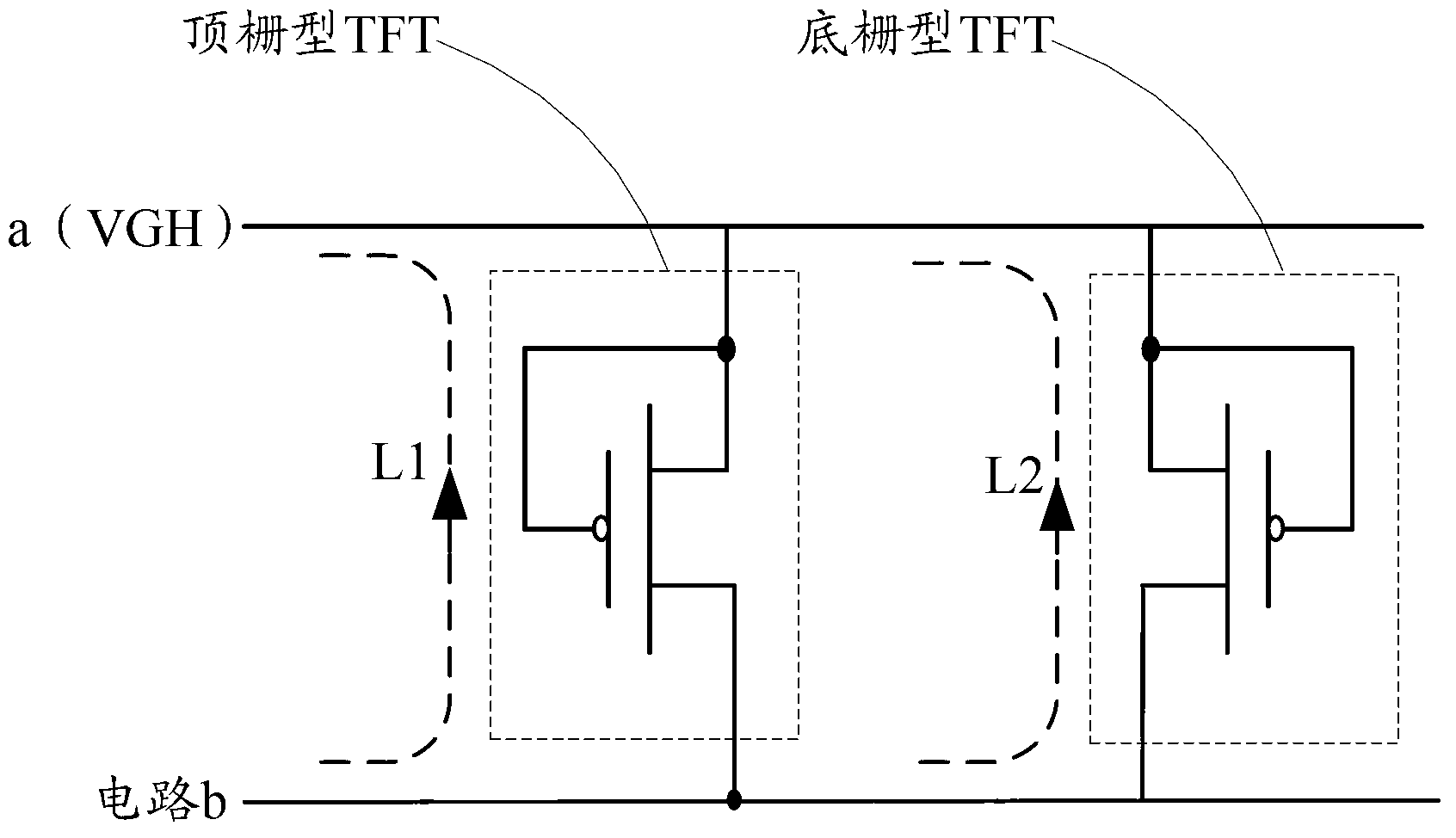

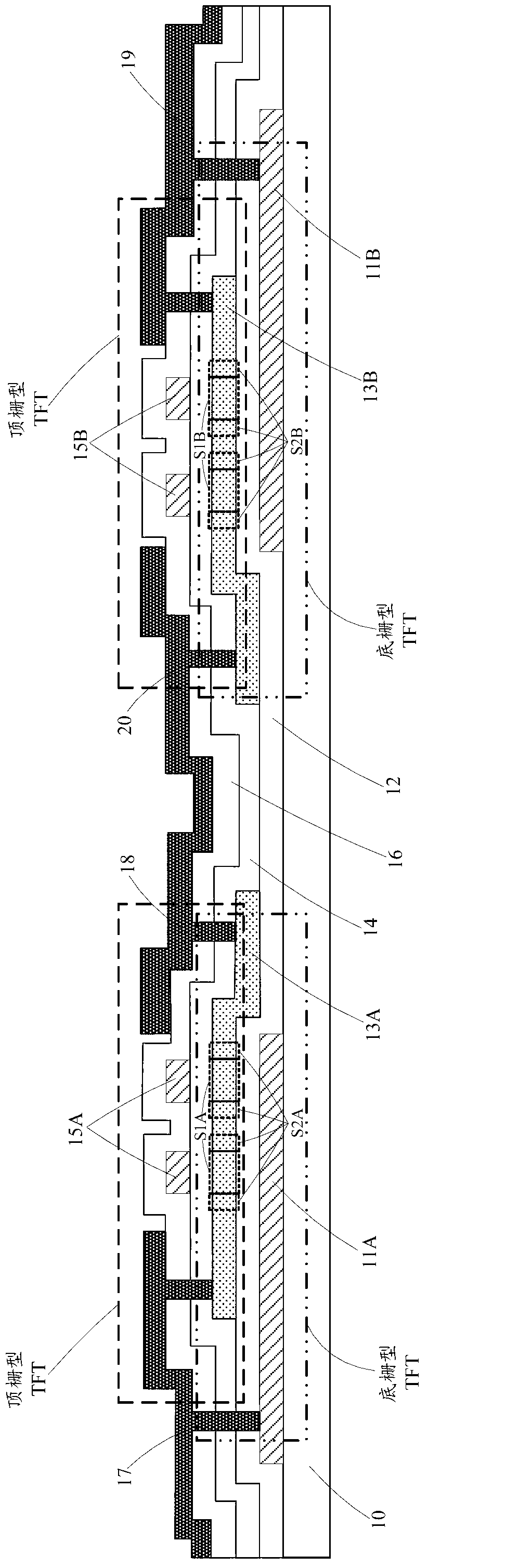

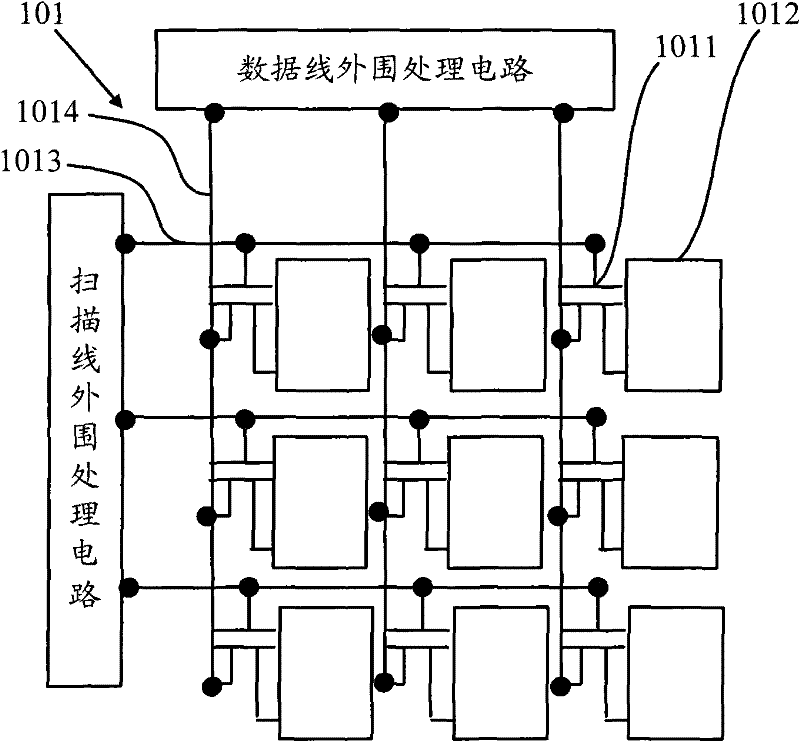

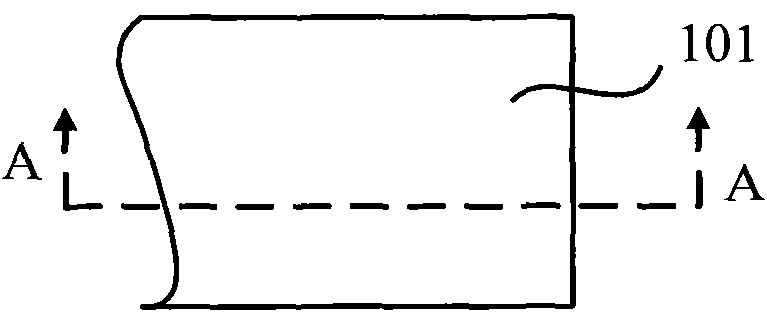

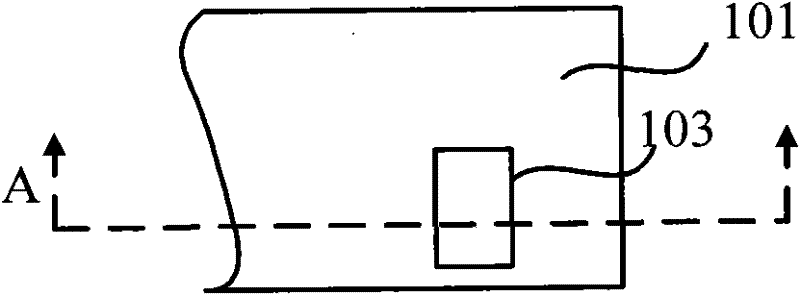

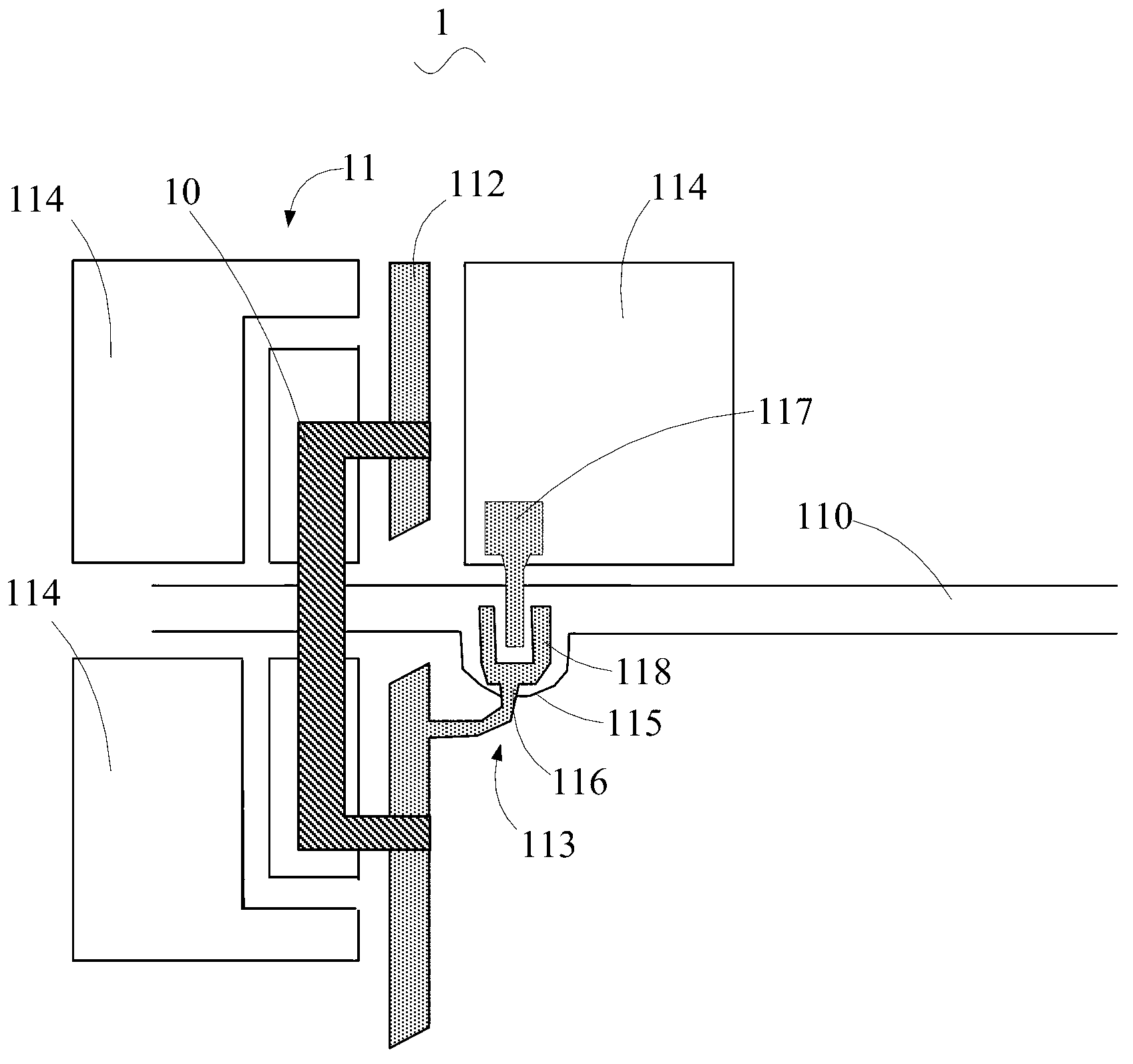

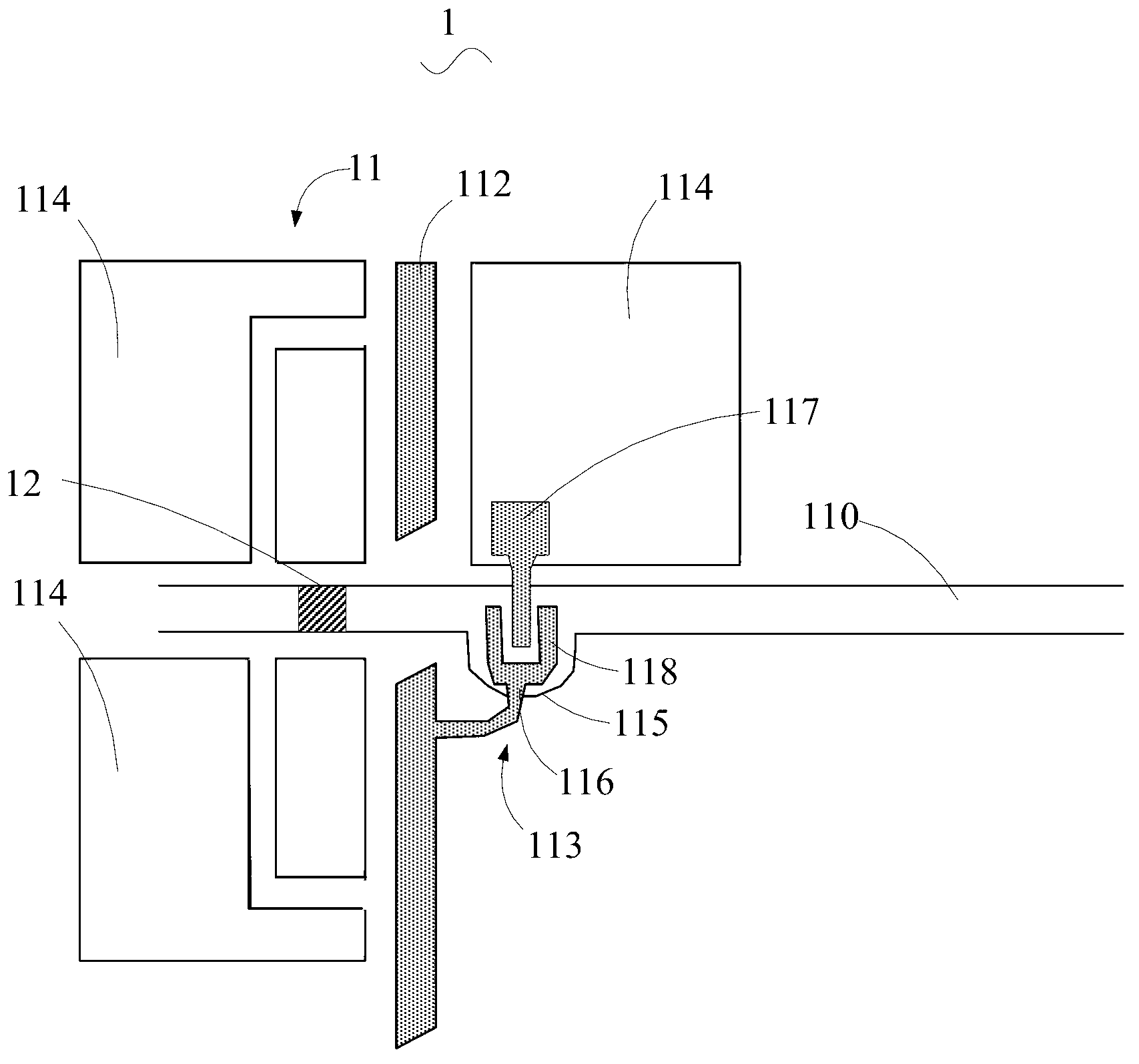

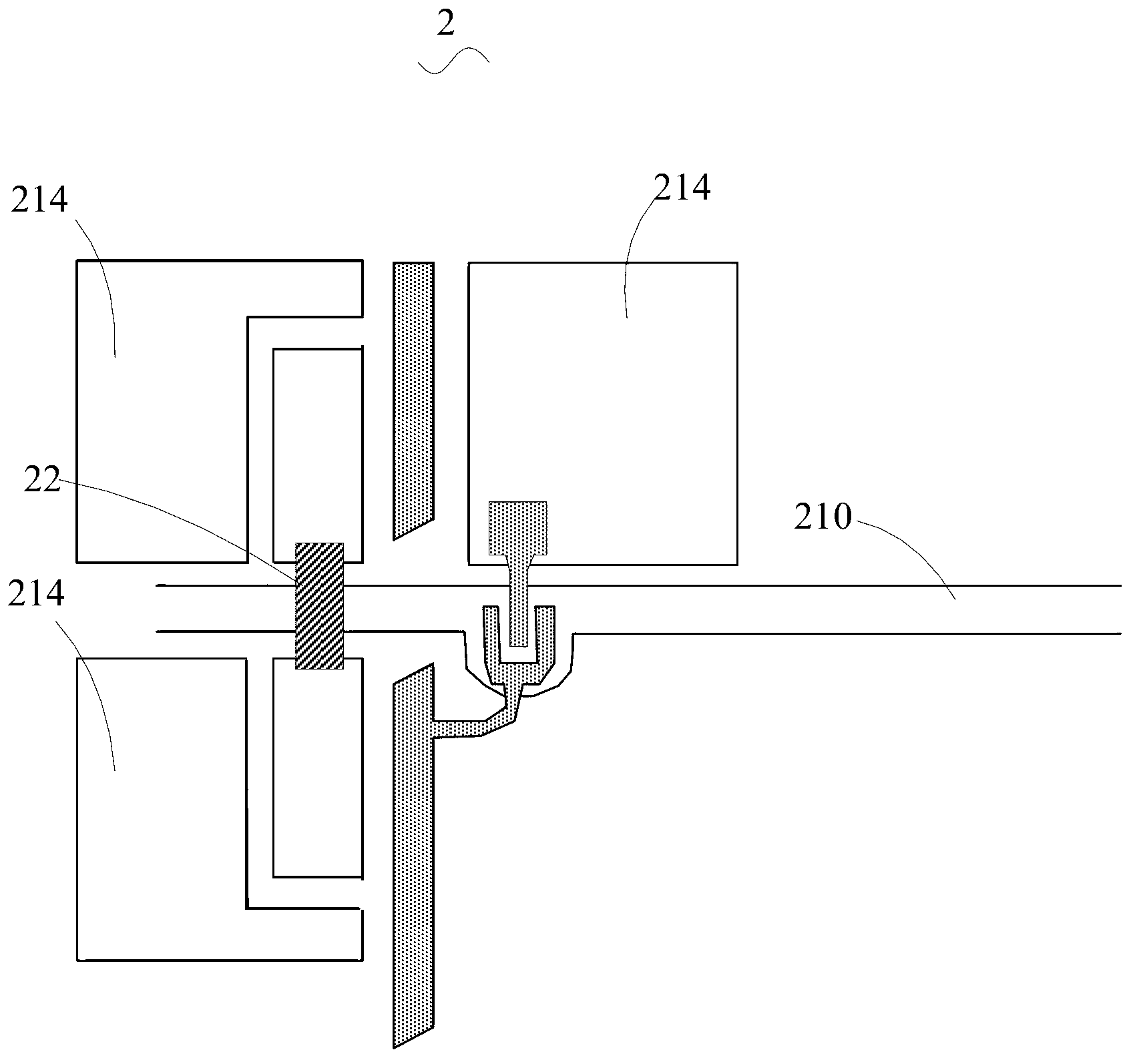

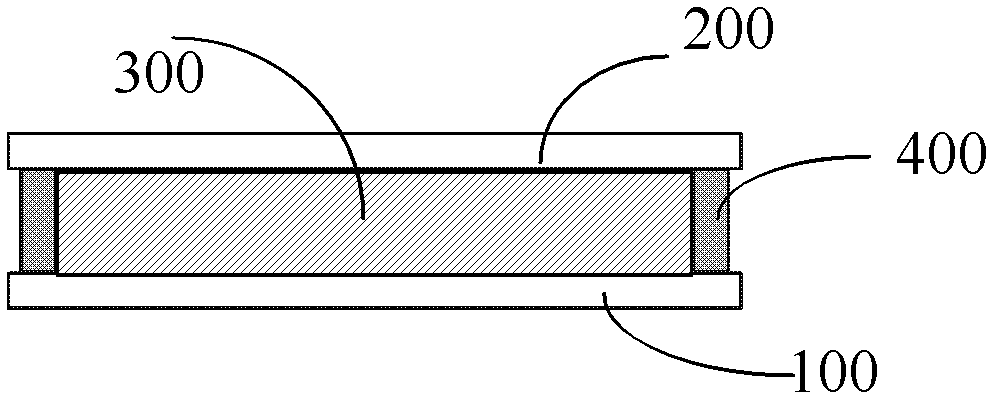

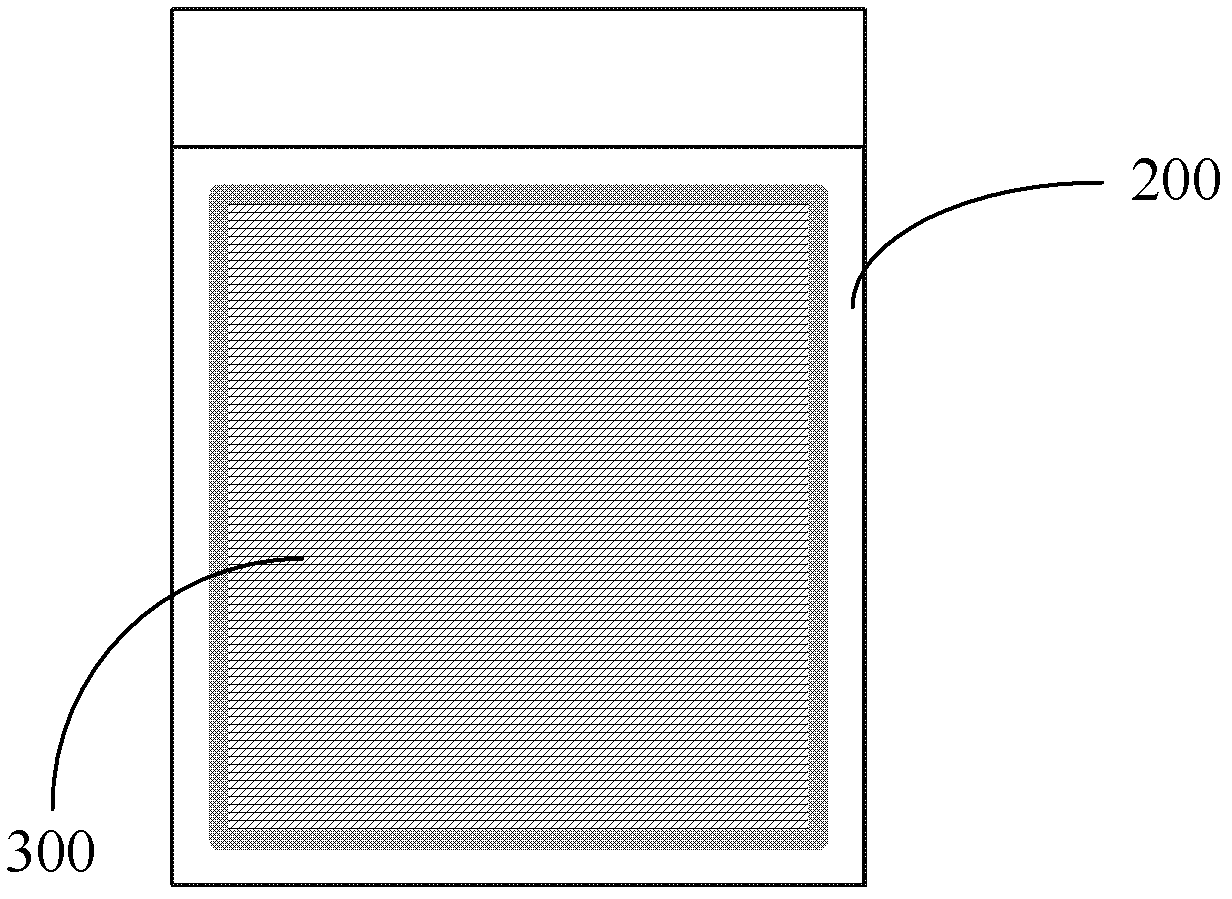

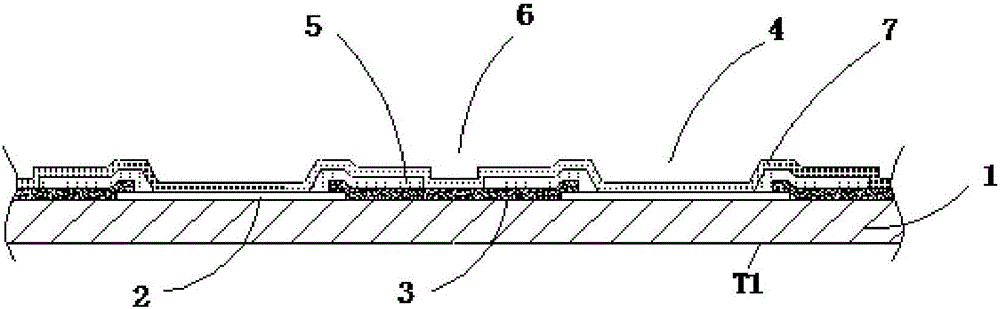

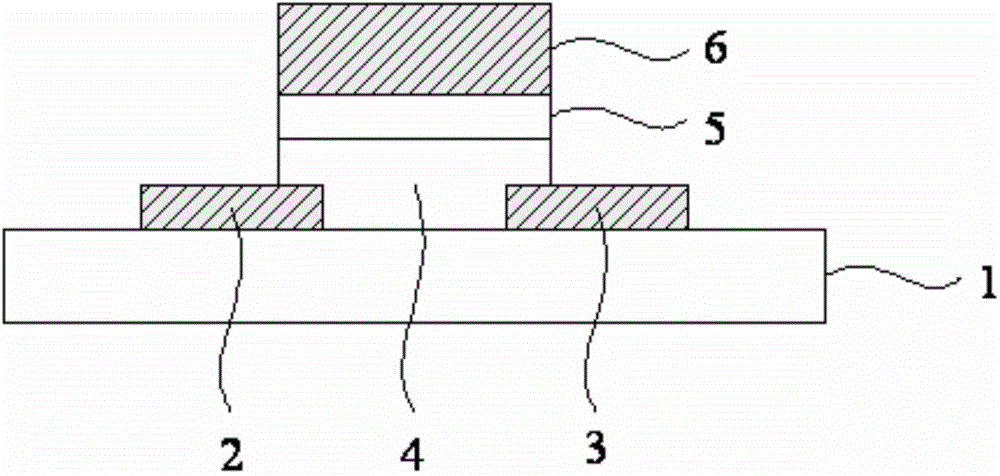

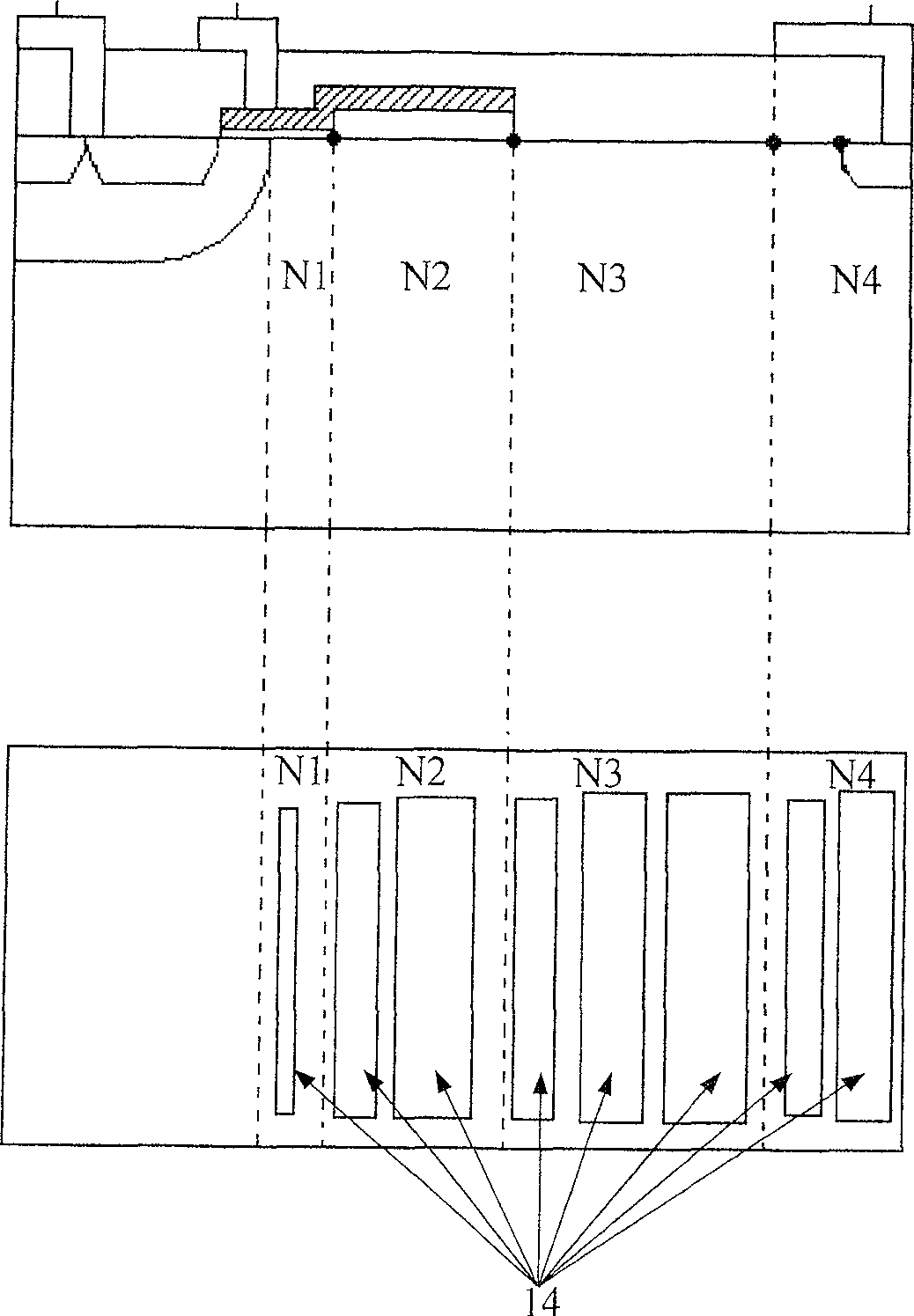

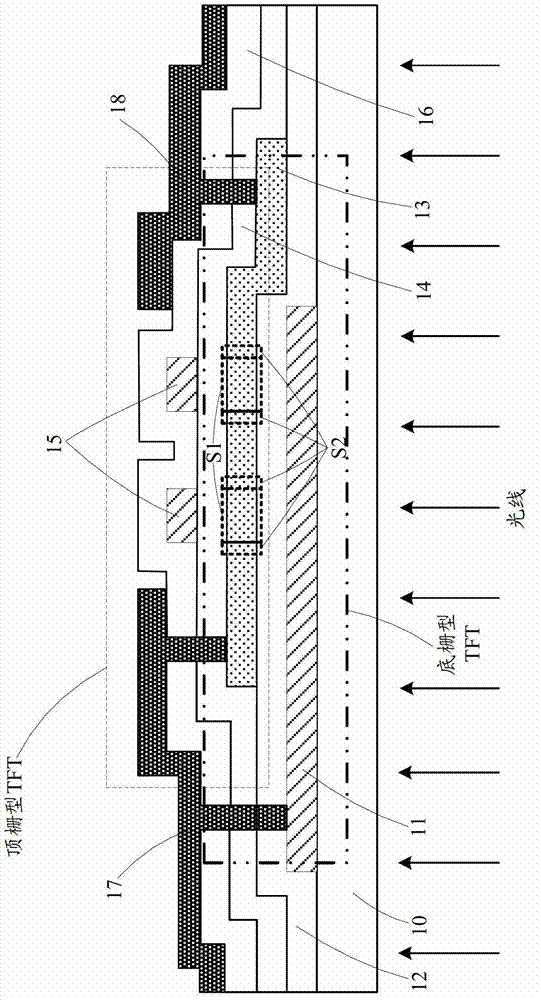

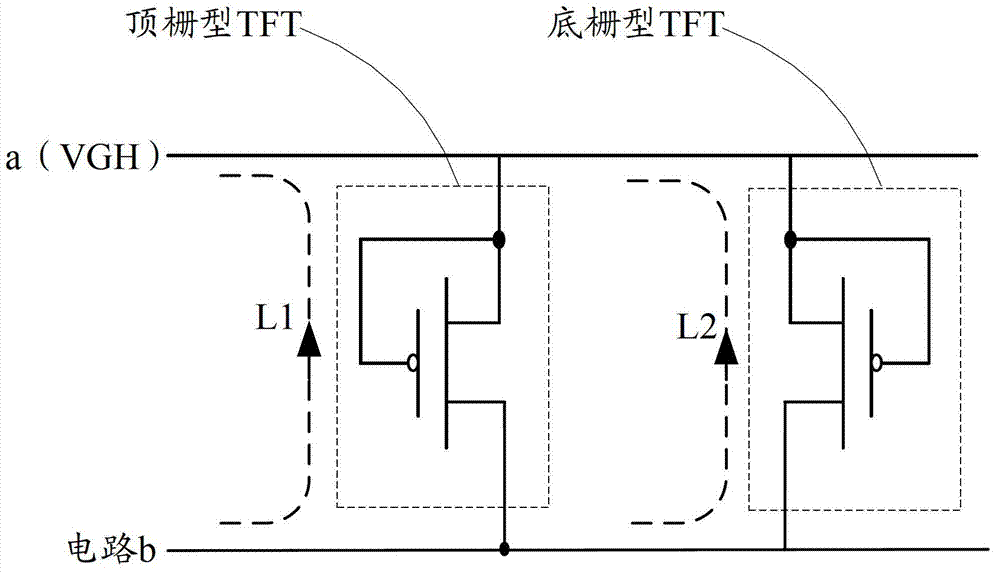

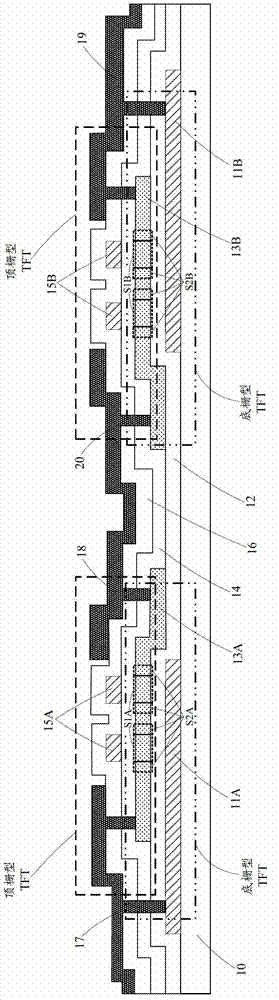

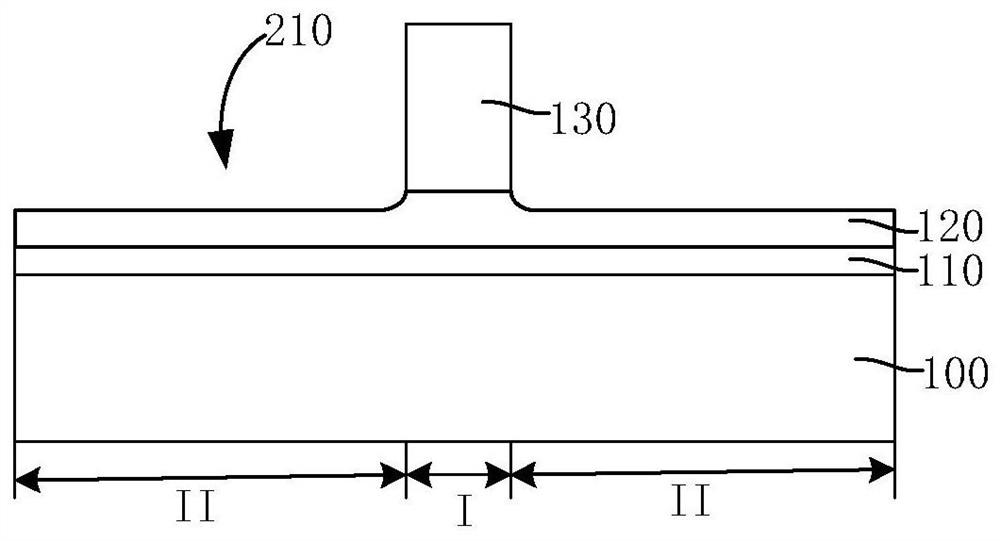

The invention relates to the field of display devices, in particular to an electrostatic discharge protection circuit, a display panel and a display device. According to the embodiment of the invention, the electrostatic discharge protection circuit comprises at least one electrostatic protection element, and the electrostatic protection element comprises a bottom gate electrode, a first insulating layer, an active layer, a second insulating layer, top gate electrodes, a third insulating layer, a first electrode and a second electrode, wherein the bottom gate electrode is positioned on a substrate; the first insulating layer is positioned on the bottom gate electrode; the active layer is positioned on the first insulating layer, and corresponds to the bottom gate electrode; the second insulating layer is positioned on the active layer; the top gate electrodes are positioned on the second insulating layer, and correspond to the active layer; the third insulating layer is positioned on the top gate electrodes; the first and second electrodes are positioned on the two sides of the top gate electrodes on the third insulating layer respectively; the bottom gate electrode and the top gate electrodes are electrically connected with the first electrode and connected with a power cord or a circuit of a display area of the display panel; and the second electrode is electrically connected with the circuit of the display area or the power cord. According to the electrostatic discharge protection circuit, an electrostatic discharge path is added, so that the anti-electrostatic capability is improved.

Owner:XIAMEN TIANMA MICRO ELECTRONICS

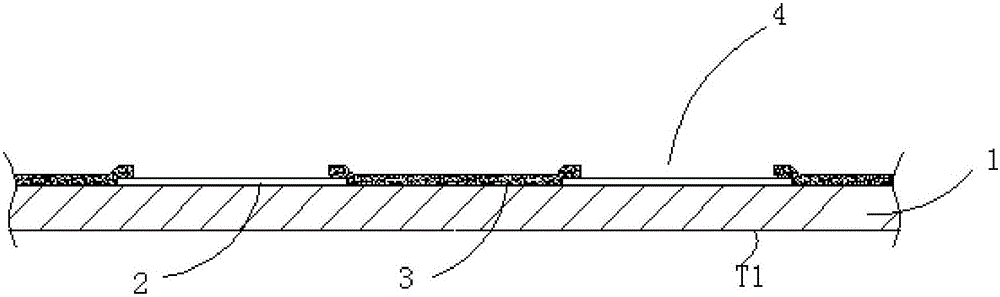

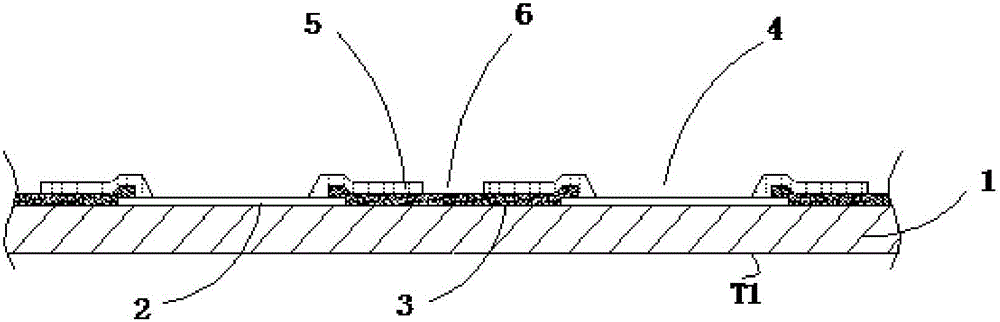

Manufacturing method of array substrate

ActiveCN102244082AAvoid destructionNo additional process stepsSemiconductor/solid-state device manufacturingRadiation controlled devicesEtchingEngineering

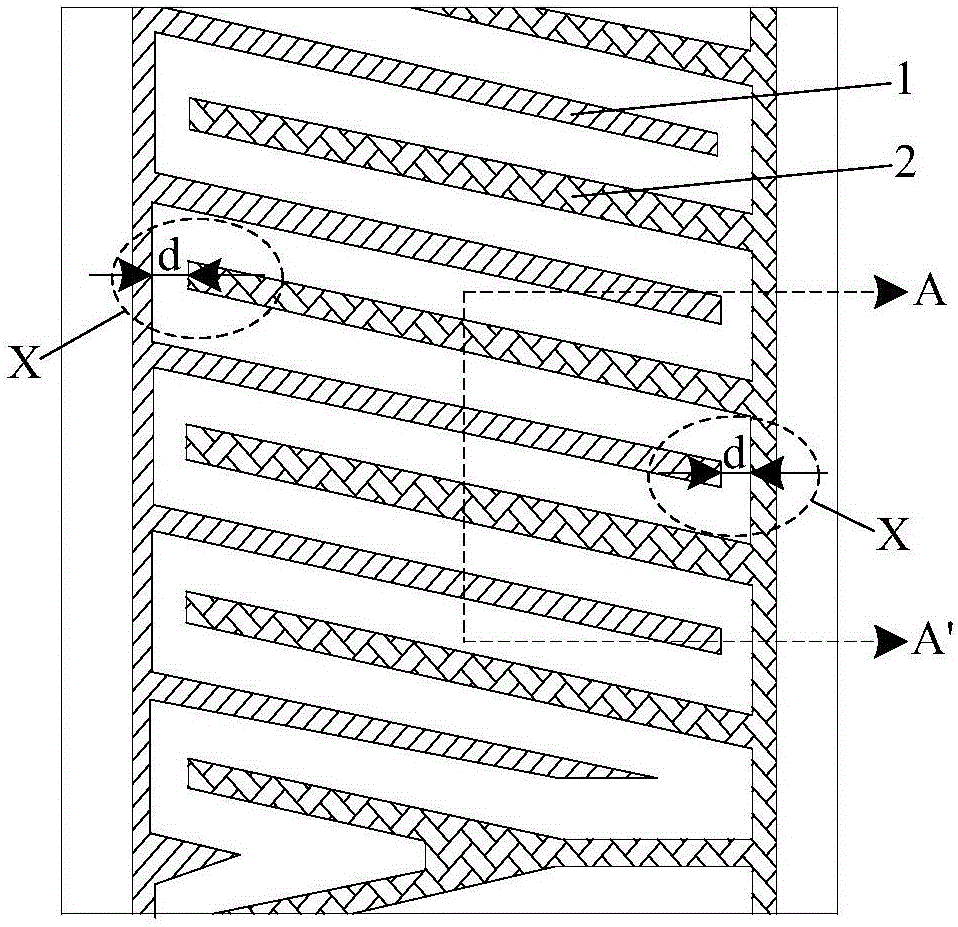

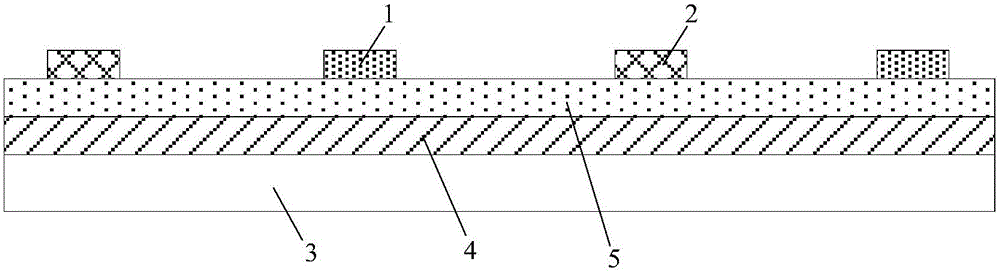

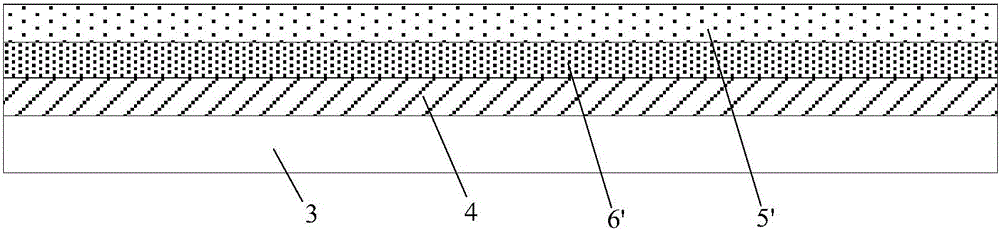

The invention relates to a manufacturing method of an array substrate. The manufacturing method comprises the following steps: providing a substrate, depositing and etching a first metal layer on the substrate, forming a first metal interconnection line, a first short-circuit line and a first electrostatic discharge protective electrode; forming and etching an insulating layer respectively above the first metal interconnection line, the first short-circuit line and the first electrostatic discharge protective electrode, respectively forming via holes on the insulating layers above the first metal interconnection line, the first short-circuit line and the first electrostatic discharge protective electrode; depositing and etching second metal layers on the insulating layers, and forming a second metal interconnection line which is electrically connected with the first metal interconnection line through a corresponding via hole, a second short-circuit line and a second electrostatic discharge protective electrode electrically connected with the first electrostatic discharge protective electrode through a corresponding via hole, wherein the second short-circuit line connects the second metal interconnection line and the second electrostatic discharge protective electrode; etching and for disconnecting the first short-circuit line. In the method, the electrostatic discharge protection on an X-ray detector is started from the first process without increasing processing steps.

Owner:SHANGHAI TIANMA MICRO ELECTRONICS CO LTD

Circuit repair structure and method

ActiveCN103311220ANo additional process stepsSemiconductor/solid-state device detailsSolid-state devicesTransistor arrayThin membrane

Owner:TCL CHINA STAR OPTOELECTRONICS TECH CO LTD

Method for manufacturing raised grating alignment mark in imprinting lithography

InactiveCN102053509ASolve the problem of severe loss of contrastQuality improvementPhotomechanical exposure apparatusMicrolithography exposure apparatusSputteringGrating

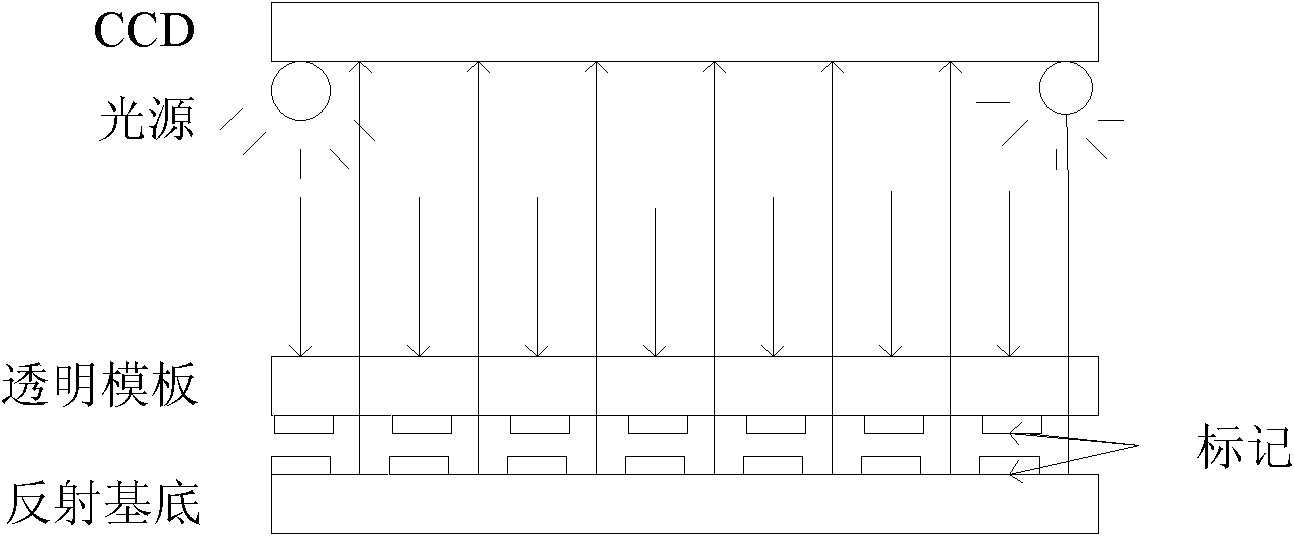

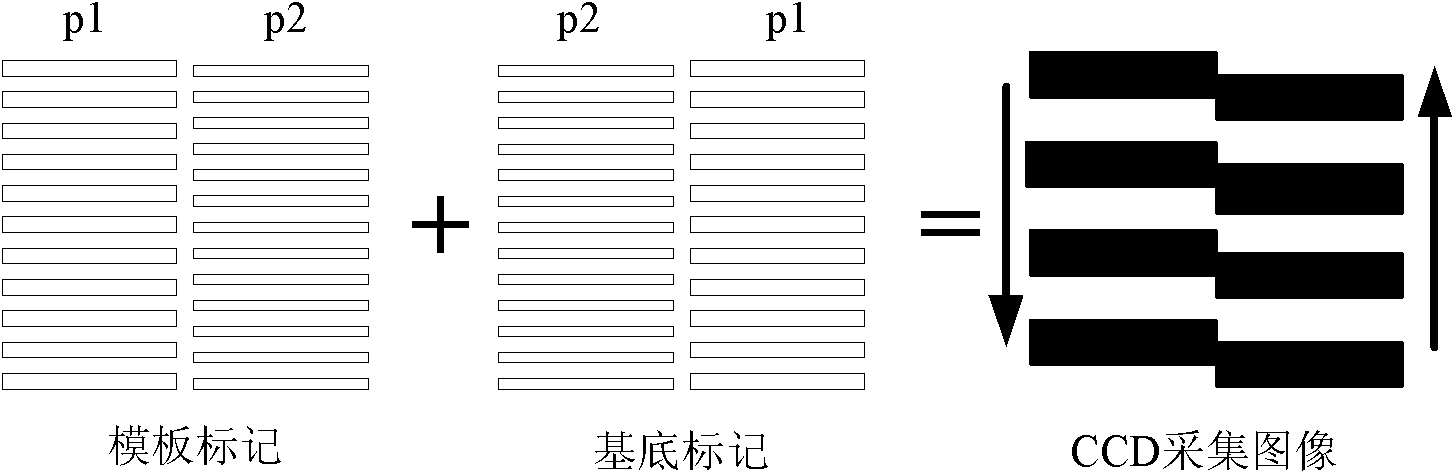

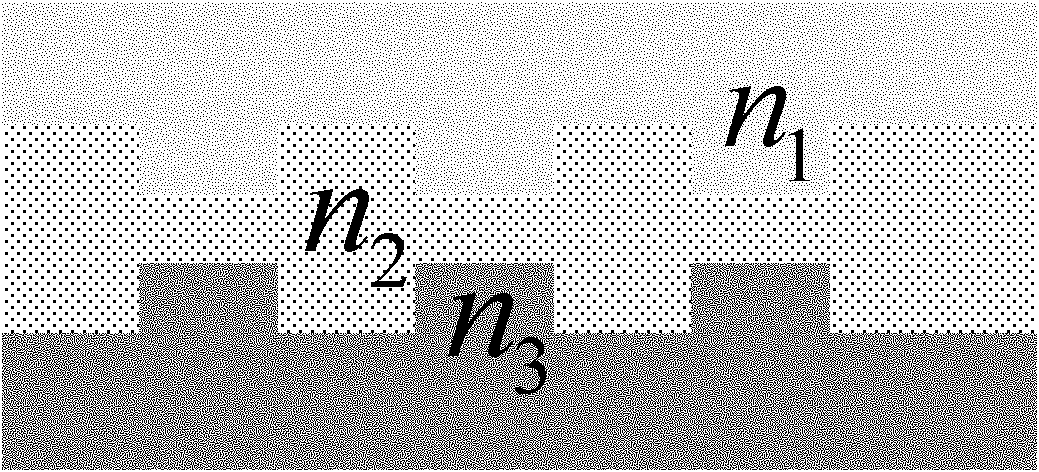

The invention discloses a method for manufacturing a raised grating alignment mark in imprinting lithography, which comprises the following steps of: (1) determining a refractive grating refraction index range for acquiring high-contrast Moire fringe images, and selecting a grating material in the range; (2) photo-etching: manufacturing a grating mark mask plate, and etching a photoresist layer by using the grating mark mask plate as a mask to respectively obtain photoresist grids on an imprinting substrate and a template; (3) sputtering: sputtering on the substrate with photoresist grid lines to optimize the grating material; and (4) peeling off: peeling the photoresist area on the substrate to obtain raised grating fringes. The method optimizes the grating mark manufacturing material by adopting interface optical theory and finite difference computation. The method solves the problem that the Moire fringe alignment image contrast of the traditional mark declines seriously due to the introduction of imprinting photoresist from the aspect of the grating manufacturing material, has wider photoresist application range, and can be applied to introduction of various common photoresists.

Owner:XI AN JIAOTONG UNIV

Liquid crystal display device

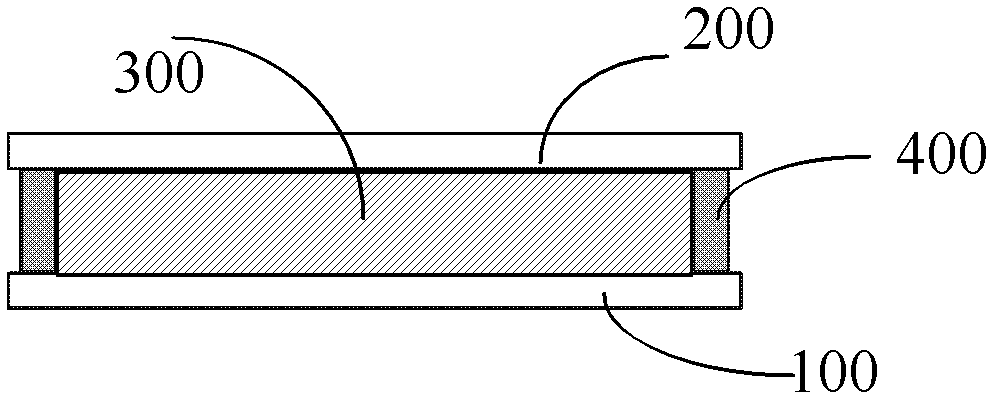

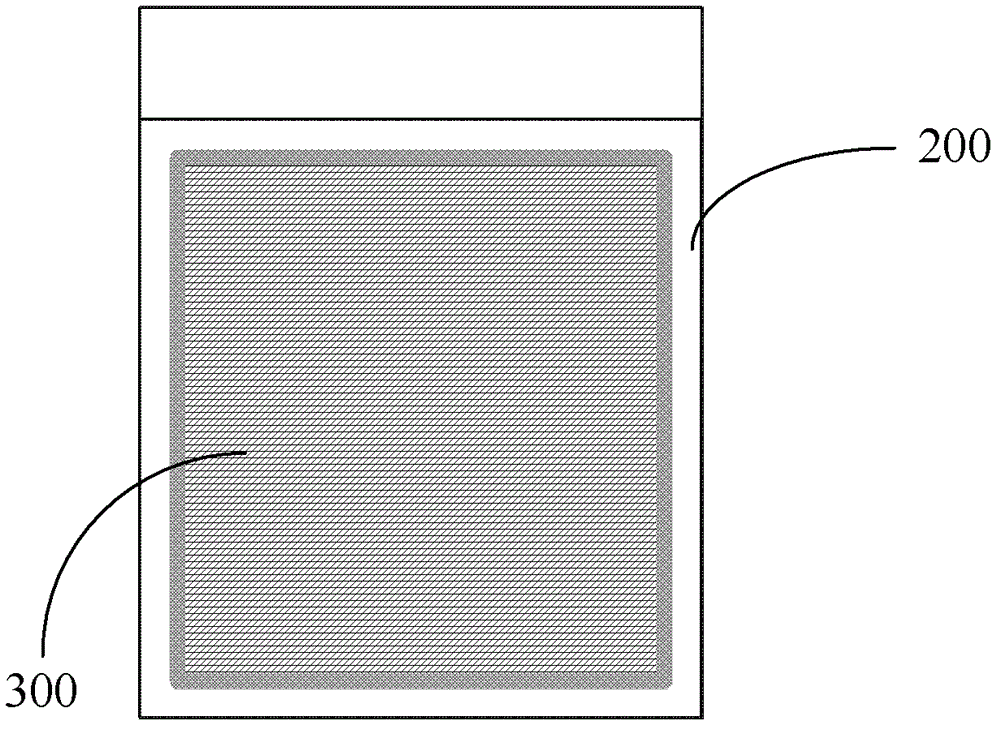

ActiveCN102830550AImprove antistatic performancePrevent electrostatic dischargeStatic indicating devicesNon-linear opticsLiquid-crystal displayEngineering

The invention provides a liquid crystal display device which comprises a first substrate, a second substrate and sealing glue, wherein the first substrate and the second substrate are relatively arranged; the sealing glue is arranged between the first substrate and the second substrate for adhering the first substrate and the second substrate; the first substrate is provided with a driving line and a first substrate common electrode toward the direction of the second substrate; the second substrate is provided with a second substrate common substrate toward the direction of the first substrate; a plurality of conductive particles are distributed into the sealing glue; the sealing glue is divided into a first sealing glue area and a second sealing glue; the conductive particles in the first sealing glue area are contacted with the first substrate common electrode and the second substrate common electrode; the conductive particles in the second sealing area are only contacted with the second substrate common electrode; a conductive housing layer is also arranged in the second sealing glue area, and positioned between the conductive parts and the driving line; and a first insulating layer is also arranged between the conductive housing layer and the driving line. With the adoption of the liquid crystal display device, the problems that the yield is reduced due to the discharging of the top ends of the conductive particles can be prevented.

Owner:SHANGHAI TIANMA MICRO ELECTRONICS CO LTD

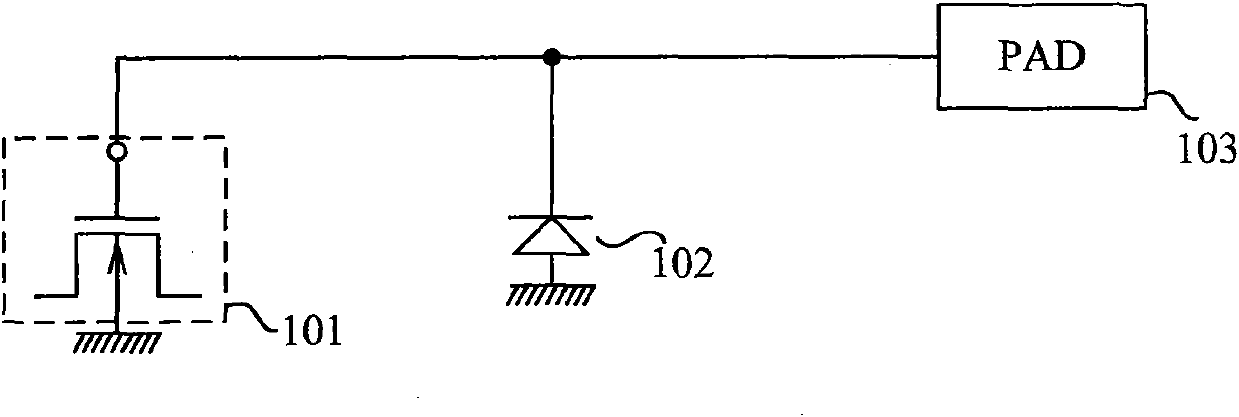

Protection device and method for semiconductor apparatus

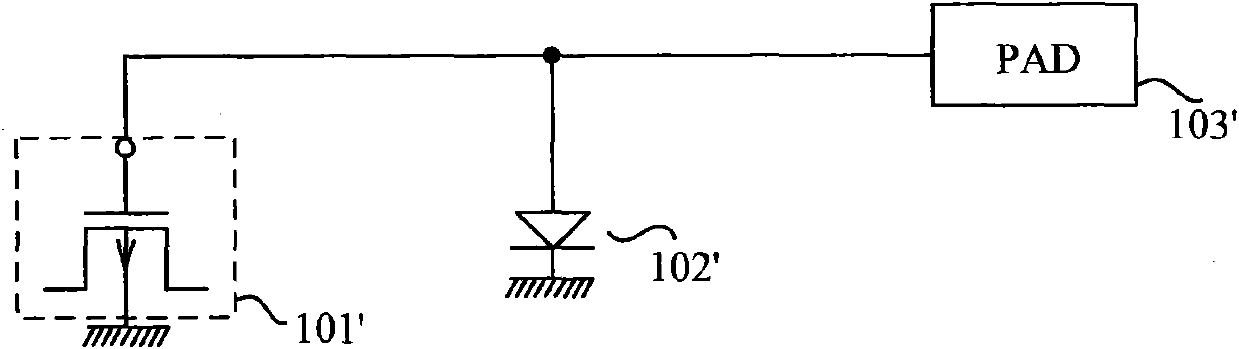

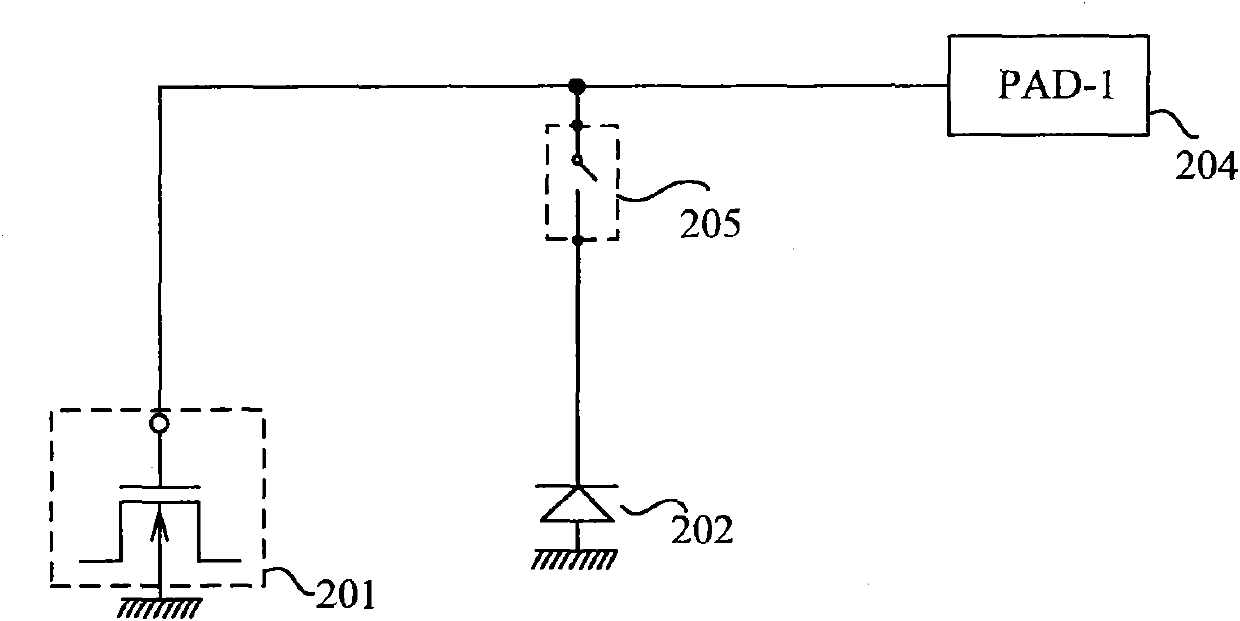

InactiveCN102024807ASimple structureSimple processSemiconductor/solid-state device detailsSolid-state devicesReverse modeEngineering

The invention provides a protection device for a semiconductor apparatus, which comprises a transistor, a first pad connected to the grid of the transistor, and a switch element and a diode in turn connected between the ground and the join point of the first pad and the grid of the transistor. The protection device of the invention can be used for protecting the semiconductor apparatus, particularly for preventing MOS transistor from being damaged by plasma in the manufacturing process and for testing the MOS elements under reverse mode and accumulating mode.

Owner:SEMICON MFG INT (SHANGHAI) CORP

Fabrication method of wafer level bump package structure

InactiveCN105140200AAvoid the problem of excessive stress pulling on the insulationImprove package reliabilitySemiconductor/solid-state device detailsSolid-state devicesProtection layerMetal

The invention relates to a fabrication method of a wafer level bump package structure. The method comprises the following steps: (1) providing a wafer integrated with a chip electrode and an insulating layer; (2) fabricating a protective layer on the wafer; (3) removing the protective layer above the chip electrode to form a first opening, and removing the protective layer at a chip cutting position on the wafer to form a second opening; (4) fabricating an under bump metal layer and a bump layer at the first opening; and (5) carrying out cutting along the position of the second opening to obtain a single wafer level bump package structure. According to the fabrication method, the problem of overlarge stress, for pulling the insulating layer, of the protective layer due to thermal mismatching is avoided, so that the package reliability is improved; and when the reliability is improved, the processing step is not increased. In the wafer cutting process, protection glue at the preset cutting position is removed, so that the protective layer avoids a cutting channel; pulling of the insulating layer by the protective layer during cutting is removed; and the edge breakage phenomenon of a chip body during cutting is reduced.

Owner:NAT CENT FOR ADVANCED PACKAGING

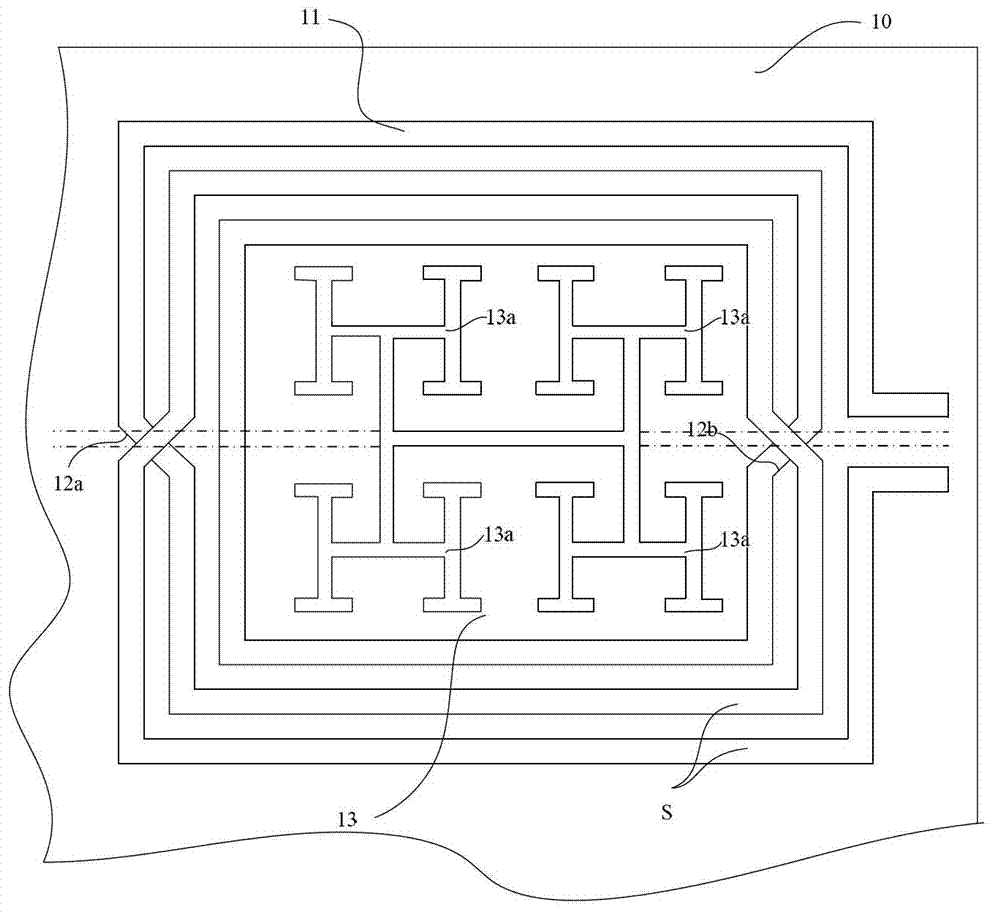

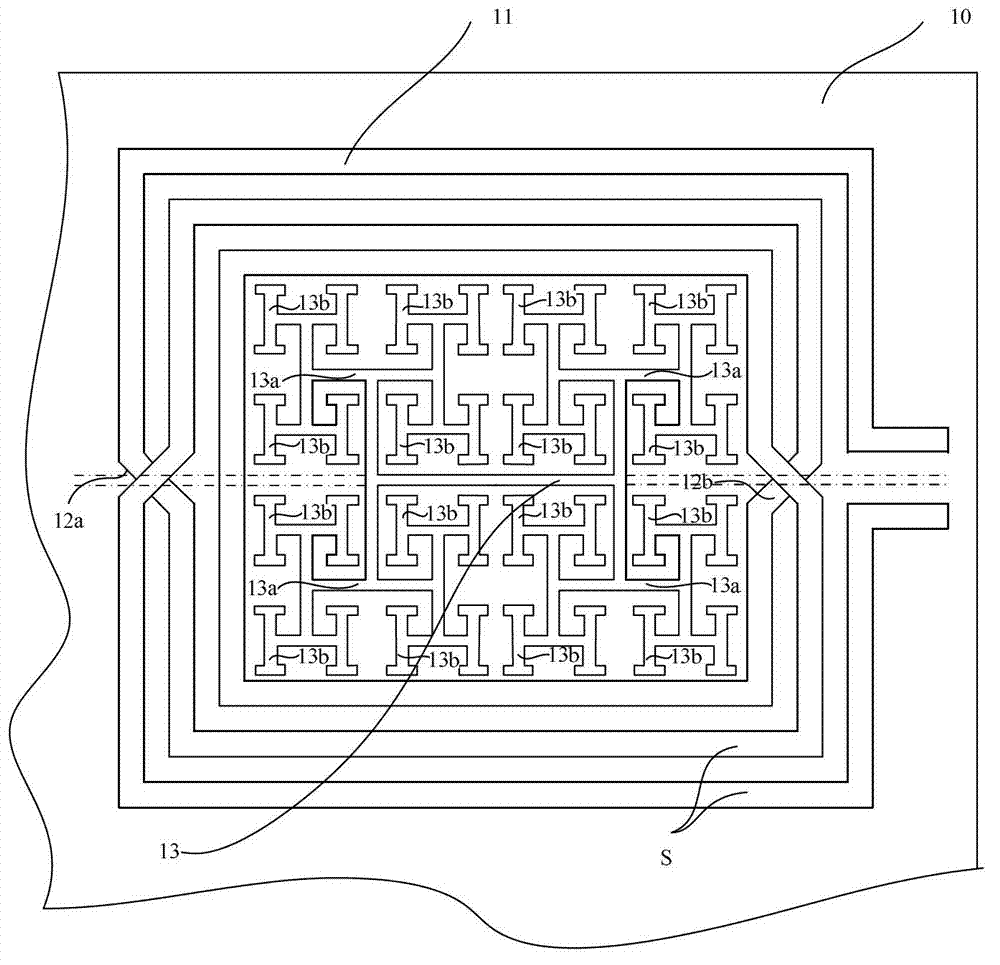

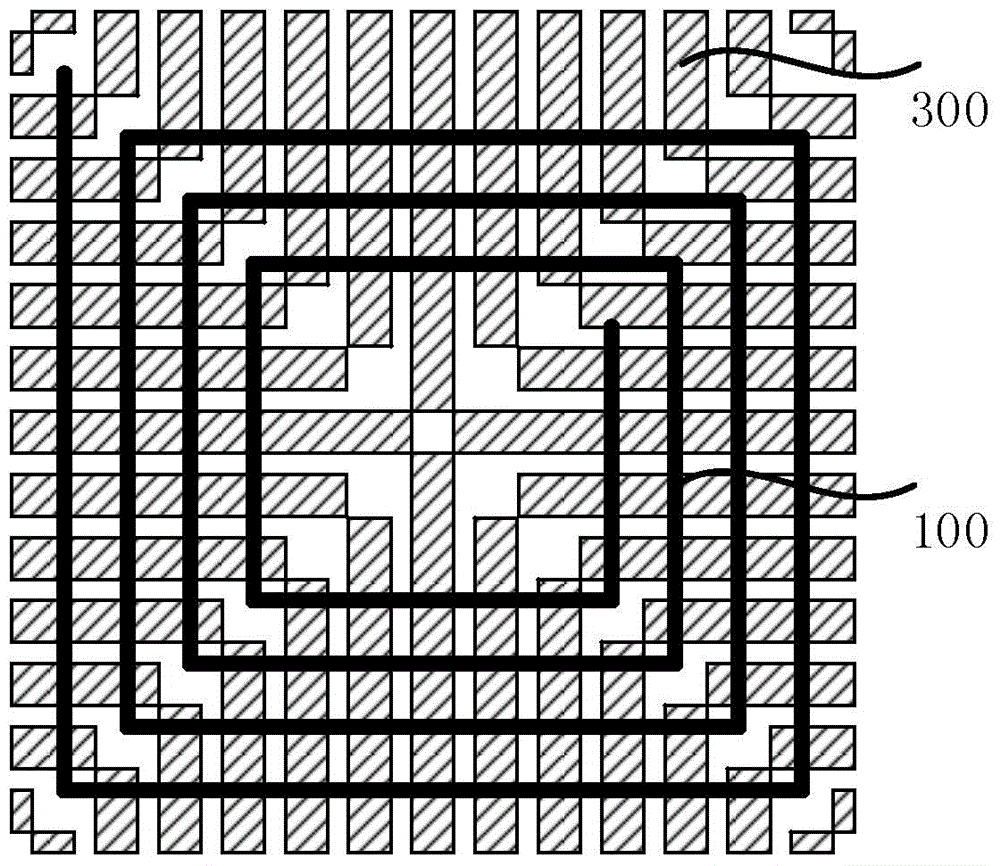

Novel fractal pattern grounding shield structure

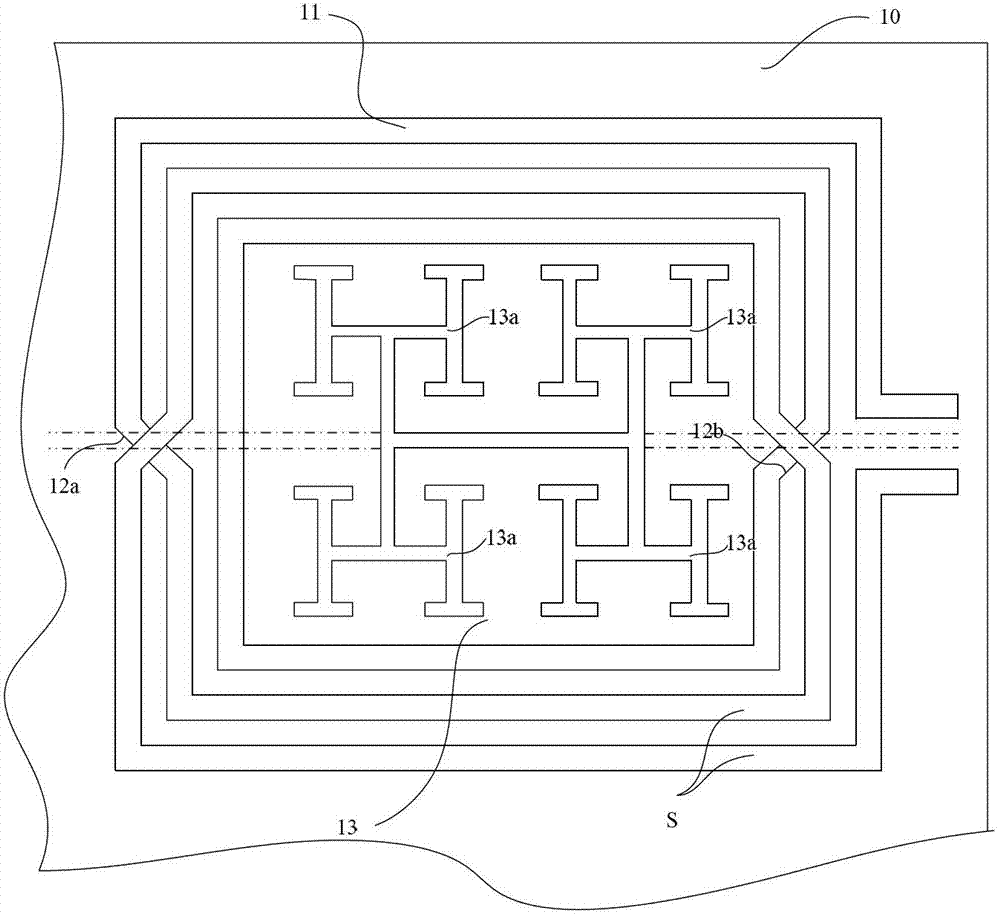

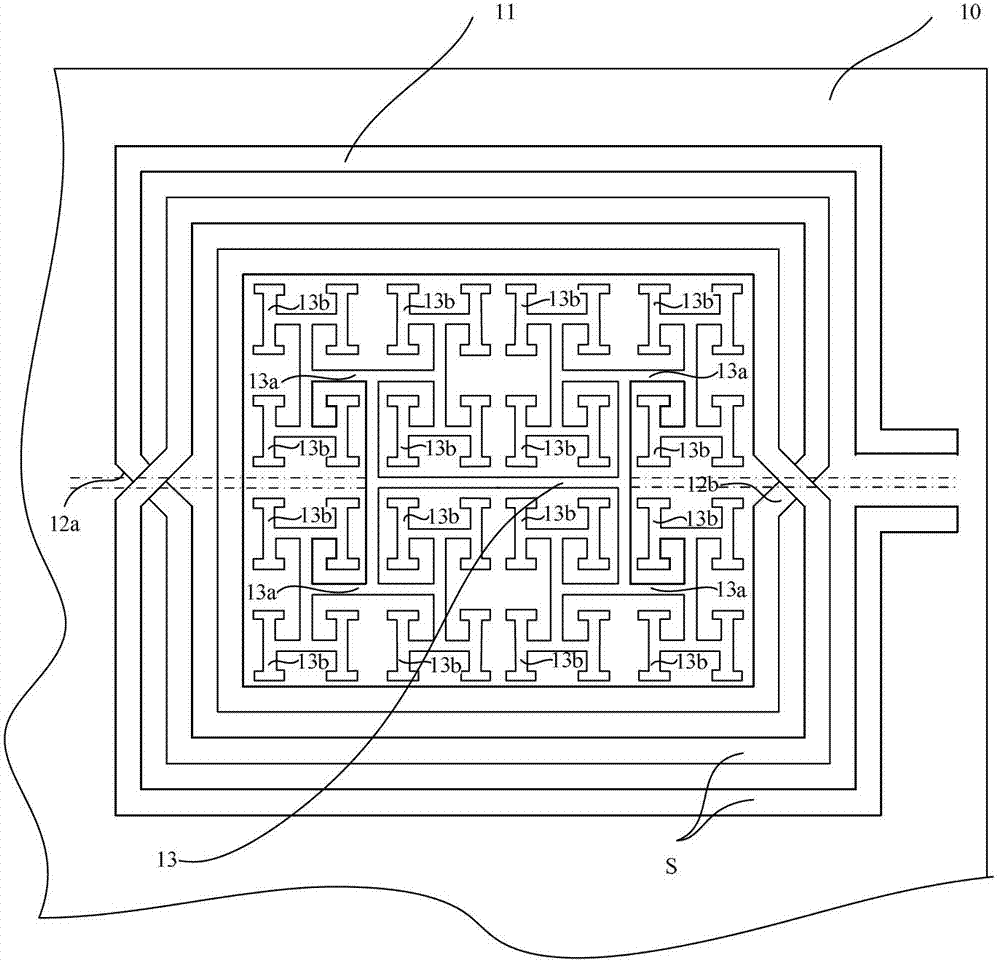

ActiveCN102738124AEffective shieldingReduce energy lossSemiconductor/solid-state device detailsSolid-state devicesPatterned ground shieldTransformer

The invention relates to a grounding shield structure which applies a fractal theory. In existing on-chip spiral inductors and transformers, because an alternating electromagnetic field is produced, induction current is produced on a substrate, energy loss is produced, and an induction value and a Q value are reduced. The shield structure is arranged in the center of an inductor / transformer which is wound from a coil, and a pattern grounding shield layer of a first order, a second order, a third order and even a higher order is constructed with metal layers M1 and M2 with thin bottom layers based on H-shaped and crisscross basic units through the self similarity and iterative principle of the fractal theory. According to the novel fractal pattern grounding shield structure, the electromagnetic field which penetrates to the substrate is effectively shielded, so that the induction current which can be produced on the substrate and on the surface area of the substrate is reduced, and the effects of reducing the energy loss of the substrate and improving the induction value and a quality factor are achieved.

Owner:HANGZHOU DIANZI UNIV

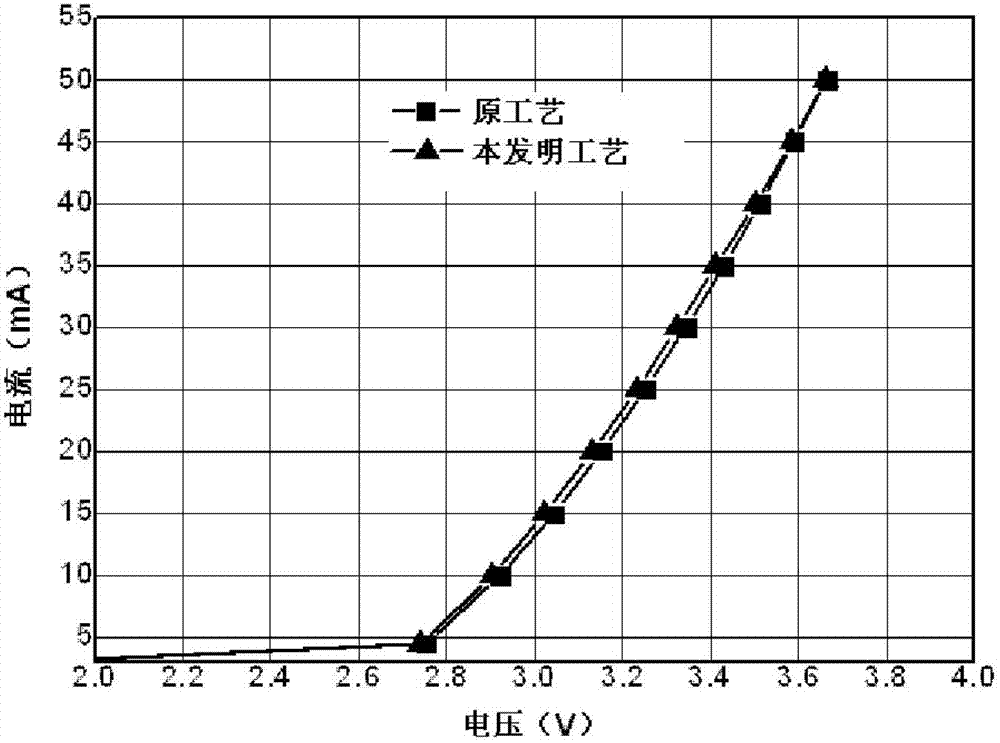

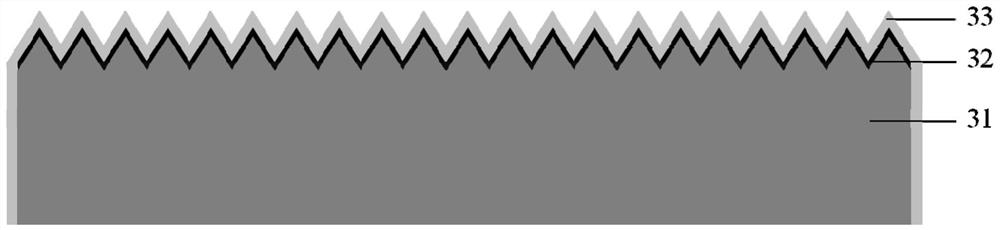

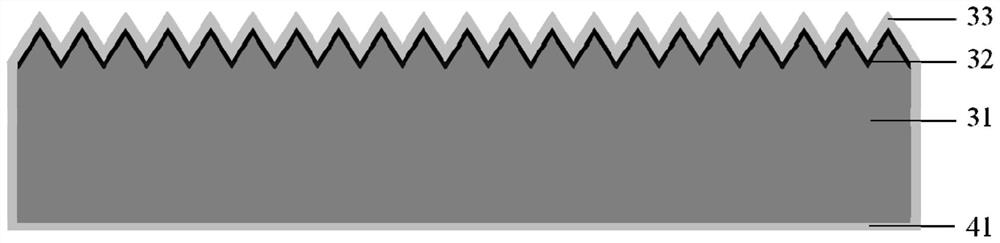

Method for manufacturing brightness-improved GaN-based light emitting diode (LED) chip

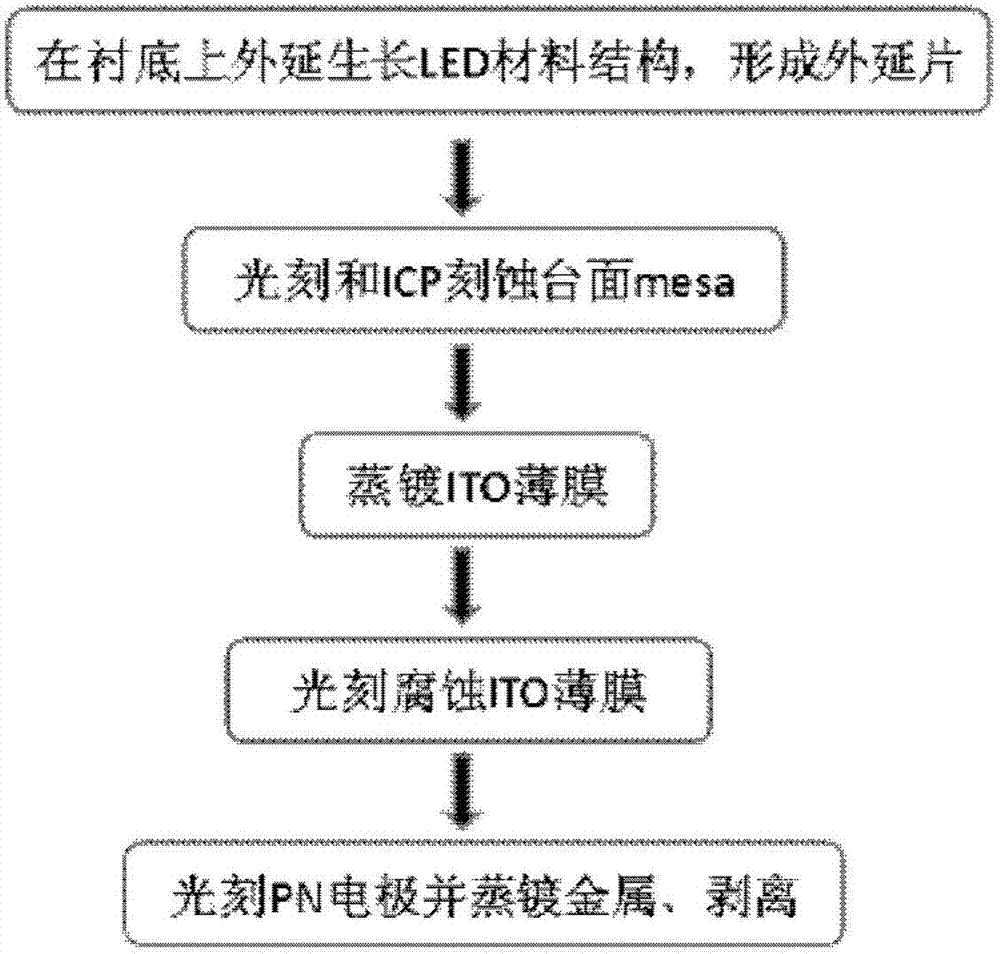

InactiveCN103165780AIncrease brightnessImprove light extraction efficiencySemiconductor devicesElectrical conductorGas phase

The invention discloses a method for manufacturing a brightness-improved GaN-based light emitting diode (LED) chip. The method comprises the following steps of: 1, taking a semiconductor substrate; 2, sequentially growing a low-temperature GaN buffer layer, a non-doped GaN layer, an N-GaN layer, a multi-quantum well light emitting layer and a P-GaN layer on the semiconductor substrate by adopting a metal organic chemical vapor deposition method to form a GaN epitaxial sheet; 3, performing downward etching on one side of the surface of the GaN epitaxial sheet till reaching the N-GaN layer, and forming a mesa on one side of the N-GaN layer; 4, performing vapor deposition on the upper surface of the GaN epitaxial sheet to form an indium tin oxide (ITO) film; 5, photo-etching a groove on the ITO film on the P-GaN layer, corroding the ITO film on the side walls of the multi-quantum well light emitting layer and the P-GaN layer, and reserving the ITO film on the mesa; and 6, manufacturing a P electrode in the groove on the ITO film, manufacturing an N electrode on the ITO film on the mesa, and thus obtaining the GaN-based LED chip.

Owner:INST OF SEMICONDUCTORS - CHINESE ACAD OF SCI

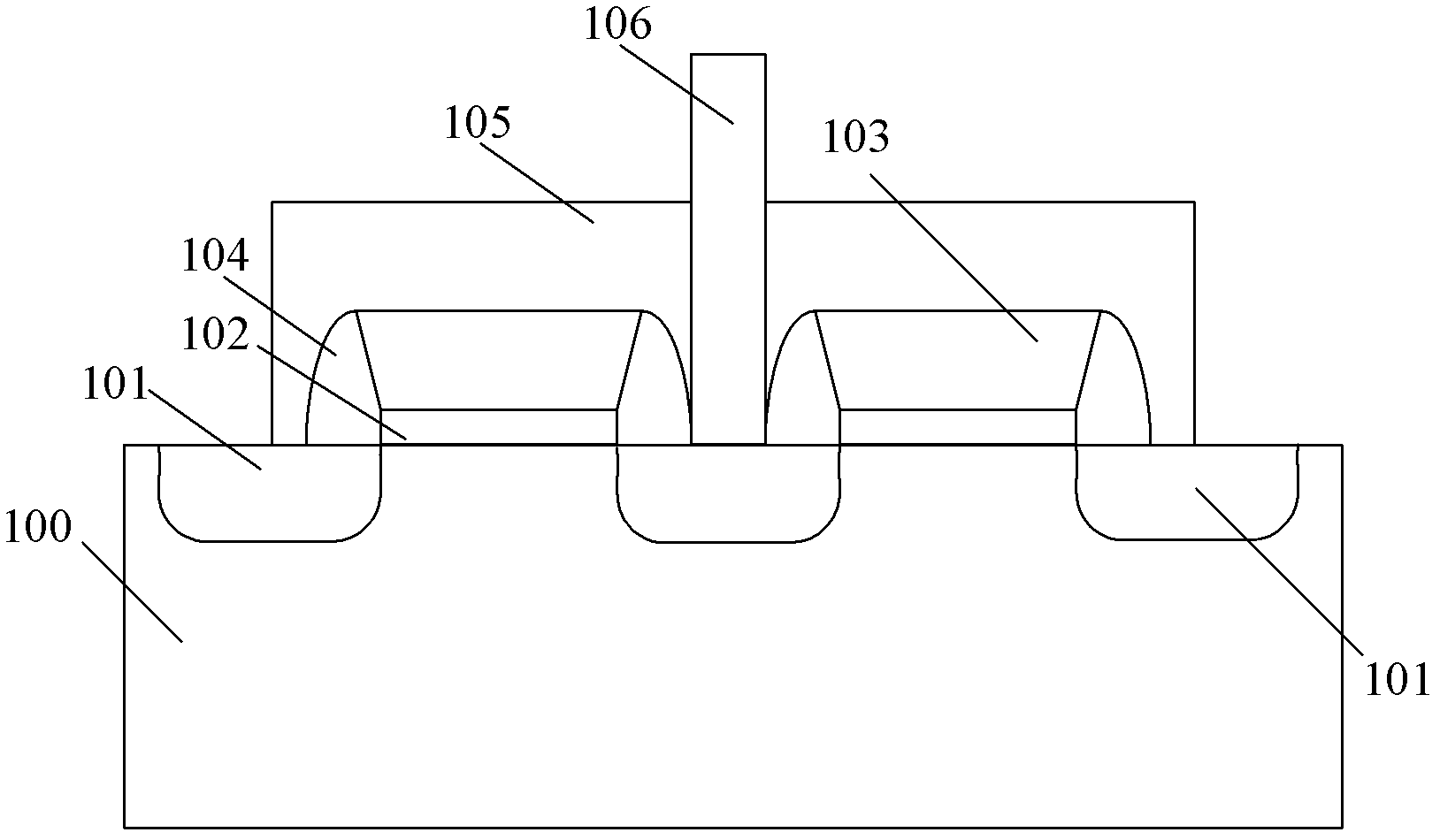

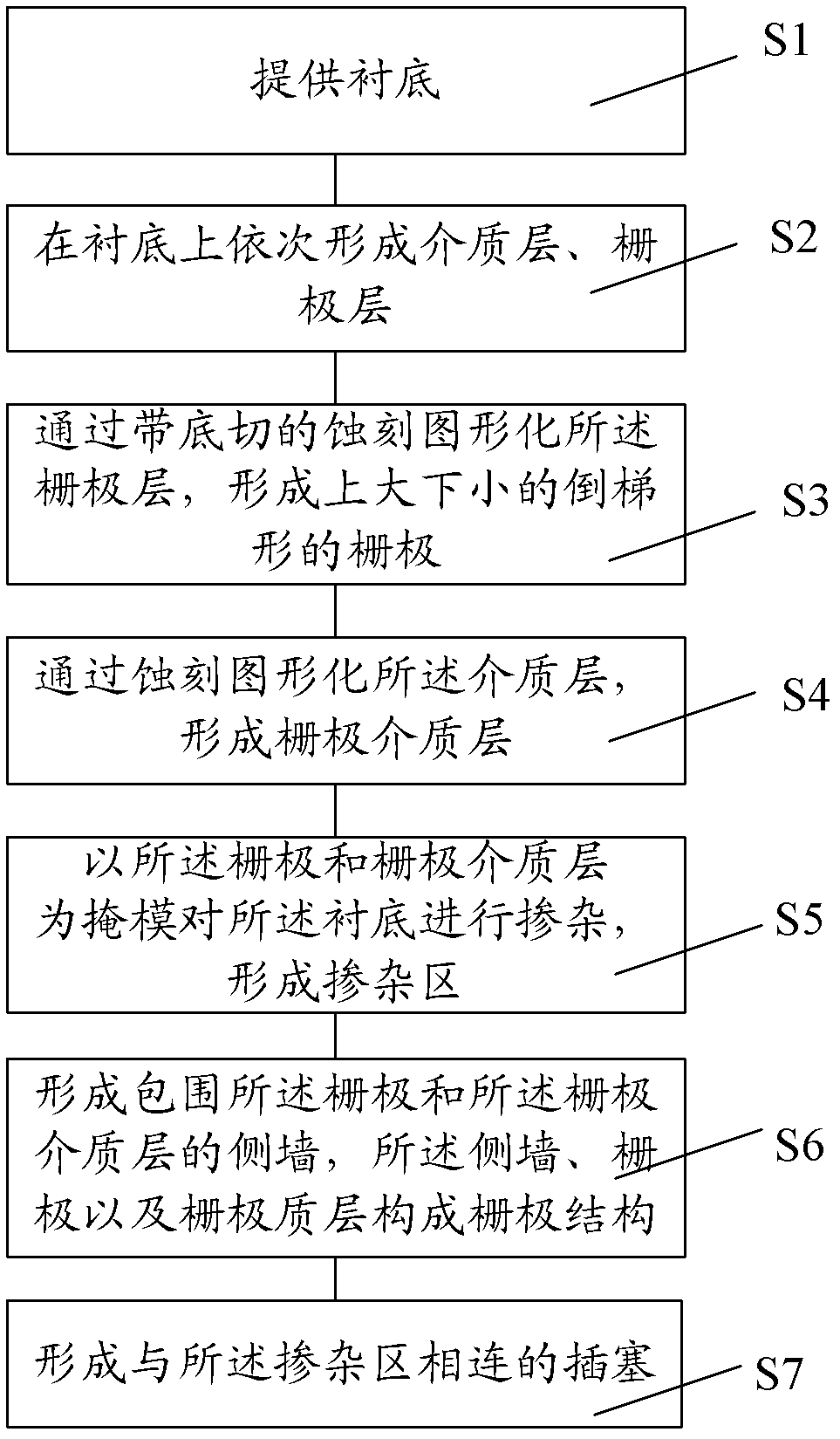

One-time programmable memory and manufacturing method

ActiveCN102522408AImprove data retentionReduce churnSolid-state devicesSemiconductor/solid-state device manufacturingGate dielectricOne time programmable

The invention discloses a one-time programmable memory and a manufacturing method. The one-time programmable memory comprises a plurality of memory cells, each memory cell comprises a control MOS (metal oxide semiconductor) tube and a read MOS tube in serial connection, and each read MOS tube comprises a floating gate in an inverted trapezoidal structure with the big end up. The read MOS tube manufacturing method includes steps: providing a substrate; sequentially forming a dielectric layer and a gate layer on the substrate; imaging the gate layer by etching with undercutting to form a gate in an inverted trapezoidal shape with the big end up; imaging the dielectric layer by etching to form a gate dielectric layer; doping the substrate by using the gate and the gate dielectric layer for masking to form a doped area; and forming a side wall enclosing the gate and the gate dielectric layer, wherein the side wall, the gate and the gate dielectric layer form a gate structure. By means of the one-time programmable memory and the manufacturing method, data retention of the one-time programmable memory can be improved.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

Array substrate and manufacturing method thereof, and display device

ActiveCN105826328AAlleviate the problem of light transmittance dropHigh light transmittanceSolid-state devicesSemiconductor/solid-state device manufacturingComposition processDisplay device

The invention provides an array substrate and manufacturing method thereof and display device, relates to the technical field of display, and can solve the problem of low light transmissivity when an array substrate of a comb-shaped electrode structure is adopted. The manufacturing method of the array substrate includes the steps of: forming a first conductive thin film and a passivation layer thin film on a lining substrate in sequence; adopting a one-time composition process, removing the passivation layer thin film and the first conductive thin film except a to-be-formed first electrode area, and forming a graph of a passivation layer and a graph of a first electrode; forming a second conductive thin film on the lining substrate having the graph of the passivation layer and the graph of the first electrode; and adopting the one-time picture composition process, removing the second conductive thin film except a to-be-form second electrode area, and forming a graph of a second electrode. The manufacturing method of the abovementioned array substrate is used for manufacturing the array substrate.

Owner:BOE TECH GRP CO LTD

Novel fractal PGS (Program Generation System) structure

ActiveCN102738127AEffective shieldingReduce energy lossSemiconductor/solid-state device detailsSolid-state devicesPatterned ground shieldTransformer

The invention relates to a novel fractal PGS (Program Generation System) structure. As the existing the on-chip spiral inductor and transformer generate an alternating electromagnetic field, induced current is caused on a substrate to generate energy consumption and reduce the inductance and the Q value. The PGS is located in the central part of a coil-wound inductor / transformer, a first-order, second-order, third-order, or even higher order pattern grounded shield layer is constructed by a metal layer with a thin bottom on the basis of an H-shaped basic unit and a cross-shaped basic unit through the self-similarity of fractal theory and the iterative theory. The novel fractal PGS structure screens out the electromagnetic field which permeates the substrate effectively, reduces the induced current which is capable of generating on the substrate and the substrate surface area, achieves the substrate energy consumption and improves the function of inductance and quality factor.

Owner:HANGZHOU DIANZI UNIV

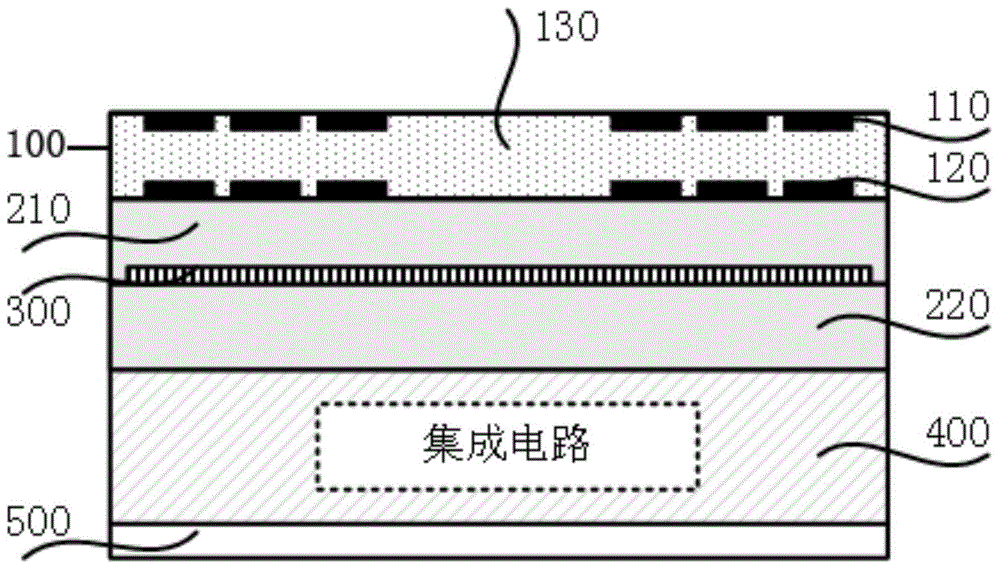

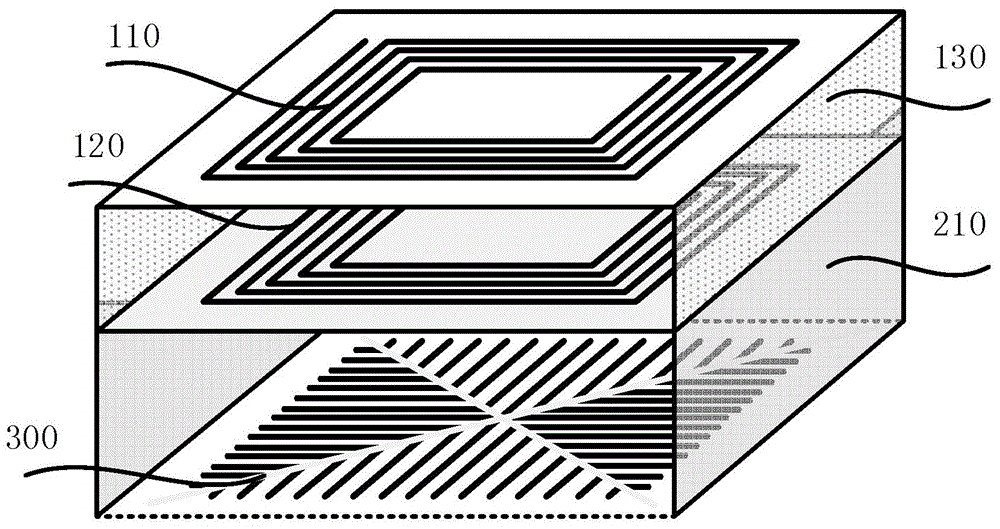

On-chip integrated transformer

InactiveCN105185778AReduce areaReduce manufacturing costSemiconductor/solid-state device detailsTransformers/inductances coils/windings/connectionsTransformerEngineering

The invention discloses an on-chip integrated transformer, which comprises a circuit layer, a transformer layer and a shielding layer, wherein the transformer layer is stacked on the circuit layer; and the shielding layer is arranged between the transformer layer and the circuit layer and is used for shielding an electric field formed on the transformer layer. Through a stacked design, high chip integration of a system is achieved; through adding the shielding layer, interlayer crosstalk on the transformer layer can be shielded; and the signal and power transmission performance of the transformer layer is ensured.

Owner:INST OF AUTOMATION CHINESE ACAD OF SCI

Nitrogen and phosphorus zinc oxide thin film, preparation method thereof and thin film transistor

ActiveCN103560147AEliminate oxygen vacanciesLower the barrierTransistorVacuum evaporation coatingNitrogenCharge carrier mobility

The invention discloses a nitrogen and phosphorus zinc oxide thin film, a preparation method thereof and a thin film transistor. The nitrogen and phosphorus zinc oxide thin film is composed of ZnxPyO1-x-y-zNz, wherein x is larger than or equal to 55% and smaller than or equal to 65%, y is larger than or equal to 1% and smaller than or equal to 10%, and z is larger than or equal to 10% and smaller than or equal to 22%, and the percentage sum of the number of atoms of each atom is 100%. The nitrogen and phosphorus zinc oxide thin film is deposited through ion sputtering, and the thin film transistor made of given thin film materials has high carrier mobility and stability.

Owner:SHENZHEN DANBANG INVESTMENT GROUP

Tobacco bale leaf identity calibration method and tobacco bale leaf identity identification system

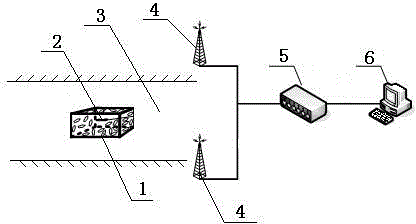

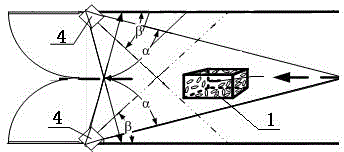

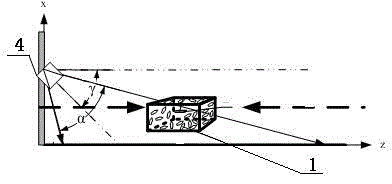

InactiveCN103150586ANo additional process stepsImprove efficiencyData processing applicationsCo-operative working arrangementsEngineeringTobacco leaf

The invention discloses a tobacco bale leaf identity calibration method and a tobacco bale leaf identity identification system. The calibration method comprises the steps of information collection, writing-in into electronic labels, placing into a tobacco bale and encapsulation. The identification system comprises a detection passage arranged on a path required to be passed by the tobacco bale, the electronic labels are arranged in the tobacco bale, two electronic label reading and writing antennas are respectively erected and arranged above the two sides of a detection passage inlet, the height from the antennas to the ground is 1.7 to 2.3m, the axial line of the antennas and the edge line of the detection passage form an included angle beta being 40 to 50 degrees in the horizontal direction, the center point axial line of the antennas and the horizontal plane form an included angle gamma being 40 to 50 degrees, the antennas are connected with the reading and writing device through connecting wires, and the reading and writing device is connected with a computer system through a data wire. When the carried tobacco bale marked with the tobacco leaf identity passes through the detection passage, the tobacco bale data can be fast, accurately and reliably identified and read, in addition, the environment pollution is reduced, and the cost is saved.

Owner:GUIZHOU TOBACCO REDRYING +1

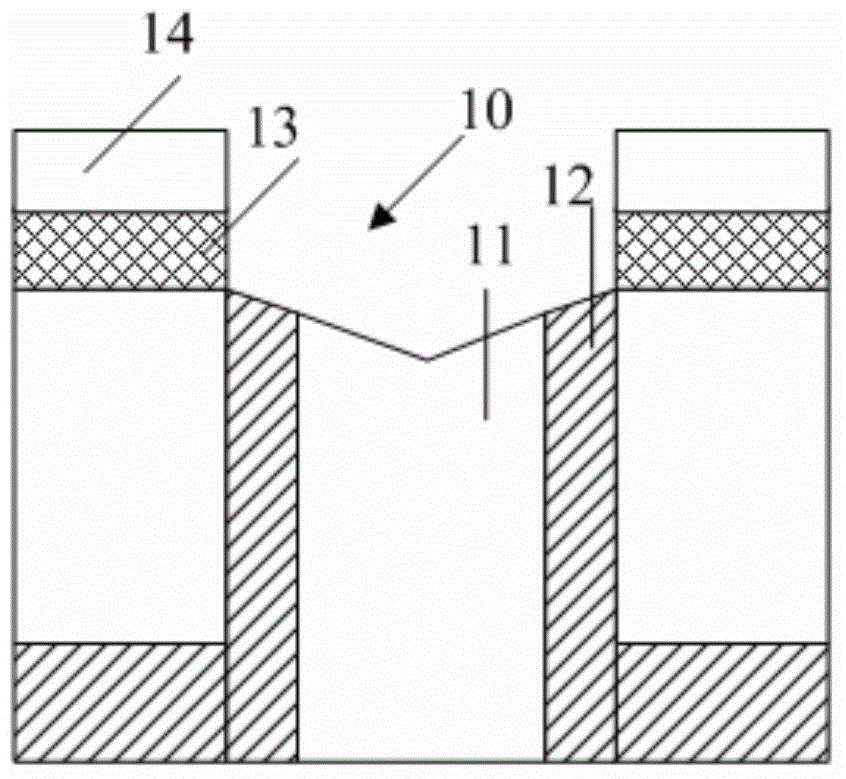

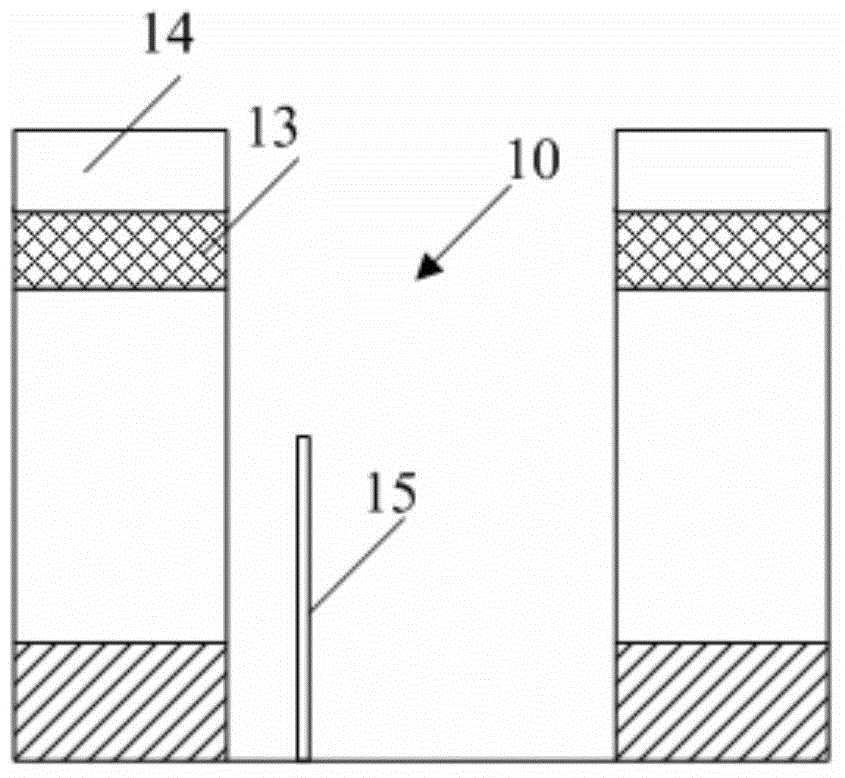

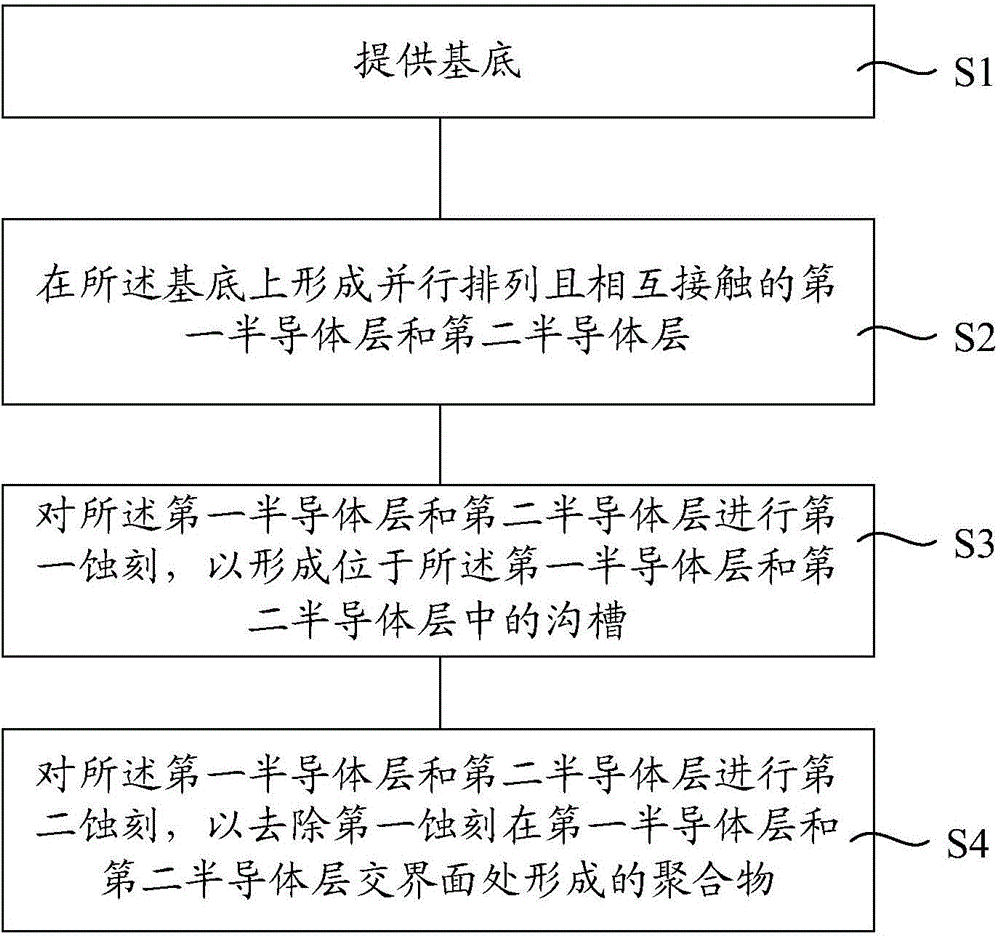

Etching method and semiconductor device

ActiveCN104658896AReduce the chance of occurrenceSolve residual problemsSemiconductor/solid-state device manufacturingSemiconductor devicesEtchingSemiconductor

The invention provides an etching method and a semiconductor device. The etching method comprises the following steps: providing a substrate; forming a semiconductor layer stacking structure on the substrate, wherein the semiconductor layer stacking structure comprises at least two semiconductor layers arranged in parallel on the substrate and contacting each other; performing first etching on the semiconductor layer stacking structure to realize patterning; and performing second etching on the semiconductor layer stacking structure to remove a polymer formed at the interface of the semiconductor layers through the first etching. The invention further provides the semiconductor device which is formed by the etching method. The performance and output of the semiconductor device can be improved.

Owner:SEMICON MFG INT (SHANGHAI) CORP

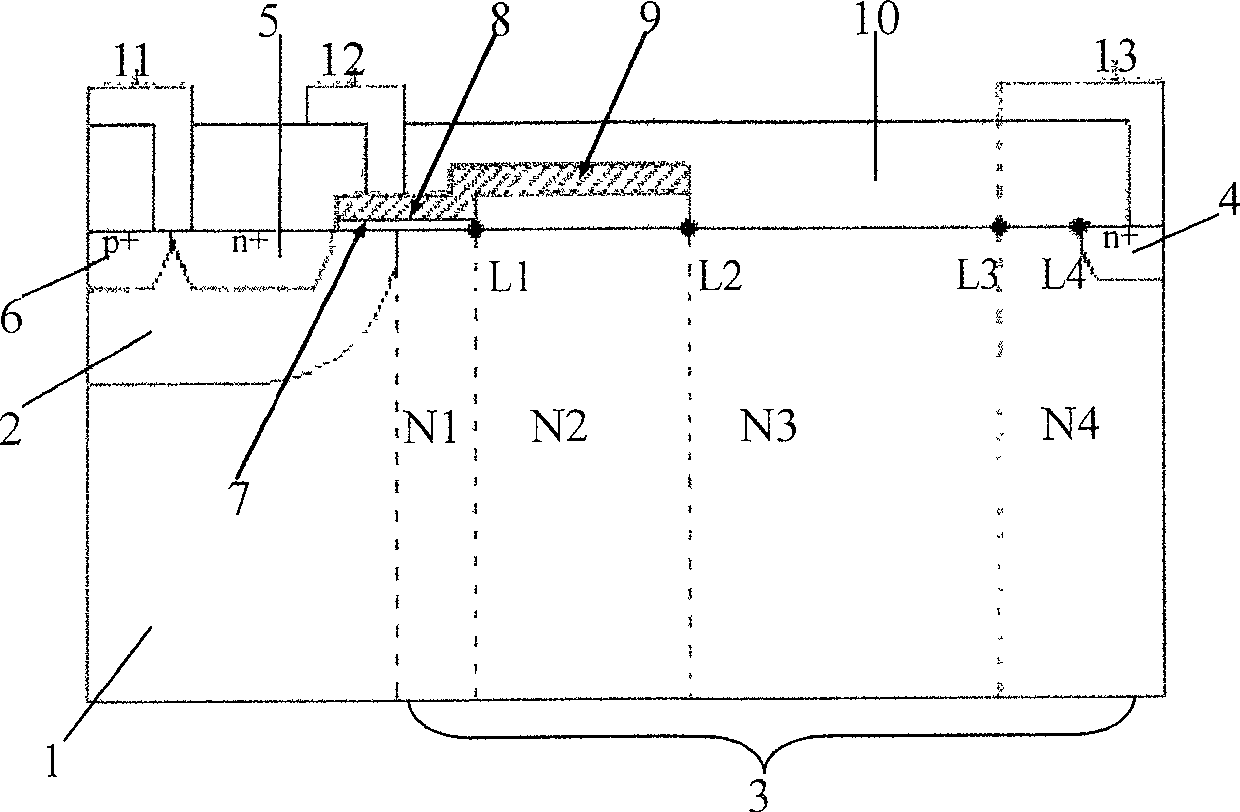

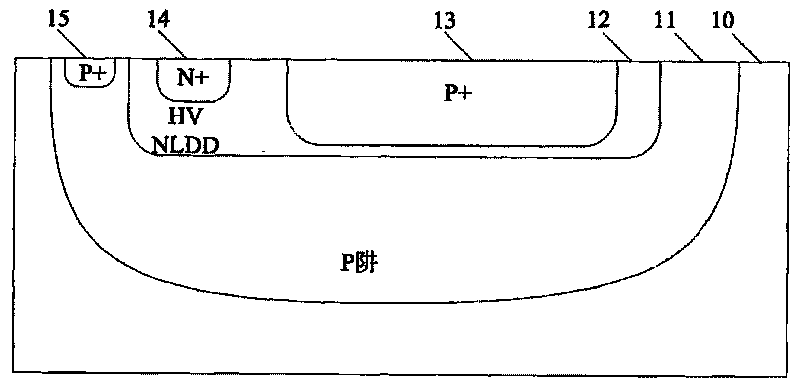

High voltage N-shape metal oxide semiconductor tube and its preparing method

InactiveCN100470840CIncrease concentrationReduce peak electric fieldSemiconductor/solid-state device manufacturingSemiconductor devicesPhysical chemistryPolysilicon gate

This invention relates to a high pressure N-type MOS tube with linear dope, in which, a P-type trap and a N-type drift region are set on the N-type substrate, a P-type contact hole and a N-type source are set in the P-type trap, a N-type leak is set in the N-type drift region, a grid oxidation layer is set above the P-type trap and the N-type drift region, a polysilicon grid is set above the grid oxidation layer and above the interface of the trap and the drift region, a filed oxidation layer is set above the grid oxidation layer and the polysilicon grid, Al leads are connected on the contact hole, the N-type sourc, the polysilicon grid and the N-type leak, polysilicon field pole plates connected with the polysilicon grid are set in the field oxidation layer, the N-type drift region is composed of a first, second, third and fourth regions arrayed along the source and the leak orderly, the doped concentration becomes smaller from the fourth, third, second and the first region.

Owner:SOUTHEAST UNIV

Method of preparing carbon fibers through crosslinked reaction of boron trichloride and polyacrylonitrile precursors

ActiveCN102383224BUniform chemical modificationReduced release of hydrogen cyanideFibre chemical featuresToxic gasCarbon fibers

Owner:NAT UNIV OF DEFENSE TECH

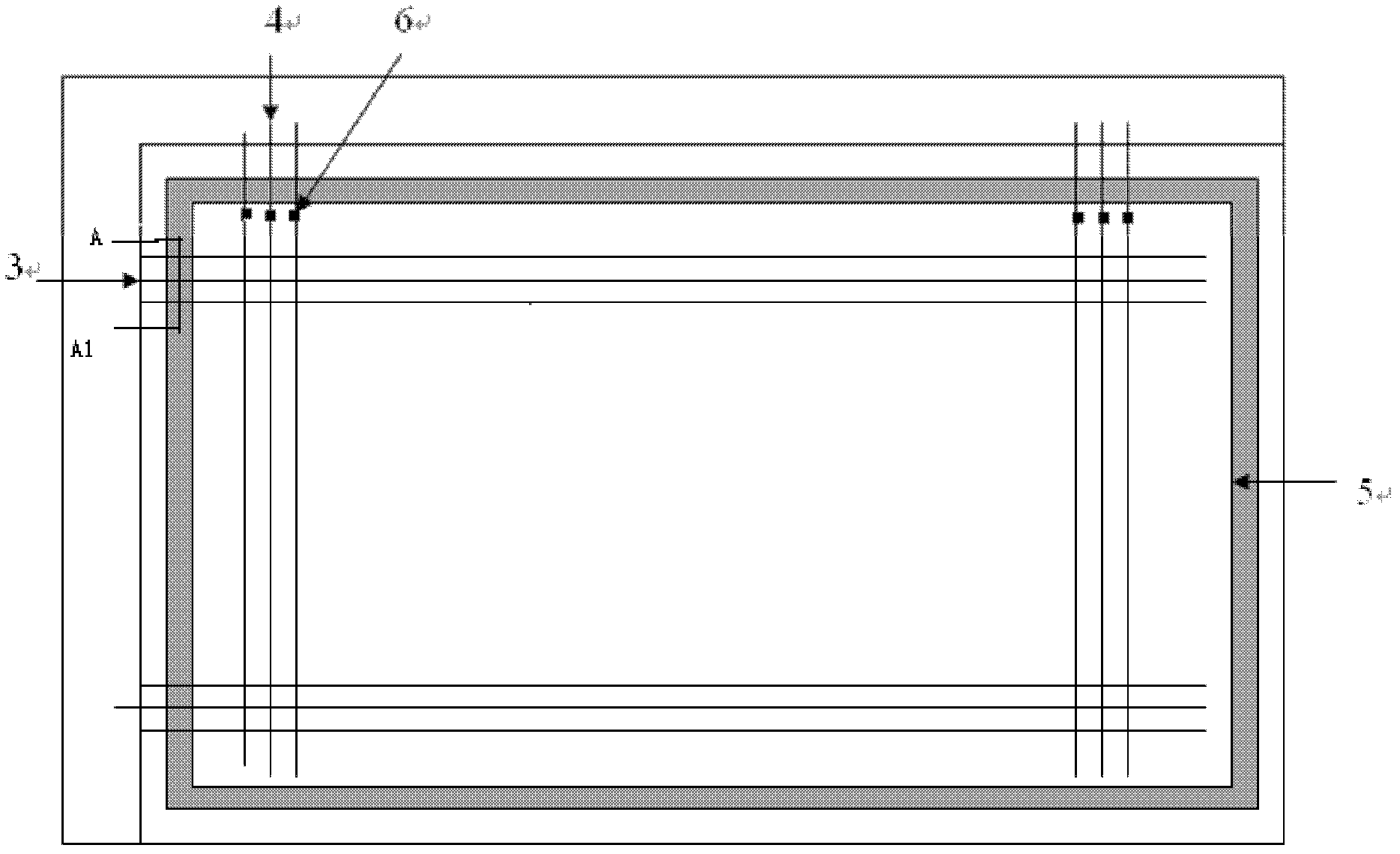

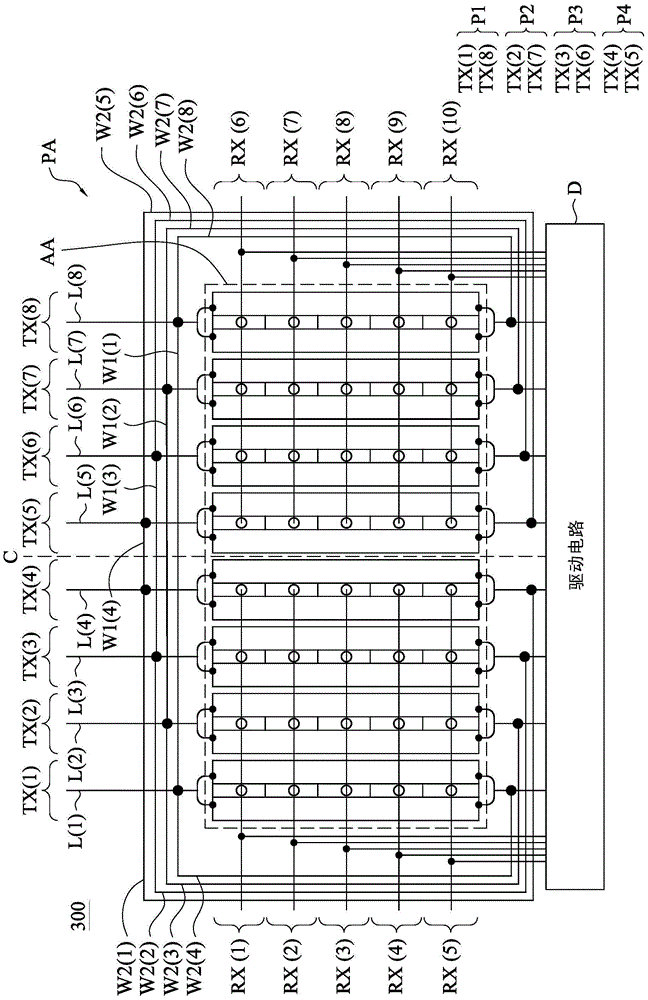

Embedded touch display panel

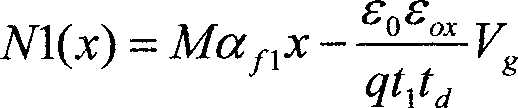

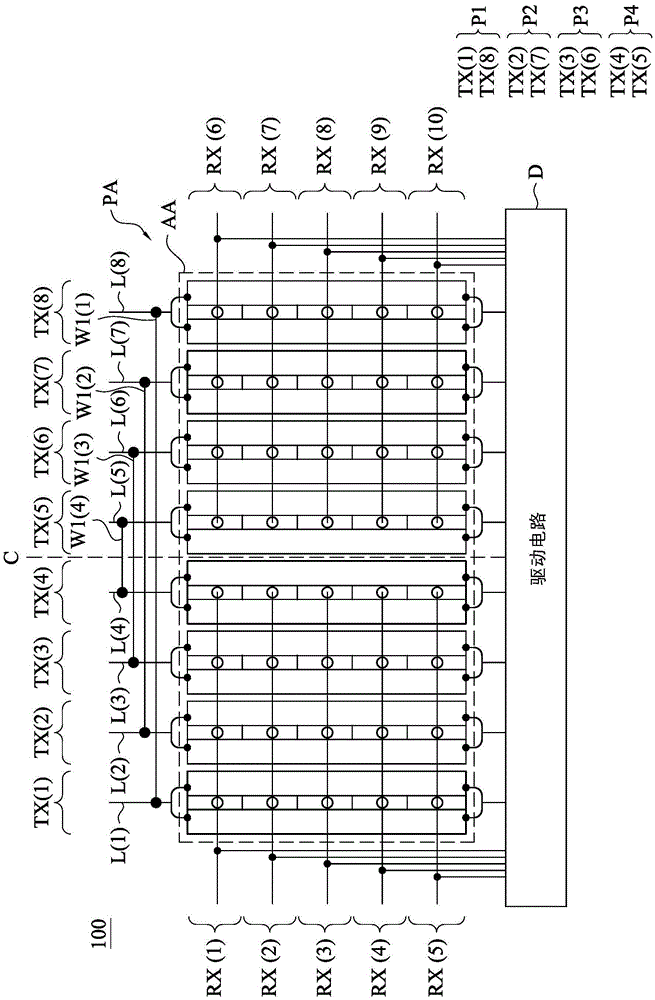

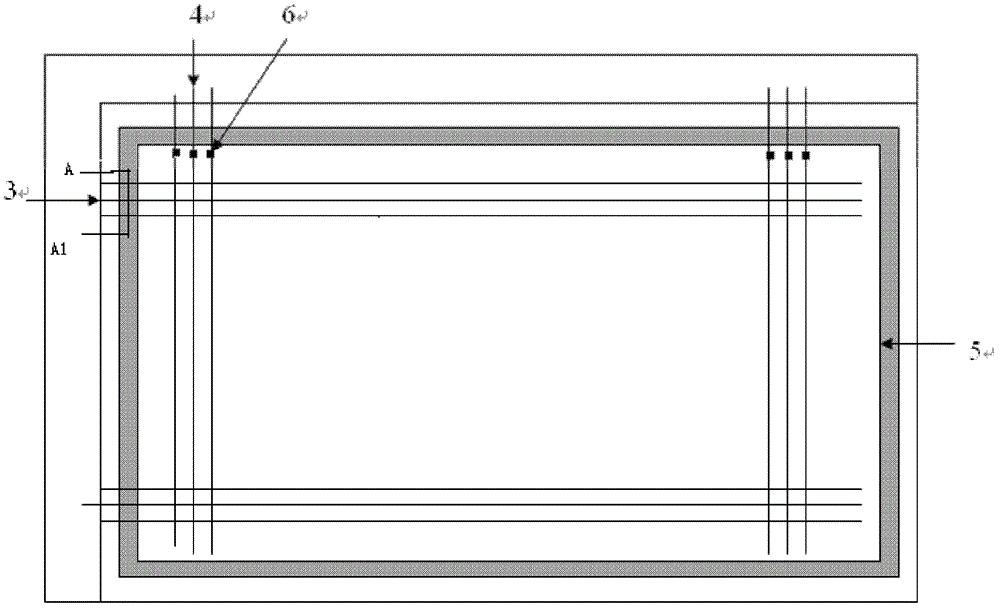

ActiveCN106775037ANo additional process stepsImprove voltage uniformityInput/output processes for data processingPeripheral zoneEmbedded system

The invention provides an embedded touch display panel which comprises multiple touch driving electrodes and multiple touch sending electrodes. The multiple touch driving electrodes and the multiple touch sending electrodes are located in a display zone of the embedded touch display panel and are arranged in staggered mode. The multiple touch driving electrodes are divided into multiple touch driving electrode groups, each of the multiple touch driving electrode groups comprises two of the touch driving electrodes, and the touch driving electrodes in each of the multiple touch driving electrode groups are mutually and electrically connected through connecting leads in a peripheral zone located outside the display zone of the embedded touch display panel.

Owner:HIMAX TECH LTD

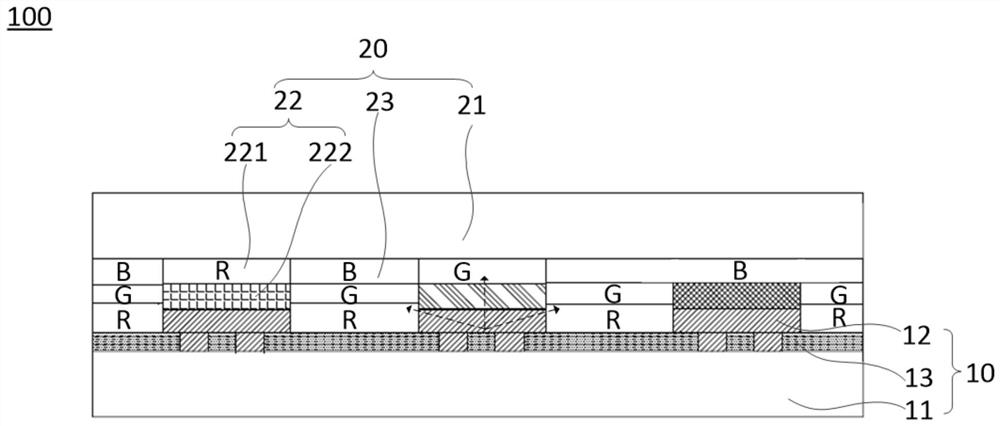

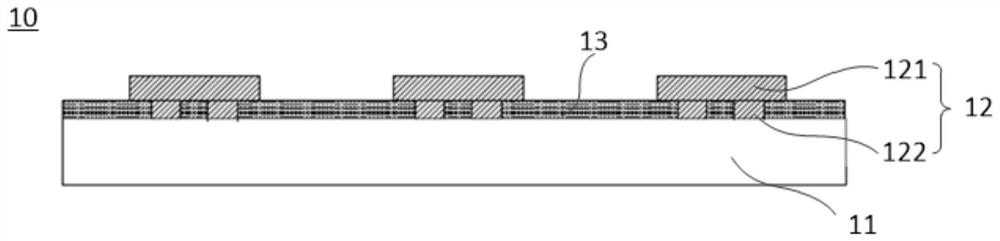

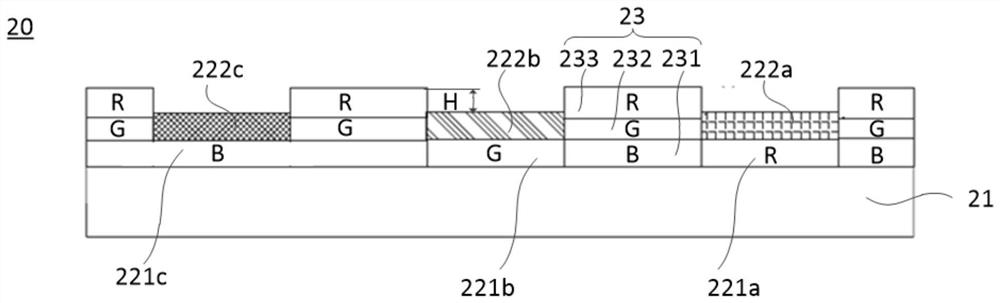

Display panel and display panel manufacturing method

PendingCN114566581AImprove the display effectAvoid cross-colorSolid-state devicesSemiconductor devicesConvertersColor transformation

The invention is suitable for the technical field of display, and provides a display panel which comprises a first substrate and a second substrate which are oppositely arranged. The plurality of micro LEDs are arrayed on the first substrate at intervals; the plurality of color converters are arranged on the second substrate and are opposite to the micro LEDs respectively, each color converter comprises a color filter film and a quantum dot layer which are stacked, and the quantum dot layer is used for changing the wavelength of light; the shading part is located between the adjacent color converters, the shading part at least comprises a first color resistance layer and a second color resistance layer which are sequentially arranged on the second substrate in an overlapped mode and are different in color, and the shading part is right opposite to a gap between the adjacent micro LEDs. The invention further provides a manufacturing method of the display panel. According to the display panel and the display panel manufacturing method provided by the invention, color crossing between the sub-pixels can be effectively avoided, the manufacturing process is simple, and the cost is relatively low.

Owner:CHUZHOU HKC OPTOELECTRONICS TECH CO LTD +1

IPS liquid crystal display screen liquid crystal box preparation method

The invention relates to the technical field of IPS liquid crystal display screen manufacturing, in particular to an IPS liquid crystal display screen liquid crystal box preparation method. The methodincludes: A, arranging at least one preset liquid crystal coverage area at intervals on a CF substrate, wherein a small frame is formed on the periphery of each preset liquid crystal coverage area through frame glue; B, enclosing to form a large frame, which encloses all small frames in the step A, on the periphery of the CF substrate through frame glue; C, dropping liquid crystal on a TFT substrate through a liquid crystal dropping process; D, fitting the surface, with the dropped liquid crystal in the step C, of the TFT substrate to the surface, with the frame, of the CF substrate in the step B to form a Cell liquid crystal box. The large frame is provided with an opening to prevent water vapor from entering the Cell box in cleaning and causing adverse influences on subsequent products.The whole Cell box is uniformly stressed, and frame impression is avoided.

Owner:TRULY HUIZHOU SMART DISPLAY

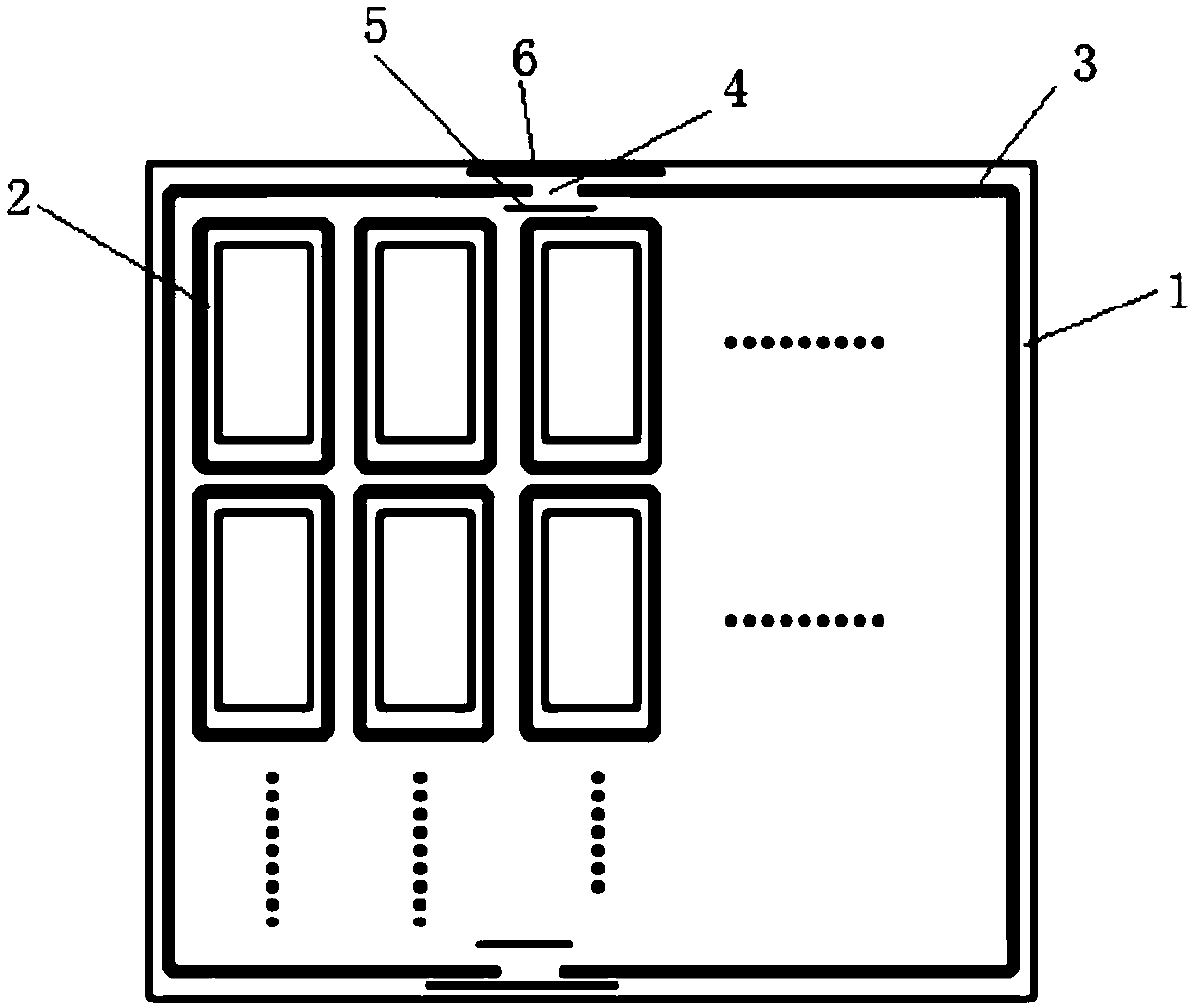

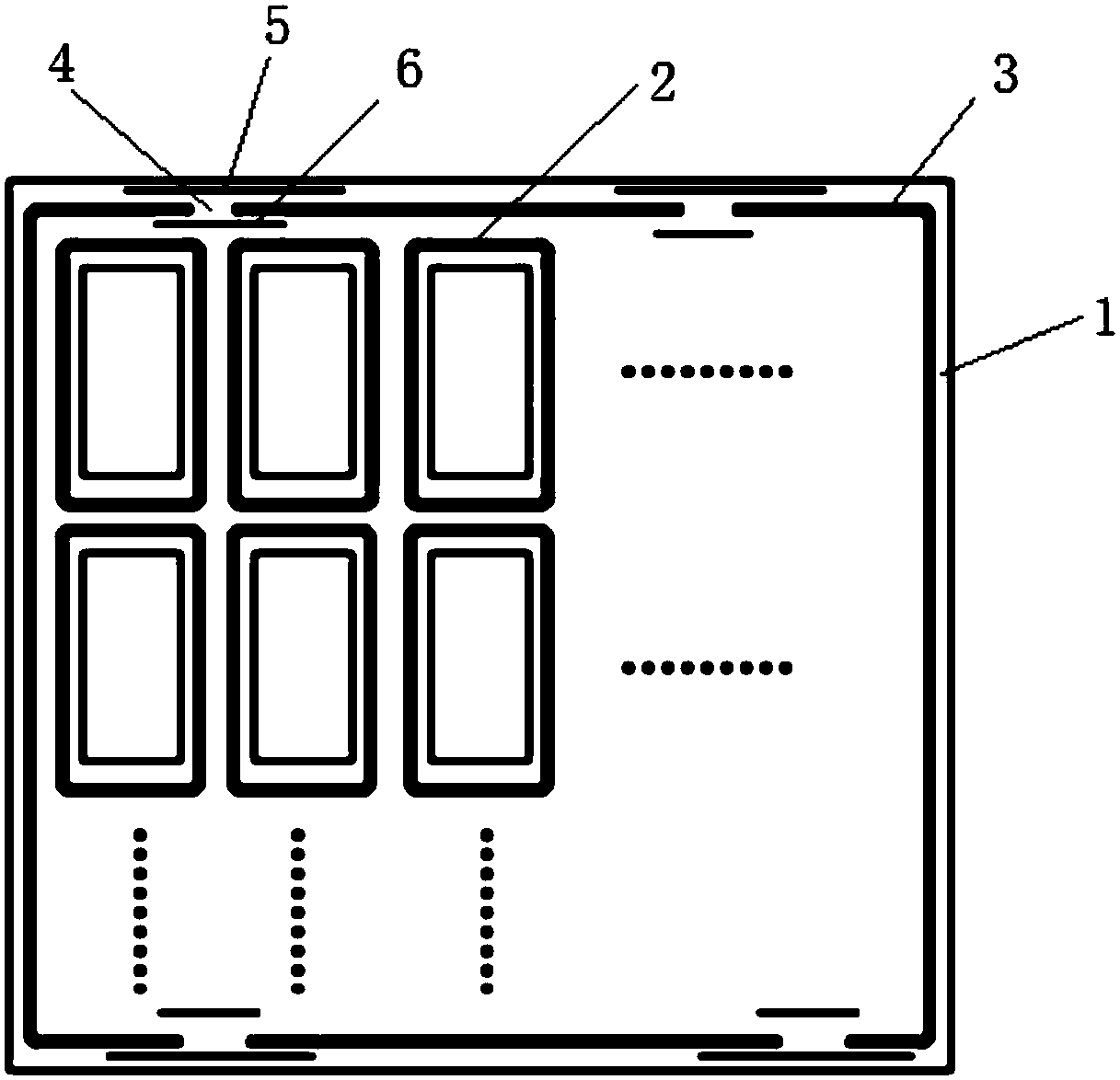

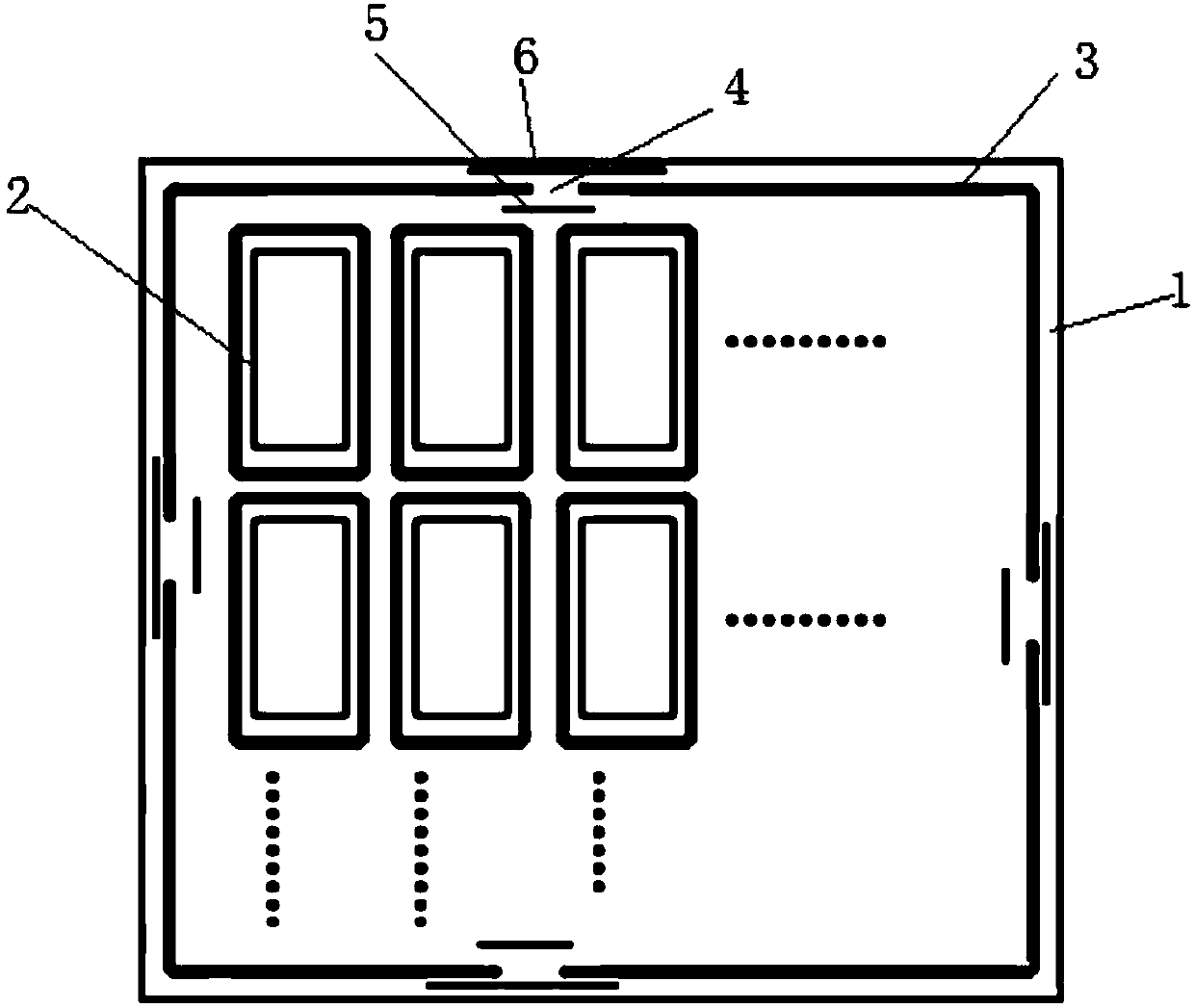

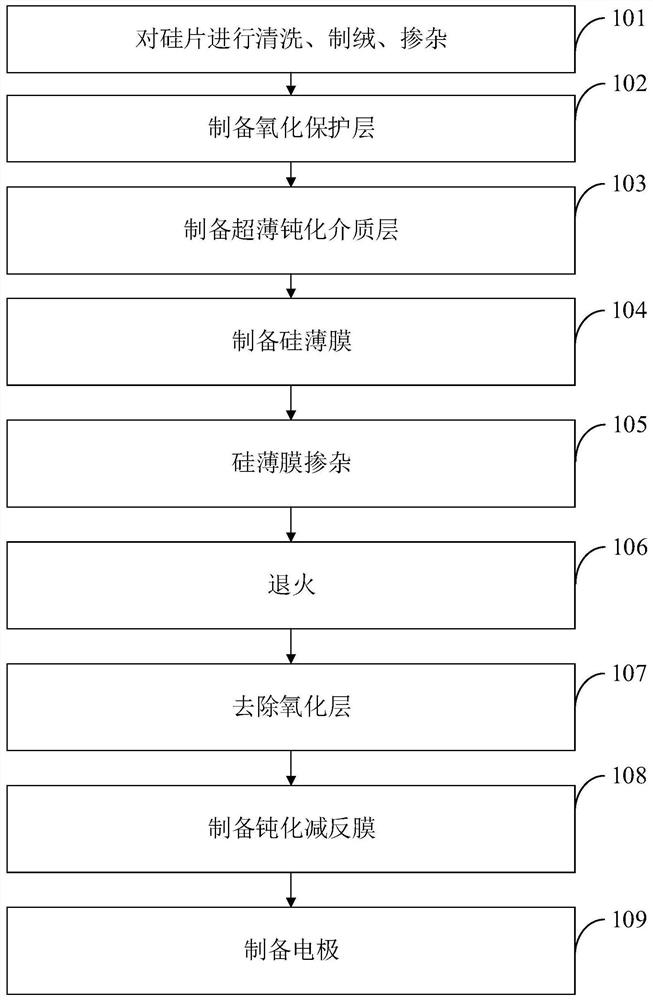

Preparation method of passivation contact solar cell

InactiveCN111816732AWill not polluteReduce leakageFinal product manufacturePhotovoltaic energy generationCell fabricationSolar battery

The invention relates to a preparation method of a passivation contact solar cell, and relates to the field of solar cell manufacturing. The method comprises the following step: forming an oxidation protection layer on a first surface of a doped silicon wafer, wherein the first surface of the silicon wafer comprises a doped surface of one surface of the silicon wafer and a side surface of the silicon wafer. According to the technical scheme provided by the invention, the process can be simplified, and the productivity of the solar cell can be improved.

Owner:JA SOLAR TECH YANGZHOU

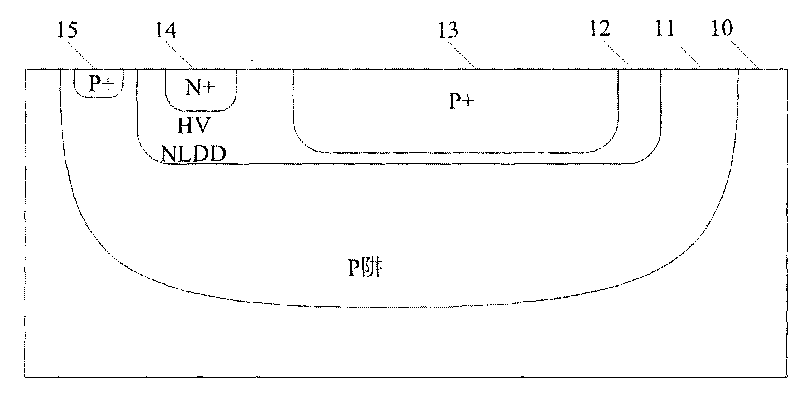

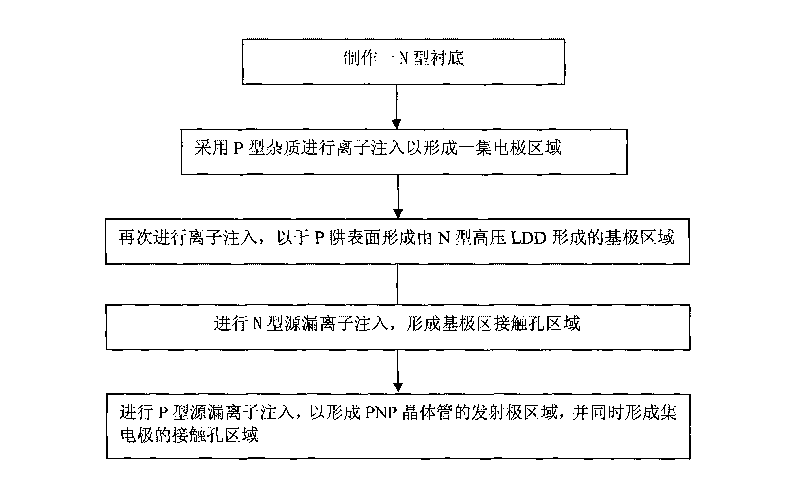

Vertical bipolar transistor and method for manufacturing same

InactiveCN101692424AImprove performanceNo additional process stepsSemiconductor/solid-state device manufacturingSemiconductor devicesHigh voltage transistorsParasitic bipolar transistor

The invention discloses a vertical bipolar transistor and a method for manufacturing the same. The vertical bipolar transistor comprises a collector electrode area formed by a trap of a CMOS transistor, a base electrode area formed by using a high-voltage lightly doped drain electrode of a high-voltage transistor and an emitter electrode area formed on the surface of the base electrode area and by a source-drain of the CMOS transistor. The method fully uses the prior CMOS process, avoids the use of additional process steps and uses the base electrode formed by the high-voltage LDD of the high-voltage transistor; and because the junction depth of a PN junction formed by the high-voltage LDD and the trap is slightly deeper than that of the PN junction formed by the source-drain and the LDD, the base electrode of the formed vertical bipolar transistor has quite thin thickness, and consequentially the performance of the bipolar transistor is improved.

Owner:GRACE SEMICON MFG CORP

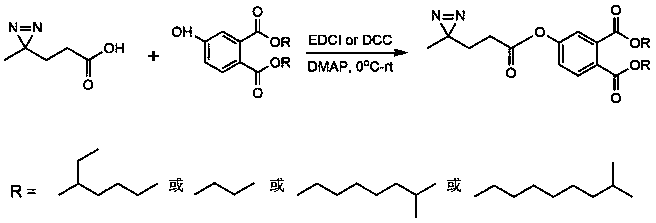

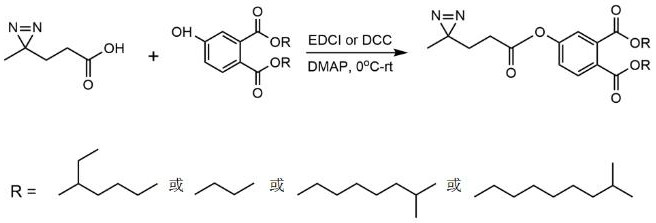

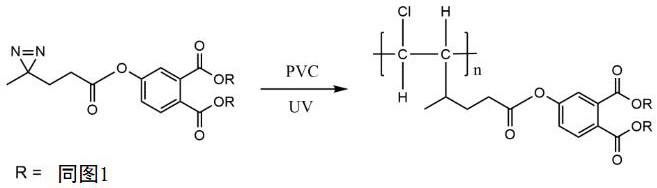

Method for manufacturing polyvinyl chloride artificial leather based on synchronous internal plasticization of light-sensitive reaction type plasticizer

ActiveCN109162110AInhibit migrationIncreased durabilityOrganic chemistryTextiles and paperPolyvinyl chlorideCarbene

The invention discloses a method for manufacturing polyvinyl chloride artificial leather based on synchronous internal plasticization of a light-sensitive reaction type plasticizer. The method is characterized by comprising the following steps: introducing a biethylene imine light-sensitive group into an o-benzene plasticizer, carrying out synchronous ultraviolet radiation with a wavelength of 330-370nm while a polyvinyl chloride artificial leather coating is plasticized, promoting biethylene imine to rapidly generate active Cabbeen which is inserted into C-H bonds of polyvinyl chloride molecules, furthermore carrying out in-situ covalent grafting on the o-benzene plasticizer with a PVC (Polyvinyl Chloride) resin, thereby achieving synchronous internal plasticization of the polyvinyl chloride artificial leather coating. By adopting the method, conventional process steps of polyvinyl chloride artificial leather are not changed, the plasticization time of the polyvinyl chloride artificial leather is not prolonged, grafting reactions and polyvinyl chloride artificial leather processing are synchronously carried out, plasticizer migration can be effectively inhibited, the problem of toxicity caused by o-benzene plasticizer migration can be substantially solved, the durability and the service life of the polyvinyl chloride artificial leather can be prolonged, and practical engineering application values can be made.

Owner:SICHUAN UNIV

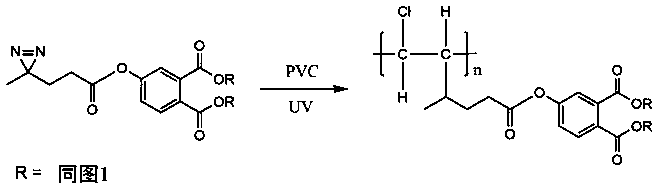

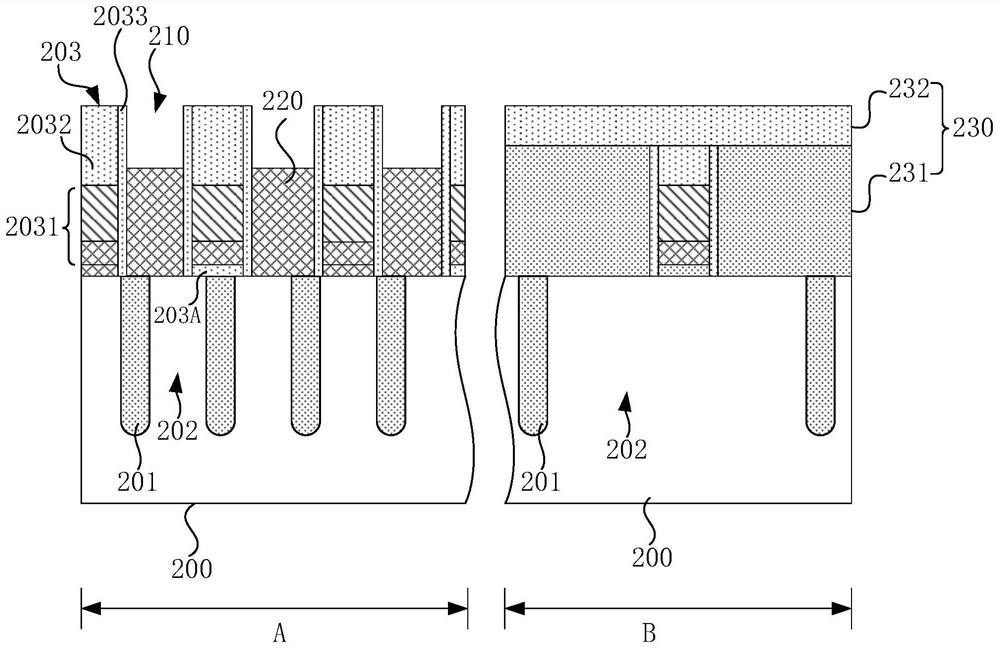

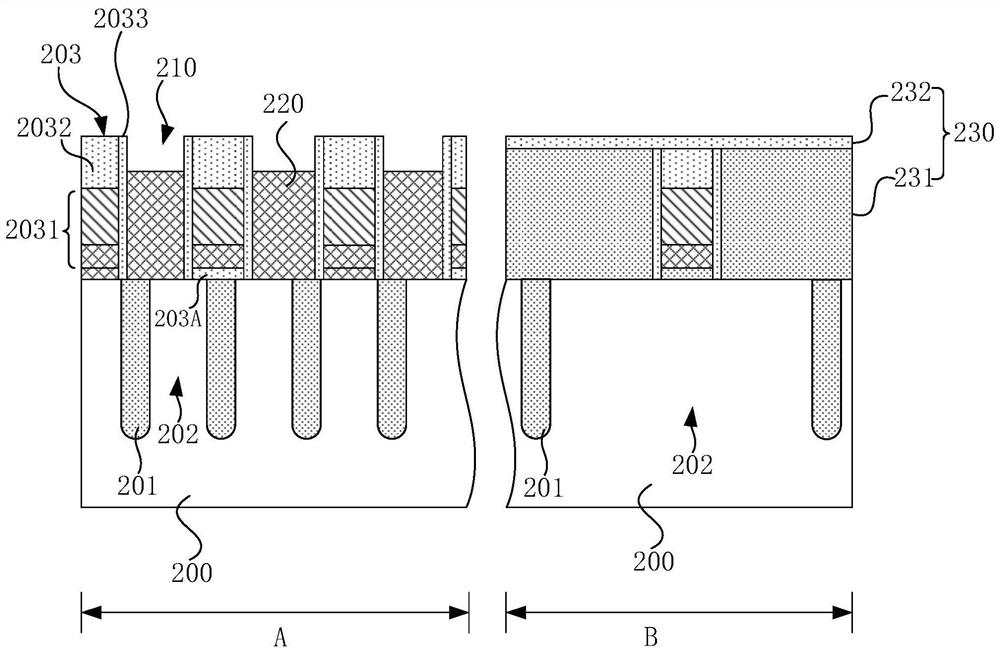

Semiconductor structure and preparation method thereof

PendingCN114078778AImprove electrical conductivityPrevent leakageTransistorSemiconductor/solid-state device manufacturingPhysicsElectrically conductive

The invention provides a semiconductor structure and a preparation method thereof. the preparation method comprises the following steps: providing a semiconductor substrate which comprises an array region and a peripheral circuit region, wherein the array region and the semiconductor substrate are provided with a plurality of capacitor contact holes, the bottoms of the capacitor contact holes are provided with first conductive layers, and in the peripheral circuit region, a device layer is arranged on the semiconductor substrate; processing the first conductive layer to increase the roughness of the first conductive layer; forming a wire contact hole in the peripheral circuit area, wherein the wire contact hole exposes the semiconductor substrate; forming a transition layer, wherein the transition layer at least covers the surface of the first conductive layer and the surface of the semiconductor substrate exposed by the wire contact hole; and forming a second conductive layer which covers the transition layer and fills the capacitor contact hole and the wire contact hole. Transition layers with different thicknesses can be formed in the array area and the peripheral circuit area, and the performance of the semiconductor structure is greatly improved.

Owner:CHANGXIN MEMORY TECH INC

A method for producing polyvinyl chloride artificial leather based on synchronous internal plasticization of photosensitive response plasticizer

ActiveCN109162110BInhibit migrationIncreased durabilityOrganic chemistryTextiles and paperBenzenePolymer science

The invention discloses a method for manufacturing polyvinyl chloride artificial leather based on synchronous internal plasticization of a light-sensitive reaction type plasticizer. The method is characterized by comprising the following steps: introducing a biethylene imine light-sensitive group into an o-benzene plasticizer, carrying out synchronous ultraviolet radiation with a wavelength of 330-370nm while a polyvinyl chloride artificial leather coating is plasticized, promoting biethylene imine to rapidly generate active Cabbeen which is inserted into C-H bonds of polyvinyl chloride molecules, furthermore carrying out in-situ covalent grafting on the o-benzene plasticizer with a PVC (Polyvinyl Chloride) resin, thereby achieving synchronous internal plasticization of the polyvinyl chloride artificial leather coating. By adopting the method, conventional process steps of polyvinyl chloride artificial leather are not changed, the plasticization time of the polyvinyl chloride artificial leather is not prolonged, grafting reactions and polyvinyl chloride artificial leather processing are synchronously carried out, plasticizer migration can be effectively inhibited, the problem of toxicity caused by o-benzene plasticizer migration can be substantially solved, the durability and the service life of the polyvinyl chloride artificial leather can be prolonged, and practical engineering application values can be made.

Owner:SICHUAN UNIV

Electrostatic discharge protection circuit, display panel and display device

ActiveCN103268876BAdd release pathImprove anti-static performanceSolid-state devicesEmergency protective arrangements for limiting excess voltage/currentBottom gateDisplay device

The invention relates to the field of display devices, in particular to an electrostatic discharge protection circuit, a display panel and a display device. According to the embodiment of the invention, the electrostatic discharge protection circuit comprises at least one electrostatic protection element, and the electrostatic protection element comprises a bottom gate electrode, a first insulating layer, an active layer, a second insulating layer, top gate electrodes, a third insulating layer, a first electrode and a second electrode, wherein the bottom gate electrode is positioned on a substrate; the first insulating layer is positioned on the bottom gate electrode; the active layer is positioned on the first insulating layer, and corresponds to the bottom gate electrode; the second insulating layer is positioned on the active layer; the top gate electrodes are positioned on the second insulating layer, and correspond to the active layer; the third insulating layer is positioned on the top gate electrodes; the first and second electrodes are positioned on the two sides of the top gate electrodes on the third insulating layer respectively; the bottom gate electrode and the top gate electrodes are electrically connected with the first electrode and connected with a power cord or a circuit of a display area of the display panel; and the second electrode is electrically connected with the circuit of the display area or the power cord. According to the electrostatic discharge protection circuit, an electrostatic discharge path is added, so that the anti-electrostatic capability is improved.

Owner:XIAMEN TIANMA MICRO ELECTRONICS

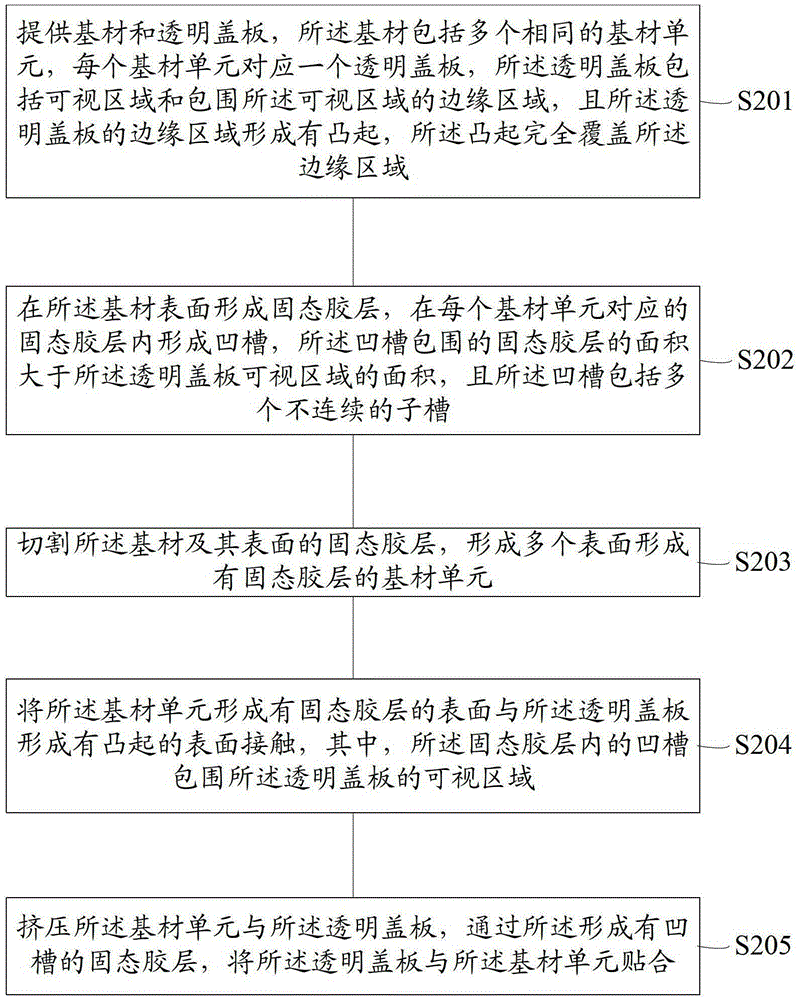

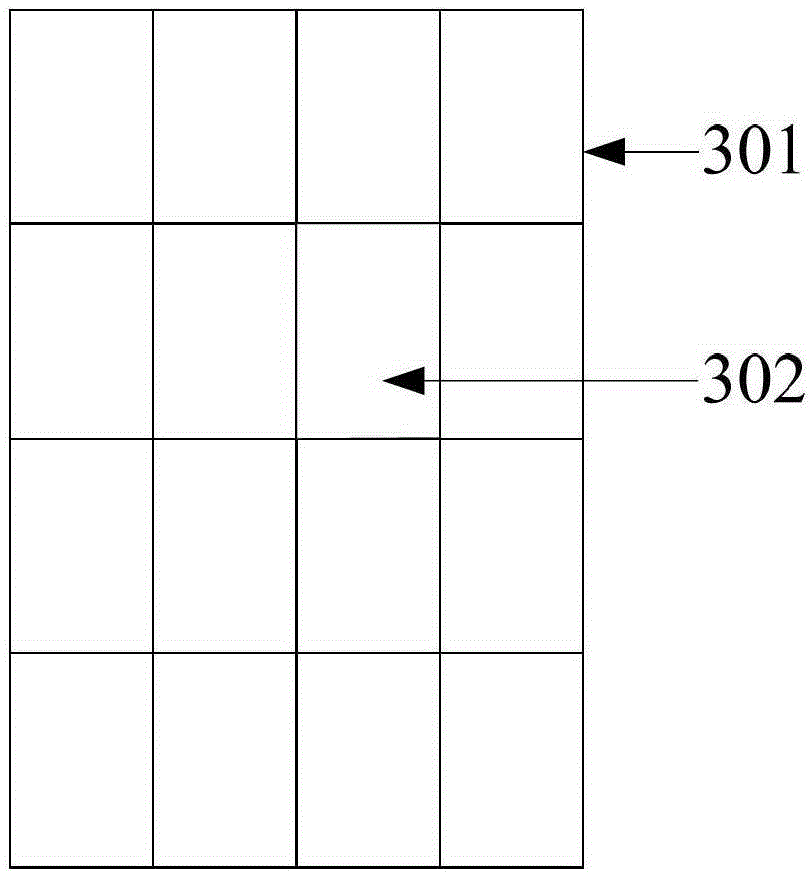

A kind of display and bonding method thereof

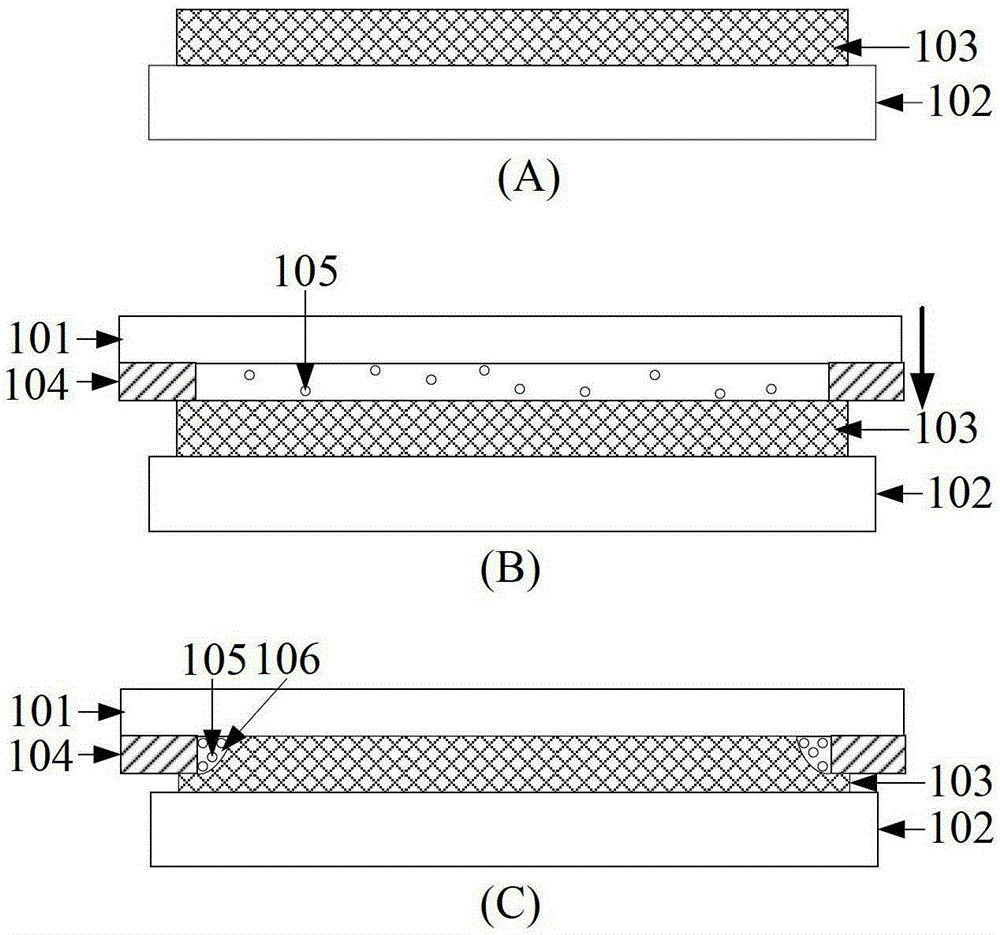

ActiveCN103192583BWill not affect the displayAffect the display effectLaminationLamination apparatusDisplay deviceEngineering

The invention provides a laminating method, and is applied to the manufacturing process of a display. The laminating method comprises the following steps of: providing base material and a transparent cover plate, wherein the base material comprises a plurality of same base material units; forming a solid adhesive layer on the surface of the base material, and forming a groove inside the solid adhesive layer corresponding to each base material unit; contacting the surfaces of the base material units provided with the solid adhesive layer with the surface of the transparent cover plate provided with bulges, and extruding the base material units and the transparent cover plate; and laminating the transparent cover plate and the base material units through the solid adhesive layer provided with the grooves. According to the laminating method, gas between the transparent cover plate and the base material units can be extruded into the grooves of the solid adhesive layer during the laminating process, and the grooves and bubbles inside the grooves cannot influence the display effect of the transparent cover plate, so that the display effect of the transparent cover plate is prevented from being influenced by the bubbles simultaneously when the laminating quality between the transparent cover plate and the base material units is ensured.

Owner:TRULY OPTO ELECTRONICS

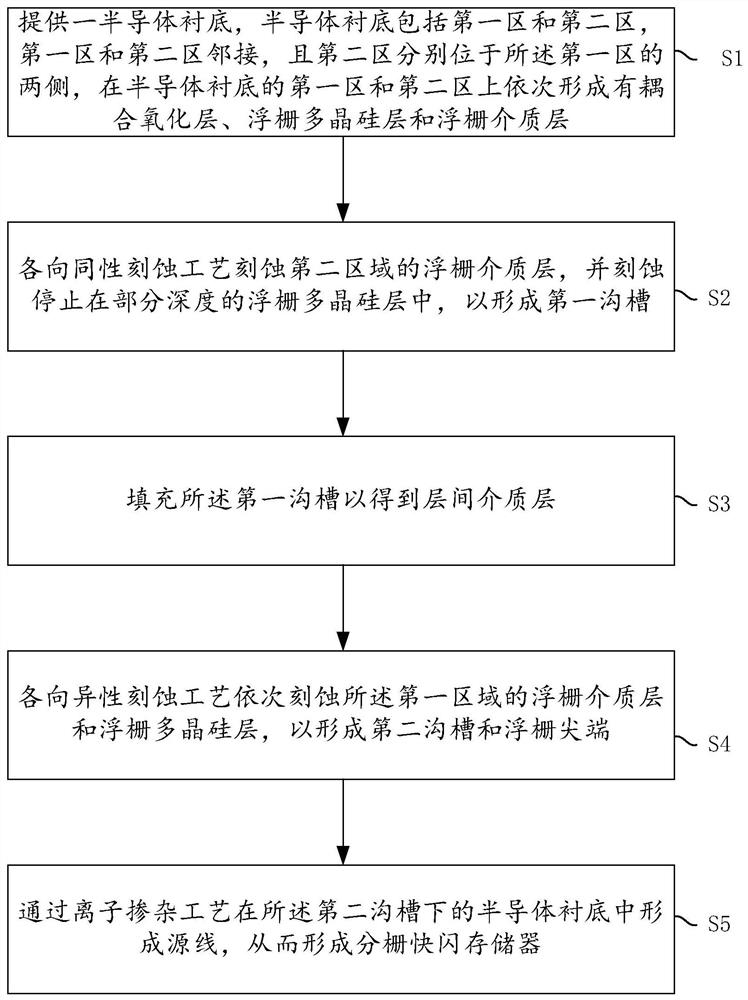

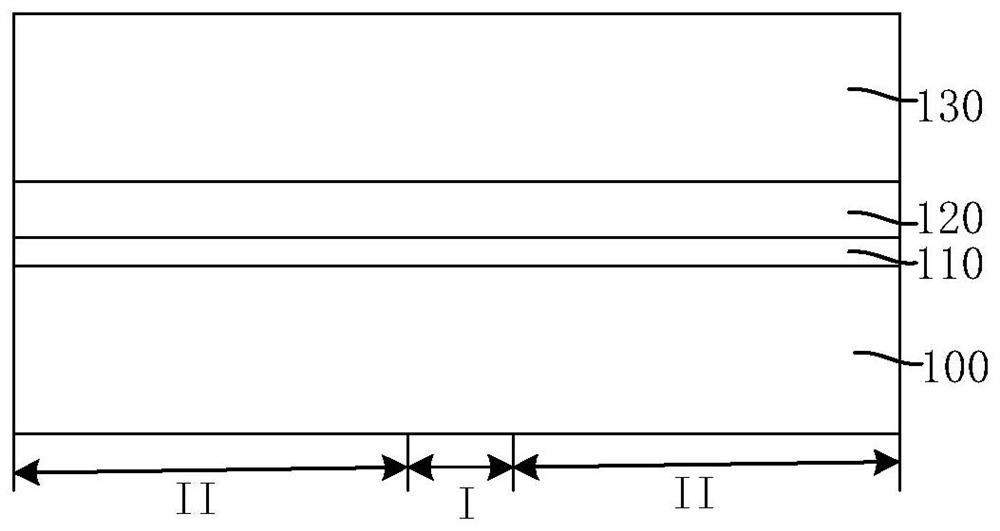

Split-gate flash memory and forming method thereof

PendingCN112530956AImprove erase effectImproved Durability PropertiesTransistorSolid-state devicesMemory cellDynamic power dissipation

According to the split-gate flash memory and the forming method thereof provided by the invention, in the forming method of the split-gate flash memory, the floating gate tip is formed while the floating gate is formed, no process step is added in the whole process, and meanwhile, the newly added floating gate tip enhances the erasure capability of a memory cell and greatly improves the numericalvalue of current Ir1, so reliability of the memory cell is improved; the erase voltage on the erase gate during erase is reduced, so that the read operation interference is reduced, and the static power consumption and the dynamic power consumption of the split-gate flash memory for low-voltage read operation are reduced; in addition, the source line formed by the subsequent process only influences the erasing efficiency and does not influence the channel, so durability characteristic of the memory unit can be improved.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

Liquid crystal display device

ActiveCN102830550BImprove antistatic performancePrevent electrostatic dischargeStatic indicating devicesNon-linear opticsLiquid-crystal displayEngineering

Owner:SHANGHAI TIANMA MICRO ELECTRONICS CO LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com