Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

84results about How to "Improve test yield" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

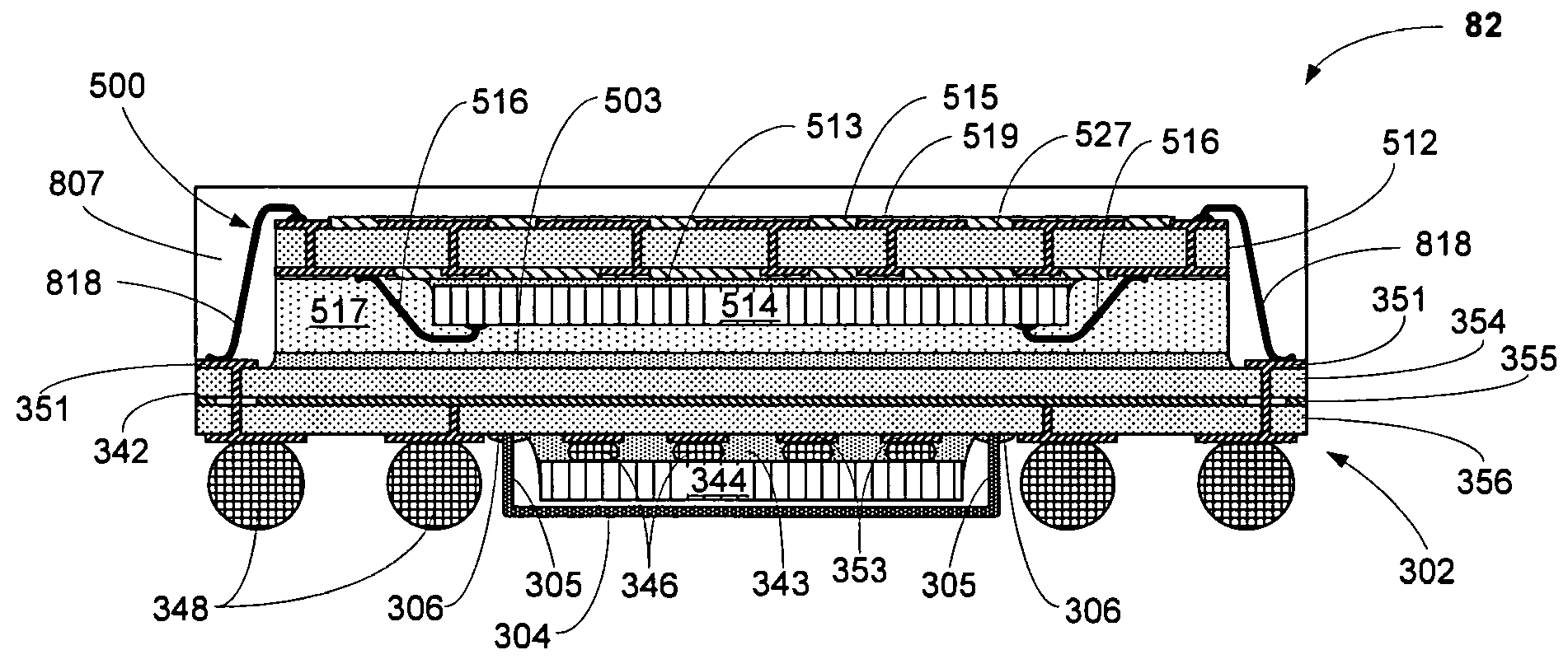

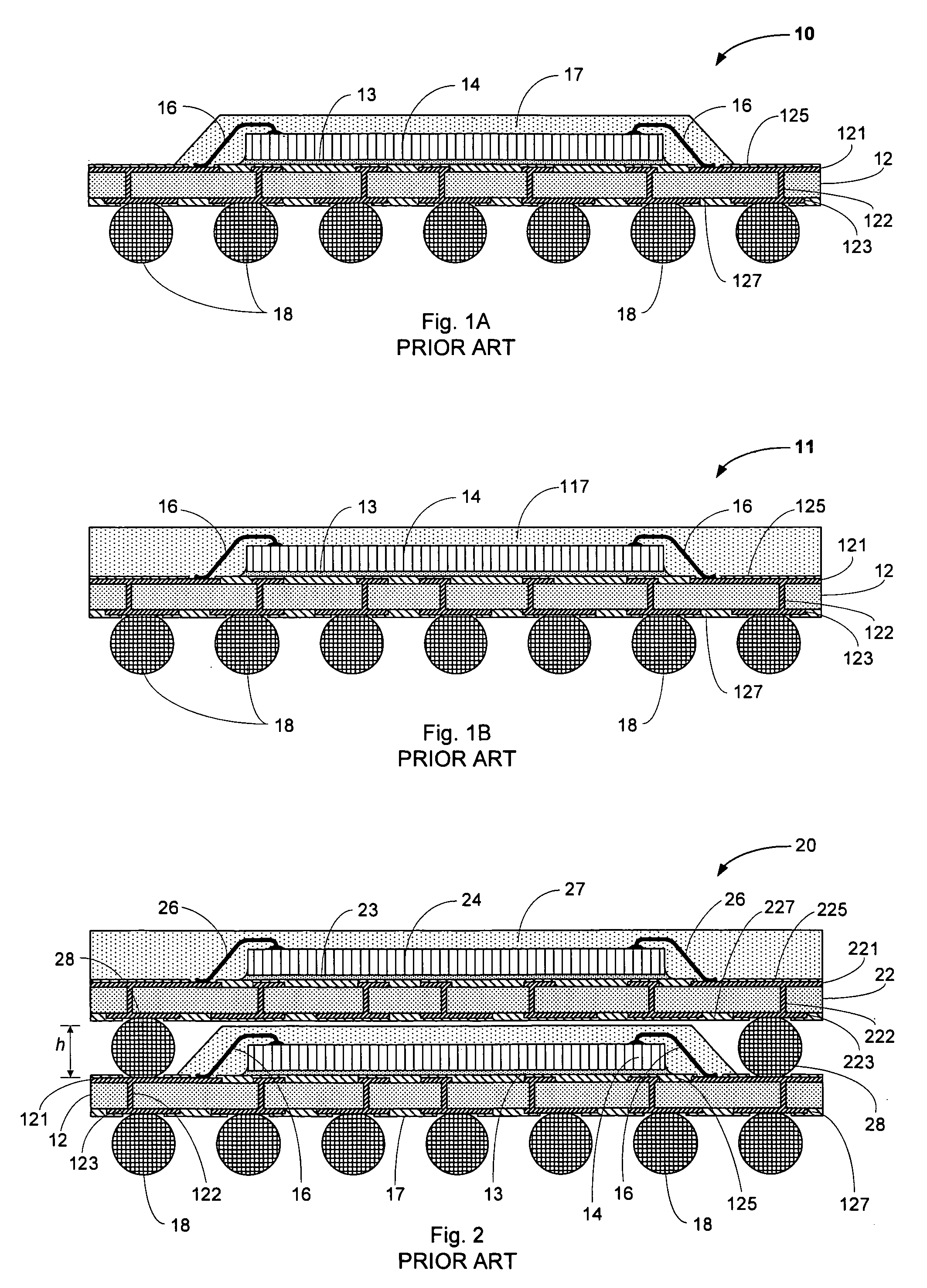

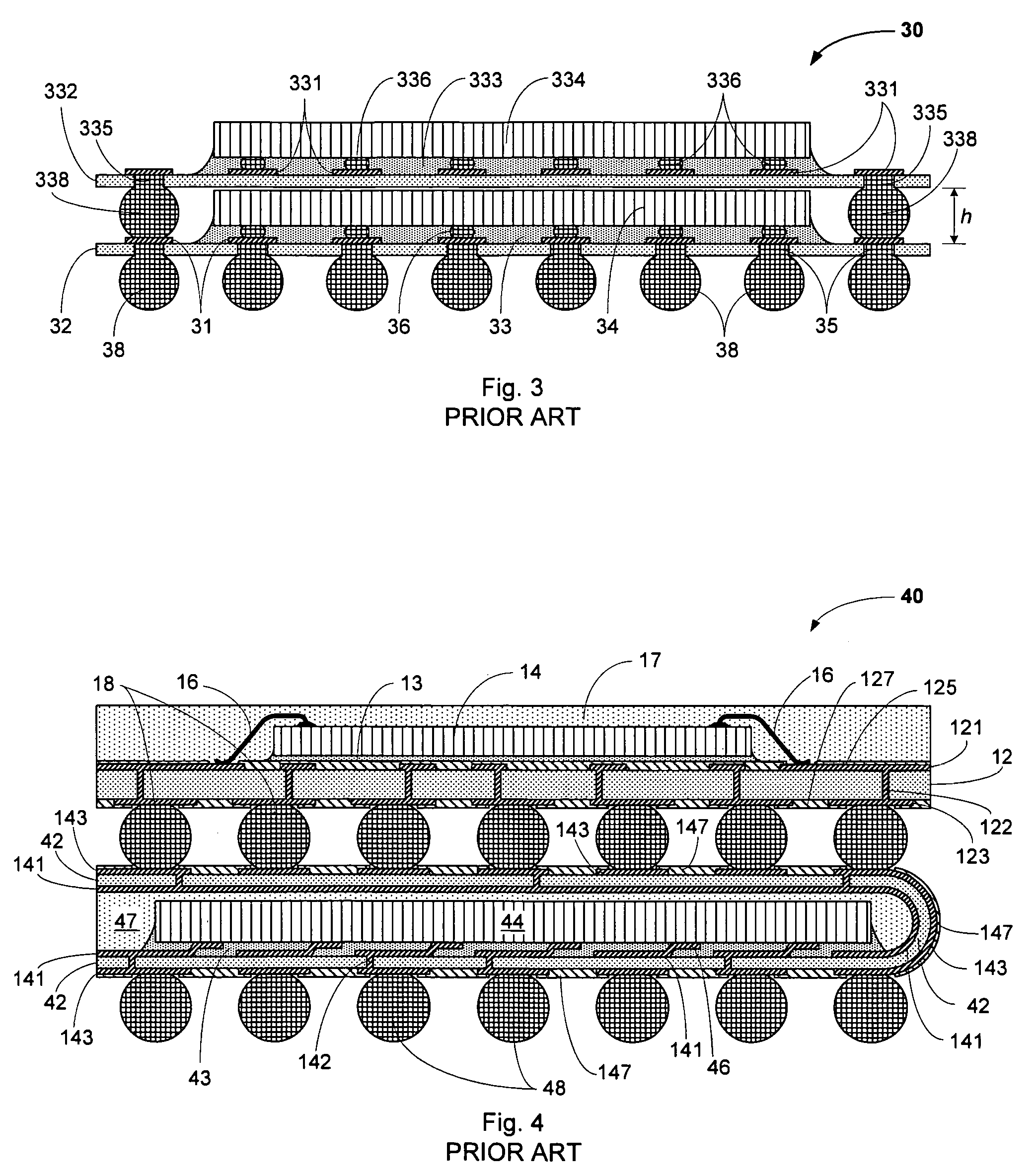

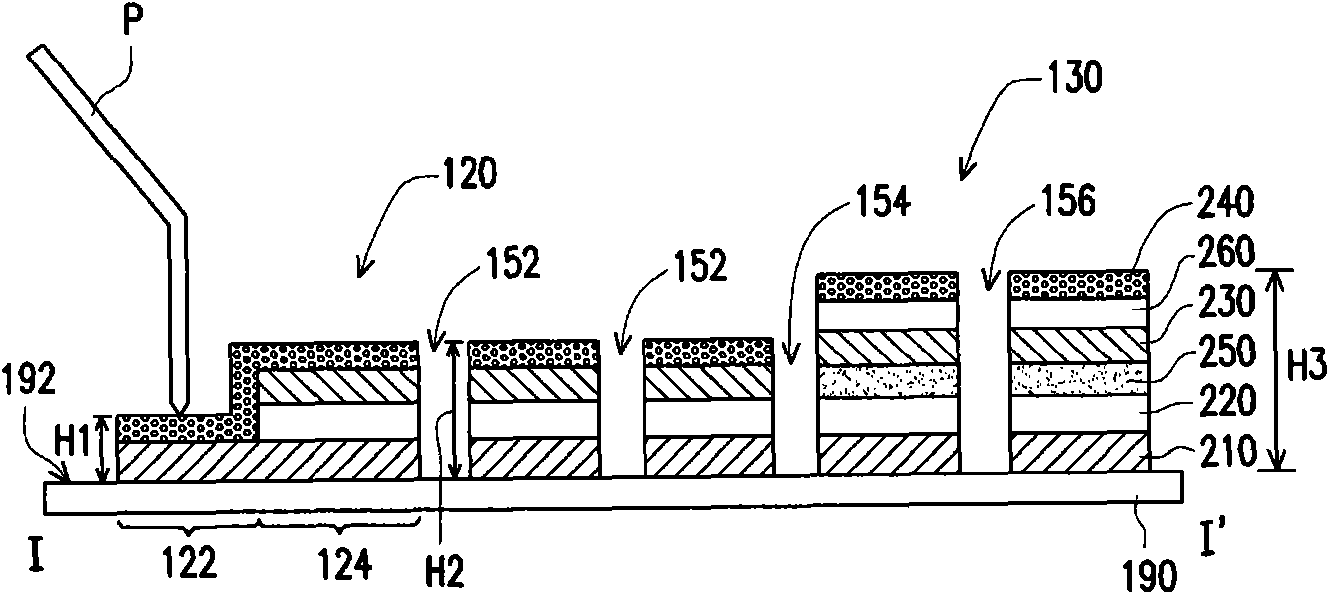

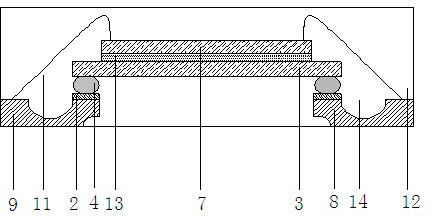

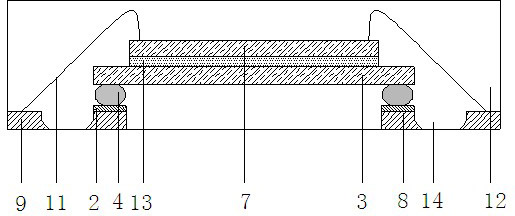

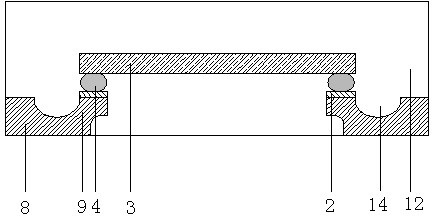

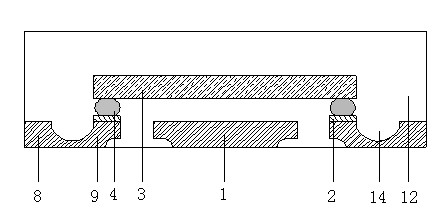

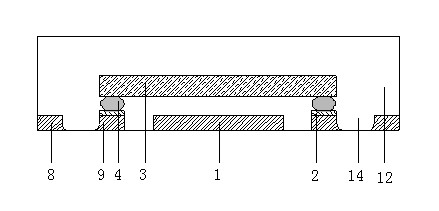

Semiconductor multi-package module having inverted second package stacked over die-up flip-chip ball grid array (BGA) package

ActiveUS7101731B2Low production costOverall design flexibilitySemiconductor/solid-state device detailsSolid-state devicesSemiconductor packageEngineering

A semiconductor multi-package module has stacked lower and upper packages, each of which includes a die attached to a substrate, in which the second package is inverted, and in which the first and second substrates are interconnected by wire bonding, and in which the first package includes a flip-chip ball grid array package having a flip-chip in a die-down configuration. Also, a method for making a semiconductor multi-package module, by providing a lower molded package including a lower substrate and a flip-chip in a die-down configuration, affixing an upper molded package including an upper substrate in inverted orientation onto the upper surface of the lower package, and forming z-interconnects between the upper and lower substrates.

Owner:STATS CHIPPAC LTD

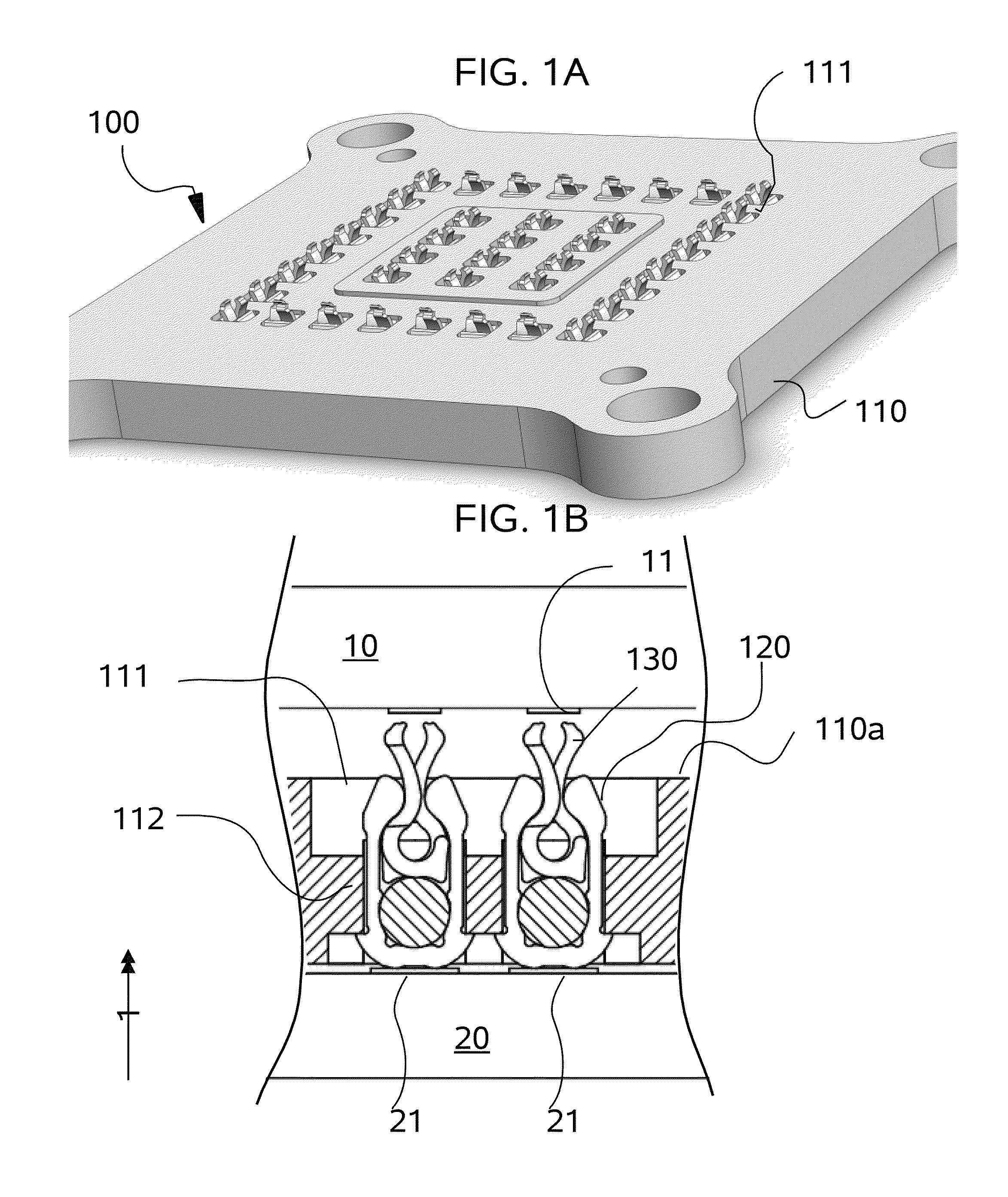

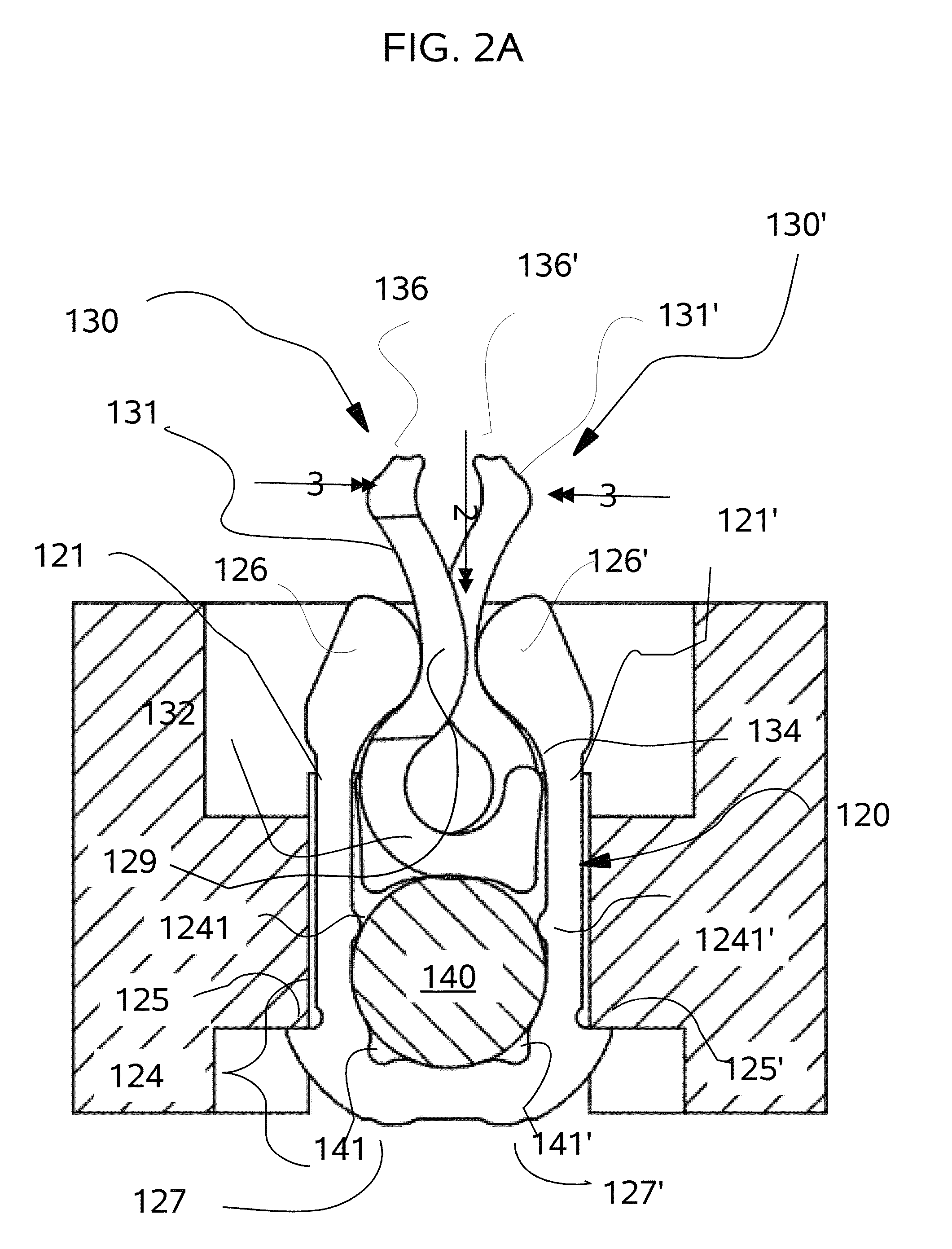

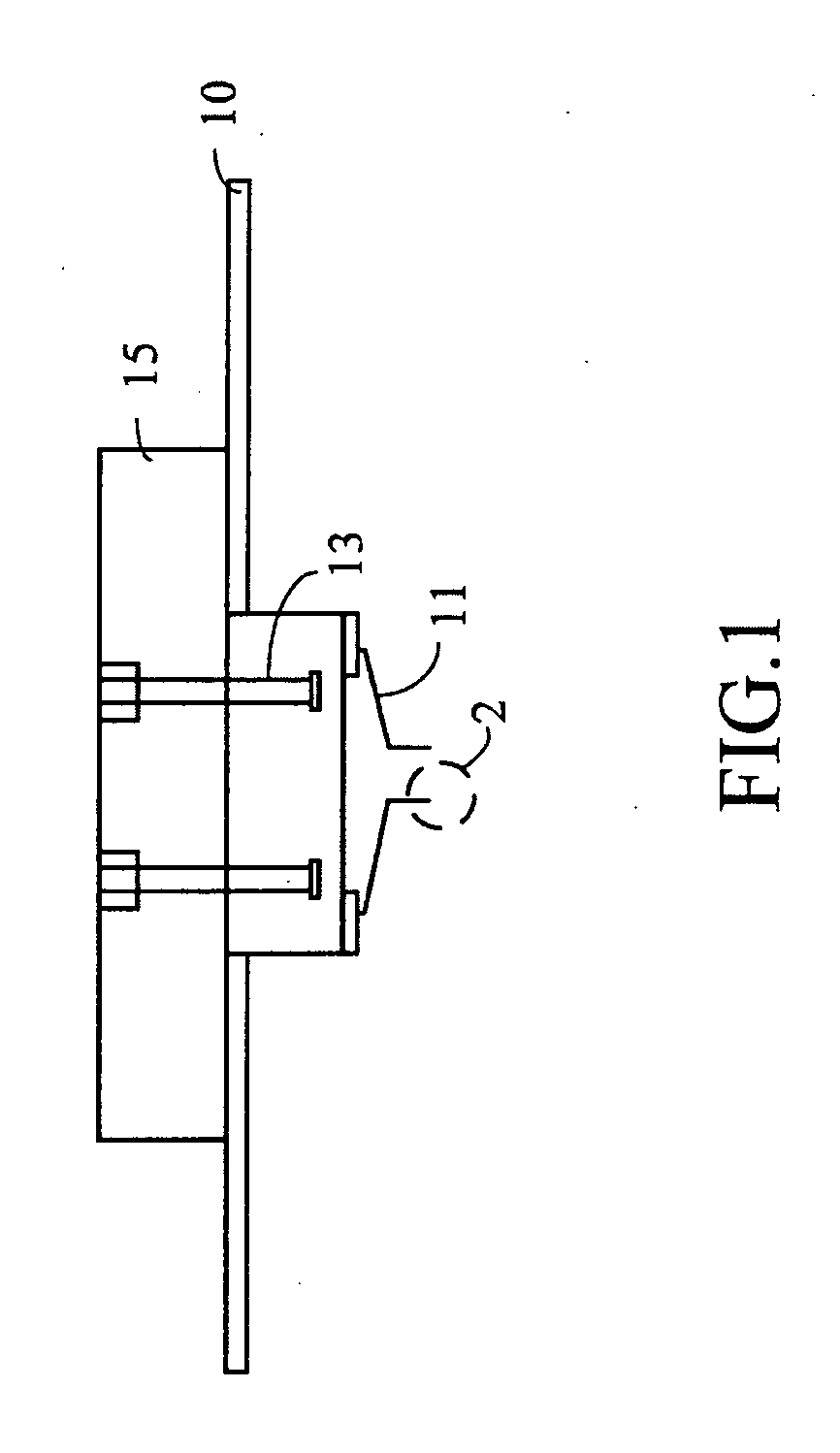

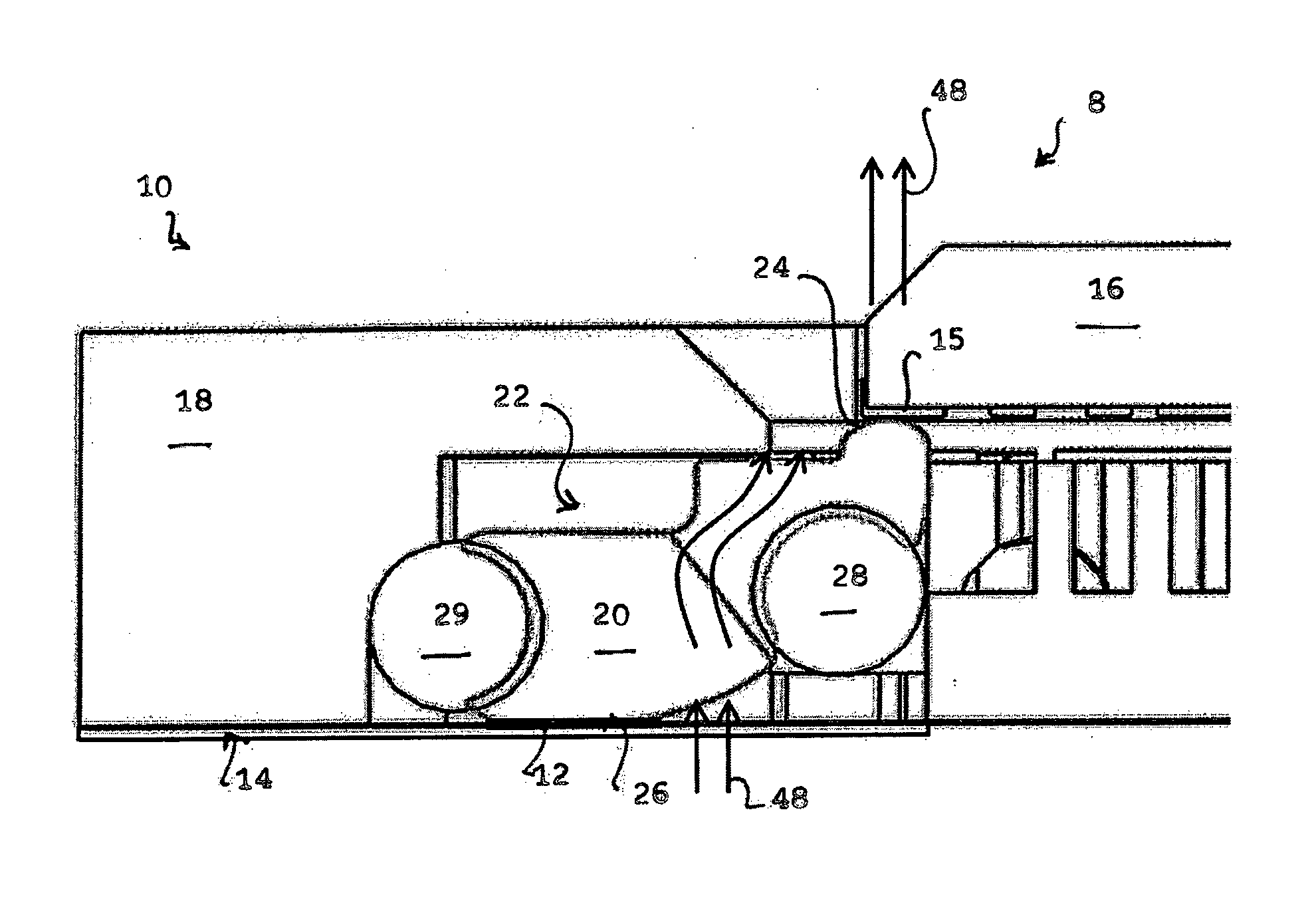

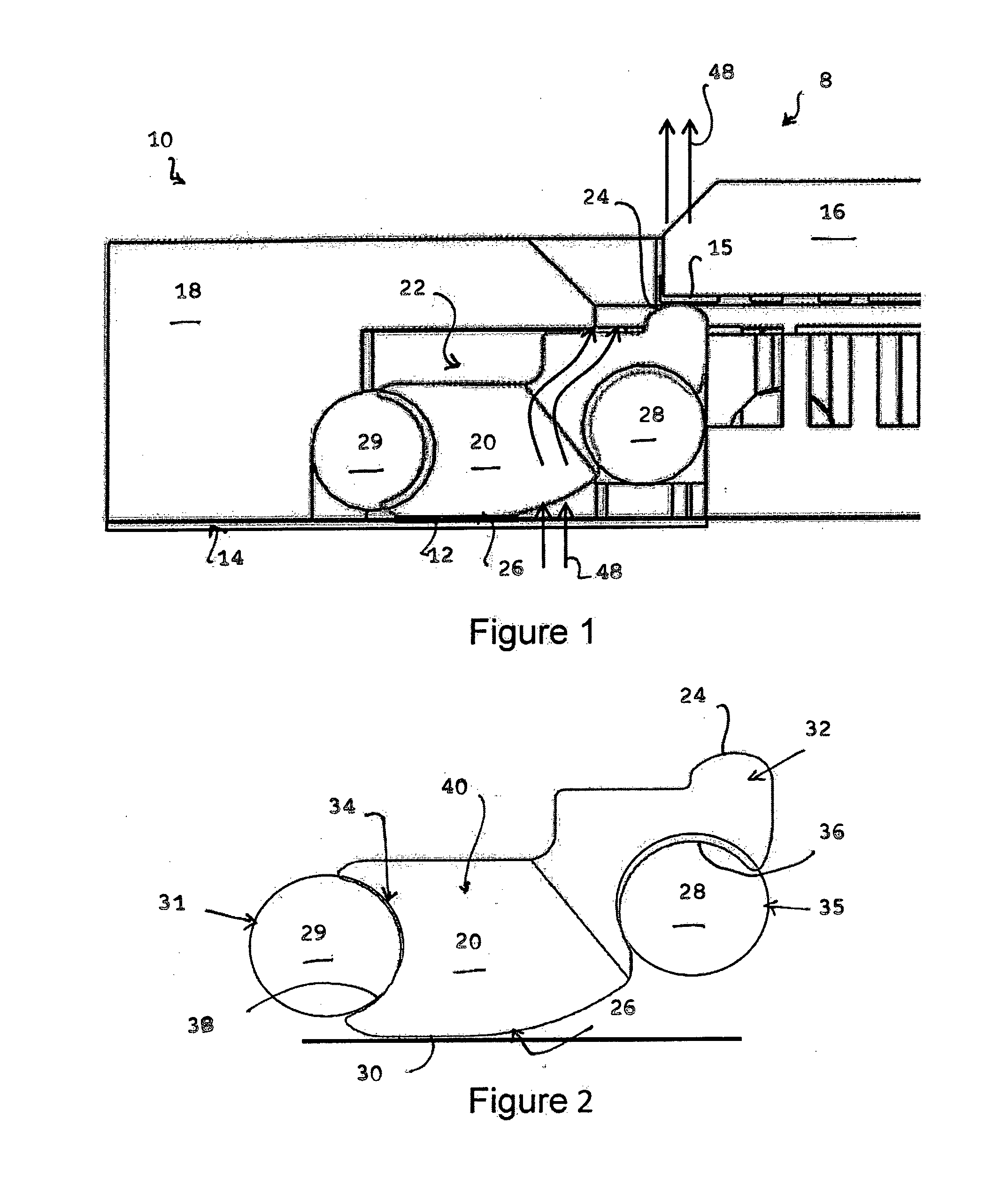

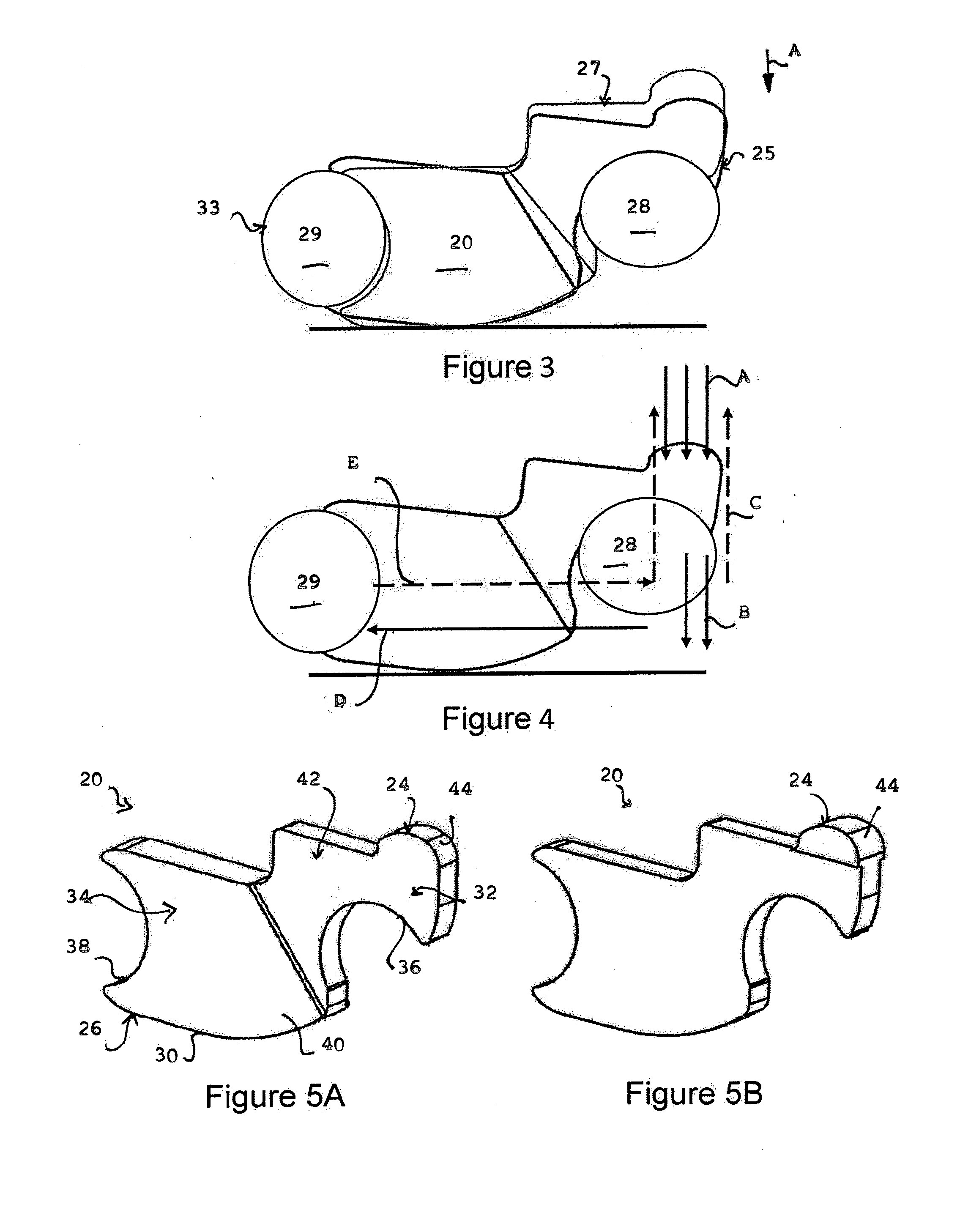

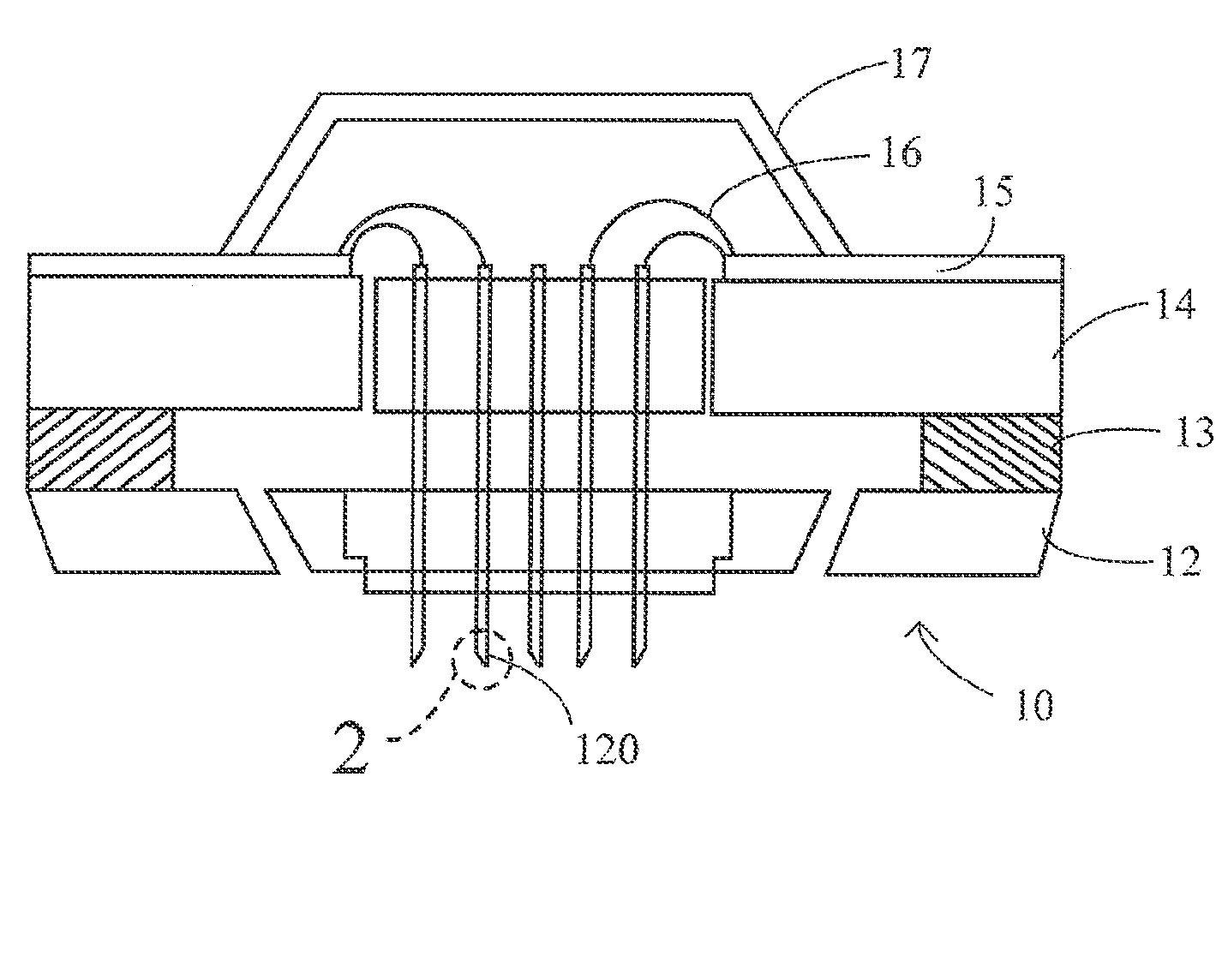

Electronic device test fixture

InactiveUS8441275B1Minimization requirementsImprove accuracyElectrical measurement instrument detailsPrinted circuitsElectrical junctionEngineering

An electronic device test fixture deploys a plurality of contact elements in a dielectric housing. The plumb arrangement of contact elements each include an armature or transversal configured to first depress and then slide laterally when urged downward by the external contacts of a device under test. The rotary movement of the transversal is optimized via the configuration of a surrounding forked regulator such that surface oxide deposition on the external device under test terminal is disrupted to reliably minimize contact resistance without damaging or unduly stressing the electrical junction of the device under test.

Owner:TAPT INTERCONNECT

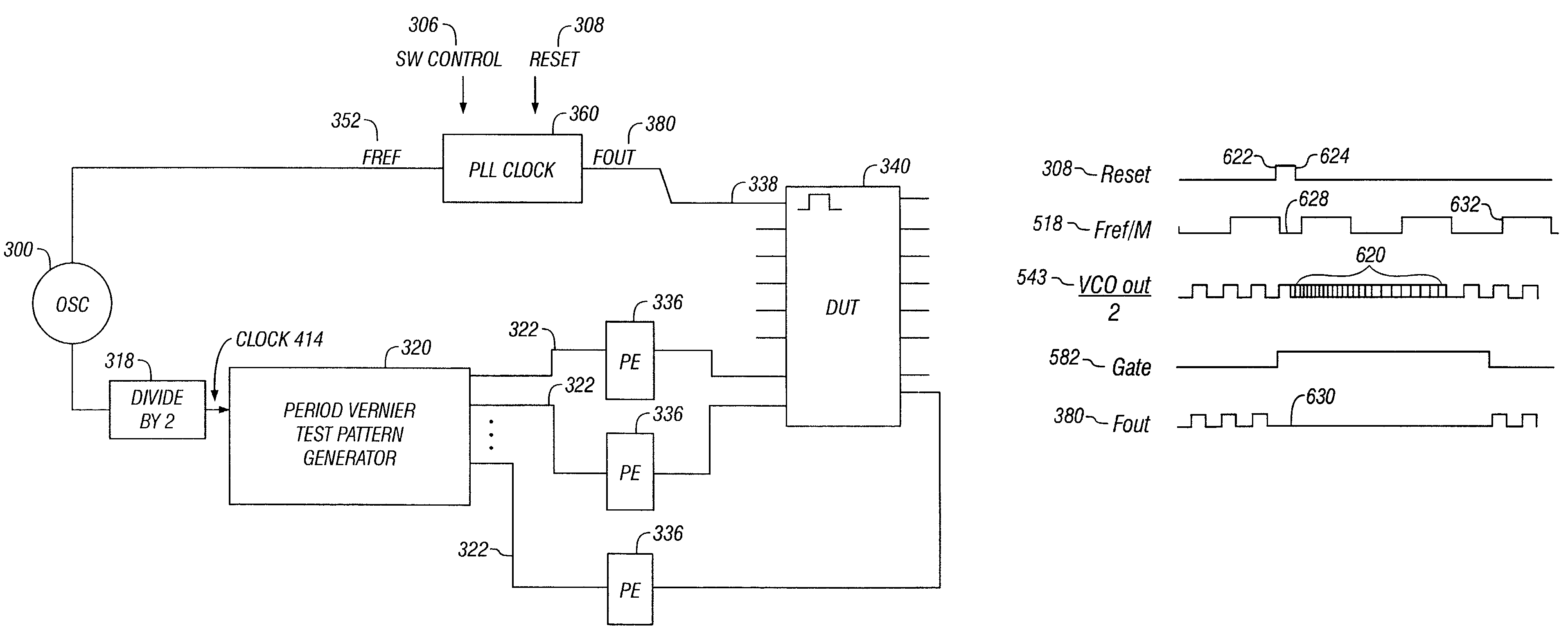

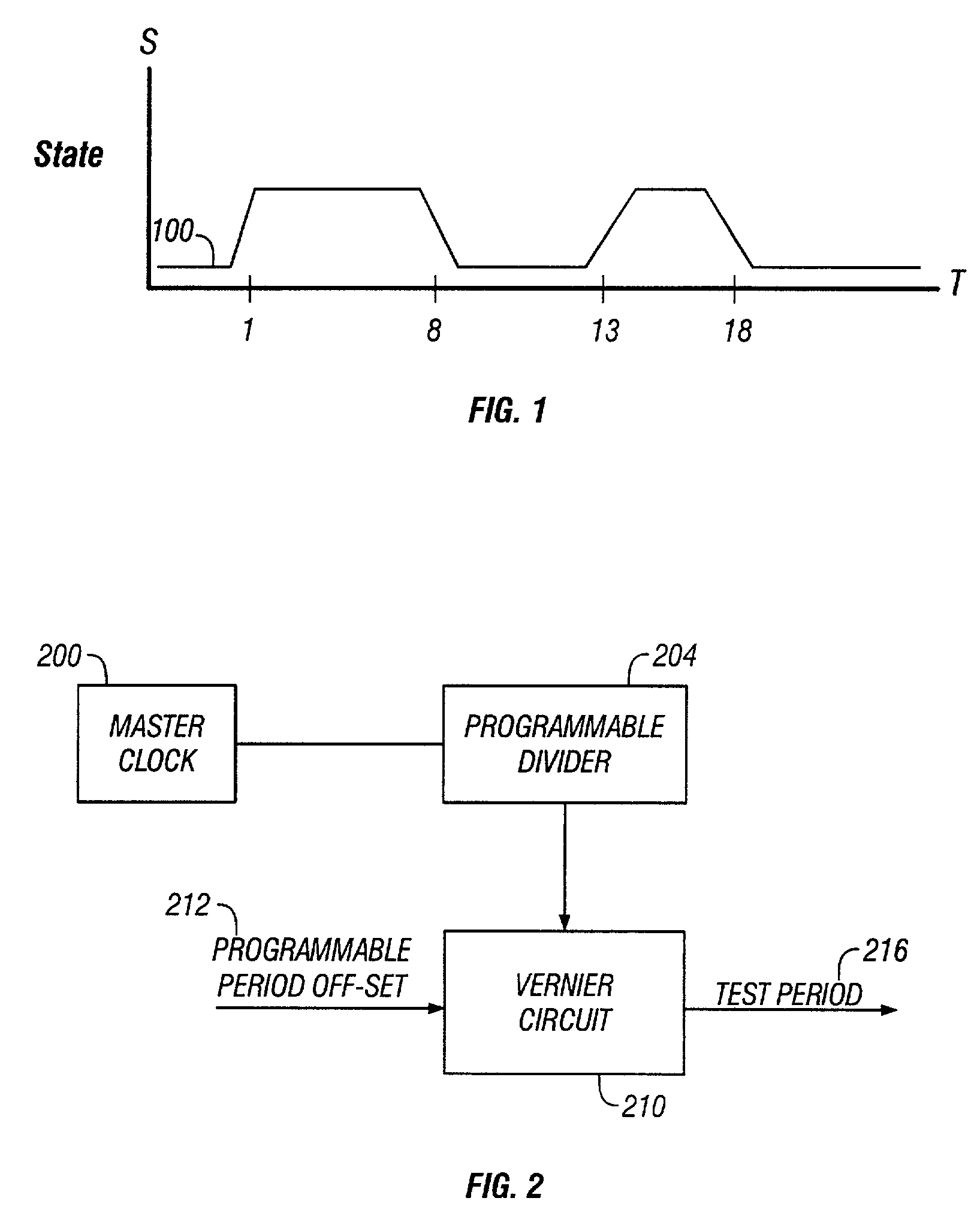

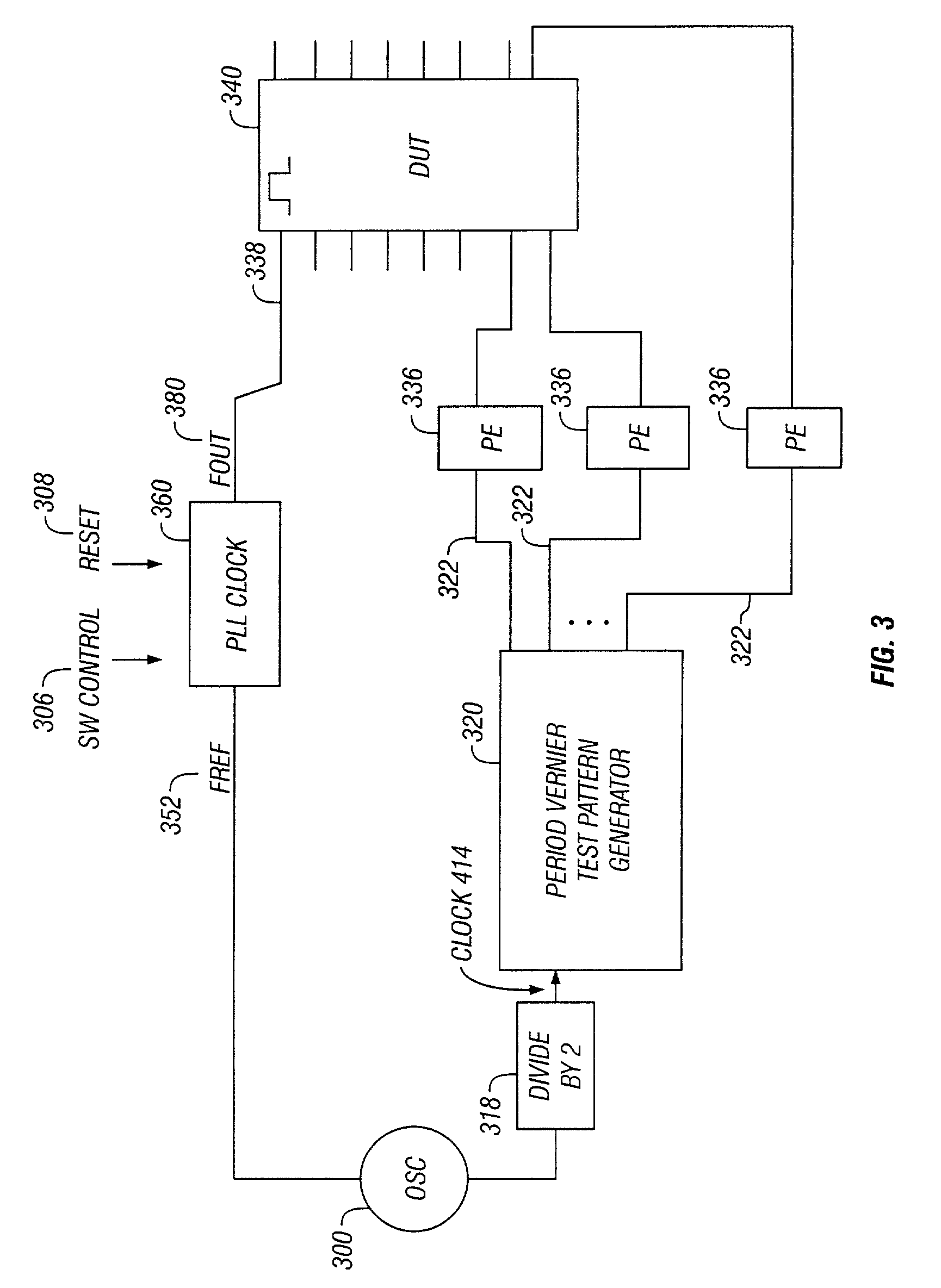

Low-jitter clock for test system

InactiveUS7093177B2Easy to moveOptimize timingDigital circuit testingError detection/correctionLow jitterEngineering

Generating test signals for a device under test (DUT) involves generating a master reference signal, using a vernier technique to generate test pattern signals based on the master reference signal, generating a test clock signal that is phase-matched with and frequency similar to the test pattern signals by providing the master reference signal as input to a phase-locked loop (PLL) and controlling one or more programmable dividers in the PLL to adjust the test clock signal to be a multiple or sub-multiple of a frequency of the test pattern signals, applying the test clock signal to the clock input pin of the DUT, and applying the test pattern signals to data pins of the DUT. When the frequency of the test pattern signals is changed, the test clock signal frequency may be adjusted to calibrate to the changed frequency of the test pattern signals by re-programming the programmable dividers.

Owner:SCHLUMBERGER TECH CORP

Probe of cantilever probe card

InactiveUS20090212807A1Reduce cleaning frequencyExtended run timeElectrical measurement instrument detailsElectrical testingEpoxyProbe card

A probe of a cantilever probe card (Epoxy probe card) is disclosed. The probe has a tip and a surface region extended from the tip of the probe about 5-10 mil is coated with a nano-film of high electro-conductive nanomaterial. The thickness of the nano-film is about 1-20 nm. Through the coating process, the nano-film coated on the probe of the cantilever probe card can efficiently provide the excellent advantages of no-clean, stable electro-conductivity, minimum overdrive force and longer usage lifetime for the probe of cantilever probe card. Accordingly, the yield of wafer testing can be improved and the frequency of cleaning the probe can be decreased. Furthermore, the total testing cost can be reduced.

Owner:IPWORKS TECH CORP

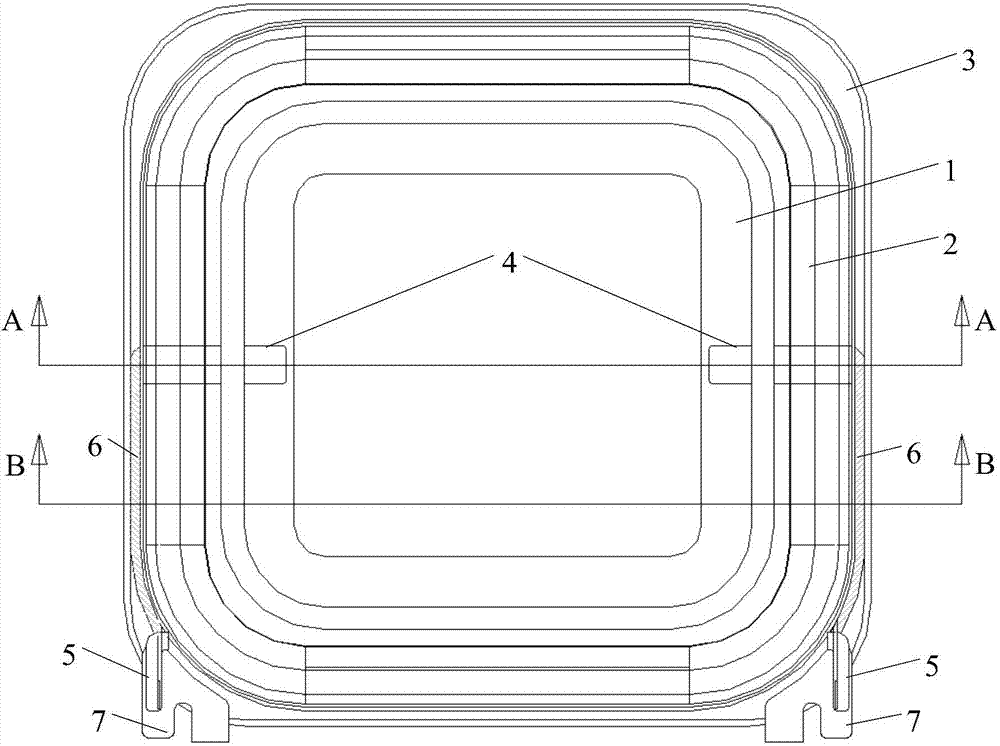

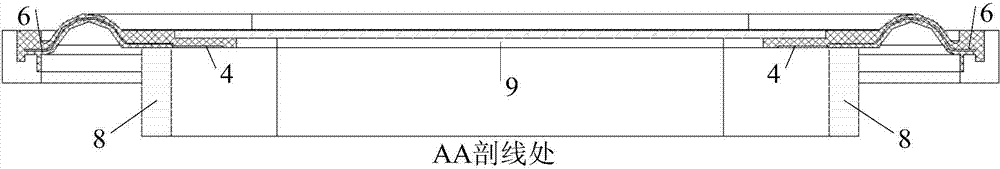

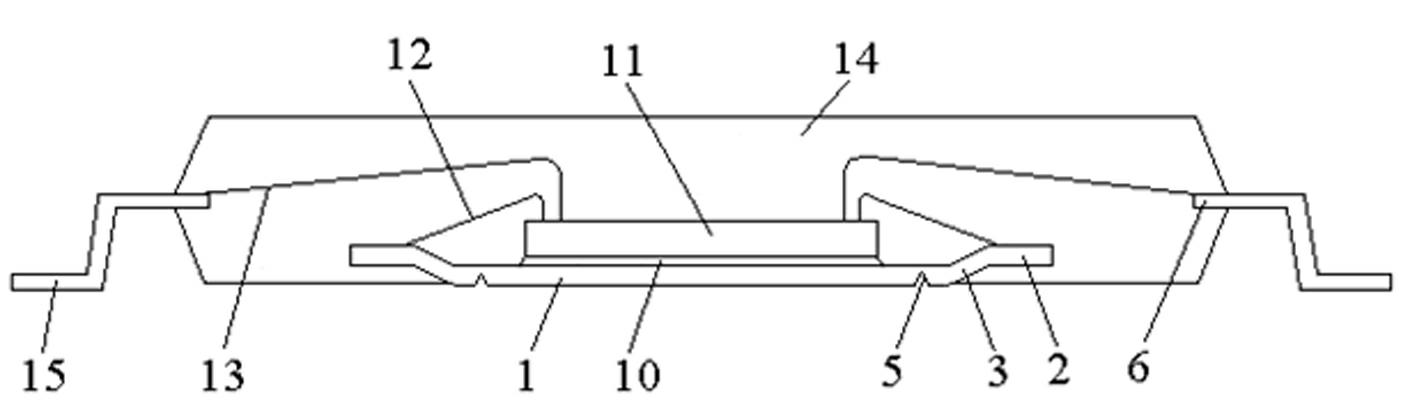

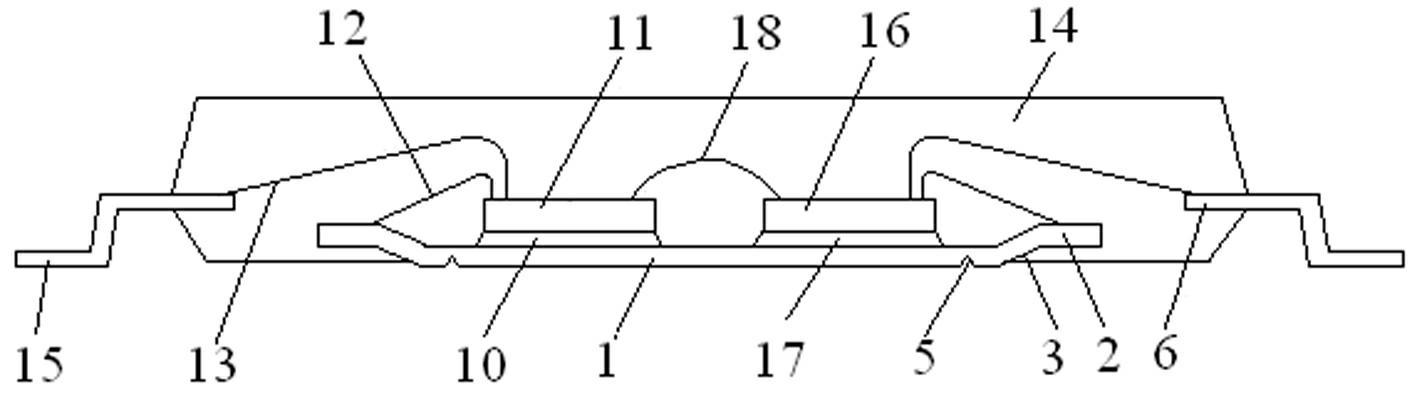

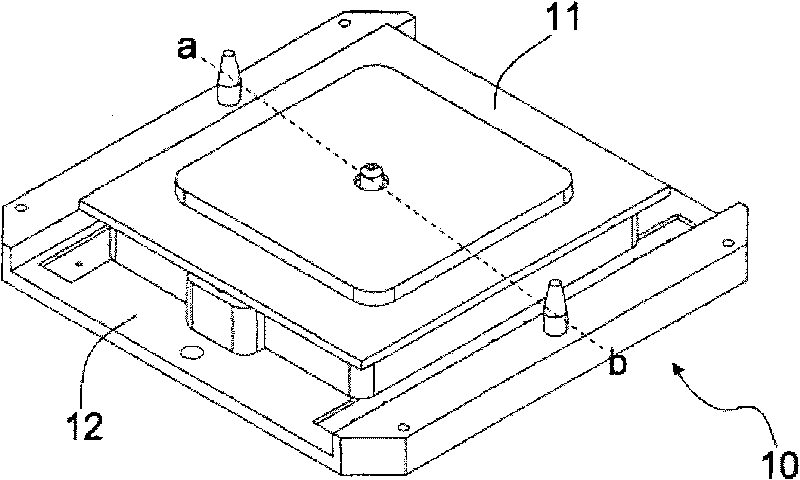

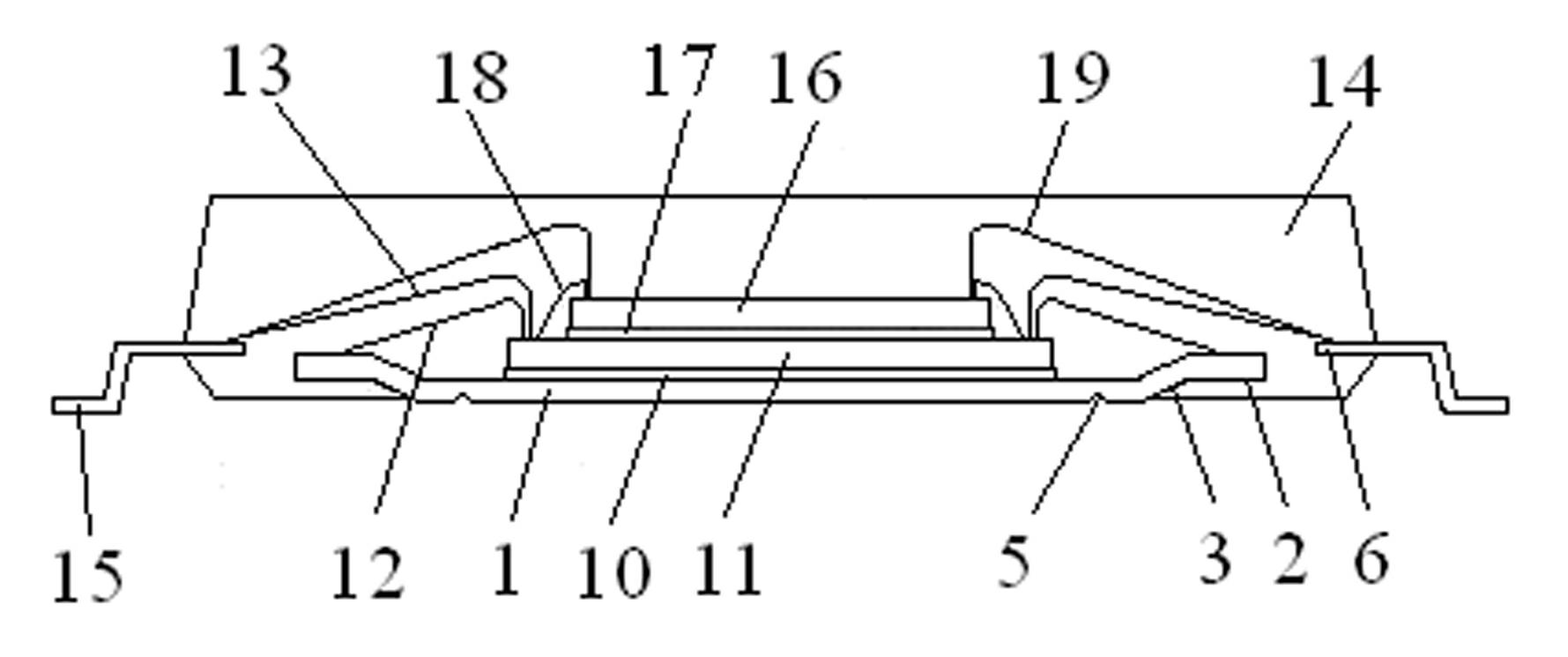

Silicone vibrating diaphragm, receiver module and method for processing silicone vibrating diaphragm

InactiveCN104853304AAchieve connectionTroubleshoot hearing problemsEarpiece/earphone attachmentsPlane diaphragmsSilica gelInjection moulding

The invention discloses a silicone vibrating diaphragm, a receiver module and a method for processing the silicone vibrating diaphragm. Two blocks of sheet metal are integrally formed on the silicone vibrating diaphragm through injection molding, the two blocks of sheet metal are embedded in the silicone vibrating diaphragm symmetrically, and both ends of each sheet metal are provided with a first welding part and a second welding part; each first welding part is embedded in a plane part, close to a folded ring part, of the silicone vibrating diaphragm, and is used for welding a coiling tap of a voice coil on the inner side of the voice coil; each second welding part extends out of or is embedded in a fixing part of the silicone vibrating diaphragm, and is used for welding a welding pad on an outer shell; and a connecting part connecting each first welding part and the corresponding second welding part is embedded in the silicone vibrating diaphragm to form a conductive path. By adopting the technical scheme of replacing lead wires of the voice coils with the two blocks of sheet metal of the silicone vibrating diaphragm, the problem of poor listening effect caused by collision of lead wires of the voice coils can be solved thoroughly, a wire-break risk of the lead wires of the voice coils can be avoided through the sheet metal embedded in the silicone vibrating diaphragm, and the product stability is improved.

Owner:GOERTEK INC

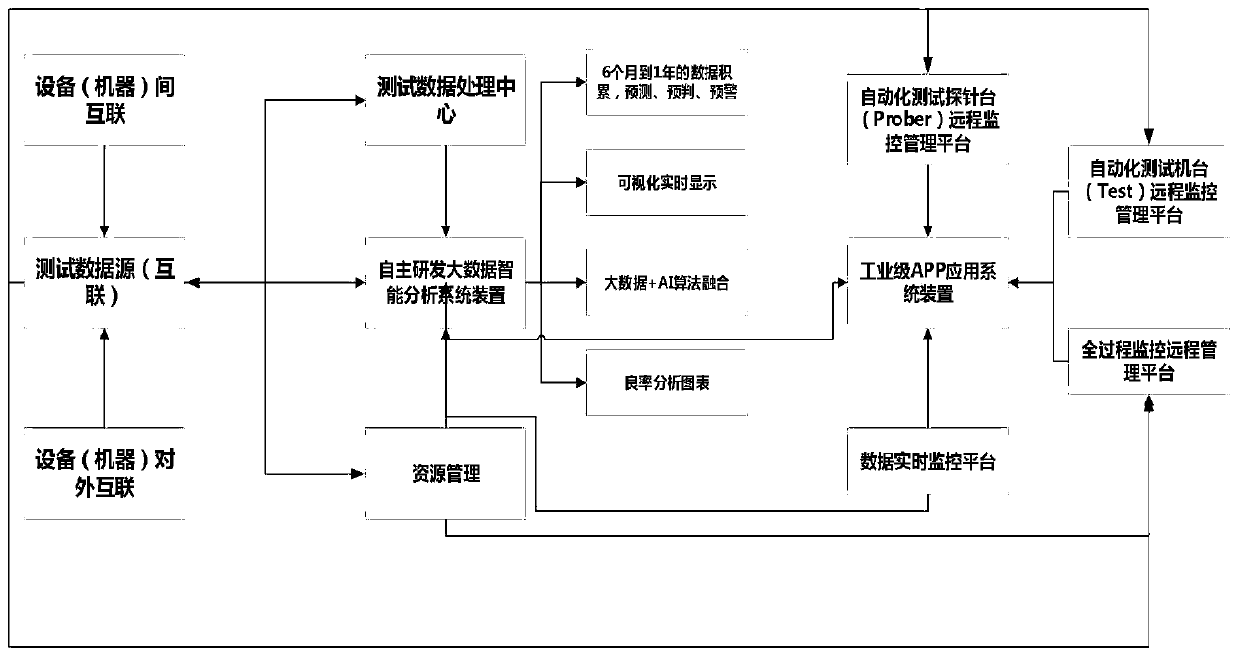

An integrated circuit test informatization management system based on the industrial Internet

ActiveCN109726234ARich and fast online servicesImprove test efficiencyDatabase management systemsDatabase distribution/replicationInformatizationResource Management System

The invention discloses an integrated circuit test informatization management system based on industrial Internet, which comprises an equipment interconnection and data source fusion module subsystem,a resource management system subsystem, a big data intelligent analysis subsystem and a similar unmanned workshop industrial-grade APP application system. According to the integrated circuit test information management system based on the industrial Internet, rich and rapid online services can be provided, the test efficiency can be improved, the test capacity can be improved, and all states (including a test prober, a test machine, test data and information charting) of a cleanliness workshop can be integrated on the information system in real time.

Owner:SINO IC TECH

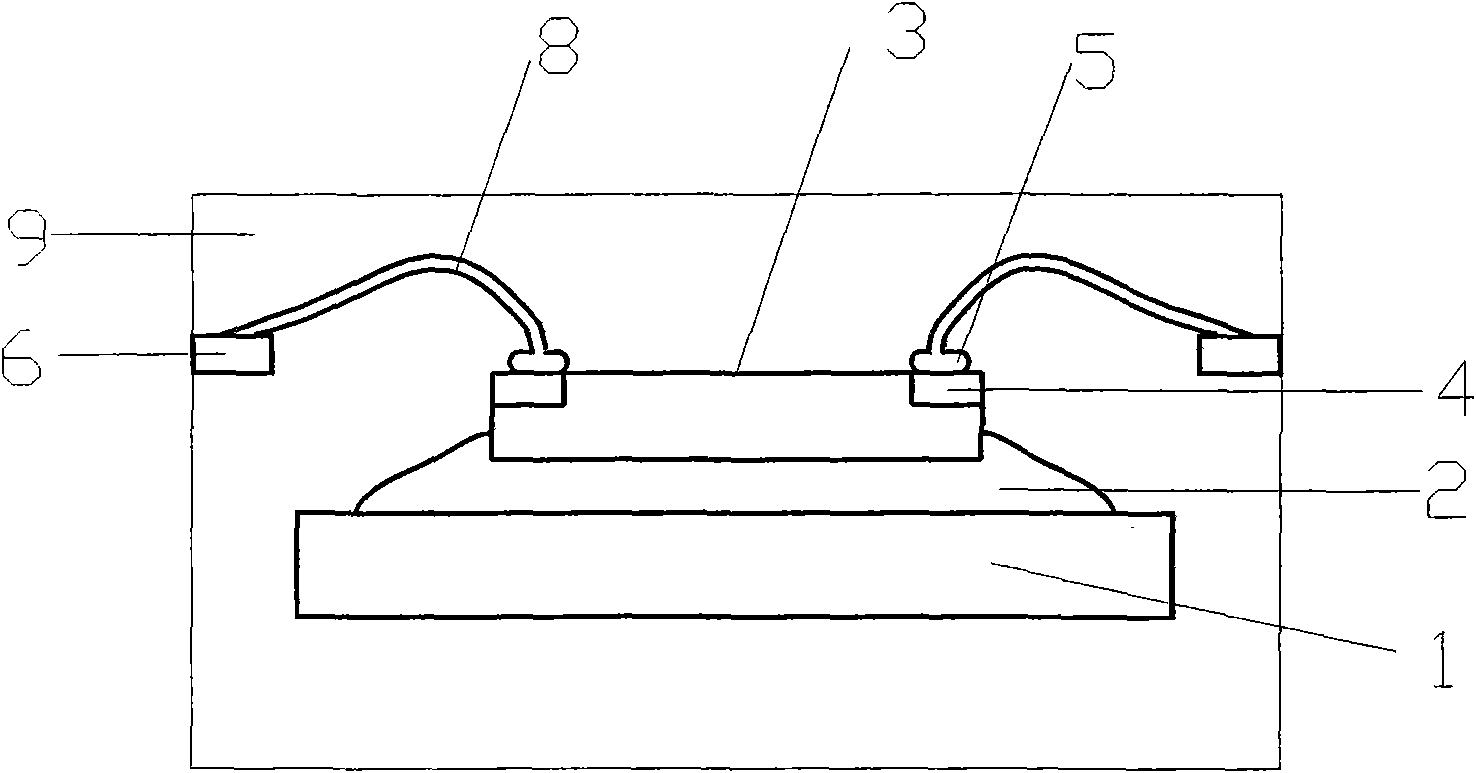

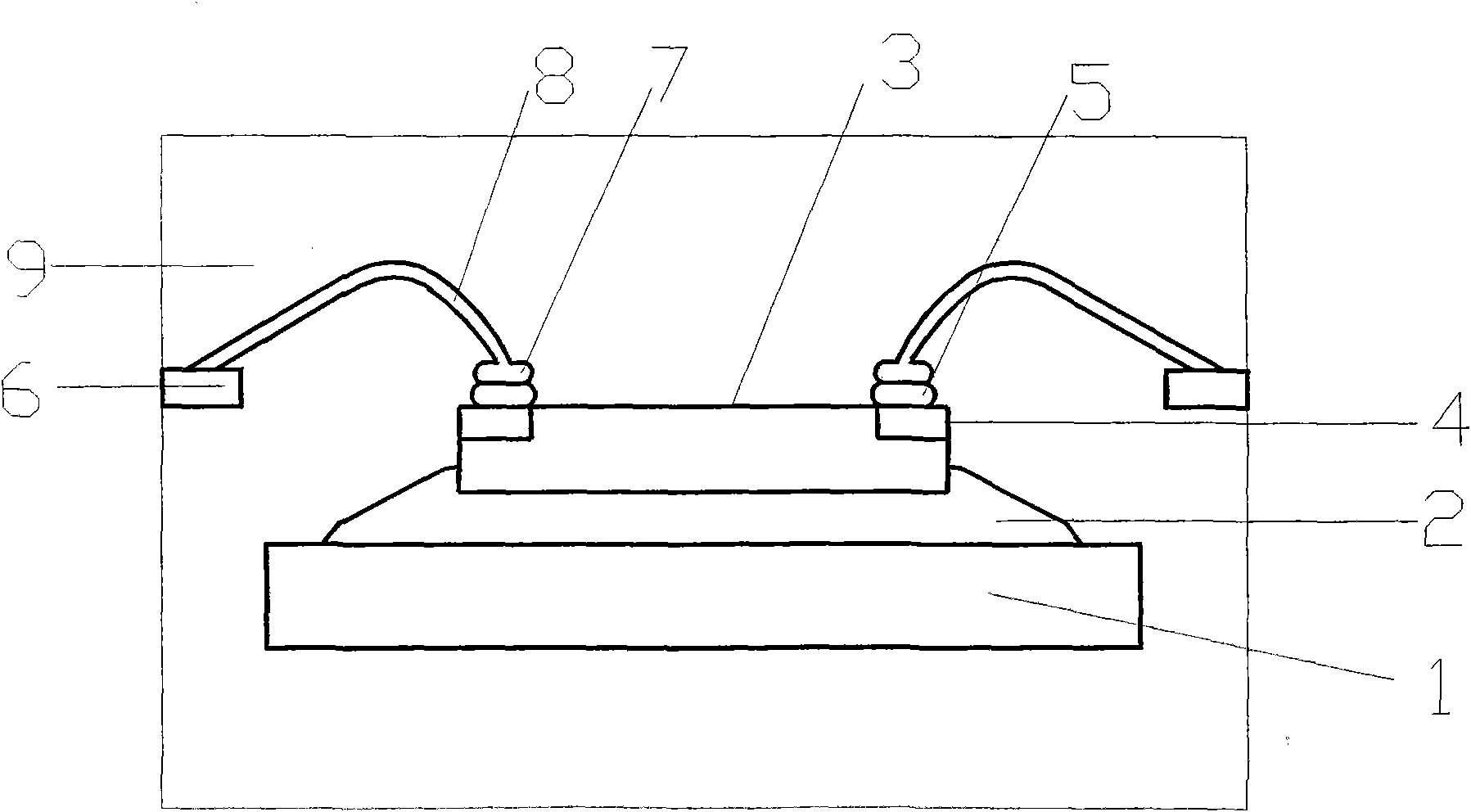

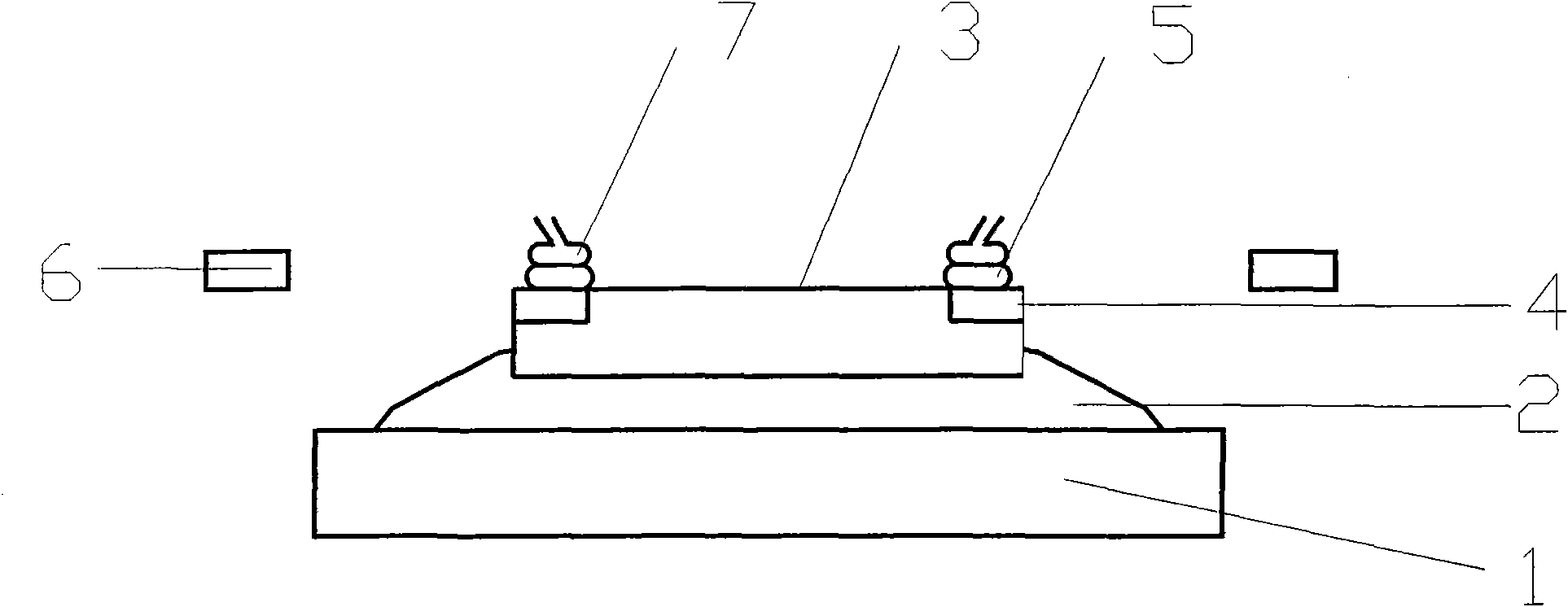

Production method of encapsulated component of copper wire bonding IC chip

InactiveCN101626008ASolving the crater puzzleSaving wire costSemiconductor/solid-state device detailsSolid-state devicesGold ballPlastic packaging

The invention relates to a production method of an encapsulated component of a copper wire bonding IC chip. A welding plate of the IC chip is provided with a golden ball on which copper bonding balls are stacked, an arch wire is provided with a copper welding point on an inner pin of a lead frame, and a welding plate of the IC chip is connected with the pin of the lead frame. A plastic packaging body is covered on the IC chip, the copper balls stacked on the packed golden ball, the copper welding point of the arch wire on the inner pin of the lead frame and partial inner pins of the lead frame to form a whole circuit. The production method comprises wafer grinding, wafer scribing, core installing, press welding, plastic package, post curing, printing, punching separation, inspection, packaging and warehousing. The invention has simple and reasonable structure, easy use and high qualified rate in encapsulation and testing as well as high reliability, avoids craters, the intensity of the welding point is improved, the pull force of copper welding wires and the shearing strength of the welding point through the production method are greater than that in a copper (golden) bonding production method through direct wire threading, and unsoldering can not happen to the inner welding point.

Owner:TIANSHUI HUATIAN TECH

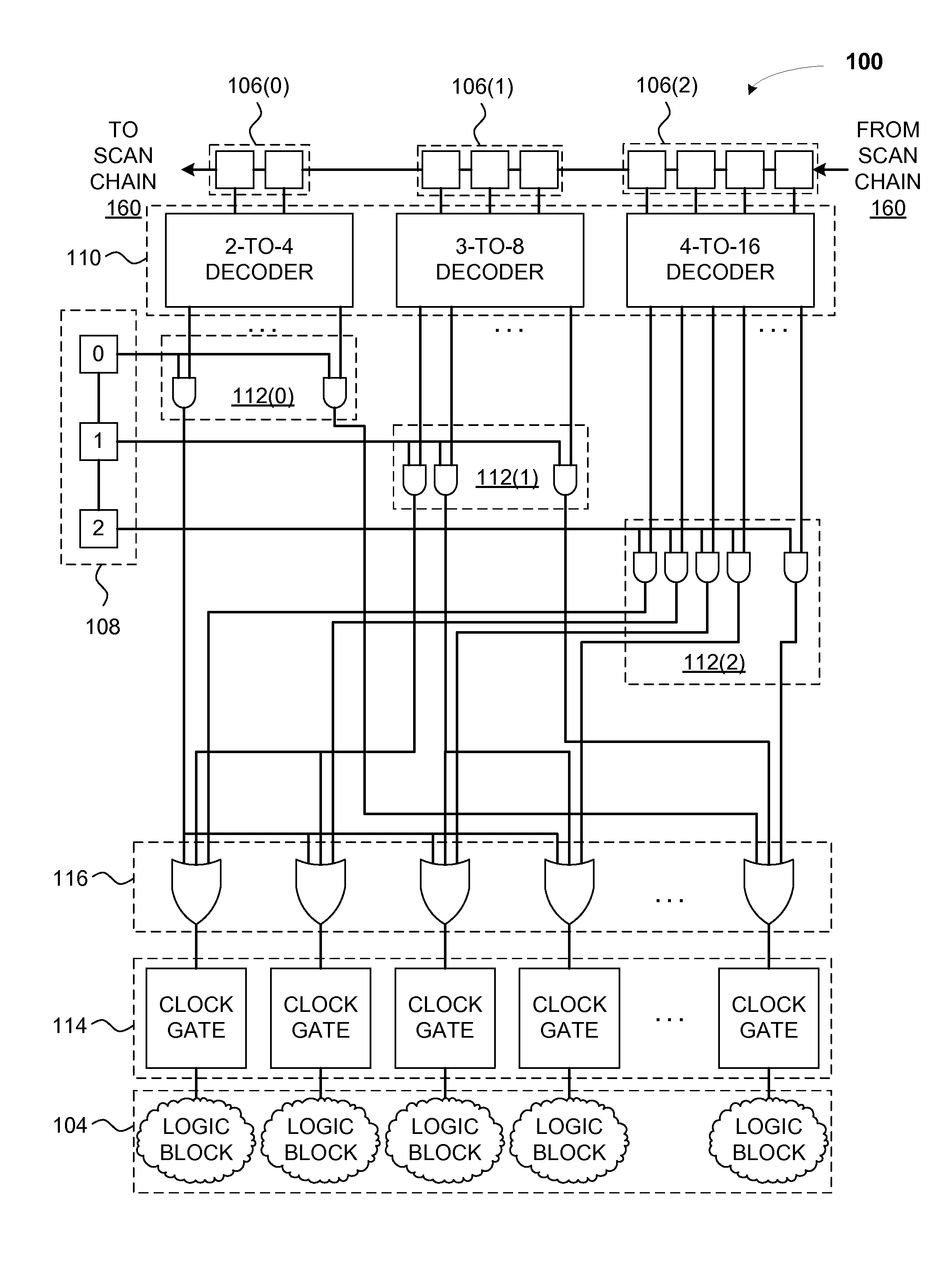

Power droop reduction via clock-gating for at-speed scan testing

InactiveUS20130271197A1Improve test yieldShort test timeElectrical testingPulse generation by logic circuitsControl powerControl system

A clock gating mechanism controls power within an integrated circuit device. One or more clock gating circuits are configured to couple a system clock to a different portion of the integrated circuit device. A logic circuit applies an enabling signal to one of the clock gating circuits to control whether the system clock passes through the clock gating circuit to a portion of the integrated circuit device associated with the clock gating circuit. A plurality of scan flip-flops is configured to provide a binary code to the logic circuit, where the binary code indicates to the logic circuit that the enabling signal should be applied to the clock gating circuit. One advantage of the disclosed technique is that power droop during at-speed testing of a device is reduced without significantly increasing the quantity of test vectors or reducing test coverage, resulting in greater test yields and lower test times.

Owner:NVIDIA CORP

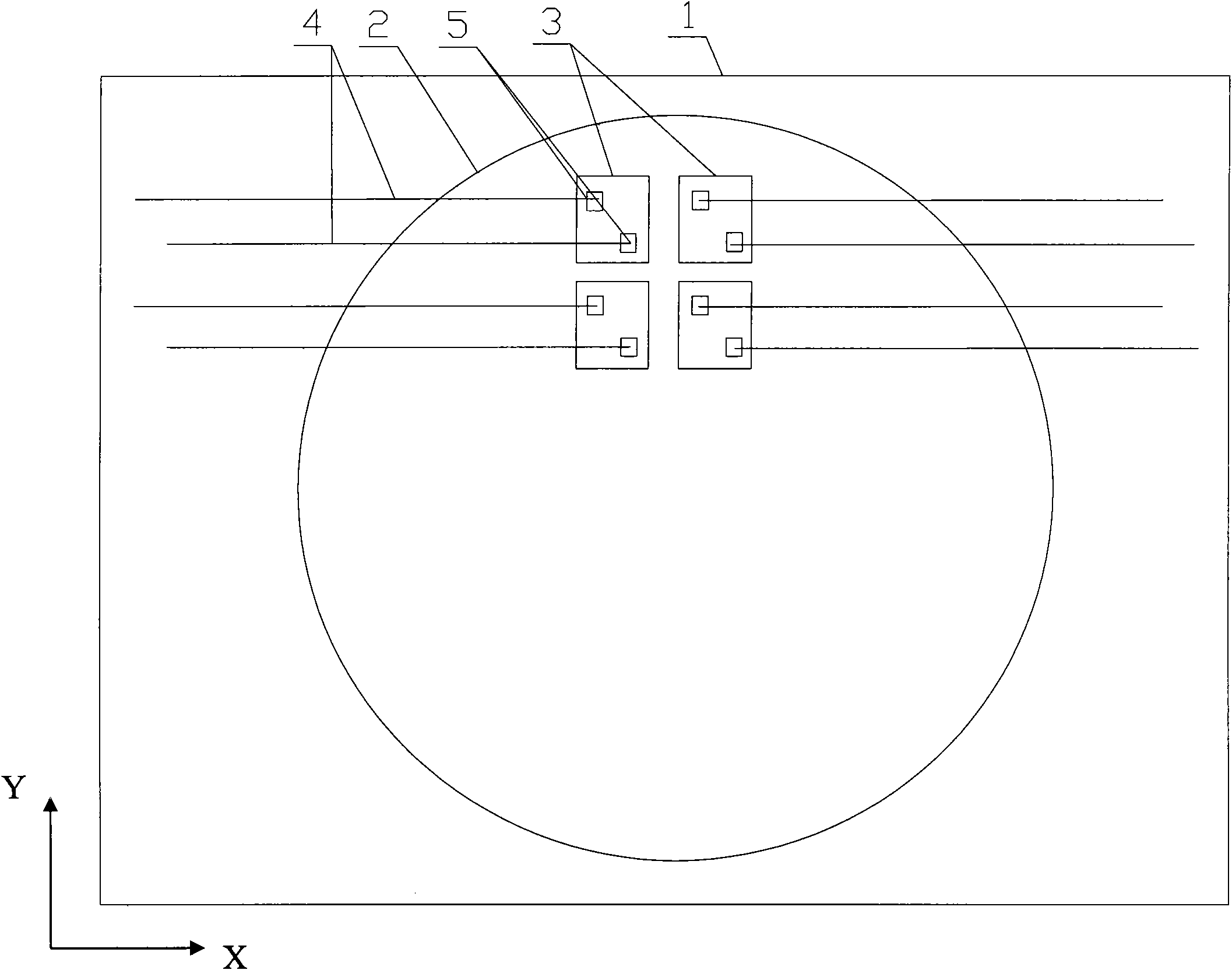

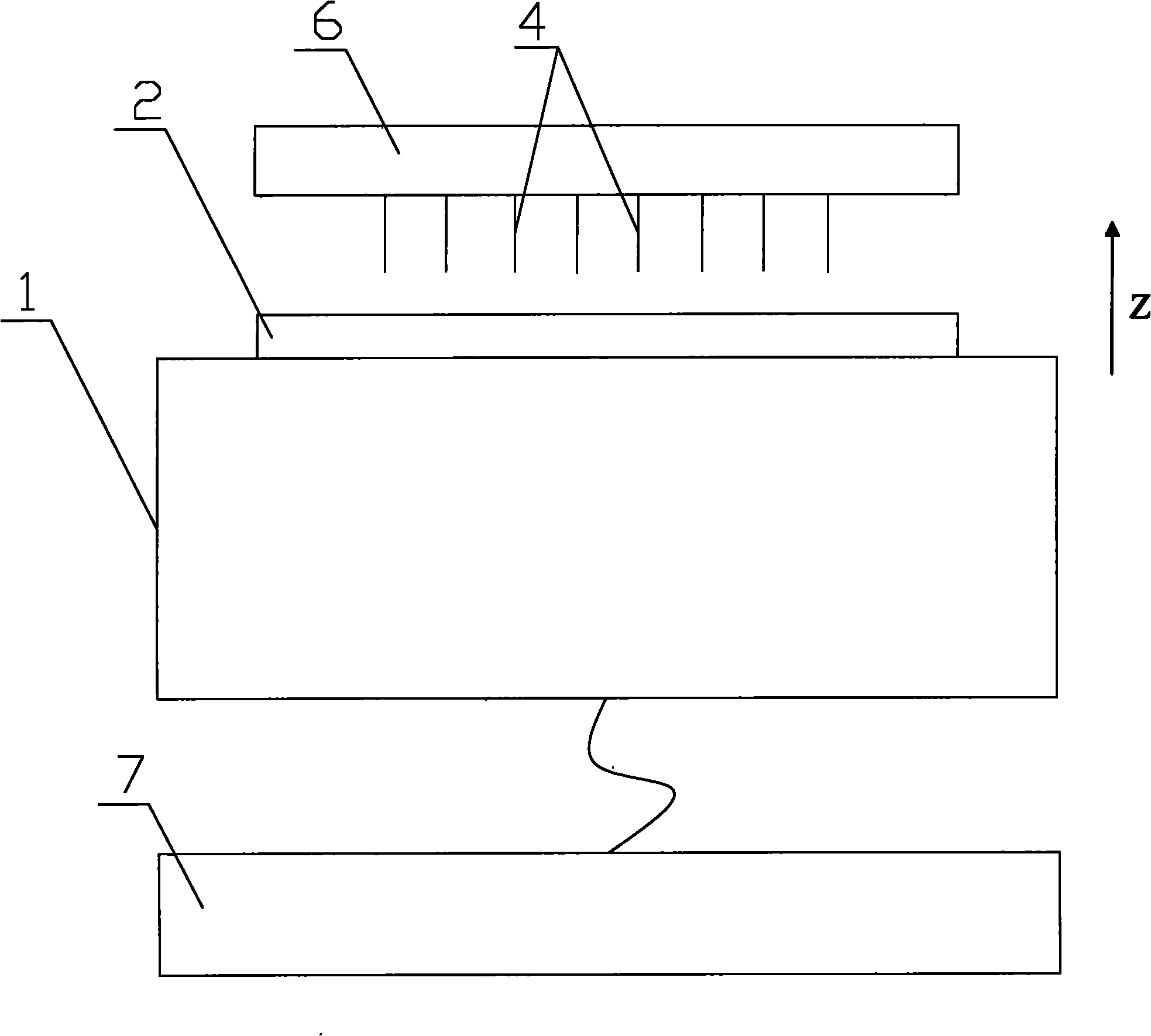

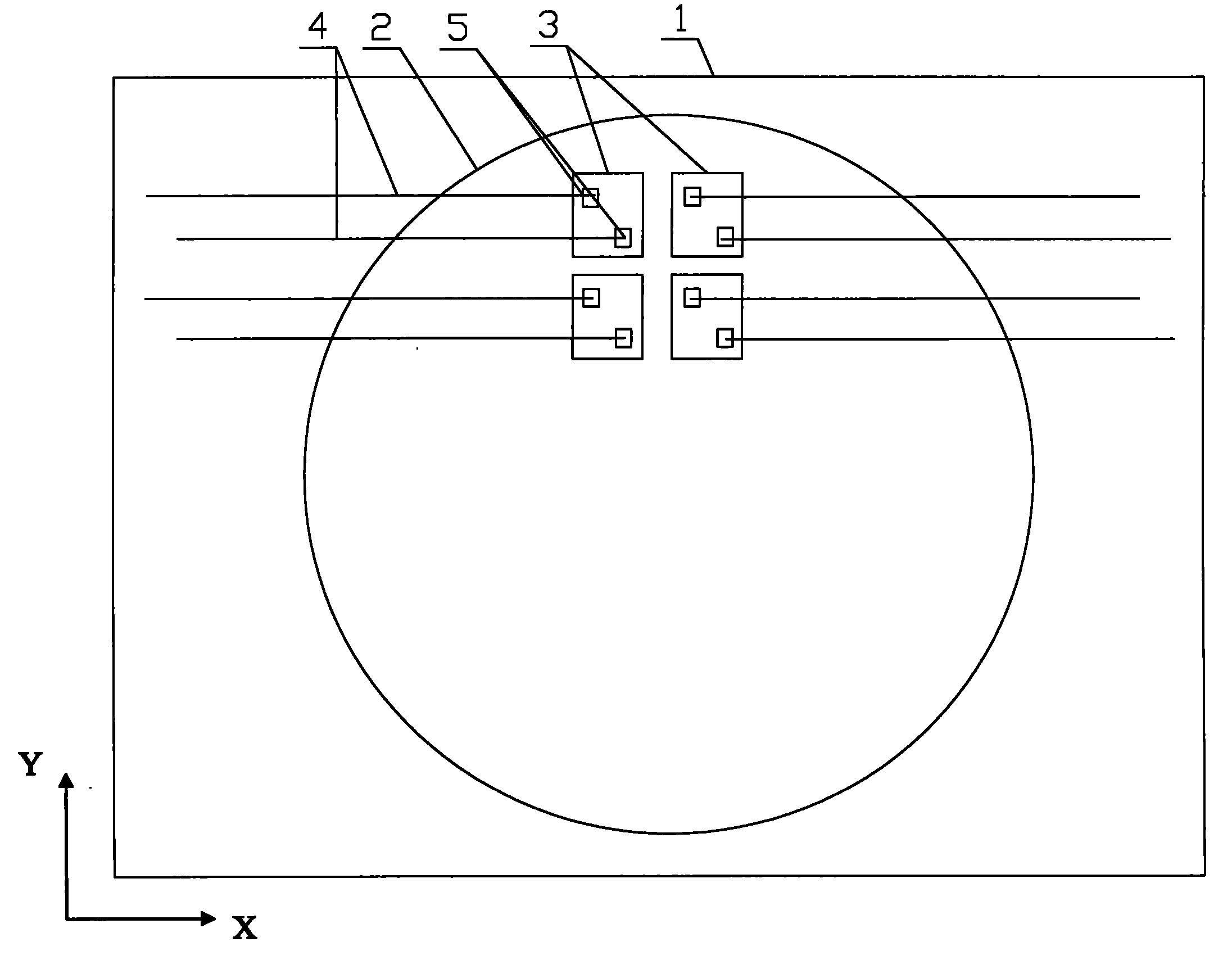

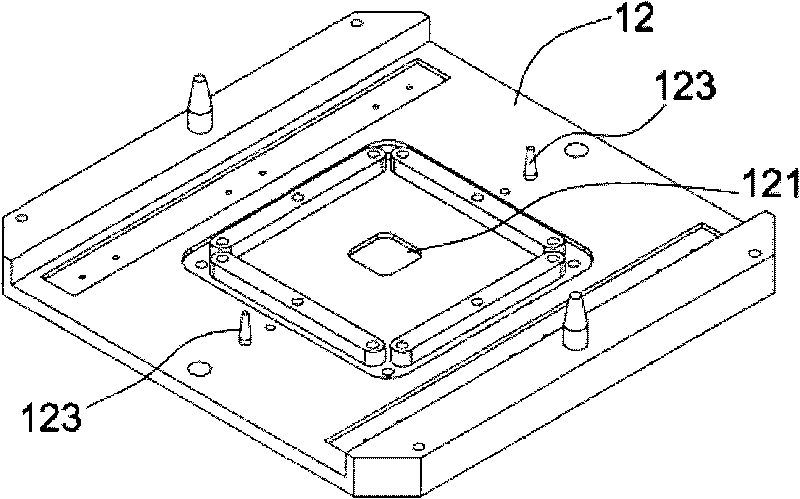

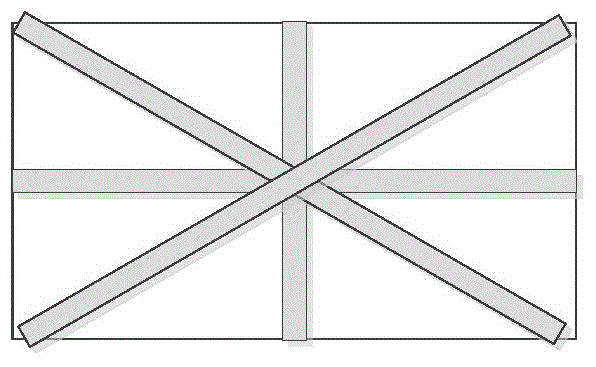

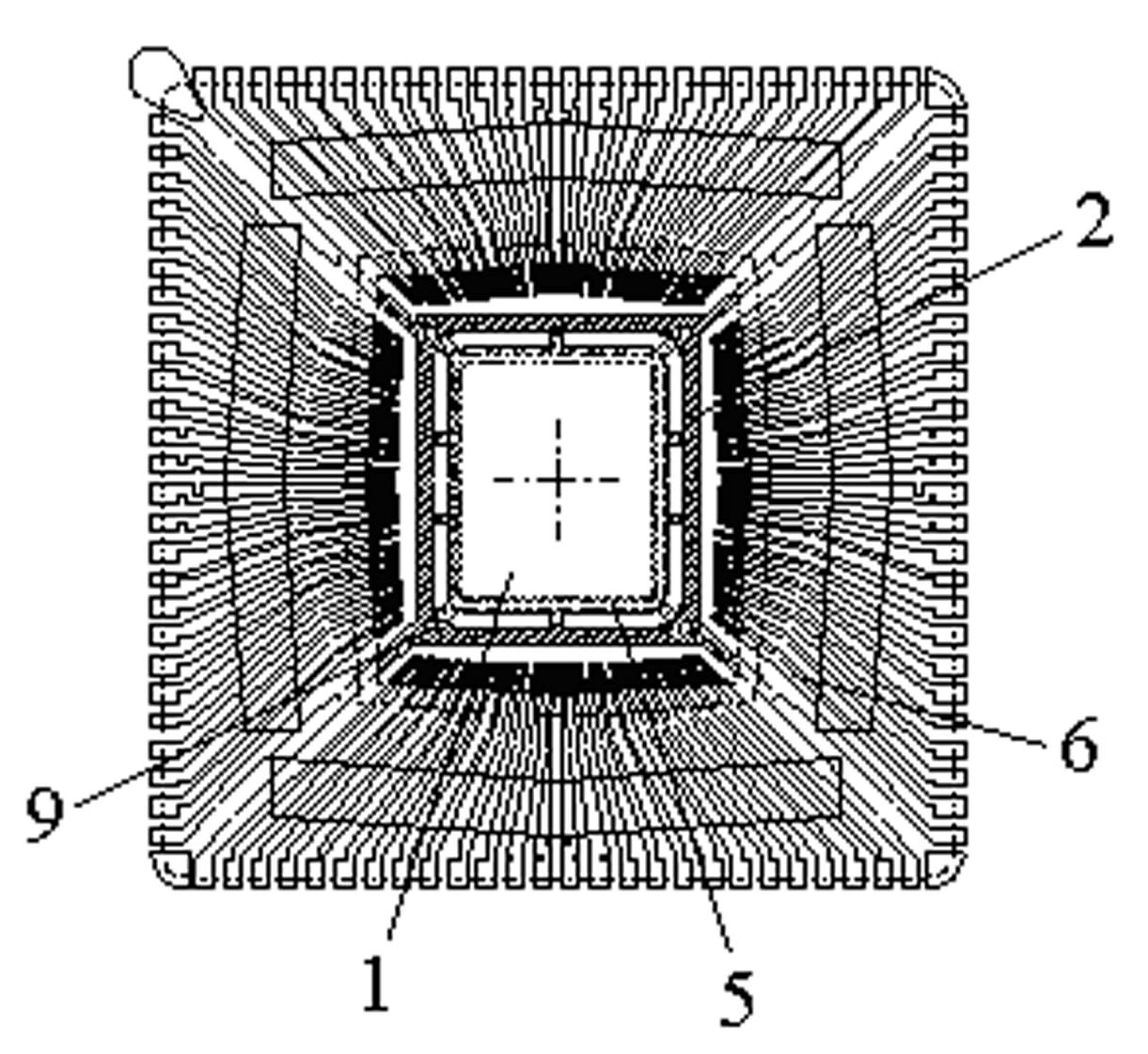

RFID high-frequency chip four-channel test device and method

InactiveCN102401873AReduce signal interferenceImprove test yieldElectric signal transmission systemsSemiconductor/solid-state device testing/measurementProbe cardEmbedded system

The invention discloses an RFID (Radio Frequency Identification Device) high-frequency chip four-channel test device and a method, wherein the device at least comprises a probe station, an upper computer and an RFID reader; the probe station comprises a moveable platform and a probe card; the movable platform bears a wafer to be tested and is used for providing directional movement in the directions of X-axis, Y-axis and Z-axis; a plurality of RFID high-frequency chips to be tested are regularly distributed on the wafer; a probe on the probe card is contacted with the chips during the test; the upper computer is connected with the probe station and controls the movement of the movable platform; the probe card is provided with eight probes; every two probes are in one group and are arranged in parallel; each chip to be tested corresponds to one group of probes; the upper computer is connected with the RFID reader and controls the RFID reader to send a test signal; and the signal is returned according to the chip to be tested so as to judge the test result and store the test result in a database. Due to the RFID high-frequency chip four-channel test device and the method, the test yield and test speed of products are improved, and the test cost is saved.

Owner:JIANGSU KILOWAY ELECTRONICS

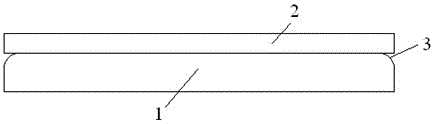

A novel wafer thinning method

ActiveCN105702563AQuality improvementImprove test yieldSemiconductor/solid-state device manufacturingWafer thinningUV coating

According to a novel wafer thinning method, polytetrafluoroethylene is added into a polyimide solution which is to be rolled and stirred uniformly to form coating liquid; the coating liquid is coated on the front surface of an original wafer to cover the surface of the original wafer and chamfers between the front surface of the original wafer and edges to form a cover layer; otherwise, a polytetrafluoroethylene coating or a UV coating is made to cover the front surface of the original wafer and subjected to low-temperature baking to enable a cover layer to form on the surface of the original wafer and the chamfers between the front surface of the original wafer and edges to form a cover layer; coarse grinding and fine grinding are carried out on the original wafer according to present technology; illumination is carried out to enable cracking of the cover layer; and plasma cleaning is carried out to remove the cracked cover layer so as to obtain the thinned wafer. The thinning method can prevent secondary pollution to the surface of the wafer in a thinning process; the wafer thinning quality and the test yield rate can be raised; cleaning by a lot of water is not needed; a lot of water resources are saved; and a good basis is provided for subsequent pressure welding technology.

Owner:TIANSHUI HUATIAN TECH

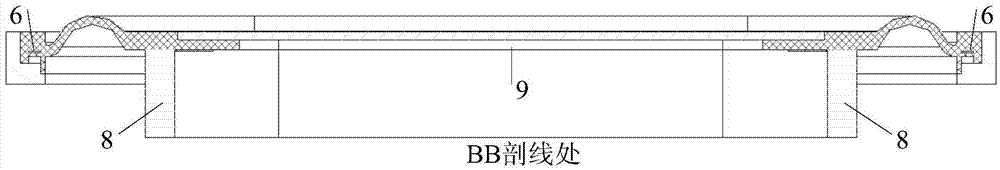

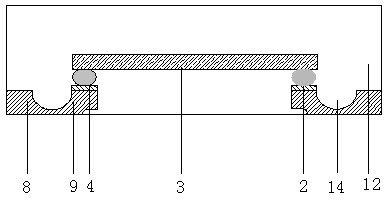

e/LQFP (low-profile quad flat package) planar packaging part with grounded ring and production method of e/LQFP planar packaging part with grounded ring

ActiveCN102522392ASimple structureImprove bindingSemiconductor/solid-state device detailsSolid-state devicesPlastic packagingEngineering

The invention discloses an e / LQFP (low-profile quad flat package) planar package with a grounded ring, which comprises a carrier and the grounded ring, wherein one to two IC (integrated circuit) chips are adhered to the carrier. The IC chips are connected with an inner pin through bonding wires, the inner pin is connected with an outer pin, the lower end face of the grounded ring is higher than the upper end face of the carrier, and the carrier is connected with the grounded ring through a ribbed plate. The end face, without the IC chips, of the carrier is provided with an anti-overflow ring, the grounded ring, the bonding wires, the ribbed plate and the inner pin are packaged in a plastic packaging part which is fixedly packaged on the carrier, the outer pin is positioned outside the plastic packaging part, the outer pin and the plastic packaging part are coplanar, and the lower end face of the carrier is positioned outside the plastic packaging part or packaged inside the plastic packaging part. The e / LQFP planar package with the grounded ring is produced by procedures of wafer thinning, scribing, coring, bonding and the like. Layering or shedding of a ground wire caused by making the ground wire on the carrier can be avoided, the carrier is free of silver coating, and packaging reliability is improved.

Owner:TIANSHUI HUATIAN TECH +1

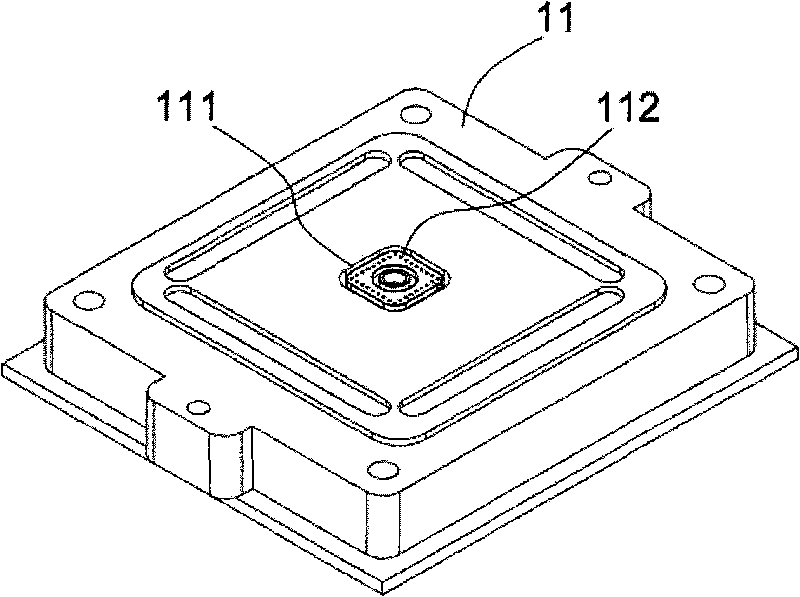

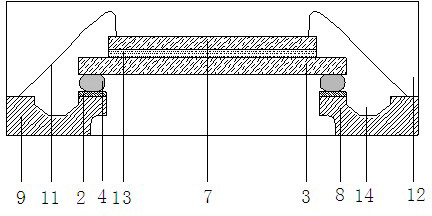

IC test device

InactiveCN101726699AAvoid pressure lossAvoid test failuresElectronic circuit testingElectrical measurement instrument detailsEngineeringIc testing

The invention relates to an IC test device which is used for testing the encapsulated IC. The IC test device mainly comprises an upper cover plate and a base which match each other. The invention is characterized in that a through hole is contained in the upper cover plate, a plurality of test probes are arranged near the through hole and used for contacting the IC, and a test spring is contained in each test probe. In addition, at least one bearing seat corresponding to the through hole in the upper cover plate is contained in the base and used for bearing the IC. At least one bearing spring is arranged between the lower part of the bearing seat and the base, the distance between the through hole and the bearing seat is smaller than the thickness of the encapsulated IC, and the coefficient of the elasticity of the bearing spring is greater than the sum of the coefficients of the elasticity of the plurality of test springs.

Owner:KING YUAN ELECTRONICS

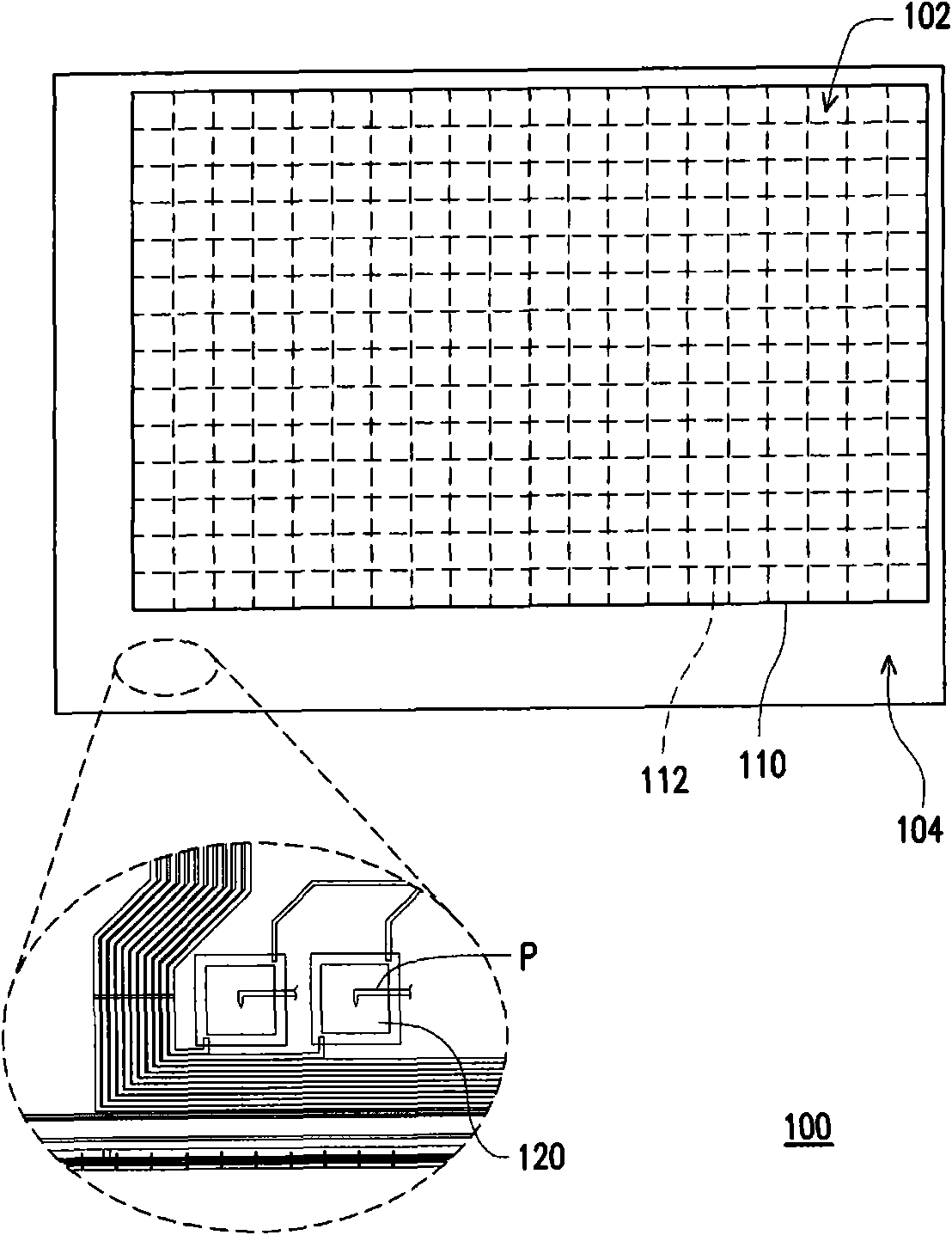

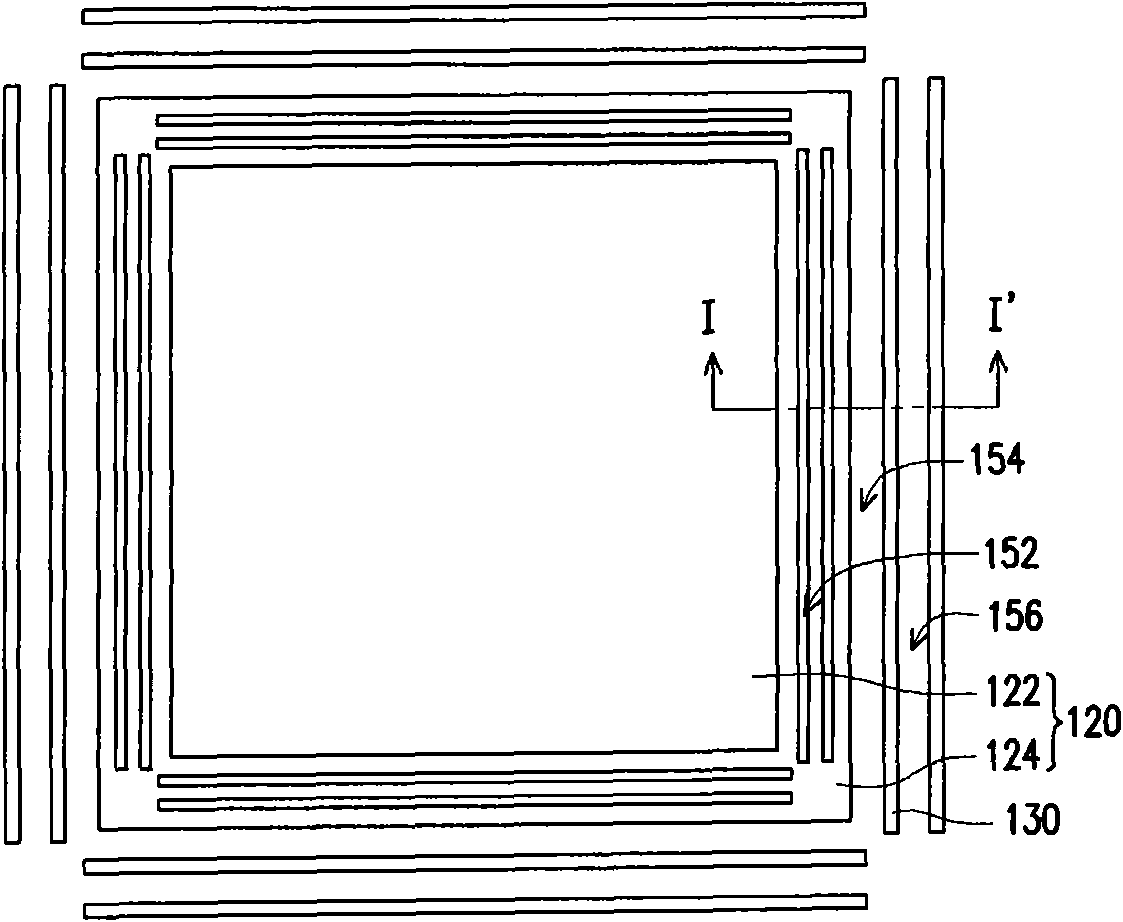

Display panel

InactiveCN102122092AStrengthen the restraint effectImprove test yield and test accuracyNon-linear opticsPixel arrayBiomedical engineering

The invention provides a display panel, comprising a substrate, a pixel array, and a test pad. The substrate is provided with a support surface, a display district, and a circumferential line district at the periphery of the display district. The pixel array is disposed on the support surface and located in the display district. The test pad is disposed on the support surface and located in the circumferential line district. The test pad is electrically connected with the pixel array. The test pad comprises a central part and a peripheral part surrounding the central part, wherein the height of the peripheral part is greater than the height of the central part, and the peripheral part is provided with a plurality of first grooves. The first grooves are exposed out of the support surface.

Owner:AU OPTRONICS CORP

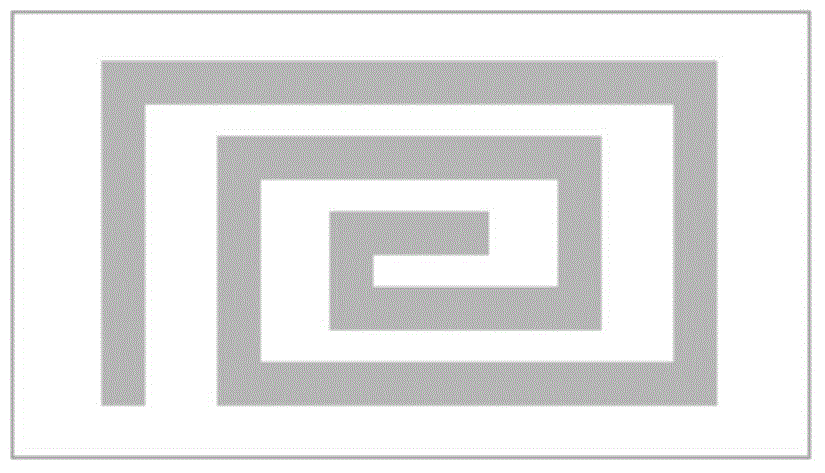

Touch panel lineation detecting and judging system and method

ActiveCN104881176AIncrease flexibilityImprove test yieldInput/output processes for data processingAlgorithmComputer module

The invention discloses a touch panel lineation detecting and judging system and method. The system comprises a touch panel lineation track collection module, a test file generation module, a pattern partitioning module, a comparison module and a judgment module, wherein the touch panel lineation track collection module is used for collecting touch coordinates in the lineation detection process; the test file generation module is used for receiving edit of an outside user and generating to-be-tested lineation patterns; the pattern partitioning module is used for decomposing strokes of the lineation patterns generated by the test file generation module and partitioning the mark areas; the comparison module is used for receiving the partitioning condition of the pattern partitioning module and performs comparison according to the partitioned mark areas; the judgment module is used for setting judgment and detection types and procedures, receiving a comparison result generated by the comparison module and performing lineation judgment according to the types and the procedures. According to the judgment system and the judgment method, the editable adjustment of the testing process is improved, and the method and the system can be applied to multi-standard and extremely complicated lineation tests.

Owner:WUHAN JINGCE ELECTRONICS GRP CO LTD

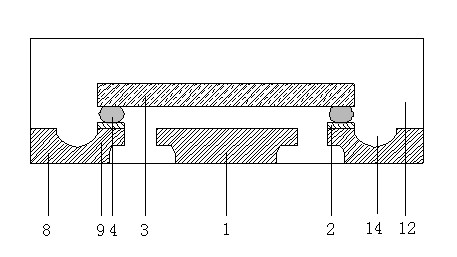

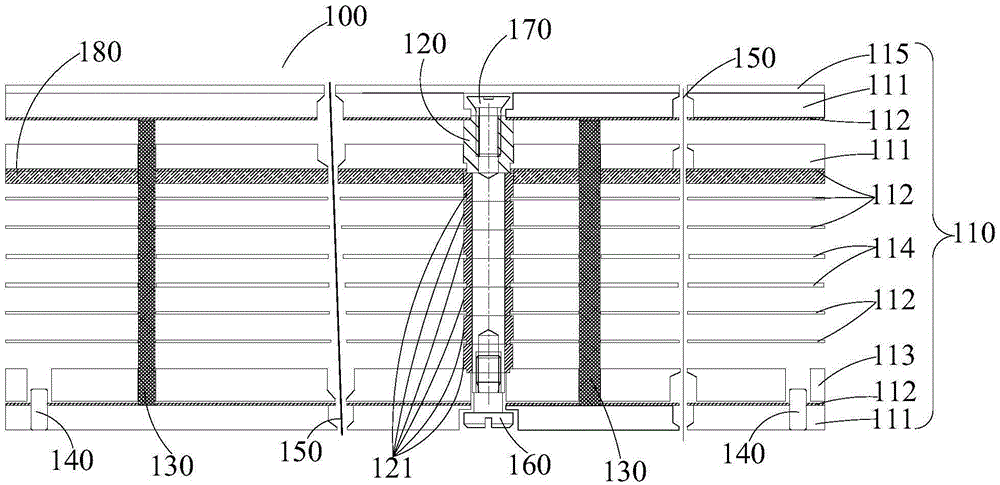

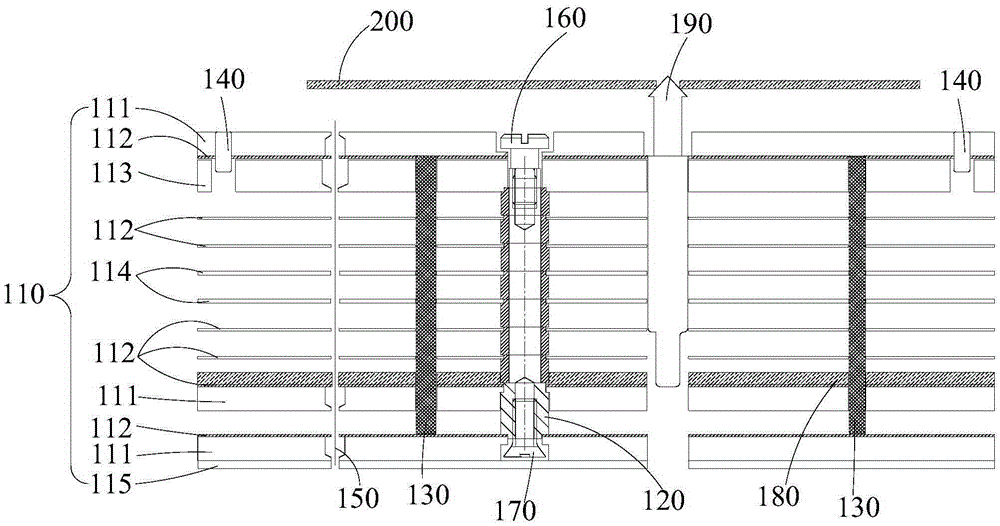

Multi-cycle arrangement carrier-free double-integrated chip (IC) package and production method

ActiveCN102231376AReduce capacitanceReduce thicknessSemiconductor/solid-state device detailsSolid-state devicesCapacitanceHemt circuits

Owner:TIANSHUI HUATIAN TECH +1

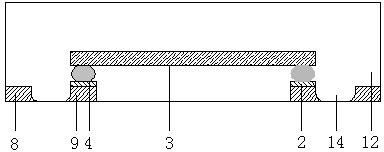

e/LQFP (low-profile quad flat package) stacked package with grounded ring and production method of e/LQFP stacked package with grounded ring

ActiveCN102522391ASimple structureImprove bindingSemiconductor/solid-state device detailsSolid-state devicesPlastic packagingStructural engineering

The invention discloses an e / LQFP (low-profile quad flat package) stacked package with a grounded ring and a production method of the e / LQFP stacked package with the grounded ring. Two IC (integrated circuit) chips are adhered to a carrier in a stacked manner and connected with an inner pin through bonding wires, the inner pin is connected with an outer pin, the carrier is connected with the grounded ring through a ribbed plate, and the lower end face of the grounded ring is higher than the upper end face of the carrier. The lower end face of the carrier is provided with an anti-overflow ring, the grounded ring, the bonding wires, the ribbed plate and the inner pin are packaged in a plastic packaging part, the lower end face of the carrier is packaged in the plastic packaging part or positioned outside the plastic packaging parte. A wafer is thinned and scribed prior to being subjected to coring, bonding, plastic packaging and subsequent procedures to produce the e / LQFP stacked packaging part with the grounded ring. The carrier of the stacked packaging part is free of ground wire, layering caused by stress generated by making the ground wire and bonding failure of the ground wire can be avoided, and thereby reliability and testing yield of the package are improved.

Owner:TIANSHUI HUATIAN TECH +1

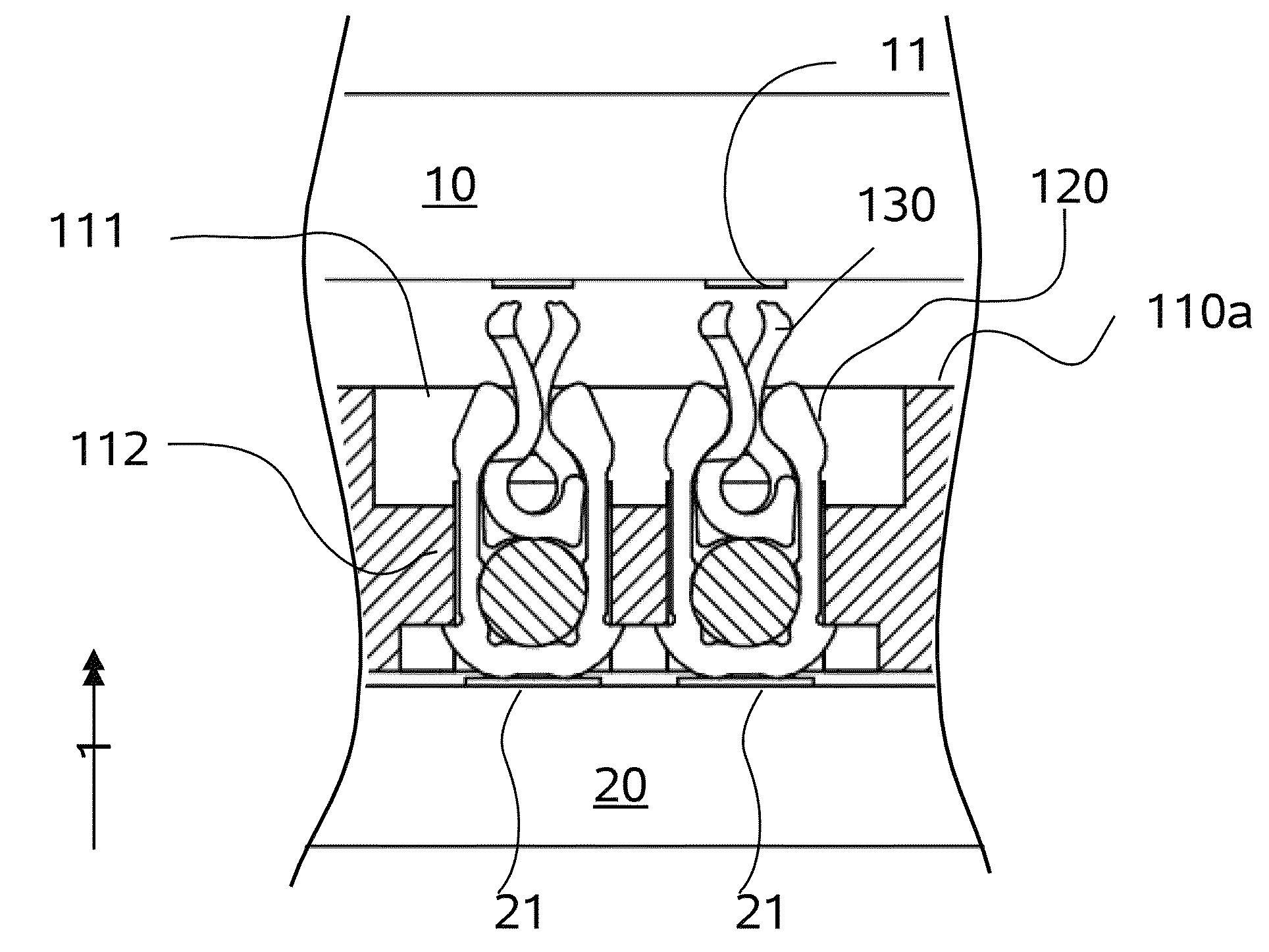

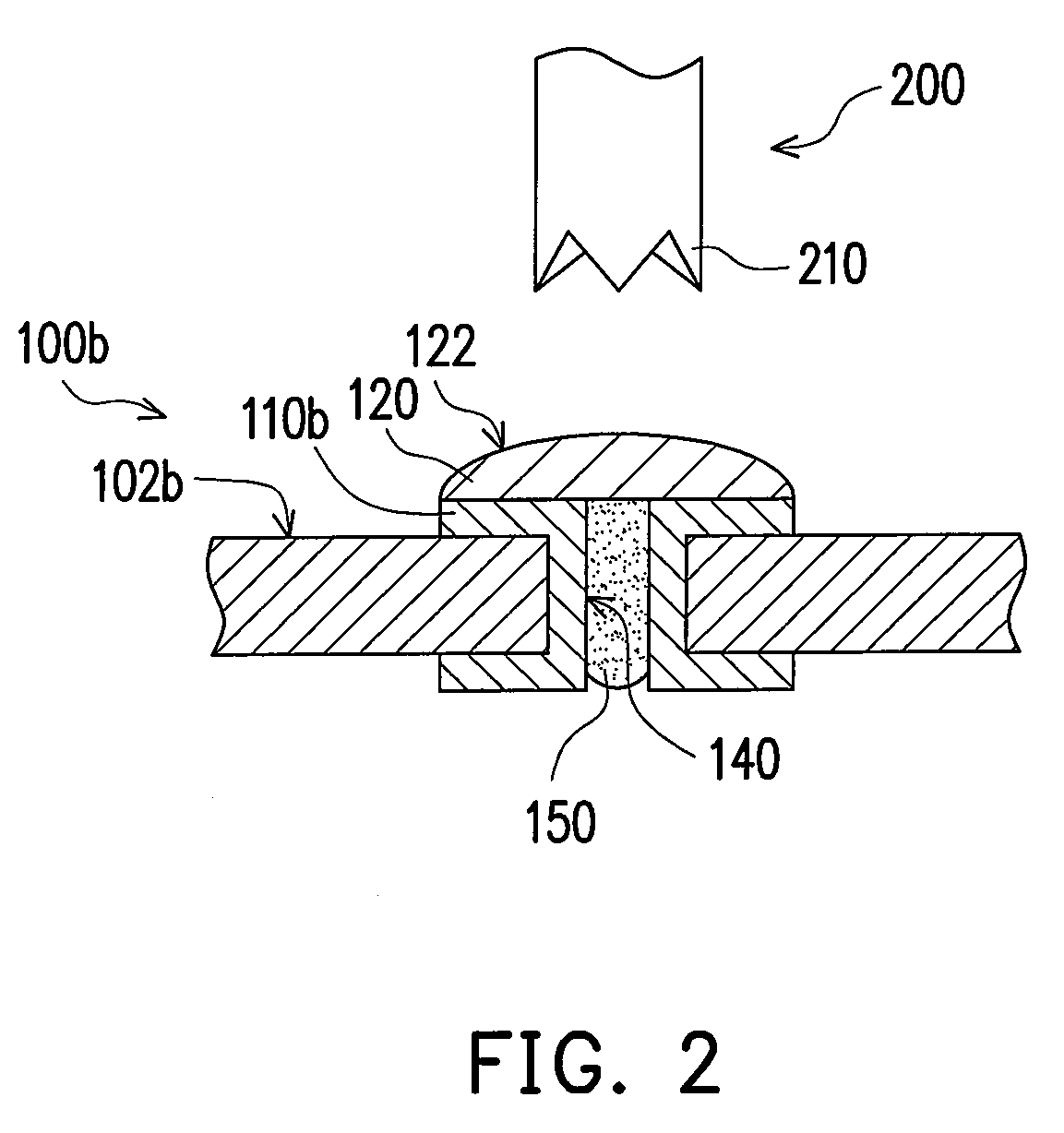

Electrical interconnect assembly

ActiveUS20140127953A1Extend load board lifeImprove test yieldElectrical measurement instrument detailsCoupling contact membersEngineeringIc devices

An electrical test contact electrically connects a test terminal of an Integrated Circuit (IC) test assembly with an IC terminal of an IC device in an electrical interconnect assembly. The test contact is formed of electrically conductive material and includes a head portion and a foot portion. The head portion includes a first electrical contacting portion for electrically engaging an IC terminal of an IC device during use, and the foot portion includes a second electrical contacting portion for electrically engaging a test terminal of a test assembly during use. The head portion includes a head receiving portion that receives a first resiliently biasing member to retain the first resiliently biasing member in contact with the test contact. The first resiliently biasing member biases the first electrical contacting portion against the IC terminal of the IC device during use. An electrical interconnect assembly having multiple test contacts is also disclosed.

Owner:JF MICROTECH

Multi-turn arranged carrier-free IC (Integrated Circuit) chip packaging component and manufacturing method thereof

ActiveCN102231372ASimple structureGood thermal propertiesSemiconductor/solid-state device detailsSolid-state devicesCapacitancePlastic packaging

The invention discloses a multi-turn arranged carrier-free IC (Integrated Circuit) chip packaging component and a manufacturing method thereof. The multi-turn arranged carrier-free IC chip packaging component comprises a lead frame, inner pins, an IC chip and a plastic packaging body, wherein the lead frame is a carrier-free lead frame, the inner pins of the lead frame are arranged around four sides of the lead frame in turns, the IC chip is provided with bumps, and the bumps are connected to the inner pins. The number of pins of the packaging component in the invention is increased by over 40% compared with the number of the pins of a single-row lead frame with the same area; and bonding lines are not needed for the connection of the pins and the lead frame, and the structure is simple and reasonable. The heat conduction distance is short, the heat performance is excellent, the inner welding inductance and capacitance of a circuit are reduced due to direct contact between the bumps and the frame (a base plate and a chip), the signal transmission is fast, the little distortion is caused, and the electric performance is excellent; in addition, the thickness and the weight of packaging are reduced, thus the crossing and the open circuit of bonding wires are avoided, and the test yield and reliability are improved.

Owner:TIANSHUI HUATIAN TECH +1

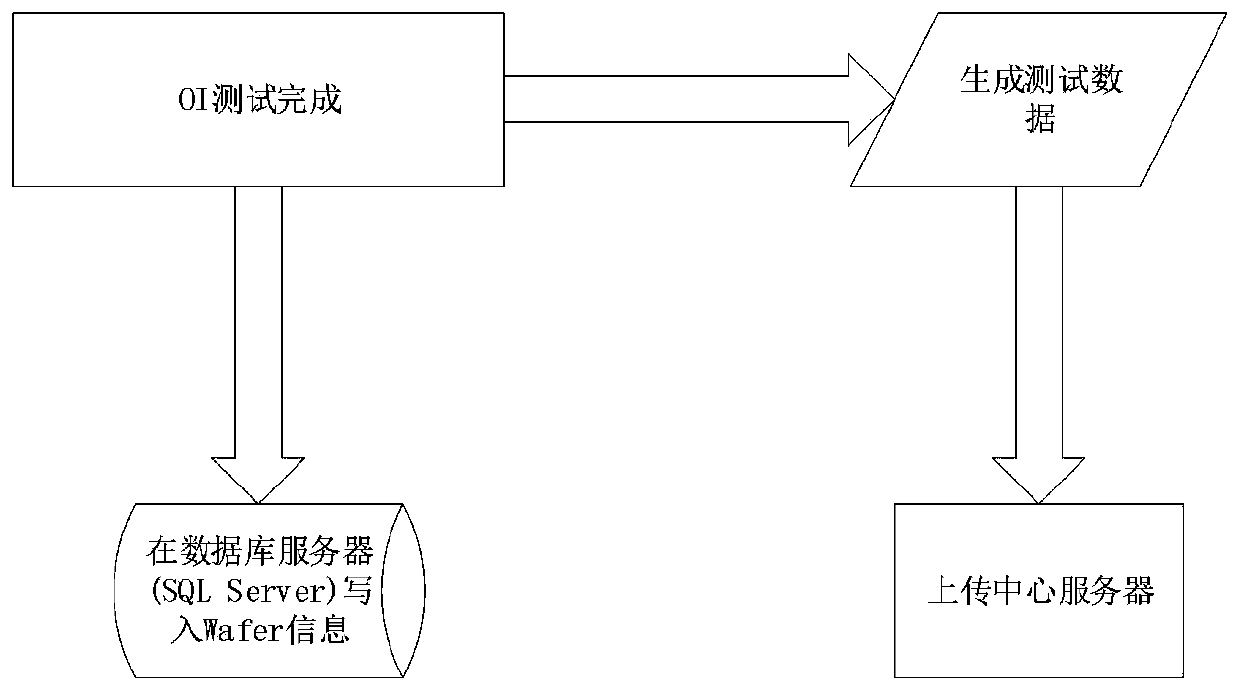

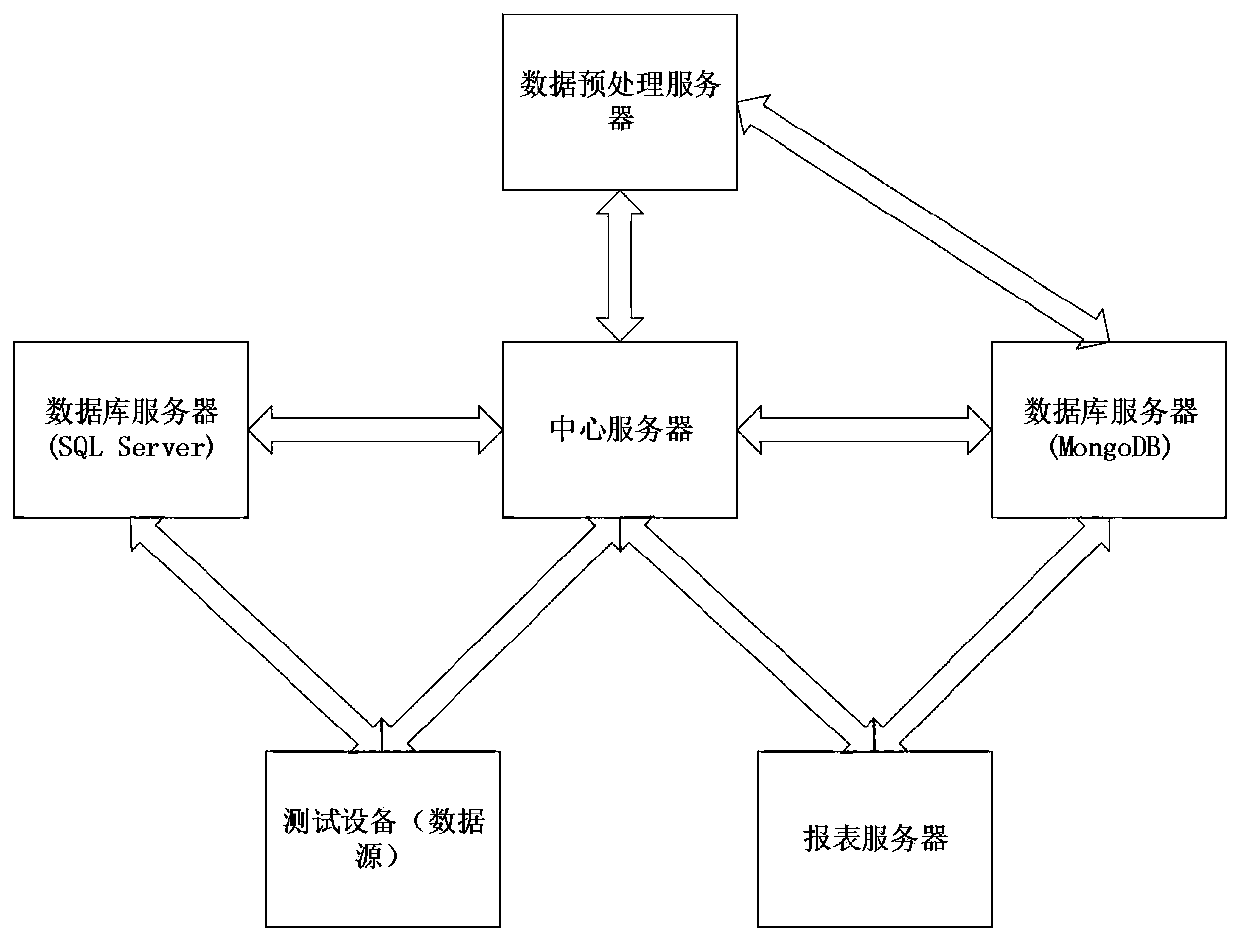

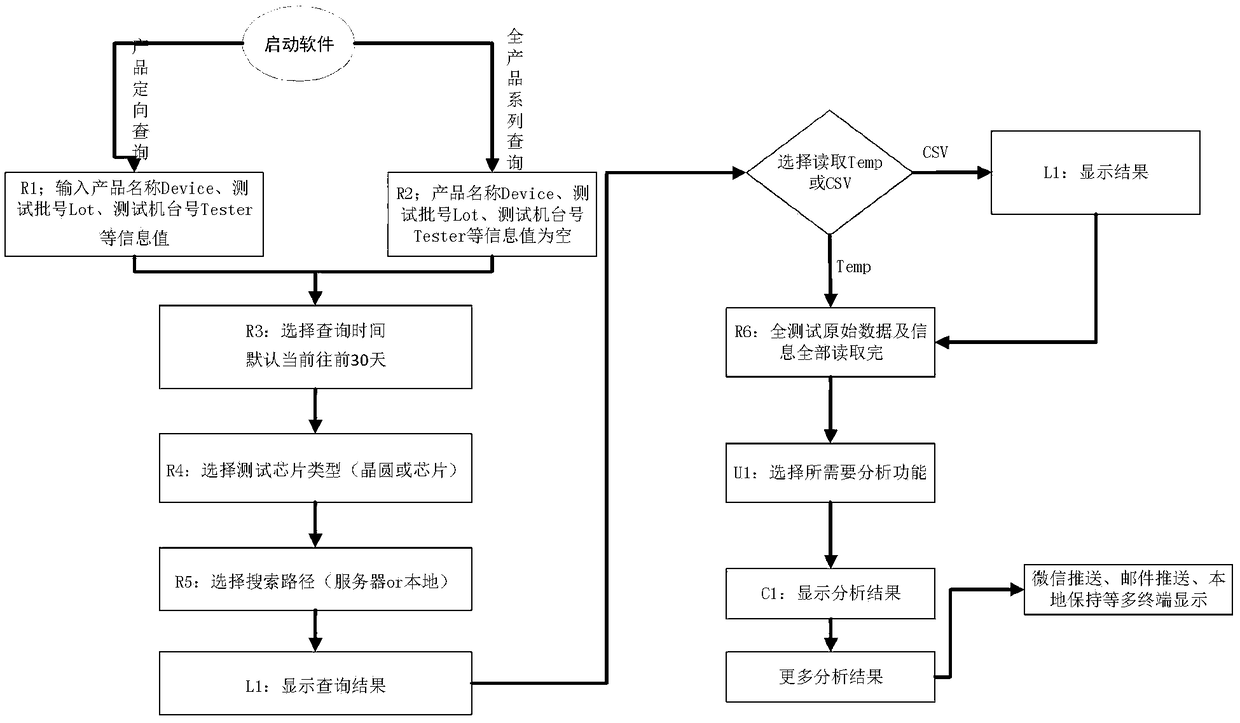

Integrated circuit total ecological chain intelligent test analysis method

ActiveCN109406984ARealize interconnectionAnalysis results are fastElectronic circuit testingData acquisitionIntegrated circuit

The present invention discloses an integrated circuit total ecological chain intelligent test analysis method. A data collection layer, a big data processing analysis layer and an application layer are provided. The method comprises the steps of: integrated circuit test parameter index analysis, wafer test yield analysis, test time analysis, wafer MAP information, an SummaryCheck and analysis, TouchDown, Report and SQLHistory analysis. The integrated circuit total ecological chain intelligent test analysis method achieves timeliness, mobility and intelligence of company office, has remote dataintercommunication and remote data backup, is high in safety, introduces an industrial big data analysis model based on data accumulation for 6 months and 12 months through continuous data accumulation to achieve data retrieval, tracking, analysis, early warning and pre-determination of the total ecological chain test information, is used to guide production and improves the production efficiencyand test yield.

Owner:SINO IC TECH

Multi-circle arranged IC (integrated circuit) chip packaging member and producing method thereof

ActiveCN102222658ASimple and reasonable structureShort heat conduction distanceSemiconductor/solid-state device detailsSolid-state devicesDistortionCapacitance

The invention relates to a multi-circle arranged IC (integrated circuit) chip packaging member, which comprises a lead frame, inner pins, an IC chip and a plastic package body. The multi-circle arranged IC chip packaging member is characterized in that the lead frame is provided with a load; the inner pins of the lead frame are arranged around the lead frame in circles; the IC chip is provided with convex points; and the convex points are connected to the inner pins. Compared with a single-row lead frame with a same area, the multi-circle arranged IC chip packaging member has the advantage ofincreasing the number of the pins of the multi-circle arranged IC chip packaging member by over 40%; the pins can be connected with the lead frame without bonding wires; and the structure is simple and reasonable. In addition, as the heat conducting distance is short, the multi-circle arranged IC chip packaging member has better thermal property; as the convex points are in direct contact with the lead frame (a substrate, the chip), the inductance and the capacitance welded inside a circuit are reduced, the signal transmission speed is high, the distortion is little, and excellent electrical property is obtained; and the thickness and the weight of a package are reduced, thus reeling and disconnecting of a bonding wire are avoided, and the yield and the reliability for testing are improved.

Owner:TIANSHUI HUATIAN TECH +1

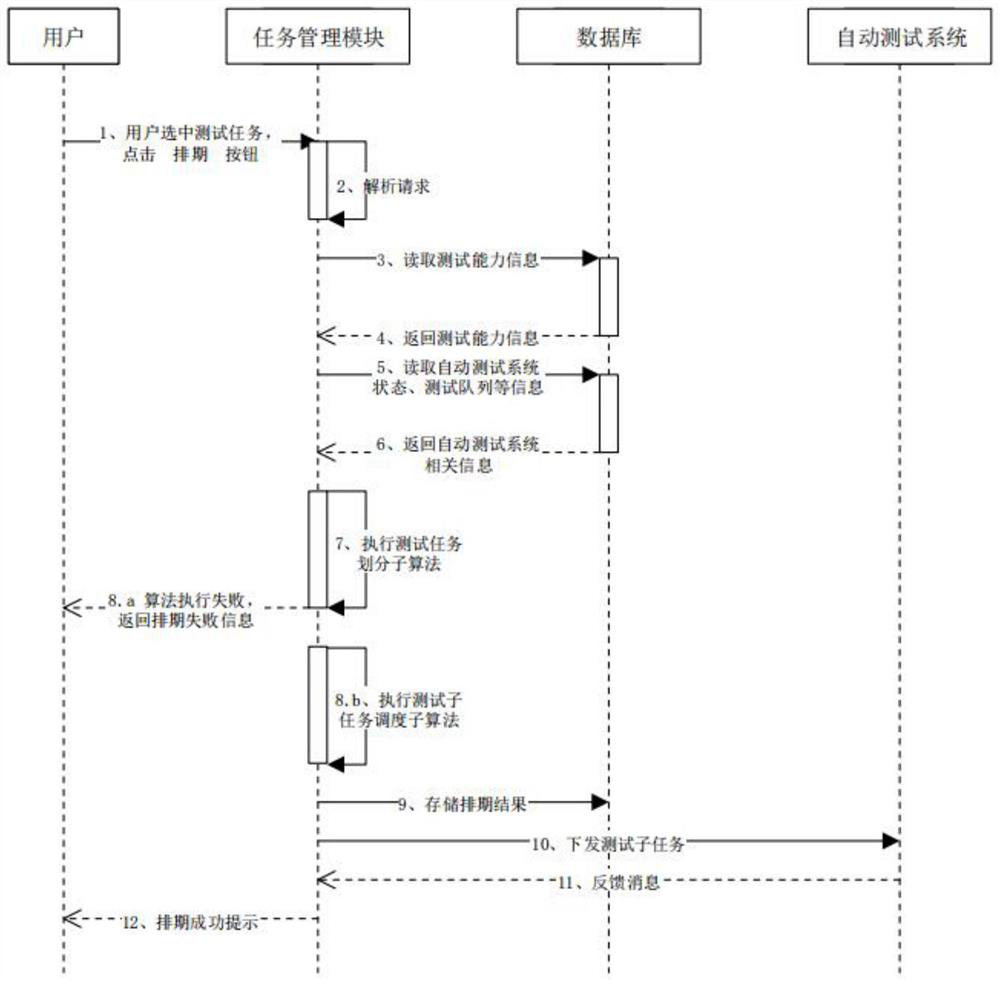

Internet of Things test cloud platform and method

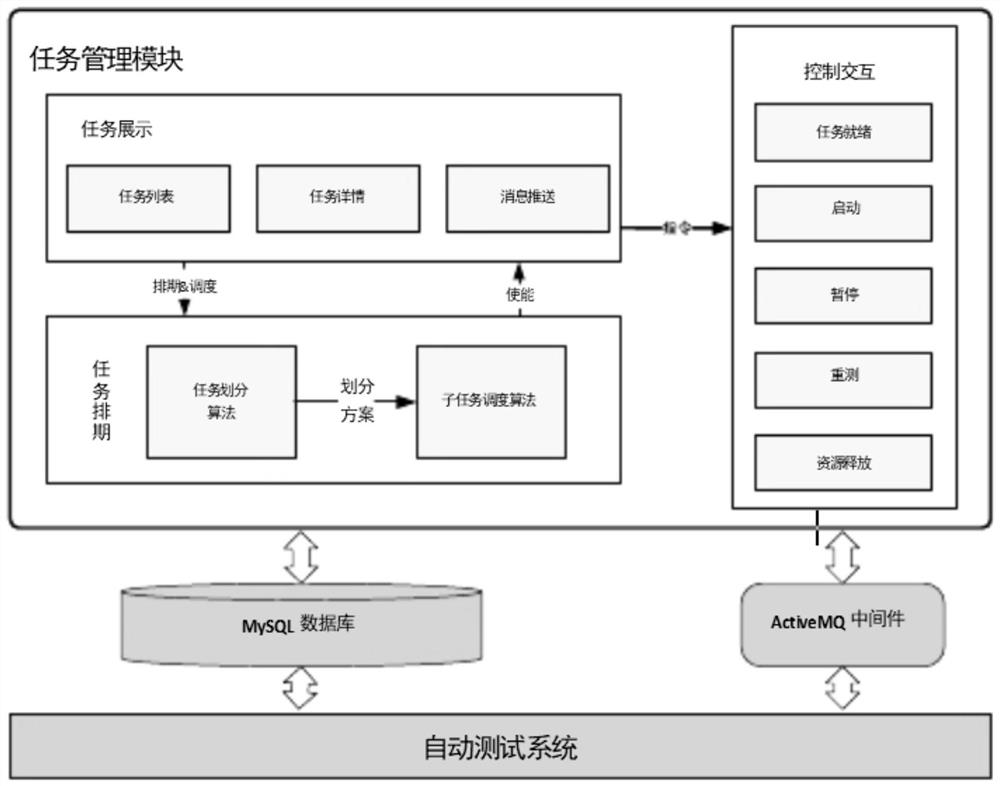

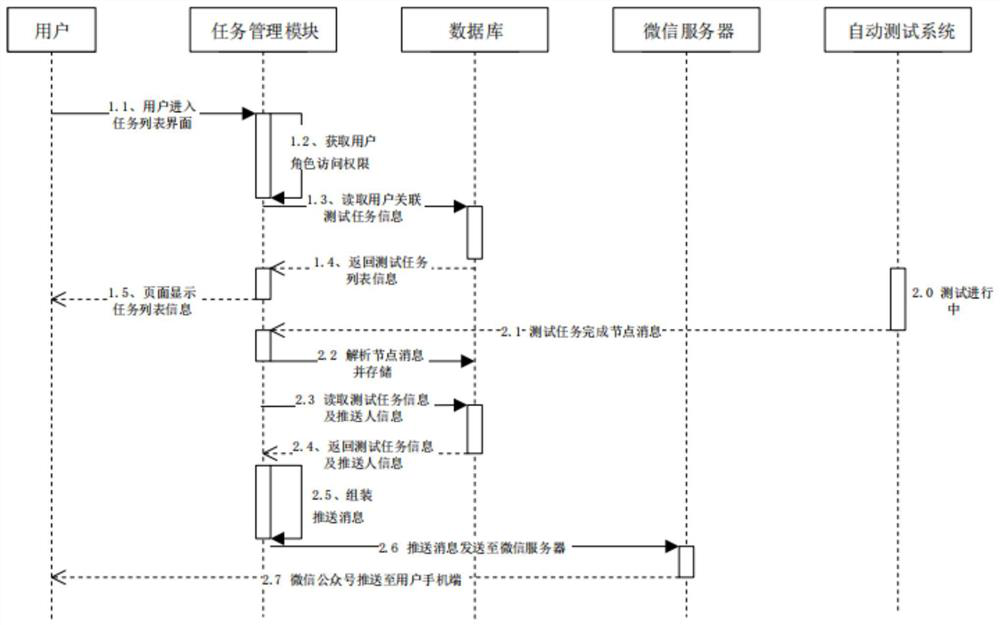

ActiveCN111654416AOptimize execution orderImprove test management efficiencyData switching networksTest efficiencyStatistical analysis

The invention belongs to the technical field of Internet of Things, and particularly relates to an Internet of Things test cloud platform and method, and the test cloud platform comprises: an application management module which is used for managing and auditing a test application submitted by a user, converting the test application passing the auditing into a test task, and transmitting the test task to a task management module; a task management module which is used for dividing and scheduling the test tasks, assigning the divided and scheduled test tasks to an automatic test system, and maintaining and managing the whole life cycle of the test tasks from test preparation to test completion; and a result and statistical analysis module which is used for summarizing the test results and forming a corresponding test report after the test is completed. After the test tasks are divided and dispatched, the test tasks are issued and dispatched to the corresponding automatic test systems, the execution sequence of the different test tasks is optimized, the test efficiency is improved, the test income is increased, and therefore the test management efficiency of testing the Internet of Things equipment is improved.

Owner:北京智网信测科技有限公司

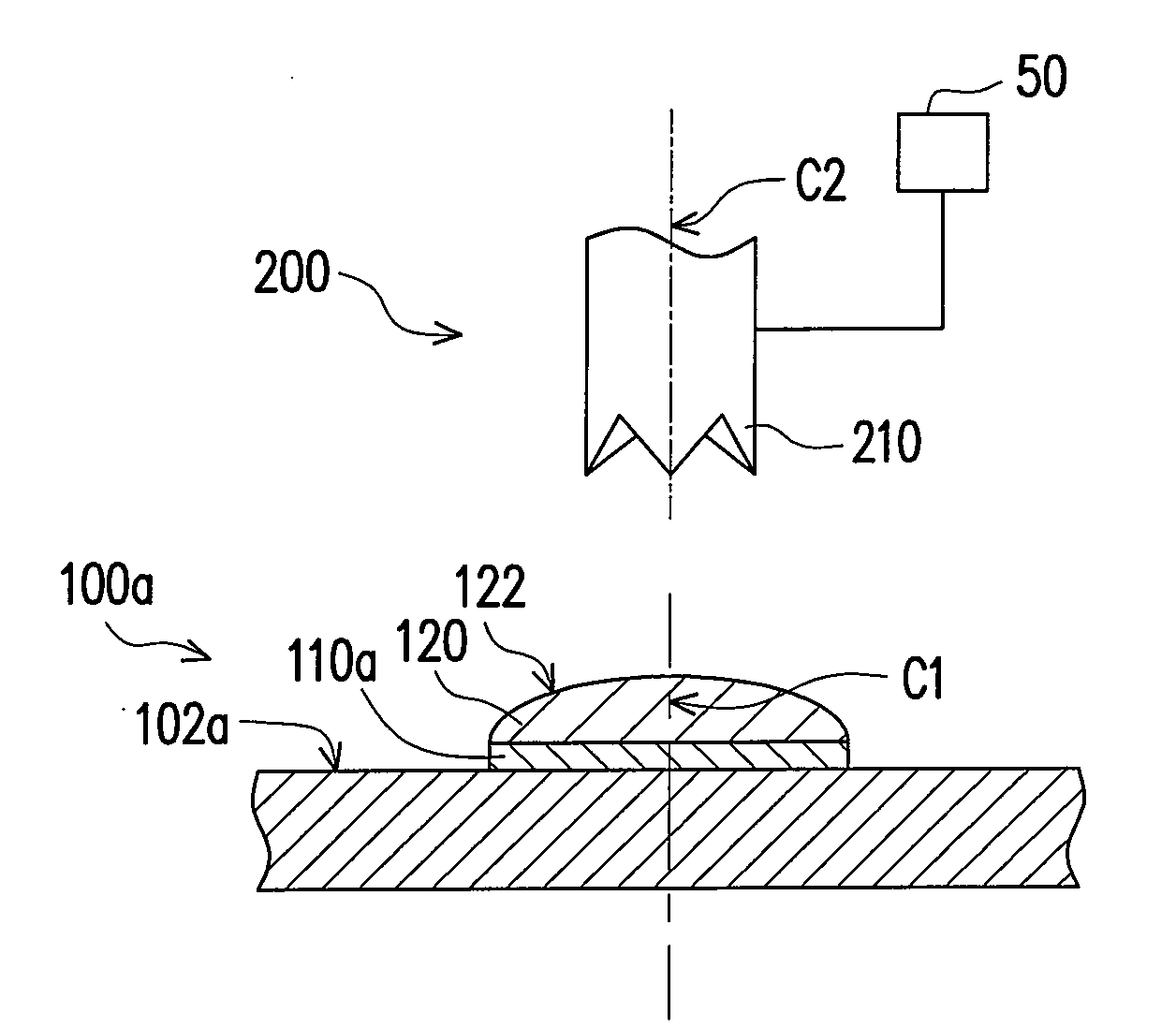

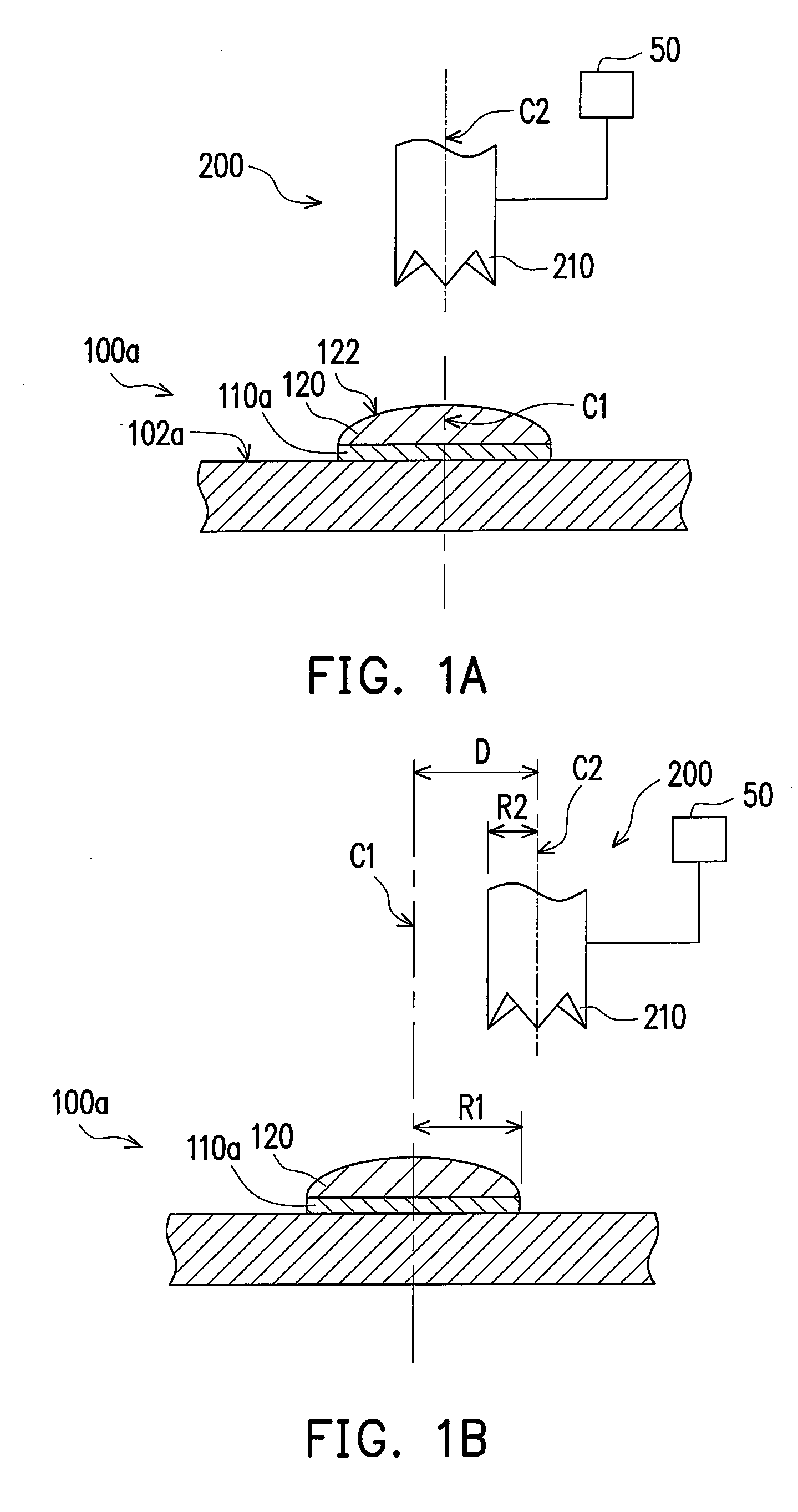

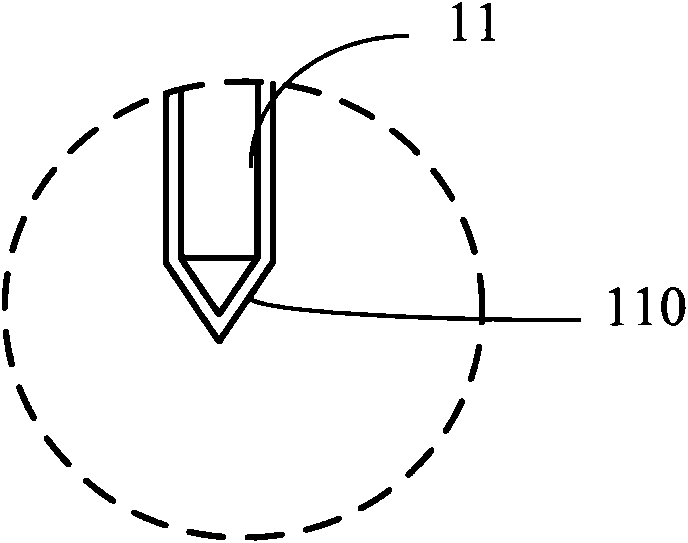

Testing probe and electrical connection method using the same

InactiveUS20090096473A1Large position toleranceIncrease contactElectrical measurement instrument detailsPrinted circuit aspectsElectricityElectrical connection

A testing probe including a shaft body and a plurality of claws is provided. Each cross section of the shaft body has a substantially identical shape and a substantially identical outer diameter. The claws are formed integrally with the shaft body at an end thereof. An orthogonal projection of the claws on any one of the cross sections of the shaft body is within the contour of the cross section. Contacting a solder bump on a test pad of a circuit board with the claws of the testing probe increases the test yield of the circuit board.

Owner:COMPAL ELECTRONICS INC

Test probe

InactiveUS20090289646A1Reduce cleaning frequencyIncrease profitElectrical measurement instrument detailsElectrical testingConductive polymerMetallic materials

A test probe pin is disclosed. The test probe has a plurality of probes, each of which has a probe tip surface coated with a nano-film of conducting polymer, and the thickness of the nano-film is about 1-20 nm. The probes coated with the nano-film are installed on a test fixture for testing IC components, so that the probes can efficiently provide excellent no-clean property and stabler electro-conductivity for lowering the cleaning frequency of the probes, enhancing the yield of IC component testing, increasing the utility rate of the test fixture, reducing the total testing cost, elongating the usage lifetime of the test probe, and reducing the cost of probe material. Thus, due to the nano-film of conducting polymer, the probes made of metal material can provide almost the same electro-conductivity as a traditional probe by only plating a gold layer of one fifth of original thickness, so that the cost of whole probe material can be reduced.

Owner:IPWORKS TECH CORP

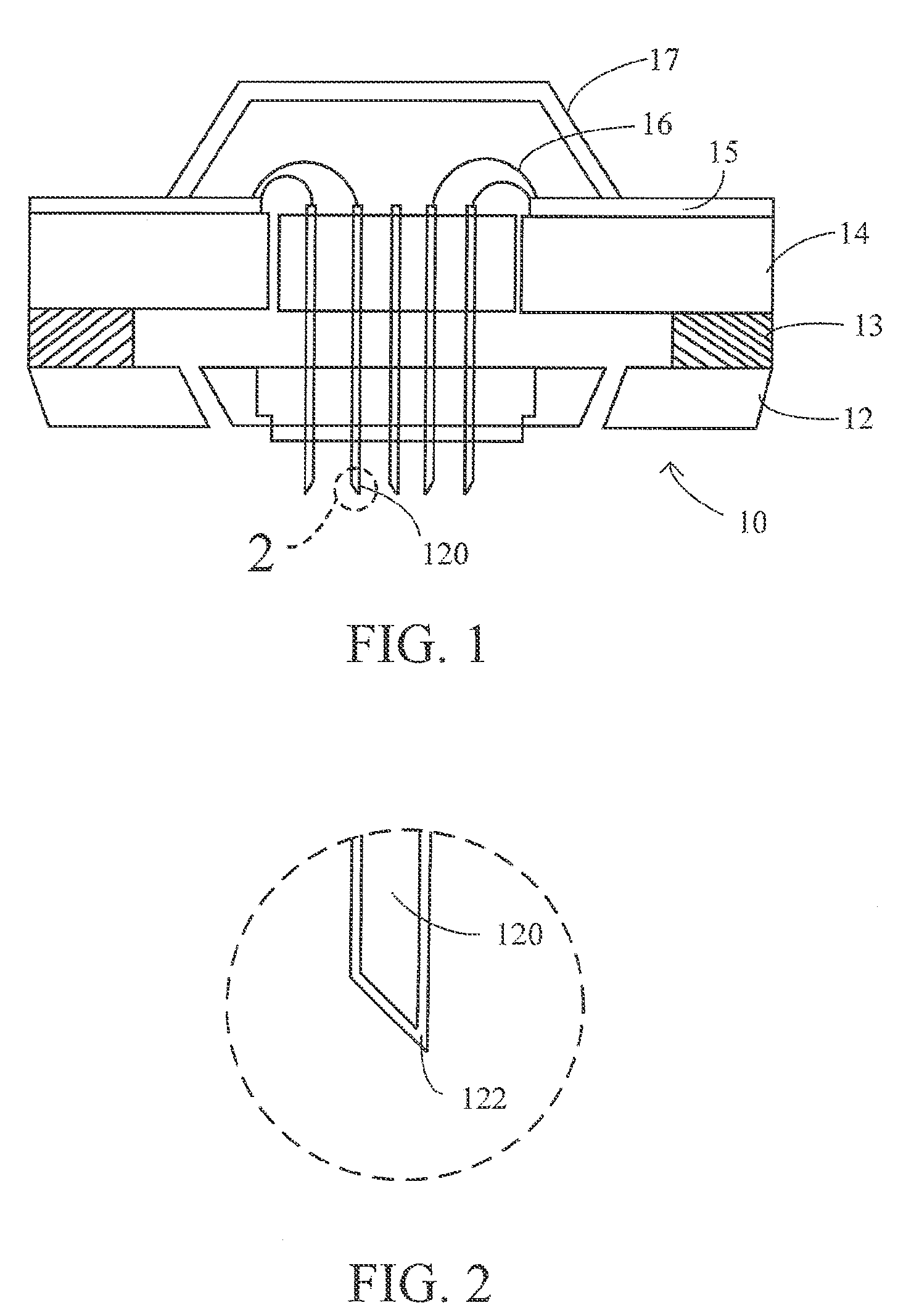

Probe clearing method of probe and probe

InactiveCN105583695AReduce lossReduce needle breakage rateEdge grinding machinesPolishing machinesFragilityBiomedical engineering

The invention discloses a probe clearing method of a probe and the probe. The probe clearing method comprises the following steps of performing polishing treatment on the surface of the probe so as to clear pollutants on the surface of the probe, and cutting and activating the surface of the probe; and performing grinding treatment on a probe tip of the probe so as to passivate the probe tip of the probe. According to the probe clearing method and the probe disclosed by the invention, the surface of the probe is subjected to polishing treatment so as to clear the pollutants on the surface of the probe, and the length of the probe has no significant loss; then the probe tip of the probe is subjected to grinding treatment for passivating the probe tip of the probe, thereby reducing the condition that a test bond pad is punched caused by excessive acuteness of the probe tip, and reducing the probability that the probe is broken caused by excessive fragility of the probe tip. Therefore, after the probe is cleared by adopting the probe clearing method provided by the invention, the length of the probe tip has no significant change, further the loss of the probe in the probe clearing process is reduced, and the aim of improving the test yield of a functional test performed by adopting the probe is achieved.

Owner:SEMICON MFG INT (SHANGHAI) CORP

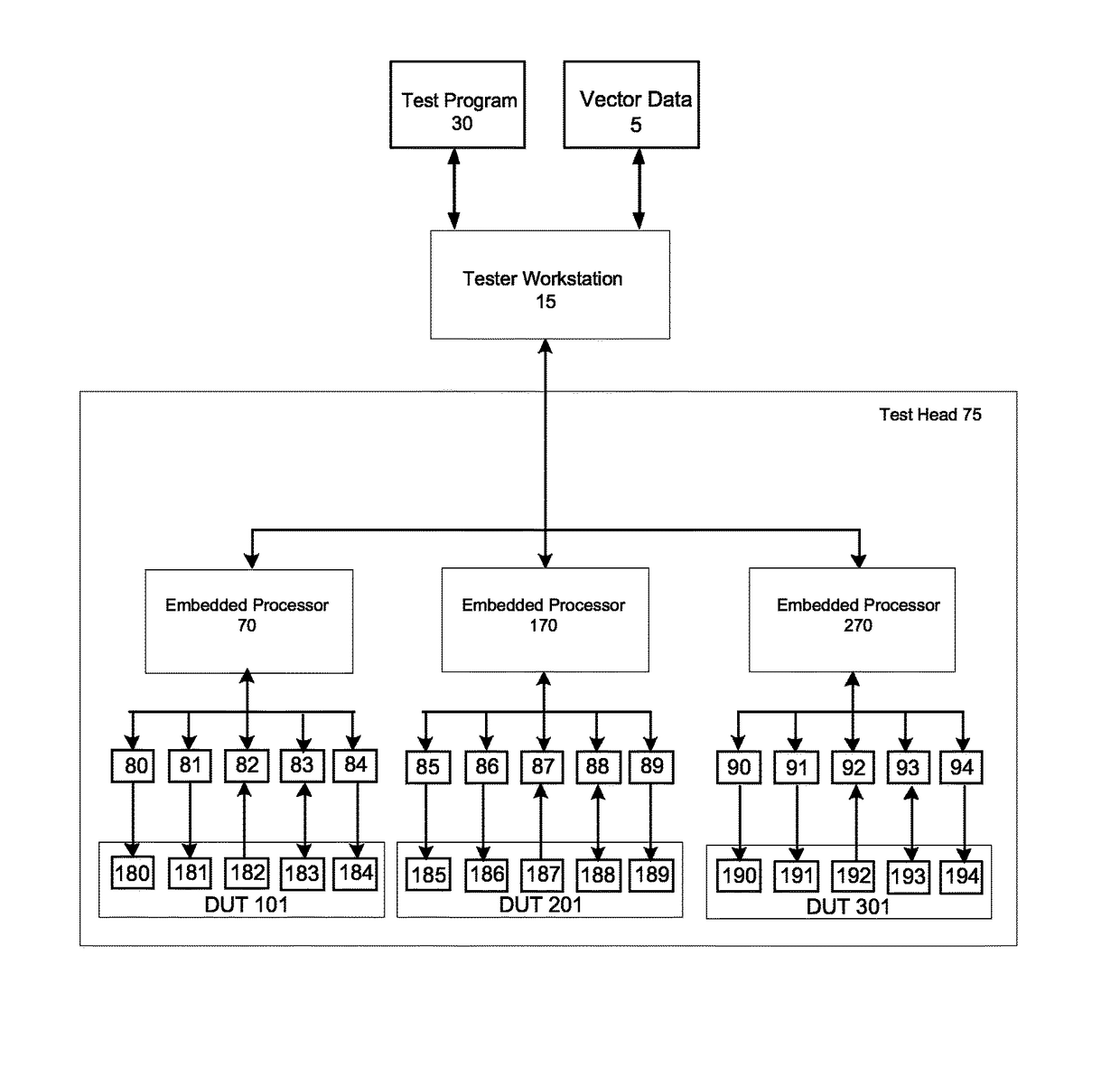

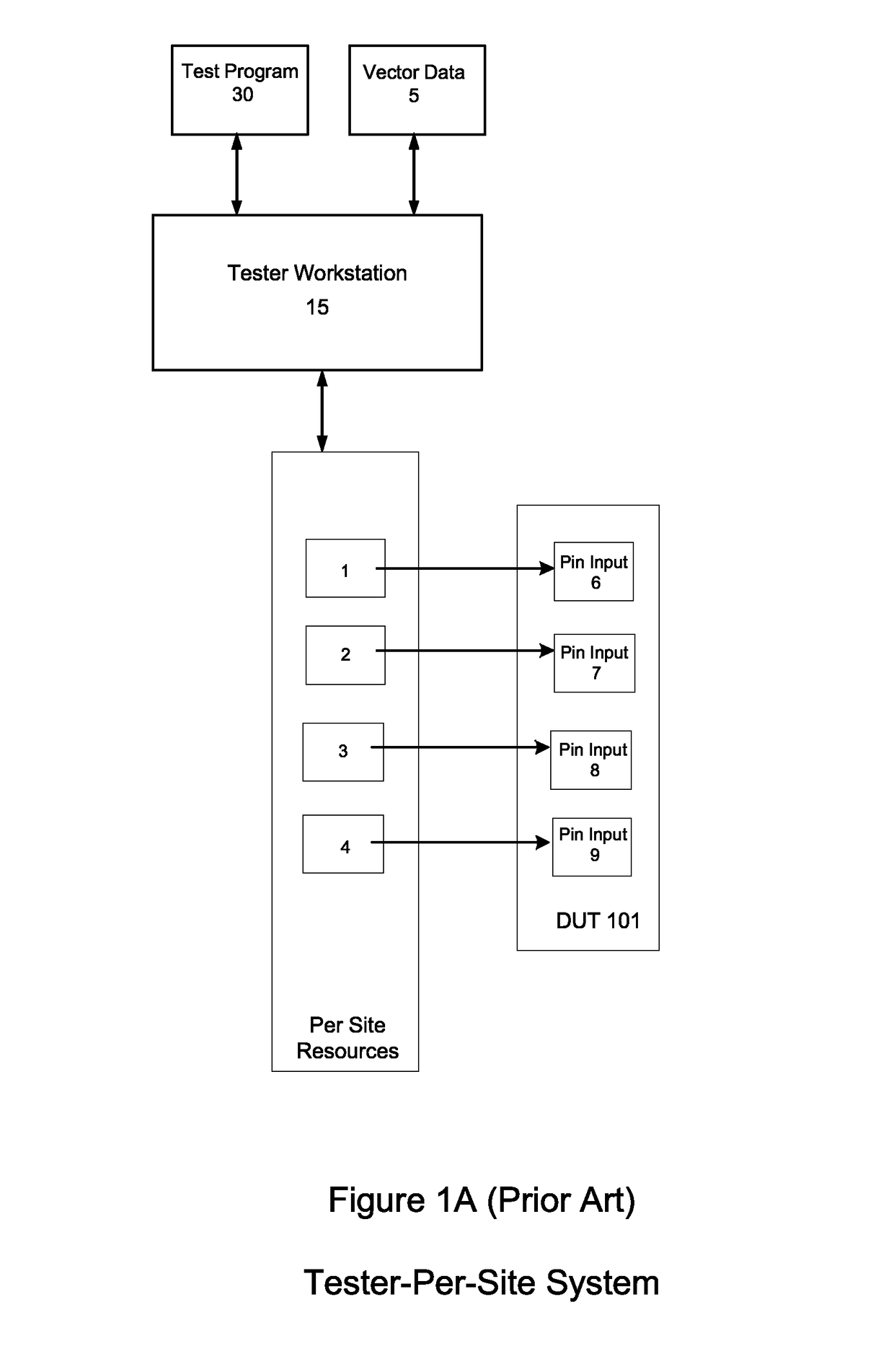

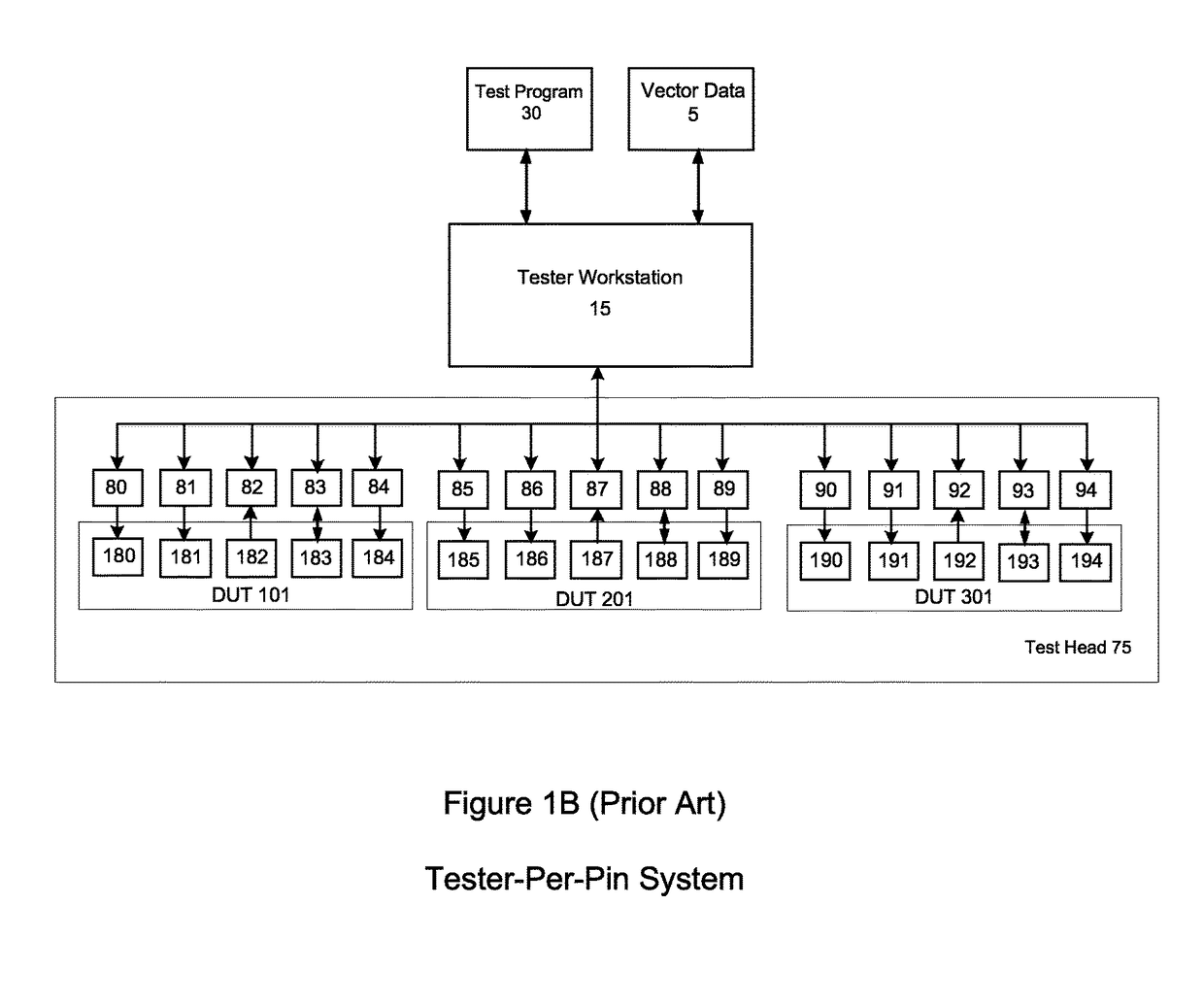

Pseudo tester-per-site functionality on natively tester-per-pin automatic test equipment for semiconductor test

ActiveUS9606183B2Effective distributionMinimize timeDigital circuit testingAutomatic test equipmentControl signal

Owner:ADVANTEST CORP

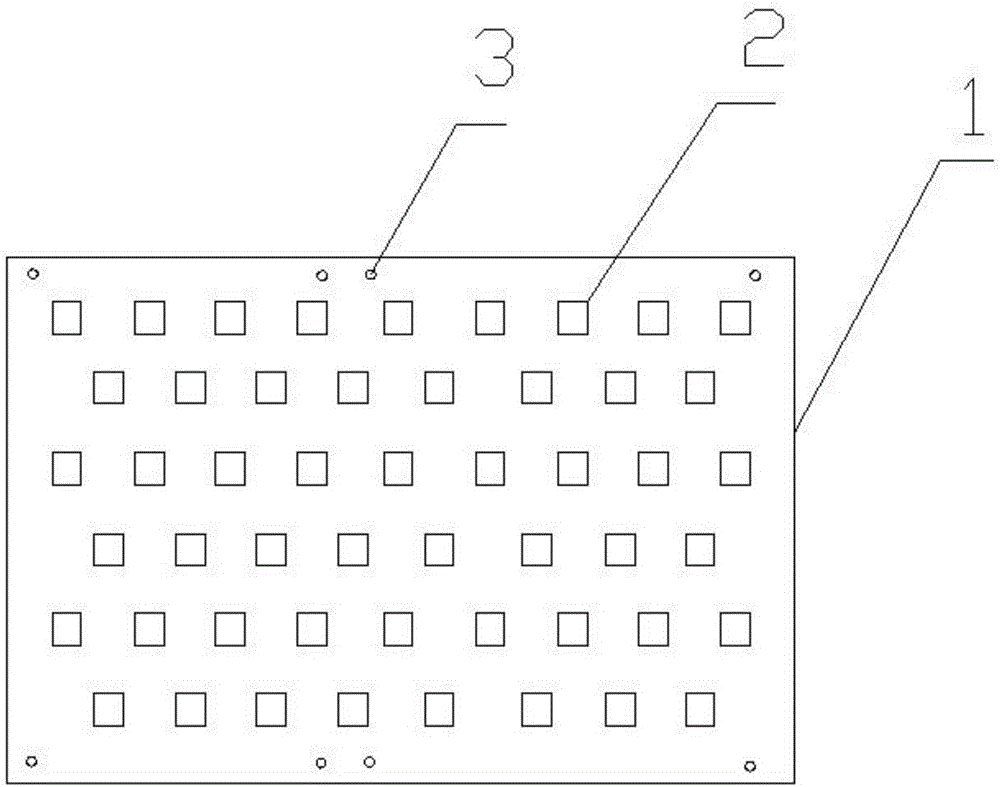

General short needle and micro needle clamp

InactiveCN105424984AImprove test yieldReduce layer spacingPrinted circuit testingMeasurement instrument housingFiberCopper

The invention provides a general short needle and micro needle clamp. The general short needle and micro needle clamp comprises a composite fiber board in a multi-layer structure, fixing copper columns, steel needles and sponge, wherein the composite fiber board comprises a top fiber board, a middle fiber board and a lower fiber board which are sequentially laminated, the top fiber board, the middle fiber board and the lower fiber board each comprise multi-layer fiber boards, a preset gap is further arranged between two adjacent fiber boards, a preset gap scope is 0.01-4mm, the composite fiber boards are each provided with through holes and penetration needle holes, the fixing copper columns are arranged in the through holes, the steel needles are mounted in the needle holes, two ends of the steel needles are respectively exposed out of surfaces of the fiber boards, diameters of the steel needles are greater than or equal to 0.08mm, the sponge is arranged on the surface of one of the fiber boards, so the steel needles are not easy to generate deformation when the steel needles having relatively small diameters are utilized to test, the loss rate is reduced, the test yield of the clamp is improved, and thereby detection on PCBs with smaller bonding pads are convenient for users.

Owner:HANS LASER TECH IND GRP CO LTD +1

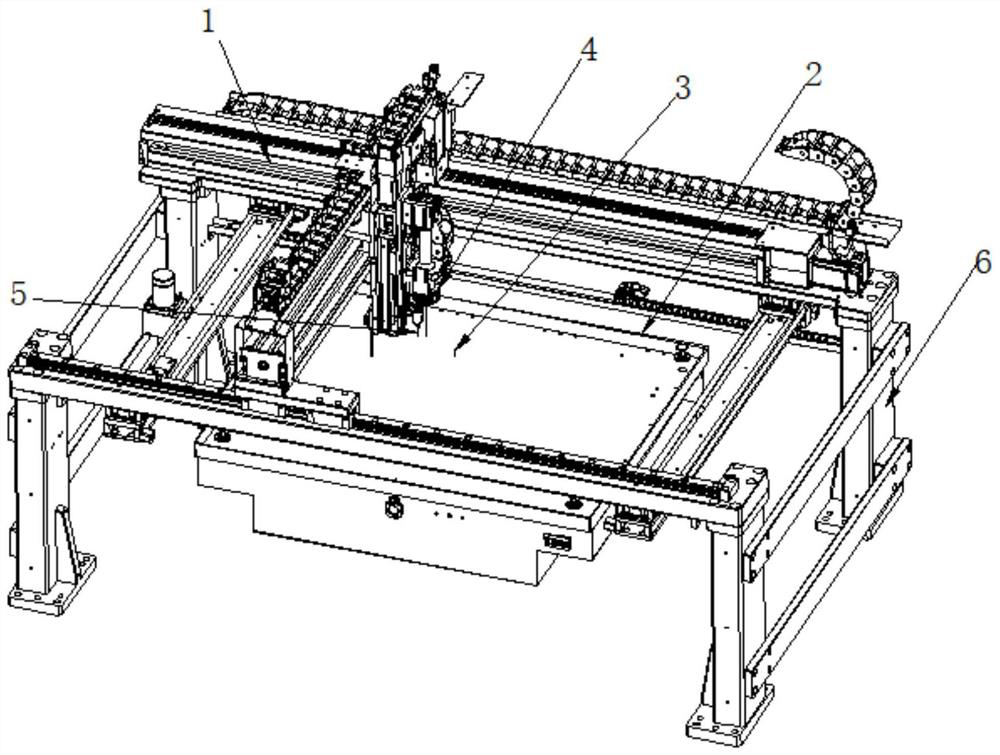

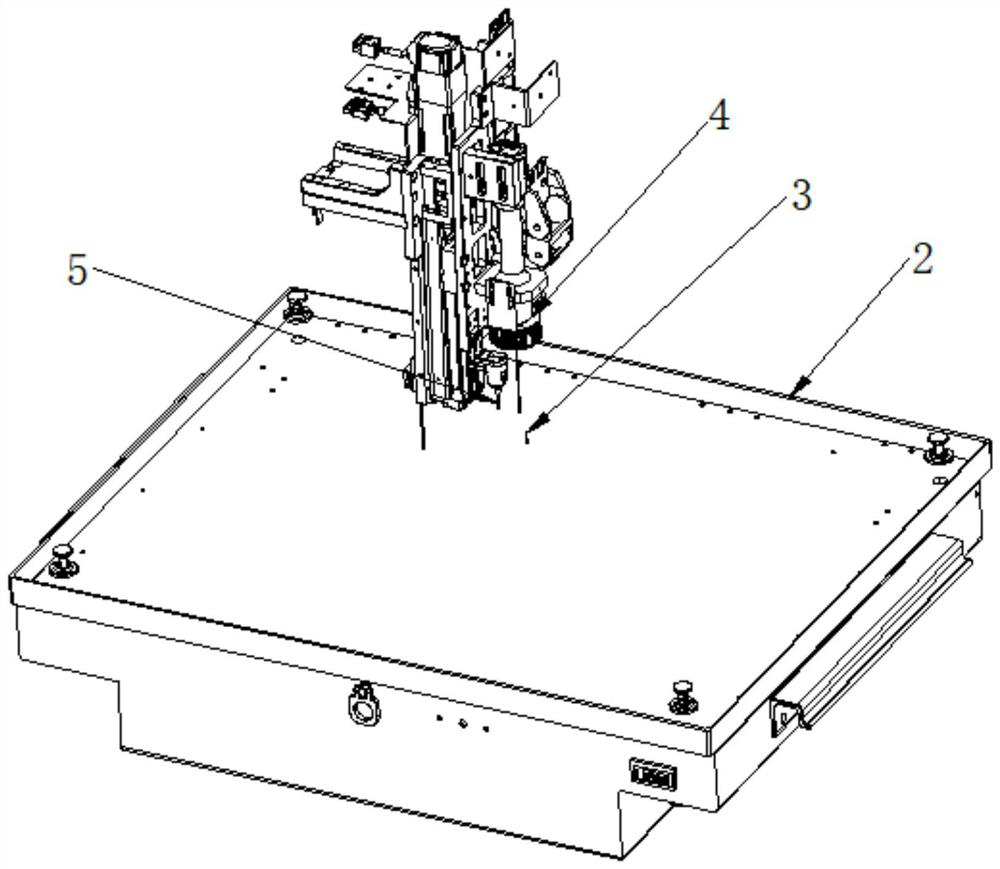

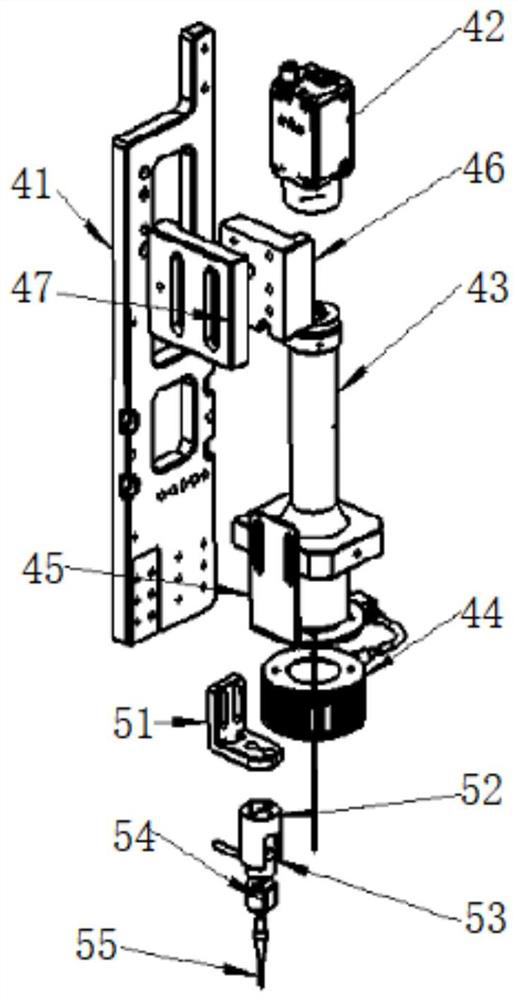

ICT clamp probe elasticity detection equipment

PendingCN111638482AImprove versatilitySimple structureElectrical testingMeasurement instrument housingTest efficiencyControl system

The invention discloses ICT clamp probe elasticity detection equipment, and relates to the technical field of detection equipment. A gantry three-axis module, a vision module and a pressure head module are arranged; the visual module is controlled by a software control system to automatically search a MARK point; the actual MARK point is compared with original coordinates to position an ICT clamp;further from coordinate positioning, points are routed according to original data, every time the upper of a probe body is reached, the pressure is measured; the problems that the labor cost is high,the misjudgment rate is high, manual operation cannot be automatic accurate, and long time manual detection causes fatigue when a maintainer judges whether the elasticity of the probe meets the requirement or not by means of personal feeling are solved. The equipment is simple in structure, easy to be compatible and interchanged, high in efficiency, safe, low in cost, high in universality and lowin development cost, the labor intensity of manual detection is reduced, the test efficiency and test yield are improved, and the equipment can be widely applied in future.

Owner:深圳市明信测试设备股份有限公司

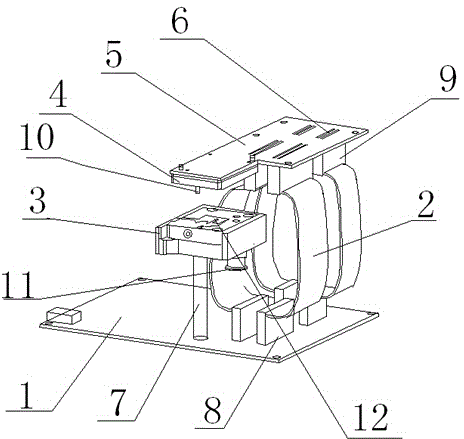

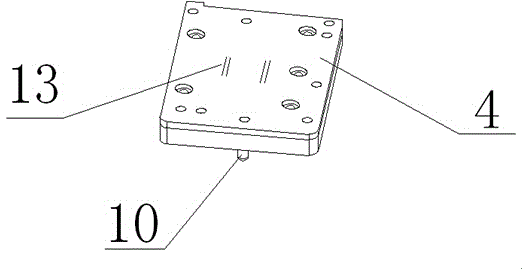

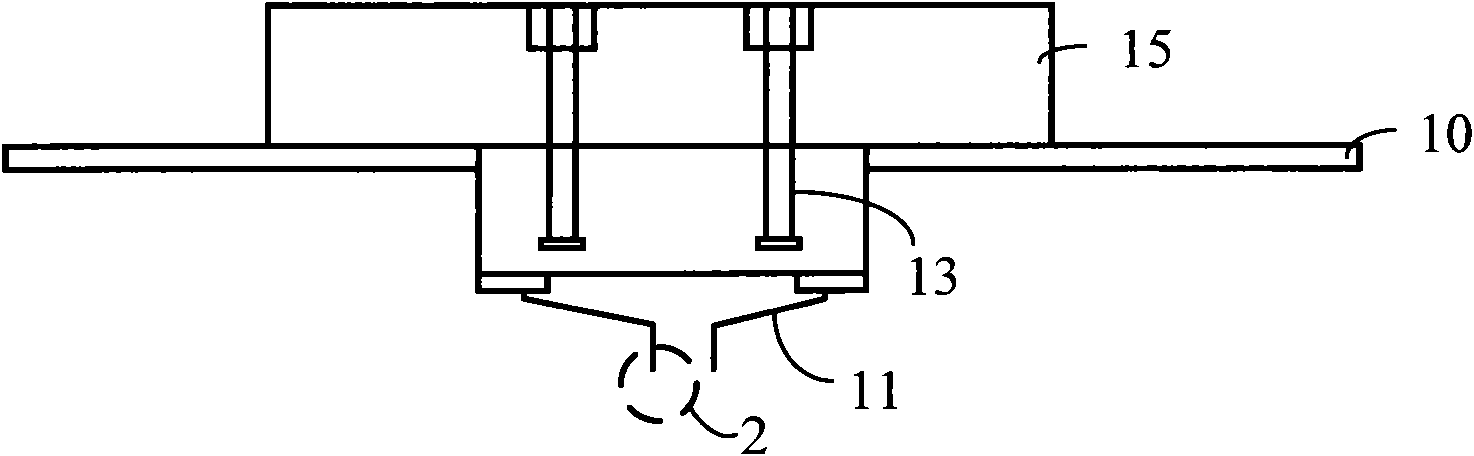

Adapter plate needle die mechanism

InactiveCN104155486AExtended service lifePrecise positioningElectrical testingMeasurement instrument housingTest efficiencyEngineering

The invention discloses an adapter plate needle die mechanism which comprises a test plate, a flat cable, a lower needle die, an upper needle die, a cover plate and an adapter plate. A cavity and a lower fixation plate are arranged on the test plate. The lower needle die is fixedly arranged on the cavity. One end of the flat cable is connected with the lower fixation plate, and the other end is connected with an upper fixation plate. The upper fixation plate is arranged at the lower part of the cover plate. The upper needle die is fixedly arranged at the lower part of the cover plate. The upper needle die is arranged right above the lower needle die. A pin is arranged at the lower part of the upper needle die. The adapter plate is arranged on the upper surface of the cover plate. A vacuum suction head is arranged on the lower needle die. A positioning groove is arranged on the lower needle die. A probe is arranged on the upper needle die. The test plate is connected with the lower needle die through the cavity. According to the invention, the test mechanism carries out an automatic test, and can accurately position a product; the test efficiency and the test yield are improved; and the service life of the mechanism is improved, and the service life is more than 17000 times.

Owner:KUNSHAN LTK AUTOMATION EQUIP TECH

Probe of cantilevel probe card

InactiveCN101592682ANon-stickImprove conductivitySemiconductor/solid-state device testing/measurementElectronic circuit testingEpoxyProbe card

The invention discloses a probe of a cantilevel probe card (epoxide resin probe card). The technical scheme is achieved as follows: high electroconductive polymer materials, nanometer plating of which is thick in 1-20 nm, are plated on the surface of a probe point far away from 5-10mil about. The nanometer plating of the probe effectively enables the probe to have better qualities of no adhesive, high conductivity, contact force reduction and long service life through the plating process, thereby improving the test yield of washers, lowering the frequency of cleaning the probe and reducing the whole test cost.

Owner:IPWORKS TECH CORP

PCB thin board vertical flying probe test bracing frame

InactiveCN106338621ALoss reduction rateShake EliminationMeasurement instrument housingLoss rateTest efficiency

The invention relates to a PCB thin board vertical flying probe test bracing frame. The PCB thin board vertical flying probe test bracing frame comprises a bracing frame body, wherein the bracing frame body is arranged on a PCB surface, and the bracing frame is provided with through holes enabling probes penetrating through the bracing frame body to contact with a welding pad on a PCB or passage openings. Through the additionally-equipped PCB thin board vertical flying probe test bracing frame, the thin board is supported and is prevented from shaking, test points at a back surface can be further exposed, dual-surface simultaneous detection is realized, test accuracy is improved, a test yield is improved, and an electric measurement operation board loss rate can be reduced; the bracing effect of the bracing frame is excellent, dual-surface measurement and full-measurement-point measurement of 0.05-0.10mm thin boards are realized, measurement reliability is improved, and PCB flying probe test efficiency is greatly improved.

Owner:GUANGDE BAODA PRECISION CIRCUIT CO LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com