Multi-turn arranged carrier-free IC (Integrated Circuit) chip packaging component and manufacturing method thereof

A technology of chip package and production method, which is applied in the fields of electrical solid-state devices, semiconductor devices, semiconductor/solid-state device manufacturing, etc., to achieve good high-frequency performance, good electrical performance, and the effect of improving test yield and reliability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0055](1), wafer thinning thickness 250μm

[0056] Coarse grinding thickness range, from original wafer to final thickness + adhesive film thickness + 50 μm, rough grinding speed 5 μm / s; fine grinding thickness range, from final thickness + adhesive film thickness + 50 μm to final wafer thickness + adhesive film thickness , Grinding speed: 0.4μm / s, wafer thinning method ordinary QFN thinning, 6-inch to 8-inch wafer VG-502MKⅡ8B automatic thinning machine, 8-inch to 12-inch wafer adopts PG300RM / TCN;

[0057] (2), scribing

[0058] Wafers up to 8 inches use DISC3350 or double-knife dicing machines, and wafers from 8 inches to 12 inches use A-WD-300TXB dicing machines. Application of anti-fragmentation and anti-crack scribing software control technology, the scribing speed is controlled at ≤10mm / s;

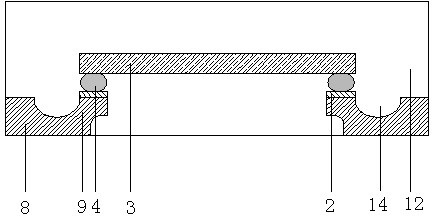

[0059] (3), single chip flip chip and reflow soldering

[0060] Single-chip flip-chip bonding, using IC chip 3 with bumps, flip-chip bonding is performed on a carrier frame with a ...

Embodiment 2

[0076] (1), wafer thinning thickness 250μm

[0077] Coarse grinding thickness range, from original wafer to final thickness + adhesive film thickness + 50μm, rough grinding speed 2μm / s; fine grinding thickness range, from final thickness + adhesive film thickness + 50μm to final wafer thickness + adhesive film thickness , Grinding speed: 0.9μm / s, ordinary QFN thinning method for wafer thinning, VG-502MKⅡ8B automatic thinning machine for 6-inch to 8-inch wafers, PG300RM / TCN for 8-inch to 12-inch wafers;

[0078] (2) Scribing

[0079] With embodiment 1;

[0080] (3), single chip flip chip and reflow soldering

[0081] With embodiment 1;

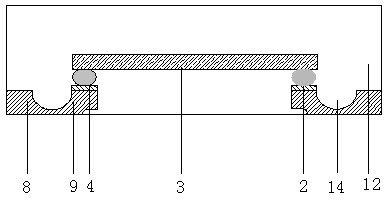

[0082] (4), bottom filling

[0083] Choose a material with a low thermal expansion coefficient, heat the underfill to 80°C, use vacuum technology to underfill the bumps 4 and the pins in the frame, and finally bake the finished product after the underfill in a QFN general-purpose baking oven Bake for about 15 minutes;

[0084] (5)~(7)

...

Embodiment 3

[0093] (1)~(7)

[0094] With embodiment 1;

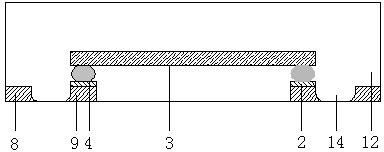

[0095] (8), separate pins

[0096] The pins are separated from each other by laser cutting method, and the cutting depth is 0.13μm;

[0097] (9), electroplating

[0098] The electroplating is the same as that of ordinary QFN packages, directly plating 7μm pure tin in the electroless plating system, and the baking conditions and methods after electroless plating are the same as those of ordinary QFN packages after electroplating;

[0099] (10), cutting and separating products

[0100] With embodiment 1.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com