Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

77results about How to "Improve data access speed" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

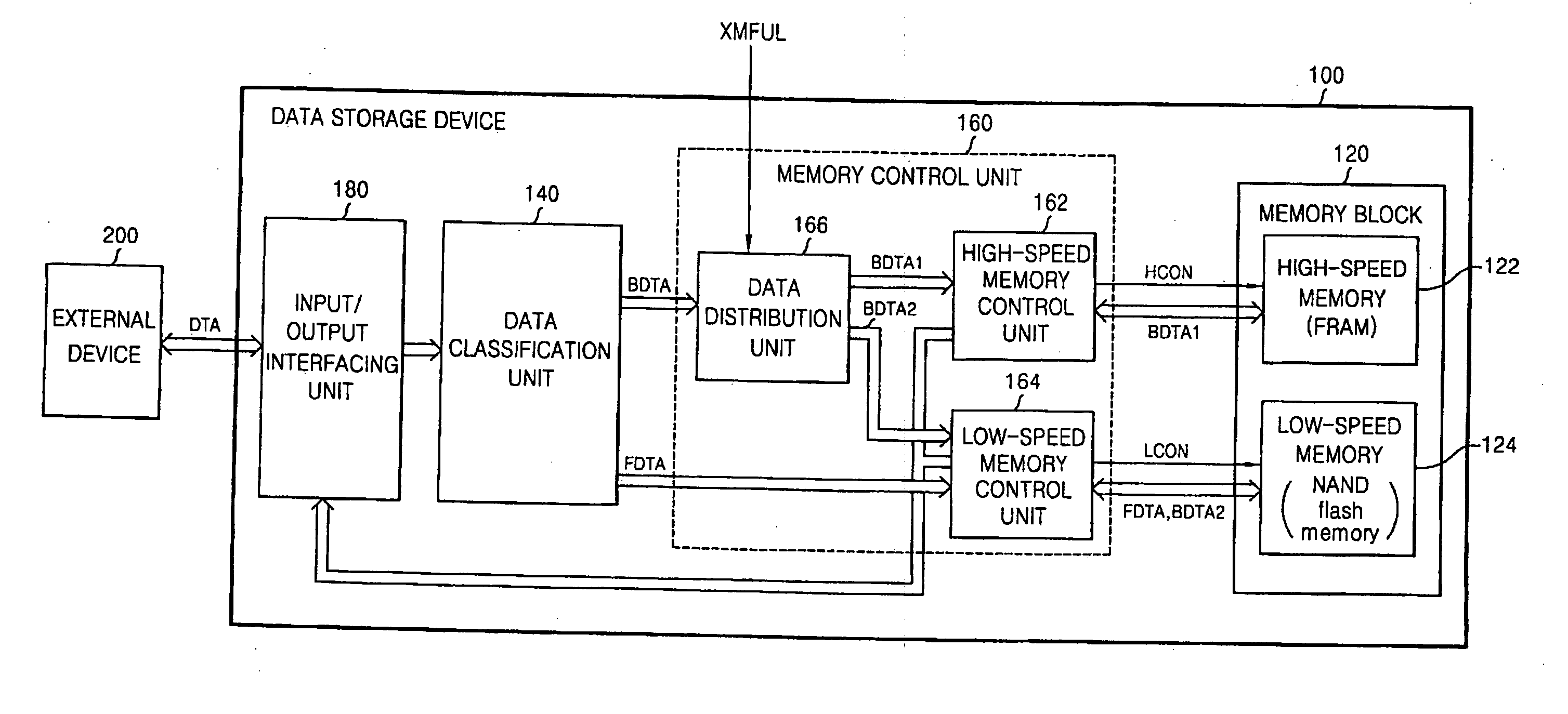

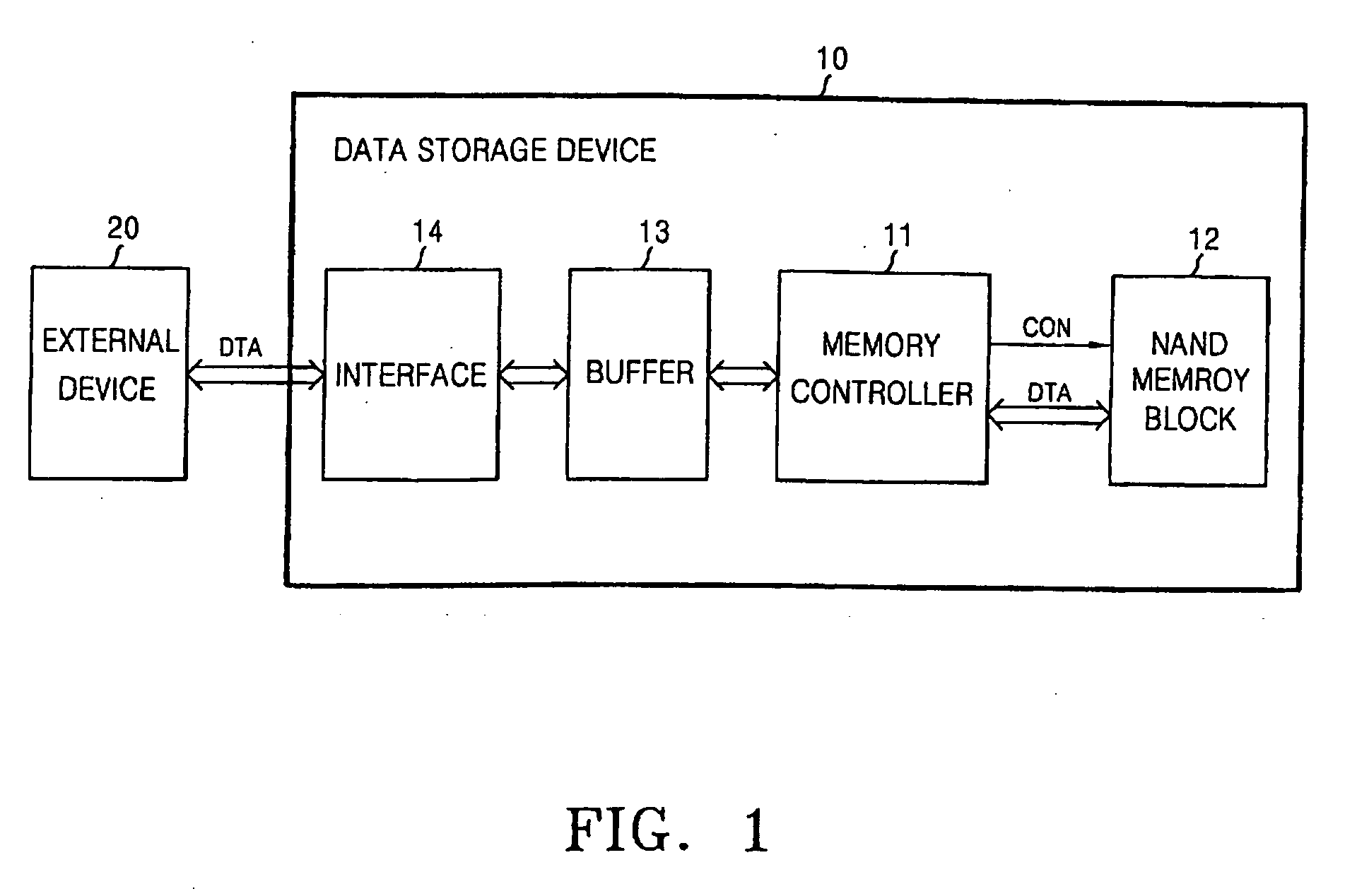

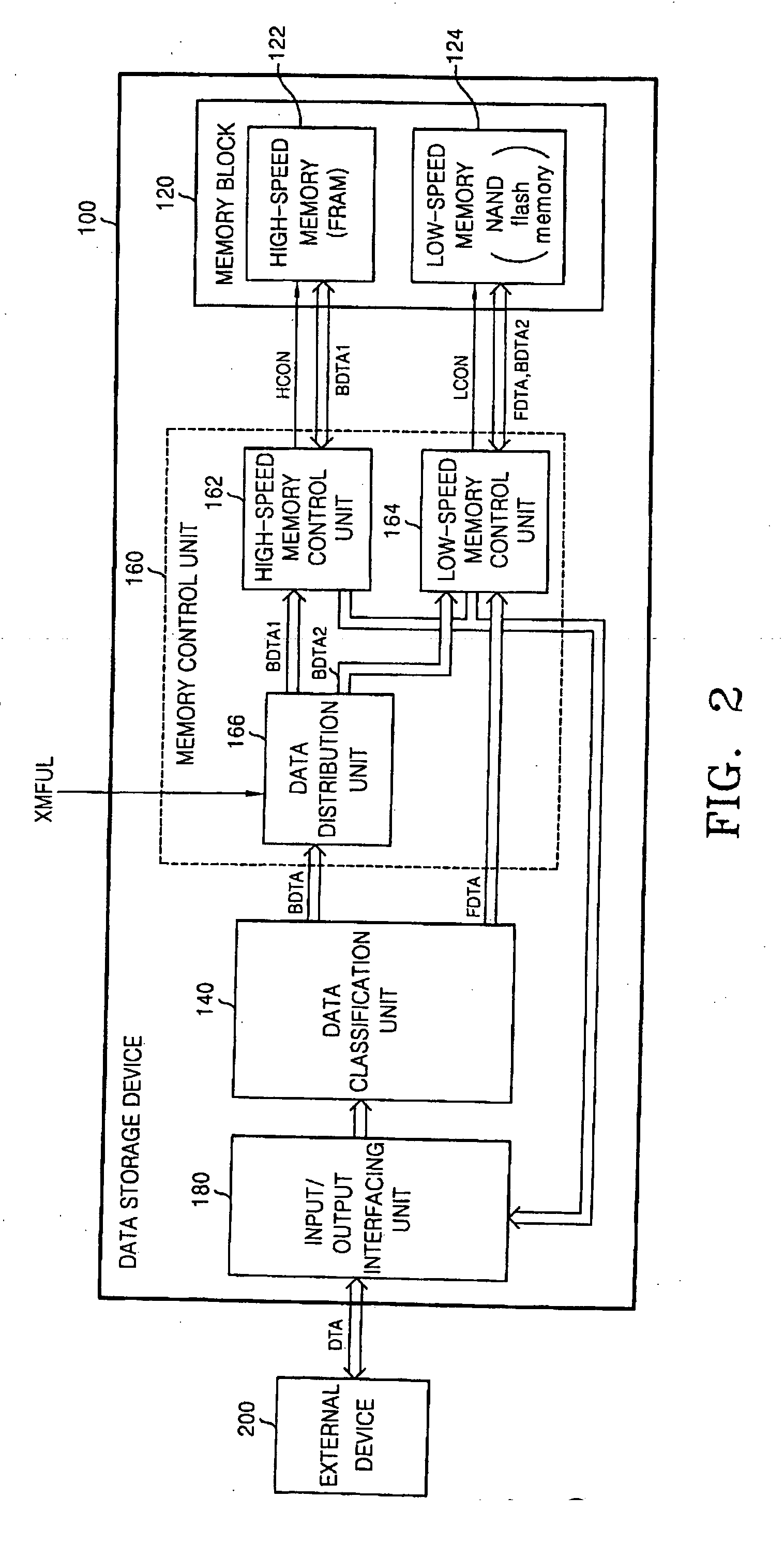

Data storage device and method using heterogeneous nonvolatile memory

ActiveUS20060248259A1Great access frequencyImprove data access speedMemory architecture accessing/allocationMemory adressing/allocation/relocationLow speedParallel computing

A data storage device includes a memory block, a data classification unit, and a memory control unit. The memory block includes a high-speed nonvolatile memory and a low-speed nonvolatile memory, wherein a data access speed of the high-speed nonvolatile memory is greater than a data access speed of the low-speed nonvolatile memory. The data classification unit classifies the externally input data into data groups including busy data and free data, where the busy data has greater access frequency than the free data. The memory control unit configured to store the externally input data classified by the data classification unit as busy data in the high-speed nonvolatile memory, and to store the externally input data classified by the data classification unit as free data in the low-speed nonvolatile memory.

Owner:SAMSUNG ELECTRONICS CO LTD

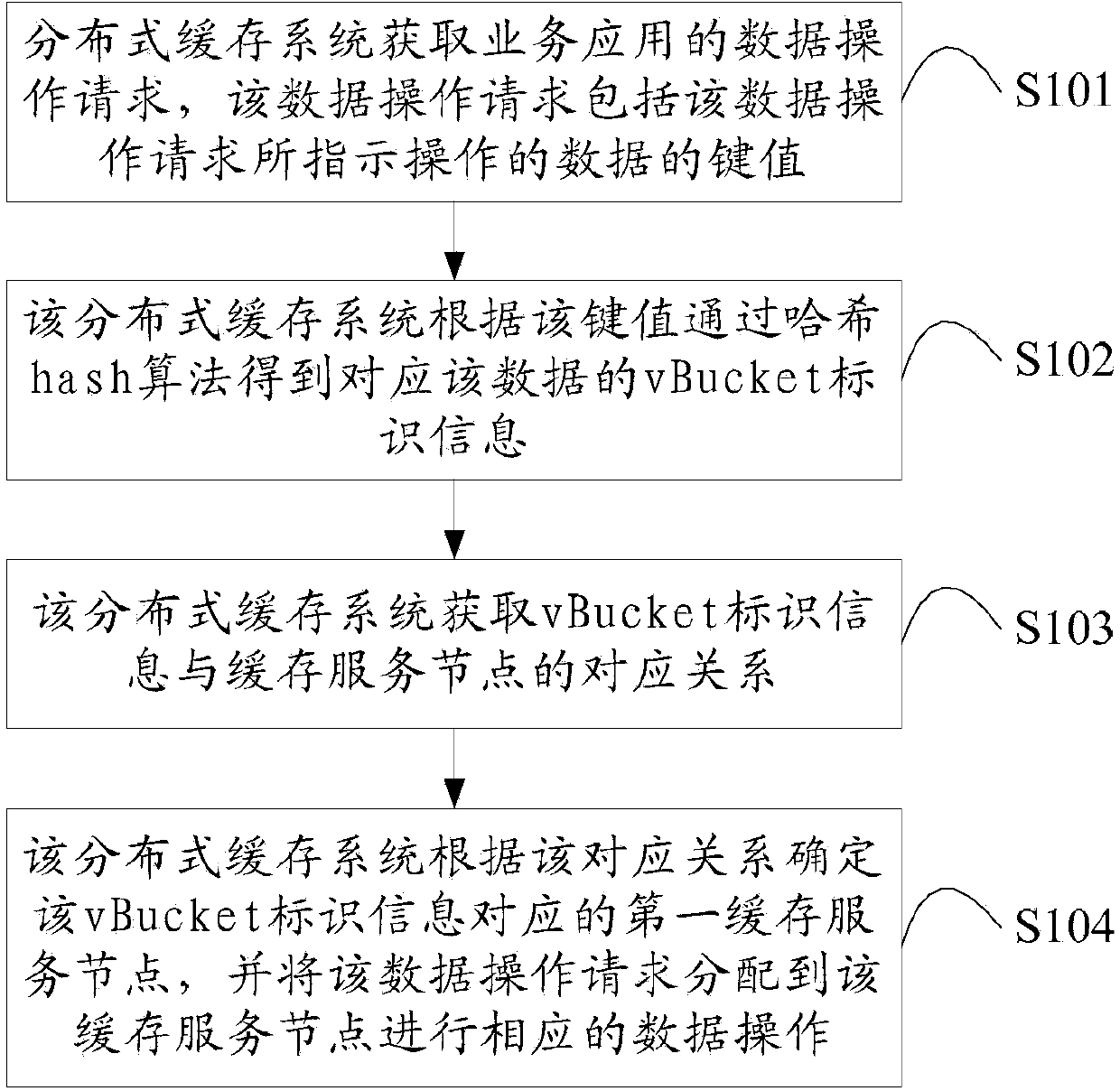

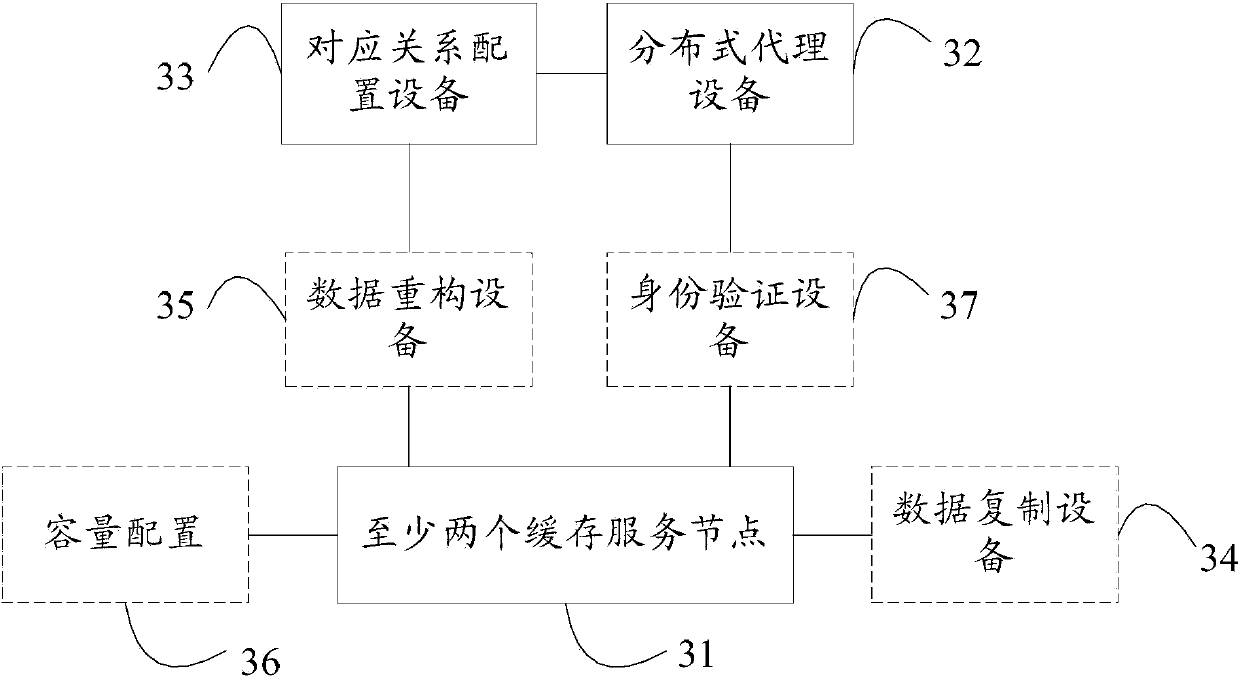

Distributed caching method and system

The embodiment of the invention provides a distributed caching method and a distributed caching system, and relates to the field of data storage. The data access speed of the distributed caching system is increased. The method comprises the following steps that the distributed caching system acquires a data operation request of a service application, and performs hash operation according to a key value of data indicated to be operated by the data operation request to obtain the identification information of a virtual queue vBucket corresponding to the data; the distributed caching system acquires a corresponding relationship between the identification information of the vBucket and a caching service node, determines a first caching service node corresponding to the identification information of the vBucket according to the corresponding relationship, and allocates the data operation request to the first caching service node for corresponding data operation. The embodiment of the invention is used for distributed data caching.

Owner:LETV CLOUD COMPUTING CO LTD

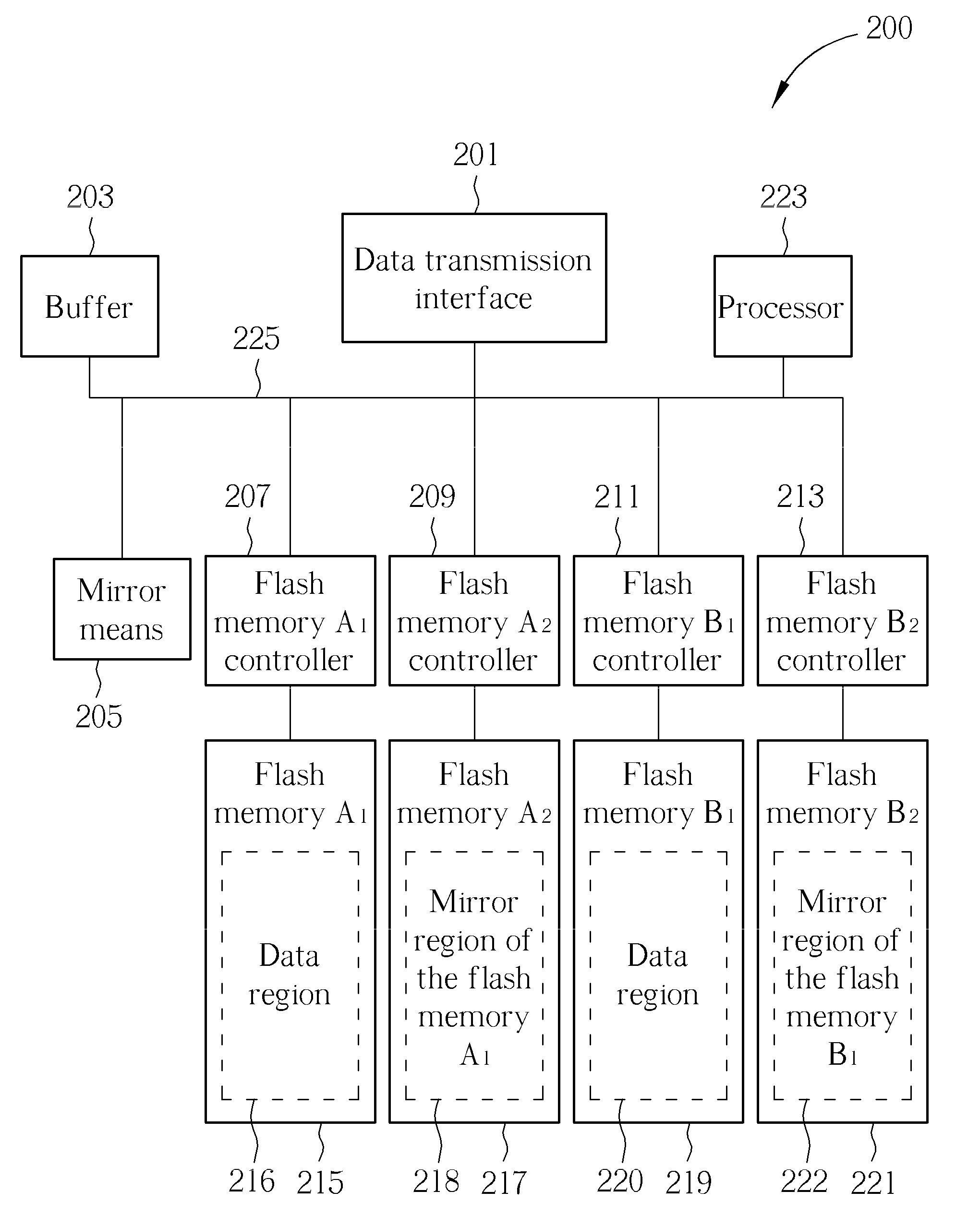

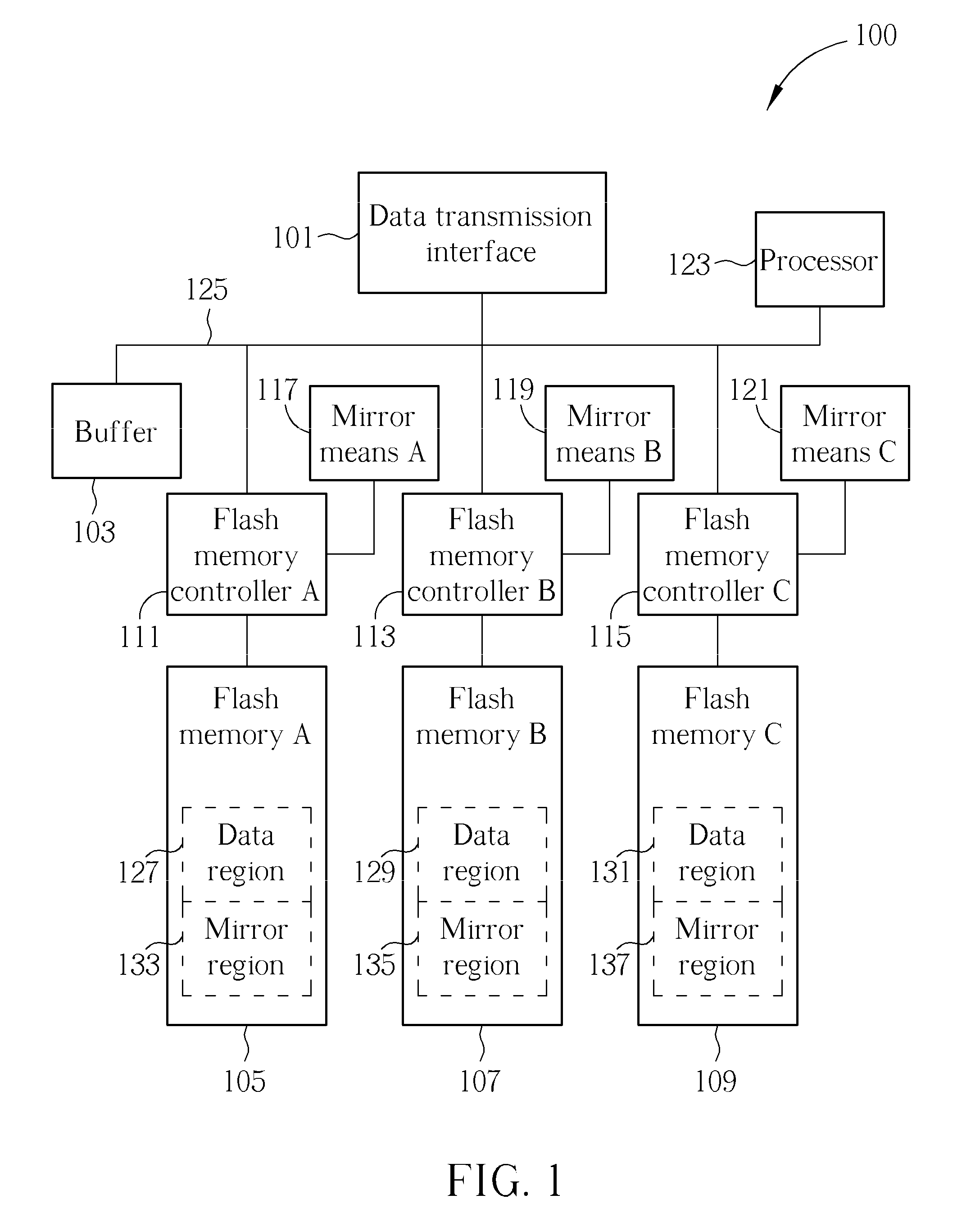

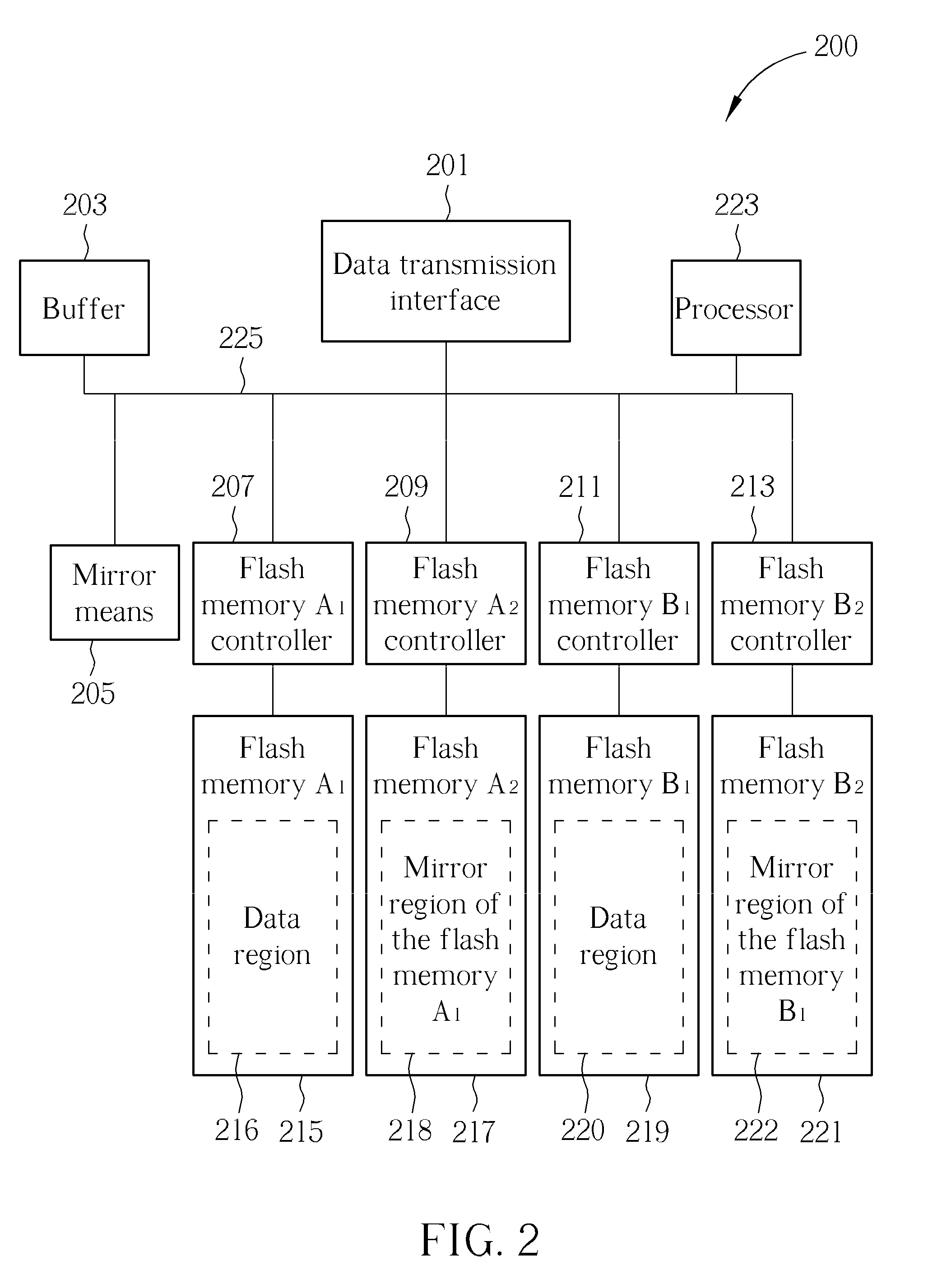

Data access apparatus and data access method

ActiveUS20100287433A1High data accuracyImprove access speedError preventionTransmission systemsAccess methodData access

A data access apparatus includes: a flash memory controller; a mirror means; and a flash memory including at least one data region and at least one mirror region. The mirror means copies data to form mirror data to the mirror region when the flash controller writes the data into the data region. The flash memory controller reads the mirror data to replace the data if the flash memory controller determines that the data include error(s) while the data are being read.

Owner:SILICON MOTION INC (TW)

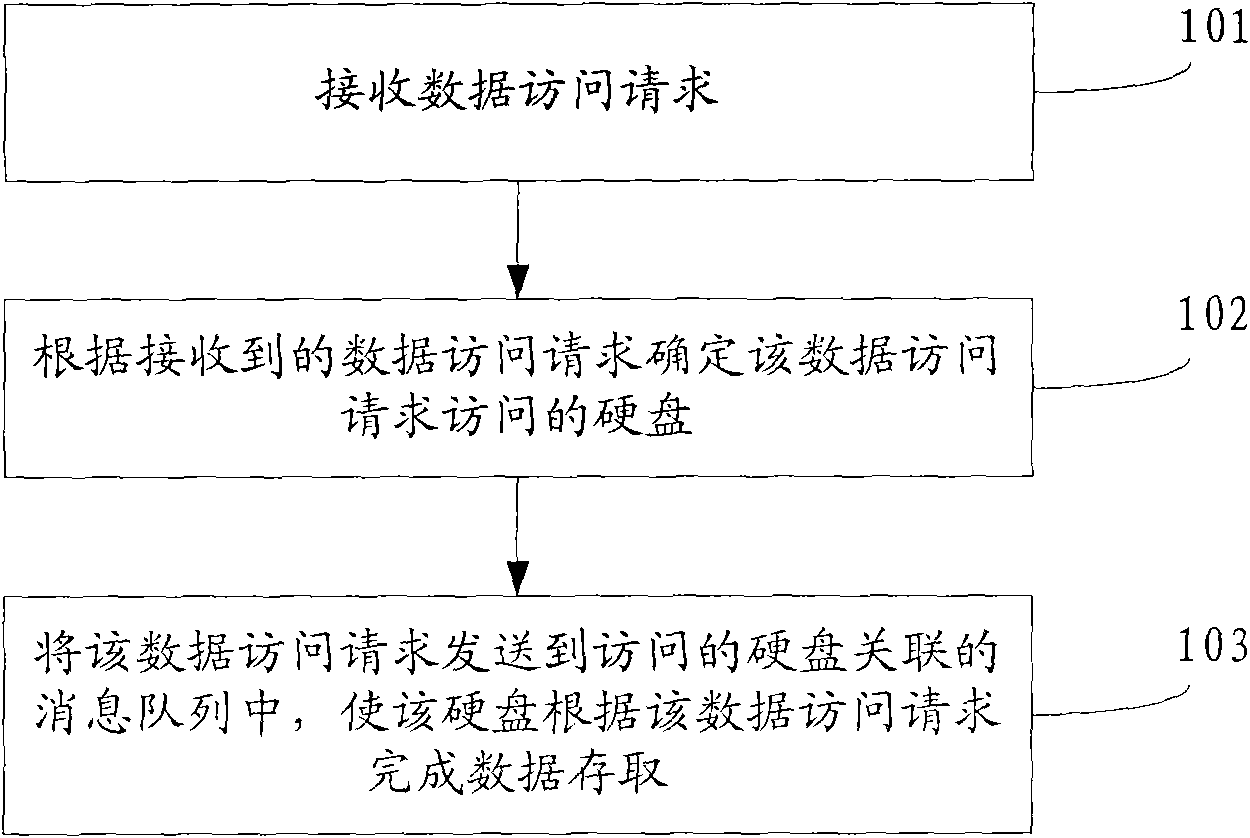

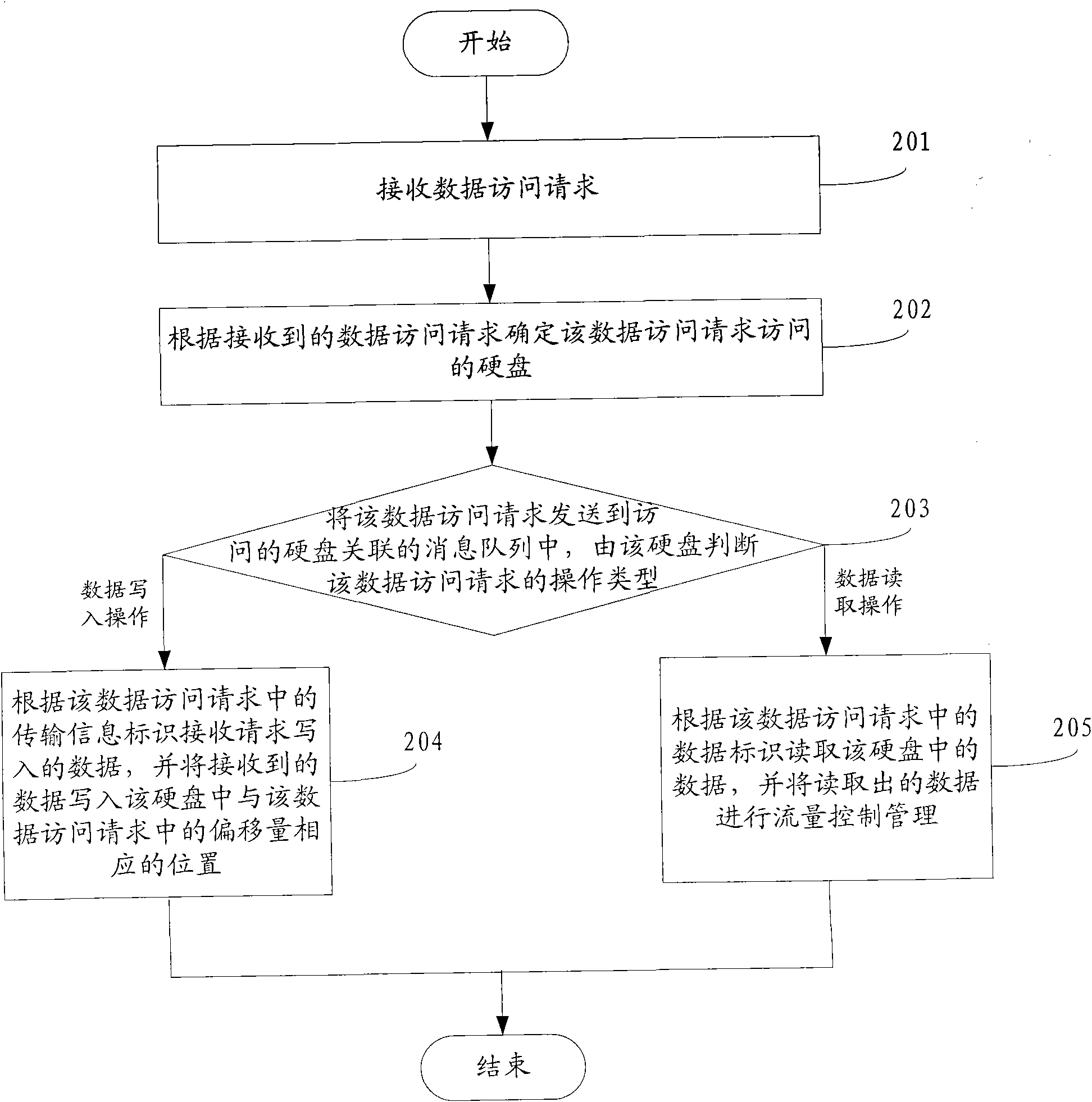

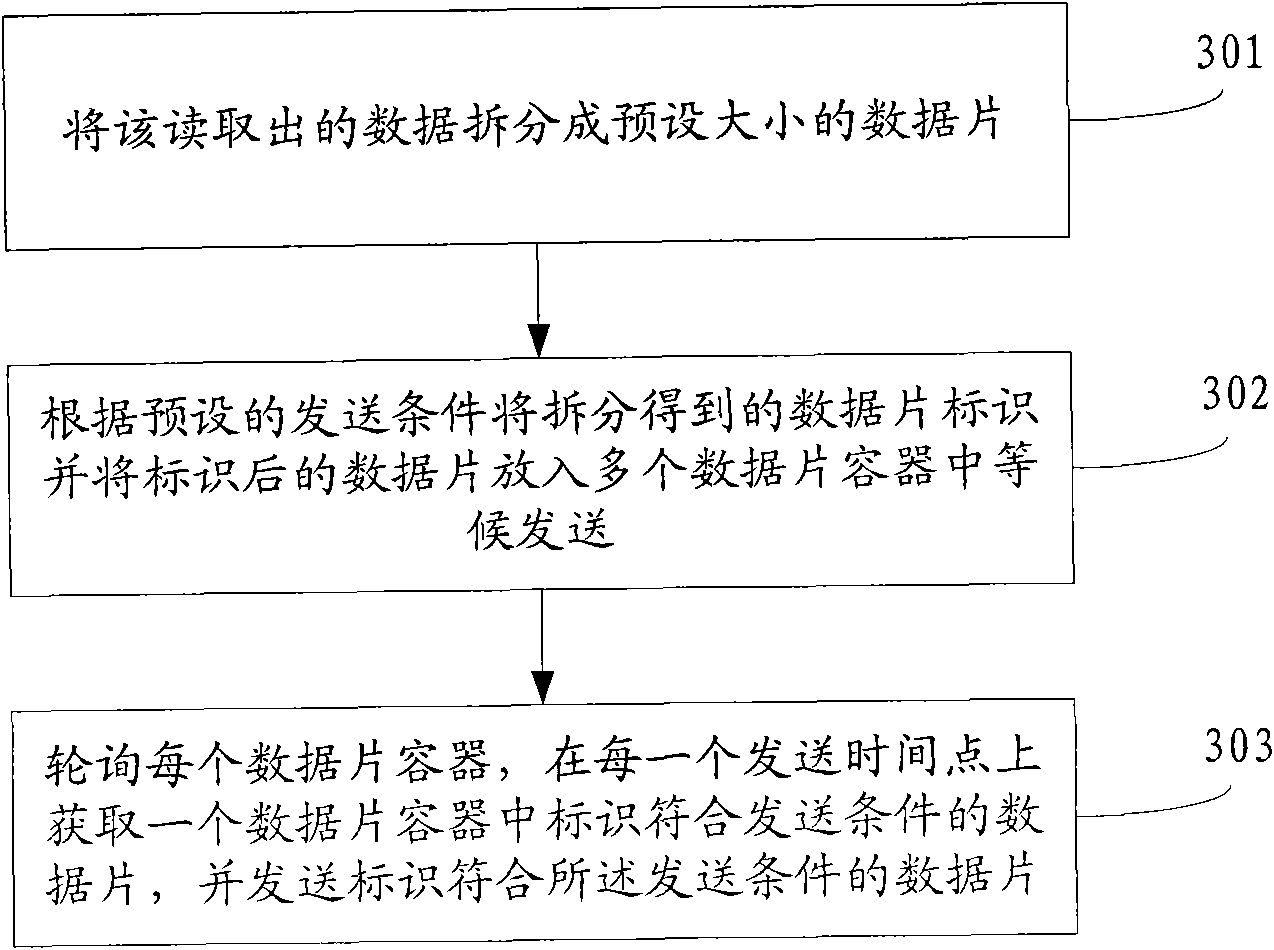

Data access method, message receiving resolver and system

InactiveCN102053800AEasy accessImprove data access speedInput/output to record carriersMessage queueComplete data

Owner:HUAWEI TECH CO LTD

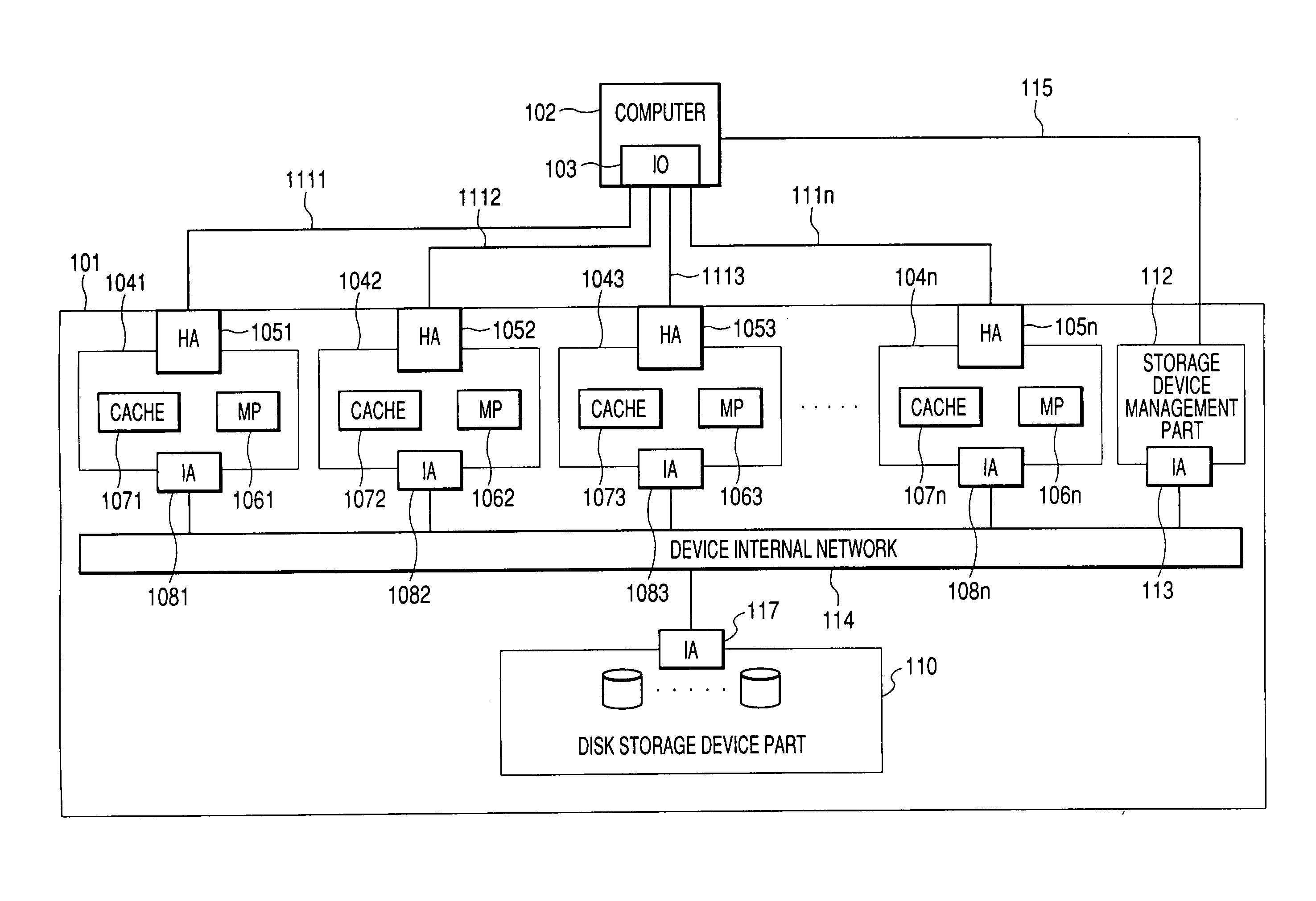

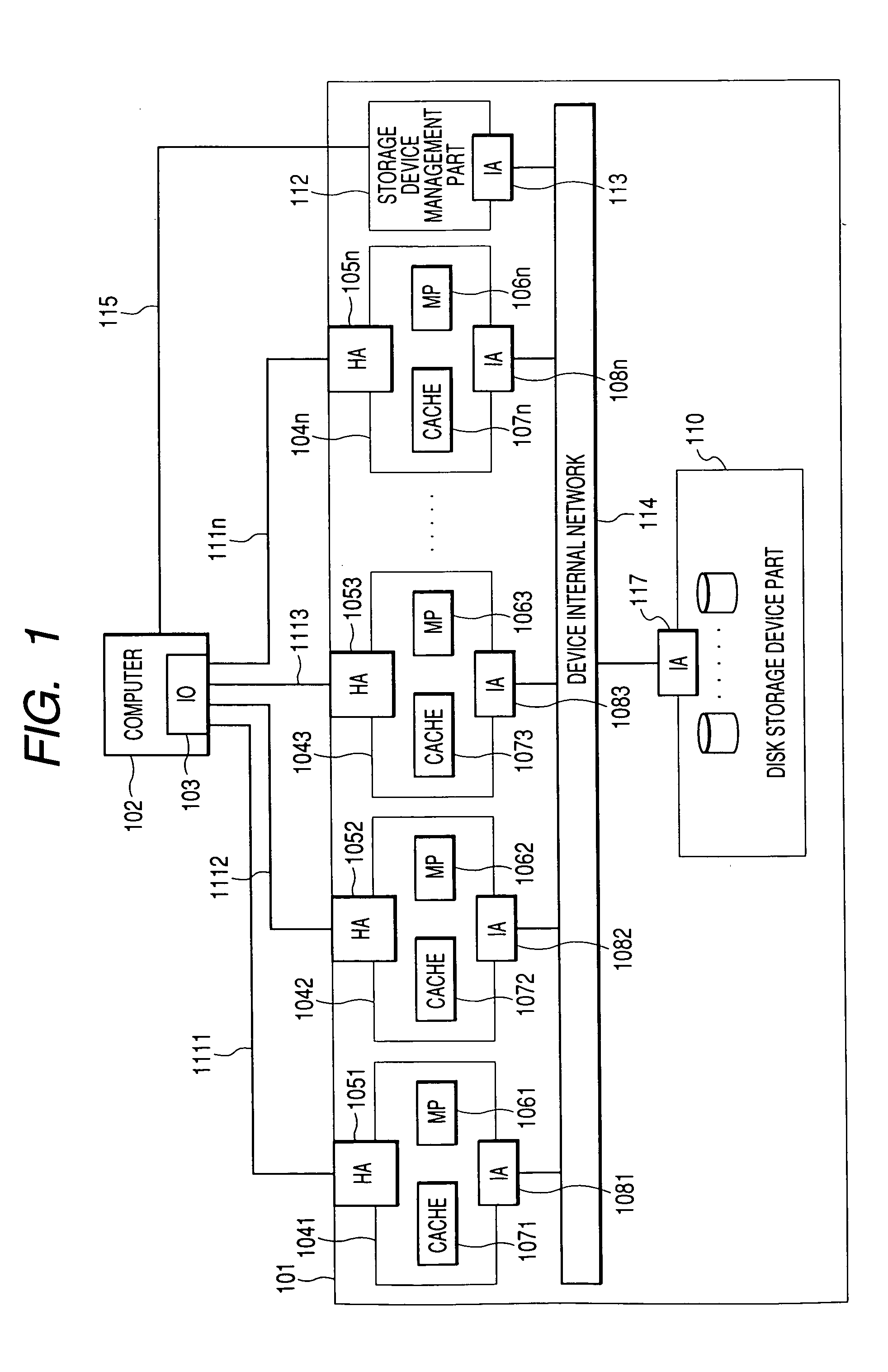

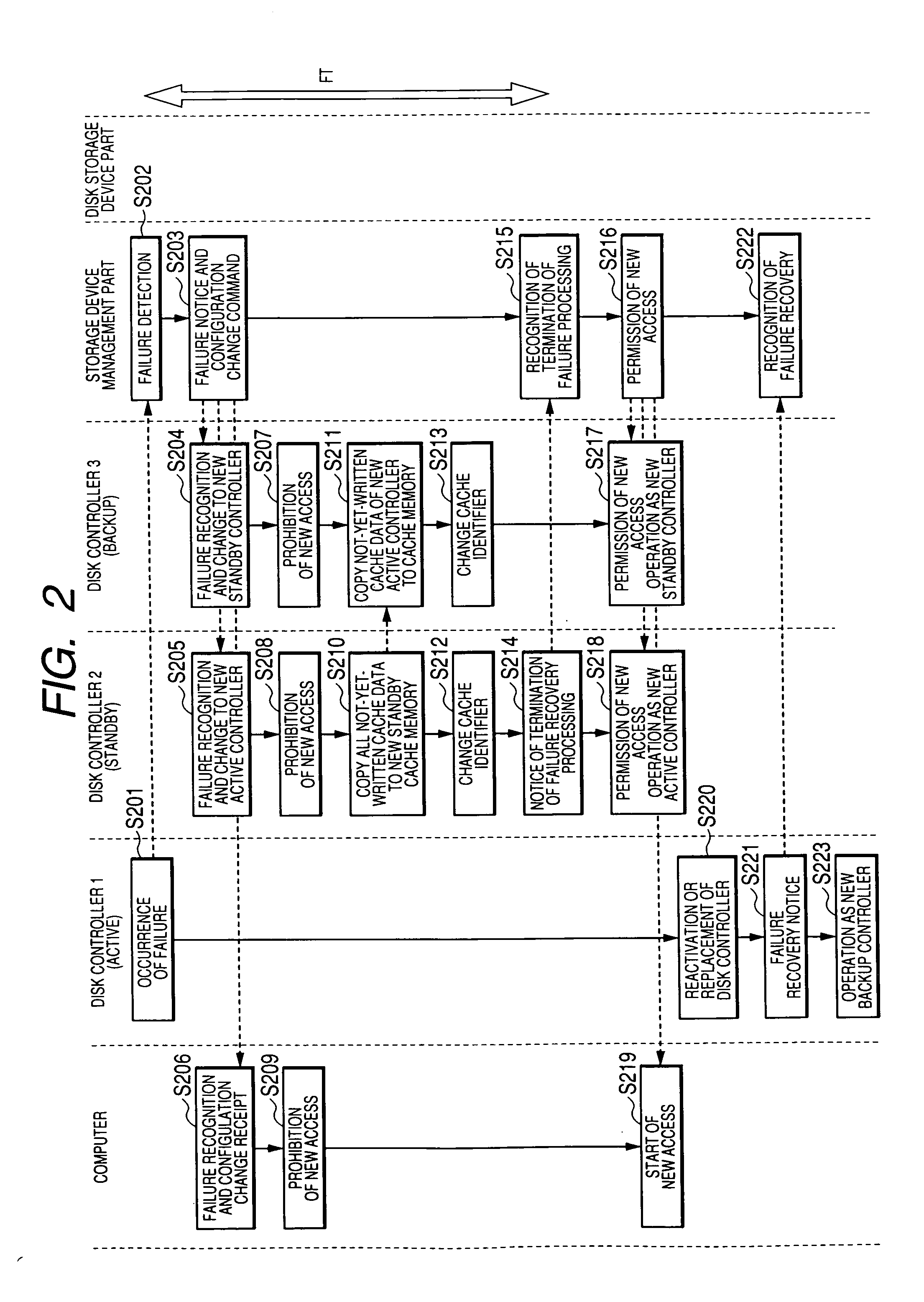

Cache control method in a storage system with multiple disk controllers

InactiveUS20050097402A1High reliable and high-speed data accessShorten speedInput/output to record carriersMemory systemsDisk controllerOperating system

In a storage device including plural disk controllers, the invention reduces time required for failure recovery when a failure occurs in the disk controllers. The storage device includes n (n>2, where n is an integer) disk controllers. The disk controller includes a cache memory. Data of the cache memory is copied to another cache memory. When a failure occurs in the disk controller, data not written to a disk of the data copied to the cache memory is transferred to further another cache memory.

Owner:HITACHI LTD

Circuit and method for supplying page mode operation in semiconductor storing device

A semiconductor memory device having a partial activation framework, which provides an efficient page mode operation while operating in a partial activation mode. Control circuits and methods are provided to enable a page mode operation (for read and write data accesses) in a semiconductor memory device (such as a DRAM, FCRAM) having a partial activation framework, resulting in an improved data access speed when data is written / read from memory locations having the same wordline address. In one aspect, a method for accessing data in a memory device comprises activating a first wordline corresponding to a first address to perform a data access operation, receiving a second address after the first address, if the second address is the same as the first address, generating a page mode enable signal for maintaining an activated state of the first wordline corresponding to the first address while activating a second wordline corresponding to the second address, and deactivating the first and second wordlines in response to disabling of the page mode enable signal.

Owner:SAMSUNG ELECTRONICS CO LTD

Auction bidding system based on distributed non-blocking asynchronous message processing mode and operation method thereof

ActiveCN107093138ARelieve pressureTroubleshoot out-of-sync issuesInterprogram communicationCommerceMessage queueComputer module

The invention relates to an auction bidding system based on a distributed non-blocking asynchronous message processing mode and an operation method thereof. The auction bidding system comprises an nginx server, a node server, a Tomcat cluster, a message queue, a bidding logic processing module cluster, and an Oracle database. A user initiates a request through a user terminal, and sends the request to the Tomcat cluster through the nginx server. The Tomcat cluster converts the request into a message, saves the message to the message queue, and gives a feedback to the user for response, wherein the feedback is used to remind the user that the request has been received and is being processed. The bidding logic processing module cluster processes the message in the message queue, and notifies the user of the processing result through the node server.

Owner:山东佳联电子商务有限公司

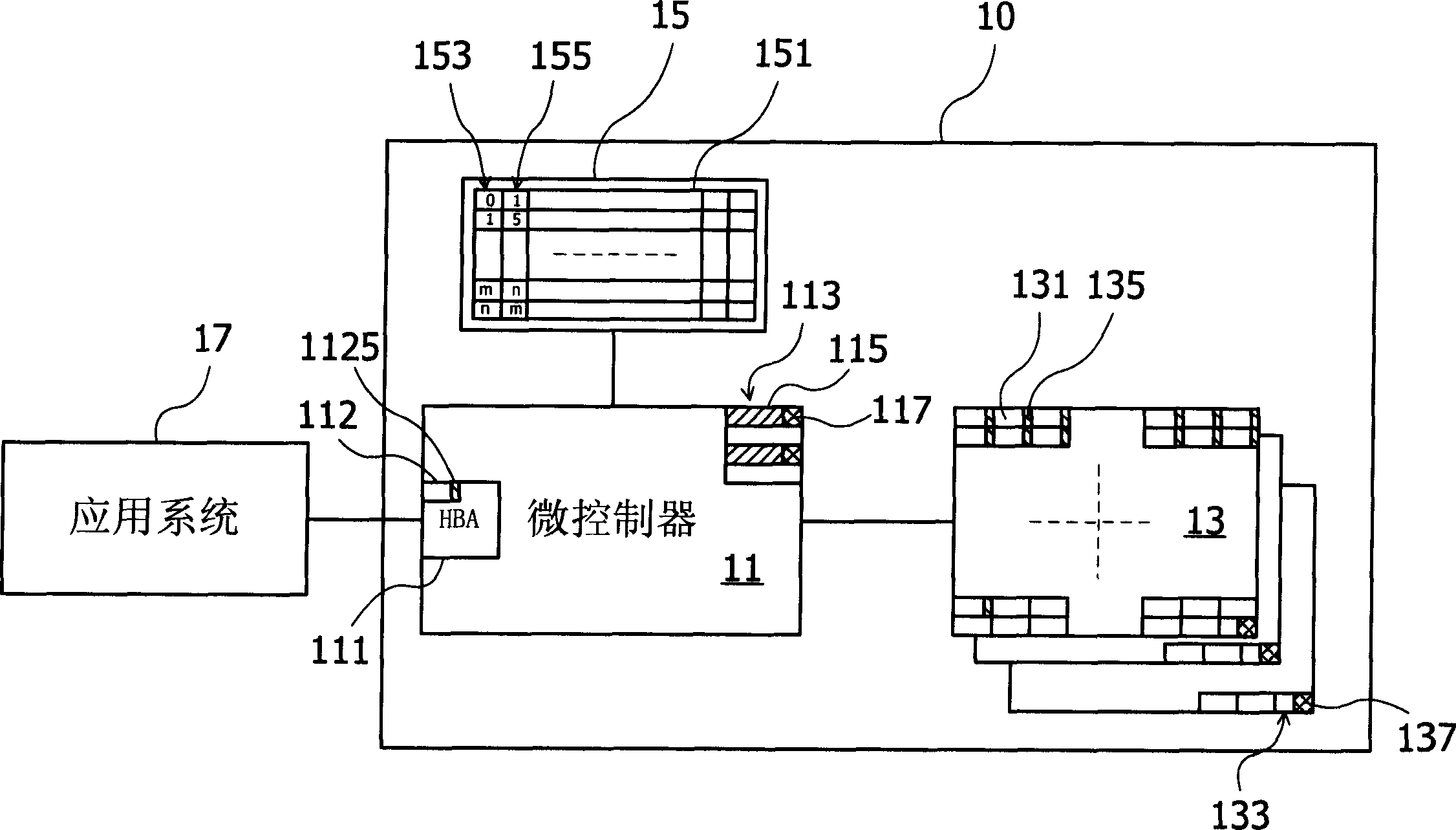

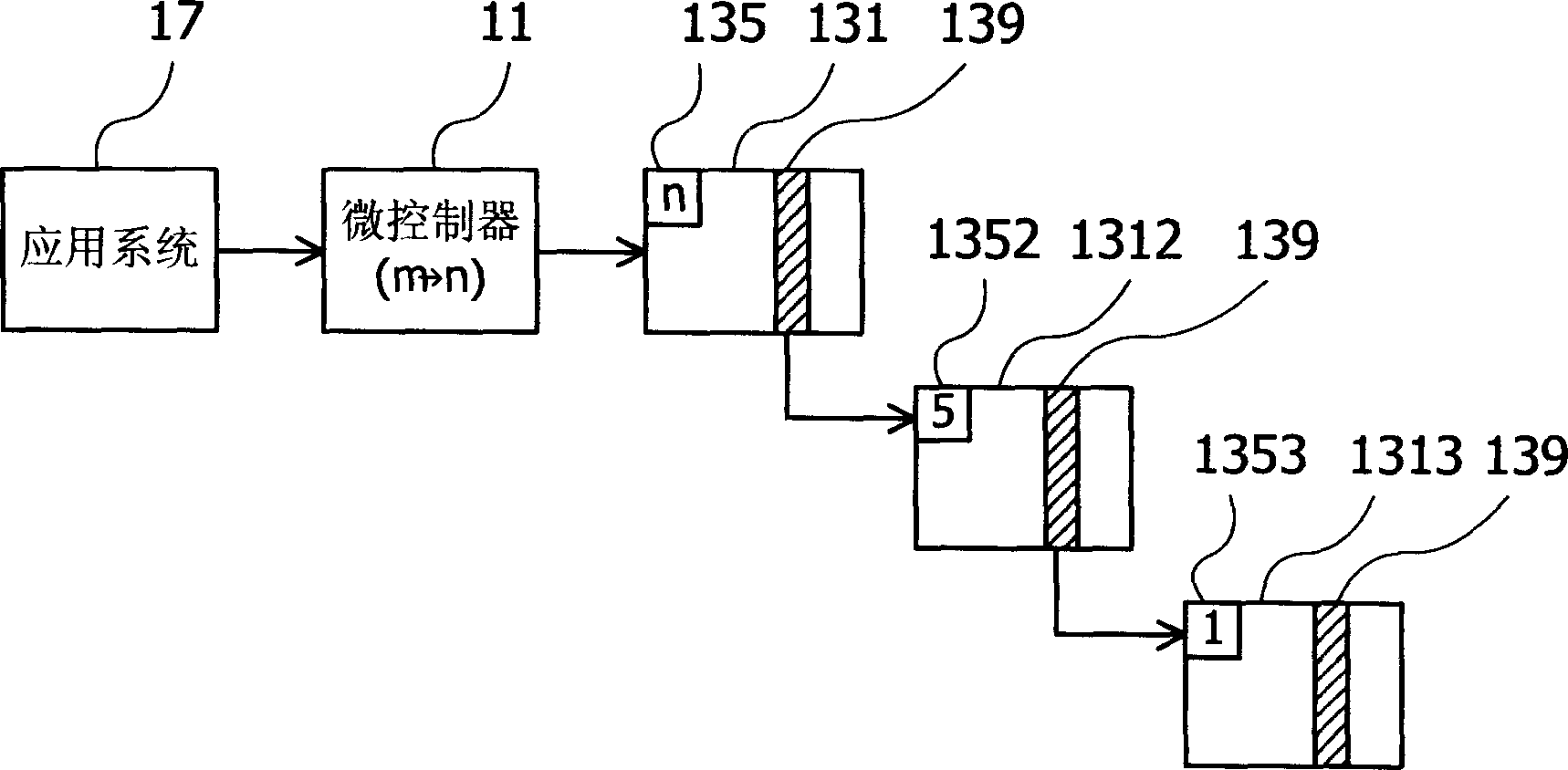

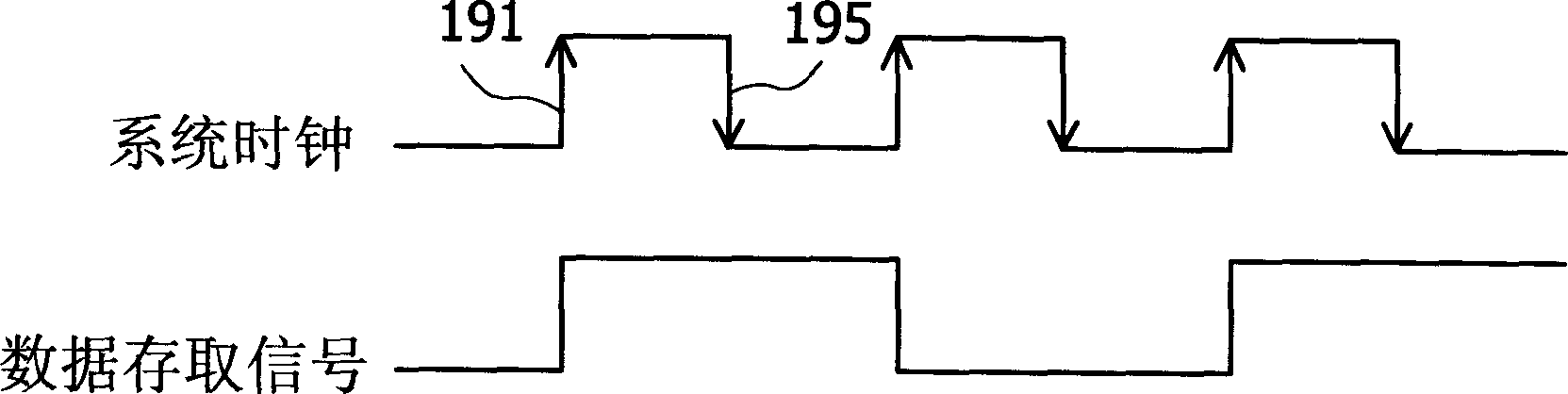

Flash memory system

InactiveCN1700189AEnsure safetySave memory capacityMemory adressing/allocation/relocationRead-only memoriesLogical addressElectric energy

The invention relates to a flash memory storage system which comprises microcontroller, at least one flash memory of microcontroller with each flash memory including many entity storage blocks. Each entity storage block includes an entity address and many entity sectors which comprise at least one user data area and a logical address orienting fence, wherein each logical address orienting fence can write a logical address orienting data at user data area when it storage a entity data; logical address orienting data can log a corresponding logical address; a temporary storage which is connected with microcontroller can storage a connecting look-up table which can log each entity block's address and the corresponding logical address of logical storage block.

Owner:PROLIFIC TECH INC

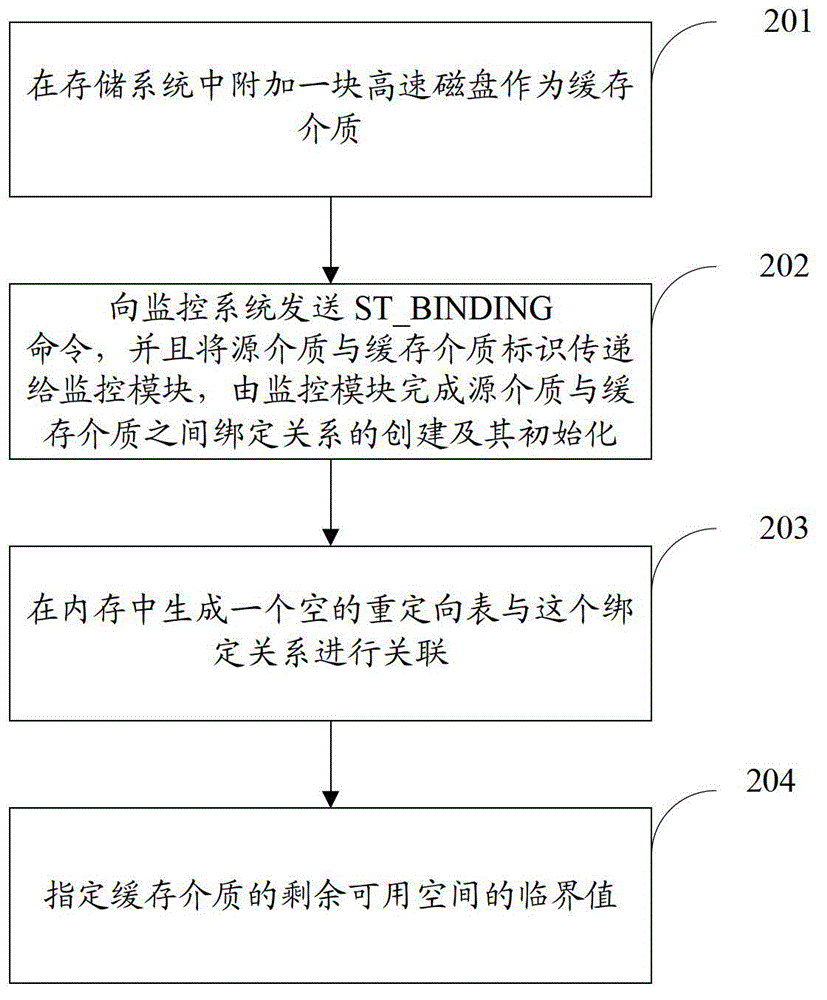

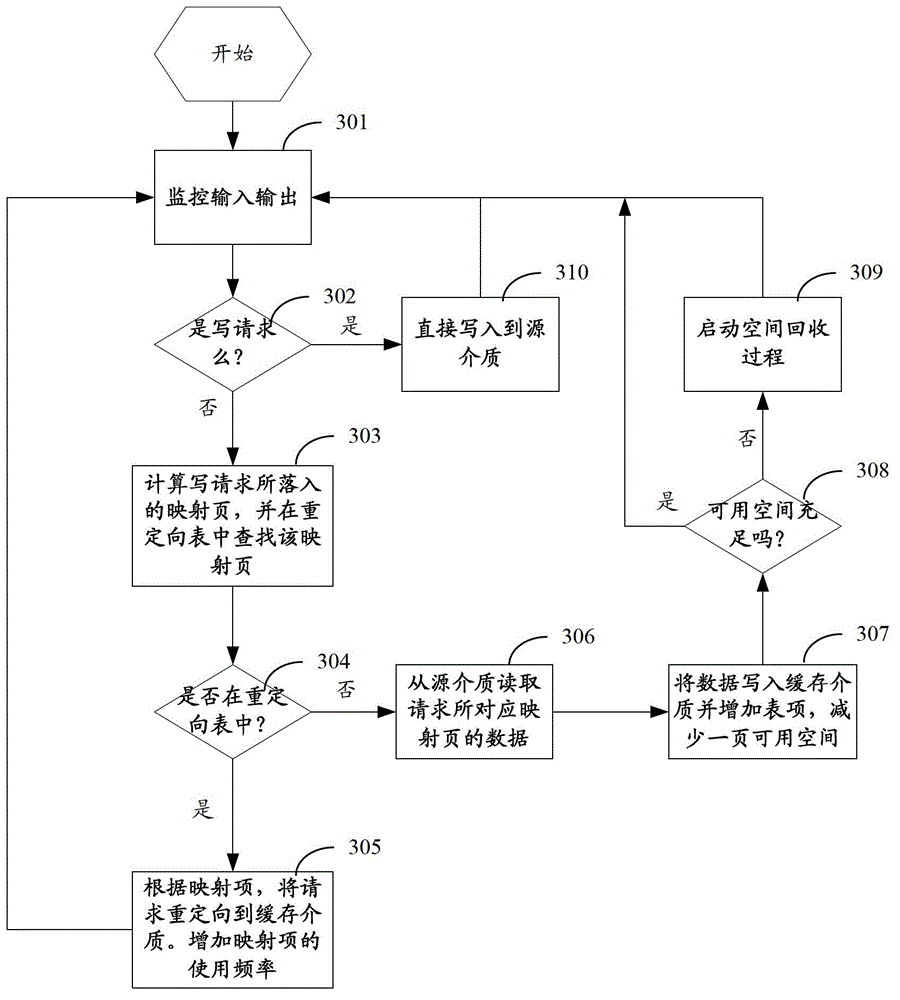

Method for improving speed of storage system data access

InactiveCN102981979AImprove data access speedMemory adressing/allocation/relocationInput/outputLow speed

The invention discloses a method for improving speed of storage system data access. The method for improving the speed of the storage system data access is capable of obtaining all the input output requests for low speed storage media, and redirecting the input output requests to high speed storage media according to an access situation. Therefore the aim of improving the speed of the storage system data access is achieved.

Owner:EISOO SOFTWARE

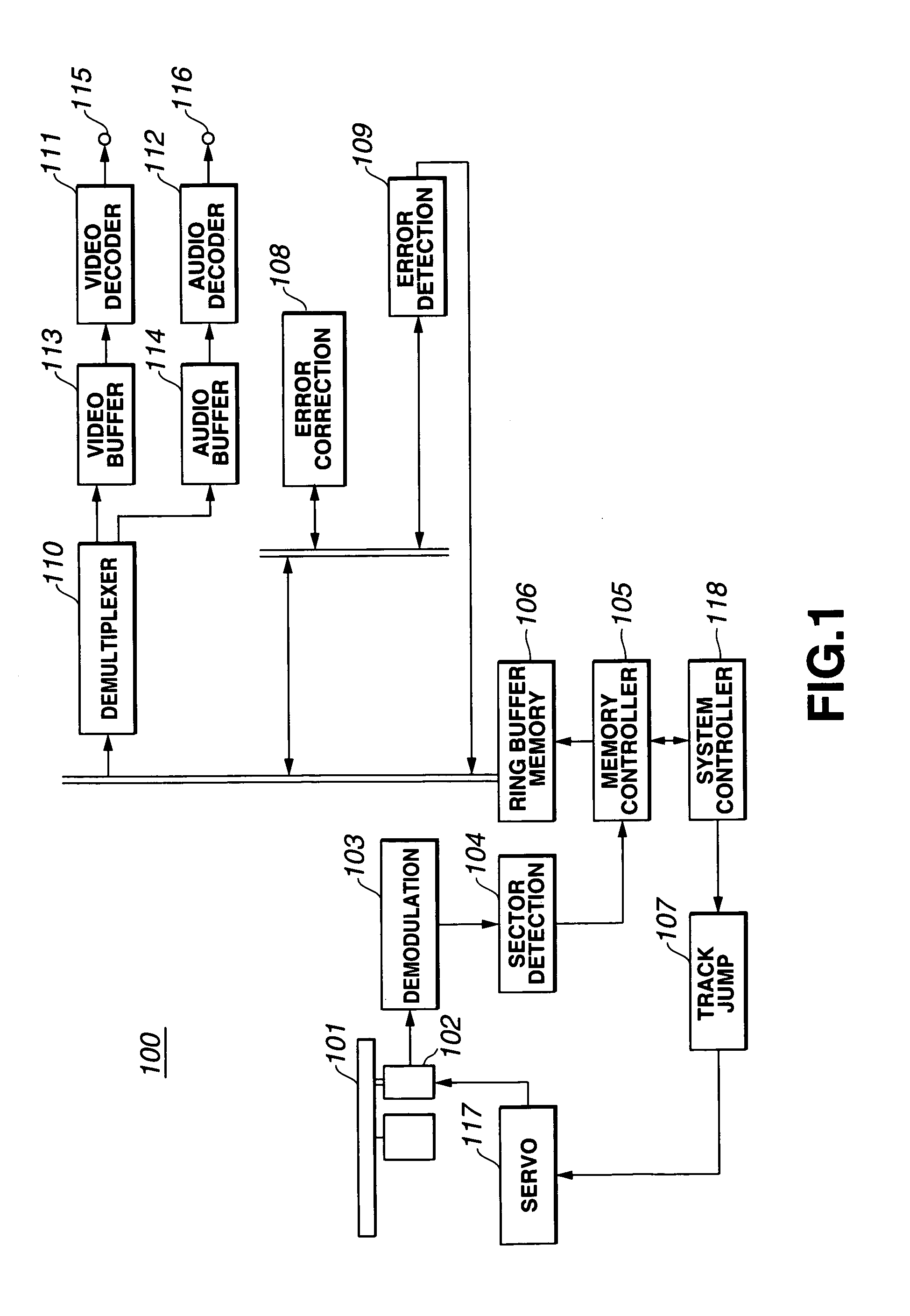

Data reproduction apparatus and method

InactiveUS6965725B1Reduce throughputImprove data access speedTelevision system detailsColor television signals processingComputer hardwareControl signal

The objectives of the present invention are to reduce the throughput required for a rapid reproduction or other special types of reproduction and to improve also the data access speed at the time of a rapid reproduction. In order to achieve these objectives, the system controller 19 controls so that the address information of the MPEG data reproduced by a pickup 2 may be used to create the first reproduction control information at a sector detection circuit 4, that the second reproduction control information corresponding to the starting point of pictures contained in the MPEG data destined to be reproduction signals by the first reproduction control signal and subjected to an error correction in an error correction circuit 7 may be created in a stream detection circuit 9, and that some MPEG data out of the entire MPEG data may be outputted for a rapid reproduction by referring to the second reproduction control information, and through these steps, the interval of reproducing I pictures in a rapid reproduction by using for example only I pictures is reduced and a smooth reproduction is achieved.

Owner:SONY CORP

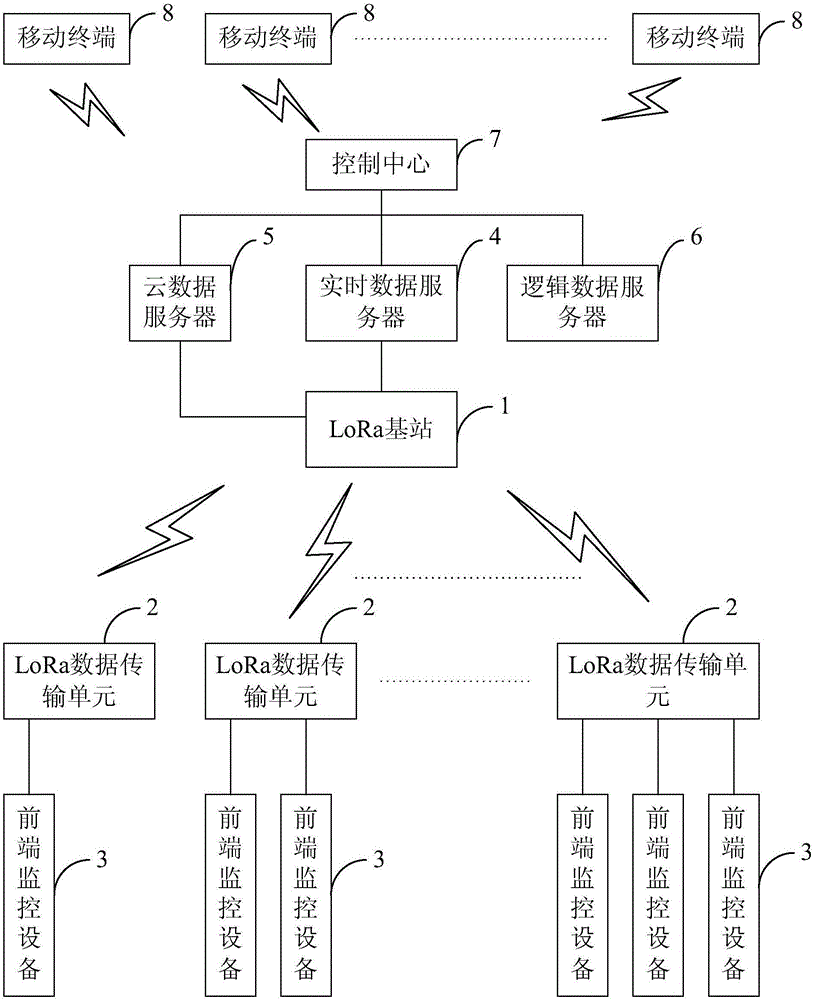

Residential area monitoring system based on Internet of things

InactiveCN106713413ARealize real-time monitoringImprove data access speedMeasurement devicesTransmission systemsReal-time dataThe Internet

The invention relates to the technical field of the Internet of things and discloses a residential area monitoring system based on the Internet of things. The system comprise an LoRa base station, LoRa data transmission units, front end monitoring devices, a real-time data sever, a cloud data server, a logic data server and a control center. The front end monitoring devices are connected with the LoRa data transmission units. The LoRa data transmission units are connected with the LoRa base station. The LoRa base station is connected with the real-time data sever and the cloud data server. The front end monitoring devices transmit monitored or collected front end data to the real-time data sever and the cloud data server through the LoRa data transmission units and the LoRa base station. The control center is connected with the cloud data server, the logic data server and the control center. According to the system, real-time monitoring is carried out a residential area with relatively large area in a wireless networking mode of the LoRa base station and LoRa data transmission units, the real-time monitoring data and the processed data are stored separately, and the subsequent data access speed is increased.

Owner:云南佳海网络科技有限责任公司

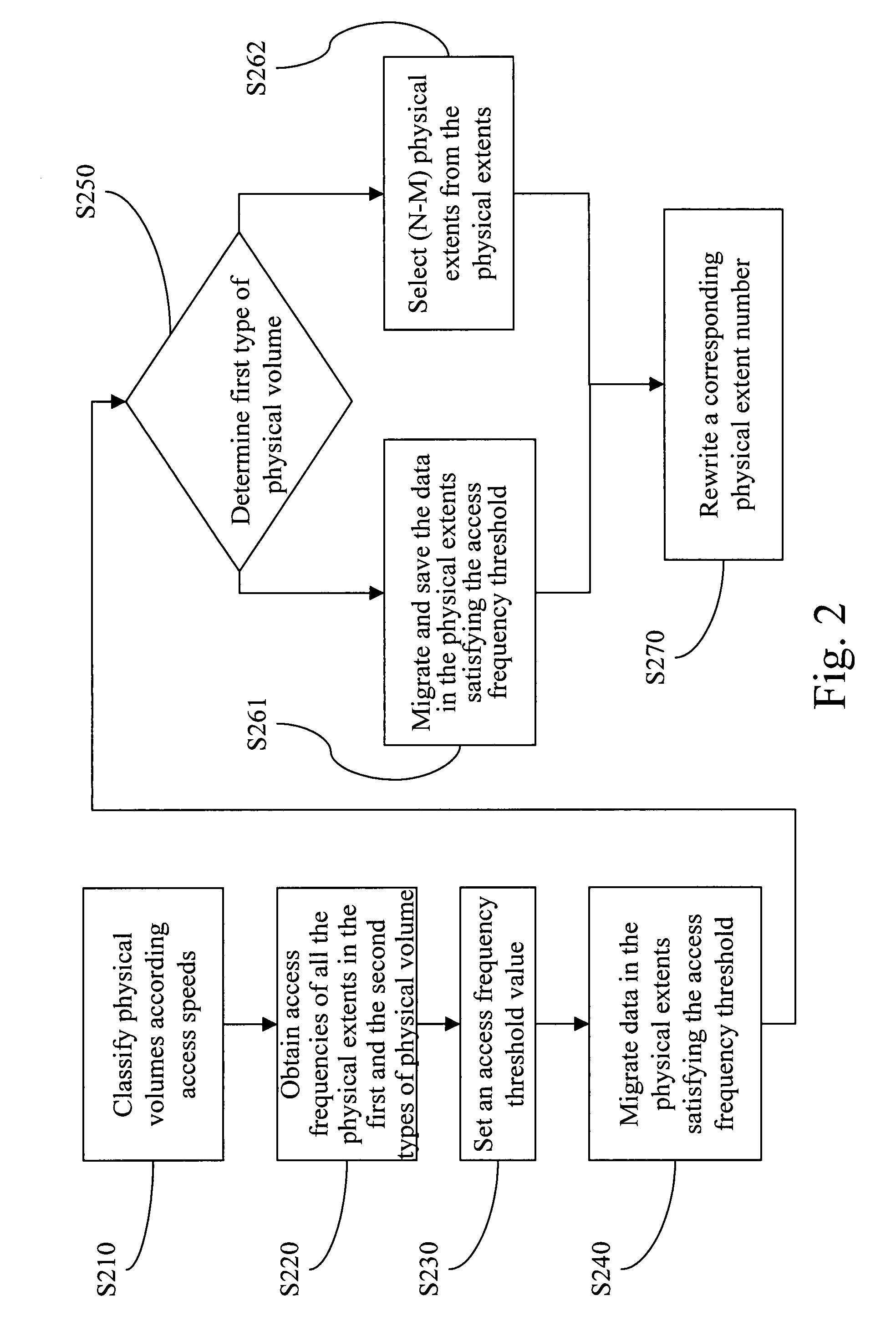

Data management method for logical volume manager

InactiveUS20090138530A1Improve data access speedMemory systemsInput/output processes for data processingAccess frequencyData management

A data management method for logical volume manager (LVM), called LVM includes a first type of physical volume and a second type of physical volume. Access speed of the first type of physical volume is higher than that of the second type of physical volume. Each physical volume has a plurality of physical extents, and a data storage method includes the following steps. Obtaining access frequencies of all the physical extents in statistics; performing a data migration operation, migrating and saving data in the physical extents satisfying an access frequency threshold value in the second type of physical volume to the physical extents without any data in the first type of physical volume; and rewriting a corresponding physical extent number for the migrated data.

Owner:INVENTEC CORP

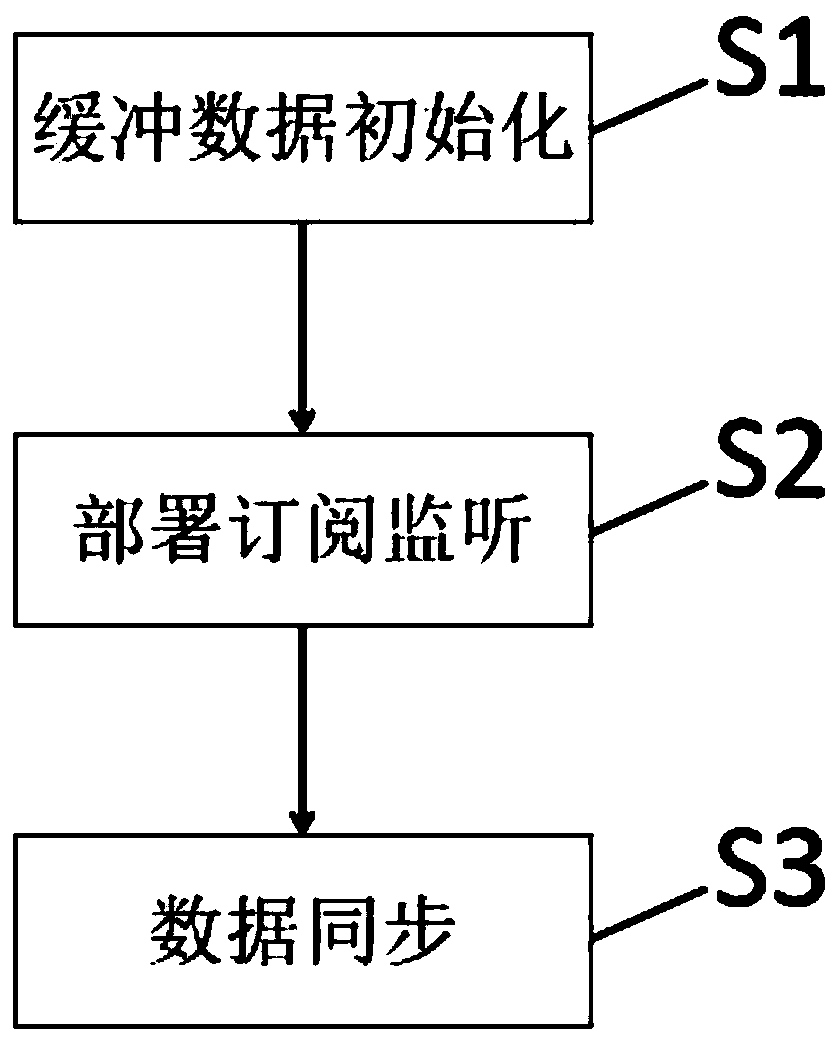

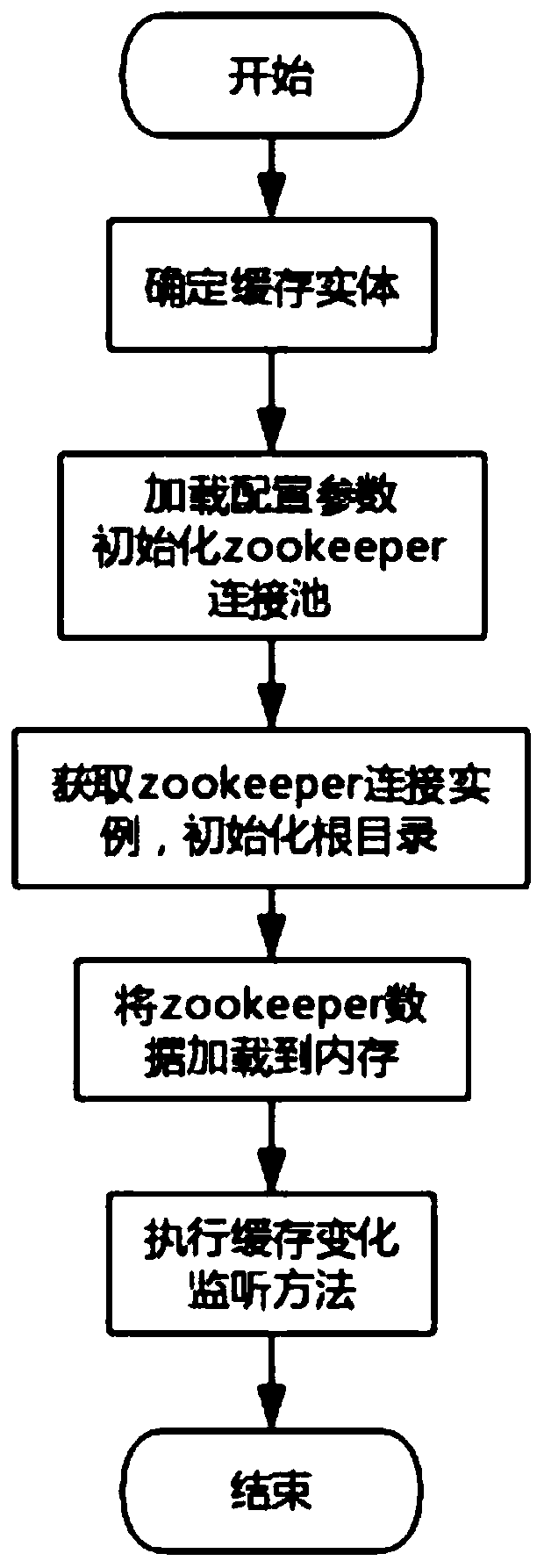

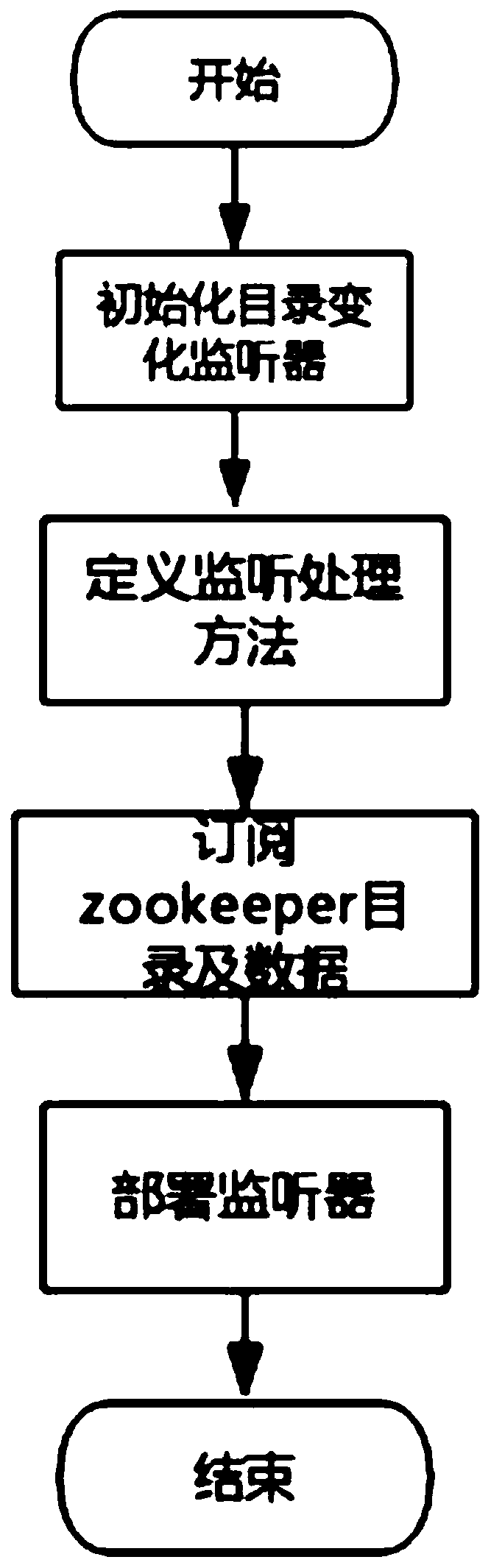

A distributed architecture data consistency method based on a Zookeeper

ActiveCN109815248AImprove data access speedImproved performance and data consistencyDatabase updatingSpecial data processing applicationsDistributed computing

The invention discloses a distributed architecture data consistency method based on a Zookeeper, and relates to the technical field of data processing. The method comprises the following steps of: initializing buffer data: loading data in a Zookeeper into a memory of each node after each node of the distributed system is started; defining a subscription monitoring method, each node subscribes to aZookeeper directory and data, deploying monitoring; and data synchronization: after monitoring the data change in the Zookeeper, updating the memory data of each node through a deployed monitoring method, and keeping the data synchronization among the nodes. According to the invention, a Zookeeper component is used as a cache data synchronization manager in a distributed architecture system; thedistributed multi-node cache data is synchronized in real time by utilizing a release and subscription mechanism of the Zookeeper, and meanwhile, the data access speed is greatly increased based on aZookeeper database of a memory, so that the performance and the data consistency are well improved in a distributed architecture system.

Owner:科大国创云网科技有限公司

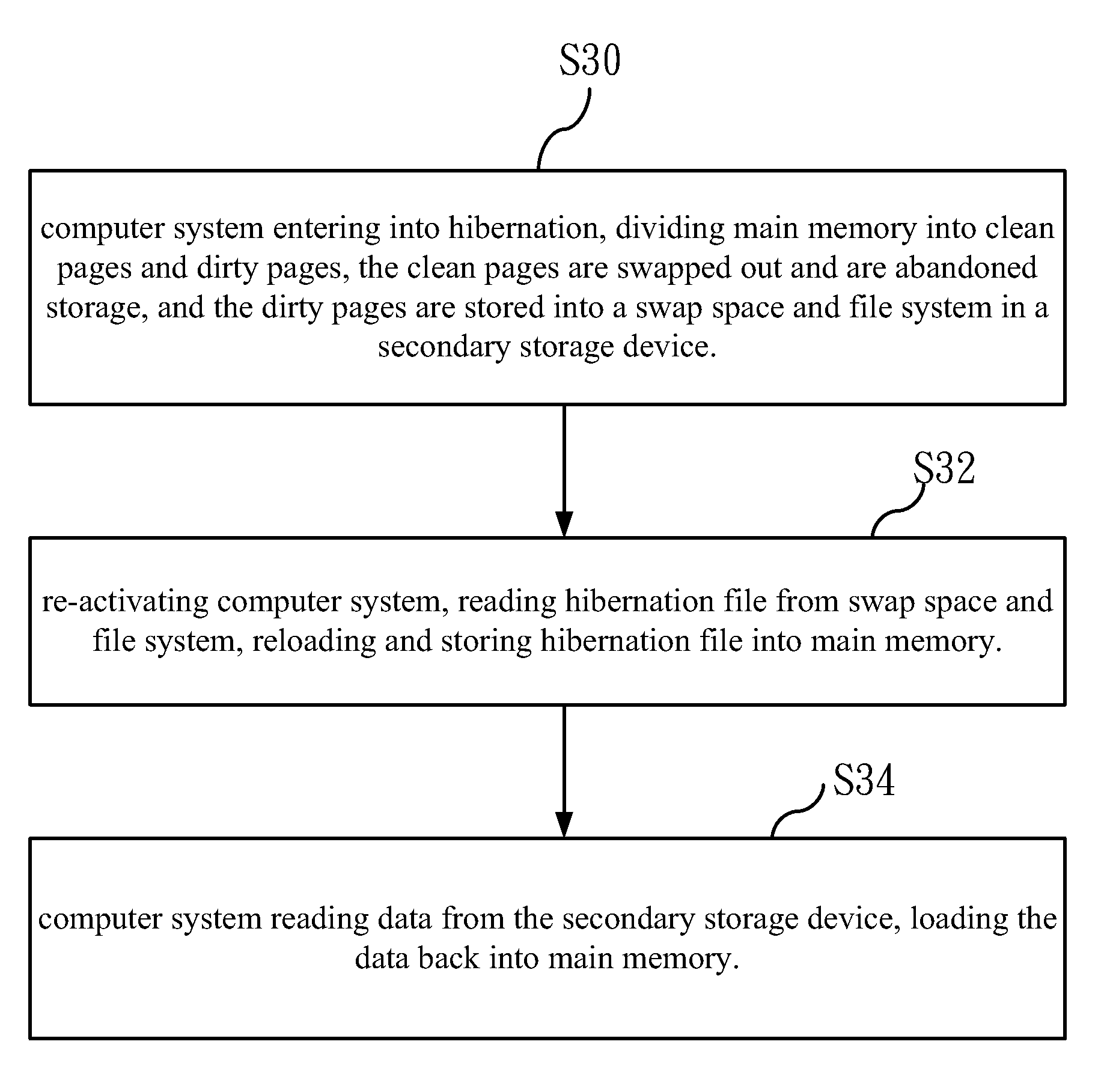

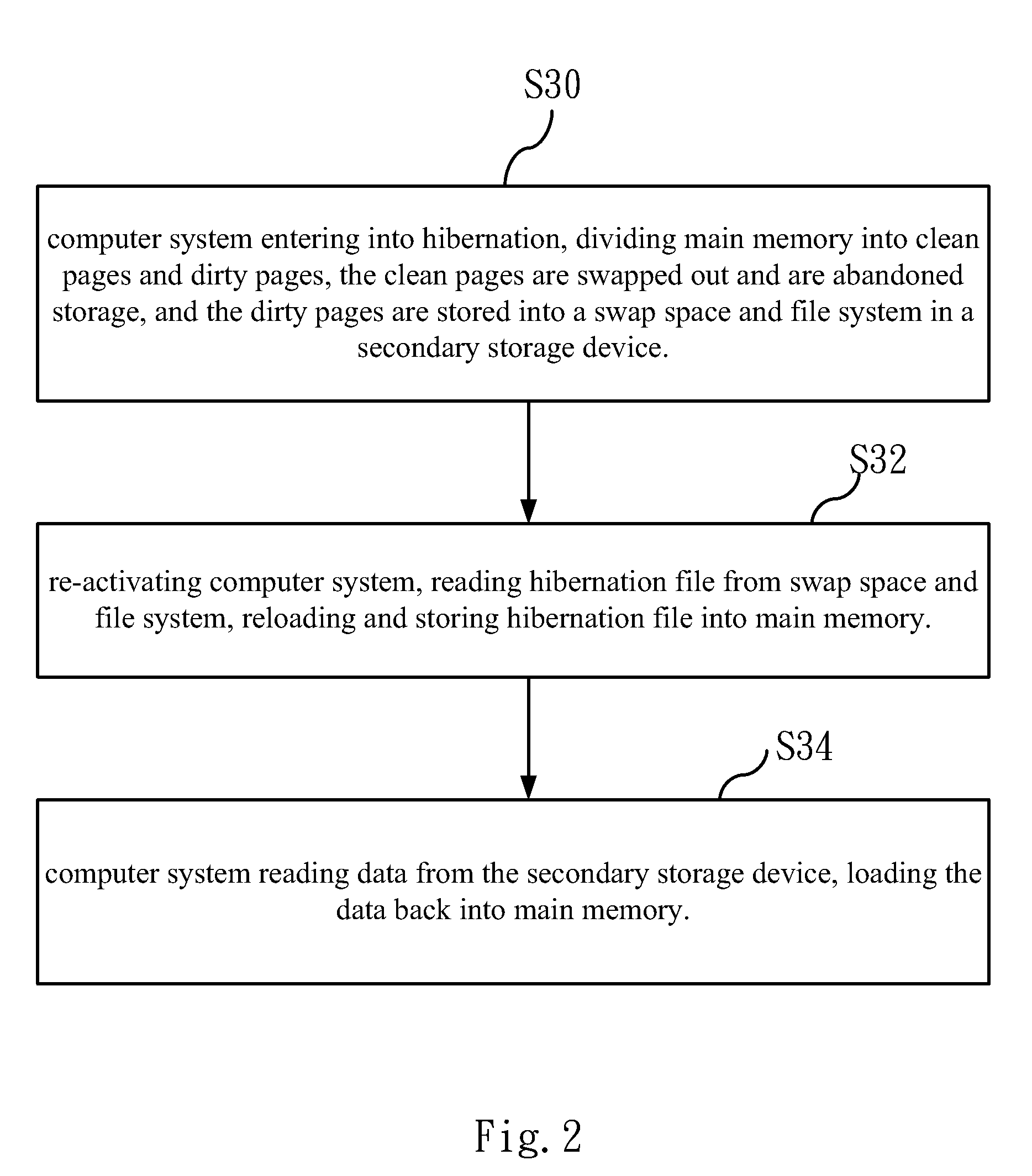

Fast speed computer system power-on & power-off method

ActiveUS20110087901A1Reduce the amount of memoryIncrease computing speedError detection/correctionPower supply for data processingElectricityComputer architecture

A fast speed computer system power-on & power-off method, that is used to reduce an amount of main memory transferred and stored from a main memory into a second storage device, thus speeding up a speed of re-activation of a computer system from a hibernation state into a full speed operation state. Said fast speed computer system power-on & power-off method is applicable to various types of computer systems, and can be used to write in and load back data in cooperation with a random access processing technology. In addition, said method can be used to reduce extent of data loss and damage of said computer system due to a sudden power outage of said computer system.

Owner:NATIONAL CHUNG CHENG UNIV

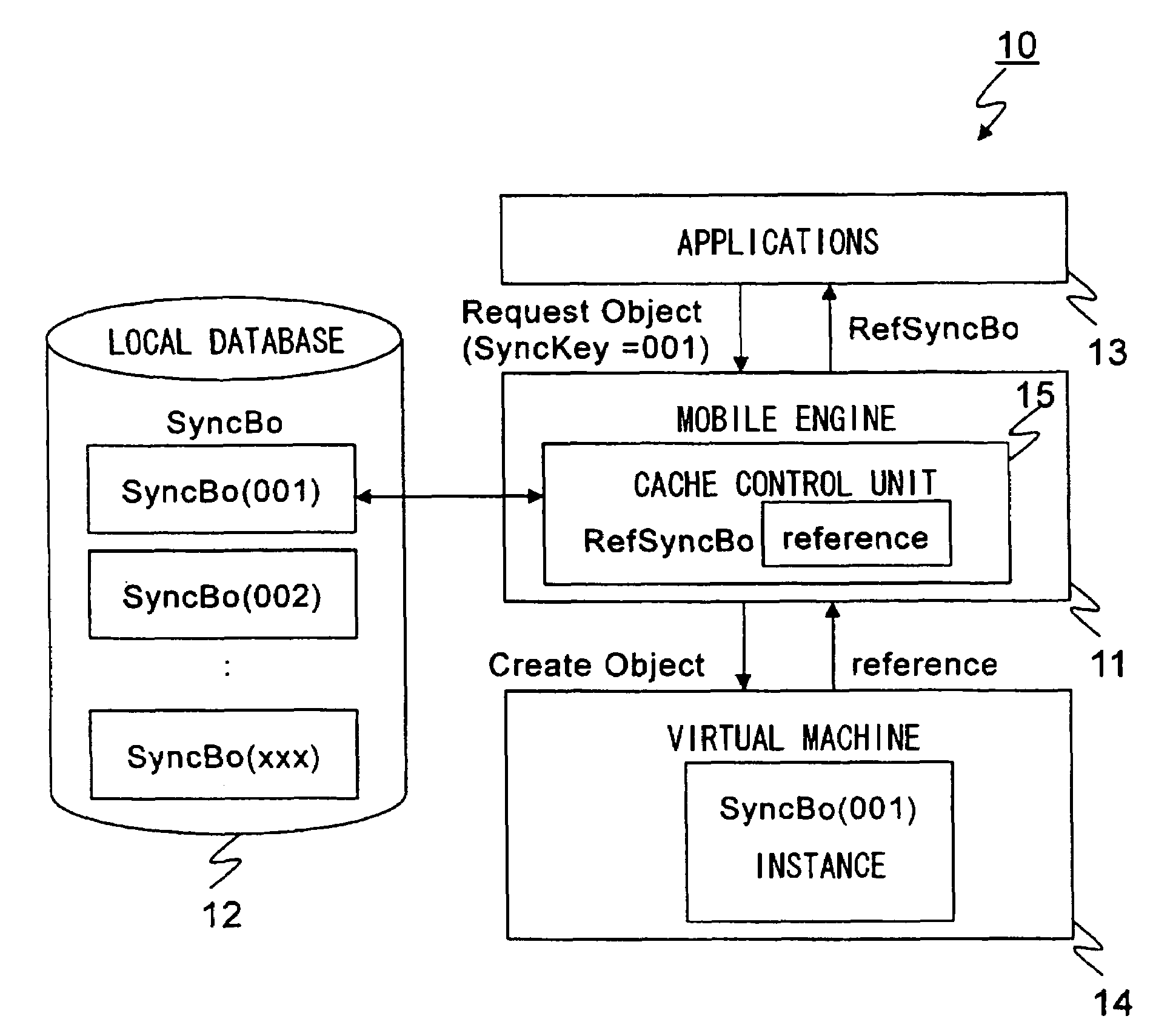

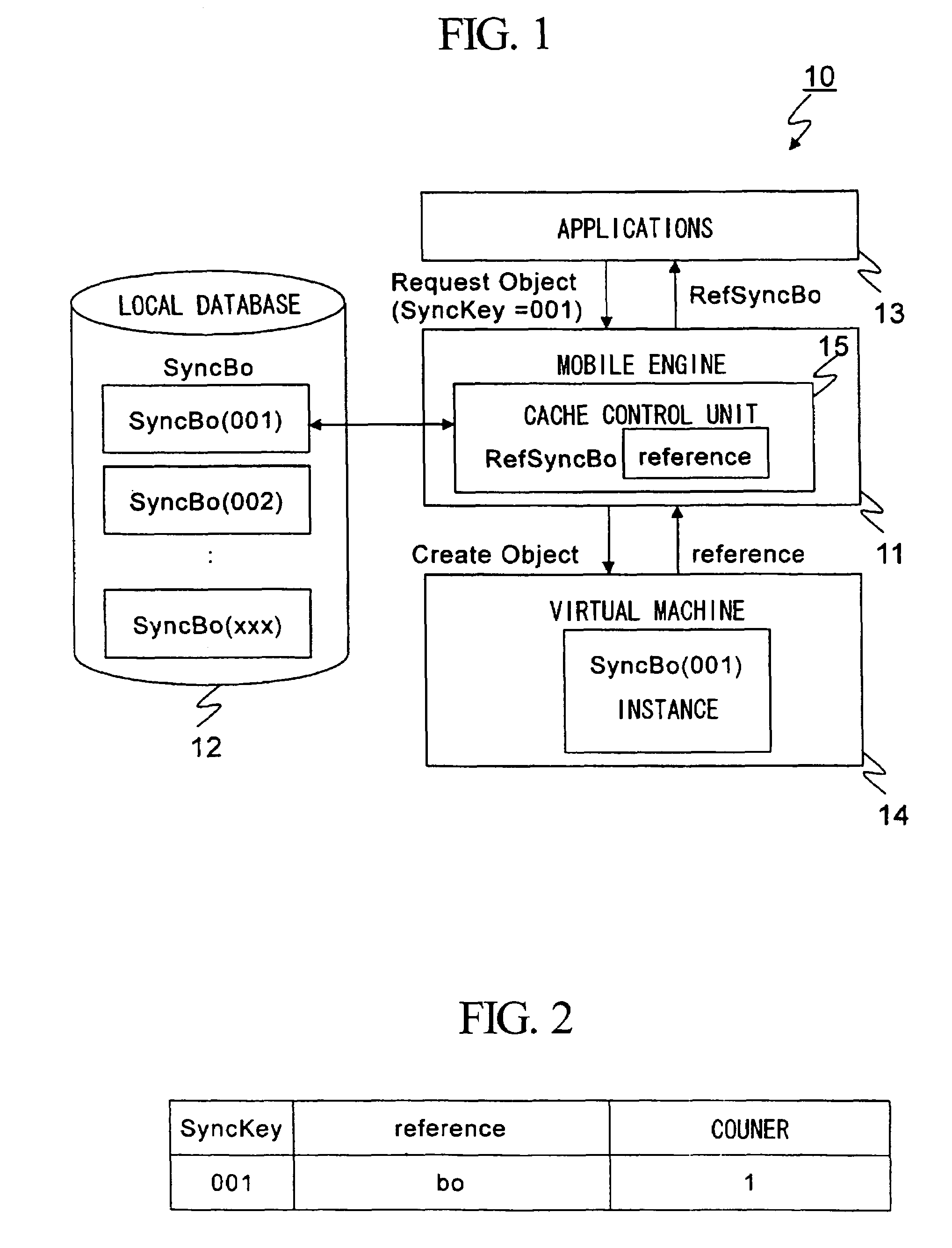

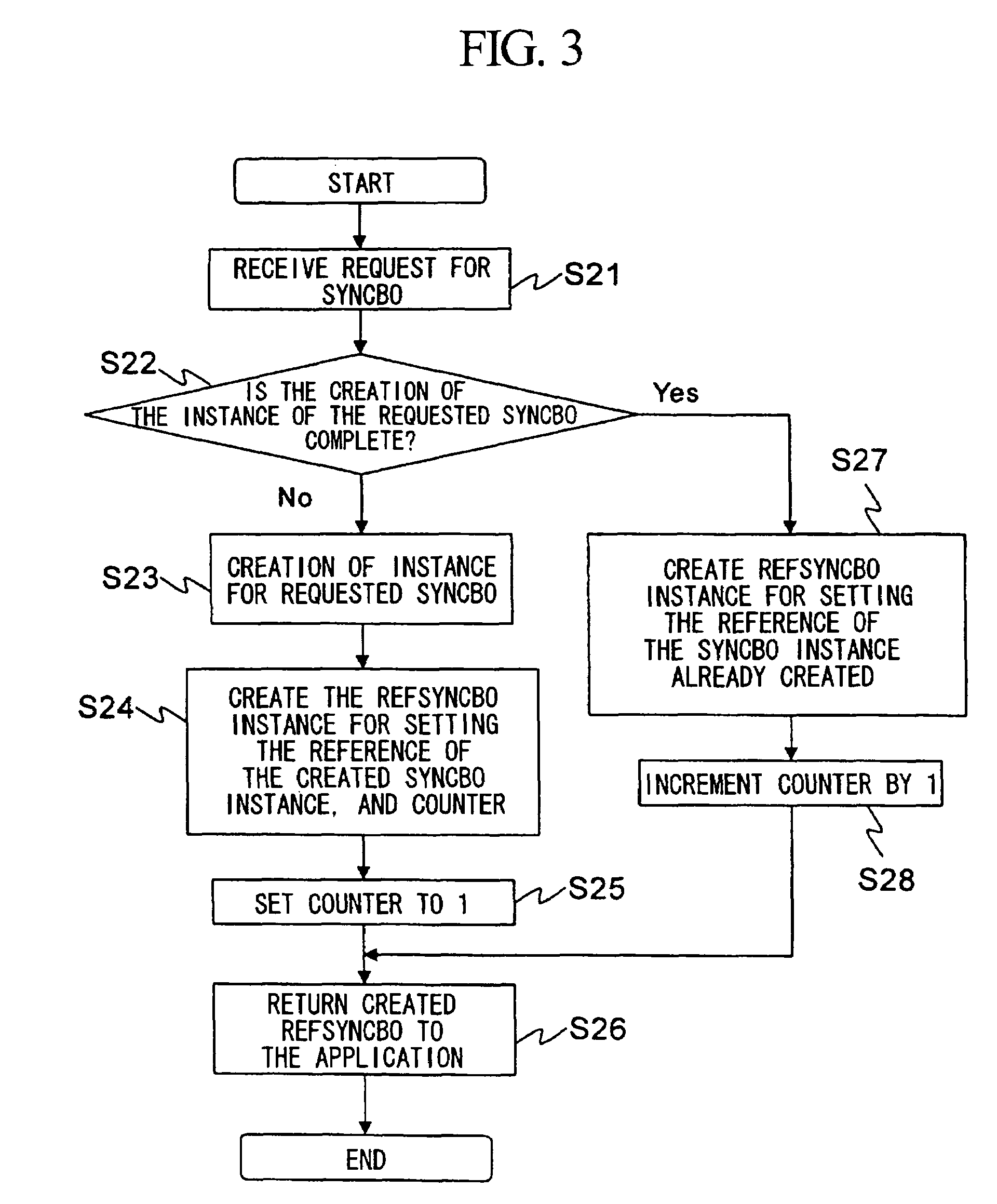

Cache control device, and method and computer program for the same

ActiveUS20050188380A1Increase speedEnsure data consistencyMemory adressing/allocation/relocationMultiprogramming arrangementsDistributed computingControl unit

The cache control unit 15 of the mobile terminal 10 receives an access request for an instance of an object that specifies data to which applications 13 refers, and in the case that an instance of the object does not exist, creates an instance of the object and a counter. In addition, an instance of a reference setting class is created, the reference that refers to the instance of the requested object is set and the result is returned to the application 13, and the counter is incremented by 1. In the case that a release notification for the instance of the reference setting class is received, the counter is decremented by 1, and when the counter has reached 0, the instance of the object is released.

Owner:SAP AG

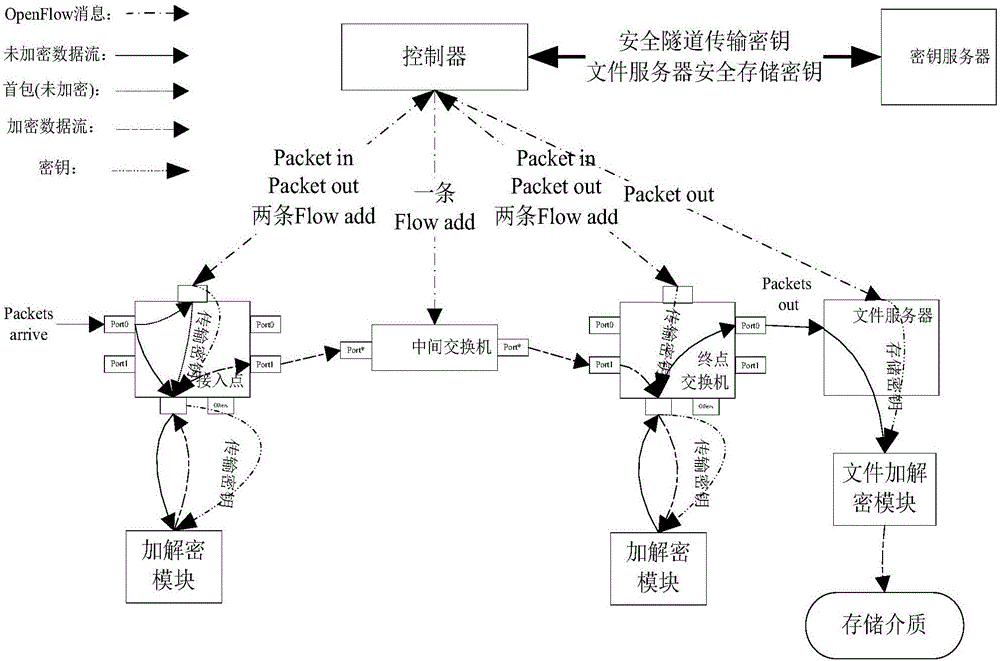

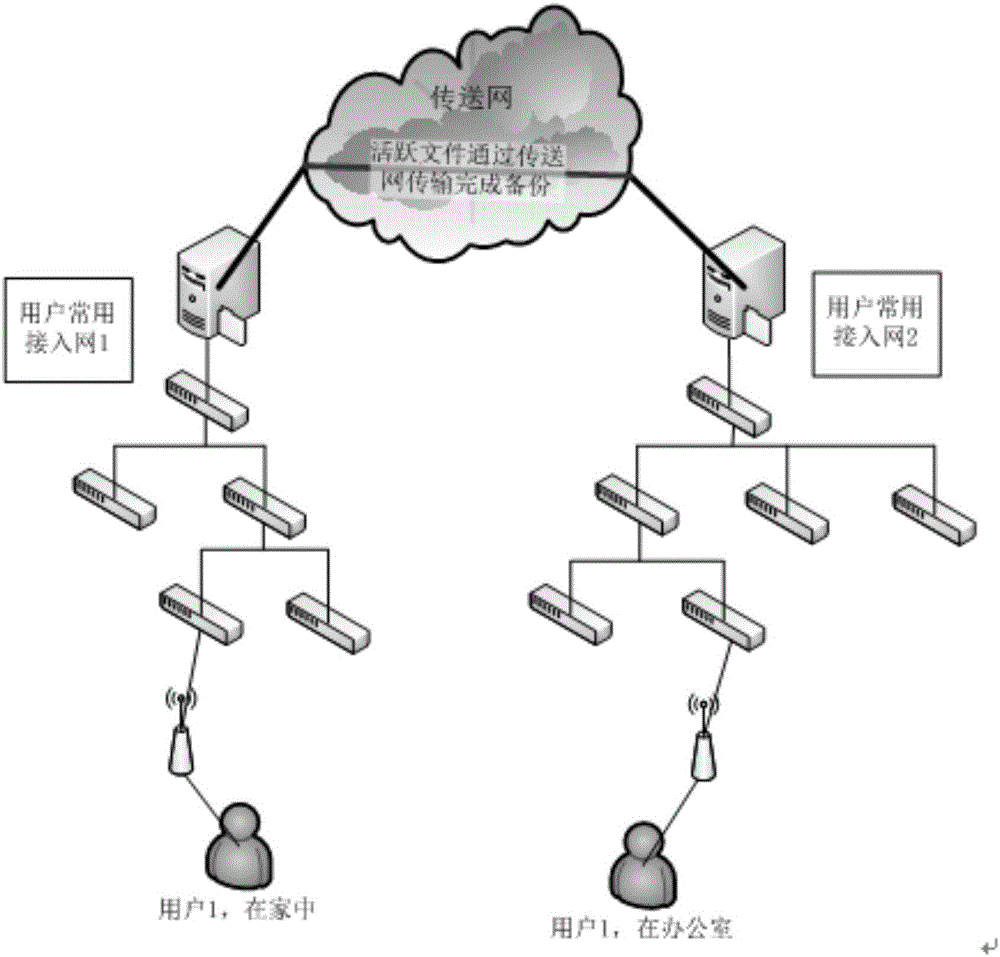

Method for realizing follow-up safe access of user data

The invention discloses a method for realizing follow-up safe access of user data. A safe tunnel triggered by a user is realized to achieve safe transmission of non-inductive user data, then the isolation and safe access of the user data are accomplished by encryption technology irrelevant to a storage service provider, and the safe storage architecture method, which both has the speed and safety of private cloud and can provide the convenience of public cloud, can enable the user to truly experience the same safety and convenience of storing data on the cloud just like storing the data in local.

Owner:UNIV OF ELECTRONIC SCI & TECH OF CHINA

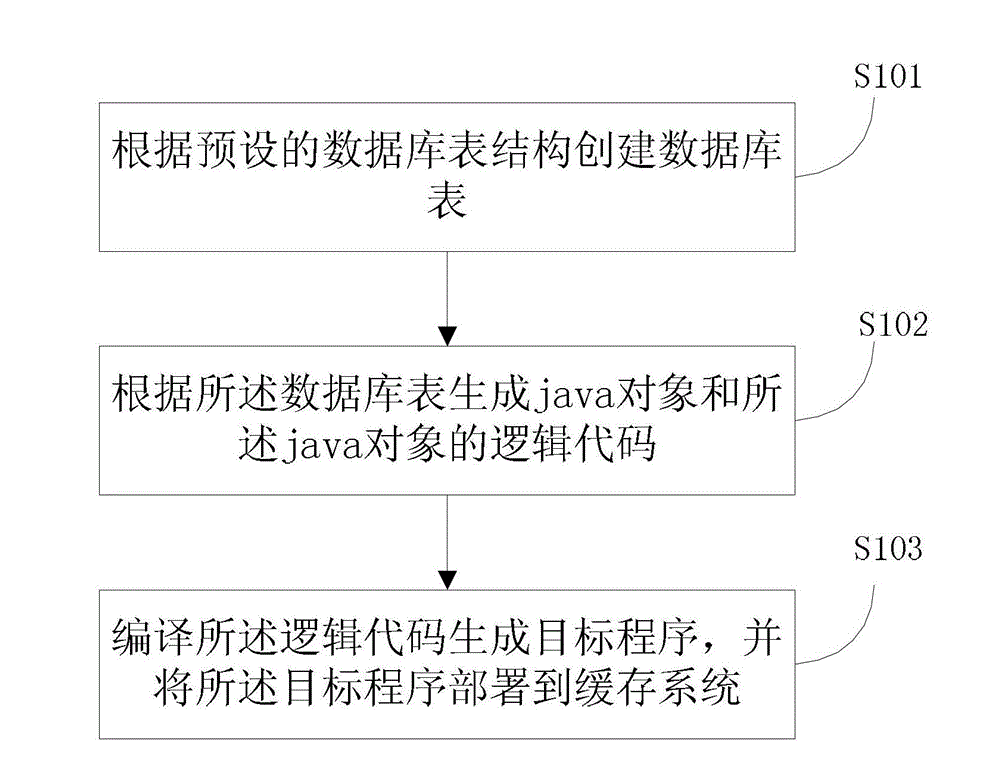

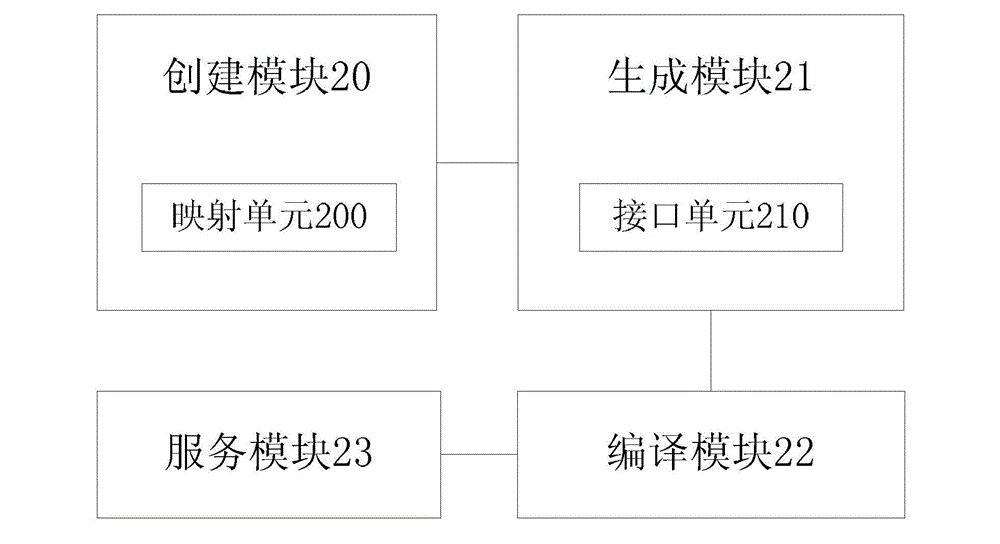

Data caching method and device based on Java object

InactiveCN102945156AReduce dependenceReduce waiting timeSpecial data processing applicationsSpecific program execution arrangementsTime delaysData access

The invention discloses a data caching method and a data caching device based on a Java object. By the method, data in the database is cached in form of the Java object, a cache system provides the Java object in form of a jar packet, and the dependence on database in the data caching process in the application program accessing is avoided, so that in the accessing process of each application program, only the data object structure is considered by transferring the Java object in the cache data jar pocket and by using the java method for fast accessing, and the database data structure is not required to be considered; the data is acquired and displayed by using the uniform data reading method in the cache system, so that the development speed is greatly improved, and the waiting time of user is shortened. The data accessing speed after the application program is accessed is improved, and the network time delay caused by the object packaging and database visiting when the database is accessed is avoided.

Owner:融创天下(上海)科技发展有限公司

Cache control device, and method and computer program for the same

ActiveUS7441252B2Improve data access speedSave areaMemory adressing/allocation/relocationMultiprogramming arrangementsControl equipmentDistributed computing

Owner:SAP AG

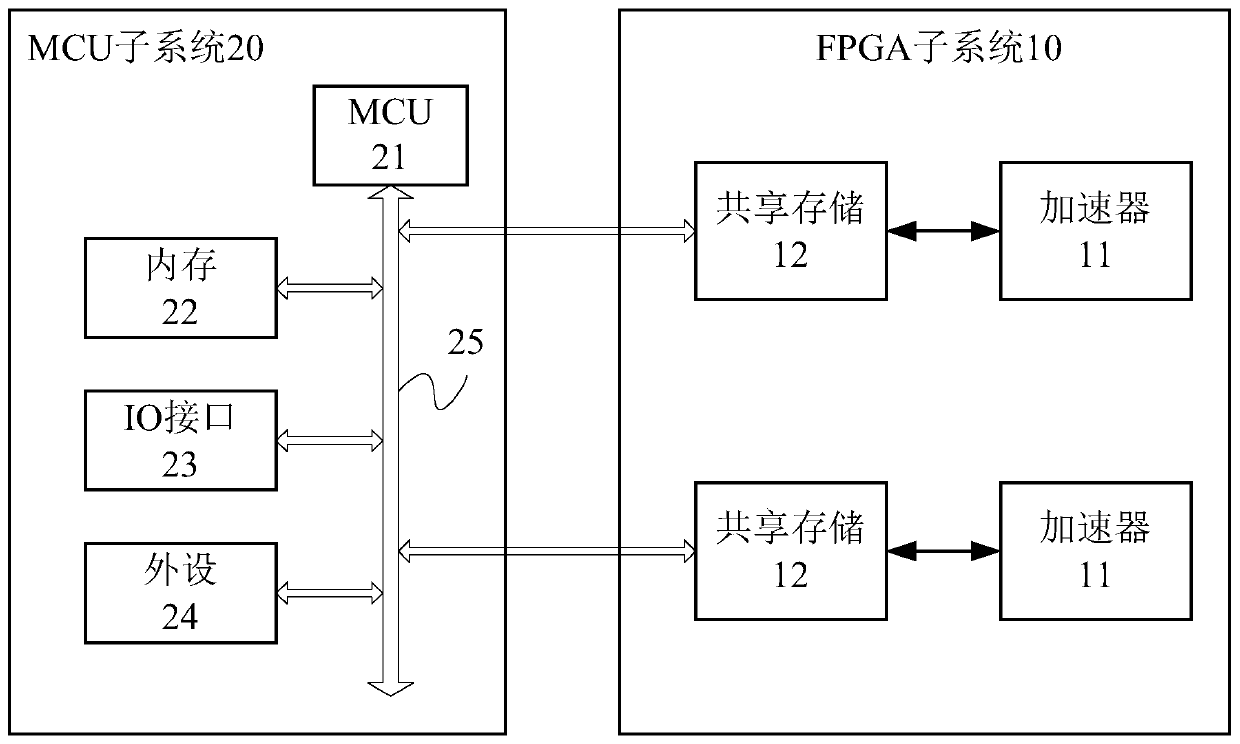

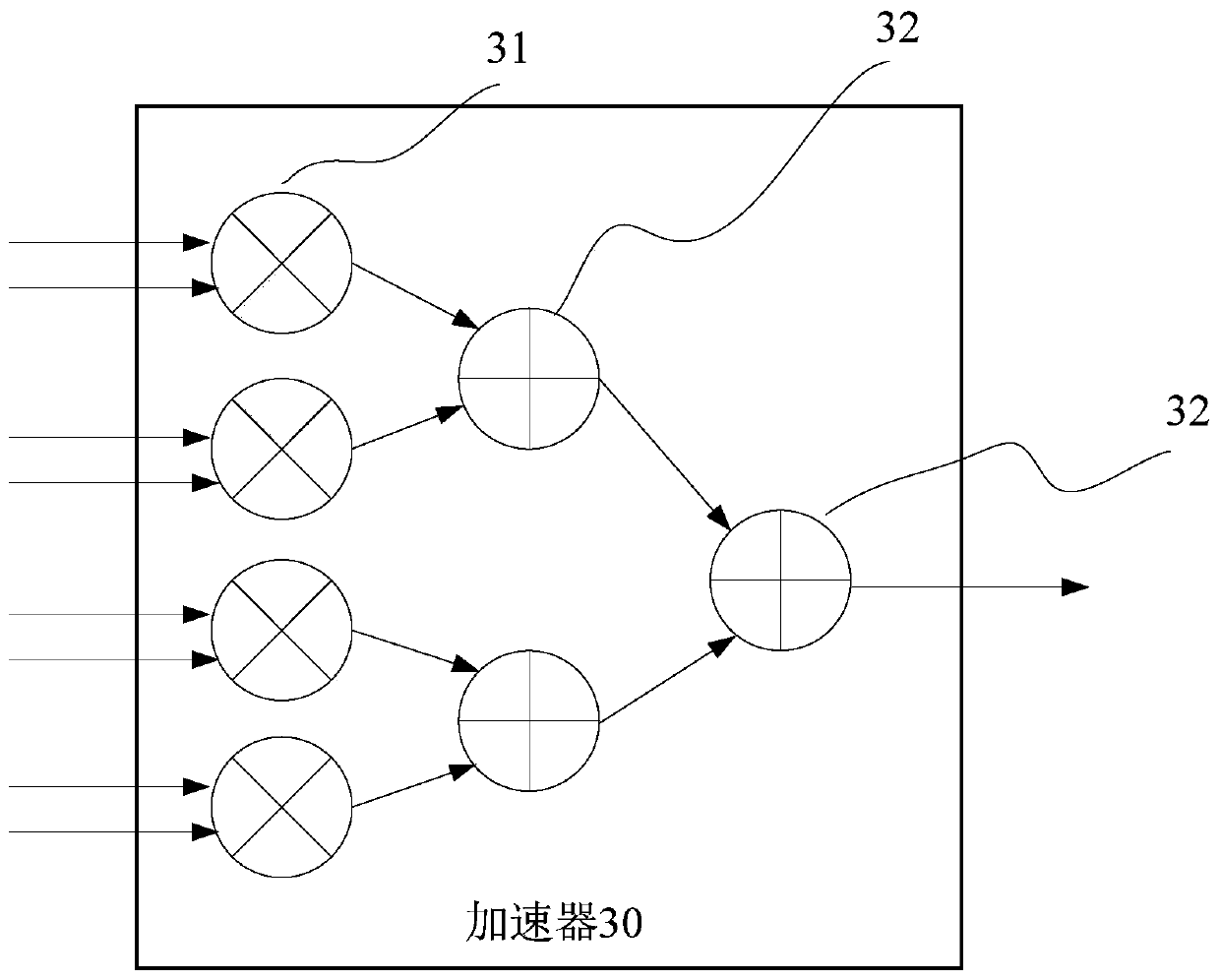

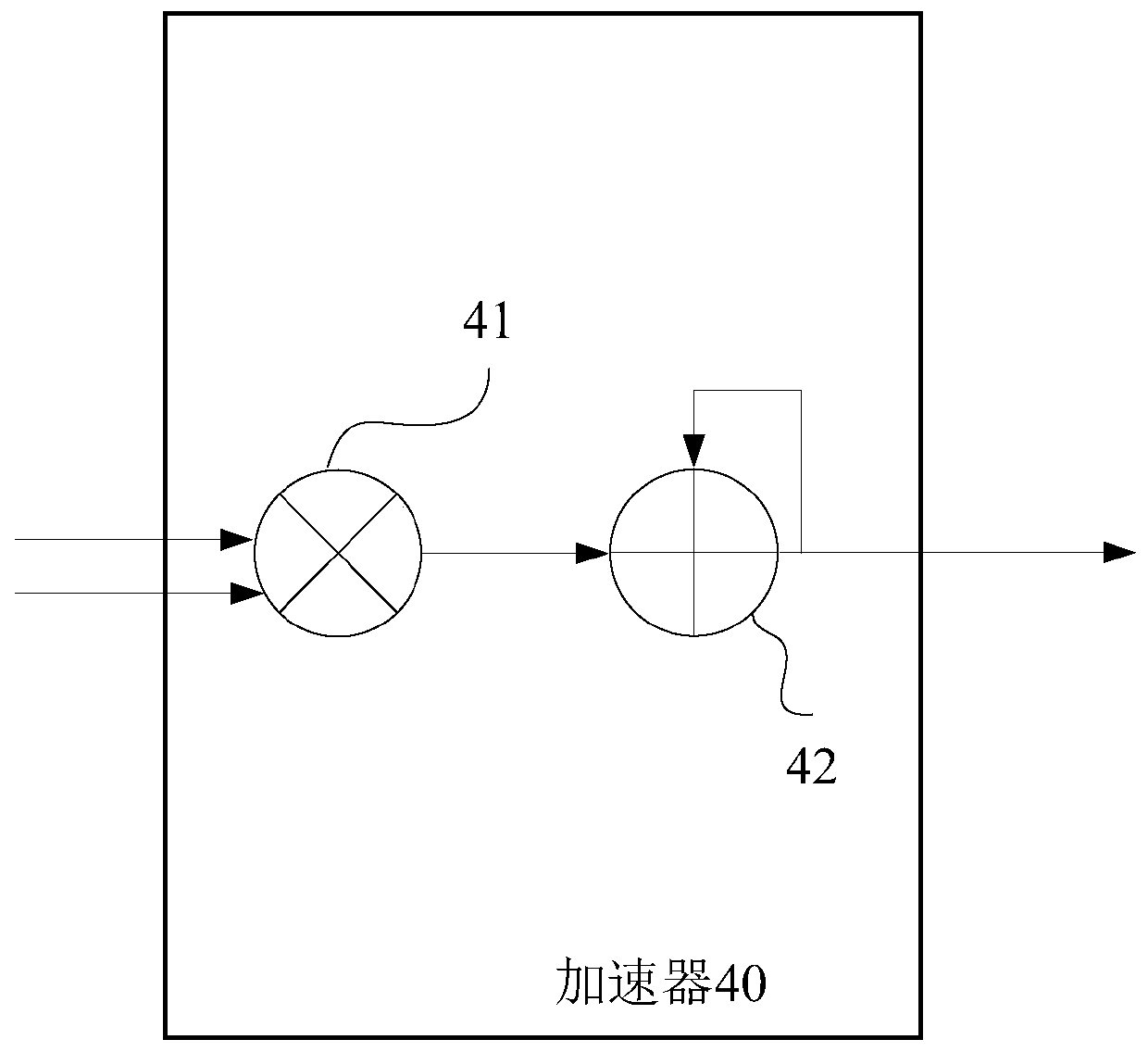

Edge artificial intelligence computing system framework based on SoC FPGA

PendingCN110727633AAccelerated implementationReduce power consumptionGeneral purpose stored program computerPhysical realisationAlgorithmEngineering

An edge artificial intelligence computing system framework based on an SoC FPGA comprises an MCU subsystem and an FPGA subsystem, and the FPGA subsystem comprises an accelerator used for carrying outacceleration operation on an artificial intelligence algorithm; a shared memory used as an interface of the accelerator and the MCU subsystem; wherein the MCU subsystem uploads data to be calculated to the shared memory, and retrieves an operation result; and the accelerator independently reads data from the shared memory for operation and writes back an operation result. The system architecture has the advantages of small hardware area, low power consumption, high operational performance and high usability, and the design process is simple and flexible.

Owner:GOWIN SEMICON CORP LTD

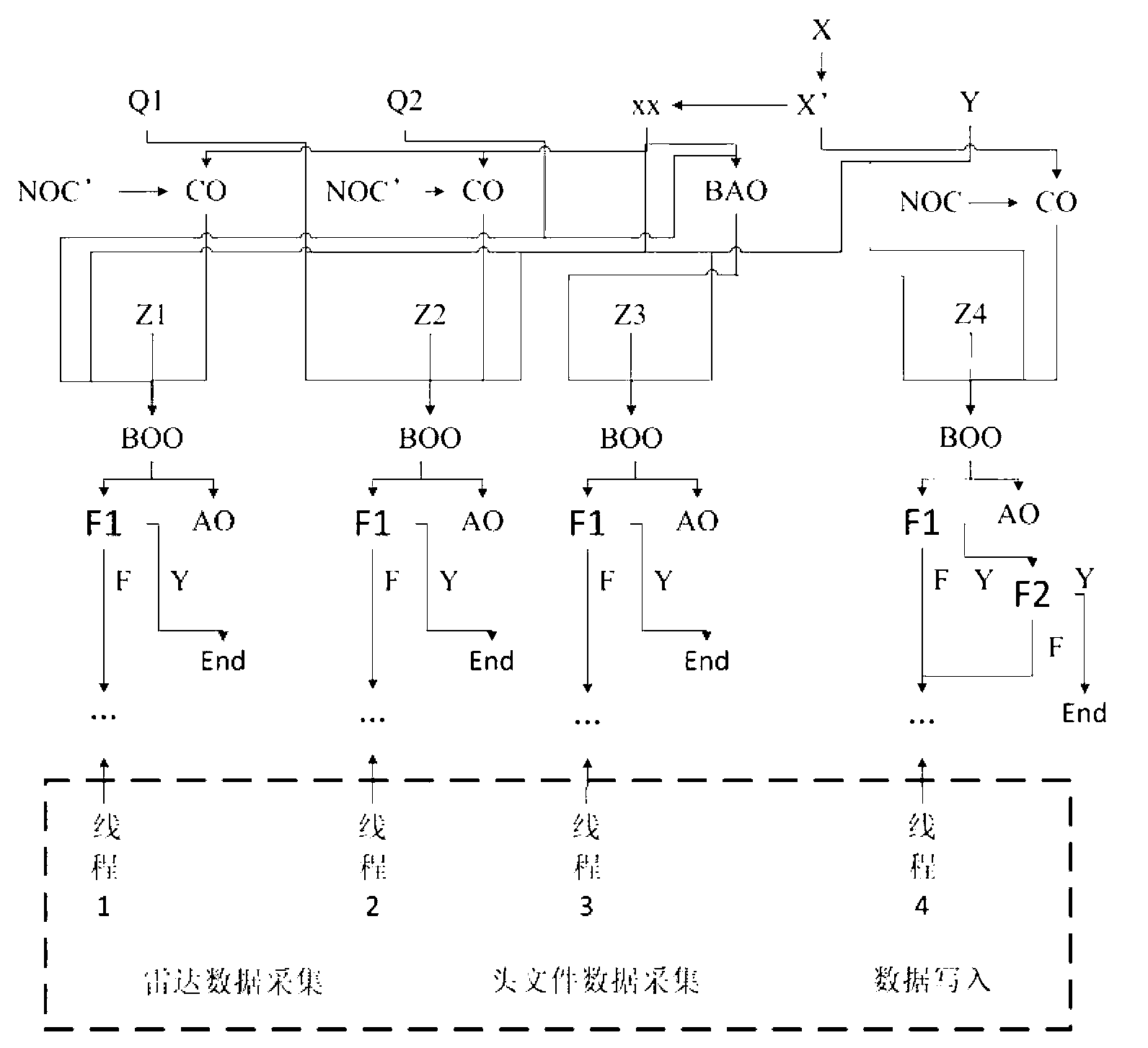

Synchronous control method of multithreading data acquisition system in acquisition times control mode

InactiveCN103226328AImprove data access speedImprove overall performanceConcurrent instruction executionAdaptive controlControl variableComputer based

The invention relates to a synchronous control method of a multithreading data acquisition system in an acquisition times control mode, and belongs to the technical field of ground penetrating radars. The method comprises the steps that a times integer variable for controlling data acquisition is pre-established; a value after addition processing and a value after division processing of the times integer variable are subjected to Boolean operation together with two control variables respectively; results of the Boolean operation serve as synchronous control signals of different threads; synchronous control of multithreading in the mode is achieved by criterion functions of the threads and assignments of the control variables; and all the acquisition data can be stored by the preset criterion functions written in the threads. According to the method, a control function of the ground penetrating radar multithreading acquisition system is achieved on the basis of a computer control theory.

Owner:CHINA UNIV OF MINING & TECH (BEIJING)

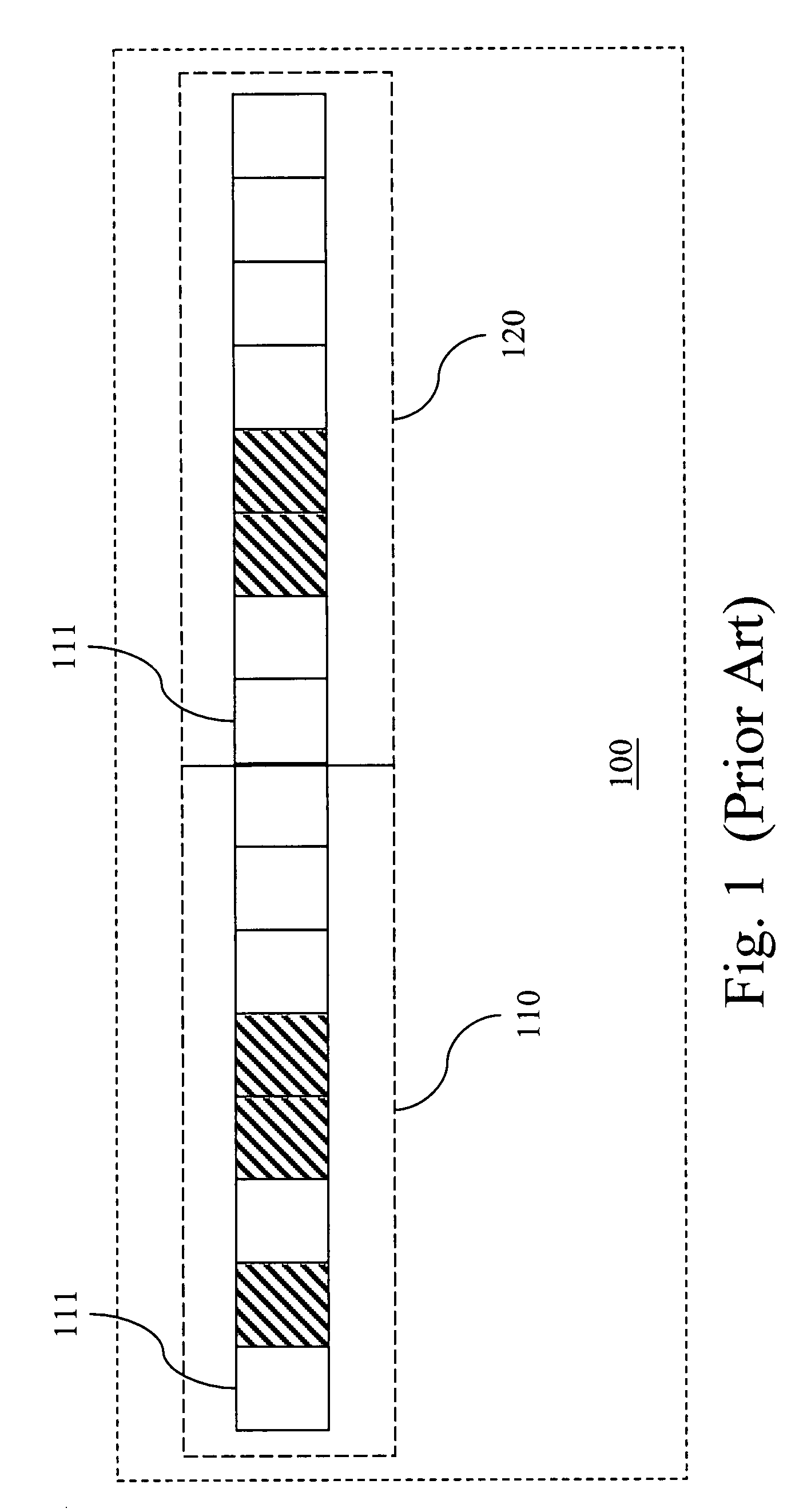

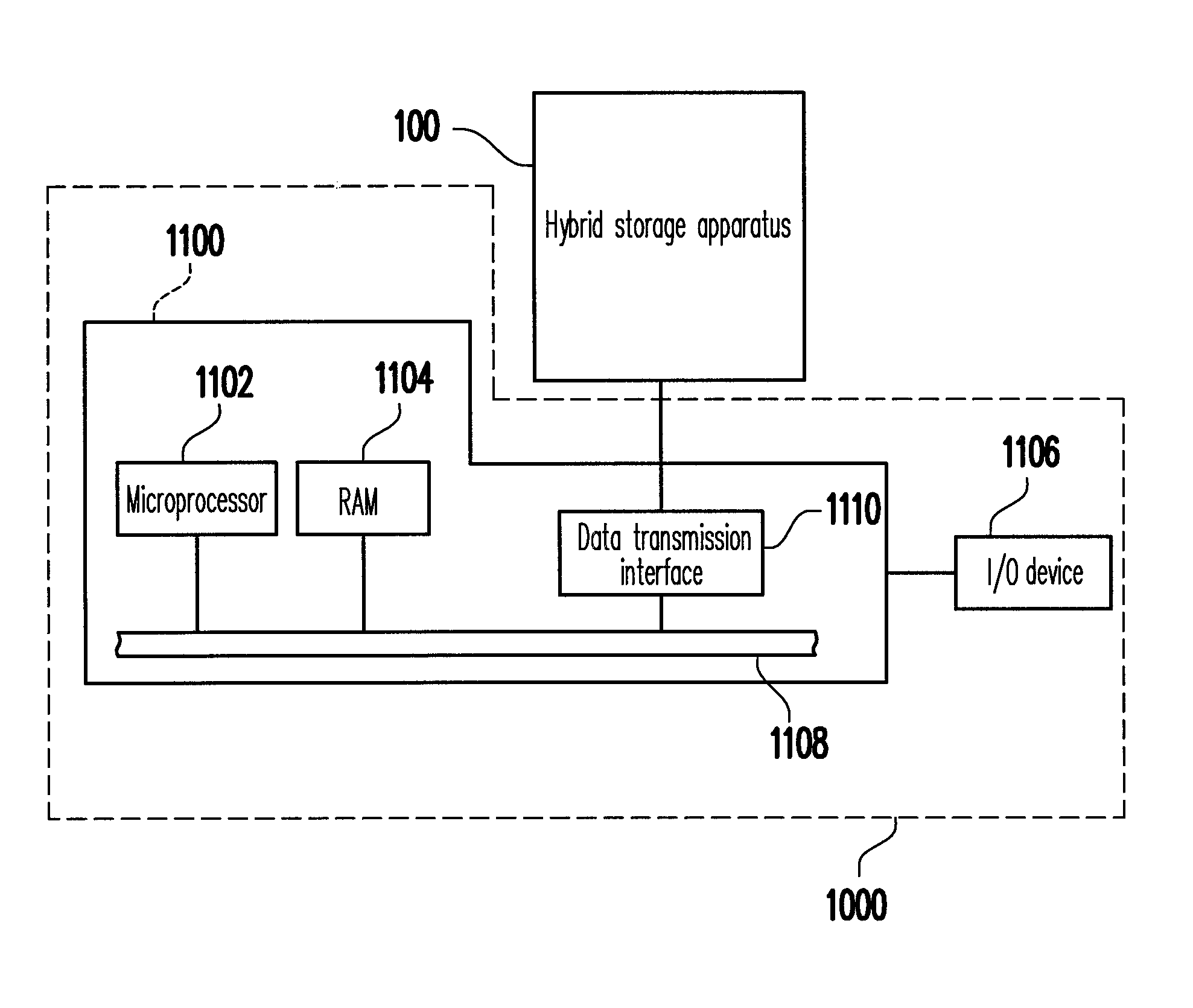

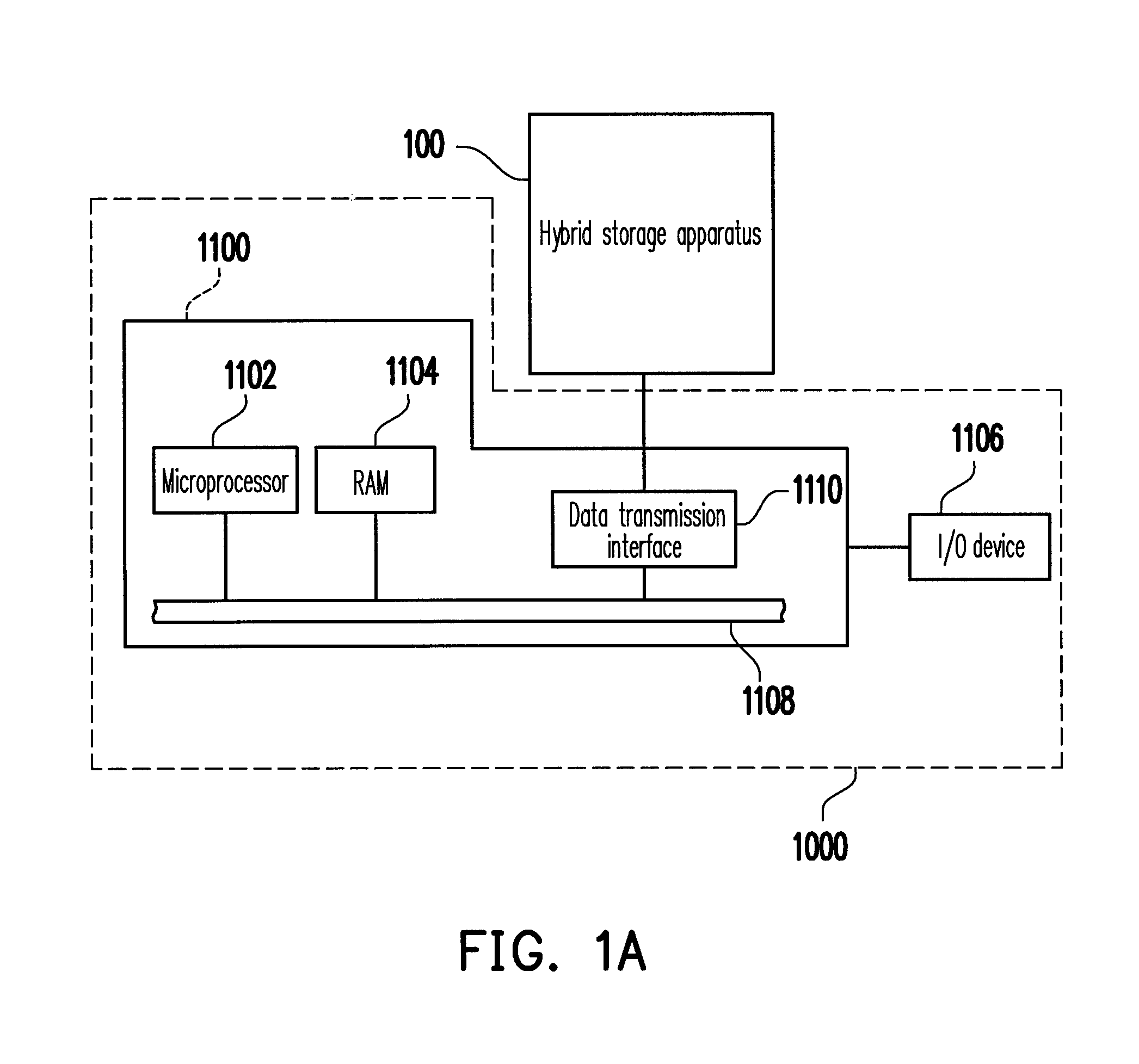

Hybrid storage apparatus and hybrid storage medium controller and addressing method thereof

ActiveUS8417869B2Improve data access speedExtend your lifeMemory architecture accessing/allocationInput/output to record carriersData accessLogical disk

A hybrid storage apparatus including a non-volatile memory module, a hard disk module, and a hybrid storage medium controller is provided. The hybrid storage medium controller groups physical blocks of the non-volatile memory module into at least a storage area and a replacement area, and the hybrid storage medium controller configures a plurality of logical blocks for mapping to the physical blocks in the storage area and configures a plurality of logical disk addresses for mapping to physical disk addresses of the hard disk module. The hybrid storage medium controller further configures a plurality of logical access addresses to be accessed by a host system and initially maps a portion of the logical access addresses to the logical blocks and the other logical access addresses to a portion of the logical disk addresses. Accordingly, the hybrid storage apparatus can have improved data access performance and prolonged lifespan.

Owner:PHISON ELECTRONICS

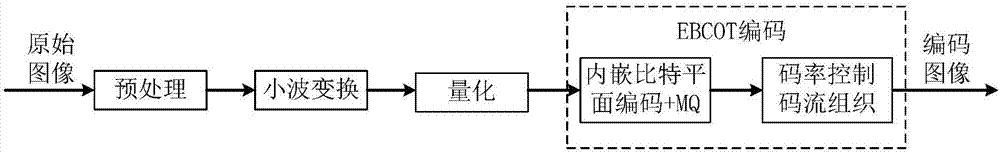

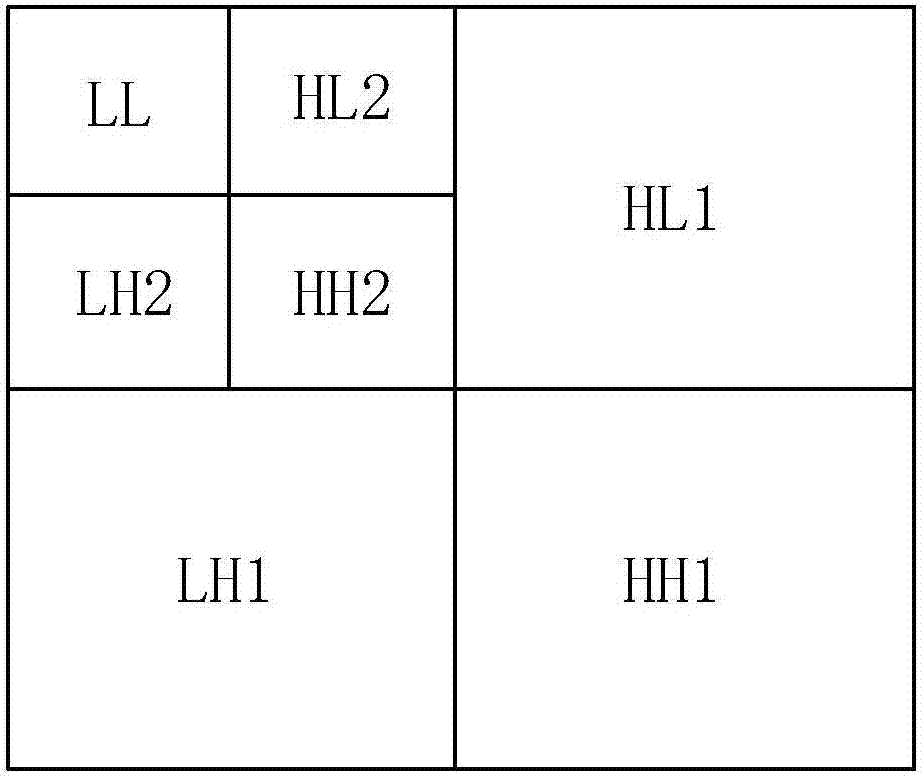

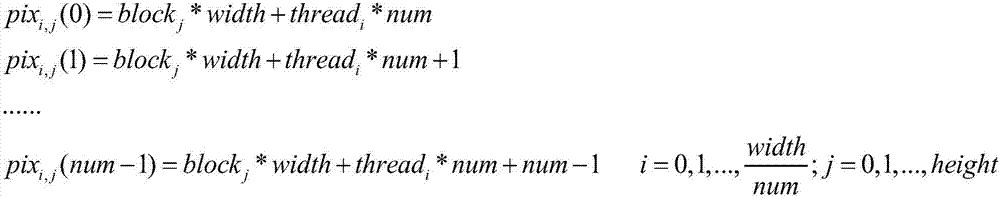

Acceleration method for realizing inverse wavelet transform in JPEG2000 decompression algorithm by using GPU

InactiveCN107483964AImprove decompression speedSimple structureImage memory managementImage codingParallel processingComputer science

The invention discloses an acceleration method for realizing inverse wavelet transform in an JPEG2000 decompression algorithm by using a GPU. The method comprises the following steps: firstly, performing optimized storage for inverse wavelet transform coefficients in a shard memory by using the advantage that the GPU shared memory is high in access speed; and secondly, adopting a parallel processing mode that one block processes a line (column) of pixels according to the characteristics that the line-line processing and column-column processing in the inverse wavelet transform process are independent of each other, adopting a parallel processing mode that one thread processes a plurality of pixels according to the characteristics that the processing of the same line (column) of pixels has dependence, but part of the processing procedure can still be parallel, and completing the inverse wavelet transform in a horizontal direction and a vertical direction. According to the inverse wavelet transform acceleration method disclosed by the invention, the advantages that the GPU has a large number of cores and is suitable for parallel computation are fully used, and the decompression speed of JEPG2000 can be improved effectively; and moreover, the algorithm structure is simple and reasonable, and is easy to implement on the GPU.

Owner:SHANDONG JIAOTONG UNIV

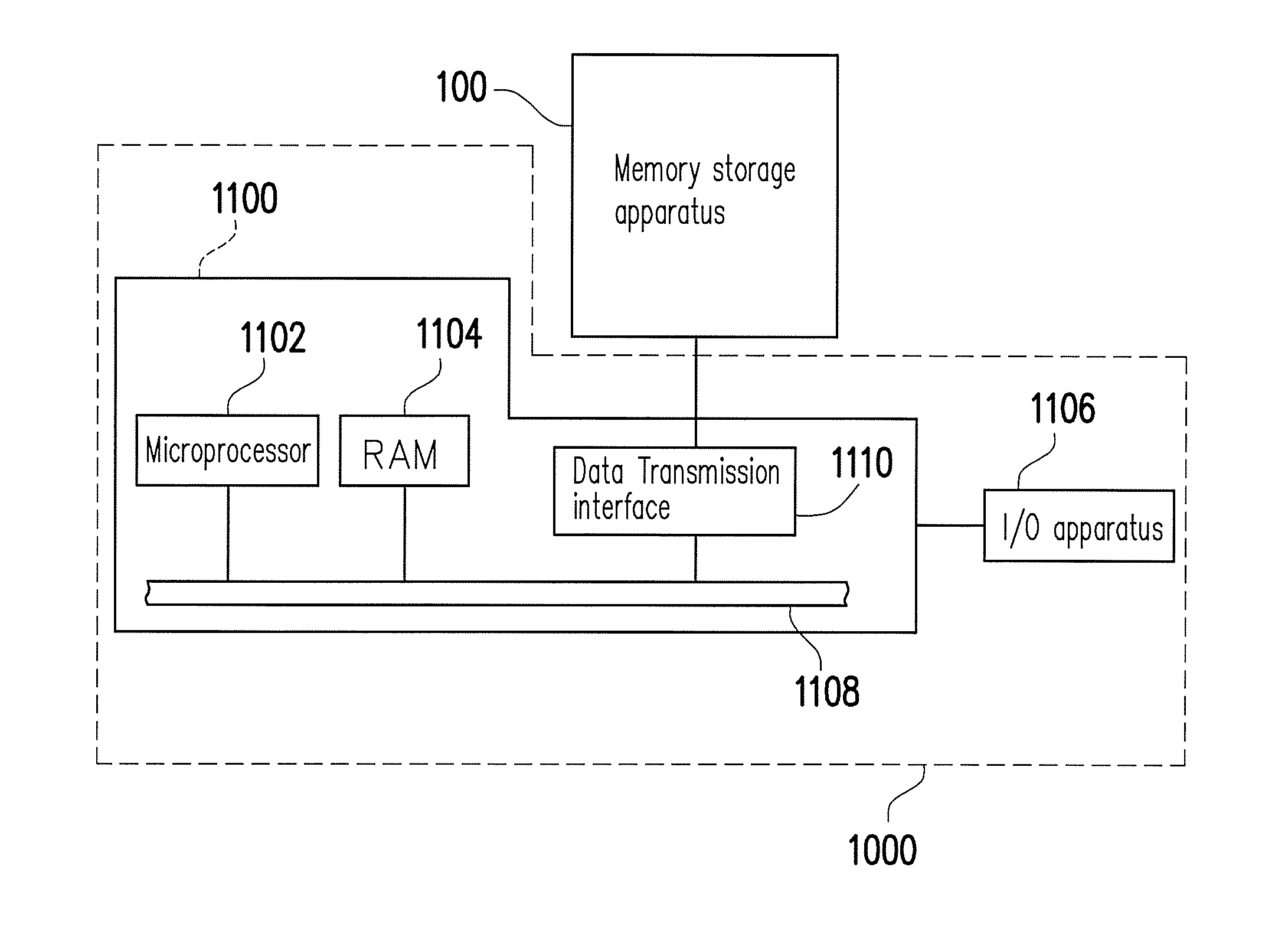

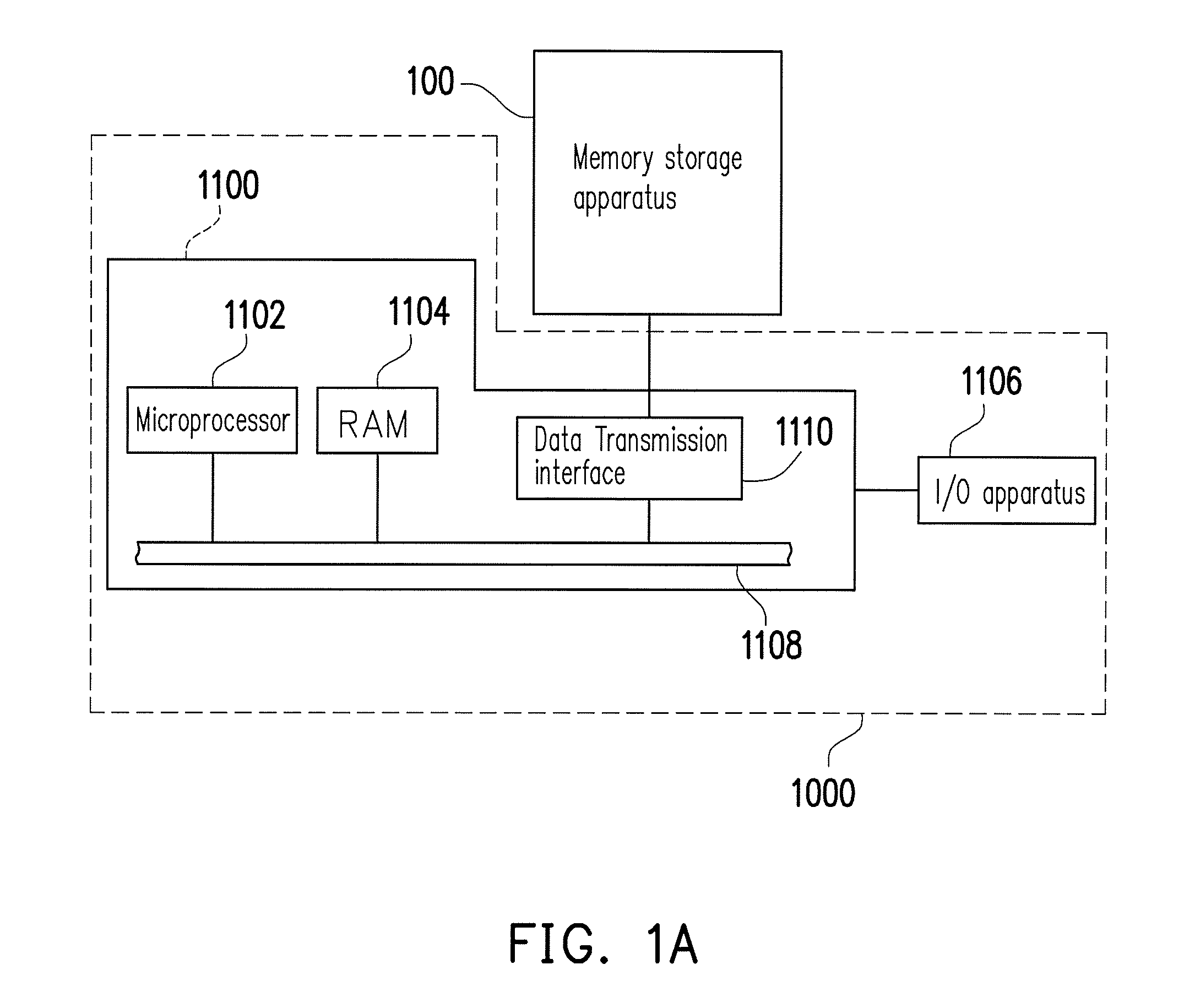

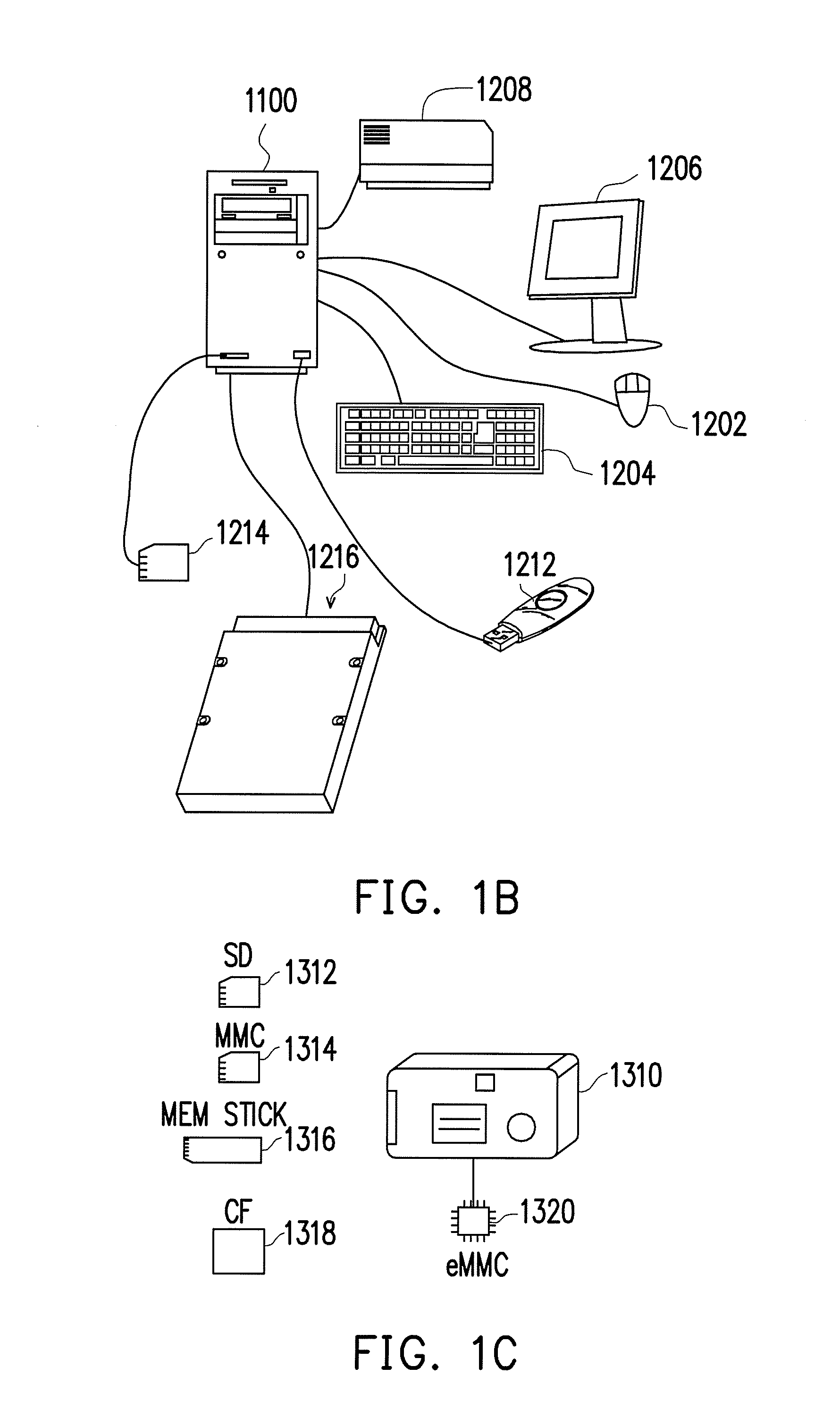

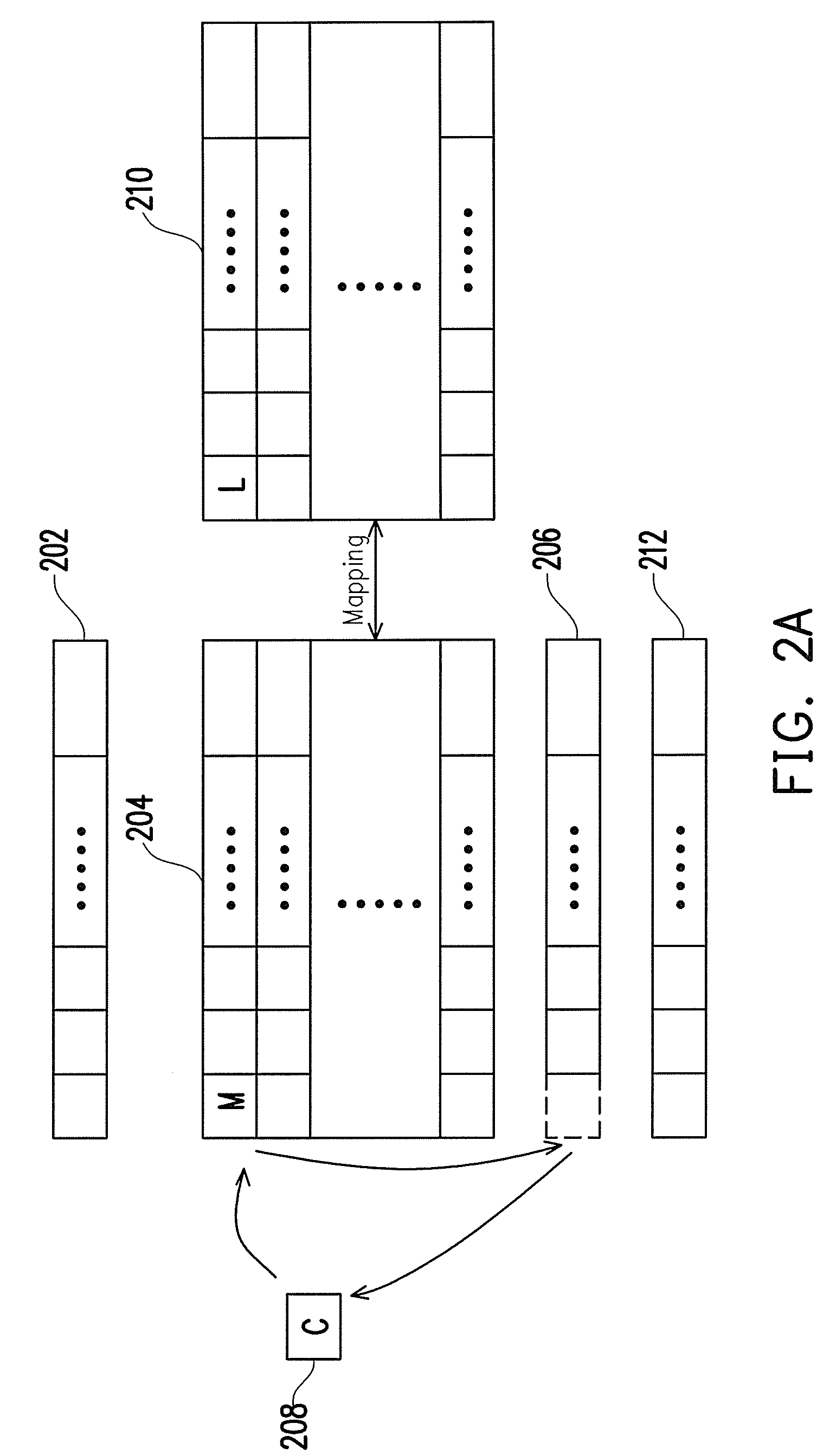

Memory management method, memory control circuit unit, and memory storage apparatus

ActiveUS20160364141A1Improve data access speedEasy data accessMemory architecture accessing/allocationInput/output to record carriersPhysical unitControl circuit

A memory management method is provided according to an exemplary embodiment. The method includes: receiving a write command and determining whether a usage status of physical units associated to a storage area conforms to a first predetermined status; storing write data corresponding to the write command to at least one of physical units associated to a temporary area if the usage status of the physical units associated to the storage area conforms to the first predetermined status; associating the at least one physical unit storing the write data to the storage area; and allocating at least one logical unit to map the at least one physical unit associated to the storage area.

Owner:PHISON ELECTRONICS

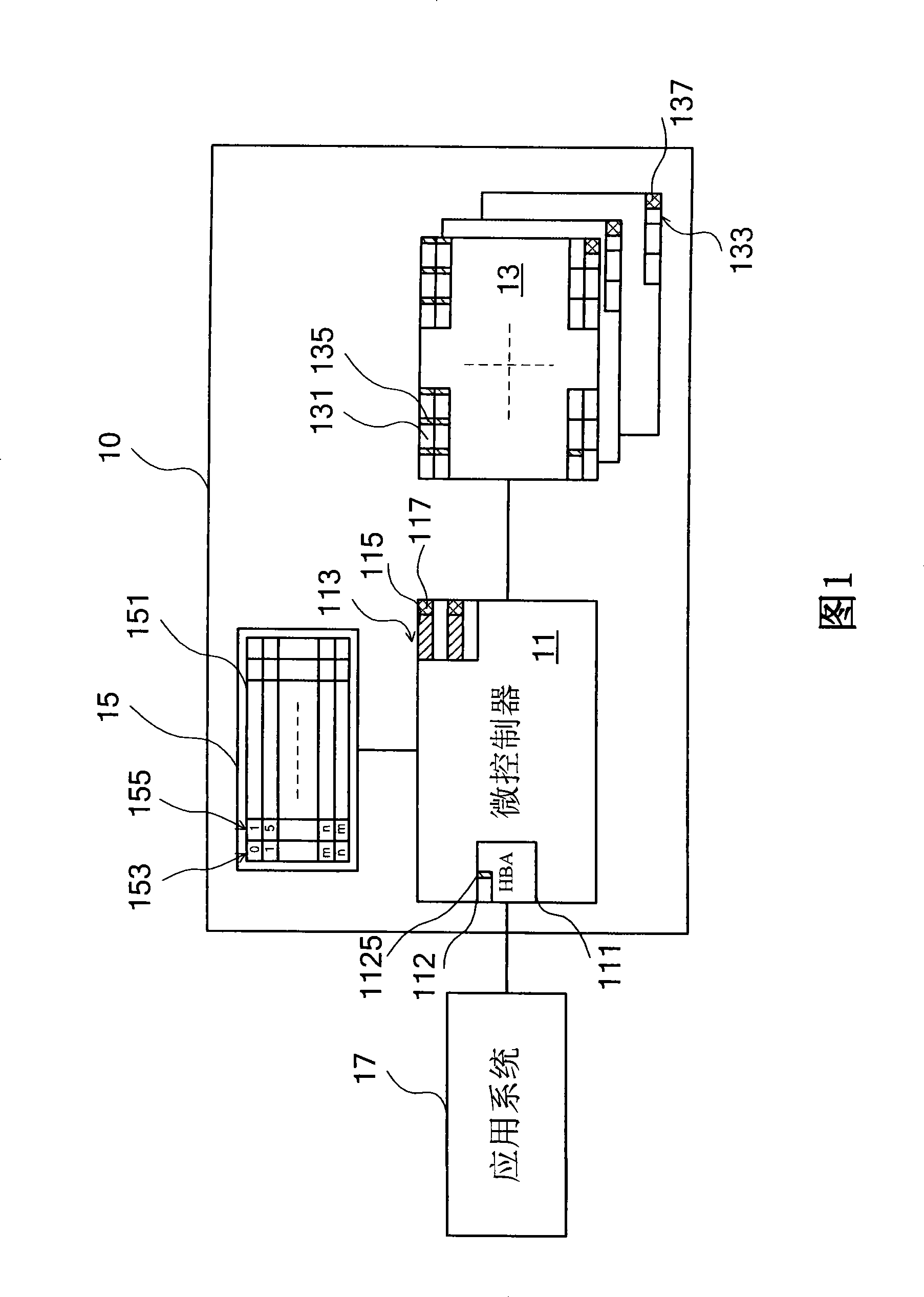

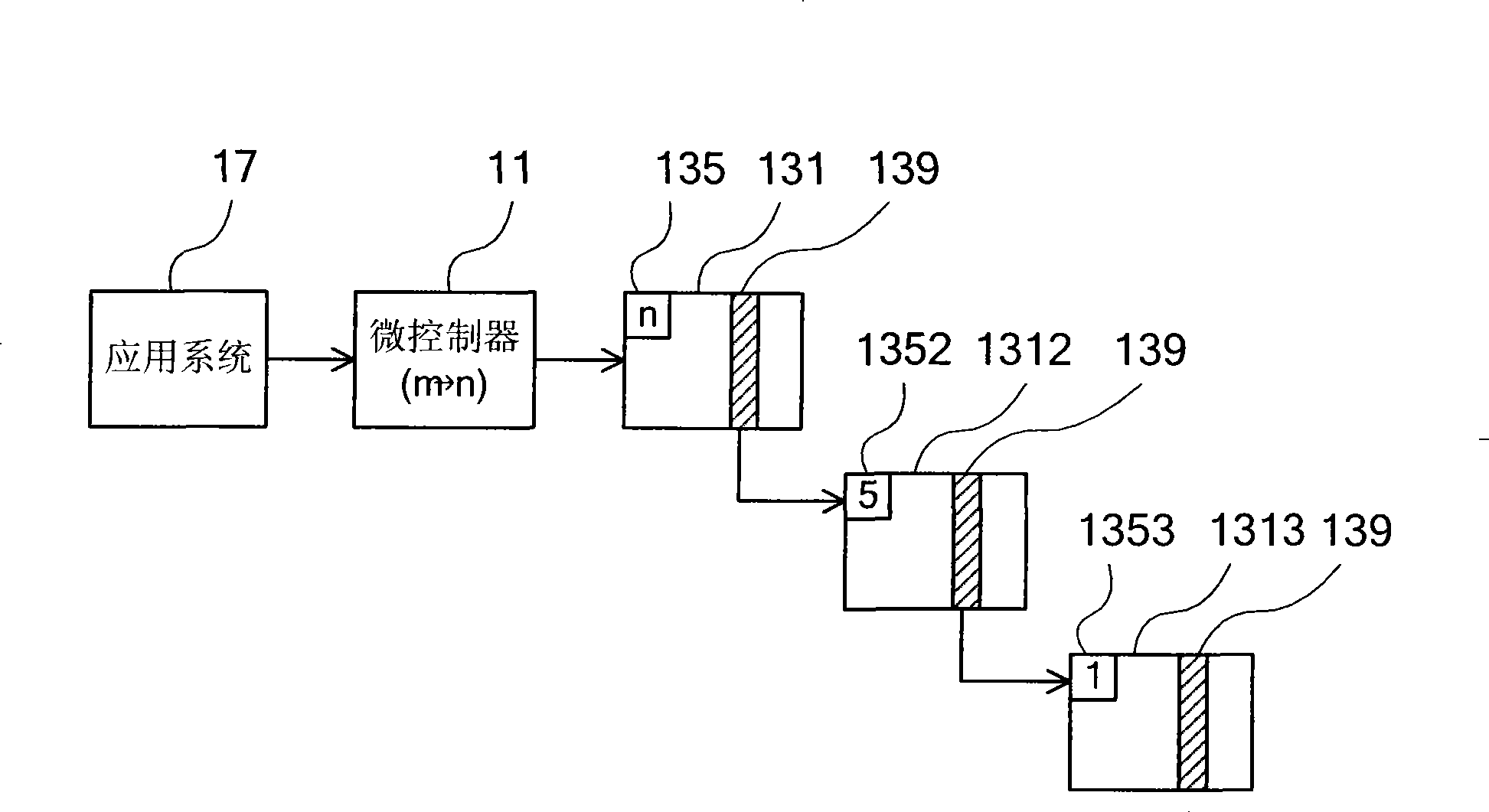

Flash memory system

InactiveCN101364205AEnsure safetySave memory capacityMemory adressing/allocation/relocationMicrocontrollerData access

The invention relates to a storage system with flash memories, which mainly comprises a microcontroller, at least a flash memory connected with the microcontroller, and a scratch pad storage. A plurality of entity storage area blocks are included in each flash memory; an entity address and a plurality of entity sectors are included in each entity storage area block; each entity sector at least comprises a user data field and a logical address pointing column, wherein logical address pointing data can be written into each logical address pointing column when entity data is stored in the user data field; a logical address of a logical storage area block corresponding to each entity storage area block can be recorded in the logical address pointing data; the scratch pad storage is connected with the microcontroller, and can be used for storing a connection comparison table; and the entity address of each entity storage area block and the logical address of one of the logical storage area blocks corresponding to the entity storage area blocks can be recorded in the connection comparison table. The storage system with the flash memories can not only ensure secure data access, but also save the internal storage capacity and the electric energy loss of the scratch pad storage.

Owner:PROLIFIC TECH INC

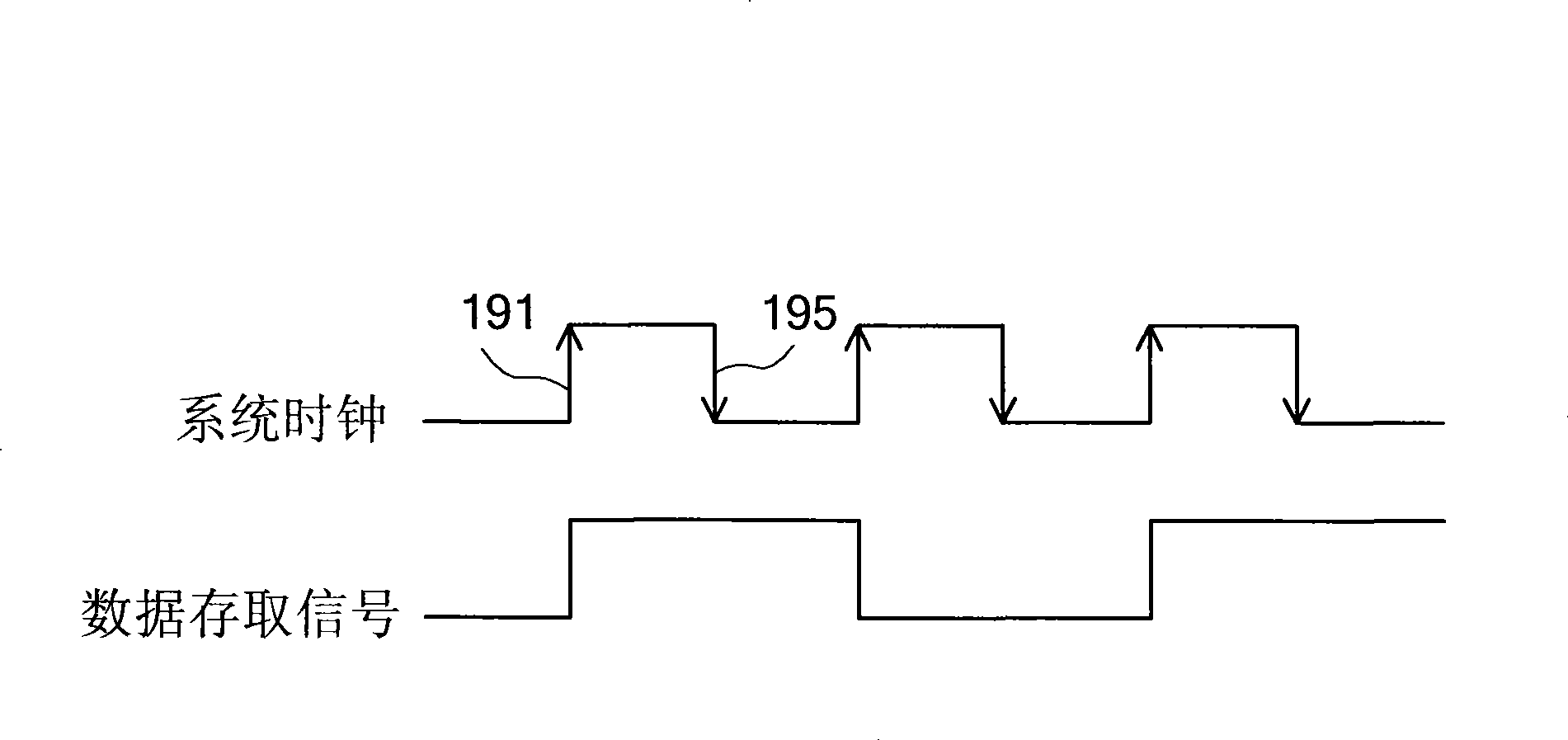

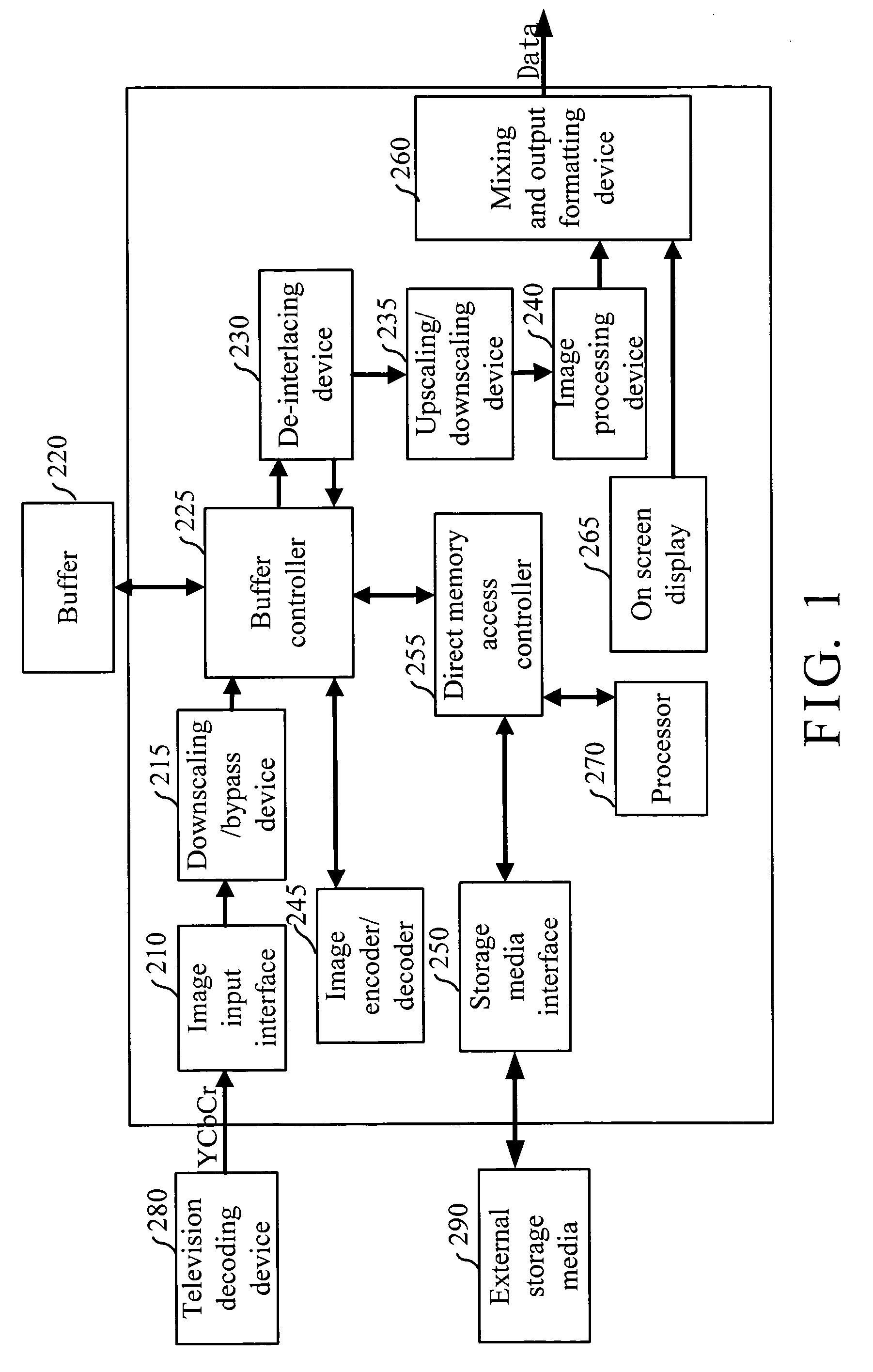

Liquid crystal display system with a storage capability

InactiveUS20050212784A1Improve image qualityImprove data access speedTelevision system detailsColor television detailsImaging processingData stream

A liquid crystal display system with a storage capability includes an image input interface, a buffer, a de-interlacing device, an upscaling / downscaling device, an image processing device, an image processing device, a buffer controller, a storage media interface and a direct memory access controller. The image input interface is used for receiving an image data stream. The buffer is coupled to the image input interface and used for temporarily storing the image data stream. The storage media interface is coupled to external storage media and the buffer and used for sending an image data stream stored in the storage media to the buffer for display, or sending an image data stream stored in the buffer to the storage media for storage. The direct memory access buffer controller is used for increasing a data access speed between the storage media interface and the buffer.

Owner:SUNPLUS TECH CO LTD

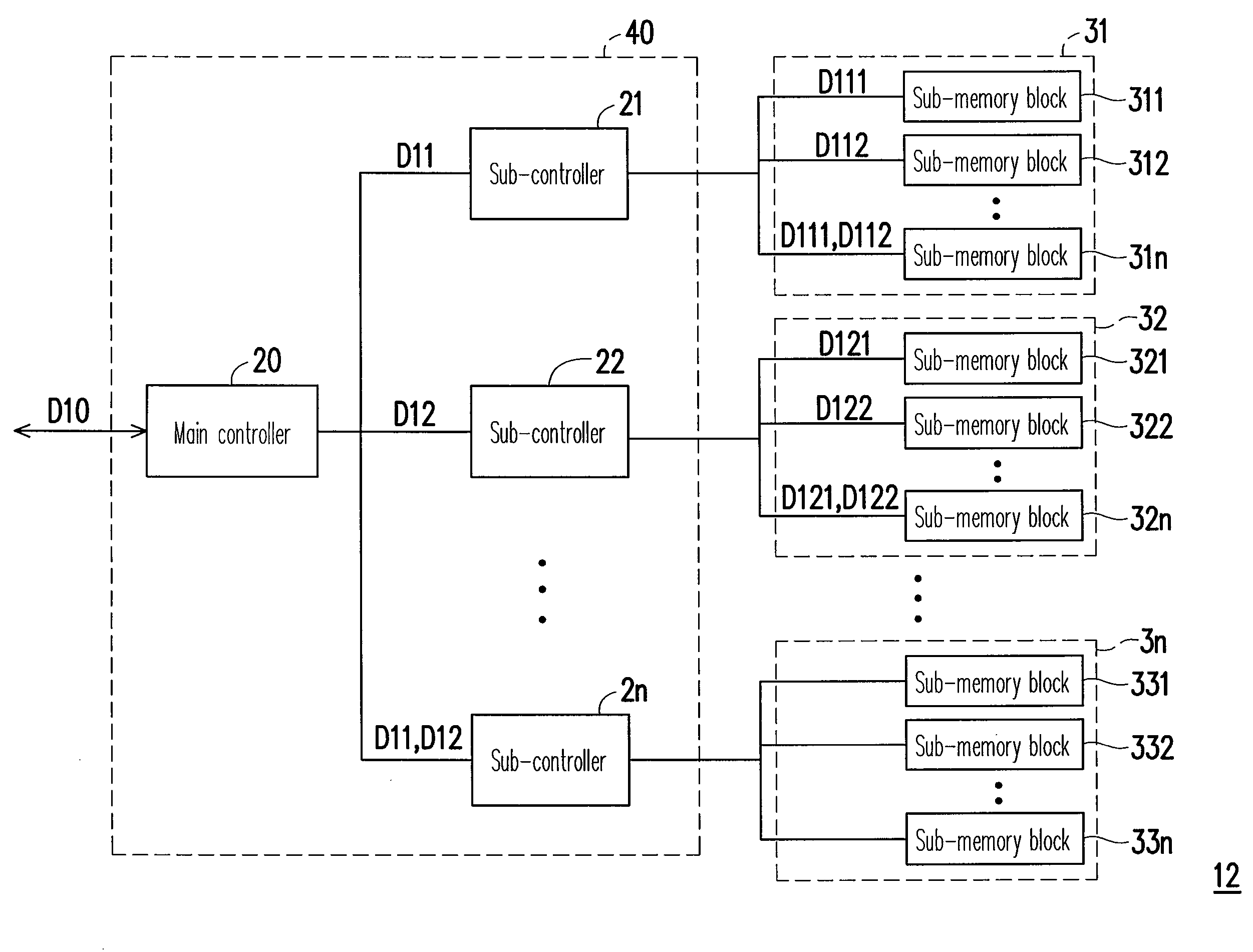

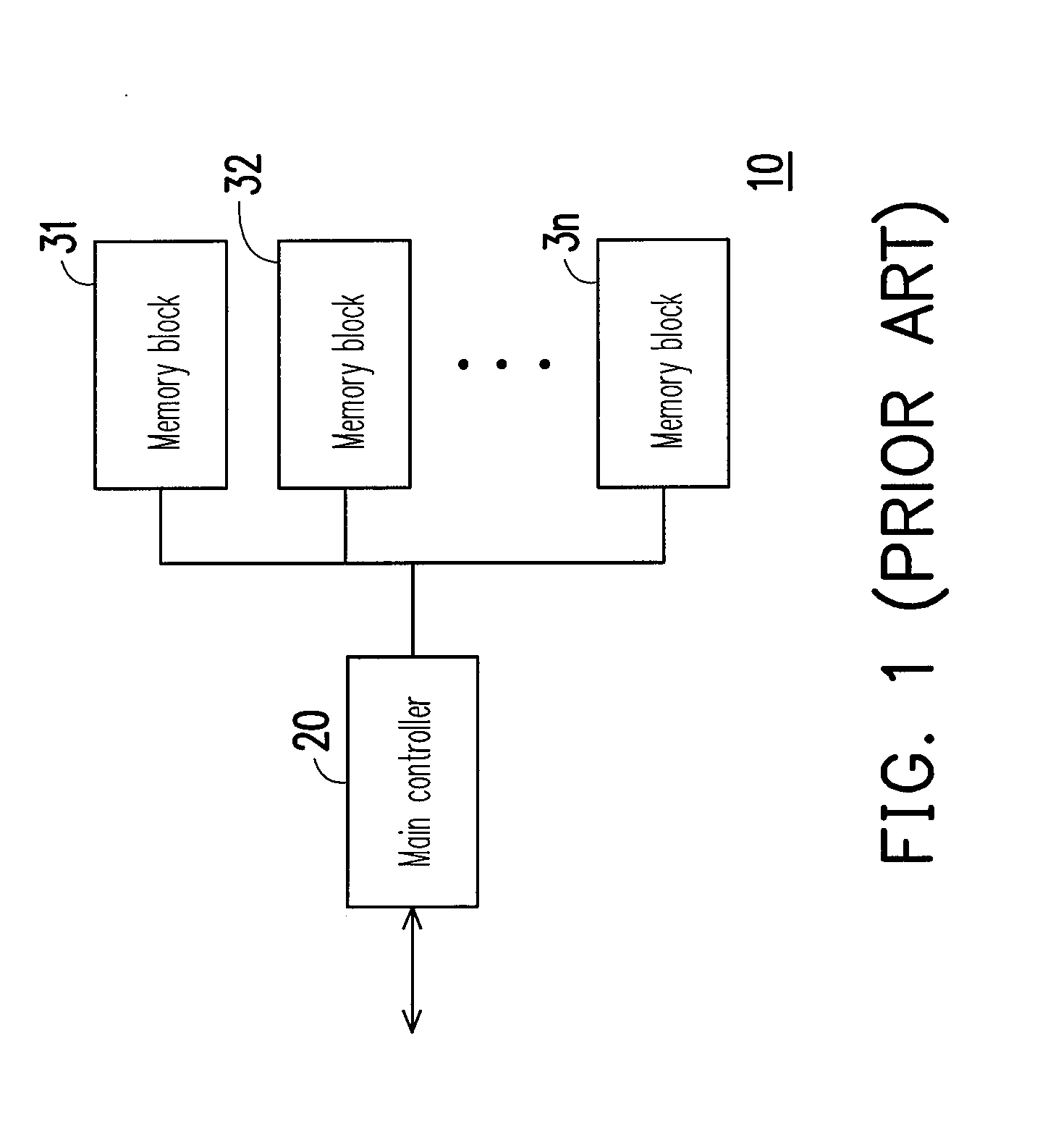

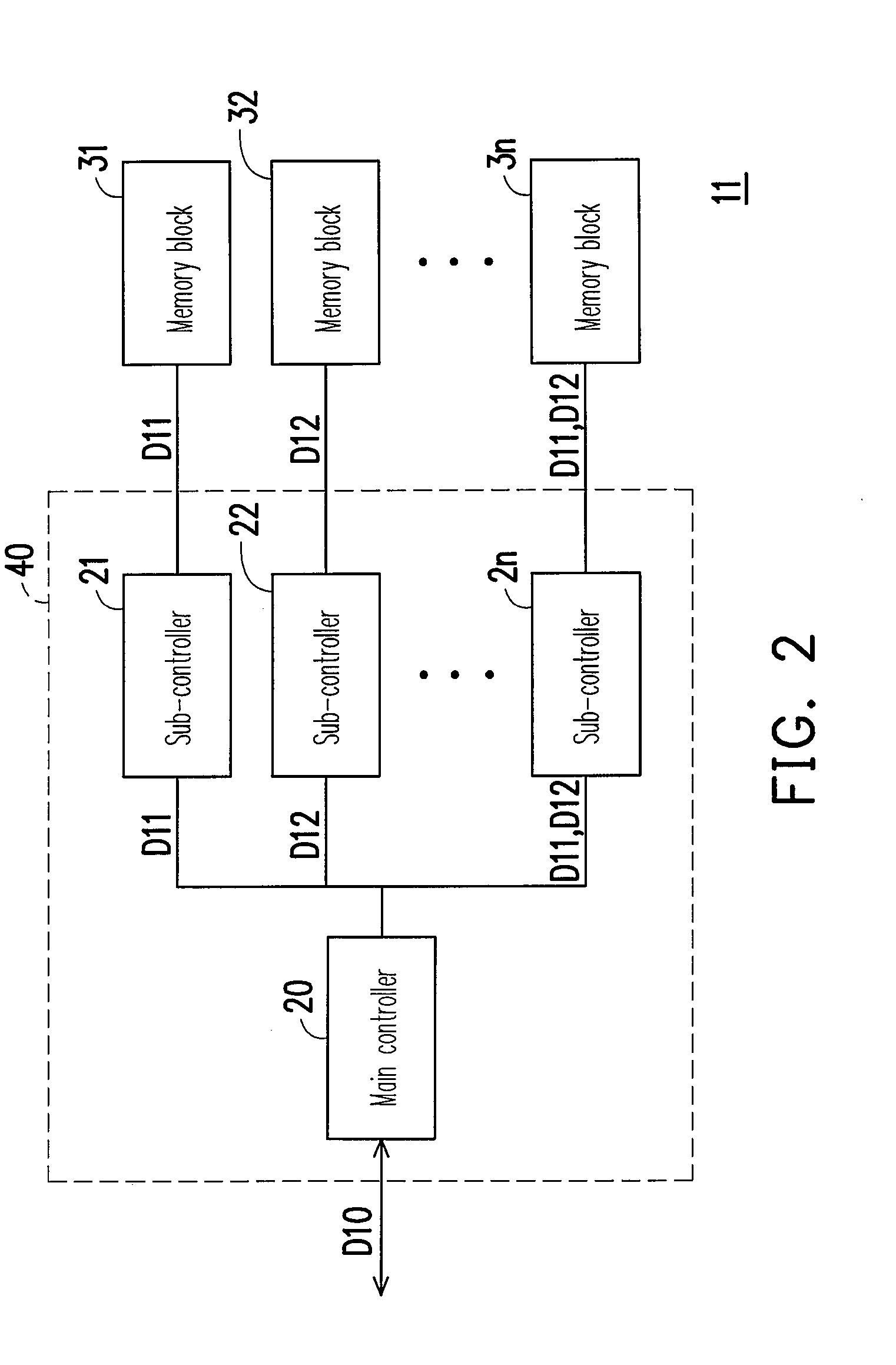

Non-volatile memory device and data access circuit and data access method

ActiveUS20090037645A1Easy to processImprove data processing speedError detection/correctionMemory systemsAccess methodData access

A non-volatile memory device, a data access circuit and a data access method are provided. The non-volatile memory device includes a main controller, a plurality of sub-controllers and a plurality of memory blocks. The sub-controllers are coupled to the main controller and are used to execute the tasks assigned by the main controller. The memory blocks are respectively coupled to the corresponding sub-controllers. The main controller is used to divide a received main data into a plurality of sub-data, and the sub-data are respectively saved in the memory blocks through corresponding sub-controllers. Therefore, the data access speed of the non-volatile memory device is substantially speeded-up.

Owner:TRANSCEND INFORMATION

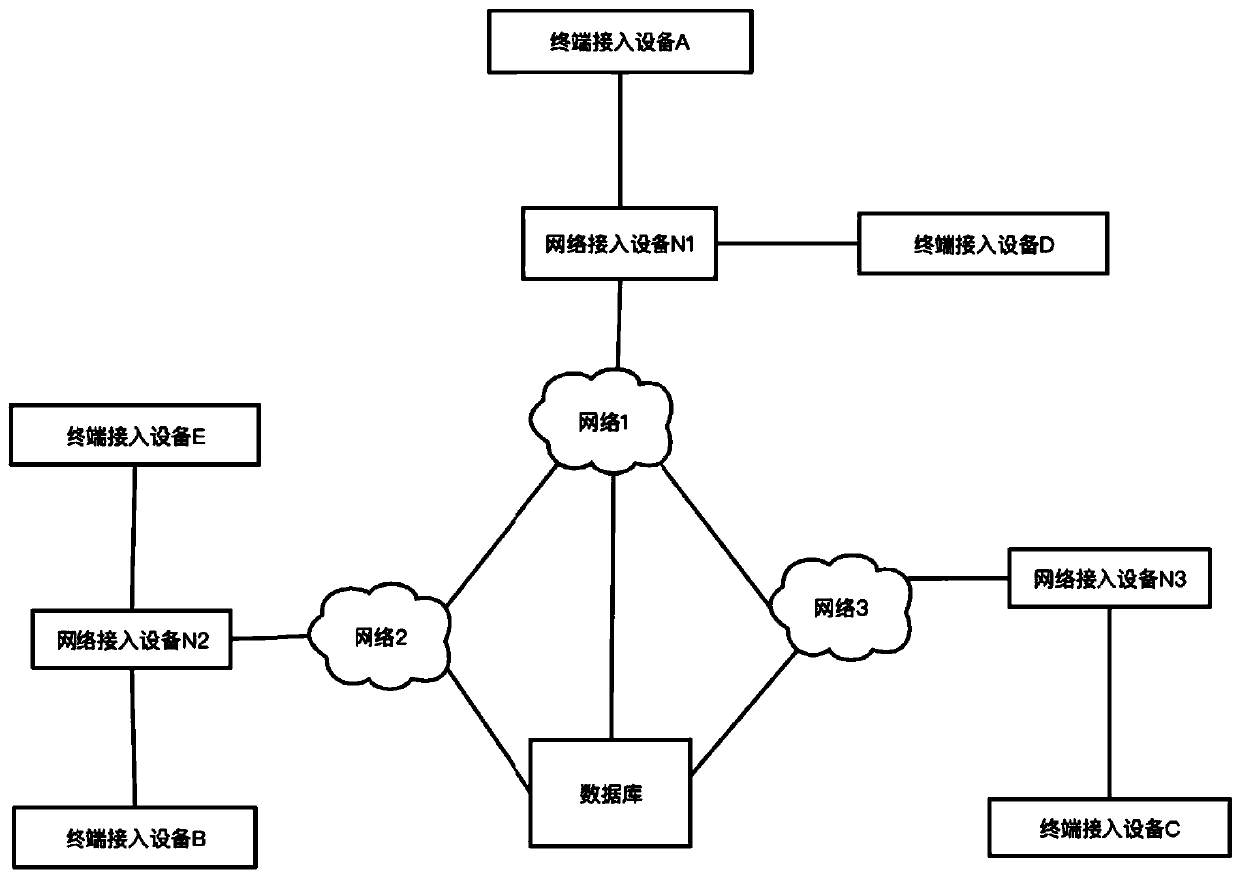

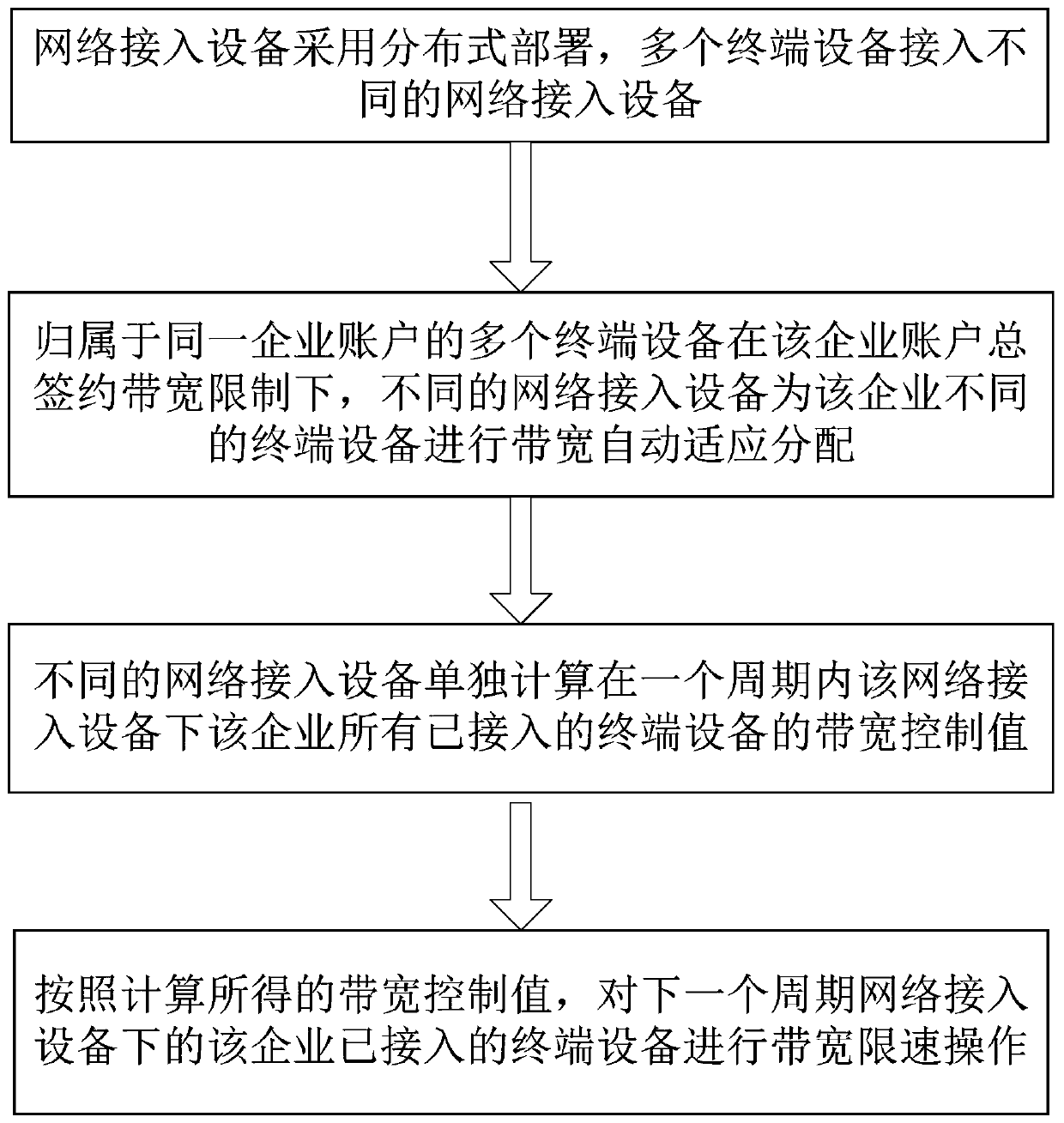

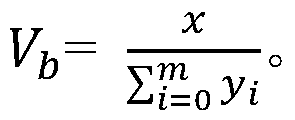

Adaptive bandwidth control method

ActiveCN110177056ADecoupling linkHigh Availability GuaranteeData switching networksTerminal equipmentEnterprise level

The invention discloses an adaptive bandwidth control method. The method comprises the following steps that: network access equipment adopts distributed deployment, a plurality of terminal devices areaccessed to different network access devices, wherein the plurality of terminal devices belonging to the same enterprise account are limited by the total signing bandwidth of the enterprise account;different network access devices carry out bandwidth automatic adaptive distribution on different terminal devices of the enterprise, and different network access devices independently calculate bandwidth control values of all accessed terminal devices of the enterprise under the network access device in one period; and according to the calculated bandwidth control value, carrying out bandwidth speed limiting operation on the terminal equipment accessed by the enterprise under the network access equipment in the next period. According to the method disclosed by the invention, the enterprise-oriented network access system can provide a bandwidth of a shared resource for different users belonging to the same enterprise, and dynamically adjust the bandwidth control value distributed by each terminal access device in real time according to the bandwidth use condition.

Owner:杭州商湾网络科技有限公司

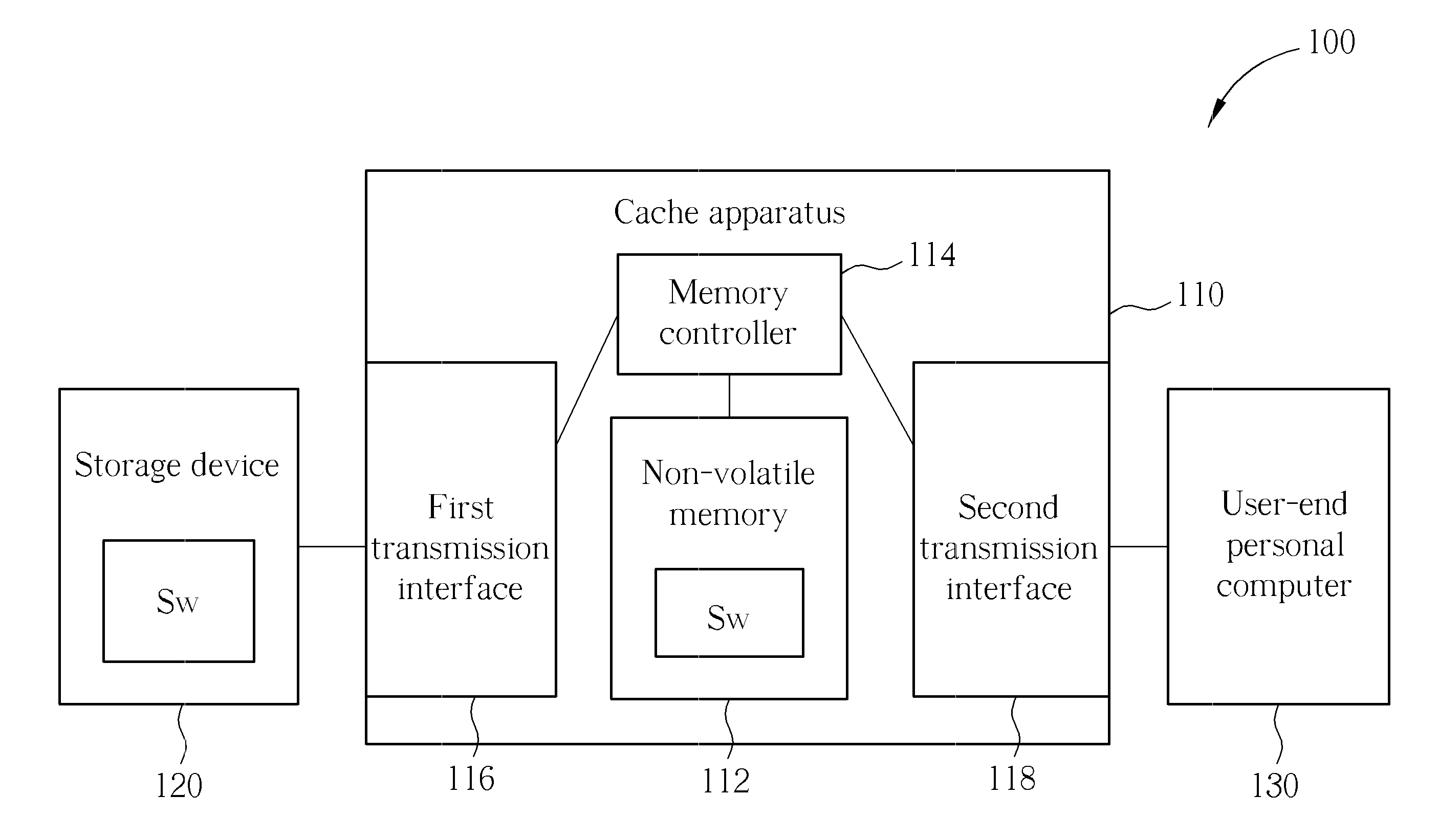

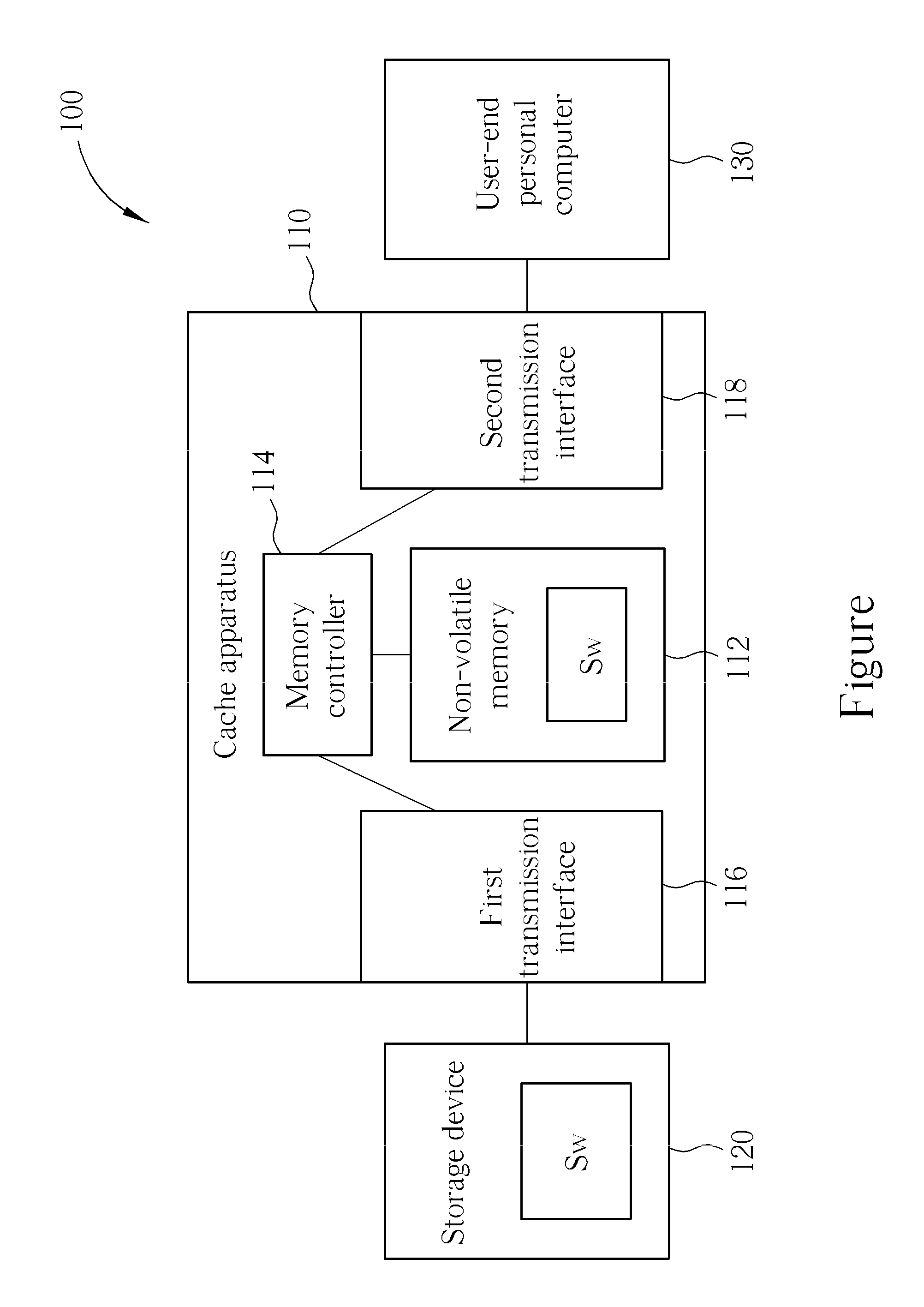

Cache apparatus for increasing data accessing speed of storage device

InactiveUS20110173376A1Increase data access speedImprove data access speedMemory adressing/allocation/relocationMemory controllerEmbedded system

A cache apparatus for increasing data accessing speed of a storage device includes: a non-volatile memory, for storing data; a memory controller, coupled to the non-volatile memory, for controlling data accessing operations of the non-volatile memory; a first transmission interface, coupled to the memory controller, for electrically connecting the memory controller to the storage device; and a second transmission interface, coupled to the memory controller, for electrically connecting the memory controller to a user-end personal computer.

Owner:JMICRON

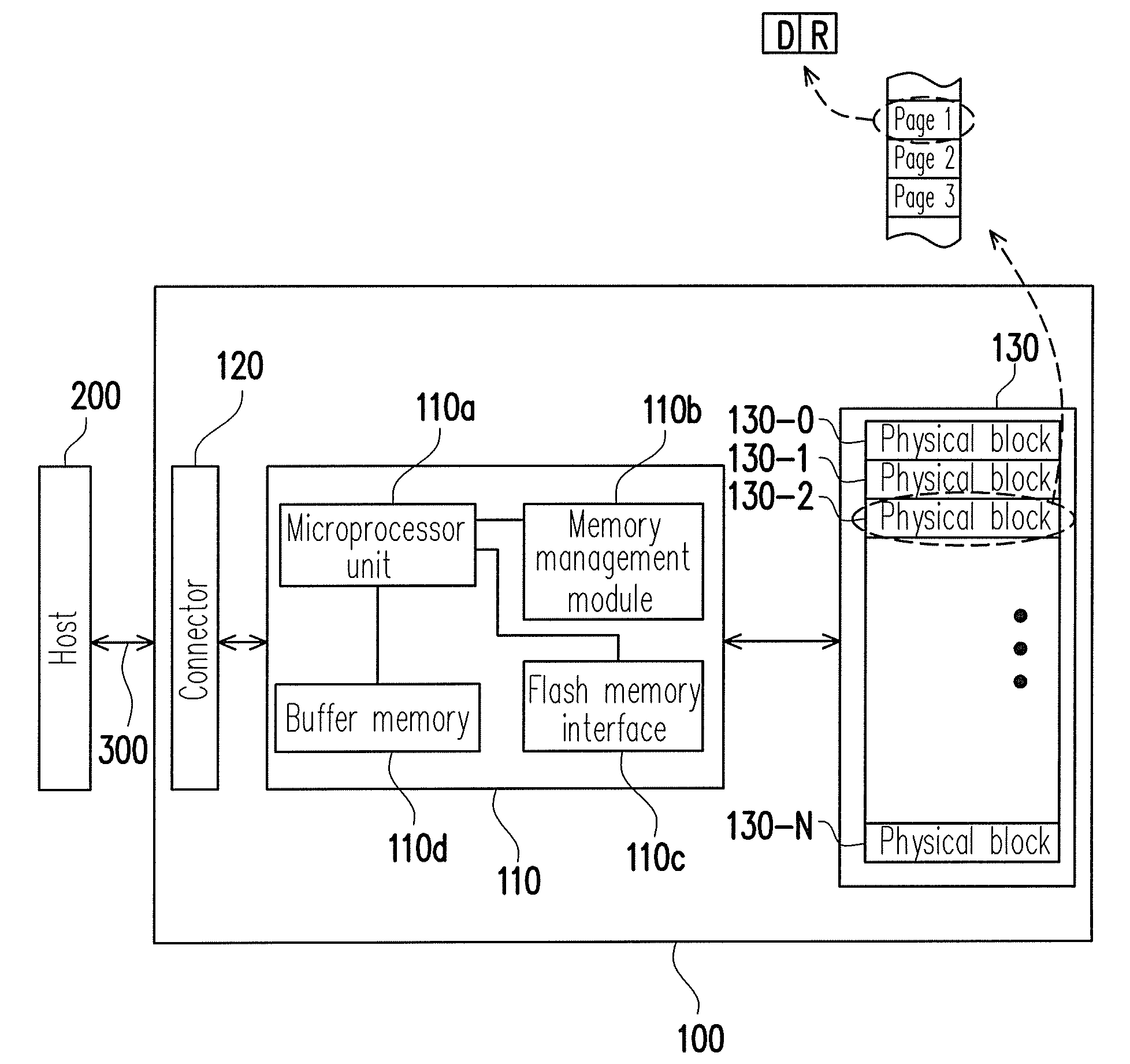

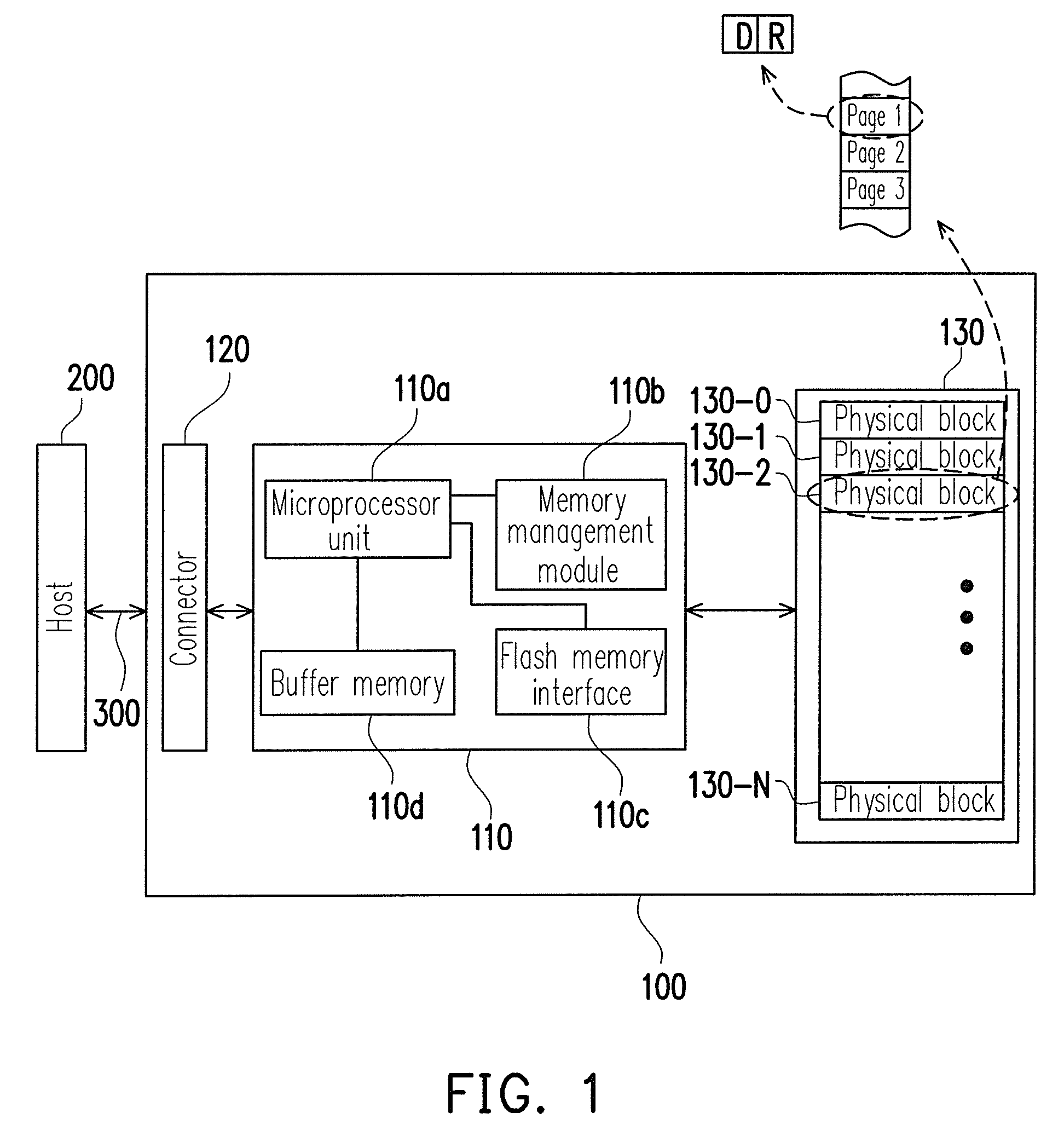

Data accessing method for flash memory and storage system and controller using the same

ActiveUS8386698B2Improve data access speedReduce in quantityMemory architecture accessing/allocationMemory systemsData accessContinuous data

A data accessing method for a flash memory and a storage system and a controller using the same are provided. The data accessing method includes grouping a plurality of physical blocks of the flash memory into a data area, a spare area, and a random area and when a write command and a new data to be written are received from a host, determining whether the new data is a continuous data, wherein the new data is written temporarily into the physical blocks in the random area if the new data is not a continuous data. Thereby, the number of data moving and physical block erasing is reduced and accordingly the data accessing speed in a random writing mode is increased.

Owner:PHISON ELECTRONICS

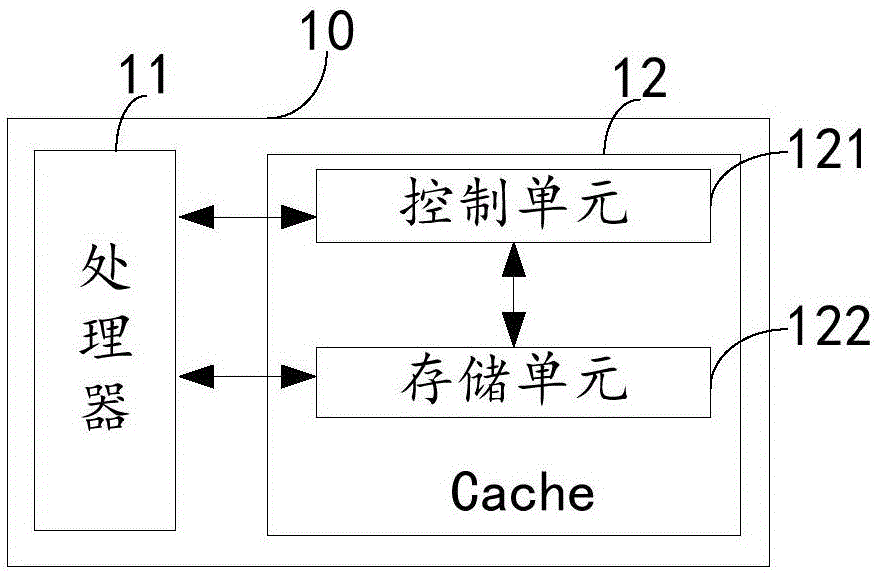

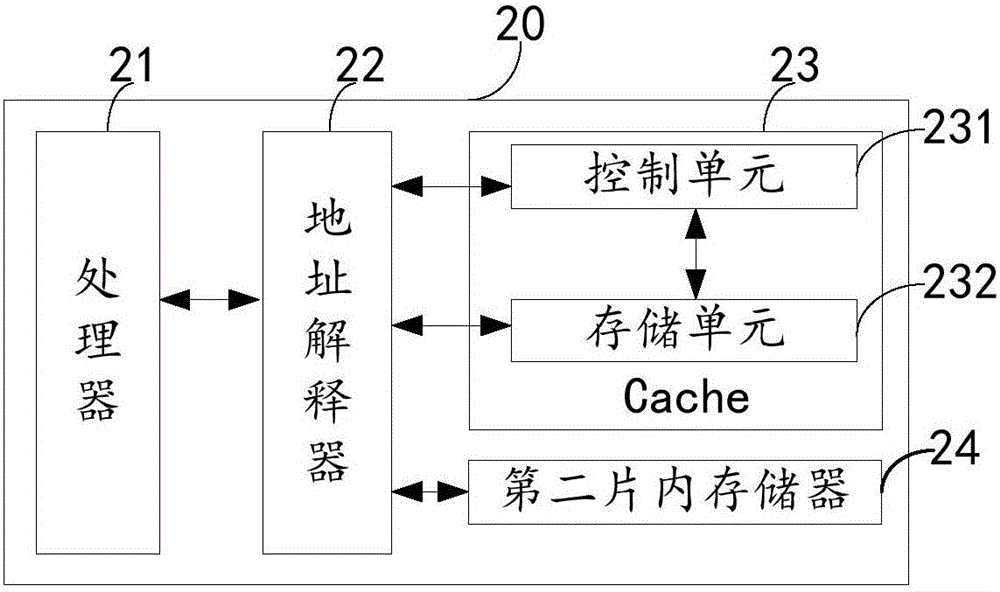

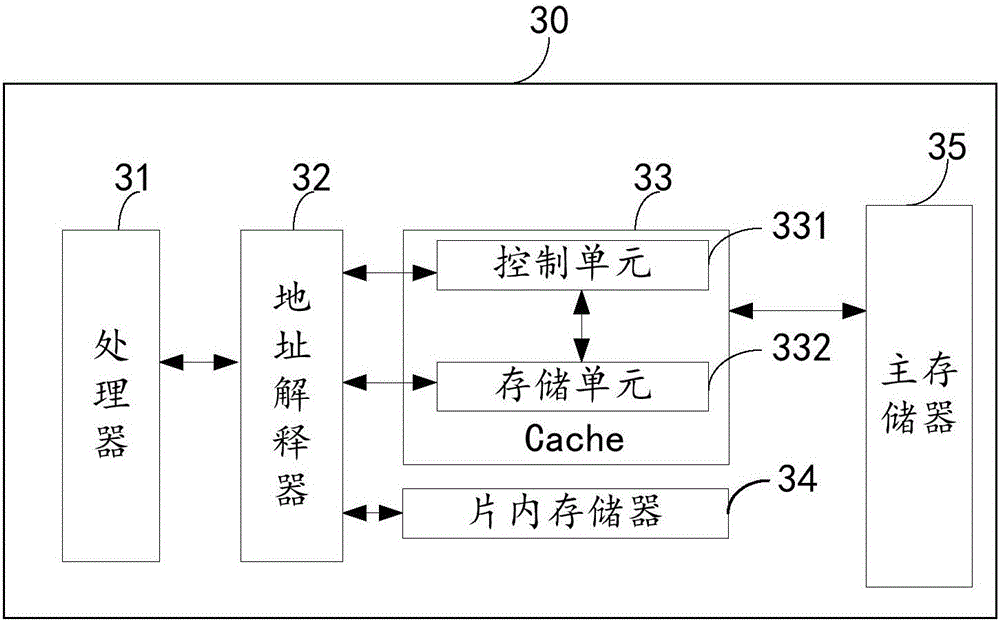

Chip and electronic device

ActiveCN106776360AExpand on-chip storage spaceImprove data access speedMemory adressing/allocation/relocationData accessParallel computing

The invention relates to the technical field of cache using, in particular to a chip and an electronic device. The chip comprises a processor and a cache. The cache comprises a caching mode and a storage mode; when the cache is located in the caching mode, the cache is used as a caching storage, and when the cache is located in the storage mode, the cache is used as a first on-chip storage. By means of the application mode of the chip and the electronic device in the embodiment, the on-chip storage space of the processor is enlarged, the data access speed of the processor is increased, and the performance of the chip is improved.

Owner:APPOTECH

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com