Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

291 results about "Logical analysis" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

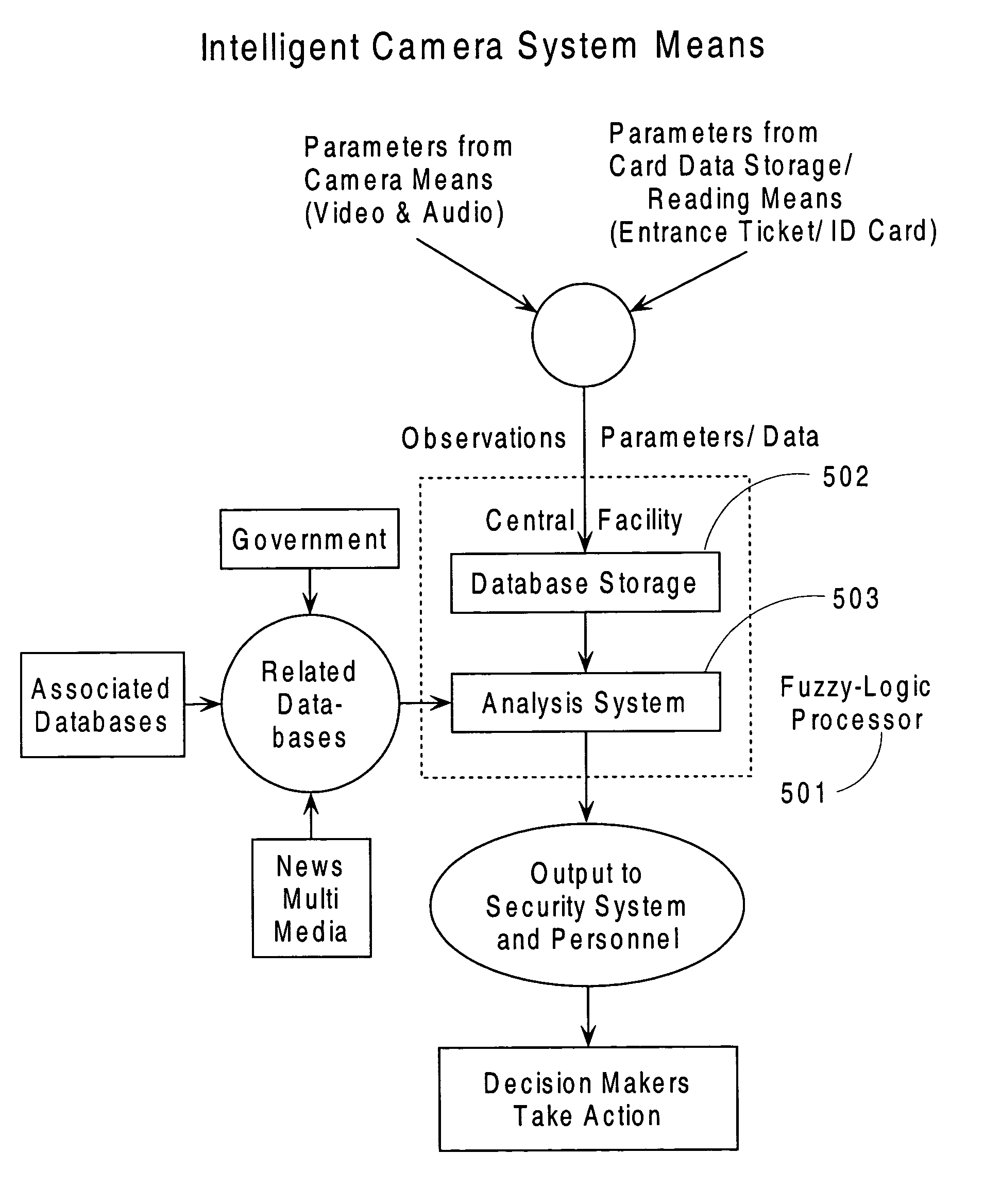

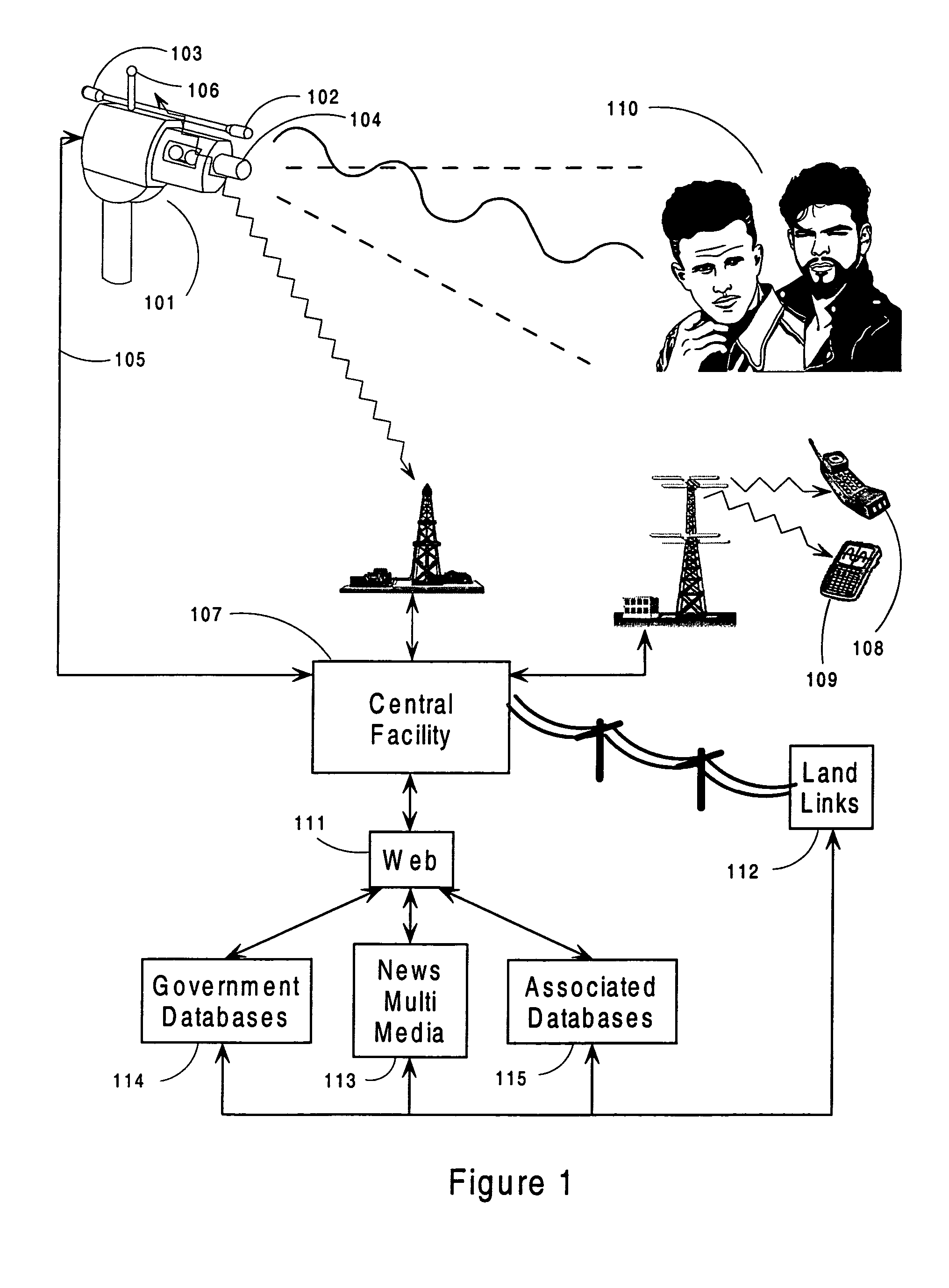

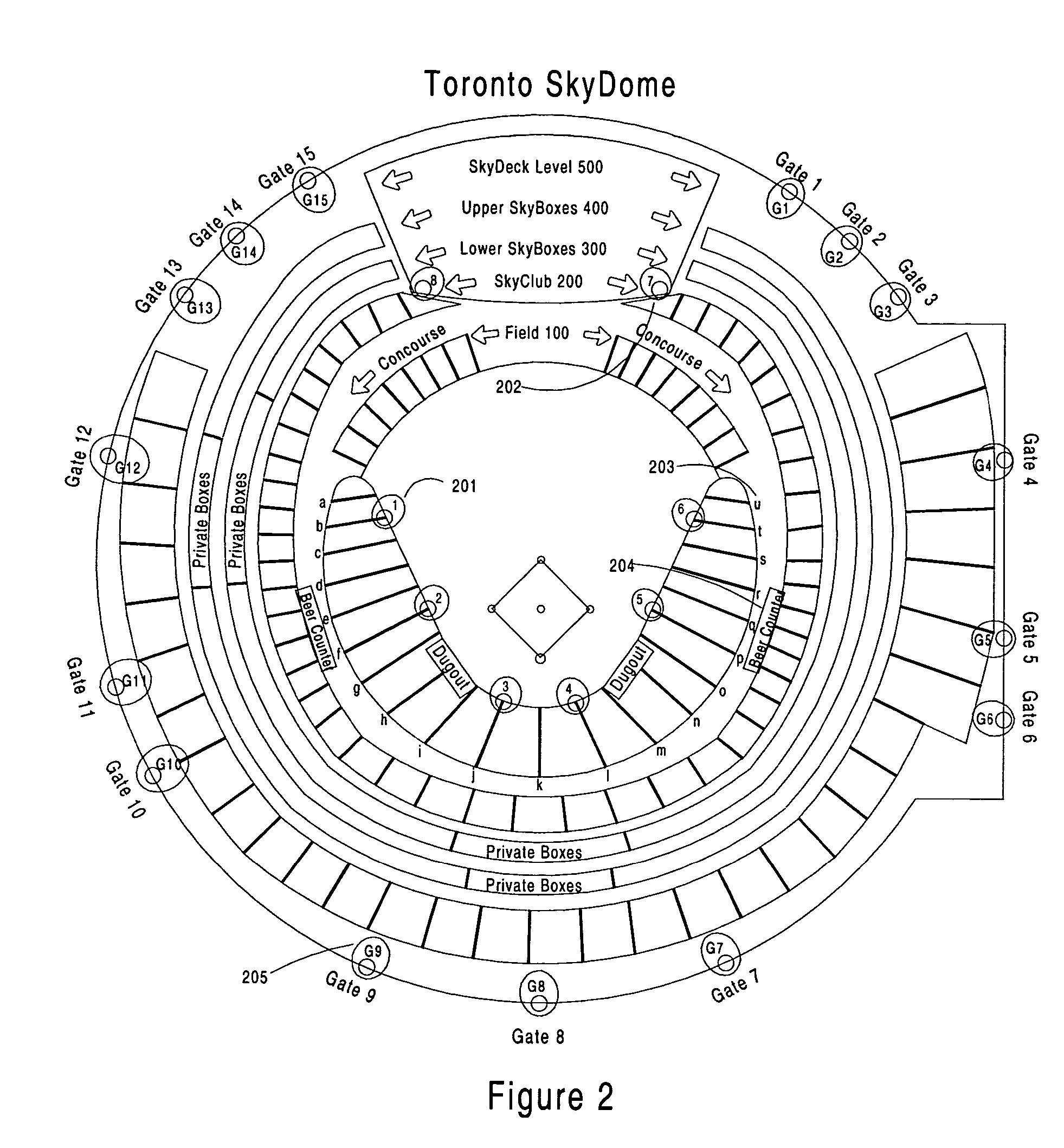

Voice, lip-reading, face and emotion stress analysis, fuzzy logic intelligent camera system

InactiveUS7999857B2Improve abilitiesMaintain integrityTelevision system detailsColor television detailsPattern recognitionCrowds

Revealed is an intelligent camera security monitoring, fuzzy logic analyses and information reporting system that includes video / audio camera, integrated local controller, interfaced plurality of sensors, and input / output means, that collects and analyses data and information observations from a viewed scene and communicates these to a central controller. The central controller with fuzzy logic processor receives, stores these observations, conducts a plurality of computer analyses techniques and technologies including face, voice, lip reading, emotion, movement, pattern recognition and stress analysis to determine responses and potential threat of / by a person, crowd, animal, action, activity or thing. This invention recognizes possible terrorists, criminals, enraged or dangerous persons and also can identify a person's level of intoxication or impairment by alcohol or drugs via a new “Visual Response Measure”. The invention provides an intelligent tool to assist security systems and personnel, improving capability to record, display and share information and maintain security.

Owner:STRESSCAM OPERATIONS & SYST

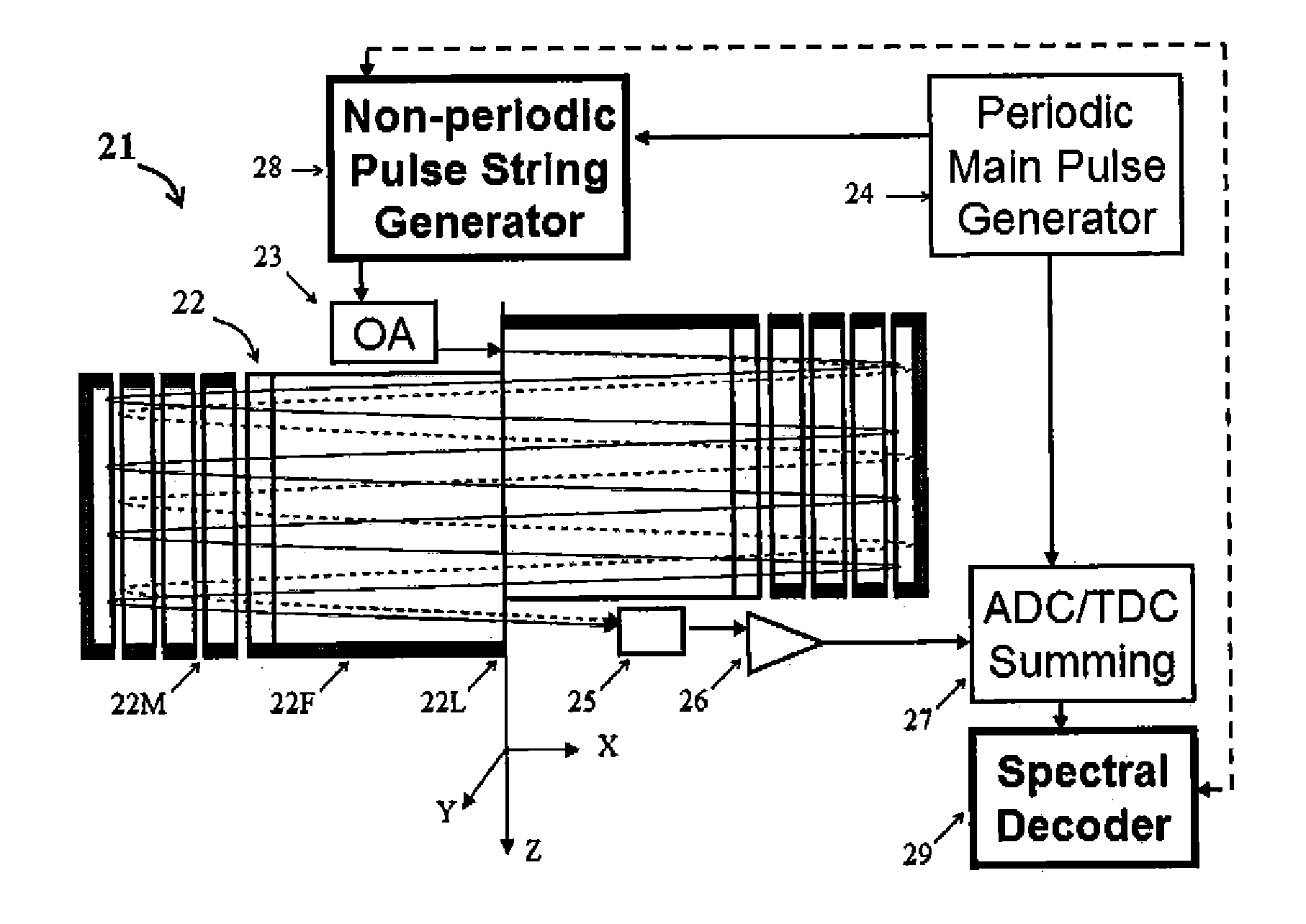

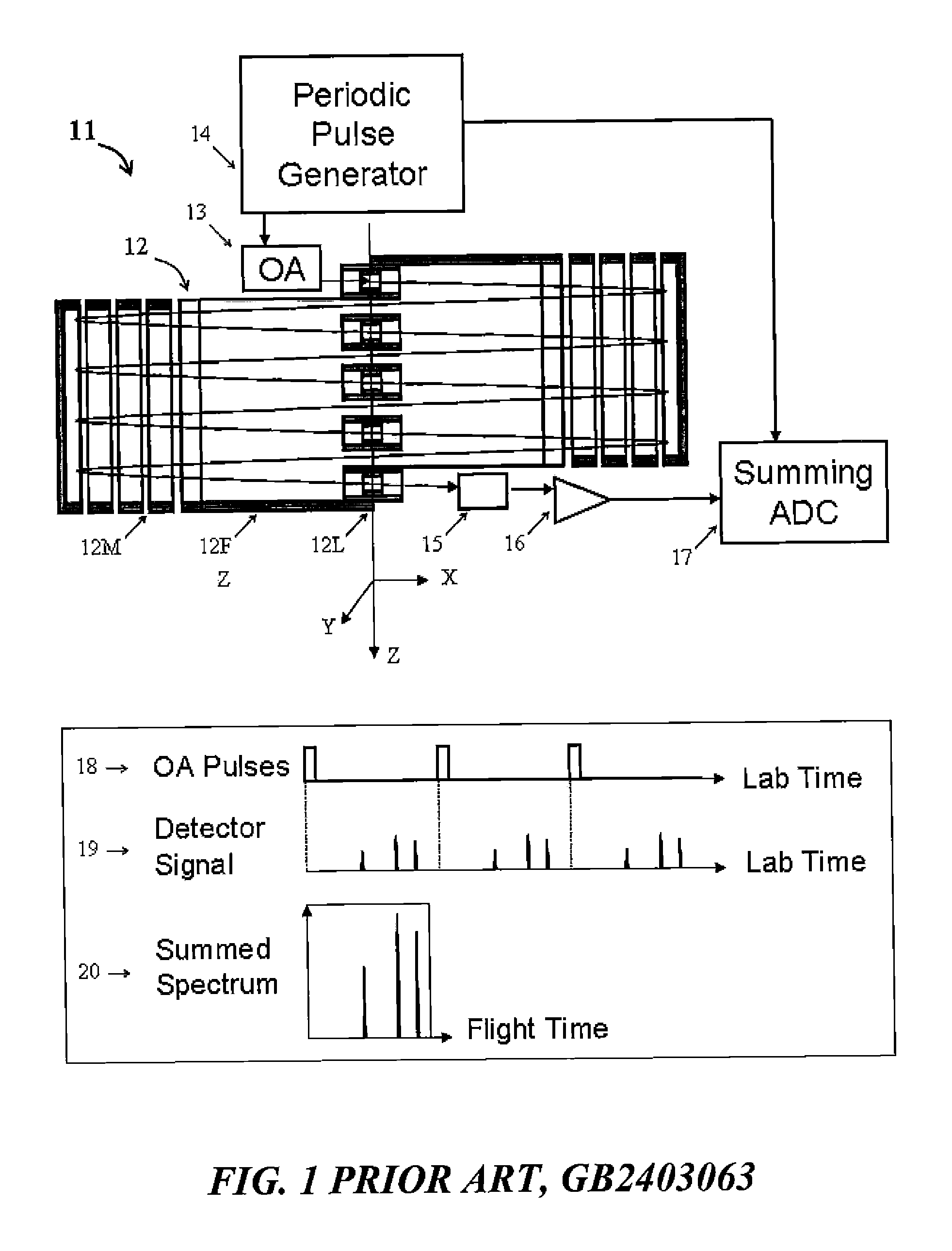

Electrostatic Mass Spectrometer with Encoded Frequent Pulses

ActiveUS20130048852A1Increase rangeHigh responseTime-of-flight spectrometersIsotope separationLogical analysisProtein mass spectrometry

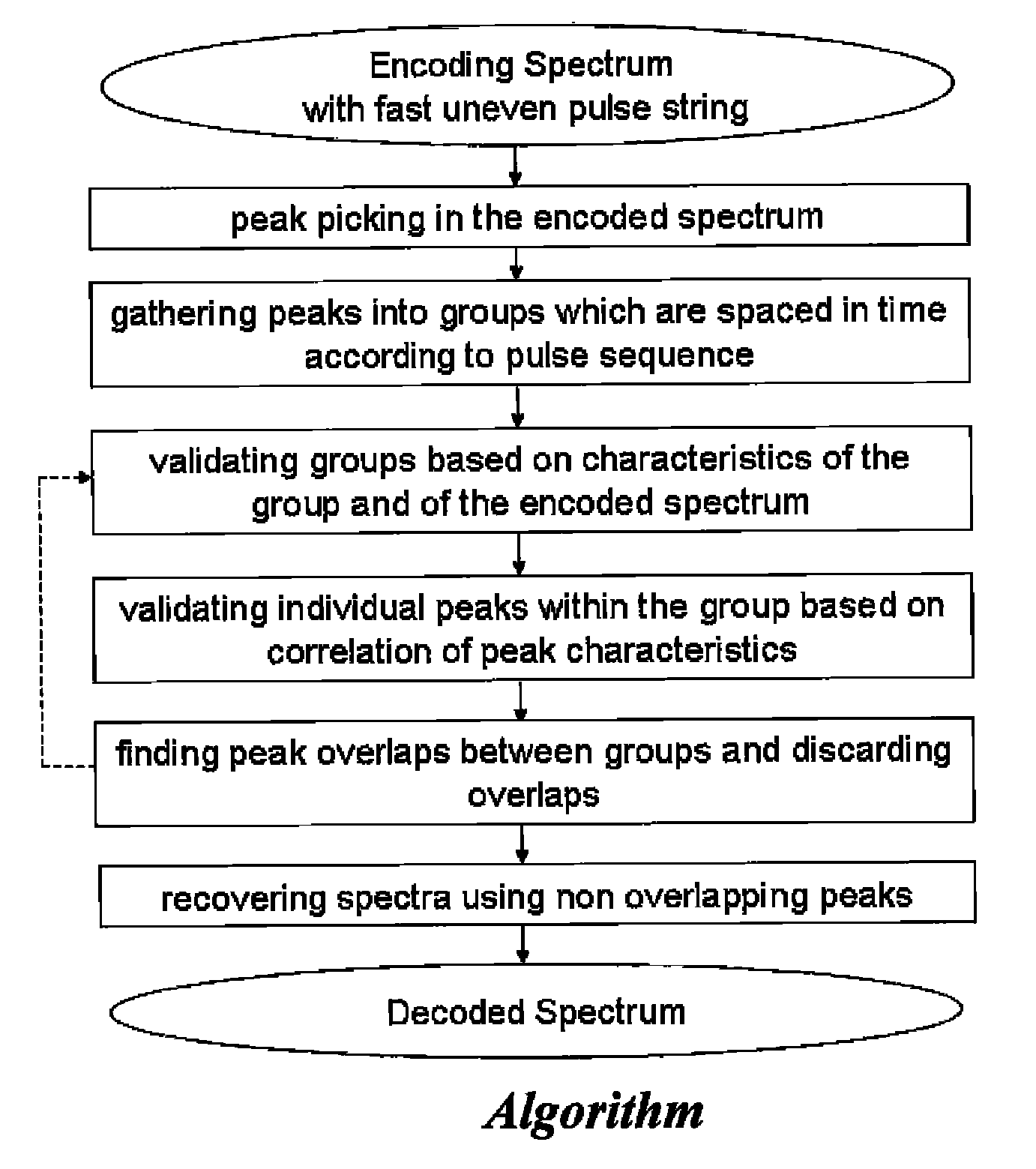

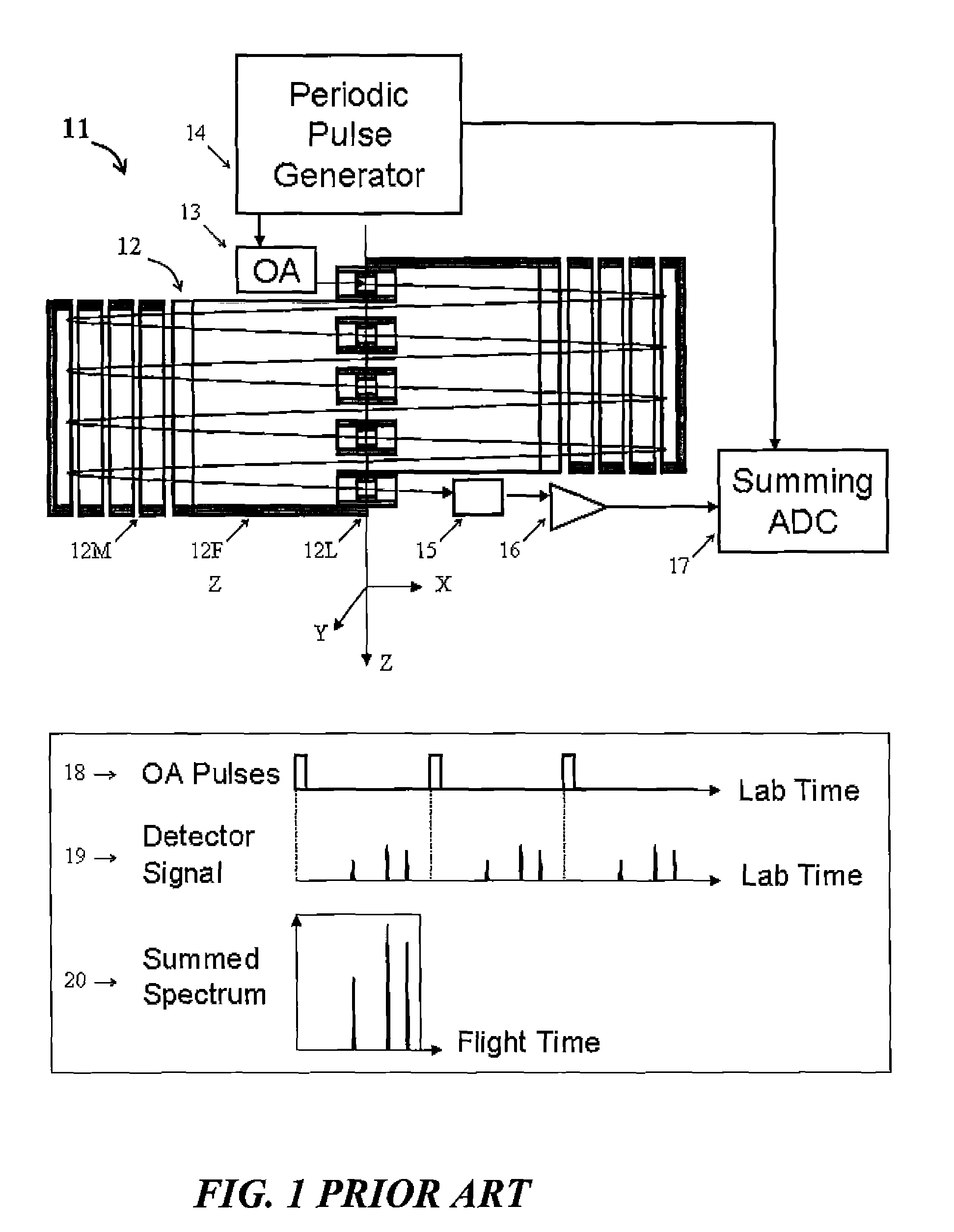

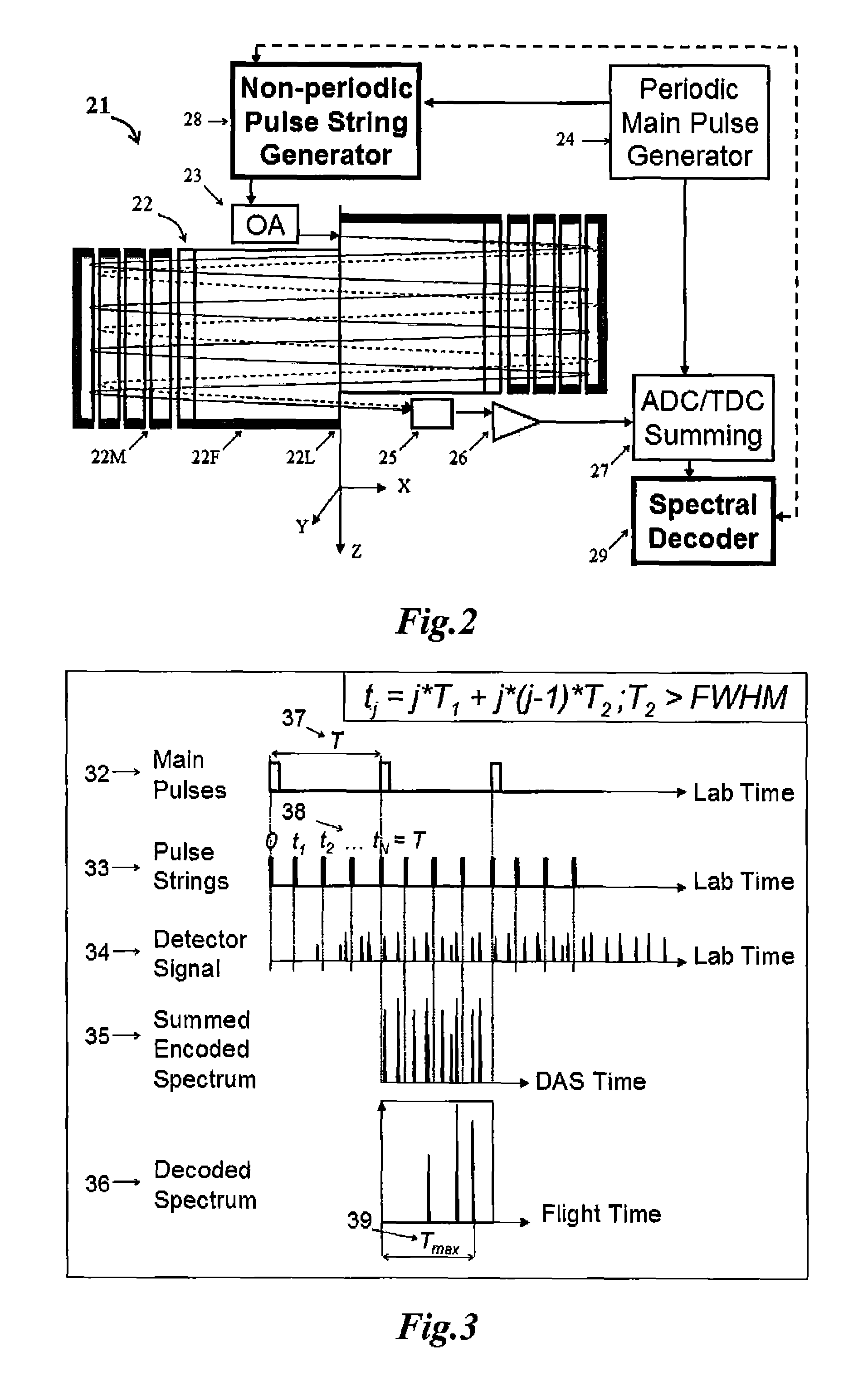

A method, apparatus and algorithms are disclosed for operating an open electrostatic trap (E-trap) or a multi-pass TOF mass spectrometer with an extended flight path. A string of start pulses with non equal time intervals is employed for triggering ion packet injection into the analyzer, a long spectrum is acquired to accept ions from the entire string and a true spectrum is reconstructed by eliminating or accounting overlapping signals at the data analysis stage while using logical analysis of peak groups. The method is particularly useful for tandem mass spectrometry wherein spectra are sparse. The method improves the duty cycle, the dynamic range and the space charge throughput of the analyzer and of the detector, so as the response time of the E-trap analyzer. It allows flight extension without degrading E-trap sensitivity.

Owner:LECO CORPORATION

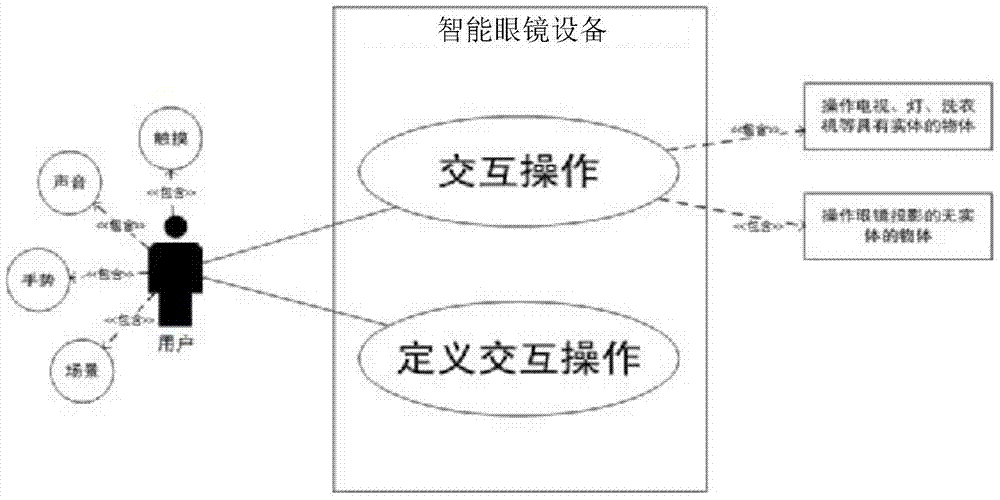

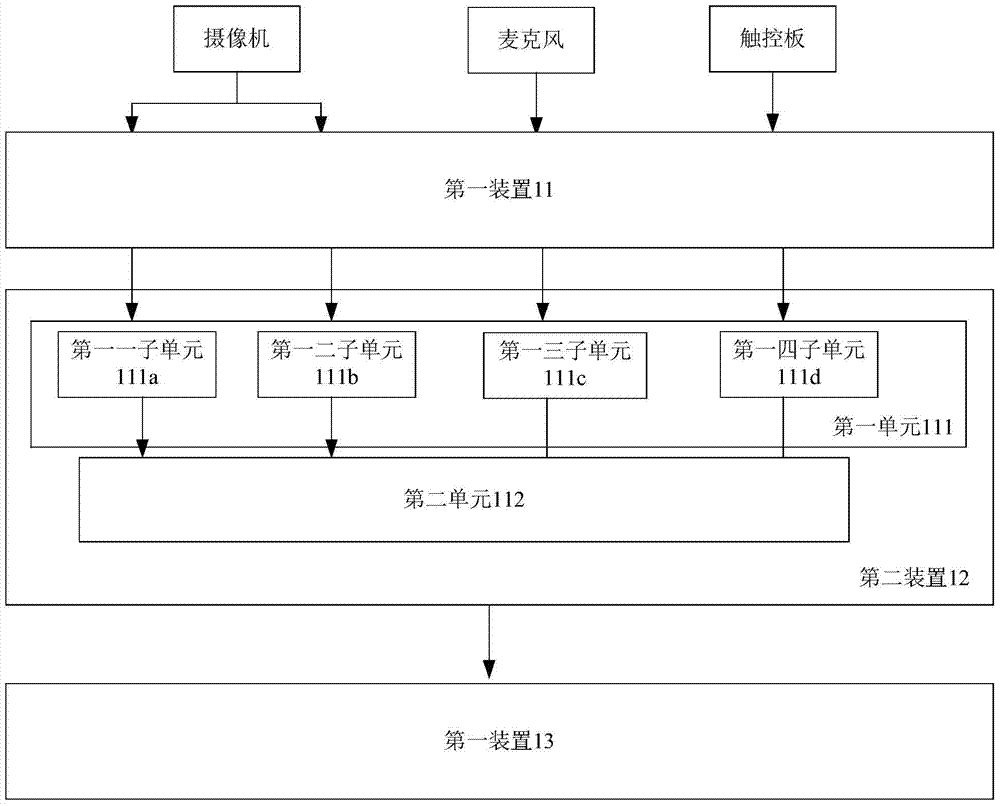

Multimodal input-based interactive method and device

ActiveCN106997236AImprove interactive experienceIncrease flexibilityInput/output for user-computer interactionCharacter and pattern recognitionObject basedComputer module

The invention aims to provide an intelligent glasses device and method used for performing interaction based on multimodal input and capable of enabling the interaction to be closer to natural interaction of users. The method comprises the steps of obtaining multiple pieces of input information from at least one of multiple input modules; performing comprehensive logic analysis on the input information to generate an operation command, wherein the operation command has operation elements, and the operation elements at least include an operation object, an operation action and an operation parameter; and executing corresponding operation on the operation object based on the operation command. According to the intelligent glasses device and method, the input information of multiple channels is obtained through the input modules and is subjected to the comprehensive logic analysis, the operation object, the operation action and the operation element of the operation action are determined to generate the operation command, and the corresponding operation is executed based on the operation command, so that the information is subjected to fusion processing in real time, the interaction of the users is closer to an interactive mode of a natural language, and the interactive experience of the users is improved.

Owner:HISCENE INFORMATION TECH CO LTD

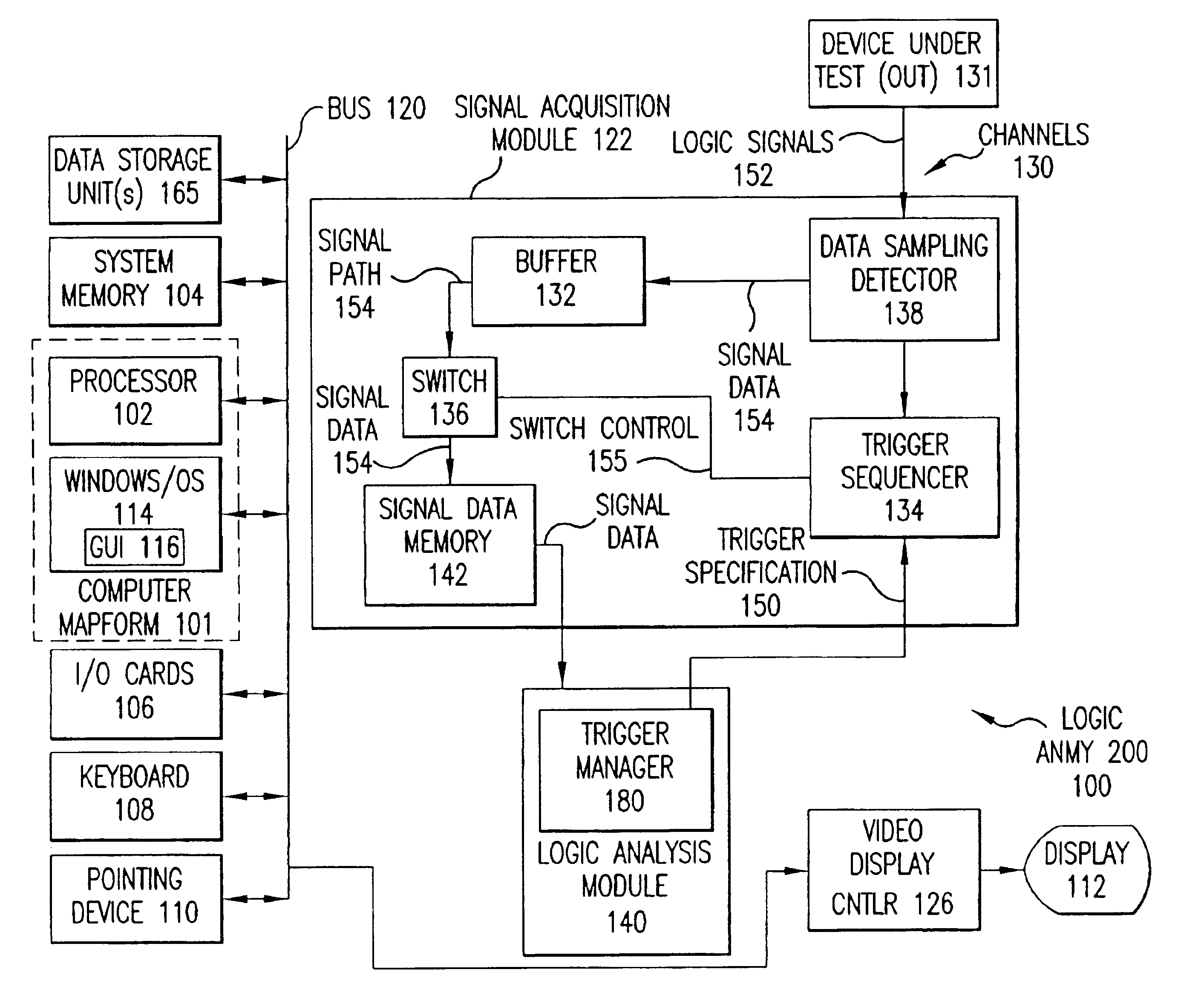

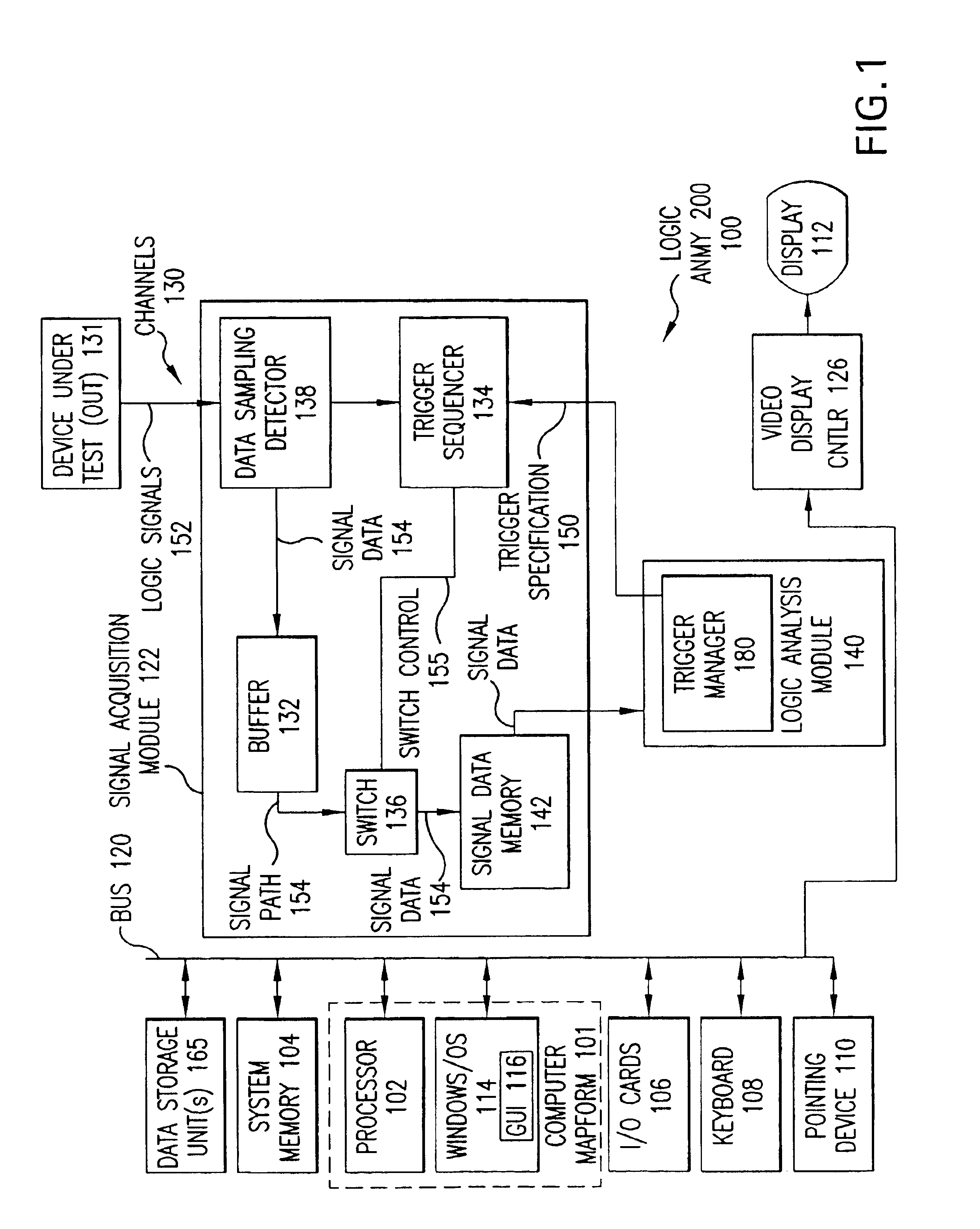

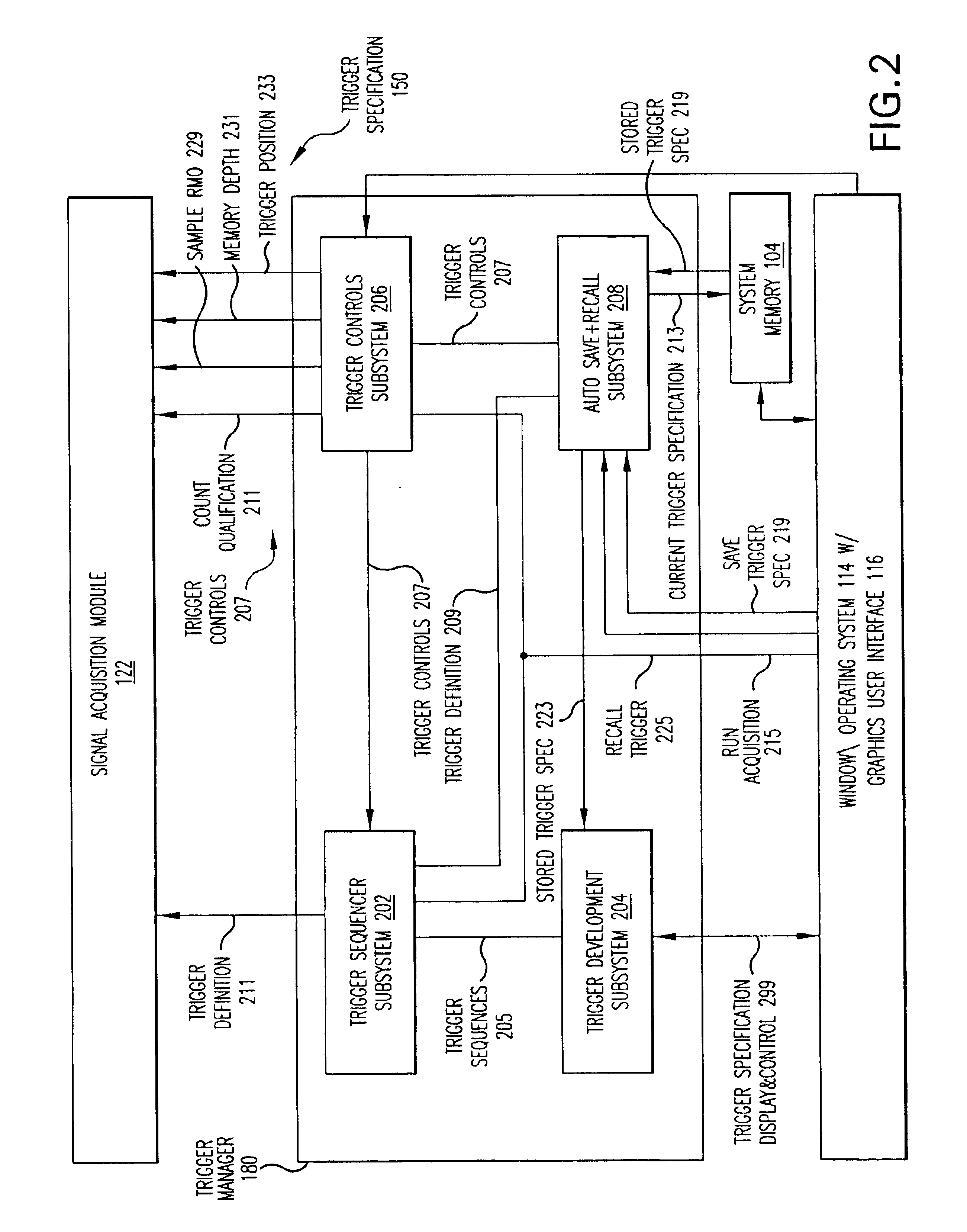

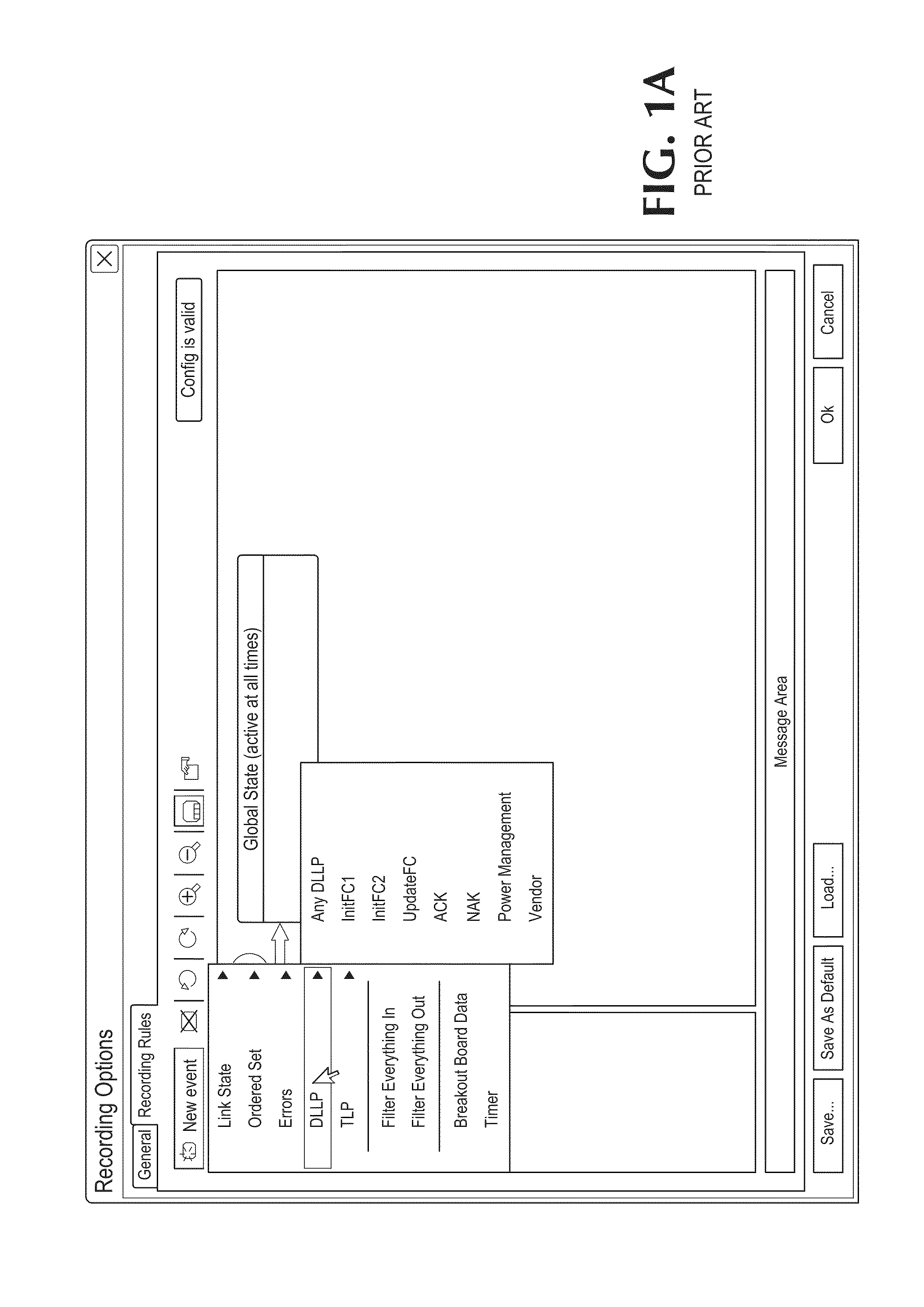

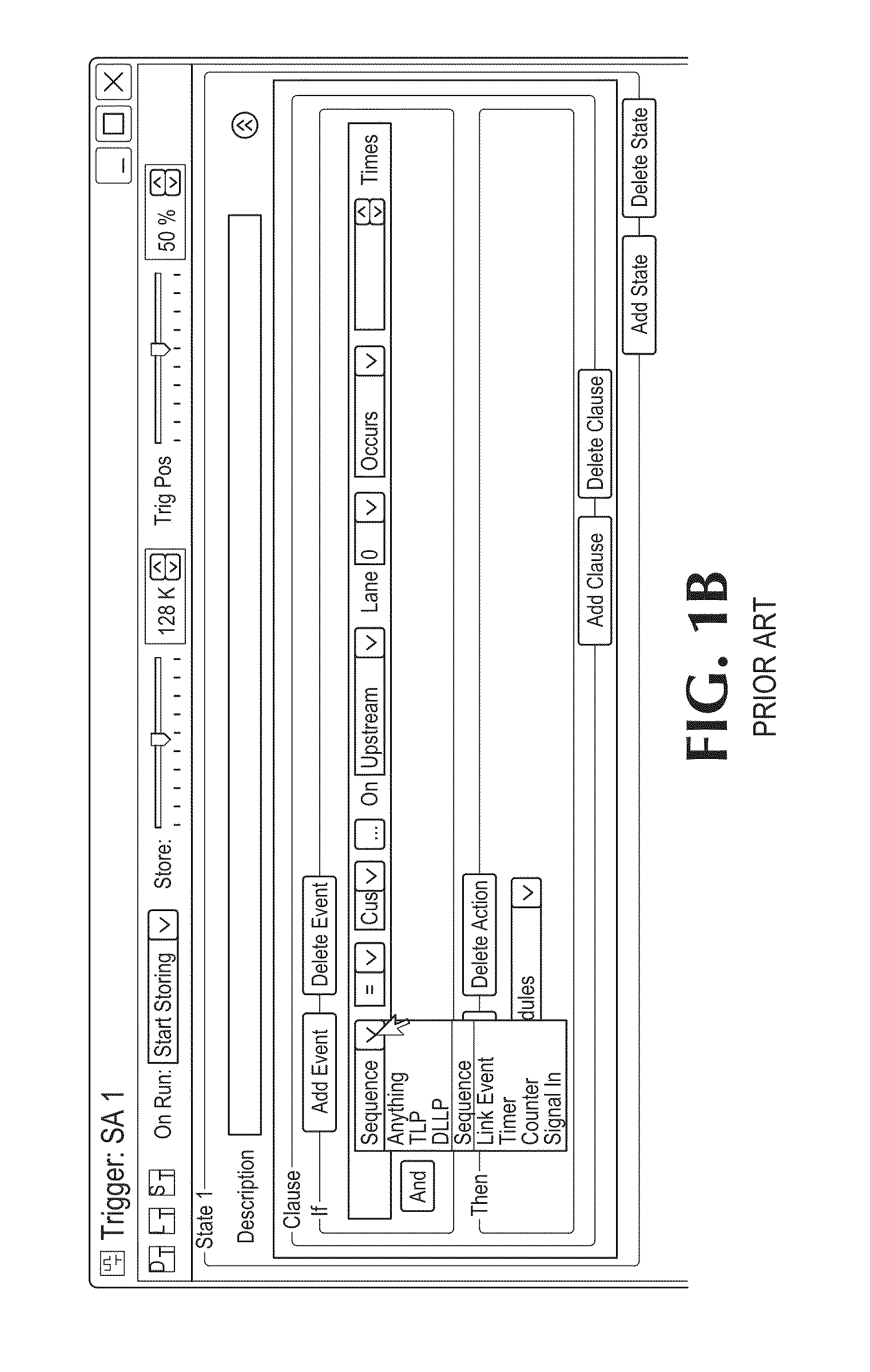

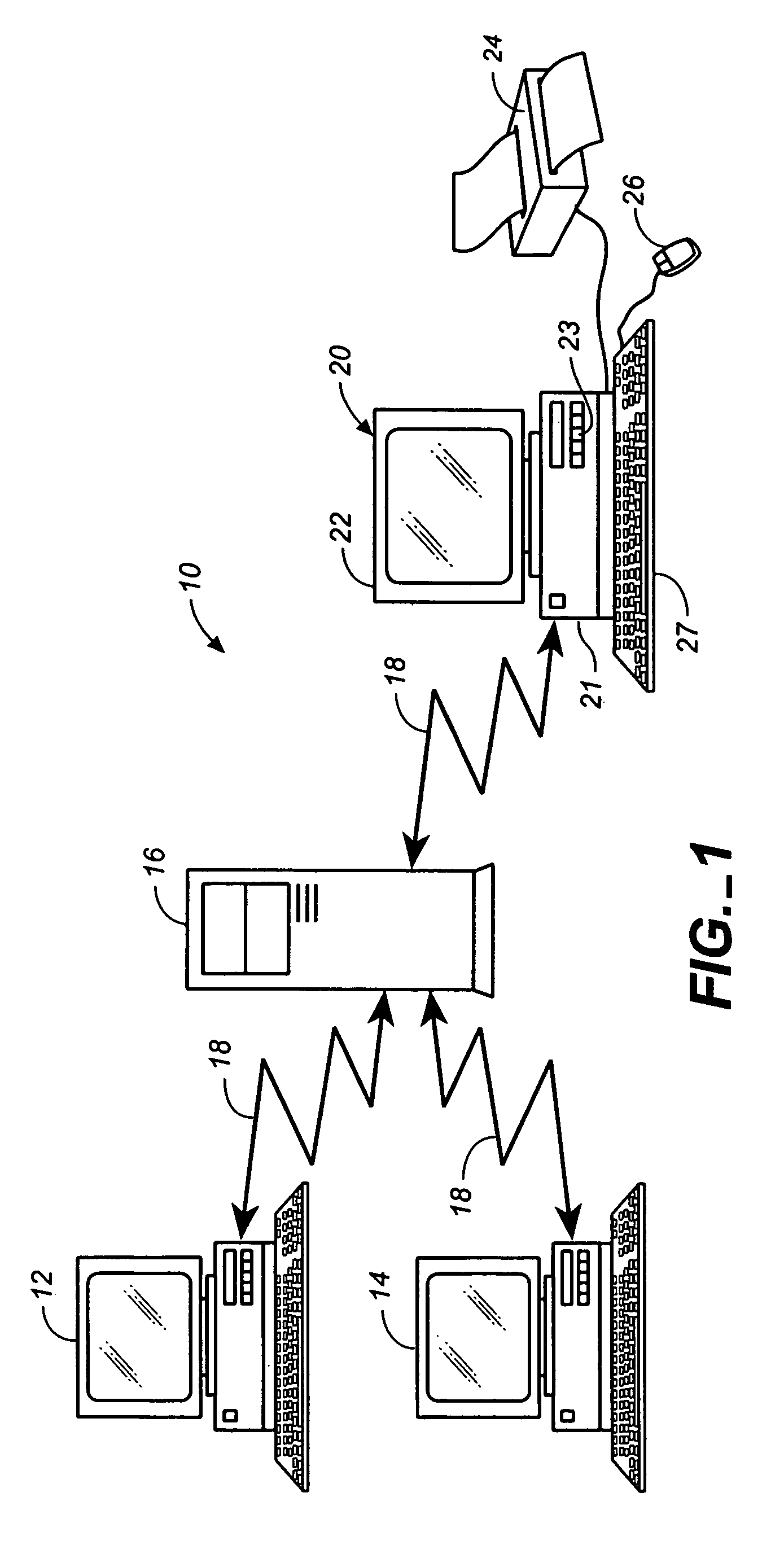

System and method for configuring a logic analyzer to trigger on data communications packets and protocols

InactiveUS6850852B1Digital variable displayData processing applicationsGraphicsGraphical user interface

A trigger function display system and methodology for trigger definition development in a signal measurement system having a graphical user interface. The system displays a plurality of graphically selectable icons and an associated protocol profile window. The protocol profile window includes at least a protocol descriptor field and a protocol editors field. The user inputs data into the protocol editors field which causes the system to automatically construct a bit sequence utilizing a plurality of event definitions stored in memory. The event definitions are two bit blocks resulting from the parsing of protocol definition text files. The bit sequence is used to then construct a series of trigger primitives. An optimizing routine is used to consolidate consecutive multiple occurrences of identical bit patterns in the bit sequence into single trigger primitives.

Owner:AGILENT TECH INC

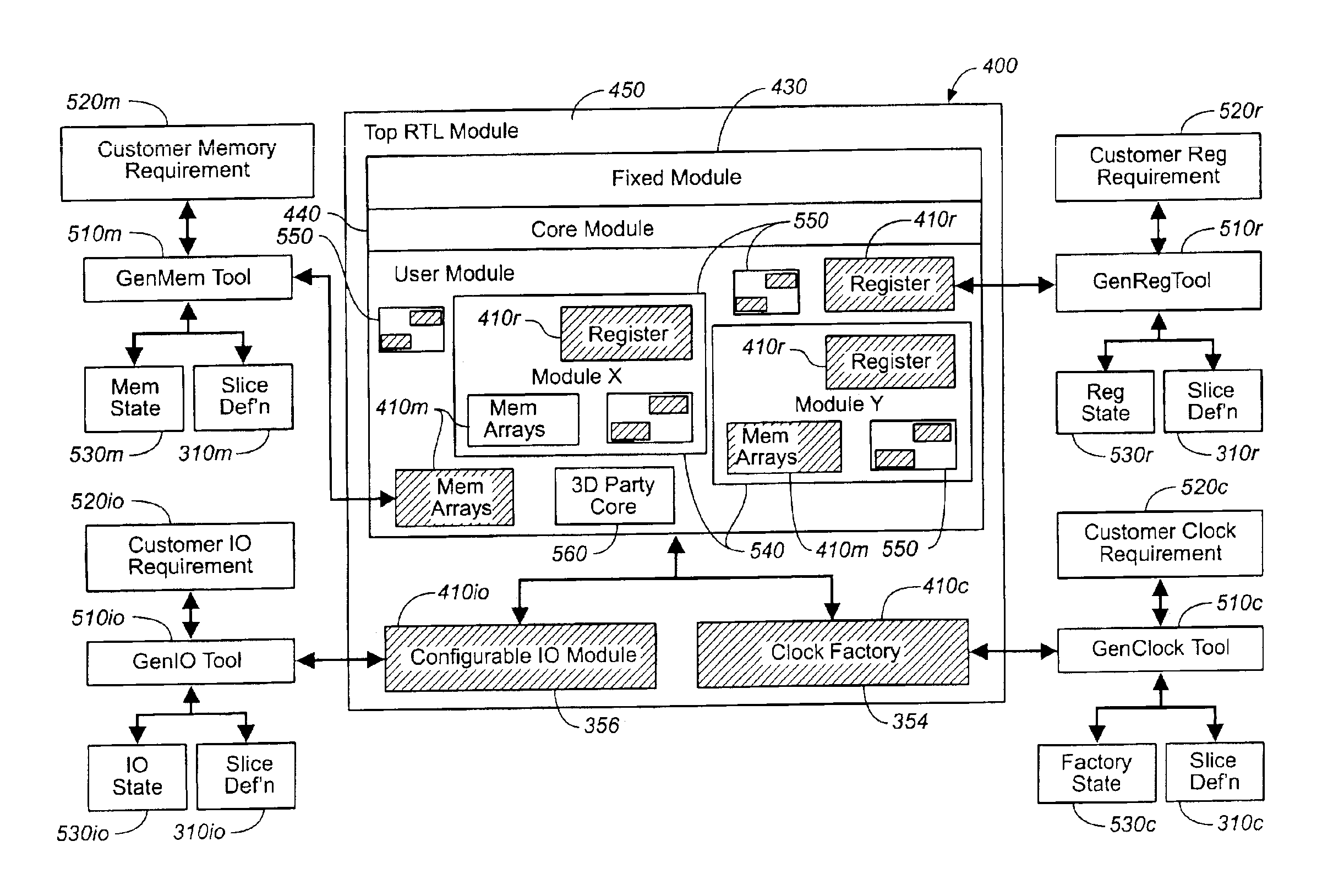

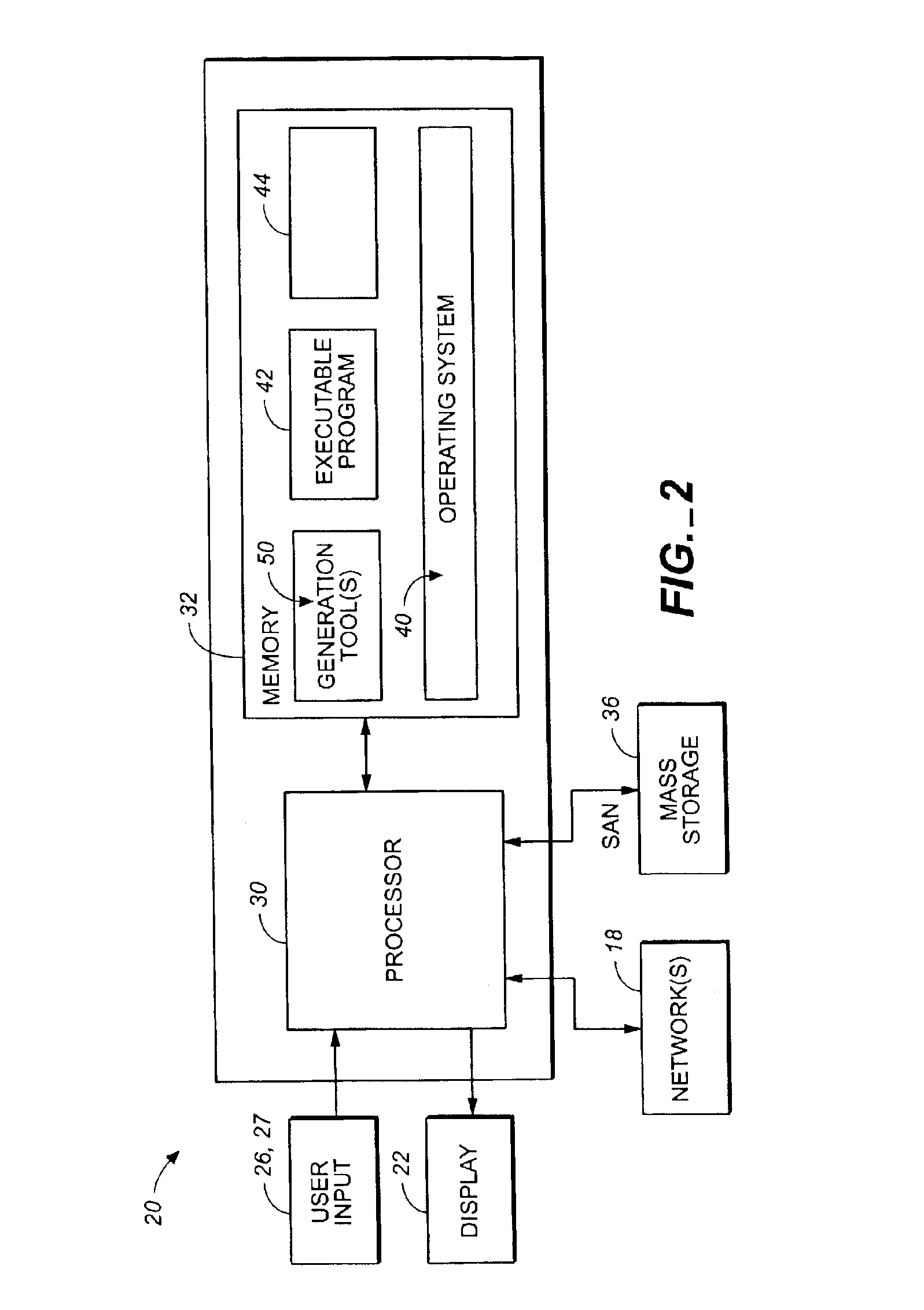

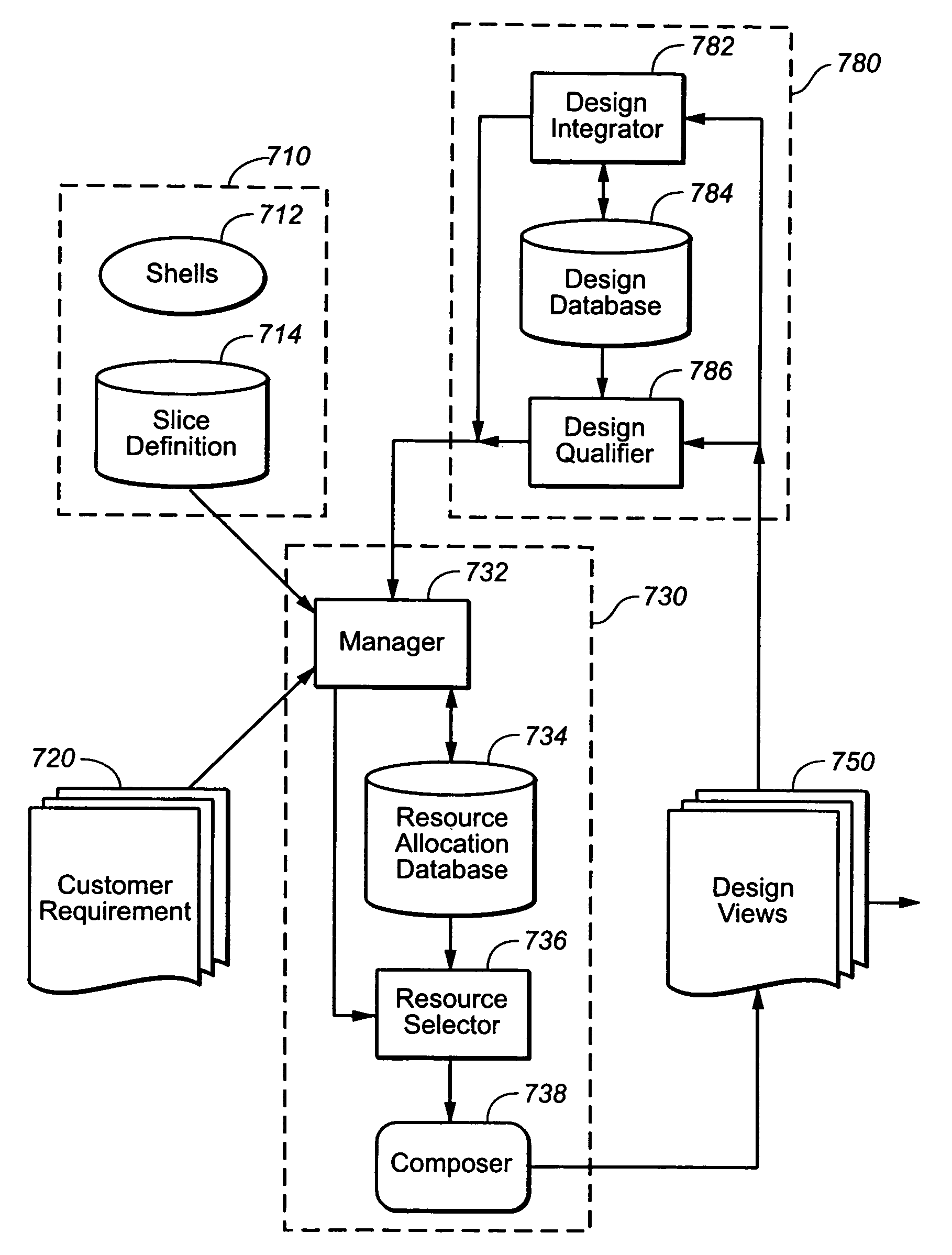

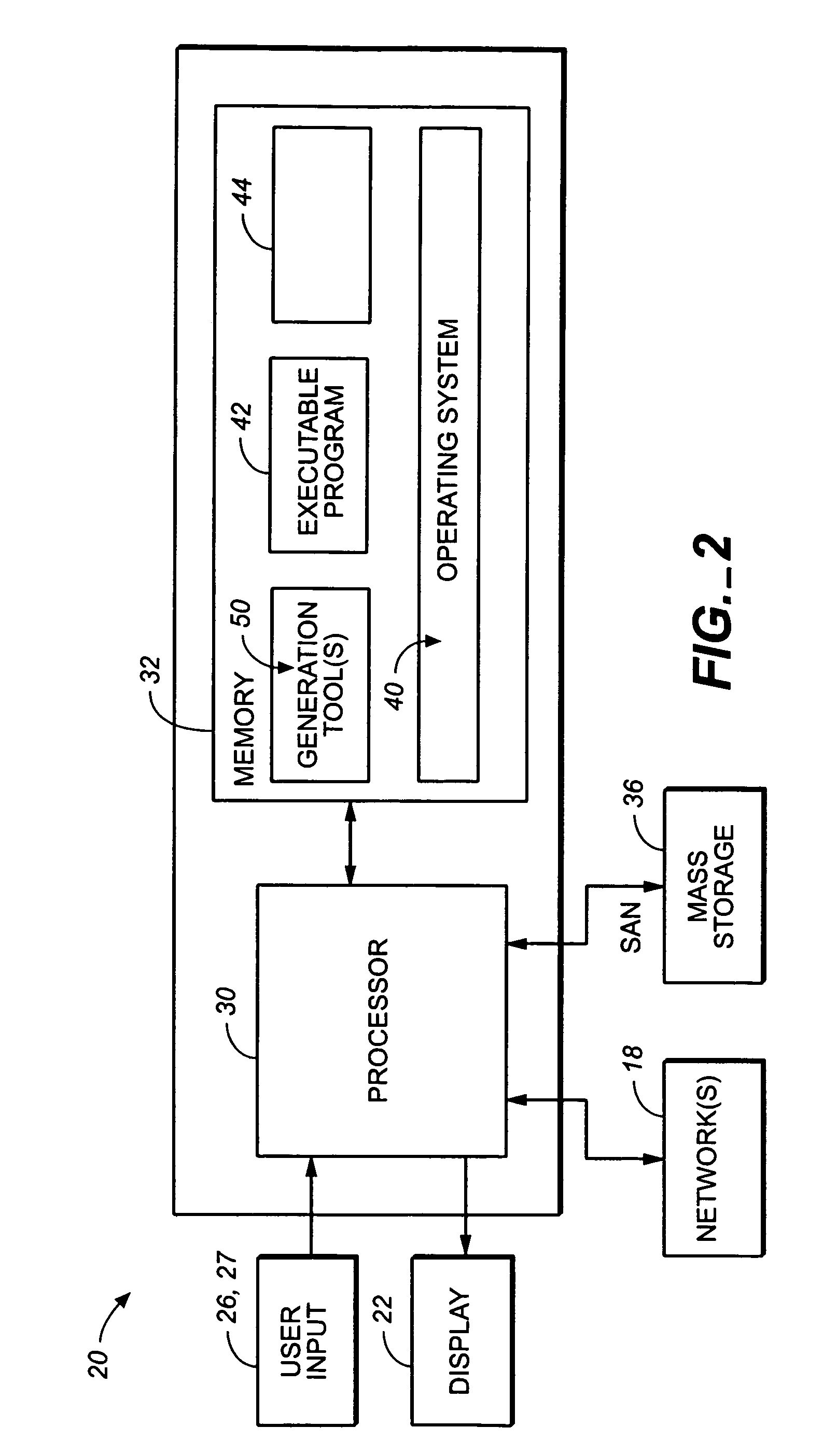

Simplified process to design integrated circuits

ActiveUS7055113B2Computer aided designSoftware simulation/interpretation/emulationCustomer requirementsFoundry

A set of tools is provided herein that produces useful, proven, and correct integrated semiconductor chips. Having as input either a customer's requirements for a chip, or a design specification for a partially manufactured semiconductor chip, the tools generate the RTL for control plane interconnect; memory composition, test, and manufacture; embedded logic analysis, trace interconnection, and utilization of spare resources on the chip; I / O qualification, JTAG, boundary scan, and SSO analysis; testable clock generation, control, and distribution; interconnection of all of the shared logic in a testable manner from a transistor fabric and / or configurable blocks in the slice. The input customer requirements are first conditioned by RTL analysis tools to quickly implement its logic. The slice definition and the RTL shell provides the correct logic for a set of logic interfaces for the design specification to connect. The tools share a common database so that logical interactions do not require multiple entries. The designs are qualified, tested, and verified by other tools. The tools further optimize the placement and timing of the blocks on the chip with respect to each other and with respect to placement on a board. The suite may be run as batch processes or can be driven interactively through a common graphical user interface. The tools also have an iterative mode and a global mode. In the iterative mode, one or more of the selected tools can generate the blocks or modify a design incrementally and then look at the consequences of the addition, or change. In the global mode, the semiconductor product is designed all at once in a batch process as above and then optimized altogether. This suite of generation tools generates design views including a qualified netlist for a foundry to manufacture.

Owner:BELL SEMICON LLC

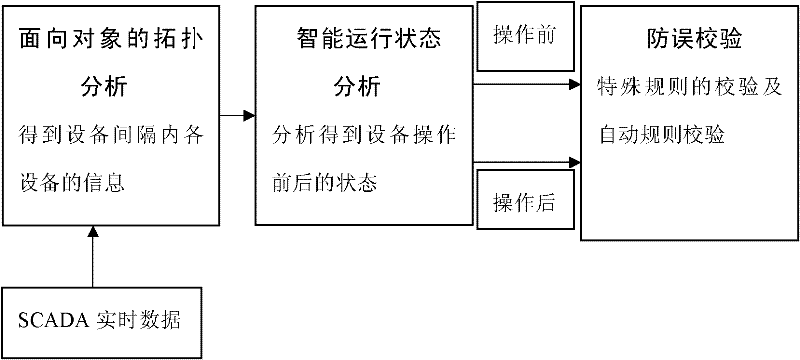

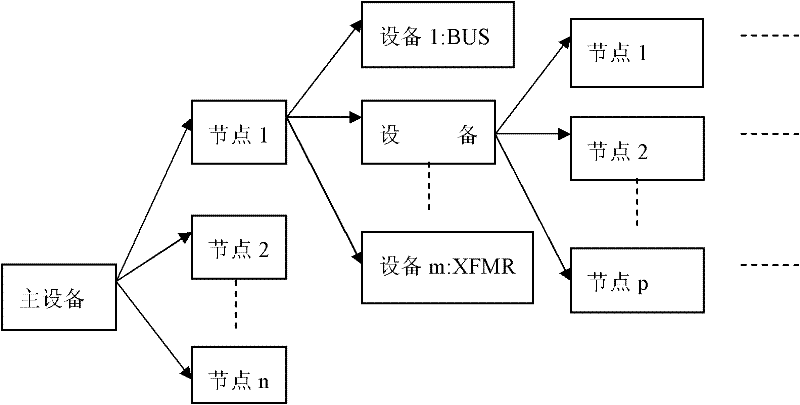

Topology error-preventing checking method based on intelligent identification of state of equipment

InactiveCN102508059AGuaranteed real-timeGuaranteed correctnessPower network operation systems integrationCircuit arrangementsElectric power systemData acquisition

The invention provides a topology error-preventing checking method based on intelligent identification of a state of equipment. The method comprises the following steps of: based on power grid real-time data, combining an SCADA (Supervisory Control and Data Acquisition) monitoring system to carry out object-oriented partial topology analysis to obtain information and real-time opening / closing states of a circuit breaker, an isolation switch, a bypass disconnecting link / earth wire in an equipment gap; and then, obtaining the state of electrical equipment through a logic analysis and analyzing whether the state of the equipment is normal or not; and obtaining influences to a power grid by equipment operations through analyzing changes of a power system before and after the equipment operations, so as to calculate a checked result and give out a prompt to realize the topology error-preventing checking. According to the invention, an intelligent identification function of the state of the equipment is realized and operation conditions of the equipment gap can be monitored in real time; once erroneous states are found, the system sends out an alarming prompt to accelerate a user to find and correct errors, so as to ensure the safe operation of the power grid. By comparing the changes of the power grid before and after the equipment operations to carry out checking, the accuracy of checking operations is ensured.

Owner:BEIJING KEDONG ELECTRIC POWER CONTROL SYST

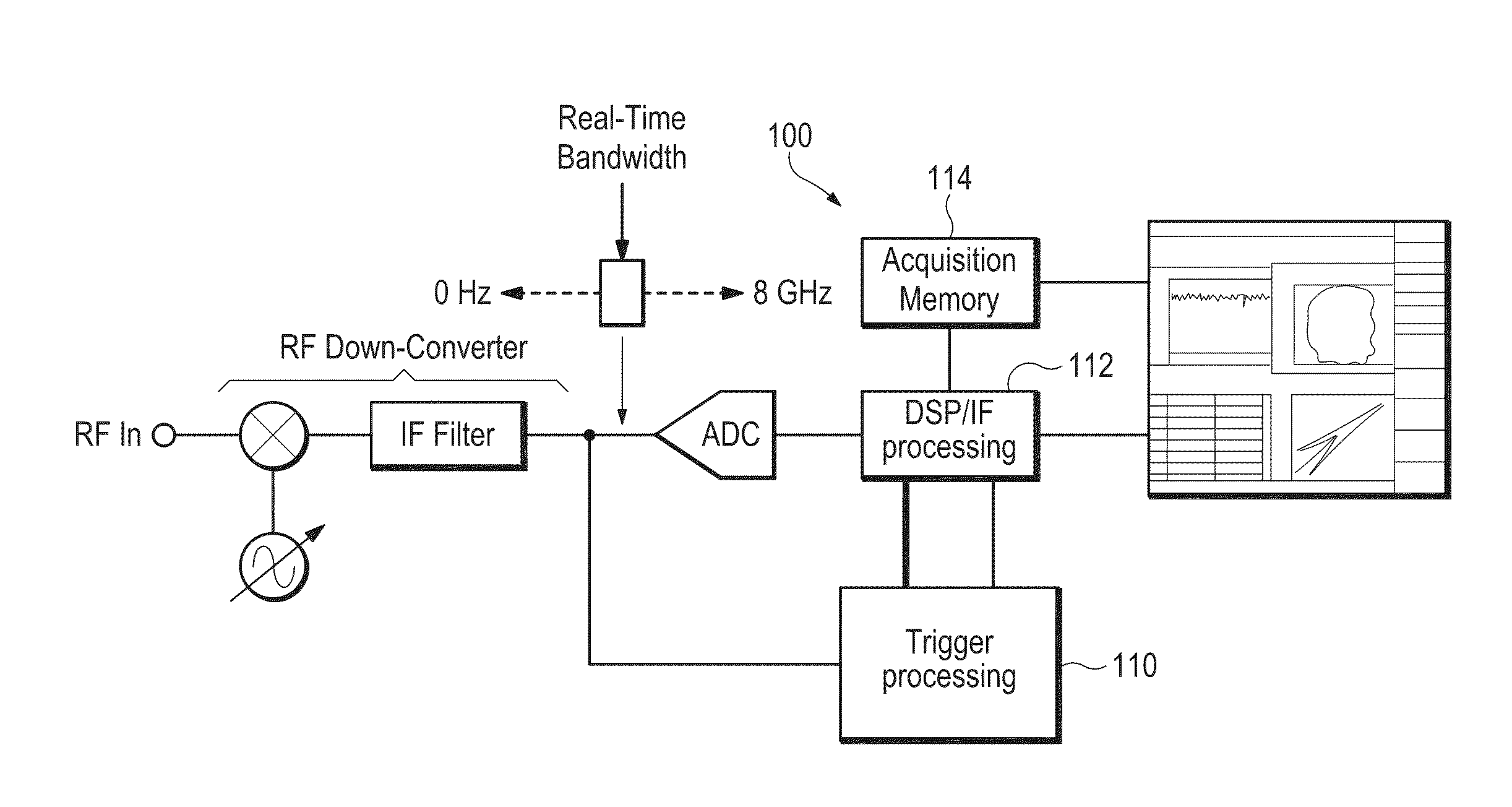

Real Time Statistical Triggers on Data Streams

InactiveUS20110246134A1Digital computer detailsLogical operation testingData streamSpectrum analyzer

Logic analyzers and real-time spectrum analyzers use real-time statistical processes as a basis for creating a trigger. The statistical displays within a test and measurement system such as a Logic Analyzer (LA) or Spectrum Analyzer (SA) or other instrument are used in a user interface to define a trigger based on the statistical event itself. In brief, the invention is a Real Time Statistical trigger established by the user through a direct interaction with the Real Time Statistics displays. This interaction can be via a graphical user interface, or the user interface can employ a non-visible display (e.g., a speaker) or input device (e.g., a microphone).

Owner:TEKTRONIX INC

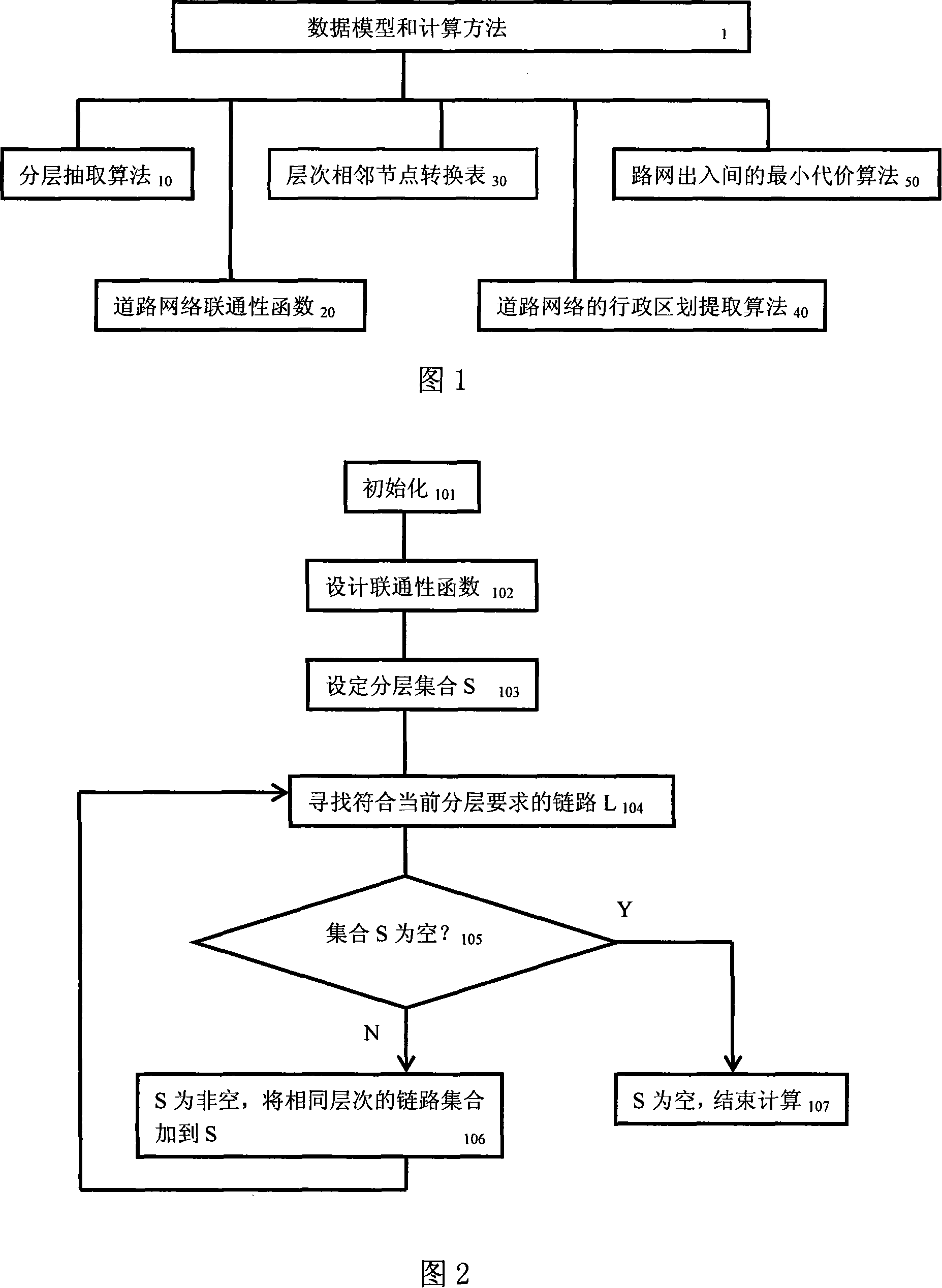

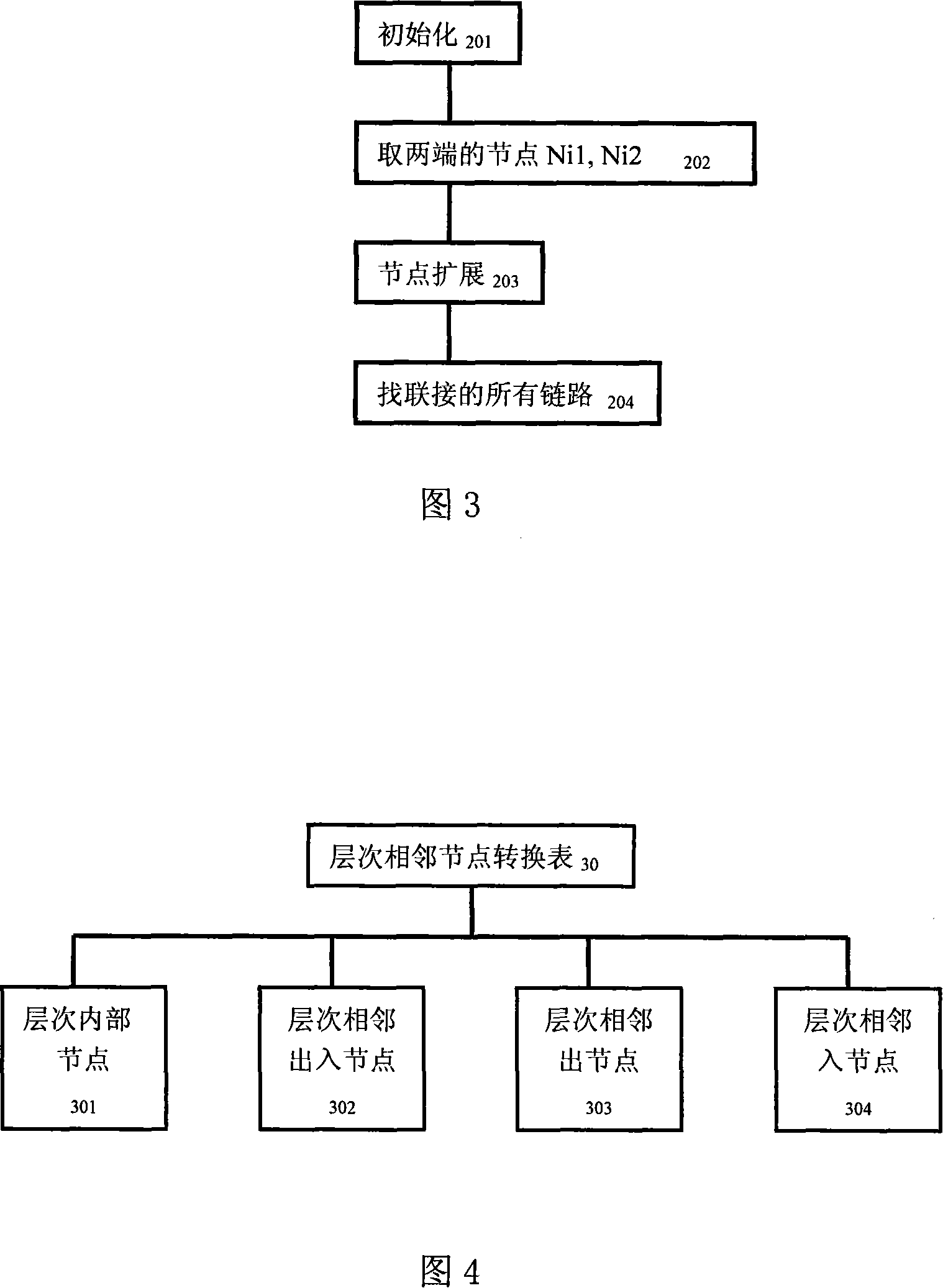

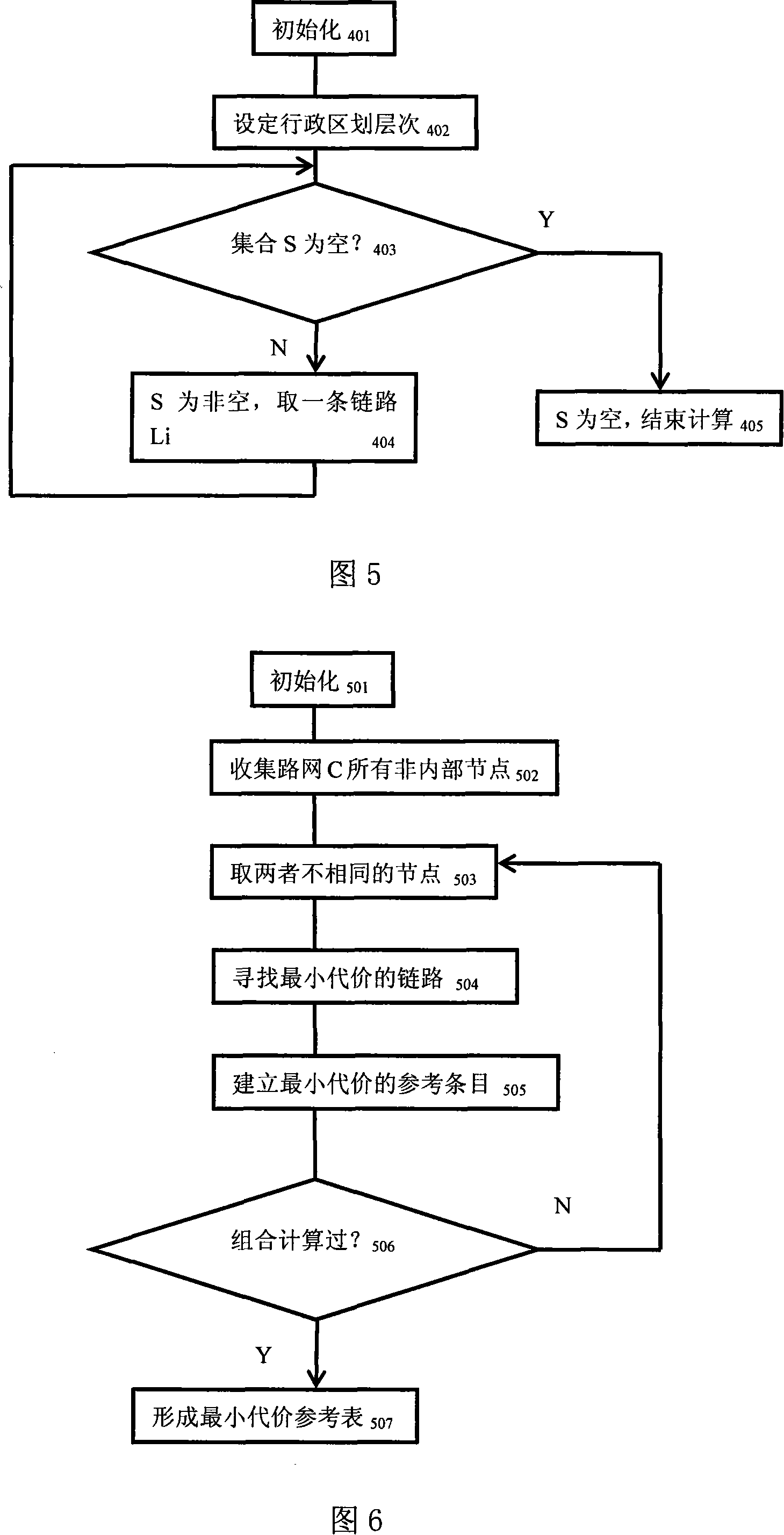

Road topology data model for navigation and calculation method

InactiveCN101149268AGuaranteed connectivityRetain heuristic dataInstruments for road network navigationNavigational calculation instrumentsLeast costLogical analysis

An application technology field relates to the navigation, especially the analysis and picking method of the road topological data used in the navigation and setting the data model, which is a road topological data model and computing method used in navigation to treat the road with big area and long distance in navigation map data. The method includes the stratified extracting arithmetic, the road connection calculation function, the hierarchical adjacent node transition table, the road web canton extracting arithmetic and the least cost arithmetic of road net in-out; it mainly solves the technology problem of route calculation of long distance and big area. The invention can insure the connection of whole road web; it can store the starting data of route calculation and improves the route calculation efficient; so it can get the logical analysis result in the logical time and cost range.

Owner:上海上大鼎正软件股份有限公司

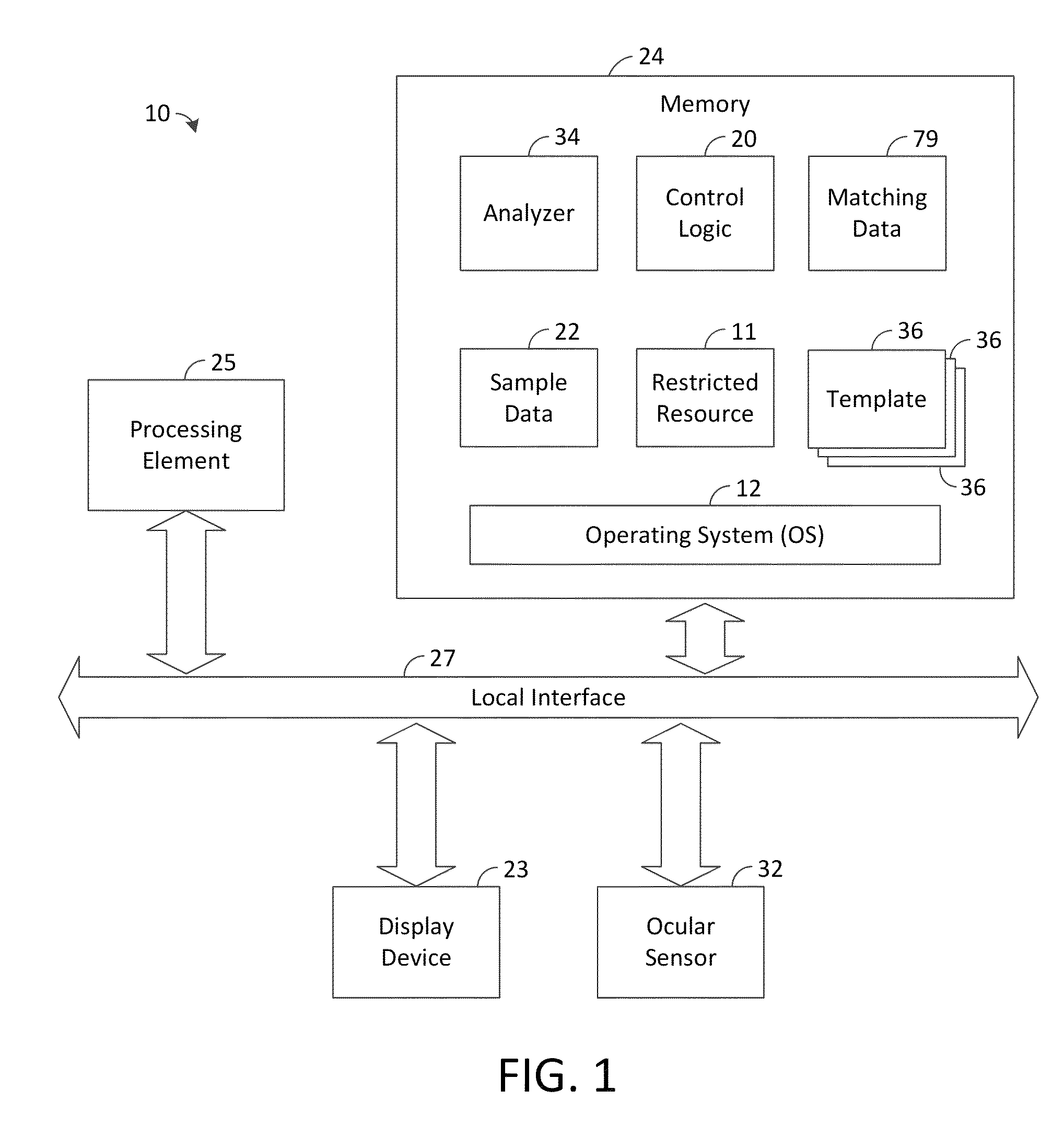

Systems and methods for user authentication using eye movement and pupil size change matching

A system for eye movement and pupil size change matching for user authentication includes an ocular sensor that is configured to sense eyes of a user and collect data indicative of the user's eye movement and pupil size changes. When a user's eyes are detected, the logic analyzes data collected by the ocular sensor in order to determine whether the sensed data match data extracted from a template defined by the eye movement and pupil size changes of an authorized user. If so, the user is authenticated and is permitted to access at least one restricted resource. As an example, the user may be permitted to access an application or sensitive data stored on a computer system or to access a restricted area, such as a room of a building.

Owner:UNIVERSITY OF ALABAMA

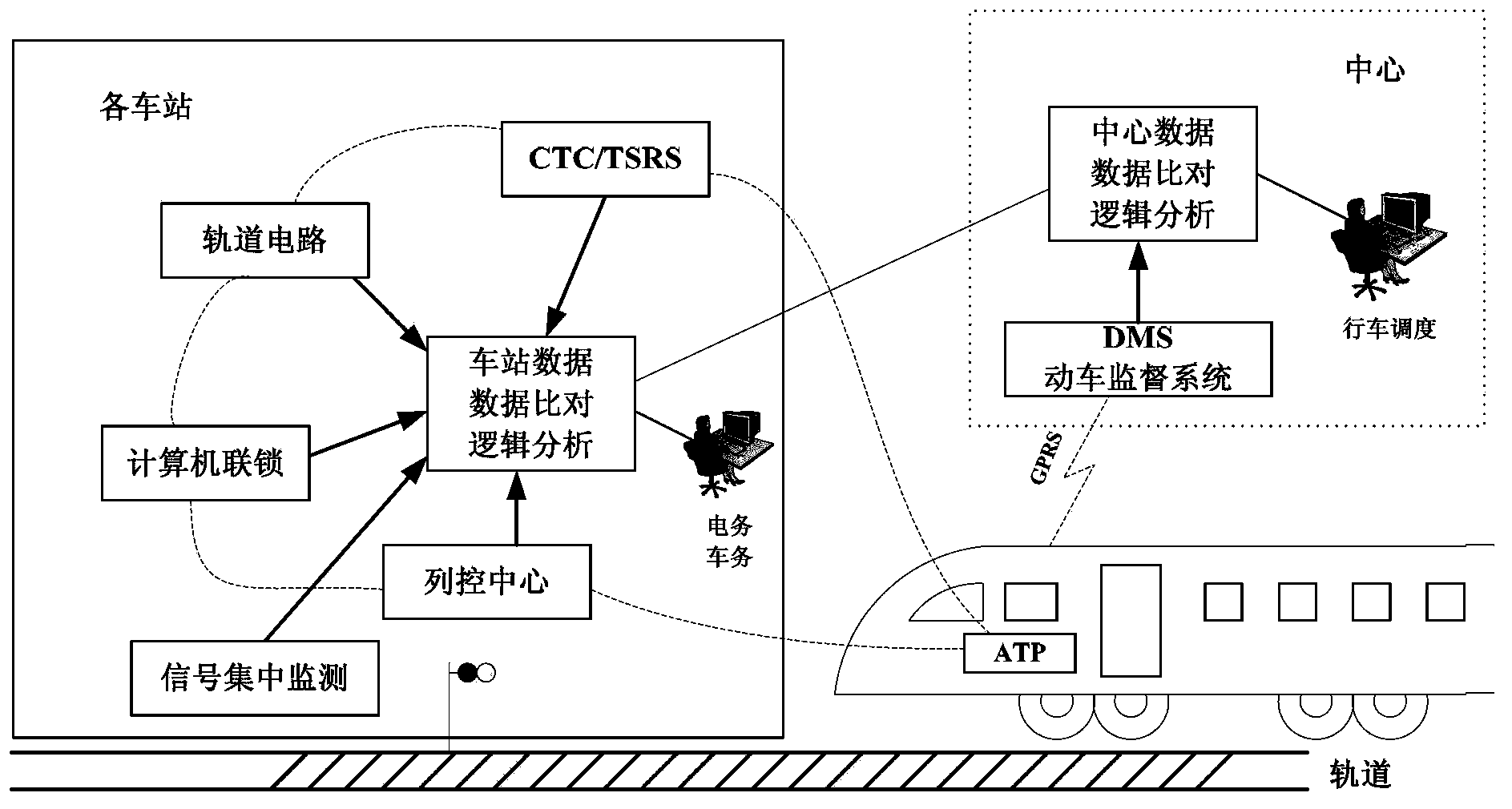

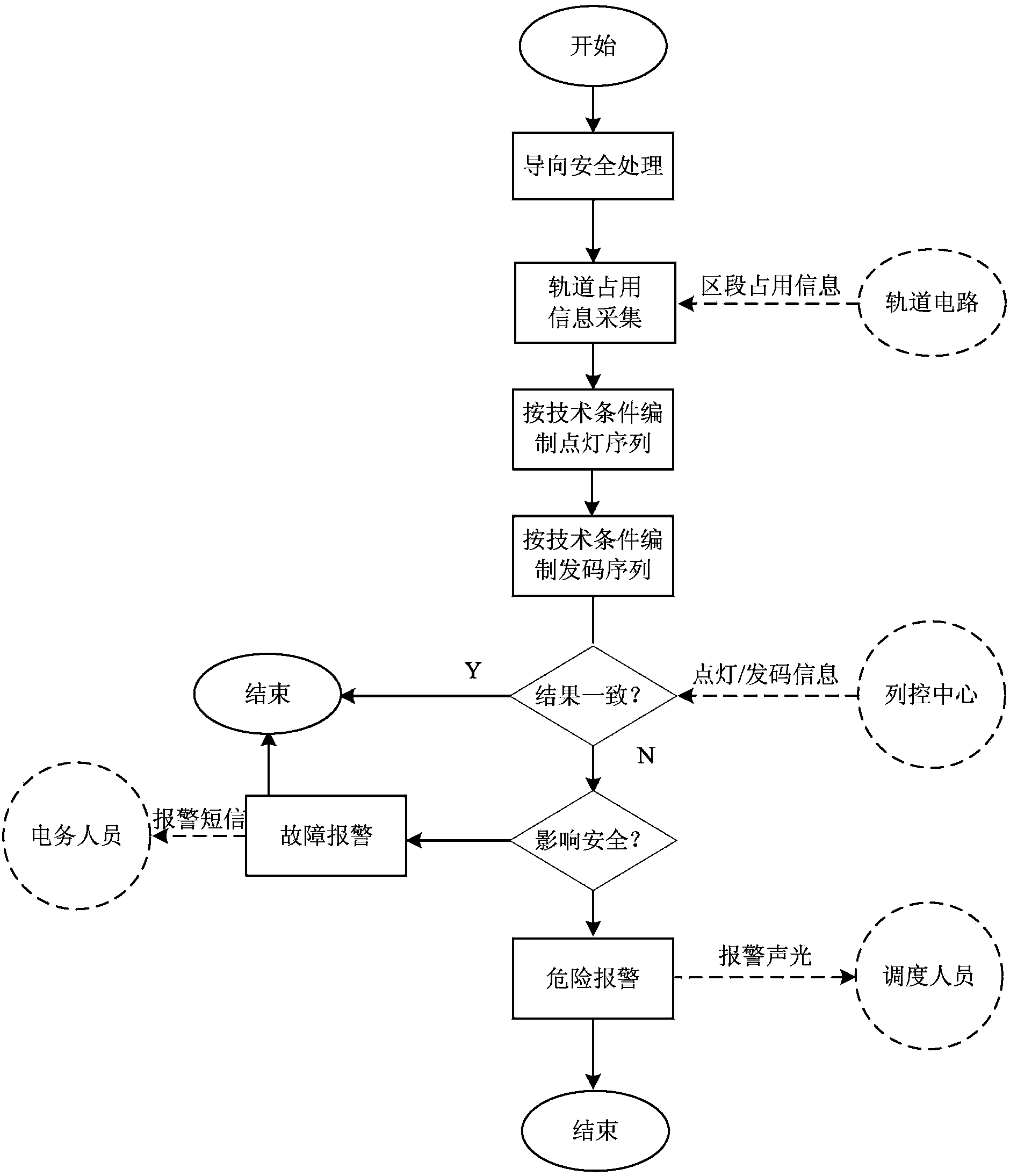

Railway signal equipment operation alarming method based on data comparison and logical analysis

ActiveCN103569161AGuaranteed uptimeEnsure safetyRailway signalling and safetyLogical operationsFile comparison

The invention discloses a railway signal equipment operation alarming method based on data comparison and logical analysis. The method comprises the following steps: collecting service data and state data of signal equipment in a real-time and online manner; comparing key data publicly adopted or associated backwards and forwards between the signal equipment; analyzing service logical correlation relation between the signal equipment; alarming an abnormal condition obtained by comparison or logical analysis. By virtue of collecting and concentrating the operation data and equipment state data of each railway signal equipment in an online manner and comparison and logical analysis on the key data are performed, the service logical operation safety and equipment interface operation normality of the signal equipment are monitored in an auxiliary way, and finally the normal operation and correct signal logical correlation of the signal equipment are ensured, so that the operation safety of a train is ensured.

Owner:BEIJING SWJTU RICHSUN TECH

Electrostatic mass spectrometer with encoded frequent pulses

ActiveUS8853623B2Increase rangeHigh responseTime-of-flight spectrometersIsotope separationMass analyzerParticle physics

A method, apparatus and algorithms are disclosed for operating an open electrostatic trap (E-trap) or a multi-pass TOF mass spectrometer with an extended flight path. A string of start pulses with non equal time intervals is employed for triggering ion packet injection into the analyzer, a long spectrum is acquired to accept ions from the entire string and a true spectrum is reconstructed by eliminating or accounting overlapping signals at the data analysis stage while using logical analysis of peak groups. The method is particularly useful for tandem mass spectrometry wherein spectra are sparse. The method improves the duty cycle, the dynamic range and the space charge throughput of the analyzer and of the detector, so as the response time of the E-trap analyzer. It allows flight extension without degrading E-trap sensitivity.

Owner:LECO CORPORATION

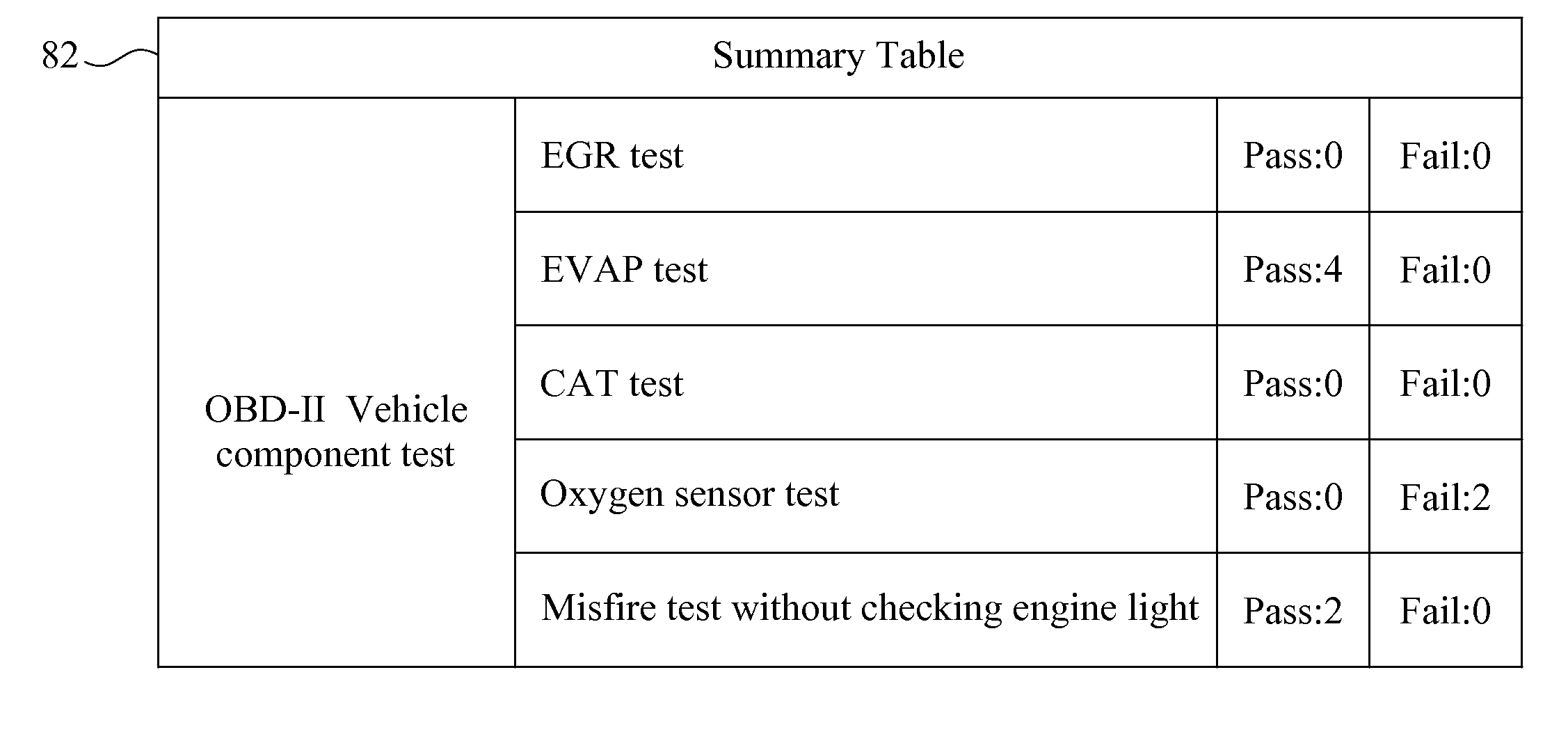

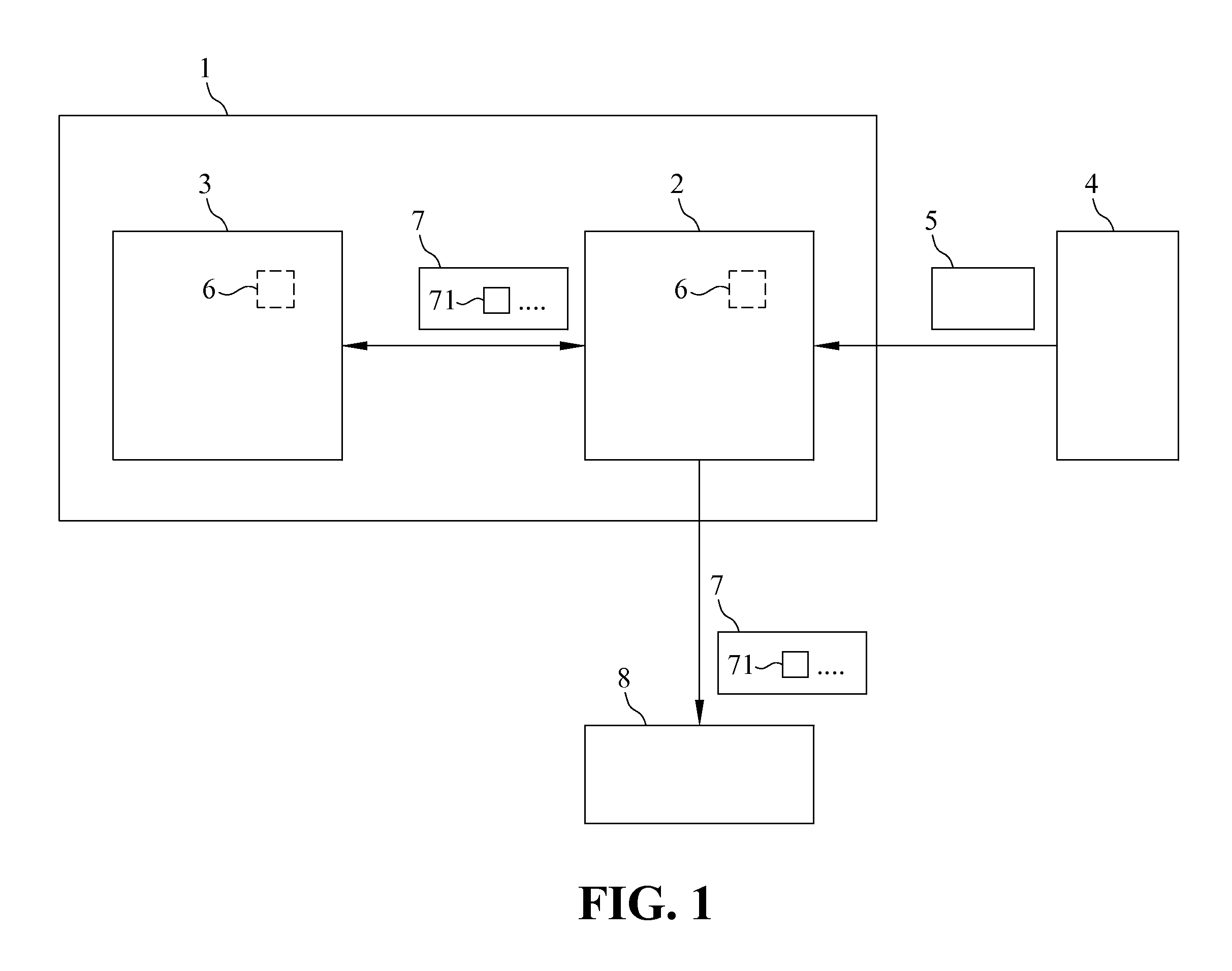

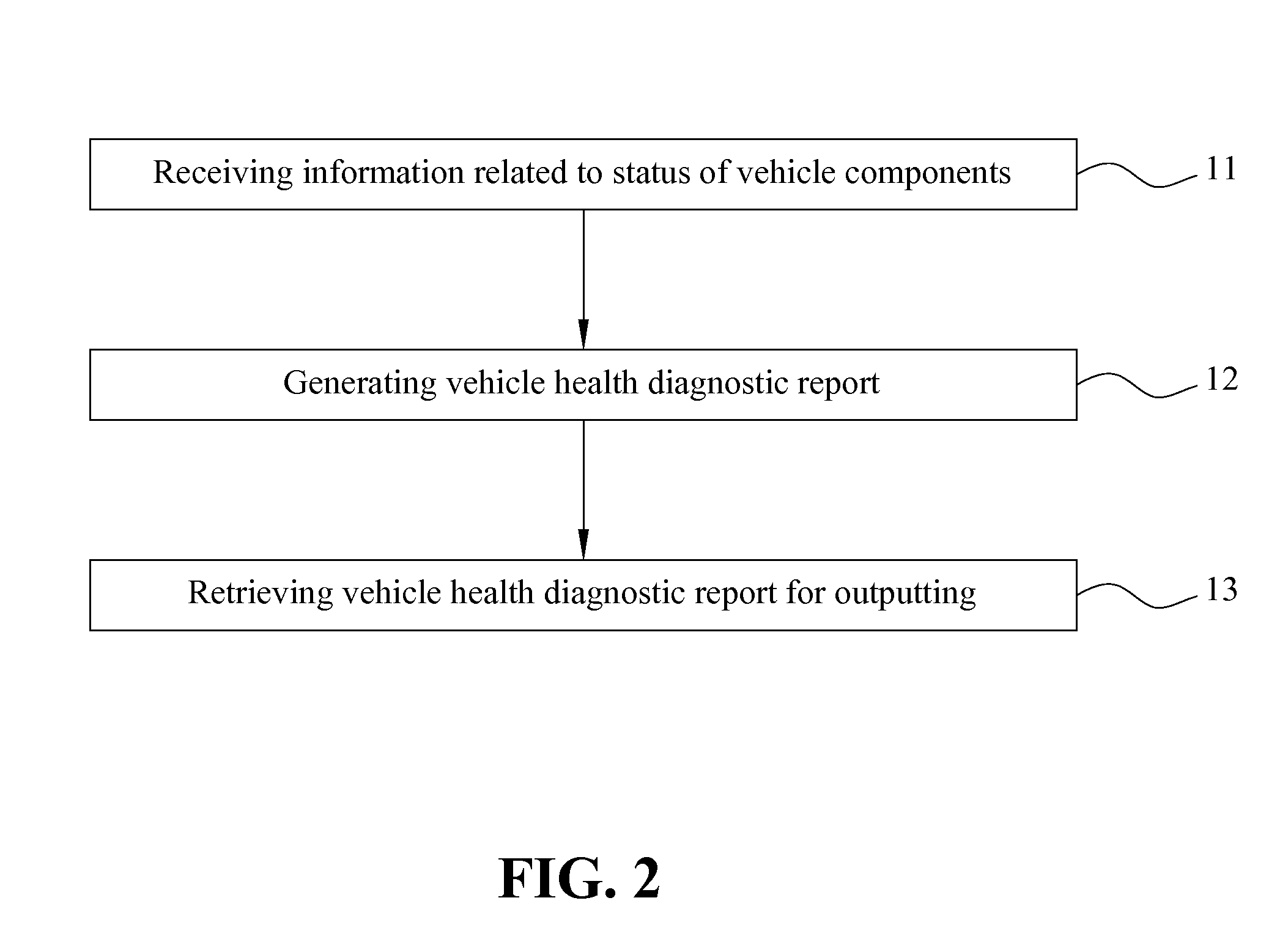

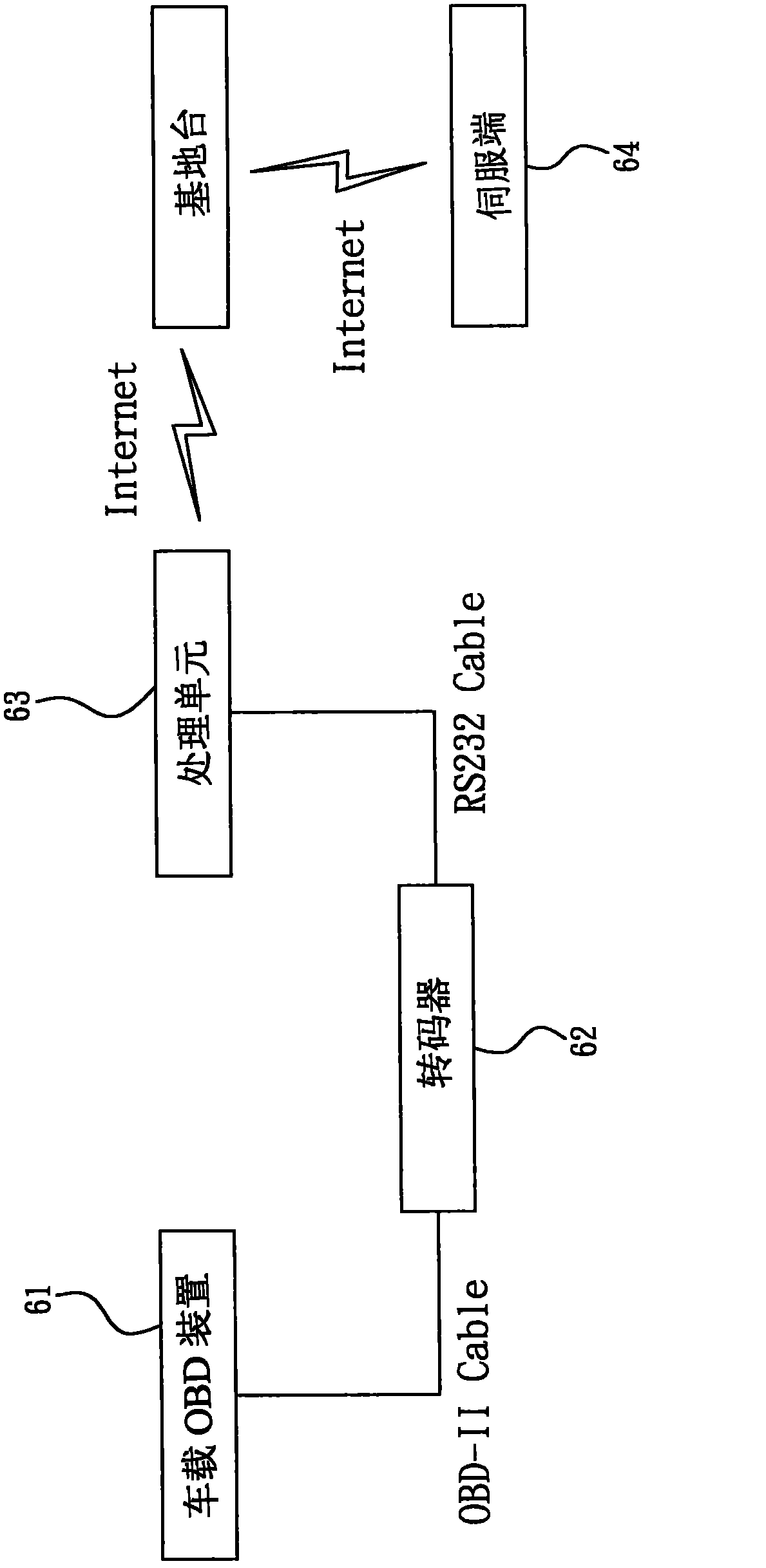

Vehicle Diagnostic System And Method Thereof

InactiveUS20110077817A1Vehicle testingRegistering/indicating working of vehiclesLogical analysisDiagnostic system

A vehicle diagnostic system and a method are provided. The vehicle diagnostic system includes a receiving / processing module, and a database. The receiving / processing module is adapted for receiving the information related to a status of vehicle components from an OBD-II interface connected thereto. The information is then analyzed by a processing logic, so as to generate a vehicle health diagnostic report with respect to the corresponding vehicle components. In the vehicle health diagnostic report including the one or more table, in addition to enumerating the operation status of the vehicle components as “Pass / Fail”, there is also shown a testing result of the vehicle components, and there are also provided additional information and suggestions related to the vehicle components. The processing logic is stored in receiving / processing module and / or in the database.

Owner:SUN CHIN YANG +1

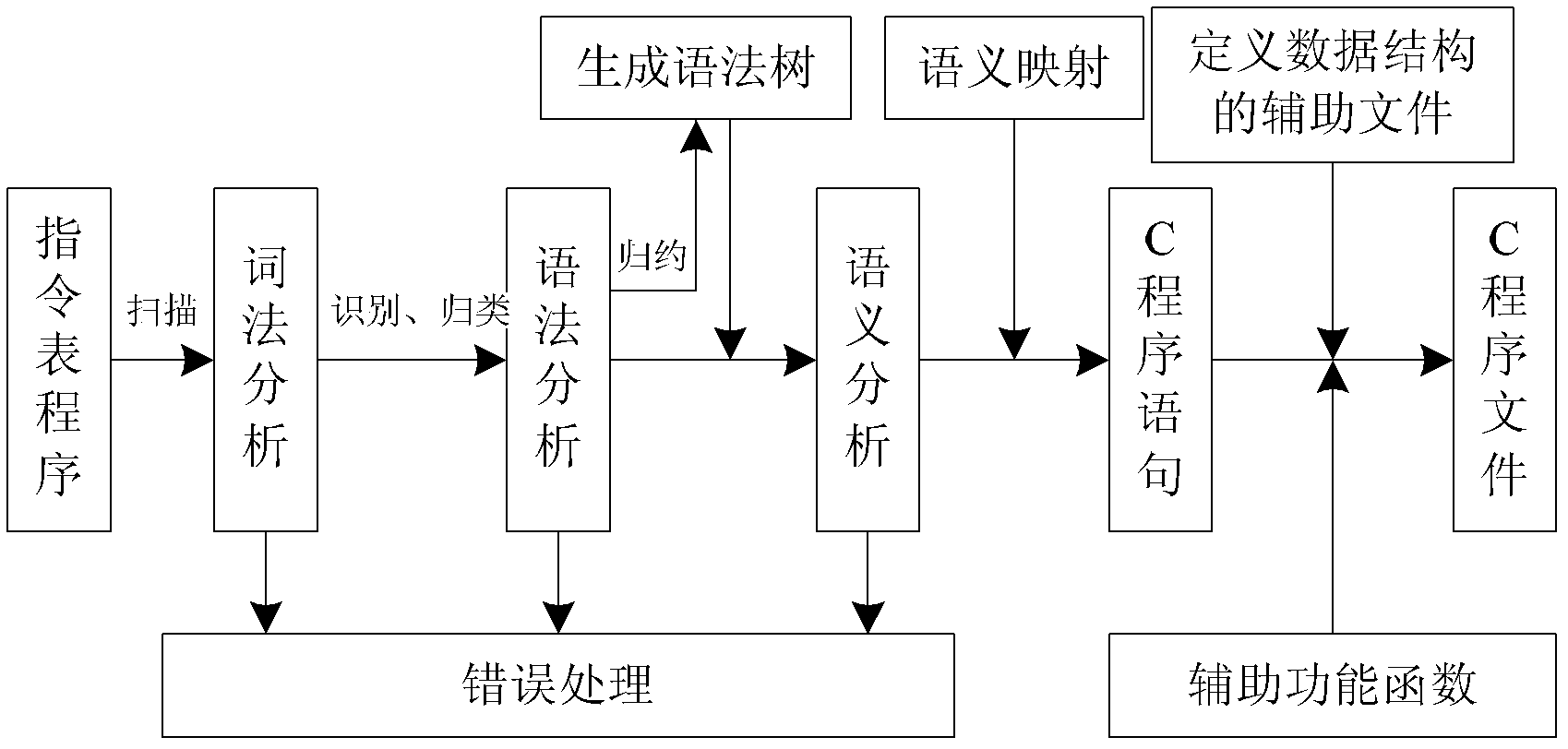

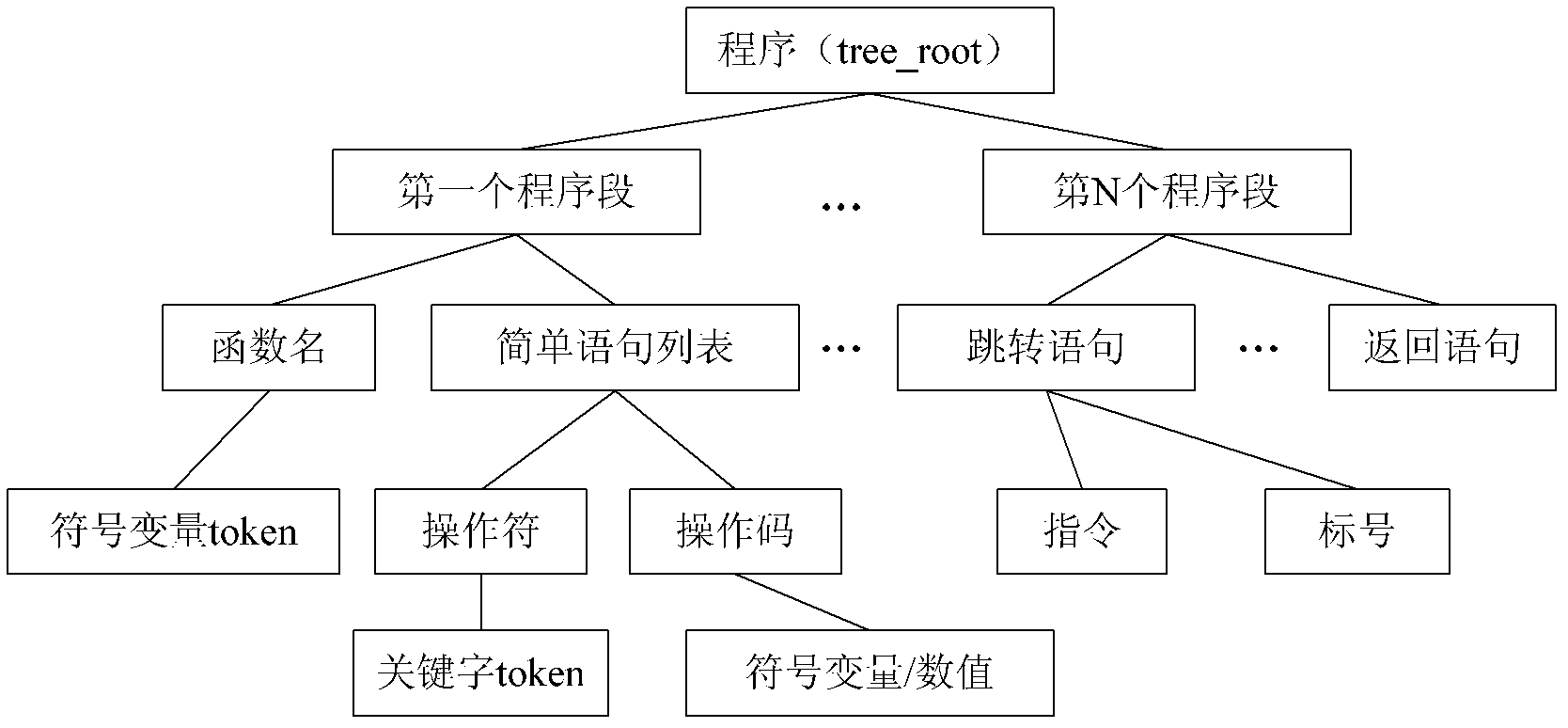

Compiling method from intermediate language (IL) program to C language program of instruction list

InactiveCN103123590AFeasible grammatical conventionFeasible semantic analysisProgram controlMemory systemsPerformance functionLexical analysis

The invention discloses a compiling method from an intermediate language (IL) program to a C language program of an instruction list. The method comprises the steps: building a middle storage structure syntax tree according to results of lexical analysis and grammatical analysis through logical analysis on a program of the instruction list and logistic mapping relation between semanteme of the instruction list and semanteme of the C language; combining an auxiliary performance function and an auxiliary data structure define file, and generating an integrated file of the C language program through program data of an original instruction list according to a C language programming method, wherein the program data of the original instruction list is stored in the structure of the syntax tree. The generated C language program completely corresponds to the logic program of the original instruction list and has the advantages of a high-level C language, wherein the advantages include strong transportability, strong compatibility and the like. Due to the structure of the syntax tree and an analytic method of semanteme mapping, compiling is standardized and mass-produced, complexity of the compiling is reduced through adoption of functions and modularization of an auxiliary function of a function block, compiling time is shortened, and speed of the whole compiling process is improved.

Owner:中国科学院沈阳计算技术研究所有限公司

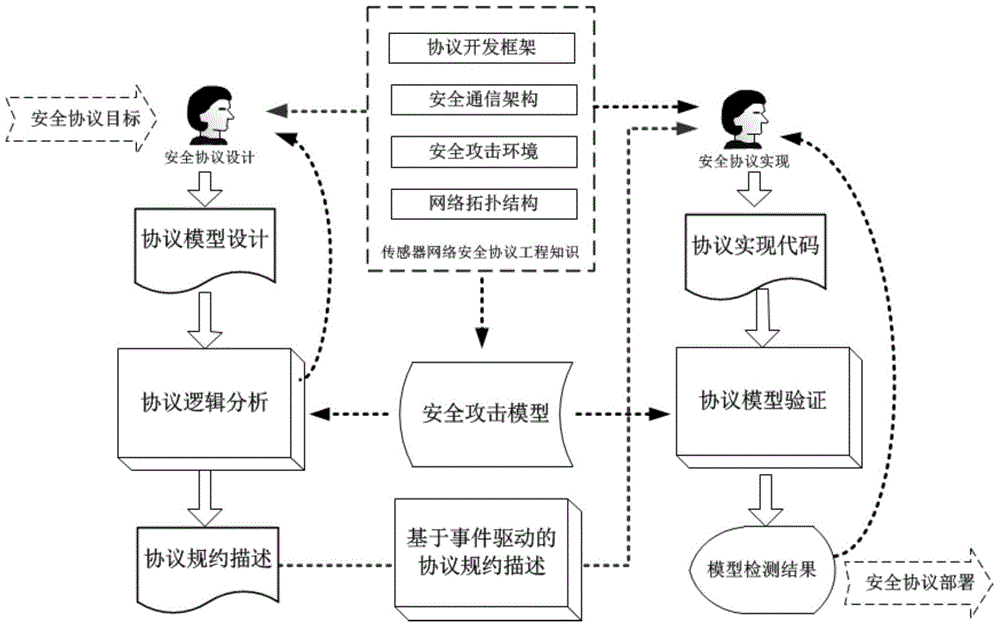

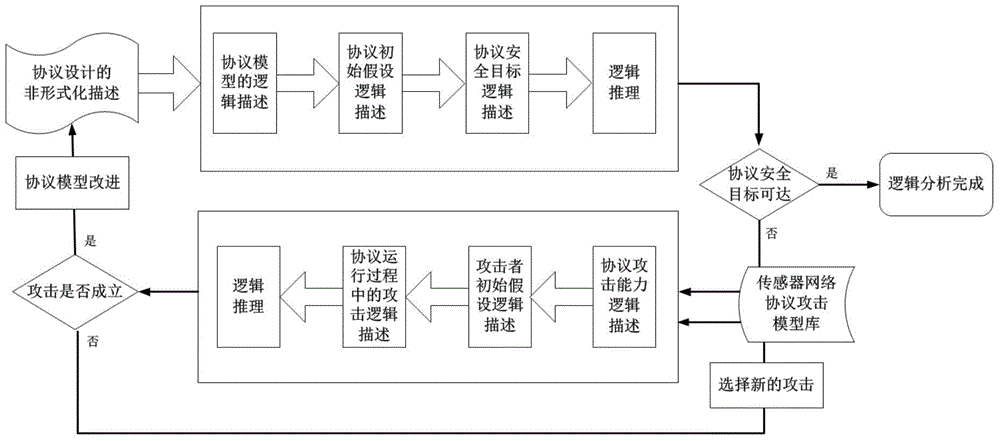

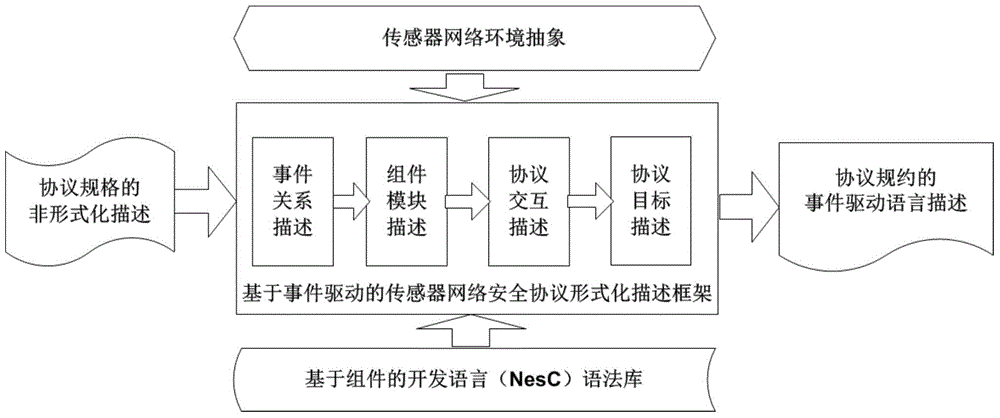

Formal verification method for facing design and accomplishment of wireless sensing network safety protocol

ActiveCN104135397ASimple designImprove development efficiencyData switching networksProtocol designValidation methods

A formal verification method for facing design and accomplishment of a wireless sensing network safety protocol, comprises the following steps: (1) a sensing network safety protocol design method based on logical analysis: a designer of the sensor network safety protocol accepting a protocol design goal, and designing a protocol rudiment based on analysis of sensor network environmental factors; establishing a logical reasoning system to accomplish protocol modeling and logical analysis, amending the protocol design plan according to the analysis result, and repeating logical analysis until the logic of the protocol is correct; and giving description of the protocol specification which is not formalized finally; (2) a safety protocol specification description language facing the sensing network developing environment; and (3) a safety protocol code automatic verification method based on model checking. The present invention effectively ensures safety and efficiency of the design and development and has good expansibility.

Owner:ZHEJIANG UNIV OF TECH

Configurable IC with trace buffer and/or logic analyzer functionality

InactiveUS20080191733A1Quick configurationEasy to operateReliability increasing modificationsFail-safe circuitsHemt circuitsLogic analyzer

Some embodiments of the invention provide a configurable integrated circuit (IC) that includes several configurable circuits for configurably performing different operations and several user design state (UDS) circuits for storing user-design state values. The IC further includes a trace buffer for storing user-design state values associated with an operational trigger event of the IC. In some embodiments, the configurable circuits, UDS circuits, and tracer buffer are on a single IC die.

Owner:TAHOE RES LTD

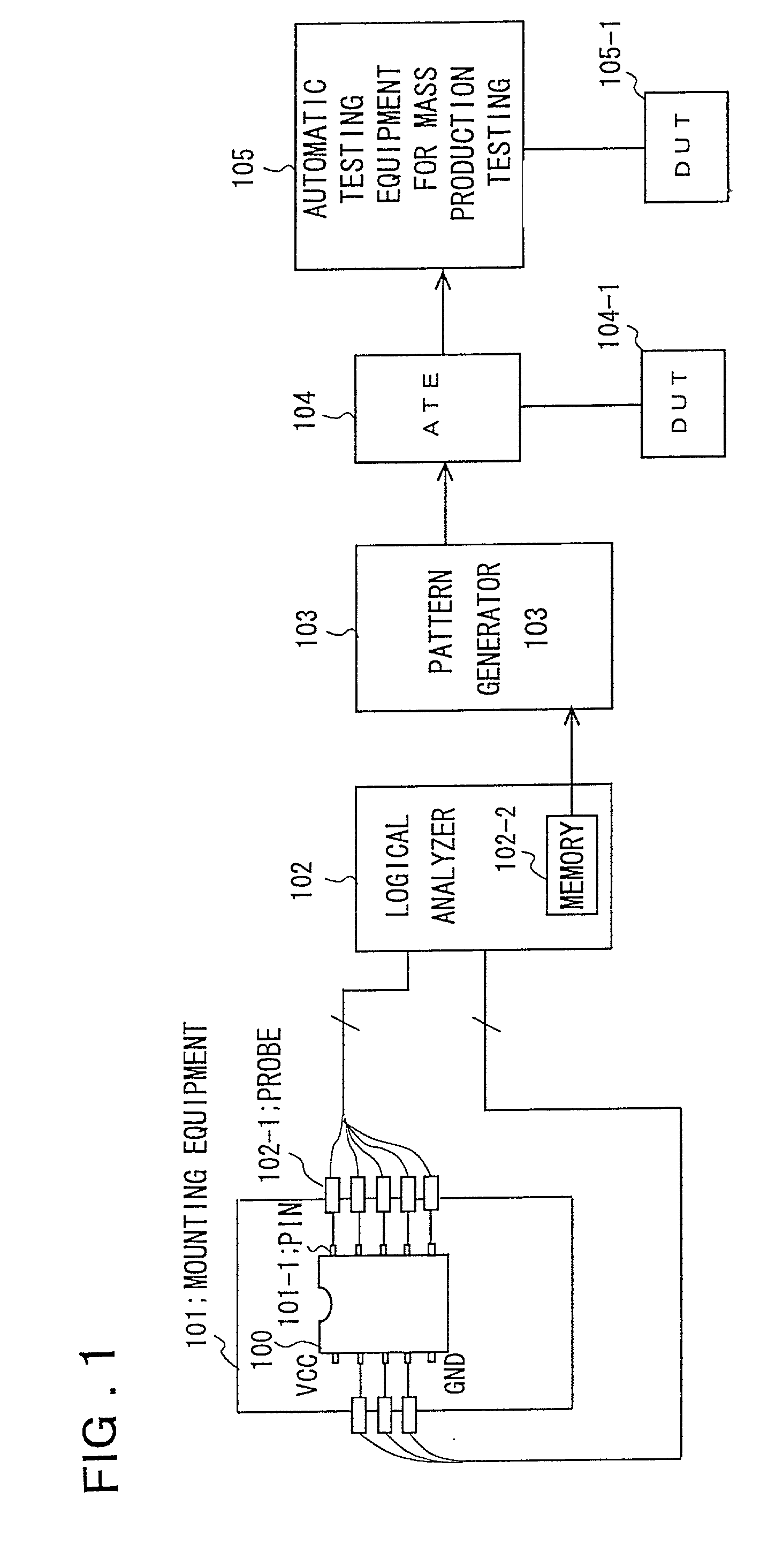

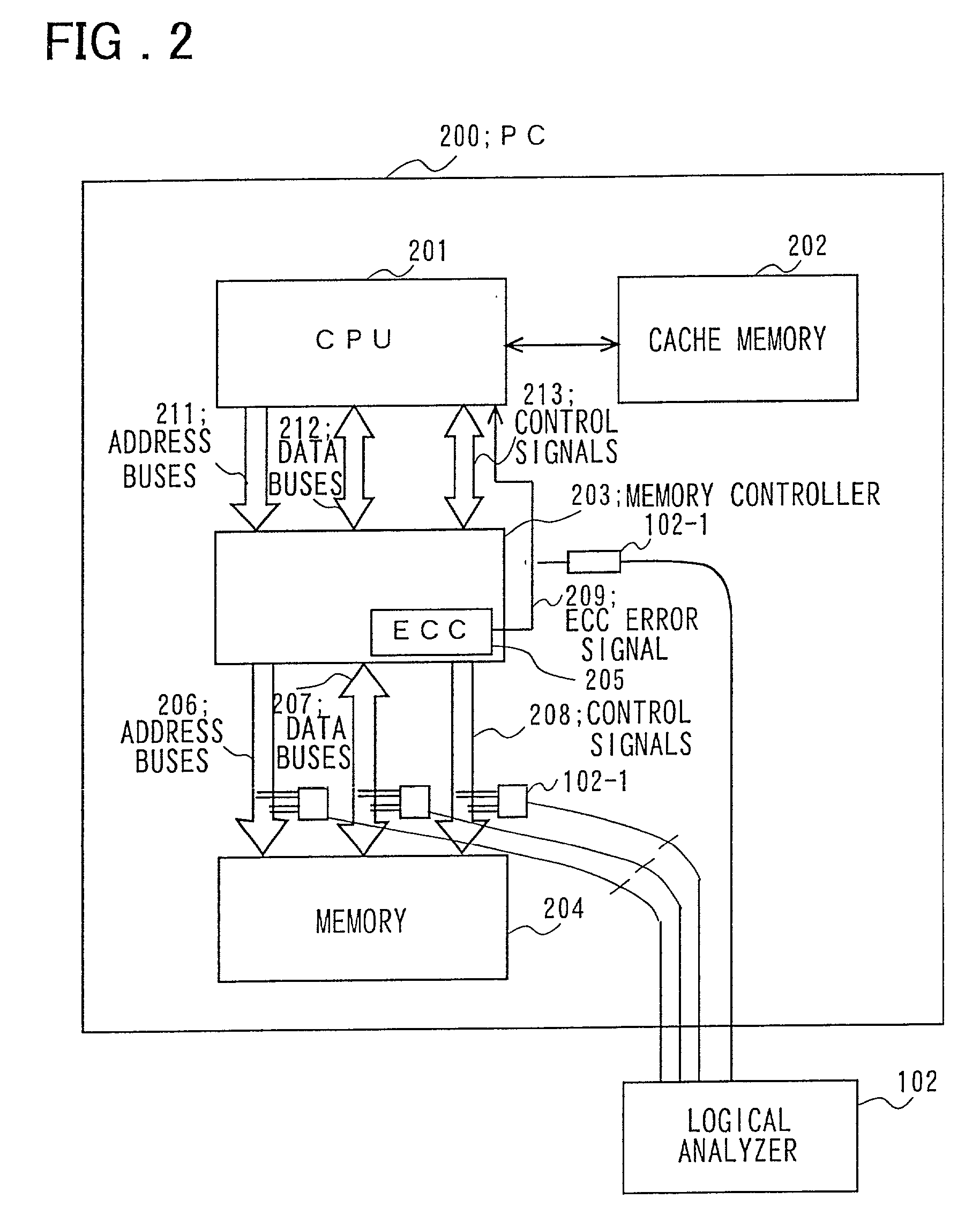

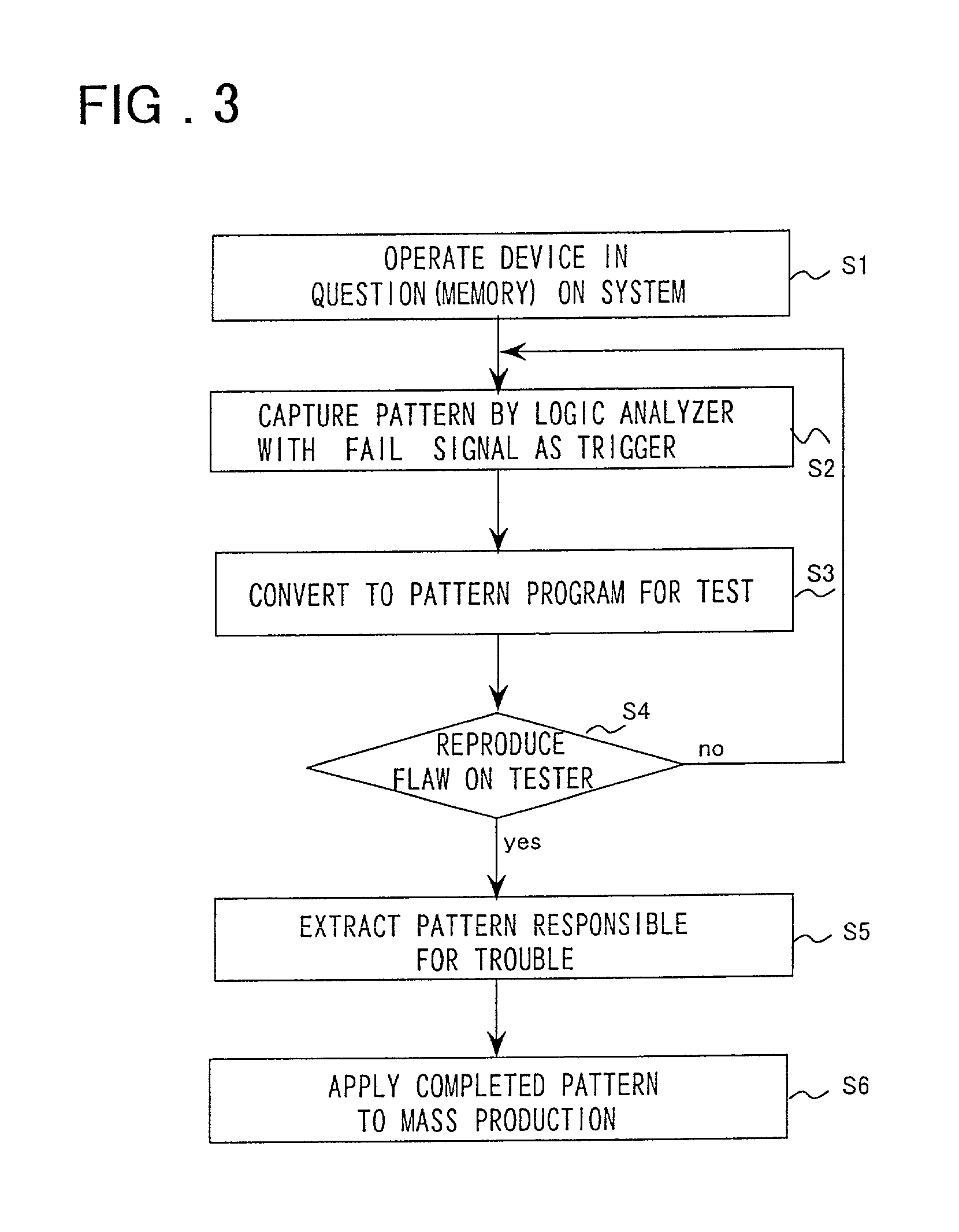

Semiconductor device testing method and system and recording medium

InactiveUS20010005132A1Electronic circuit testingElectrical measurement instrument detailsEngineeringTest fixture

A method and apparatus for generating a test Pattern enabling the detection of malfunctions produced on loading on an actual equipment in advance such as at the time of production testing. Using a logical analyzer, signal waveform data during a time period beginning with a first time point going back from the time of the malfunction and running until a second time point including the malfunctioning time is acquired. This signal waveform data is converted by a test pattern generating device into a test pattern for an automatic testing equipment for testing a semiconductor device as a device to be test. The test pattern so generated is output and used to change data at the time of malfunction into normal data to generate a pattern of expected values for an output signal of the semiconductor device. It is then checked whether or not input signal setting required in connection with an output signal of the semiconductor device is present in the signal waveform data. If the result is negative, a test pattern for setting the input signal to the semiconductor device is generated. If the malfunction is reproduced in the testing equipment, the test pattern is used for a mass production test.

Owner:PS4 LUXCO SARL

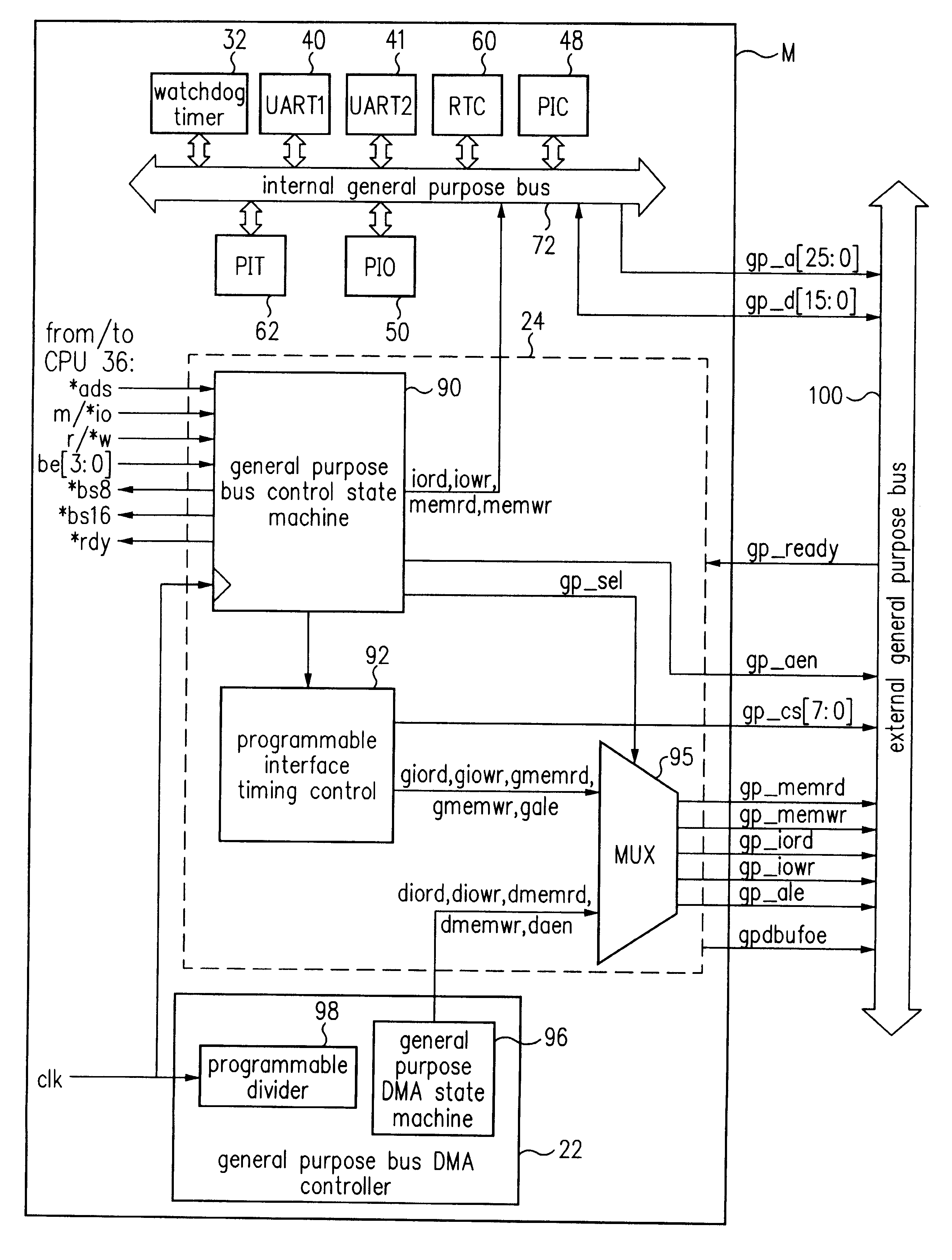

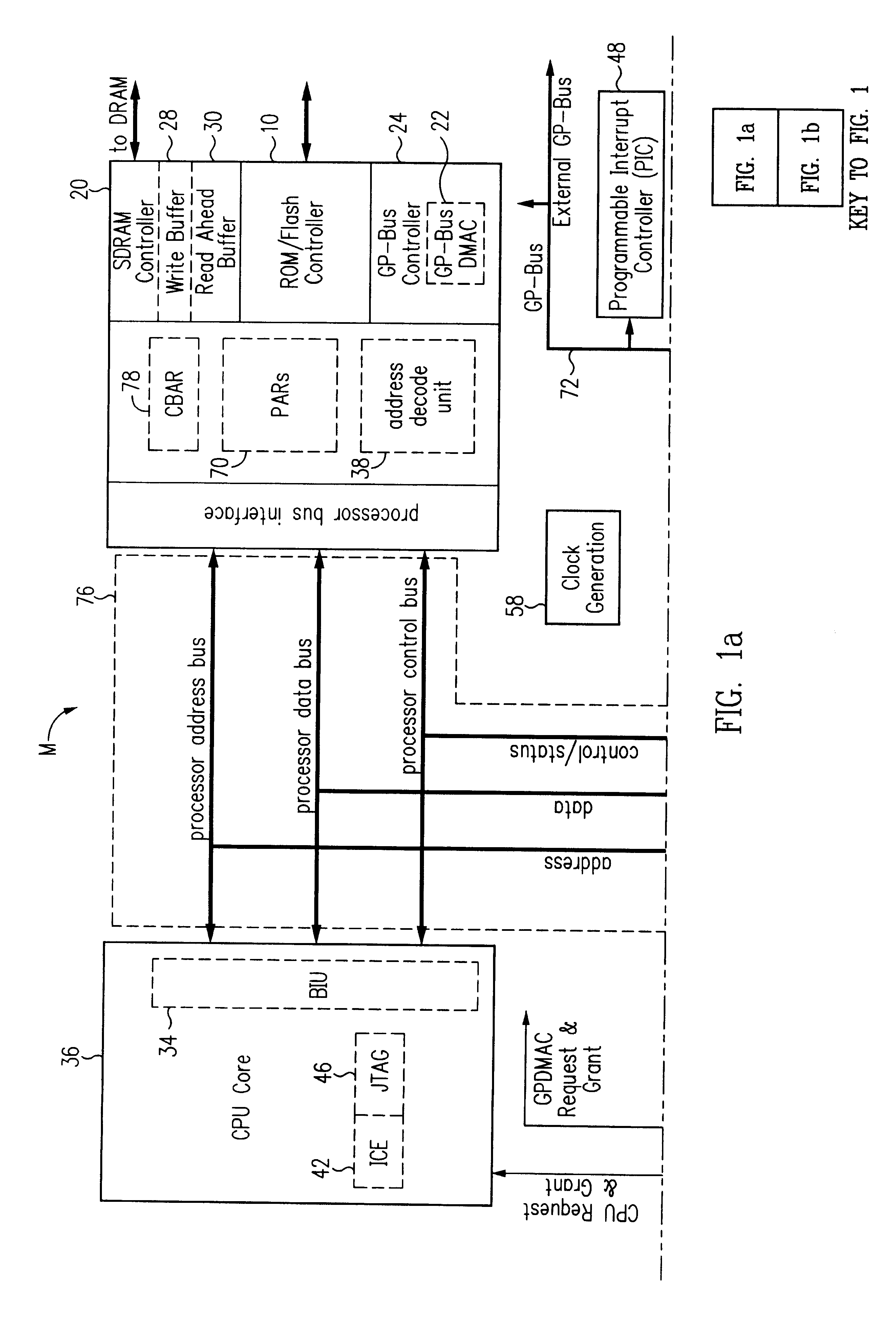

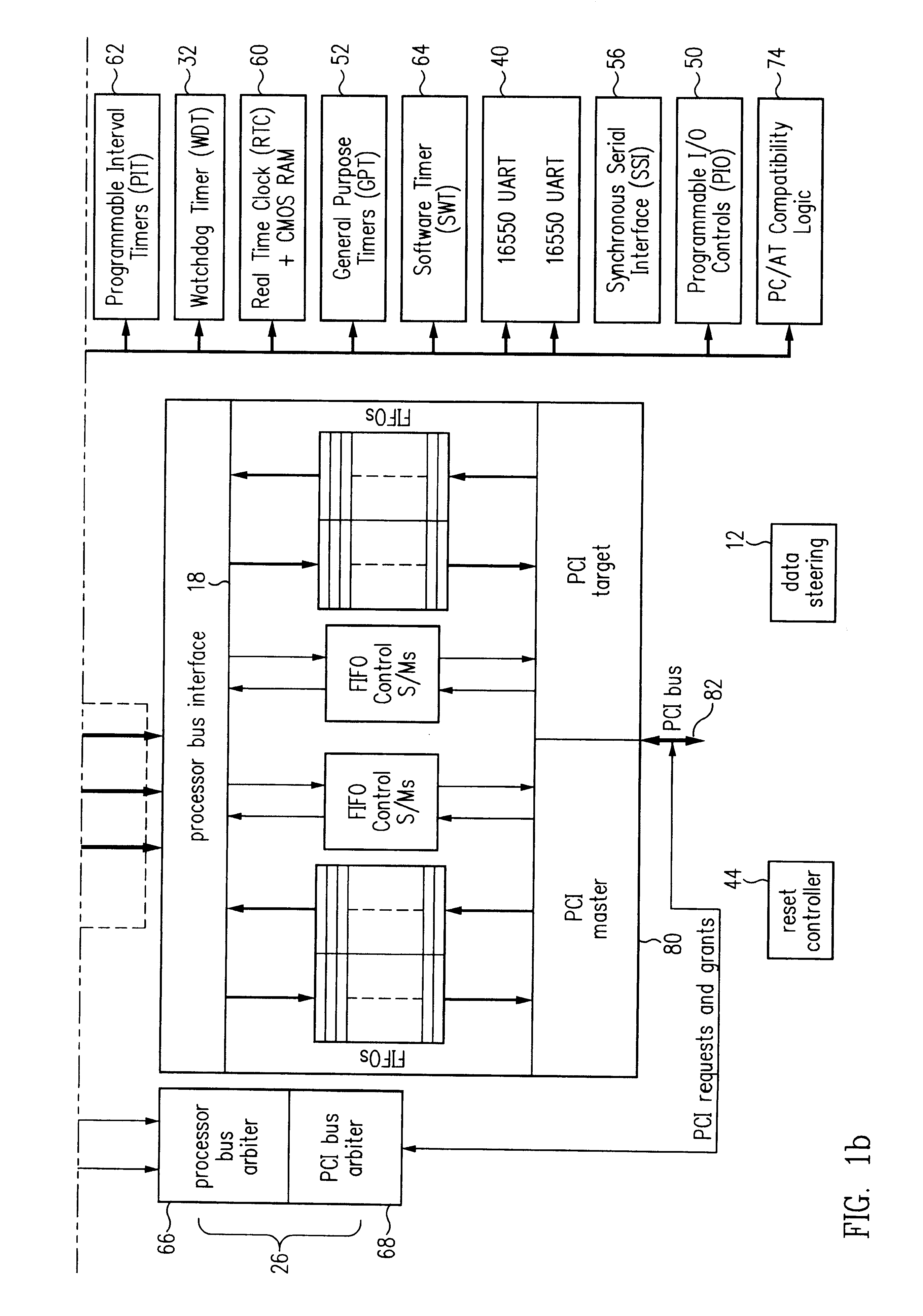

General purpose bus with programmable timing

InactiveUS6490638B1Generating/distributing signalsInput/output processes for data processingGeneral purposeMicrocontroller

A system provides a general purpose bus with programmable timing capability. As part of a microcontroller, this general purpose bus provides a mechanism for communication between general purpose peripherals connected to the bus and enables external devices to be connected with proper timing to the microcontroller. The general purpose bus controller includes programmable interface timing control logic which allows the bus cycle length for commands from a processor or other bus master to be programmed. Accordingly, memory and I / O read and write commands are customized to suit the timing requirements of peripheral devices connected externally to the microcontroller. A significant variety of peripheral devices may thus be coupled to the microcontroller without requiring additional glue logic. The general purpose bus controller further includes an echo mode which permits accesses to internal peripheral devices to be interpreted by a logic analyzer or other debugging equipment.

Owner:GLOBALFOUNDRIES INC

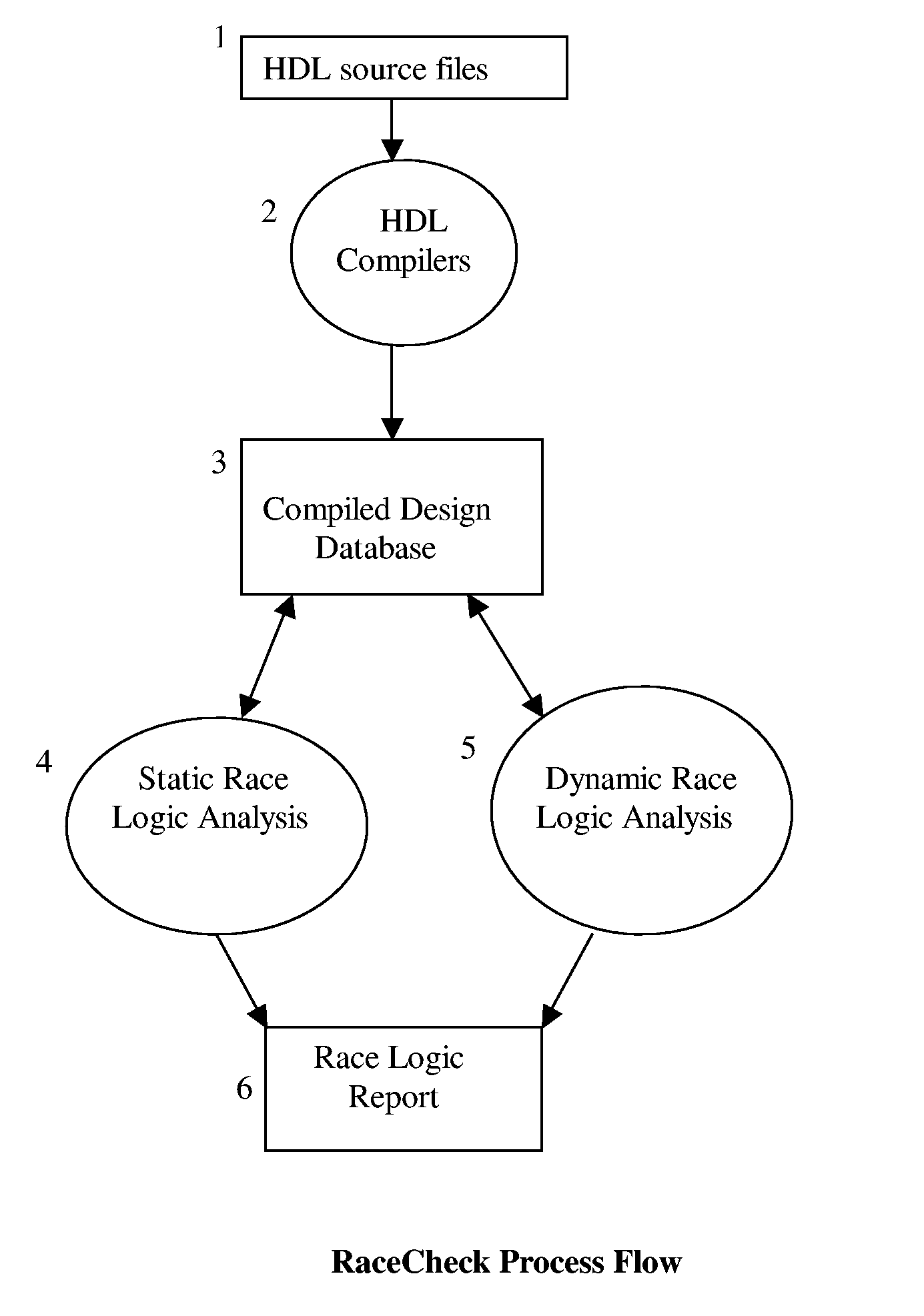

RaceCheck: A Race Logic Ana,yzer Program for Digital Integrated Circuits

ActiveUS20060075367A1Reduce effortShorten the timeElectrical testingDesign optimisation/simulationTime informationSystemC

This invention describes a race logic audit program, RaceCheck, which is unique from the prior arts. Specifically, RaceCheck can perform both static and dynamic race logic analysis, and it works with a plurality of hardware description languages (HDL), which include but not limited to: VHDL, Verilog, SystemVerilog, and SystemC. Furthermore, RaceCheck makes use of both structural and timing information of IC designs, as well as binary-decision diagram (BDD) and automatic test pattern generation (ATPG) techniques to derive accurate race logic analysis results with few false violations. Finally, RaceCheck can detect concurrent invocation races of the $random system function, concurrent invocation races of user-defined tasks and functions, zero-delay combination loops, and RaceCheck's dynamic analysis engine uses a HDL simulation kernel to perform timing-accurate race logic analysis. All these aforementioned features are unique for the invention and have not been reported in any prior arts.

Owner:DYNETIX DESIGN SOLUTIONS

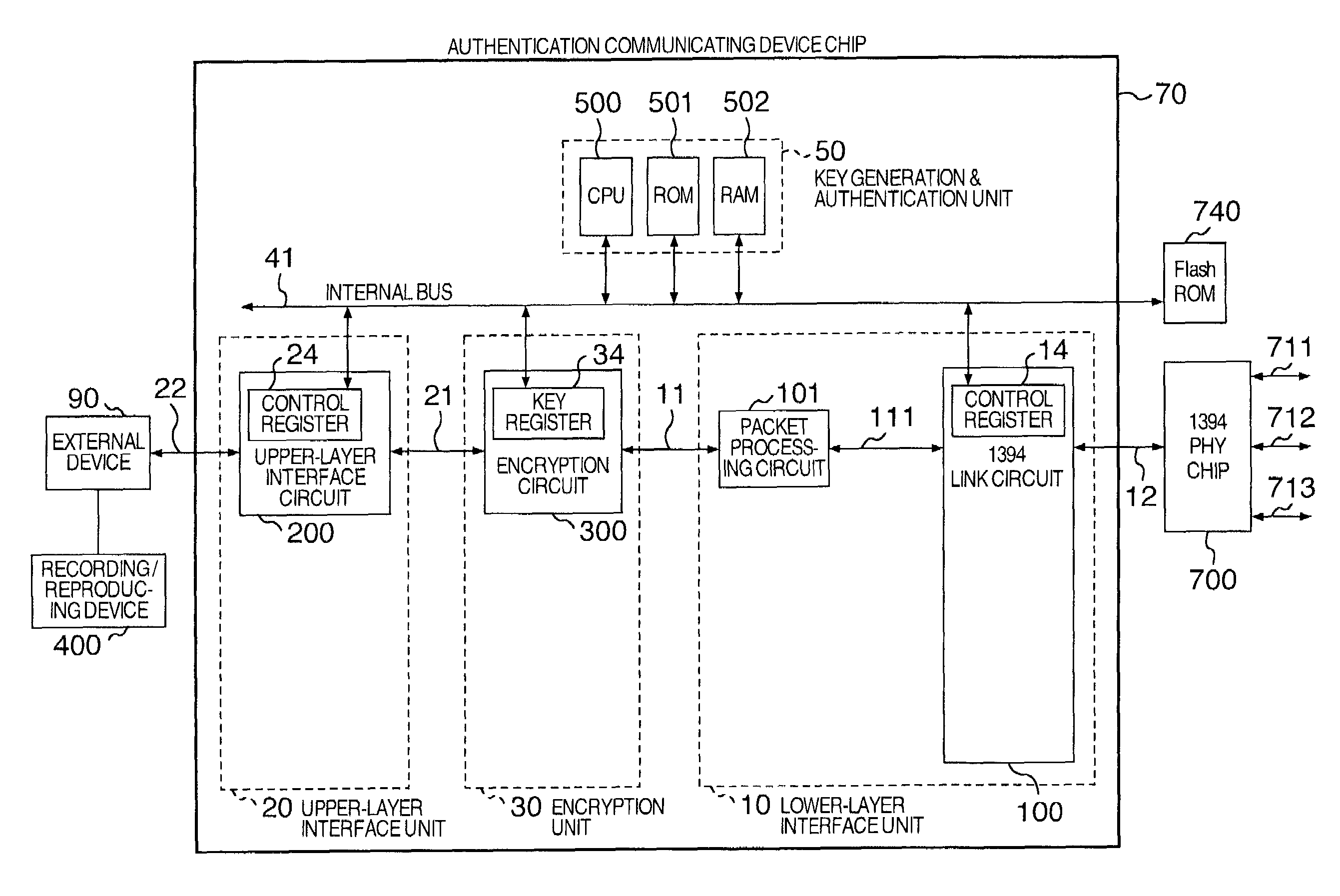

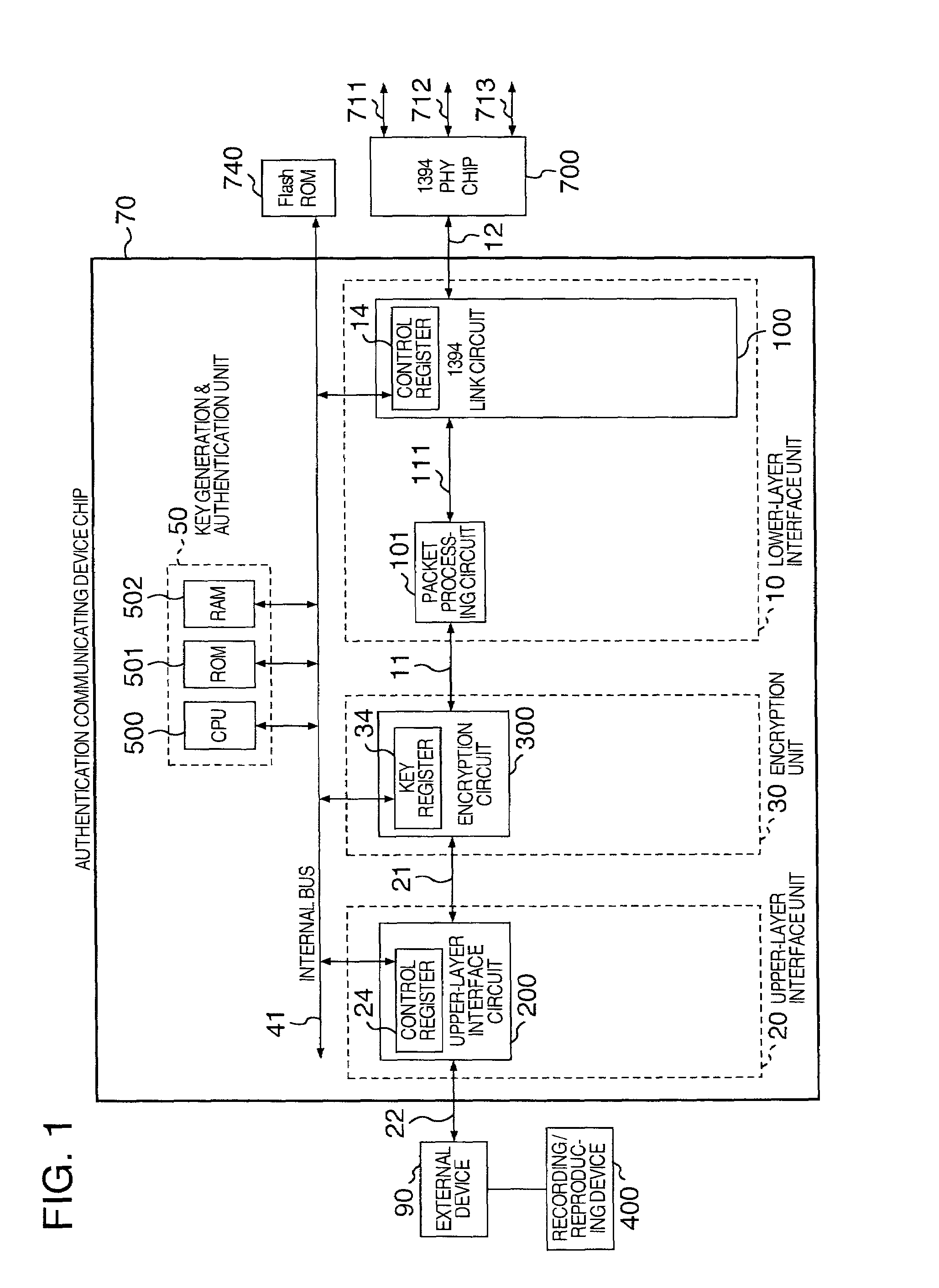

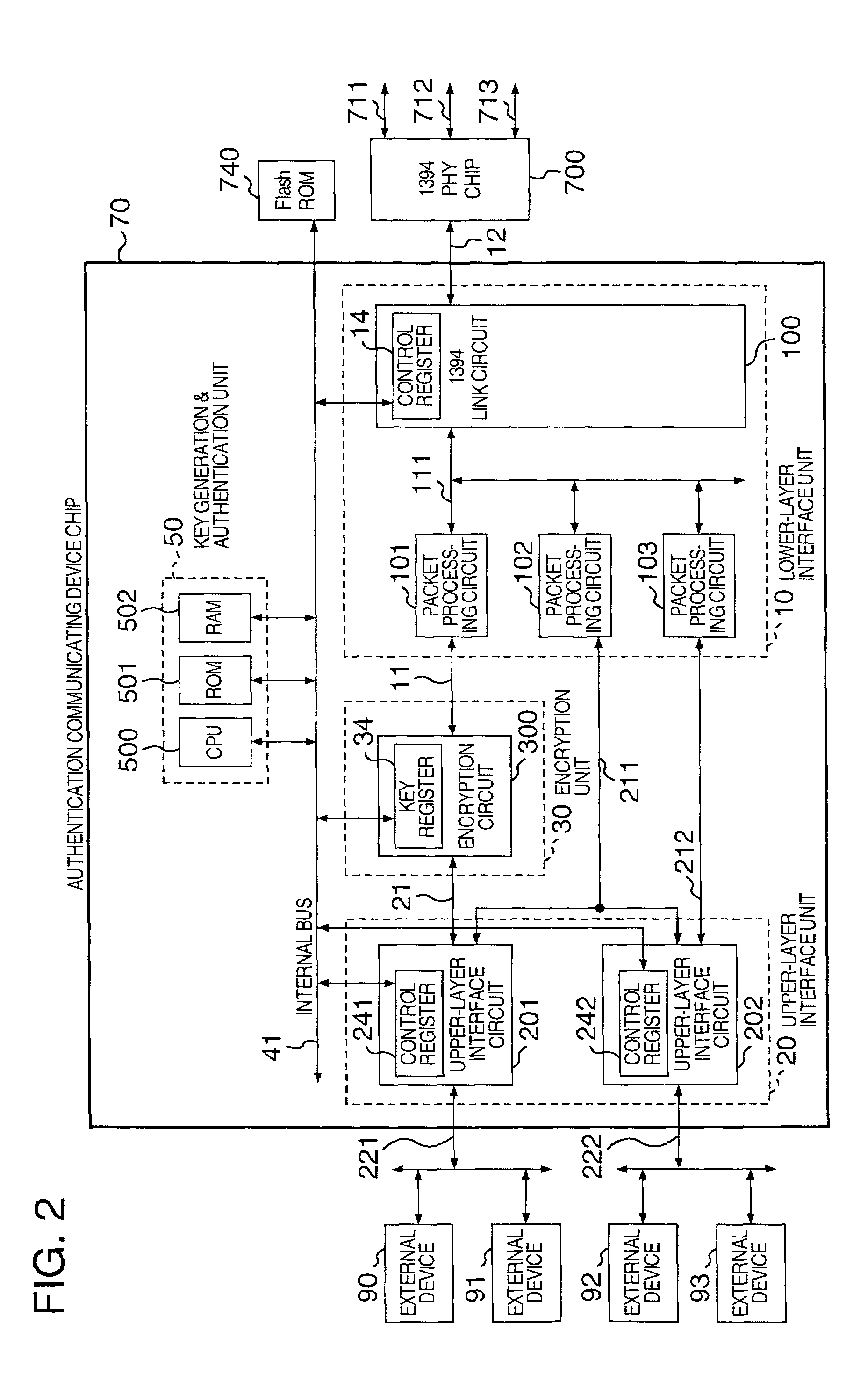

Authentication communicating semiconductor device

InactiveUS7107458B2Improve securityLow costTelevision system detailsDigital data processing detailsMain processing unitControl communications

In an authentication communicating semiconductor device to enhance protection against illegal copying, a logic analyzer probe or the like is connected to a CPU bus to suppress possibility in which the authentication process is intercepted and is analyzed to break the mechanism of illegal copy protection and the electronic device is modified to set a tampered encryption key to the CPU bus. The authentication communicating semiconductor device includes a semiconductor chip, a main processing unit formed on the chip for generating a key code according to a predetermined algorithm, for determining approval / non-approval of communication of data with an external device, and for controlling the communication; an encryption unit formed on the chip for encrypting and decoding communication data using the key code generated by the main processing unit, and an interface unit formed on the chip for conducting communication with an upper-layer or a lower-layer according to a predetermined protocol.

Owner:RENESAS ELECTRONICS CORP

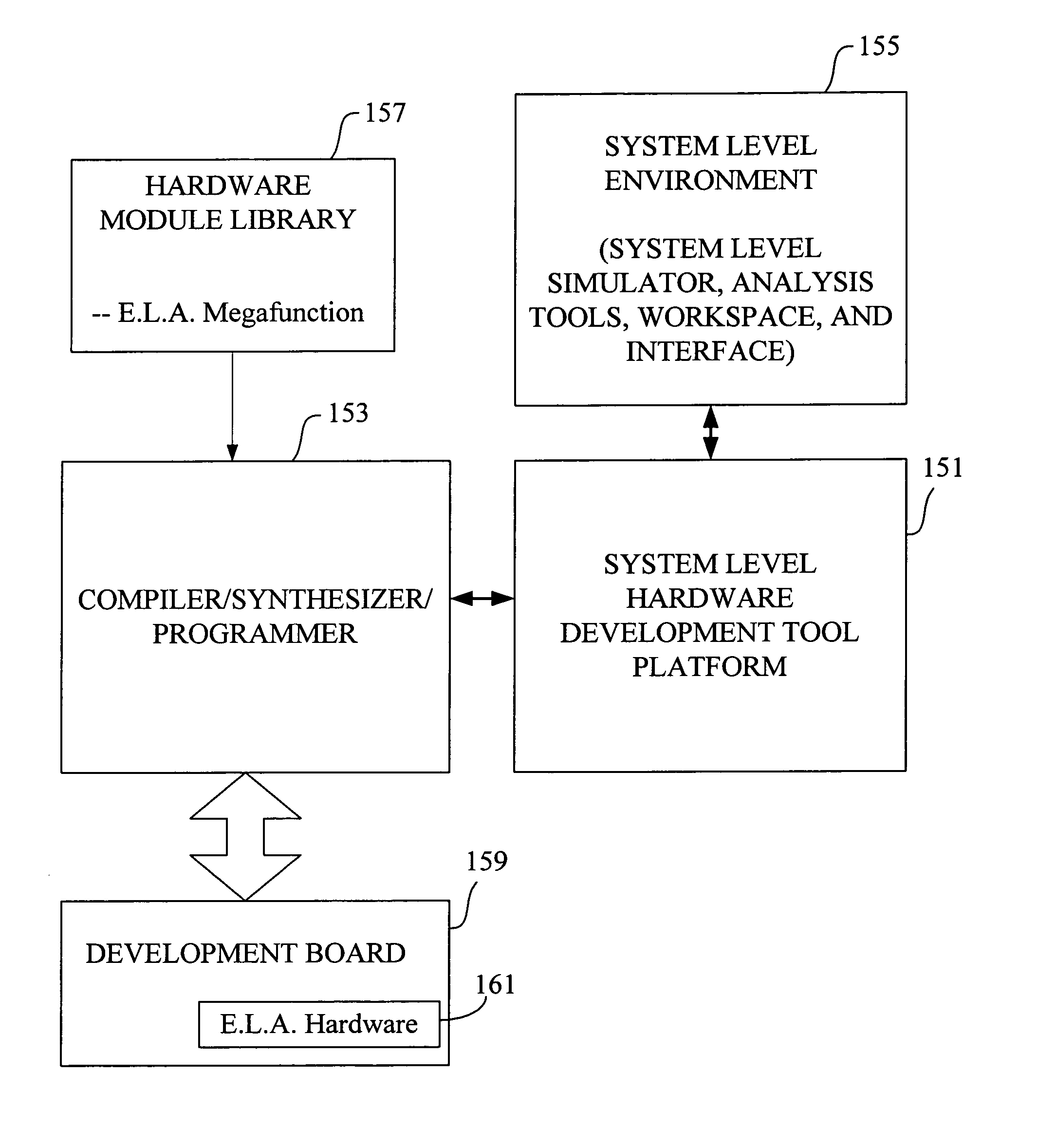

Embedded logic analyzer functionality for system level environments

ActiveUS7991606B1CAD circuit designSoftware simulation/interpretation/emulationLogic analyzerElectronic design automation

An electronic design automation system merges embedded logic analyzer technology with system level design and analysis technology. Embedded logic analyzers provide hardware to allow board-level signal capture and subsequent analysis of test devices programmed with a hardware design generated using electronic design automation. System level environments provide interactive tools for entering, modeling, simulating and analyzing multi-domain systems such as DSP designs. Typically, a user enters a system level design as a block diagram, including embedded logic analyzer blocks. The user inserts such blocks at nodes in the design where he or she wishes to capture signals to verify the design.

Owner:ALTERA CORP

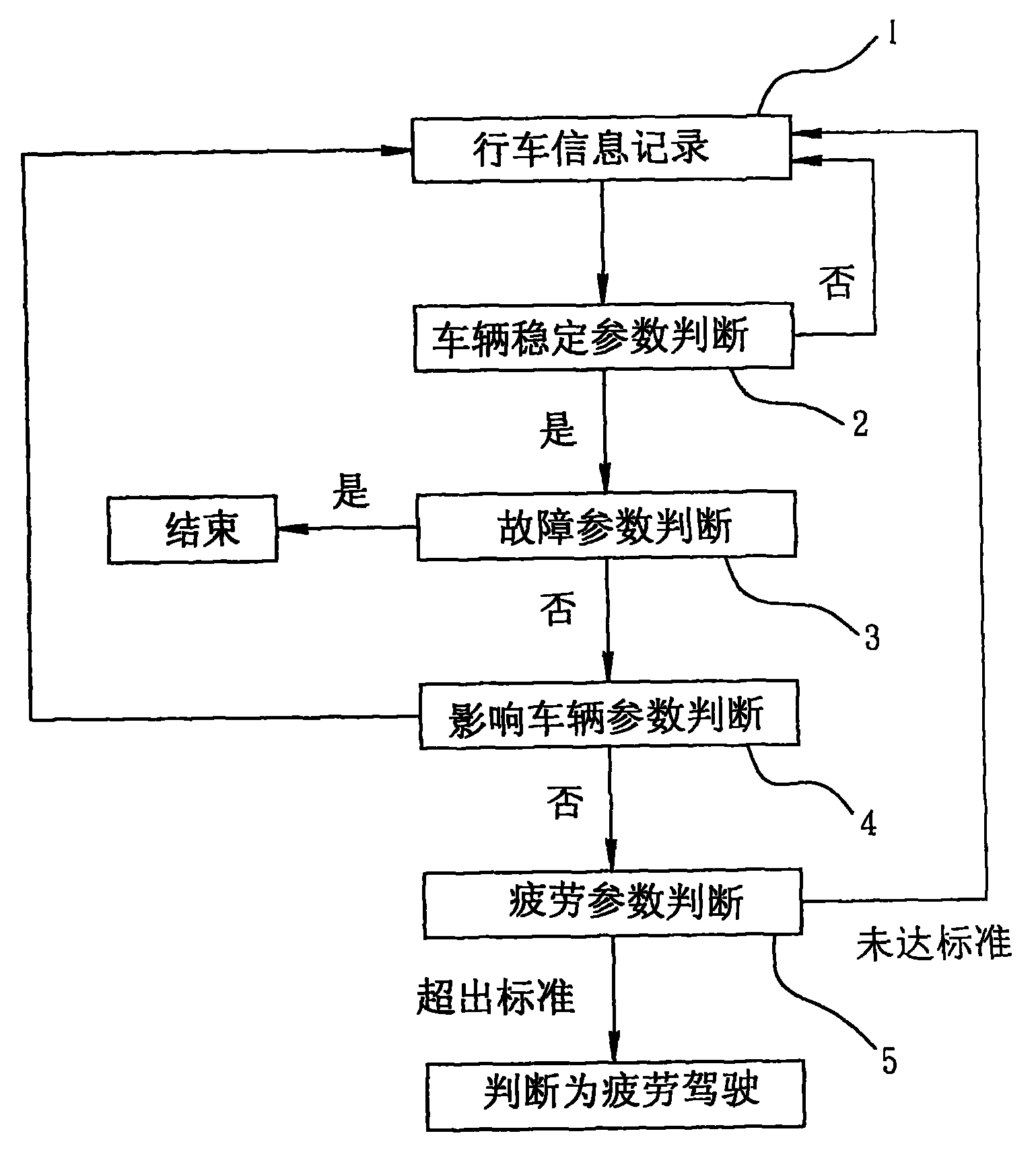

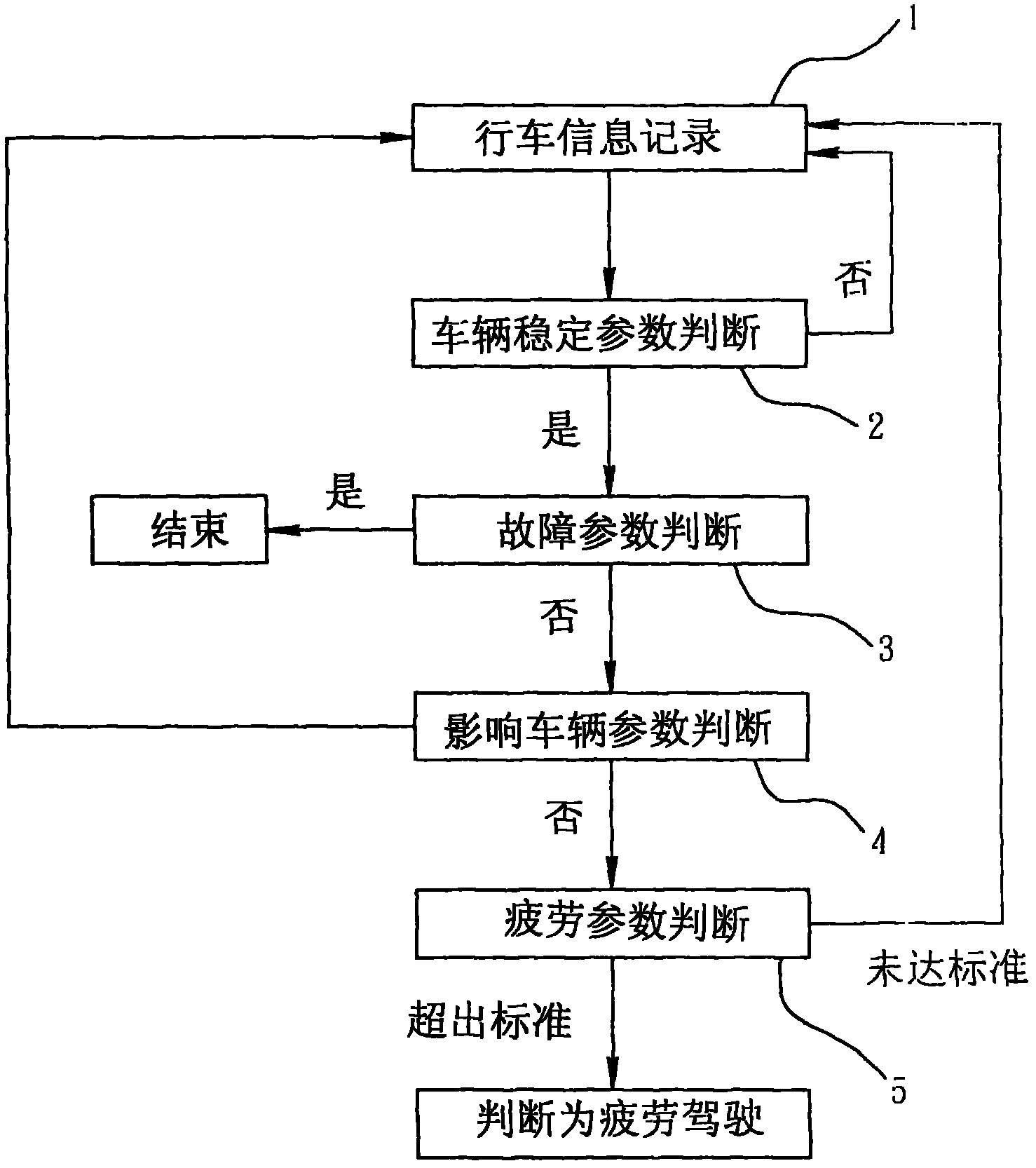

Method and device for judging fatigue driving

The invention discloses a method and device for judging fatigue driving. A driving information record generated by a vehicle OBD (On-Board Diagnostics) device when a vehicle is driven serves as a resource parameter; a driver driving behaviour logically manually analyzed serves as a comparison parameter; a processing unit takes a comparison parameter as a basis to carry out data judgement and accumulation on the resource parameter; and when the accumulated resource parameter reaches the set standard, an automobile driver is judged to be in the fatigue driving state.

Owner:AUTOMOTIVE RES & TESTING CENT

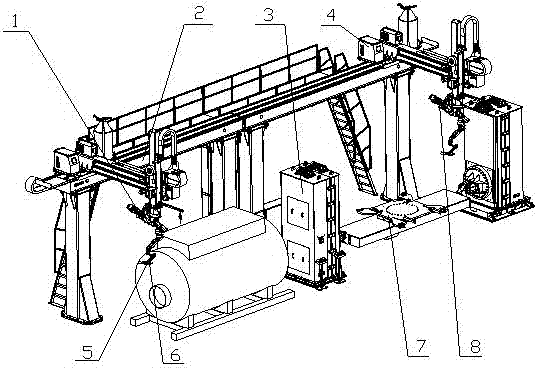

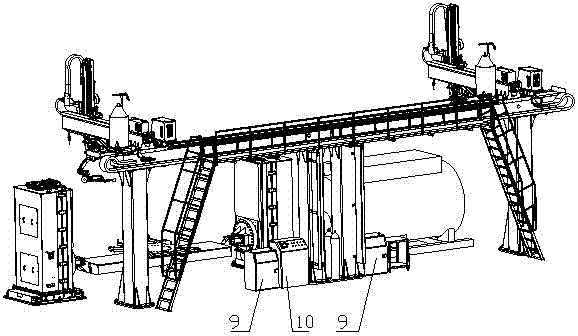

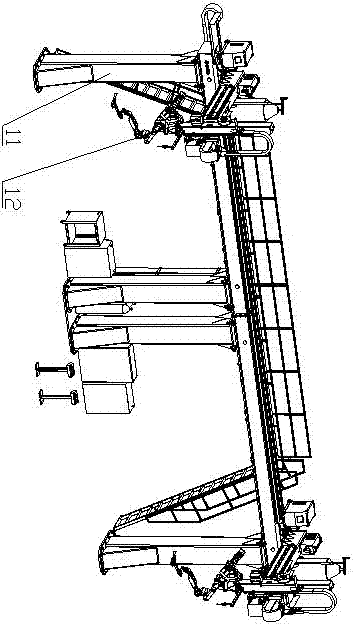

Boiler heat exchanger welding robot workstation

InactiveCN107234383AReduce labor intensityImprove work efficiencyWelding/cutting auxillary devicesAuxillary welding devicesEngineeringWorkstation

The invention discloses a boiler heat exchanger welding robot workstation, which comprises a welding robot, a gantry frame, a liftable double-rotation positioner, tooling fixtures and a walking device; two gantry frames are connected side by side, and one of them A liftable double-rotation positioner is installed in front of the gantry frame, the tooling fixture is installed on the liftable double-turn positioner, the traveling device is movably installed on the gantry frame, and the welding robot is installed on the traveling device. The invention uses welding robots instead of manual labor to complete automatic welding of different types of boiler converters, which has high work efficiency, reduces production costs, and reduces labor intensity of workers; a universal tooling fixture is designed for boiler heat exchangers, which can realize fast clamping of workpieces , The fixture can be applied to the clamping of different types of boiler converters; it realizes that the robot can replace the manual to complete more complex logic analysis, and complete various actions more accurately than manual, with a high degree of automation.

Owner:湖南蓝天机器人科技有限公司

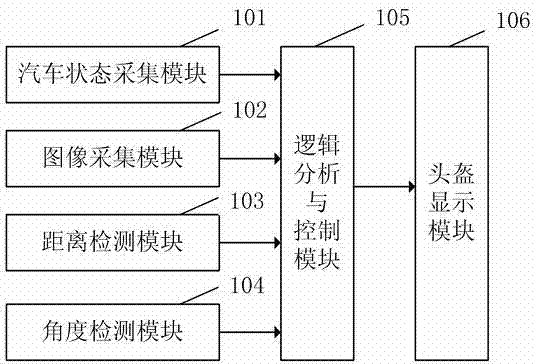

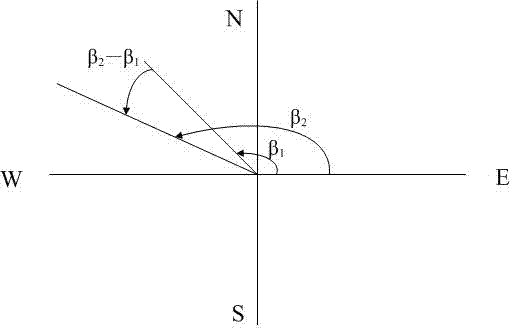

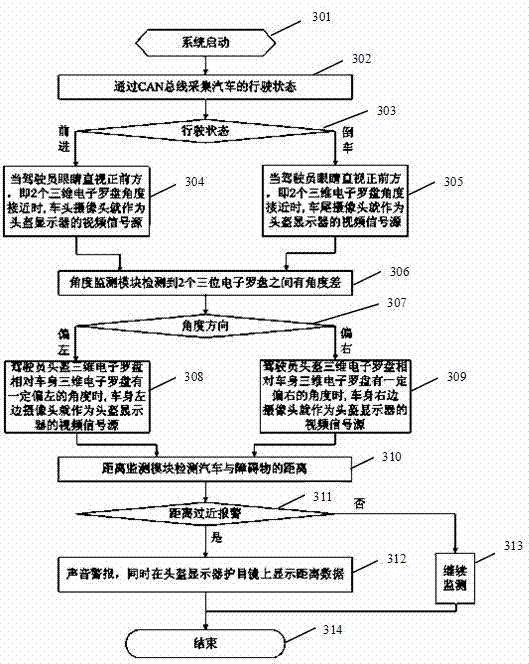

Driving assistance system and method based on head-mounted display and used for automatic scene selection for display

InactiveCN103802728AHumanized operationAvoid traffic accidentsHelmetsHelmet coversDriver/operatorDisplay device

The invention discloses a driving assistance system and method based on head-mounted display and used for automatic scene selection for display. Four wide-angle cameras and six groups of radar transmitting and receiving devices are mounted all around a car body so as to collect images around the car and detect distances between the car and surrounding obstacles in real time, a relative direction (angle) between a diver head (sight) and an automobile is calculated through relative angles collected by a three-dimensional electronic compass on a driver helmet and a three-dimensional electronic compass mounted on the car body, then a logical analysis and process function module performs operation processing, and finally, real-time synchronous display is performed on the head-mounted display (goggles). Therefore, through a panoramic parking helmet, the driver can see the position of the car and the obstacles around the car conveniently and intuitively when sitting in the car.

Owner:GUANGDONG COAGENT ELECTRONICS SCI & TECH

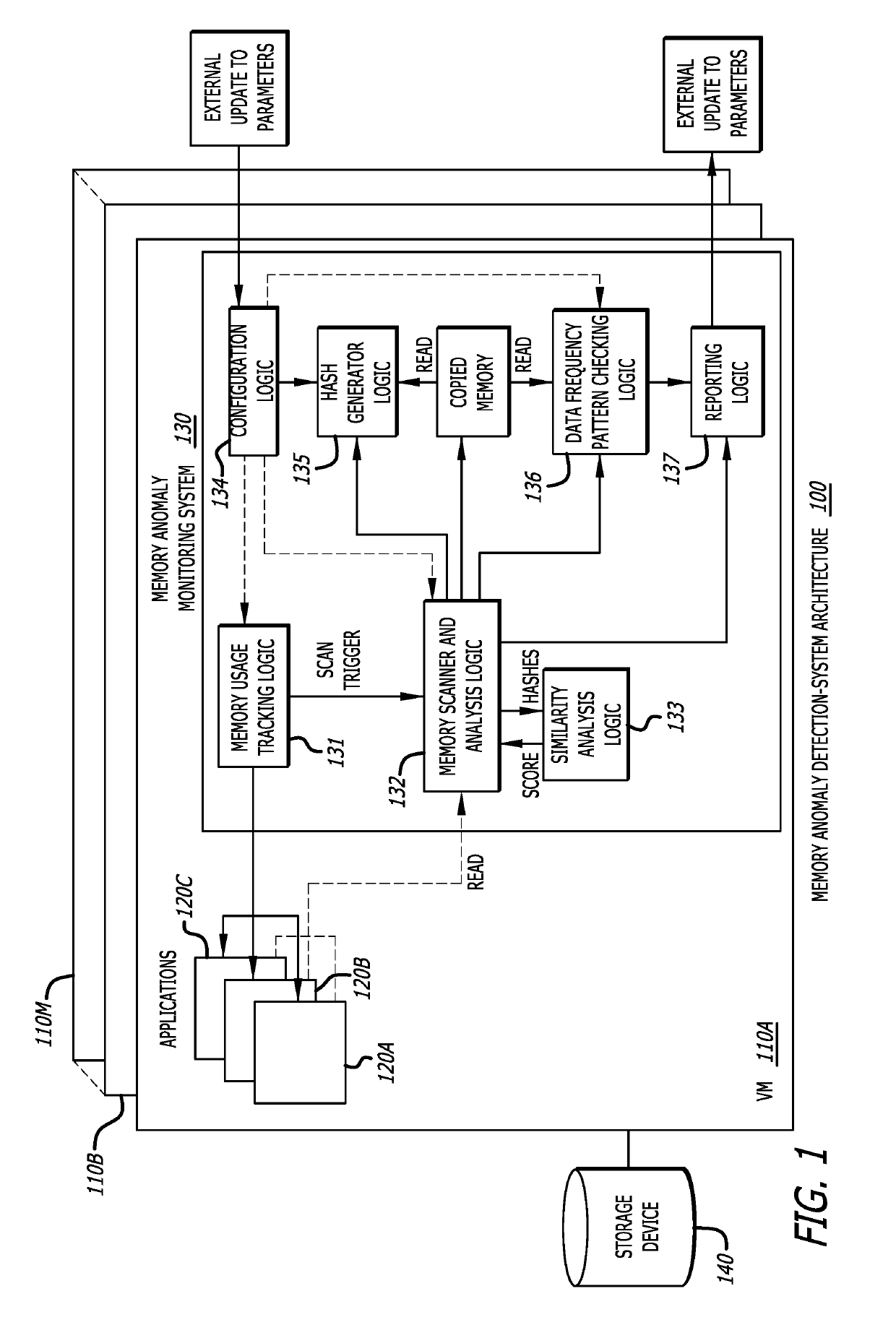

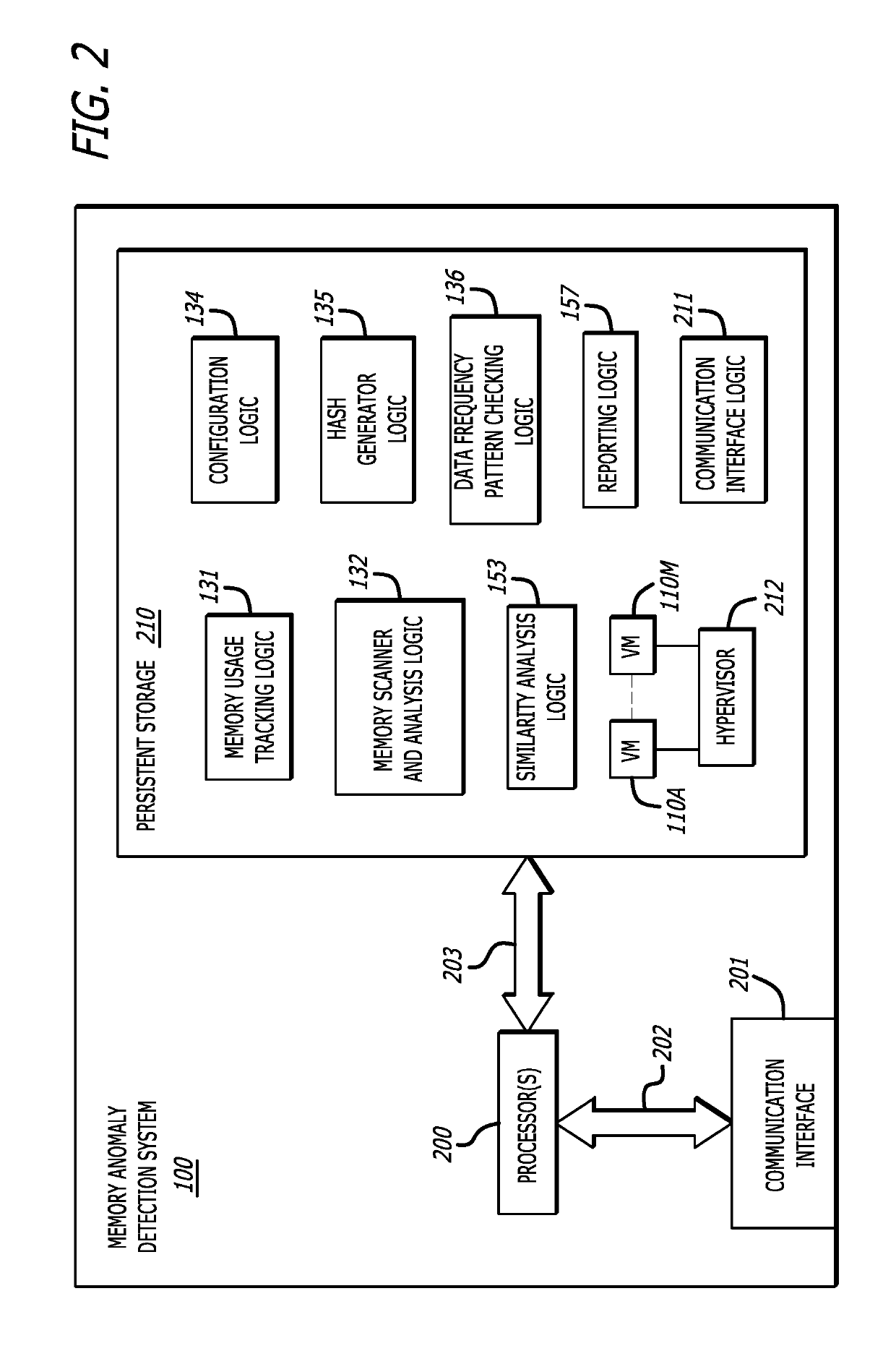

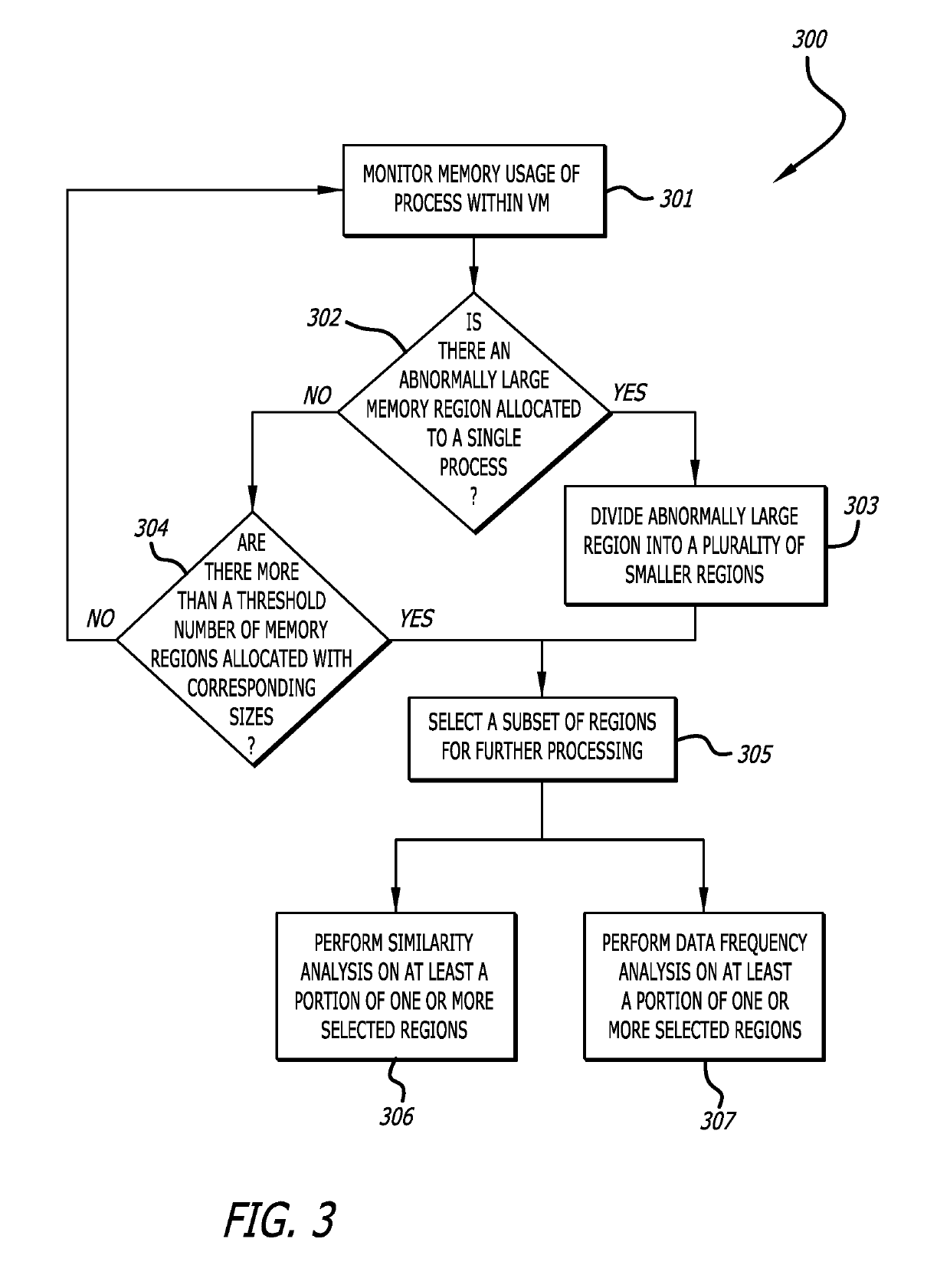

Methods of identifying heap spray attacks using memory anomaly detection

ActiveUS10430586B1Input/output to record carriersPlatform integrity maintainanceAnomaly detectionParallel computing

A non-transitory storage medium including instructions that are executable by one or more processors to perform operations including instrumenting a VM is shown. The VM is used to process an object to determine whether the object is associated with malware. Logic within the VM analyzes memory allocated for a process within the VM for a point of interest (POI), the POI being an address of one of a set predetermined instructions likely to be associated with malware. The VMM detects a memory violation during processing of the object and responsive to detecting the memory violation, injects a transition event at the POI on the page on which the POI is located in memory. Further, responsive to detecting an attempted execution of the transition event, the VMM (i) emulates an instruction located at the POI, and (ii) the logic within the VM performs one or more malware detection routines.

Owner:FIREEYE SECURITY HLDG US LLC

Suite of tools to design integrated circuits

InactiveUS7430725B2Detecting faulty computer hardwareComputer programmed simultaneously with data introductionComputer architectureBatch processing

A set of tools is provided herein that produces useful, proven, and correct integrated semiconductor chips. Having as input either a customer's requirements for a chip, or a design specification for a partially manufactured semiconductor chip, the tools generate the RTL for control plane interconnect; memory composition, test, and manufacture; embedded logic analysis, trace interconnection, and utilization of spare resources on the chip; I / O qualification, JTAG, boundary scan, and SSO analysis; testable clock generation, control, and distribution; interconnection of all of the shared logic in a testable manner from a transistor fabric and / or configurable blocks in the slice. The input customer requirements are first conditioned by RTL analysis tools to quickly implement its logic. The slice definition and the RTL shell provides the correct logic for a set of logic interfaces for the design specification to connect. The tools share a common database so that logical interactions do not require multiple entries. The designs are qualified, tested, and verified by other tools. The tools further optimize the placement and timing of the blocks on the chip with respect to each other and with respect to placement on a board. The suite may be run as batch processes or can be driven interactively through a common graphical user interface. The tools also have an iterative mode and a global mode. In the iterative mode, one or more of the selected tools can generate the blocks or modify a design incrementally and then look at the consequences of the addition, or change. In the global mode, the semiconductor product is designed all at once in a batch process as above and then optimized altogether. This suite of generation tools generates design views including a qualified netlist for a foundry to manufacture.

Owner:BELL SEMICON LLC

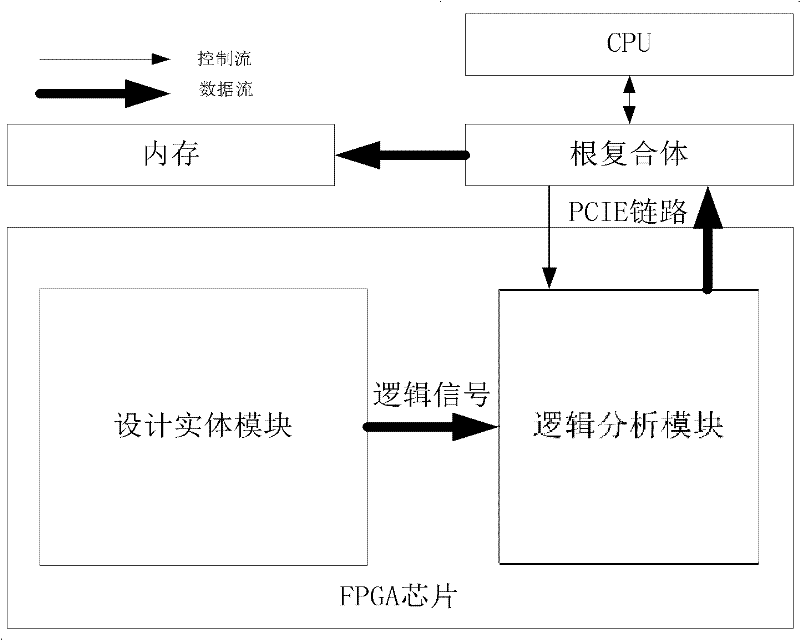

Integrated logic analysis module based on PCIe (peripheral component interconnection express) for FPGA (field programmable gate array)

ActiveCN102495920ASolve the situation where the margin is not enoughMeet the transmission protocol requirementsSpecial data processing applicationsInternal memoryComputer architecture

An integrated logic analysis module based on PCIe (peripheral component interconnection express) for an FPGA (field programmable gate array), which comprises a trigger controller, a DMA (direct memory access) controller, a message transmitting engine, a message receiving engine and a PCIe receiving and transmitting controller. The integrated logic analysis module not only can realize all functions of SignalTap or Chipscope, but also can solve the problem of insufficient allowance of a Block RAM (random access memory) in a large-size design, and at the moment, as data are exported and stored in an internal memory of a CPU (central processing unit) side instead of being stored in a chip, sufficient data can be collected under permission of the internal memory. In addition, a trigger module is a register-level code, accordingly, more complicated triggering setting can be realized only by means of modifying the code, and the integrated logic analysis module is far more flexible than the SignalTap or the Chipscope. Besides, in the large-sized design, a CPU and an FPGA are commonly arranged in the same system, a PCIe link is a common channel of multiple high-speed systems, and accordingly the integrated logic analysis module is wide in application.

Owner:南京中新赛克科技有限责任公司

FPGA (Field Programmable Gata Array) with embedded logical analysis function and logical analysis system

InactiveCN103049361AFlexible collectionFunction increaseLogical operation testingElectrical testingComputer moduleLogical analysis

The invention provides an FPGA with an embedded logical analysis function and a logical analysis system. The FPGA comprises a working module, a storing module embedded in the FPGA, a logical analysis module and an interface module. The logical analysis module connected with the working module and the storing module is used for collecting signals input by the corresponding working module of FPGA based on received collecting commands, storing the collected signals in the storing module and outputting signals stored in the storing module when the collection is finished. The interface module connected with outer devices and the logical analysis module is used for performing protocol encapsulation / parsing processing on data transmitting between the logical analysis module and the outer devices. The data comprises collecting commands input into the interface module by the outer devices and signals input into the interface module by the logical analysis module. The logical analysis system comprises the FPGA and the outer devices connected with the FPGA.

Owner:CELESTICA TECH CONSULTANCY SHANGHAI

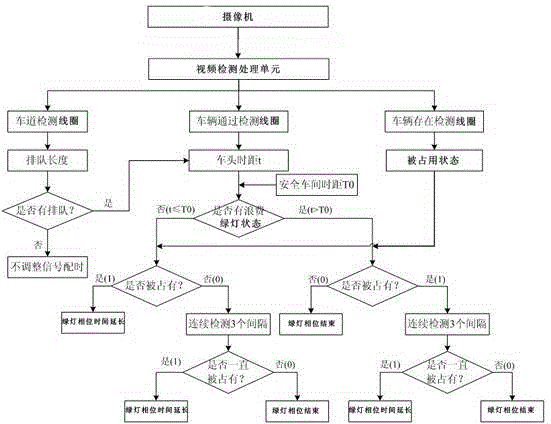

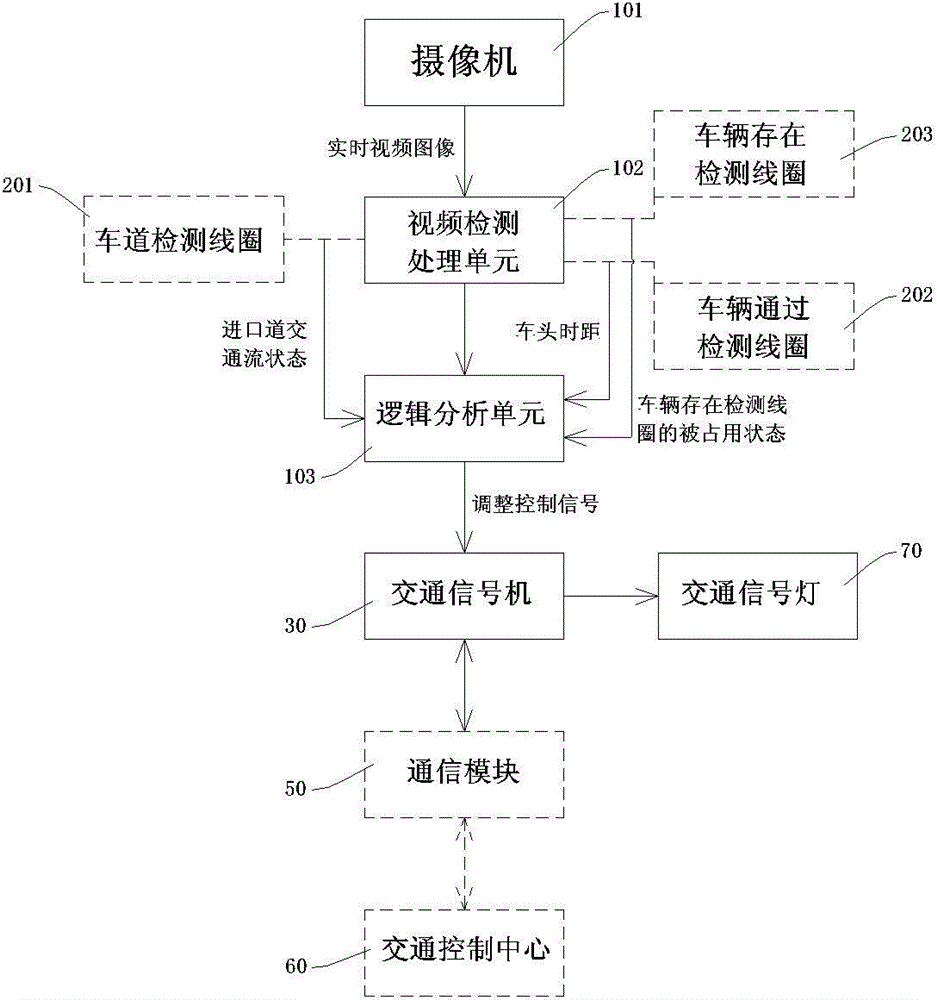

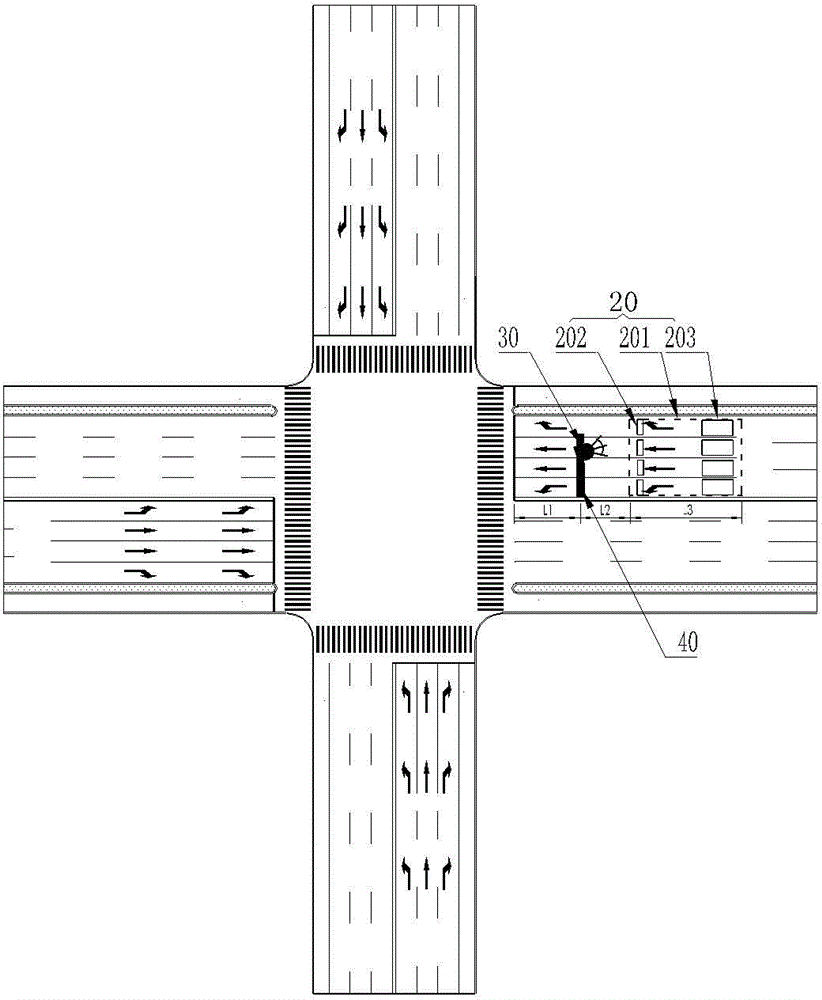

Real-time optimization signal control method and system based on video traffic state monitoring

ActiveCN104658279ARealize real-time sensing signal controlExpand the scope of detectionControlling traffic signalsTraffic signalLogical analysis

The invention provides a real-time optimization signal control method and system based on video traffic state monitoring. According to the method and the system, the problems of high detecting coil damage rate, inflexible setting and poor data reliability of traditional intersection actuated signal control can be solved. The method comprises steps as follows: a camera is erected above an entrance driveway of an intersection and used for collecting real-time video images of an entrance section of each guide driveway of the entrance driveway; a video detecting and processing unit is used for setting virtual detecting coils on the real-time video images and detecting the traffic state in the entrance driveway through the virtual detecting coils; a logical analysis unit is used for logically analyzing the traffic state in the entrance driveway, and a control adjustment signal is generated according to a logical analysis result and is transmitted to a traffic signal instrument; the traffic signal instrument is used for controlling or adjusting a timing plan of the entrance driveway according to the control adjustment signal.

Owner:TRAFFIC MANAGEMENT RES INST OF THE MIN OF PUBLIC SECURITY

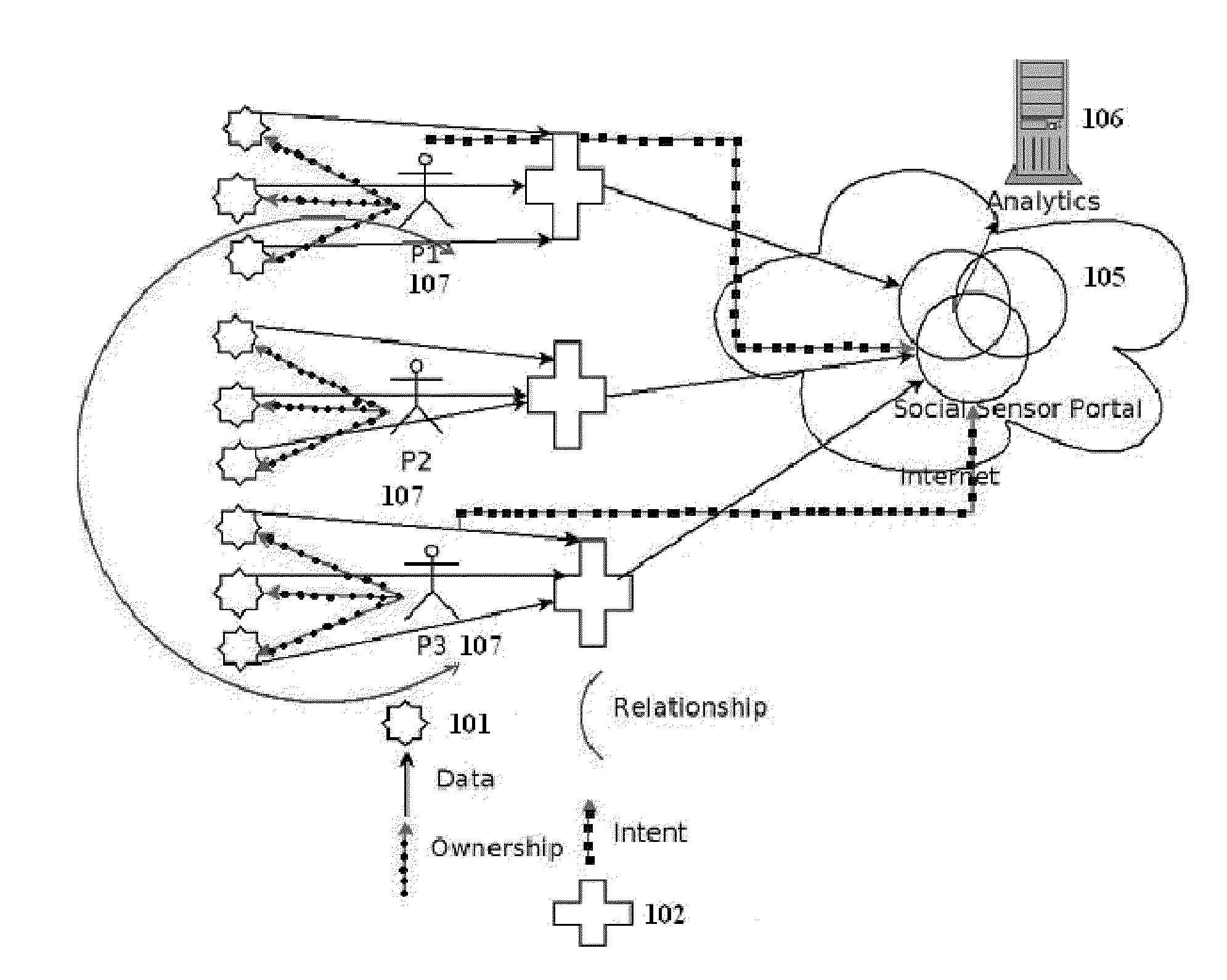

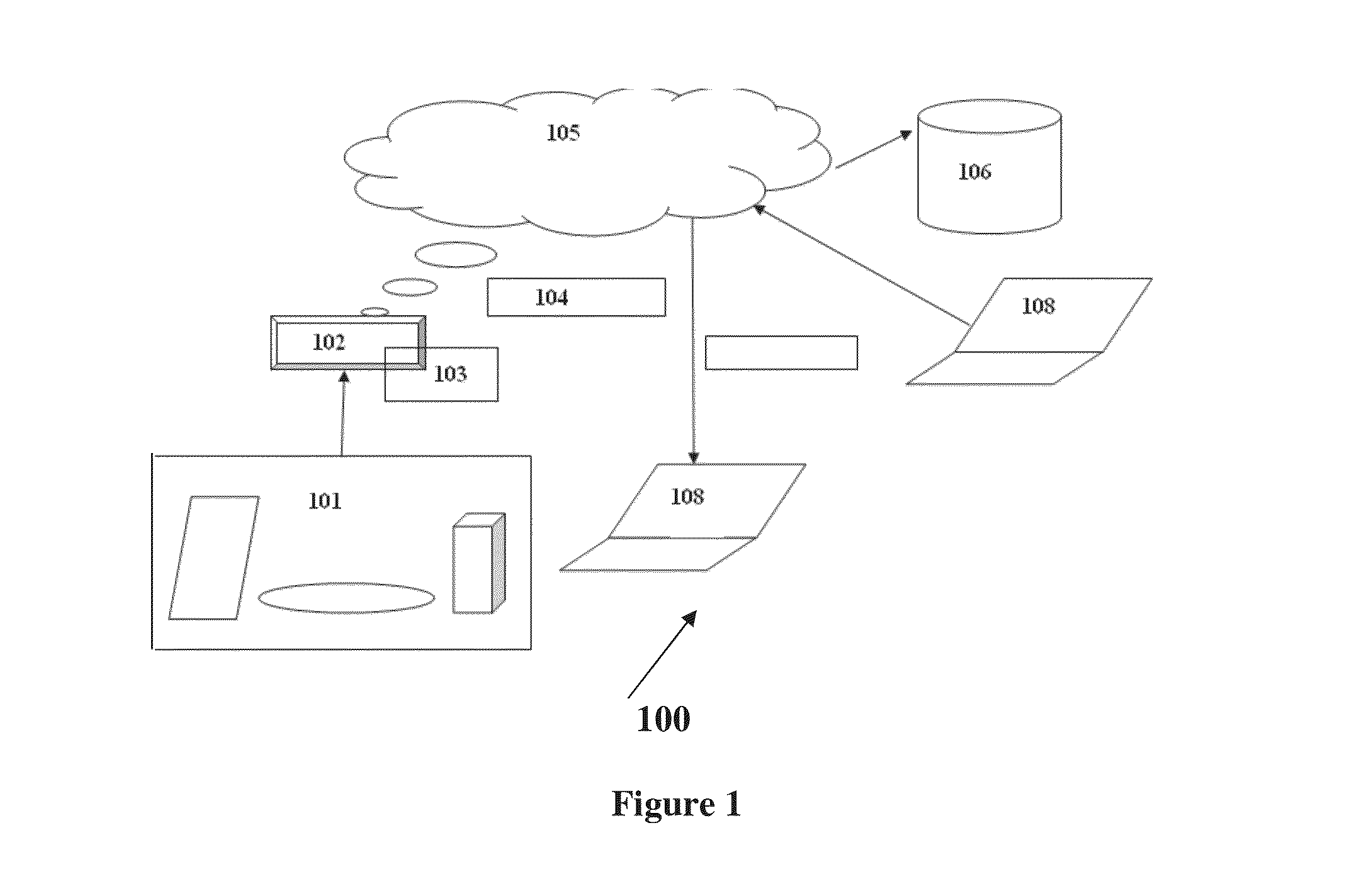

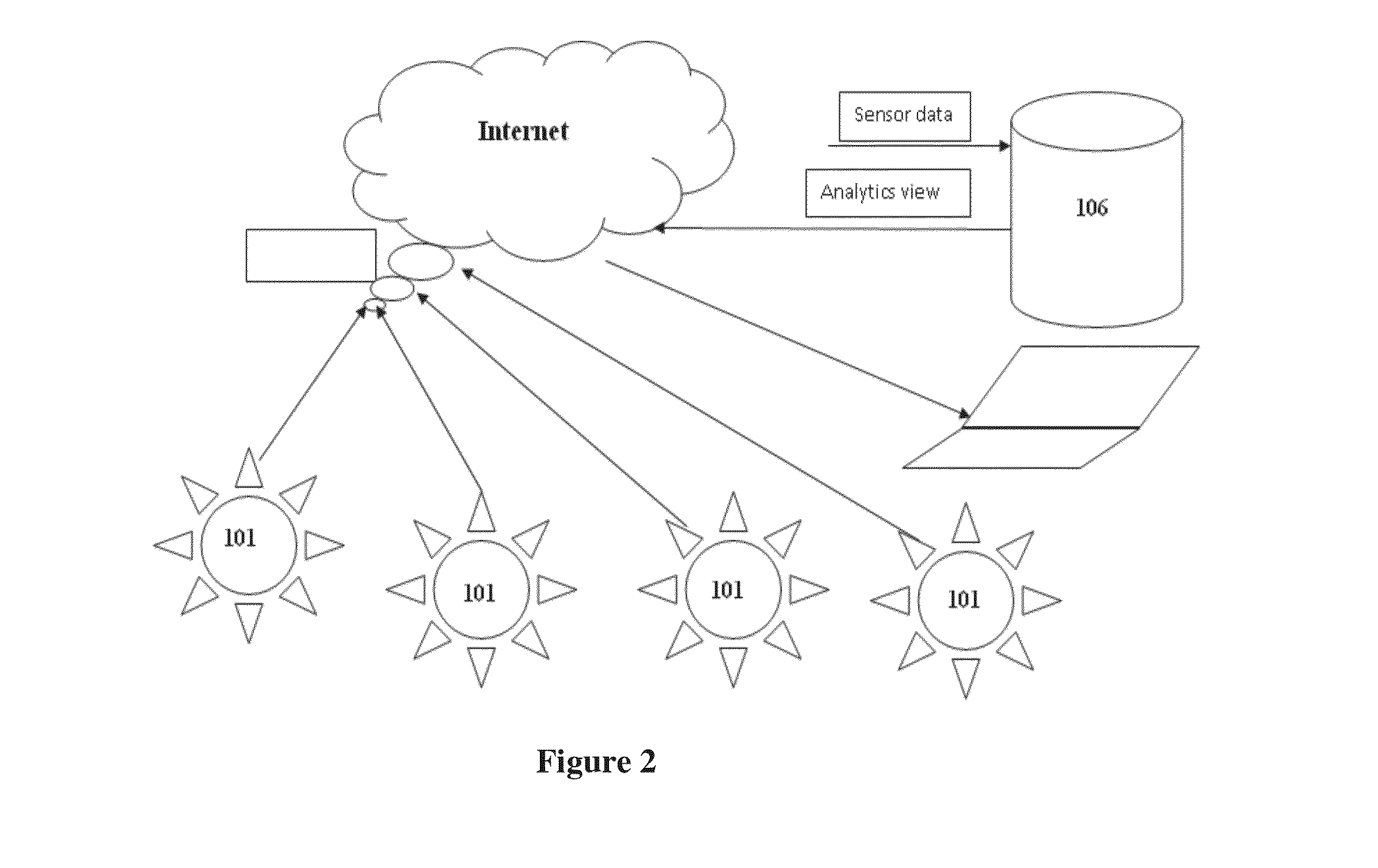

Social network graph based sensor data analytics

ActiveUS20140101255A1Reduce settingsEffectiveTransmissionMachine-to-machine/machine-type communication serviceData setData aggregator

The present invention relates to a system and method of effective physical data aggregation and its logical analytics by way of utilizing socially interacting and networking platforms to create meaningful association and relevancy between the captured physical data. The physical data associated by social networking platforms results in creation of reduced data set for analytics and requires low processing requirements for application usage.

Owner:TATA CONSULTANCY SERVICES LTD

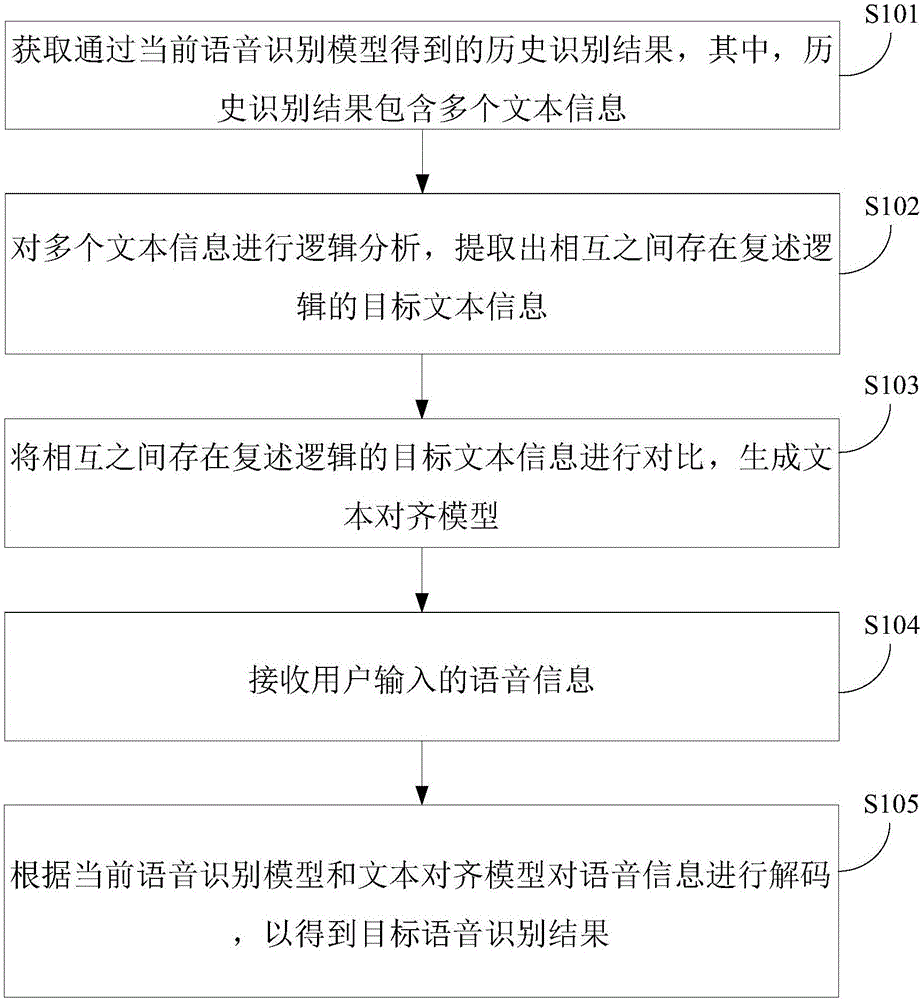

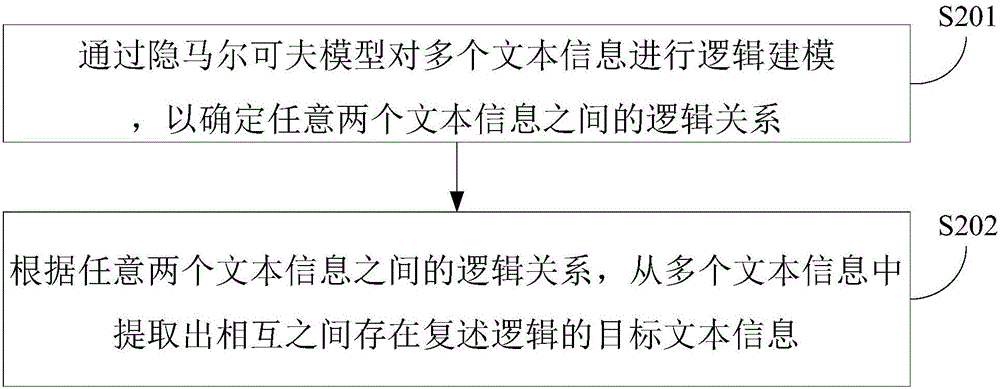

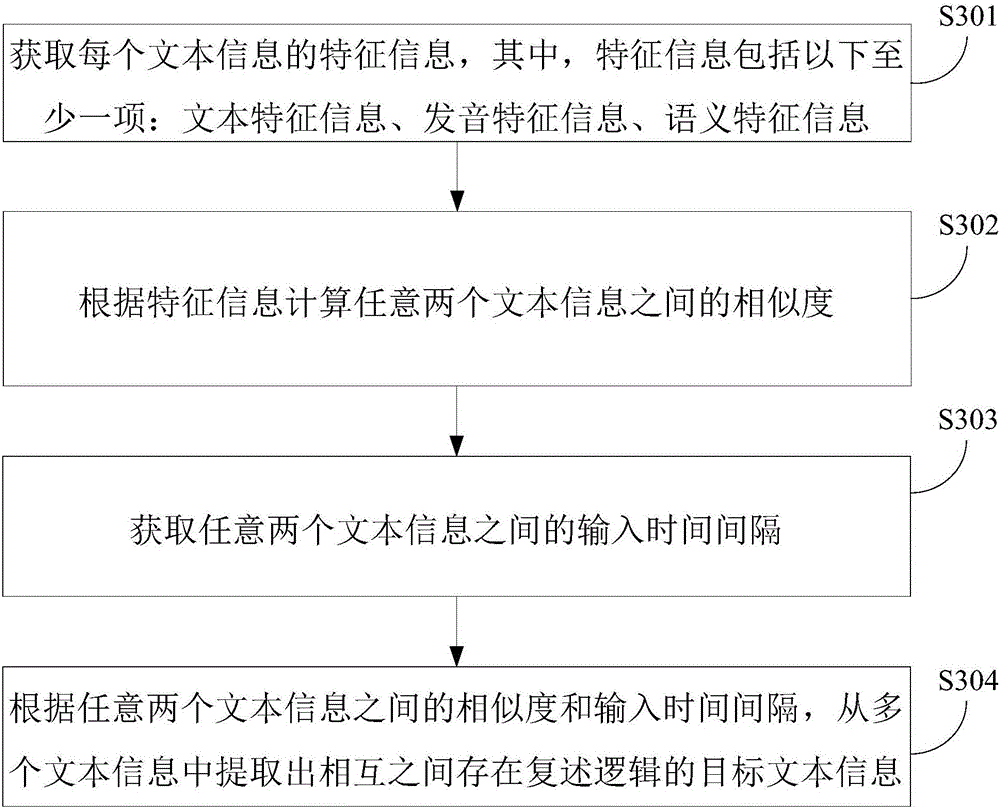

Speech recognition error correction method and device

The present invention relates to a speech recognition error correction method and device. The method includes the following steps that: historical recognition results obtained by a current speech recognition model are acquired, wherein the historical recognition results include a plurality of pieces of text information; logical analysis is performed on the plurality of pieces of text information, and target text information with repeat logic is extracted; the target text information with repeat logic is subjected to wrong channel statistics, so that a text alignment model can be generated; speech information inputted by a user is received; and the speech information is decoded according to the current speech recognition model and the text alignment model, so that a target speech recognition result is obtained. With the speech recognition error correction method and device provided by the technical schemes of the invention adopted, the obtained speech recognition result can be more accurate and better meet the requirements of the user, and therefore, the use experience of the user can be enhanced.

Owner:BEIJING UNISOUND INFORMATION TECH +1

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com