Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

109 results about "Automatic test pattern generation" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

ATPG (acronym for both Automatic Test Pattern Generation and Automatic Test Pattern Generator) is an electronic design automation method/technology used to find an input (or test) sequence that, when applied to a digital circuit, enables automatic test equipment to distinguish between the correct circuit behavior and the faulty circuit behavior caused by defects. The generated patterns are used to test semiconductor devices after manufacture, or to assist with determining the cause of failure (failure analysis). The effectiveness of ATPG is measured by the number of modeled defects, or fault models, detectable and by the number of generated patterns. These metrics generally indicate test quality (higher with more fault detections) and test application time (higher with more patterns). ATPG efficiency is another important consideration that is influenced by the fault model under consideration, the type of circuit under test (full scan, synchronous sequential, or asynchronous sequential), the level of abstraction used to represent the circuit under test (gate, register-transfer, switch), and the required test quality.

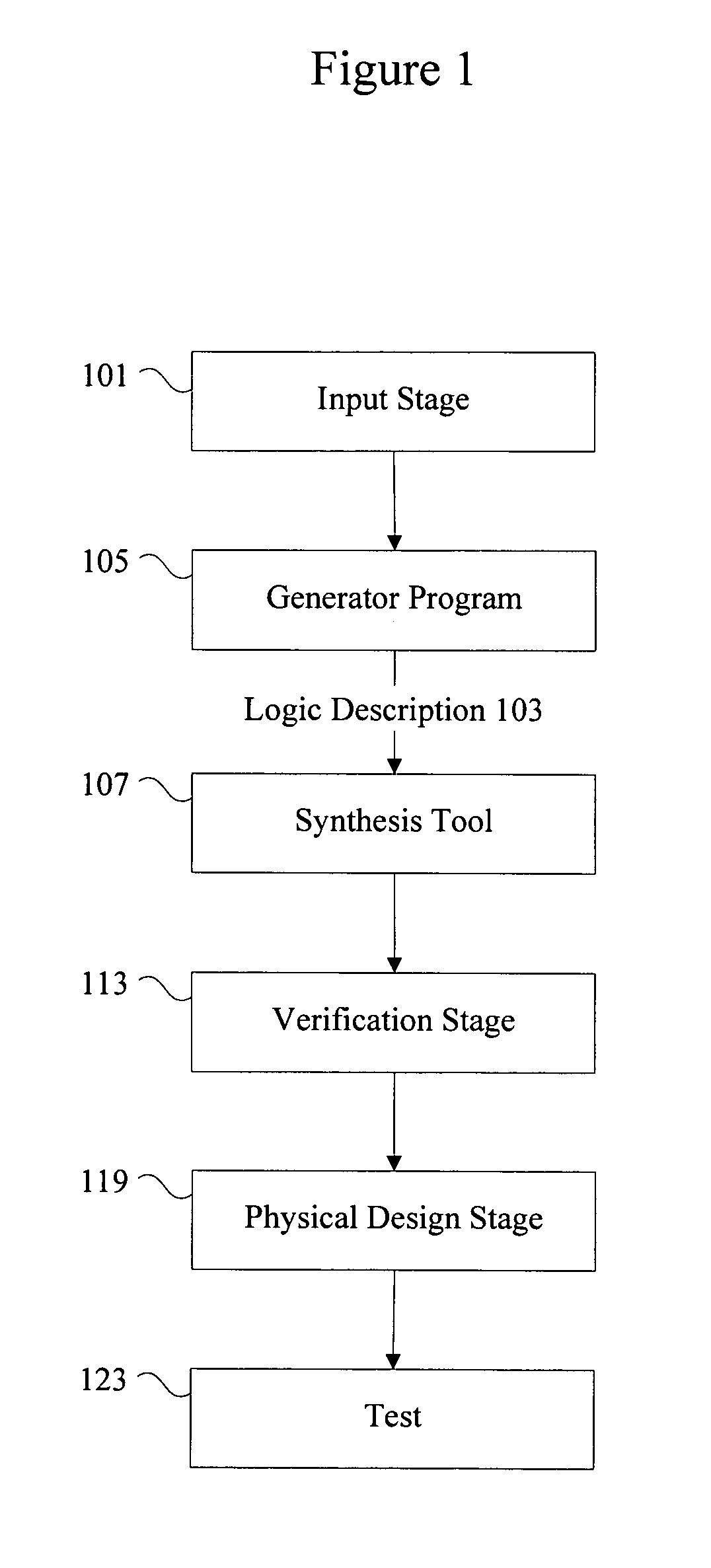

System and method for automatic test case generation

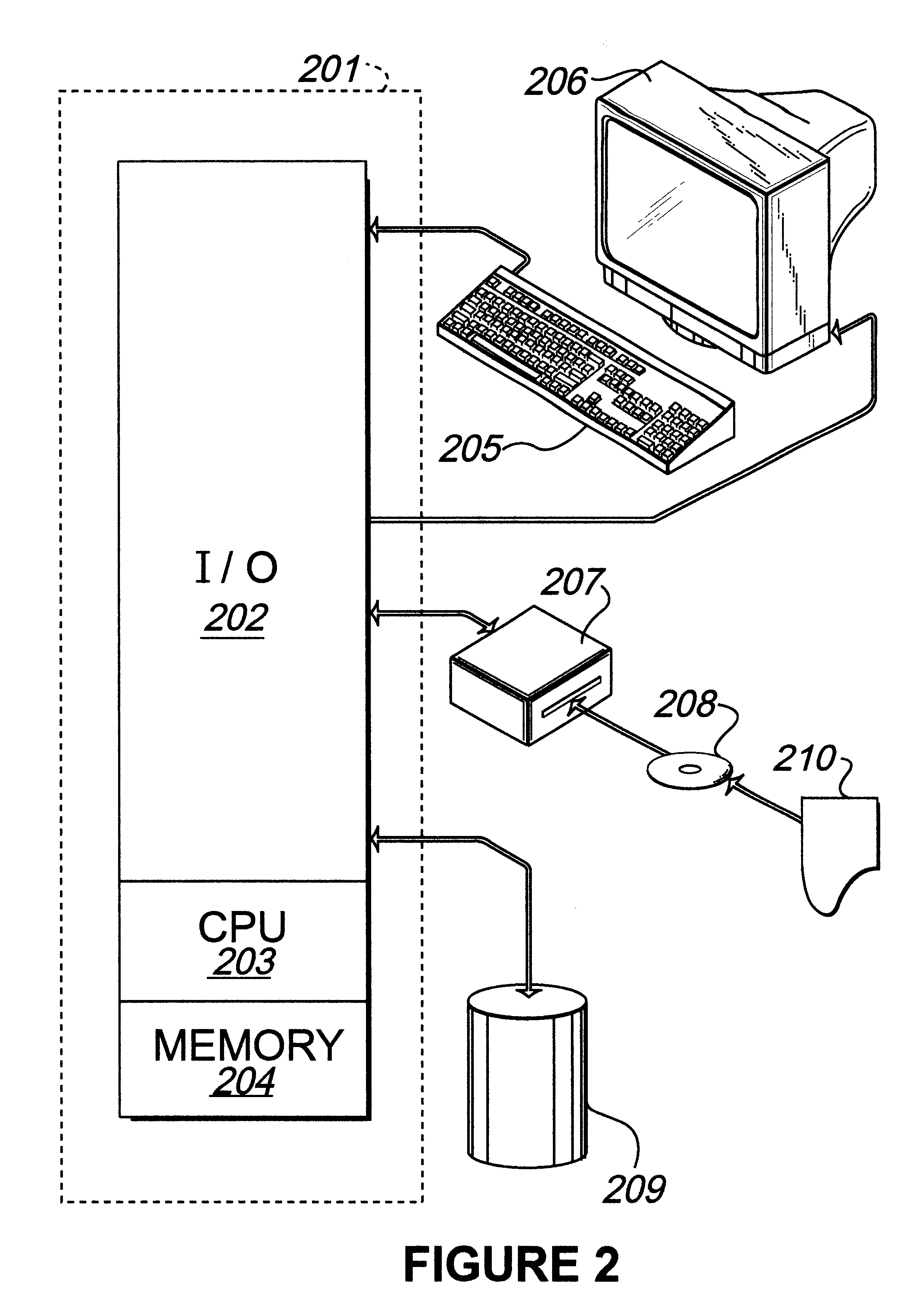

ActiveUS7299382B2Error preventionSoftware testing/debuggingComputer moduleAutomatic test pattern generation

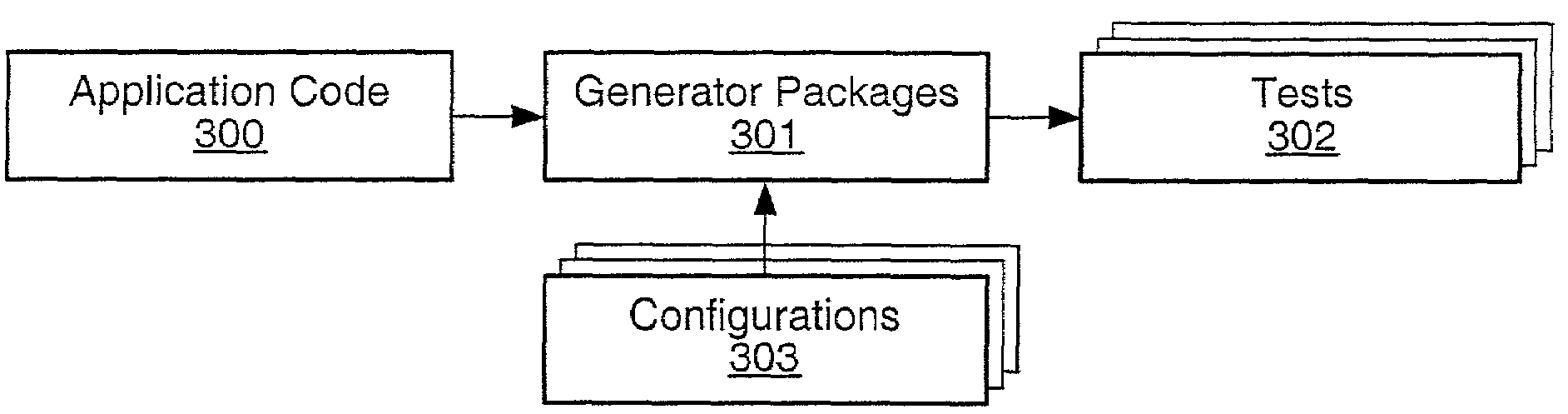

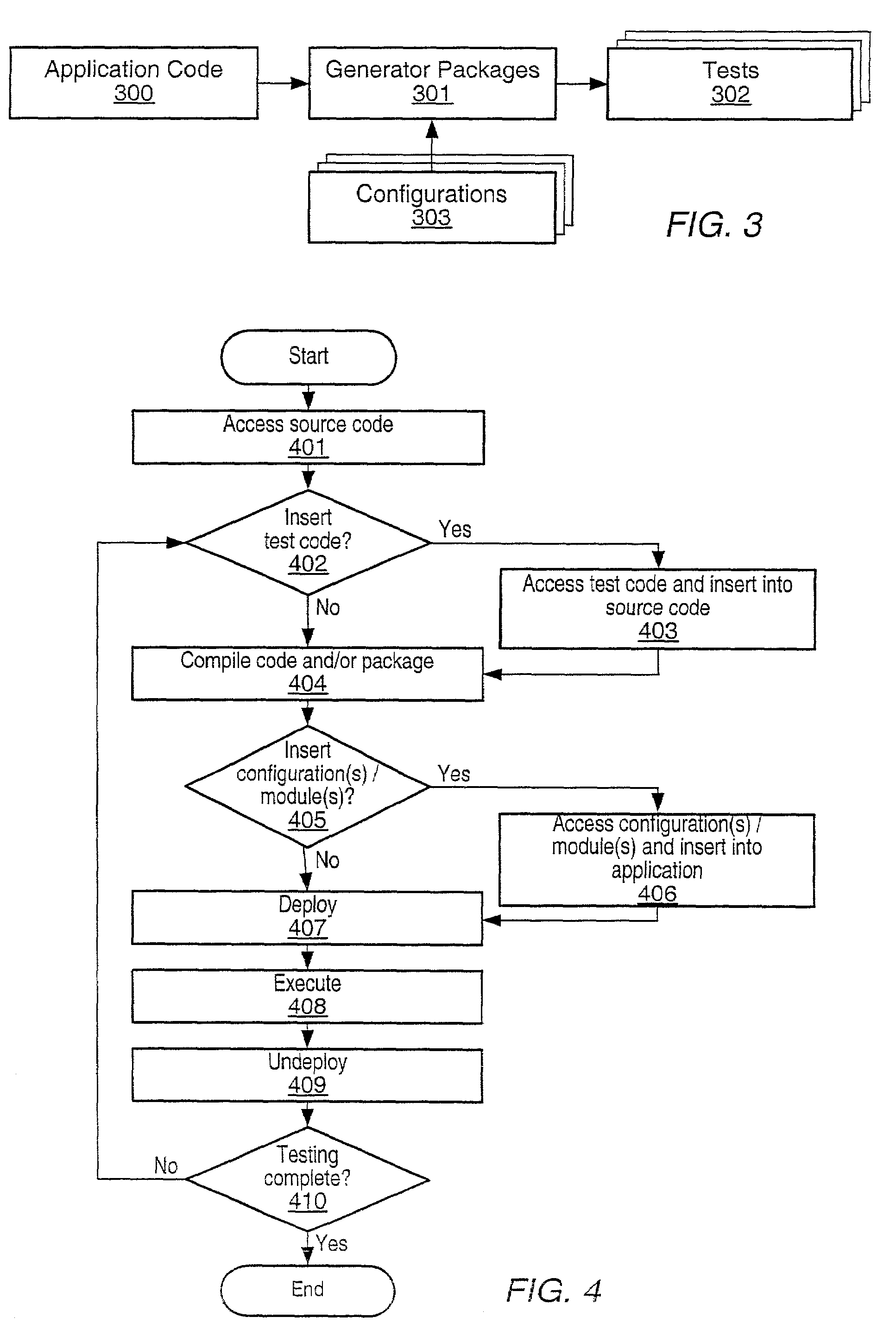

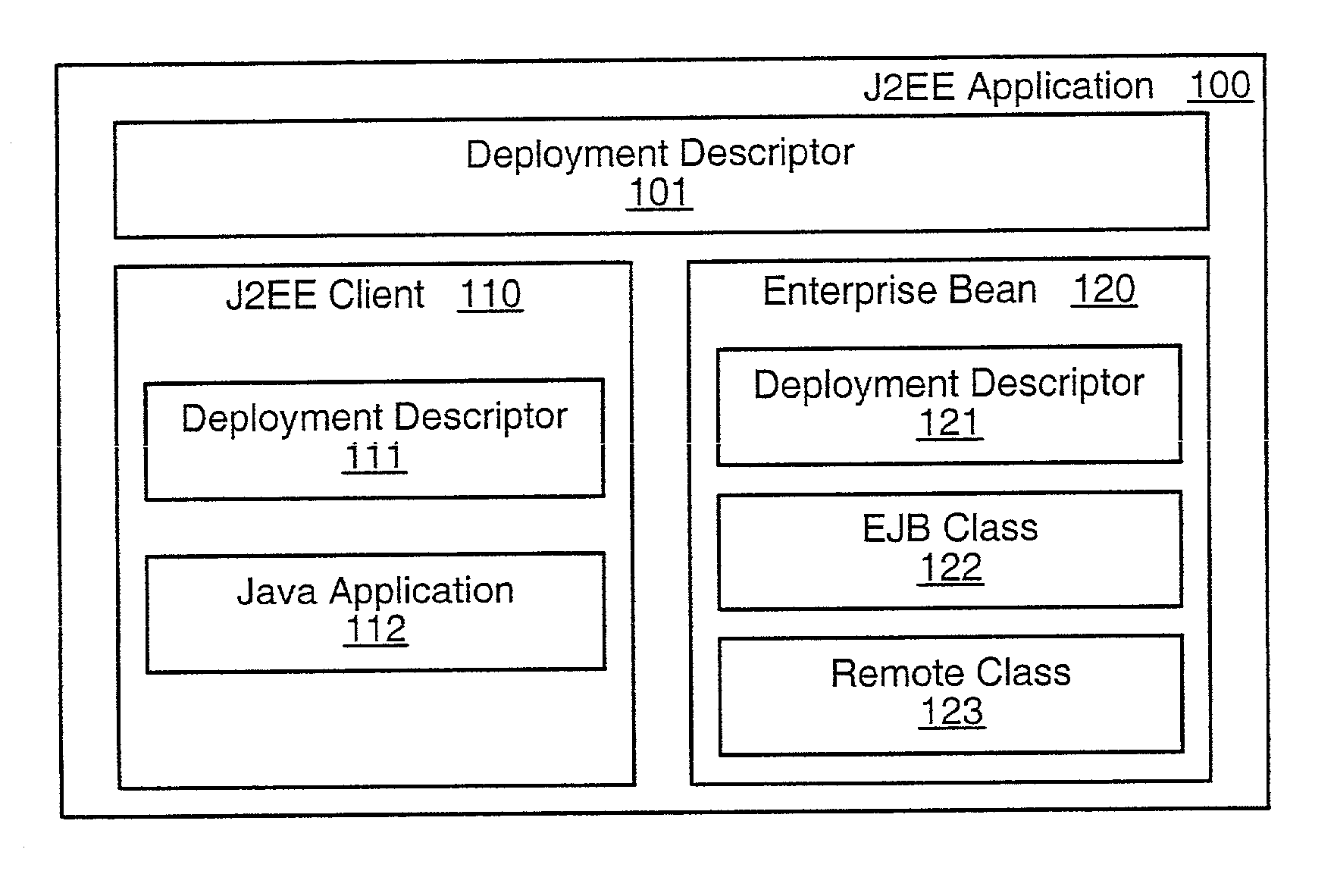

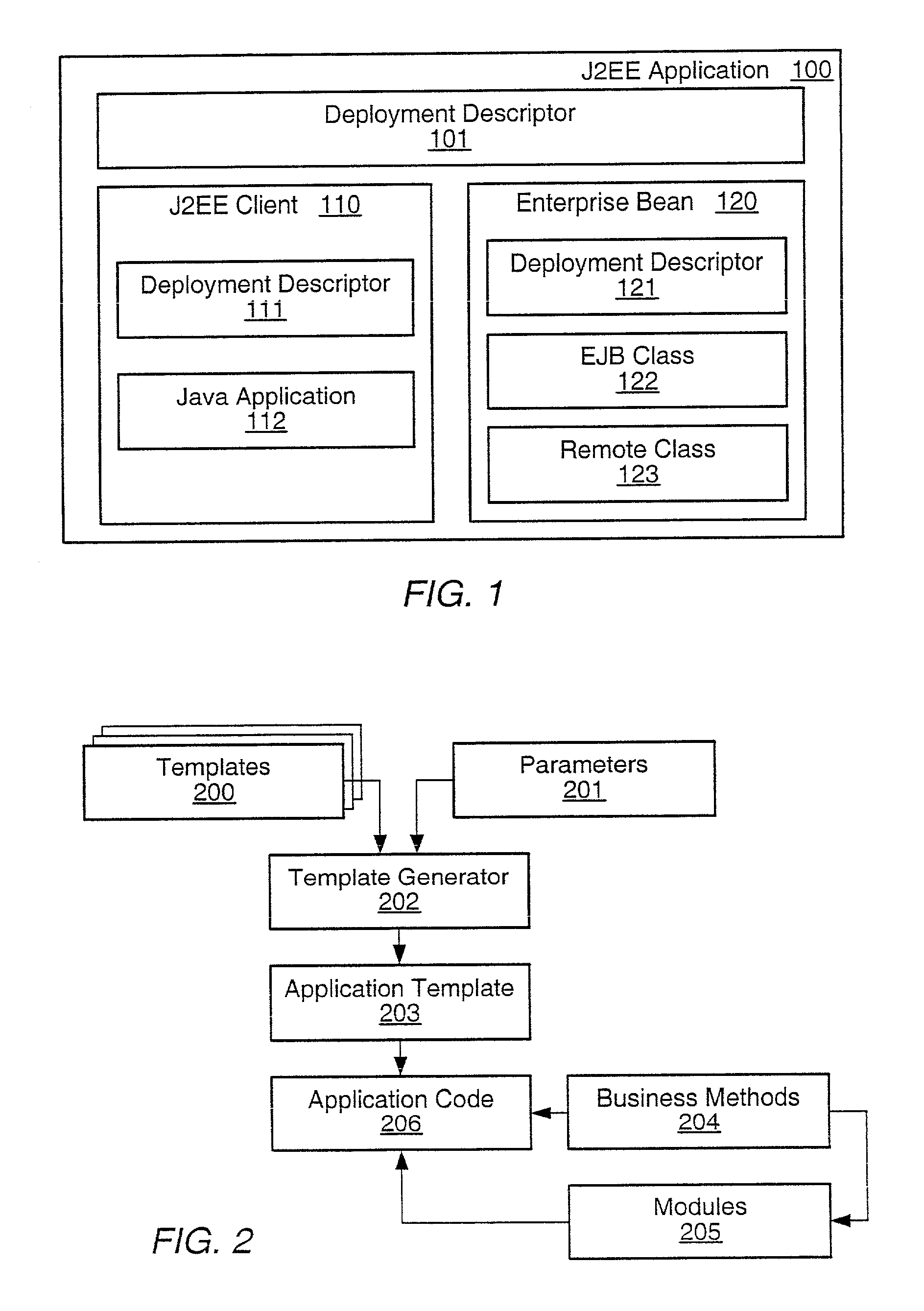

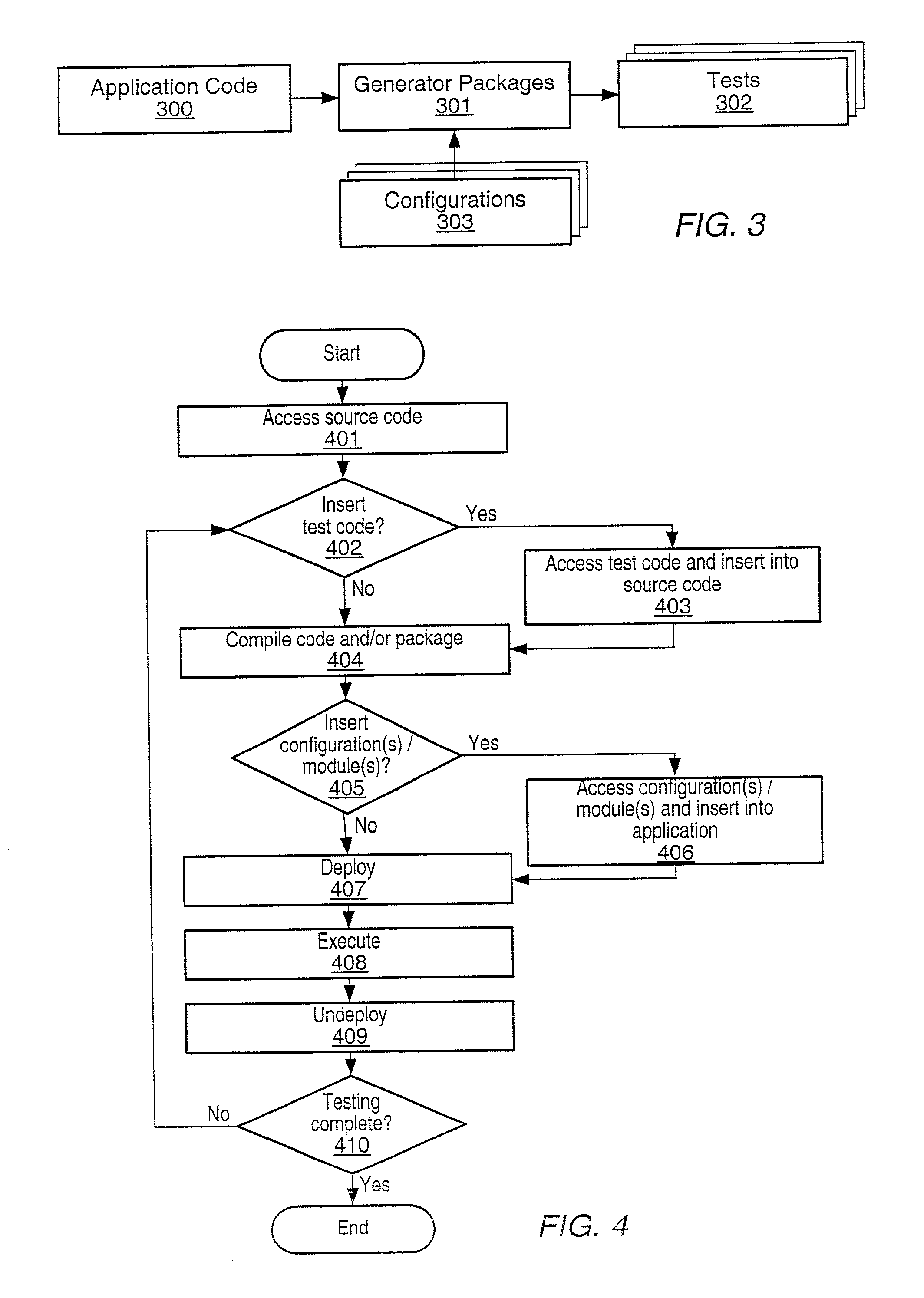

A system and method provide testing of software in different configurations automatically. Templates may be provided for developers to create an application or for generating tests. One or more tests may be generated for testing the application. The testing scope may range between a plurality of configurations for the application in one or more environments. Tests may include test blocks corresponding to parts of the application for testing according to the execution order of the parts of the application. Tests may change input values, modules in the application, configuration settings, data types, communication parameters, and / or other application elements for testing. Such changes may be generated automatically during testing. Test code may be inserted in the application for testing. Application generation and compilation may be automated during testing. Deployment and undeployment of applications may also be automated for testing.

Owner:ORACLE INT CORP

System and method for automatic test case generation

ActiveUS20030204784A1Error preventionSoftware testing/debuggingApplication procedureAutomatic test pattern generation

A system and method provide testing of software in different configurations automatically. Templates may be provided for developers to create an application or for generating tests. One or more tests may be generated for testing the application. The testing scope may range between a plurality of configurations for the application in one or more environments. Tests may include test blocks corresponding to parts of the application for testing according to the execution order of the parts of the application. Tests may change input values, modules in the application, configuration settings, data types, communication parameters, and / or other application elements for testing. Such changes may be generated automatically during testing. Test code may be inserted in the application for testing. Application generation and compilation may be automated during testing. Deployment and undeployment of applications may also be automated for testing.

Owner:ORACLE INT CORP

Defect location identification for microdevice manufacturing and test

InactiveUS20060069958A1Error detection/correctionElectrical testingManufacturing technologyEngineering

A defect identification tool is disclosed that predicts locations at which defects in a microdevice are most likely to occur. The tool may identify both a type of defect and the particular netlists in which that defect is likely to occur. A test circuit generation tool can then subsequently use this defect information to generate a test circuit that tests for the defect in the identified portions of the microcircuit. Similarly, an automatic test pattern generation tool may use the defect location information to generate test data custom-tailored to check for faults corresponding to the identified defect in the specified portions of the microcircuit. Various implementations of the tool may be used both to identify the locations at which defects caused by systematic errors, such as manufacturing process deficiencies or flaws, are most likely to occur and the locations at which randomly-created defects are most likely to occur.

Owner:MENTOR GRAPHICS CORP

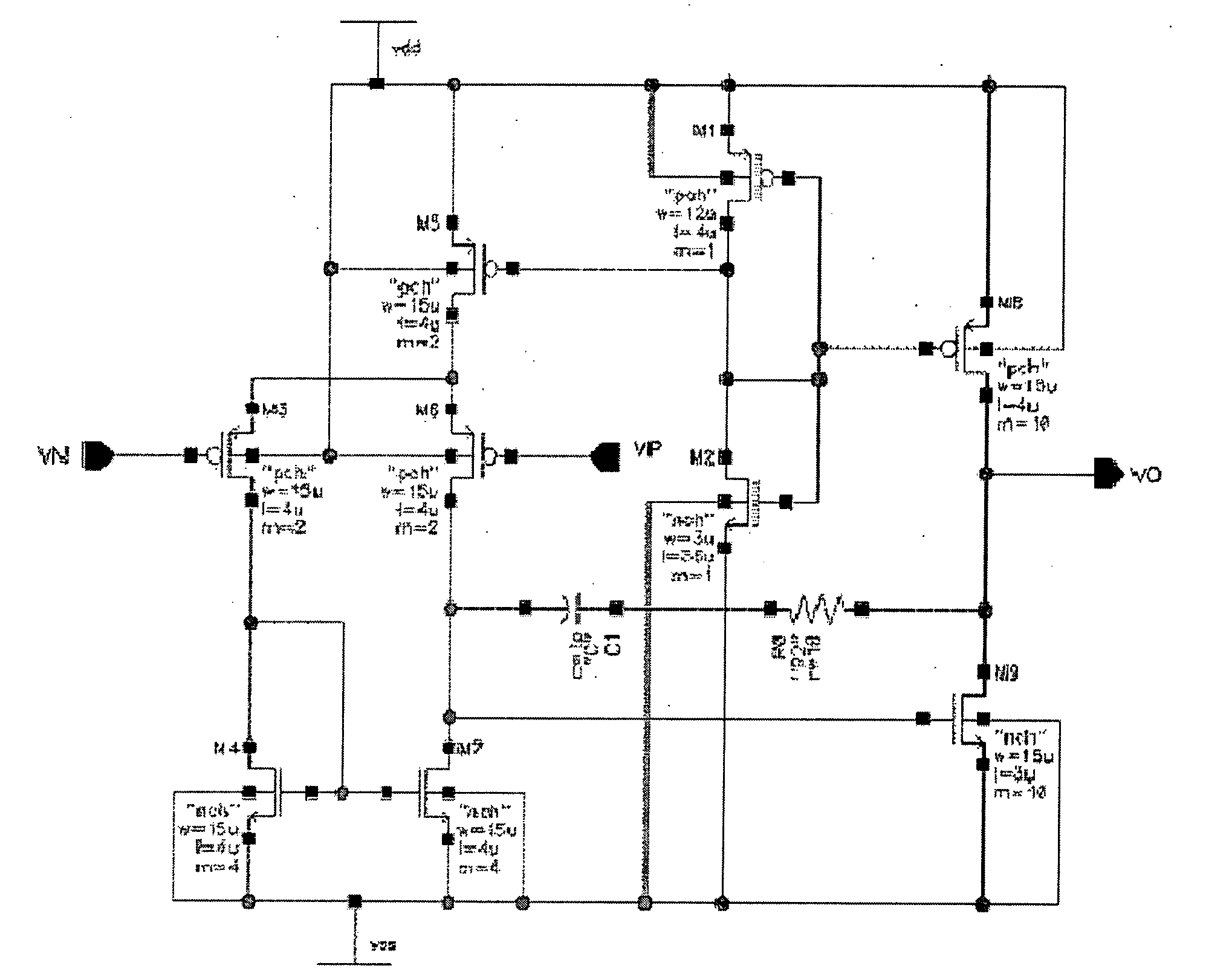

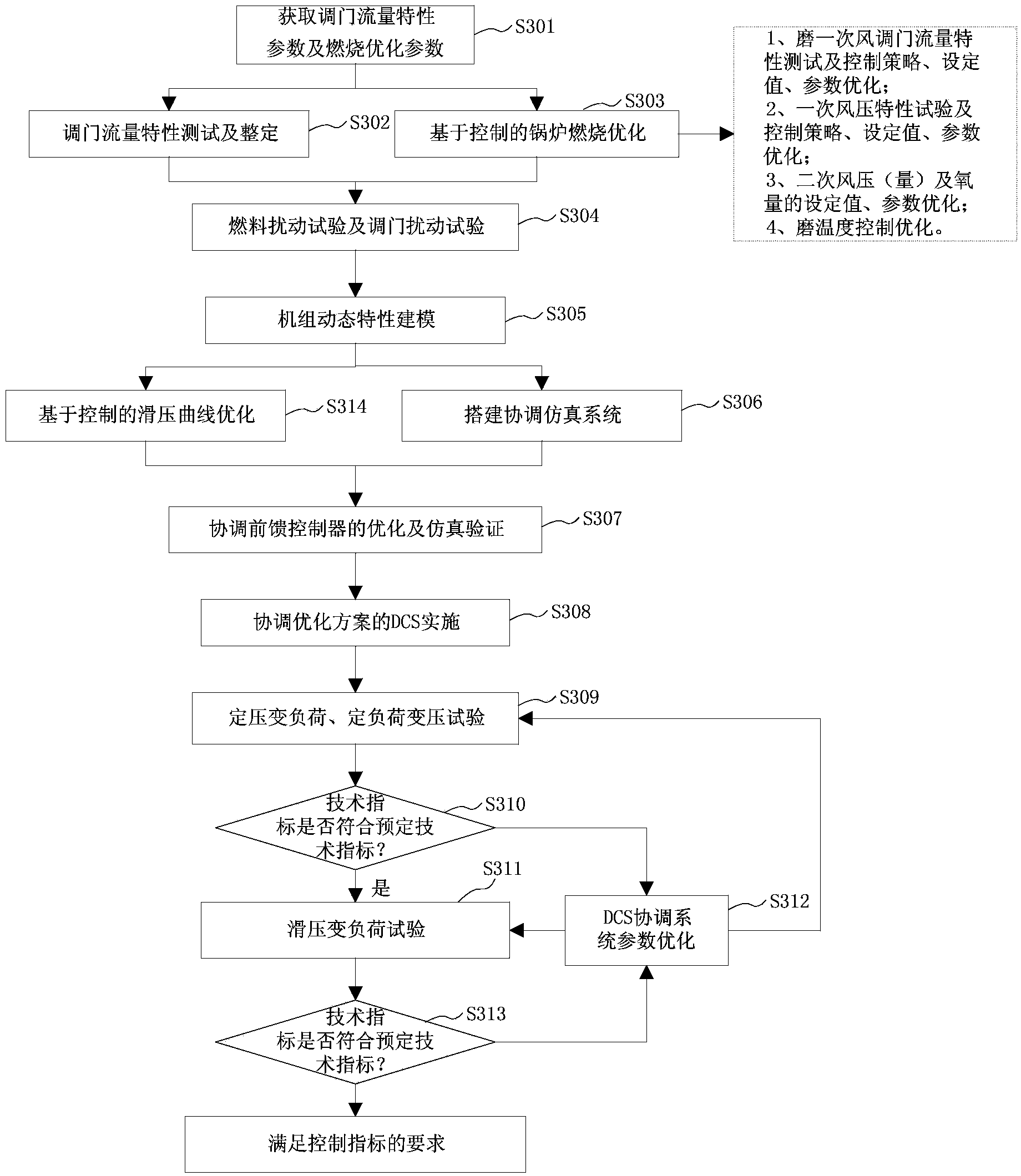

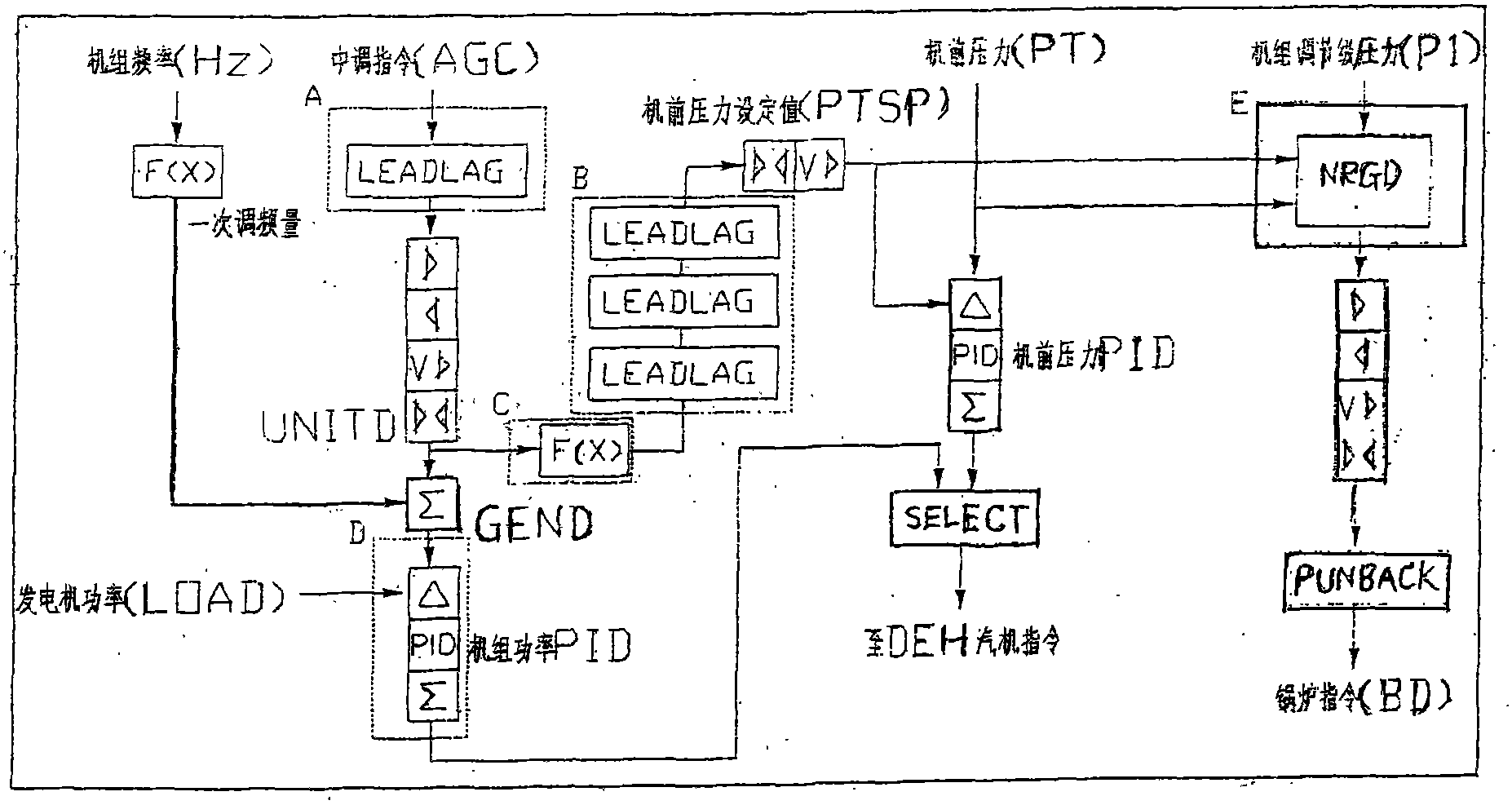

Integral optimization method and system for automatic power generation system of coal-fired unit

ActiveCN103513640AImprove variable load capacityImprove adaptabilityProgramme total factory controlSteam pressureDynamic models

The invention provides an integral optimization method and system for an automatic power generation system of a coal-fired unit. The method comprises the steps of carrying out control valve flow characteristic test and adjustment according to control valve flow characteristic parameters, carrying out combustion optimization on a wind and smoke subsystem and a combustion subsystem, carrying out a fuel disturbance test and a control valve disturbance test to generate typical test parameters, using the typical test parameters to generate a dynamic unit model, constructing a coordinating simulation system according to a coordinating controller and the dynamic unit model, using the dynamic unit model to optimize a feedforward controller and carry out simulation verification on the coordinating simulation system simultaneously, carrying out DCS configuration and parameter debugging in the simulation system, carrying out a constant-voltage slide-voltage variable-load test and a constant-load voltage-transformation test to generate technical indexes of the variable-load rate, the variable-load accuracy, variable-load response time and the main steam pressure accuracy, judging whether the technical indexes meet the preset technical indexes, and if on yes judgment, carrying out a slide-voltage variable-load test to enable the coal-fired unit to operate normally.

Owner:STATE GRID CORP OF CHINA +1

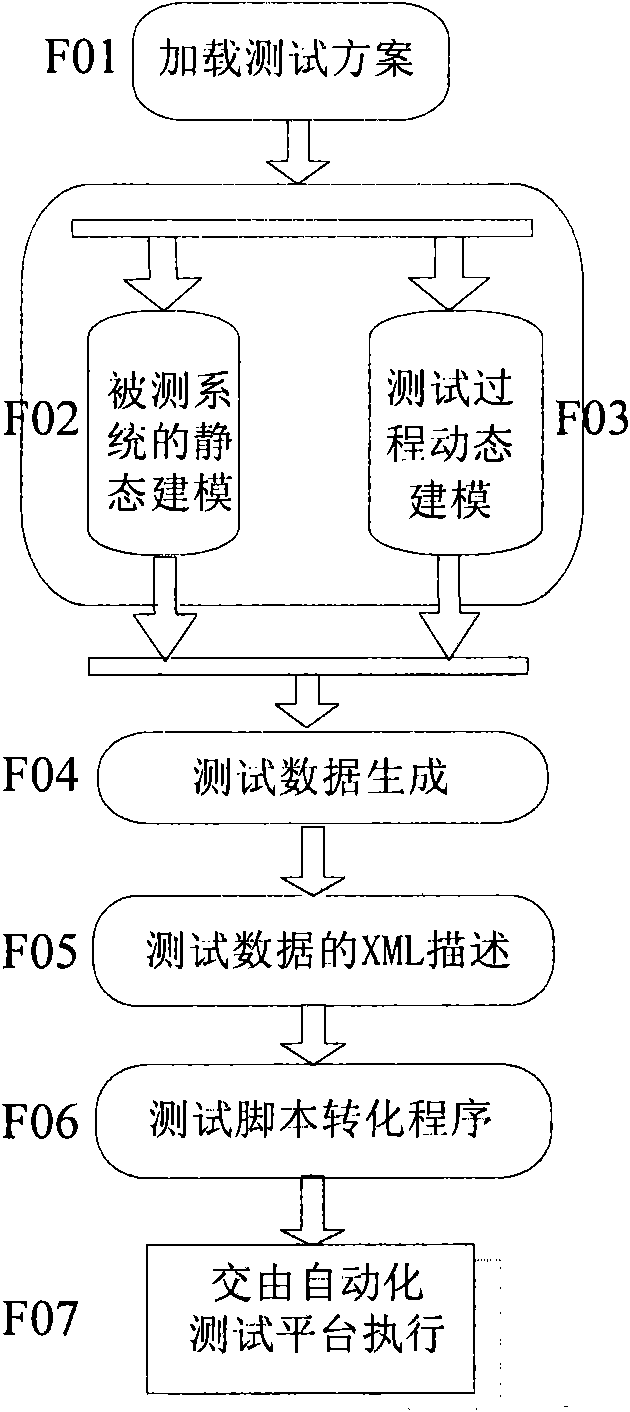

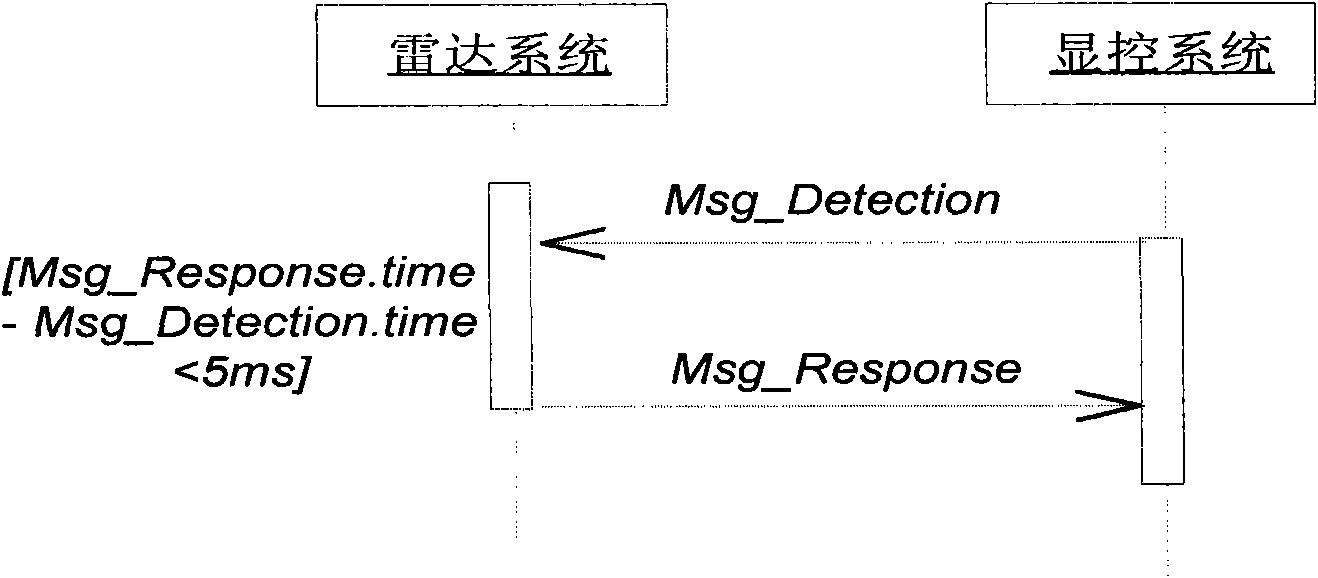

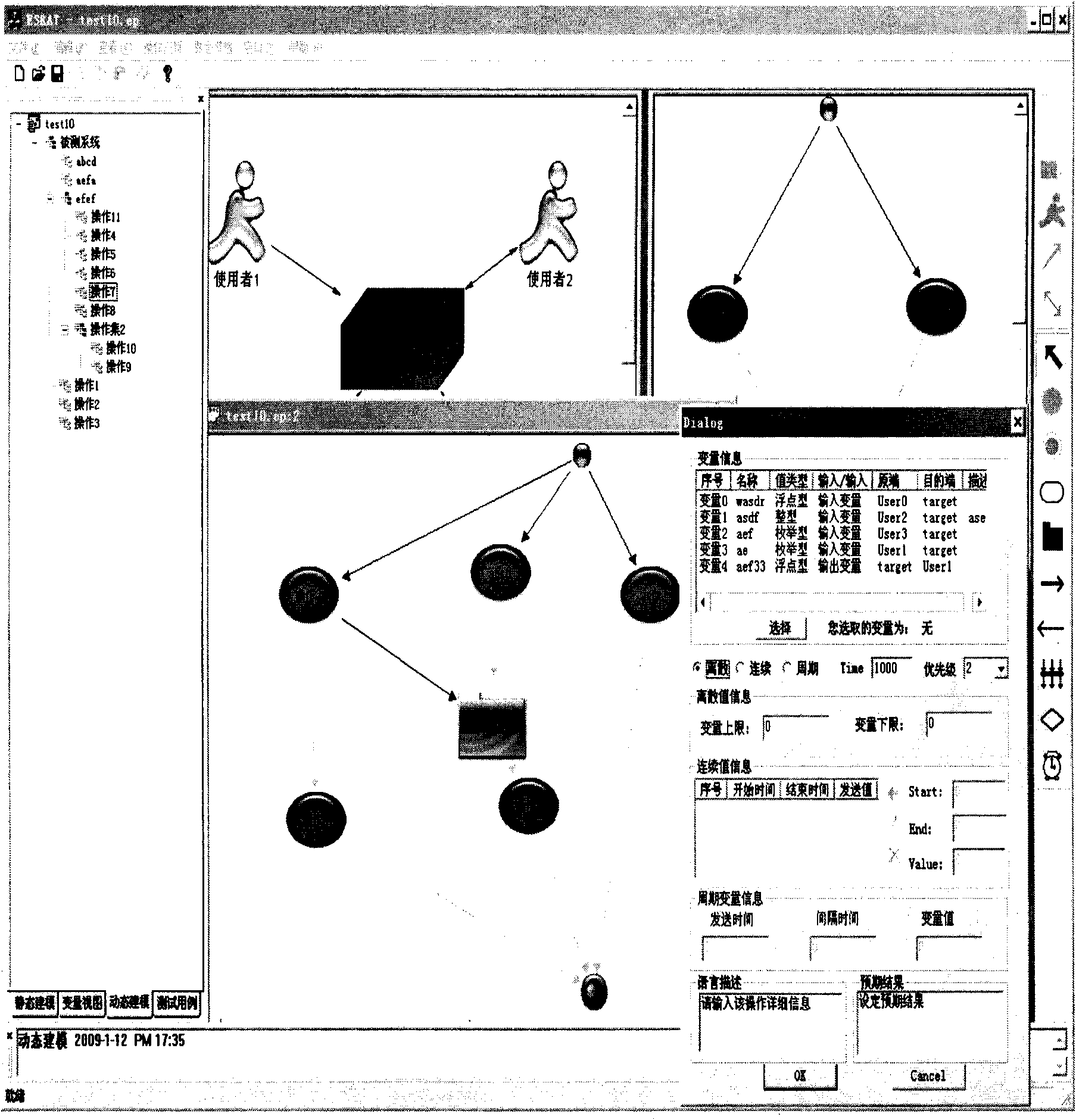

Visualization automatic generation method of embedded software test data and system thereof

InactiveCN101571802AIncrease the level of automationTime consumingSoftware testing/debuggingSpecific program execution arrangementsSpecific testTest script

The invention relates to a visualization automatic generation method of embedded software test data and a system thereof. The method comprises the following steps: adopting a de facto industrial standard--universality and flexibility of a unified modeling language (UML), performing real-time expansion on the UML, and introducing a scene technology to realize automatic generation of the embedded software test data in a visualization manner. The developed automatic test data generation system can automatically transform the test data into a test script required for a specific test platform, and running of the test script can drive the test for running to realize automatic testing for the embedded software.

Owner:BEIHANG UNIV

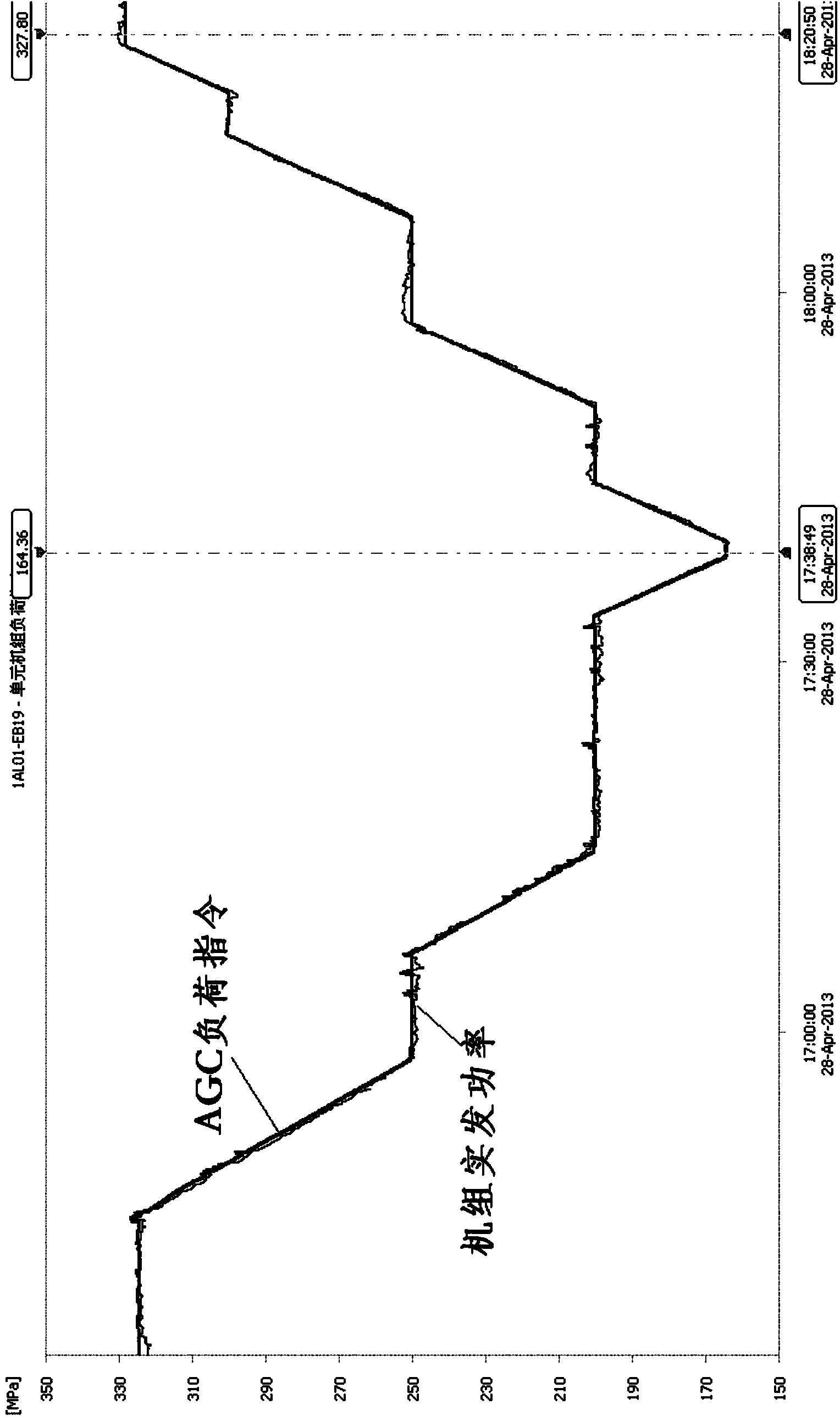

Control method for coordination and automatic power generation of coal quality self-adaptive thermal power generating unit

InactiveCN101788155AEnsure coordinationGuaranteed AGC control indicatorsFuel supply regulationSteam pressureAir volume

The invention provides a control method for coordination and automatic power generation of a coal quality self-adaptive thermal power generating unit. The method comprises the following steps of: 1, compressively determining the coal quality according to parameters including first-level pressure of a steam engine, drum pressure, coal feed, unit load and the like; 2, by the determined coal quality, performing the coal quality self-adaptive control over main control systems of fuel, coordination, air delivery and the like; 3, by core control strategies of boiler load commands, main steam pressure settings, a coal quality self-checking positive load upper limit and the like, realizing the control over the coal quality self-adaptive coordination and automatic power generation of the thermal power generating unit; and 4, realizing the automatic safe operation of the thermal power generating unit by improving safety locking conditions of the thermal power generating unit. The method has the following obviously advantages that: under a fluctuating condition of the coal quality of the thermal power generating unit, the automatic power generation and the coordination control of the thermal power generating unit are unnecessarily intervened by people, and the scheduling requirements are still met; and compared with the conventional control method, the control method of the invention has the advantages that: the accuracies of the main controlled parameters of the thermal power generating unit are further improved; and simultaneously, the automatic power generation control indexes and the safety and the economy of the thermal power generating unit are enhanced.

Owner:云南电力试验研究院(集团)有限公司

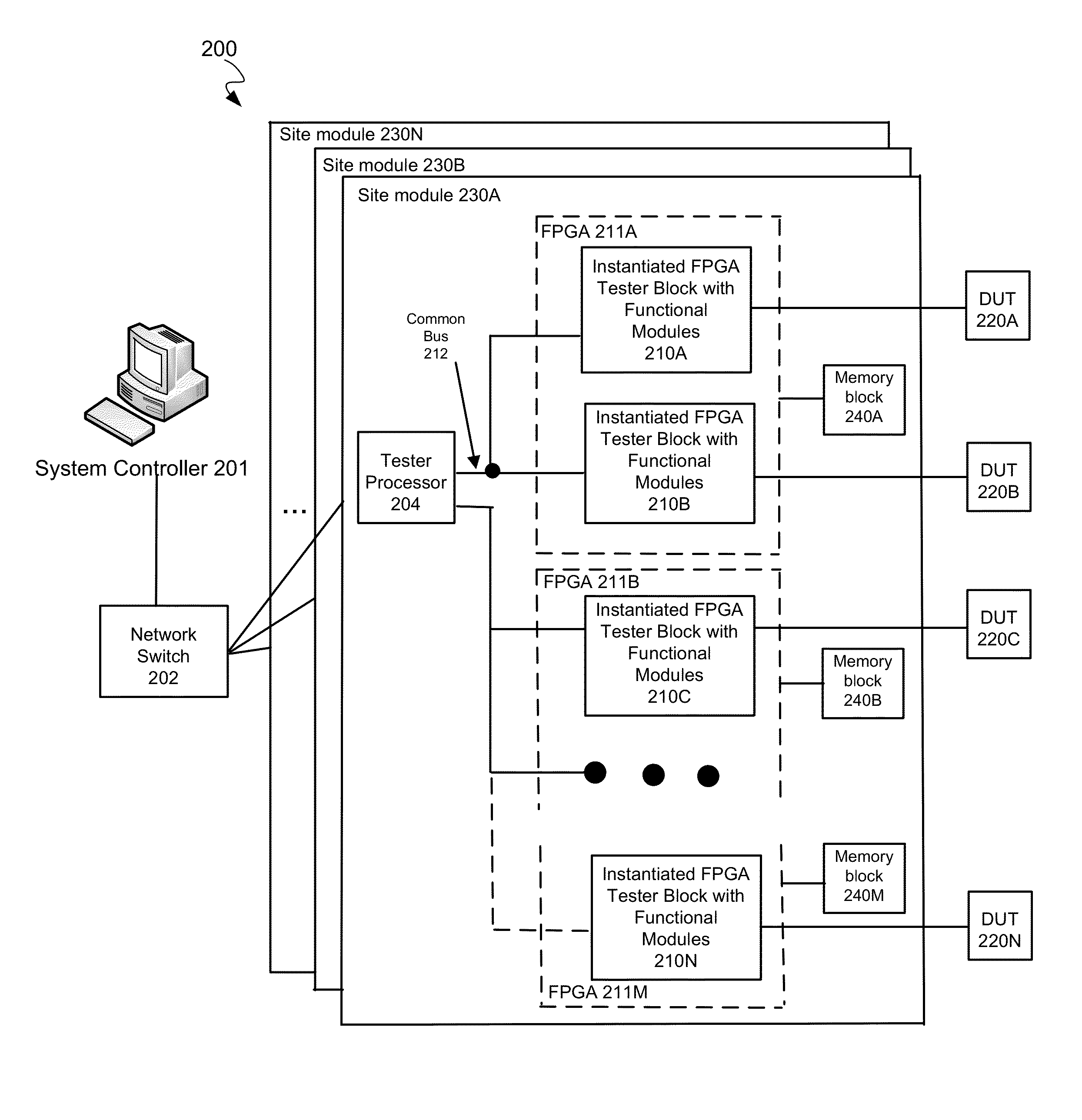

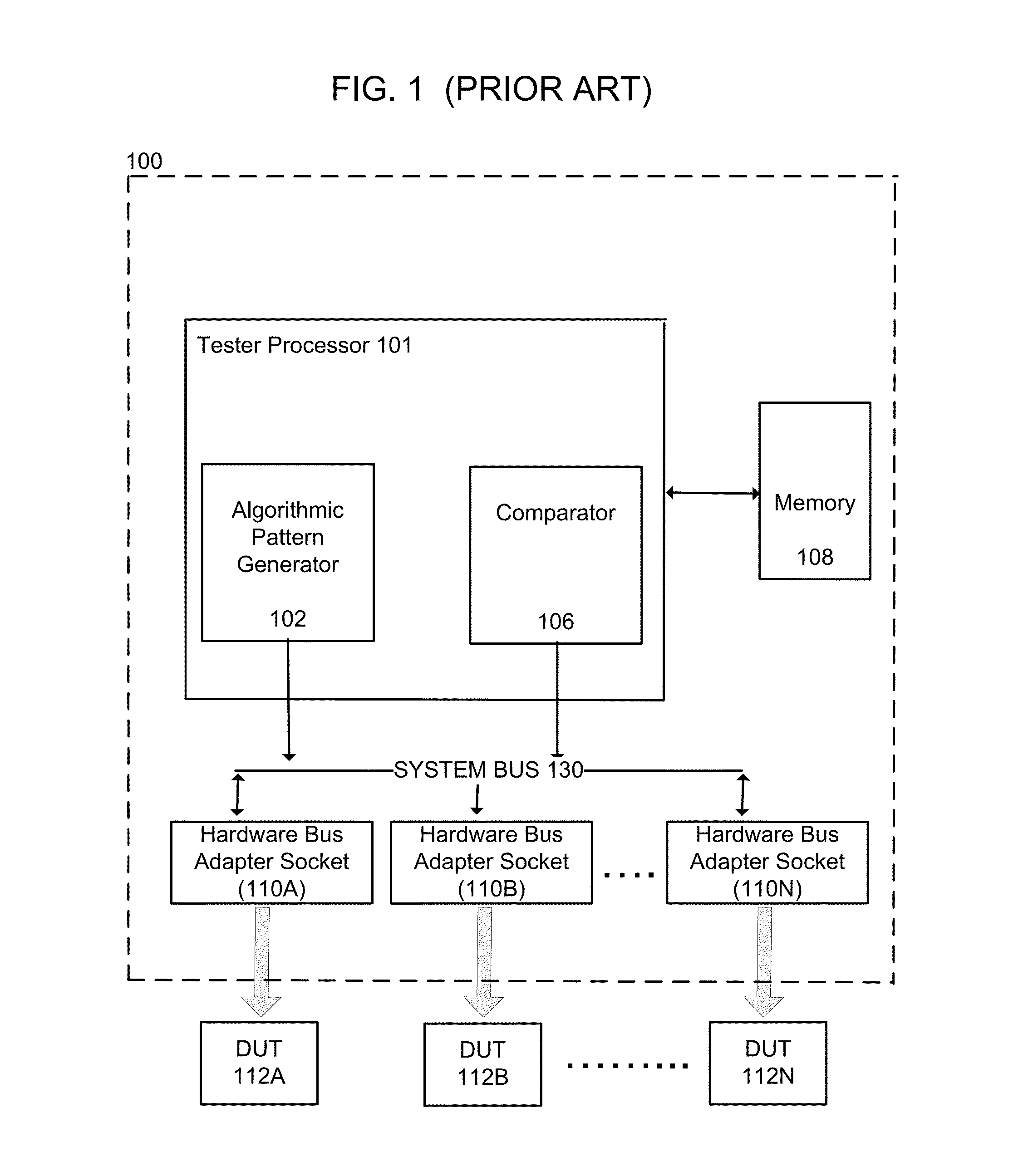

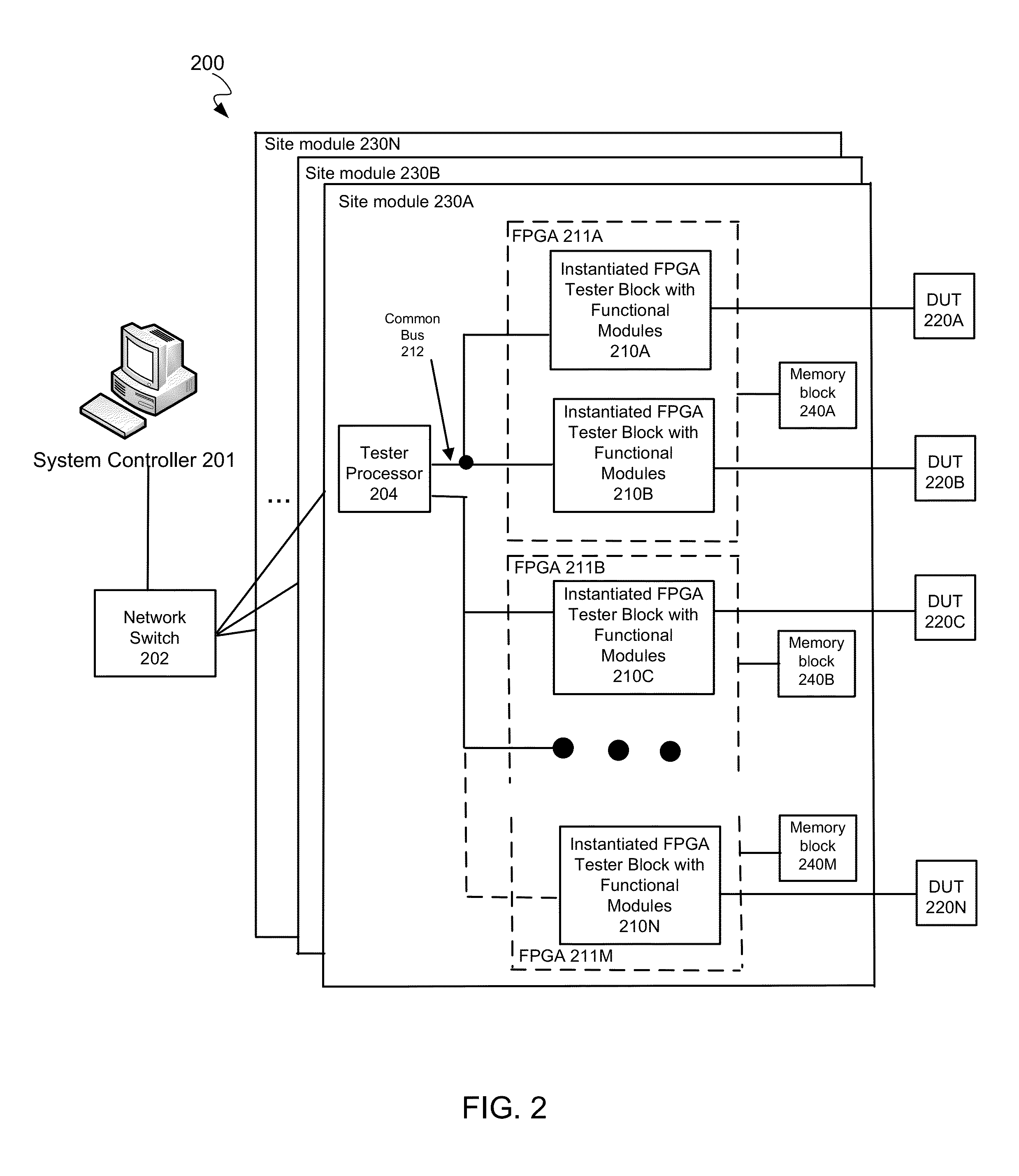

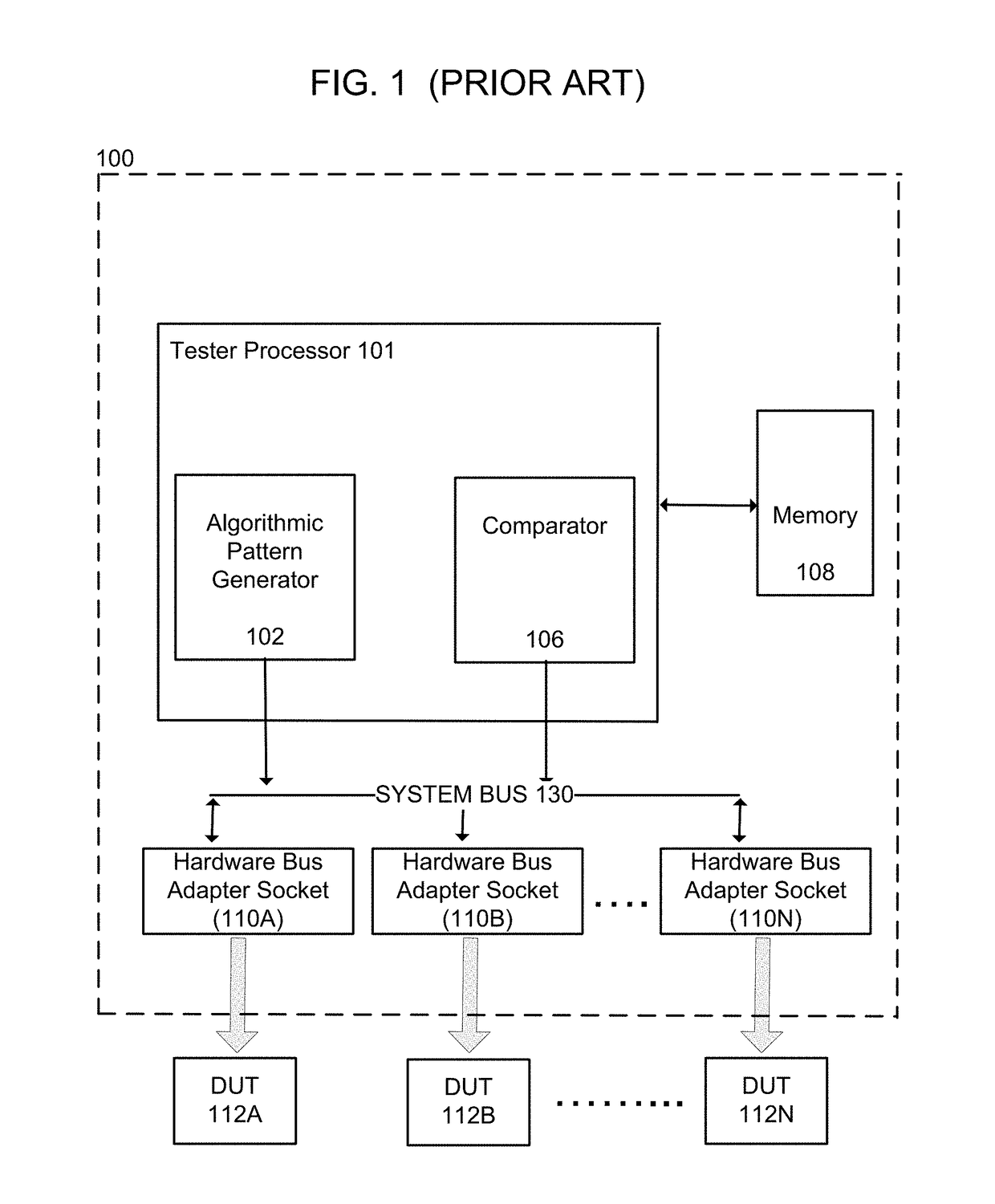

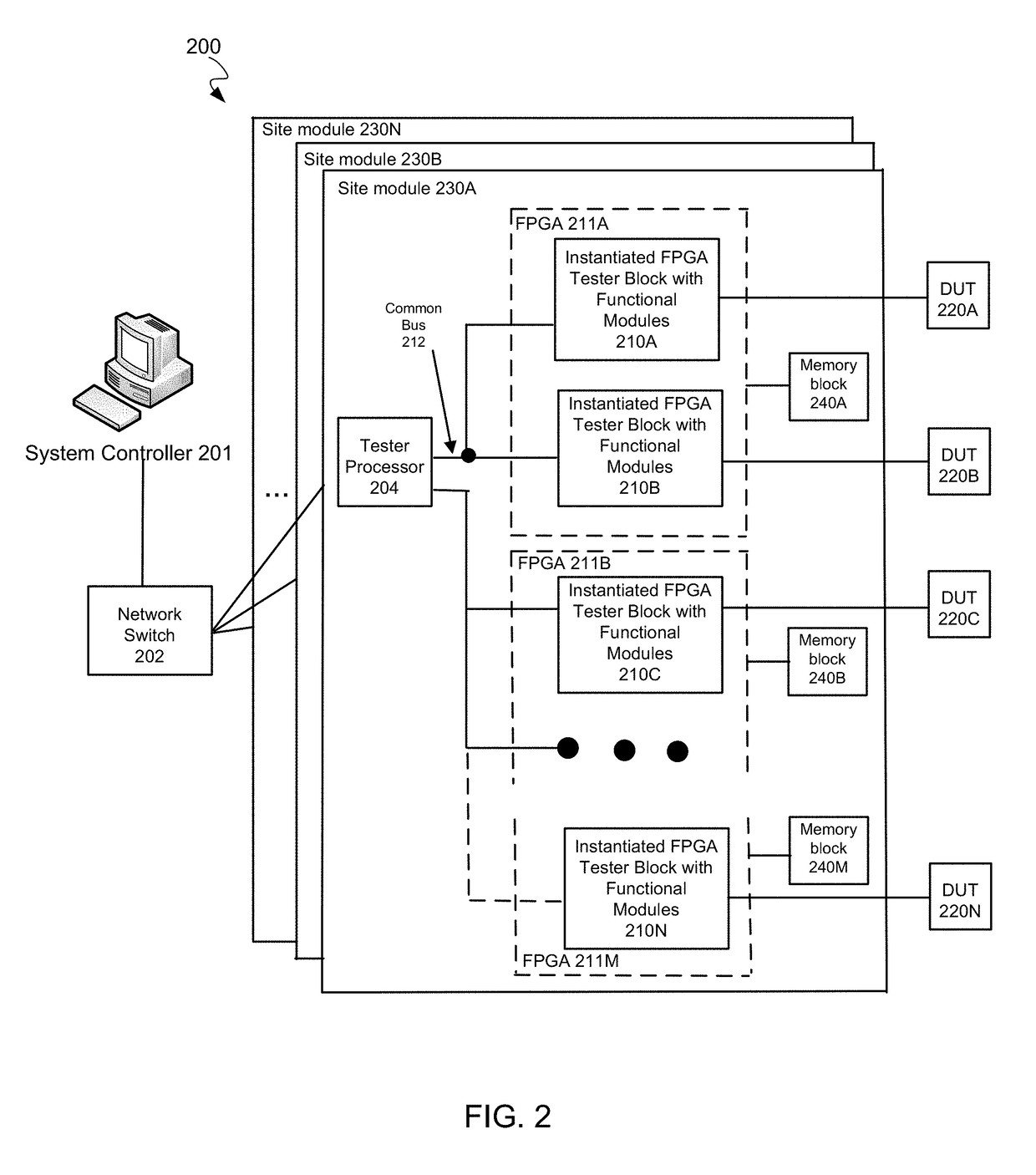

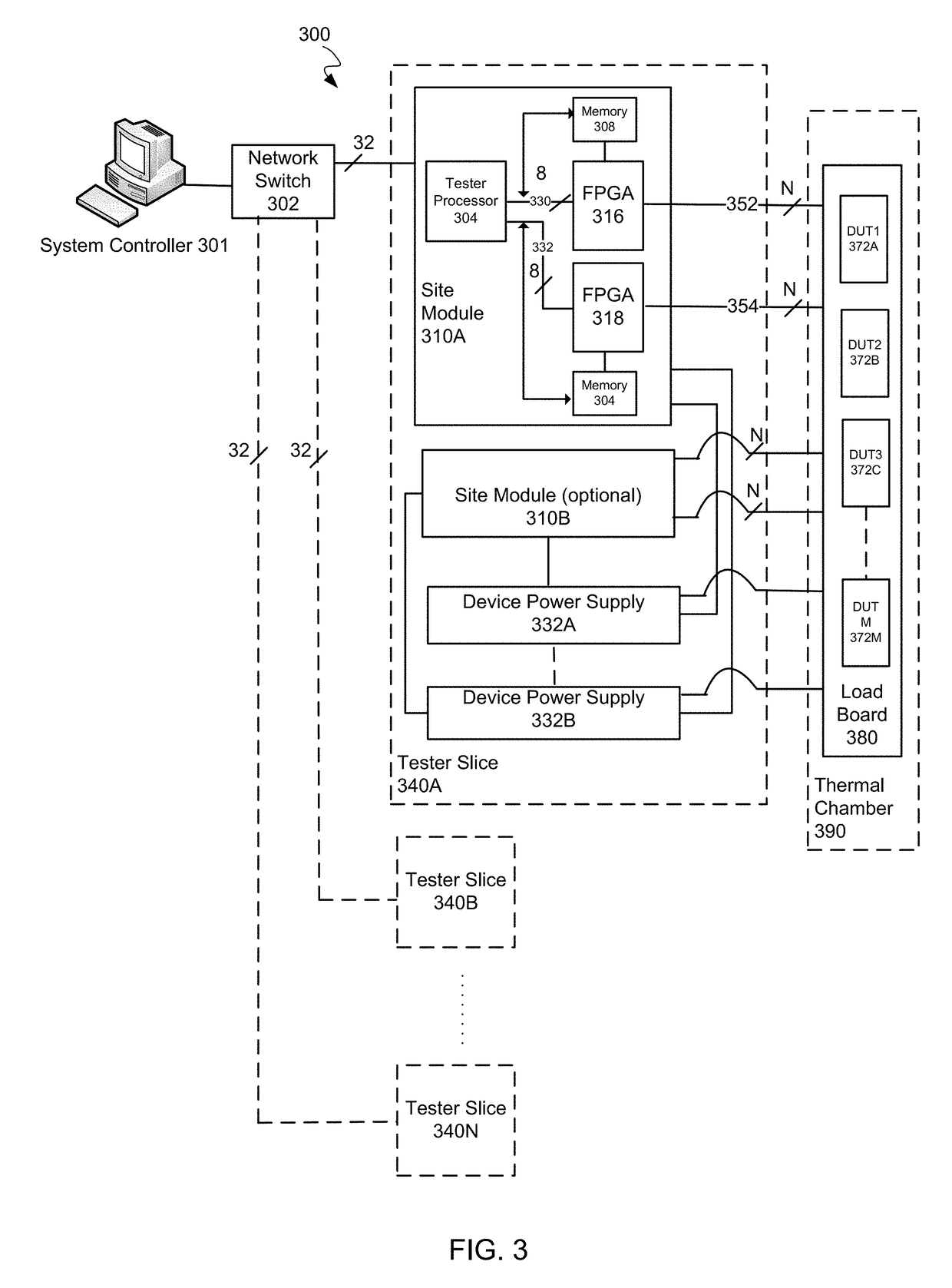

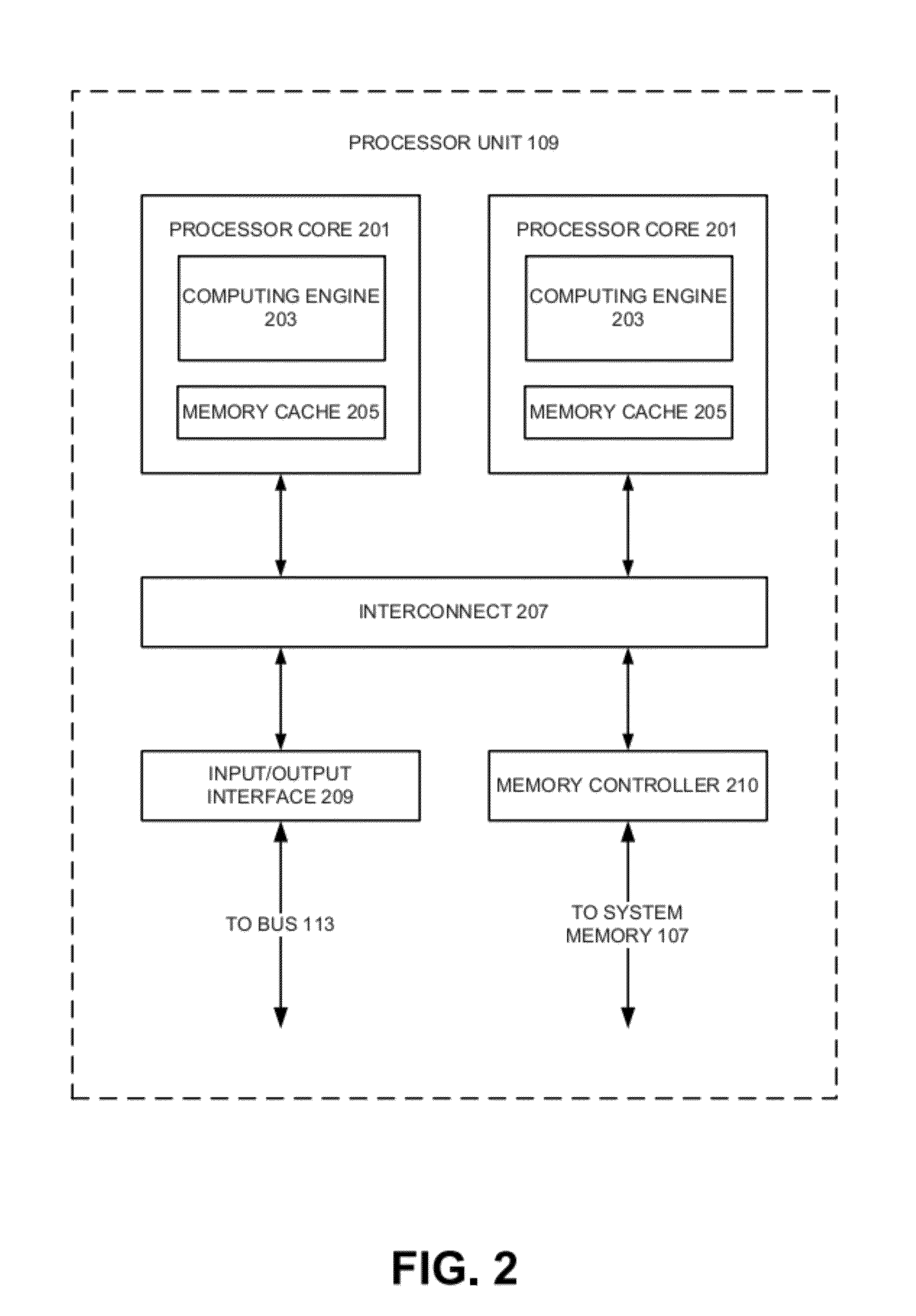

Tester with acceleration on memory and acceleration for automatic pattern generation within a FPGA block

ActiveUS20140236524A1Bandwidth requirement can be keptMinimal processing loadTesting/calibration of speed/acceleration/shock measurement devicesSpecial data processing applicationsAutomatic test pattern generationHardware acceleration

Automated test equipment capable of performing a high-speed test of semiconductor devices is presented. The automated test equipment apparatus comprises a computer system comprising a tester processor, wherein the tester processor is communicatively coupled to a plurality of FPGA components. Each of the plurality of FPGA components is coupled to a memory module and comprises: an upstream port operable to receive commands and data from the tester processor; a downstream port operable to communicate with a respective DUT from a plurality of DUTs; and a plurality of hardware accelerator circuits, wherein each of the accelerator circuits is configured to communicate with one of the plurality of DUTs. Each of the plurality of hardware accelerator circuits comprises a pattern generator circuit configurable to automatically generate test pattern data to be written to the one of the plurality of DUTs and a comparator circuit configured to compare data read from the one of the plurality of DUTs with test pattern data written to the one of the plurality of DUTs

Owner:ADVANTEST CORP

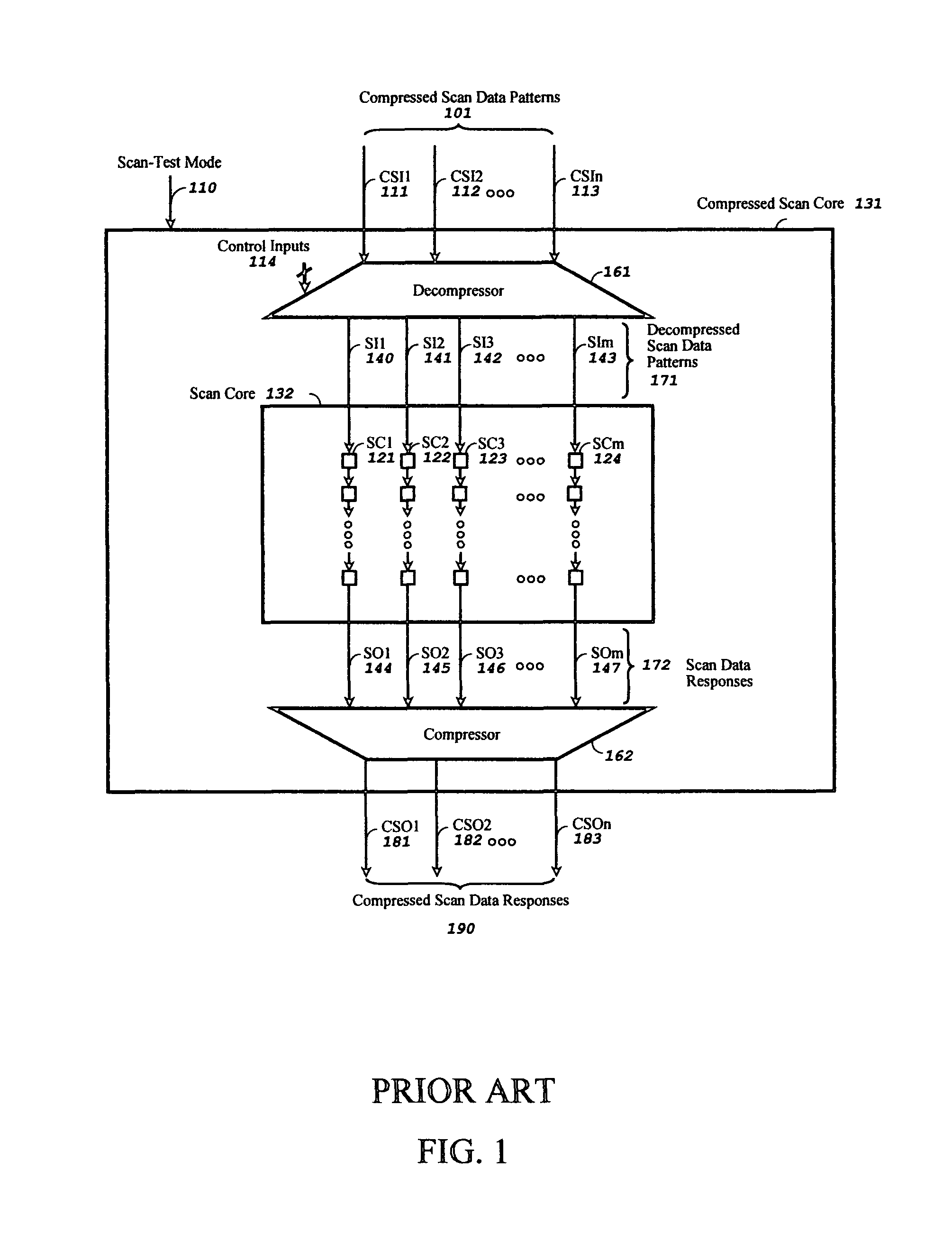

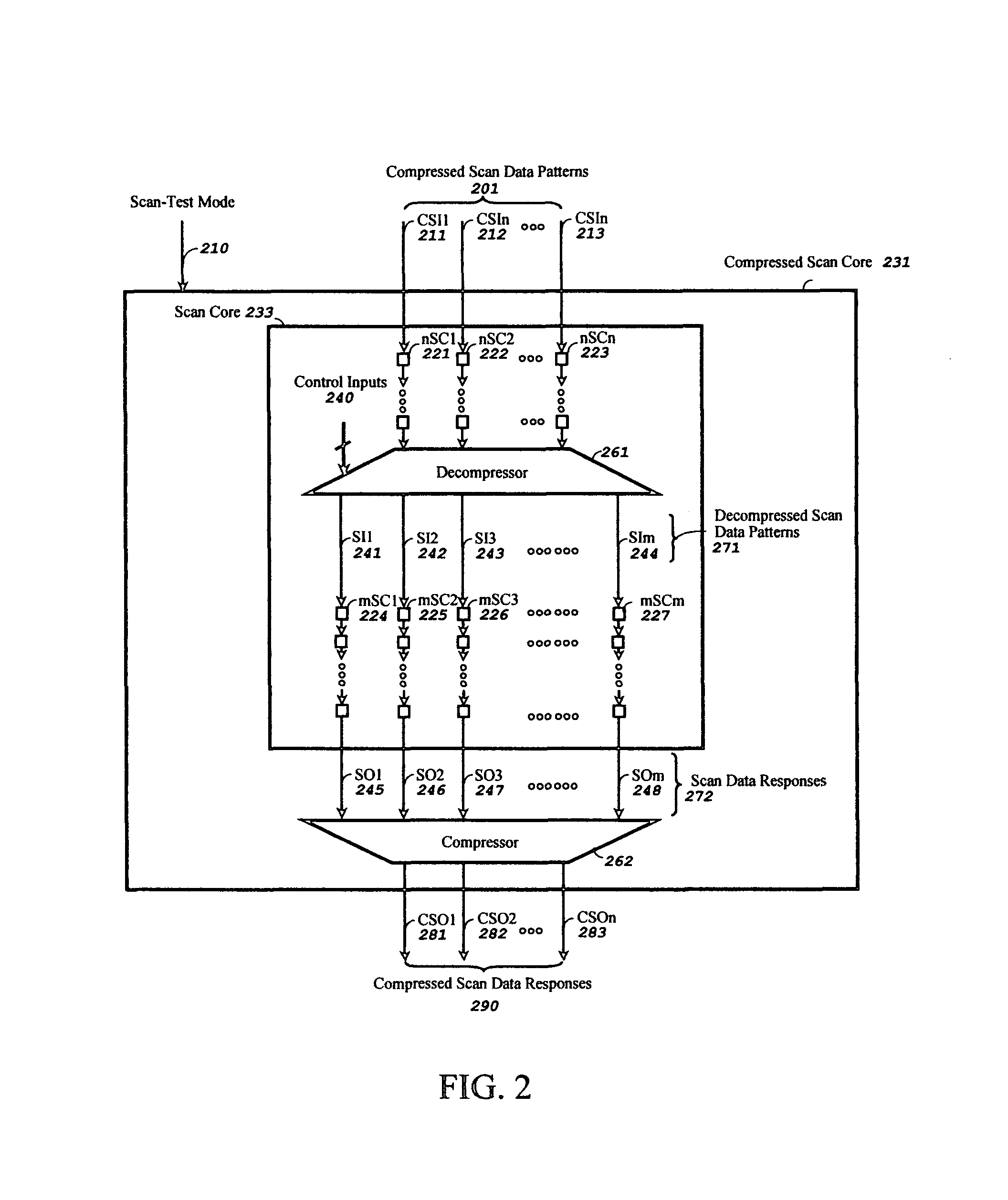

Smart capture for ATPG (automatic test pattern generation) and fault simulation of scan-based integrated circuits

InactiveUS7124342B2Improve performanceHigh simulationError detection/correctionMarginal circuit testingHemt circuitsAutomatic test pattern generation

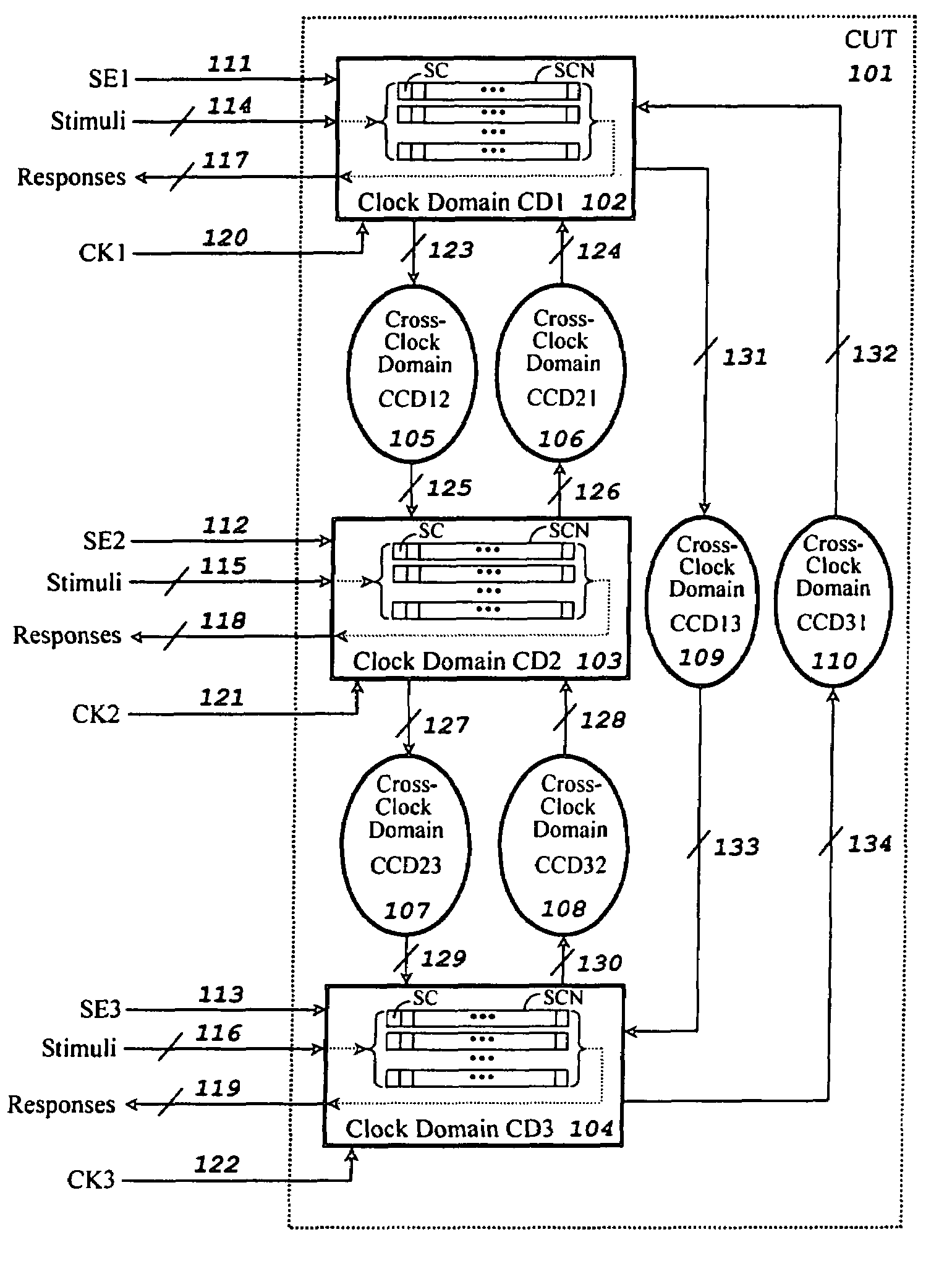

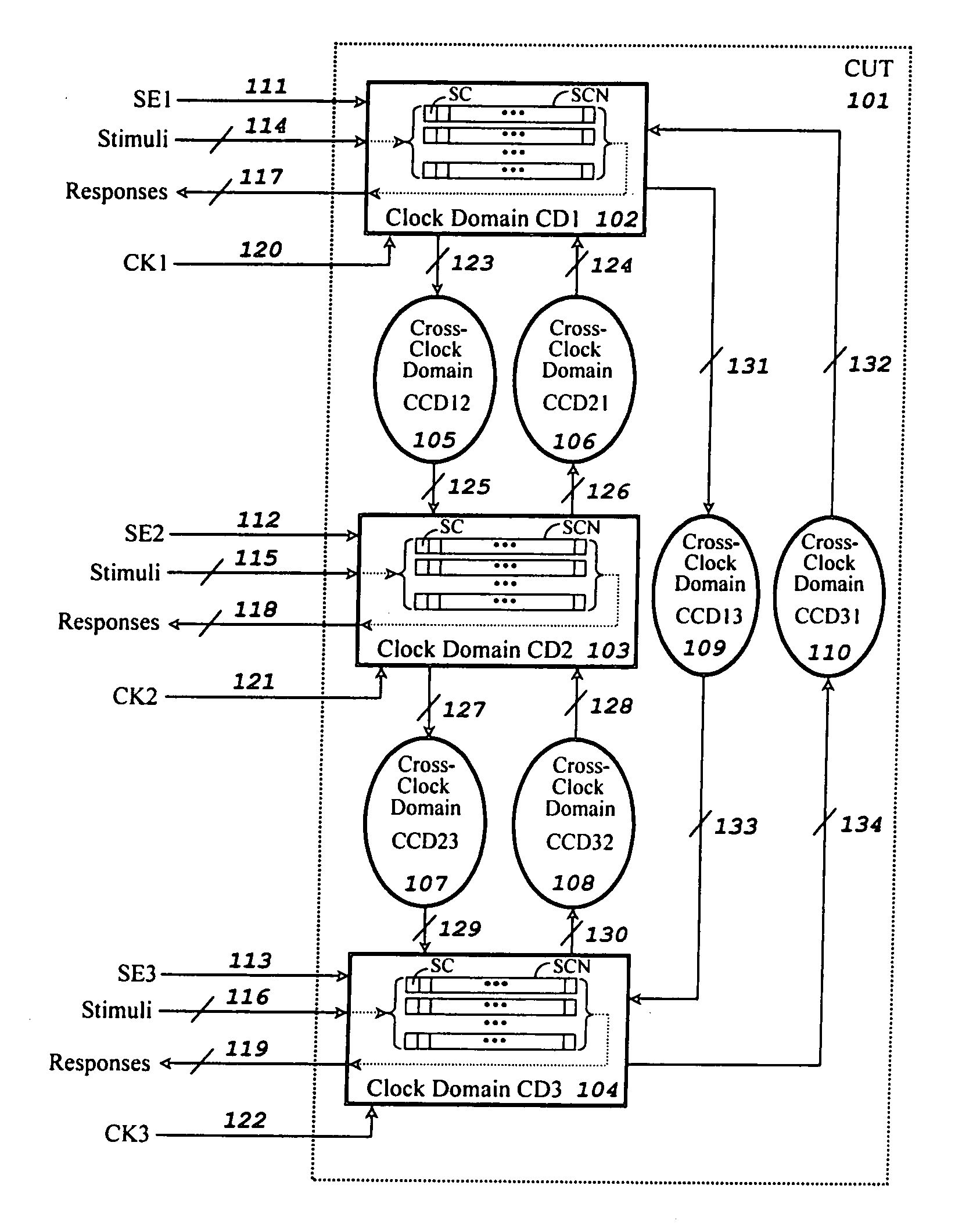

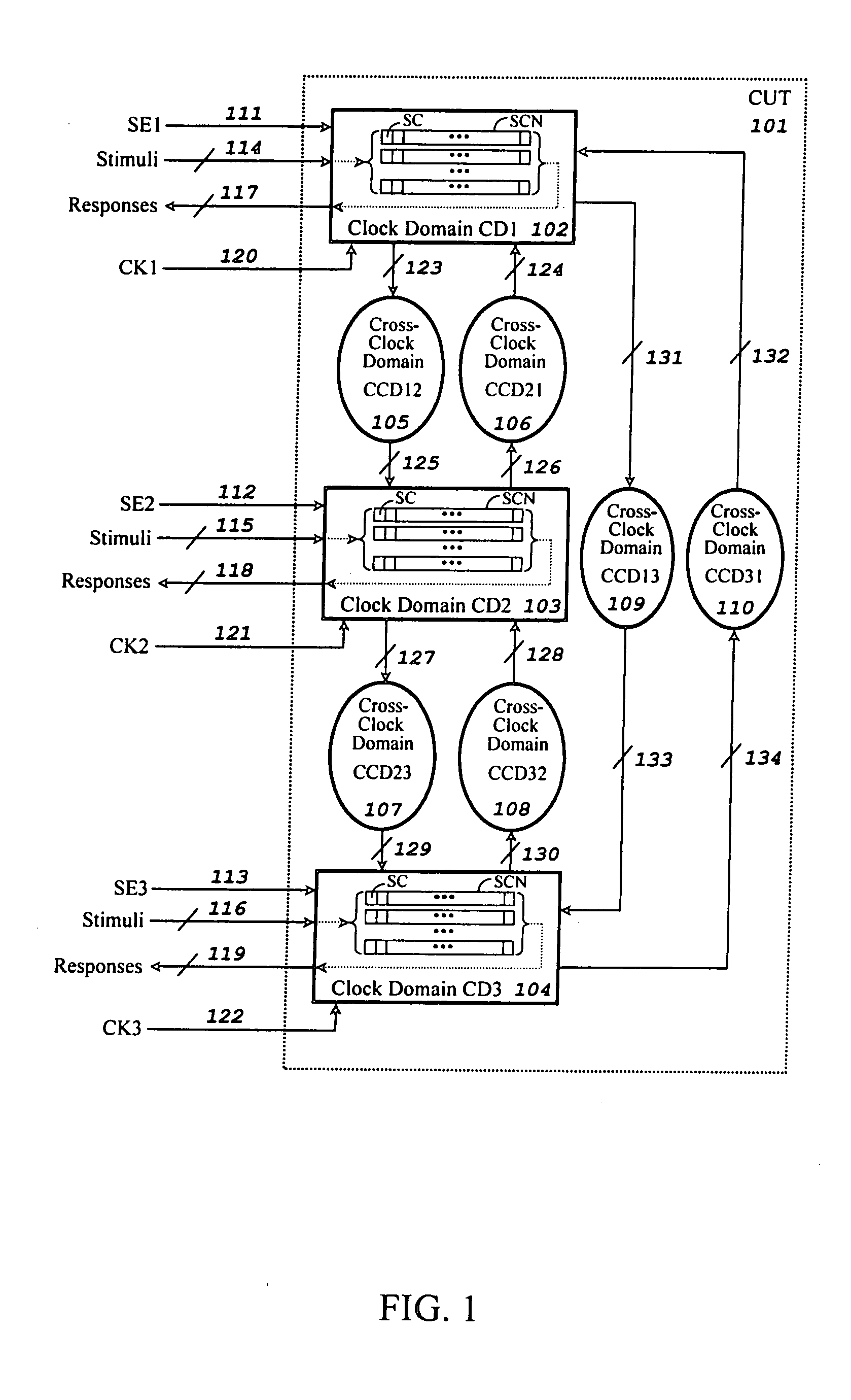

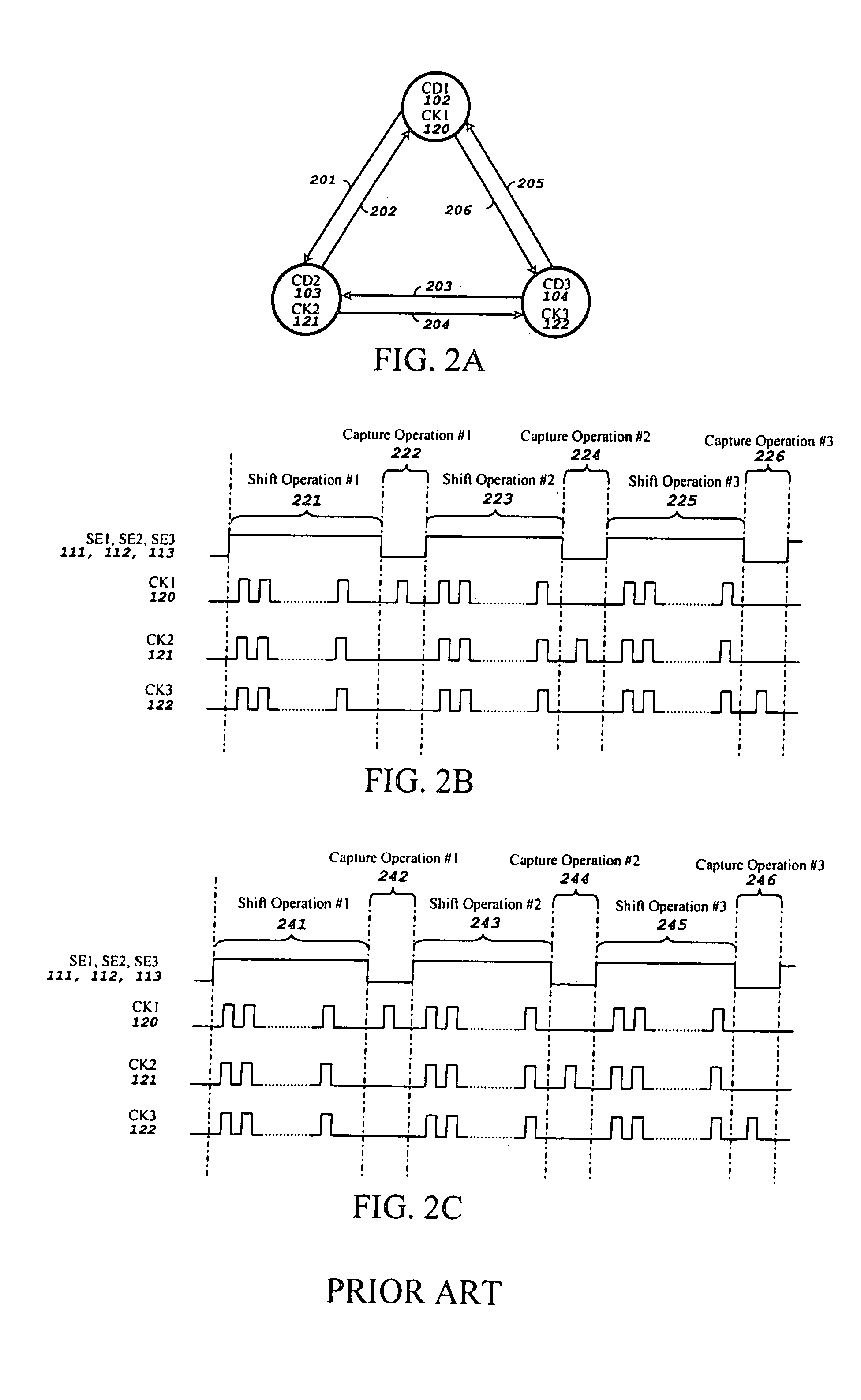

A method for generating stimuli and test responses for testing faults in a scan-based integrated circuit in a selected scan-test mode or a selected self-test mode, the scan-based integrated circuit containing a plurality of scan chains, N clock domains, and C cross-clock domain blocks, each scan chain comprising multiple scan cells coupled in series, each clock domain having one capture clock, each cross-clock domain block comprising a combinational logic network. The method comprises compiling the scan-based integrated circuit into a sequential circuit model; specifying input constraints on the scan-based integrated circuit during a shift and capture operation; specifying a clock grouping to map the N clock domains into G clock domain groups, where N>G>1; transforming the sequential circuit model into an equivalent combinational circuit model according to the input constraints and the clock grouping; and generating the stimuli and test responses on the equivalent combinational circuit model according to the input constraints.

Owner:SYNTEST TECH

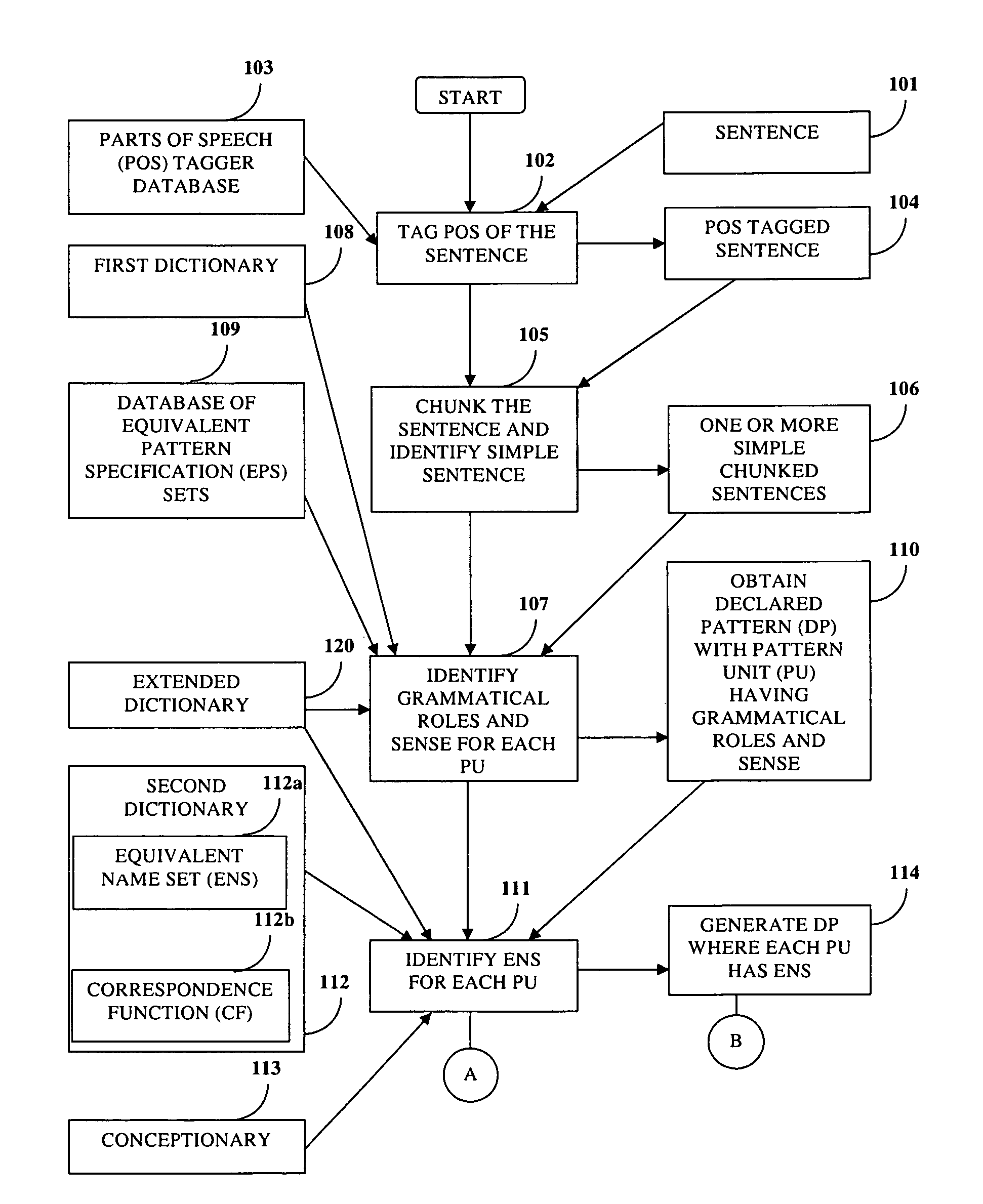

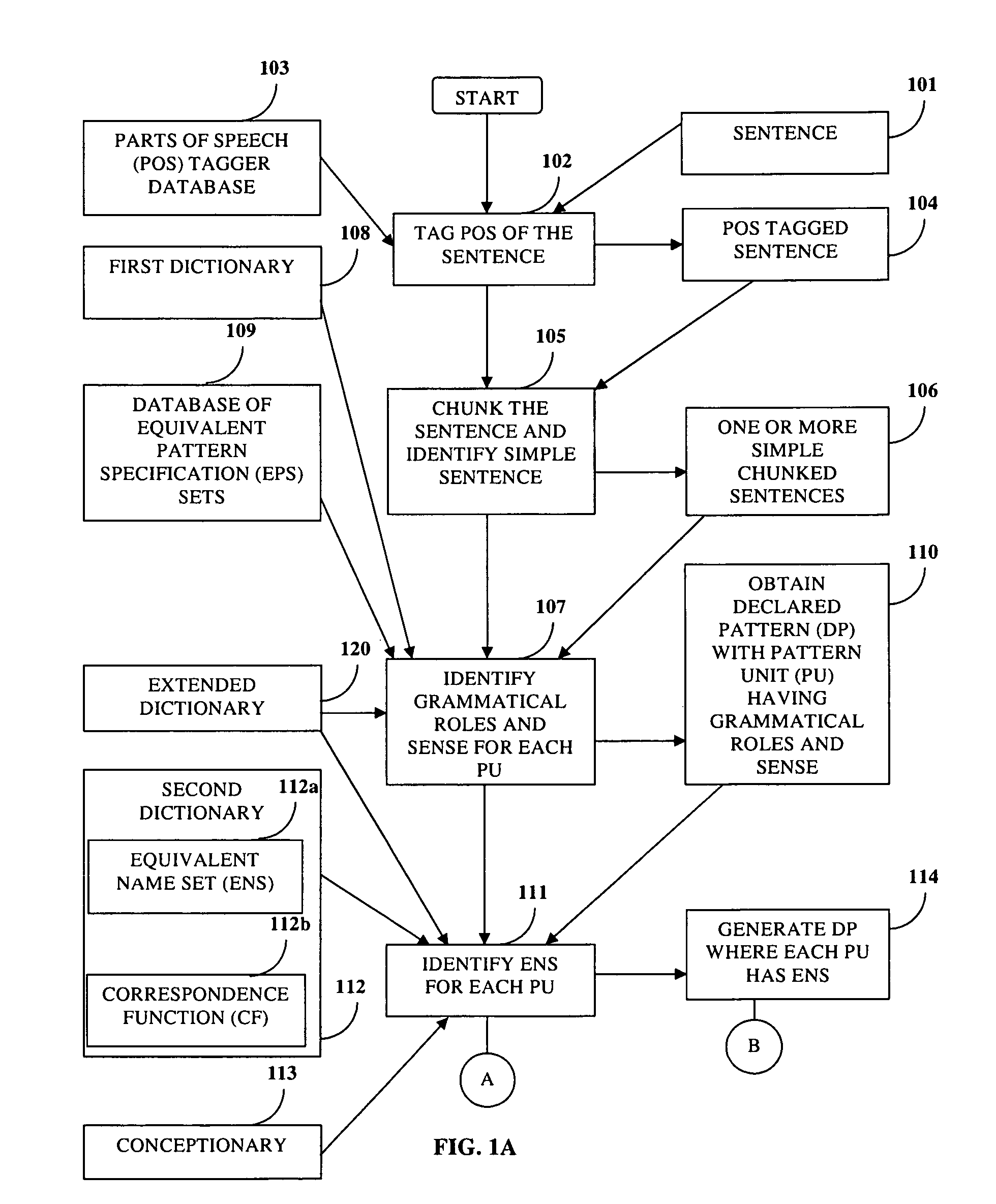

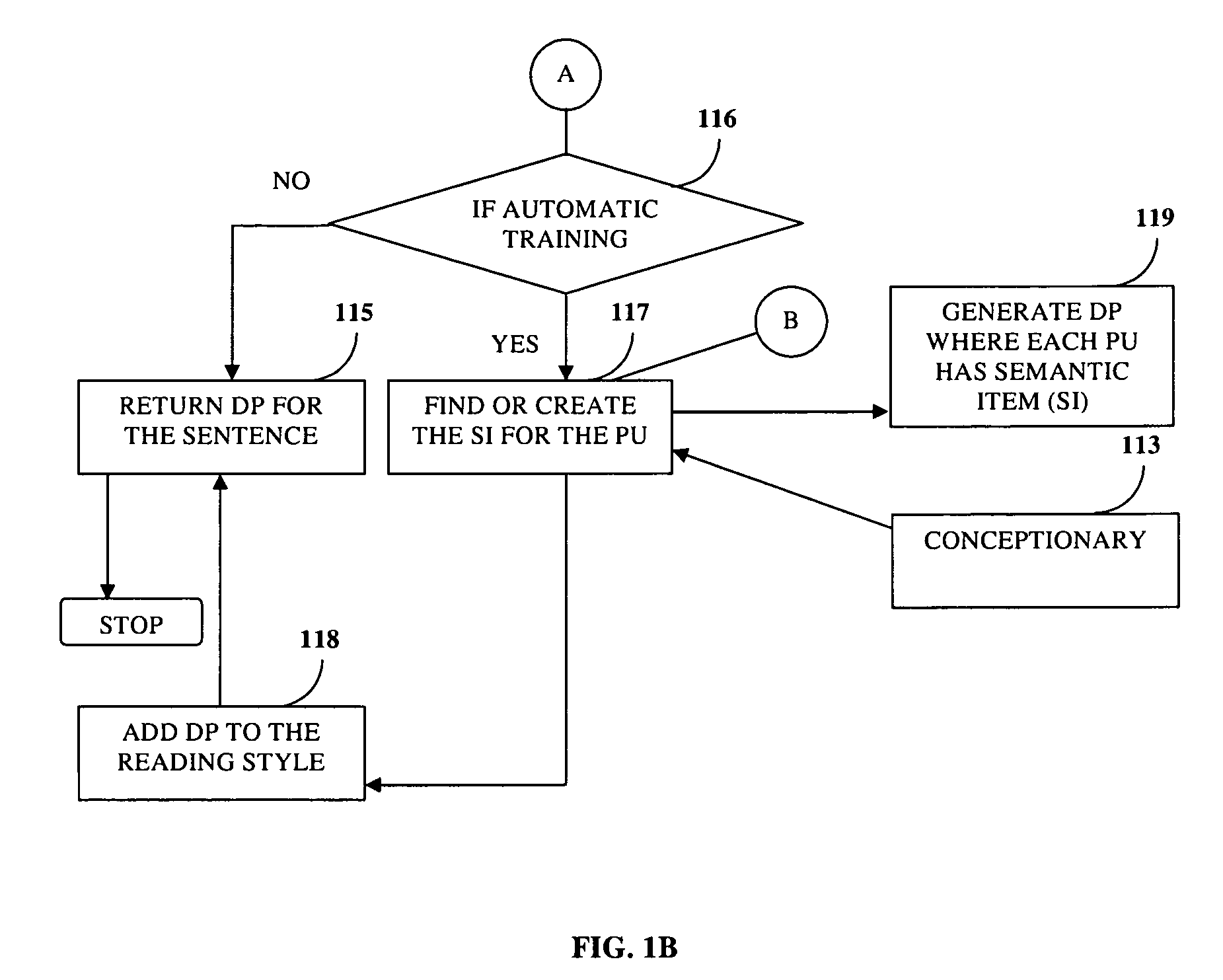

Automatic pattern generation in natural language processing

Disclosed herein is a computer implemented method and system of generating declared patterns from components of a sentence. Parts of speech in the sentence are tagged for identifying parts of speech of each word and phrase in the sentence. Sentence chunking is then performed using the identified parts of speech of each word and phrase to generate pattern units. A first dictionary and a database of equivalent pattern specification sets are then applied to identify grammatical roles and senses of the generated pattern units. A second dictionary and a conceptionary are then applied to identify an equivalent name set for each of the generated pattern units. The declared patterns are then generated for the sentence using the identified equivalent name set for each of the generated pattern units.

Owner:TRIGENT SOFTWARE

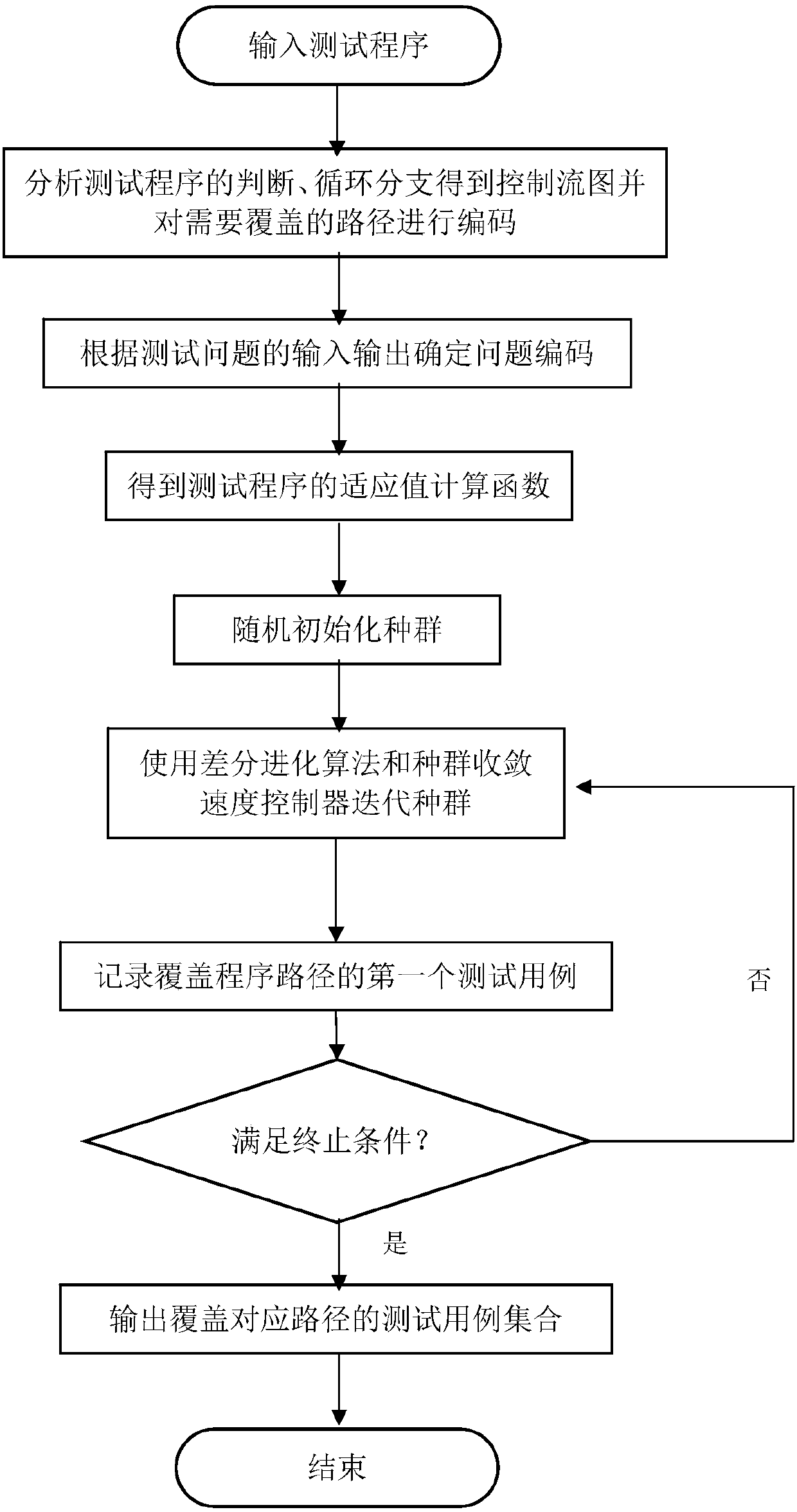

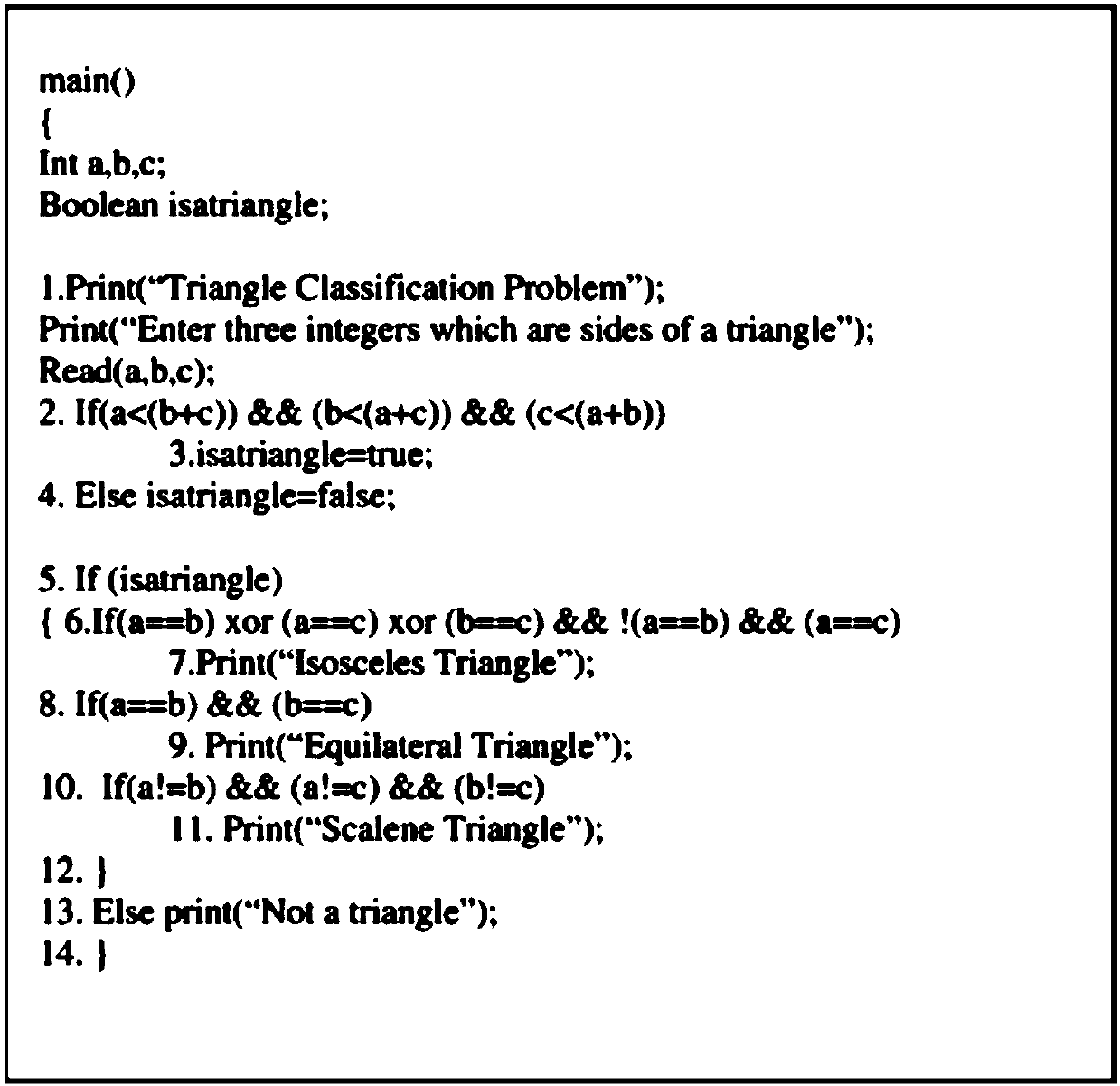

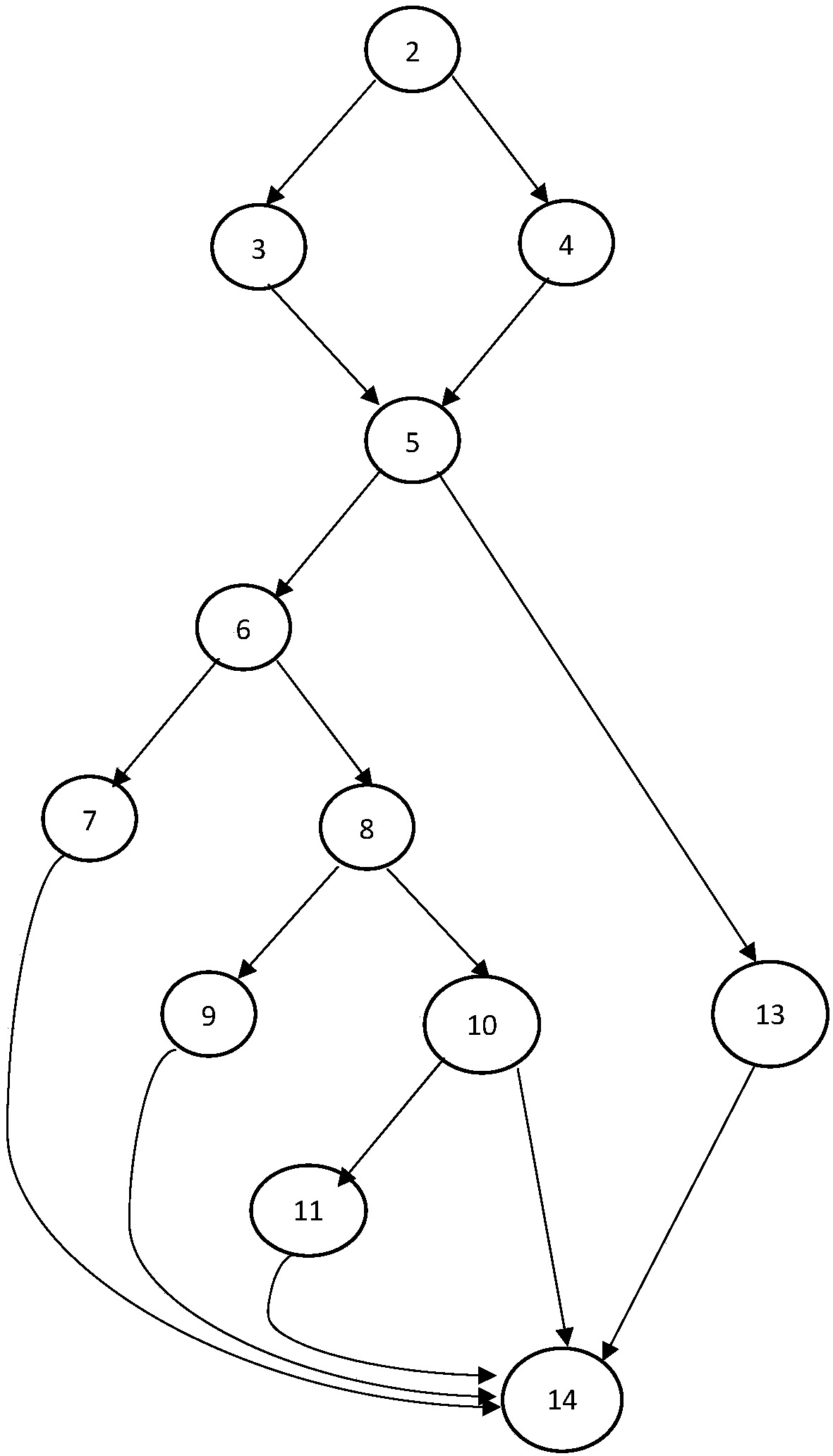

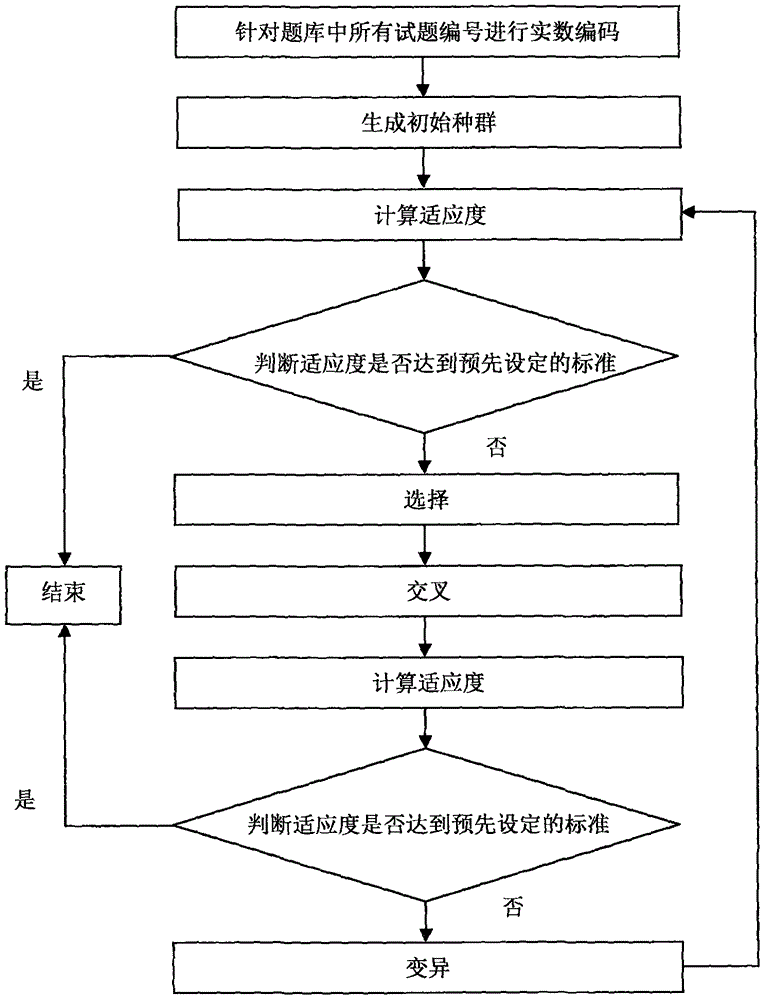

Path coverage software test-based automatic test case generation method

ActiveCN107590073AImprove the ability to solveStrong error correction abilitySoftware testing/debuggingProgramming languageWorking environment

The invention provides a path coverage software test-based automatic test case generation method. The method comprises the following steps of: analyzing a code of a tested program to obtain a controlflow graph (CFG) of the program and a path of the program; obtaining and calculating a fitness function of a group of corresponding test cases according to the control flow graph obtained in the laststep and a branch distance-based method; carrying out iterative updating on a randomly initialized population by using the fitness function through a differential evolution algorithm and a convergencespeed controller; and recording the first test case of paths corresponding to a coverage program until the test cases of all the paths are obtained or the iteration frequency of the algorithm exceedsa limit, and outputting a test case set of the paths corresponding to the coverage program. The method is capable of effectively utilizing the tested program to cover heuristic information of the test cases on the basis of the paths, and can be applied to practical software test work environment.

Owner:微科智检(佛山市)科技有限公司

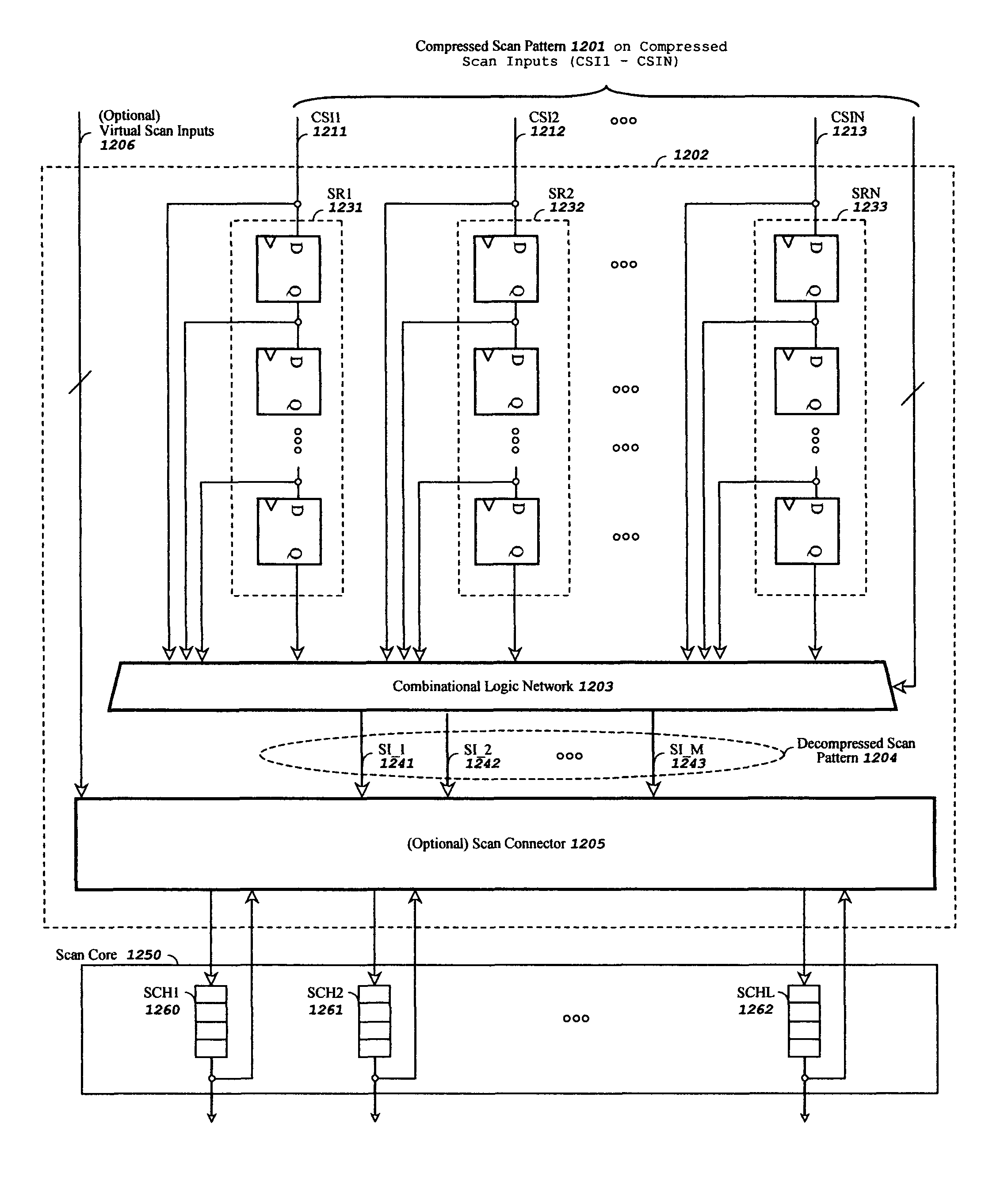

Method and apparatus for pipelined scan compression

InactiveUS7945833B1Reduce loadImprove balanceElectronic circuit testingPower supply testingShift registerEngineering

A pipelined scan compression method and apparatus for reducing test data volume and test application time in a scan-based integrated circuit without reducing the speed of the scan chain operation in scan-test mode or self-test mode. The scan-based integrated circuit contains one or more scan chains, each scan chain comprising one or more scan cells coupled in series. The method and apparatus includes a decompressor comprising one or more shift registers, a combinational logic network, and an optional scan connector. The decompressor decompresses a compressed scan pattern on its compressed scan inputs and drives the generated decompressed scan pattern at the output of the decompressor to the scan data inputs of the scan-based integrated circuit. Any input constraints imposed by said combinational logic network are incorporated into an automatic test pattern generation (ATPG) program for generating the compressed scan pattern for one or more selected faults in one-step.

Owner:SYNTEST TECH

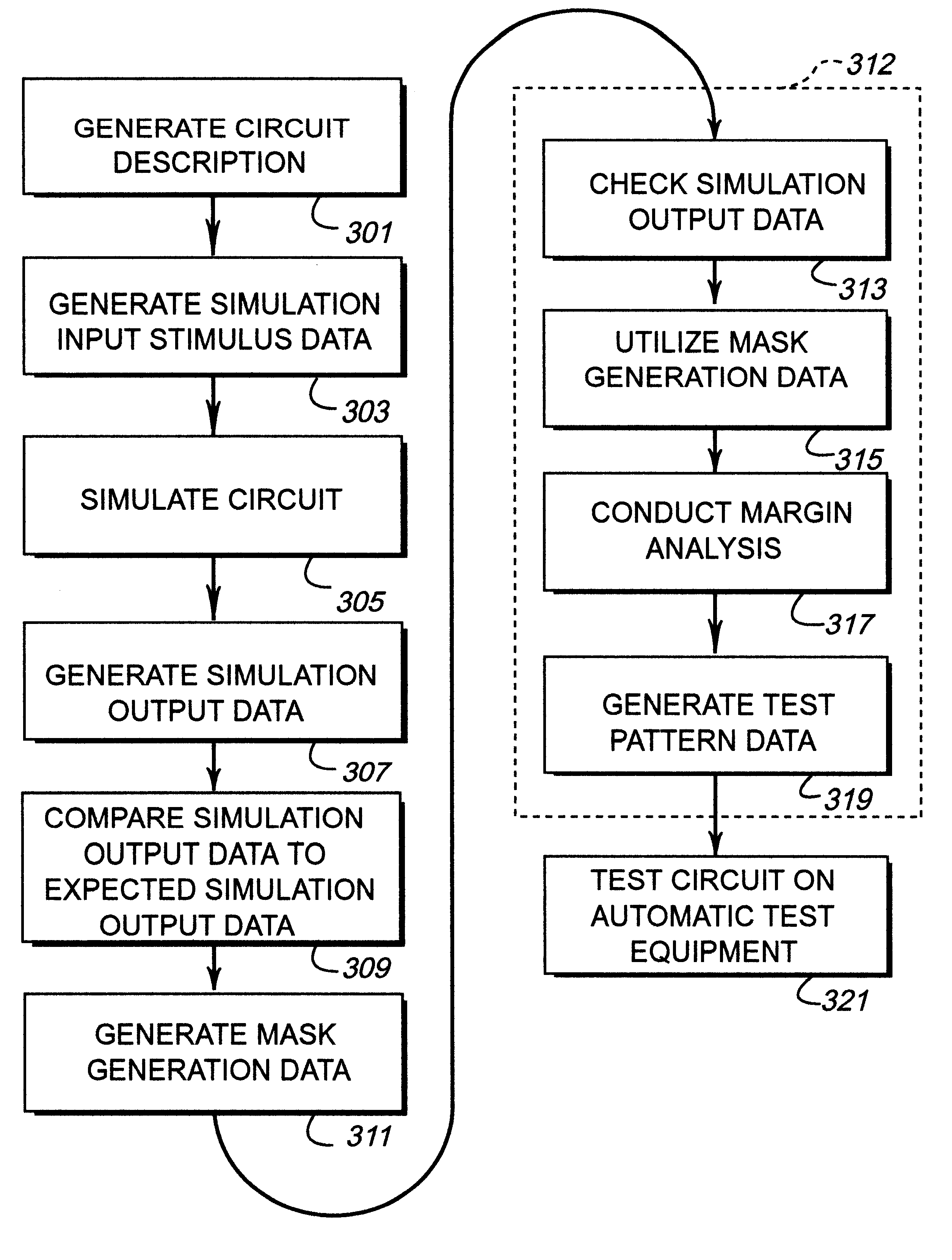

File driven mask insertion for automatic test equipment test pattern generation

InactiveUS6308292B1Electronic circuit testingError detection/correctionAutomatic test equipmentComputer architecture

A method, system, and program for selectively testing output signals of an integrated circuit. The system comprising a mask generation file specifying output signals and test cycles and a verification module to check simulation output data and generate test pattern data. The verification module further comprising an extractor routine which receives the mask generation file and processes the simulation output data such that the test pattern data is coded to mask the specified output signals at the specified test cycles. The verification module further comprising margin analysis for determining if margin times of the coded test patterns fall below a minimum margin time setting.

Owner:BELL SEMICON LLC

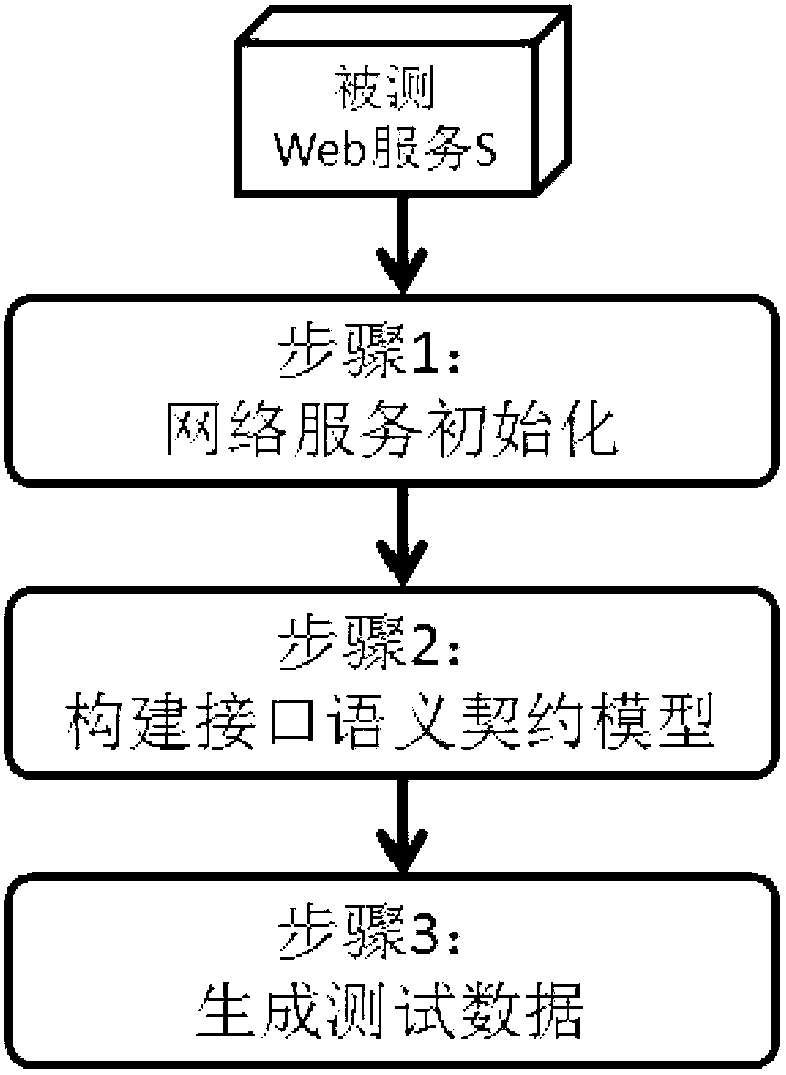

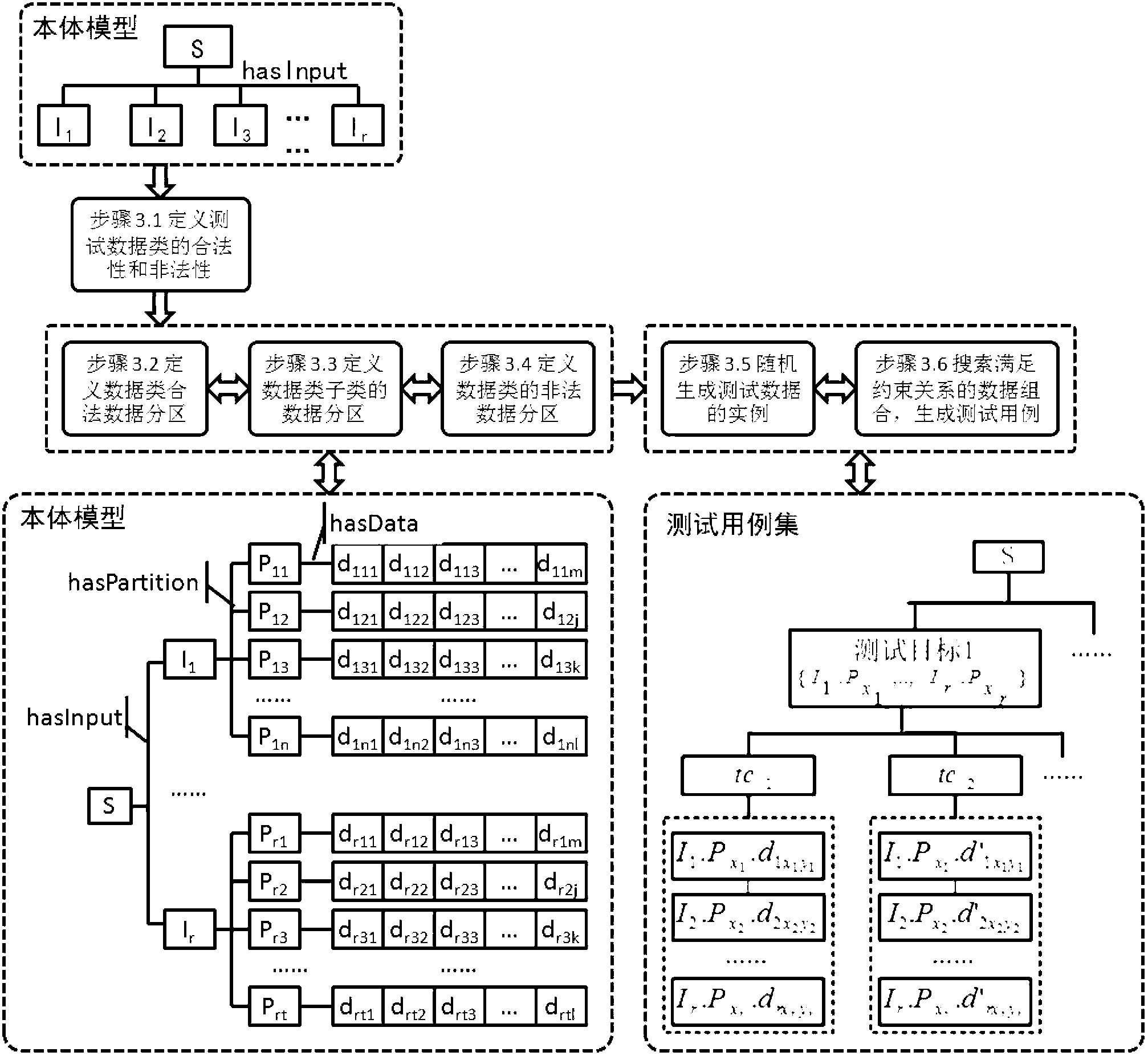

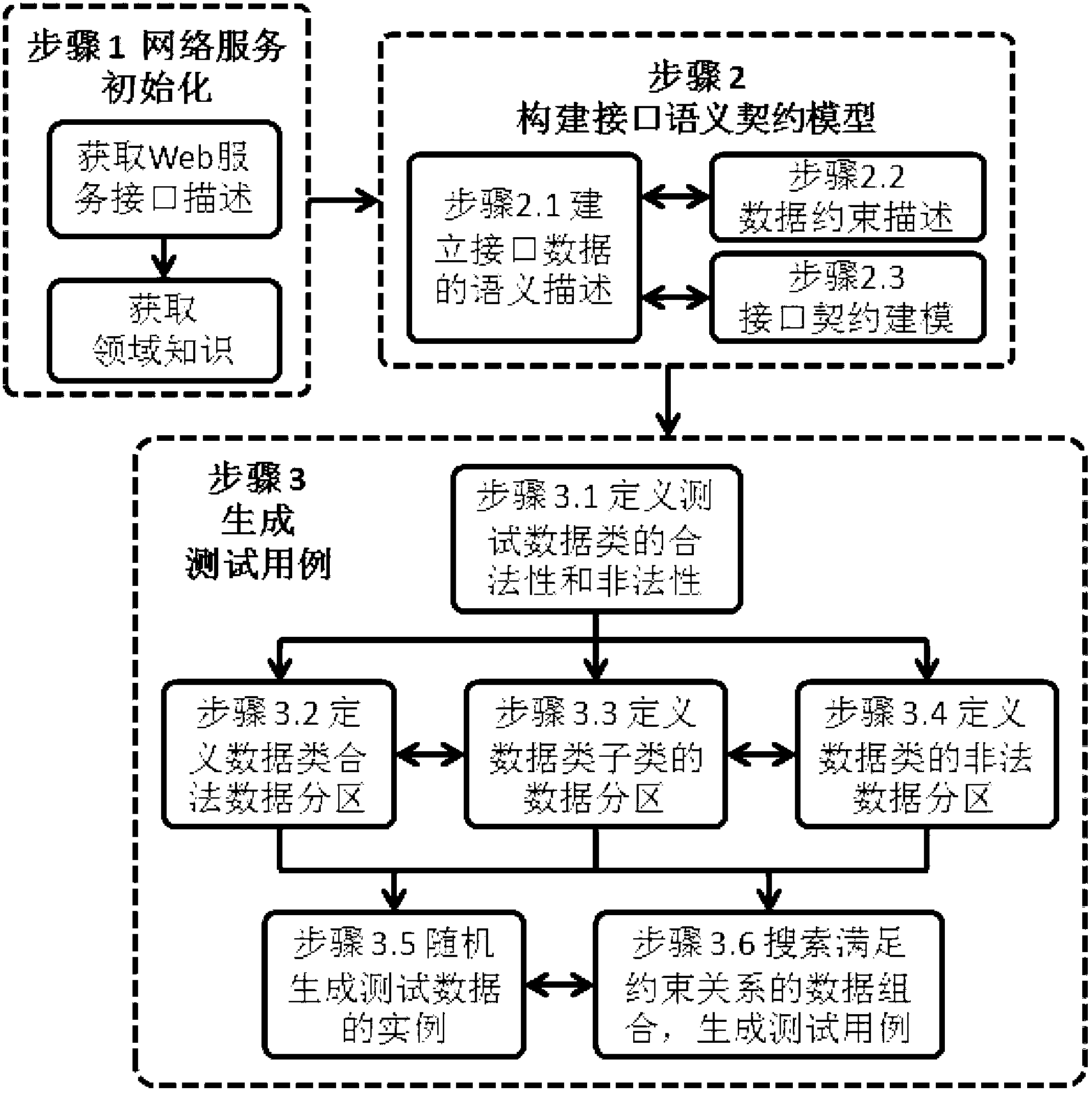

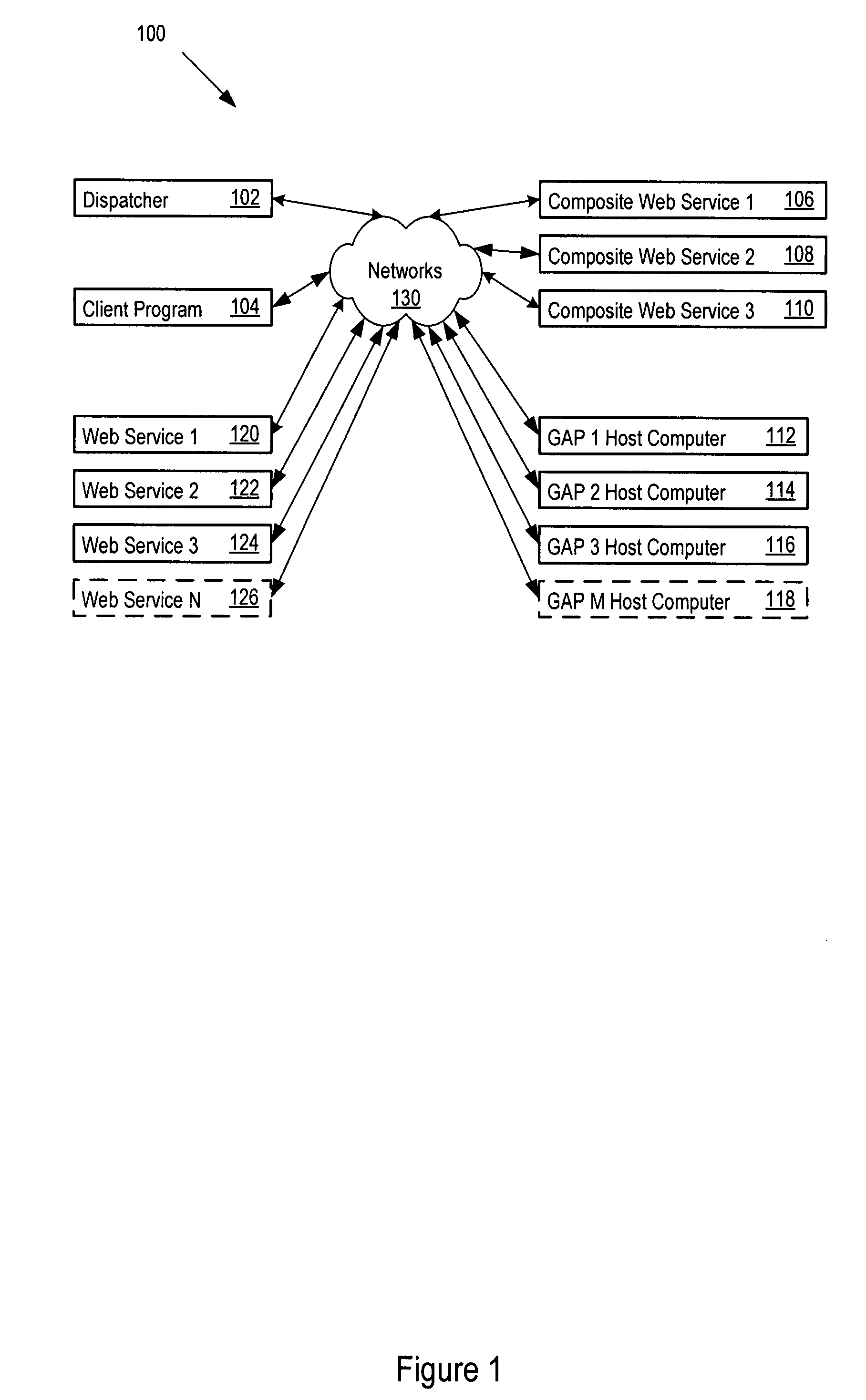

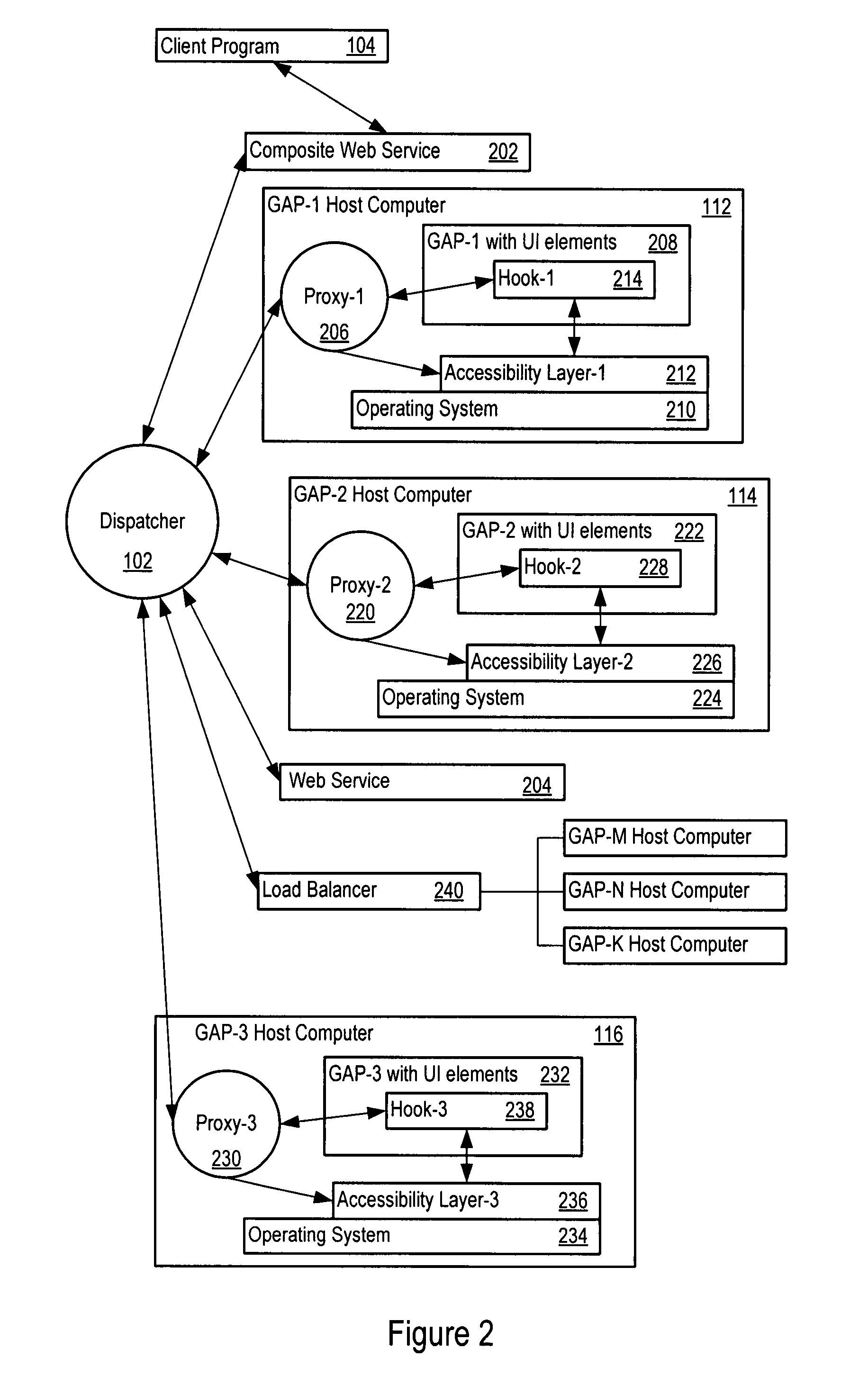

Web service modeling and test method based on interface semantic contract model

ActiveCN103064788AEnhanced description abilityGuaranteed correctnessSoftware testing/debuggingSpecific program execution arrangementsTest inputWeb service

A web service modeling and the test method based on an interface semantic contract model relate to the fields of software test modeling and automatic test case generation. The web service test method comprises (1) building a service interface semantic contract model to expand descriptive capability of an existing service interface; (2) generating test input data and a test case according to description of the interface data ontology to provide input data for the test case; and (3) providing an expected output result for the test case according to regular test data. The web service modeling and the test method based on the interface semantic contract model have the advantages of being applicable to a web service test, capable of expanding the descriptive capability of the existing service interface, capable of being used for generating the test data and the test case and improving the degree of automation and intelligentization of test generation through knowledge descriptions and reasoning technologies.

Owner:TSINGHUA UNIV

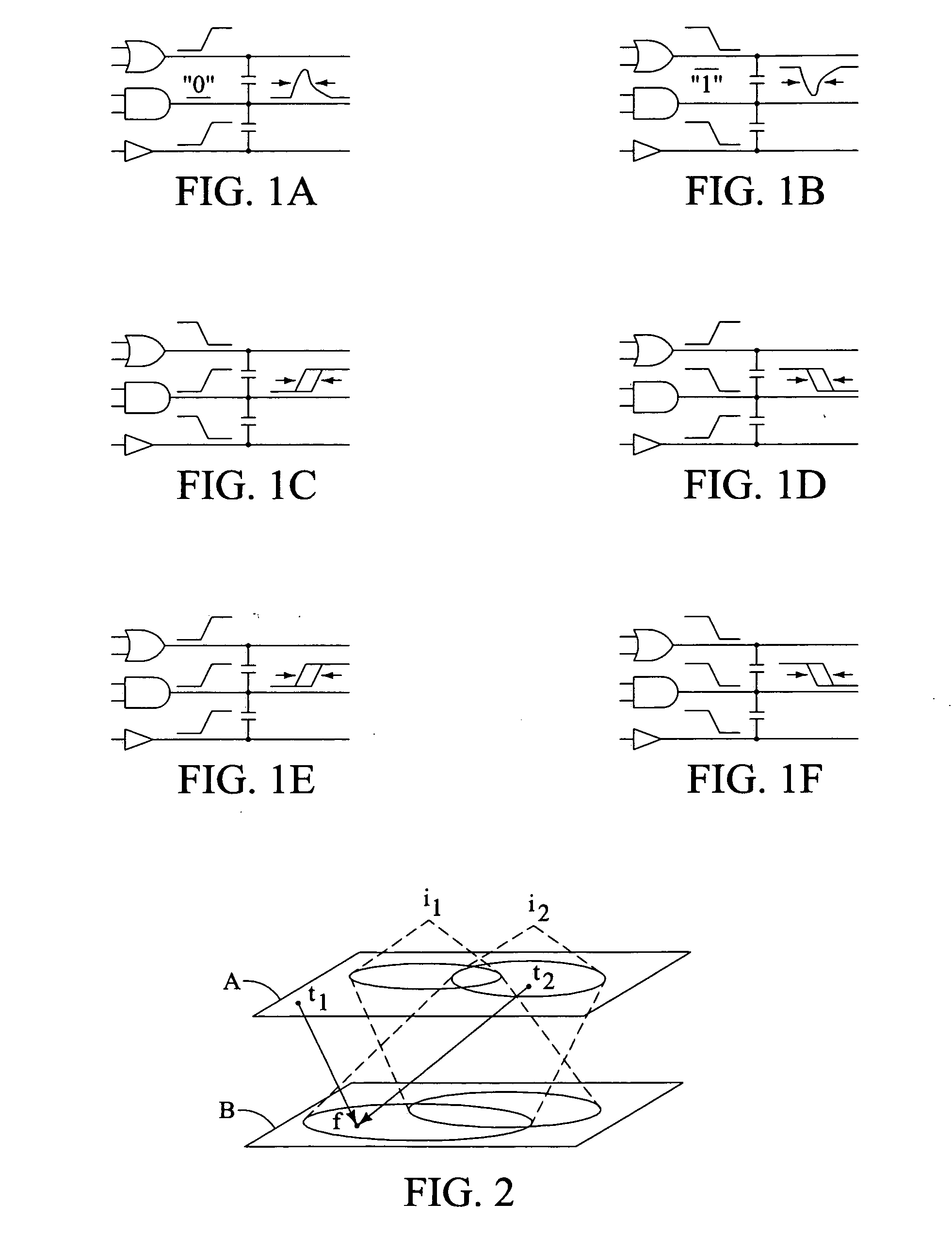

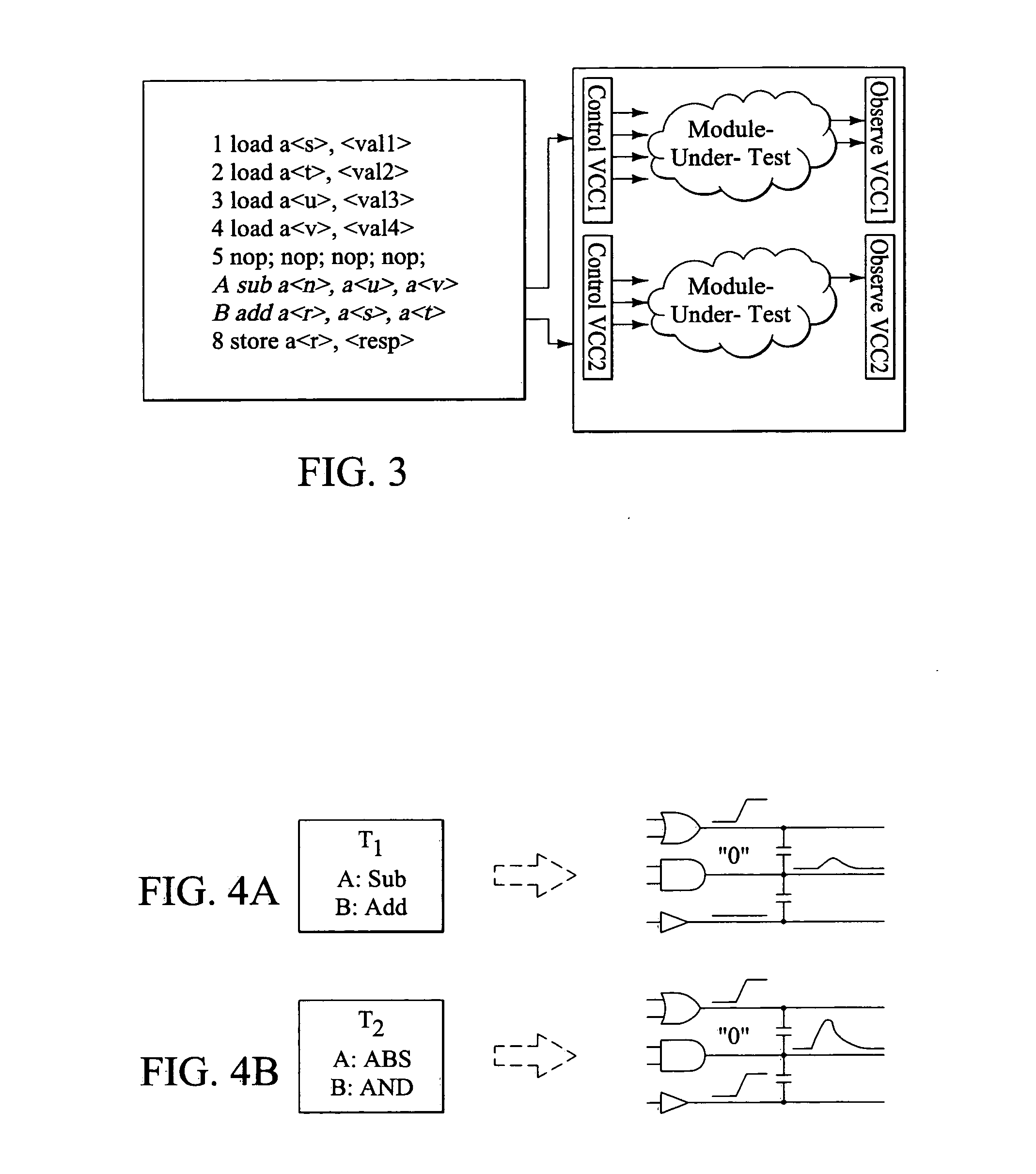

Method for test application and test content generation for AC faults in integrated circuits

InactiveUS20050102594A1Digital circuit testingError detection/correctionPattern generationAutomatic test pattern generation

A method for generating a software-based self-test in an integrated circuit includes extracting constraints for corresponding instructions for the integrated circuit, modeling the constraints for a plurality of timeframes and performing constrained test pattern generation on the integrated circuit using the models. An automatic test pattern generation method for an AC fault in an integrated circuit includes identifying a current desired condition for triggering the AC fault, determining whether the current desired condition is feasible, and identifying a subsequent desired condition for triggering the AC fault if the current desired condition is not feasible. The method further includes determining whether the subsequent desired condition for triggering the AC fault is feasible, and searches for test vectors for realizing the current desired condition or subsequent desired condition which is determined to be feasible.

Owner:RGT UNIV OF CALIFORNIA

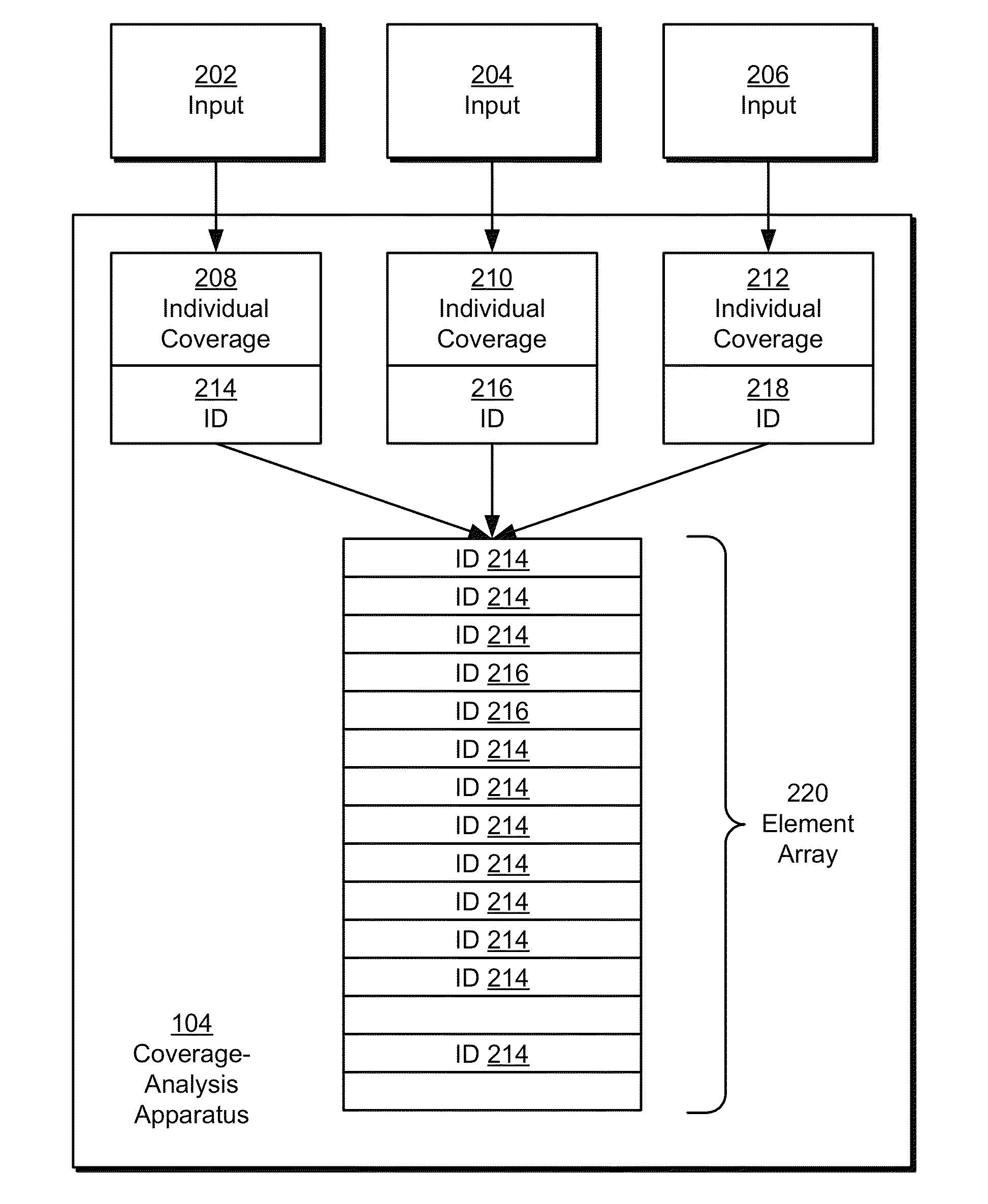

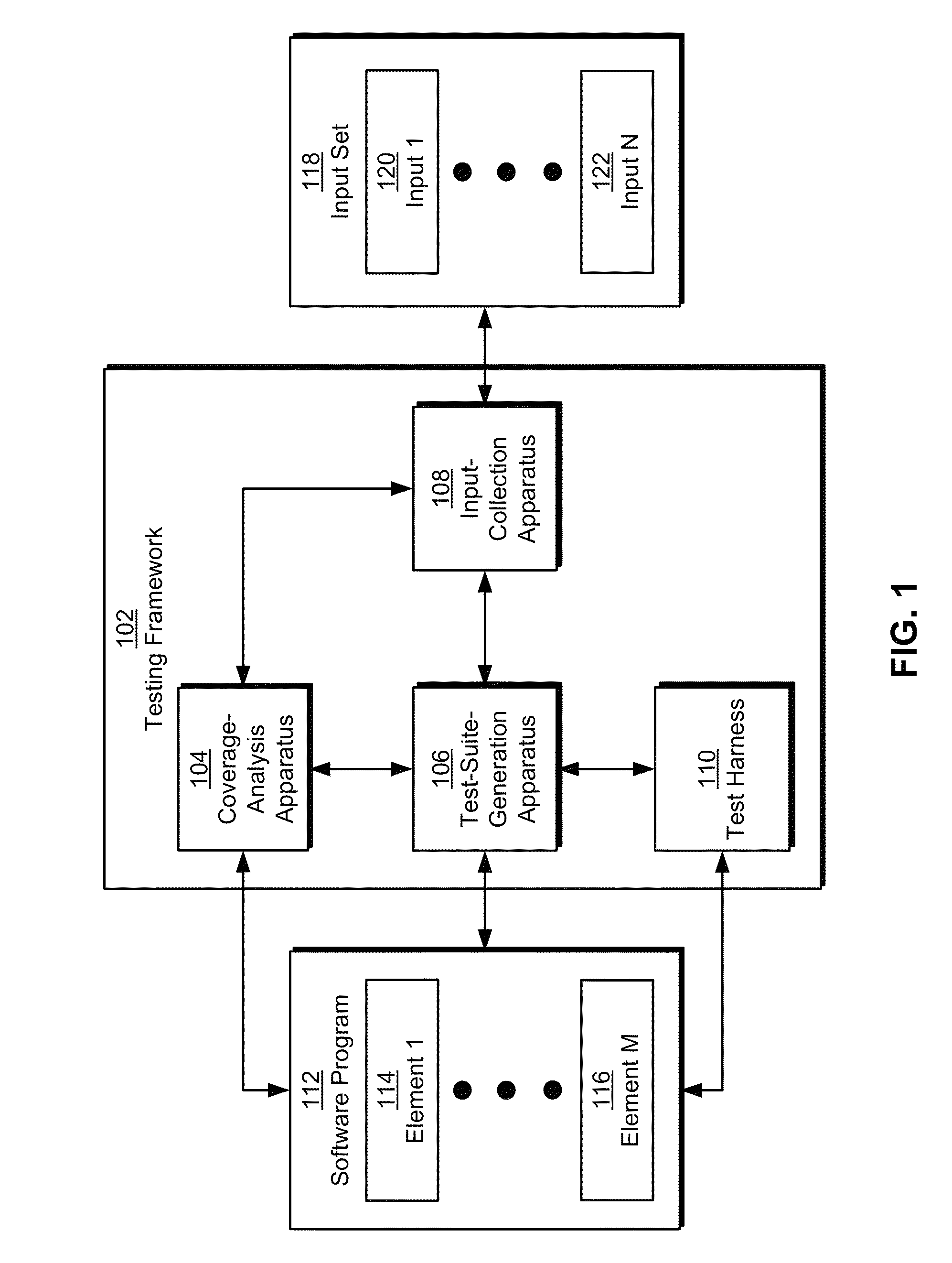

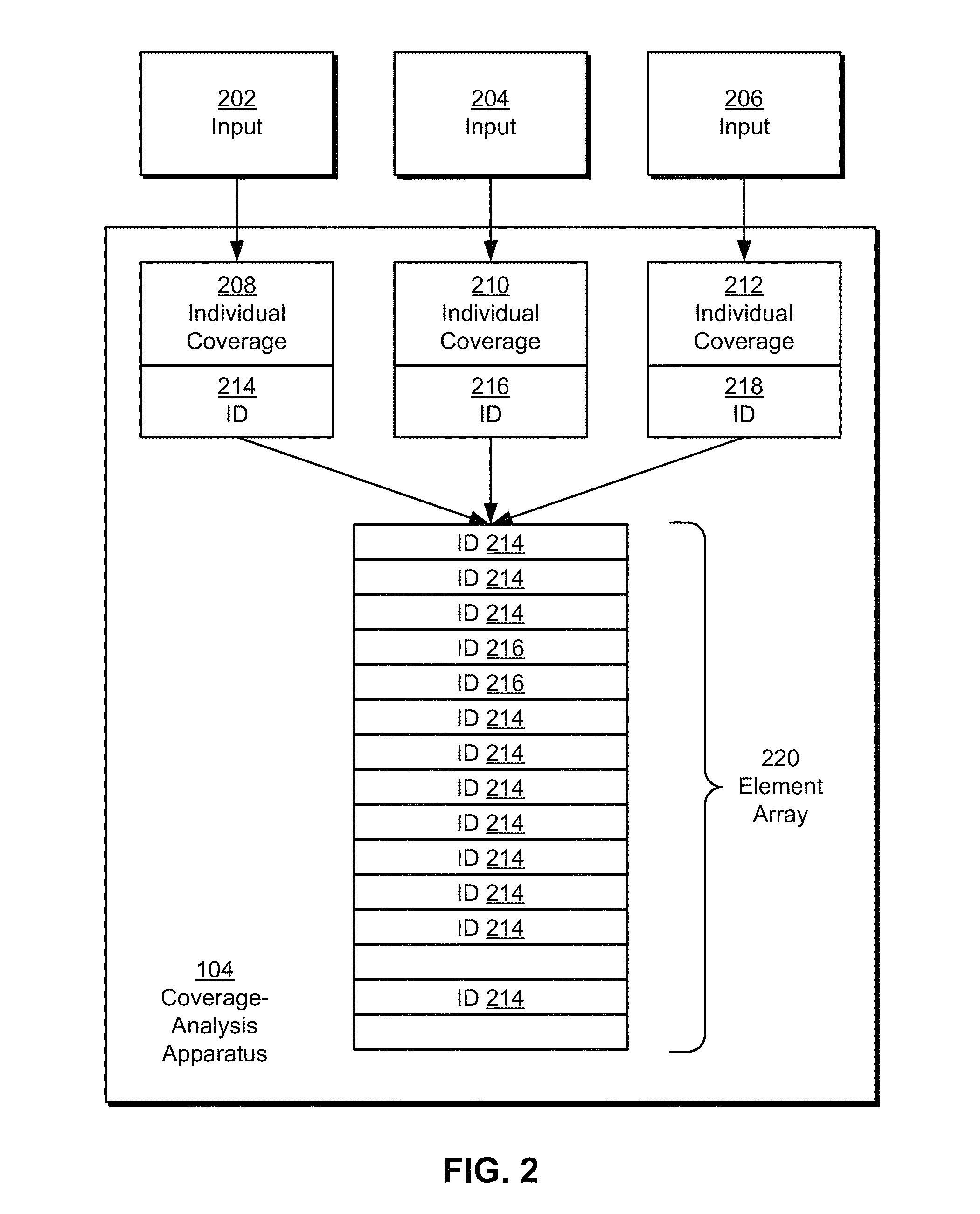

Input selection for automatic test suite generation

InactiveUS8745592B1Error detection/correctionSpecific program execution arrangementsInput selectionTest suite

Some embodiments provide a system that generates a test suite for a software program. During operation, the system obtains a set of inputs for the software program and determines a coverage of the software program associated with the set of inputs. Next, the system determines a subset of the inputs which substantially provides the coverage of the software program. Finally, the system uses the subset of inputs as the test suite for the software program.

Owner:GOOGLE LLC

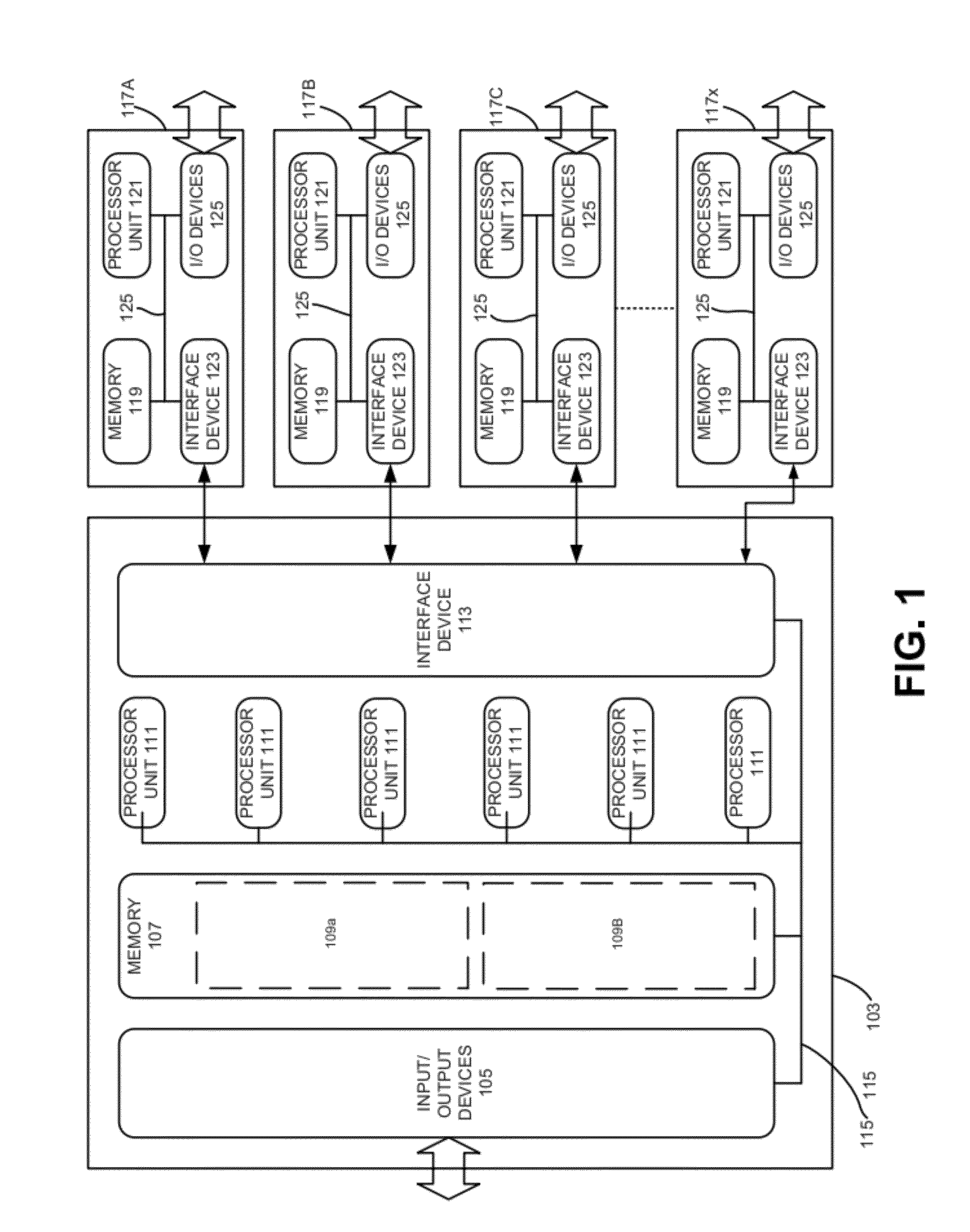

Tester with acceleration on memory and acceleration for automatic pattern generation within a FPGA block

ActiveUS10161993B2Bandwidth requirement can be keptMinimal processing loadDigital circuit testingError detection/correctionAutomatic test pattern generationHardware acceleration

Automated test equipment capable of performing a high-speed test of semiconductor devices is presented. The automated test equipment apparatus comprises a computer system comprising a tester processor, wherein the tester processor is communicatively coupled to a plurality of FPGA components. Each of the plurality of FPGA components is coupled to a memory module and comprises: an upstream port operable to receive commands and data from the tester processor; a downstream port operable to communicate with a respective DUT from a plurality of DUTs; and a plurality of hardware accelerator circuits, wherein each of the accelerator circuits is configured to communicate with one of the plurality of DUTs. Each of the plurality of hardware accelerator circuits comprises a pattern generator circuit configurable to automatically generate test pattern data and a comparator circuit configured to compare data.

Owner:ADVANTEST CORP

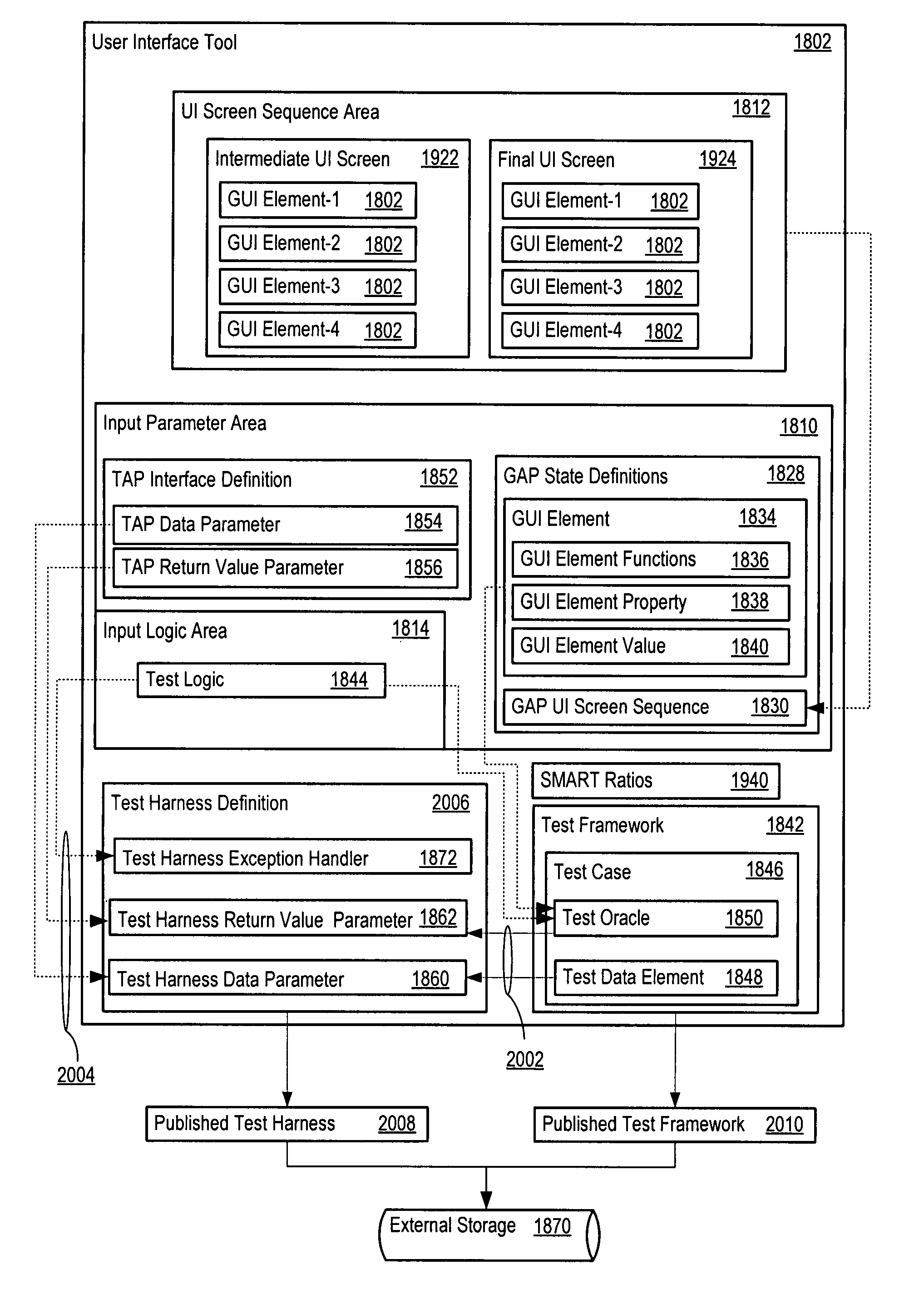

Automatic test generation for reference testing

ActiveUS7979846B2Increase valueError detection/correctionSpecific program execution arrangementsDrag and dropSoftware development process

A system for application reference testing (SMART) solves the technical problem of generating test data and test cases from graphical user interface applications (GAPs) to test web services, effectively and non-invasively. SMART allows organizations to easily and promptly identify and resolve software bugs, ensure higher quality software and development productivity, complete software projects faster, deliver software products to market quicker, and improve the return on investment for software development projects. SMART provides a user friendly visualization mechanism that interacts with an accessibility layer to enable organizations to economically and easily define user interactions with GAPs, by performing point-and-click, drag-and-drop operations on the GAPs, and generate reusable test data and test cases for web services.

Owner:ACCENTURE GLOBAL SERVICES LTD

Smart capture for ATPG (automatic test pattern generation) and fault simulation of scan-based integrated circuits

InactiveUS20050262409A1Improve accuracyGreat measured fault coverageError detection/correctionMarginal circuit testingTest responseCircuit models

A method for generating stimuli and test responses for testing faults in a scan-based integrated circuit in a selected scan-test mode or a selected self-test mode, the scan-based integrated circuit containing a plurality of scan chains, N clock domains, and C cross-clock domain blocks, each scan chain comprising multiple scan cells coupled in series, each clock domain having one capture clock, each cross-clock domain block comprising a combinational logic network. The method comprises compiling the scan-based integrated circuit into a sequential circuit model; specifying input constraints on the scan-based integrated circuit during a shift and capture operation; specifying a clock grouping to map the N clock domains into G clock domain groups, where N>G>1; transforming the sequential circuit model into an equivalent combinational circuit model according to the input constraints and the clock grouping; and generating the stimuli and test responses on the equivalent combinational circuit model according to the input constraints.

Owner:SYNTEST TECH

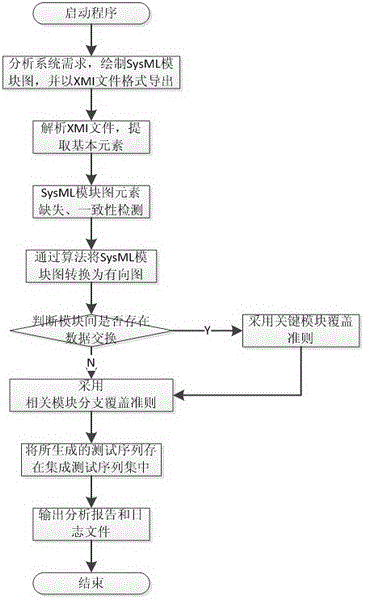

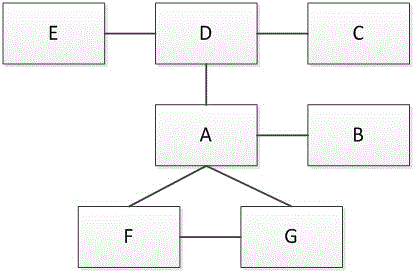

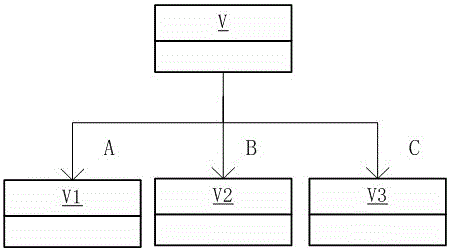

Integrated test sequence generating method based on SysML module diagrams

ActiveCN105677563AImprove test efficiencyIntegration tests are adequateSoftware testing/debuggingDirected graphIntegration testing

The invention discloses an integrated test sequence generating method based on SysML module diagrams. The method is applicable to an embedded system having higher integration complex and more crosslinking relations among application systems. An integrated test strategy from constraint to combination, from pairing to grouping, from inside to outside and from bottom to top is provided according to the logic functional combination relation of the embedded system; modeling is conducted on the strategy by analyzing the demands and design of the system and by using the SysML module diagrams; the SysML module diagrams are analyzed and converted into directed graphs; a relevant module branch coverage criterion is provided according to the combination relation of functional modules; a key module coverage criterion is provided according to existing data exchange of the modules; then directed graphs are traversed under the guidance of the coverage criterions to automatically generate an integrated test sequence set. The integrated test sequence generating method combines with a model driven engineering technology, achieves automatic test sequence generation and improves the software testing efficiency.

Owner:NANCHANG HANGKONG UNIVERSITY

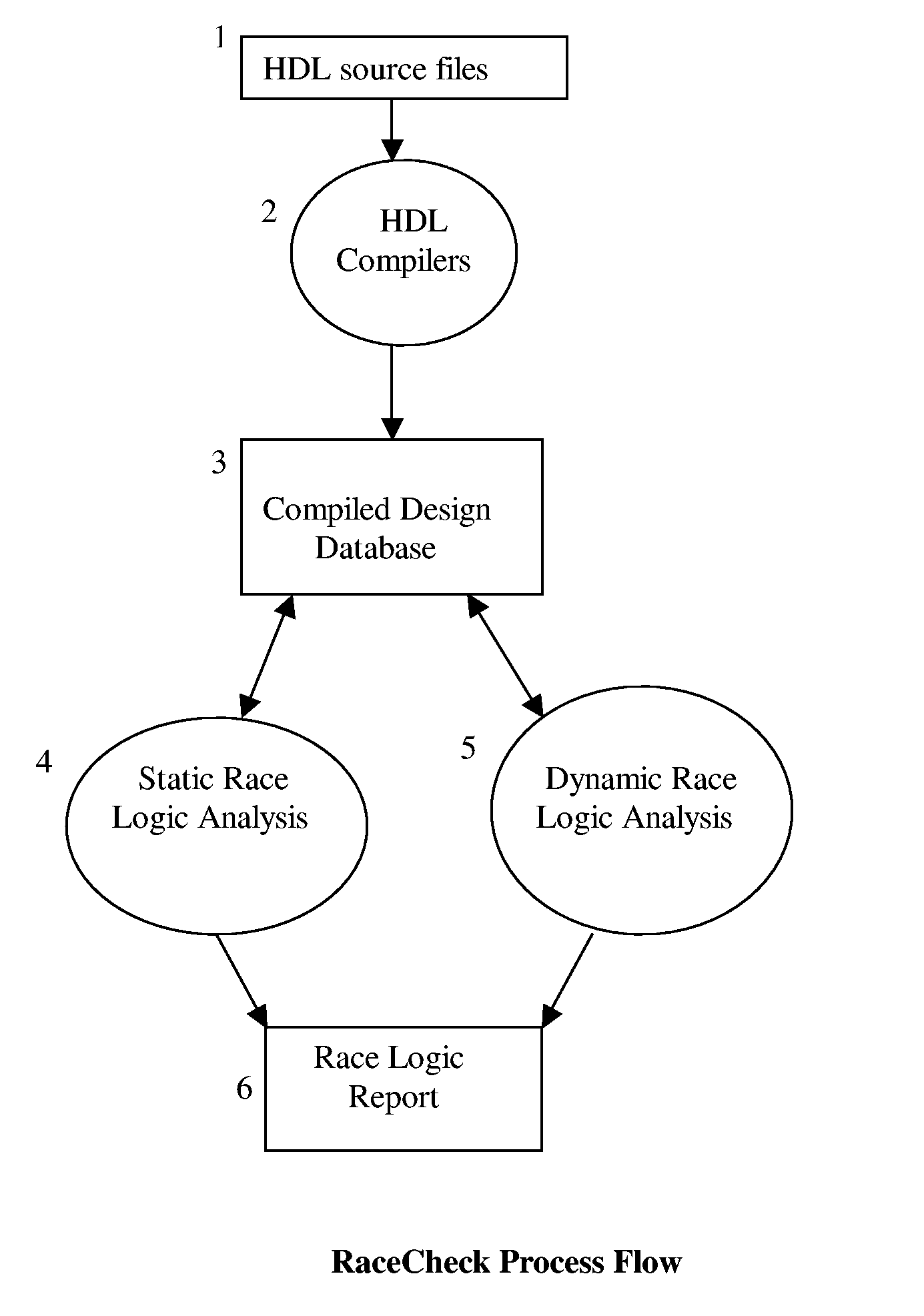

RaceCheck: A Race Logic Ana,yzer Program for Digital Integrated Circuits

ActiveUS20060075367A1Reduce effortShorten the timeElectrical testingDesign optimisation/simulationTime informationSystemC

This invention describes a race logic audit program, RaceCheck, which is unique from the prior arts. Specifically, RaceCheck can perform both static and dynamic race logic analysis, and it works with a plurality of hardware description languages (HDL), which include but not limited to: VHDL, Verilog, SystemVerilog, and SystemC. Furthermore, RaceCheck makes use of both structural and timing information of IC designs, as well as binary-decision diagram (BDD) and automatic test pattern generation (ATPG) techniques to derive accurate race logic analysis results with few false violations. Finally, RaceCheck can detect concurrent invocation races of the $random system function, concurrent invocation races of user-defined tasks and functions, zero-delay combination loops, and RaceCheck's dynamic analysis engine uses a HDL simulation kernel to perform timing-accurate race logic analysis. All these aforementioned features are unique for the invention and have not been reported in any prior arts.

Owner:DYNETIX DESIGN SOLUTIONS

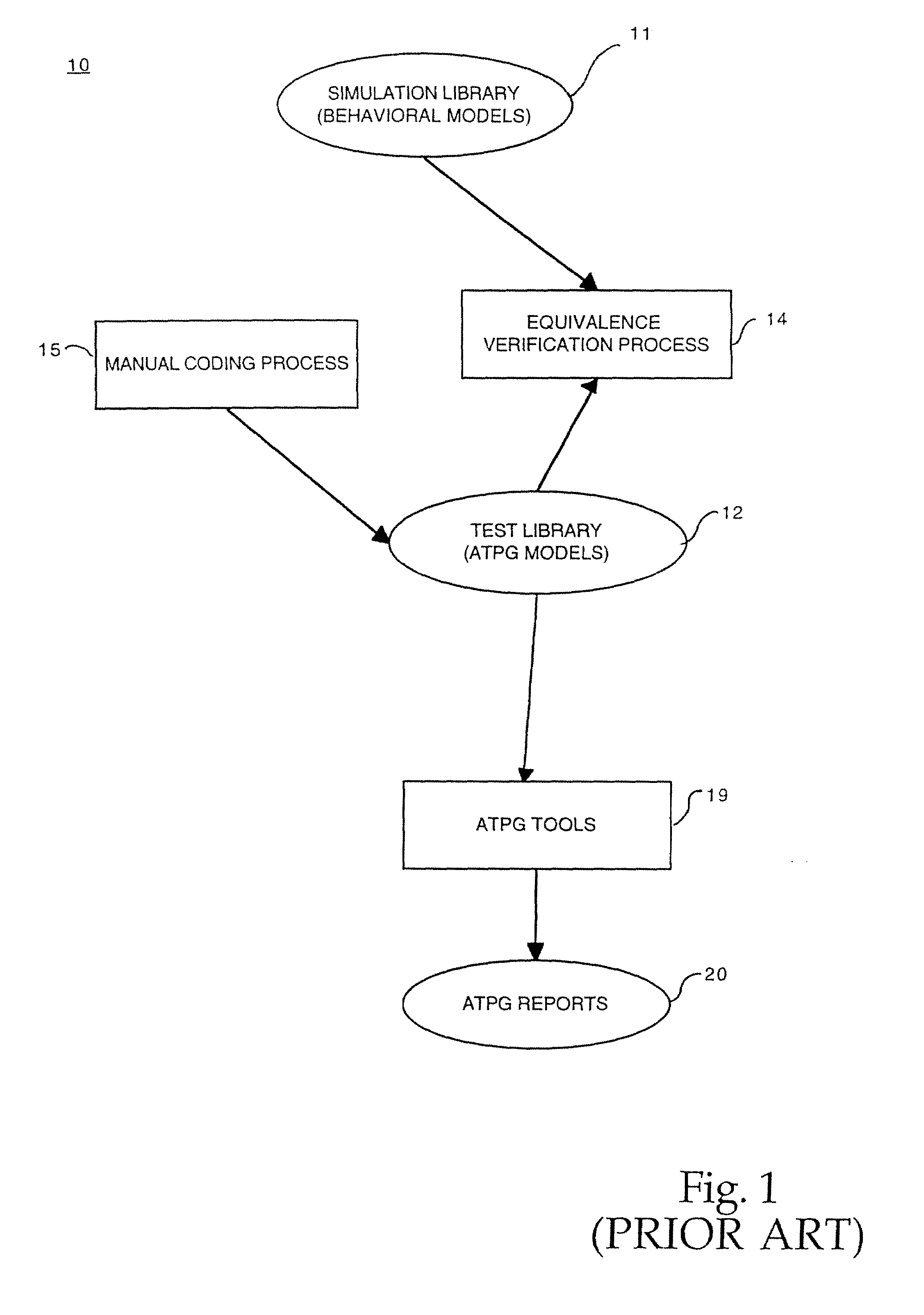

Method and system for generating an atpg model of a memory from behavioral descriptions

InactiveUS20040167764A1Tedious, time-consuming, error-prone and difficult tasksFacilitate the processDigital circuit testingCAD circuit designRandom access memoryTheoretical computer science

Abstract of the Disclosure 42Method and system for constructing a structural model of a memory for use in ATPG (Automatic Test Pattern Generation). Behavioral models of memories of simulation libraries are re-coded into simplified behavioral models using behavioral hardware description language (e.g., Verilog). Simplified behavioral models are automatically converted into structural models that include ATPG memory primitives. Structural models are stored for subsequent access during pattern generation. In another embodiment for modeling random access memories (RAMs), the ATPG memory primitives include memory primitives, data bus primitives, address bus primitives, read-port primitives and macro output primitives. In another embodiment for modeling content addressable memories (CAMs), the ATPG memory primitives include memory primitives, compare port primitives and macro output primitives. Functional equivalence between simplified behavioral models and simulation models can be verified with the same behavioral hardware description language simulator (e.g., Verilog). Another advantage is complicated memories, such as CAMs, can be accurately modeled for ATPG.

Owner:SYNOPSYS INC

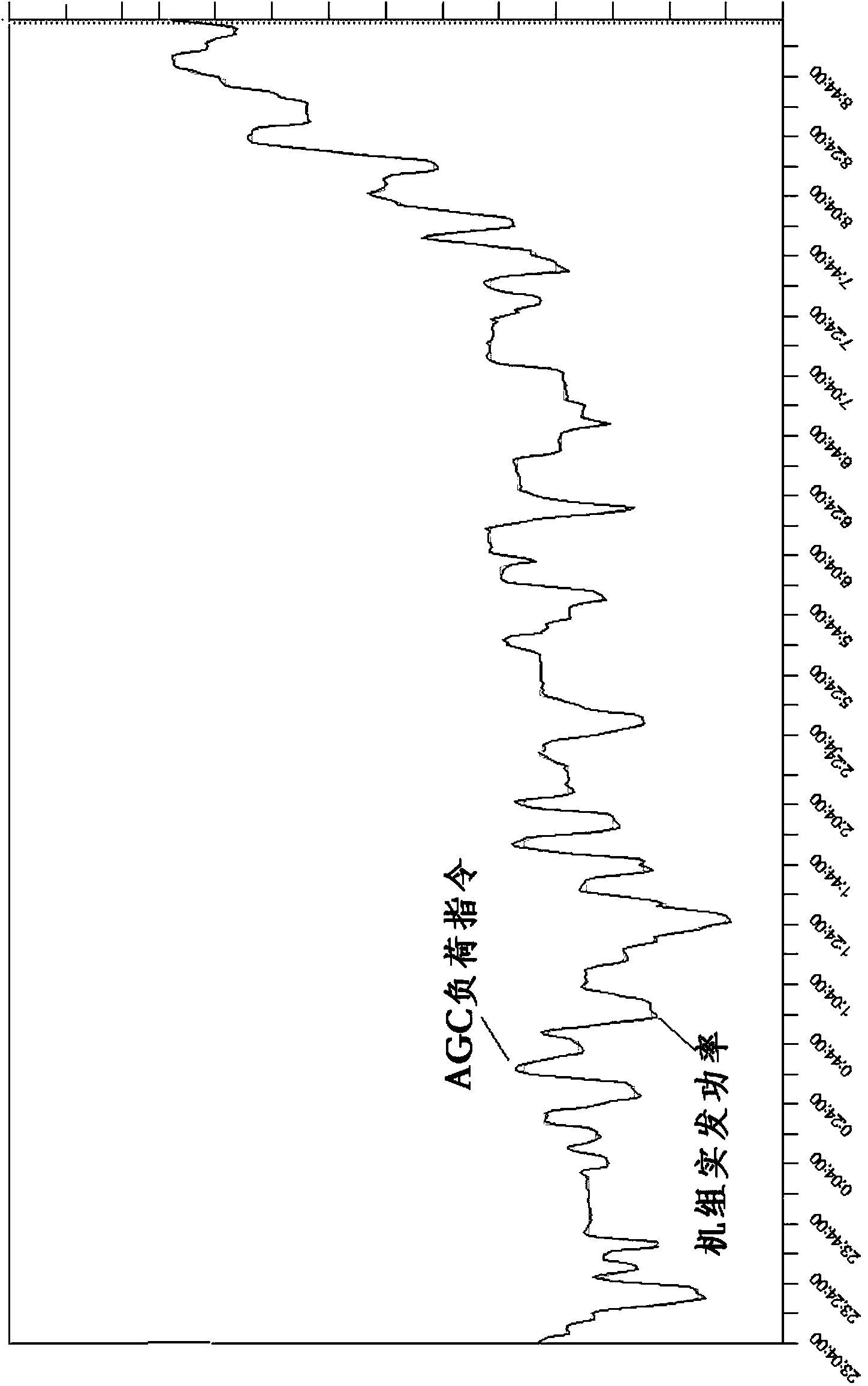

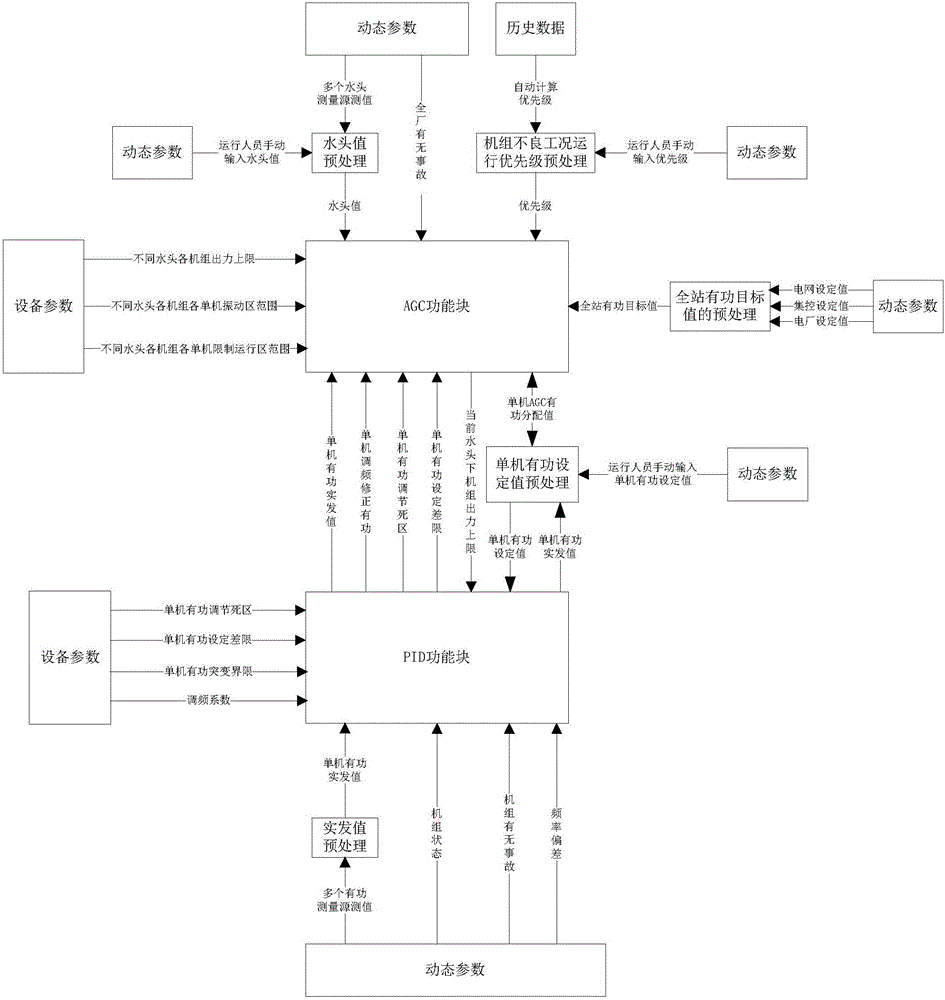

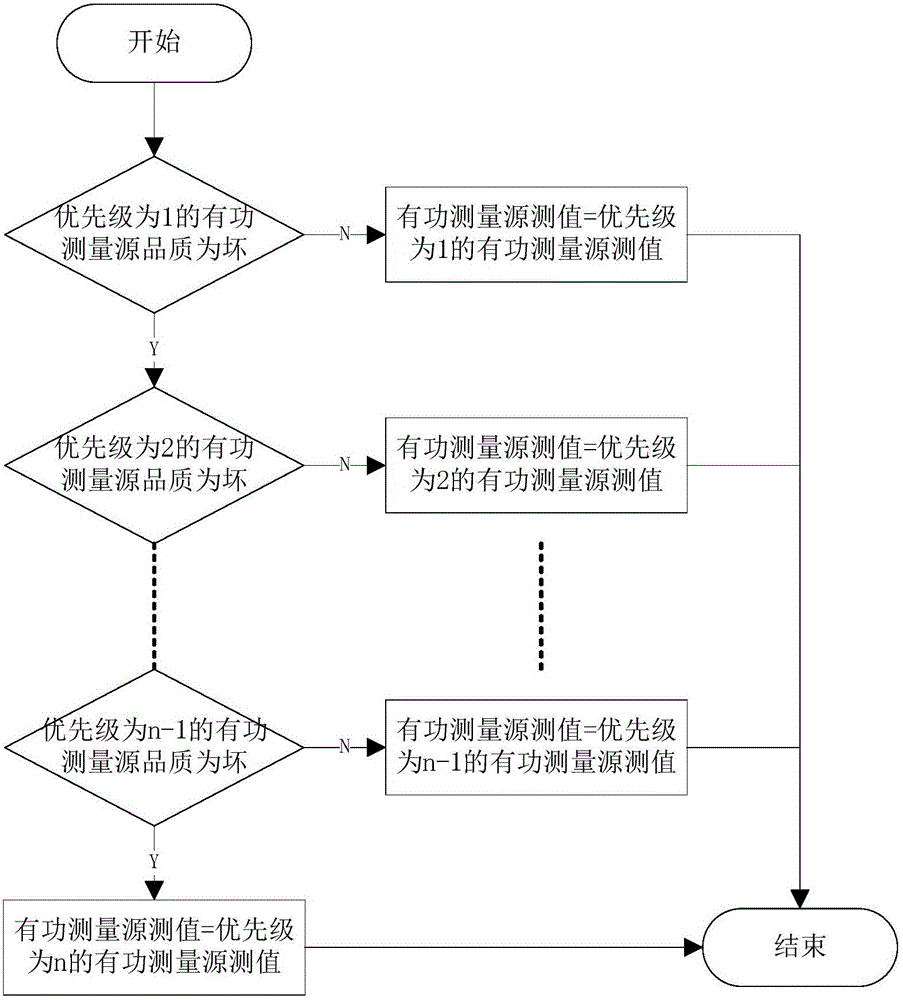

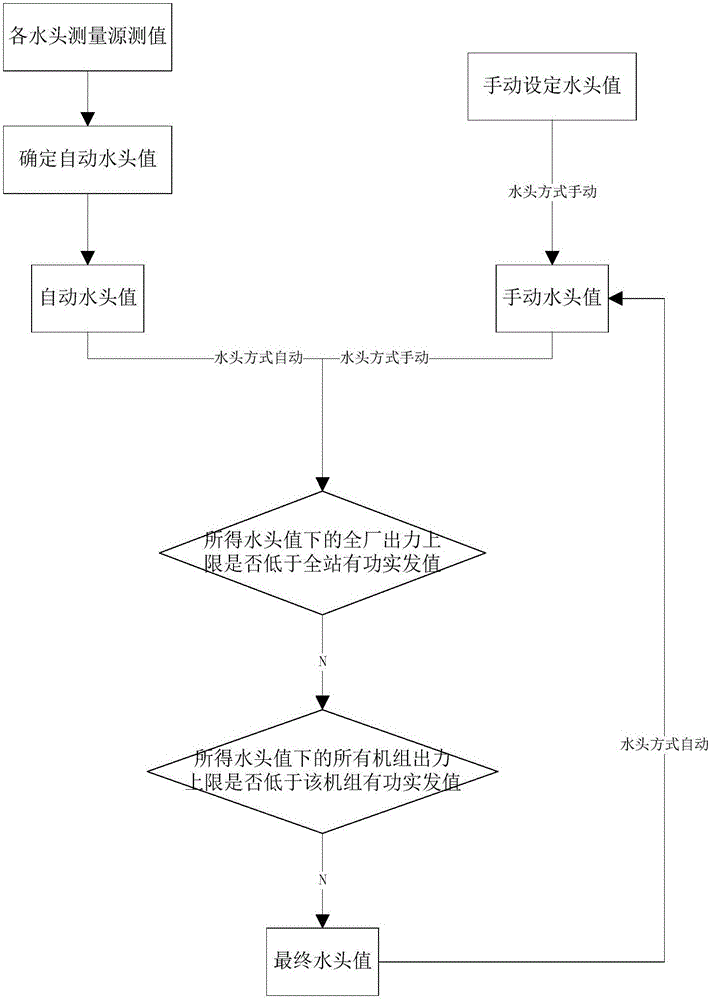

Active power output control parameter pre-processing method for hydropower station during automatic power generation

ActiveCN105811473AReduce computing loadReduce complexitySingle network parallel feeding arrangementsClosed loopEngineering

The invention discloses an active power output control parameter pre-processing method for a hydropower station during automatic power generation. The method involves an automatic generation control (AGC) functional block, a proportion integration differentiation (PID) functional block and a pre-processing functional block, and a device parameter and a dynamic parameter are directly input or processed by the pre-processing functional block and then are sent to the AGC functional block and the PID functional block for updating. An active power set value of a single machine of each power generation set can be calculated according to a full-station active power target value of the hydropower station, PID closed-loop adjustment is carried out on the active power actual value of the single machine, and the running requirements of the power generation seat evading from a vibration region and one-time frequency adjustment of the hydropower station are met; and a pre-built mode of inputting a combination output model of an AGC machine set is adopted, data conversion existing in a machine set form is data in a power station form, the solution efficiency is improved, and the automatic active power output control demands of different large- and medium-size hydropower stations with multiple vibration regions and multiple types of machines sets can be met.

Owner:HUANENG LANCANG RIVER HYDROPOWER

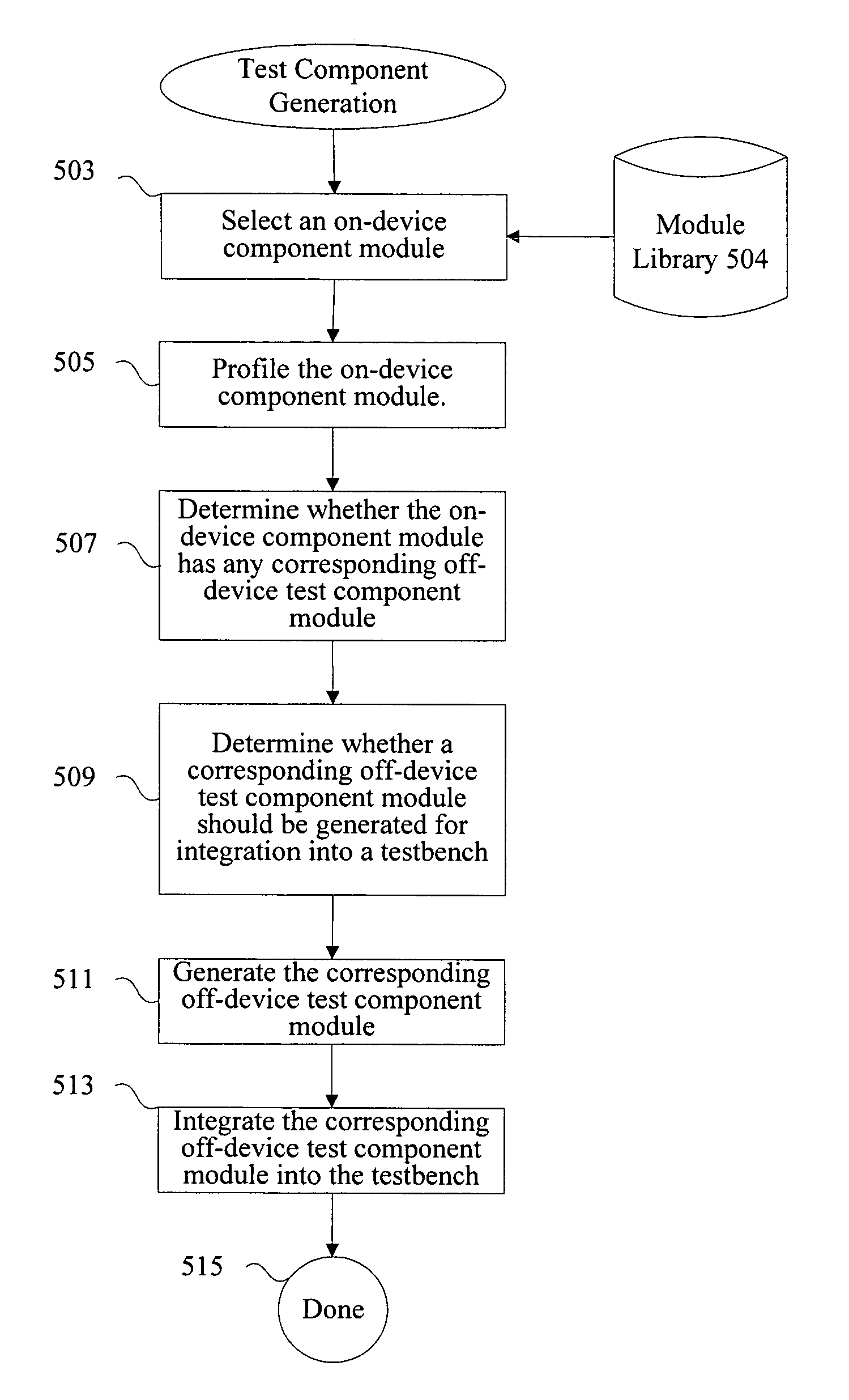

Methods and apparatus for automatic test component generation and inclusion into simulation testbench

InactiveUS7225416B1Generate efficientlyDetecting faulty computer hardwareElectrical testingConfiguration designEngineering

Methods and apparatus are provided for efficiently generating test components for testing and evaluating a design under test. As a design is being configured, generated test components are made available. In one example, test components are automatically generated and included in a simulation testbench based on selected components in the design. Generally, the test components complement the selected components in the design. Moreover, the test components can be automatically seeded with initial contents.

Owner:ALTERA CORP

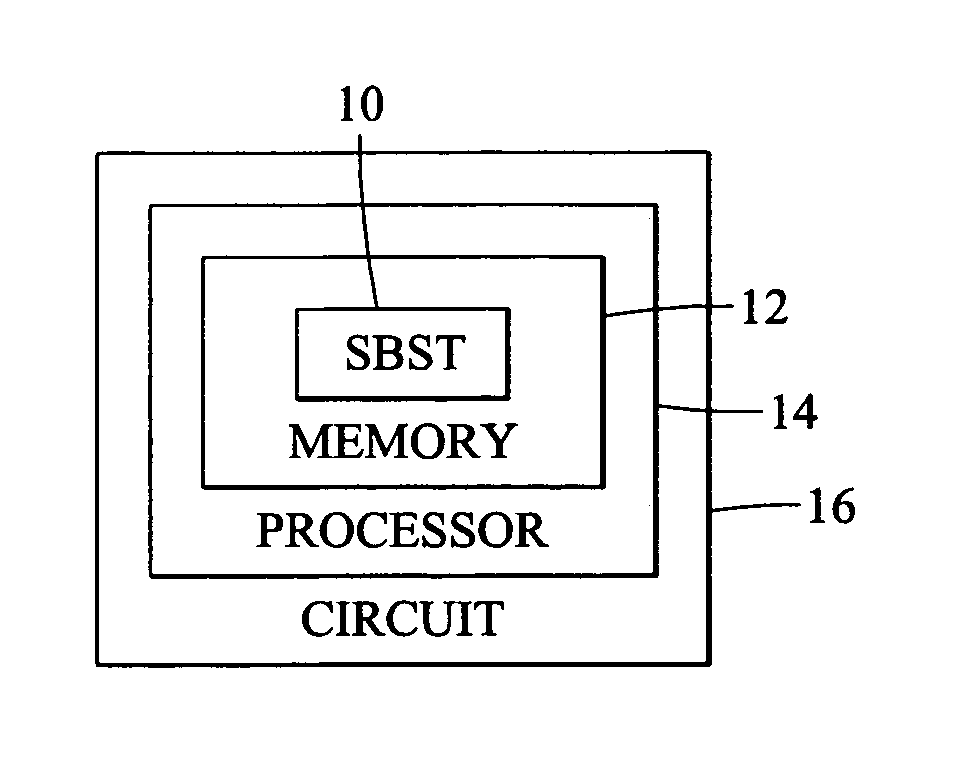

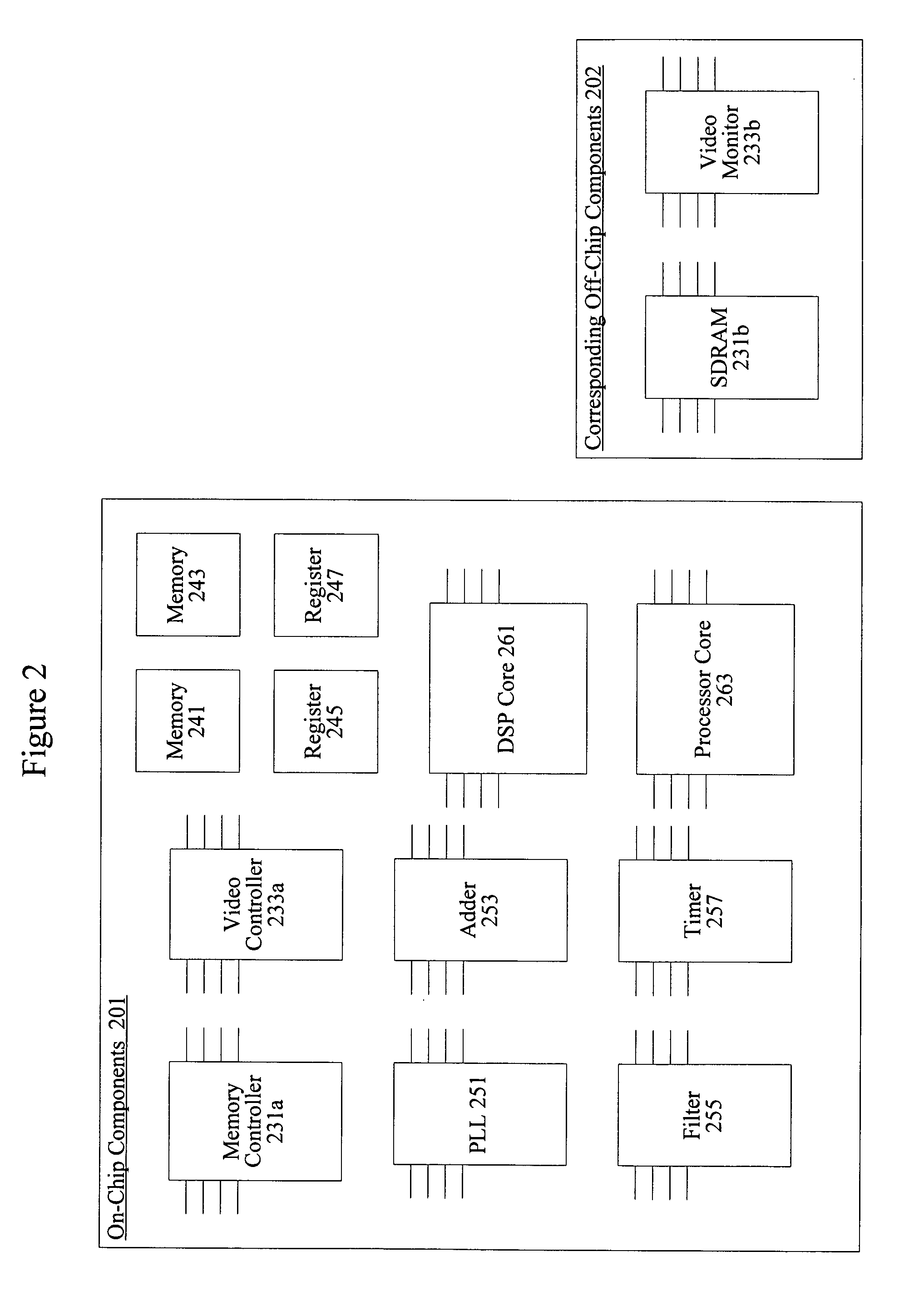

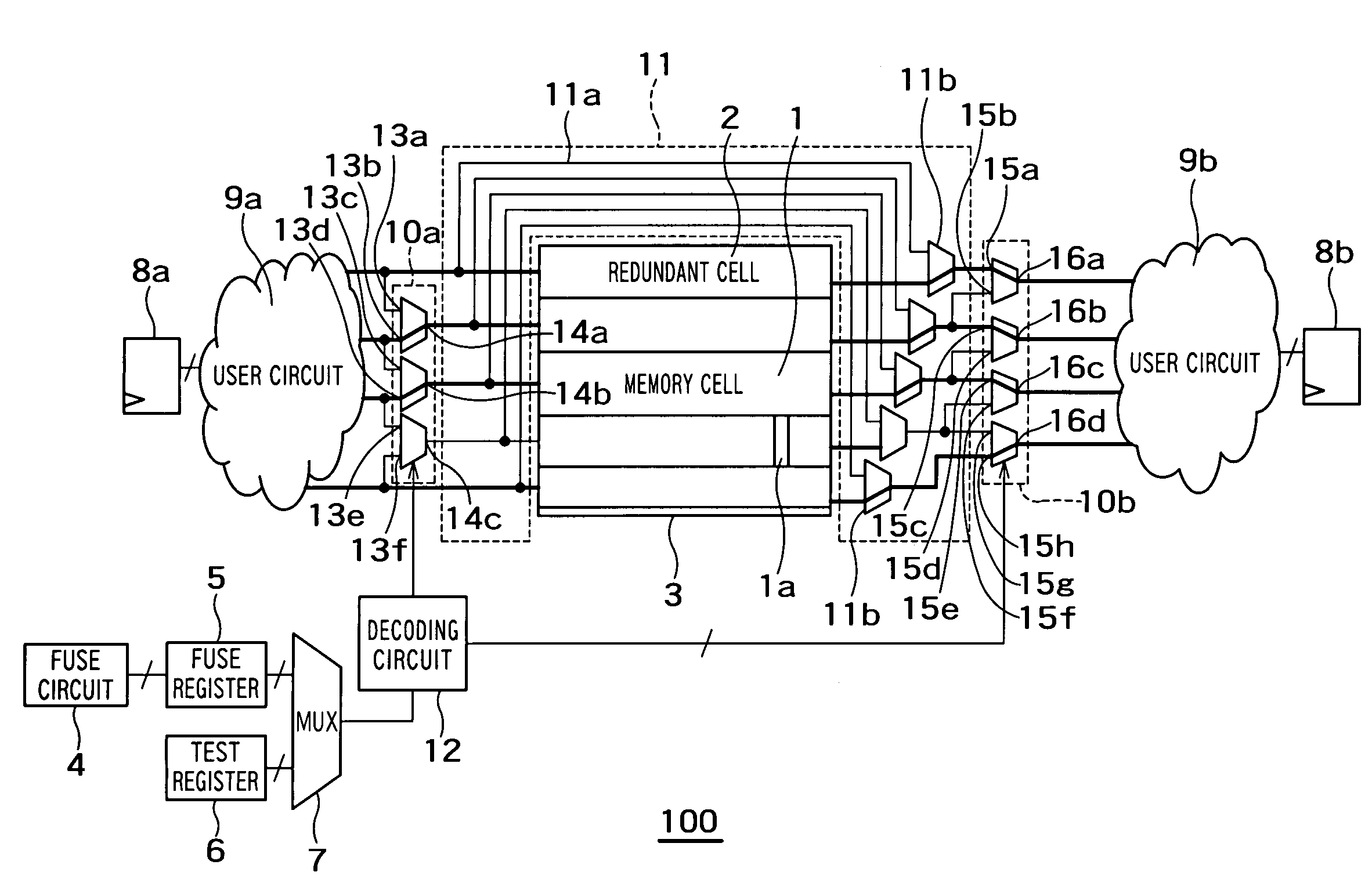

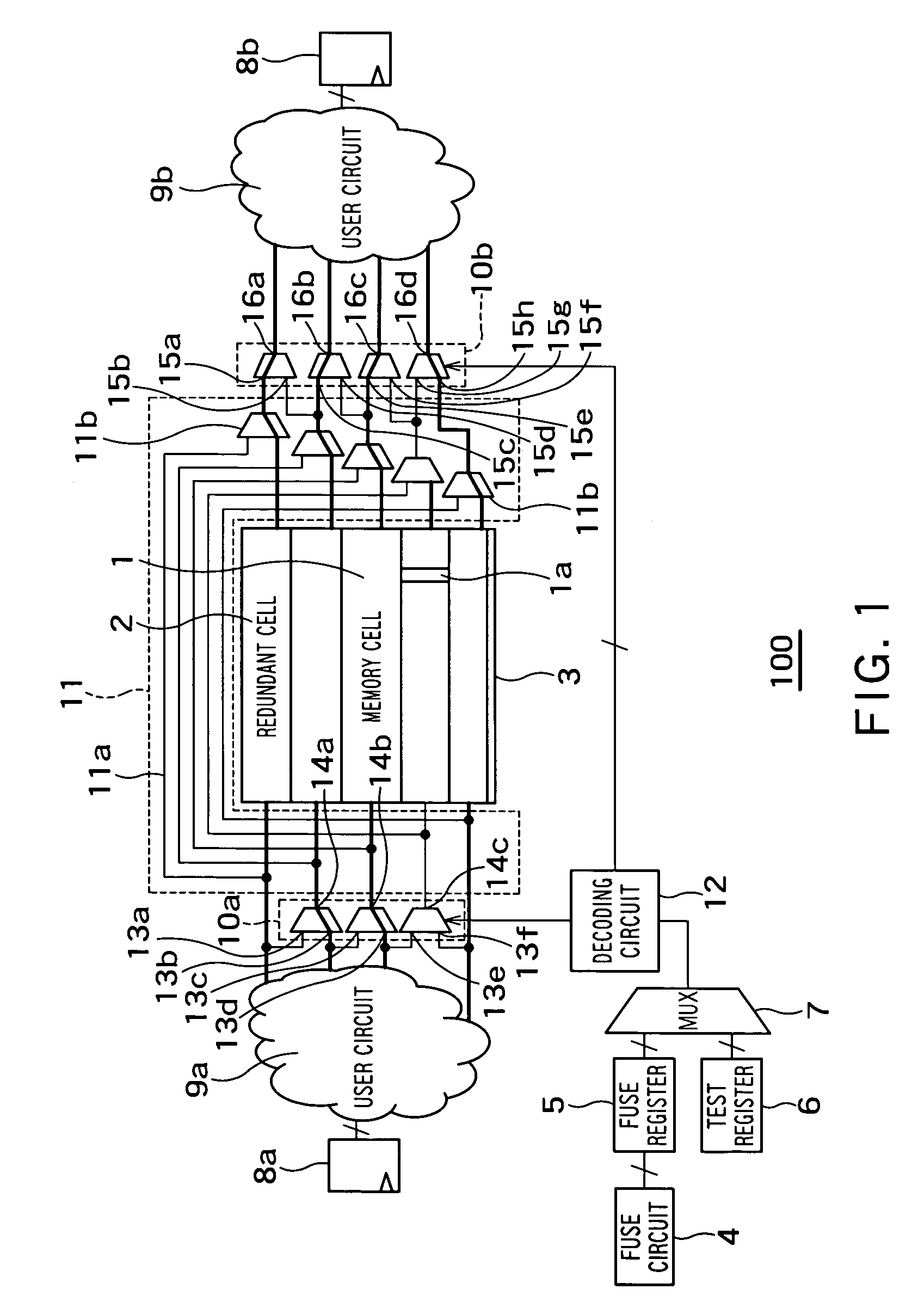

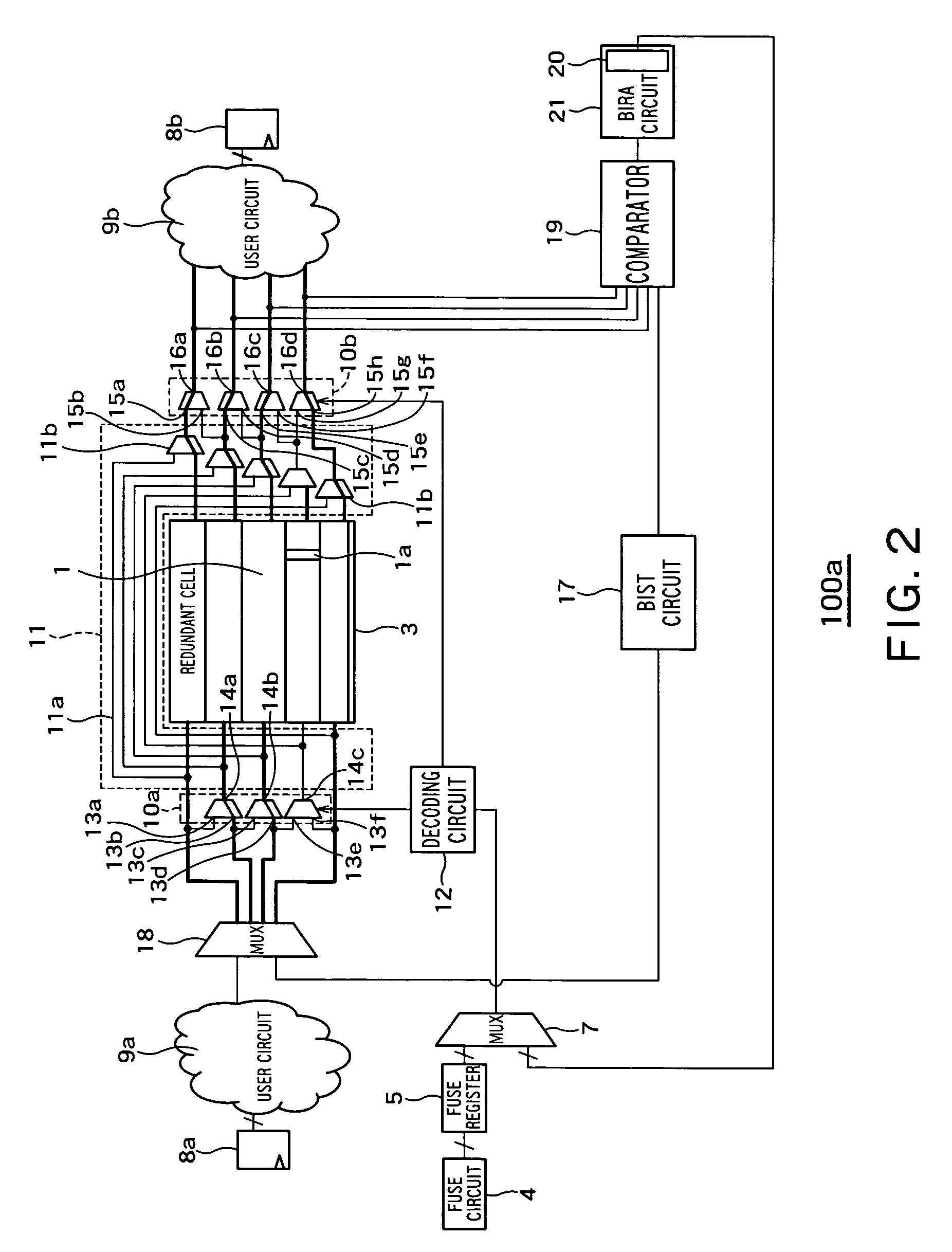

Semiconductor integrated circuit, design support software system and automatic test pattern generation system

ActiveUS7577885B2Electronic circuit testingError detection/correctionProcessor registerSoftware system

A semiconductor integrated circuit has a memory circuit having memory cells, a first register, a second register, a register selection circuit having an input to which an output of the first register and an output of the second register are connected, a memory bypass circuit which is located between a first switching circuit and a second switching circuit, and connected to the inputs and the outputs of the memory circuit. The register selection circuit is switched to the output signals of the first register when performing testing by way of the memory circuit, and switched to output signals of the second register when performing testing by way of the memory bypass circuit.

Owner:KK TOSHIBA

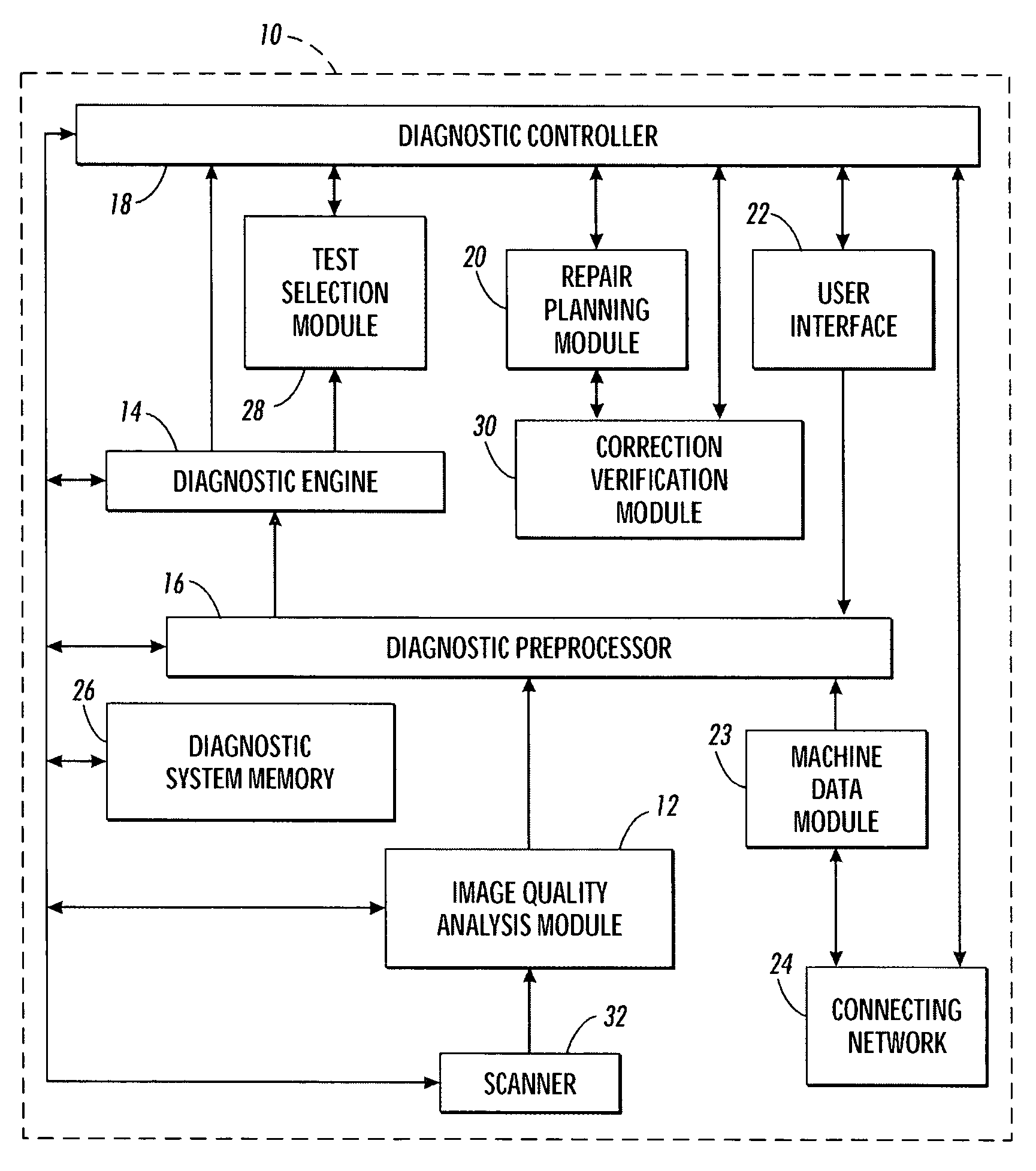

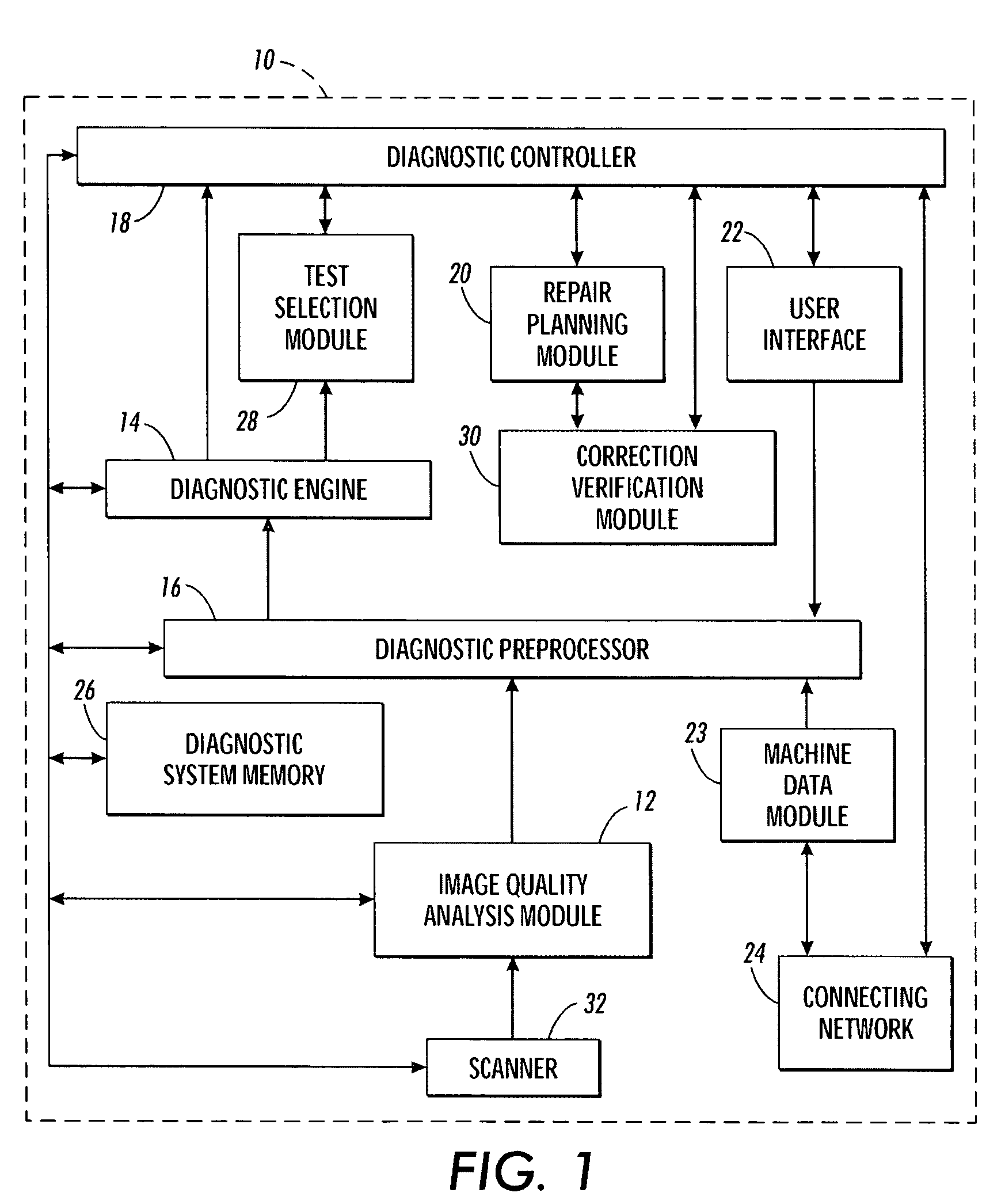

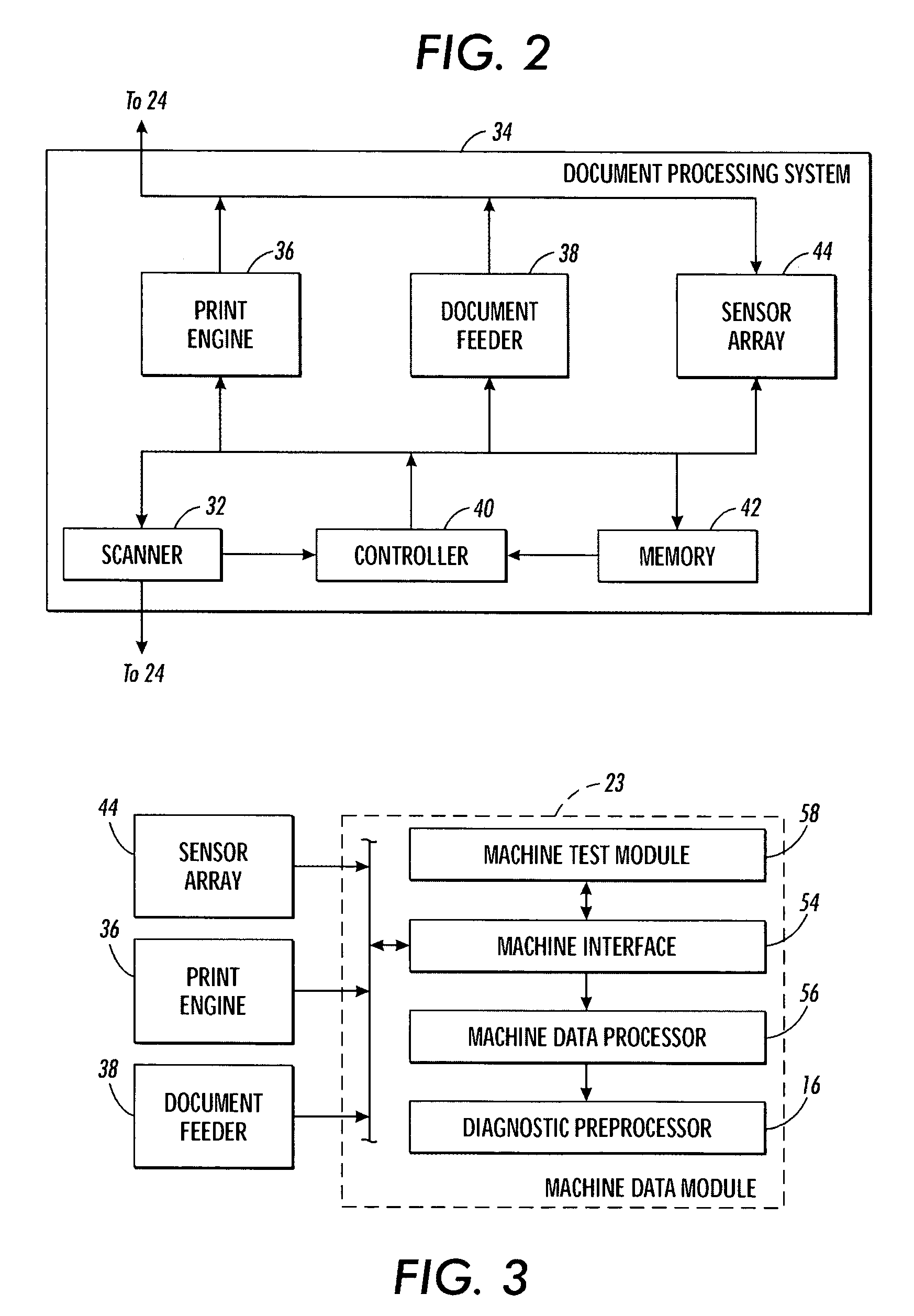

Dynamic test pattern composition for image-analysis based automatic machine diagnostics

The present invention is directed to a system and method for test target selection in conjunction with dynamic test pattern generation. In the invention, a test pattern page(s) is composed using an optimal set of test targets, which can be accommodated or adjusted to fit within size constraints of the test pattern. The method of the present invention makes use of layout optimization to ensure that related and optimized test targets are accommodated on a single test pattern. For example, it may be preferable to “squeeze in” a smaller-than-normal uniform area target, rather than not to print it at all during a test.

Owner:XEROX CORP

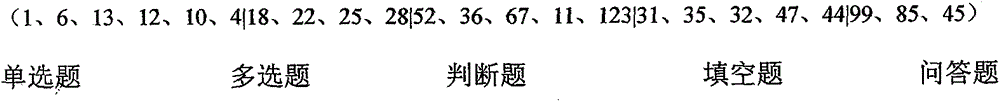

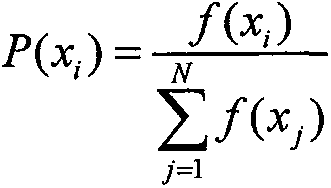

Automatic test paper generation method for test questions in question bank through genetic algorithm

InactiveCN105825270ACancel decoding timeShorten the formation timeGenetic modelsSoftware engineeringGenetic algorithm

The invention relates to a method for automatically forming test papers in a test bank by using a genetic algorithm. It adopts real number codes for the test questions in the test bank, which can overcome the shortcomings of using binary codes in the past that the search space is too large and the code length is too long. The decoding time of the test papers to be assembled improves the speed of obtaining the final test papers. In addition, the present invention generates the initial population of the test papers to be grouped by randomly generating the initial population according to the total number of questions, the proportion of questions, and the total score of the test papers to be grouped, which can speed up the convergence of the genetic algorithm and reduce the number of iterations, thereby reducing Formation time of the test paper. Therefore, the present invention can be widely used in the field of automatic paper formation.

Owner:EDUCATION TRAINING & EVALUATION CENT OF YUNNAN POWER GRID CO LTD

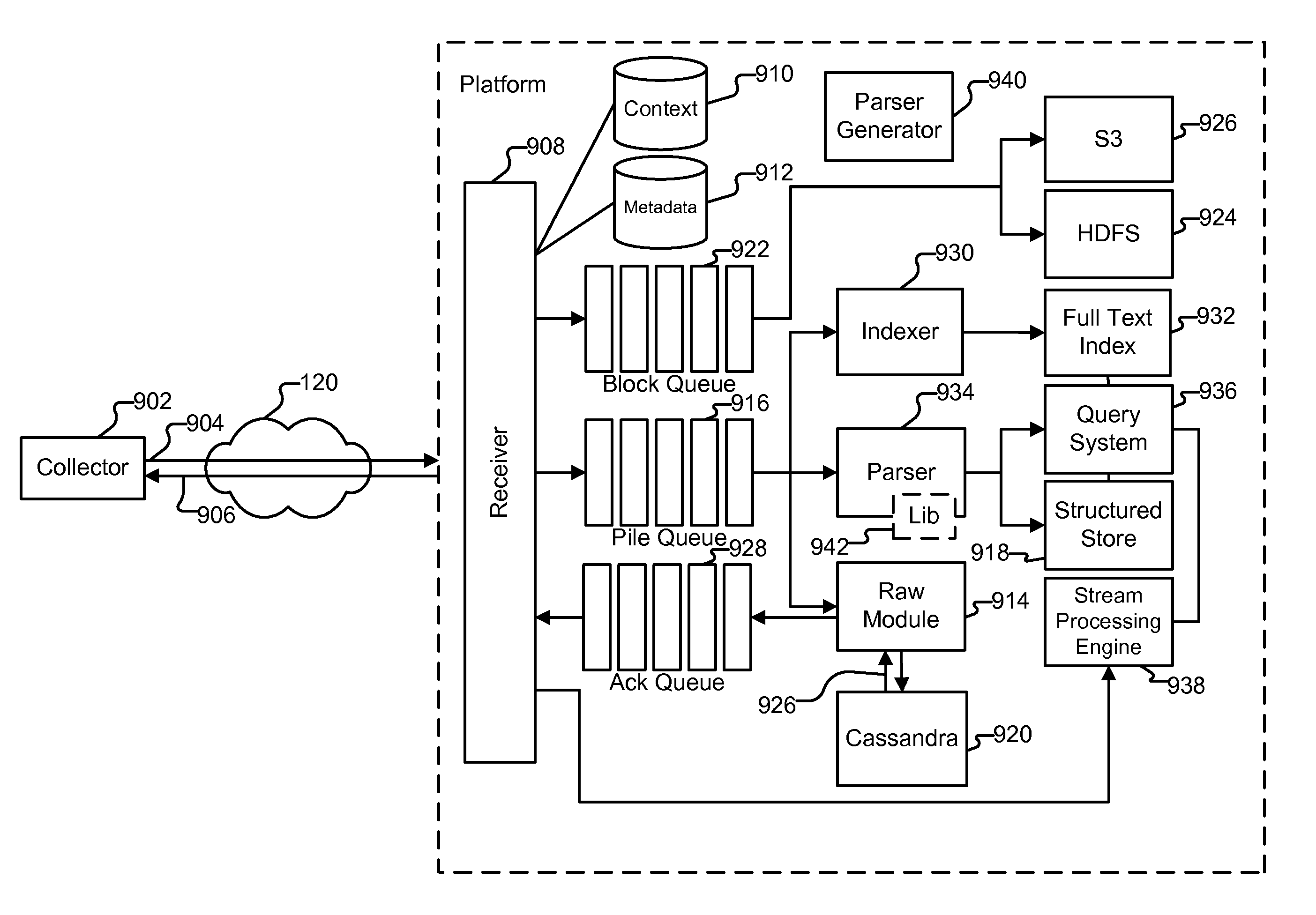

Automatic parser generation

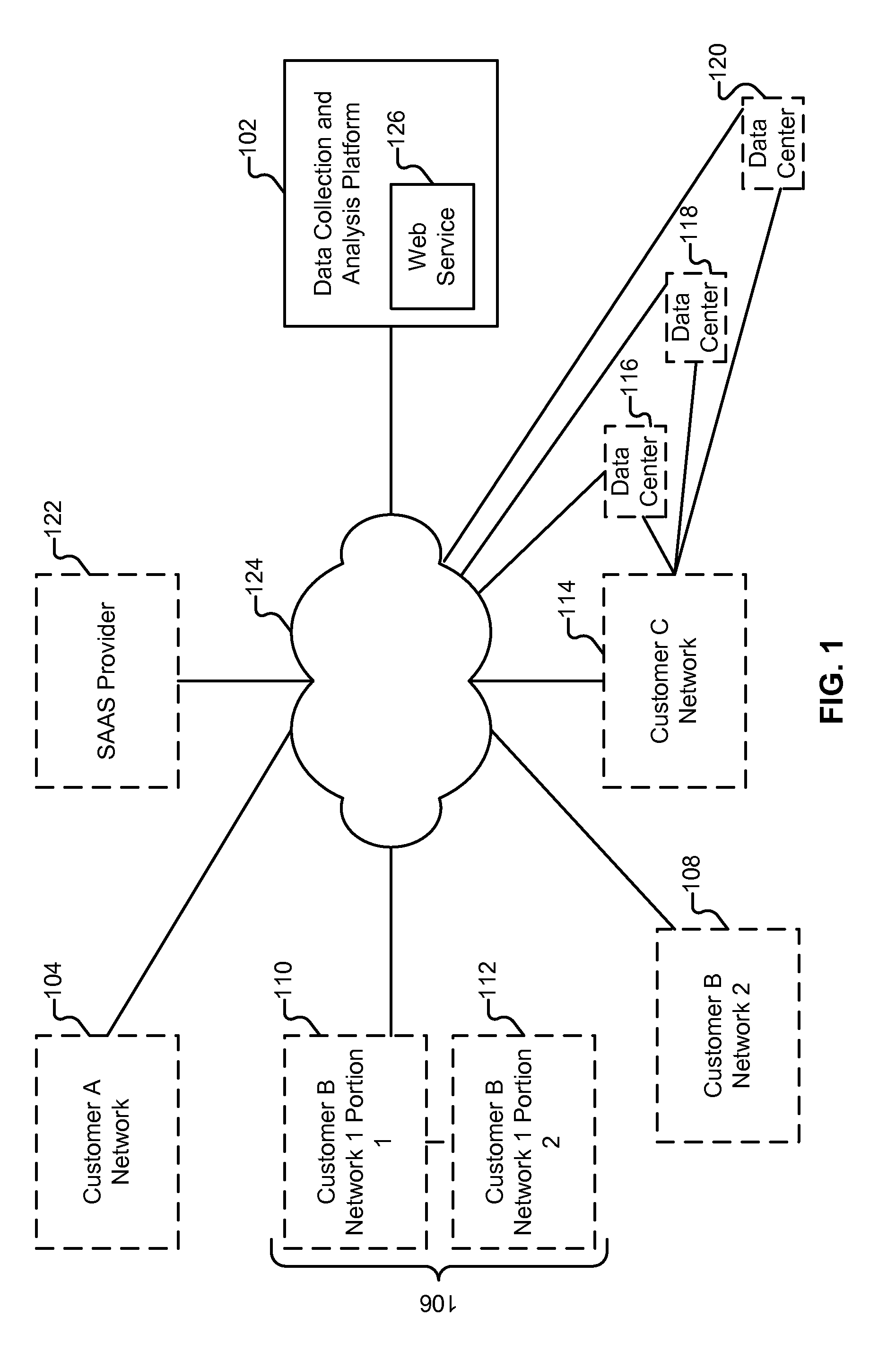

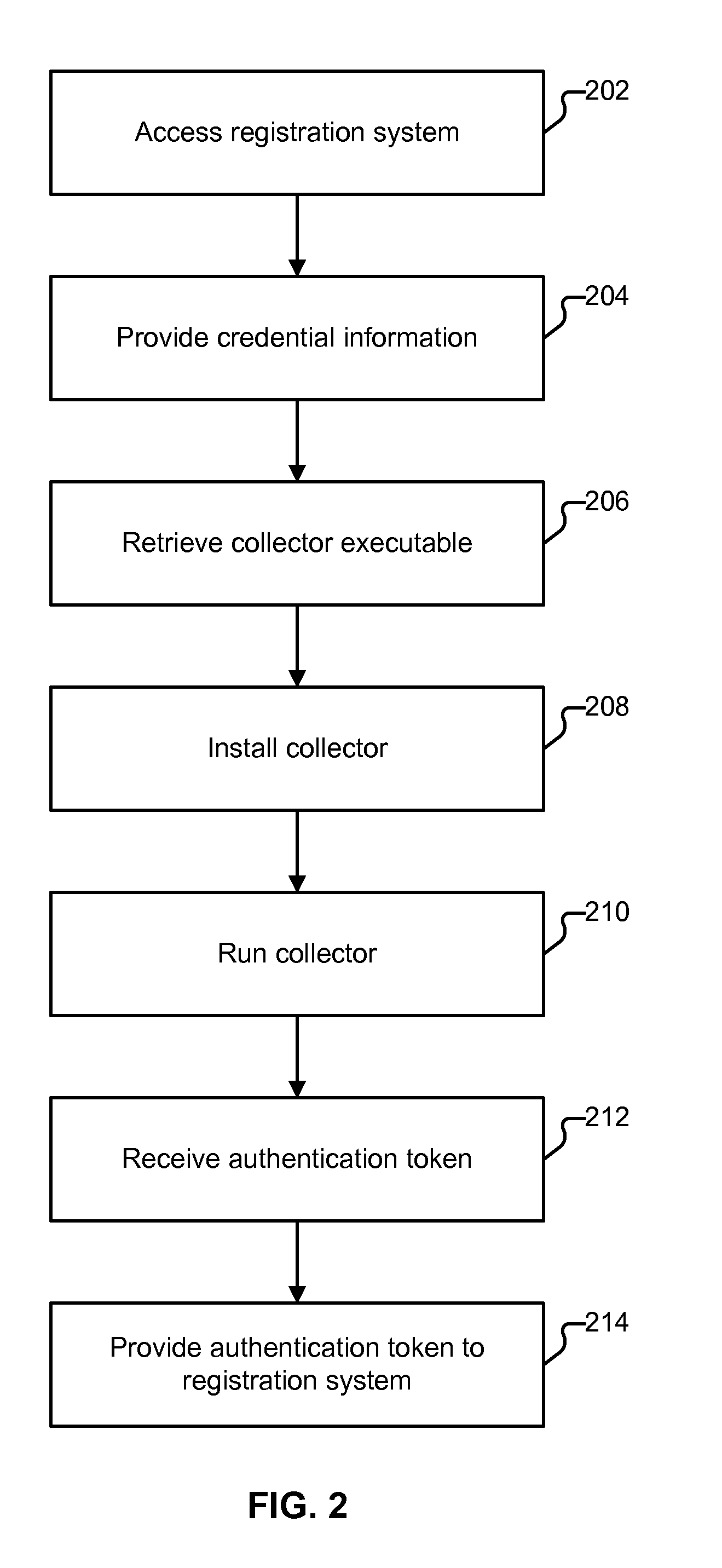

Automatically generating a parser is disclosed. Raw data is received from a first remote device. A determination that the raw data does not, within a predefined confidence measure, conform to any rules included in a set of rules is made. A clustering function is performed on the raw data. At least one parser rule is generated based on the clustering.

Owner:SUMO LOGIC INC

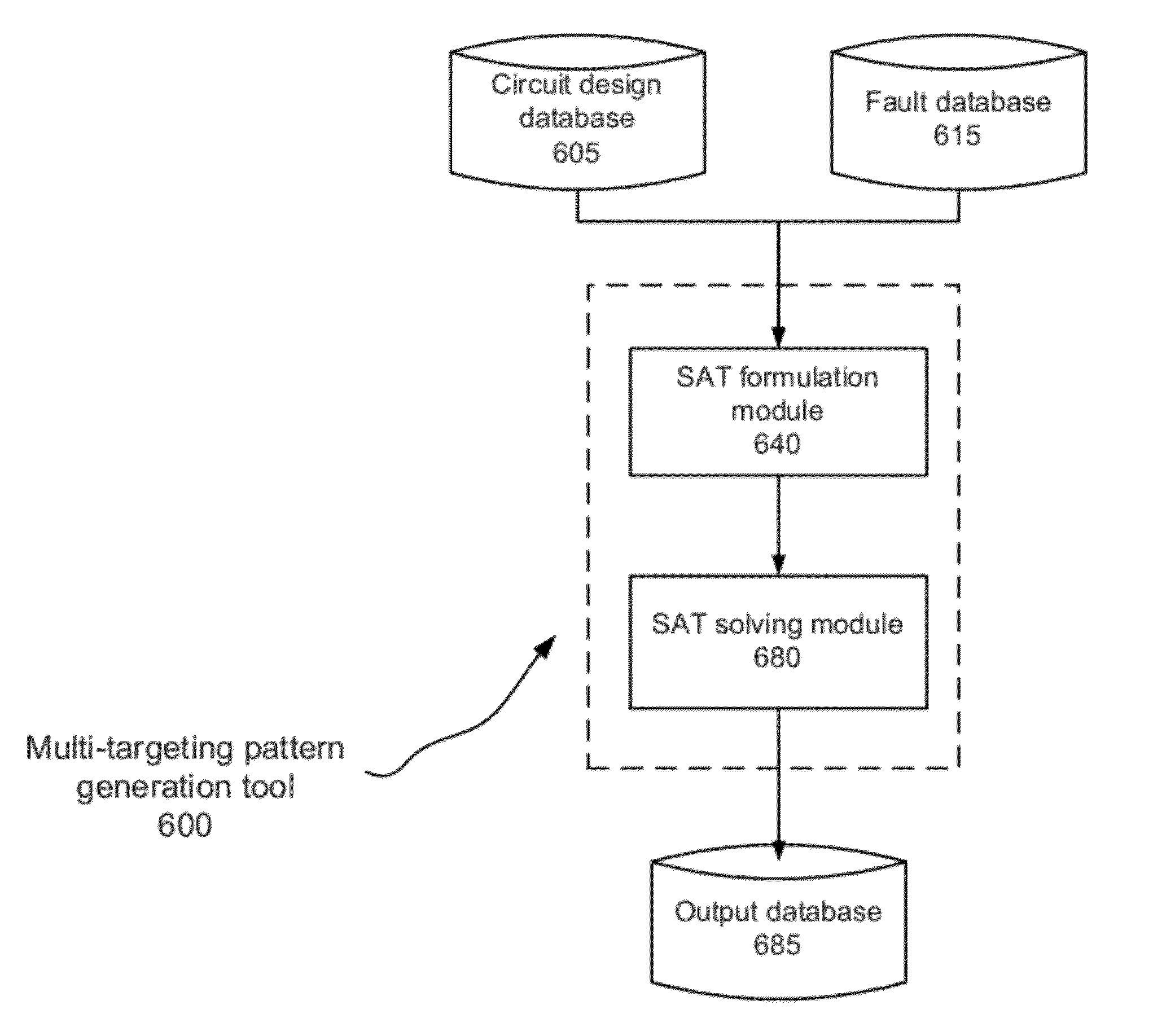

Multi-targeting boolean satisfiability-based test pattern generation

ActiveUS20120317454A1Electronic circuit testingError detection/correctionPattern generationAutomatic test pattern generation

Disclosed are representative examples of methods, apparatus, and systems for generating test patterns targeting multiple faults using Boolean Satisfiability (SAT)-based test pattern generation methods. A SAT instance is constructed based on the circuit design information and a set of faults being targeted. A SAT solving engine is applied to the SAT instance to search for a test pattern for detecting the set of faults. The SAT instance or the SAT solving engine may be modified so that the SAT solving engine will search for a test pattern for detecting a maximum number of faults in the set of faults.

Owner:SIEMENS PROD LIFECYCLE MANAGEMENT SOFTWARE INC

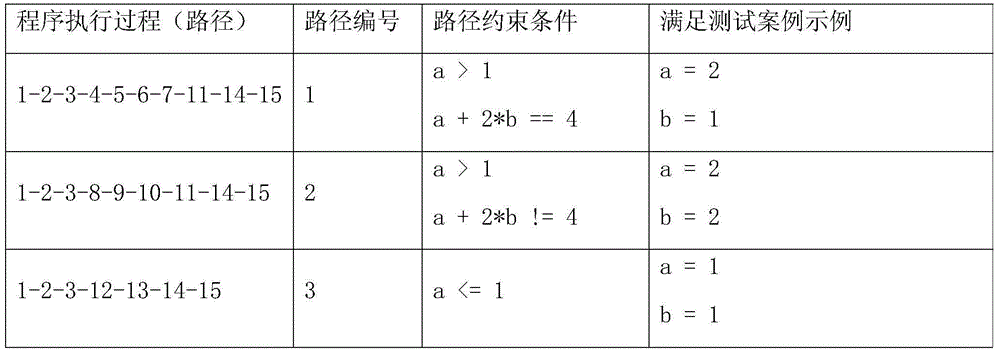

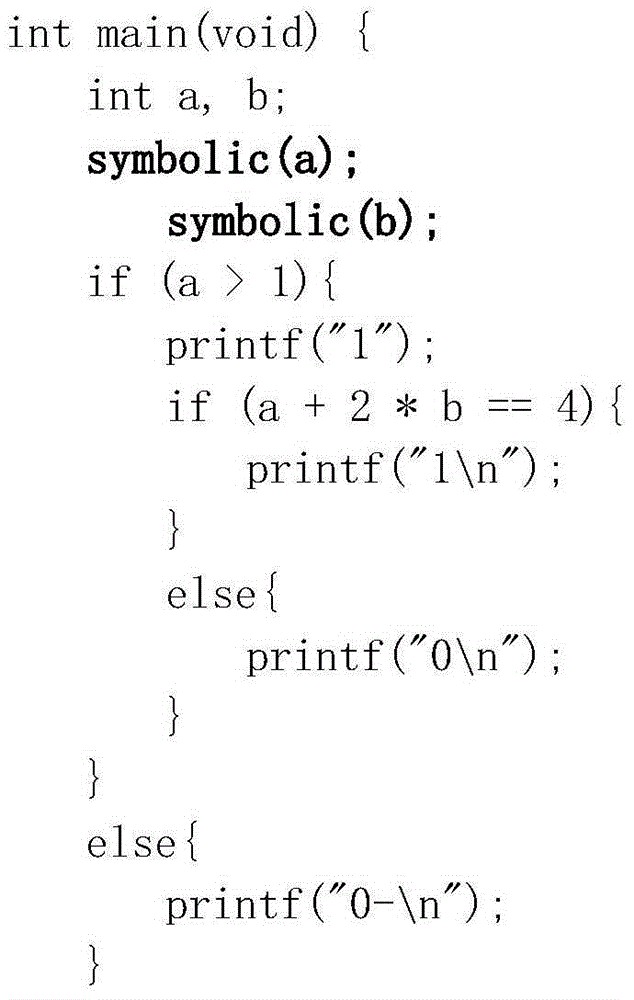

Distributed automatic test case generation method based on dynamic symbolic execution

ActiveCN105117341AAchieve independenceEasy to analyze and processSoftware testing/debuggingTest efficiencySemantics

The invention belongs to a distributed automatic test case generation method based on dynamic symbolic execution in the technical field of software test case automatic generation. The method comprises the following steps of: configuration of a test device, pre-processing of a program under test, extraction of a path constraint condition, and automatic generation of the test case. According to the invention, the program under test is separated from a test case automatic generation tool, and the program under test can run on a real platform in test, thus, the collected path constraint condition follows own semantics of the program, is accurate, and is helpful for analyzing complex data structures, thereby improving reliability and validity of test; moreover, multiple programs under test can be tested at the same time, and multiple parallel multi-path selection methods are provided. Therefore, the distributed automatic test case generation method based on dynamic symbolic execution has the characteristics of running the program under test on the real platform, having high reliability, being capable of performing multiple tests at the same time, effectively improving test reliability, test accuracy and test efficiency, having high utilization rate of test tools, and so on.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

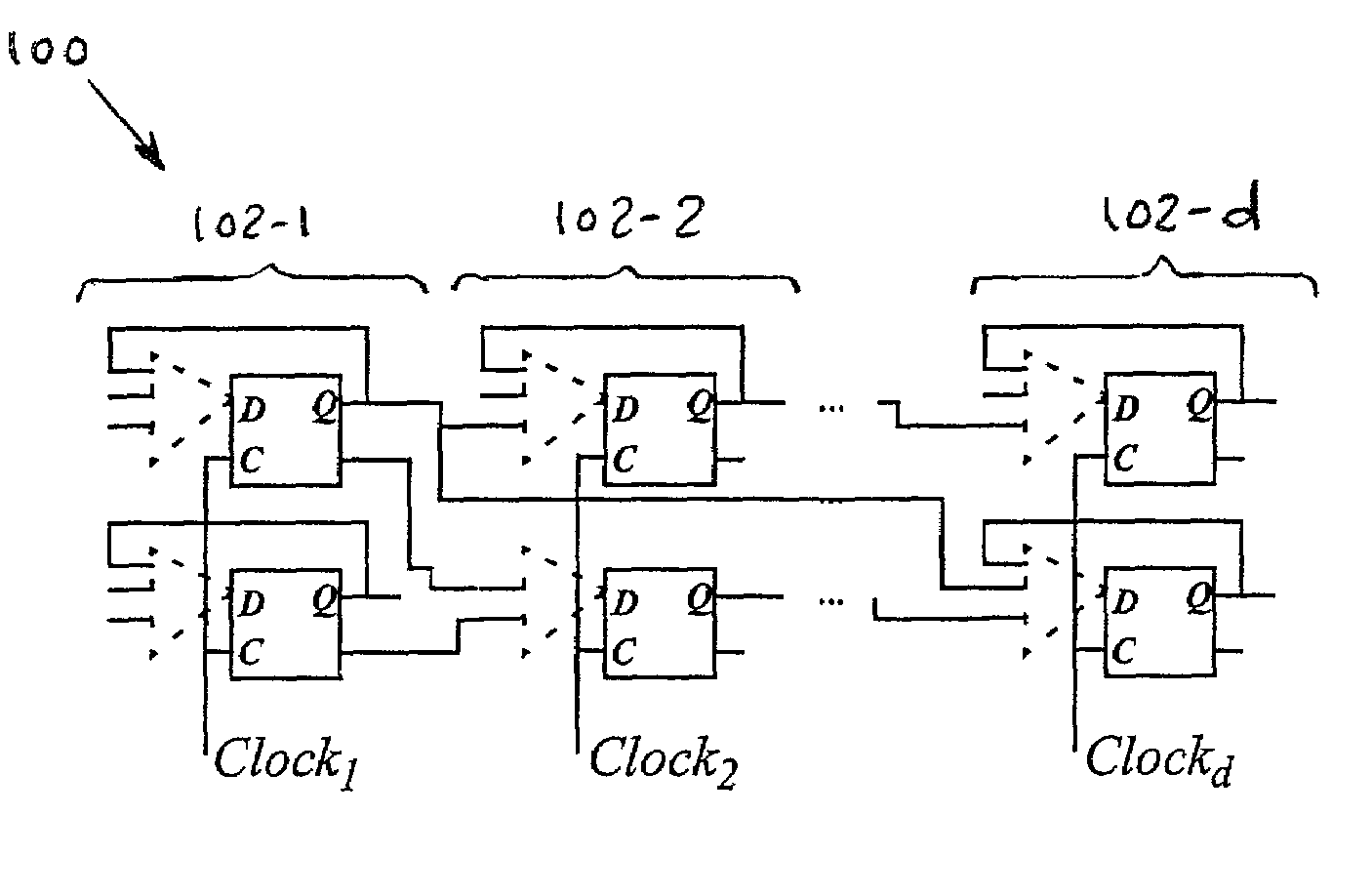

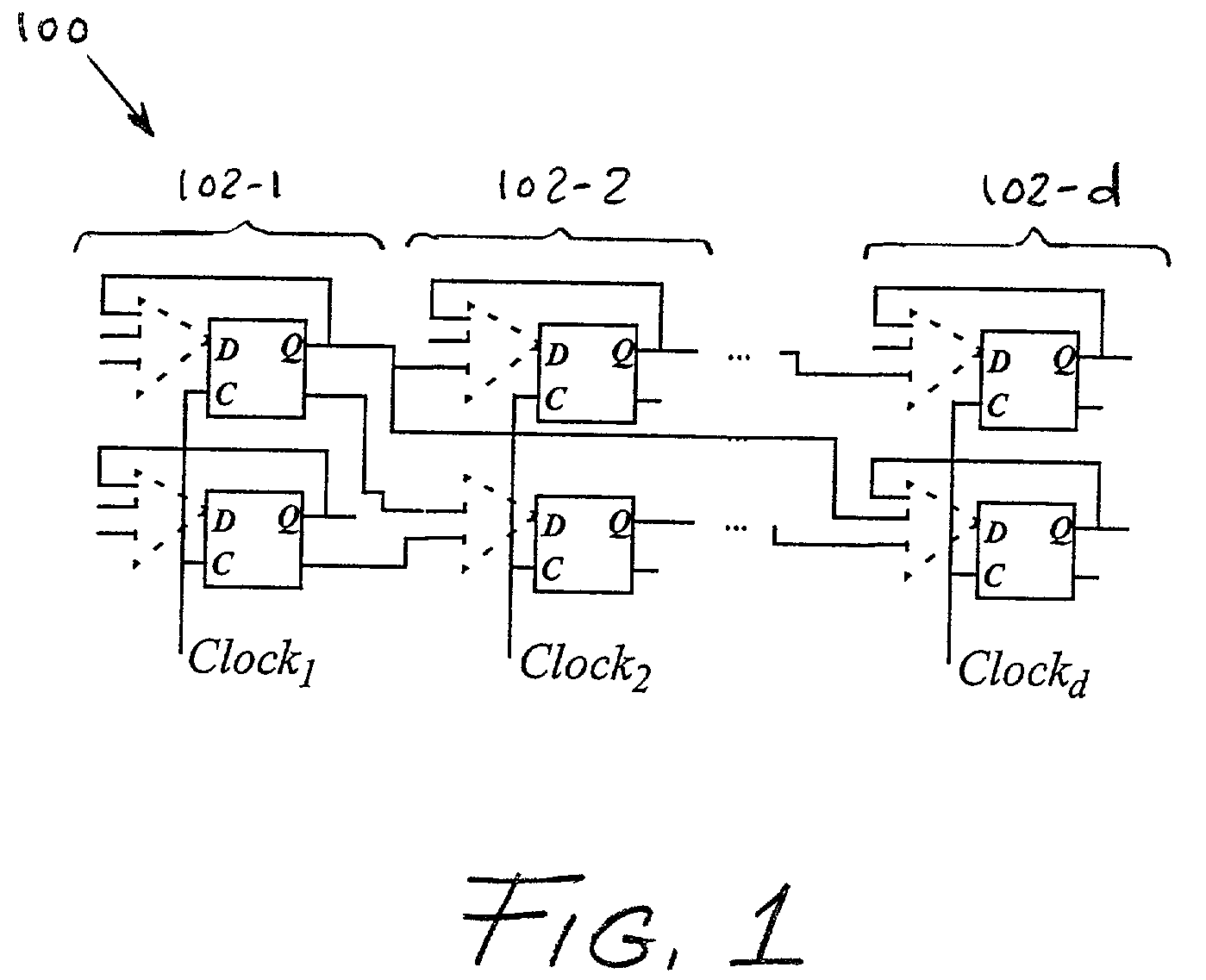

Sequential test pattern generation using clock-control design for testability structures

InactiveUS7017096B2No delay penaltiesSmall area overheadDigital circuit testingError detection/correctionProcessor registerPattern generation

Techniques for testing a sequential circuit comprising a plurality of flip-flops or other types of registers. The circuit is first configured such that substantially all feedback loops associated with the registers, other than one or more self-loops each associated with a corresponding one of the registers, are broken. Test patterns are then generated for application to the circuit. The test patterns are applied to the circuit in conjunction with partitioned clock signals each of which is associated with a corresponding level of the circuit containing at least one of the self-loops.

Owner:BELL SEMICON LLC

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com