Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

123 results about "High density packaging" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

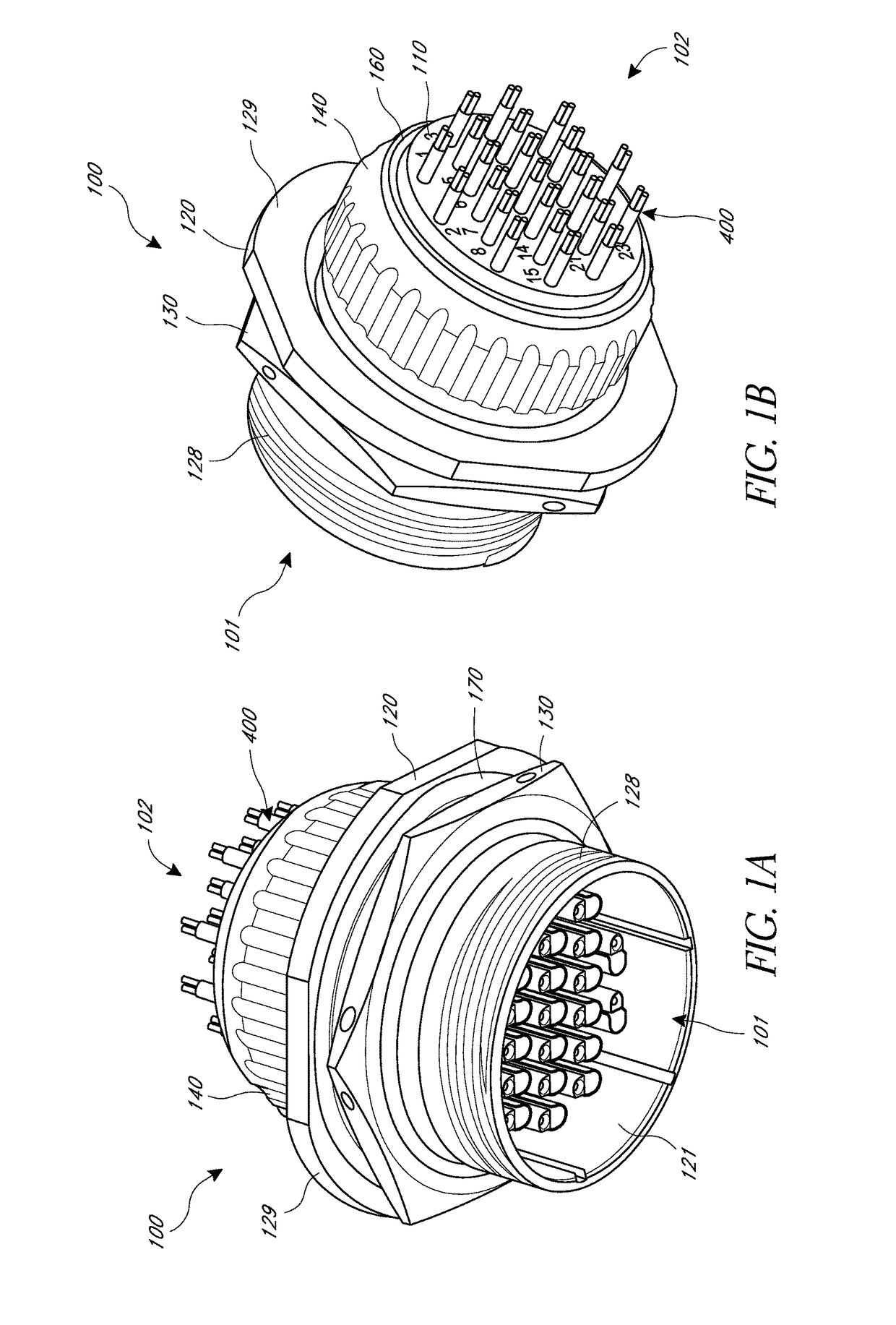

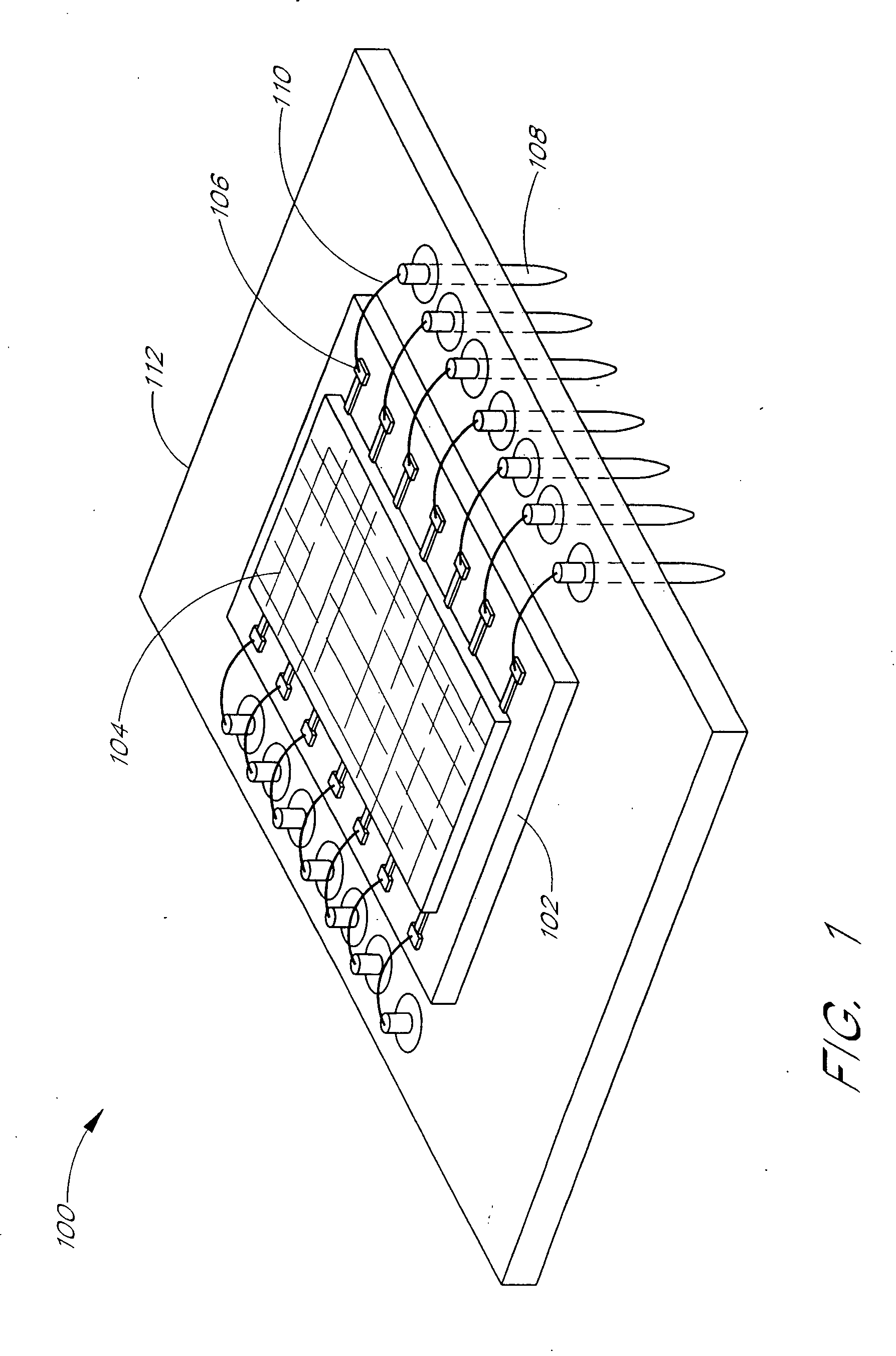

Genderless electrical connectors

ActiveUS9680268B1Reduce noiseReduce electric fluxSecuring/insulating coupling contact membersCoupling contact membersHigh density packagingElectrical and Electronics engineering

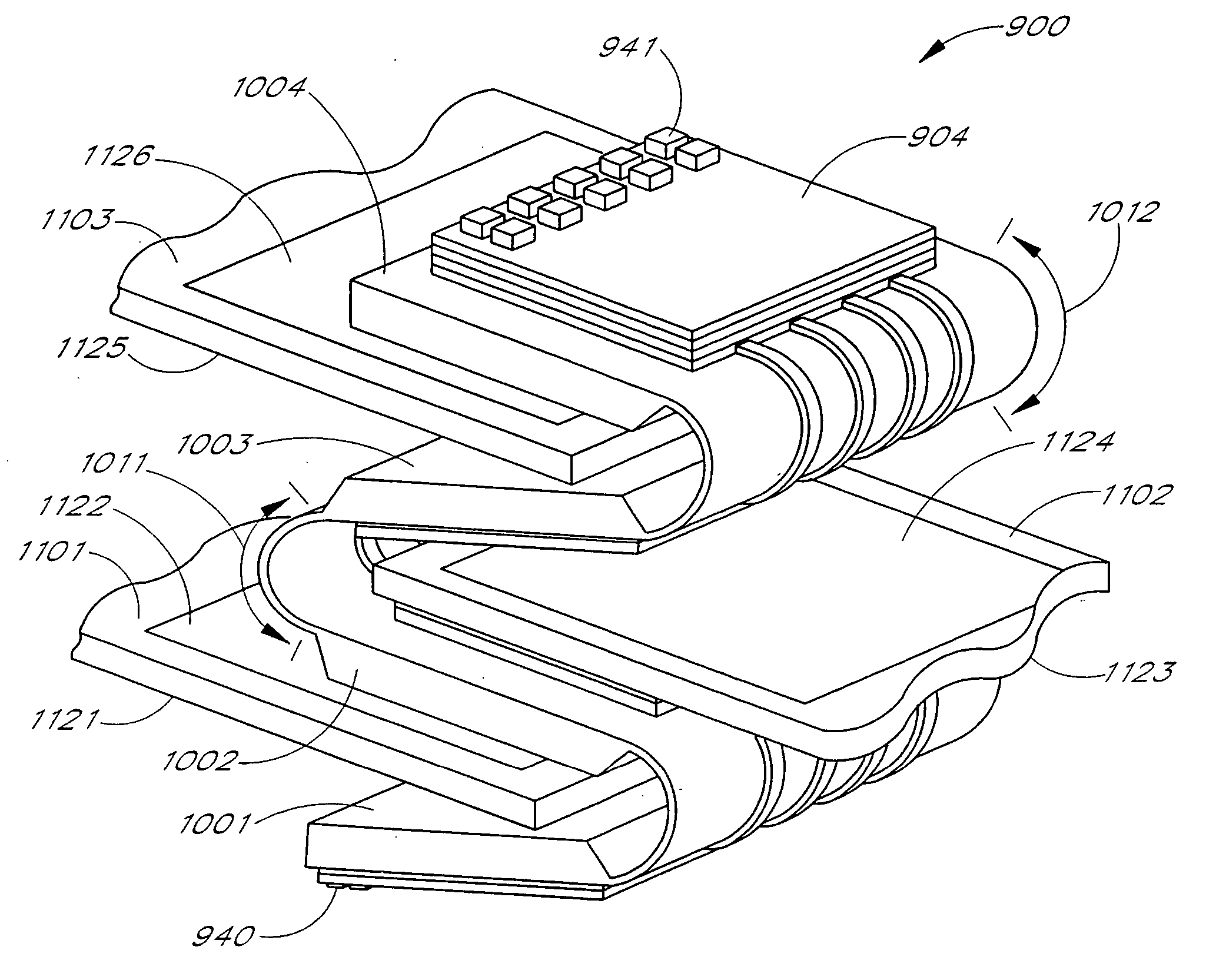

Various components and methods related to electrical connectors are disclosed. The electrical connectors can be configured to receive a plurality of cables. The electrical connectors can be configured to accommodate a plurality of cables so as to provide a high density packaging within each of the pair of electrical connectors. In order to provide appropriate shielding against electric flux and to reduce noise, each of the plurality of cables can be retained within a genderless insert that can be inserted through each of the pair of electrical connectors. Each of the genderless inserts can include an engagement end that allows the interconnection of the cables retained within the pair of electrical connectors. In some examples, the engagement end of each of the genderless inserts includes both a male and female component.

Owner:ITT MFG ENTERPRISES LLC

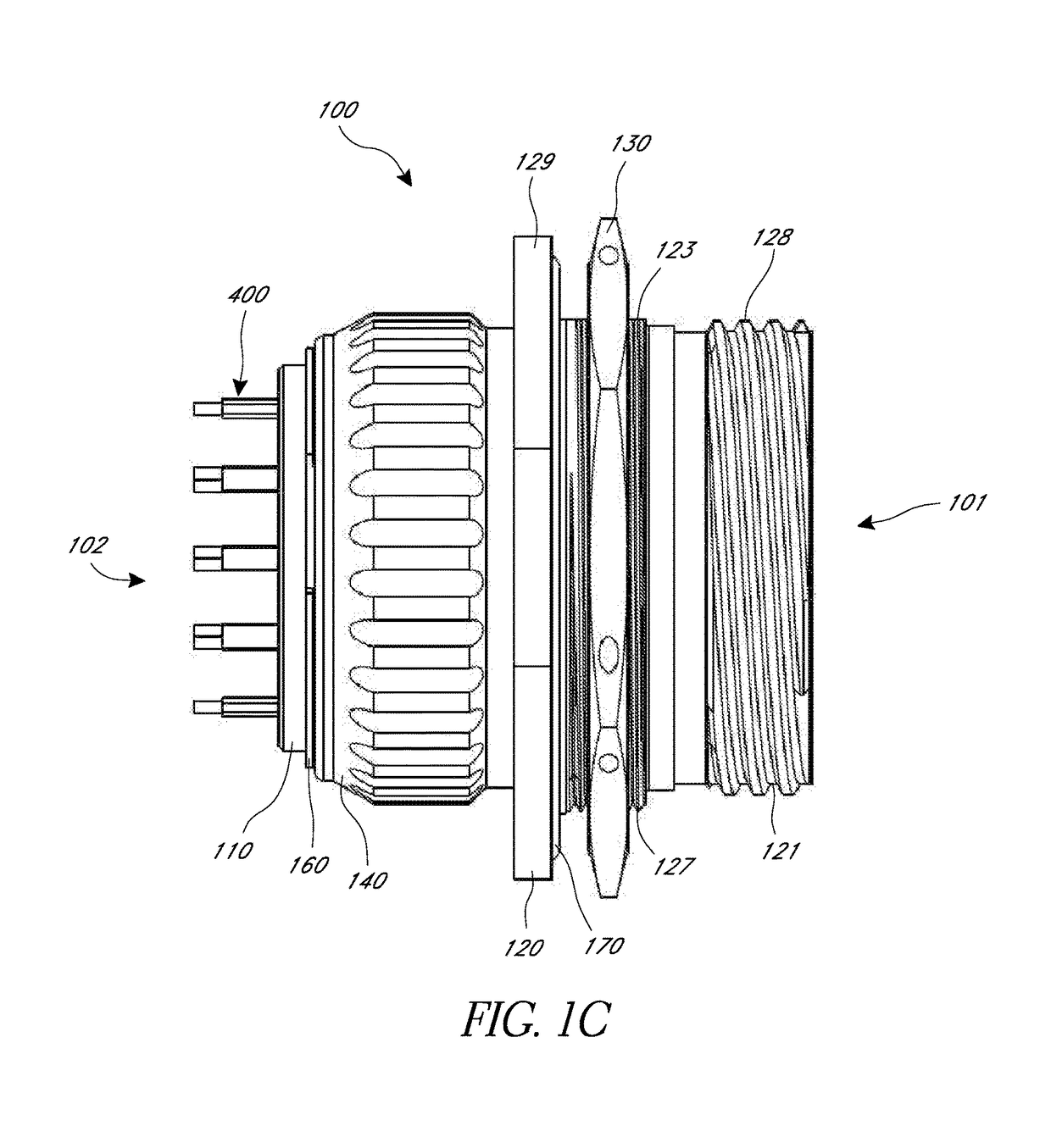

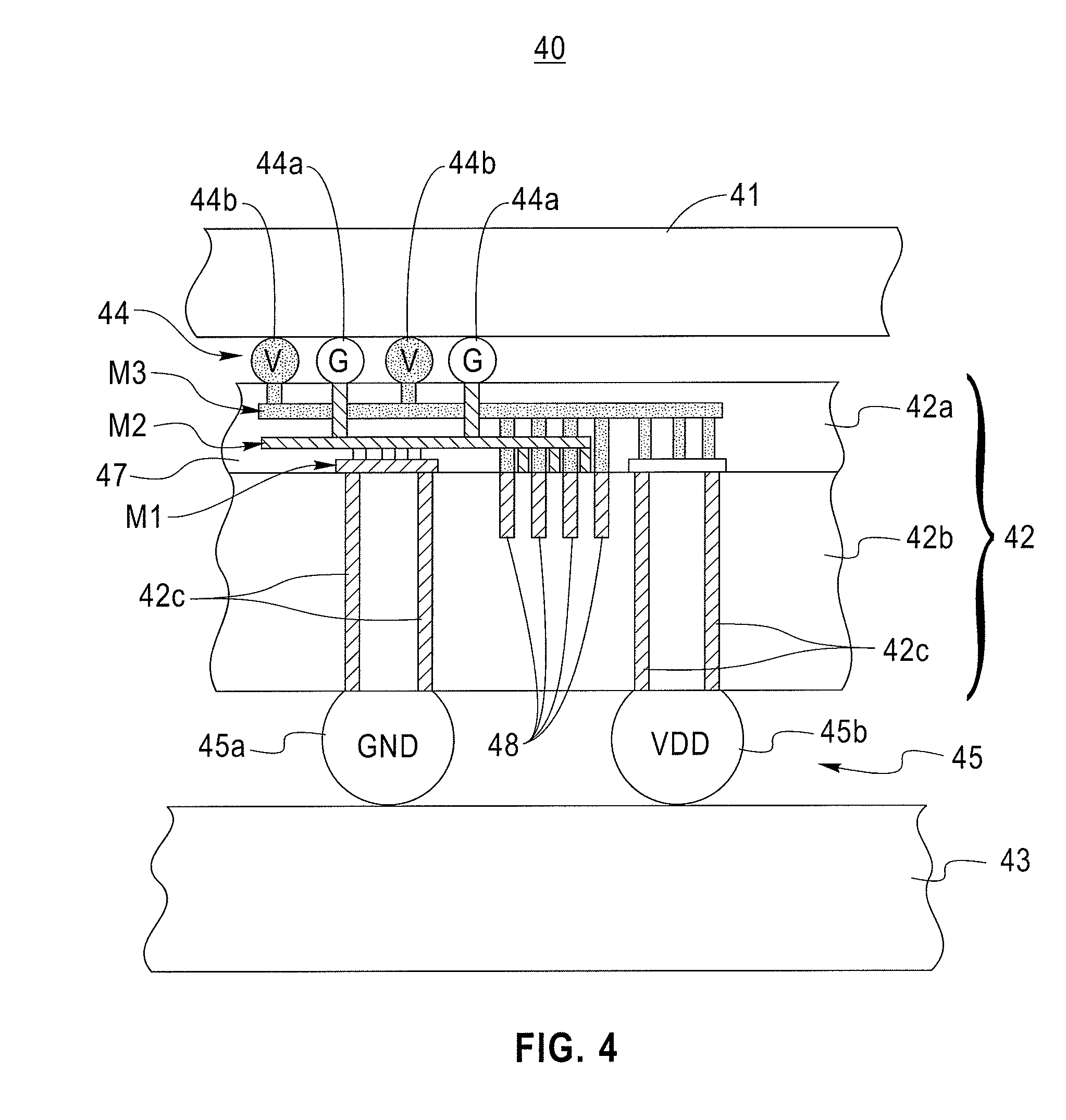

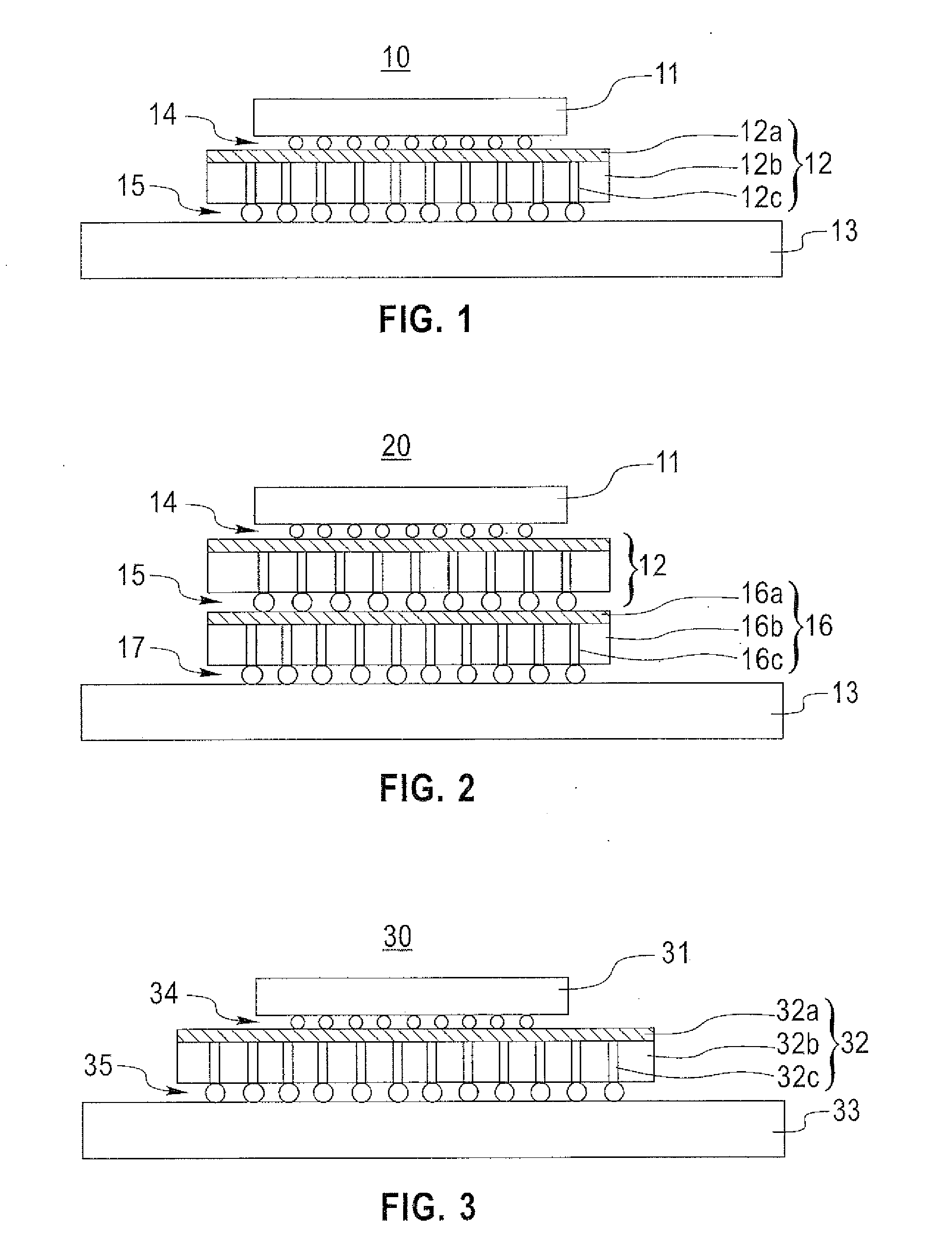

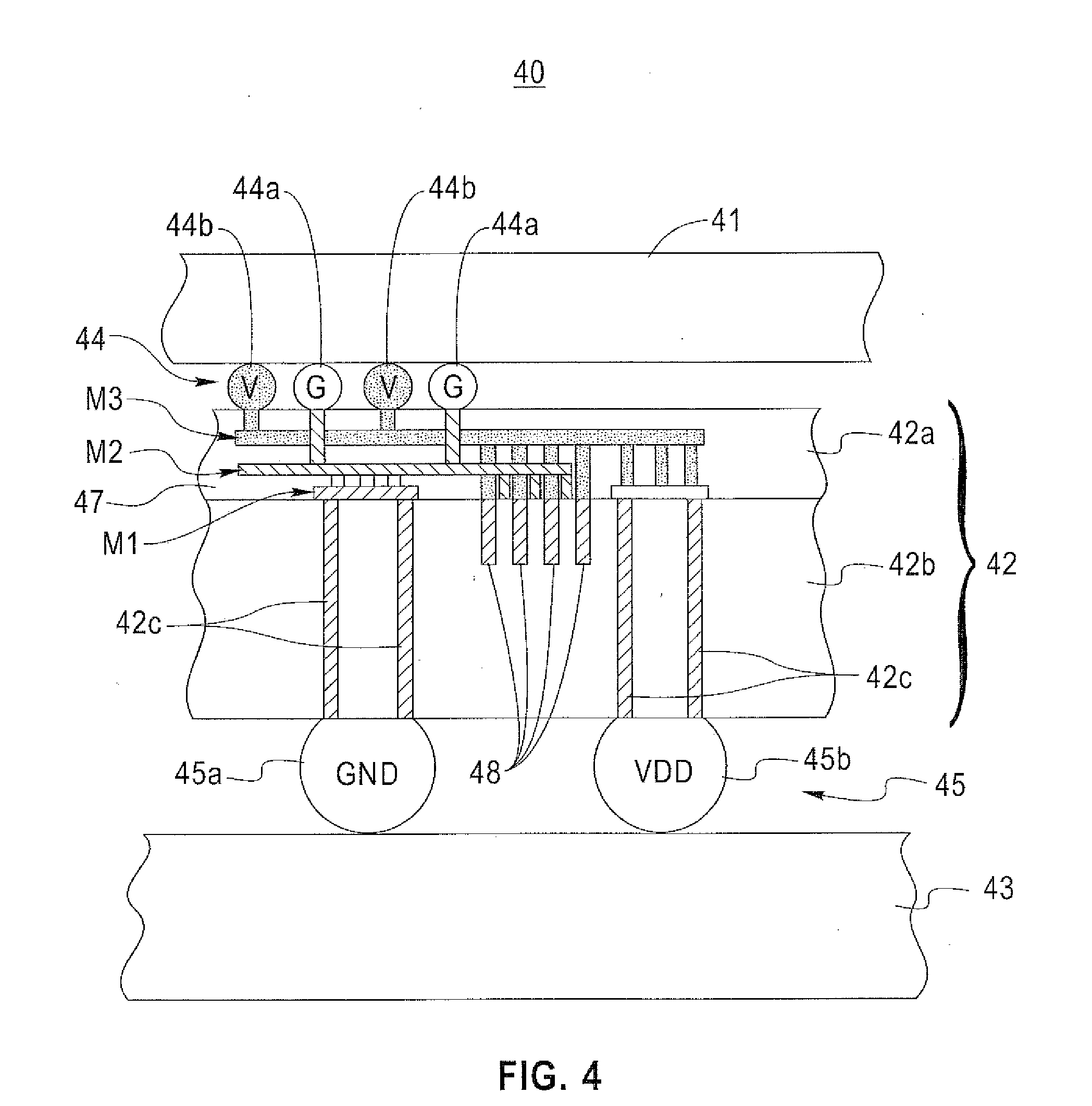

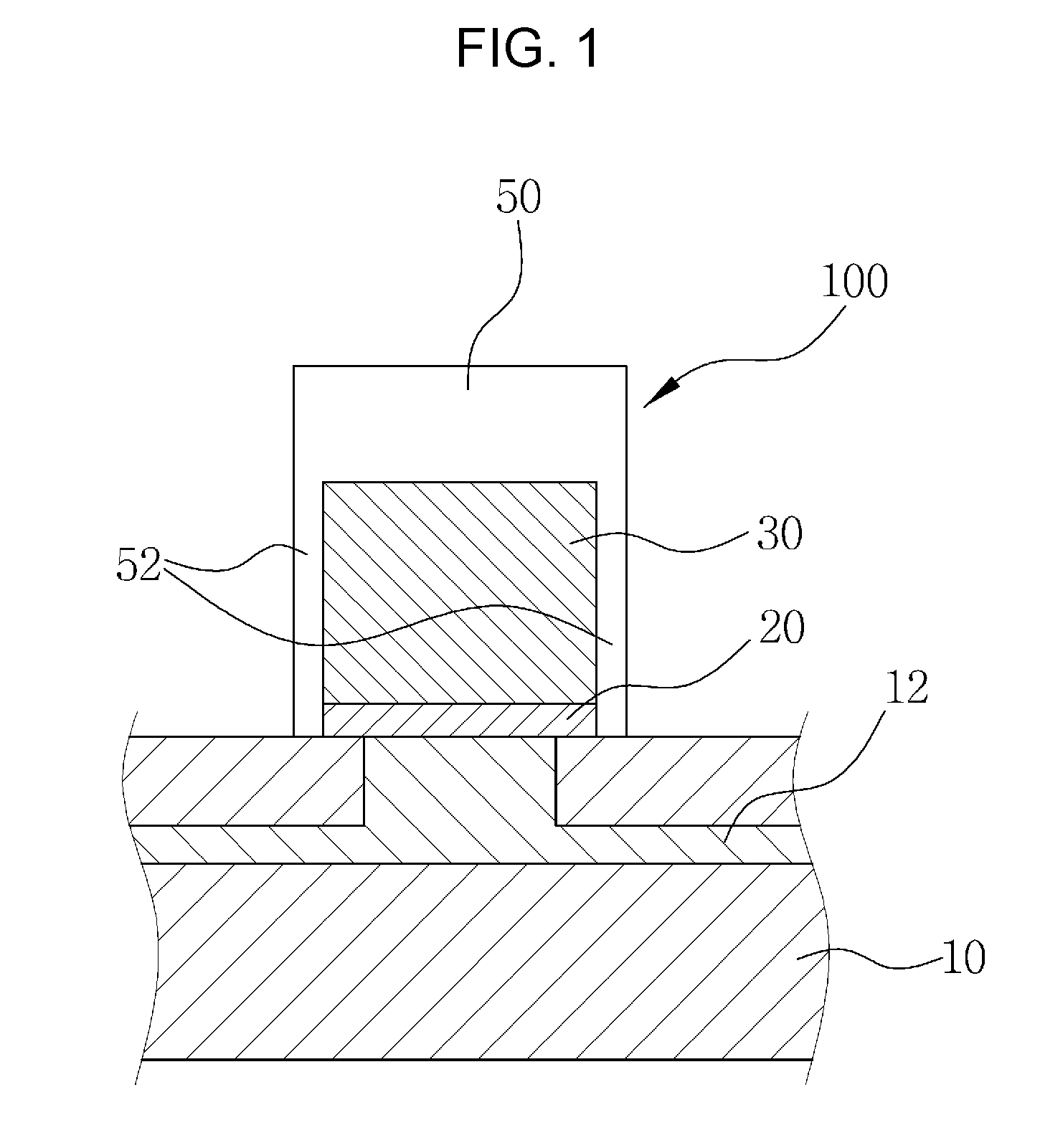

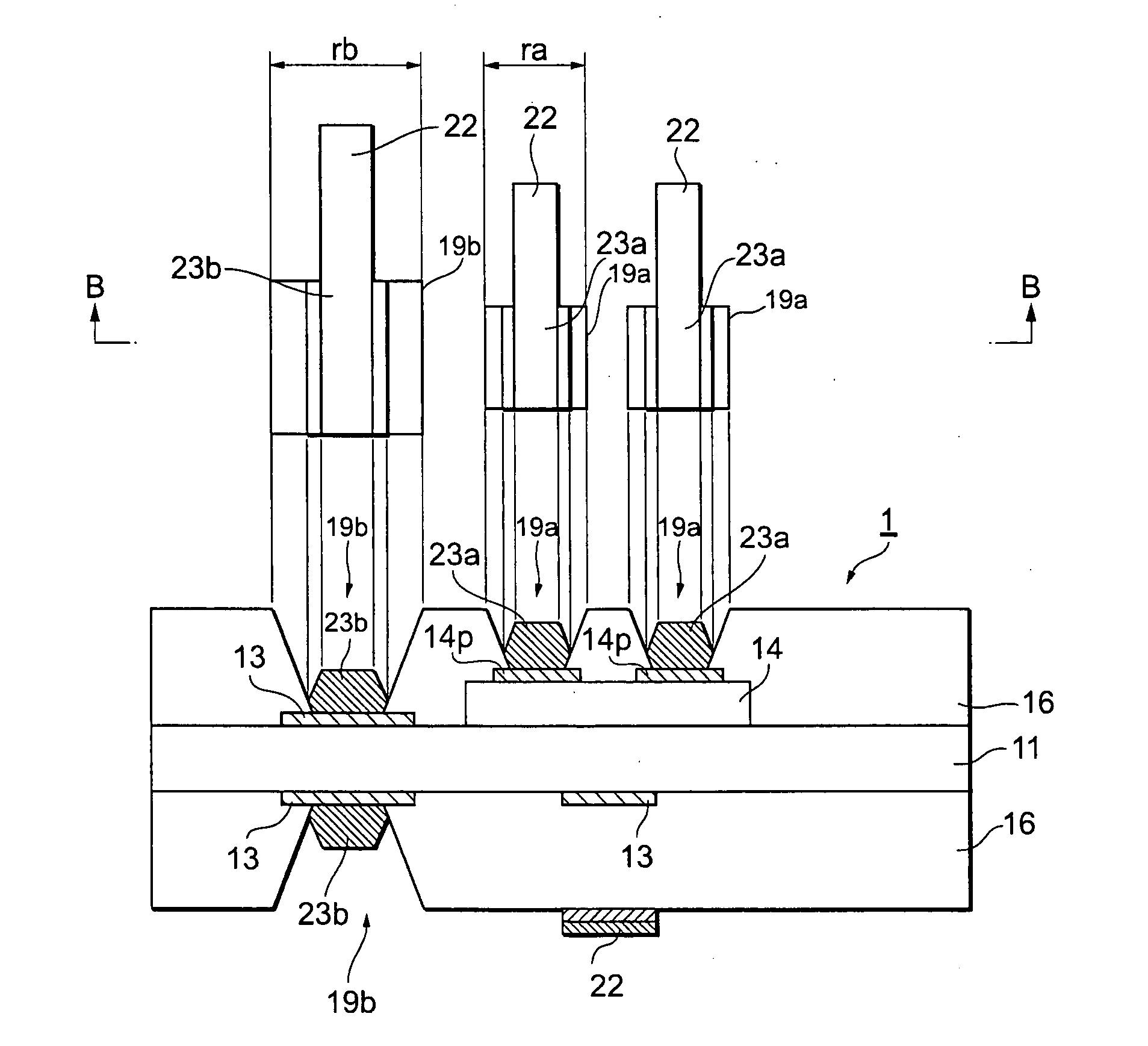

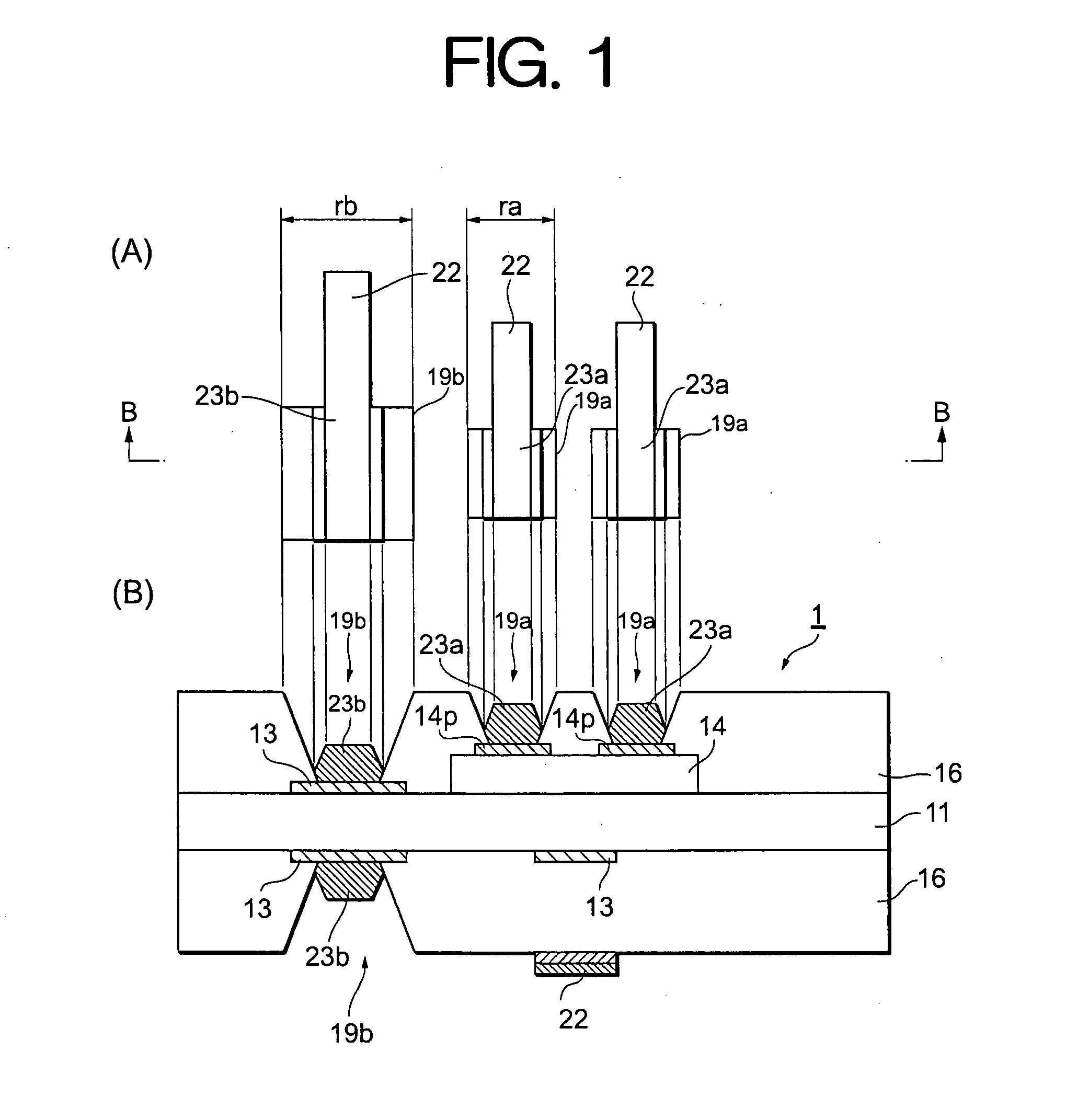

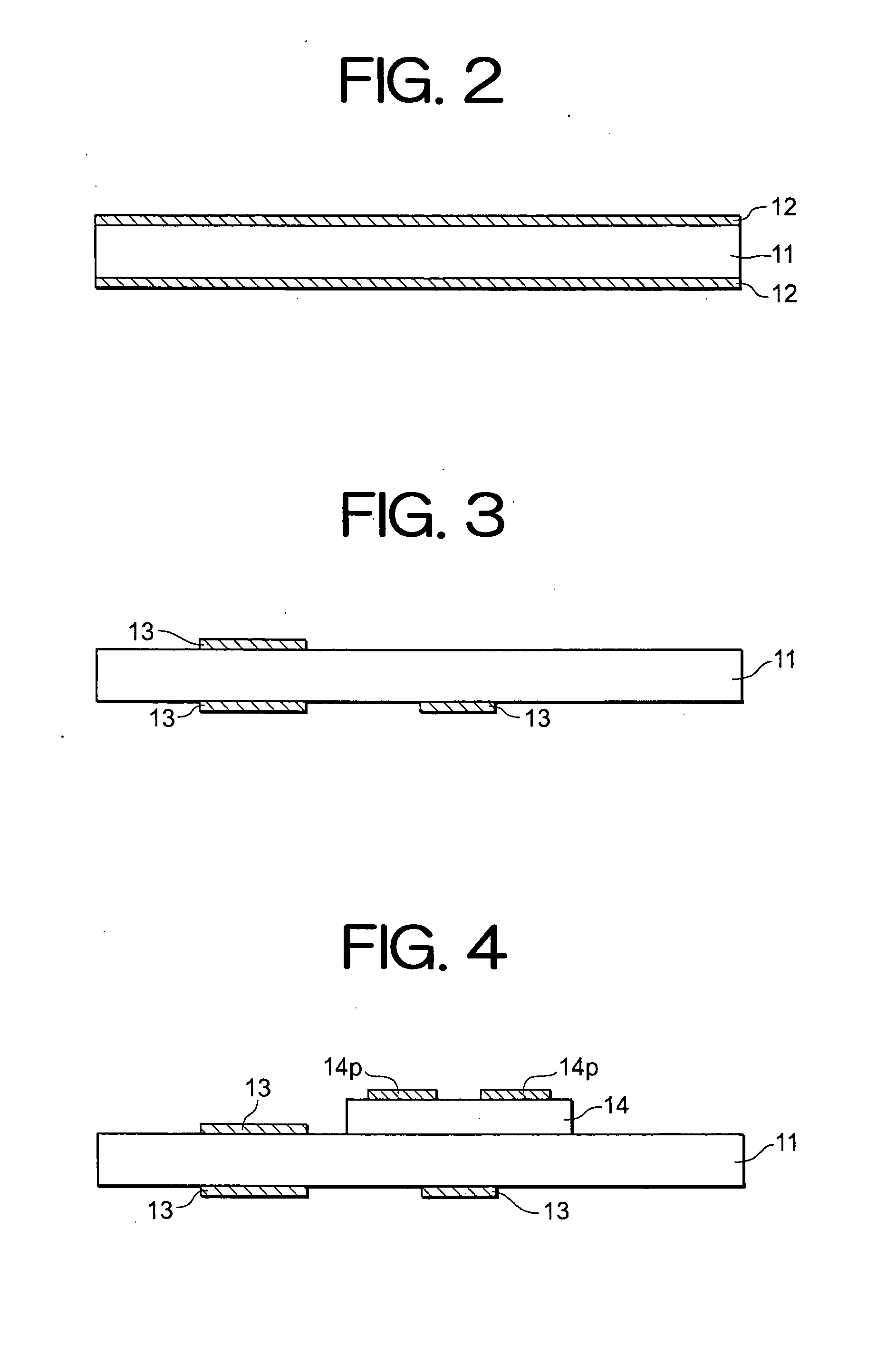

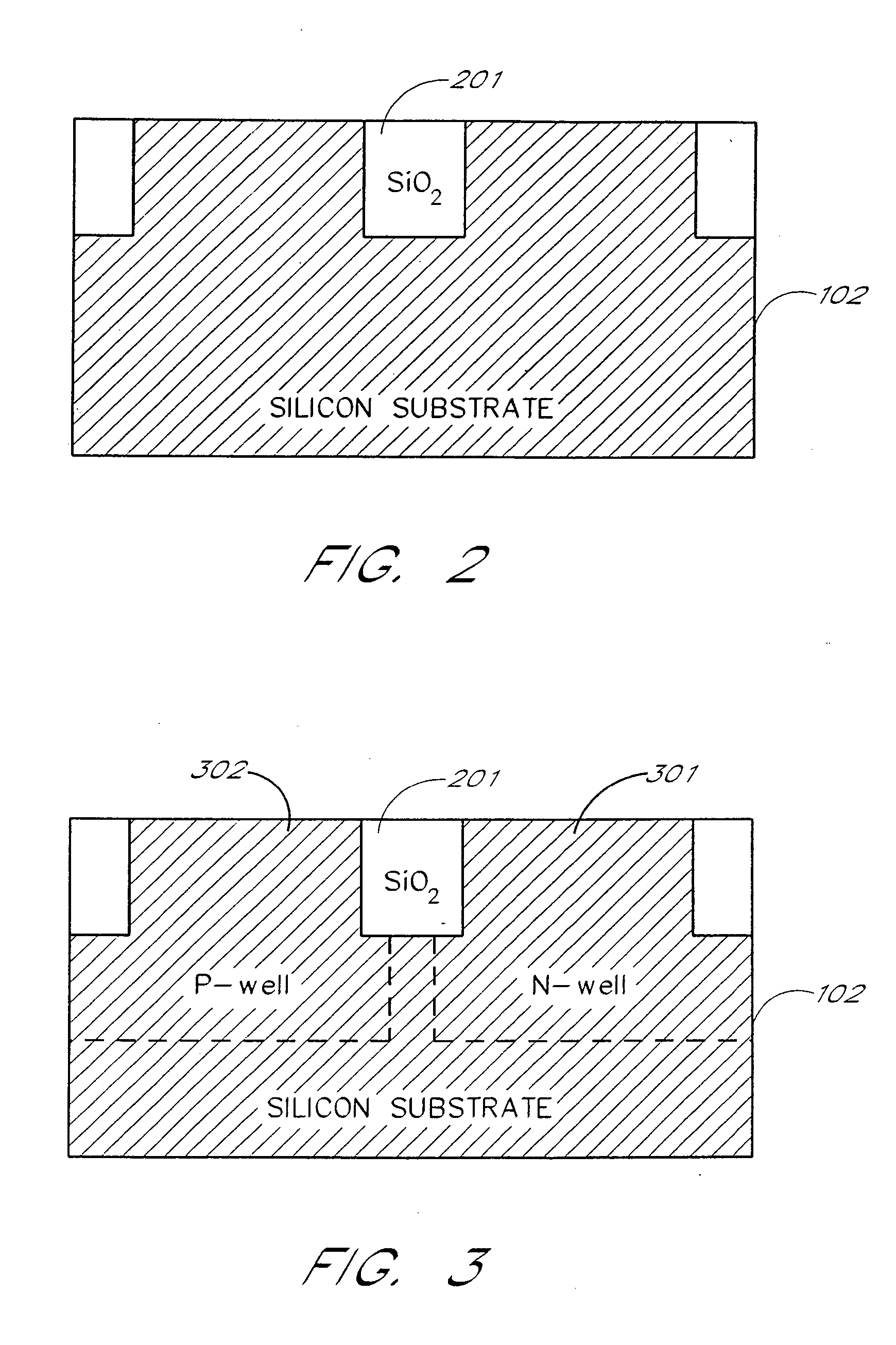

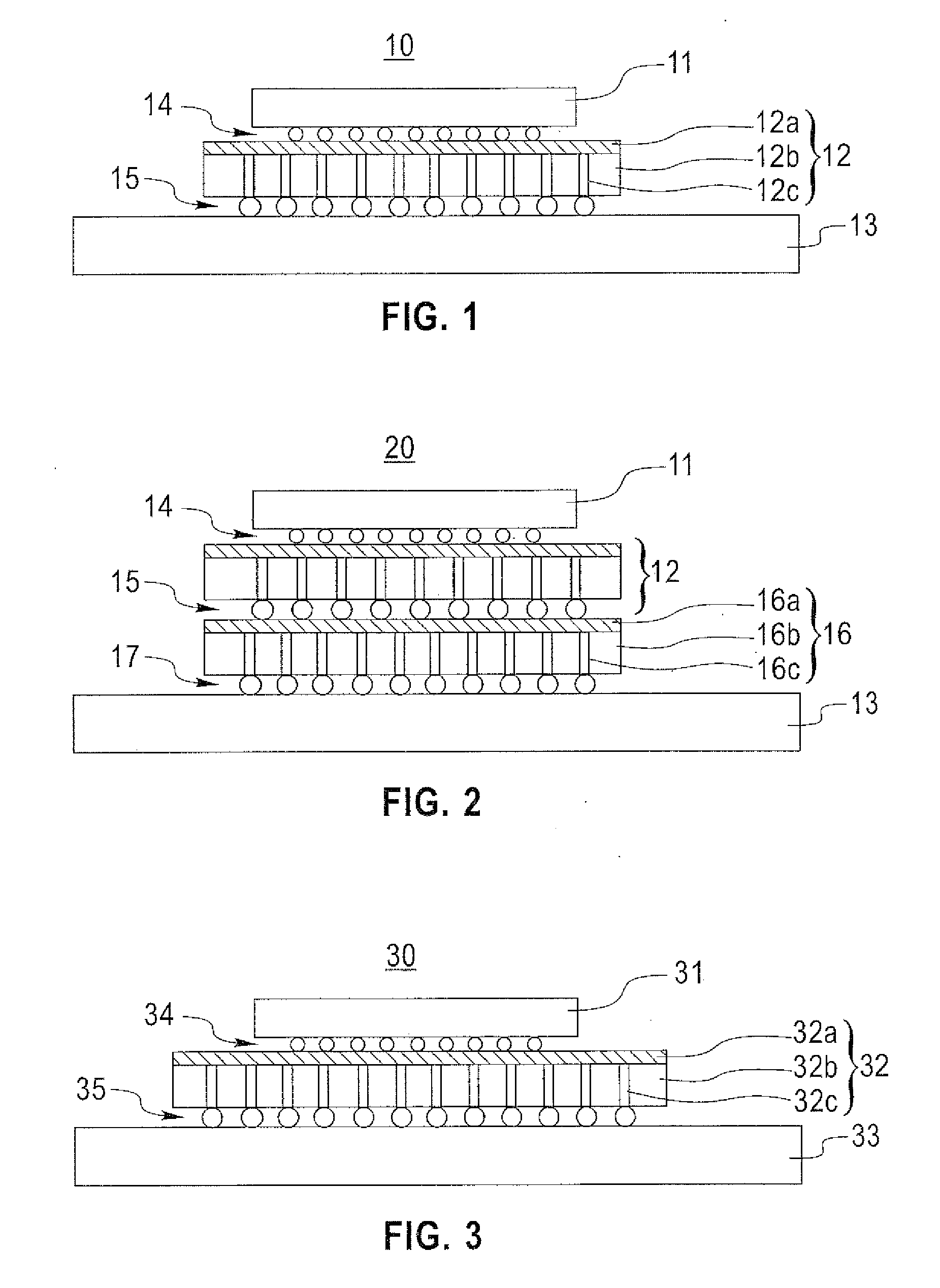

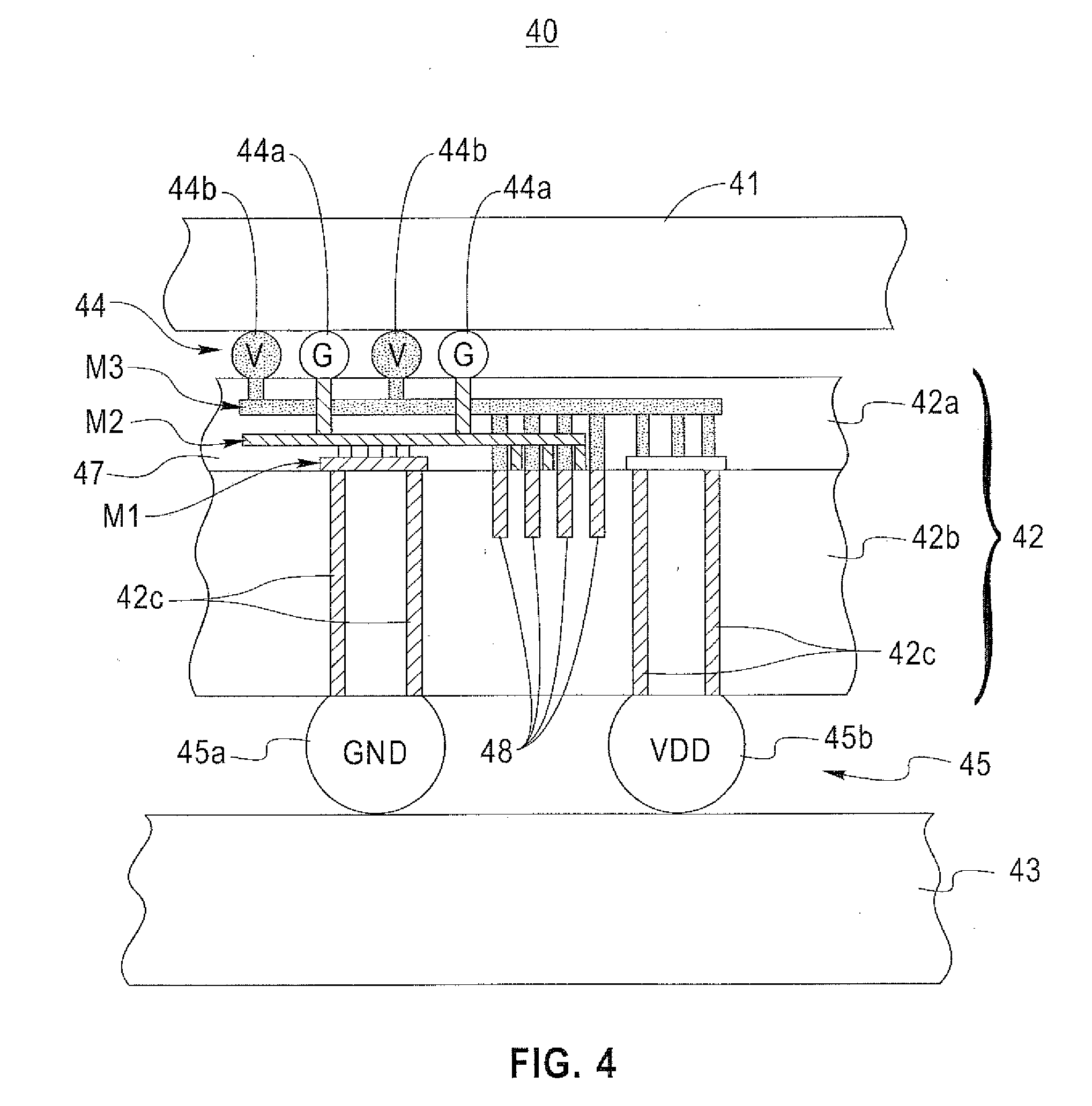

Apparatus and Methods for Constructing Semiconductor Chip Packages with Silicon Space Transformer Carriers

InactiveUS20080284037A1Cost assemblyCost handlingSemiconductor/solid-state device detailsSolid-state devicesHigh densityTransformer

Apparatus and methods are provided for high density packaging of semiconductor chips using silicon space transformer chip level package structures, which allow high density chip interconnection and / or integration of multiple chips or chip stacks high I / O interconnection and heterogeneous chip or function integration.

Owner:IBM CORP

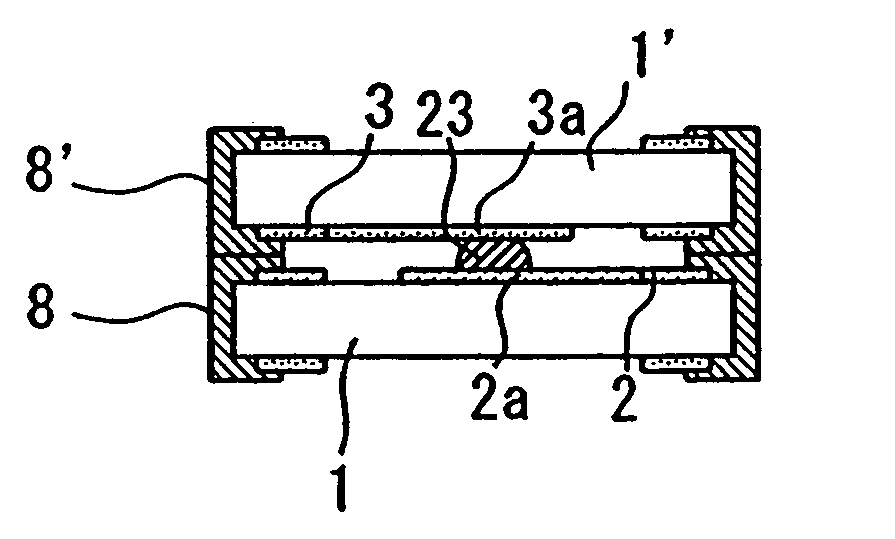

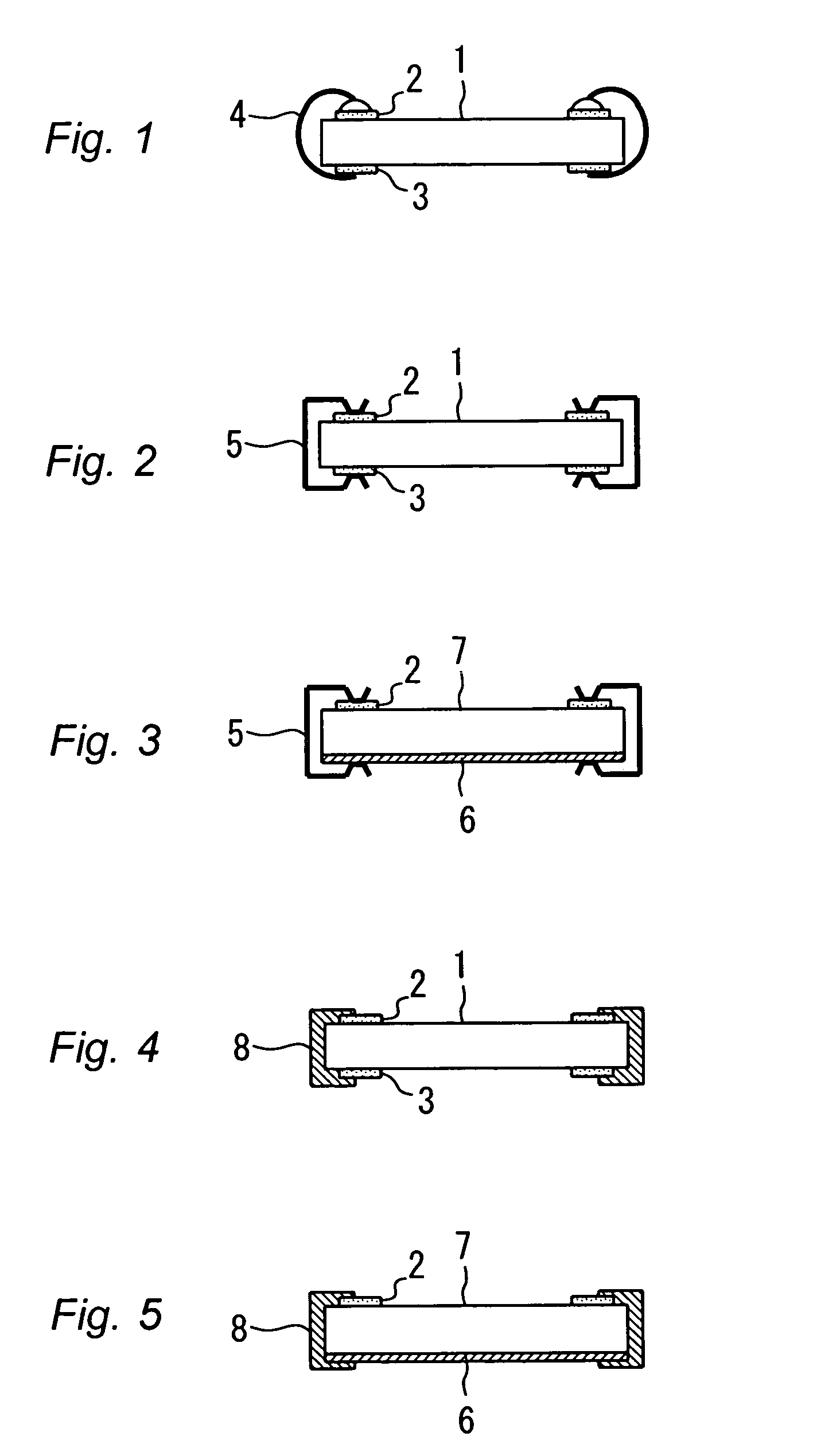

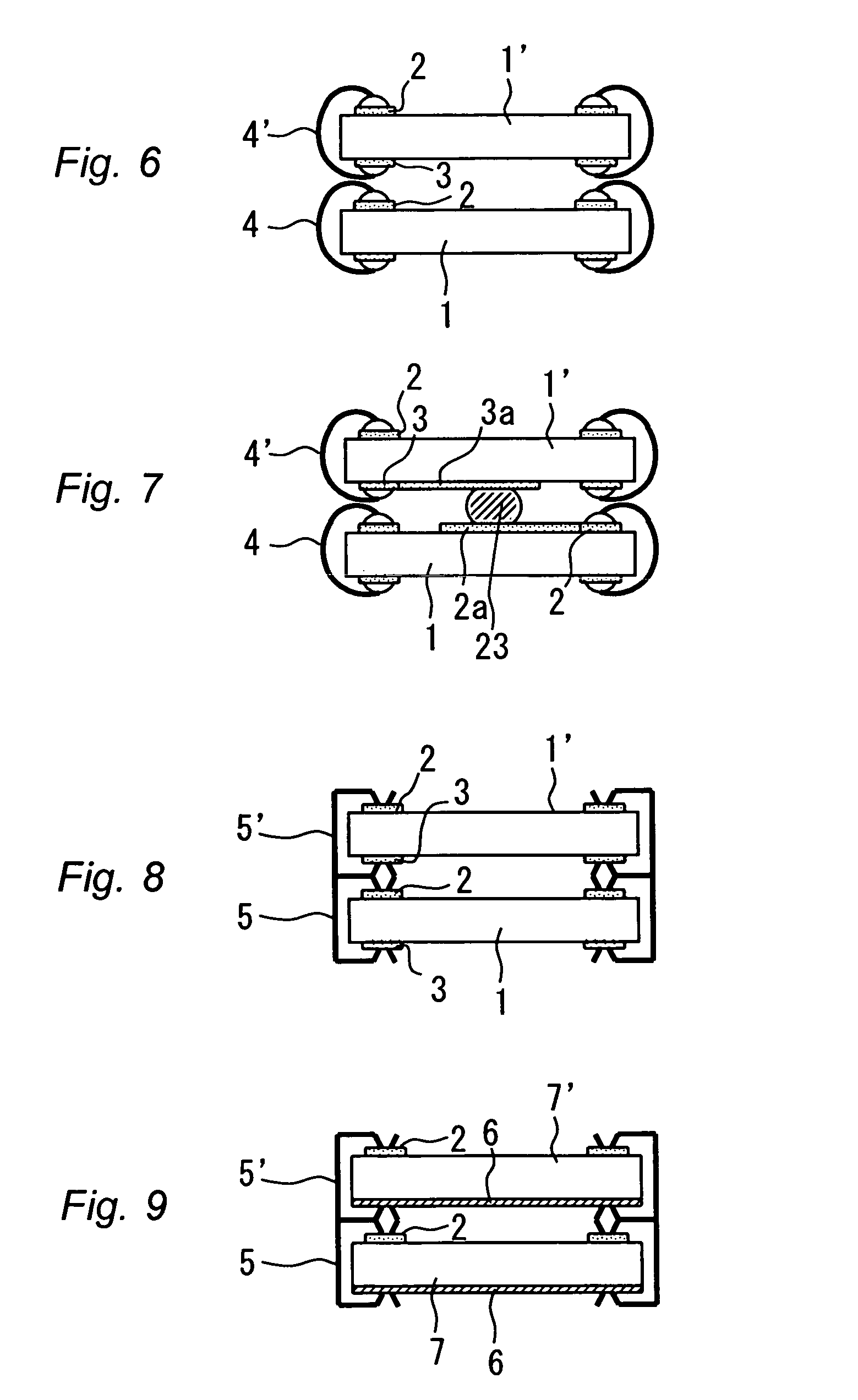

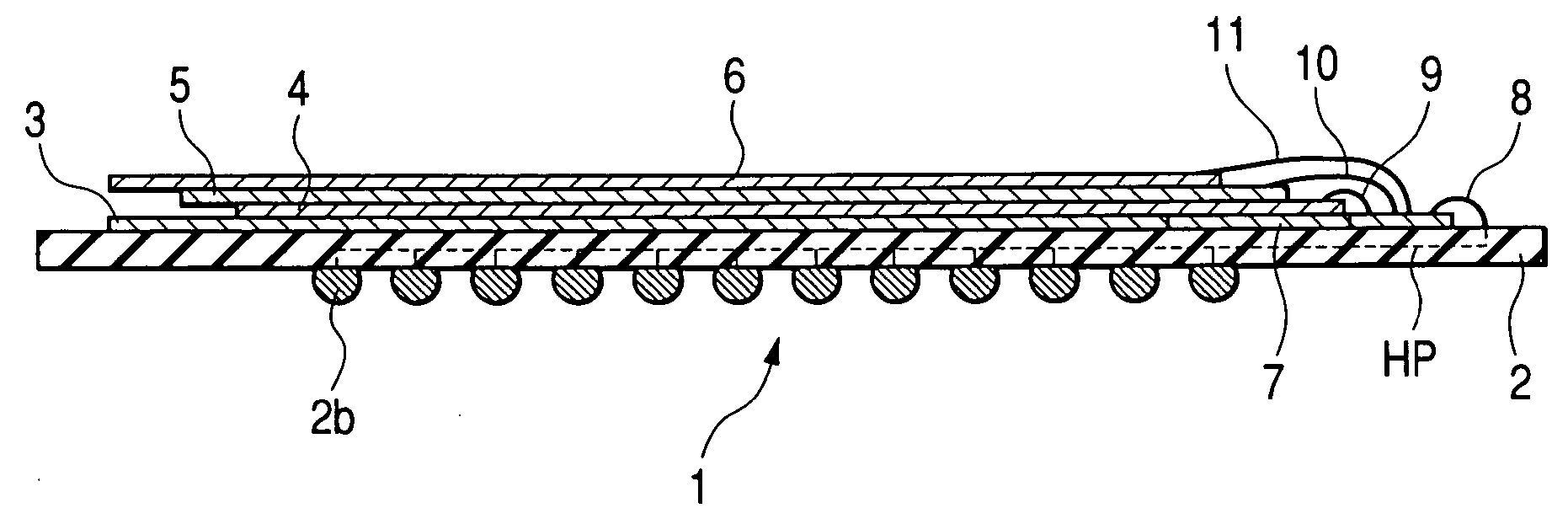

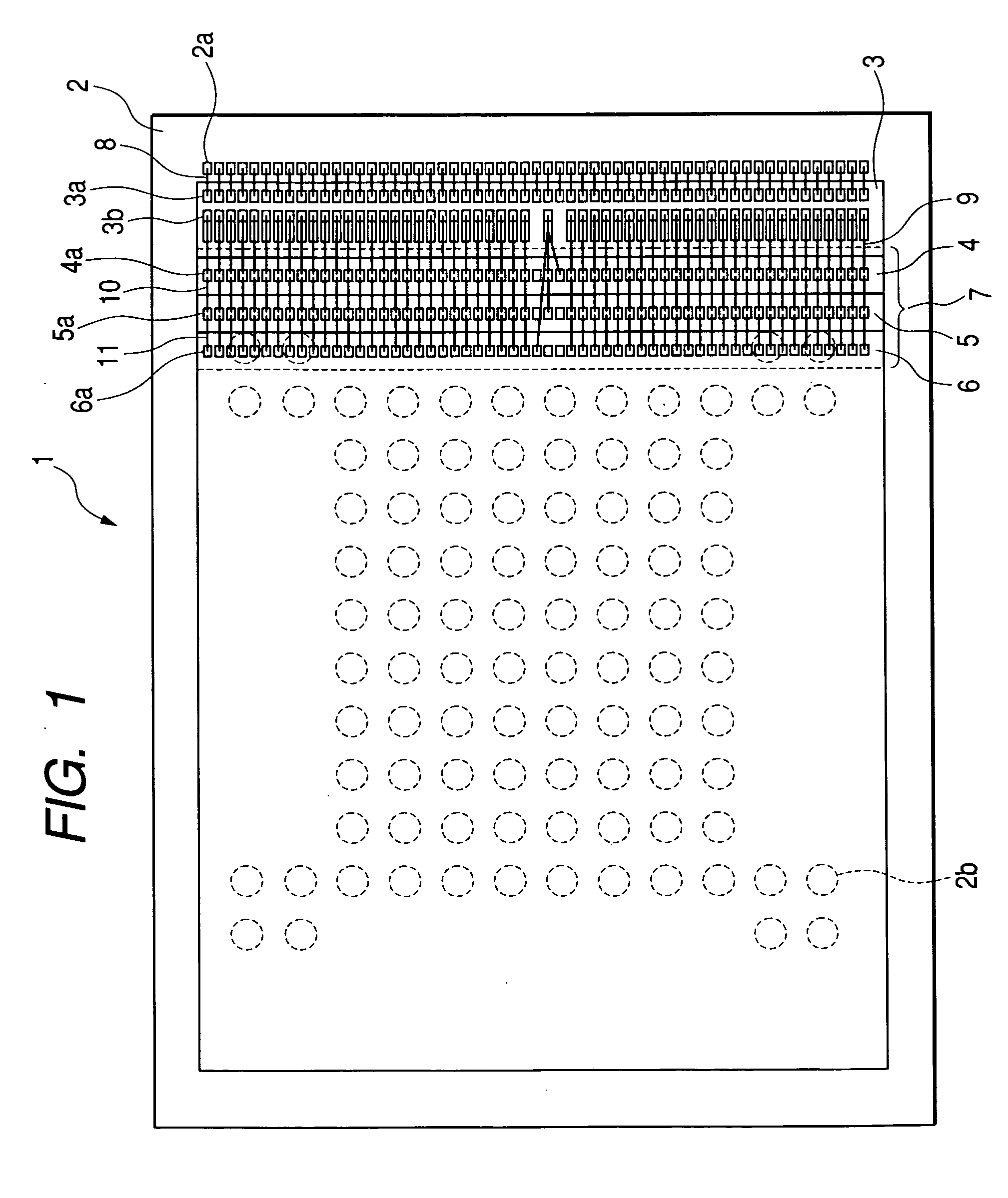

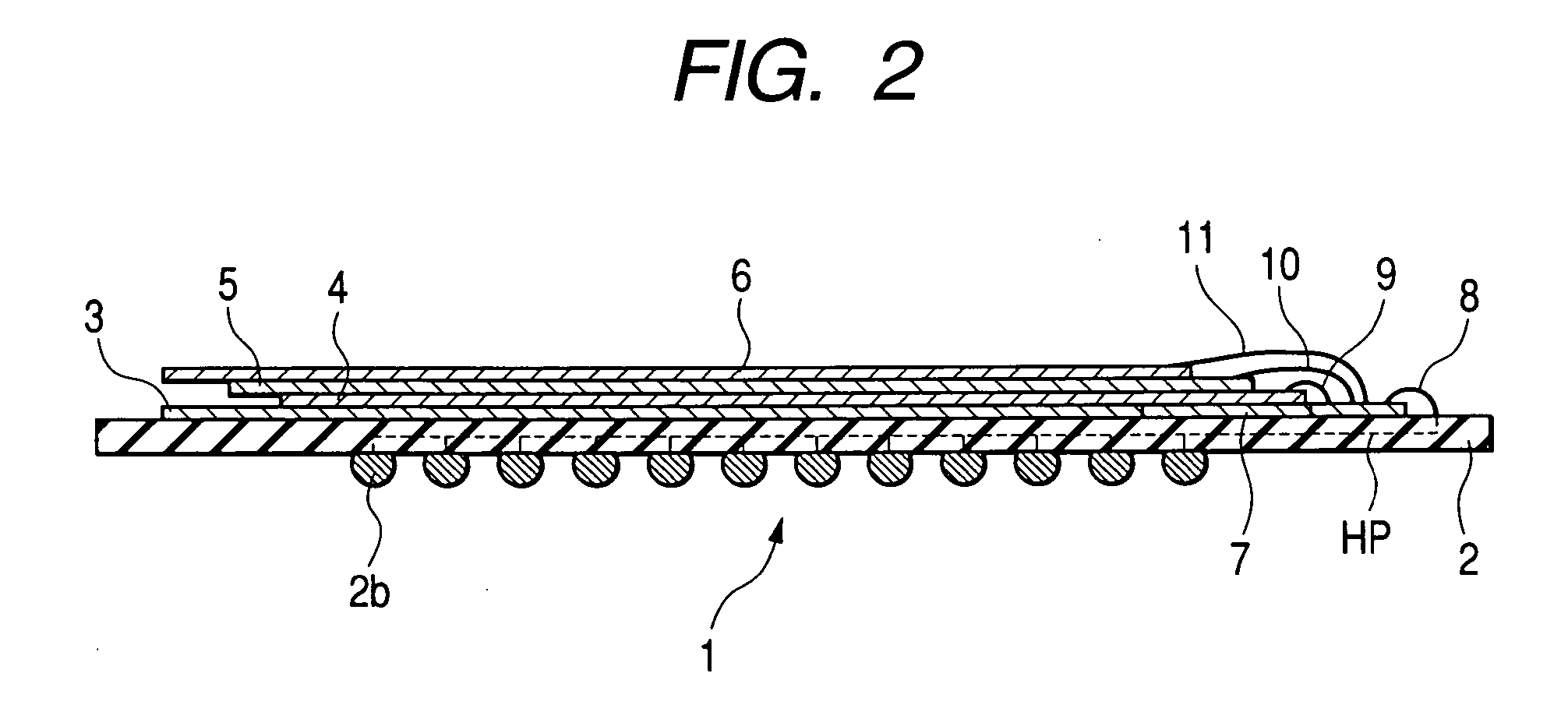

Semiconductor device having densely stacked semiconductor chips

InactiveUS6984885B1High-density packagingSemiconductor/solid-state device detailsSolid-state devicesInsulation layerLead bonding

In a semiconductor chip having electrodes formed on the top surface, and electrodes or an insulation layer formed on the back surface, the top-surface electrodes are loop-connected with the back-surface electrodes by wire bonding, or, the top-surface electrodes are connected with the back-surface electrodes or an insulation layer by conductive clip, or by deposited conductive materials. The semiconductor chips thus produced are stacked, and wires, conductive clips, or conductive materials are connected and fixed to each other to produce a stacked semiconductor device in which semiconductor chips of the same size are densely packaged. Thus, a semiconductor device is provided which enables high-density packaging of semiconductor chips even of the same size.

Owner:RENESAS ELECTRONICS CORP

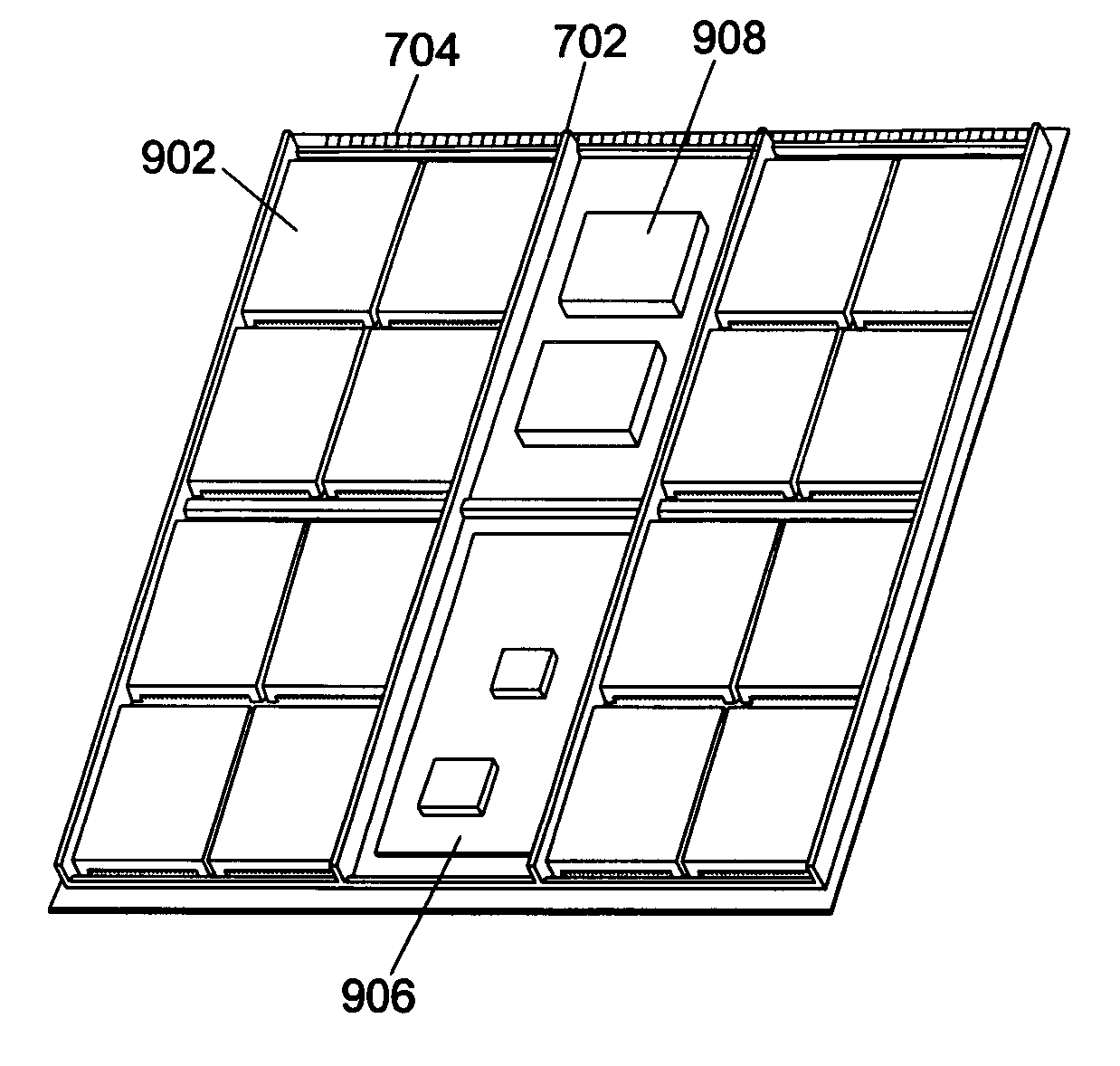

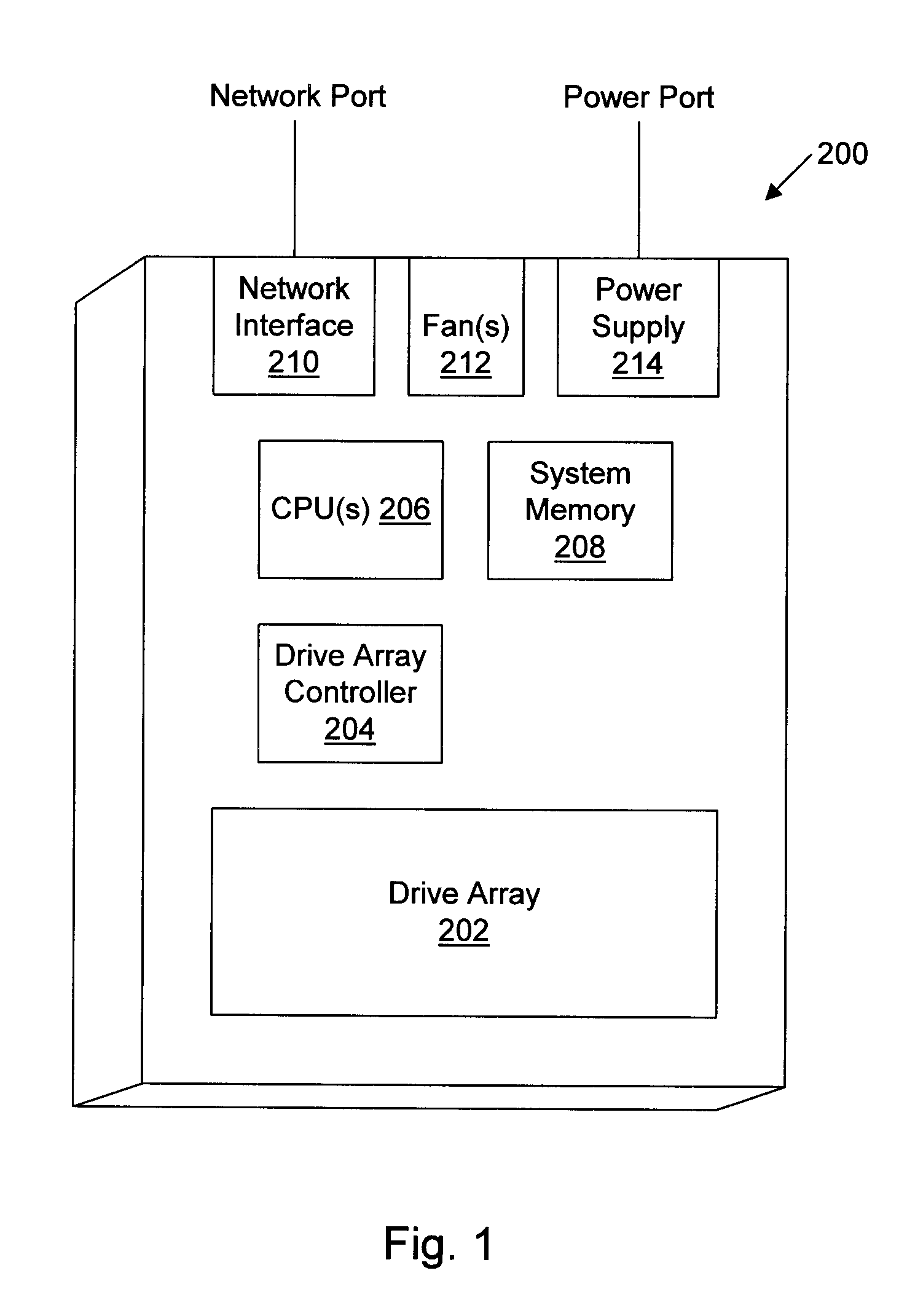

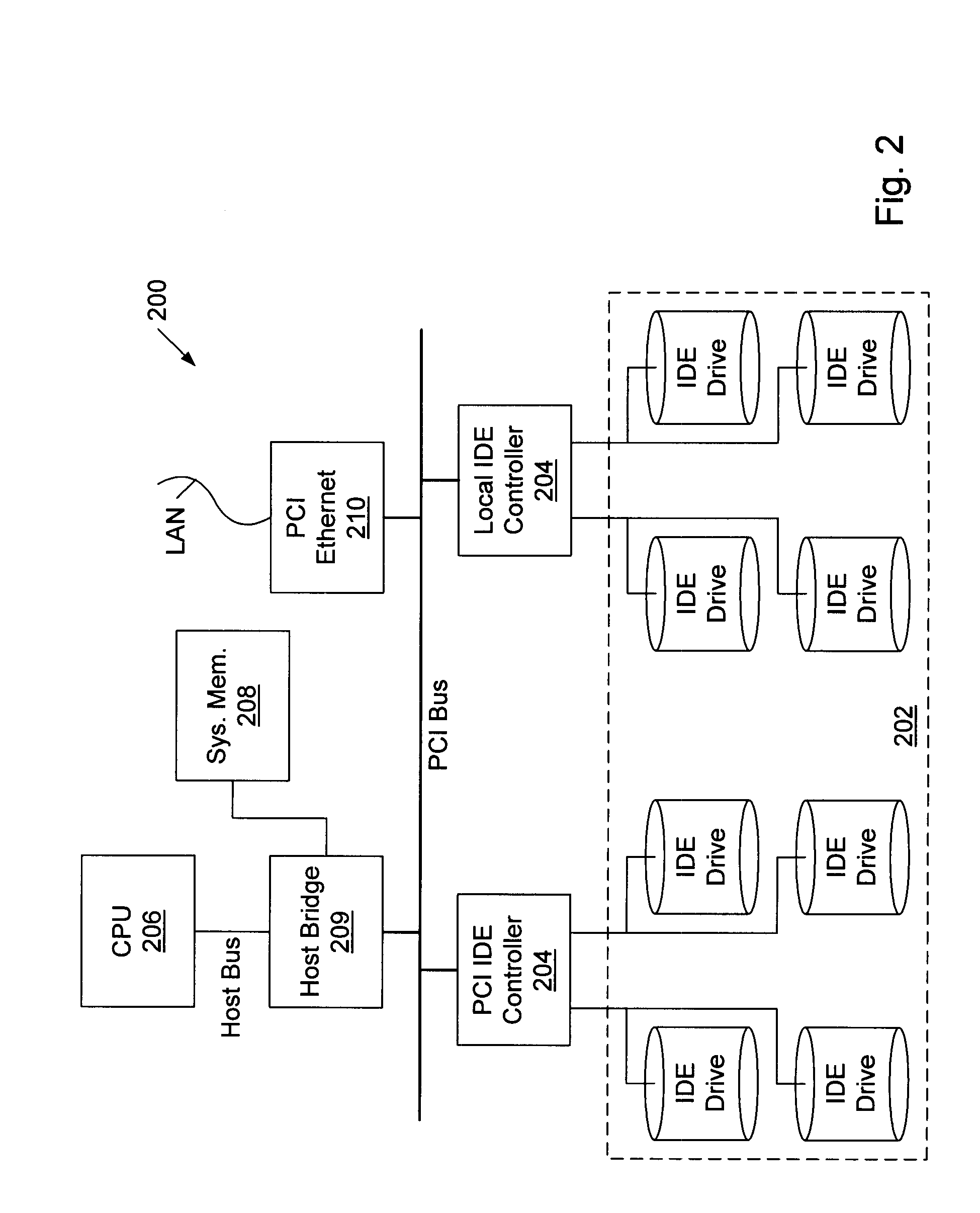

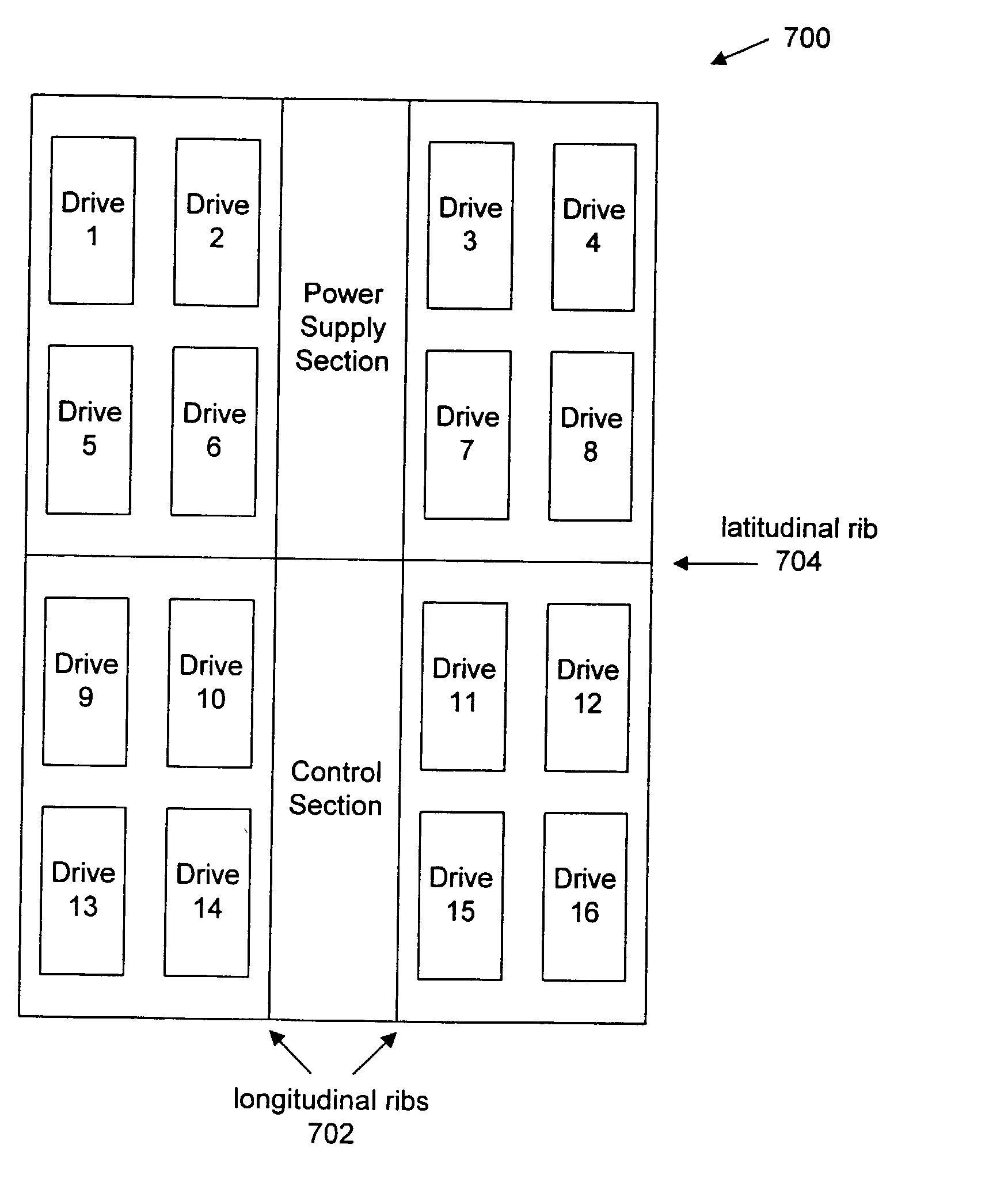

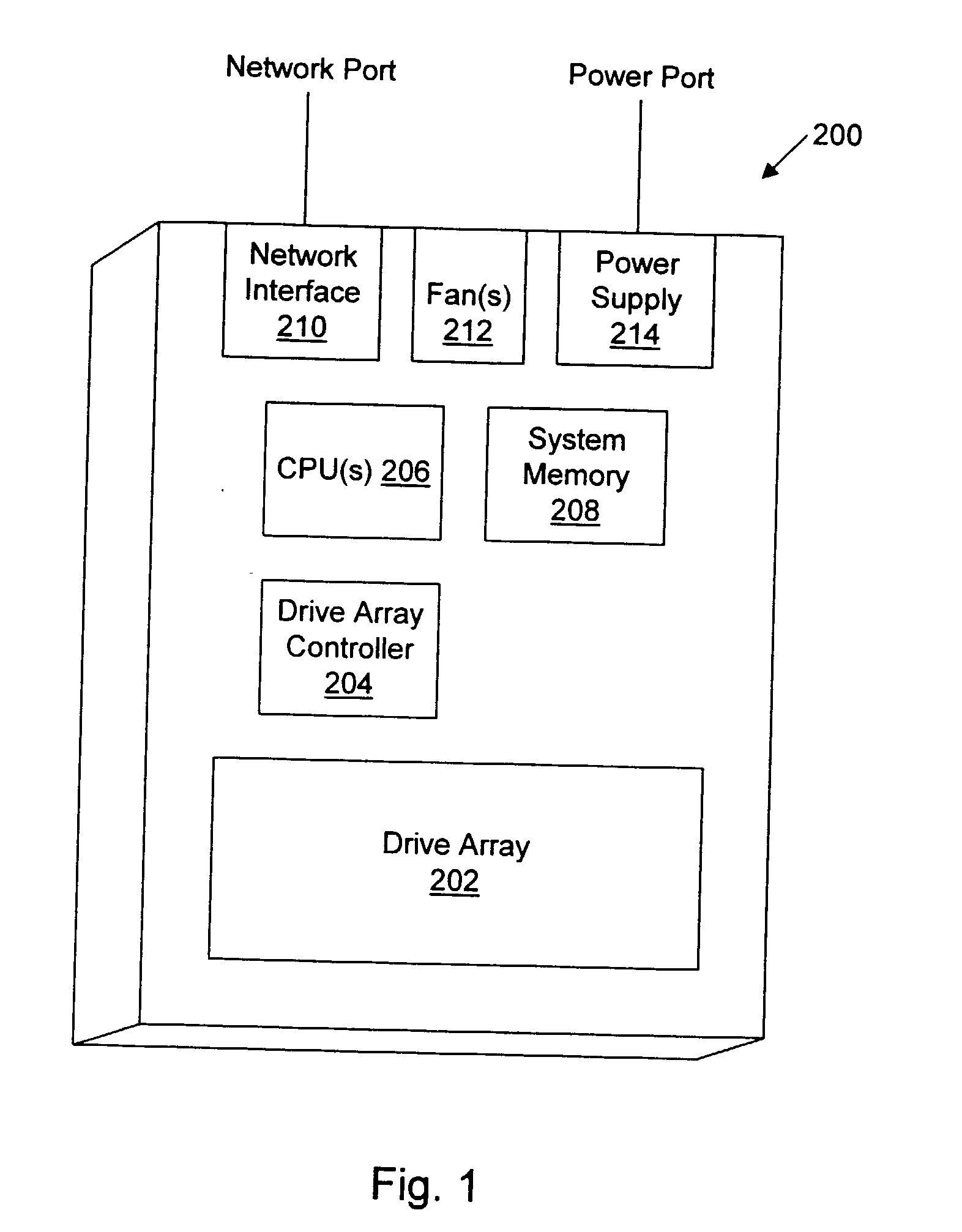

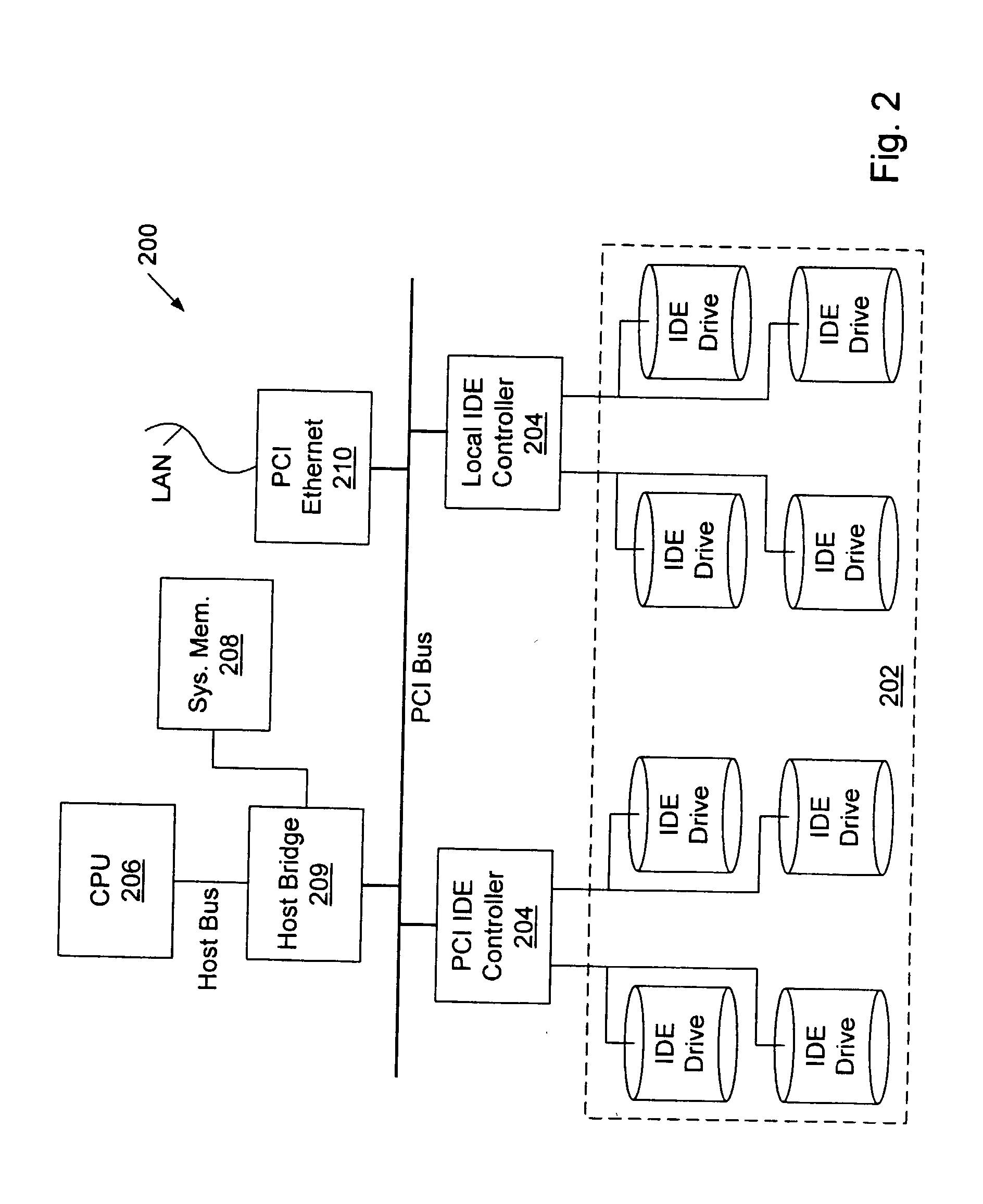

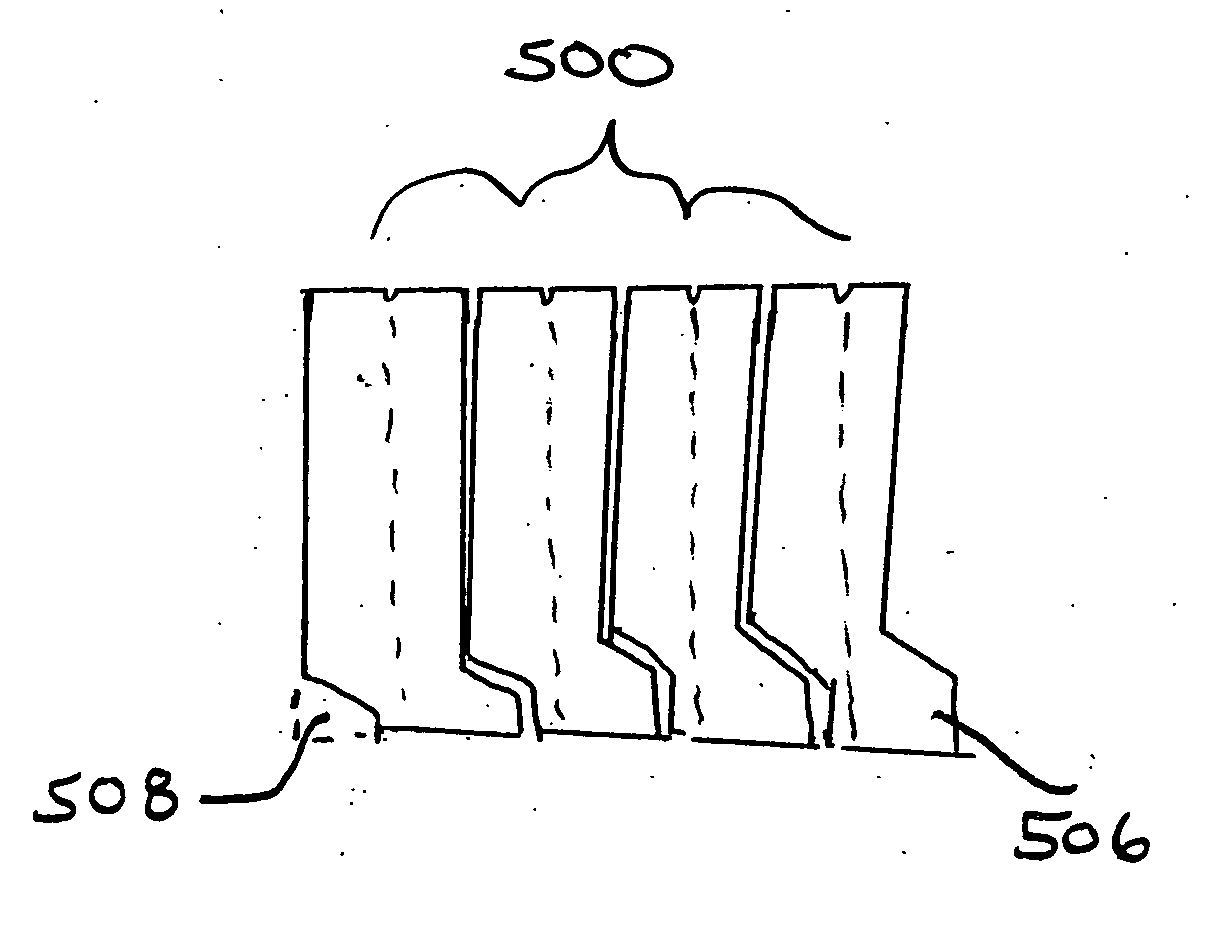

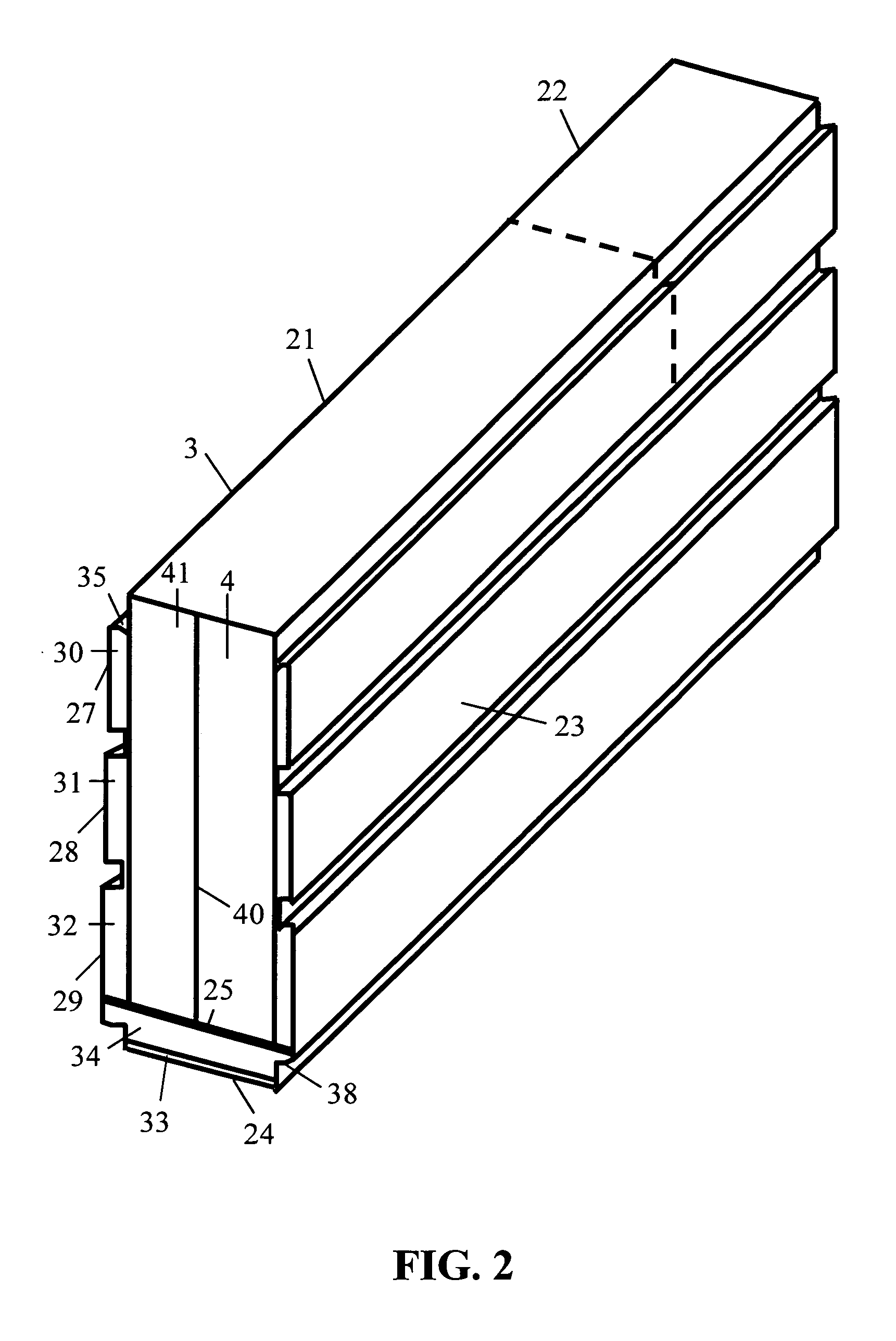

High density packaging for multi-disk systems

InactiveUS6510050B1Carrier constructional parts dispositionDigital data processing detailsElectricityHigh density

A substrate for packaging a storage or server system may include one or more sections of the substrate configured to hold a two-dimensional array of disk drives. Another section of this substrate may be configured to hold circuitry for accessing the array of disk drives. This circuitry may include one or more processors. The substrate also includes a first plurality of ribs positioned in the first access of the substrate. The first plurality of ribs separate the sections from one another. The section configured to hold the control circuitry may also be configured to hold one or more power supplies for supplying power to the array of disk drives and control circuitry. This section, as well as other sections, may be divided in two by one or more additional ribs in a transverse direction. The substrate may be configured to be mounted in a cage or rack and may include an edge connector at one edge of the substrate to provide electrical connectivity to a back plane in the cage or rack. A lateral protrusion may extend along each parallel edge of the substrate for mounting the substrate in the cage or rack by sliding the substrate into the cage or rack.

Owner:ORACLE INT CORP

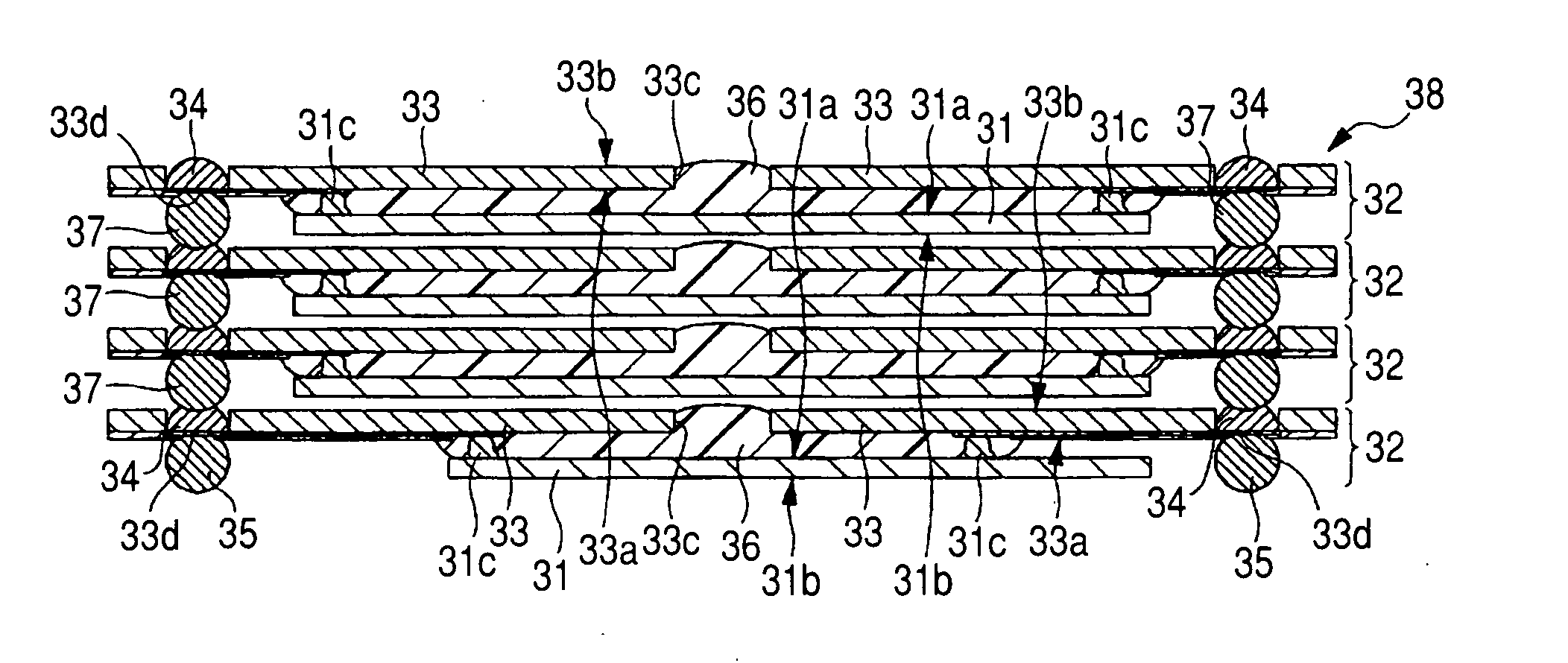

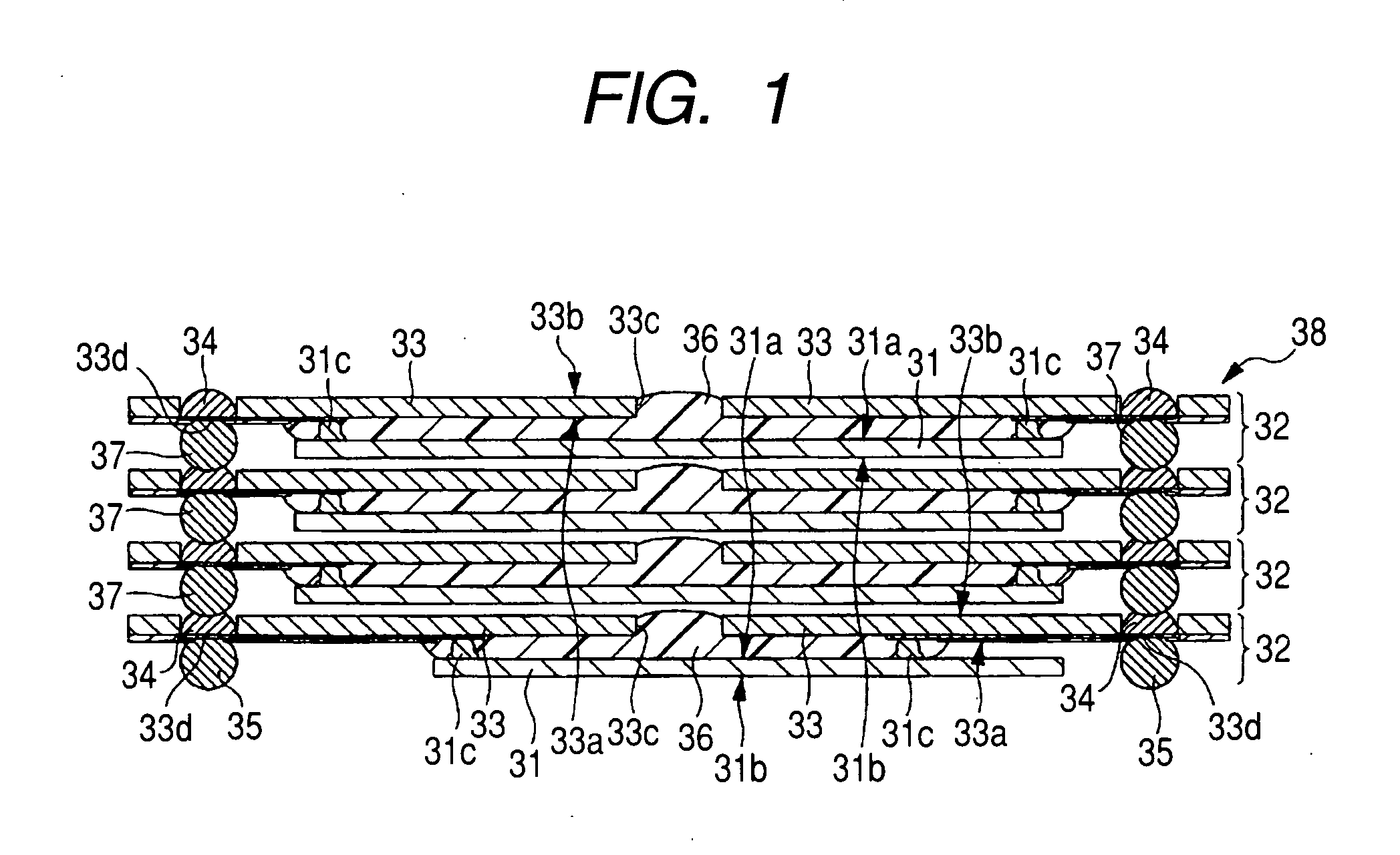

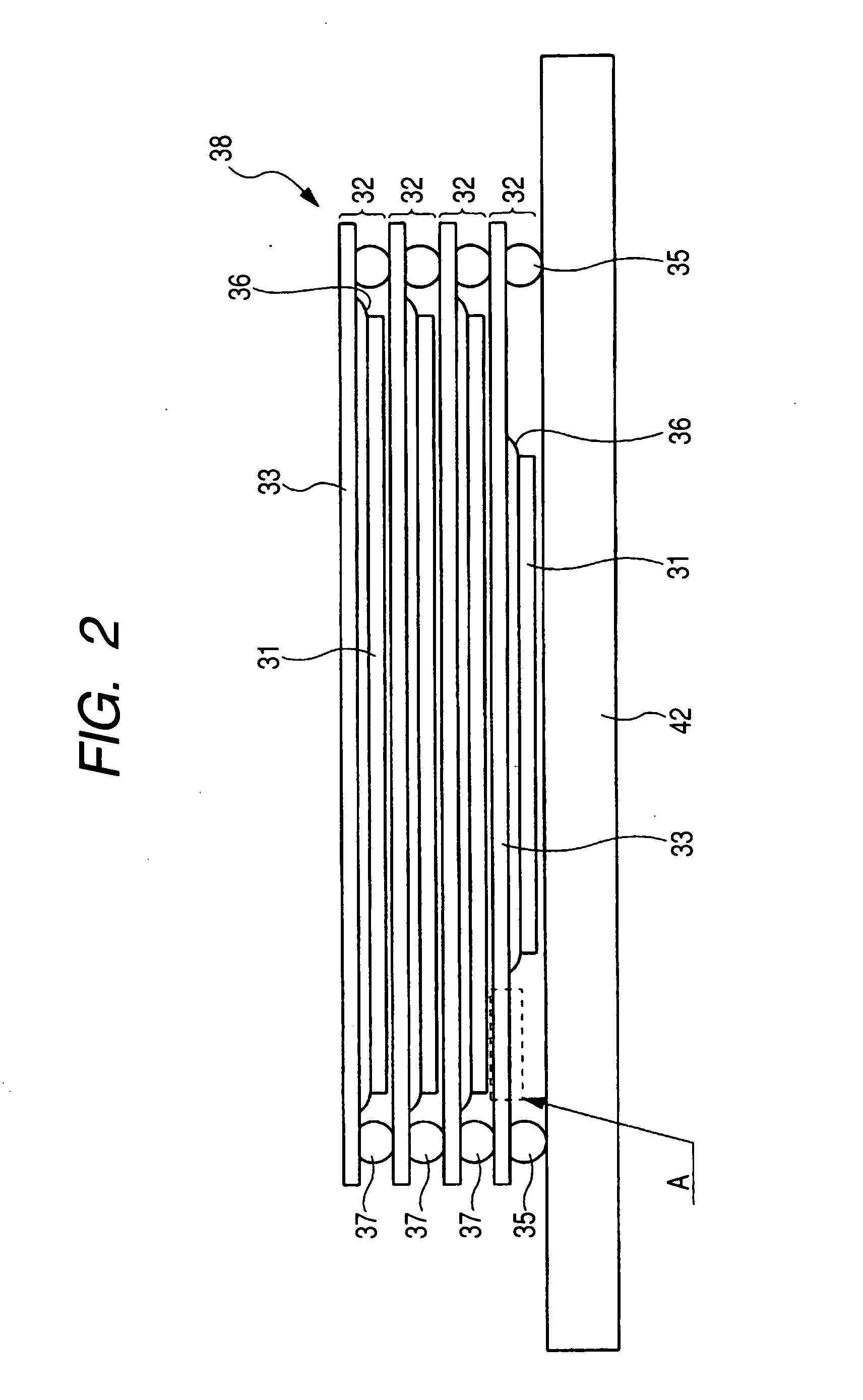

Nonaqueous-electrolyte secondary battery

ActiveUS20070048607A1Good effectIncrease capacityNon-aqueous electrolyte accumulatorsCell seperators/membranes/diaphragms/spacersLithiumParticulates

A subject for the invention is to improve the cycle characteristics of a high-capacity secondary battery containing an active material packed at a high density, by using a particulate active material having a low aspect ratio. The invention relates to a nonaqueous-electrolyte secondary battery comprising a negative electrode and a positive electrode each capable of occluding / releasing lithium, a separator, and a nonaqueous electrolyte solution comprising a nonaqueous solvent and a lithium salt, characterized in that the separator comprises a porous film made of a thermoplastic resin containing an inorganic filler, and at least either of the following is satisfied: the active material contained in the negative electrode is a particulate active material having an aspect ratio of from 1.02 to 3; and the active material contained in the positive electrode is a particulate active material having an aspect ratio of from 1.02 to 2.2.

Owner:MITSUBISHI CHEM CORP

Apparatus and methods for constructing semiconductor chip packages with silicon space transformer carriers

ActiveUS20100013073A1Cost assemblyCost handlingSemiconductor/solid-state device detailsSolid-state devicesHigh densityTransformer

Owner:INT BUSINESS MASCH CORP

Blister display package having tear-resistant security tape

Owner:SMURFIT STONE CONTAINER ENTERPRISES INC

High density packaging for multi-disk systems

InactiveUS20020196601A1Carrier constructional parts dispositionDigital data processing detailsHigh density packagingBackplane

A substrate for packaging a storage or server system may include one or more sections of the substrate configured to hold a two-dimensional array of disk drives. Another section of this substrate may be configured to hold circuitry for accessing the array of disk drives. This circuitry may include one or more processors. The substrate also includes a first plurality of ribs positioned in the first access of the substrate. The first plurality of ribs separate the sections from one another. The section configured to hold the control circuitry may also be configured to hold one or more power supplies for supplying power to the array of disk drives and control circuitry. This section, as well as other sections, may be divided in two by one or more additional ribs in a transverse direction. The substrate may be configured to be mounted in a cage or rack and may include an edge connector at one edge of the substrate to provide electrical connectivity to a back plane in the cage or rack. A lateral protrusion may extend along each parallel edge of the substrate for mounting the substrate in the cage or rack by sliding the substrate into the cage or rack.

Owner:LEE WHAY S +4

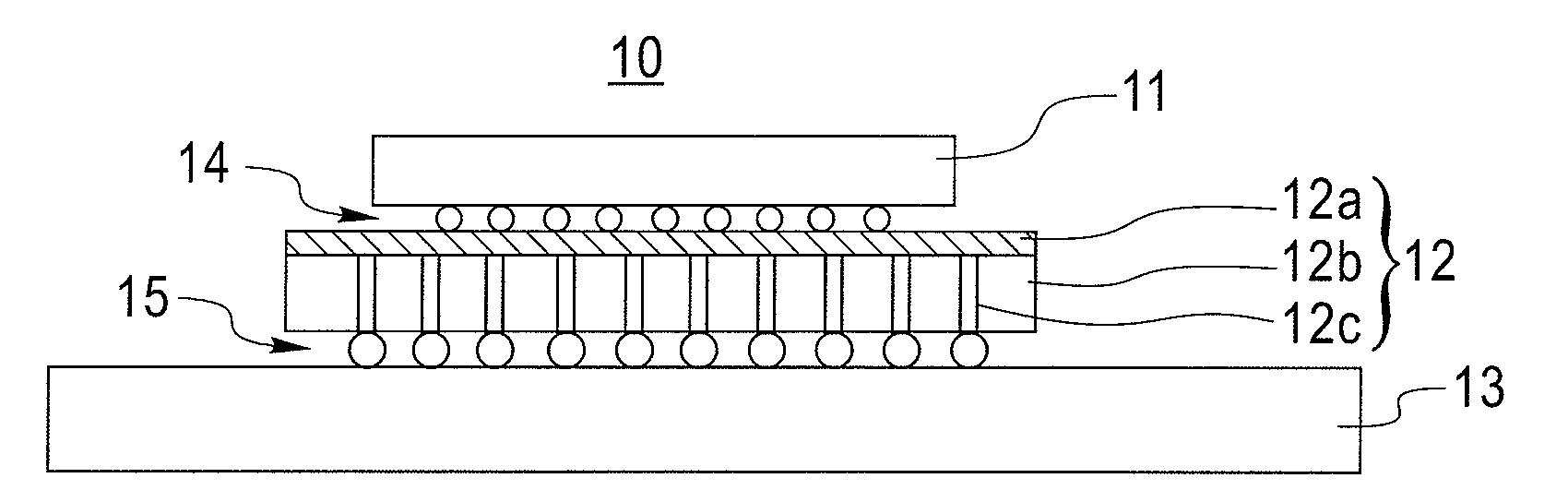

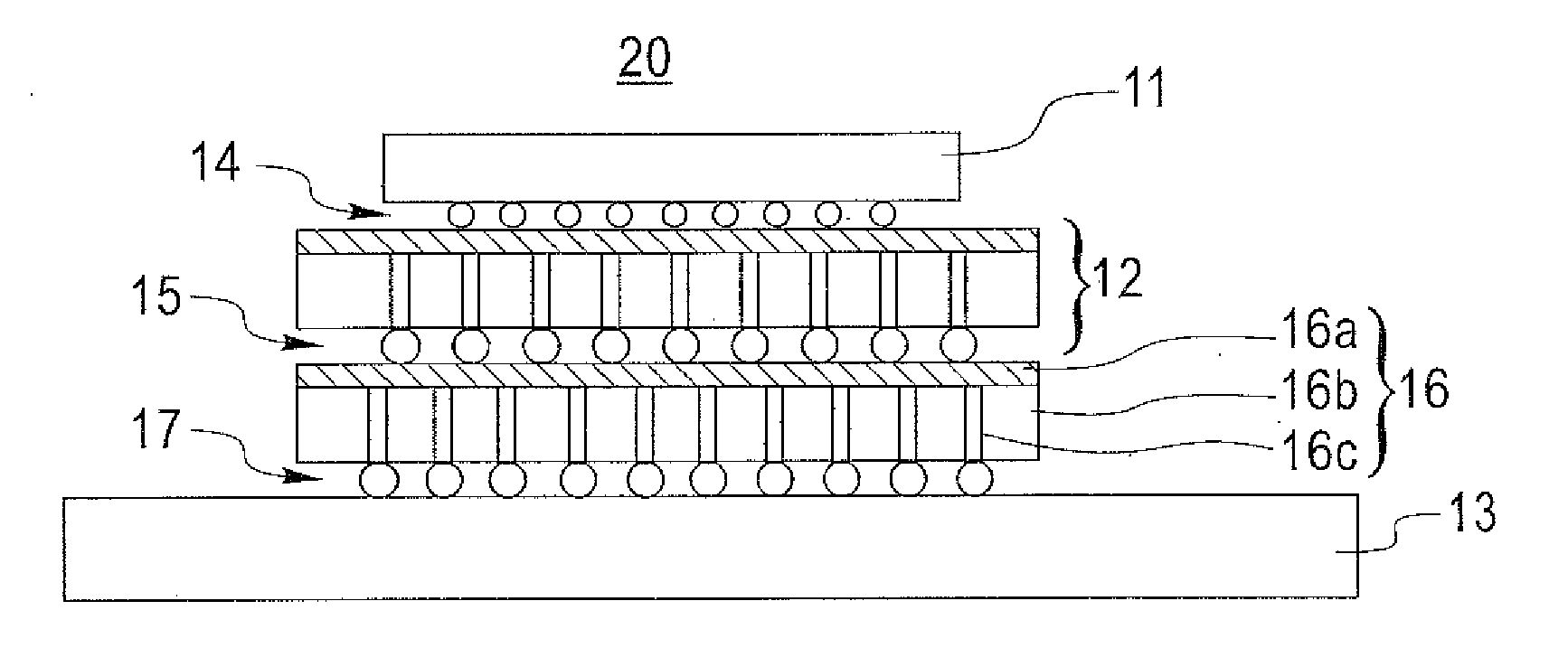

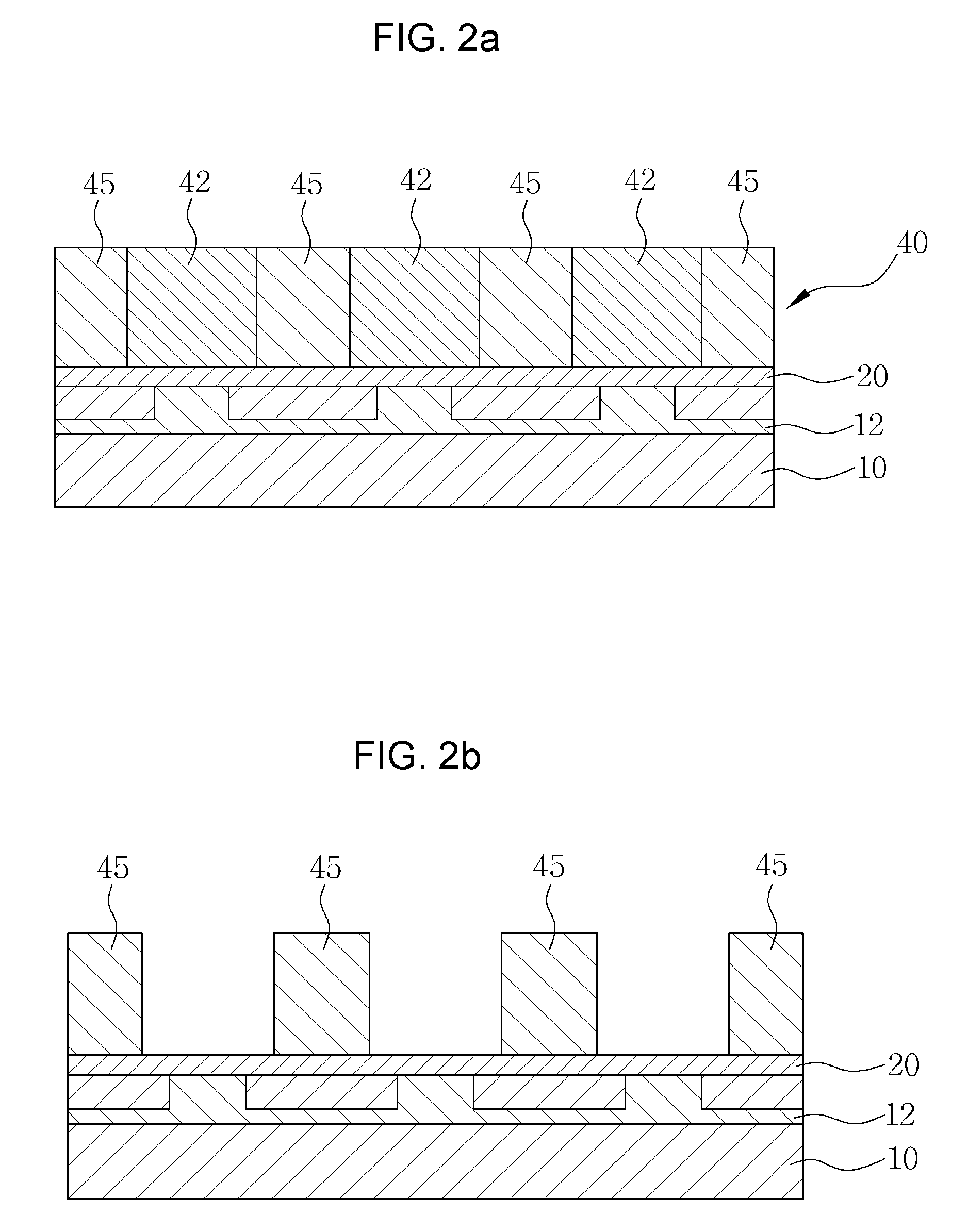

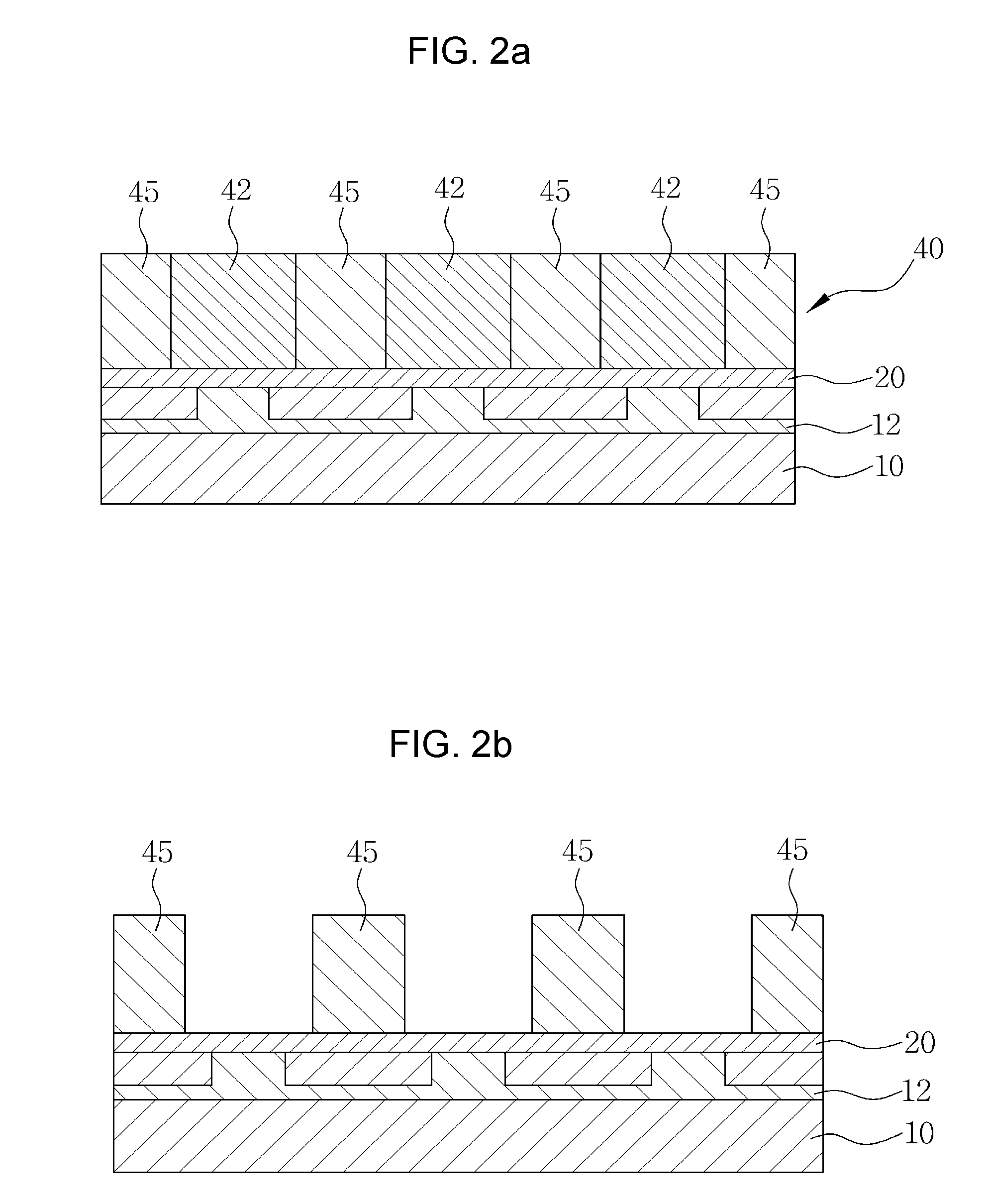

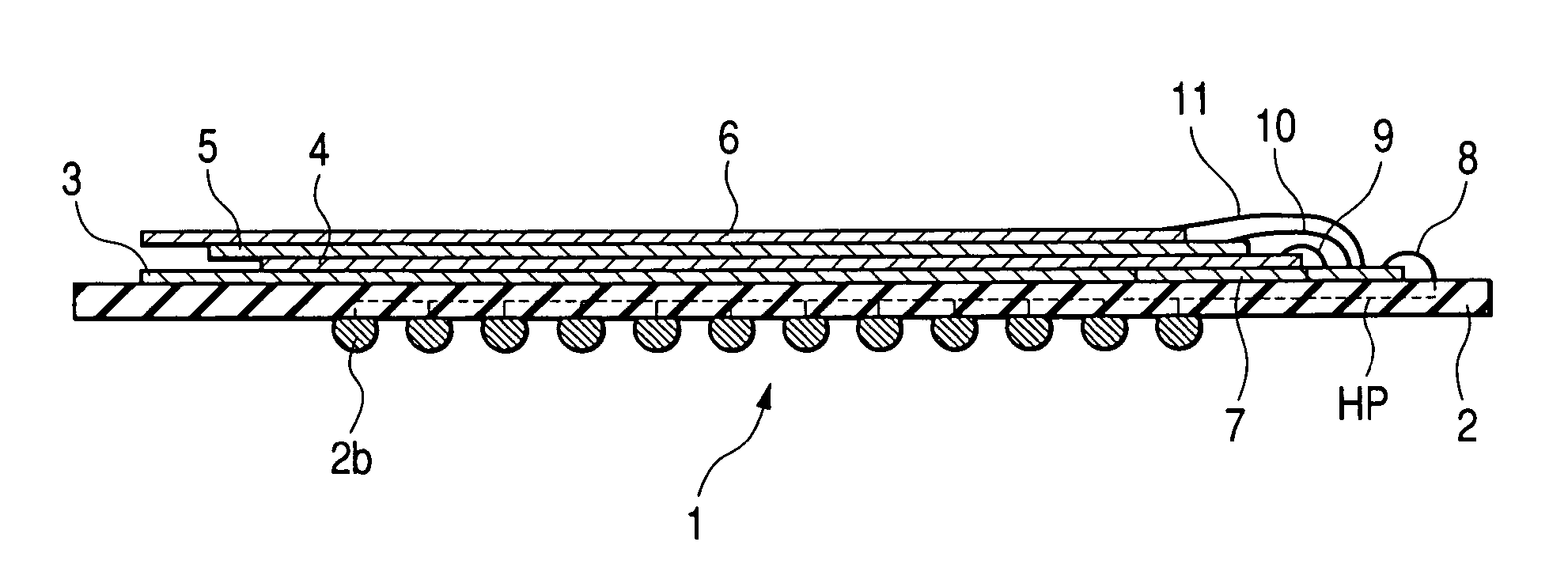

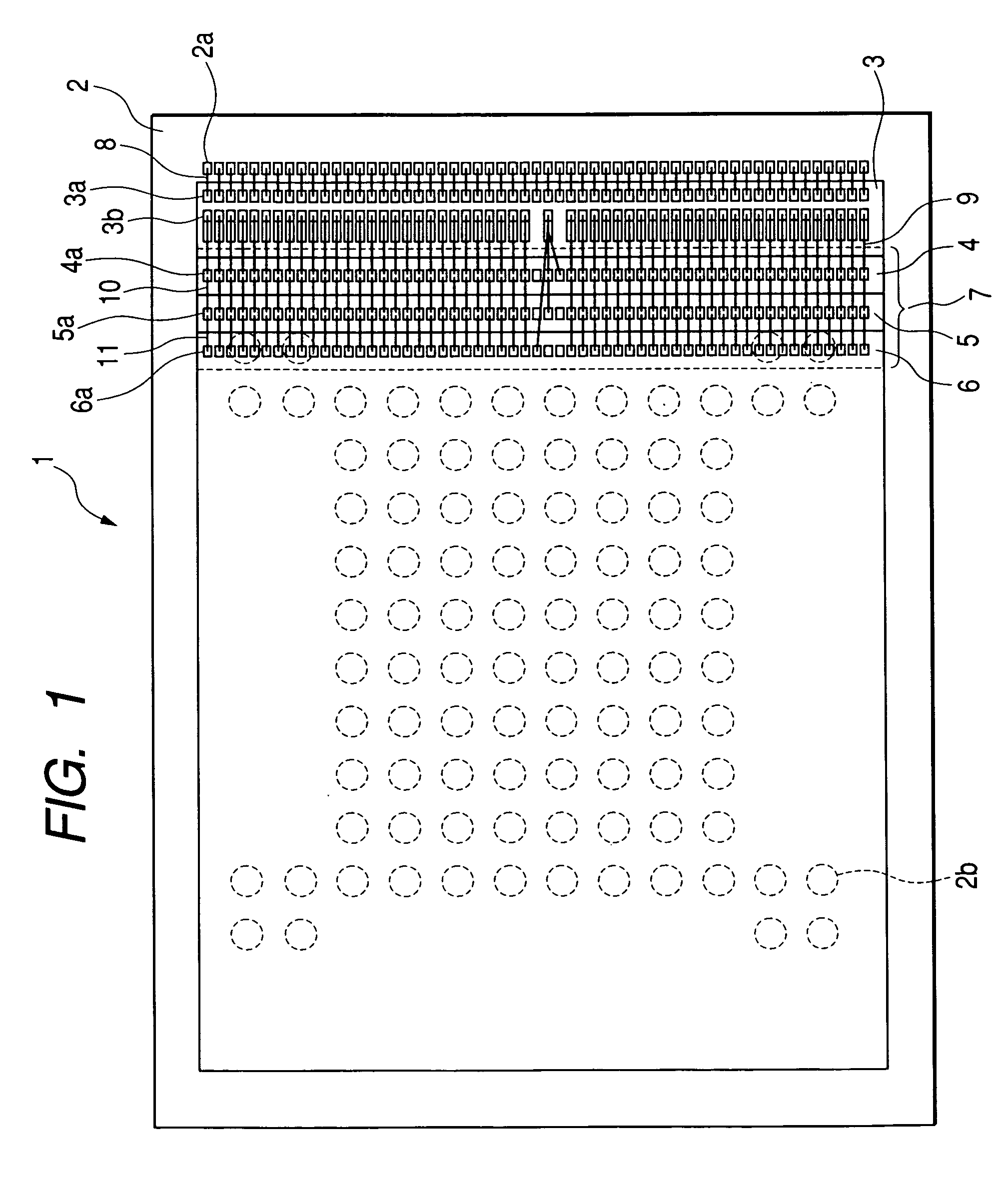

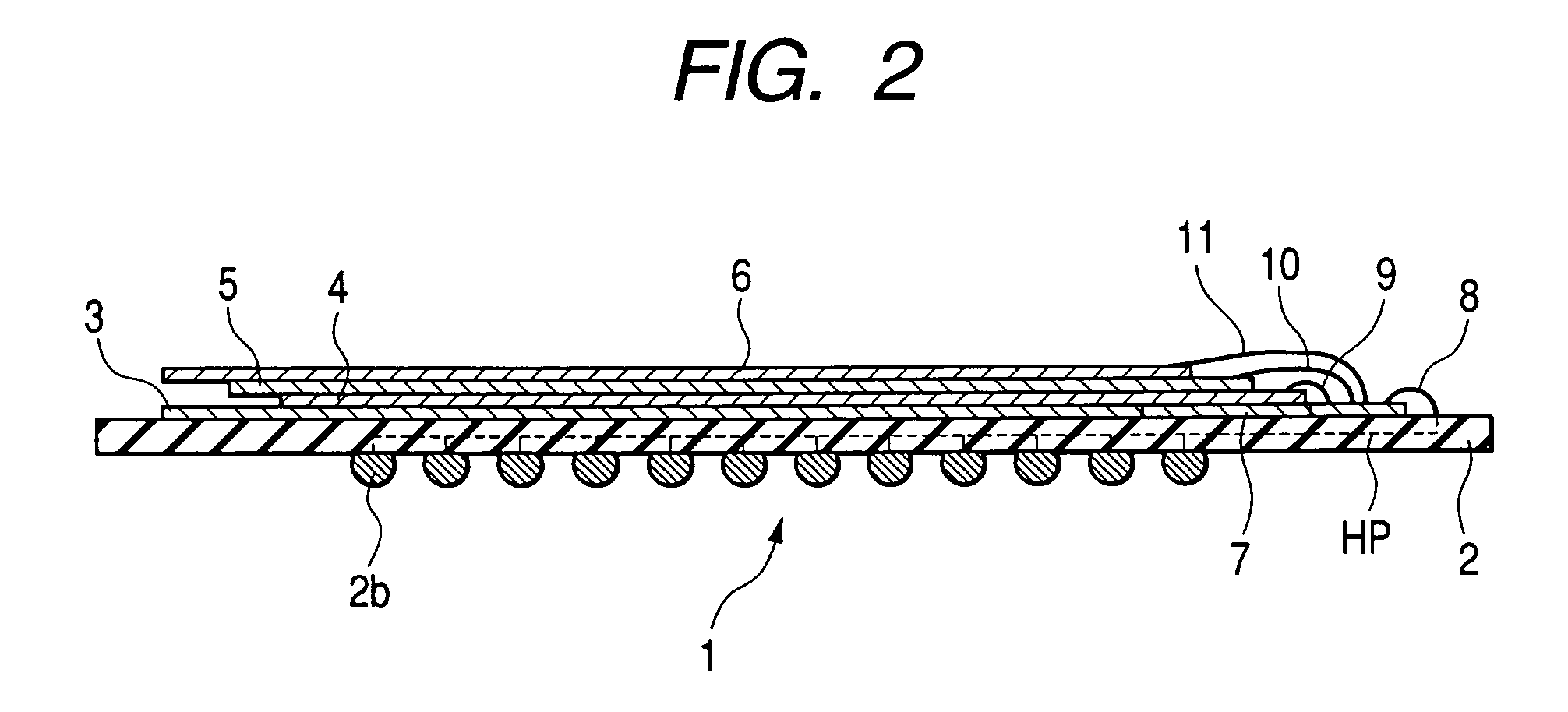

Thin film capacitor, high-density packaging substrate incorporating thin film capacitor, and method for manufacturing thin-film capacitor

InactiveUS20050111162A1Sufficient capacitanceSolid-state devicesSemiconductor/solid-state device manufacturingEngineeringFilm capacitor

A capacitor capable of being incorporated into a packaging substrate, characterized in that the capacitor comprises a high-dielectric-constant layer, and an upper electrode layer and a lower electrode layer sandwiching the high-dielectric-constant layer from the upper side and the lower side. A packaging substrate containing the capacitor, and a method for producing the same are also provided.

Owner:WASEDA UNIV +2

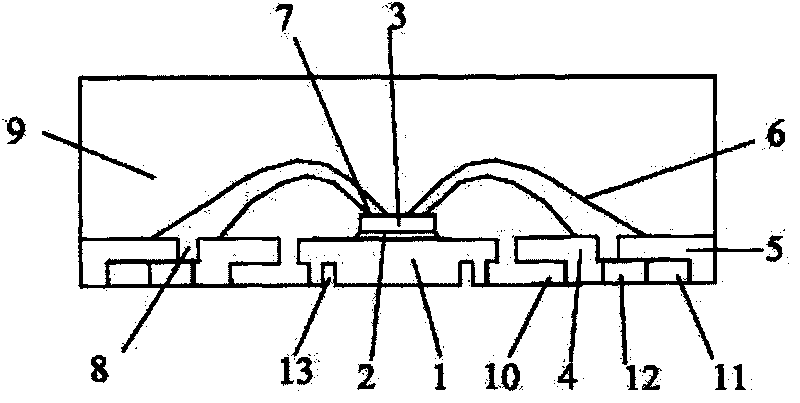

Packaging part with double-row pins and four flat and pin-free surfaces and production method thereof

ActiveCN101694837AShort wirePrevent flowSemiconductor/solid-state device detailsSolid-state devicesHigh density packagingBond line

The invention relates to a packaging part with double-row pins and four flat and pin-free surfaces and a production method thereof. The packaging part comprises a lead frame carrier, an IC chip, a bonding pad, inner lead pins, bonding lines and a plastic packaging body and is characterized in that the inner lead pins are arranged into two rows, i.e. the inner lead pin (4) and the inner lead pin (5), each pair of lead pins are connected together, a groove is arranged in the middle of the connected pins, the bonding pads are respectively connected with the inner lead pin (4) and the inner lead pin (5) through the bonding lines, an anti-spilling groove is arranged at the bottom of the carrier, and grooves are arranged at the bottoms of the inner lead pins. The packaging part is processed and produced through the processes of reduction, scribing, chip installation, press welding, plastic packaging, electroplating, cutting and the like. The carrier is diminished, the inner lead pins are inwards extended and designed into double rows, and the packaged I / O number is increased, thereby not only markedly saving the cost of plastic packaging materials, but also realizing the thin and miniaturized packaging of portable products, being suitable for multi-pin high-density packaging, and improving the packaging density.

Owner:TIANSHUI HUATIAN TECH

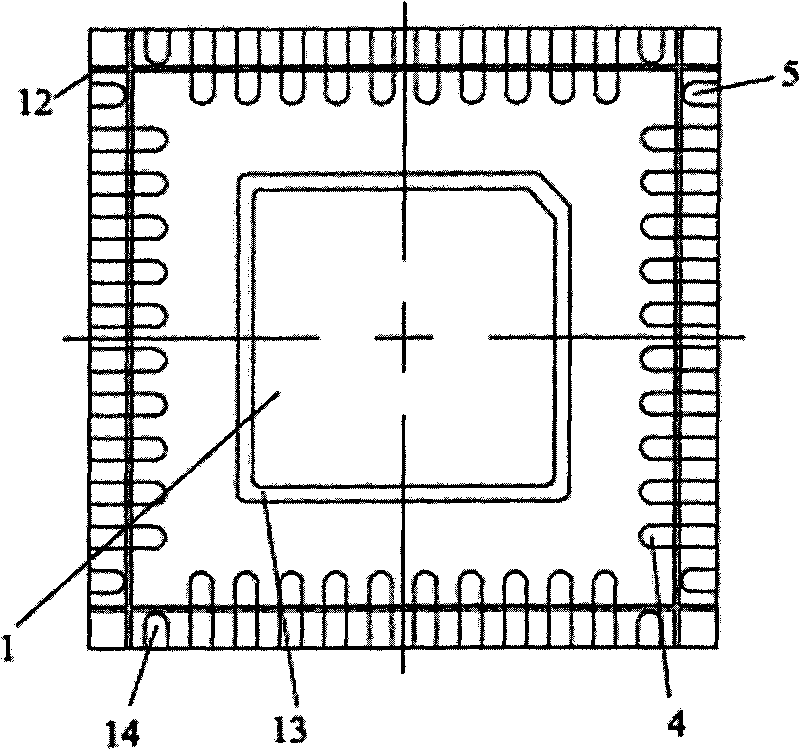

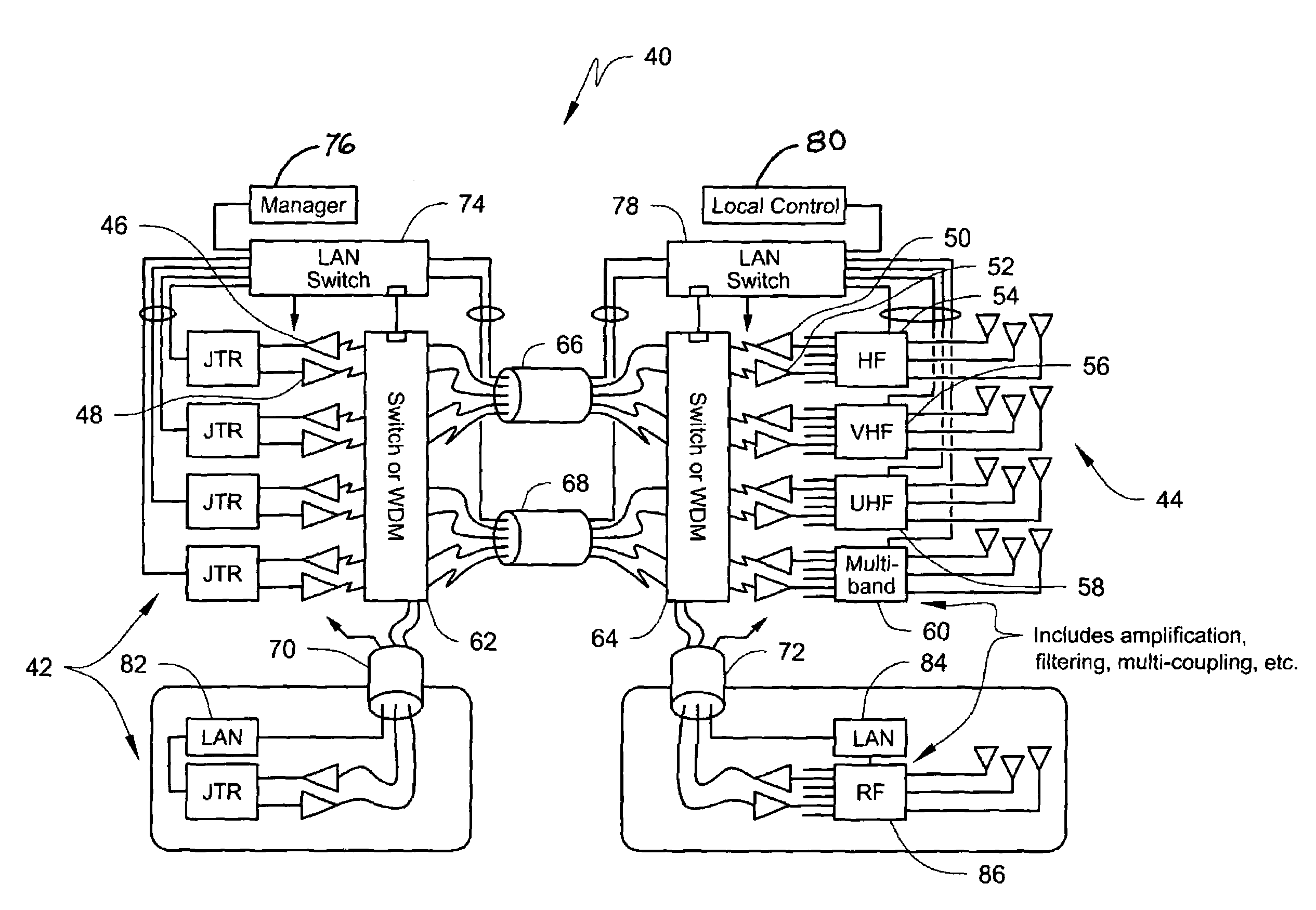

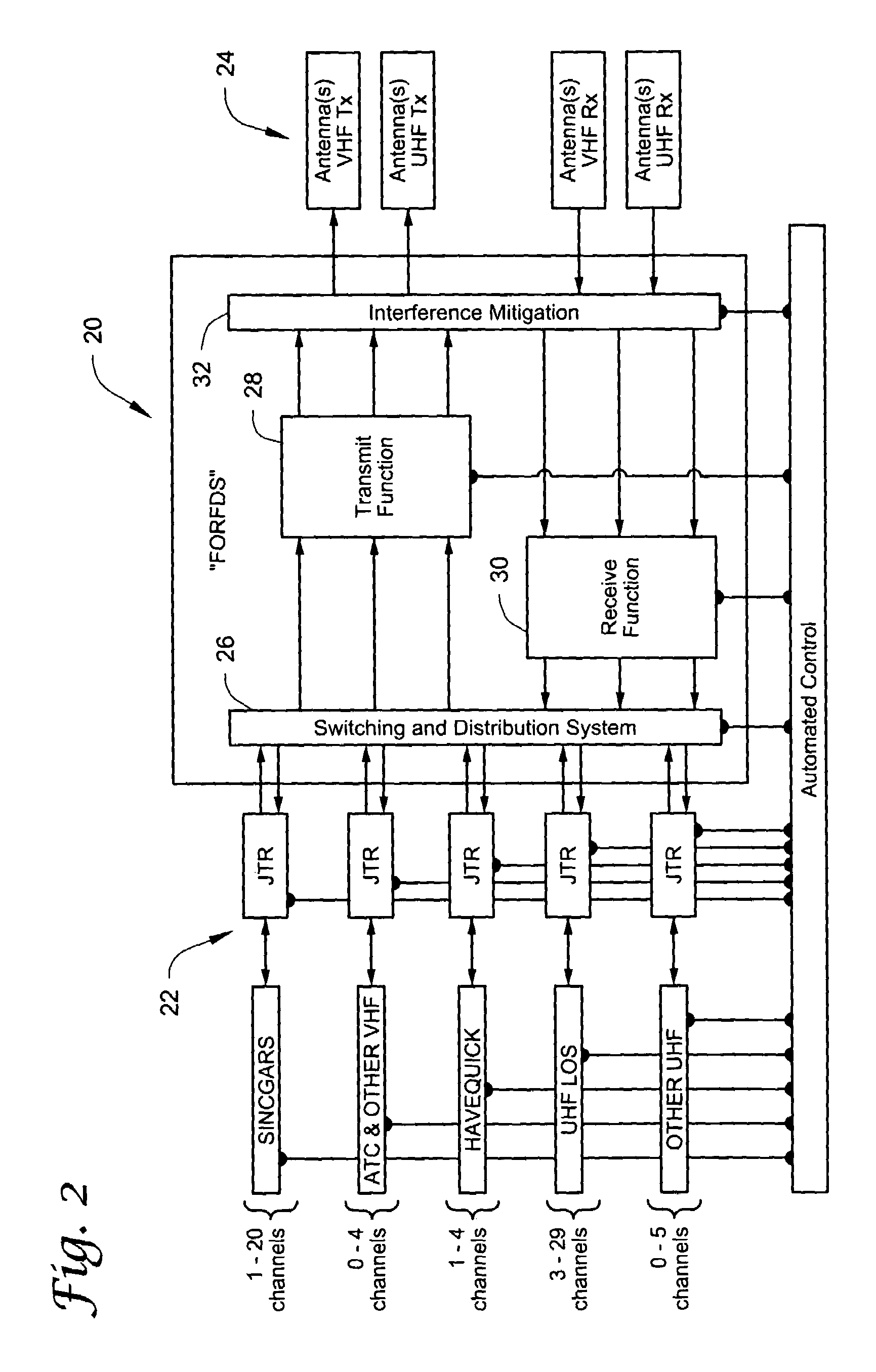

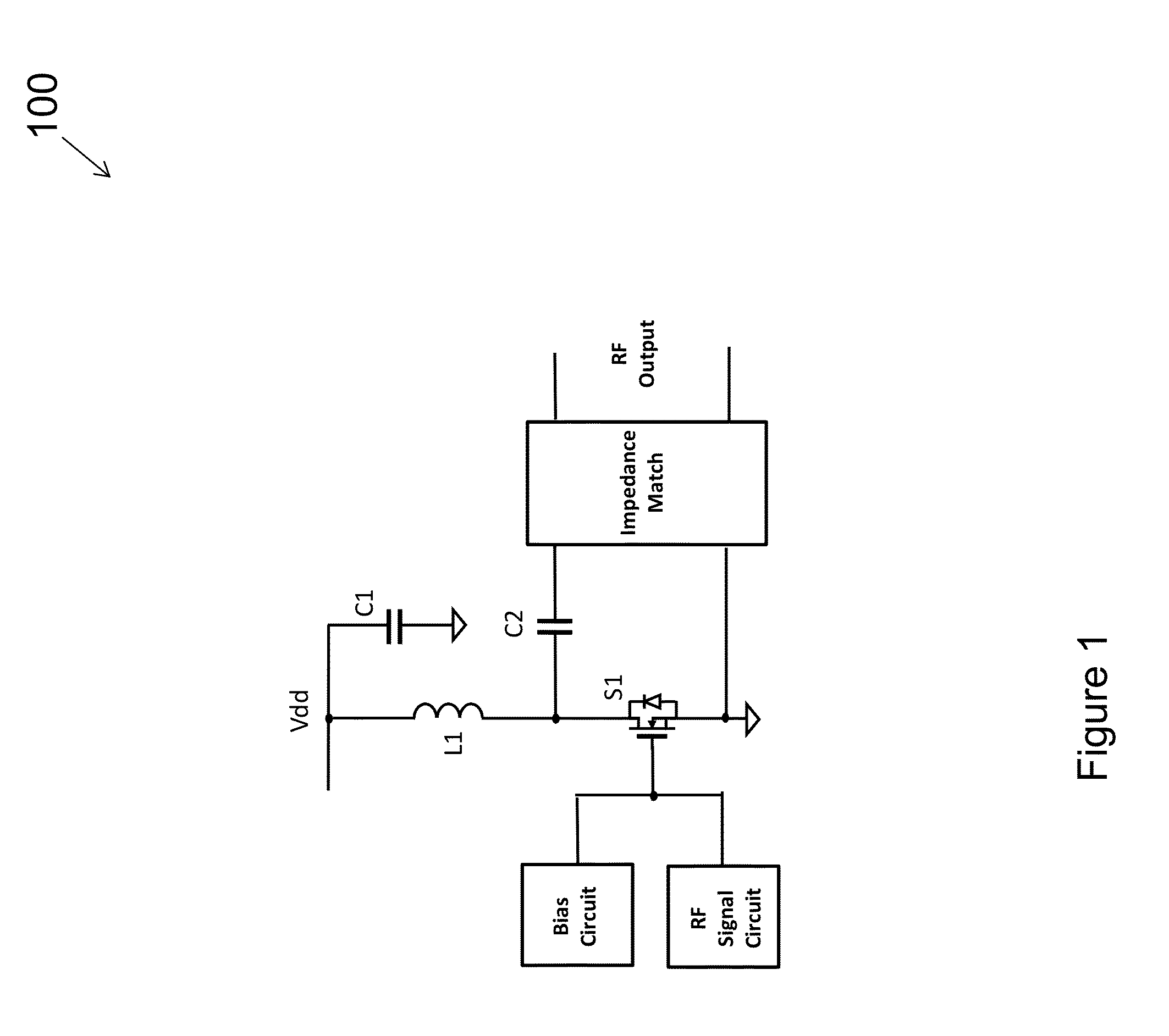

Fiber optic radio frequency distribution system

InactiveUS7715722B1Accurate transferHigh densitySubstation equipmentRadio transmission for post communicationExtensibilityFiber

A scalable, flexible, automated radio frequency distribution system (FORFDS) employs fiber optics to eliminate the need for metallic / coaxial type interconnections between onboard and fixed-site radios and antennas. Key elements of the FORFDS may include, for example, 1) electrical to optical conversion (and vice versa) of RF signals, 2) optical switching, 3) automated control and monitoring, including Ethernet interfaces, and 4) high density packaging. The system is compatible with JTRS (2 MHz to 2000 MHz), is scalable and cost effective (no longer in the laboratory or concept high cost ranges), compared with known technologies.

Owner:LOCKHEED MARTIN CORP

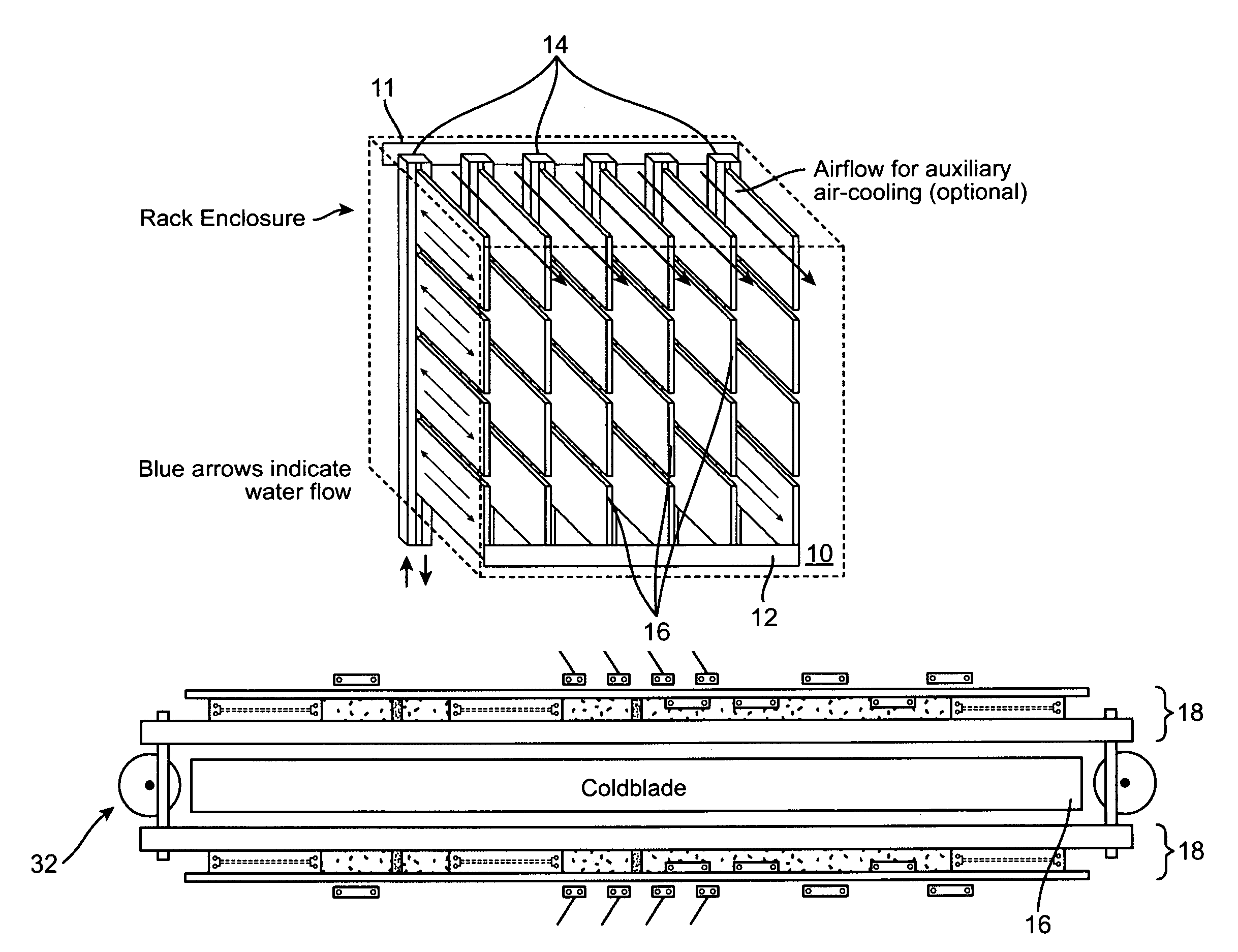

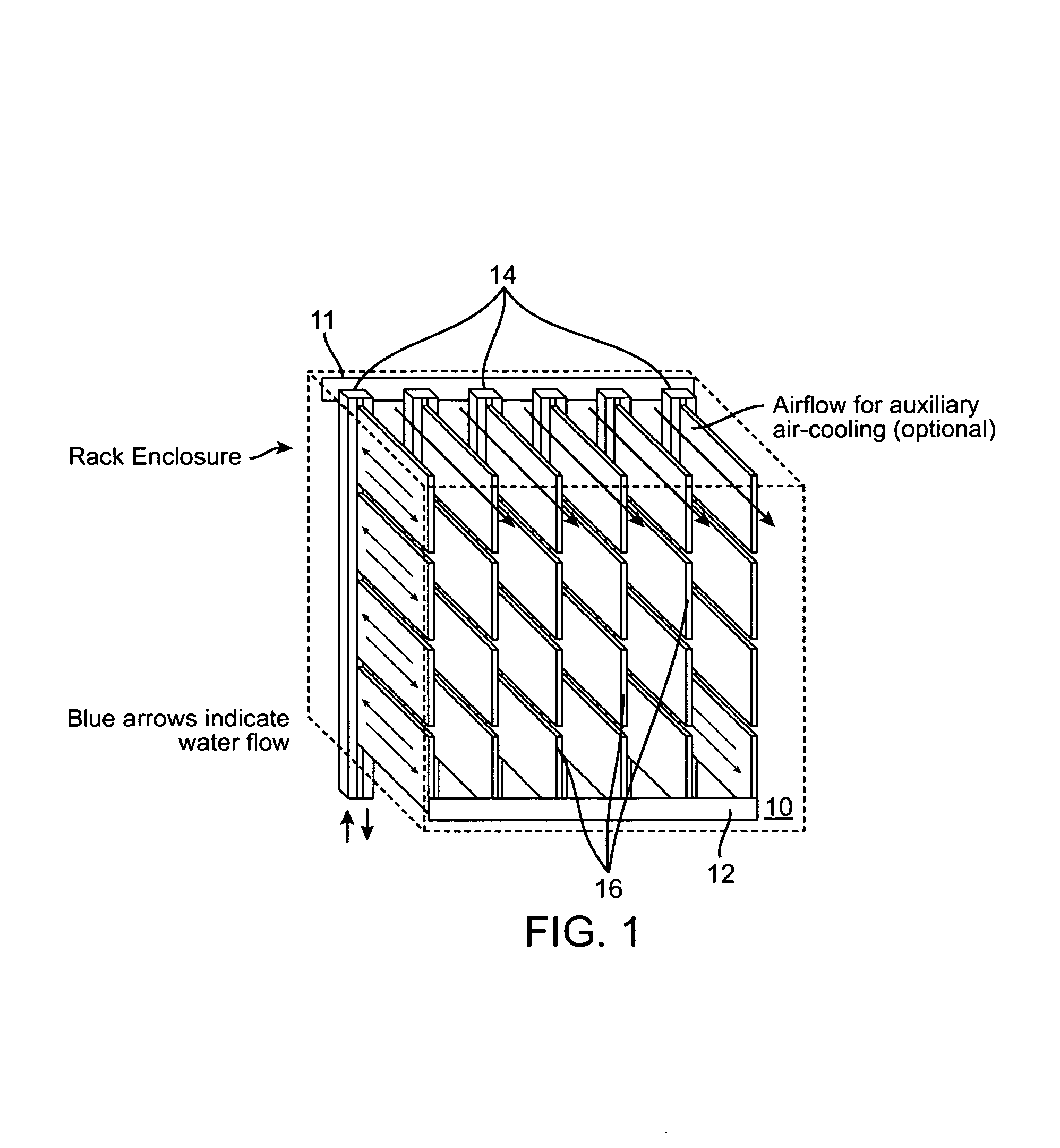

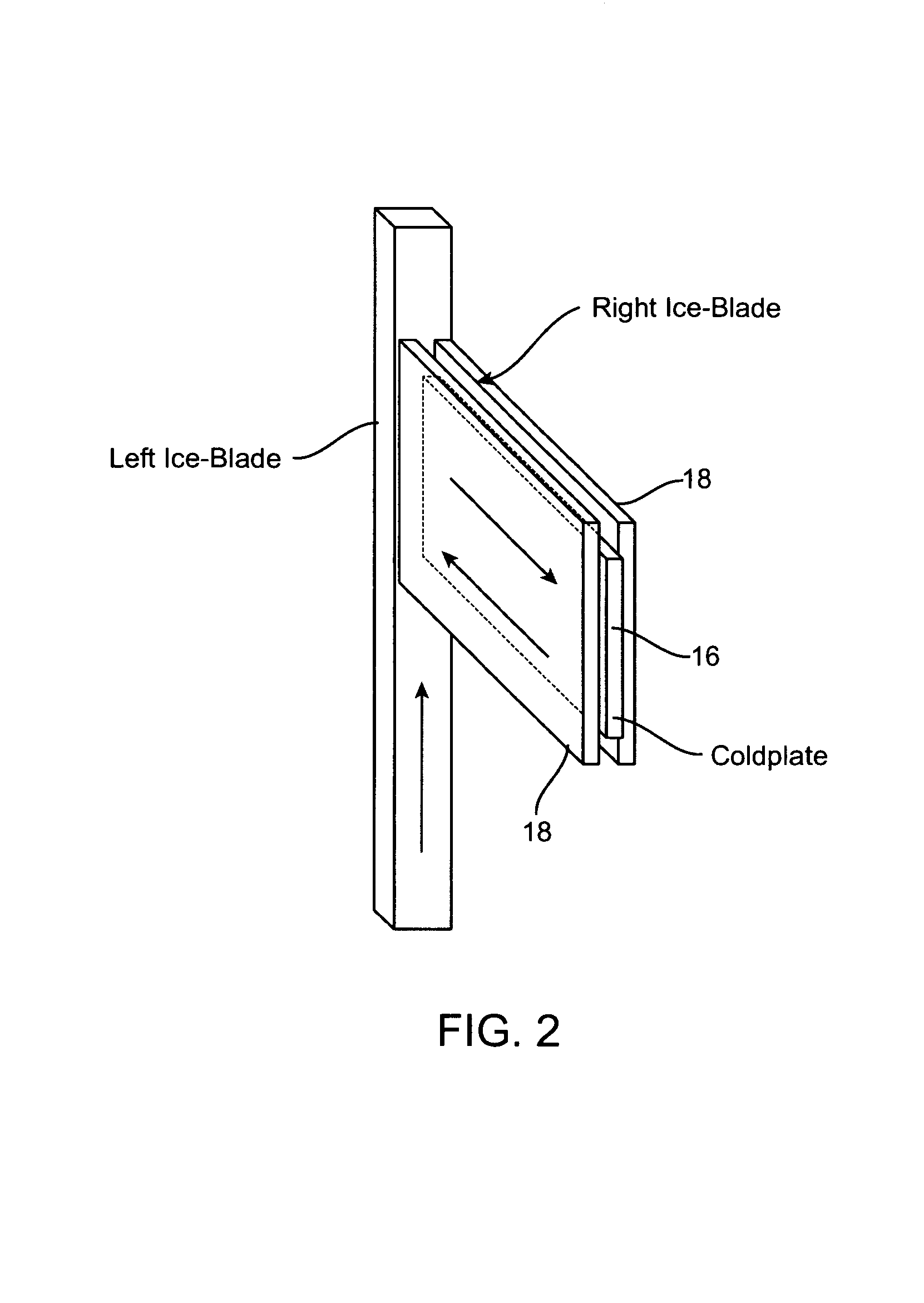

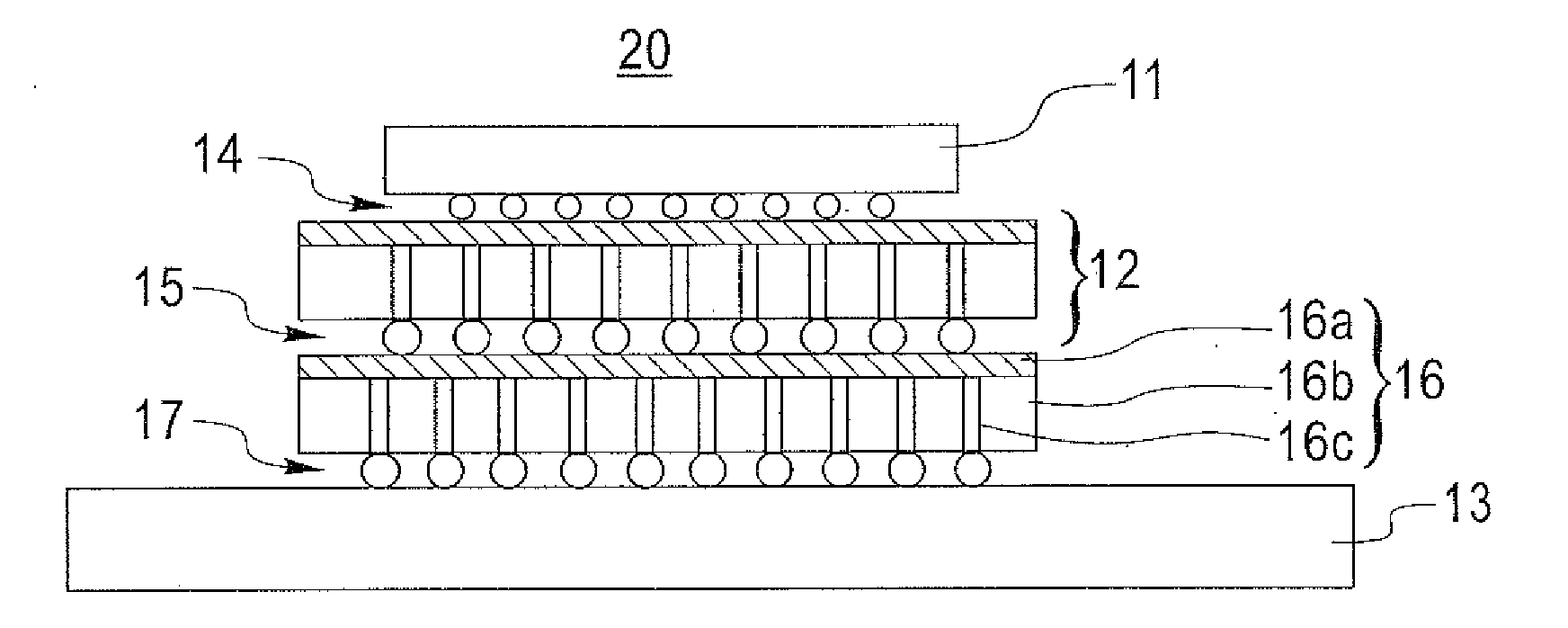

Method for high-density packaging and cooling of high-powered compute and storage server blades

InactiveUS7552758B2Modifications using gaseous coolantsLaminated elementsEngineeringHigh density packaging

According to the present invention, there is provided a system for removing heat from server blades densely packaged in a rack of server blades. The system includes a liquid distribution manifold. In addition, the system includes a plurality of cold blades attached to the liquid distribution manifold, wherein liquid is circulated through the liquid distribution manifold and the cold blades. Moreover, the system includes at least one server blade attached to each of the cold blades.

Owner:GLOBALFOUNDRIES INC

Copper pillar tin bump on semiconductor chip and method of forming the same

InactiveUS7781325B2Reduce spacingHigh densitySolid-state devicesSemiconductor/solid-state device manufacturingResistSemiconductor chip

Copper pillar tin bump on semiconductor chip comprises a copper layer composed on chip and a tin layer entirely wrapping whole outer surface of said copper layer. A method for forming of the copper pillar tin bump on semiconductor chip comprises: composing the first copper layer on said chip; applying photoresist to said first copper layer, exposing and developing a part of said photoresist, composing the copper pillar layer at the developed part of photoresist, composing the upper tin layer, removing said photoresist, removing said the first copper layer except disposing place of copper pillar layer, composing side tin layer. The minute pattern makes it possible to form a high density packaging by reducing a pitch of copper pillar tin bump. Signal delay can be reduced by low electric resistance, and underfill can be easily soaked.

Owner:HWABEAK ENG

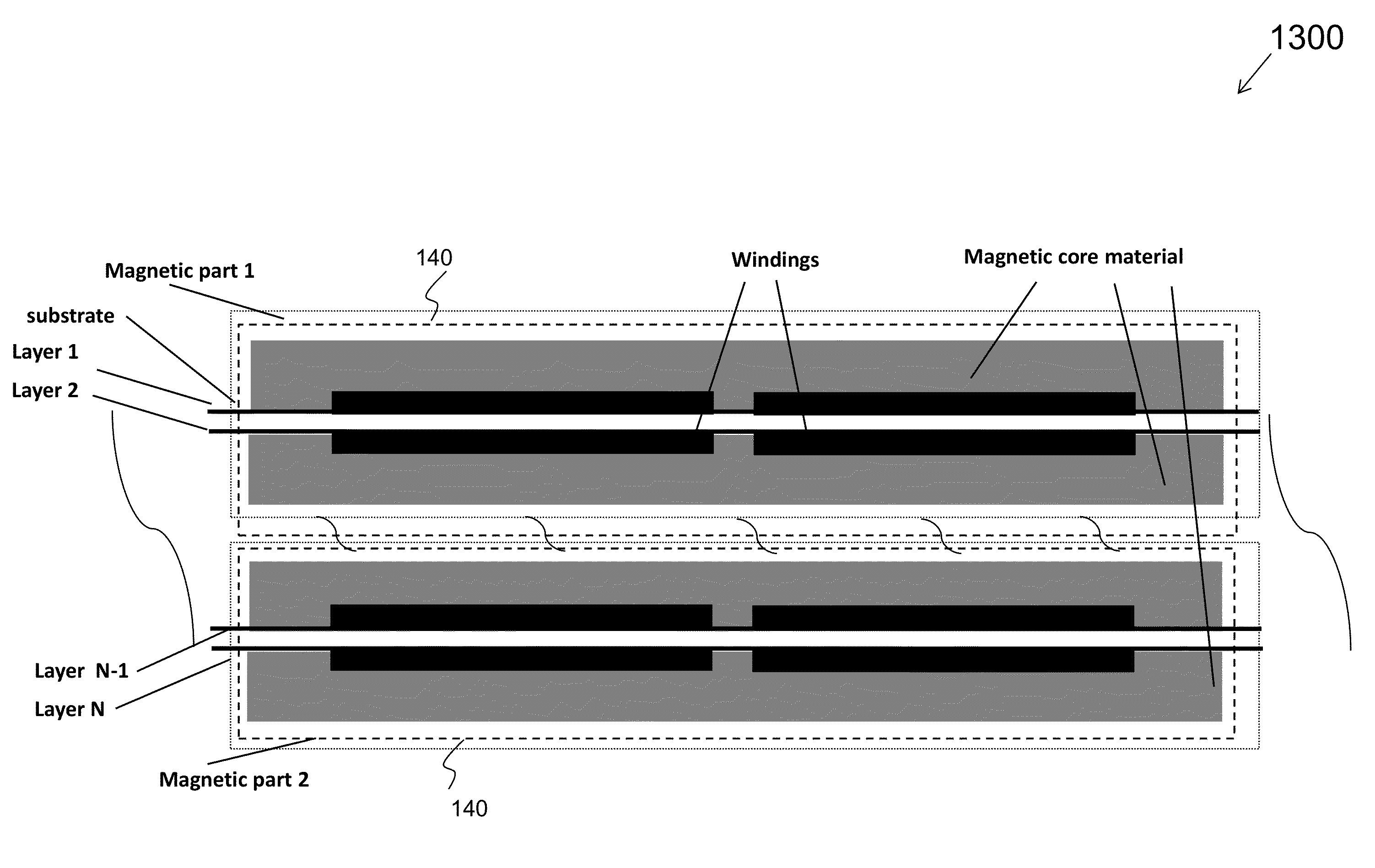

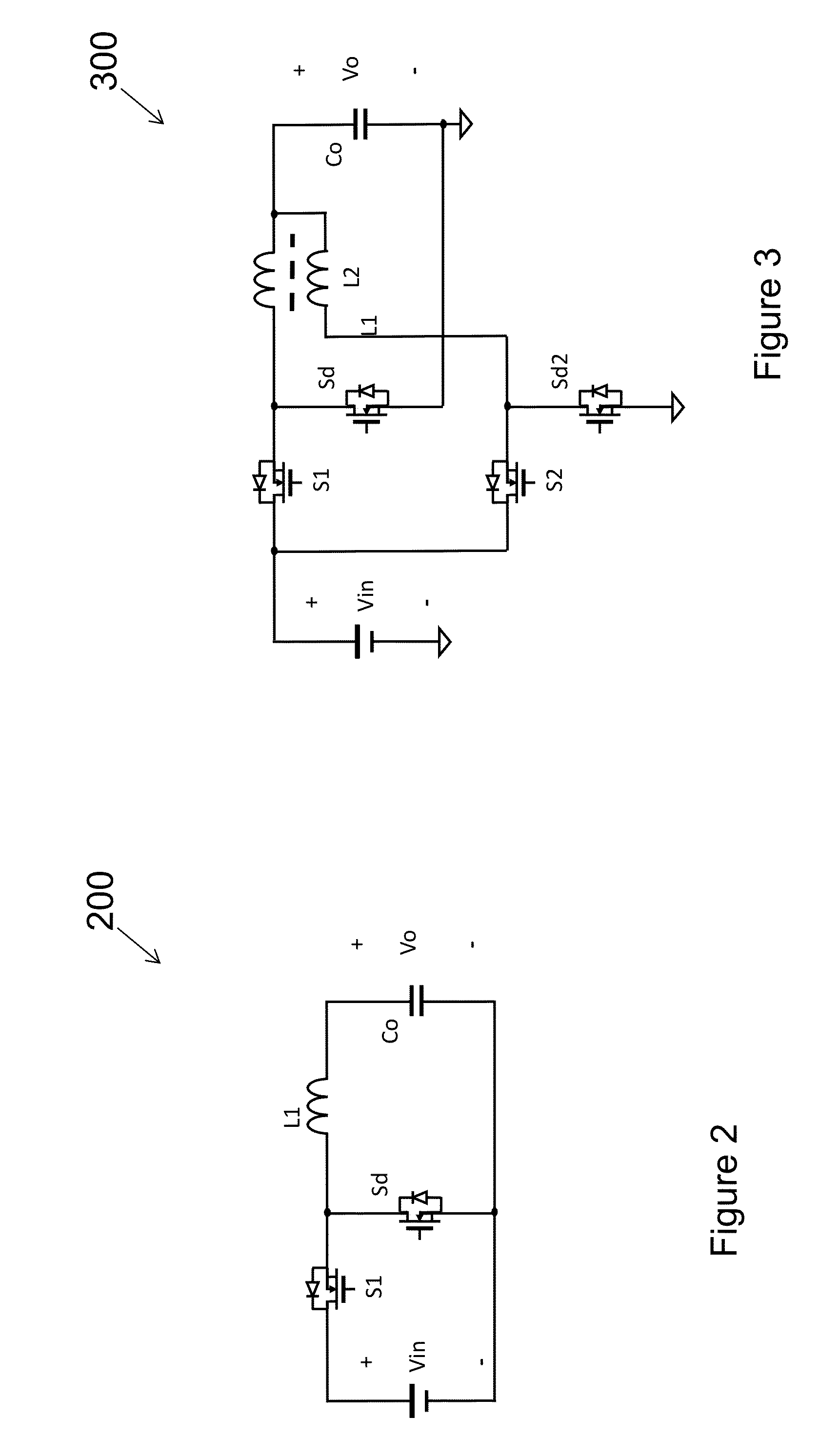

High Density Packaging for Efficient Power Processing with a Magnetic Part

InactiveUS20140266546A1Improved resonant power conversionTransformers/inductances coils/windings/connectionsCoils manufacturePower processingEngineering

Owner:MAO HENGCHUN

Wiring structure of printed wiring board and method for manufacturing the same

ActiveUS20080149379A1High densityMaintain insulation propertiesPrinted circuit assemblingElectrically conductive connectionsSemiconductorSemiconductor device

Provided is a wiring structure and the like which can completely connect a wiring layer to a body to be wired while keeping insulation between two adjacent wiring layers and realize high density packaging due to a narrowed pitch.In a semiconductor-embedded substrate, a conductive pattern is formed on both sides of a core substrate and a semiconductor device is placed in a resin layer stacked over the core substrate. The resin layer has via-holes so that the conductive pattern and a bump of the semiconductor device protrude from the resin layer. Inside the via-holes, the bump and conductive pattern are respectively connected to via-hole electrode portions whose cross-sectional area has been increased toward the bottom of the via-hole. A void is defined between the via-hole electrode portion and upper portion of the inner wall of the via-hole.

Owner:TDK CORPARATION

Stacked chip semiconductor device

ActiveUS20050116331A1Reduce power consumptionSemiconductor/solid-state device detailsSolid-state devicesDevice materialSemiconductor chip

A stacked chip semiconductor device whose size is substantially reduced by high density packaging of two or more semiconductor chips. In the semiconductor device, four semiconductor chips are stacked over a printed wiring board. The bottom semiconductor chip has an interface circuit which includes a buffer and an electrostatic discharge protection circuit. All signals that these semiconductor chips receive and send are inputted or outputted through the interface circuit of the bottom semiconductor chip. Since the other semiconductor chips require no interface circuit, the semiconductor device is compact.

Owner:RENESAS ELECTRONICS CORP

High-density packaging of integrated circuits

InactiveUS20050095745A1Small sizeSuitable for installationTelevision system detailsSemiconductor/solid-state device detailsSmall form factorEngineering

An integrated circuit constructed on a folded integrated circuit is described. The folded integrated circuit has a much smaller form-factor than the original (unfolded) circuit and is thus more suitable for use in miniature devices, such as, for example, electronic camera, electronic-film cartridge, cellular telephone, handheld computer, handheld digital music device, portable devices, handheld devices, and the like. In one embodiment, the integrated circuit is folded by thinning an area of the substrate such that the thinned area of the substrate becomes flexible. Conducting traces on the upper surface of the substrate connect an active region on one side of the thinned area to an active region on the other side of the thinned area. The substrate is folded at the thinned area to thereby reduce the size of the substrate. In one embodiment, a heat-sink is inserted between the folds to carry heat away from the substrate.

Owner:SAPIR ITZHAK

Copper pillar tin bump on semiconductor chip and method of forming the same

InactiveUS20090127708A1High-density packagingHigh densitySemiconductor/solid-state device detailsSolid-state devicesResistSemiconductor chip

Copper pillar tin bump on semiconductor chip comprises a copper layer composed on chip and a tin layer entirely wrapping whole outer surface of said copper layer. A method for forming of the copper pillar tin bump on semiconductor chip comprises: composing the first copper layer on said chip; applying photoresist to said first copper layer, exposing and developing a part of said photoresist, composing the copper pillar layer at the developed part of photoresist, composing the upper tin layer, removing said photoresist, removing said the first copper layer except disposing place of copper pillar layer, composing side tin layer. The minute pattern makes it possible to form a high density packaging by reducing a pitch of copper pillar tin bump. Signal delay can be reduced by low electric resistance, and underfill can be easily soaked.

Owner:HWABEAK ENG

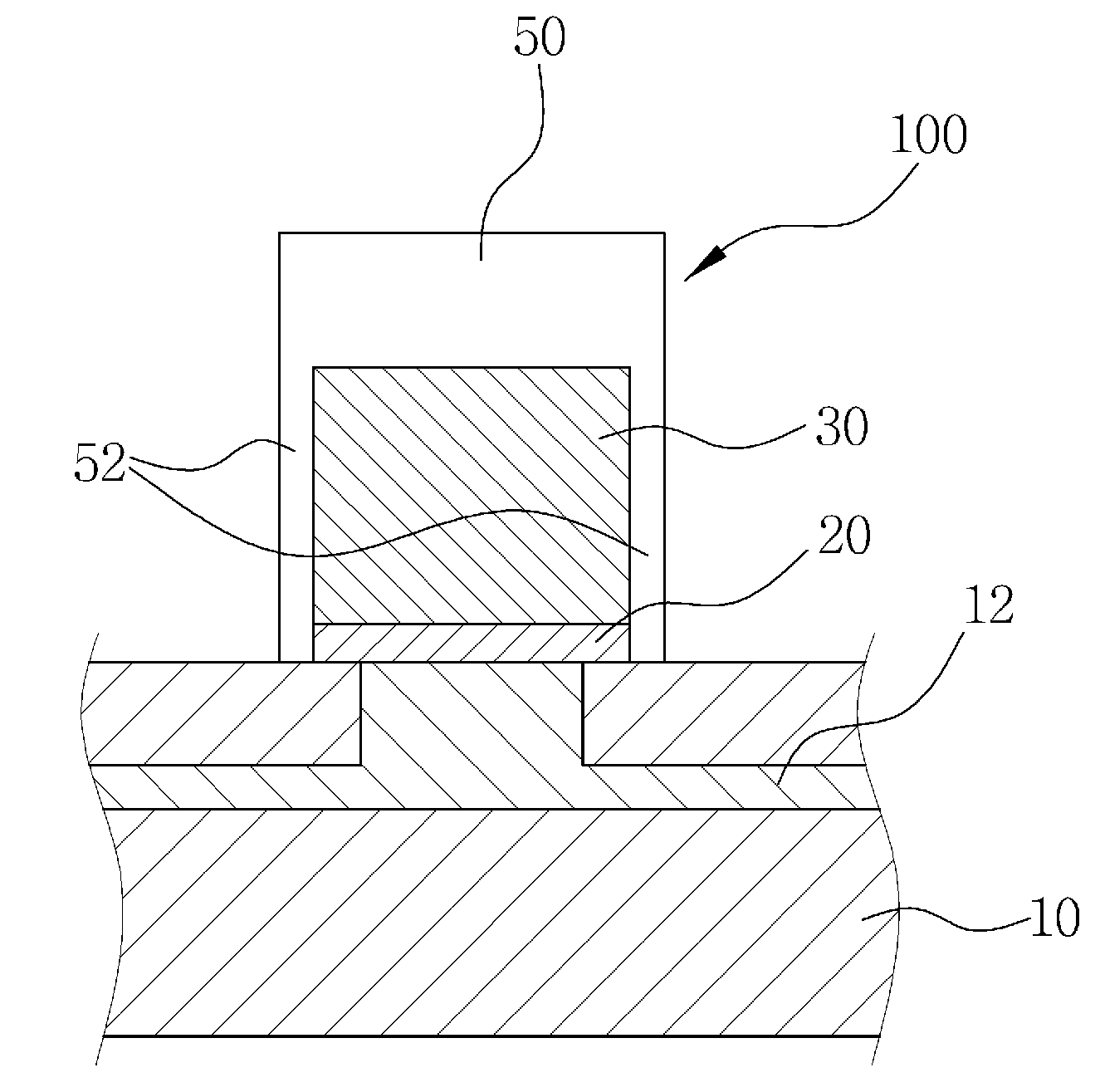

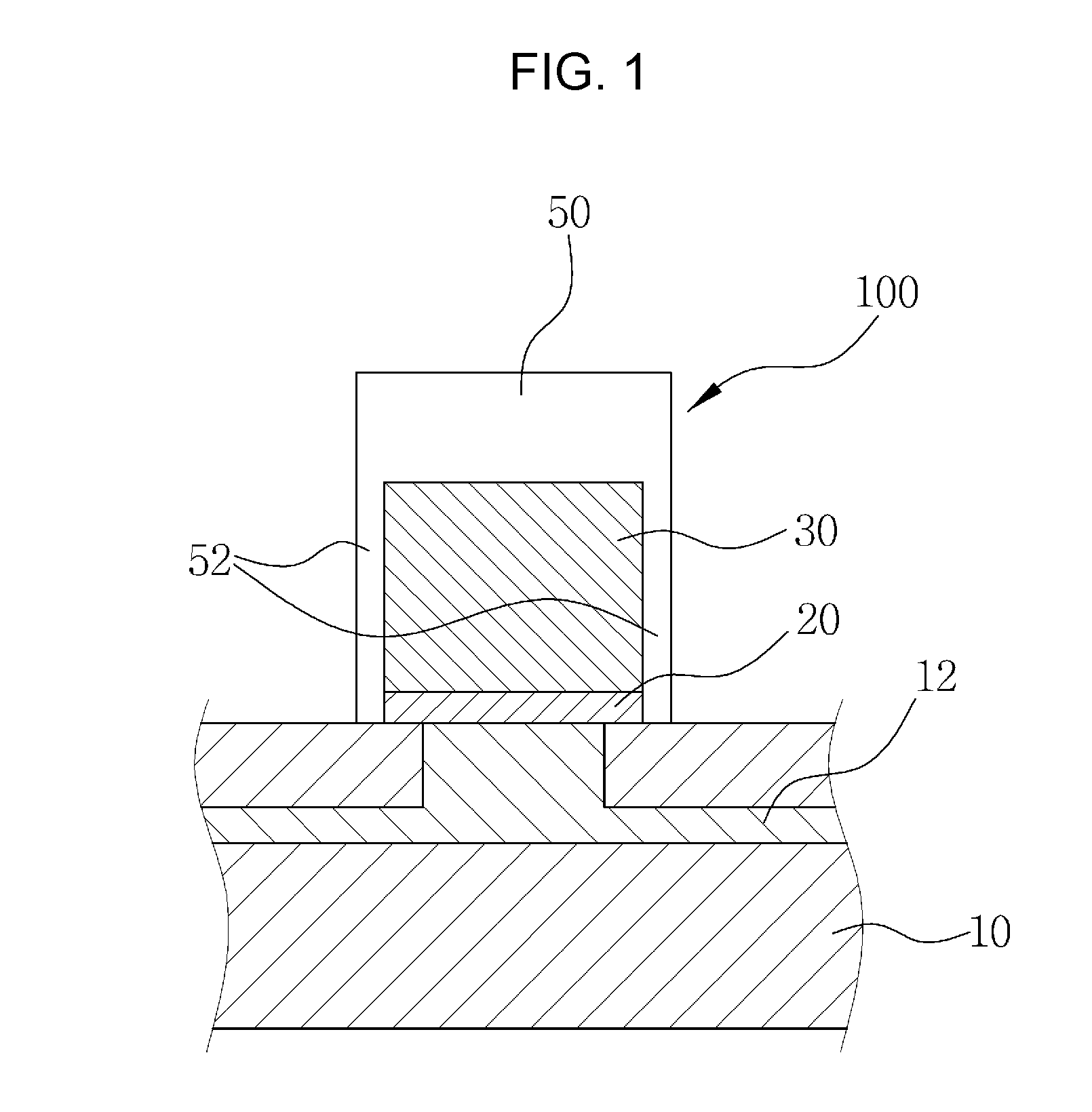

Semiconductor device

InactiveUS20050040509A1High-density packagingImprove reliabilitySemiconductor/solid-state device detailsSolid-state devicesMemory chipDevice material

For high density packaging of a semiconductor device, the semiconductor device has a multi-layer substrate, a first-stage chip connected electrically to the multi-layer substrate, other package substrates stacked in three stages on the multi-layer substrate and each connected to an underlying wiring substrate through solder balls, second-, third- and fourth-stage chips electrically connected respectively to the other package substrates, and solder balls provided on the bottom multi-layer substrate. The number of wiring layers in the bottom multi-layer substrate which has a logic chip is larger than that in the package substrates which have memory chips, whereby the semiconductor device can have a wiring layer not used for distribution of wires to the solder balls and wiring lines in the wiring layer can be used for the mounting of another semiconductor element or a passive component to attain high density packaging of the semiconductor device as a stacked type package.

Owner:RENESAS ELECTRONICS CORP

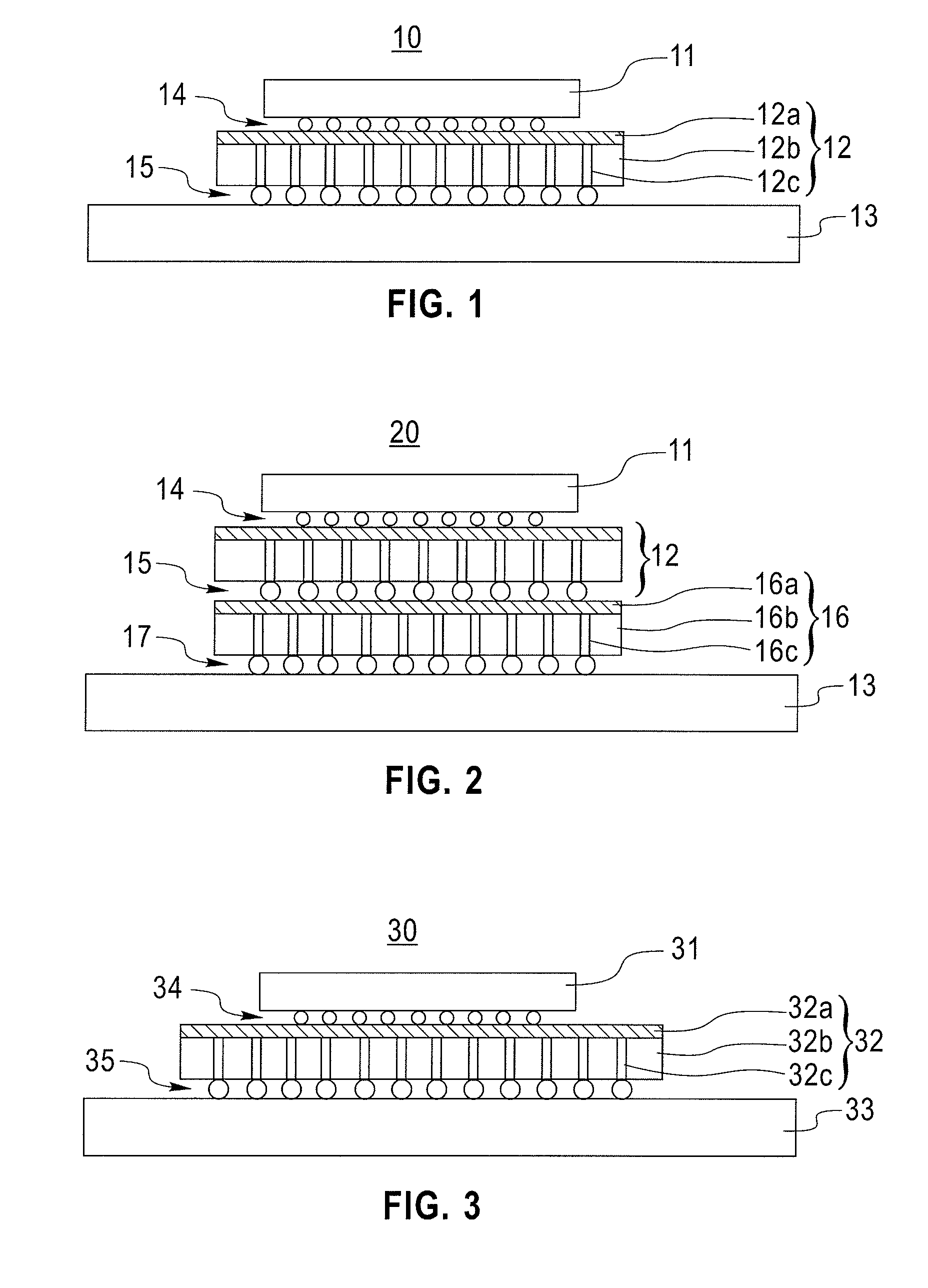

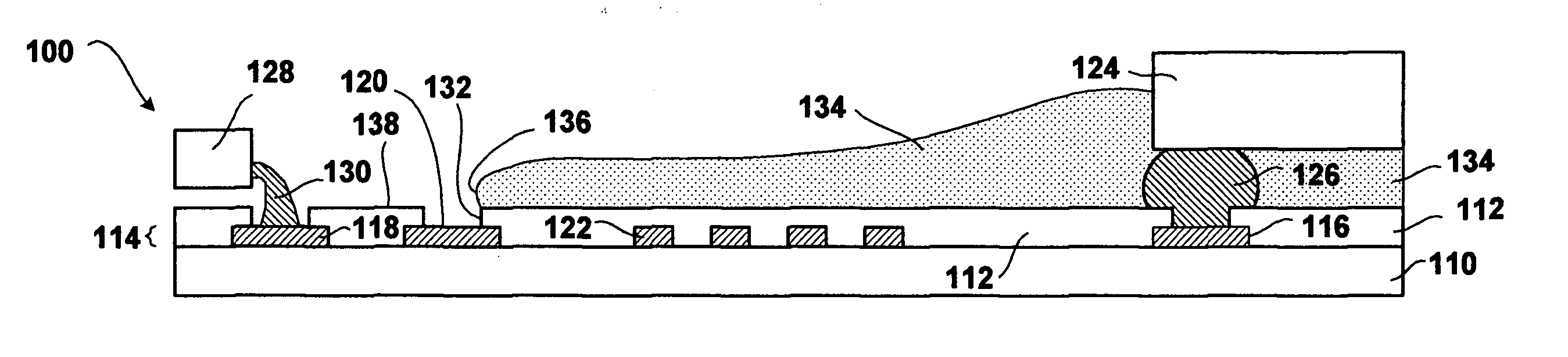

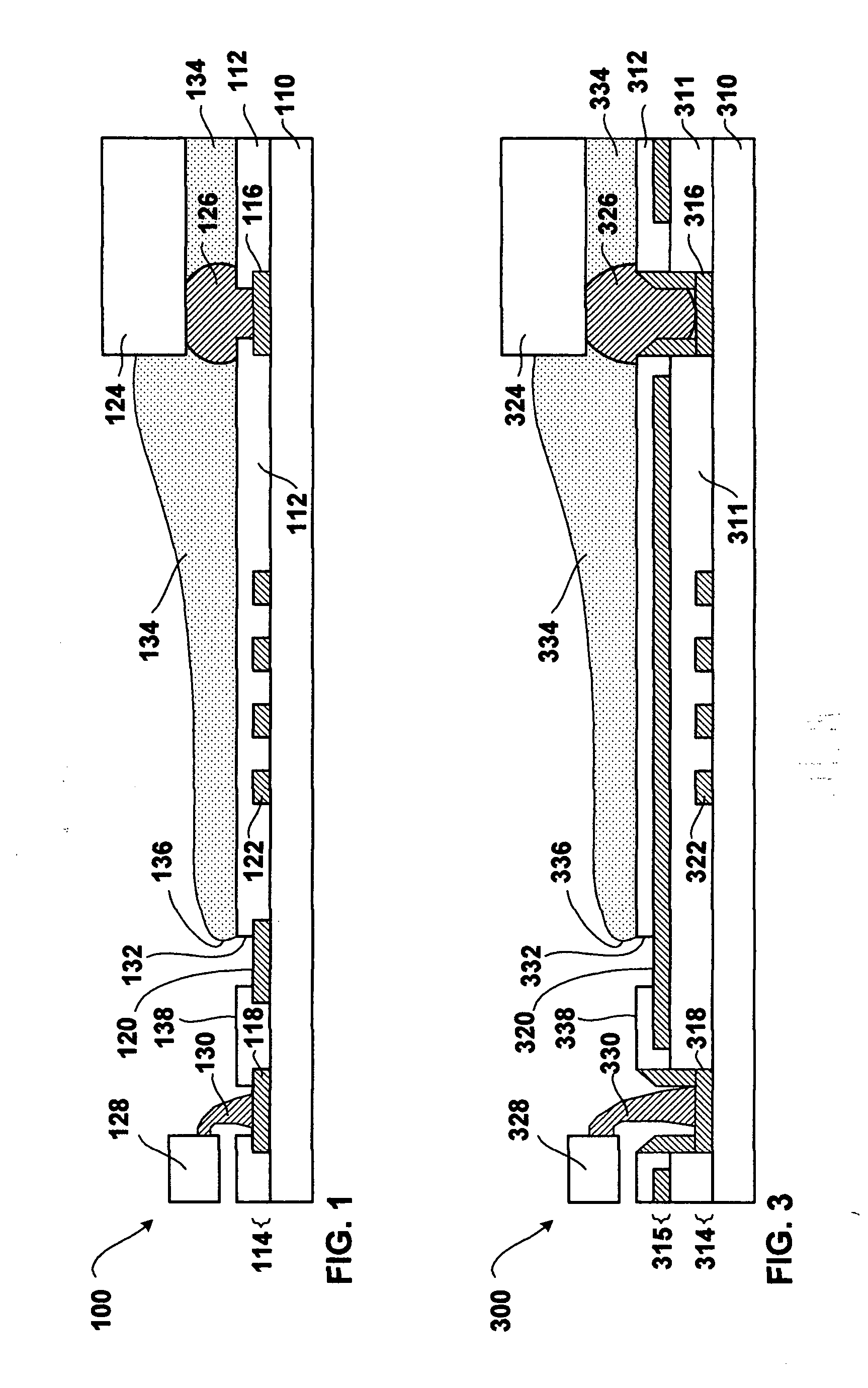

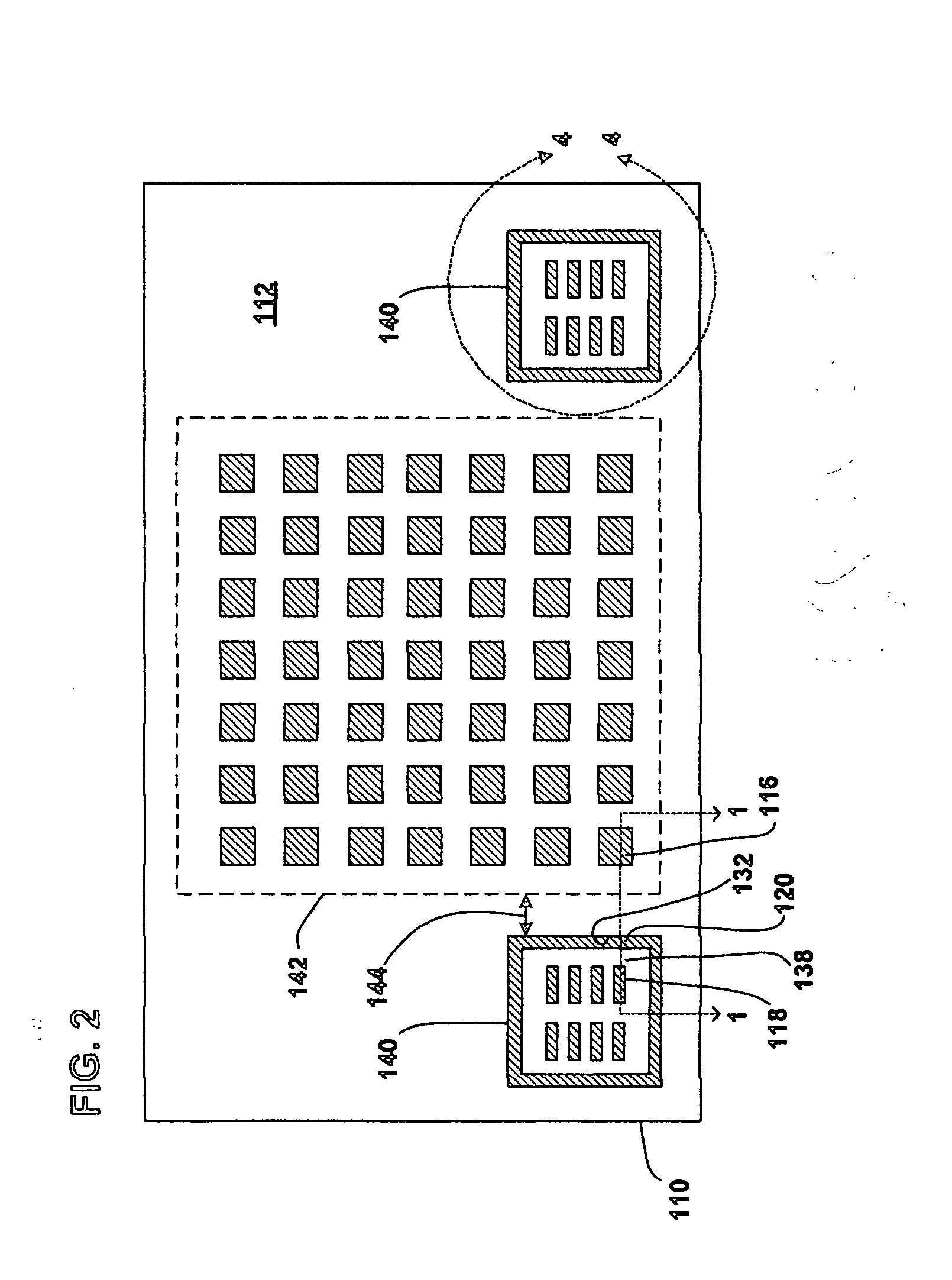

Local control of underfill flow on high density packages, packages and systems made therewith, and methods of making same

ActiveUS20050195582A1Semiconductor/solid-state device detailsPrinted circuit aspectsHigh densityActive component

An article includes a mounting substrate, a passive component site on the mounting substrate, and an active component site on the mounting substrate. The article also includes a fluid flow barrier disposed local to the passive component site and spaced apart from the active component site. The fluid flow barrier can be a recess that resists fluid flow thereinto because of surface tension of the fluid when it meets the recess edge. The fluid flow barrier can include a boundary that diverts fluid flow due to the angle of the recess edge as the fluid approaches it. An embodiment also includes a packaging system that includes the article and at least one passive component. An embodiment also includes a method of assembling the article or the packaging system.

Owner:INTEL CORP

Apparatus and methods for constructing semiconductor chip packages with silicon space transformer carriers

InactiveUS20090311828A1Cost assemblyCost handlingSemiconductor/solid-state device detailsSolid-state devicesHigh densityTransformer

Owner:INT BUSINESS MASCH CORP

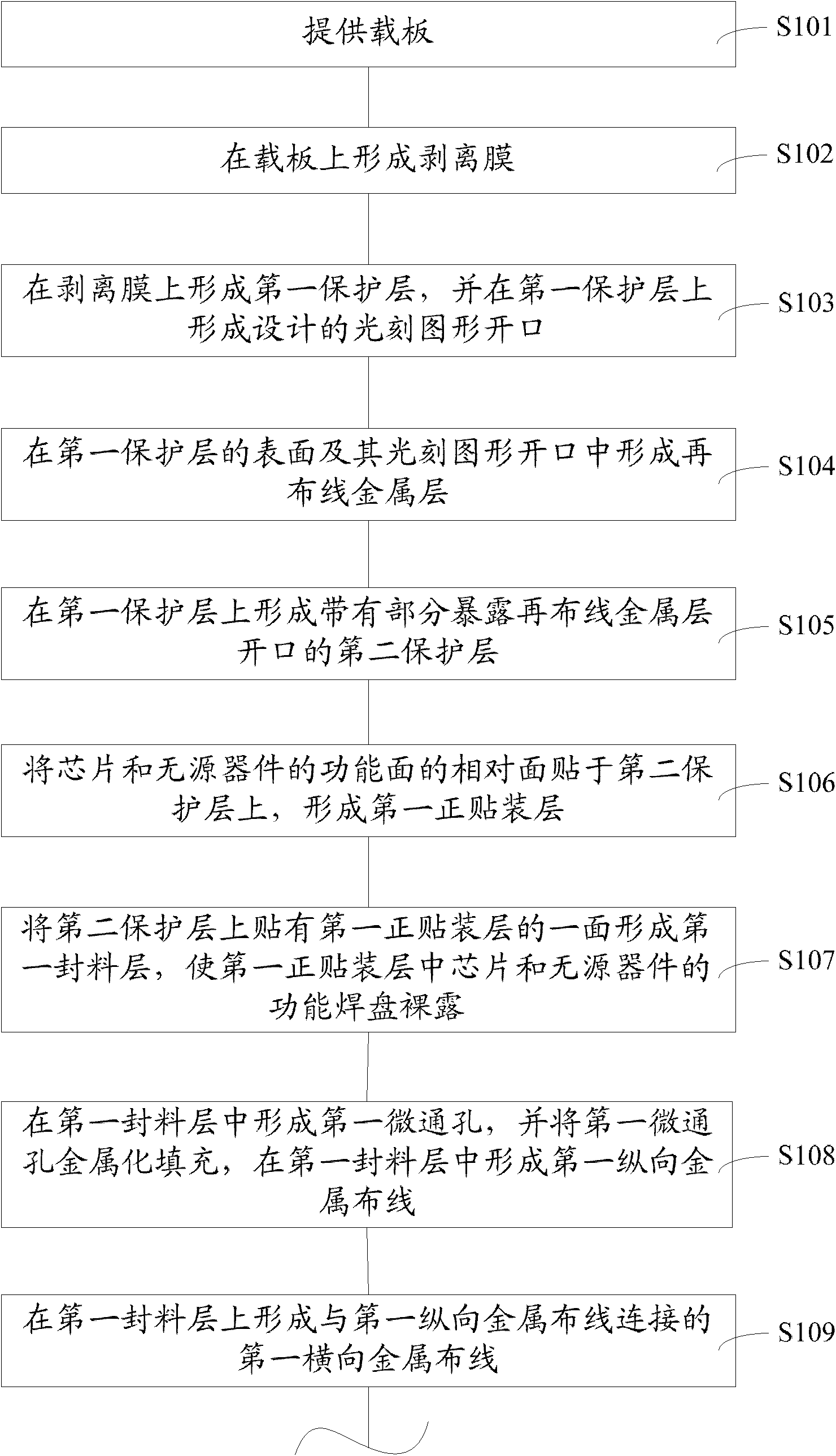

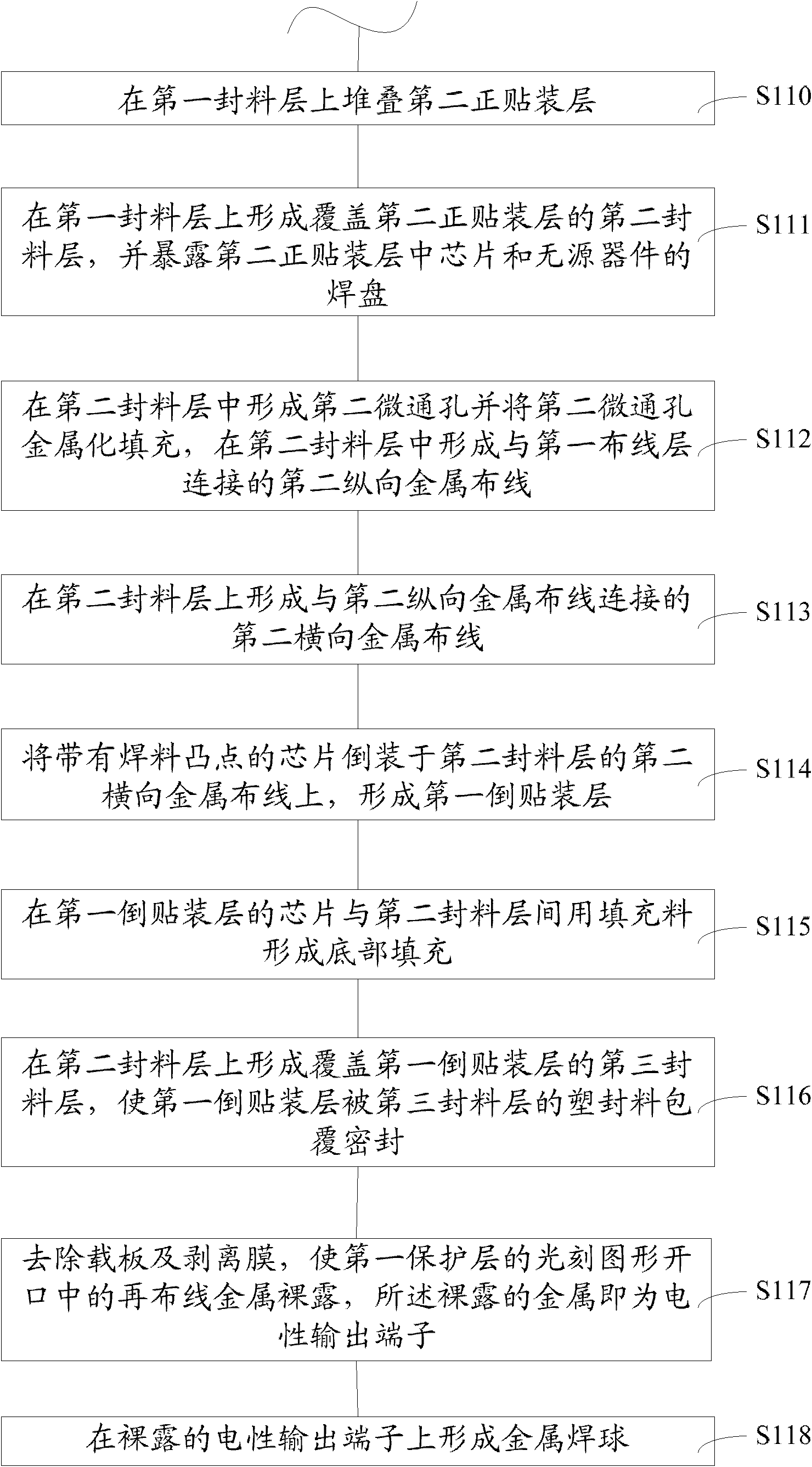

Fan-out high-density packaging method

ActiveCN102157393ALess distracting factorsComply with the trend of light, thin and shortSolid-state devicesSemiconductor/solid-state device manufacturingInterference factorEngineering

The invention relates to a fan-out high-density packaging method, which comprises the following steps of: providing a carrier plate; forming a stripping membrane on the carrier plate; forming protective layers on the stripping membrane; forming a rewiring metal layer in the protective layers; forming wiring packaging layers which are conductive with the rewiring metal layer on the protective layers; forming inversion packaging layers on the wiring packaging layers, wherein the packaging layers are connected electrically and mutually by wiring layers and welding flux salient points; removing the carrier plate and the stripping membrane, so that rewiring metal in a first protective layer is exposed; and forming a metal welded ball on the exposed rewiring metal. Compared with the prior art, the fan-out high-density packaging method has the advantages that: a final packaging product with an integral systemic function instead of a single chip function can be formed, and the resistance and inductance in a system and interference factors among chips are reduced. In addition, a complex multi-layer interconnection structure can be formed, so that the wafer system-level packaging of a higher integration level is realized.

Owner:NANTONG FUJITSU MICROELECTRONICS

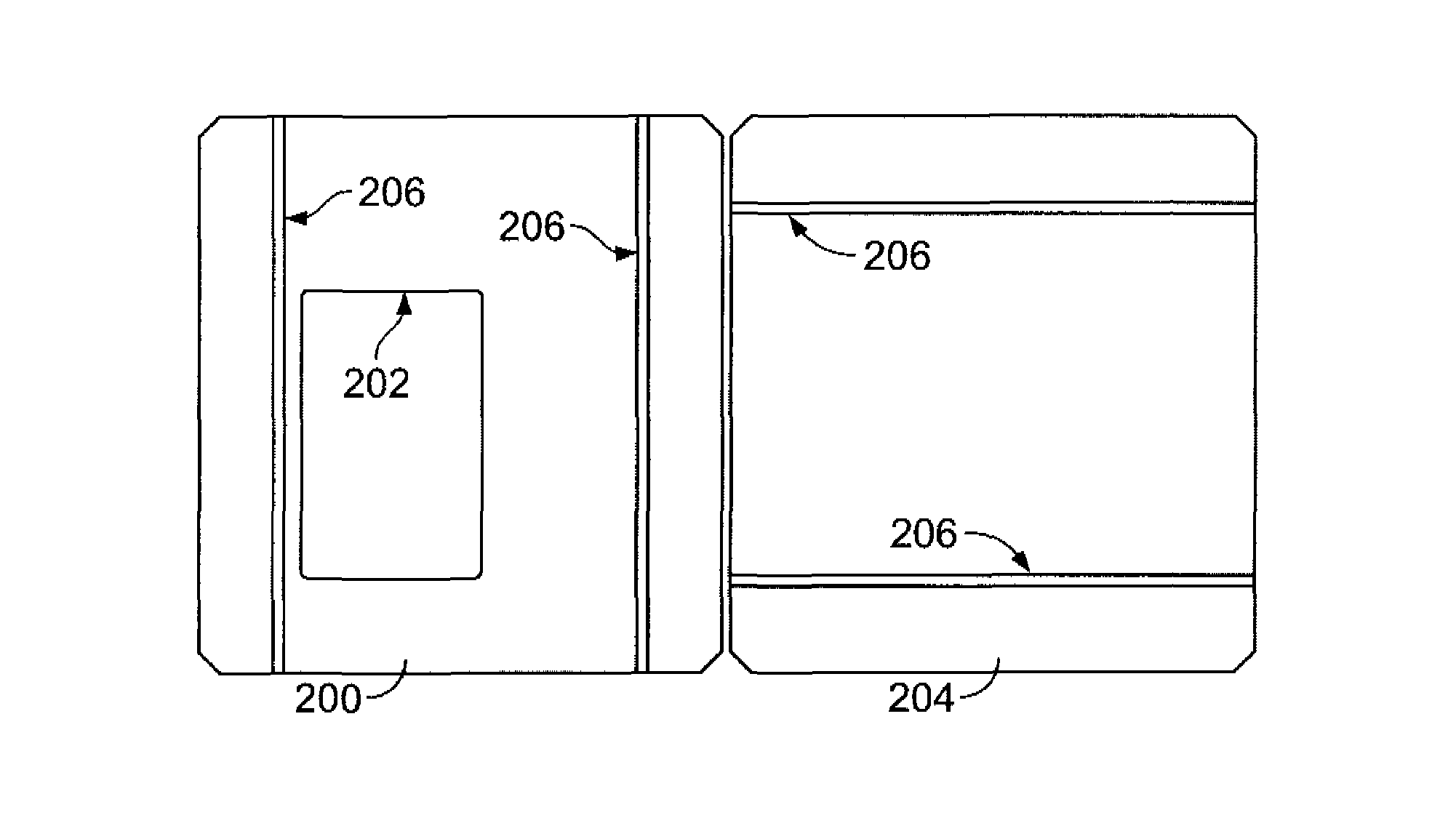

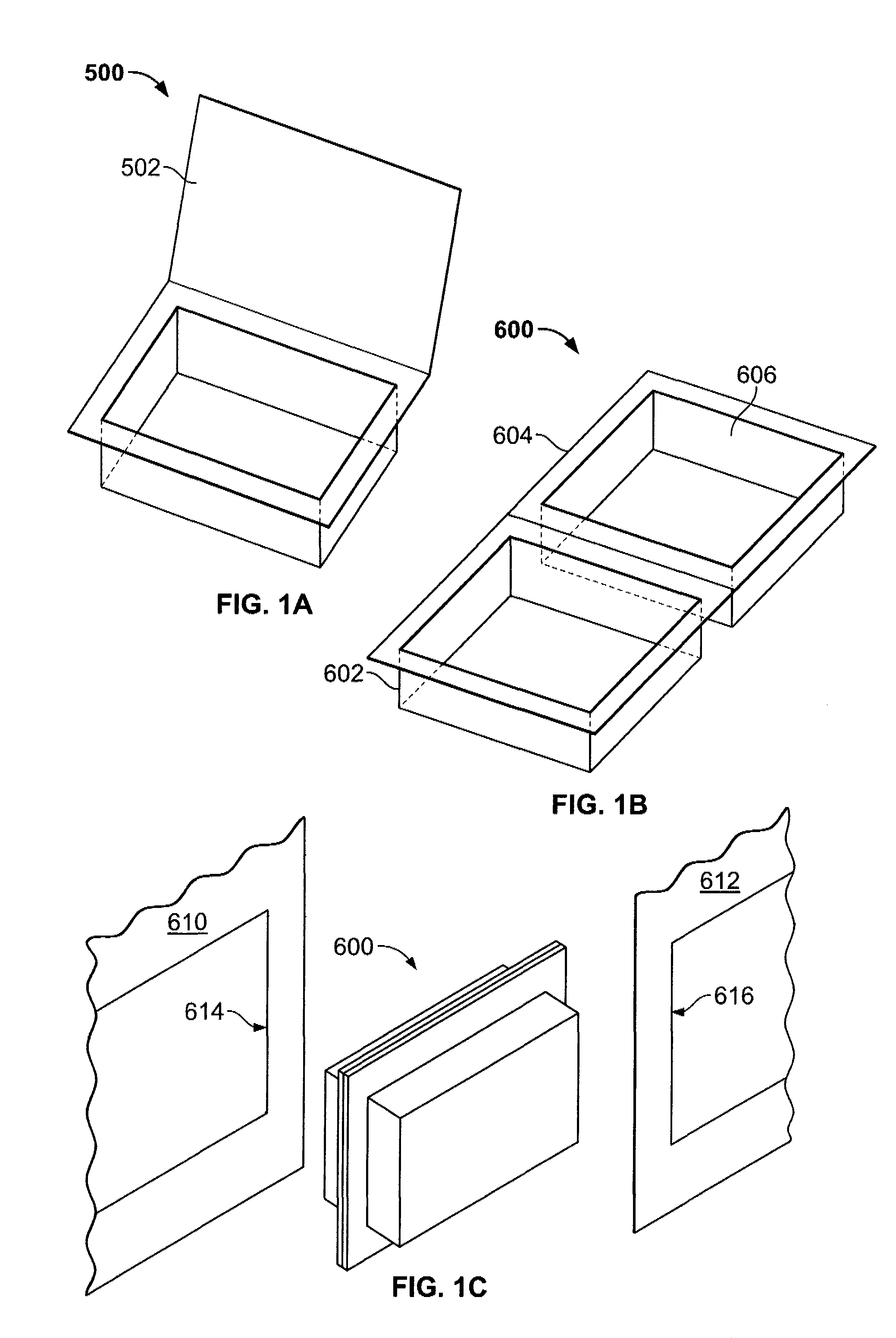

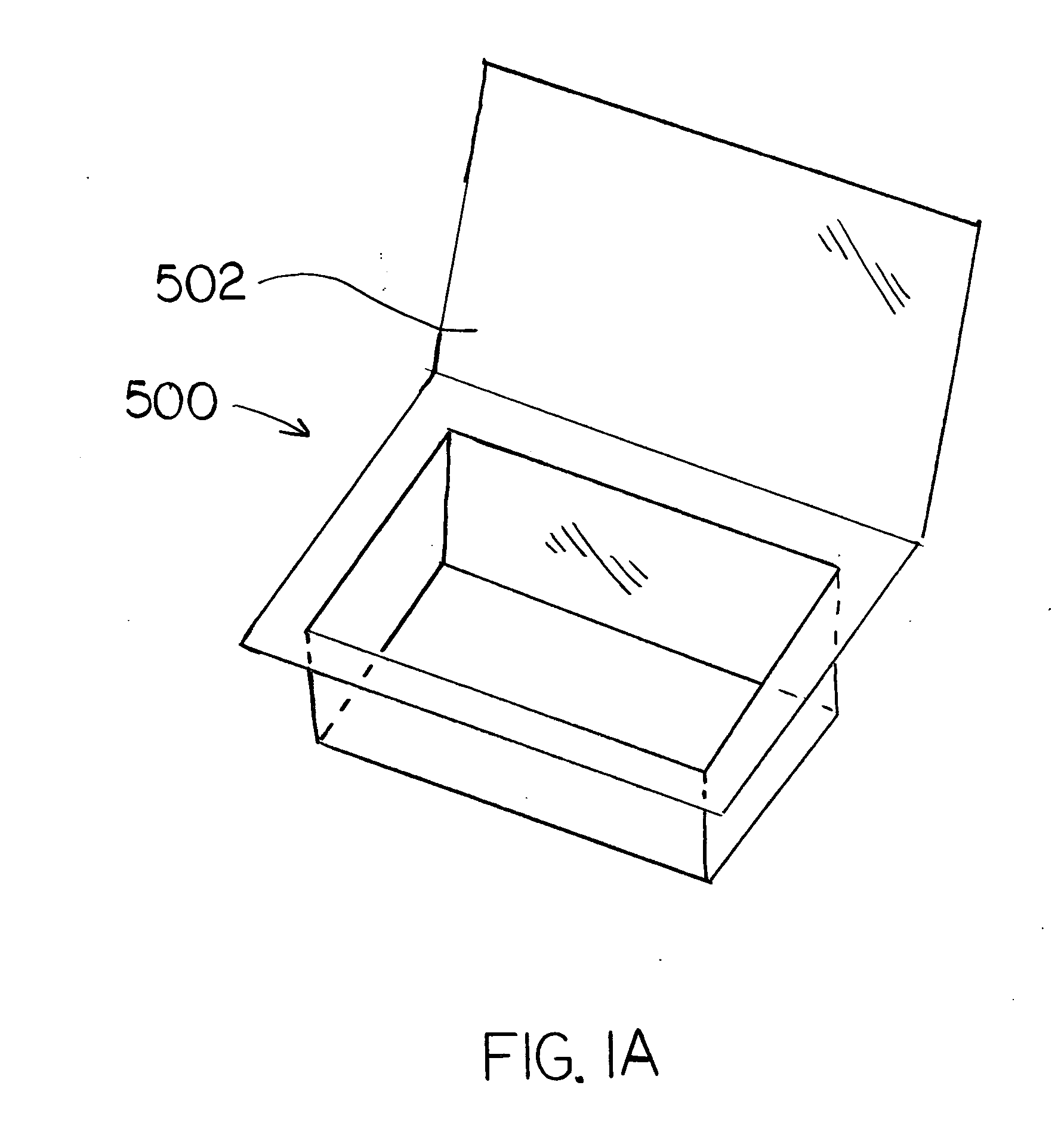

Display package constructions

Display packaging constructions incorporating a plastic blister cavity, sandwiched between layers of paperboard material, preferably corrugated paperboard material, are disclosed. Variations of the basic construction include a high-density packaging configuration, display packages having security features for precluding unauthorized access to the interior of the display package, and a reclosable construction to enable the display package to be used as a storage container. When corrugated paperboard is used for the layers, the corrugations may be arranged to extend transversely to one another, to resist warping caused during the heat sealing process. A plastic blister construction is provided, having a forward stabilizing foot, and a rear concavity, for receiving a similar foot from a like blister, for facilitated nested packing together of pluralities of such blisters.

Owner:SMURFIT STONE CONTAINER ENTERPRISES INC

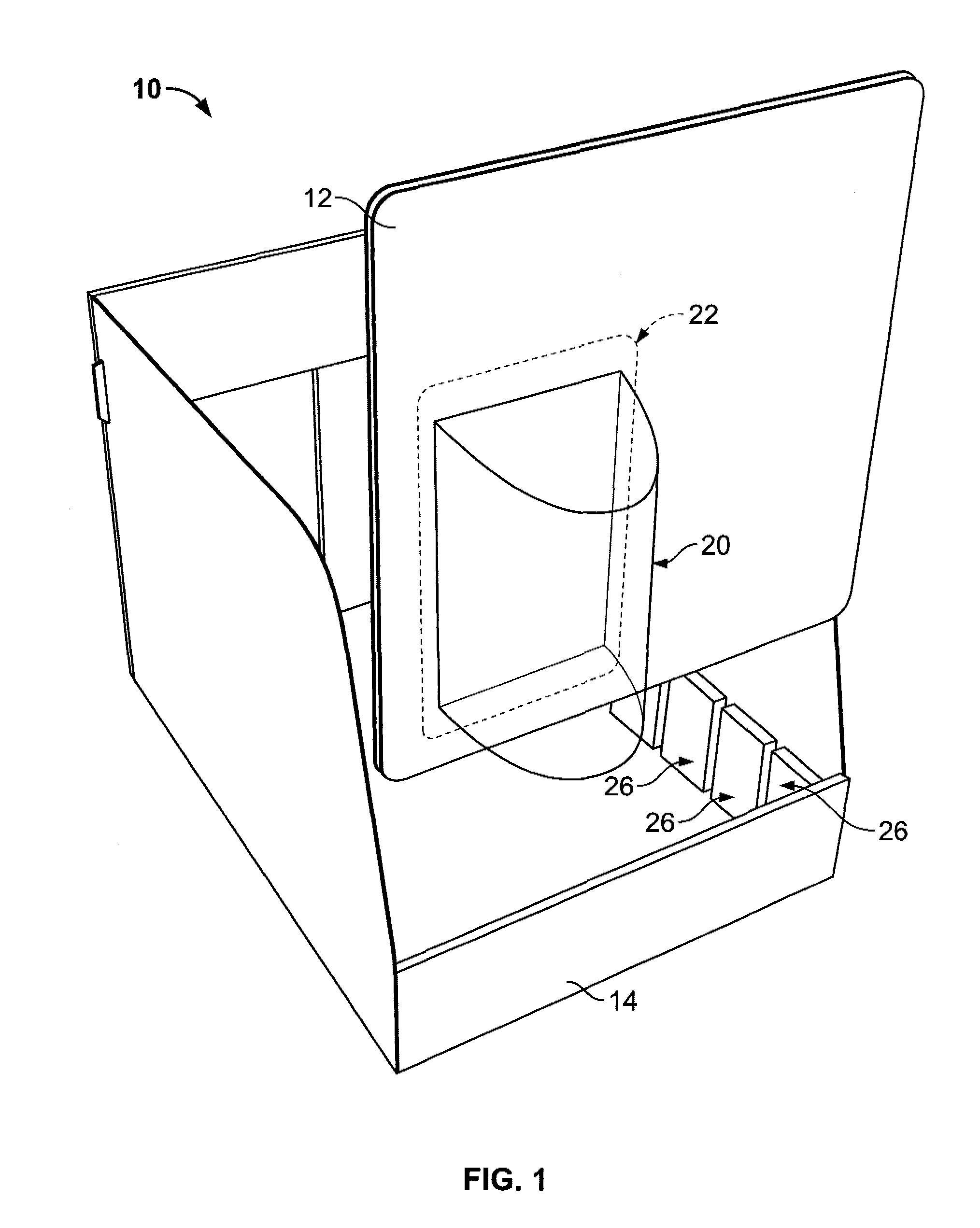

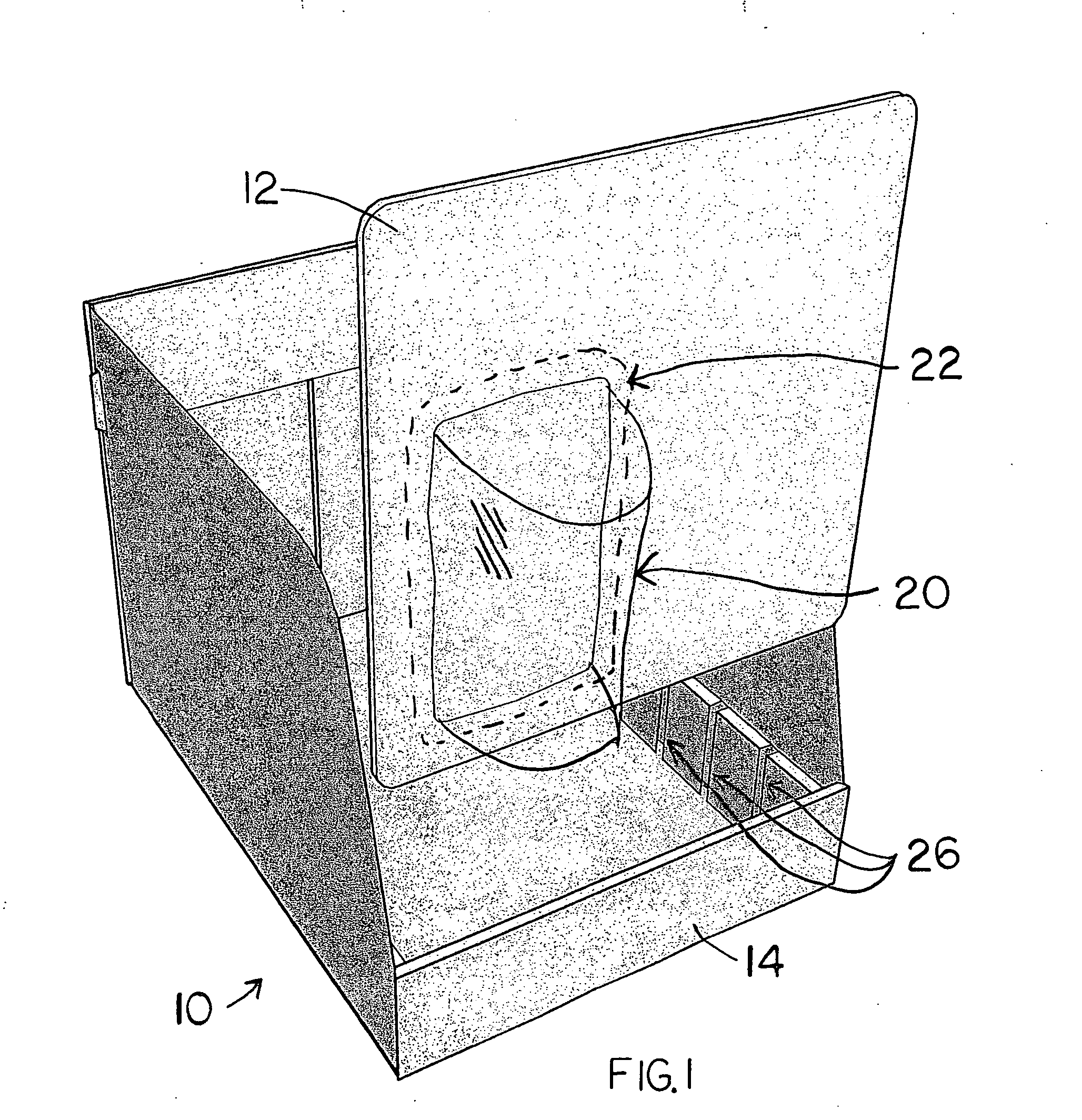

Method and apparatus of packaging disk drives in a data storage system

InactiveUS7145770B1Easy to useIncrease packing densityDigital data processing detailsRecord information storageEngineeringAir channel

A high density storage device packaging apparatus in which storage devices are oriented to have lateral faces parallel to each other and to edges of a module in which the storage devices are mounted. The storage devices are connected to a board contained in the module by a plug-in action. The board contains a controller to control the operation of the storage devices including the READ and WRITE operations. The RSM is capable of holding a large number of storage devices and capable of being inserted into a cabinet by a plug-in connection. The RSM includes a housing that covers and protects the storage devices and includes air channels to allow the storage devices to cool. The invention provides a solution for high density packaging of the storage devices and allows for easy access to the storage devices and allows for replacement of failed storage devices without disruption of the remainder of storage devices in the RSM or in the cabinet.

Owner:RPX CORP +1

Chip-level bottom filling adhesive and preparation method thereof

InactiveCN102559115ADoes not affect memoryCuring shrinkage is smallSemiconductor/solid-state device detailsSolid-state devicesCross-linkEpoxy

The invention relates to a chip-level bottom filling adhesive, which comprises following components by weight percentage: 15 to 50 percent of epoxy resin, 1 to 20 percent of toughening agent, 0.1 to 1 percent of dispersing agent, 0.01 to 1 percent of defoaming agent, 0.8 to 10 percent of cross-linking agent, 0.1 to 0.5 percent of pigment, 40 to 70 percent of filler, 3 to 30 percent of curing agent and 1 to 20 percent of diluting agent. A preparation method of the chip-level bottom filling adhesive comprises the steps that the epoxy resin, toughened resin, the dispersing agent, the defoaming agent, the cross-linking agent and the pigment are weighed according to the proportion, thrown into reaction kettle and mixed to form a homogeneous solution; and afterwards, the filler, the curing agent and the diluting agent are weighed according to the proportion, thrown into the reaction kettle in sequence and evenly mixed with the homogeneous solution, and then the chip-level bottom filling adhesive is obtained. The bottom filling adhesive prepared by adopting the method has the characteristics of low curing shrinkage rate, high reliability, and the like, simultaneously satisfies the requirement of low radioactivity and is suitable for primary high-density packaging of memory chips.

Owner:YANTAI DARBOND TECH

Stacked chip semiconductor device

ActiveUS7420281B2Reduce power consumptionMiniaturizationSemiconductor/solid-state device detailsSolid-state devicesSemiconductor chipInterface circuits

A stacked chip semiconductor device whose size is substantially reduced by high density packaging of two or more semiconductor chips. In the semiconductor device, four semiconductor chips are stacked over a printed wiring board. The bottom semiconductor chip has an interface circuit which includes a buffer and an electrostatic discharge protection circuit. All signals that these semiconductor chips receive and send are inputted or outputted through the interface circuit of the bottom semiconductor chip. Since the other semiconductor chips require no interface circuit, the semiconductor device is compact.

Owner:RENESAS ELECTRONICS CORP

Bottom filling glue for packaging inverted chip type semiconductor

ActiveCN102002209AExcellent performance indexImprove moisture resistanceSemiconductor/solid-state device detailsSolid-state devicesEpoxyThermal expansion

The invention discloses bottom filling glue for packaging an inverted chip type semiconductor, which is prepared from the following raw materials in percentage by weight: 5.8-59 percent of liquid epoxy resin, 2-10 percent of rubber toughening agent, 5.8-59 percent of modified organic silicon resin, 0.5-14.8 percent of multifunctional epoxy resin, 1.5-10.5 percent of epoxy diluent, 0.5-14.8 percent of aromatic amine curing agent, 1.1-10.8 percent of silane coupling agent, 20-59 percent of silicon micropowder and 0-6 percent of pigment. The invention has the advantages of low viscosity, proper flow property, no defect, no bubble and good heat resistance of resin condensate, low thermal expansion coefficient, low modulus, small internal stress, less warping degree, high bonding strength, low halogen content and high insulating performance, can maintain favorable bonding reliability and curing performance during thermal cycling treatment and improve the seal performance and the operating performance of the surface of a silicon wafer containing photosensitive polyimide and a silicon nitride film, can be widely used for the technical field of inverted chip packaging and is especially suitable for the field of high-end devices in a Flip-chip process and high-density packaging.

Owner:深圳市库泰克电子材料技术有限公司

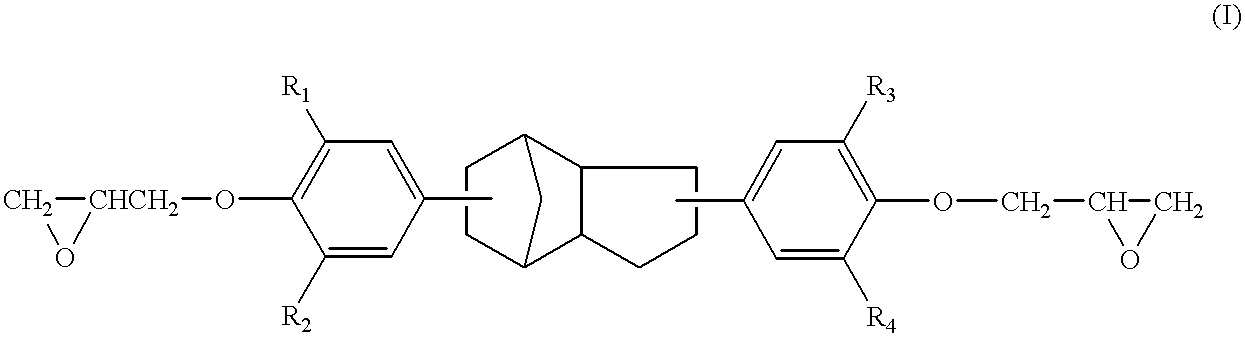

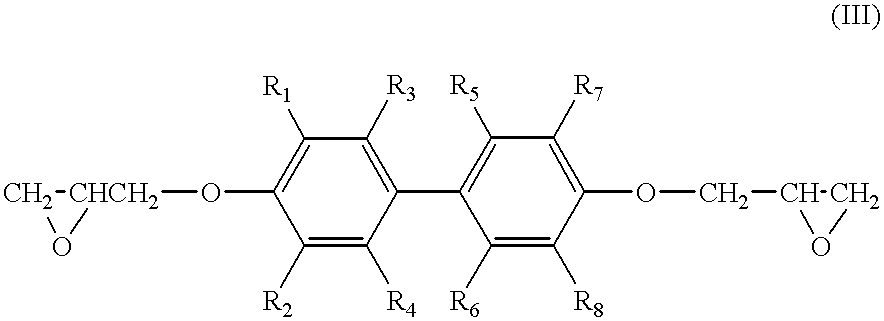

Adhesive sheet for semiconductor connecting substrate, adhesive-backed tape for TAB, adhesive-backed tape for wire bonding connection, semiconductor connecting substrate, and semiconductor device

InactiveUS20020025431A1Moderate modulusModerate coefficientSemiconductor/solid-state device detailsSolid-state devicesEpoxyTectorial membrane

An adhesive sheet for a semiconductor connecting substrate consisting of a laminate having an adhesive layer on a substrate, wherein said adhesive layer contains a thermoplastic resin (A) and an epoxy resin (B) and said epoxy resin (B) contains at least one epoxy resin (B) selected from (I) dicyclopentadiene skeleton-containing epoxy resins, (II) terpene skeleton-containing epoxy resins, and (III) biphenyl skeleton-containing epoxy resins, as an essential component; an adhesive-backed tape for TAB consisting of a laminate having an adhesive layer and a protective film layer on a flexible organic insulating film. The adhesive sheet for a semiconductor connecting substrate, the adhesive-backed tape for TAB and the adhesive-backed tape for wire bonding connection of the present invention are excellent in adhesive strength, insulatability, dimensional accuracy, etc., and can improve the reliability of a semiconductor integrated circuit connecting substrate and a semiconductor device respectively for high density packaging.

Owner:TORAY IND INC

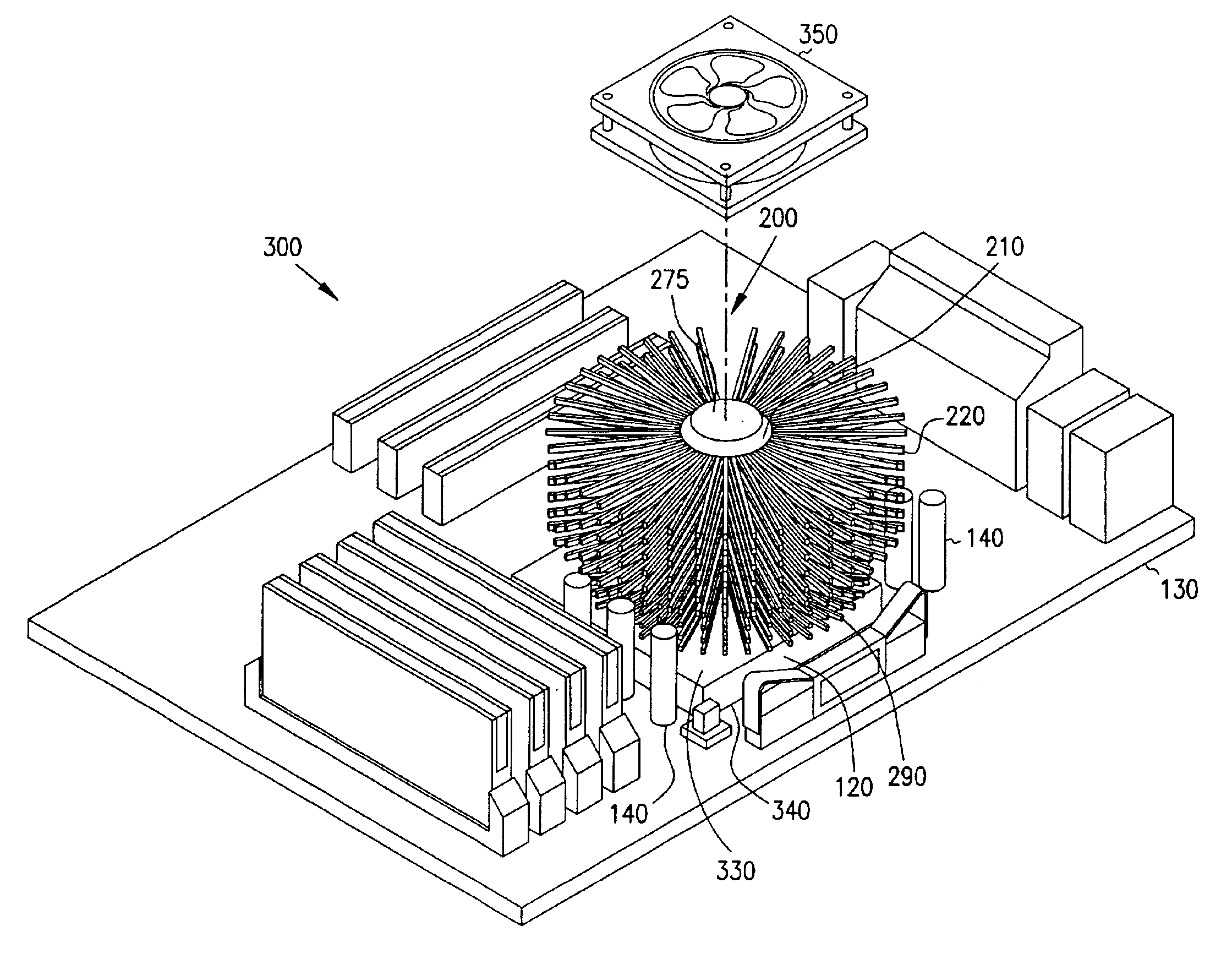

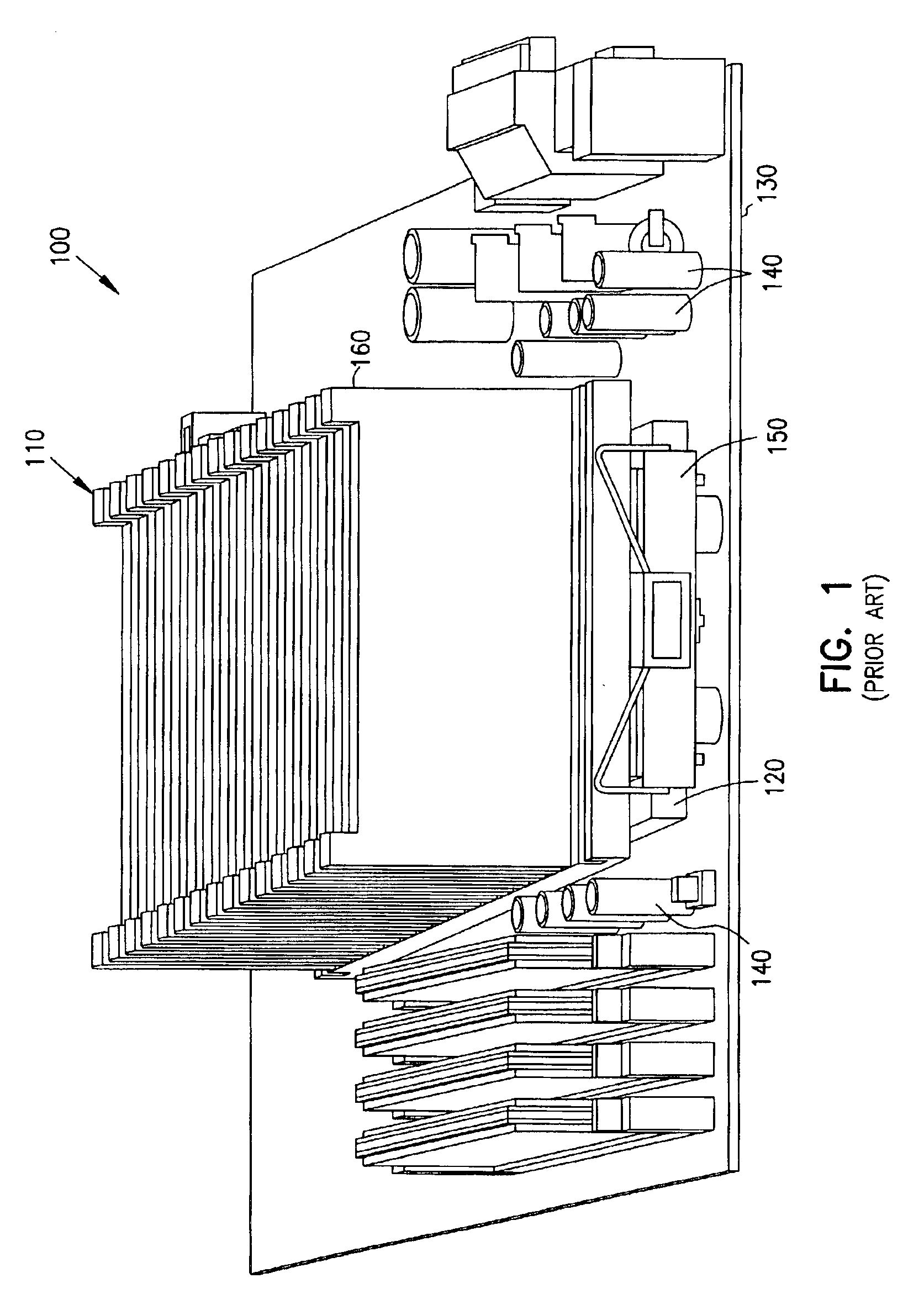

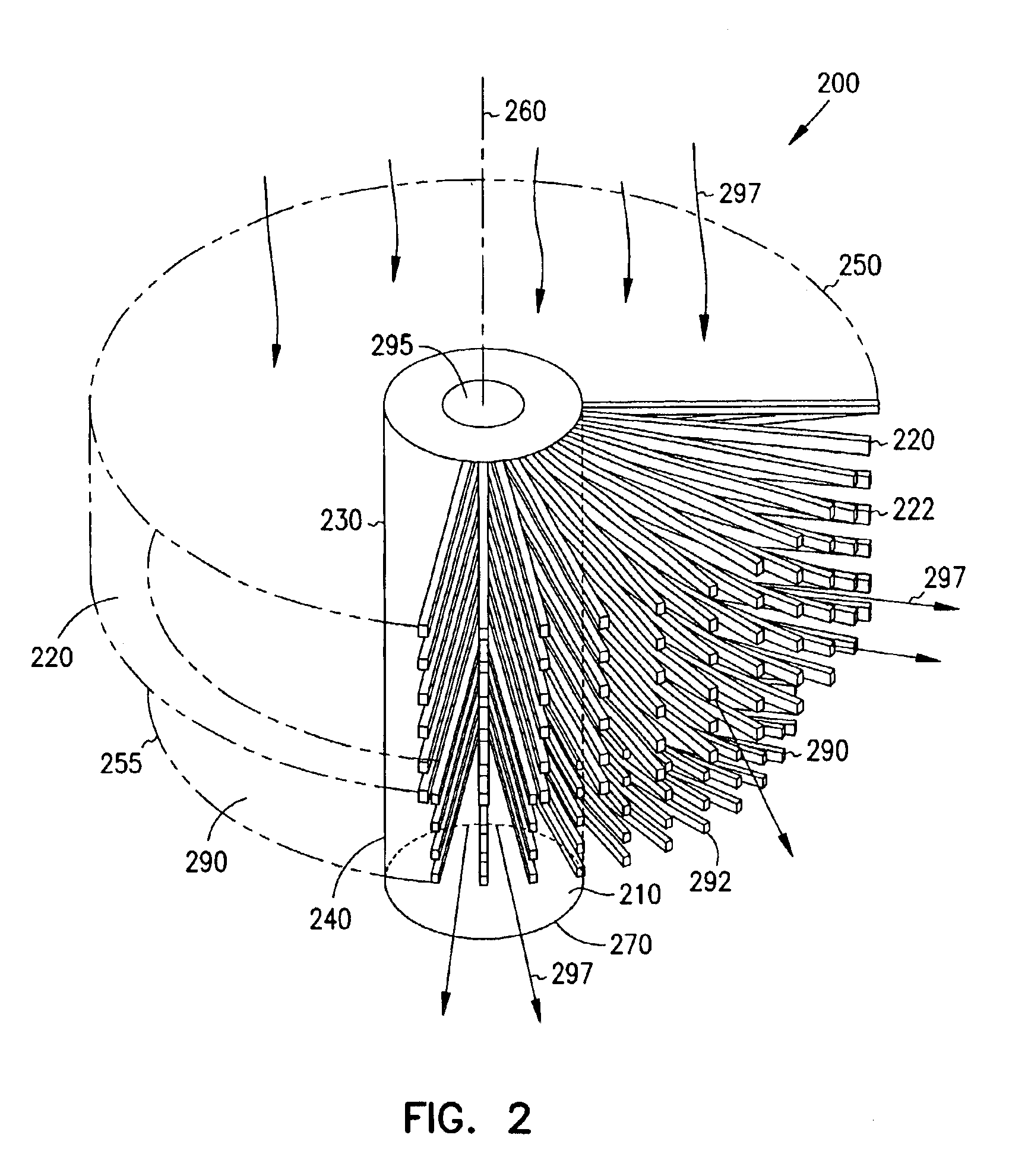

High performance heat sink configurations for use in high density packaging applications

InactiveUS6845010B2Improve cooling effectDissipating heat away from the integrated circuit deviceSemiconductor/solid-state device detailsSolid-state devicesHigh densityEngineering

An enhanced heat dissipation device to extract heat from an integrated circuit device includes a thermally conductive core having upper and lower outer surface areas. The device further includes a first array of radially extending pin fin structures. The first array is thermally coupled to the upper surface area such that a cooling medium introduced around the core and the first array creates an omni-directional flow around the first array and the core to enhance heat dissipation from the integrated circuit device. The core including the first array and the lower surface area are of sufficient size to allow components on a motherboard to encroach onto the integrated circuit device when the heat dissipation device is mounted onto the integrated circuit device.

Owner:INTEL CORP

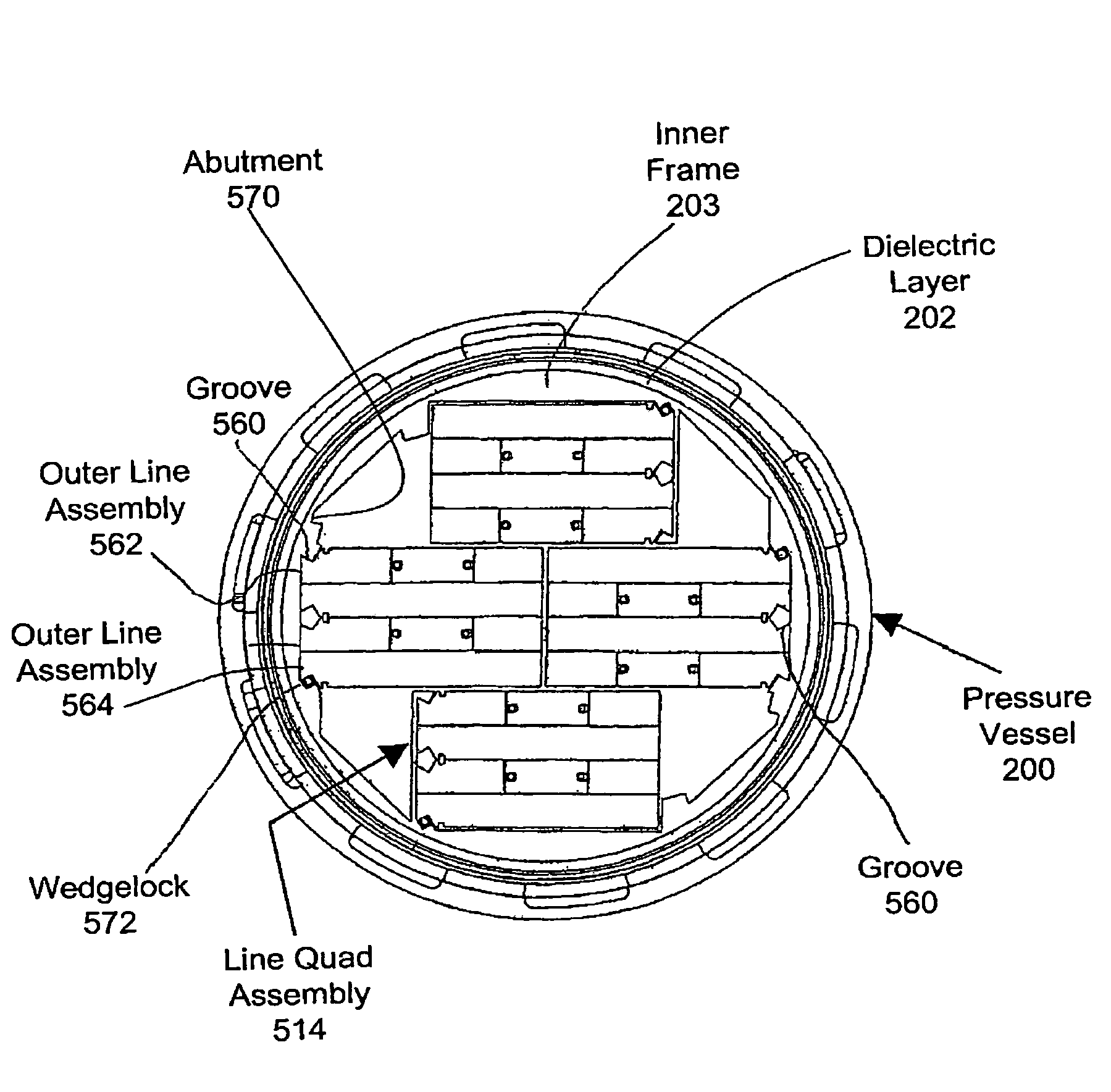

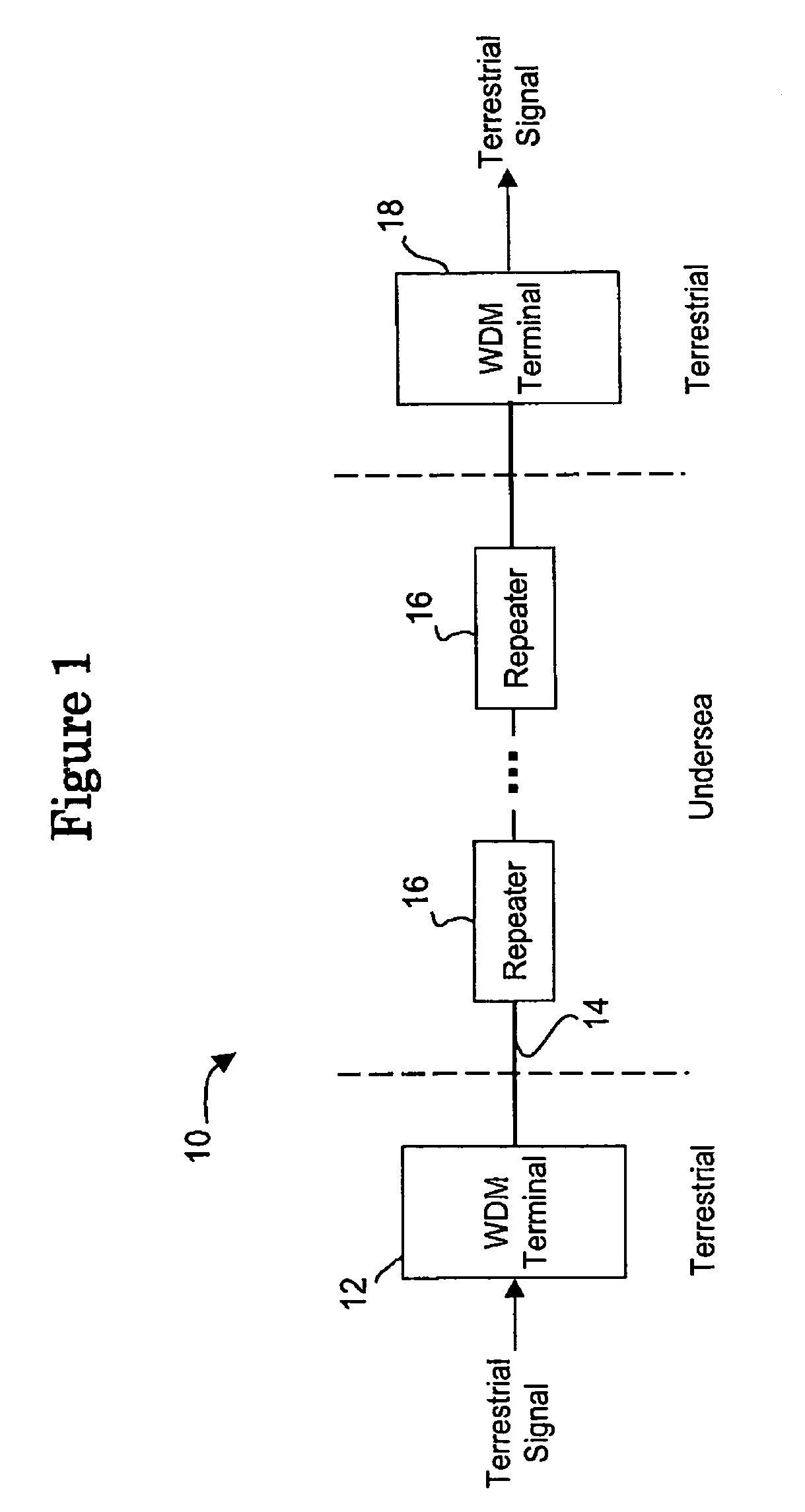

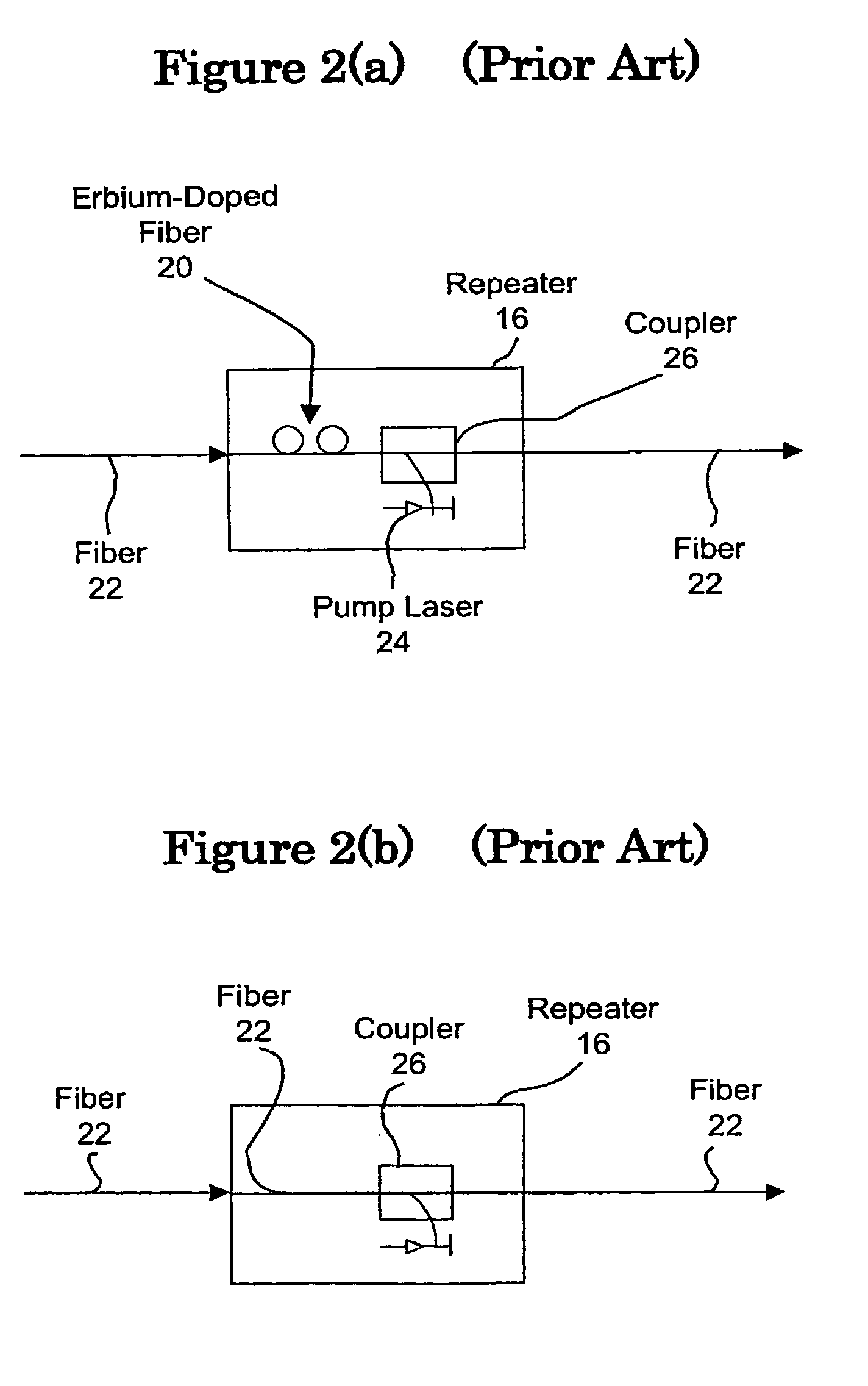

High density optical packaging

Repeaters for use in amplifying optical data signals transmitted through undersea fiber optic cables are disclosed. Raman amplification schemes using 100 or more pump lasers are integrated into industry standard sized pressure vessels for amplifying optical data signals transmitted through one or more fiber optic pairs. Such repeaters include high density packaging to permit numerous active and passive optical components, as well as significant lengths of optical fiber, to reside within legacy sized pressure vessels.

Owner:OPTIC153 LLC

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com