Fan-out high-density packaging method

A packaging method and high-density technology, applied in semiconductor devices, electrical components, circuits, etc., can solve the problem of inappropriate multi-layer packaging structure, and achieve the effect of high density

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0026] In the following description, numerous specific details are set forth in order to provide a thorough understanding of the present invention. However, the present invention can be implemented in many other ways different from those described here, and those skilled in the art can make similar extensions without violating the connotation of the present invention, so the present invention is not limited by the specific implementations disclosed below.

[0027] Secondly, the present invention is described in detail by means of schematic diagrams. When describing the embodiments of the present invention in detail, for convenience of explanation, the schematic diagrams are only examples, which should not limit the protection scope of the present invention.

[0028] The specific embodiments of the present invention will be described in detail below in conjunction with the accompanying drawings.

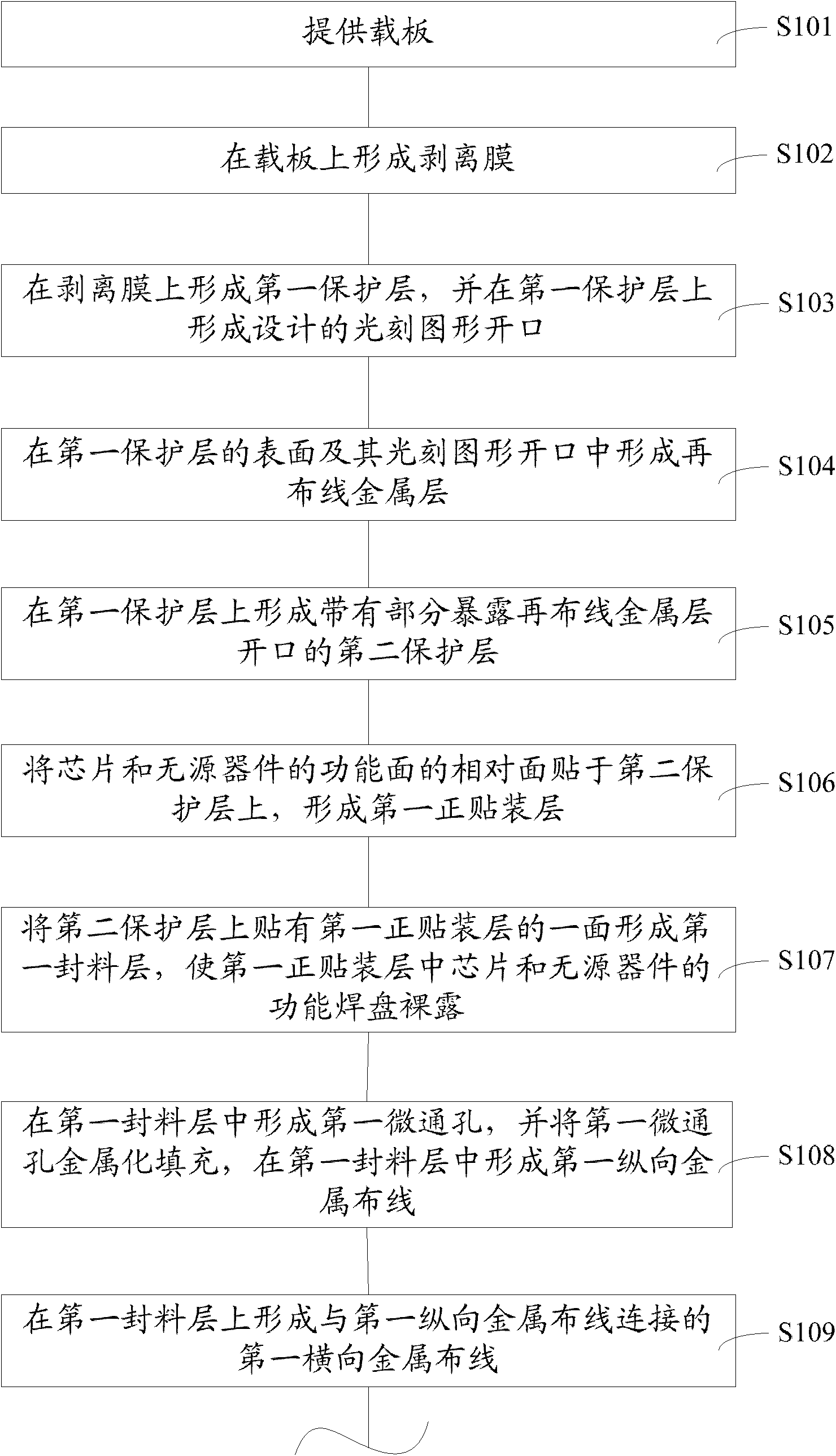

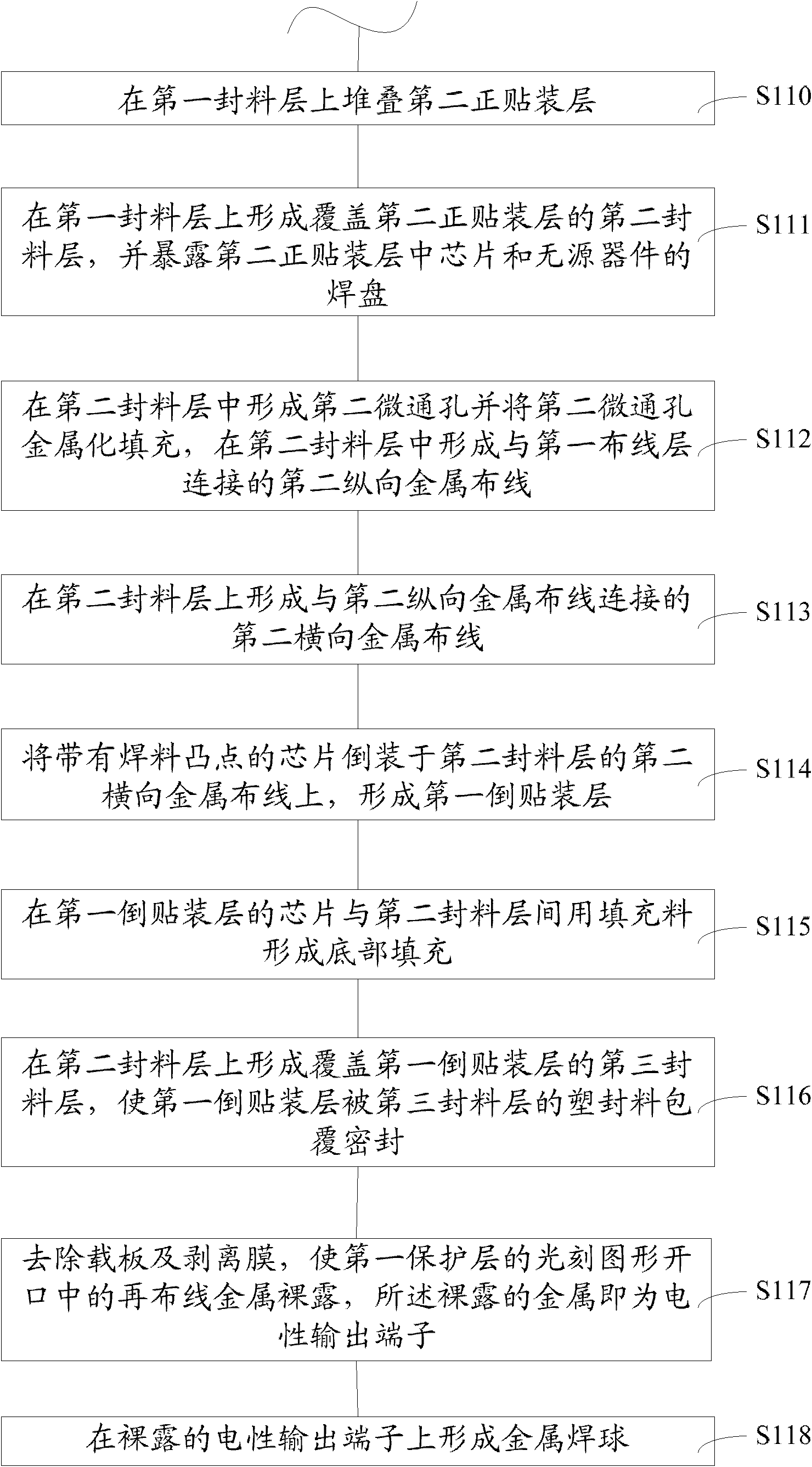

[0029] Such as figure 1 with figure 2 As shown, in one embodiment of the prese...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com