Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

63 results about "Fermi level pinning" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

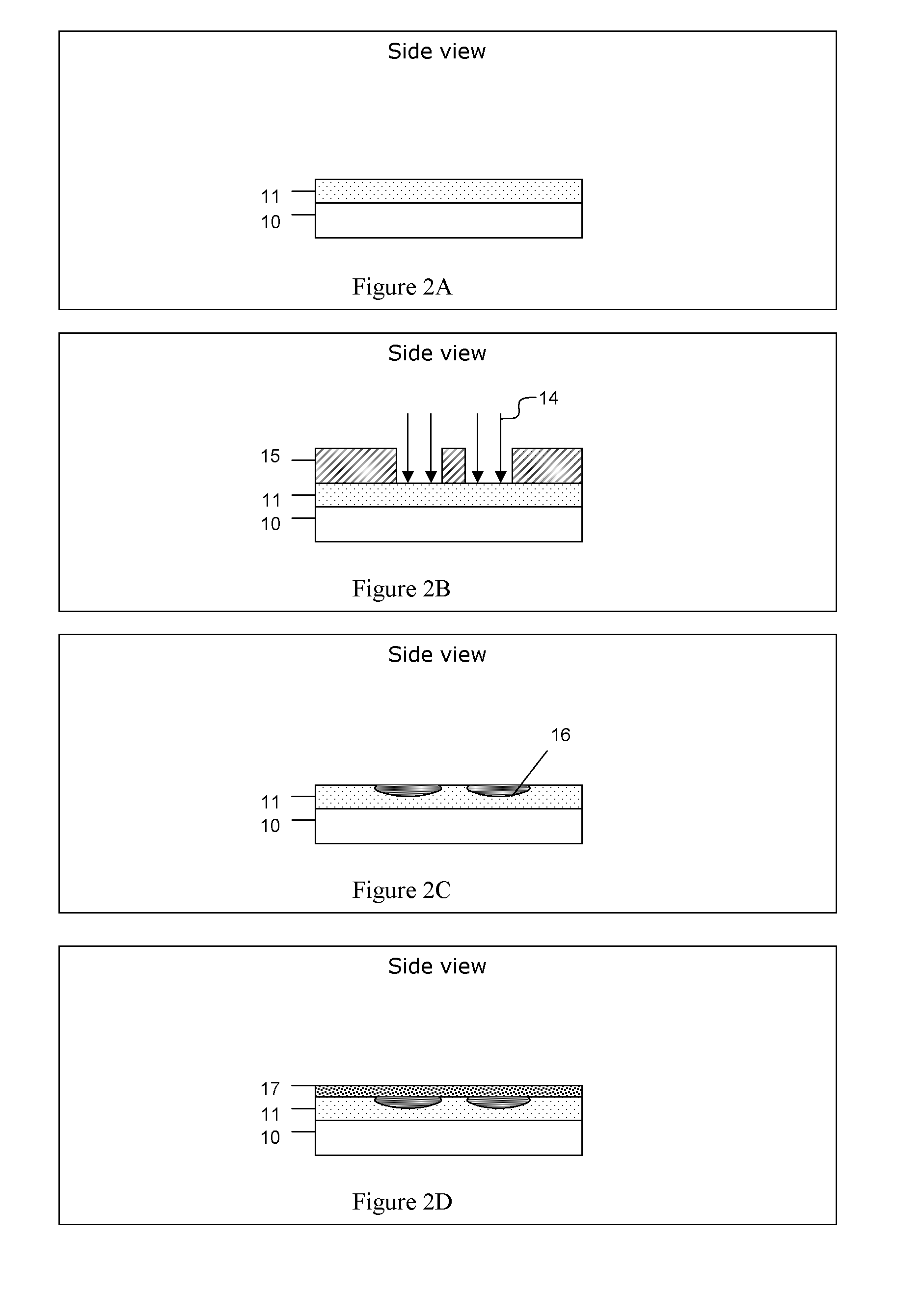

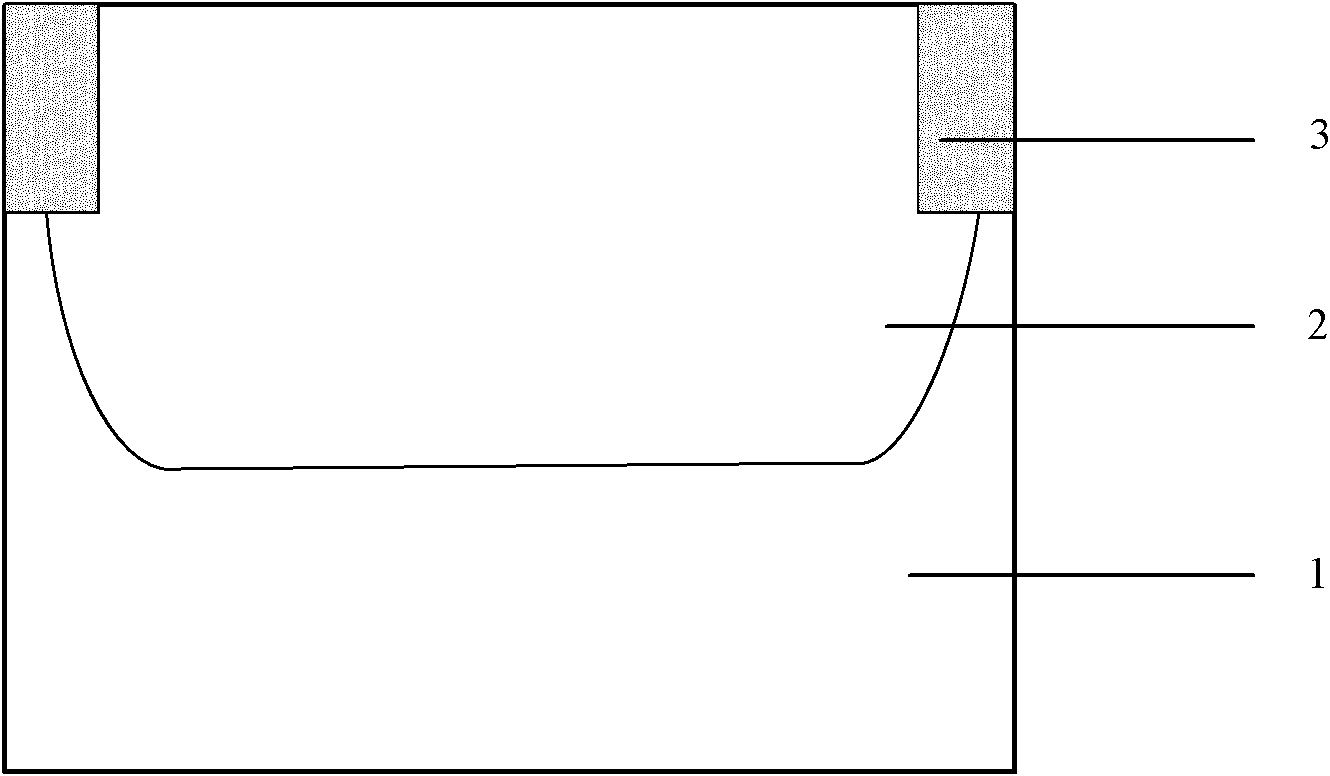

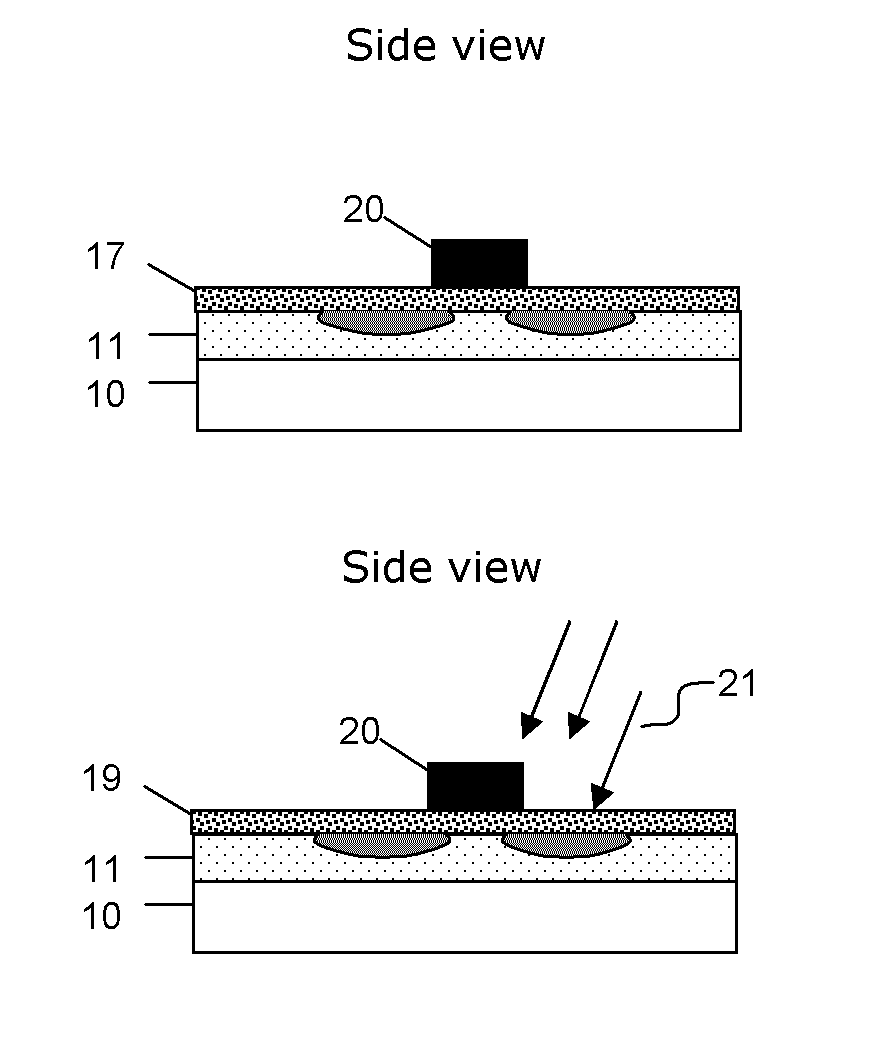

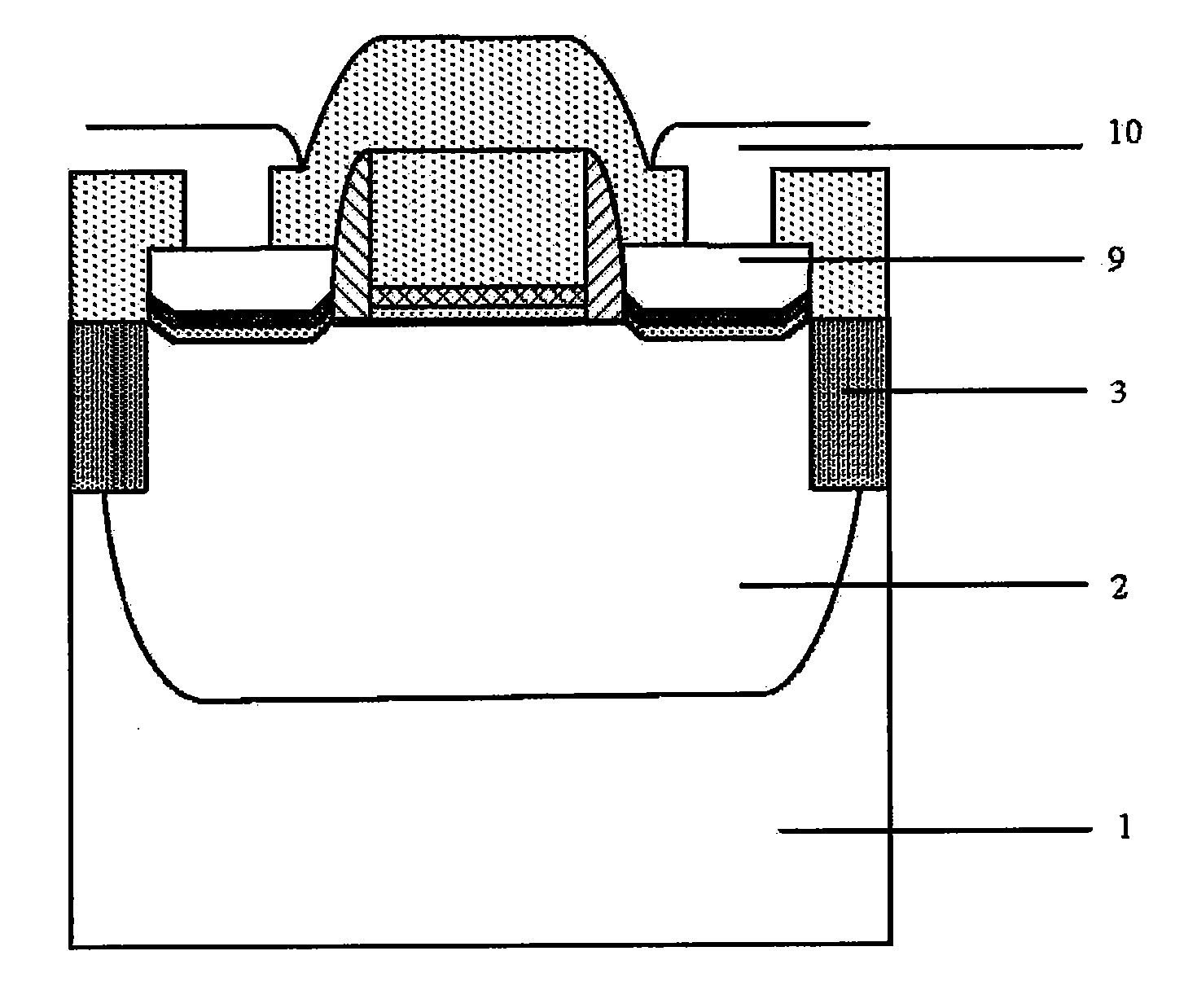

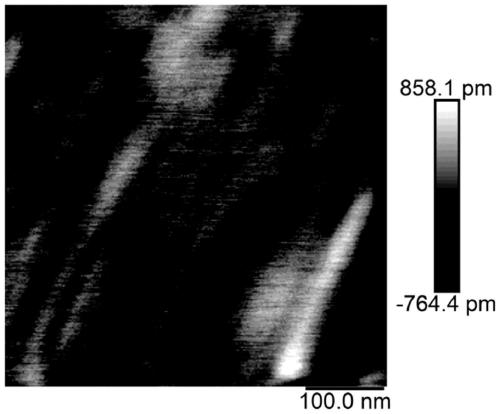

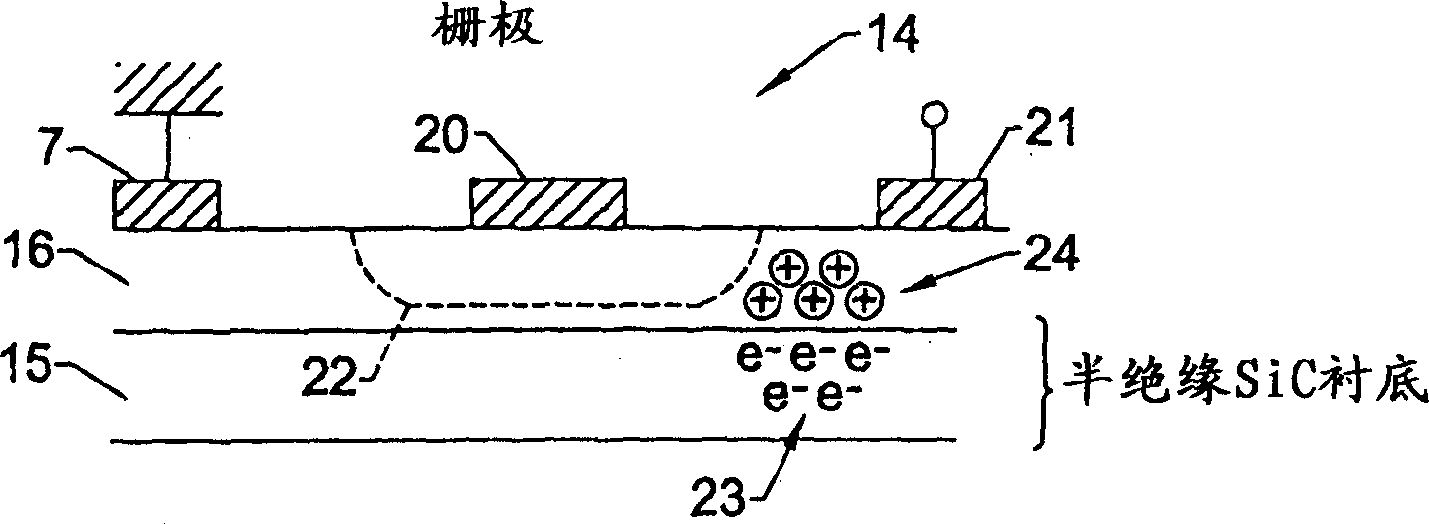

Fermi level pinning is behavior at semiconductor/metal interface that defies Schottky–Mott model and creates unexpected height of the Schottky barrier. This - in most modern transistors - create a big challenge for device engineering. The figure below is from Wikipedia.

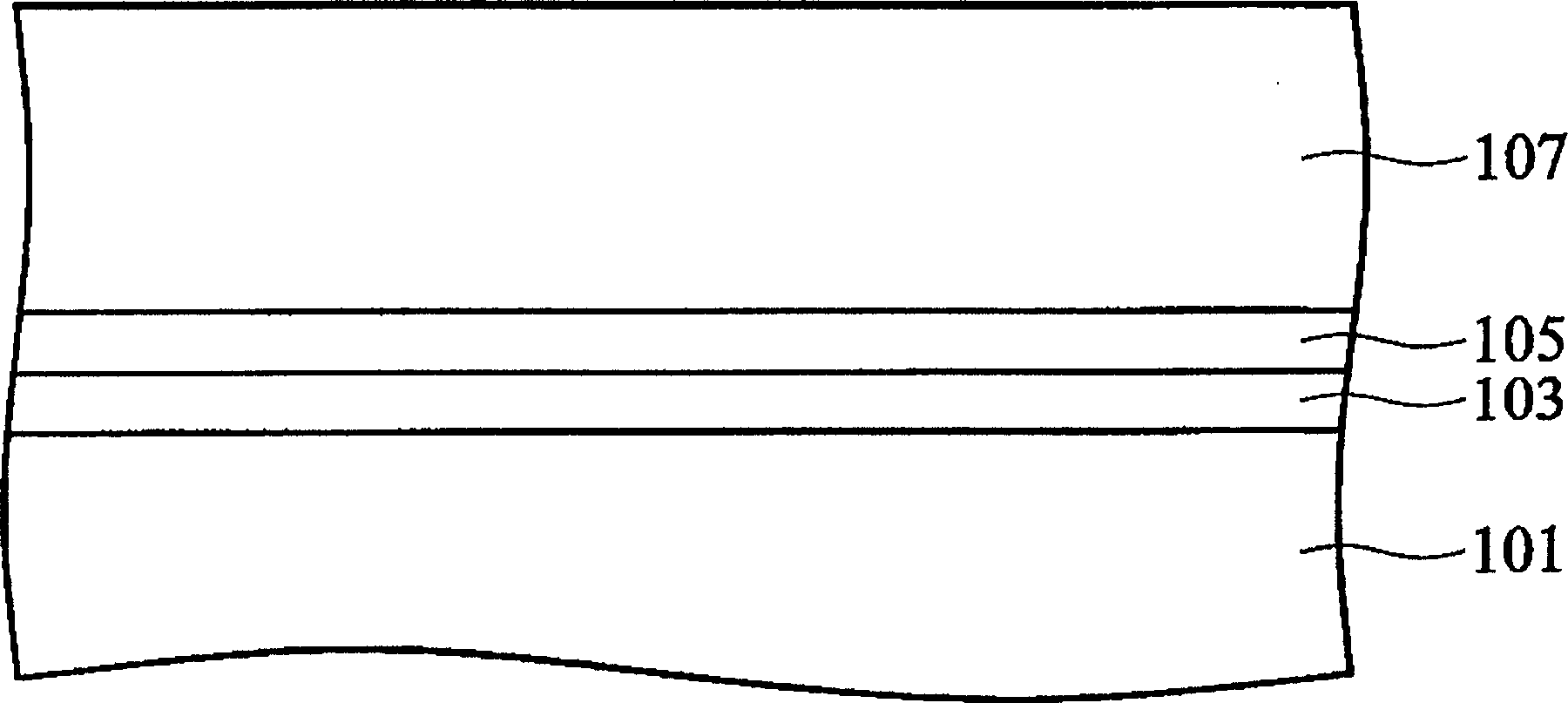

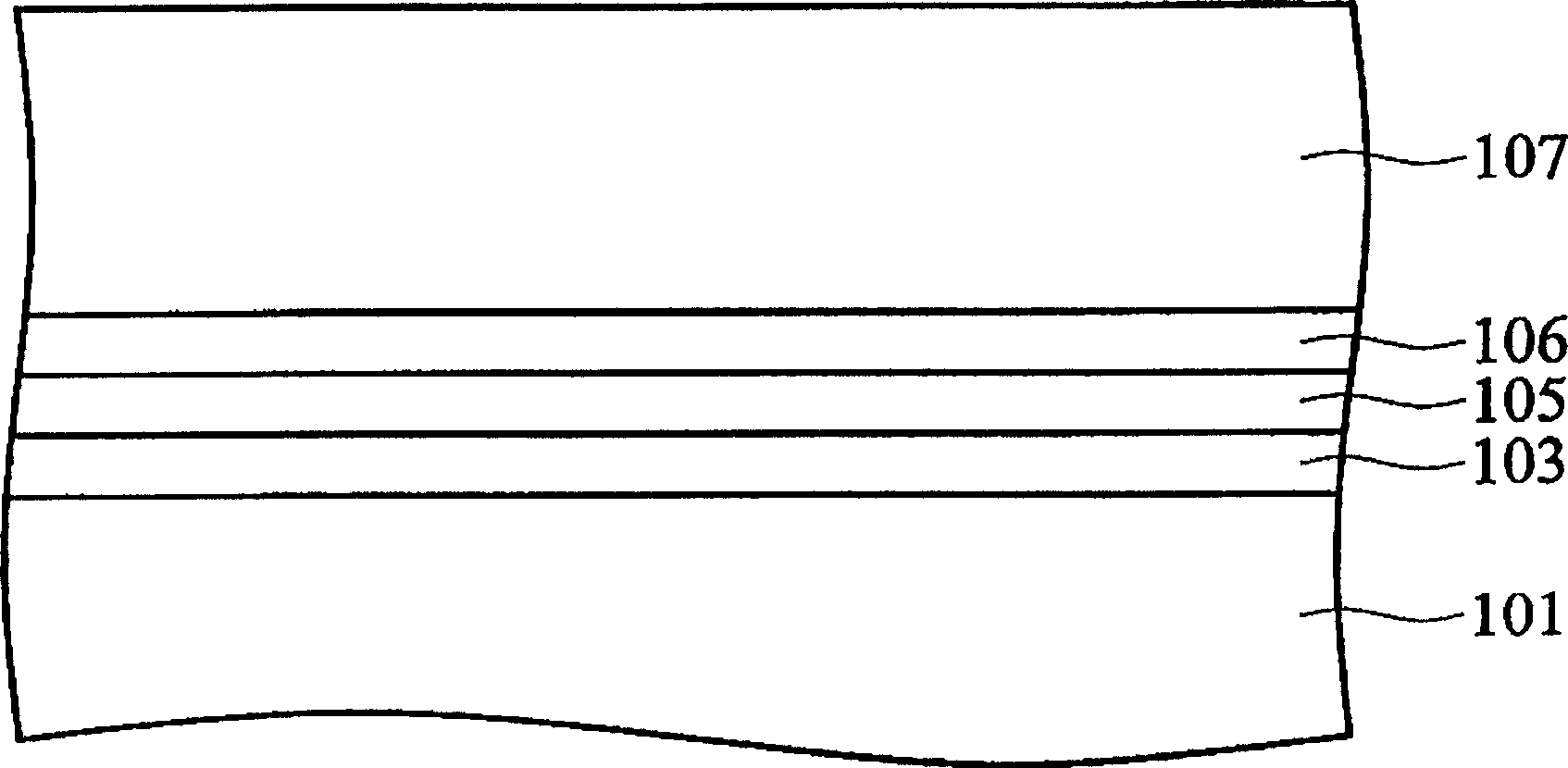

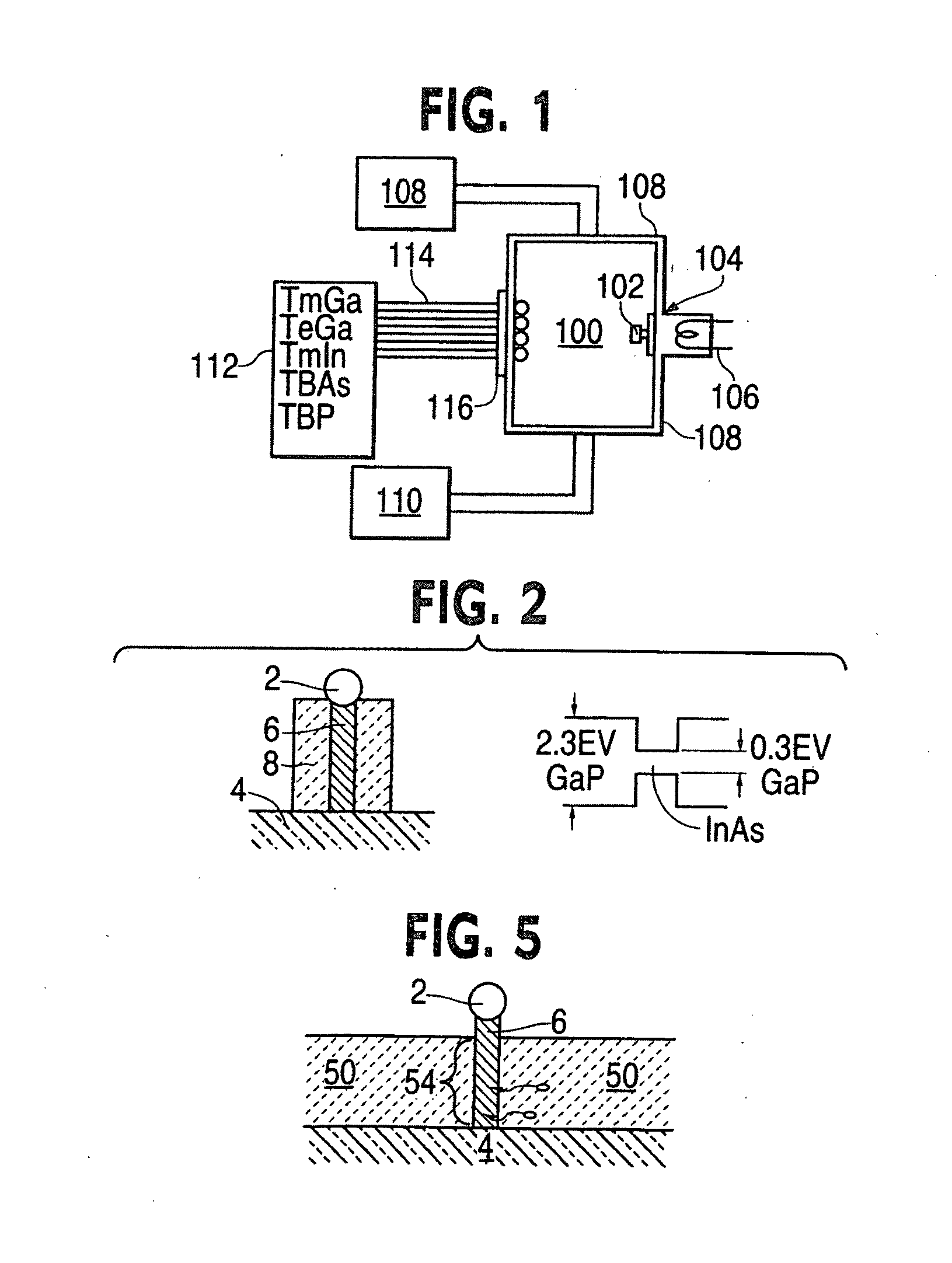

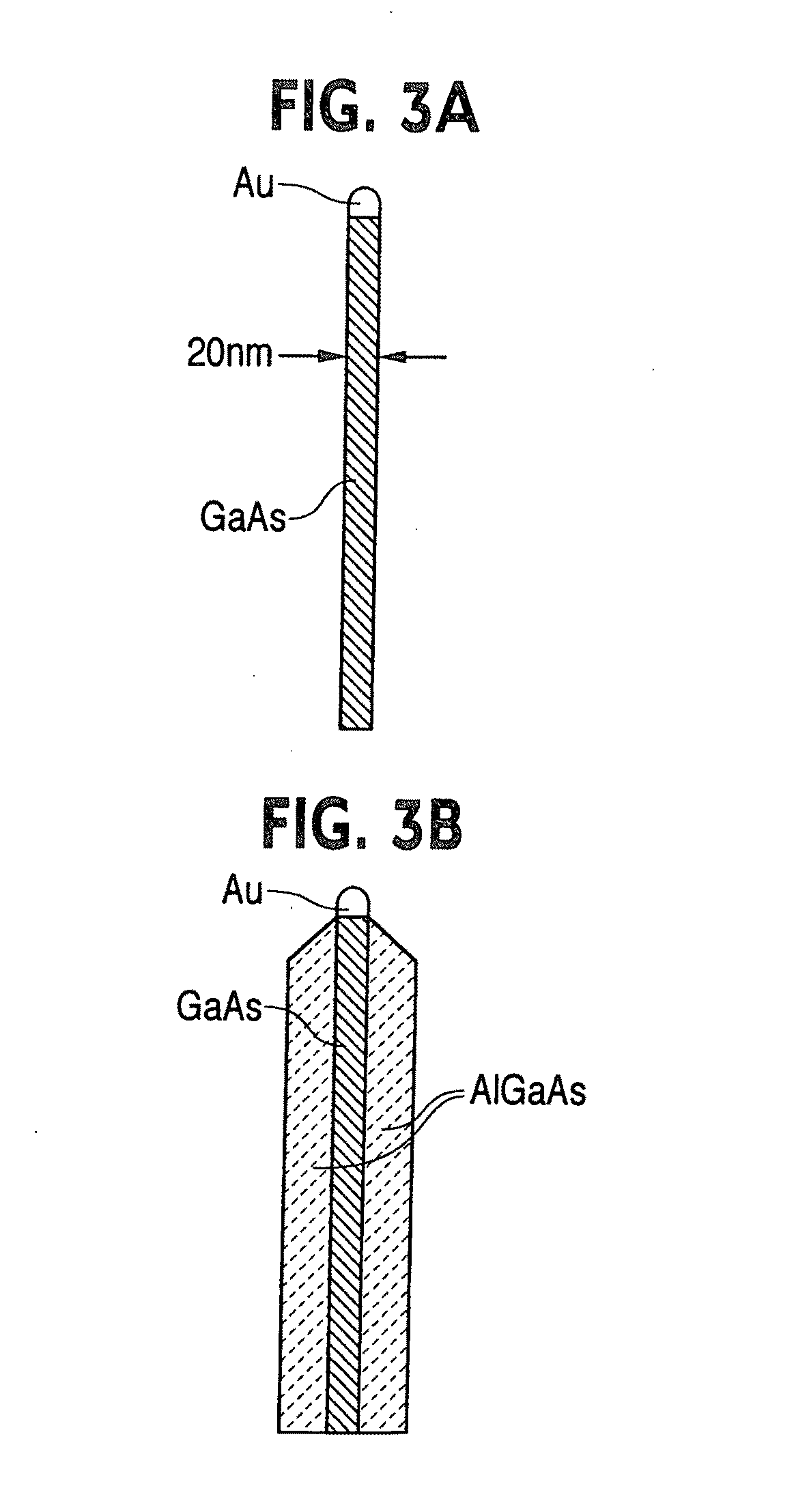

Nanowhiskers with PN junctions, doped nanowhiskers, and methods for preparing them

InactiveUS20050006673A1Good electrical conductivityPermitted diffusionPolycrystalline material growthNanoinformaticsHeterojunctionP–n junction

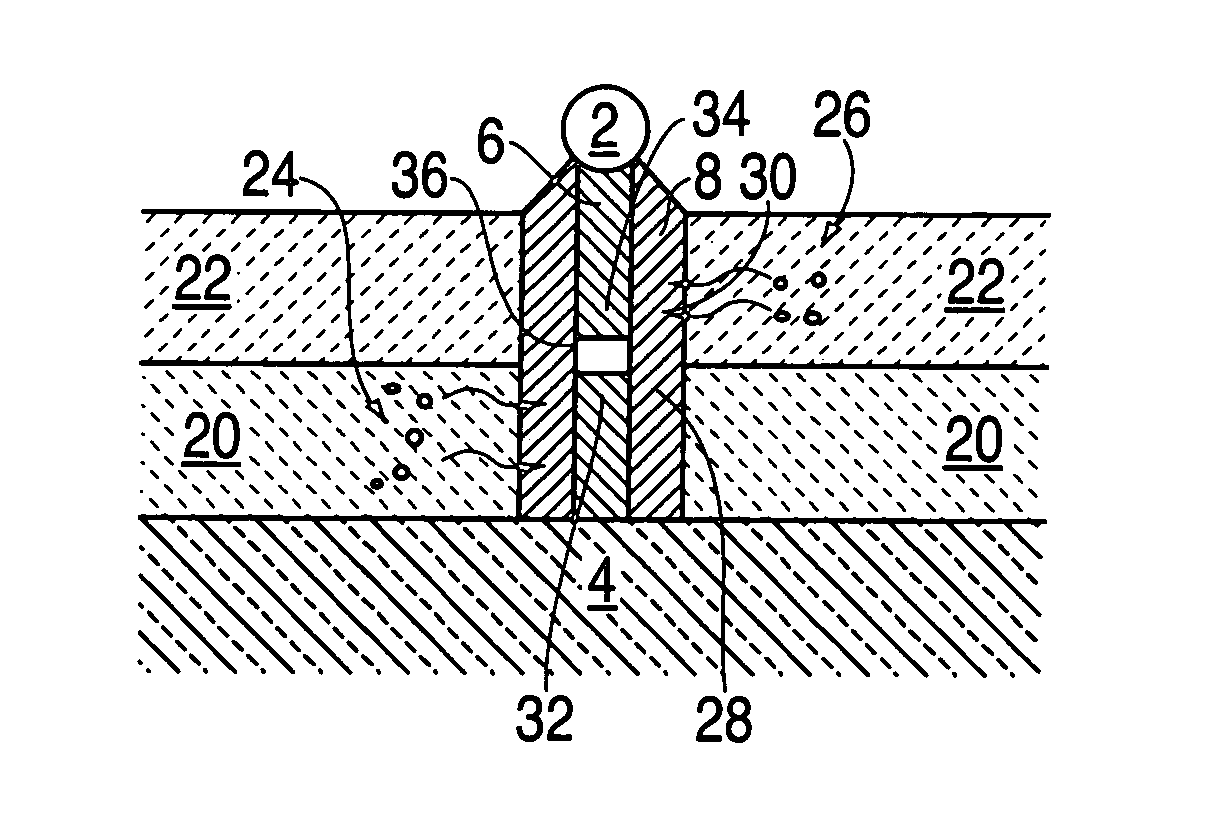

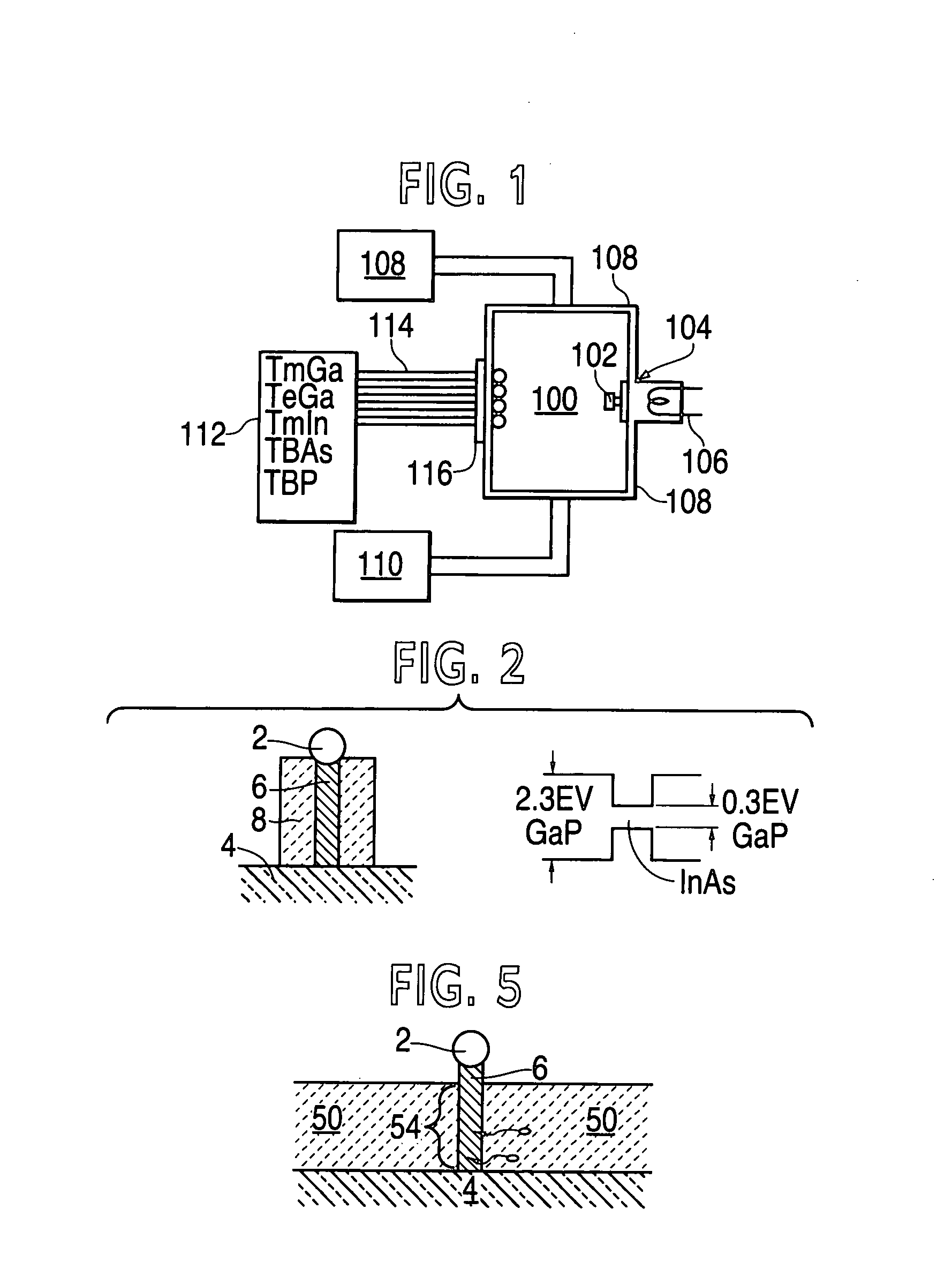

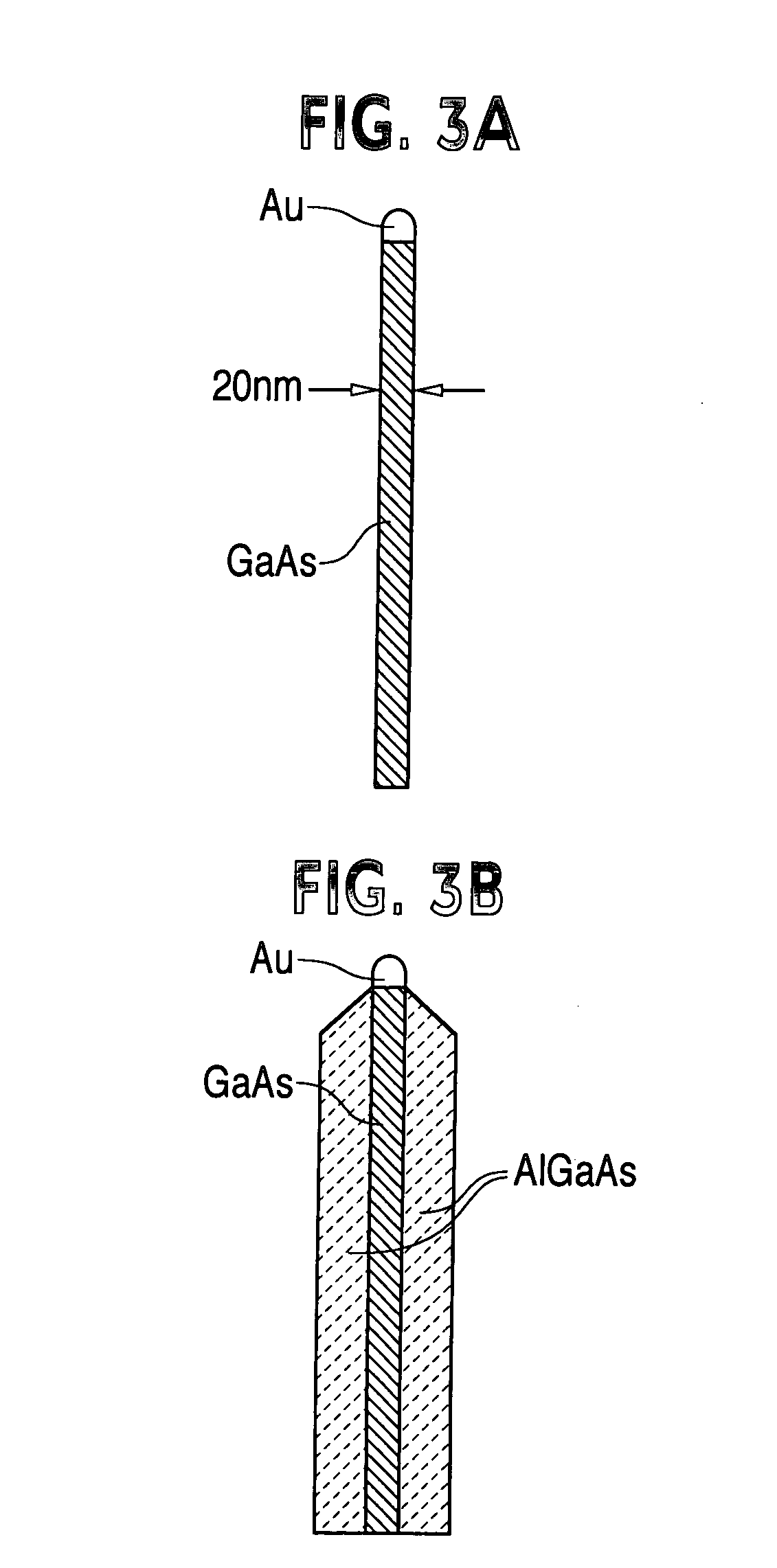

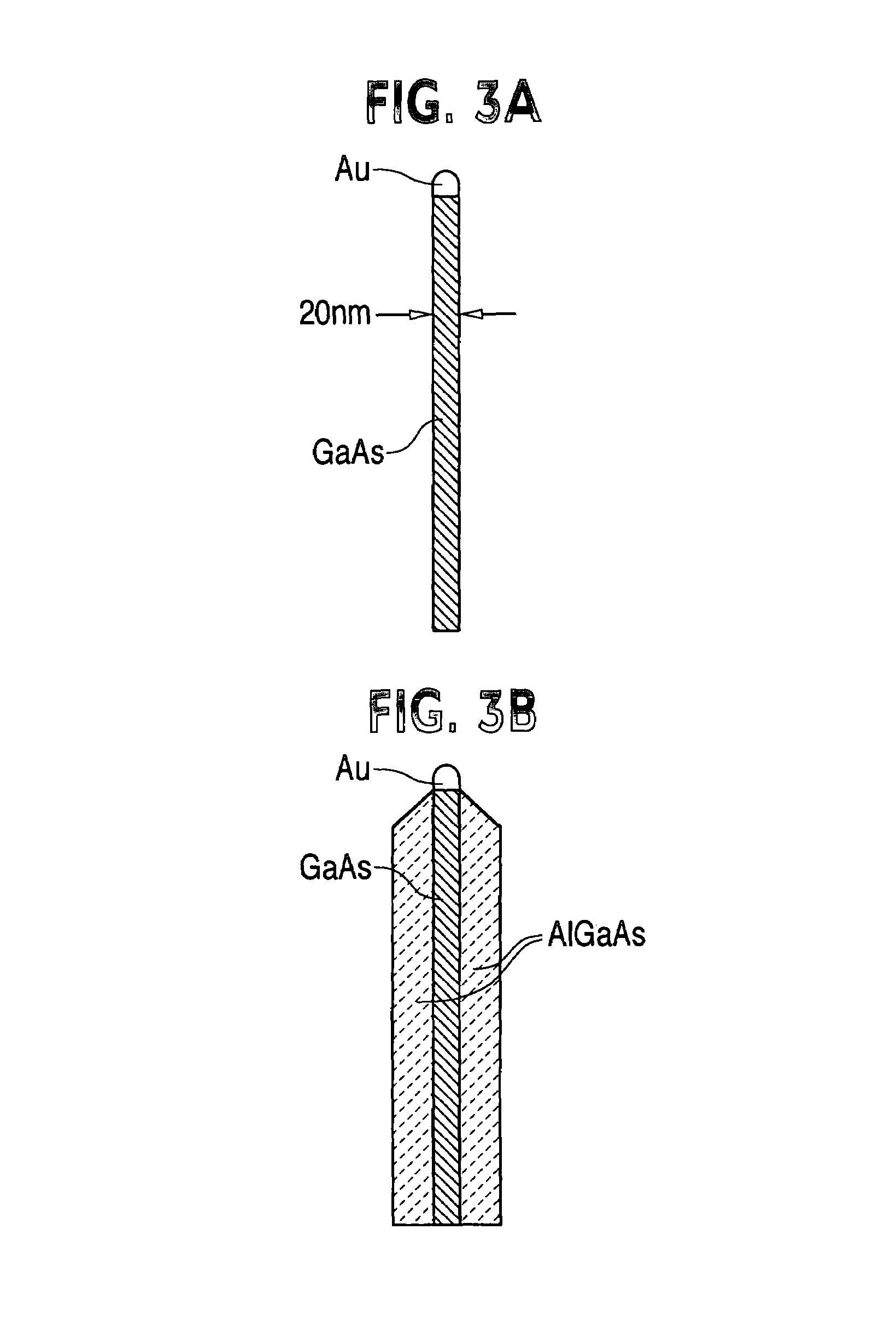

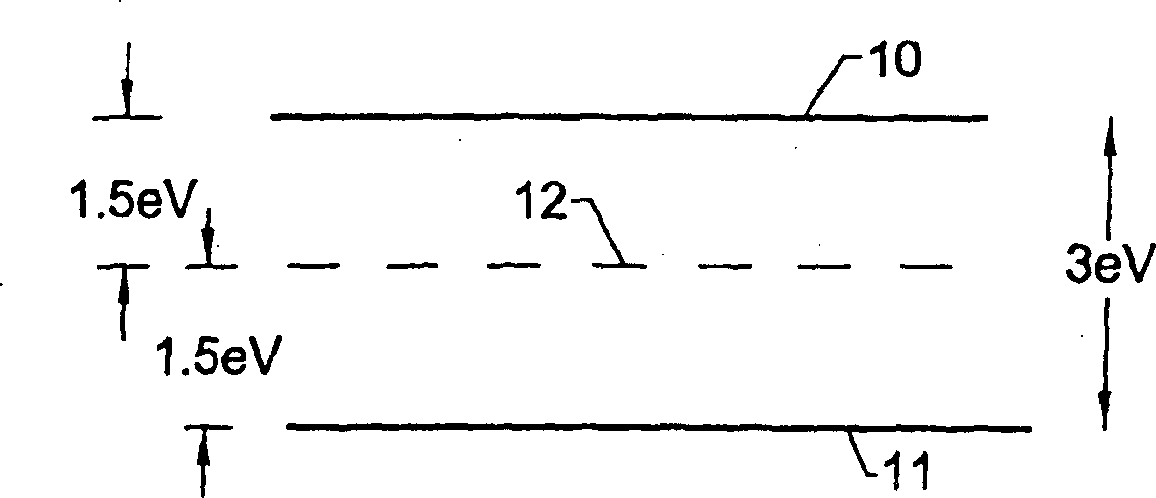

Nano-engineered structures are disclosed, incorporating nanowhiskers of high mobility conductivity and incorporating pn junctions. In one embodiment, a nanowhisker of a first semiconducting material has a first band gap, and an enclosure comprising at least one second material with a second band gap encloses said nanoelement along at least part of its length, the second material being doped to provide opposite conductivity type charge carriers in respective first and second regions along the length of the of the nanowhisker, whereby to create in the nanowhisker by transfer of charge carriers into the nanowhisker, corresponding first and second regions of opposite conductivity type charge carriers with a region depleted of free carriers therebetween. The doping of the enclosure material may be degenerate so as to create within the nanowhisker adjacent segments having very heavy modulation doping of opposite conductivity type analogous to the heavily doped regions of an Esaki diode. In another embodiment, a nanowhisker is surrounded by polymer material containing dopant material. A step of rapid thermal annealing causes the dopant material to diffuse into the nanowhisker. In a further embodiment, a nanowhisker has a heterojunction between two different intrinsic materials, and Fermi level pinning creates a pn junction at the interface without doping.

Owner:QUNANO

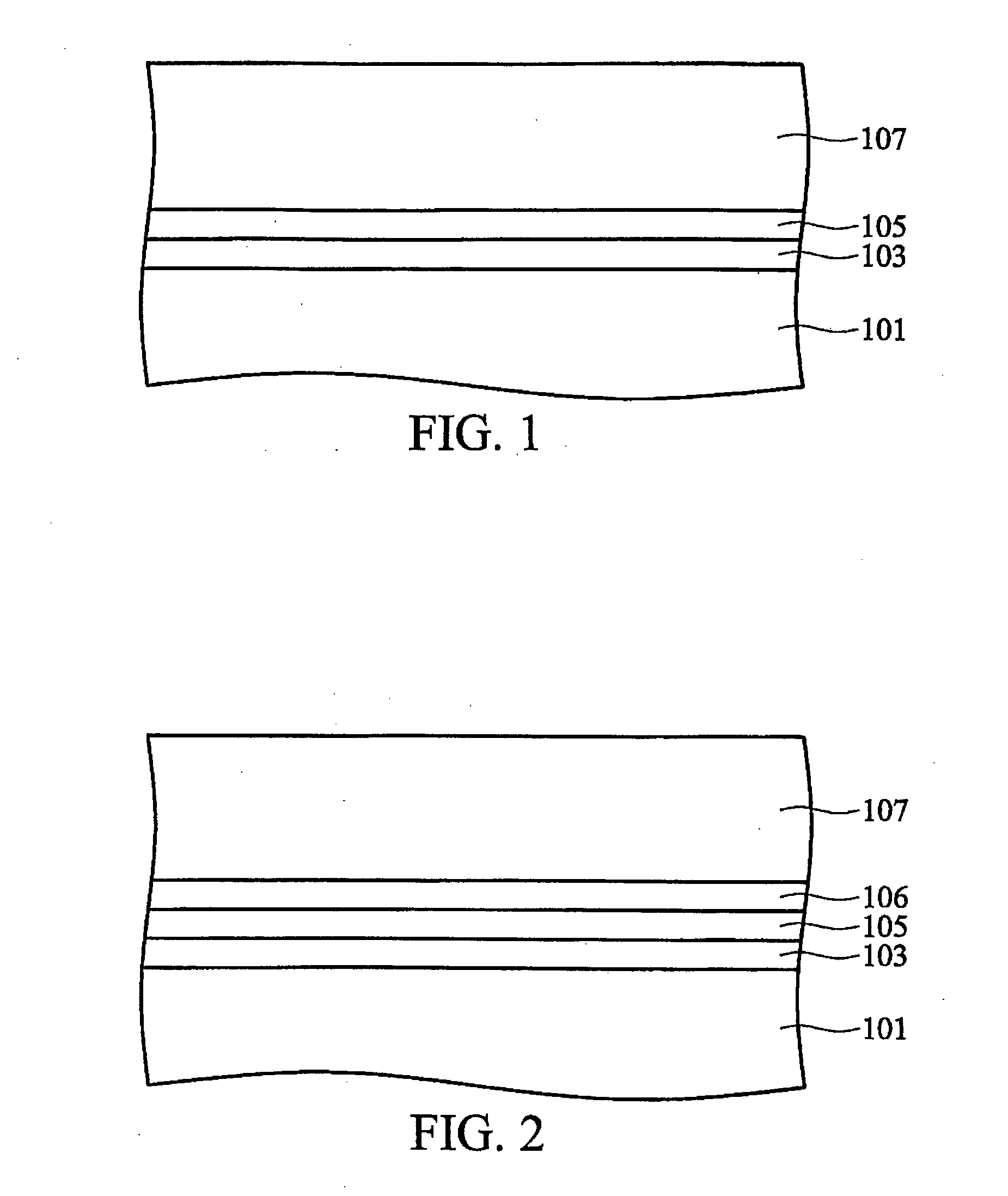

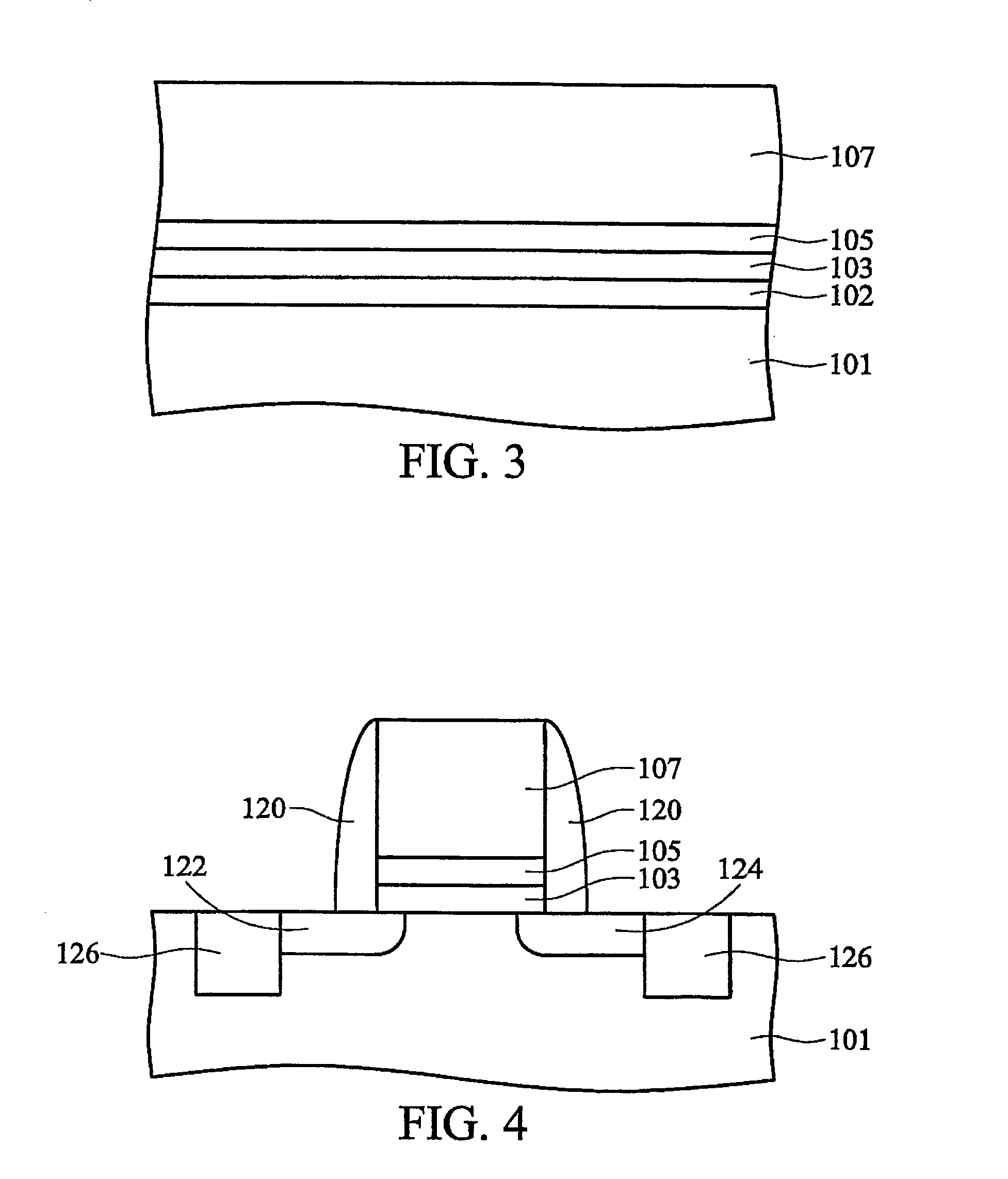

Semiconductor device and method for high-K gate dielectrics

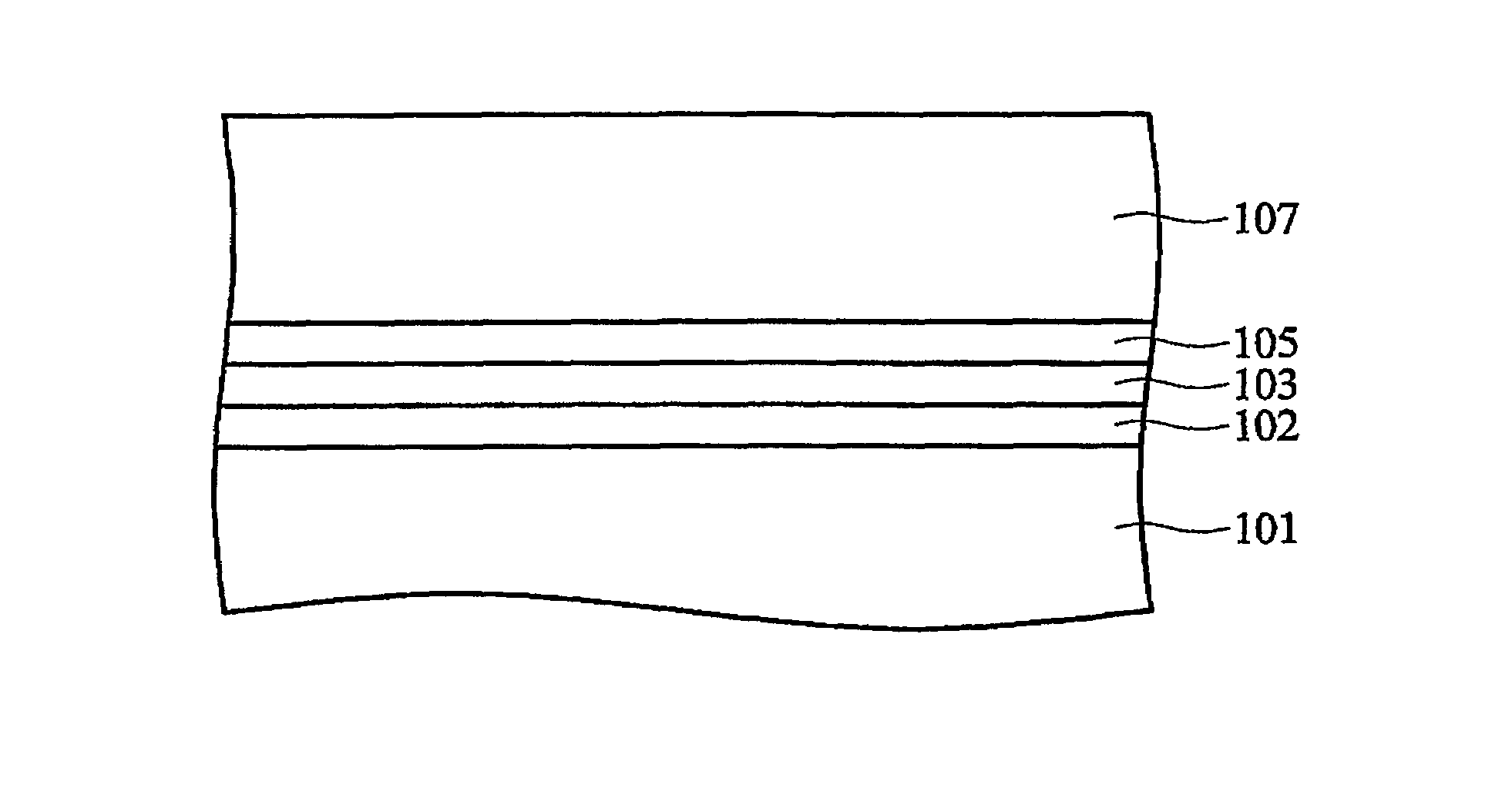

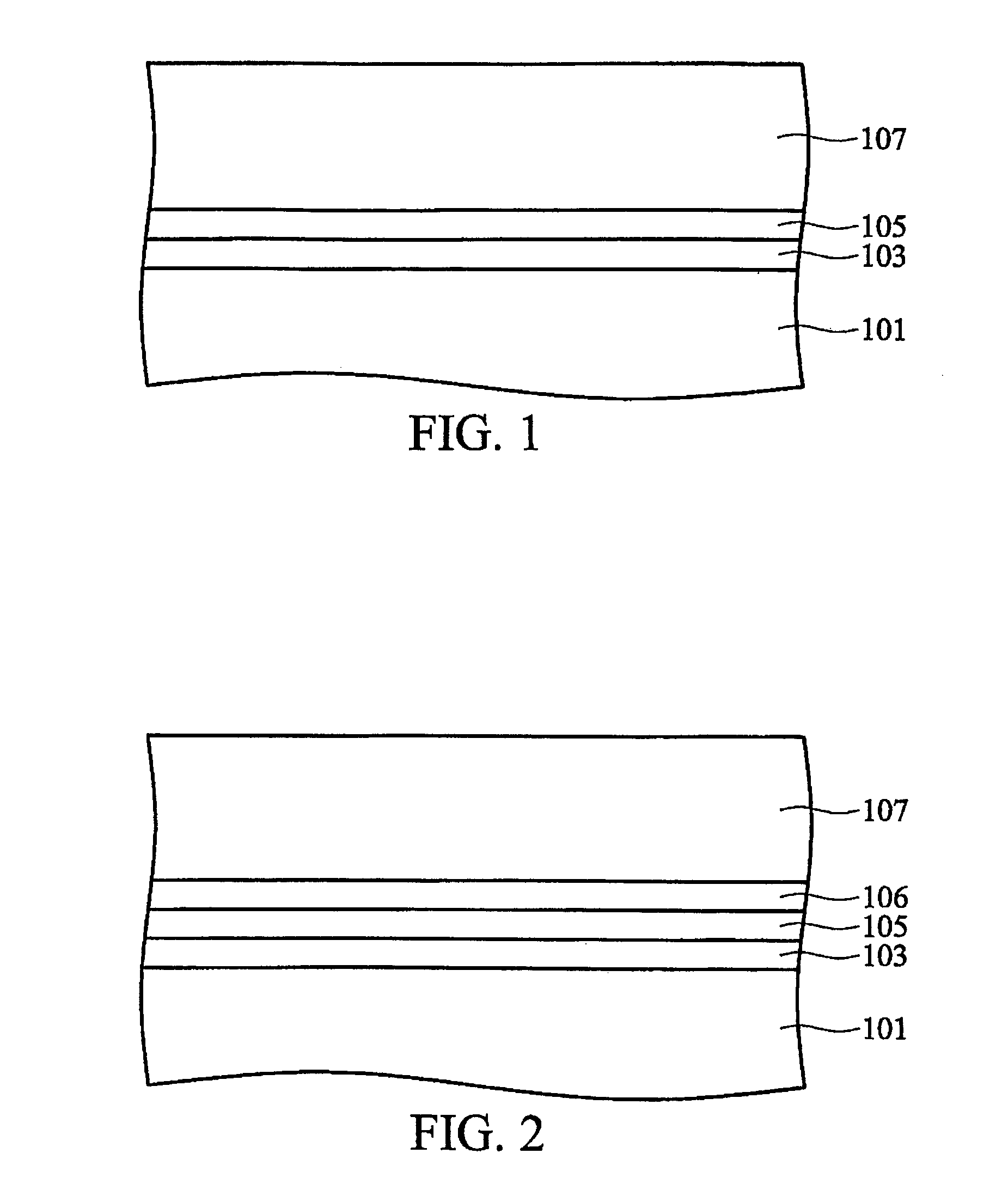

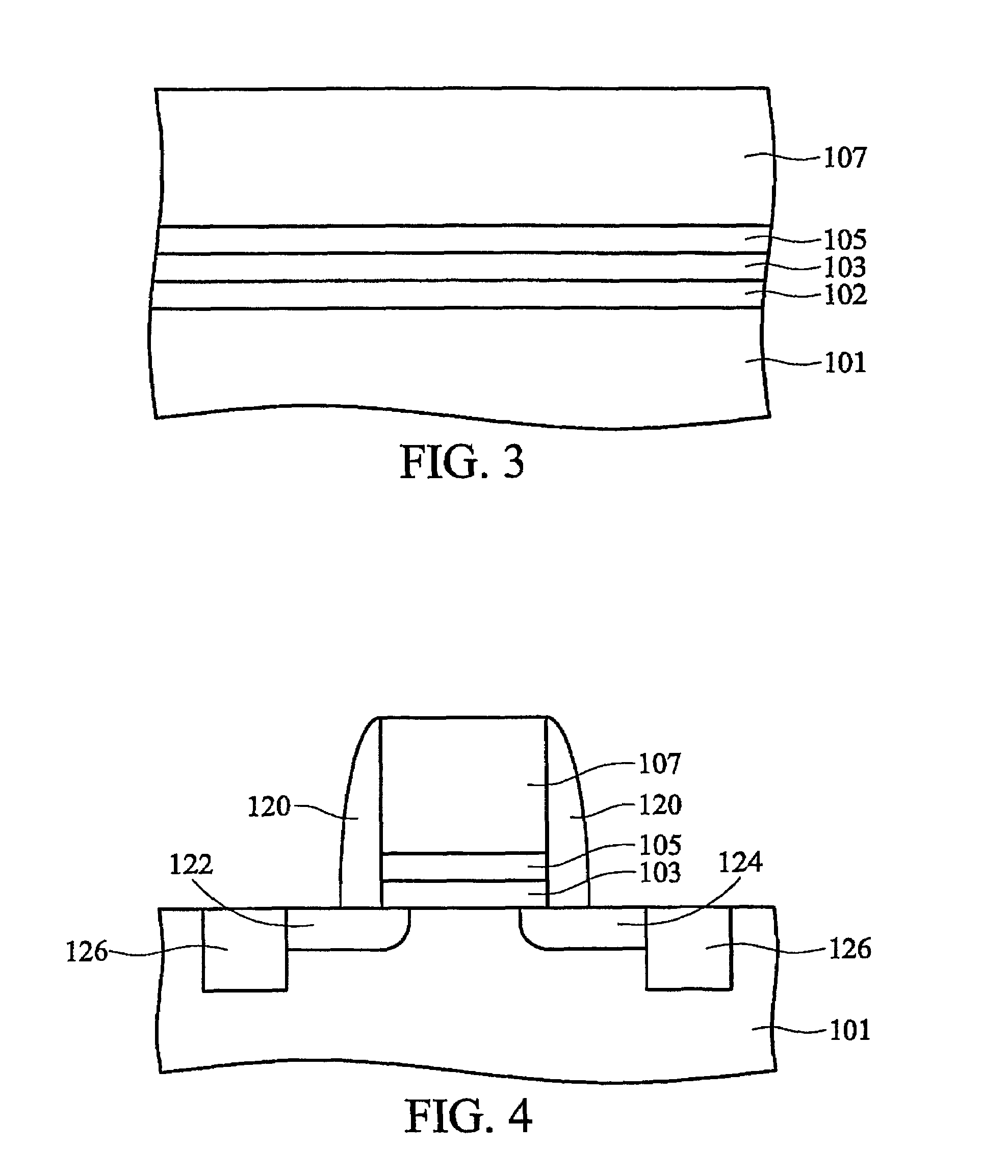

ActiveUS20060131675A1Improve performanceHigh carrier mobilityTransistorSolid-state devicesDielectricGate dielectric

A semiconductor device and process including a high-k gate dielectric is described. A substrate is provided, and a high-k gate dielectric material, preferably amorphous HfSiON, is deposited over the substrate. In preferred embodiments, the high-k dielectric material includes nitrogen. In a preferred embodiment, a silicon nitride layer is deposited using jet vapor deposition (JVD) on the high-k dielectric material. When the JVD nitride layer is deposited according to preferred embodiments, the layer has a low density of charge traps, it maintains comparable carrier mobility and provides better EOT compared to oxide or oxynitride. A second nitrogen-containing layer formed between the high-k dielectric and the gate electrode acts as a diffusion barrier. It also reduces problems relating to oxygen vacancy formation in high-k dielectric and therefore minimizes Fermi-level pinning.

Owner:TAIWAN SEMICON MFG CO LTD

Method for reducing fermi-level-pinning in a non-silicon channel mos device

InactiveUS20100065824A1Reduce decreaseLowering the Fermi levelSemiconductor/solid-state device manufacturingSemiconductor devicesGate dielectricHydrogen

A method to reduce (avoid) Fermi Level Pinning (FLP) in high mobility semiconductor compound channel such as Ge and III-V compounds (e.g. GaAs or InGaAs) in a Metal Oxide Semiconductor (MOS) device. The method is using atomic hydrogen which passivates the interface of the high mobility semiconductor compound with the gate dielectric and further repairs defects. The methods further improve the MOS device characteristics such that a MOS device with a quantum well is created.

Owner:INTERUNIVERSITAIR MICRO ELECTRONICS CENT (IMEC VZW)

Nanowhiskers with pn junctions, doped nanowhiskers, and methods for preparing them

InactiveUS7432522B2Permitted diffusionReduce the amount requiredPolycrystalline material growthNanoinformaticsHeterojunctionNon doped

Nano-engineered structures are disclosed, incorporating nanowhiskers of high mobility conductivity and incorporating pn junctions. In one embodiment, a nanowhisker of a first semiconducting material has a first band gap, and an enclosure comprising at least one second material with a second band gap encloses said nanoelement along at least part of its length, the second material being doped to provide opposite conductivity type charge carriers in respective first and second regions along the length of the of the nanowhisker, whereby to create in the nanowhisker by transfer of charge carriers into the nanowhisker, corresponding first and second regions of opposite conductivity type charge carriers with a region depleted of free carriers therebetween. The doping of the enclosure material may be degenerate so as to create within the nanowhisker adjacent segments having very heavy modulation doping of opposite conductivity type analogous to the heavily doped regions of an Esaki diode. In another embodiment, a nanowhisker is surrounded by polymer material containing dopant material. A step of rapid thermal annealing causes the dopant material to diffuse into the nanowhisker. In a further embodiment, a nanowhisker has a heterojunction between two different intrinsic materials, and Fermi level pinning creates a pn junction at the interface without doping.

Owner:QUNANO

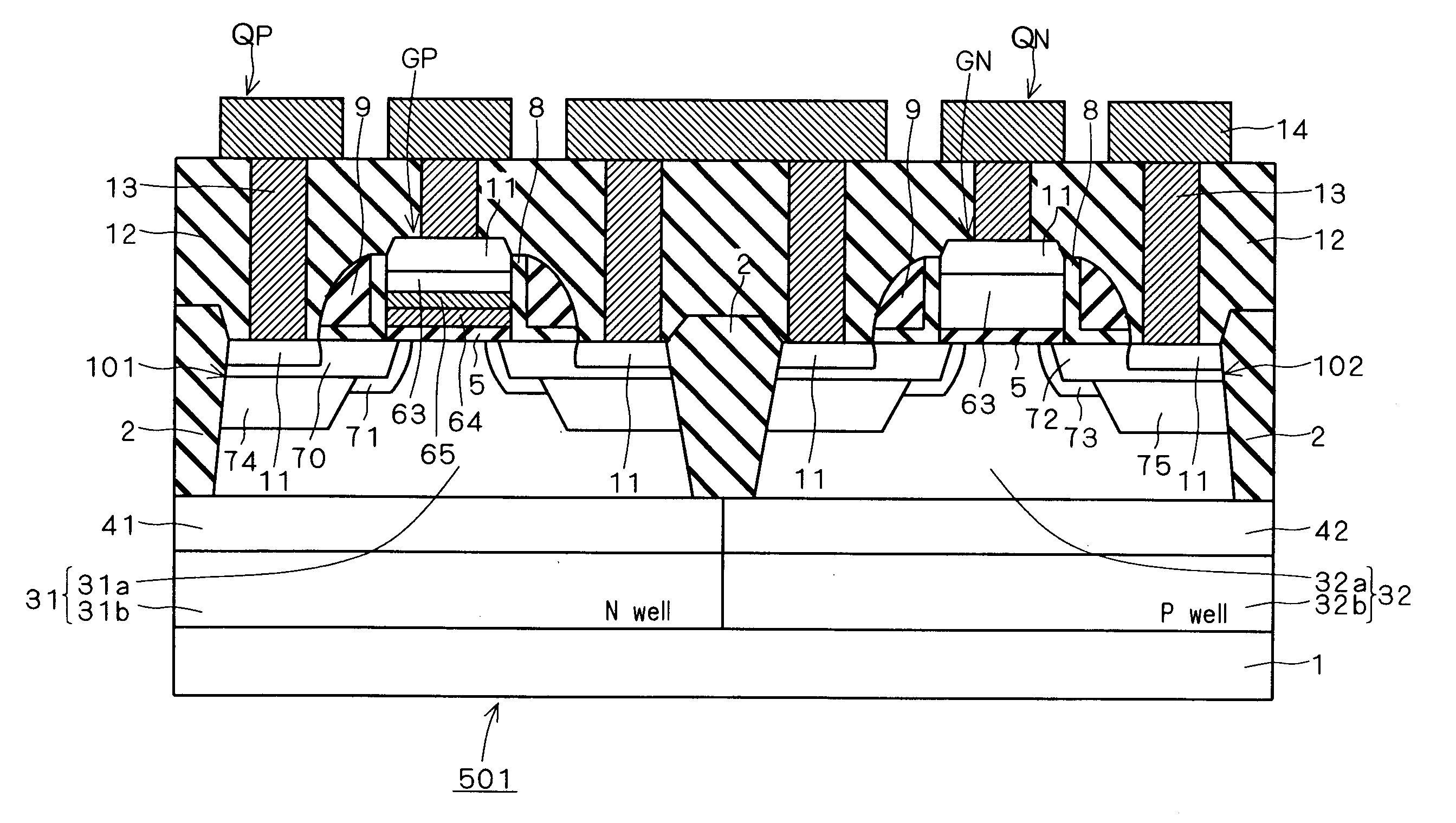

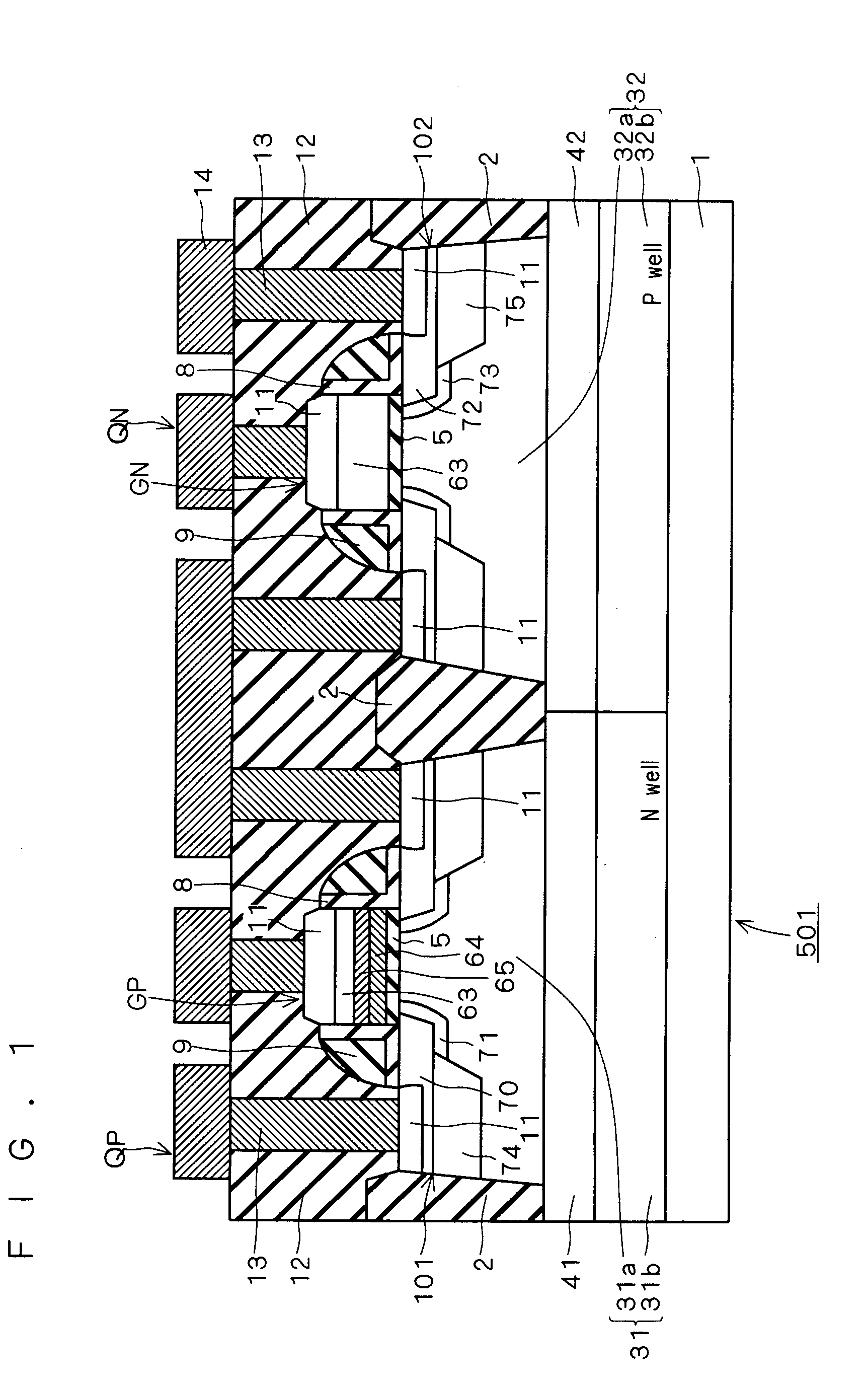

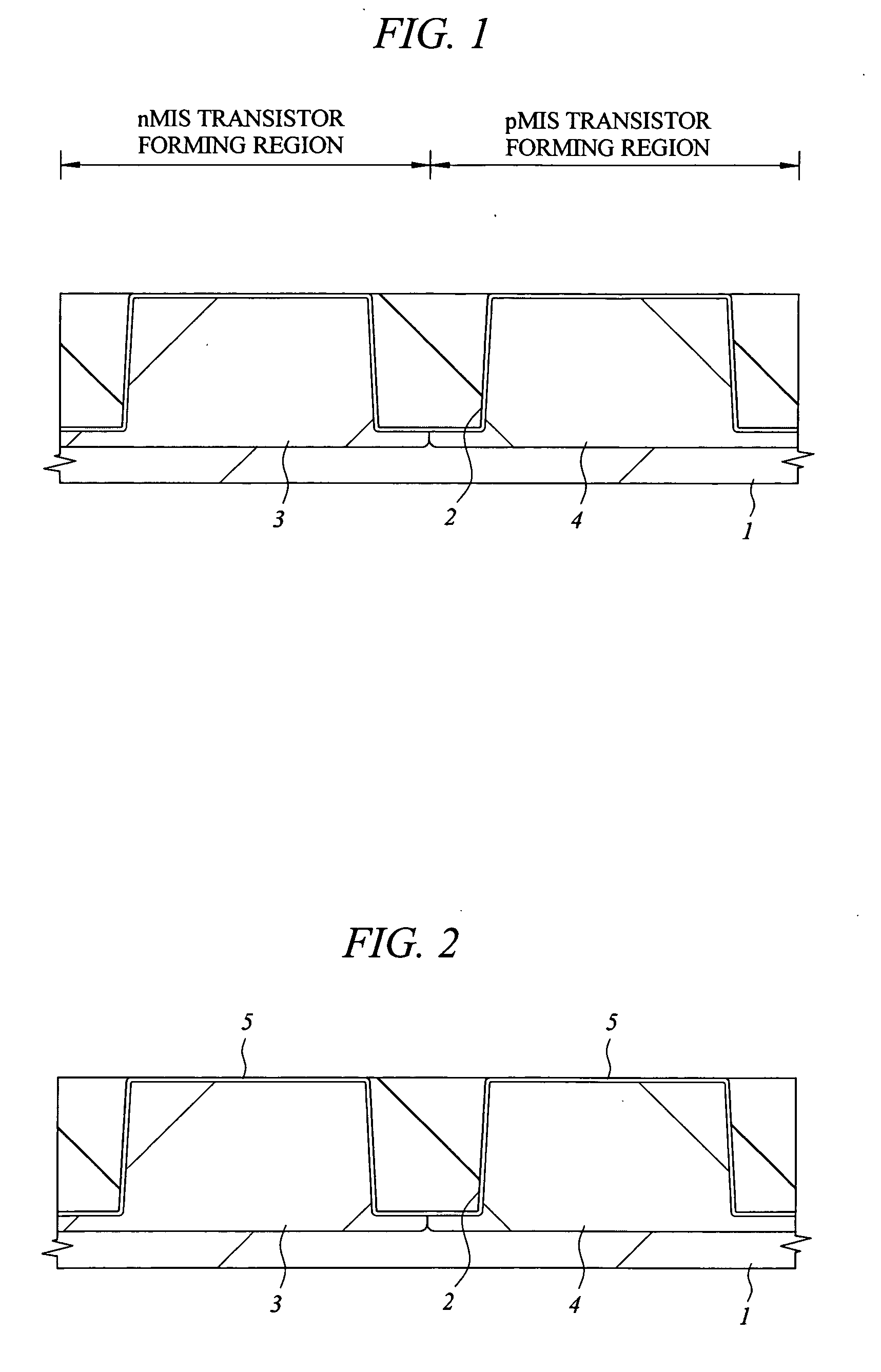

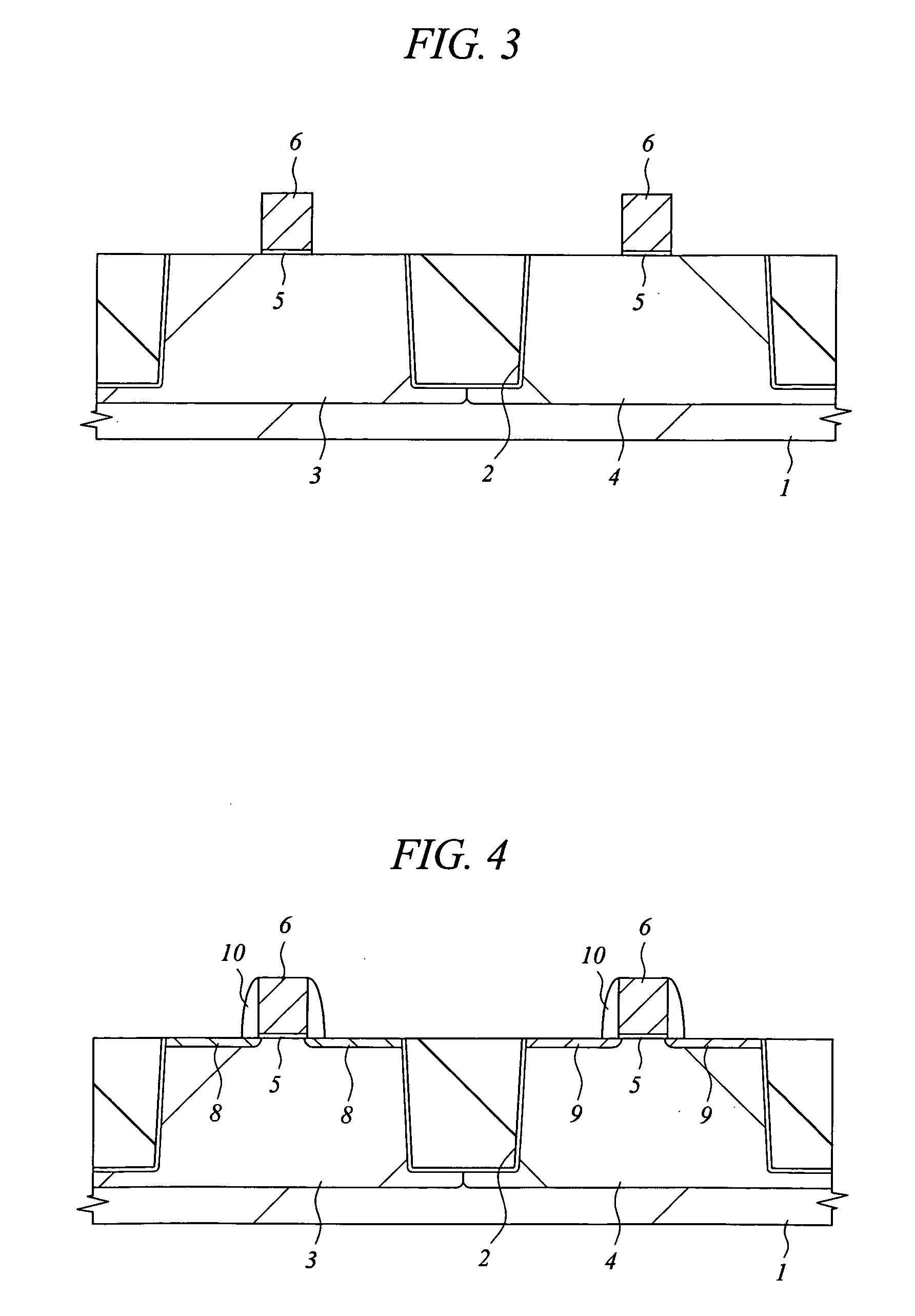

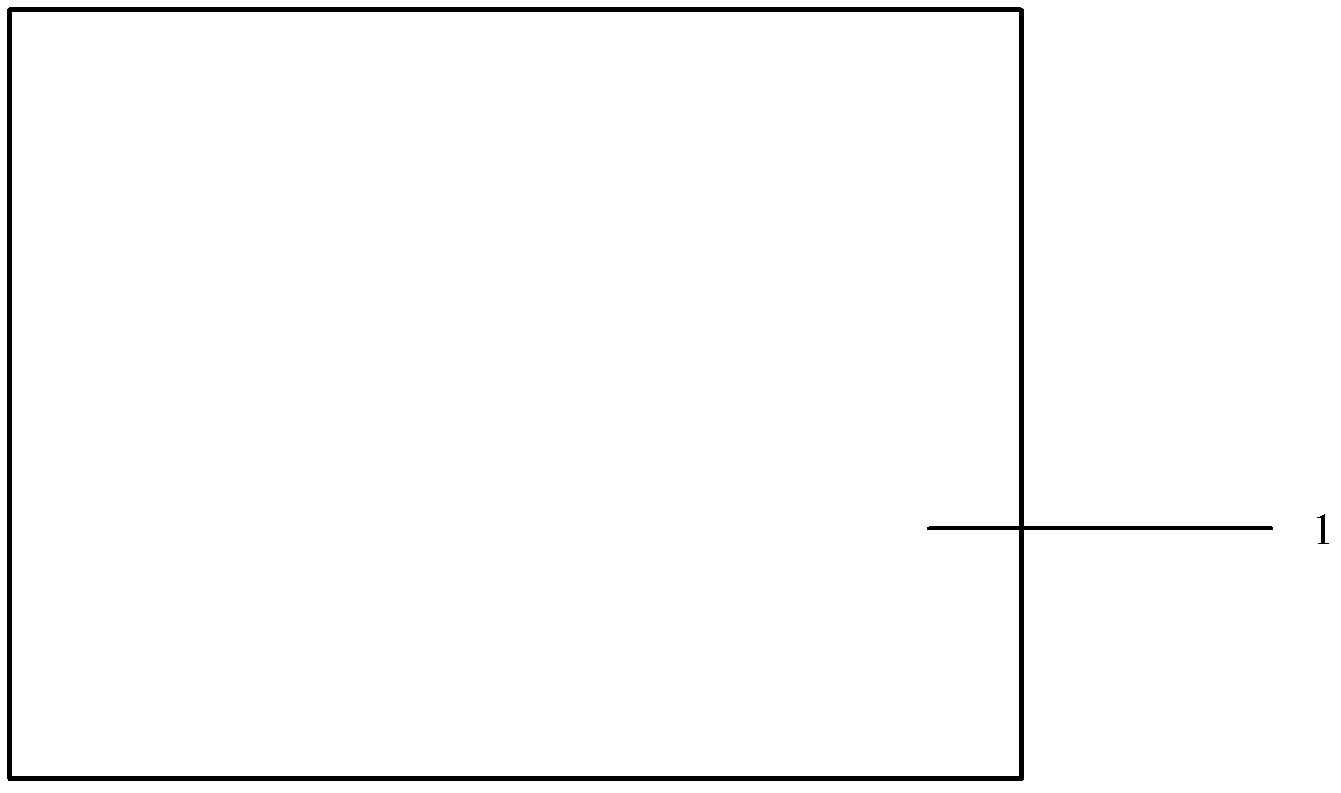

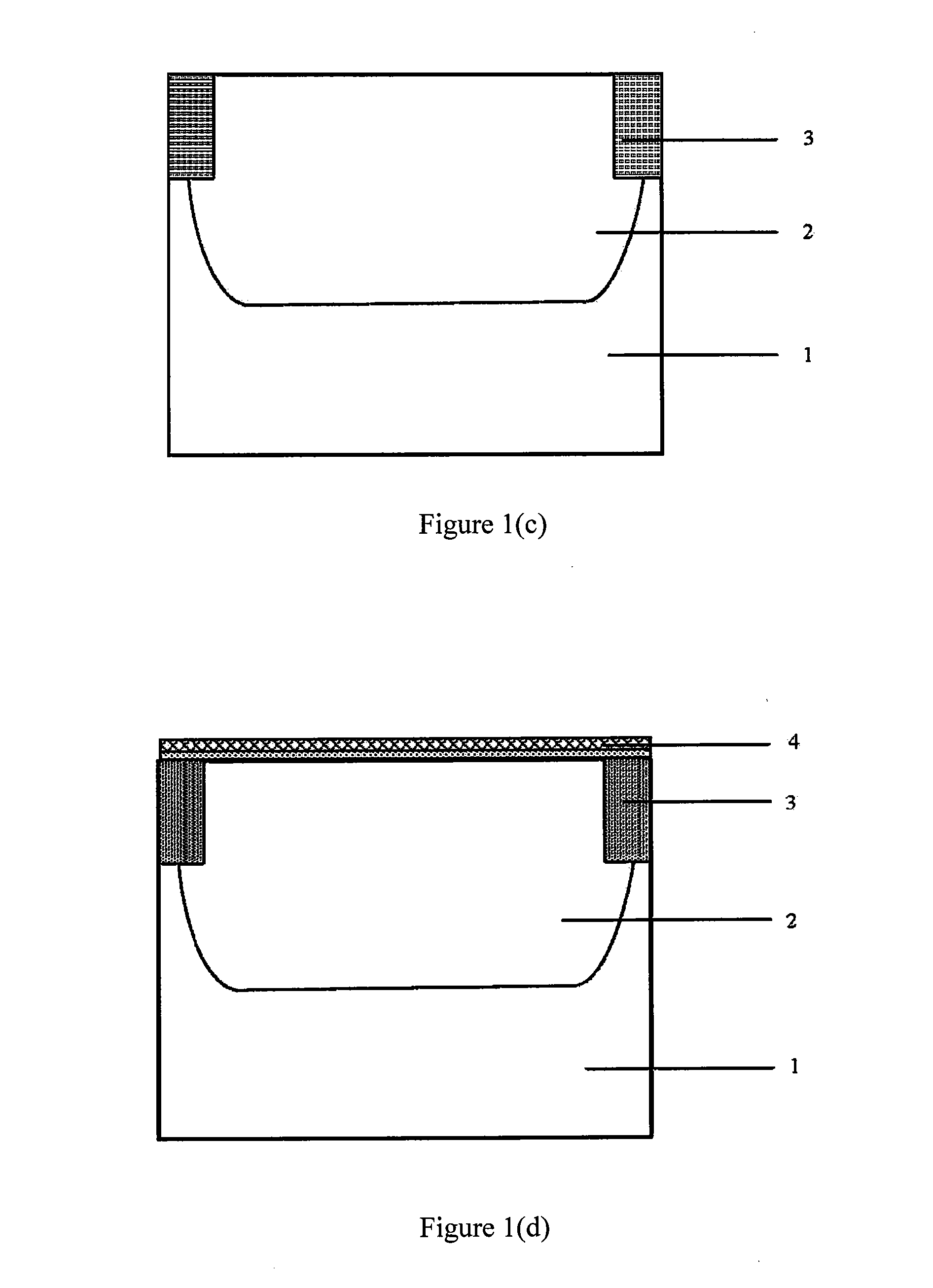

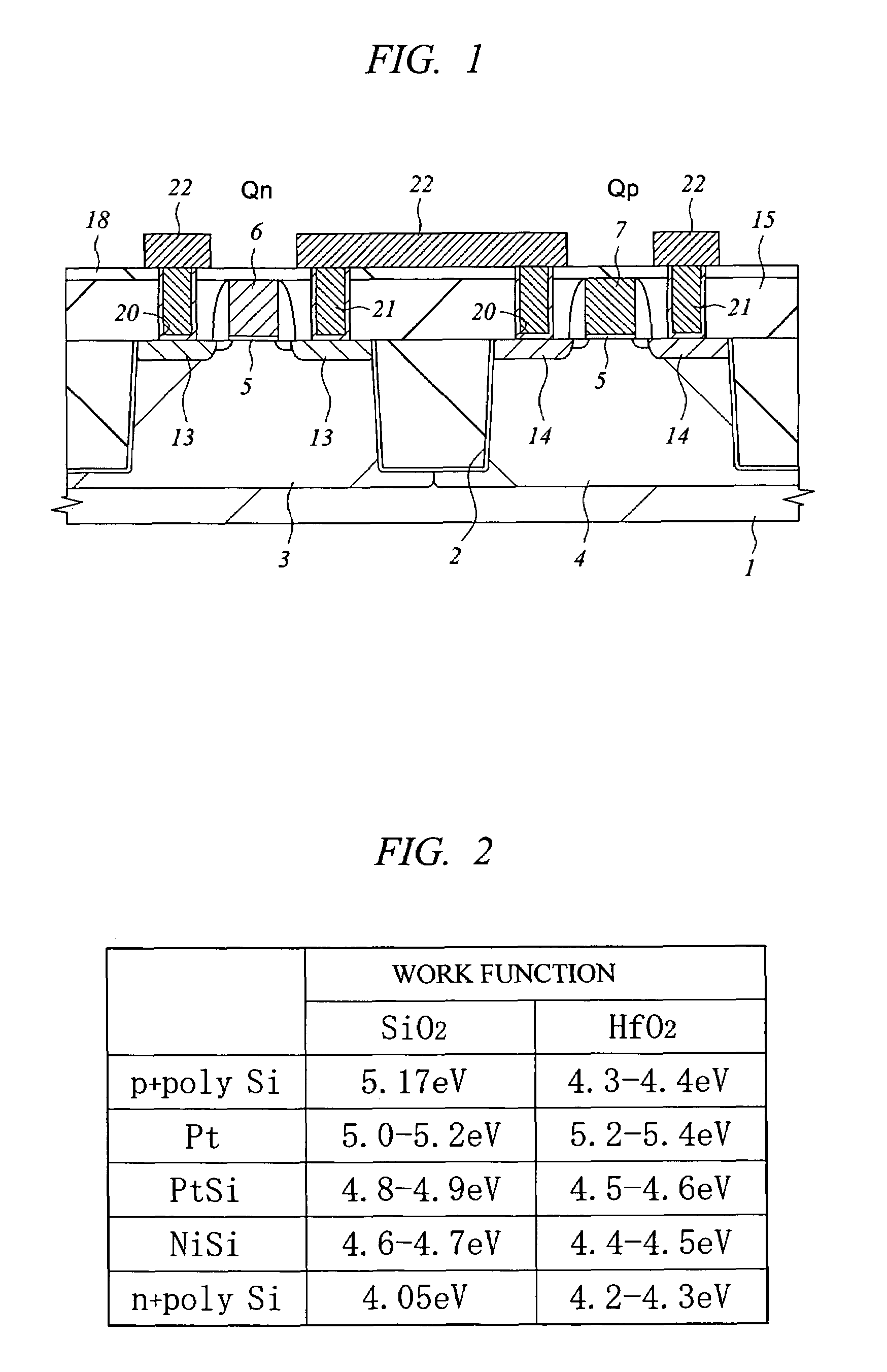

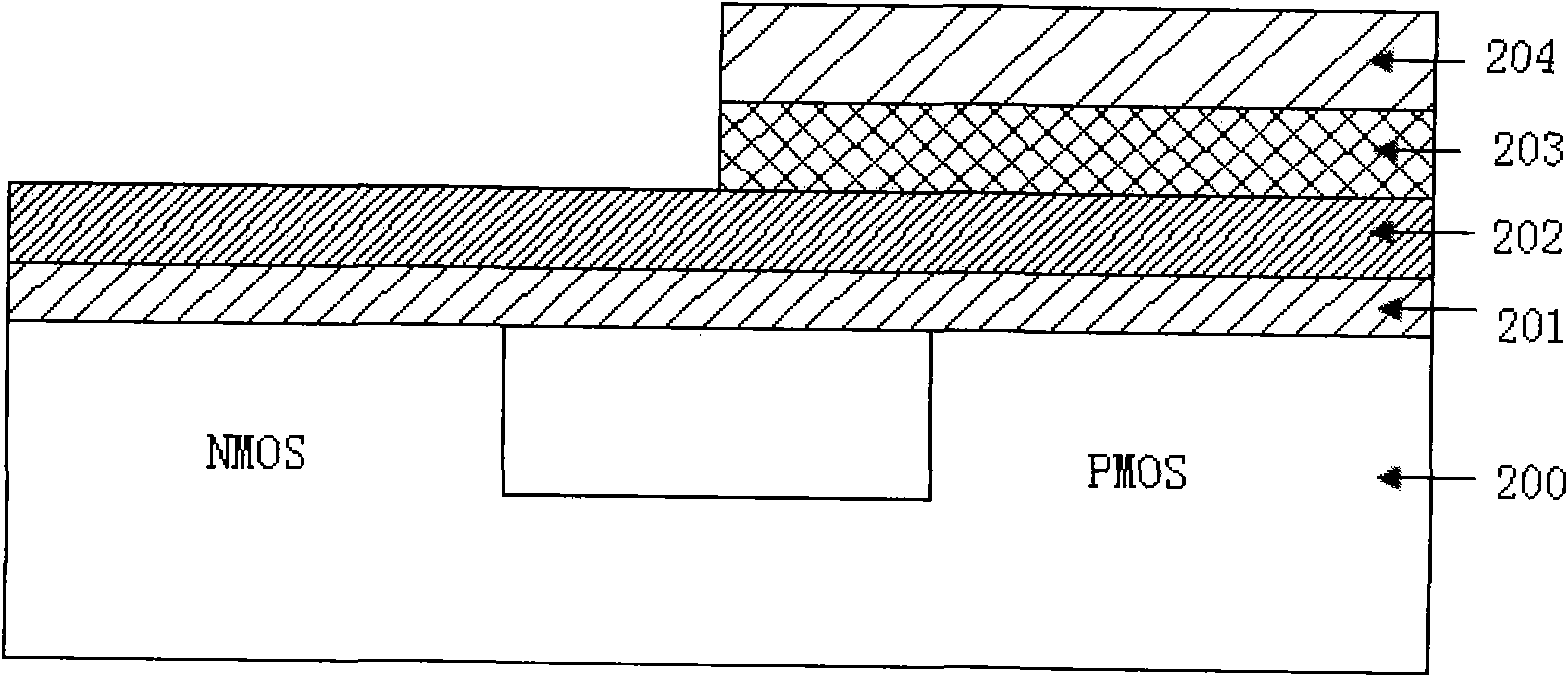

Semiconductor device which has mos structure and method of manufacturing the same

InactiveUS20080121999A1Simple manufacturing processEasy to manufactureTransistorSemiconductor/solid-state device manufacturingSemiconductorMetal

The present invention offers the semiconductor device which can solve each problem, such as Fermi level pinning, formation of gate electrode depletion, and a diffusion phenomenon, can adopt a material suitable for each gate electrode of the MOS structure from which threshold voltage differs, and can adjust (control) threshold voltage appropriately by the manufacturing process simplified more and which has a MOS structure.In the semiconductor device which has a MOS structure concerning the present invention, a PMOS transistor has the structure in which the gate insulating film, first metal layer, second metal layer, and polysilicon layer was formed in the order concerned. An NMOS transistor has the structure by which a gate insulating film and polysilicon were formed in the order concerned.

Owner:RENESAS ELECTRONICS CORP

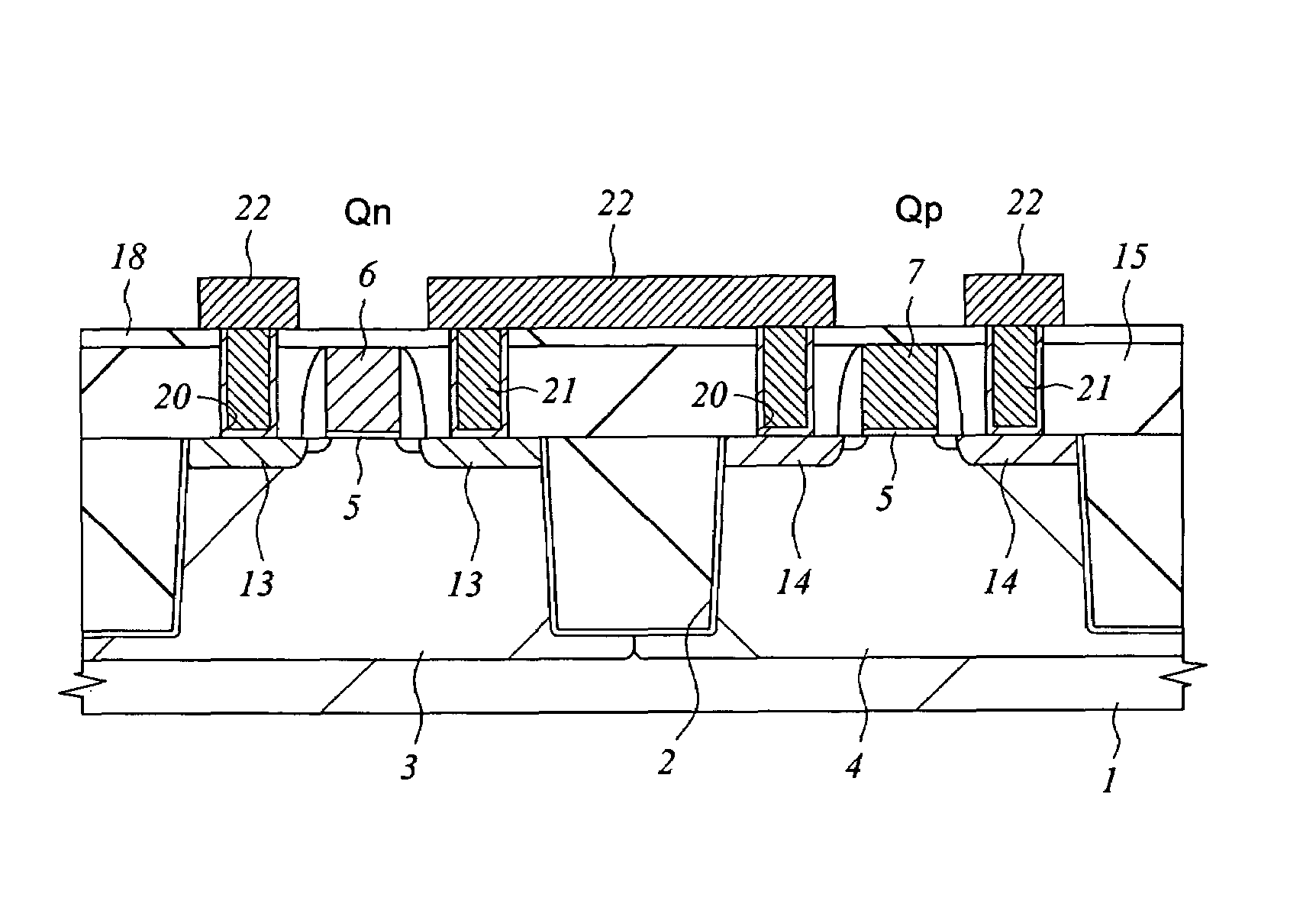

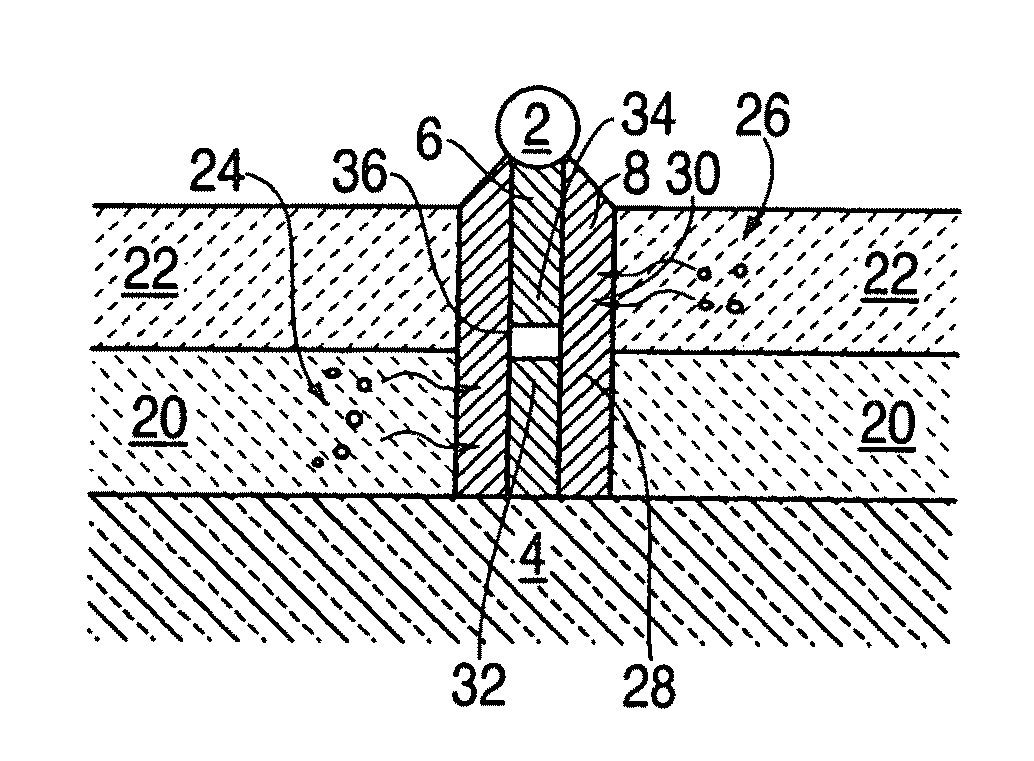

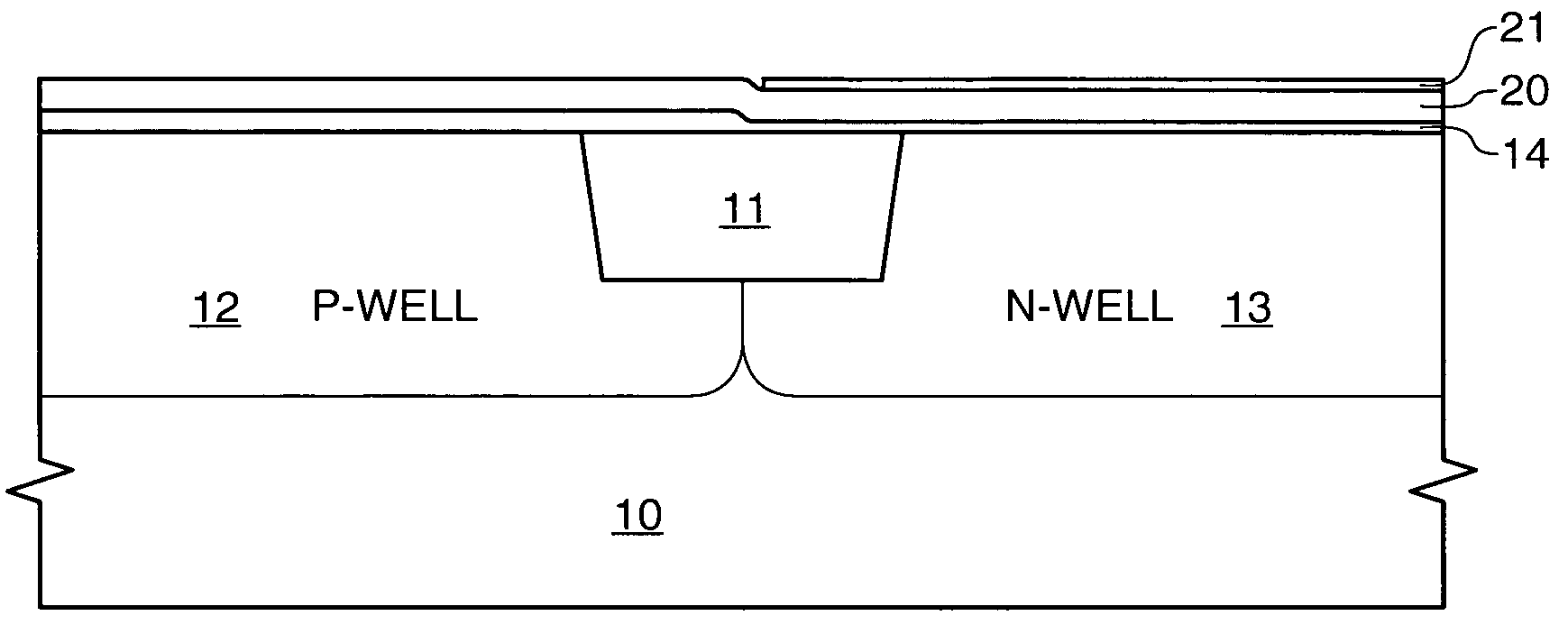

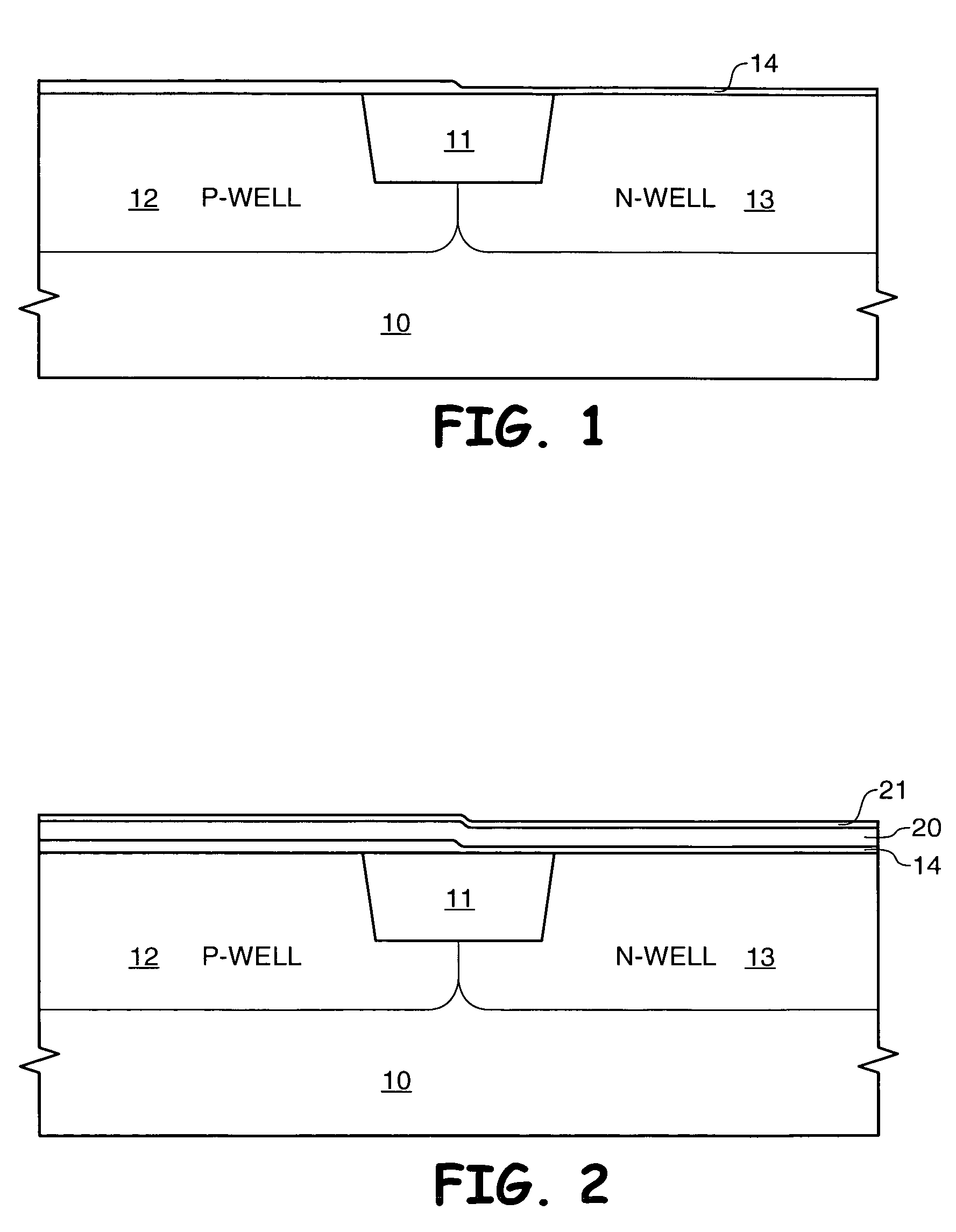

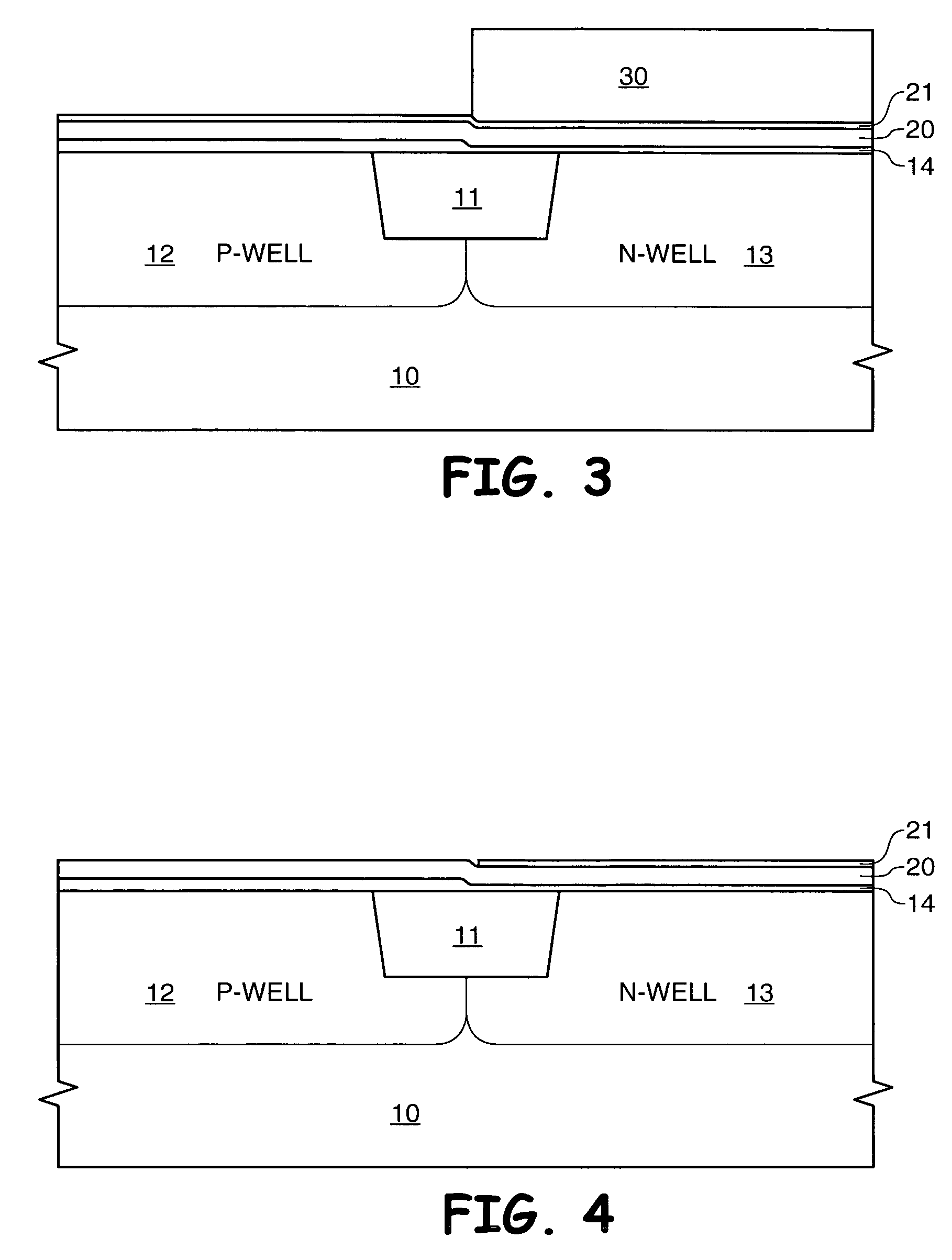

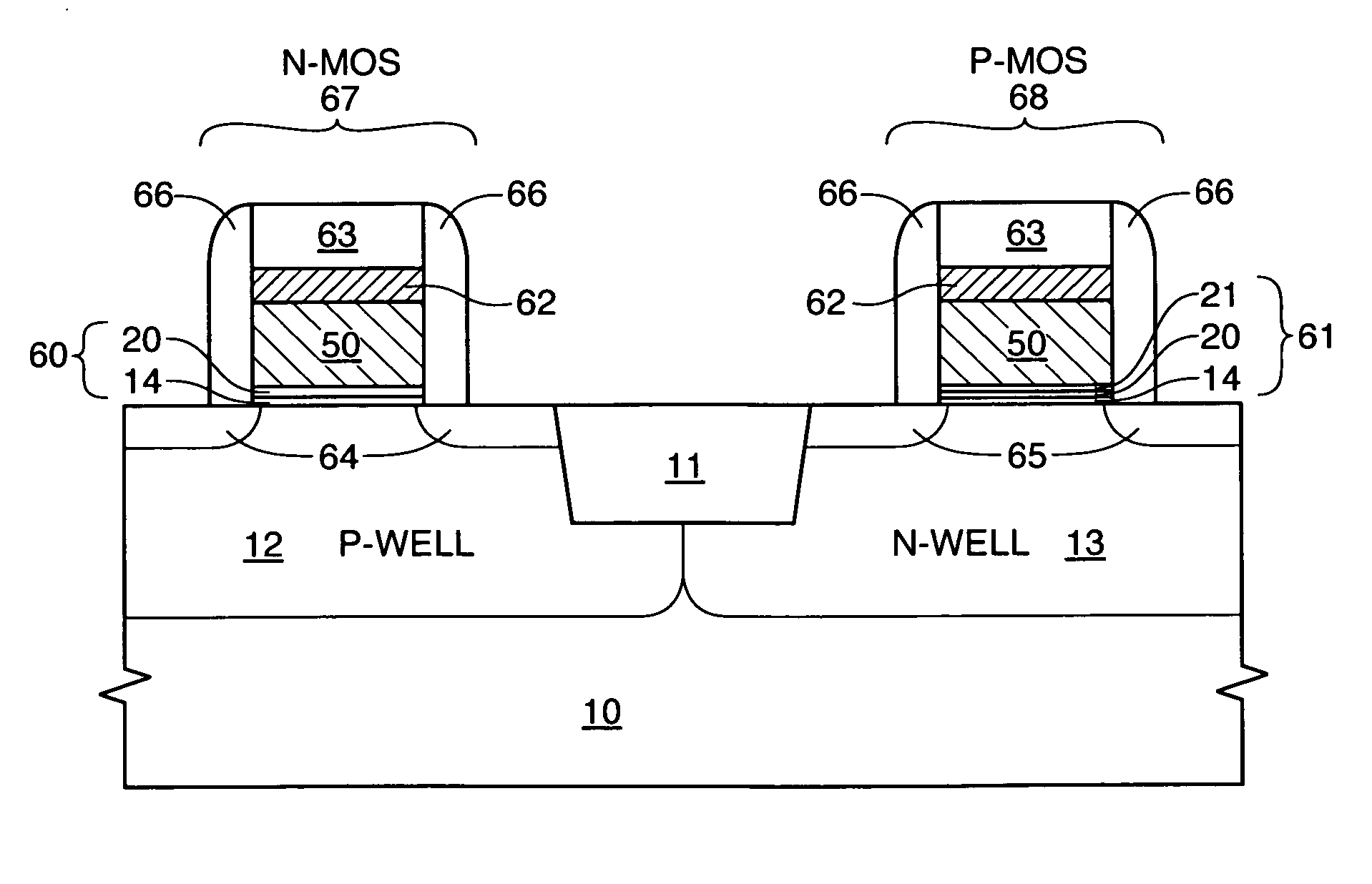

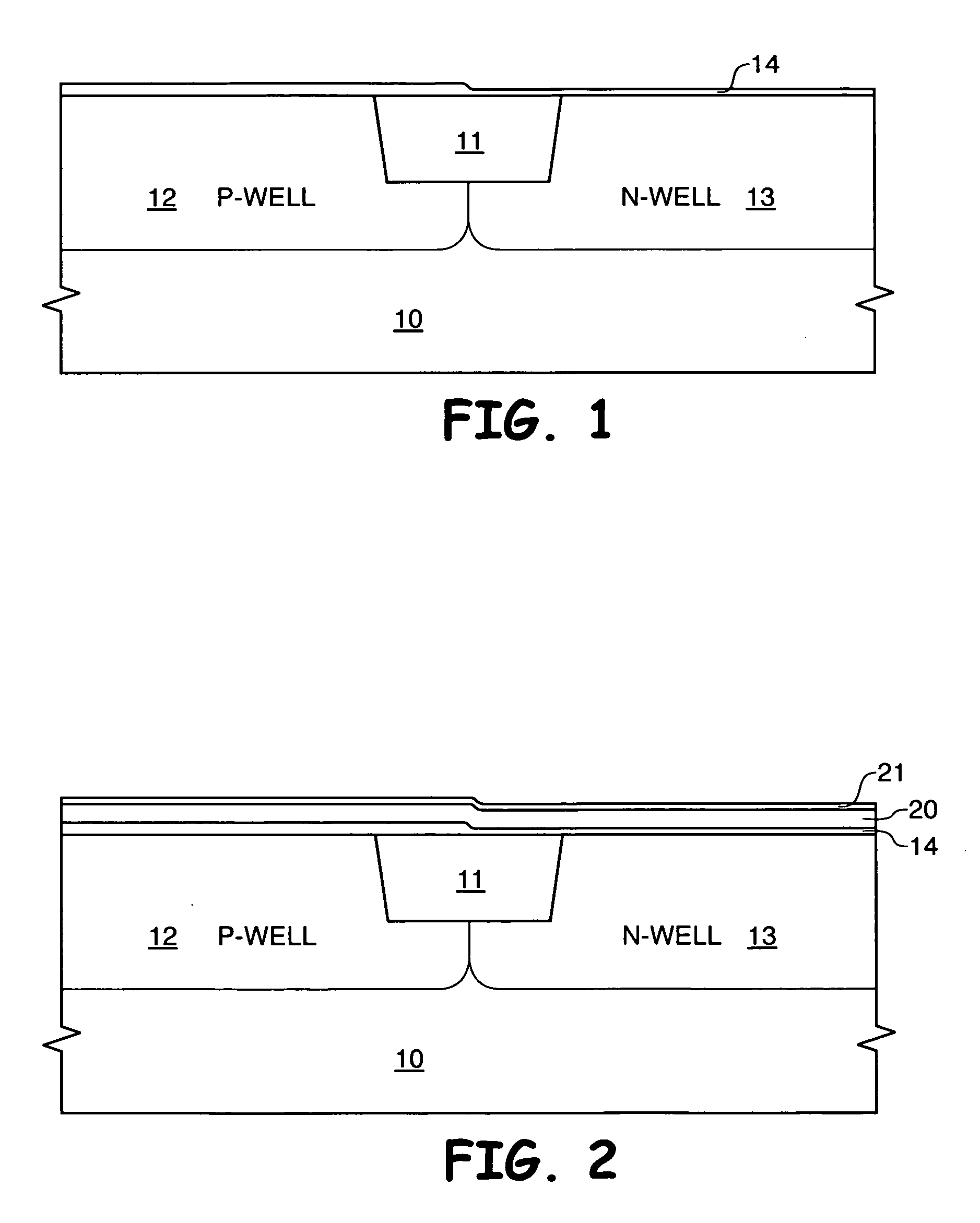

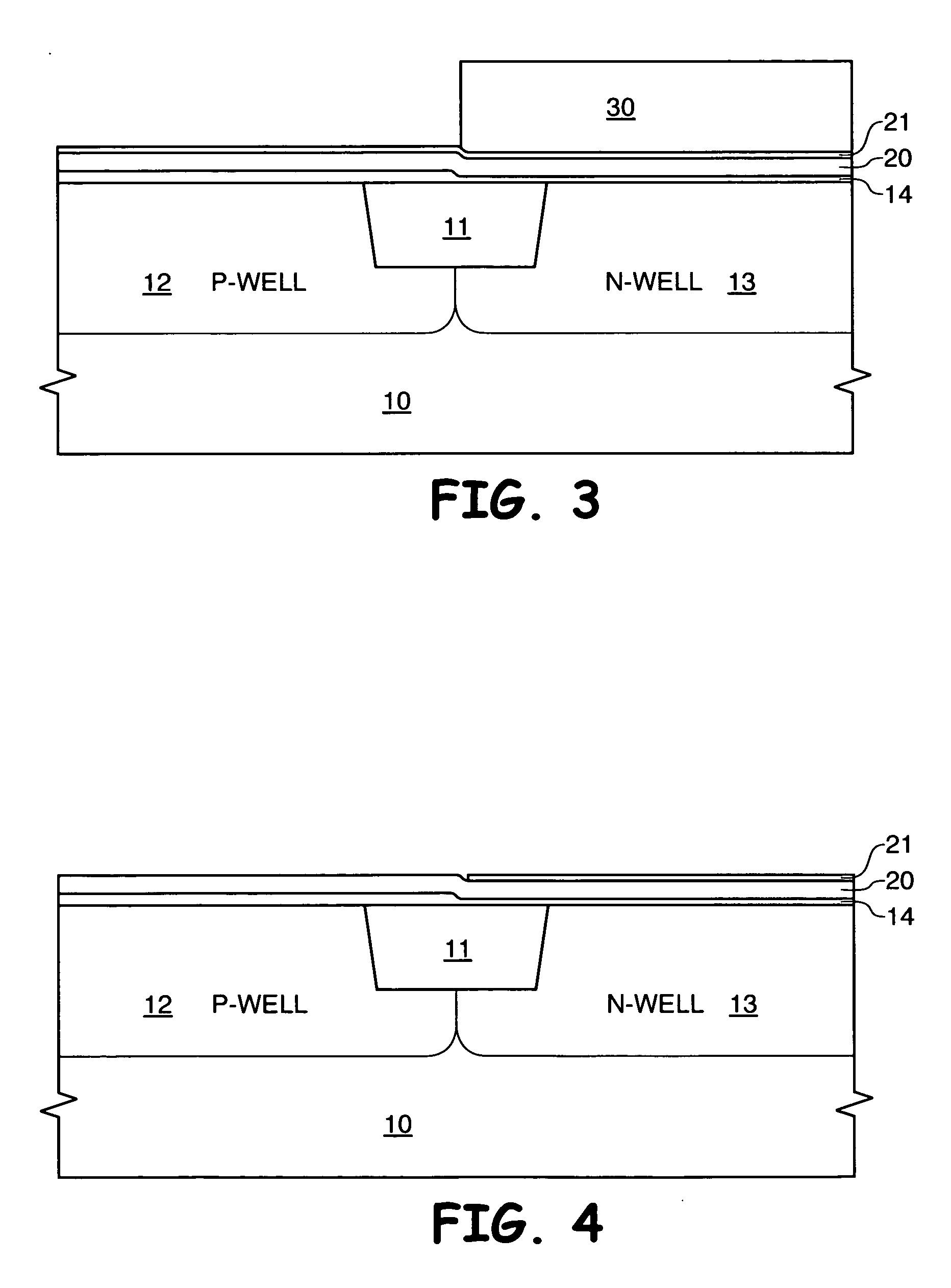

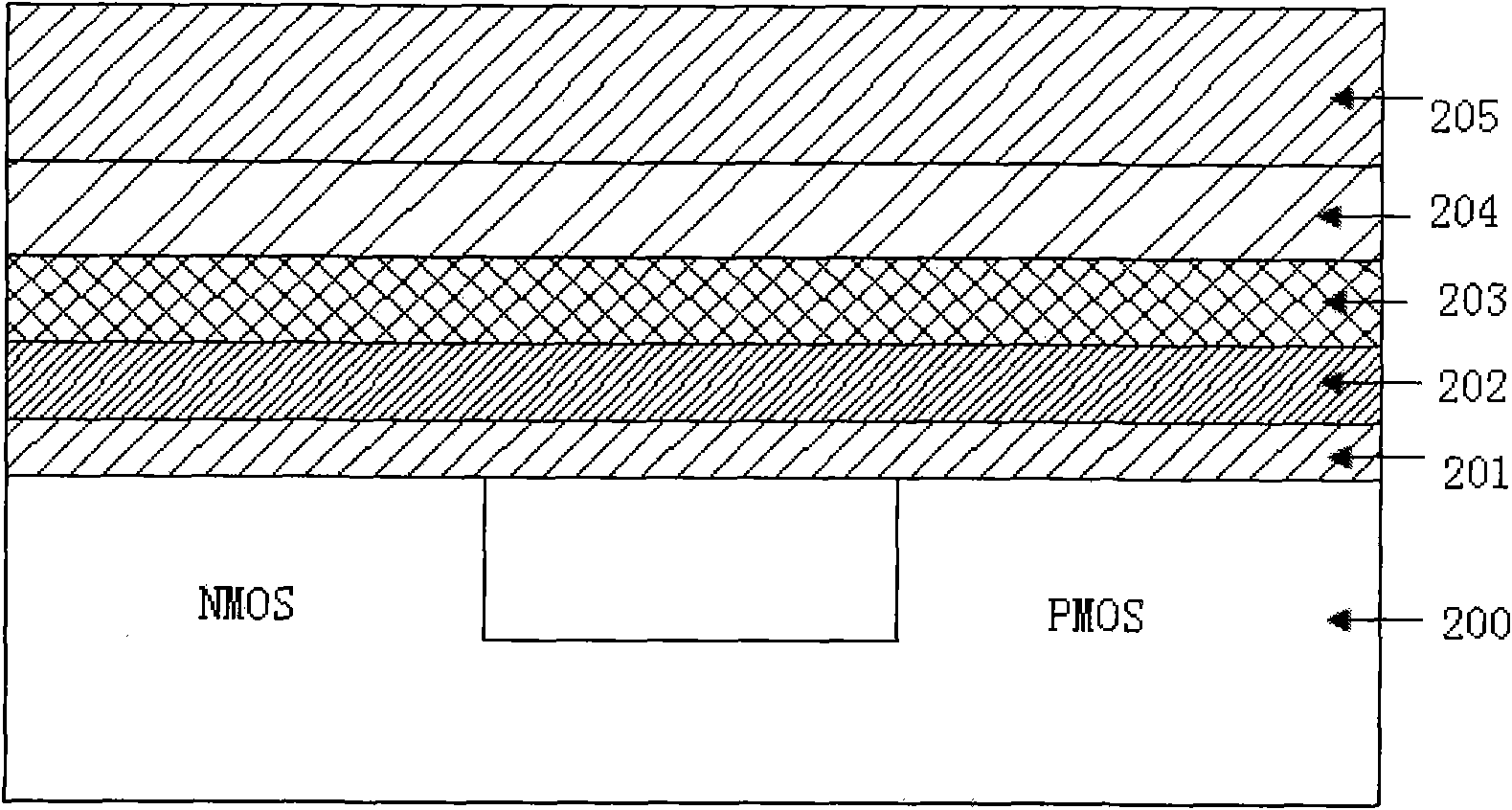

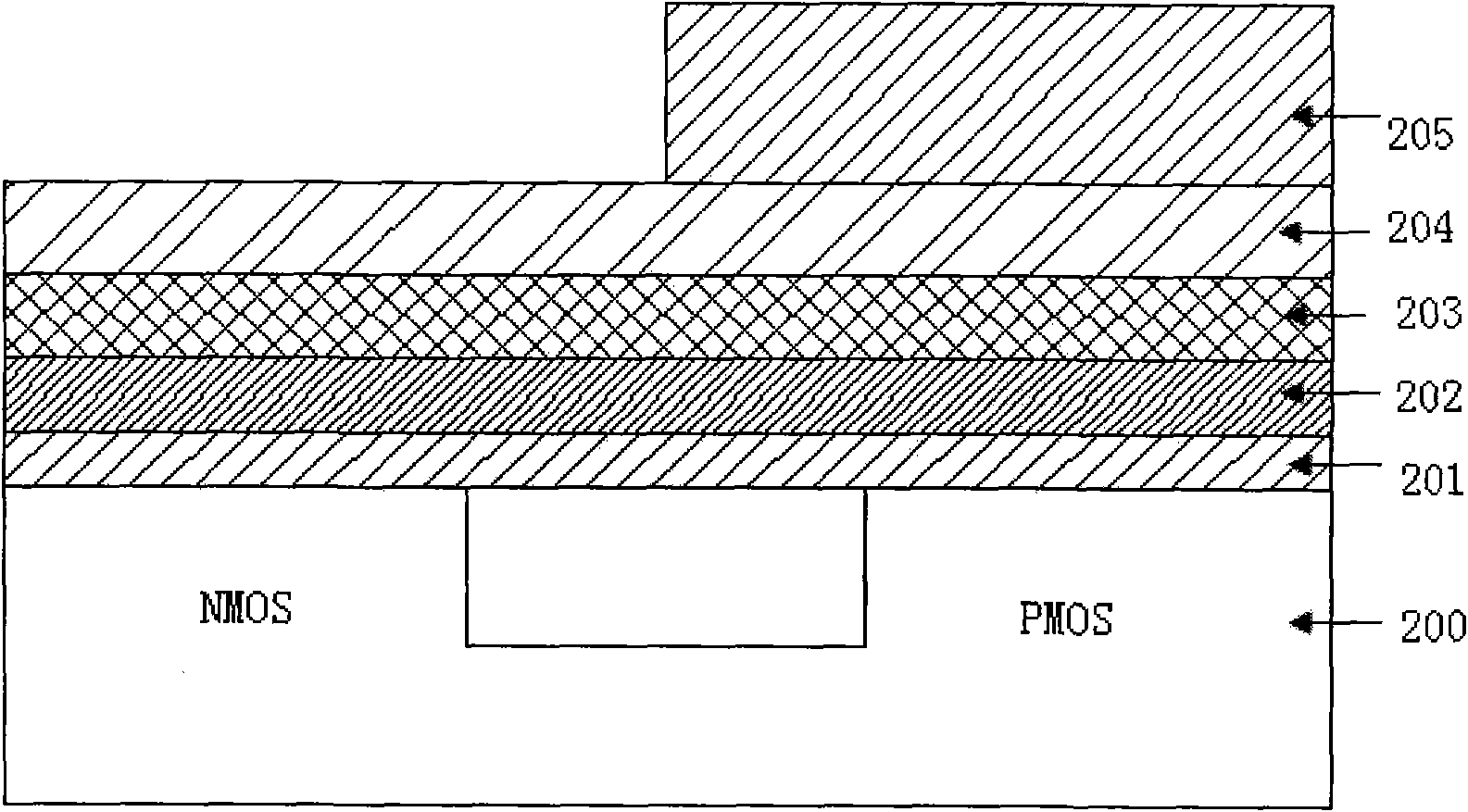

Methods of enabling polysilicon gate electrodes for high-k gate dieletrics

ActiveUS20060030096A1Semiconductor/solid-state device manufacturingSemiconductor devicesDielectricInterfacial oxide

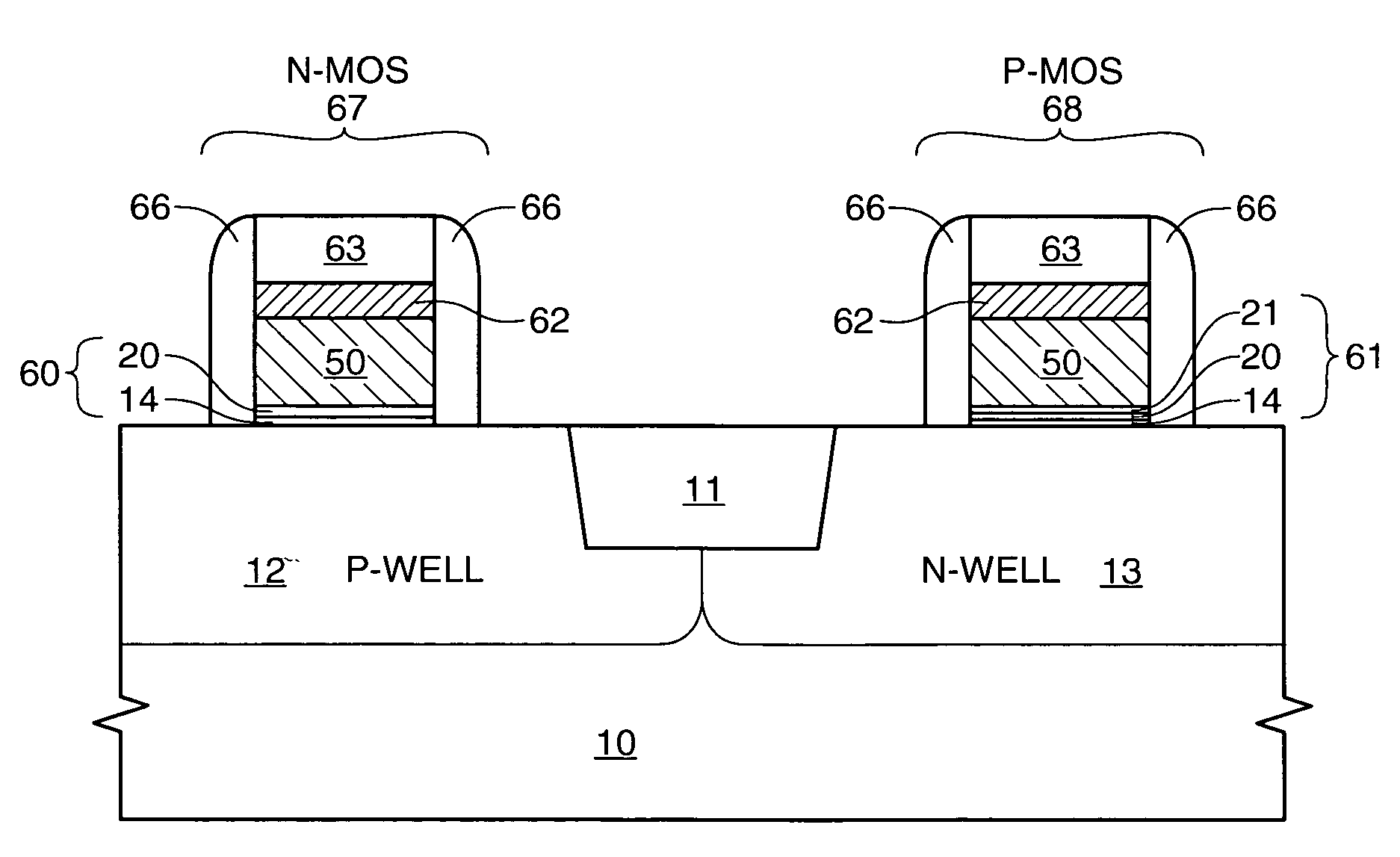

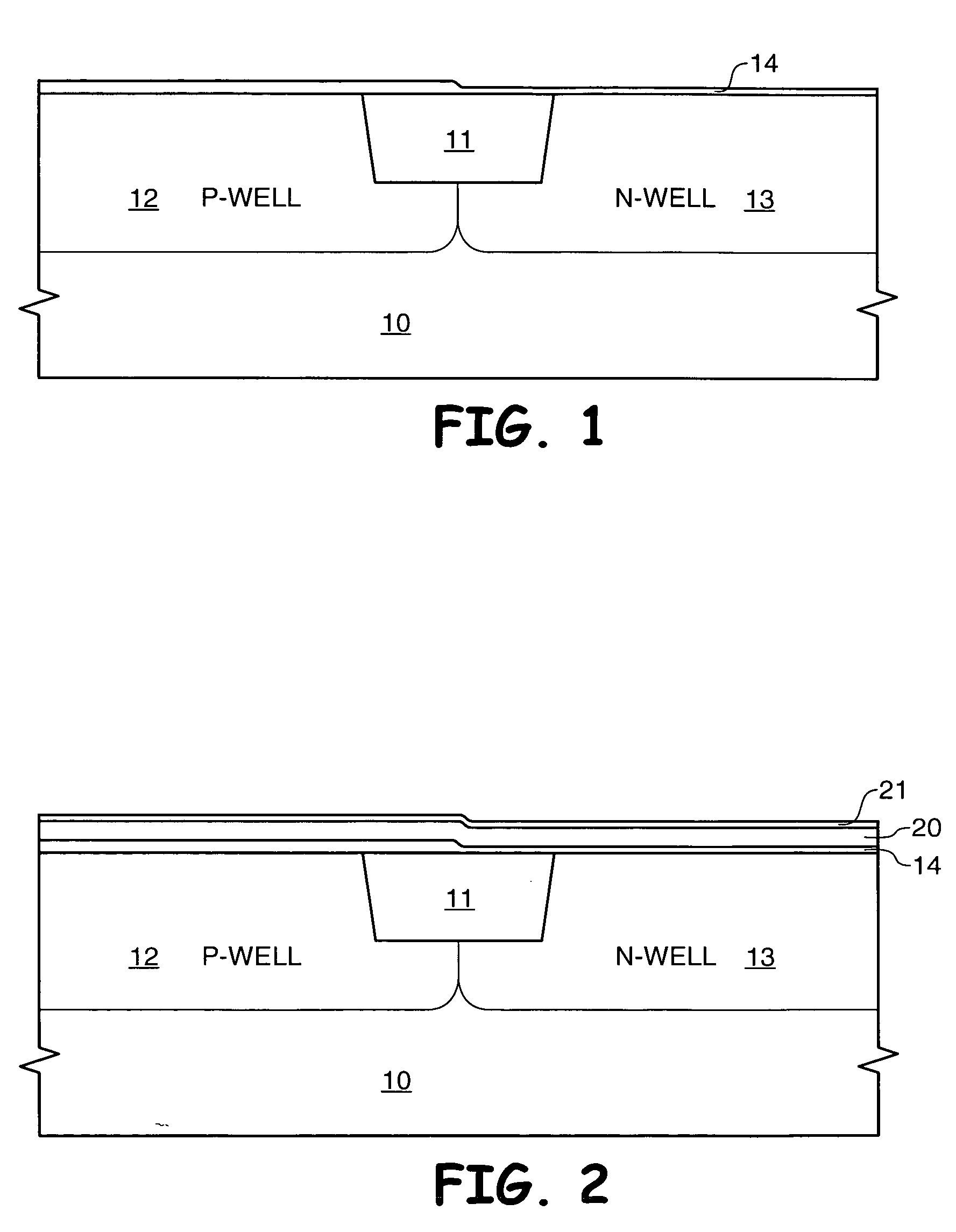

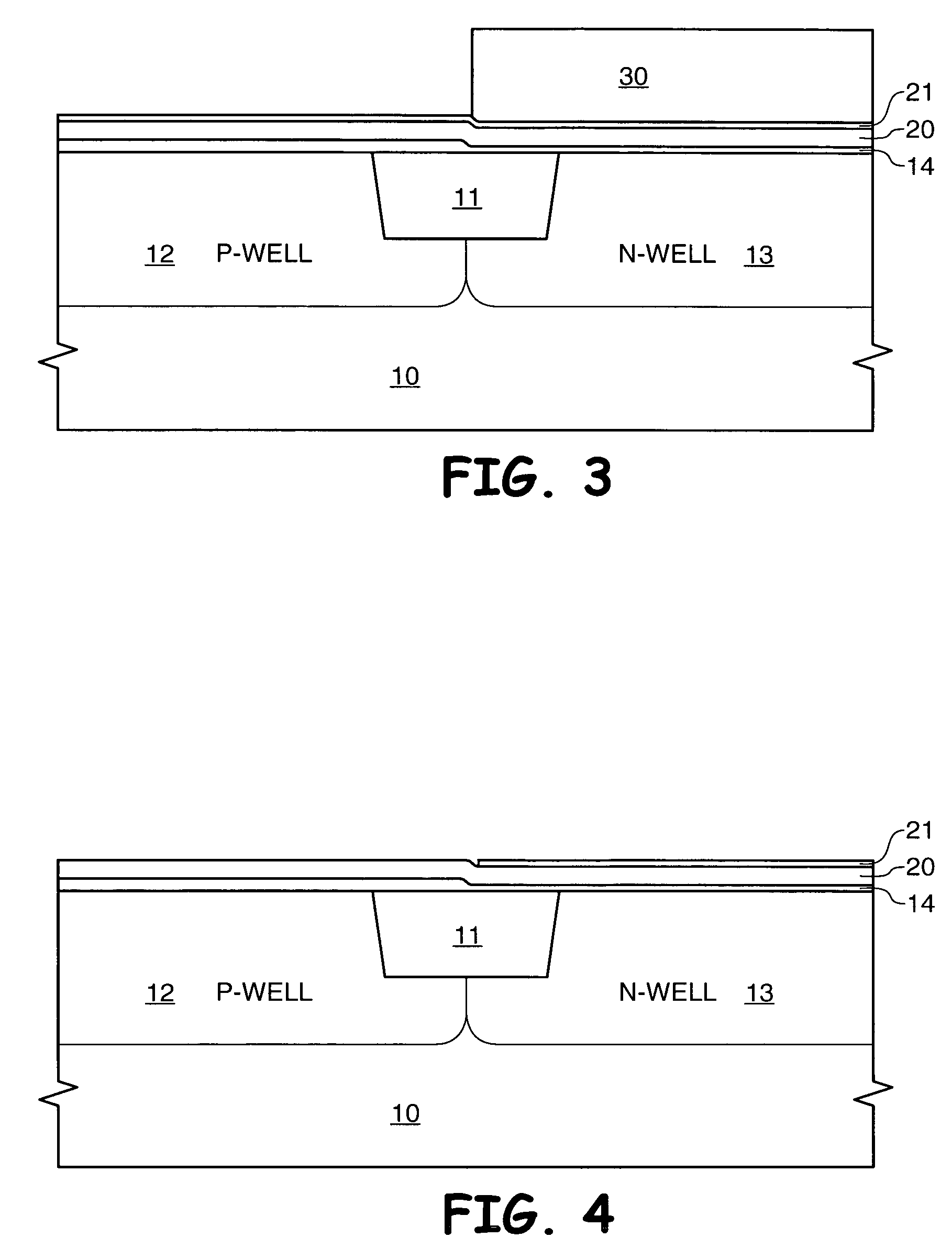

Complementary transistors and methods of forming the complementary transistors on a semiconductor assembly are described. The transistors are formed with an optional interfacial oxide, such as SiO2 or oxy-nitride, to overlay a semiconductor substrate which will be conductively doped for PMOS and NMOS regions. Then a dielectric possessing a high dielectric constant of least seven or greater (also referred to as a high-k dielectric) is deposited on the interfacial oxide. The high-k dielectric is covered with a thin monolayer of metal oxide (i.e., aluminum oxide, Al2O3) that is removed from the NMOS regions, but remains in the PMOS regions. The resulting NMOS transistor diffusion regions contain predominately metal to silicon bonds that create predominately Fermi level pinning near the valence band while the resulting PMOS transistor diffusion regions contain metal to silicon bonds that create predominately Fermi level pinning near the conduction band.

Owner:MICRON TECH INC

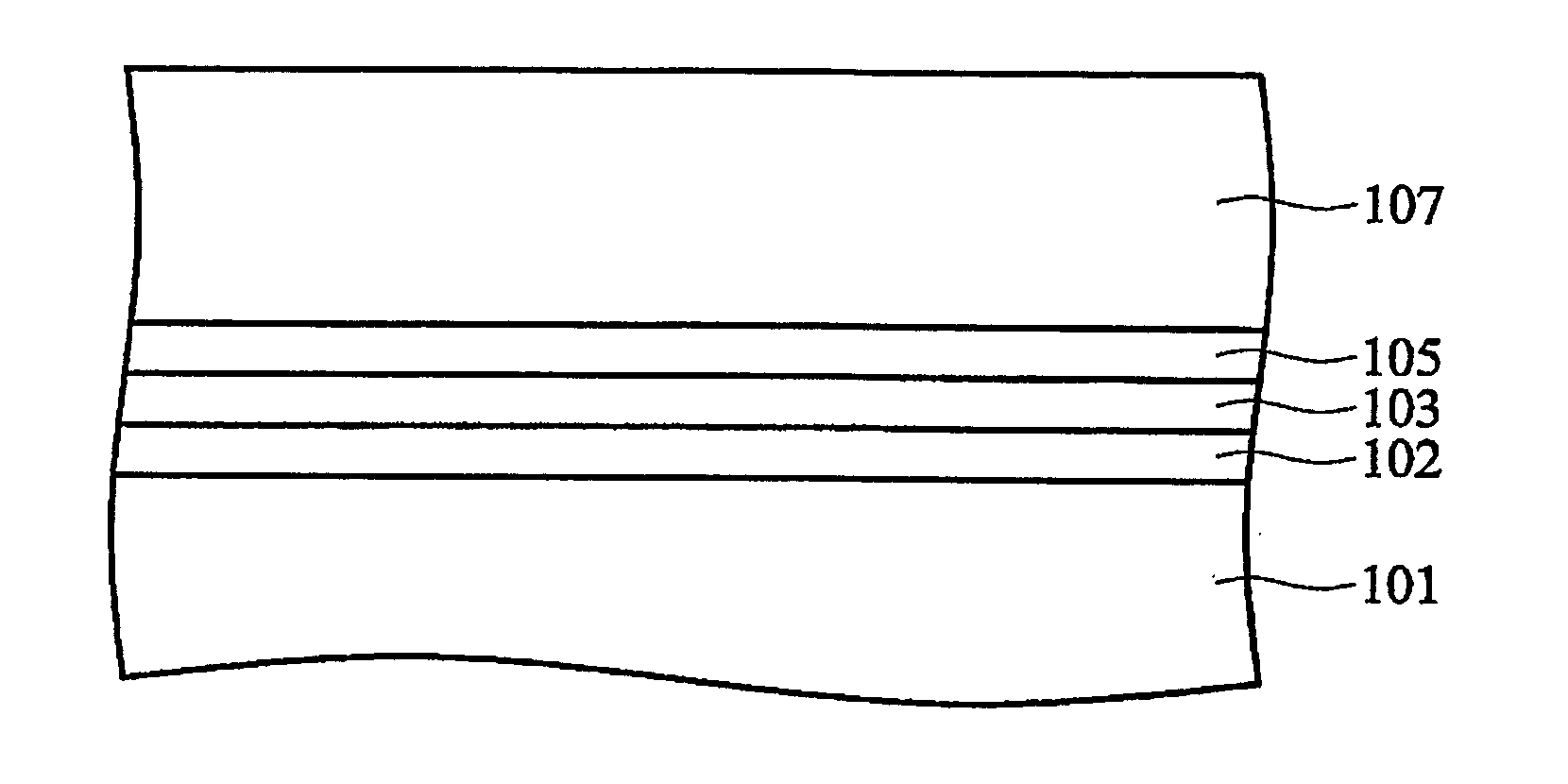

Semiconductor device and method for high-k gate dielectrics

ActiveUS7355235B2High carrier mobilityImprove performanceTransistorSolid-state devicesDielectricGate dielectric

A semiconductor device and process including a high-k gate dielectric is described. A substrate is provided, and a high-k gate dielectric material, preferably amorphous HfSiON, is deposited over the substrate. In preferred embodiments, the high-k dielectric material includes nitrogen. In a preferred embodiment, a silicon nitride layer is deposited using jet vapor deposition (JVD) on the high-k dielectric material. When the JVD nitride layer is deposited according to preferred embodiments, the layer has a low density of charge traps, it maintains comparable carrier mobility and provides better EOT compared to oxide or oxynitride. A second nitrogen-containing layer formed between the high-k dielectric and the gate electrode acts as a diffusion barrier. It also reduces problems relating to oxygen vacancy formation in high-k dielectric and therefore minimizes Fermi-level pinning.

Owner:TAIWAN SEMICON MFG CO LTD

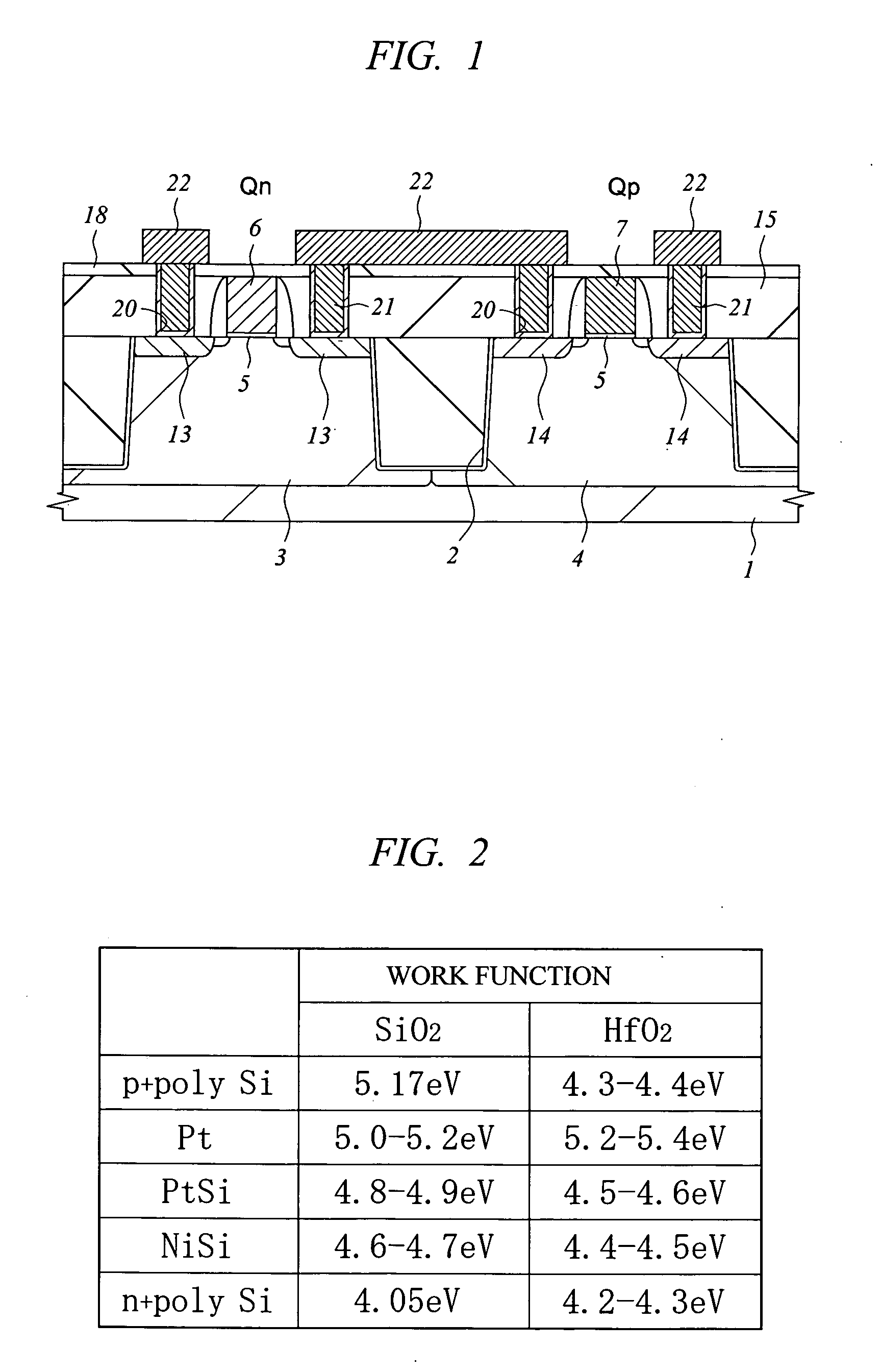

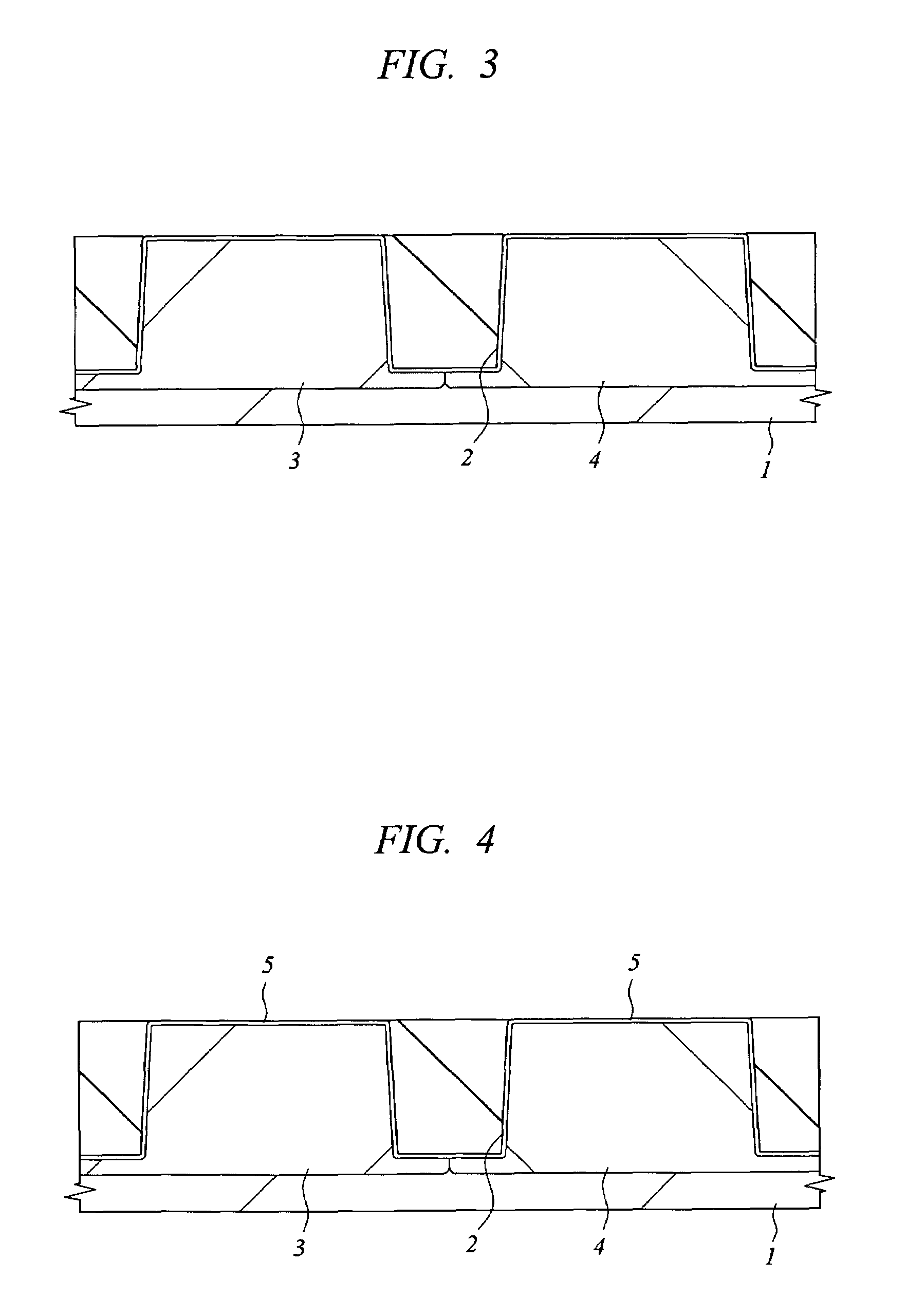

Semiconductor device and manufacturing method thereof

InactiveUS20060071282A1High currentReduce power consumptionSemiconductor/solid-state device manufacturingSemiconductor devicesDevice materialEngineering

A structure of a MIS transistor for realizing a CMOS circuit capable of simultaneously achieving the high ON current and the low power consumption is provided. Each of the gate insulators of a n channel MIS transistor and a p channel MIS transistor is composed of a hafnium oxide film. Also, the gate electrode is composed of a Pt silicide film with a ratio of Si atoms to Pt atoms of approximately 1 (PtSix: x=1) in the vicinity of a region in contact with the gate insulator. Also, the gate electrode of the p channel MIS transistor is composed of a Pt silicide film with a ratio of Si atoms to Pt atoms of less than 1 (PtSix: x<1) in the vicinity of a region in contact with the gate insulator. Therefore, the Fermi level pinning of the gate electrode is suppressed.

Owner:RENESAS TECH CORP +1

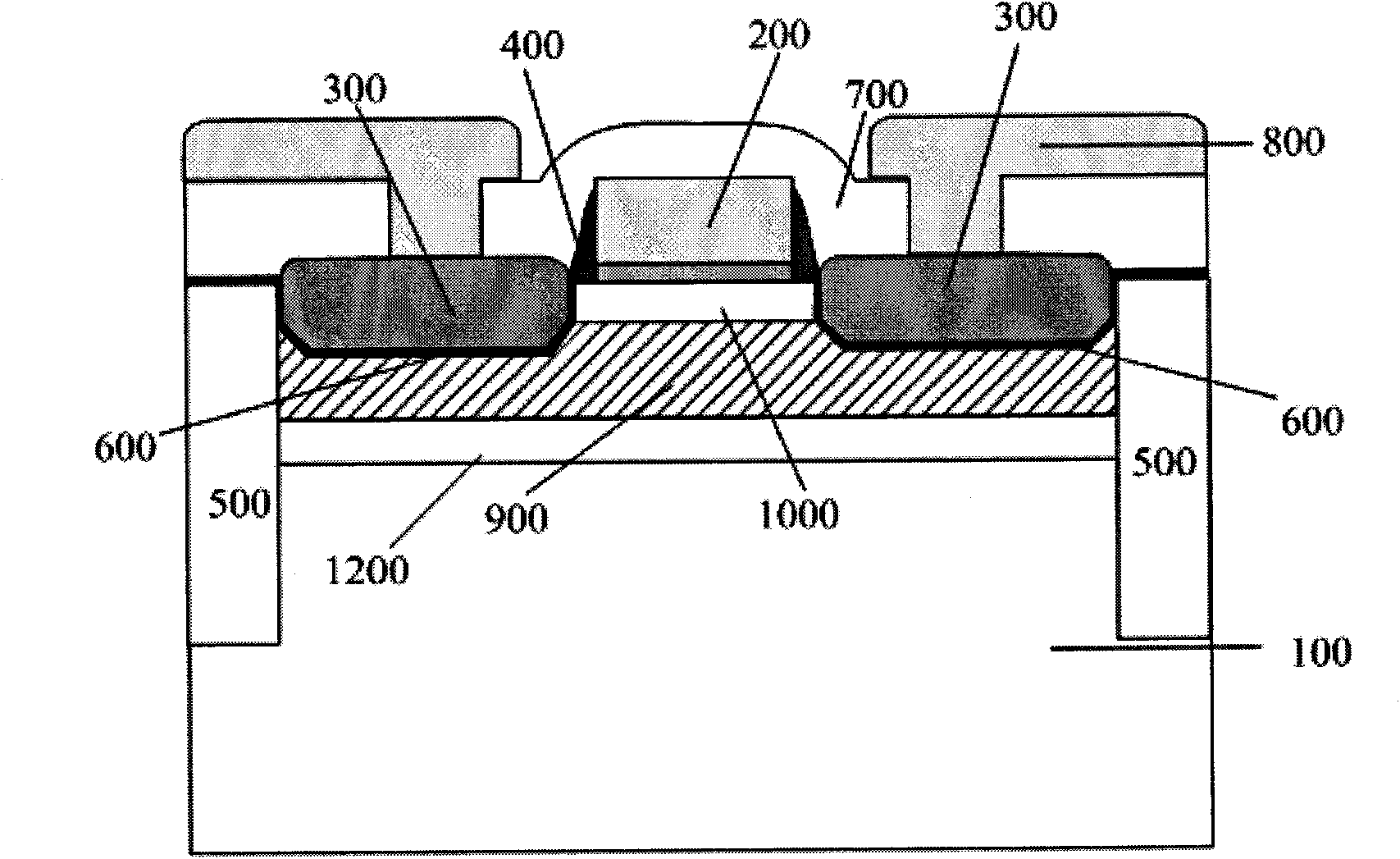

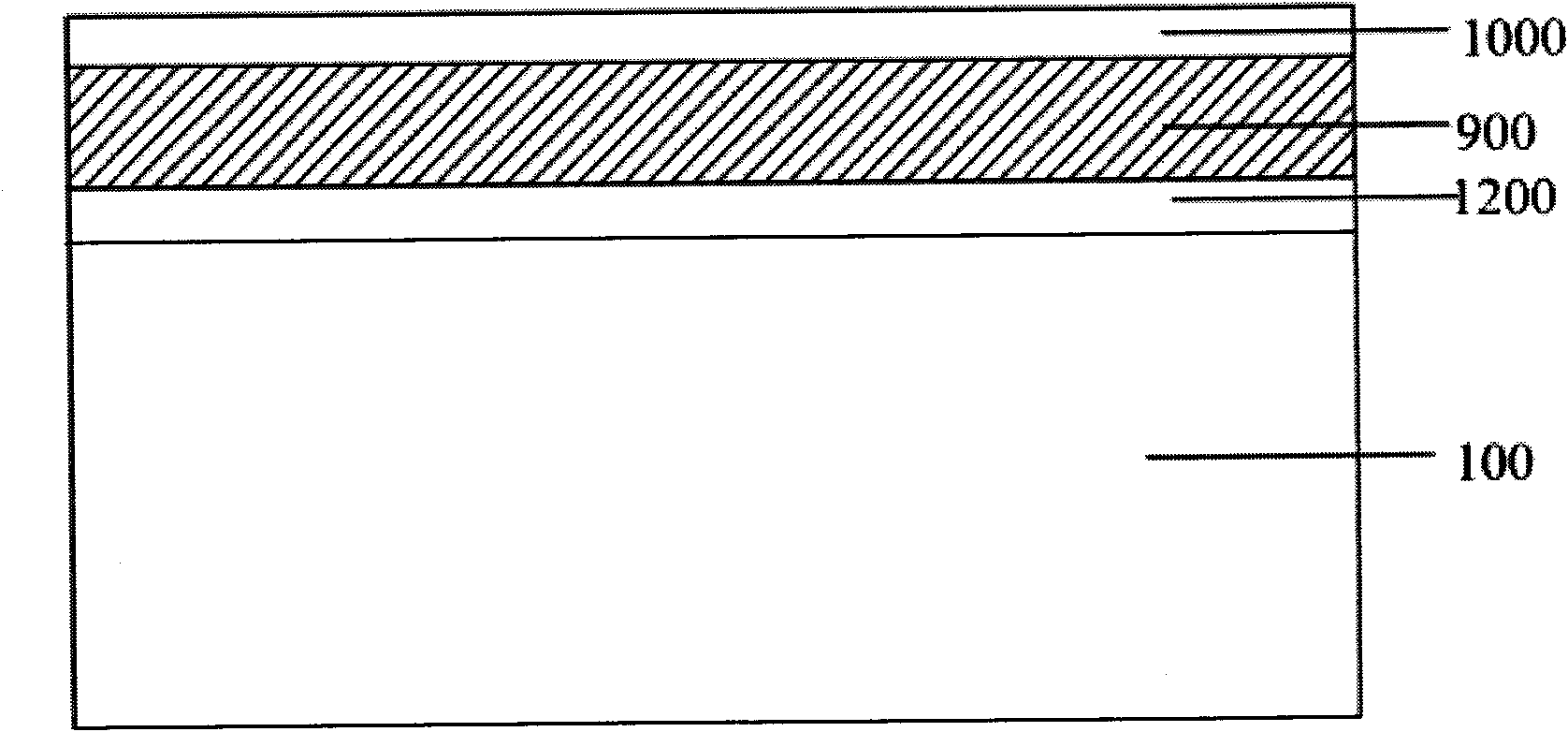

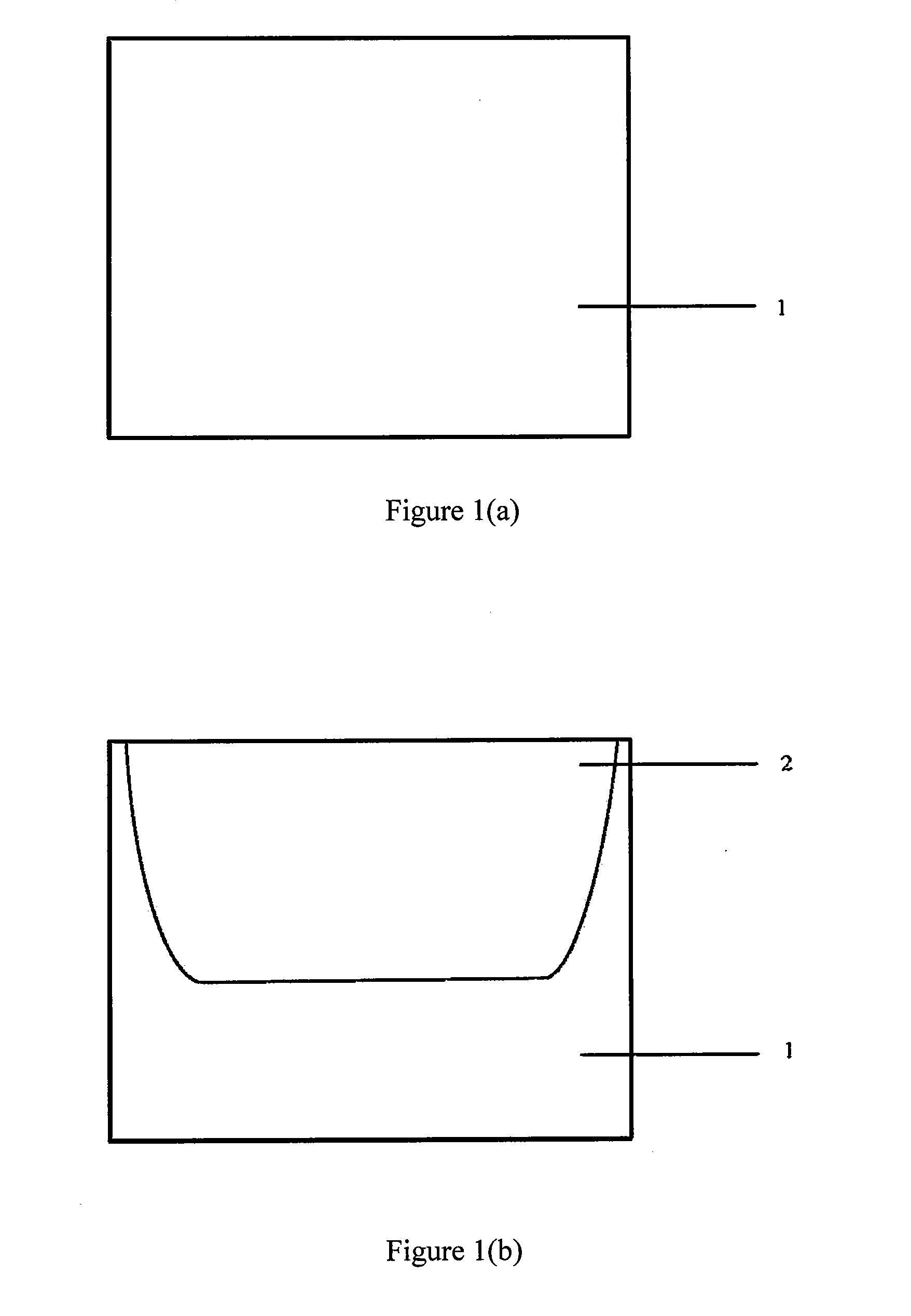

Germanium-based NMOS (N-metal-oxide-semiconductor) device and preparation method thereof

ActiveCN102222687AHigh switching current ratioSmall subthreshold slopeSemiconductor/solid-state device manufacturingSemiconductor devicesHafniumOxygen

The invention provides a germanium-based NMOS (N-metal-oxide-semiconductor) device and a preparation method thereof, belonging to the technical field of ultra large scale integration (ULSI) circuit manufacturing. Two layers of insulation medium material are inserted among metal source and drain electrodes and a substrate of the germanium based-NMOS device, and the bottom layer is S medium material with high pinning coefficient, such as hafnium oxide, silicon nitride or hafnium silica, and the upper layer of medium material is delta EC medium material with low conduction band offset, such as titanium dioxide, gallium oxide or strontium titanium oxygen. According to the invention, the fermi energy level pinning effect can be weakened, the electronic potential barrier is reduced, and furtherthe performances of a germanium-based schottky NMOS device are improved; and compared with the traditional method in which a single layer of insulation medium material such as AL2O3 is adopted, the preparation method can be used for effectively reducing the schottky potential barrier and maintaining lower source and drain resistance, therefore, the performances of the device are improved to a large extent.

Owner:SEMICON MFG INT (BEIJING) CORP +1

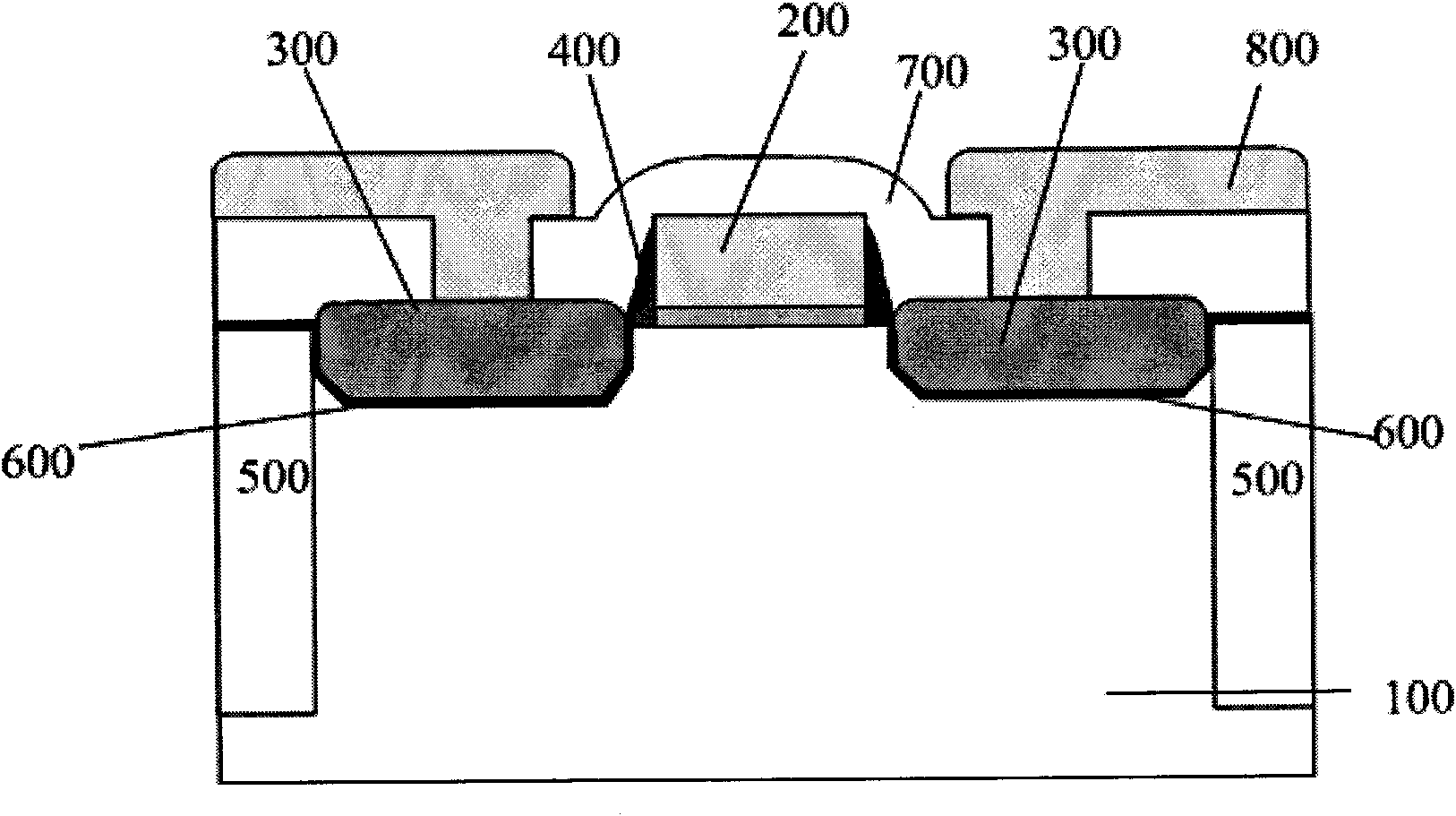

Low Schottky barrier semiconductor structure and formation method thereof

ActiveCN101866953ALower barrier heightHigh switching current ratioSemiconductor/solid-state device manufacturingSemiconductor devicesSwitched currentSemiconductor structure

The invention provides a low Schottky barrier semiconductor structure. The semiconductor structure comprises a substrate, a gate stack, one or more layers of side walls, metal source and drain electrodes and an insulating layer film, wherein the gate stack is formed on the substrate, the one or more layers of side walls are located at two sides of the gate stack, the metal source and drain electrodes are formed at two sides of the gate stack and located in the substrate, and the insulating layer film is located between the substrate and the metal source and drain electrodes. Through the embodiment of the invention, the insulating layer film formed between the substrate and the metal source and drain electrodes can prevent the band gap state caused by the metal source and drain electrodes from entering a channel, thereby the Fermi energy level pinning phenomenon is relieved, the Schottky barrier height is reduced, and the switching current ratio of a transistor is increased.

Owner:TSINGHUA UNIV

Preparation method of germanium-based Schottky N-type field effect transistor

ActiveCN102136428ADoes not significantly increase parasitic resistanceIncrease the current switch ratioSemiconductor/solid-state device manufacturingSemiconductor devicesField-effect transistorSchottky transistor

The invention provides a preparation method of a germanium-based Schottky N-type field effect transistor, belonging to the technical field of technical manufacturing of ultra large scale integrations (ULSI). In the preparation method, a high-k medium thin layer is formed among a germanium substrate, a metal source and a metal drain. On one hand, the thin layer can prevent an electron wave function in metal from introducing an MIGS (Metal Induction Gap Strip) interface state into a semiconductor forbidden band and can passivate a dangling bond of a germanium interface; and on the other hand, an insulating medium layer is very thin and electrons can freely pass through the insulating medium layer basically, so that the parasitic resistances of the source and the drain cannot be increased remarkably. By adopting the method, the Fermi level pinning effect can be wakened, the Fermi level is close to the conduction band position of germanium, and the electronic barrier is lowered, therefore, the electric current on-off ratio of the germanium-based Schottky transistor is increased, and the performance of an NMOS (Negative Channel Metal Oxide Semiconductor) device is improved.

Owner:SEMICONDUCTOR MANUFACTURING INTERNATIONAL (BEIJING) CORP +1

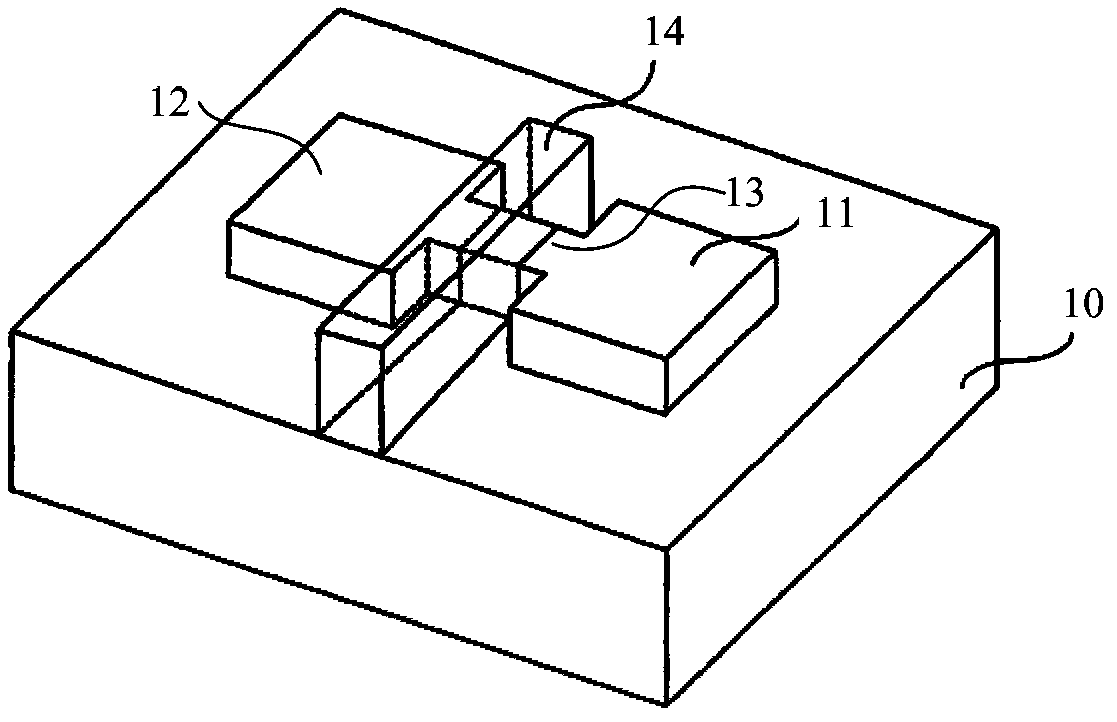

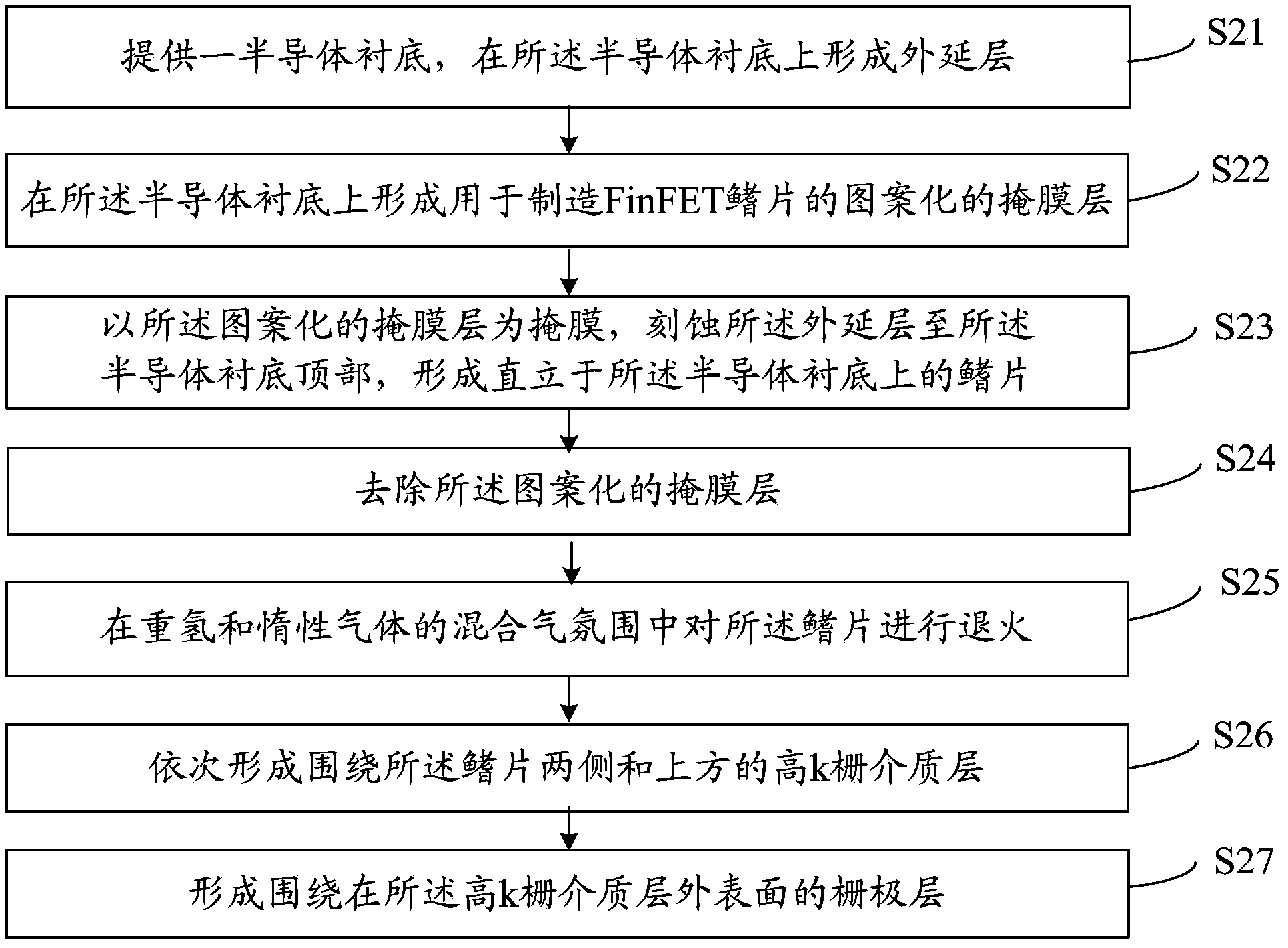

FinFET manufacturing method

InactiveCN103515223AImprove Fermi level pinning problemReduce the number of defectsSemiconductor/solid-state device manufacturingSemiconductor devicesGate dielectricOxygen vacancy

The invention provides a FinFET manufacturing method. Before or after a step of forming a high-k gate dielectric layer surrounding the two sides and the upper side of a fin, the fin is annealed in a mixed atmosphere of heavy hydrogen and inert gas, dangling bonds of silicon in the fin are eliminated, induced band gap state or oxygen vacancy at a fin interface are reduced, the problem of Fermi energy level pinning in the high-k dielectric layer is improved, and the fin interface is smoothed, thereby reducing the number of defects in the high-k dielectric layer, suppressing the charge trap effect, improving the threshold voltage drift and improving the performance of FinFET devices.

Owner:SEMICON MFG INT (SHANGHAI) CORP

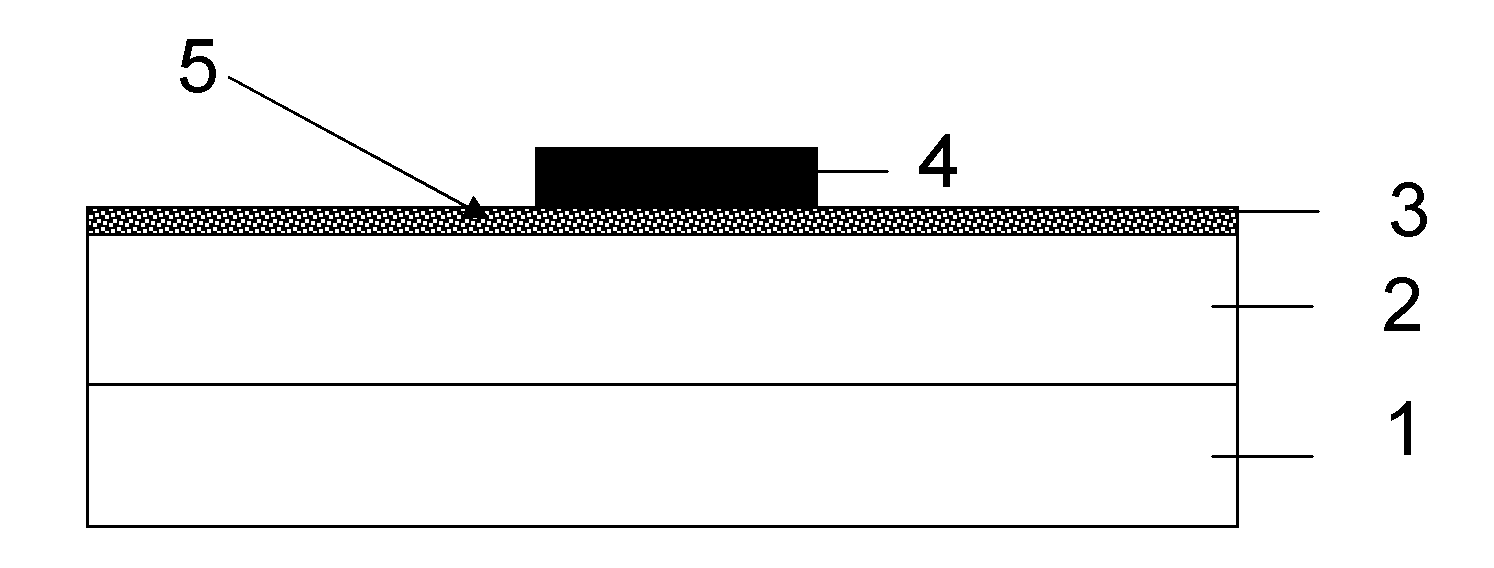

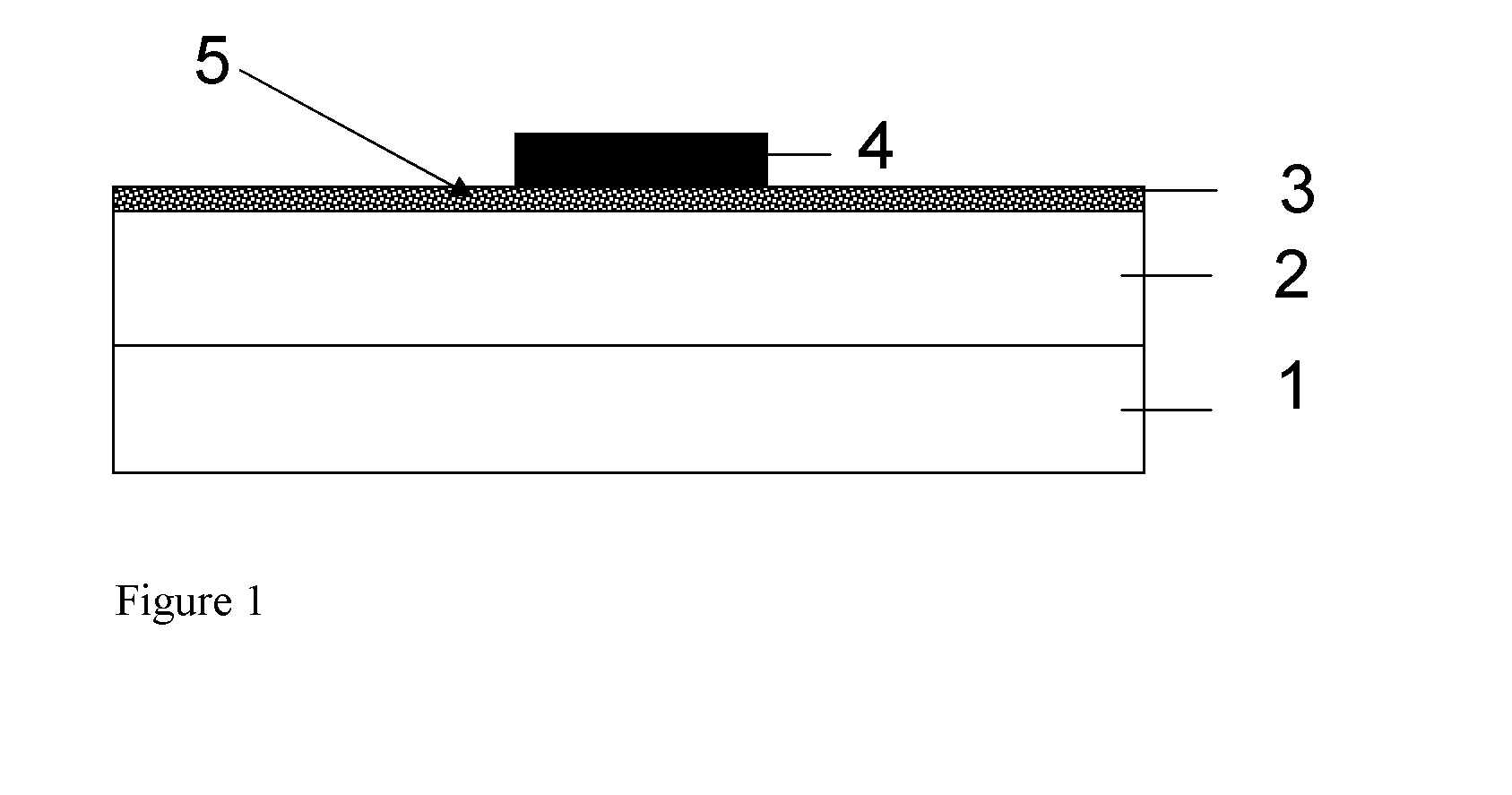

OLED backplane structure and method for OLED backplane

ActiveCN108091674ALower on-resistanceOmit annealingSolid-state devicesSemiconductor/solid-state device manufacturingWhole bodyContact resistance

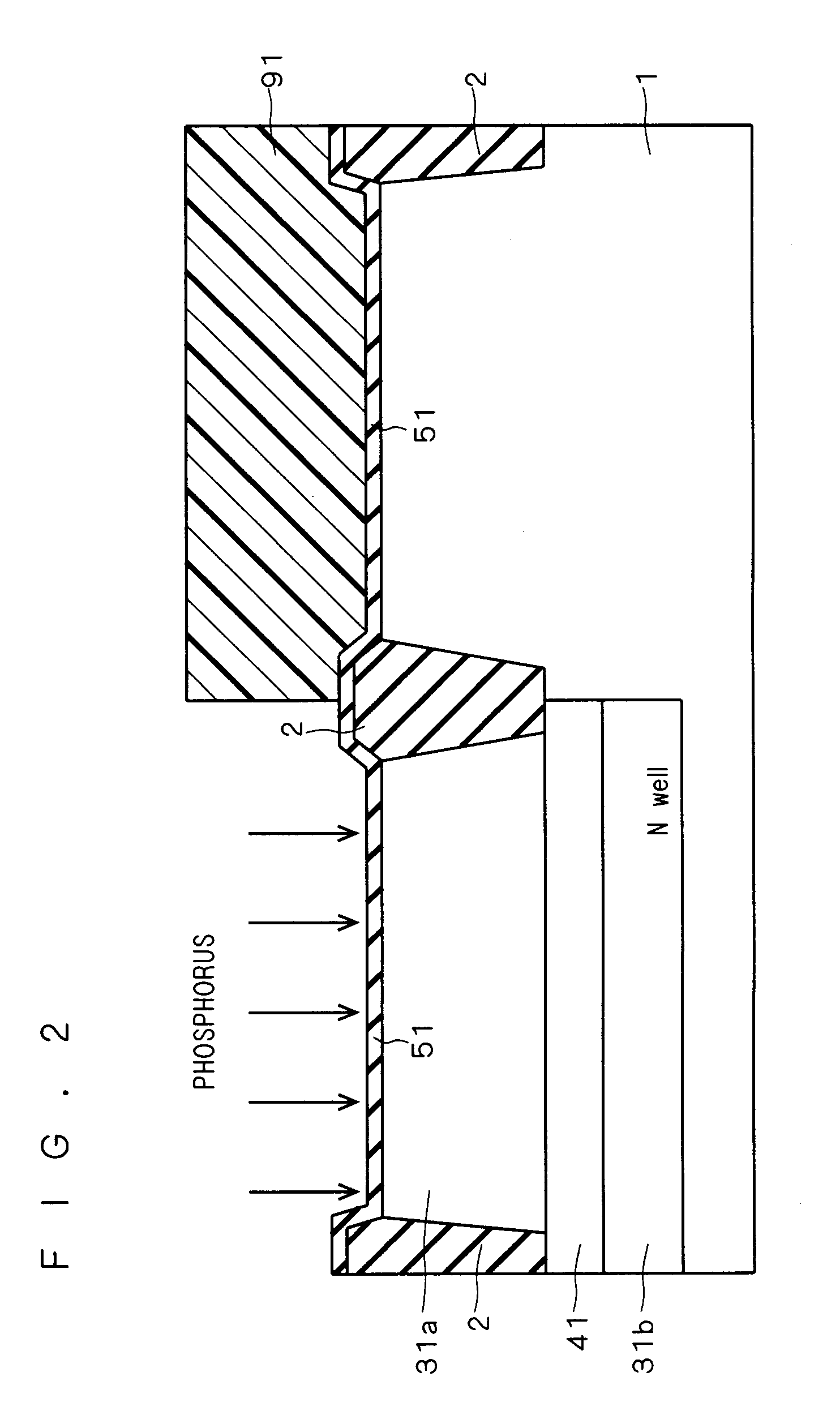

The invention provides an OLED backplane structure and a method for manufacturing the OLED backplane. The OLED backplane structure is provided with a composite electrode (5). On one hand, the materialof the contact part (51) of the composite electrode (5) in contact with a semiconductor layer (111) of a thin film transistor (11) is conductive metal oxide. While the Fermi level pinning effect between a metal and a semiconductor is reduced, a large series resistance is not caused, and the contact resistance of the metal and the semiconductor can be greatly reduced. On the other hand, an anode and a drain electrode of the thin film transistor (11) are integrated to be a whole body, the contact resistance between the anode and the drain electrode of the thin film transistor (11) is eliminated, thus the on-resistance of an OLED display can be greatly reduced, and the power consumption is reduced.

Owner:WUHAN CHINA STAR OPTOELECTRONICS SEMICON DISPLAY TECH CO LTD

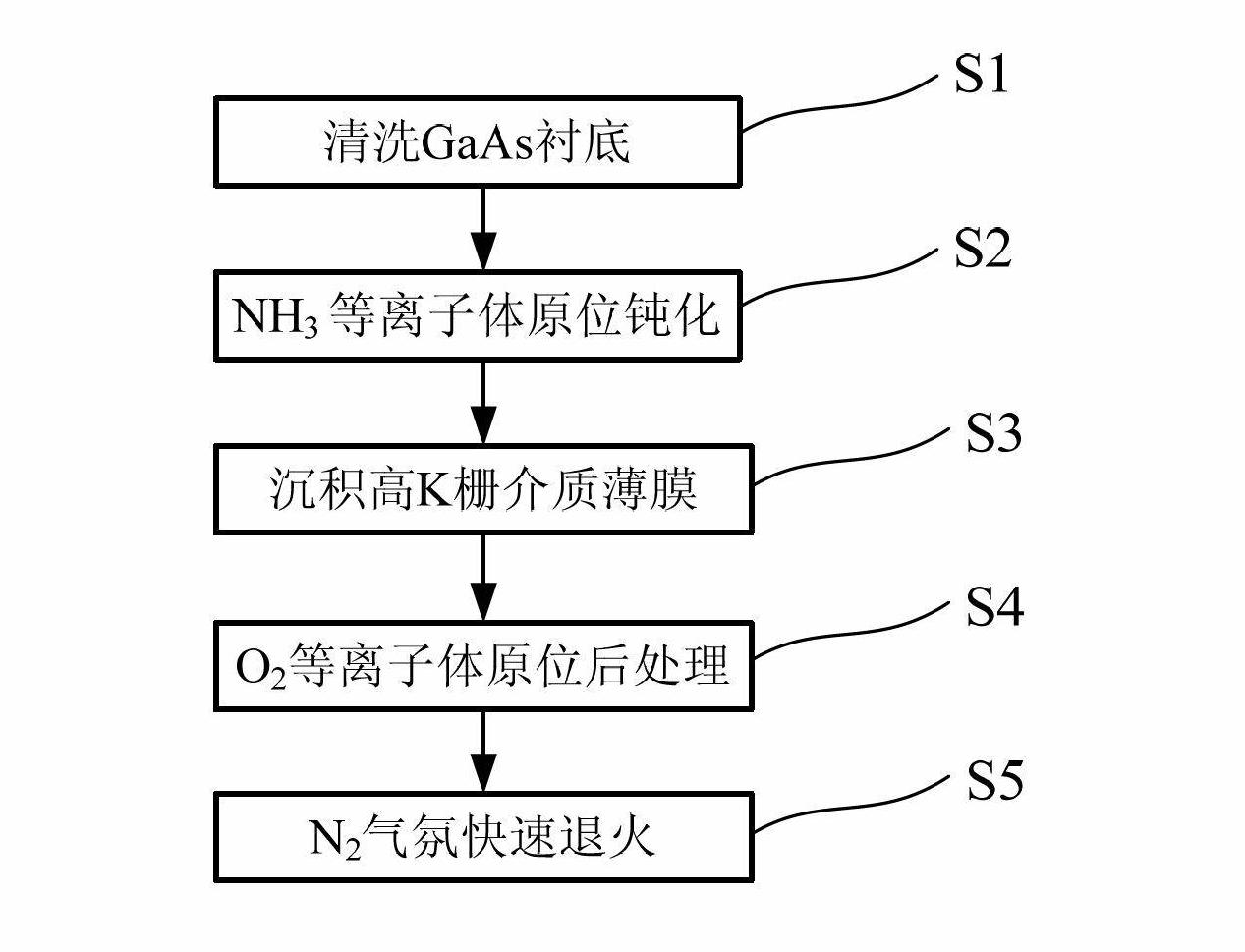

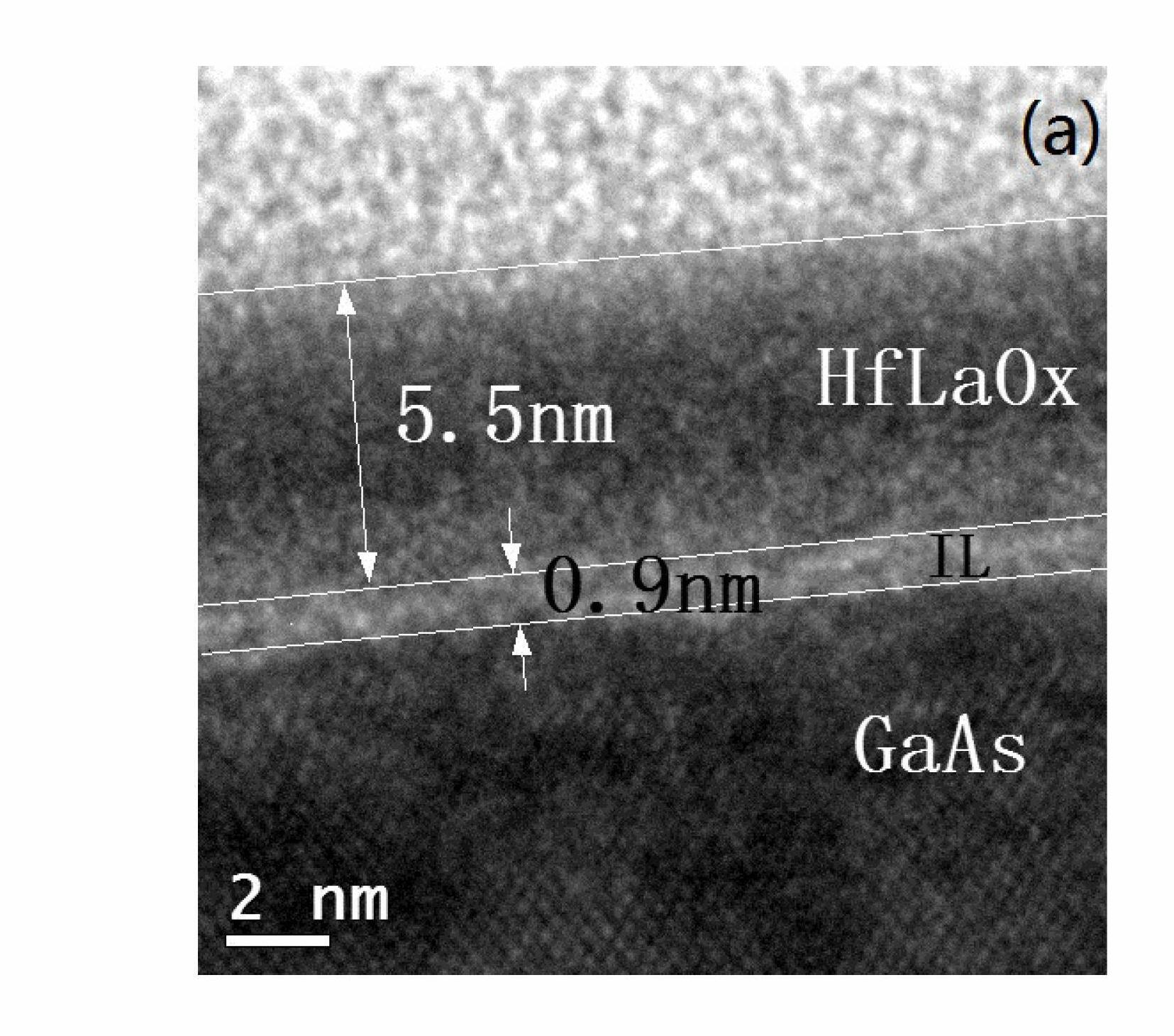

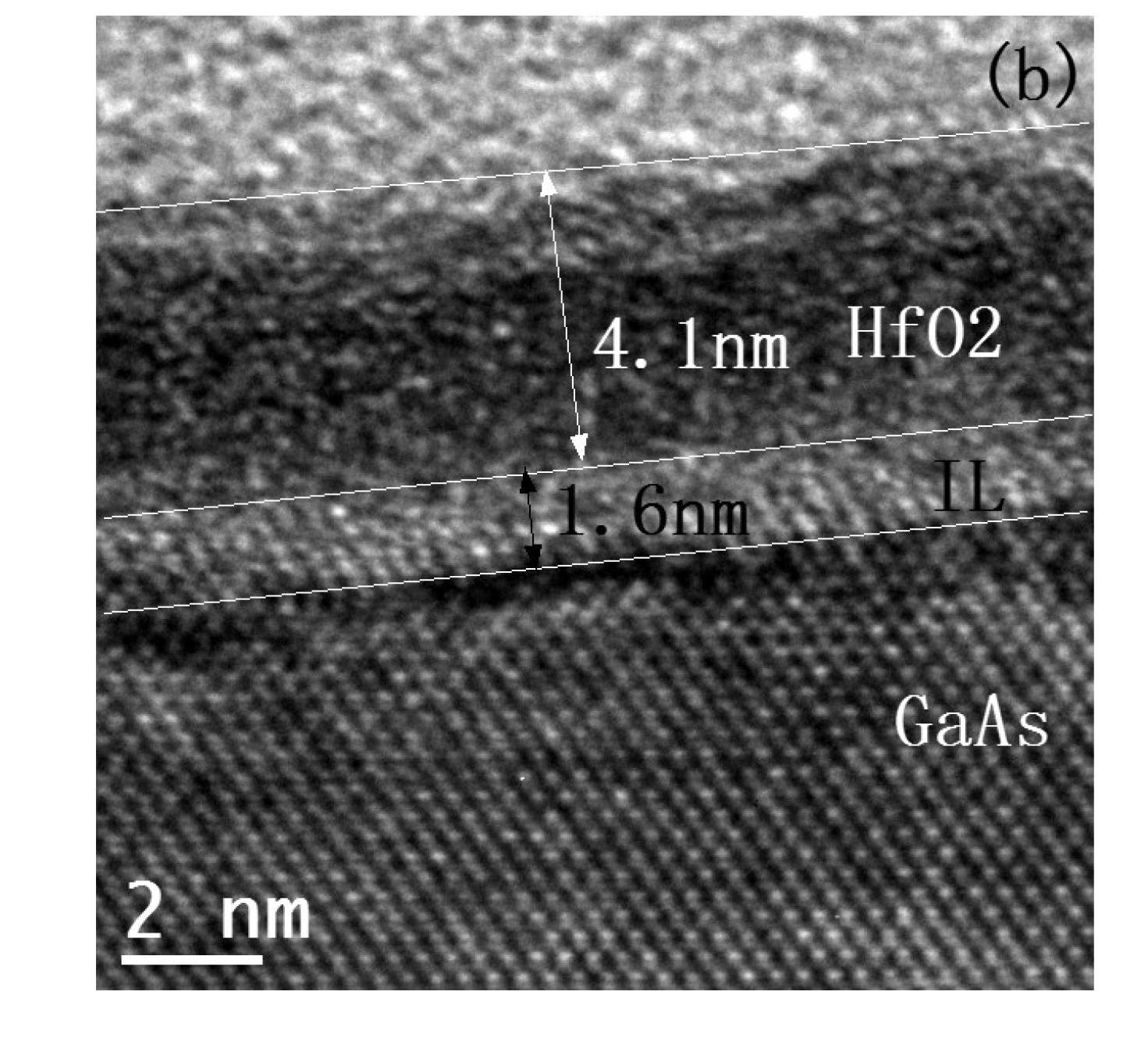

Method for preparing Hf-based high-K gate dielectric film on GaAs substrate

InactiveCN102664147AImprove compactnessImprove film qualitySemiconductor/solid-state device manufacturingDielectricGate dielectric

The invention discloses a method for preparing an Hf-based high-K dielectric film on a GaAs substrate. The method comprises the following steps of: firstly providing a GaAs wafer as a substrate, cleaning the substrate, and placing the cleaned GaAs substrate wafer into an ALD (Atomic Layer Deposition) reaction cavity; then carrying out plasma in-situ pretreatment on the GaAs substrate by utilizing plasma, and then despoisting a high-K gate dielectric film; and finally carrying out in-situ aftertreatment on the high-K gate dielectric film by adopting oxygen plasma. According to the method disclosed by the invention, the GaAs substrate is passivated by virtue of the plasma in-situ pretreatment before the high-K gate dielectric film is deposited, interface characteristic between the high-K gate dielectric and the GaAs substrate is improved, influence of Fermi level pinning effect is reduced, and density and quality of the high-K film are improved by virtue of the oxygen plasma in-situ aftertreatment after the high-K gat dielectric film is formed.

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI

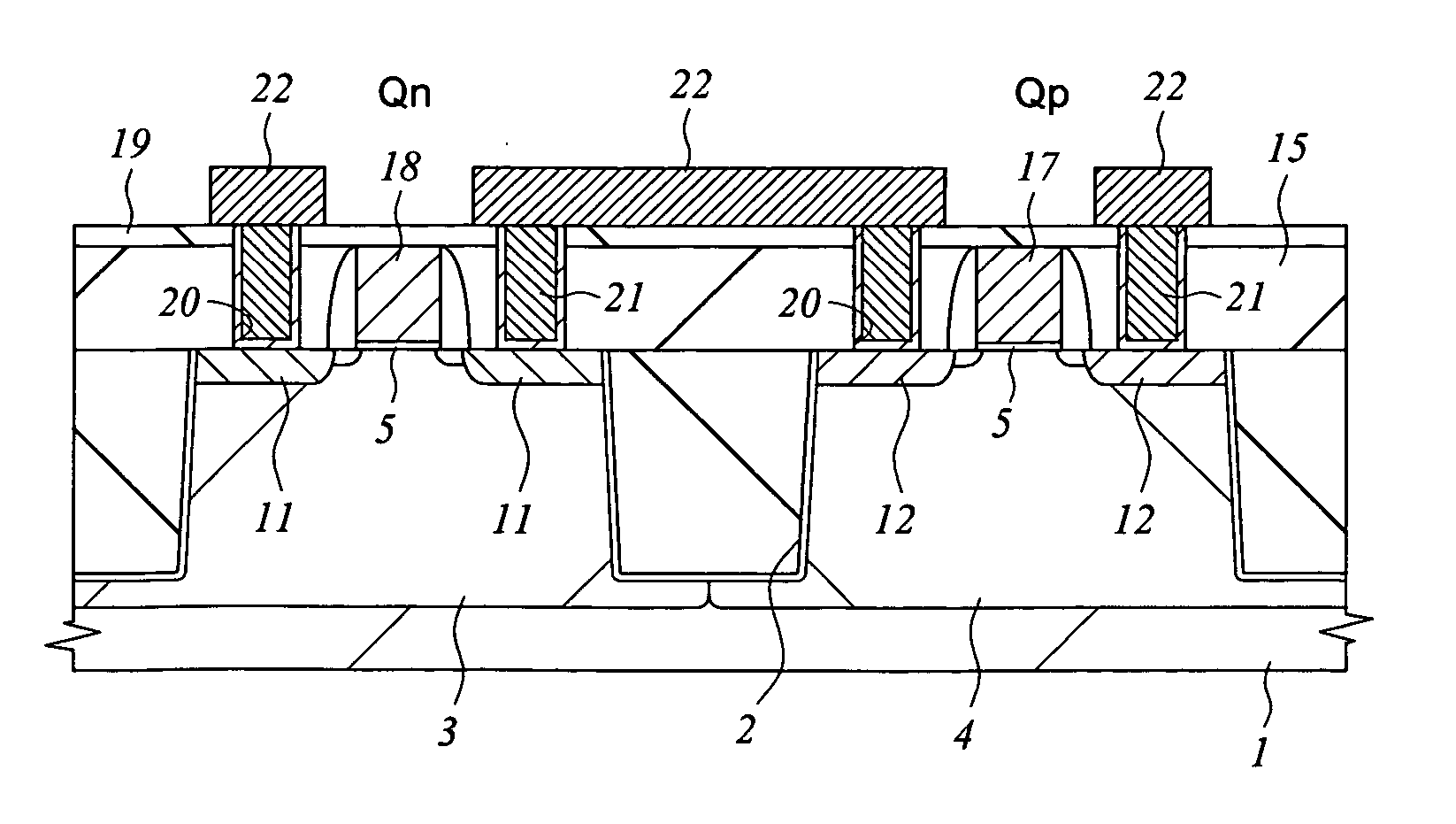

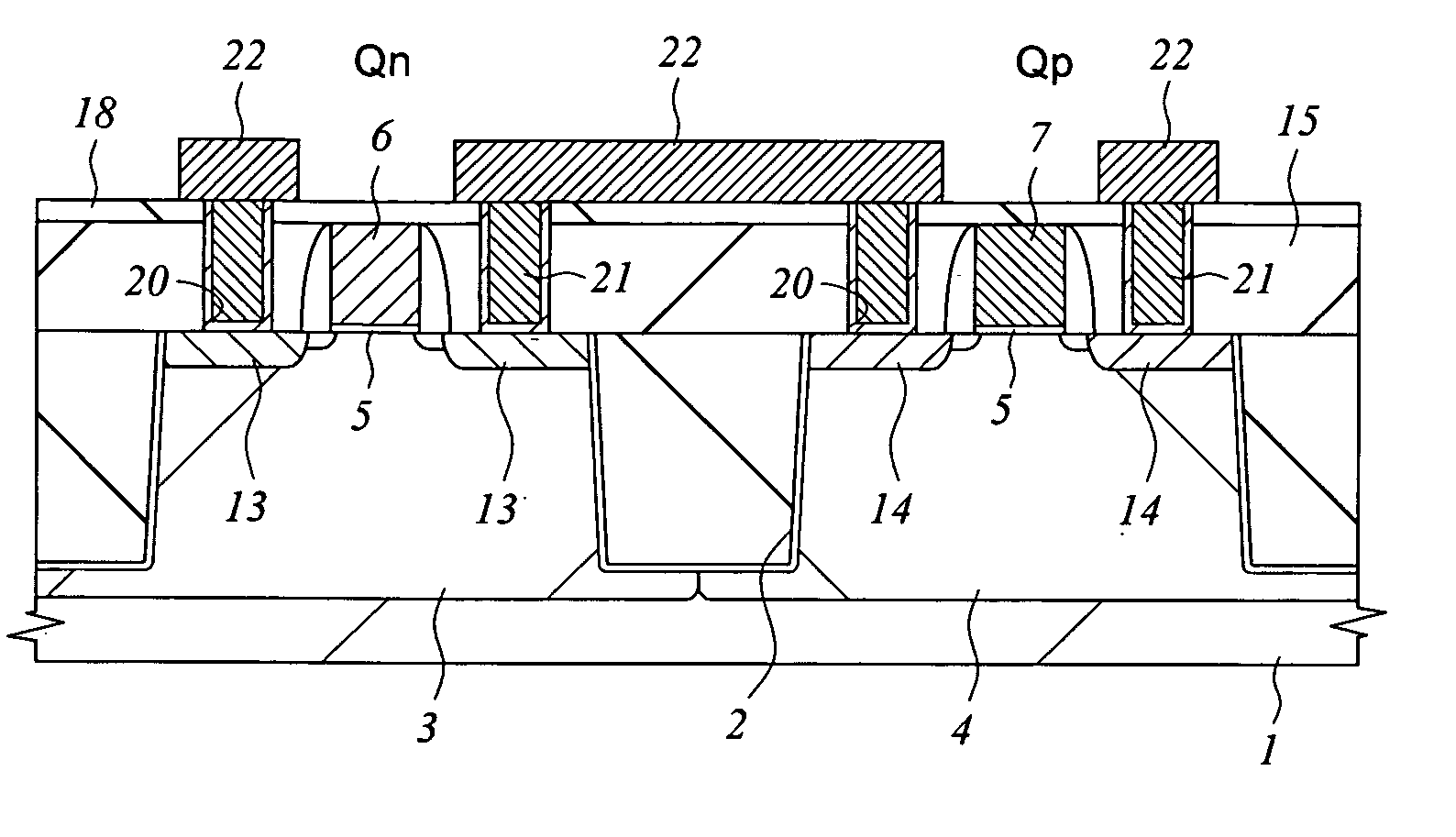

Semiconductor device and manufacturing method thereof

ActiveUS20060051915A1High currentReduce power consumptionSemiconductor/solid-state device manufacturingSemiconductor devicesDevice materialP channel

A structure of a MIS transistor for realizing a CMOS circuit capable of simultaneously achieving the high ON current and the low power consumption is provided. Each of the gate insulators of an n channel MIS transistor and a p channel MIS transistor is composed of a hafnium oxide (HfO2) film. Also, the gate electrode of the n channel MIS transistor is composed of an Ni (nickel) silicide film, and the gate electrode of the p channel MIS transistor is composed of a Pt (platinum) film. In this structure, Fermi level pinning of the gate electrodes can be prevented. Therefore, the increase of the threshold voltage of the n channel MIS transistor and the p channel MIS transistor can be inhibited.

Owner:RENESAS ELECTRONICS CORP

Method for reducing Fermi-Level-Pinning in a non-silicon channel MOS device

InactiveUS8524562B2Lowering the Fermi levelReduce FLPSemiconductor/solid-state device manufacturingSemiconductor devicesGate dielectricHydrogen

A method to reduce (avoid) Fermi Level Pinning (FLP) in high mobility semiconductor compound channel such as Ge and III-V compounds (e.g. GaAs or InGaAs) in a Metal Oxide Semiconductor (MOS) device. The method is using atomic hydrogen which passivates the interface of the high mobility semiconductor compound with the gate dielectric and further repairs defects. The methods further improve the MOS device characteristics such that a MOS device with a quantum well is created.

Owner:INTERUNIVERSITAIR MICRO ELECTRONICS CENT (IMEC VZW)

Germanium-based nmos device and method for fabricating the same

InactiveUS20130069126A1On-off ratio can be increasedLittle resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesSilicon oxideHafnium

An embodiment of the invention provides a germanium-based NMOS device and a method for fabricating the same, which relates to fabrication process technology of an ultra-large-scale-integrated (ULSI) circuit. The germanium-based NMOS device has two dielectric layer interposed between a metal source / drain and a substrate. The bottom dielectric layer includes a dielectric material having a high pinning coefficient S such as hafnium oxide, silicon nitride, hafnium silicon oxide or the like, and the top dielectric layer includes a dielectric material having a low conduction band offset ΔEC such as titanium oxide, gallium oxide, strontium titanium oxide or the like. According to the method, Fermi level pinning effect can be alleviated, electron barrier height can be lowered, and thus performance of the germanium-based Schottky NMOS device can be improved. Compared with a conventional single dielectric layer such as aluminum oxide (Al2O3), Schottky barrier height can be lowered while low source / drain resistances can be maintained, and thus performance of the device can be significantly improved.

Owner:PEKING UNIV

Semiconductor device and manufacturing method thereof

ActiveUS7323381B2Raise the threshold voltageIncrease the on-currentSemiconductor/solid-state device manufacturingSemiconductor devicesP channelSilicide

A structure of a MIS transistor for realizing a CMOS circuit capable of simultaneously achieving the high ON current and the low power consumption is provided. Each of the gate insulators of an n channel MIS transistor and a p channel MIS transistor is composed of a hafnium oxide (HfO2) film. Also, the gate electrode of the n channel MIS transistor is composed of an Ni (nickel) silicide film, and the gate electrode of the p channel MIS transistor is composed of a Pt (platinum) film. In this structure, Fermi level pinning of the gate electrodes can be prevented. Therefore, the increase of the threshold voltage of the n channel MIS transistor and the p channel MIS transistor can be inhibited.

Owner:RENESAS ELECTRONICS CORP

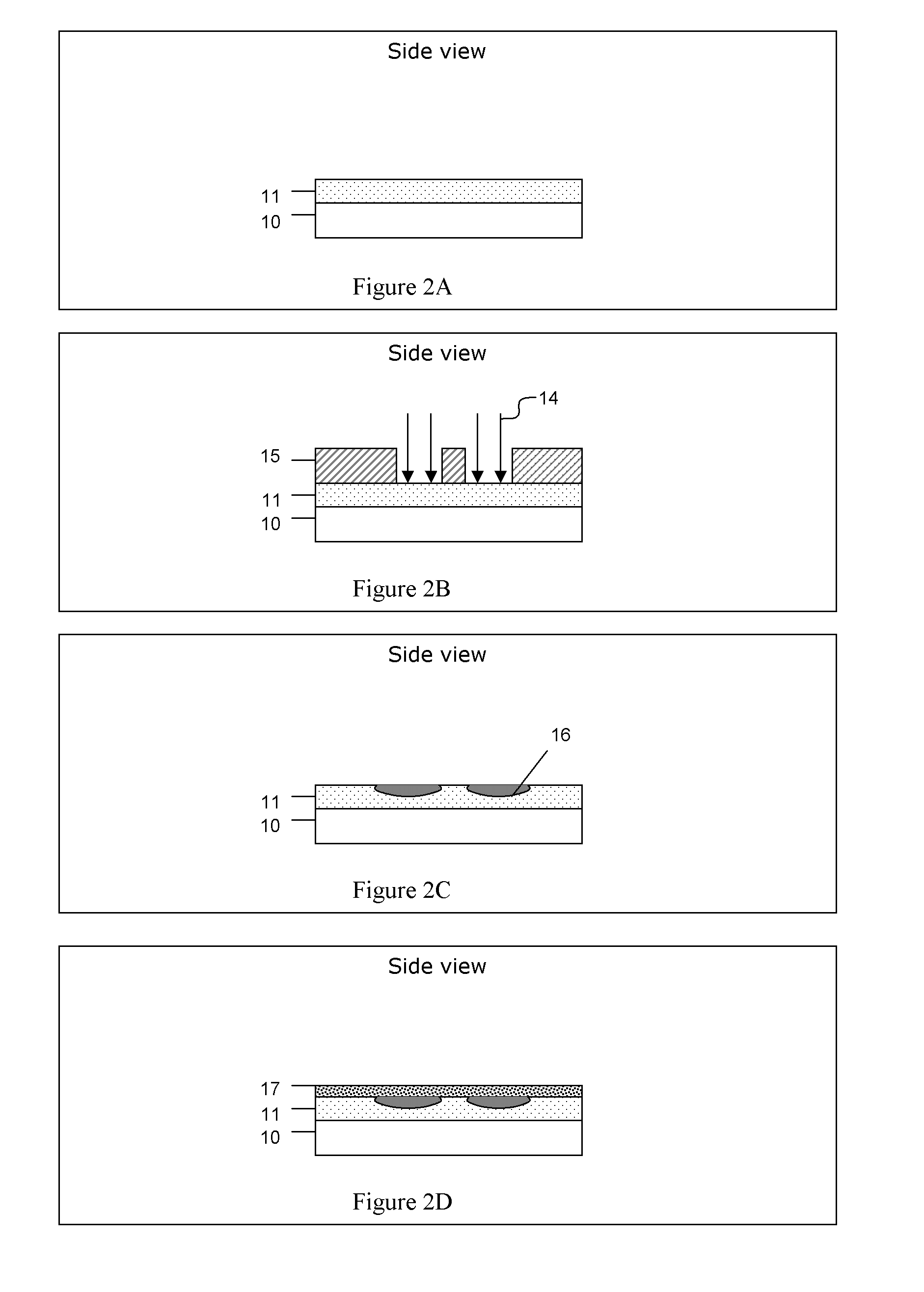

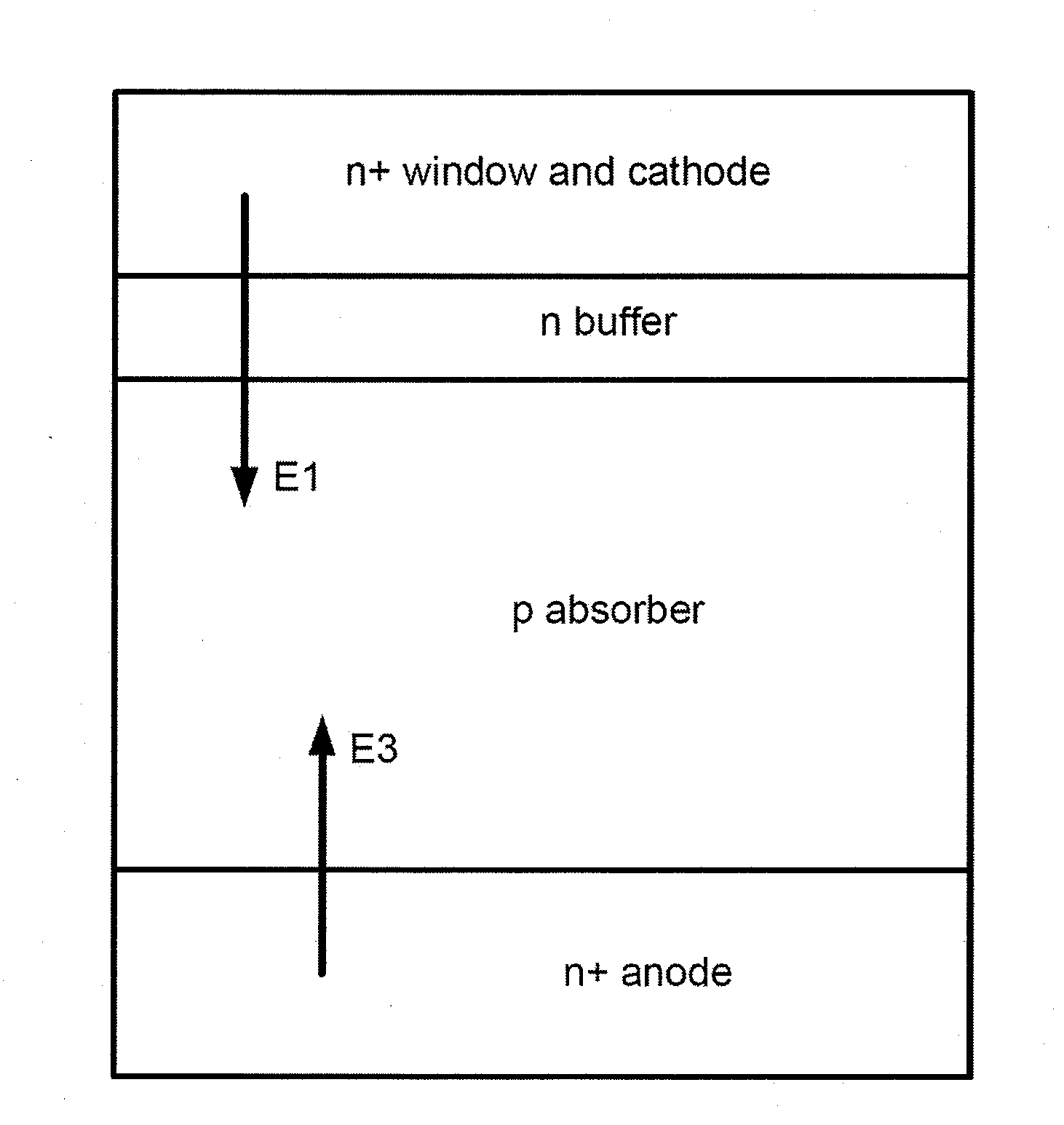

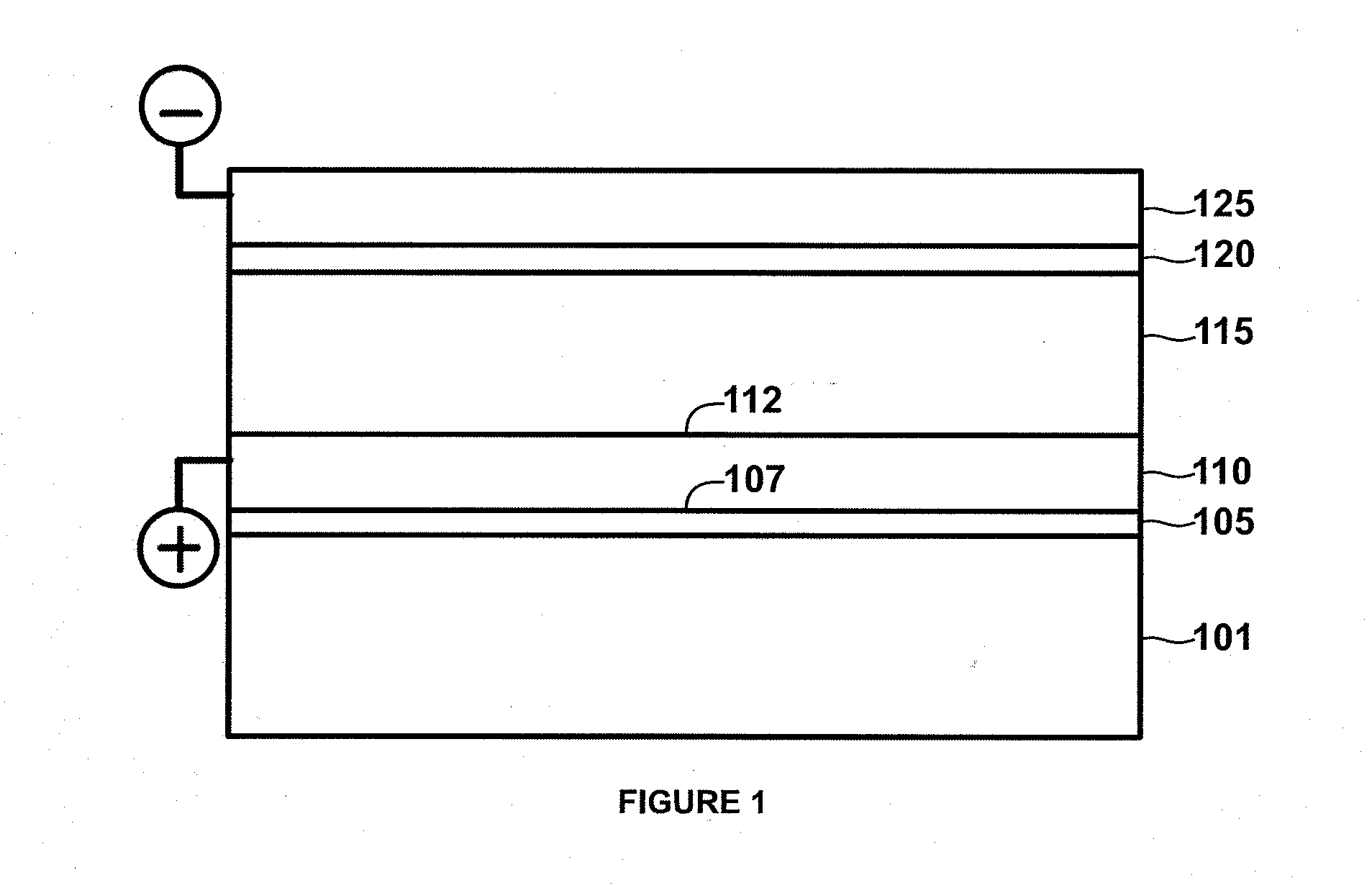

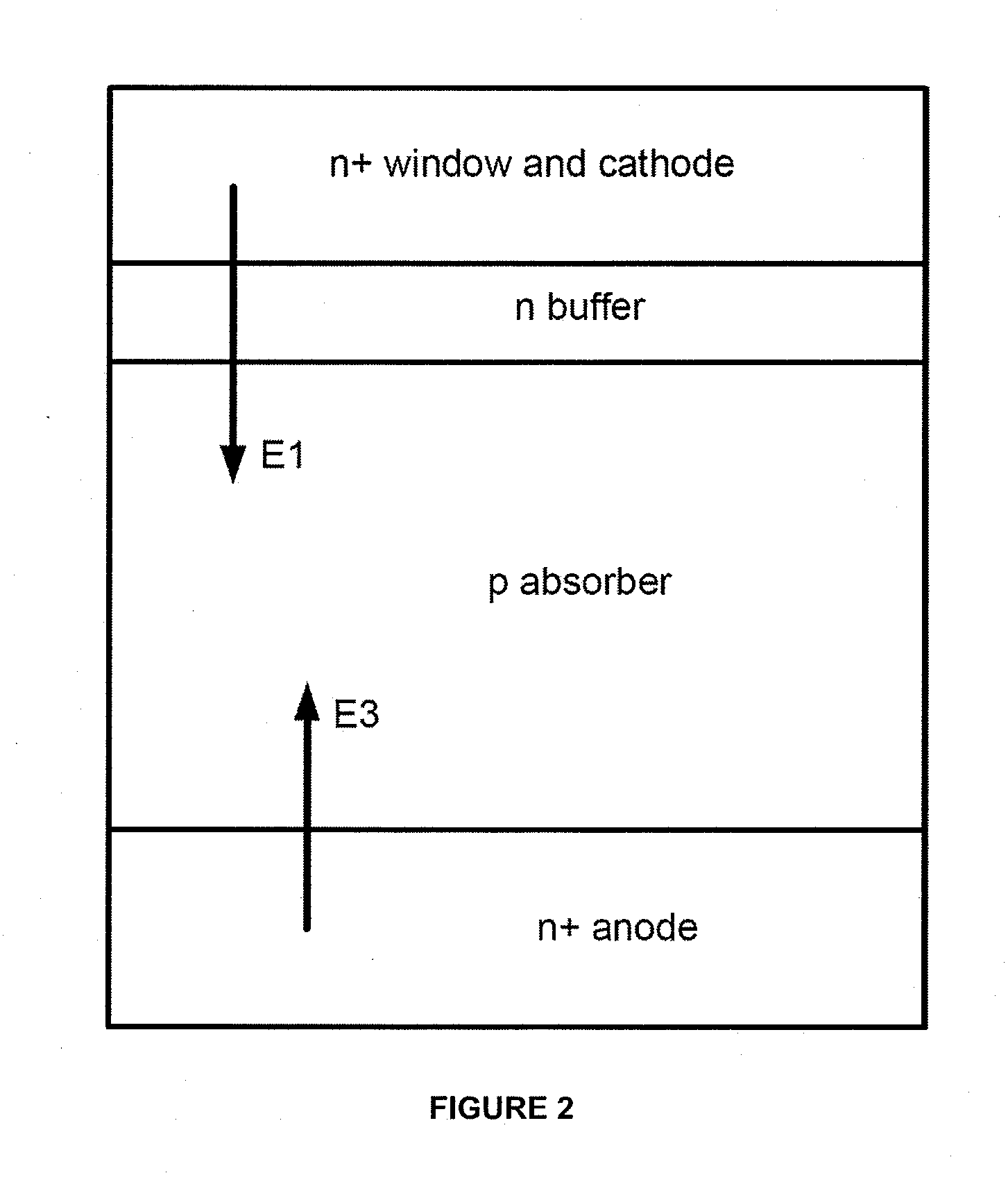

Method and Device Utilizing Strained AZO Layer and Interfacial Fermi Level Pinning in Bifacial Thin Film PV Cells

InactiveUS20110220198A1Reduce electric field strengthEasy tunnelingSemiconductor/solid-state device manufacturingPhotovoltaic energy generationInter layerAluminum doped zinc oxide

A method for forming a bifacial thin film photovoltaic cell includes providing a glass substrate having a surface region covered by an intermediate layer and forming a thin film photovoltaic cell on the surface region. Additionally, the thin film photovoltaic cell includes an anode overlying the intermediate layer, an absorber over the anode, and a window layer and cathode over the absorber mediated by a buffer layer. The anode comprises an aluminum doped zinc oxide (AZO) layer forming a first interface with the intermediate layer and a second interface with the absorber. The AZO layer is configured to induce Fermi level pinning at the first interface and a strain field from the first interface to the second interface.

Owner:CM MFG

Semiconductor device and method for manufacturing it

ActiveCN1815755ASemiconductor/solid-state device manufacturingSemiconductor devicesDielectricEquivalent oxide thickness

Owner:TAIWAN SEMICON MFG CO LTD

Nanowhiskers with PN junctions, doped nanowhiskers, and methods for preparing them

ActiveUS20090014711A1Reduce the amount requiredPolycrystalline material growthNanoinformaticsHeterojunctionNon doped

Nano-engineered structures are disclosed, incorporating nanowhiskers of high mobility conductivity and incorporating pn junctions. In one embodiment, a nanowhisker of a first semiconducting material has a first band gap, and an enclosure comprising at least one second material with a second band gap encloses said nanoelement along at least part of its length, the second material being doped to provide opposite conductivity type charge carriers in respective first and second regions along the length of the of the nanowhisker, whereby to create in the nanowhisker by transfer of charge carriers into the nanowhisker, corresponding first and second regions of opposite conductivity type charge carriers with a region depleted of free carriers therebetween. The doping of the enclosure material may be degenerate so as to create within the nanowhisker adjacent segments having very heavy modulation doping of opposite conductivity type analogous to the heavily doped regions of an Esaki diode. In another embodiment, a nanowhisker is surrounded by polymer material containing dopant material. A step of rapid thermal annealing causes the dopant material to diffuse into the nanowhisker. In a further embodiment, a nanowhisker has a heterojunction between two different intrinsic materials, and Fermi level pinning creates a pn junction at the interface without doping.

Owner:QUNANO

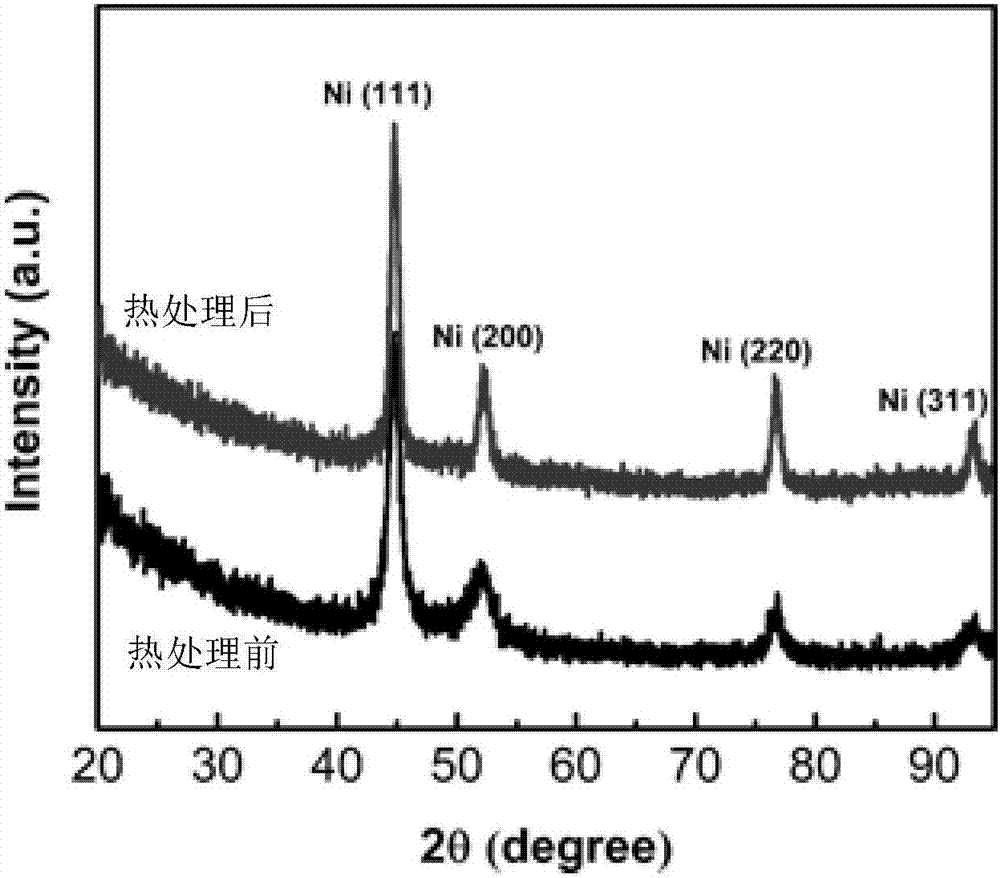

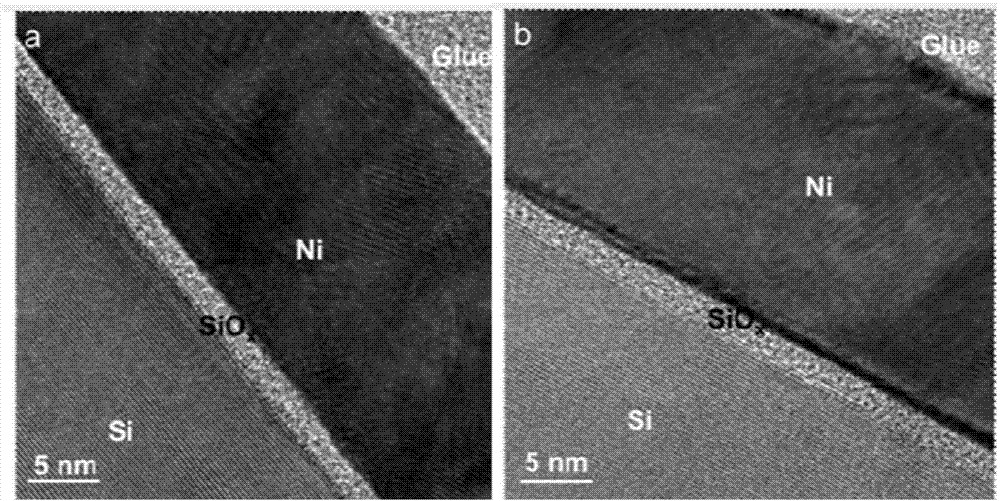

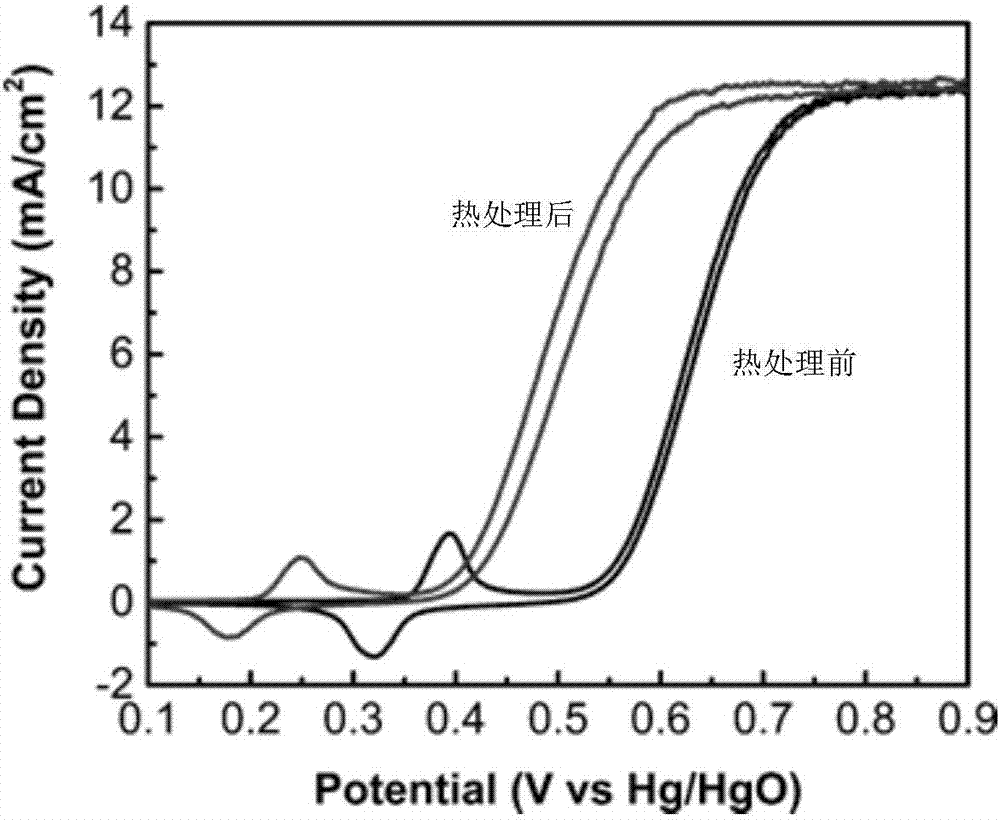

Method for reducing photoelectrochemistry water decomposition starting potential of Ni/n-Si photo-anode

ActiveCN107513723ALower interface stateImprove developmentEnergy inputElectrodesDecompositionPhotoelectrochemistry

The invention discloses a method for reducing the photoelectrochemistry water decomposition starting potential of a Ni / n-Si photo-anode. A simple rapid heat treatment process is conducted on the prepared Ni / n-Si photo-anode, the interface states existing between Ni / n-Si interfaces are reduced, the Fermi level pinning effect caused by the interface states is released, the schottky barrier height formed by Ni / n-Si is increased, accordingly the Ni / n-Si photo-anode generates the higher photovoltage during illumination, and finally the photoelectrochemistry water decomposition starting potential of the Ni / n-Si photo-anode is reduced. The method for reducing the photoelectrochemistry water decomposition starting potential of the Ni / n-Si photo-anode is easy to operate, low in cost and suitable for being applied to a metal / n-Si photo-anode system on a large scale, and positive significance is achieved for promoting development and application of the photoelectrochemistry water decomposition technology.

Owner:TECHNICAL INST OF PHYSICS & CHEMISTRY - CHINESE ACAD OF SCI

Methods of enabling polysilicon gate electrodes for high-k gate dielectrics

ActiveUS7416933B2Semiconductor/solid-state device manufacturingSemiconductor devicesInterfacial oxideDielectric

Complementary transistors and methods of forming the complementary transistors on a semiconductor assembly are described. The transistors are formed with an optional interfacial oxide, such as SiO2 or oxy-nitride, to overlay a semiconductor substrate which will be conductively doped for PMOS and NMOS regions. Then a dielectric possessing a high dielectric constant of least seven or greater (also referred to as a high-k dielectric) is deposited on the interfacial oxide. The high-k dielectric is covered with a thin monolayer of metal oxide (i.e., aluminum oxide, Al2O3) that is removed from the NMOS regions, but remains in the PMOS regions. The resulting NMOS transistor diffusion regions contain predominately metal to silicon bonds that create predominately Fermi level pinning near the valence band while the resulting PMOS transistor diffusion regions contain metal to silicon bonds that create predominately Fermi level pinning near the conduction band.

Owner:MICRON TECH INC

Methods of enabling polysilicon gate electrodes for high-k gate dielectrics

InactiveUS20060263962A1TransistorSemiconductor/solid-state device manufacturingDielectricInterfacial oxide

Complementary transistors and methods of forming the complementary transistors on a semiconductor assembly are described. The transistors are formed with an optional interfacial oxide, such as SiO2 or oxy-nitride, to overlay a semiconductor substrate which will be conductively doped for PMOS and NMOS regions. Then a dielectric possessing a high dielectric constant of least seven or greater (also referred to as a high-k dielectric) is deposited on the interfacial oxide. The high-k dielectric is covered with a thin monolayer of metal oxide (i.e., aluminum oxide, Al2O3) that is removed from the NMOS regions, but remains in the PMOS regions. The resulting NMOS transistor diffusion regions contain predominately metal to silicon bonds that create predominately Fermi level pinning near the valence band while the resulting PMOS transistor diffusion regions contain metal to silicon bonds that create predominately Fermi level pinning near the conduction band.

Owner:WEINER RONALD A

Surface passivation method for Ge

InactiveCN102005390APrevent re-oxidationElimination of Fermi level pinningSemiconductor/solid-state device manufacturingSemiconductorMaterials science

The invention belongs to the technical field of semiconductor manufacturing, and particularly discloses a surface passivation method for Ge. By adopting a thioacetamide (CH3CSNH2) solution to passivate a Ge sheet, the natural oxide on the surface of the Ge sheet can be removed, and an even and compact GeSx passivation layer can be generated to prevent the reoxidation of the surface of the Ge sheet and eliminate the Fermi level pinning. A layer of high-quality Al2O3 film is deposited on the passivated Ge sheet by adopting an atom layer deposition method to prevent the reoxidation of the surface of the Ge sheet, and therefore, a good Al2O3 / Ge interface can be obtained.

Owner:FUDAN UNIV

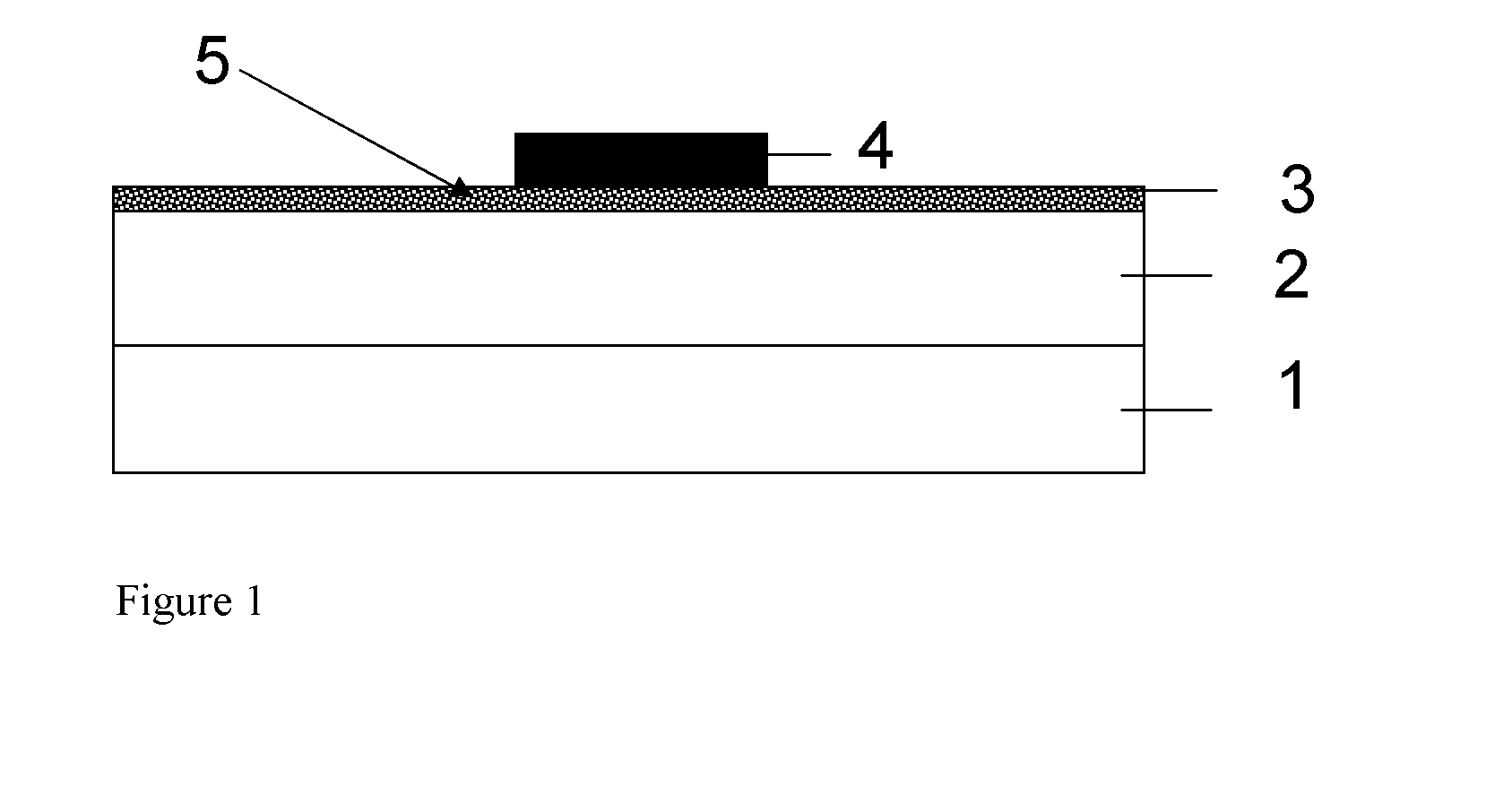

High performance flexible substrate thin film transistor and method

InactiveUS7772589B1Reduce interfaceSolid-state devicesSemiconductor/solid-state device manufacturingGate dielectricSemiconductor materials

A high performance thin film transistor includes a flexible substrate, a layer of metal oxide semiconductor material deposited on the flexible substrate, and a layer of self-assembled organic gate dielectric material deposited on the metal oxide semiconductor material. The metal oxide semiconductor material has high carrier mobility and is transparent. An interface is formed between the layer of metal oxide semiconductor material and the layer of organic gate dielectric material that is substantially free of reactions and Fermi level pinning. The polymer materials are not polar and do not give rise to gap state formation and interface scattering.

Owner:FULL STRENGTH GRP LTD

Silicon-based photoelectrode and preparation method and application thereof

ActiveCN109943857AImprove photoelectric performanceImprove electrocatalytic activityVacuum evaporation coatingSputtering coatingProtection layerFilm material

The invention relates to a silicon-based photoelectrode and a preparation method and application thereof. The silicon-based photoelectrode includes a Si layer, a passivation layer, a buffer layer anda catalytic protection layer, wherein the passivation layer, the buffer layer and the catalytic protection layer are sequentially disposed on the surface of the Si layer. The passivation layer, the buffer layer and the catalytic protection layer in the silicon-based photoelectrode are all made of dense film materials, wherein the catalytic protection layer has high electrocatalytic activity and can effectively reduce the reaction overpotential and maintain high stability in a solution; the passivation layer on the surface of the Si layer can reduce the surface state of Si, reduce Fermi level pinning and inhibit the recombination of electrons and holes on the silicon surface; the buffer layer can protect the passivation layer from damage in the process of preparing the catalytic protectionlayer, and the photoelectric property of the photoelectrode is improved from two aspects including thermodynamics and kinetics.

Owner:THE NAT CENT FOR NANOSCI & TECH NCNST OF CHINA

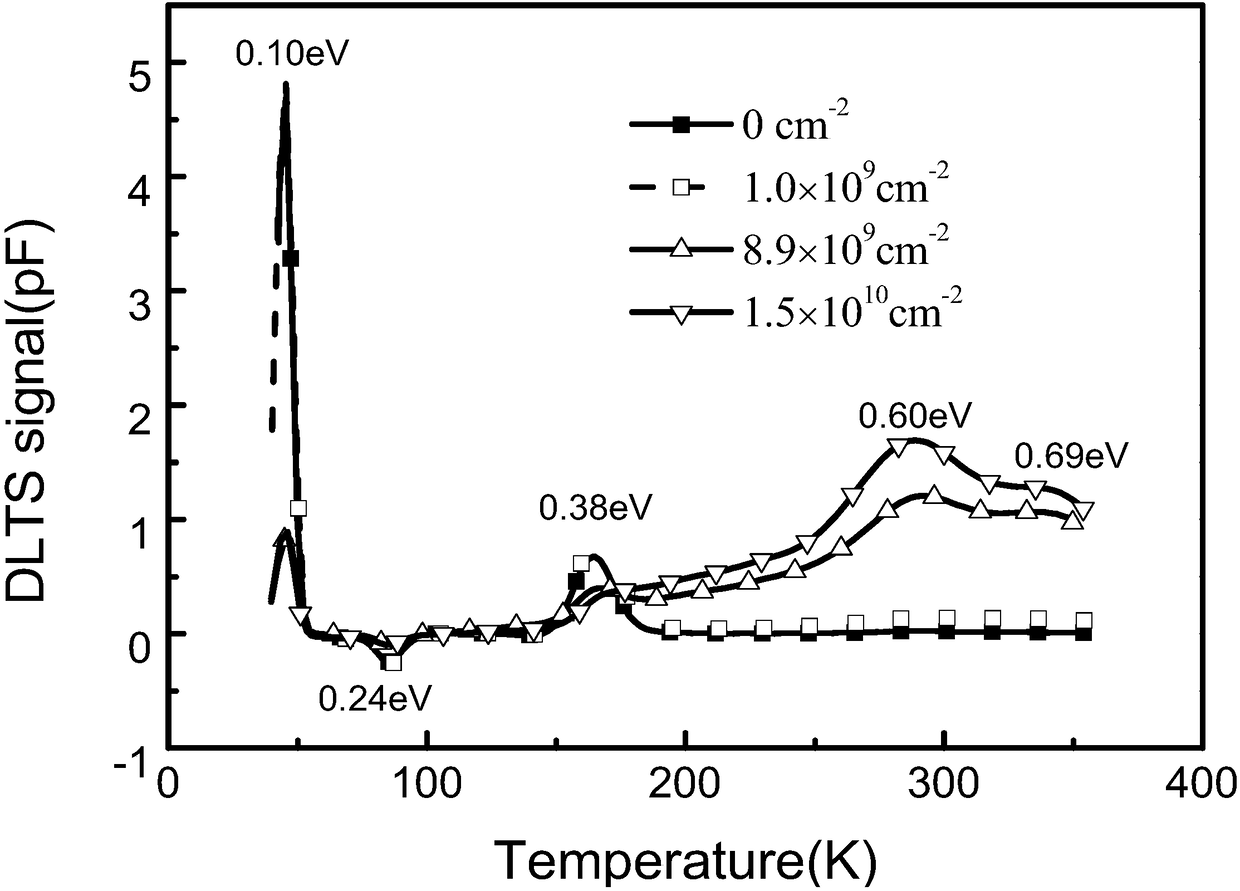

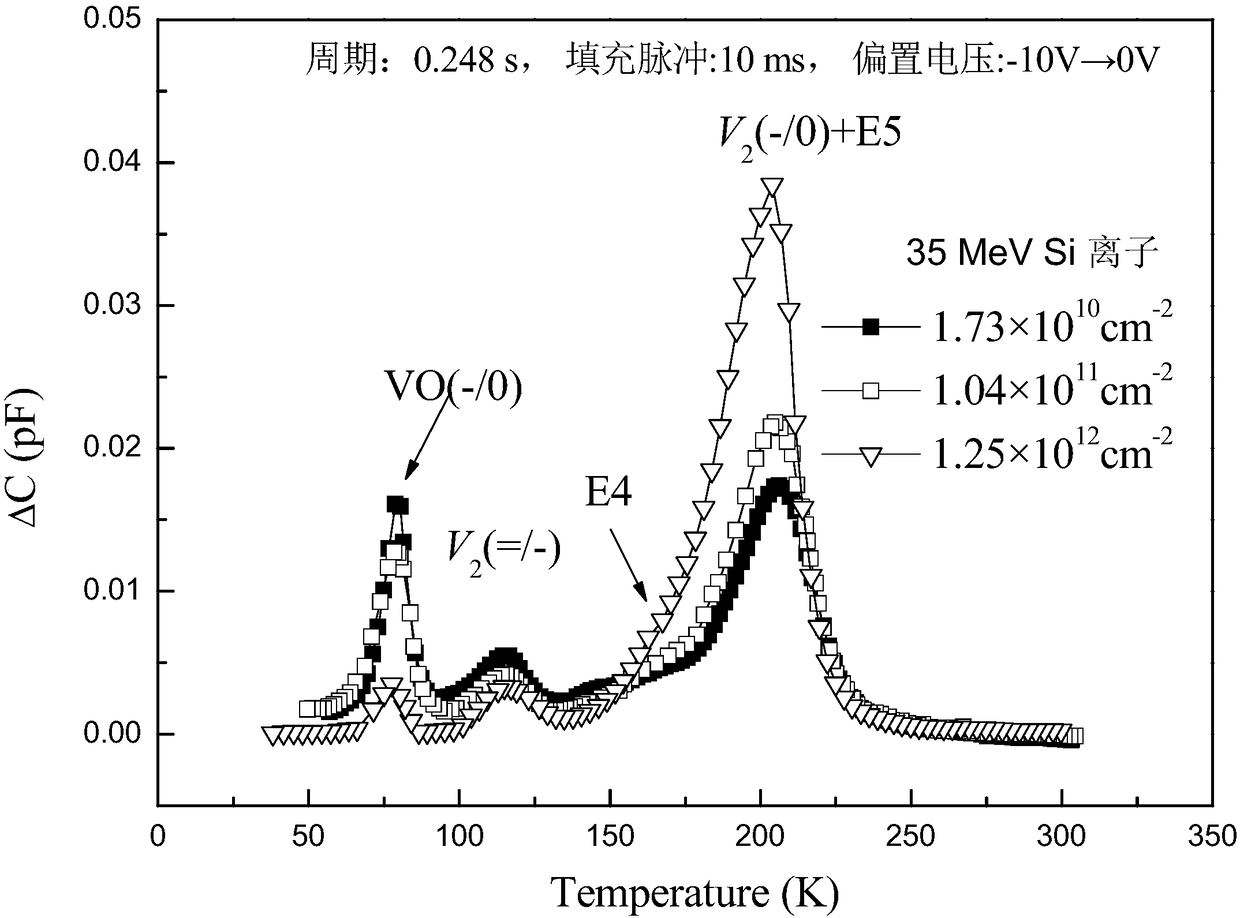

Method for judging Fermi energy level pinning effect of electronic device

ActiveCN108335984ASimple processEasy to operateSemiconductor/solid-state device manufacturingSemiconductor devicesDevice materialInjection point

The invention relates to a method for judging a Fermi energy level pinning effect of an electronic device and relates to a determination method for the Fermi energy level pinning effect of the electronic device. In order to solve the problem that no determination method for the Fermi energy level pinning effect of the electronic device in a particle radiation environment is generated, the method utilizes software to calculate vacancy numbers generated by a single radiation particle of radiation particles in a chip material, the type and the energy of the radiation particle are determined, radiation test is performed by selecting different radiation injection quantities, the radiation injection points are not less than 3, deep energy level transient spectrum test is performed on the deviceafter radiation, deep energy level transient spectroscopy (DLTS) curves according to different radiation injection quantities are compared, signal peaks corresponding to deep energy level defect and shallow energy level defect are compared, the device material generates Fermi energy level pinning effect if the concentration of the deep energy level defect is raised and the concentration of the shallow energy level defect is reduced with increase of the radiation injection quantity. The method is suitably used for detecting the Fermi energy level pinning effect of the electronic device.

Owner:HARBIN INST OF TECH

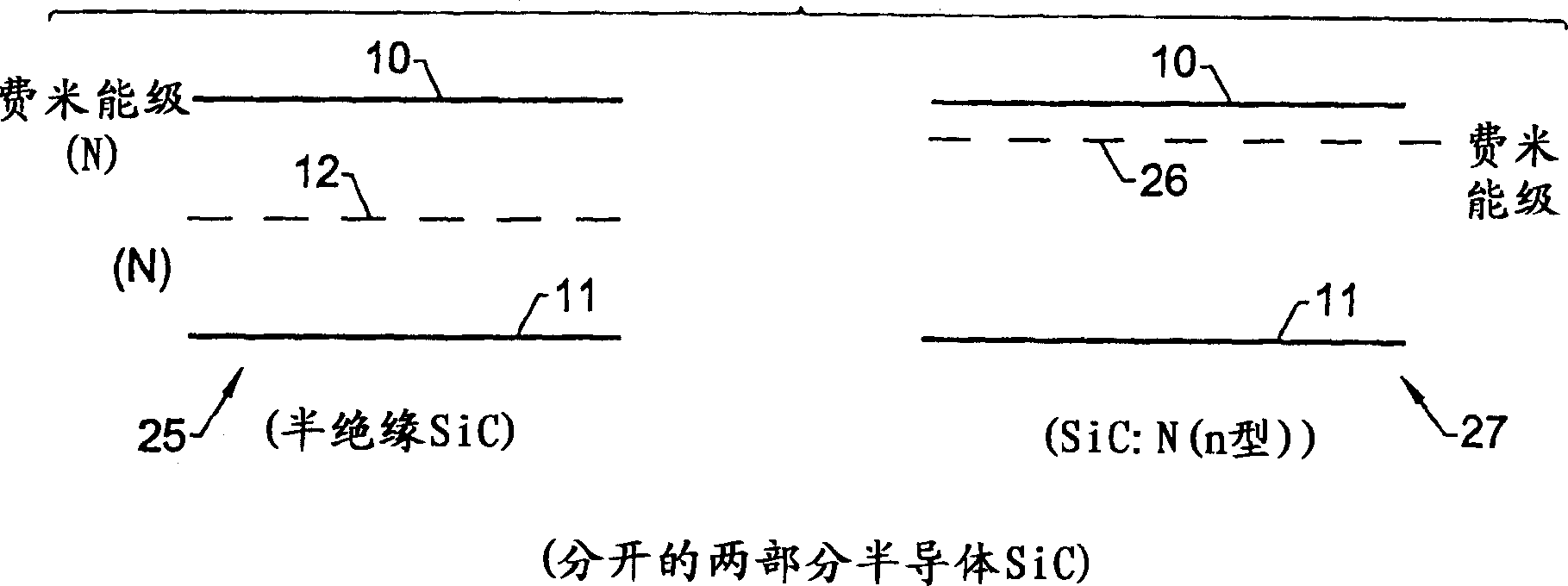

High-resisting silicon carbide substrate for semiconductor devices with high breakdown voltage

InactiveCN1507506AAvoid disadvantagesPolycrystalline material growthSemiconductor/solid-state device manufacturingHigh resistivity siliconSingle crystal

A high-resistivity silicon carbide single crystal is disclosed that includes at least one compensated dopant having an electronic energy level far enough from an edge of the silicon carbide bandgap to avoid conductive behavior, while far enough from mid-gap towards the band edge to create a greater band offset than do mid-level states when the substrate is in contact with a doped silicon carbide epitaxial layer and when the net amount of the dopant present in the crystal is sufficient to pin the Fermi level at the dopant's electronic energy level. The silicon carbide crystal has a resistivity of at least 5000 ohms-centimeters at room temperature.

Owner:CREE INC

Structure taking part of metal grid as grid medium etching blocking layer with high dielectric constant and integration method

InactiveCN101673710AFix damageSimplify integration complexitySemiconductor/solid-state device manufacturingSemiconductor devicesSemiconductor chipFermi energy

The invention relates to a structure taking part of a metal grid as a grid medium etching blocking layer with high dielectric constant and an integration method, belonging to the technical field of semiconductor chips. The method comprises the following steps: taking part of the metal grid as the etching blocking layer for etching a high-K material when etching the high-K material; after integrating, enabling the threshold voltage of NMOS and PMOS to conform to requirements by simplified steps. The invention has the advantages of overcoming the nail pricking effect of the fermi energy level ofa PMOS grid, solving the problem that the traditional technique damages a high-K medium when removing photoengraving glue, and simplifying the integration complexity of a high-K metal grid greatly.

Owner:FUDAN UNIV

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com