Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

87results about How to "Reduce threading dislocation density" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

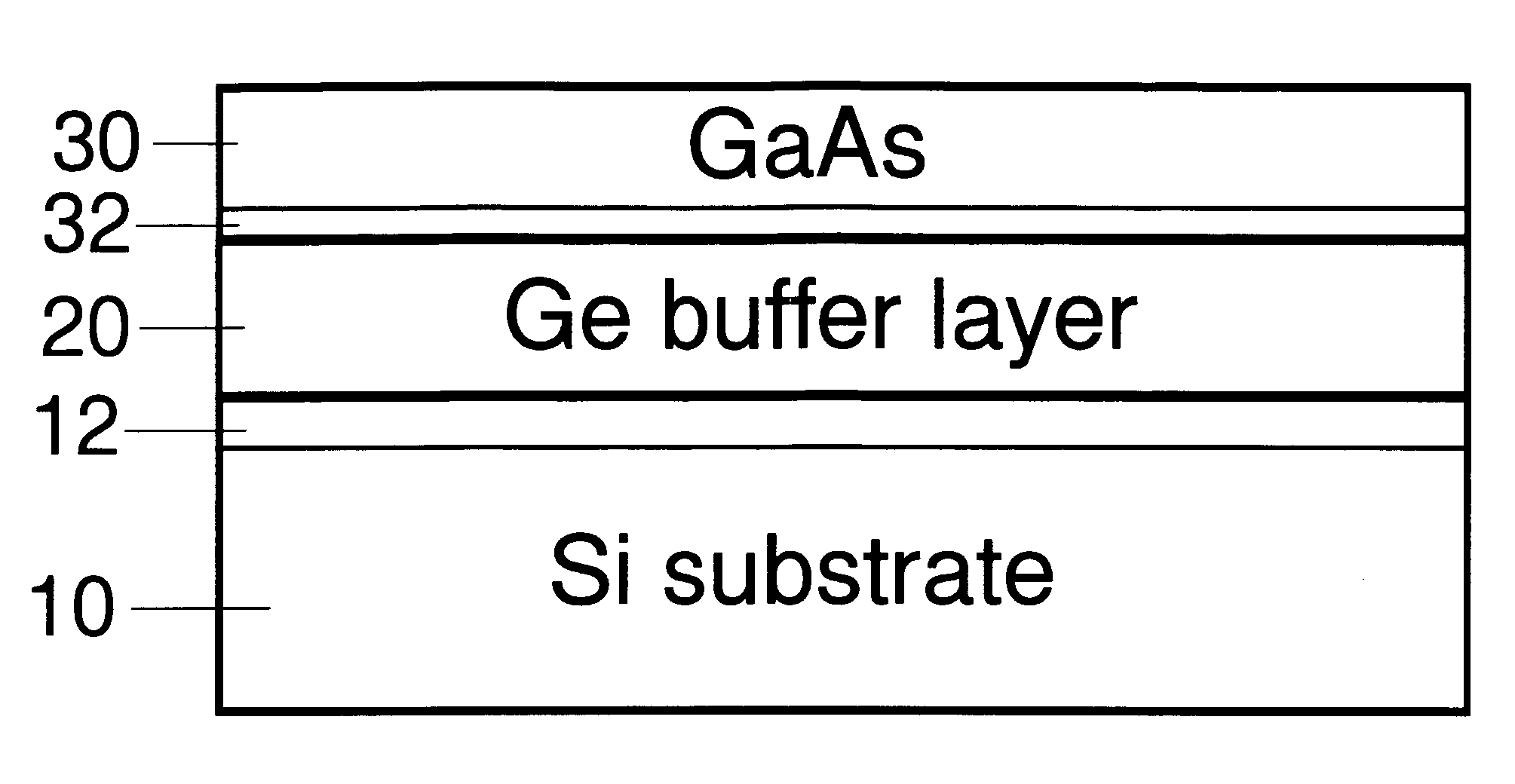

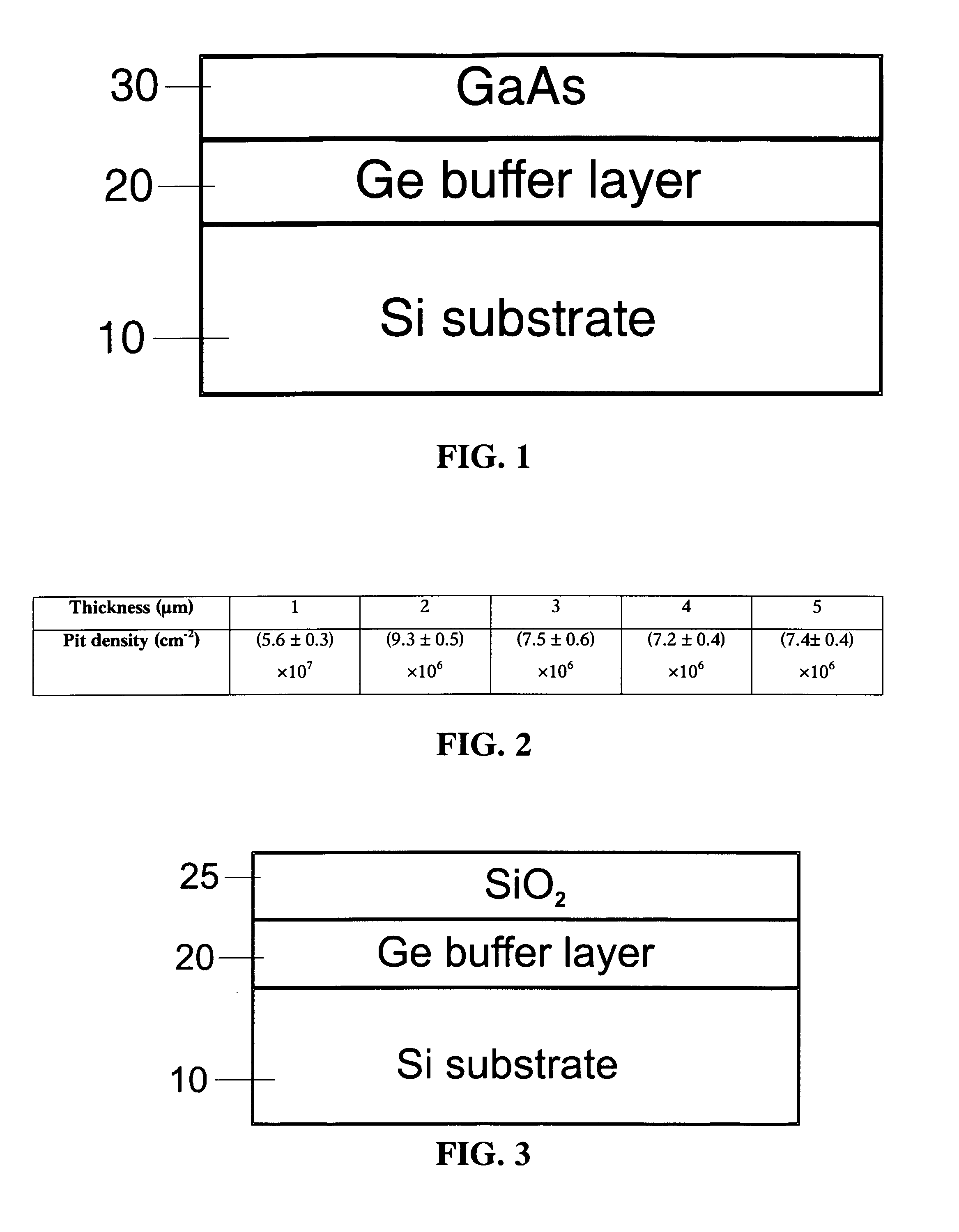

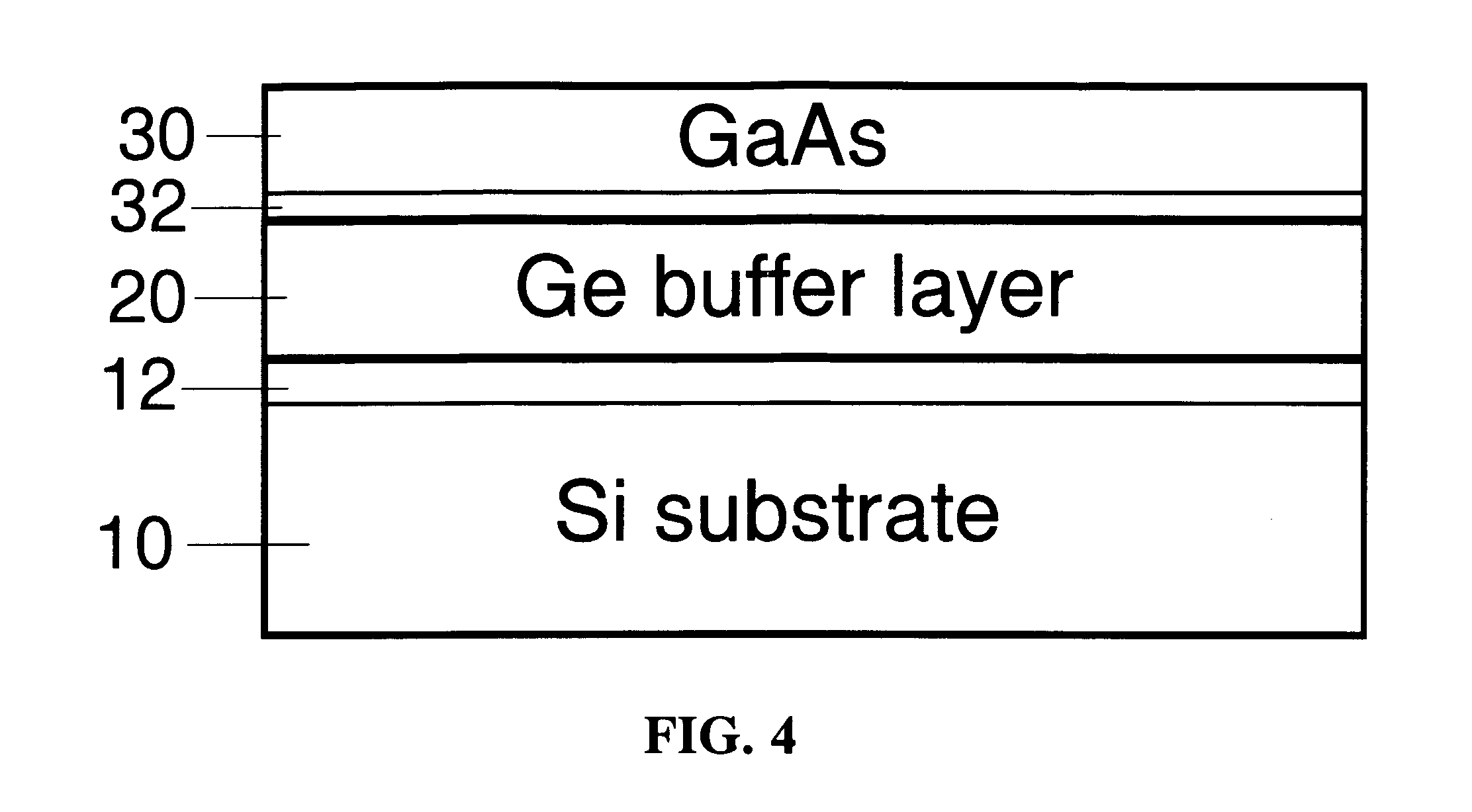

Method for Producing Virtual Ge Substrates for III/V-Integration on Si(001)

InactiveUS20070231488A1Fast epitaxial growthCheap methodSolid-state devicesSemiconductor/solid-state device manufacturingField-effect transistorSolar cell

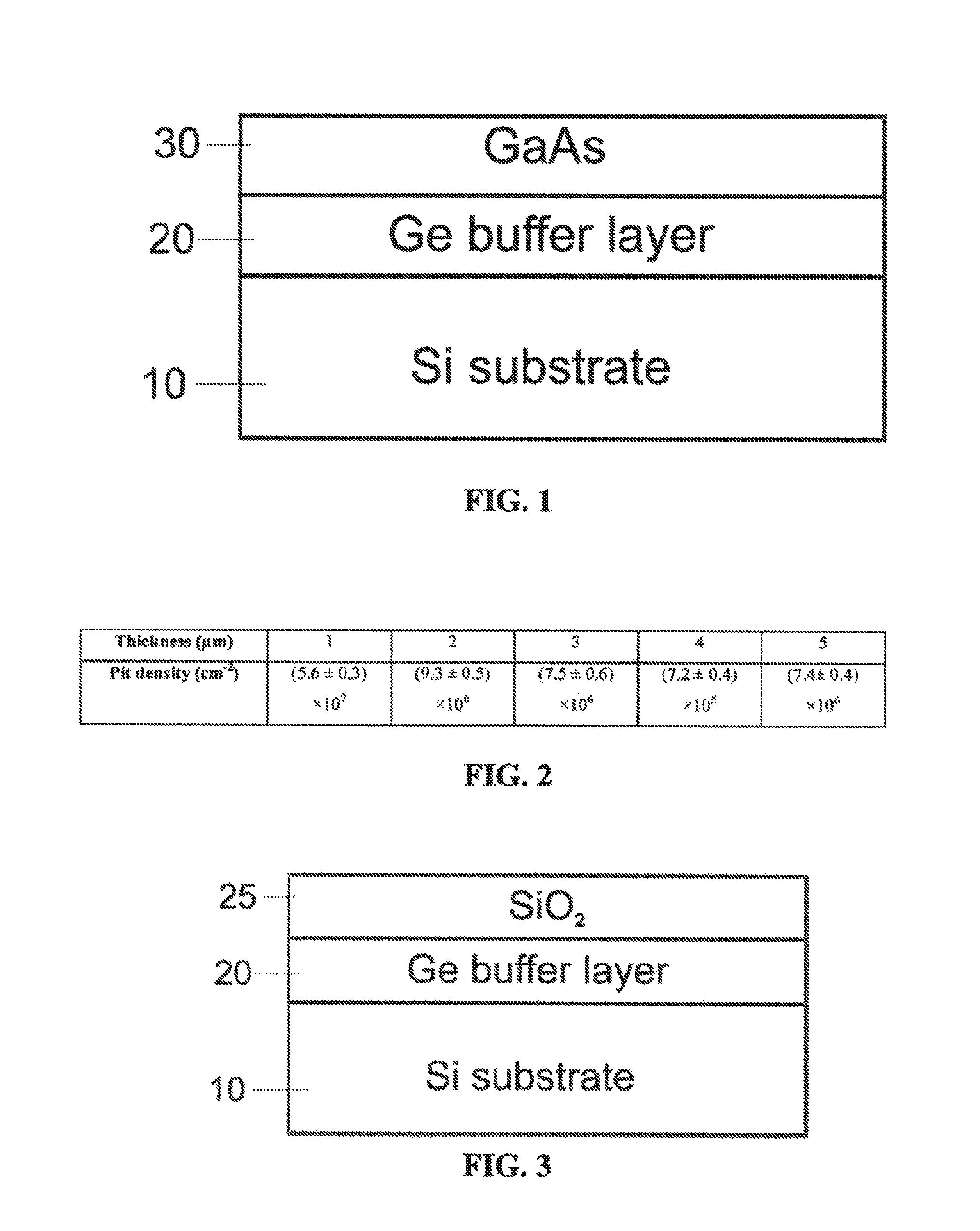

Relaxed germanium buffer layers can be grown economically on misoriented silicon wafers by low-energy plasma-enhanced chemical vapor deposition, in conjunction with thermal annealing and / or patterning, the buffer layers can serve as high-quality virtual substrates for the growth of crack-free GaAs layers suitable for high-efficiency solar cells, lasers and field effect transistors.

Owner:DICHROIC CELL

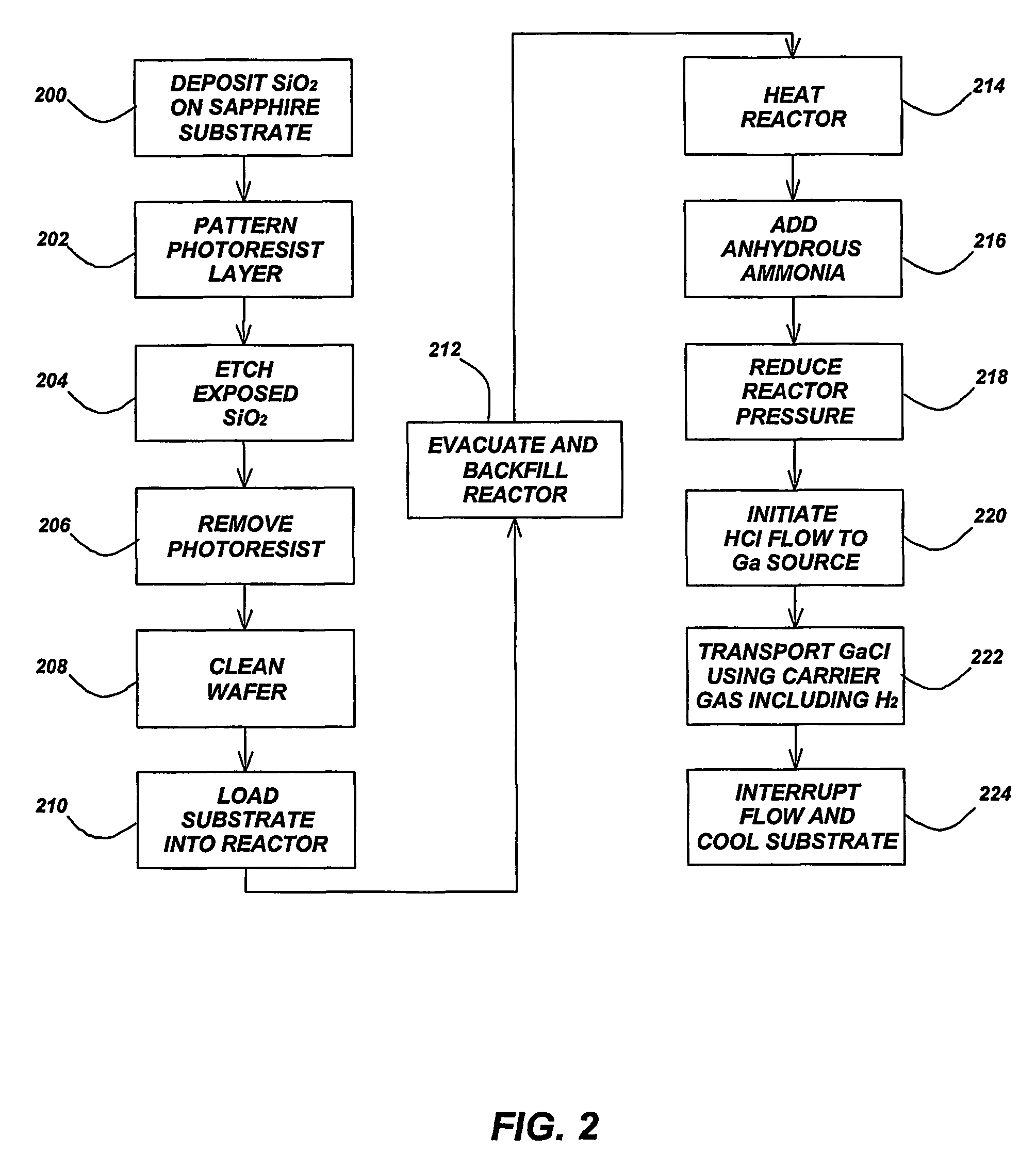

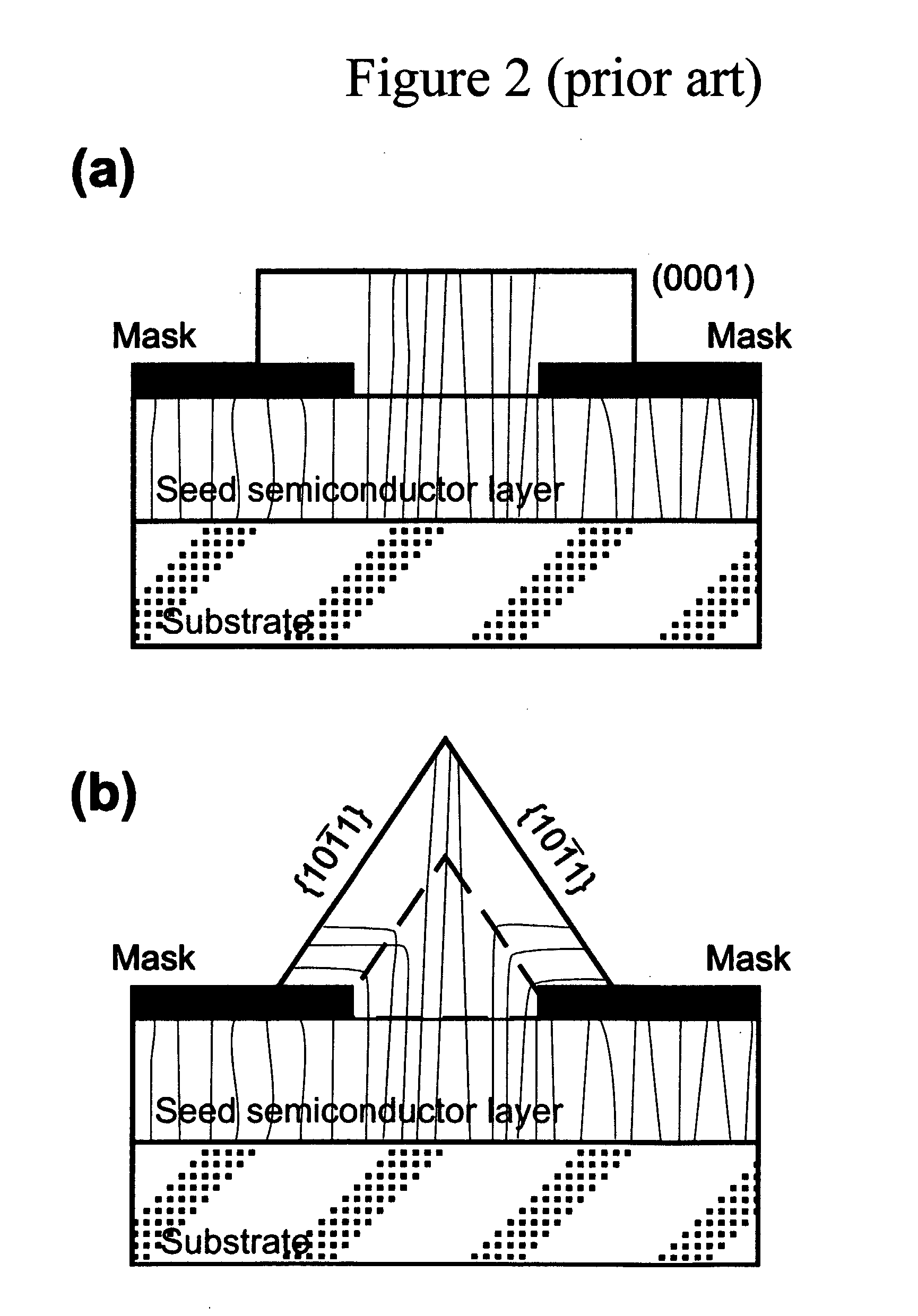

Growth of reduced dislocation density non-polar gallium nitride by hydride vapor phase epitaxy

InactiveUS7220658B2Reduce threading dislocation densityPolycrystalline material growthSemiconductor/solid-state device manufacturingGallium nitrideVapor phase

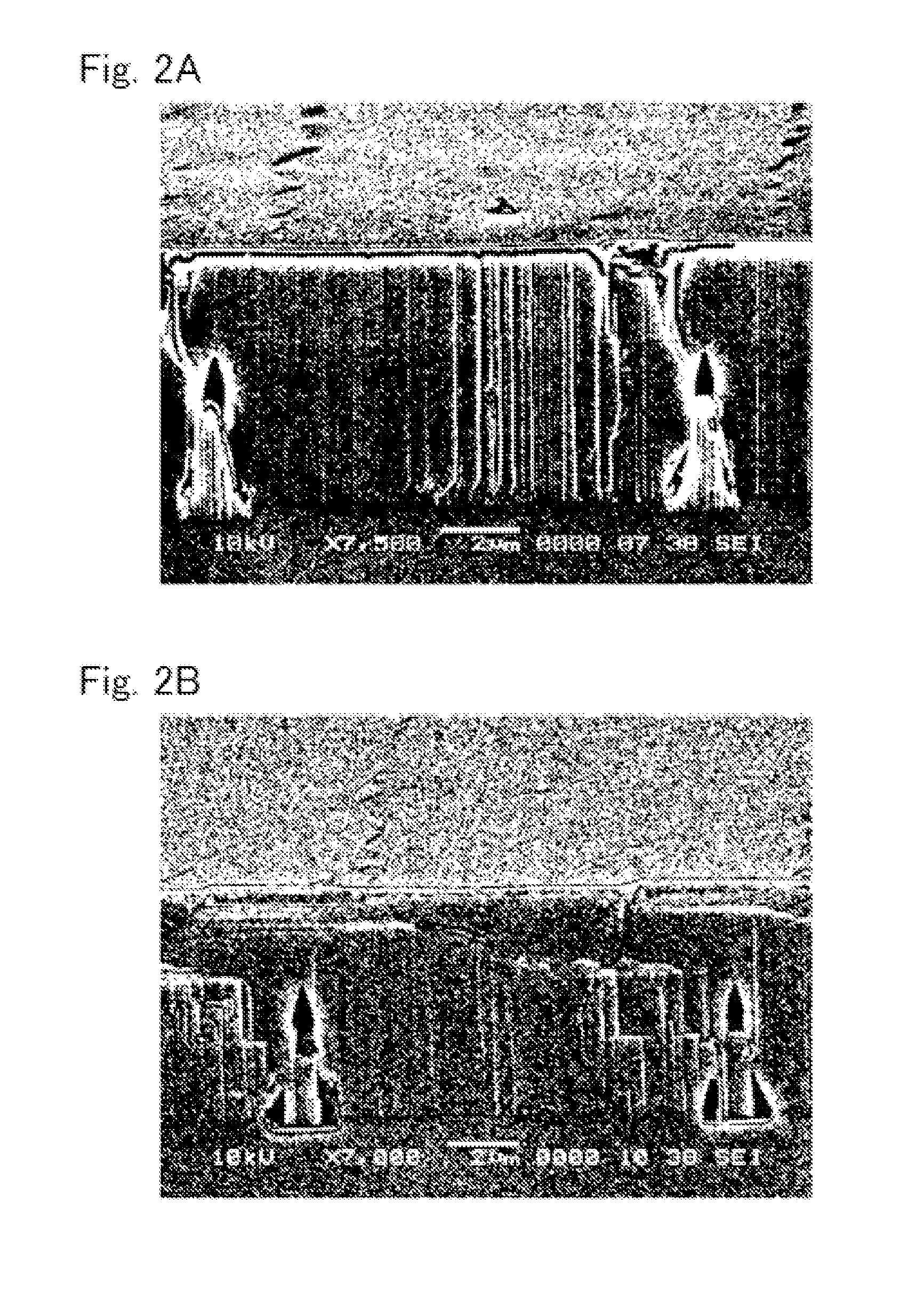

Lateral epitaxial overgrowth (LEO) of non-polar a-plane gallium nitride (GaN) films by hydride vapor phase epitaxy (HVPE) results in significantly reduced defect density.

Owner:JAPAN SCI & TECH CORP +1

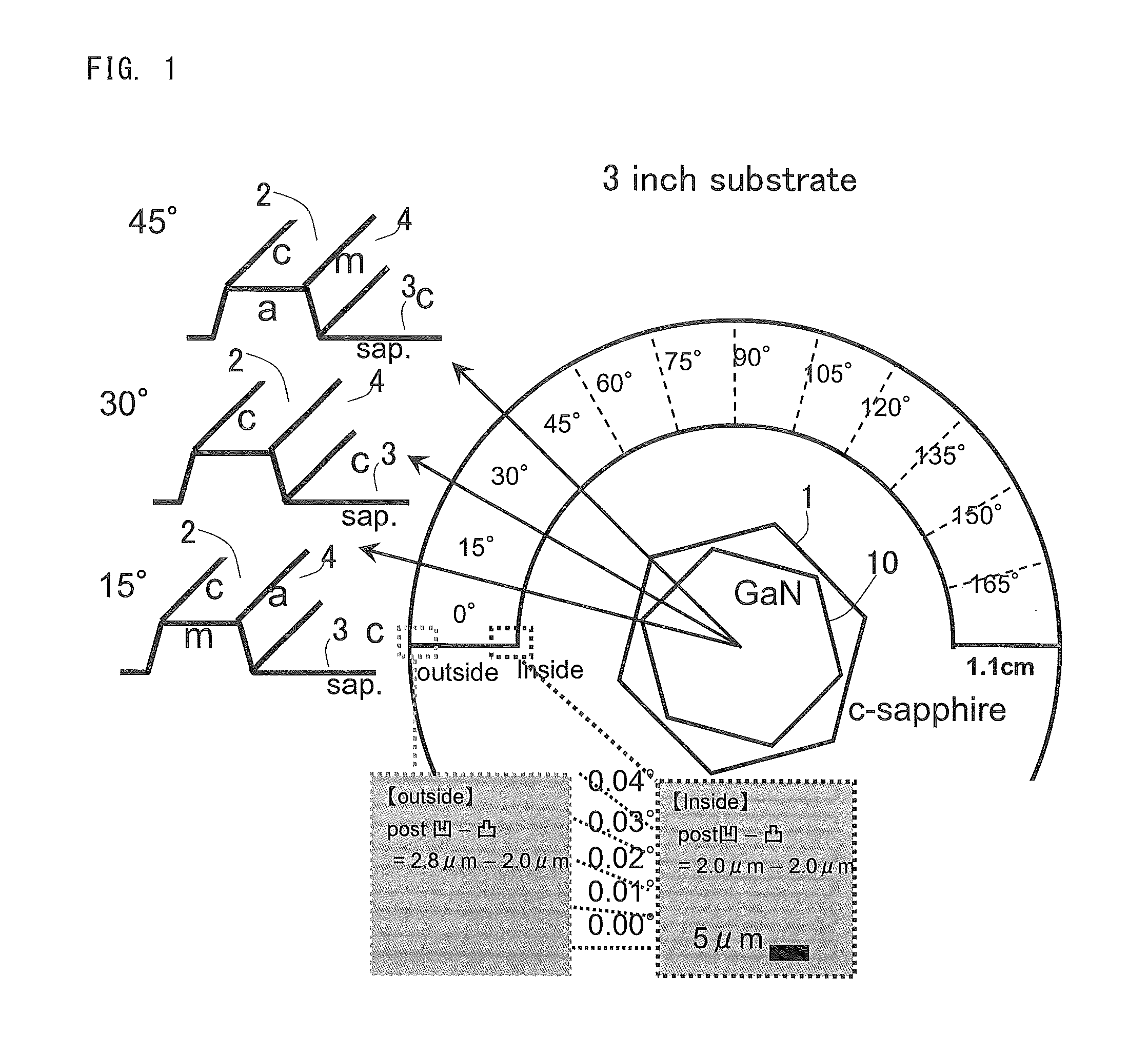

Sapphire substrate, epitaxial substrate and semiconductor device

An epitaxial substrate for manufacturing field effect transistor (FET) that has heterojunction structure consisting of at least a channel layer made of gallium nitride or gallium indium nitride and a barrier layer made of aluminum gallium nitride formed successively on the principal plane of the sapphire substrate, wherein the principal plane of the sapphire substrate semiconductor is inclined from (01-12) plane toward (0001) plane by an off-angle α that is in a range of 0°<x≦5°. With this constitution, an epitaxial substrate for manufacturing field effect transistor having high smoothness is provided.

Owner:KYOCERA CORP

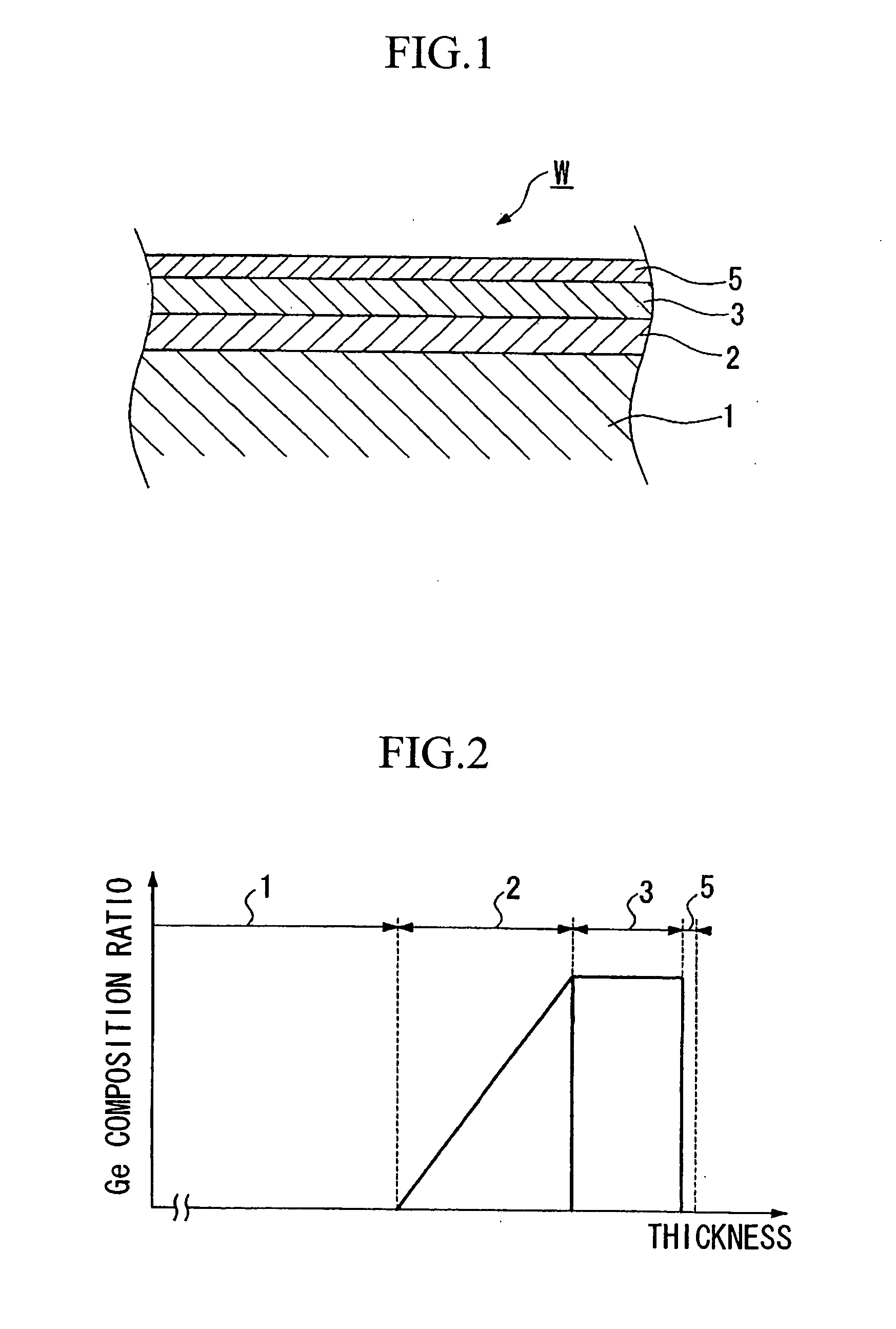

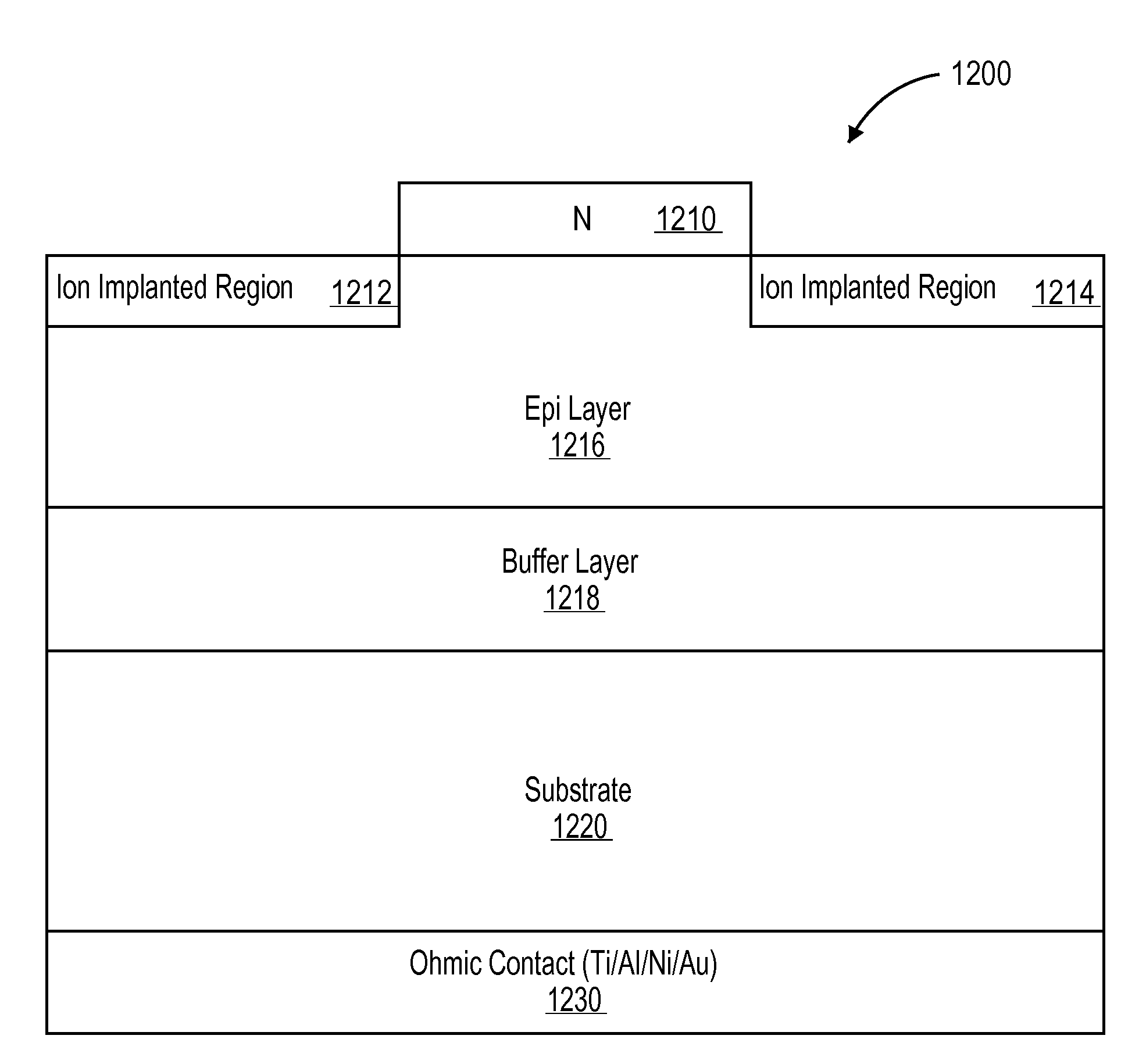

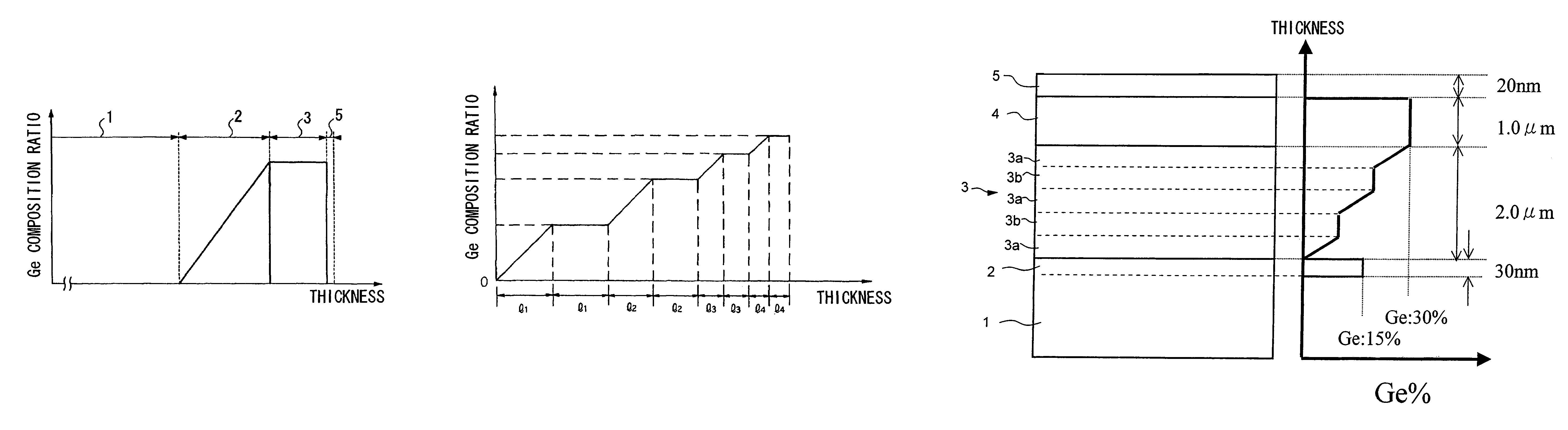

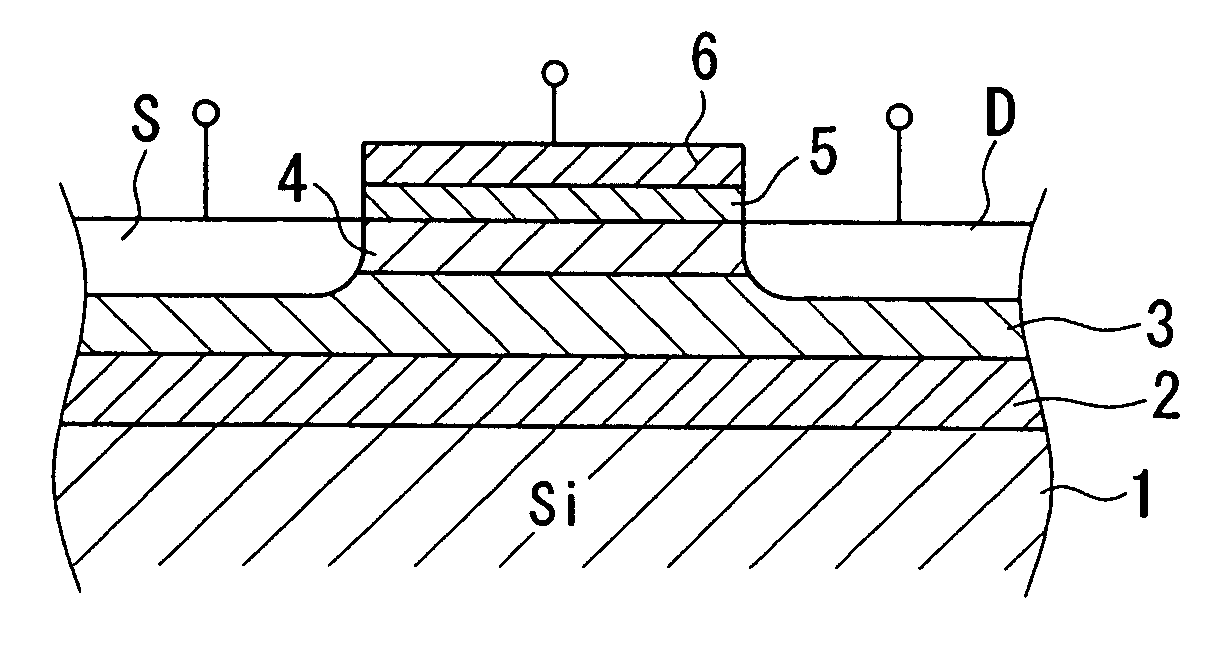

Semiconductor substrate, field-effect transistor, and their production methods

ActiveUS20060258126A1Low penetrate dislocation densityReduce surface roughnessSemiconductor/solid-state device manufacturingSemiconductor devicesDislocationField-effect transistor

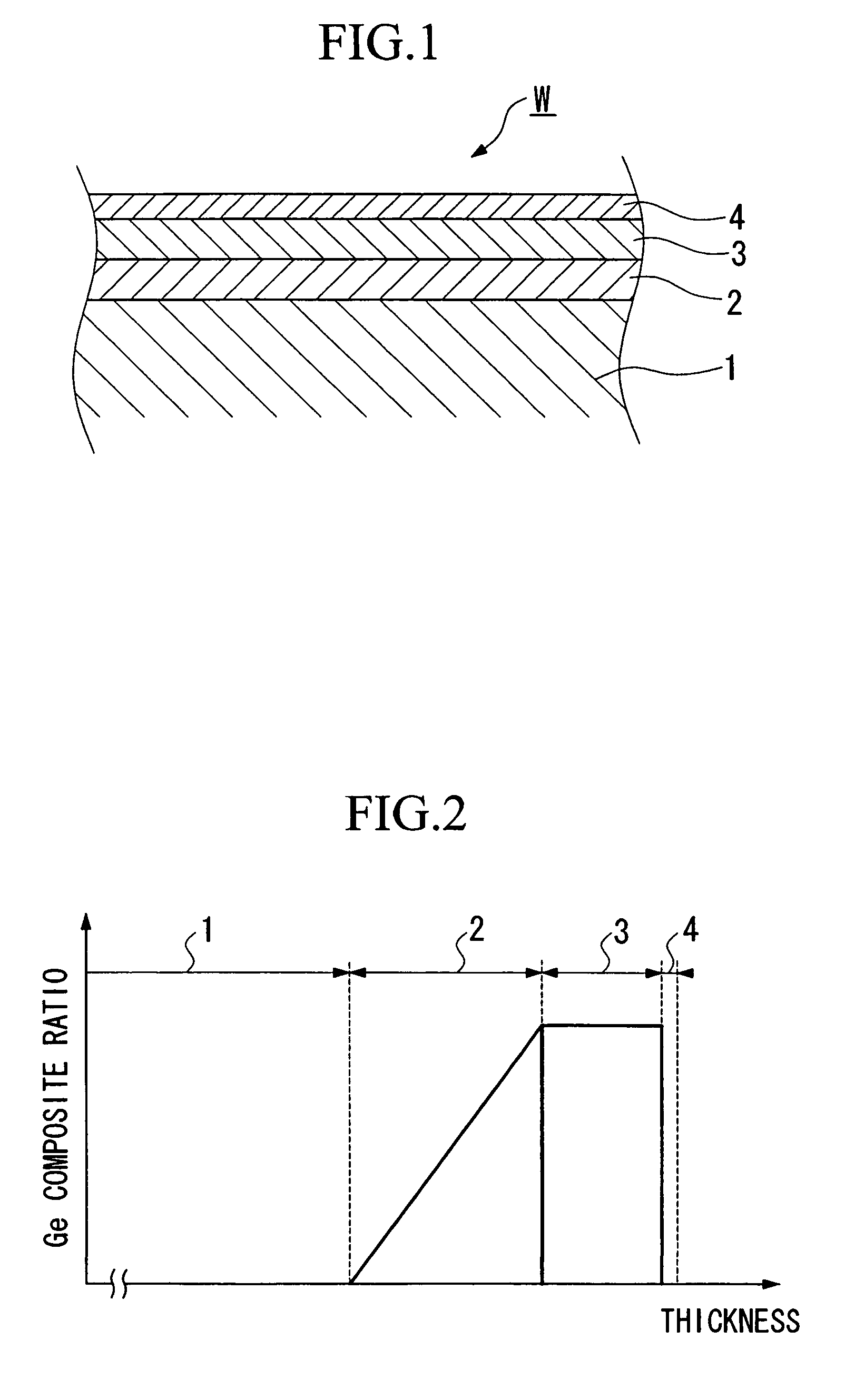

A semiconductor substrate manufacturing method has a first layer formation process, a second layer formation process, a heat treatment process, and a polishing process; in the first layer formation process, the thickness of the first SiGe layer is set to less than twice the critical thickness, which is the film thickness at which dislocations appear and lattice relaxation occurs due to increasing film thickness; in the second layer formation process, the Ge composition ratio of the second SiGe layer is at least at the contact face with the first SiGe layer or with the Si layer, set lower than the maximum value of the Ge composition ratio in the first SiGe layer, and moreover, a gradient composition region in at least a portion of which the Ge composition ratio increases gradually toward the surface is formed. By this means, the penetrating dislocation density is kept low, surface roughness is low, and worsening of roughness at the surface and at interfaces due to heat treatment in device manufacturing processes or similar is prevented.

Owner:SUMCO CORP

Growth of reduced dislocation density non-polar gallium nitride

InactiveUS20070126023A1Reduce threading dislocation densityPolycrystalline material growthSemiconductor/solid-state device manufacturingGallium nitrideDislocation

Owner:RGT UNIV OF CALIFORNIA +1

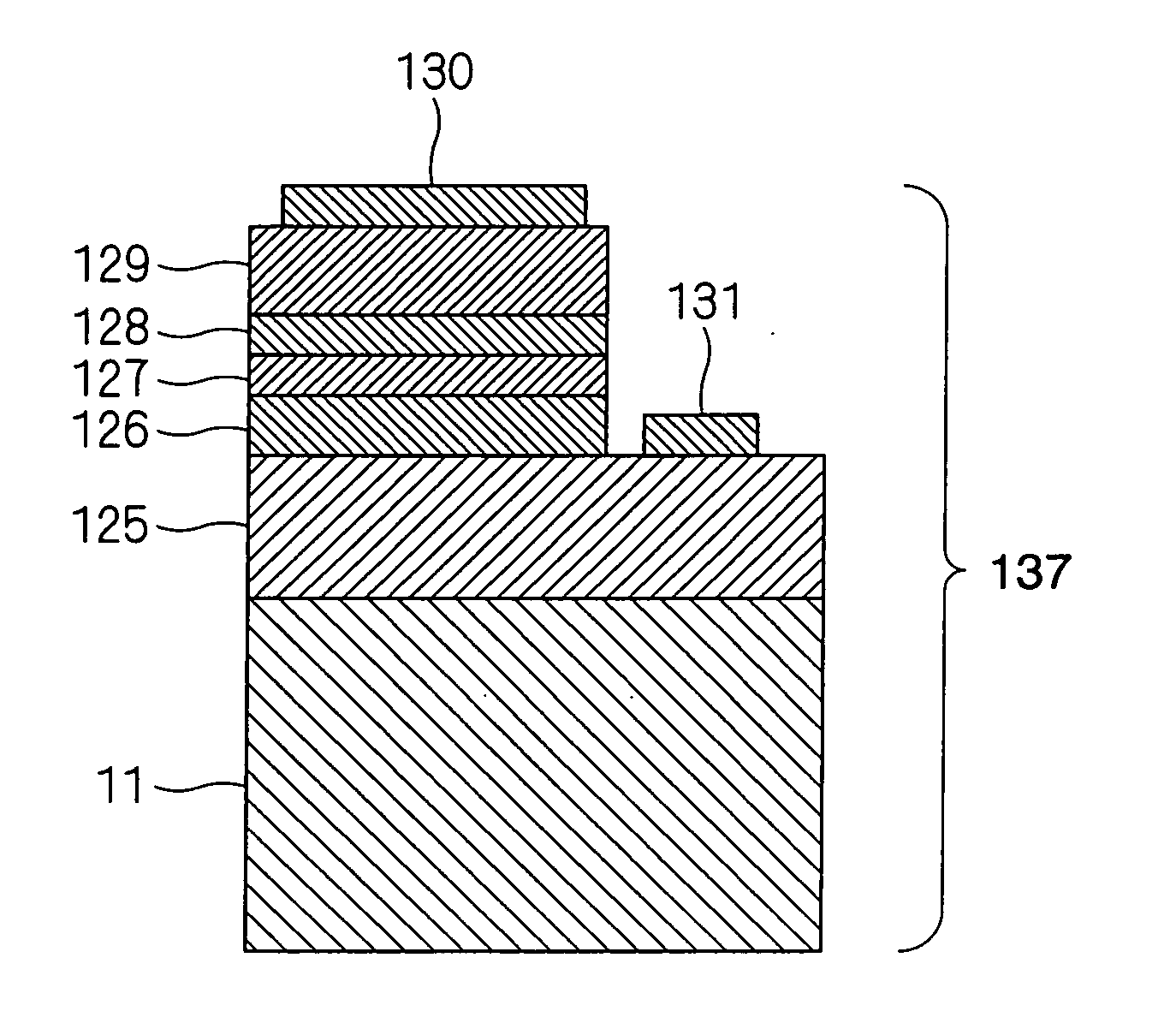

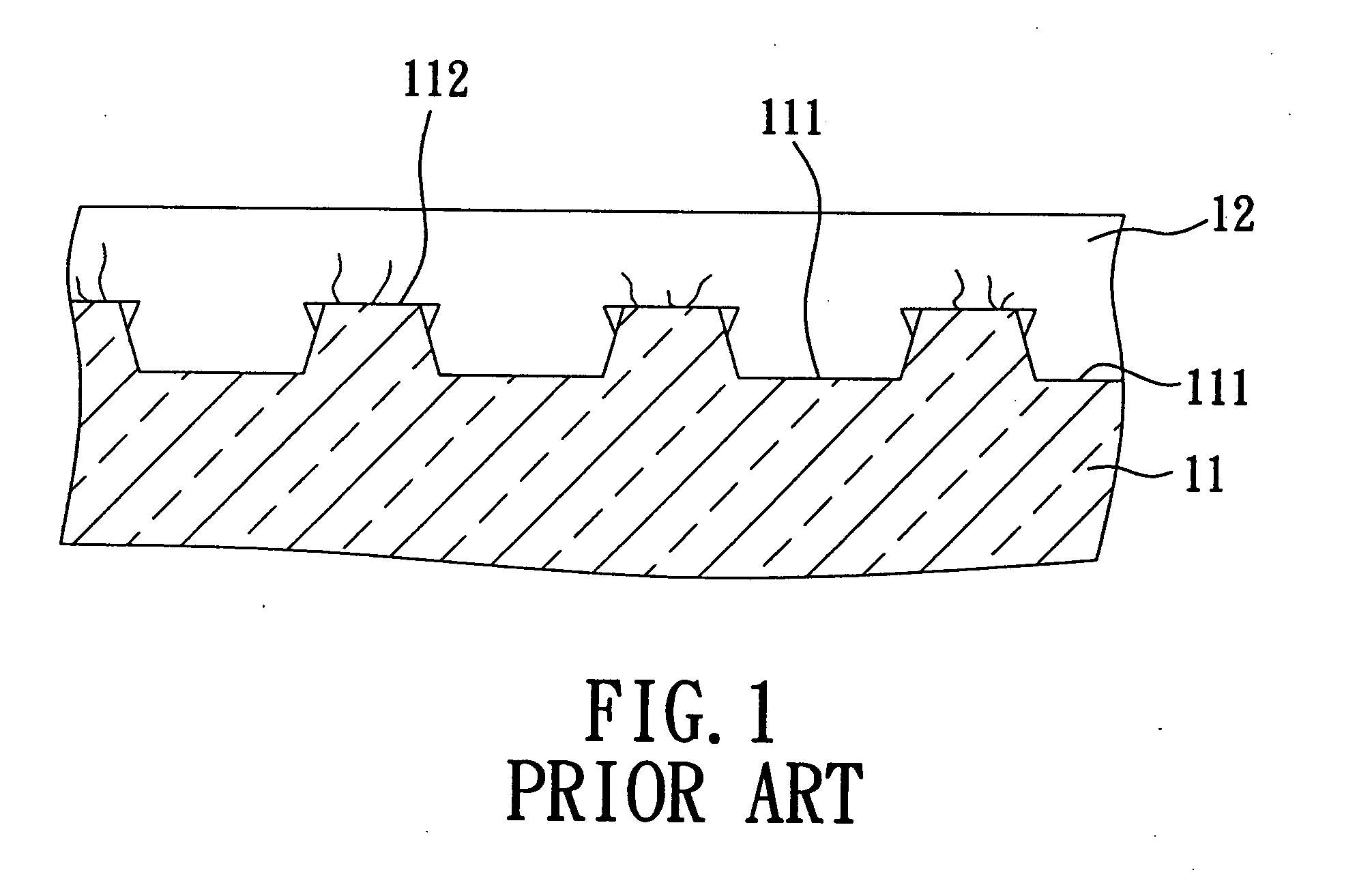

Light emitting device and method for making the same

InactiveUS20080277686A1Reduce threading dislocation densityOvercomes drawbackSemiconductor/solid-state device manufacturingSemiconductor devicesLight emitting deviceLight-emitting diode

A light emitting diode includes: an epitaxial substrate having a roughened side and formed with alternately disposed ridges and valleys at the roughened side, each of the ridges having a roughened surface that is formed with a dense concentration of alternately disposed pits and protrusions; and an epitaxial layered structure formed on and covering the ridges and the valleys of the epitaxial substrate. A method for making the light emitting diode involves forming the epitaxial substrate with the ridges and valleys prior to the formation of the epitaxial layered structure.

Owner:EPISTAR CORP

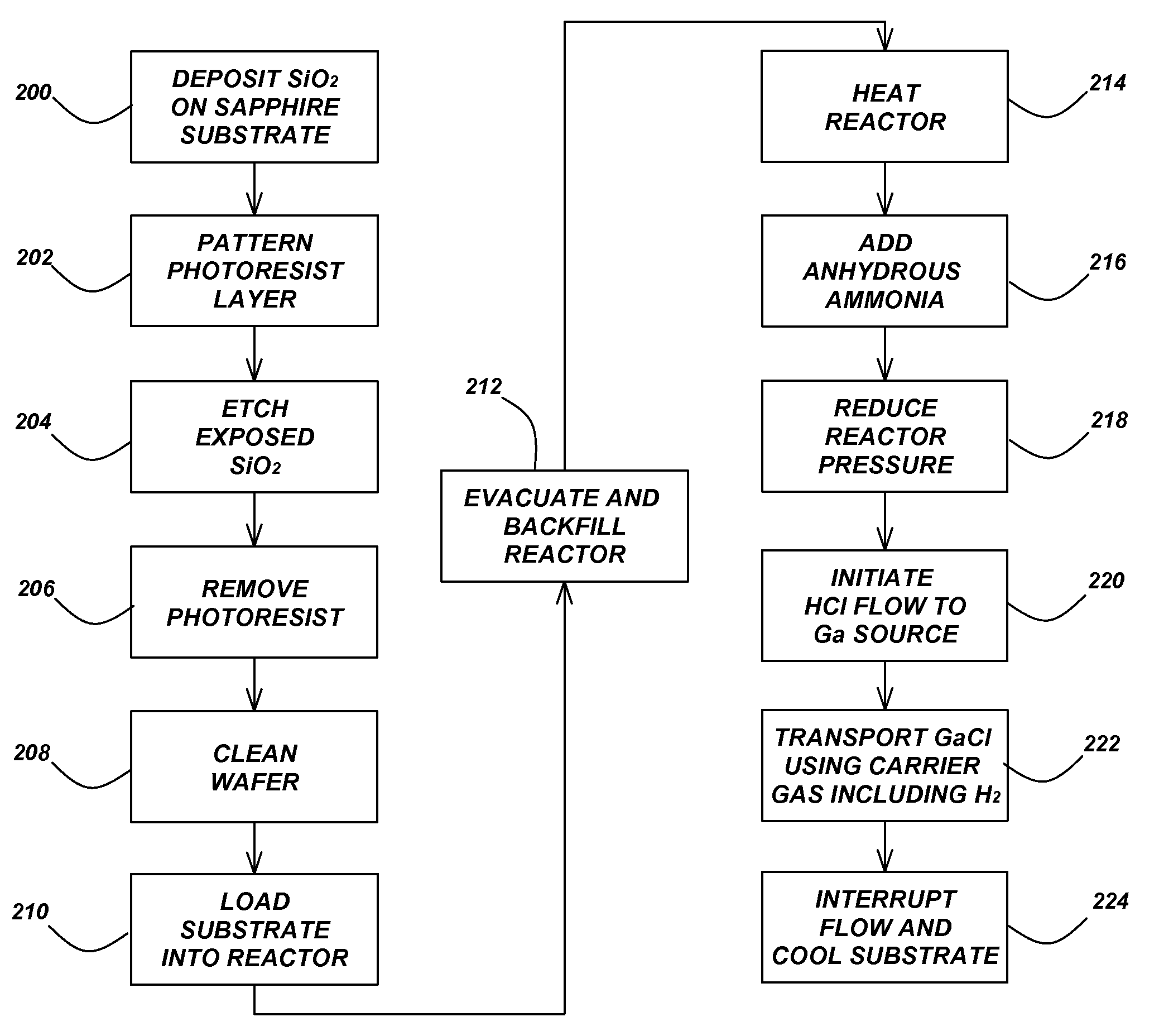

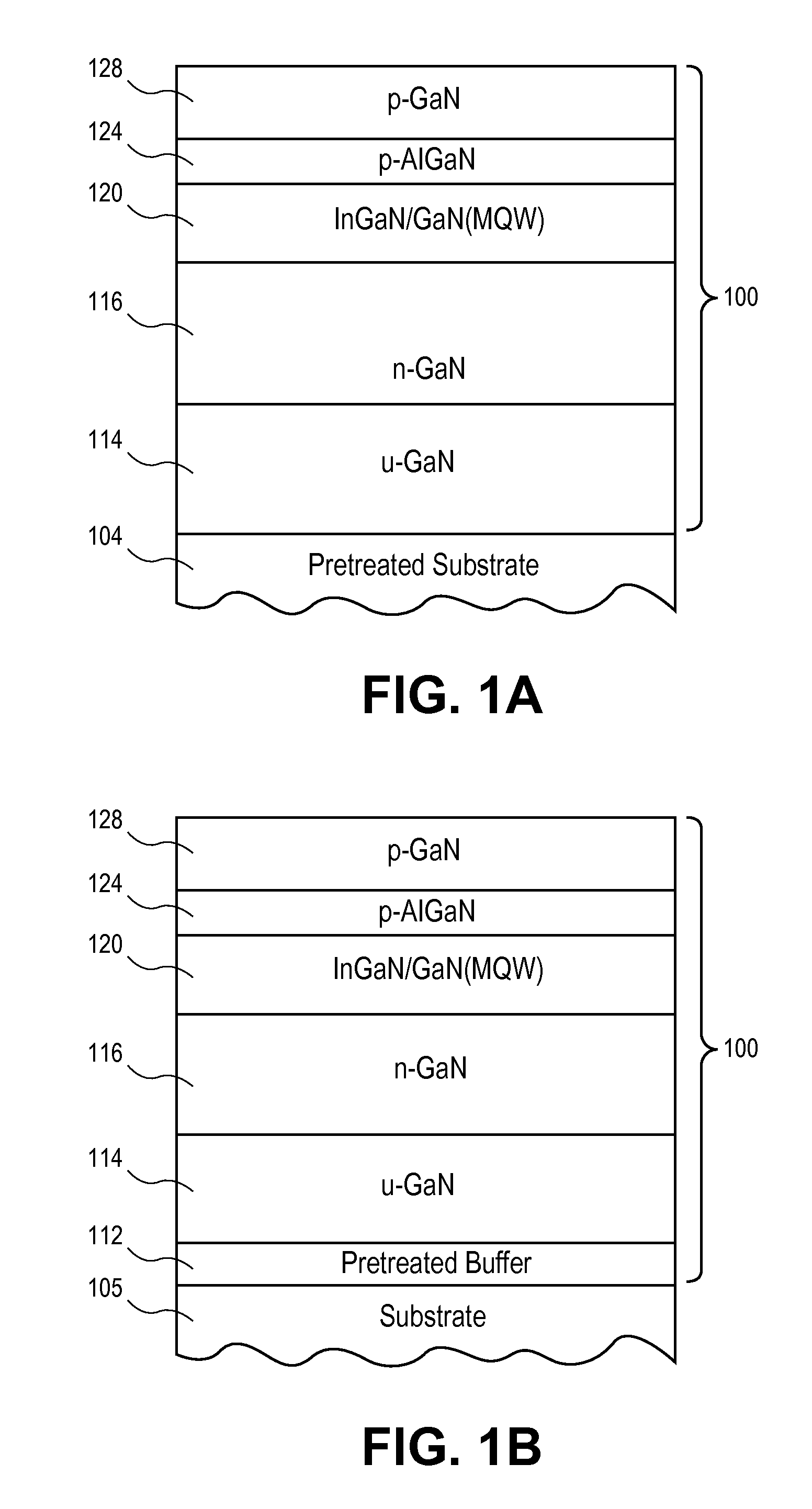

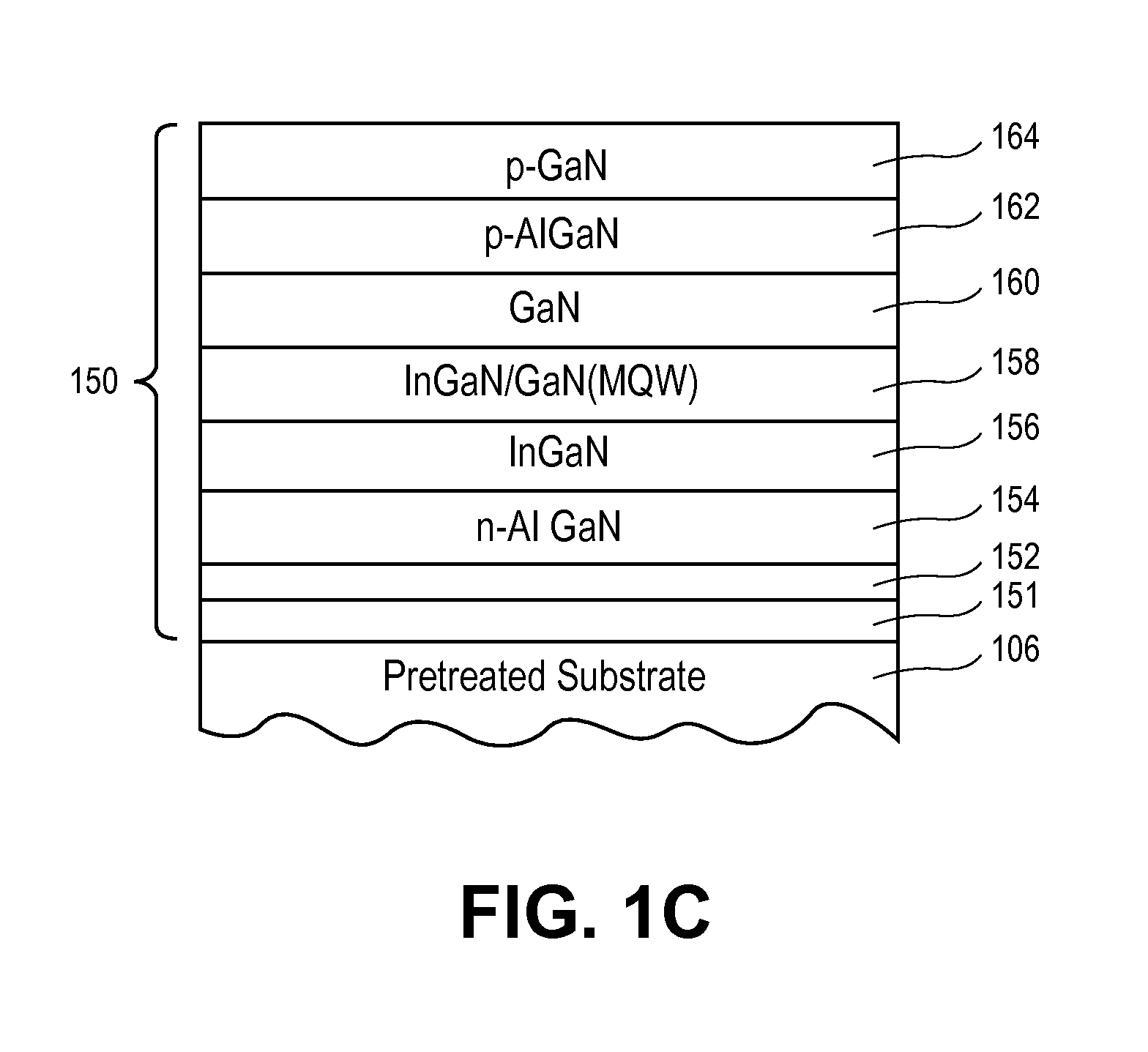

Methods for pretreatment of group iii-nitride depositions

InactiveUS20120295428A1Reduce threading dislocation densityLower regulation pressureSemiconductor/solid-state device manufacturingSemiconductor devicesHydrogen halidePre treatment

Embodiments of the present disclosure relate to methods for pretreatment of substrates and group III-nitride layers for manufacturing devices such as light emitting diodes (LEDs), laser diodes (LDs) or power electronic devices. One embodiment of the present disclosure provides a method including providing one or more substrates having an aluminum containing surface in a processing chamber and exposing a surface of each of the one or more substrates having an aluminum containing surface to a pretreatment gas mixture to form a pretreated surface. The pretreatment gas mixture includes ammonia (NH3), an aluminum halide gas (e.g., AlCl3, AlCl) and an etchant containing gas that includes a halogen gas (e.g., Cl2) or hydrogen halide gas (e.g., HCl).

Owner:APPLIED MATERIALS INC

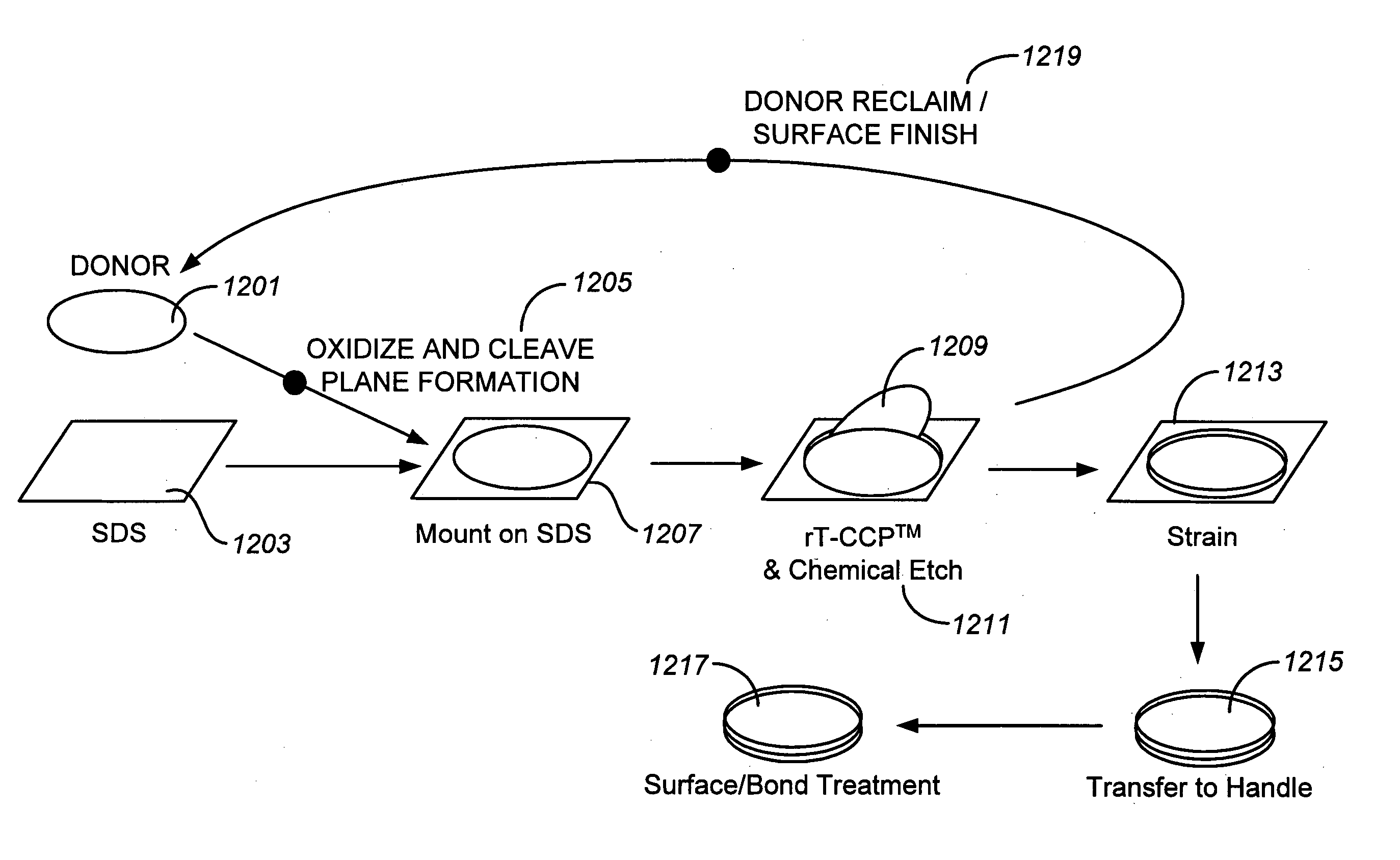

Method and system for lattice space engineering

InactiveUS7390724B2Easy to useHigh device yieldSemiconductor/solid-state device manufacturingStressed stateMechanical engineering

A system for manufacturing multilayered substrates. The system has a support member is adapted to process a film of material comprising a first side and a second side from a first state to a second state. The support member is attached to the first side of the film of material. The second state comprises a stressed state. The system has a handle substrate comprising a face, which is adapted to be attached to the second side of the film of material. The support member is capable of being detached from the first side of the film of material thereby leaving the handle substrate comprising the film of material in the second state being attached to the face of the handle substrate.

Owner:SILICON GENERAL CORPORATION

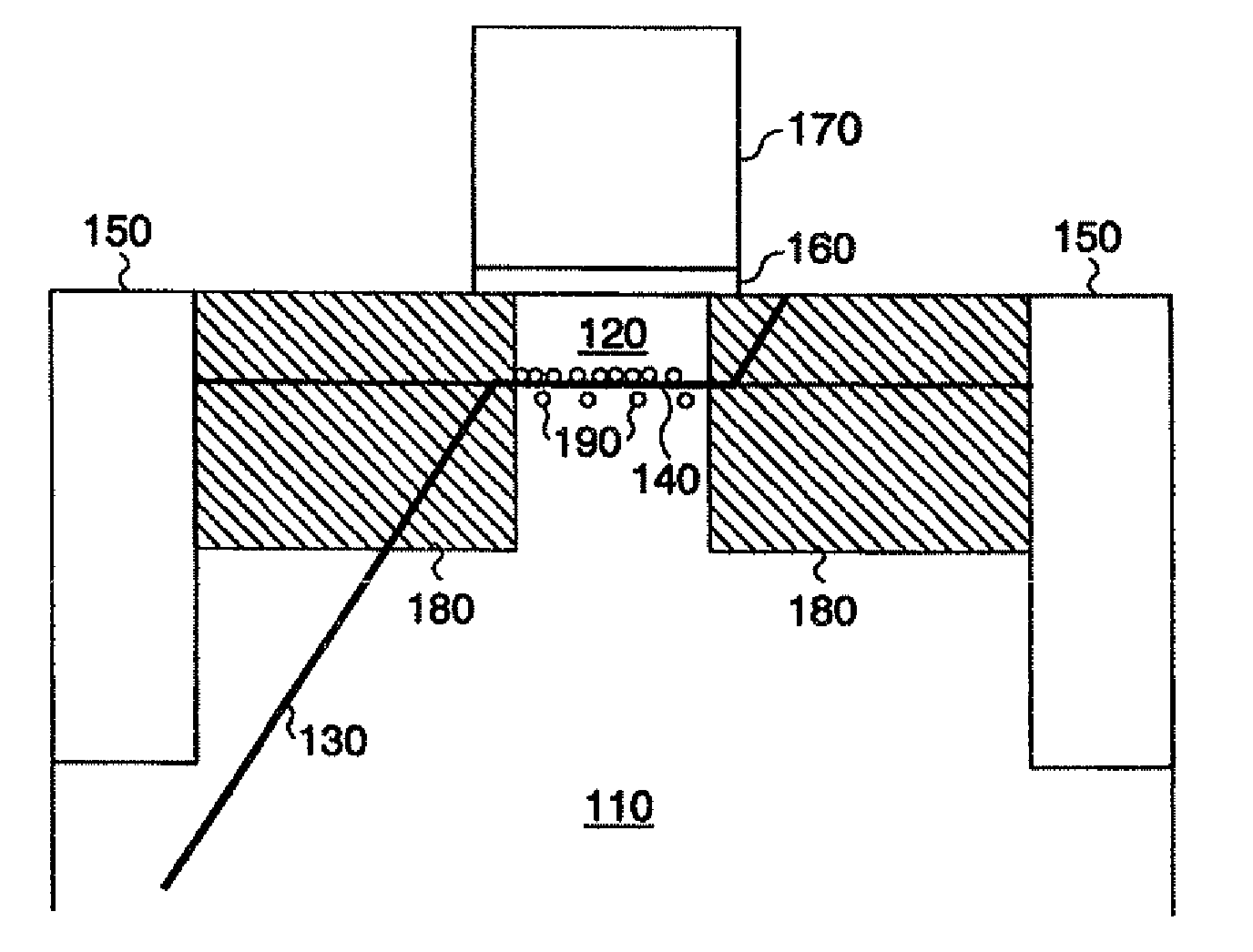

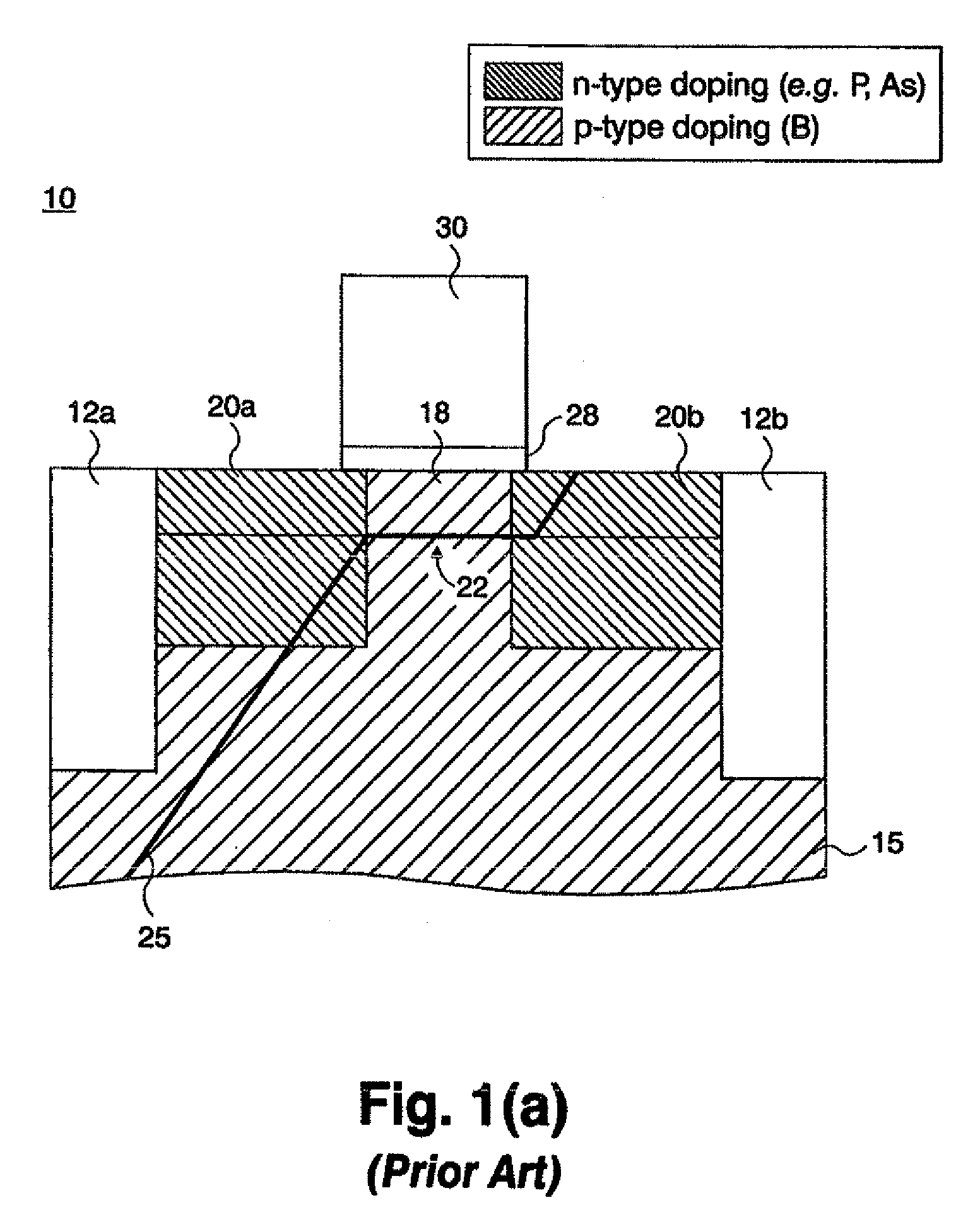

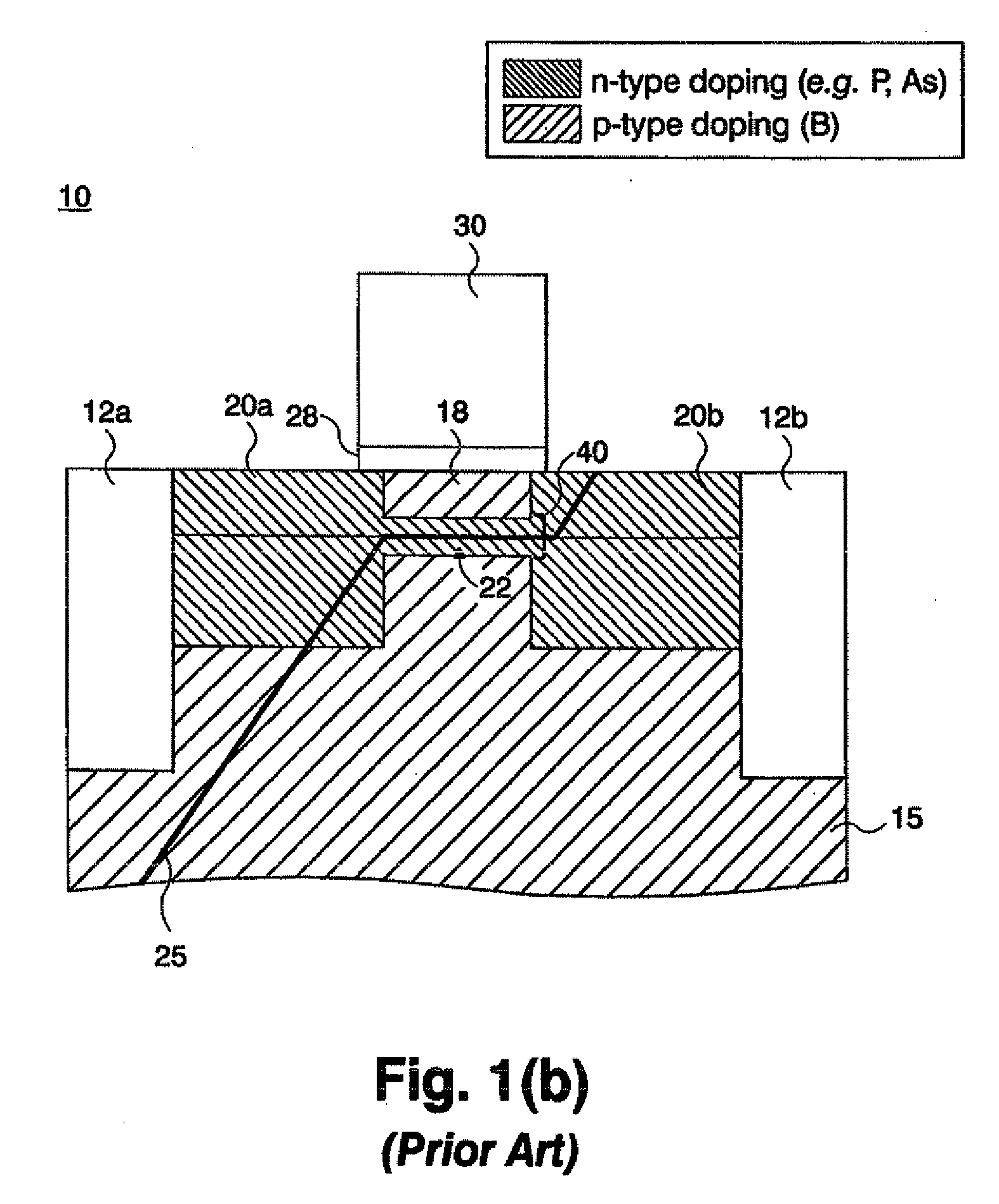

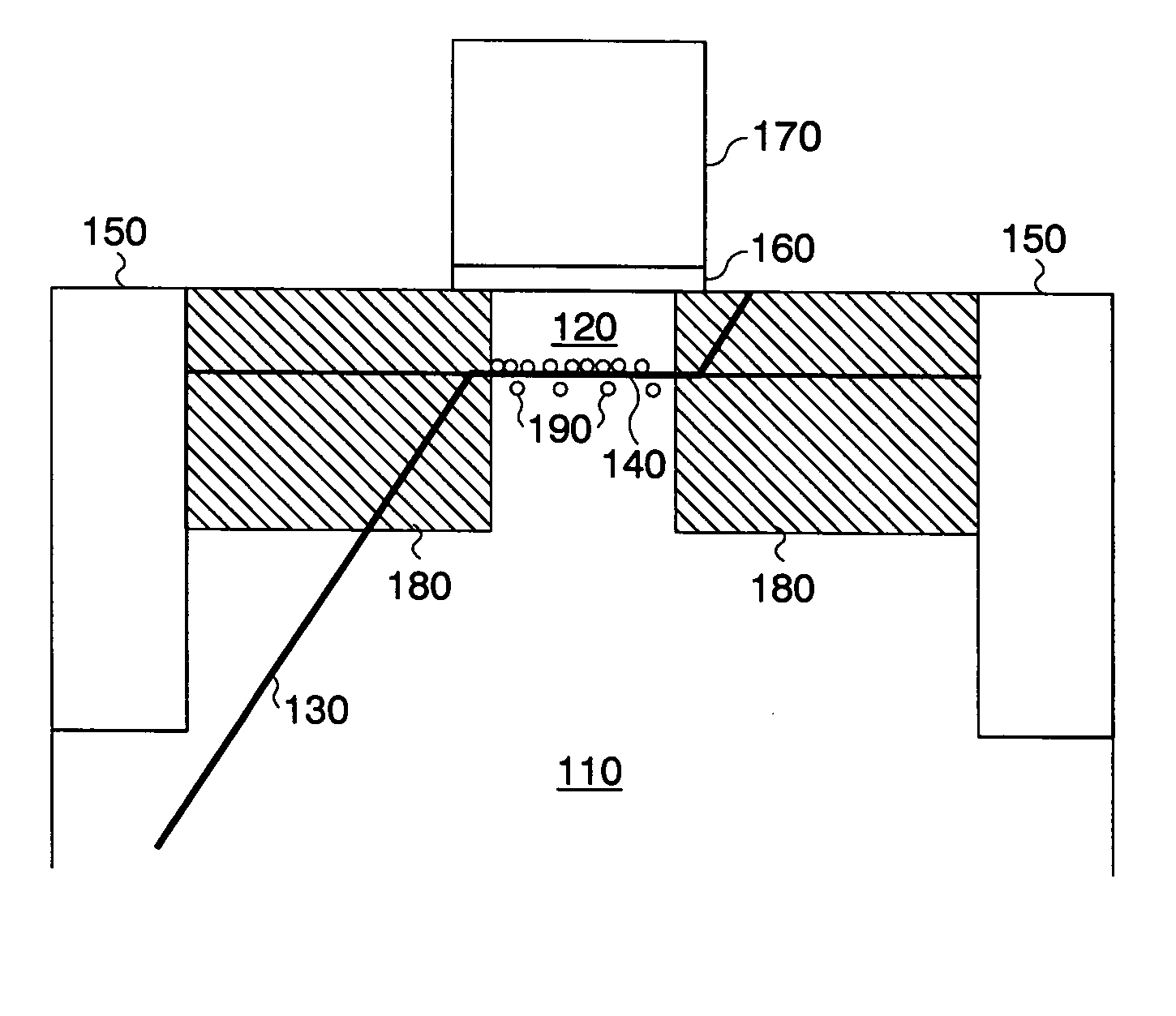

Method of reducing dislocation-induced leakage in a strained-layer field-effect transistor

ActiveUS20090325358A1Reduce leakagePrevent leakageSemiconductor/solid-state device manufacturingSemiconductor devicesMOSFETDopant

A structure and method of fabricating a semiconductor field-effect transistor (MOSFET) such as a strained Si n-MOSFET where dislocation or crystal defects spanning from source to drain is partially occupied by heavy p-type dopants. Preferably, the strained-layer n-MOSFET includes a Si, SiGe or SiGeC multi-layer structure having, in the region between source and drain, impurity atoms that preferentially occupy the dislocation sites so as to prevent shorting of source and drain via dopant diffusion along the dislocation. Advantageously, devices formed as a result of the invention are immune to dislocation-related failures, and therefore are more robust to processing and material variations. The invention thus relaxes the requirement for reducing the threading dislocation density in SiGe buffers, since the devices will be operable despite the presence of a finite number of dislocations.

Owner:TAIWAN SEMICON MFG CO LTD

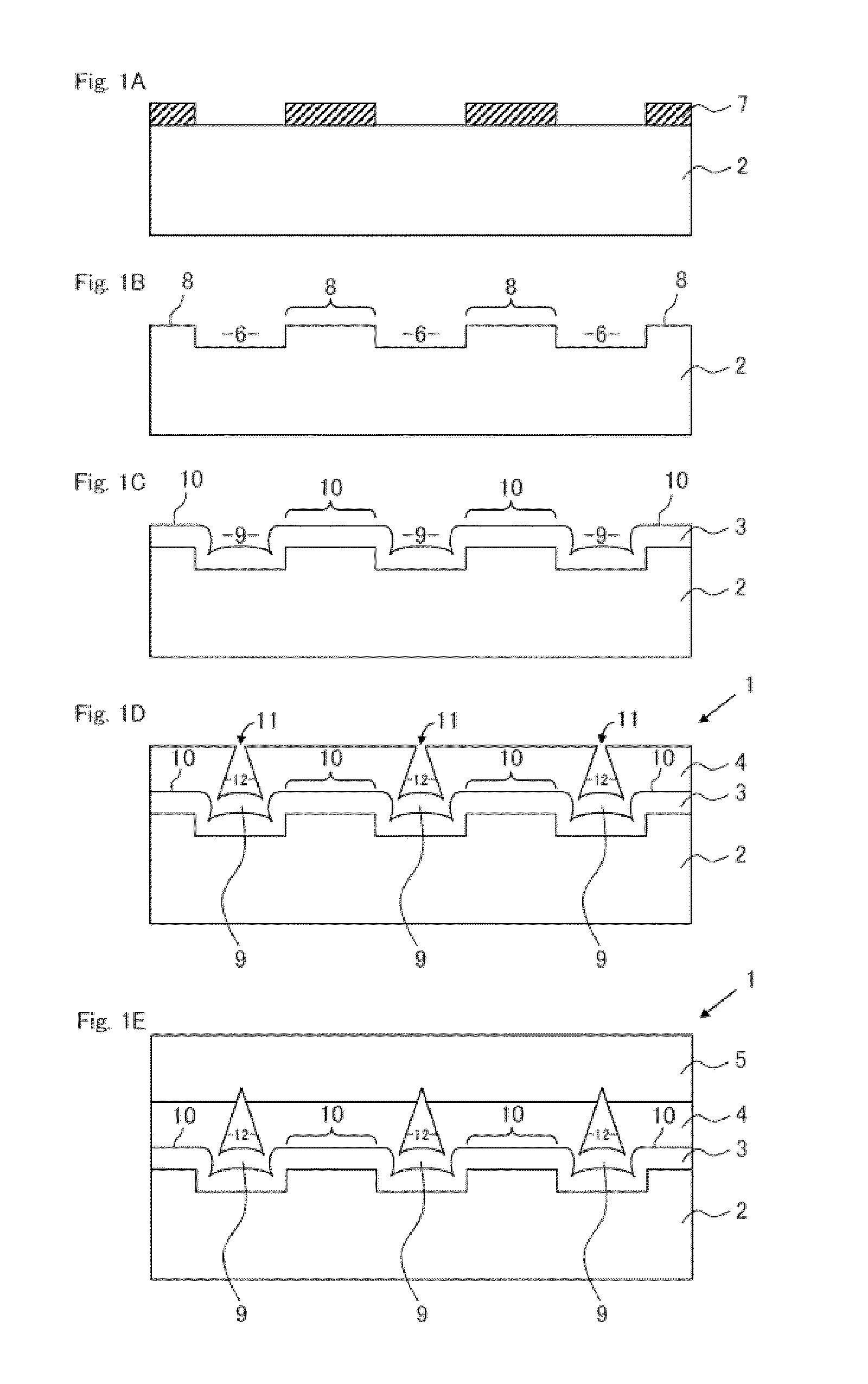

Template for Epitaxial Growth and Process for Producing Same

ActiveUS20120258286A1Increasing manufacturing costMaintain good propertiesPolycrystalline material growthLayered productsLateral overgrowthOptoelectronics

A surface of a sapphire (0001) substrate is processed to form recesses and protrusions so that protrusion tops are flat and a given plane-view pattern is provided. An initial-stage AlN layer is grown on the surface of the sapphire (0001) substrate having recesses and protrusions by performing a C+ orientation control so that a C+ oriented AlN layer is grown on flat surfaces of the protrusion tops, excluding edges, in such a thickness that the recesses are not completely filled and the openings of the recesses are not closed. An AlxGayN(0001) layer (1≧x>0, x+y=1) is epitaxially grown on the initial-stage AlN layer by a lateral overgrowth method. The recesses are covered with the AlxGayN(0001) layer laterally overgrown from above the protrusion tops. Thus, an template for epitaxial growth having a fine and flat surface and a reduced threading dislocation density is produced.

Owner:NIKKISO COMPANY

Method and system for lattice space engineering

InactiveUS20050233545A1Easy to useHigh device yieldSemiconductor/solid-state device manufacturingEngineeringStressed state

A system for manufacturing multilayered substrates. The system has a support member is adapted to process a film of material comprising a first side and a second side from a first state to a second state. The support member is attached to the first side of the film of material. The second state comprises a stressed state. The system has a handle substrate comprising a face, which is adapted to be attached to the second side of the film of material. The support member is capable of being detached from the first side of the film of material thereby leaving the handle substrate comprising the film of material in the second state being attached to the face of the handle substrate.

Owner:SILICON GENERAL CORPORATION

Method of producing high quality relaxed silicon germanium layers

InactiveUS7041170B2Reduce depositionIncrease probabilityPolycrystalline material growthSemiconductor/solid-state device manufacturingSemiconductor materialsMetallurgy

A method for minimizing particle generation during deposition of a graded Si1-xGex layer on a semiconductor material includes providing a substrate in an atmosphere including a Si precursor and a Ge precursor, wherein the Ge precursor has a decomposition temperature greater than germane, and depositing the graded Si1-xGex layer having a final Ge content of greater than about 0.15 and a particle density of less than about 0.3 particles / cm2 on the substrate.

Owner:TAIWAN SEMICON MFG CO LTD

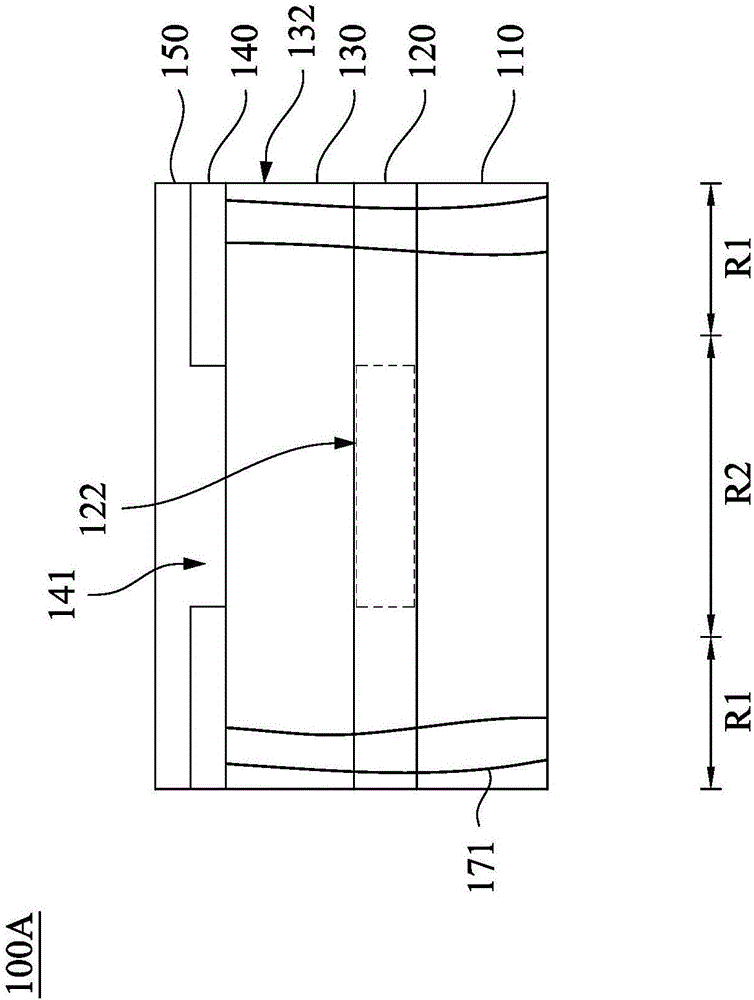

Semiconductor substrate and field-effect transistor, and manufacturing method for same

InactiveUS7405142B2Reduce threading dislocation densityReduce surface roughnessSemiconductor/solid-state device manufacturingSemiconductor devicesSurface roughnessCritical thickness

Owner:SUMCO CORP

Method of Producing Template for Epitaxial Growth and Nitride Semiconductor Device

ActiveUS20130069079A1Reduce threading dislocation densityEasy to optimizePolycrystalline material growthSemiconductor/solid-state device manufacturingLateral overgrowthSapphire

A surface of a sapphire (0001) substrate is processed so as to have recesses and protrusions so that protrusion tops are made flat and have a given plan-view pattern. An initial-stage AlN layer is epitaxially grown on the surface of the sapphire (0001) substrate so that new recesses are formed over the recesses, by performing C axis orientation control so that a C+ axis oriented AlN layer grows on flat surfaces of the protrusion tops, excluding edges. A first ELO layer including an AlN (0001) layer is epitaxially grown on the initial-stage AlN layer by an epitaxial lateral overgrowth method, and stops growing before a recess upper region above the new recesses is completely covered with the first ELO layer that is laterally grown from a protrusion upper surface of the initial-stage AlN layer. A second ELO layer including an AlxGa1-xN (0001) layer (1>x>0) is epitaxially grown on the first ELO layer by an epitaxial lateral overgrowth method. The recess upper region is completely covered with the second ELO layer that is laterally grown from an upper surface of the first ELO layer.

Owner:NIKKISO COMPANY

Nitride semiconductor substrate and method of manufacturing the same

InactiveUS20080054294A1Reduce manufacturing costSimple manufacturing processSemiconductor/solid-state device manufacturingSemiconductor devicesBlock structureDislocation

The present invention relates to a method of forming a nitride semiconductor substrate. This method includes steps of providing a substrate and then forming an epitaxy layer on the substrate. A patterned mask layer is formed on the epitaxy layer, wherein the patterned mask layer exposes a portion of the epitaxy layer. Next, an oxidation process is performed to oxidize the exposed epitaxy layer so as to form a plurality of dislocation blocking structures. The patterned mask layer is then removed. Further, a nitride semiconductor layer is formed on the epitaxy layer having the dislocation blocking structures.

Owner:IND TECH RES INST

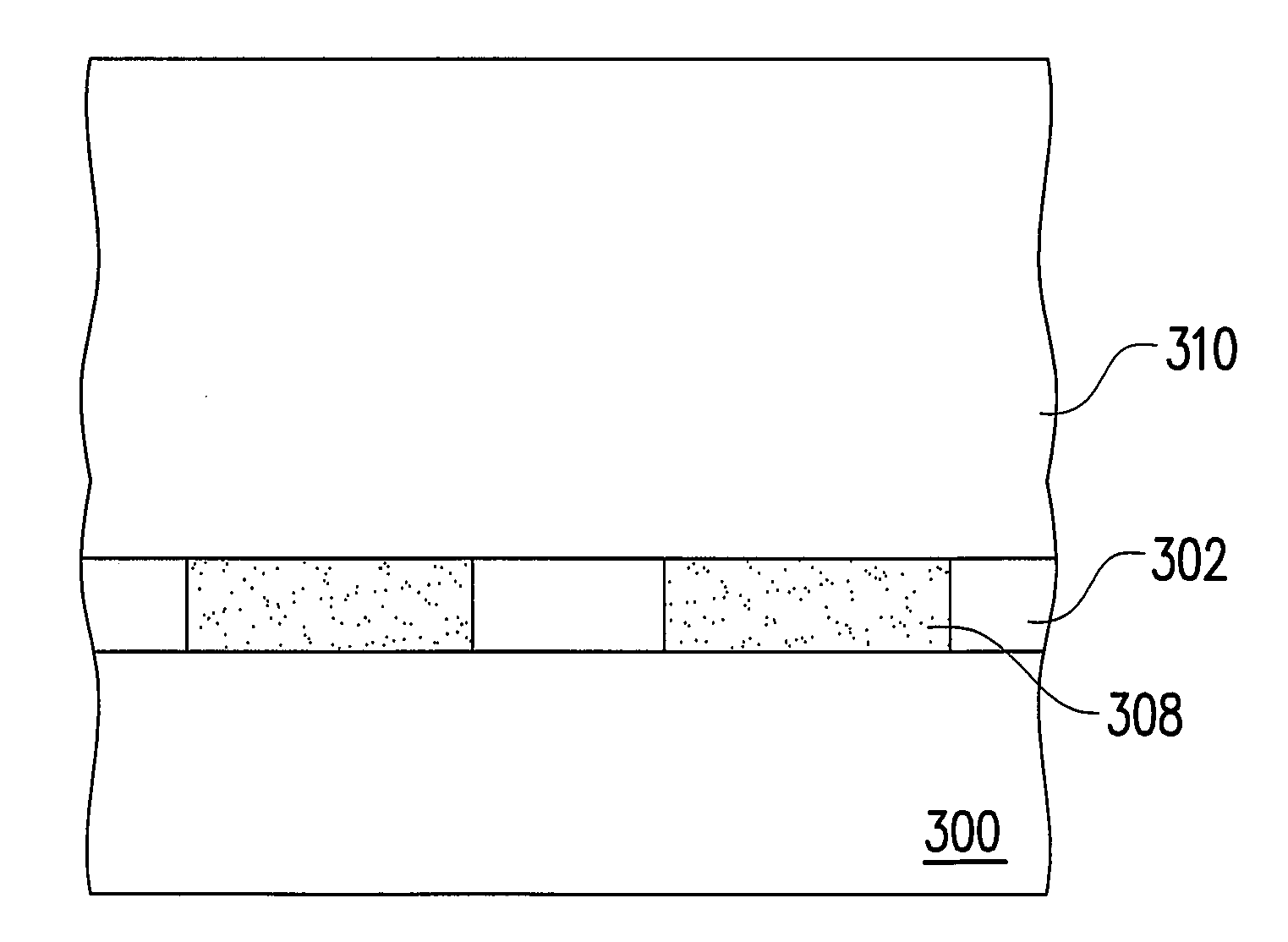

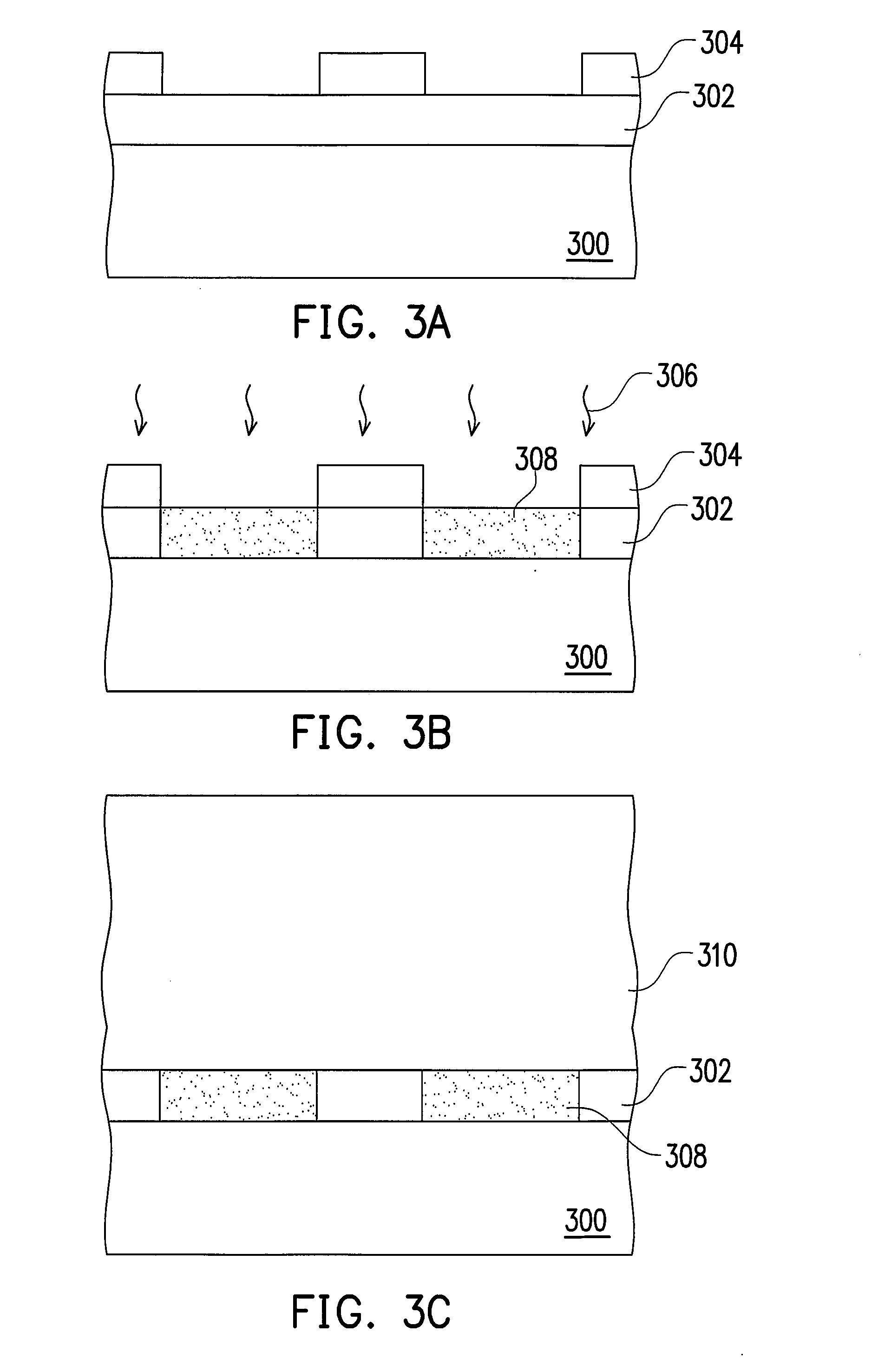

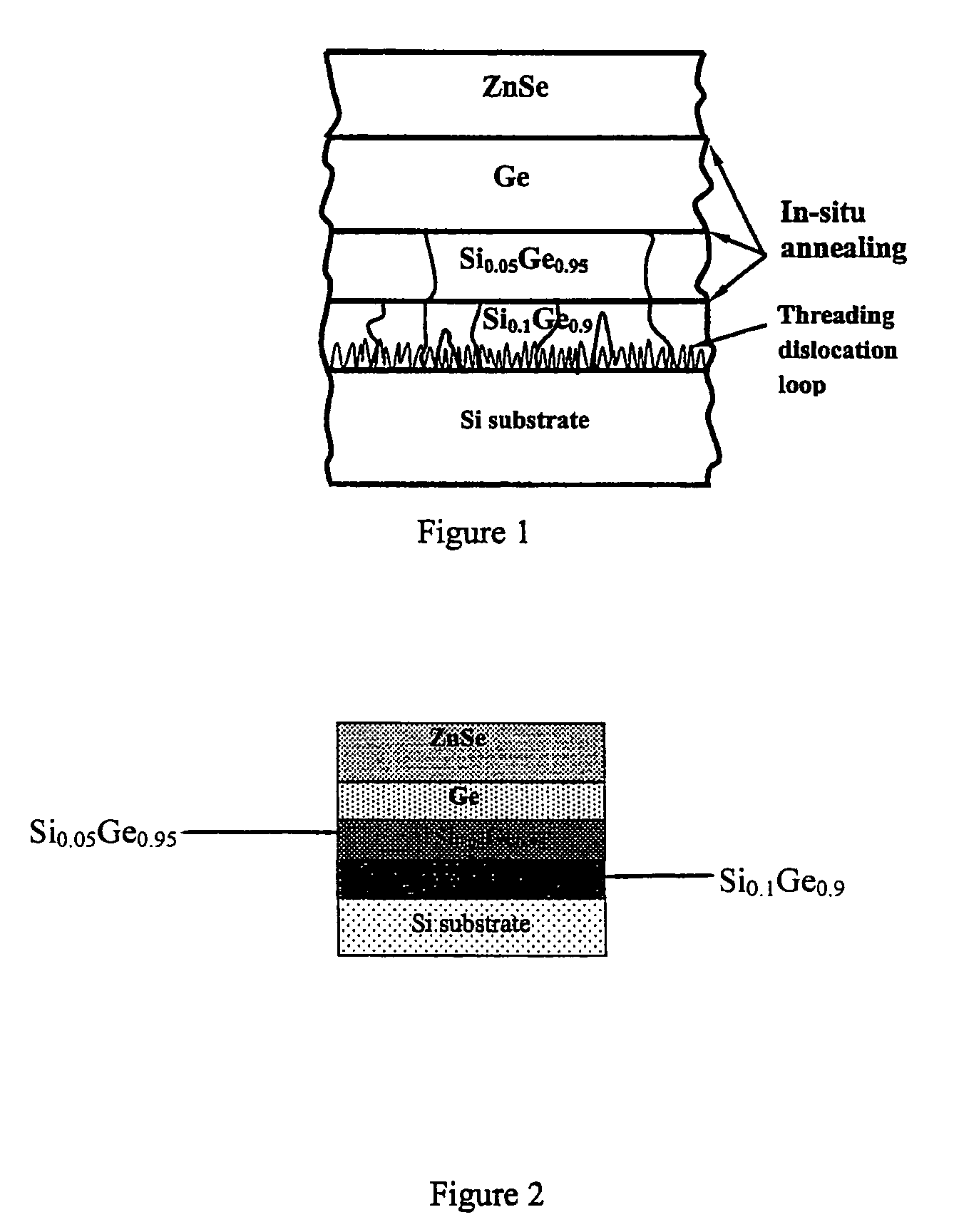

Technique to grow high quality ZnSe epitaxy layer on Si substrate

InactiveUS7071087B2Improve photoelectric performanceReduce threading dislocation densityPolycrystalline material growthVacuum evaporation coatingDiffusionUltra-high vacuum

A technique to grow high quality and large area ZnSe layer on Si substrate is provided, comprising growing GexSi1−x / Ge epitaxial layers on Si substrate by using ultra-high vacuum chemical vapor deposition (UHVCVD), and finally growing a ZnSe film on top Ge buffer layers.Two concepts are applied in the process of this invention, the first one is to block the dislocations generated from GexSi1−x epitaxial layers and to terminate the propagated upward dislocations by using strained interfaces, accordingly the dislocation density of ZnSe layer is greatly reduced and the surface roughness is improved; the second concept is to solve the problems of anti-phase domain due to growth of polar materials on non-polar material using off-cut angle Si substrate, and that is free from diffusion problems between different atoms while generally growing ZnSe layers on Si substrate.

Owner:WITTY MATE CORP

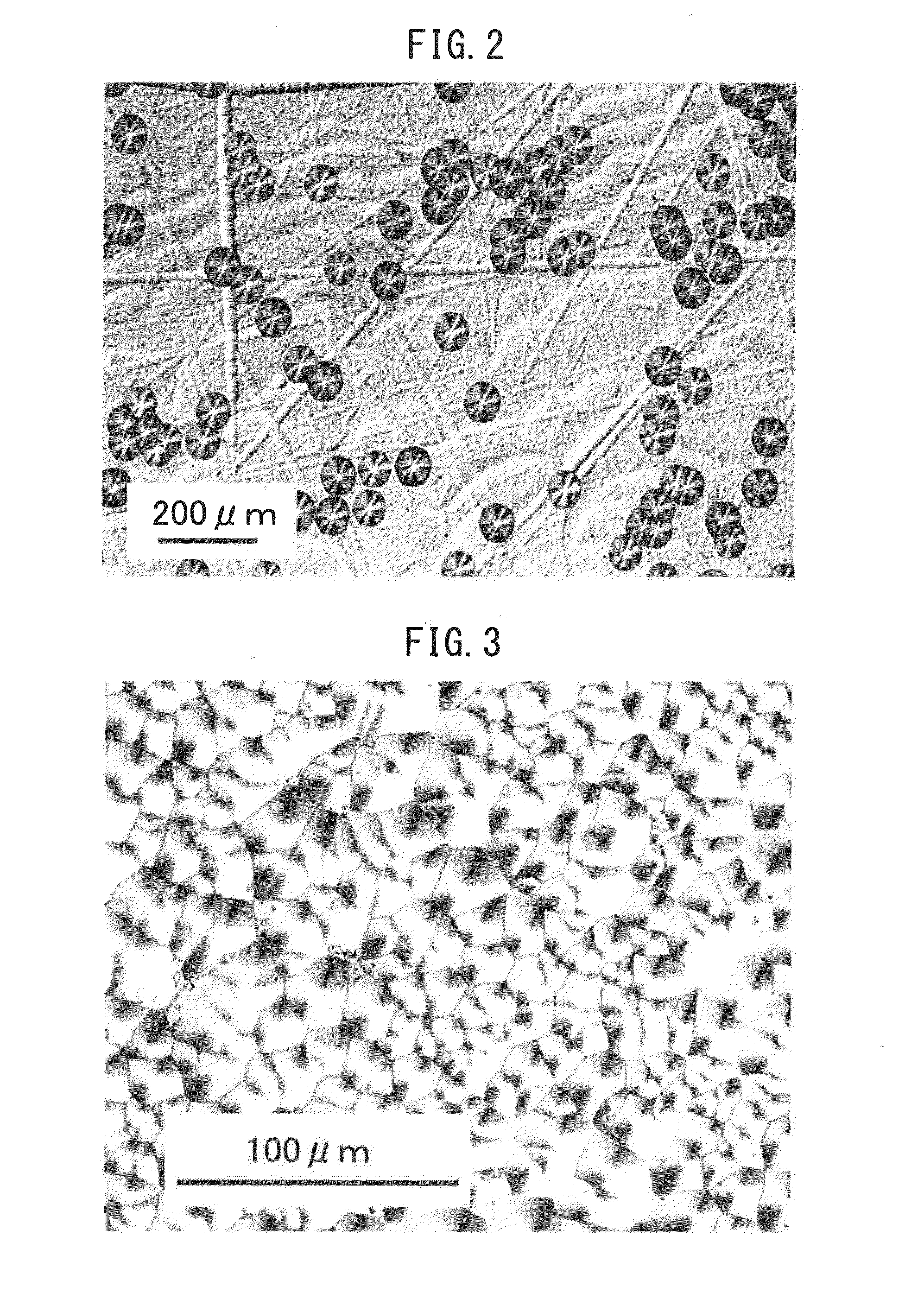

SiC Single-Crystal Ingot, SiC Single Crystal, and Production Method for Same

ActiveUS20150191849A1Reduce threading dislocation densityLow resistivityPolycrystalline material growthFrom normal temperature solutionsNitrogenDislocation

Provided are an SiC single-crystal ingot containing an SiC single crystal having a low threading dislocation density and low resistivity; an SiC single crystal; and a production method for the SiC single crystal. The SiC single crystal ingot contains a seed crystal and a grown crystal grown by a solution process in which the seed crystal is the base point, the grown crystal of the SiC single crystal ingot containing a nitrogen density gradient layer in which the nitrogen content increases in the direction of growth from the seed crystal.

Owner:TOYOTA JIDOSHA KK

Method of reducing dislocation-induced leakage in a strained-layer field-effect transistor

InactiveUS20050104092A1Reduce leakagePrevent leakageSemiconductor/solid-state device manufacturingSemiconductor devicesMOSFETDislocation

A structure and method of fabricating a semiconductor field-effect transistor (MOSFET) such as a strained Si n-MOSFET where dislocation or crystal defects spanning from source to drain is partially occupied by heavy p-type dopants. Preferably, the strained-layer n-MOSFET includes a Si, SiGe or SiGeC multi-layer structure having, in the region between source and drain, impurity atoms that preferentially occupy the dislocation sites so as to prevent shorting of source and drain via dopant diffusion along the dislocation. Advantageously, devices formed as a result of the invention are immune to dislocation-related failures, and therefore are more robust to processing and material variations. The invention thus relaxes the requirement for reducing the threading dislocation density in SiGe buffers, since the devices will be operable despite the presence of a finite number of dislocations.

Owner:ALSEPHINA INNOVATIONS INC

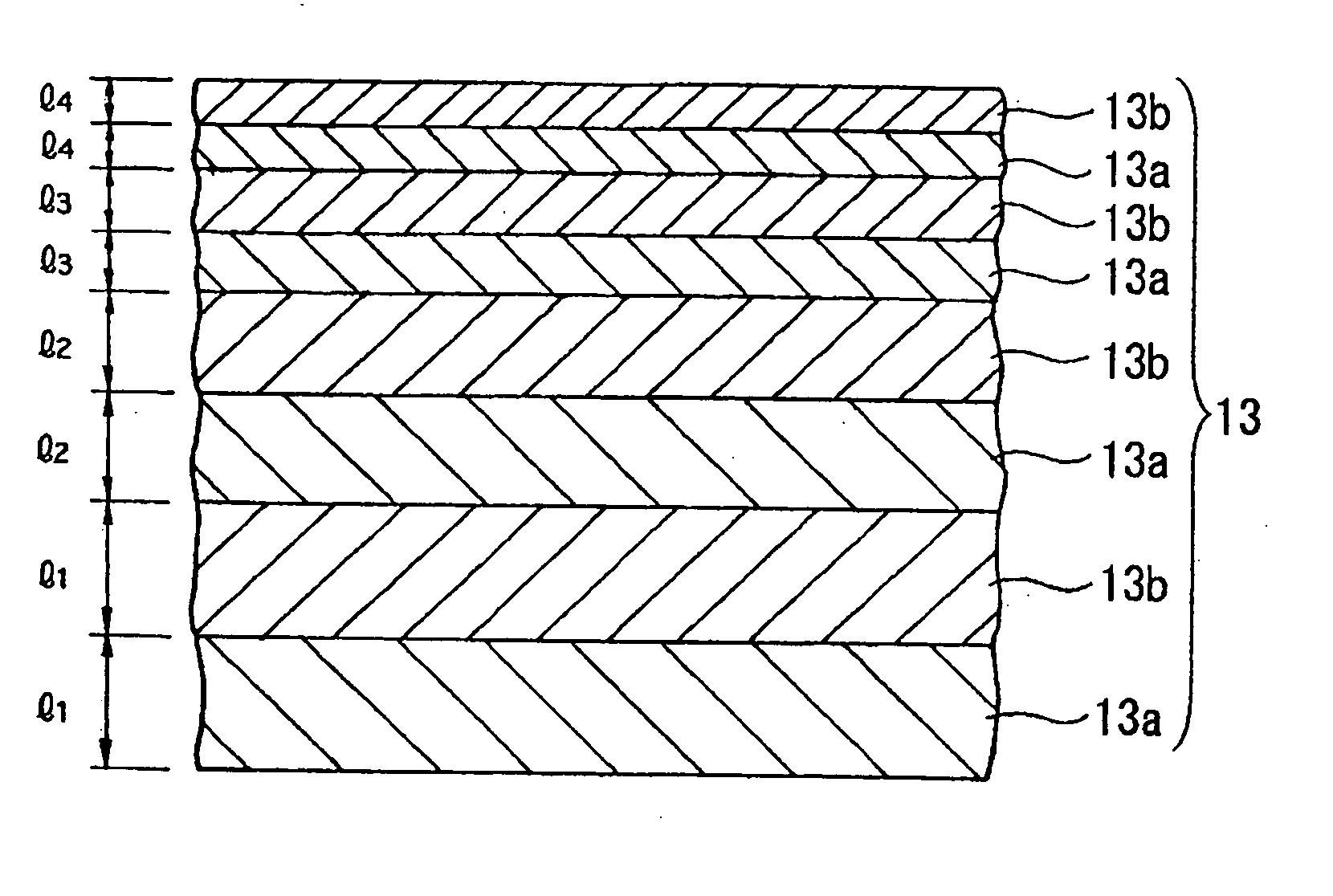

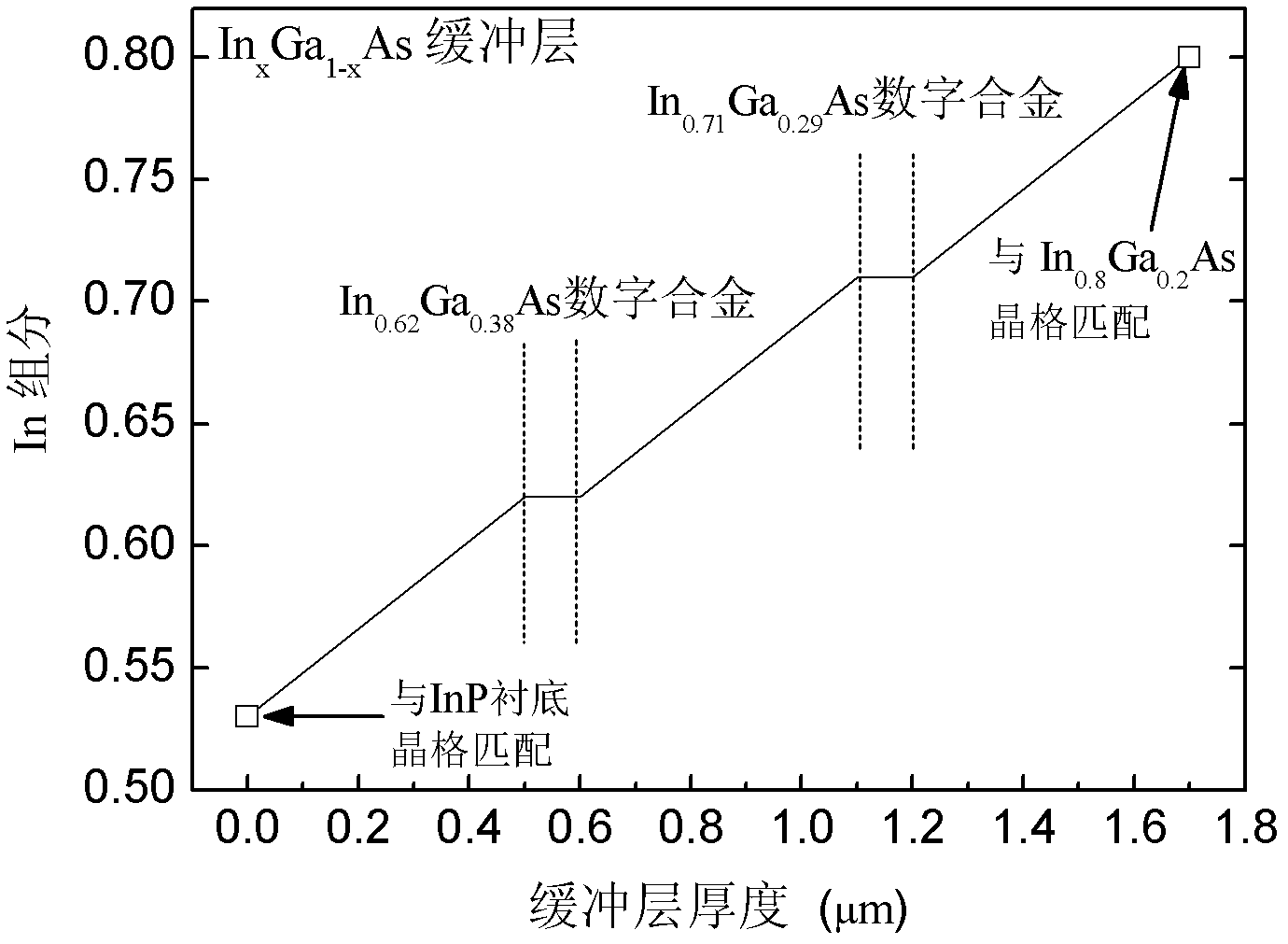

Macrolattice mismatch epitaxial buffer layer structure containing digital dislocation separating layers and preparation method thereof

InactiveCN102254954AReduce threading dislocation densityImproved lattice quality and optoelectronic propertiesFinal product manufactureSemiconductor devicesDislocationBeam source

The invention relates to a macrolattice mismatch epitaxial buffer layer structure containing digital dislocation separating layers and a preparation method thereof. The structure is characterized in that n layers of digital alloy dislocation separating layer materials are inserted into an ingredient gradual changing buffer layer. The preparation method comprise the following steps: adjusting beam source temperature, growing a ingredient gradual changing buffer layer on a substrate, and according to present gradual changing ingredient, forming a digital alloy dislocation separating layer through growing short period superlattice; adjusting the beam source temperature again, growing a ingredient gradual changing buffer layer, regrowing a digital alloy dislocation separating layer according to present gradual changing ingredient; regrowing a ingredient gradual changing buffer layer in above sequence until the buffer layer ingredient gradually changes to a desirable value to obtain the macrolattice mismatch epitaxial buffer layer structure. According to the invention, the macrolattice mismatch epitaxial material takes place relaxation and releases stress rapidly and effectively in the buffer layer and isolates penetrating dislocation, thus penetrating dislocation density of the epitaxial material on the buffer layer is reduced, and crystal lattice quality and photoelectric characteristic of the macrolattice mismatch epitaxial material on the buffer layer are improved.

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI

Semiconductor device

InactiveUS20110260175A1Reduce leakage currentRestrains generationSemiconductor devicesSemiconductor packageSingle crystal

A silicon carbide layer is provided on a substrate, has a hexagonal single-crystal structure, and has a surface at which a depletion layer is formed. A protective film is insulative and provided on the silicon carbide layer to directly cover the surface. The surface thus directly covered with the protective film includes a portion having an off angle of not more than 10° relative to the {0-33-8} plane of the silicon carbide layer. This results in reduced leakage current flowing in an interface between the protective film and the semiconductor layer.

Owner:SUMITOMO ELECTRIC IND LTD

Light-emitting diode and manufacturing method thereof

ActiveCN106129202AImprove luminous efficiencyReduce threading dislocation densitySemiconductor devicesVertical projectionThreading dislocations

The invention discloses a light-emitting diode and a manufacturing method thereof. The light-emitting diode (LED) includes a first type semiconductor layer, a second type semiconductor layer, an active layer, a dielectric layer and an electrode. The active layer is disposed between the first type semiconductor layer and the second type semiconductor layer. The active layer has at least one threading dislocation therein. The dielectric layer is disposed on the second type semiconductor layer. The dielectric layer has at least one first opening therein to expose a part of the second type semiconductor layer. The vertical projection of the threading dislocation on the dielectric layer is separated from the first opening. The electrode partially is disposed on the dielectric layer and electrically coupled to the second type semiconductor layer through the first opening. Light-emitting efficiency of the light-emitting diode is improved.

Owner:MIKRO MESA TECH

Semiconductor wafer comprising gallium nitride layer having one or more silicon nitride interlayer therein

ActiveUS9142723B2Reduce threading dislocation densitySemiconductor/solid-state device manufacturingNanoopticsGallium nitrideSilicon nitride

A semiconductor wafer comprising a substrate layer and a first GaN layer having one or more SiNx interlayers therein, wherein in the first GaN layer at least one SiNx interlayer has GaN penetrated through one or more portions of said SiNx interlayer and preferably has a thickness of from 0.5 to 10 nm.

Owner:INTELLEC

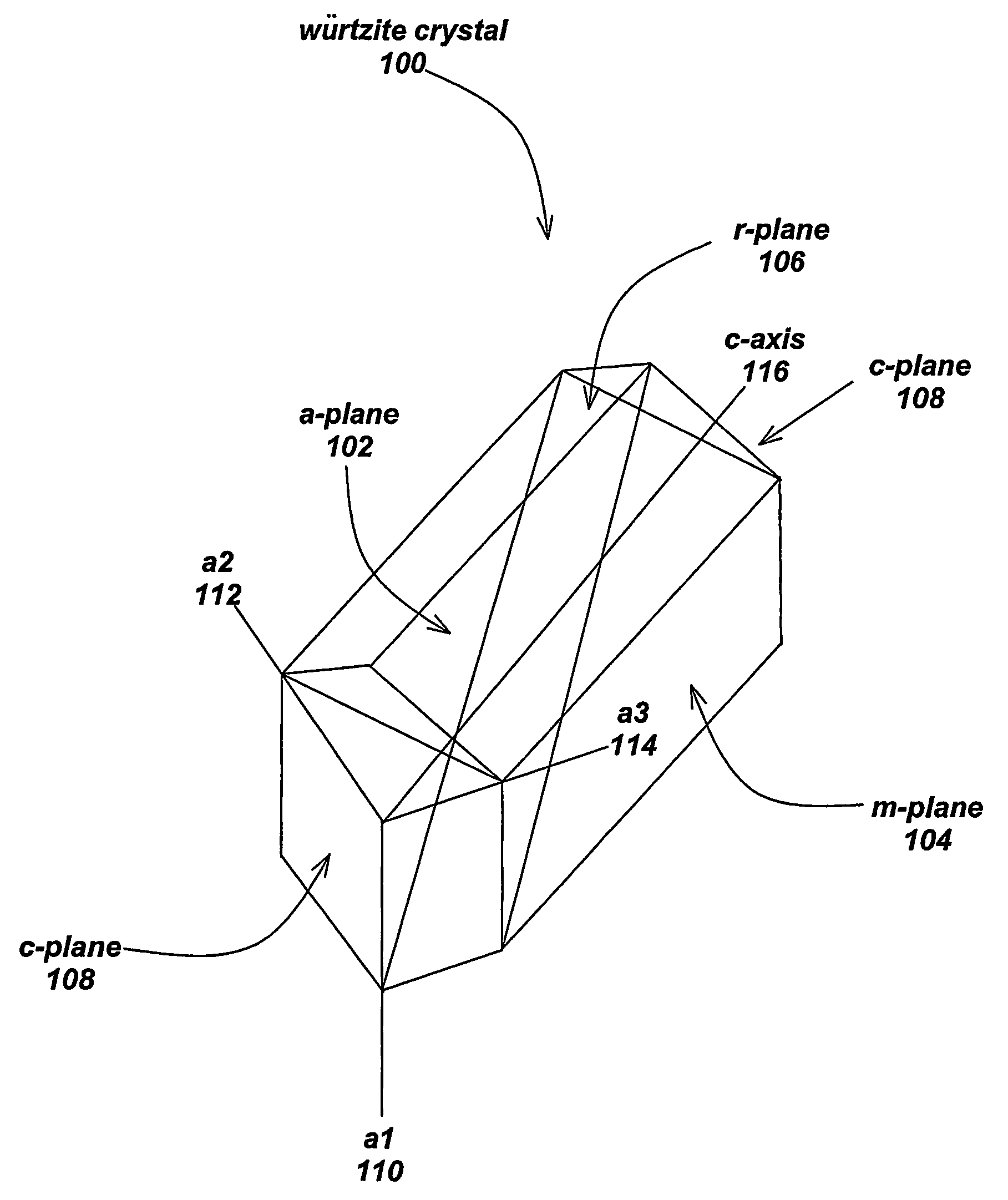

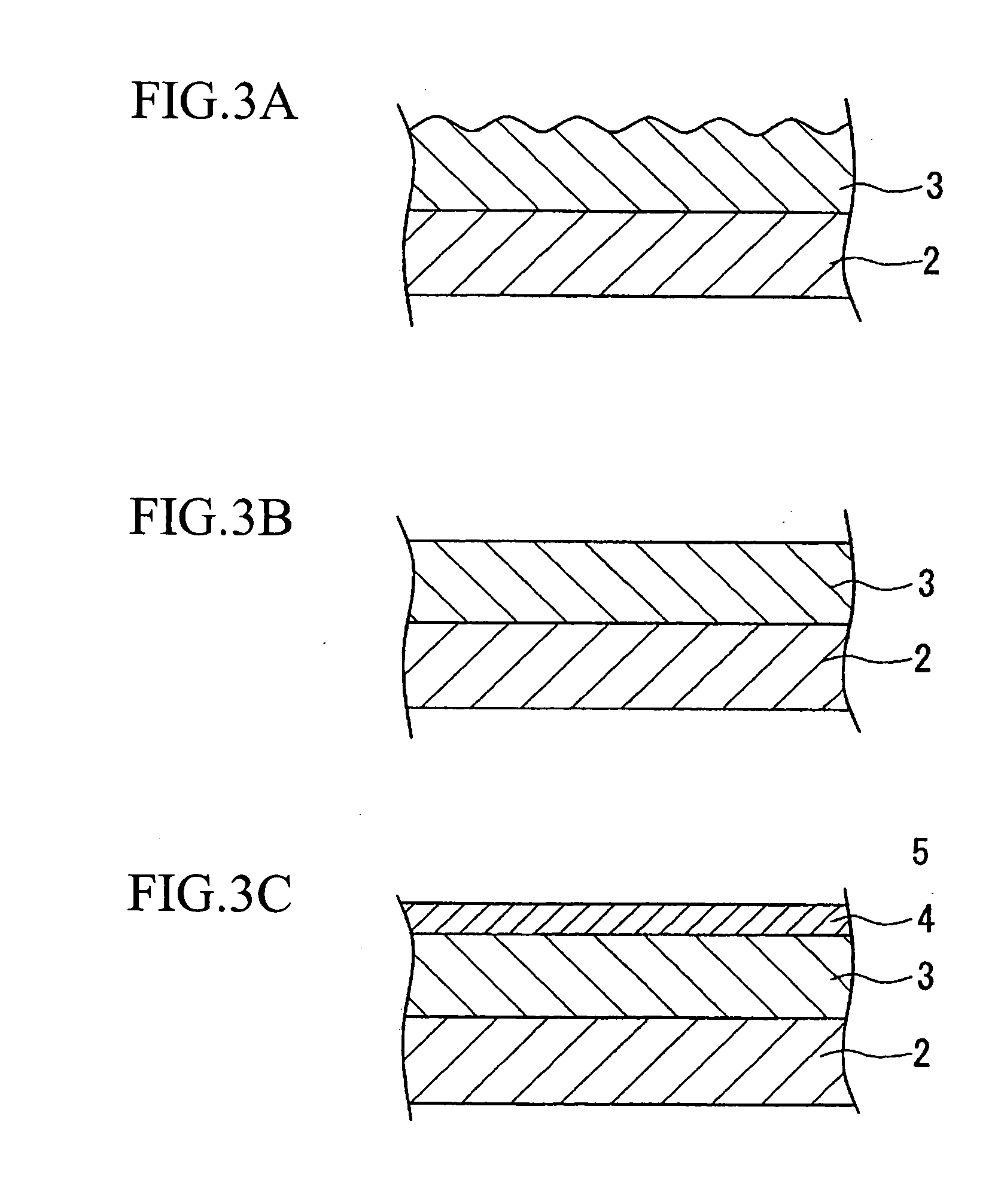

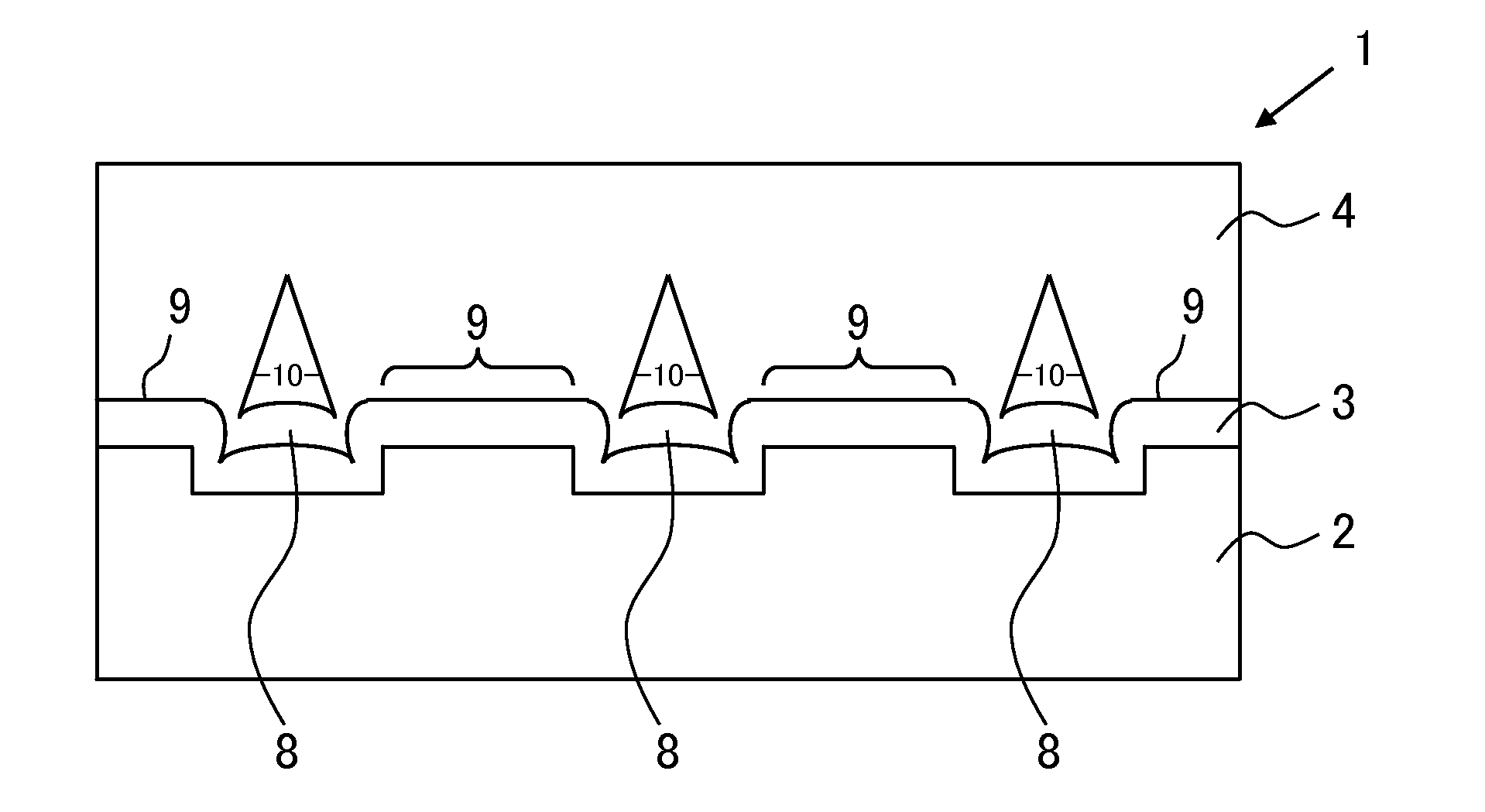

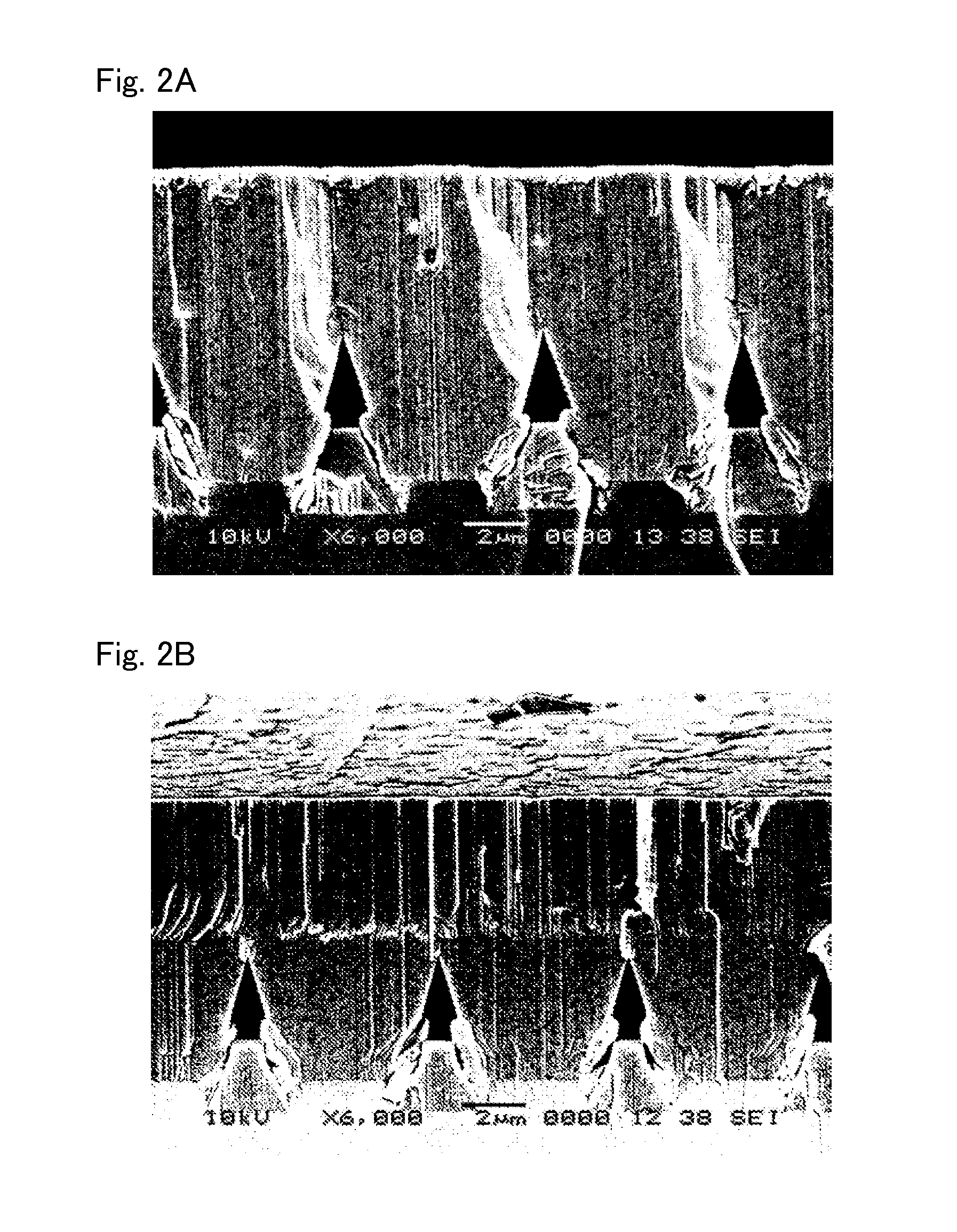

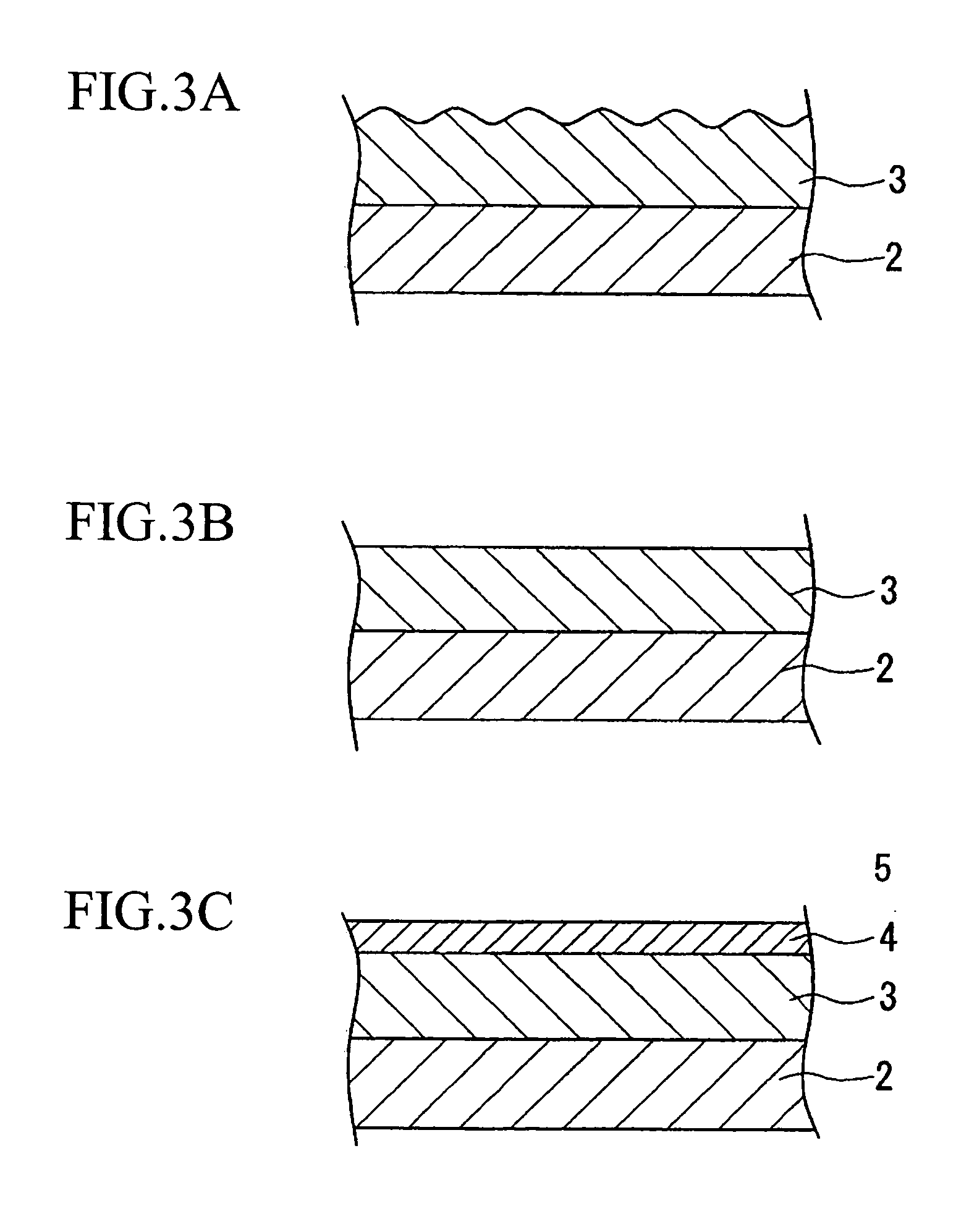

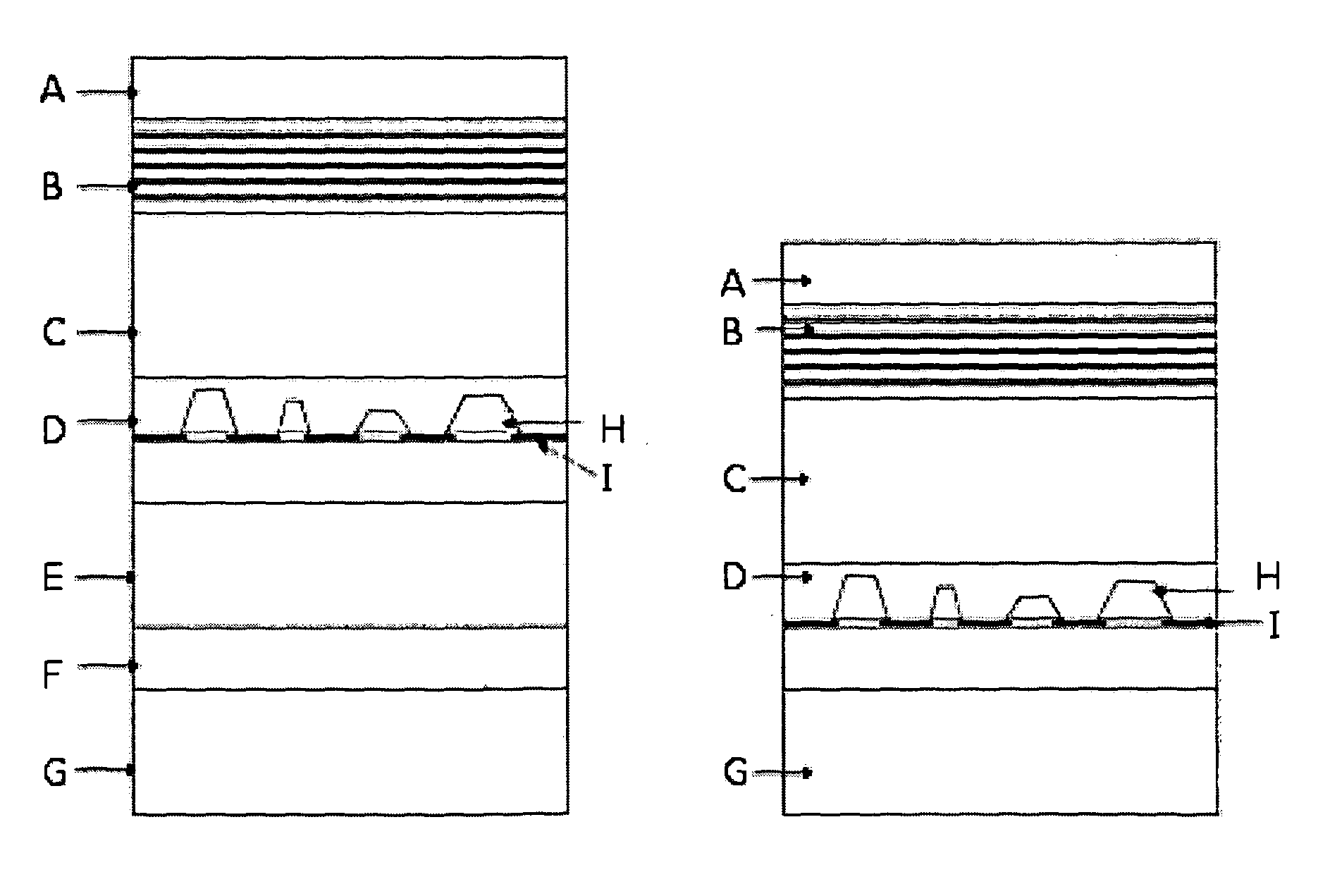

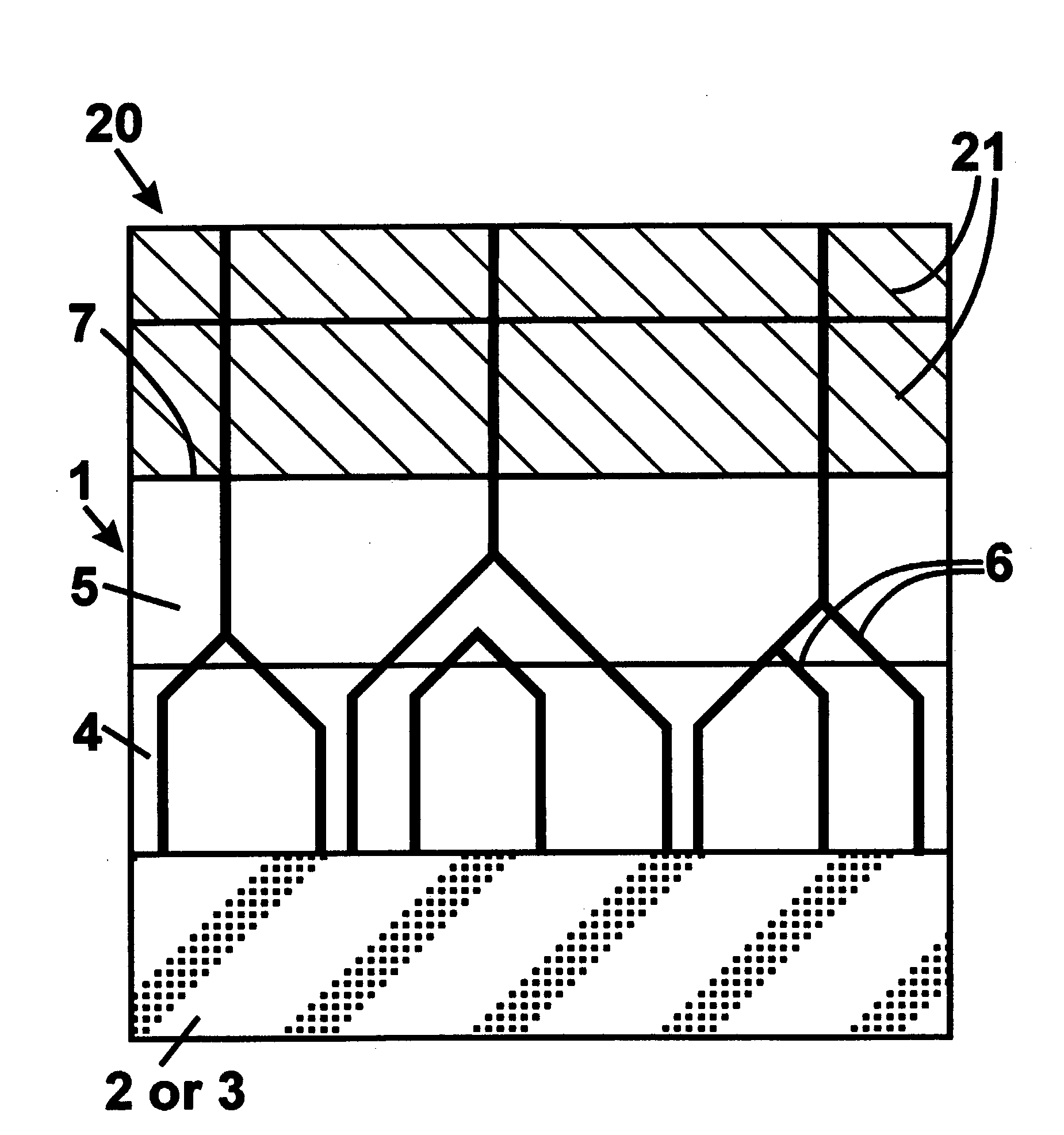

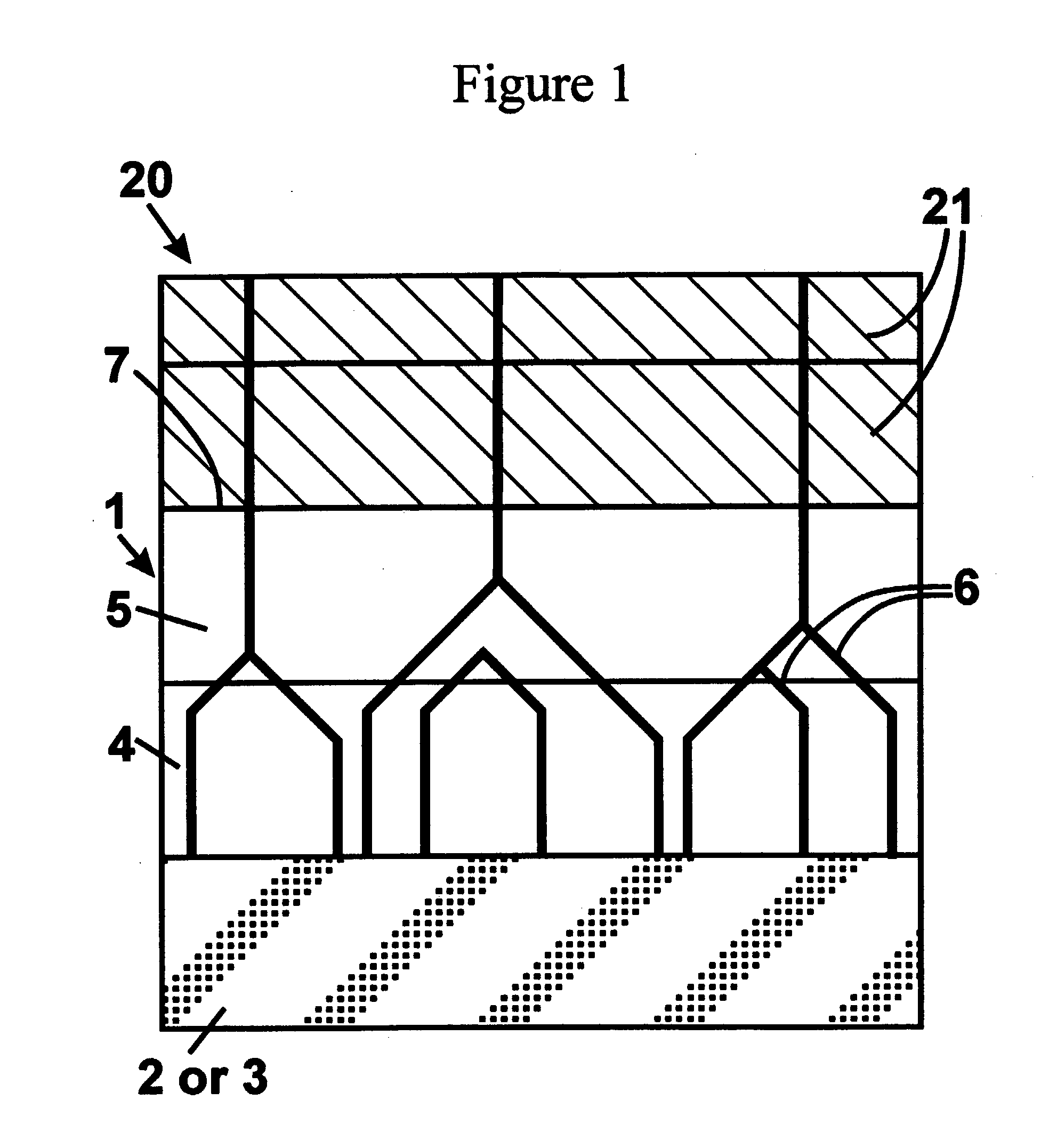

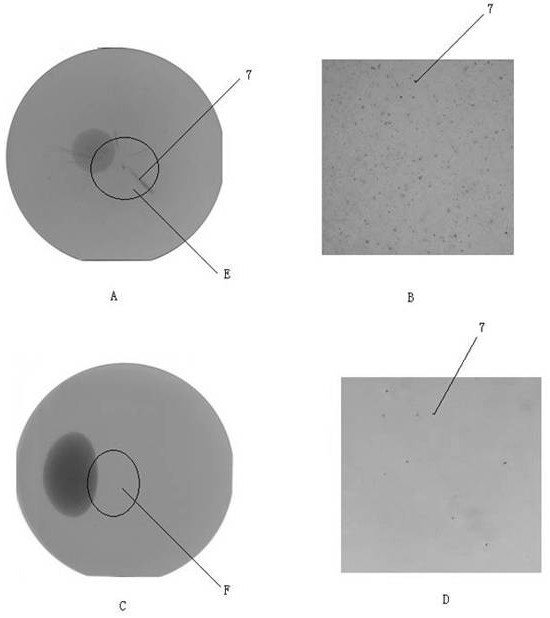

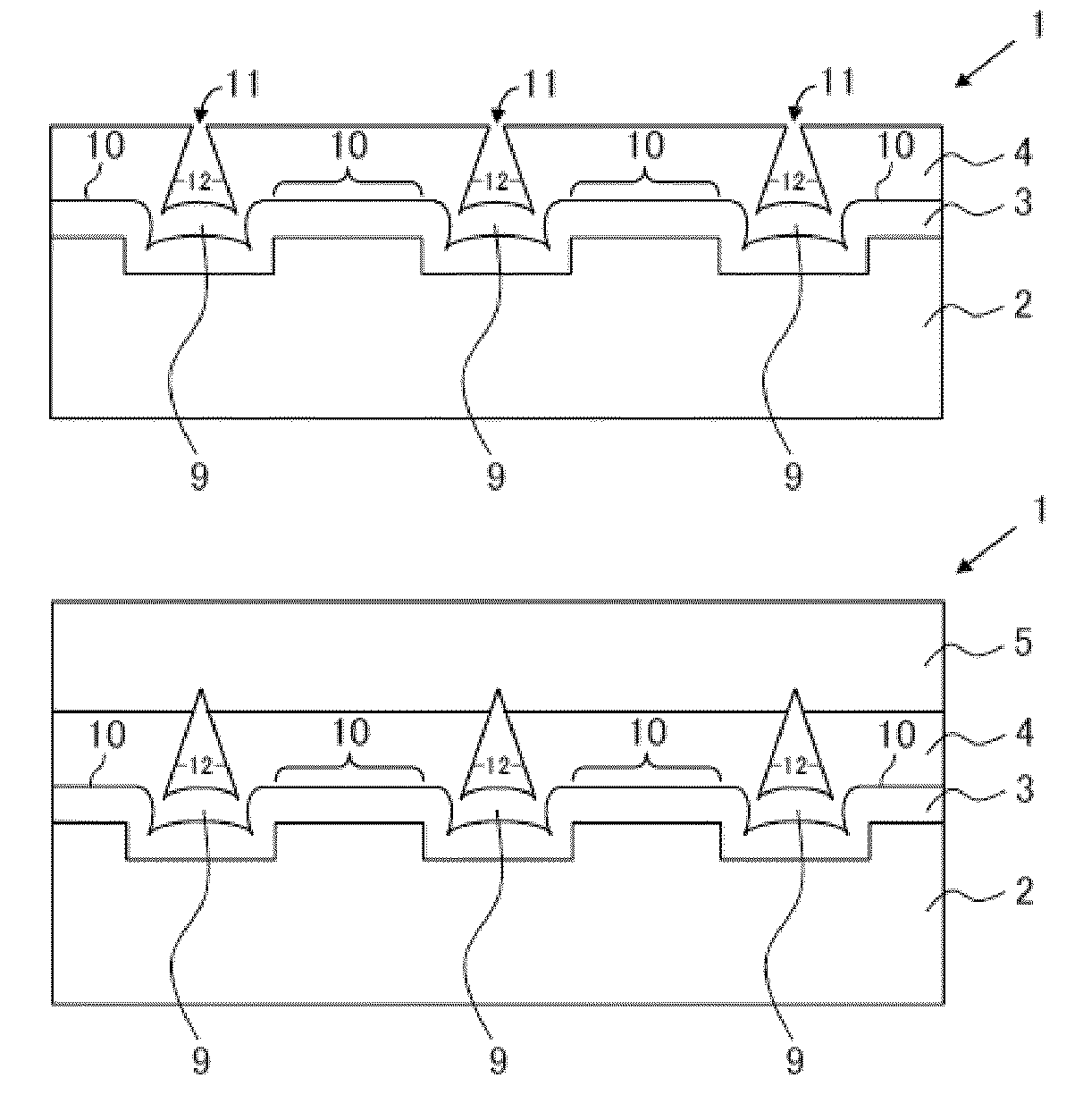

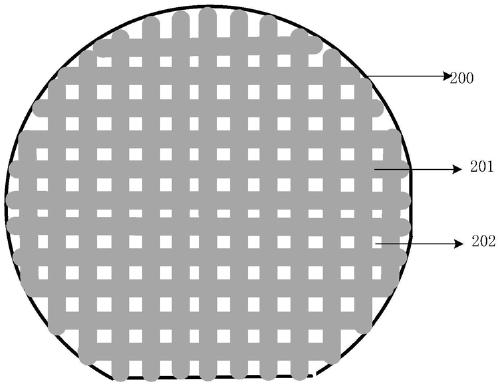

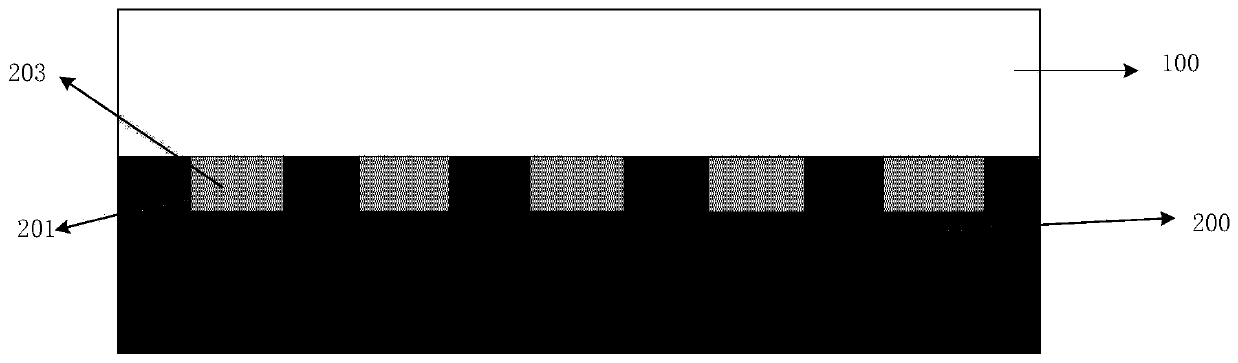

Semiconductor Substrate, Semiconductor Device and Method of Manufacturing a Semiconductor Substrate

InactiveUS20080308841A1Increase the areaIncrease probabilitySemiconductor/solid-state device manufacturingSemiconductor devicesReaction layerDevice material

A semiconductor substrate (1) of the present invention is made of nitrides of group III metals having wurtzite crystal structure and is grown in vapor phase either on a (0001) oriented foreign substrate (2), lattice mismatched to the semiconductor substrate materials, or on existing (0001) oriented highly dislocated layer (3) of the semiconductor substrate materials and has a highly reduced dislocation density. According to the present invention, a structure is utilized for the dislocation density reduction, which comprises a dislocation redirection layer (4) providing intentional inclination of threading dislocations (6) towards high index crystallographic planes having crystallographic indexes other than (0001) and those of the type {1 100}, in order to enhance the probability for dislocation reactions; and a dislocation reaction layer (5) positioned above said dislocation layer (4), in which the threading dislocations (6) coalesce with each other resulting in reduced threading dislocation density at the semiconductor substrate surface (7).

Owner:OPTOGAN OY

METHOD OF GROWING PURE Ge THIN FILM WITH LOW THREADING DISLOCATION DENSITY

InactiveUS20100144124A1Reduce threading dislocation densityPolycrystalline material growthSemiconductor/solid-state device manufacturingReduced pressure chemical vapor depositionSingle crystal

Provided is a method of growing a pure germanium (Ge) thin film with low threading dislocation density using reduced pressure chemical vapor deposition (RPCVD), which includes growing a Ge thin film on a silicon (Si) substrate at a low temperature, performing real-time annealing for a short period of time, and growing the annealed Ge thin film at a high temperature. The grown Ge single crystal thin film can overcome conventional problems of generation of a Si—Ge layer due to Si diffusion, and propagation of misfit dislocation to a high-temperature Ge thin film.

Owner:ELECTRONICS & TELECOMM RES INST

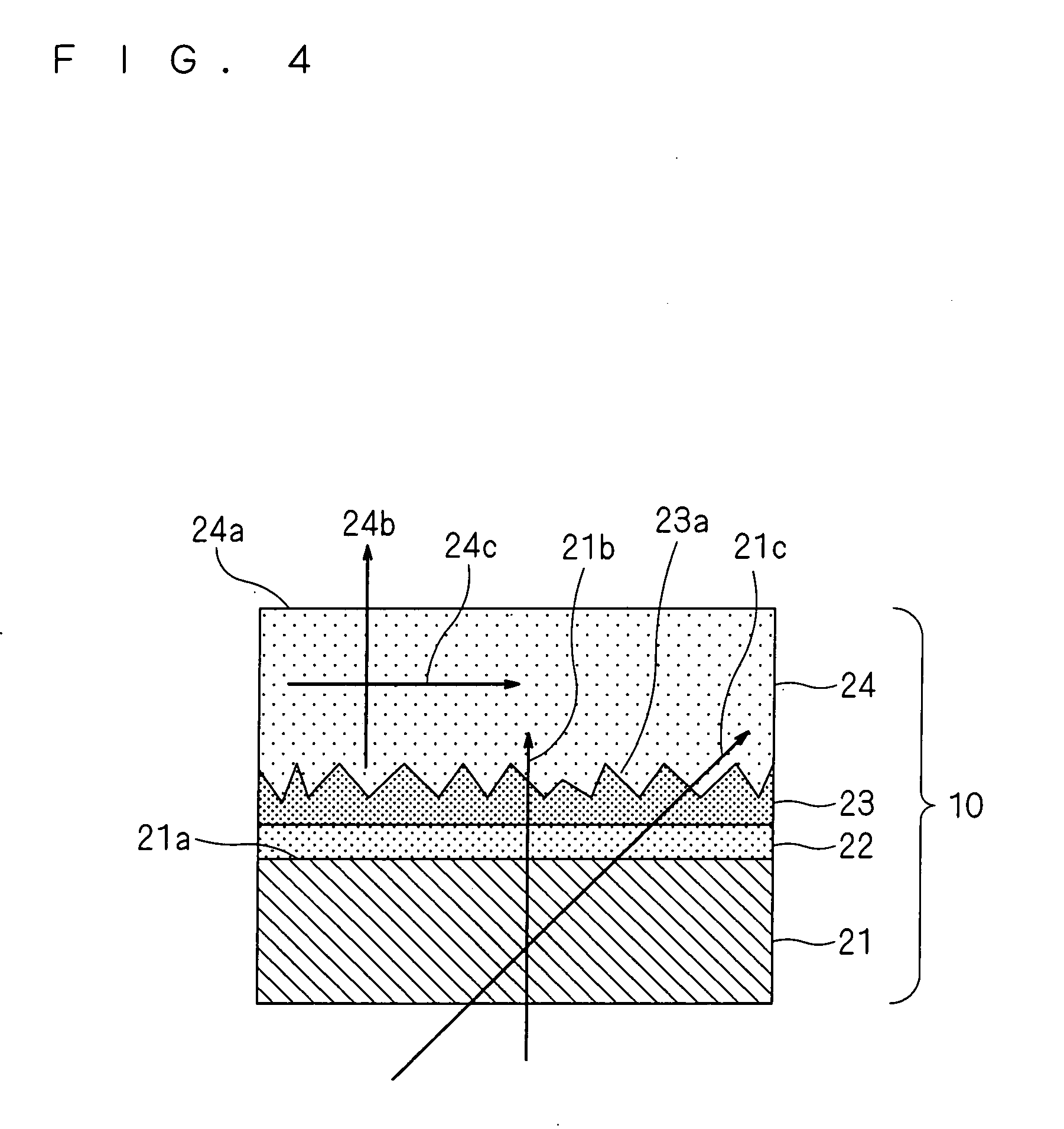

Method for Producing Group III Nitride Semiconductor and Group III Nitride Semiconductor

ActiveUS20140353804A1Improve external quantum efficiencyReduce threading dislocation densitySemiconductor/solid-state device manufacturingSemiconductor devicesPhysicsRefractive index

A first side surface of post of the first stripe is formed so that a plane which is most parallel to the first side surface among low-index planes of the growing Group III nitride semiconductor is a m-plane (10-10), and a first angle between the first lateral vector obtained by orthogonally projecting a normal vector of the first side surfaces to the main surface and a m-axis projected vector obtained by orthogonally projecting a normal vector of the m-plane of the growing semiconductor to the main surface is from 0.5° to 6°. A second side surface of post of the second stripe is formed so that a plane which is most parallel to the second side surface among low-index planes of the growing semiconductor is an a-plane (11-20), and a second angle between the second lateral vector and an a-axis projected vector of the a-plane is from 0° to 10°.

Owner:TOYODA GOSEI CO LTD

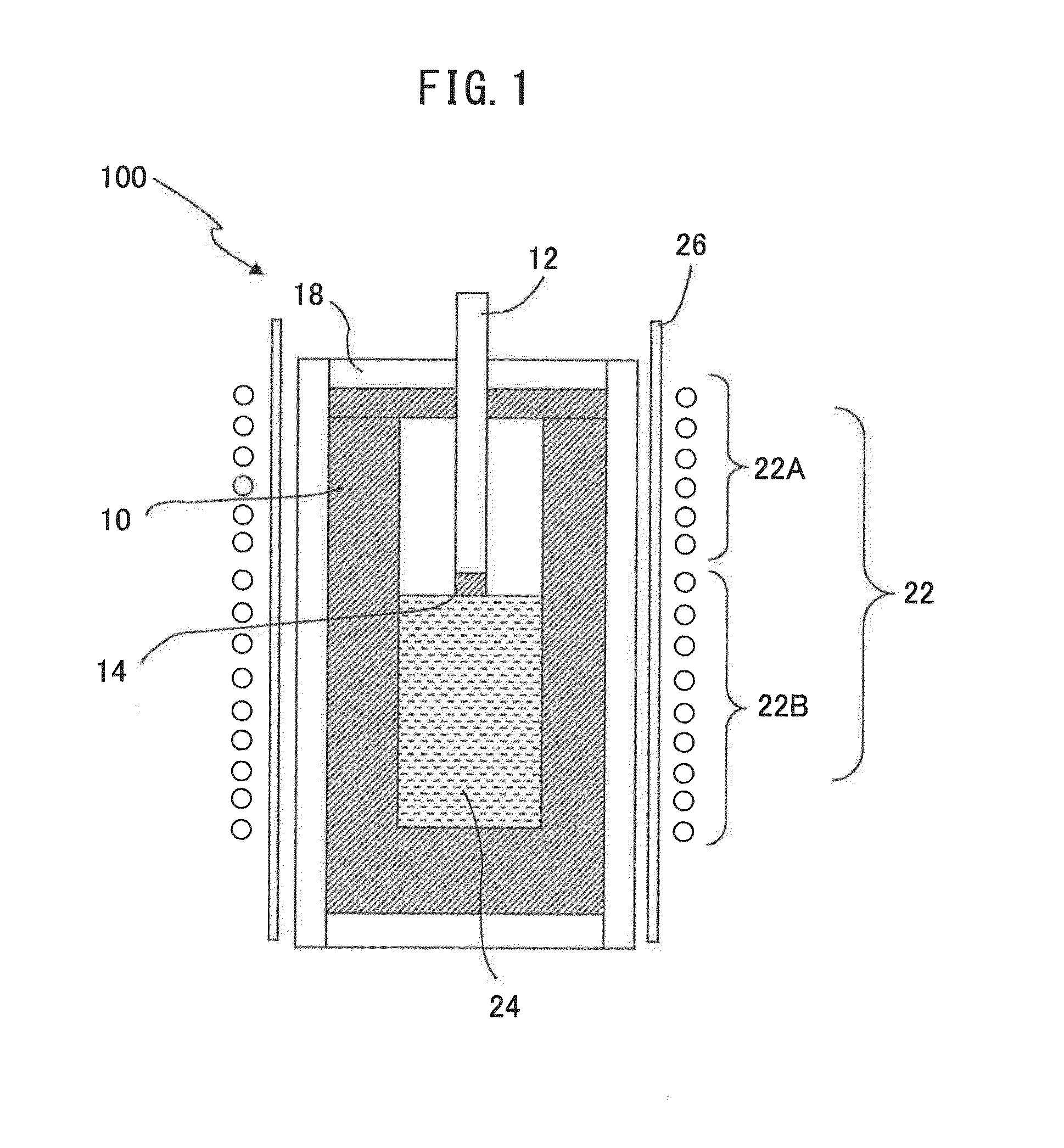

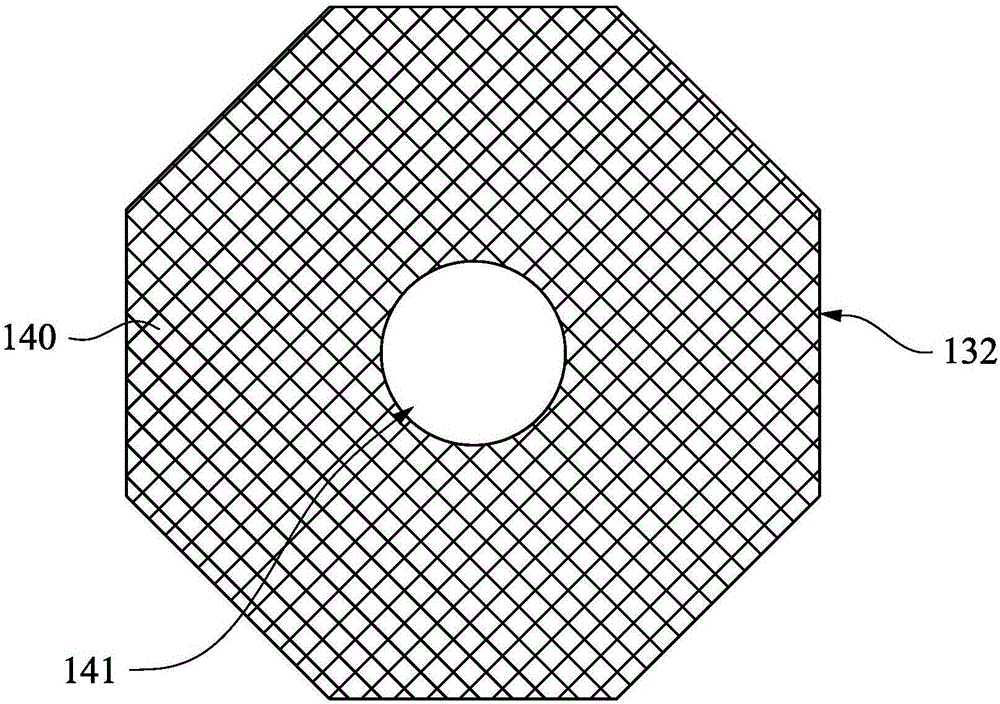

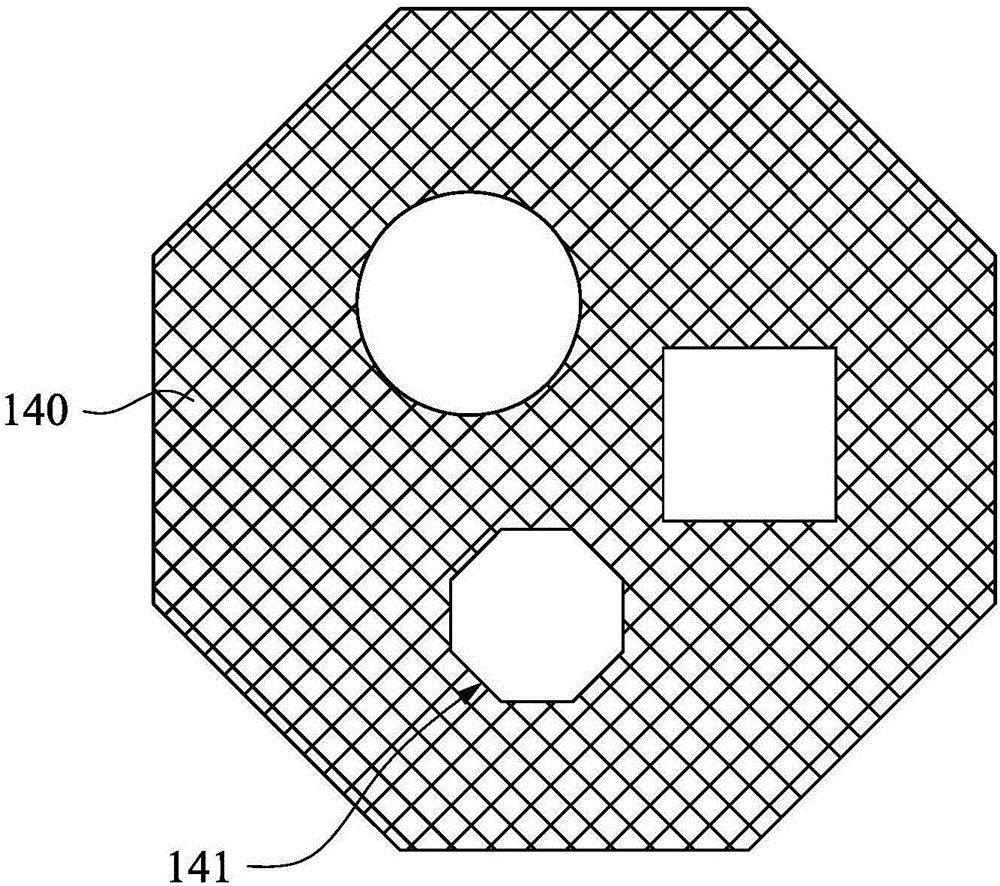

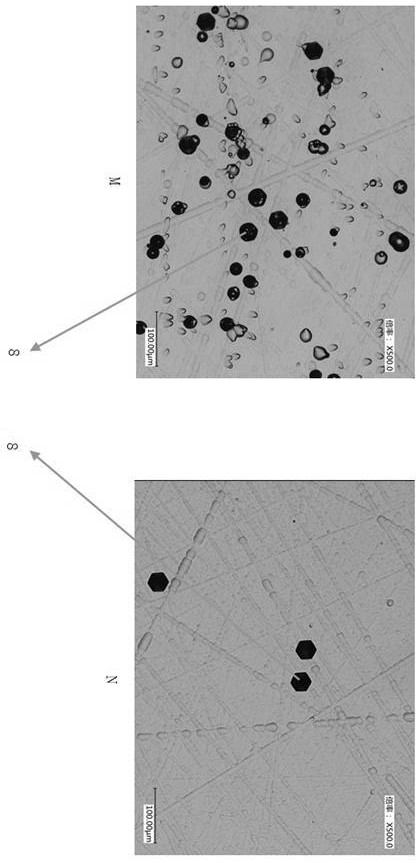

Device and method for preparing high-quality large-diameter SiC single crystal

PendingCN111793826AQuality improvementReduce threading dislocation densityPolycrystalline material growthFrom condensed vaporsInsulation layerThermal insulation

The invention discloses a device and a method for preparing a high-quality large-diameter SiC single crystal, which belong to the field of SiC crystal growth, the device comprises a crucible, a thermal insulation layer, a heating device and a porous graphite barrel; wherein the crucible is positioned in the thermal insulation layer; the heating device is located on the outer side of the thermal insulation layer; the seed crystal and a porous graphite barrel are positioned in the crucible and are coaxial with the crucible; according to the invention, a transportation mode of the SiC growth components is from raw materials on the outer side of the crucible to seed crystals on the inner side of the crucible, the crystal growth process is a natural expanding process, expanding of the diameterof the crystal is not limited, meanwhile, the crystal grows along a non-polar growth face, and the penetration dislocation density is greatly reduced compared with that of the crystal growing along aC axis; C particles generated by the SiC raw material which is heated and carbonized next to the crucible wall are effectively blocked by the SiC raw material on the inner side and the porous graphitelayer, so that C inclusions in the crystal are reduced, and the quality of the crystal is effectively improved.

Owner:河北同光科技发展有限公司

Method of producing template for epitaxial growth and nitride semiconductor device

ActiveUS8659031B2Reduce threading dislocation densityEasy to optimizePolycrystalline material growthSemiconductor/solid-state device manufacturingLateral overgrowthSapphire

Owner:NIKKISO COMPANY

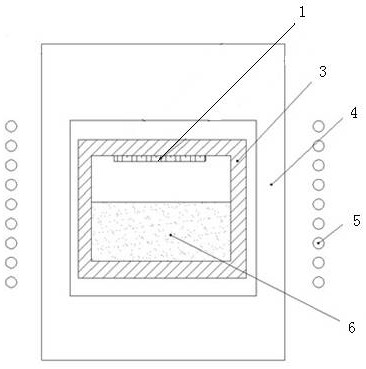

Seed crystal support and method for reducing penetration type dislocation density in silicon carbide single crystal

PendingCN111334855AReduce threading dislocation densityPolycrystalline material growthFrom condensed vaporsThin membraneDislocation

The invention provides a seed crystal support and a method for reducing penetration type dislocation density in a silicon carbide single crystal. The grooves are formed in the seed crystal support, the grooves are filled with the materials with the heat conductivity different from that of graphite, or the seed crystal support is directly plated with the thin film with the heat conductivity different from that of the graphite, so that two substances with the different heat conductivities exist on the surface of the seed crystal support during crystal growth, heat dissipation is uneven, and thenuneven distribution of a temperature field on the surface of the seed crystal is caused. Therefore, periodic distribution of two substances with different thermal conductivities on the seed crystal support can be utilized; according to the method, the distribution of a seed crystal surface temperature field in the SiC physical vapor transport growth process is modulated, preferential nucleation is forced to be carried out in a low-temperature area corresponding to a predefined pattern, selective preferential growth is carried out according to the predefined pattern, and then lateral growth iscarried out, so that the purpose of reducing the penetration type dislocation density is achieved.

Owner:广州南砂晶圆半导体技术有限公司

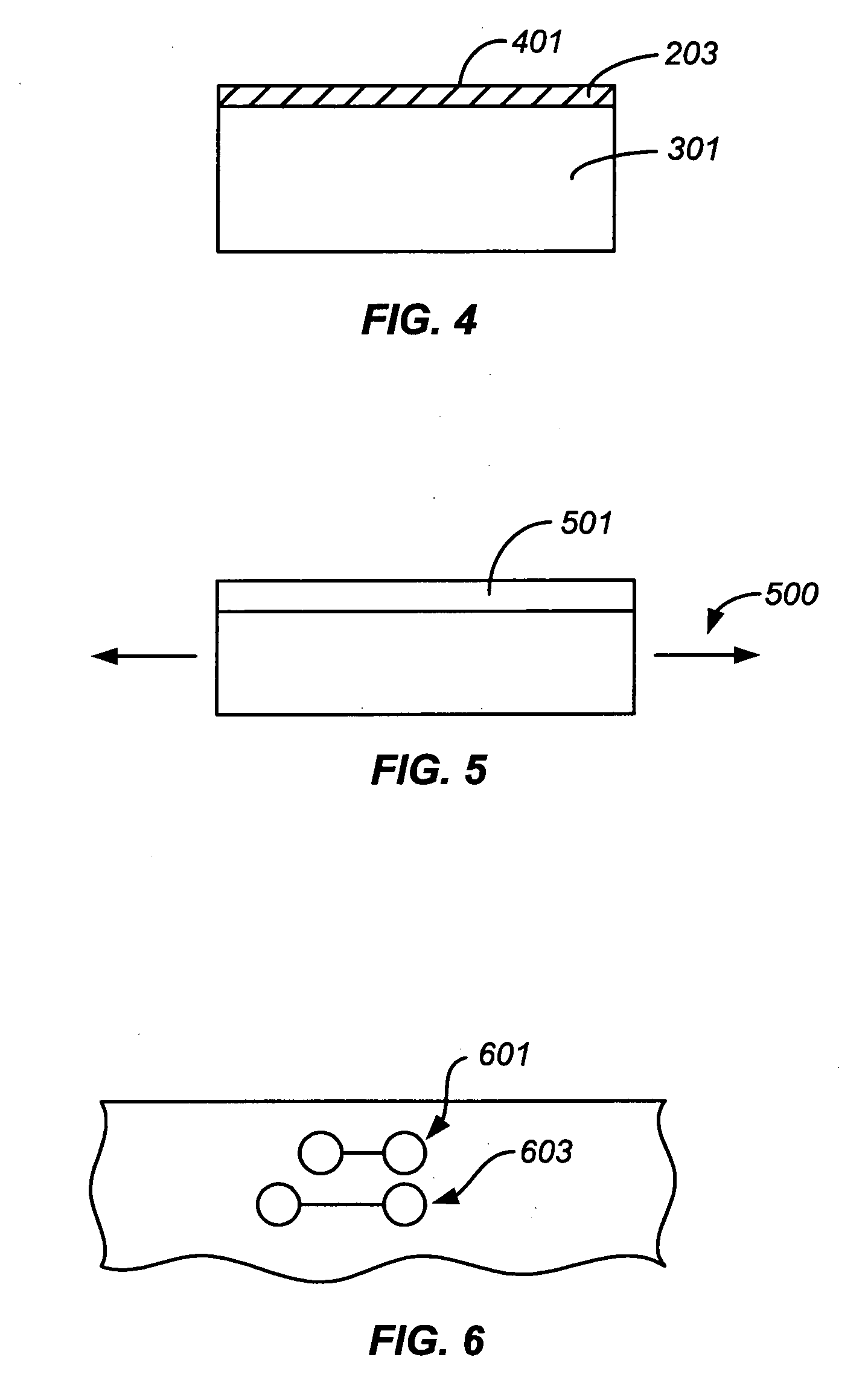

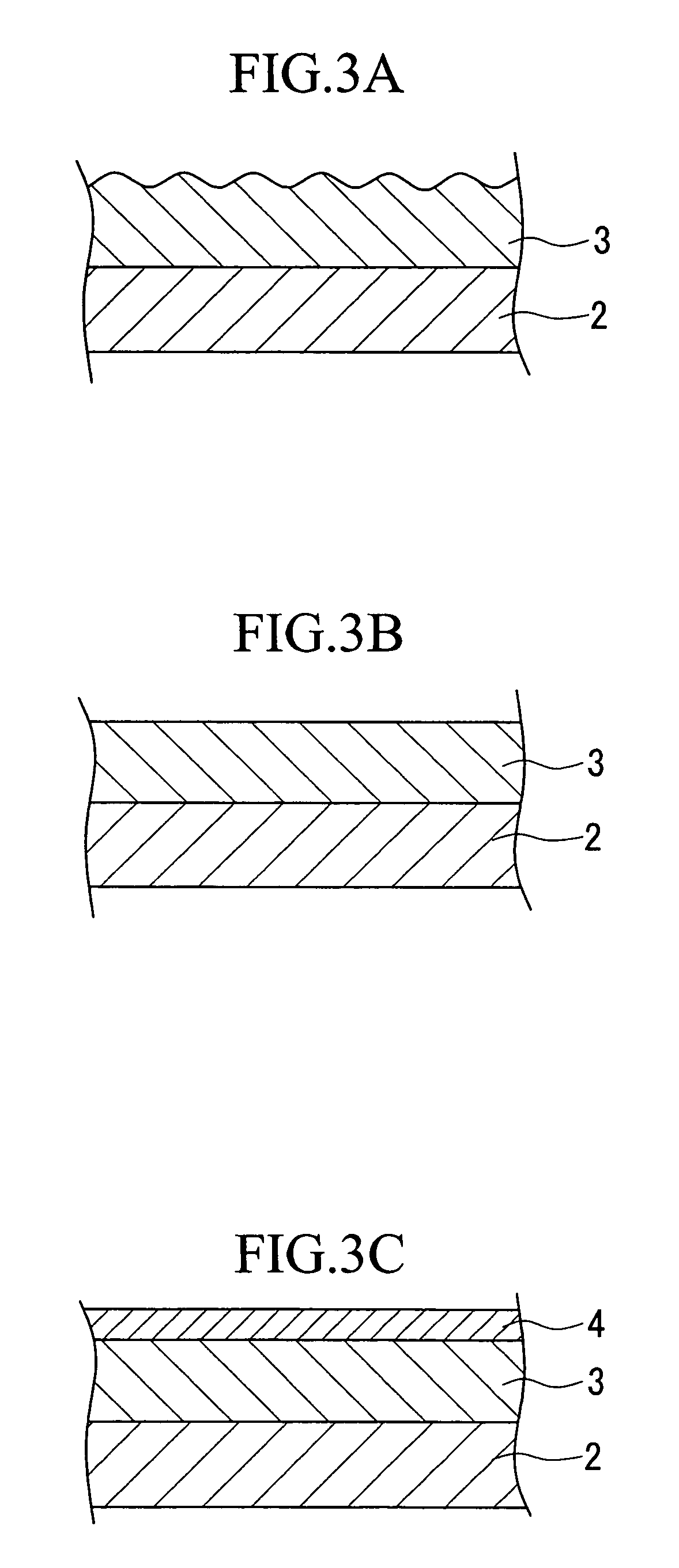

Production method for semiconductor substrate and production method for field effect transistor and semiconductor substrate and field effect transistor

InactiveUS7056789B2Worsening of roughnessWorsening of surfaceSolid-state devicesSemiconductor/solid-state device manufacturingSurface roughnessEngineering

The present invention relates to a semiconductor substrate production method, field effect transistor production method, semiconductor substrate and field effect transistor which, together with having low penetrating dislocation density and low surface roughness, prevent worsening of surface and interface roughness during heat treatment of a device production process and so forth. A production method of a semiconductor substrate W, in which SiGe layers 2 and 3 are formed on an Si substrate 1, is comprised of a heat treatment step in which heat treatment is performed either during or after the formation of the SiGe layers by epitaxial growth, at a temperature that exceeds the temperature of the epitaxial growth, and a polishing step in which irregularities in the surface formed during the heat treatment are removed by polishing following formation of the SiGe layers.

Owner:SUMITOMO MITSUBISHI SILICON CORP

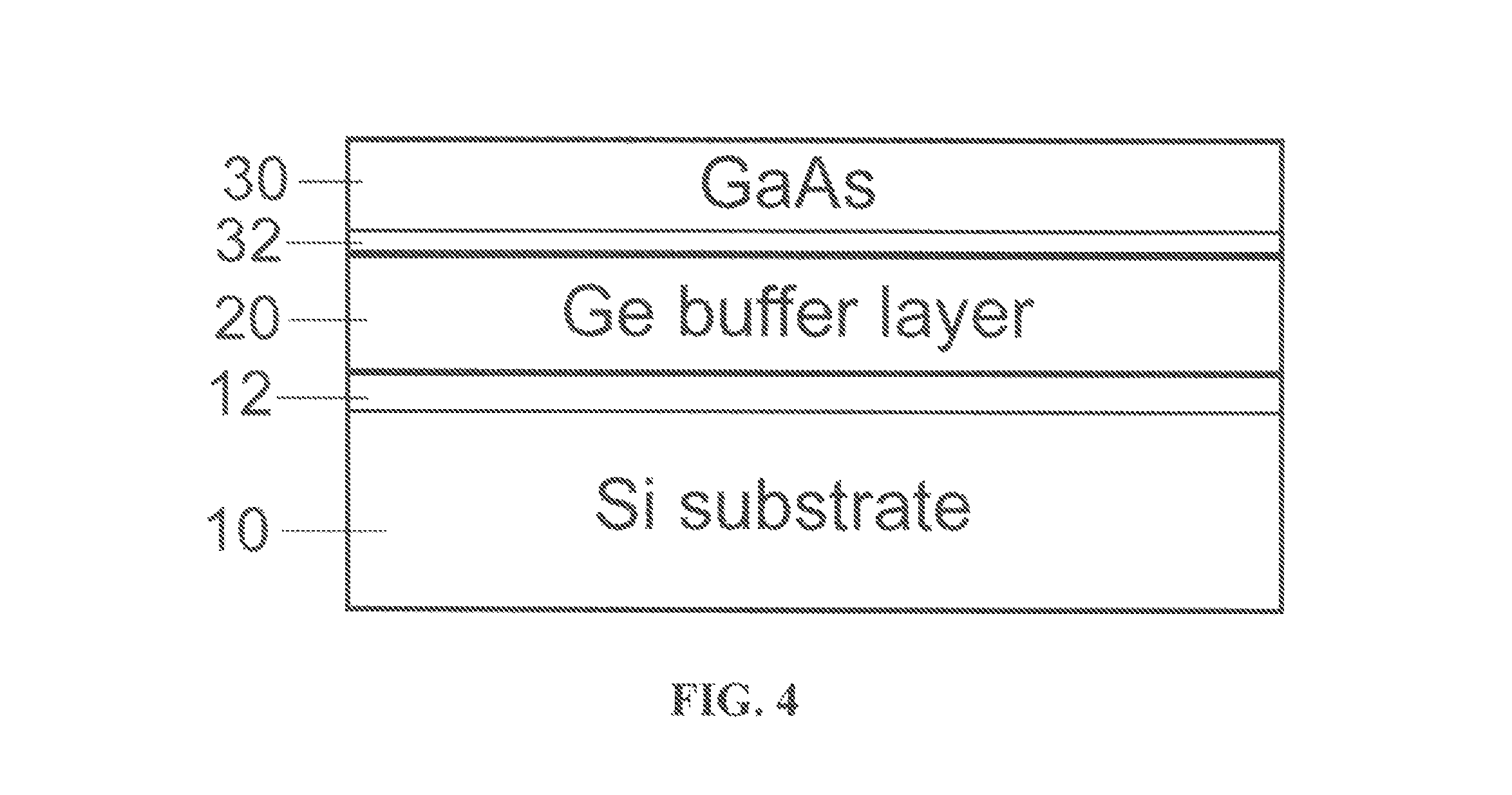

Method for producing virtual Ge substrates for III/V-integration on Si(001)

InactiveUS8882909B2Cheap methodReduce threading dislocation densityPolycrystalline material growthSolid-state devicesCrack freeField-effect transistor

Relaxed germanium buffer layers can be grown economically on misoriented silicon wafers by low-energy plasma-enhanced chemical vapor deposition. In conjunction with thermal annealing and / or patterning, the buffer layers can serve as high-quality virtual substrates for the growth of crack-free GaAs layers suitable for high-efficiency solar cells, lasers and field effect transistors.

Owner:DICHROIC CELL

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com