Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

65results about How to "No design changes required" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

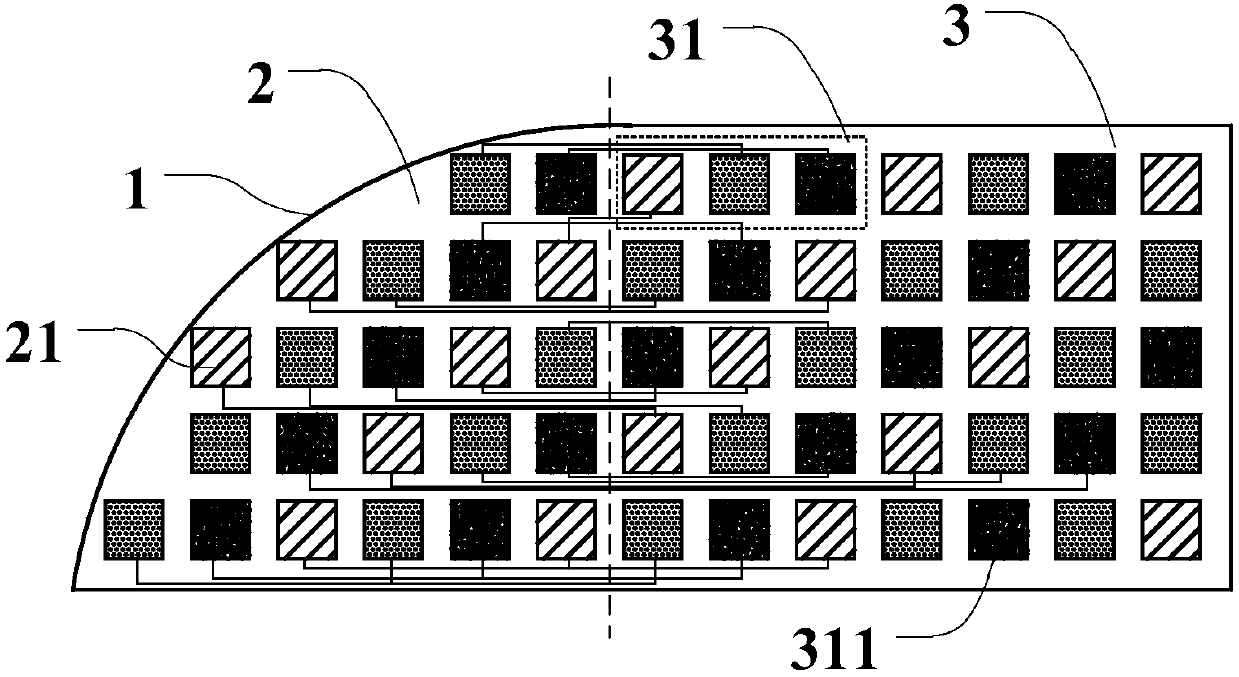

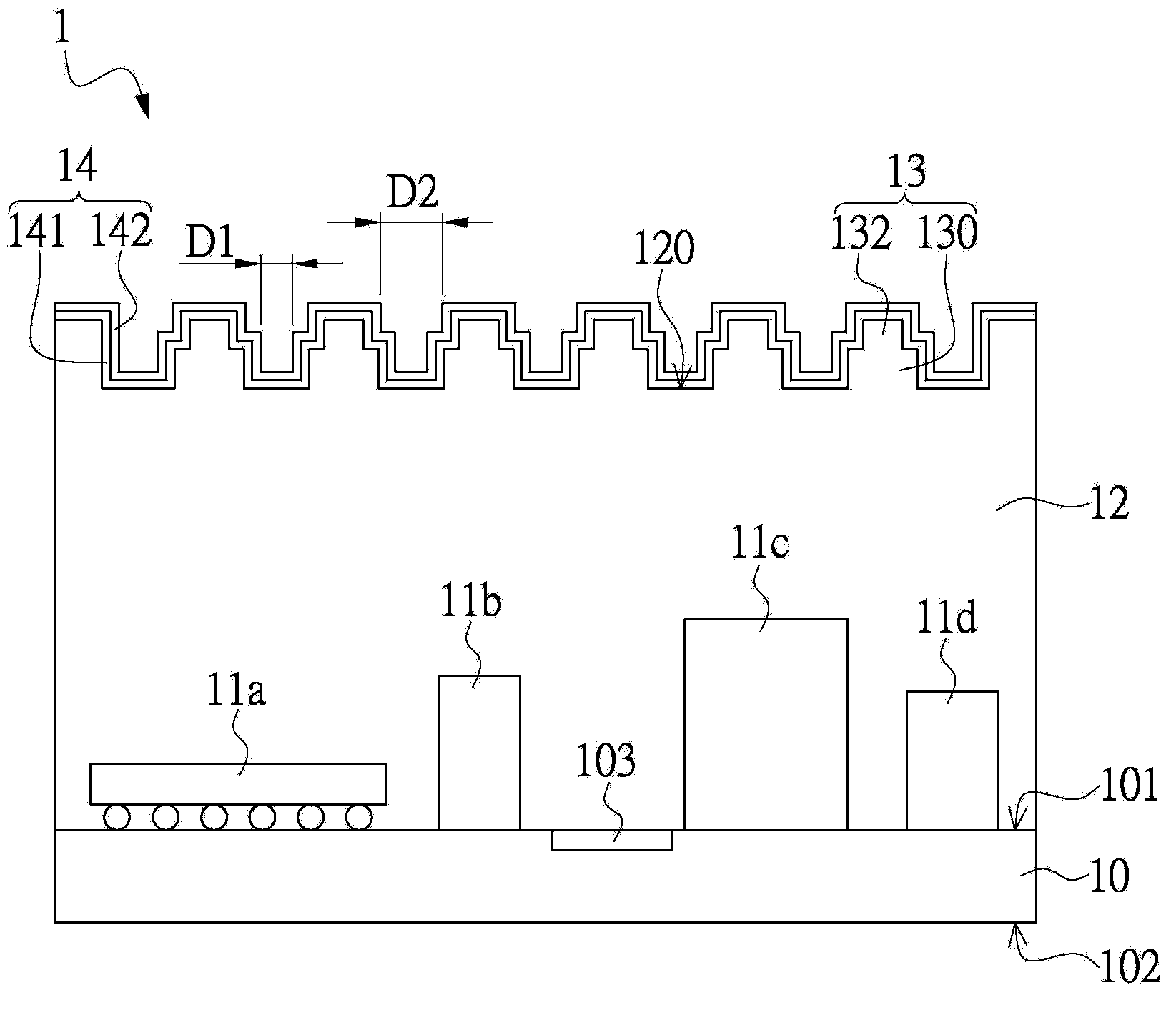

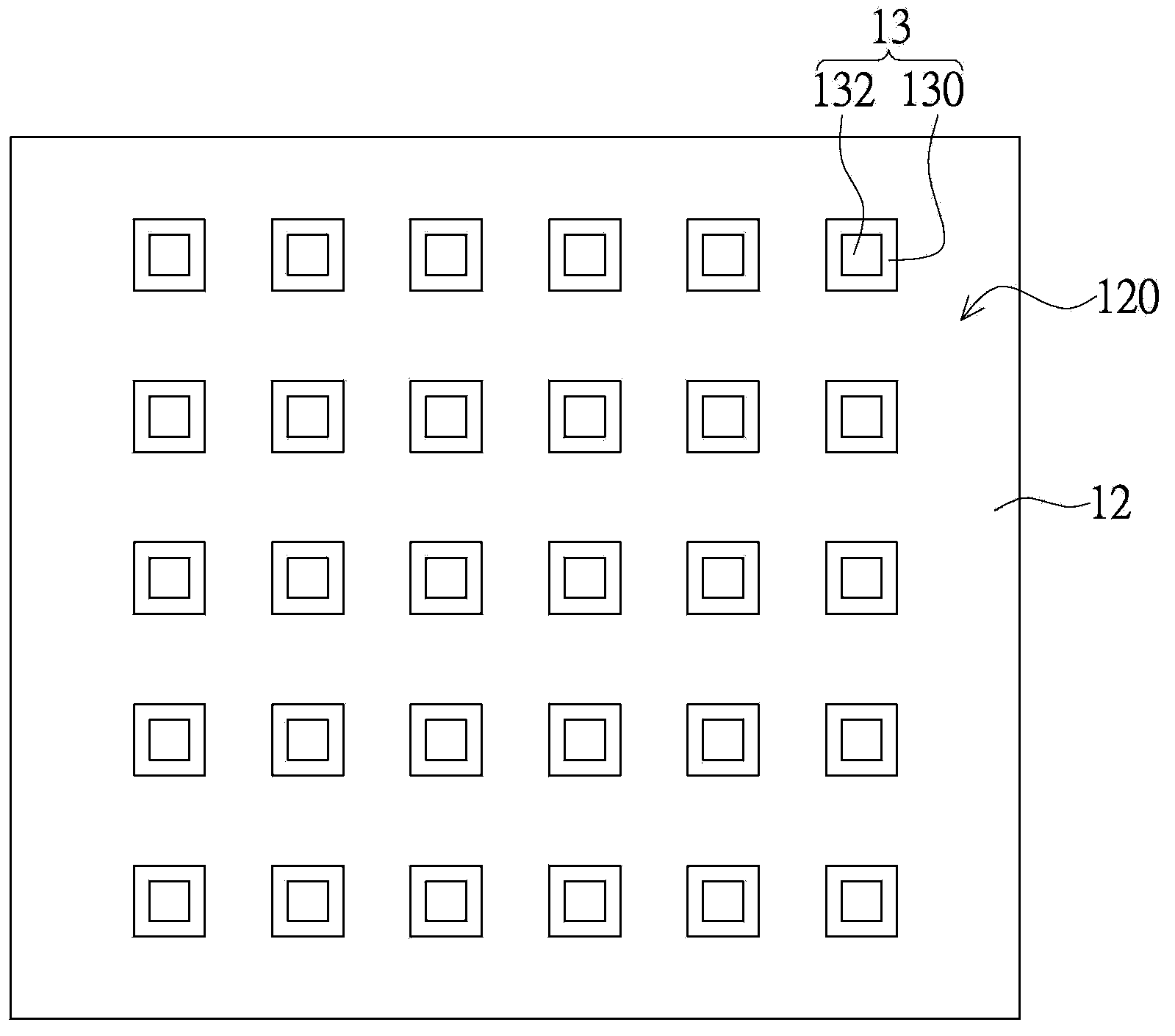

Organic light-emitting display panel and display device

ActiveCN107819023AVisible jaggednessImprove the display effectSolid-state devicesSemiconductor devicesElectricityDisplay device

The invention discloses an organic light-emitting display panel and a display device to weaken the sawtooth phenomenon of a shaped edge of a shaped display panel and to improve the display effect of the display panel near the shaped edge. The organic light-emitting display panel comprises a display area with the shaped edge, wherein the display area comprises a first display area and a second display area which are sequentially arranged along the direction far away from the shaped edge; the first display area comprises a plurality of first subpixels arranged in an array; the second display area comprises a plurality of pixel units arranged in an array; each pixel unit comprises second subpixels of at least three colors; the second display area is provided with a plurality of pixel circuits; each second subpixel is electrically connected with the corresponding pixel circuit; the same pixel circuit is shared by the first subpixels and the second subpixels of the same color; and the firstsubpixels of the same color connected with the second subpixels of various colors in the same pixel unit are the same in quantity.

Owner:WUHAN TIANMA MICRO ELECTRONICS CO LTD

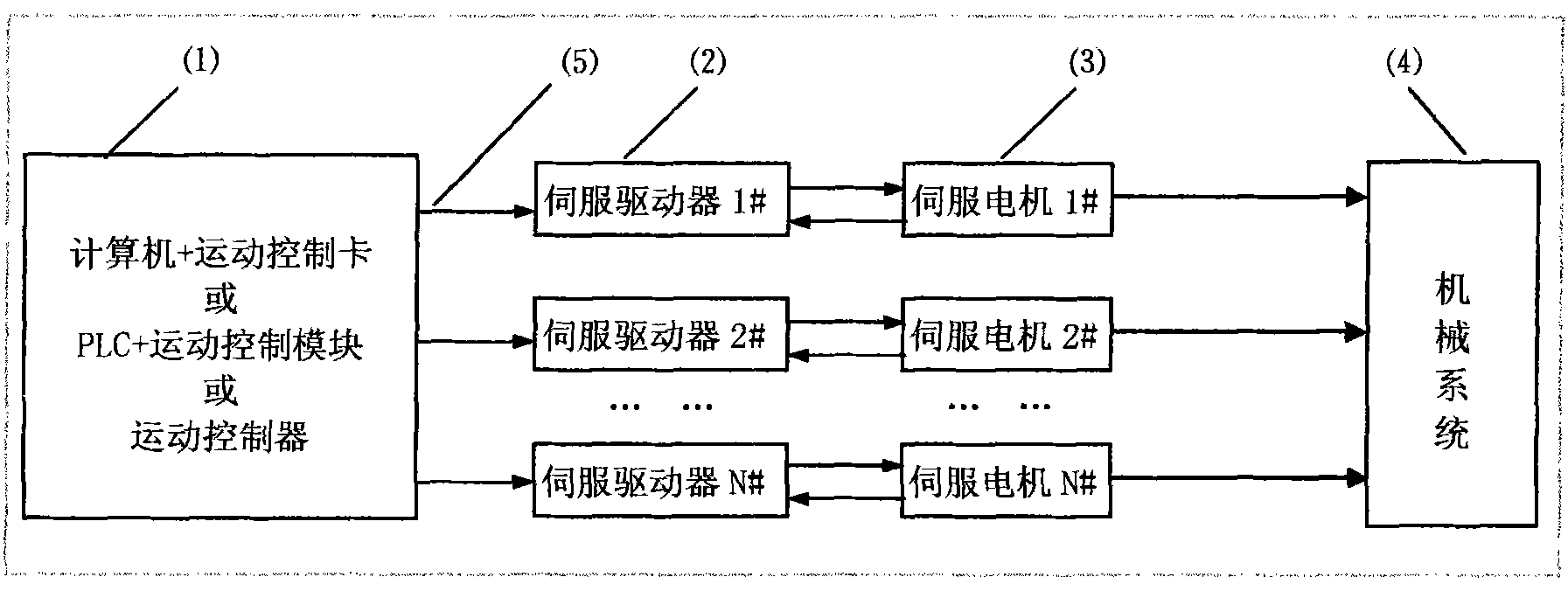

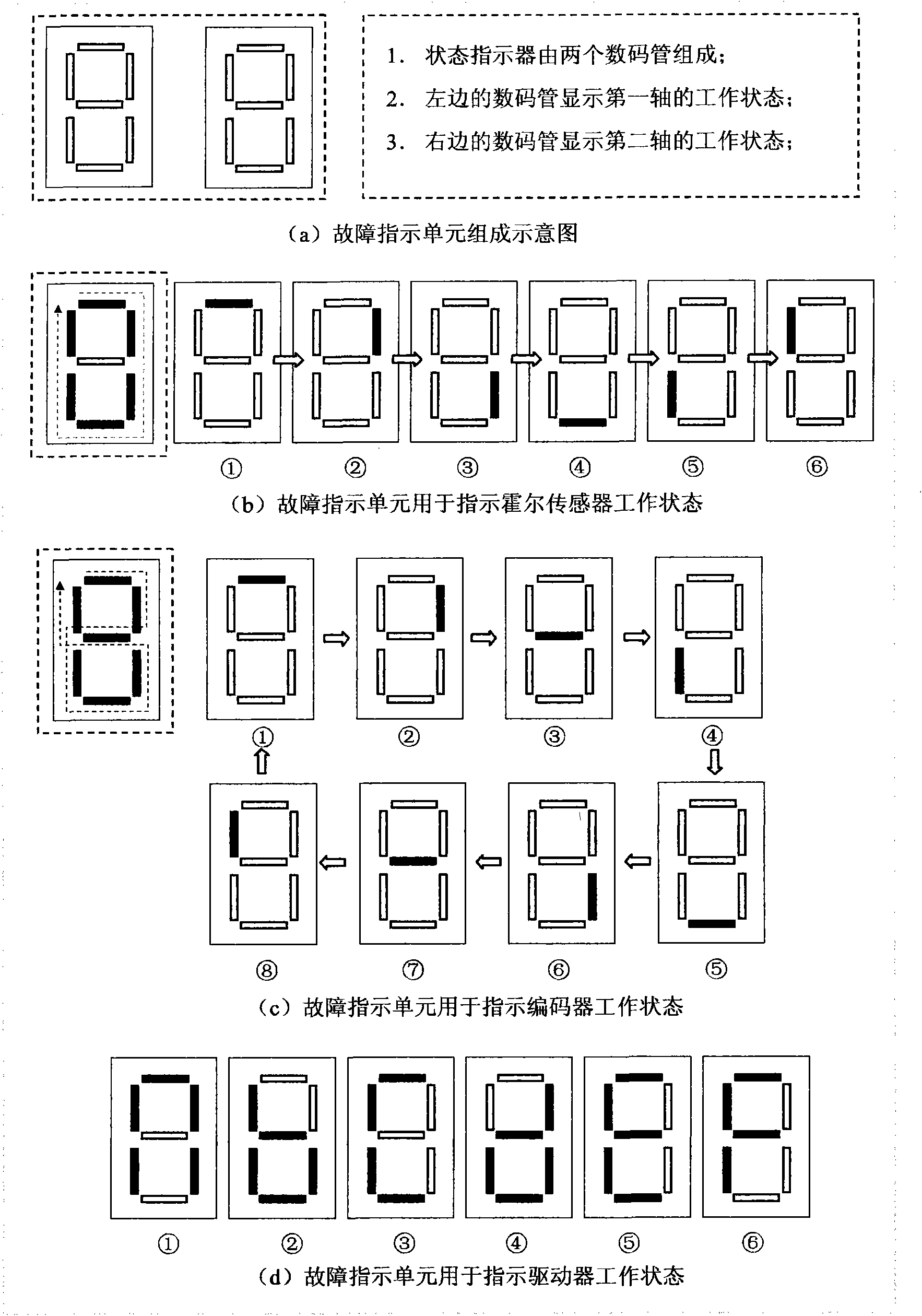

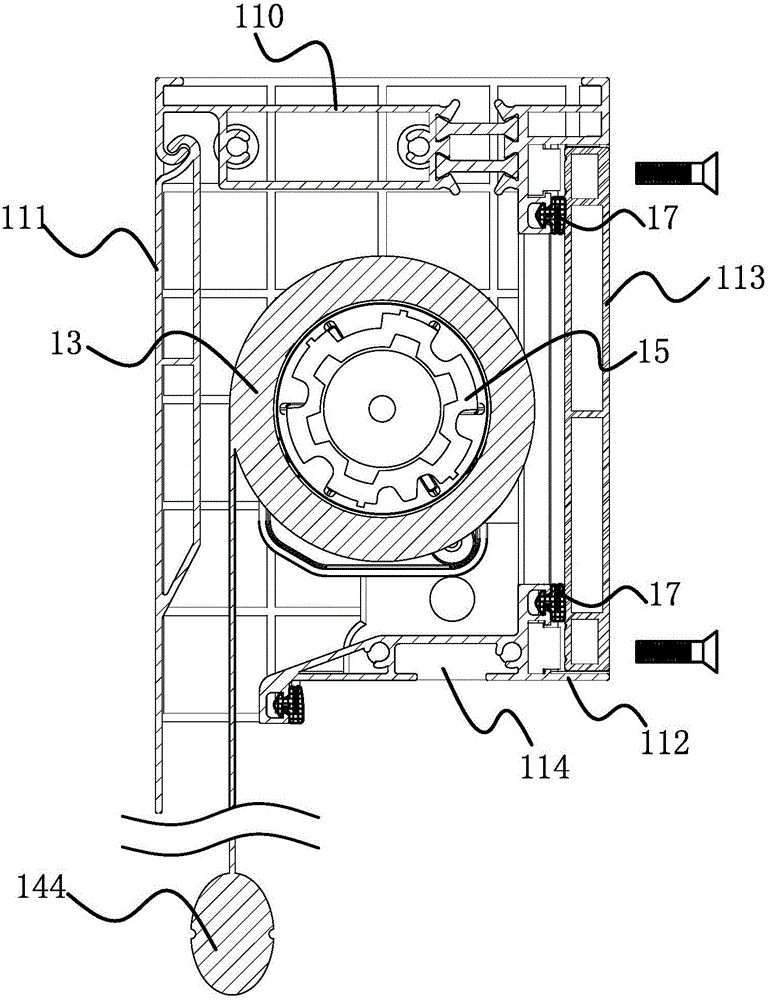

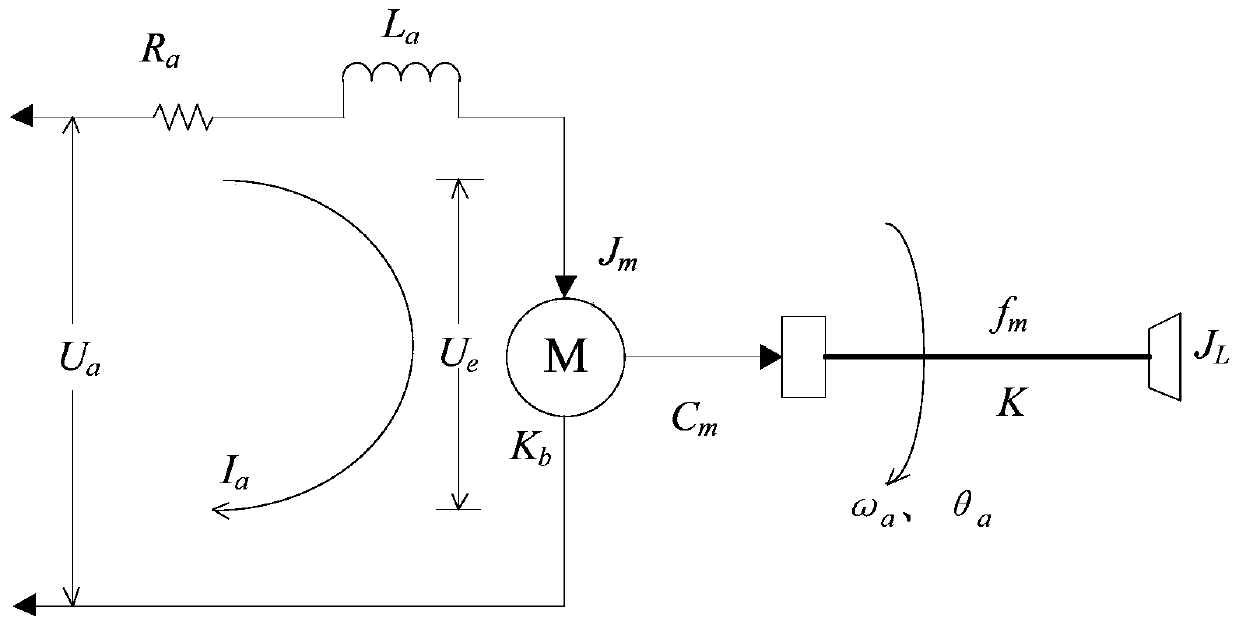

Full digitalized distributed intelligent servo driver

InactiveCN102073302AReduce points of failureLow costElectric motor controlNumerical controlModularityField-programmable gate array

The invention discloses a full digitalized distributed intelligent servo driver which adopts a full digitalized DSP (Digital Signal Processor) + FPGA (Field Programmable Gate Array) structure. The intelligent servo driver provided by the invention integrates the functions of motion control, motor control and a simple PLC (Programmable Logic Controller) and can conveniently construct a motion control system without an upper computer motion controller (card). The intelligent servo driver can be used for controlling and driving a direct current brush (brushless) motor, an alternating current servo motor and a linear motor only through software configuration without changing hardware. The intelligent servo driver can realize the following operation modes: A. an RS232 network control mode; B. an RS485 distributed network control mode; C. an independent driver running mode without the upper computer; D. a pulse command running mode; and E. an analog signal running mode. The servo driver provided in the invention adopts a modularized structure, the same control module can be matched with driving modules of different power levels to form intelligent servo driving systems of different power levels. By utilizing the full digitalized distributed intelligent servo driver, a motion control system with the advantages of low cost, flexible system configuration, simpleness and convenience for operation, reliable performance and convenience of maintenance can be realized.

Owner:北京诺信泰伺服科技有限公司

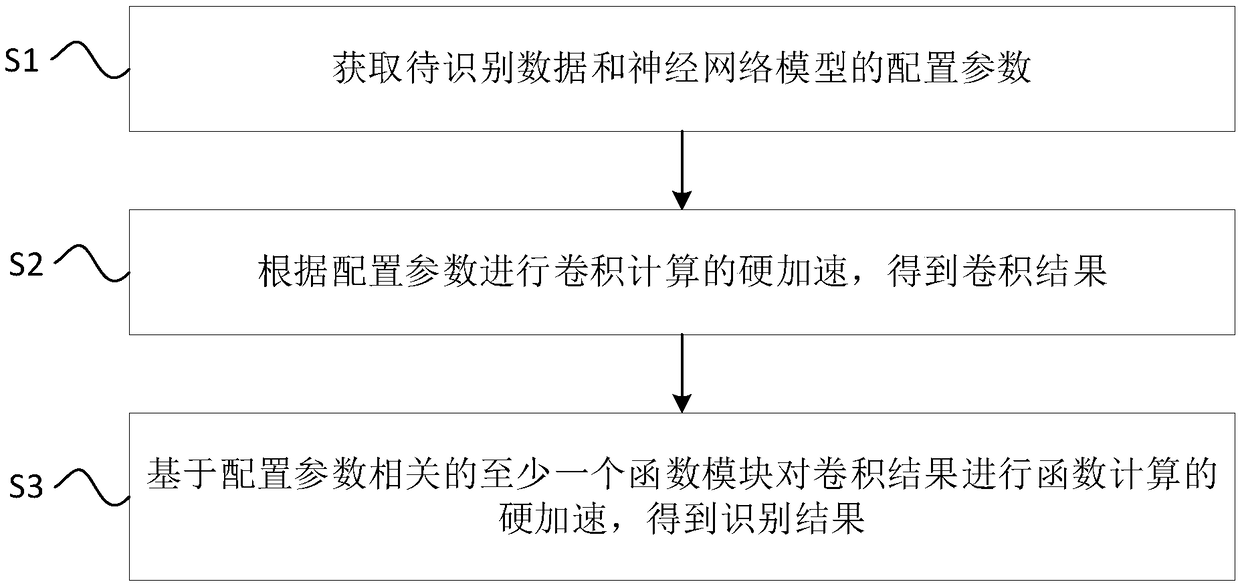

Hard acceleration method and device for neural network model of electronic equipment

PendingCN108710941ANo design changes requiredImplementation supportNeural architecturesPhysical realisationNerve networkNetwork model

The invention discloses a hard acceleration method and device for a neural network model of first electronic equipment. The method and the device relate to the technical field of deep learning in artificial intelligence. The method includes the following steps: obtaining to-be-recognized data and configuration parameters of the neural network model; performing hard acceleration of convolution calculation matching the neural network model according to the configuration parameters, and obtaining a convolution result of the to-be-recognized data by the neural network model; performing the hard acceleration of function calculation on the convolution result by calling at least one function module matching the neural network model from at least one preset function module based on the configuration parameters, and obtaining a recognition result of the to-be-recognized data by the neural network model. The method and the device can support the neural network model established by various open source development environments, and also support a user-defined neural network model; and when an algorithm of the neural network model is updated, only the parameters of the first electronic equipment need to be reconfigured without changing hardware design.

Owner:HANGZHOU FEISHU TECH CO LTD

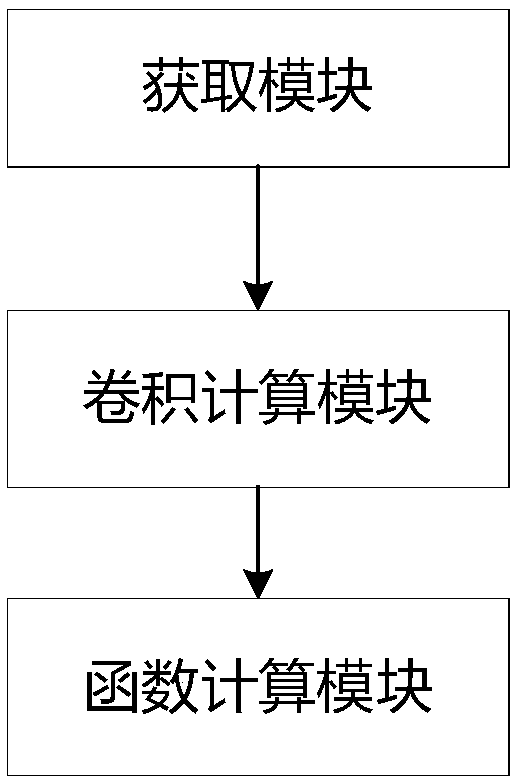

Embedded system power on self test method

InactiveCN103176875AImprove diagnostic coverageImprove execution efficiencyDetecting faulty computer hardwareElectricityInternal memory

The invention relates to an embedded system power on self test method. The method comprises the following steps: (1), electrifying a system, and detecting a center processing unit (CPU) register; (2), detecting internal memory by a cross blocking method being used, and judging whether breakdowns exist in the internal memory or not; (3), classifying instructions used by the system, testing the various instructions, comparing test results with an expected test result vector quantity, and judging whether all the instructions pass a test, if yes, executing the step (4), if no, carrying out failure process; (4), carrying out read only memory (ROM) integrity detection on operation system files which are loaded, application programs and data, and judging whether the loaded files are integrated or not, if yes, quitting detection, if no, entering error process. Compared with the prior art, the embedded system power on self test method has the advantages of being reliable, effective, and high in fault detect covering rate.

Owner:CASCO SIGNAL

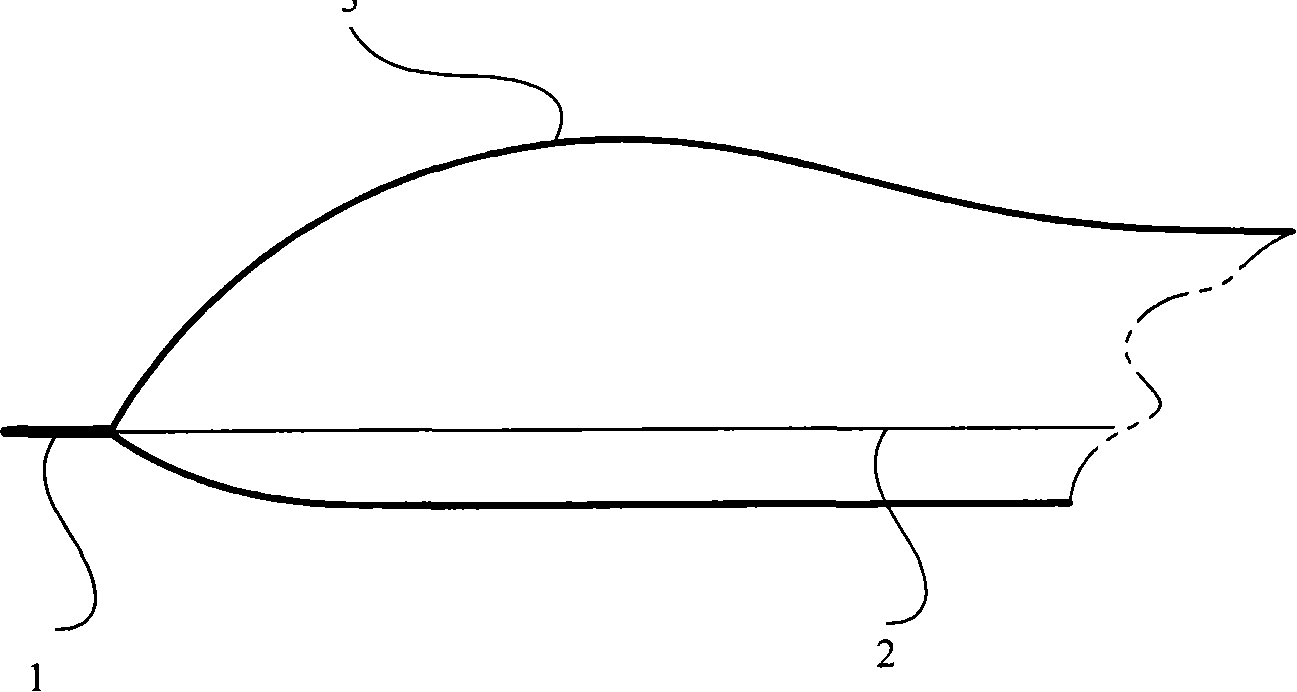

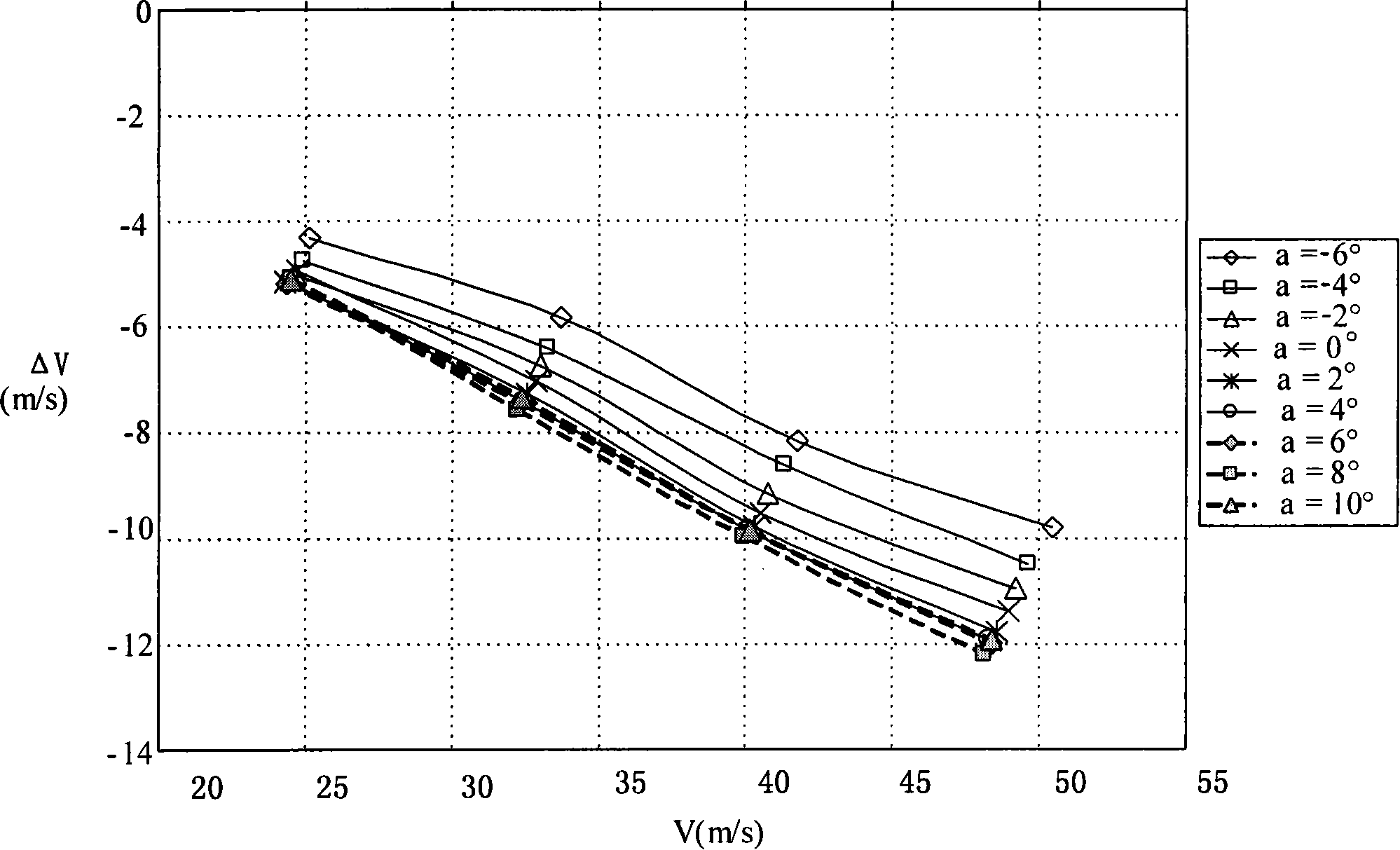

Amending method for positional error of total static pressure sensor on low-speed unmanned aerial vehicle

InactiveCN101246078ANo design changes requiredNo need to change the general arrangementAerodynamic testingFluid pressure measurementLow speedUncrewed vehicle

The present invention discloses a method for modifying the position error of the total static pressure pick-up. The method uses a wind tunnel experiment to obtain a simple modifying method for modifying the flight speed of the unmanned plane and the atmosphere static pressure data. When the modifying method provided by the invention is applied, the designing of the total static pressure pick-up and the general arrangement of the plane do not need modifying; besides the provided modifying formula is simple and definite formulated, the inner algorithm of the air data computer does not need modifying and the data can be automatically modified in the flight control software; and a higher modifying precision is provided to the typical flight condition.

Owner:BEIHANG UNIV

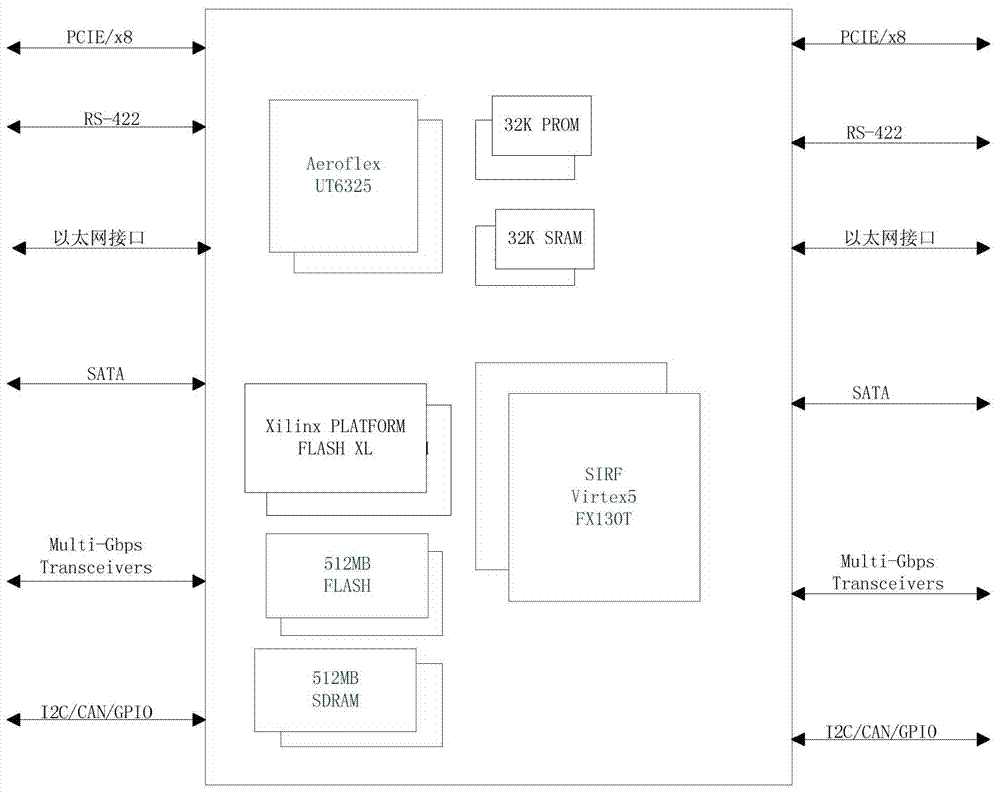

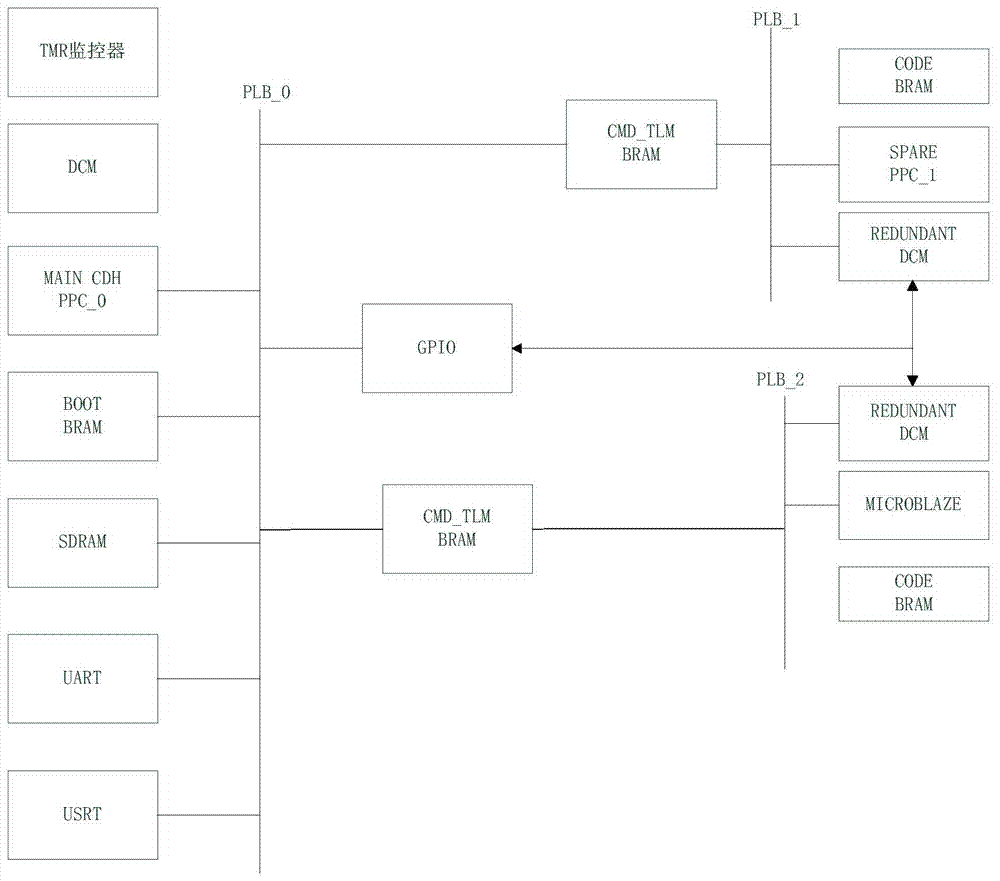

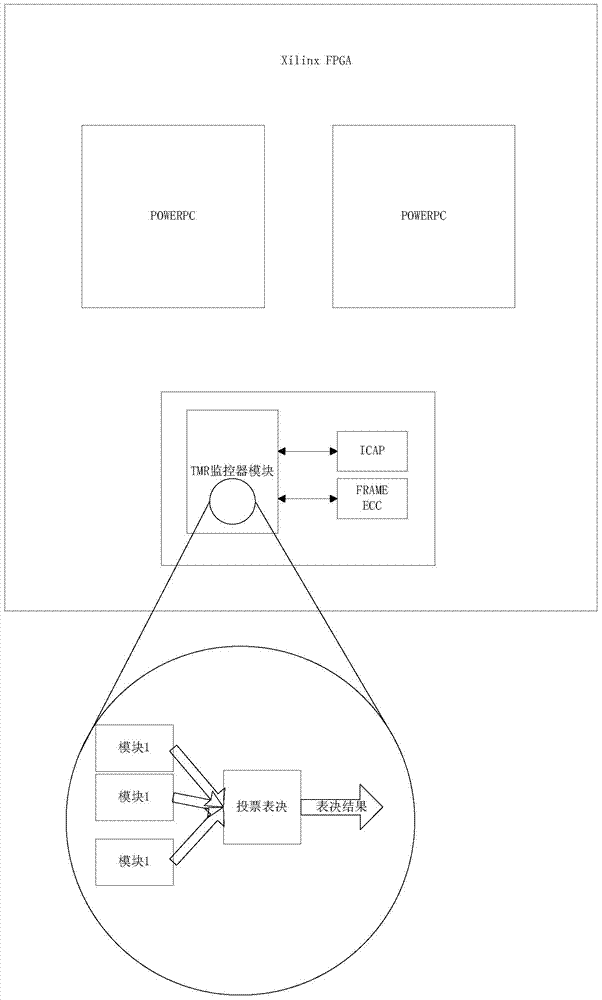

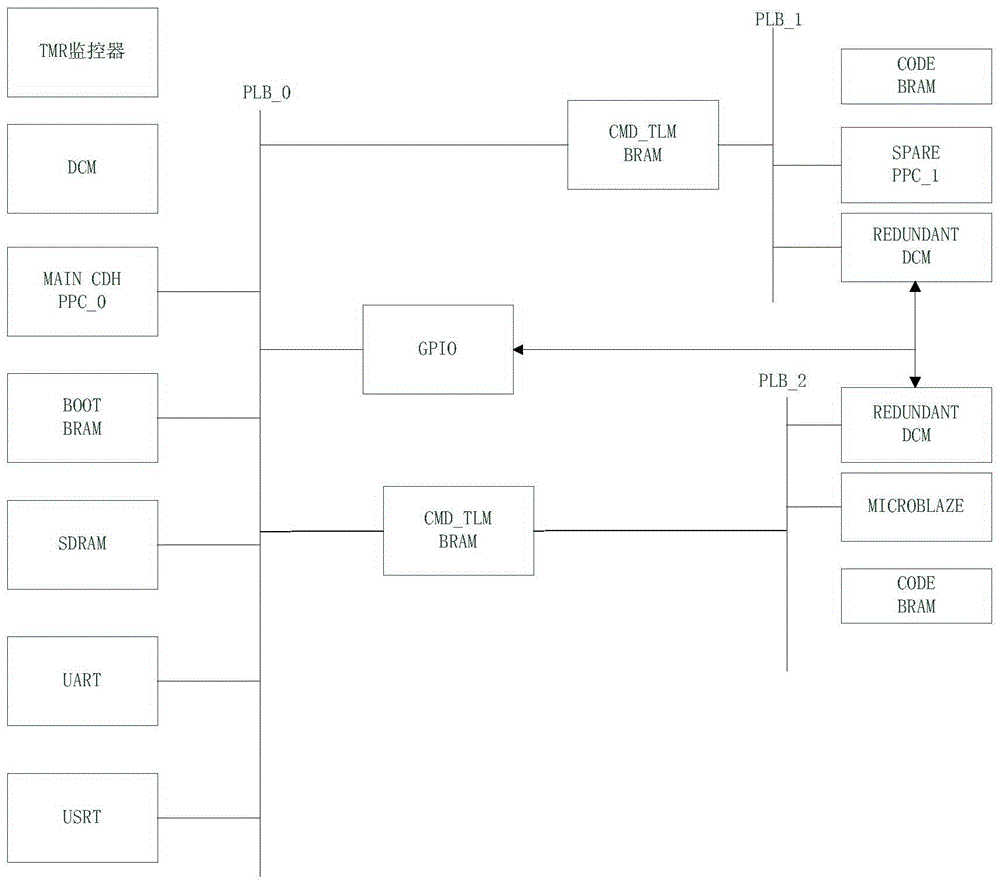

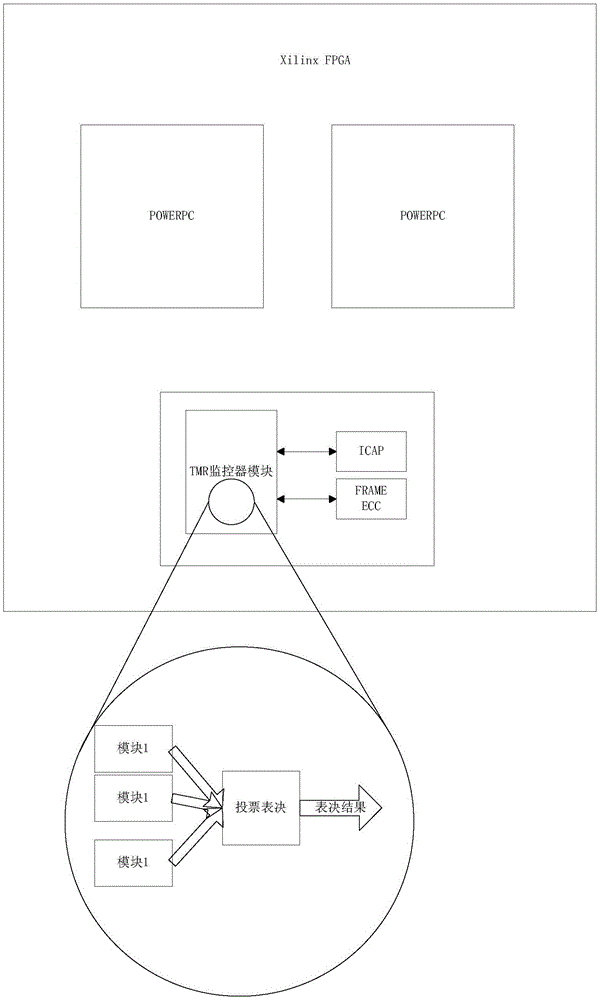

Anti-radiation data processing system and method based on FPGA

InactiveCN103500125AEasy to useEasy to handleError detection/correctionData processing systemProcess module

The invention discloses an anti-radiation data processing system and method based on an FPGA. The data processing system comprises a data processing card applicable to severe environments such as radiation environments and comprising the double-port RAM commercial SPAM structure FPGA. The data processing card comprises two pieces of anti-radiation antifuse Aeroflex UT6235FPGAs, two pieces of incomplete anti-radiation Xilinx Virtex-5FX130T FPGAs and relevant storages, interfaces and other peripheral chips. Each piece of Xilinx Virtex-5FX130T FPGA comprises three parts, namely a control and processing part, a first path data processing module used for processing input data and storing a data processing result into a first part of a double-port RAM and a second path data processing module identical with the first path data processing module and identically processing the same input data. A data processing result is stored into a second part of the double-port RAM. A control and processing module compares the processing results of the two path processing modules. If the results are identical, the processing results are stored into a designated storage and if the results are not identical, processing is repeated.

Owner:SHANGHAI INST OF TECHNICAL PHYSICS - CHINESE ACAD OF SCI

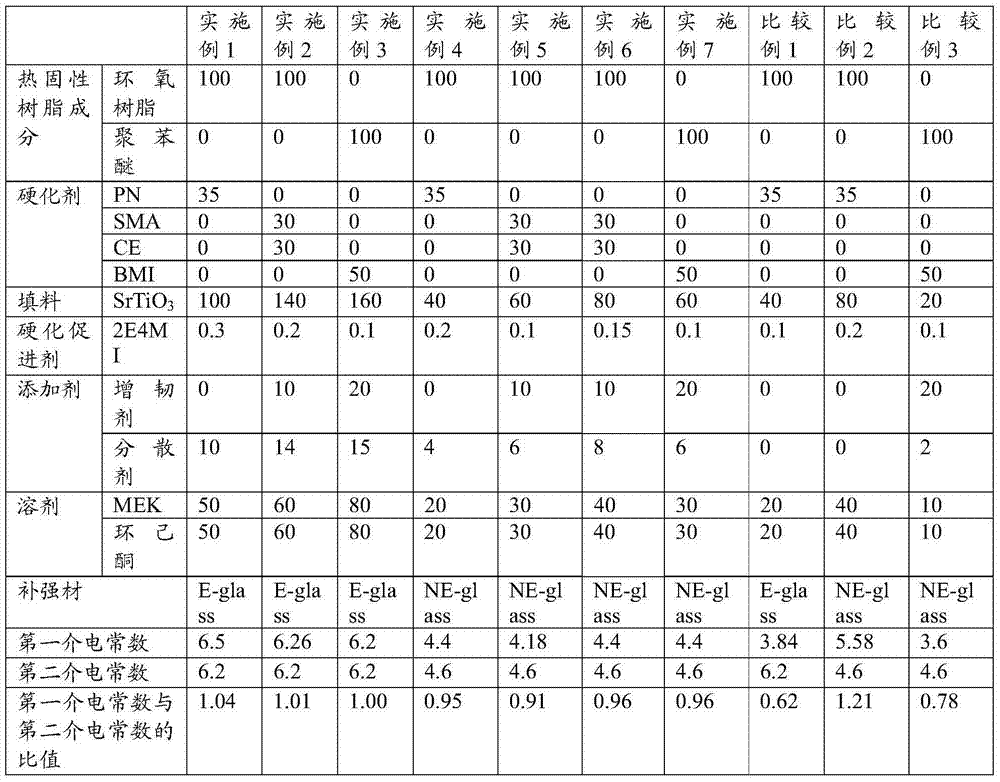

Prepreg And Uses Of The Same

InactiveCN104744891ANo design changes requiredSolve the signal skew problemPrinted circuit aspectsElectrical equipmentDielectric

A prepreg is provided. The prepreg is prepared by immersing a reinforcing material into a resin composition and drying the immersed reinforcing material, wherein the resin composition has a first dielectric constant and comprises a thermosetting resin component, a hardener and a filler. The reinforcing material has a second dielectric constant, and the ratio of the first dielectric constant to the second dielectric constant ranges from 0.8 to 1.05.

Owner:TAIWAN POWDER TECH CO LTD

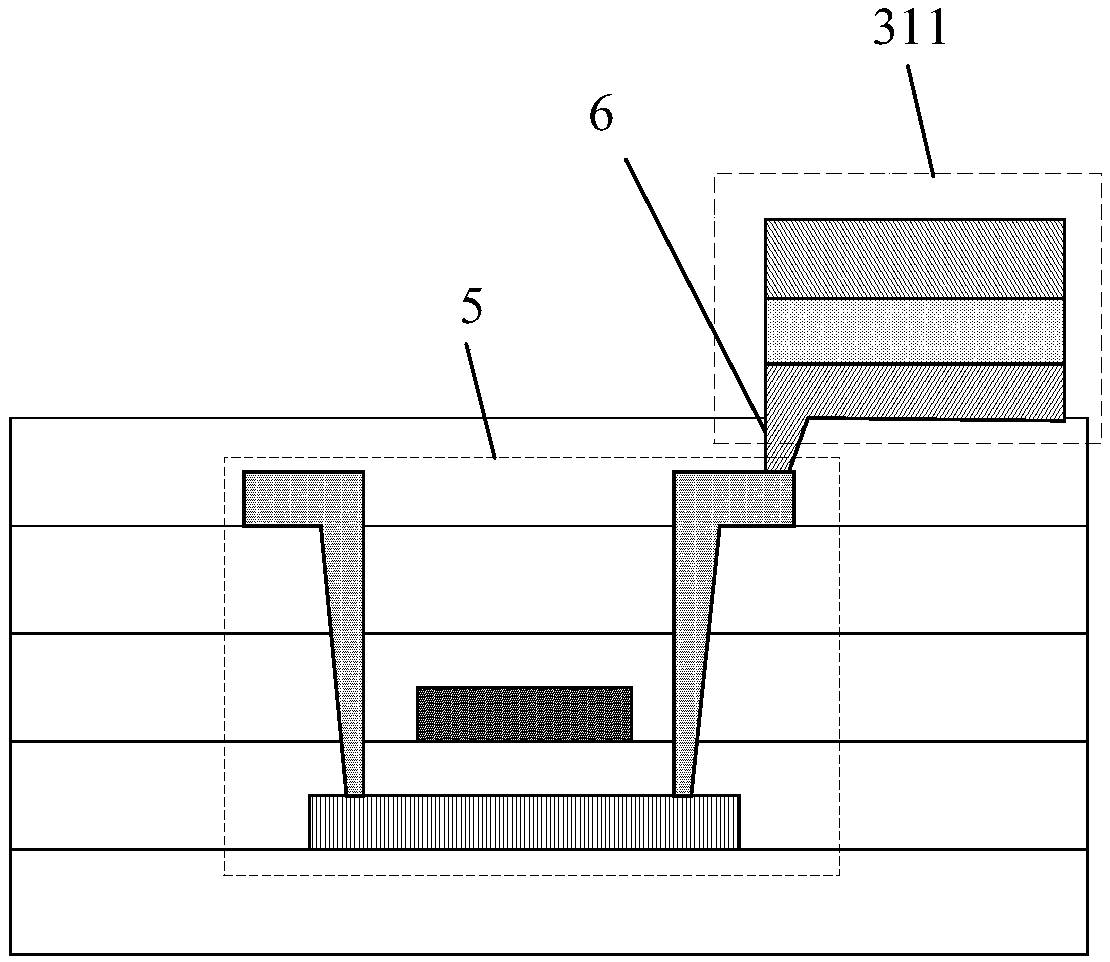

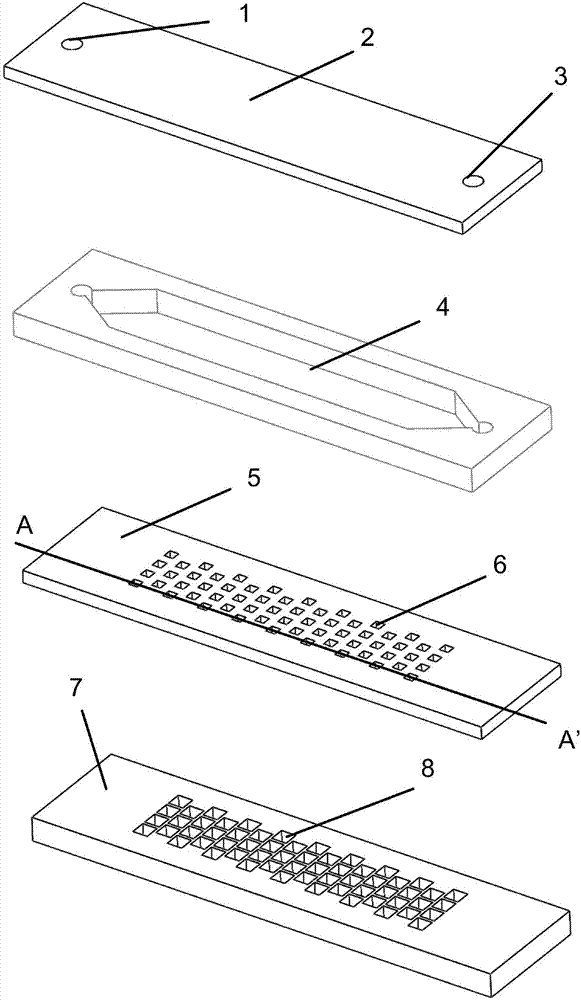

Microfluidic chip for study of tumor single cell invasion and epithelial-mesenchymal transition

ActiveCN107497503AReduce stepsImprove experiment success and reliabilityBioreactor/fermenter combinationsBiological substance pretreatmentsMicrofluidic chipCell invasion

The invention provides a microfluidic chip for studying the tumor single cell invasion and epithelial-mesenchymal transition process capability. The microfluidic chip includes four layers of structures that are stacked together in order and sealed to each other, and falls into a top cover, a microfluidic channel layer, a substrate with micropore array and a baseplate with a cavity group from top to bottom. The invention also provides a system that matches with the chip and is used for single cell detection. The microfluidic chip and the corresponding detection system provided by the invention can achieve rapid, simple and low-cost sorting of single cells and study of invasion ability and epithelial-mesenchymal transition, and performs gene analysis on a target single cell.

Owner:THE NAT CENT FOR NANOSCI & TECH NCNST OF CHINA

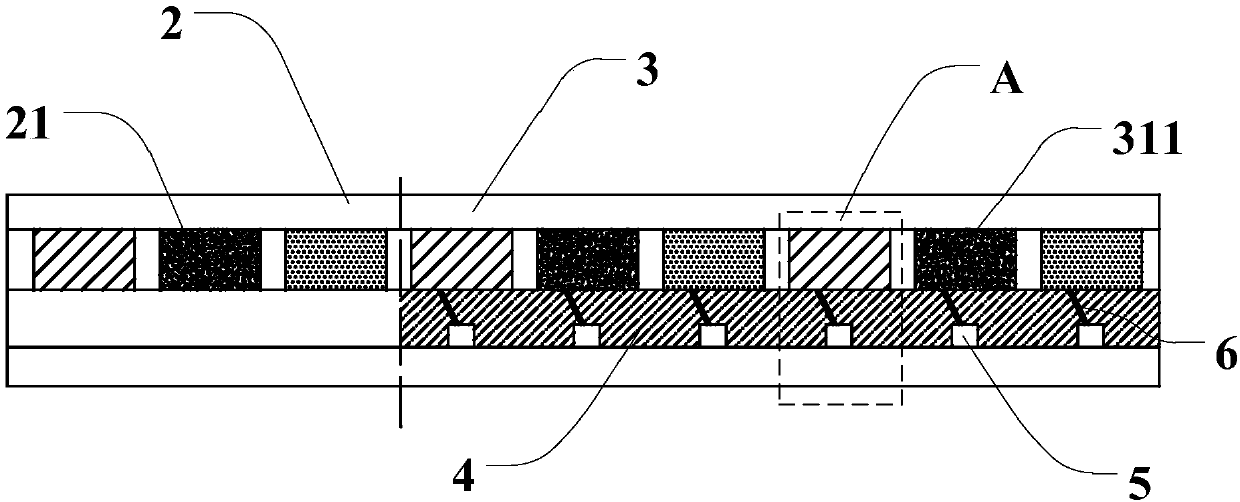

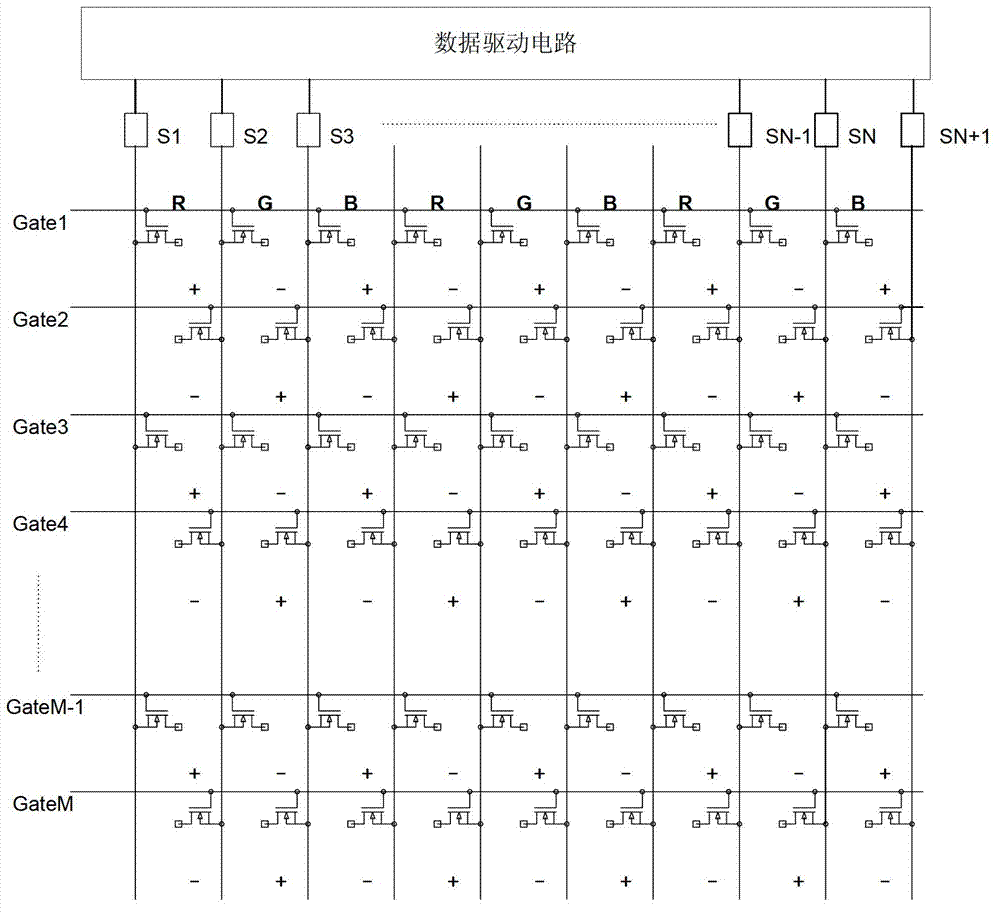

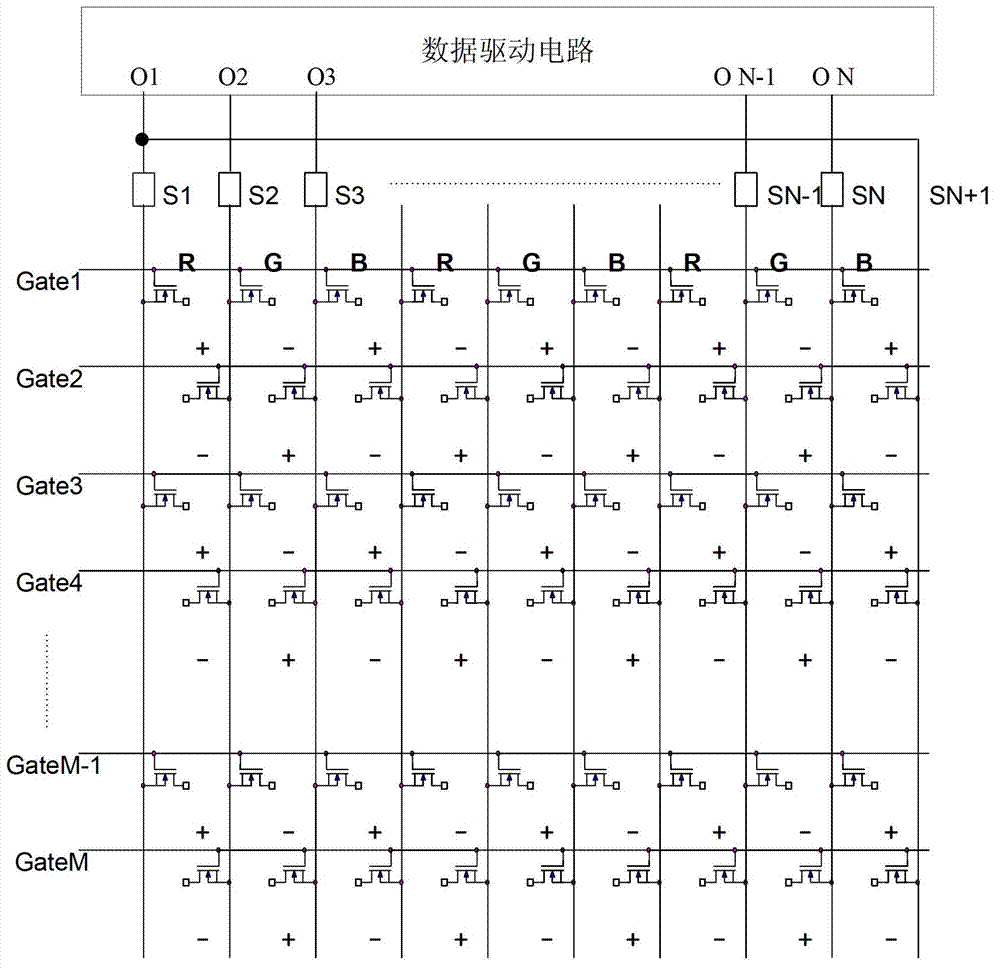

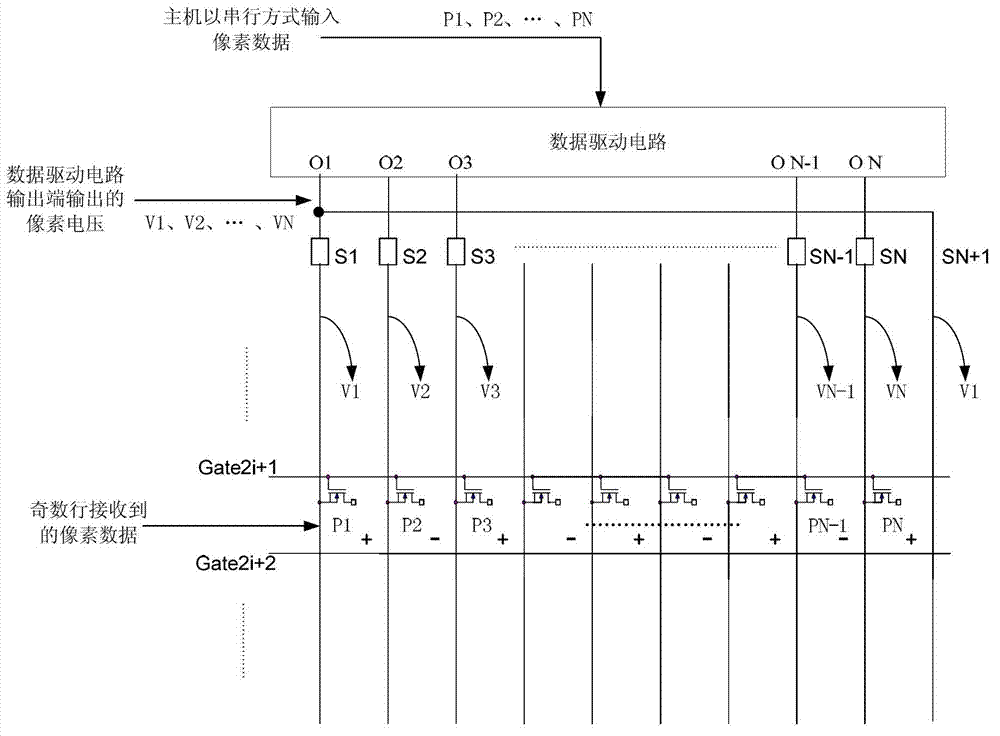

Liquid crystal display panel and liquid crystal display device

ActiveCN103592800ANo design changes requiredLow costStatic indicating devicesNon-linear opticsLiquid-crystal displayComputer science

The invention discloses a liquid crystal display panel and a liquid crystal display. The liquid crystal display panel comprises sub-pixels, N+1 data lines and M scanning lines; the sub-pixels are arranged according to the matrix way of M rows by N columns; every data line receives pixel data; the M scanning lines are intersected with the data lines to form the pixel area; a grid electrode of the <i+1>th sub-pixel which is in coupling connection with the first data line is in coupling connection with the <2i+1>th scanning line; a grid electrode of the <i+1>th sub-pixel which is in coupling connection with the <i+2>th data line is in coupling connection with the <i+1>th scanning line; a grid electrode of the <i+1>th sub-pixel which is in coupling connection with the <n+1>th data line is in coupling connection with the <2i+2>th scanning line; the first data line and the <n+1>th data line are connected at the pixel data received end; I is a nonnegative integer which is smaller than or equal to n-2. According to the liquid crystal display panel and the liquid crystal display, the design that a data driving circuit does not need to be changed can be achieved and the cost is reduced.

Owner:SHANGHAI TIANMA MICRO ELECTRONICS CO LTD

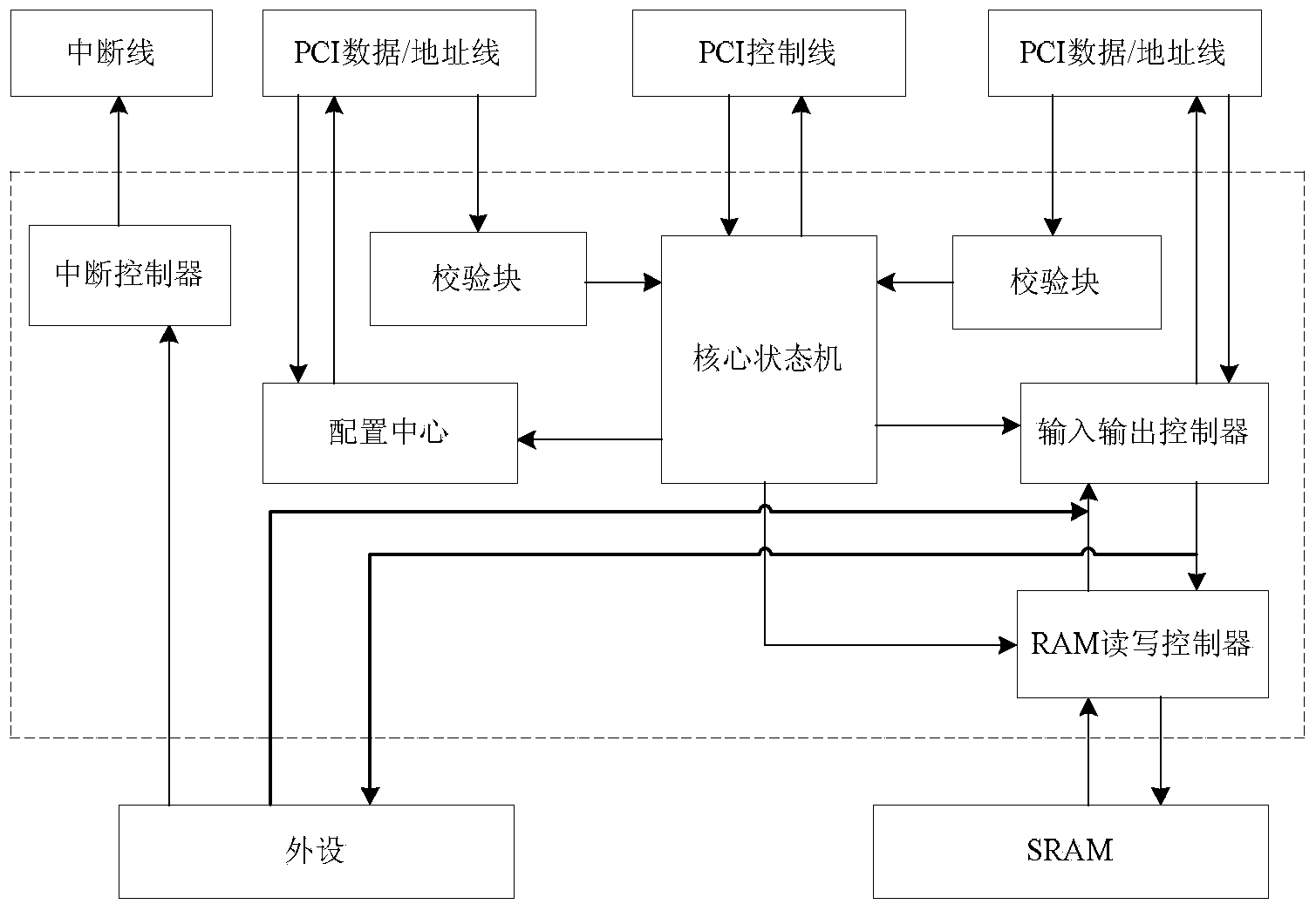

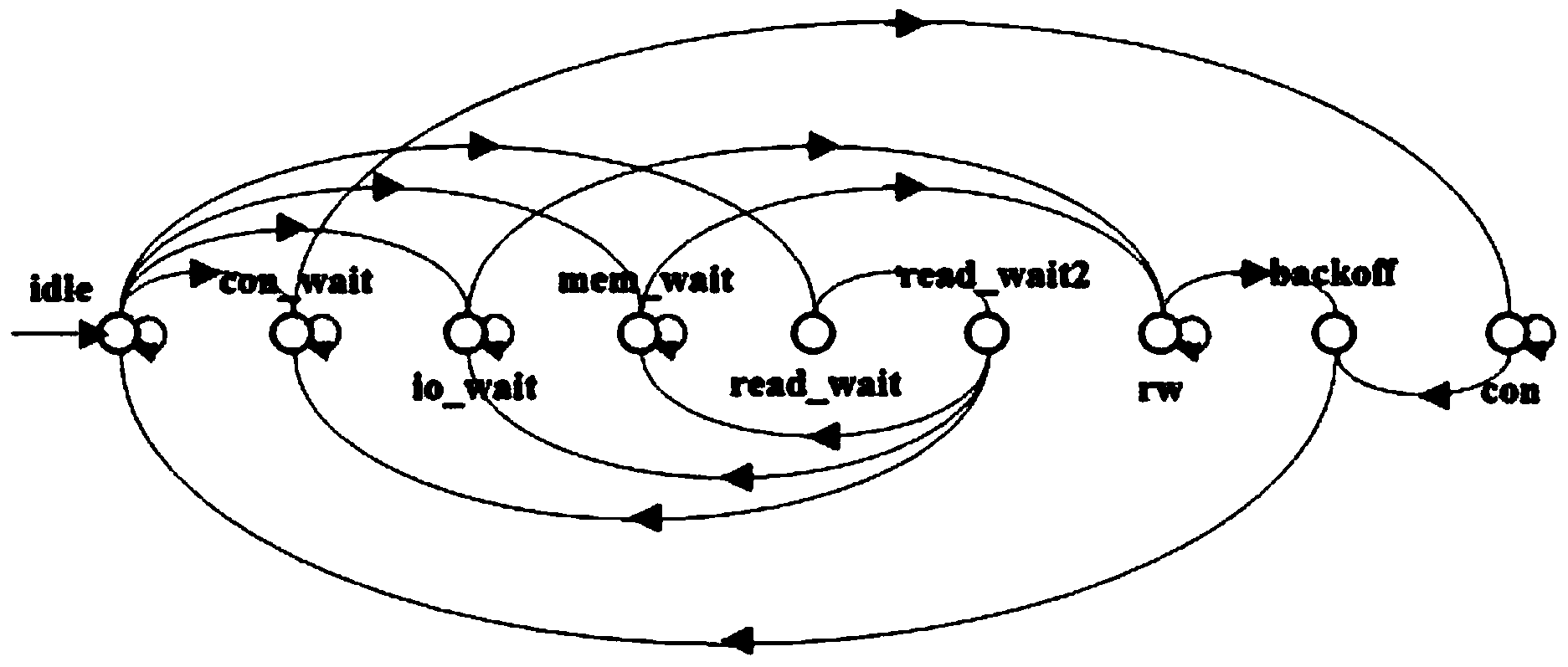

PCI (peripheral component interconnect) slave unit core control module applied to high-speed motion control system

The invention relates to a PCI (peripheral component interconnect) slave unit core control module applied to a high-speed motion control system, which relates to a PCI slave unit core control module, and solves the problem that an existing PCI slave unit occupies a large space, the function cannot be customized, the cost is high, and the design of an embedded system is limited. The PCI slave unit core control module comprises a core state machine, a configuration unit, an input-output controller, a verifying block, an RAM (random access memory) reading-writing controller and an interruption controller, wherein the core state machine comprises an idle state idle, a configuration operation waiting state con_wait, a port operation waiting state io_wait, a storage operation waiting state mem_wait, a reading-writing state read-wait, a configuration reading-writing state con, a port or storage reading-writing state rw and an ending state backoff. The PCI slave unit core control module is applied to the development of the PCI slave unit.

Owner:HARBIN INST OF TECH

Touch panel repair circuit

InactiveCN101794037ANo design changes requiredStatic indicating devicesAudio power amplifierOperational amplifier

The invention provides a touch panel repair circuit. The repair circuit comprises a connecting wire, a data wire, a read wire, a data wire repair wire, a read wire repair wire, a data wire operational amplifier, and a read wire operational amplifier, wherein the data wire is electrically connected with a plurality of display units; one end of the data wire is transversely arranged on the connecting wire in an insulated way; the read wire is electrically connected with a plurality of touch units; one end of the read wire is transversely arranged on the connecting wire in the insulated way; one end of the data wire repair wire is arranged above or under the connecting wire in the insulated way, while the other end is transversely arranged on the other end of the data wire and the read wire in the insulated way; the read wire repair wire is insulated from the data wire repair wire; one end of the read wire repair wire is arranged above or under the connecting wire in the insulated way, while the other end is arranged above or under the data wire repair wire in the insulated way; the data wire operational amplifier is arranged on the data wire repair wire; and the read wire operational amplifier is arranged on the read wire repair wire and opposite to the data wire operational amplifier. The touch panel repair circuit is used for repair of the data wire and the read wire, does not need increase space occupied by the original repair wire, and keeps the same panel design.

Owner:AU OPTRONICS CORP

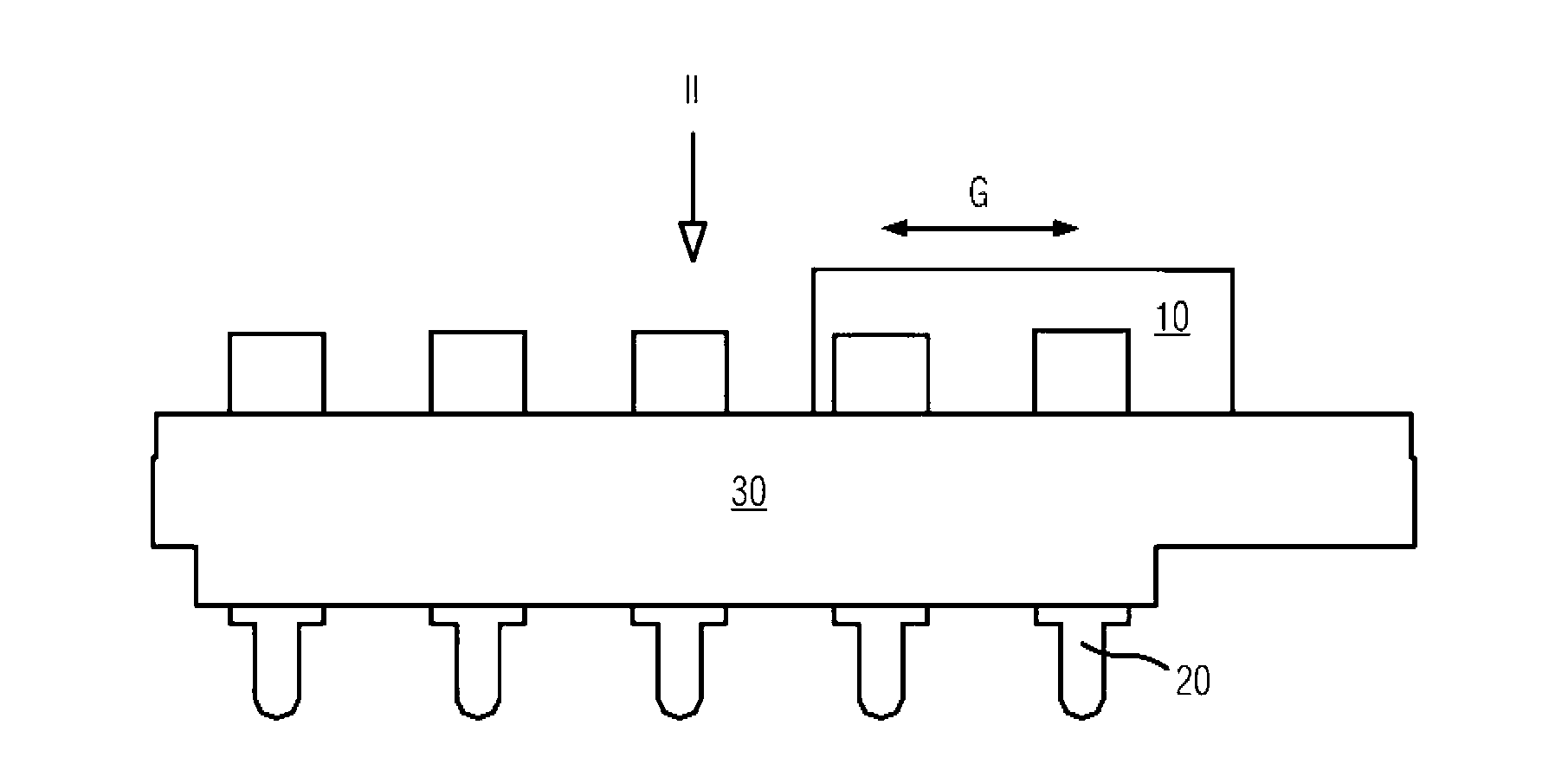

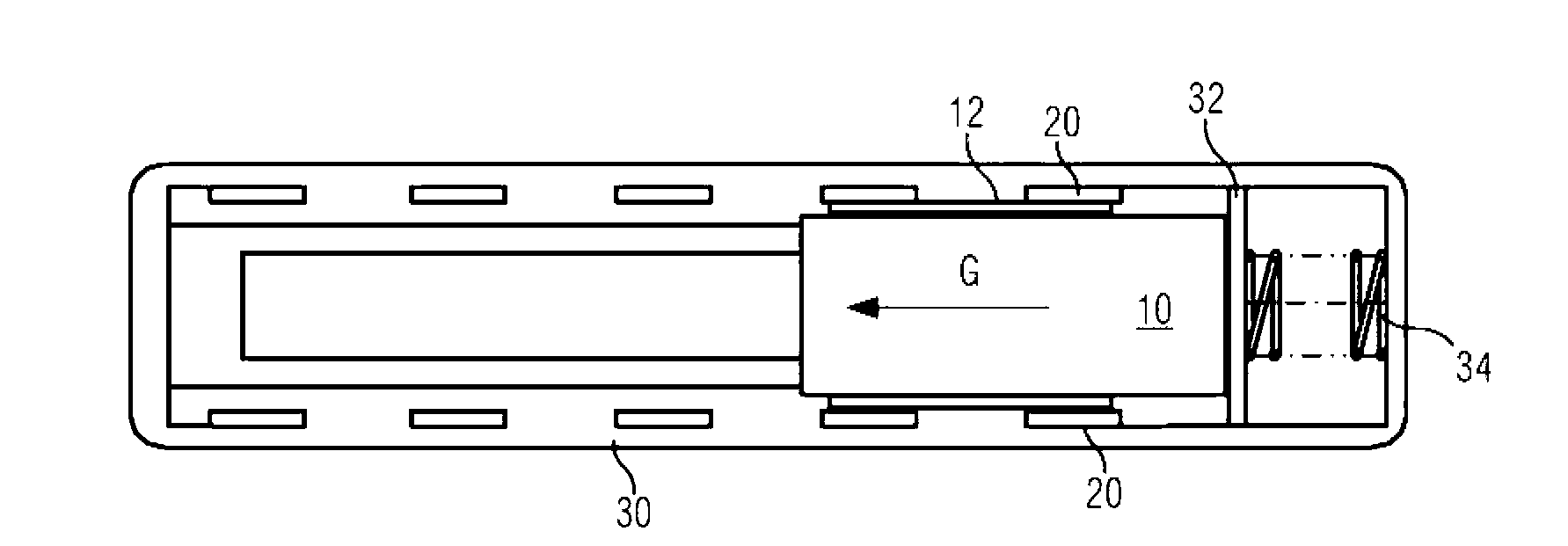

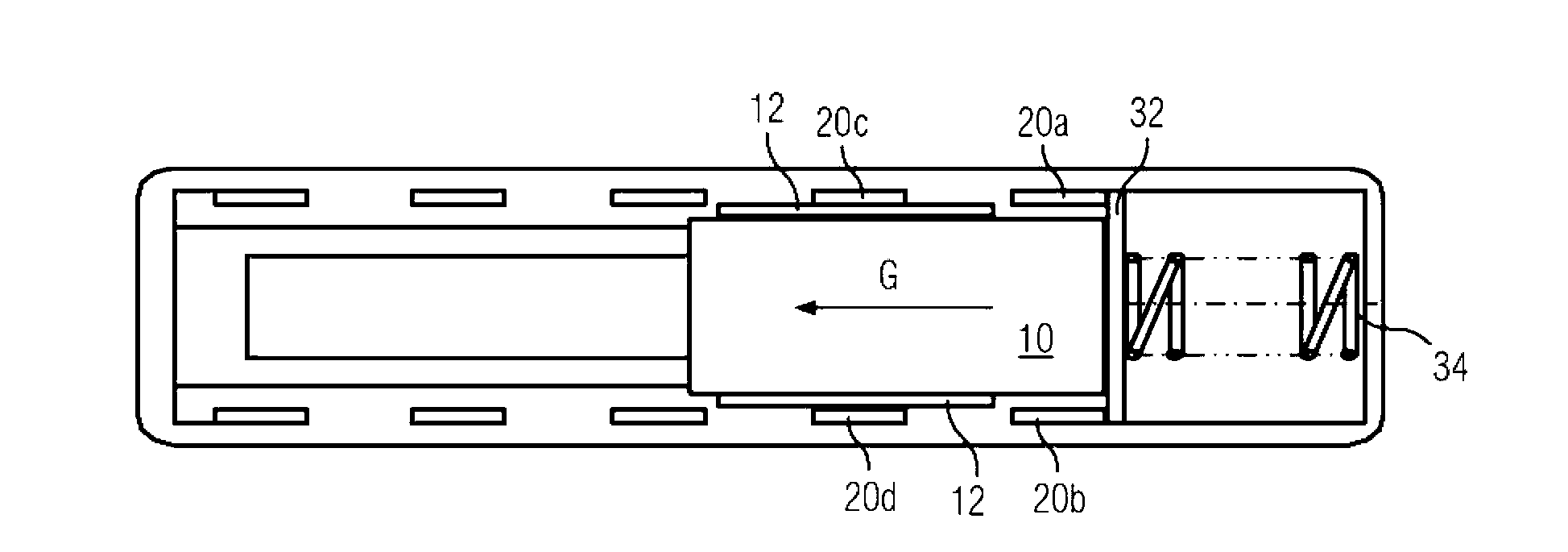

Slider switch and thermostat controller using the same

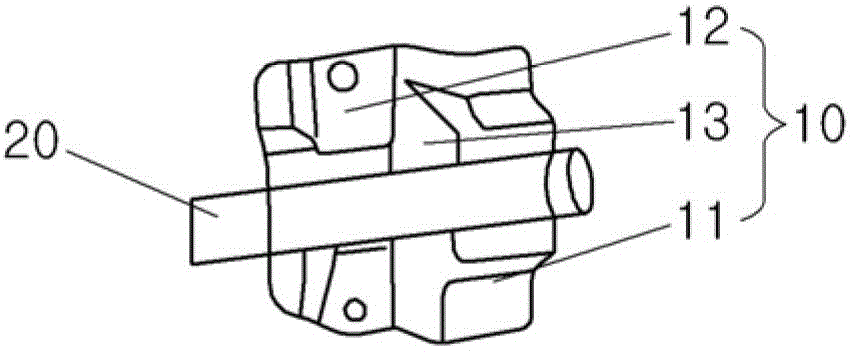

A slider switch and a thermostat controller using the same are provided. The switch comprises a base (30), a slider (10), several pins (20) arranged in two rows, and a contact element (12) for electrically connecting a pair of neighboring pins in the same row. A first elastic element (34) and a contact sheet (32) are provided along the glide direction. One end of the first elastic element is connected with the base, the other end of the first elastic element is connected with the contact sheet, and one end surface of the slider adjacent to the contact sheet can be pressed against the contact sheet from a direction opposite to the first elastic element. When each of the contact elements is in contact with a pair of the pins closest to the contact sheet, the contact sheet is separate from the two pins closest to the contact sheet with the pressure from the slider; and when each of the contact elements is in contact with other pins of pins other than those closest to the contact sheet, the contact sheet is pressed against the two pins closest to the contact sheet by the first elastic element. The slider switch can be used for fan control in the thermostat controller as well as occasions requiring switch and connection among multiple circuits.

Owner:SIEMENS SWITZERLAND

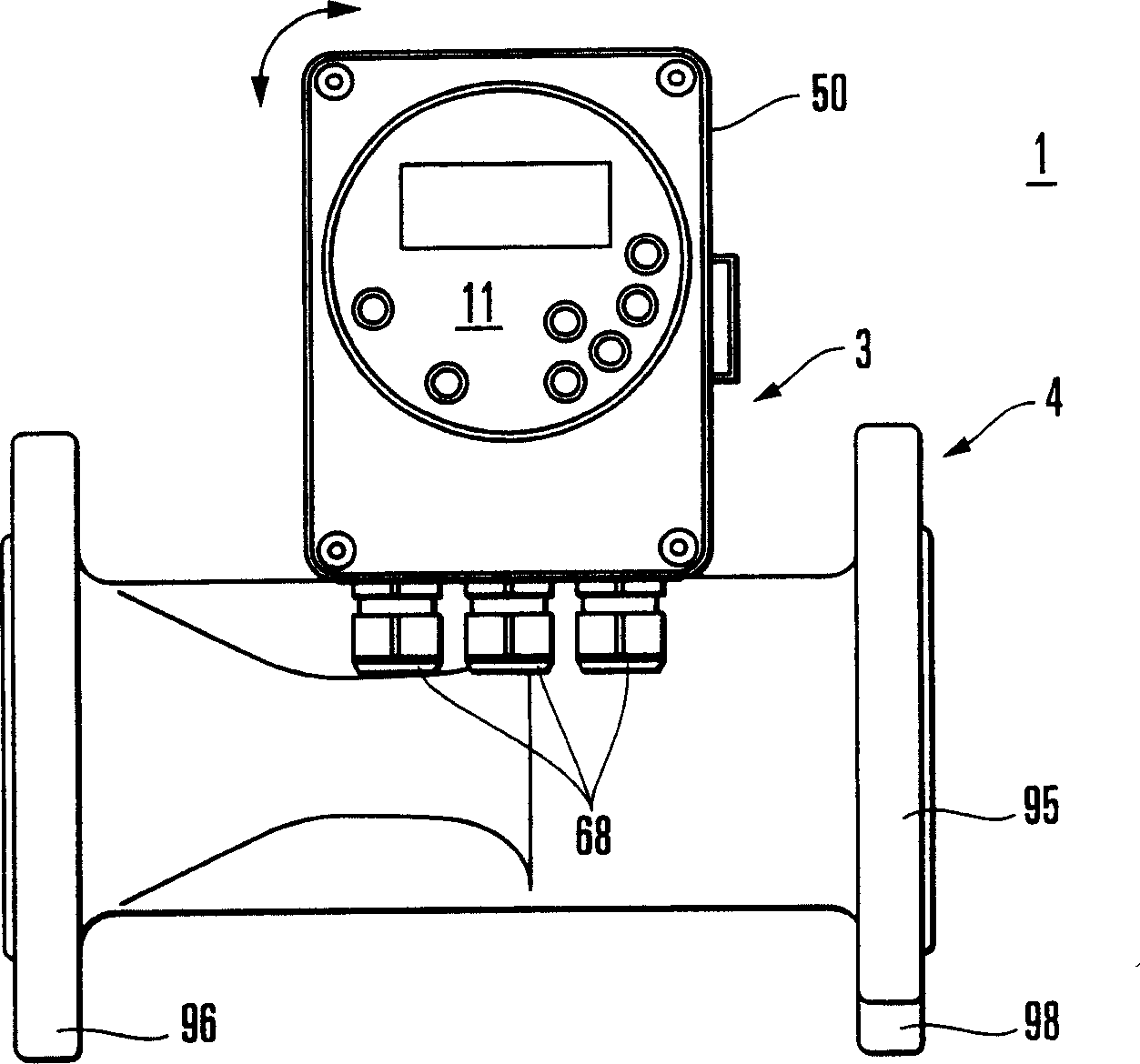

Differential/pressure transmitter

ActiveCN1512141AChange the installation angleEasy to installFluid pressure measurement by electric/magnetic elementsVolume/mass flow by differential pressureDifferential pressureEngineering

Owner:YAMATAKE HONEYWELL CO LTD

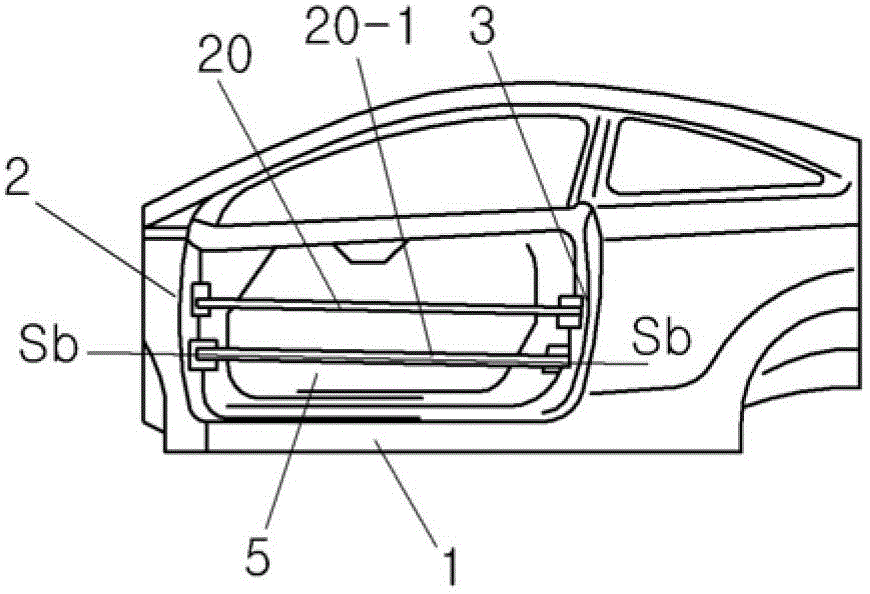

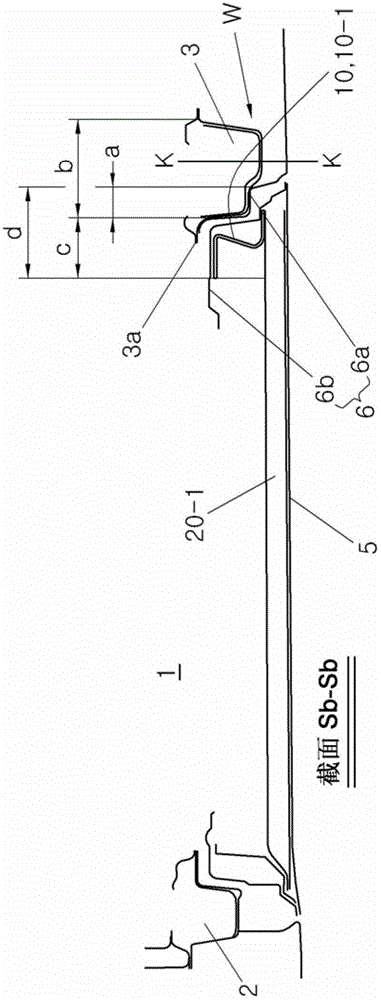

Door impact beam unit for 2-door vehicle

ActiveCN103144594AImprove stabilityImprove structural stabilityPedestrian/occupant safety arrangementSuperstructure subunitsCar door

The invention relates to a door impact beam unit for 2-door vehicles. Wide brackets of door impact beams are formed in a Z shape such that beam contact parts are extended horizontally in one direction above oblique force support parts and wide overlap parts are extended horizontally in the opposite direction below the oblique force support parts. Therefore, while an overlap section of a door with respect to a B pillar is further widened, a body frame and a B pillar of a 2-door coupe vehicle exhibit the same safety performance as a body frame and a B pillar of a 4-door sedan vehicle.

Owner:HYUNDAI MOTOR CO LTD +1

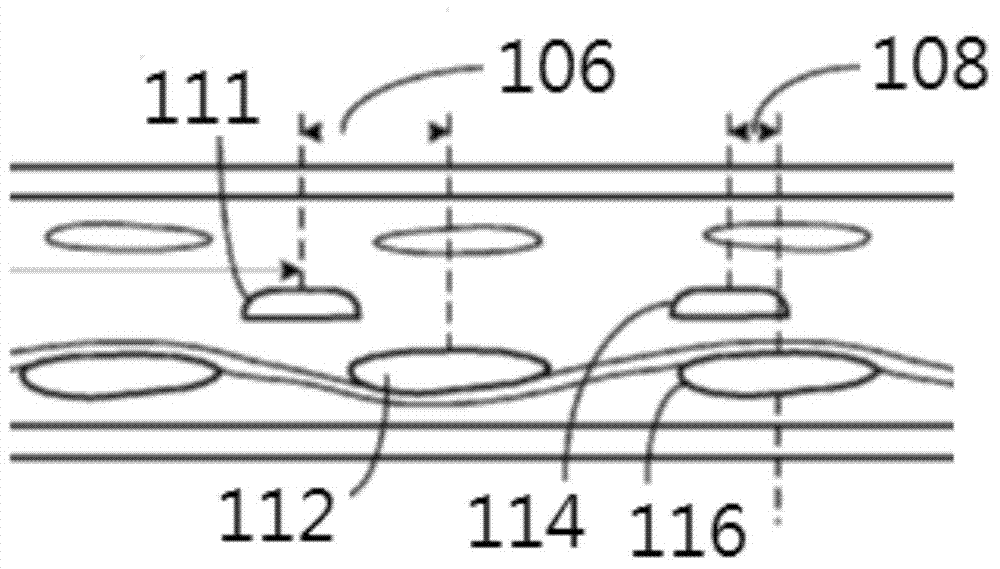

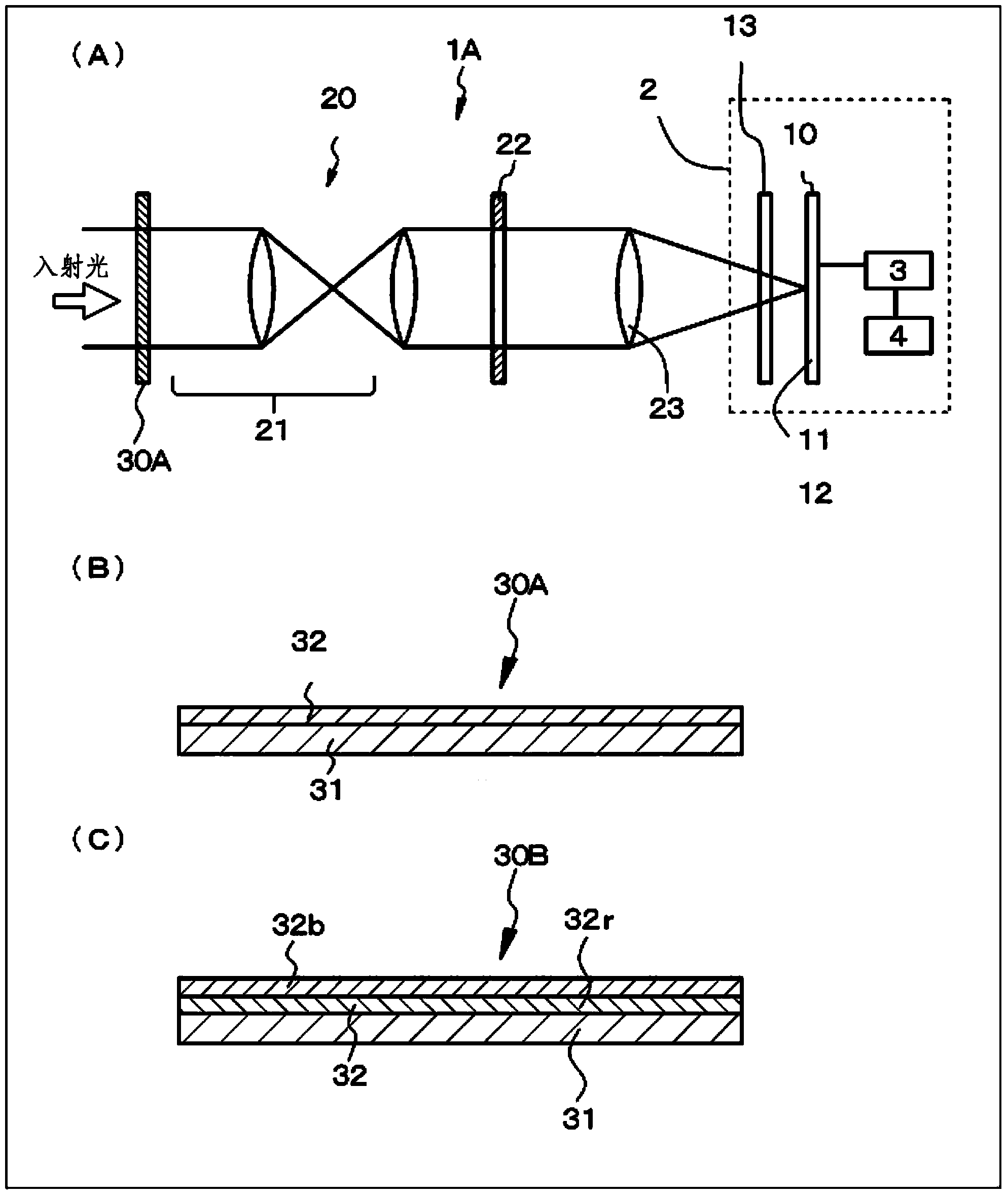

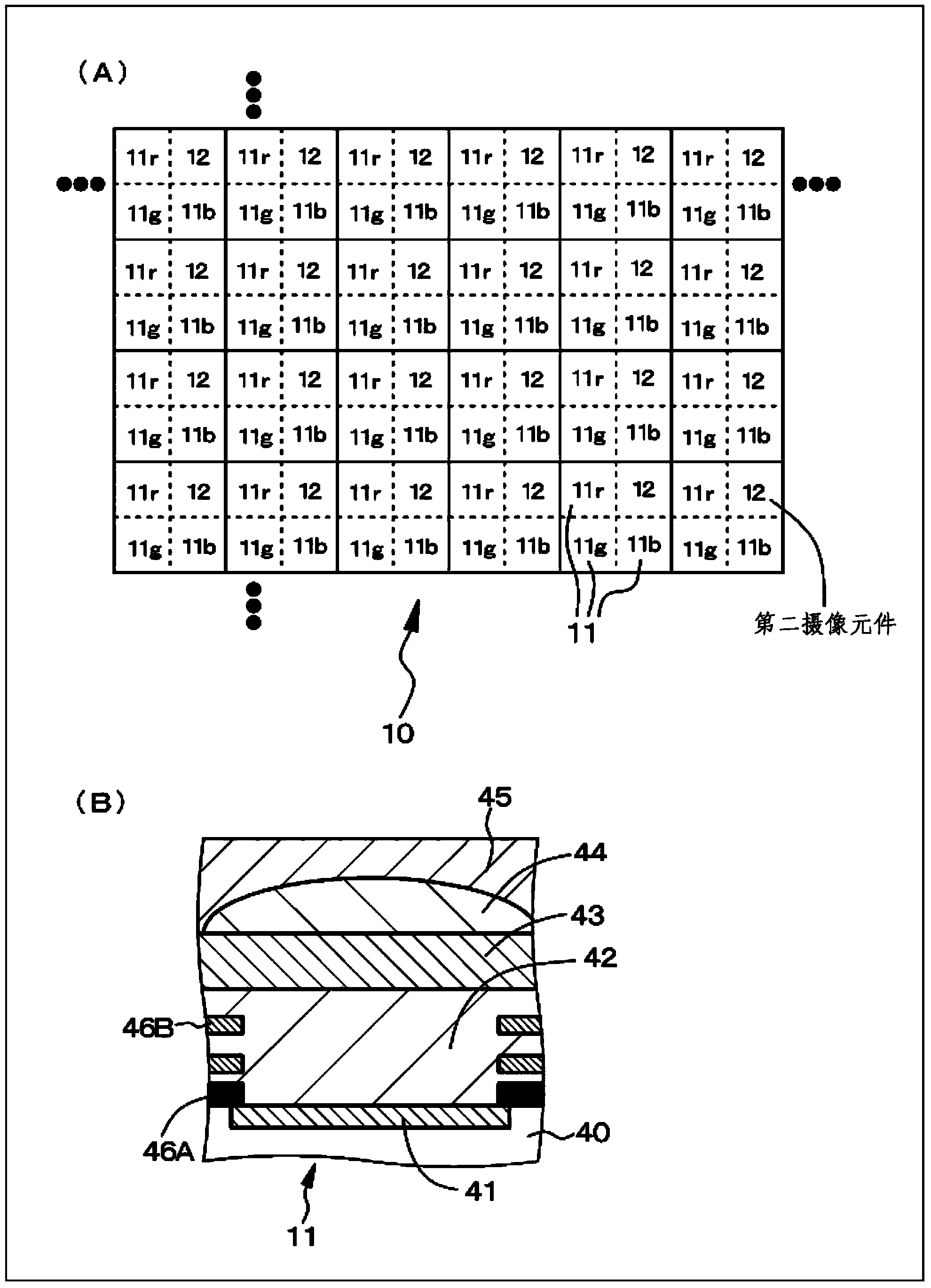

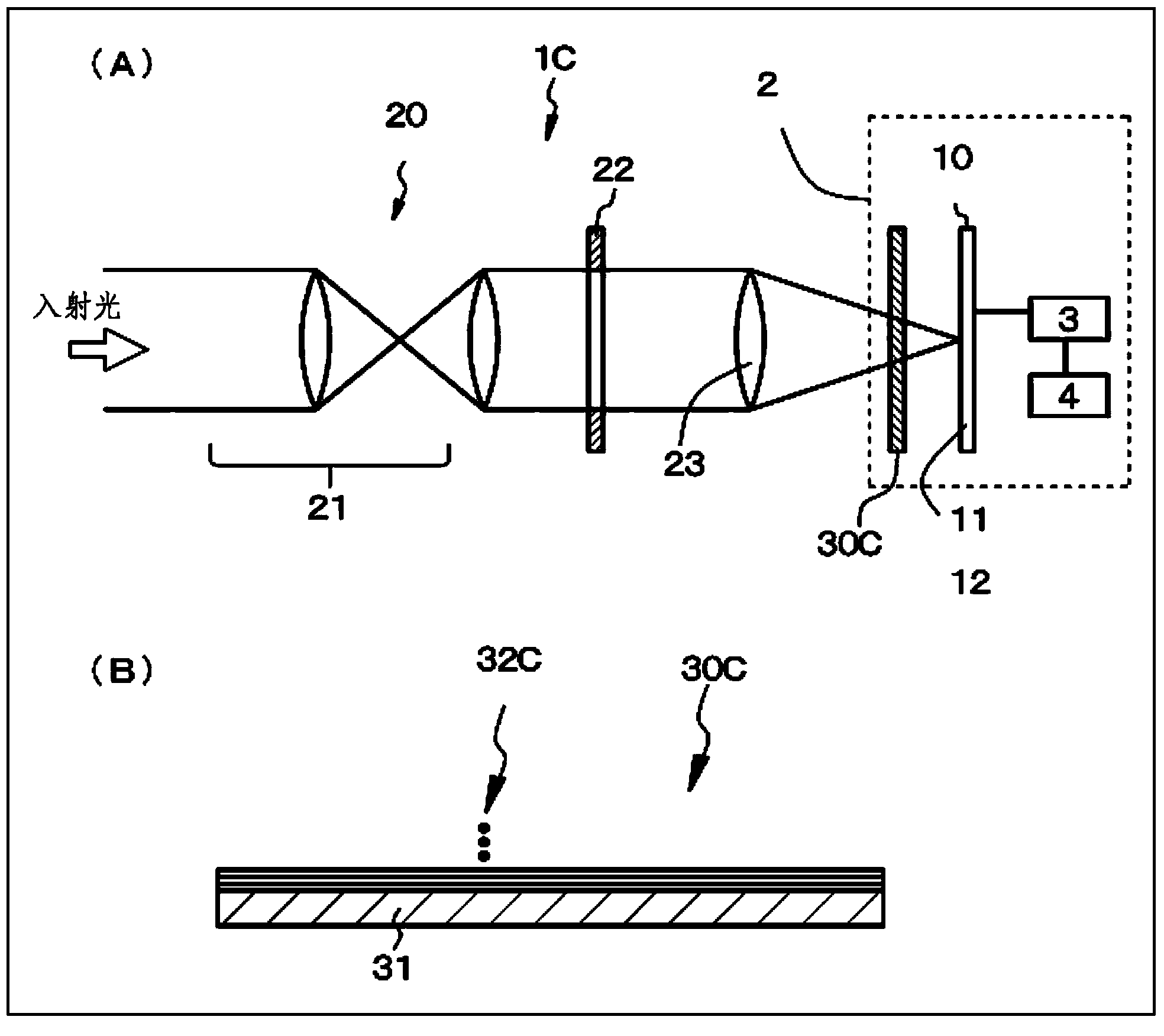

Image pickup apparatus and filter

InactiveCN103814571AChange manufacturing stepsNo design changes requiredSolid-state devicesSignal generator with single pick-up deviceUltraviolet lightsLuminous flux

The present technology relates to an image pickup apparatus and a filter, said technology being capable of providing an image pickup apparatus that can detect infrared light or ultraviolet light and visible light in a same manner. An image pickup apparatus 1A is provided with a lens system 20, and an image pickup unit 10 having inputted thereto light that has passed through the lens system 20. The image pickup unit 10 has a plurality of first image pickup elements 11, which receive light in a first wavelength band; and a plurality of second image pickup elements 12, which receive light in a second wavelength band different from the first wavelength band. The lens system 20 or the image pickup unit 10 is provided with an optical element 30A, which makes the light in the first wavelength band reach the image pickup unit, said light having a light quantity smaller than that of the light in the second wavelength band.

Owner:SONY CORP

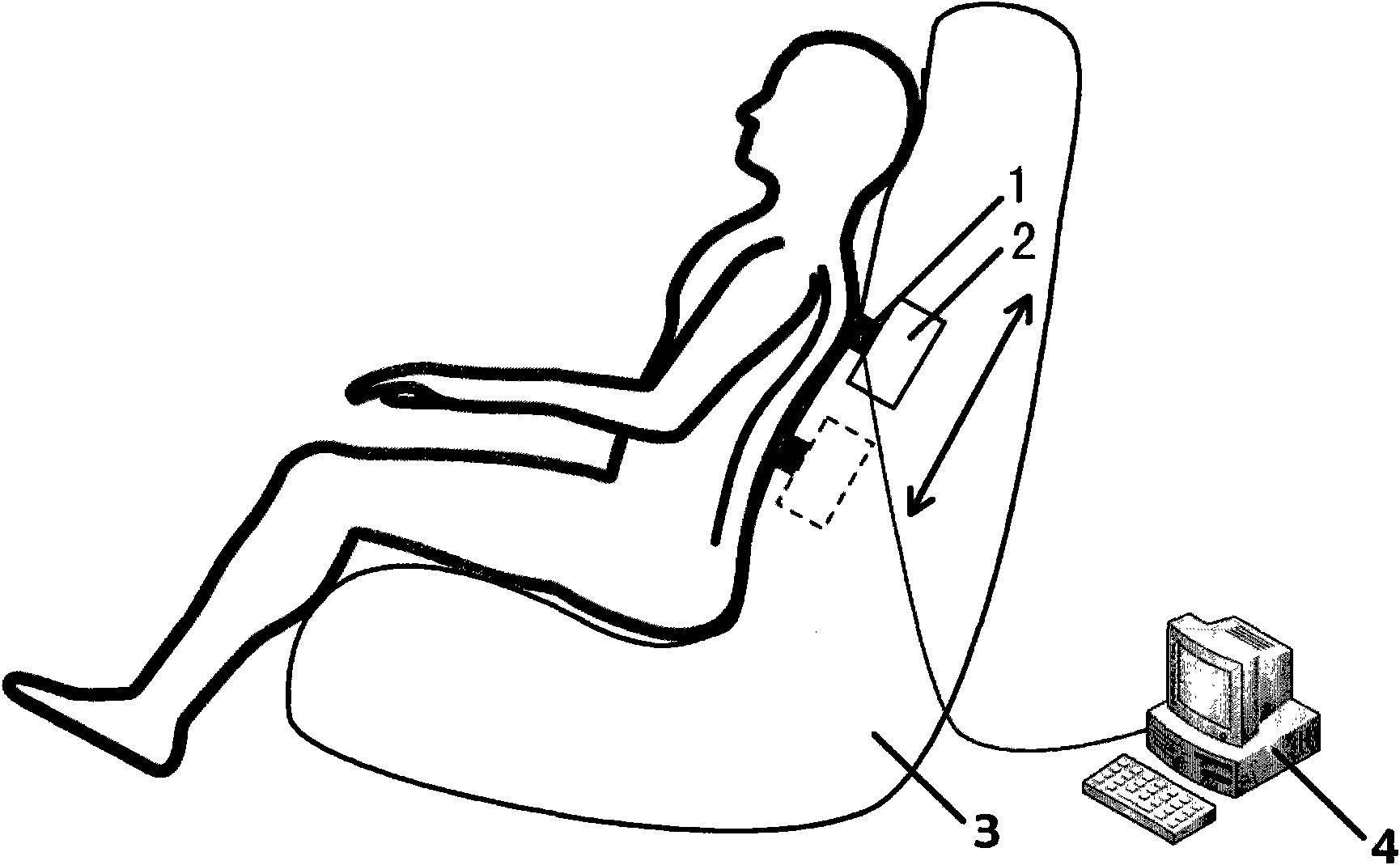

Detection device for S curve on back of human body

InactiveCN101966082ASimple structureReasonable designDiagnostic recording/measuringSensorsMicrocontrollerEngineering

The invention relates to a detection device for an S curve on a back of a human body, which comprises a massage armchair, a pressure detection module and an upper computer, wherein the pressure detection module is arranged in the massage armchair and is connected with the upper computer; the pressure detection module can be fixed in a flat position on a walkable massager clock mechanism in the massage armchair; the pressure detection module can detect the suffered extrusion of the back of the human body in the course of walking up and down along with the massager clock mechanism; the upper computer carries out real-time data processing to obtain the gravity distribution of each position on the back of the human body so that the S curve on the back of the human body can be detected; and the method provides a foundation to enhance the comfort level of massage. The detection method has the advantages that a singlechip is taken as a core processing chip; the method is combined with the traditional pressure sensing technique; the accuracy, the reliability and the anti-interference performance in the course of data transmission of the traditional angle sensing technique are utilized; the accurate detection of the S curve on the back of the human body is realized to reach good massage effect; the structure is simple; the reliability is strong; and the cost performance is high.

Owner:SHANGHAI UNIV +1

A fpga-based anti-radiation data processing system and method

InactiveCN103500125BEasy to useEasy to handleError detection/correctionData processing systemRadiation resistant

The invention discloses an FPGA-based anti-radiation data processing system and method, including a commercial SRAM structure FPGA with dual-port RAM, which can be used for data processing boards in harsh environments such as radiation. The data processing board includes two anti-radiation anti-fuse Aeroflex UT6235FPGAs, two non-complete anti-radiation Xilinx Virtex-5FX130T FPGAs and related storage and interface peripheral chips. Each Xilinx FPGA includes three parts: the control and processing part; the first data processing module, which is used for input data processing and stores the data processing results in the first part of the dual-port RAM; and the first data processing module The same second data processing module performs the same processing on the same input data, and the data processing result is stored in the second part of the dual-port RAM. The control and processing module compares the processing results of the two processing modules, and if they are consistent, the processing results are stored in a designated memory. If inconsistent, re-process.

Owner:SHANGHAI INST OF TECHNICAL PHYSICS - CHINESE ACAD OF SCI

Semiconductor apparatus

InactiveCN1741372ANo design changes requiredElectronic switchingAmplifier protection circuit arrangementsPower semiconductor deviceElectrical resistance and conductance

Owner:MITSUBISHI ELECTRIC CORP

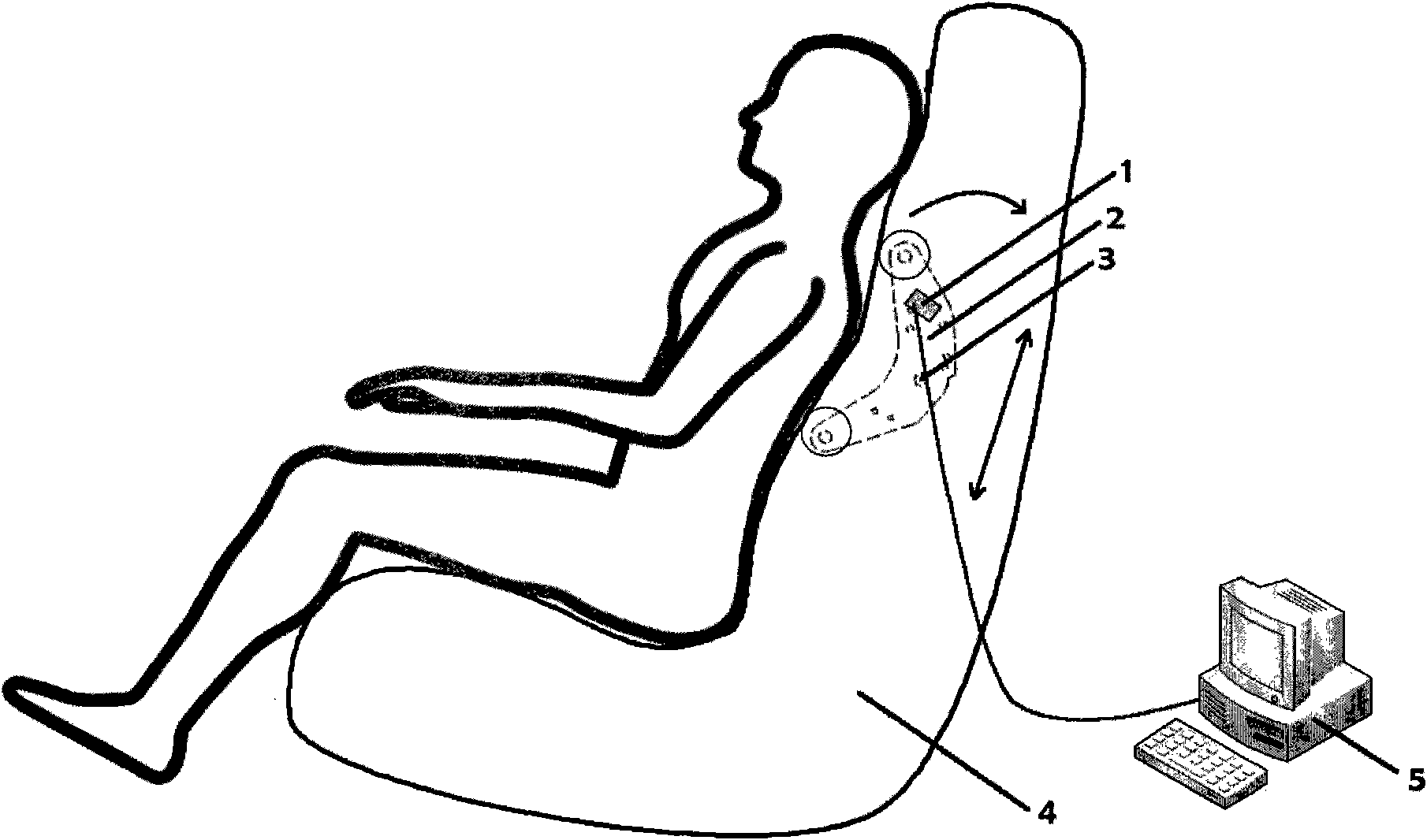

Human shoulder position detection device

InactiveCN102028601ASimple structureReasonable designChiropractic devicesUsing electrical meansMicrocontrollerPhysical medicine and rehabilitation

The present invention relates to a human shoulder position detection device, comprising a massage chair, an angle detection module and an upper computer. The angle detection module is fixed at a flat position at a side of a swinging massage arm in the massage chair; the angle detection module is connected to the upper computer. The angle detection module can rotate with the swinging of the massage swinging arm; and the angle detection module can collect data for the rotating angles of the massage swinging arm and transmit the data to the upper computer for data processing. Therefore the position of human shoulder is detected, and the massage chair can massage the human shoulder exactly. The detection device uses a single chip to be as the core processing chip which is combined with the prior angle sensing technology, and the accuracy and reliability of the prior angle sensing technology and interference immunity of data transmission are used. The accurate detection of human shoulder position during massage is realized; a good massage effect is reached; the structure is simple; the reliability and transportability are strong; and the cost performance is high.

Owner:SHANGHAI UNIV +1

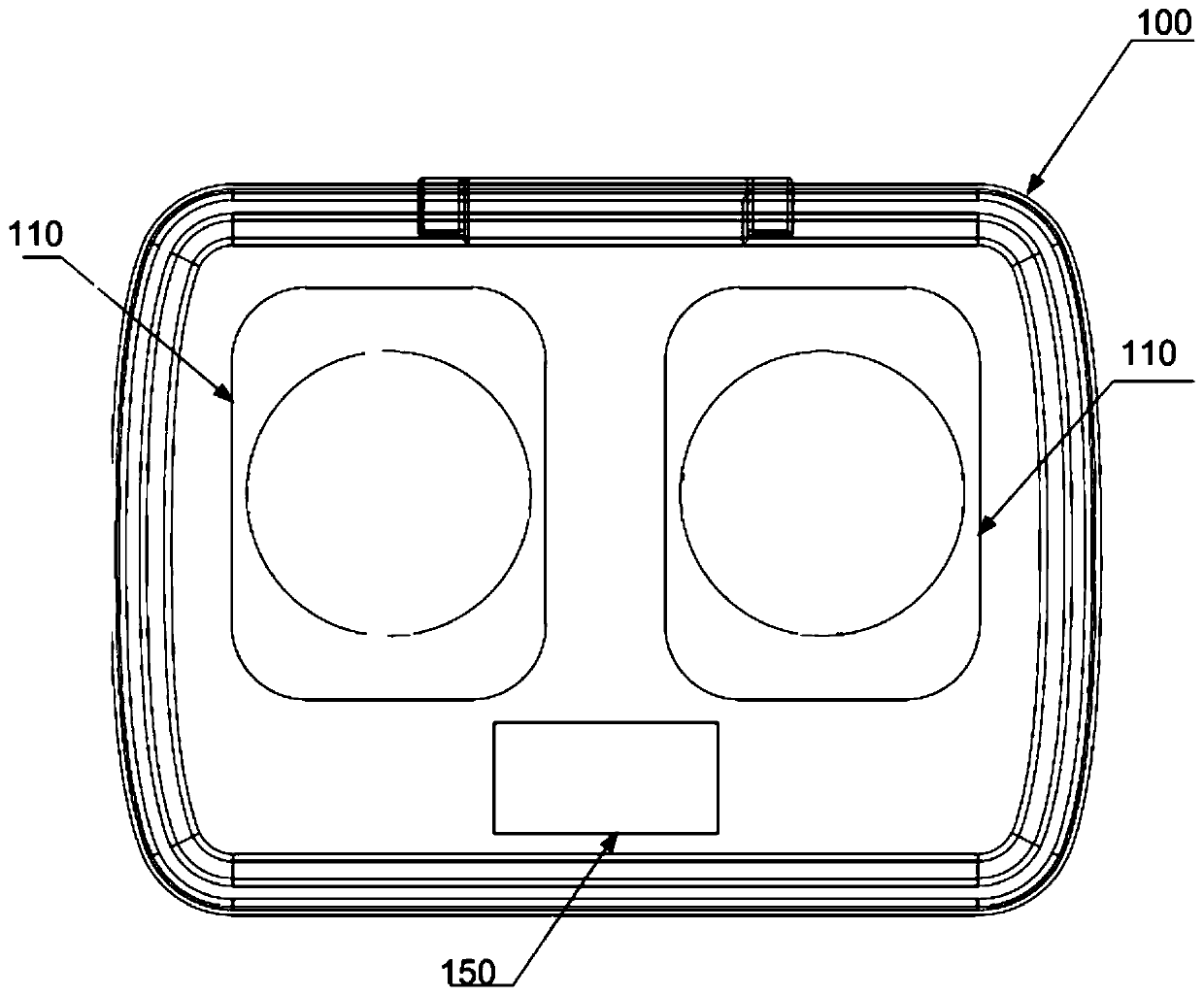

Multi-head charging system for myofascial gun battery pack and battery charging system

InactiveCN111313504AFast chargingNo design changes requiredBatteries circuit arrangementsCurrent conducting connectionsAutomotive engineeringElectrical battery

The invention provides a multi-head charging system for a myofascial gun battery pack and a battery charging system. At least one battery pack comprises a battery pack shell and also comprises a battery management chip, a plurality of battery units and a plurality of first terminals which are arranged in the battery pack shell; a power switch is used for switching on or switching off the electricconnection between the plurality of first terminals of the battery pack and the outside; the charger interface is electrically connected to the battery management chip and is used for charging the battery units through an external charger; a multi-head charger includes a charging management chip and a detection circuit disposed within a base. The at least one battery pack is configured to detect its on-state by the detection circuit when it is inserted into a charging dock, and control the charging management chip to charge the battery pack via a second terminal and the first terminals in response to the power-on of the battery pack. By means of the charging system, charging and using can be achieved at the same time, the battery pack can be detached to replace batteries, and an under-voltage battery pack is placed in the charging dock to be rapidly charged.

Owner:NANJING BINDE TECH CO LTD

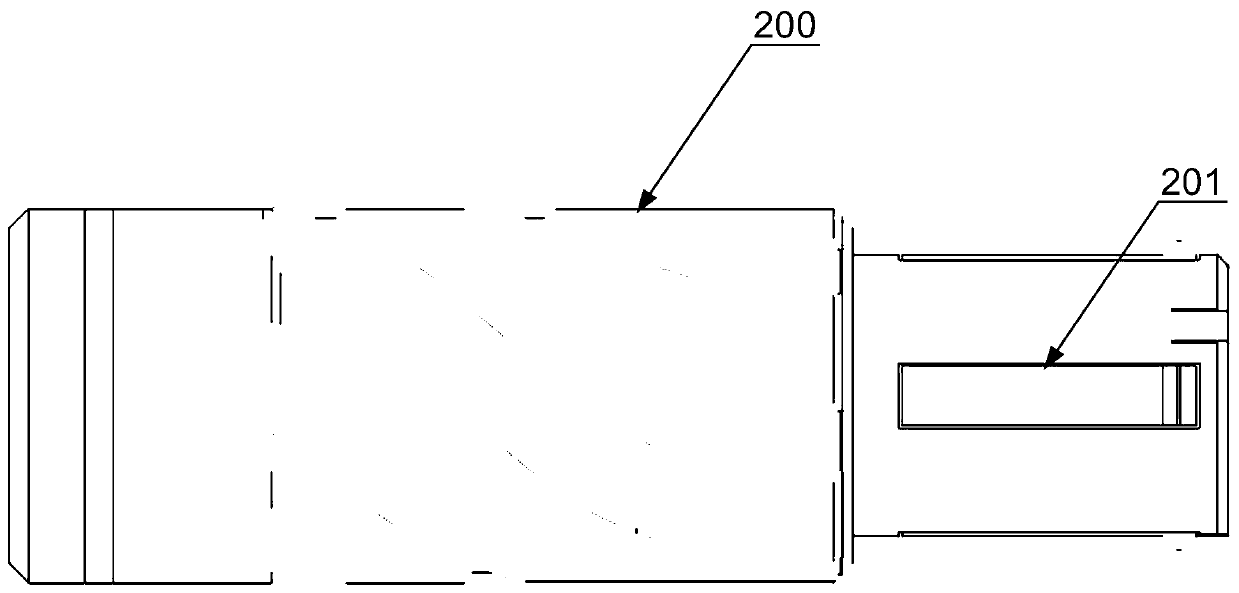

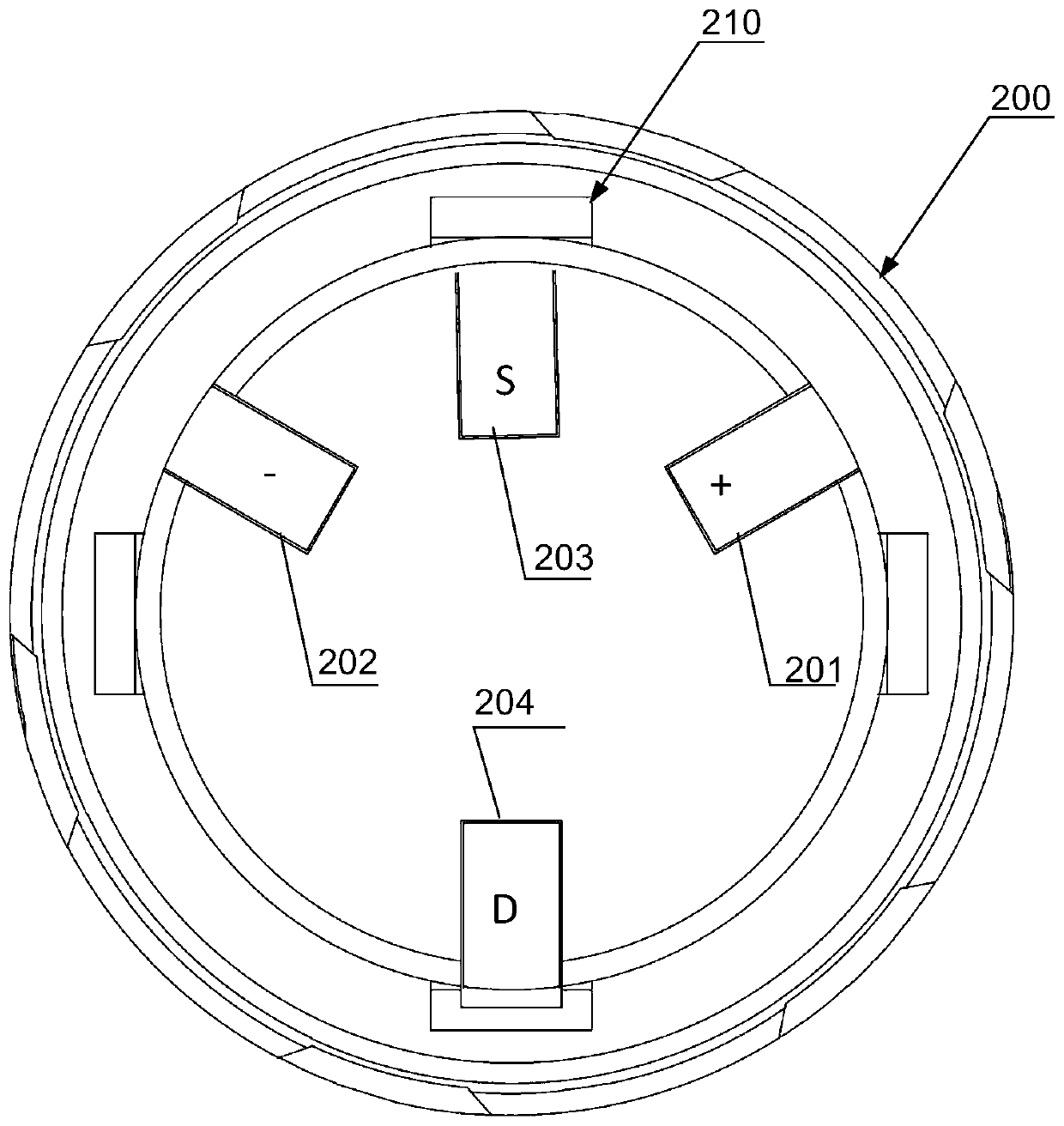

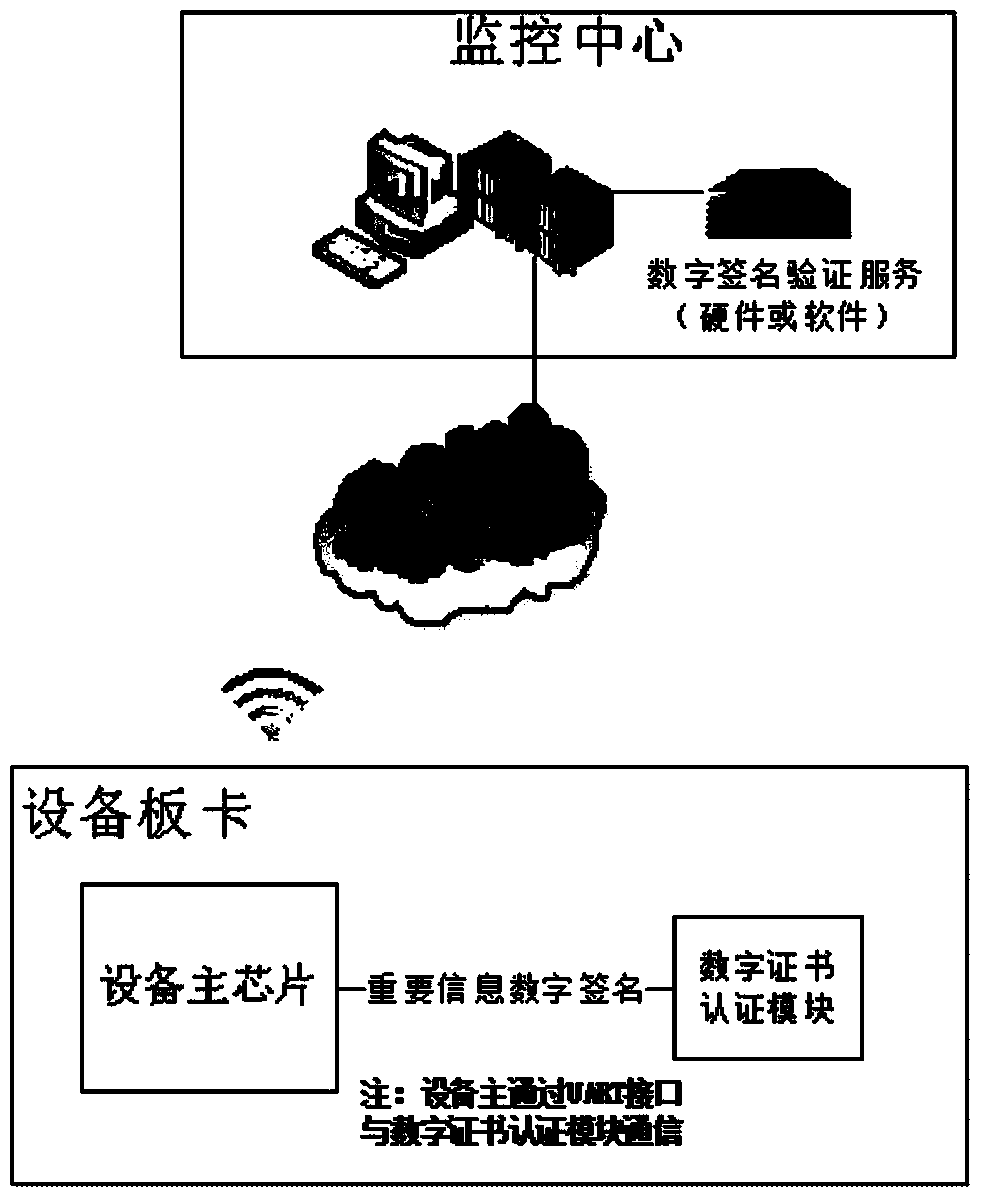

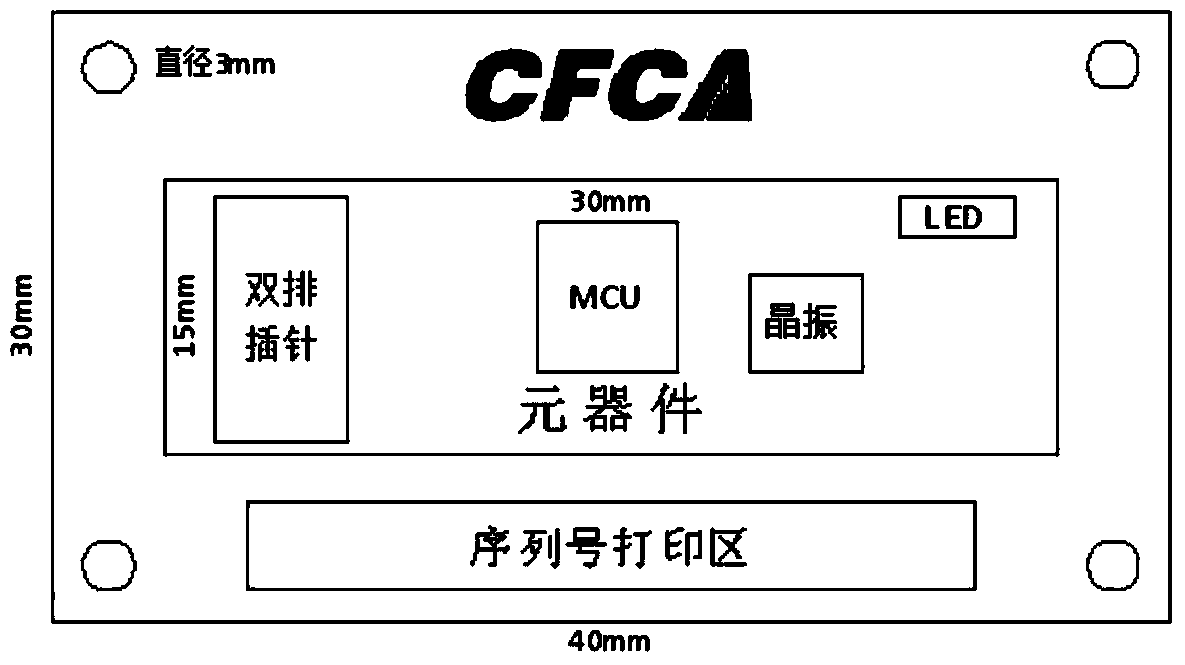

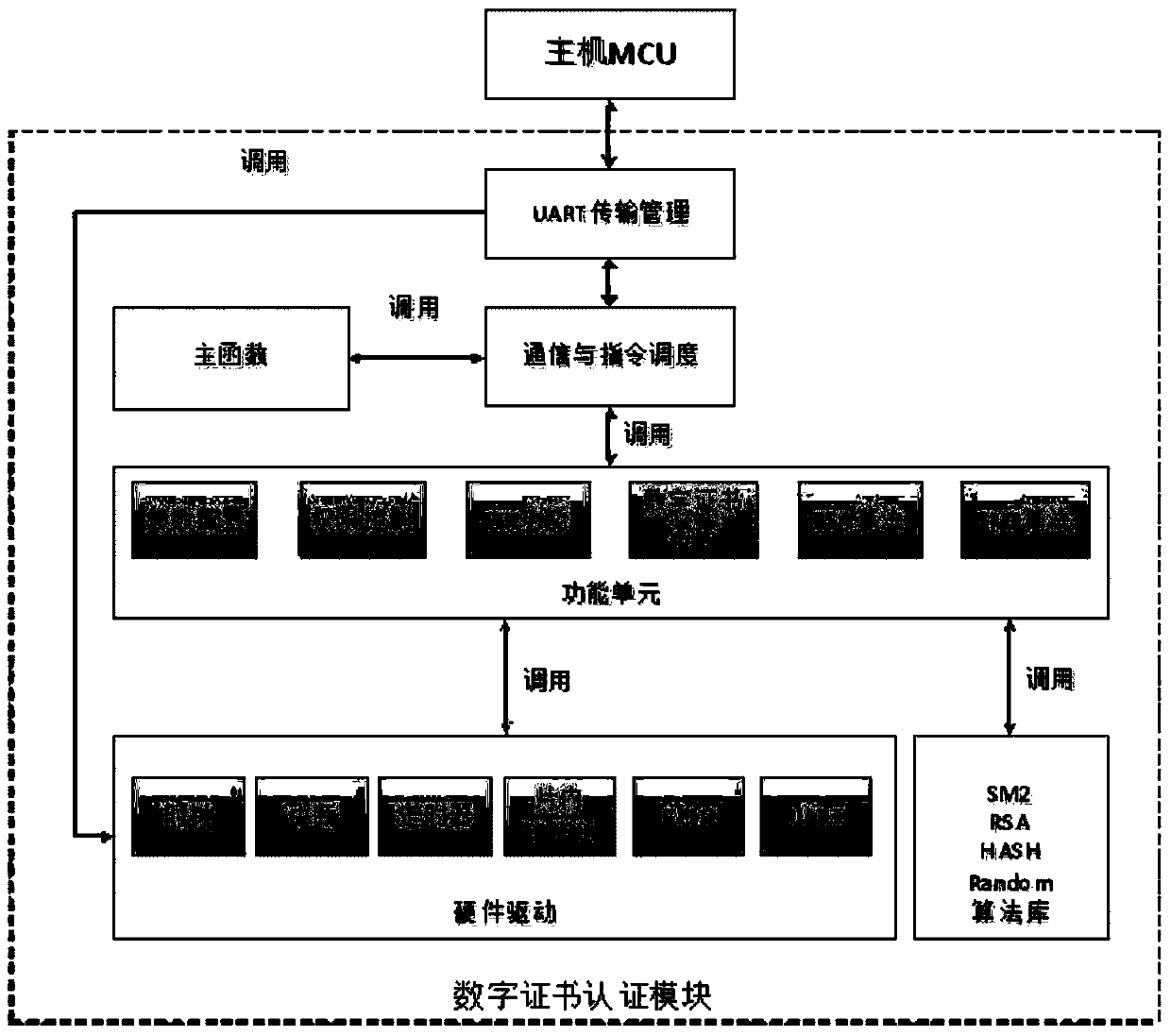

Digital certificate authentication device and digital certificate authentication system

ActiveCN103731262ANo design changes requiredSimple hardware interfacePublic key for secure communicationUser identity/authority verificationHardware structureOperational system

The invention relates to the technical field of Public Key Infrastructure (PKI), and provides a digital certificate authentication device and a digital certificate authentication system. The digital certificate authentication device comprises a software portion and a hardware portion, wherein the software portion comprises a COS and a guide system, the hardware portion comprises hardware loading the COS and the guide system, and the COS comprises a UART transmission and management module, a hardware drive module, a function module, an algorithm library, a communication and instruction dispatch module and a main function module. The digital certificate authentication device and the digital certificate authentication system can meet the requirements that an equipment hardware structure is not changed and the minimum integrated development workload is guaranteed.

Owner:CHINA FINANCIAL CERTIFICATION AUTHORITY

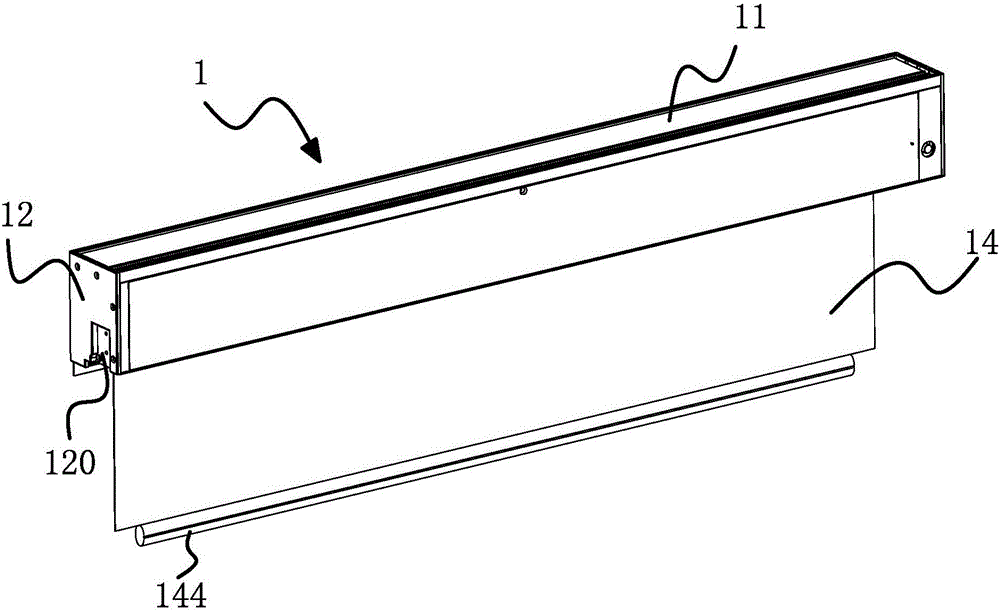

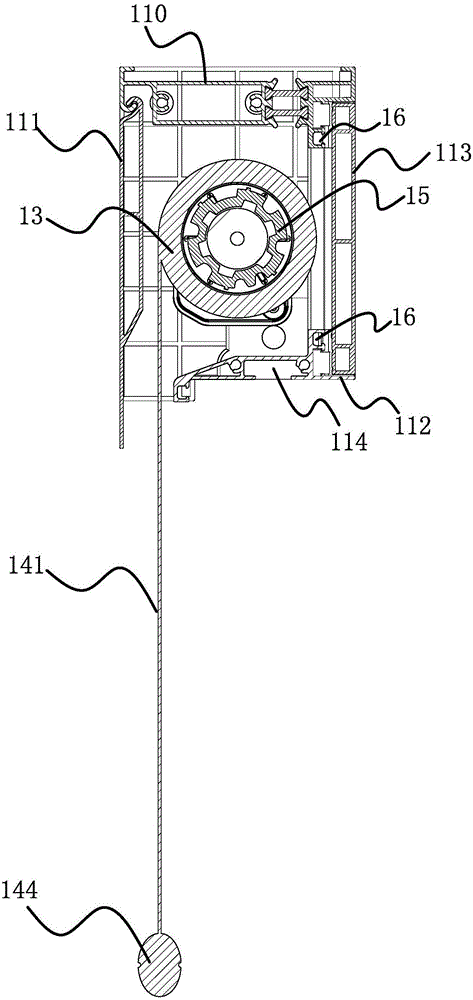

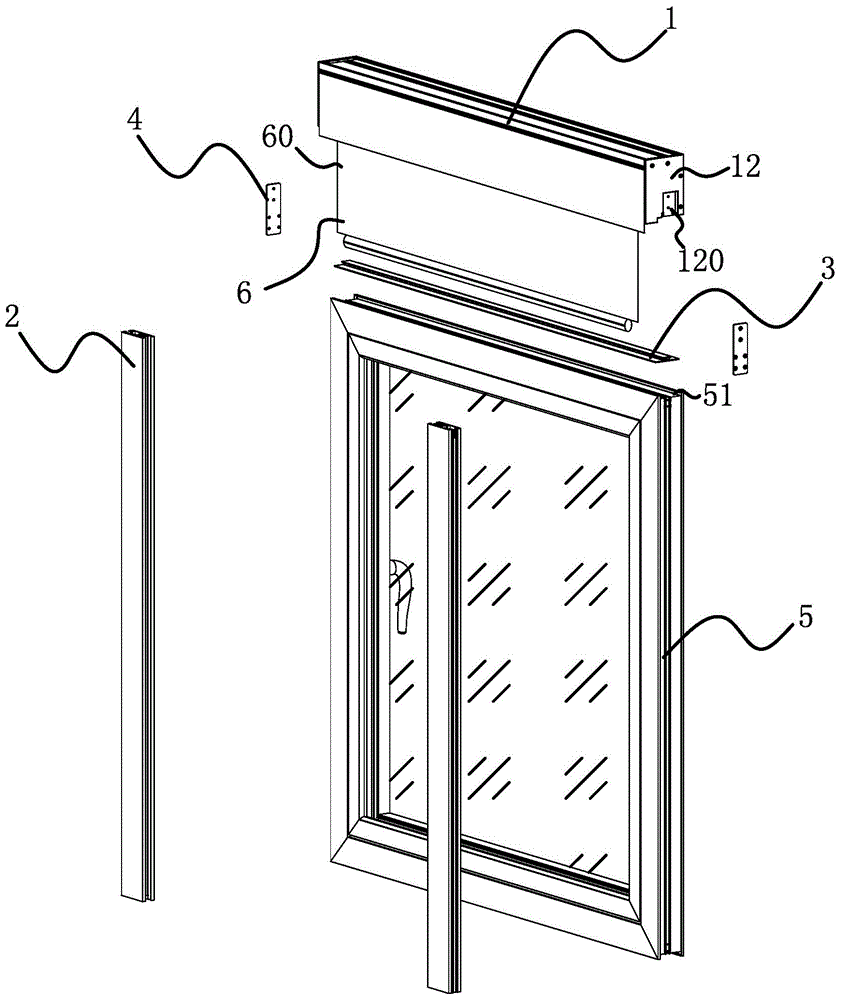

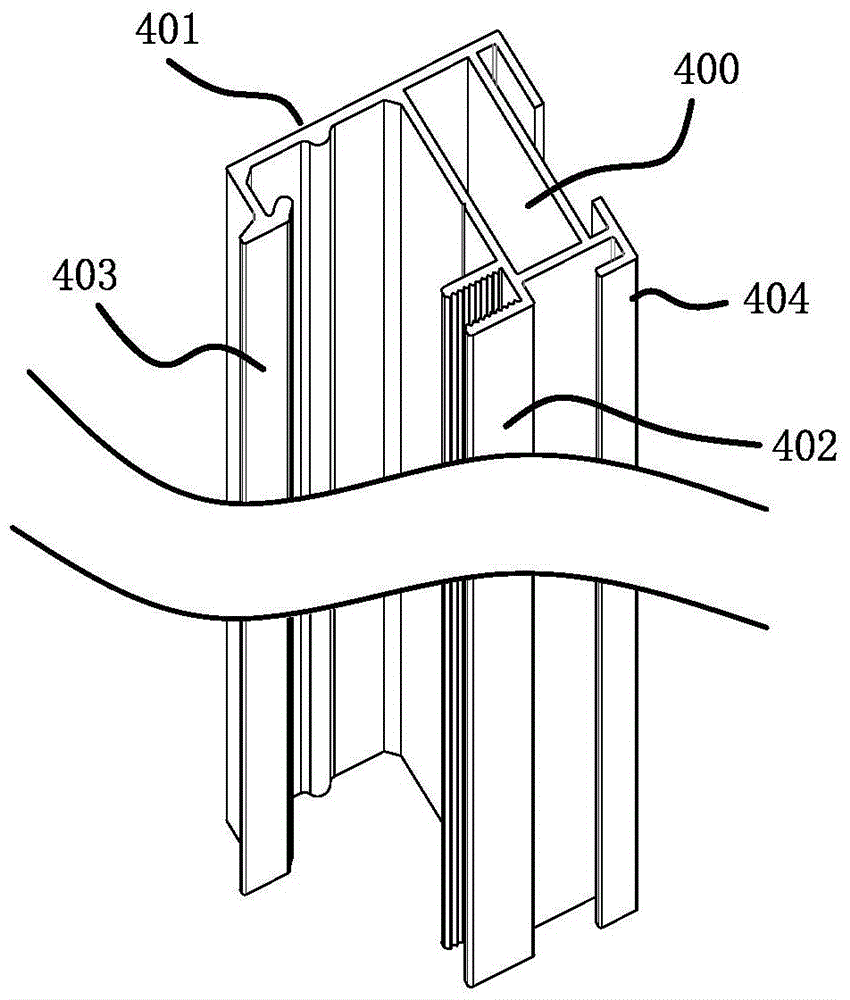

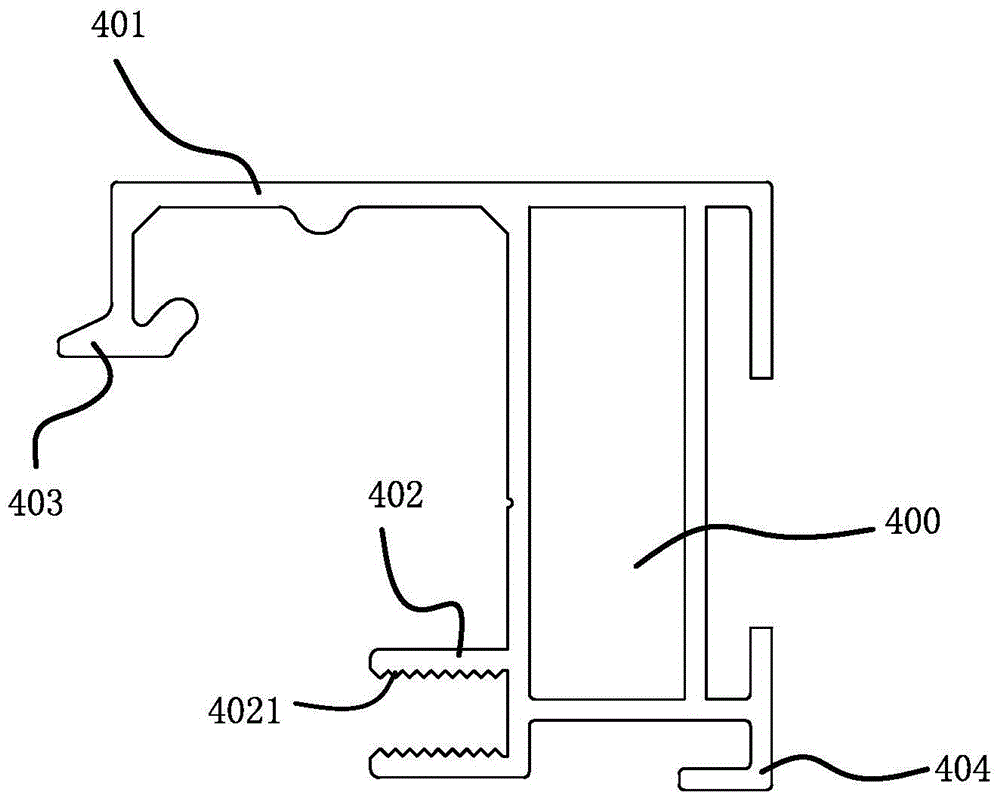

Integrated roller shutter window

InactiveCN104989262ANo design changes requiredEasy follow-up maintenanceLight protection screensAgricultural engineering

The invention provides an integrated roller shutter window, and belongs to the field of building components. The integrated roller shutter window overcomes the defect that an existing roller shutter window is not high in universality. The integrated roller shutter window comprises a sectional bar window and further comprises a roller shutter assembly. The roller shutter assembly comprises a curtain cover assembly installed on the top face of the sectional bar window, two wind resisting tracks located on the front surfaces of the two sides of the sectional bar window, a first connecting piece for detachably installing the curtain cover assembly on the top face of the sectional bar window, and second connecting pieces for detachably connecting the two wind resisting tracks to the front surfaces of the two sides of the sectional bar window. The curtain cover assembly is provided with a cord fabric assembly capable of being unfolded or folded, and the two side edges of the cord fabric assembly can move in the two wind resisting tracks respectively during unfolding. The integrated roller shutter window has the advantages of being high in universality, easy to install and suitable for various sectional bar windows.

Owner:NINGBO XIANFENG NEW MATERIAL

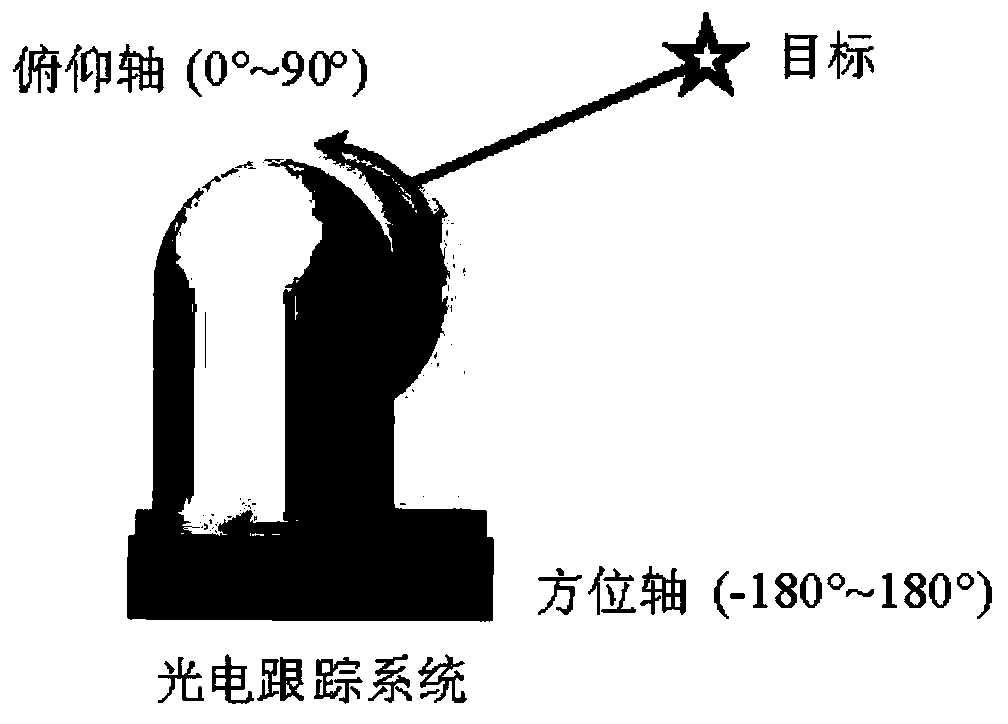

Transient process-based anti-integration saturation design method

InactiveCN110609470ANo design changes requiredGuaranteed speedControllers with particular characteristicsClosed loopEngineering

The invention provides a transient process-based anti-integration saturation design method and belongs to the field of photoelectric system tracing control. Aiming at the problem that an integral saturation phenomenon occurs in a conventional dual-closed loop control method during tracking a phase step reference signal to cause excessively large system output overshot and stability reduction, themethod for designing transient process is proposed for the integral saturation phenomenon. After the transient process and the dual-closed loop control method are effectively combined, the purpose ofanti-integration saturation is achieved, the rapidness of tracking the phase step reference signal by dual closed loops is maintained, meanwhile, the system stability is improved, and the problem of large overshot during tracking is solved. By experiment of the photoelectric tracking system, the effectiveness of the method is verified.

Owner:INST OF OPTICS & ELECTRONICS - CHINESE ACAD OF SCI

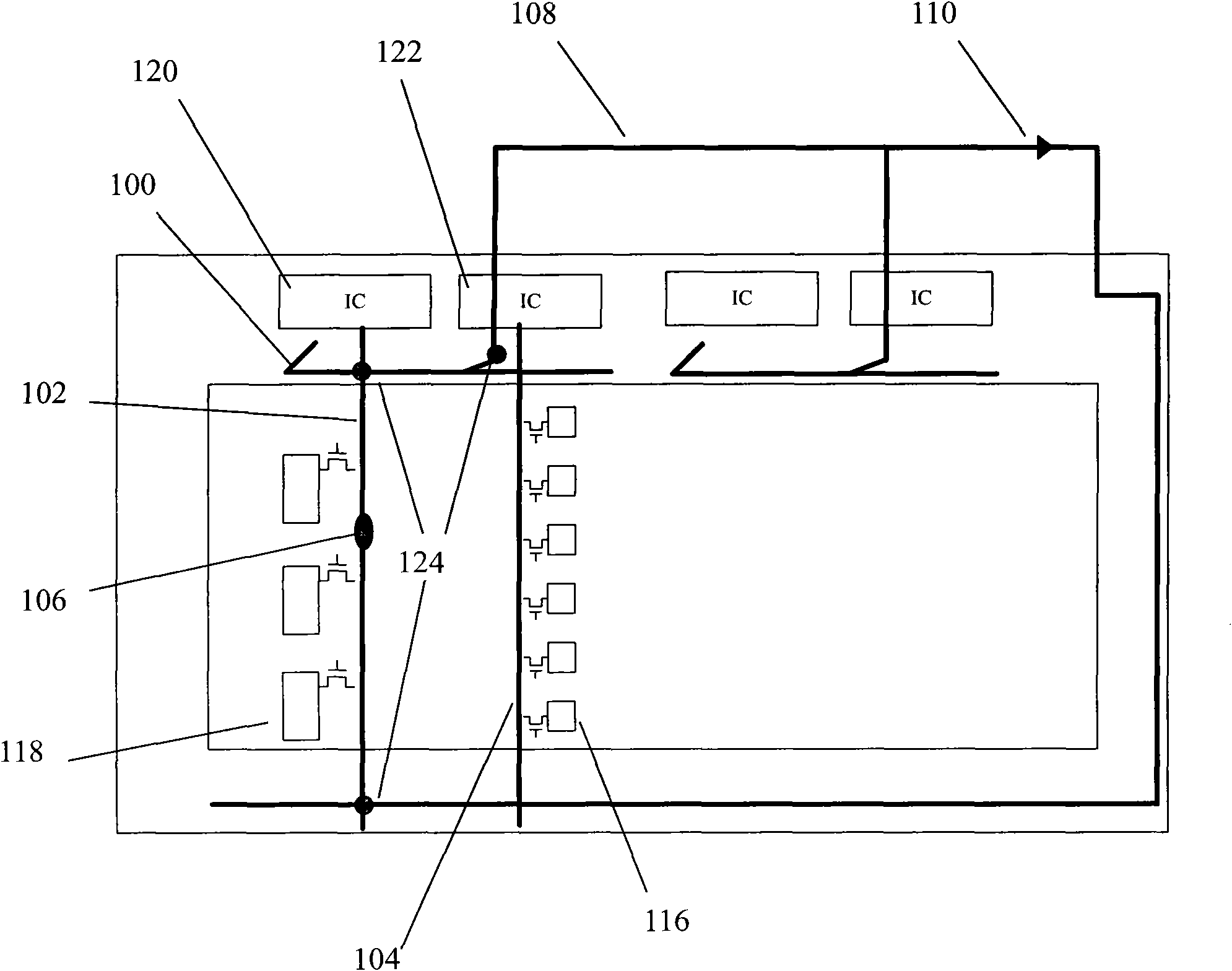

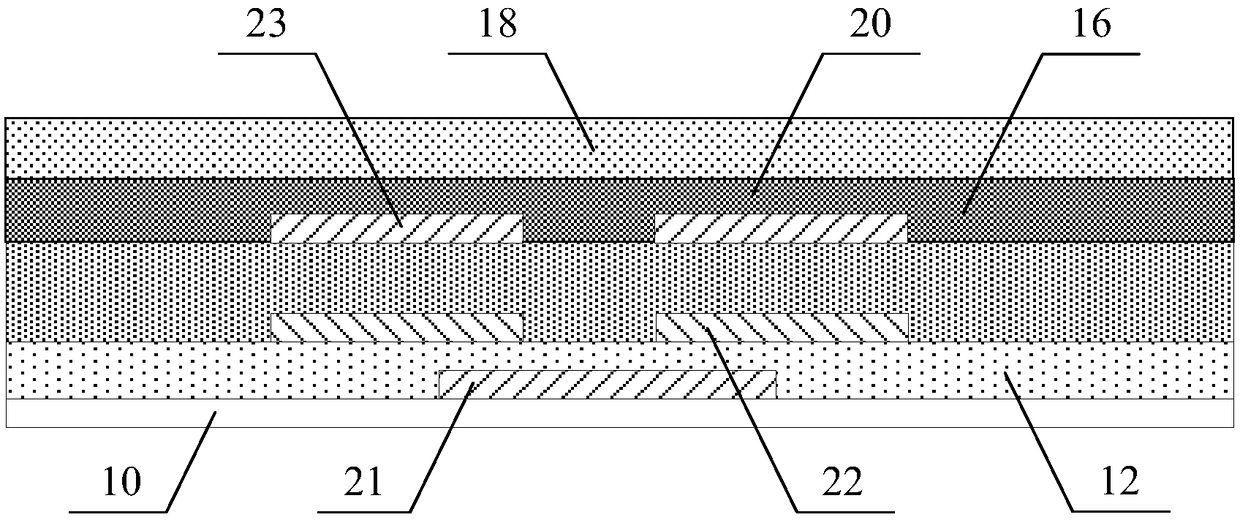

Electronic module and manufacturing method thereof

ActiveCN104103631AIncrease surface areaHas cooling effectSemiconductor/solid-state device detailsSolid-state devicesBearing surfaceEngineering

The invention discloses an electronic module and a manufacturing method thereof. The electronic module comprises a substrate, an electronic element, a mould sealing layer and a composite electromagnetic wave mask layer. The electronic element is configured on the substrate. The mould sealing layer covers a part of bearing surface of the electronic element and the substrate. The mould sealing layer is provided with an upper surface which is provided with a three-dimensional geometric pattern. The composite electromagnetic wave mask layer covers the upper surface of the mould sealing layer with the advantage of the form so that electromagnetic wave is shielded. The composite electromagnetic wave mask layer comprises a magnetic material layer and a conductive material layer.

Owner:UNIVERSAL SCIENTIFIC INDUSTRIAL (SHANGHAI) CO LTD +1

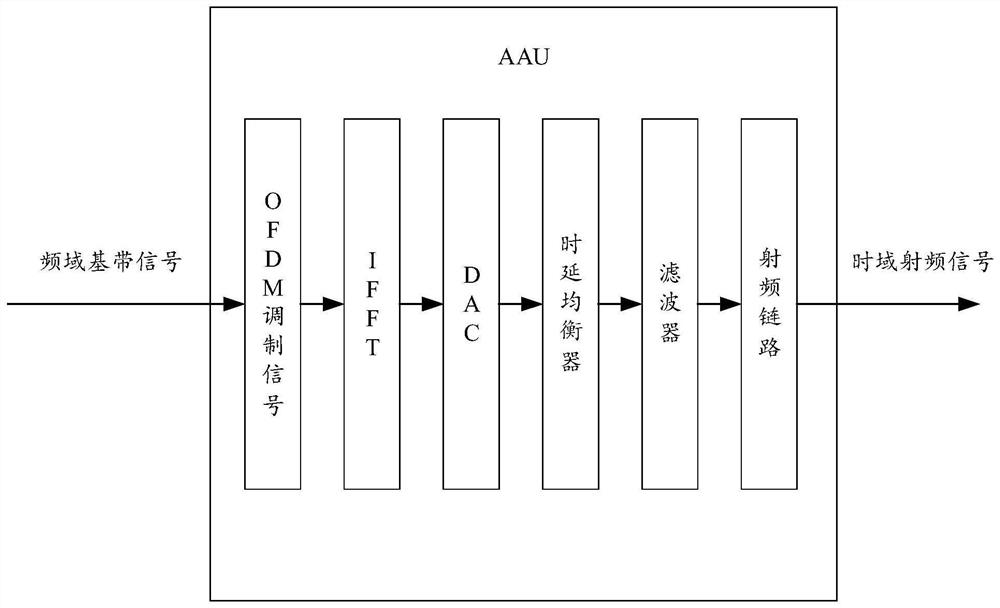

AAU group delay fluctuation compensation method and device, electronic equipment and storage medium

PendingCN114285509AGroup delay fluctuation improvementImpact of other indicatorsTime-division multiplexTransmissionTelecommunicationsControl engineering

The embodiment of the invention relates to the technical field of communication, and discloses an AAU group delay fluctuation compensation method, which comprises the following steps: acquiring a first reference signal sent to a signal receiving device by an AAU and a second reference signal generated by the signal receiving device; determining a phase value of the delay fluctuation of the AAU group according to the first reference signal and the second reference signal; and compensating the group delay fluctuation of the AAU according to the phase value. The embodiment of the invention also discloses an AAU group delay fluctuation compensation device, electronic equipment and a storage medium. According to the AAU group delay fluctuation compensation method and device, the electronic equipment and the storage medium provided by the embodiment of the invention, the group delay fluctuation of the AAU can be effectively improved, the design of AAU hardware does not need to be changed, and the cost of the hardware design is not increased.

Owner:ZTE CORP

Nickle sheet positioning method

ActiveCN1792555ANo design changes requiredAvoid deformationWelding/cutting auxillary devicesWork holdersMaterials scienceMetallic Nickel

An apparatus for locating nickel sheet whose thickness is less than 1mm is composed of upper match plate with the locating slots of nickel sheet, lower match plate with magnets, and locating pins for locating said upper and lower match plates. Its locating method includes such steps as putting upper match plate on lower one, locating the nickel sheet and its functional part in the locating slots of upper match plate, welding, removing lower match plate, and separating the nickel sheet and its functional part from upper match plate. It can prevent deformation of nickel sheet.

Owner:江西萨瑞微电子技术有限公司

Touch substrate and preparation method thereof and touch panel

ActiveCN108062183AReduce the incidence of bad defectsReduce the impactInput/output processes for data processingComputer scienceDark line

The embodiment of the invention provides a touch substrate and a preparation method thereof and a touch panel. The touch substrate comprises a display structure layer formed in a display region and afan-out structure layer formed in a fan-out region, wherein the fan-out structure layer comprises multiple signal outgoing lines, and a protective layer covering the signal outgoing lines is arrangedon the fan-out structure layer. According to the touch substrate, by adding the protective layer covering the signal outgoing lines to the fan-out region, in a subsequent cutting process, even if a cutting tool bit scratches the fan-out region, the signal outgoing lines cannot be easily broken, and therefore the occurrence rate of concealed line bad defects is effectively lowered. Through a sub-region protection scheme, little improvement is made to an existing process, implementation is convenient, production cost is low, meanwhile, it is not needed to change the design and structure of an original array substrate, the influence of the protective layer preparation process on the performance of the array substrate is small, product performance is guaranteed, and the touch substrate has a good application prospect.

Owner:BOE TECH GRP CO LTD +1

Integrated window with assembled type roller blind wind-resistant track

ActiveCN105064899ANo design changes requiredEasy to disassembleLight protection screensWing arrangementsEngineeringMechanical engineering

The invention discloses an integrated window with an assembled type roller blind wind-resistant track. The integrated window with the assembled type roller blind wind-resistant track comprises a profile window and a roller blind assembly, wherein the roller blind assembly comprises a curtain cover assembly, two assembled type roller blind tracks , a first connector and second connectors; the curtain cover assembly is arranged on the top surface of the profile window; the two assembled type roller blind tracks are positioned on front surfaces of two sides of the profile window; the curtain cover assembly is detachably arranged on the top surface of the profile window by the first connector; the two assembled type roller blind tracks are respectively connected to the front surfaces of two sides of the profile window detachably by the second connectors; the curtain cover assembly is provided with a curtain cloth assembly which can be unfolded or rolled up; and when the curtain cloth assembly is unfolded, two sides of the curtain cloth assembly move in the two assembled type roller blind tracks respectively. The assembled type roller blind tracks are more convenient to detach, repair and mount.

Owner:NINGBO XIANFENG NEW MATERIAL

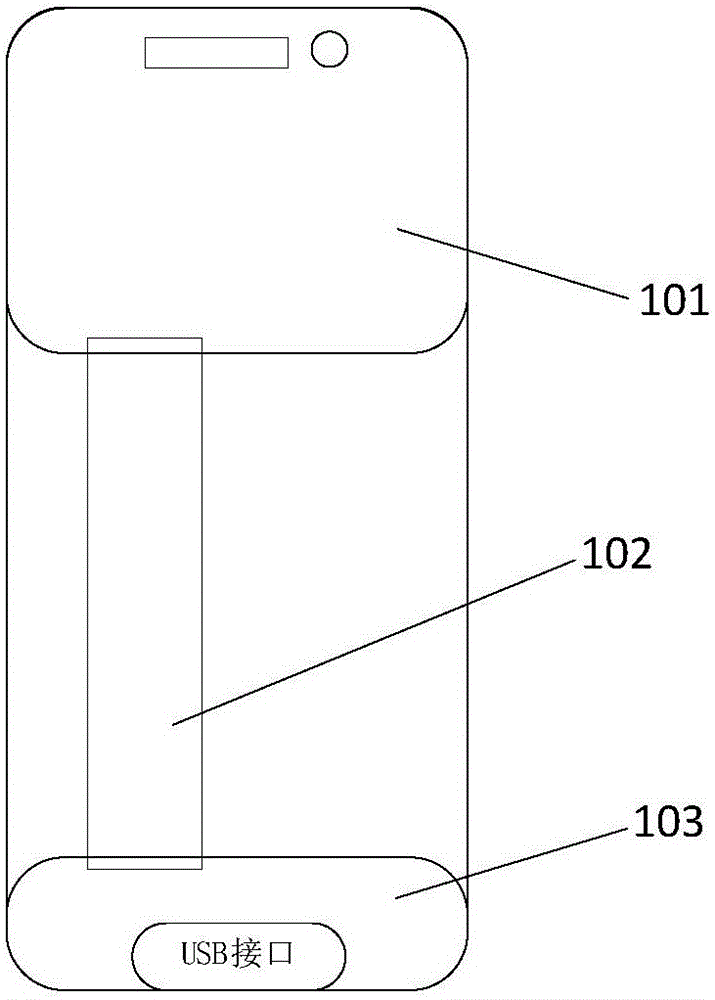

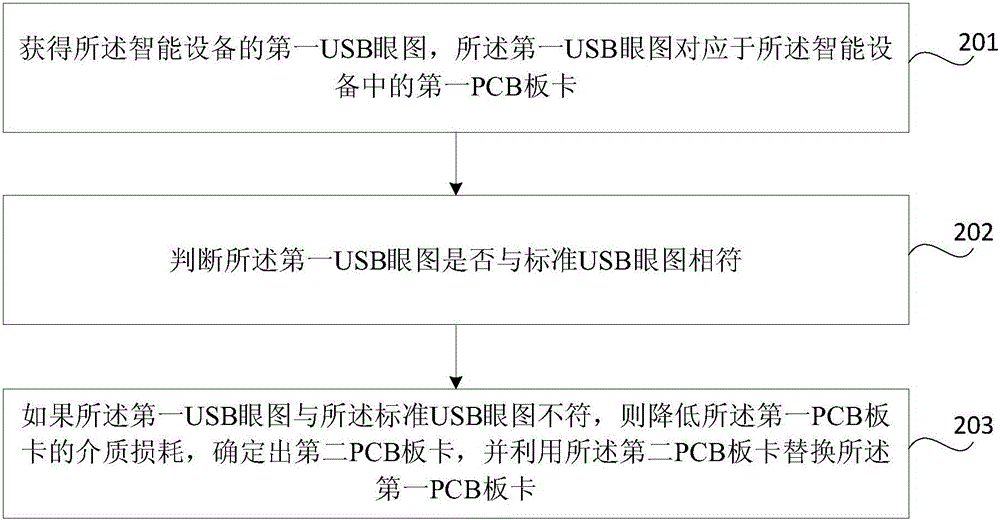

Intelligent device USB eye pattern improvement method

InactiveCN105808395ASimplicity and practicalityImproved USB eye diagramDetecting faulty computer hardwareDielectric lossDifferential line

The present disclosure relates to an intelligent device USB eye pattern improvement method. The method comprises: obtaining a first USB eye pattern of an intelligent device, wherein the first USB eye pattern corresponds to a first PCB board card in the intelligent device; determining whether the first USB eye pattern coincides with a standard USB eye pattern; and if the first USB eye pattern does not coincide with the standard USB eye pattern, reducing a dielectric loss of the first PCB board card, determining a second PCB board card, and replacing the first PCB board card with the second PCB board card. The method facilitates improvement of signal transmission quality of strip differential lines and effectively improves USB eye patterns.

Owner:BEIJING XIAOMI MOBILE SOFTWARE CO LTD

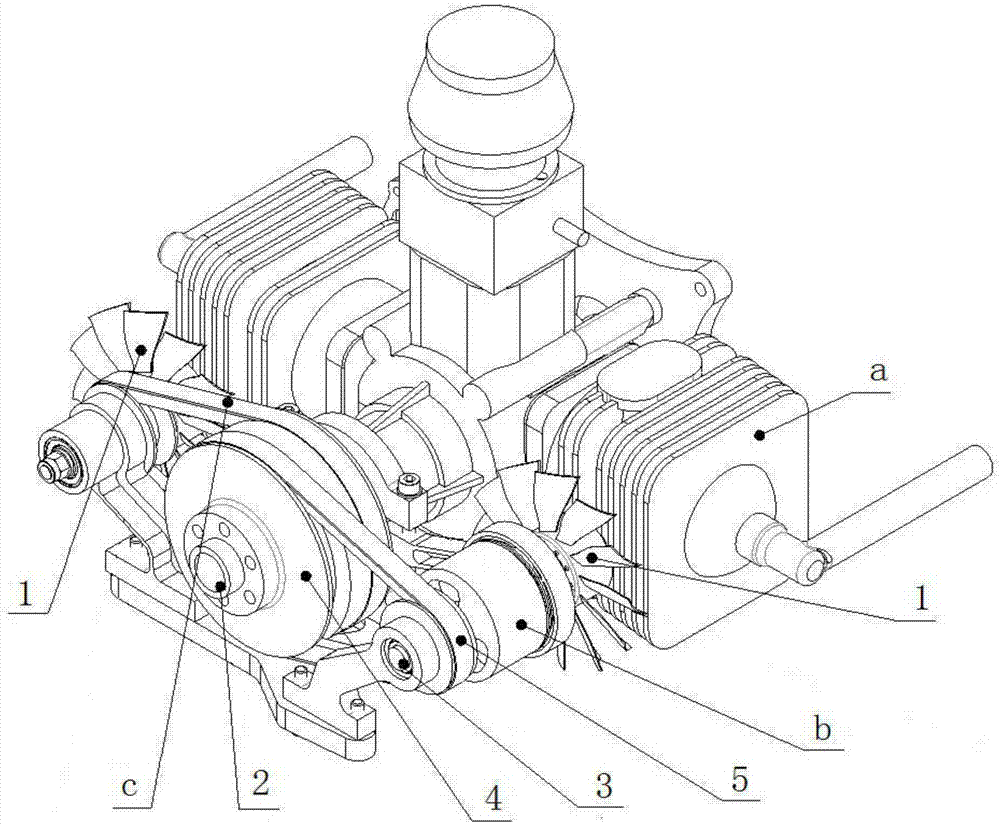

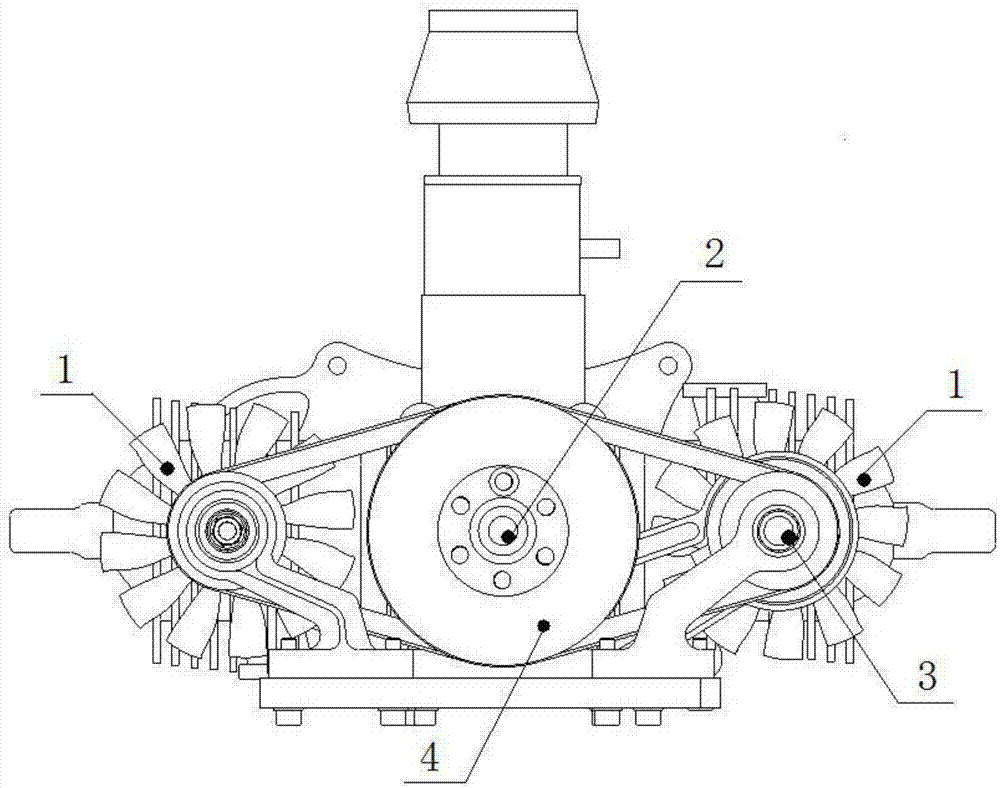

Air cooling system for helicopter

PendingCN107489513AGuaranteed cooling effectCooling Stability GuaranteePower plant cooling arrangmentsMachines/enginesAir cooling systemUncrewed vehicle

The invention discloses an air cooling system for a helicopter. The air cooling system comprises a fan (1), wherein the shaft of the fan (1) is in belt connection with an engine output end (2), and the engine output end (2) rotates to drive the fan (1) to rotate. The air cooling system is suitable for being installed in a narrow space in an unmanned aerial vehicle, the structure is compact, the shape of the unmanned aerial vehicle does not need to be changed, and the air cooling system can adapt to engine cooling requirements of unmanned aerial vehicles of various models.

Owner:湖南省库塔科技有限公司

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com