Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

50results about How to "Effective stress" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

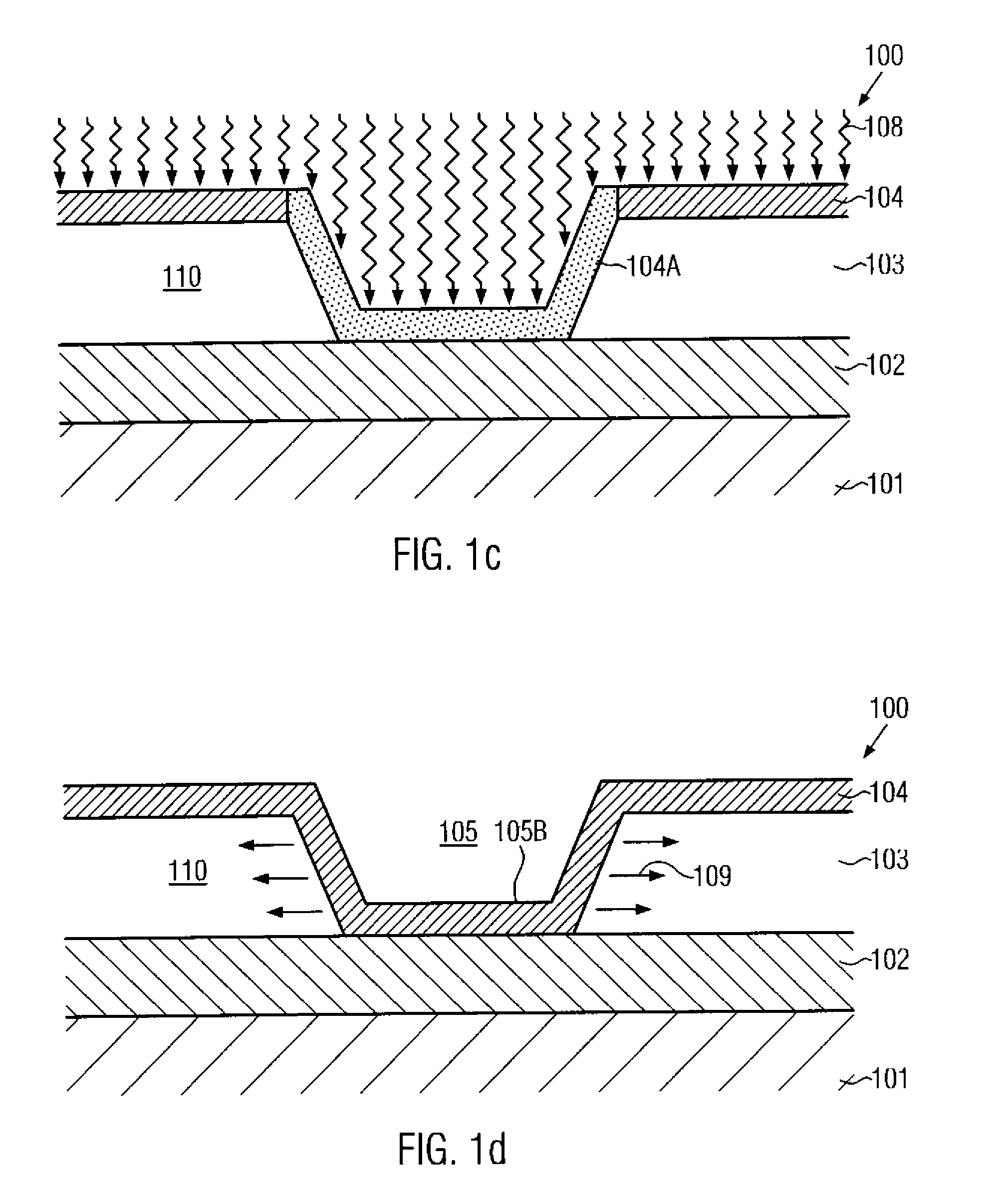

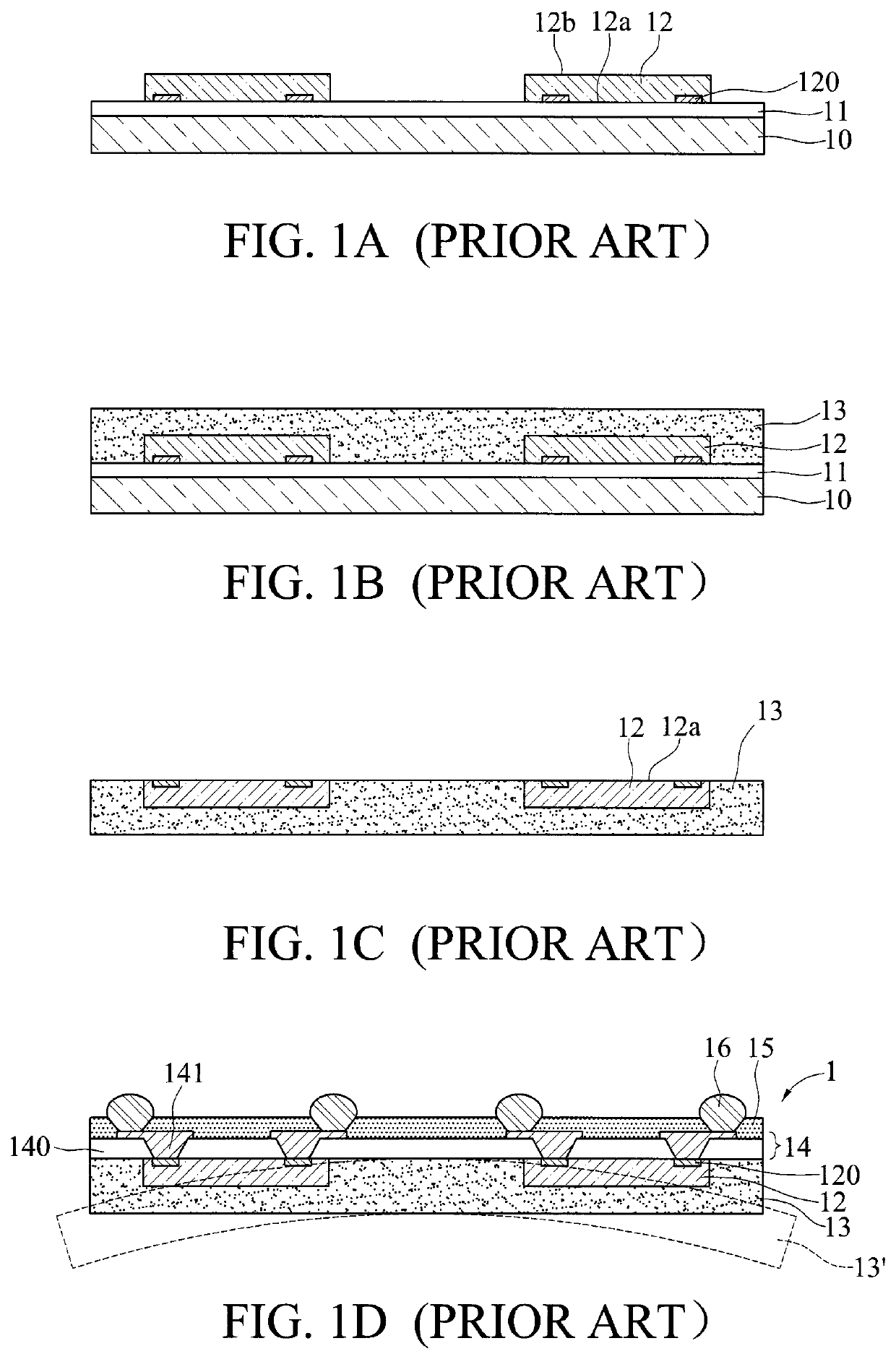

Method for manufacturing semiconductor device and semiconductor device

ActiveUS20100001323A1High carrier mobilityPrevent crystal defectTransistorSemiconductor/solid-state device manufacturingMixed crystalSemiconductor

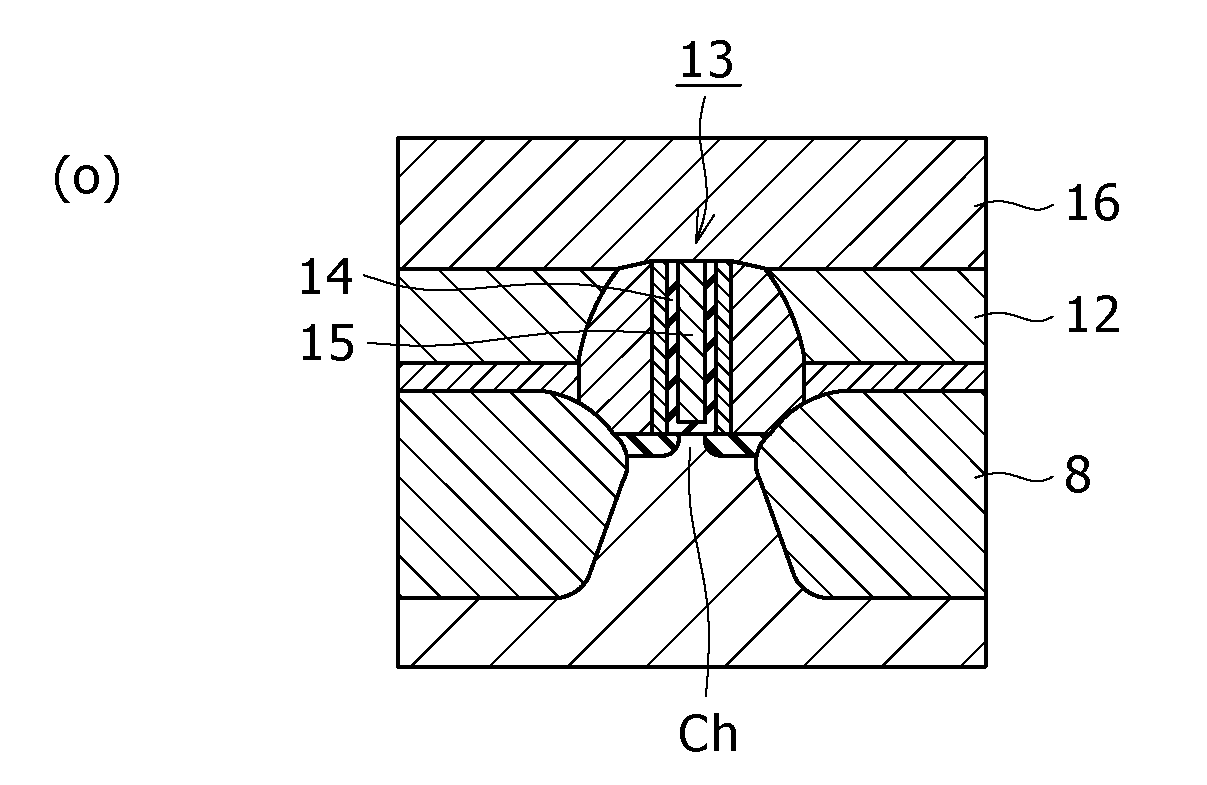

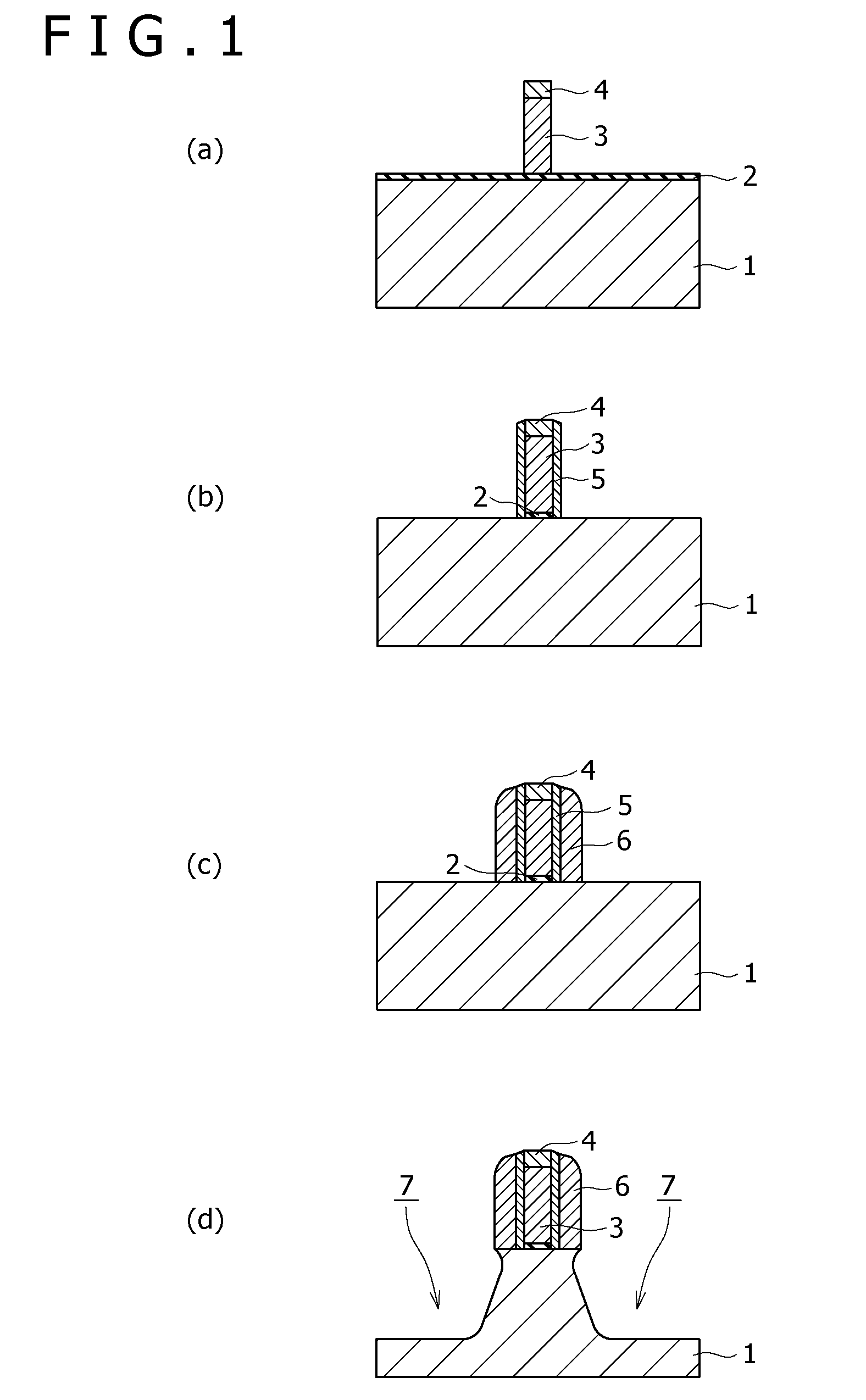

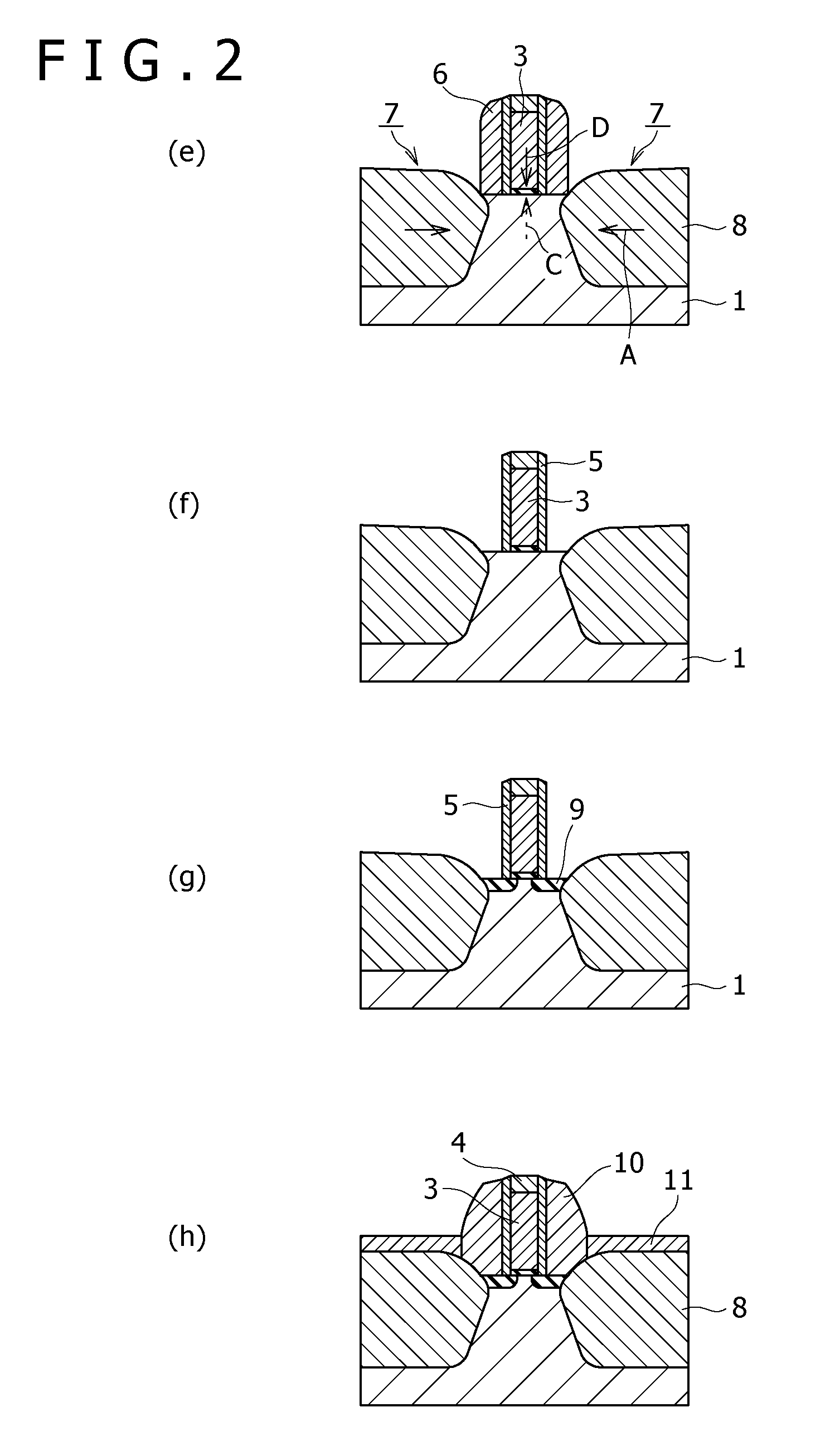

Provided is a semiconductor device manufacturing method by which sufficient stress can be applied to a channel region within allowable ranges of concentrations of Ge and C in a mixed crystal layer. A semiconductor device is also provided. A dummy gate electrode 3 is formed on a Si substrate 1. Then, a recess region 7 is formed by recess etching by using the dummy gate electrode 3 as a mask. Next, on the surface of the recess region 7, a mixed crystal layer 8 composed of a SiGe layer is epitaxially grown. Subsequently, an interlayer insulating film 12 is formed on the mixed crystal layer 8 to cover the dummy gate electrode 3, and the interlayer insulating film 12 is removed until the surface of the dummy gate electrode 3 is exposed. A recess 13 is formed on the interlayer insulating film 12 to expose the Si substrate 1 by removing the dummy gate electrode 3. Then, a gate electrode 15 is formed in the recess 13 by having a gate insulating film 14 in between.

Owner:SONY CORP

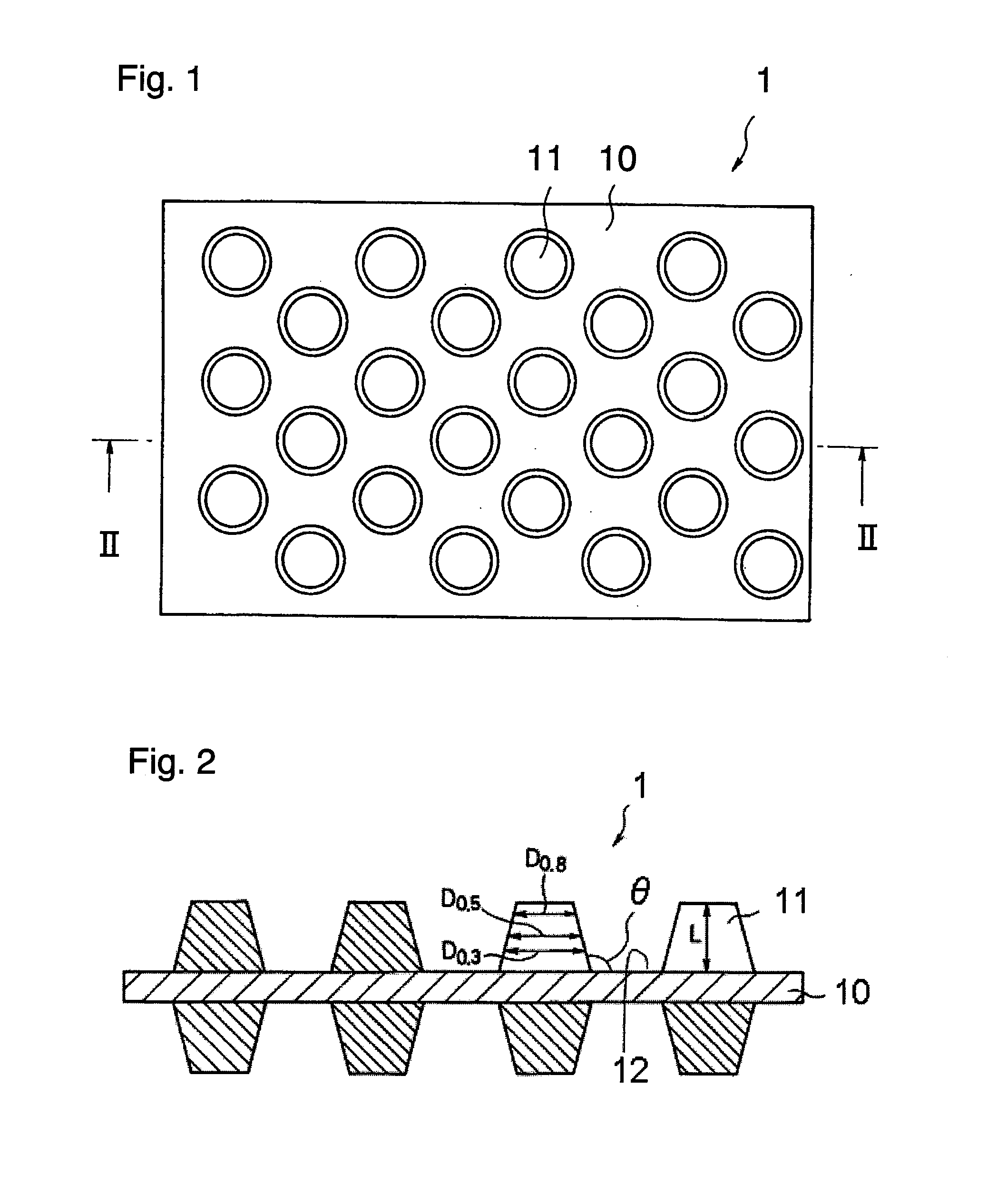

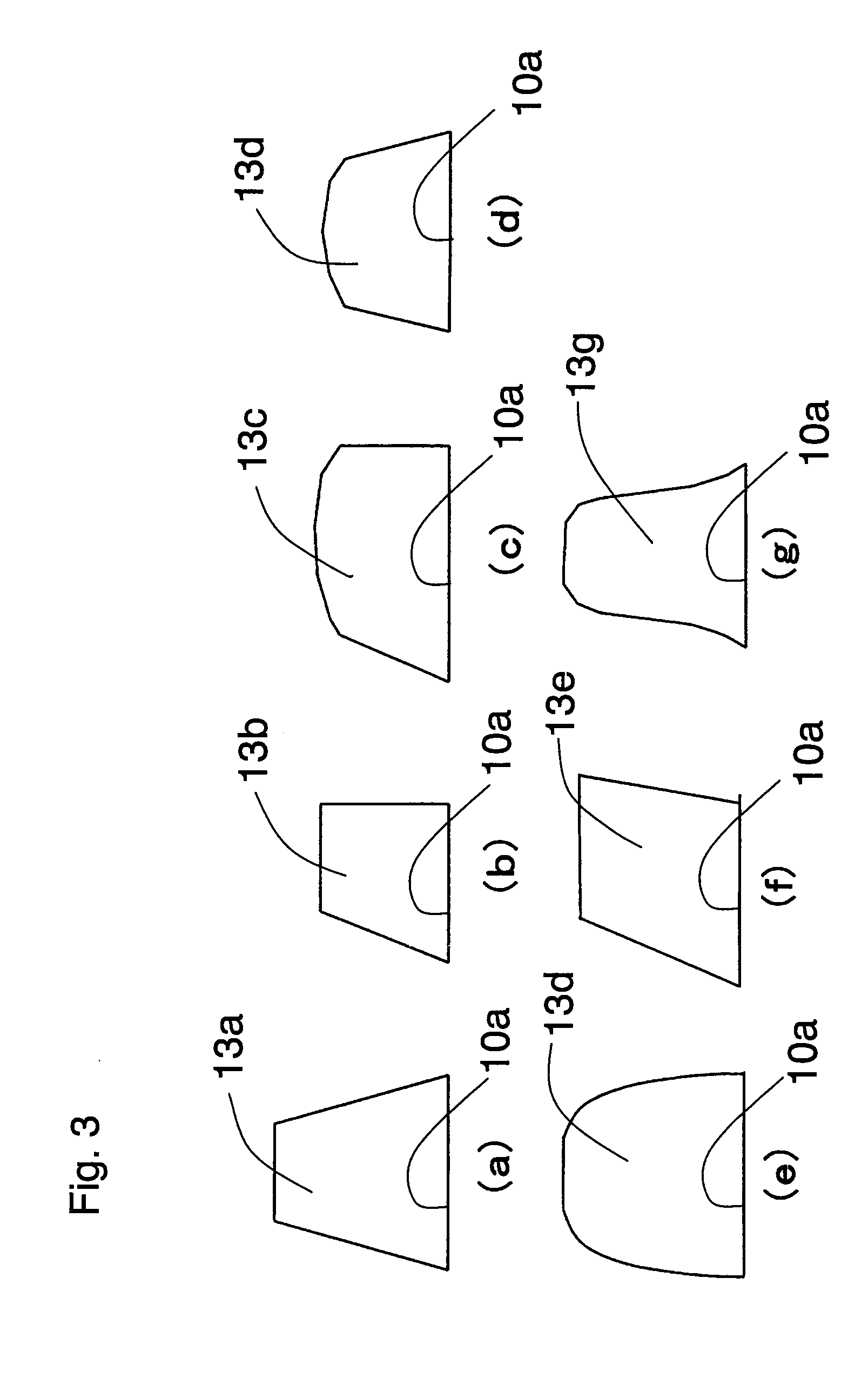

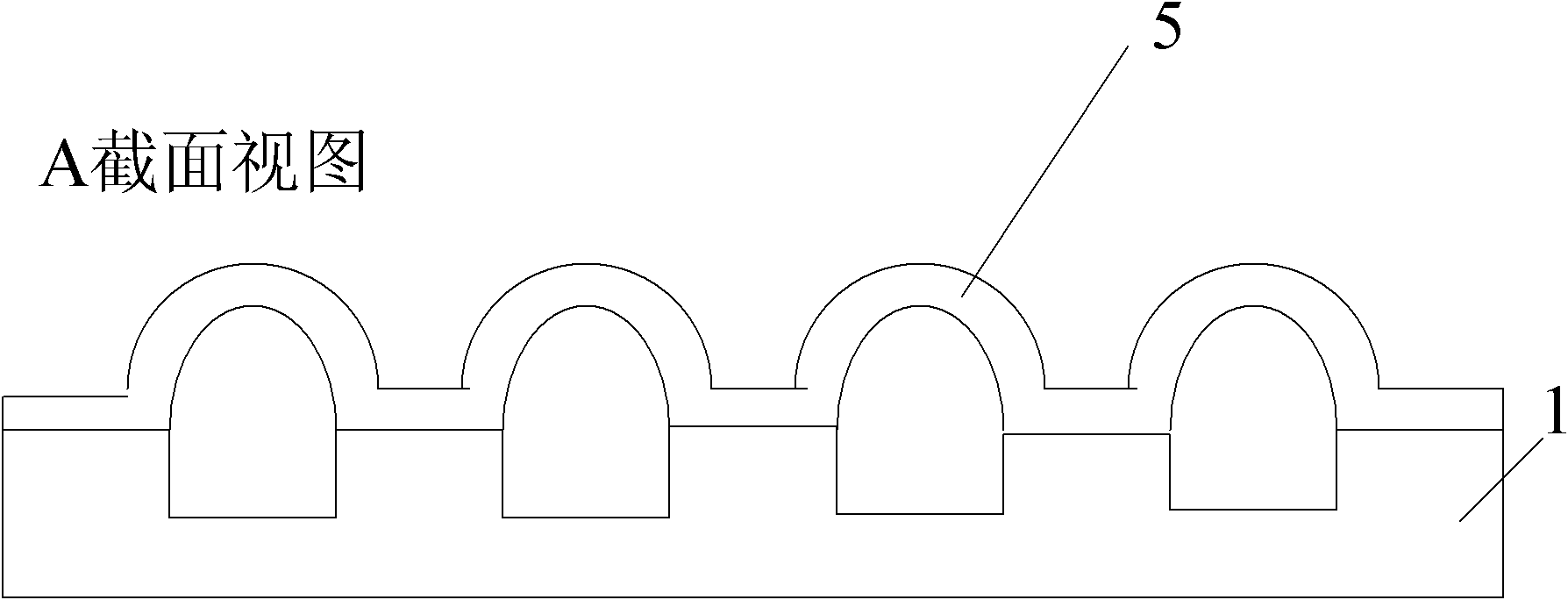

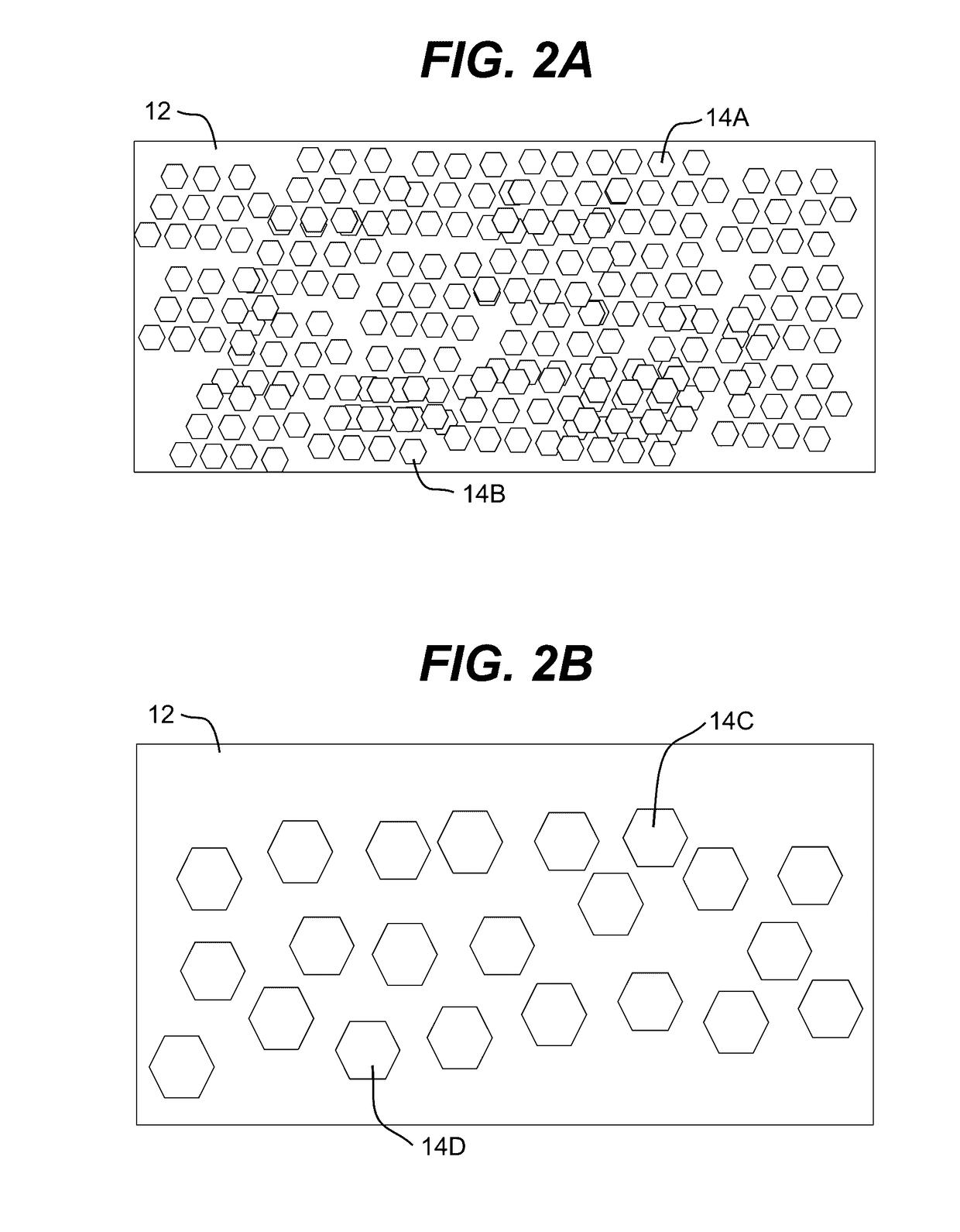

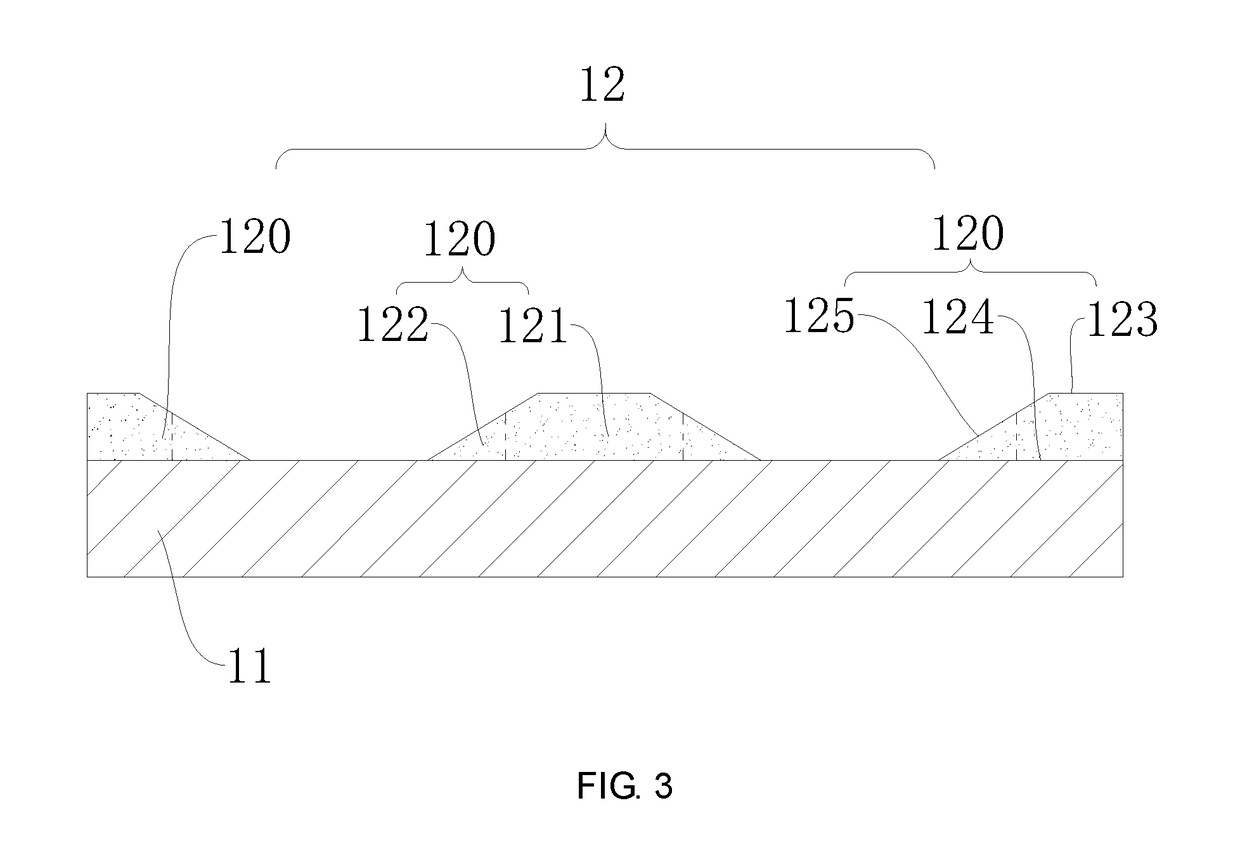

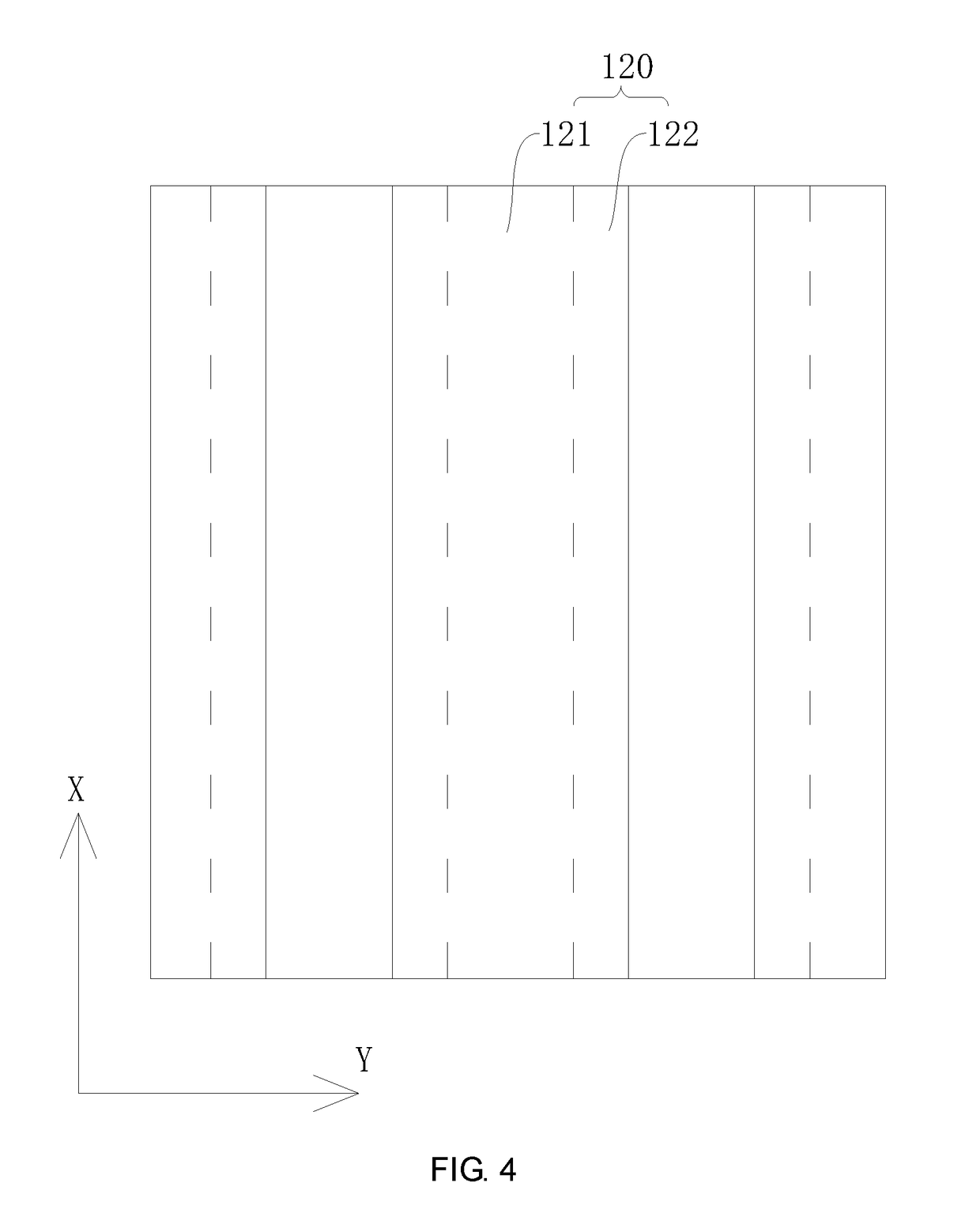

Current collector, electrode, and non-aqueous electrolyte secondary battery

InactiveUS20090202908A1Relieving and dispersing stressEffective stressFinal product manufactureElectrode carriers/collectorsEngineeringNon aqueous electrolytes

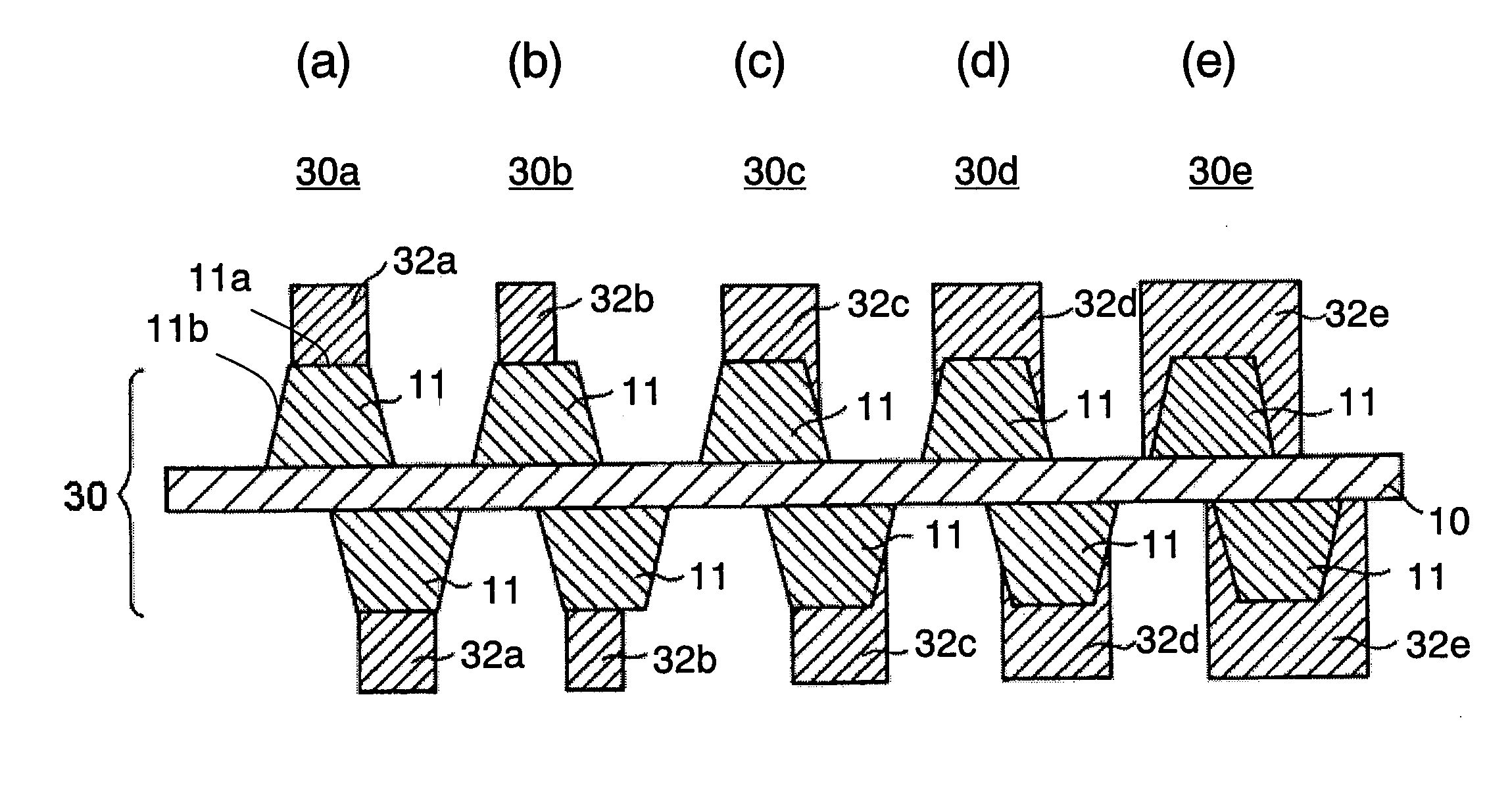

An electrode capable of effectively dispersing or relieving the stress generated in association with expansion and contraction of an active material is provided. The electrode is produced by forming an active material layer on a predetermined current collector. This current collector includes a base and a plurality of projections formed so as to extend outwardly from a surface of the base. The cross section of the projections in a thickness direction of the current collector has a tapered shape in which a width in a direction parallel to the surface of the base narrows from the surface of the base along an extending direction of the projections.

Owner:PANASONIC CORP

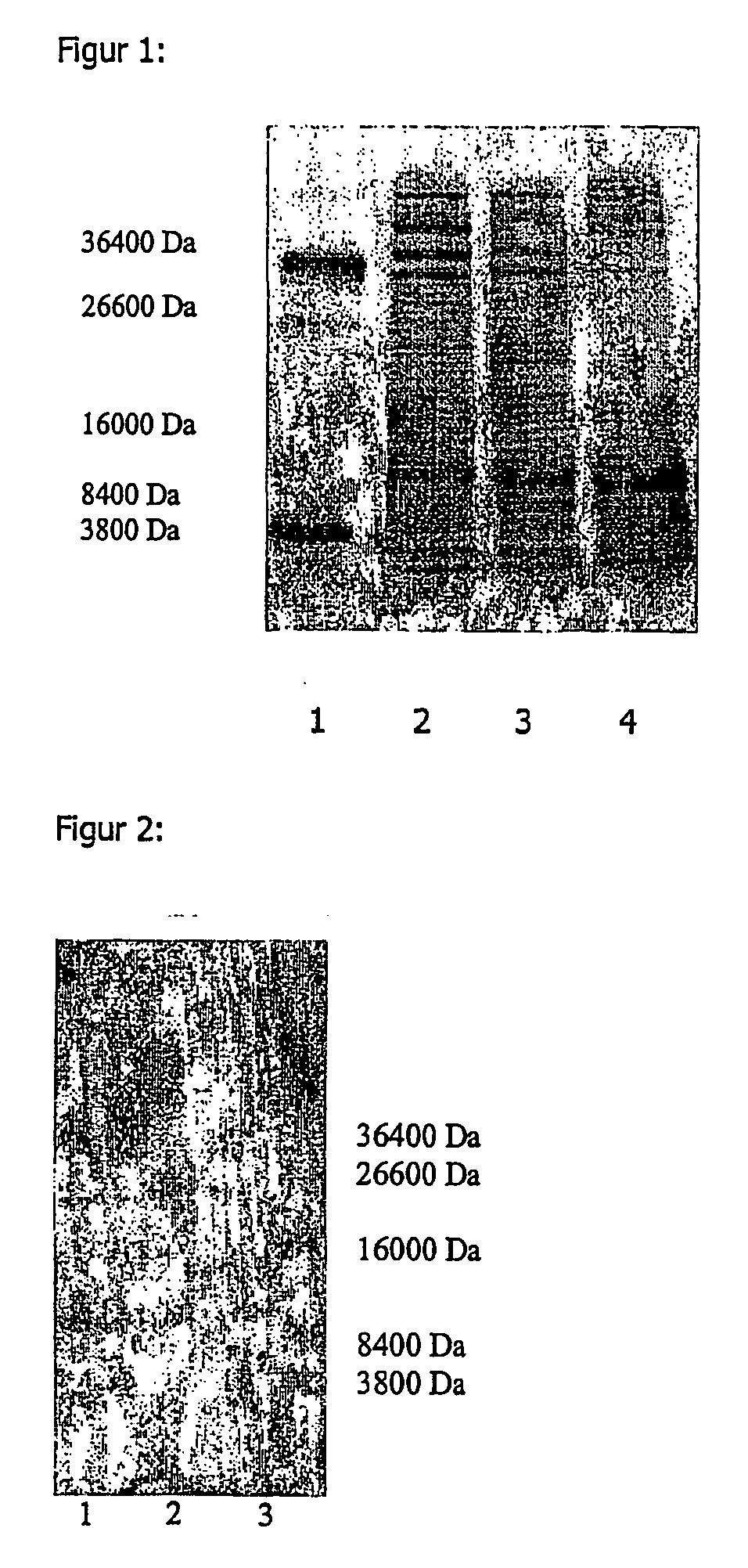

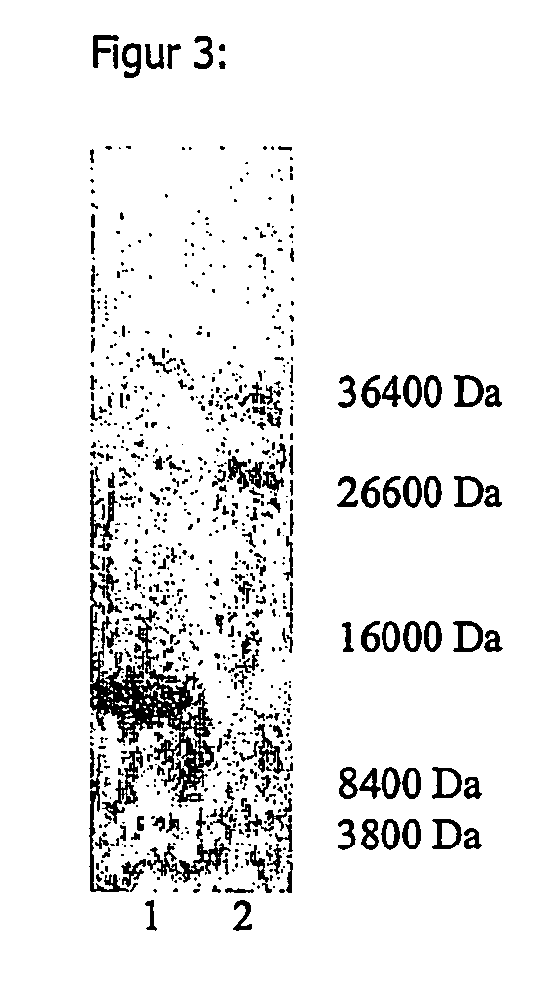

Cosmetic and/or pharmaceutical preparations

InactiveUS20040109880A1Improve heat resistanceEffective stressCosmetic preparationsOrganic active ingredientsHeat shockBULK ACTIVE INGREDIENT

A cosmetic or pharmaceutical composition containing an active ingredient selected from the group consisting of late embryogenesis abundant proteins, heat shock proteins, and mixtures thereof.

Owner:COGNIS FRANCE SA +1

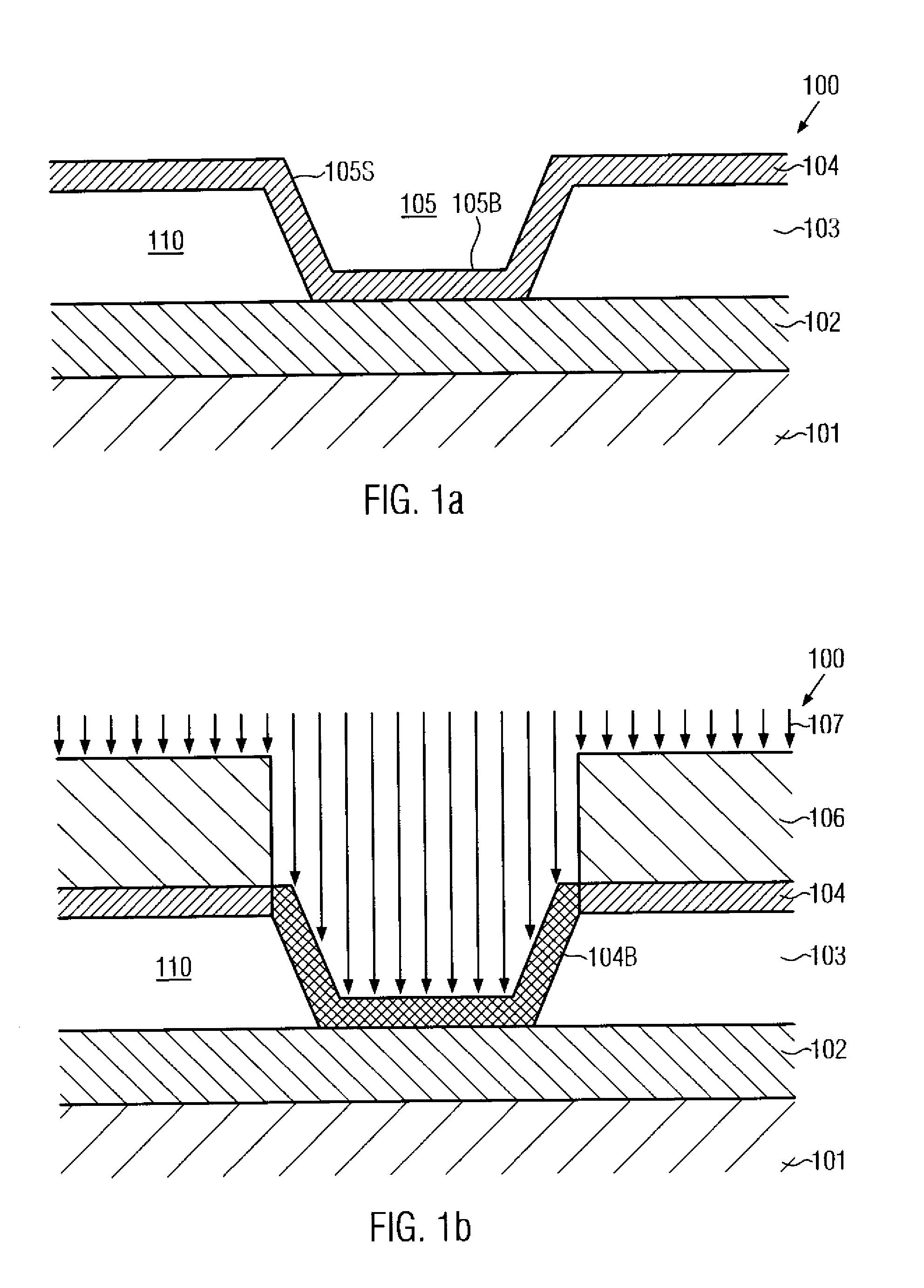

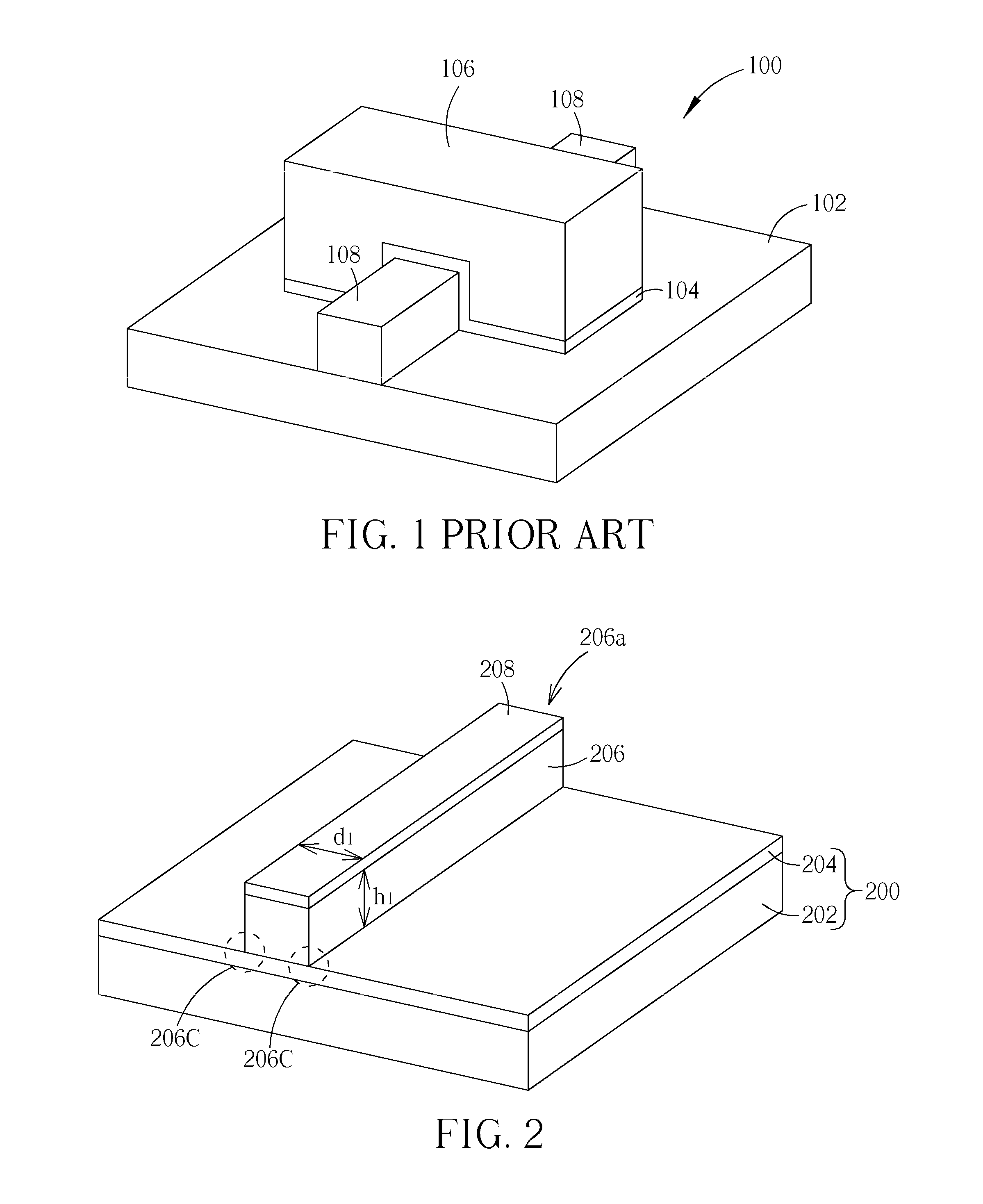

Technique for forming an isolation trench as a stress source for strain engineering

InactiveUS20070155121A1Increase compressive stressEfficient stress engineeringSemiconductor/solid-state device detailsSolid-state devicesIon bombardmentEngineering

By forming a non-oxidizable liner in an isolation trench and selectively modifying the liner within the isolation trench, the stress characteristics of the isolation trench may be adjusted. In one embodiment, a high compressive stress may be obtained by treating the liner with an ion bombardment and subsequently exposing the device to an oxidizing ambient at elevated temperatures, thereby incorporating silicon dioxide into the non-oxidizable material. Hence, an increased compressive stress may be generated within the non-oxidizable layer.

Owner:GLOBALFOUNDRIES INC

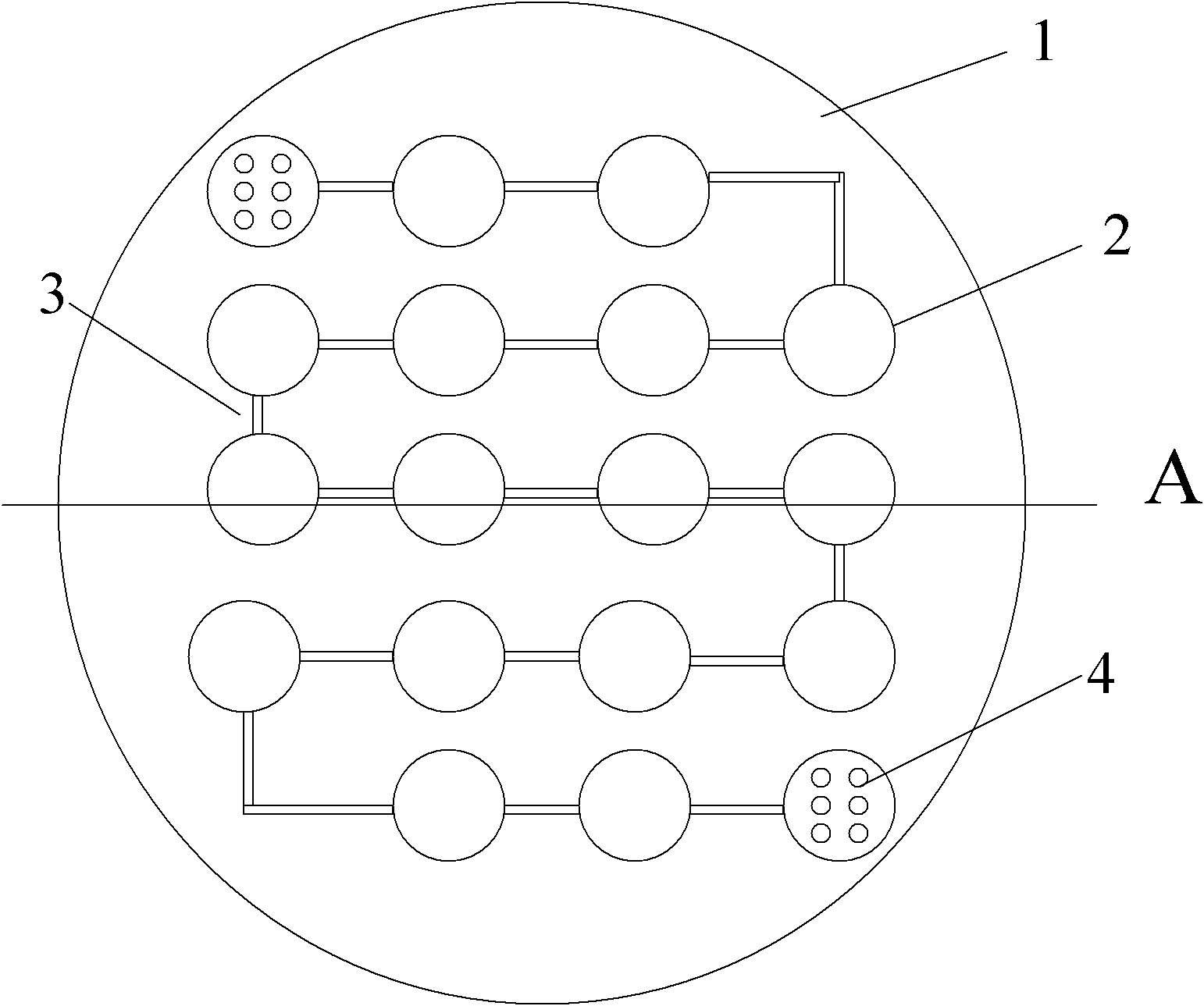

Preparation method for high-density interposer for microelectronic system-in-package

ActiveCN102070120AImprove reliabilitySmall coefficient of thermal expansionDecorative surface effectsChemical vapor deposition coatingThermal dilatationElectrical conductor

The invention discloses a preparation method for a high-density interposer for microelectronic system-in-package. The preparation method comprises the following steps of: 1, preparing a drectionally growing carbon nanotube bundle array, wherein the diameter of each carbon nanotube bundle is 0.5 to 30 microns, the gap of the carbon nanotube bundle is 0.8 to 100 microns, and the carbon nanotube bundle is 40 to 500 microns long; 2, depositing metal tungsten on the surface of the drectionally growing carbon nanotube bundle so as to form a conductor array; 3, melting borosilicate glass and compounding the melted borosilicate glass with the conductor array so as to form a compound body; and 4, grinding the upper surface and the lower surface of the formed compound body so as to expose the end of the carbon nanotube bundle deposited with the metal tungsten, and obtaining the high-density interposer for the system-in-package. The material adopted by the preparation method has low thermal expansivity and the process method is low in time consumption, so the prepared high-density interposer has the advantages of high density, high reliability and low cost.

Owner:SOUTHEAST UNIV

Mechanical stress crystallization of thermoplastic polymers

InactiveUS6479625B1Effective stressSufficient stressCeramic shaping apparatusChemical/physical processesChemistryPolyester

A method of crystallizing particles of amorphous thermoplastic polymer particles in a mechanically fluidizing horizontal cylindrical crystallizer so that each particle is crystallized to substantially the same degree without particle agglomeration or stickiness in the crystallizer or the product. The method comprises mechanically fluidizing the particles with fluidizing blades providing mechanical friction, heat, and deformation stress until the stress orients the polymer molecules to form polymer crystals. The method is particularly useful with polyesters, polyester copolymers and low melting blends thereof. A new crystallized polymer composition prepared by the mechanical stress method is disclosed.

Owner:AGRINUTRIENTS TECH GRP INC

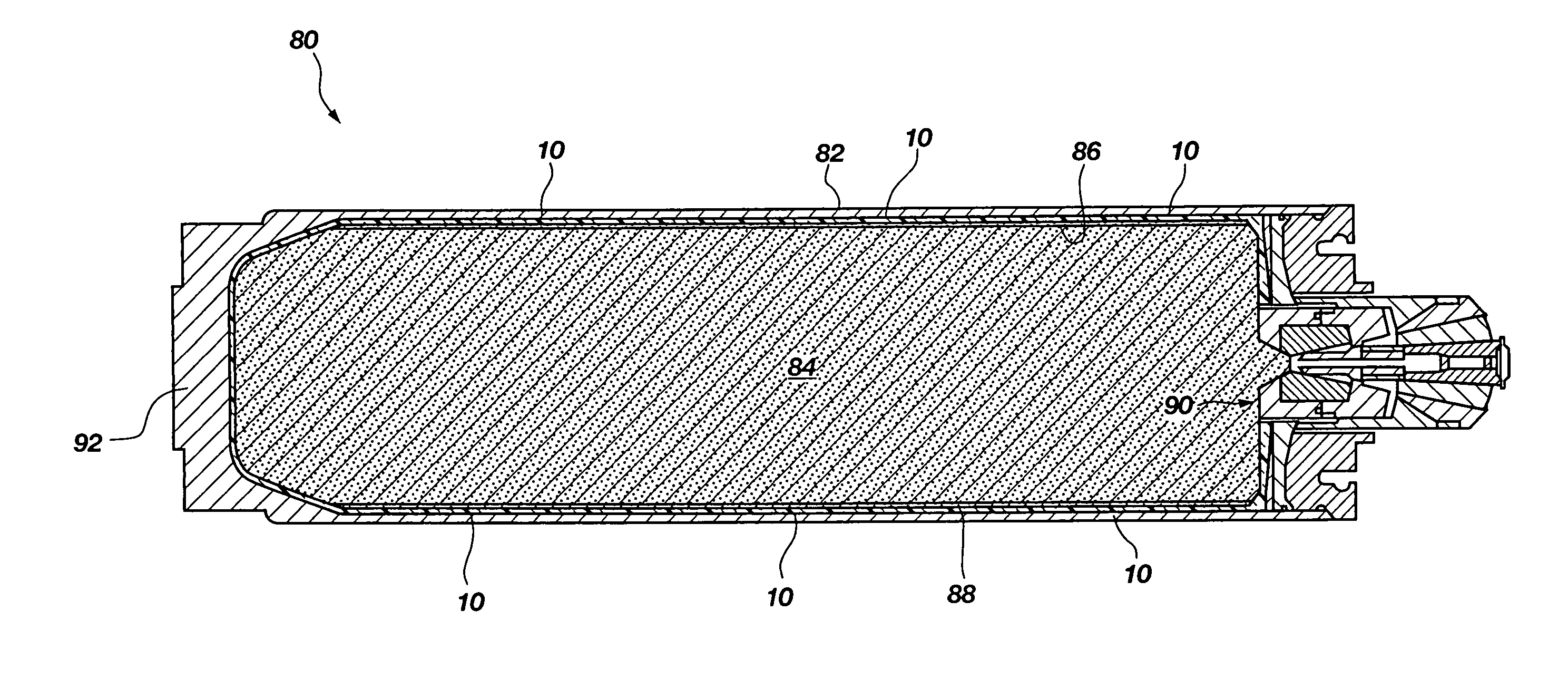

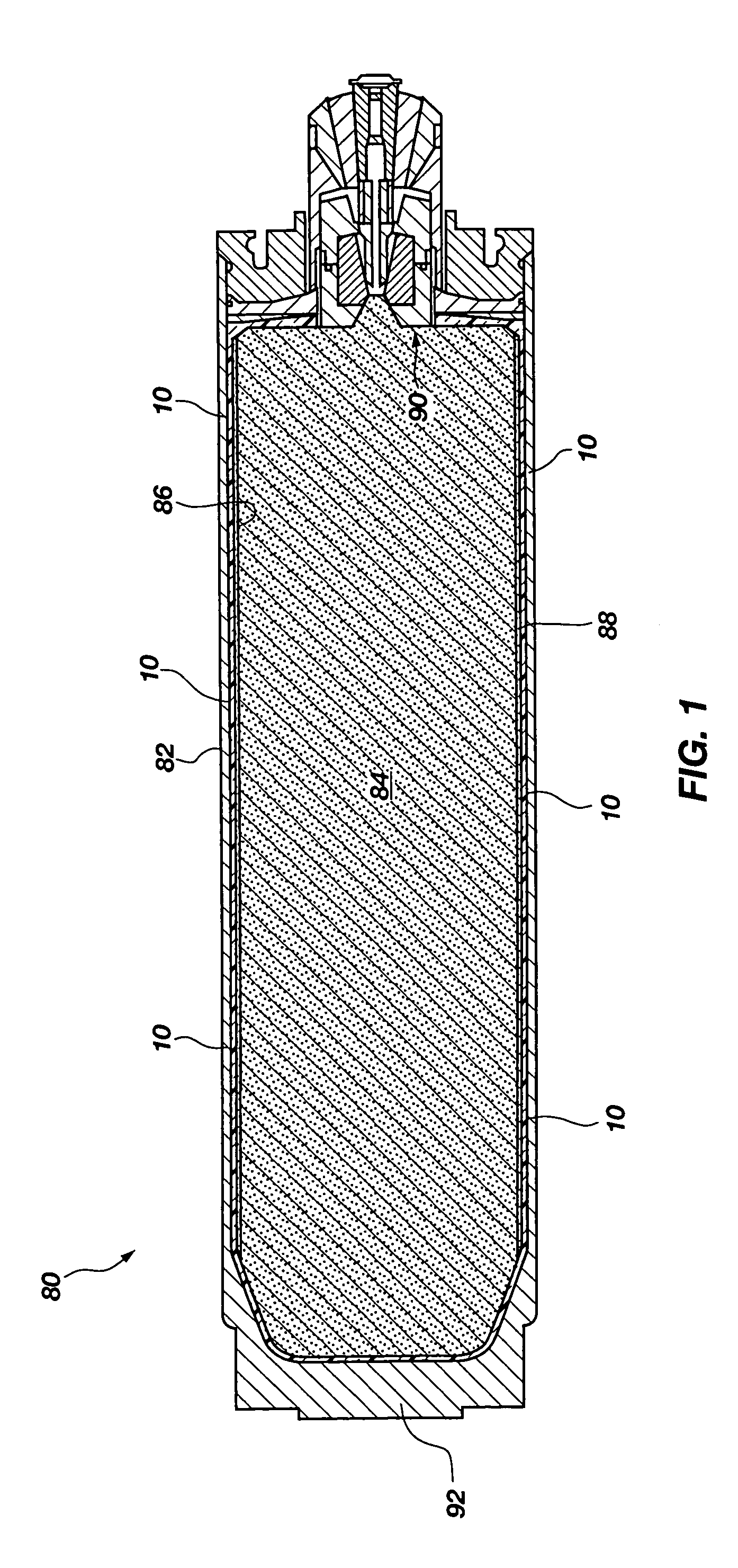

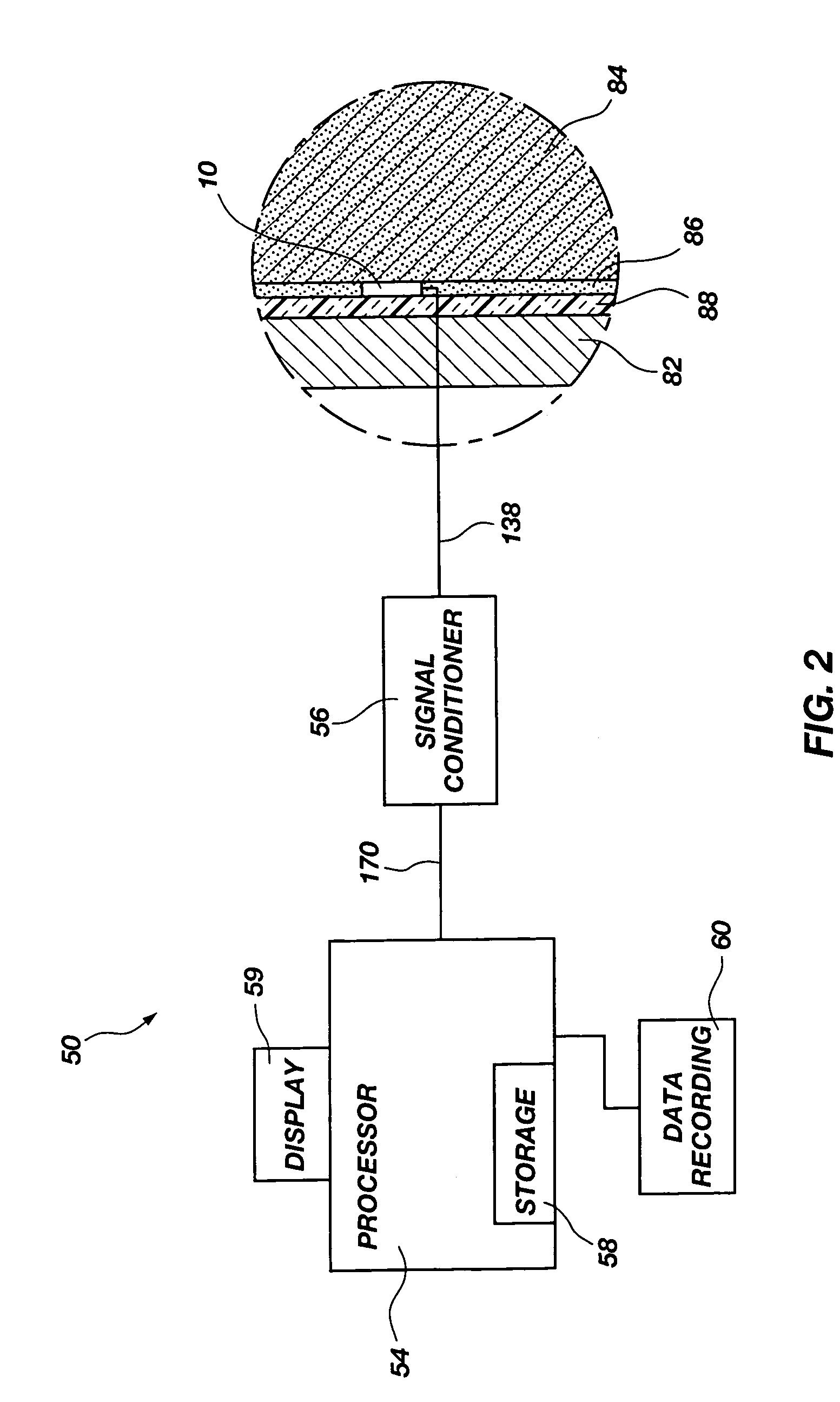

Apparatus and method for measuring stress at an interface

InactiveUS7077011B2Effectively stress and stress componentEffective stressWeighing apparatus using elastically-deformable membersForce measurement by measuring optical property variationAcousticsNormal component

An apparatus for measuring stress is provided that includes a stress sensor including, in part, a sensing device configured for generating and outputting sensor measurement signals representative of a stress or a component of a stress. In one embodiment, the stress sensor permits sensing and measurement of a shear component of a stress substantially exclusive of a normal component thereof. The stress sensor may be suited for measuring stress between mated bodies, such as at an interface between the mated bodies. A method of measuring stress using the stress sensor and a rocket motor including at least one stress sensor are also provided.

Owner:NORTHROP GRUMMAN INNOVATION SYST INC

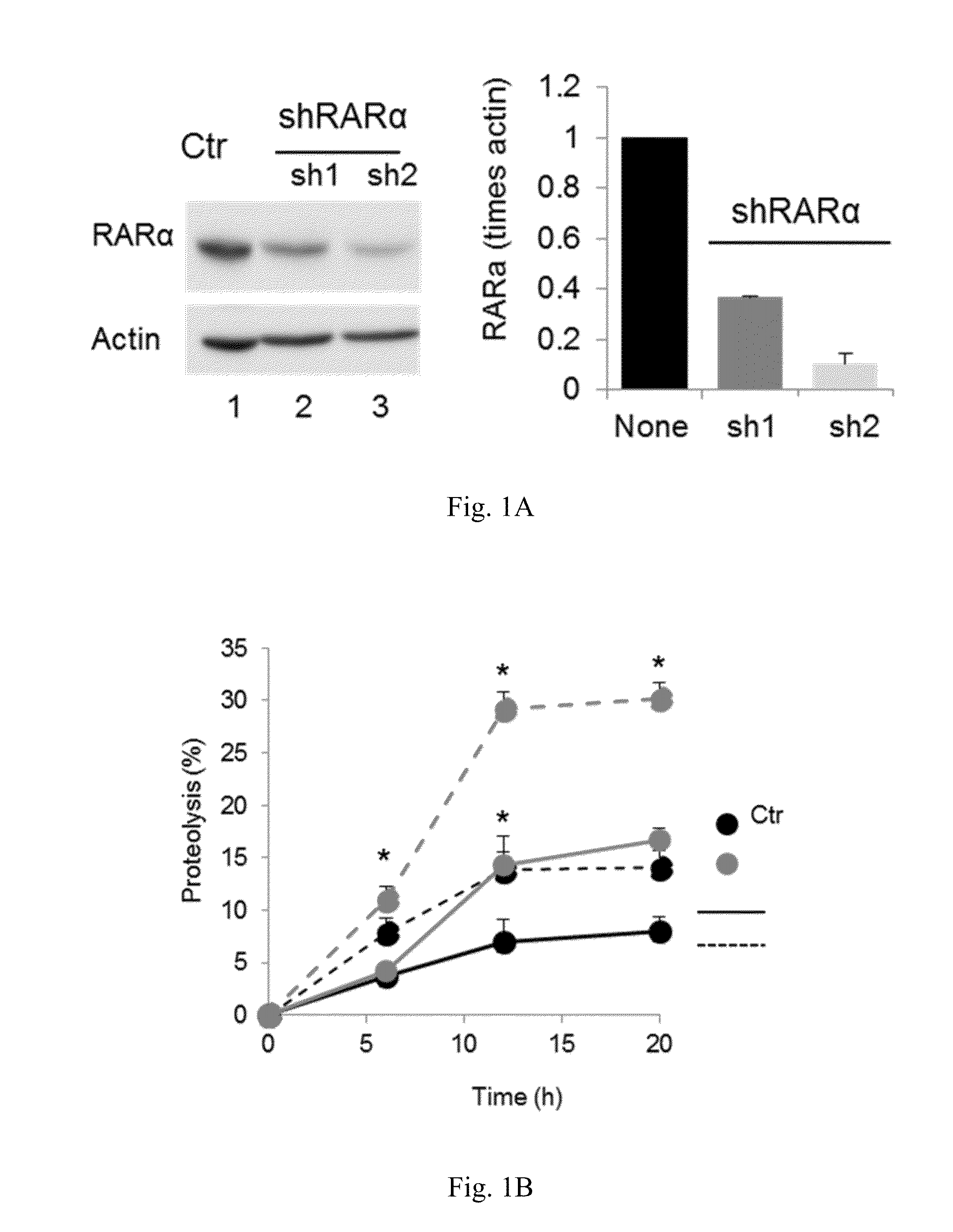

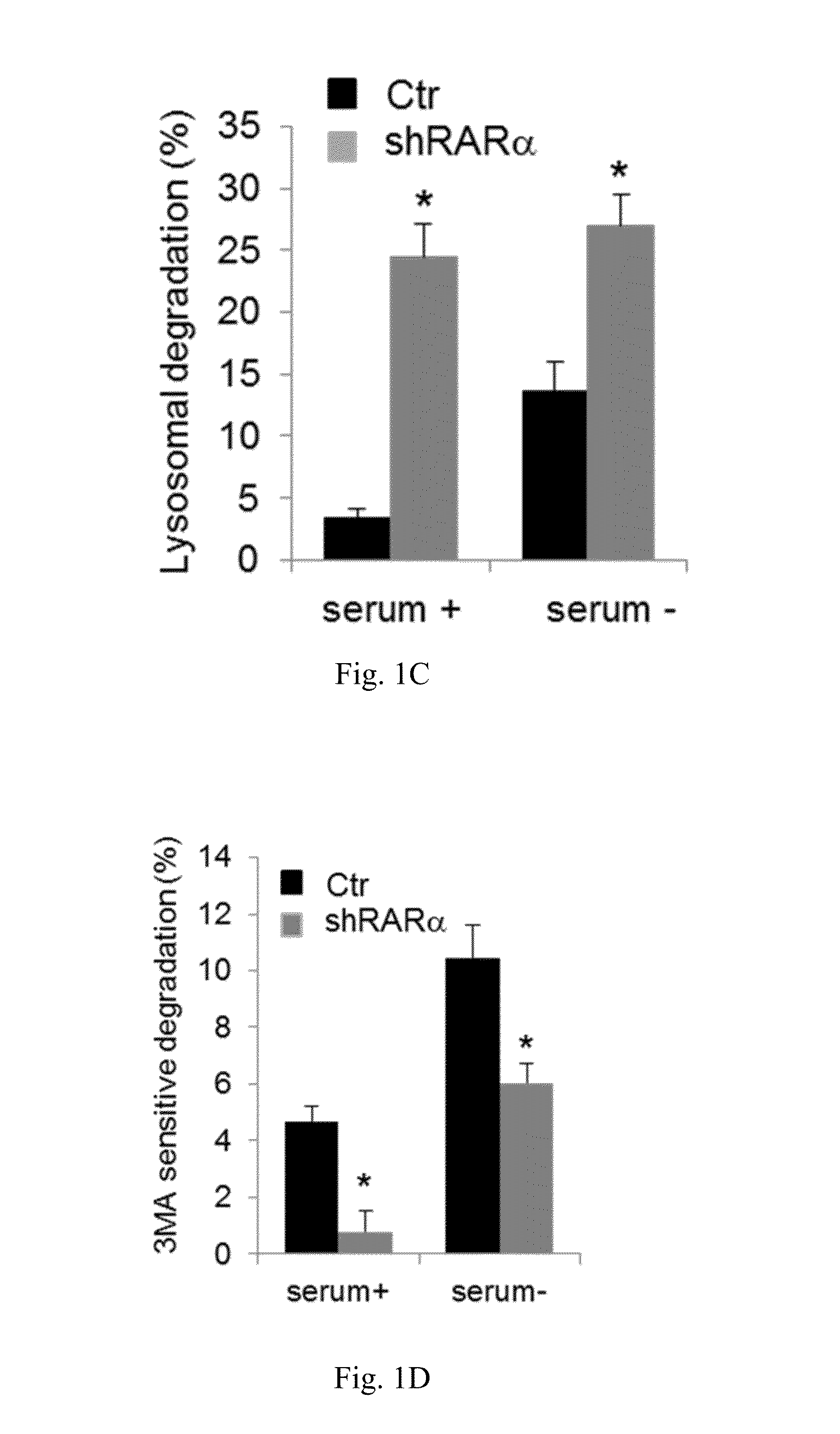

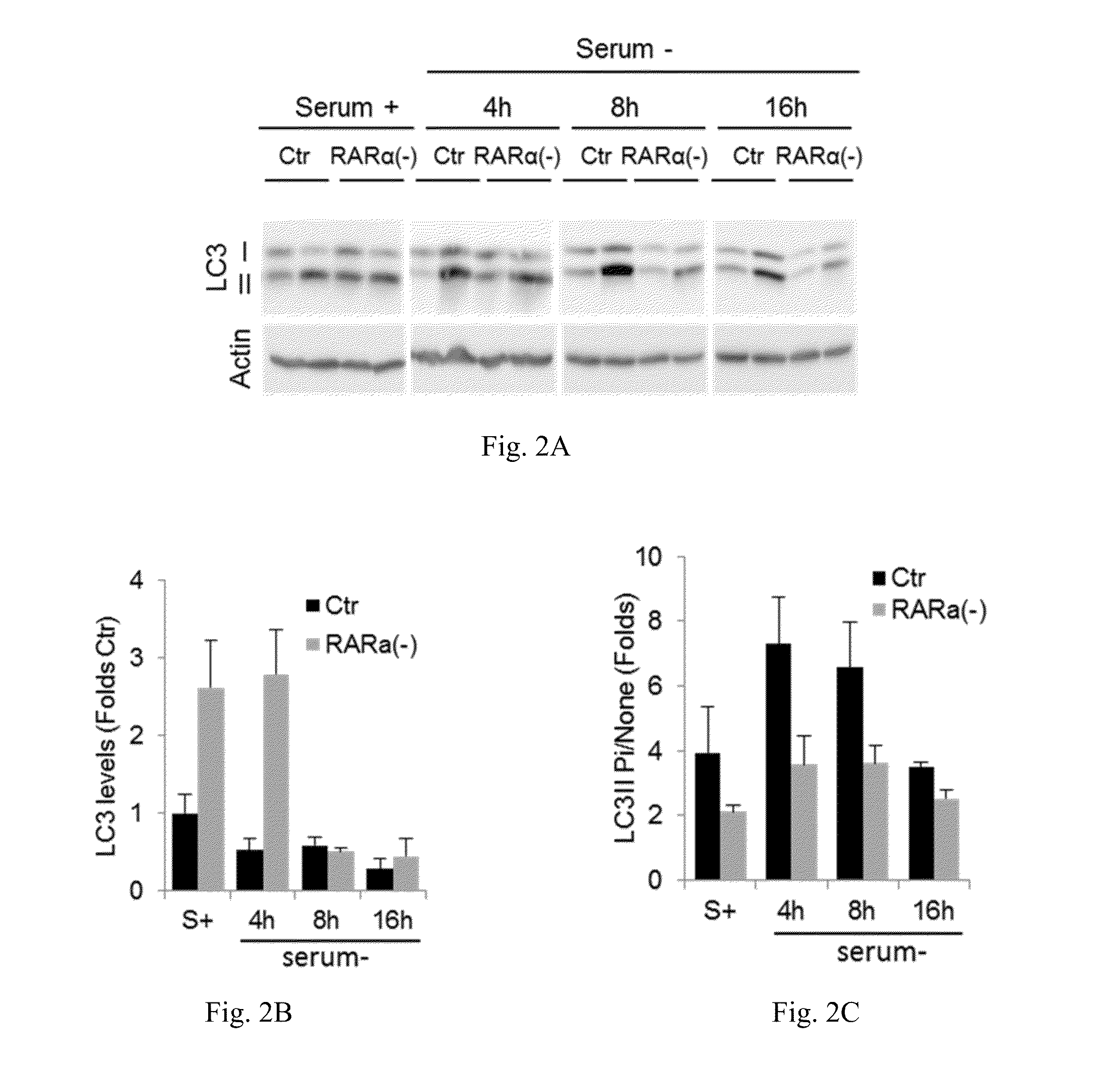

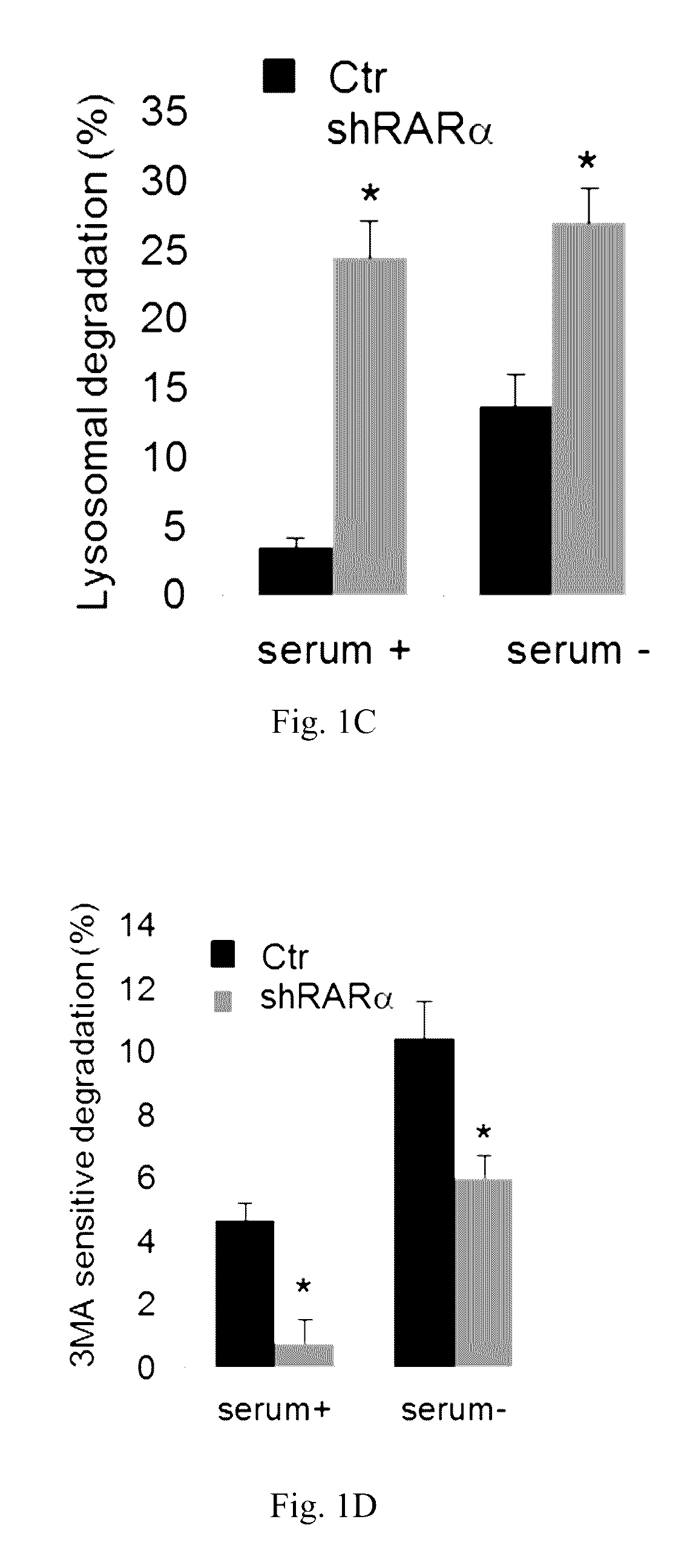

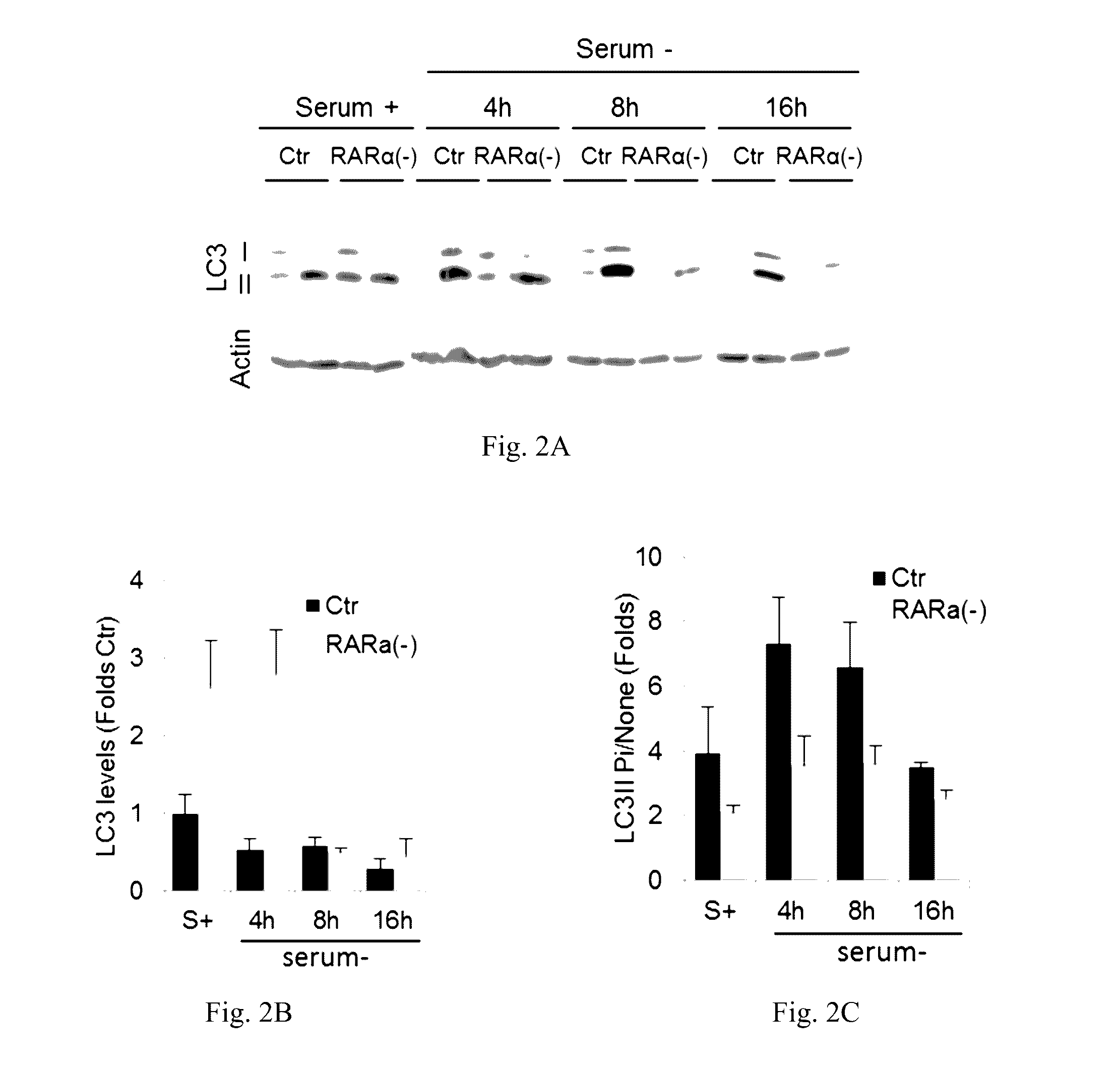

Retinoic acid receptor antagonists as chaperone-mediated autophagy modulators and uses thereof

Compounds, compositions and methods are provided for selectively activating chaperone-mediated autophagy (CMA), protecting cells from oxidative stress, proteotoxicity and lipotoxicity, and / or antagonizing activity of retinoic acid receptor alpha (RARα) in subjects in need thereof.

Owner:ALBERT EINSTEIN COLLEGE OF MEDICINE OF YESHIVA UNIV

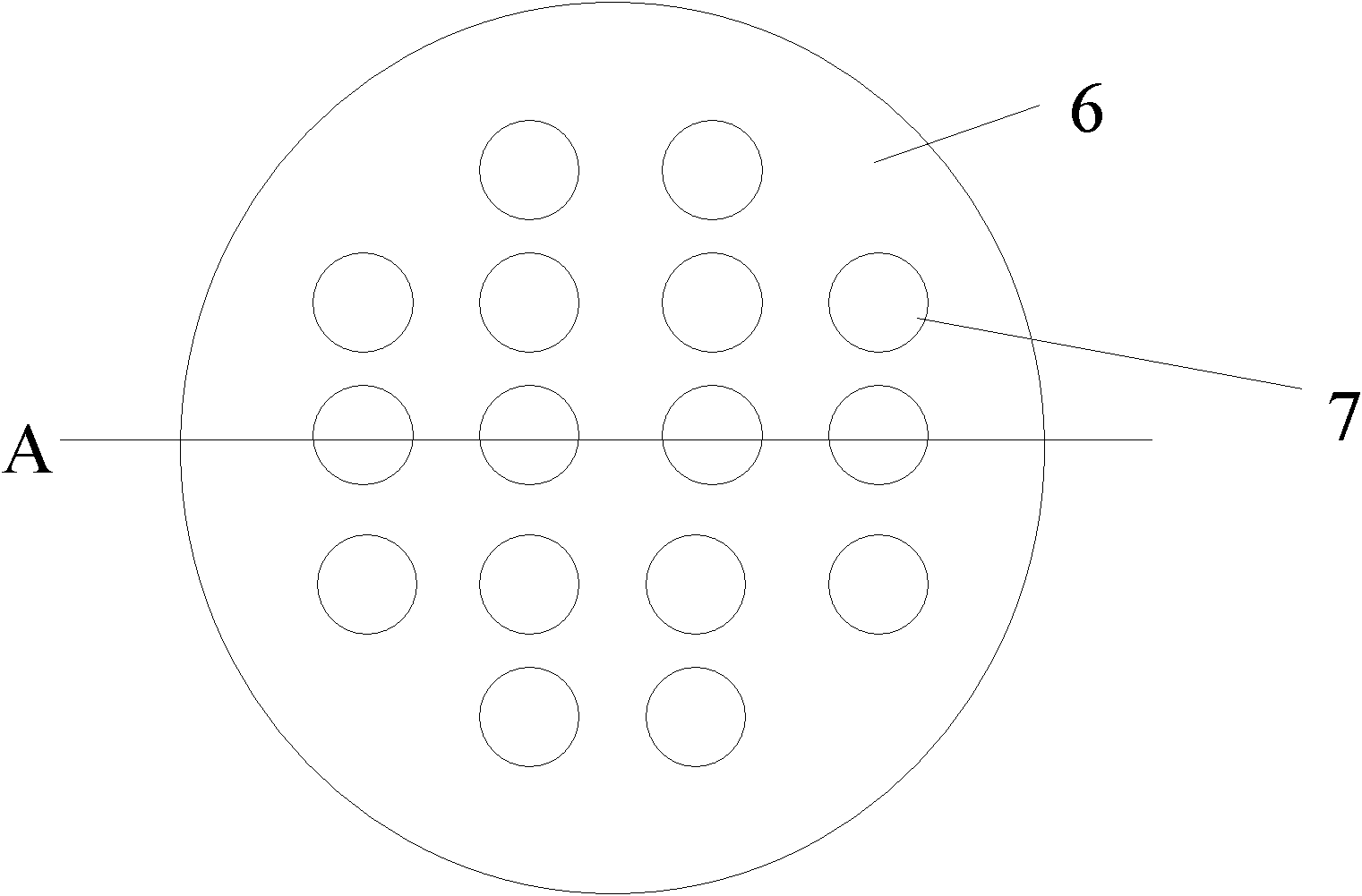

Method for packaging glass-silicon wafer-grade chiponboard (COB) of light emitting diode (LED)

ActiveCN102097545AReduce luminous attenuationImprove performanceSolid-state devicesSemiconductor devicesHeat resistanceSilica gel

The invention discloses a method for packaging a glass-silicon wafer-grade chiponboard (COB) of a light emitting diode (LED). The method comprises the following steps: 1, etching a silicon micro slot array with the micro slots communicated with each other through micro channels, and placing a proper amount of heat outgas agent in the micro slots; 2, performing anodic bonding on the Si wafer with patterns and the heat outgas agent and borosilicate glass wafer in air or in vacuum to form a sealed cavity; 3, heating and preserving heat to form a spherical glass micro cavity, cooling the cavity to normal temperature, annealing and removing silicon to obtain a wafer-grade glass micro cavity; 4, preparing a lead substrate; 5, mounting a chip and leading a wire; 6, carrying out wafer-grade bonding; and 7, filling silica gel to realize the wafer-grade packaging of the LED. By achieving the integration with the wafer-grade LED reflecting cup, the method reduces heat resistance and cost.

Owner:SOUTHEAST UNIV

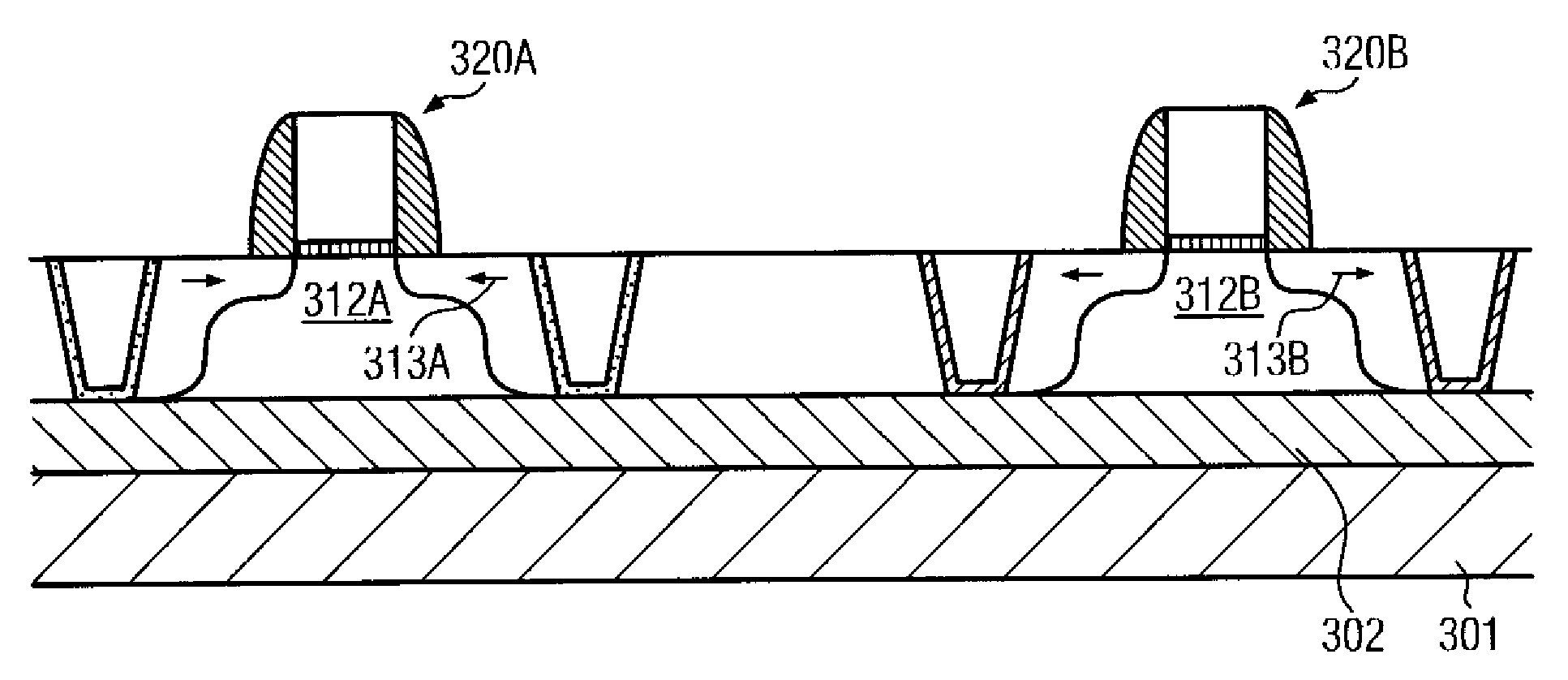

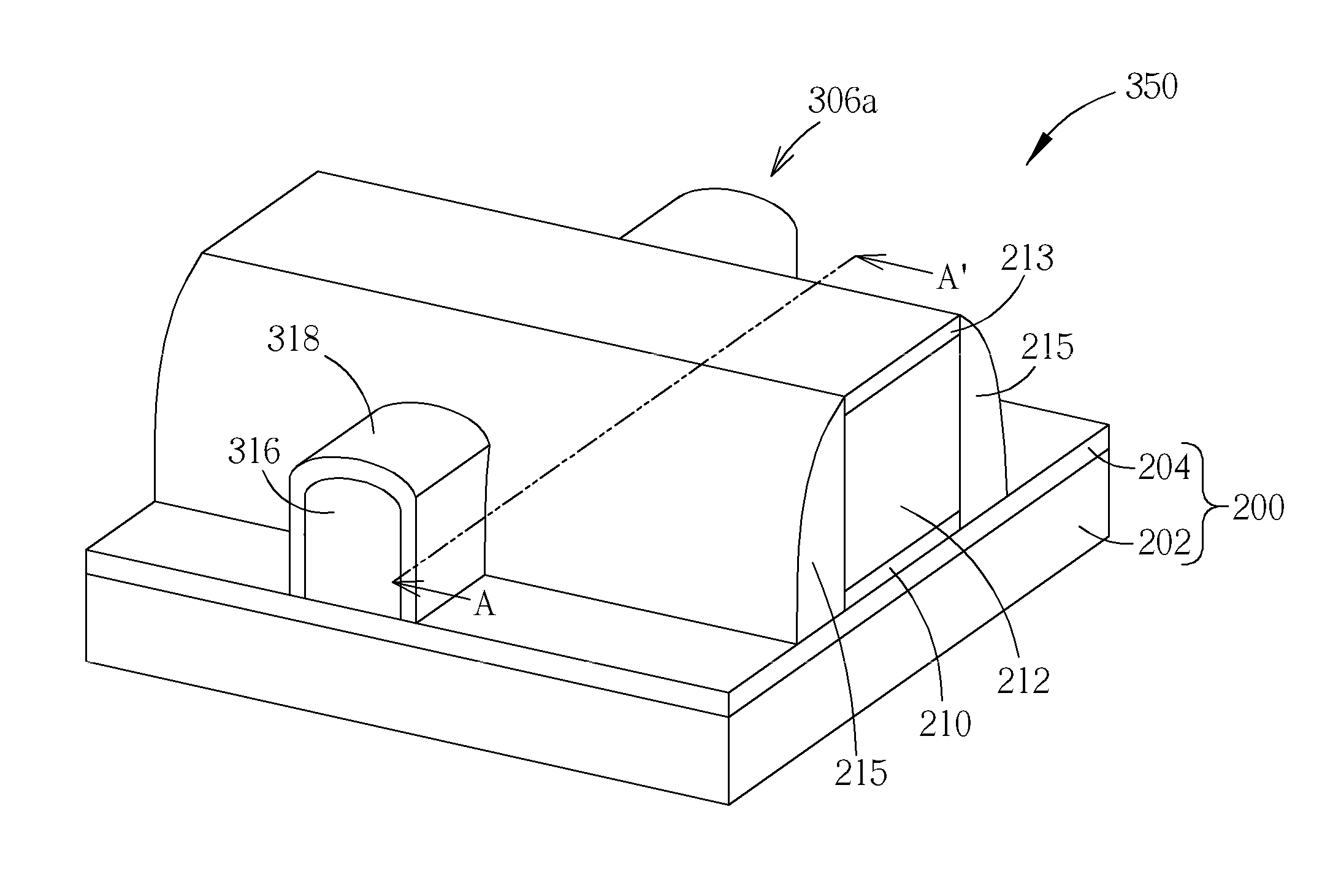

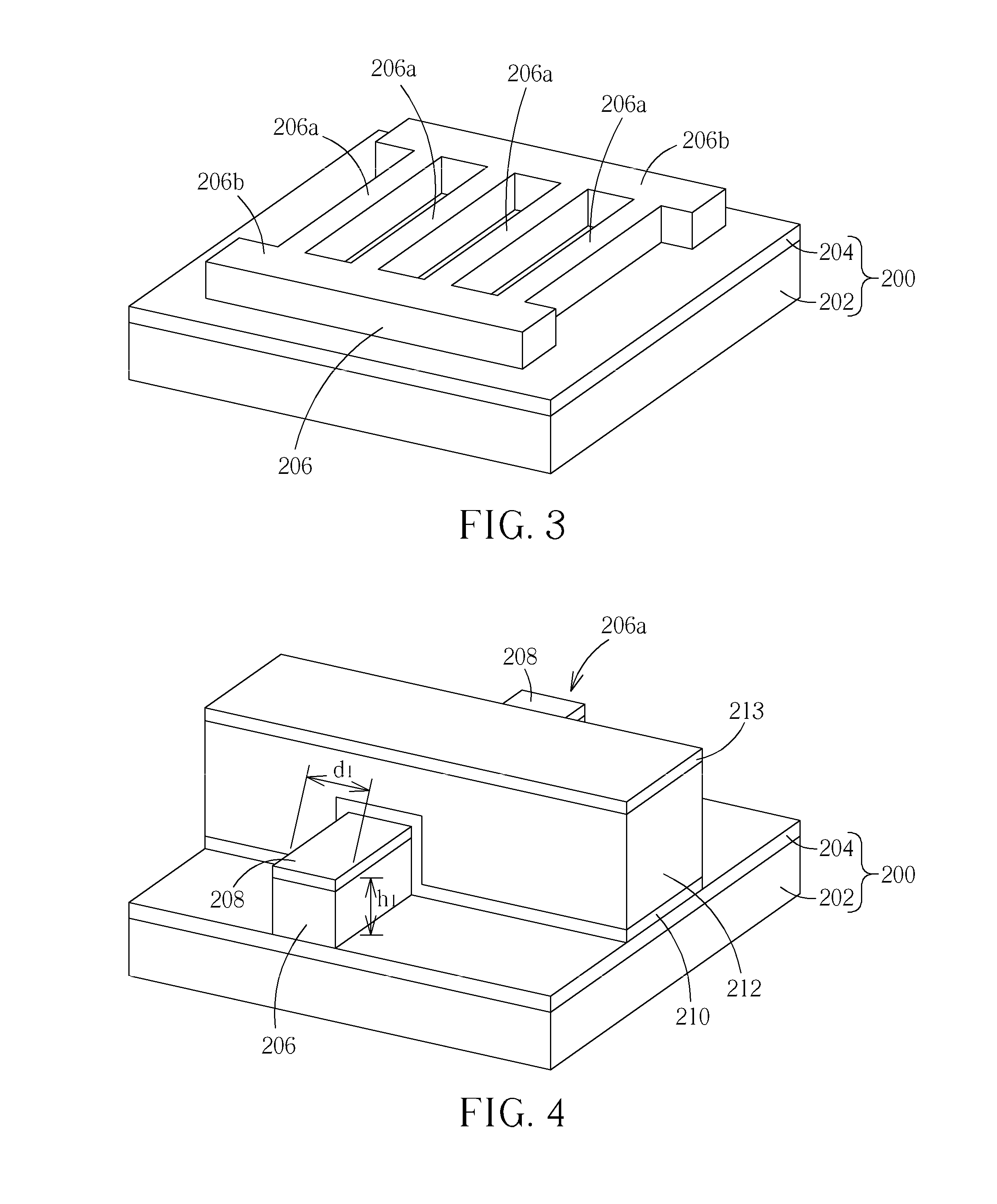

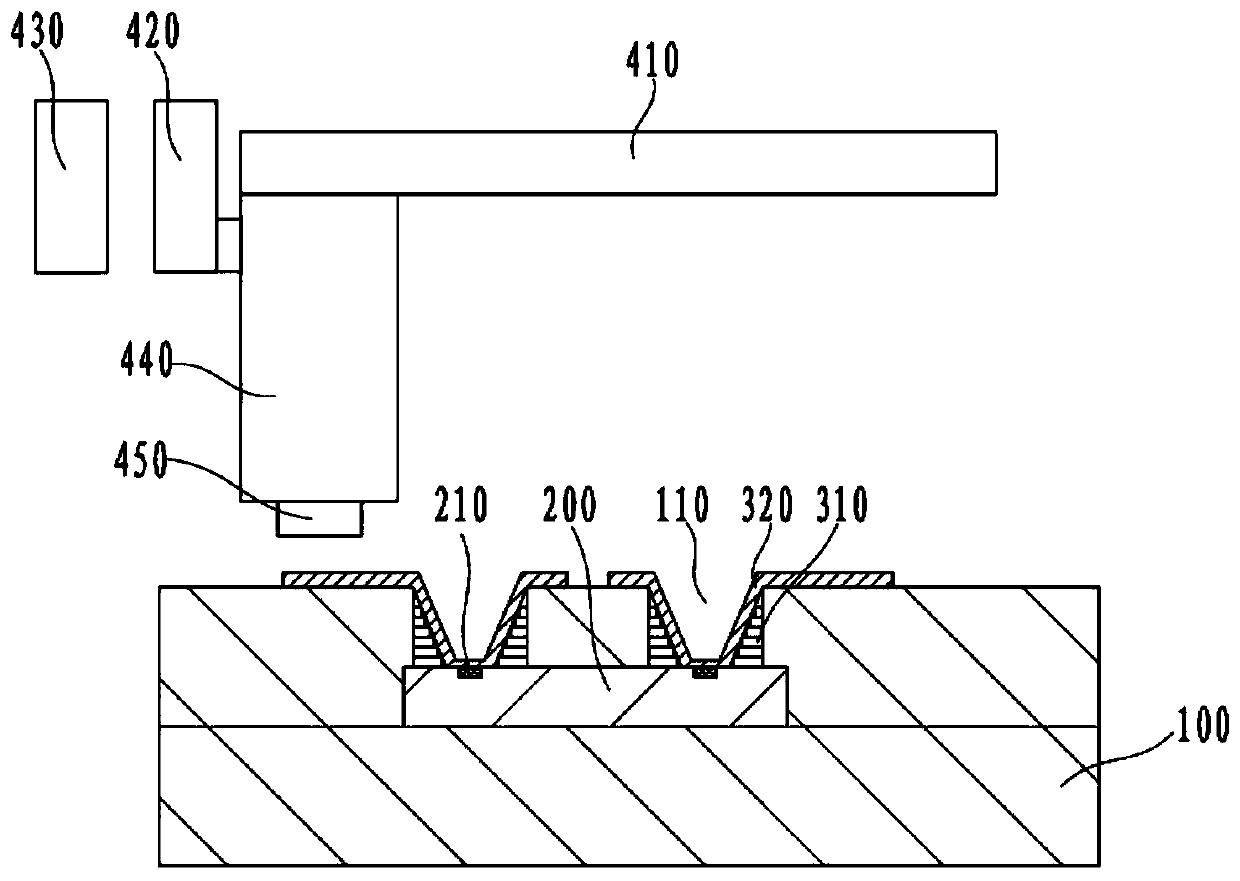

Method for manufacturing multi-gate transistor device

ActiveUS8551829B2Strain stress is provided to the channel regionImprove mobilitySemiconductor/solid-state device manufacturingSemiconductor devicesGate dielectricEngineering

Owner:UNITED MICROELECTRONICS CORP

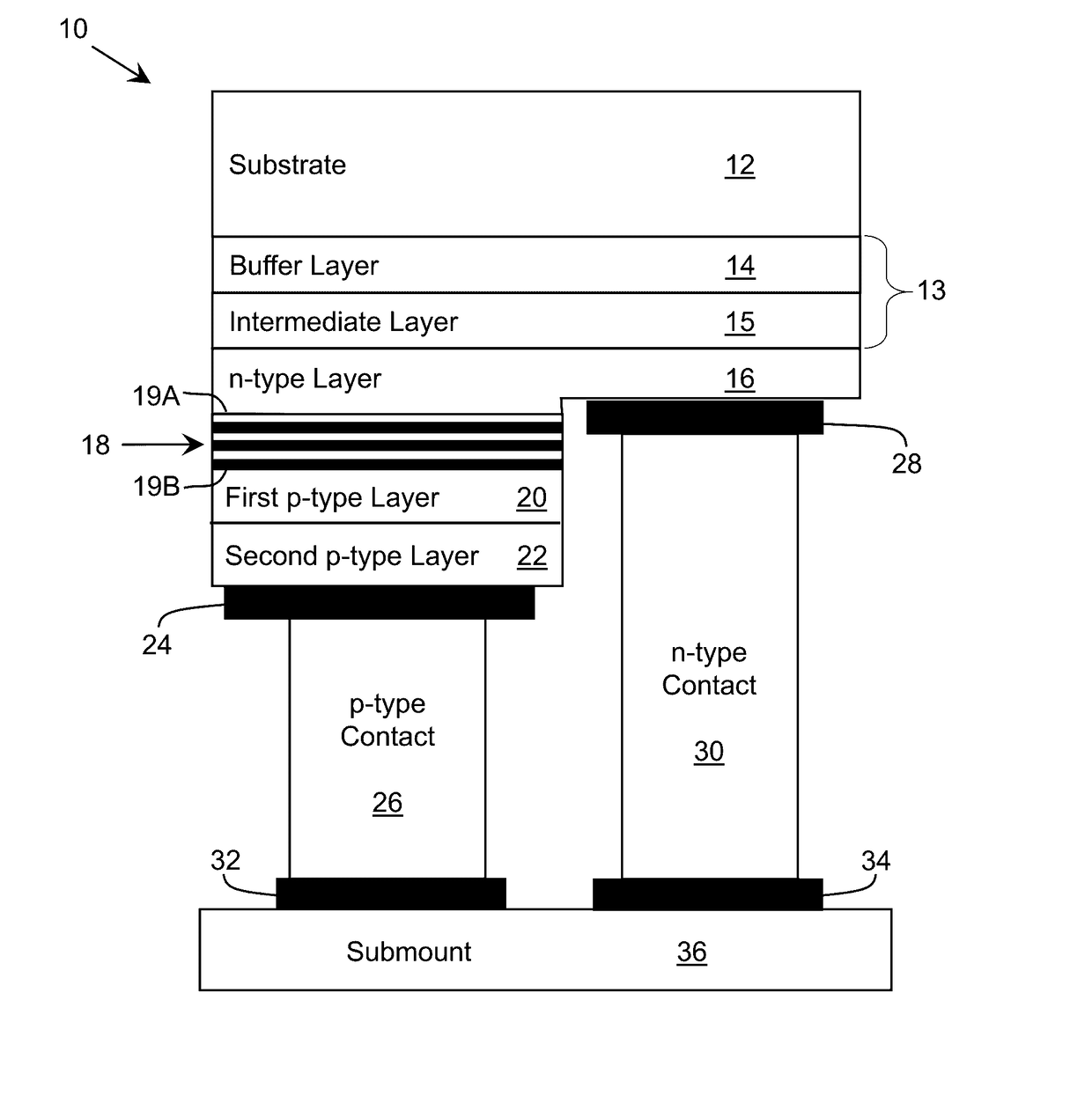

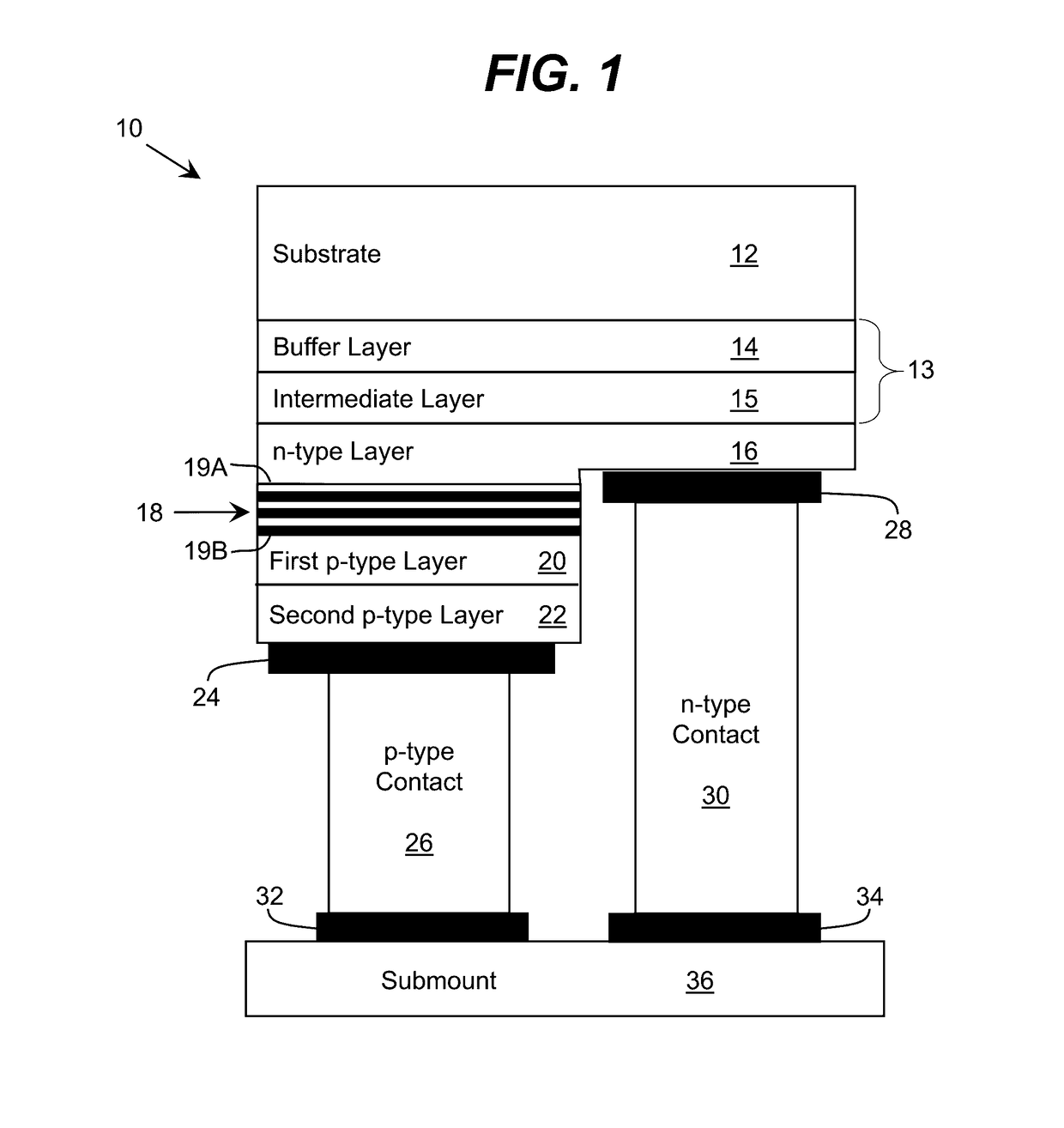

Semiconductor Structure with Stress-Reducing Buffer Structure

ActiveUS20170110628A1Effective stressCompressive stressPolycrystalline material growthSpecial data processing applicationsGrowth parameterSemiconductor structure

A semiconductor structure comprising a buffer structure and a set of semiconductor layers formed adjacent to a first side of the buffer structure is provided. The buffer structure can have an effective lattice constant and a thickness such that an overall stress in the set of semiconductor layers at room temperature is compressive and is in a range between approximately 0.1 GPa and 2.0 GPa. The buffer structure can be grown using a set of growth parameters selected to achieve the target effective lattice constant a, control stresses present during growth of the buffer structure, and / or control stresses present after the semiconductor structure has cooled.

Owner:SENSOR ELECTRONICS TECH

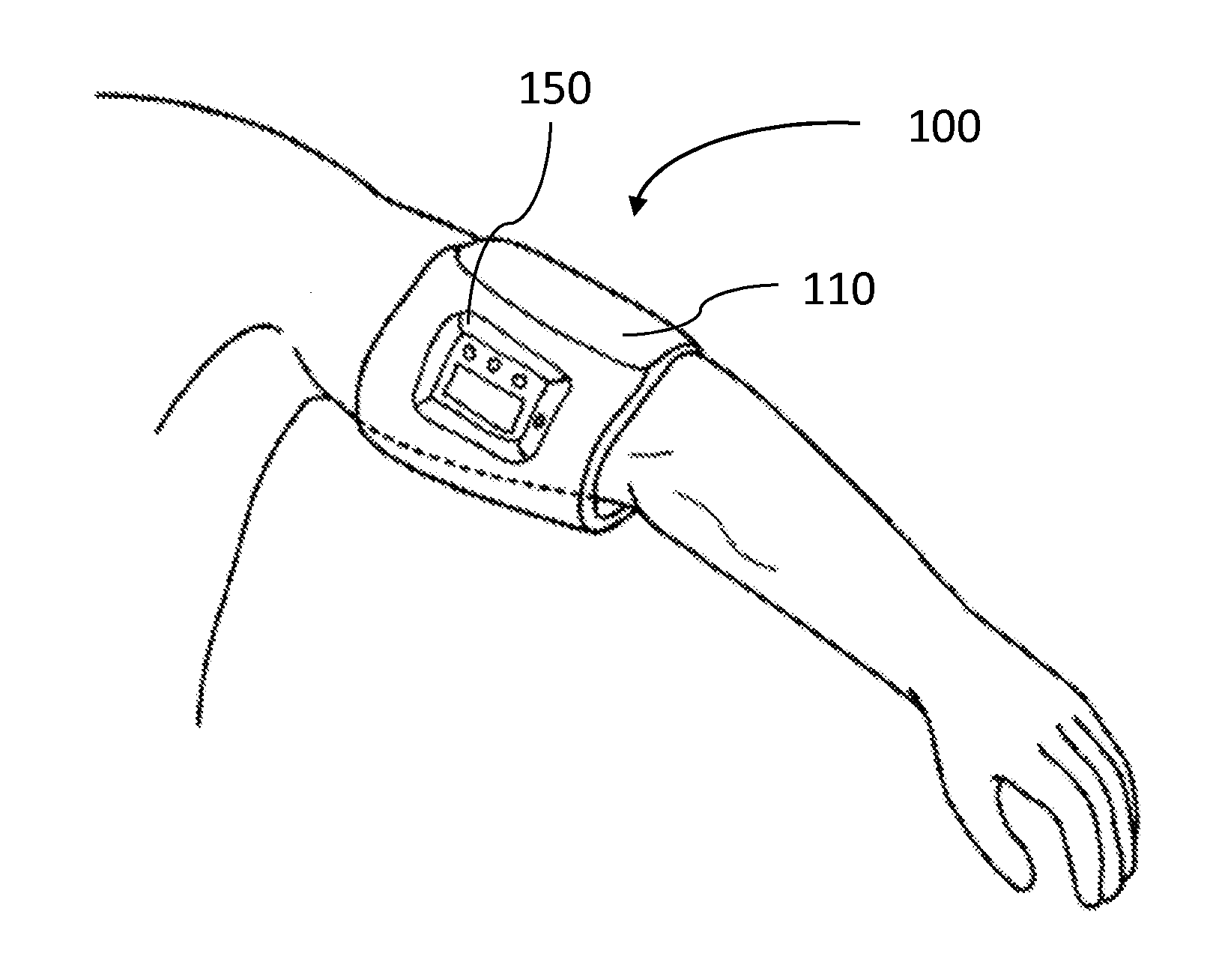

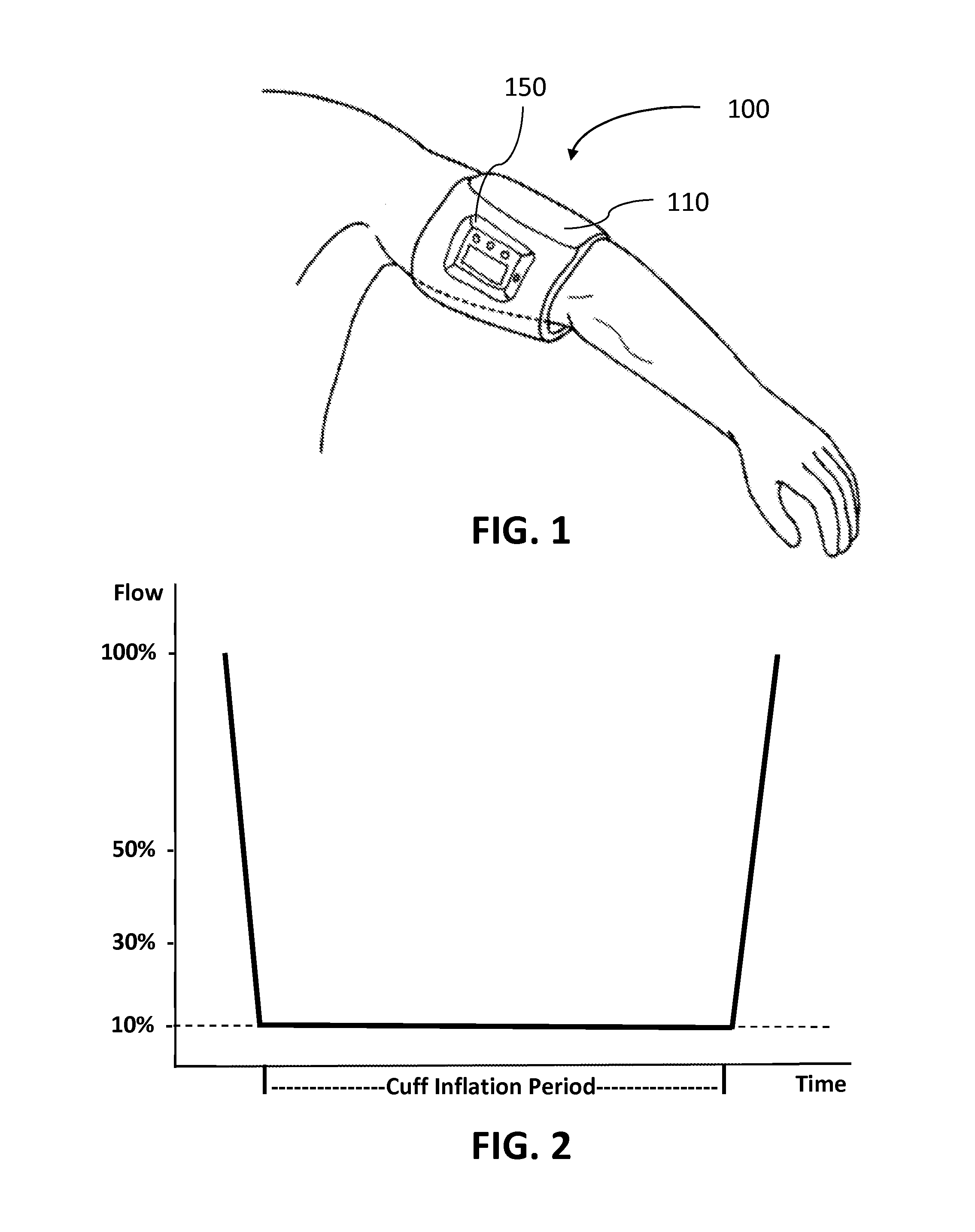

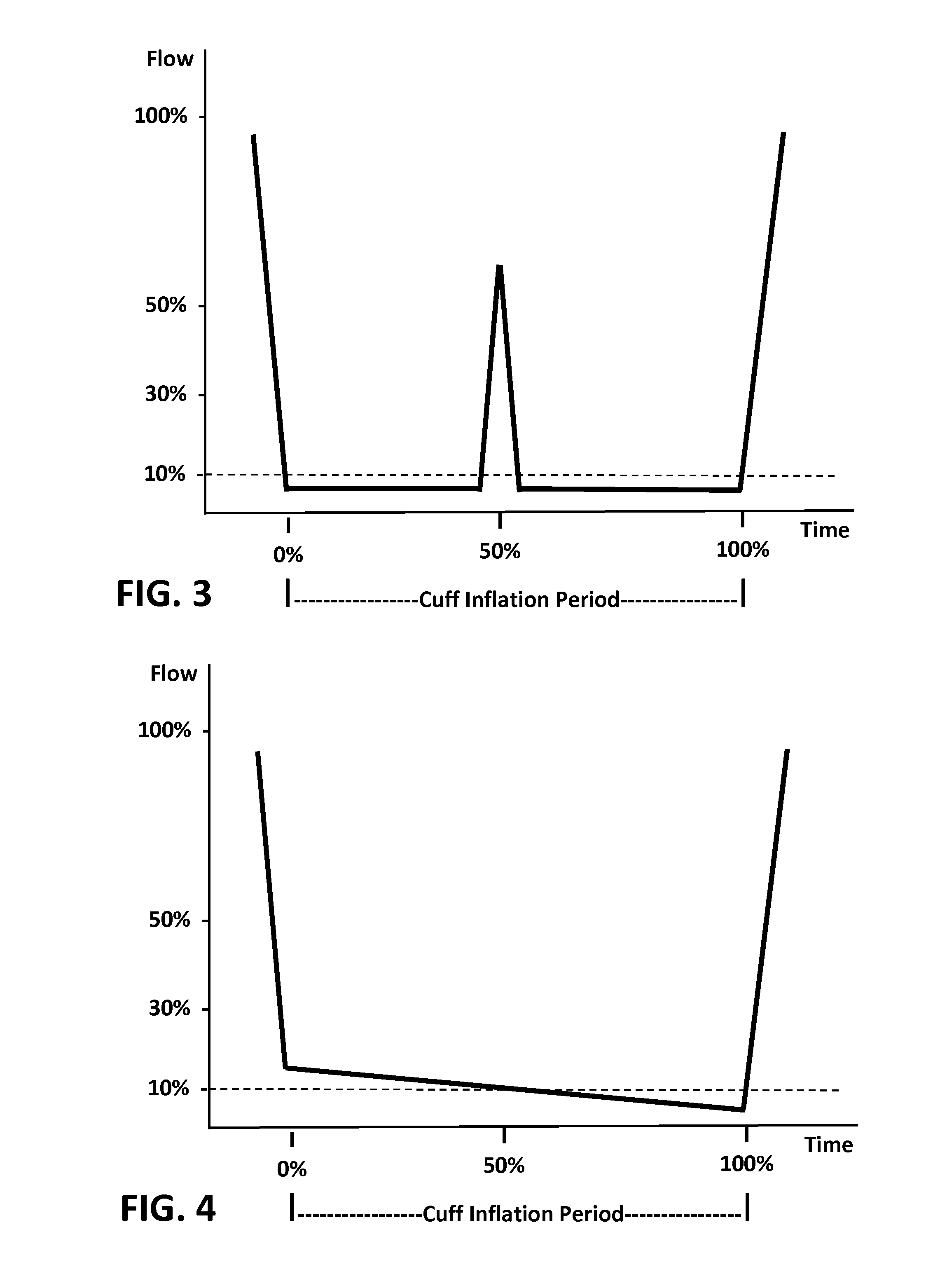

Methods and devices for remote ischemic conditioning via partial limb occlusion

ActiveUS20150190301A1Minimizing pain and discomfortRisk minimizationPneumatic massageGenitals massageBlood flowClot formation

Single- or dual-bladder devices for automated delivery of remote ischemic conditioning treatment via partial limb occlusion involve various methods of operating the cuff in which partial or full limb occlusion is achieved during the periods of cuff inflation. Achieving clinical benefits of remote ischemic conditioning without extended cessation of limb blood flow are advantageous due to lower required cuff pressure and reduced risk of clot formation in the limb vasculature.

Owner:INFARCT REDUCTION TECH

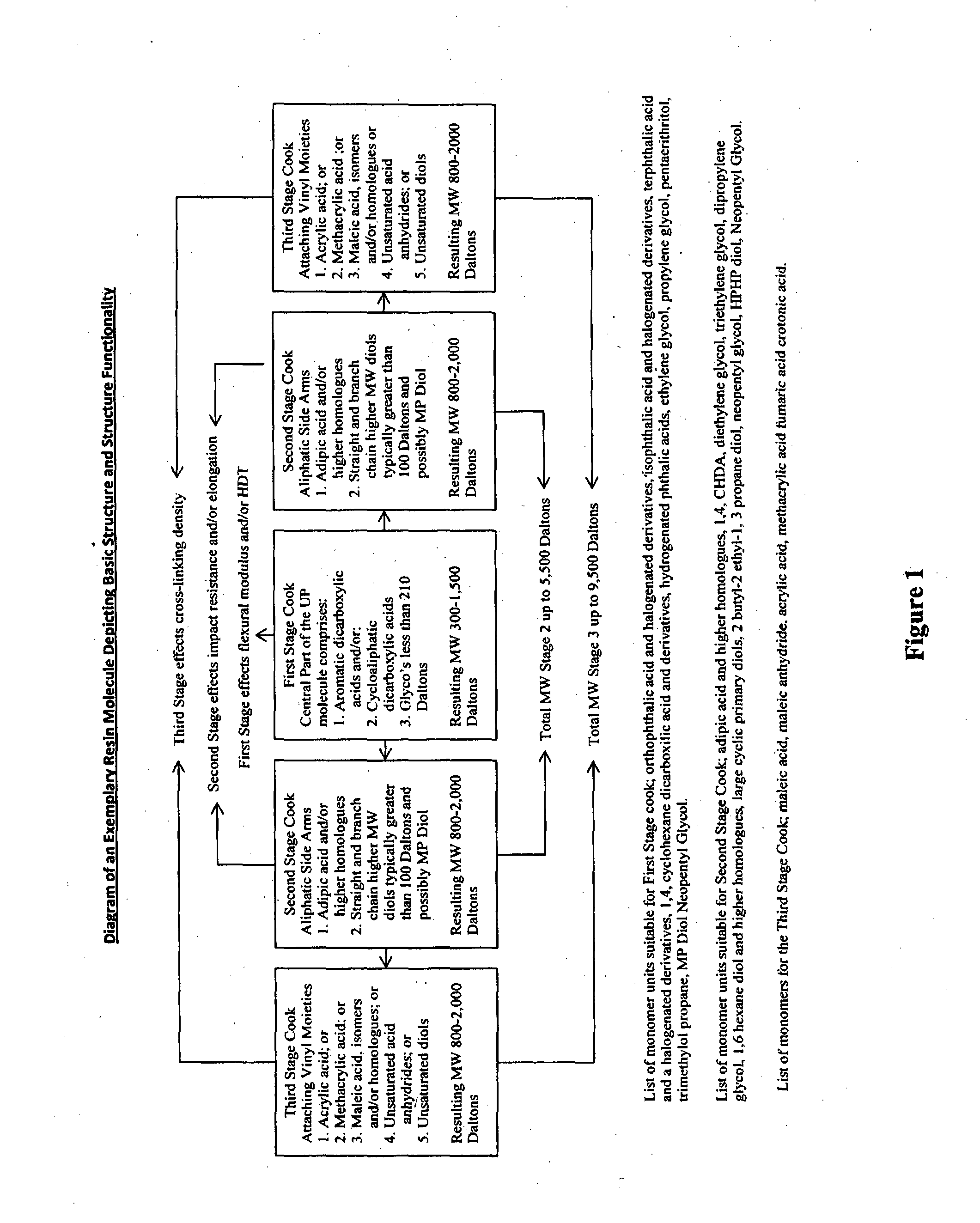

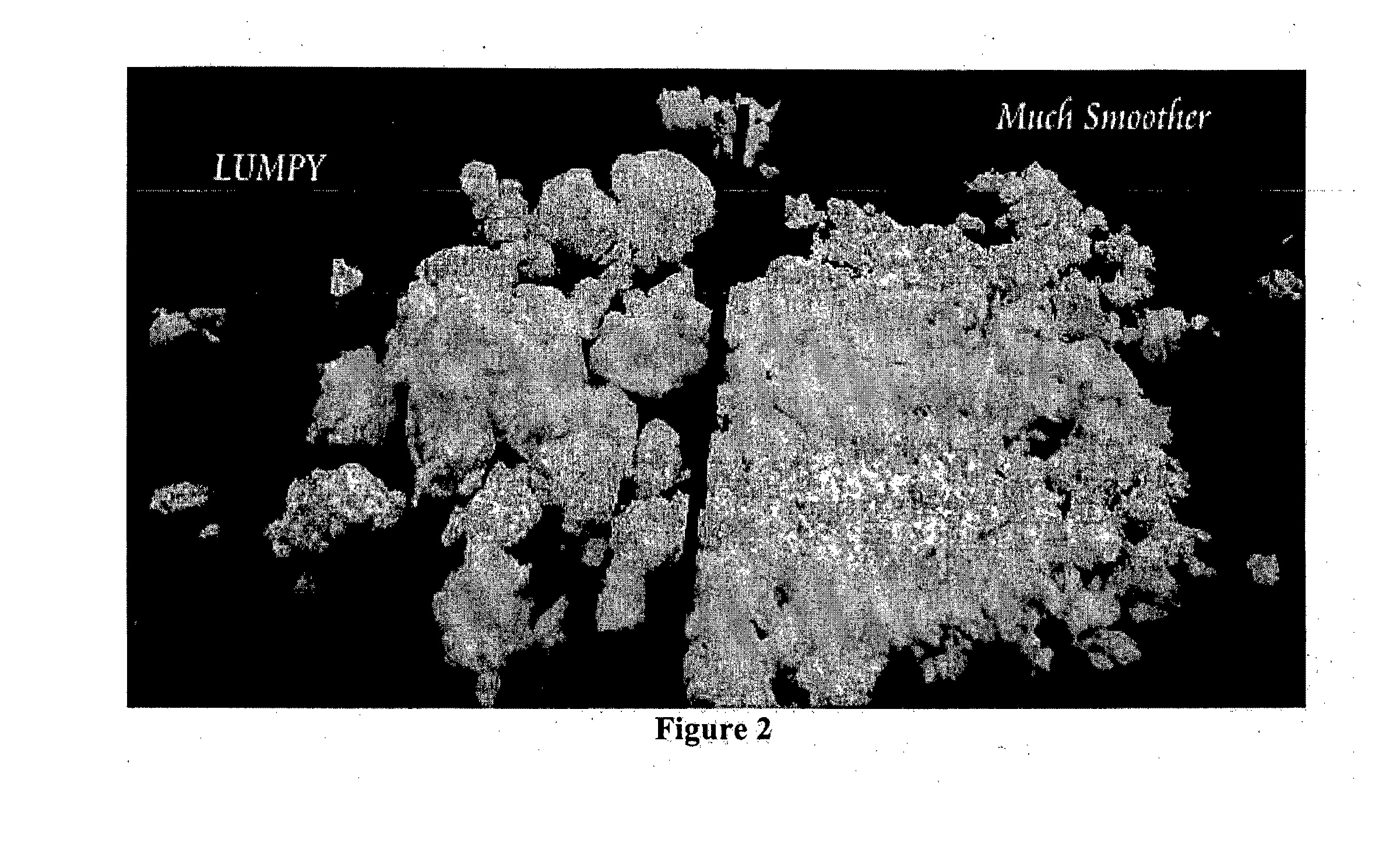

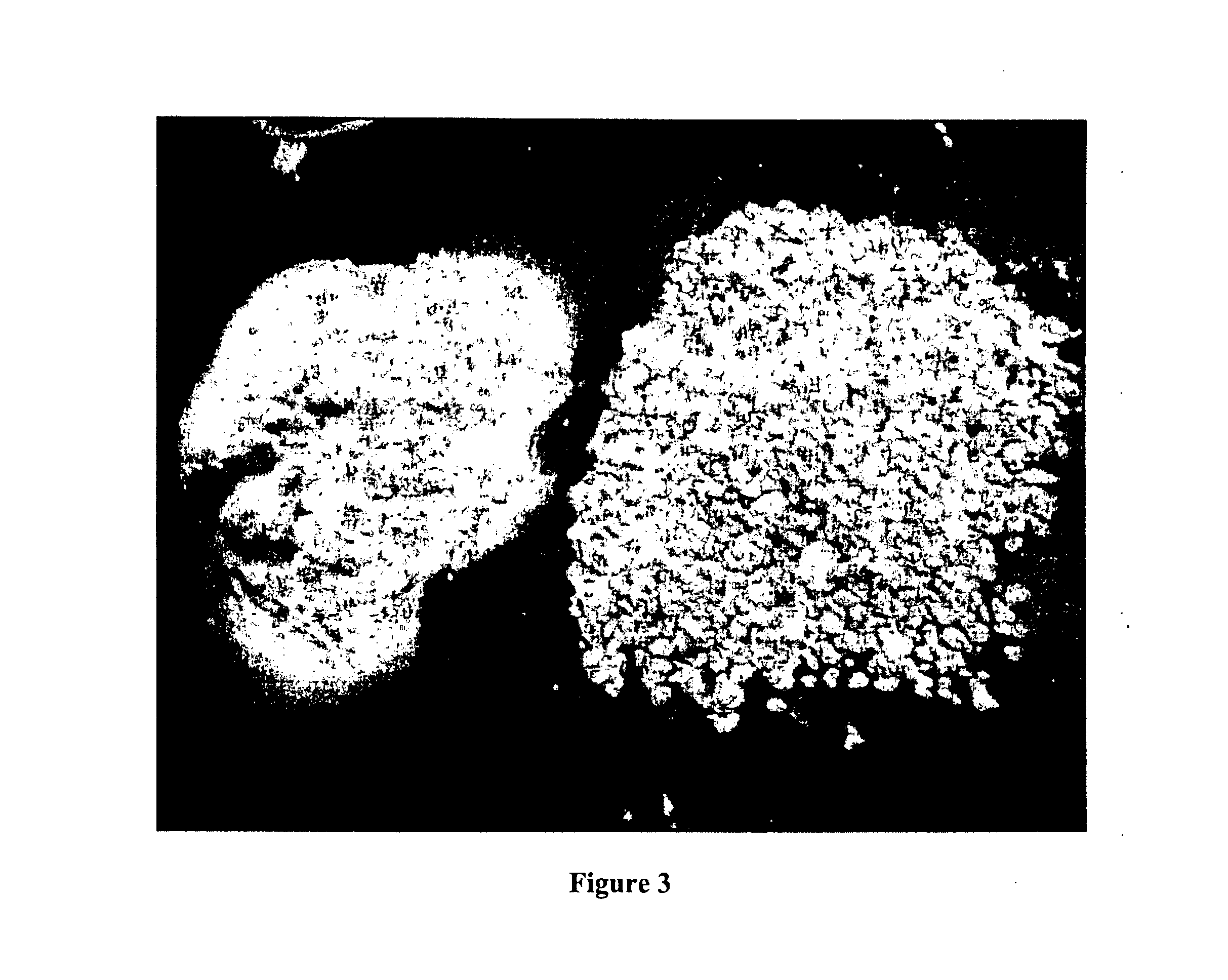

Resins, Resin/Fibre Composites, Methods of Use and Methods of Preparation

Owner:SPOKE HLDG LLC

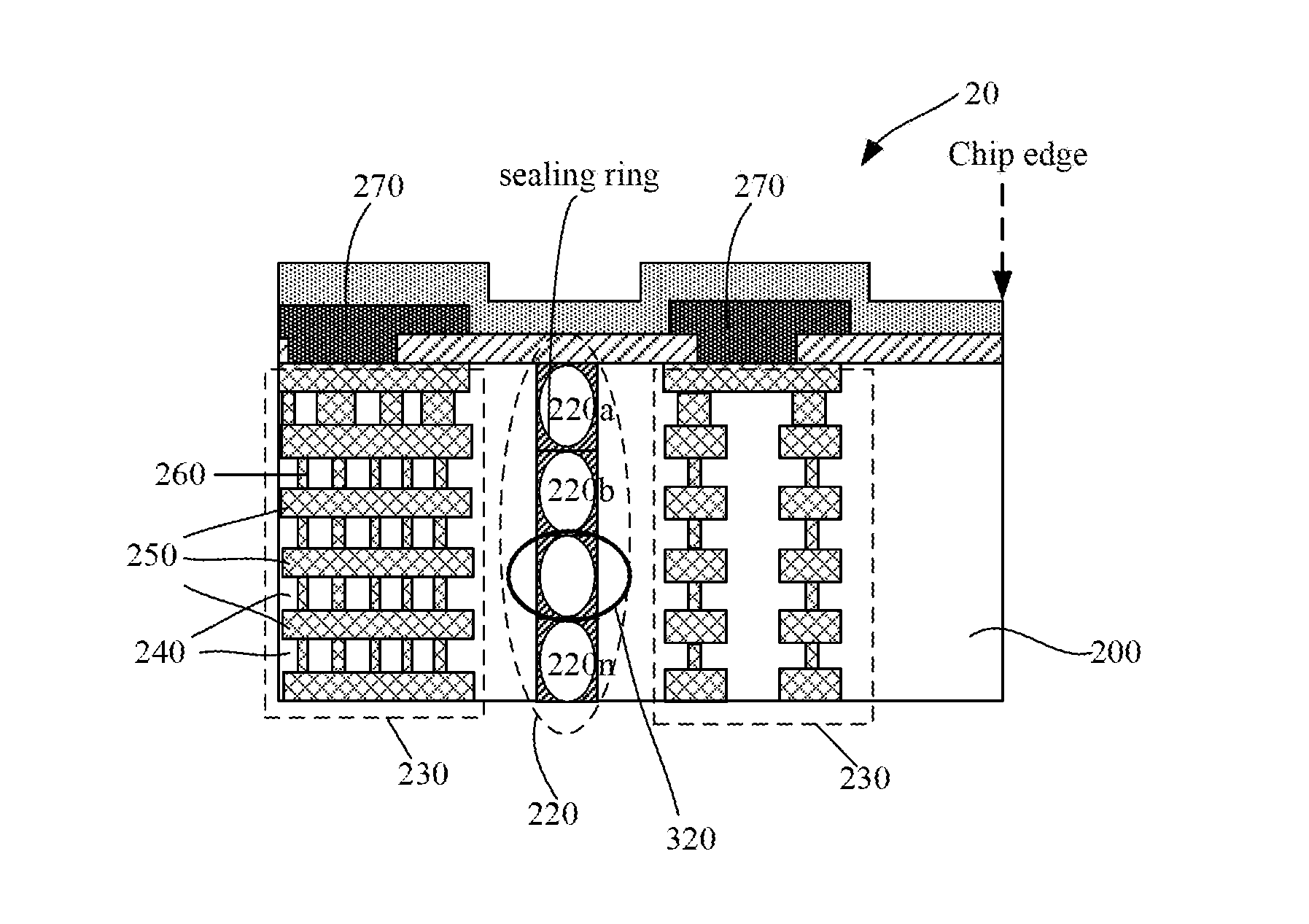

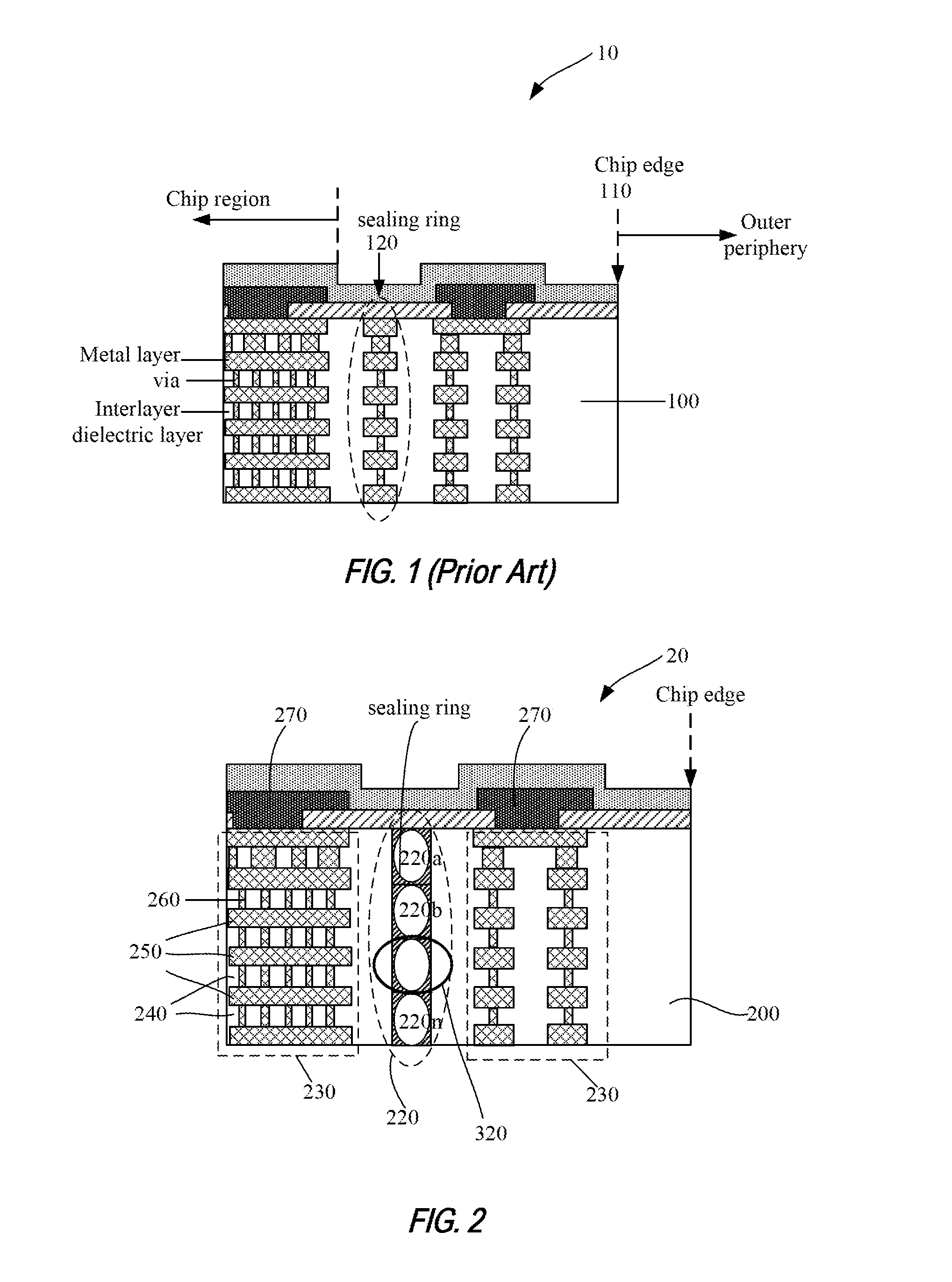

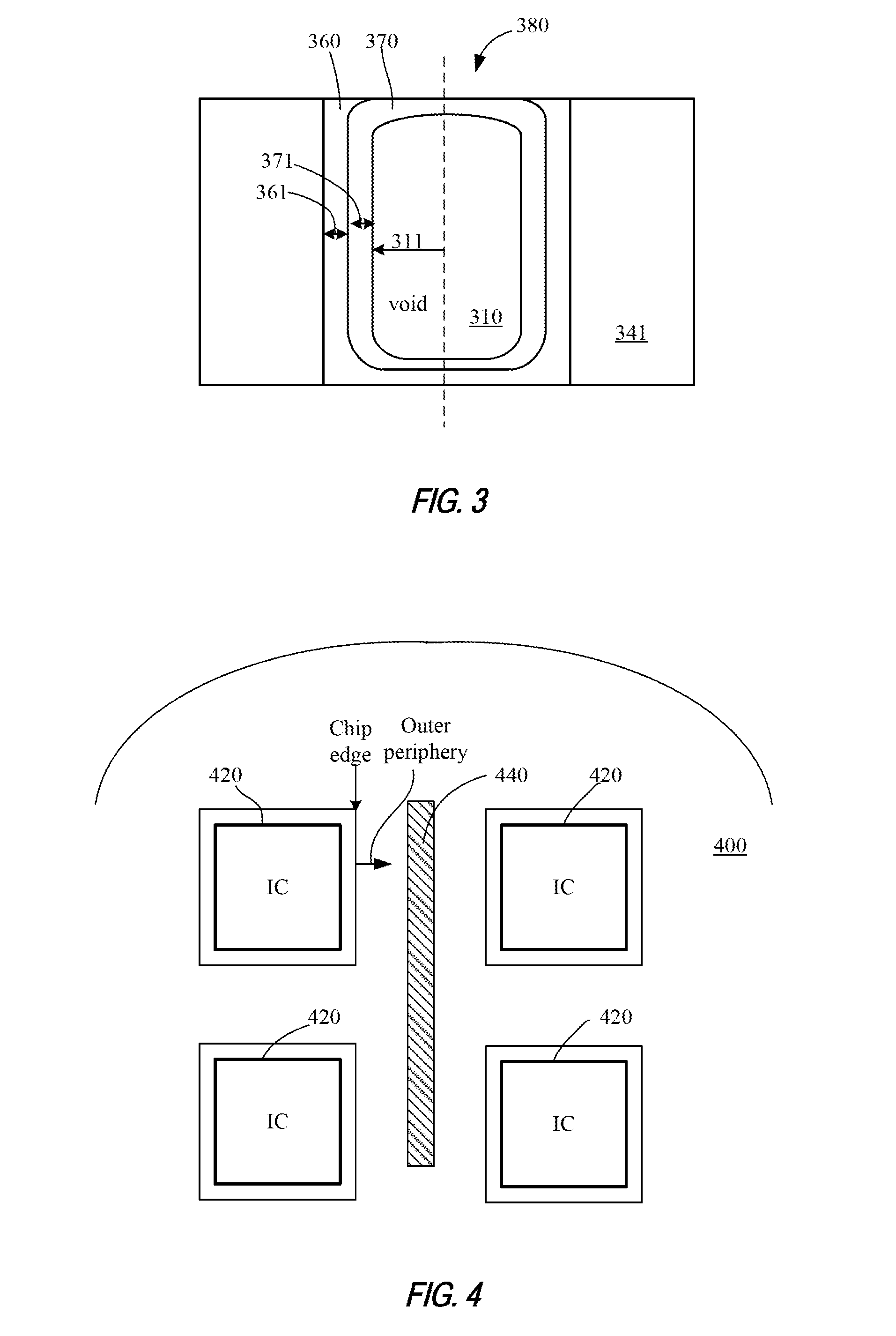

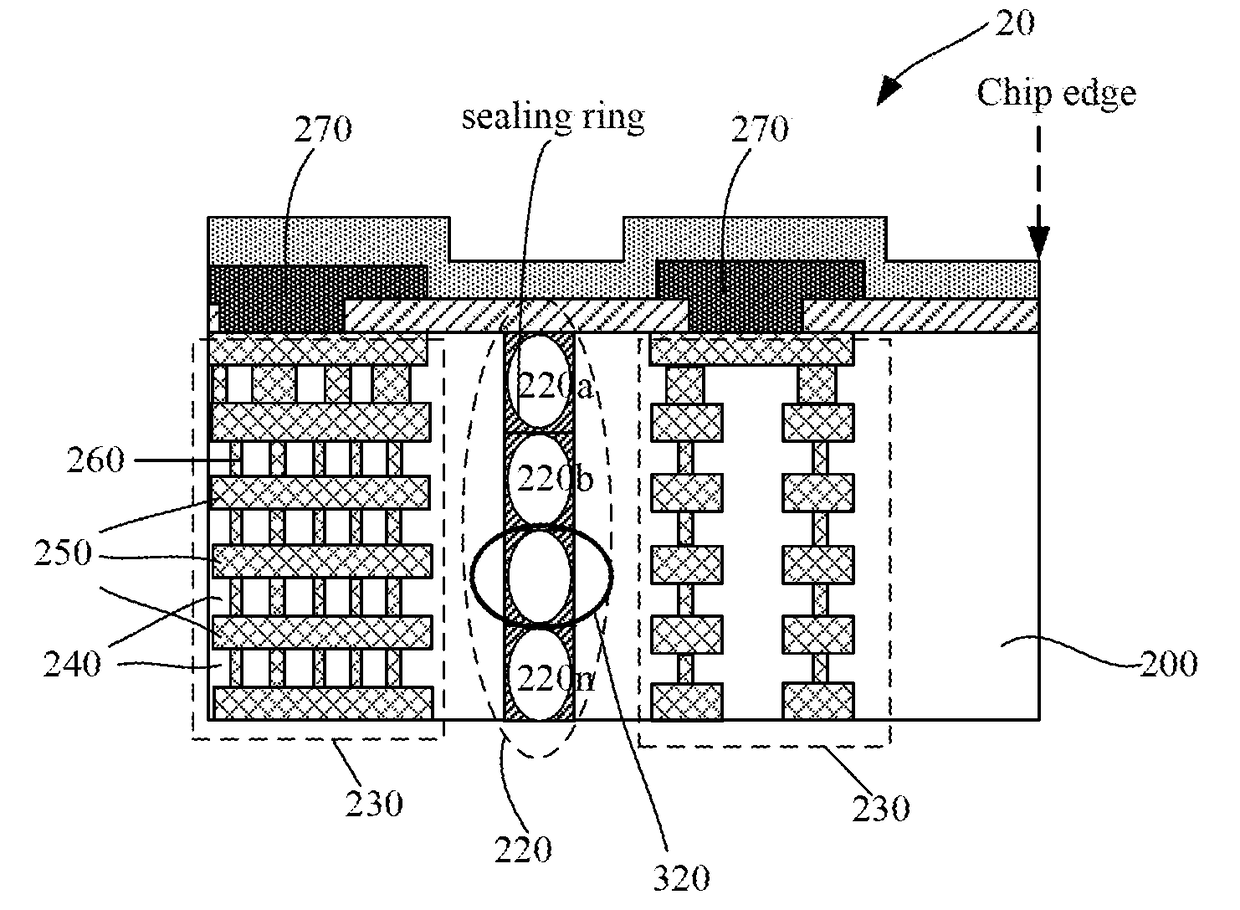

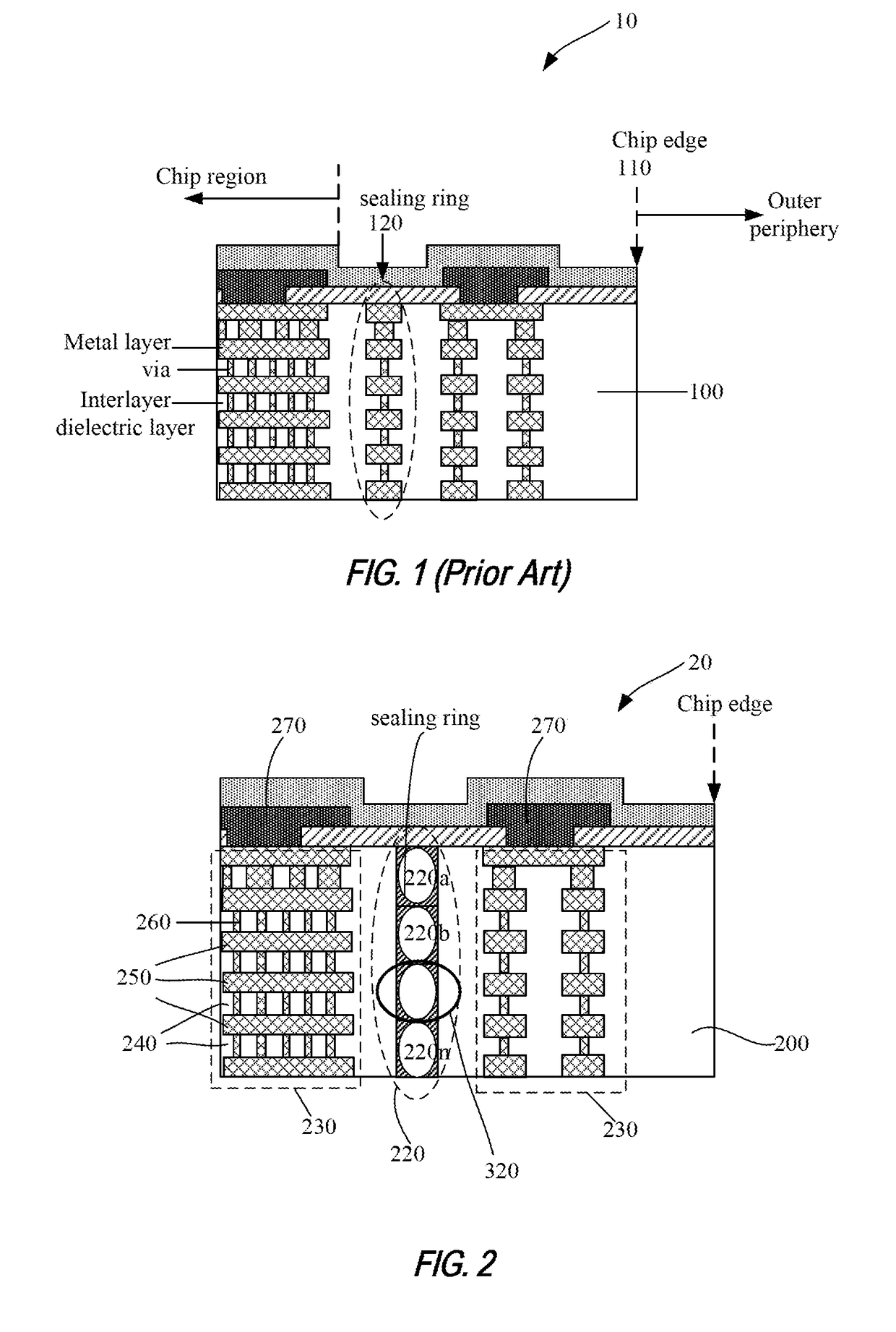

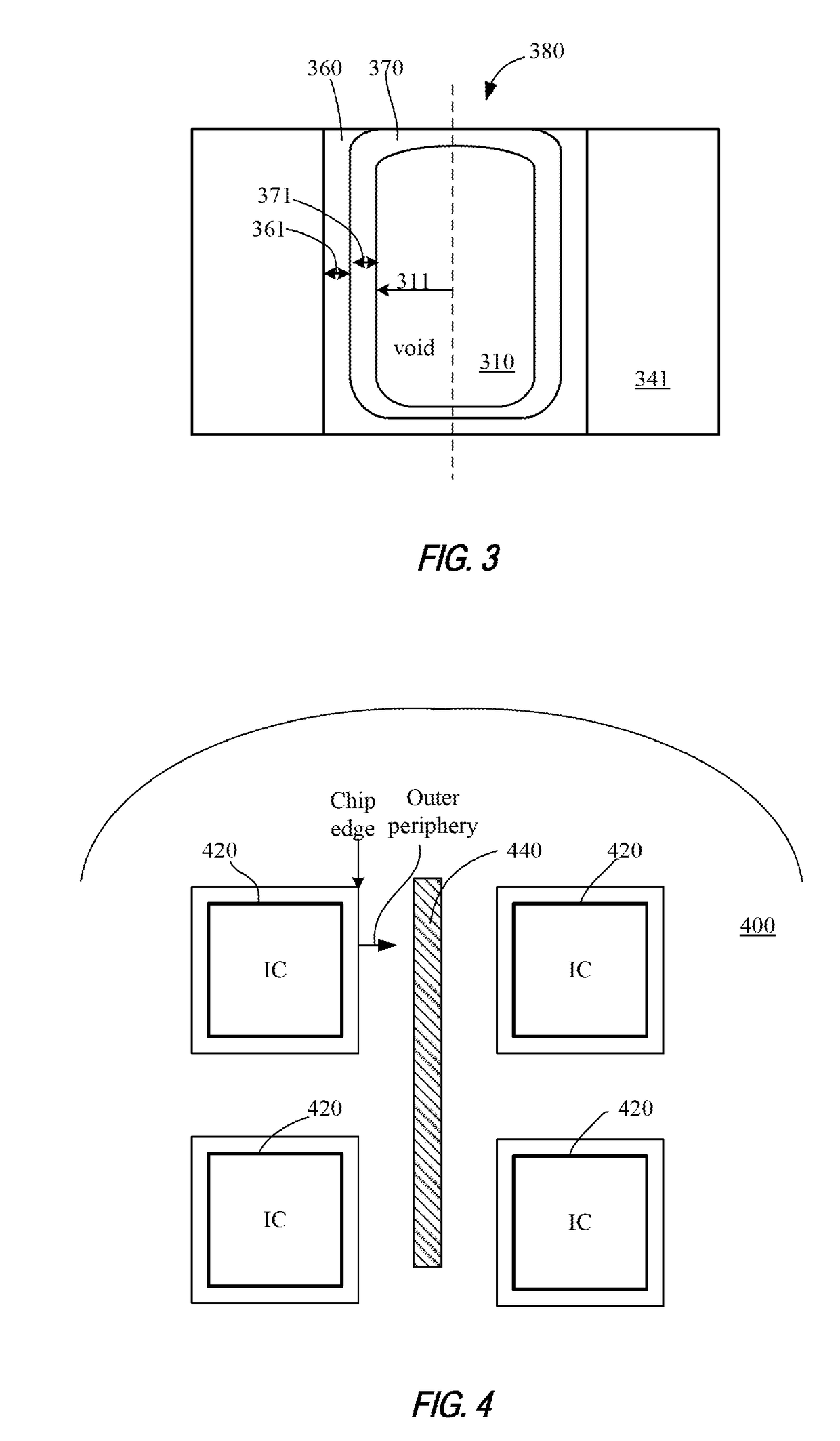

Seal ring structure to avoid delamination defect

ActiveUS20160343673A1Improve performanceHigh yieldSemiconductor/solid-state device detailsSolid-state devicesDiffusion barrierDielectric layer

A semiconductor device includes a semiconductor substrate, a plurality of integrated circuit devices on the semiconductor substrate, and a seal ring structure surrounding each one of the integrated circuit devices. The seal ring structure includes a plurality of interlayer dielectric layers and a plurality of hollow through-hole structures disposed within each of the interlayer dielectric layers. Each of the hollow through-hole structure within an interlayer dielectric layer includes a through-hole disposed within one of the interlayer dielectric layers, a diffusion barrier layer formed at the bottom, sidewalls and the top of the through-hole, and a seed layer disposed on the diffusion barrier layer. The diffusion barrier layer and the seed layer cover the top of the through-hole so that the through-hole has a void to form the hollow through-hole structure.

Owner:SEMICON MFG INT (SHANGHAI) CORP

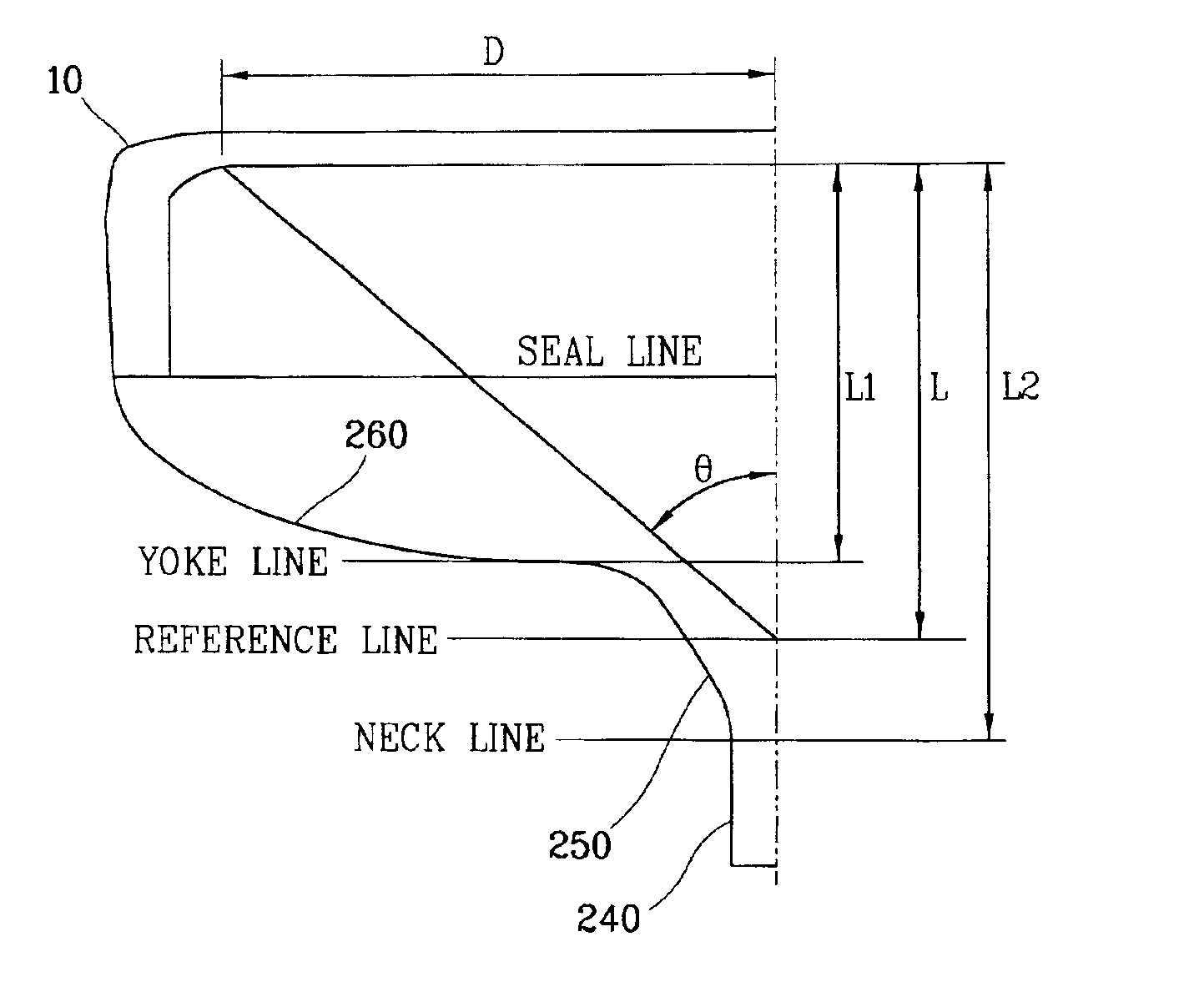

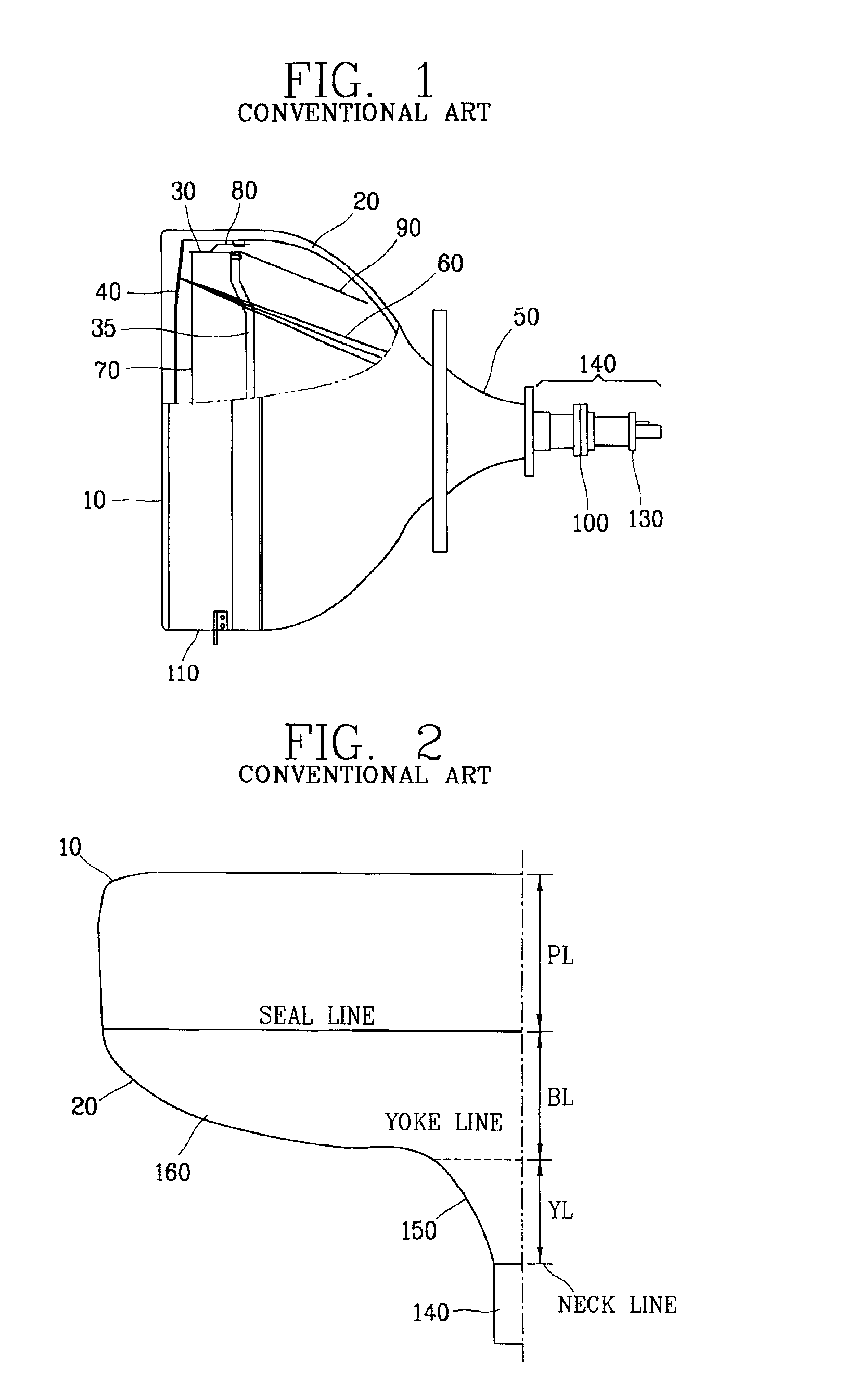

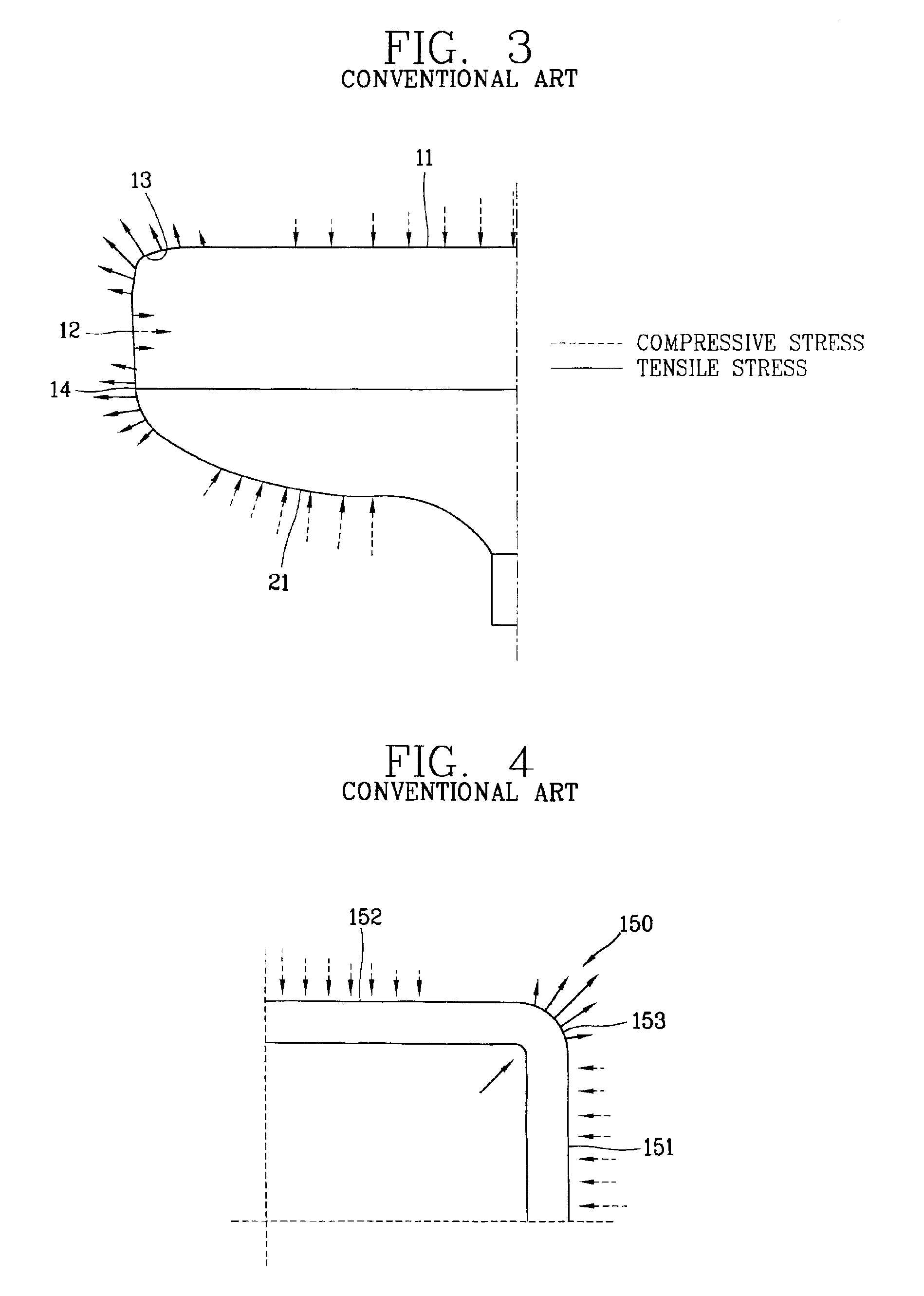

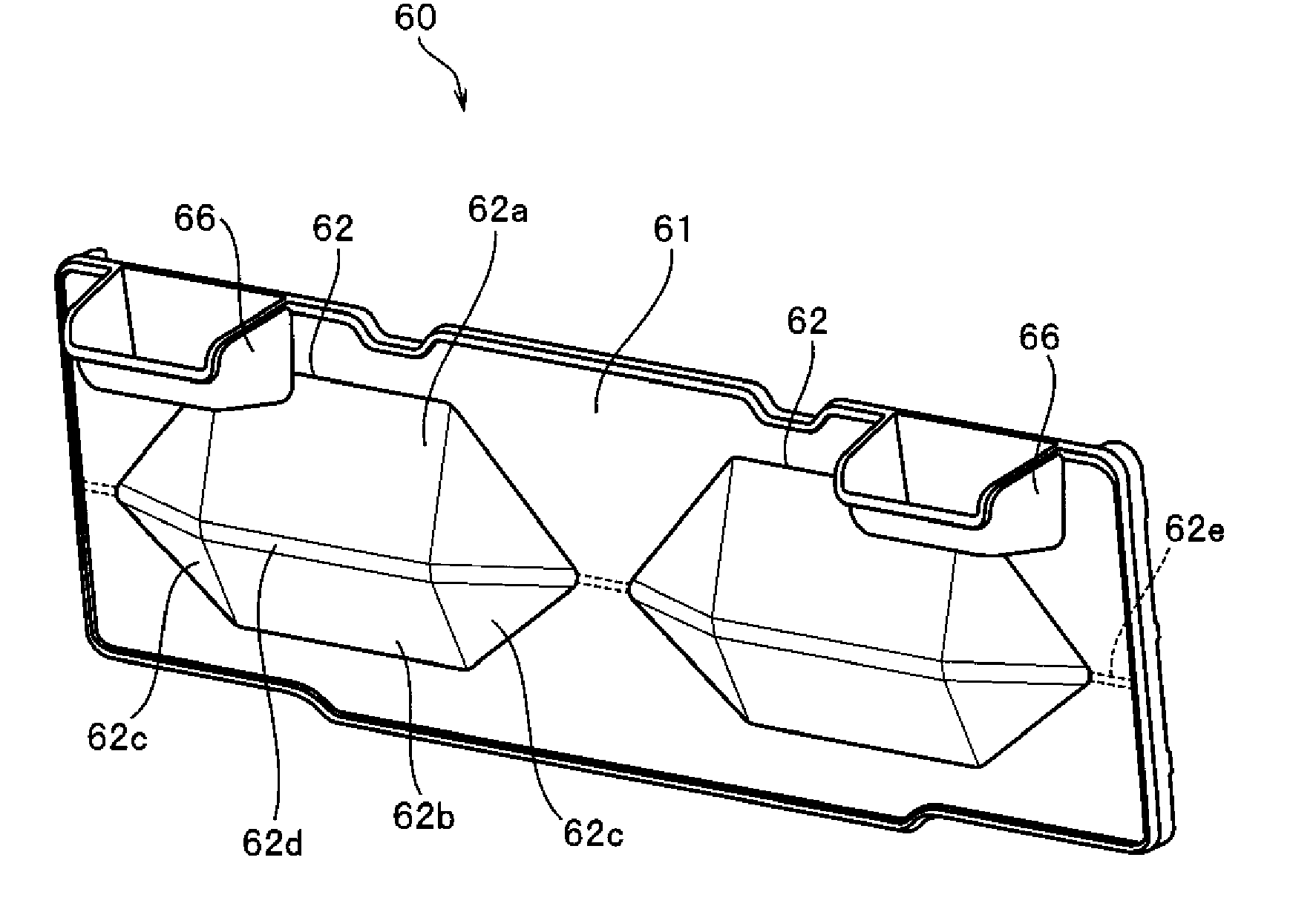

CRT with funnel having quadrangular yoke portion

InactiveUS6876138B2Lowering efficientlySimple structureCathode-ray/electron-beam tube electrical connectionCathode-ray/electron-beam tube vessels/containersProduction rateEngineering

In a color cathode ray tube, by optimizing an outer radios of curvature, an inner radius of curvature on a corner portion, a thickness of a long side, a thickness of a short side, a thickness of the corner portion, the total length of the panel, the total length of the funnel body and the total length of a yoke portion of the funnel determining a section shape of the yoke portion of the funnel, a stress concentrated on the yoke portion can be lowered. In addition, according to the increase of an inner radius of curvature of the corner portion of the yoke portion, a crash phenomenon of an electron beam is decreased, and an impact resistance and productivity improvement in fabrication process can be secured by lowering a high stress occurrence on the funnel in vacuum.

Owner:MERIDIAN SOLAR & DISPLAY

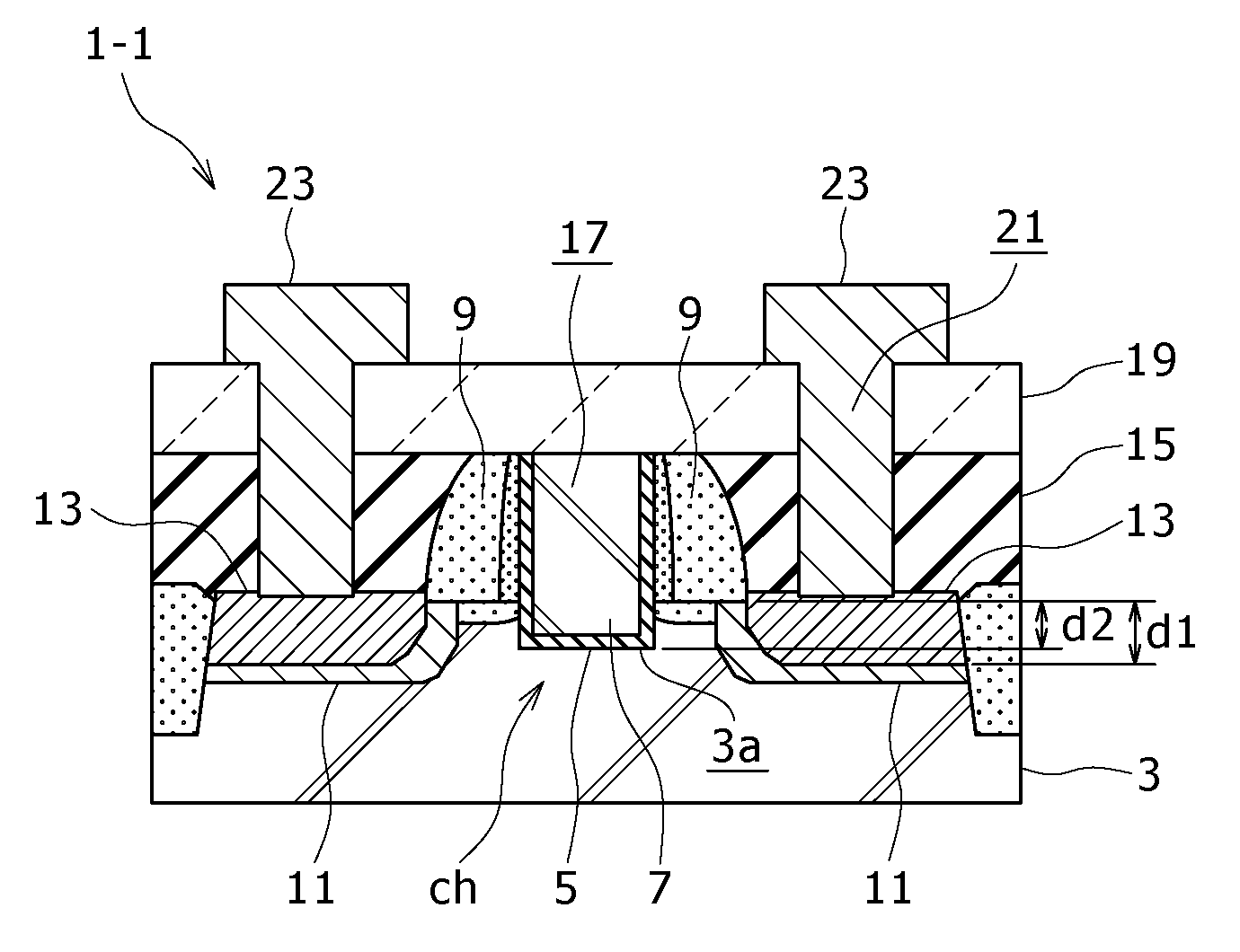

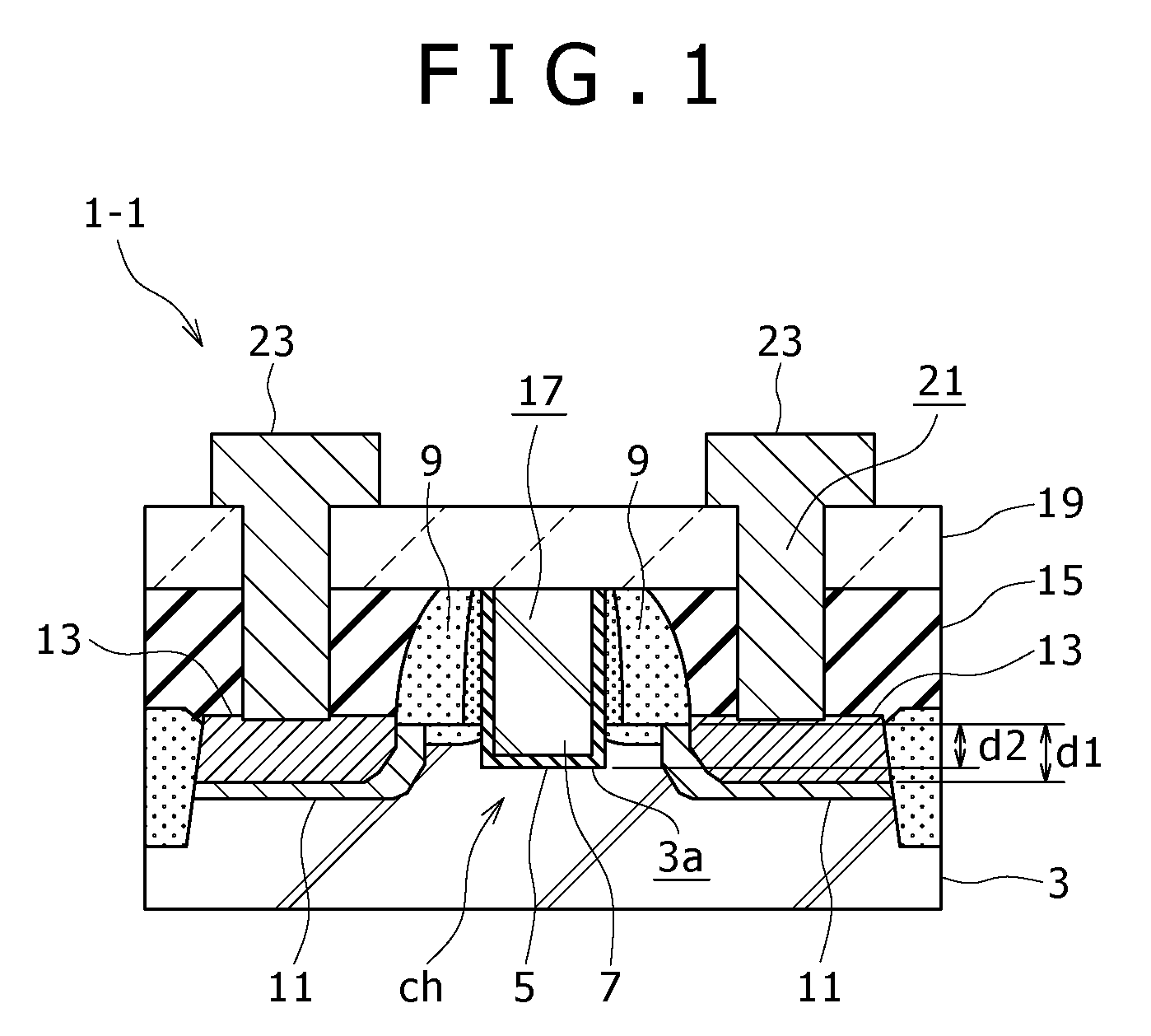

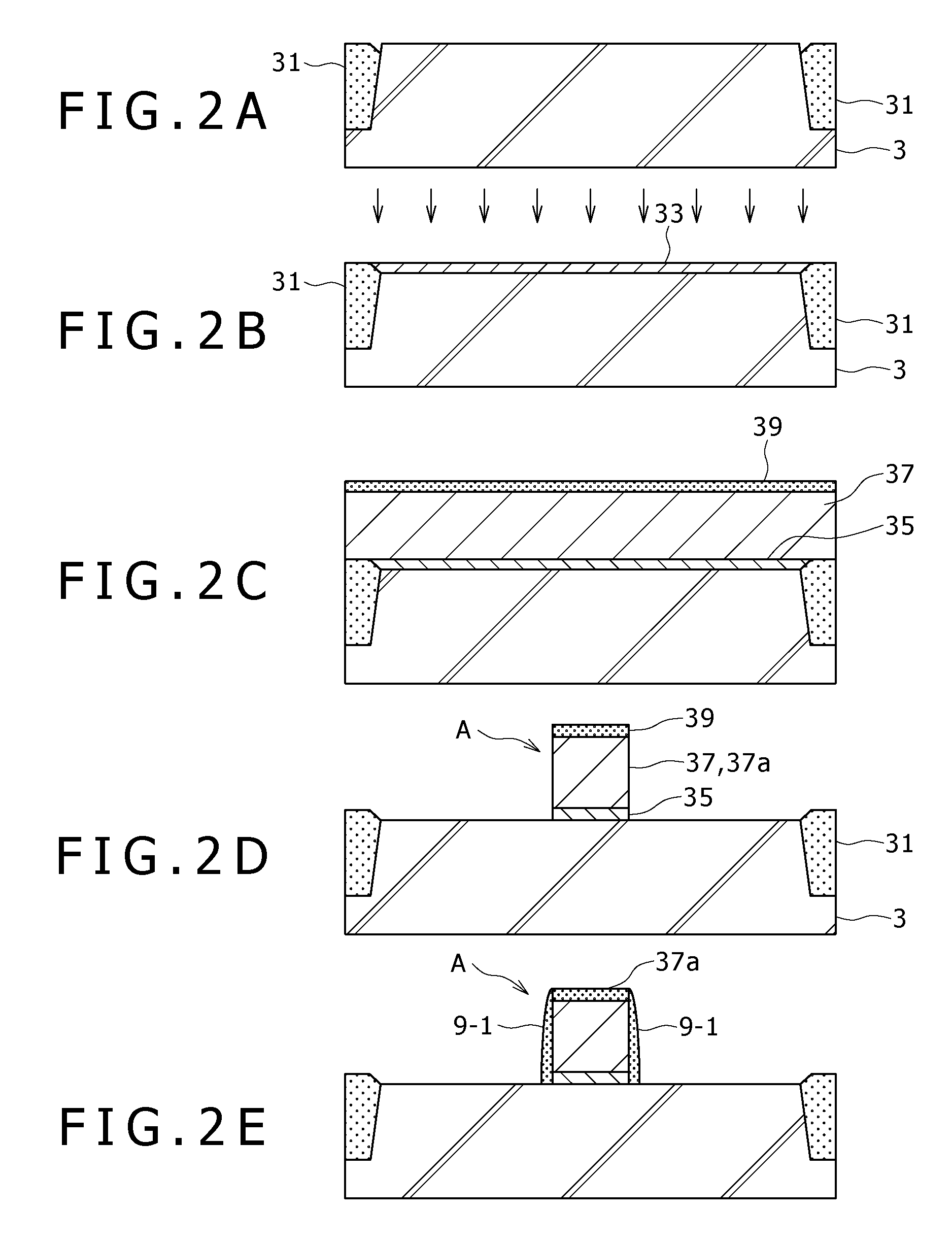

Semiconductor device and method for production of semiconductor device

ActiveUS8242558B2High carrier mobilityImprove performanceTransistorSemiconductor/solid-state device manufacturingCondensed matter physicsSemiconductor

Owner:SONY CORP

Body Controlled Double Channel Transistor and Circuits Comprising the Same

ActiveUS20110080772A1Improve compatibilityIncrease compressive stressSolid-state devicesDigital storageIon bombardmentEngineering

By forming a non-oxidizable liner in an isolation trench and selectively modifying the liner within the isolation trench, the stress characteristics of the isolation trench may be adjusted. In one embodiment, a high compressive stress may be obtained by treating the liner with an ion bombardment and subsequently exposing the device to an oxidizing ambient at elevated temperatures, thereby incorporating silicon dioxide into the non-oxidizable material. Hence, an increased compressive stress may be generated within the non-oxidizable layer.

Owner:TAIWAN SEMICON MFG CO LTD

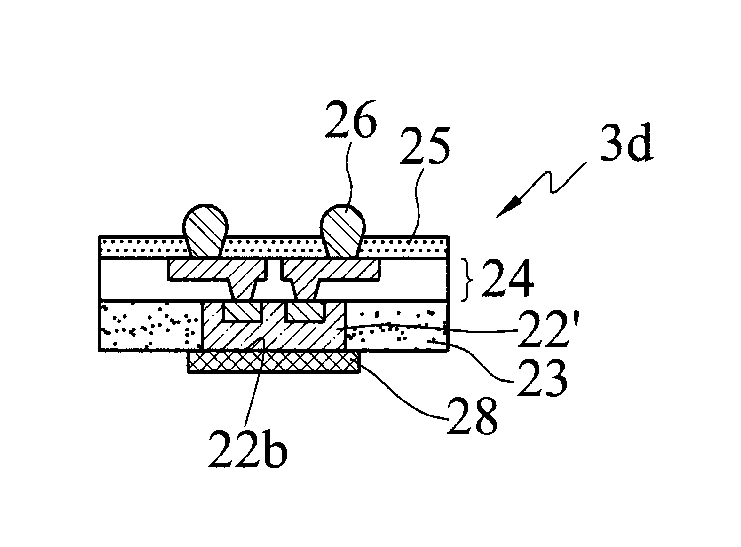

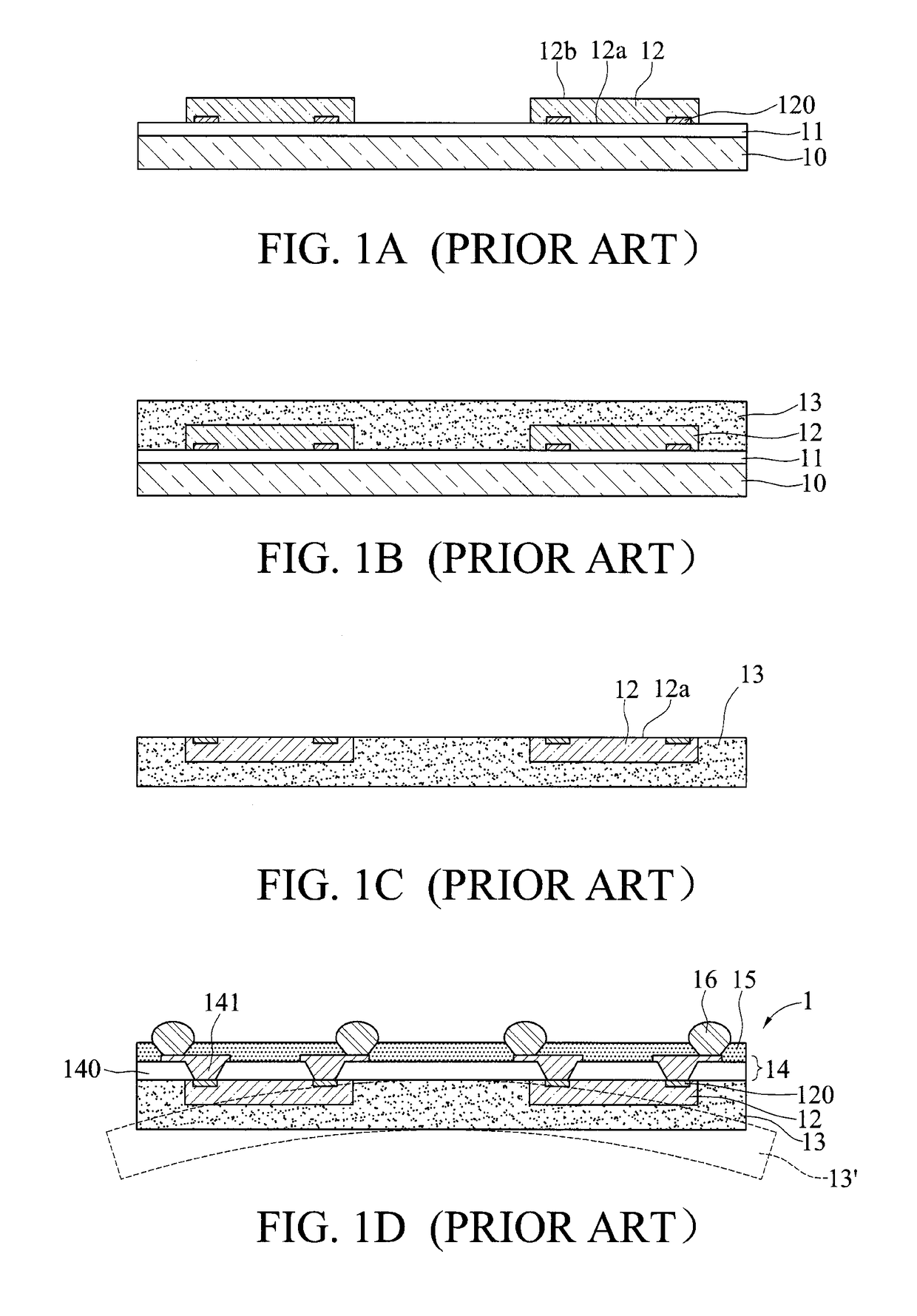

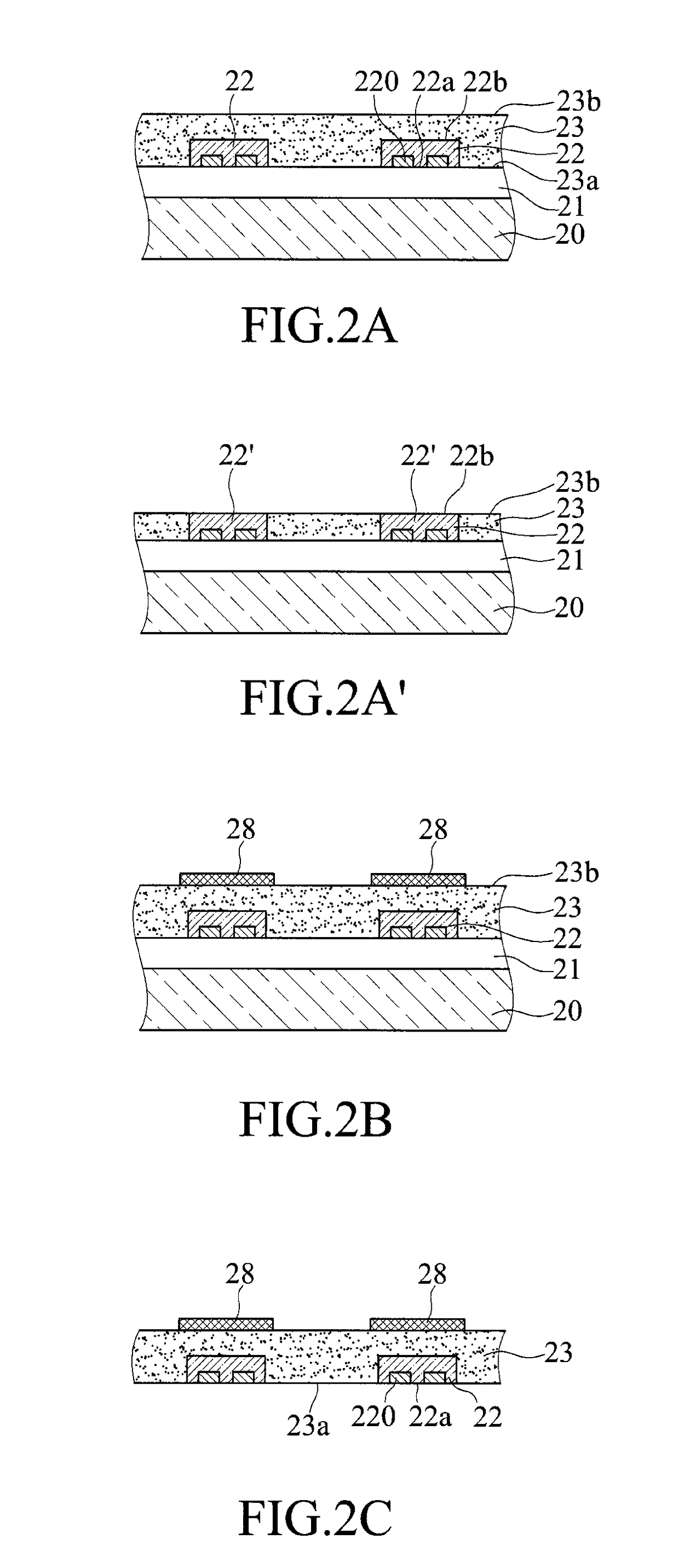

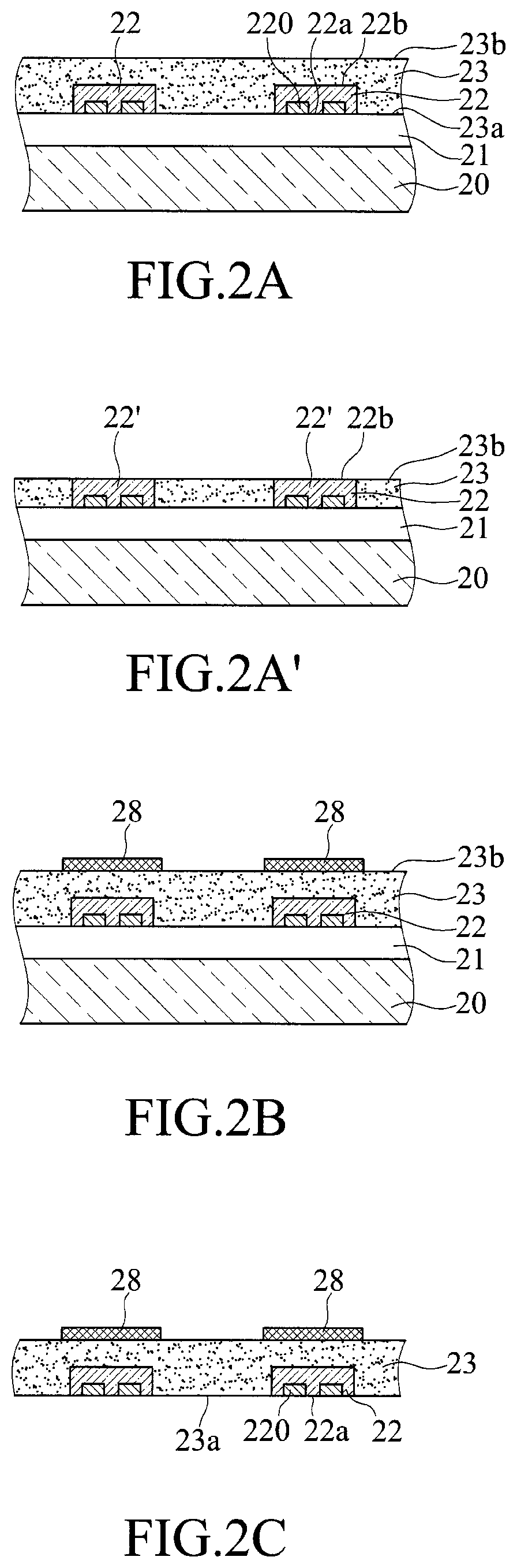

Electronic package and method for manufacturing the same

ActiveUS20180254232A1Reduce warpageBalance the stress of the packaging layerSemiconductor/solid-state device detailsSolid-state devicesElectronic componentElectronic packages

The disclosure provides an electronic package and a method of manufacturing the same. The method is characterized by encapsulating an electronic component with a packaging layer and forming on an upper surface of the packaging layer a circuit structure that is electrically connected to the electronic component; and forming a stress-balancing layer on a portion of the lower surface of the packaging layer to balance the stress exerted on the upper and lower surfaces of the packaging layer, thereby reducing the overall package warpage and facilitating the manufacturing process.

Owner:SILICONWARE PRECISION IND CO LTD

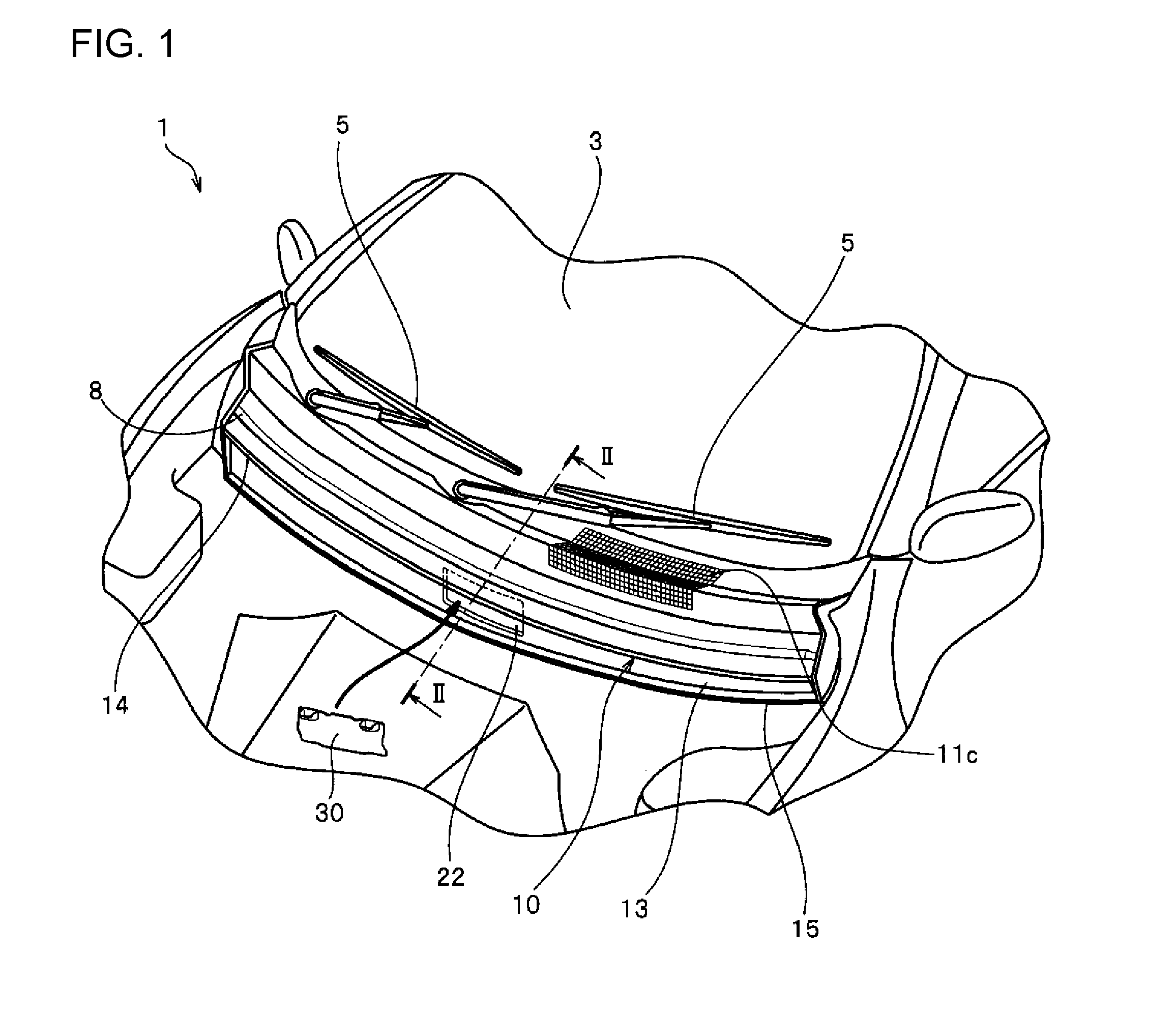

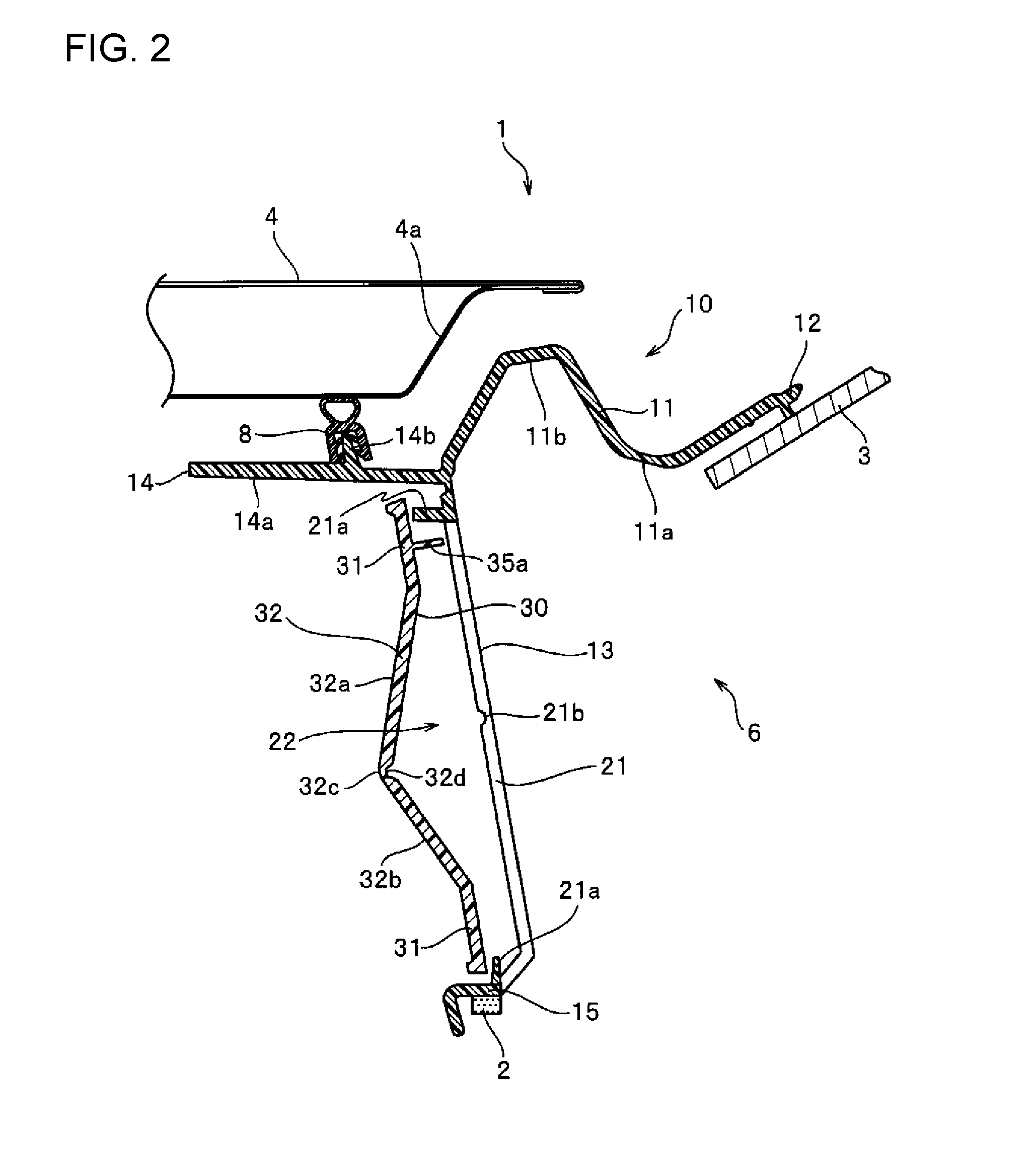

Cowl top cover

ActiveUS20160229459A1Improve appearance qualityDecrease total amount of swellingPedestrian/occupant safety arrangementSuperstructure subunitsStructural engineering

This cowl top cover has a cover body section and a vertical wall section which extends vertically from the front end of the cover body section. The vertical wall section is provided with a vertical wall body, an opening which is formed in the vertical wall body, and a cover section has a cover-side bending promotion section which extends in the width direction of the vehicle and which promotes the bending and deformation of the cover section to one side of the length direction of the vehicle. As a result of this configuration, the cowl top cover can consistently exhibit a sufficient impact absorption function when subjected to an impact.

Owner:NIHON PLAST CO LTD +1

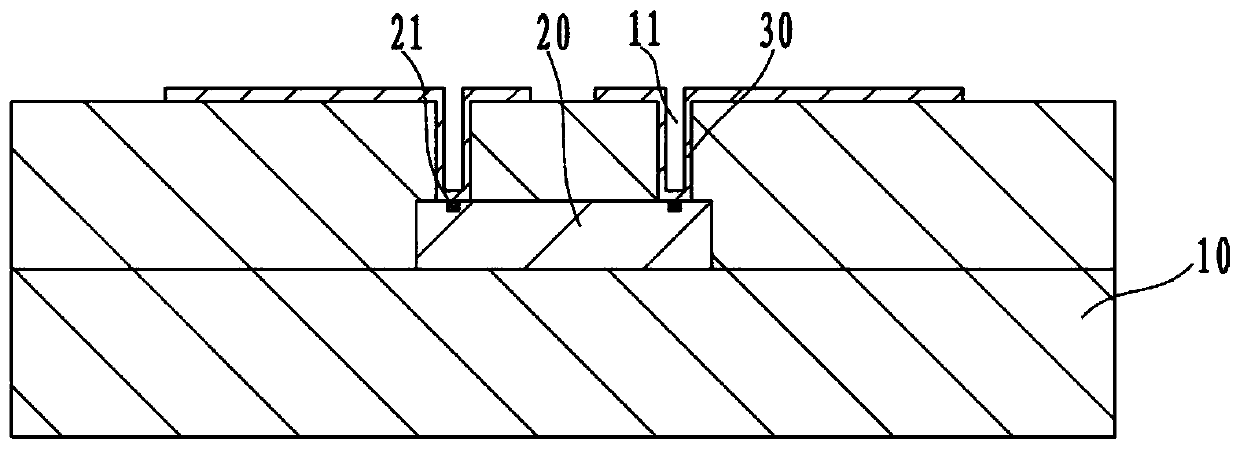

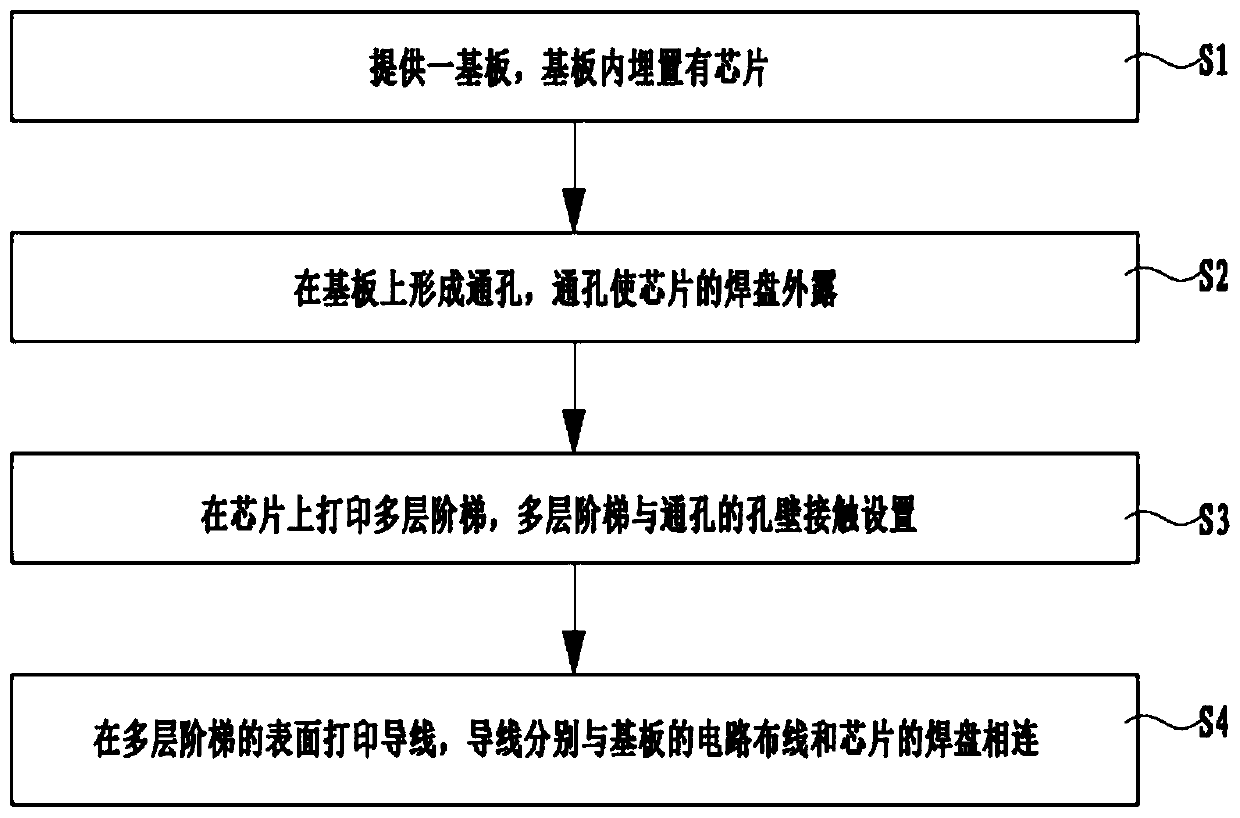

Chip interconnection packaging method and interconnection packaging structure

InactiveCN110459509ADistribute stressImprove reliabilitySemiconductor/solid-state device detailsSolid-state devicesFlexible electronicsElectrical connection

The invention provides a chip interconnection packaging method and an interconnection packaging structure, which are suitable for a flexible electronic packaging technology. The chip interconnection packaging method comprises steps: the chip is firstly packaged in a substrate by embedding, a hole is then punched in the substrate to obtain a through hole, and a pad of the chip is exposed; a multi-level step is then printed at the included angle between the hole wall of the through hole and the chip; and a wire is finally printed on the surface of the multi-level step, the wire is respectively connected with the circuit wiring of the substrate and the pad of the chip, and chip inter-layer interconnection is realized. According to the chip interconnection packaging method and the interconnection packaging structure provided in the invention, the multi-level step is then printed at the included angle between the hole wall of the through hole and the chip, wire printing in the through holebecomes simpler and more reliable, instable conductive performance of the wire caused by factors such as the gravity and a bonding force can be avoided, the inter-layer interconnection reliability isimproved, and the electrical connection reliability of the chip interconnection packaging structure is thus improved.

Owner:浙江荷清柔性电子技术有限公司

Composition for slowing cellular ageing, associated food supplement

InactiveUS20170333337A1Effective stressPrevents hypomethylation and hypermethylationOrganic active ingredientsCosmetic preparationsS-Adenosyl-l-methionineVitamin C

The invention relates to a composition for slowing cellular ageing which comprises at least: S-Adenosyl-methionine; an extract of at least one adaptogenic plant selected among plants belonging to the Astragalus, Dioscorea, Schisandra, Panax, Eleuterococcus, Rosmarinus, Pfaffia, Morinda, Cordyceps or Lepidium genera; a vitamin selected among the B vitamins, vitamin C, or a mixture thereof; except for compositions comprising 7-keto-DHEA and an extract of one or more adaptogenic plants belonging to the Dioscorea or Lepidium genera. A liquid or solid food supplement can be characterised in that it comprises the composition. A dermatologically acceptable composition can be characterised in that it comprises at least 10 wt % of the composition.

Owner:FREY MICHEL

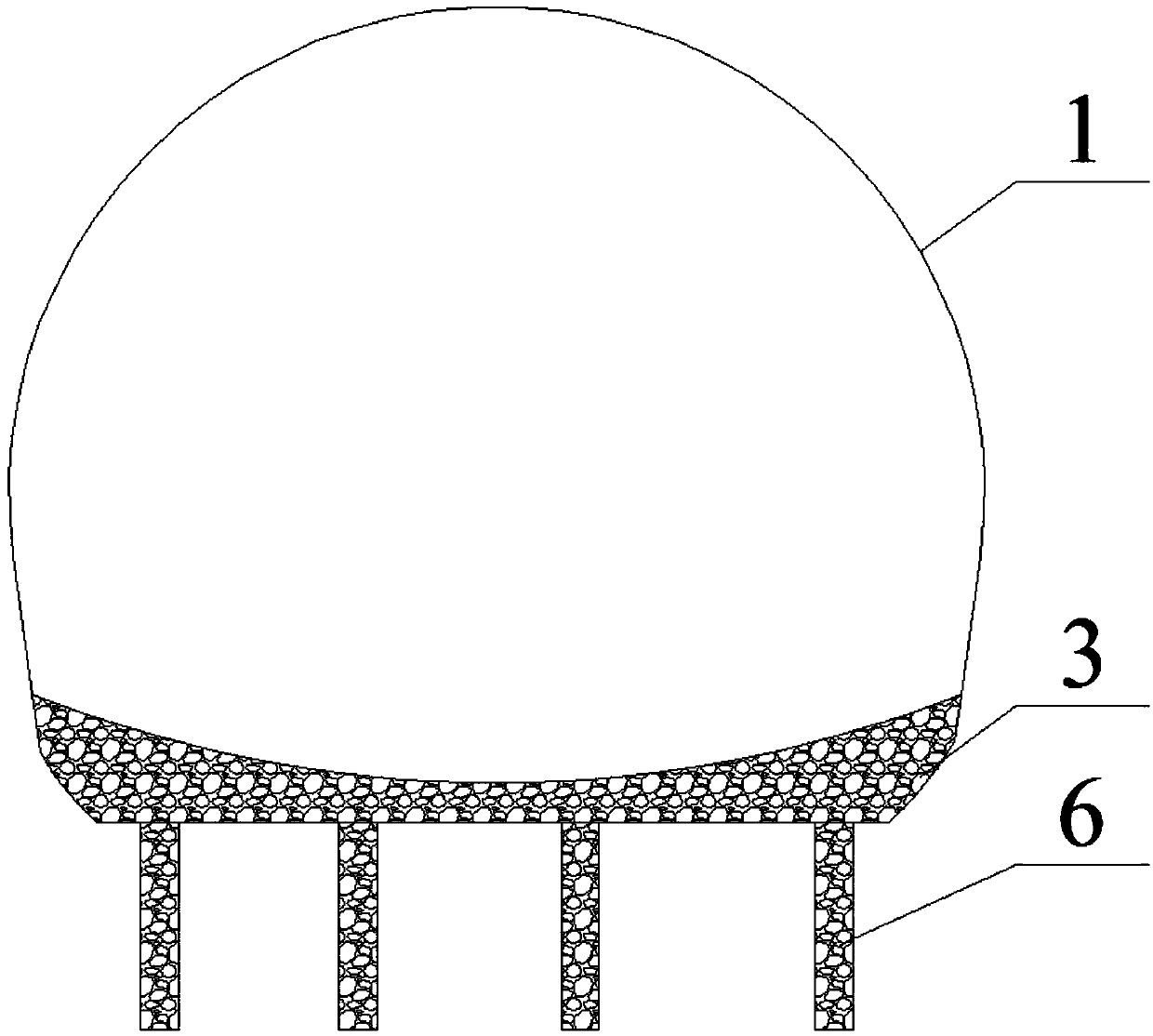

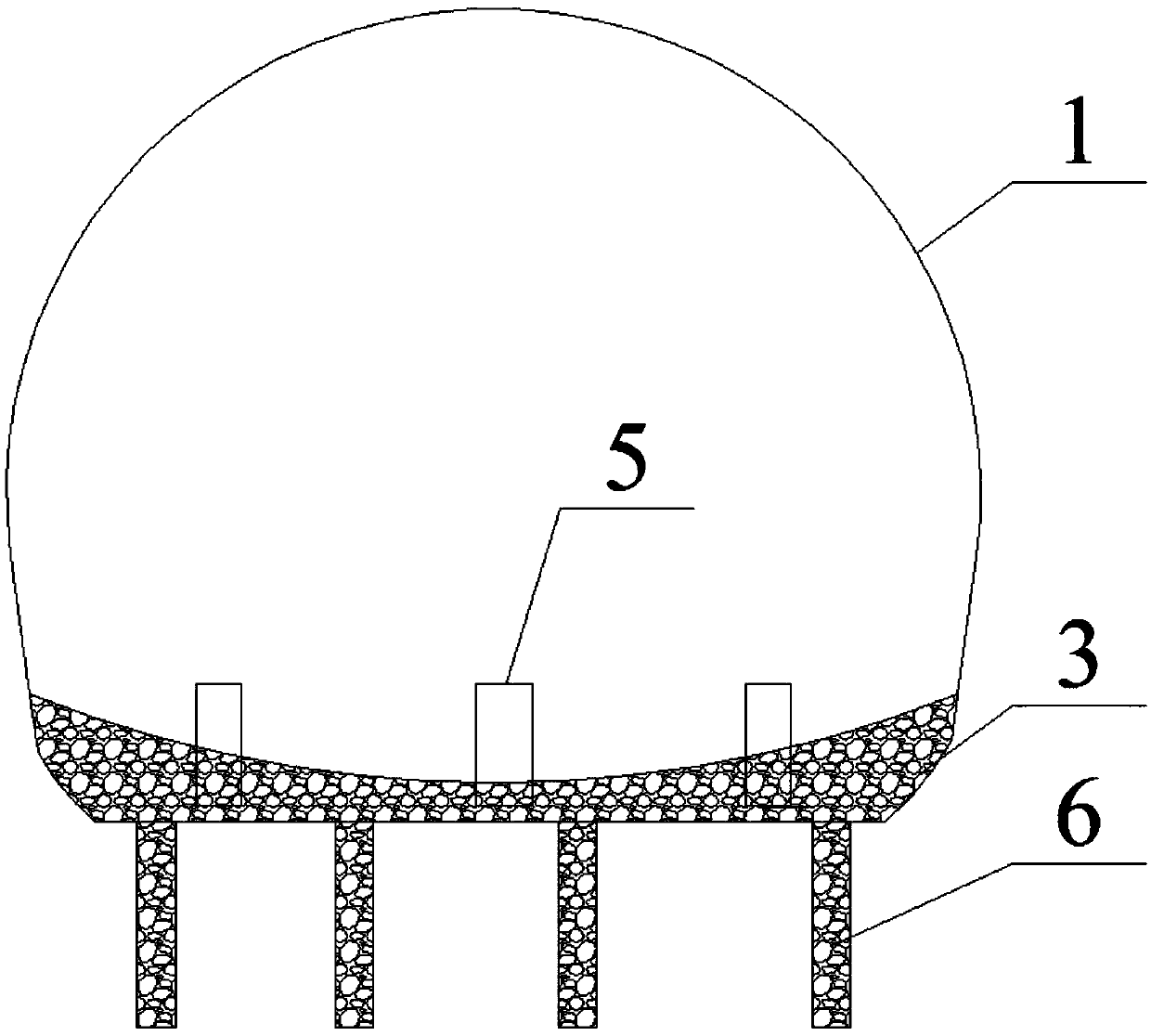

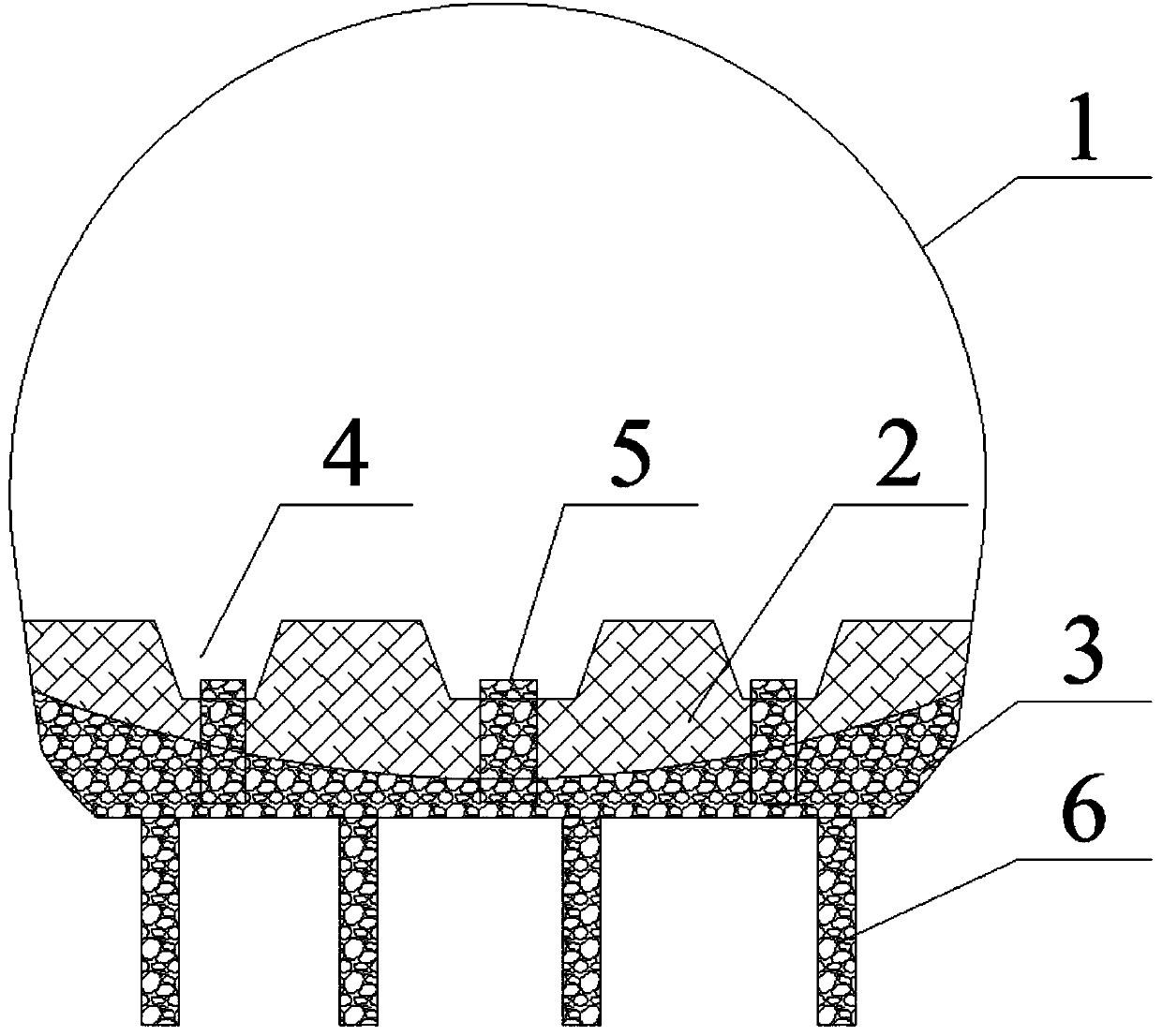

Tunnel bottom structure and construction method capable of eliminating uplifts of inverted arches of tunnel in area with high ground pressure

ActiveCN107630706AAvoid damageEffectively elicitUnderground chambersHydro energy generationStructure of the EarthStructural engineering

The invention relates to the field of tunnel defect rectification technology structures, in particular to a tunnel bottom structure and a construction method capable of eliminating uplifts of invertedarches of a tunnel in an area with high ground pressure. The structure comprises the inverted arches and an over-break back-filling layer; multiple sets of pressure releasing holes are formed in theinterior of the over-break back-filling layer in the transverse direction of the tunnel at intervals in a drilled mode, and each set of the pressure releasing holes comprises the multiple pressure releasing holes which are arranged in the longitudinal direction of the tunnel at intervals; the lower ends of the pressure releasing holes stretch into surrounding rock under the tunnel bottom; multipledrainage ditches arranged in the transverse direction of the tunnel at intervals are formed in the inverted arches, a set of steel pipes are arranged in each drainage ditch, the steel pipes are filled with gravel, and the steel pipes, the over-break back-filling layer and pores in the pressure releasing holes are communicated. According to the tunnel bottom structure, arrangement is orderly, theconstruction process is convenient, fast and compact, and the economical and environmentally-friendly effects are significant; when uplift destruction of the inverted arches generated due to the action of vertically-upward high compression stress needs to be prevented, by means of the method, ground stress can be effectively released, and underground water with high water levels can be effectivelydrained, so that potential safety hazards of late operation of the tunnel are eliminated, and the effect of fundamentally preventing the uplifts of the inverted arches is achieved.

Owner:CCCC SECOND HARBOR ENG

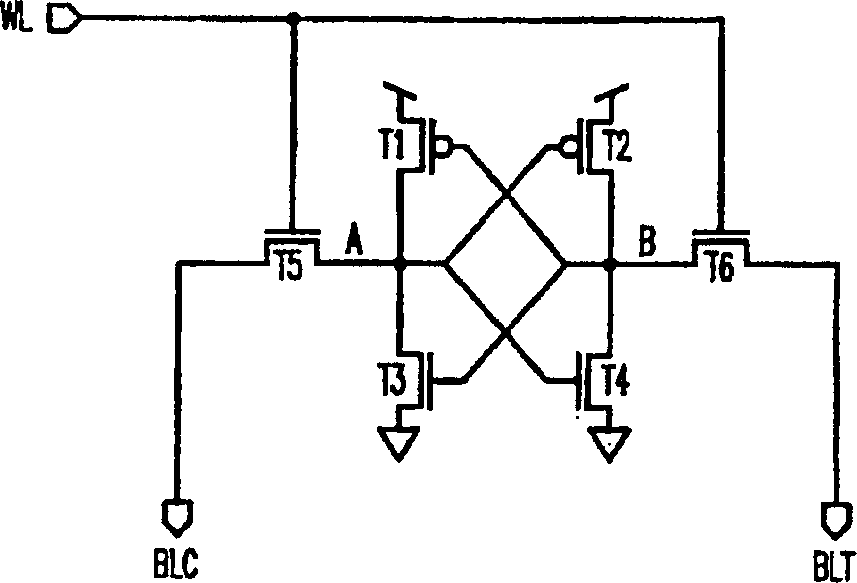

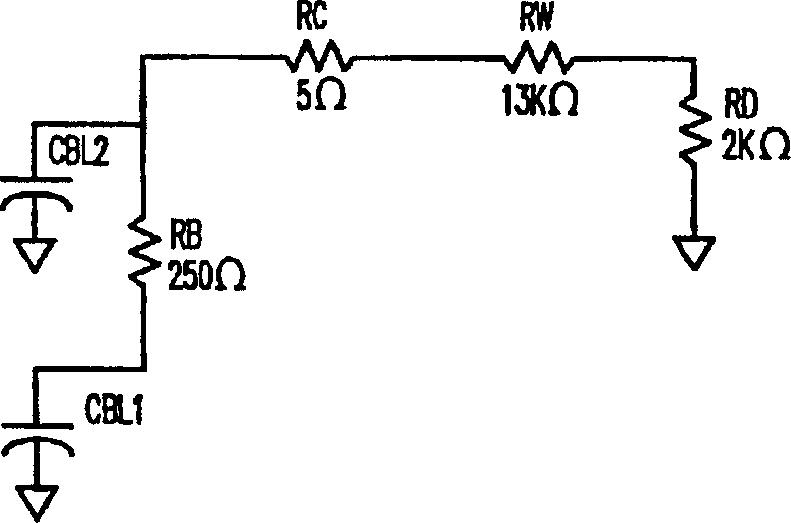

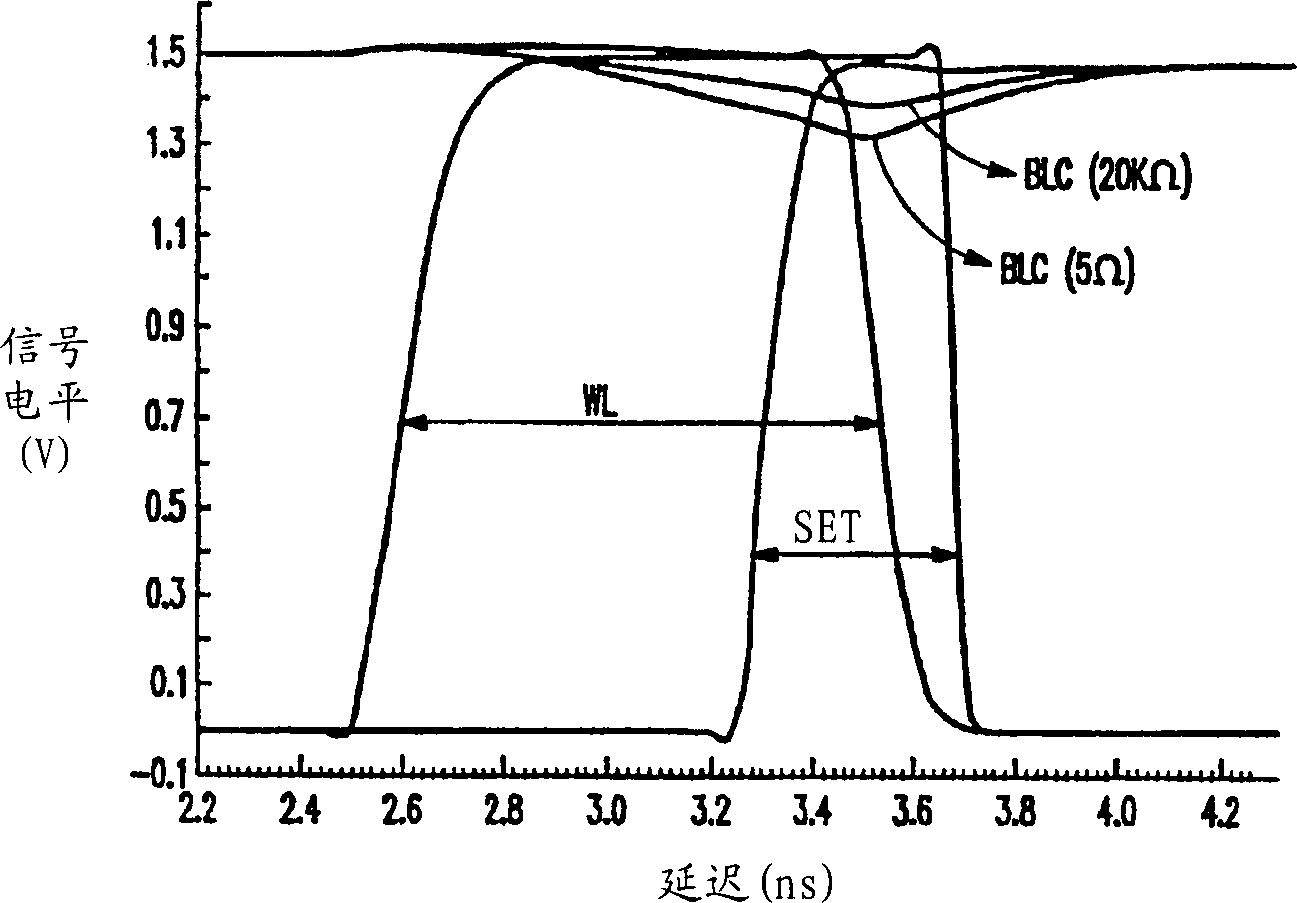

Duty-cycle-efficent SRAM cell test

A method and structure for the invention includes an integrated memory structure having a built-in test portion. The integrated memory structure has memory cells, bitlines and wordlines connected to the memory cells, wordline decoders connected to a plurality of the wordlines, bitline restore devices connected to the bitlines for charging the bitlines during read and write operations, and a clock circuit connected to the wordlines. During a test mode the wordline decoders simultaneously select multiple wordlines that the bitline restore devices maintain in an active state and the clock circuit maintains the multiple wordlines and the bitline restore devices in an active state for a period in excess of a normal read cycle. The invention also includes transistors which are connected to the memory cells. The transistors include bitline contacts which are stressed during the test mode.

Owner:INT BUSINESS MASCH CORP

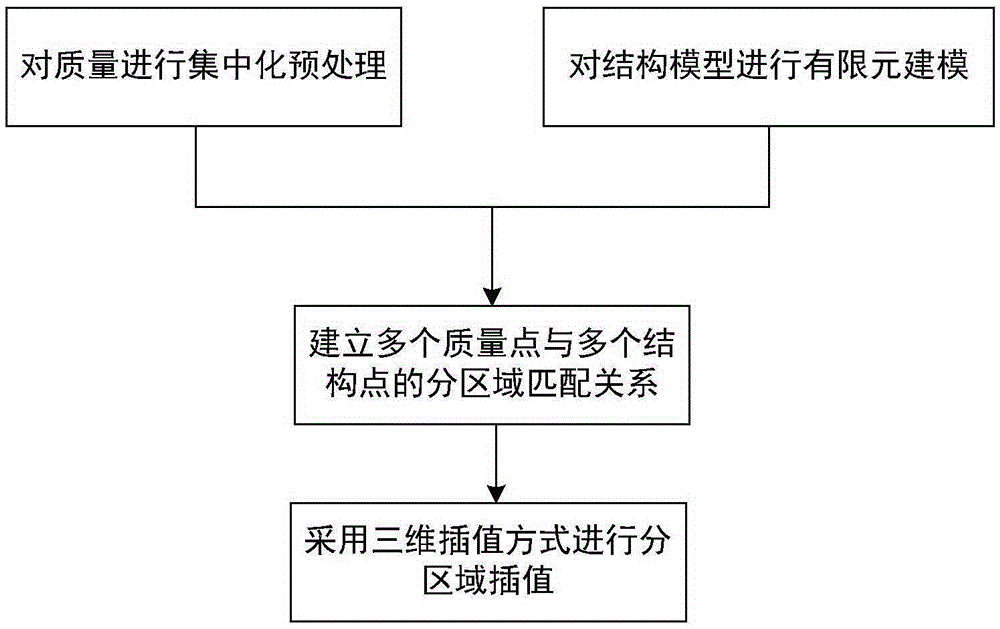

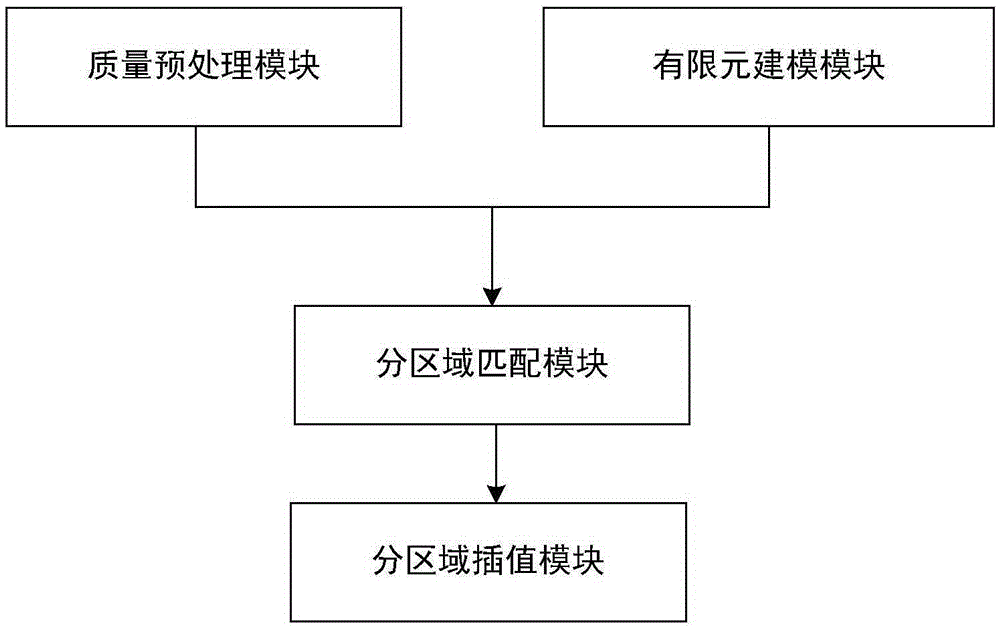

Mass loading method and system

ActiveCN105243192ATrue reflection of physical behaviorMass distributionSpecial data processing applicationsMass loadingElement modeling

The present invention relates to a mass loading method and system. The mass loading method and system applies the mass to load on a structural model. The method comprises: intensively preprocessing the mass to obtain multiple discrete mass points; carrying out finite element modeling on the structural model to obtain multiple structural nodes; establishing a sub-regional matching relation between the multiple discrete mass points and the multiple structural nodes; and using a three-dimensional interpolation function to carry out sub-regional interpolation, thereby realizing that the mass is uniformly loaded on the structural model. The mass loading method and system of the present invention exert the following beneficial technical effects that: the mass is enabled to distribute on the structural nodes of the structural model as uniform as possible, and the physical behavior can be truly reflected.

Owner:COMAC +1

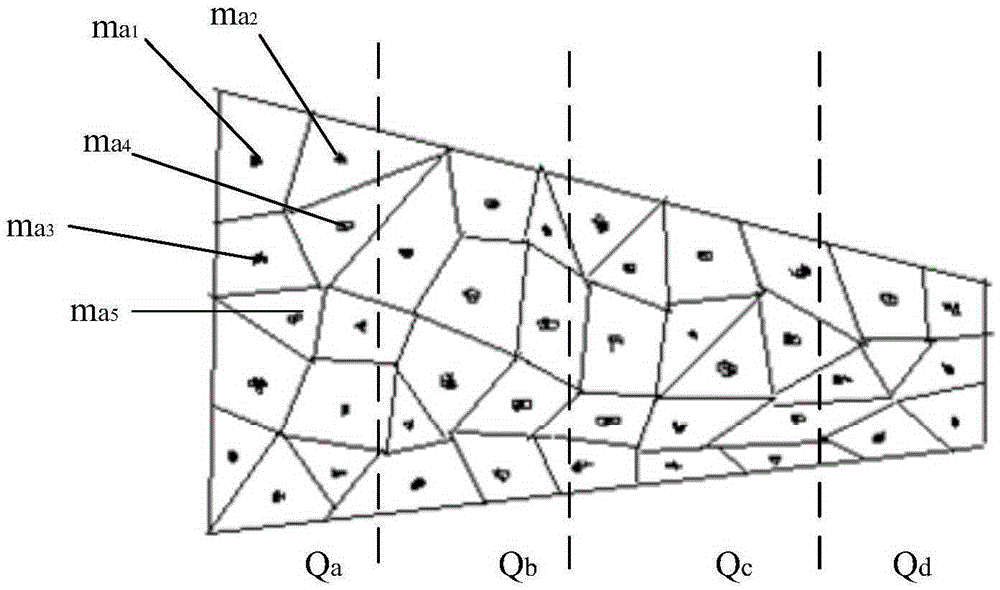

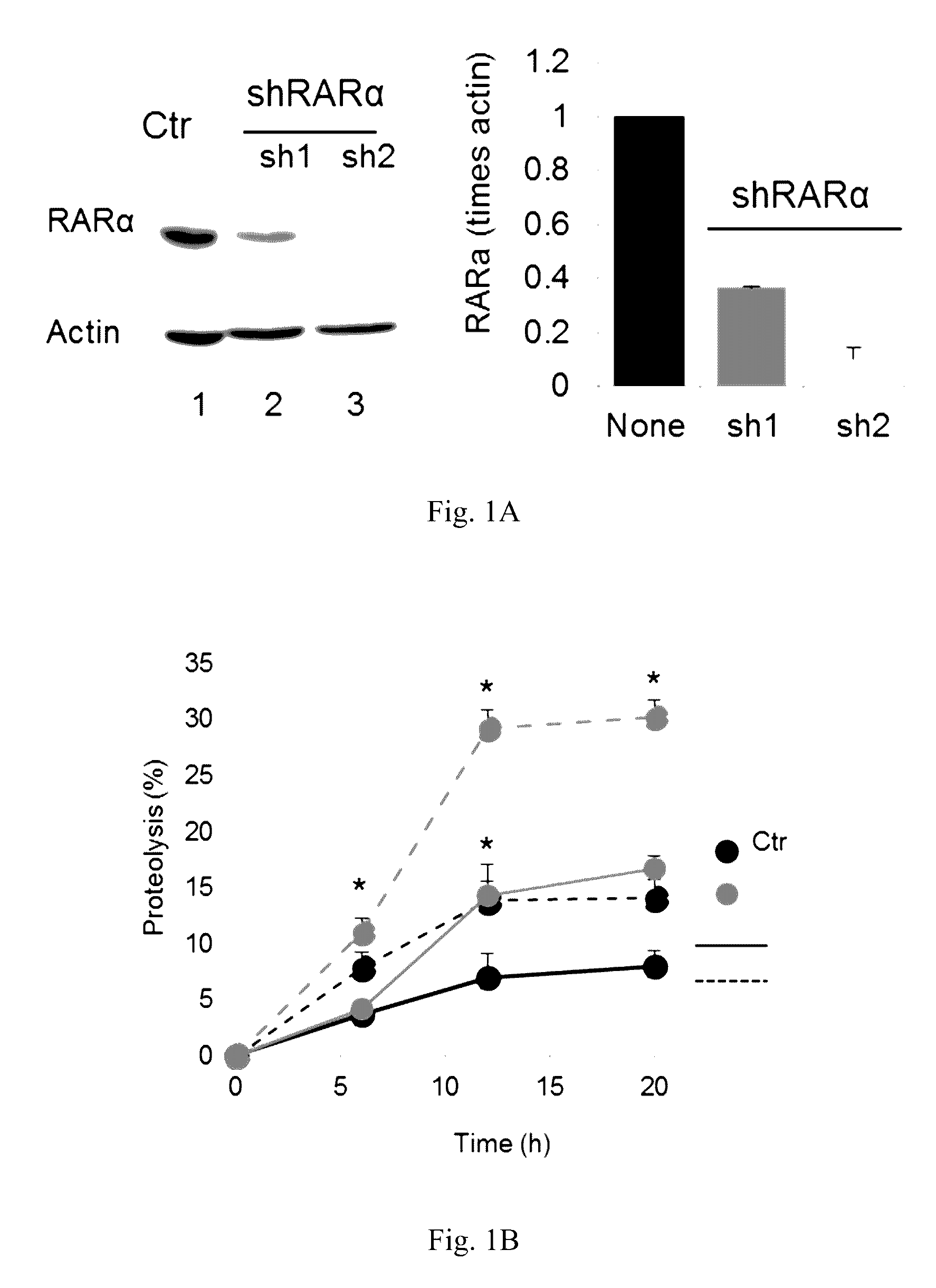

Method for manufacturing a seal ring structure to avoid delamination defect

ActiveUS20170317037A1Effective stressImprove performanceSemiconductor/solid-state device detailsSolid-state devicesDielectric layerSemiconductor

A method for manufacturing a semiconductor device includes providing a semiconductor substrate, forming a plurality of integrated circuit (IC) devices on the semiconductor substrate, and forming a seal ring structure surrounding each of the IC devices. Forming the seal ring structure includes forming a plurality of interlayer dielectric layers on the semiconductor substrate, and forming a plurality of hollow through-hole structures within each of the interlayer dielectric layers.

Owner:SEMICON MFG INT (SHANGHAI) CORP

Retinoic acid receptor antagonists as chaperone-mediated autophagy modulators and uses thereof

ActiveUS9512092B2Effective stressCompound screeningApoptosis detectionOxidative stressChaperone-mediated autophagy

Compounds, compositions and methods are provided for selectively activating chaperone-mediated autophagy (CMA), protecting cells from oxidative stress, proteotoxicity and lipotoxicity, and / or antagonizing activity of retinoic acid receptor alpha (RARα) in subjects in need thereof.

Owner:ALBERT EINSTEIN COLLEGE OF MEDICINE OF YESHIVA UNIV

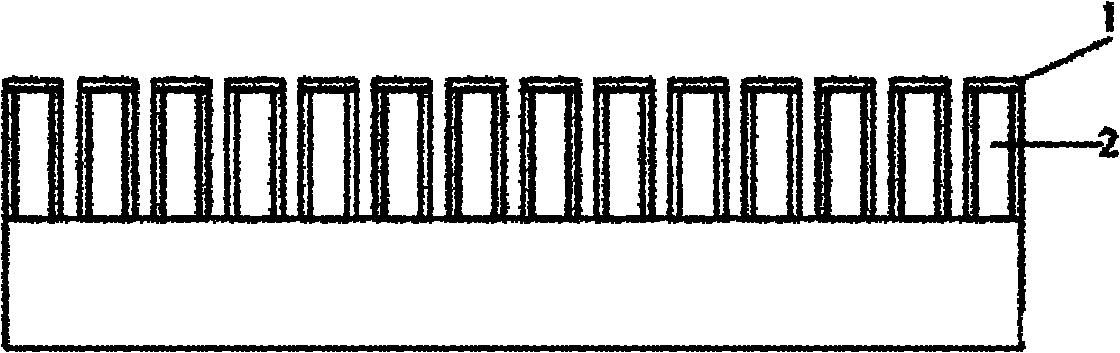

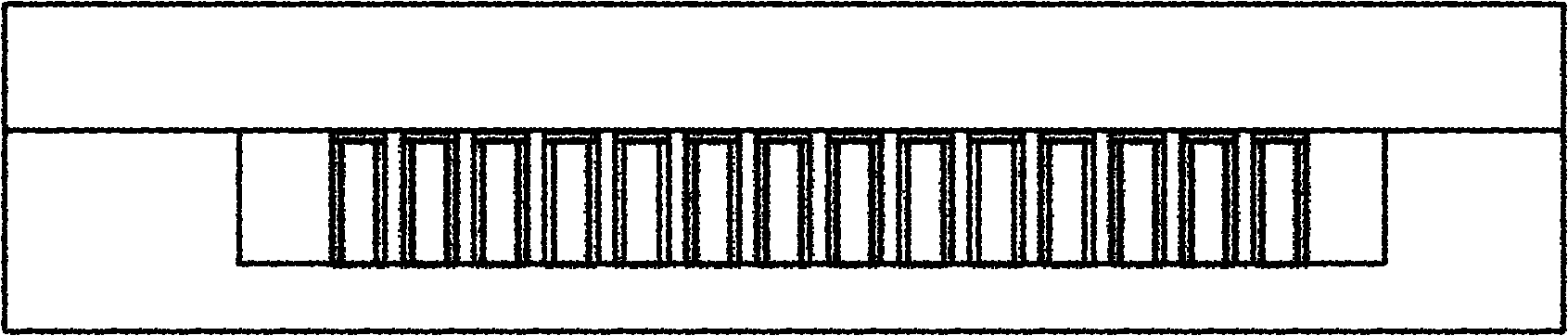

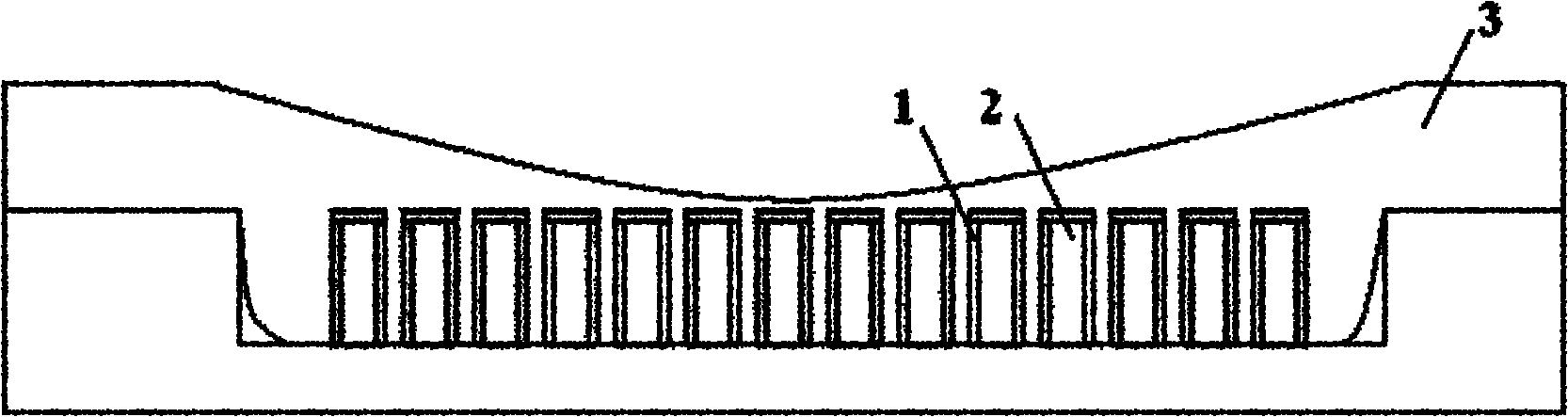

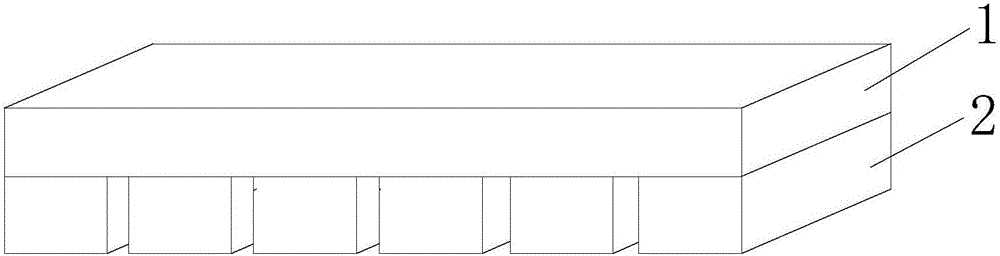

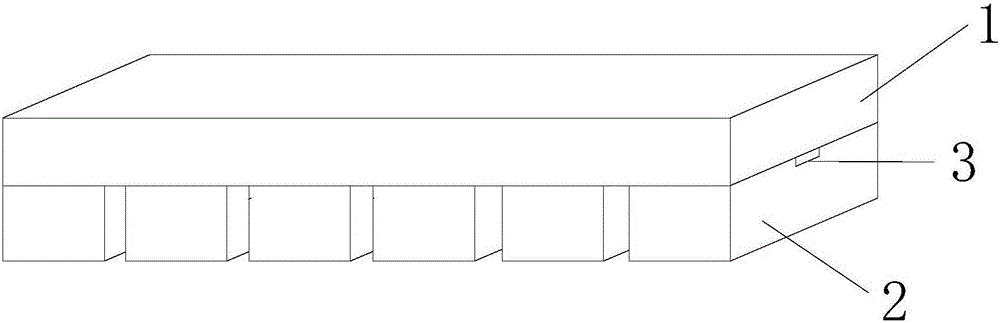

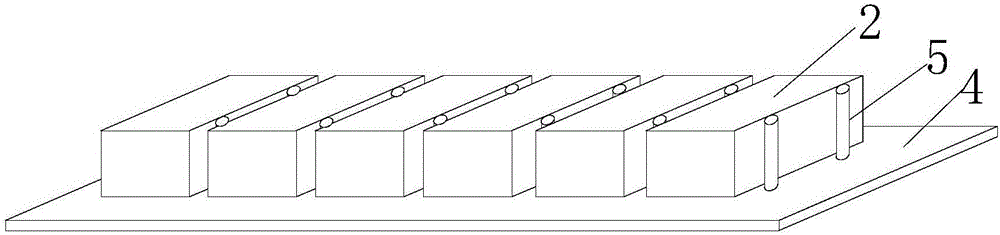

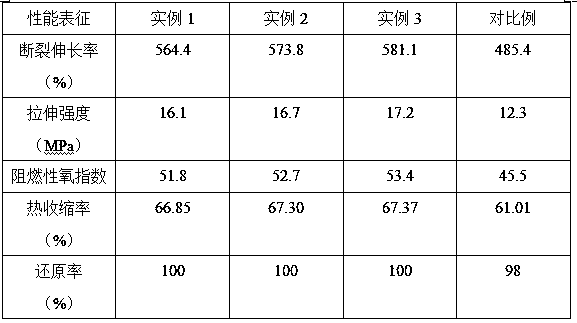

Double-layer solid wood composite floor and manufacturing method thereof

InactiveCN106049821AHigh strengthImprove stabilityWood veneer joiningFlooringSolid woodPulp and paper industry

The invention discloses a double-layer solid wood composite floor and a manufacturing method thereof. The double-layer solid wood composite floor comprises a solid wood face layer (1) with wood grains extending in the length direction of the solid wood face layer; a plurality of small long-strip-shaped battens (2) which are arranged side by side are glued under the solid wood face layer (1); and wood grains of the small long-strip-shaped battens (2) extend in the length direction of the small long-strip-shaped battens (2). The wood grain direction of the small long-strip-shaped battens (2) is perpendicular to the wood grain direction of the solid wood face layer (1), and the length of the small long-strip-shaped battens (2) is equal to the width of the solid wood face layer (1). Gaps are reserved between the adjacent small long-strip-shaped battens (2). According to the double-layer solid wood composite floor and the manufacturing method thereof, the use amount of high-quality solid wood can be reduced effectively, wood resources are saved, and simultaneously high structural strength and whole stability are achieved.

Owner:ZHEJIANG FUMA FLOOR HEATING SCI&TECH CO LTD

Electronic package and method for manufacturing the same

ActiveUS10679914B2Reduce warpageBalance the stress of the packaging layerSemiconductor/solid-state device detailsSolid-state devicesHemt circuitsElectronic component

The disclosure provides an electronic package and a method of manufacturing the same. The method is characterized by encapsulating an electronic component with a packaging layer and forming on an upper surface of the packaging layer a circuit structure that is electrically connected to the electronic component; and forming a stress-balancing layer on a portion of the lower surface of the packaging layer to balance the stress exerted on the upper and lower surfaces of the packaging layer, thereby reducing the overall package warpage and facilitating the manufacturing process.

Owner:SILICONWARE PRECISION IND CO LTD

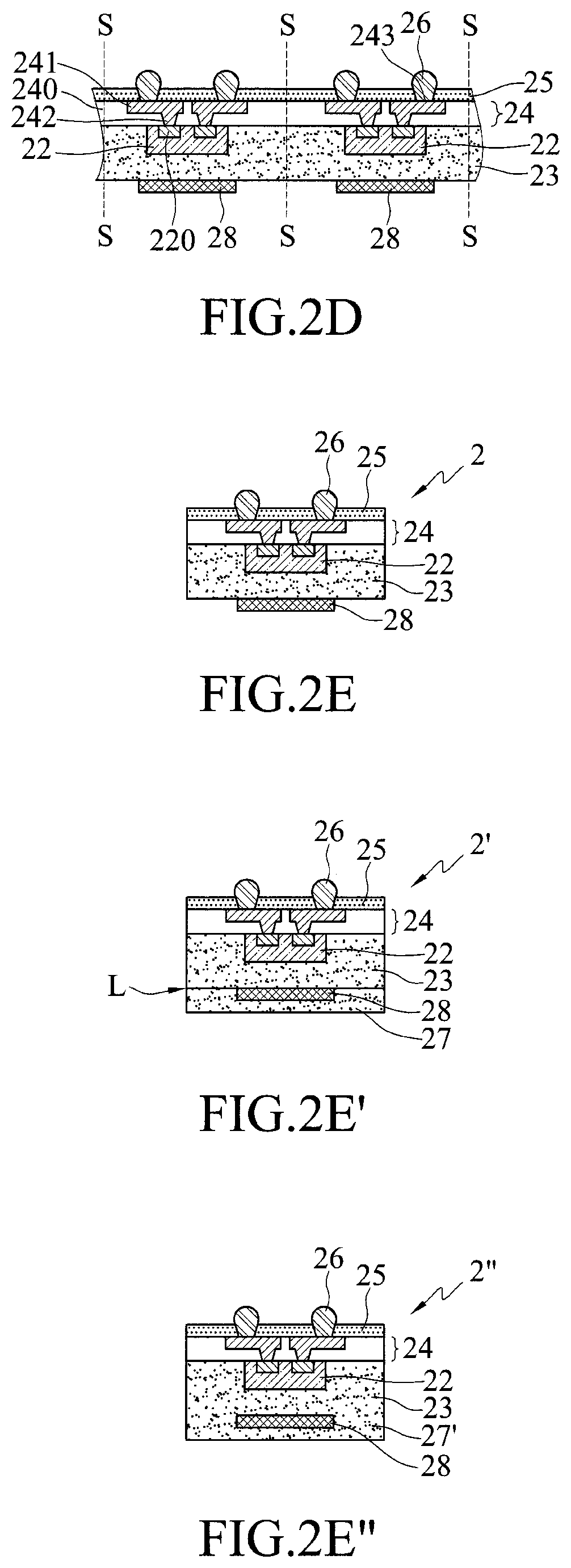

Halogen-free flame-retardant thermal-contraction material and method for preparing same

The invention relates to a halogen-free flame-retardant thermal-contraction material and a method for preparing the same, and belongs to the technical field of intelligent materials. The halogen-freeflame-retardant thermal-contraction material and the method have the advantages that an appropriate quantity of ethylene-1-octene copolymers are added into ethylene-vinyl acetate copolymers, equivalently, flexible chains are introduced, accordingly, the toughness and the processability of the halogen-free flame-retardant thermal-contraction material can be improved, and the irradiation dose can beappropriately reduced; the ethylene-vinyl acetate copolymers are combined with maleic anhydride grafted polyethylene, surface hydrophilic groups are easy to act on the surfaces of particles of flameretardants and can be wound around the particles, and accordingly dispersion of the particles in polymer matrixes can be promoted, hydrophobic groups are wound on polymer base materials by the aid ofVan der Waals force or are physically wound on the polymer base materials, accordingly, the polymer matrixes and the ultrafine particles of the flame retardants are connected with one another and are'bridged' with one another, and the interfacial bonding strength can be improved; perfect interfacial tension can be applied to the inorganic flame retardants and the polymer matrixes under 'bridged'effects, accordingly, stress and strain can be effectively transmitted and distributed between two phases by composite material systems, and the performance of composite systems can be improved.

Owner:徐冬

Flexible substrate and flexible display

ActiveUS10224497B2Improve bending performanceLong lastingSemiconductor/solid-state device detailsSolid-state devicesDisplay deviceFlexible display

Disclosed is a flexible substrate, comprising a first organic layer, a first inorganic layer, a second organic layer and a second inorganic layer. The first inorganic layer is located on the first organic layer. The first inorganic layer comprises first strips which are spaced. The first strip comprises a first middle part and two first side parts. The second organic layer covers the first inorganic layer. The second inorganic layer is located on one side of the second organic layer remote from the first organic layer. The second inorganic layer comprises second strips which are spaced. The second strip comprises a second middle part and two second side parts. An extension direction of the second strips is the same as an extension direction of the first strips, the second organic layer is partially interposed between two first strips and between two second strips which are adjacent.

Owner:WUHAN CHINA STAR OPTOELECTRONICS TECH CO LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com