Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

1915results about How to "Avoid downtime" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

System and method for detecting decreased performance in a refrigeration system

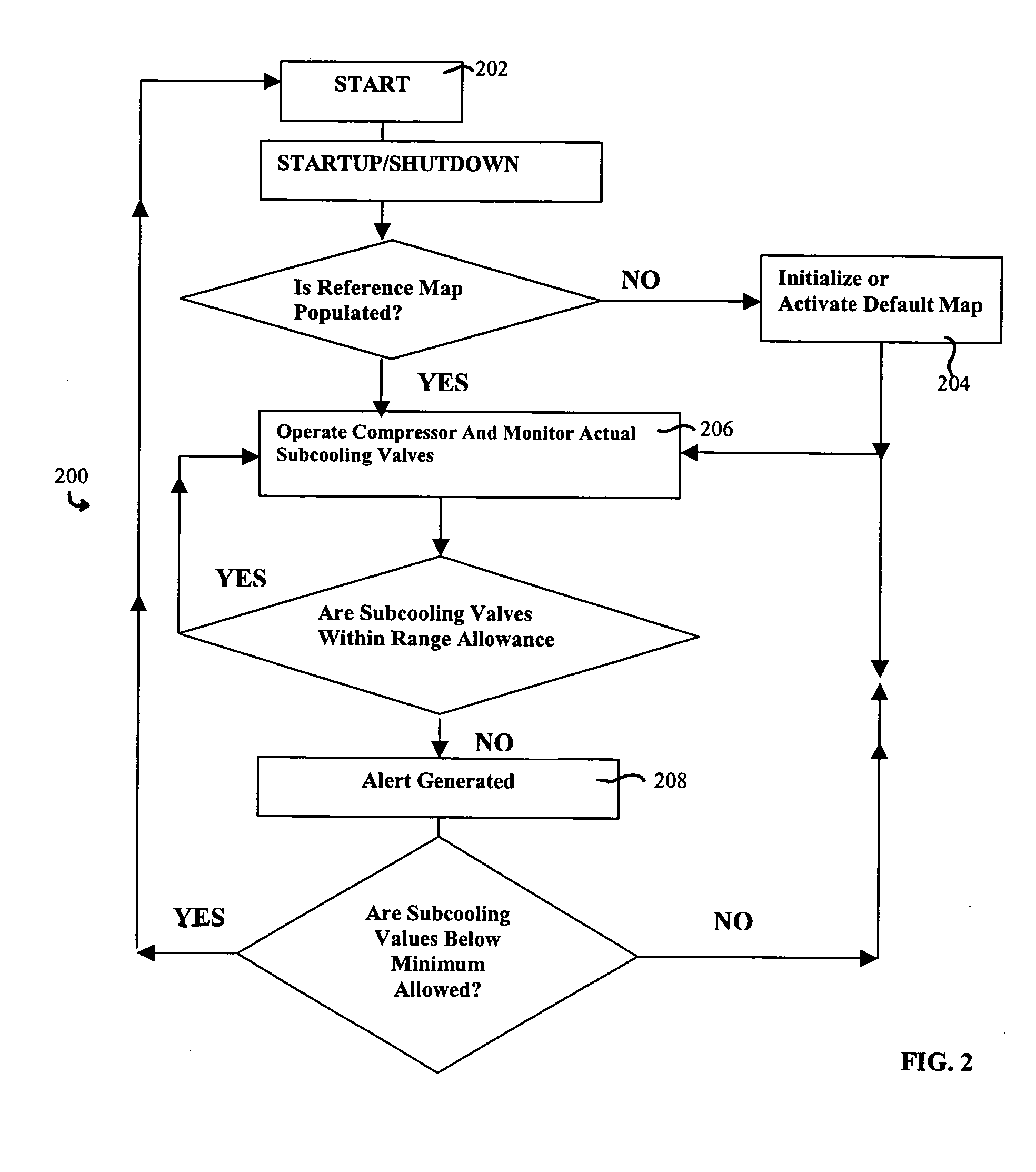

InactiveUS20060042276A1Avoid downtimeEarly detectionElectric testing/monitoringThermometer applicationsEngineeringRefrigeration

Systems and methods are provided for detecting performance degradation in a refrigeration system. Specifically, the present invention provides systems and methods for detecting, at a very early stage, a low refrigerant charge and degradation in condenser performance of a refrigeration system.

Owner:YORK INT

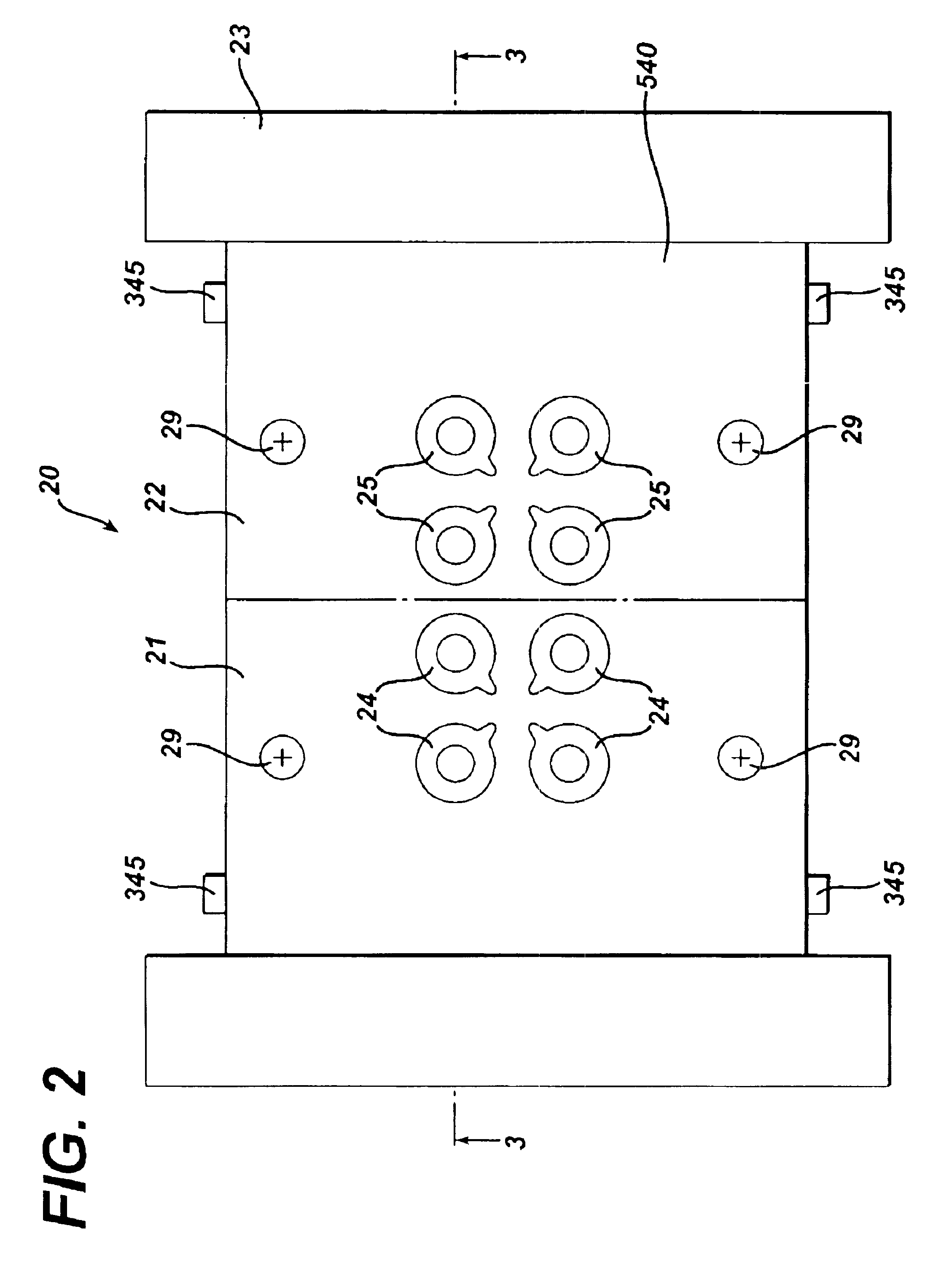

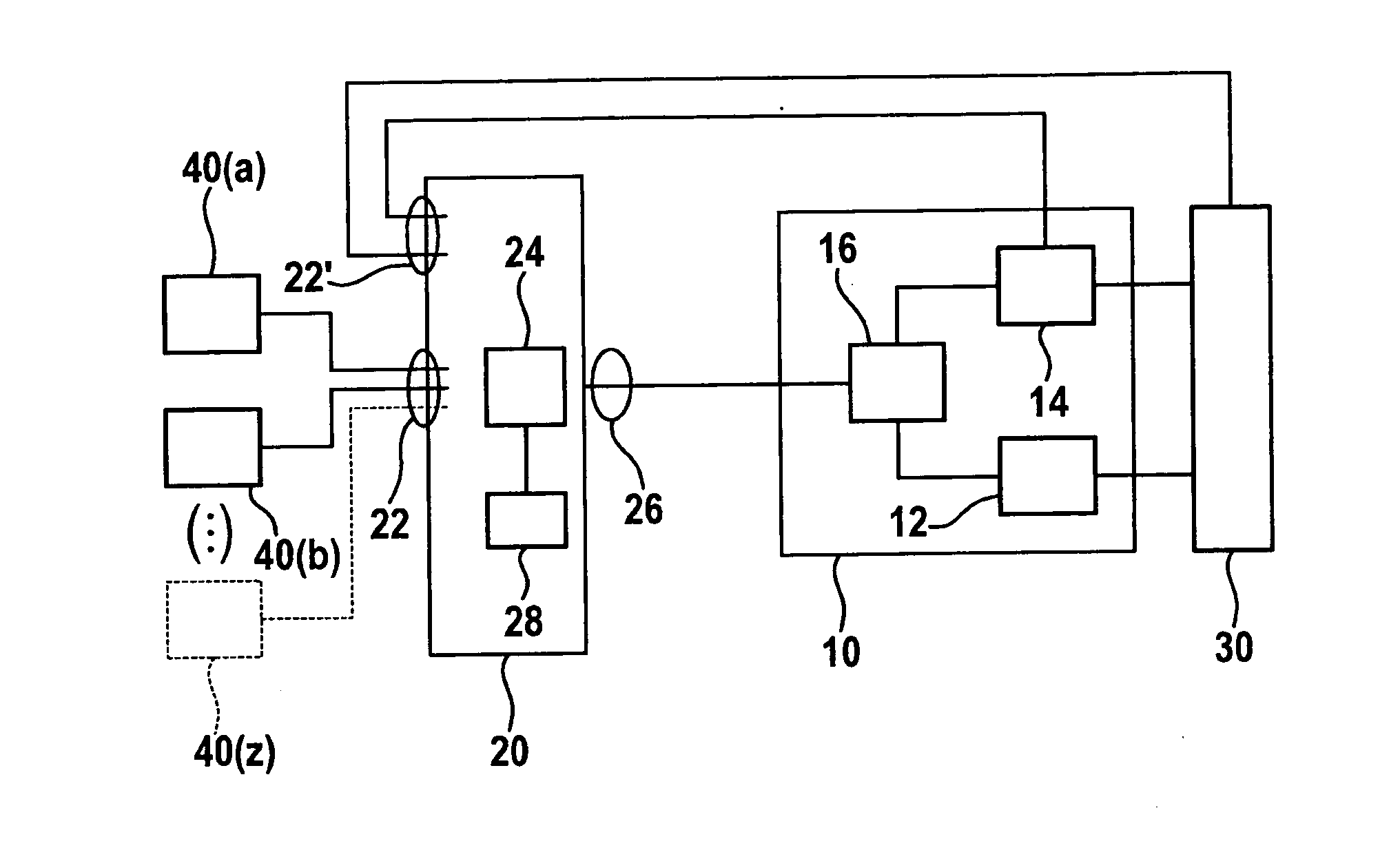

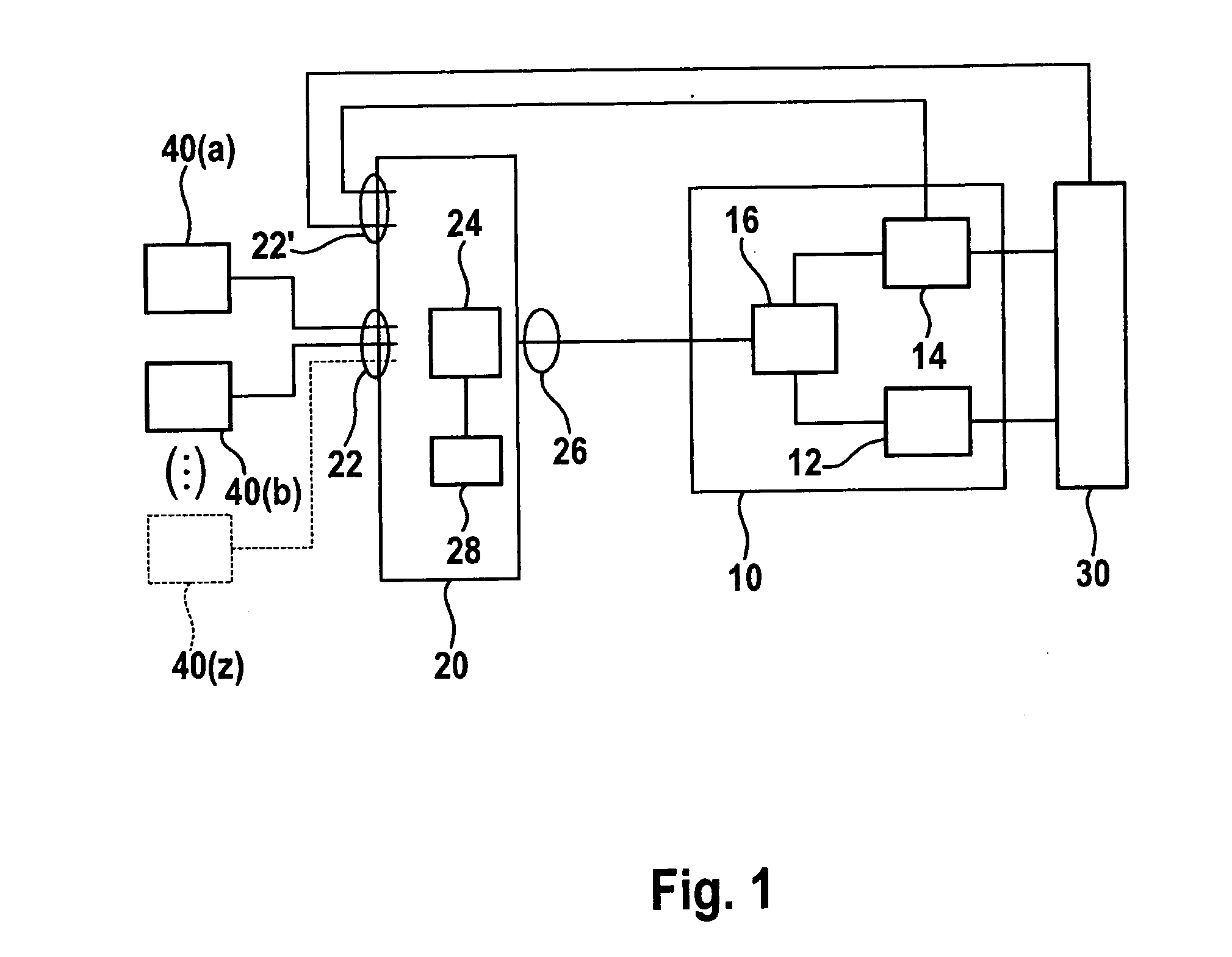

Flow battery systems

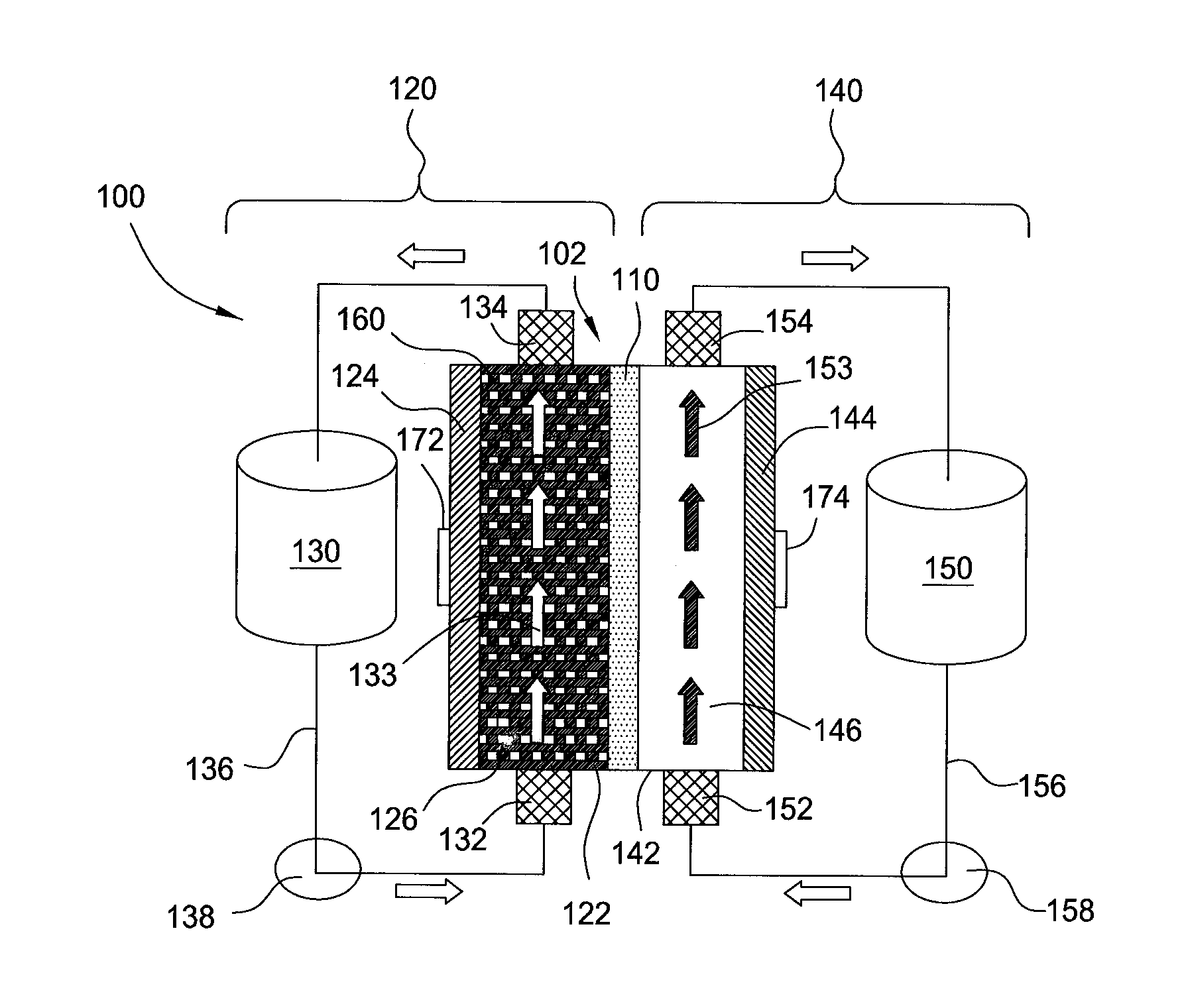

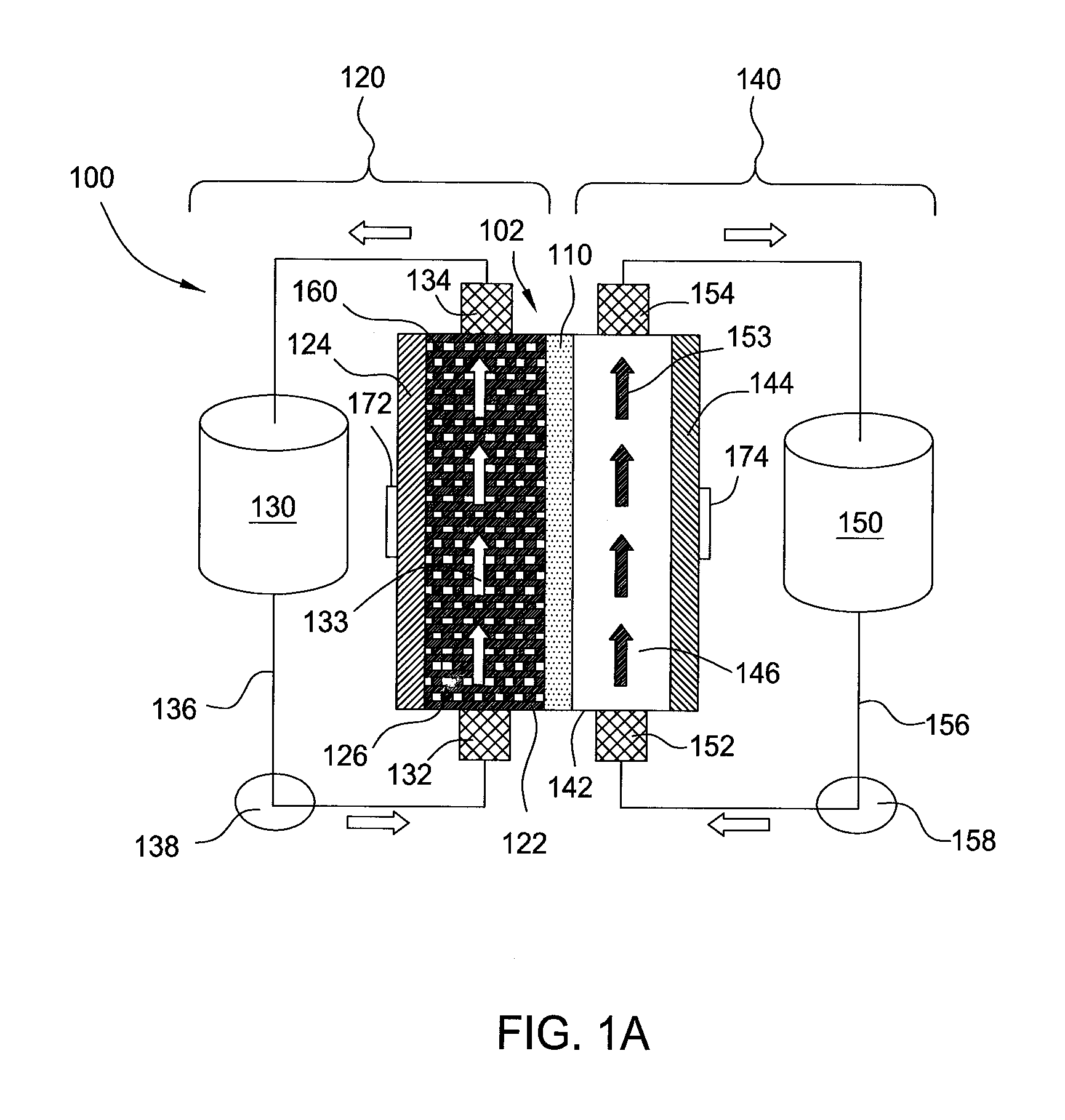

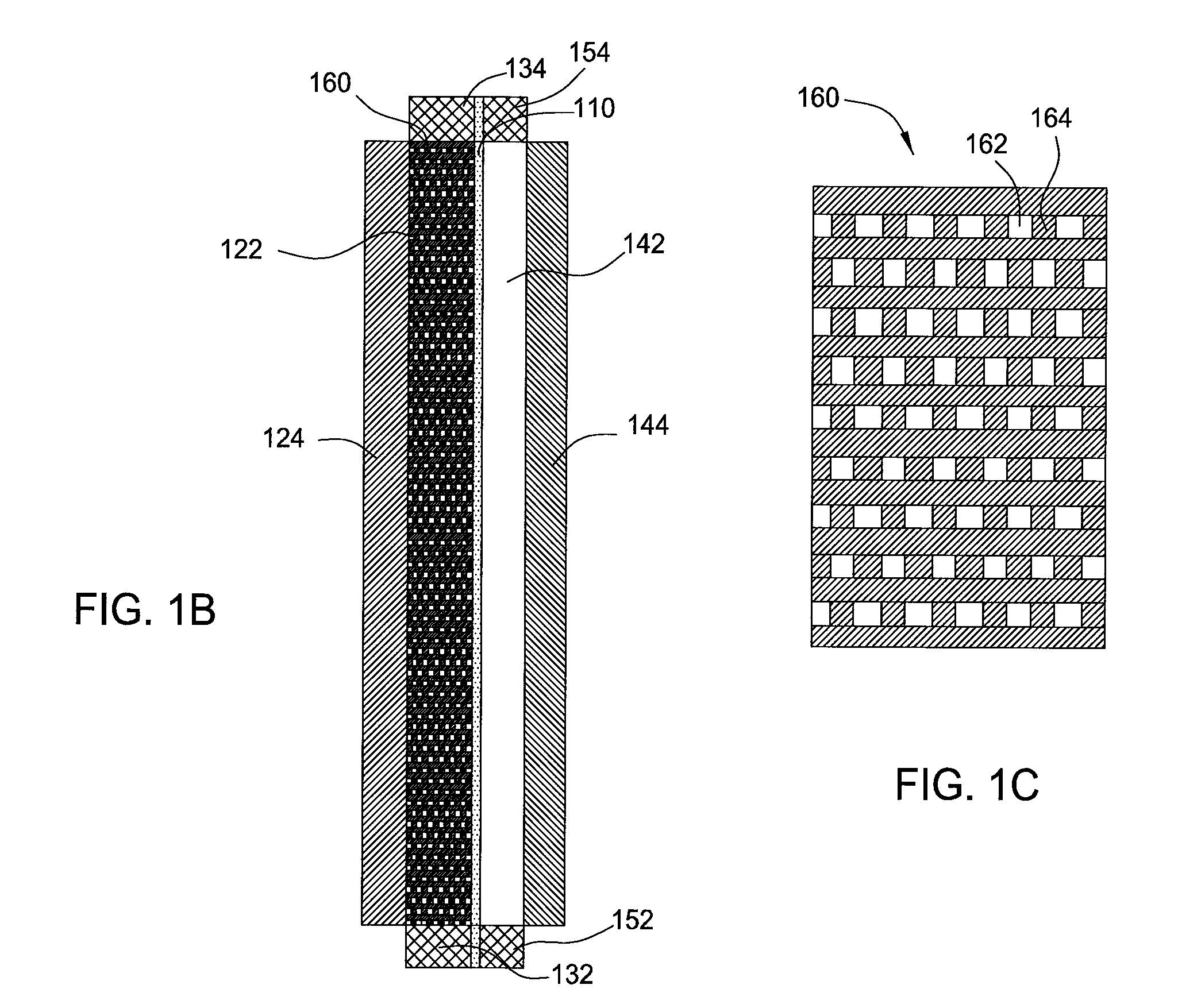

ActiveUS20120052347A1Uniform metal platingHigh cell current densityFuel and secondary cellsCell electrodesEngineeringMetal

Embodiments of the invention generally provide for flow battery cells and systems containing a plurality of flow battery cells, and methods for improving metal plating within the flow battery cell, such as by flowing and exposing the catholyte to various types of cathodes. In one embodiment, a flow battery cell is provided which includes a cathodic half cell and an anodic half cell separated by an electrolyte membrane, wherein the cathodic half cell contains a plurality of cathodic wires extending perpendicular or substantially perpendicular to and within the catholyte pathway and in contact with the catholyte, and each of the cathodic wires extends parallel or substantially parallel to each other. In some examples, the plurality of cathodic wires may have at least two arrays of cathodic wires, each array contains at least one row of cathodic wires, and each row extends along the catholyte pathway.

Owner:APPLIED MATERIALS INC

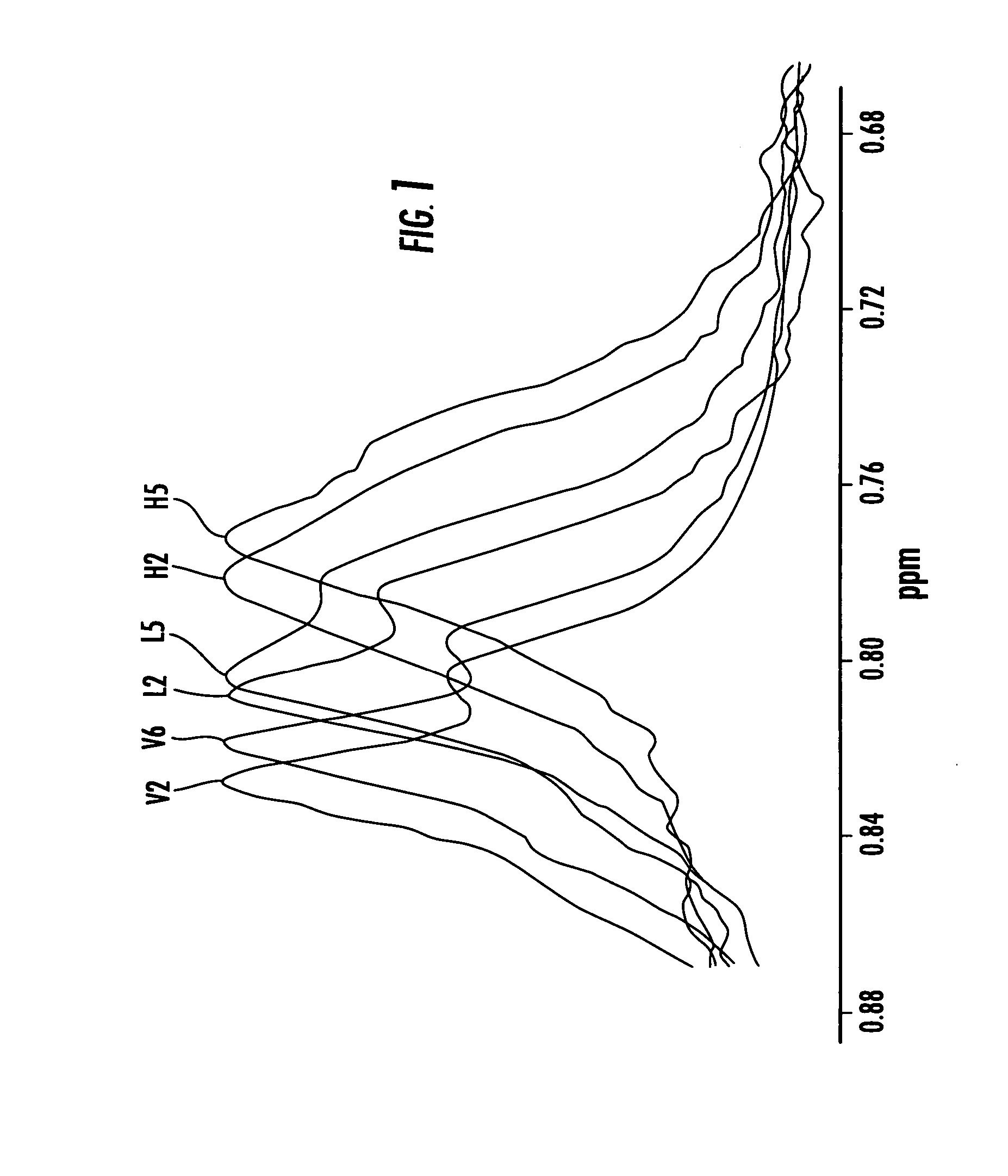

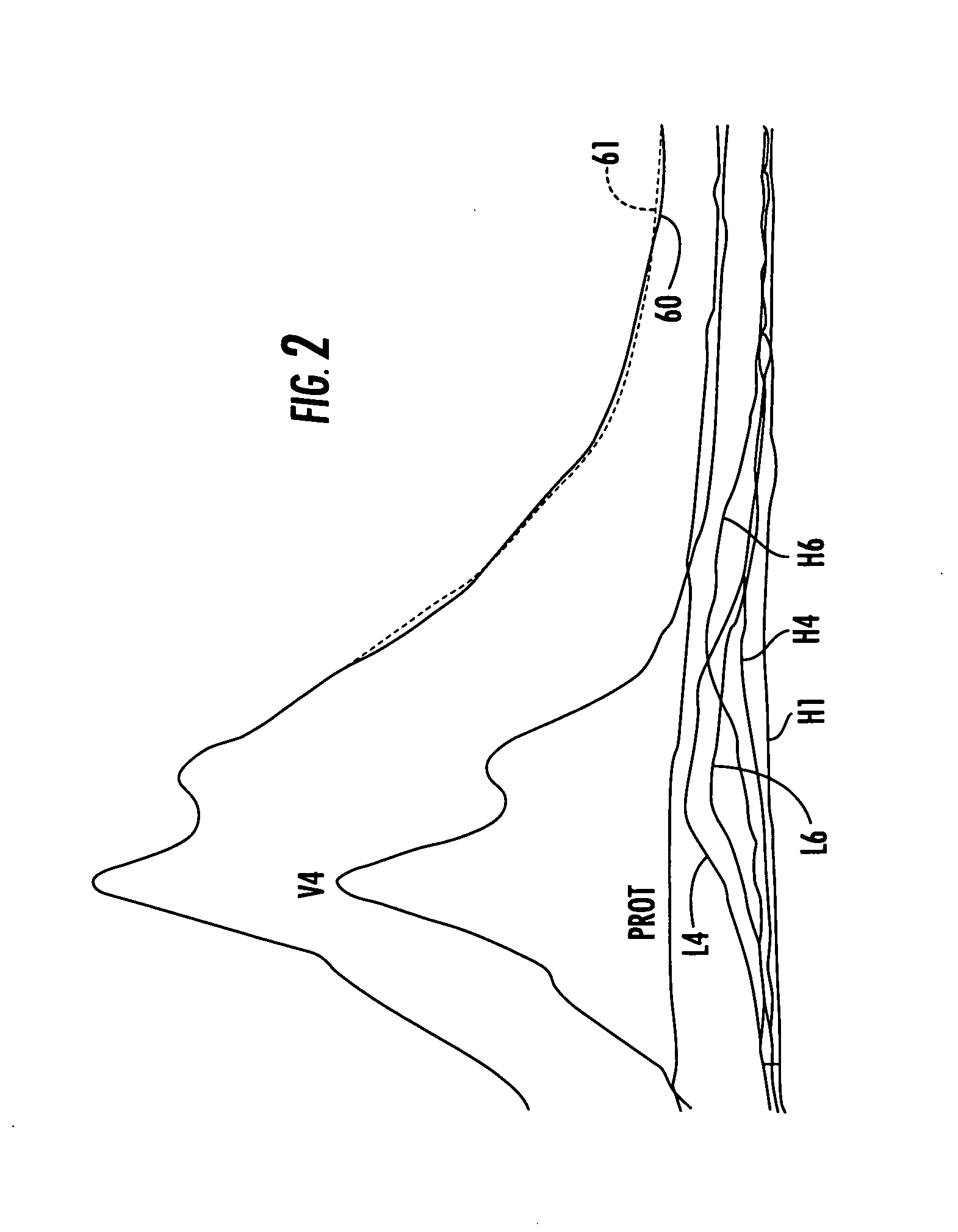

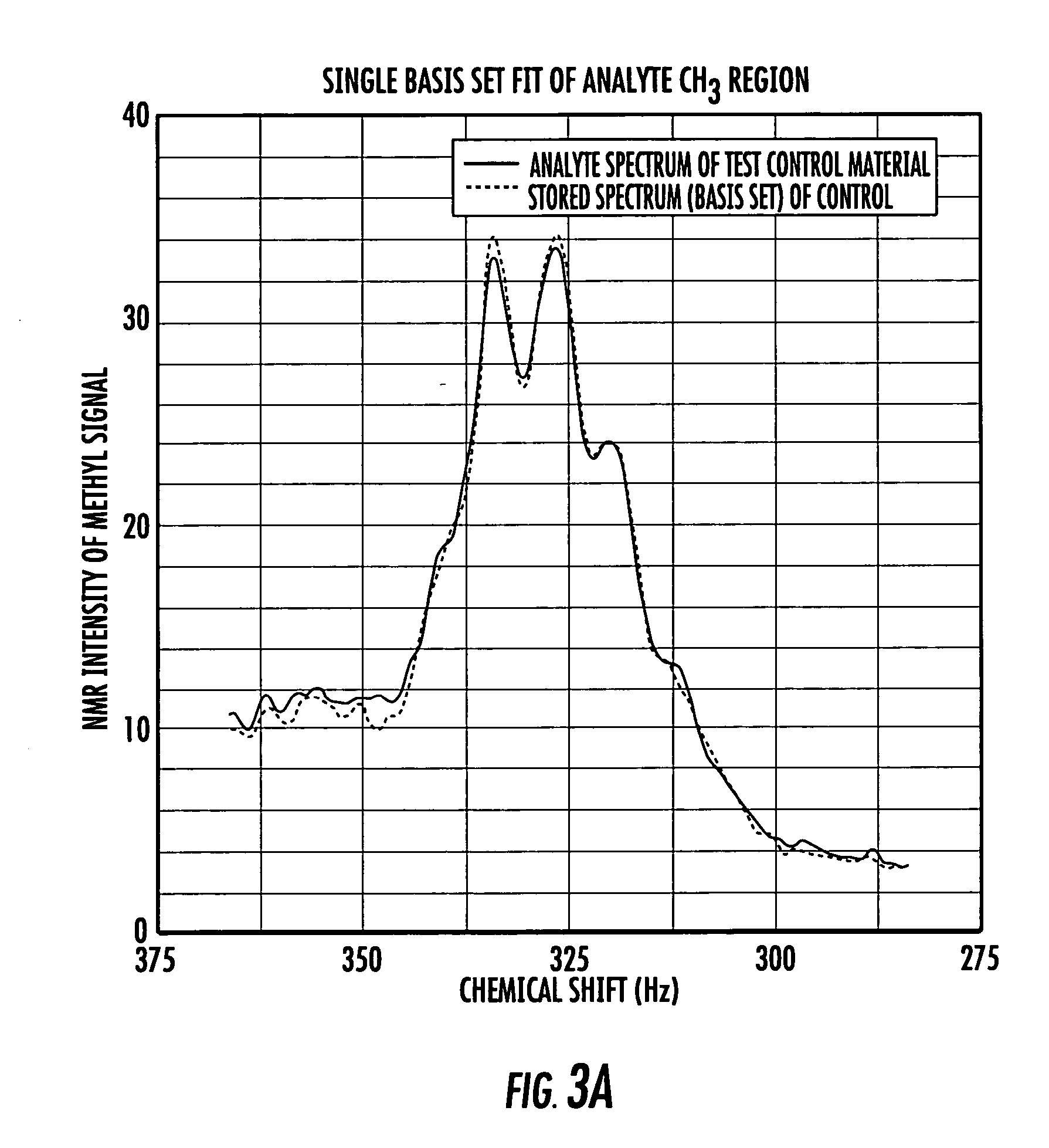

NMR clinical analyzers and related methods, systems, modules and computer program products for clinical evaluation of biosamples

ActiveUS20050222504A1Improve reliabilityAvoid downtimeMagnetic measurementsDiagnostic recording/measuringRemote systemRemote control

Methods, computer program products and apparatus automate clinical NMR in vitro diagnostic analyzers. The clinical analyzer can automatically electronically monitor selected parameters and automatically electronically adjust parameters to maintain the analyzer within desired operational ranges. The clinical NMR analyzers can be configured as a networked system with a plurality of clinical NMR analyzers located at different use sites; and at least one remote control system in communication with one or a plurality of clinical NMR analyzers, the at least one remote system configured to monitor selected local operating parameters associated with a respective clinical NMR analyzer.

Owner:LIPOSCI

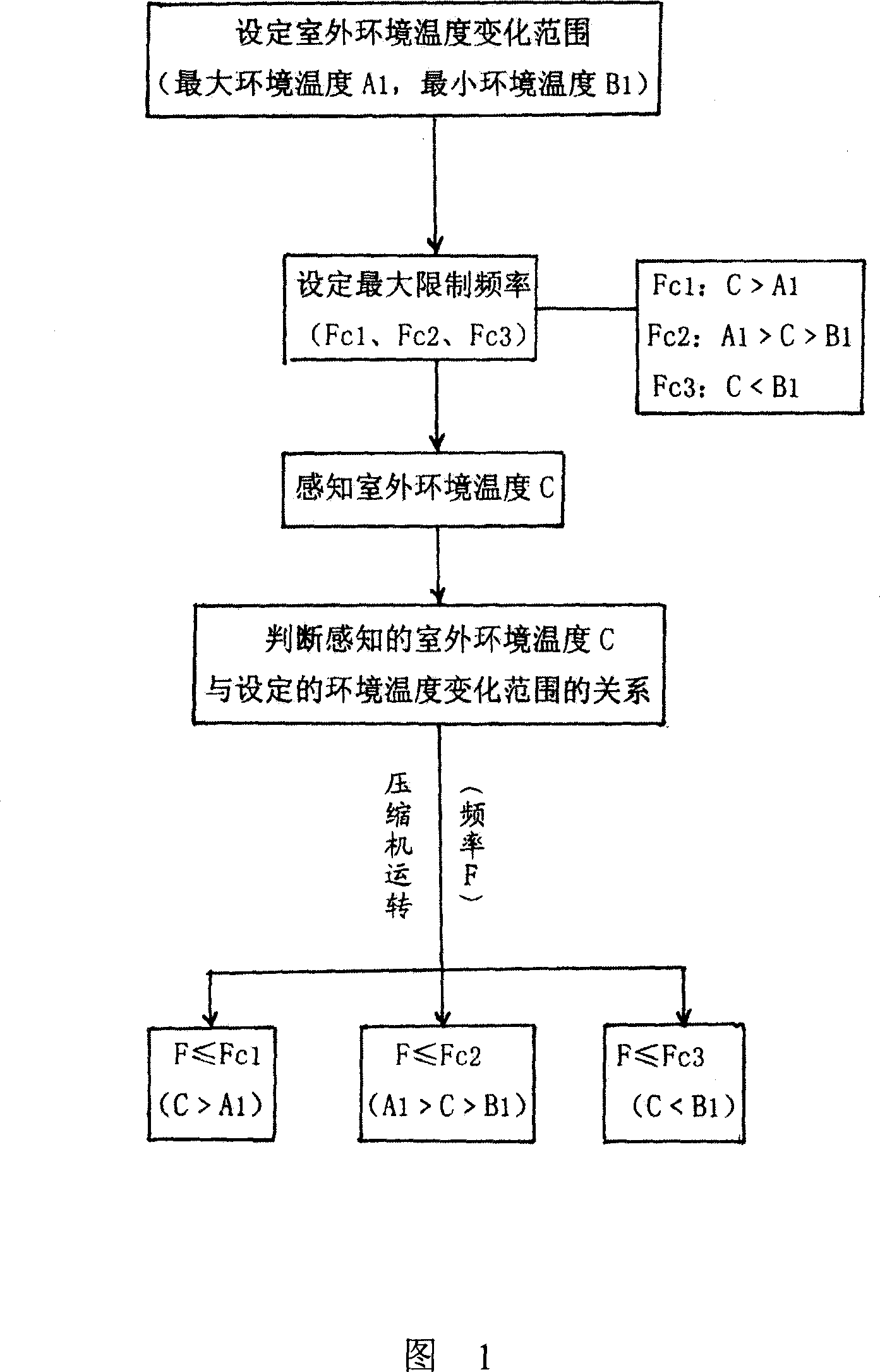

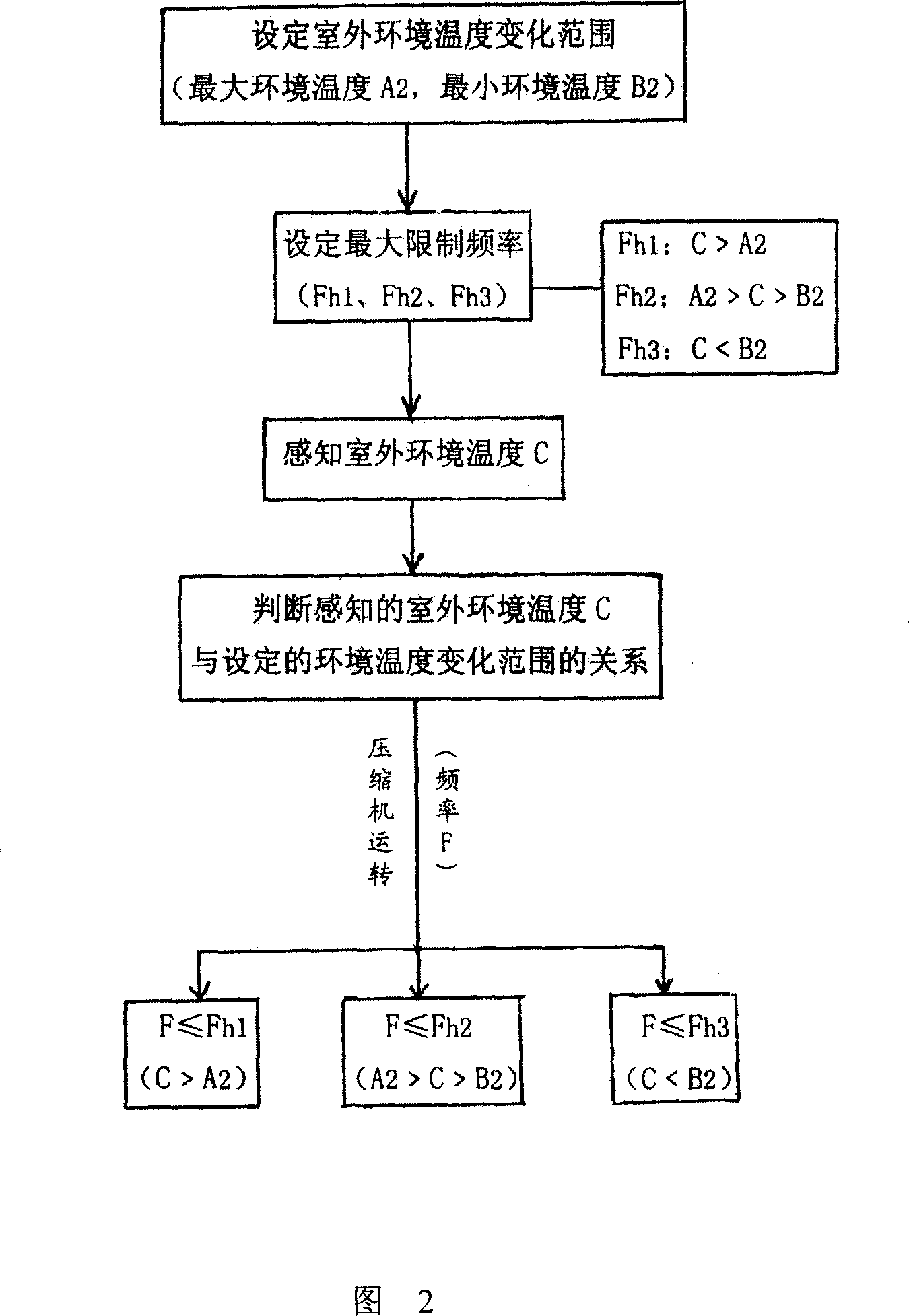

Method for limiting inverter compressor maximum frequency according to outdoor environment temperature

InactiveCN101109553ASimple control logicAvoid downtimeSpace heating and ventilation safety systemsLighting and heating apparatusFrequency conversionEngineering

The invention discloses a method for limiting the max. frequency of a frequency-conversion compressor based on outdoor environmental temperature, which comprises: the change range of outdoor environmental temperature is set; the max. limit frequency of the compressor is set based on the range of outdoor environmental temperature; a temperature sensor senses the outdoor environmental temperature; the relationship is judged between the sensed outdoor environmental temperature and the change range of environmental temperature based on which the max. limit frequency of the compressor is set; the max. limit frequency for the frequency-conversion running of the compressor is determined based on the relationship between the sensed outdoor environmental temperature and the change range of environmental temperature based on which the max. limit frequency of the compressor is set. The method improves the controlling logic for the frequency-conversion compressor, so that the compressor will not breakdown because the compressor increases frequency and accelerates without limit depending upon the outdoor environmental temperature.

Owner:LG ELECTRONICS (TIANJIN) APPLIANCES CO LTD

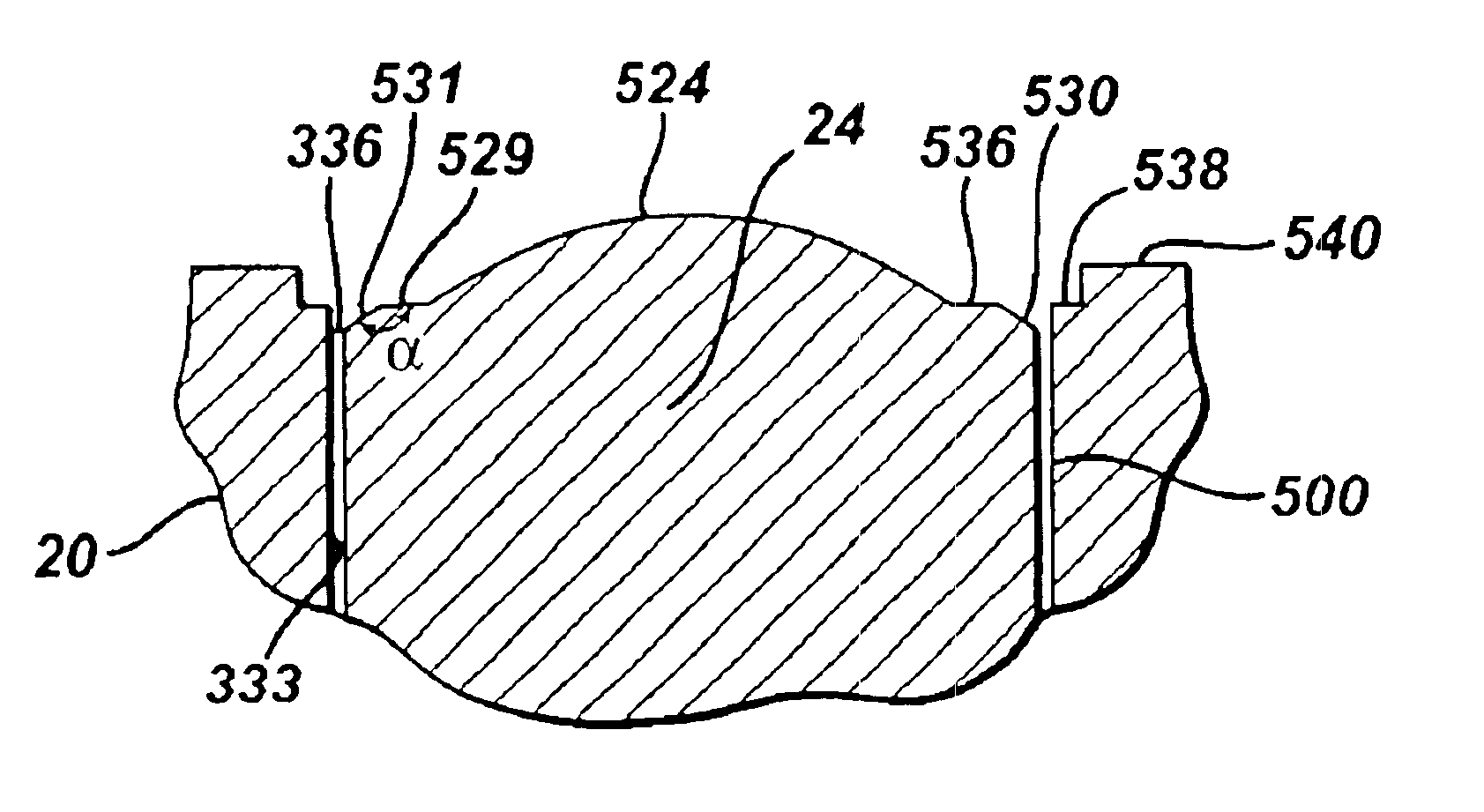

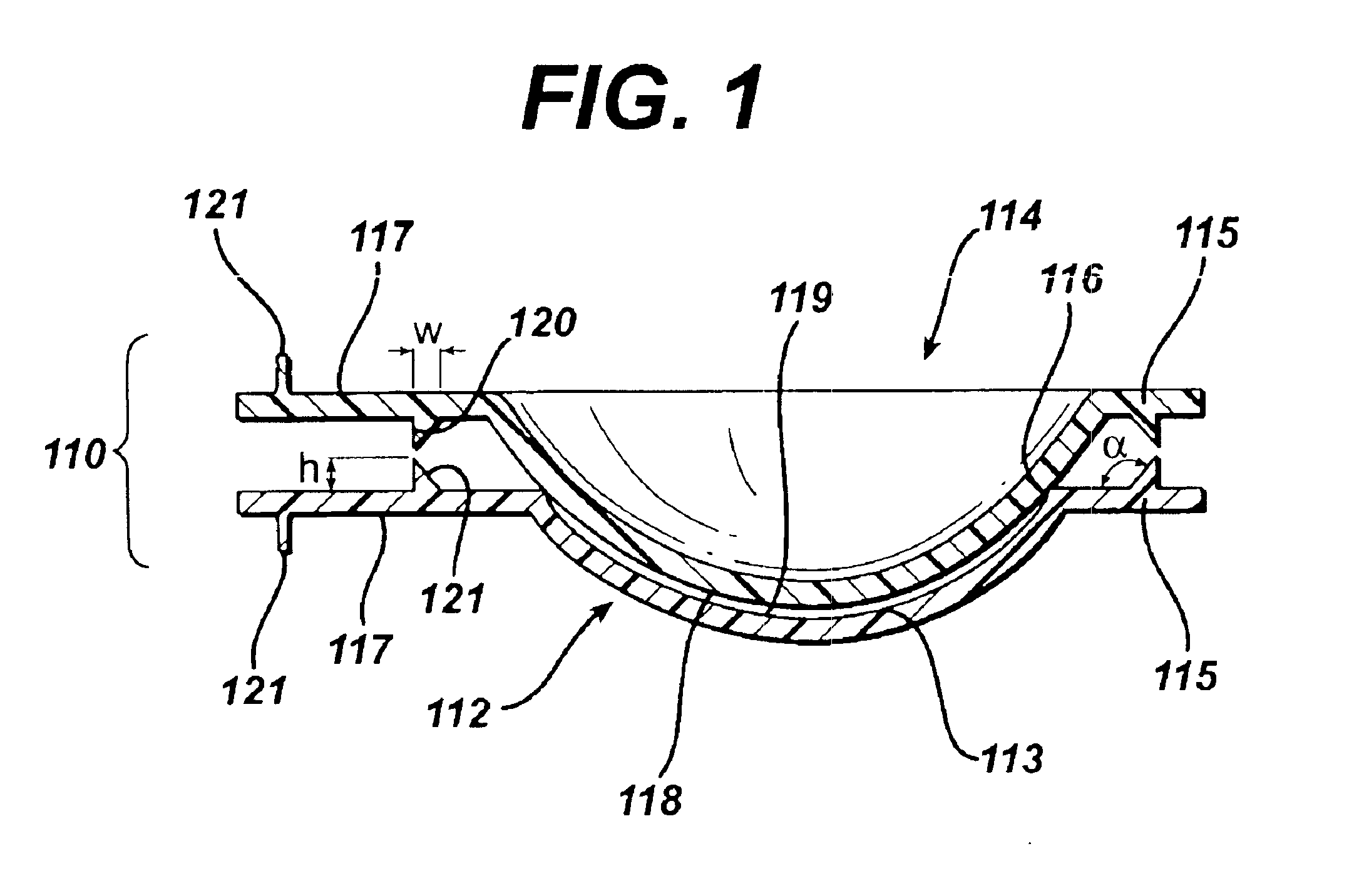

Method and mold for making ophthalmic devices

Owner:JOHNSON & JOHNSON VISION CARE INC

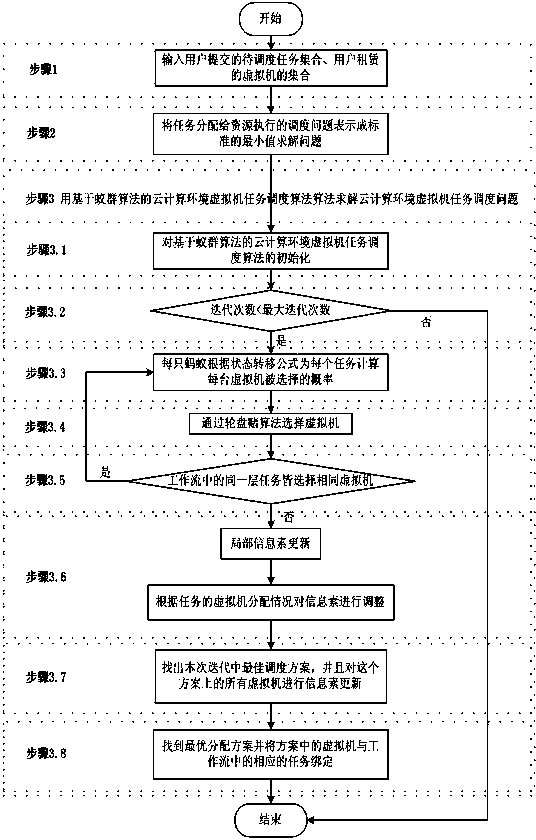

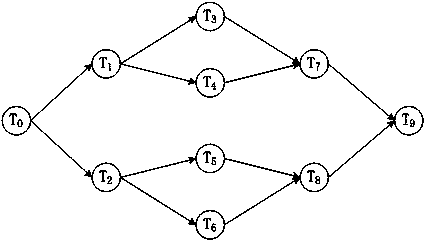

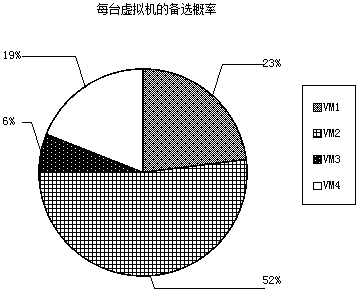

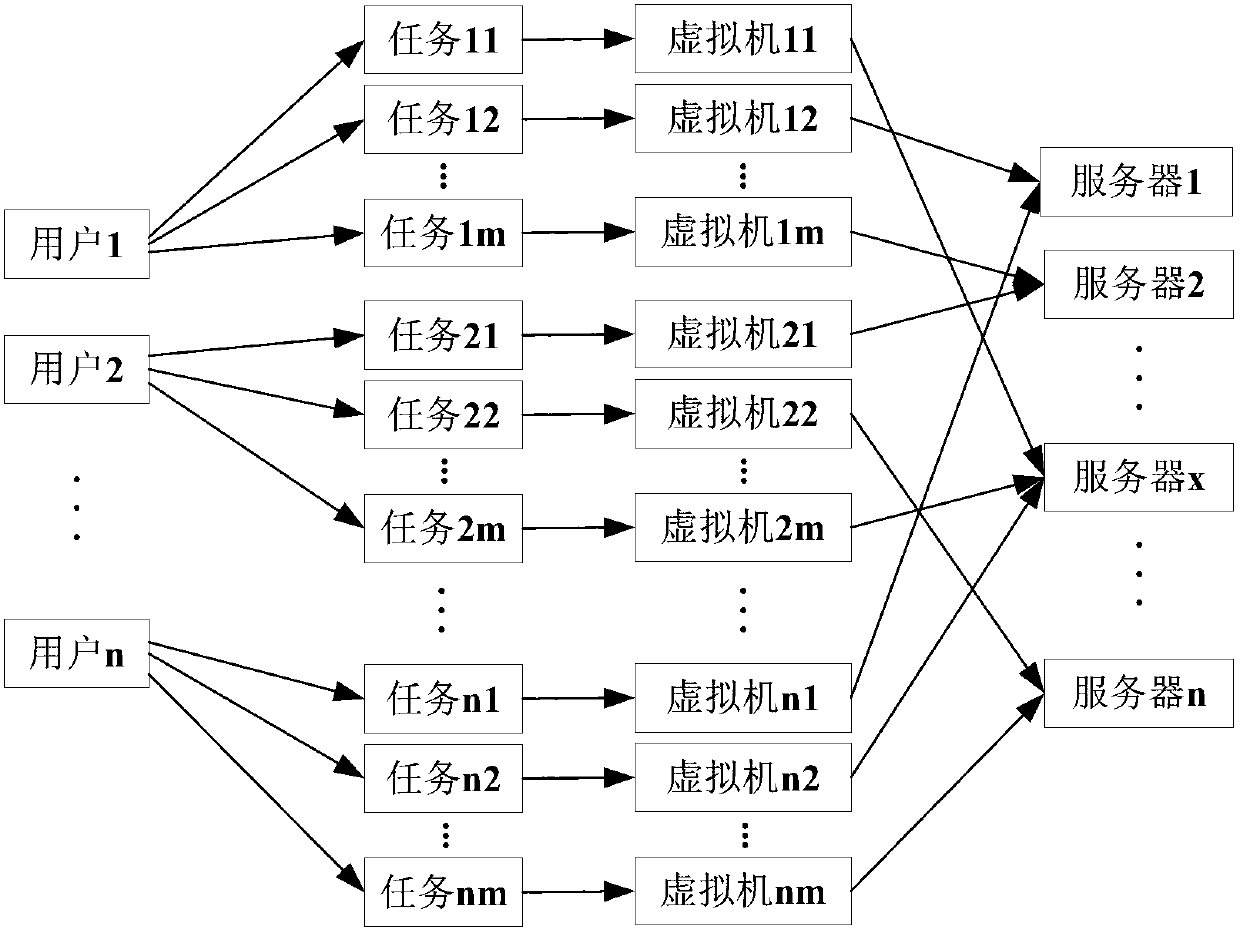

Cloud data center task scheduling method based on improved ant colony algorithm

ActiveCN103970609AAvoid downtimeAvoid issues such as wasteResource allocationBiological modelsCloud data centerTime overhead

The invention provides a cloud data center task scheduling method based on an improved ant colony algorithm, and relates to the field of cloud computing. The method comprises the following steps that (1) a to-be-scheduled workflow task set submitted by a user and a virtual machine set rent by the user are input, (2) a scheduling problem that tasks are allocated to virtual machines to be executed is represented as a standard minimum value solving problem, and (3) the virtual machine task scheduling problem in a cloud computing environment is solved through the ant colony algorithm based on information element updating. The method can adapt to the dynamic nature of the cloud environment, time for task scheduling of a user is shortened, and virtual machine load in a cloud data center can be maintained in a relative balance state.

Owner:WUHAN FIBERHOME INFORMATION INTEGRATION TECH CO LTD

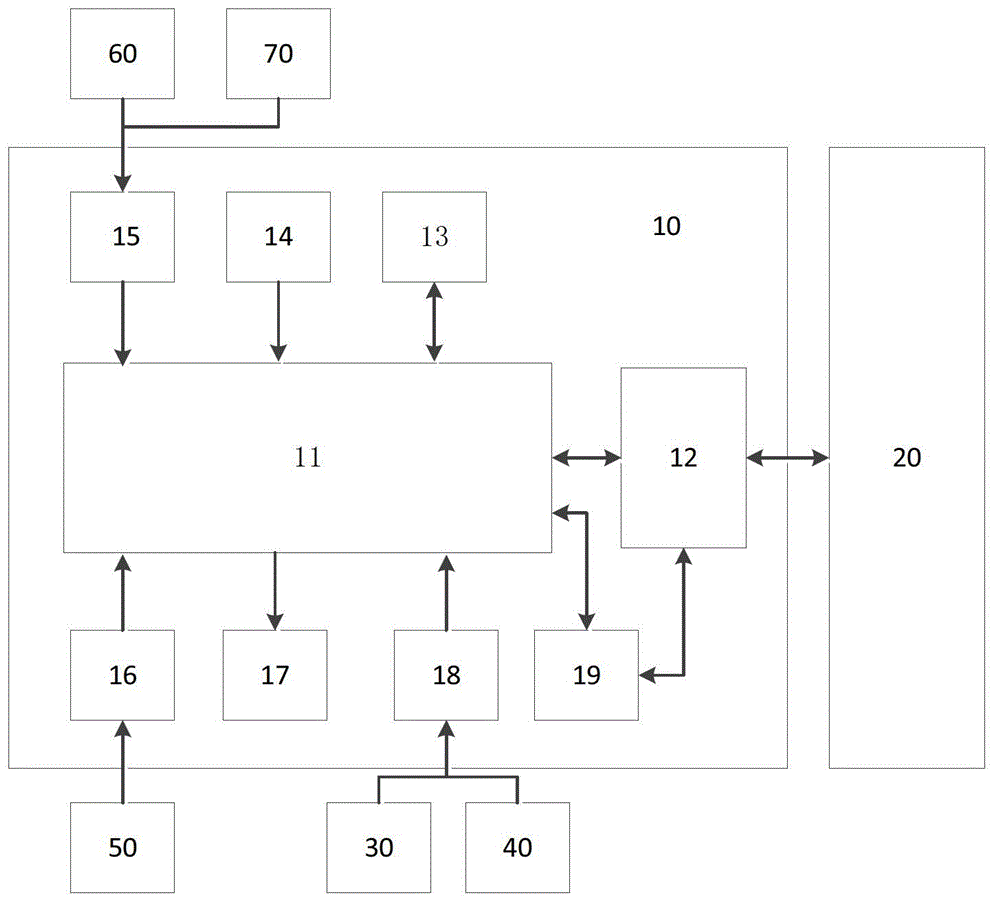

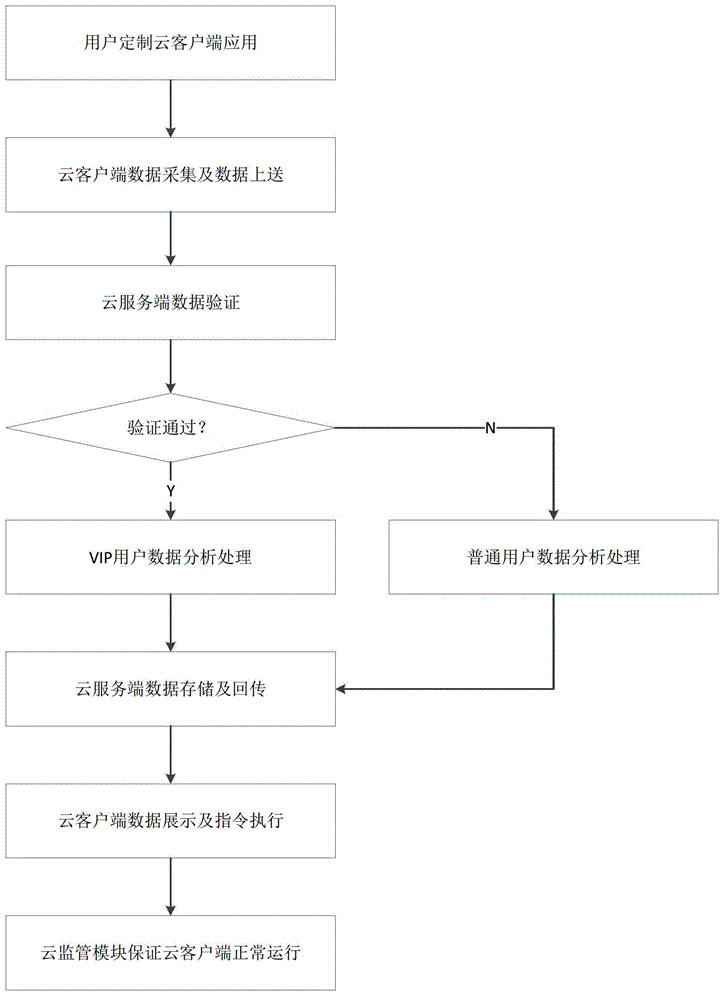

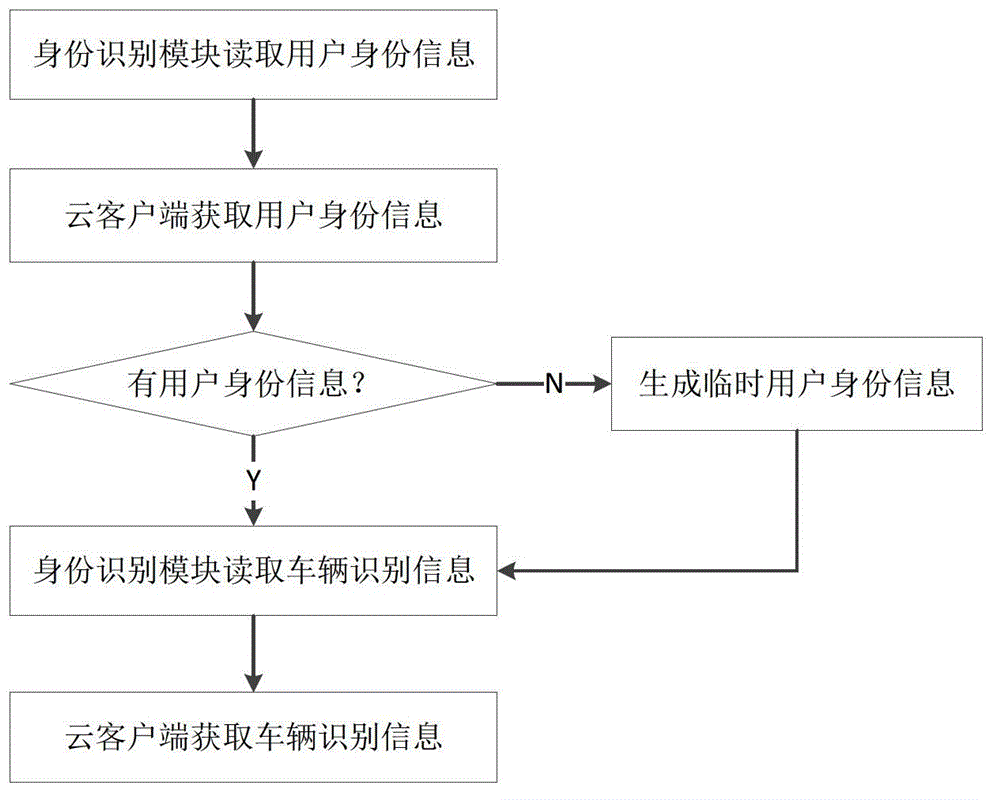

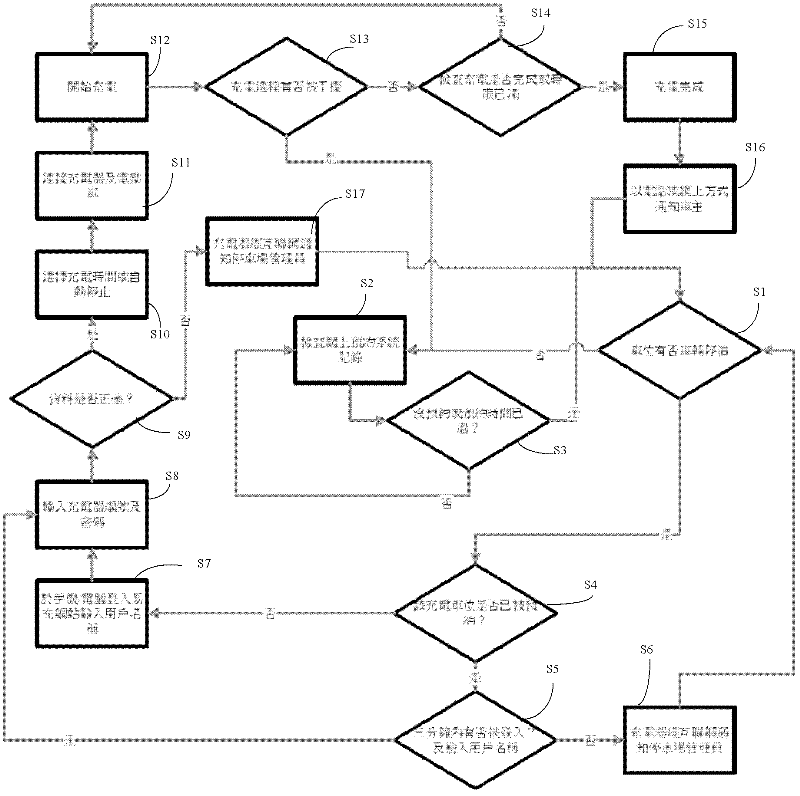

Electric vehicle-mounted terminal based on cloud computing and using method thereof

ActiveCN102752380AReduce performance requirementsImprove operational reliabilityTransmissionArea networkElectrical battery

The invention discloses an electric vehicle-mounted terminal based on cloud computing and a using method thereof. The electric vehicle-mounted terminal comprises a cloud client, a communication module, a human-machine interaction module, a positioning module, an identity identification module, an electric energy metering module, a charge / discharge control module and a CAN (controller area network) data interface. The cloud client is connected with the identity identification module, the positioning module, the human-machine interaction module, the communication module, the electric energy metering module, the charge / discharge control module and the CAN data interface respectively; a cloud server is connected with the communication module; an identity identification card and a vehicle identification card are both connected with the identity identification module; an electric energy meter is connected with the electric energy metering module; and a vehicle information system and a battery management system are both connected with the CAN data interface. Through the invention, the operation reliability of the vehicle-mounted terminal is improved; more personalized services are expanded; the structure and layout of the vehicle-mounted terminal are simplified, and the expandability of the vehicle-mounted terminal is improved; and the user does not worry about data loss, virus invasion and the like, and convenience is provided to the managers in finding the problems of the vehicle and battery in time.

Owner:ELECTRIC POWER RESEARCH INSTITUTE OF STATE GRID SHANDONG ELECTRIC POWER COMPANY +1

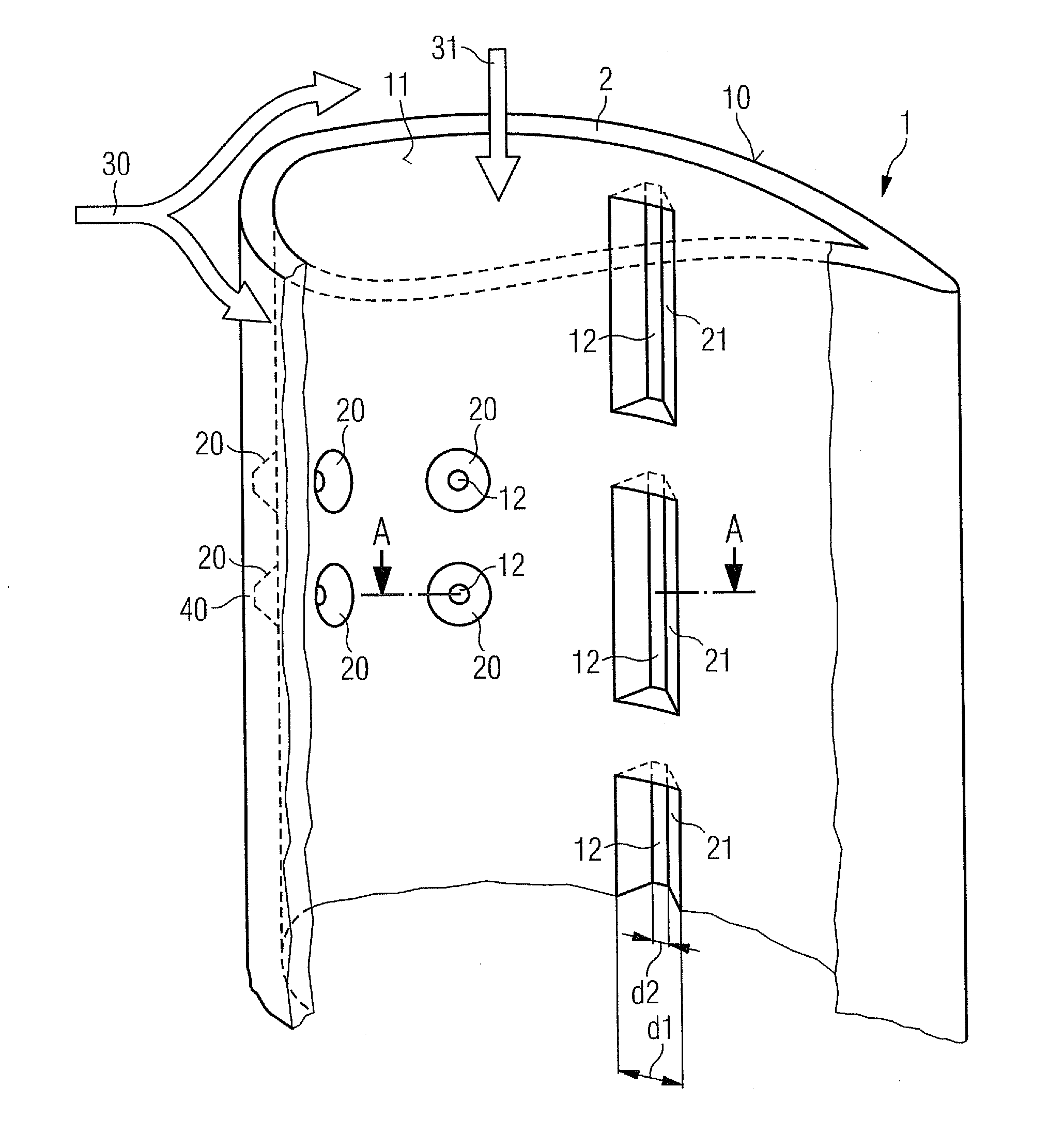

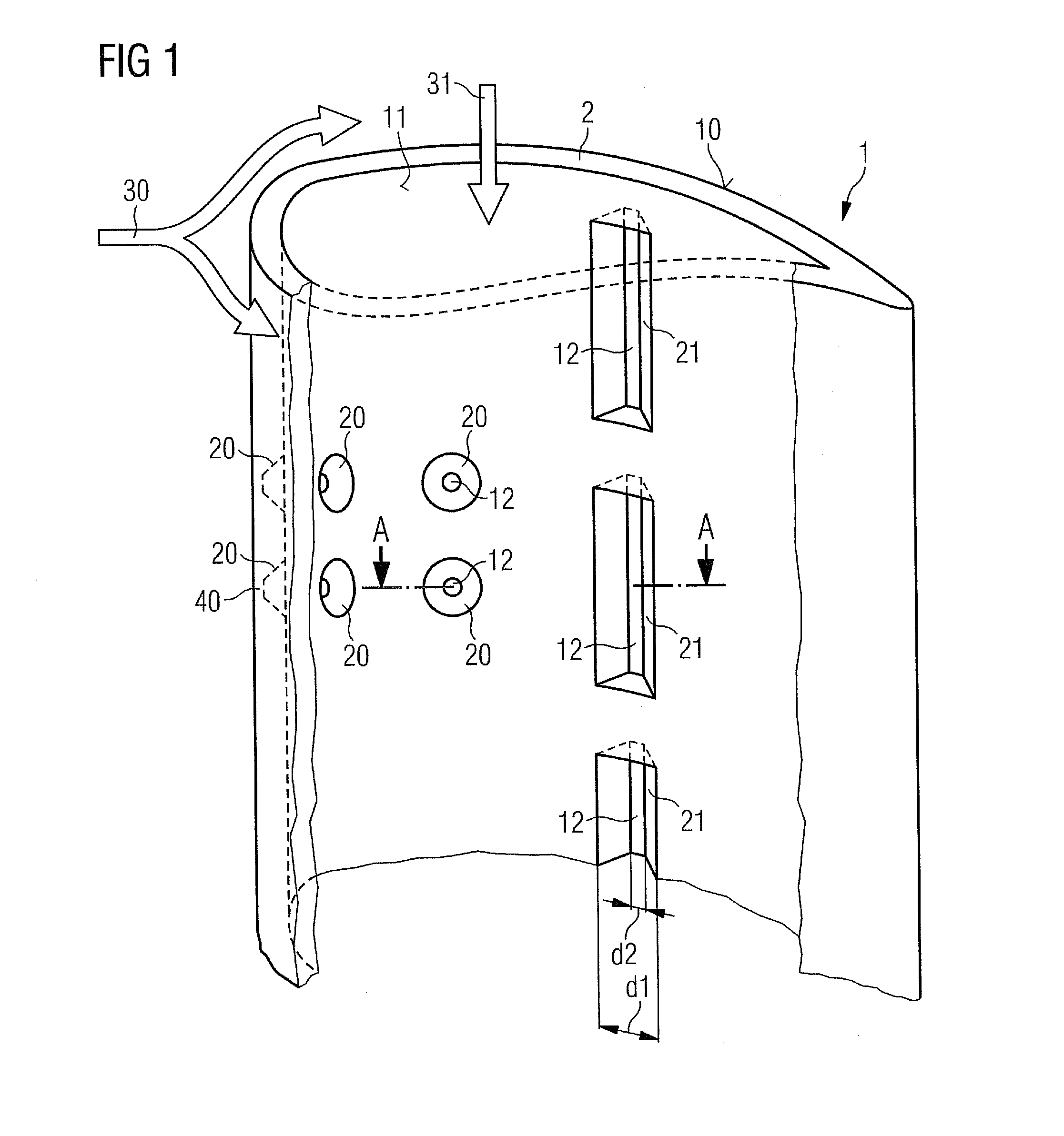

Turbine engine component for adaptive cooling

InactiveUS20110189015A1Marginal performanceAvoid downtimePropellersEngine manufactureWorking fluidEngineering

A turbine engine component, particularly an aerofoil, including a body is provided. The turbine engine component includes a first surface exposed to a working fluid of high temperatures during operation, a second surface including a depression, the depression is exposed to a cooling fluid during operation and oriented such that, starting from the second surface, the depression deepens in the direction of a back face of the first surface. Furthermore the body includes a body portion between the back face and the first surface. The depression is defined such that a diameter of the depression decreases from the second surface in direction of the back face.

Owner:SIEMENS AG

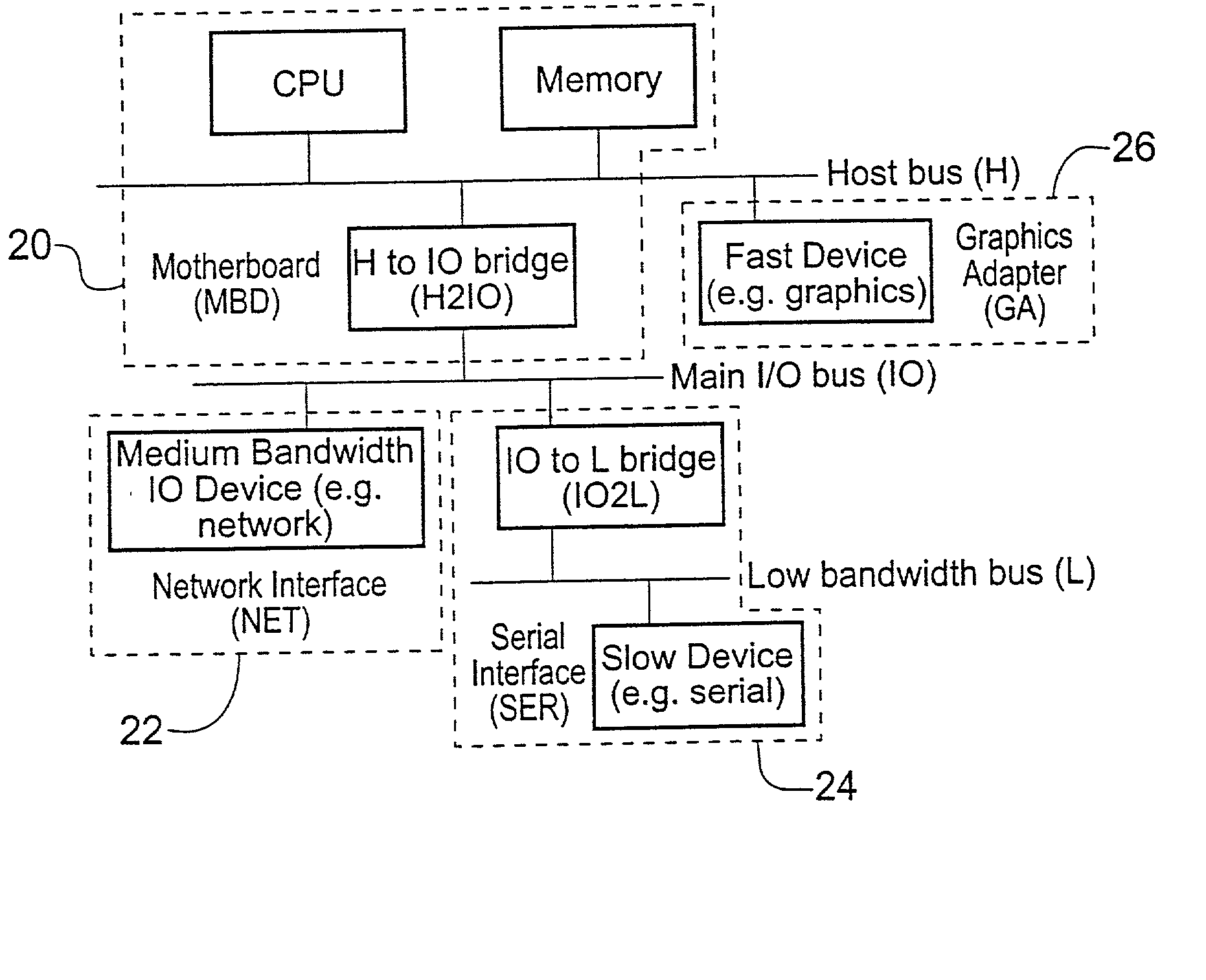

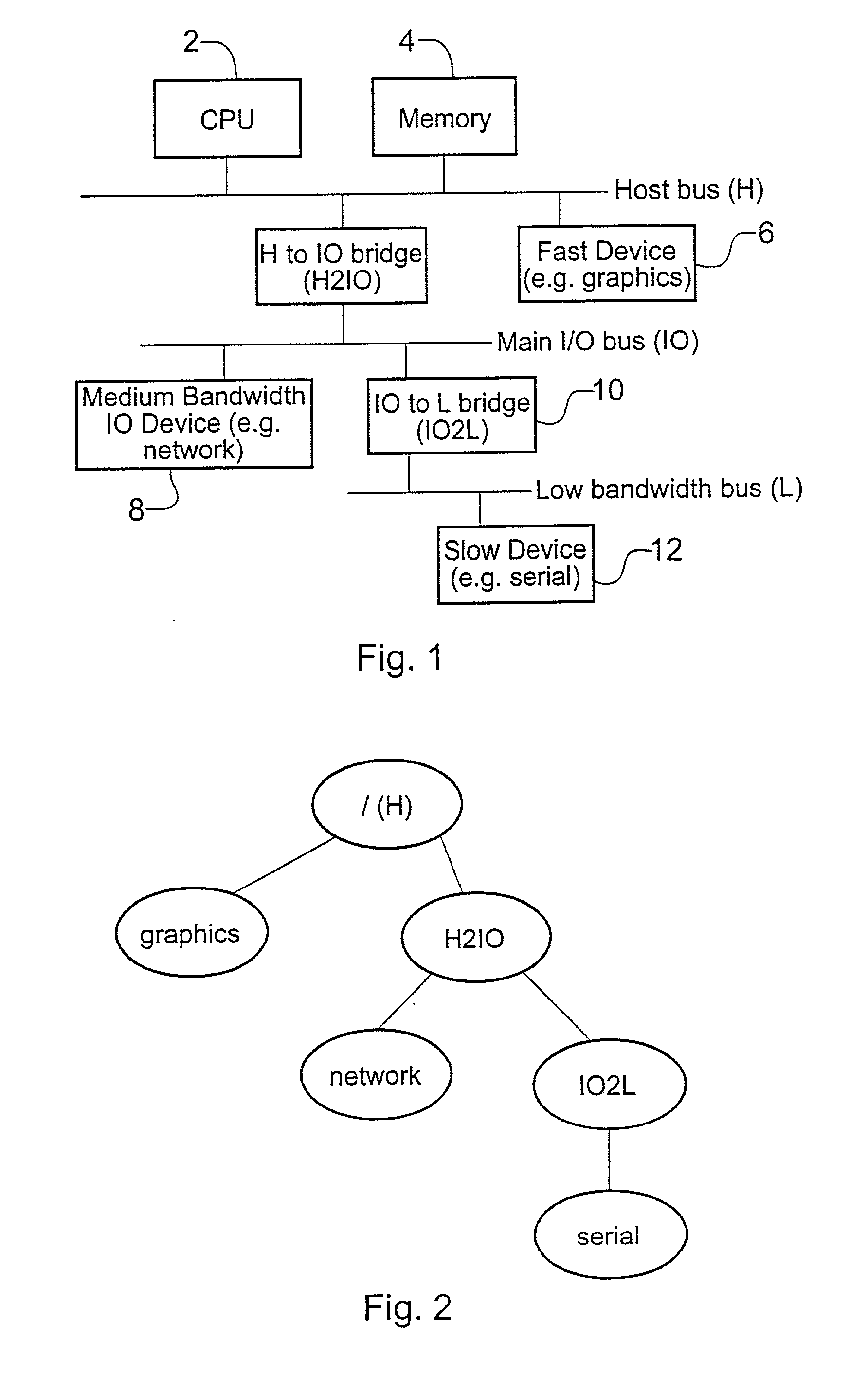

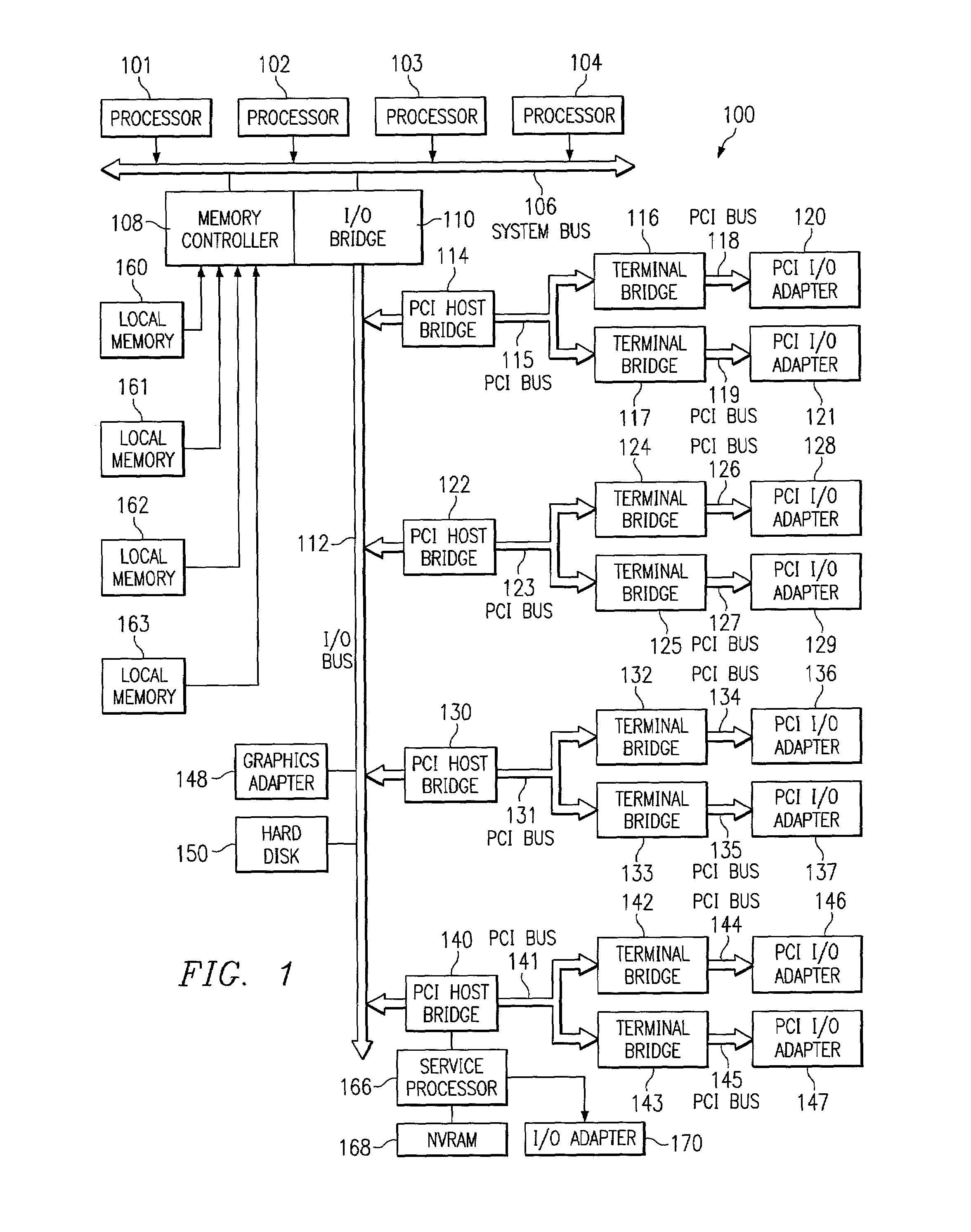

Computer system

ActiveUS20020138782A1Raise the possibilityReduce downtimeError preventionFault responseField replaceable unitConnected device

A computer system comprises a processor (2), memory (4) and a plurality of devices (6, 8, 10, 12), the processor (2) and the memory (4) being operable to effect the operation of a fault response processor (AFR), and a device driver (GRAPHICS, NETWORK, H2IO, IO2L, SERIAL) for each of the devices. The fault response processor (AFR) is operable to generate a model (81) which represents the processor (2), the memory (4) and the devices (6, 8, 10, 12) of the computer system and the inter-connection of the processor (2), memory (4) and the devices (GRAPHICS, NETWORK, H2IO, IO2L, SERIAL). The device driver (GRAPHICS, NETWORK, H2IO, IO2L, SERIAL) for each of the devices (6, 8, 10, 12) is arranged, consequent upon a change of operational status of the device, to generate fault report data indicating whether the change of status was caused internally within the device or externally by another connected device. The devices of the computer system may be formed as a plurality of Field Replaceable Units (FRU). The fault response processor (AFR) is operable, consequent upon receipt of the fault reports from the device drivers (GRAPHICS, NETWORK, H2IO, IO2L, SERIAL) to estimate the location of a FRU containing a faulty device by applying the fault indication to the model (81). In other embodiments the fault report data includes direction information indicating a connection between the device and the other connected device which caused the external fault. Having identified the faulty device the FRU may be replaced, thereby minimizing down time of the computer system.

Owner:ORACLE INT CORP

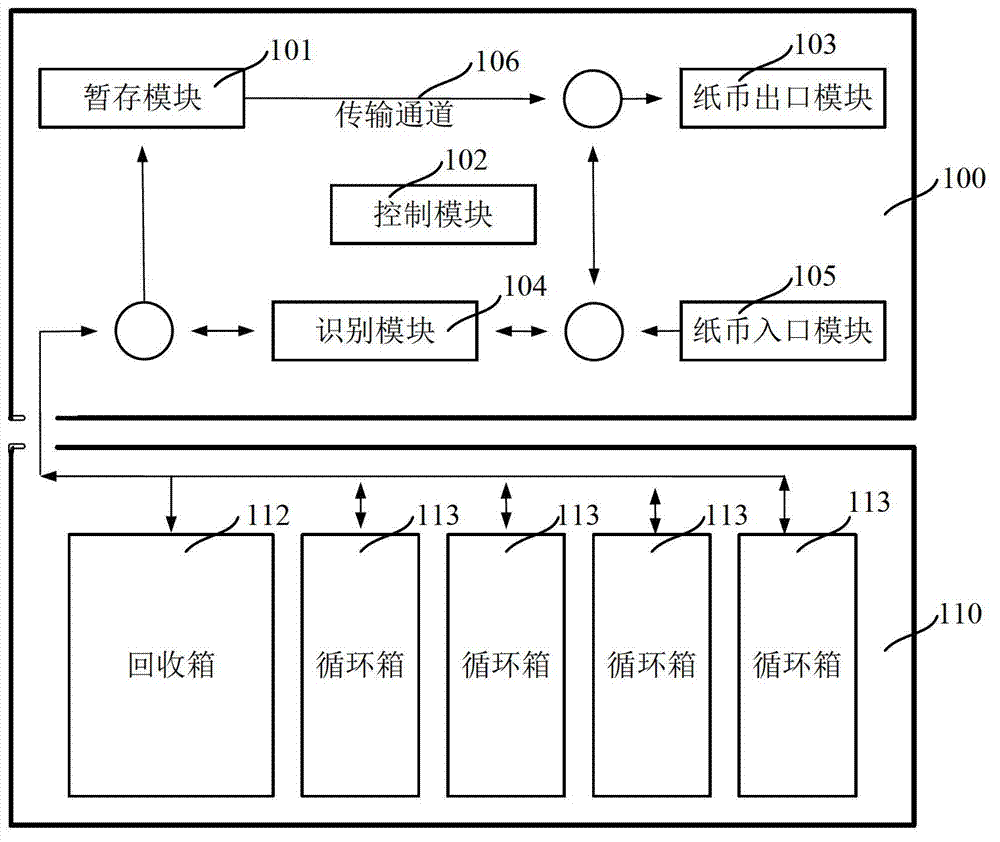

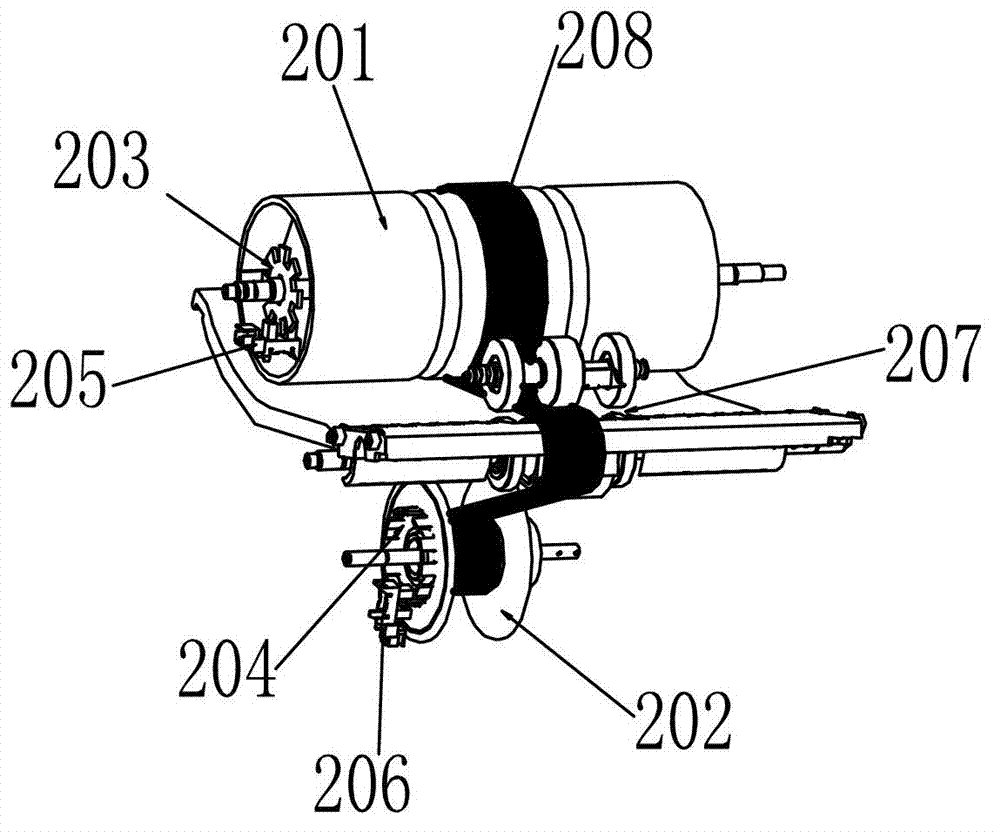

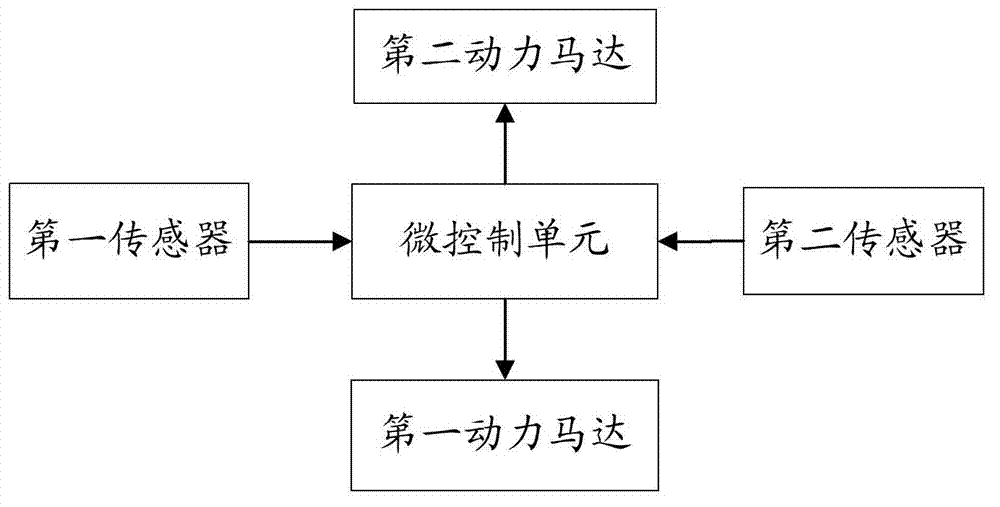

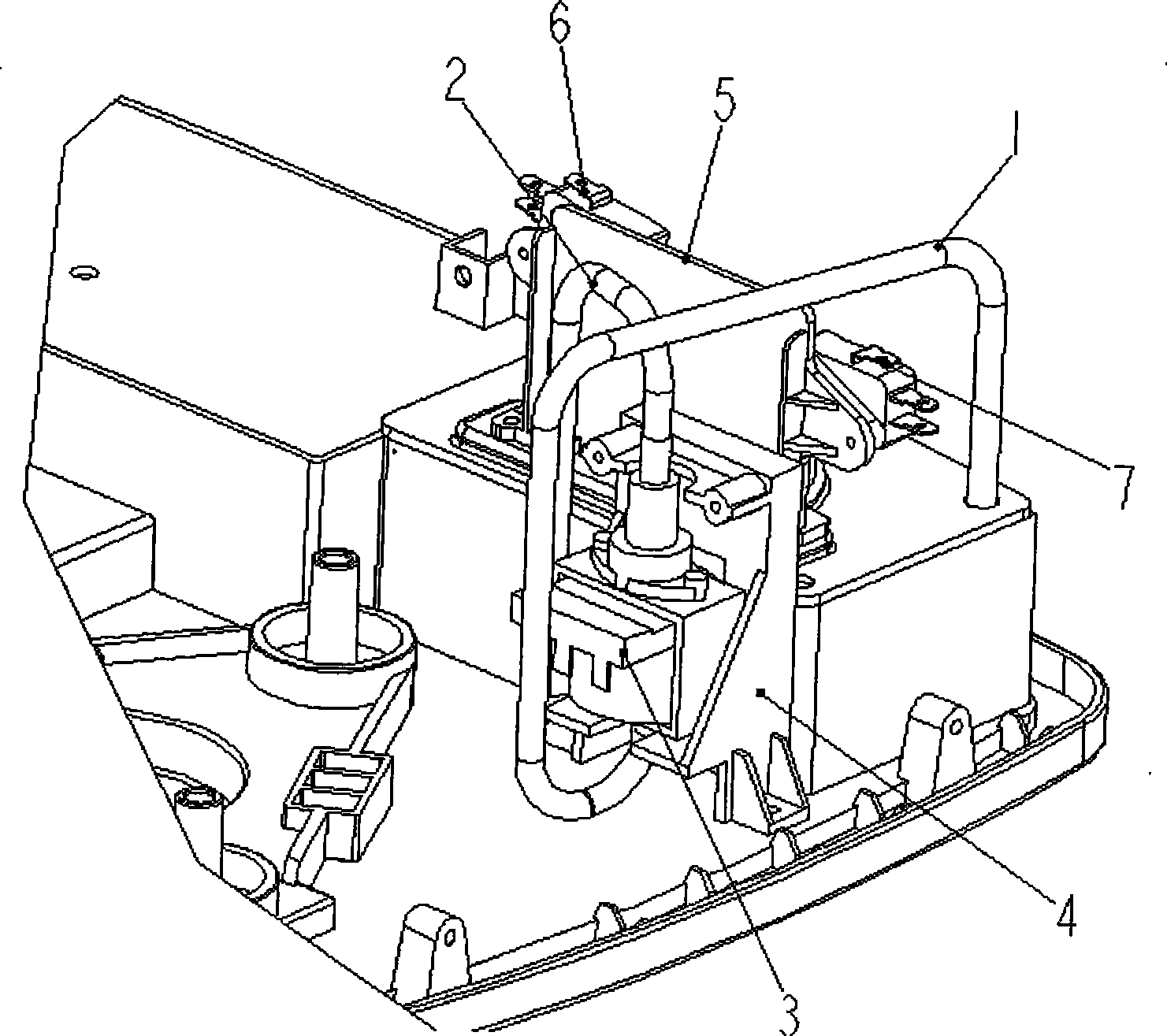

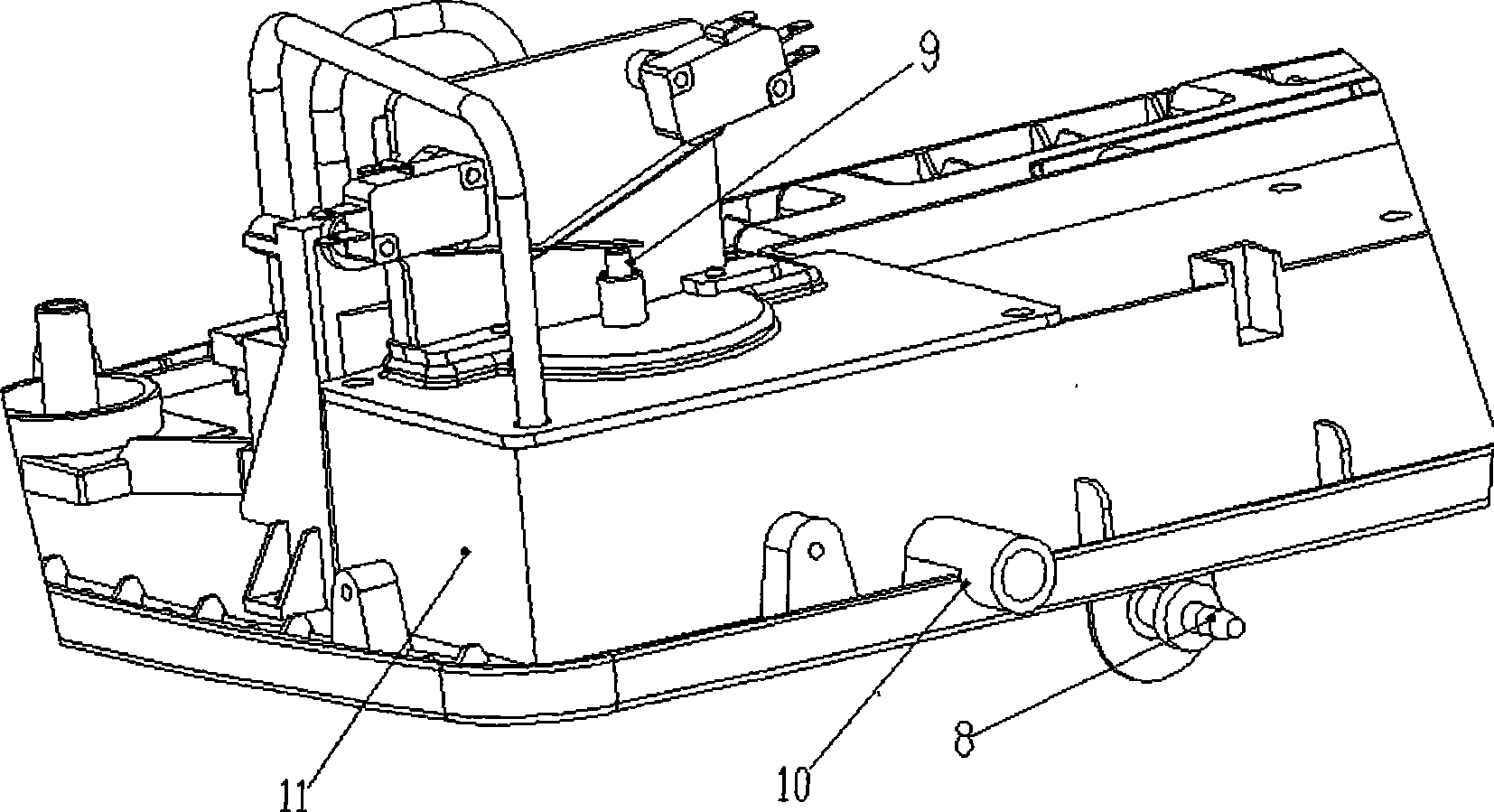

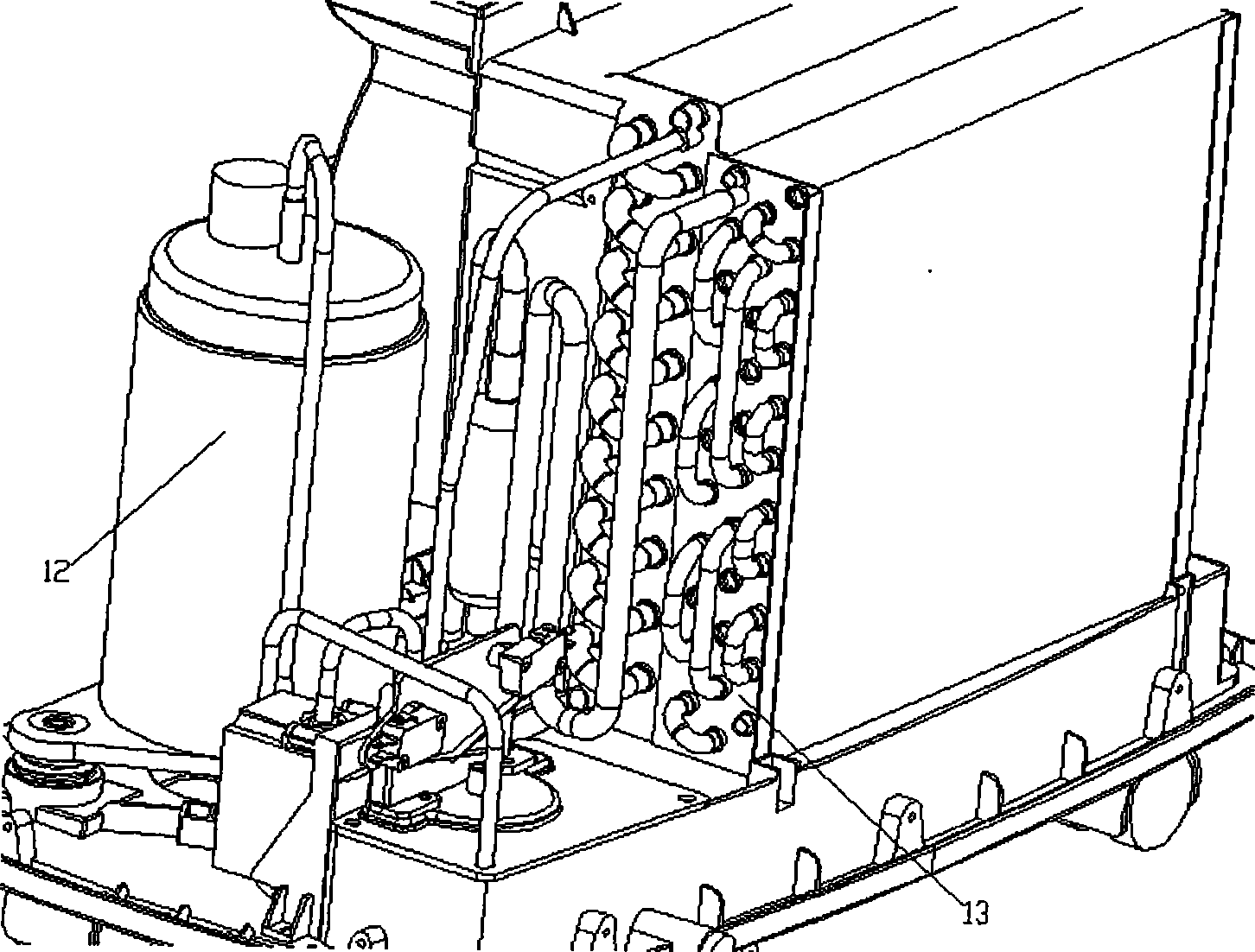

Paper money temporary storage module and reel rotating speed control method thereof

ActiveCN102930638AAvoid downtimeReduce lossFunction indicatorsCoin/currency accepting devicesAngular velocityTemporary storage

The invention relates to a paper money temporary storage module and a reel rotating speed control method thereof. The paper money temporary storage module comprises a large reel driven by a first power motor, a small reel driven by a second power motor, a coiling tape, a first coded disc, a second coded disc, a first sensor, a second sensor and a microcontroller, wherein two ends of the coiling tape are respectively fixed on the large reel and the small reel and the coiling tape is retracted and wound between the large reel and the small reel; the first coded disc is fixed on a rotating shaft of the large reel; the second coded disc is fixed on a rotating shaft of the small reel; the first sensor is arranged corresponding to the first coded disc and is used for monitoring the rotating angle of the large reel; the second sensor is arranged corresponding to the second coded disc and is used for monitoring the rotating angle of the small reel; and the microcontroller is used for calculating the length of the coil tape released by the small reel when the large reel rotates for a circle according to output signals of the first sensor and the second sensor and further calculating the current radius of the large reel, and thus angular velocities of the large reel and the small reel are controlled and the linear velocity of the large reel is enabled to be consistent with that of the small reel.

Owner:GRG BAKING EQUIP CO LTD

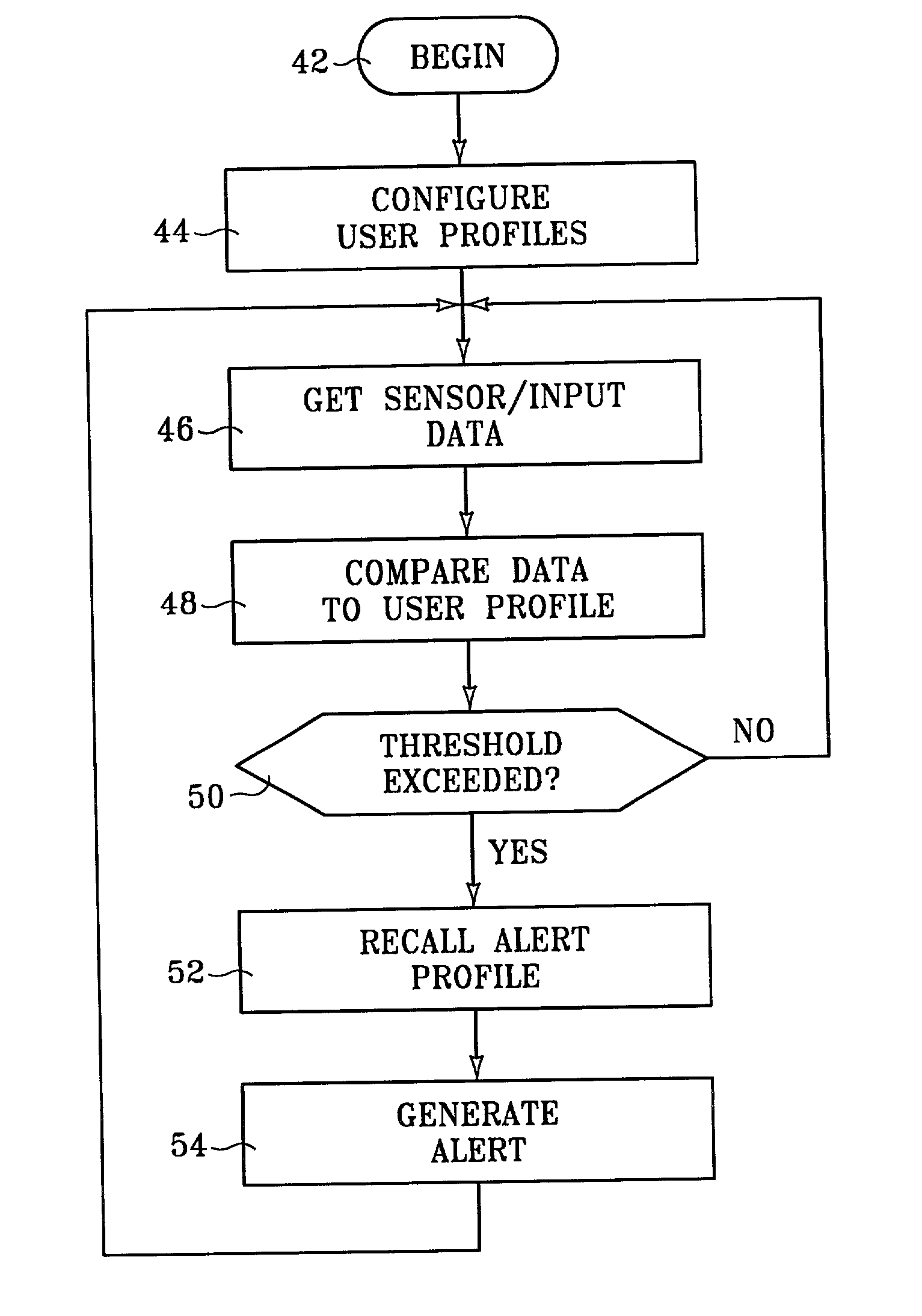

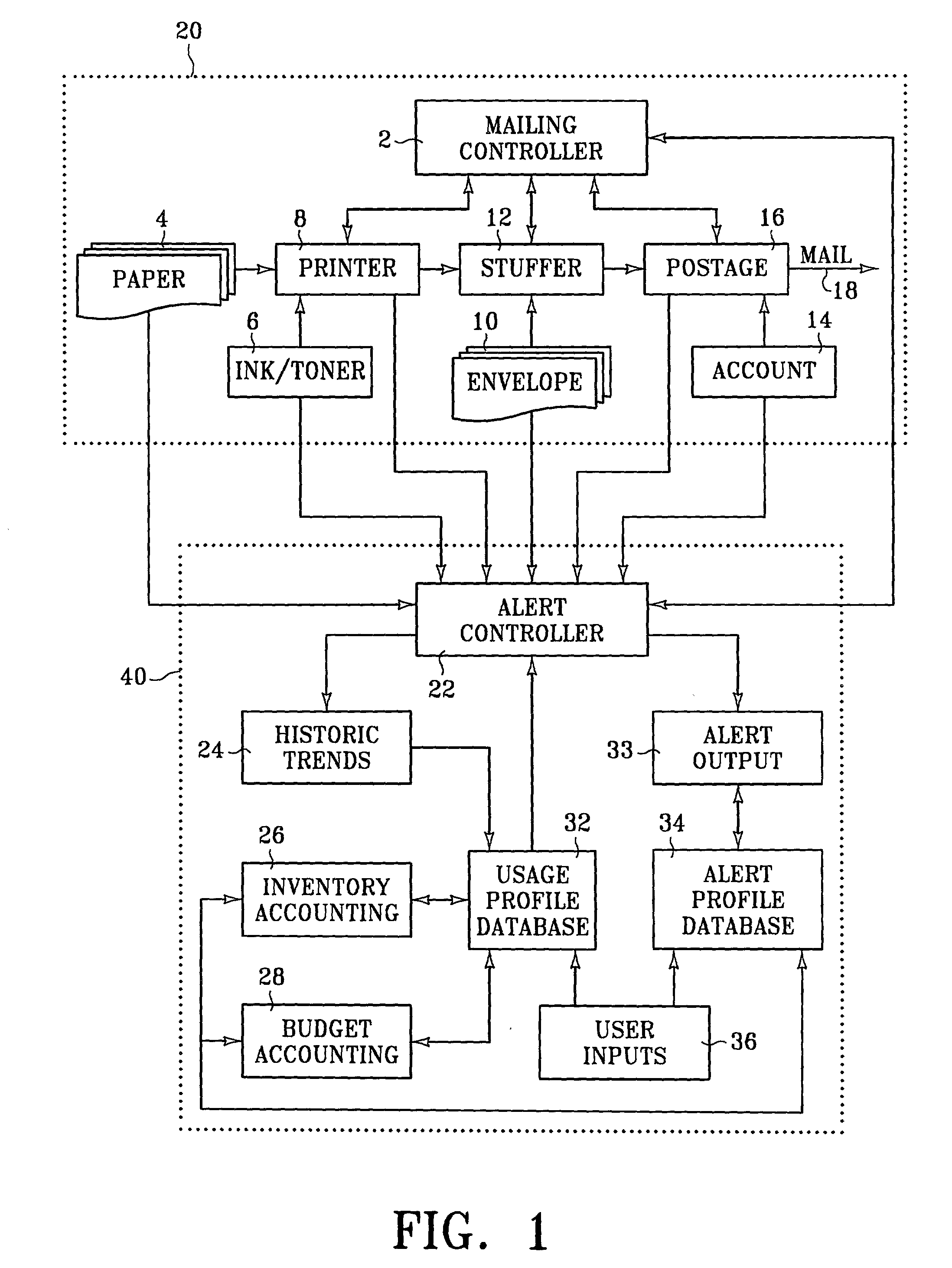

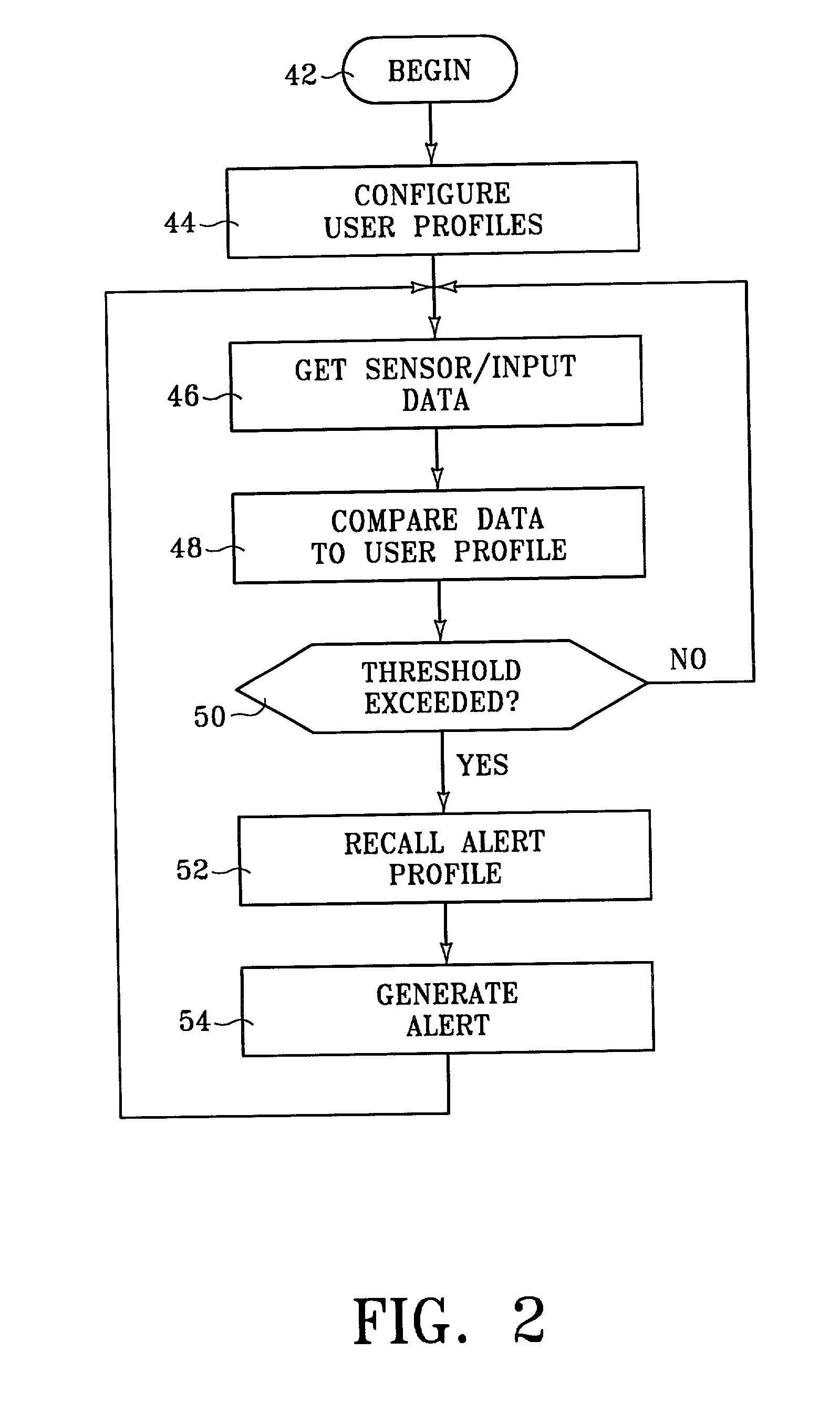

Cost and usage based configurable alerts

InactiveUS20030110103A1Avoid downtimeAvoid wastingAlarmsLogisticsSystem parametersParameter analysis

A method and apparatus for notification of deviation from predetermined threshold in a system that utilizes consumable and wear components. In one embodiment, a usage rate profile database is configured with one or more thresholds. A controller monitors one or more system parameters and compares them with the database. An alert is generated when deviation beyond the threshold exists. The metrics of the threshold can be quantity, value, or time. The alert action can also be configured to provide simple notification, a description of the deviance, or it can enable a corrective action, such as replenishment of the depletion. In addition, analysis of parameters can occur on a system-wide level, or can be sub-divided by task, user, or budget items.

Owner:HEWLETT PACKARD DEV CO LP

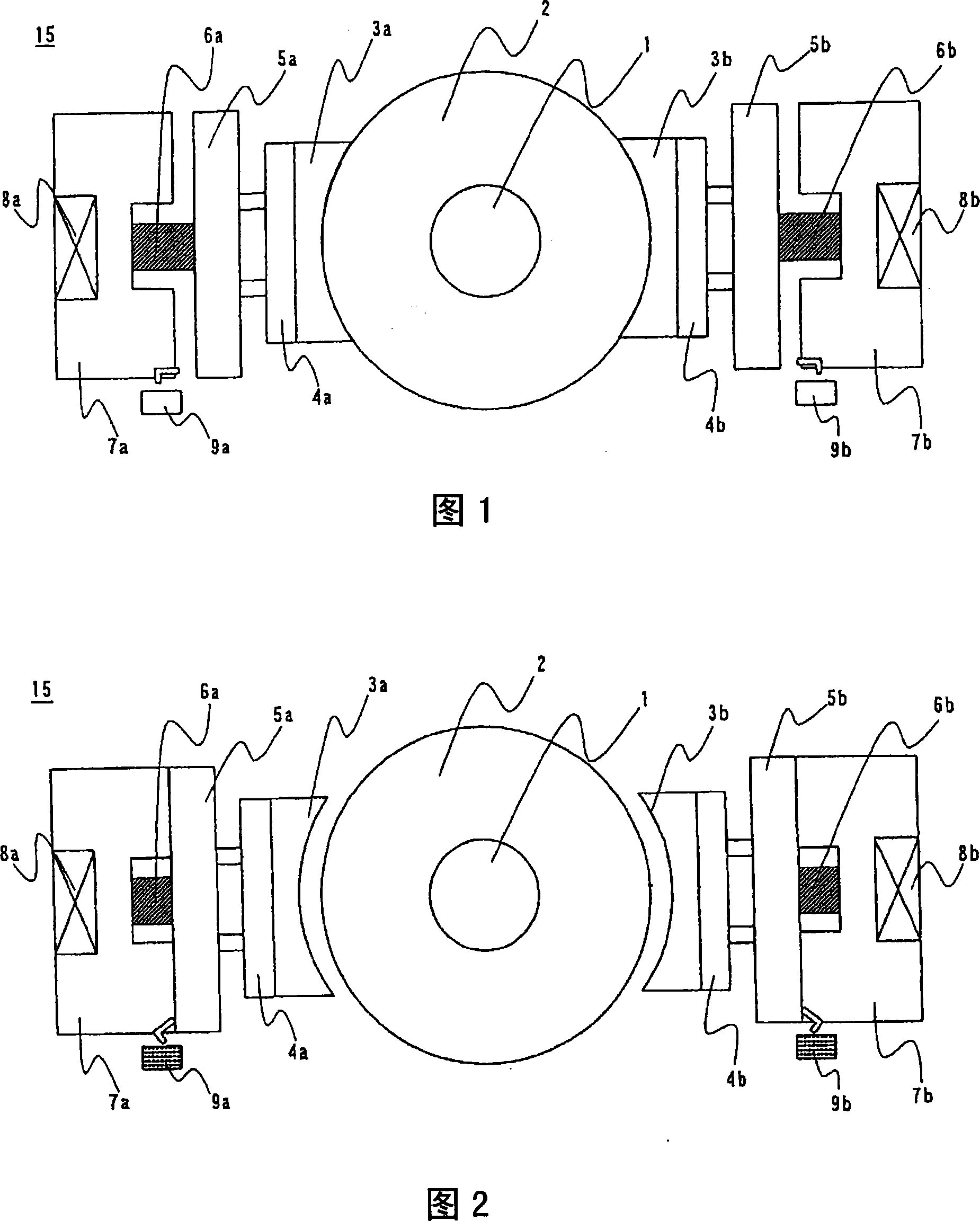

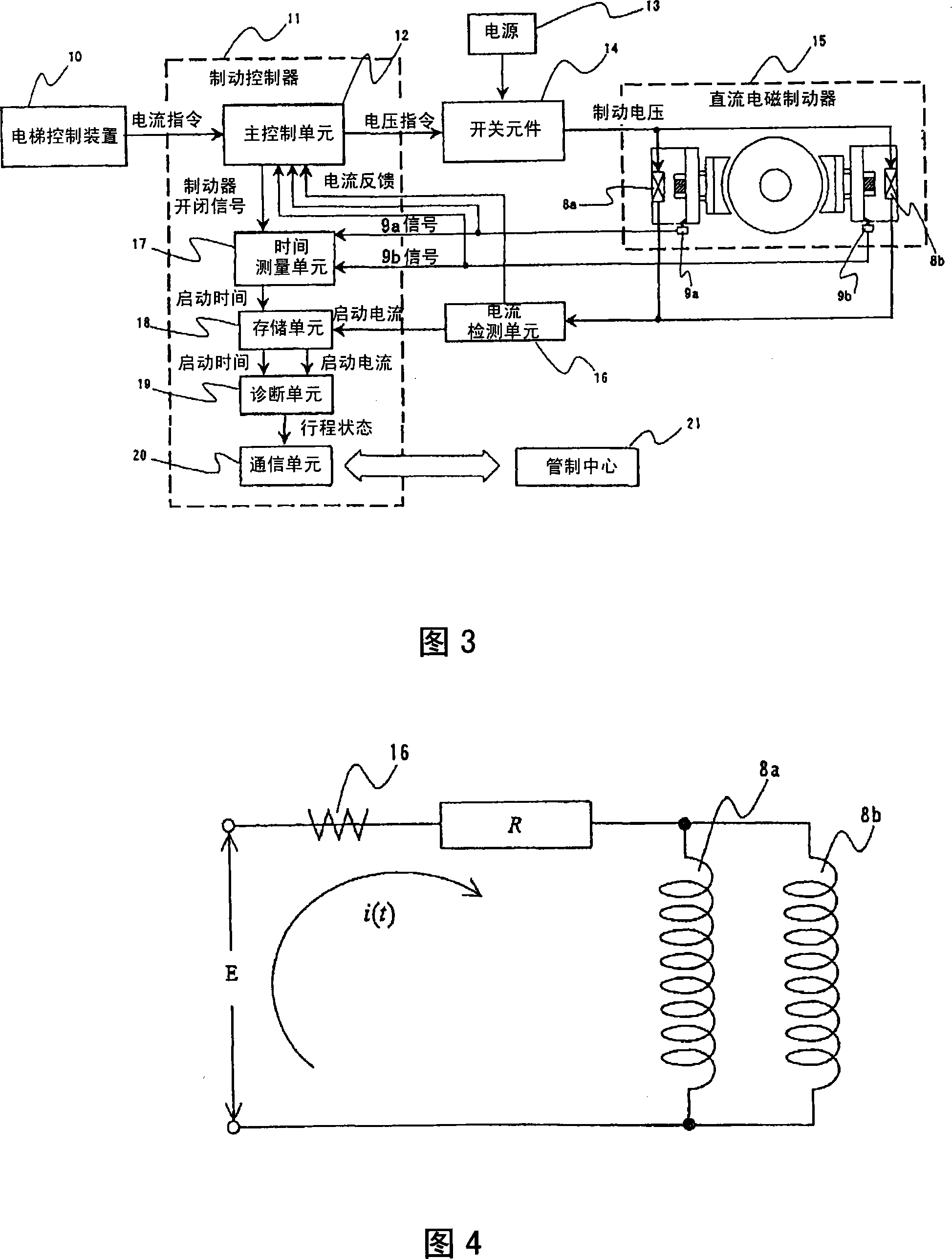

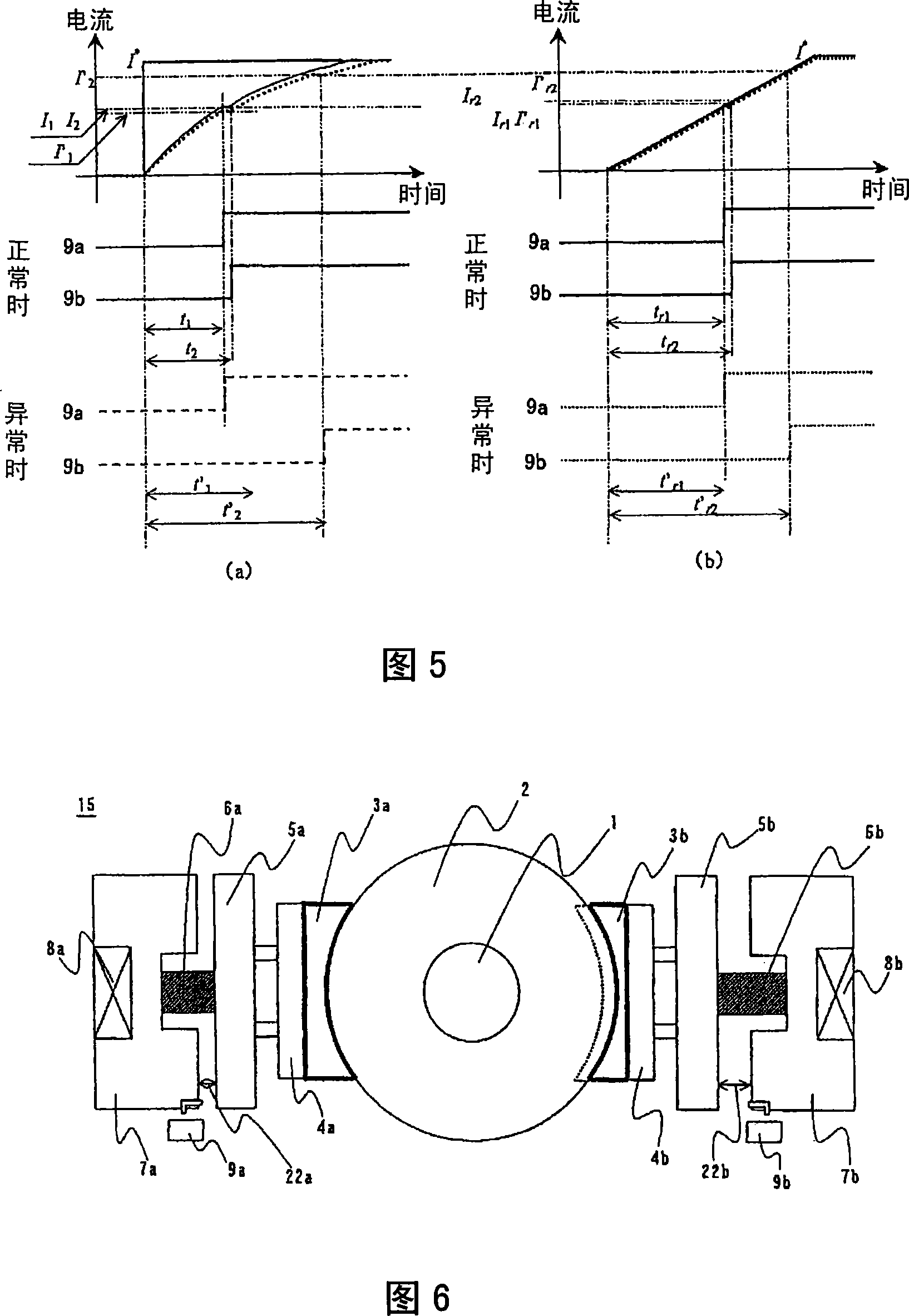

Elevator brake control device

ActiveCN101224831ASolve difficult-to-detect problemsPrecise Exception CheckingElevatorsPower flowExcitation current

The invention provides an elevator brake control device capable of detecting the abnormity of the direct-current magnetic brake without special device and free from the effect of current staining during the brake operating and the act position of the brake detecting switch. The elevator brake control device comprises: at least above two direct-current magnetic brakes; a brake detecting switches mounted in each direct-current magnetic brake and used for detecting the switching state of the direct-current magnetic brake; a main control unit for commanding the switch of the direct-current magnetic brake; a current detecting unit for detecting the exciting current flowing through the brake coil of the direct-current magnetic brake; a storage cell for storing the normal current value detected by the current detecting unit and a diagnosis cell for diagnosing the state of the direct-current magnetic brake by comparing the normal current value with the abnormal current value.

Owner:HITACHI LTD +2

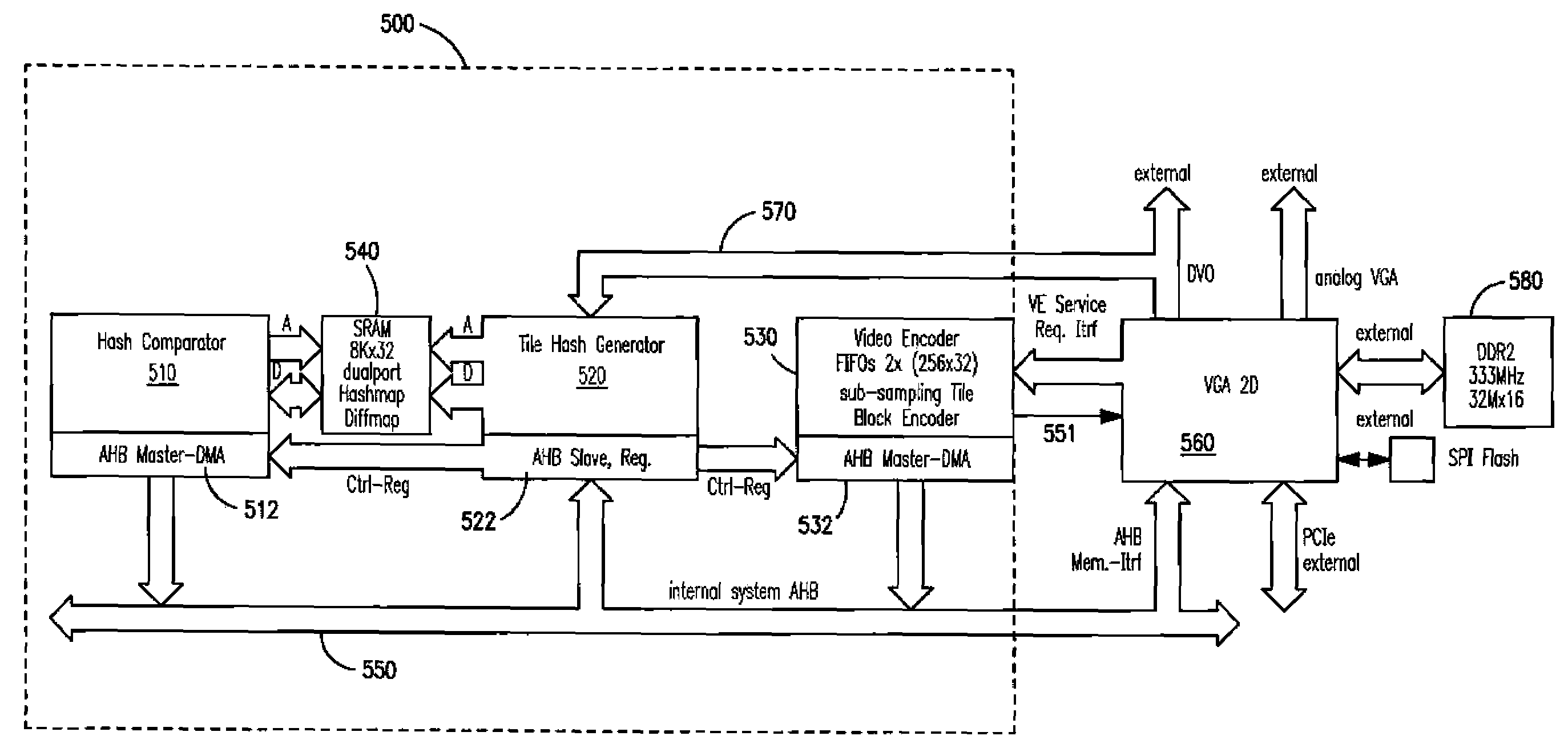

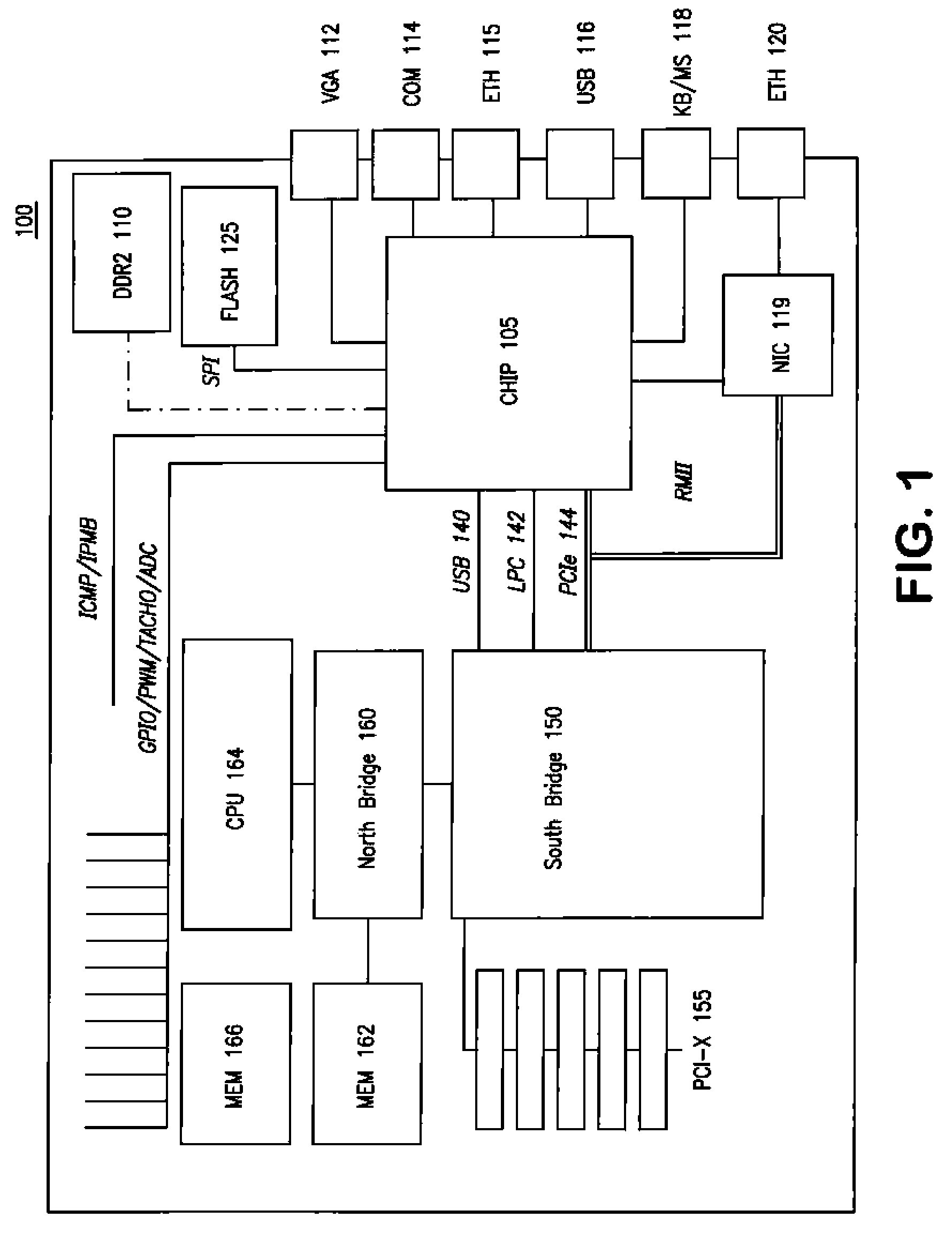

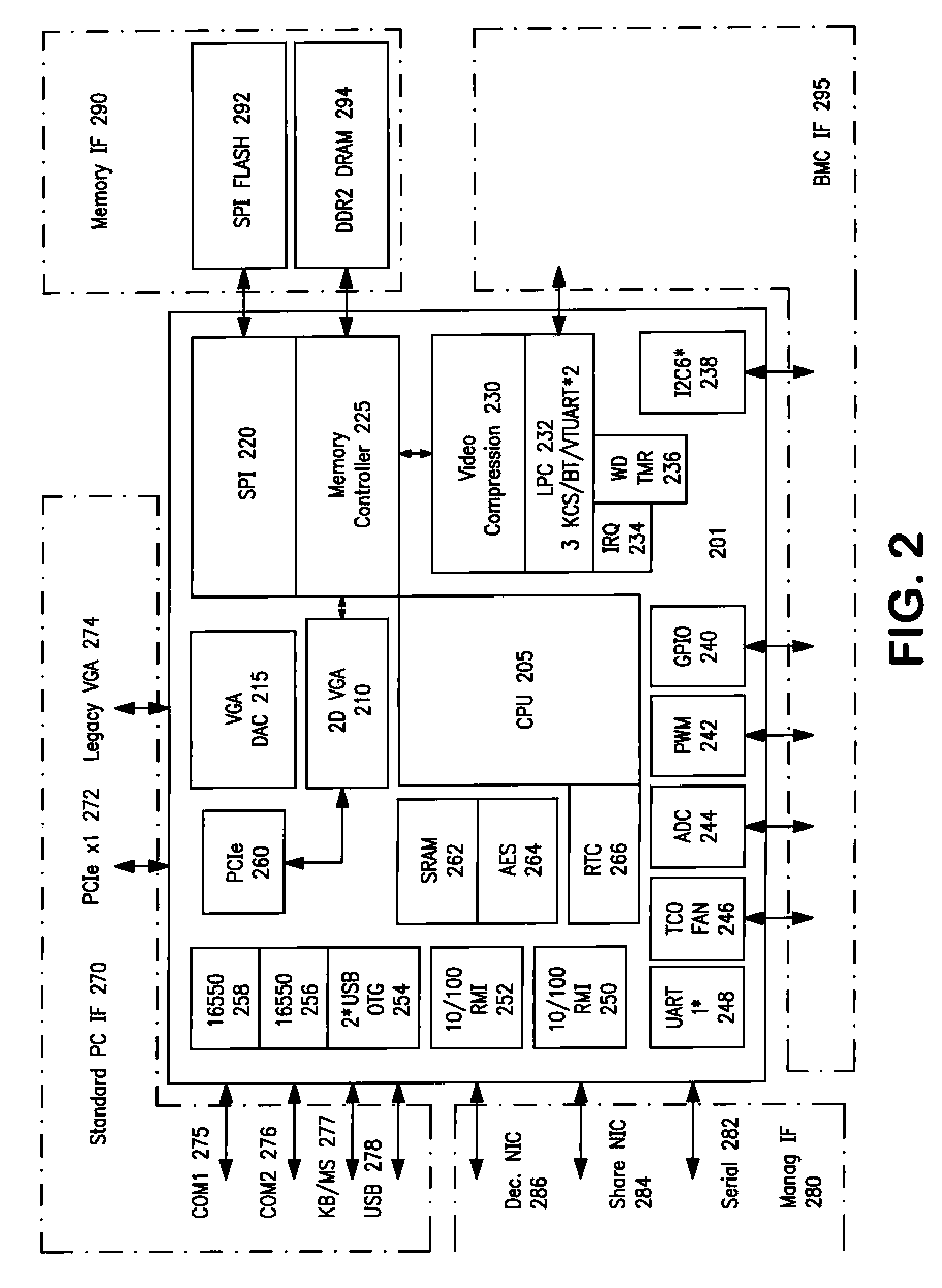

Architecture and Method for Remote Platform Control Management

InactiveUS20080278508A1Minimizes server downtimeImprove productivityCharacter and pattern recognitionCathode-ray tube indicatorsDifference-map algorithmVideo processing

An integrated circuit is a baseboard management controller that is a fully integrated system-on-a-chip microprocessor incorporating function blocks and interfaces that provide remote management solution. The integrated circuit uses a microprocessor, and a video compression accelerator in combination with a unified memory architecture to accelerate video processing, and a set of system and peripheral functions that are useful in a variety of remote management applications. The video compression accelerator generates hash map values for received image data, compares the hash map values to generate a difference map and encodes the image data corresponding to the difference map prior to the microprocessor sending the encoded video data to a client.

Owner:RARITAN AMERICA

Modular multi-level multi-terminal flexible direct current system direct current fault handling method

ActiveCN103066573ATroubleshooting method is simple and easyReliable methodEmergency protective circuit arrangementsModularityFault handling

The invention provides a modular multi-level multi-terminal flexible direct current system direct current fault handling method which comprises the following steps that (1) a relay protection device detects a multi-terminal flexible direct current system in real time, if a direct current fault point is detected, breakers at two ends of a direct current line are switched off, and converters of stations are kept in a running state; (2) the switched-off breakers are switched on, whether the fault disappears is detected, if the fault does not disappear, the breakers are switched off again, and if the fault disappears, a step (3) is carried out; (3) the direct current line is used, and the system runs normally. The modular multi-level multi-terminal flexible direct current system direct current fault handling method is simple, easy to implement and reliable, influences on a plurality of converter stations of temporary direct current faults are reduced, timely recovery and running of the system after the temporary direct current faults are removed are guaranteed effectively, and device running safety is guaranteed at the same time.

Owner:GLOBAL ENERGY INTERCONNECTION RES INST CO LTD +2

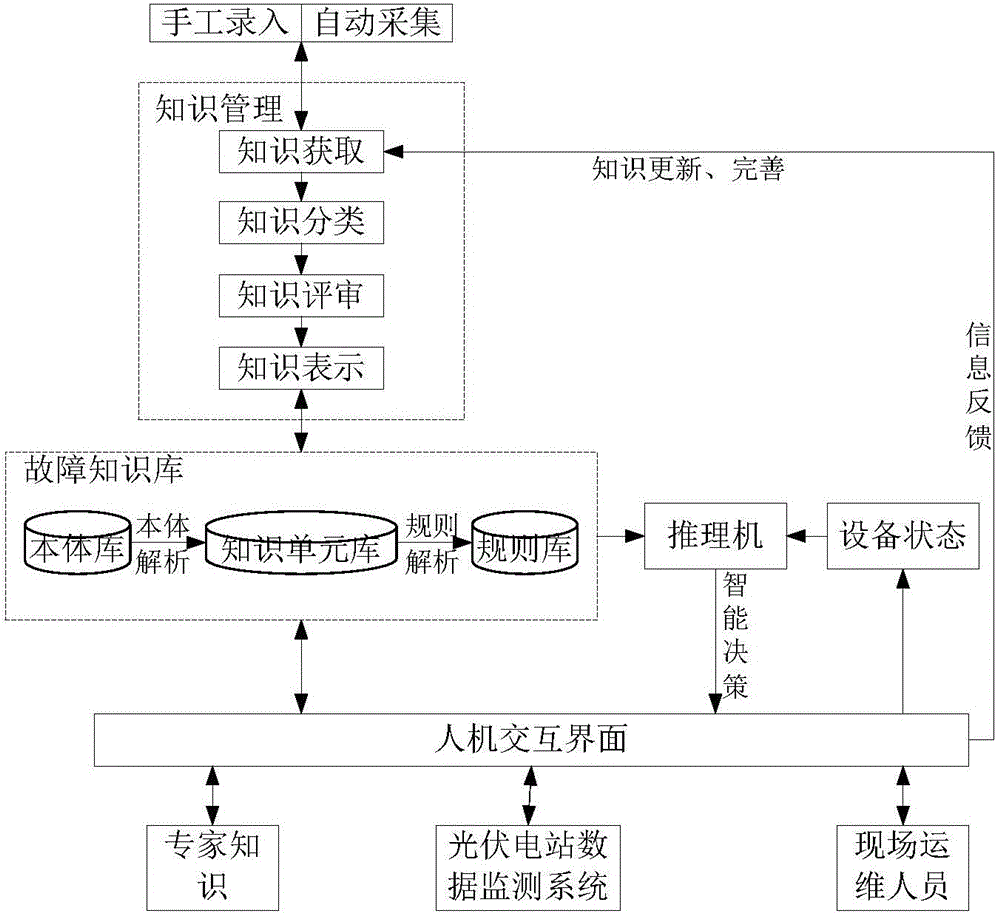

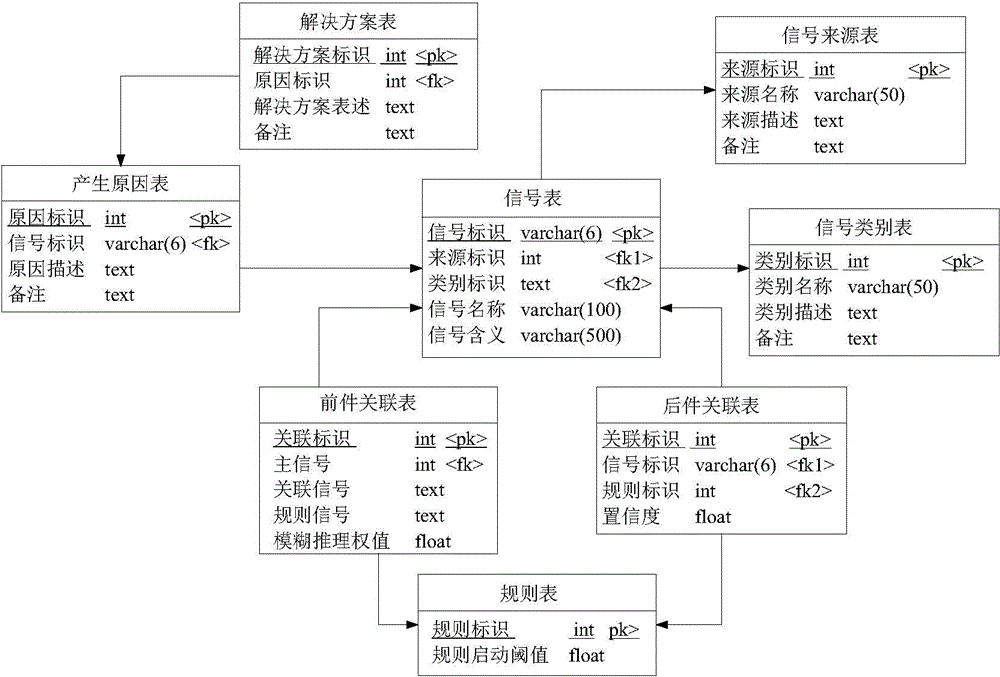

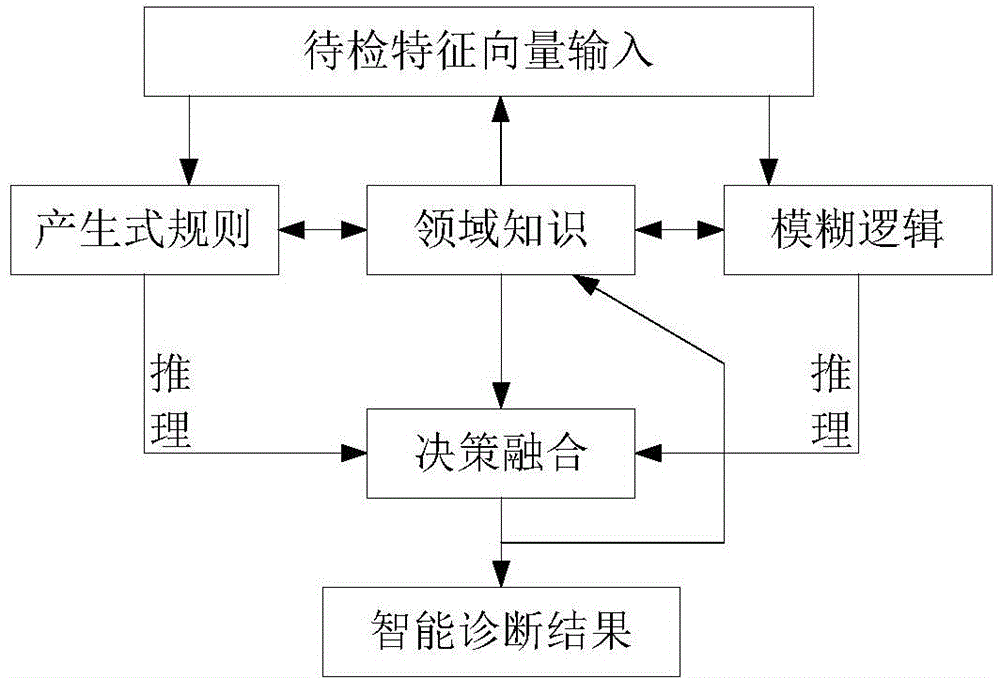

Photovoltaic power station fault diagnosis method based on fuzzy production rule knowledge base

InactiveCN104133981AReduce downtimeAvoid downtimeSpecial data processing applicationsInformation repositoryDecision scheme

The invention relates to a photovoltaic power station fault diagnosis method based on a fuzzy production rule knowledge base, and belongs to the technical field of electric engineering informatization. According to the method, firstly, the field knowledge of photovoltaic power station equipment warning and fault information is stored in a fact and rule form for forming a fault information knowledge base; then, fuzzy logics are adopted for carrying out qualitative analysis on the fault information base of photovoltaic power station equipment, and a judging rule between a fault phenomenon and a reason is determined; detected fault feature vectors are subjected to fuzzy matching with each rule antecedent in a rule base; and according to the matching relationship between the fault phenomenon and the judging rule, the fault diagnosis reason and the result are determined, the fault is positioned, and an overhaul decision scheme is given. The photovoltaic power station fault diagnosis method has the advantages that the final fault or the most possible fault can be fast searched and positioned; meanwhile, the knowledge base is inquired to obtain the overhaul decision; the overhaul decision is provided for overhaul personnel, so that the overhaul personnel can shorten the fault inquiry time; the goal of fast repairing fault equipment is achieved; and the power station machine halt time is reduced, or the power station machine halt is avoided.

Owner:STATE GRID CORP OF CHINA +1

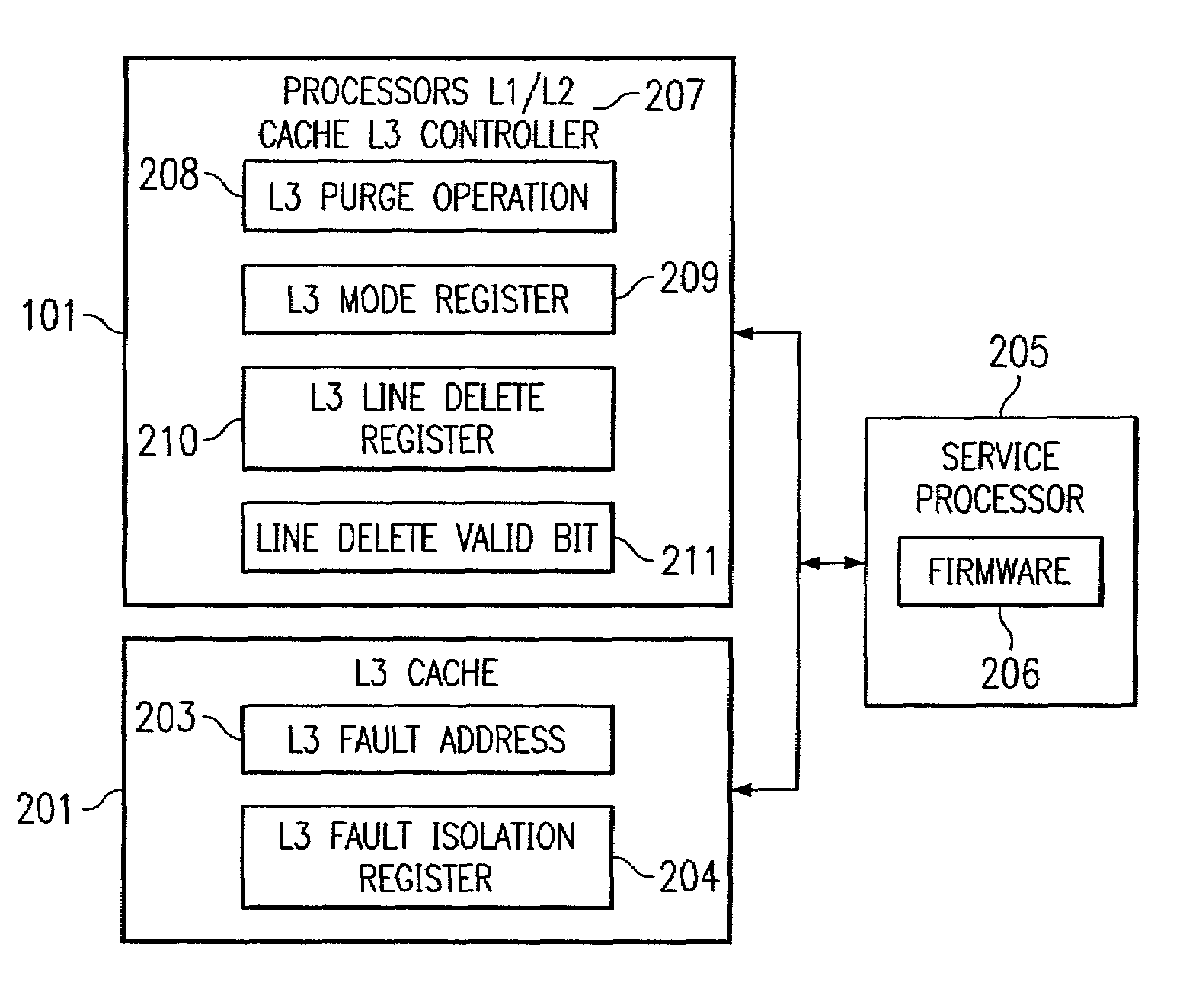

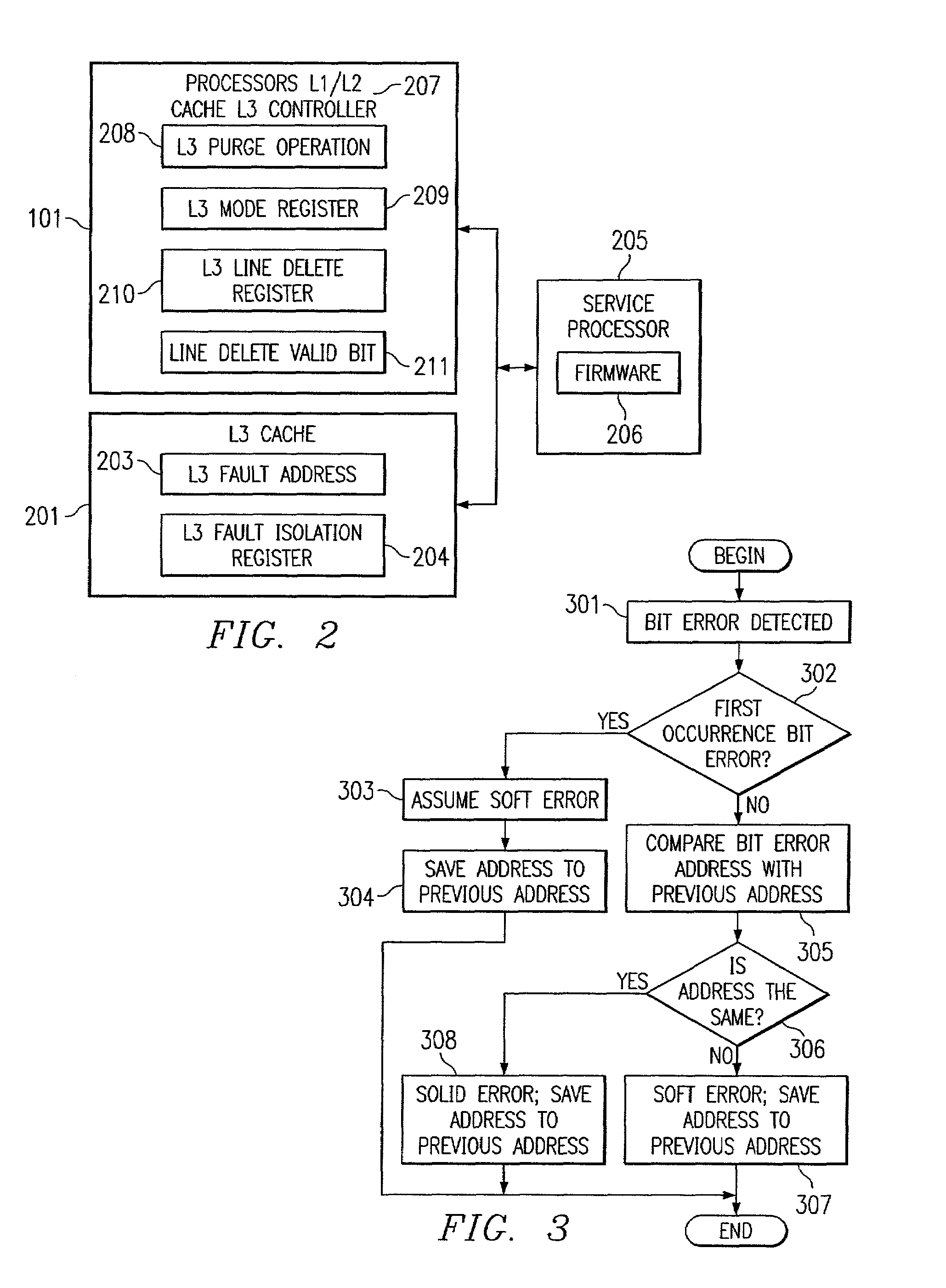

Method and system for handling multiple bit errors to enhance system reliability

ActiveUS7007210B2Avoid downtimeNon-redundant fault processingStatic storageData processing systemParallel computing

The present invention provides an improved method, an system, and a set of computer implemented instructions for handling a cache containing multiple single-bit hard errors on multiple addresses within a data processing system. Such handles will prevent any down time by logging in the parts to be replaced by an operator when certain level of bit errors is reached. When a hard error exists on a cache address for the first time, serviceable first hard error, that cache line is deleted. Thus the damaged memory device is no longer used by the system. As a result, the system is running with “N−x” lines wherein “N” constitutes the total number of existing lines and “x” is less than “N”. An alternative method is to exchange the damaged memory device to a spare memory device. In order to provide such services, the system must first differentiate whether an error is a soft or hard error.

Owner:IBM CORP

Method and control module for controlling the drive mode of a hybrid drive to prevent jerky movements

InactiveUS20110112708A1Efficiency of drive is not substantially impairedAvoid changeInternal combustion piston enginesDigital data processing detailsComputer moduleJerky movements

The drive mode of a hybrid drive is controlled by: detecting a drive mode change signal characterizing a planned drive mode change, and determining a torque shortfall, which would occur due to the drive mode change. Furthermore, the method provides for comparing the torque shortfall with a threshold value, and blocking a drive mode change, if the comparison step reveals that the torque shortfall is above the threshold value. Otherwise, the method provides for: automatically performing a drive mode change according to the drive mode change signal, if the comparison step reveals that the torque shortfall is not above the threshold value.

Owner:ROBERT BOSCH GMBH

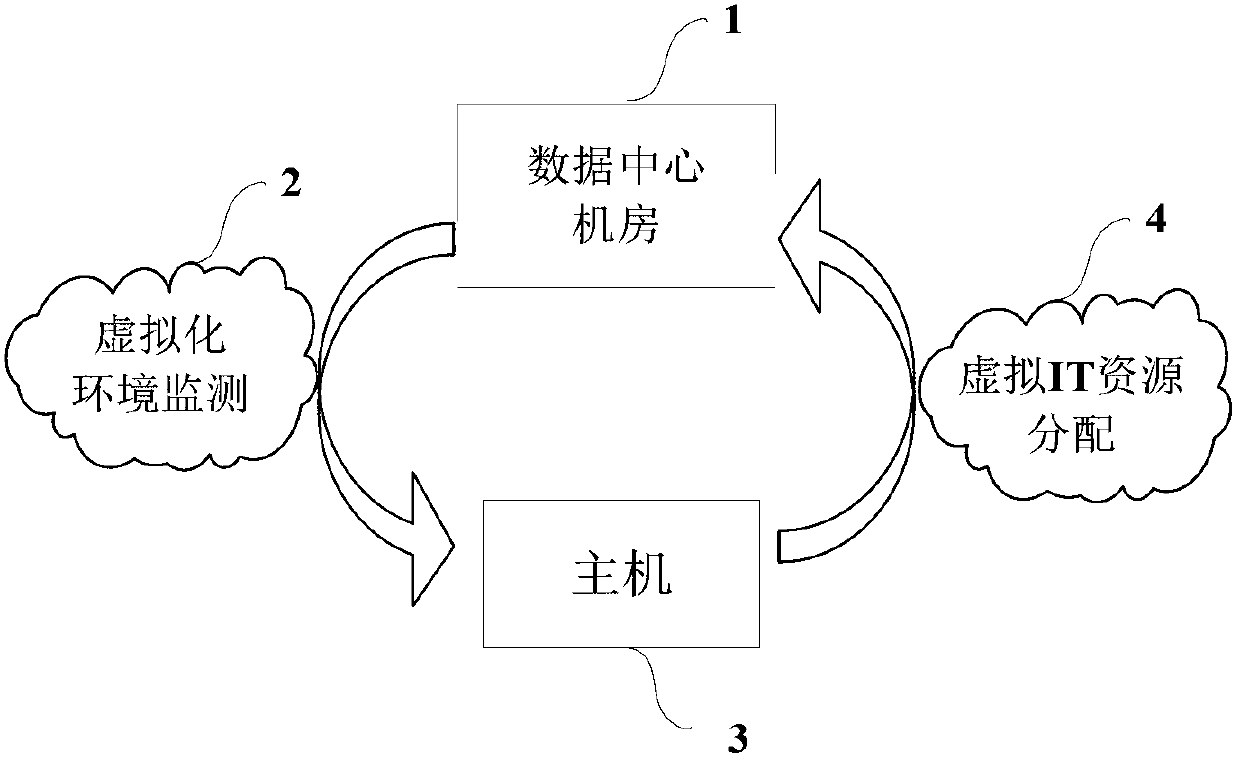

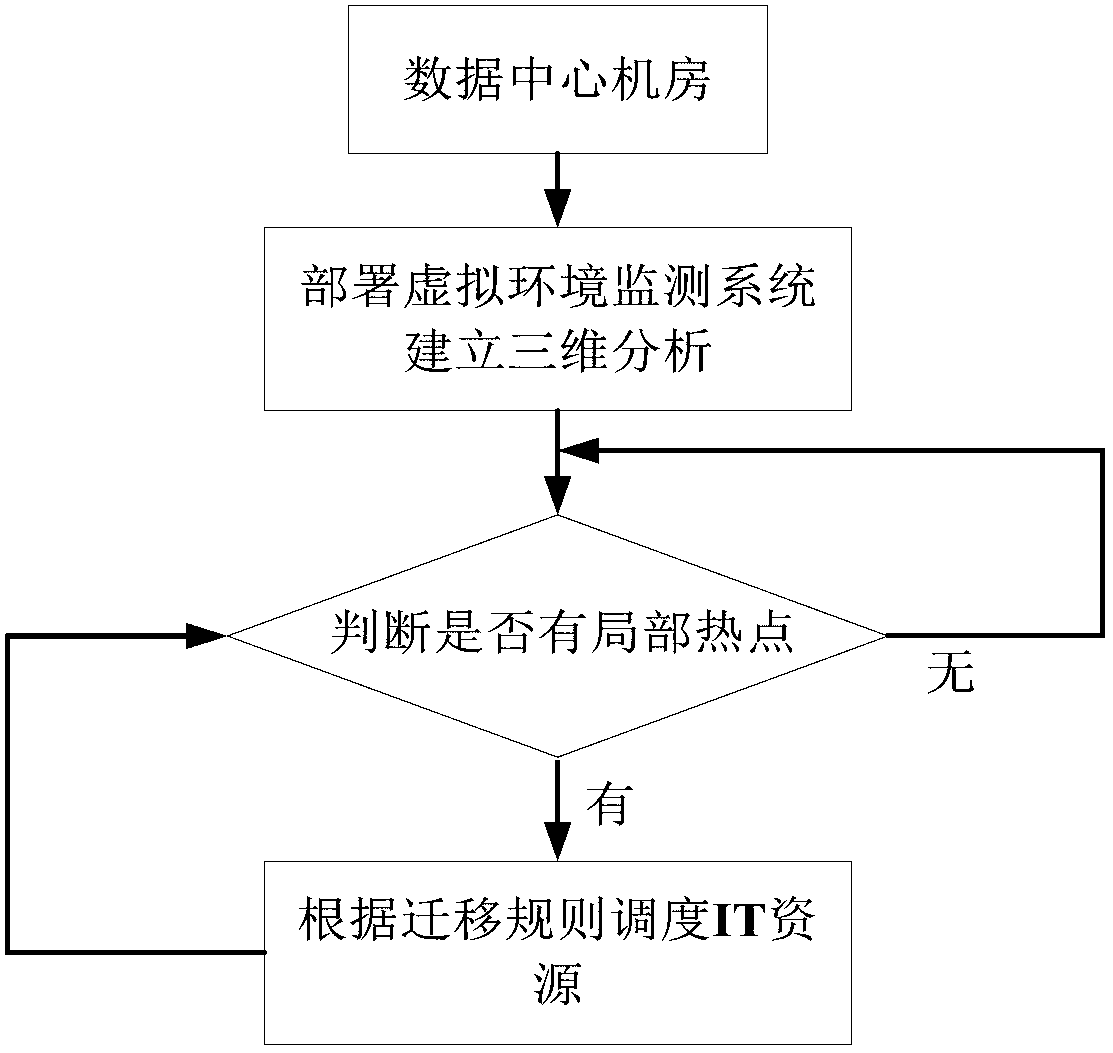

Data center energy saving system and method based on virtual IT resource distribution technology

ActiveCN103345298AImprove stability and longevityImprove energy efficiencyResource allocationPower supply for data processingMagnetic disksEnvironmental monitoring

The invention relates to a data center energy saving method based on a virtual IT resource distribution technology. Virtual environment resources in a data center are monitored to acquire a three-dimensional temperature and humidity nephogram and operation data of a CPU of a server, a magnetic disk and an internal storage, and accordingly limited IT resources are dynamically migrated and adjusted, air conditioner resources are reasonably dispatched and can be fully utilized, and unnecessary waste is reduced. Meanwhile, the virtual environment is continuously monitored to guarantee reasonable and effective resource allocation. The closed loop feedback monitoring mechanism effectively increases the use ratio of the resources in the data center, and finally achieves an environment-friendly operation and maintenance target of the data center.

Owner:SHANDONG COMP SCI CENTNAT SUPERCOMP CENT IN JINAN

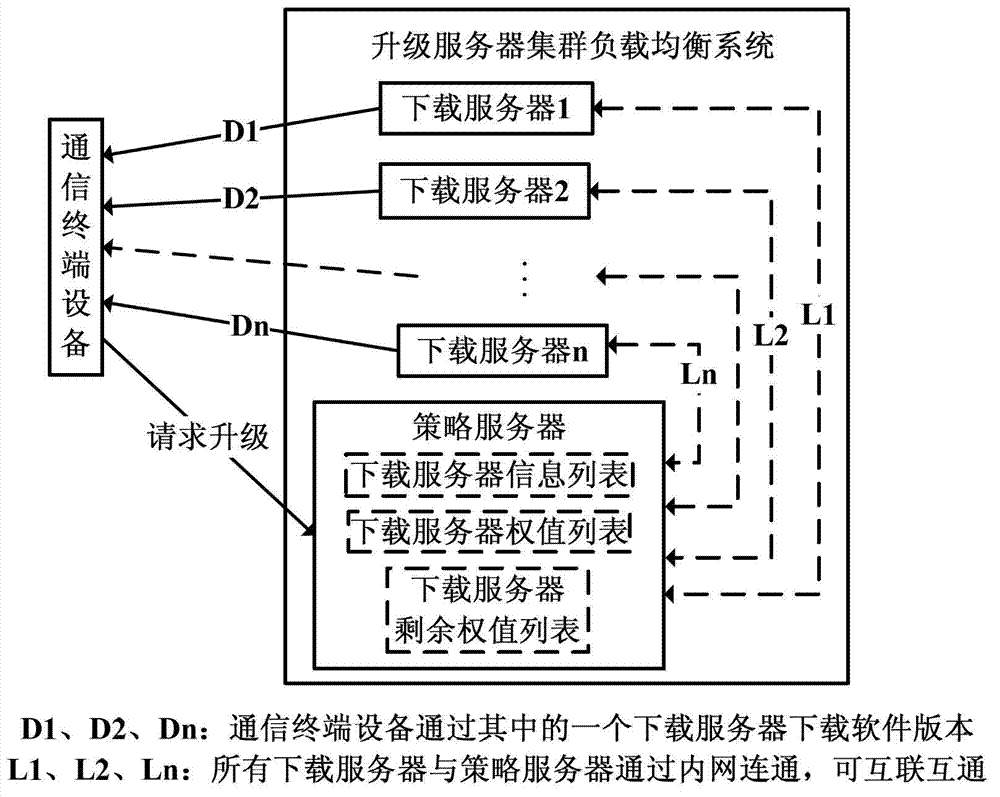

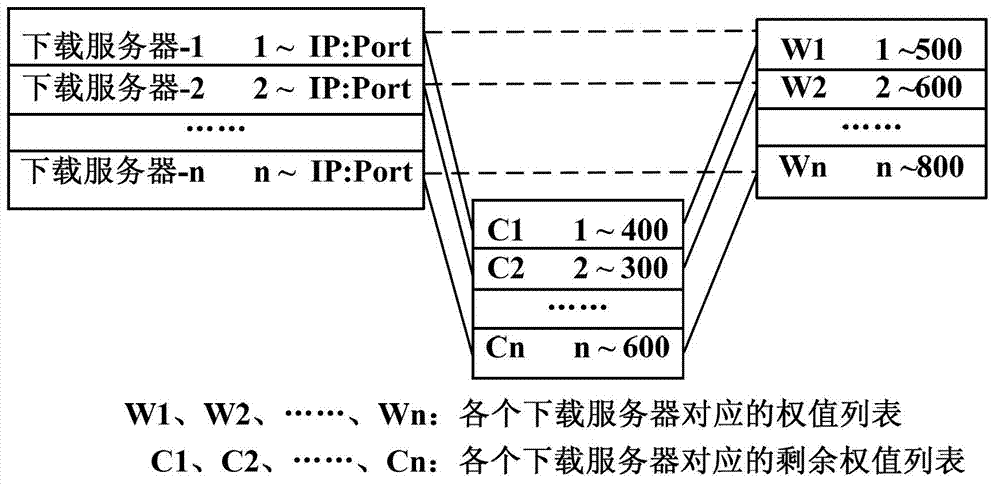

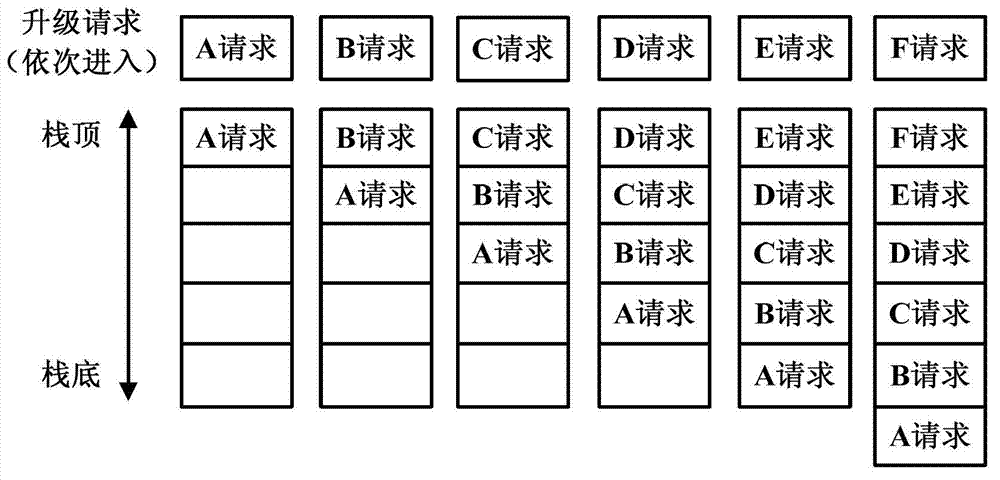

Upgraded server cluster system and load balancing method thereof

ActiveCN103118076ARealize rationalityGuaranteed stabilityTransmissionCluster systemsTerminal equipment

The invention discloses an upgraded server cluster system and a load balancing method thereof and relates to the field of server clusters. The upgraded server cluster system comprises a policy server and a plurality of download servers, wherein the policy server is a unified access entrance, a weight number is distributed to each of the download servers by the upgraded server cluster system, the weight number means the maximum access volume of the corresponding download server in unit time, the weight number of each of the download servers minus a real-time linking number of each of the download servers, then a residual weight number of each of the download servers is obtained, an information list , a weight number list and a residual weight number list of each of the download servers are stored in an accessible data base of the policy server or an accessible configuration file of the policy server by the policy server, and the information list of each of the download servers is corresponding to the weight number list and the residual weight number list of each of the download servers in a one-to-one mode. According to the upgraded server cluster system and the load balancing method thereof, through combining the number of communication terminal equipment which accesses to the download servers and the maximum access weight number of each of the download servers, and scientific dynamic scheduling and reasonable allocation of access requirements are achieved.

Owner:FENGHUO COMM SCI & TECH CO LTD

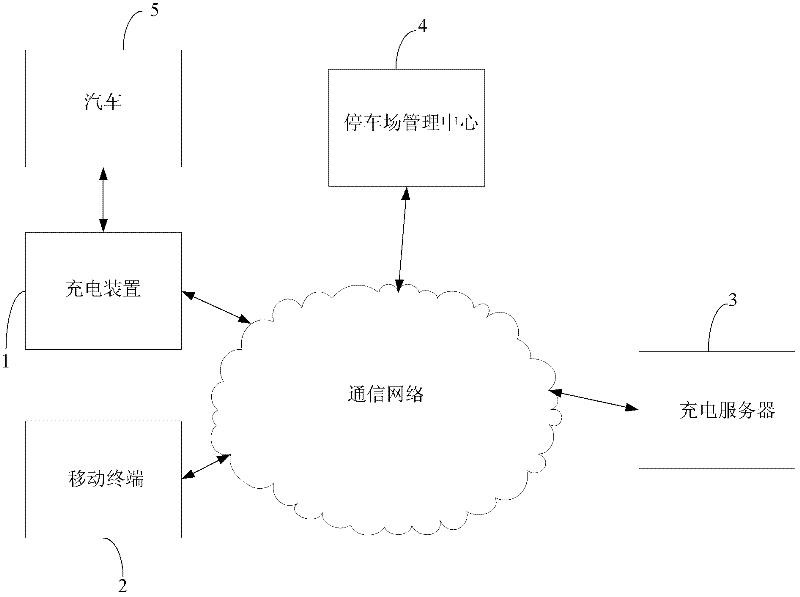

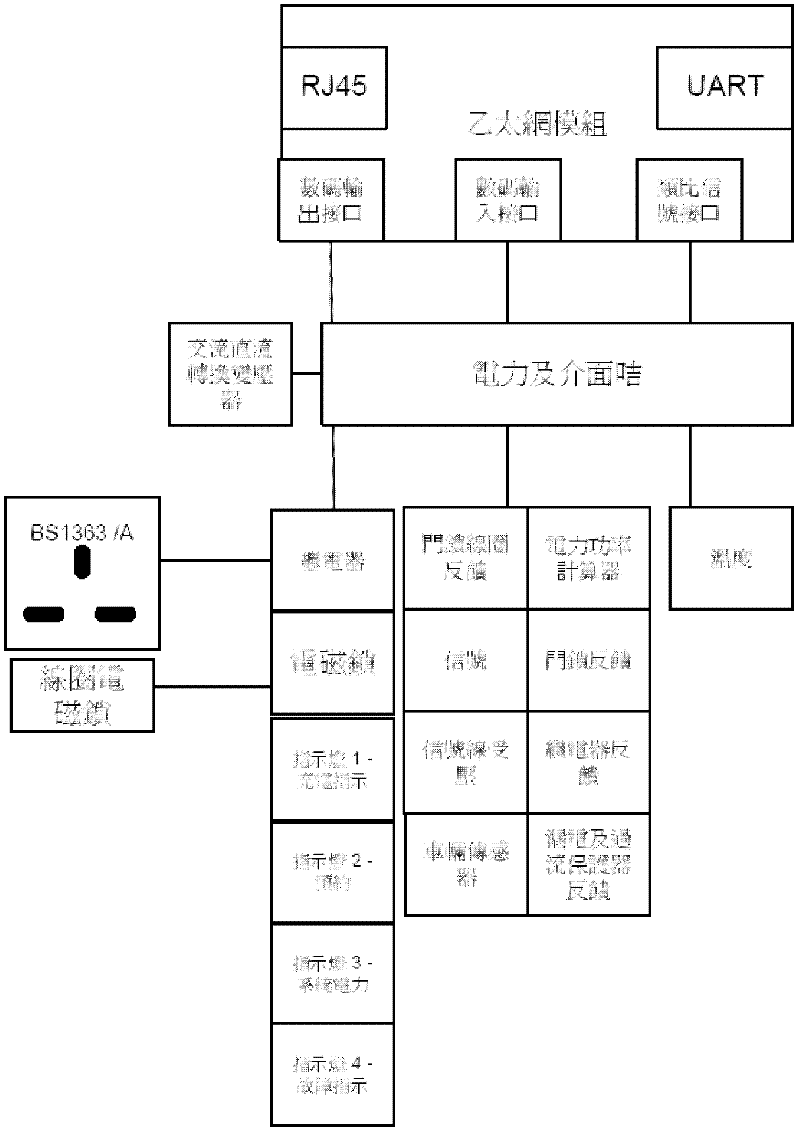

Charging device, charging system of electric automobile and control method of the charging system

InactiveCN102570537AEasy to control and useEasy to expandBatteries circuit arrangementsCharging stationsEngineeringElectrical and Electronics engineering

The invention relates to a charging device, a charging system of an electric automobile and a control method of the charging system of the electric automobile. The system comprises a mobile terminal, a charging server and the charging device. The mobile terminal is used to send charging service request information and a charging mode to the charging server. The charging server is used to control the charging device to charge the automobile connected with the charging device when user information and information of the charging device are verified to be valid and to send charging completion information to the mobile terminal. The charging server, the mobile terminal and the charging device are connected through wire and wireless networks to form network control and matched with a charger or a vehicle sensor in a charging stall to control and manage charge for the parked electric automobile. The invention supports appointment making function, has the function of self-detection and automatic error report, and is easy to use and control. Hardware is easy to expand, different charging plugs can be replaced, and use of an electronic card is obviated. Charging can be performed only by login authentication and the invention can indicate various work states in the charging process.

Owner:HONG KONG POWER

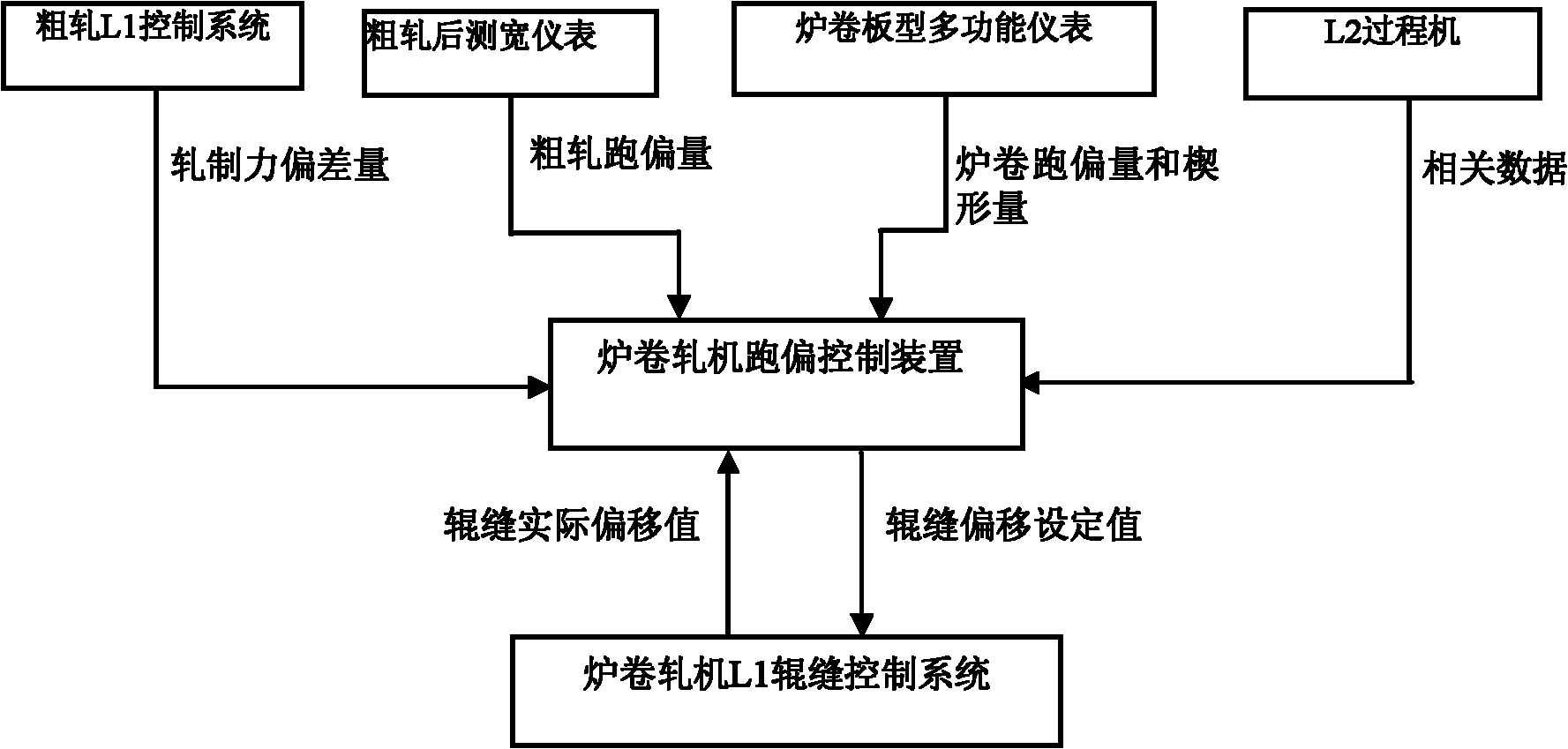

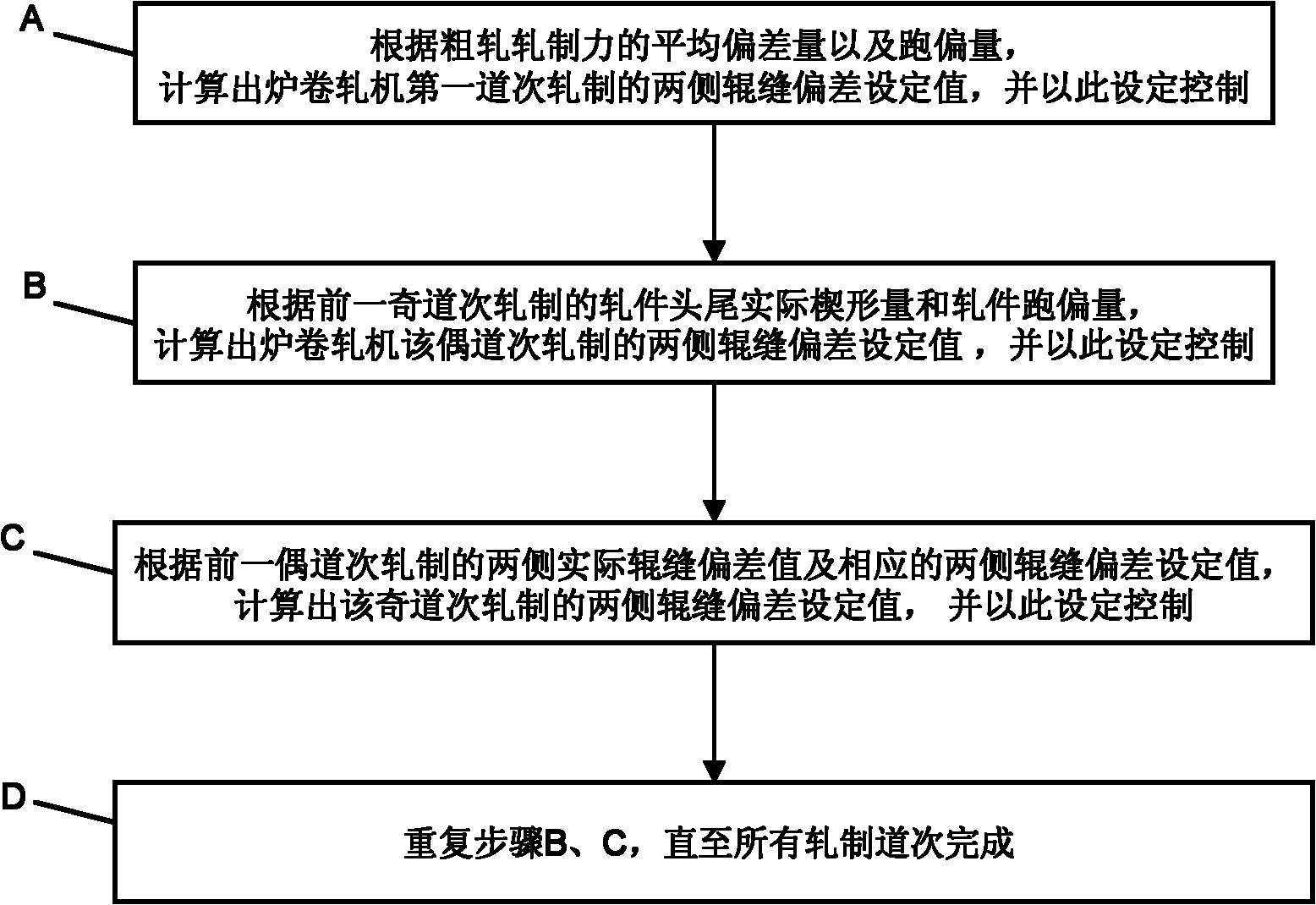

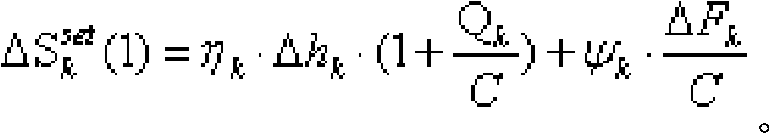

Steckel mill rolled piece head-and-tail deviation control method

InactiveCN102641903AImprove rolling stabilityPrevent set controlRare end control deviceRoll force/gap control deviceStrip millStrip steel

The invention discloses a steckel mill rolled piece head-and-tail deviation control method which comprises the following steps that: based on existing equipment configuration, different modes are distinguished by integrating the rolling information of a steckel mill according to the rolled piece deviation and rough rolling force in the final step of rough rolling, then the deviation controlled by roll gaps on both sides of the steckel mill is determined, and roll gap setting control for preventing deviation is carried out. Through the method, the hand-and-tail deviation of strip steel can be reduced, shut-down accidents caused by the deviation of strip steel can be prevented, and the rolling stability of the steckel mill can be improved.

Owner:BAOSHAN IRON & STEEL CO LTD

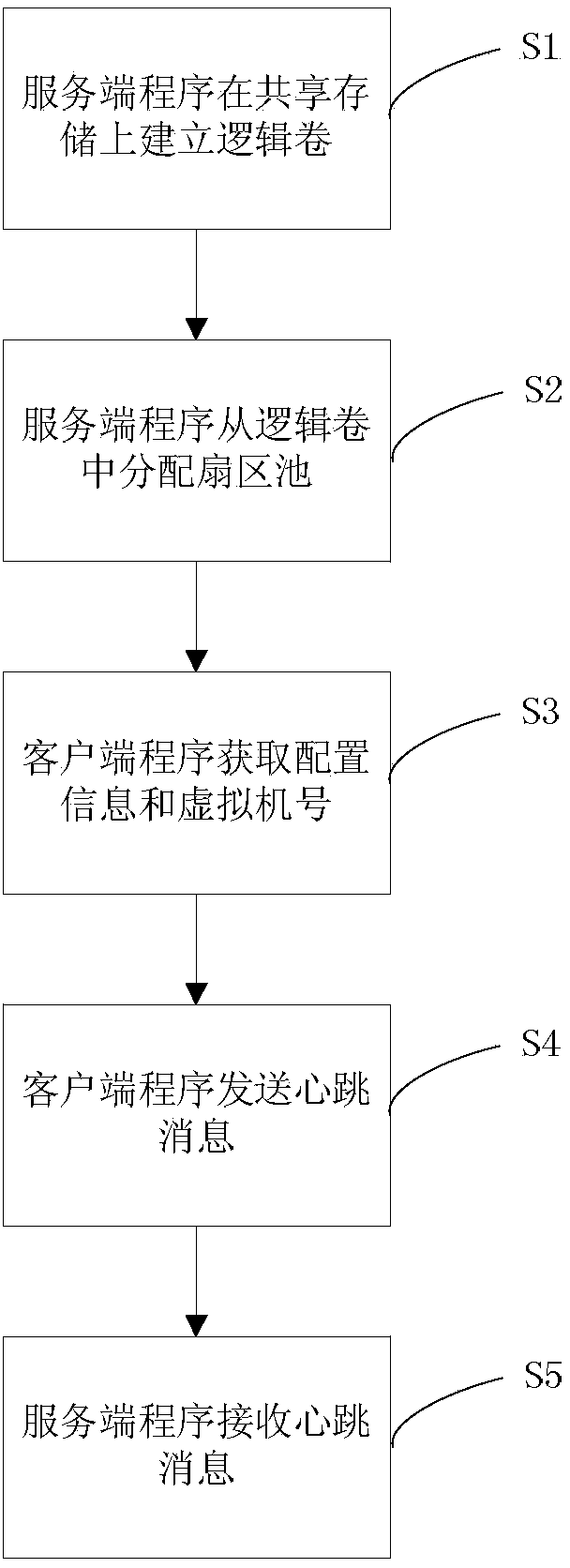

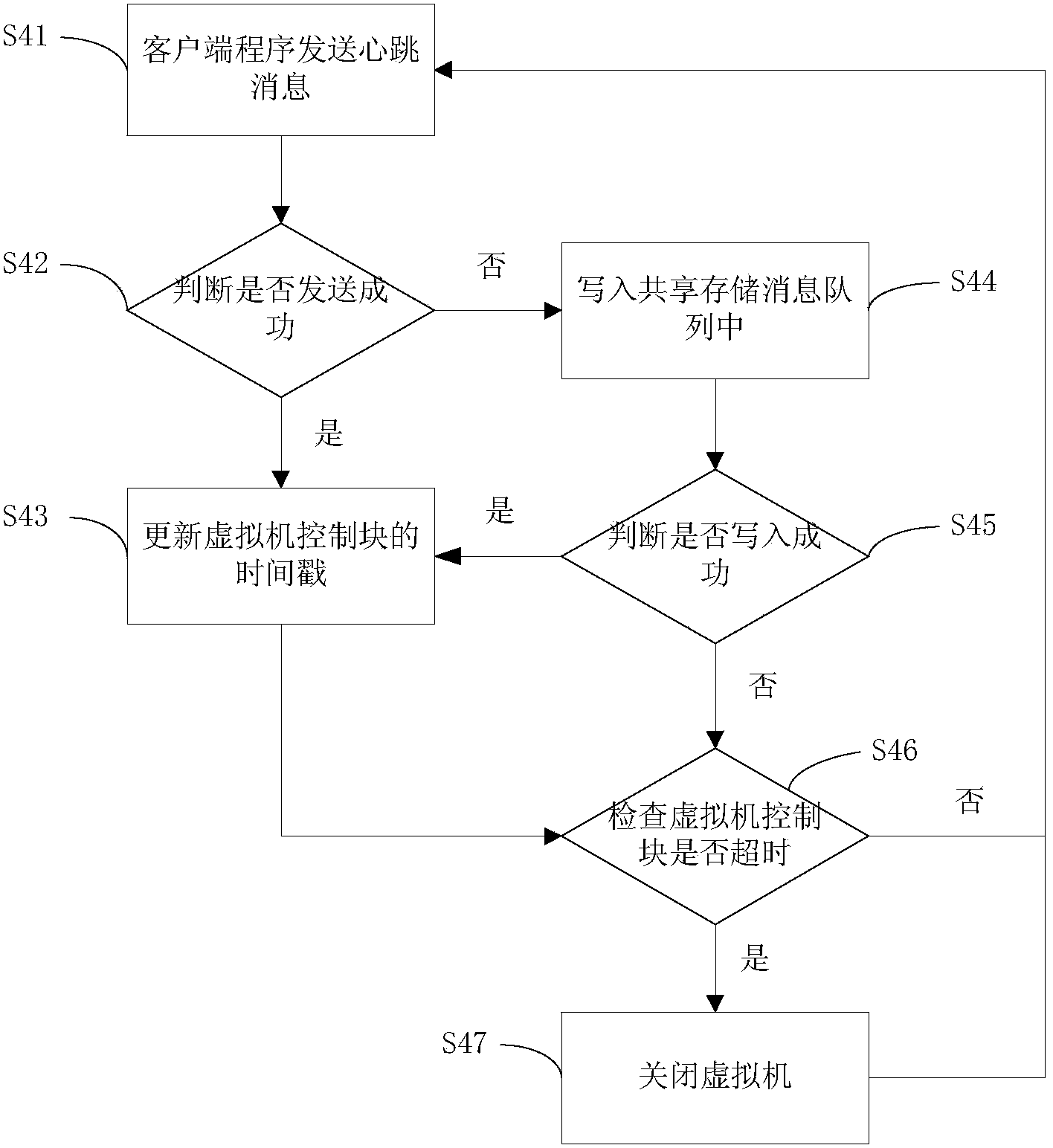

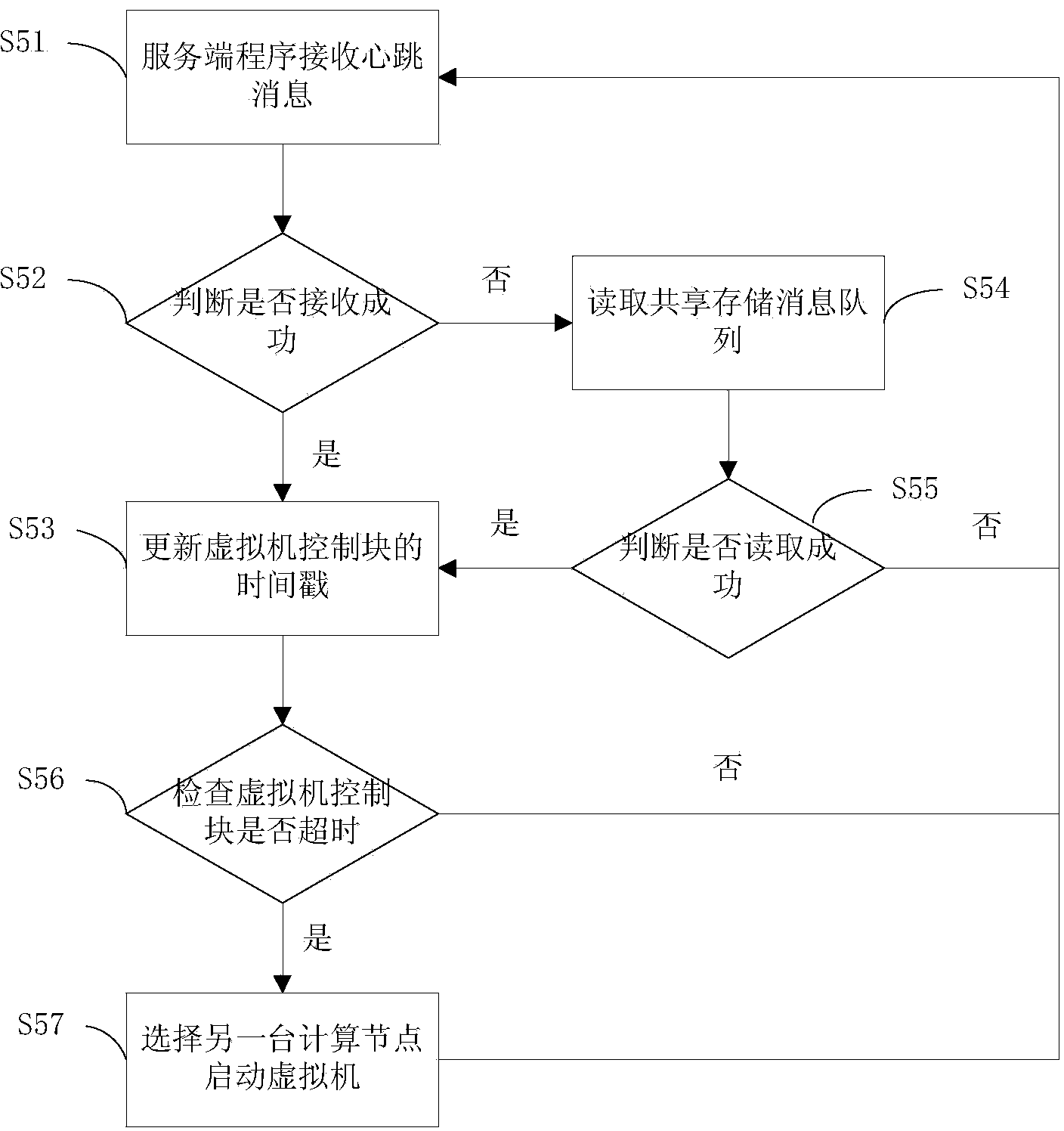

Shared storage message queue-based implementation method for high availability of virtual machines

The invention discloses a shared storage message queue-based implementation method for high availability of virtual machines and relates to the field of cloud computing. The shared storage message queue-based implementation method for the high availability of the virtual machines comprises the following steps: initializing a piece of contiguous space on shared storage by a server program to serve as a logical volume; distributing a plurality of contiguous sectors from the logical volume to serve as a sector pool of a client program; acquiring the configuration information of the sector pool and the number of a virtual machine, of which the high availability is enabled, by the client program; sending a heartbeat message by the client program, and updating the timestamp of a virtual machine control block maintained by the client program; receiving the heartbeat message by the server program, and updating the timestamp of the virtual machine control block maintained by the server program by utilizing the timestamp carried in the heartbeat message. According to the shared storage message queue-based implementation method disclosed by the invention, the unnecessary stop time of the virtual machines is avoided; system resource consumption is low by adopting a heartbeat detection mechanism; the performance is high; the service life of the disk of the shared storage is prolonged.

Owner:WUHAN OPENKER COMPUTING

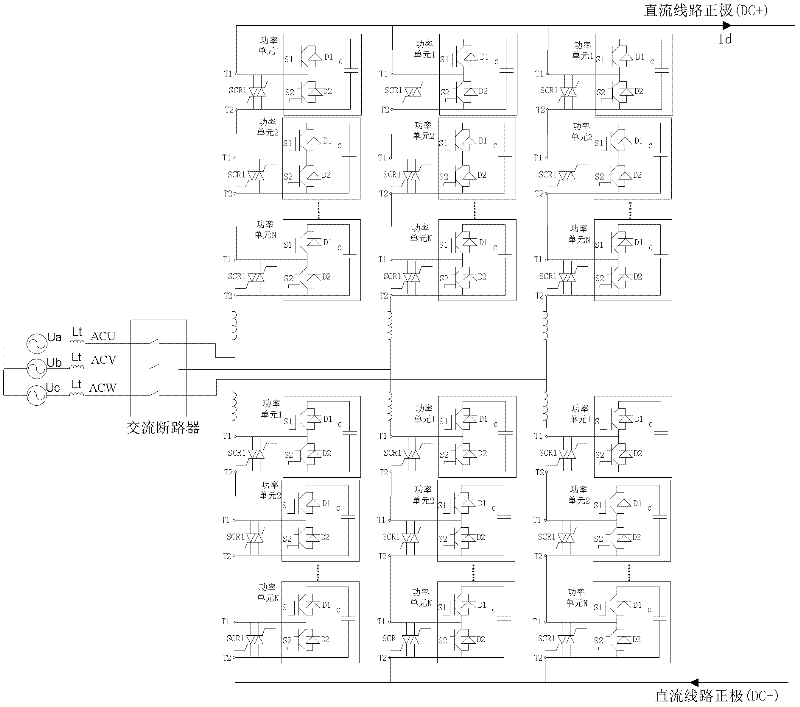

Method for protecting direct current line transient short-circuit fault of modular multiple-level converter

InactiveCN102403886AProtection securitySo as not to damageEmergency protective arrangements for limiting excess voltage/currentPower conversion systemsPower flowLevel converter

The invention relates to a method for protecting a direct current line transient short-circuit fault of a modular multiple-level converter, belonging to the technical field of direct current transmission. A group of two-way thyristor switch is connected on alternating current ports of each power unit of the modular multiple-level converter in parallel, when a direct current line has a transient short-circuit fault, control pulses of all of the power units are closed, and all of the two-way thyristor switches are triggered to be switched on at the same time, so that the short-circuit point of the direct current line is in natural arc extinction and disappears. When short-circuit current of the direct current line is detected to be zero, all of the two-way thyristor switches are controlled to be switched off, and the control pulses of all of the power units are opened, so that the converter runs again. With the adoption of the method, a switch device of the converter can be quickly protected from damage during a failure, and the direct current short-circuit point is in the natural arc extinction after failure, therefore, the device can automatically run again, thereby avoiding the complete off-stream of the device and greatly improving the reliability and the availability factor of the device.

Owner:ELECTRIC POWER RESEARCH INSTITUTE, CHINA SOUTHERN POWER GRID CO LTD +1

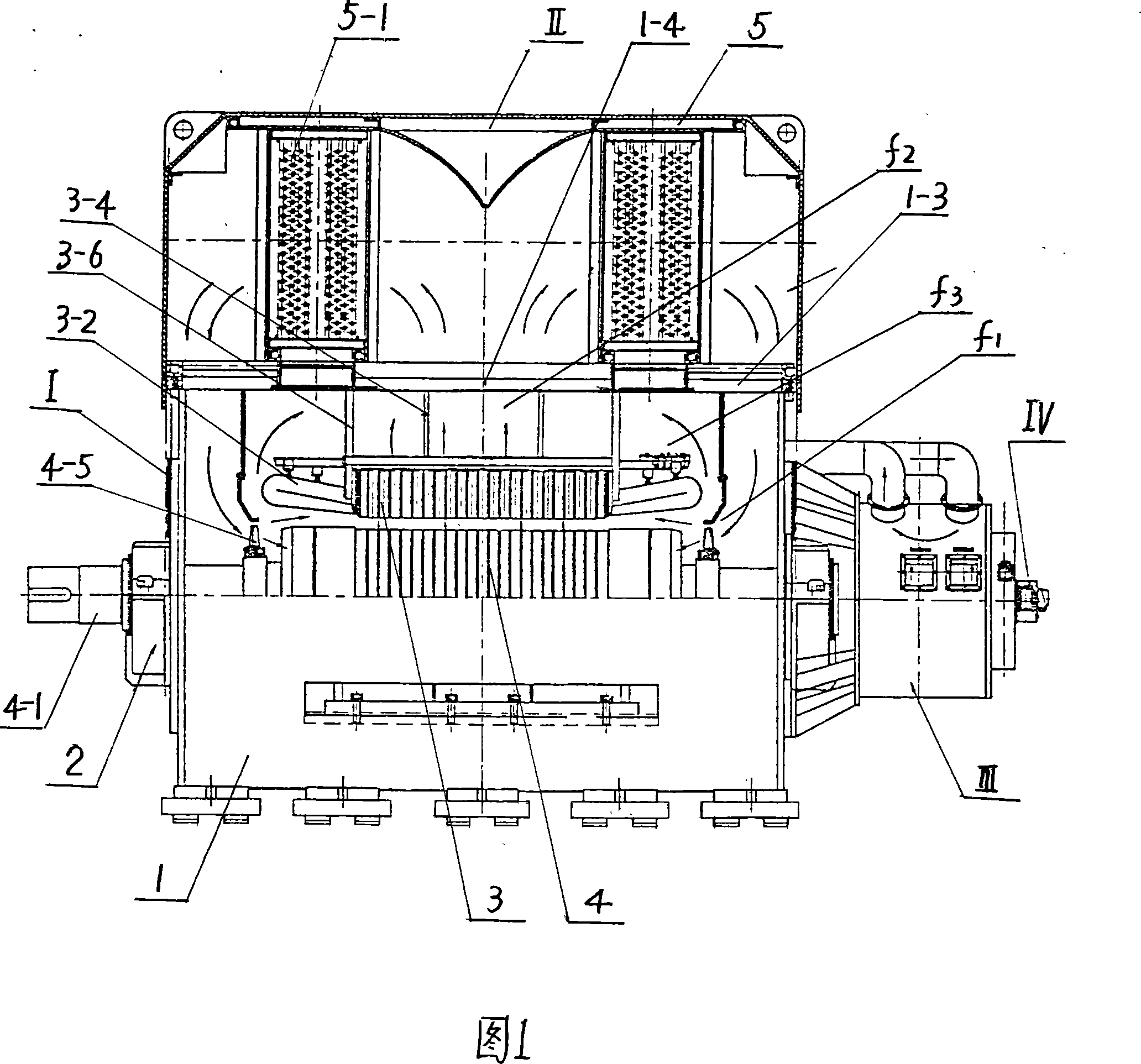

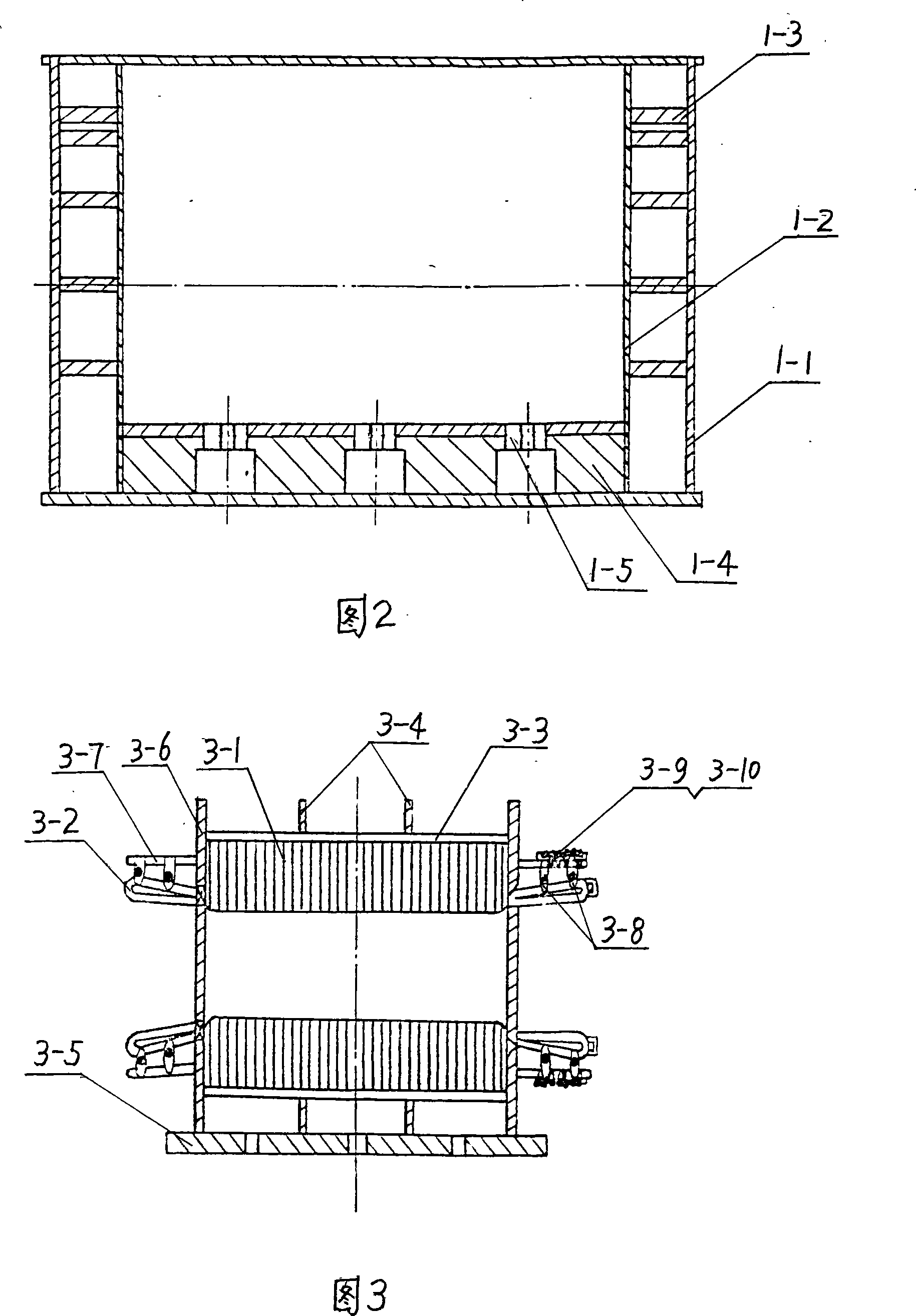

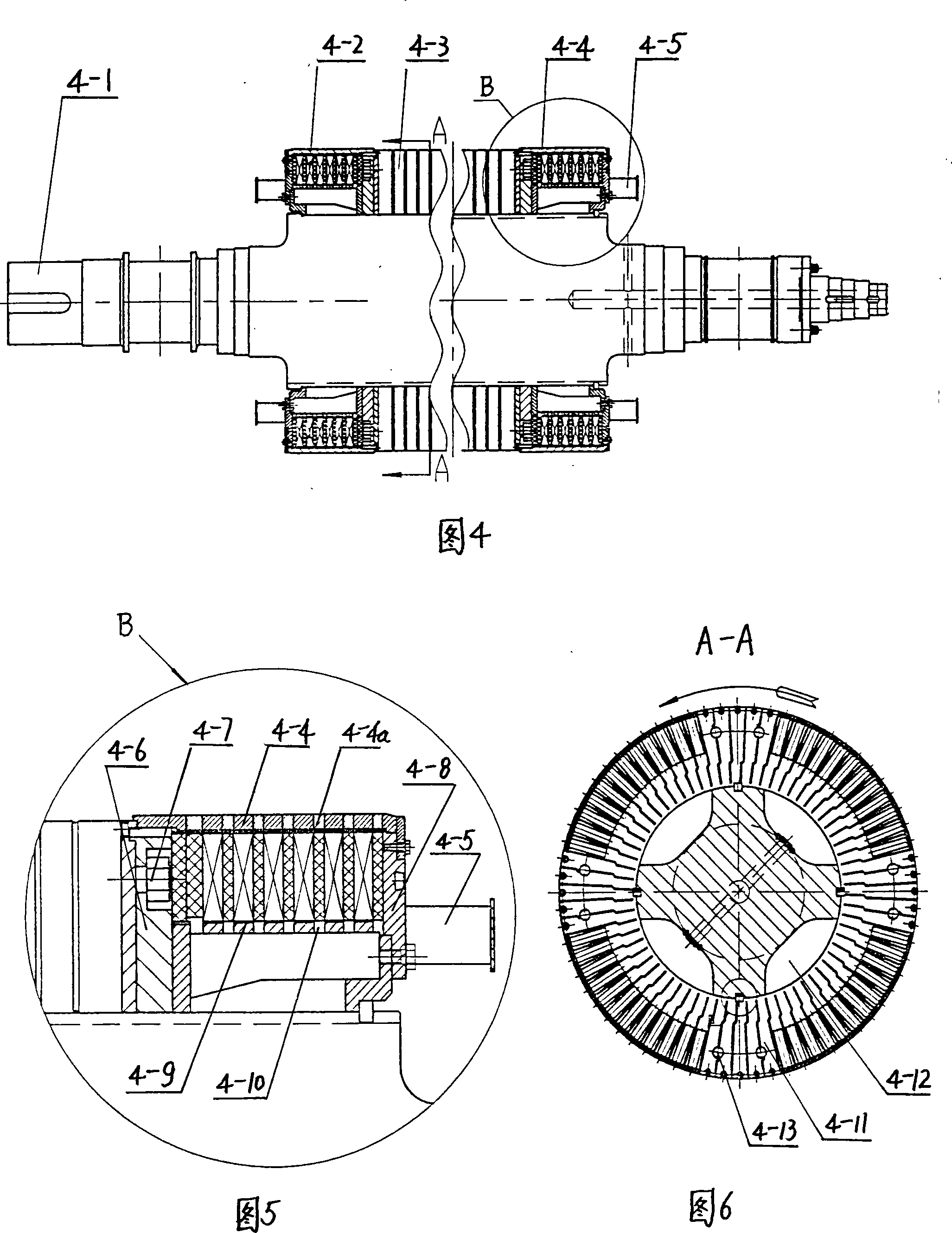

High-capacity non-salient pole nest plate type synchronous generator

ActiveCN101227129AEasy offlineGuaranteed accuracySynchronous generatorsMagnetic circuit rotating partsEngineeringDynamo

The invention relates to a large capacity non-salient pole plate fine type synchronous generator, which is characterized in that a main generator is provides with a stator which is sleeved with a motor base split unit and a rotor which is connected with a motor base through an end cover bearing, an exciting end of a rotor rotating shaft is provided with a brushless excitation system with a high pole number, the tail end of the system is provided with a grounding detecting device, and a cooling system comprises a cooling device which is positioned on the main generator, four ducted cooling paths which circulates in multiply return circuits and is formed by a stator ventilating circuit, a rotor ventilating circuit, an air gas ventilating circuit and an exciting dynamo ventilating circuit of the main generator. The generator has the advantages of reasonable design of the whole system, compact structure, complete function of each portion, convenient installation and maintenance, reliable operating property, high quality of voltage and electric current which are produced and the like, which saves manufacturing cost.

Owner:WOLONG ELECTRIC NANYANG EXPLOSION PROTECTION GRP CO LTD

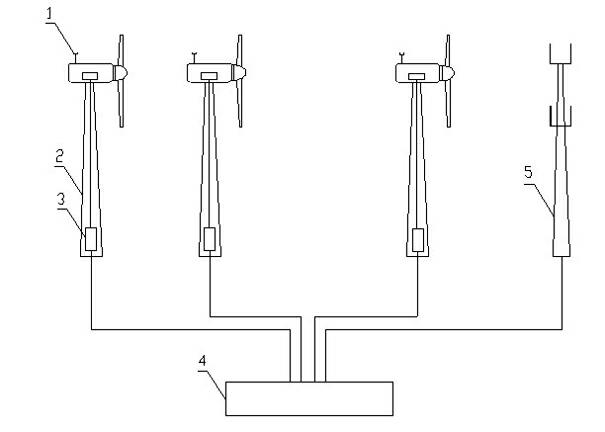

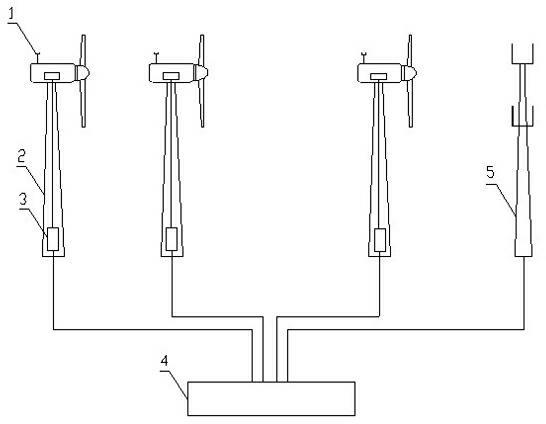

Wind speed and wind direction sharing system of wind electric field set

InactiveCN102434392AAutomatically achieve automatic switchingAvoid downtimeWind motor controlMachines/enginesWind drivenData acquisition

The invention relates to a wind speed and wind direction sharing system of a wind electric field set, which belongs to the technical field of wind driven generation. The technical scheme includes relating meteorological information of each wind generating set to wind speed and wind direction meteorological information of a plurality of sets and / or wind electric field booster stations on the periphery with similar positions and topography according to relevant positions and topography of each wind driven generating set in the wind electric field; sharing the meteorological information of the relevant wind generating set under special conditions by means of a wind electric field supervisory control and data acquisition (SCADA) system; automatically achieving automatic switch of local meteorological information and remote shared meteorological information by a fault set local control system; simultaneously performing backup protection on safety operation of the set under strong wind operation mode based on an pitch angle and generated output, and finally ensuring continuous and safe operation of the set. The wind speed and wind direction sharing system of the wind electric field set can well solve the problem that a machine is halted while the wind generating set continues generating power due to faults of a wind speed and / or a wind direction sensor and is simple in structure, high in safety, strong in practicality and good in economy.

Owner:BAODING TIANWEI WIND POWER TECH

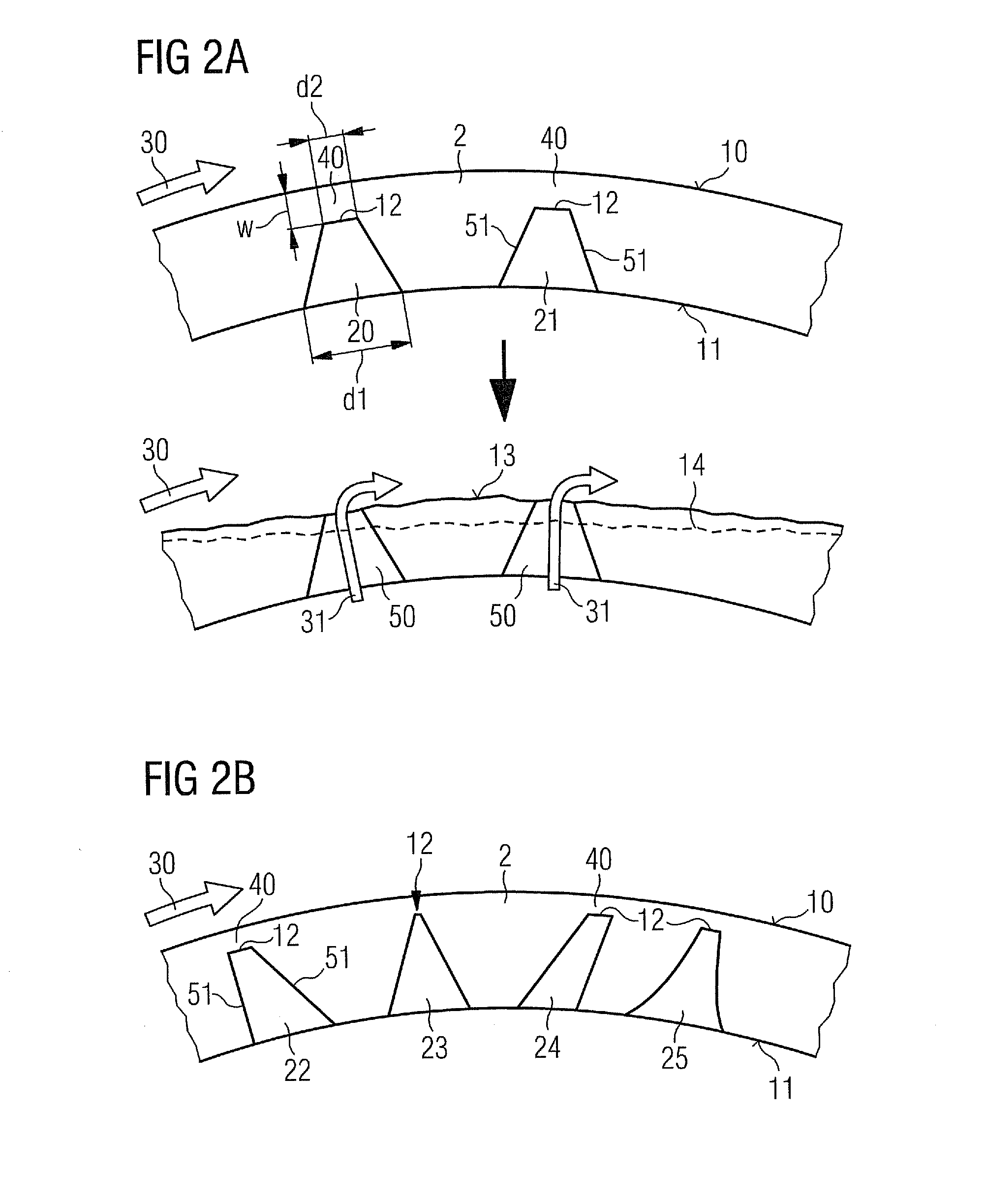

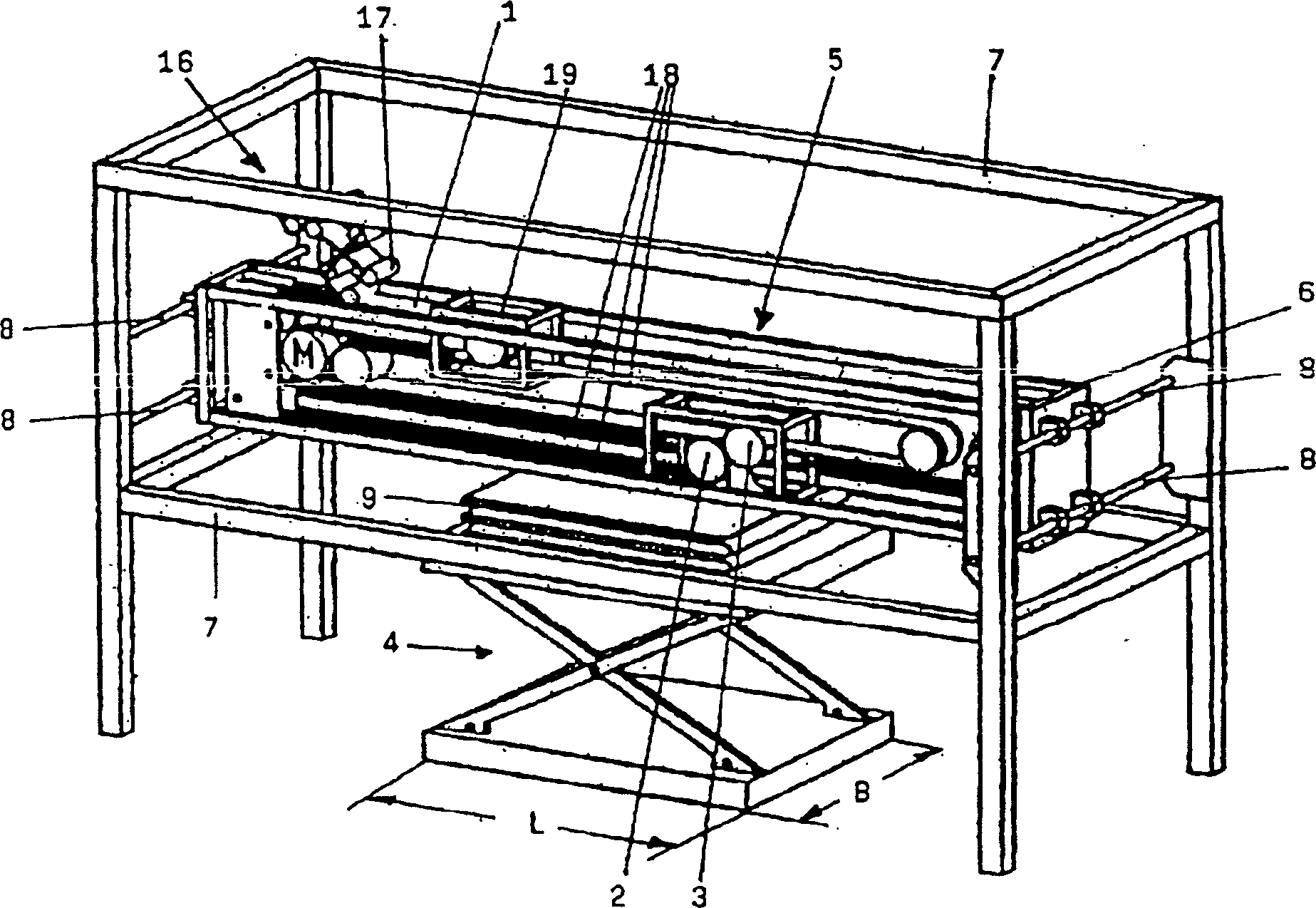

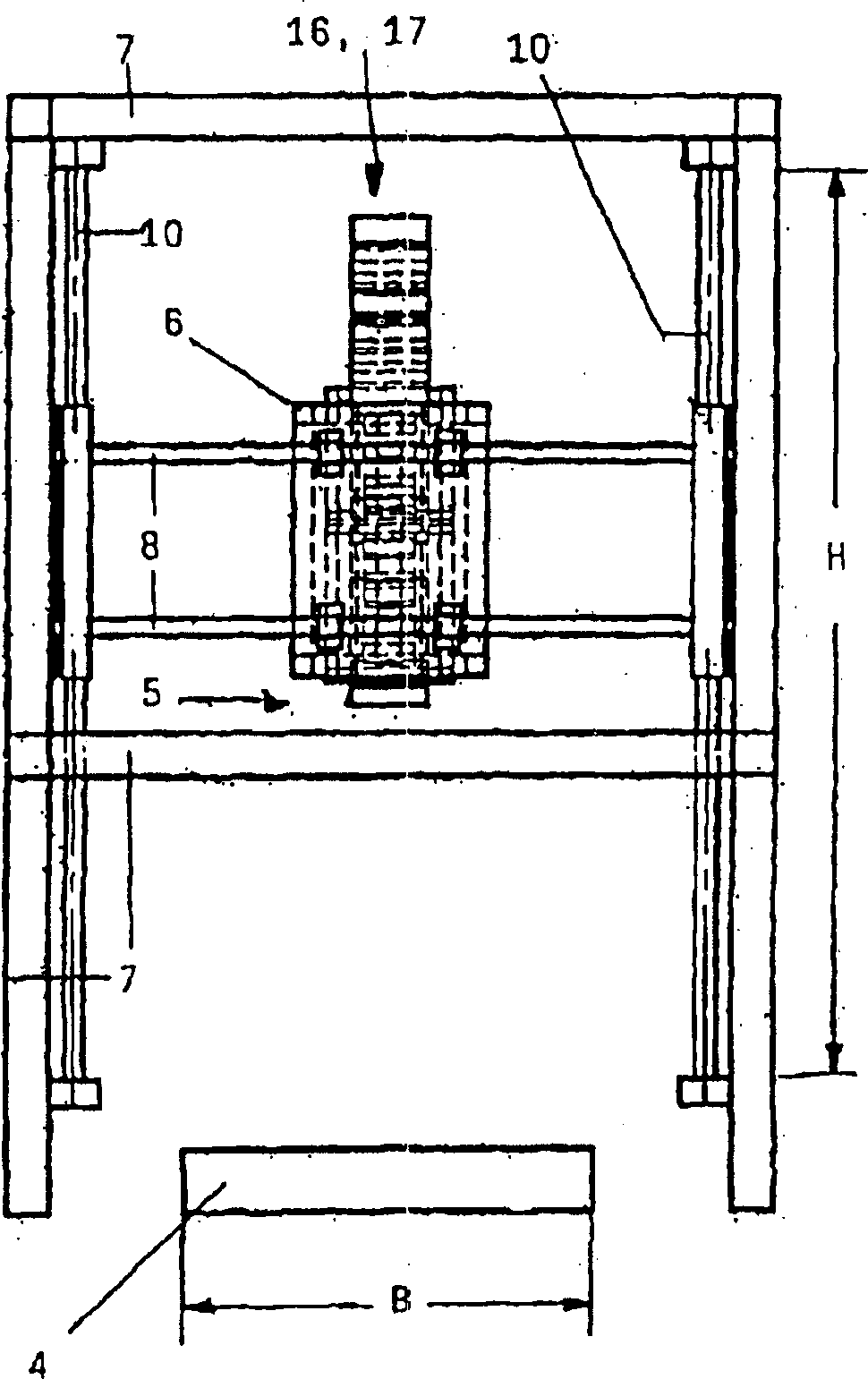

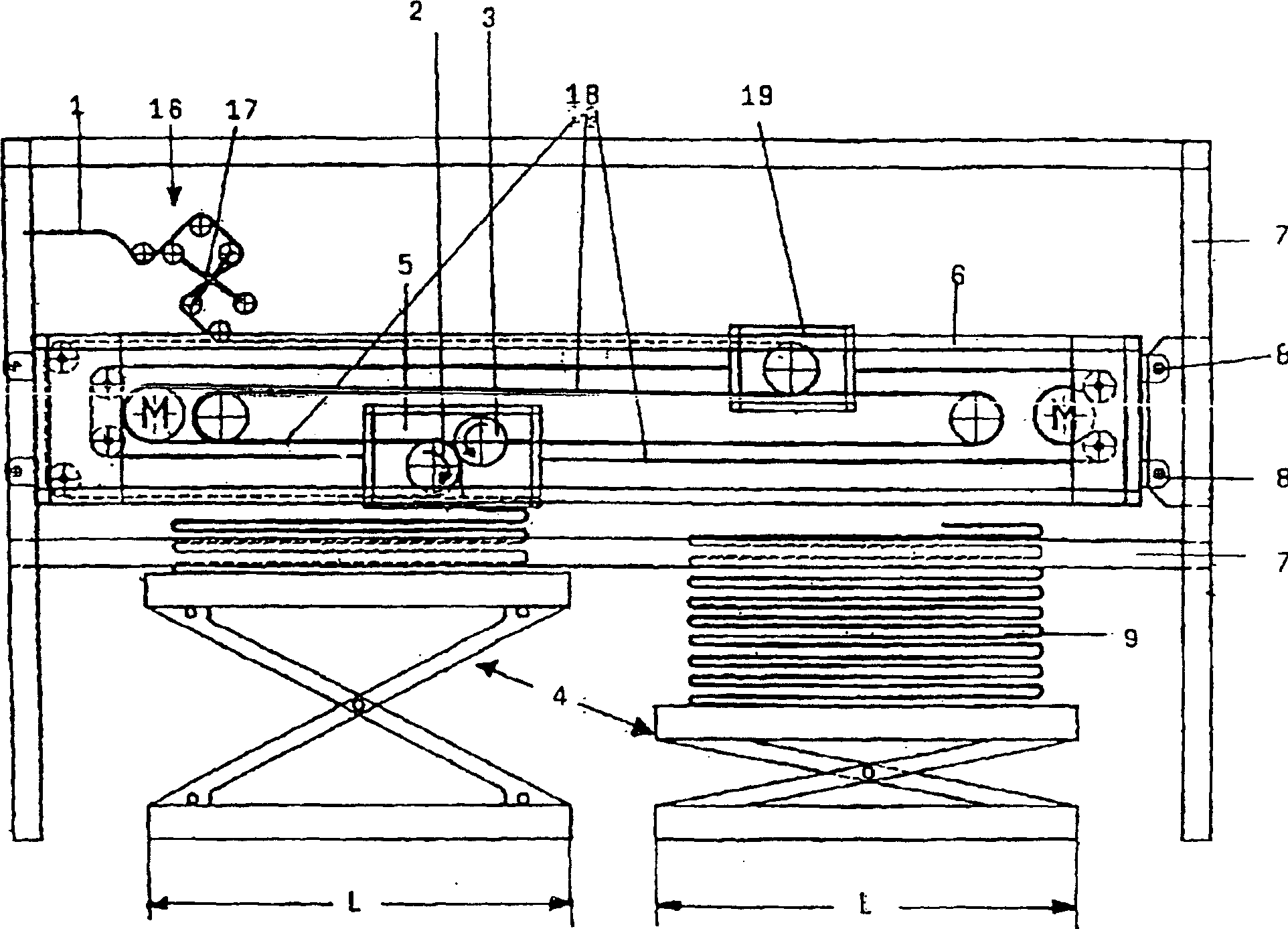

Device for laying a flexible material web

A device for laying a flexible material web 1 on a point of deposit 4 and which has at least one pair of deposit rollers 2, 3 that rotate in opposite directions. The deposit rollers 2, 3 form part of a deposit carriage 5 which is reciprocated in a reversible direction over at least the deposit length L of the material web 1. The device is more cost-effective in that the deposit carriage 5 has a smaller width than the point of deposit 4 and is reciprocated in a reversible direction over at least the deposit width B of the point of deposit 4.

Owner:SAURER GMBH & CO KG

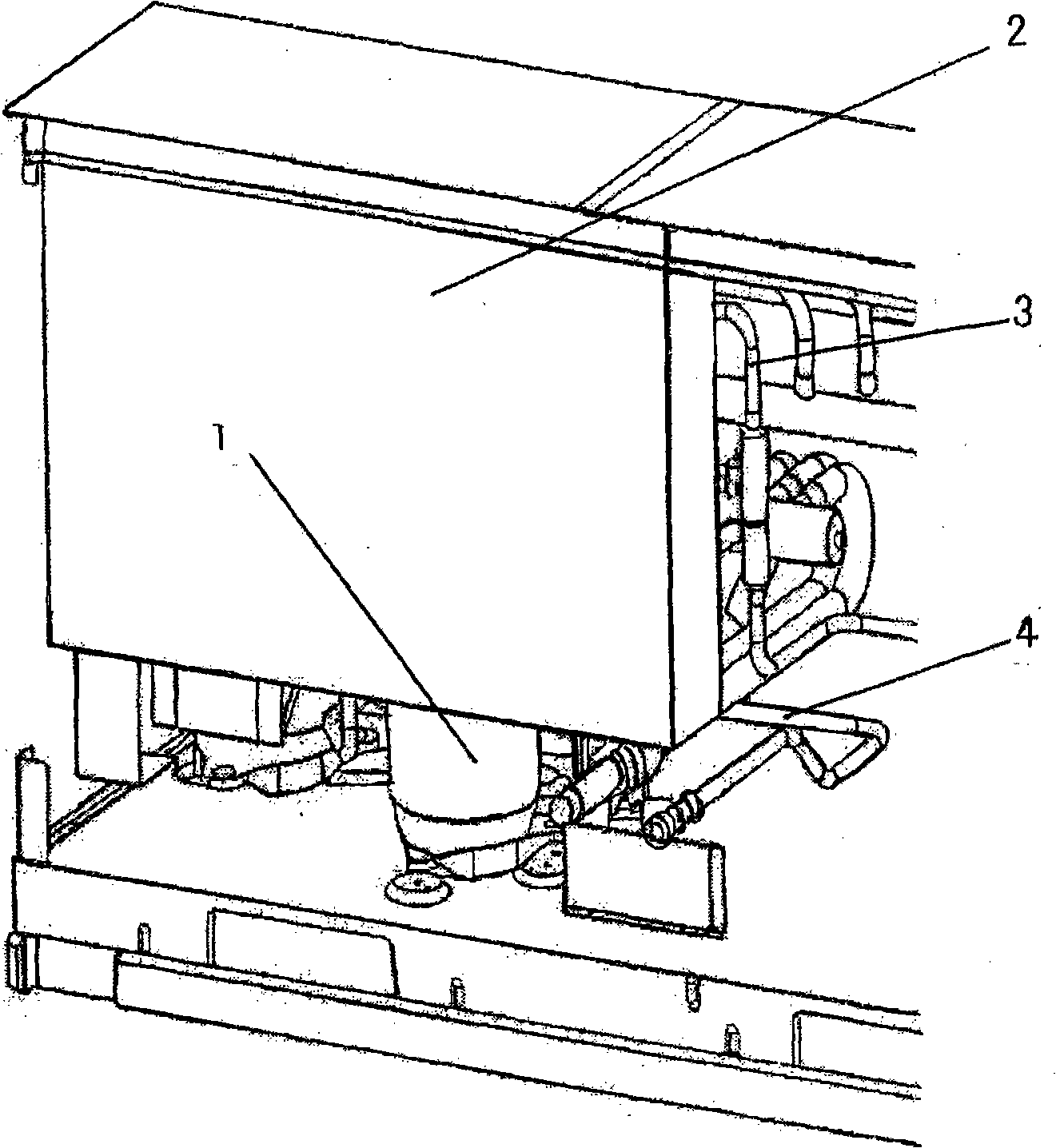

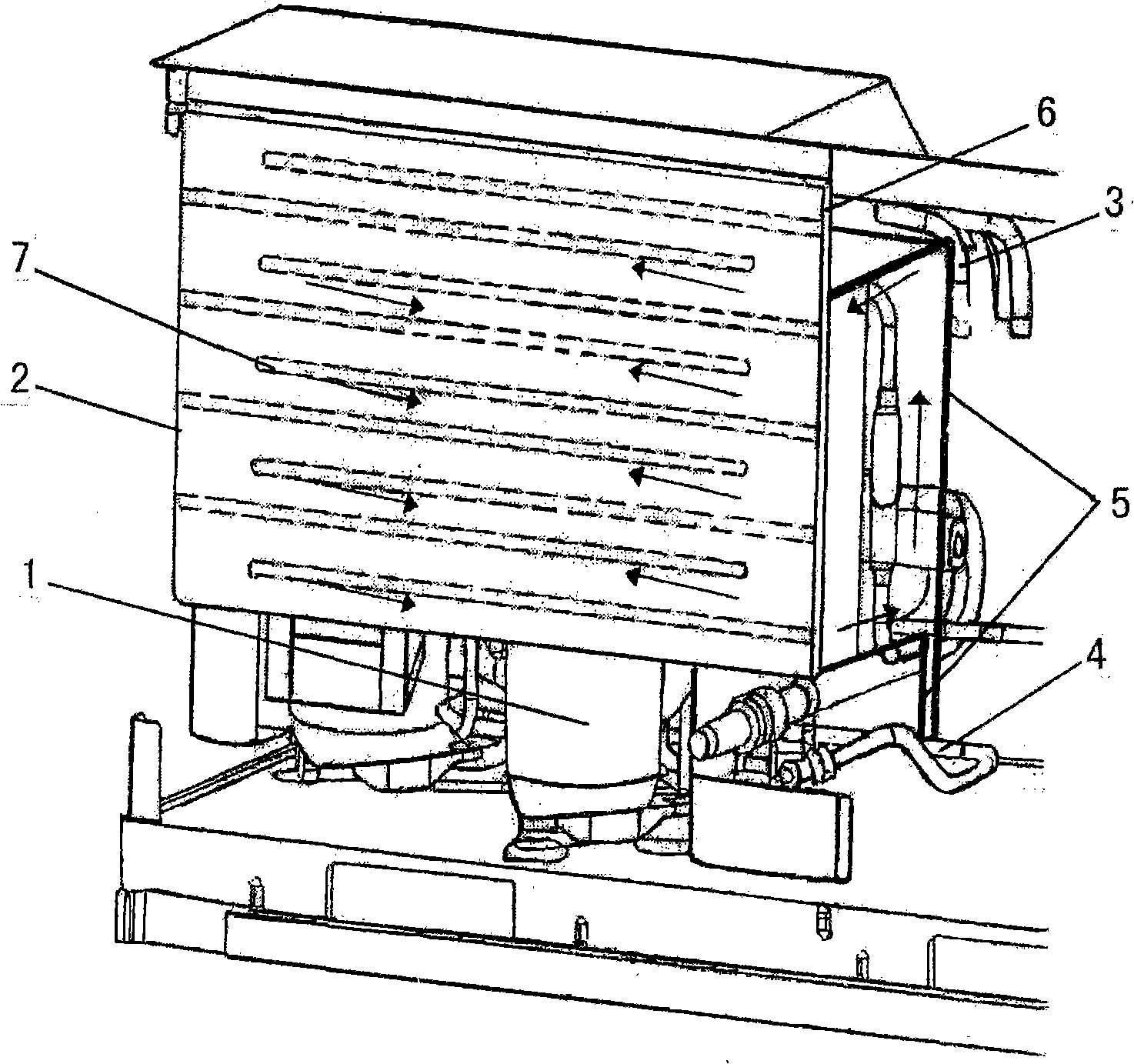

Automatic level-controlling draining dehumidifier and draining method thereof

InactiveCN101520214AReduce structure use spaceTimely exclusionCondensate preventionLighting and heating apparatusEngineeringDrainage tubes

An automatic level-controlling draining dehumidifier mainly comprises a water pump suction pipe, a water pump drainage pipe, an electromagnetic water pump, a water pump fixing cover, an inductive switch fixing part, a water fullness alarming switch, a pumping alarming switch, a drainage quick adapter assembly, a level measuring floater, a water-collecting tray, an osculum, an osculum plug, a compressor and a heat exchanger; the connection is as follows: one end of the water pump suction pipe is connected with the water-collecting tray and the other end is connected with the electromagnetic water pump; one end of the electromagnetic water pump is connected with the water pump suction pipe; the other end of the water pump drainage pipe is connected with the quick adapter assembly; the level measuring floater is arranged below the water pump fixing cover; and the water fullness alarming switch and the pumping alarming switch are fixed by the inductive switch fixing part. The draining method of the dehumidifier comprises the following steps: one electromagnetic water pump is arranged on the side surface of the water-collecting tray; when the dehumidifier is working, the condensed water is generated by the heat exchanger and falls into the water-collecting tray; the level measuring floater rises slowly under the effect of buoyancy with the increase of water quantity so as to measure the height of the water collected in the water-collecting tray; the floater firstly touches the pumping alarming switch with the rising of level and then the electromagnetic water pump starts to work; the quick adapter at the bottom of a chassis can be connected with a rubber drainage tube with length of about 5M; then the electromagnetic water pump drains the water inside the water-collecting tray out of the room through the water pump suction pipe and the water pump drainage pipe; if the floater touches the pumping alarming switch firstly but the electromagnetic water pump does not work.

Owner:NINGBO ERYE & ELECTRONICS

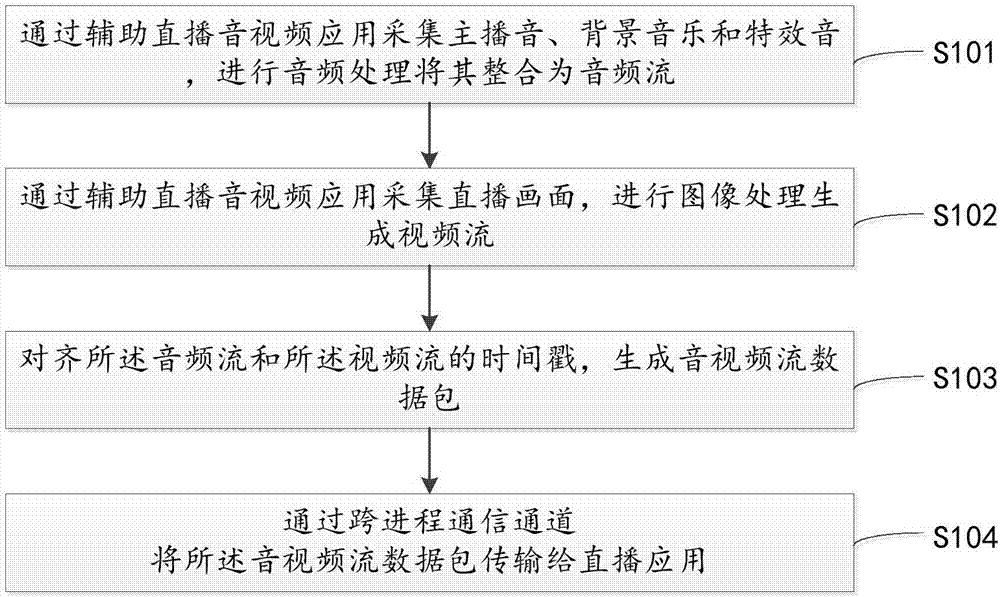

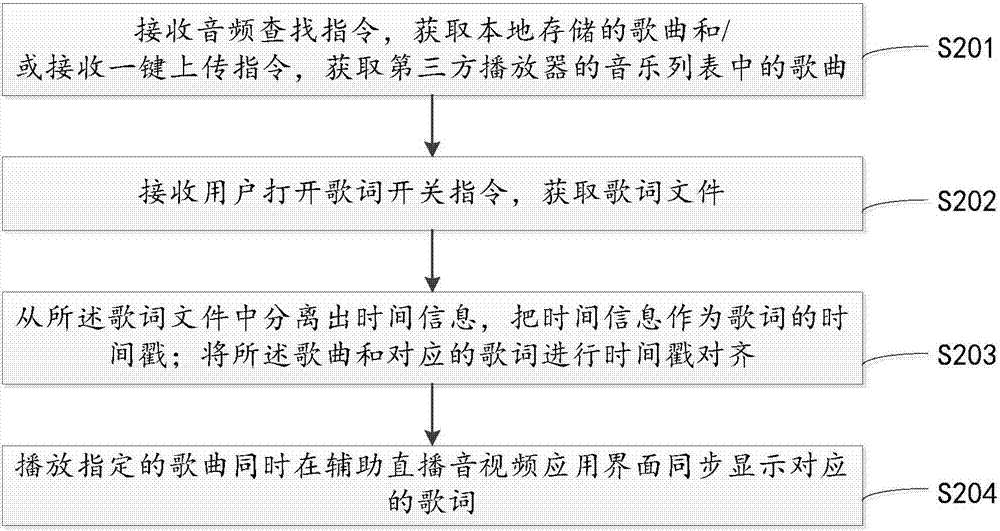

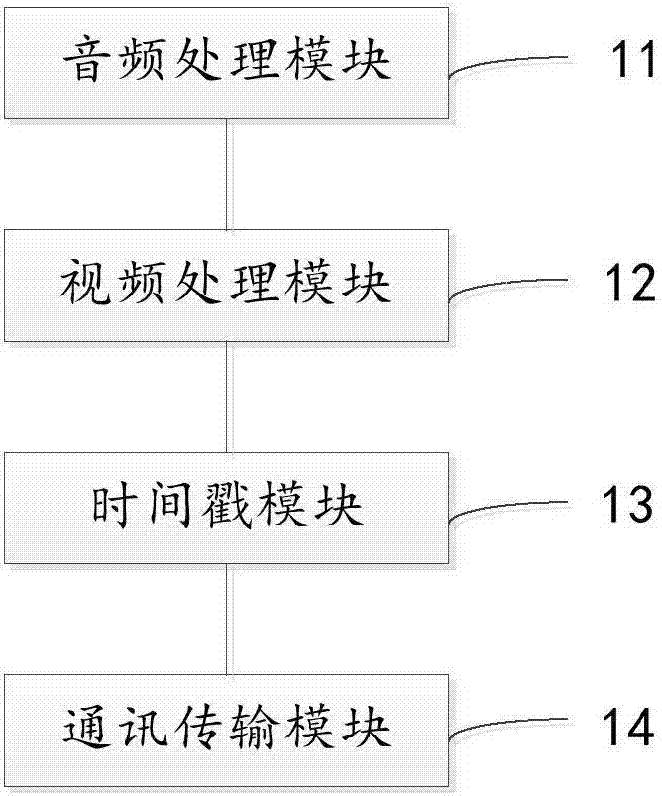

Live broadcast assistant audio/video processing method and device for

ActiveCN107027050AIncrease resource consumptionIncreased flexibility of useSelective content distributionImaging processingNetwork packet

The invention relates to the technical field of the Internet and discloses a live broadcast assistant audio / video processing method and device. The method comprises the steps of collecting anchor audios, background music and special effect audios through a live broadcast assistant audio / video application, carrying out audio processing and integrating the anchor audios, the background music and the special effect audios into an audio stream; collecting live broadcast images through the live broadcast assistant audio / video application, carrying out image processing to generate a video stream; aligning time stamps of the audio stream and the video stream to generate an audio / video stream data packet; and transmitting the audio / video stream data packet to a live broadcast application through a cross-process communication channel. The audios in the live broadcast process are effectively integrated into the audio stream, the time stamps of the audio stream and the video stream are aligned, the audio stream and the video stream are transmitted to the live broadcast application, various audios in the live broadcast process are prevented from mutual interference, and the fusion effect of the live broadcast application for the audios in the live broadcast process is relatively good.

Owner:广州方硅信息技术有限公司

Cooling by-pass structure of electric appliance control box of frequency conversion type air conditioner outdoor unit

InactiveCN101294727AReduce the temperatureAvoid burnsLighting and heating apparatusAir conditioning systemsFrequency conversionEngineering

The invention relates to a cooling bypass structure of an electric control box for the outdoor unit of an inverter air conditioner. The structure includes a thickened control box faceplate and capillaries communicating the faceplate interior with a low temperature refrigerant pipe. A hollow cavity is formed between the front side and the back side of the thickened control box faceplate; skirt plates in up / down parallel arrangement are positioned in the hollow cavity of the faceplate, thereby forming rotary type up / down circulating passages. The upper part and the lower part of the control box faceplate are respectively connected with the capillaries, two capillaries are connected with the low temperature refrigerant pipe leading to an evaporator, and the hollow cavity of the control box faceplate communicates with the low temperature refrigerant pipe via the capillaries. When the air conditioner is in operation, the temperature of the control box is lowered by the low temperature refrigerant passing through the control box faceplate, so as to avoid fuse burnout and stoppage phenomena caused by over-high temperature of the electric control box. At the same time, the capillaries of the bypass structure can play the role of throttling decompression to the refrigerant system, thereby facilitating heat conversion of the refrigerant to the evaporator and optimizing the operation performance of the system.

Owner:LG ELECTRONICS (TIANJIN) APPLIANCES CO LTD

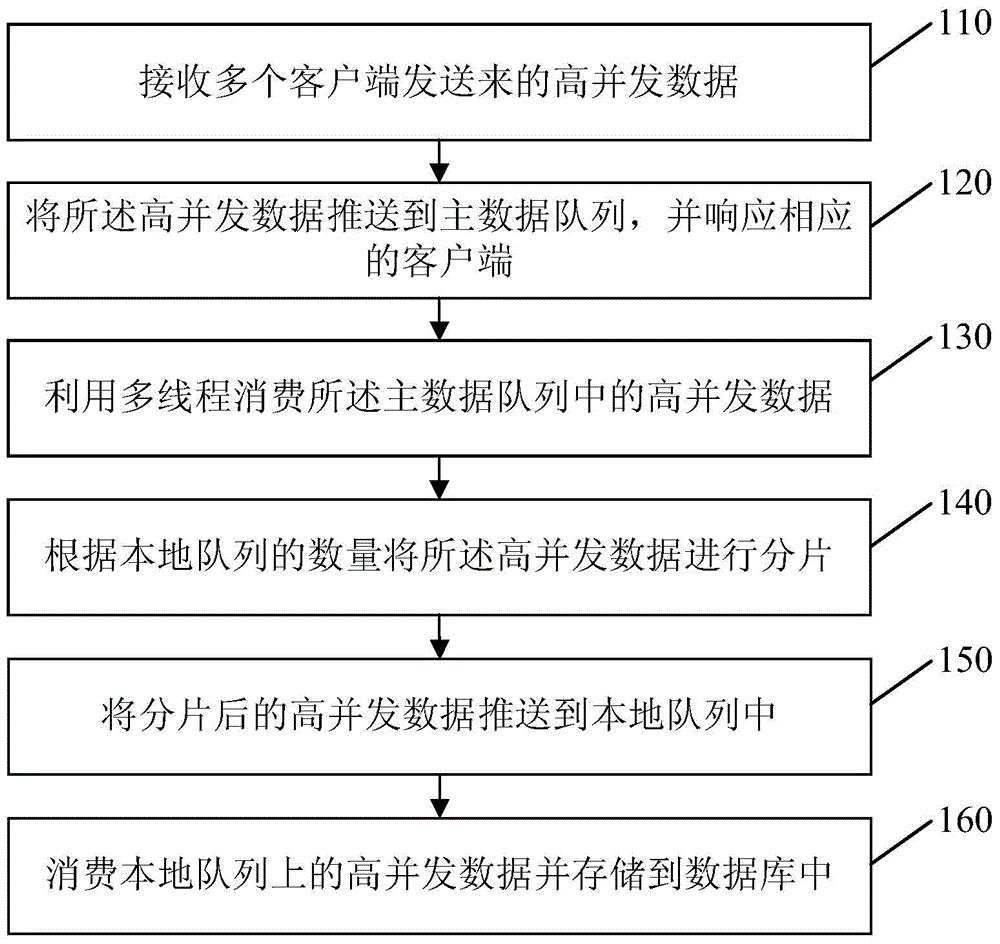

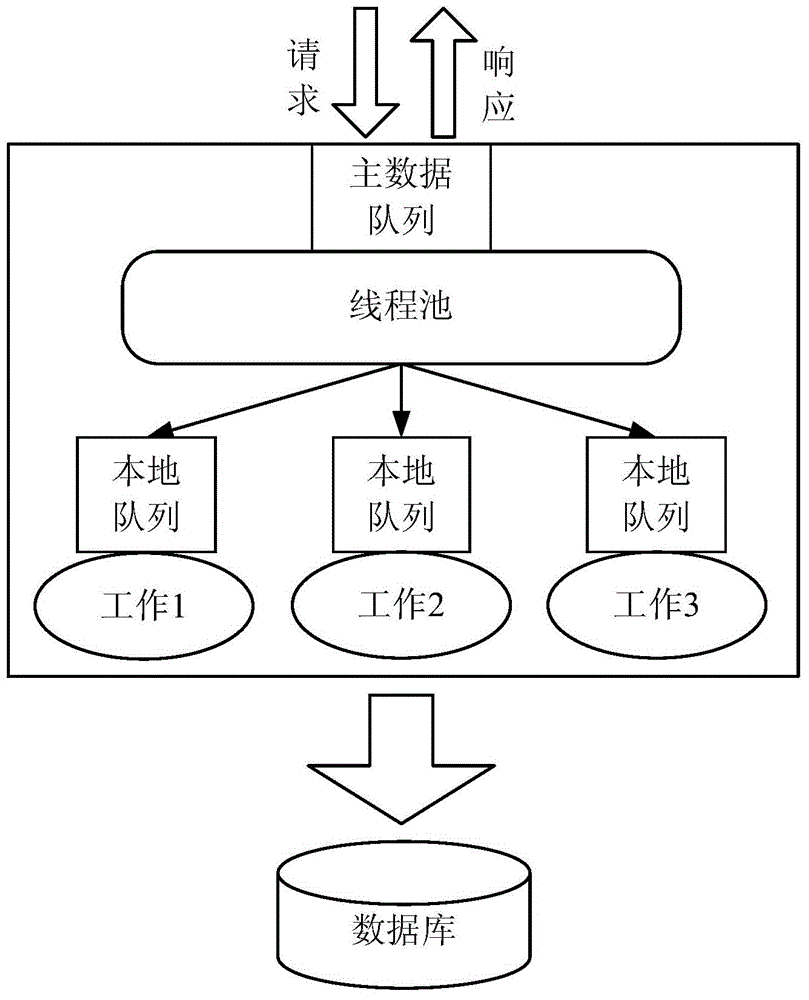

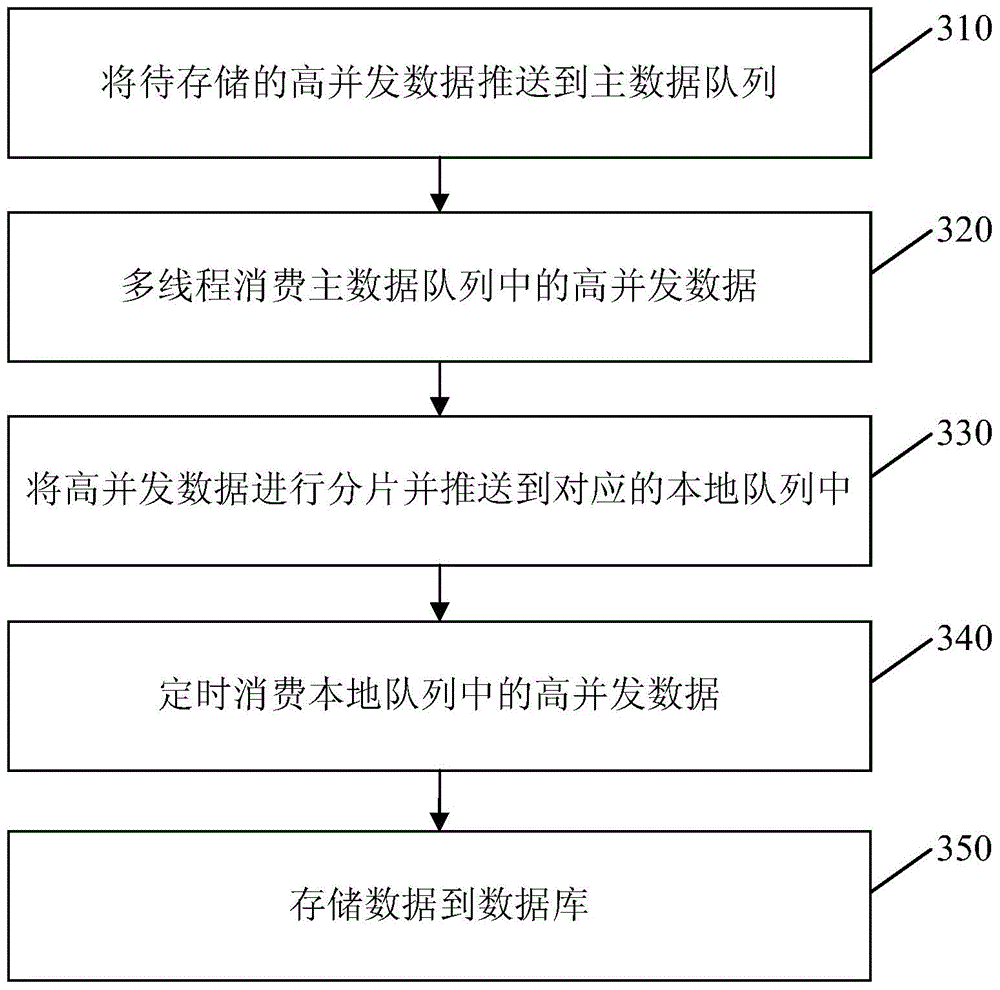

High concurrency data storage method and device

ActiveCN104598563AImprove storage efficiencyAvoid downtimeSpecial data processing applicationsProgram saving/restoringDowntimeClient-side

The invention discloses a high concurrency data storage method and device. The method comprises the steps; receiving high concurrency data transmitted by a plurality of clients; pushing the high concurrency data to a main data queue, and responding to the corresponding client; consuming the high concurrency data in the main data queue by utilizing a multithread; fragmenting the high concurrency data according to the quantity of a local queue; pushing the fragmented high concurrency data to the local queue; consuming the high concurrency data in the local queue, and storing the high concurrency data into a database. The high concurrency data is cashed by utilizing the main data queue and the local queue, the data storage is carried out by adopting an asynchronous storage way, the pressure of the database is alleviated, the downtime problem of the database under the high concurrency storage situation can be avoided, and the storage efficiency of the high concurrency data can be improved.

Owner:BEIJING JINGDONG SHANGKE INFORMATION TECH CO LTD +1

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com