Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

114 results about "Short loop" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Wireline communication system and method of frequency allocation therein

InactiveUS6650697B1Reduce impactImprove performanceTelephonic communicationLink quality based transmission modificationModem deviceFrequency spectrum

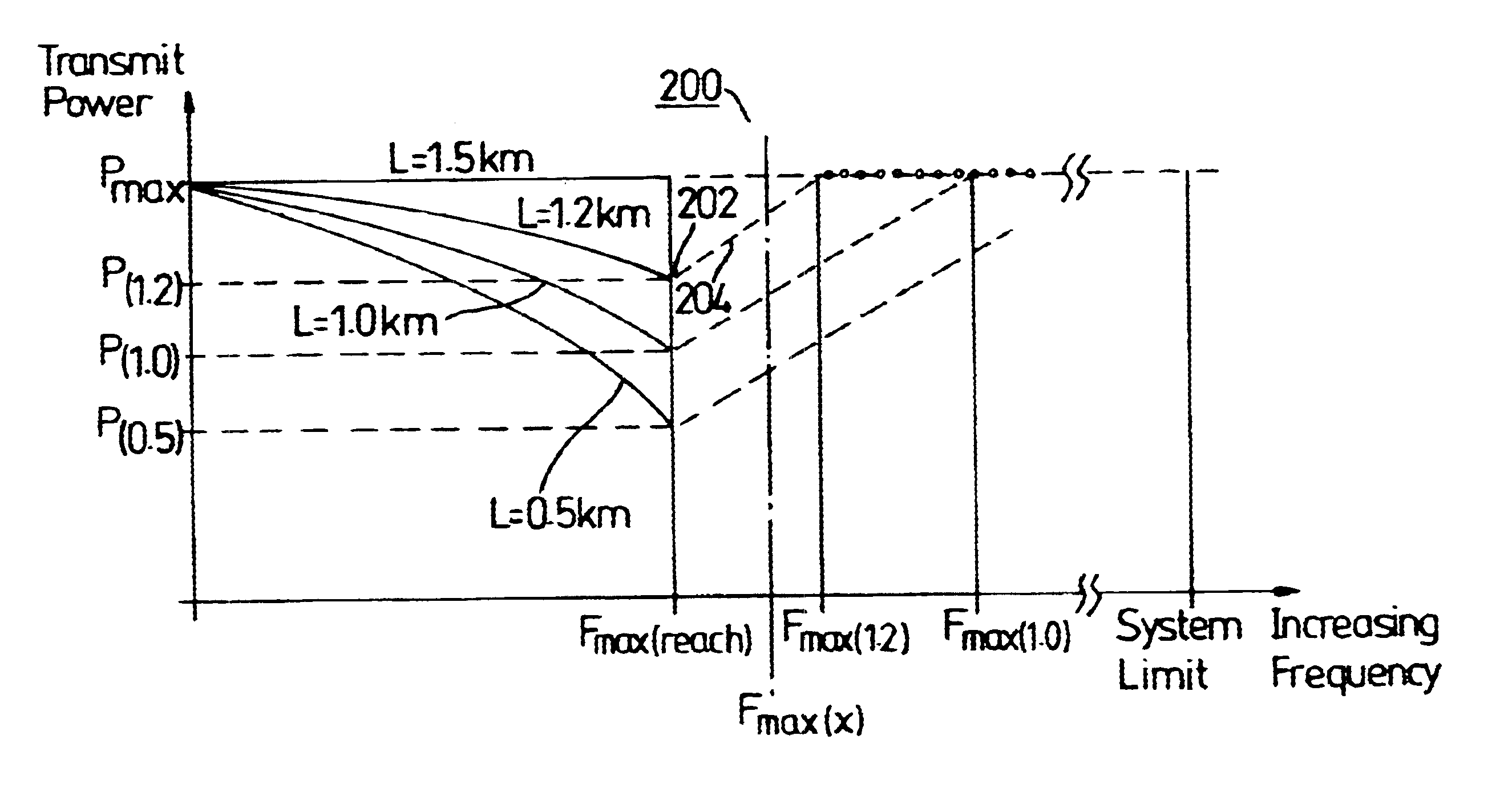

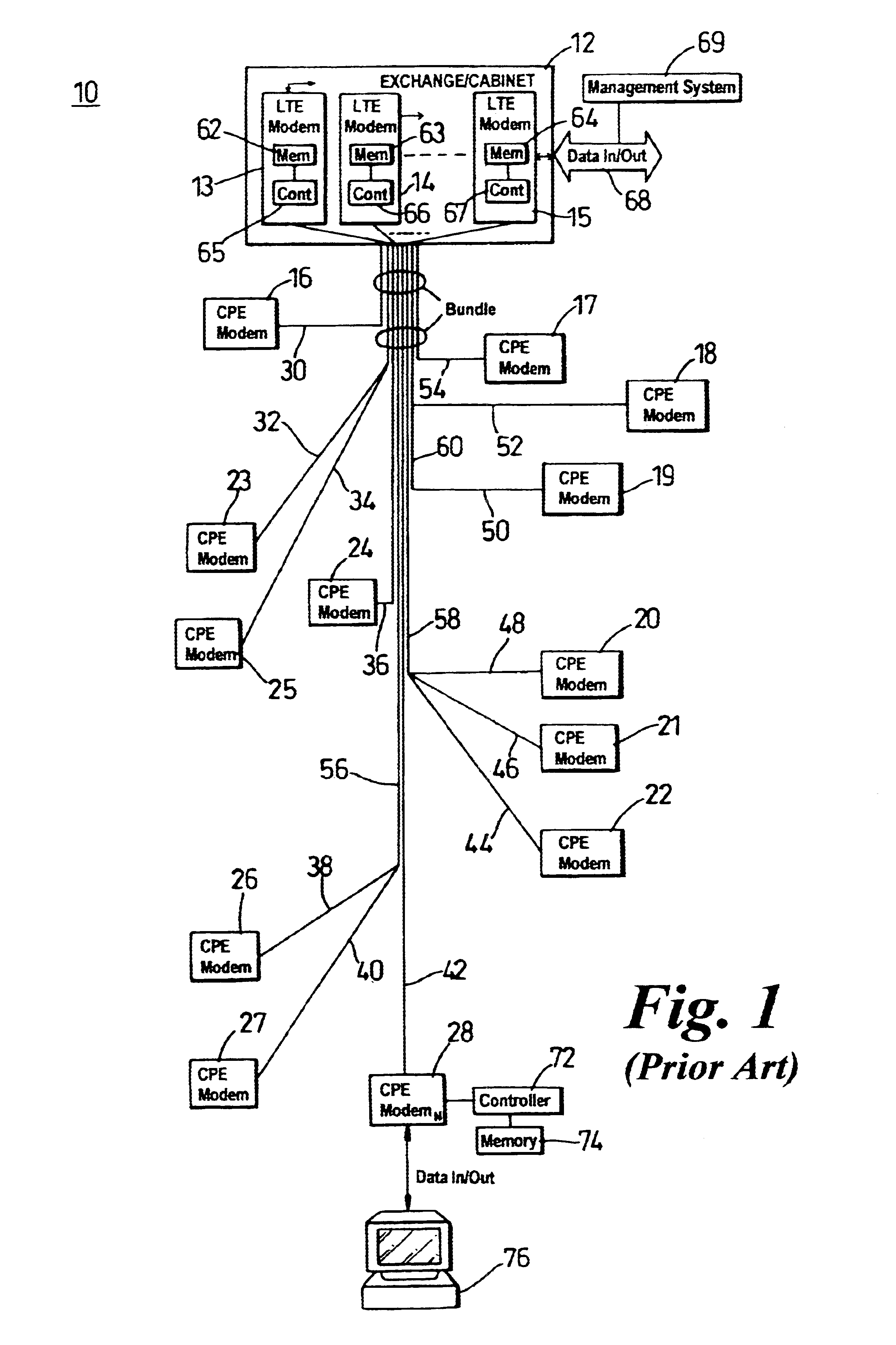

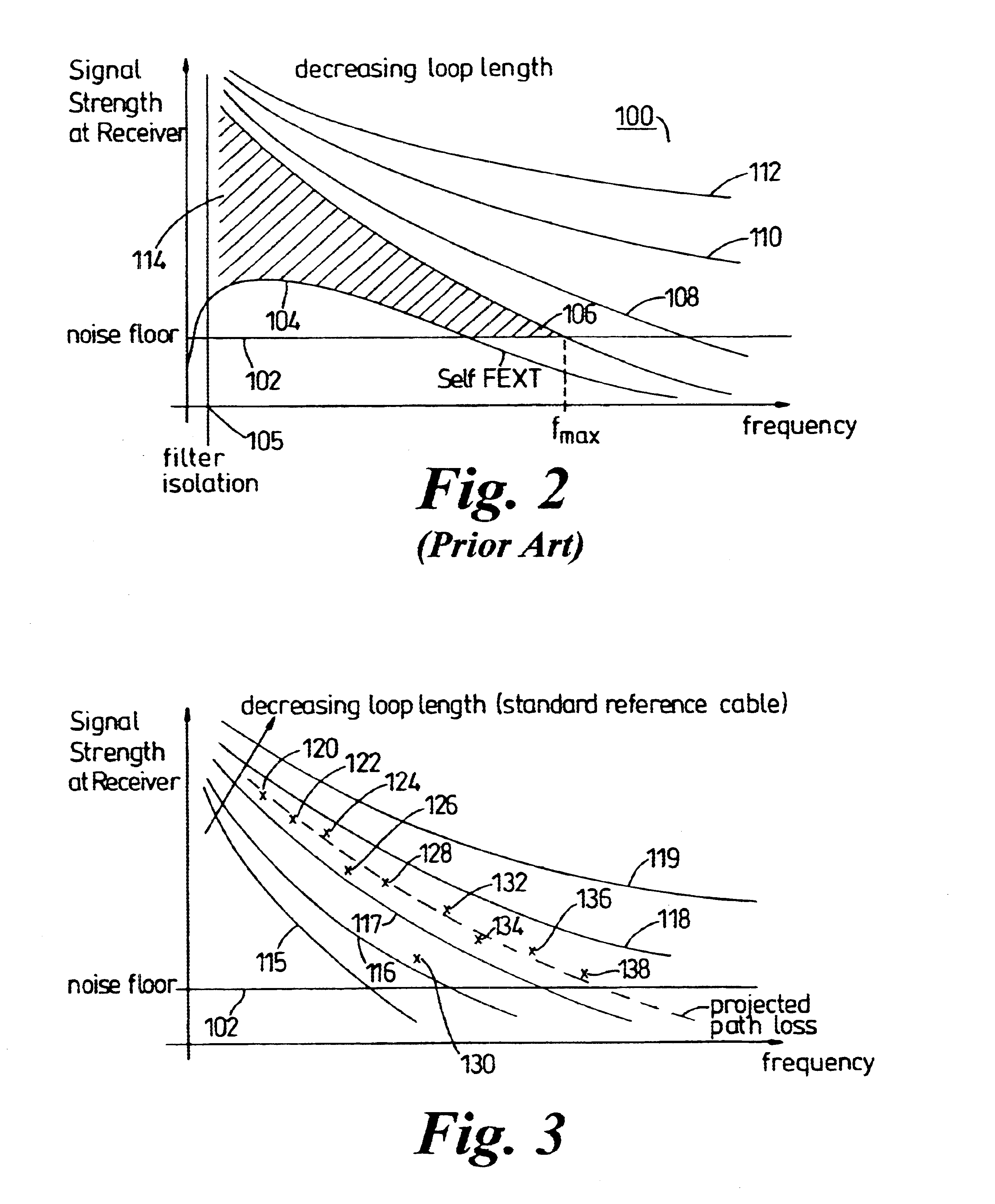

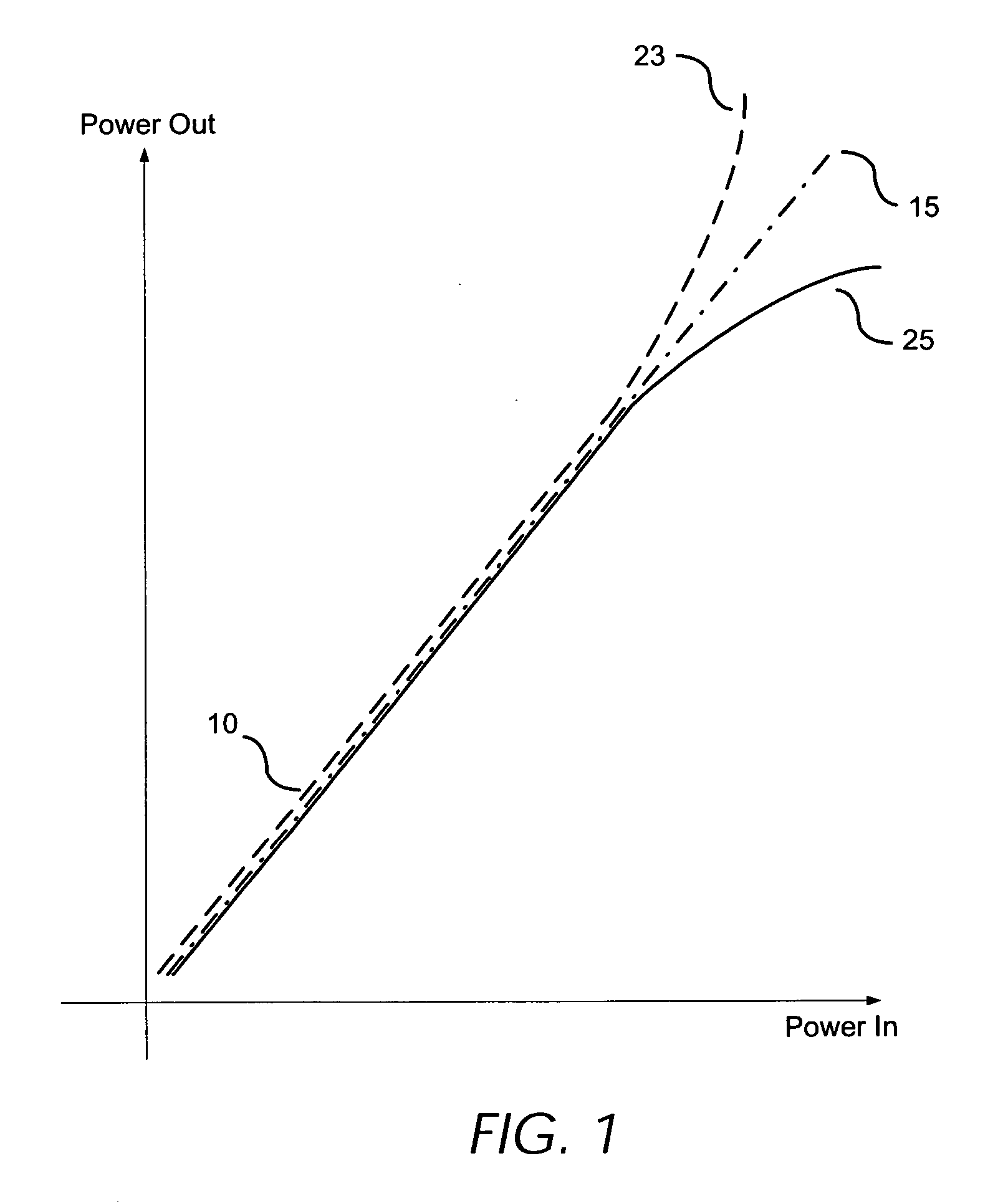

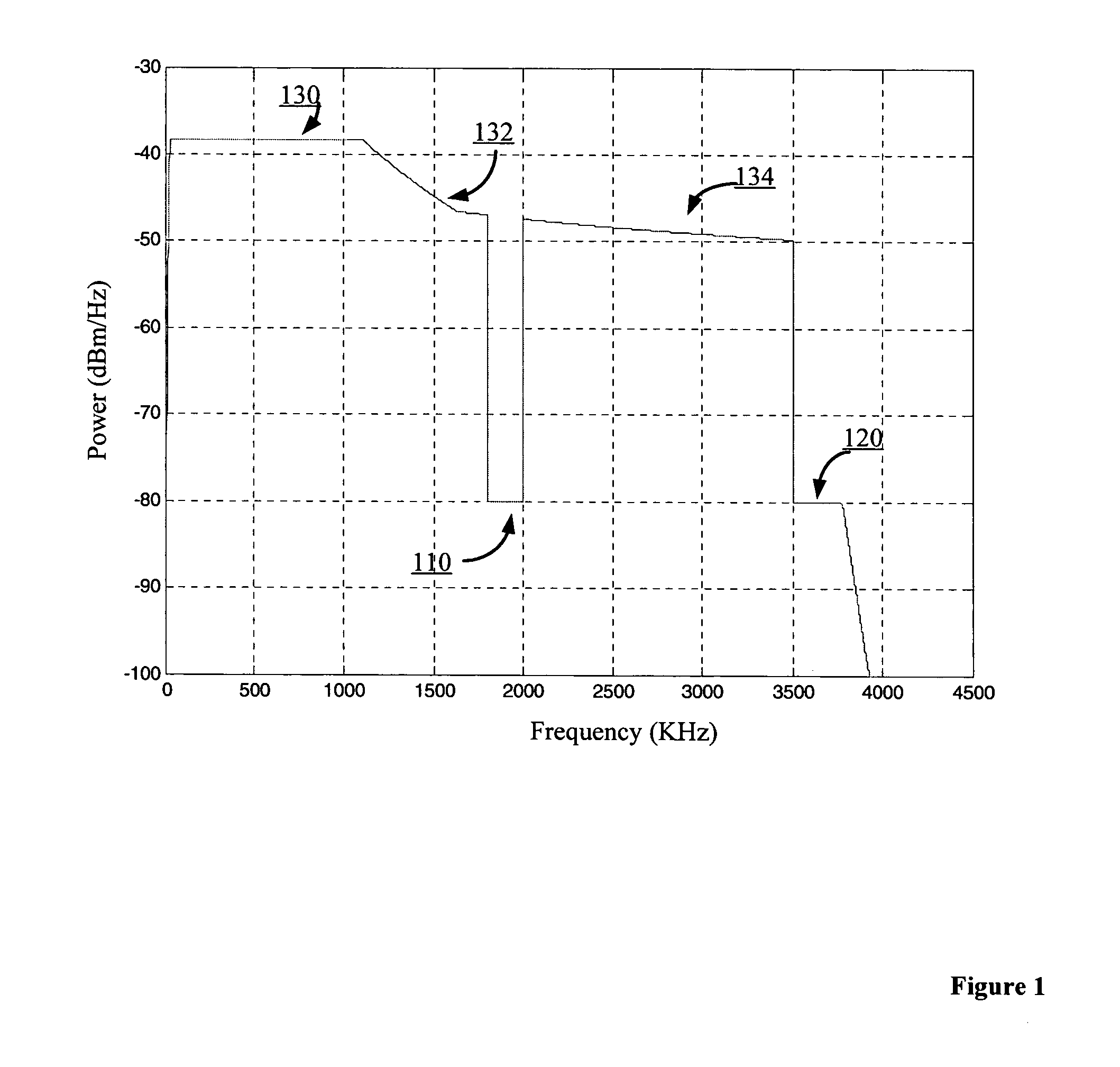

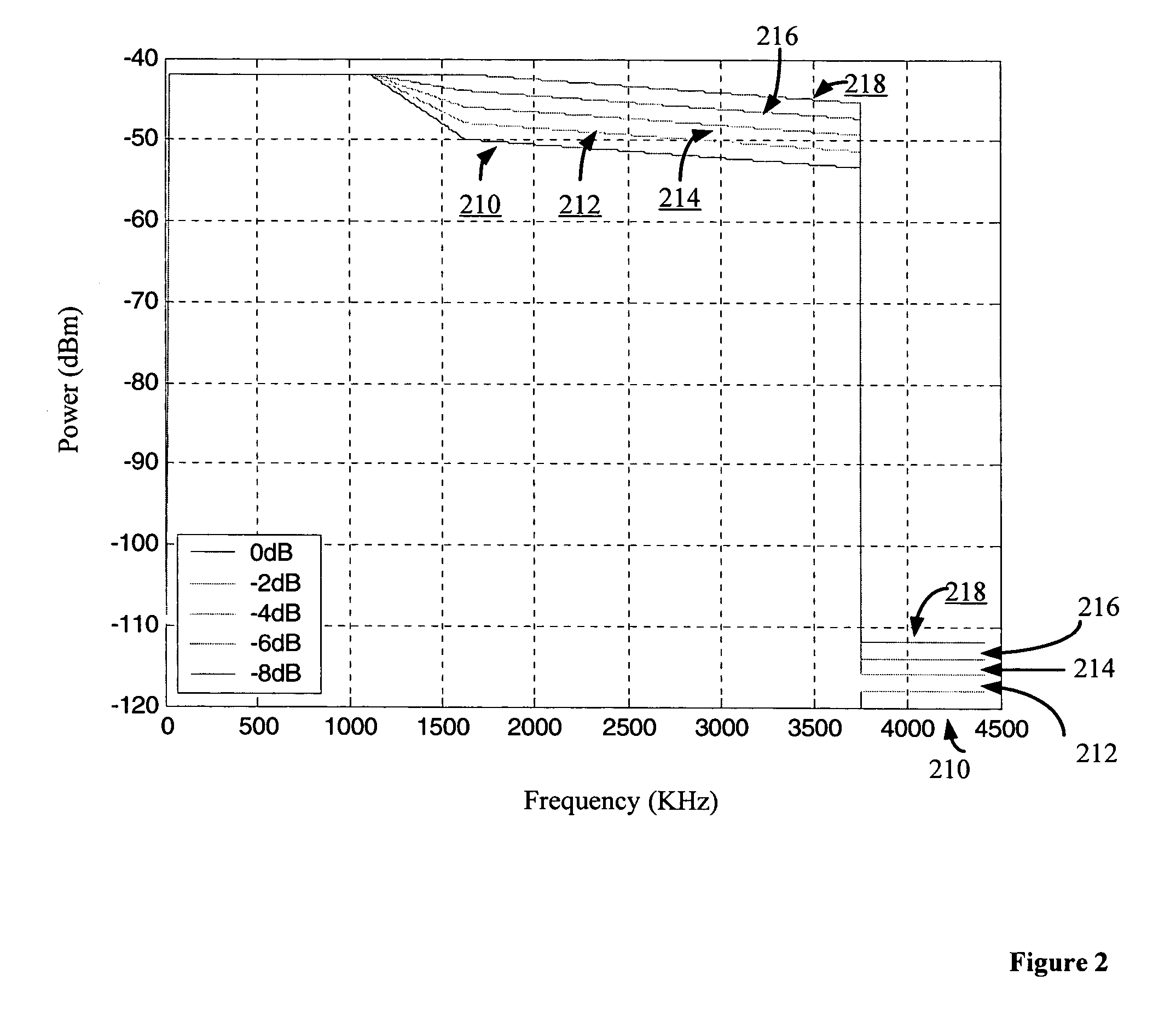

To alleviate the requirement to back-off all up-link performance, such as by limiting power spectral density, to overcome far-end cross-talk problems otherwise associated with relatively short loop-length wireline links, the present invention partitions the frequency spectrum based on an estimate of the loop length of a subscriber unit (CPE) modem from an exchange (LTE) modem. Up to a threshold frequency (fmax) at which received transmissions from a subscriber having a longest loop length (115) become indistinguishable by the LTE modem from a noise floor (102), up-link performance on all loop lengths is limited to correspond to that of the longest loop. At frequencies above the threshold frequency (fmax), subsets of subscribers (152-154) having relatively short loop lengths (116-119) use high frequency carriers that have signal to noise ratios sufficient to support information transmission in these elevated frequency bands.

Owner:NORTEL NETWORKS LTD

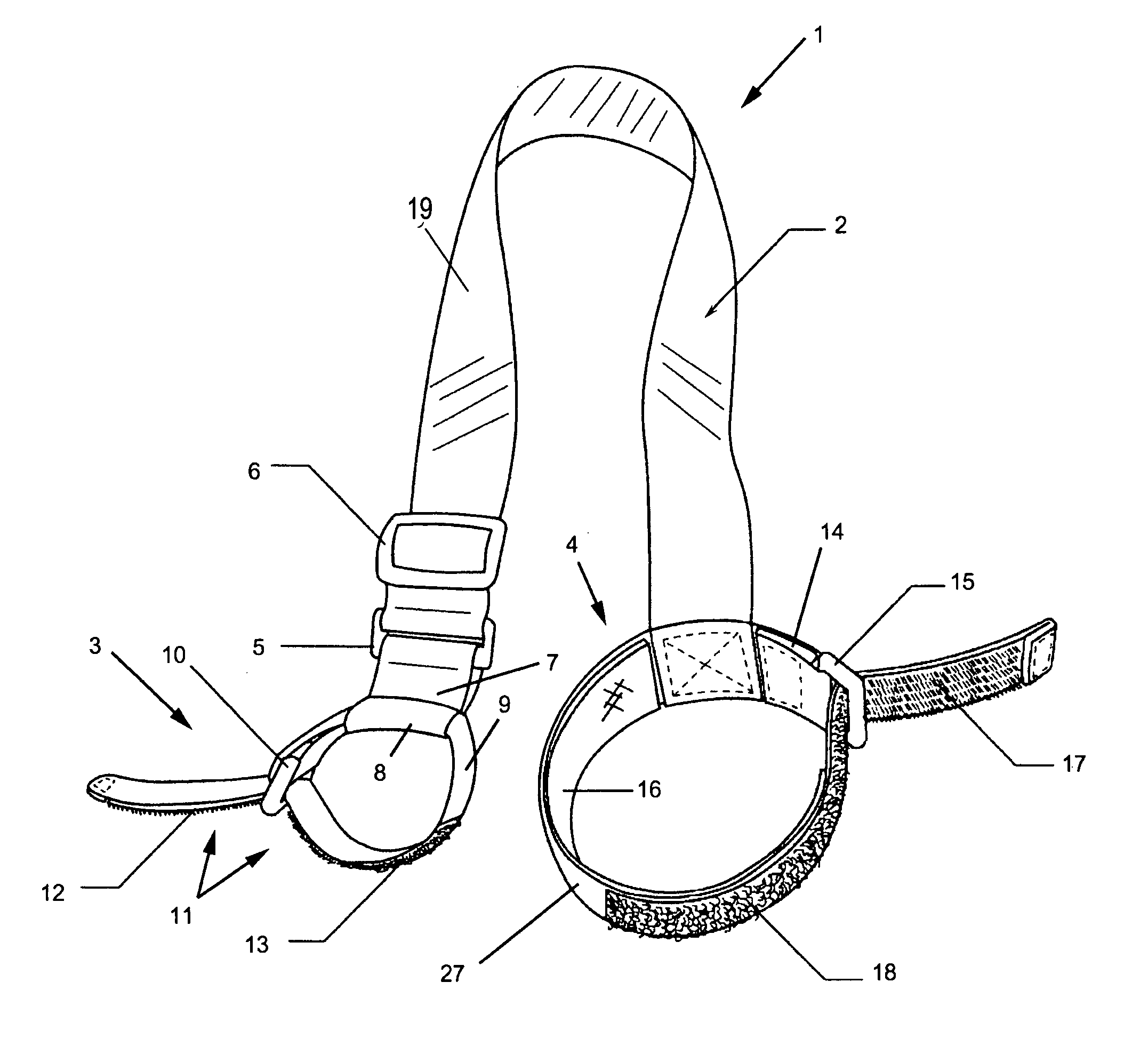

Bottle/can tethers

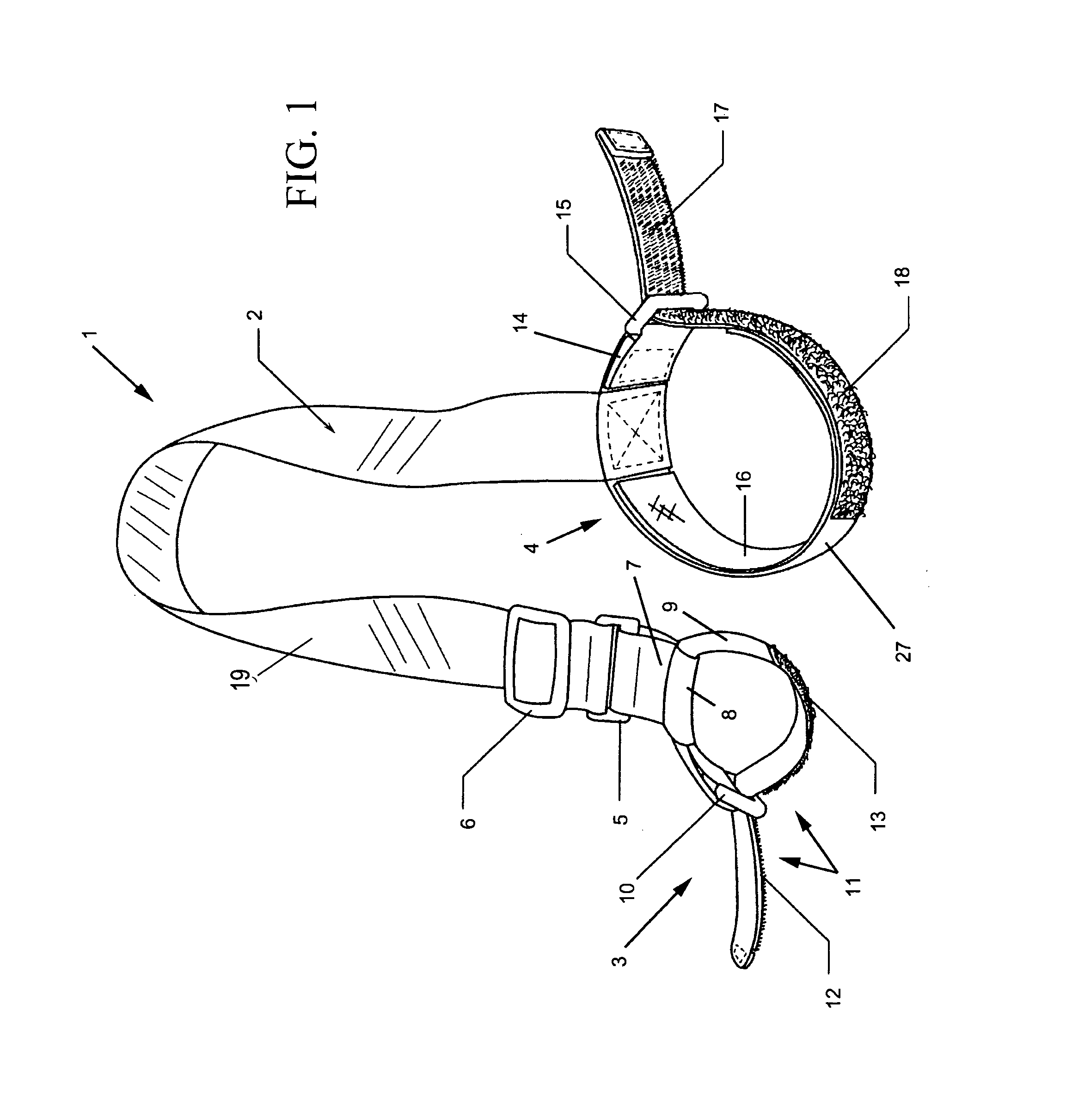

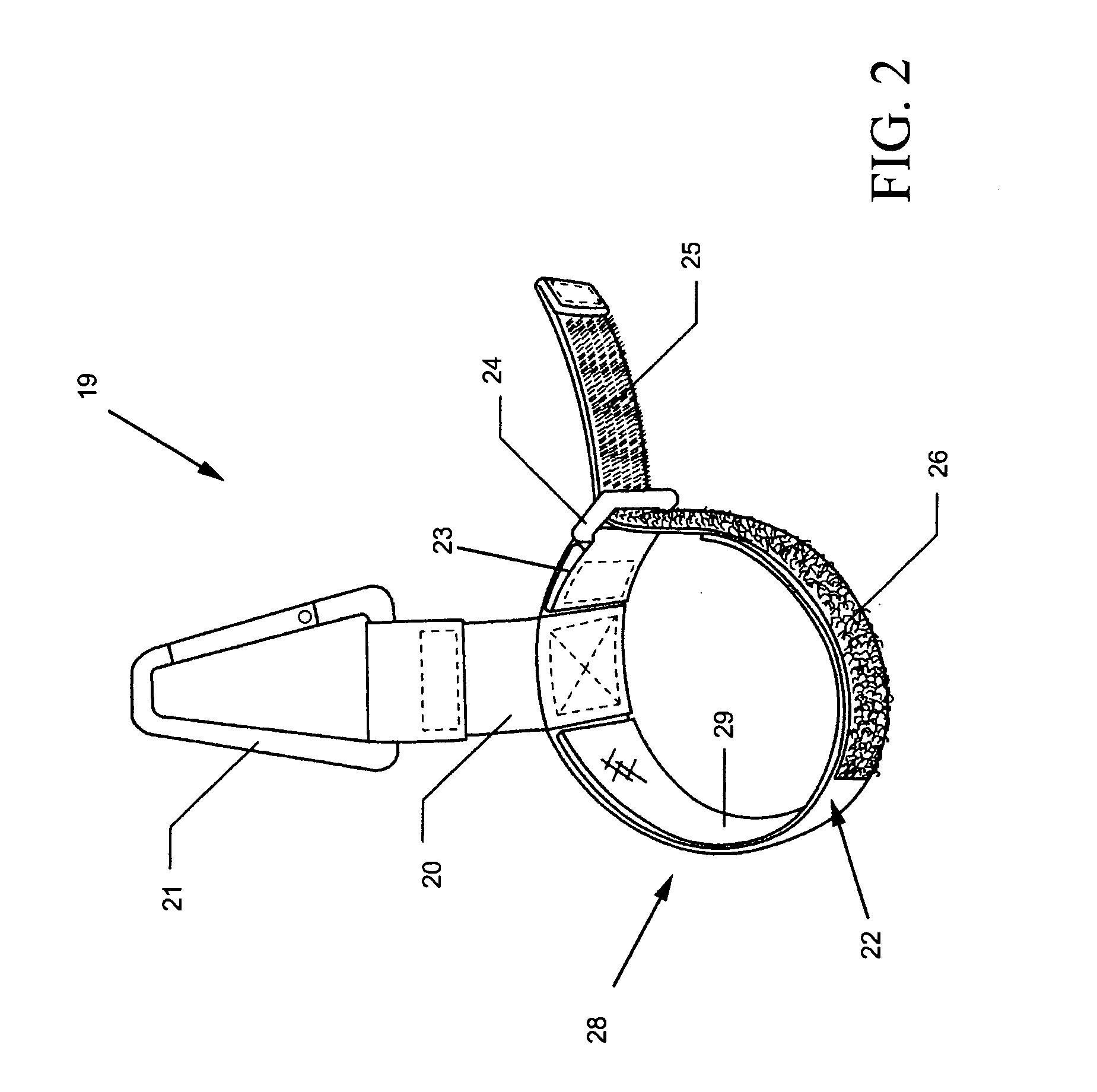

InactiveUS20080296325A1Safely attachedSimple and scalable designTravelling sacksTravelling carriersGround contactShort loop

A bottle and / or can holder including a strap of nylon webbing looped at one end through a square ring and back through a cinch buckle for length adjustment. The ring is also connected to a short loop of webbing that encircles a Velcro-adjustable cuff for attachment to a child carrier, car seat, wrist or the like. The other end of the strap is sewn to a larger Velcro-adjustable compression cuff for attachment around a bottle, can or the like. The compression cuff has a non-slip rubber (neoprene) strip sewn into the cuff to securely grip the container that it holds. An alternate embodiment of the invention comprises a bottle / can tether including a fixed strap attached to a triangular carabiner at one end, and to a Velcro-adjustable cuff at the opposing end. This cuff is for attachment around a bottle, can or the like, and it has a non-slip rubber (neoprene) strip sewn into it to securely grip the container that it holds. When applied, the devices will securely tether a bottle or can and prevent ground contact and spillage if, for instance, a baby throws his bottle.

Owner:TEPPER GINA

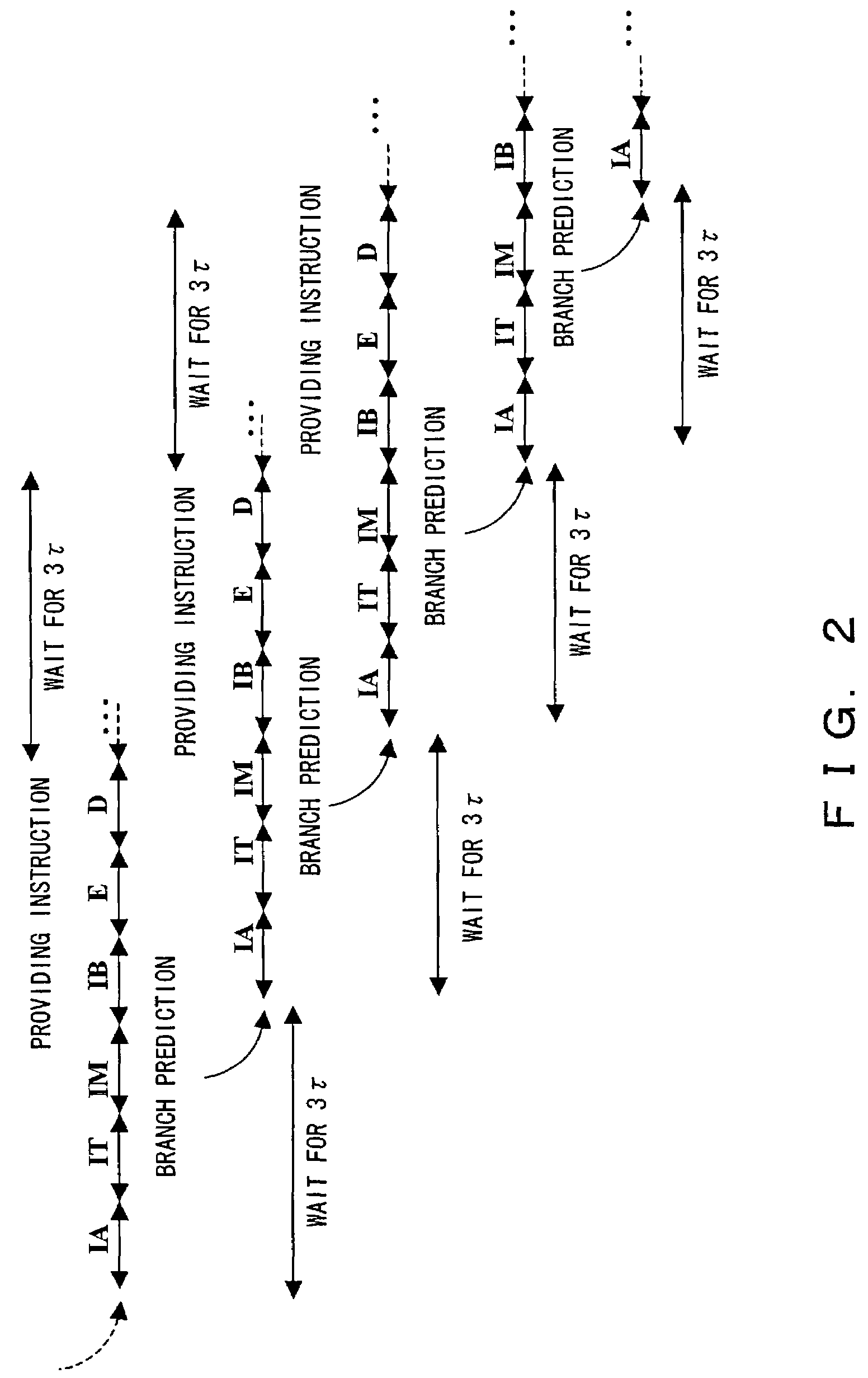

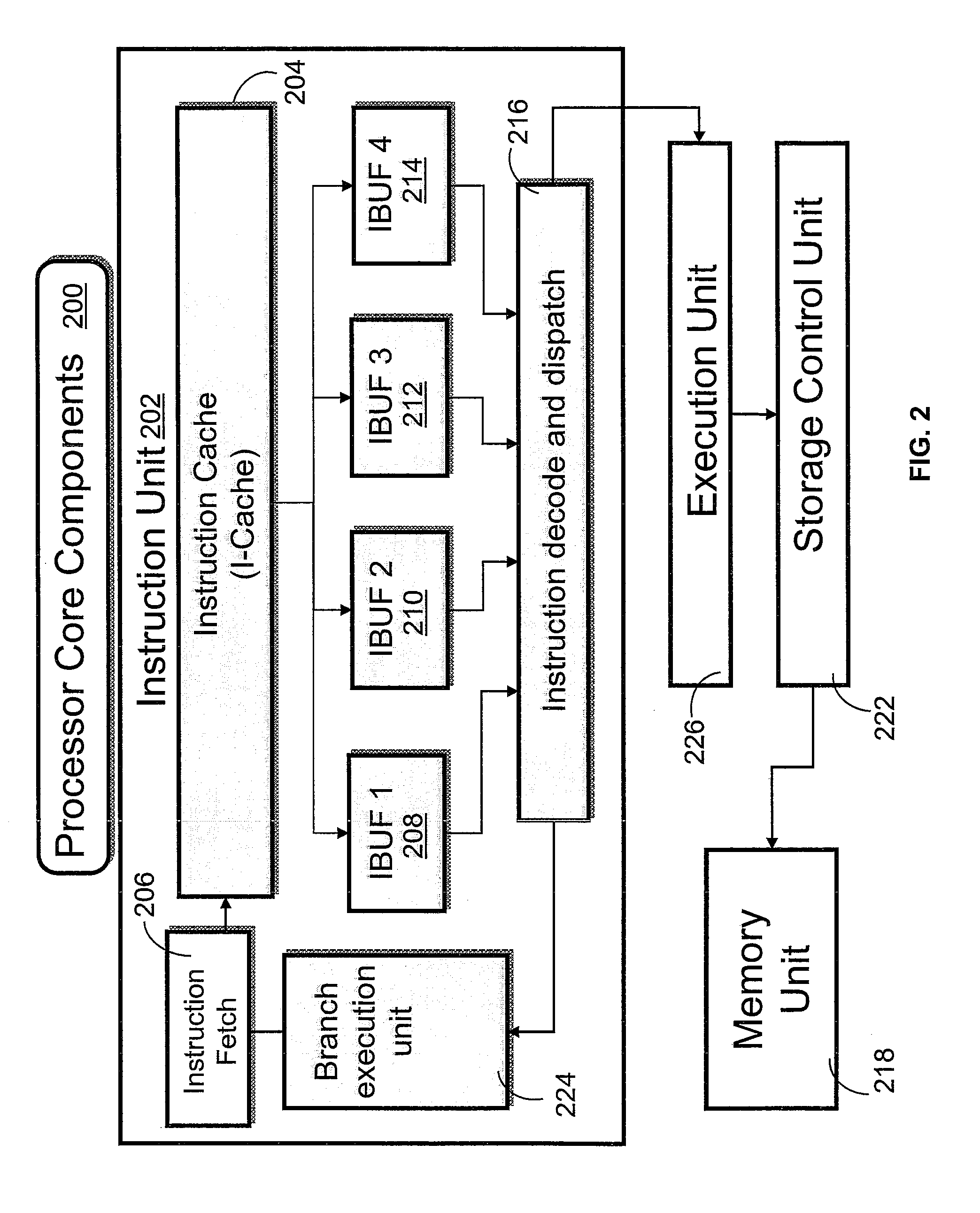

Apparatus for controlling instruction fetch reusing fetched instruction

InactiveUS7676650B2Reducing performance of information processingQuickly executing instructionDigital computer detailsConcurrent instruction executionShort loopParallel computing

When an instruction stored in a specific instruction buffer is the same as another instruction stored in another instruction buffer and logically subsequent to the instruction in the specific instruction buffer, a connection is made from the instruction buffer storing a logically and immediately preceding instruction, not the instruction in the other instruction buffer, to the specific instruction buffer without the instruction in the other instruction buffer, and a loop is generated by instruction buffers, thereby performing a short loop in an instruction buffer system capable of arbitrarily connecting a plurality of instruction buffers.

Owner:FUJITSU LTD

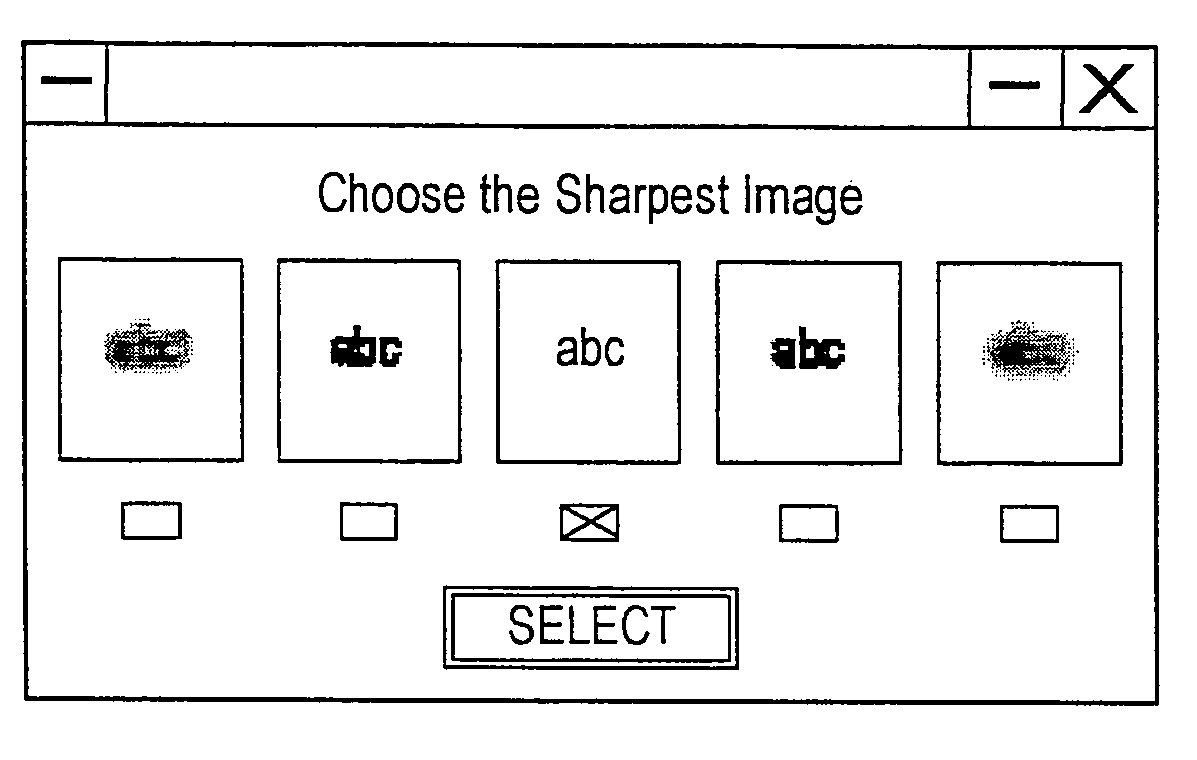

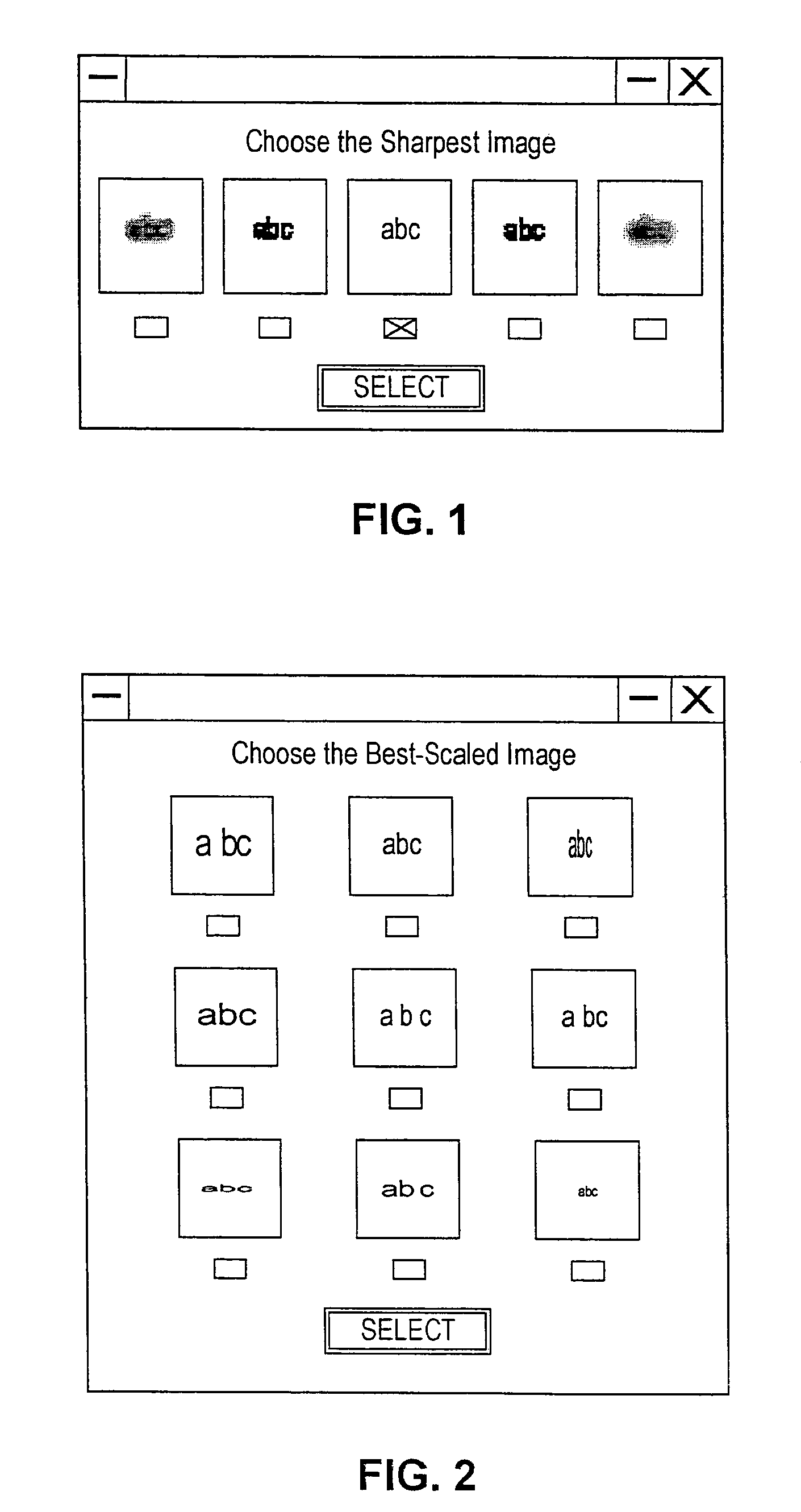

Parameterized preview array for iterative image optimization in remote applications

ActiveUS7071969B1Minimize transmission bandwidthSatisfactory qualityTelevision system detailsMaterial analysis using wave/particle radiationArray data structureShort loop

A method of adjusting focus and / or other image parameters in a remotely-operated image capturing system, such as a scanning electron microscope (SEM), is provided. The method minimizes transmission bandwidth and allows a remote user to perform adjustment quickly without requiring real-time feedback. In accordance with the method, rather than adjusting a knob or slider while viewing a real-time image as is done in prior art systems, the user selects among several still images representing a wide range of values of the adjustment in question. The user then selects from another set of images which represent a small subrange of values determined by the first choice. The process is repeated until the adjustment resolution of the instrument is reached or the user is satisfied. Adjustments, like objective lens alignment, which require “focus wobble” can also be made using this method. Since focus wobble is a periodic motion, it can be represented using a short loop of animation. This animation, when used in accordance with the present invention, can either be captured directly as a short burst of video or captured as a sequence of still images.

Owner:NAT SEMICON CORP

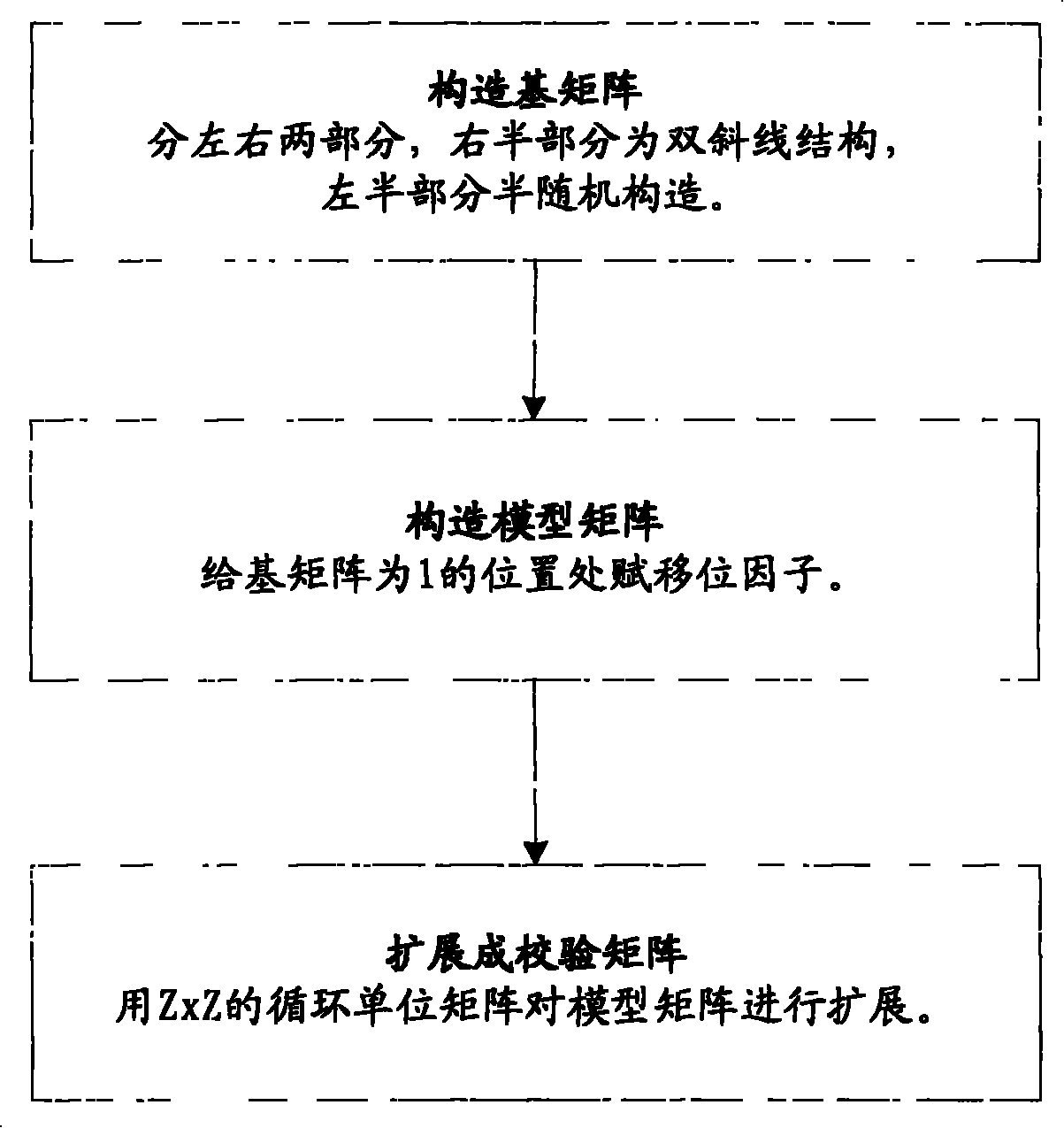

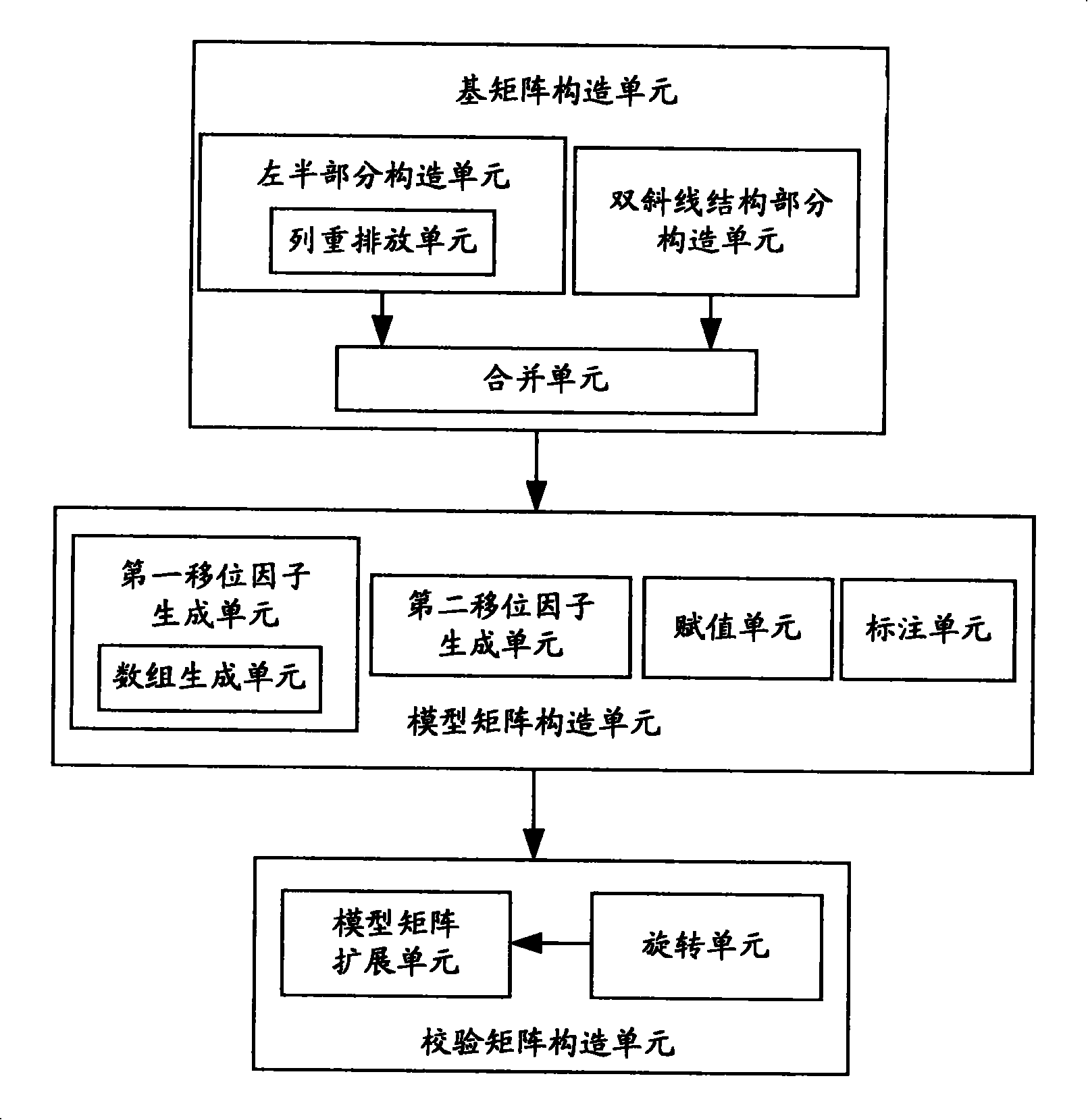

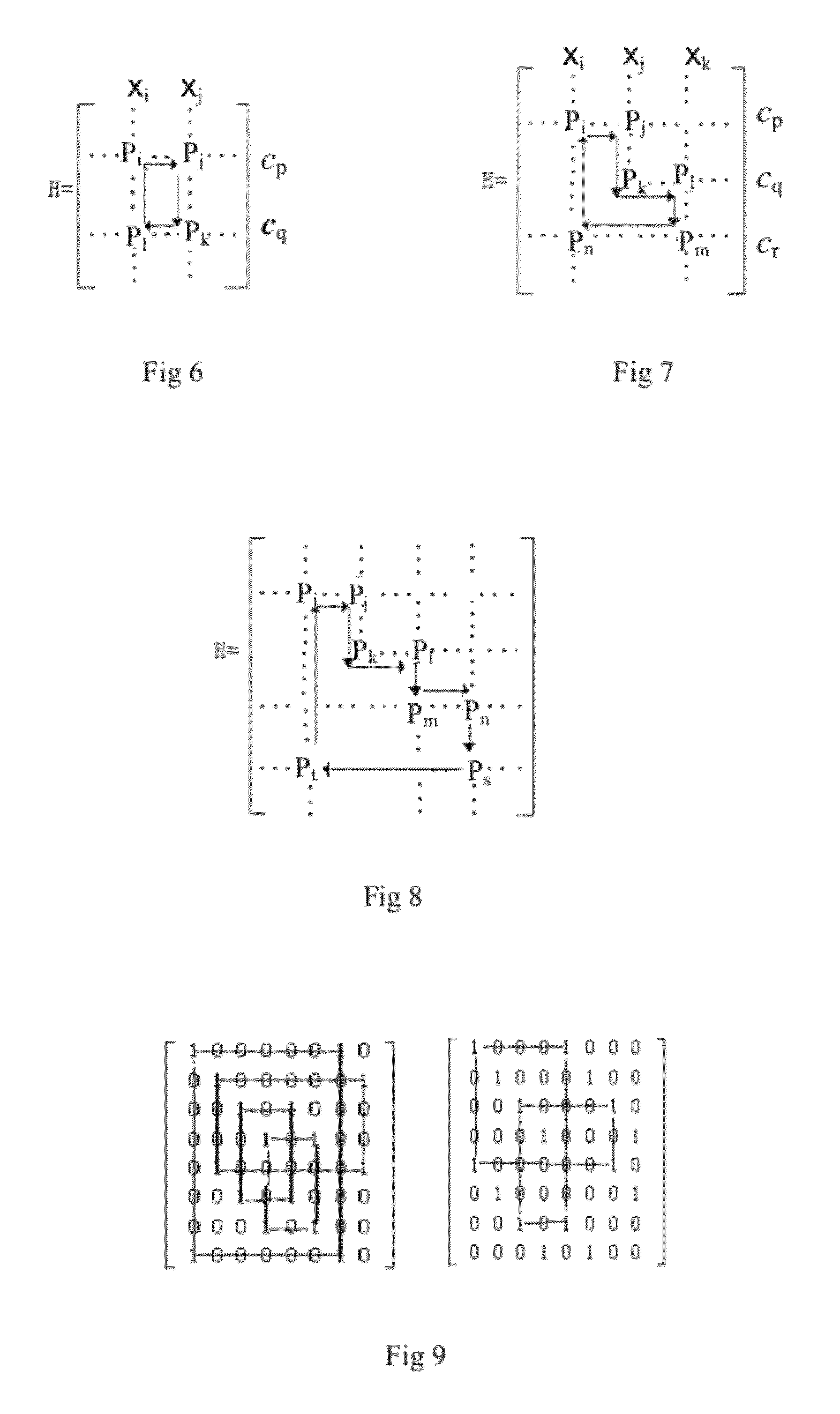

Method and device for constructing low-density parity code check matrix

InactiveCN101162907AImprove performanceEasy to implementError preventionError correction/detection using multiple parity bitsShort loopLow-density parity-check code

The invention relates to a method and device for constructing low-density parity check-code checking matrix. The constructing method is easy and flexible to implement, because the combination of semirandom constructing mode and structured constructing mode is adopted; besides, the arrays in the basis matrix are arranged in a special manner, the characteristics of irregular codes are achieved and the regularity is ensured. Therefore, the invention not only ensures excellent performance of low-density parity check-code, but also facilitates realization of coding hardware. In addition, short-loop is avoided in the basis matrix during the constructing process, and equal circular shift factors occur in the model matrix; thereby, the checking matrix has no short loop after expansion, and the decoding effect is improved. The invention also provides a group of selected model matrixes that can be expanded into multi-code length. The low-density parity check-code checking matrix with multi-code rate has an extensive application scope and excellent performance.

Owner:HUAWEI TECH CO LTD

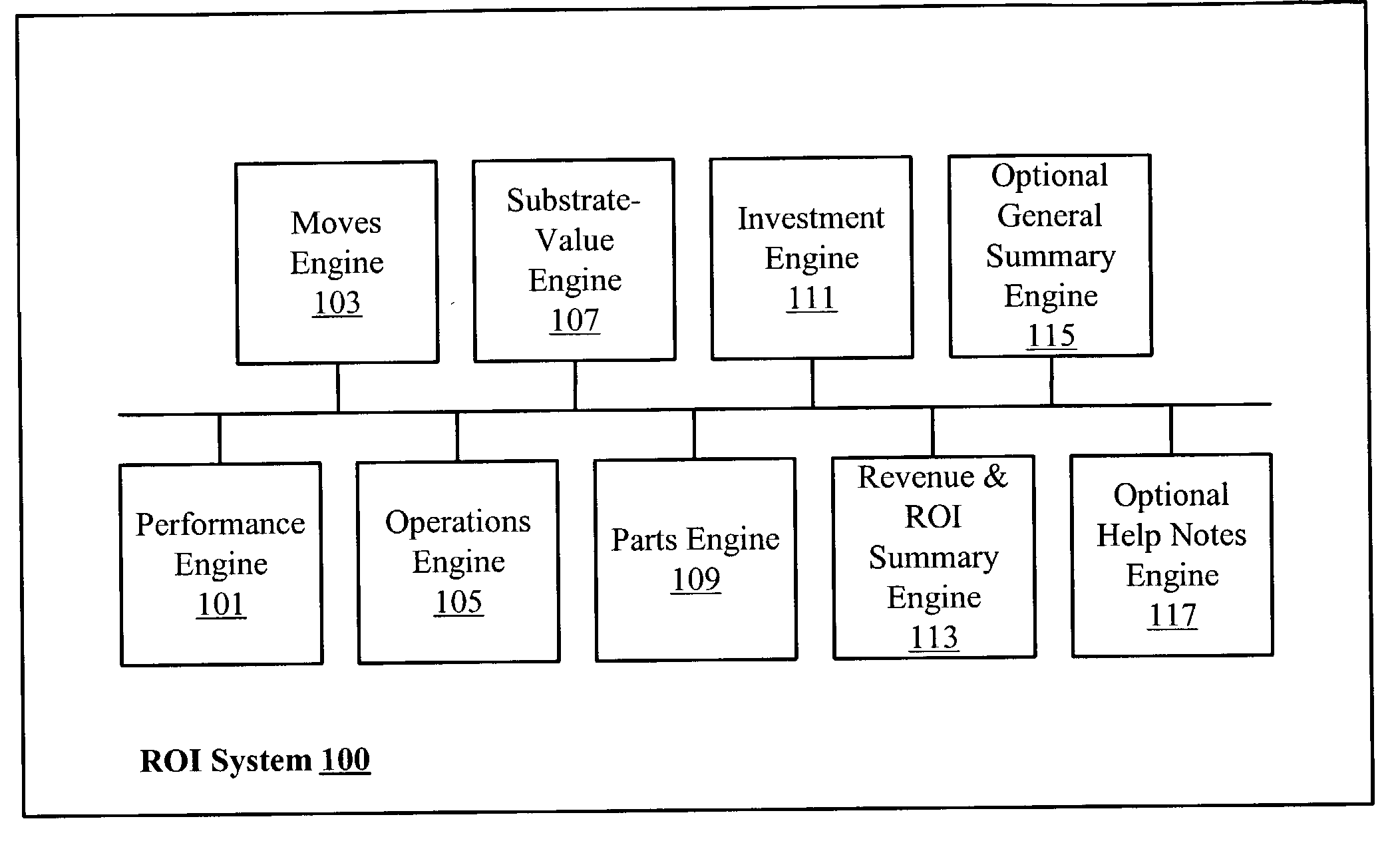

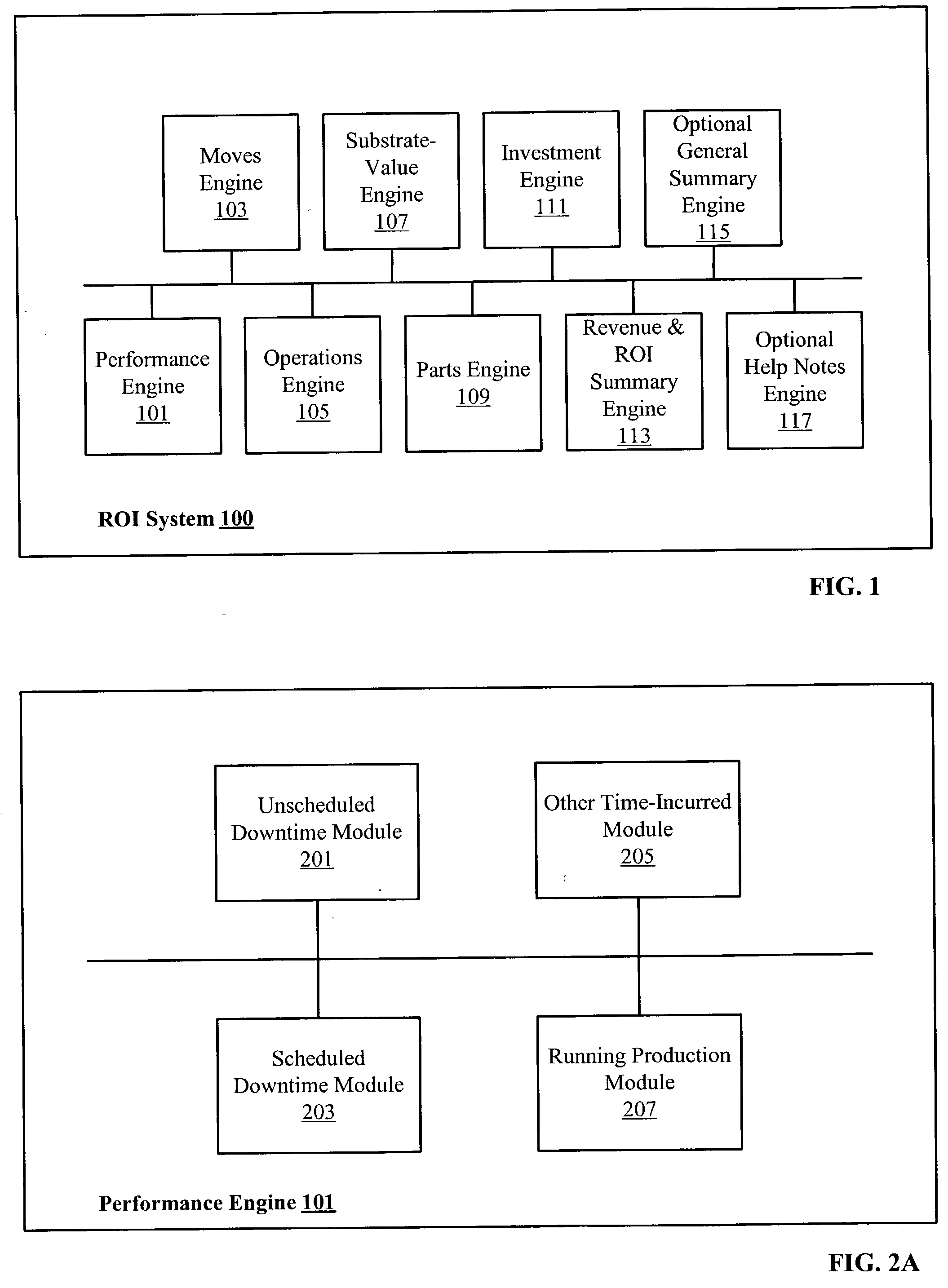

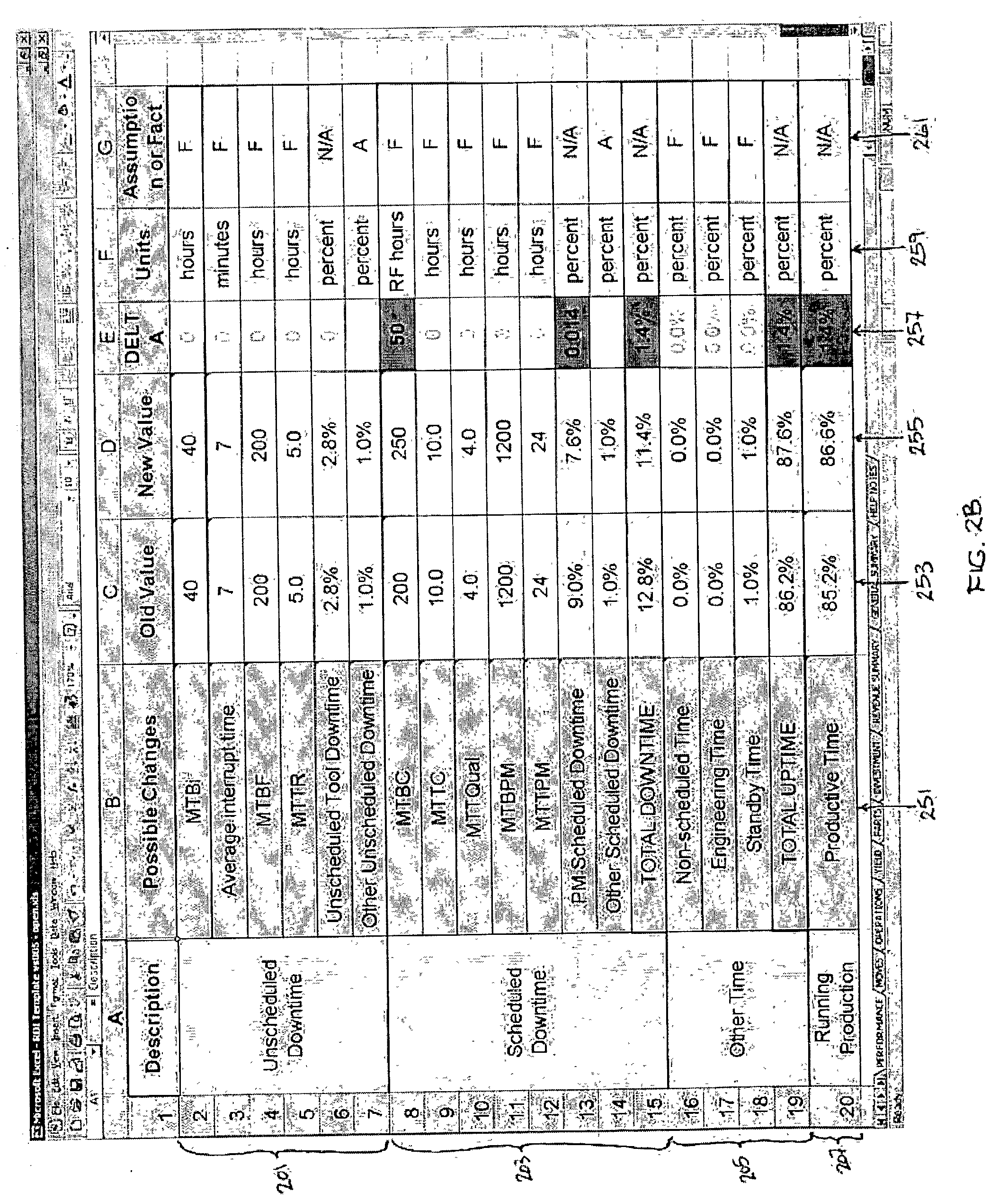

System and method for determining a return-on-investment in a semiconductor or data storage fabrication facility

A return-on-investment (ROI) modeling system and method of the present invention calculates a return-on-investment for various scenarios in a semiconductor or data storage fabrication facility ("fab"). The ROI system and method of the present invention calculates the ROI based upon having fab operational details entered. The ROI calculation may be performed for an entire fab or a particular fab processing line. The present invention compares the ROI of a current operation with a contemplated change or set of changes. A complete set of pertinent factors having a relevant or significant impact on an accurate ROI calculation is taken into consideration. Further, the present invention determines costs associated with, for example, the installation of a new tool, downtime costs, short-loop test runs, split-lot testing, design-rule shrinks, and wafer-size changes. If a fab is not currently operating at maximum capacity, an embodiment of the invention calculates an increased capacity capability.

Owner:LAM RES CORP

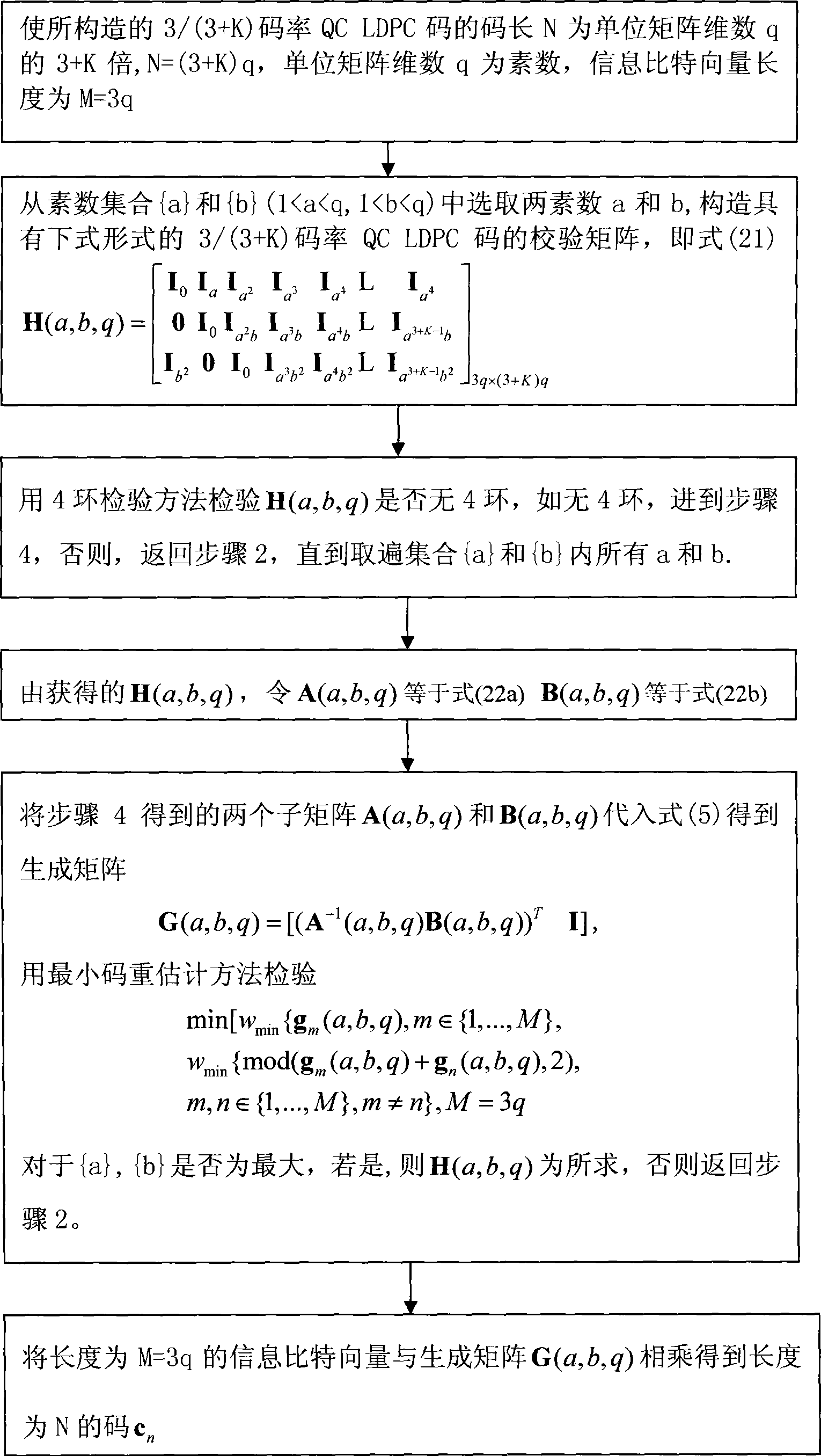

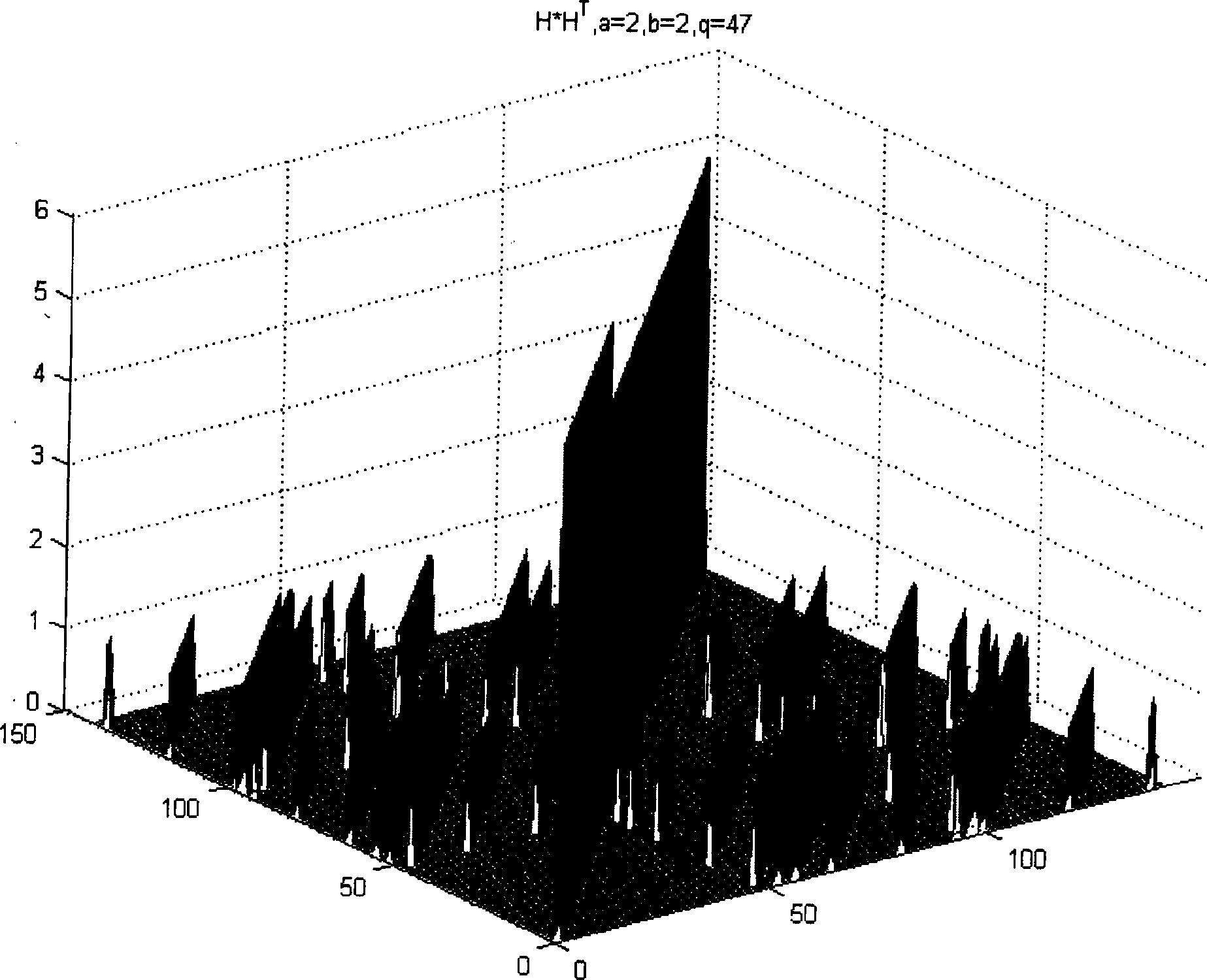

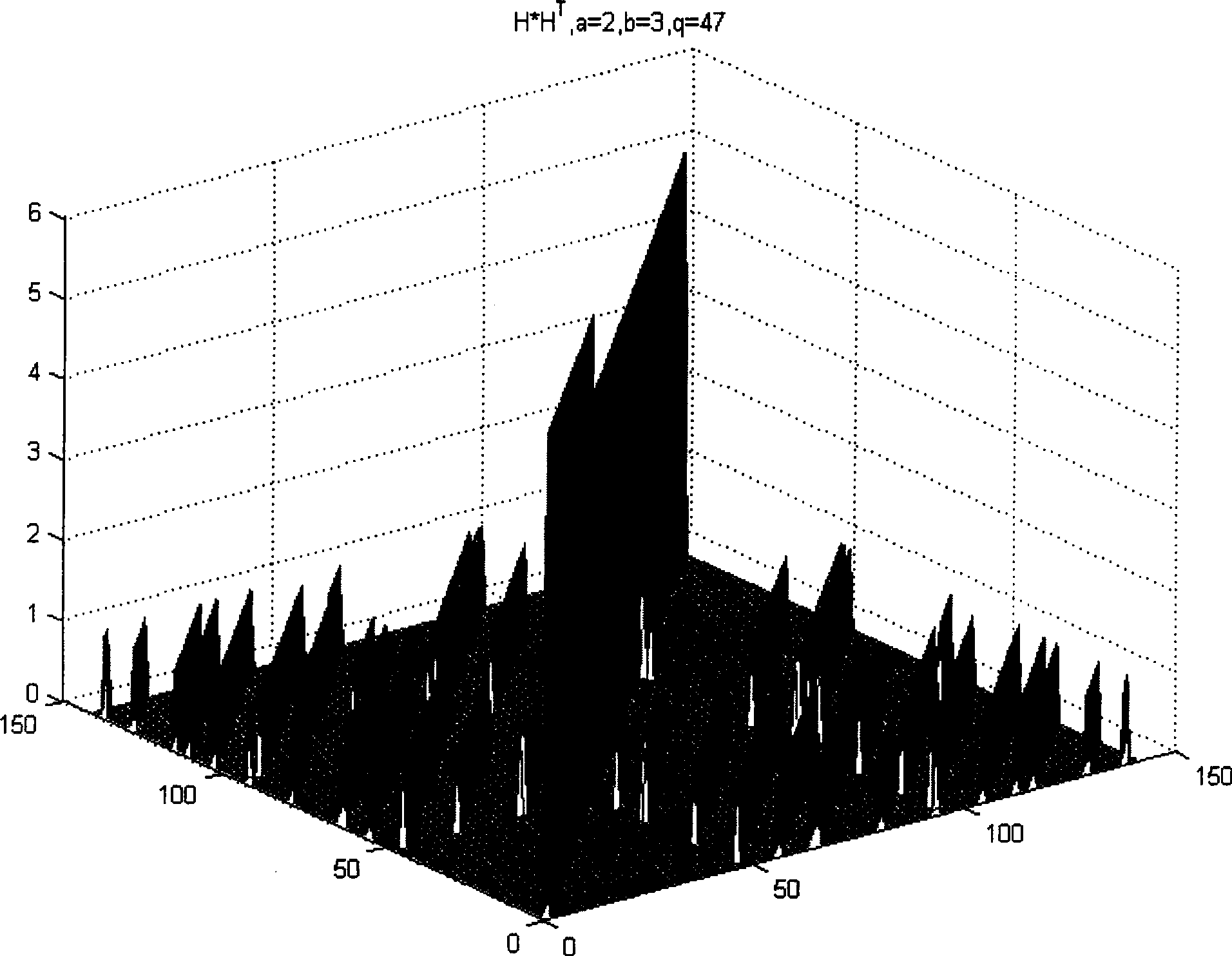

LDPC constructing method with short ring or low duplicate code

InactiveCN101488761ASolve the problem of low-code repeated code wordsCode majorError correction/detection using multiple parity bitsLinear codingShort loop

The invention discloses an algebraic construction method of LDPC (Low Density Parity Check) code based on cyclic matrixes; design parameters of cyclic matrixes are adjusted by short-loop check and minimum code weight check, which are nonnegative prime numbers a and b meeting two constraint conditions, and dimension q of an identity matrix, wherein the magnitude of dimension q of a shift identity matrix and whether the error rate characteristics of the designed LDPC code are influenced by prime numbers. The invention solves the problems of short-loop and low code coincident code word appearing in the existing QC LDPC code design. The method can check the existence of low code coincident code word in the designed code, thereby checking the existence of 4-loop. An irregular quasi-cyclic LDPC code structure disclosed by the invention divides the check matrix H into two submatrixes A and B, the nonsingular structure of the submatrix A is disclosed, and a matrix is generated by the two submatrixes A and B. Direct linear coding is carried out by generating the matrix. The embodiment validates the efficiency and good bit rate performance of the method disclosed by the invention.

Owner:BEIJING JIAOTONG UNIV

Short loop ADSL power spectral density management

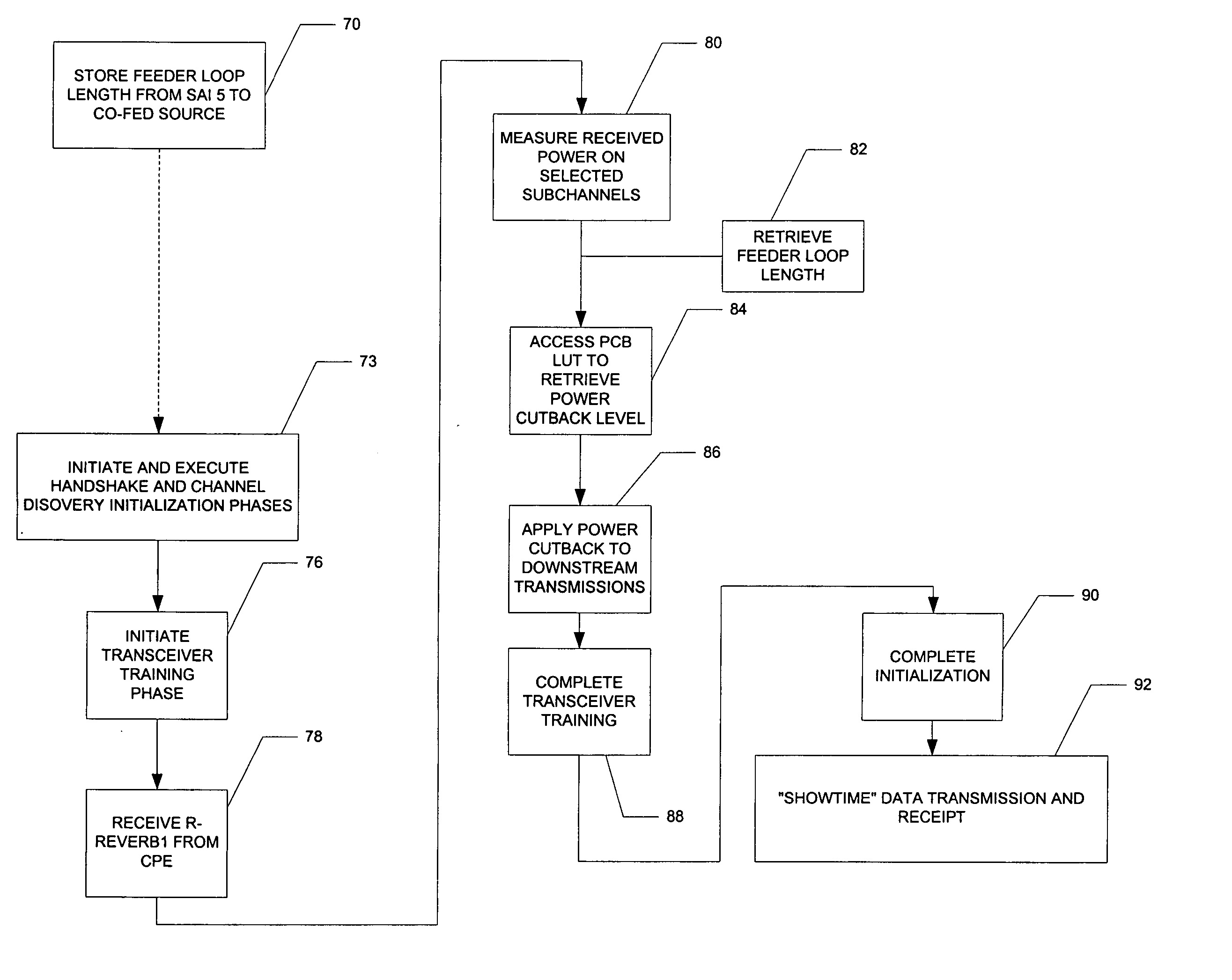

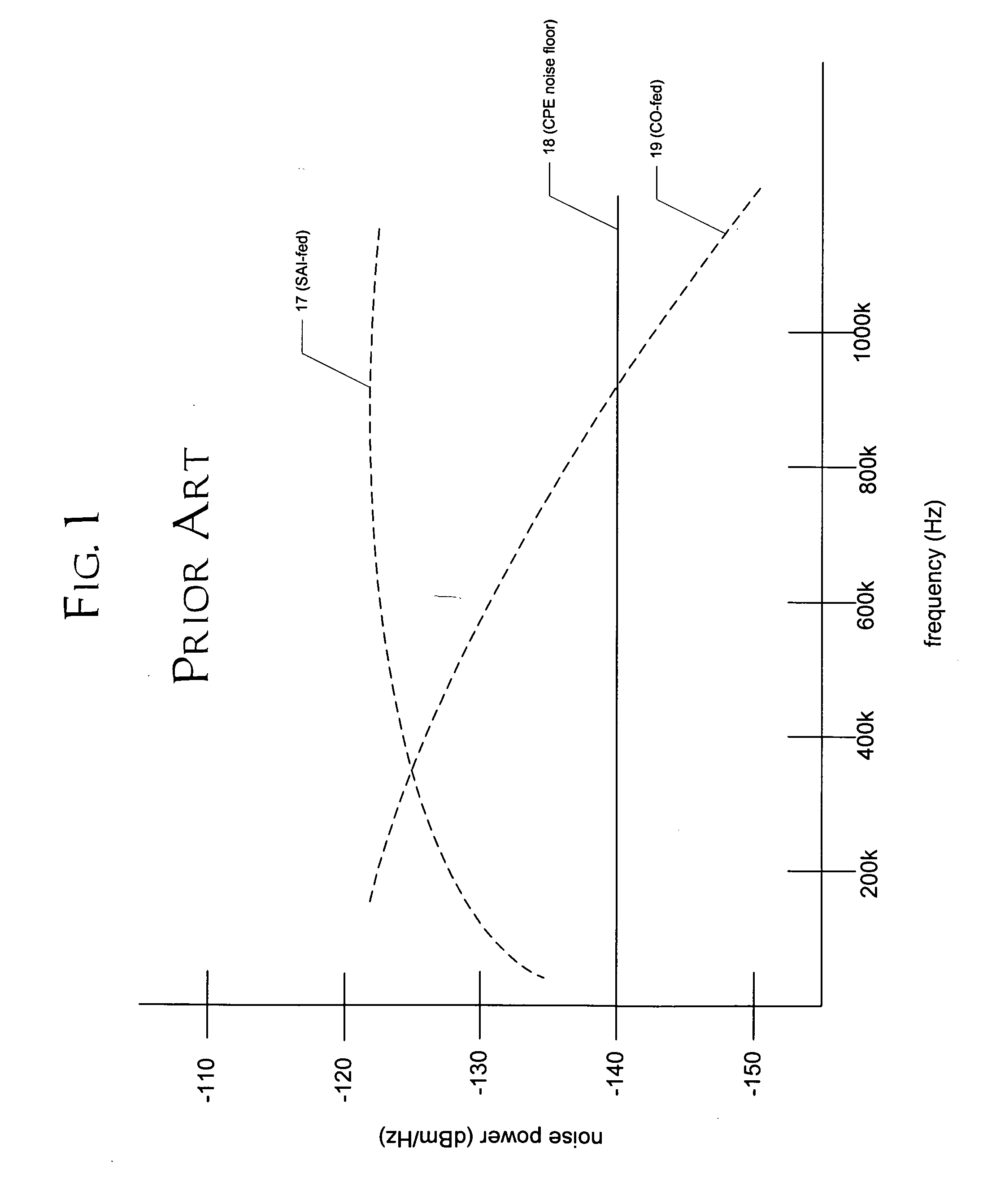

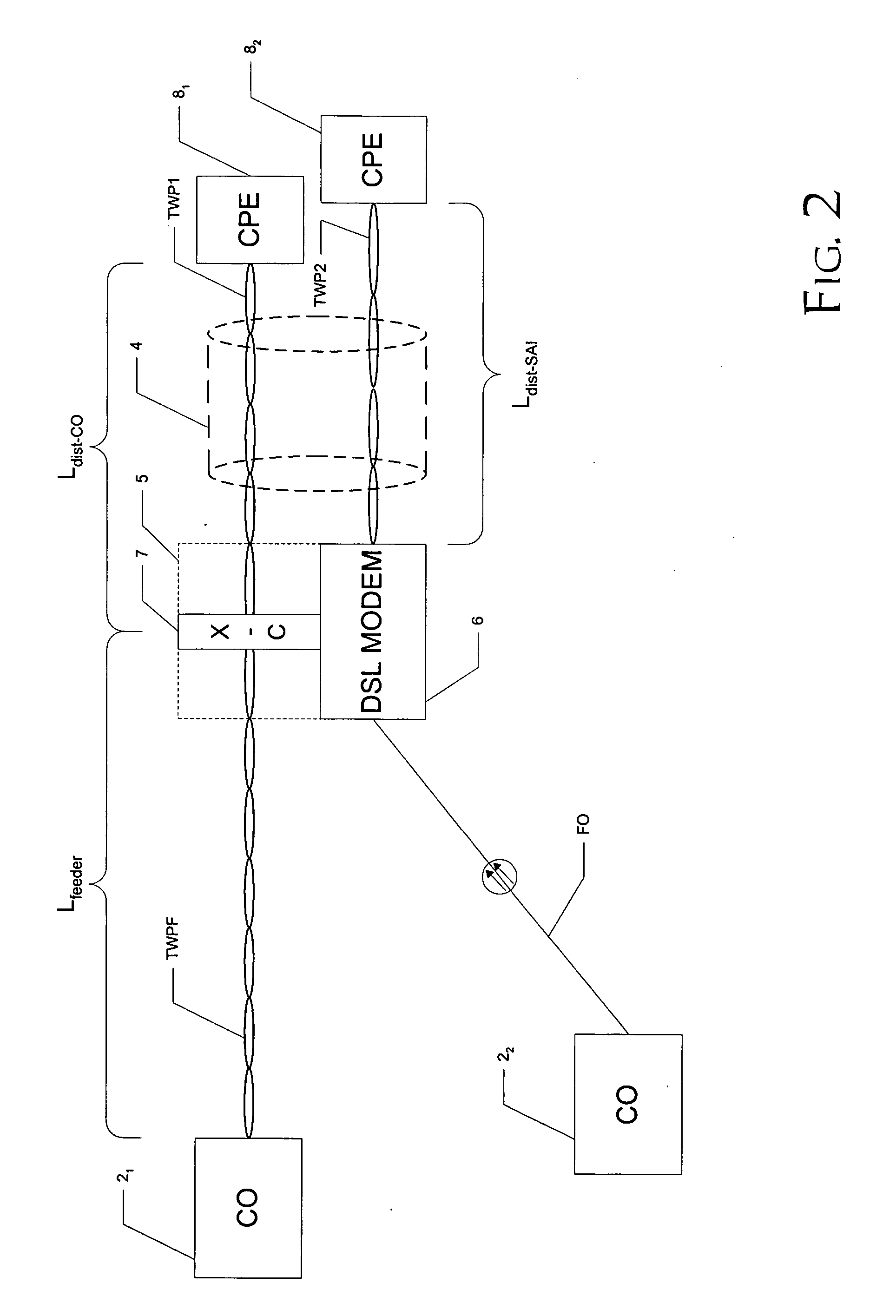

InactiveUS20060062288A1Reducing the far-end crosstalkReduce power consumptionModulated-carrier systemsCross-talk reductionFiberTransceiver

A digital subscriber line (DSL) modem for a service area interface, which controls the power of its downstream transmissions to minimize far-end crosstalk (FEXT), is disclosed. The disclosed modem has an interface to a low-attenuation upstream facility, such as fiber optic, and includes a digital transceiver and an analog front end that is coupled to a twisted-pair wire facility in a binder. The modem also includes a memory location for storing the feeder distance between a DSL central office and the service area interface, the service area interface also coupled to a subscriber of the CO-fed communications via twisted-pair wire. Power cutback levels are applied to the downstream transmissions from the modem according to the feeder distance, so that the FEXT on the CO-fed signal is minimized without undue data rate degradation.

Owner:TEXAS INSTR INC

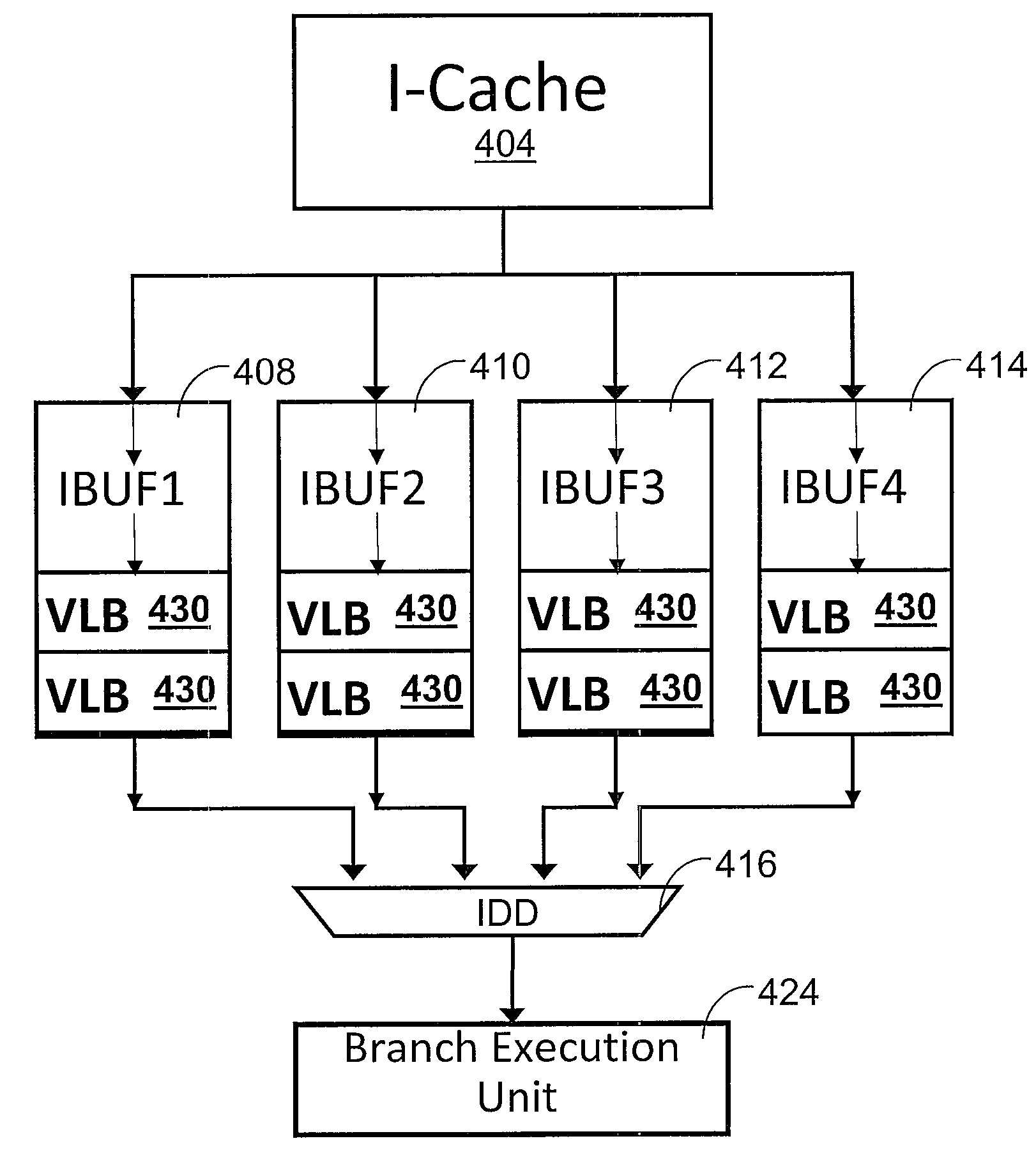

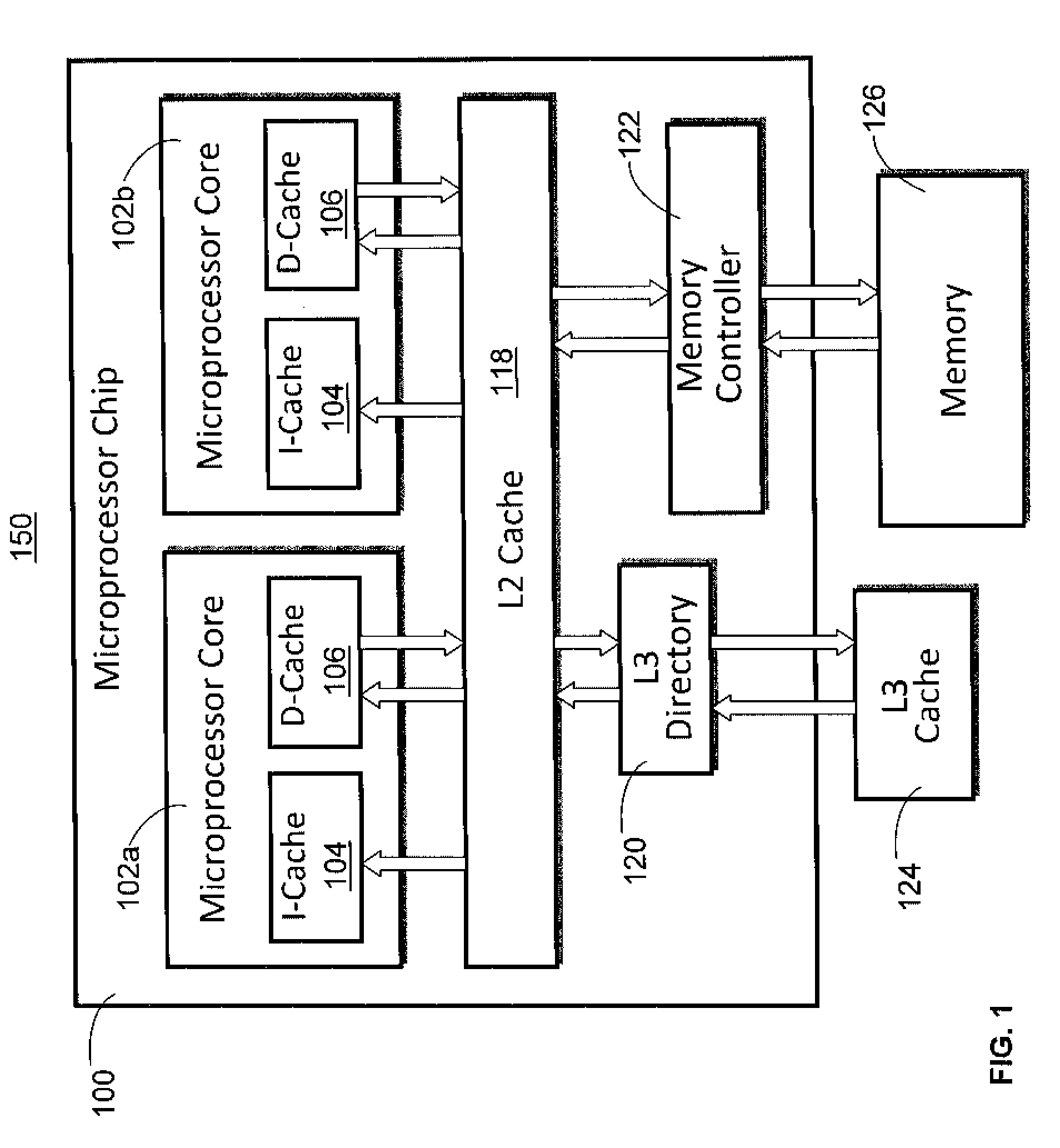

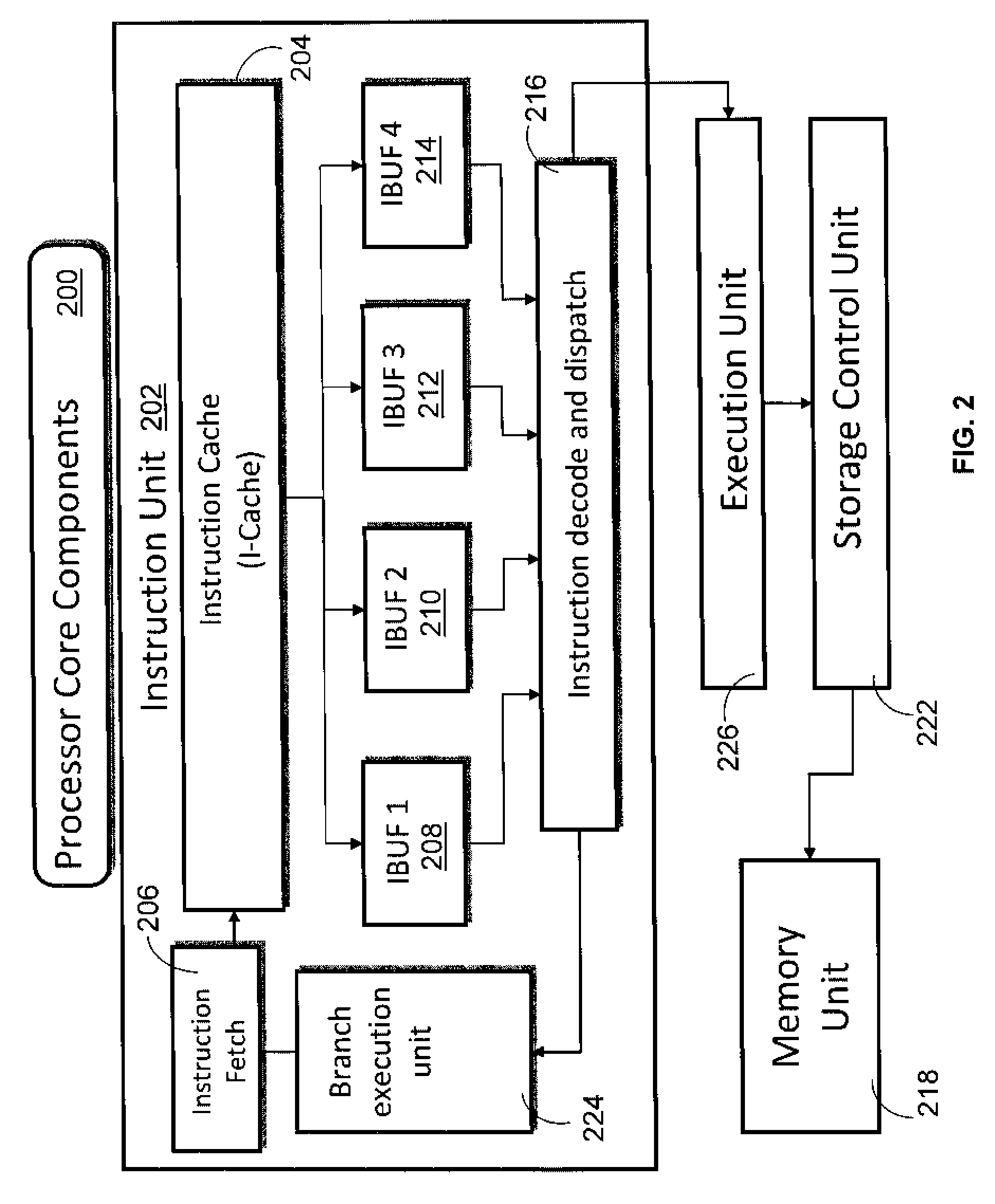

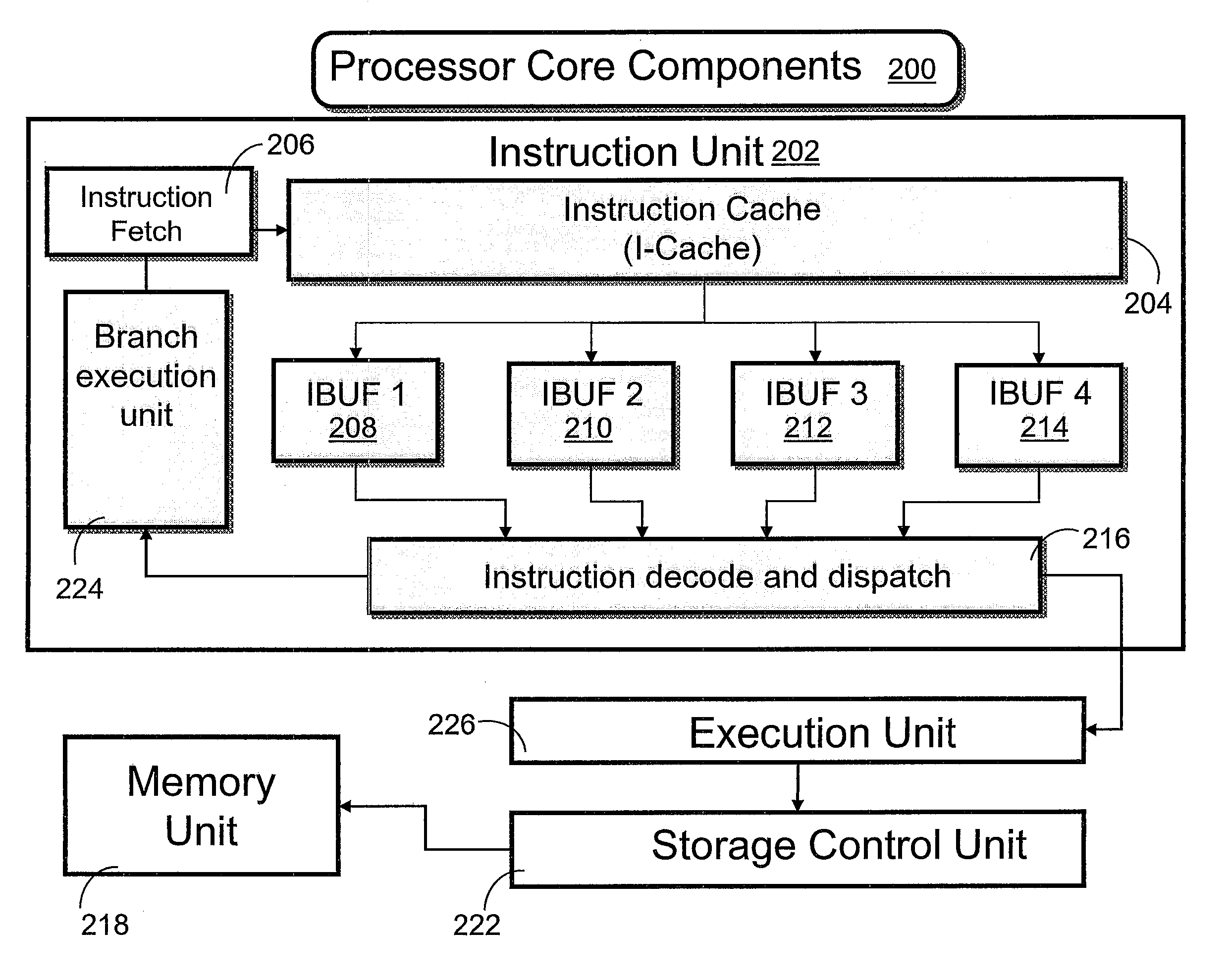

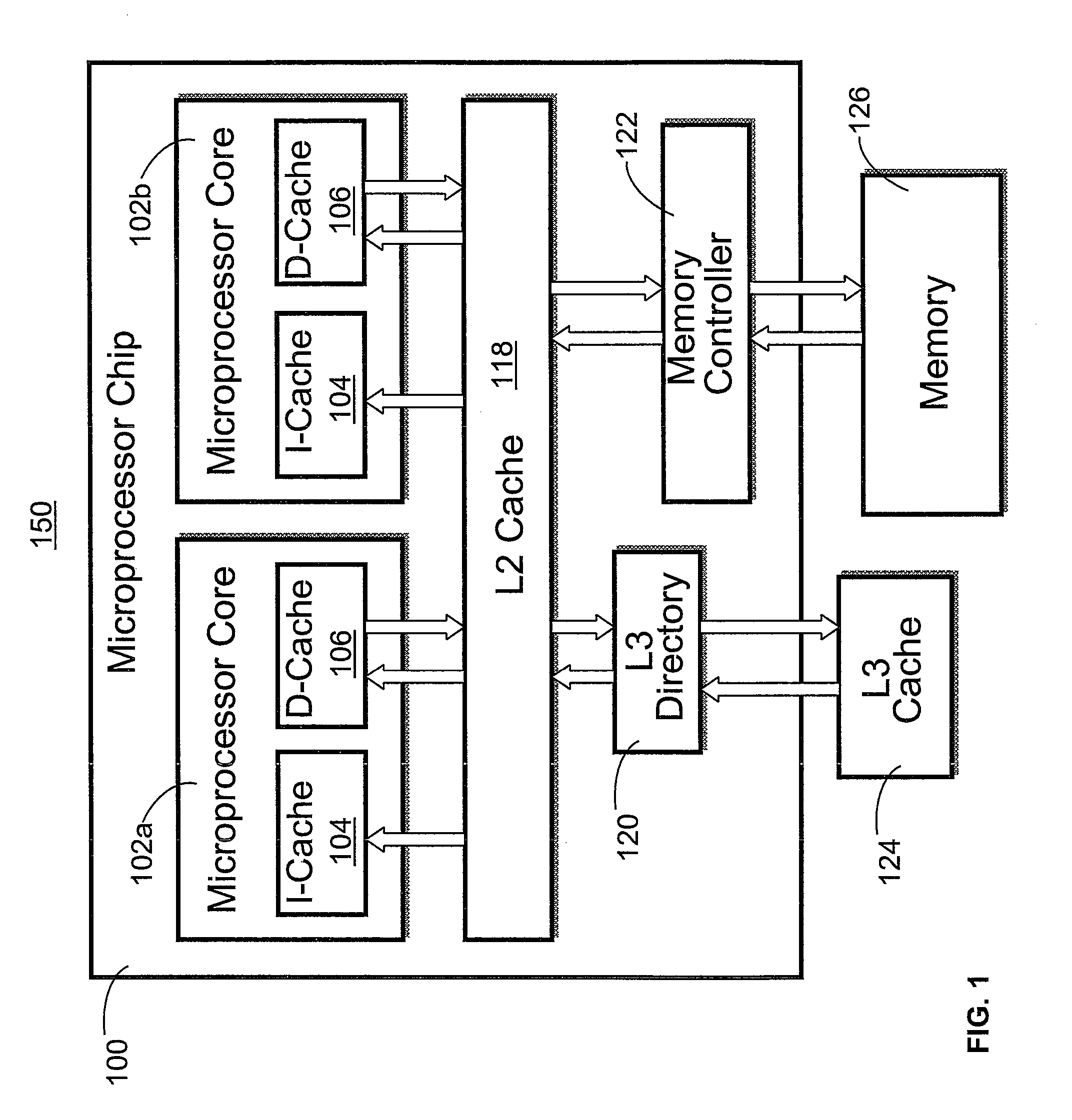

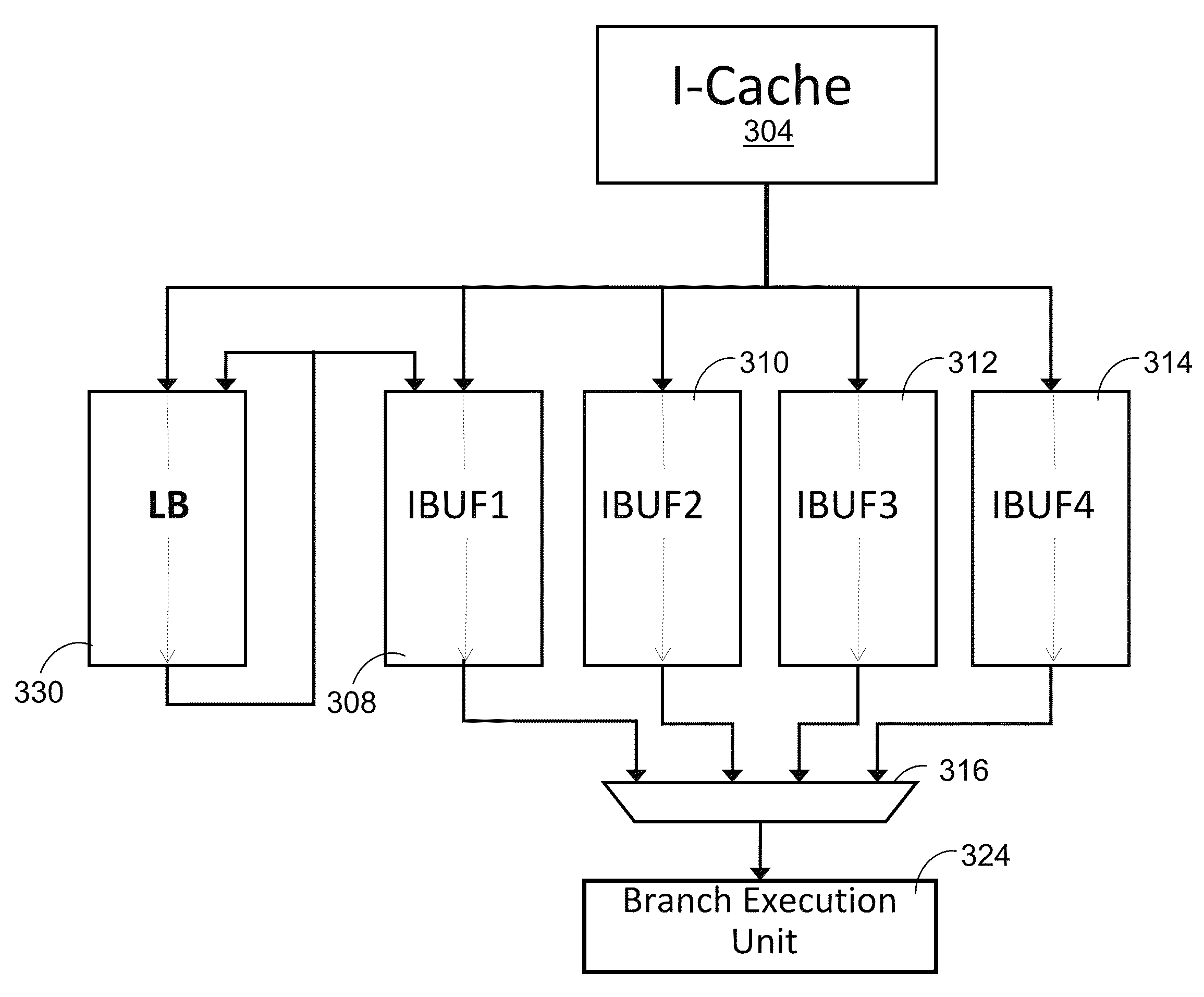

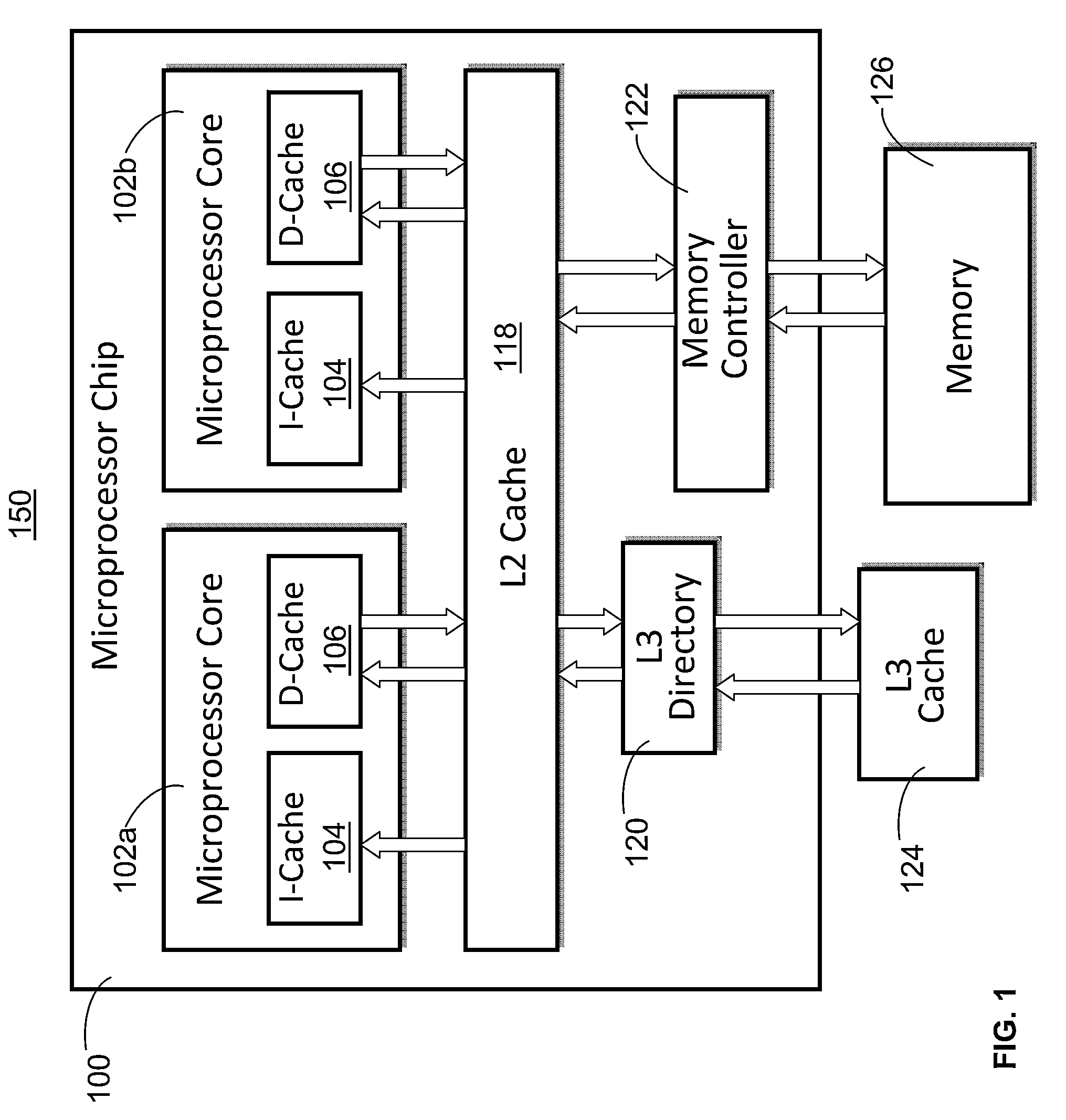

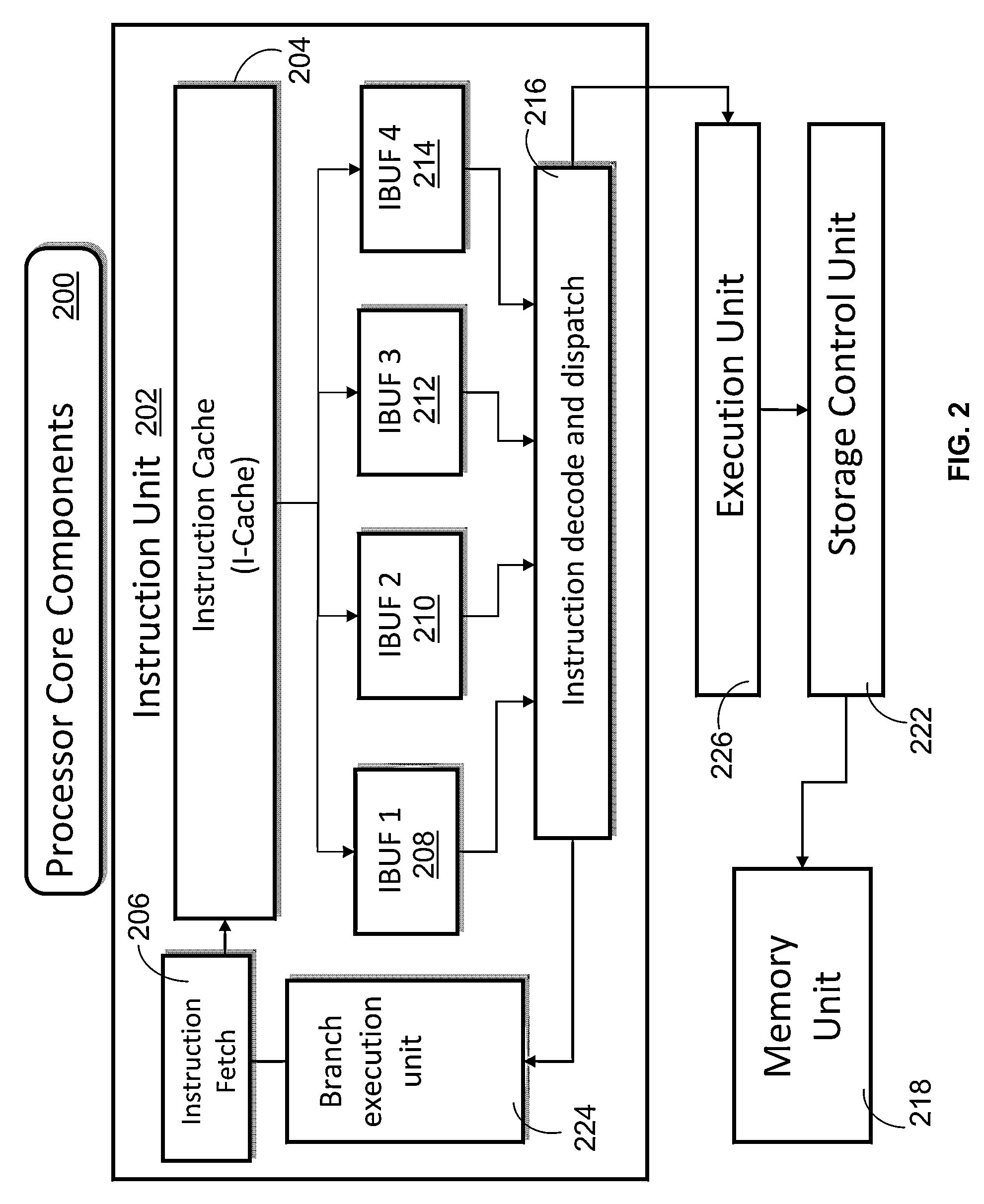

Apparatus and Method for Improving Efficiency of Short Loop Instruction Fetch

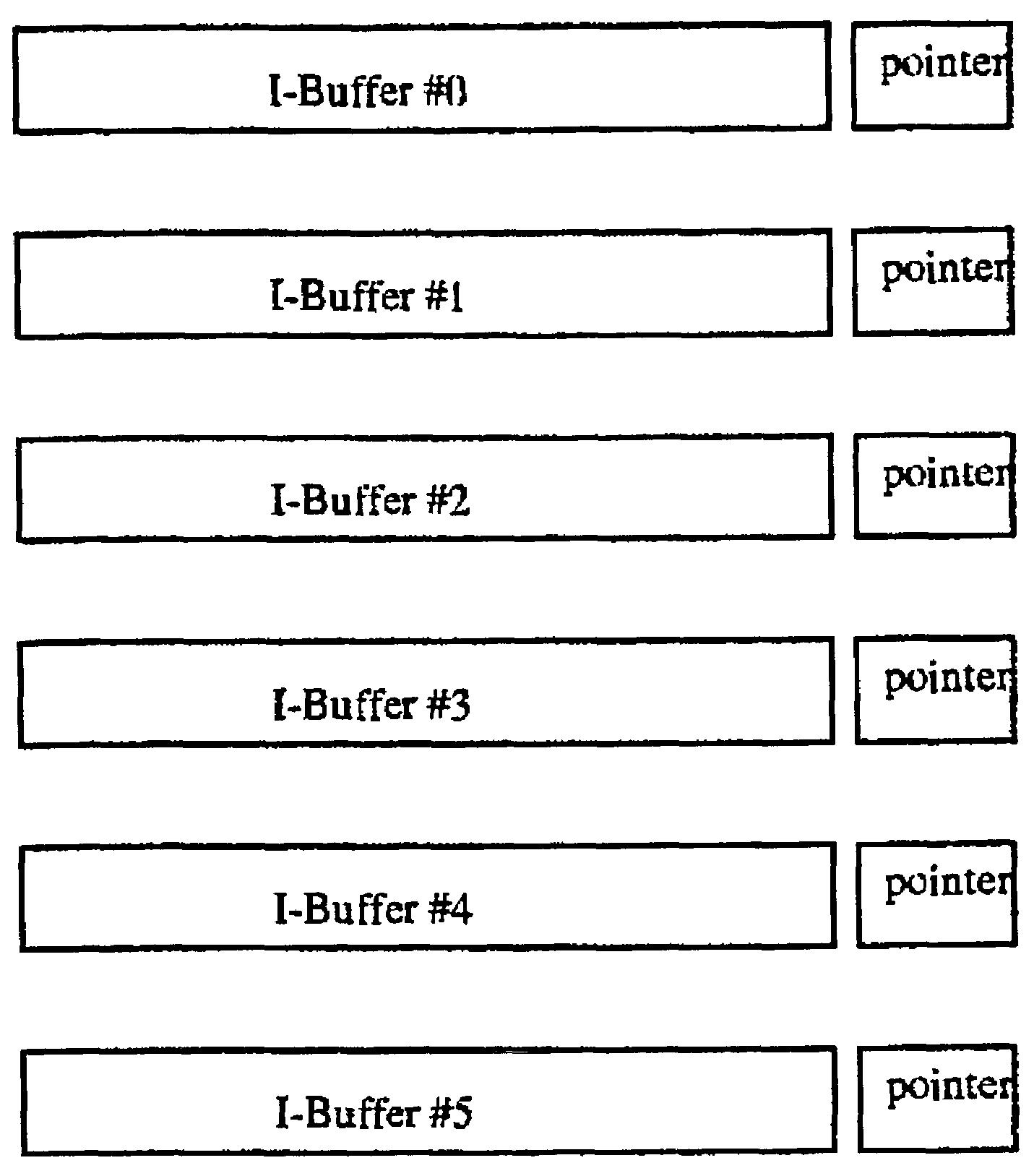

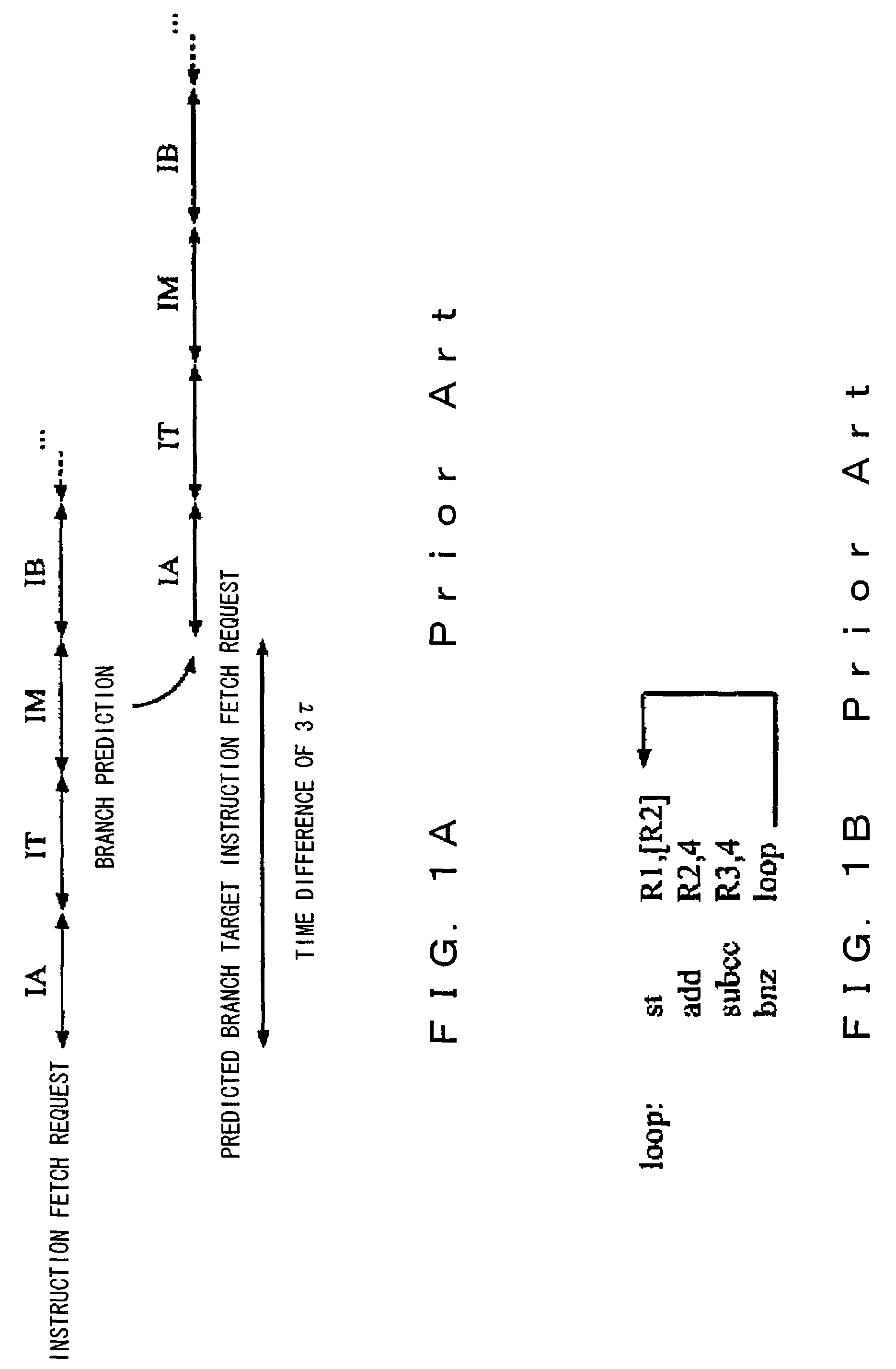

InactiveUS20090113191A1Reduce power consumptionImprove processor performanceMemory architecture accessing/allocationDigital computer detailsInstruction unitShort loop

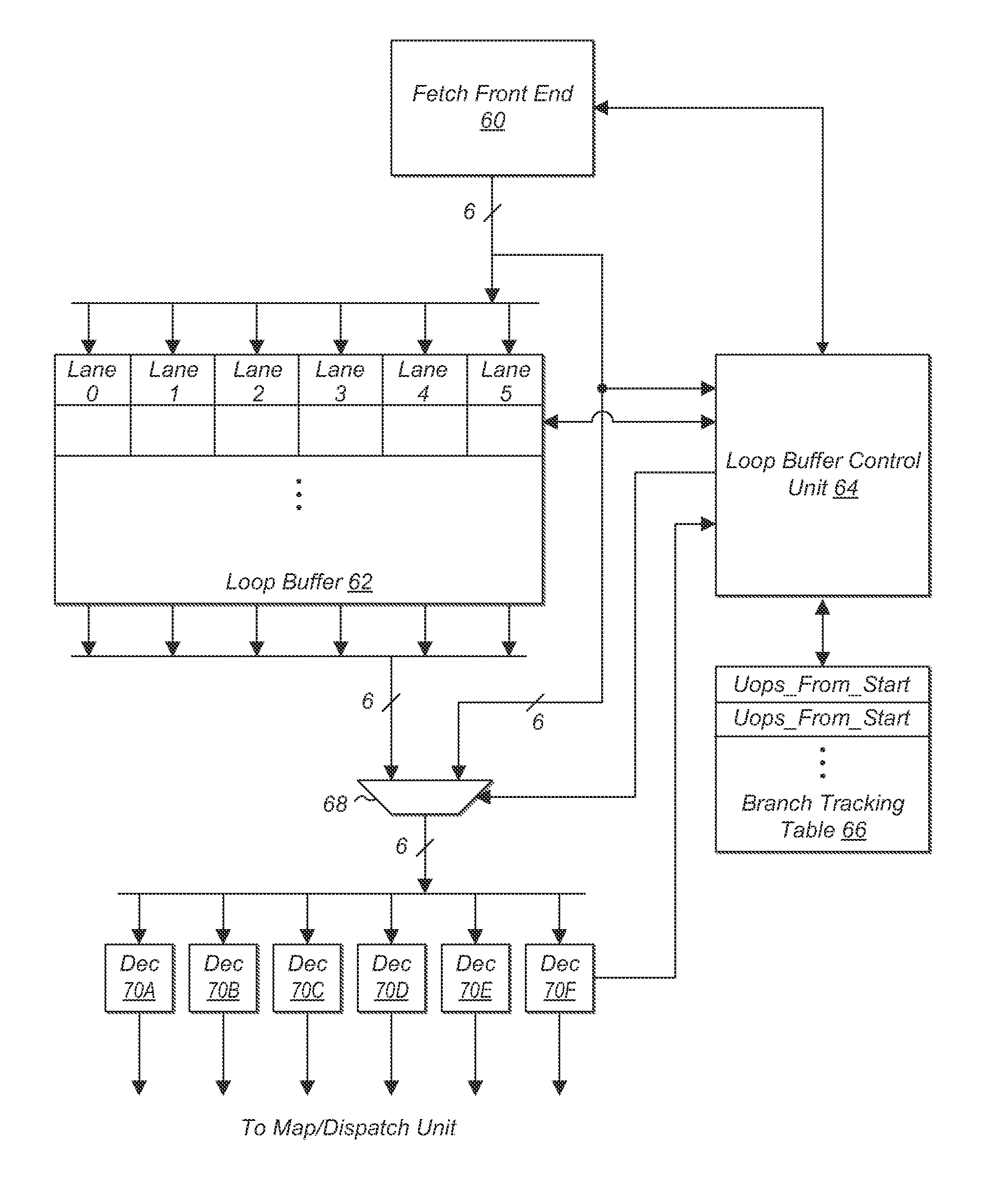

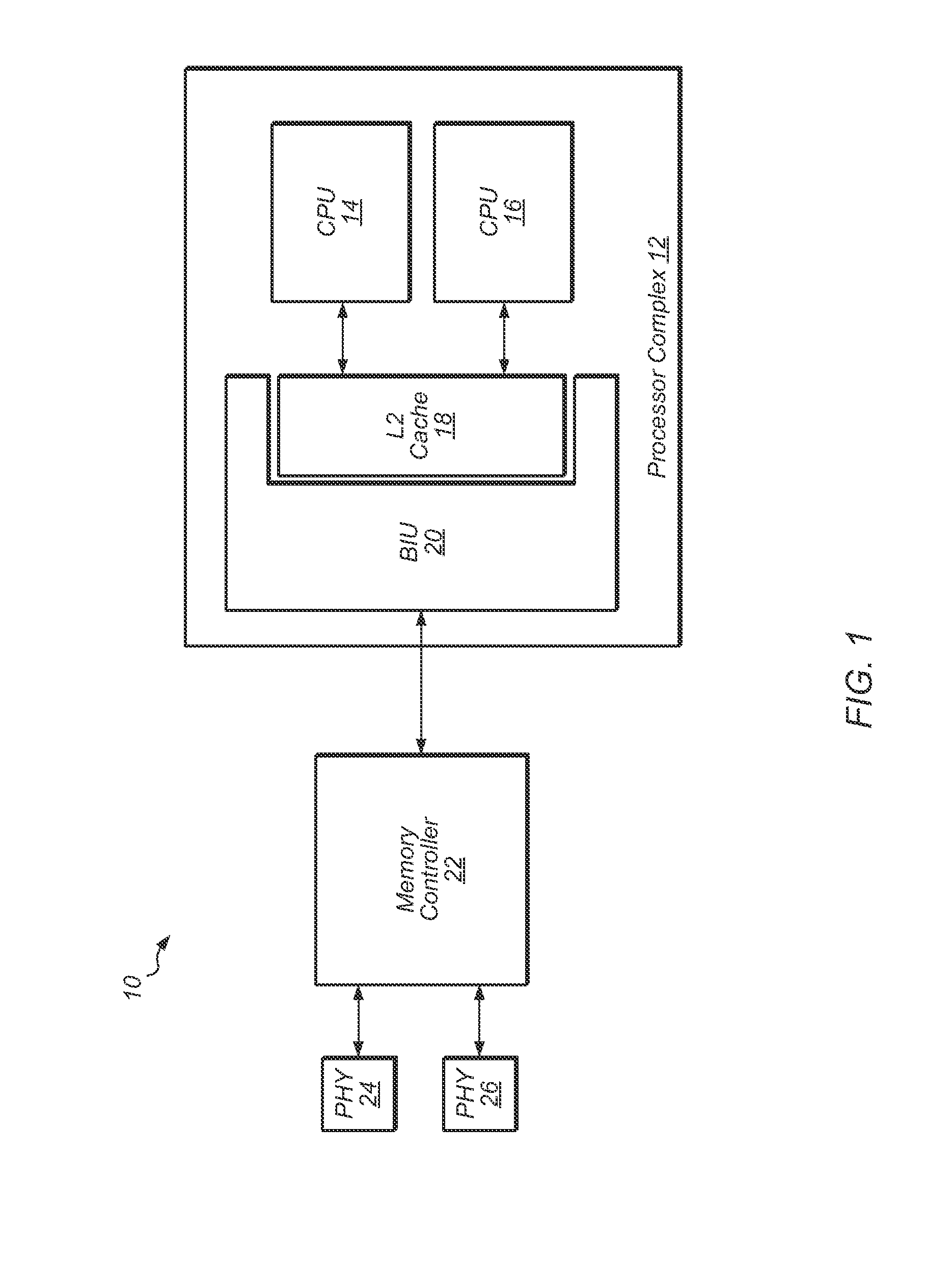

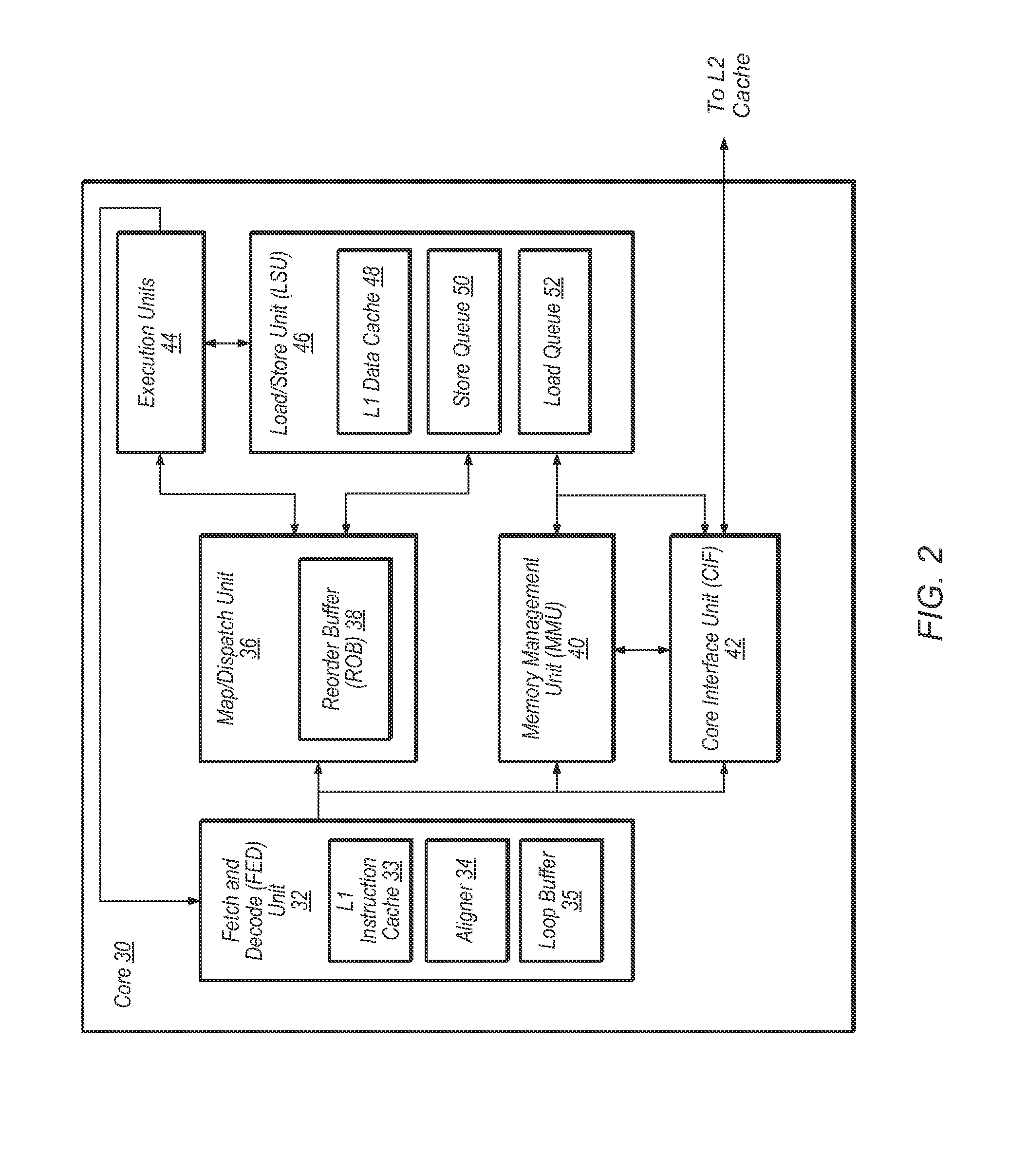

A method, system and computer program product for instruction fetching within a processor instruction unit, utilizing a loop buffer, one or more virtual loop buffers, and / or an instruction buffer. During instruction fetch, modified instruction buffers coupled to an instruction cache (I-cache) temporarily store instructions from a single branch, backwards short loop. The modified instruction buffers may be a loop buffer, one or more virtual loop buffers, and / or an instruction buffer. Instructions are stored in the modified instruction buffers for the length of the loop cycle. The instruction fetch within the instruction unit of a processor retrieves the instructions for the short loop from the modified buffers during the loop cycle, rather than from the instruction cache.

Owner:IBM CORP

Design structure for improving efficiency of short loop instruction fetch

InactiveUS20090113192A1Reduce power consumptionImprove processor performanceDigital computer detailsConcurrent instruction executionInstruction unitShort loop

A design structure provides instruction fetching within a processor instruction unit, utilizing a loop buffer, one or more virtual loop buffers, and / or an instruction buffer. During instruction fetch, modified instruction buffers coupled to an instruction cache (I-cache) temporarily store instructions from a single branch, backwards short loop. The modified instruction buffers may be a loop buffer, one or more virtual loop buffers, and / or an instruction buffer. Instructions are stored in the modified instruction buffers for the length of the loop cycle. The instruction fetch within the instruction unit of a processor retrieves the instructions for the short loop from the modified buffers during the loop cycle, rather than from the instruction cache.

Owner:IBM CORP

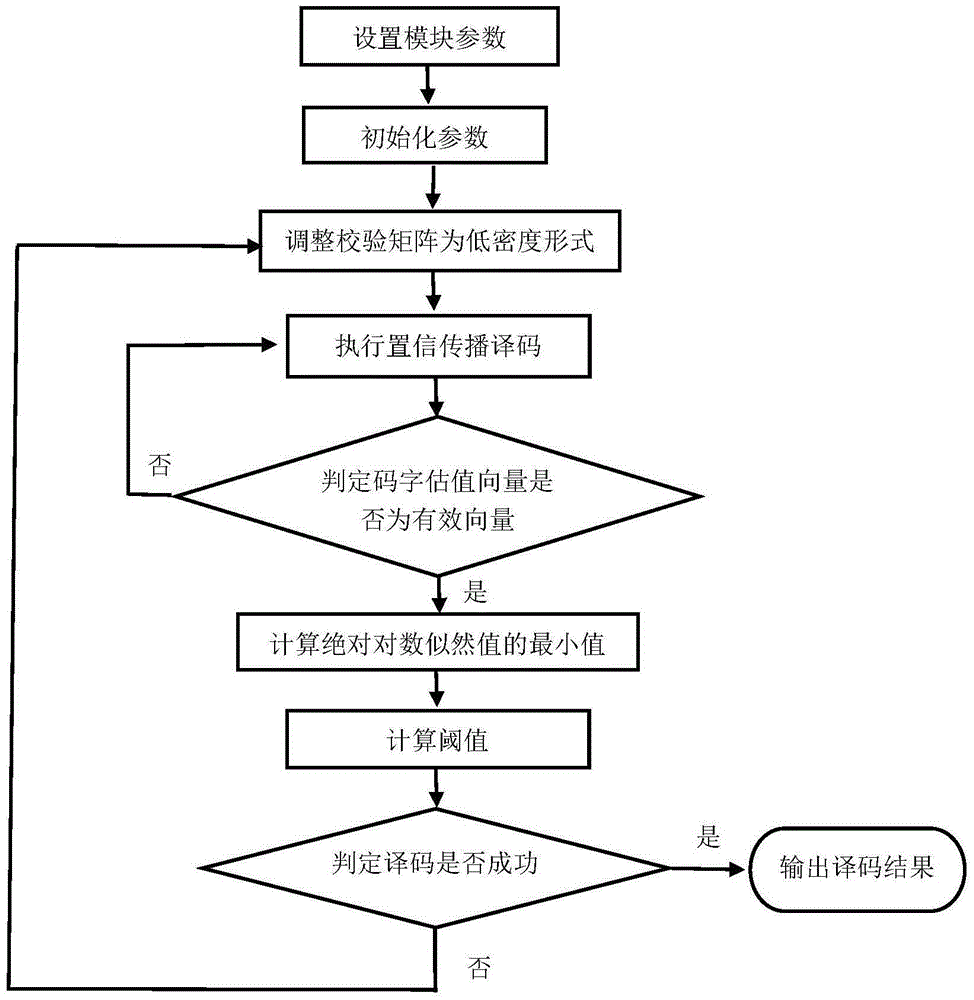

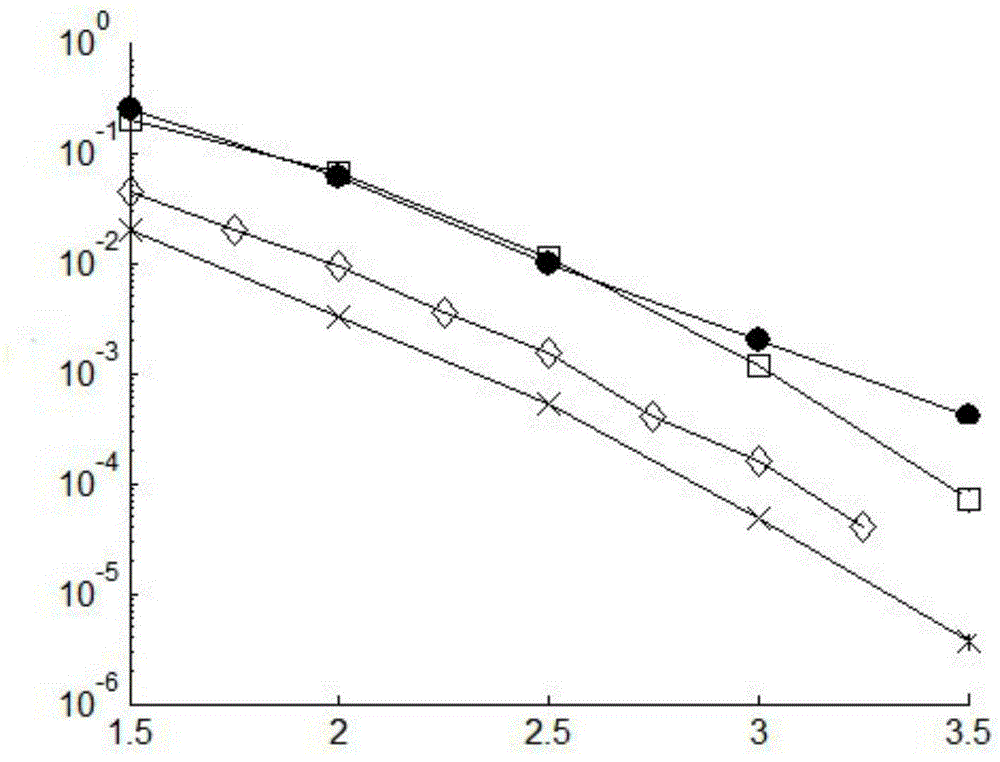

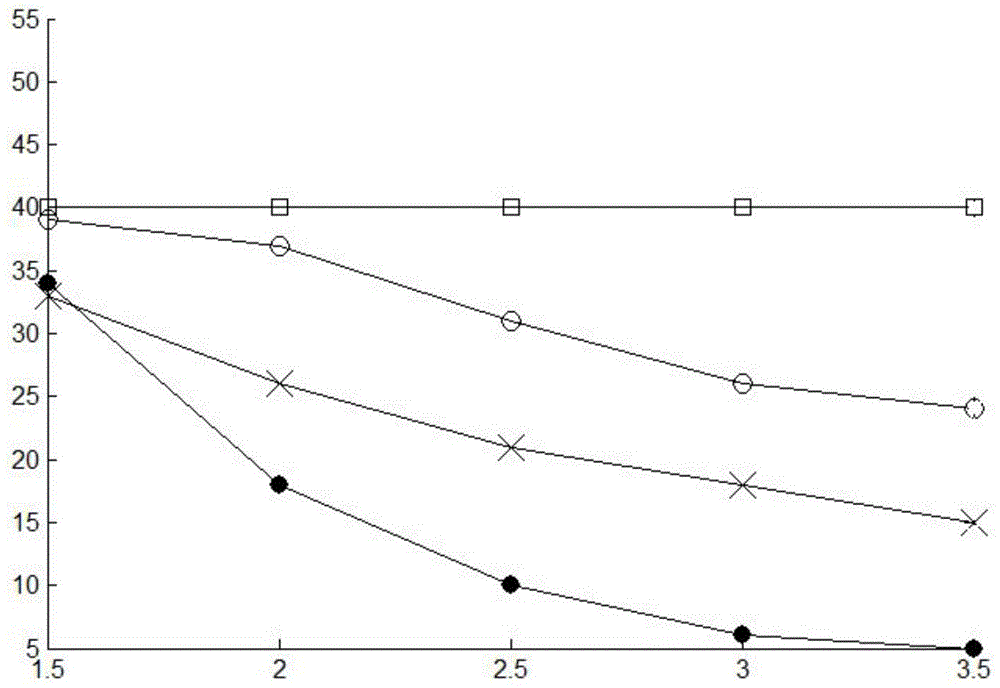

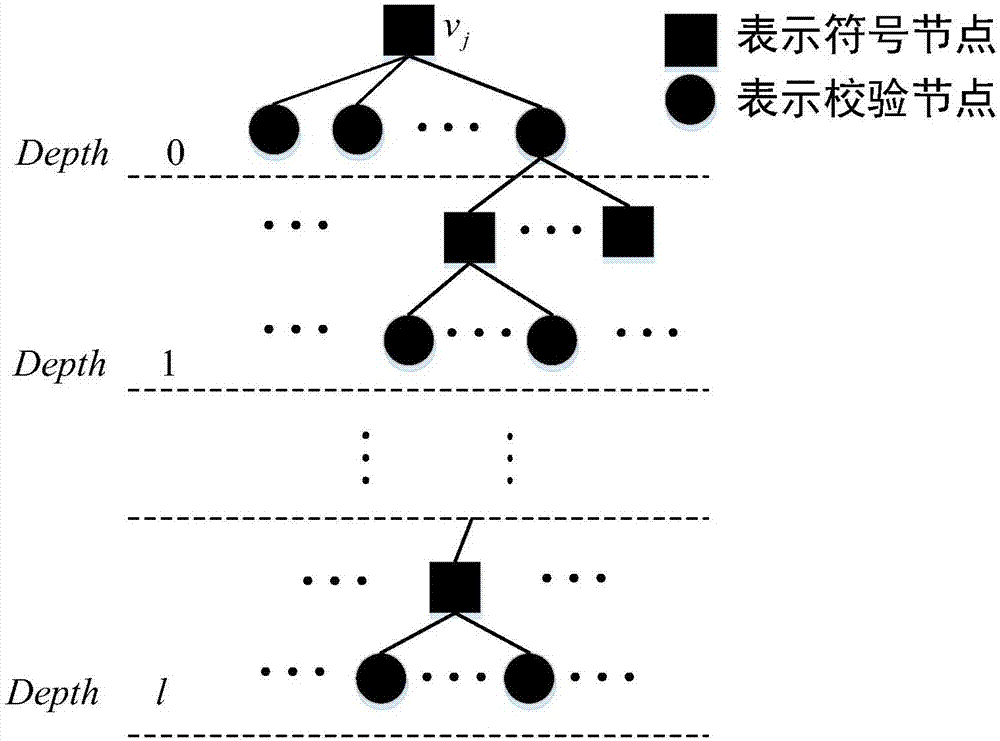

Polarization code belief propagation decoding method based on dynamic check matrix

ActiveCN105207682AImprove reliabilityImprove decoding performanceCode conversionError correction/detection using linear codesShort loopCoding decoding

The invention discloses a polarization code belief propagation decoding method based on a dynamic check matrix to solve the problems of the prior art that performance is low and time complexity is high when a traditional BP decoding algorithm is used. The method comprises the steps of 1, setting module parameters; 2, initializing parameters; 3, adjusting the check matrix to be in a low-density form; 4, executing belief propagation decoding; 5, judging whether a codon estimation vector is an effective vector; 6, calculating the minimum value of an absolute log likelihood; 7, calculating a threshold value; 8, judging whether decoding succeeds; 9, outputting a decoding result. By adjusting the polarization code check matrix and reducing the number of short loops of the check matrix, rapid convergence of the BP algorithm is achieved, and low time complexity is maintained while polarization code decoding performance is improved by means of the early-stage stop standard.

Owner:XIDIAN UNIV

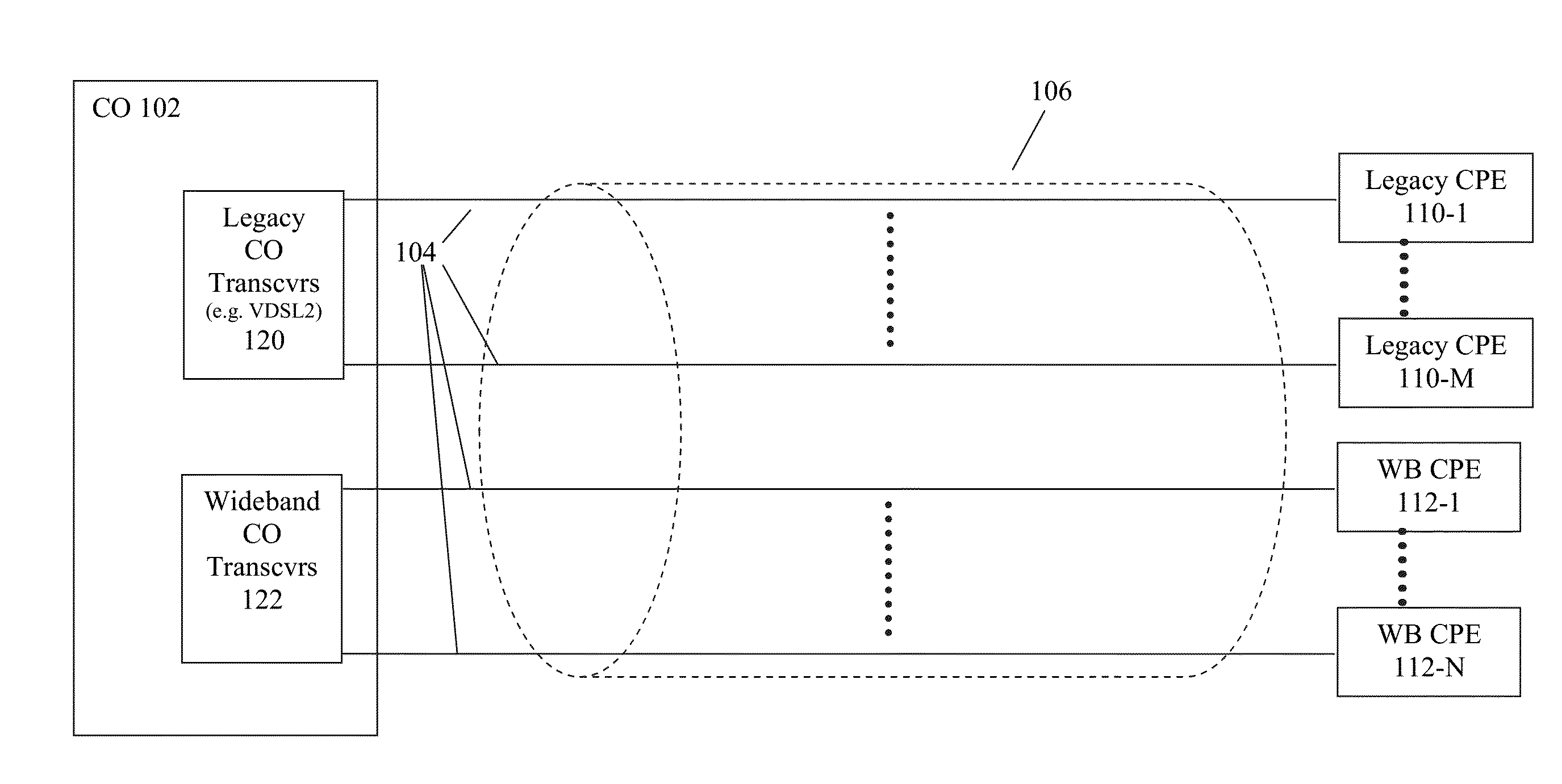

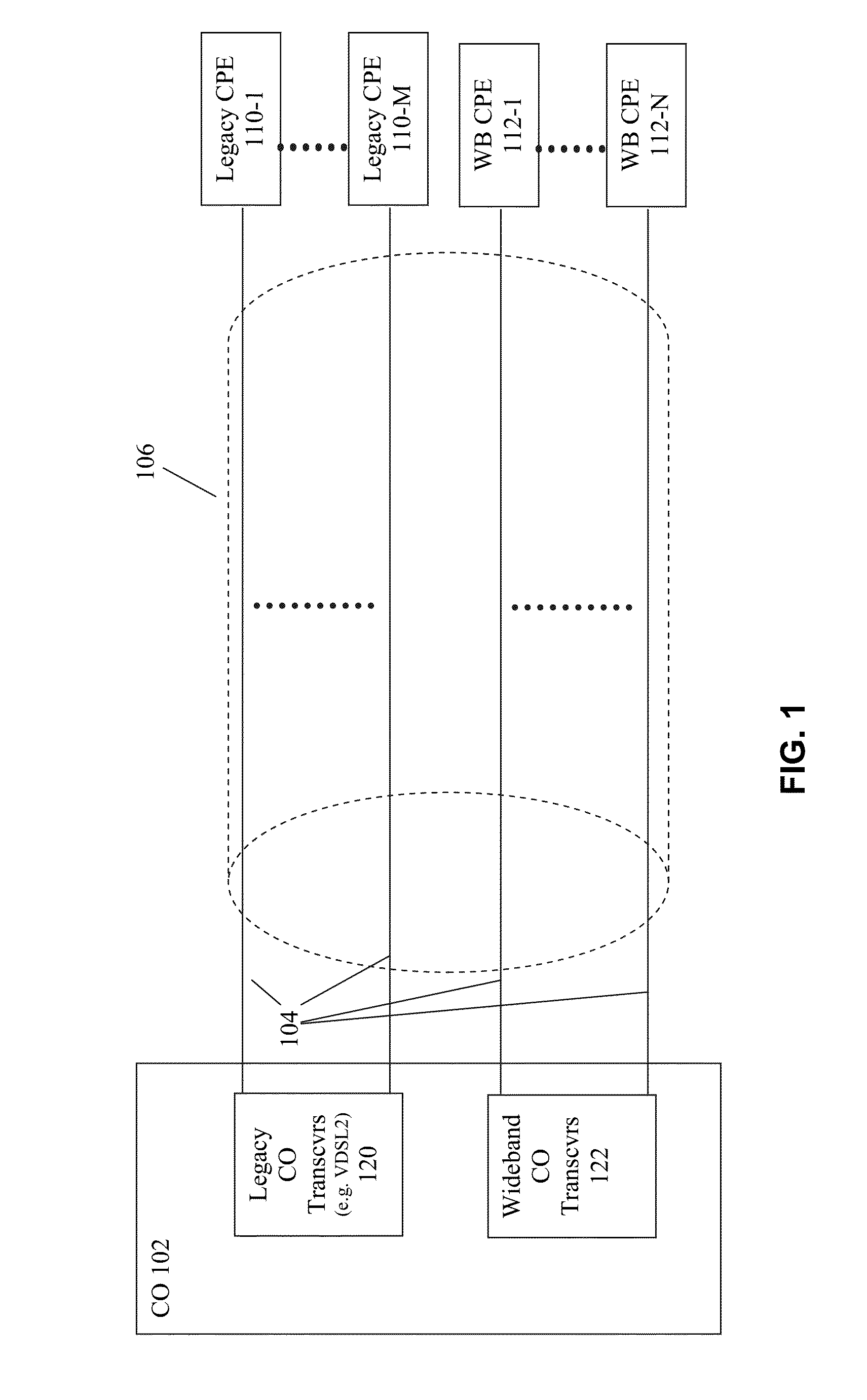

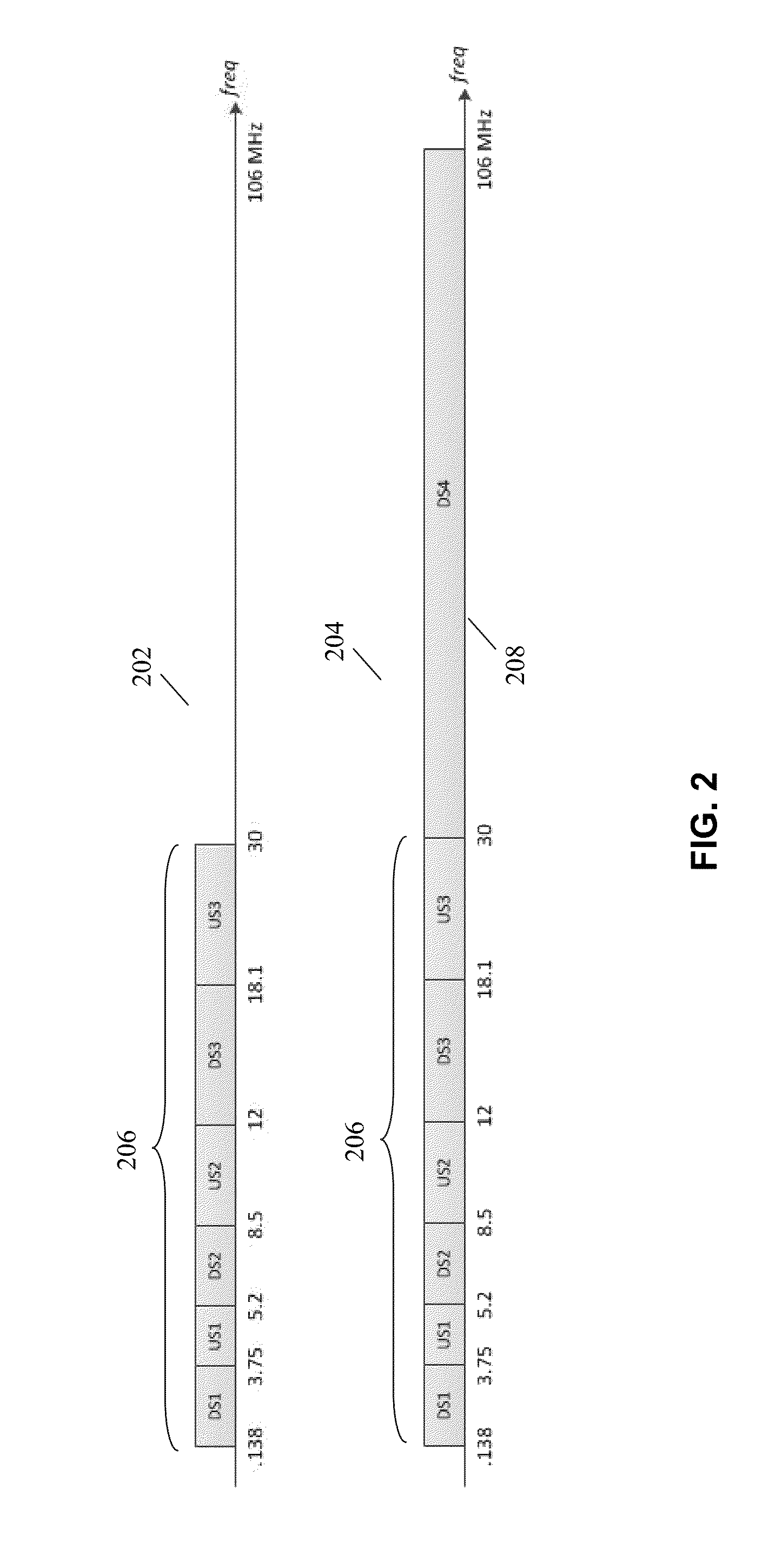

Methods and systems for maintaining spectral compatibility between co-existing legacy and wideband DSL services

InactiveUS20150270942A1Maintain compatibilityDuplex signal operationComputer hardwareFrequency spectrum

According to certain general aspects, the present invention relates to methods for transmitting signals on twisted wire-pairs above 30 MHz using frequency division duplexing (FDD) in support of 1 Gb / s aggregate services on short loop lengths while maintaining spectral compatibility with legacy ADSL2 (≦2.2 MHz bandwidth) and VDSL2 services (≦30 MHz bandwidth). An advantage of the FDD approach for Gb / s transmission according to the invention is spectral compatibility with legacy DSL services without the sacrifice of any capacity of the wider band.

Owner:IKANOS COMMUNICATIONS

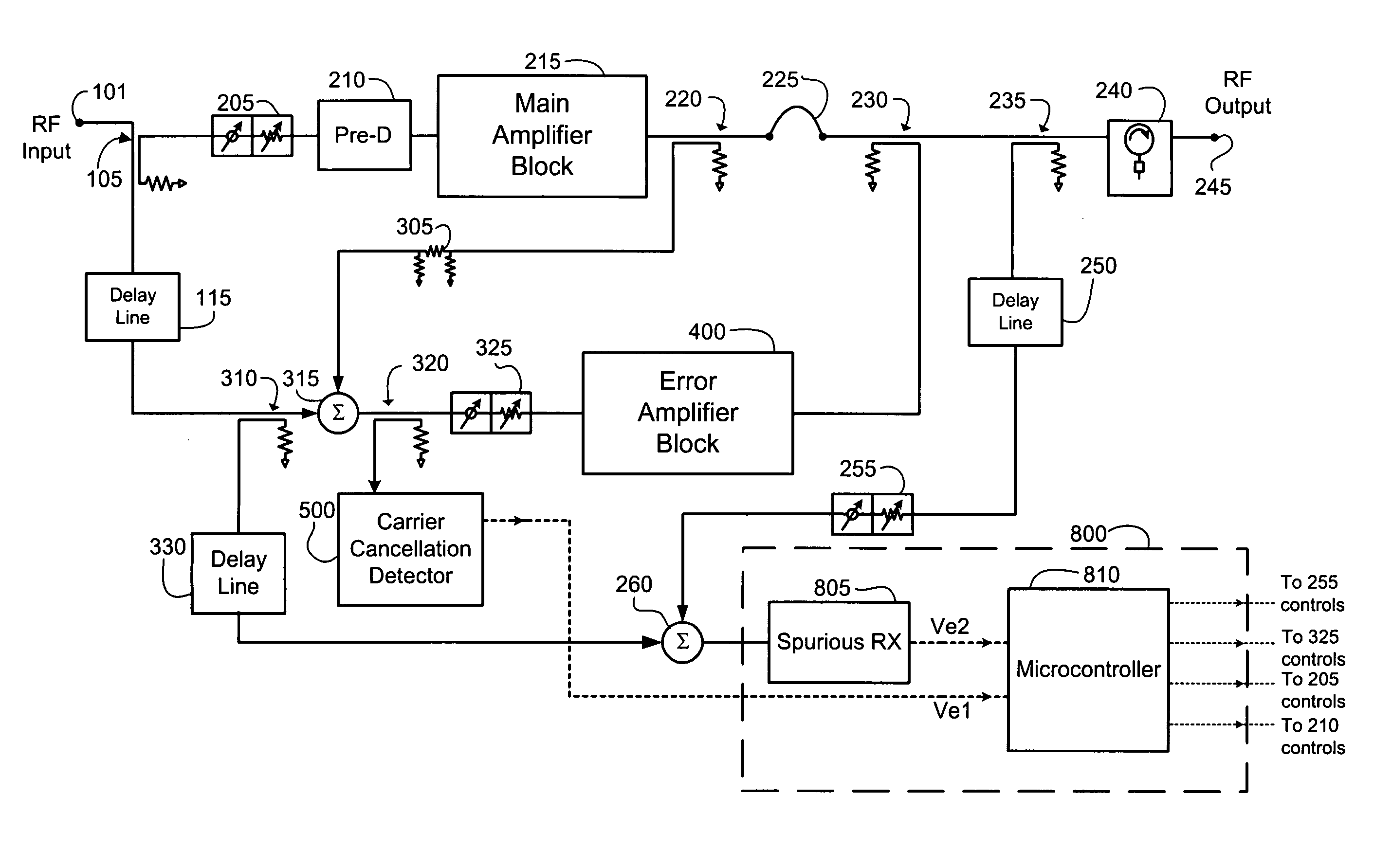

Enhanced efficiency feed forward power amplifier with delay mismatched error cancellation loop

ActiveUS7301397B2Avoid excessive delayAmplifier modifications to reduce non-linear distortionAmplifier with control circuitsLow distortionShort loop

Owner:INTEL CORP

Enhanced efficiency feed forward power amplifier utilizing reduced cancellation bandwidth and small error amplifier

ActiveUS7038540B2Minimizing detectionLess delayAmplifier modifications to reduce non-linear distortionAmplifier modifications to reduce noise influenceMicrocontrollerLow distortion

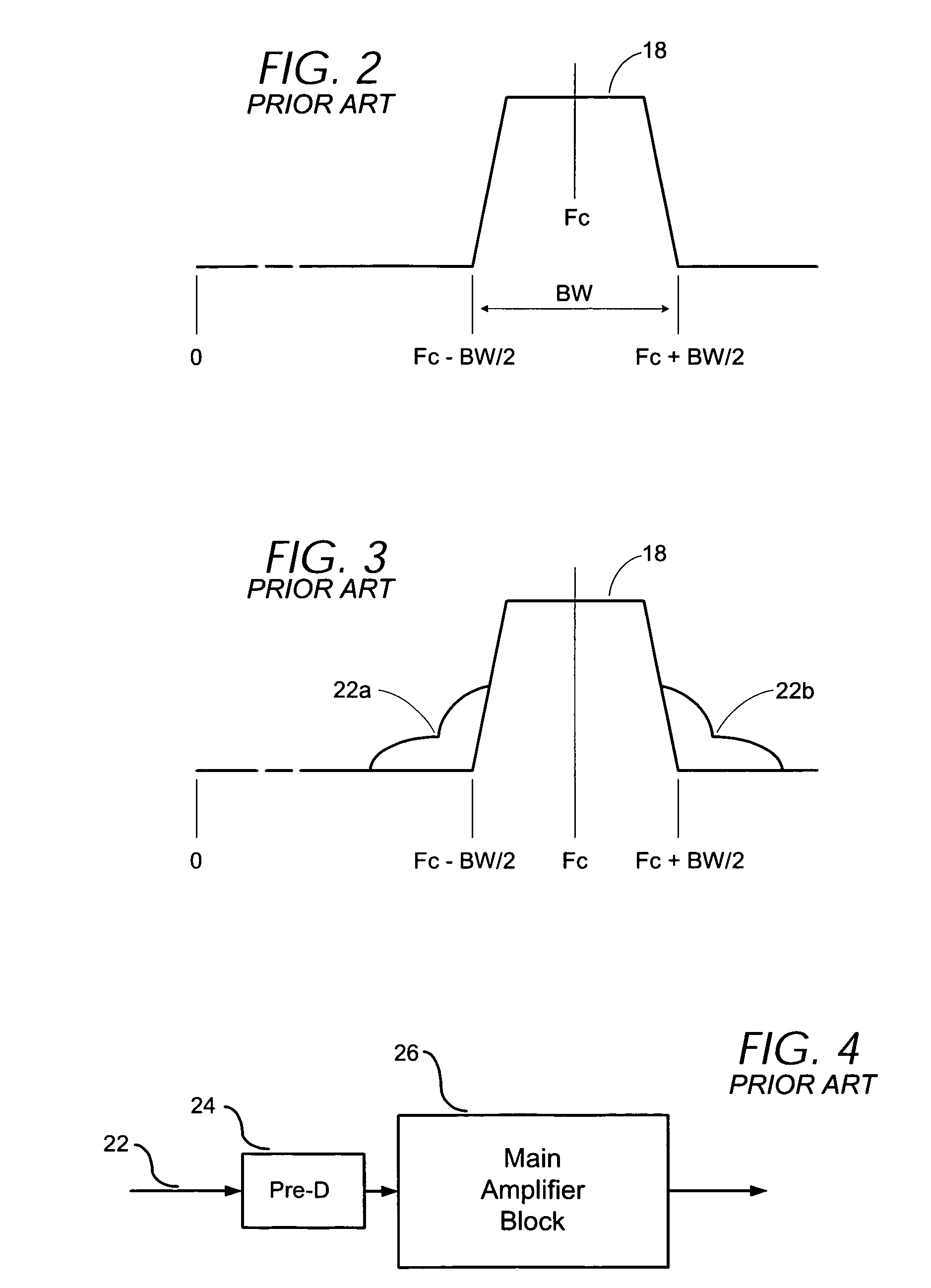

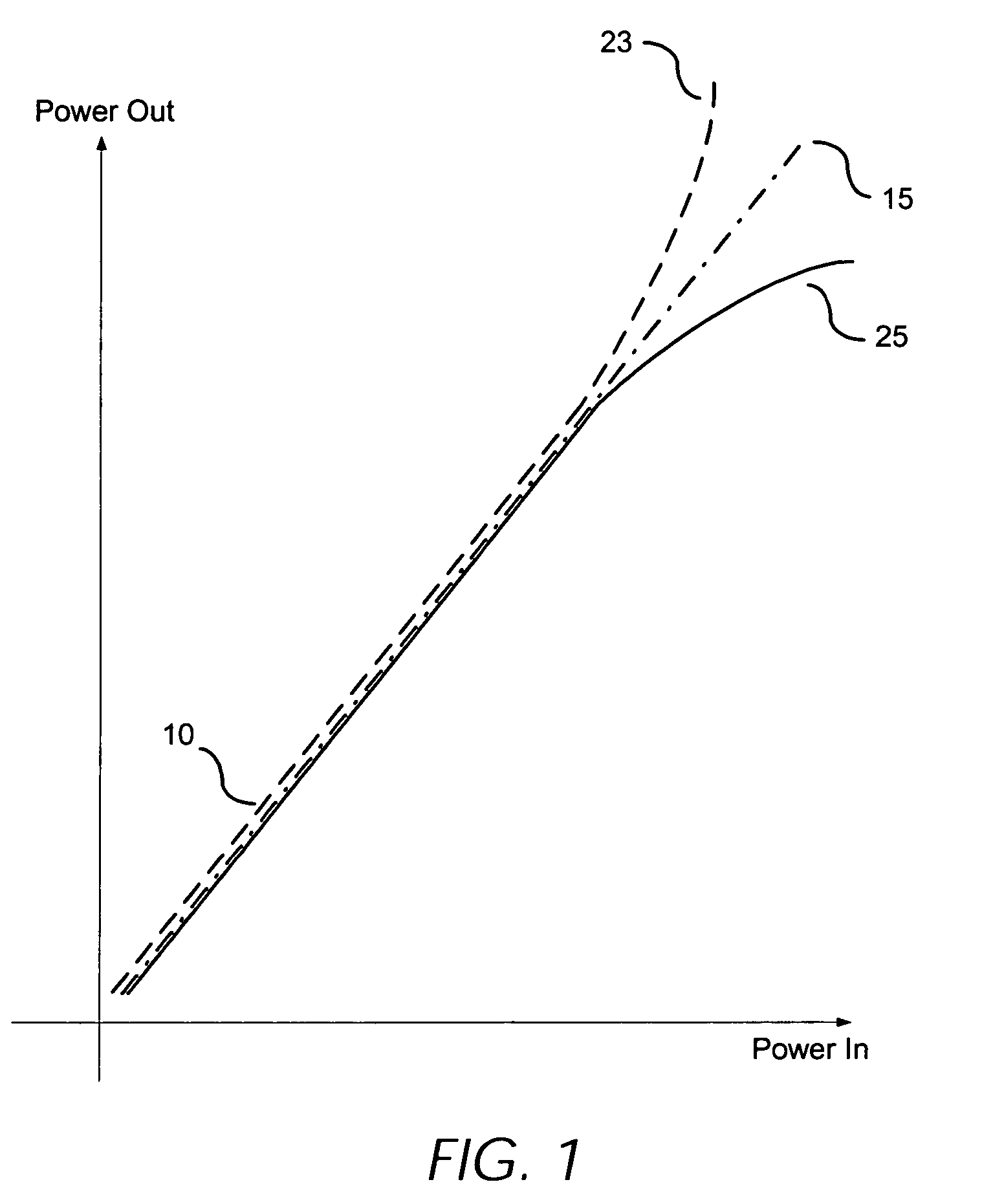

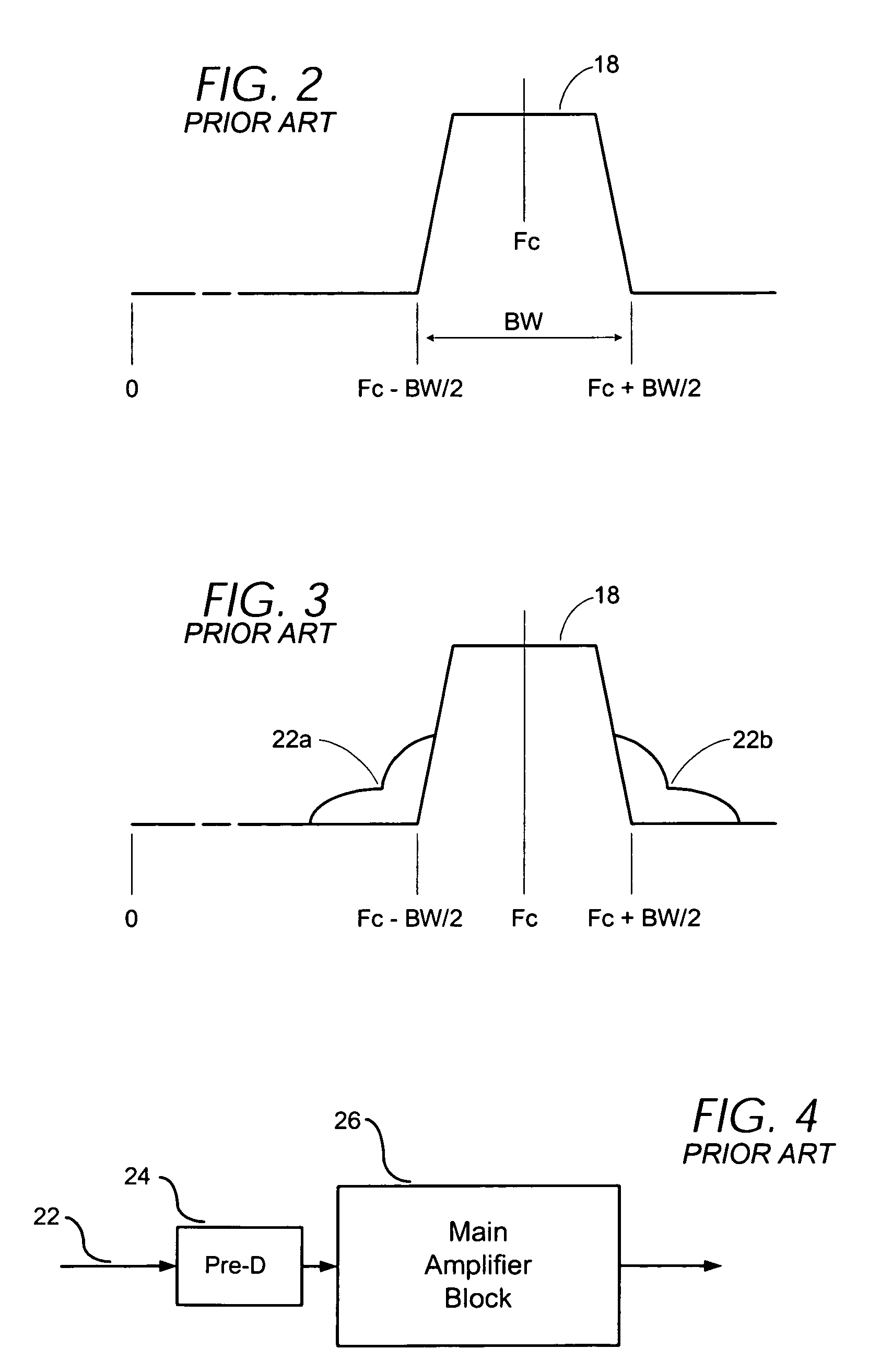

A feed forward power amplifier is disclosed which utilizes three signal cancellation loops. Loop 1 includes a main amplifier and is used to derive a carrier cancelled sample of the main amplifier output. Loop 2 includes an error amplifier used to amplify the carrier cancelled signal derived from Loop 1 operation in order to cancel distortion products generated due to the nonlinear nature of the main amplifier. Loop 2 also utilizes a very short Loop 2 delay line. A significant efficiency gain is provided due to reduced output power losses associated with the Loop 2 delay line. Lower output losses also results in lower distortion levels produced by the main amplifier. This, in turn, reduces the size and performance requirements placed on the error amplifier. A smaller and more efficient error amplifier is employed resulting in further amplifier system efficiency improvement. A spurious signal detector for out-of-band distortion detection and an associated microcontroller for Loop 1 and Loop 2 control are also provided. A third signal cancellation loop is utilized to sample the amplifier output and reduce the carrier level of the signals sampled at the output of the amplifier before providing the sampled output to the spurious signal detector. By significantly reducing the carrier power level relative to distortion power levels a cost effective spurious signal detector can be utilized. This also provides a faster conversion time in Loop 2 cancellation and enhanced cancellation of out-of-band distortion products due to a greater useful dynamic range available for the DSP employed in the spurious signal detector.

Owner:INTEL CORP

Loop buffer packing

ActiveUS20130339699A1Maximize instruction per cycle throughputMaximize throughputProgram control using stored programsInstruction analysisShort loopInstruction stream

Methods, apparatuses, and processors for packing multiple iterations of a loop in a loop buffer. A loop candidate that meets the criteria for buffering is detected in the instruction stream being executed by a processor. When the loop is being written to the loop buffer and the end of the loop is detected, another iteration of the loop is written to the loop buffer if the loop buffer is not yet halfway full. In this way, short loops are written to the loop buffer multiple times to maximize the instruction operations per cycle throughput out of the loop buffer when the processor is in loop buffer mode.

Owner:APPLE INC

Enhanced efficiency feed forward power amplifier with delay mismatched error cancellation loop

ActiveUS20070018723A1Avoid excessive delayAmplifier modifications to reduce non-linear distortionAmplifier with control circuitsLow distortionAudio power amplifier

A delay mismatched feed forward power amplifier is disclosed. Loop 1 includes a main amplifier and is used to derive a carrier cancelled sample of the main amplifier output. Loop 2 includes an error amplifier used to amplify the carrier cancelled signal derived from Loop 1 operation in order to cancel distortion products generated due to the nonlinear nature of the main amplifier. Loop 2 also utilizes a very short Loop 2 delay line. A significant efficiency gain is provided due to reduced output power losses associated with the Loop 2 delay line. Lower output losses also results in lower distortion levels produced by the main amplifier. This, in turn, reduces the size and performance requirements placed on the error amplifier. A smaller and more efficient error amplifier is employed resulting in further amplifier system efficiency improvement. The delay mismatch is compensated by a third control loop, a special adaptive control algorithm or a combination thereof.

Owner:INTEL CORP

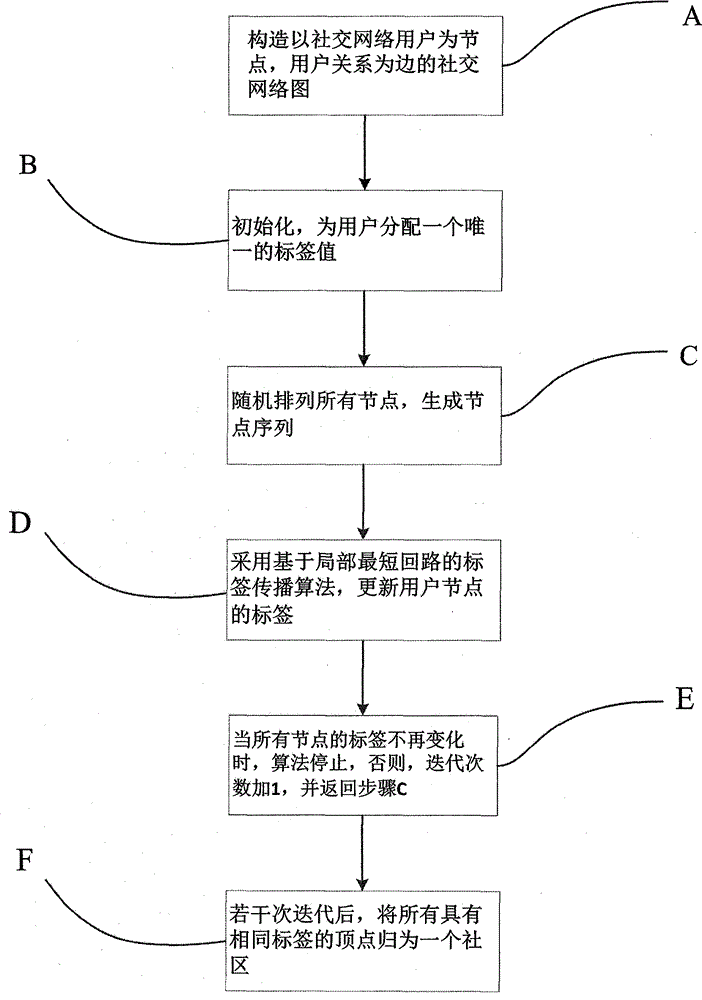

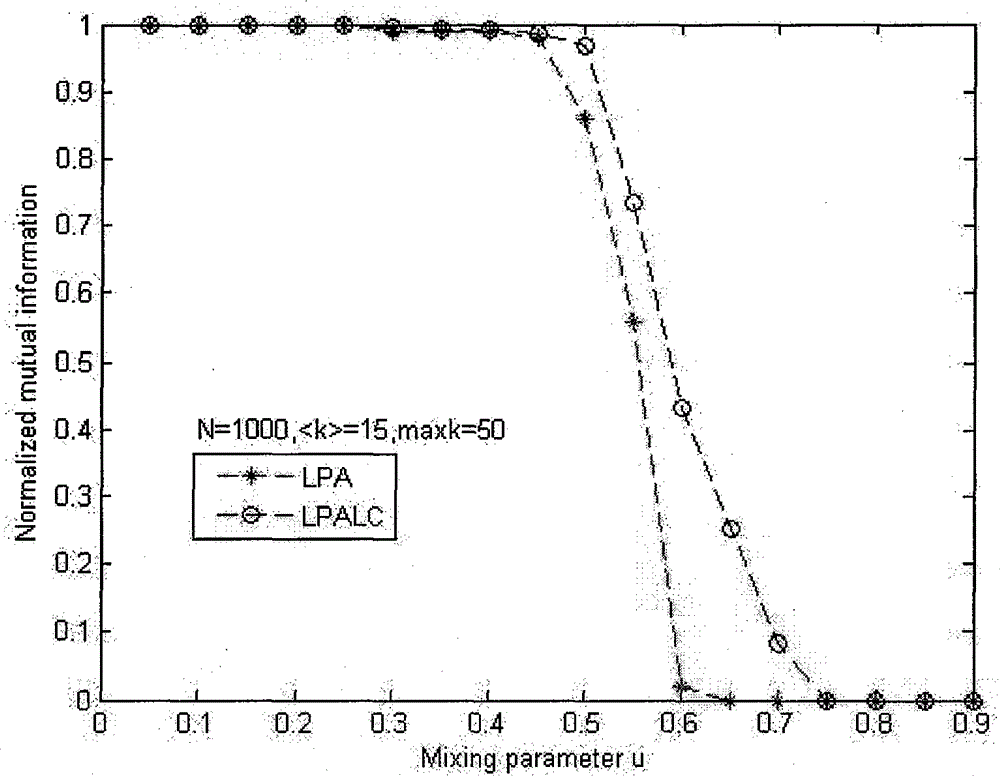

Local shortest loop based social network group division method

The invention relates to a local shortest loop based social network group division method. The method specifically comprises the steps of reading social network data, and constructing a social network graph taking social network users as nodes and user relationships as edges; endowing each user with a unique tag value representing a community that the user belongs to; and updating tags of user nodes by adopting a local shortest loop based tag propagation algorithm to obtain a community structure of a social network, wherein the closely relevant nodes have the same tag values through iterative updating for multiple times. According to the social network group division method provided by an embodiment of the invention, a tag propagation algorithm is improved with an attribute whether a local loop is constructed or not in a user relationship graph; and compared with an existing community network division method, the division of user groups is favorable for improving the accuracy of community division, the community structure in the social network is effectively mined, and division results have relatively high application values in the fields of network public opinion monitoring, search engines, commercial target mining and the like.

Owner:TIANJIN UNIV OF SCI & TECH

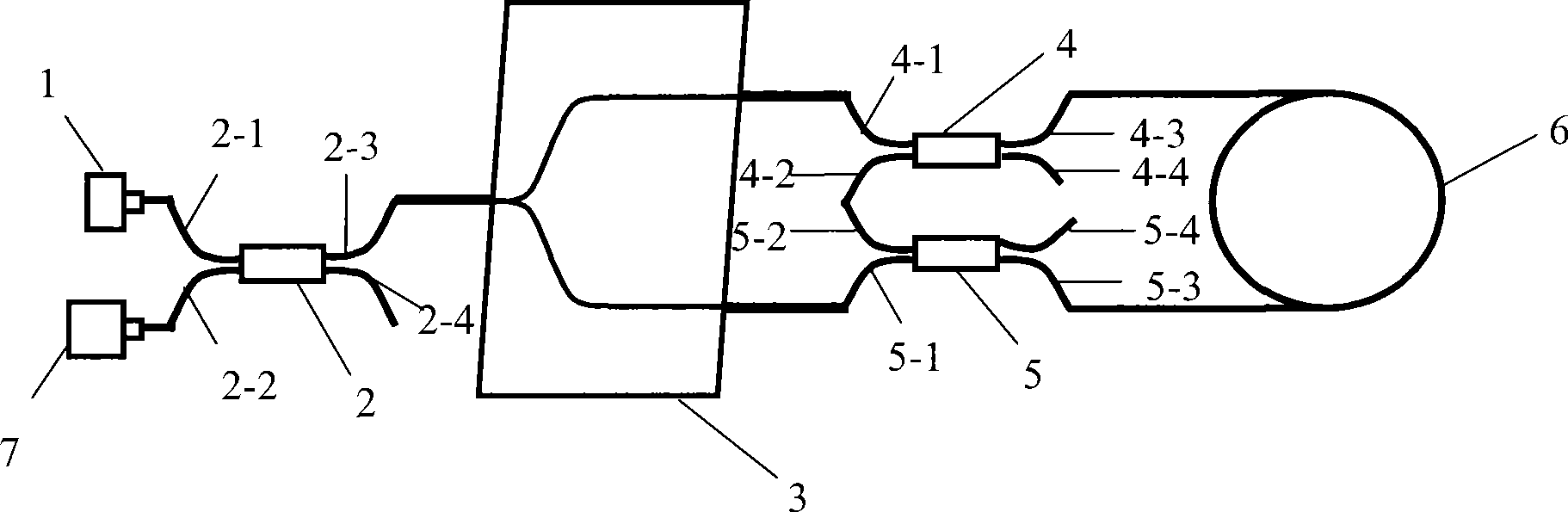

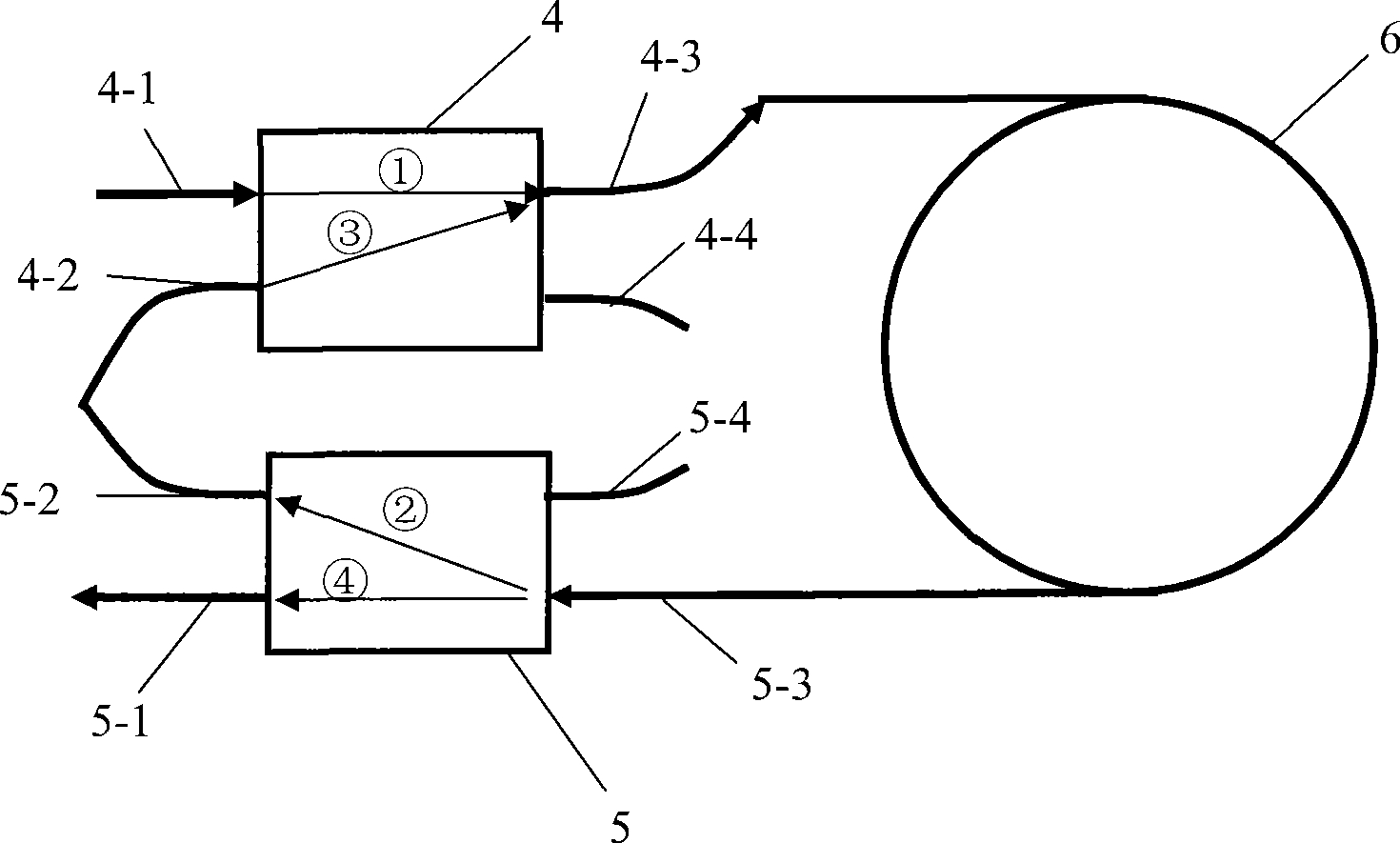

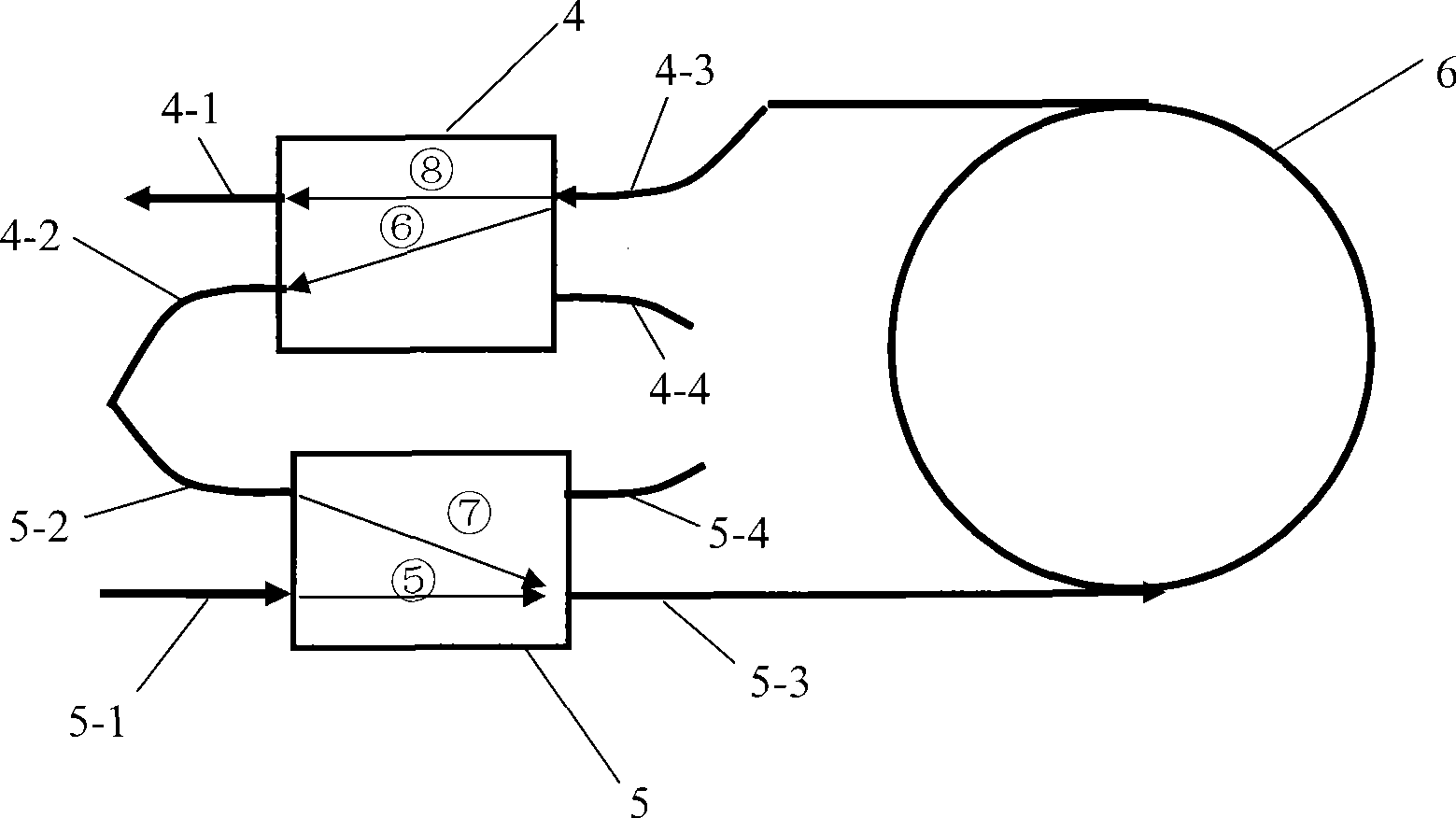

Short-loop optical fiber gyroscope

The invention relates to a short-loop fiber optic gyroscope. The prior method for improving the precision of the fiber optic gyroscope by increasing the length of a fiber optic ring leads to the great limitation of the dynamic range of the gyroscope and the reduction in bandwidth. According to the method, an input port at one end of a first coupler is connected with a broadband light source, an output port of the first coupler is connected with a detector, and a port at the other end of the first coupler is connected with a single-end port of a Y waveguide. One port of double-end ports of the Y waveguide is connected with a port at one end of a second coupler, the other port of the double-end ports of the Y waveguide is connected with a port at one end of a third coupler, and the other port at the end of the second coupler is connected with the other port at the end of the third coupler. Two ends of the fiber optic ring are connected with a port at the other end of the second coupler and a port at the other end of the third coupler respectively. The gyroscope has larger dynamic range and bandwidth, reduces poor reciprocity caused by a winding defect of the fiber optic ring and improves the adaptability of the gyroscope.

Owner:ZHEJIANG UNIV

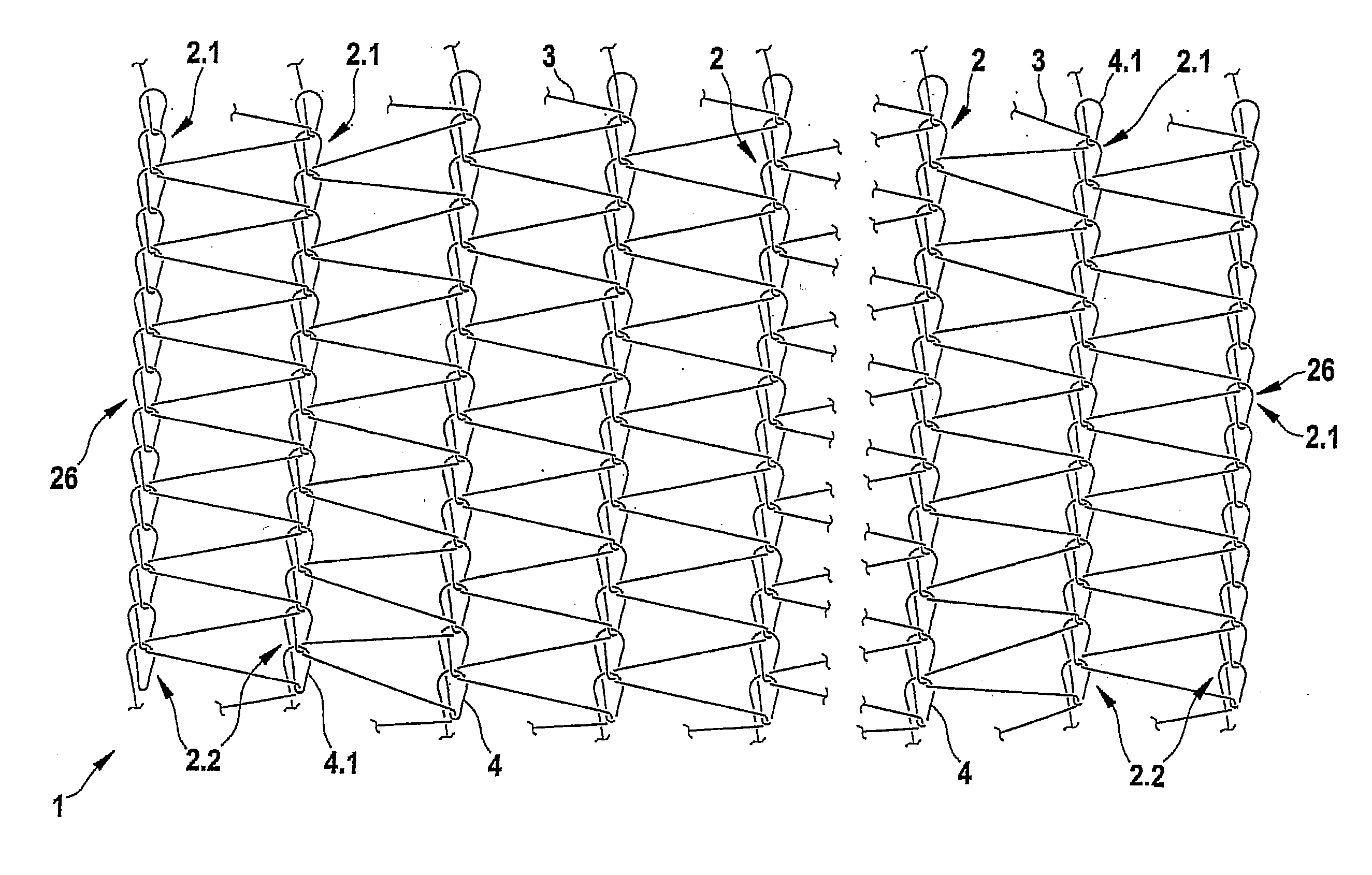

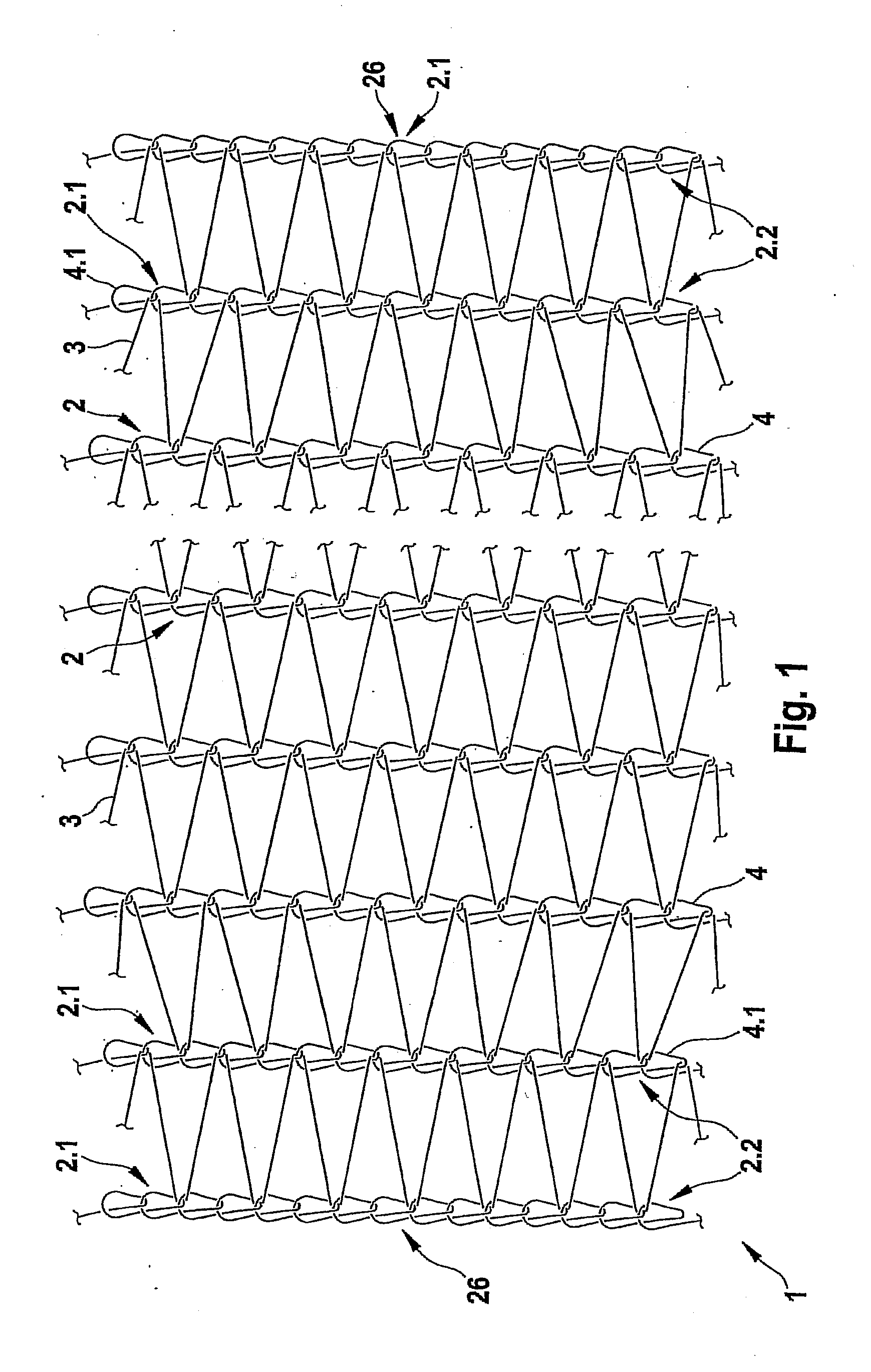

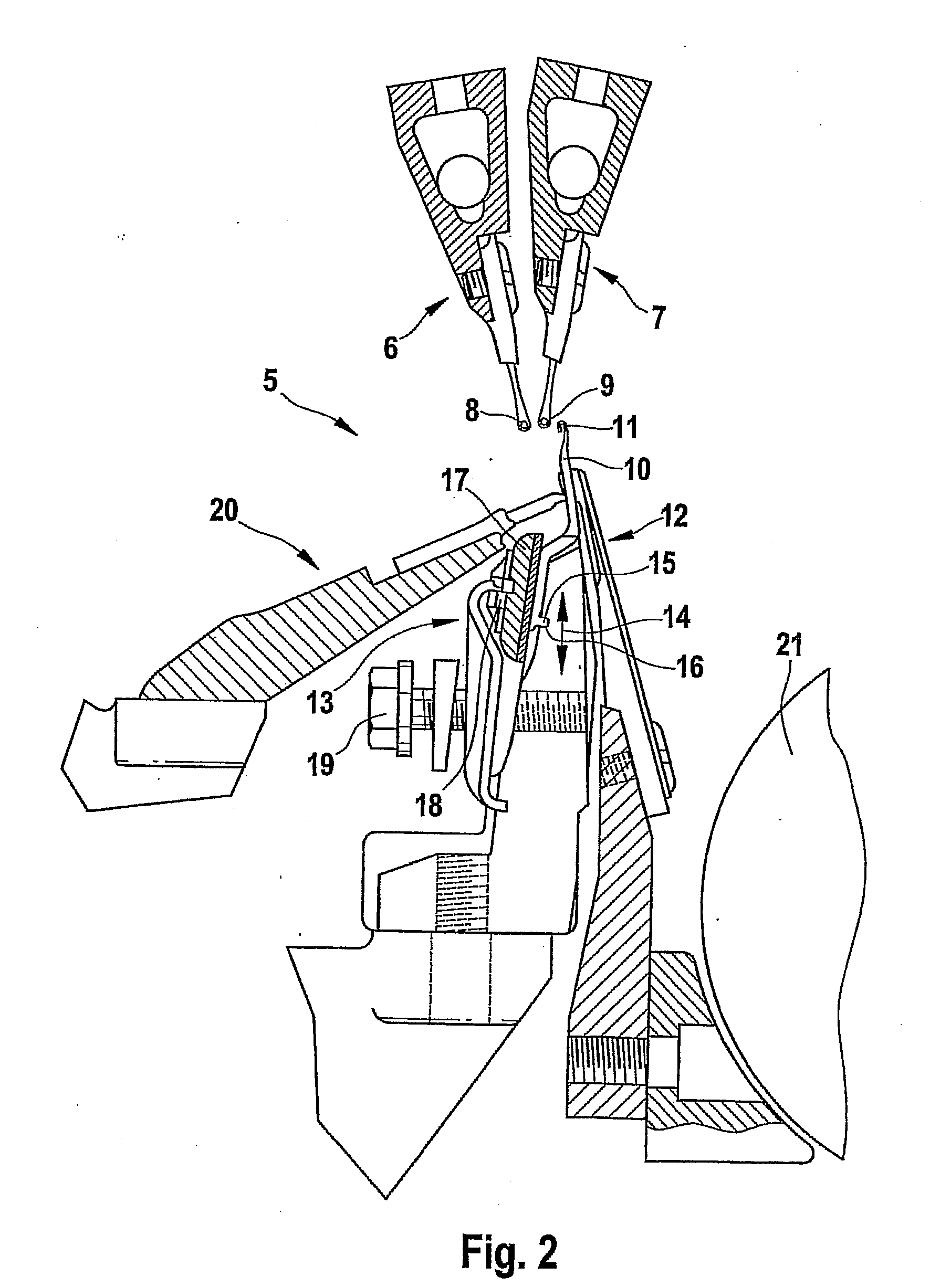

Knitted net for enveloping round bales, and method and device for the production thereof

InactiveUS20080053158A1Avoid wear and tearFraying of the round bale in the edge region is preventedBalingFlat-bed knitting machinesShort loopBiomedical engineering

A netting, knitted from fringes and weft threads is provided in which at least one fringe in at least one marginal region of the netting is shorter than the remaining fringes of the netting. The invention relates, furthermore, to a method for producing the netting on a knitting machine, during the knitting of the netting shorter loops for forming stitches from which the fringes are knitted being generated in at least one marginal region than in the remaining regions of the netting. Moreover, a knitting machine for producing a netting is described, which comprises a first lay bar for feeding the weft threads, a second lay bar for feeding the longitudinal threads, a needle bar with needles and a take-up device, at at least one position on the needle bar at which the marginal region of the netting is knitted the needle being positioned higher than the remaining needles.

Owner:RKW SE

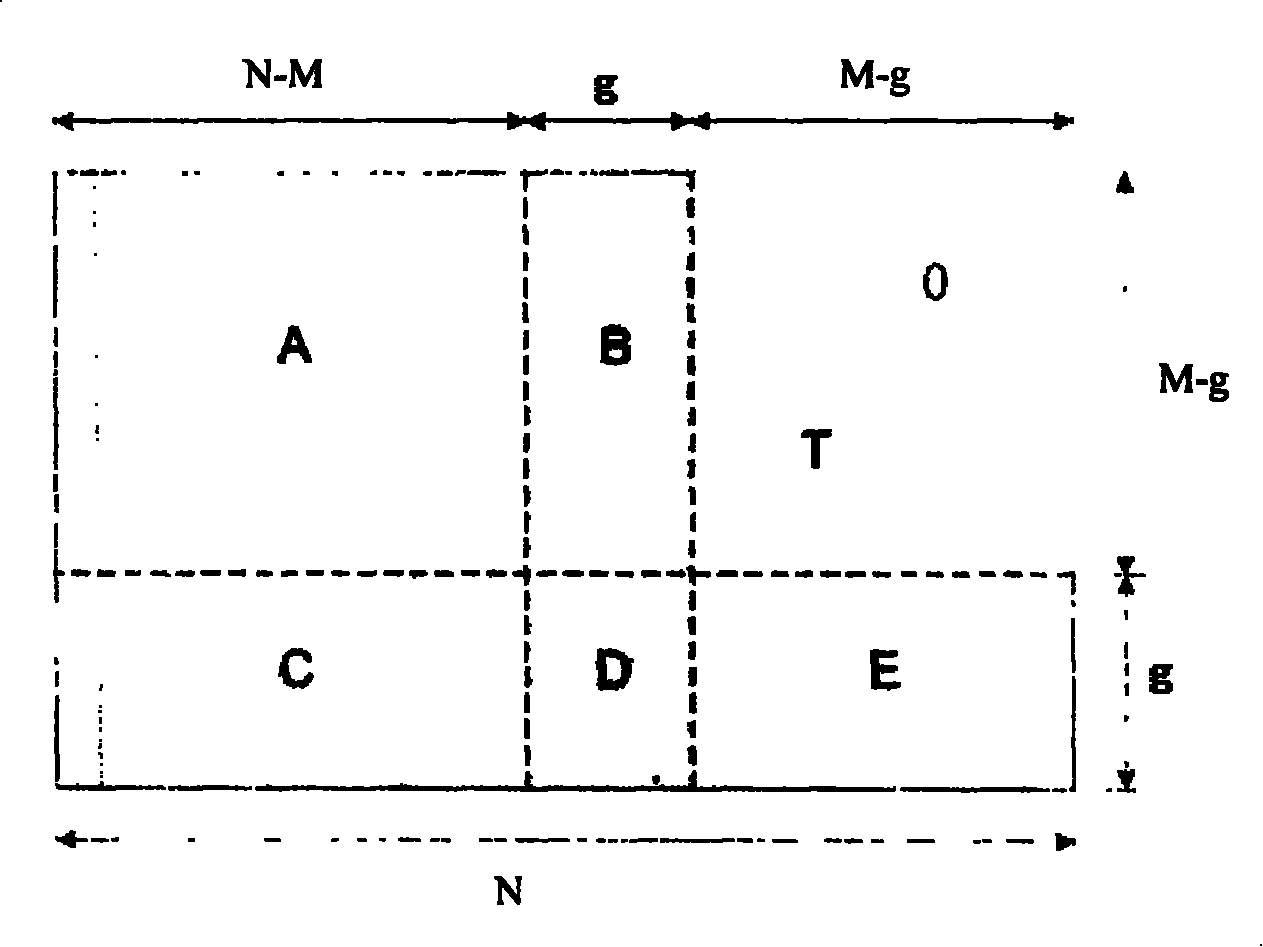

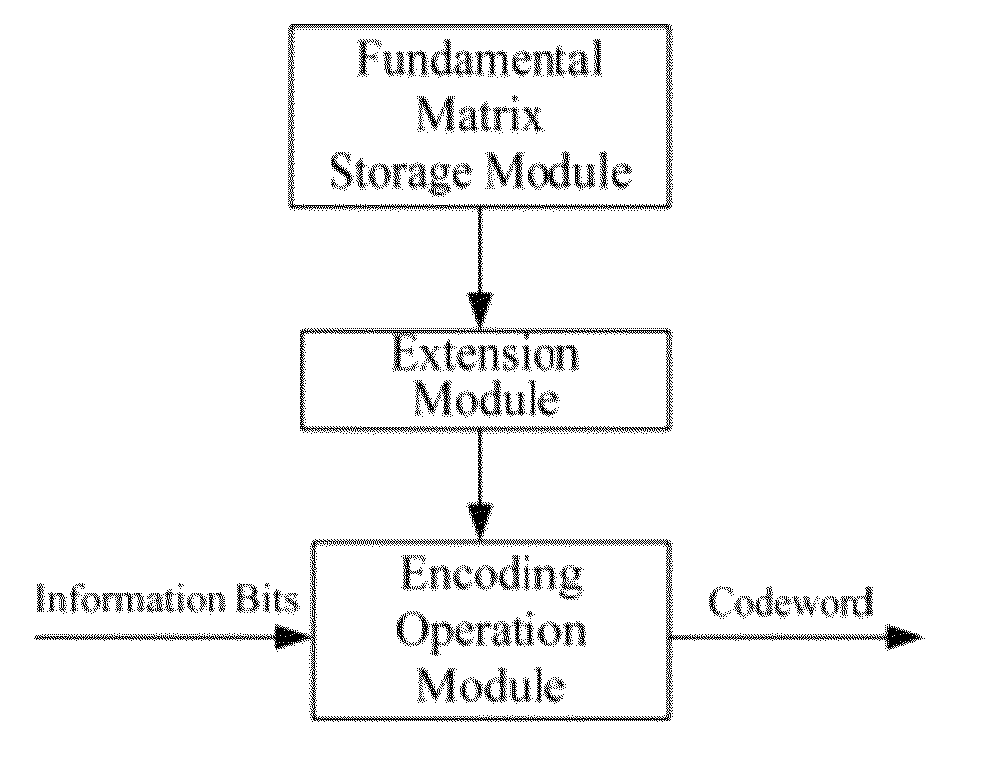

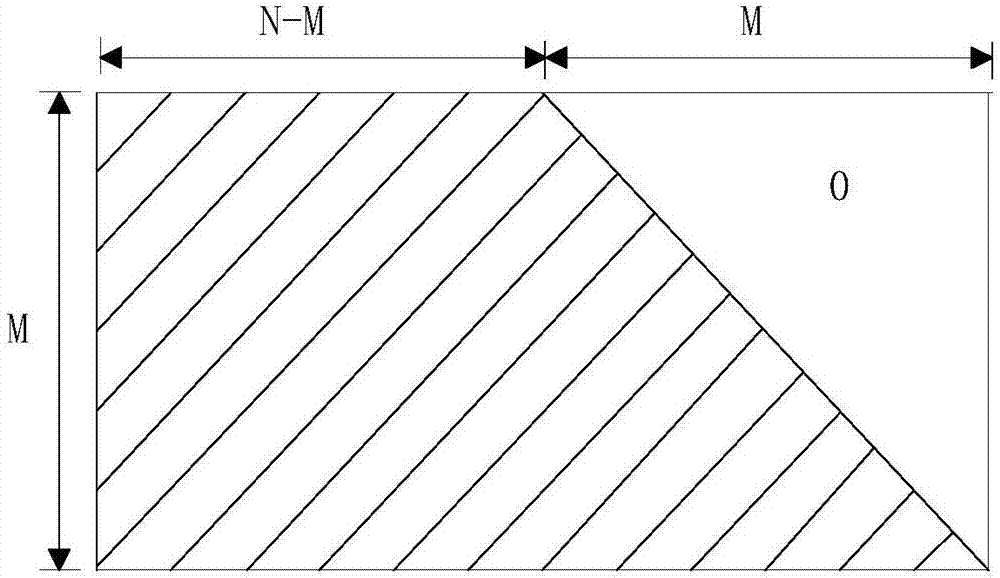

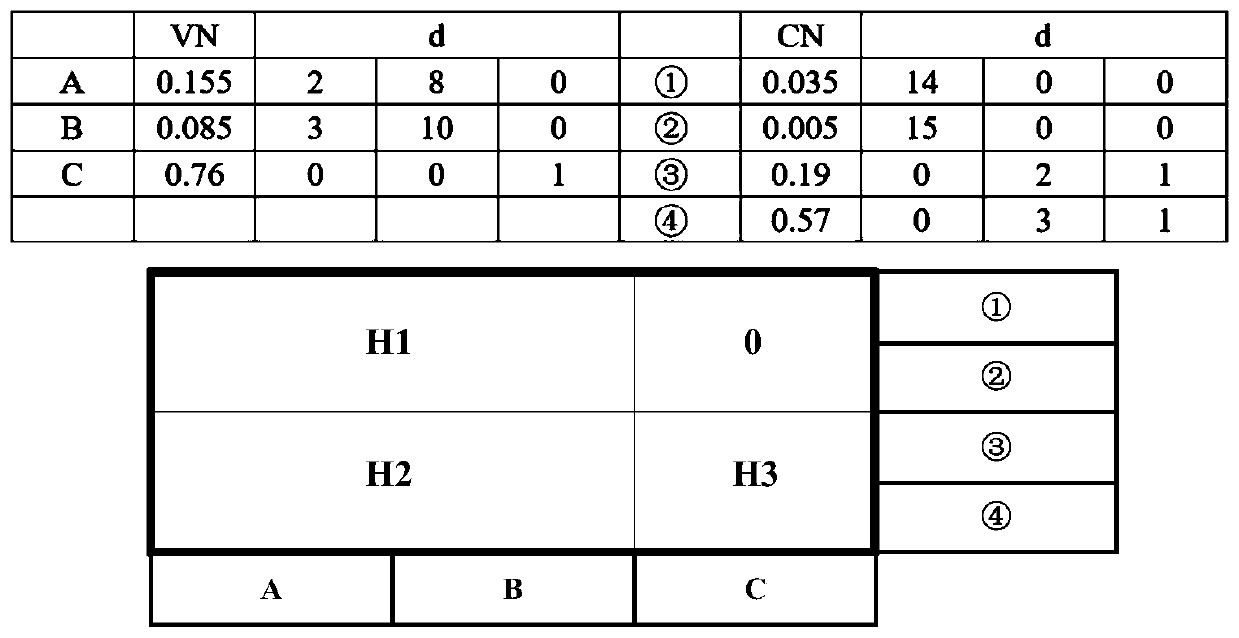

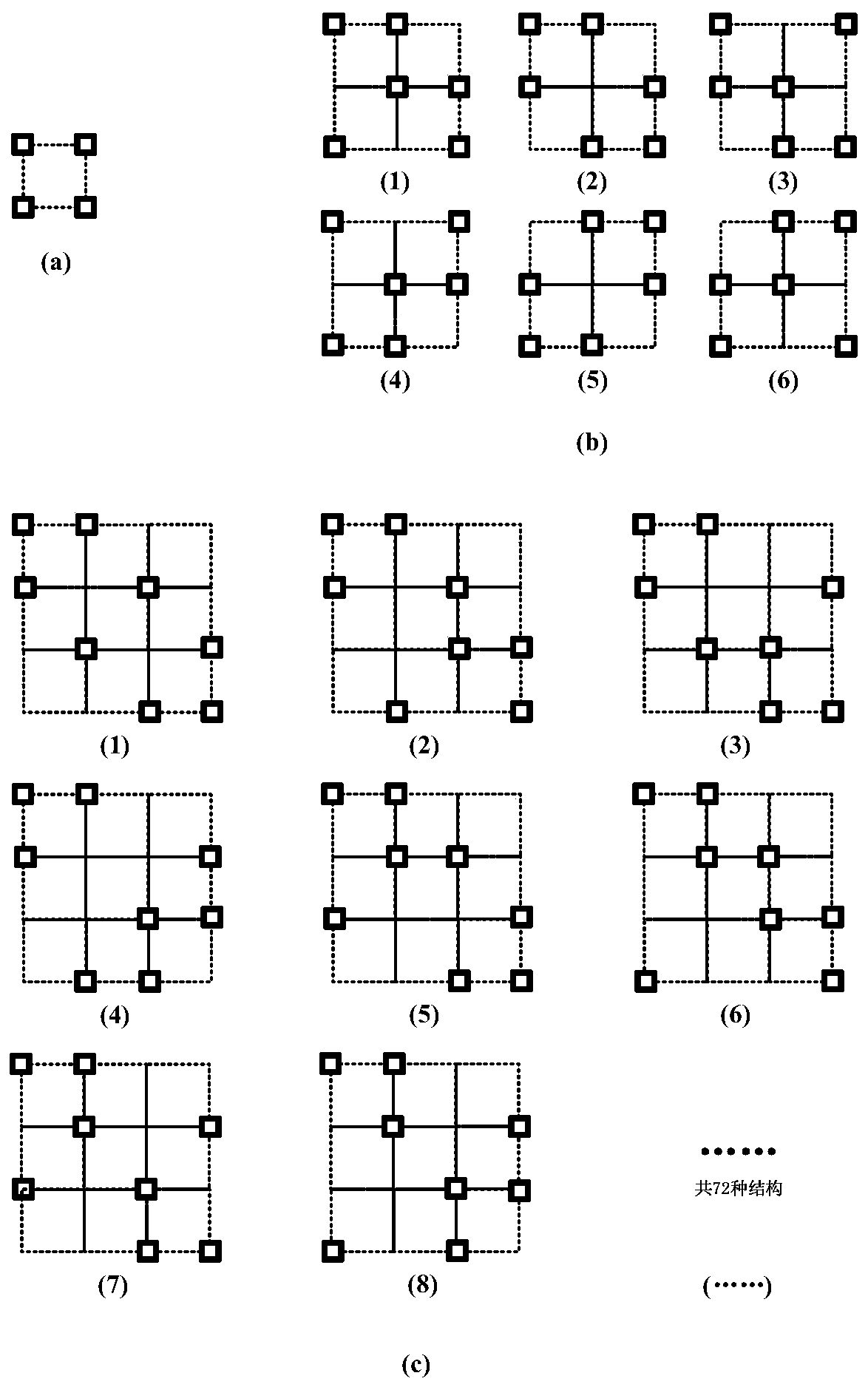

Basic matrix, coder/encoder and generation method of the low density parity check codes

ActiveUS8185797B2Eliminate error floorIncrease the speed of descentError detection/correctionError correction/detection using multiple parity bitsShort loopParity-check matrix

The invention relates to a base matrix, a encoder / decoder of Low Density Parity Check (LDPC) codes and a generation method thereof. The encoder / decoder is determined uniquely by the parity check matrix of the LDPC codes. With different code sizes, said parity check matrix can be obtained by expanding different base matrixes, and also can be obtained by expanding a unique base matrix after correction. Elements of said base matrix must meet an inequation in which the girth value is up to the standard, e.g. when girth≧6, for any element i, j, k, l in the matrix which forms the short loop having a length of 4 in anticlockwise, there are always mod(i−j+k−l, z) unequal to 0. By this invention, the girth of the constructed base matrix is made as large as possible, the amount of the shortest loops is as few as possible when it is the same girth, thus the curve of bit error ratio (BER) is dropped quickly, the error floor of the LDPC codes is eliminated effectively, and the optimal performance of the LDPC codes is obtained.

Owner:ZTE CORP

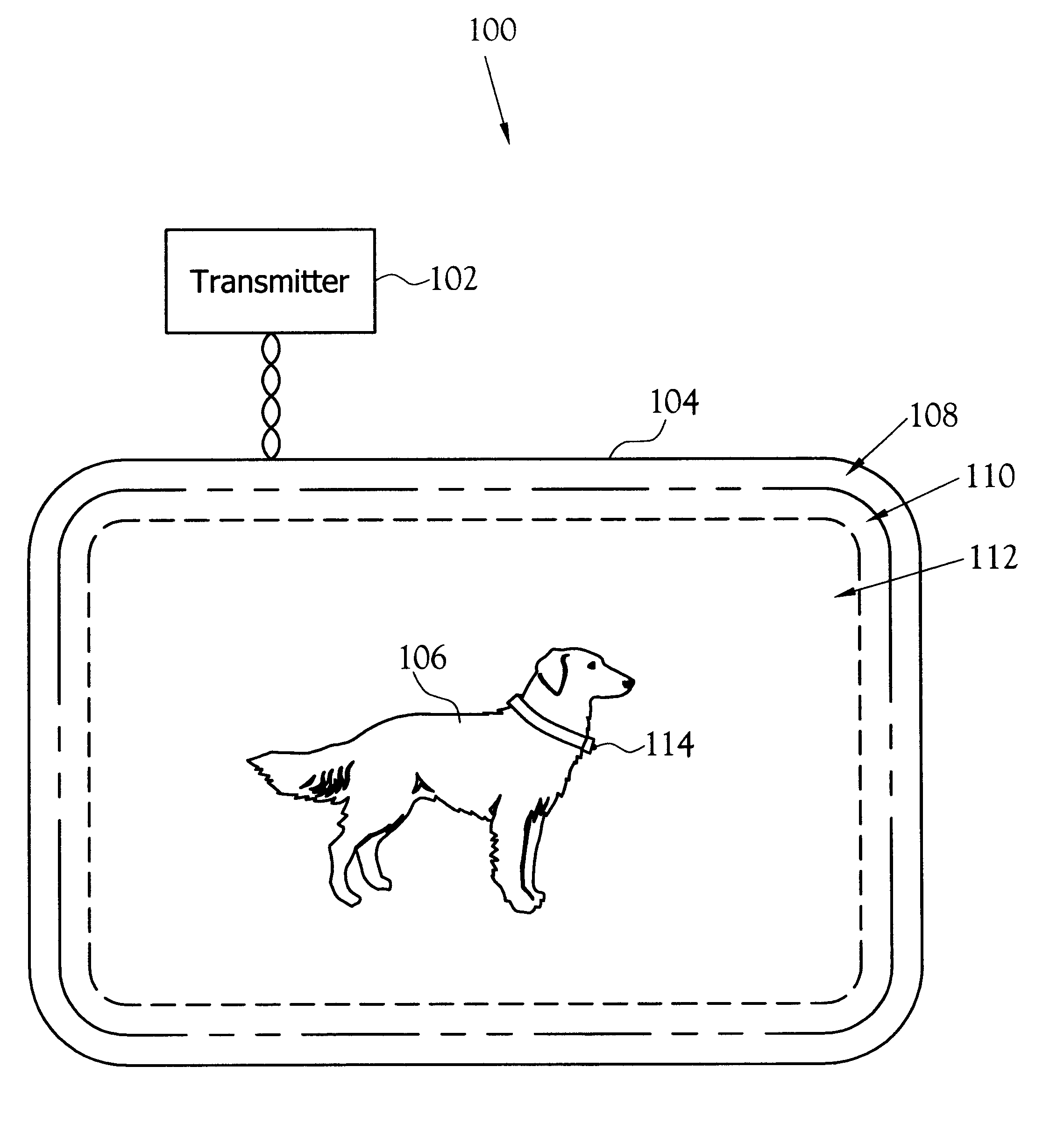

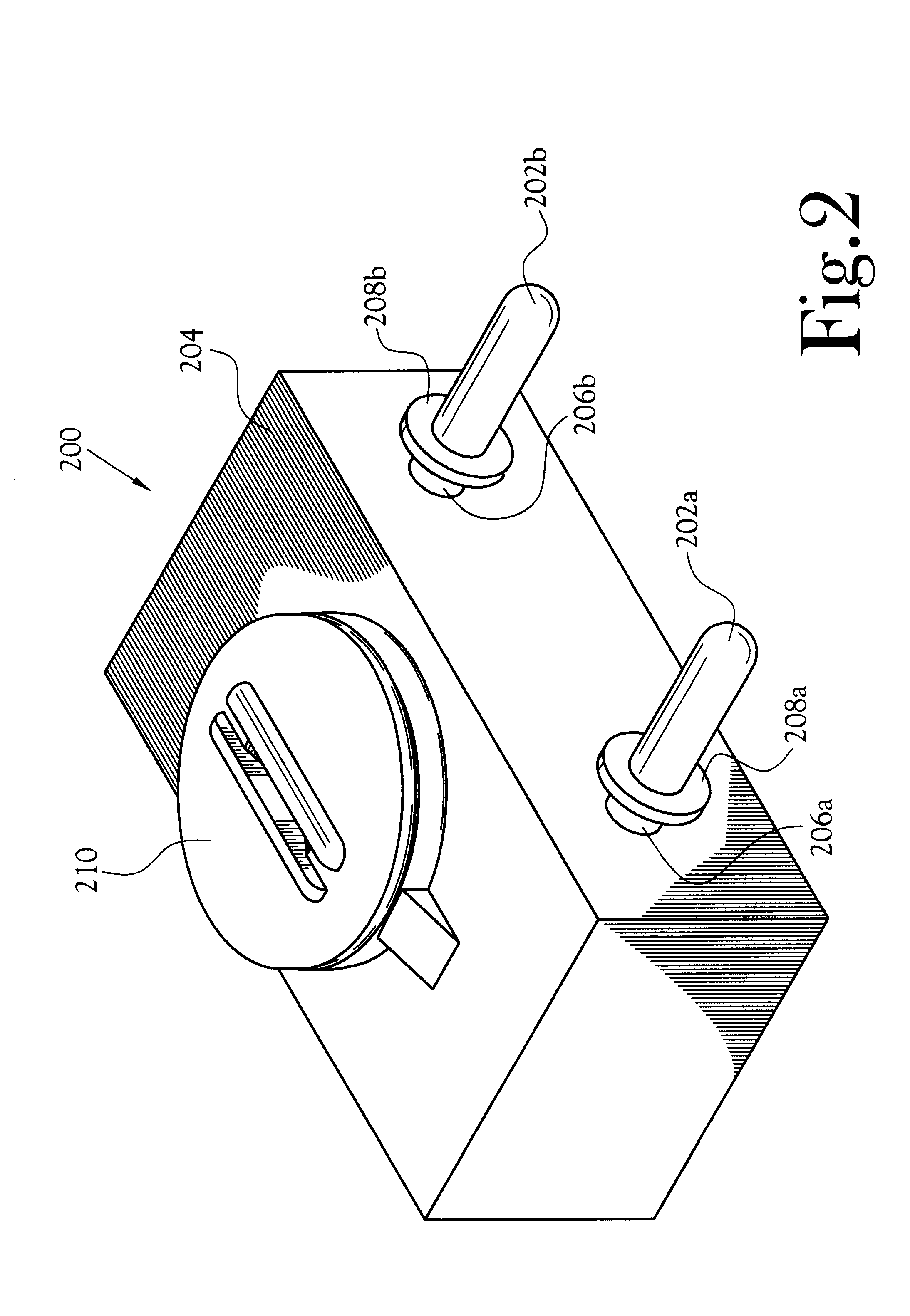

Method and apparatus for testing an electronic pet containment transmitter

A method and apparatus for testing the proper operation of an electronic pet containment transmitter. The transmitter includes an internal short loop antenna that is used to activate the receiver unit when it is brought into close proximity of the transmitter.

Owner:RADIO SYST CORP

Method and system for enhancing bit rate in DMT quad spectrum systems

InactiveUS20050135495A1Enhance and optimize bit allocationLarge bit rateError preventionTelephonic communicationFrequency spectrumShort loop

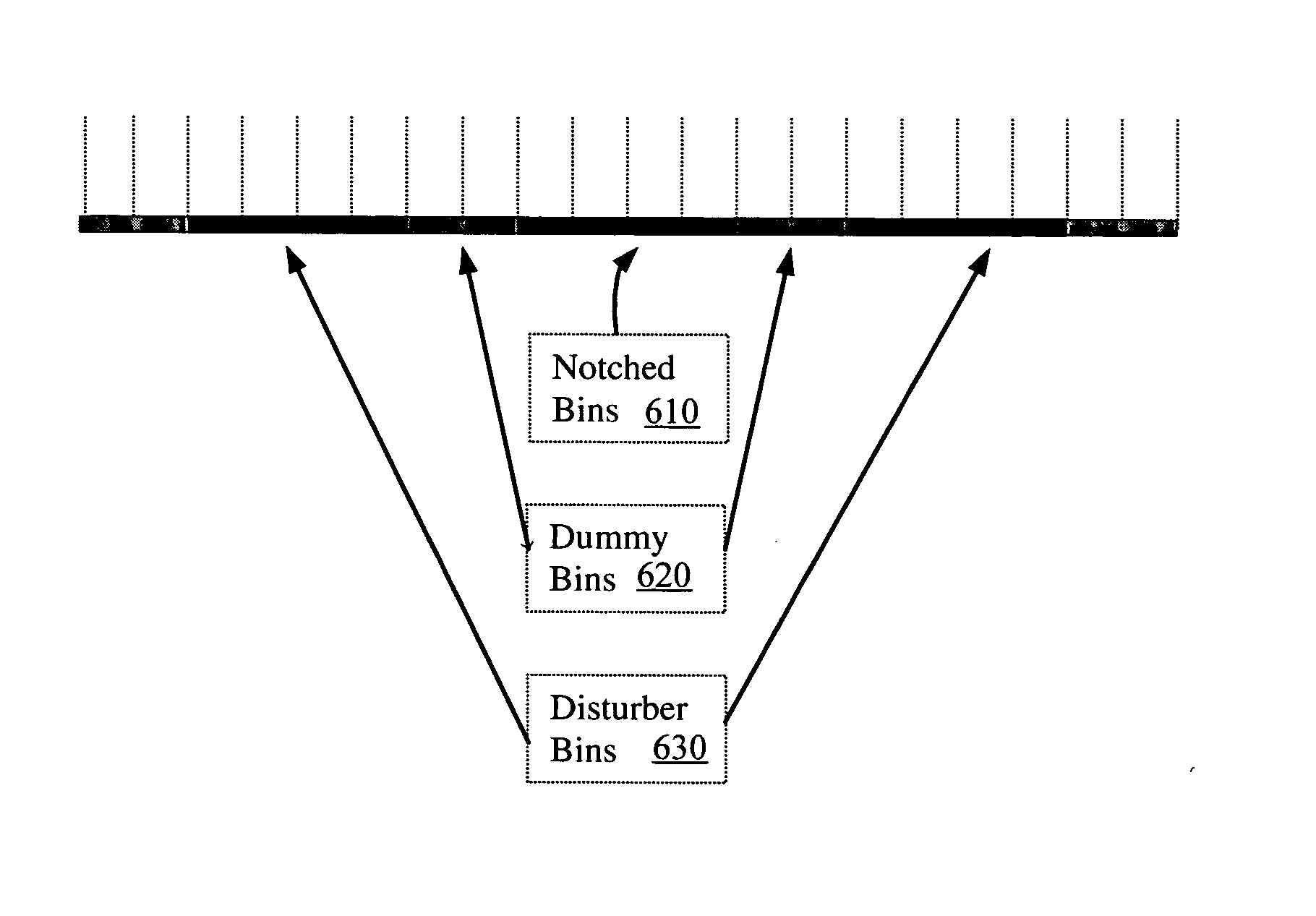

A method and system for achieving a maximum bit rate in a DMT system using a quad spectrum under constraints of avoiding interference with radio frequency interference (RFI). The methods of an embodiment of the present invention, when combined in various combinations, optimize bit allocation and utilizes bins in notched areas for transmission over short loops without violating the power spectral density (PSD) mask.

Owner:IKANOS COMMUNICATIONS

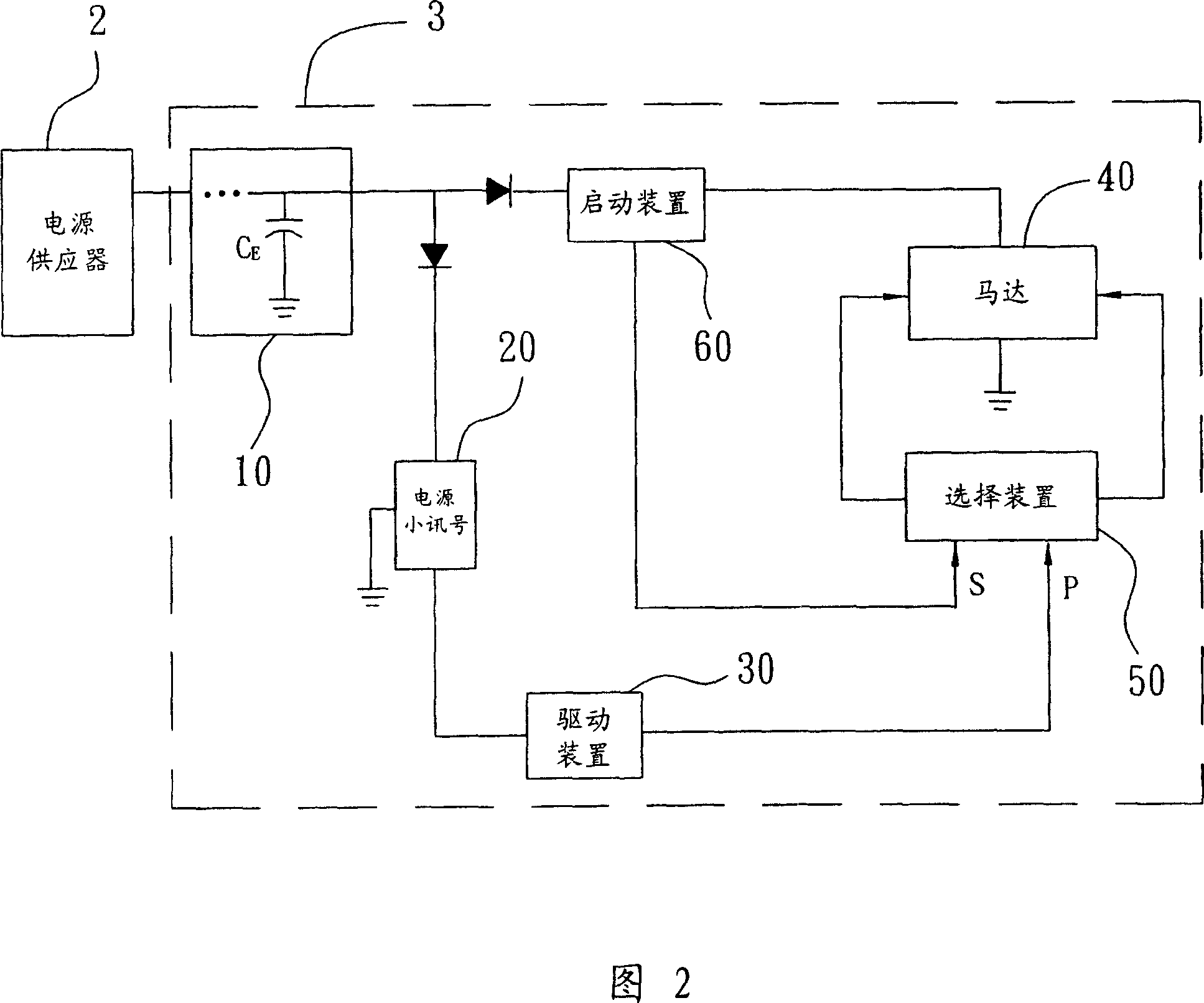

Fan system and its braking method

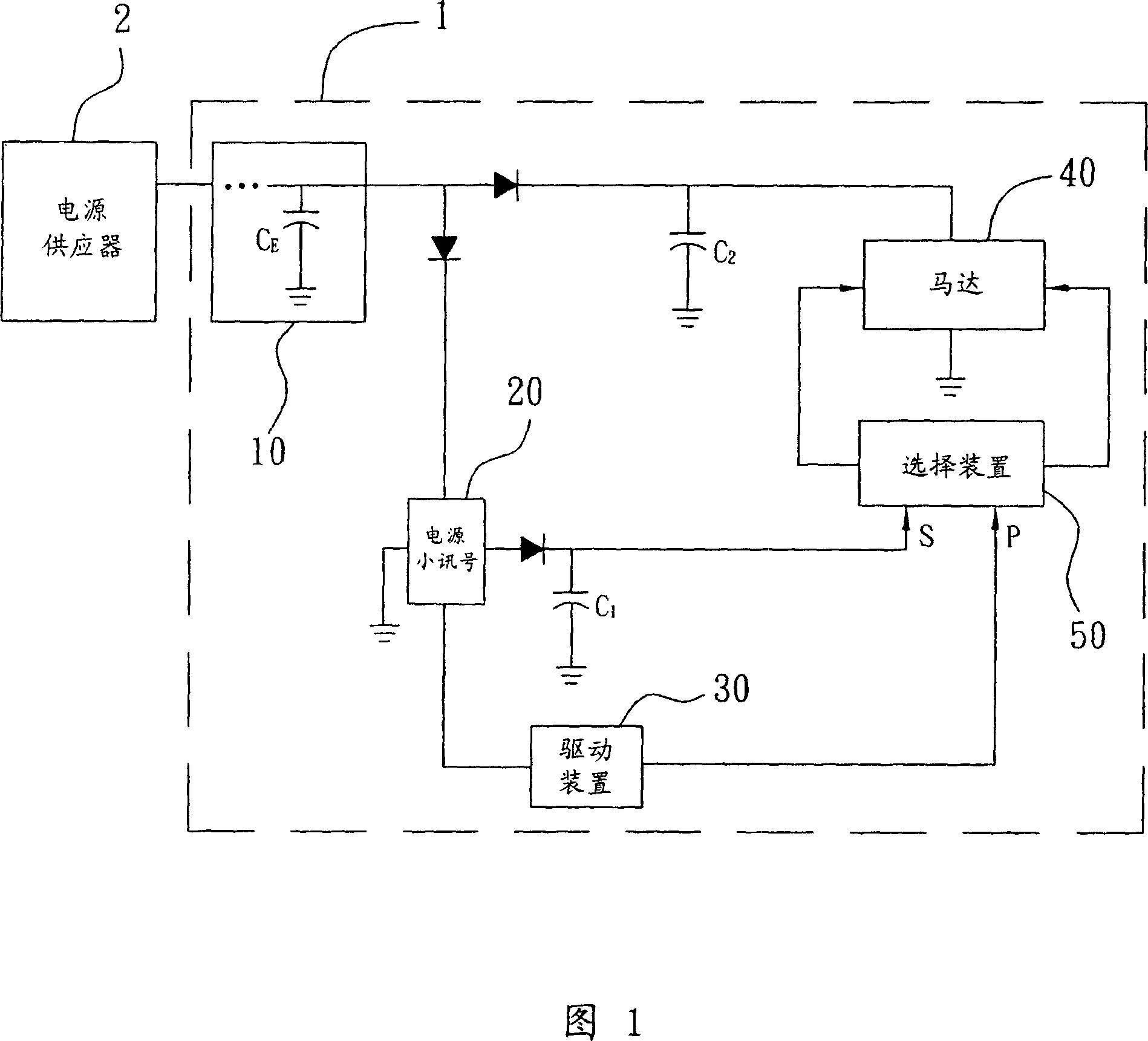

This invention provides a fan system connected to a supply provider and receiving a supply generated by the provider composed of an energy storage device, a motor, a drive device and a start up device, in which, the energy storage device receives and stores said supply, said motor is connected with said energy storage device and receives said supply, said drive device is connected between the energy storage device and the motor to form a control path, said start up device is connected between the energy storage device and said motor to form a supply path. When said fan system does not receive the supply of said provider, said storage device will release the stored supply, and said start up device generates an initiating signal to said motor to form a short loop to brake.

Owner:DELTA ELECTRONICS INC

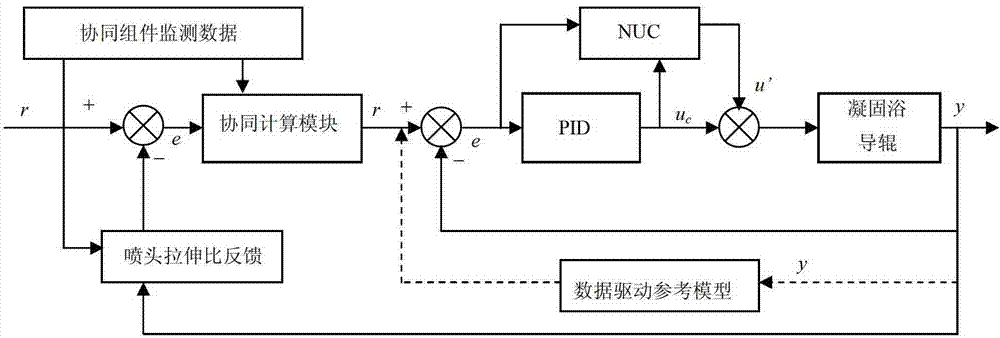

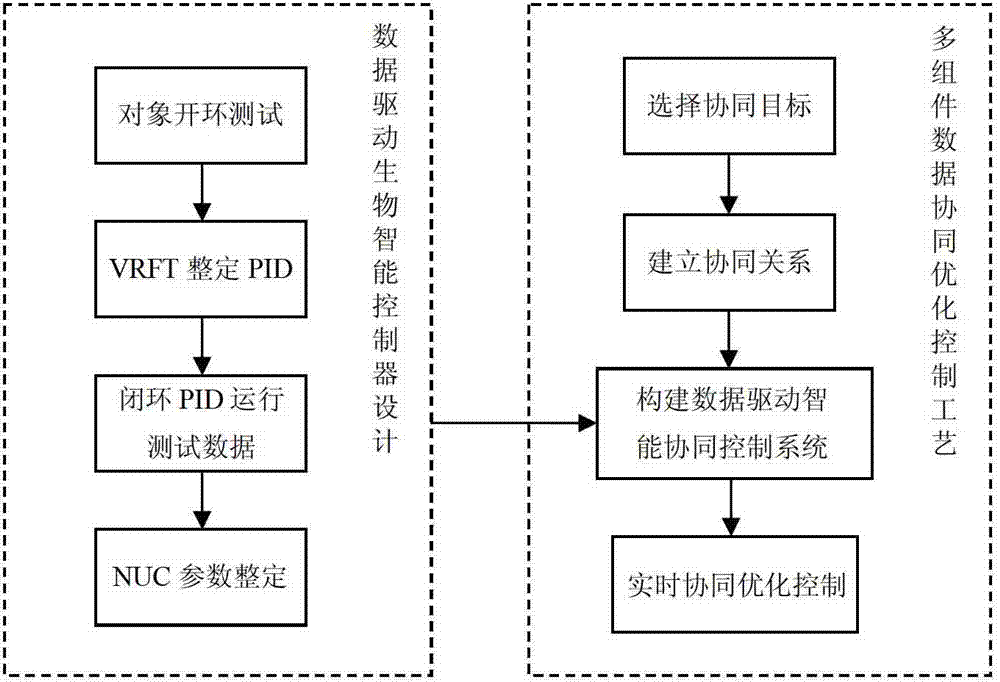

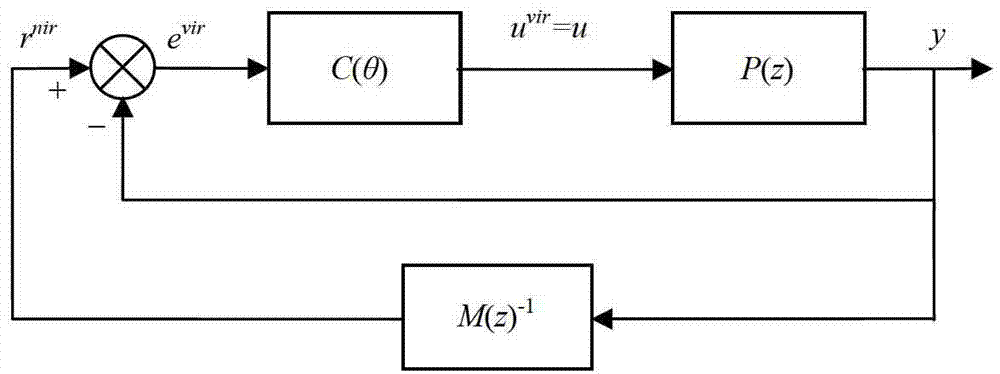

Carbon fiber precursor jet stretching process based on data driving cooperative intelligent control

InactiveCN103088448AAvoid errorsGood control effectAdaptive controlStretch-spinning methodsFiberCarbon fibers

The invention relates to carbon fiber precursor jet stretching process based on data driving cooperative intelligent control. The process route is as follows: spinning melt is accurately metered through a metering pump, enters a spinneret assembly and then enters coagulating bath after being extruded by a jet; a certain ratio of jet stretching is achieved under cooperative intelligent control of a coagulating bath guide roller; and the spinning melt leaves the coagulating bath finally. The carbon fiber precursor jet stretching process based on the data driving cooperative intelligent control is composed of biological intelligent controller design process based on data driving, and intelligent cooperative optimal control process based on multiple-component data collaboration. According to the biological intelligent controller design process based on the data driving, an endocrine ultra-short loop feedback biological intelligent controller is adopted for a controller, data driving improvement is carried out on the endocrine ultra-short loop feedback biological intelligent controller, and the endocrine ultra-short loop feedback biological intelligent controller is designed without dependence on object models; and according to the intelligent cooperative optimal control process based on the multiple-component data collaboration, the intelligent cooperative optimal control of jet stretching ratios is achieved through collecting other spinning component data with cooperative relations and carrying out cooperative optimal computation on the data.

Owner:DONGHUA UNIV

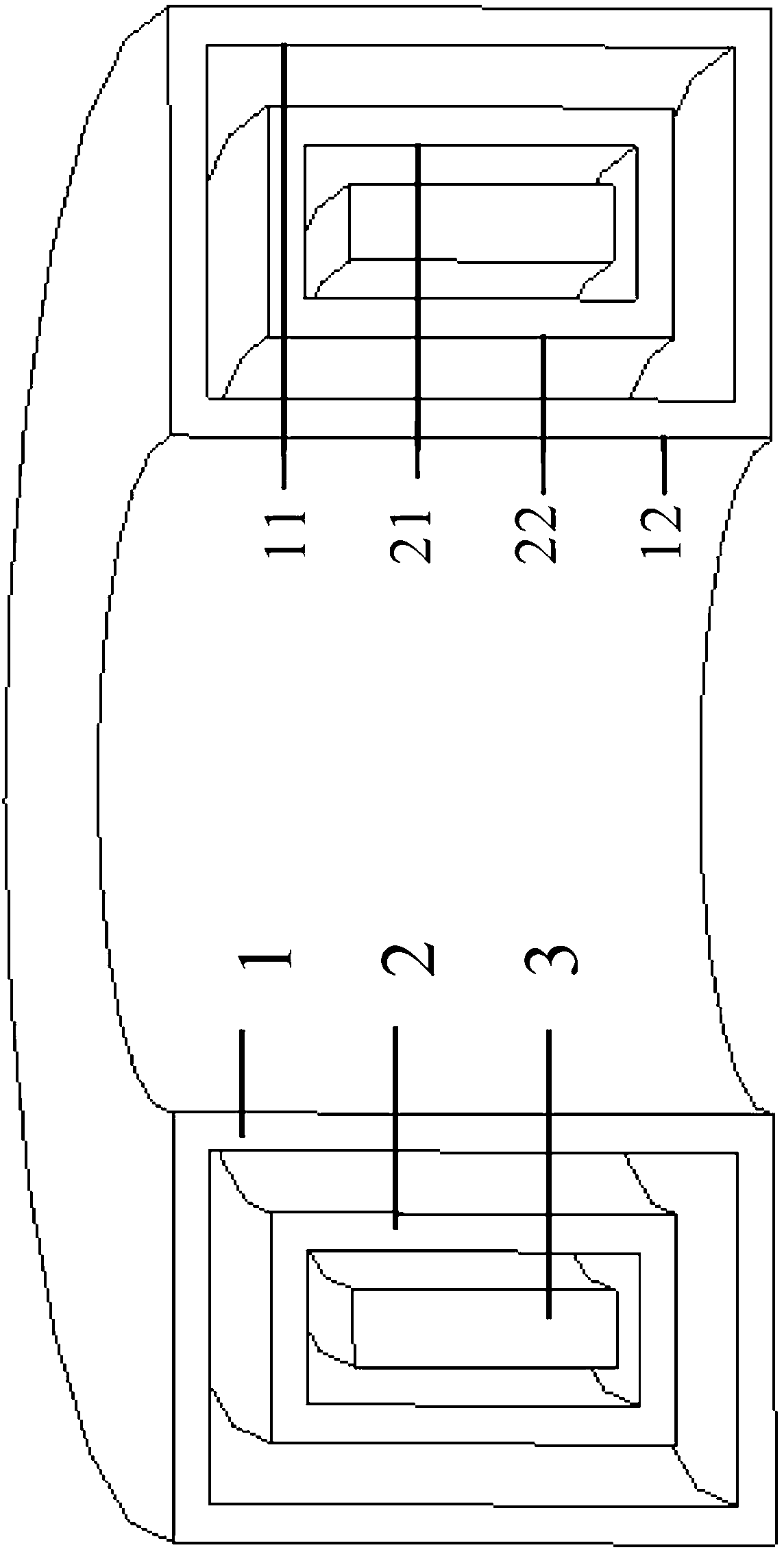

Dewar with magnetic shielding or electromagnetic shielding

InactiveCN102997037AShield or reduce negative impactImprove performancePressure vesselsShort loopSuperconducting Coils

The invention discloses a Dewar with magnetic shielding or electromagnetic shielding. The Dewar is composed of an inner barrel and an outer barrel, wherein the two closed barrels are in sleeve joint; and the space between the inner barrel and the outer barrel is vacuumized, and a group of magnetic shielding bodies or electromagnetic shielding bodies are arranged between the inner barrel and the outer magnetic field of Dewar. Each magnetic shielding body is made into a strip shape or sheet shape by the use of a silicon steel sheet, or is integrally formed by the use of an outer barrel wall made from magnetic-conduction stainless steel; the electromagnetic shielding body can adopt coils formed by winding conductive material; and the coils are closed end to end to form a short loop surrounding the main magnetic field, or metal plates are welded to form a closed barrel shape. Through the invention, adverse impacts of the outer magnetic field on a superconducting magnet can be shielded or reduced at the same time.

Owner:北京云电英纳超导电力技术有限公司 +1

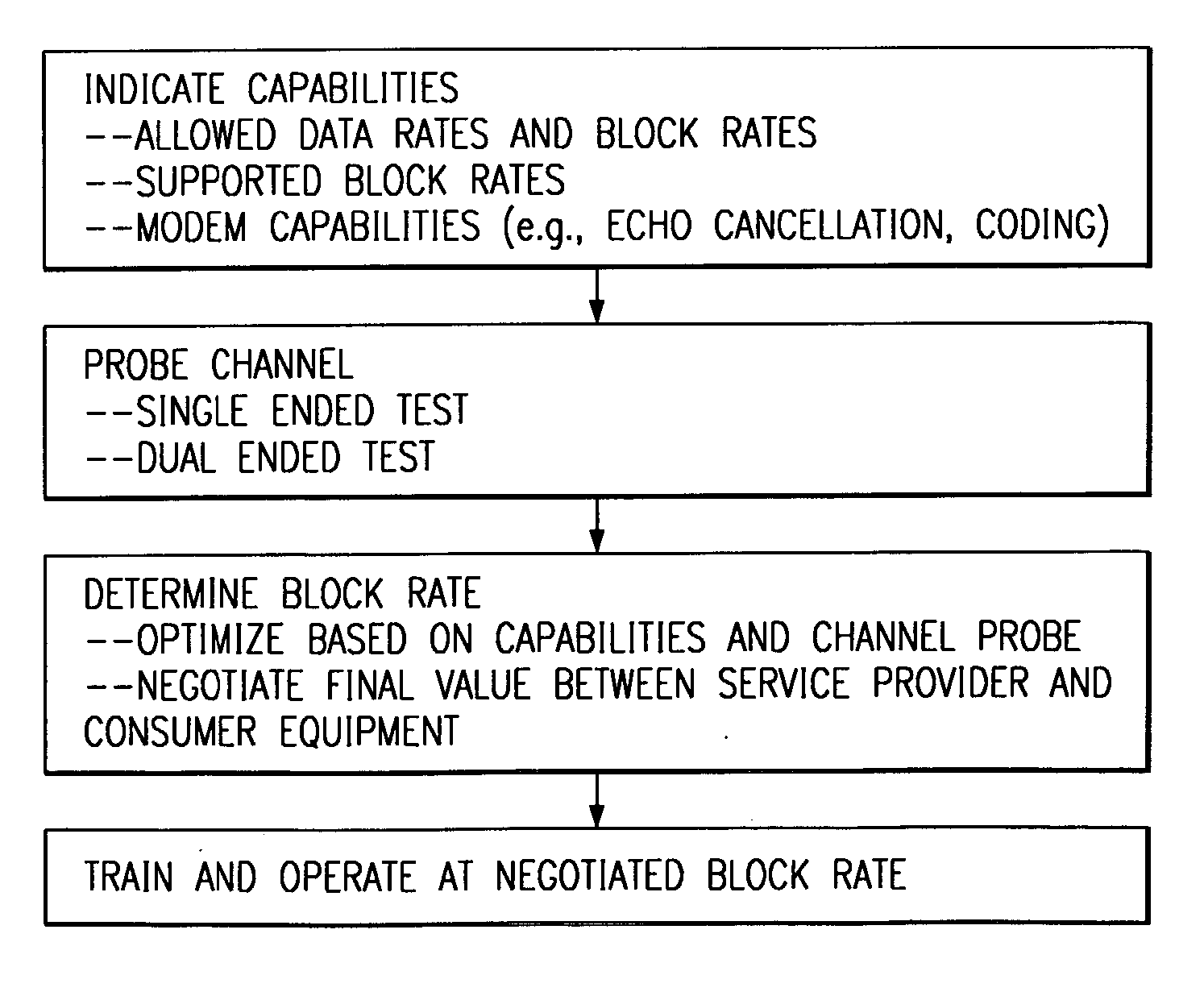

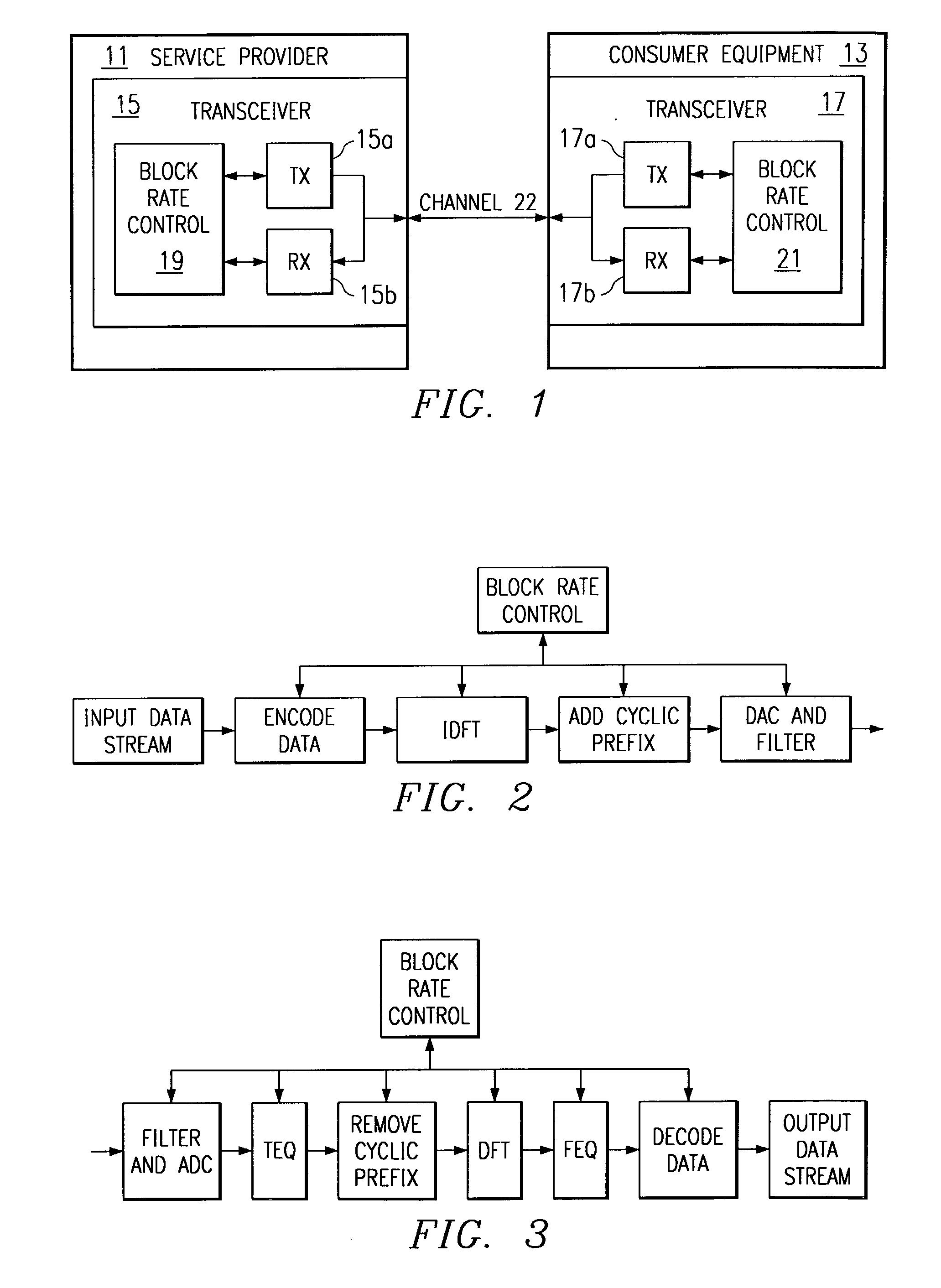

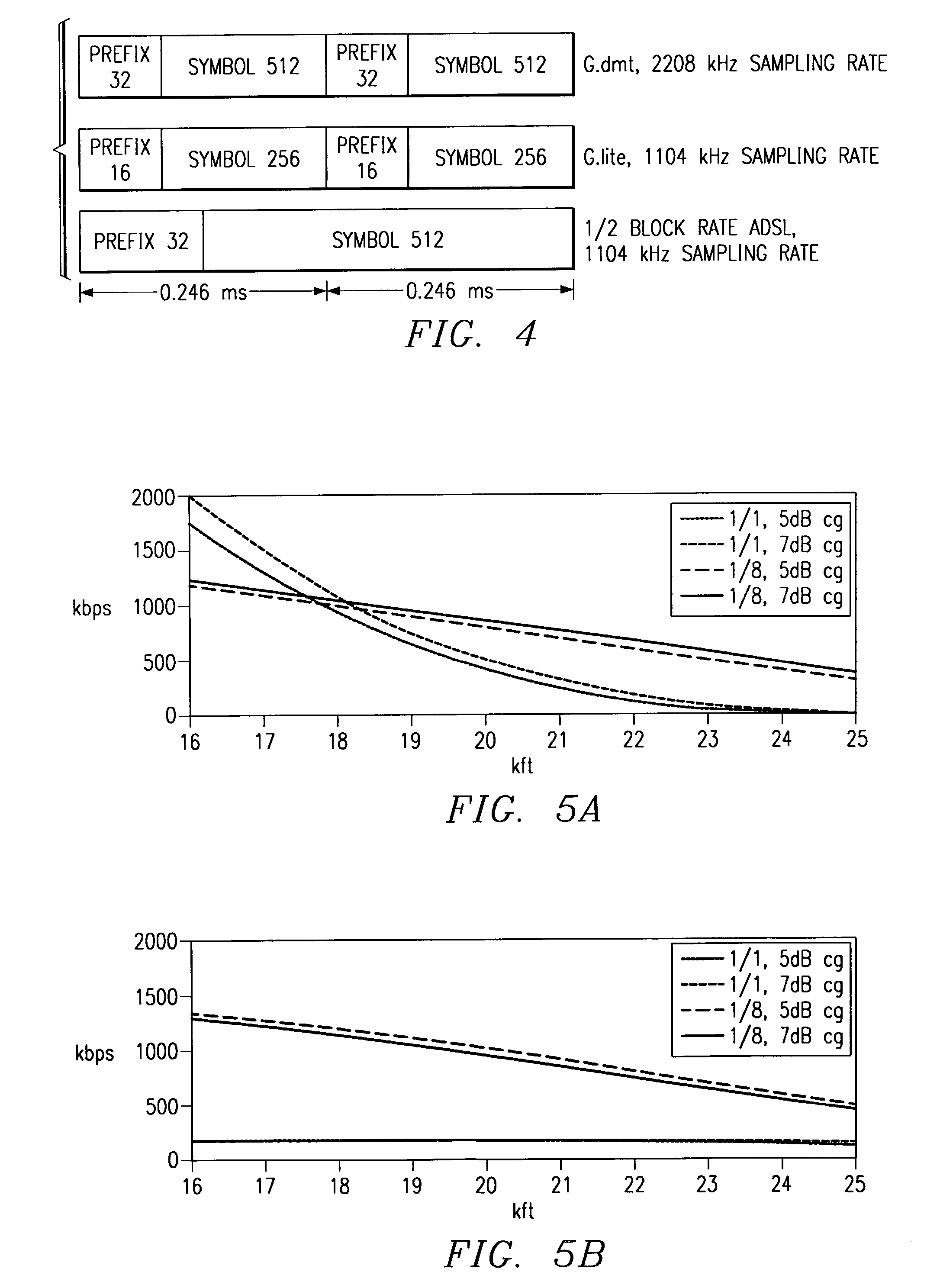

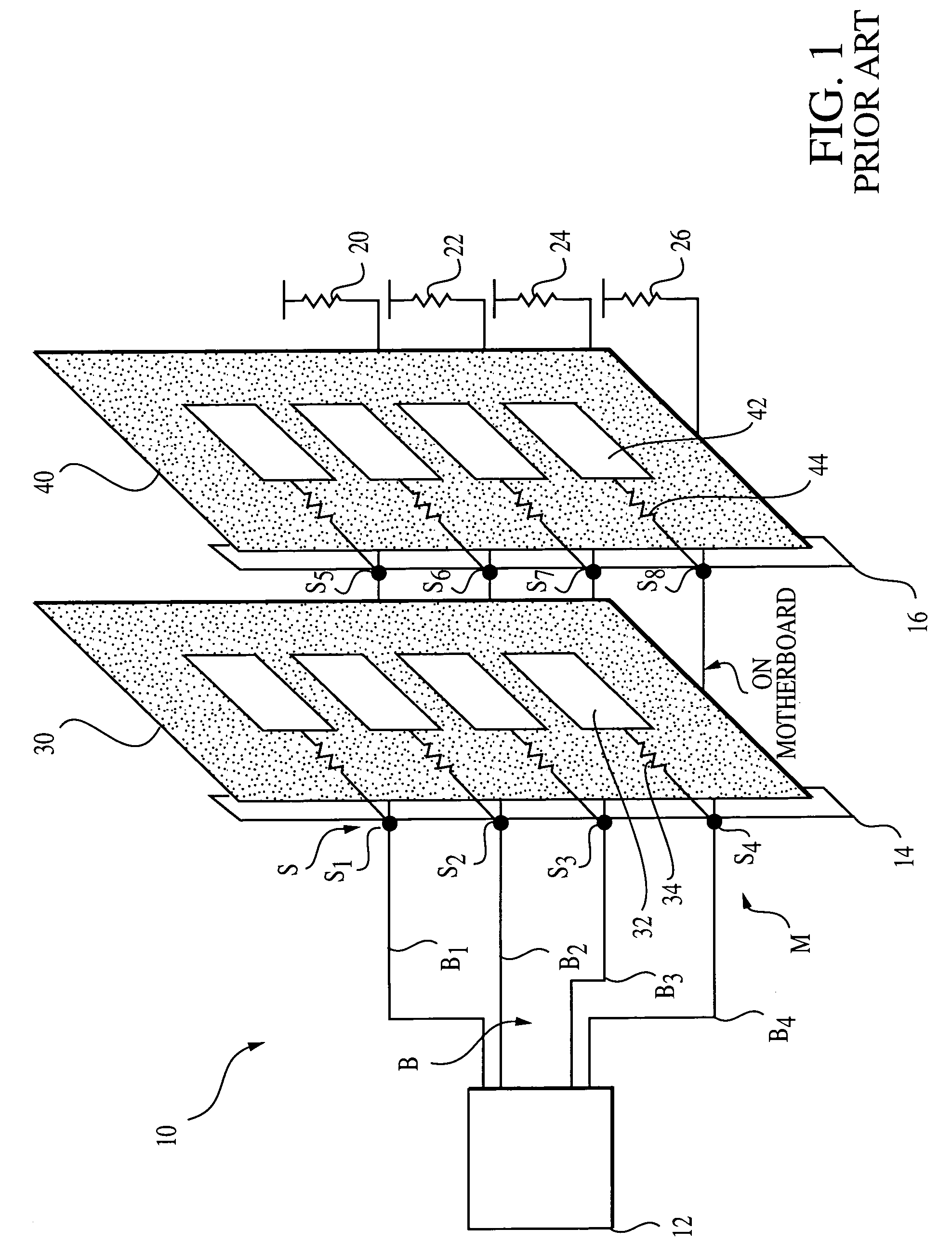

Variable block rate ADSL

ActiveUS20030118090A1Increase reachIncrease data rateTime-division multiplexFrequency-division multiplexShort loopData rate

By allowing the block rate to vary, the existing Asymmetric Digital Subscriber Line (ADSL) system is modified to better address extended reach and higher data rates. A method is disclosed for providing improved reach from the ADSL standard by reducing the block rate from the ADSL standard and providing improved data rate for short loops by increasing the block rate from the ADSL standard.

Owner:TEXAS INSTR INC

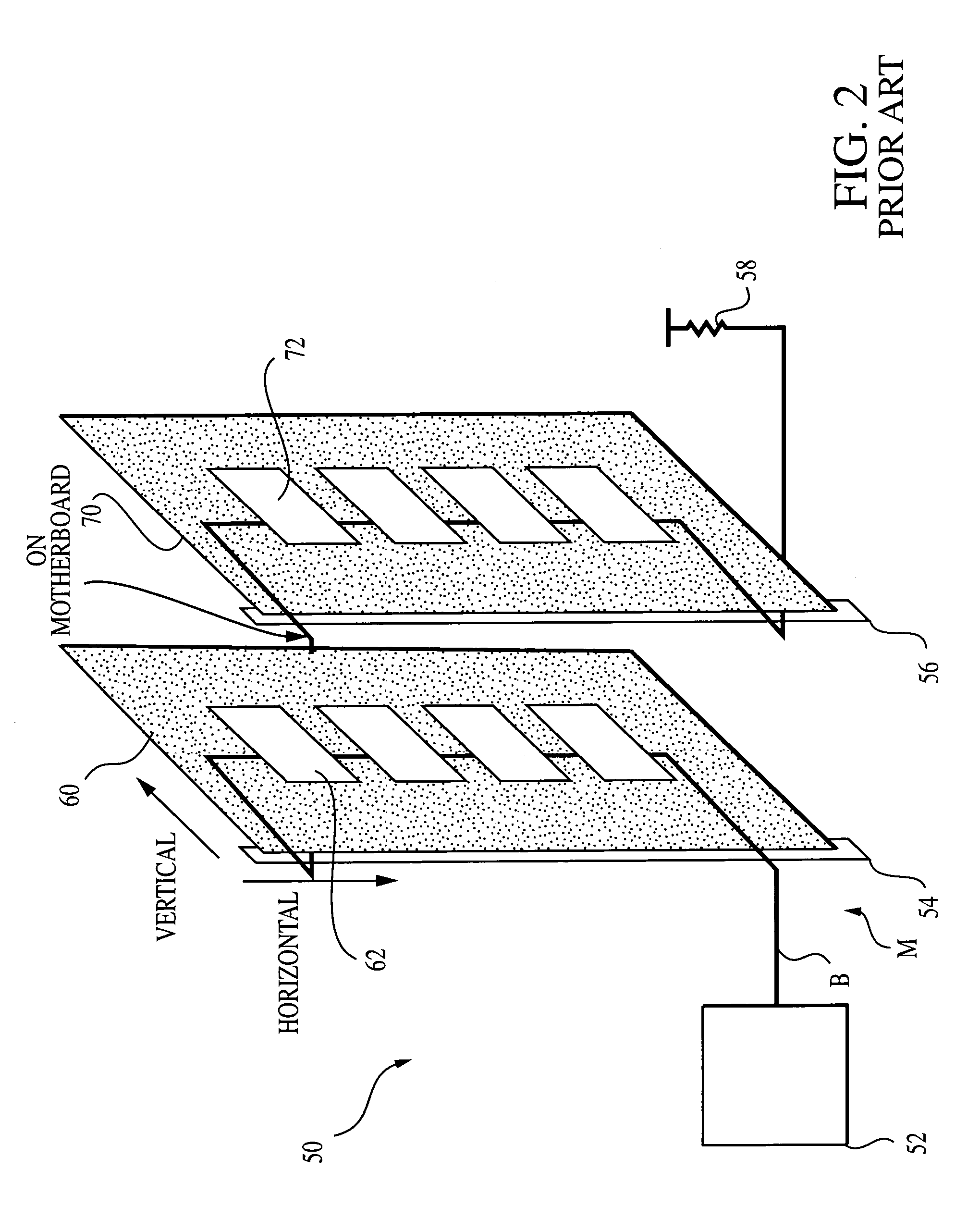

High speed bus topology for expandable systems

InactiveUS6963941B1Uniform impedanceEasy to operateElectrically conductive connectionsOrthogonal PCBs mountingScalable systemExpansion card

A high-speed short-loop bus topology that routes the bus into a first expansion connector and out of a first expansion card inserted within the connector is disclosed. The bus is not routed out of the first expansion connector. Instead, the bus is routed from the first expansion card into a second expansion card by a jumper mechanism. The bus is routed through the second expansion card and out of a second expansion connector housing the second expansion card, where the bus can be terminated or routed into another expansion connector having another expansion card. By routing the bus in this manner, it is shorter than prior art buses found in loop-through bus systems and capable of substantially maintaining a uniform transmission line impedance. Moreover, the operating bandwidth of the short-loop bus is increased since the bus is short and does not have stubs or signal reflections.

Owner:MICRON TECH INC

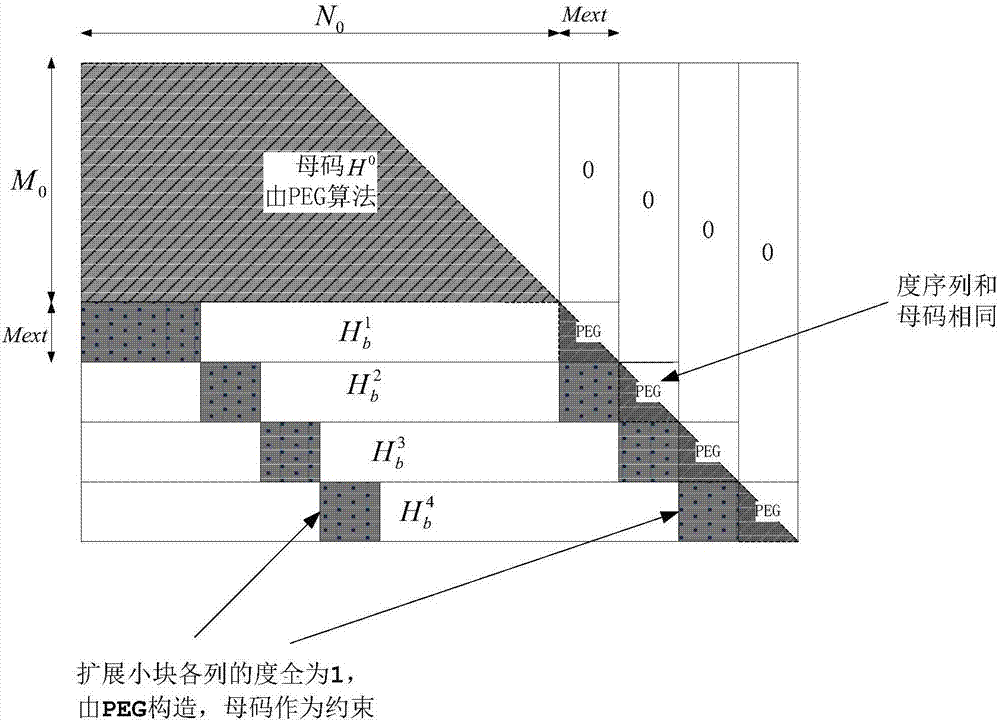

Method for generating RC-LDPC code check matrix

ActiveCN107294543AImprove bit error performanceImprove throughputError correction/detection using multiple parity bitsCode conversionRound complexityComputation complexity

The present invention belongs to the technical field of channel coding and relates to a method for generating an RC-LDPC code check matrix. The method is based on the complexity of the coding, and is modified based on the PEG algorithm to construct a check matrix with a lower triangular form. The obtained coding complexity is linear. On this basis, the method of expanding the check bit step by step is adopted to support the flexible and variable code rate, which provides a feasible channel coding method for the adaptation of a wireless link. At the same time, the obtained series of sub-codes also have a lower triangular form, which almost does not increase the complexity but can achieve linear coding with regard to the mother code. According to the invention, the method utilizes the PEG algorithm to optimize the position of the nonzero element in the expanded part and optimizes the code structure so as to eliminate the short loop, to reduce the computational complexity of the codec and to further improve the transmission performance.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

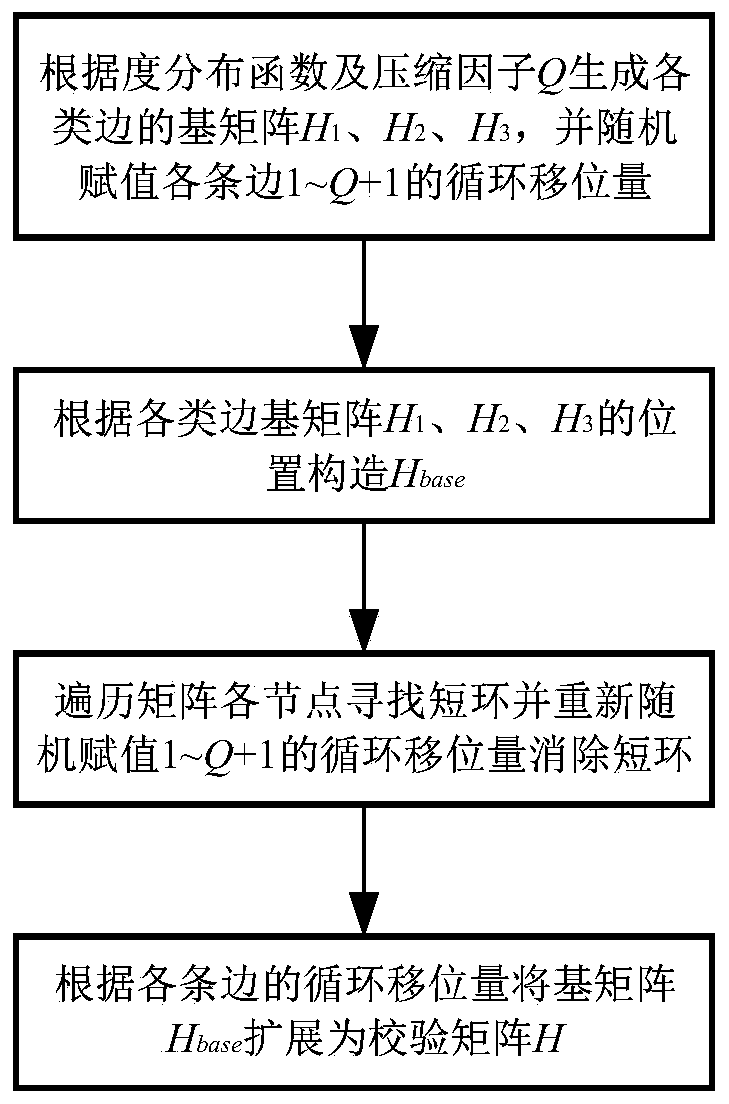

Short-loop-free QC-LDPC code rapid generation method

ActiveCN110739976AQuick buildImprove decoding performanceError correction/detection using multiple parity bitsCode conversionShort loopTheoretical computer science

The invention discloses a short-loop-free QC-LDPC code rapid generation method, which comprises the following steps: step 1, generating sub-matrixes of various edges according to a degree distributionfunction and a compression factor Q, and randomly assigning cyclic shift amounts of each edge 1-Q; step 2, arranging the sub-matrixes according to the positions of various edges to construct a basismatrix; step 3, traversing each node of the sub-matrix to search for a short ring, and randomly assigning 1-Q cyclic shift values again to eliminate the short ring; and step 4, expanding the basis matrix into a check matrix according to the cyclic shift amount of each edge. Aimed at problems in an actual QKD system, the coordination efficiency, the decoding speed and the success rate of an LDPC code check matrix are influenced due to the existence of a short loop, and then the safety code rate and the transmission distance of a system are influenced, the invention provides the short-loop-freeQC-LDPC code quick generation method suitable for the QKD system. The short-loop-free check matrix can be quickly generated, and the decoding performance is improved.

Owner:NO 30 INST OF CHINA ELECTRONIC TECH GRP CORP

Efficiency of short loop instruction fetch

InactiveUS9052910B2Useful energyEliminating repeat accessDigital computer detailsConcurrent instruction executionInstruction unitShort loop

A design structure provides instruction fetching within a processor instruction unit, utilizing a loop buffer, one or more virtual loop buffers, and / or an instruction buffer. During instruction fetch, modified instruction buffers coupled to an instruction cache (I-cache) temporarily store instructions from a single branch, backwards short loop. The modified instruction buffers may be a loop buffer, one or more virtual loop buffers, and / or an instruction buffer. Instructions are stored in the modified instruction buffers for the length of the loop cycle. The instruction fetch within the instruction unit of a processor retrieves the instructions for the short loop from the modified buffers during the loop cycle, rather than from the instruction cache.

Owner:INT BUSINESS MASCH CORP

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com