Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

33 results about "RISC-V" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

RISC-V (pronounced "risk-five") is an open-source hardware instruction set architecture (ISA) based on established reduced instruction set computer (RISC) principles. The project began in 2010 at the University of California, Berkeley, but many contributors are volunteers not affiliated with the university.

Techniques for metadata processing

ActiveUS20170177367A1Adapt quicklyMinimal overheadMemory architecture accessing/allocationRegister arrangementsData streamParallel computing

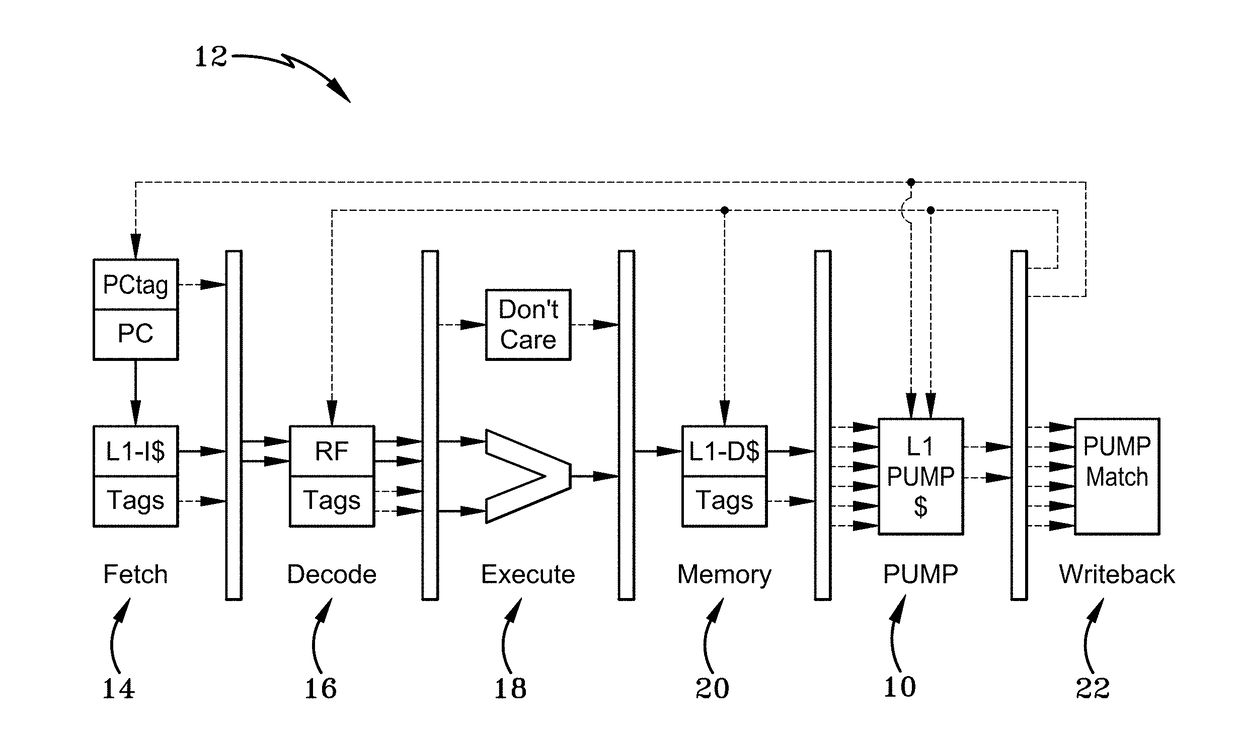

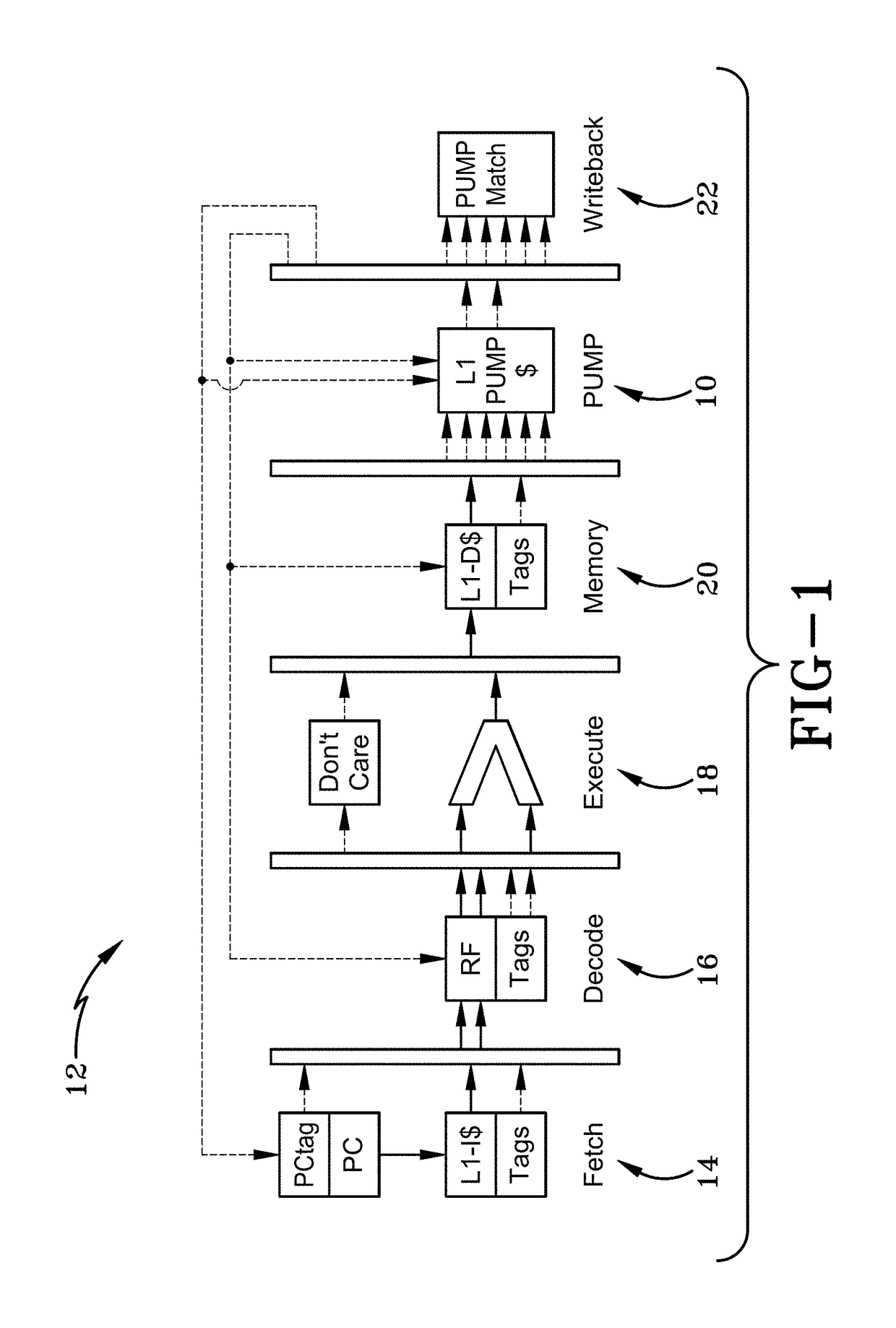

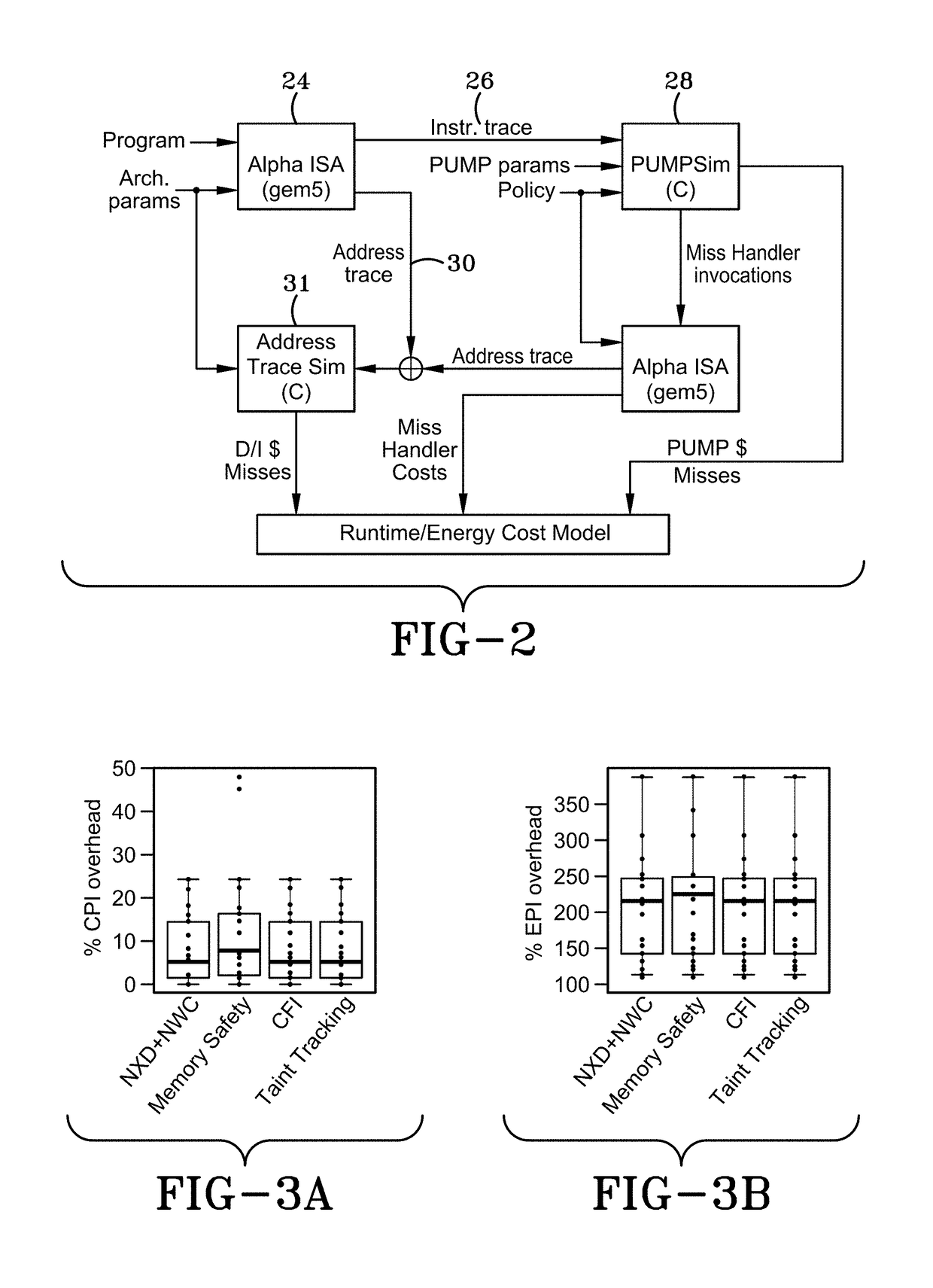

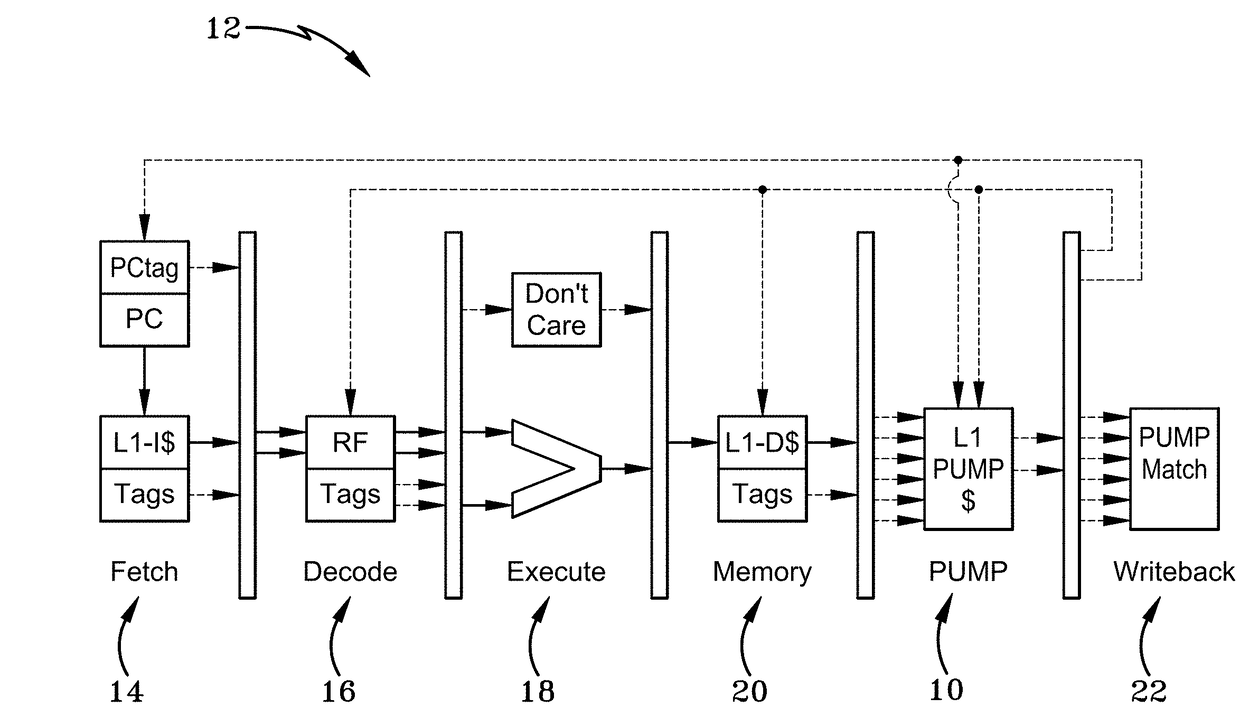

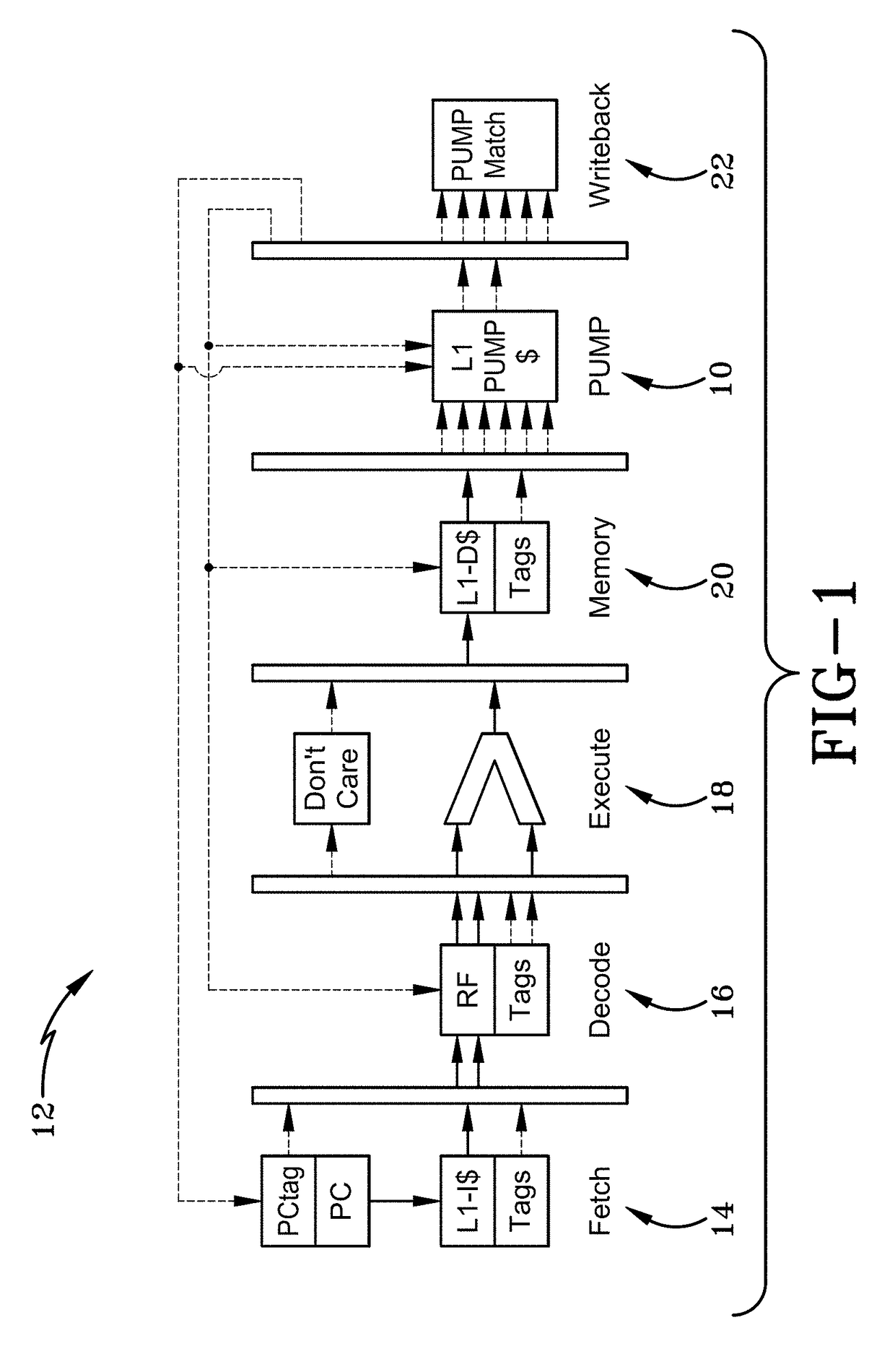

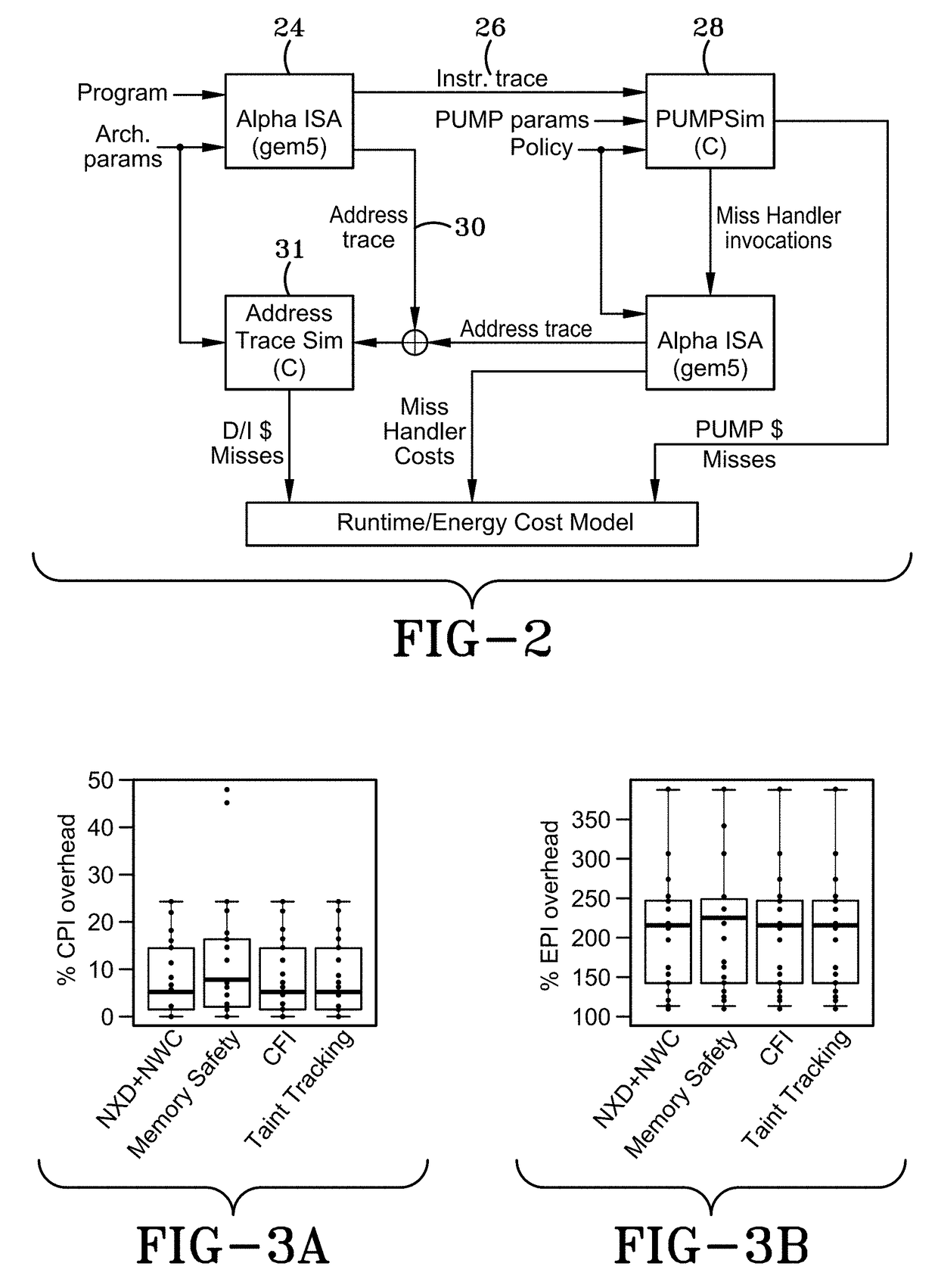

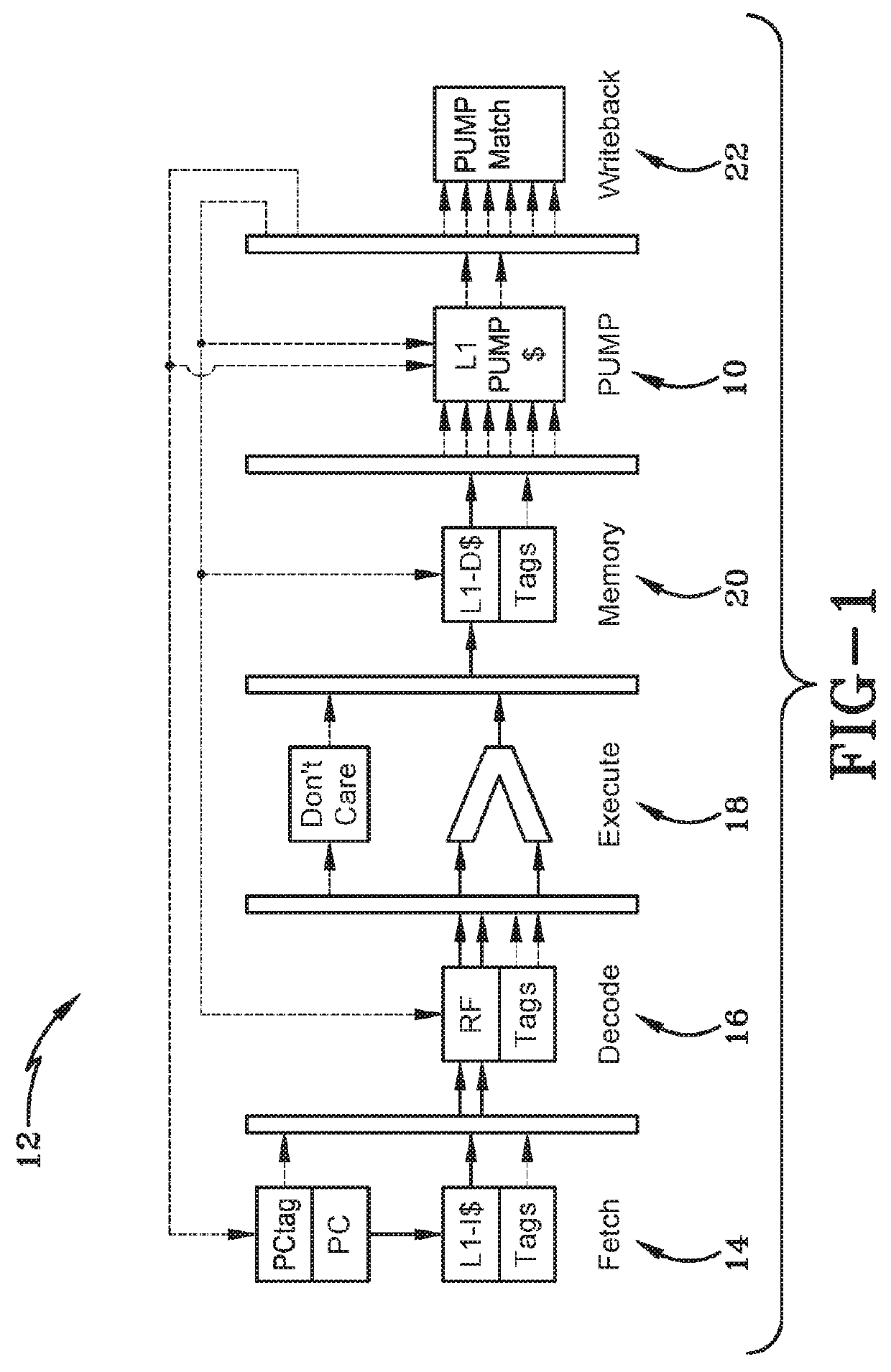

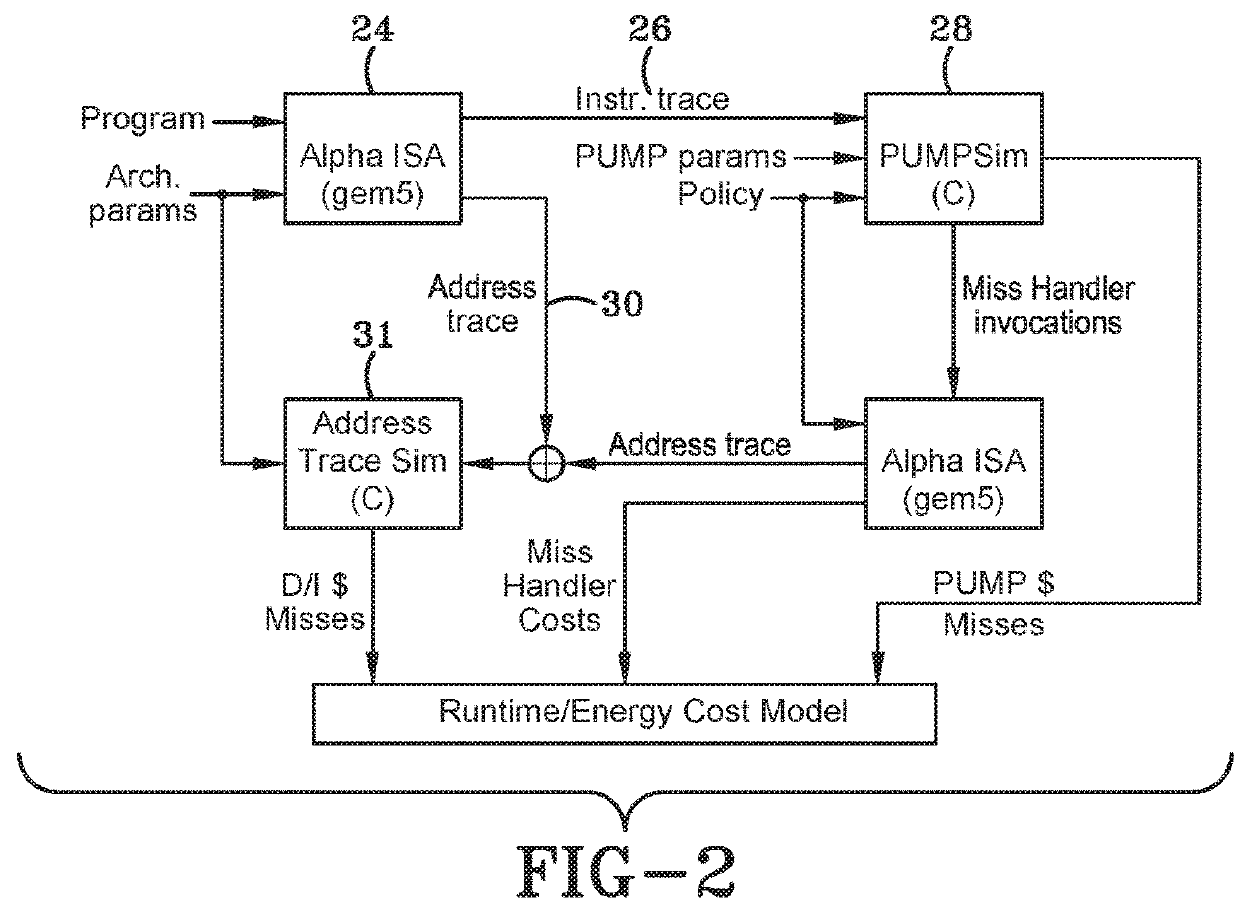

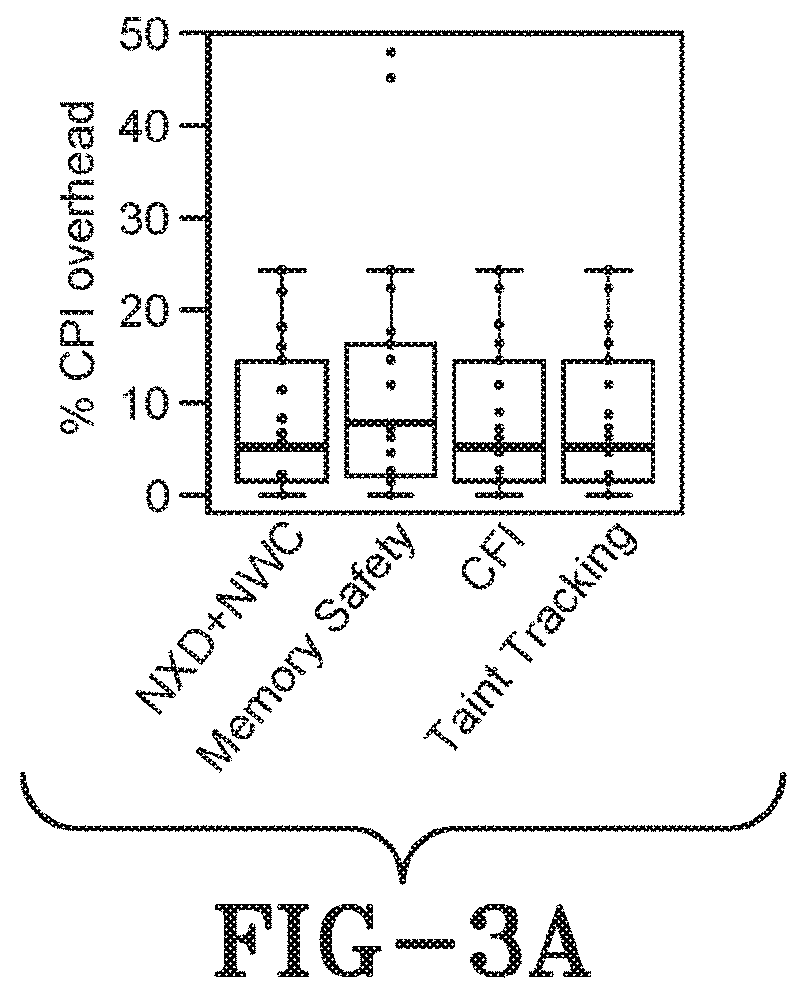

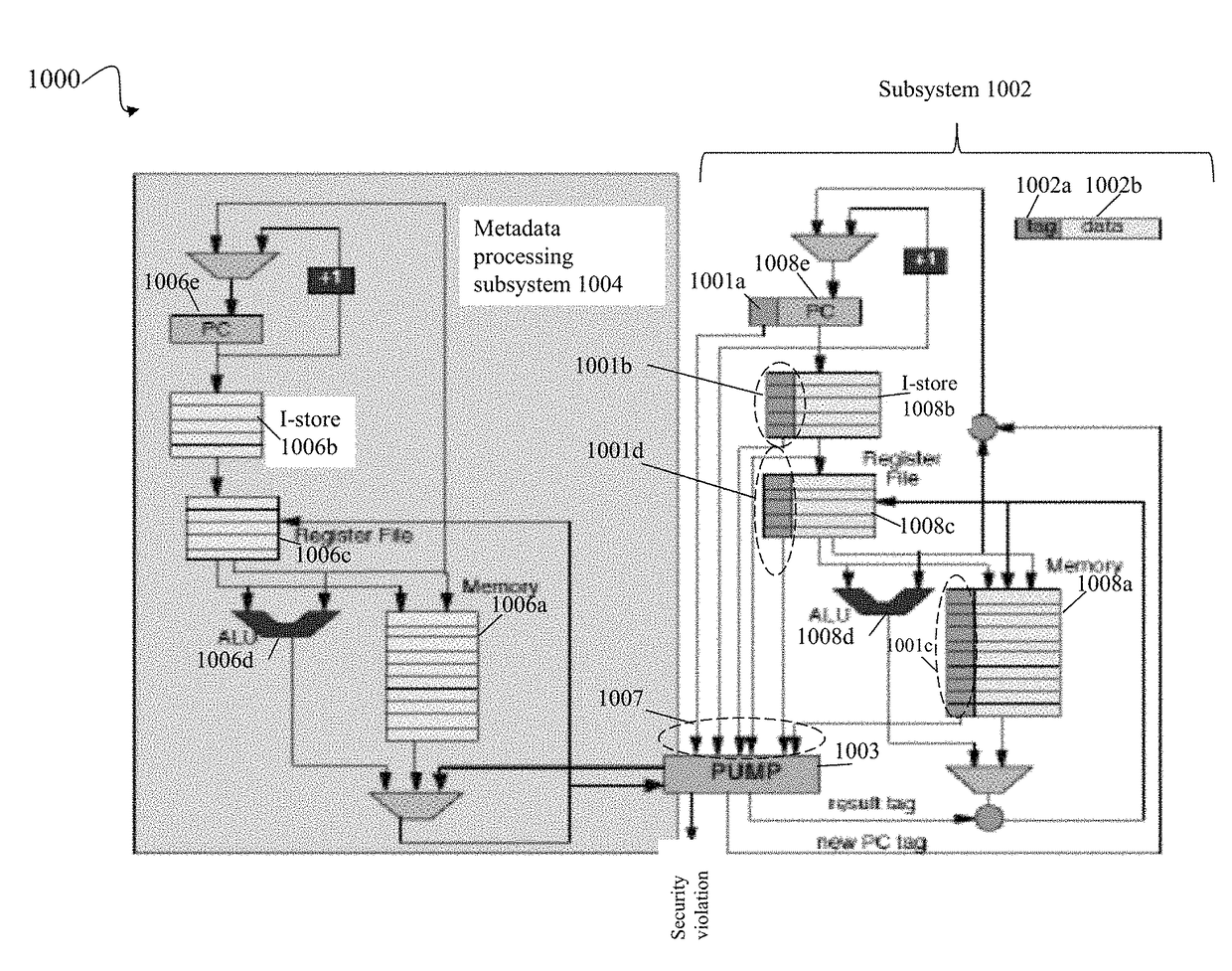

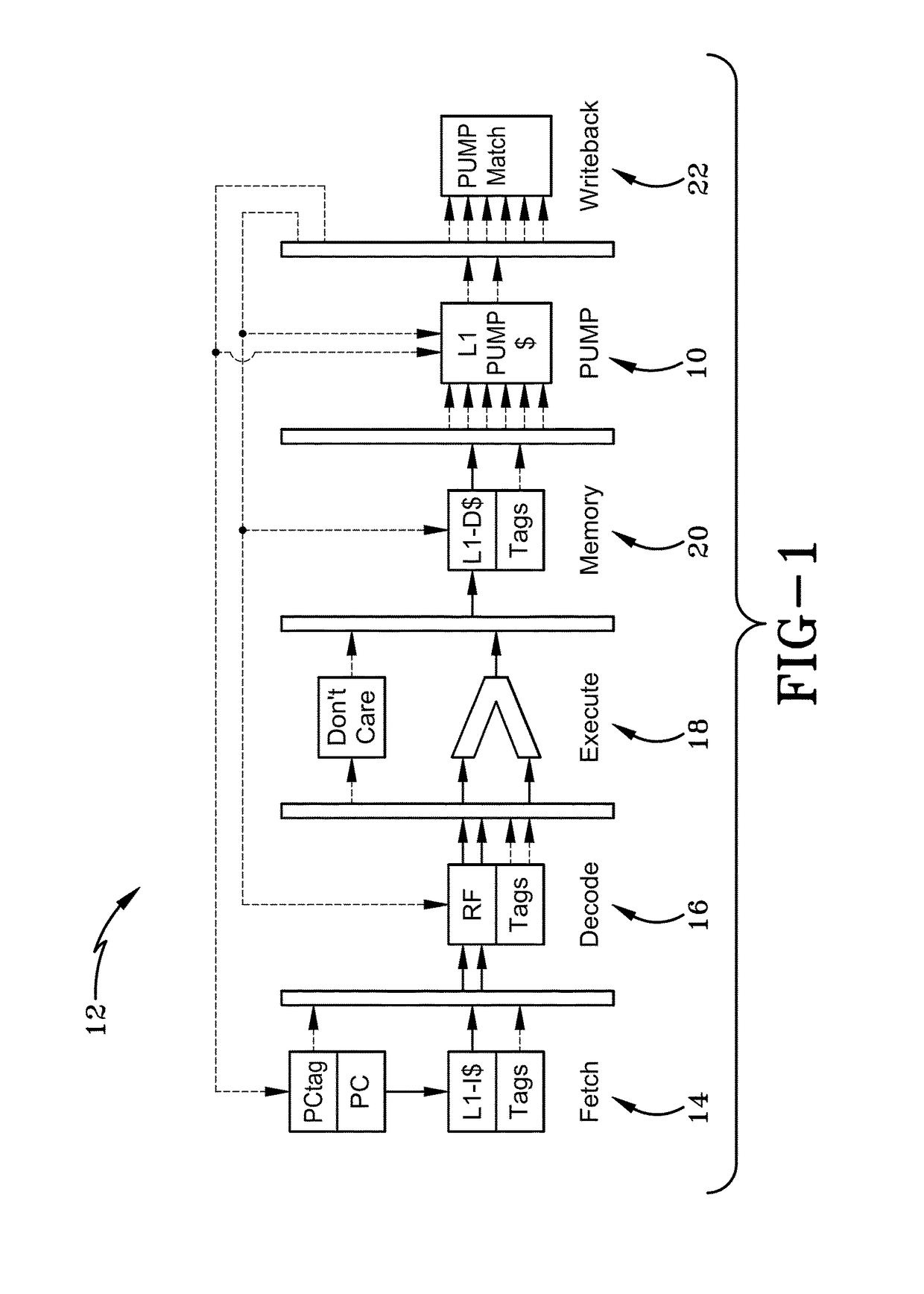

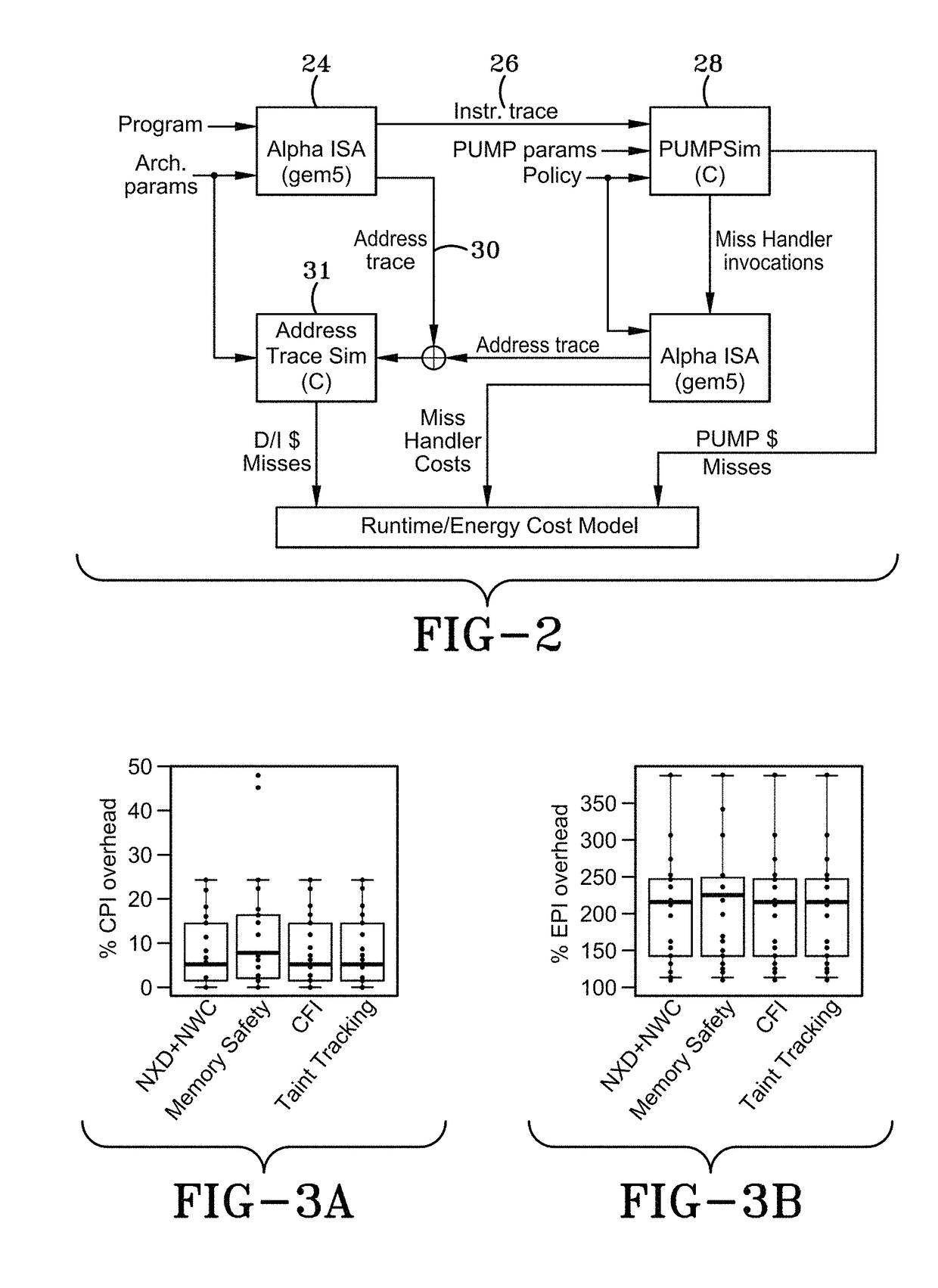

Techniques are described for metadata processing that can be used to encode an arbitrary number of security policies for code running on a processor. Metadata may be added to every word in the system and a metadata processing unit may be used that works in parallel with data flow to enforce an arbitrary set of policies. In one aspect, the metadata may be characterized as unbounded and software programmable to be applicable to a wide range of metadata processing policies. Techniques and policies have a wide range of uses including, for example, safety, security, and synchronization. Additionally, described are aspects and techniques in connection with metadata processing in an embodiment based on the RISC-V architecture.

Owner:CHARLES STARK DRAPER LABORATORY

Techniques for metadata processing

ActiveUS20170177368A1Adapt quicklyMinimal overheadMemory architecture accessing/allocationRegister arrangementsData streamParallel computing

Techniques are described for metadata processing that can be used to encode an arbitrary number of security policies for code running on a processor. Metadata may be added to every word in the system and a metadata processing unit may be used that works in parallel with data flow to enforce an arbitrary set of policies. In one aspect, the metadata may be characterized as unbounded and software programmable to be applicable to a wide range of metadata processing policies. Techniques and policies have a wide range of uses including, for example, safety, security, and synchronization. Additionally, described are aspects and techniques in connection with metadata processing in an embodiment based on the RISC-V architecture.

Owner:THE NAT INST FOR RES IN DATA PROCESSING & AUTOMATION +1

Techniques for metadata processing

ActiveUS20190213322A1Adapt quicklyMinimal overheadRegister arrangementsBootstrappingData streamParallel computing

Techniques are described for metadata processing that can be used to encode an arbitrary number of security policies for code running on a processor. Metadata may be added to every word in the system and a metadata processing unit may be used that works in parallel with data flow to enforce an arbitrary set of policies. In one aspect, the metadata may be characterized as unbounded and software programmable to be applicable to a wide range of metadata processing policies. Techniques and policies have a wide range of uses including, for example, satiety, security, and synchronization. Additionally, described are aspects and techniques in connection with metadata processing in an embodiment based on the RISC-V architecture.

Owner:CHARLES STARK DRAPER LABORATORY

Techniques for metadata processing

ActiveUS9785440B2Memory architecture accessing/allocationRegister arrangementsData streamParallel computing

Techniques are described for metadata processing that can be used to encode an arbitrary number of security policies for code running on a processor. Metadata may be added to every word in the system and a metadata processing unit may be used that works in parallel with data flow to enforce an arbitrary set of policies. In one aspect, the metadata may be characterized as unbounded and software programmable to be applicable to a wide range of metadata processing policies. Techniques and policies have a wide range of uses including, for example, safety, security, and synchronization. Additionally, described are aspects and techniques in connection with metadata processing in an embodiment based on the RISC-V architecture.

Owner:CHARLES STARK DRAPER LABORATORY

Two-level pipeline architecture based on RISC-V instruction set

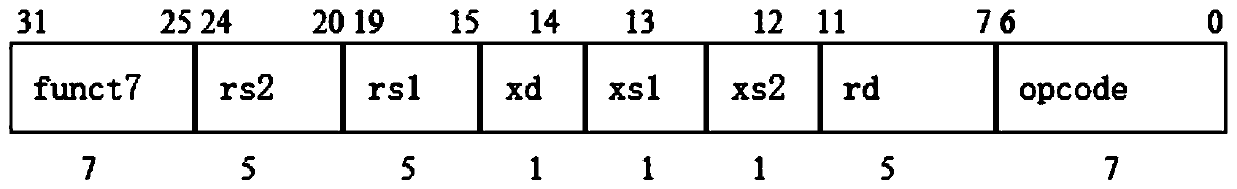

PendingCN109144573AReduce Architecture Authorization CostsImprove performanceConcurrent instruction executionGeneral purposeCoprocessor

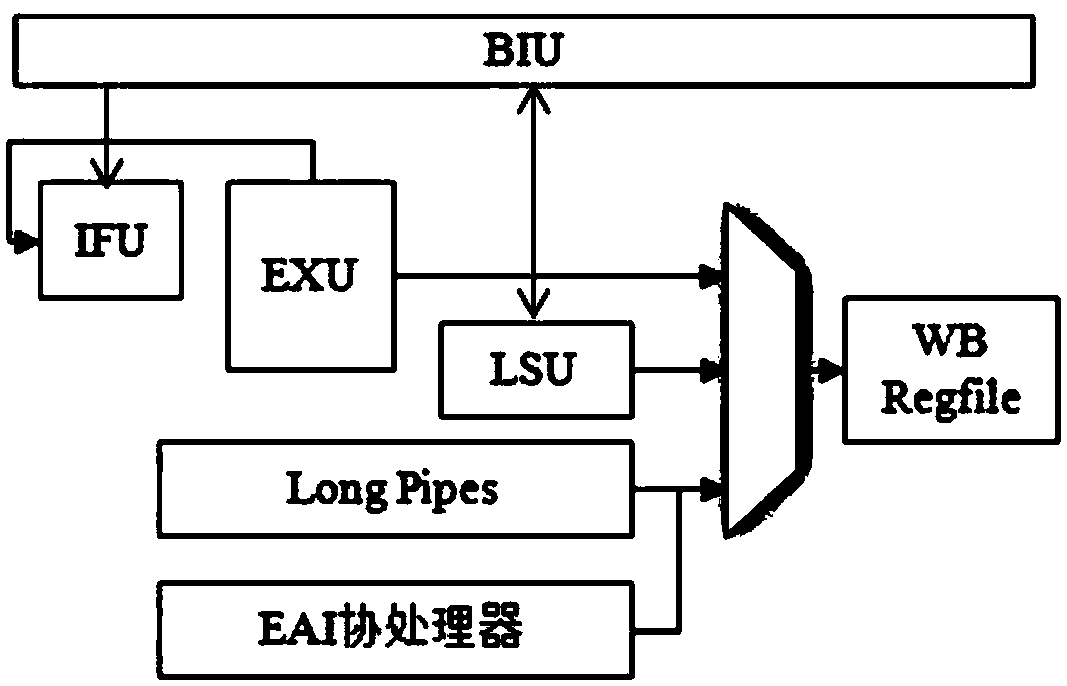

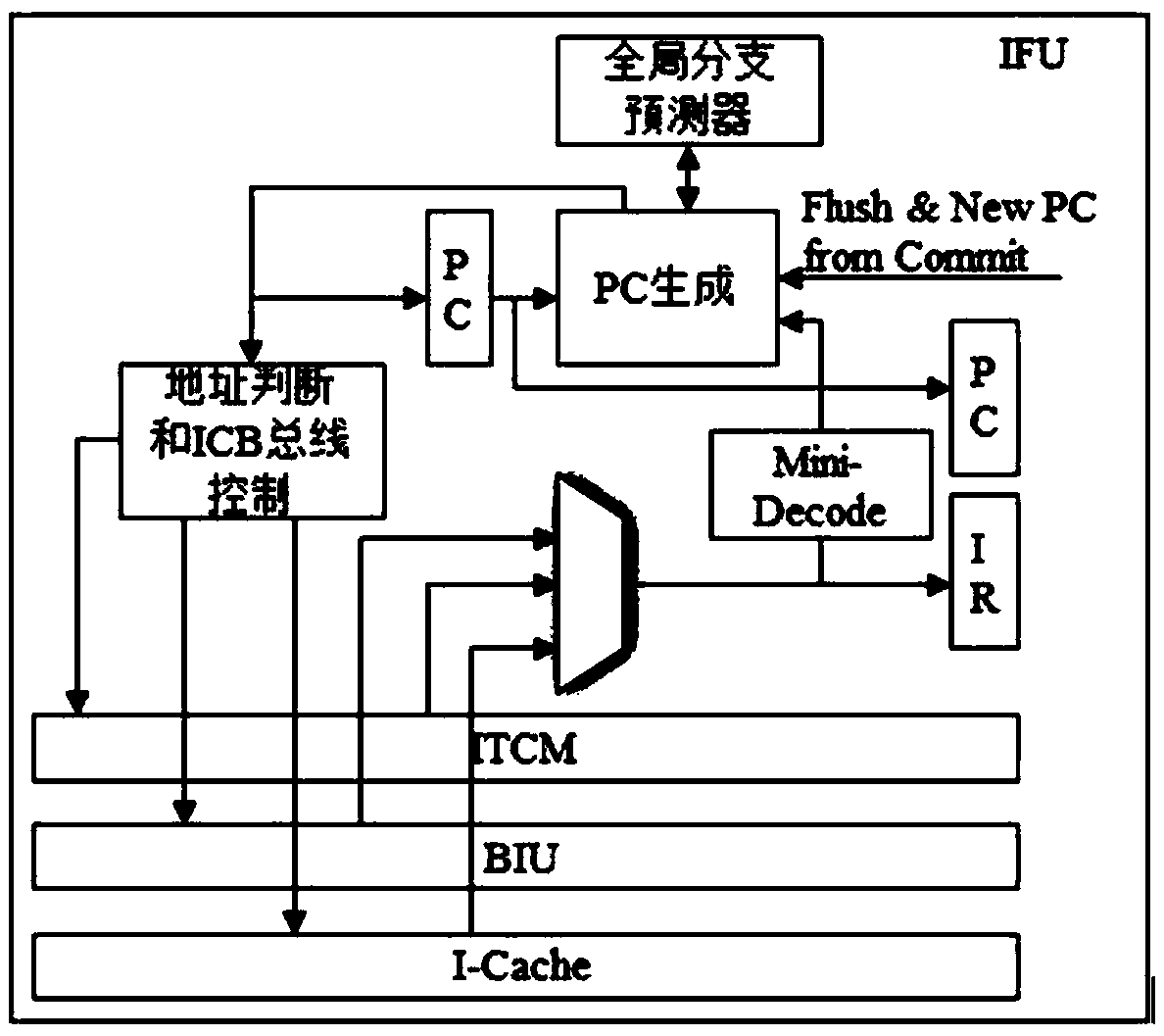

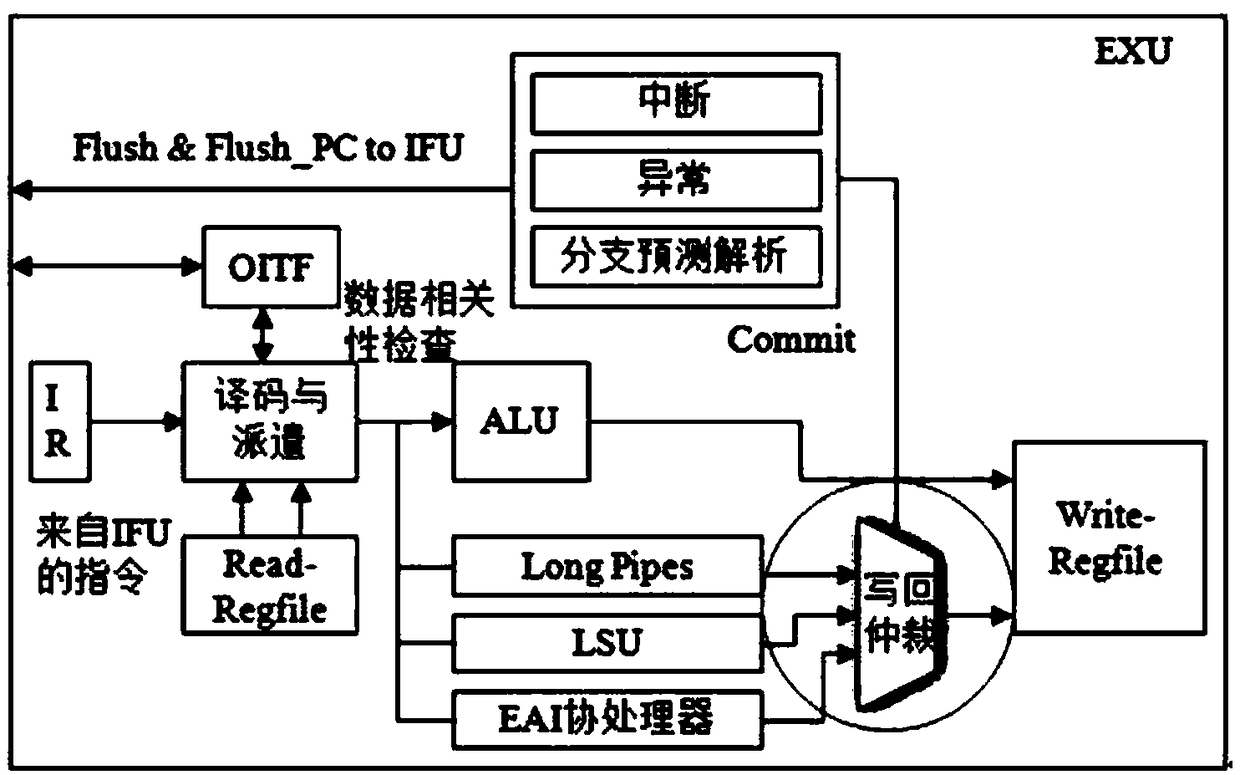

The invention discloses a two-level pipeline architecture based on an RISC-V instruction set, including a fetch instruction unit, an execution unit, a data read-write unit, a long pipeline data procesunit, an extended Acceleration Interface Coprocessor, Write-back integer general-purpose registers and bus interface units, wherein the instruction fetching unit fetches the instruction and sends theinstruction to the execution unit through the IR register, the PC value of the instruction is sent to the execution unit through the PC register, the execution unit decodes and dispatches the instruction according to the received instruction and the instruction PC value, the execution unit reads and writes back the integer general register through the decoded operand register index, the executionunit dispatches instructions to each transport module for operation, the execution unit writes back the result of the instruction operation to the write-back integer general register, the bus interface unit is used for auxiliary instruction transmission, and the two-stage pipeline architecture is adopted in the processor core, so as to reduce the cost of the processor core architecture and improve the performance of the processor.

Owner:NUCLEI SYST TECH

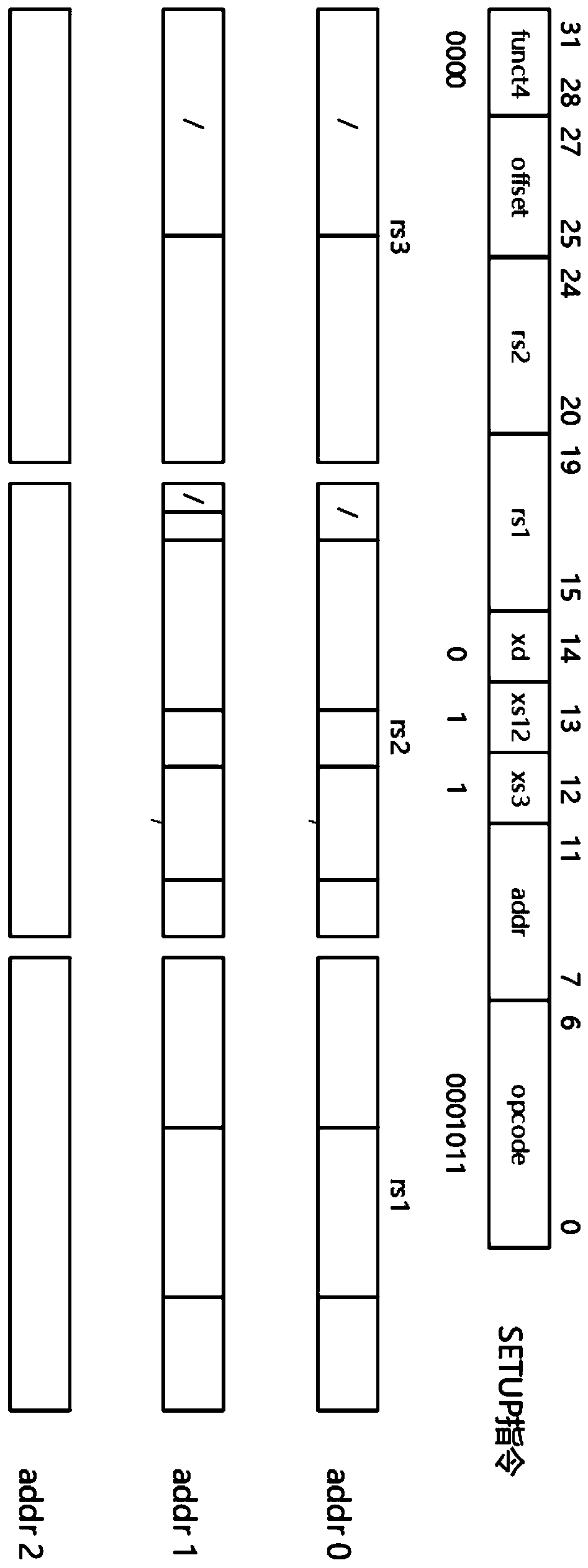

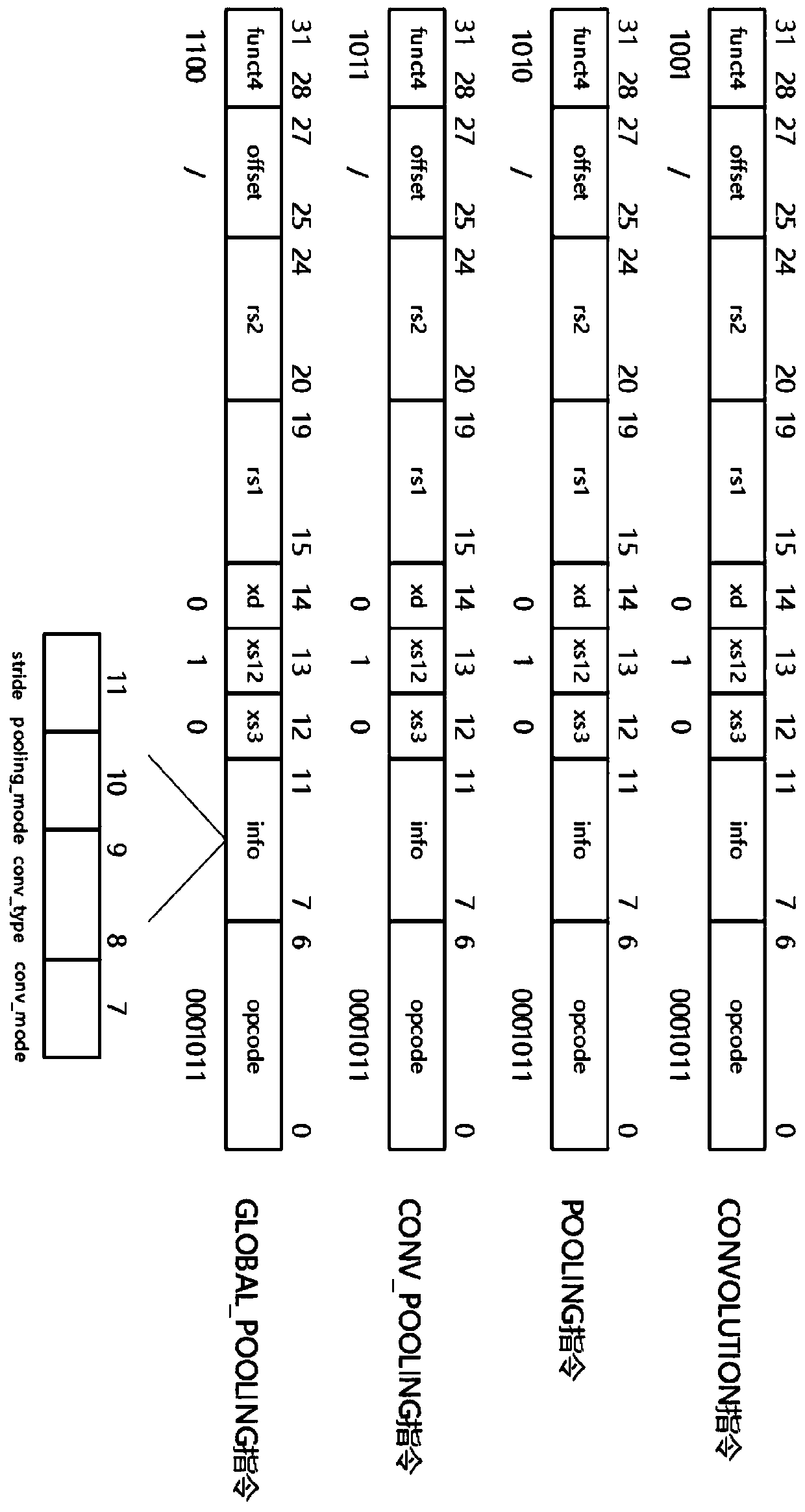

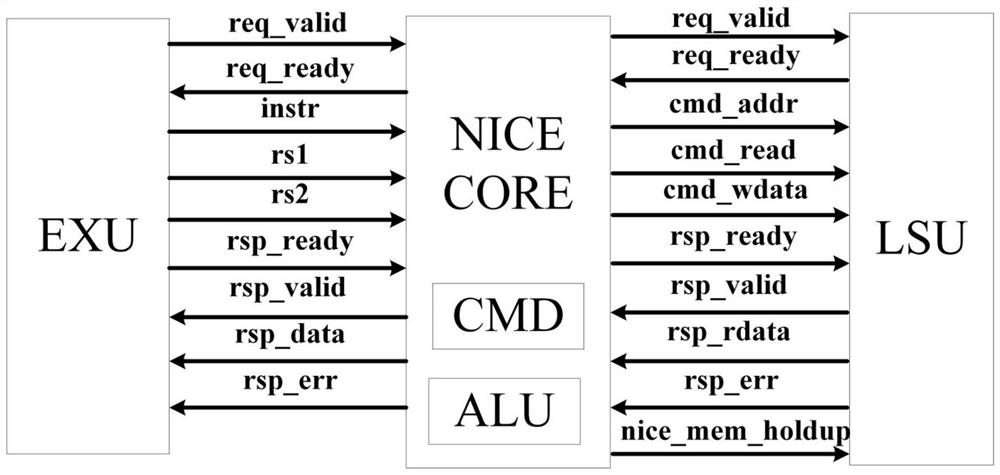

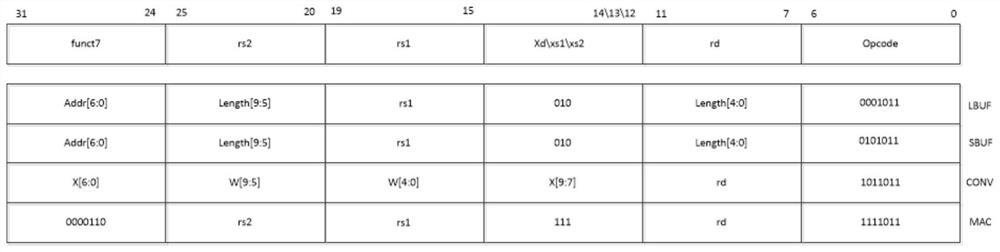

Matrix convolution calculation method, interface, coprocessor and system based on RISC-V architecture

ActiveCN109857460ACalculation speedReduce the number of memory accessesConcurrent instruction executionNeural architecturesExtensibilityProcessor design

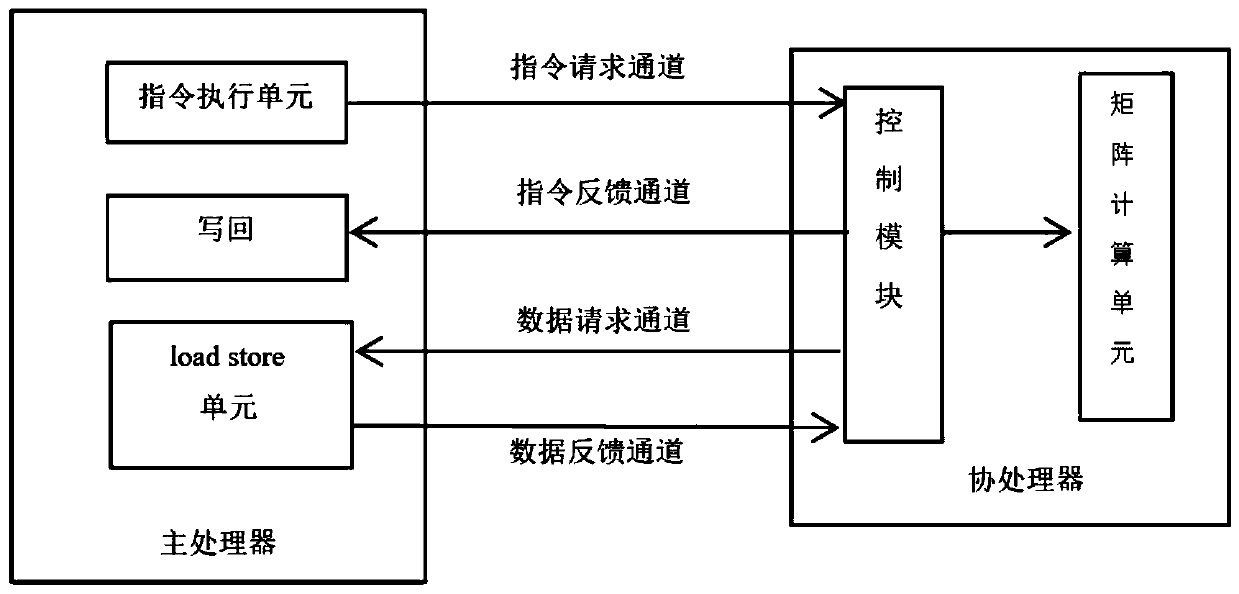

The invention discloses a set based on RISC-. According to the method and system complete mechanism of the instruction, the interface and the coprocessor for matrix convolution calculation of the V instruction set architecture, traditional matrix convolution calculation is efficiently achieved in a software and hardware combined mode, and RISC-is utilized. Extensibility of V instruction sets, a small number of instructions and a special convolution calculation unit (namely a coprocessor) are designed; the memory access times and the execution period of a matrix convolution calculation instruction are reduced, the complexity of application layer software calculation is reduced, the efficiency of large matrix convolution calculation is improved, the calculation speed of matrix convolution isincreased, flexible calling of upper-layer developers is facilitated, and the coding design is simplified. Meanwhile, RISC-is utilized. The processor designed by the V instruction set also has greatadvantages in power consumption, size and flexibility compared with ARM, X86 and other architectures, can adapt to different application scenes, and has a wide prospect in the field of artificial intelligence.

Owner:NANJING HUAJIE IMI TECH CO LTD

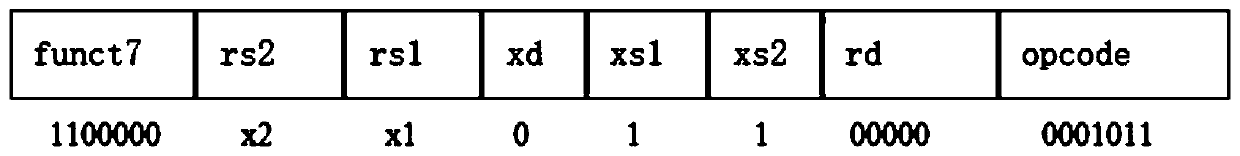

A four-stage assembly line RISC-V processor with a rapid data bypass structure

PendingCN109918130AReduce messagingSimple control logicMachine execution arrangementsInstruction memoryControl signal

The invention provides a four-stage assembly line RISC-V processor with a rapid data bypass structure. The processor has a four-stage pipeline structure, when the operation except the non-Load instruction is executed, the direct bypass is carried out, and the effective data pipeline is changed into three stages, so that the operation speed is increased. Compared with a traditional four-level assembly line, the structure reduces the instruction period of most instructions and the frequency of occurrence of data danger, and greatly improves the performance of the processor. And the four-stage pipeline structure comprises an instruction fetching module, a decoding module, an execution module and a write-back module. The fetch module can generate a PC of a next instruction according to the instruction fetched from the instruction memory in the current period and an external control signal; The decoding module is used for extracting an operation code, a function code, a source register, a destination register and an immediate of the instruction, and taking a value from the general register; The execution module is responsible for executing various arithmetic operations; And the write-back module is used for recording the information of the memory access instruction and writing the data read from the memory into the general register.

Owner:SUN YAT SEN UNIV

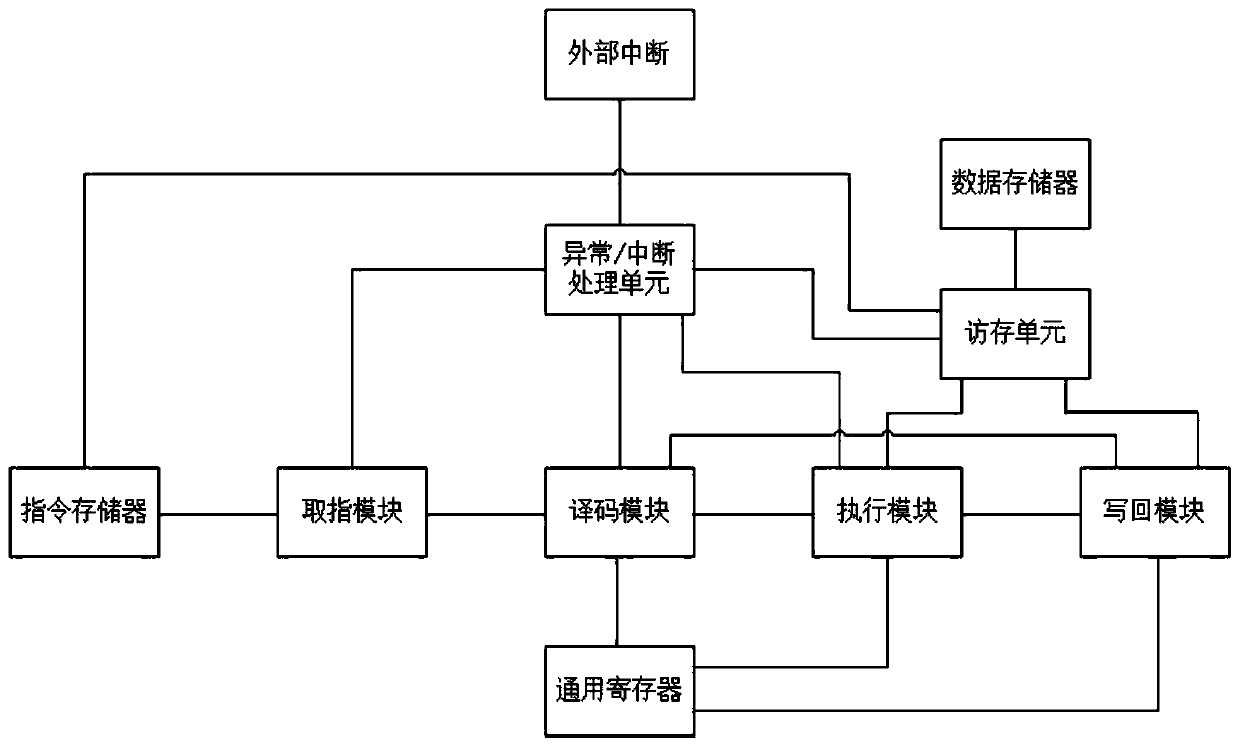

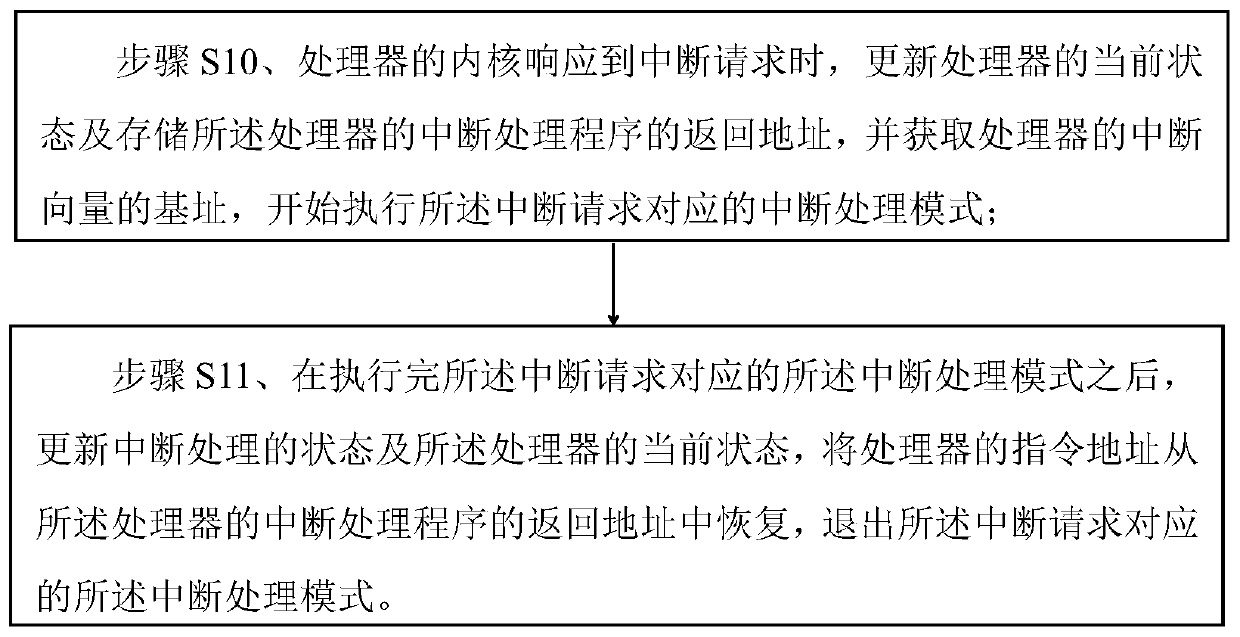

Fast interrupt control system and method for RISC-V architecture

ActiveCN109376000AImprove the efficiency of interrupt handlingSimplify interrupt control logicProgram initiation/switchingRegister arrangementsControl breakControl system

The invention discloses a fast interrupt control system and method for an RISC-V architecture, comprising a cassette port, an interrupt source priority register, an interrupt waiting register, a priority threshold register, a priority judging module, an interruptenable register, an interrupt response register, an interrupt completion register and an EIP register, wherein each interrupt source corresponds to an interrupt source priority register, and the cassette port controls the single transmission of an interrupt request of the interrupt source; the interrupt source priority register storesthe priority of the interrupt source; the interrupt waiting register is used for storing a value indicating the interrupt waiting state; the priority threshold register stores the priority threshold of the interrupt target; the priority judging module compares the priority of the interrupt source and the interrupt target; the interrupt enable register stores the status value of the masked interrupt source, and controls the transmission of interrupt requests by setting a fast interrupt control system between the interrupt source and the interrupt destination, thereby solving the problem of realizing the interrupt nesting mechanism in the RISC-V architecture.

Owner:NUCLEI SYST TECH

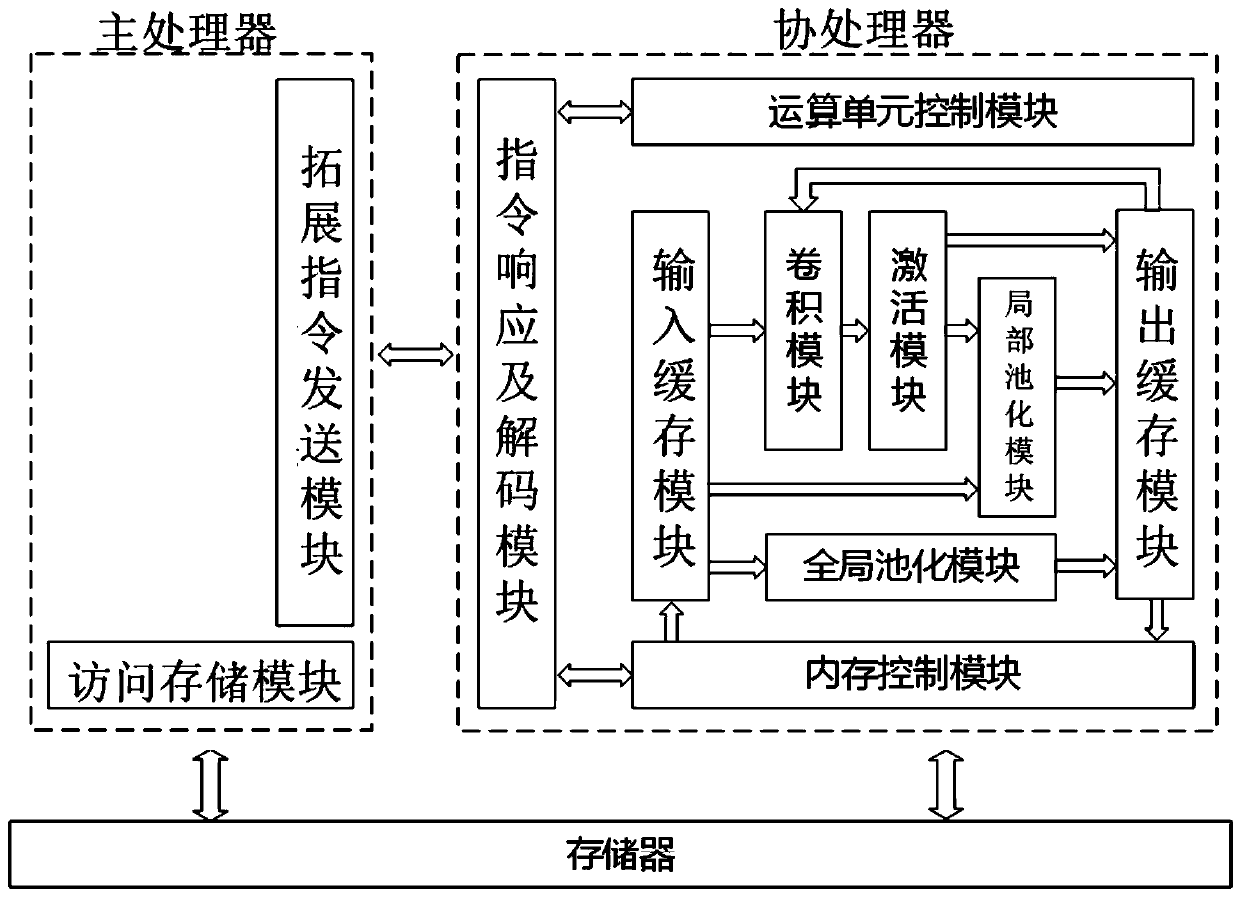

Convolutional neural network acceleration device based on RISC-V architecture and control method thereof

The invention discloses a convolutional neural network acceleration device based on an RISC-V architecture and a control method thereof, and the device comprises a memory used for storing data; a mainprocessor used for sending an expansion instruction; a coprocessor used for receiving the expansion instruction sent by the main processor, reading the input data from the memory according to the received expansion instruction, performing grouping operation processing on the input data to obtain output data, and storing the output data into the memory; the main processor is also used for readingthe output data stored by the coprocessor from the memory; wherein the operation processing comprises convolution operation, activation operation and pooling operation. According to the invention, thecoprocessor executes the time-consuming operation based on the expansion instruction, can adapt to input data of different sizes, flexibly performs combined operation on convolution, pooling and activation operations of the convolutional neural network, and can adapt to various lightweight convolutional neural networks. The method can be widely applied to the technical field of processors.

Owner:SOUTH CHINA UNIV OF TECH

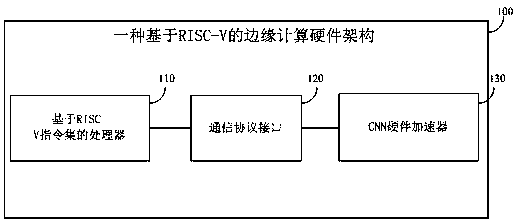

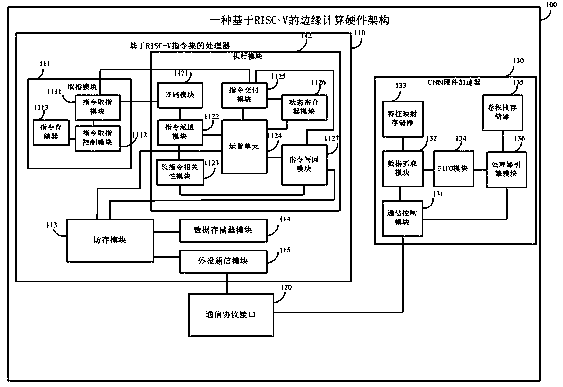

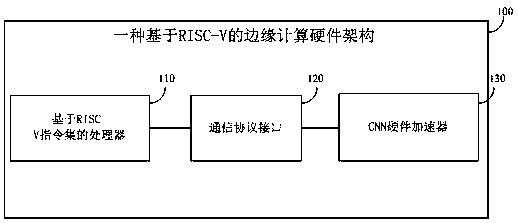

Edge computing hardware architecture based on RISC-V

ActiveCN110007961AControl AI processingReduce power consumptionNeural architecturesPhysical realisationComputer hardwareHardware architecture

The invention discloses an edge computing hardware architecture based on RISC-V. The edge computing hardware architecture comprises an edge computing controller based on an RISC-V instruction set, used for controlling a CNN hardware accelerator and processing the operation result of the CNN hardware accelerator; a communication protocol interface, realizing data communication between a RISC-V-based controller and a CNN hardware accelerator; and a CNN hardware accelerator used for carrying out convolution processing on the data in the specified memory and sending a result obtained after operation of the CNN accelerator to the controller. With the help of characteristics of free opening, concise and modular of the RISC-V instruction set, the edge computing hardware architecture solves problem of high requirements on low power consumption, low area and low cost of equipment on a edge computing end. Meanwhile, due to the fact that the RISC-V instruction set has independent expansibility and good backward compatibility, the processor designed on the basis of the RISC-V instruction set is applied to a mobile edge device end, and the problem that a traditional MCU cannot carry out lightweight artificial intelligence processing due to programming limitation can be solved.

Owner:SUN YAT SEN UNIV

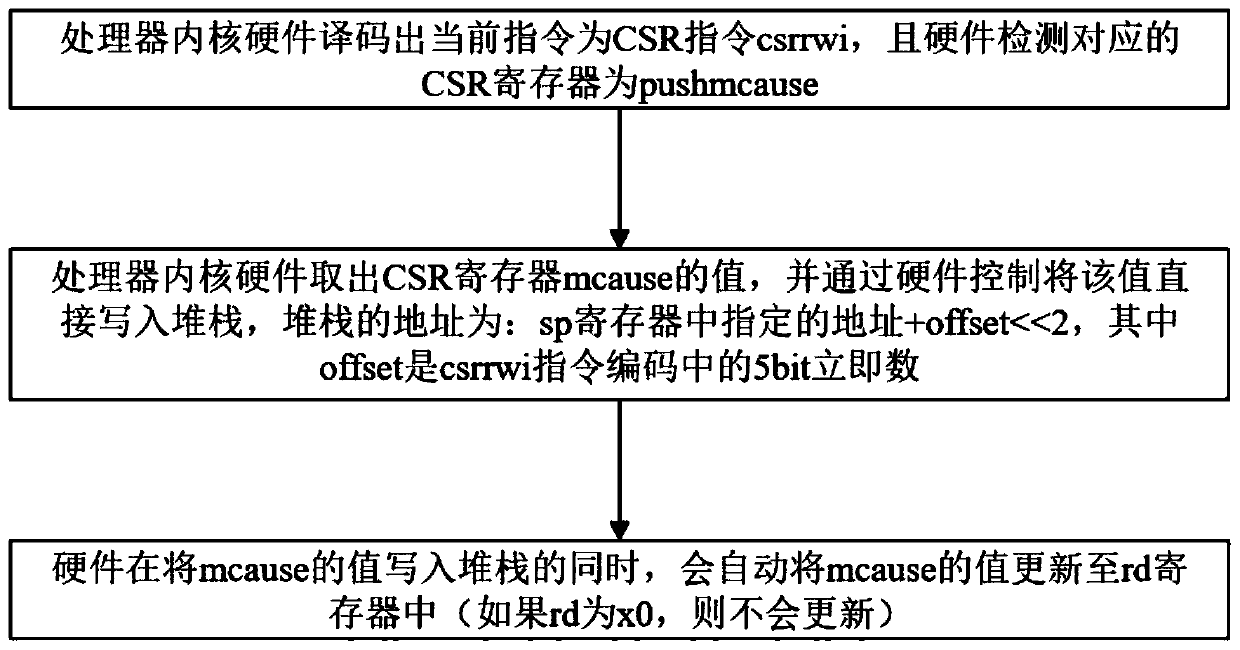

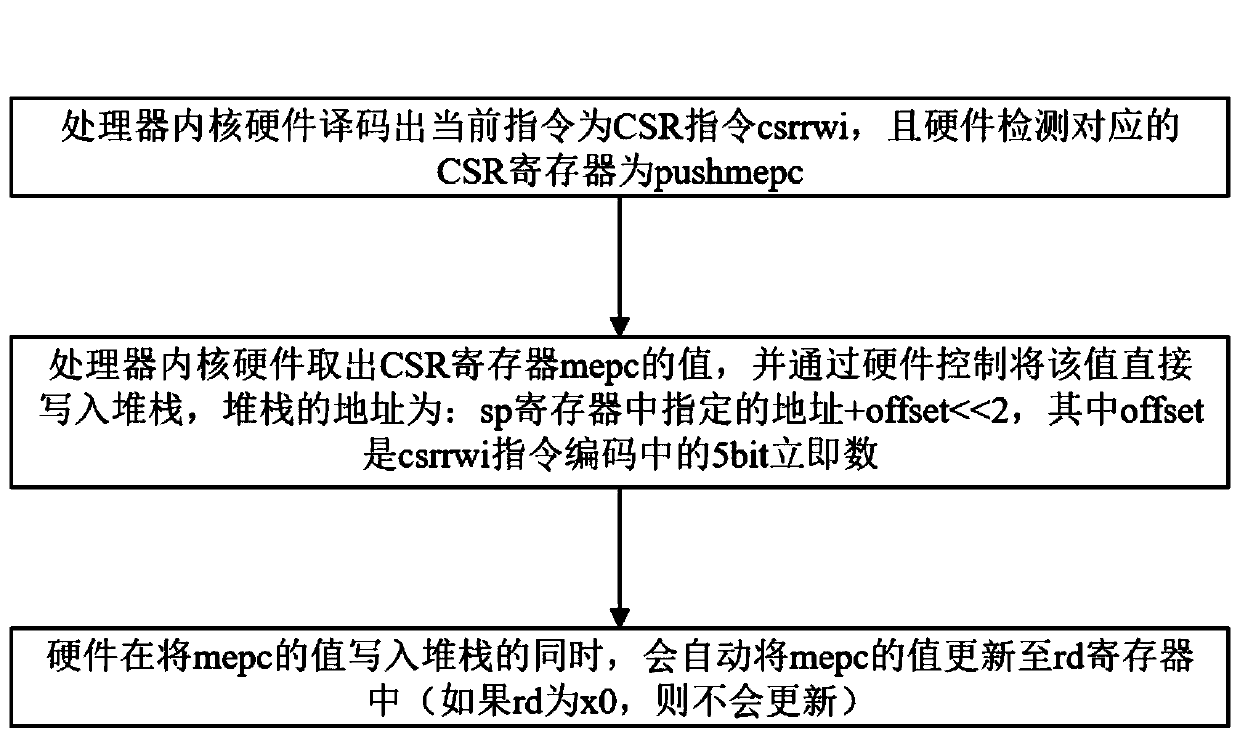

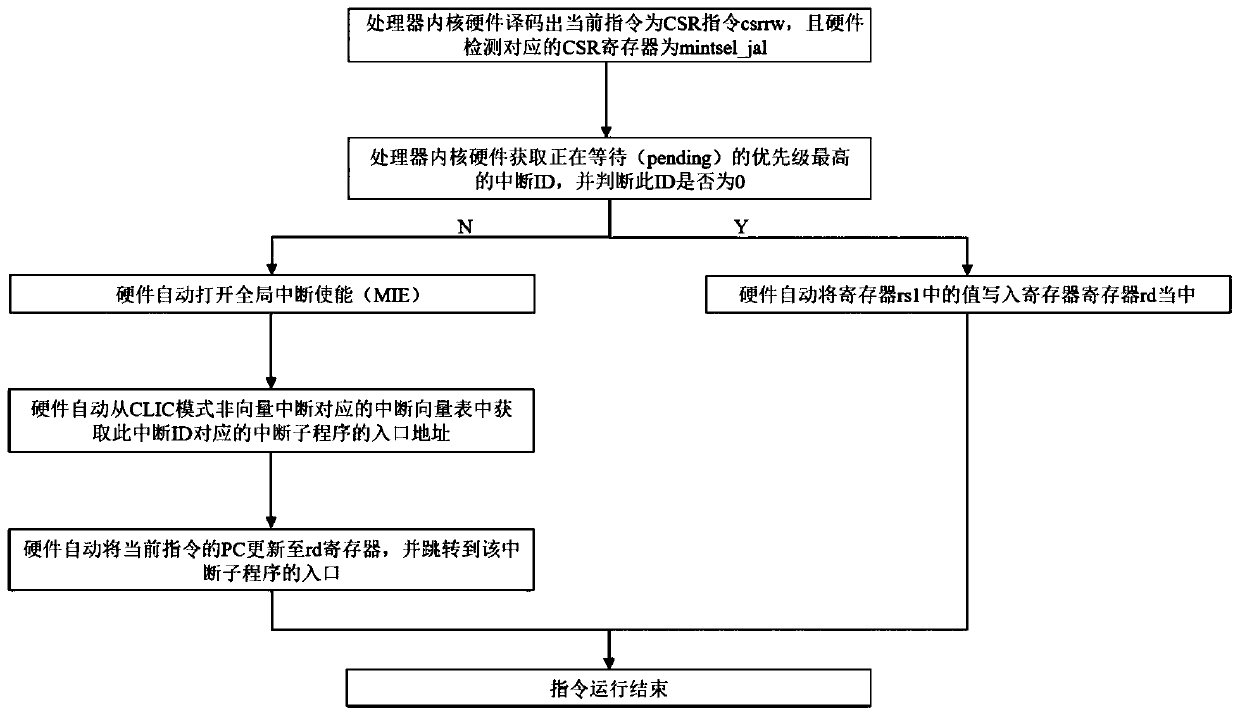

Interrupt system for RISC-V architecture

PendingCN110007964AShort storage timeShorten the timeProgram initiation/switchingRegister arrangementsProcessor registerVectored Interrupt

The invention discloses an interrupt system for an RISC-V architecture. The system comprises an original register in a CLIC, and further comprises a pushmcause register, a pushmepc register, an interrupt response register and an mtvt2 register. The pushmcause register is used for storing the value in the mcause into a stack through an instruction. The pushmepc register is used for storing the value in the mepc into a stack through an instruction. The interrupt response register is used for responding to a non-vector interrupt request sent by the CLIC through an instruction, obtaining an interrupt subprogram entry address and modifying global interrupt enabling. The mtvt2 register is used for storing the base address of the non-vector interruption in the CLIC mode, and the number of runninginstructions is reduced by increasing the register or changing part of the instructions, so that the purposes of increasing the value storage speed in the register, shortening the time of jumping tothe entrance of the corresponding interruption subprogram and improving the efficiency are achieved.

Owner:NUCLEI SYST TECH

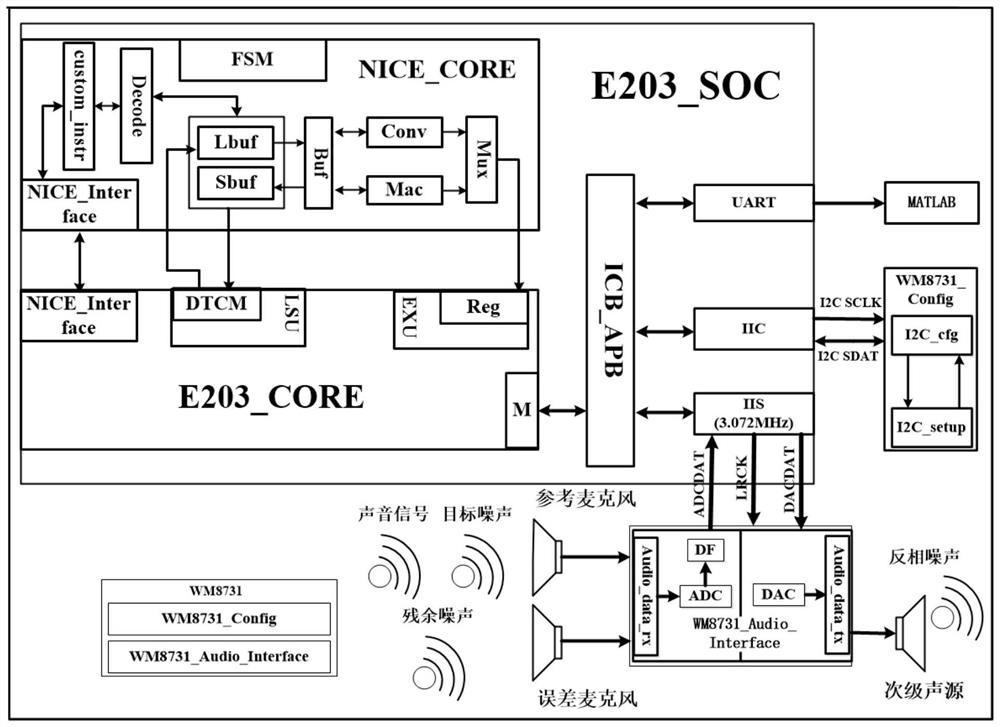

Audio noise reduction accelerator system and method based on RISC v custom instruction set expansion

PendingCN113851103AReduce wasteStrong configurabilitySound producing devicesComputer hardwareComputer architecture

The invention discloses an audio noise reduction accelerator system and method based on RISC v custom instruction set expansion, and belongs to the technical field of integrated circuits. The system mainly comprises an E203_CORE, an NICE_CORE, a NICE_Interface, an E203_SOC, an audio coding and decoding WM8731 module, and an audio noise reduction FxLMS algorithm, wherein the E203_CORE is connected with the NICE_CORE through the NICE_Interface, the E203_CORE, the NICE_CORE and a related peripheral port form the E203_SOC together, the E203_SOC is connected with the audio coding and decoding WM8731 module, and the audio noise reduction FxLMS algorithm is downloaded into a core of the RISC v processor through software programming to run. Compared with a processor of an ARM instruction set architecture, the processor adopting an RISC v custom instruction set can accelerate a specific operation part in the audio noise reduction FxLMS algorithm; and the problems of area, power consumption, granularity and the like can be better optimized, and the flexibility and feasibility of the algorithm are improved.

Owner:CHONGQING UNIV OF POSTS & TELECOMM

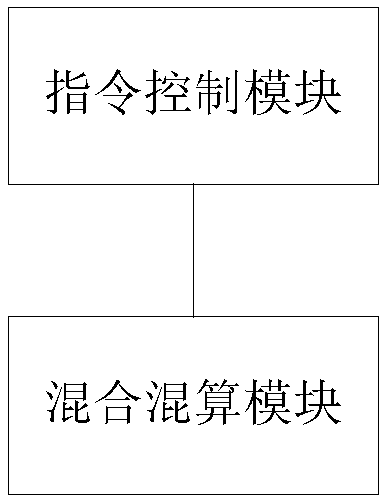

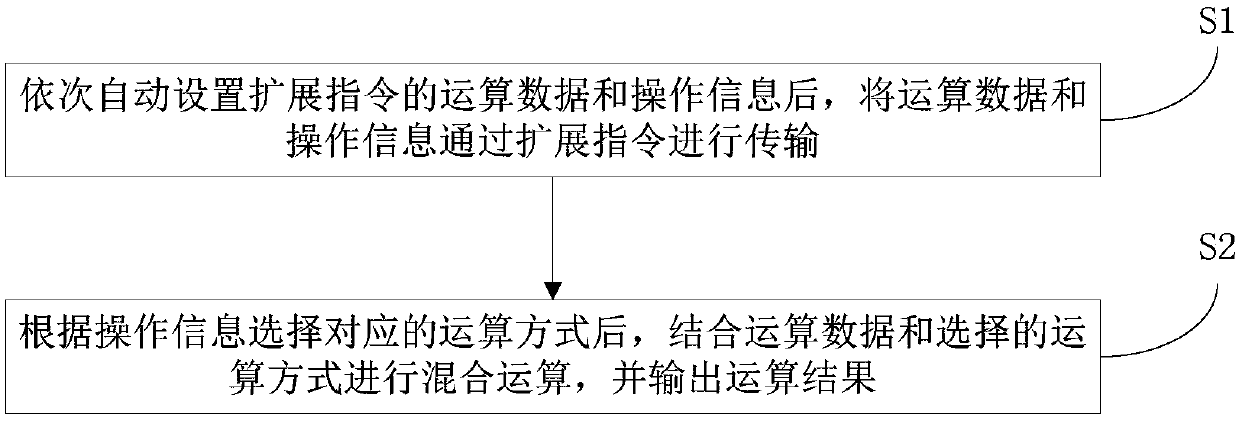

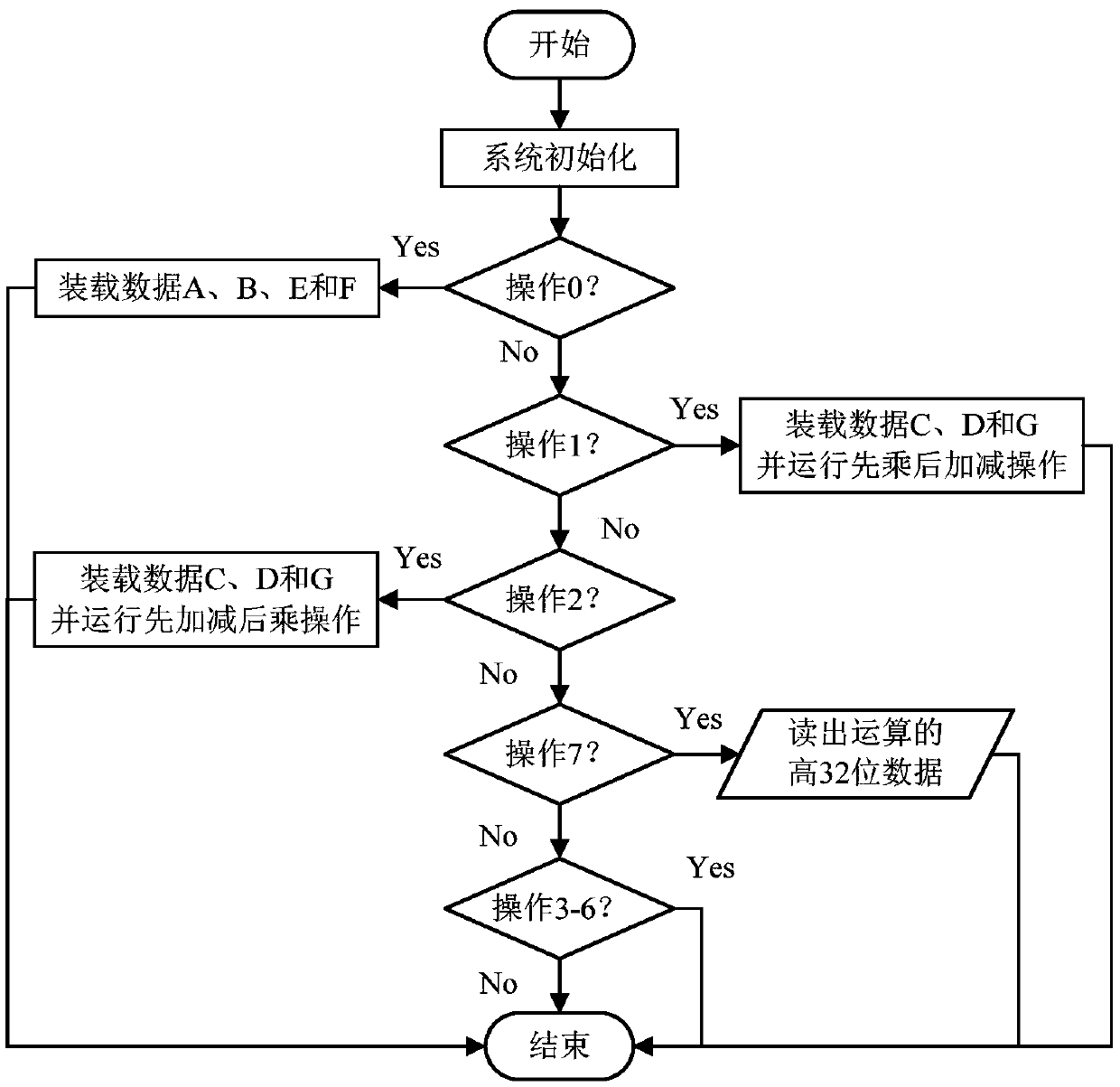

RISC-V-based hybrid mixed computing system and method

ActiveCN110018848ASimplify complex operationsReduce capacityDecompilation/disassemblyEnergy efficient computingComputer moduleComputation process

The invention discloses a RISC-V-based hybrid mixed computing system and method. The system comprises an instruction control module and a mixed calculation module, an expansion instruction is arrangedin the instruction control module, and the expansion instruction contains operation information; the instruction control module is used for automatically setting operation data and operation information in sequence and then transmitting the operation data and the operation information to the hybrid mixed calculation module through an extension instruction; and the hybrid calculation module is used for selecting a corresponding operation mode according to the operation information, performing hybrid operation by combining the operation data and the selected operation mode, and outputting an operation result. Complex hybrid operation is achieved through a single extension instruction, and some complex operations of the processor based on the RISC-V instruction set are simplified. The calculation process of complex hybrid computation is simplified; the disassembling machine code is simpler and clearer; time consumption caused by multiple times of cyclic operation is reduced, the system performance is improved, and the method can be widely applied to the technical field of communication.

Owner:ANYKA (GUANGZHOU) MICROELECTRONICS TECH CO LTD

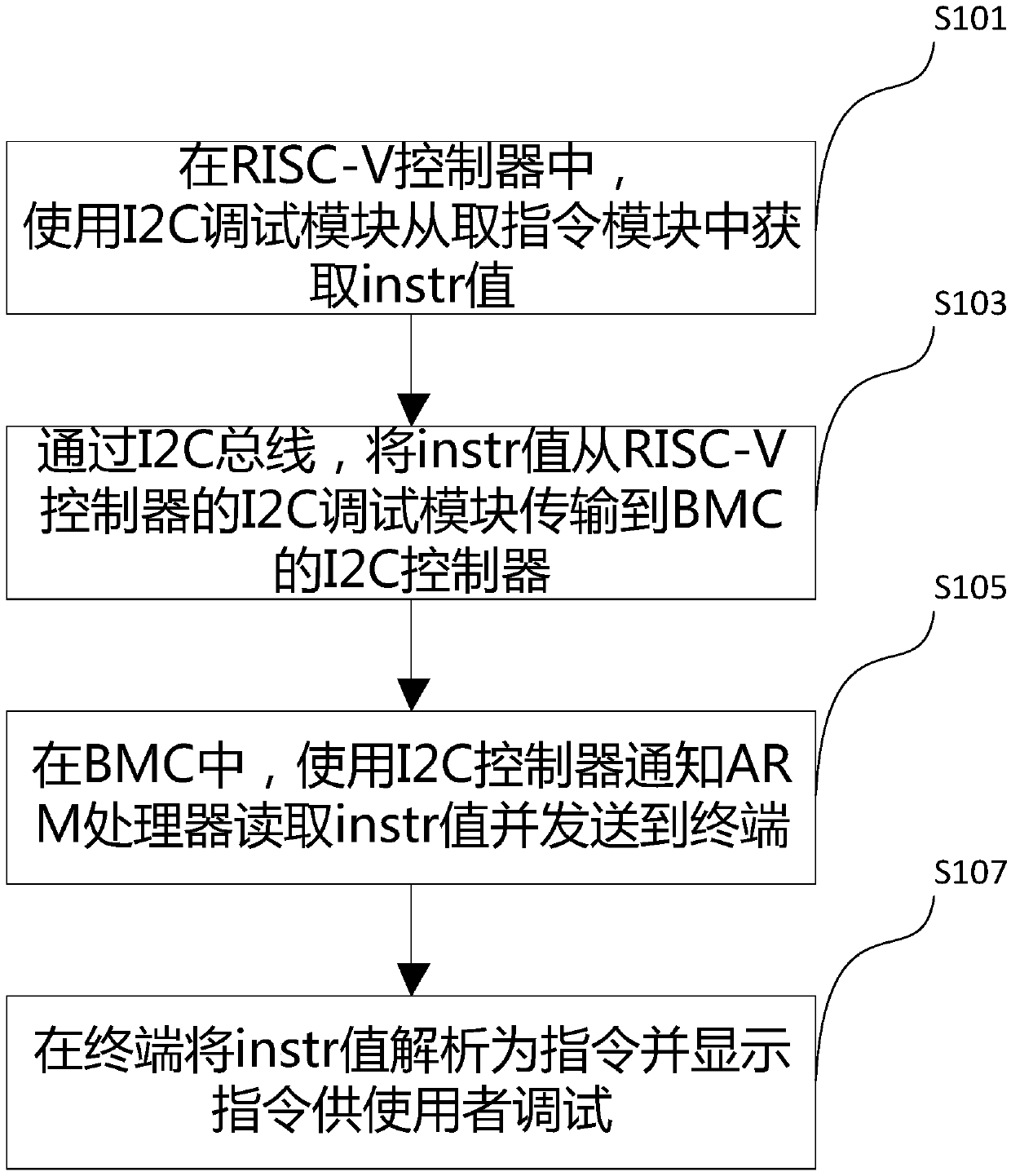

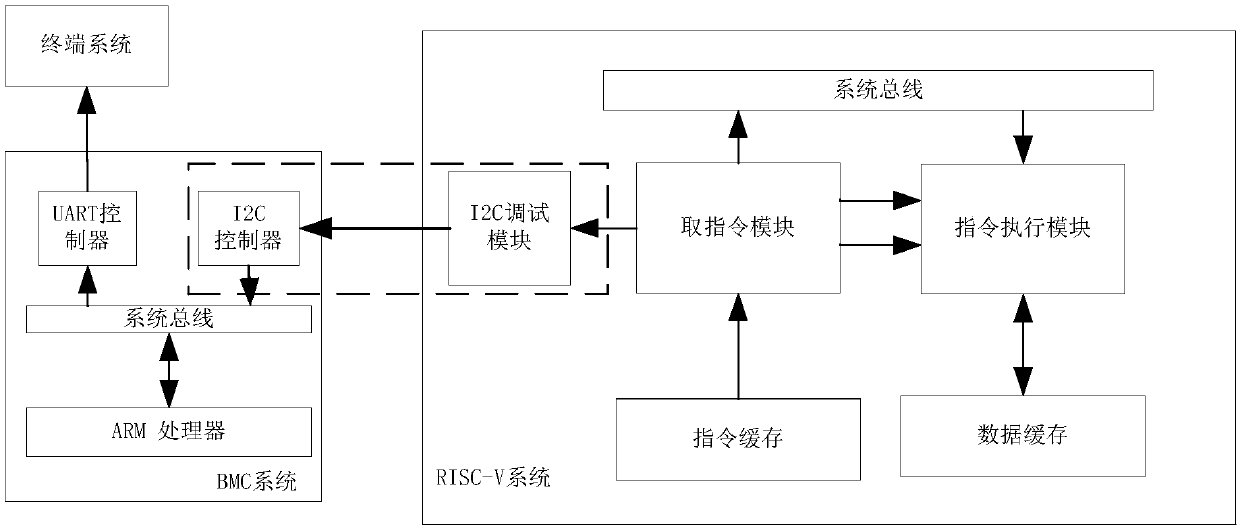

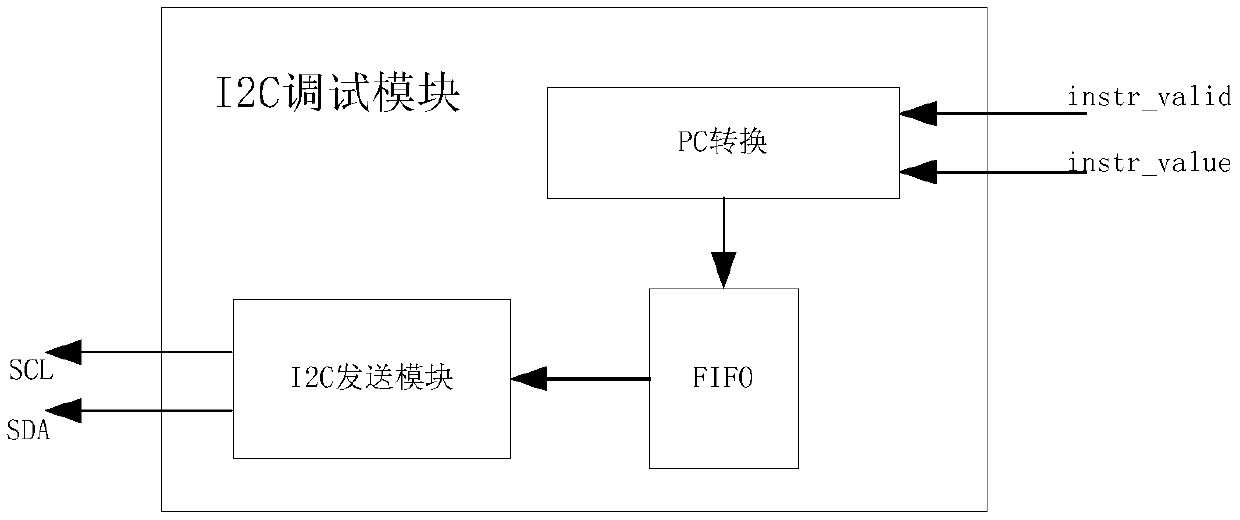

An I2C-based RISC-V controller debugging method and device

InactiveCN109684147AReduce the difficulty of debuggingFast debuggingFaulty hardware testing methodsComputer scienceRISC-V

Owner:ZHENGZHOU YUNHAI INFORMATION TECH CO LTD

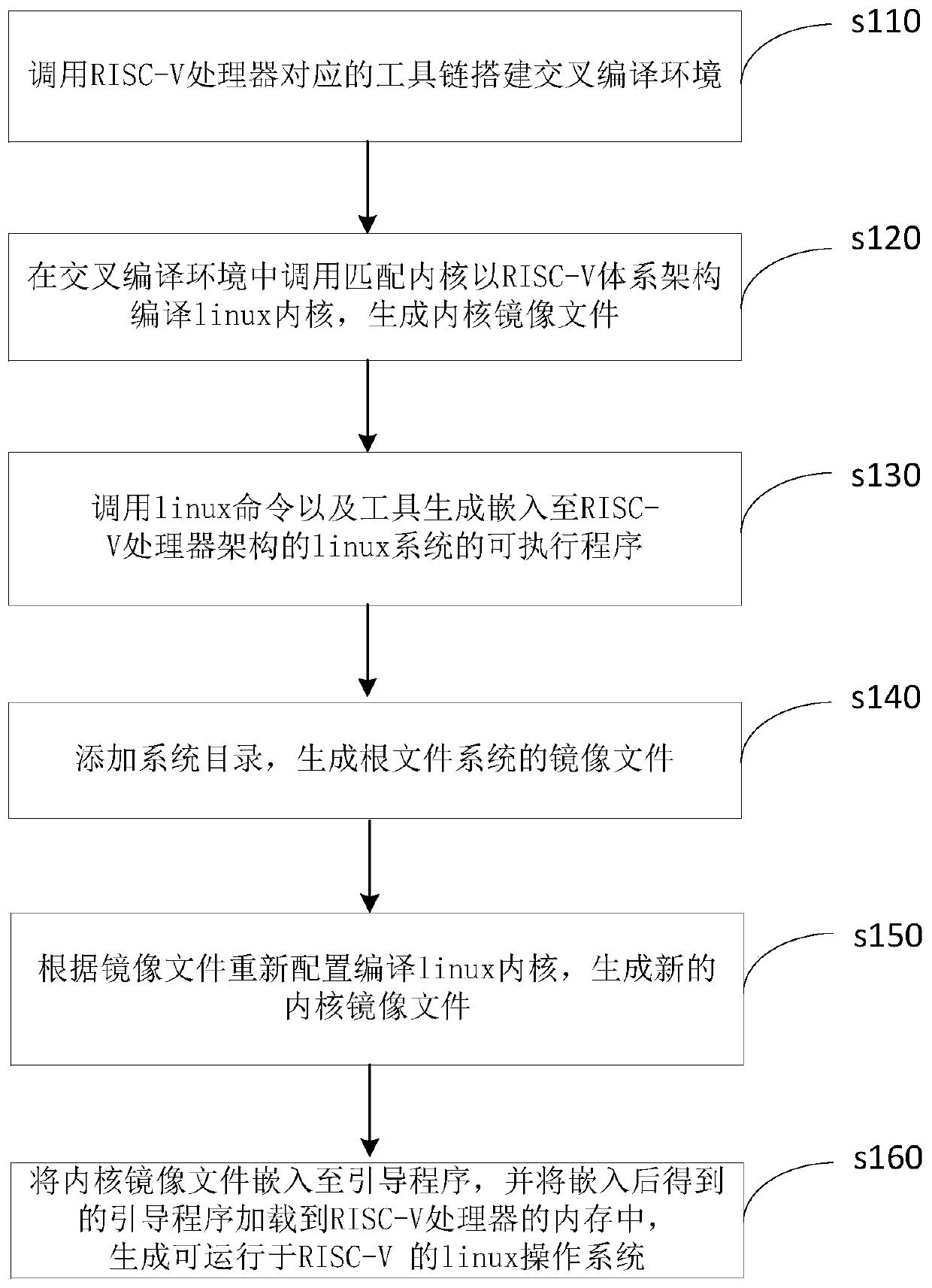

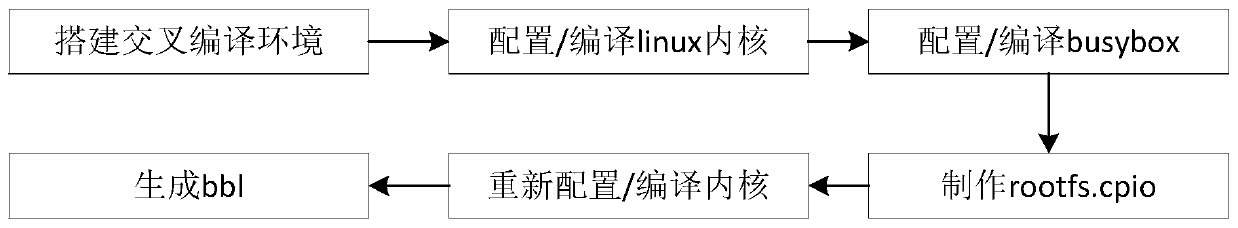

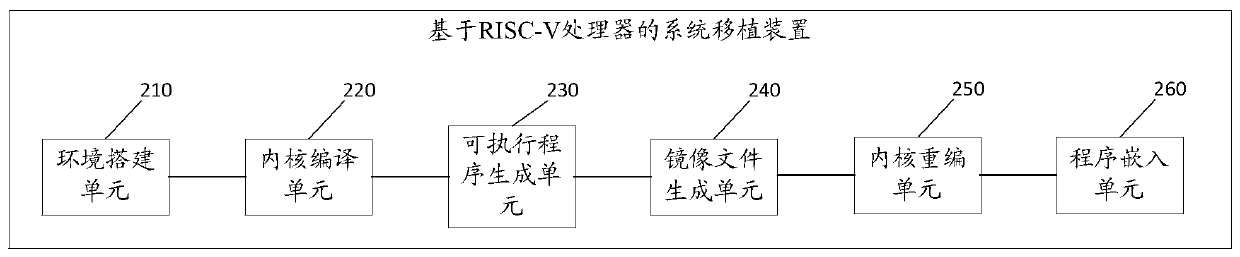

System transplanting method based on RISC-V processor and related component

The invention discloses a system transplanting method based on a RISC-V processor. The system transplanting method comprises the following steps: calling an RISC-V processor; the V processor buildinga cross compiling environment corresponding to the tool chain; calling a matching kernel in a cross compiling environment to compile the kernel by using a RISC-V system architecture, and generating akernel mirror image file without a root file system; calling a linux command and a tool to generate an executable program; adding a system preset necessary directory to generate a mirror image file; reconfiguring and compiling a linux kernel according to the mirror image file; the method comprises the steps of generating a new kernel mirror image file, embedding the generated new kernel mirror image file into a bootstrap program, and loading the bootstrap program obtained after embedding into a memory of a RISC-V processor, so that a linux operating system capable of running in the RISC-V processor can be generated, and system transplantation based on the RISC-V processor is realized. The invention also discloses a system transplanting device and equipment based on the RISC-V processor, and a readable storage medium, which have the above beneficial effects.

Owner:SUZHOU LANGCHAO INTELLIGENT TECH CO LTD

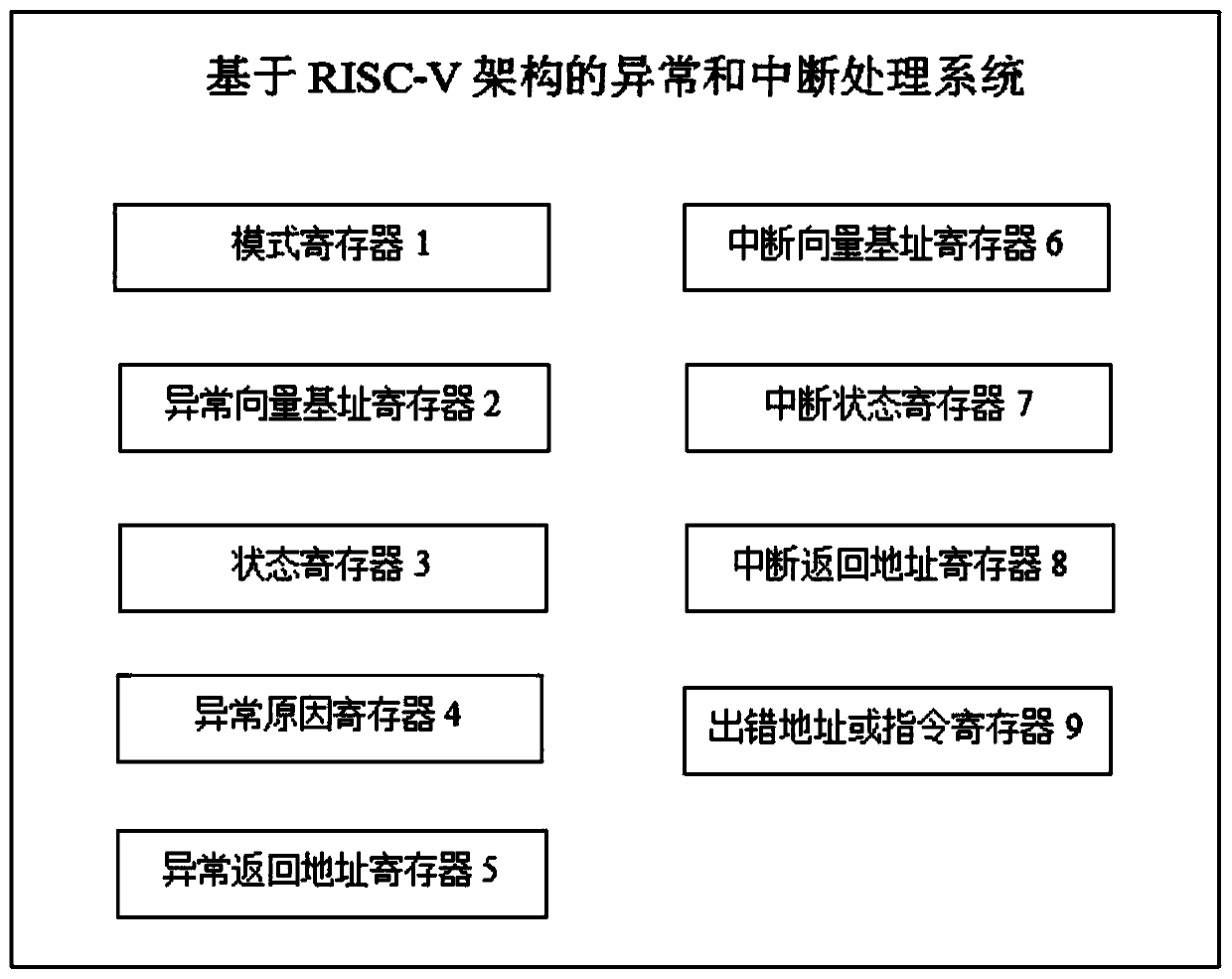

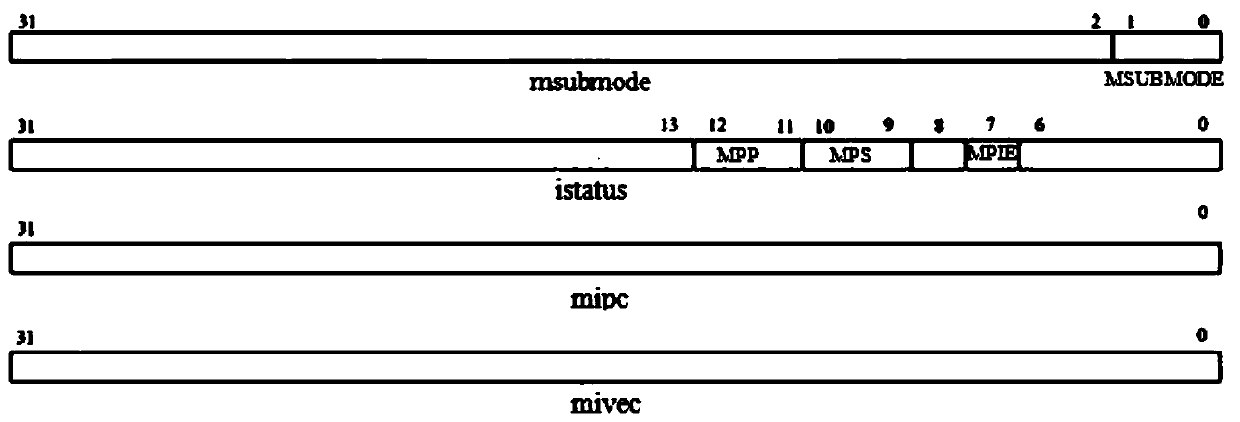

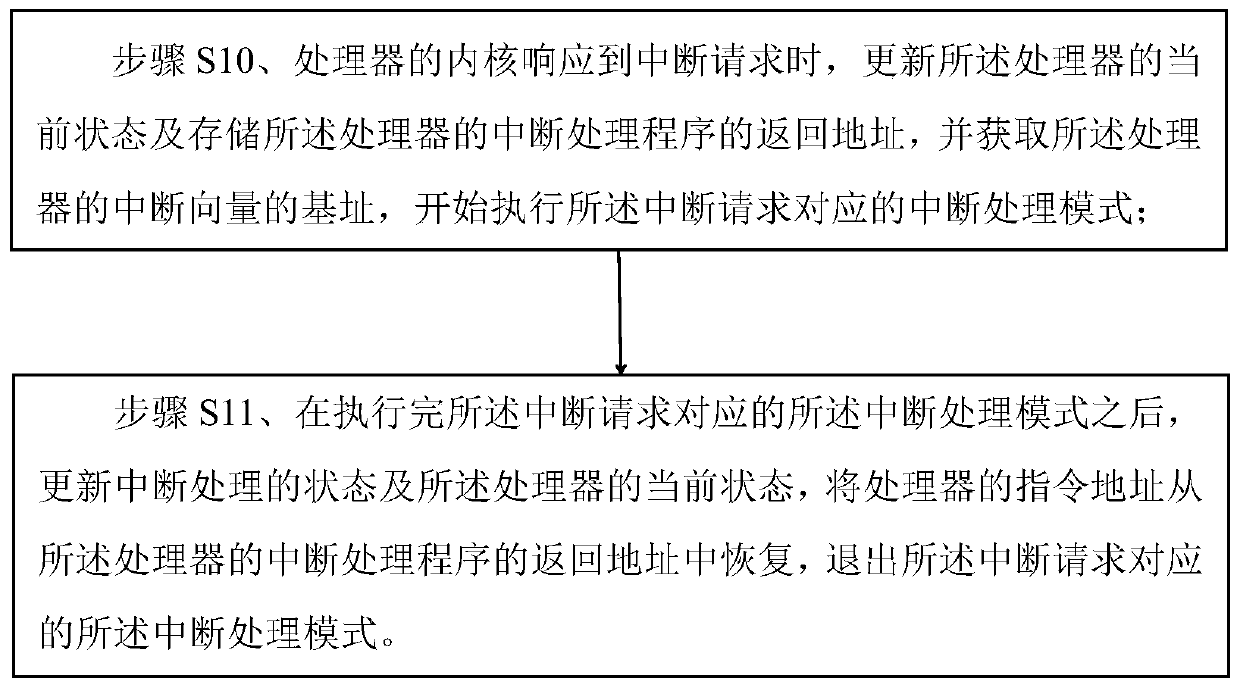

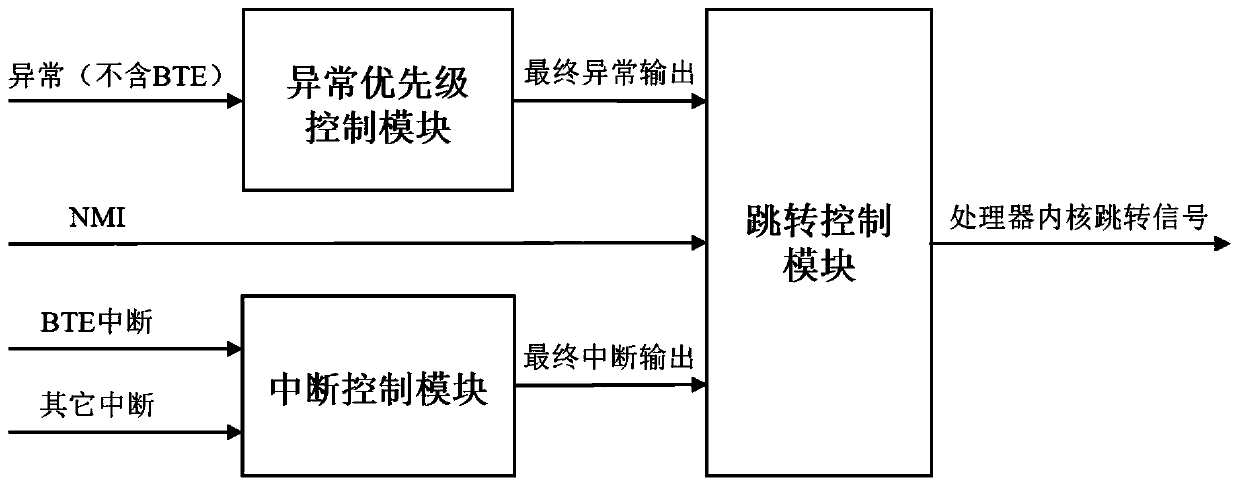

Exception and interruption processing system and method based on RISC-V architecture

The invention relates to the technical field of low-power-consumption kernel interrupt processing, in particular to an exception and interruption processing system and method based on an RISC-V architecture. The exception and interruption processing system comprises a mode register, an exception vector base address register, a state register, an exception cause register, an exception return address register, an interruption vector base address register, an interruption state register and an interruption return address register. Beneficial effects are as follows: the feed additive is A mode register is added in a kernel of a processor, and the interrupt vector base address register, the interrupt state register and the interrupt return address register are used for separately processing theinterrupt processing mode and the exception processing mode of the processor, so that a program of the processor can exit from the exception processing mode and the interrupt processing mode when theexception nesting interrupt exists, and the system can recover when the exception nesting interrupt exists.

Owner:AMOLOGIC (SHANGHAI) CO LTD

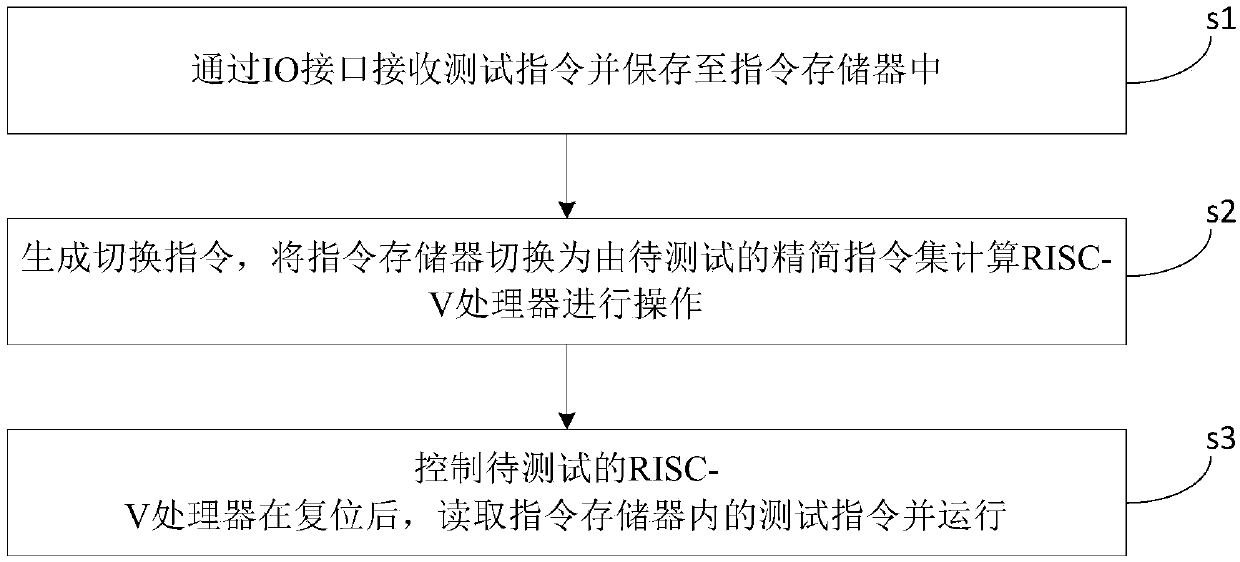

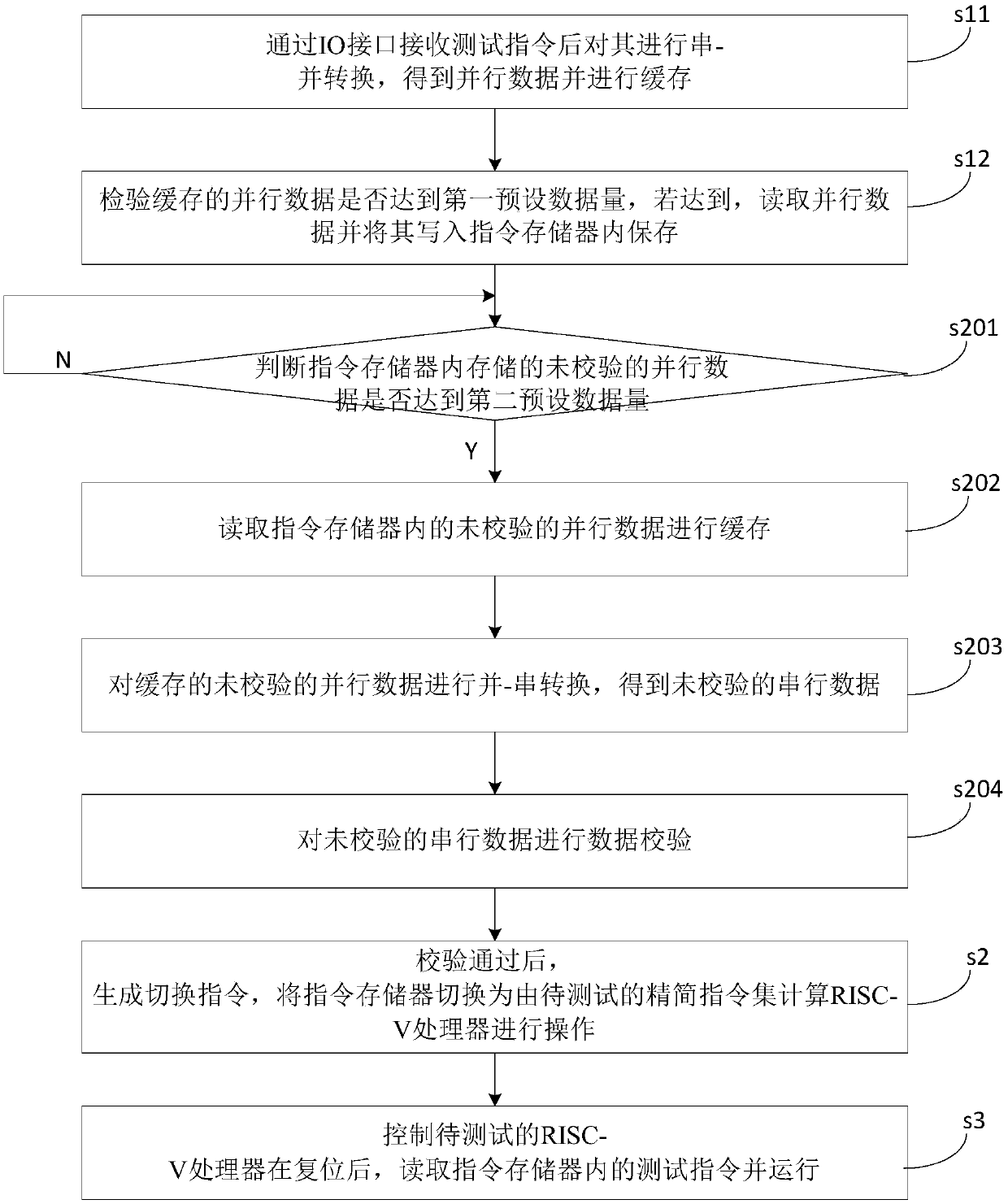

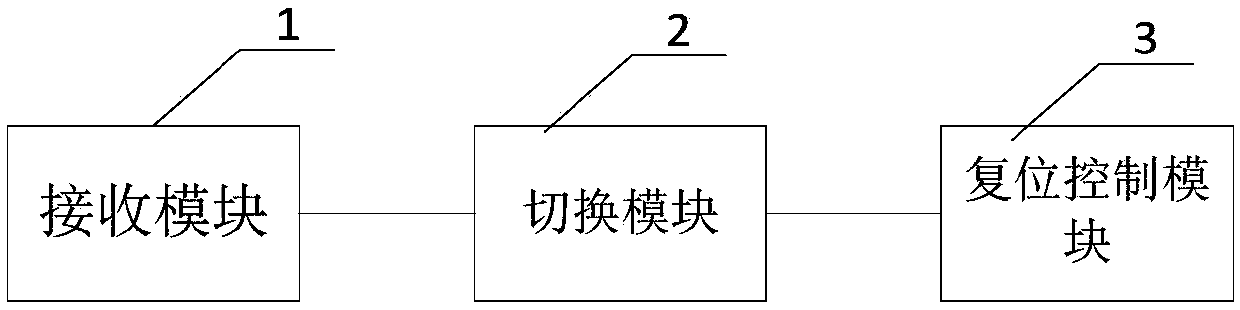

An instruction downloading method and device for an RISC-V processor

ActiveCN109684152AImprove versatilityLower specification requirementsError detection/correctionEnergy efficient computingInstruction memoryJoint Test Action Group

The invention discloses an instruction downloading method and device for an RISC-V processor based on a field programmable gate array FPGA development board, and the method comprises the steps: receiving a test instruction through an IO interface, and storing the test instruction in an instruction memory; Generating a switching instruction, and switching the instruction memory into a to-be-testedreduced instruction set calculation RISC-V processor for operation; Controlling the to-be-tested RISC-V processor to be reset, reading the test instruction in the instruction memory and operating thetest instruction. The method does not rely on the jtag interface and nand-flash but carries out instruction download through a common IO interface and an instruction memory, thereby improving universality of the test of the RISC-V processor. The invention further discloses an FPGA development board based on the method.

Owner:GUANGDONG INSPUR BIG DATA RES CO LTD

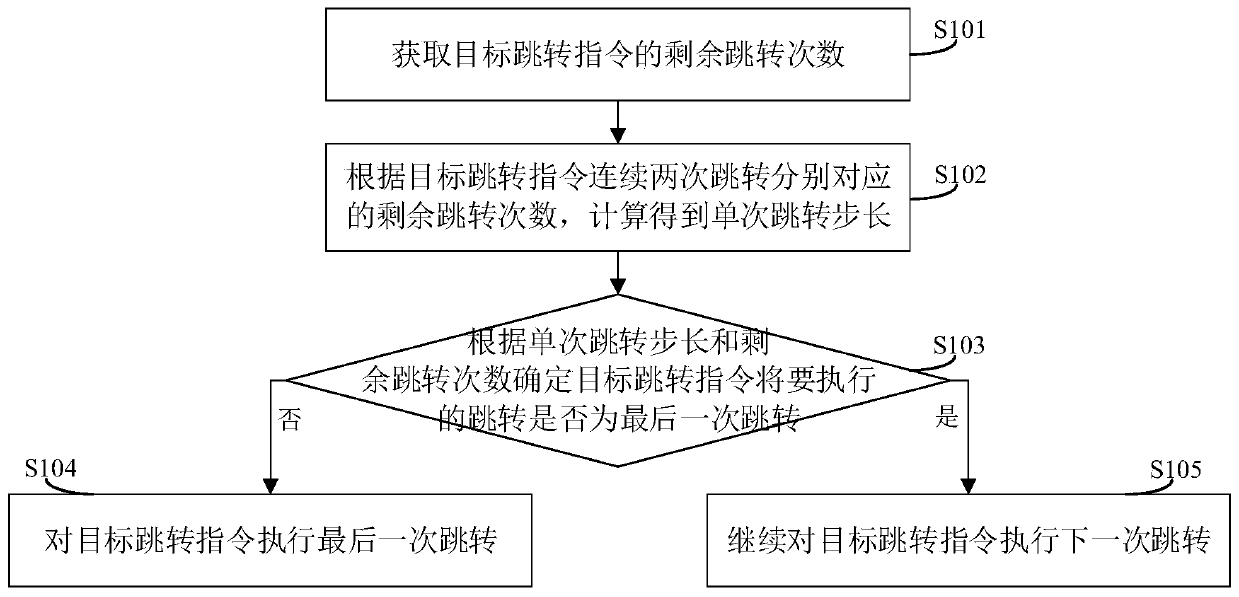

RISC-V branch prediction method and device, electronic equipment and storage medium

ActiveCN110134441AImprove processing efficiencyConcurrent instruction executionState of artPredictive methods

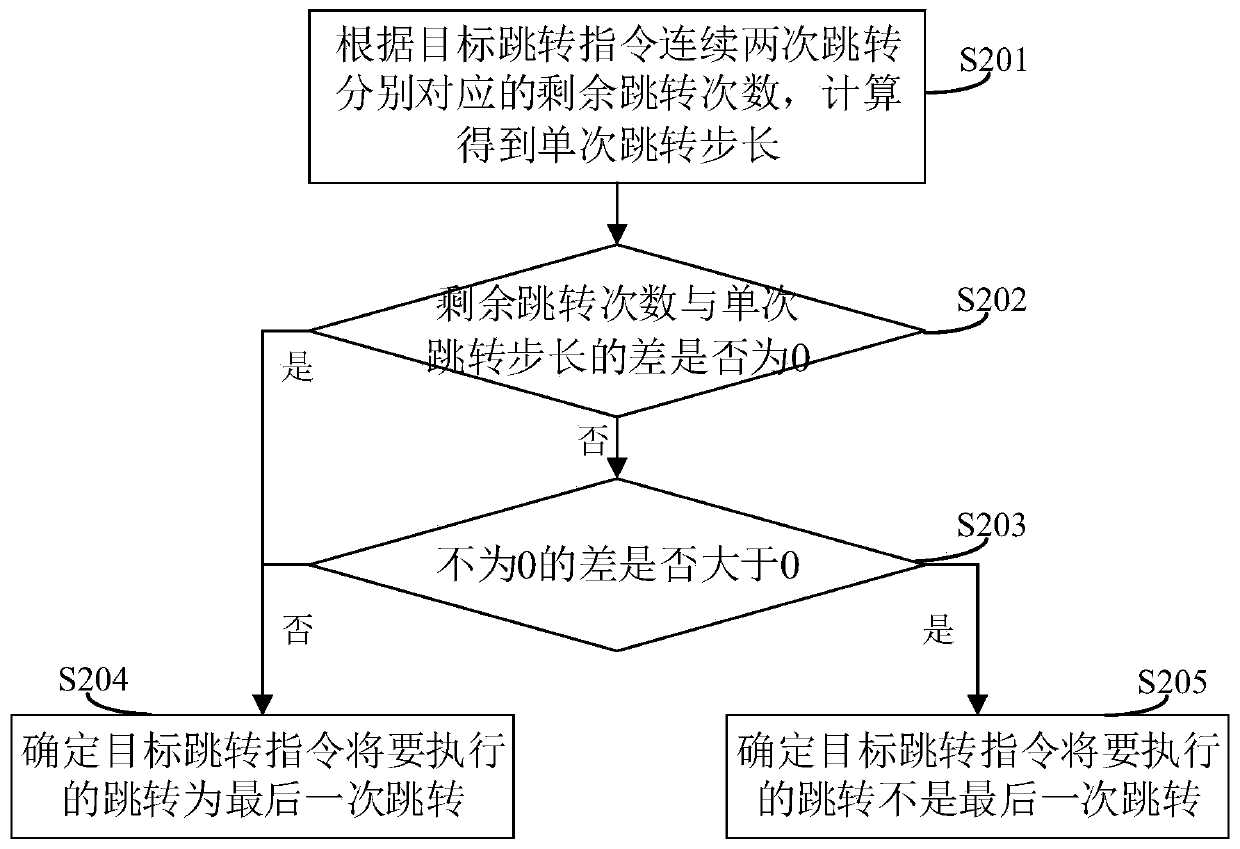

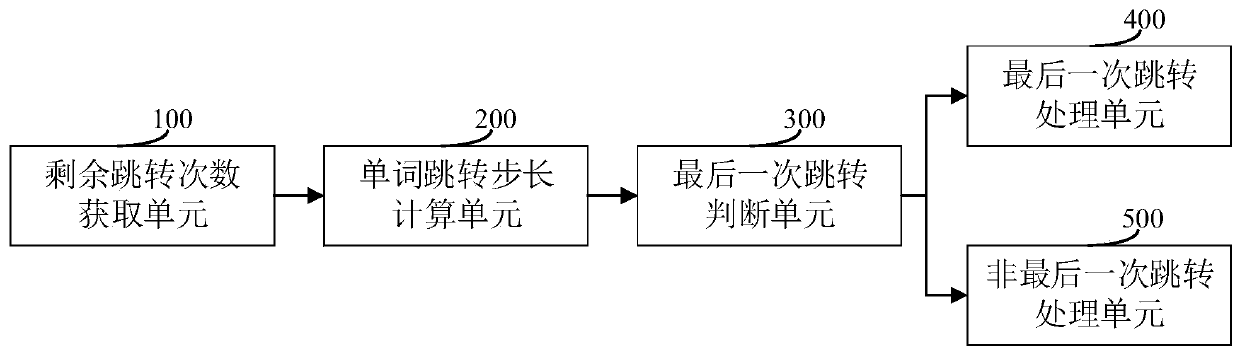

The invention discloses a RISC (Radio Service Station)-V branch prediction method. On the basis of the prior art, the remaining number of jumps of the jump instruction is additionally obtained; according to the difference value of the remaining jumping times during continuous two-time jumping, a single-time jumping step length (the single-time jumping step length is not fixed as 1) is obtained through calculation; therefore, whether the target jump instruction executes the last jump or not can be judged according to the single jump step of the jump instruction in combination with the real-timeresidual jump times, so that whether the subsequent jump times still need to be executed or not can be determined according to the judgment result. By means of the scheme, whether the jump instruction currently jumps to the last time or not can be actively judged, compared with the prior art that the same result is passively obtained, extra computing resources and instruction periods do not needto be consumed, and the processing efficiency of the processed instruction is higher. The invention further discloses the RISC-V-branch prediction device, electronic equipment and a computer readablestorage medium, which have the above beneficial effects.

Owner:INSPUR SUZHOU INTELLIGENT TECH CO LTD

Face recognition acceleration circuit system and acceleration method based on RISC-V

ActiveCN110443214ASpeed up the calculation processImprove imitation efficiencyCharacter and pattern recognitionNeural architecturesMicrocontrollerPattern recognition

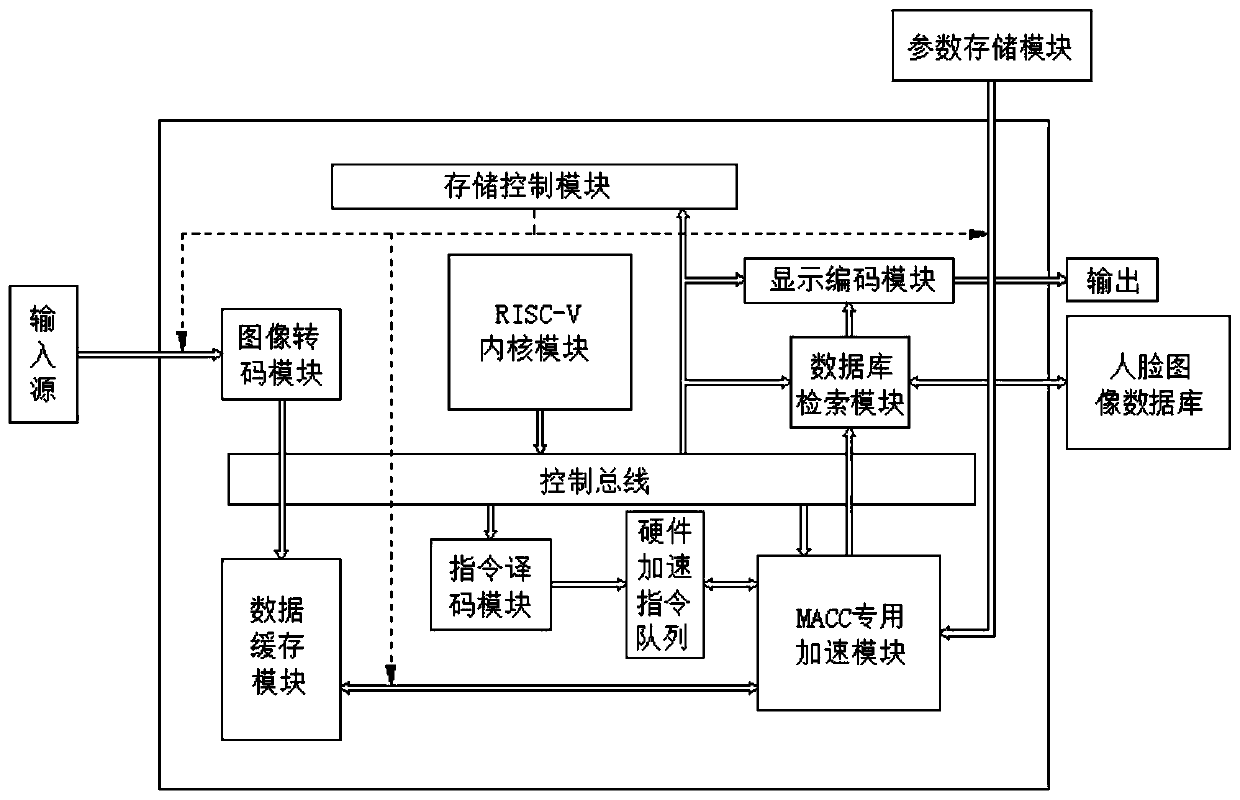

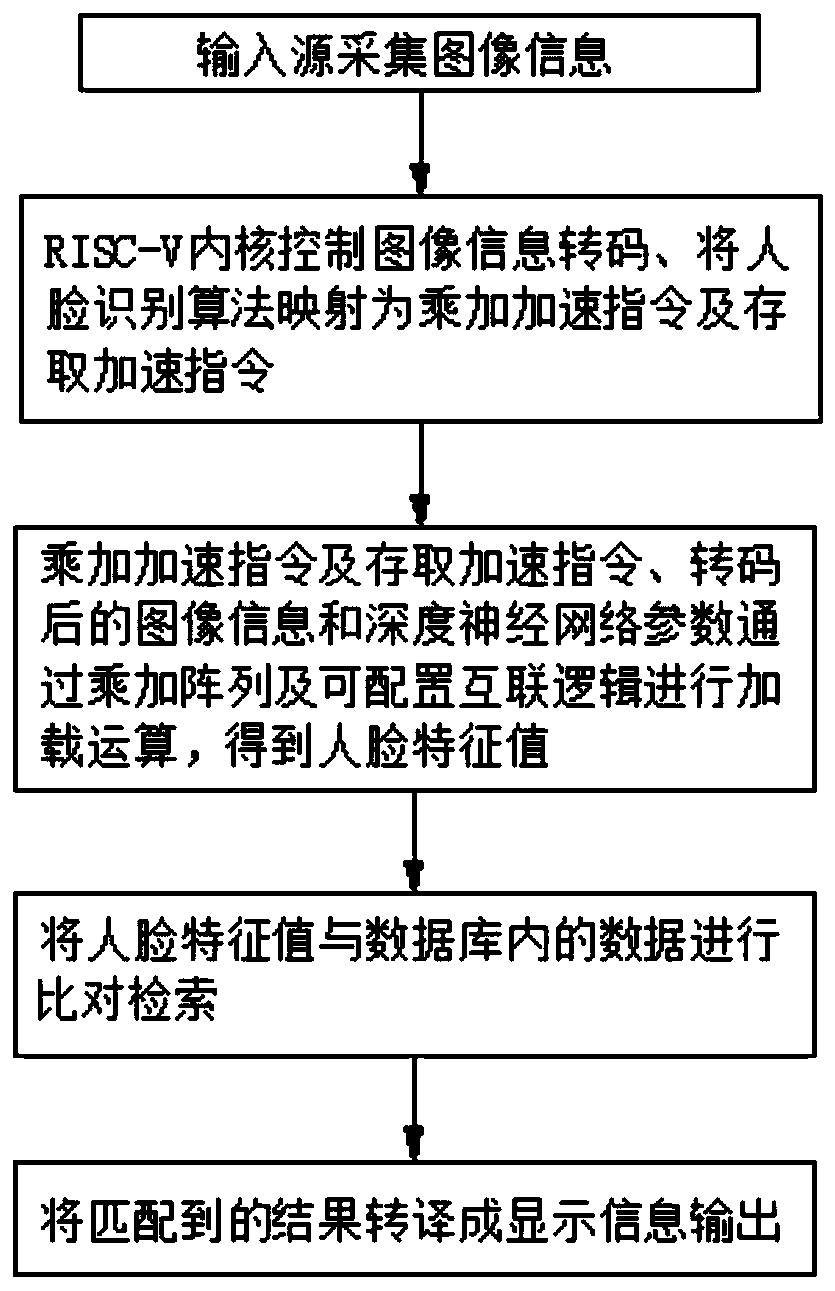

The invention discloses a face recognition acceleration circuit system and acceleration method based on RISC-V, and belongs to the field of artificial intelligence data processing. The acceleration circuit system comprises an image acquisition module, an RISC-V kernel module, an instruction processing module, an acceleration module, a parameter storage module, a storage control module and a face image processing module, and all the modules are in communication connection. According to the acceleration identification circuit system, hardware operated by deep neural network parameters is lowered, the calculation process of the face recognition process is greatly accelerated, the imitation memory efficiency is improved. The RISC-V kernel reduced instruction set serves as an instruction set framework of the on-chip microcontroller and serves as face recognition hardware acceleration master control, the framework is autonomous and controllable, and the safety and privacy confidentiality ofthe face recognition acceleration circuit can be improved.

Owner:SHANDONG INSPUR SCI RES INST CO LTD

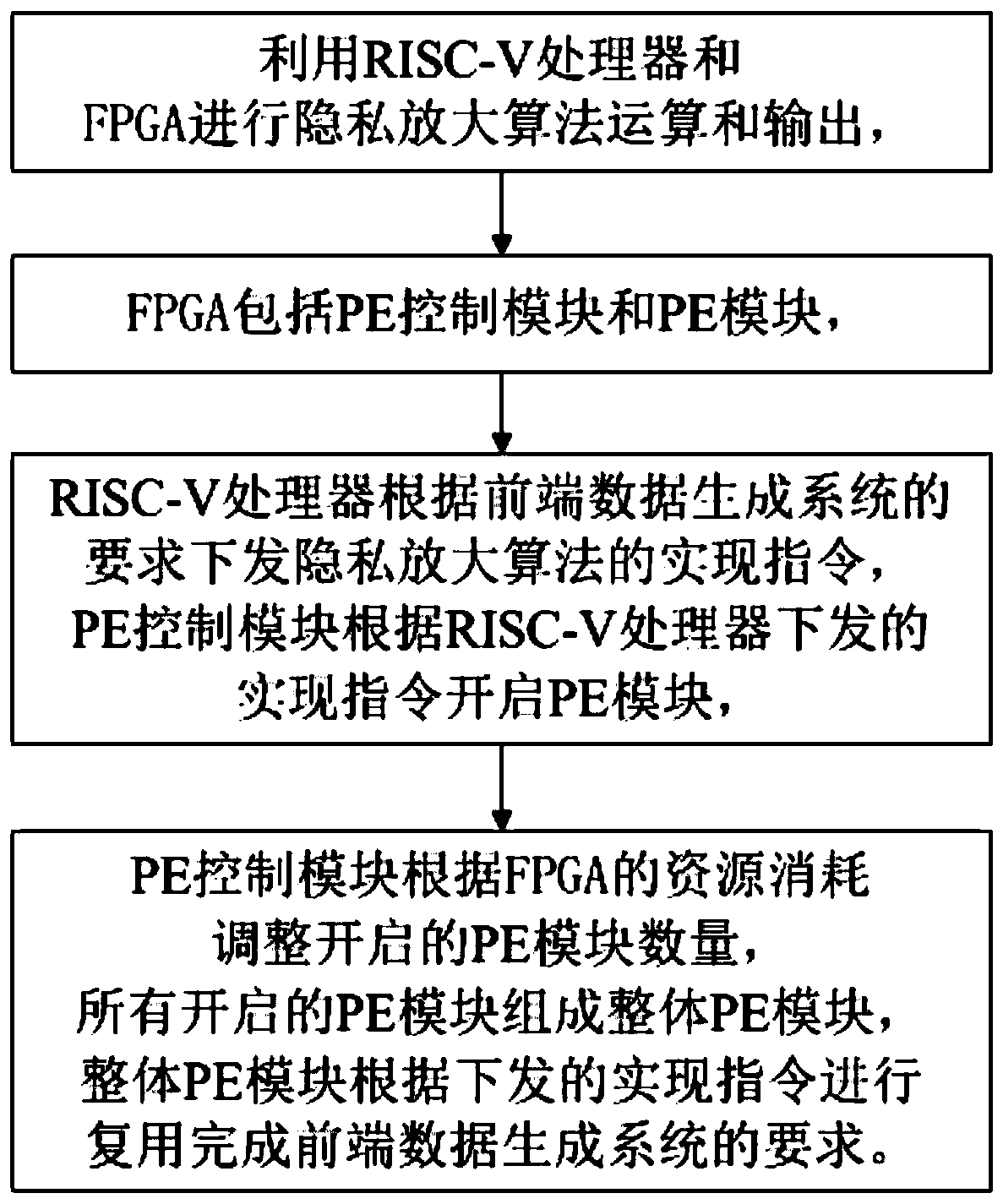

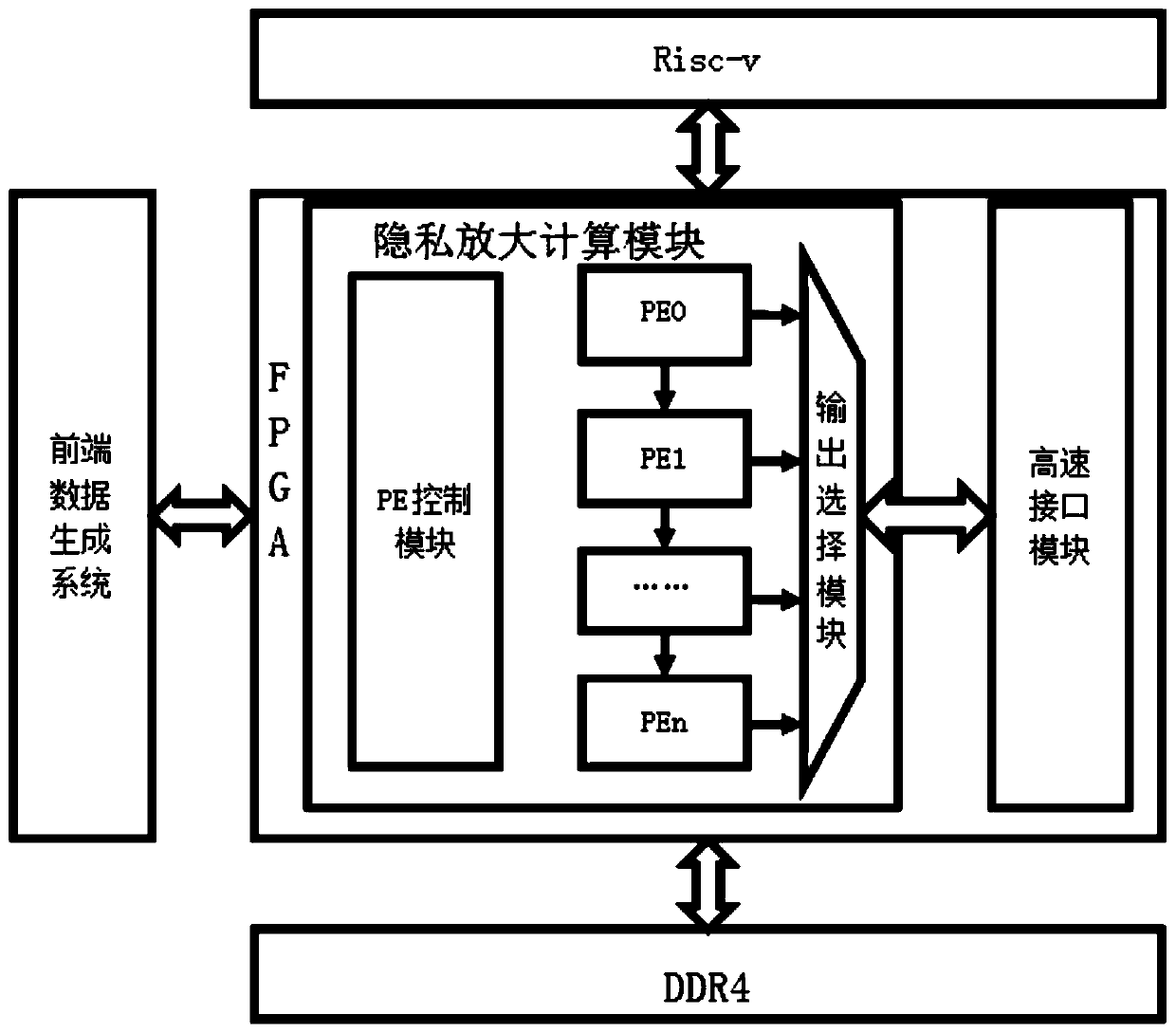

Implementation device of privacy amplification algorithm based on FPGA + RISC-V

ActiveCN110516809AHigh-speed generationHigh speed transmissionQuantum computersRandom number generatorsMultiplexingResource consumption

The invention discloses an implementation device of a privacy amplification algorithm based on FPGA + RISC-V, and relates to the field of data processing. The system comprises an RISC-V processor andan FPGA. RISC-V is used as a core processor; wherein the FPGA is mainly used for realizing a calculation task of a privacy amplification algorithm; the RISC-V realizes scheduling and management tasksof the algorithm; the PE control module of the FPGA starts the PE module according to an implementation instruction issued by the RISC-V processor; the number of the started PE modules is adjusted according to the resource consumption of the FPGA; all the opened PE modules form an integral PE module; the whole PE module performs multiplexing according to the issued implementation instruction to meet the requirements of a front-end data generation system; by utilizing the device, a privacy amplification algorithm can be realized, the flexibility is high, the algorithm speed can be adjusted according to equipment requirements, the device is applied to a quantum random number generator and QKD equipment in quantum communication, and high-speed data generation and transmission are facilitated.

Owner:SHANDONG INSPUR SCI RES INST CO LTD

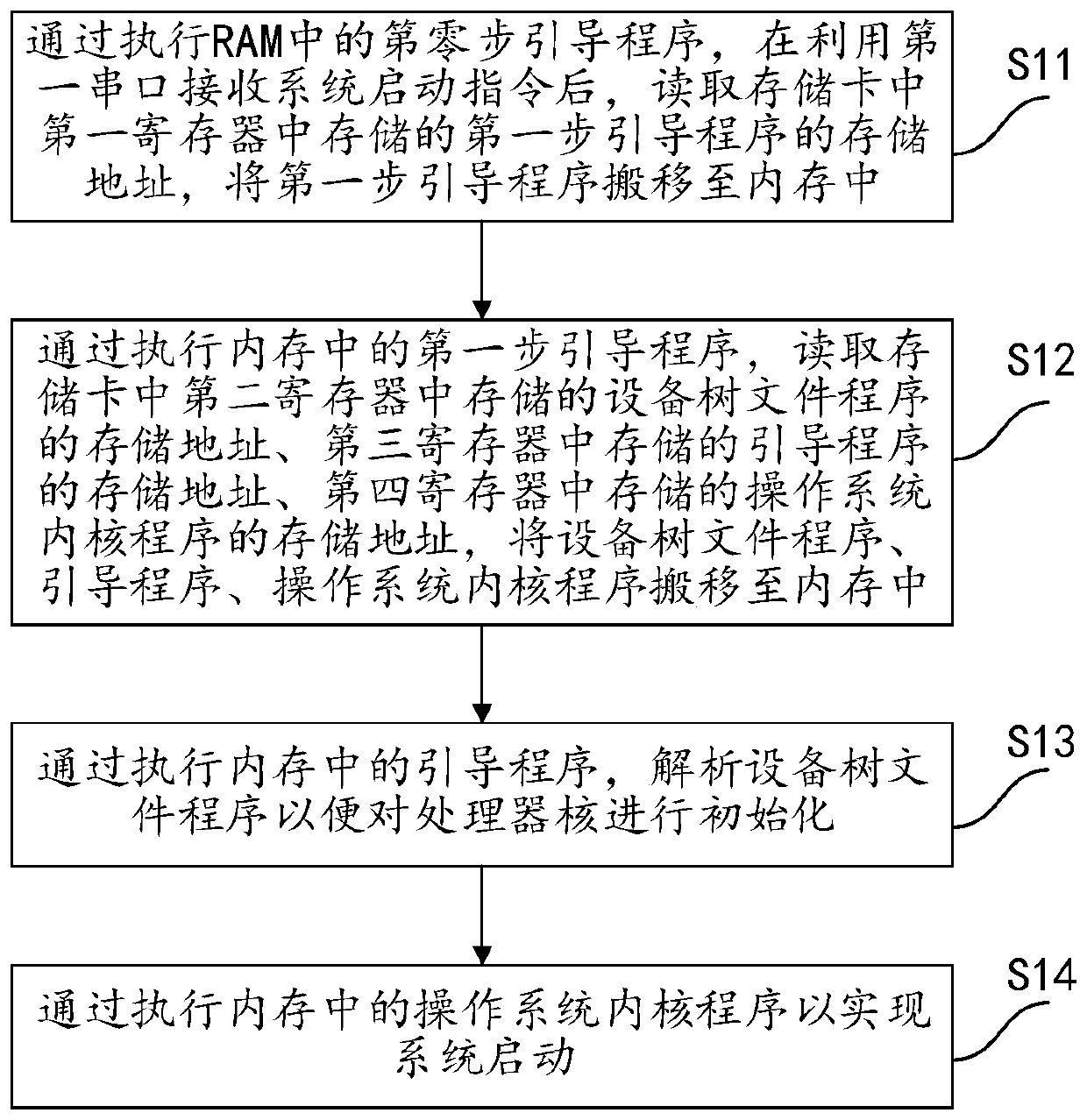

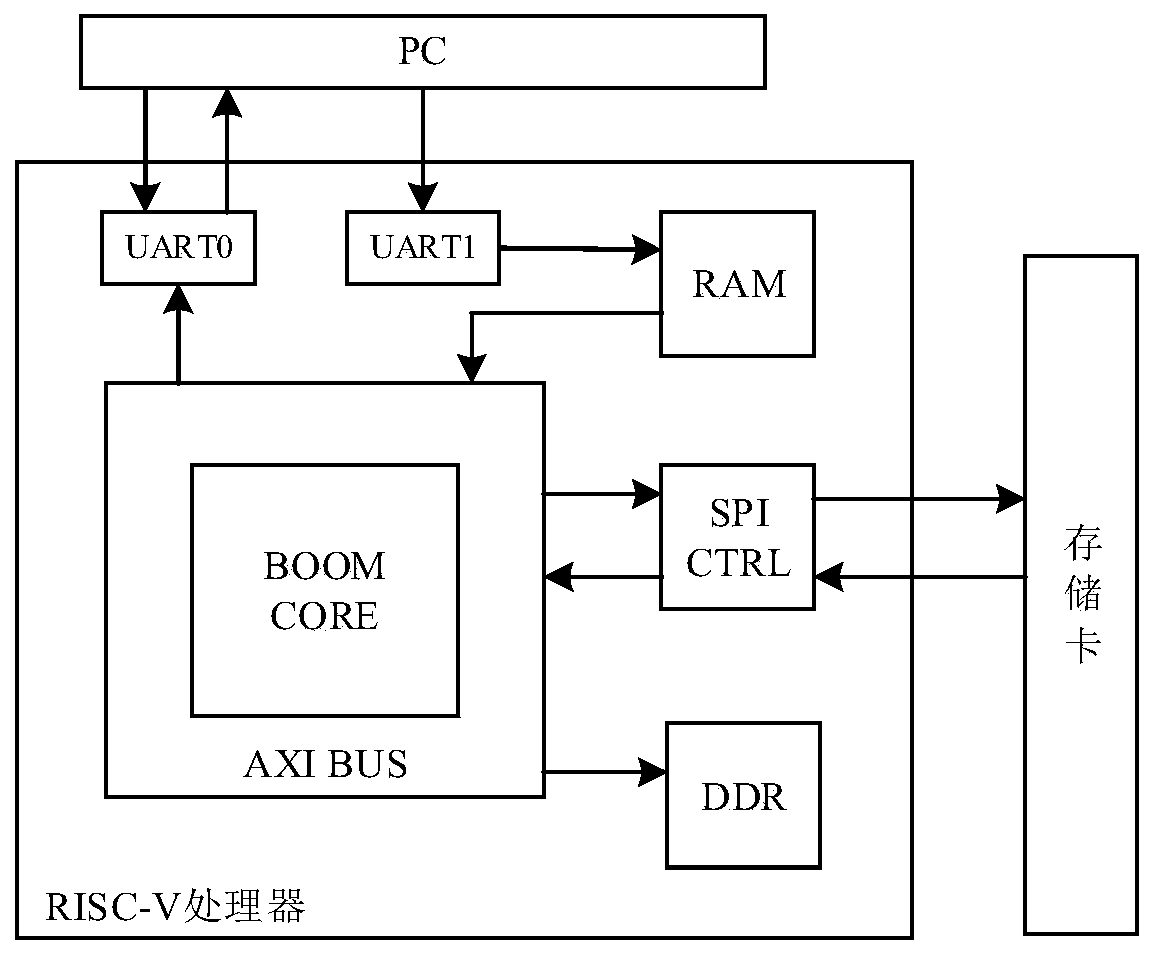

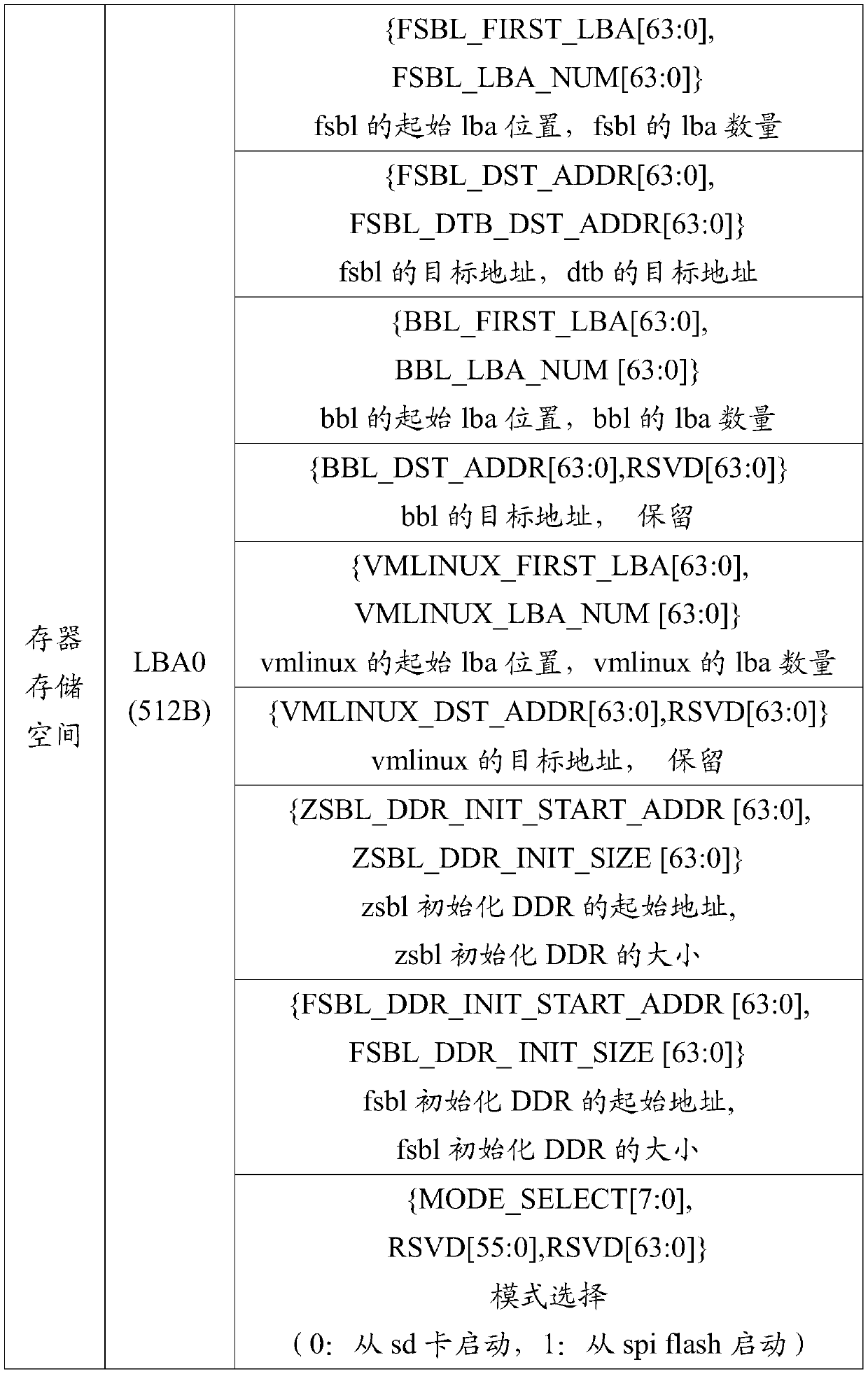

System based on RISC-V processor and system starting method thereof

PendingCN110399173AImprove developmentEasy to useBootstrappingProgram loading/initiatingOperational systemProcessor register

The invention discloses a system based on an RISC-V processor and a starting method thereof. The starting method comprises the steps: executing a zero-th bootstrap program in an RAM, reading a storageaddress of a first-step bootstrap program stored in a first register in a storage card after a system starting instruction is received, and moving the first-step bootstrap program to a memory; executing a first-step bootstrap program in the memory; reading a storage address of an equipment tree file program stored in a second register, a storage address of a bootstrap program stored in a third register and a storage address of an operating system kernel program stored in a fourth register in the memory card, and moving the equipment tree file program, the bootstrap program and the operating system kernel program into a memory; executing the bootstrap program in the memory, and analyzing the device tree file program so as to initialize the processor core; and executing an operating systemkernel program in the memory to realize system startup. According to the invention, the applicability and the operation convenience under various system configurations are effectively improved.

Owner:SUZHOU LANGCHAO INTELLIGENT TECH CO LTD

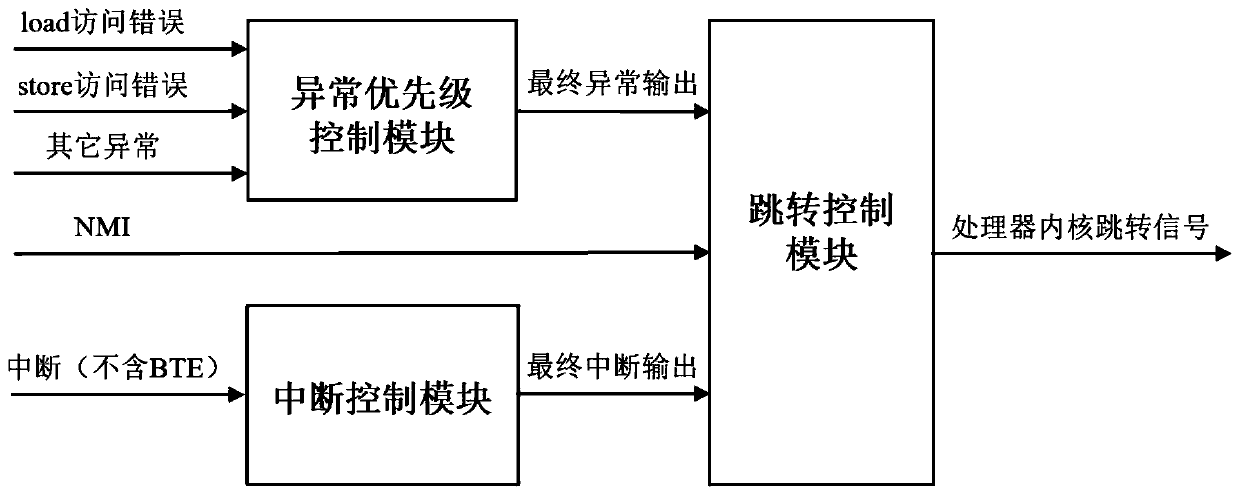

System and method for improving bus access error based on RISC-V architecture

ActiveCN110083473ADoes not interrupt processing flowIncrease flexibilityNon-redundant fault processingNon-maskable interruptRanking

The invention discloses a system for improving a bus access error based on RISC-V architecture. The system comprises an abnormal priority control module, an interrupt control module and a skip controlmodule. The system distributes interrupt numbers for the bus access error, takes the bus access error as interrupt sources for processing, and the abnormal priority control module is used for carrying out priority ranking on all abnormal types, selecting an abnormal type with the highest current priority and outputting the selected abnormal type to the skip control module; the interrupt control module is used for carrying out unified management on the bus access error and other interrupt sources, selecting the interrupt source with the highest current priority and outputting the interrupt source to the skip control module; and the skip control module is used for analyzing and processing input abnormal types, interrupt sources and unshielded interrupts and outputting analyzed and processedsignals to the processor core. According to the invention, abnormity report is changed to interrupt report for the bus access error, so that software control can be facilitated.

Owner:芯来智融半导体科技(上海)有限公司

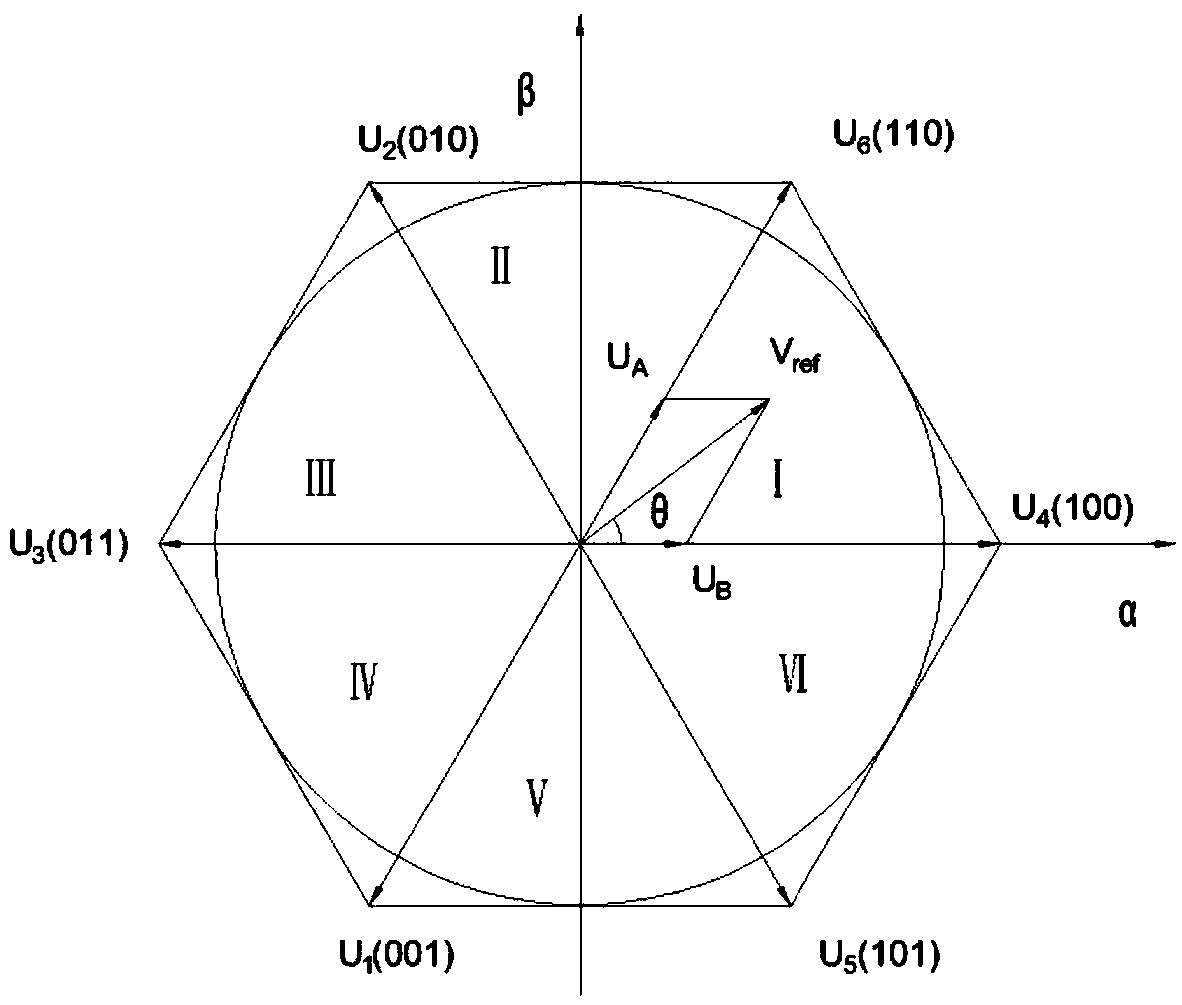

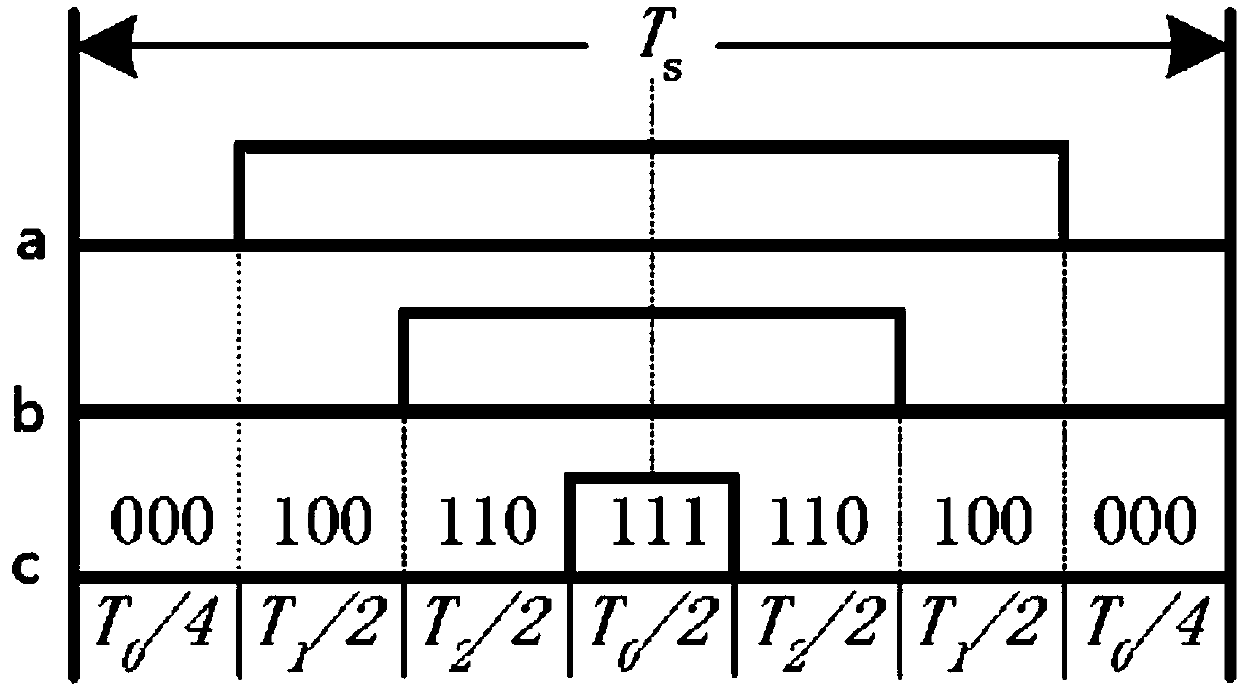

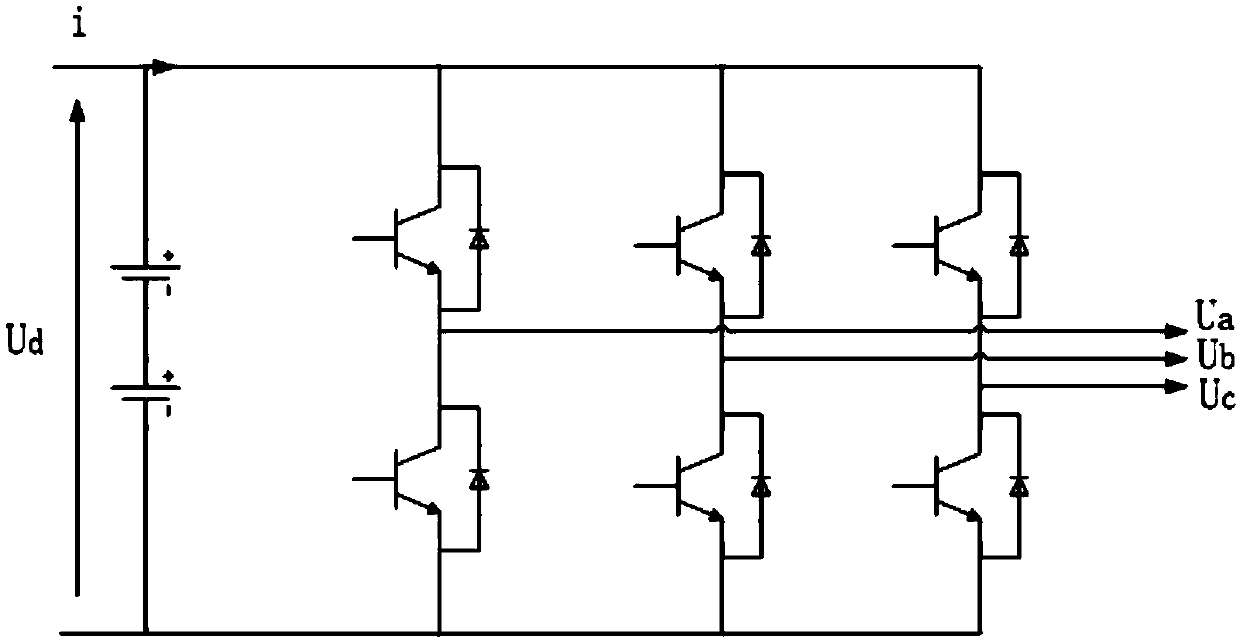

Optimization method for realizing SVPWM based on RISC-V

InactiveCN109660161AReduce the burden onReduce calculationElectronic commutation motor controlAC motor controlVoltage vectorComputer science

The invention discloses an optimization method for realizing SVPWM based on RISC-V. The optimization method comprises four steps of: firstly, determining a sector in which a reference voltage Vref islocated by means of a voltage space vector rotation amplitude; secondly, calculating action time T1 and T2 of a basic voltage vector in each sector; thirdly, calculating a voltage space vector switching point in each sector; and finally generating SVPWM modulation waveforms. The optimization method analyzes and improves the traditional SVPWM algorithm, thereby reducing the calculation loss of a trigonometric function of the traditional SVPWM algorithm through digitization, thereby reducing the consumption of CPU resources.

Owner:BEIJING UNIV OF TECH

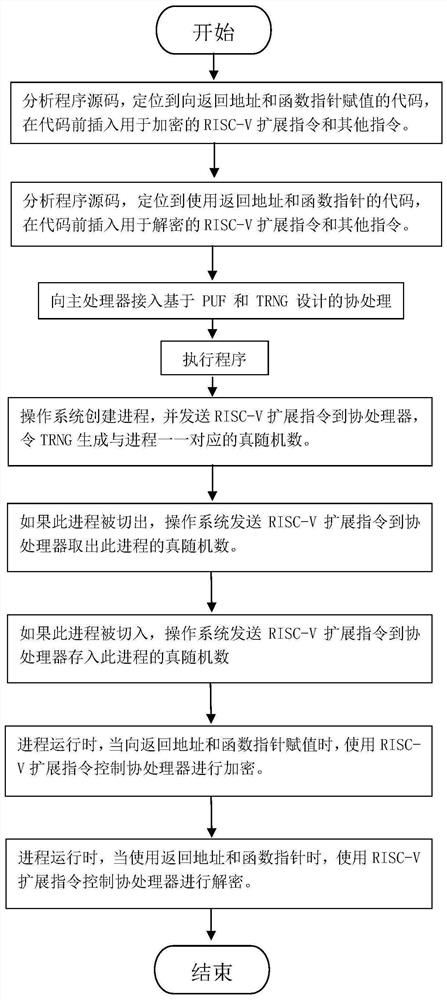

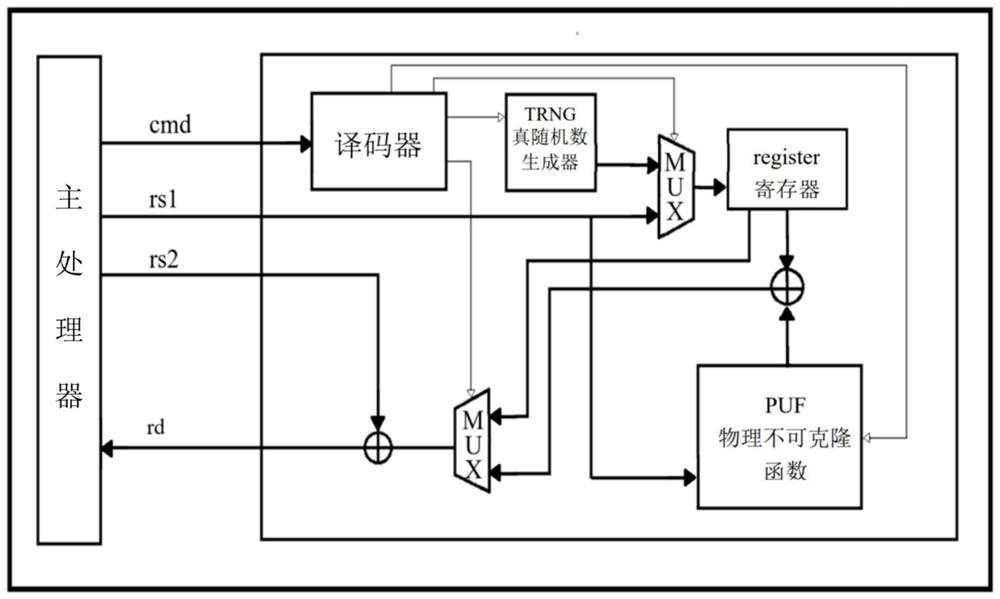

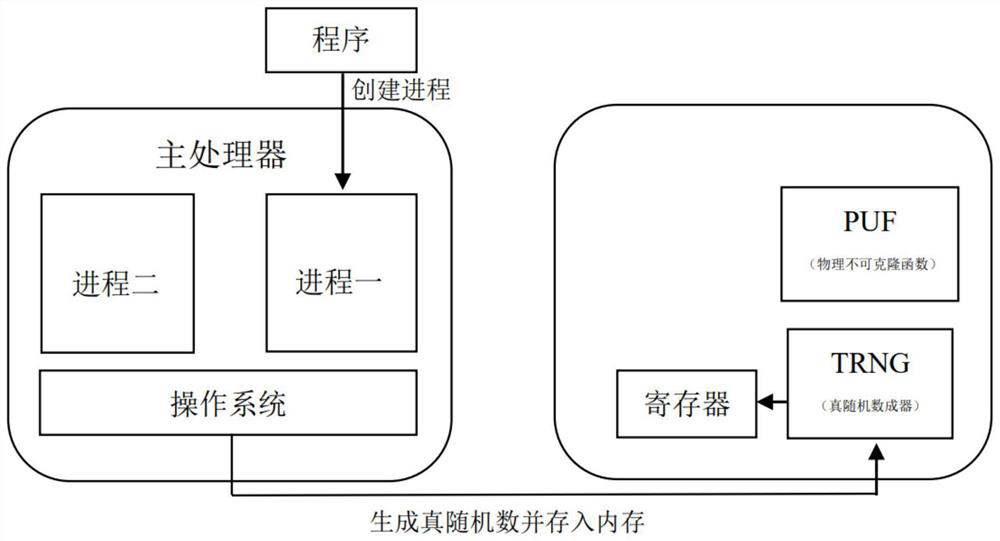

Memory overflow defense method based on pointer encryption mechanism and RISC-V coprocessor

ActiveCN113673002AReduce the impact of operating efficiencyImprove securityInternal/peripheral component protectionPlatform integrity maintainanceCoprocessorBuffer overflow

The invention discloses a memory overflow defense method based on a pointer encryption mechanism and an RISC-V coprocessor, relates to the technical field of computer system security, and aims to achieve the purpose of preventing data from jumping to a destination address through buffer overflow modification by encrypting a return address and a function pointer so as to realize security protection of an RISC-V architecture. And the safety of the RISC-V system is improved, and meanwhile, a program is not obviously influenced.

Owner:INST OF SOFTWARE - CHINESE ACAD OF SCI

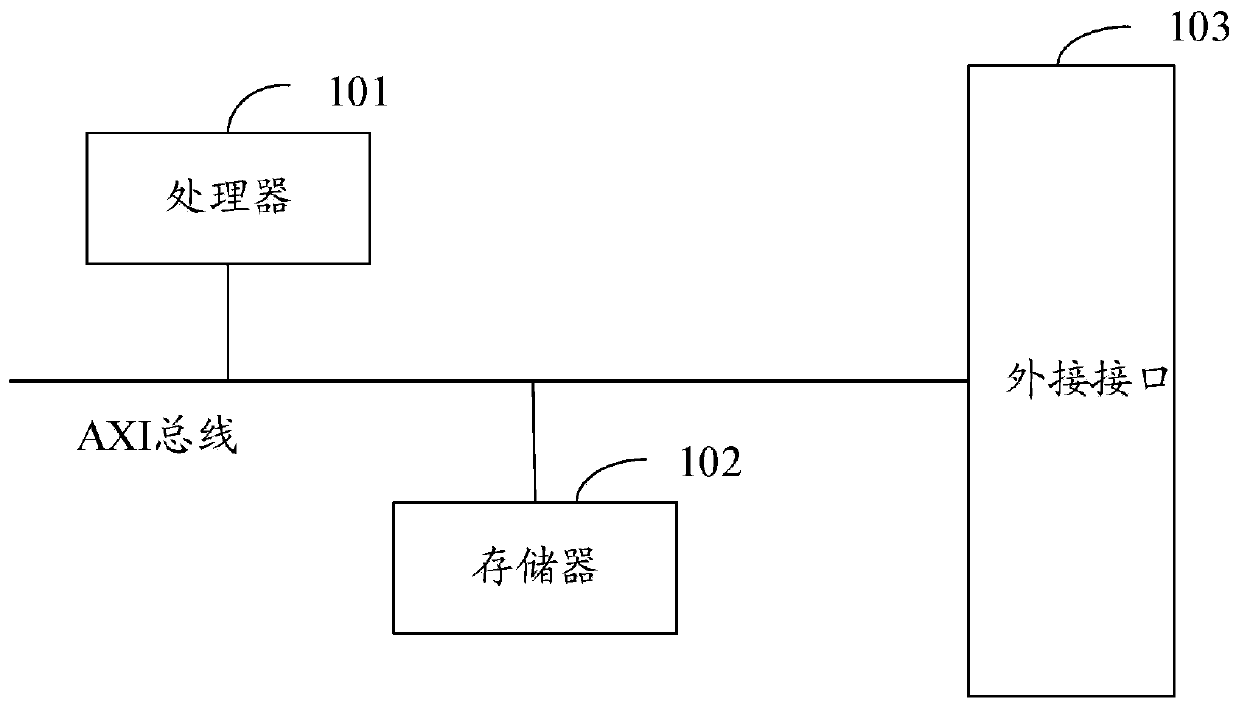

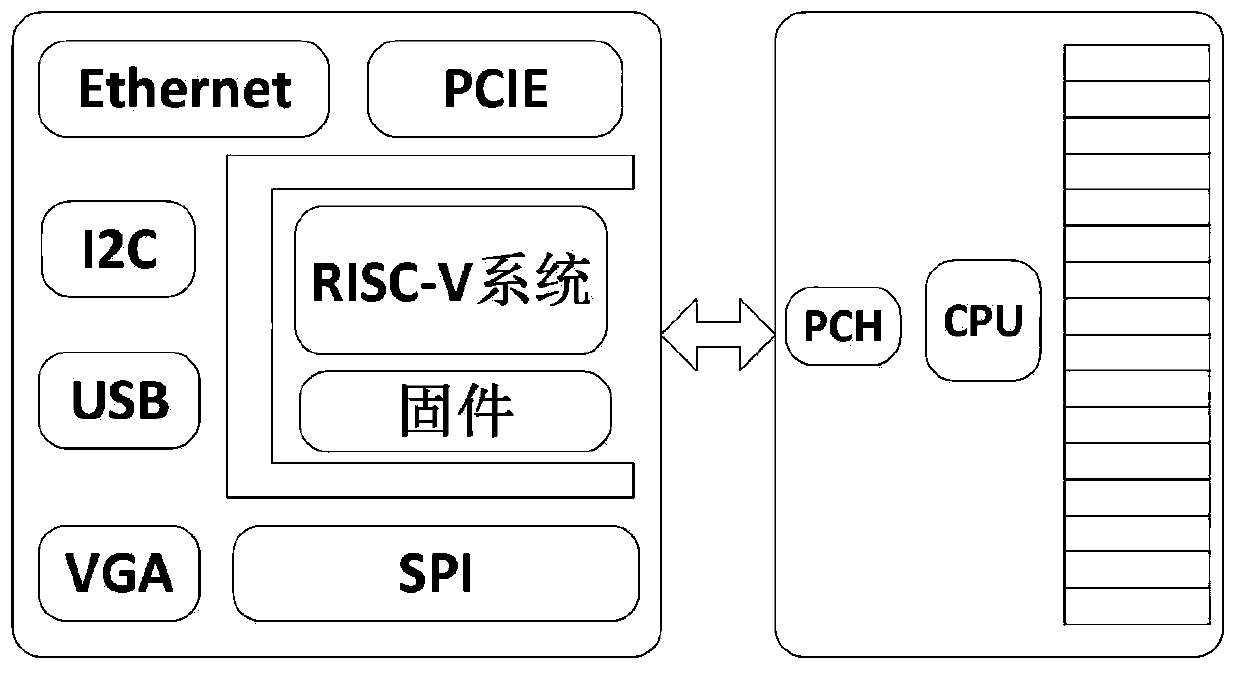

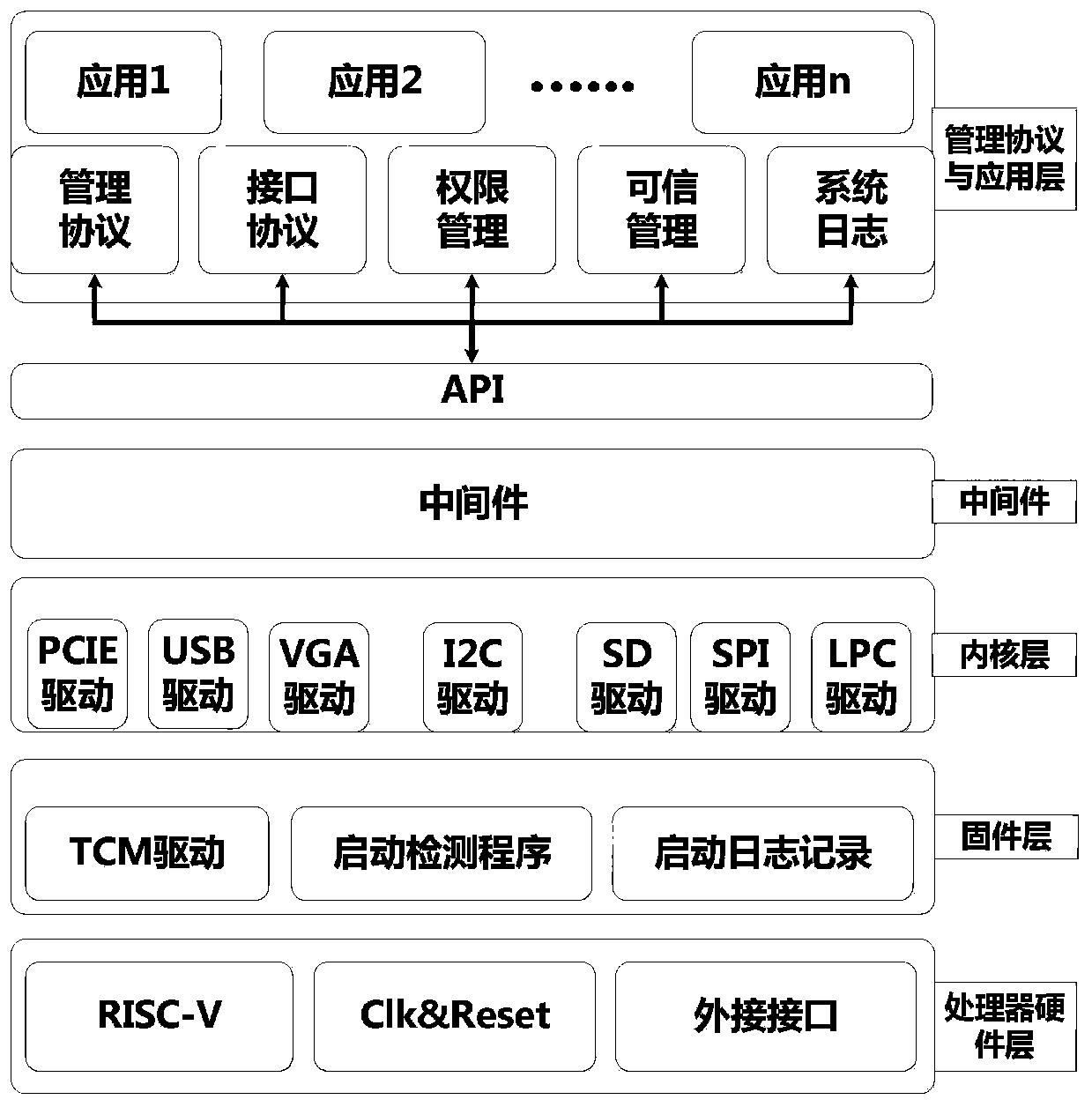

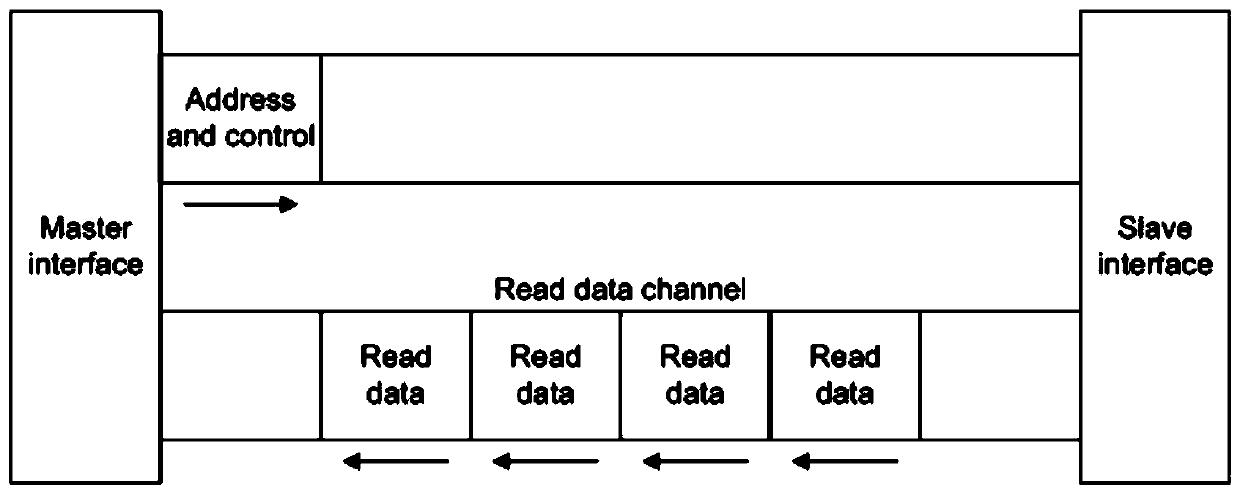

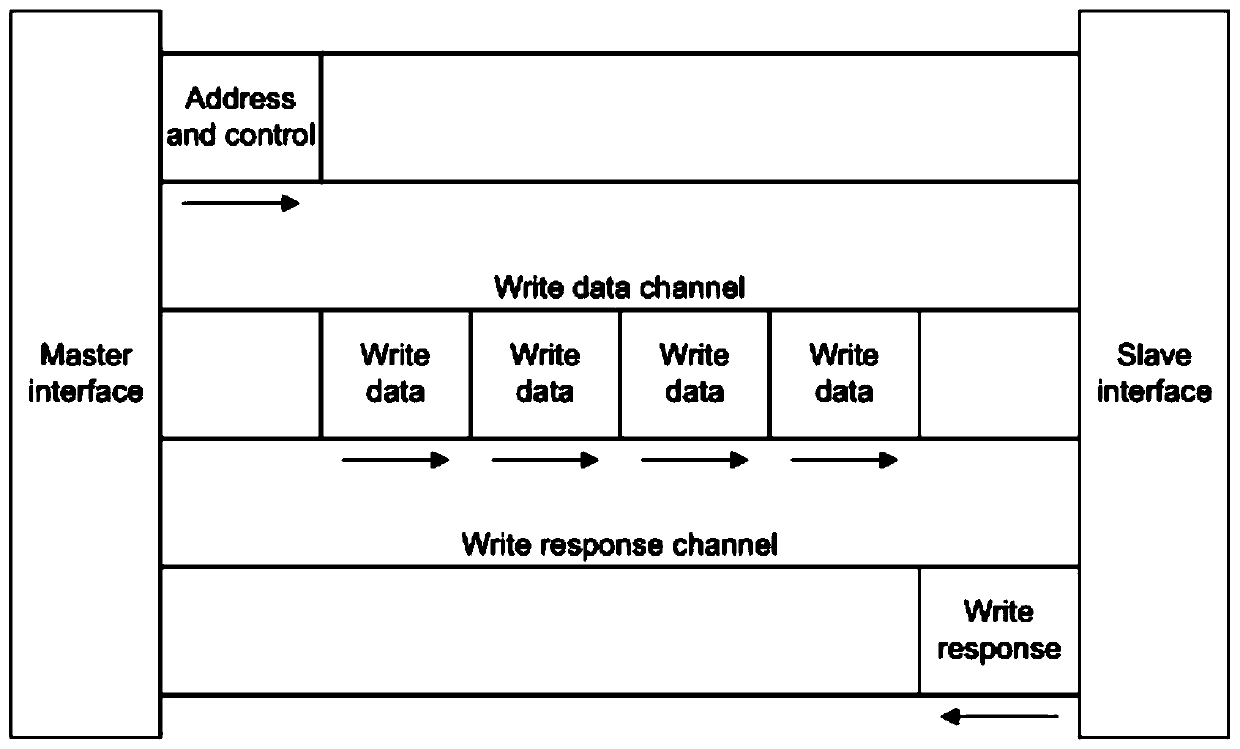

Baseboard management controller and construction method thereof

InactiveCN110532005ARealize autonomous and controllableBootstrappingArchitecture with single central processing unitOpen sourceSoftware framework

The invention provides a baseboard management controller constructed based on an RISC-V system architecture, and the baseboard management controller comprises a processor, a memory and an external interface, which are connected through an AXI bus. The memory is used for storing an OpenBMC system, and the OpenBMC system is obtained by carrying out cross compiling on an OpenBMC software framework through an RISC-V tool chain of the RISC-V framework. The processor is used for executing the OpenBMC system stored in the memory, and a soft core source code of the processor is generated by a RocketChip generator. A baseboard management controller is constructed through an RISC-V system architecture based on an open source, and an ARM architecture needing authorization is replaced to achieve the baseboard management controller. Therefore, the baseboard management controller used by the user is not limited by a manufacturer any more, and the baseboard management controller used by the user canbe completely autonomously controlled.

Owner:SUZHOU LANGCHAO INTELLIGENT TECH CO LTD

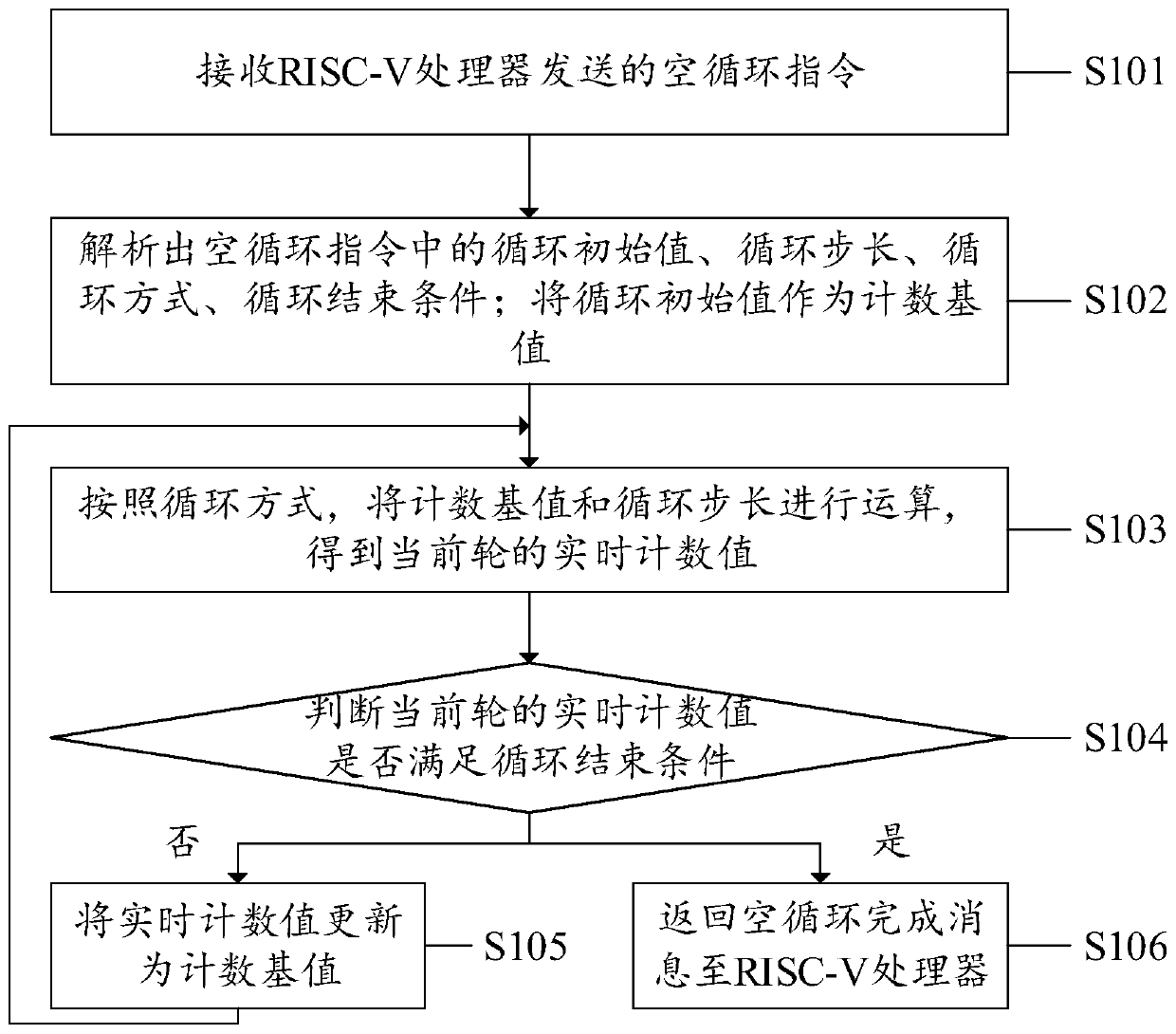

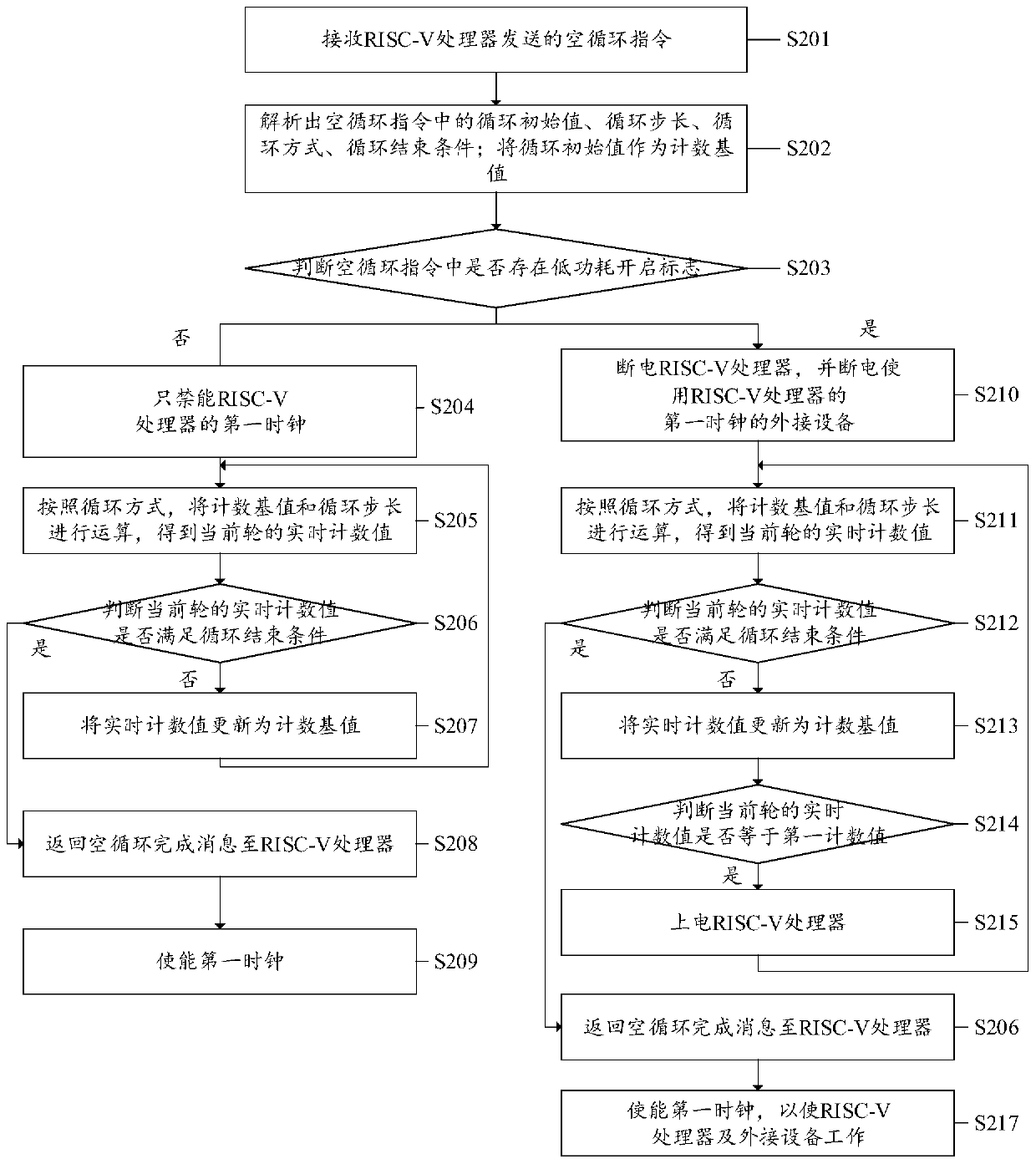

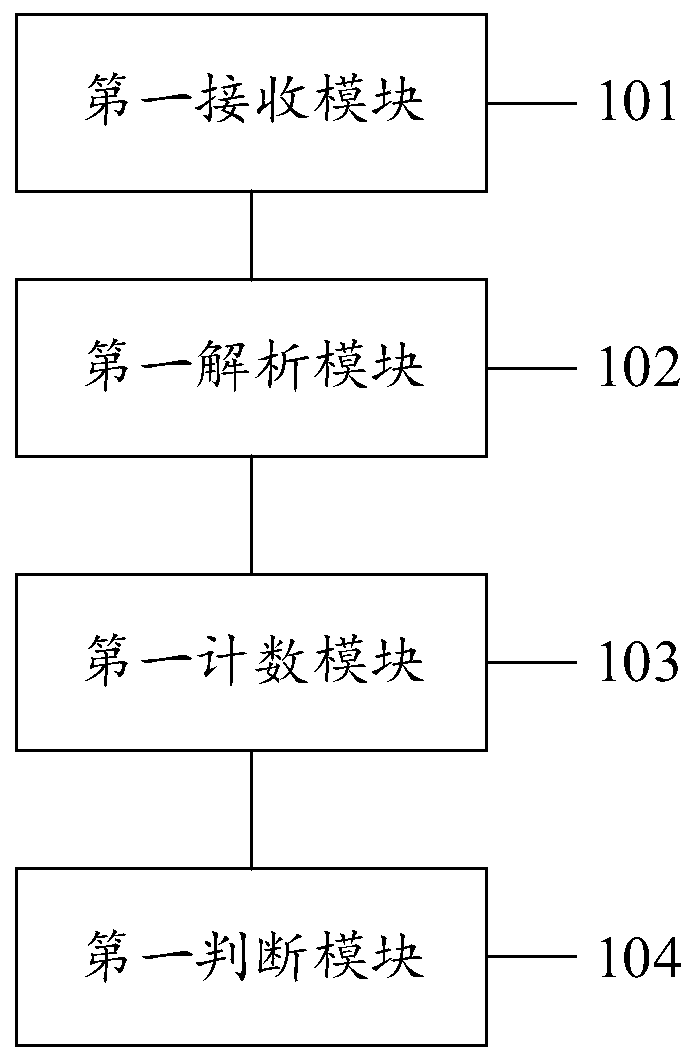

Zero-overhead circulating device and implementation method, system and equipment and computer medium

ActiveCN109739557AImprove performanceAvoid occupyingNext instruction address formationComputer scienceRISC-V

The invention discloses a zero-overhead circulating device and an implementation method, system and equipment and a computer medium. The method comprises the following steps: receiving an air circulation instruction sent by the RISC-V processor; analyzing a circulation initial value, a circulation step length, a circulation mode and a circulation ending condition in the empty circulation instruction; taking the cyclic initial value as a counting base value, and performing operation on the counting base value and the cyclic step length according to a cyclic mode to obtain a real-time counting value of the current round; judging whether the real-time count value of the current round meets a cycle ending condition or not, if not, updating the real-time count value into a counting base value,returning to the step of operating the counting base value and the cycle step length according to a cycle mode, and if yes, returning an empty cycle ending message to the RISC-V processor. According to the zero-overhead circulating device, the implementation method, system and equipment and the computer readable storage medium provided by the invention, performance of the RISC-V processor is improved.

Owner:ZHENGZHOU YUNHAI INFORMATION TECH CO LTD

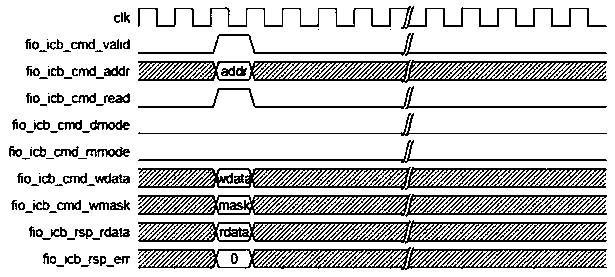

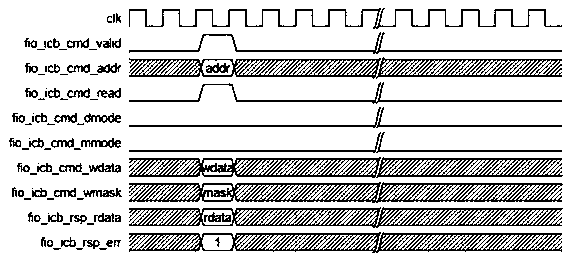

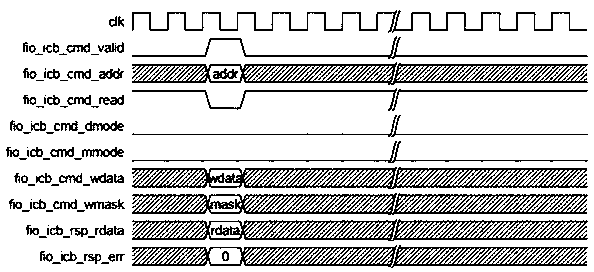

Rapid IO interface suitable for RISC-V architecture kernel

InactiveCN110069424ASimple definitionEasy to implementElectric digital data processingComputer scienceEmbedded system

The invention discloses a rapid IO interface suitable for an RISC-V architecture kernel. The rapid IO interface comprises a request channel and a feedback channel, and the request channel is used forthe processor kernel to request data writing from peripheral equipment through the fast IO interface; the feedback channel is used for the fast IO interface to return read data to the processor kernel, and the fast IO interface is directly connected with the processor; and the quick IO interface is connected with the GPIO port and the peripheral equipment. The rapid IO interface is directly connected with the processor without transferring through a bus, so that the processor can quickly and efficiently access the peripheral interface.

Owner:芯来智融半导体科技(上海)有限公司

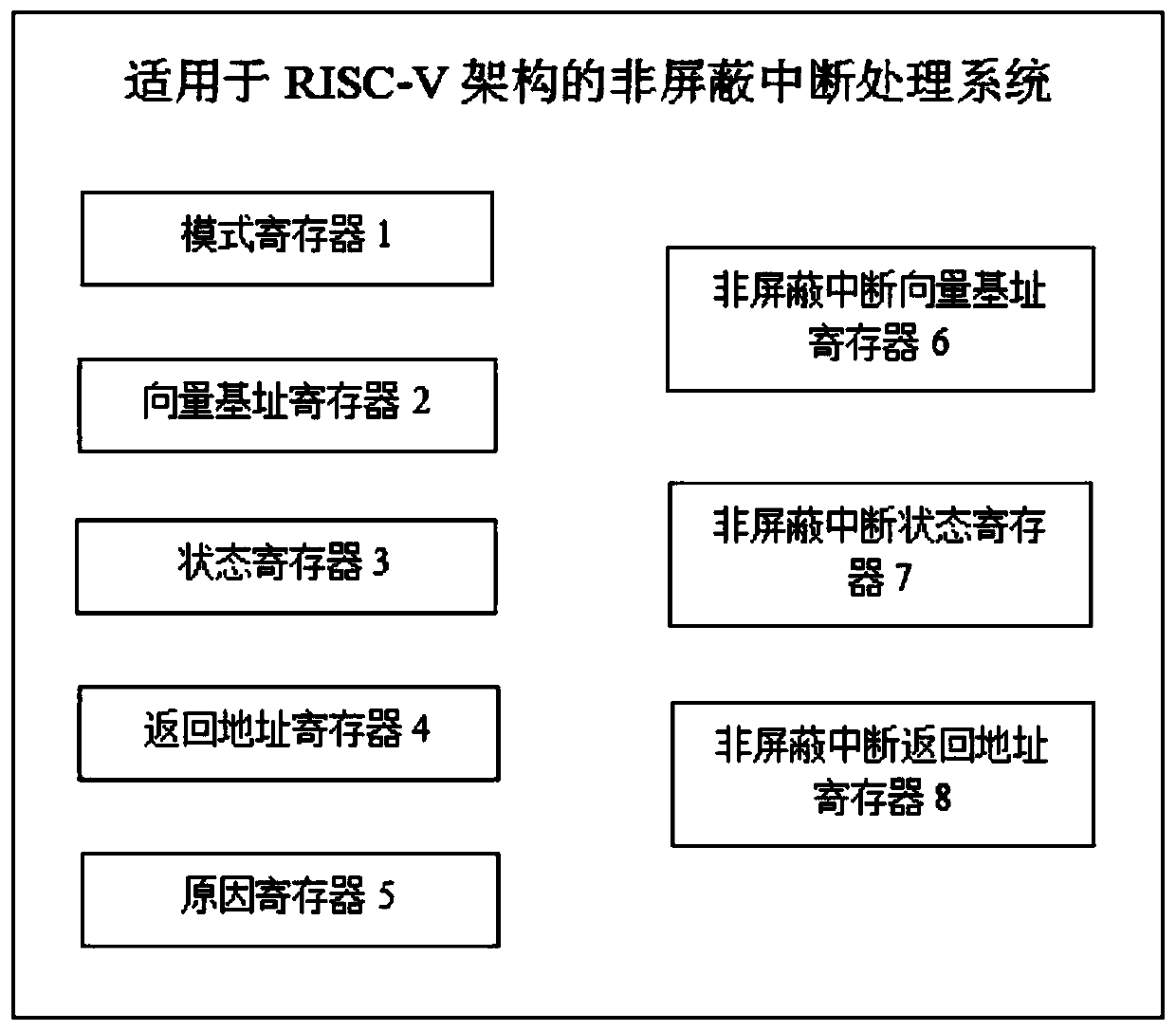

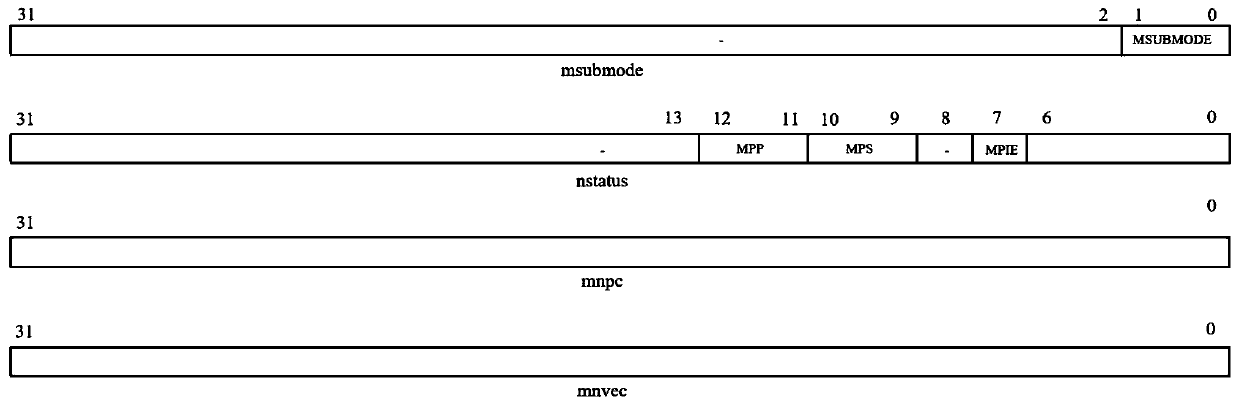

A non-shielding interrupt processing system and method suitable for a RISC-V architecture

ActiveCN109947550ARestore nestingProgram initiation/switchingEnergy efficient computingProcessor registerHandling system

The invention relates to the technical field of low-power-consumption kernel interrupt processing, in particular to a non-shielding interruption processing system and method suitable for a RISC-V architecture, and the system comprises a mode register, an abnormal vector base address register, a state register, an abnormal return address register, an abnormal reason register, a non-shielding interruption vector base address register, a non-shielding interruption state register, and a non-shielding interruption return address register. Beneficial effects are as follows: the device is simple in structure; an abnormal vector base address register is interrupted through non-shielding; the state of the processor when the non-shielding interruption occurs is stored in the non-shielding interruption state register, the values of the abnormal vector base address register and the state register are not changed, nesting of the non-shielding interruption can be recovered, and it is further guaranteed that the system can recover after the non-shielding interruption occurs.

Owner:AMOLOGIC (SHANGHAI) CO LTD

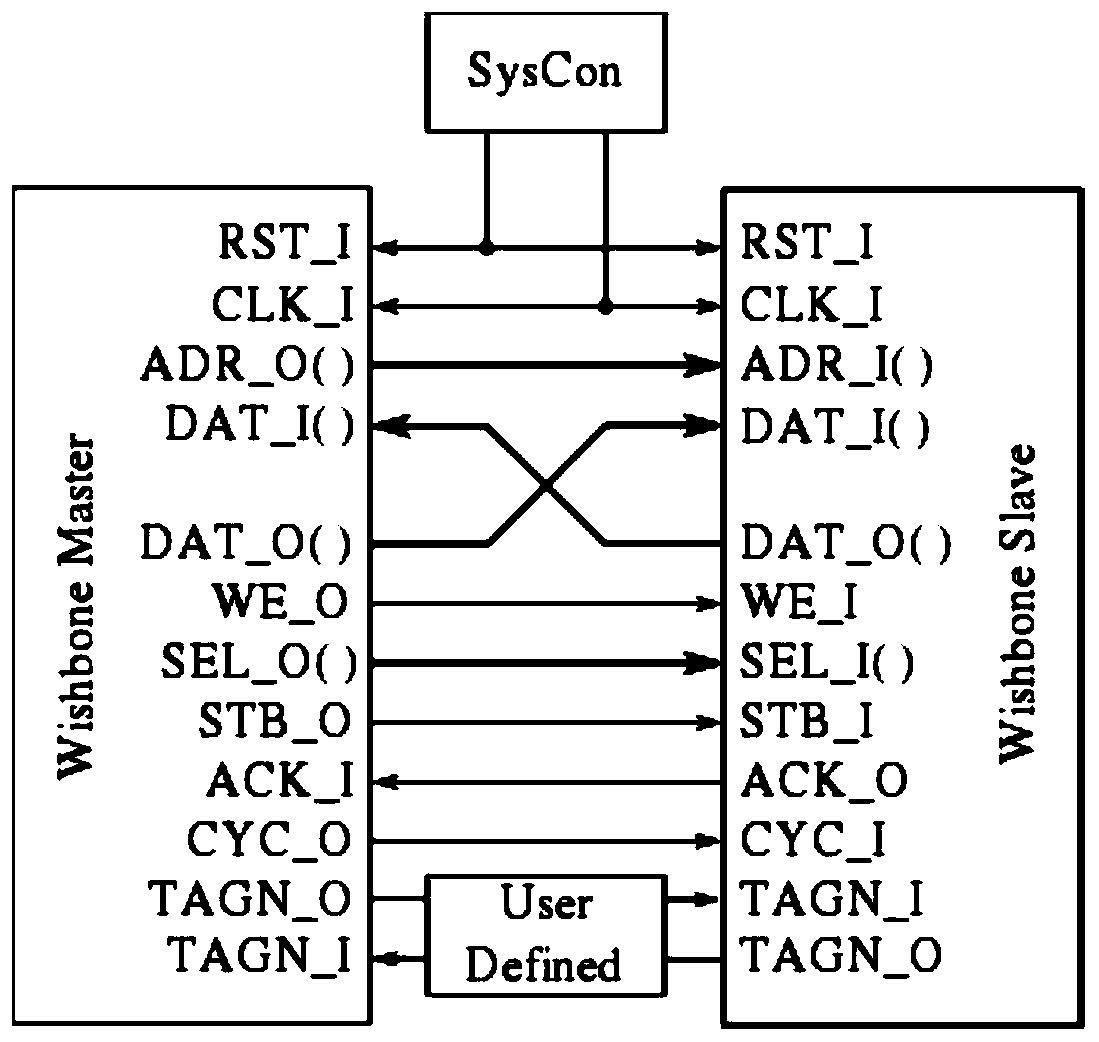

Asynchronous transceiving transmitter peripheral and system based on RISC-V processor

The invention discloses an asynchronous transceiving transmitter peripheral equipment based on an RISC-V processor. A data signal output end of the receiving module is connected with a data signal input end of the WB Interface module, and a control signal input end of is connected with a control signal output end of the UART _ Regs module to receive and process data; the data signal receiving endof the output module is connected with the data signal output end of the WB Interface module; a control signal receiving end of the output module is connected with a control signal output end of the UART _ Regs module to realize output of processed data, effective UART module mounting is realized, and the UART module can be directly mounted to n the MIMO interface of the RISC-V, data transmissionis carried out in combination with the RISC-V processor. The invention further discloses an asynchronous transceiving transmission system based on an RISC-V processor, which has the beneficial effectswhich are not repeated herein.

Owner:INSPUR SUZHOU INTELLIGENT TECH CO LTD

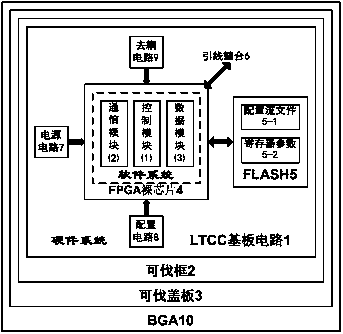

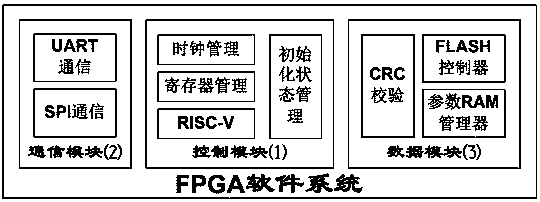

Miniaturized high-density system-level logic circuit

ActiveCN110442545AReduce volumeReduce in quantityEnergy efficient computingArchitecture with single central processing unitEngineeringCalibration function

The invention relates to a miniaturized high-density system-level logic circuit. FPGA minimum system circuits such as an FPGA bare chip, a FLASH bare chip, a power supply circuit, a decoupling circuitand a configuration circuit are realized in a miniaturized ceramic circuit; on hardware, through ten-layer high-density ceramic circuit wiring, pyramid chip stacking and a ceramic cavity opening process, three-dimensional integration miniaturization of the circuit is achieved, an oscillator calibration circuit is achieved in an FPGA, and a dynamic oscillator frequency calibration function is achieved through a negative feedback loop. Hardware potential is fully excavated, innovation is achieved from a software architecture, the parallel computing capacity of an FPGA and the storage characteristic of FLASH are brought into play, a logic control circuit, a communication circuit and a data management circuit are customized and designed, and a powerful and complex logic function and a memoryfunction are achieved in combination with an RISC-V controller; the logic circuit has the advantages of high integration level, small size, high reliability, programmability, memorability and the like.

Owner:CETC GUOJI SOUTHERN GRP CO LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com