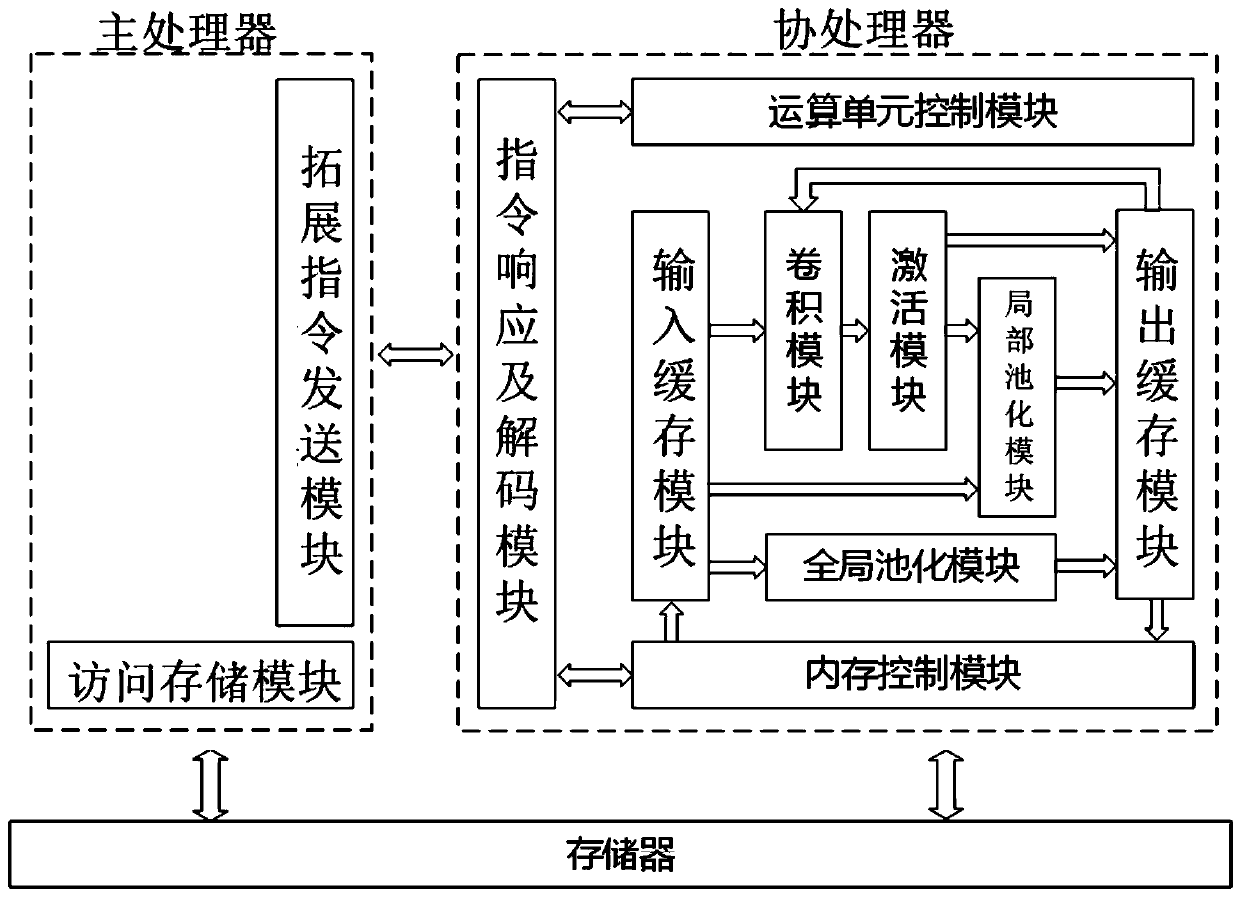

Convolutional neural network acceleration device based on RISC-V architecture and control method thereof

A convolutional neural network, RISC-V technology, applied in the processor field, can solve the problems of FPGA resource and speed limitation, GPU power consumption and cost, poor ASIC versatility, etc., to achieve the effect of high flexibility

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

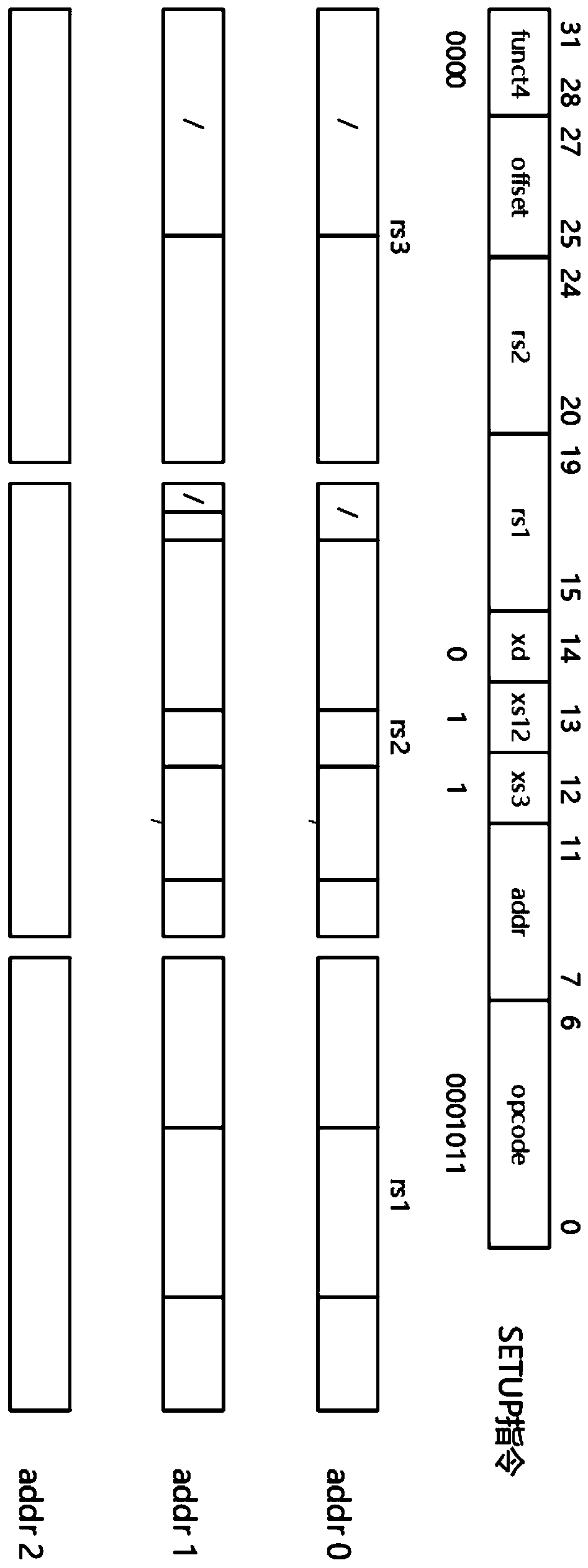

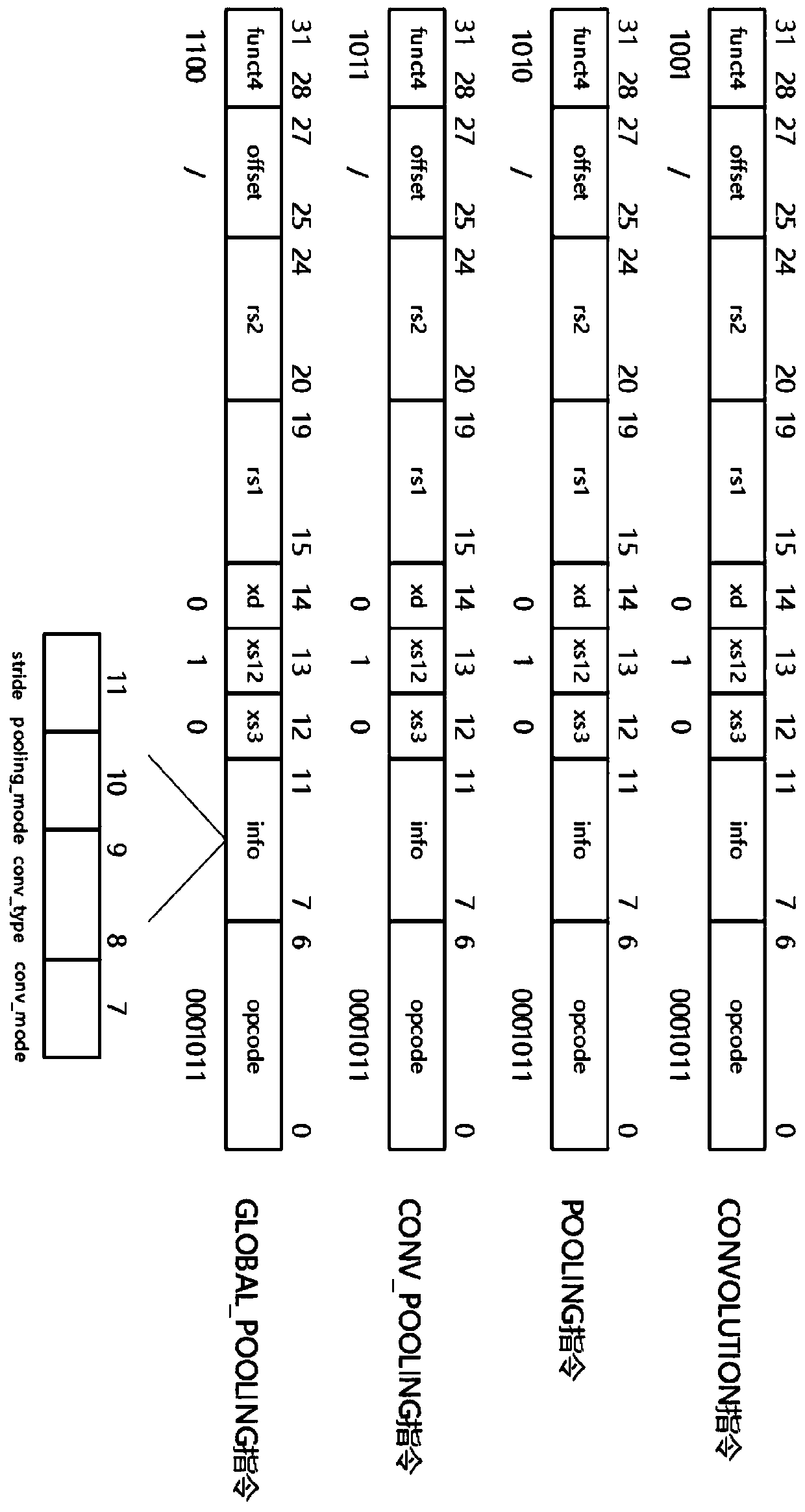

[0052] The present invention will be further described below in conjunction with the accompanying drawings and specific embodiments.

[0053]This embodiment is based on the instruction rules of the RISC-V architecture to define extended instructions. The extended instructions include the SETUP instruction for configuring the relevant information of each layer of the convolutional neural network algorithm and four operation instructions for calculation. The operations Instructions include CONVOLUTION instruction, POOLING instruction, CONV_POOLING instruction and GLOBAL_POOLING instruction. Wherein, the SETUP command is referred to as the first command in the following embodiments. The CONVOLUTION instruction is called the second instruction and is used to control the coprocessor to perform convolution operation. The POOLING instruction is called the third instruction, and is used to control the coprocessor to perform local pooling operations. The CONV_POOLING instruction is c...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com