Rapid IO interface suitable for RISC-V architecture kernel

A RISC-V, fast technology, applied in the direction of instrumentation, electrical digital data processing, etc., can solve complex problems

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

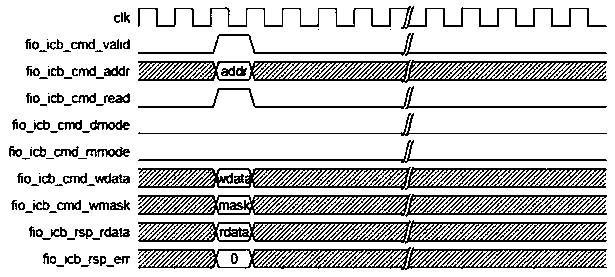

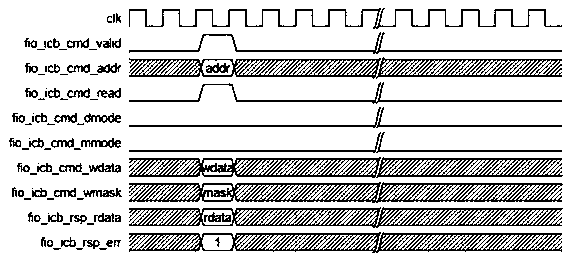

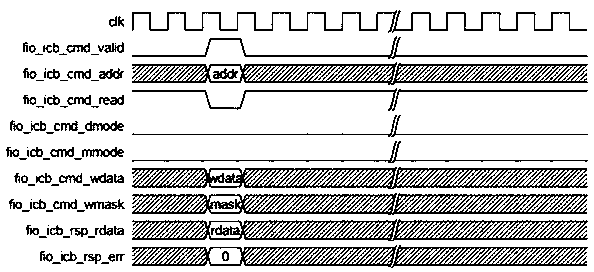

[0038] The FIO interface design of the present invention includes the following interface signals, including fio_icb_cmd_valid, fio_icb_cmd_addr, fio_icb_cmd_read, fio_icb_cmd_dmode, fio_icb_cmd_mmode, fio_icb_cmd_wdata, fio_icb_cmd_wmask, fio_icb_rsp_rdata, fio_icb_rsp_err, as shown in Table 1.

[0039] Table 1. FIO interface design signal list and description table of the present invention

[0040]

[0041] in:

[0042] The fio_icb_cmd_valid (FIO access request command valid control signal), when the signal is 1, means that the current access of the FIO interface is a valid access, and when the signal is 0, it means that the current access of the FIO interface is an invalid access .

[0043] The fio_icb_cmd_addr (FIO access request command address signal), this signal indicates the address value of the current FIO access.

[0044] The fio_icb_cmd_read (FIO access request command read and write control signal), when the signal is 1, means that the current access of the F...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com