Face recognition acceleration circuit system and acceleration method based on RISC-V

A RISC-V, face recognition technology, applied in character and pattern recognition, instruments, biological neural network models, etc., can solve the problem of unfavorable algorithm end-based rapid deployment, expensive ISA authorization, project cost control and development cycle budget It is difficult to meet expectations and other problems to achieve the effect of improving the efficiency of imitation storage and speeding up the calculation process

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

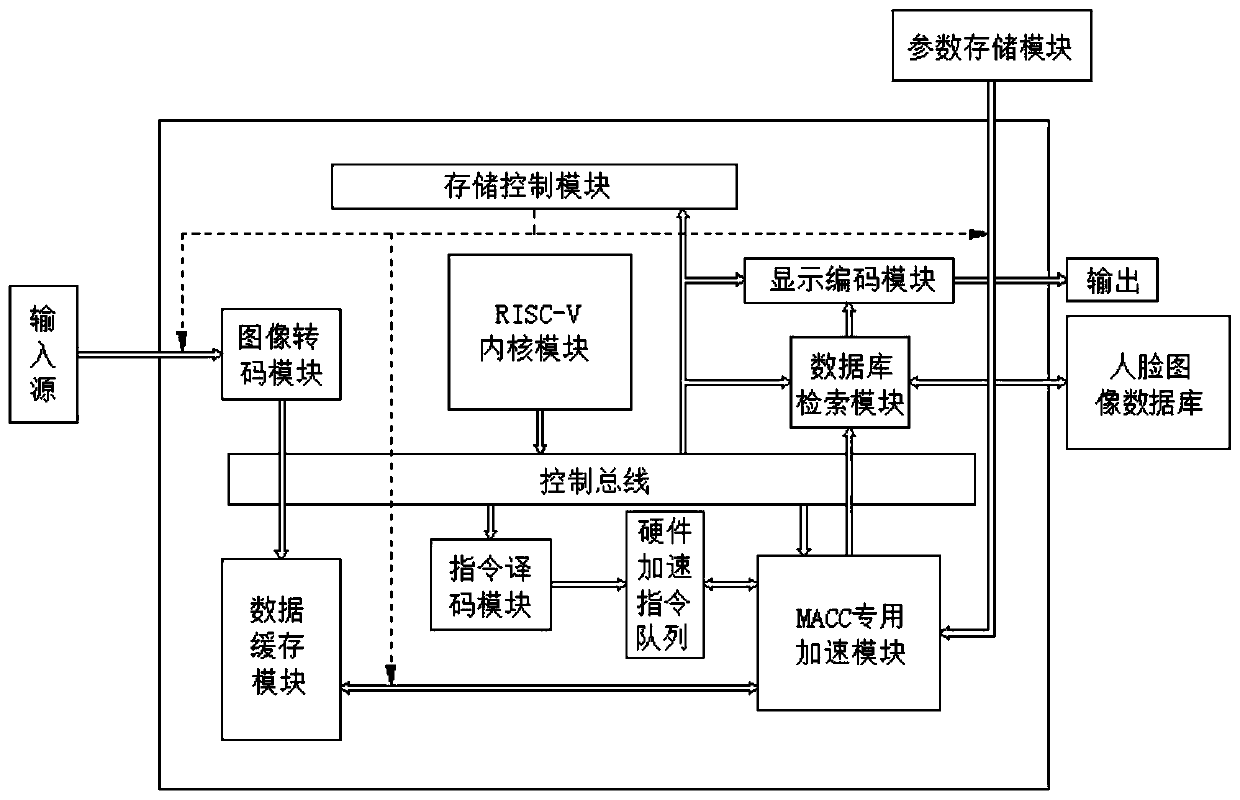

[0033] A face recognition acceleration circuit system based on RISC-V, including an image acquisition module, a RISC-V kernel module, an instruction processing module, an acceleration module, a parameter storage module, a storage control module and a face image processing module, and between each module communication connection;

[0034] The image acquisition module includes an image transcoding module and a data cache module;

[0035] The instruction processing module includes an instruction decoding module and a hardware acceleration instruction queuing module;

[0036] The face image processing module includes a database retrieval module and a display coding module;

[0037] The RISC-V kernel module is a microprocessor composed of an open source simplified instruction set architecture. The storage control module is hung on the control bus. According to the high-level language description of the face recognition algorithm, it is decoded by the compiler in the RISC-V kernel ...

Embodiment 2

[0046] On the basis of Embodiment 1, the parameters of the deep neural network include convolution kernel values, convolution kernel bias values, and convolution kernel activation thresholds for each layer of convolution;

[0047] The RISC-V kernel module controls the storage control module, and transmits the transcoded image information to the MACC dedicated acceleration module;

[0048] The RISC-V kernel module controls the MACC dedicated acceleration module to load the convolution kernel value, convolution kernel offset value, and convolution kernel activation threshold of each layer of convolution, and the MACC dedicated acceleration module controls the convolution kernel value and data cache module The image data is multiplied by the multiplication array, and after the product and the convolution kernel offset value are added and summed, the activation threshold of the convolution kernel is selected and output to obtain the face feature value; the convolution calculation i...

Embodiment 3

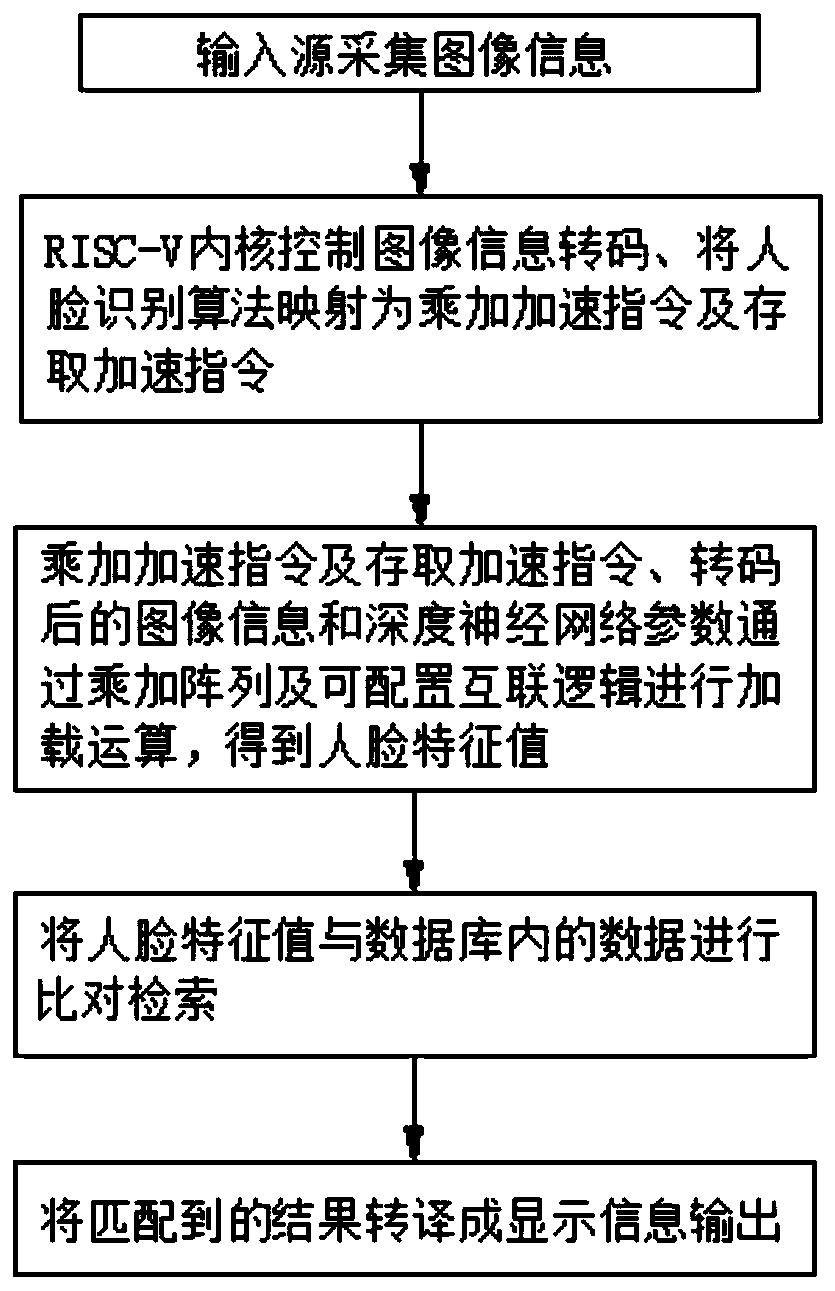

[0050] A face recognition acceleration method based on RISC-V, using the RISC-V core to build an open instruction set architecture to achieve face recognition acceleration;

[0051] The RISC-V core controls the process of transcoding and caching the data of each frame of the collected image information arranged in the form of each pixel RGB (8:8:8);

[0052] And control the process of translating and mapping the face recognition algorithm into multiplication acceleration instructions and access acceleration instructions, and temporarily storing the instructions in the order of reading;

[0053] At the same time, control the MACC dedicated acceleration module to use the multiplication acceleration instruction and the access acceleration instruction to accelerate the process of performing deep neural network parameter calculation on the transcoded image information to obtain the face feature value;

[0054] And control the search and comparison of the face feature value and the ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com