Interrupt system for RISC-V architecture

A RISC-V, a series of technologies, applied in the address formation of the next instruction, multi-program device, instrument, etc., can solve the problems of slow saving speed, low efficiency of interrupt subroutine entry, etc., and achieve the effect of shortening the time

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

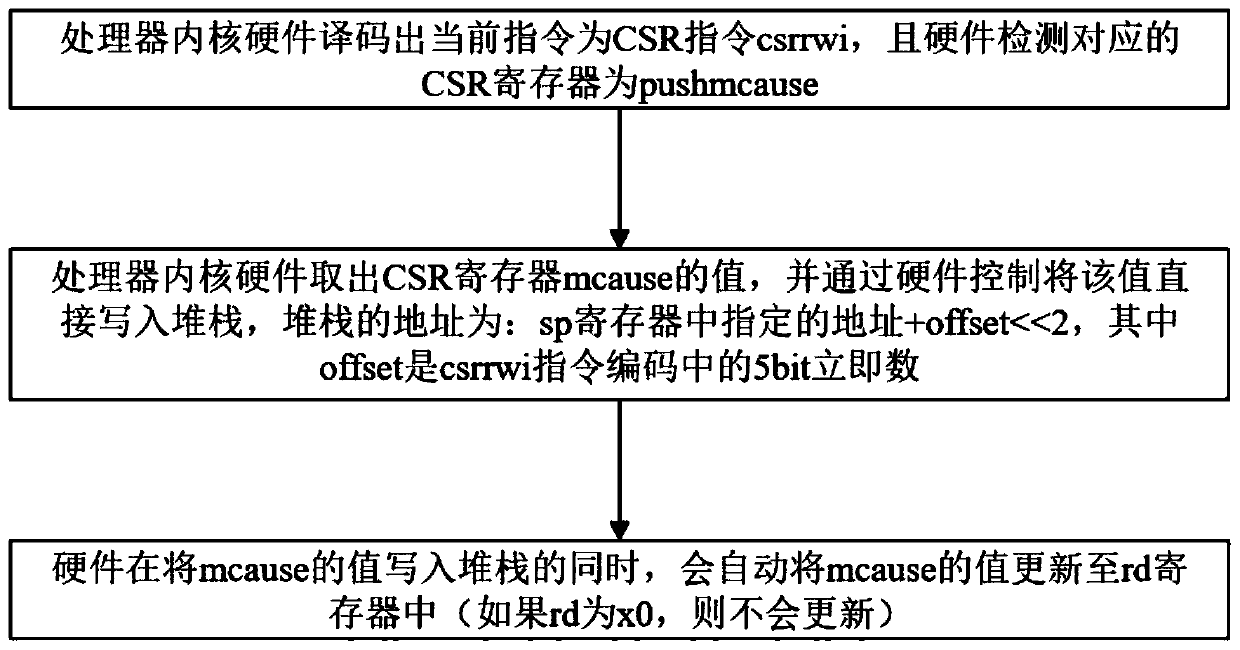

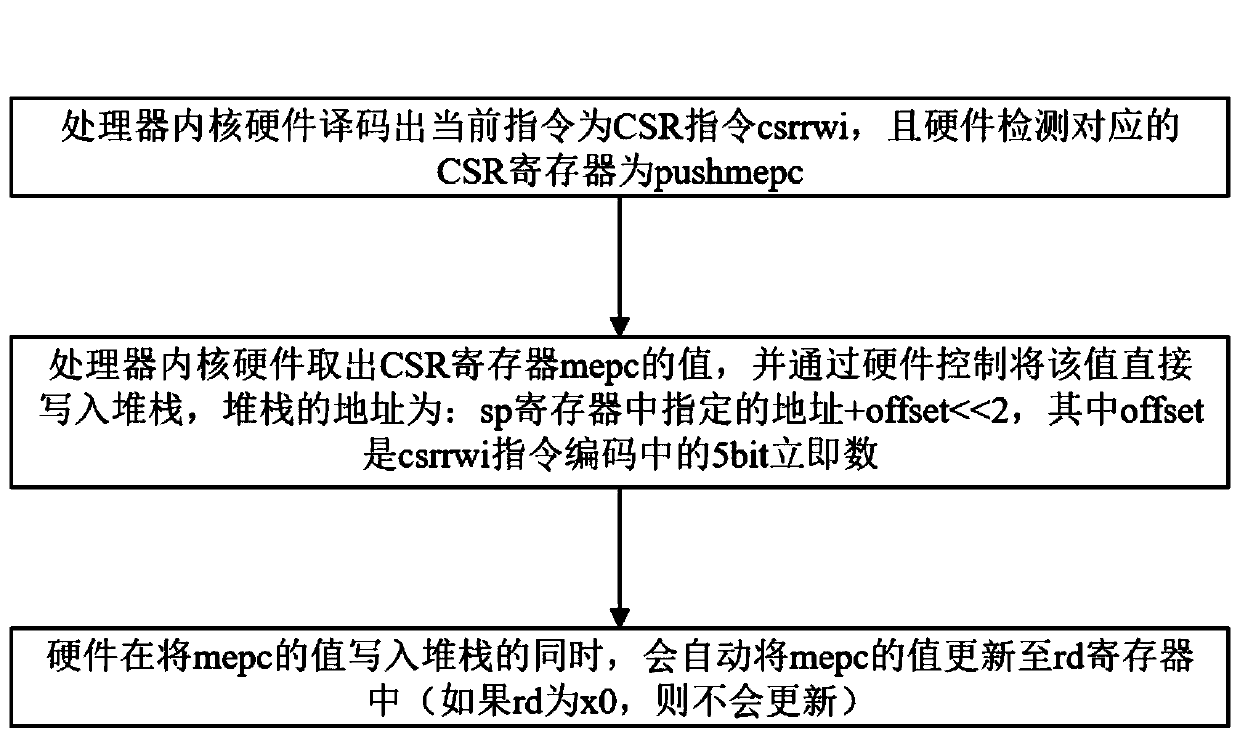

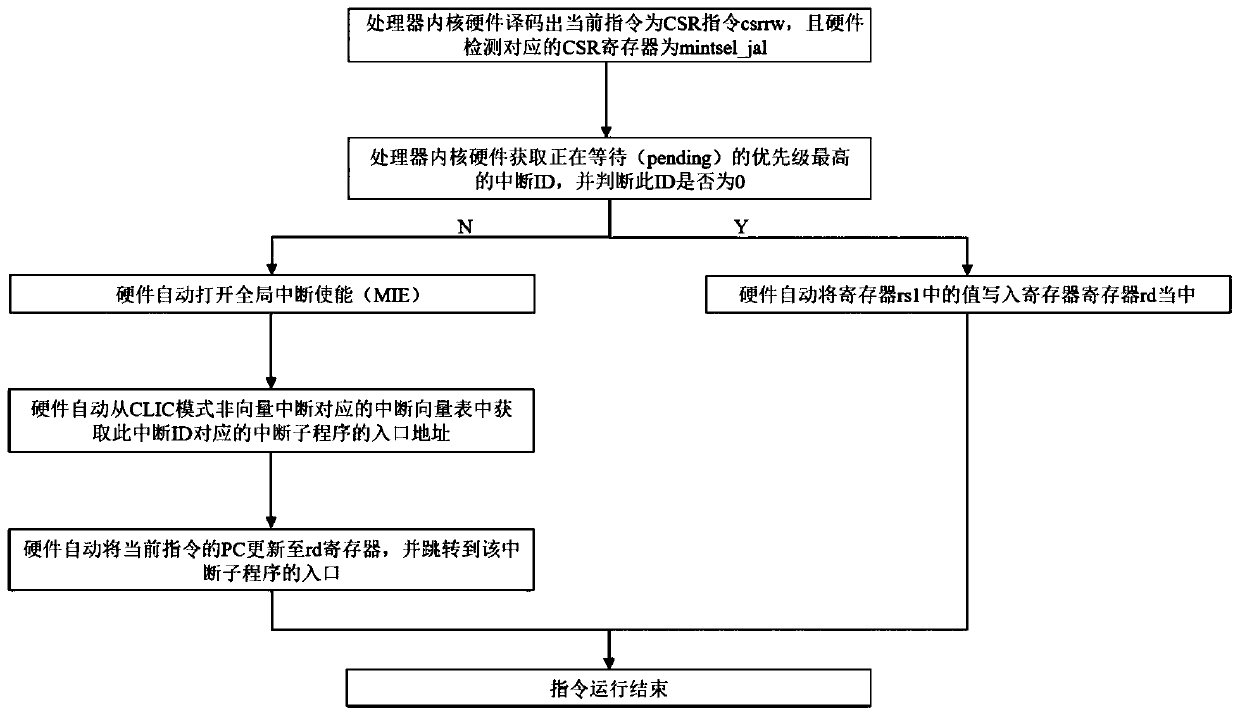

[0056] The following will clearly and completely describe the technical solutions in the embodiments of the present invention with reference to the drawings in the embodiments of the present invention.

[0057] The present invention provides an interrupt system for RISC-V architecture. Its working principle is to reduce the number of instructions to run by adding registers or changing some instructions, so as to improve the speed of saving the value in the register and shorten the jump to the corresponding Interrupt the time of subroutine entry to improve efficiency.

[0058] The present invention will be described in further detail below in conjunction with examples and specific implementation methods.

[0059] An interrupt system for RISC-V architecture, the system includes: mstatus register, medeleg register, mideleg register, mie register, mtvec register, mtvt register, mscratch register, mepc register, mcause register, mtval register, mip register, mnxti register, mintst...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com