Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

386results about How to "Reduced conversion time" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

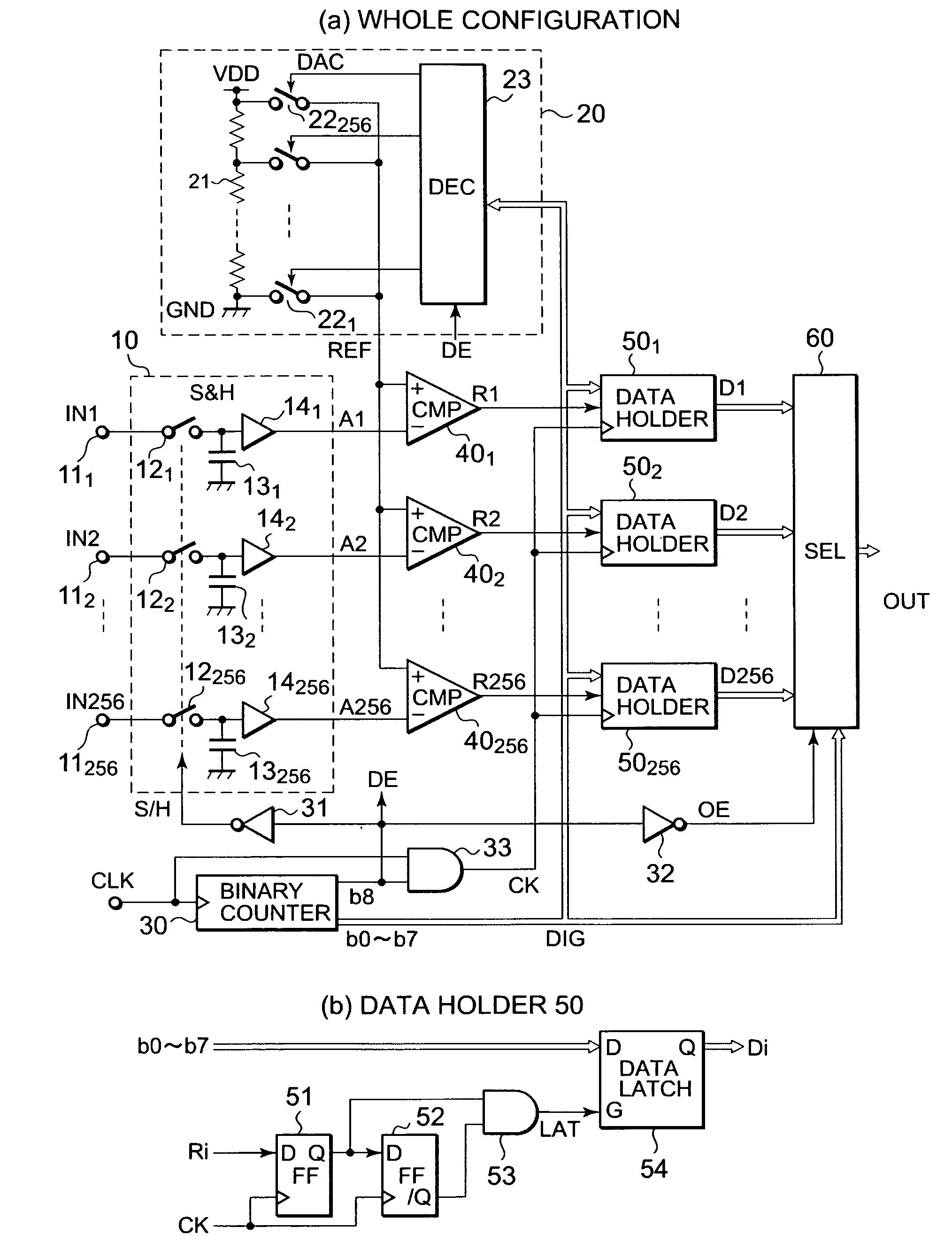

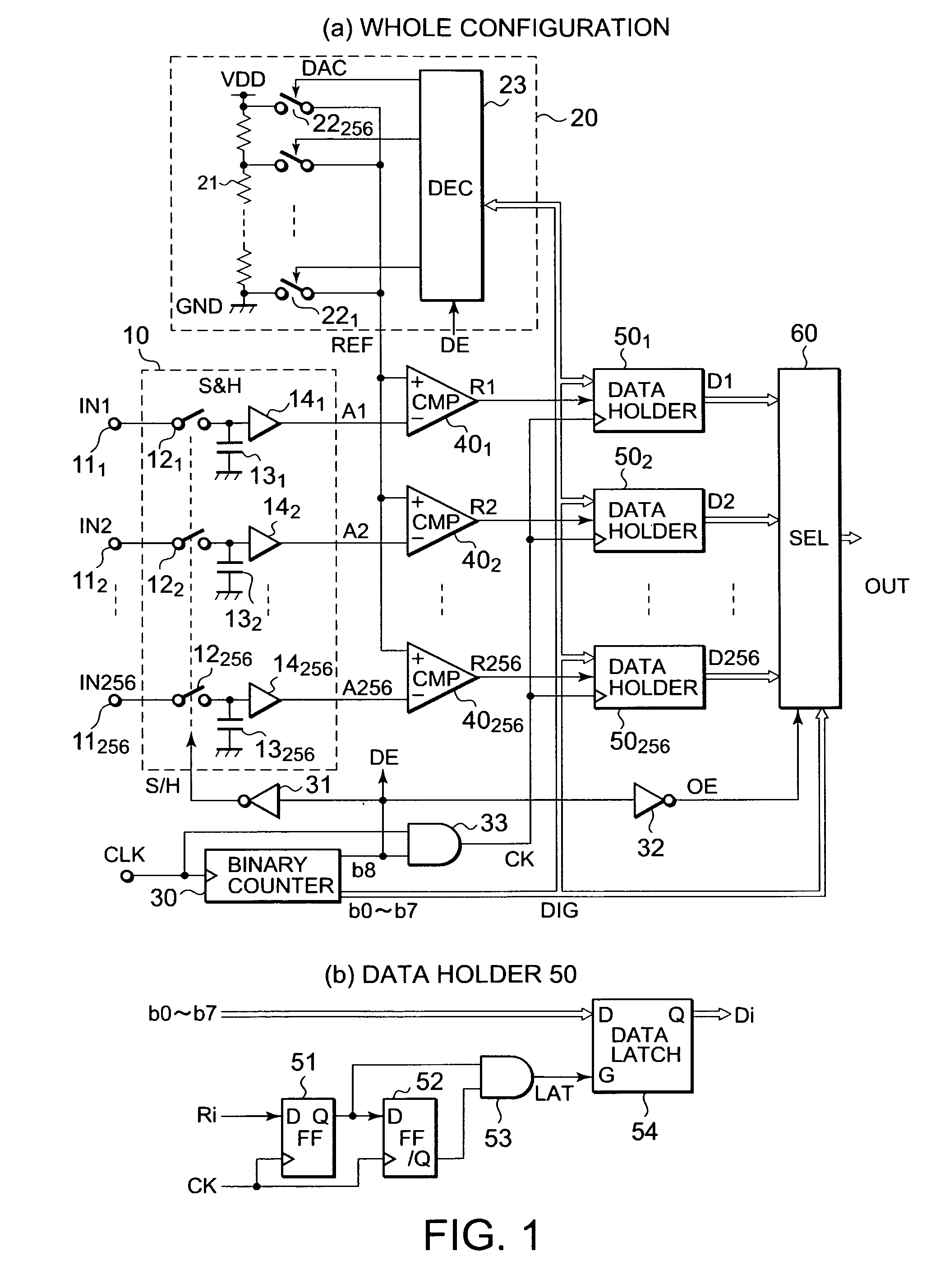

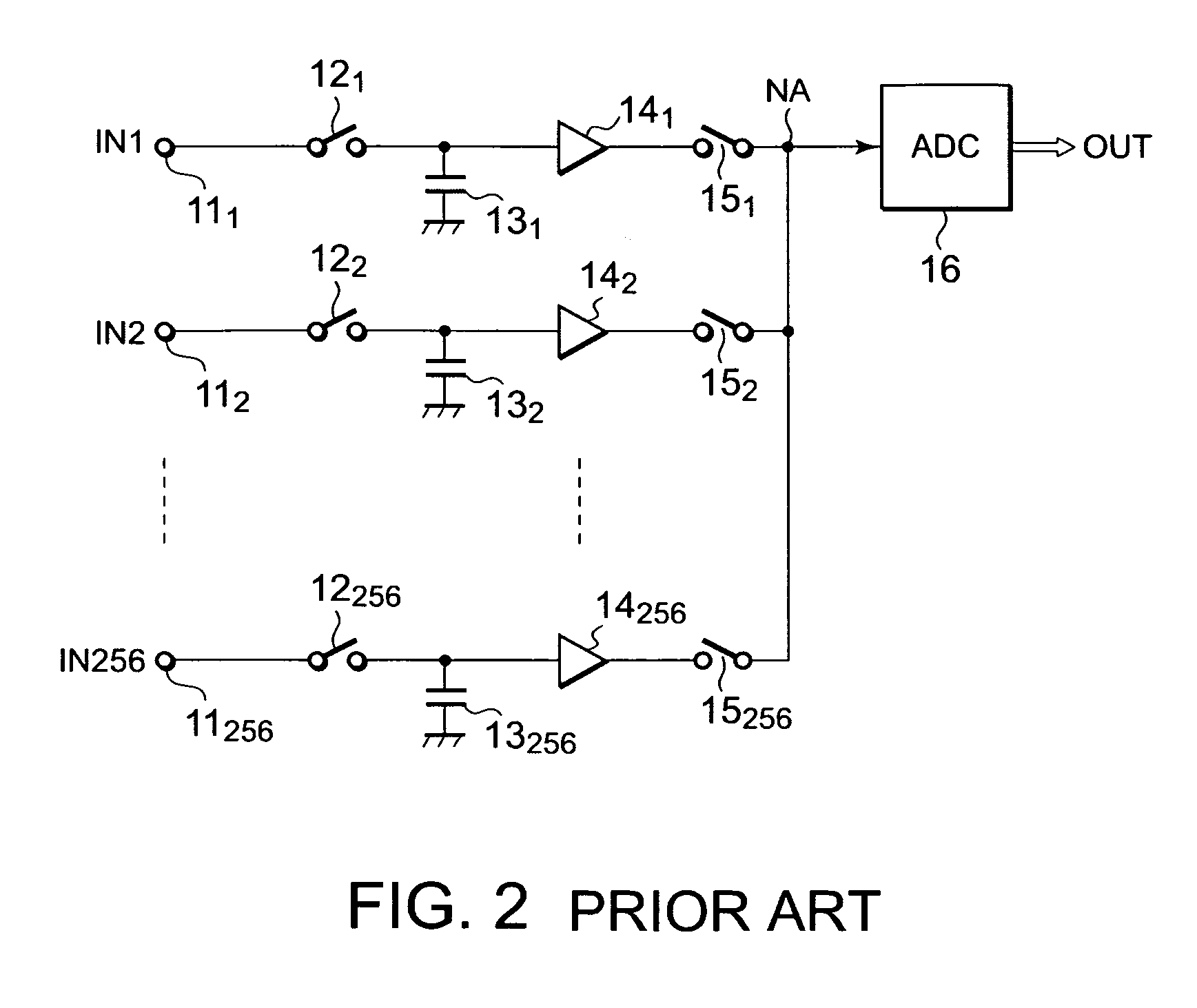

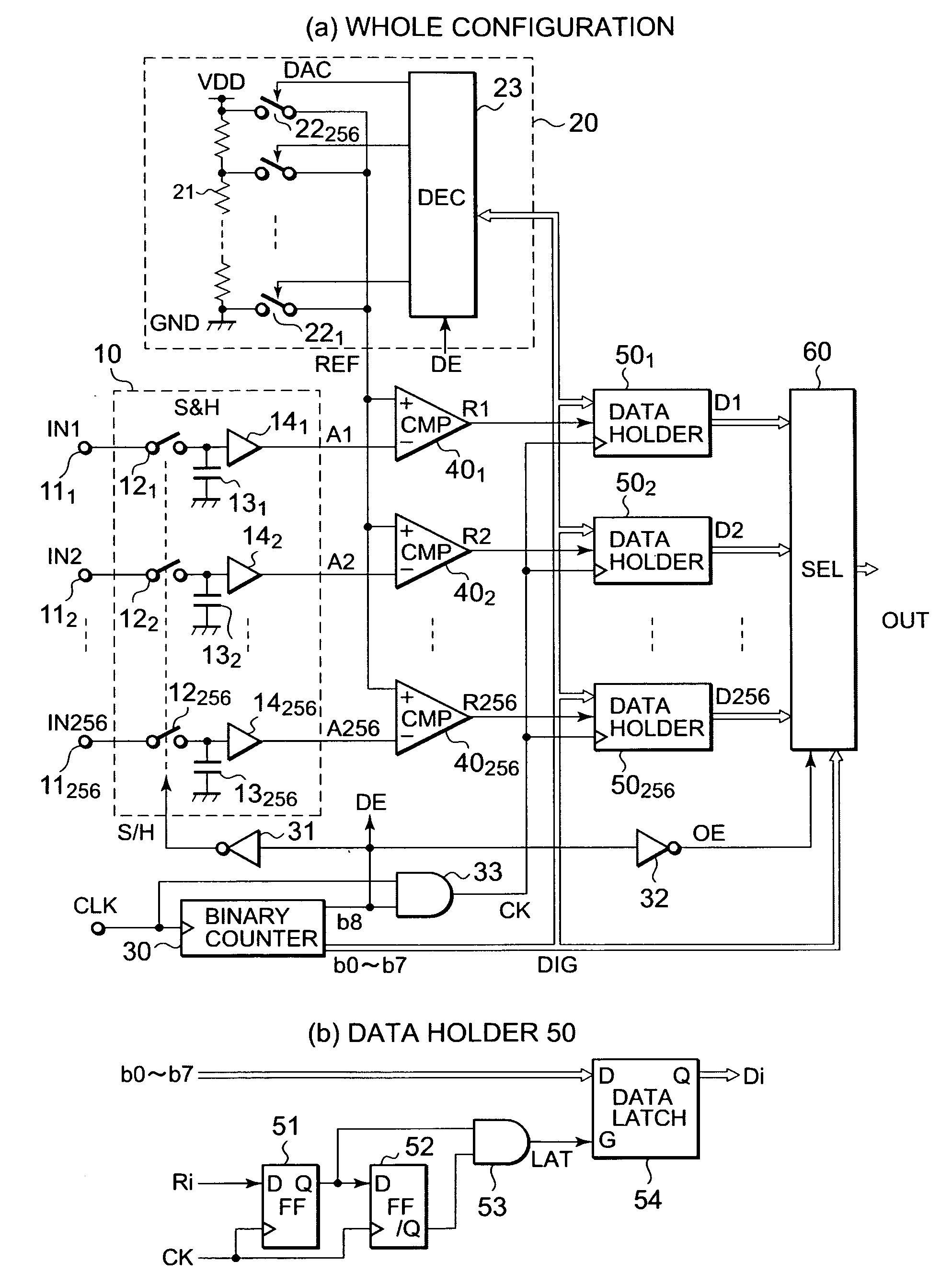

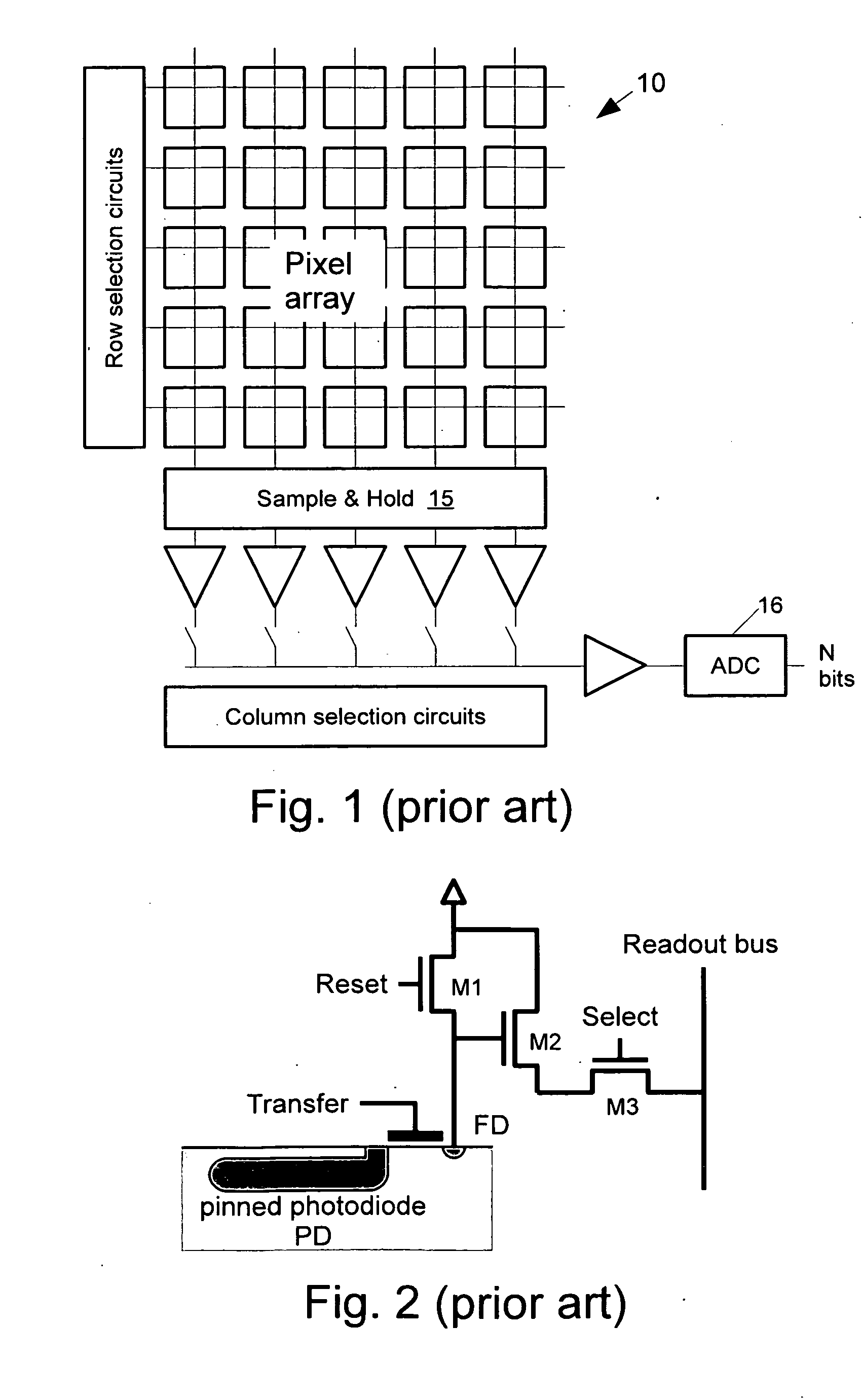

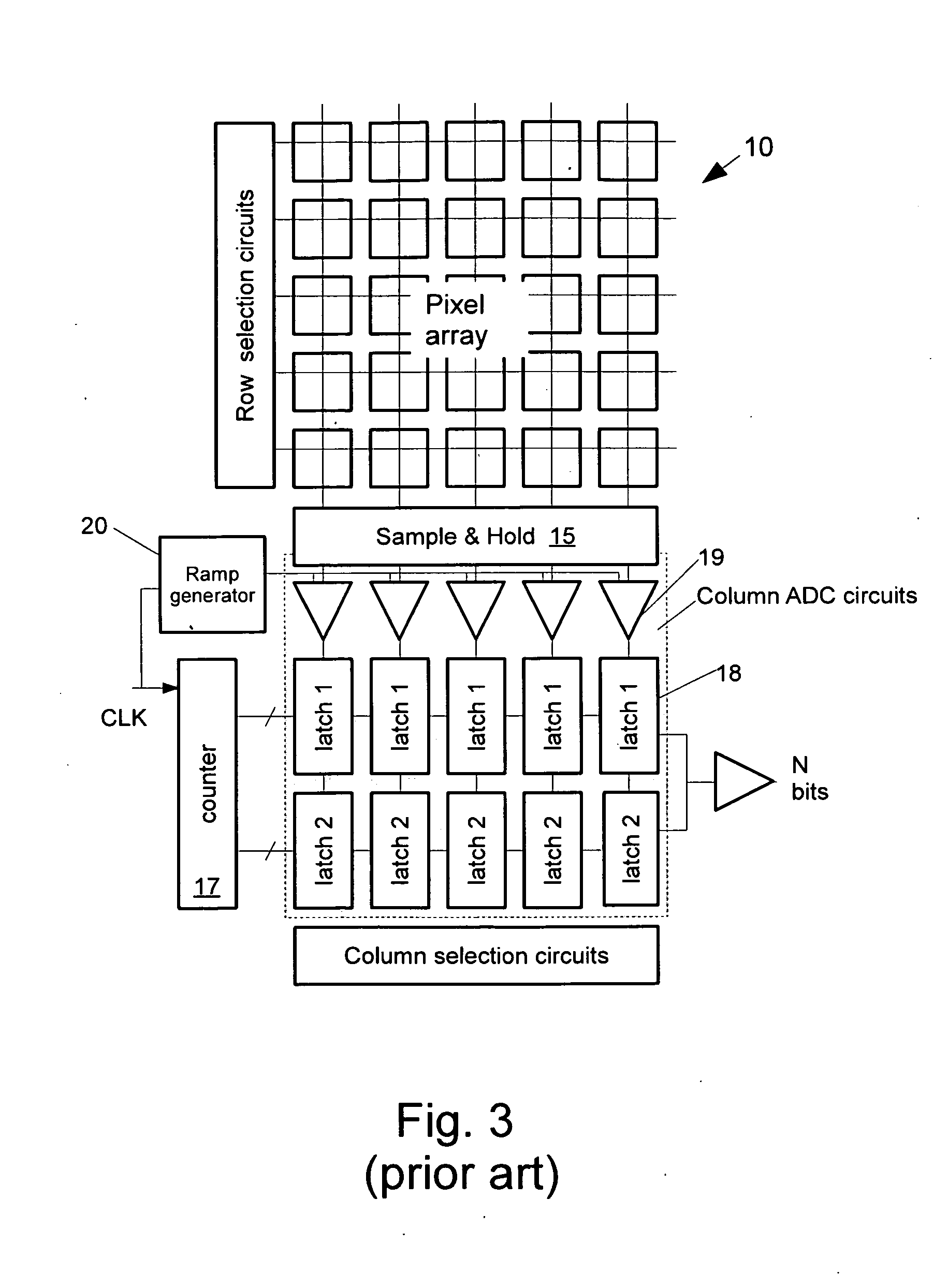

Analog-digital converter circuit

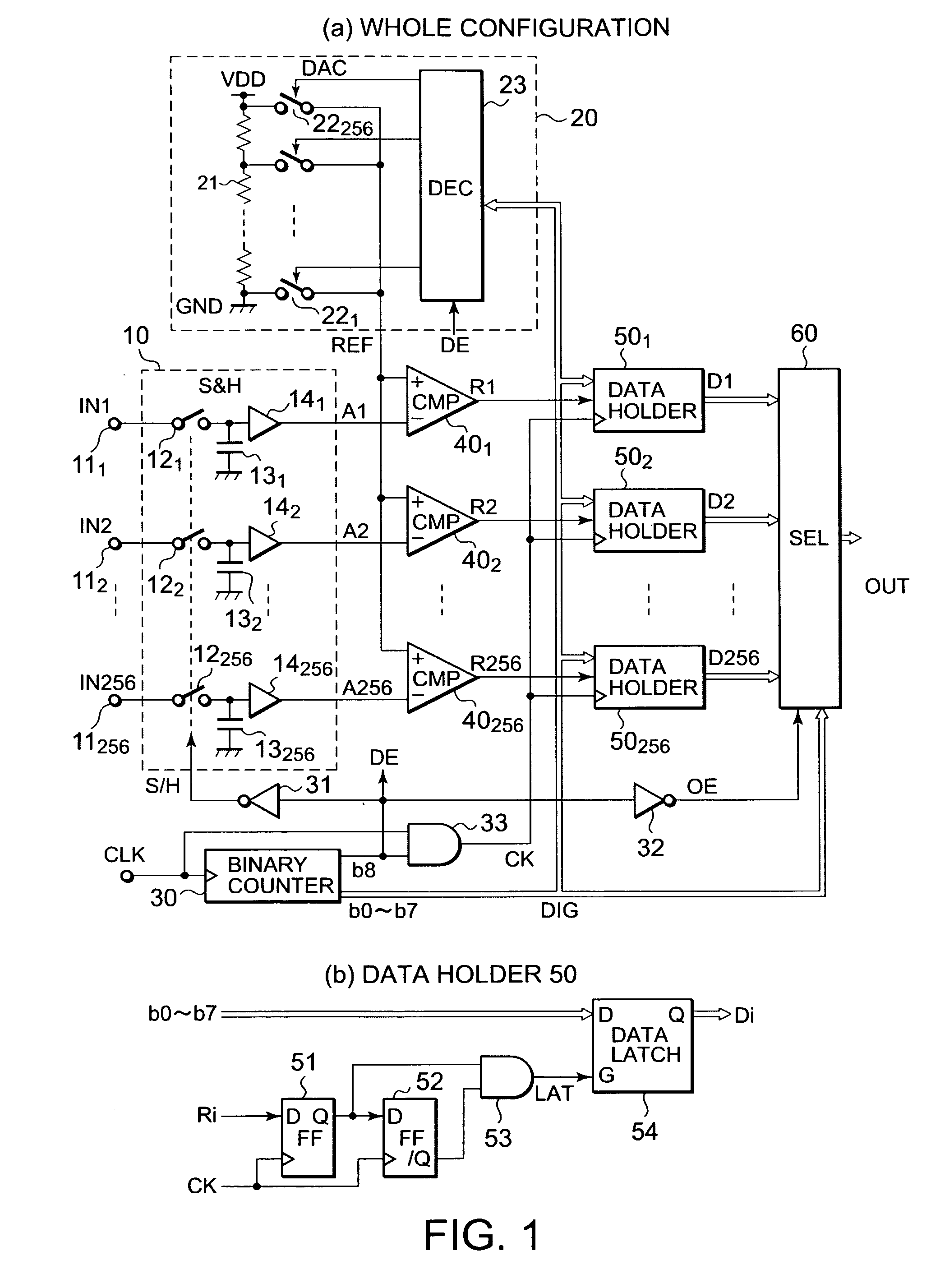

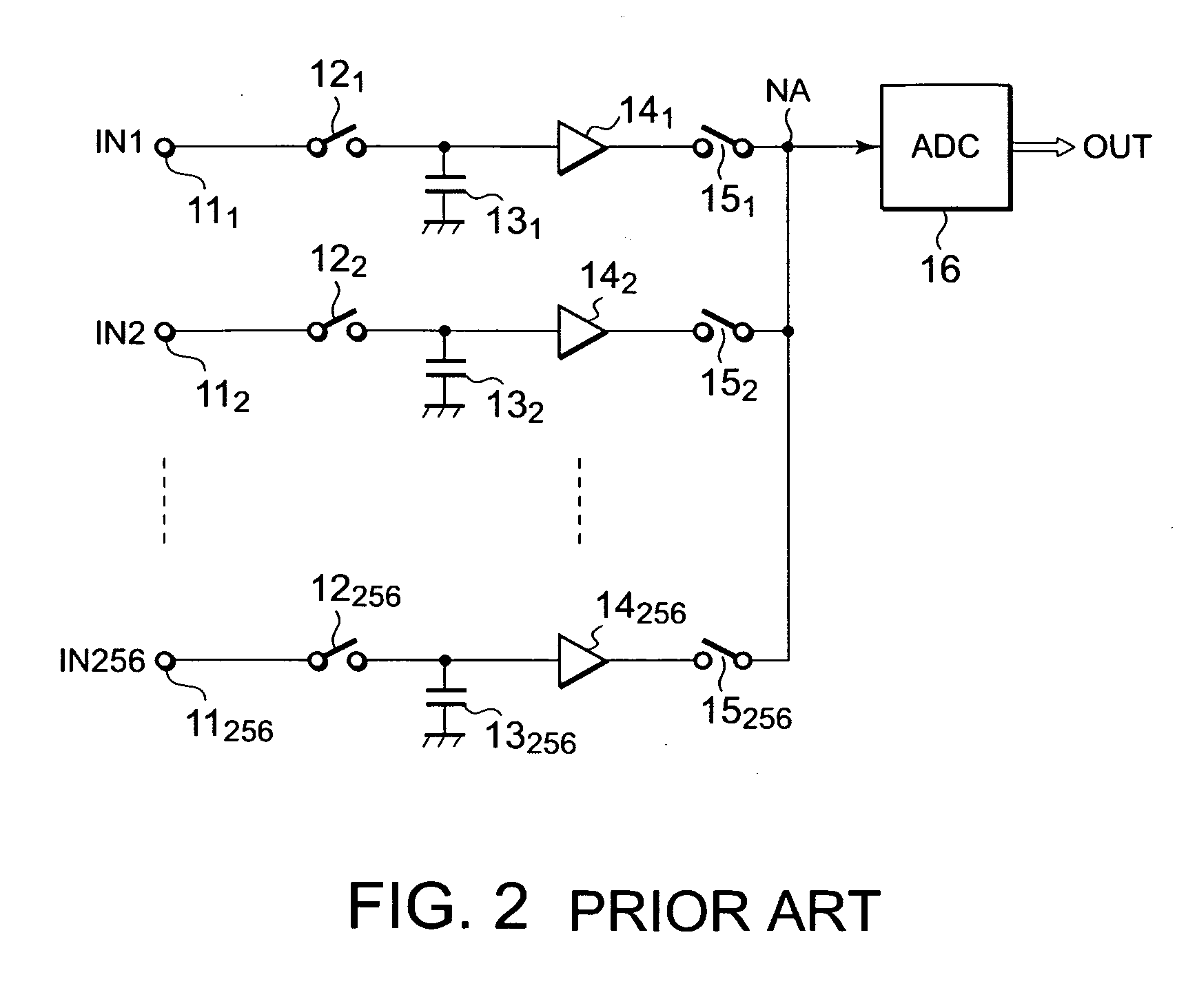

ActiveUS7372390B2Reduced conversion timeSimple circuit configurationElectric signal transmission systemsAnalogue-digital convertersMulti inputCurrent consumption

The present invention provides a multi-input A / D converter circuit capable of shorting a conversion time without increasing its layout area and current consumption. When a most significant bit of a binary counter is “L”, individual input signals are sampled by a sample and hold unit, and digital signals held in respective data holders are sequentially selected by a selector. When the most significant bit is brought to “H”, the respective input signals are held as analog signals and compared with each of reference voltages produced corresponding to a digital signal by a DAC. When decision signals outputted from comparators are changed from “L” to “H”, the digital signal at that time is held in the individual data holders as digital signals.

Owner:LAPIS SEMICON CO LTD

Analog-digital converter circuit

ActiveUS20070188367A1Reduced conversion timeSimple circuit configurationElectric signal transmission systemsAnalogue-digital convertersMulti inputA d converter

The present invention provides a multi-input A / D converter circuit capable of shorting a conversion time without increasing its layout area and current consumption. When a most significant bit of a binary counter is “L”, individual input signals are sampled by a sample and hold unit, and digital signals held in respective data holders are sequentially selected by a selector. When the most significant bit is brought to “H”, the respective input signals are held as analog signals and compared with each of reference voltages produced corresponding to a digital signal by a DAC. When decision signals outputted from comparators are changed from “L” to “H”, the digital signal at that time is held in the individual data holders as digital signals.

Owner:LAPIS SEMICON CO LTD

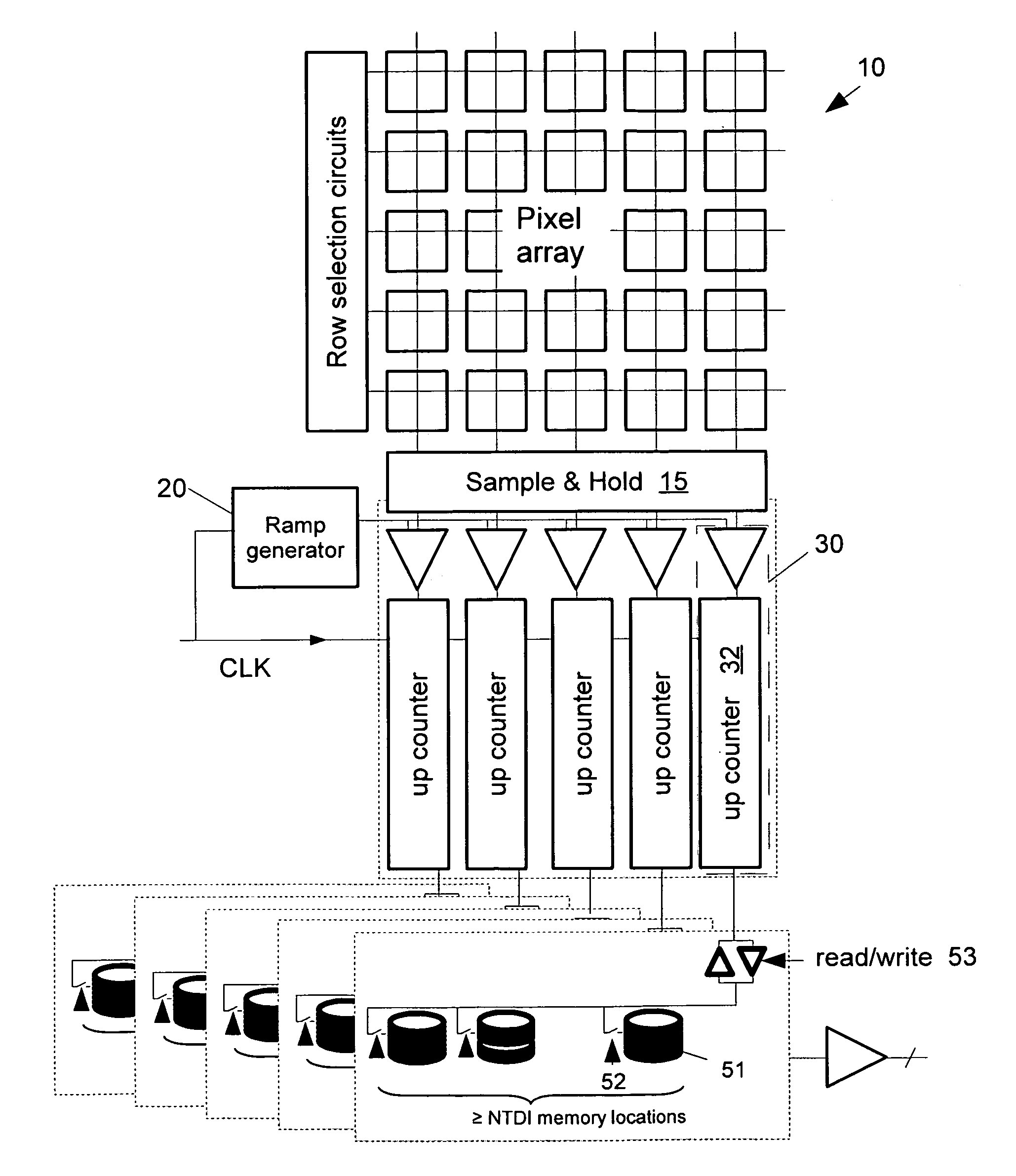

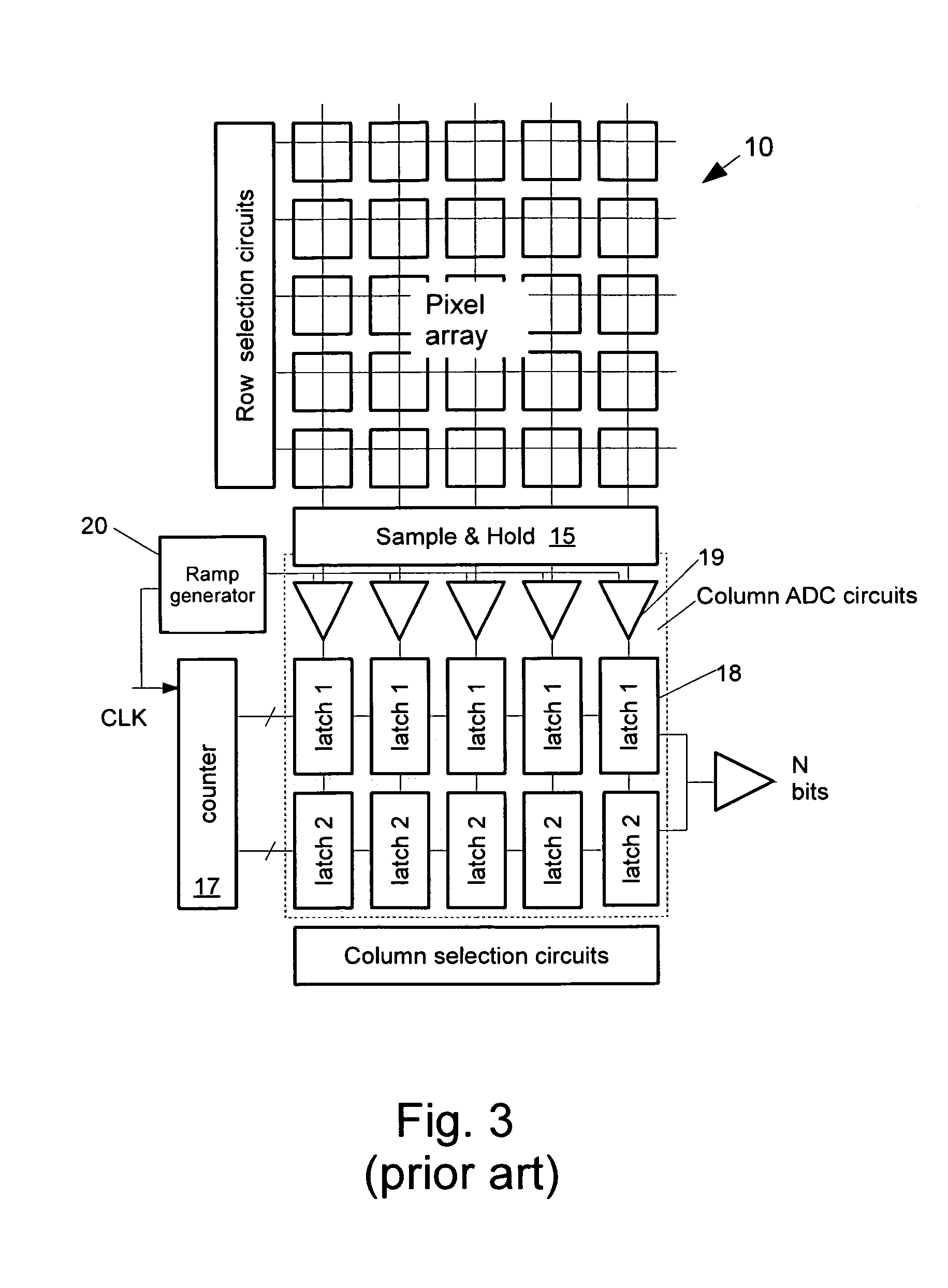

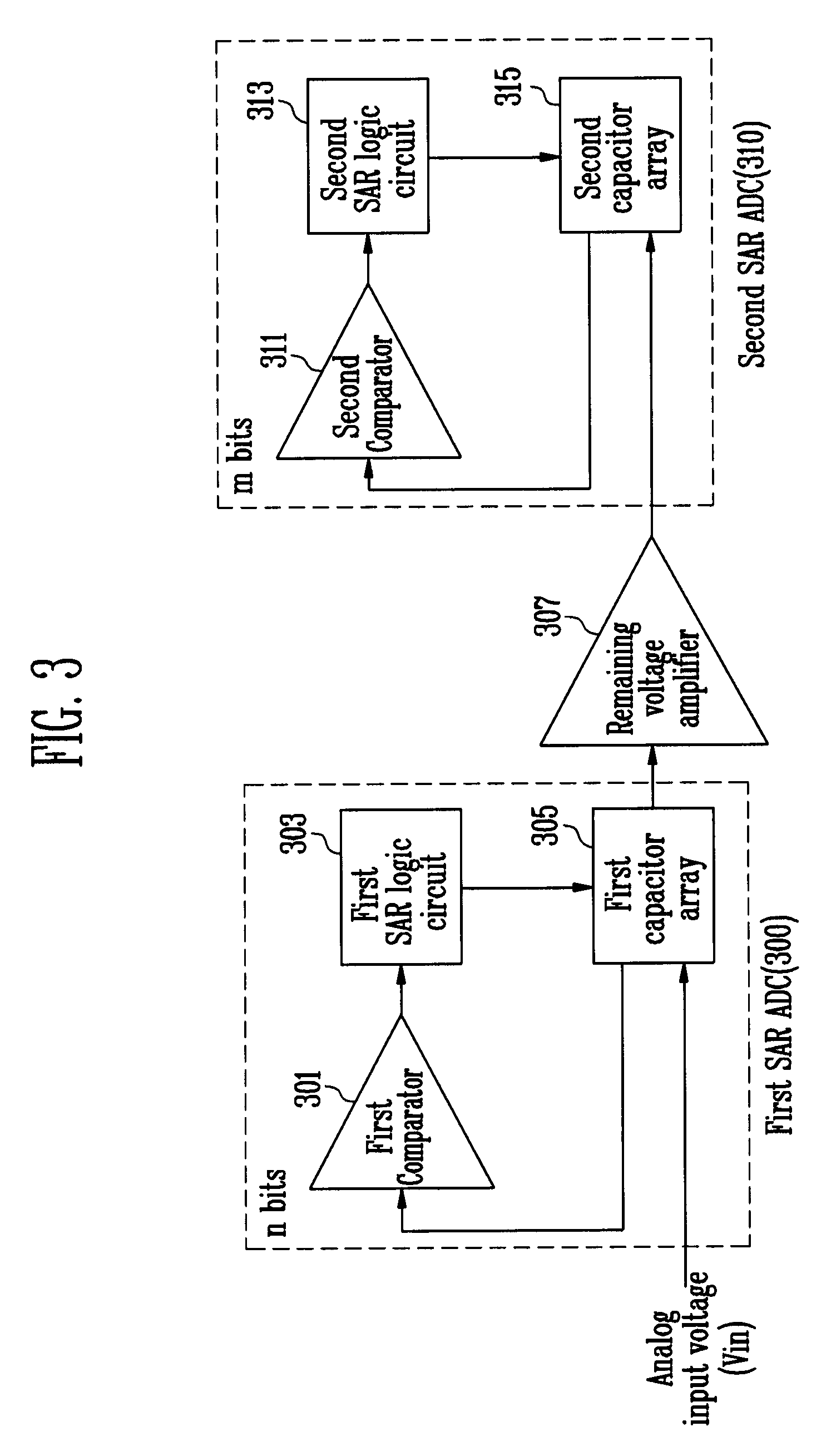

Analog-to-digital conversion in pixel arrays

ActiveUS7880662B2Improve accuracyAvoid the needAnalogue/digital conversionTelevision system detailsExposure periodAnalog signal

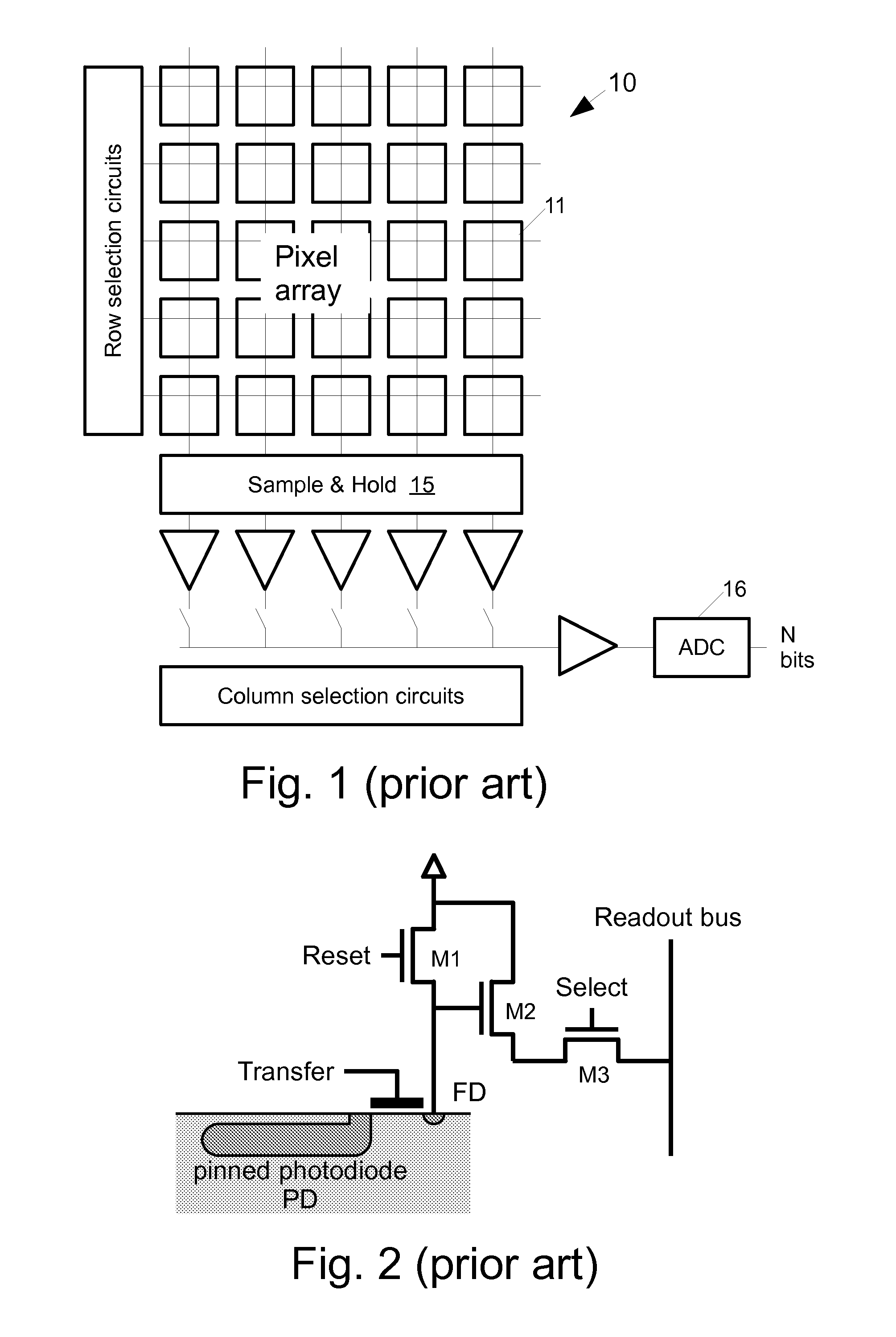

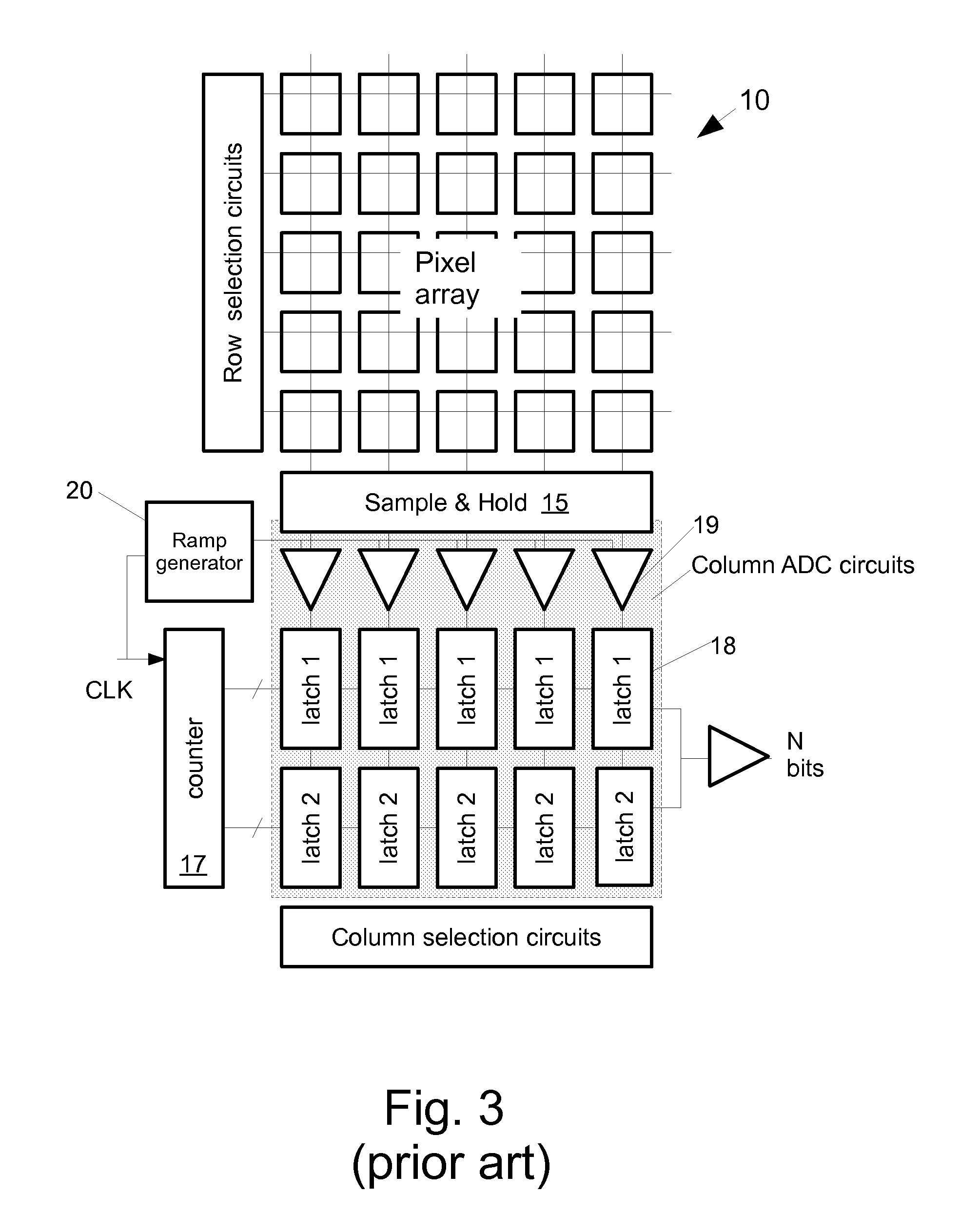

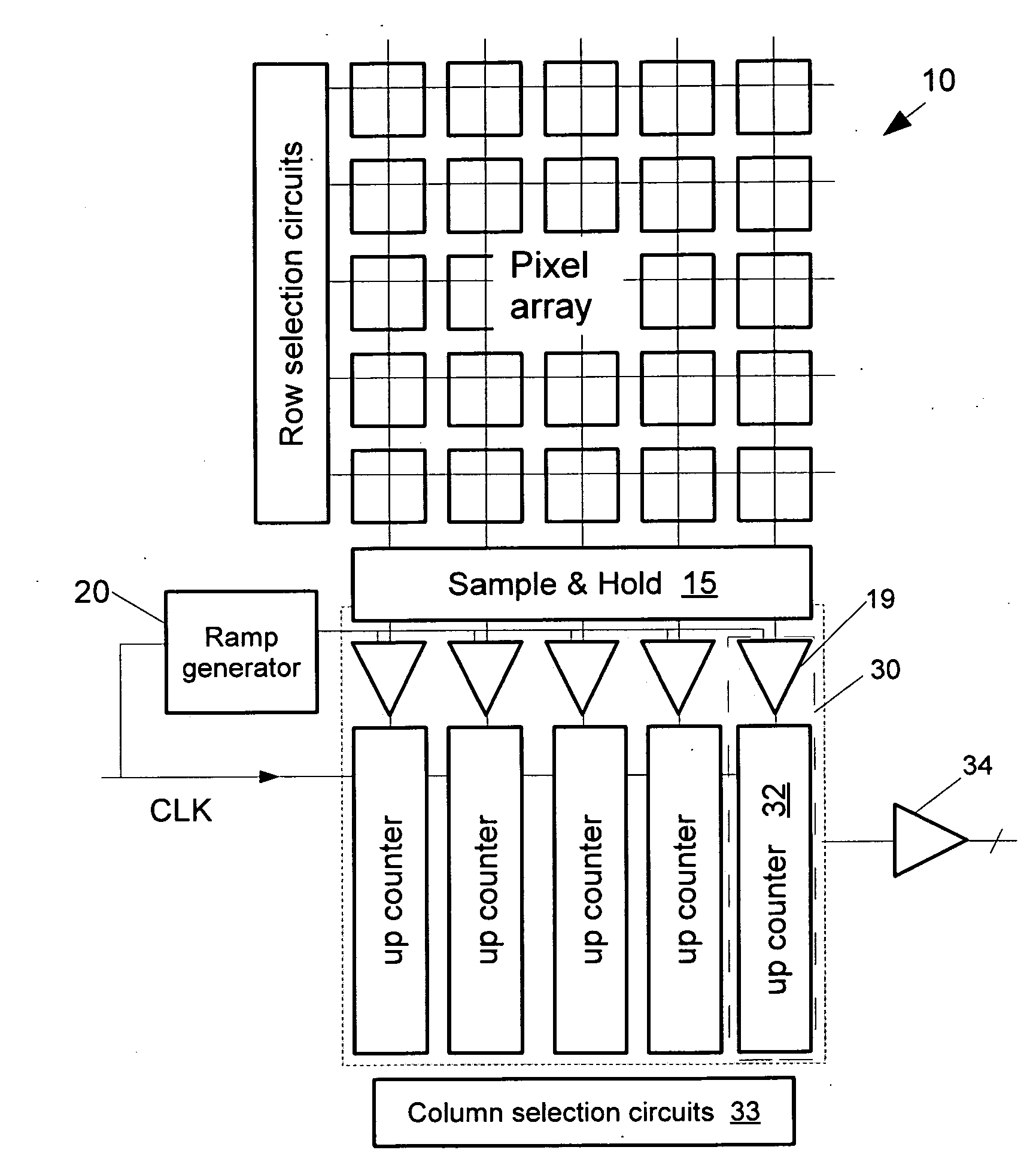

An analog-to-digital converter (ADC) generates an output digital value equivalent to the difference between two analog signal values. The ADC 30 receives a first analog signal level, a second analog signal level and a ramp signal. A counter 32 is operable to count in a single direction. A control stage is arranged to enable the counter 32 based on a comparison 19 of the ramp signal with the first analog signal and the second analog signal. A digital value accumulated by the counter during a period when it is enabled forms the output. The ADC can perform the conversion during a single cycle of the ramp signal. The counter 32 can be loaded with a starting digital value representing an exposure level accumulated during a previous exposure period. Techniques are described for reducing the conversion time.

Owner:CMOSIS

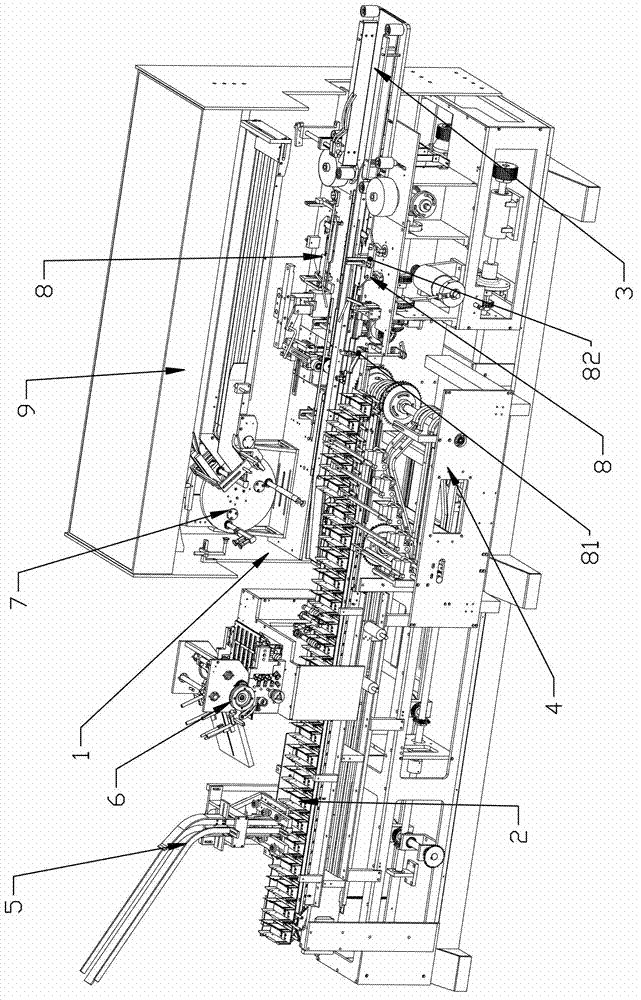

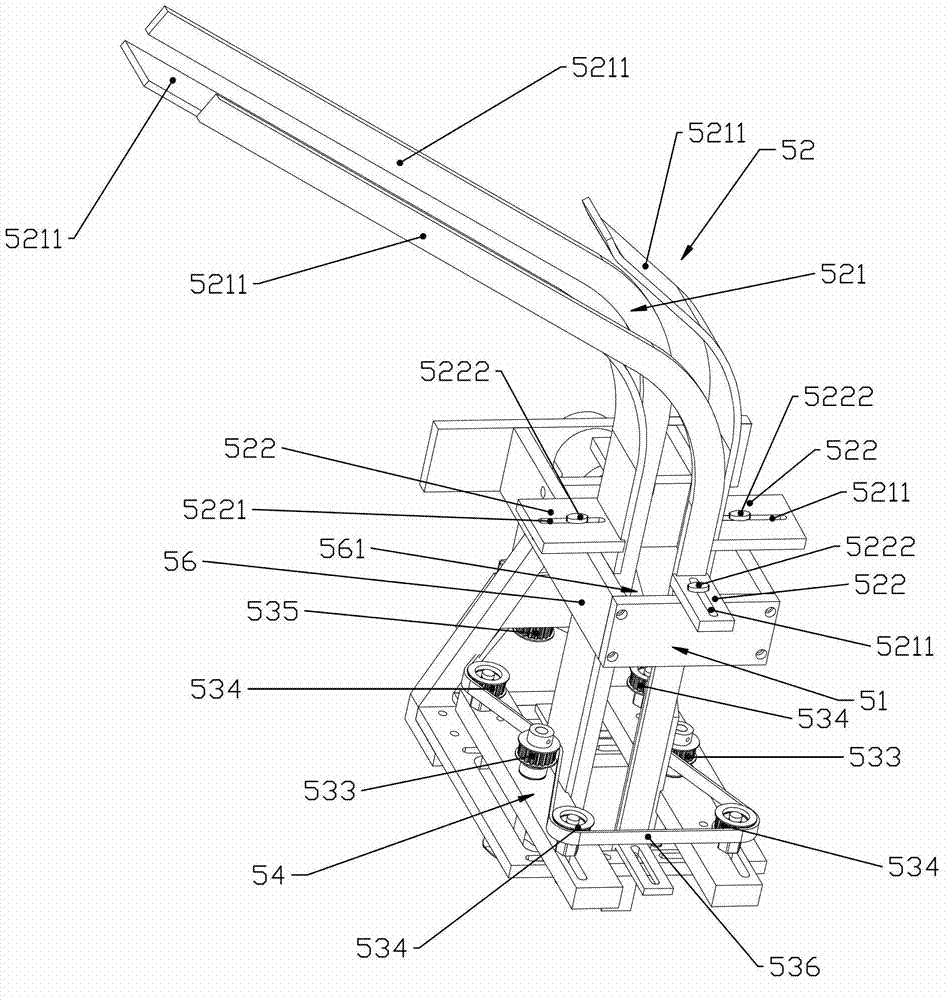

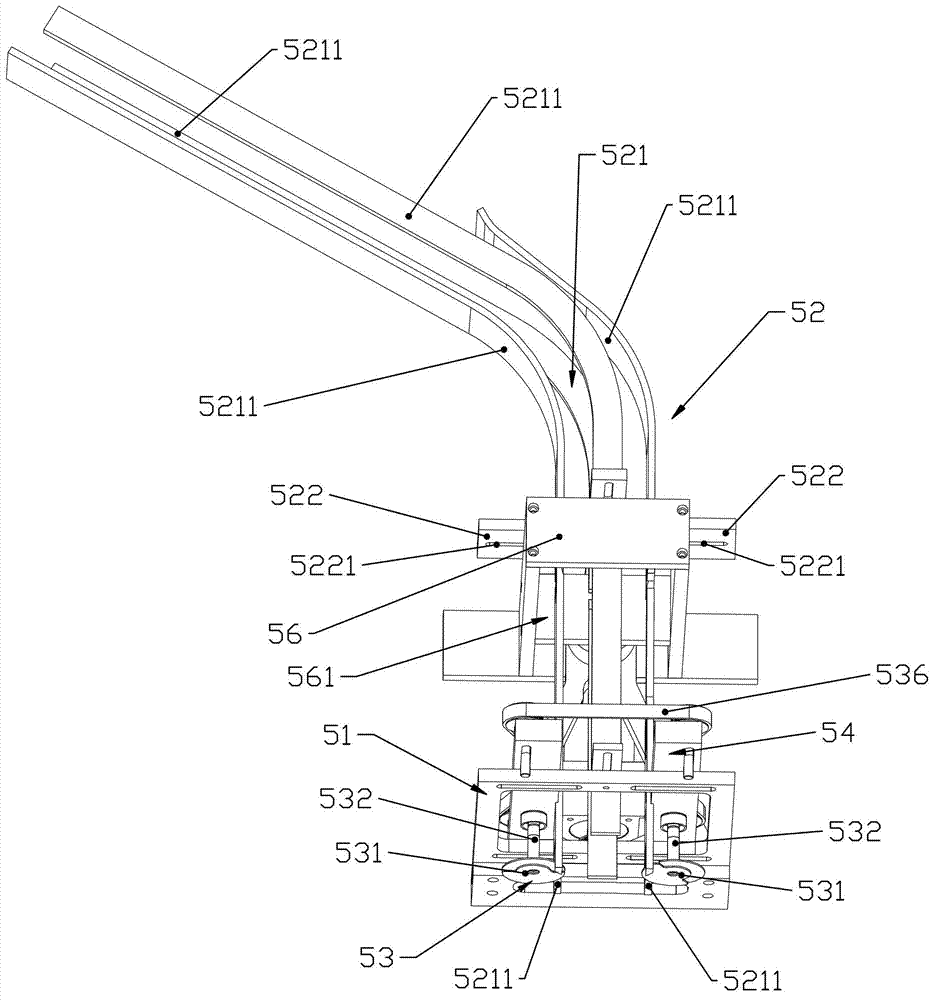

High-speed automatic medicine packing machine

The invention relates to a high-speed automatic medicine packing machine, comprising a machine frame, wherein the machine frame is provided with a medicine board conveying belt and a packaging box conveying belt; the medicine board conveying belt and the packaging box conveying belt are arranged in parallel, and parts of the medicine board conveying belt and the packaging box conveying belt are overlapped; the overlapped part of the medicine board conveying belt and the packaging box conveying belt is provided with a medicine board pushing device which is used for pushing the semi-finished products to the packaging box conveying belt from the medicine board conveying belt; a medicine adding device and a paper adding device are sequentially arranged from one end of the medicine board conveying belt, which is far away from the packaging box conveying belt to one end of the medicine board conveying belt, which is close to the packaging box conveying belt; and a box unfolding device and a sealing device are sequentially arranged from one end of the packaging box conveying belt, which is close to the medicine board conveying belt to one end of the packaging box conveying belt, which is far away from the medicine board conveying belt. The medicine adding device, the paper adding device, the box unfolding device, the sealing device, the medicine board pushing device, the medicine board conveying belt and the packaging box conveying belt are controlled by a controller through a circuit. After adopting the scheme, the high-speed automatic medicine packing machine provided by the invention is high in efficiency and attractive in appearance.

Owner:瑞安市华科包装机械有限公司

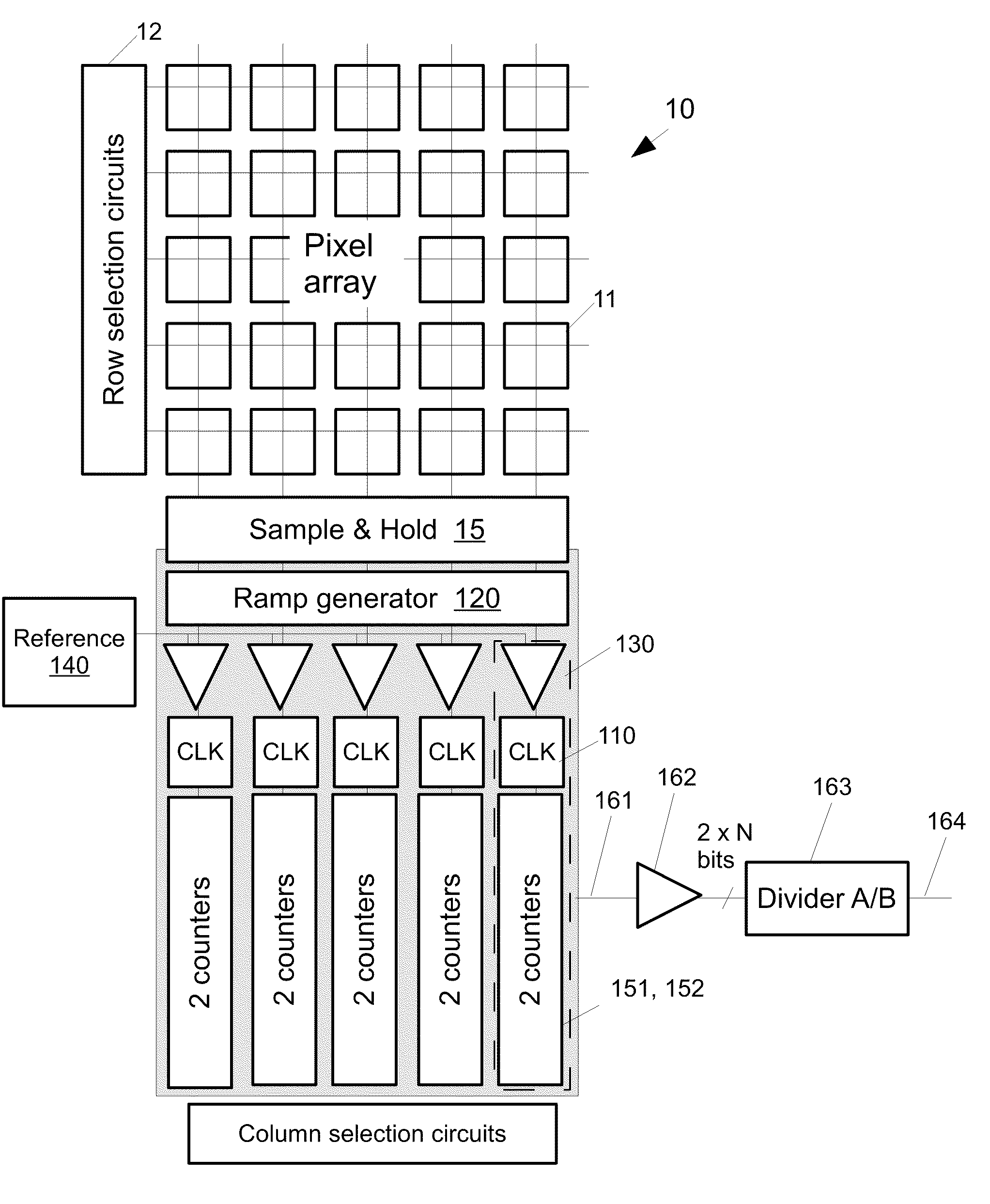

Analog-to-digital conversion in pixel array

ActiveUS20110115663A1Low powerQuick conversionElectric signal transmission systemsAnalogue-digital convertersA d converterEngineering

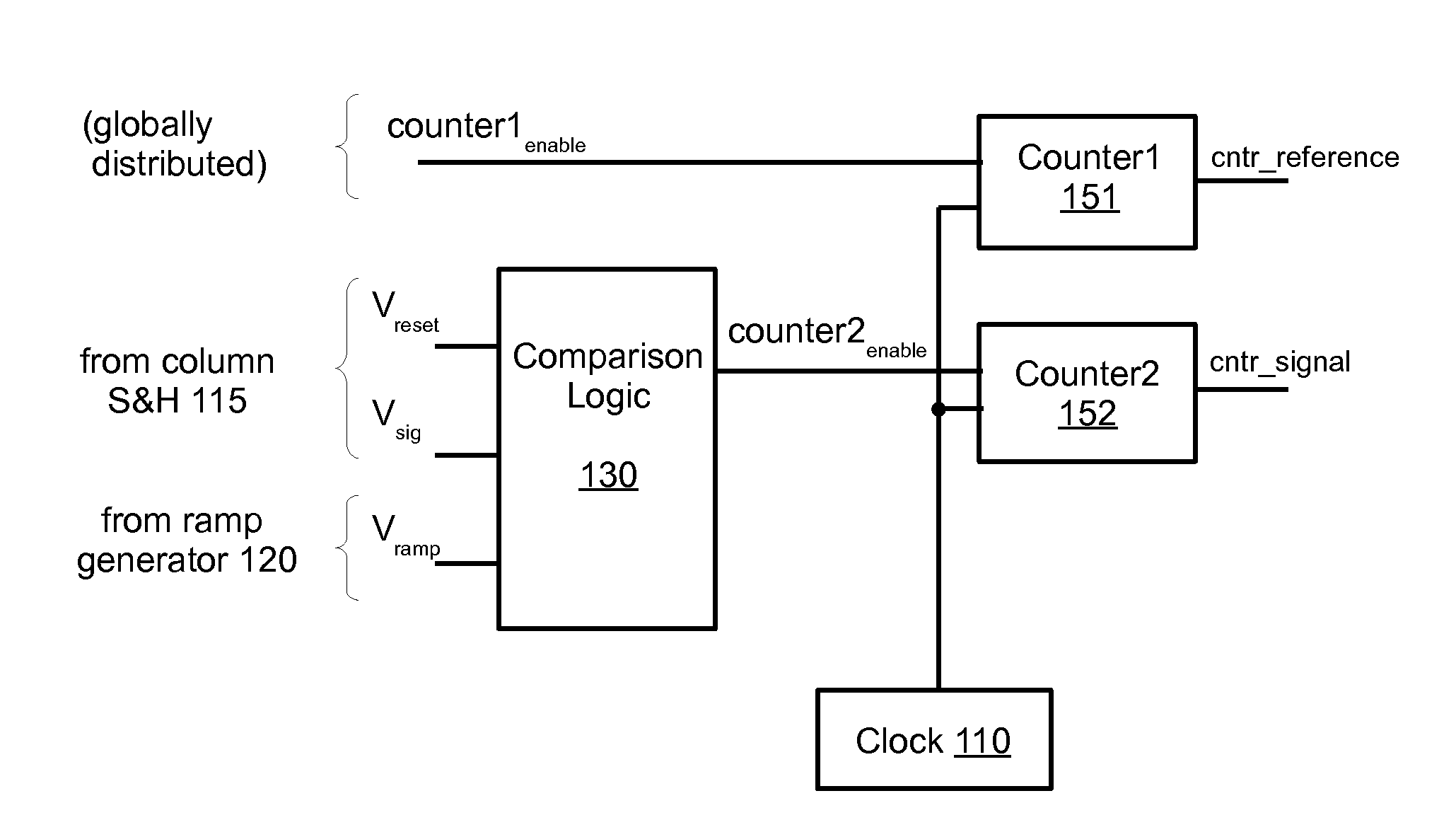

An analog-to-digital converter generates an output digital value equivalent to the difference between two analog signals. The converter forms part of a set of converters. The converter receives a first analog signal and a second analog signal (Vreset, Vsig) and a ramp signal (Vramp). A clock is dedicated to the converter, or a sub-set of converters. A control stage enables a first counter based on a comparison of the ramp signal with the first analog signal and the second analog signal. The converter can be calibrated by at least one reference signal (Vref1, Vref2) which is common to the set of converters. A-to-D conversion can include a first A-to-D conversion stage which determines a signal range, selected from a plurality of signal ranges, and a second A-to-D conversion stage which determines an M-bit digital value equivalent to the difference between the first and second analog signals by comparing the signals with a ramp signal, with the ramp signal having the signal range determined by the first analog-to-digital conversion stage.

Owner:CMOSIS

Analog-to-digital conversion in pixel arrays

ActiveUS20090256735A1Improve accuracyAvoid the needAnalogue/digital conversionTelevision system detailsExposure periodAnalog signal

An analog-to-digital converter (ADC) generates an output digital value equivalent to the difference between two analog signal values. The ADC 30 receives a first analog signal level, a second analog signal level and a ramp signal. A counter 32 is operable to count in a single direction. A control stage is arranged to enable the counter 32 based on a comparison 19 of the ramp signal with the first analog signal and the second analog signal. A digital value accumulated by the counter during a period when it is enabled forms the output. The ADC can perform the conversion during a single cycle of the ramp signal. The counter 32 can be loaded with a starting digital value representing an exposure level accumulated during a previous exposure period. Techniques are described for reducing the conversion time.

Owner:CMOSIS

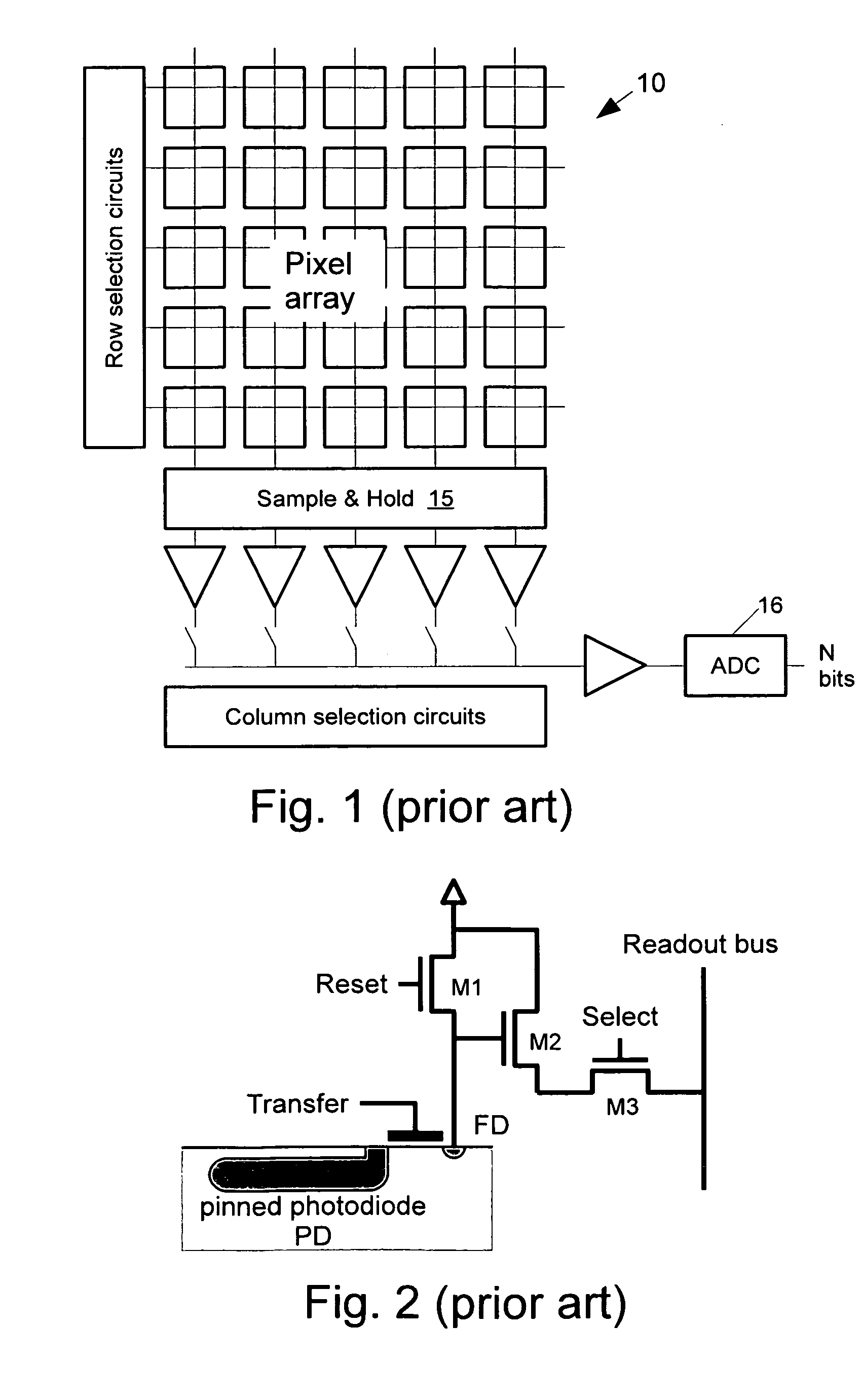

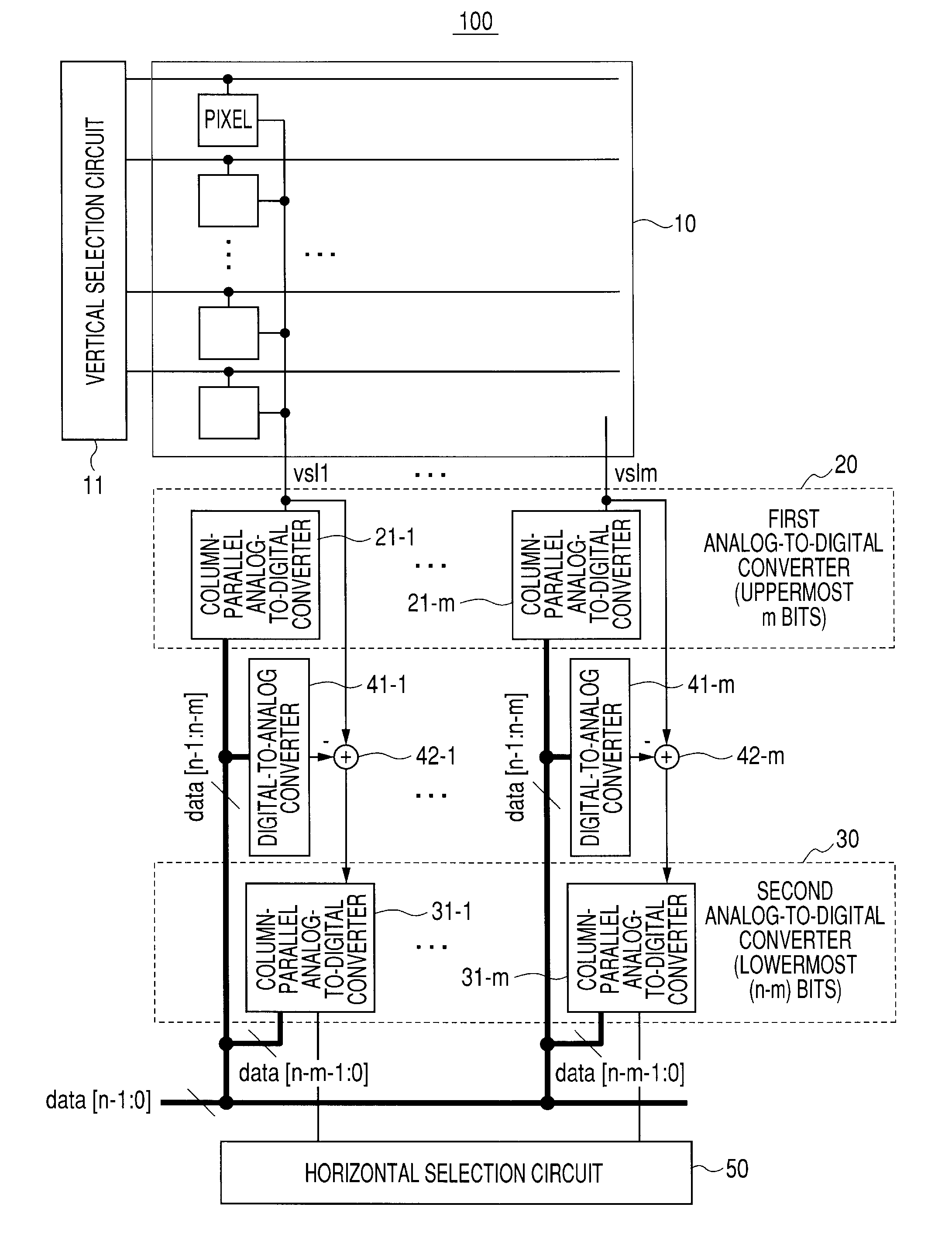

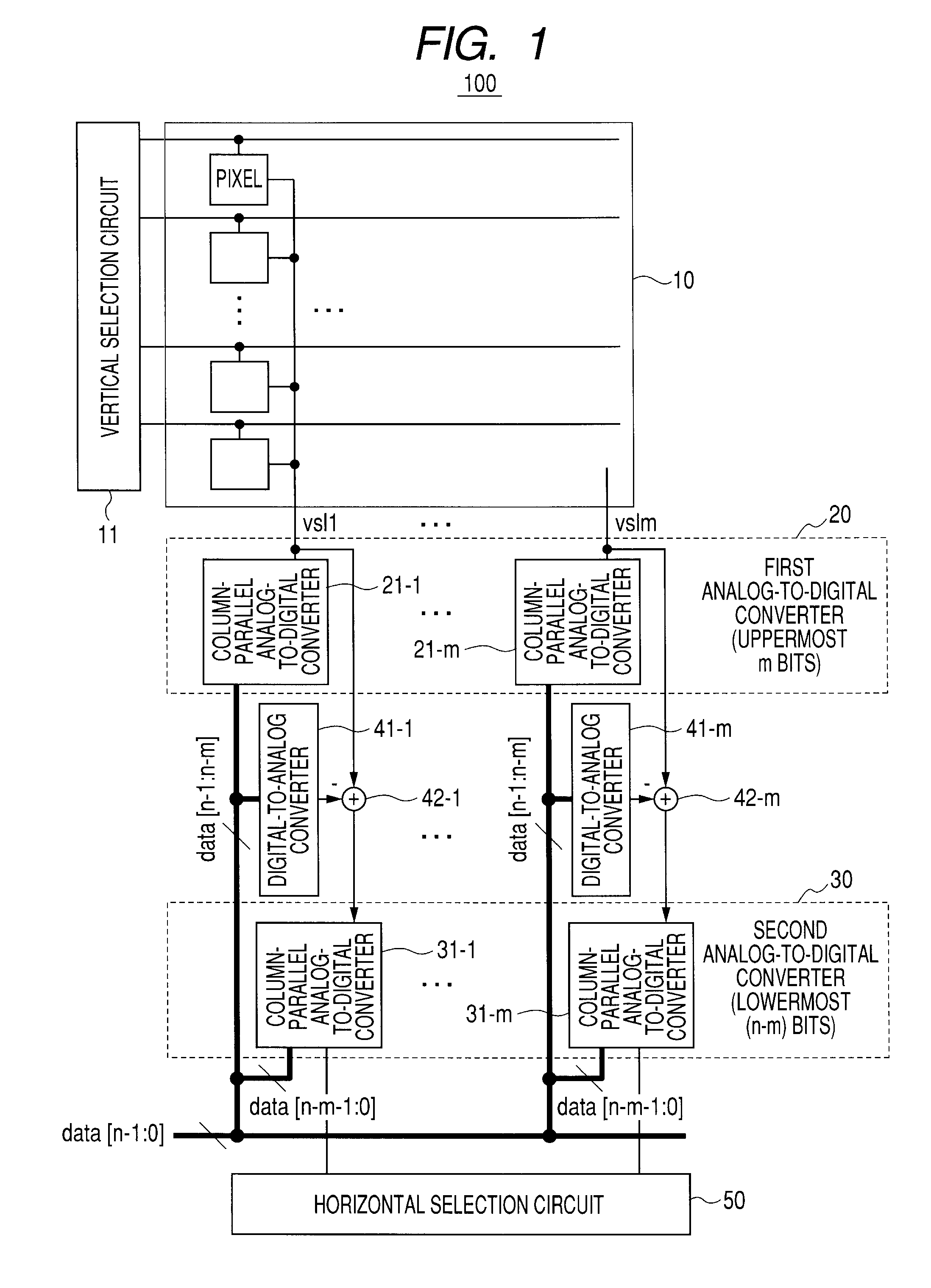

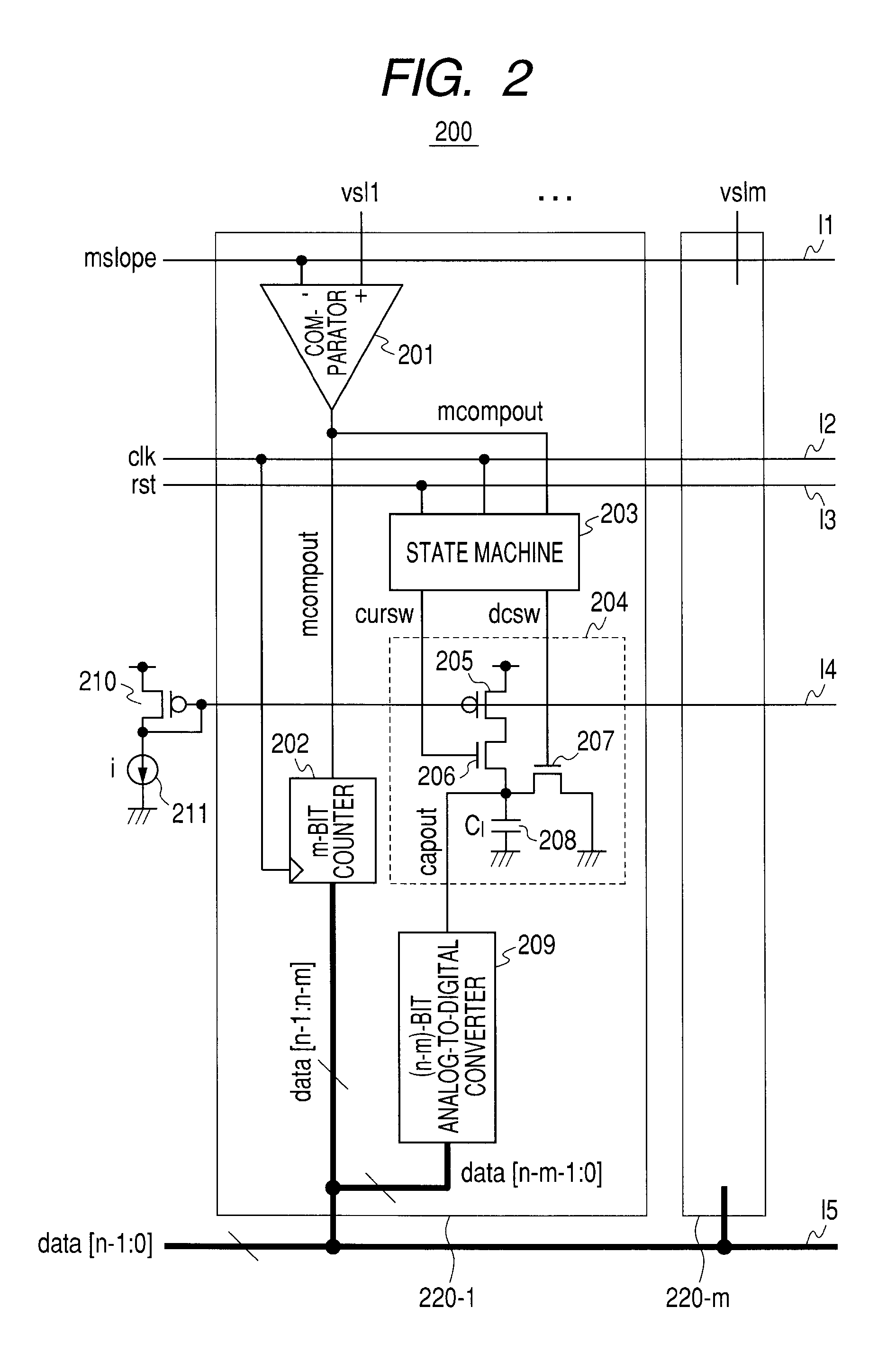

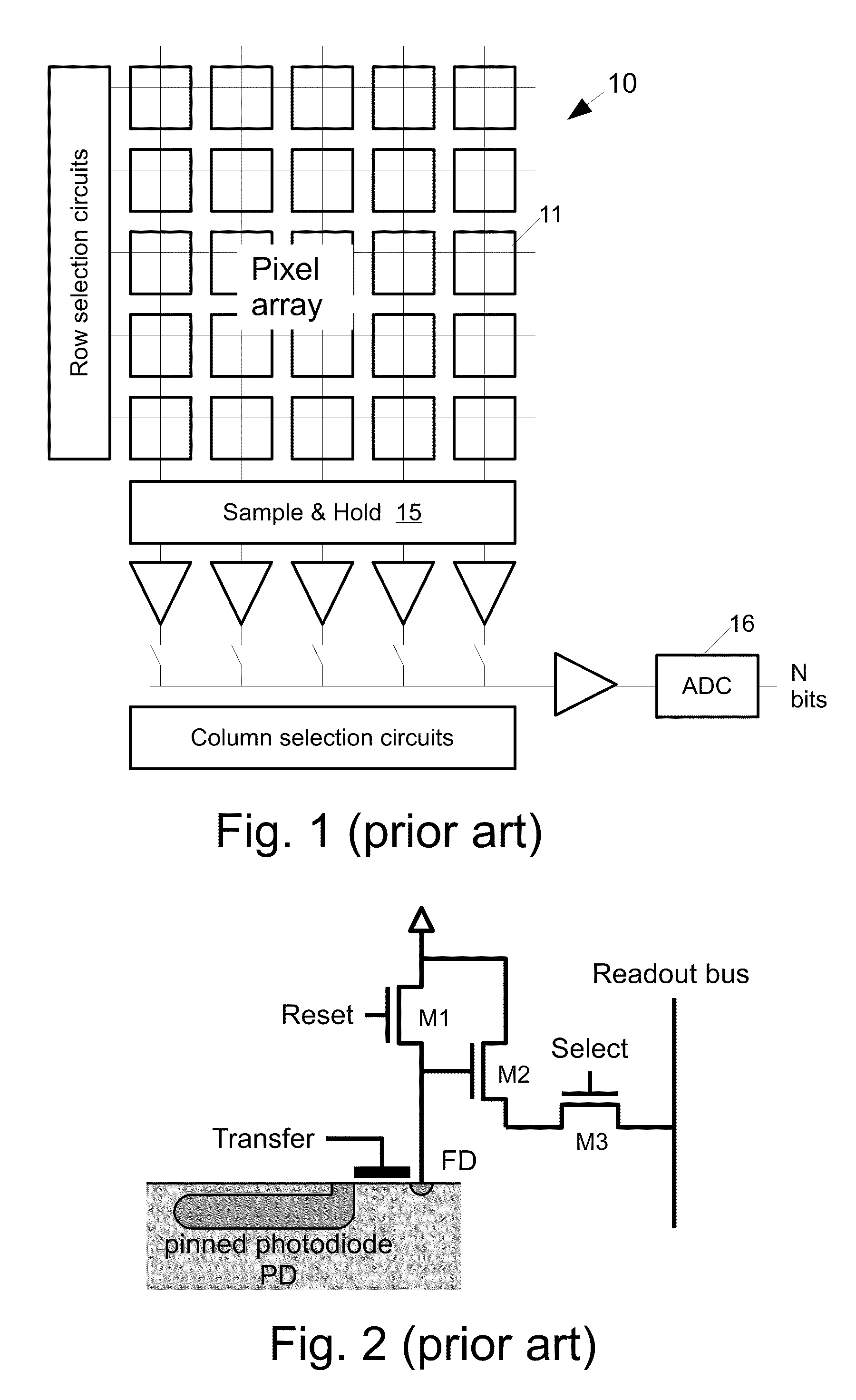

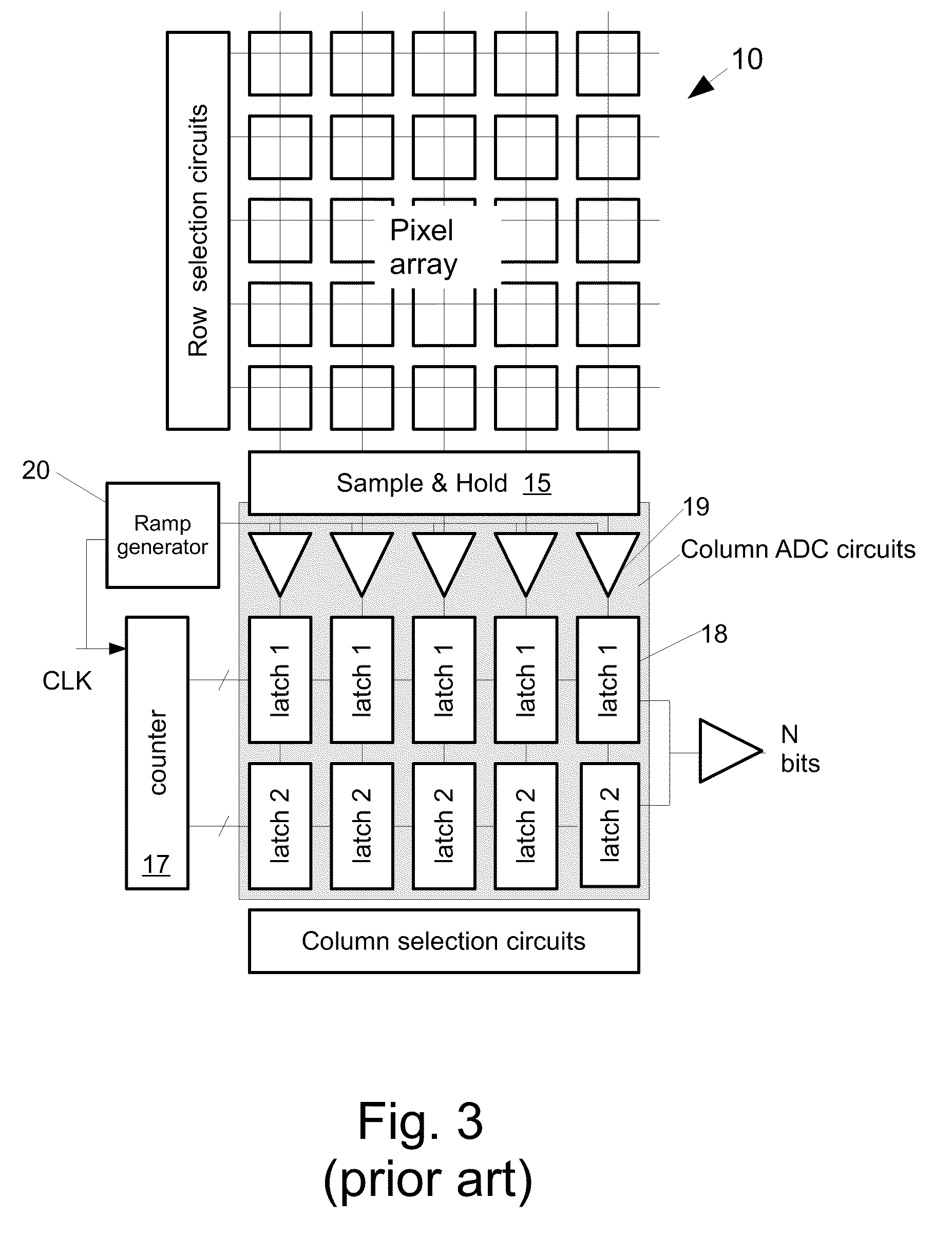

Solid-state imaging device, method of driving the same, and camera

InactiveUS20070279506A1Reduce conversion timeModerate accuracyTelevision system detailsElectric signal transmission systemsBit-lengthA d converter

A solid-state imaging device includes: a plurality of pixels which are arranged in a matrix; a sequential scanning device that selects each row of pixels; and an analog-to-digital conversion unit having a first analog-to-digital converter that is connected to a vertical signal line to which a pixel signal is supplied from the pixel and performs a first bit-length analog-to-digital conversion on an output signal from the vertical signal line or a pixel output signal obtained by sampling the output signal, and a second analog-to-digital converter that, when the first analog-to-digital converter completes the conversion operation, subtracts an analog signal corresponding to the first bit-length from the pixel output signal and then performs a second bit-length analog-to-digital conversion.

Owner:SONY SEMICON SOLUTIONS CORP

Microwave synthesis method of fiber carbamate

The invention discloses a technology of a microwave heating synthesis method of fiber carbamate; the method is that: firstly, the fiber is soaked in carbamide aqueous solution for completely adsorbing the carbamide, the fiber / carbamide even mixture is obtained by filtering and drying, and then the fiber / carbamide mixture is placed in a microwave oven for being heated, thereby obtaining the fiber carbamate. The synthesis technology of the fiber carbamate provided by the invention has no solvent pollution, organic solvents and any catalyzers do not need, the reacting time is speed, and the energy consumption is low. The synthesized fiber carbamate products has good dissolubility in 6 to 10 wt% of NaOH aqueous solution within the temperature range of -10 to 5 DEG C, and the concentrated solution which is stable, transparent and is suitable for industrial spinning and membrane manufacturing can be prepared.

Owner:WUHAN UNIV

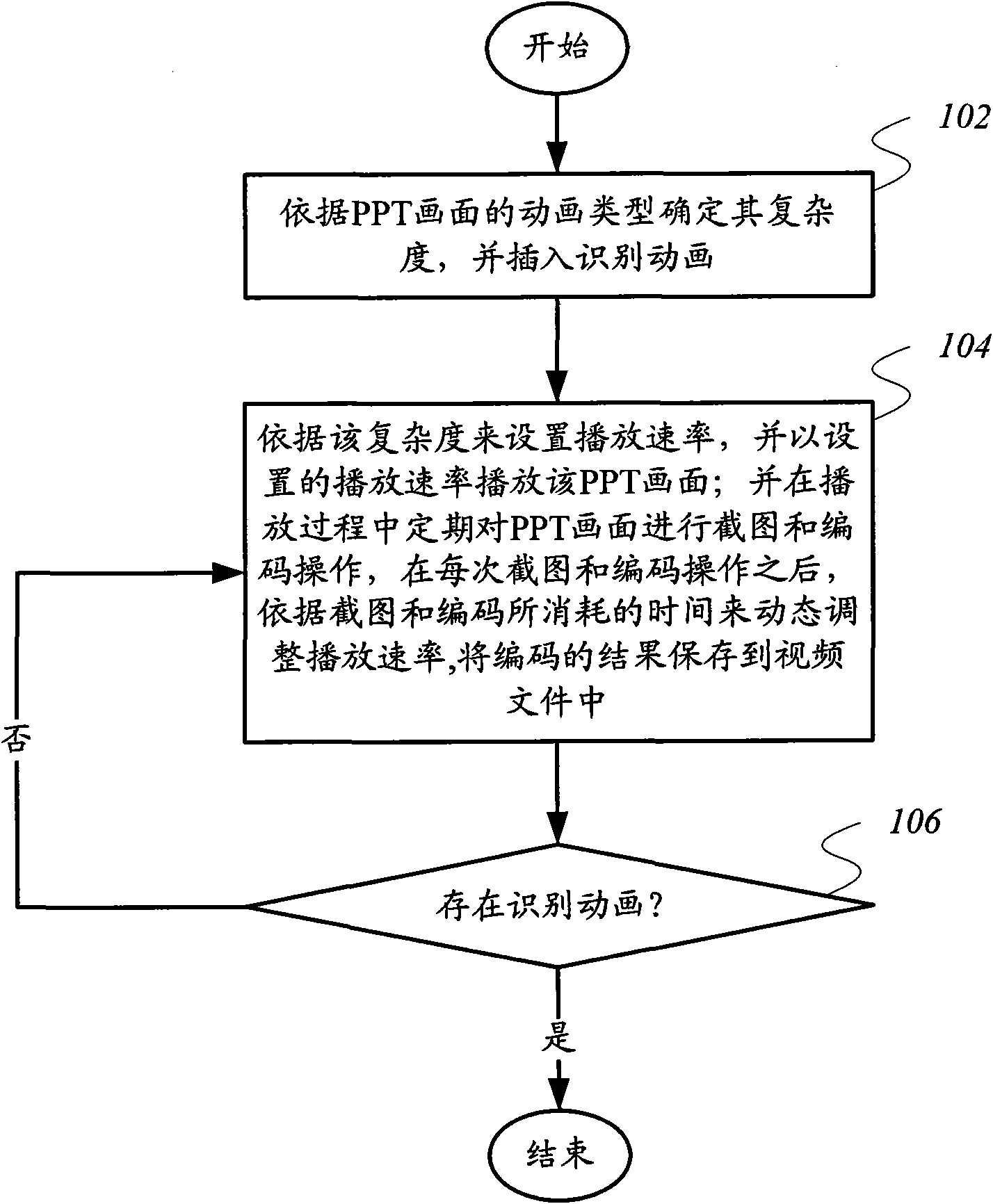

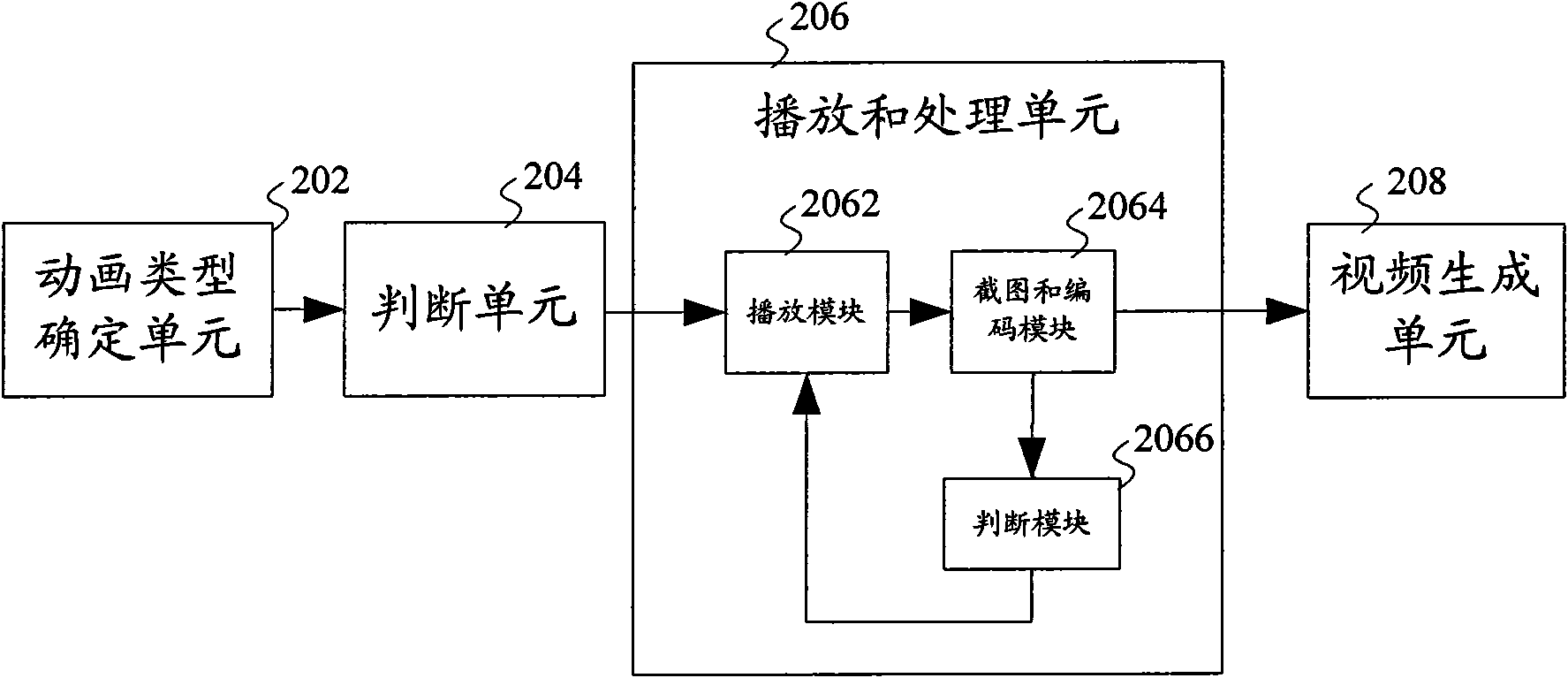

Method and system for conversing PPT into video

InactiveCN101662675AReduced conversion timeFast conversionPulse modulation television signal transmissionDigital video signal modificationAnimationGenerating unit

The invention relates to a method for conversing PPT into video. The method comprises the following steps of processing each PPT frame in a PPT file: S1) confirming the complexity thereof according tothe cartoon type of PPT frame, S2) setting a playing speed according to the complexity and playing the PPT frame with the set playing speed, performing the operations of sectional drawing and encoding on PPT frame during playing, automatically regulating the playing speed according to the time for sectional drawing and encoding after finishing the operations of sectional drawing and encoding, andS3) storing the encoding result into a video file. The invention further relates to a system for conversing PPT into video, comprising a cartoon type confirming unit, a playing and processing unit and a video generating unit. With the technical scheme, the invention can be applied to various machines, can fully utilize the machine resource to rapidly finishing conversion, can increase the conversion speed and ensure the conversion quality.

Owner:WONDERSHARE TECH CO LTD

Analog-to-digital conversion in pixel array

ActiveUS8040269B2Reduced conversion timeHigh frequencyElectric signal transmission systemsAnalogue-digital convertersA d converterEngineering

An analog-to-digital converter generates an output digital value equivalent to the difference between two analog signals. The converter forms part of a set of converters. The converter receives a first analog signal and a second analog signal (Vreset, Vsig) and a ramp signal (Vramp). A clock is dedicated to the converter, or a sub-set of converters. A control stage enables a first counter based on a comparison of the ramp signal with the first analog signal and the second analog signal. The converter can be calibrated by at least one reference signal (Vref1, Vref2) which is common to the set of converters. A-to-D conversion can include a first A-to-D conversion stage which determines a signal range, selected from a plurality of signal ranges, and a second A-to-D conversion stage which determines an M-bit digital value equivalent to the difference between the first and second analog signals by comparing the signals with a ramp signal, with the ramp signal having the signal range determined by the first analog-to-digital conversion stage.

Owner:CMOSIS

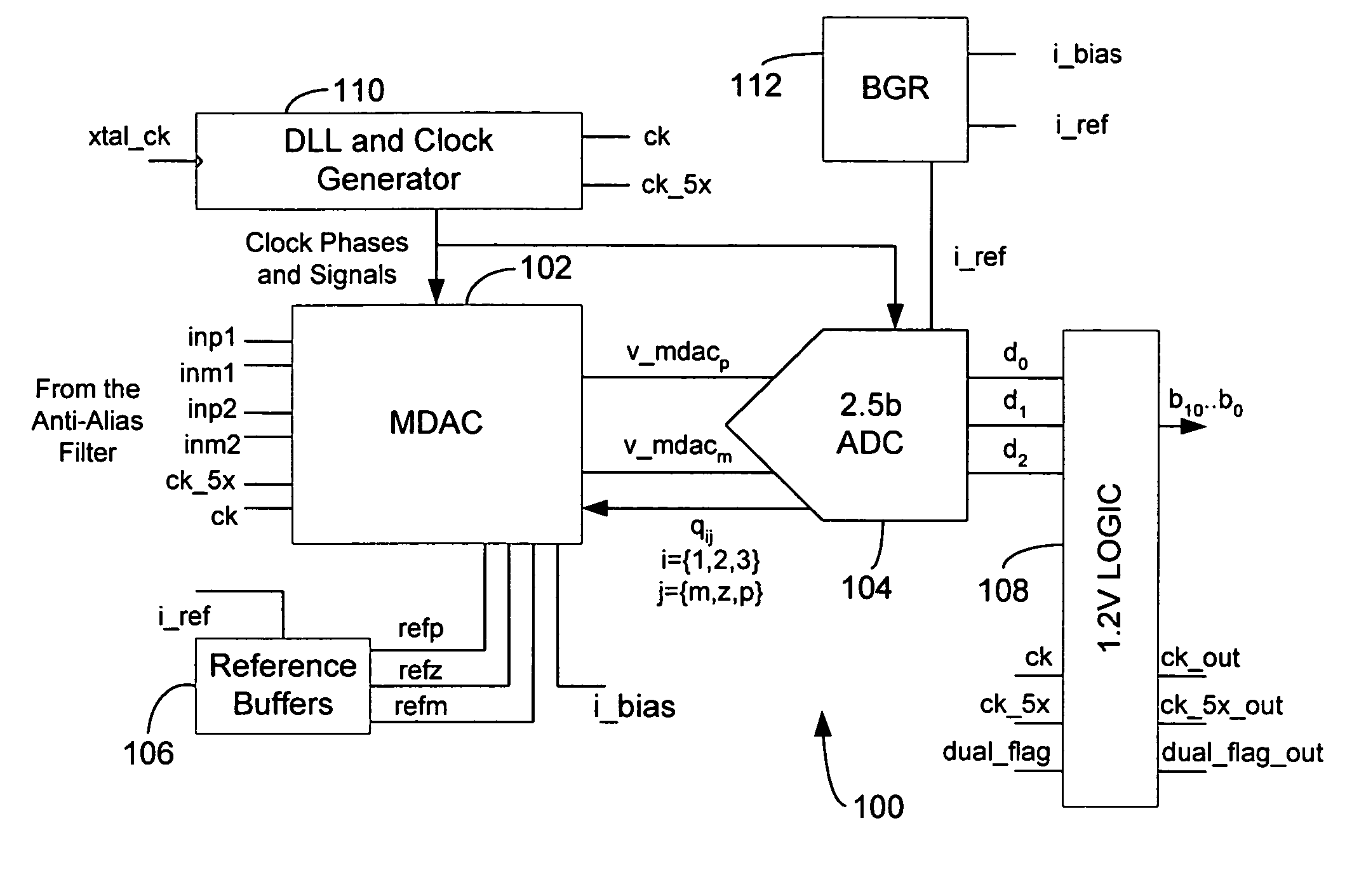

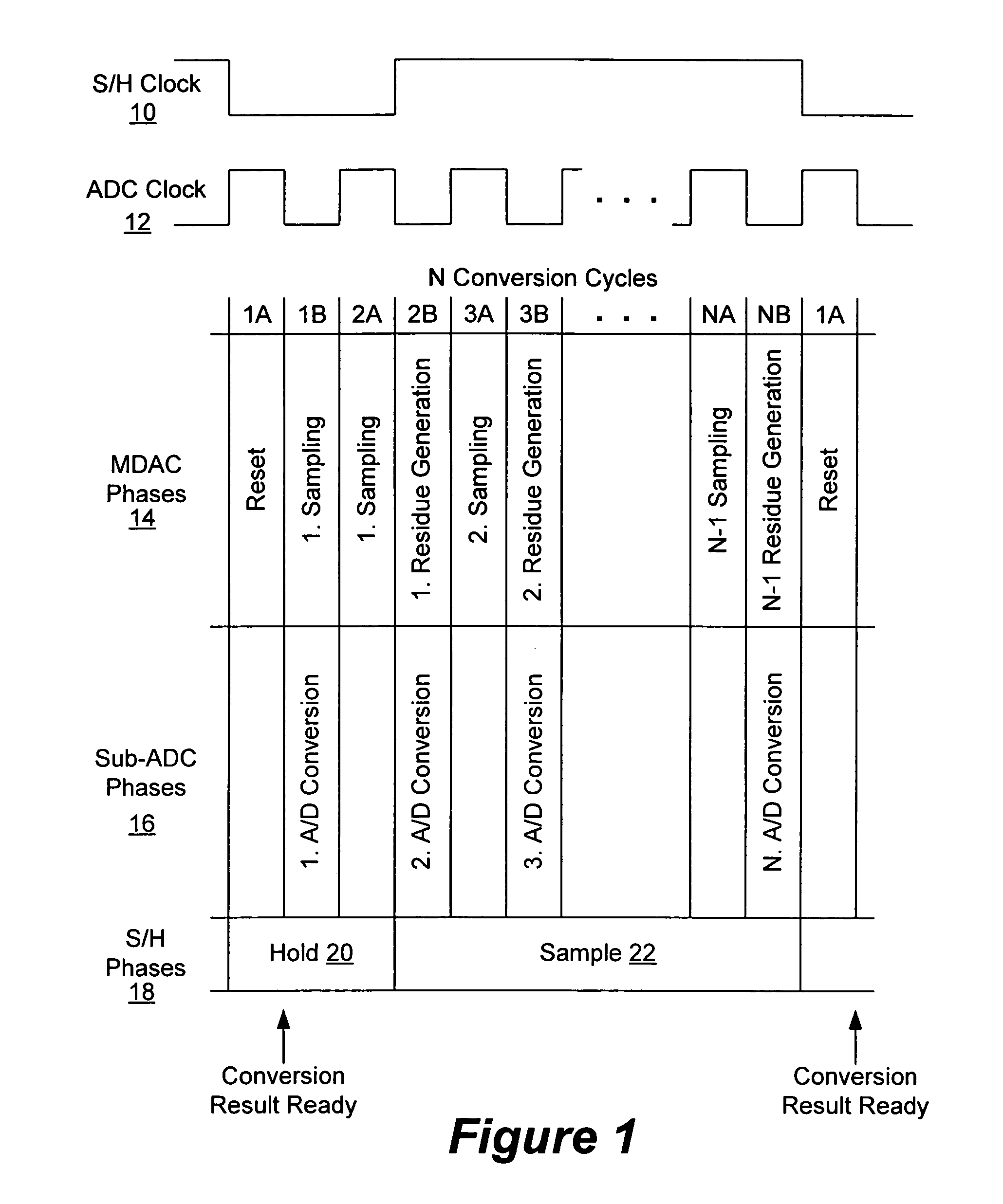

Variable clock rate analog-to-digital converter

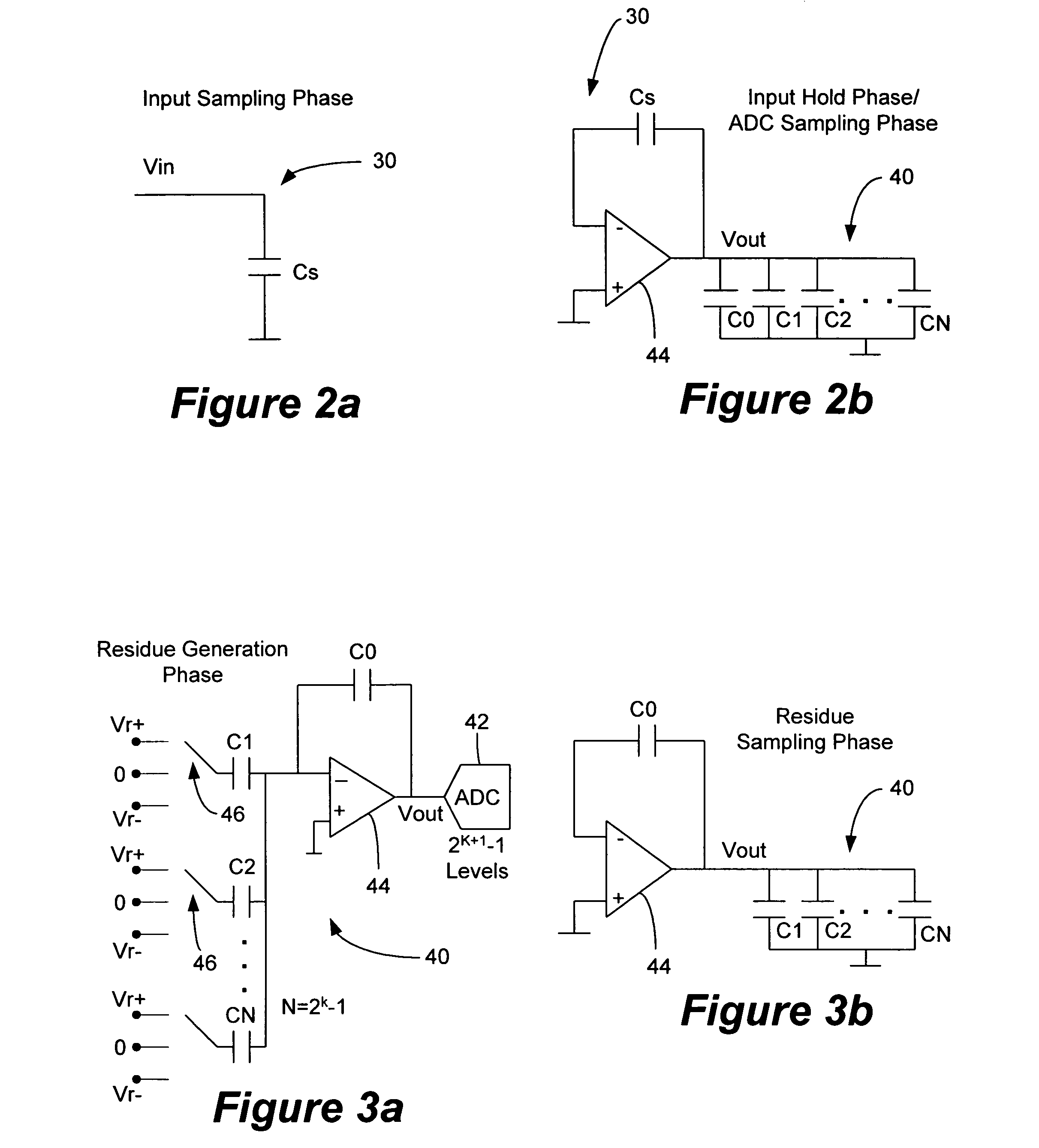

ActiveUS7088275B2Less settling timeMore accuracyElectric signal transmission systemsPulse automatic controlDigital down converterControl signal

An algorithmic analog-to-digital converter (ADC) includes a sample-and-hold circuit and an ADC processing unit operating in parallel and sharing a single operational amplifier. The ADC processing unit includes an MDAC with a switched capacitor topology and a sub-ADC. The ADC processing unit is clocked by an internal clock that is N times faster than the sample-and-hold clock. Each cycle is further sub-divided into two phases. During one phase the capacitors are coupled to a residue or sampled voltage provided by the MDAC, and during another phase the capacitor are coupled to a reference voltage determined by the switch control signals generated by the sub-ADC. A set of data bits is generated by the ADC processing unit during each ADC clock cycle. The N sets of data bits are added to generate the digital output stream. The internal clock, in turn, has a variable period allocating more time to the early operation phases where more accuracy is required and less time to the latter operation phases where less accuracy is required.

Owner:SYNAPTICS INC

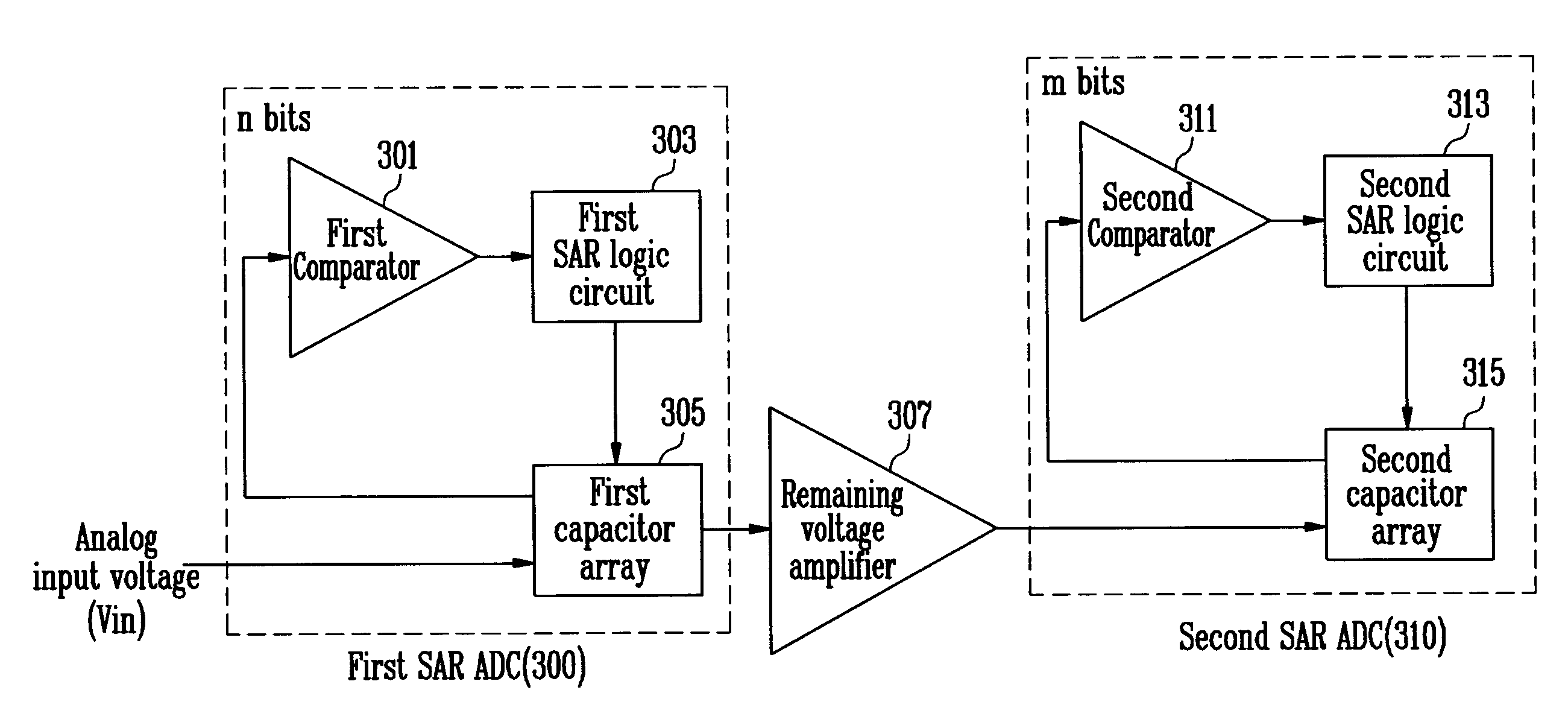

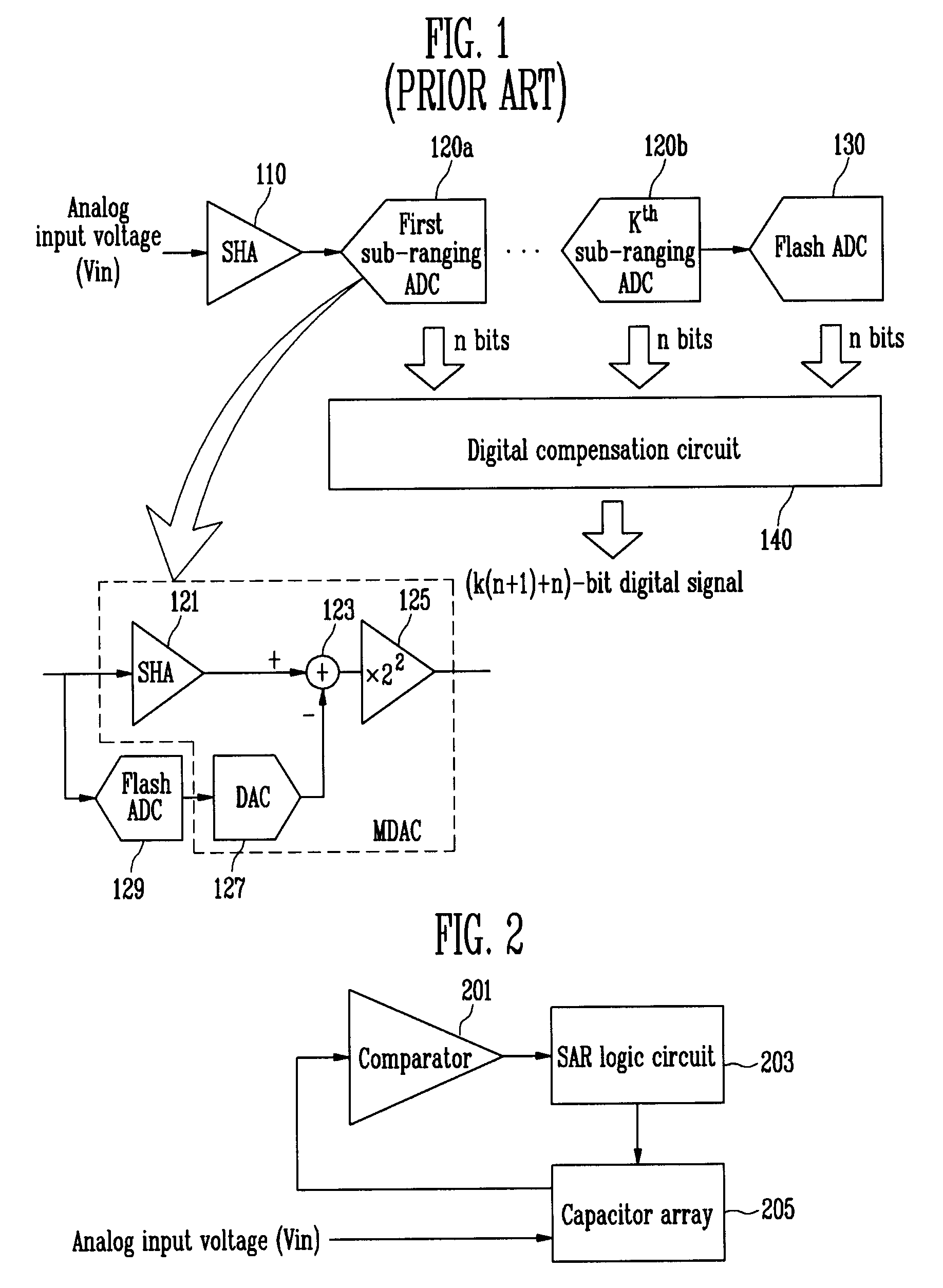

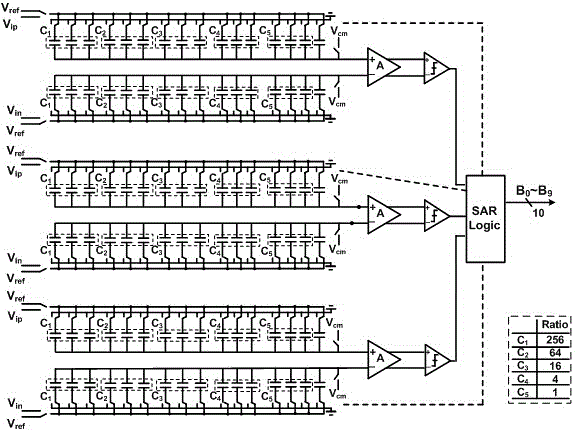

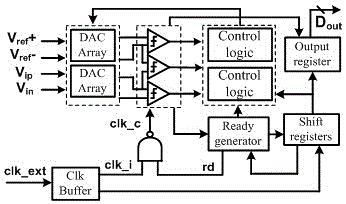

Multi-stage successive approximation register analog-todigital converter and analog-to-digital converting method using the same

InactiveUS20100066583A1Reduce power consumptionSmall sizeElectric signal transmission systemsAnalogue-digital convertersChip sizeEngineering

A multi-stage Successive Approximation Register Analog-to-Digital Converter (SAR ADC) and an analog-to-digital converting method using the same are provided. The multi-stage SAR ADC connects small-size and low-power SAR ADCs in multiple stages, thereby reducing a whole chip size and power consumption. The analog-to-digital converting method simultaneously performs analog-to-digital conversions in the SAR ADCs connected in the multiple stages, thereby reducing an analog-to-digital conversion time and maintaining an operating rate of several tens of MHz to several hundreds of MHz similar to that of a pipeline ADC.

Owner:ELECTRONICS & TELECOMM RES INST

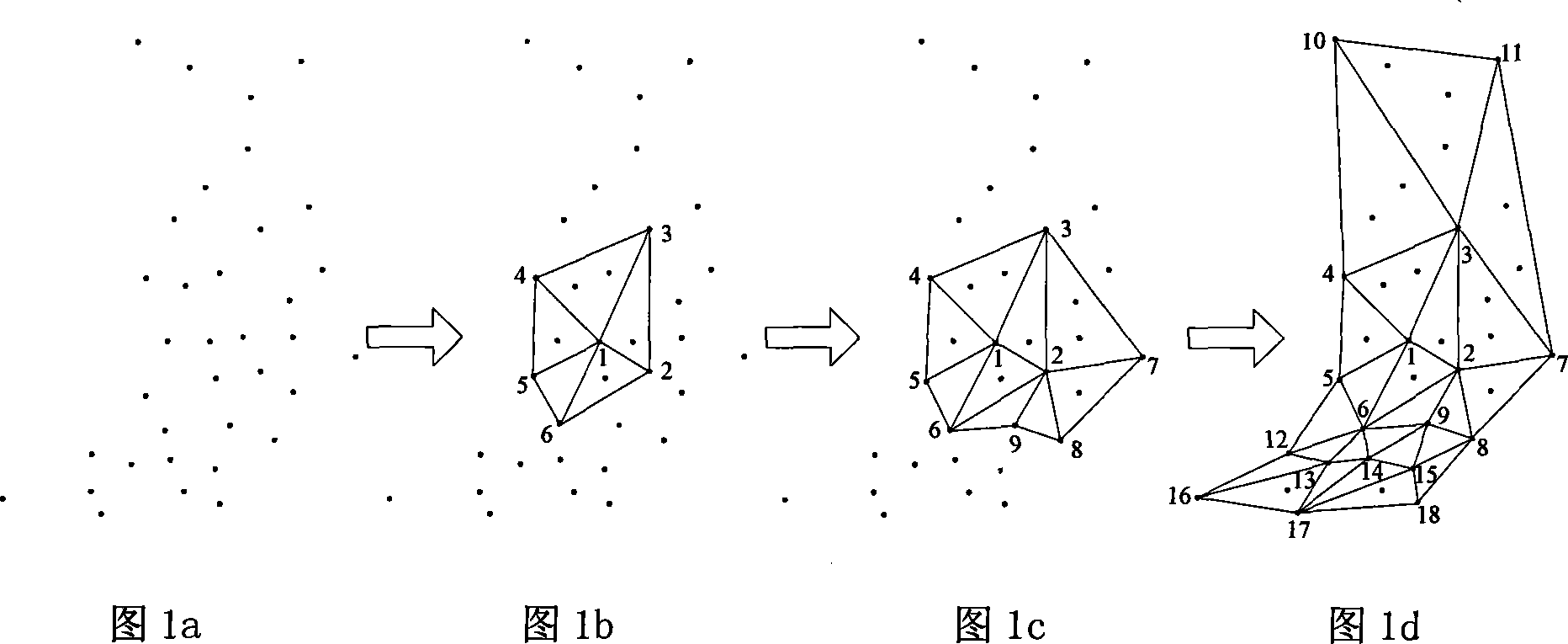

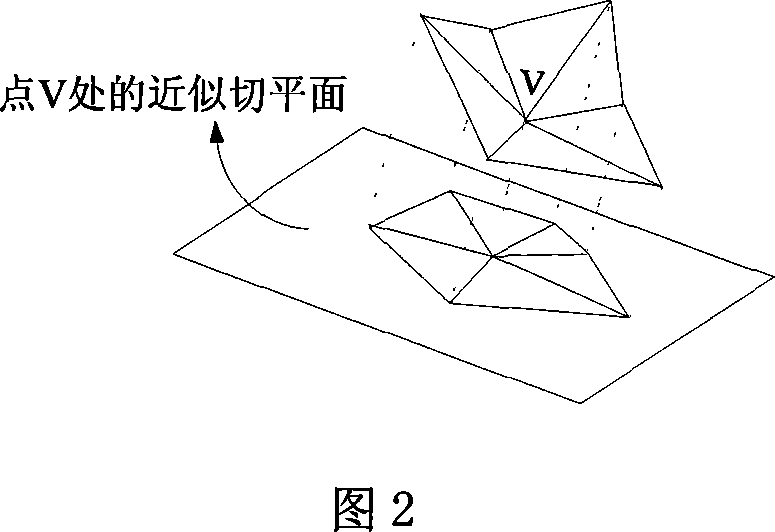

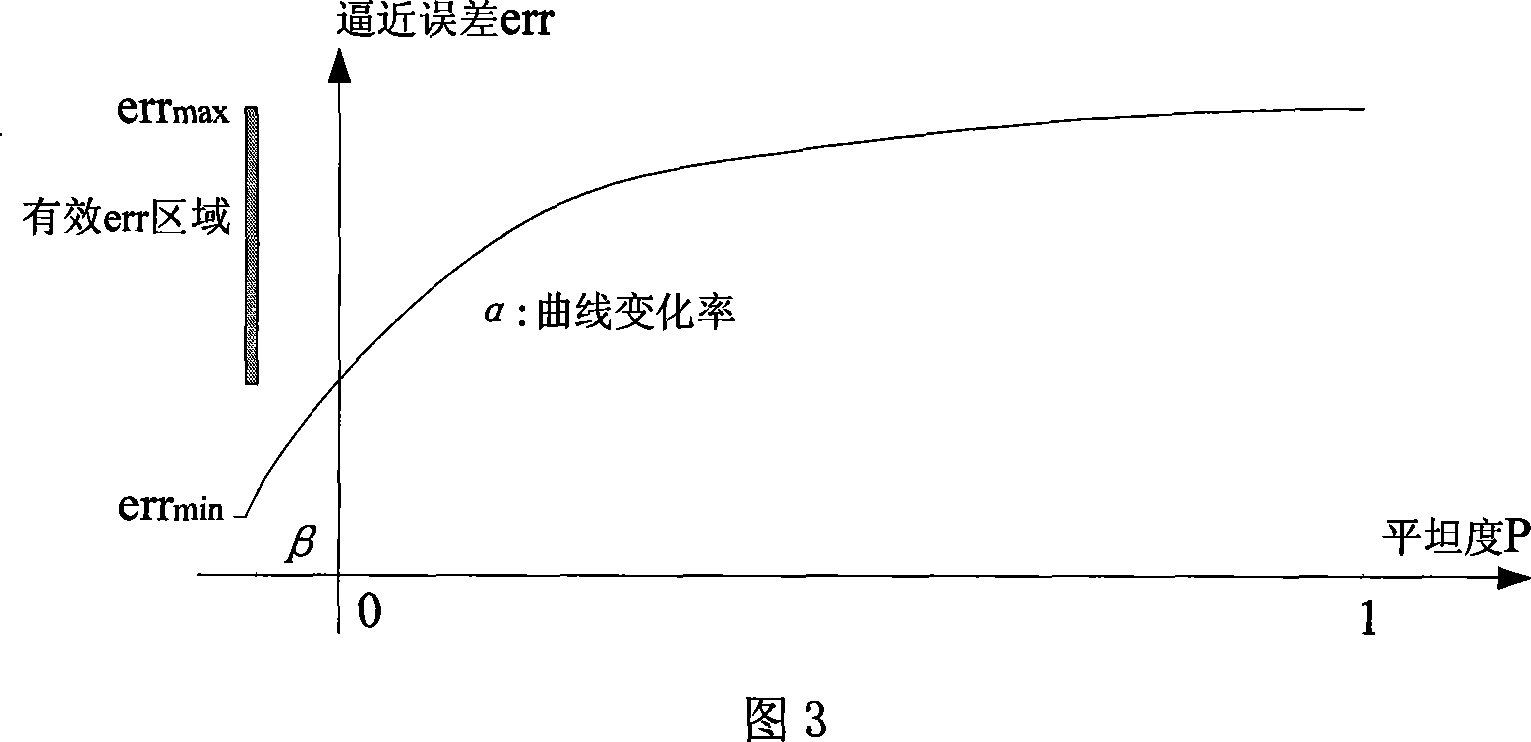

System and method for converting disordered point cloud to triangular net based on adaptive flatness

InactiveCN101067868AFast conversionReduced conversion timeFilling planer surface with attributesMesh gridAlgorithm

This invention relates to a system and a method for converting non-sequence spot-clouds into triangle griddings based on adaptive flatness, which carries out triangle analysis to spot-clouds in space directly by a non-sequence spot-cloud increment rebuilding algorithm based on adaptive flatness to structure a partial gridding ring from the initial central point based on the partial flat character of a curvature face and a Delaunary analysis rule of triangles and takes points on said gridding ring as the central point according to the generation sequence to structure the partial ring repeatedly to circulate in linearity and spread it to the entire spot set and get a topological structure finally so as to increase conversion velocity and reduce conversion time.

Owner:TONGJI UNIV

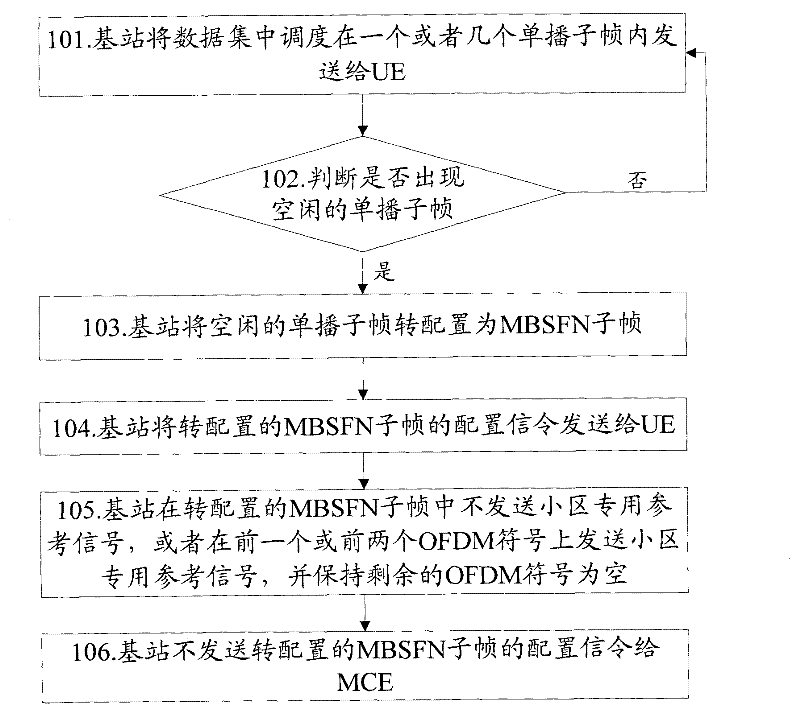

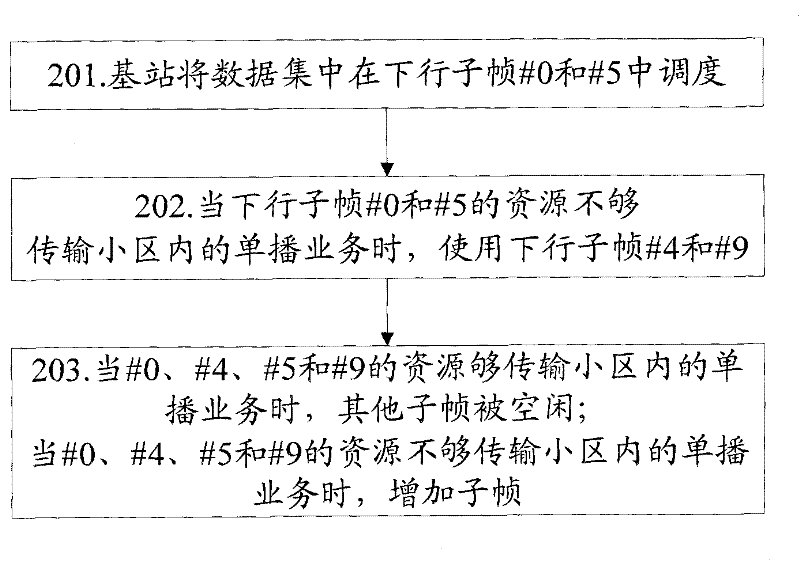

Subframe configuring method and system

ActiveCN102223604ATo achieve the purpose of saving electricity and energyReduced conversion timeBroadcast service distributionRadio transmission for post communicationElectricityConfiguration system

The invention discloses a subframe configuring method. The method comprises the following steps that: a base station reconfigures a unicast subframe into a multimedia broadcast single frequency network (MBSFN) subframe; and the base station sends a configuring signaling of the reconfigured MBSFN subframe to user equipment (UE). The invention also discloses a subframe configuring system. By the method and the system, the transmission of unicast service is not affected and the base station saves electricity and energy.

Owner:ZTE CORP

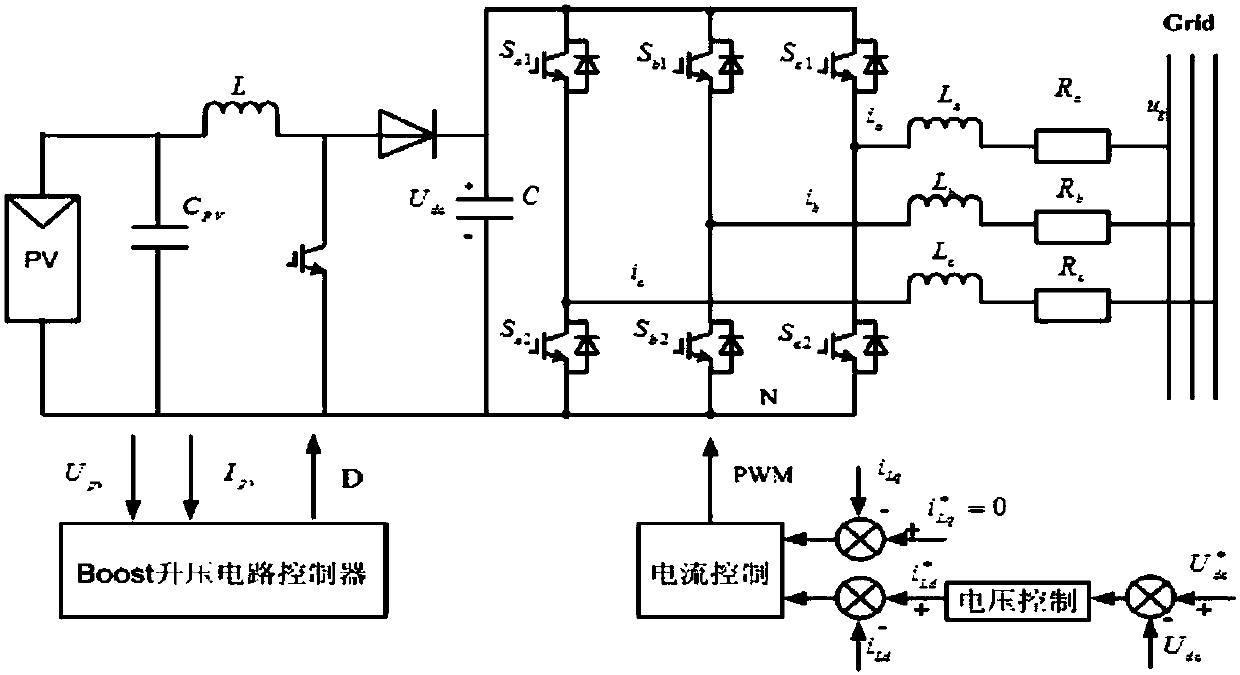

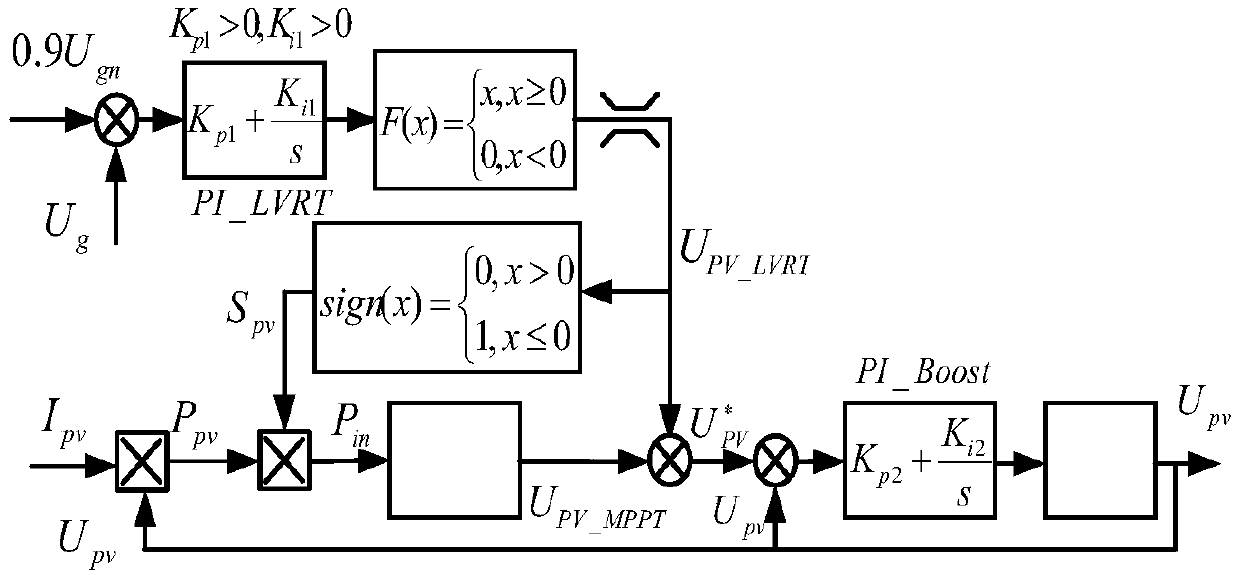

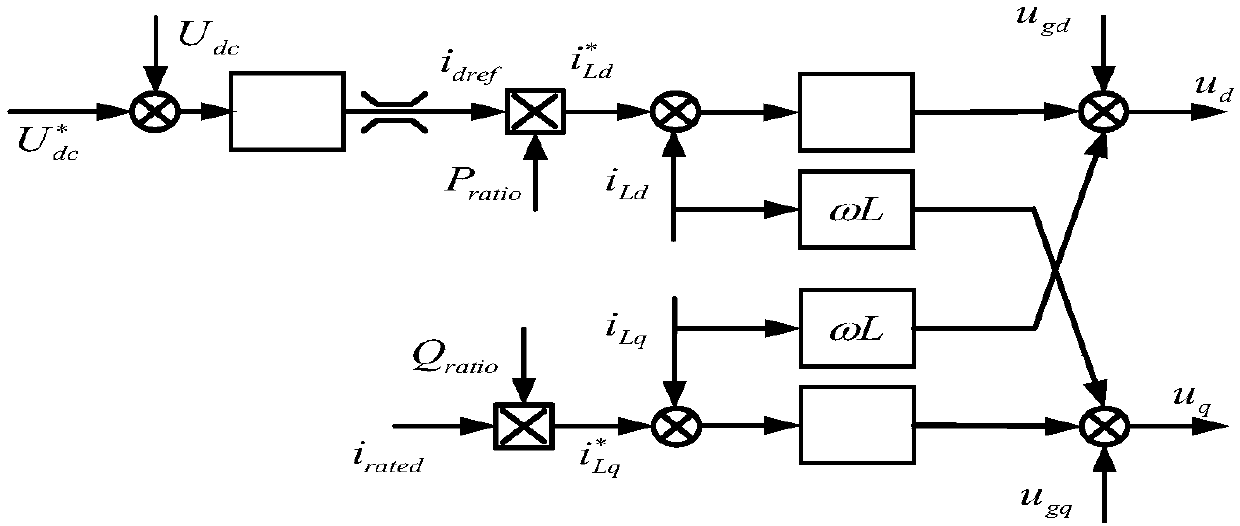

Low-voltage crossing method of two-stage type photovoltaic grid connected system of variable power tracking path

ActiveCN107732956AControl outputPrevent overcurrentSingle network parallel feeding arrangementsPhotovoltaic energy generationLow voltageNew energy

The invention discloses a low-voltage crossing method of two-stage type photovoltaic grid connected system of variable power tracking path, which belongs to the field of new energy electric power system and micro power grid technology. Under the prerequisite that the original configuration of a two-stage three phase photovoltaic grid connected system is not changed and no auxiliary device is added, the power tracking path can be adjusted through the feed-forward control of the falling amplitude of voltage, the voltage at the photovoltaic cell end can be changed in a real-time manner, and the output of the photovoltaic cell power can be rapidly and effectively controlled, and the balance of power at two sides of an inverter can be realized. Through the cooperative control with a grid connected inverter, it can be guaranteed that under the prerequisite that the grid connected output of current of the inverter is not out of limit, active power and reactive power can be provided for the power grid as more as possible, the recovery of power grid voltage can be supported to the most extent, and the zero-voltage crossing of the photovoltaic grid connected system can be realized. Comparedwith the conventional control method, the invention is advantageous in that no additional device is required; safe and stable running of the system can be realized; the cost of the photovoltaic powergeneration system can be reduced, and practicality is better.

Owner:NORTH CHINA ELECTRIC POWER UNIV (BAODING) +1

Demodulator circuit

InactiveCN104200260AGuaranteed correctnessConvenience and correctnessDifferential amplifiersRecord carriers used with machinesBandpass filteringFull wave

The invention relates to a demodulator circuit. The demodulator circuit comprises a biasing circuit, an envelope detection circuit, a comparison circuit, a shaping circuit and a control circuit, wherein the envelope detection circuit comprises a full-wave rectification circuit and a band-pass filter, the full-wave rectification circuit is used for rectifying a full-wave alternating current signal which is received by an antenna to a direct current signal, and the band-pass filter is used for performing band-pass filtering on the direct current signal to output an envelope signal within a preset bandwidth range; the comparison circuit is used for reducing amplitude of a carrier signal through voltage comparison of the envelope signal; the shaping circuit is used for extracting an ASK signal from signals which are output by the envelope detection circuit or the comparison circuit; the control circuit is used for generating a control signal according to the ASK signal so that the band-pass filter is controlled to perform discharging before the ASK signal jumps from a low level to a high level and the comparison circuit is started and the comparison circuit is controlled to be closed after the ASK signal jumps from the high level to the low level. The demodulator circuit can be excellently applied to a passive radio frequency identification (RFID) system, and the accuracy of a demodulated signal is good.

Owner:HEFEI NINGXIN ELECTRONICS TECH

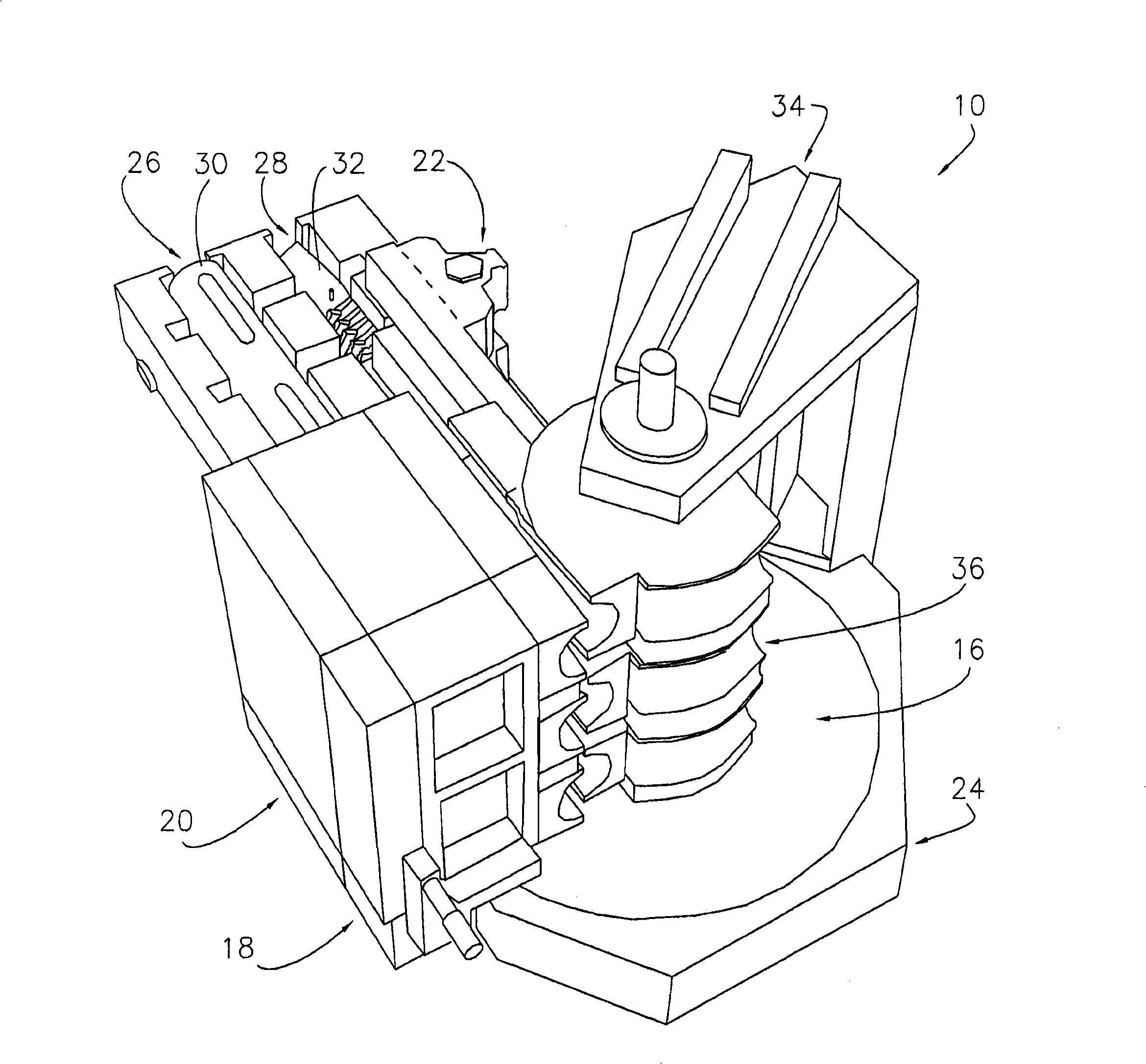

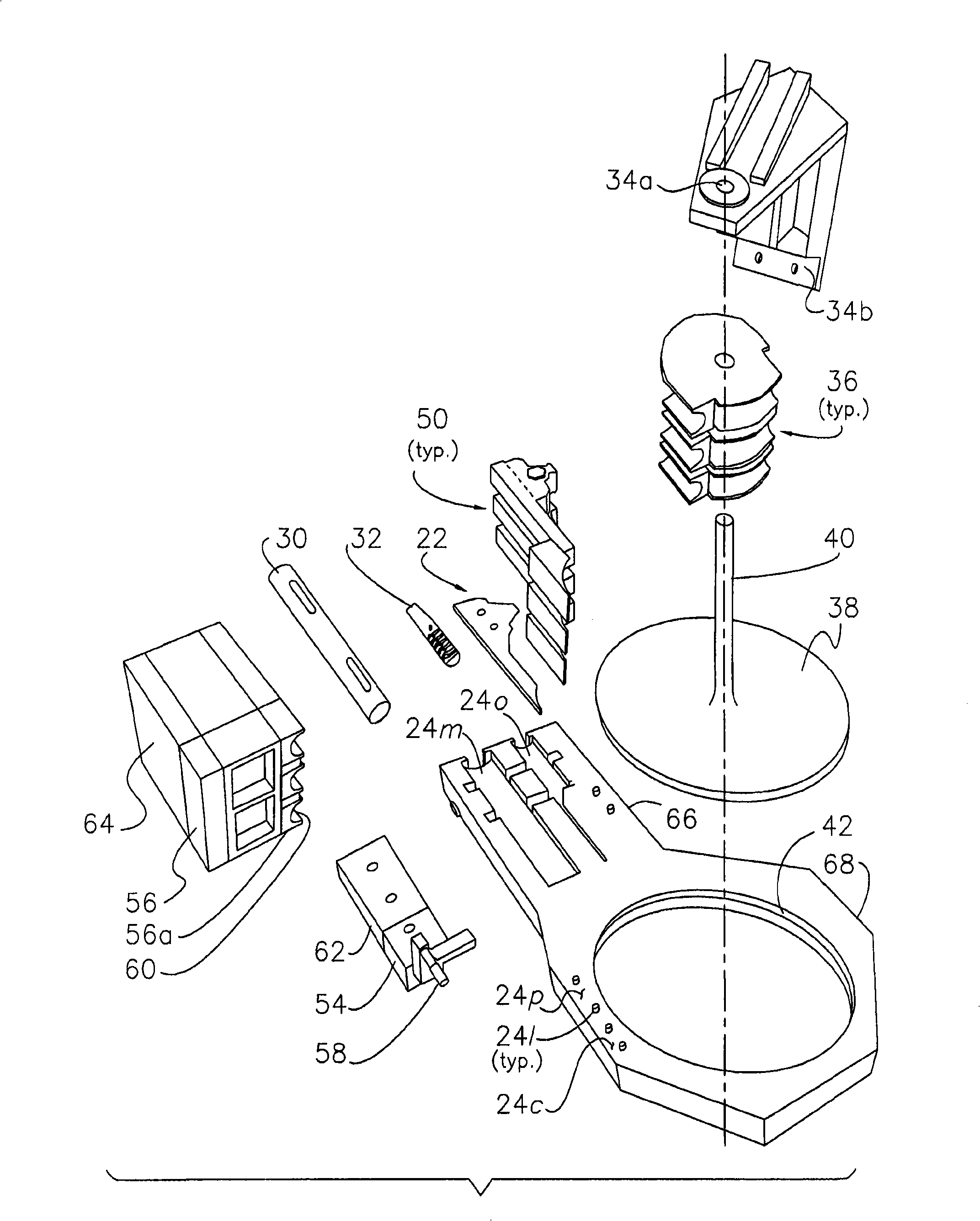

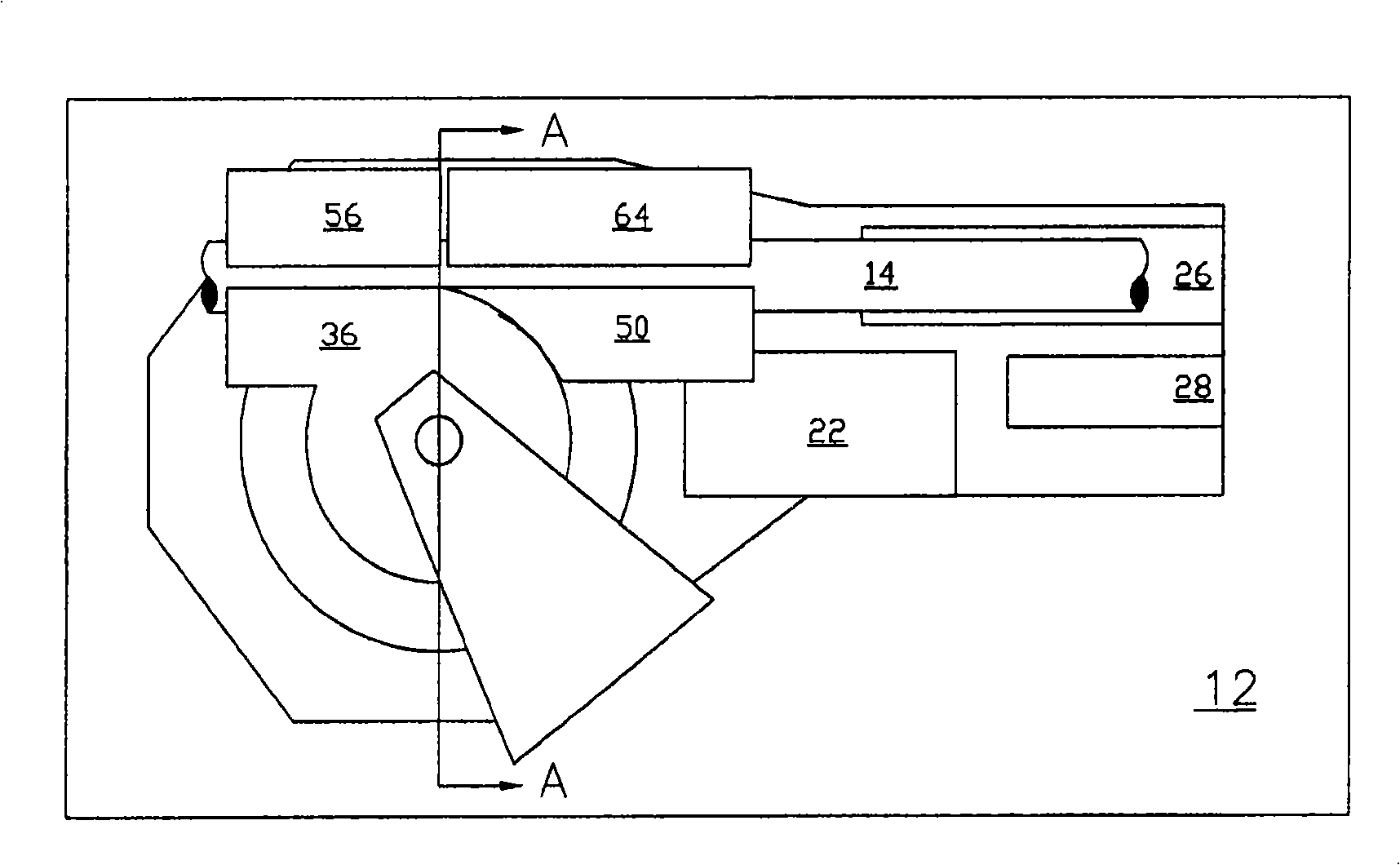

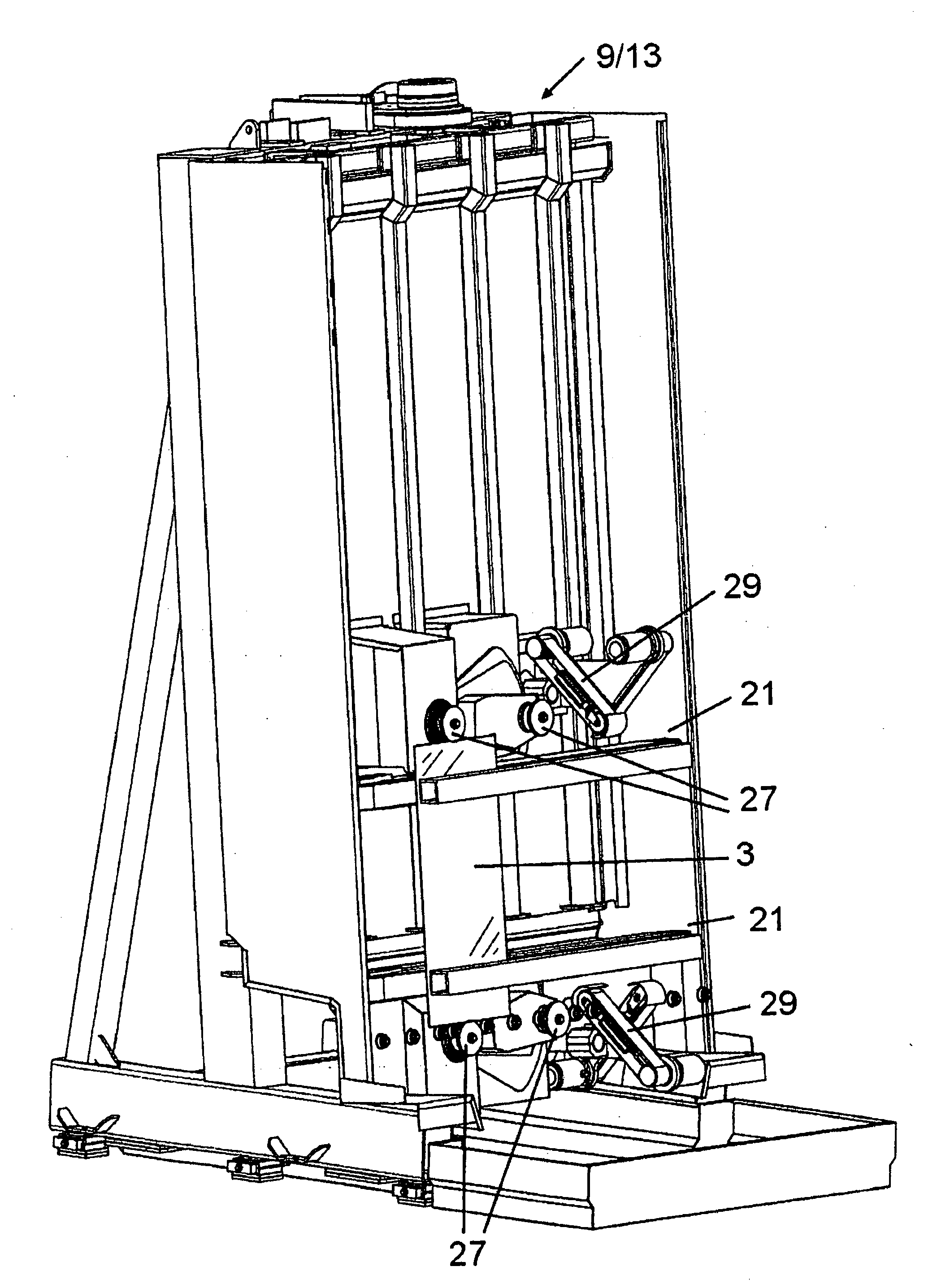

Quick changing bending machining pad pillow

A tube bending assembly adapted for use with a rotary draw bender, and preferably including a bend die mounting unit for securing a plurality of stacked bend dies drivenly coupled to the bender, a bend die tower unit for structurally supporting the bend die mounting unit, a wiper die mounting unit for securing a wiper die adjacent a selected bend die, a clamp die mounting unit for positioning and securing a clamp die, a pressure die mounting unit for securing a pressure die adjacent the clamp die, a mandrel saddle unit for positioning and enabling the utilization of a mandrel assembly, a collet saddle unit for positioning and enabling the utilization of a collet, and a bolster unit that interconnects the units, so as to present an integrated assembly capable of concurrent disconnection from and connection to the bender, and thereby reducing the tool set change-over period.

Owner:GM GLOBAL TECH OPERATIONS LLC

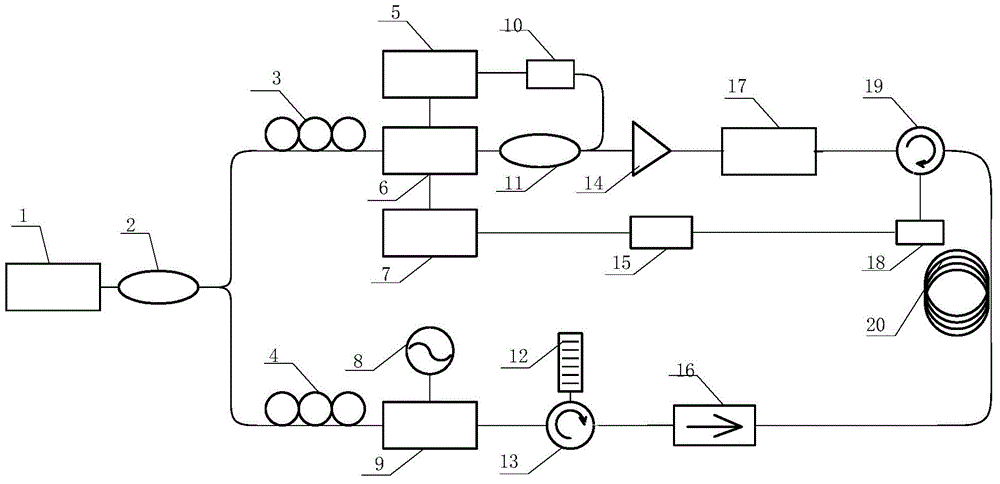

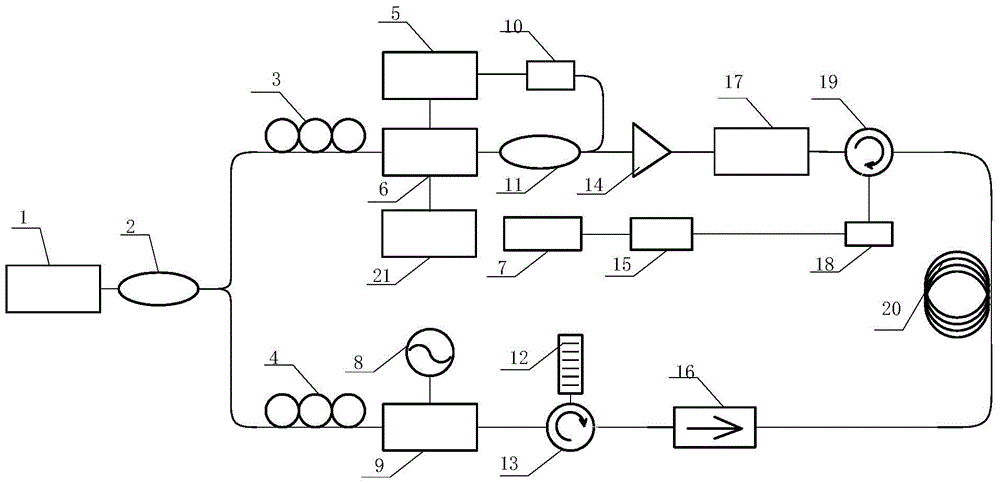

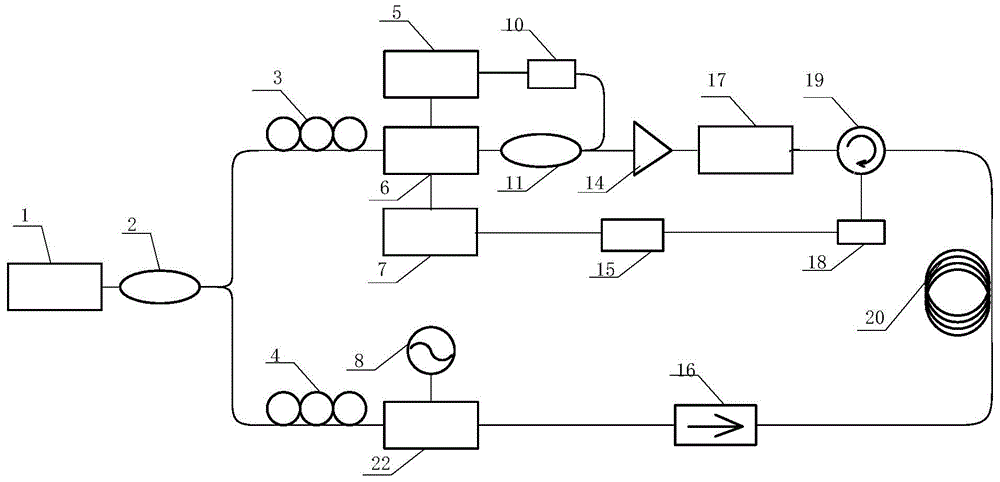

Brillouin optical-time-domain analyzer based on coherence dual-pulse pair sequence technology and method for restraining common-mode noise by utilizing same

ActiveCN104019836AReduced conversion timeAchieve inhibitionConverting sensor output opticallySpecial purpose recording/indication apparatusOptical fiber couplerSignal-to-quantization-noise ratio

The invention relates to a Brillouin optical-time-domain analyzer based on a coherence dual-pulse pair sequence technology and a method for restraining common-mode noise by utilizing the same, belongs to the field of optics, and solves the problems that a traditional Brillouin optical-time-domain analyzer is low in spatial resolution, long in measuring signal time and low in signal-to-noise ratio. A laser is adopted, an upper branch of light divided by an optical-fiber coupler I is used as pump light, pulse pairs with different pulse widths can be periodically generated by a field-programmable logic array in a programming manner, and the pulse pairs are continuously and optically modulated to form a coherence pulse pair sequence through a photoelectric modulator; a lower branch provides detection light, the detection light enters a photoelectric modulator after a polarization state is adjusted, upper marginal frequency light and lower marginal frequency light which having the frequency difference of Brillouin frequency shifting gamma B are generated on the basis of carrier light, the pump light consisting of the coherence pulse pair sequence and the modulated detection light has a Brillouin scattering phenomenon in a sensing optical fiber, and two Brillouin signals are detected by a photoelectric detector. The Brillouin optical-time-domain analyzer and the method are suitable for restraining the common-mode noise.

Owner:HARBIN INST OF TECH

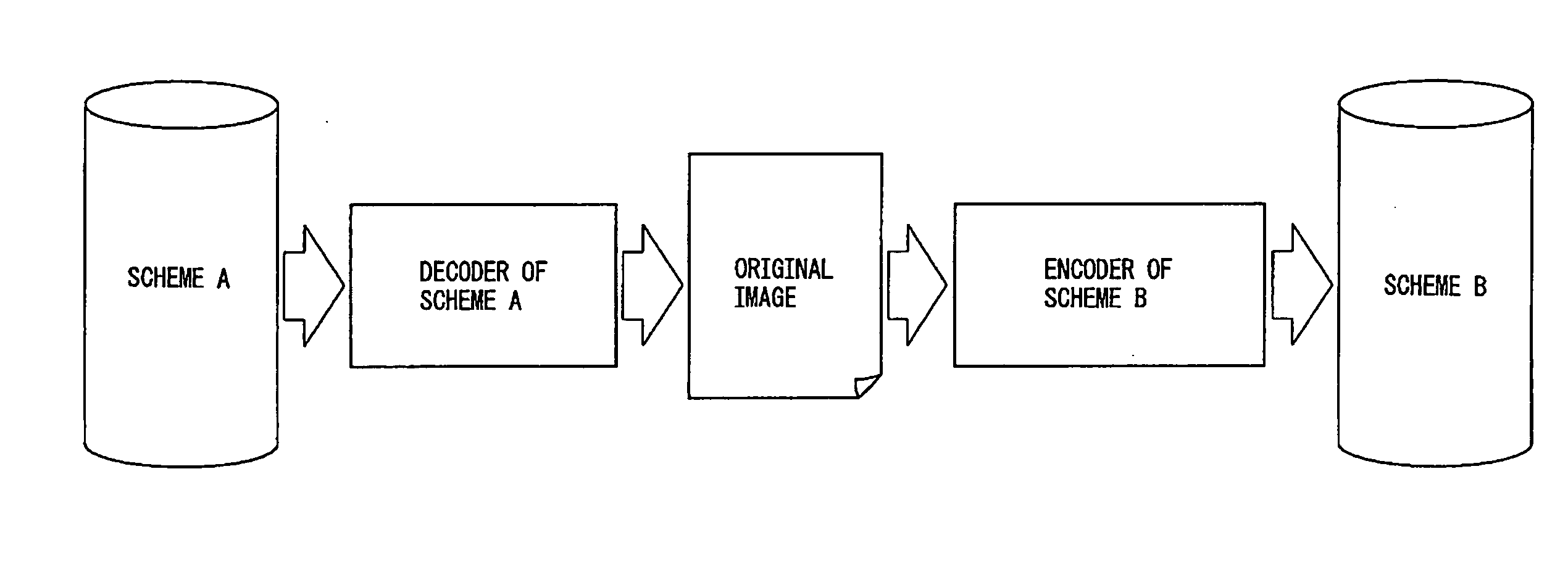

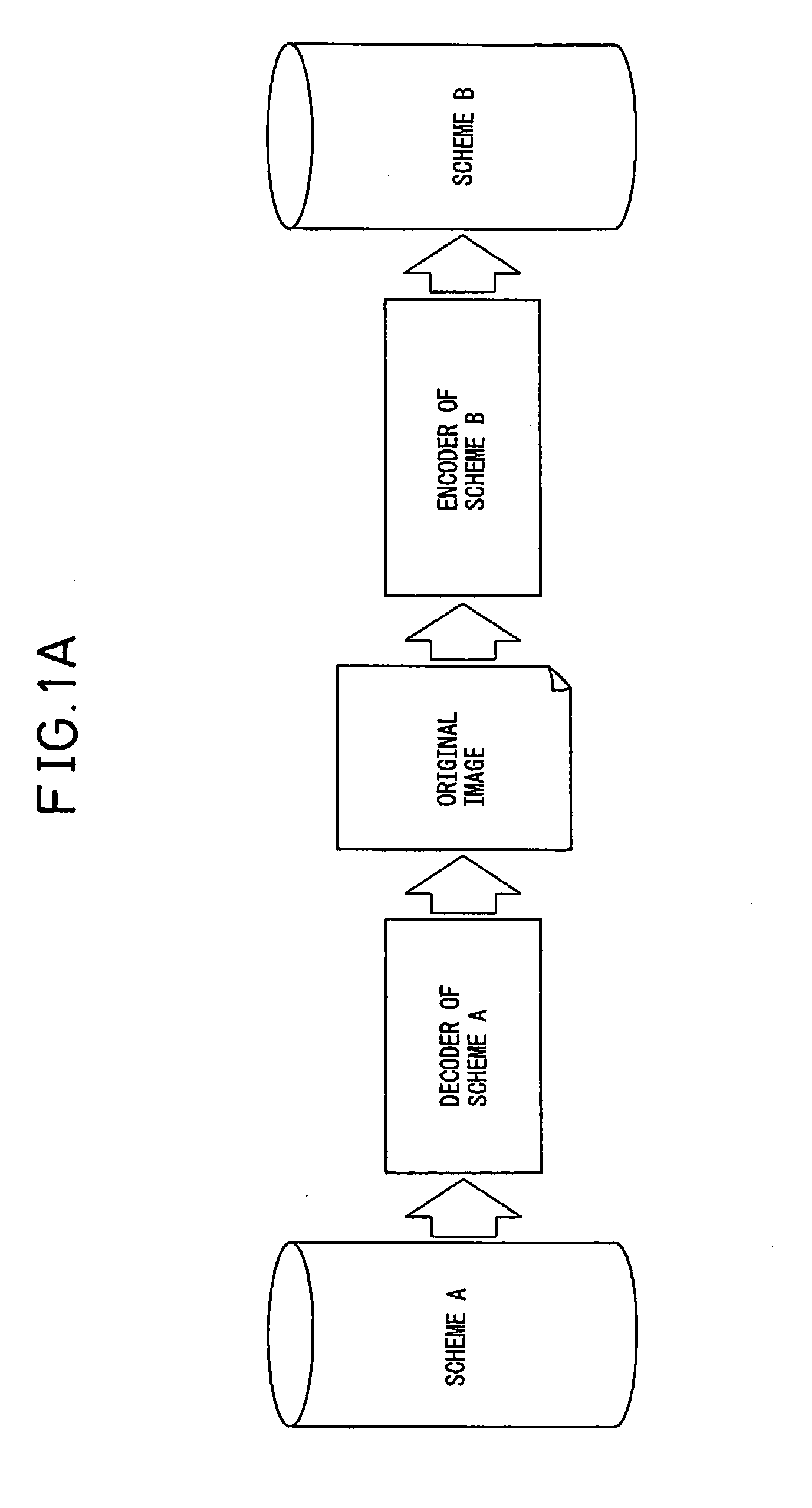

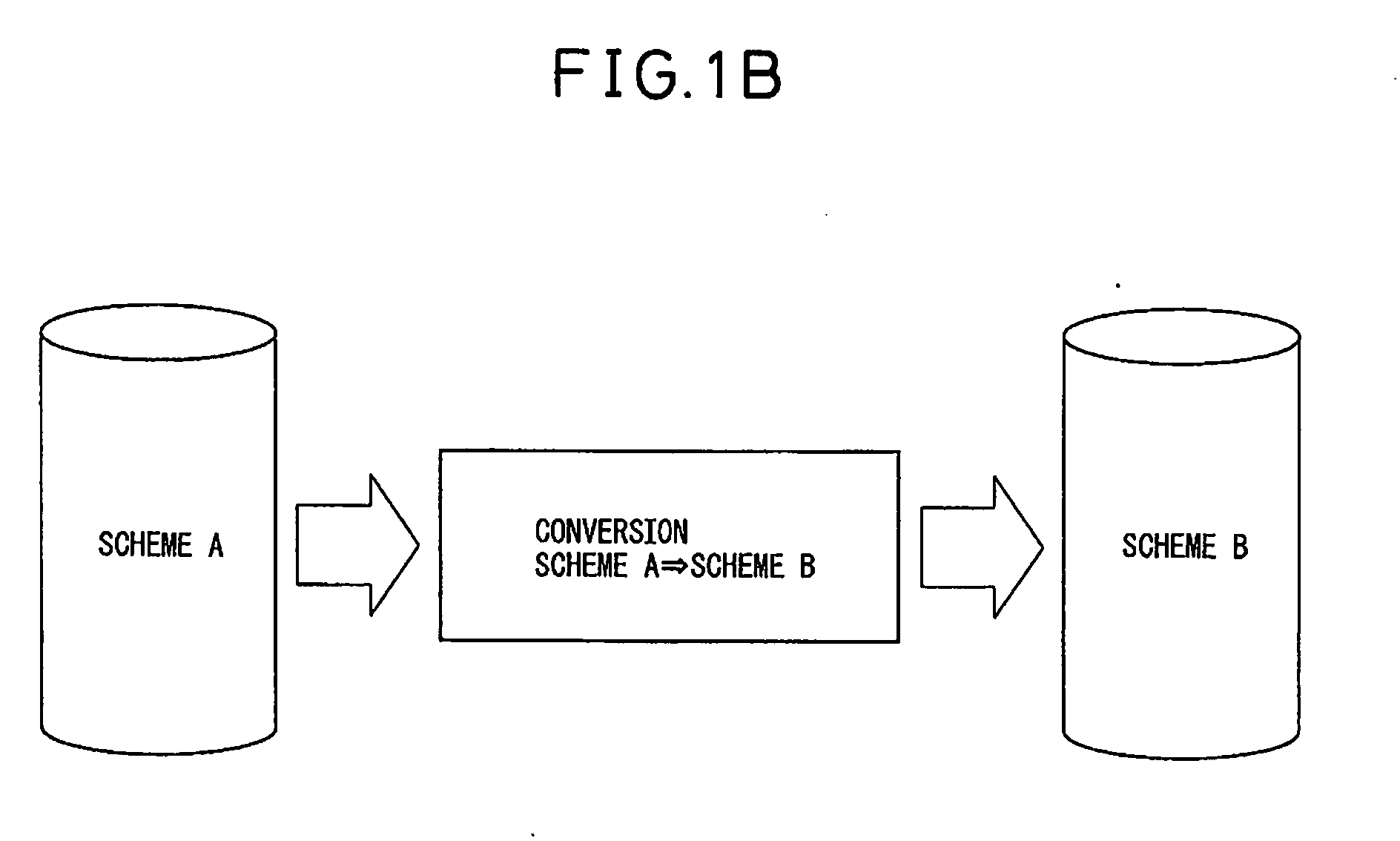

Bitstream conversion method, bitstream conversion apparatus, bitstream connecting apparatus, bitstream splitting program, bitstream conversion program, and bitstream connecting program

ActiveUS20090310669A1Suppress mutationReduced conversion timeTelevision system detailsPicture reproducers using cathode ray tubesComputer scienceTime sequence

A bitstream conversion apparatus for converting a bitstream of a first format, containing content data, into a bitstream of a second format includes: a splitting unit which splits the bitstream of the first format in time sequential fashion into a plurality of split bitstreams of the first format; a plurality of conversion units which convert the plurality of split bitstreams of the first format into a plurality of split bitstreams of the second format; and a connecting unit which connects the plurality of split bitstreams of the second format to one another.

Owner:FUJITSU LTD

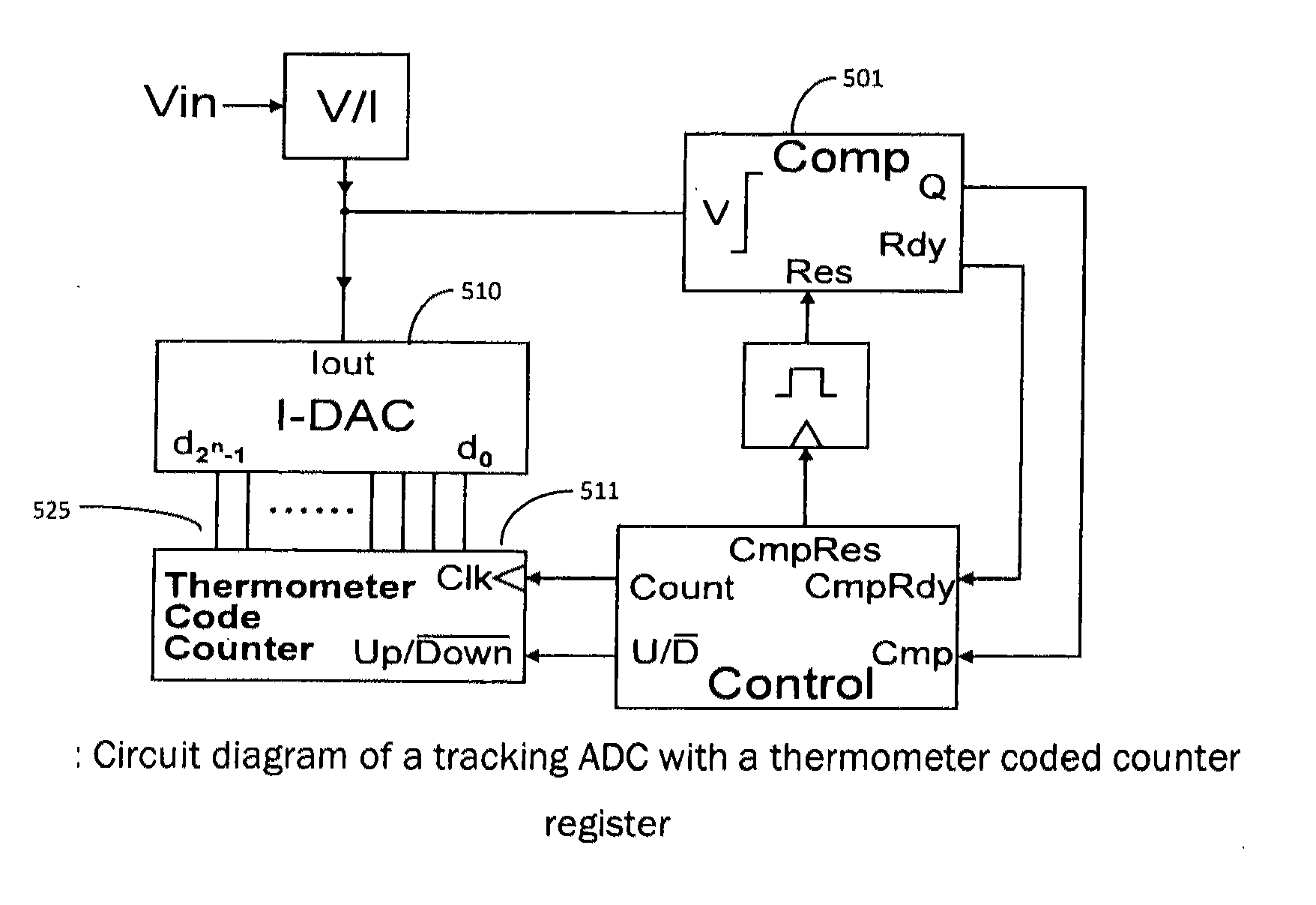

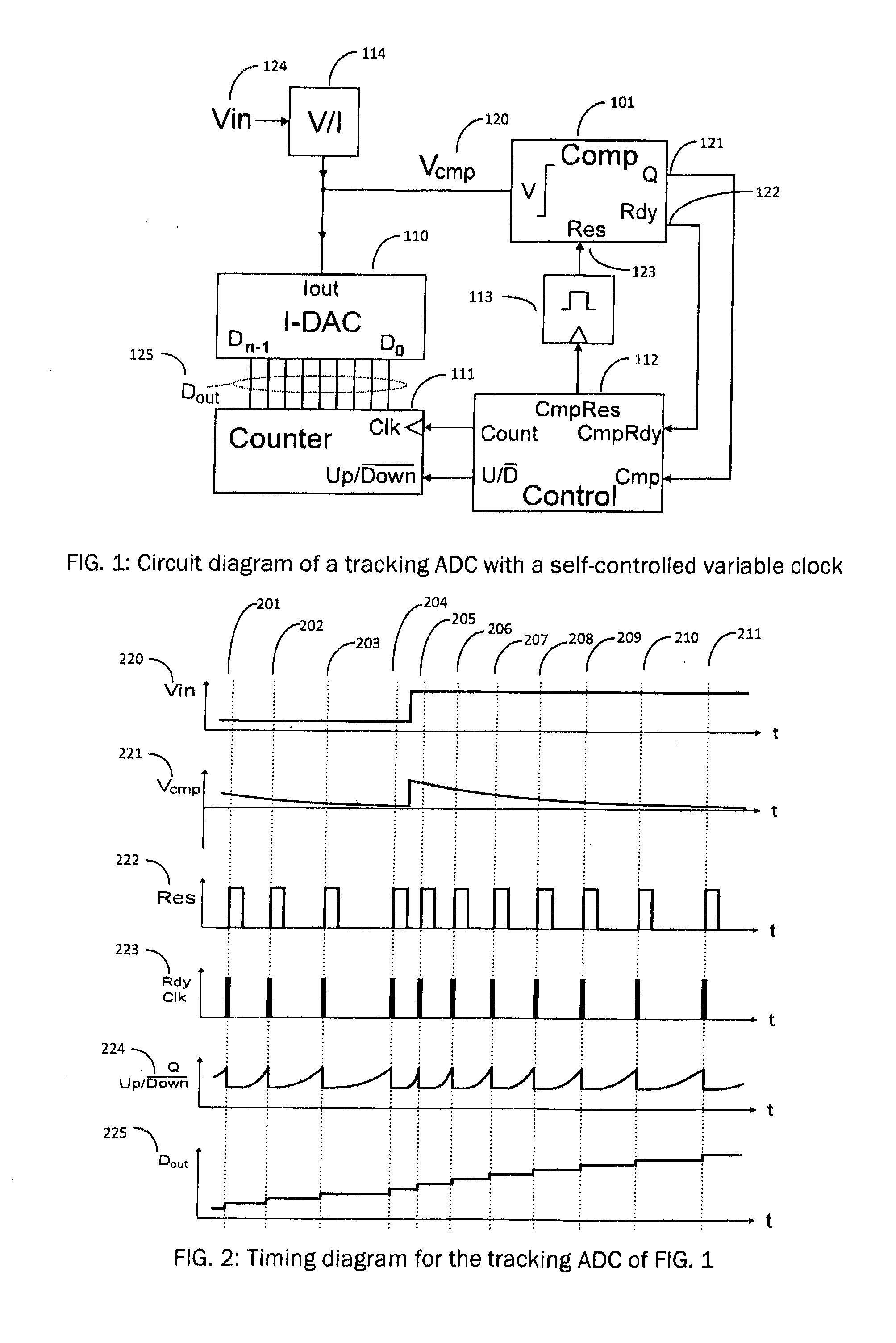

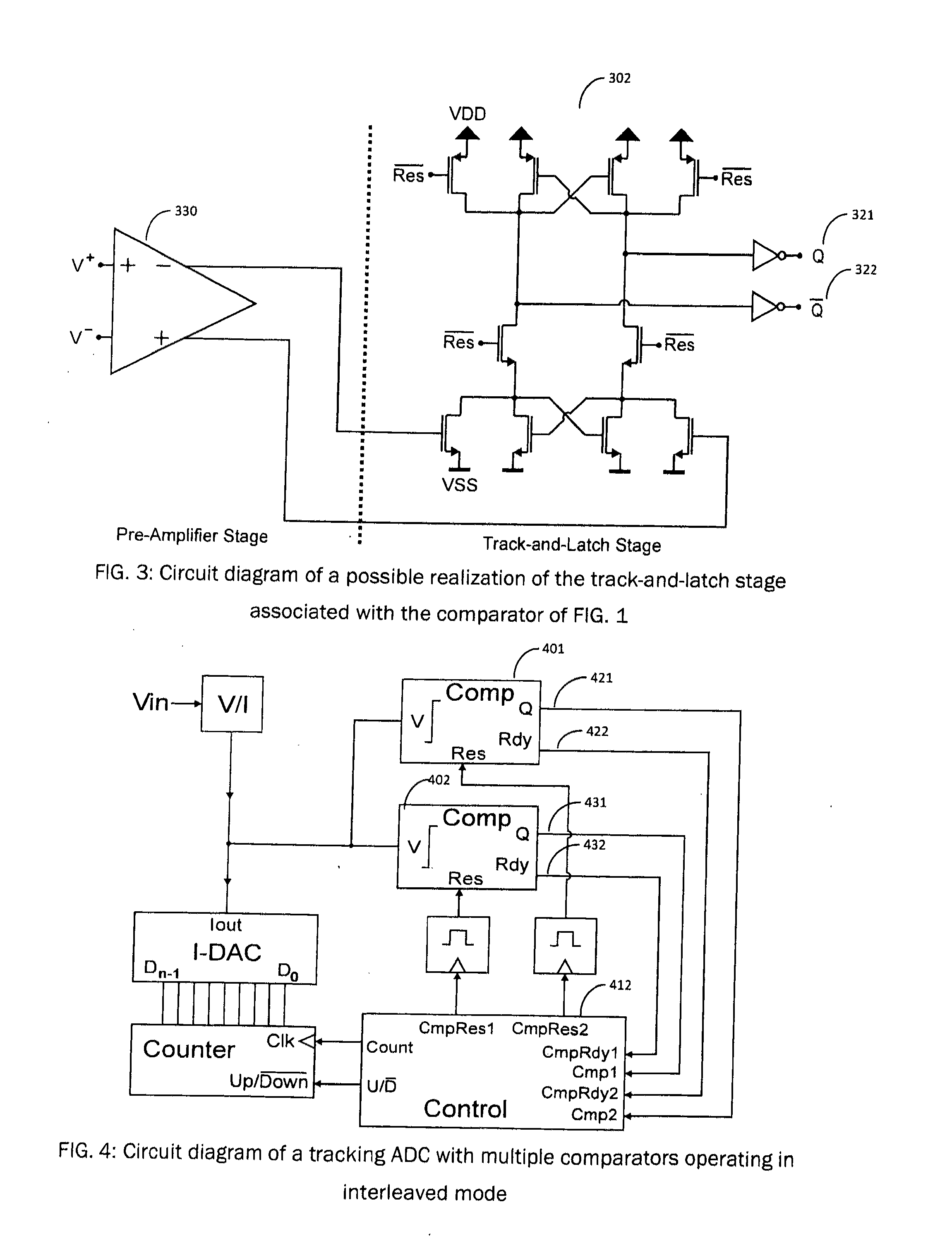

Tracking analog-to-digital converter (ADC) with a self-controlled variable clock

InactiveUS20120212356A1Increase clock frequencyReduced conversion timeElectric signal transmission systemsAnalogue-digital convertersAnalog feedbackEngineering

A tracking analog-to-digital converter “ADC” with a self-controlled variable clock comprises: a digital register; a digital-to-analog converter “DAC” coupled to said digital register providing an analog feedback signal; a comparator coupled to an analog input signal and said analog feedback signal and providing a comparison signal based on a comparison between said analog input signal and said analog feedback signal, said comparison signal being coupled to the digital register; a means for determining comparator readiness to determine if said comparator is ready, indicating that said comparison signal can be reliably read, said means for determining comparator readiness further comprising a determination of a comparison ready indicator; a means for clocking to generate a clock signal to drive said digital register in response to said means for determining comparator readiness determining that said comparator is ready; and said digital register being configured to count in response to said clock signal based on said comparison signal of the comparator.

Owner:DIALOG SEMICONDUCTOR GMBH

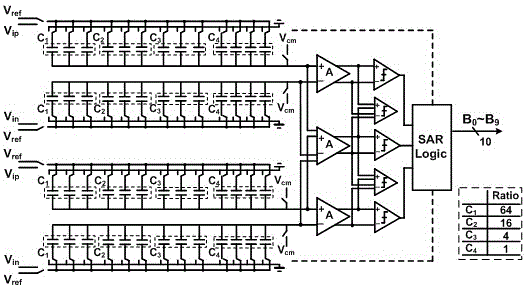

SAR ADC adopting low resolution DAC capacitor array and application method thereof

ActiveCN105141313AHigh resolutionReduce power consumptionAnalogue/digital conversionElectric signal transmission systemsCapacitanceAudio power amplifier

The invention discloses a SAR ADC adopting a low resolution DAC capacitor array and an application method thereof. The ADC comprises two DAC arrays, three preamplifiers, five comparators and a SAR control logic circuit. An interpolation structure is arranged between the two DAC arrays. Compared to the prior art, by using the ADC in the invention, one interpolation comparator is inserted between the two adjacent preamplifiers so that the number of capacitance digital-analog arrays can be reduced. A solution scheme of weighing a bandwidth and the resolution is provided for a multi-bit / periodic SAR ADC. By using the ADC and the method, there are the following advantages that for a high-precision SAR ADC design, usage of a large-scale DAC array can be avoided so that a capacitor DAC array only needs to satisfy thermal noise restraining demand.

Owner:HEFEI AICHUANGWEI ELECTRONIC TECH CO LTD

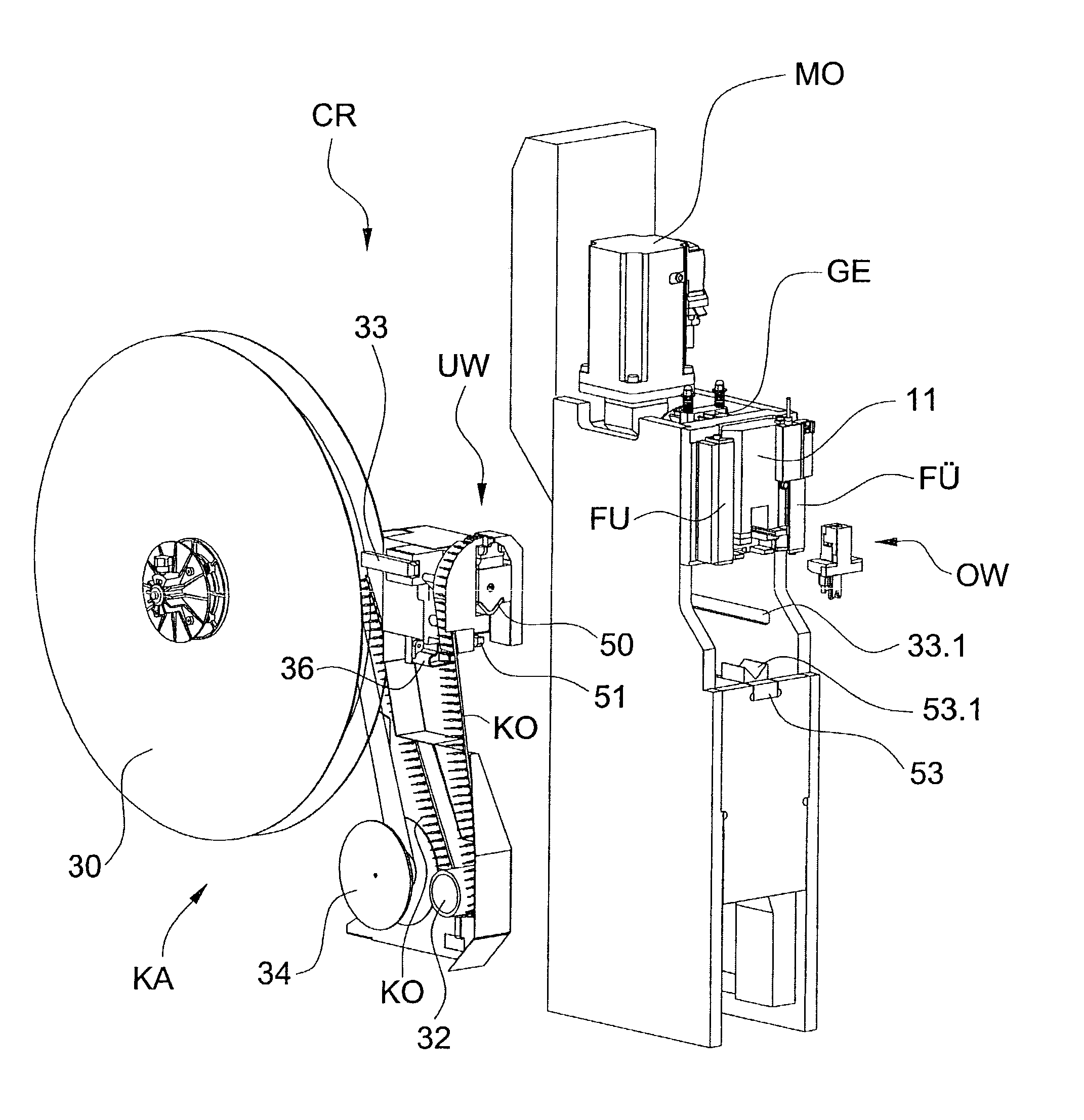

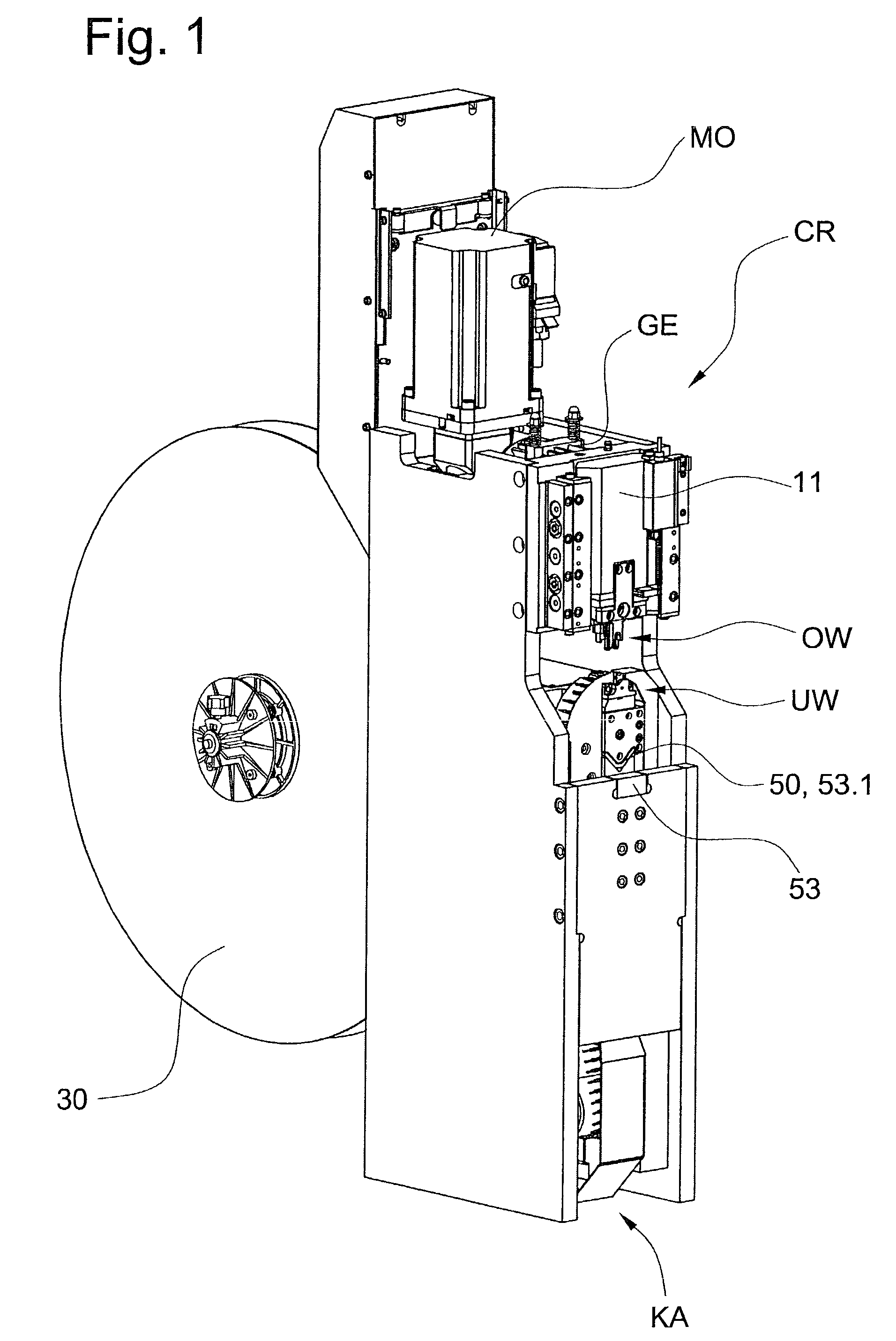

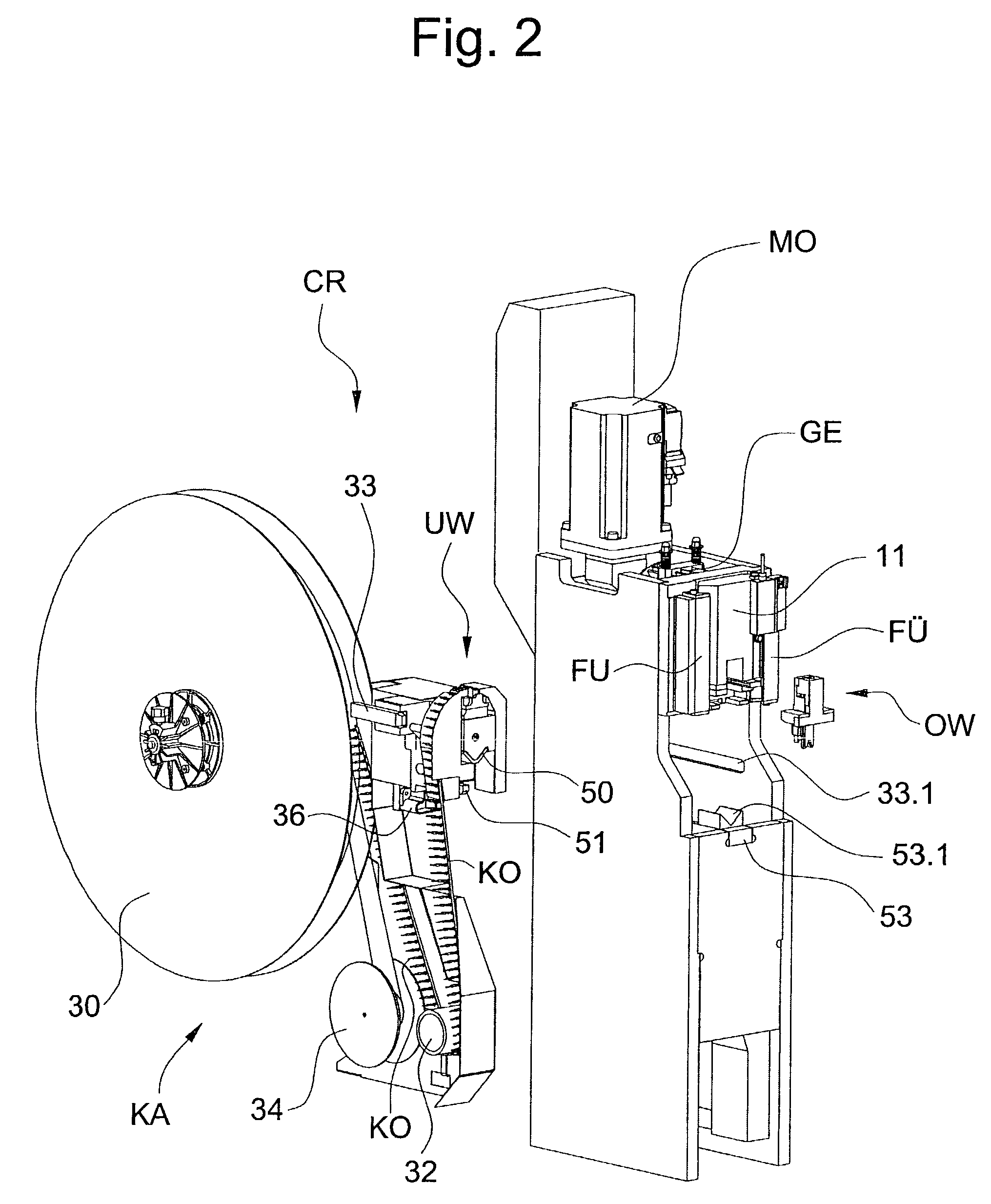

Crimping press with contact feed

ActiveUS7024752B2Avoid disadvantagesLateral space requirementShaping toolsElectronic circuit testingShaft collarSupport surface

Owner:KOMAX HOLDING

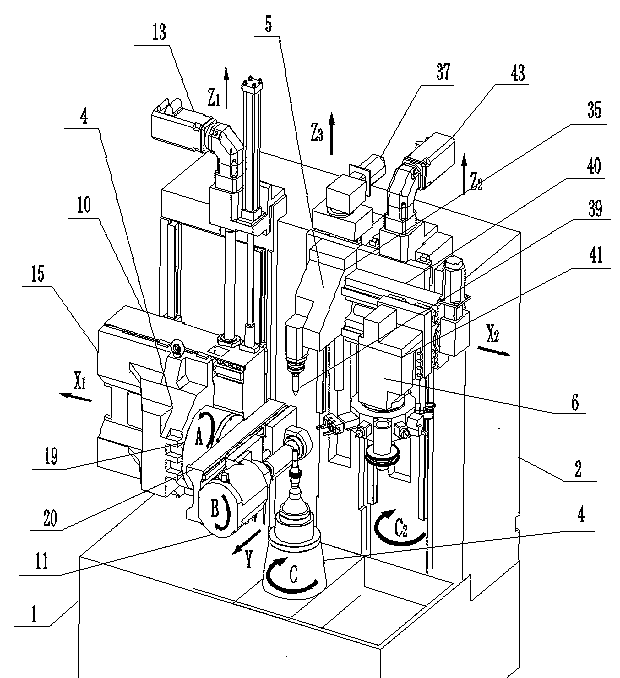

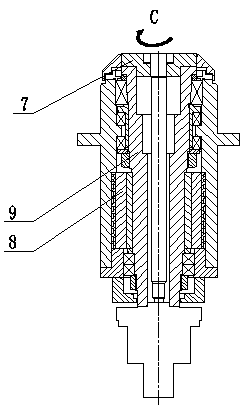

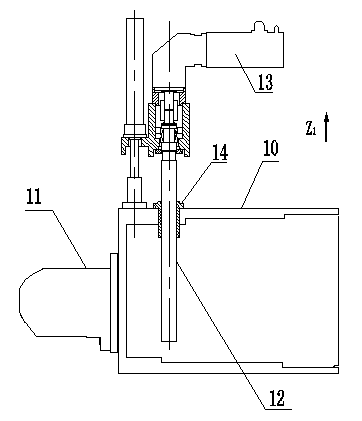

Shaft gear composite processing machine tool

ActiveCN103056629AReduced conversion timeImprove processing efficiencyGear teethEngineeringMachine tool

The invention relates to a shaft gear composite processing machine tool which comprise a tool body, a column, a rotary working platform, a hob feeding mechanism, a supporting frame feeding mechanism and a rotary knife tower feeding mechanism, wherein the column, the rotary working platform, the hob feeding mechanism, the supporting frame feeding mechanism and the rotary knife tower feeding mechanism are fixed on the tool body. The rotary working platform is fixed on the top surface of the tool body, and the hob feeding mechanism, the supporting frame feeding mechanism and the rotary knife tower feeding mechanism are horizontally and sequentially arranged on one side of the column close to the rotary working platform and matched with the column in the vertical direction in sliding mode. A workpiece is clamped once, turning, hobbing, milling, chamfering, burring, drilling and the like are performed on gears of different sizes through rotation of the working platform, switch of different processing knives, horizontal and longitudinal feeding and rotation of angles. Switching time of the workpiece between different machine tools is saved, processing efficiency is improved, and processing precision of parts is guaranteed to the maximum limit.

Owner:CHONGQING MACHINE TOOL GROUP

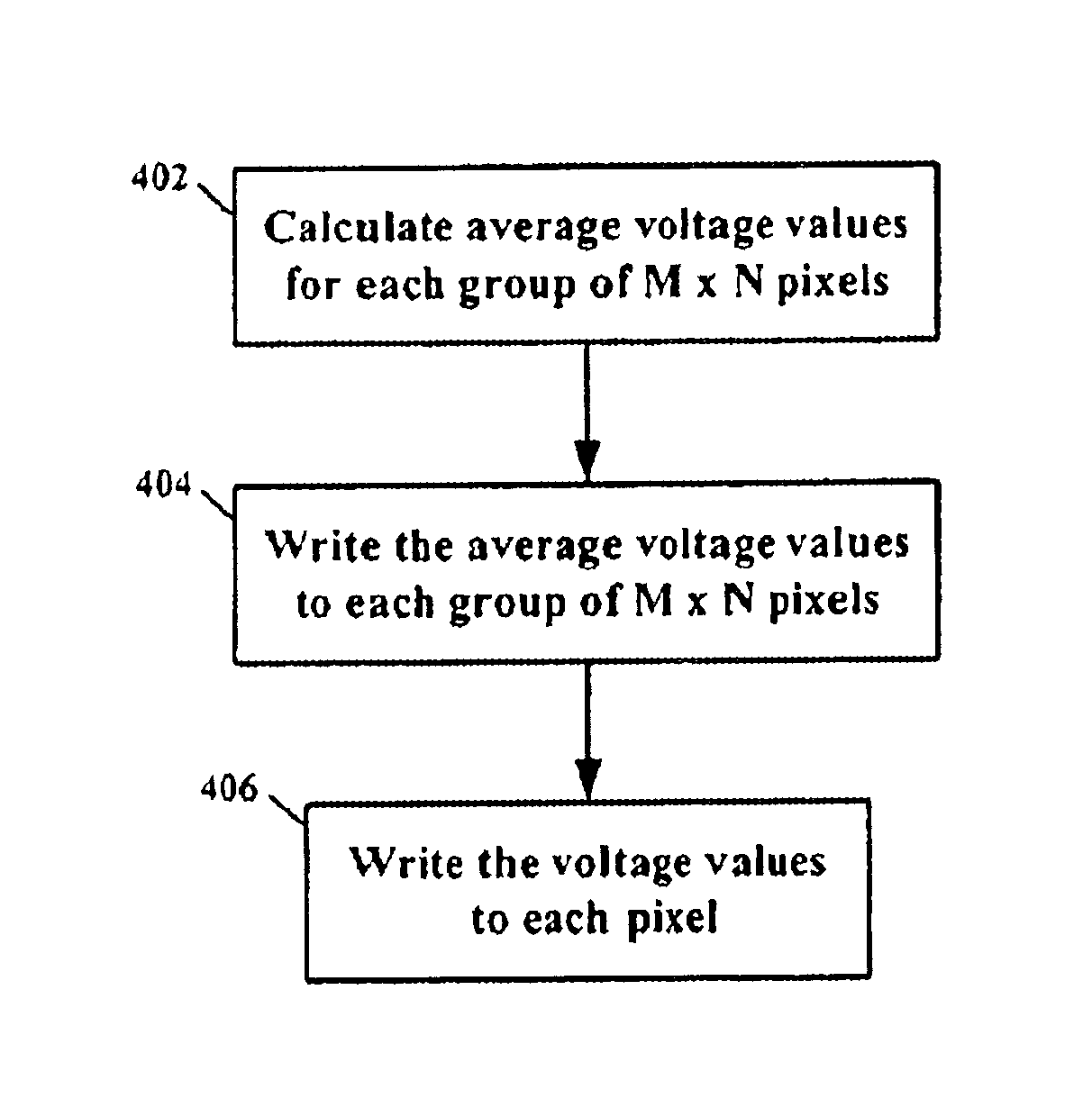

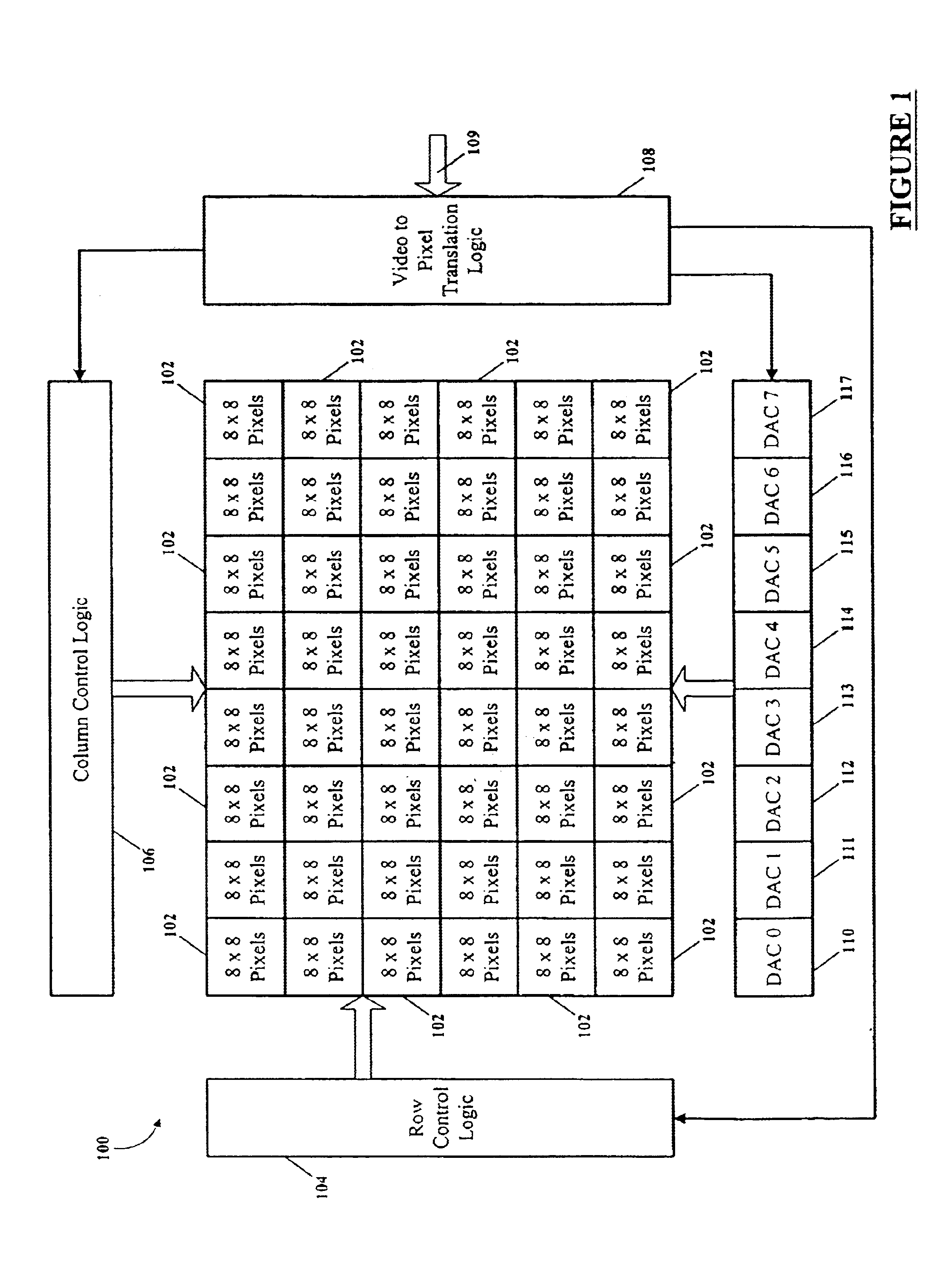

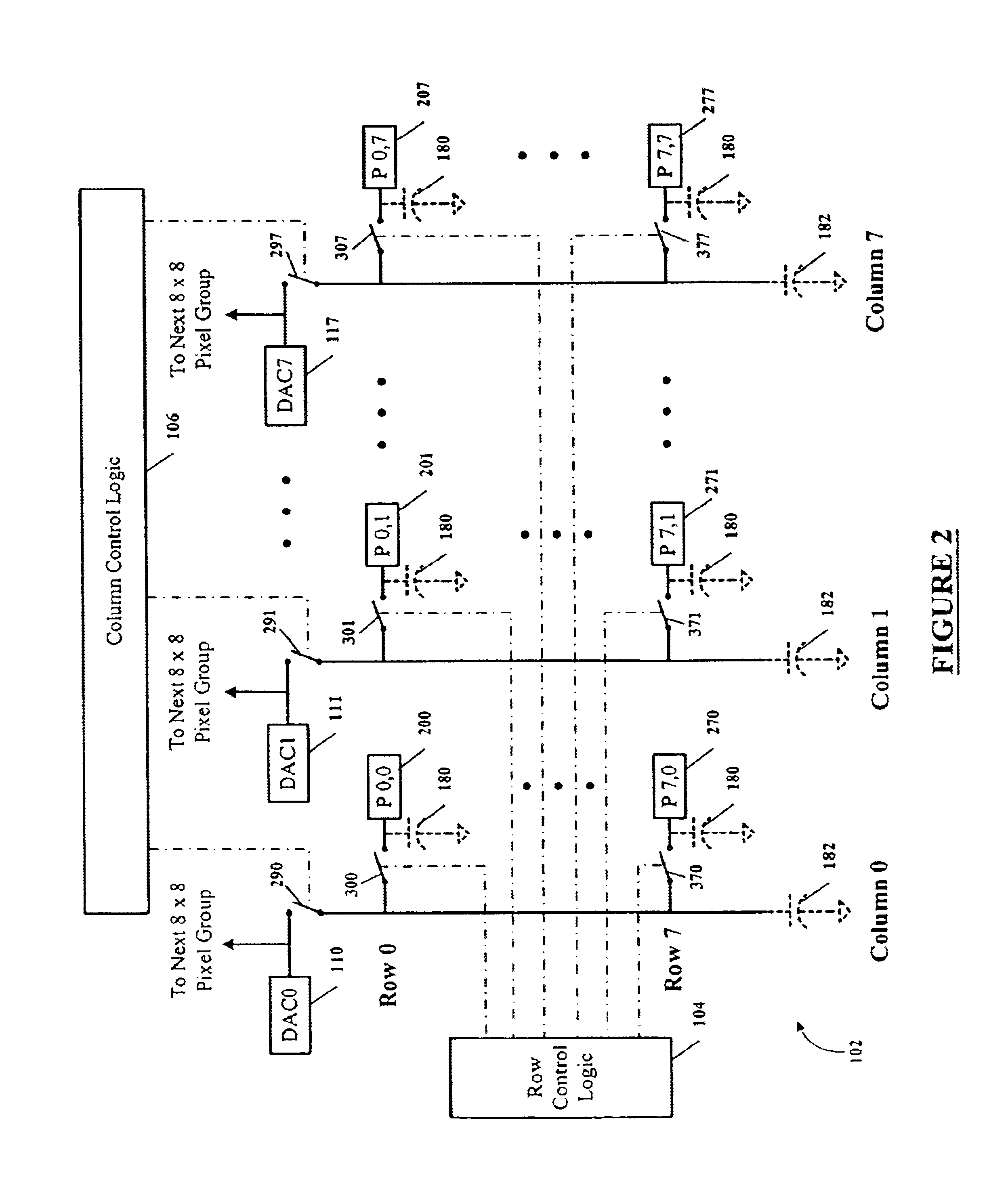

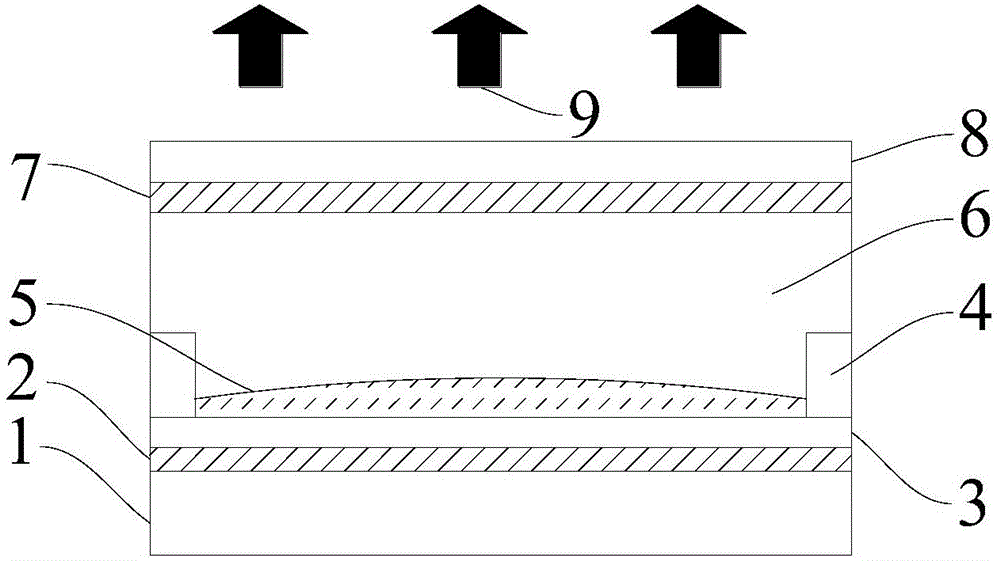

Frame prewriting in a liquid crystal display

InactiveUS6850218B2Quickly and accurately controlsFast write timeStatic indicating devicesNon-linear opticsDigital analog converterLiquid-crystal display

A liquid crystal display (LCD) having a matrix of liquid crystal pixels is provided. A plurality of digital-to-analog converters (DACs) are coupled to the LCD matrix through analog voltage switches and are adapted to produce output voltages that are applied to the pixels in the LCD matrix. Through the combination of DACs and analog voltage switches, groups of pixels are pre-written to an average value of the pixels in that group which is fairly close to their final voltage values of each pixel so that the liquid crystal material can begin slewing and settling as early as possible. Then one or more writes to each of the pixels is made of the precise voltage value desired at each of the pixels. Alternate, adjacent odd and even rows of pixels may be written together and then only the even or odd rows are finally written to obtain the desired final voltage values at each of the pixels in the LCD.

Owner:REGENMACHER +1

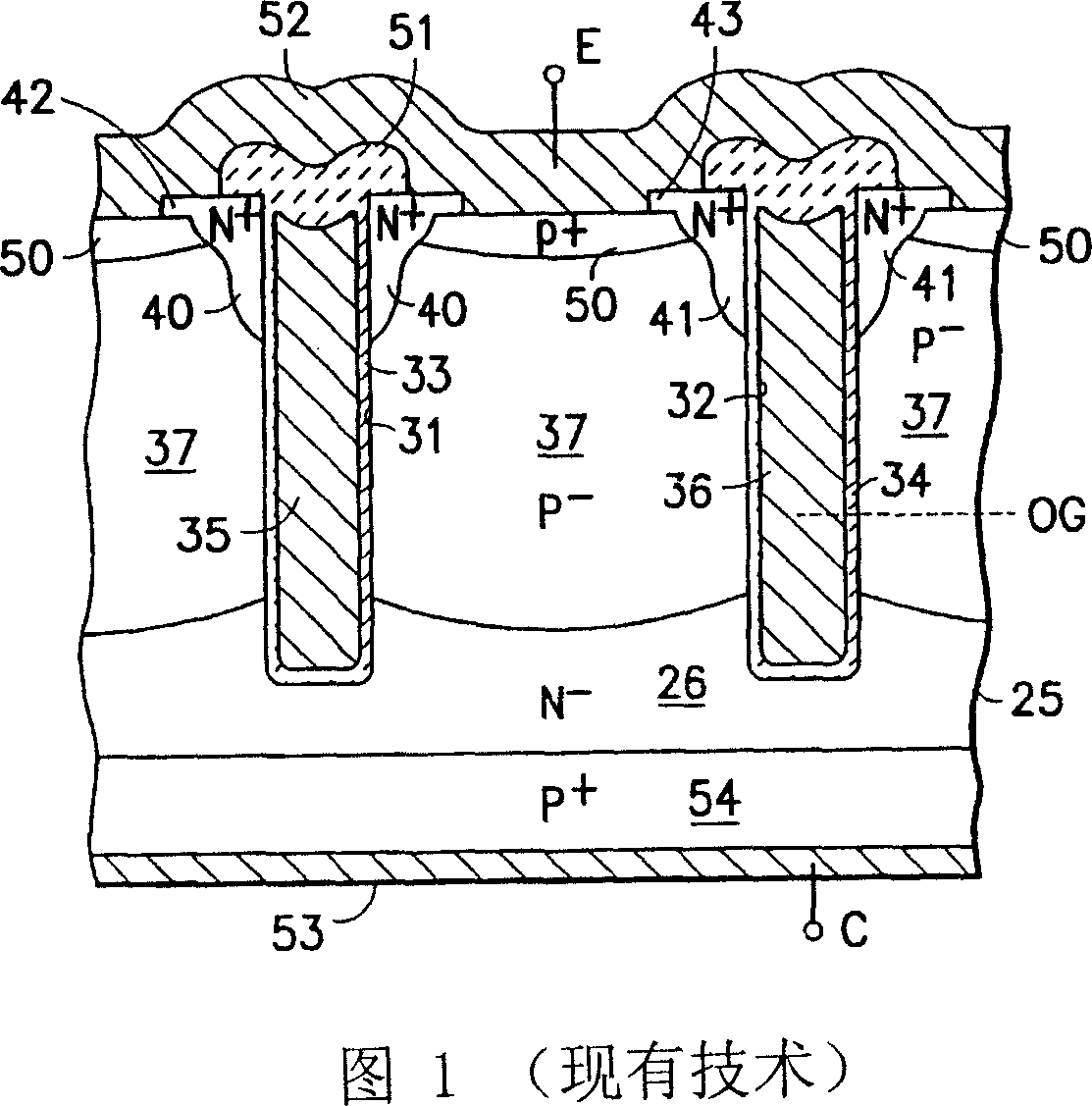

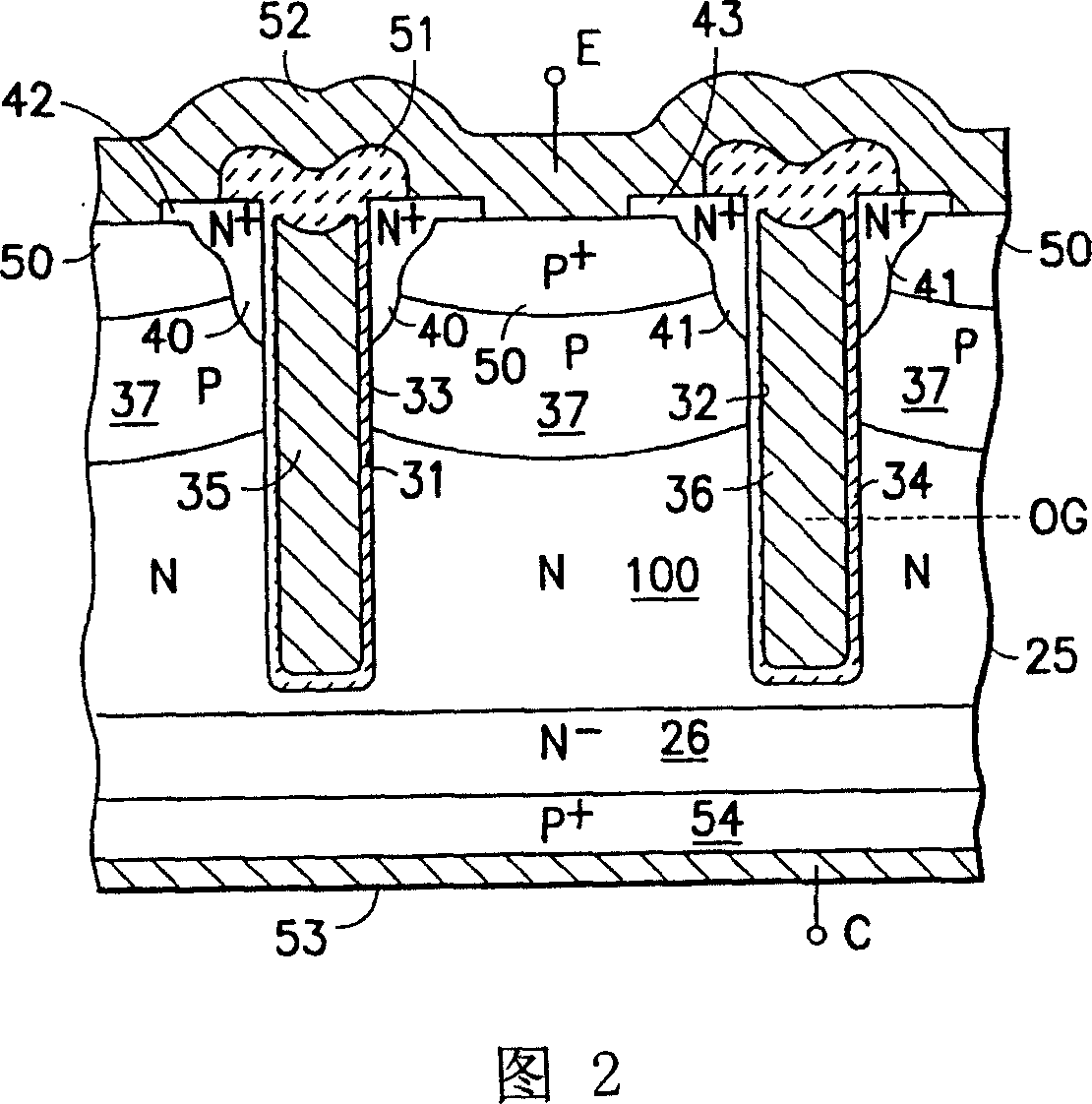

Deep N diffusion for trench IGBT

InactiveCN1921146ALower forward voltageReduce forward voltage dropTransistorTrench igbtHigh concentration

The present invention relates to a deep N diffusion for trench IGBT. An increased conductivity deep diffusion of the same conductivity type as that of the drift region is provided between adjacent trenches of a trench type IGBT and below the trenches to reduce the on resistance components of the drift region resistance and spreading resistance to current flow when the device is turned on. The deep diffusion has a higher concentration than that of the drift region, and has a width of from 4 to 10 microns. The wafer or die has a total width (or thickness) of about 70 to about 300 microns.

Owner:INTERNATIONAL RECTIFIER COEP

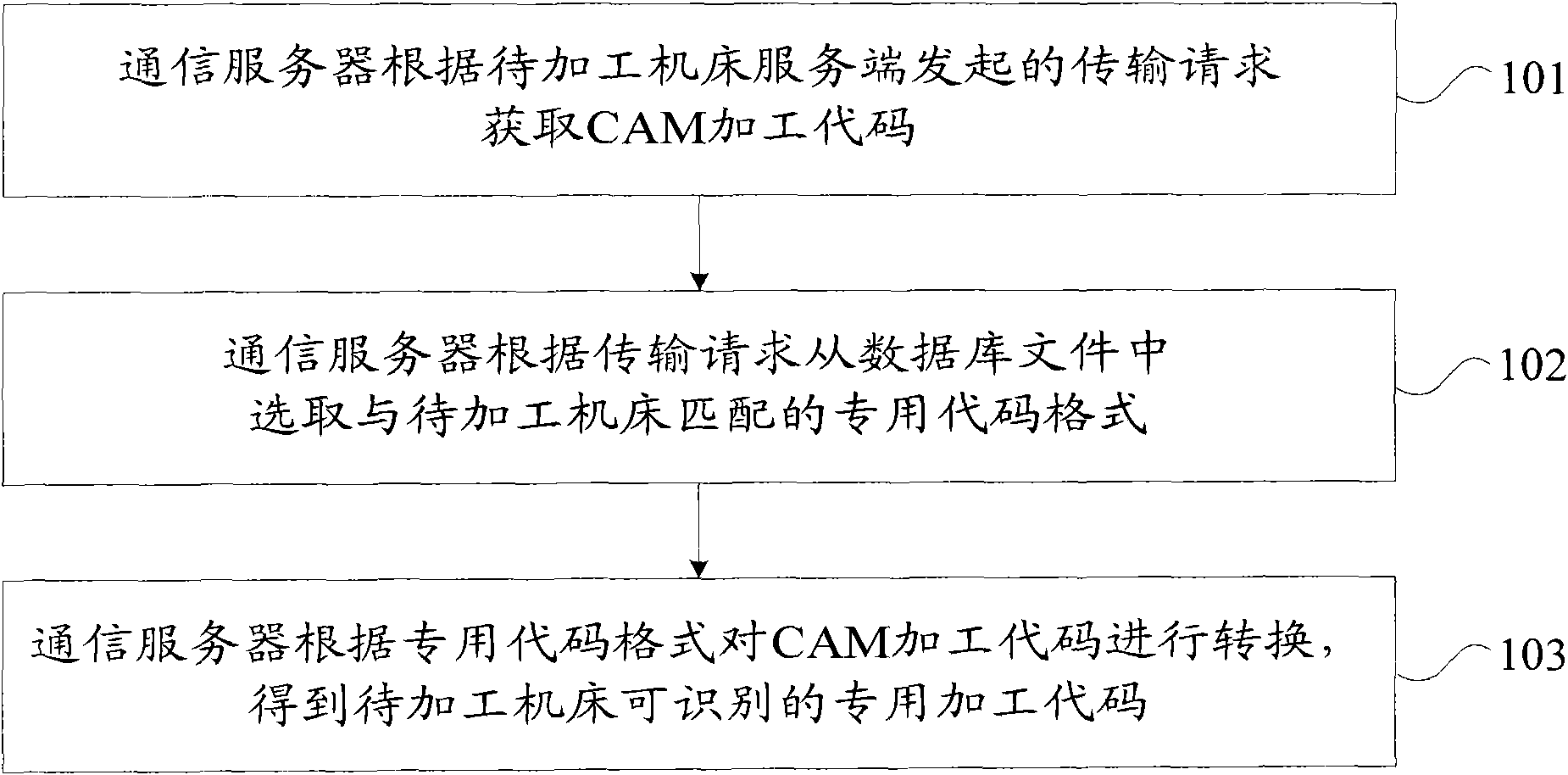

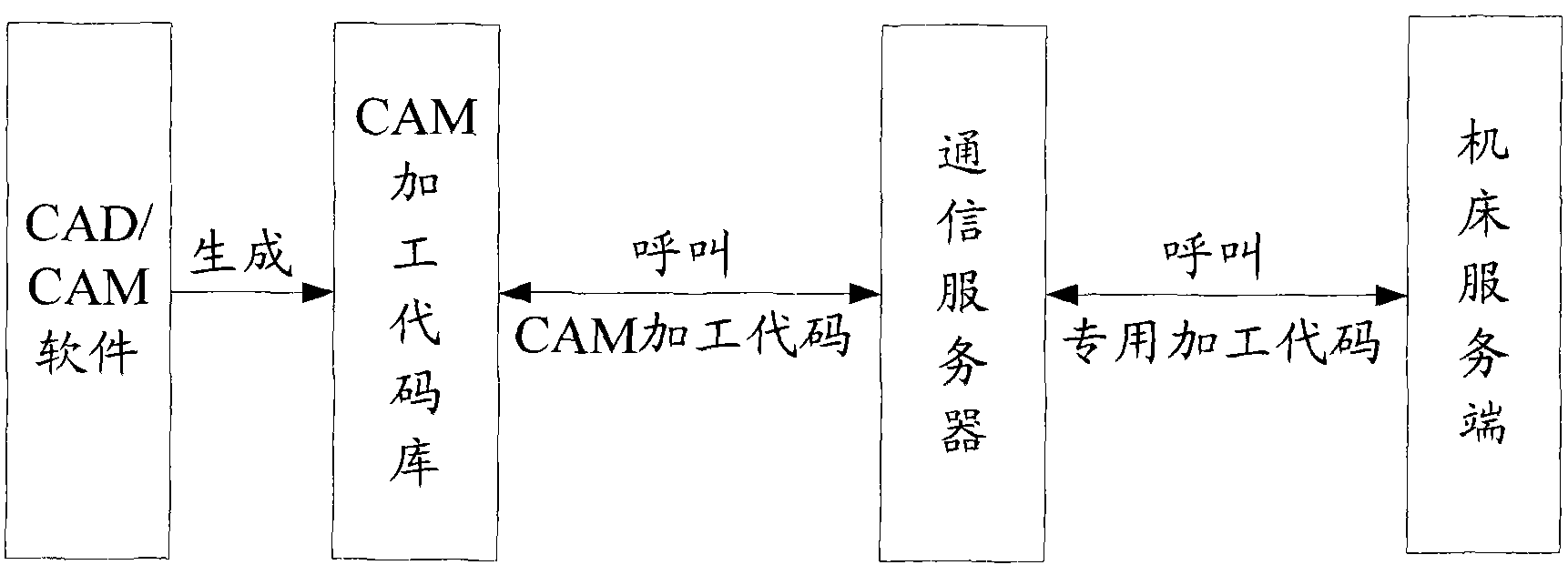

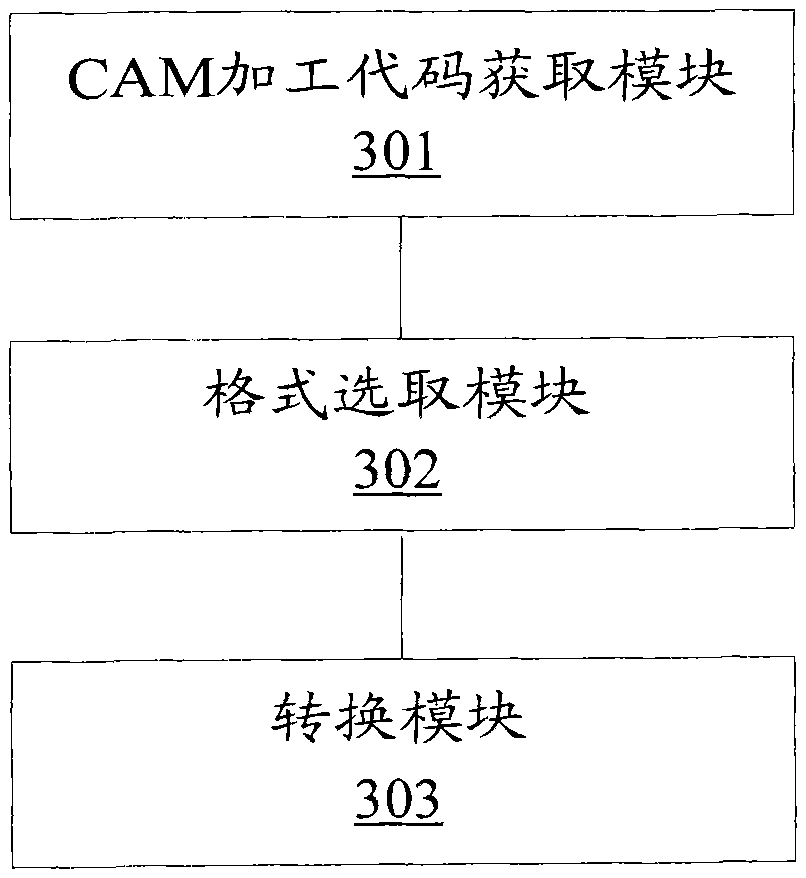

Code conversion method and device used for numerical control system

ActiveCN101794140AImplement automatic conversionReduced conversion timeProgramme controlComputer controlHigh volume manufacturingSpecific model

The invention provides a code conversion method and a device used for a numerical control system. The method comprises the following steps: obtaining CAM processing codes by a communication server according to transmission requests initiated by the service end of a machine tool to be processed; selecting a special code format matched with the machine tool to be processed from a database file by the communication server according to the transmission requests, wherein the database file is used for recording the matching relationship between the numerical control machine tool of the specific model and the special code format thereof; converting the CAM processing codes by the communication server according to the special code format to obtain the special processing code capable of being recognized by the machine tool to be processed; and sending the special processing code to the service end of the machine tool to be processed. The invention shortens the code conversion time, lowers the fault rate during batch production or processing of complicated parts, further improves the code conversion efficiency, and is favorable for improving the numerical control processing quality after the code conversion, so the invention overcomes the problem of low code conversion efficiency of a code conversion method in the correlation technique.

Owner:CAXA TECH

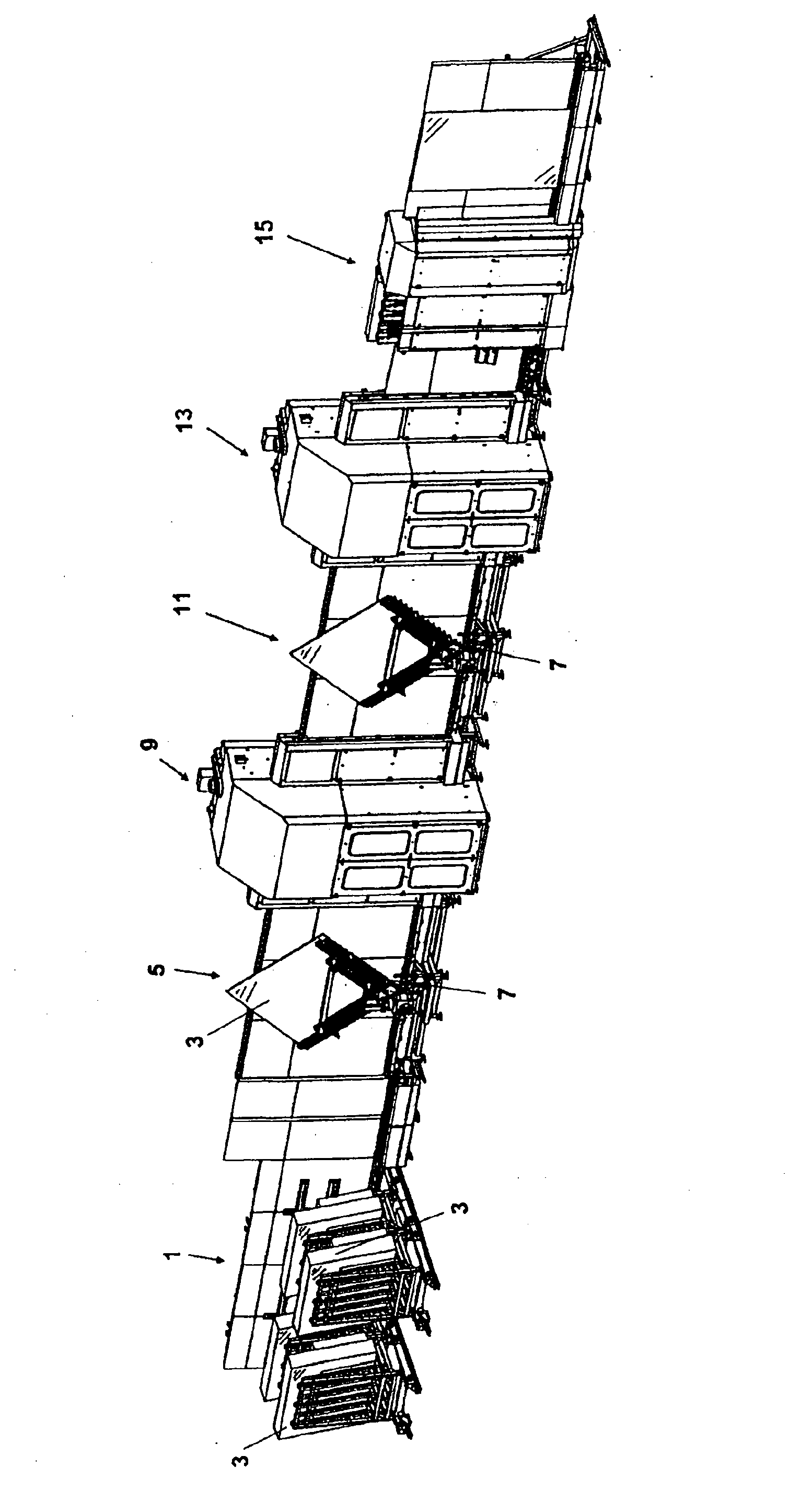

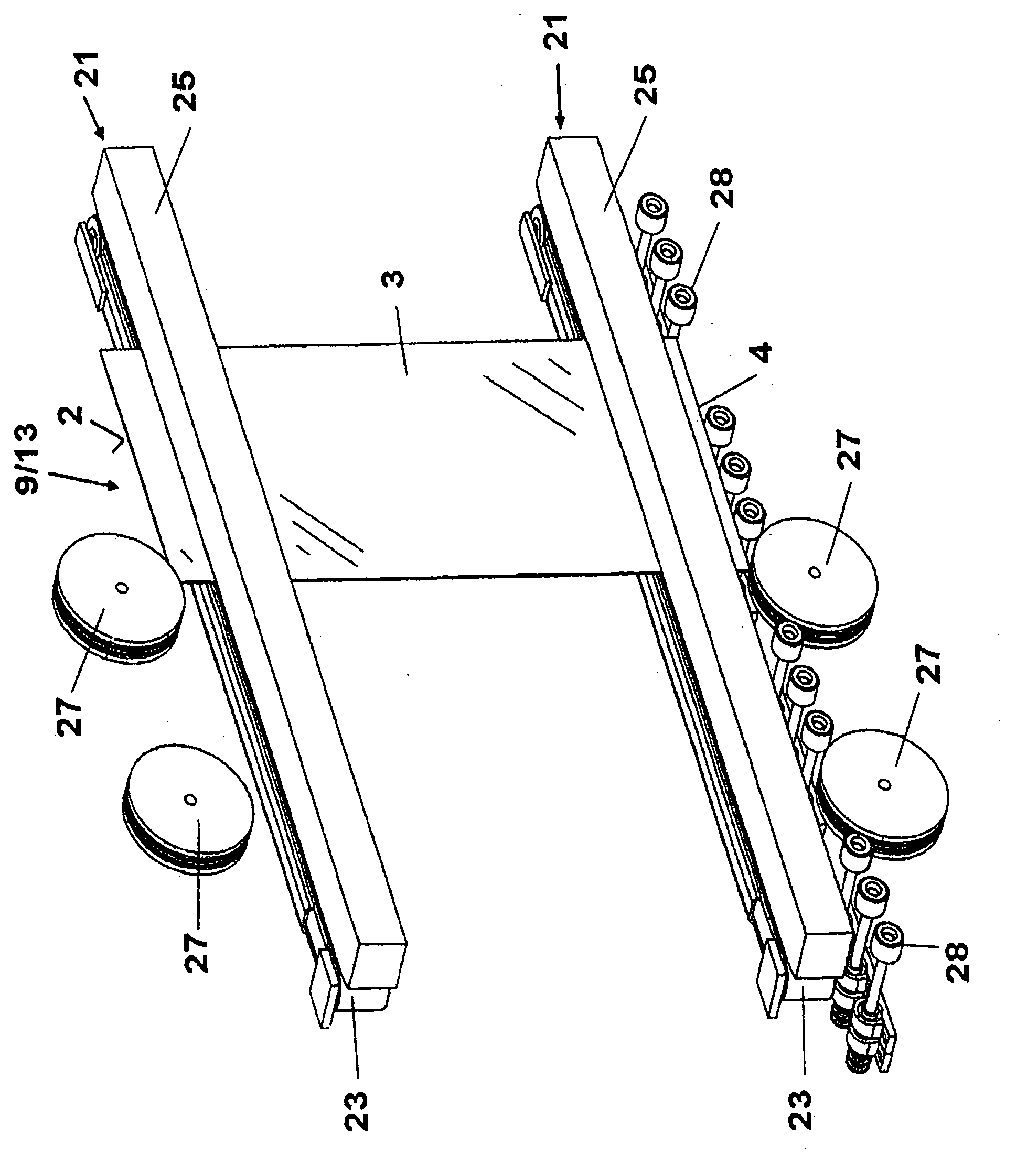

Device for conveying plate-shaped elements

The invention relates to a linear conveyor (21) for transporting glass panels (3) in the vicinity of grinding stations (9, 13) or a washing station (15) of a system for producing glass panel blanks comprising a linear conveyor (23), for example, a driven toothed belt, and opposite the driven toothed belt a beam (25), from which a fluid, in particular water, is discharged. The glass panel (3) is pressed against the linear conveyor (23) in a non-positive manner and reliably conveyed by means of the water discharged from the beam (25). Such linear conveyors (21) can be arranged at the upper or lower edge of a glass panel (3) in order to trim the glass panel using at least one grinding disk (27), for example.

Owner:LISEC AUSTRIA

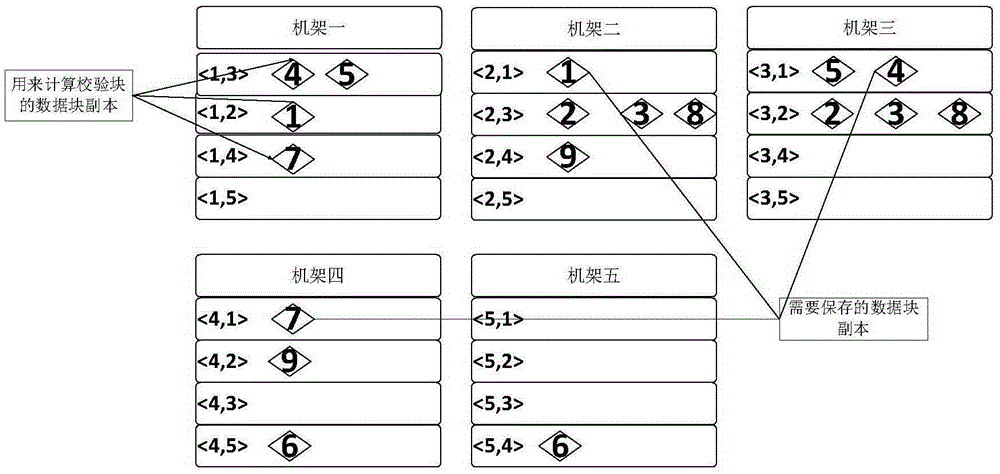

Distributed type encoding method based on dynamic band configuration

ActiveCN105302500AReduced conversion timeReduce data downloadsInput/output to record carriersQuality of serviceFault tolerance

The invention discloses a distributed type encoding method based on dynamic band configuration. The distributed type encoding method is characterized by comprising the following operation steps: acquiring data block information from a general control node, and dynamically constructing a data band according to the information; carrying out persistent storage on construction information of the data band, and distributing verification data block calculation tasks; deleting a redundant data node; and redistributing the data band which is not incompletely distributed. With the adoption of a manner of dynamically constructing the data band, compared with a traditional manner of constructing the data band by adopting a continuous data block, a rack-spanning or node-spanning data downloading amount in a conversion process is reduced under the condition of guaranteeing the fault tolerance of the data block of a system, conversion time of data from three-copy storage to erasure code storage is shortened, data bandwidth in the conversion process is reduced, and service quality and performance of the distributed type system are improved.

Owner:UNIV OF SCI & TECH OF CHINA

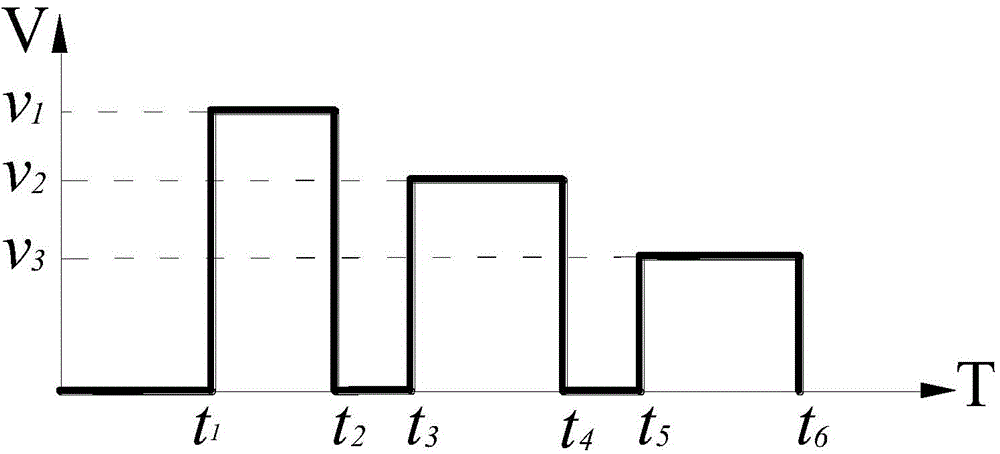

Gradation display modulating method for electrowetting display

InactiveCN104867460AExtended service lifeReduced conversion timeStatic indicating devicesDisplay contrastElectricity

The invention discloses a gradation display modulating method for an electrowetting display. The gradation display modulating method includes applying initial referential voltage between two electrodes of pixels of the electrowetting display and retaining for a while, allowing the nonpolar fluid in the electrowetting display to contract, determining a first predetermined voltage and a first predetermined time period according to target gradation of the pixels of the electrowetting display, lowering the initial referential voltage between two electrodes of pixels to the first predetermined voltage, retaining the first predetermined voltage in the first predetermined time period, releasing the contraction state of the nonpolar fluid, and the pixels displaying target gradation. The method makes full use of characteristic that nonpolar fluid is more stable during a lowering stage. The electrowetting display device is driven by lowering voltage in different phases to move nonpolar fluid stably, and the occupied area of the nonpolar fluid is accurately modulated. The visual area of each pixel grid can be accurately modulated, to control the display contrast of integral pixels and realize accurate gradation display.

Owner:SOUTH CHINA NORMAL UNIVERSITY +2

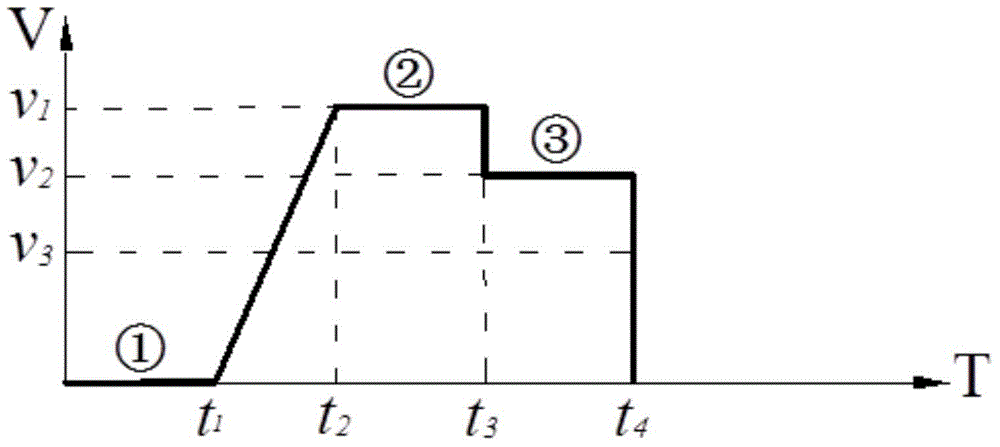

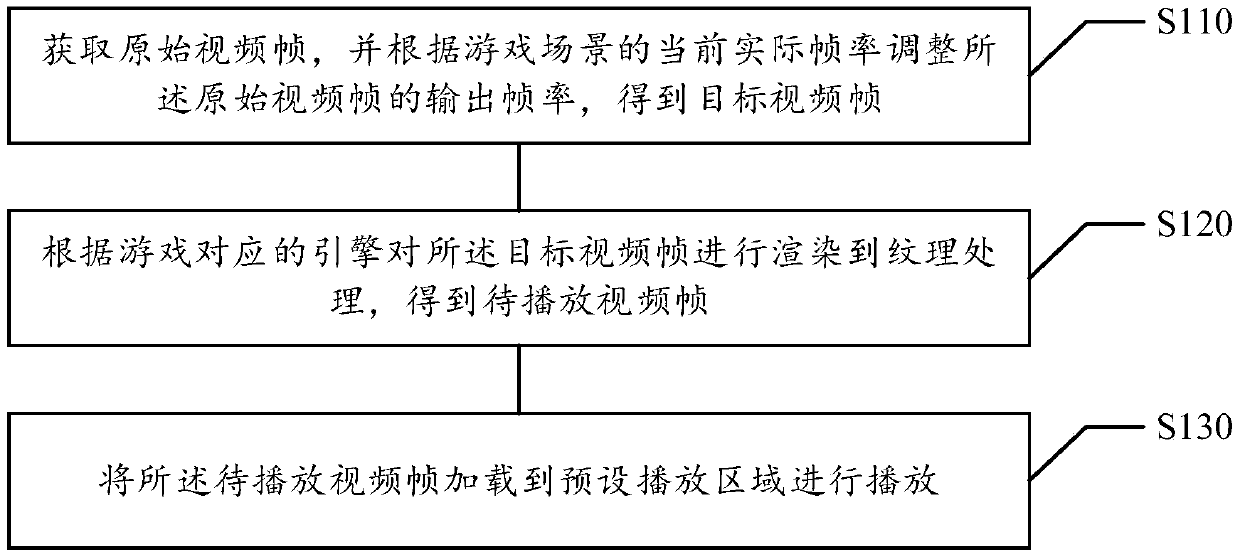

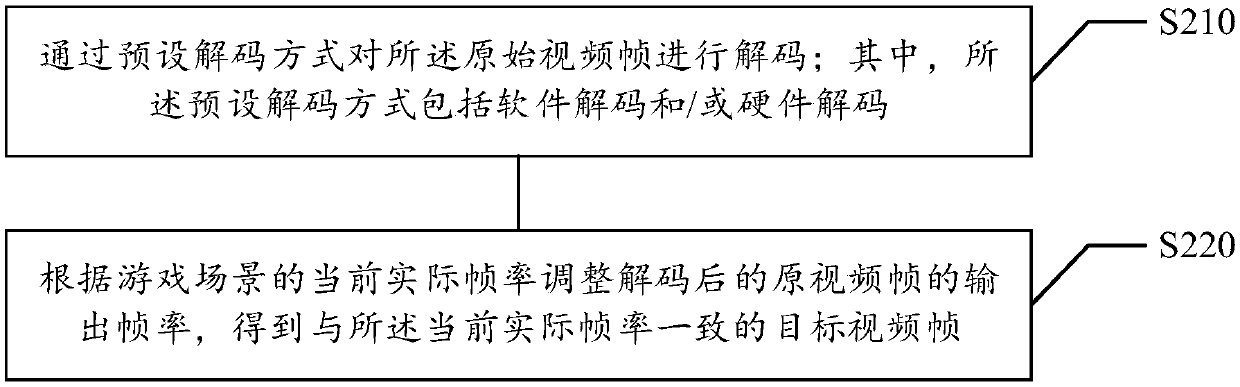

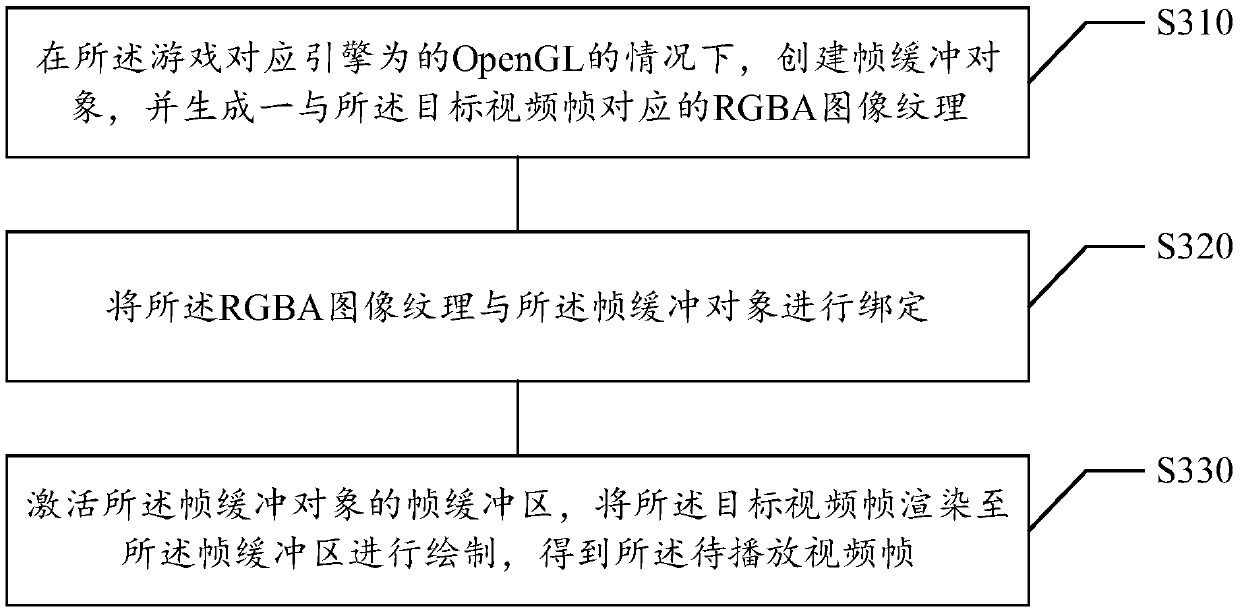

Video playing method and device in game scene, medium and electronic equipment

ActiveCN109600666AReduced conversion timeLow resolution accuracyVideo gamesSelective content distributionFrame rateComputer graphics (images)

The embodiment of the invention relates to a video playing method and device in a game scene, and belongs to the technical field of video processing. The method comprises the steps of obtaining an original video frame, and adjusting the output frame rate of the original video frame according to the current actual frame rate of the game scene, so as to obtain a target video frame; rendering the target video frame to texture processing to obtain a to-be-played video frame according to an engine corresponding to a game, and loading the to-be-played video frame to a preset playing area for playing. According to the method, the problem that in the prior art, due to the fact that the frame rate is too high, audio and video asynchronization occurs, the audio and video playing accuracy is low is solved, the audio and video playing accuracy is improved, and the burden of equipment is reduced.

Owner:NETEASE (HANGZHOU) NETWORK CO LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com