Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

206 results about "Analog feedback" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

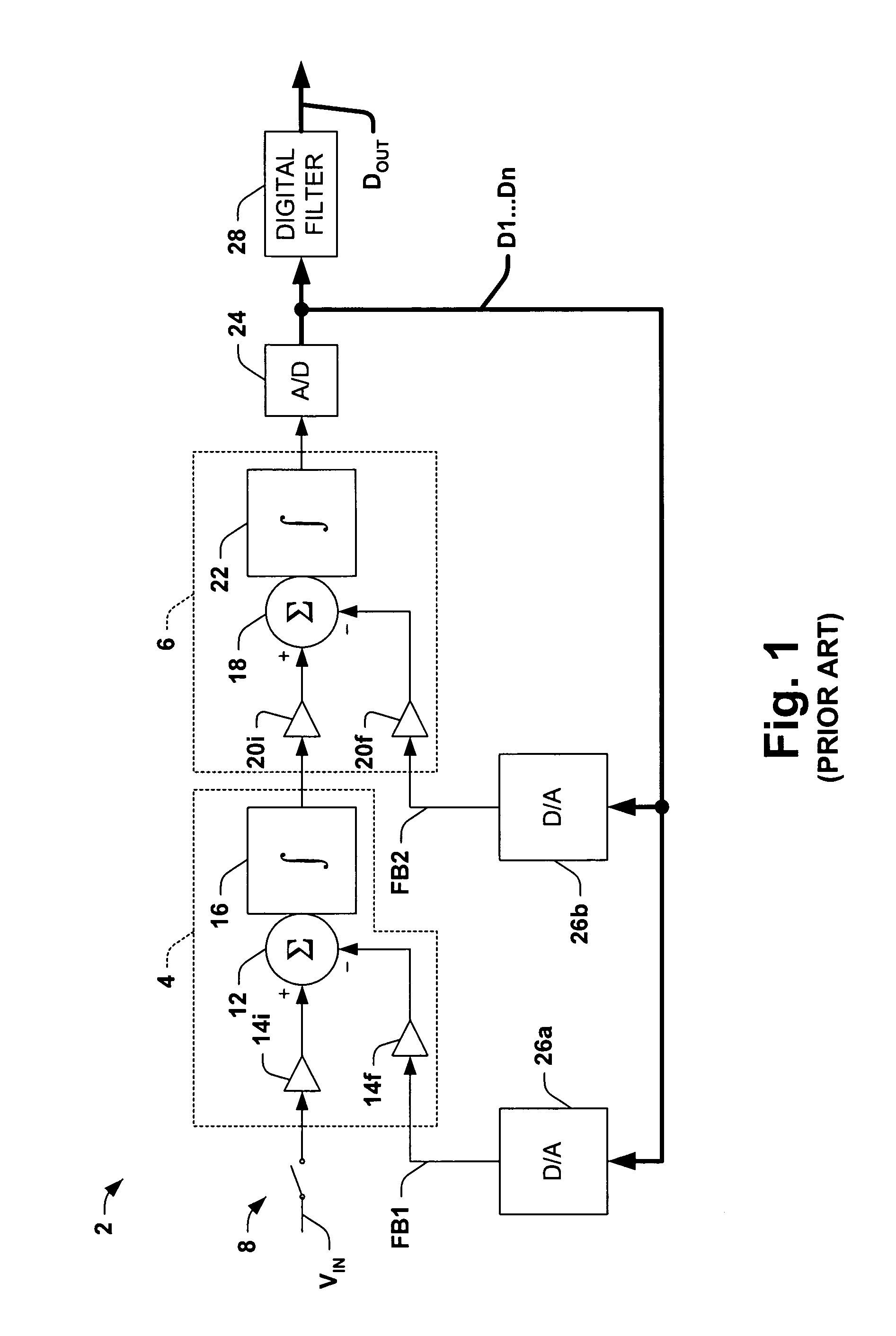

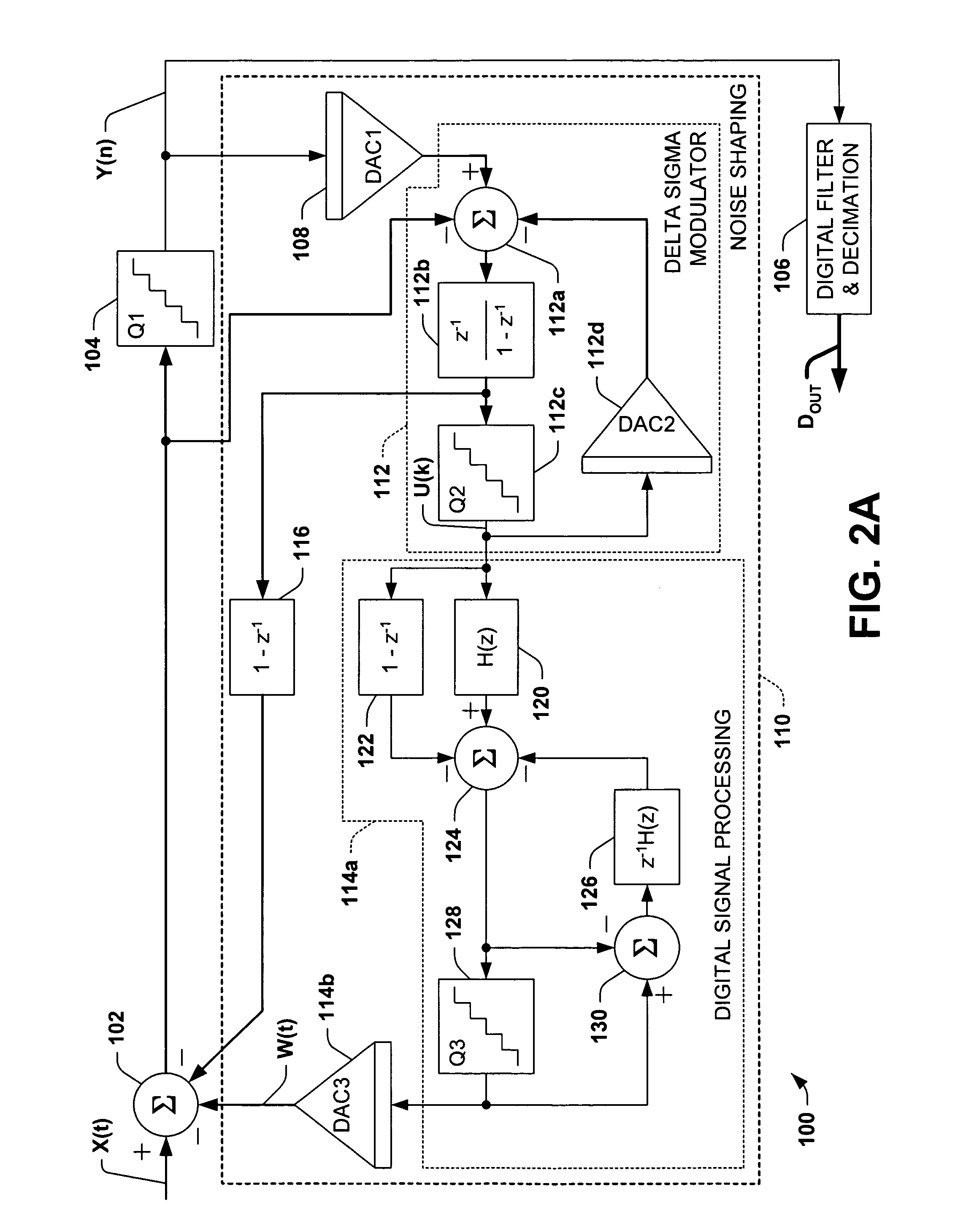

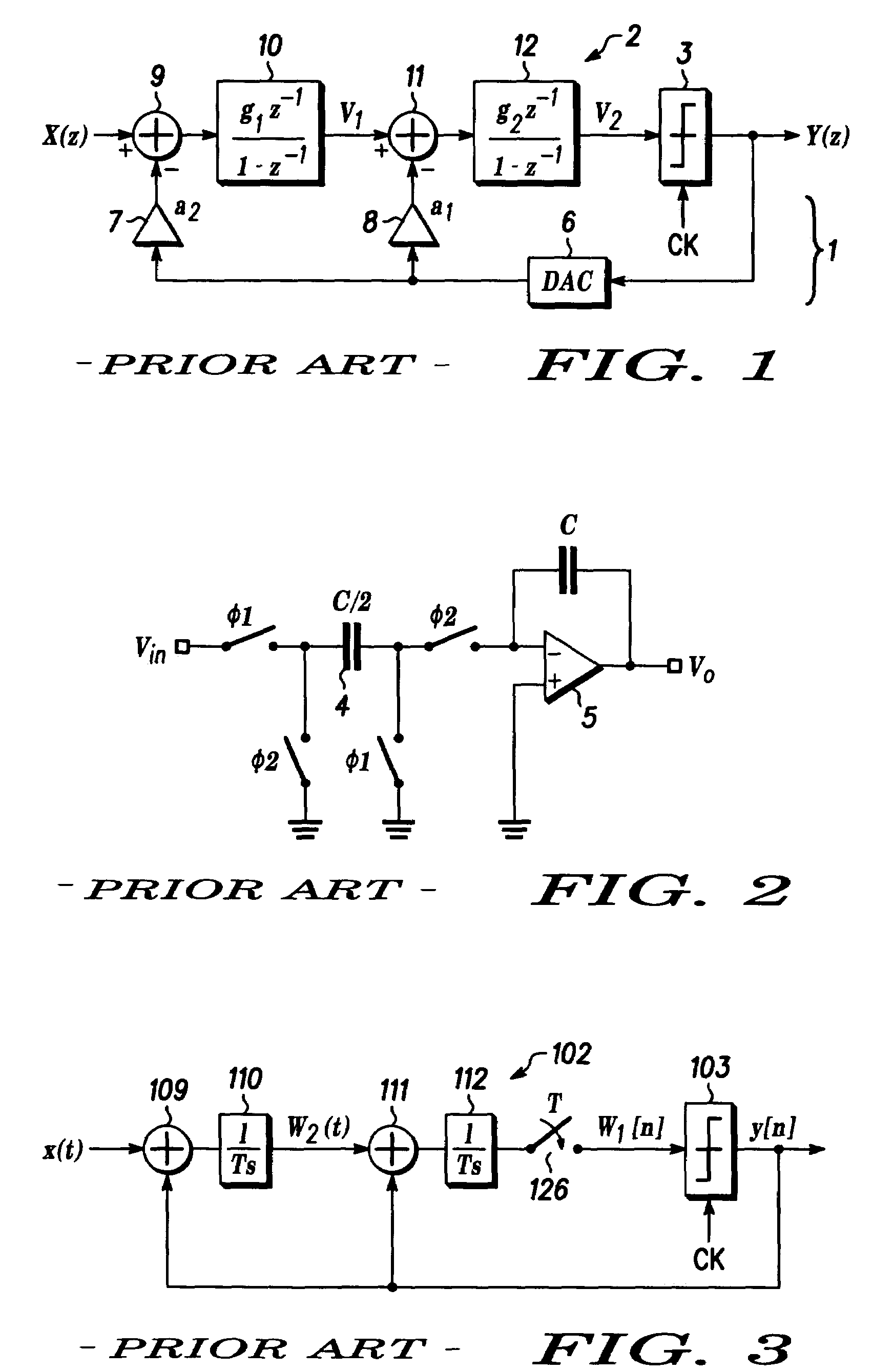

Delta-sigma A/D converter

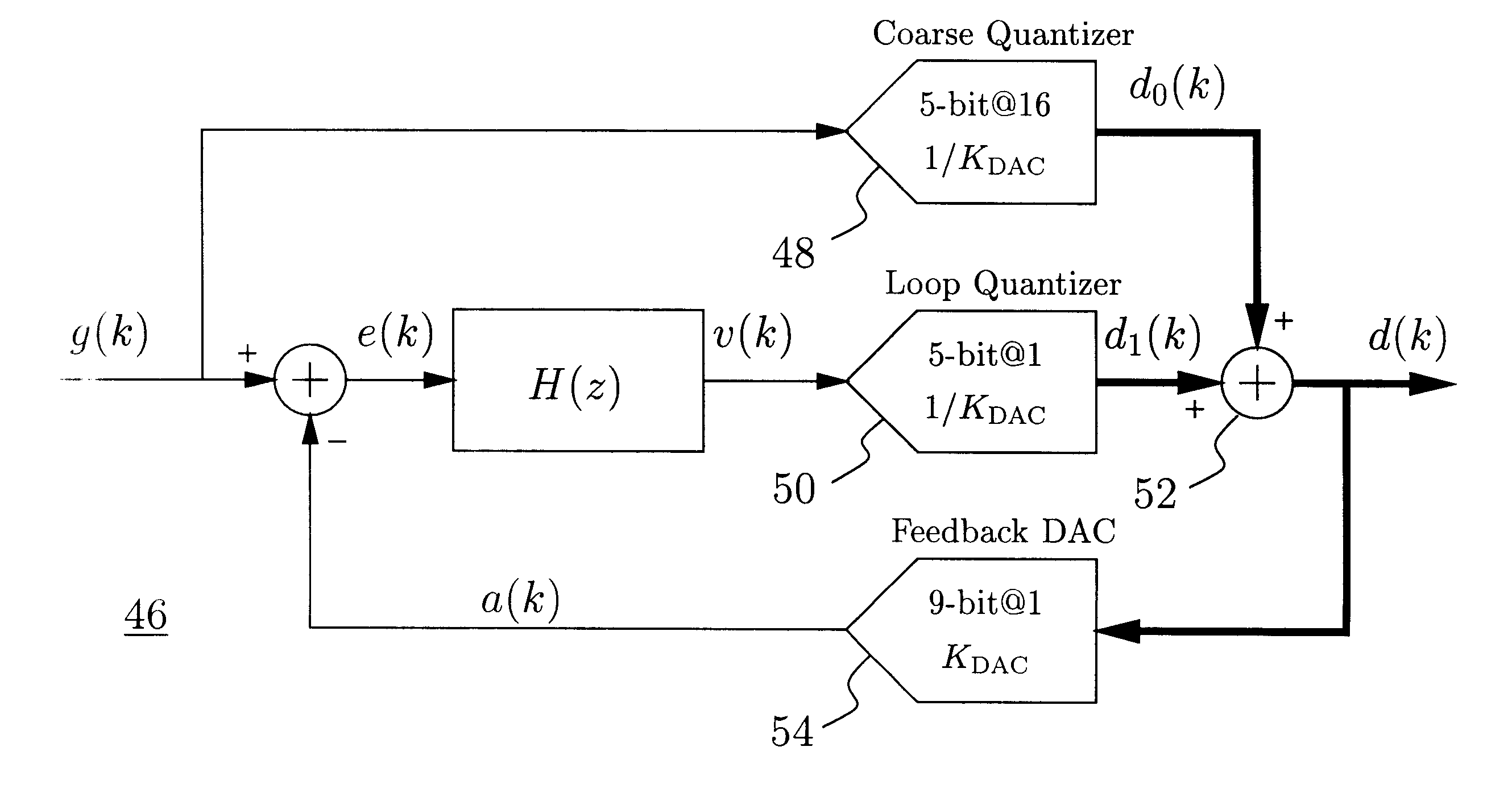

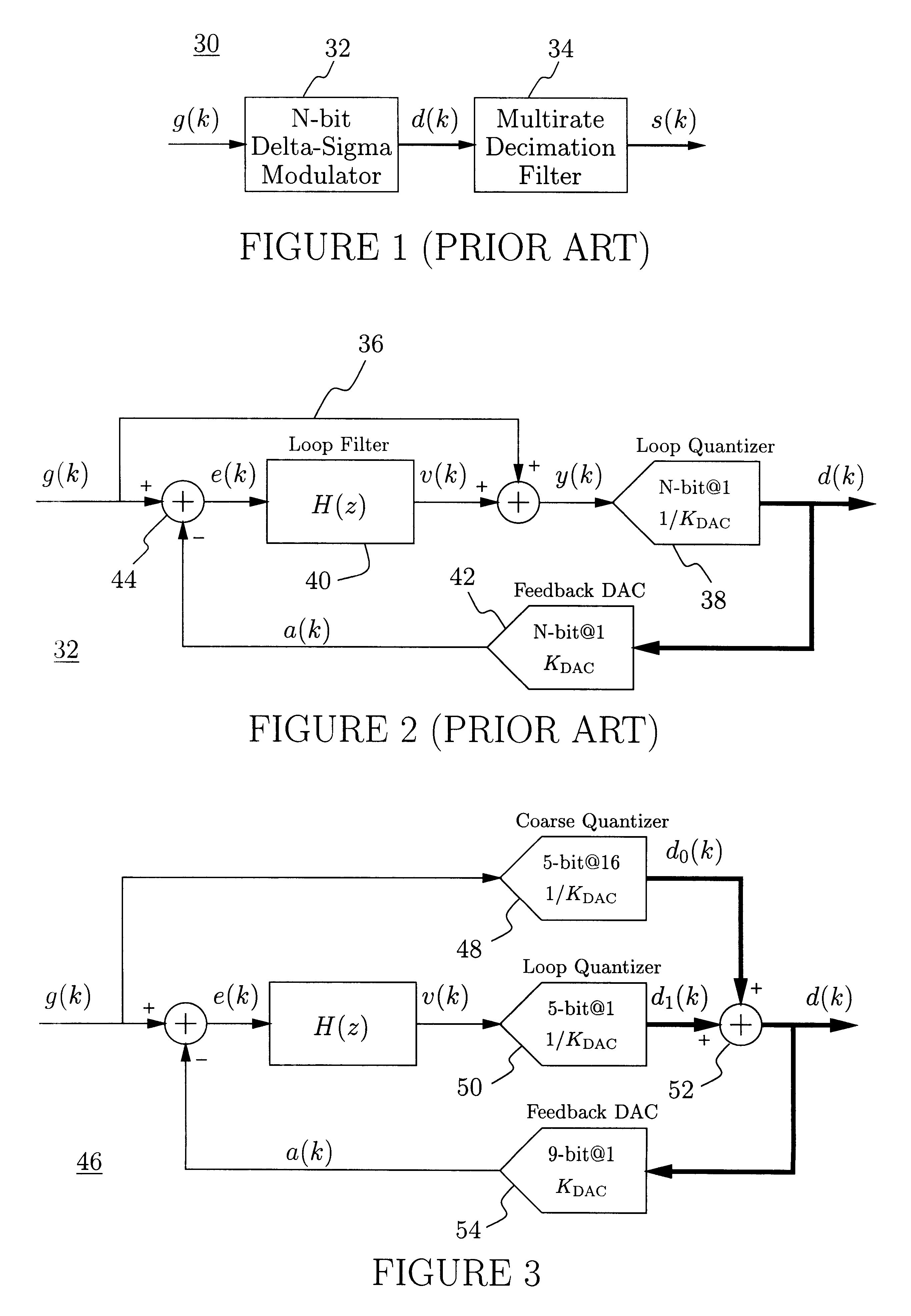

InactiveUS6271782B1Without compromising the modulator's stabilityTo overcome the large delayElectric signal transmission systemsDifferential modulationLoop filterAnalog feedback

A delta-sigma modulator comprising a first quantizer providing a first digital signal d0(k) representing the input signal g(t); a loop filter with input signal paths; a loop quantizer providing a corrective digital signal d1(k) representing the loop filter's output signal y(t); an array of feedback DACs D / A converting the sum d(k)=df(k)=d0(k)+d1(k) of the first and the corrective digital signals and injecting feedback signals into the loop filter.The loop filter's input node is applied the difference of the input signal g(t) and the global analog feedback signal a3(t). The global feedback signal a3(t) is delayed several clock cycles with respect to the digital output signal d(k). The delay is used to carry out mismatch-shaping and deglitching algorithms in the feedback DACs. The feedback DACs' different delays and gain coefficients are designed such that the modulator is stable. The filter's input signal paths and the compensating DAC are designed such that the gain from the input signal g(t) to the loop quantizer is small, ideally zero. Thus, the loop quantizer's resolving range can be a fraction of the first quantizer's resolving range, whereby the output signal's d(k) resolution can be much higher than the individual resolutions of d0(k) and d1(k).The delta-sigma modulator is well suited for the implementation of high-resolution wide-bandwidth A / D converters. Important applications include digital communication systems.

Owner:ANALOG DEVICES BV

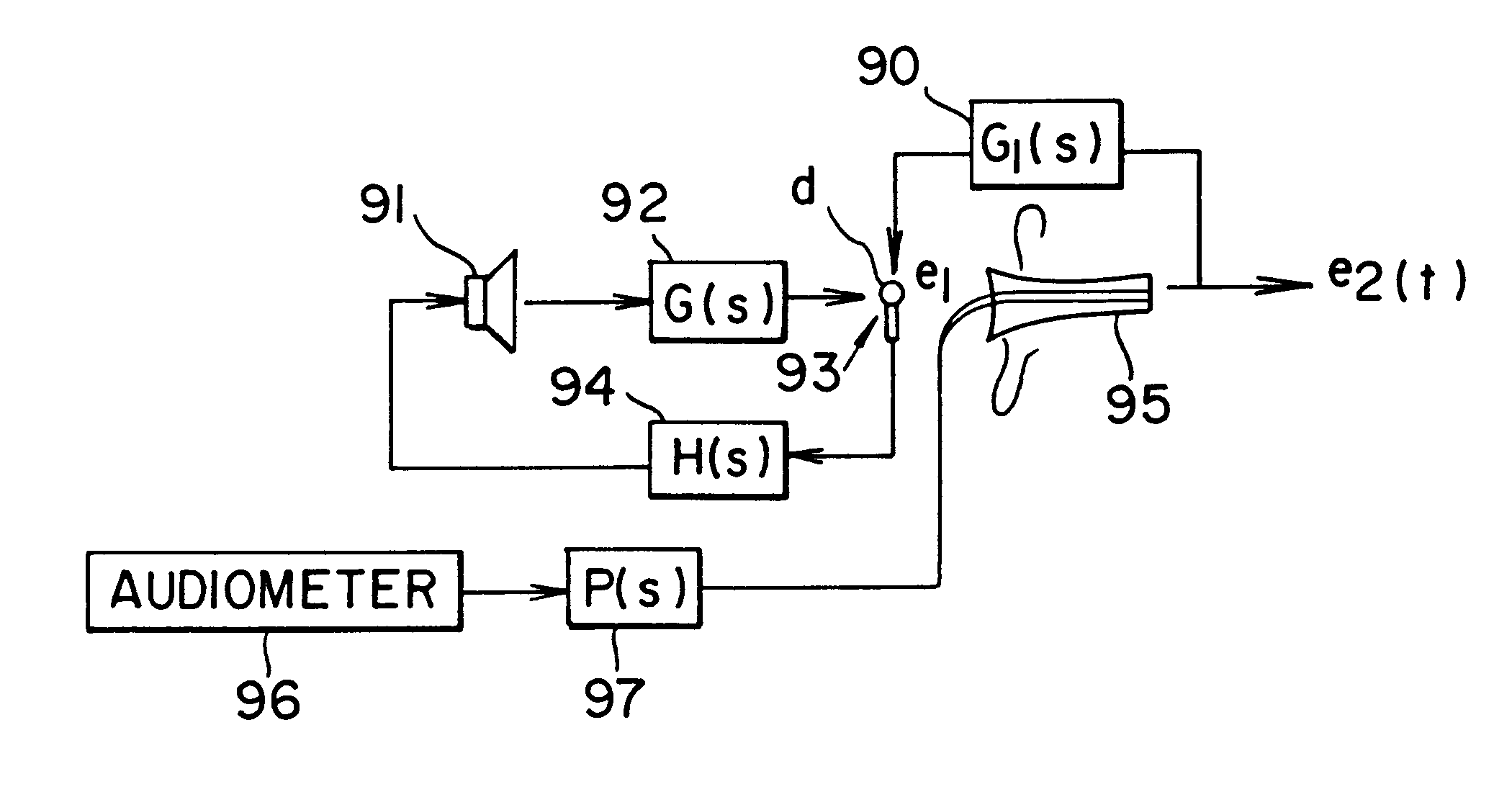

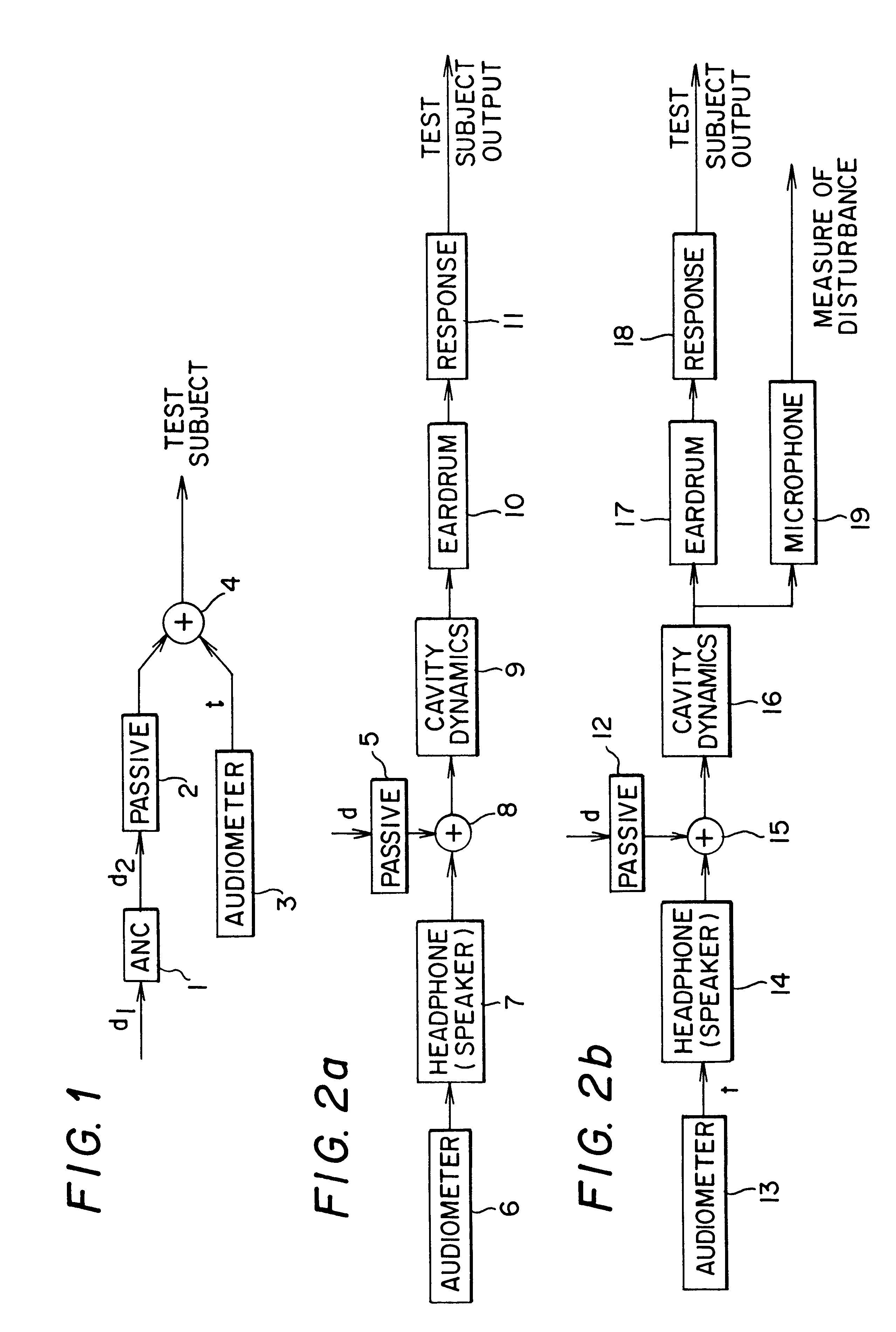

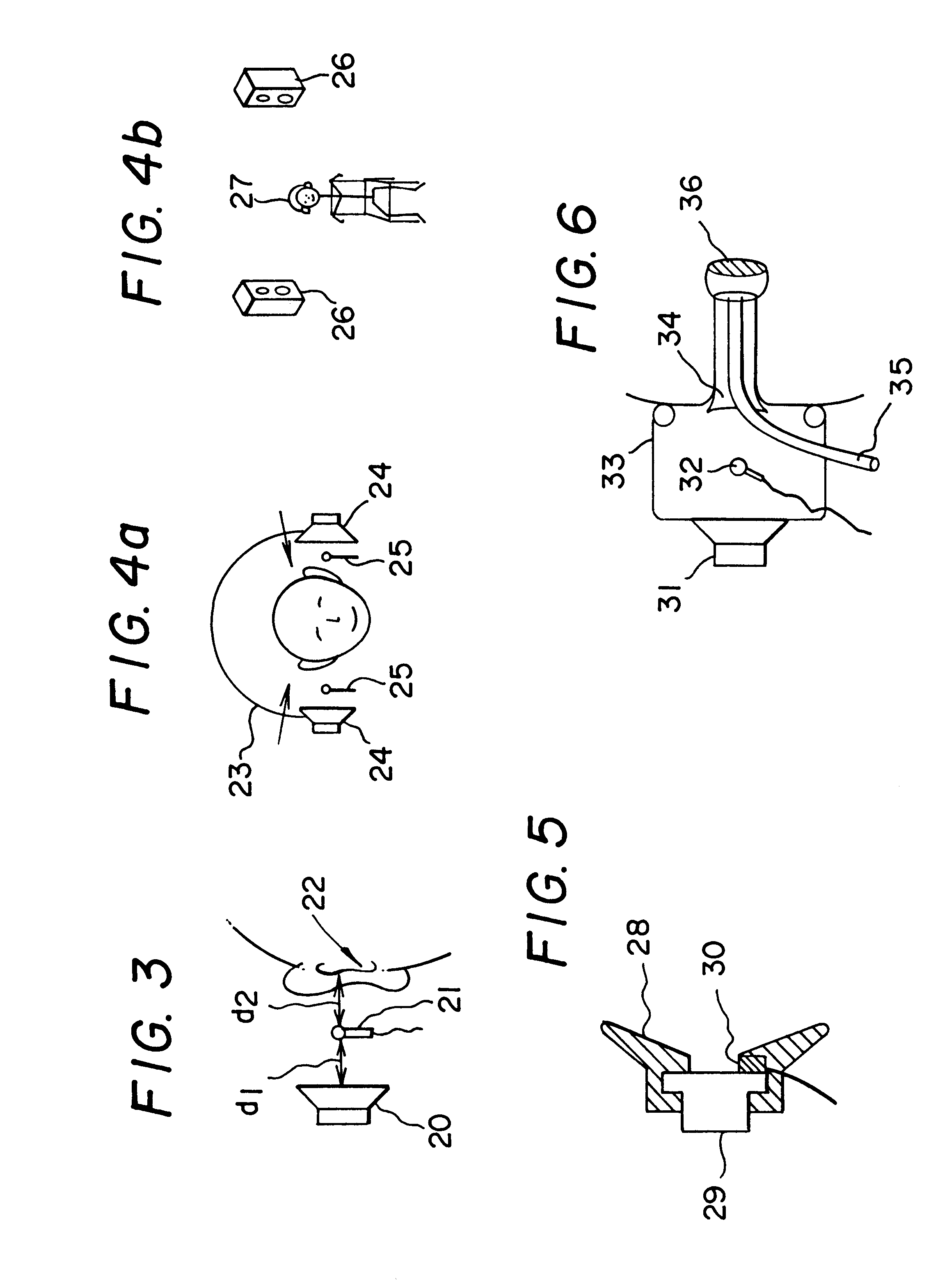

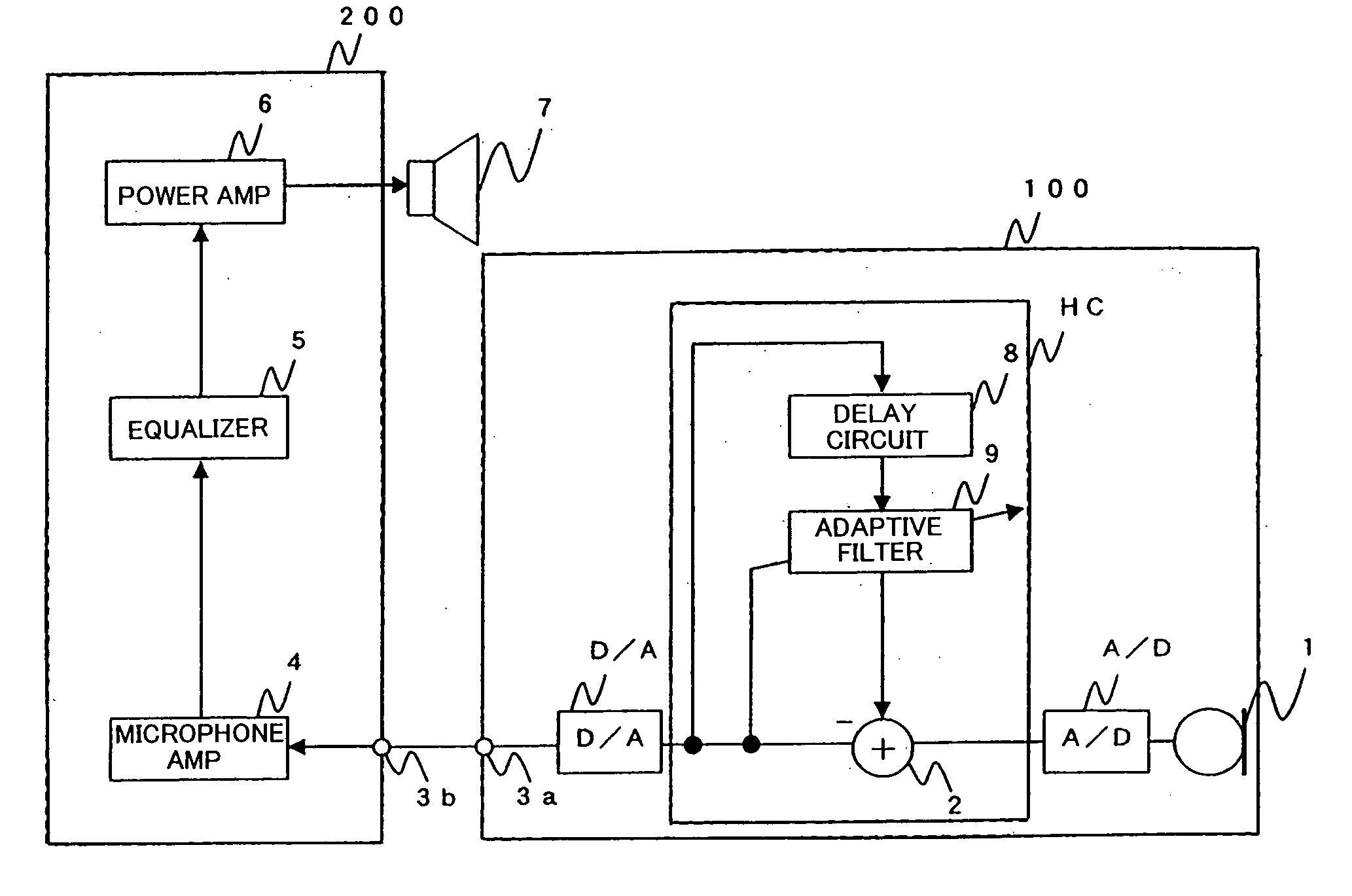

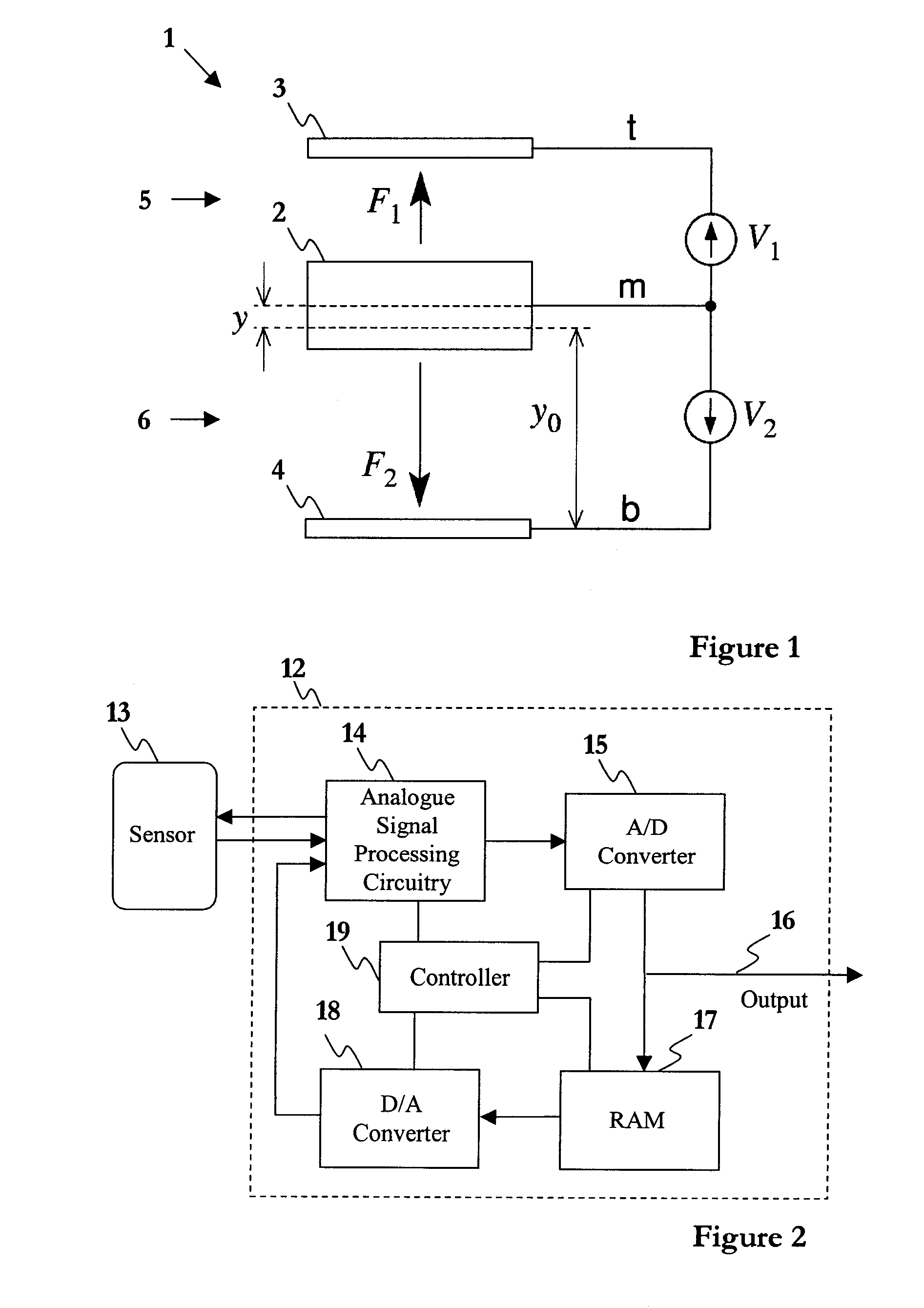

Active noise reduction for audiometry

InactiveUS6396930B1Maximize noise control performanceAccurate comparisonEar treatmentAudiometeringNoise controlNoise field

The technology of active noise reduction (ANR) is incorporated into audiometry testing in a variety of formats. Analog feedback, digital feedback, adaptive feedforward, and adaptive feedback noise control schemes are presented for use in audiometry to reduce the ambient noise heard by the test subject, allowing subject testing in higher ambient noise fields. Audiometer test signals are appropriately compensated so the test results are accurate and comply with existing calibration standards for audiometers. Existing audiometry headphone technologies are modified so that ANR can be accomplished while satisfying existing standards for audiometric testing. Embodiments are also defined for alternate headphone arrangements that may not conform to current (1997) audiometric testing standards but provide sufficient performance advantages to warrant new standards for audiometry testing in the future.

Owner:GENTEX CORP

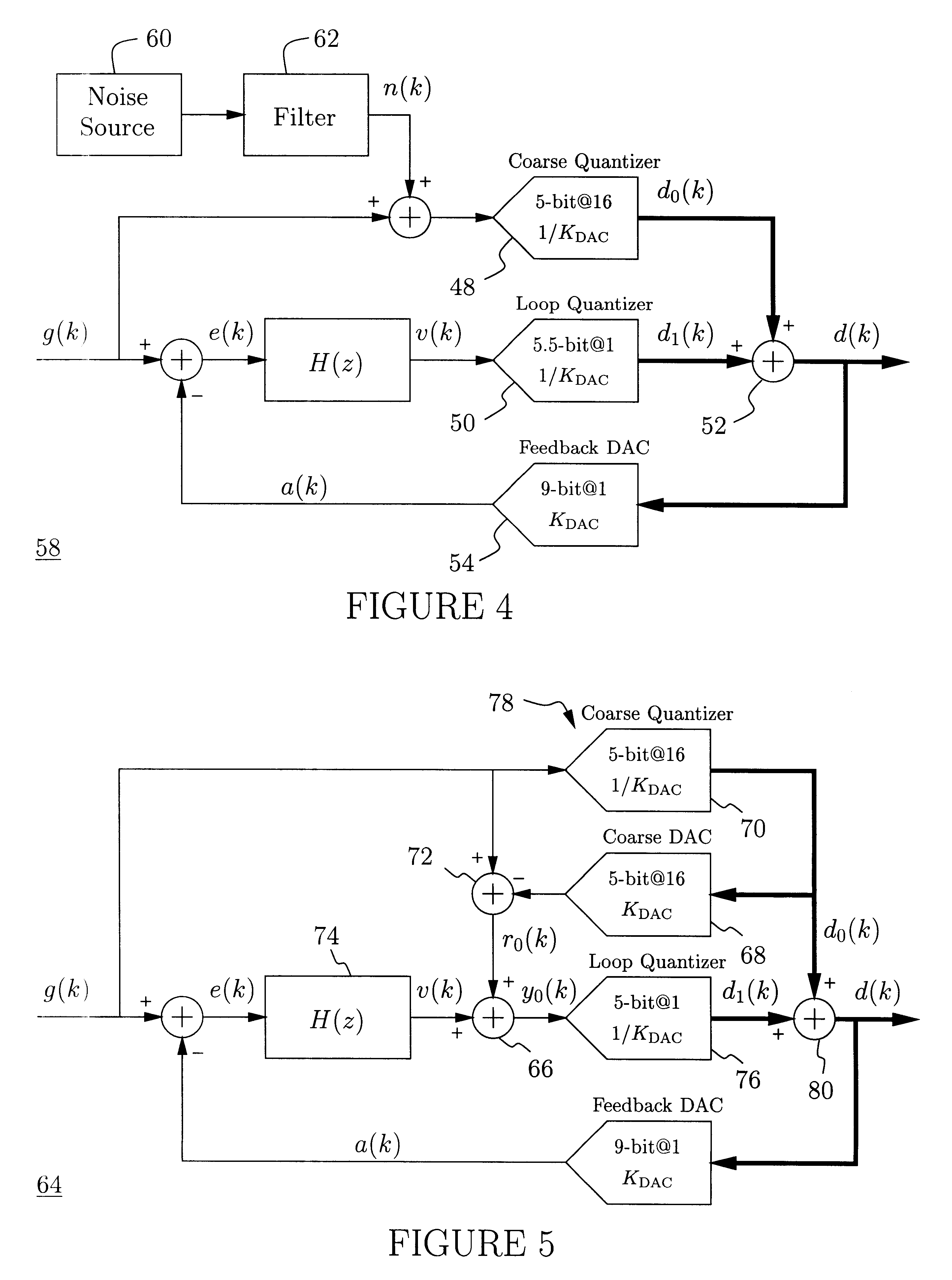

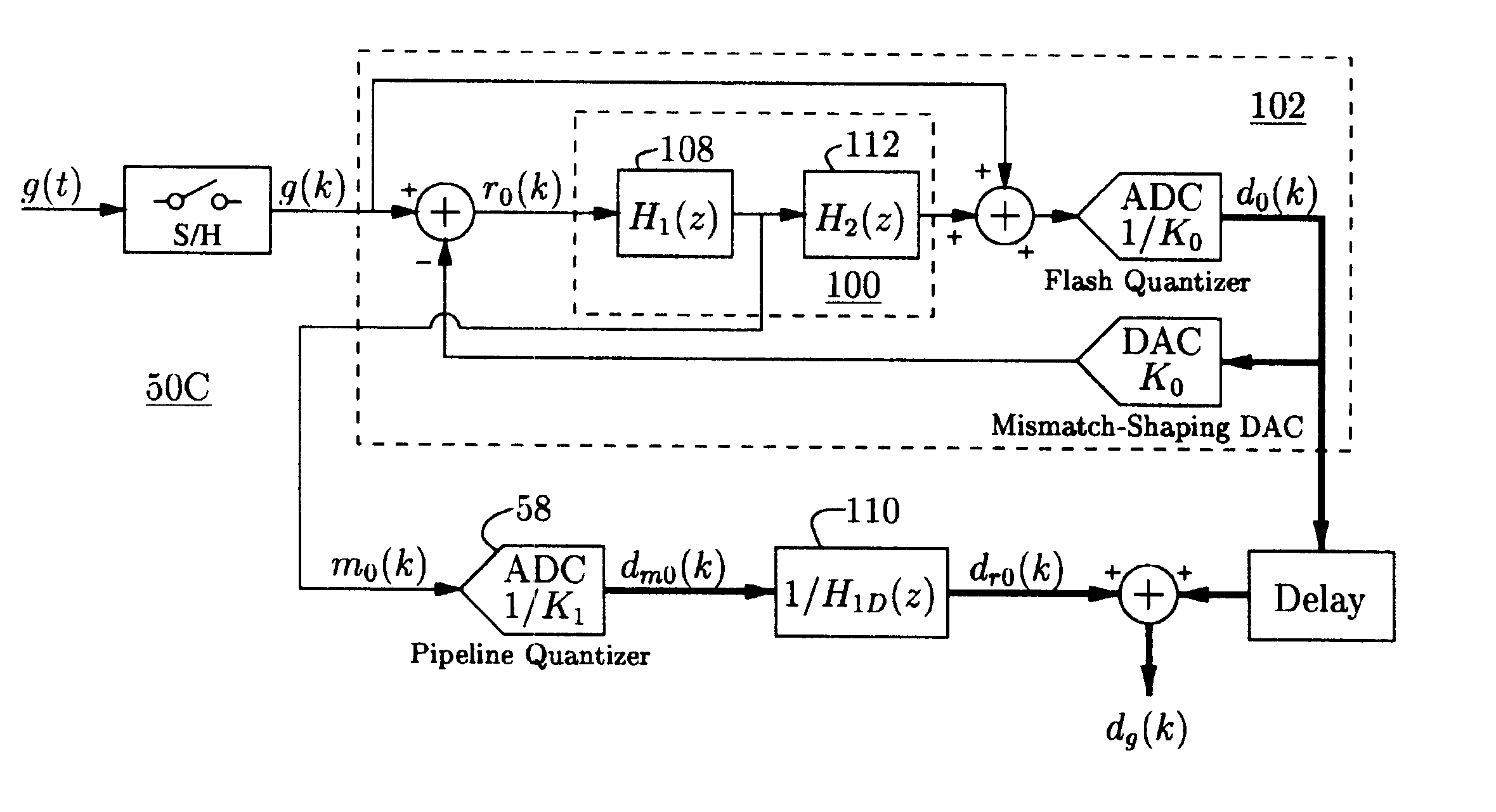

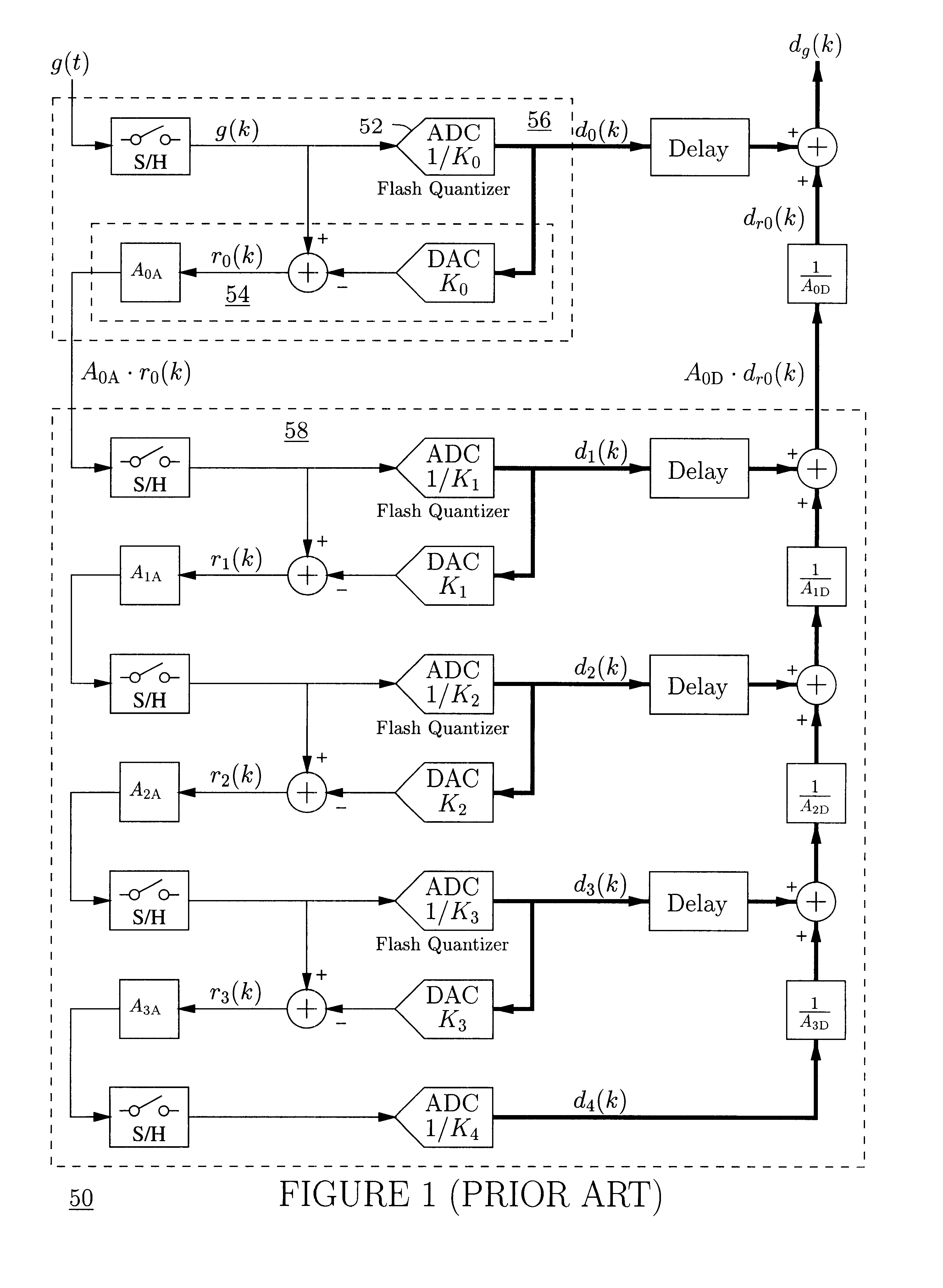

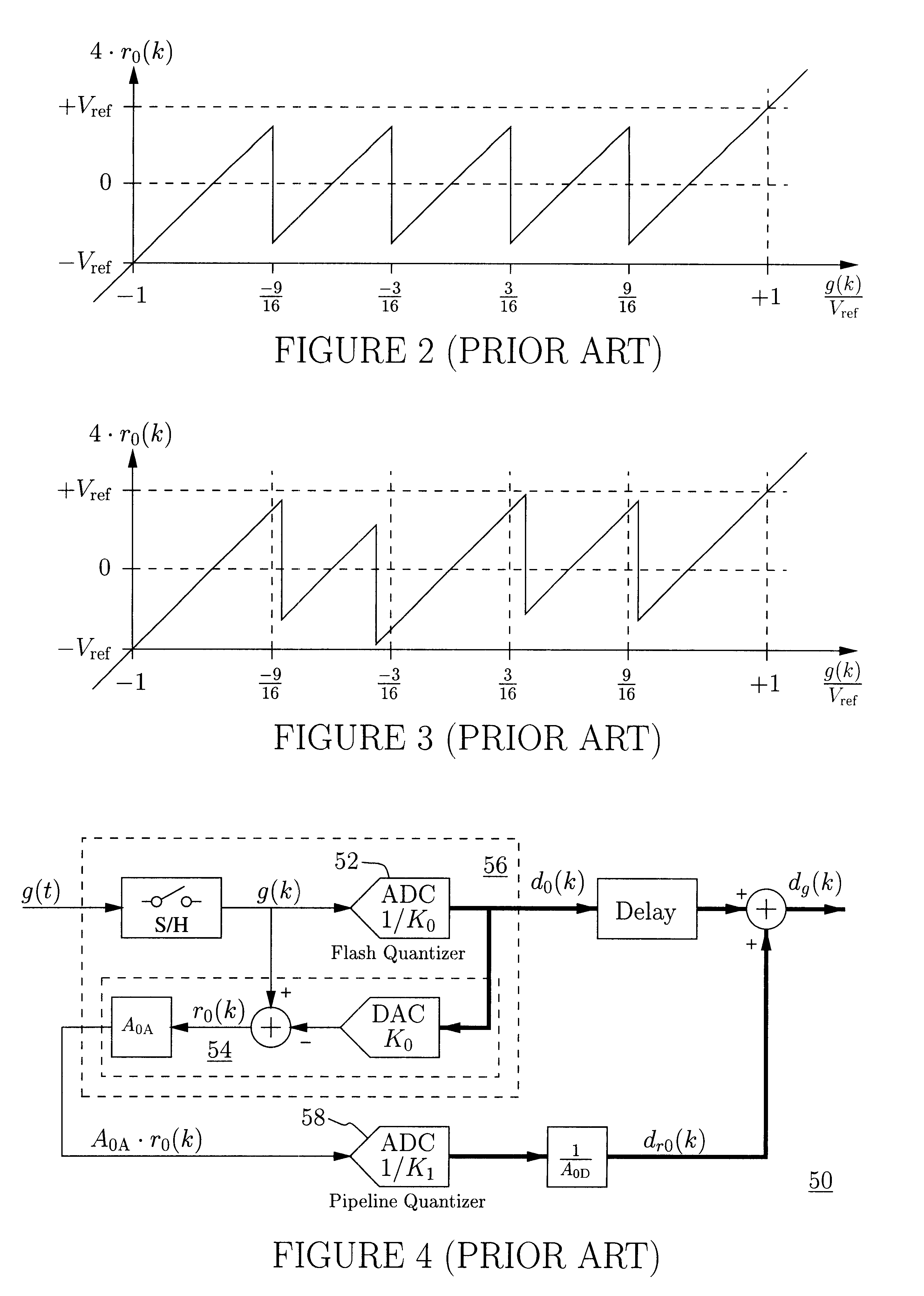

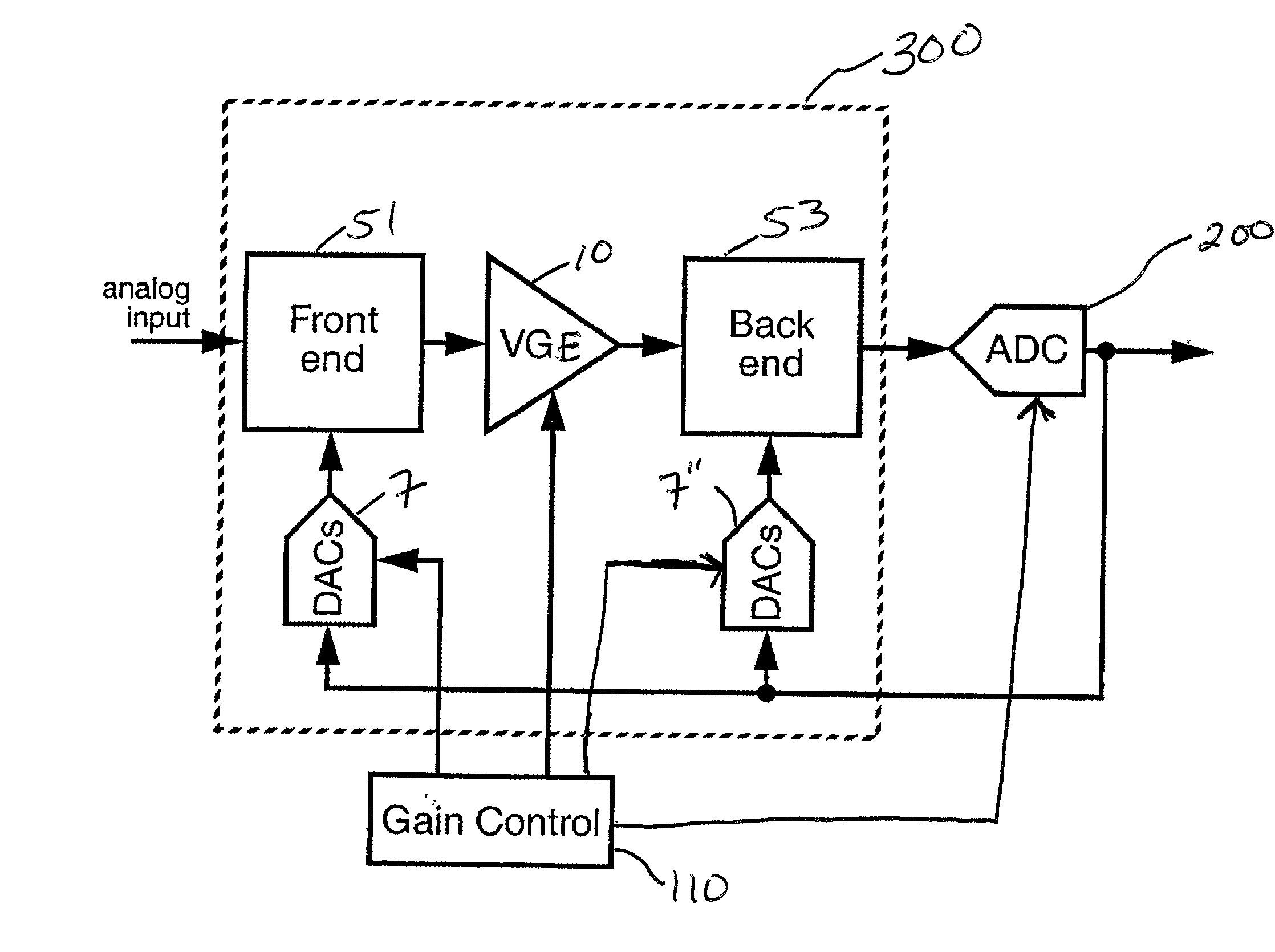

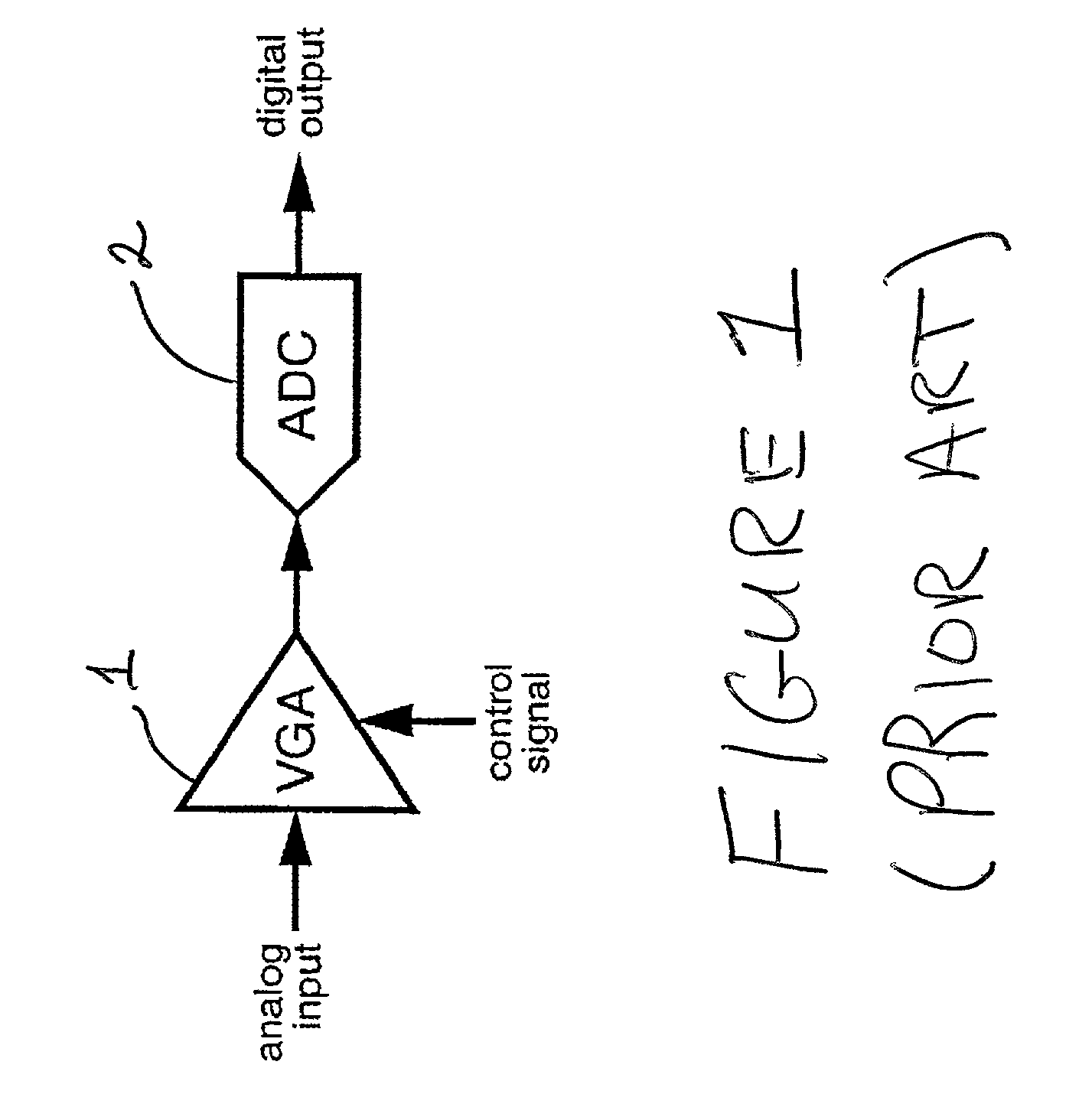

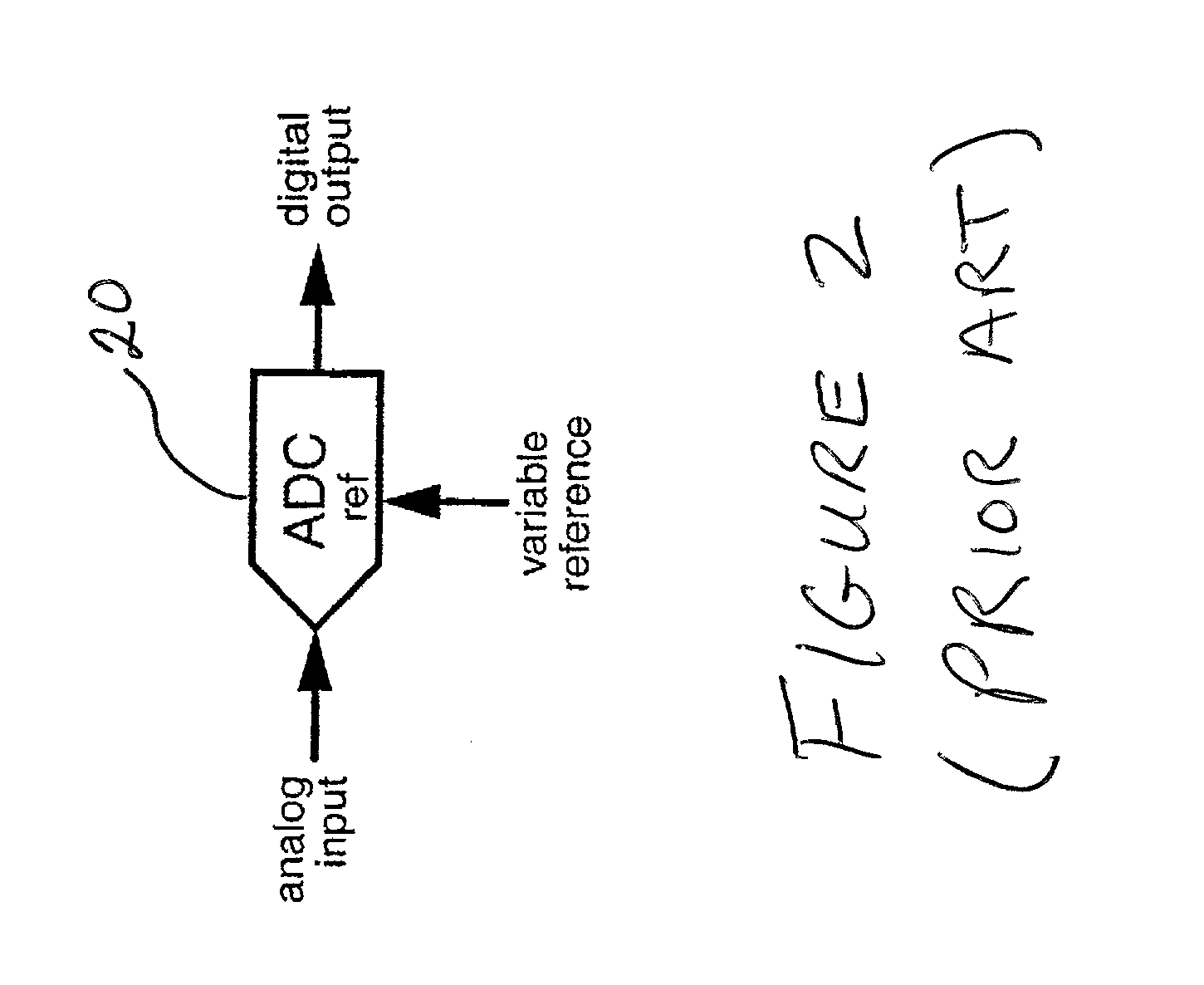

Residue-compensating A/D converter

InactiveUS6556158B2Low-cost highly-linearSuitable for useElectric signal transmission systemsDifferential modulationModem deviceFrequency spectrum

An analog-to-digital converter system [50D] processing an input signal, g, which can be either a discrete-time or a continuous-time signal. A first quantizer [154] generates a first digital signal, d0(k), representing the sum of the input signal, g, and a dithering signal, y0. A digital-to-analog converter [156] generates an analog feedback signal, alpha, representing accurately the first digital signal, d0(k). The DAC [156] may be linearized by the use of mismatch-shaping techniques. A filter [158] generates the dithering signal, y0, by selectively amplifying in the signal band the residue signal, r0, defined as the difference of the input signal, g, and the analog feedback signal, alpha. Optional signal paths [166][168] are used to minimize the closed-loop signal transfer function from g to y0, which ideally will be zero. An analog compensation signal, m0, which is described by a well-controlled relationship to the residue signal, r0, is extracted from the filter [158]. Ideally, the closed-loop signal transfer function from g to m0 will be zero, or at least small in the signal band. A second quantizer [160] converts the analog compensation signal, m0, into a second digital signal, dm0(k). The two digital signals, d0(k) and dm0(k), are filtered individually and then added to form the overall output signal, dg(k). The second digital filter [164] has a low signal-band gain, which implies that the sensitivity to signal-band errors caused by the second quantizer [160] will be low. The output signal, dg(k), is a highly-accurate high-resolution representation of the input signal, g. Circuit imperfections, such as mismatch, gain errors, and nonlinearities, will cause only noise-like errors having a very low spectral power density in the signal band.The invention facilitates the implementation of uncalibrated highly-linear high-resolution wide-bandwidth A / D converters [50D], e.g., for use in digital communication systems, such as xDSL modems and other demanding consumer-market products for which low cost is of the essence.

Owner:ANALOG DEVICES BV

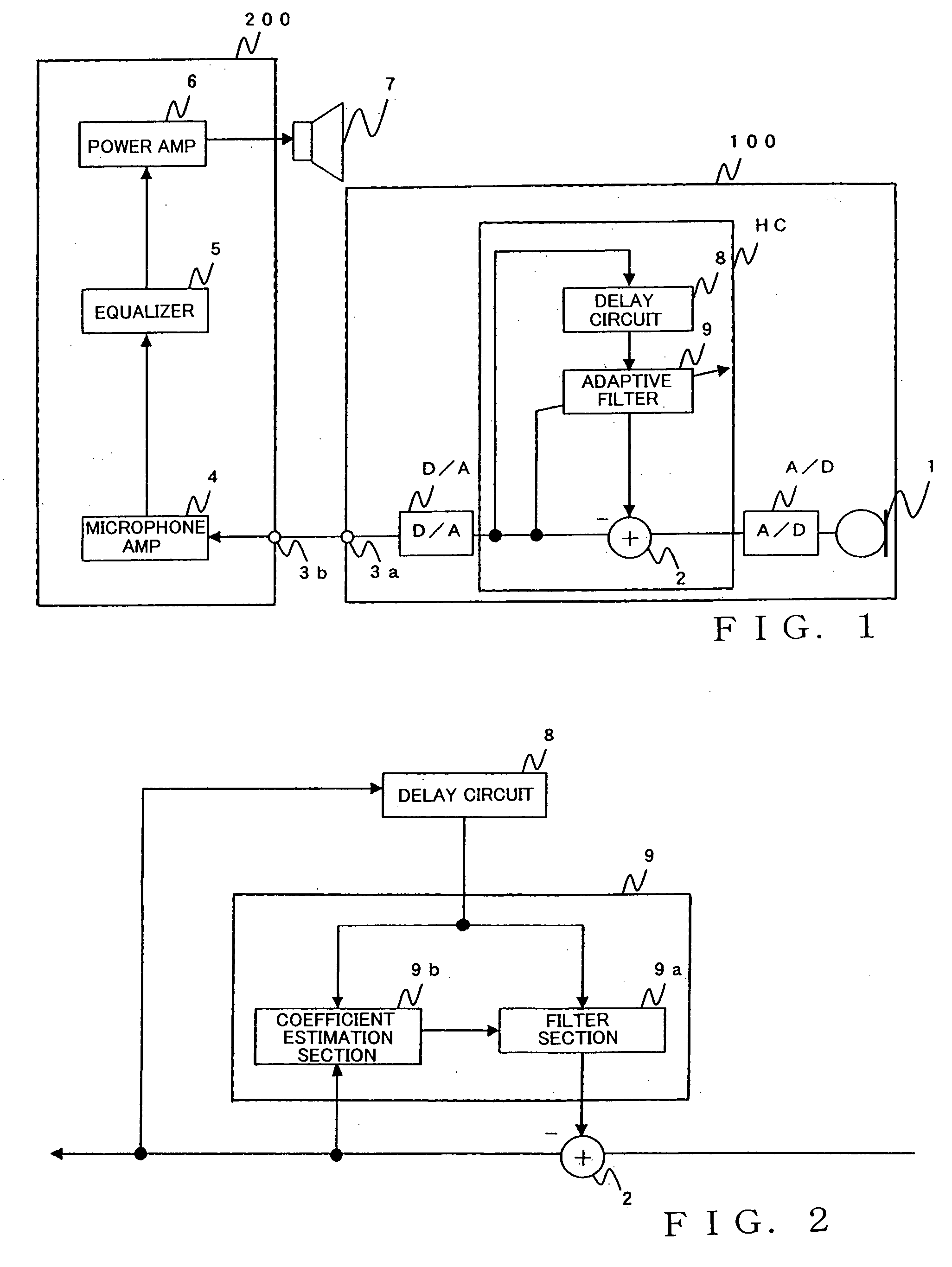

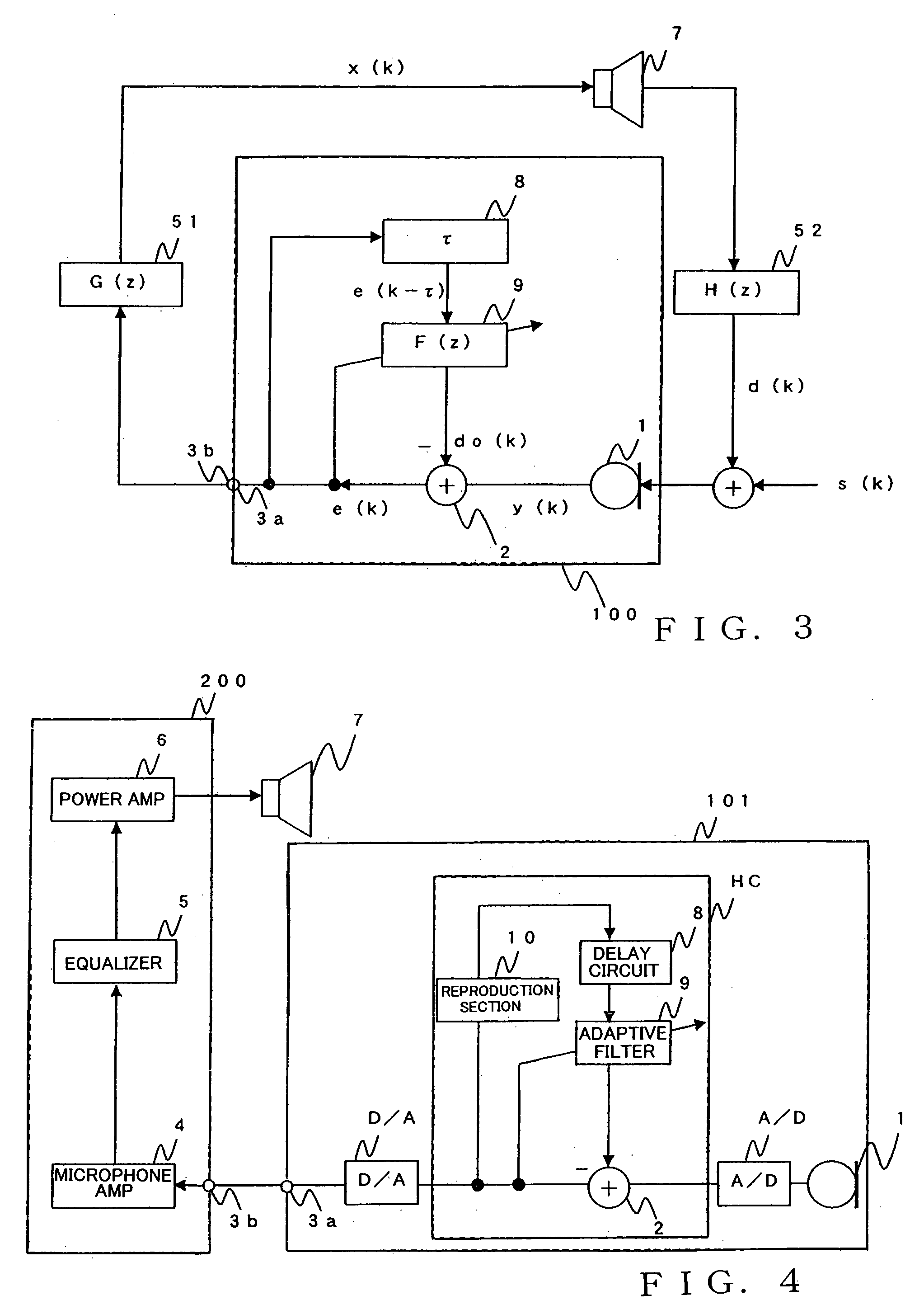

Microphone and sound amplification system

InactiveUS20060153400A1Reliably cancel howlingTransducer acoustic reaction preventionLine-transmissionAnalog feedbackAudio power amplifier

Microphone includes: a microphone element; a simulative feedback signal generation section that generates a simulative feedback signal simulating a feedback signal generated by a sound, produced via a speaker, returning the microphone element; and an arithmetic operator that subtracts the simulative feedback signal, generated by the simulative feedback signal generation section, from a sound signal collected by the microphone element, to thereby output the subtraction result as a residual signal. The residual signal output by the arithmetic operator is supplied to an amplifier device of the speaker as an output signal of the microphone. The simulative feedback signal generation section includes a delay circuit that delays the residual signal, output by the arithmetic operator, by a given time, and an adaptive filter that generates the simulative feedback signal by filtering a previous residual signal delayed by the delay circuit. The adaptive filter updates a filter coefficient on the basis of the previous residual signal delayed by the delay circuit and a current residual signal output by the arithmetic operator.

Owner:YAMAHA CORP

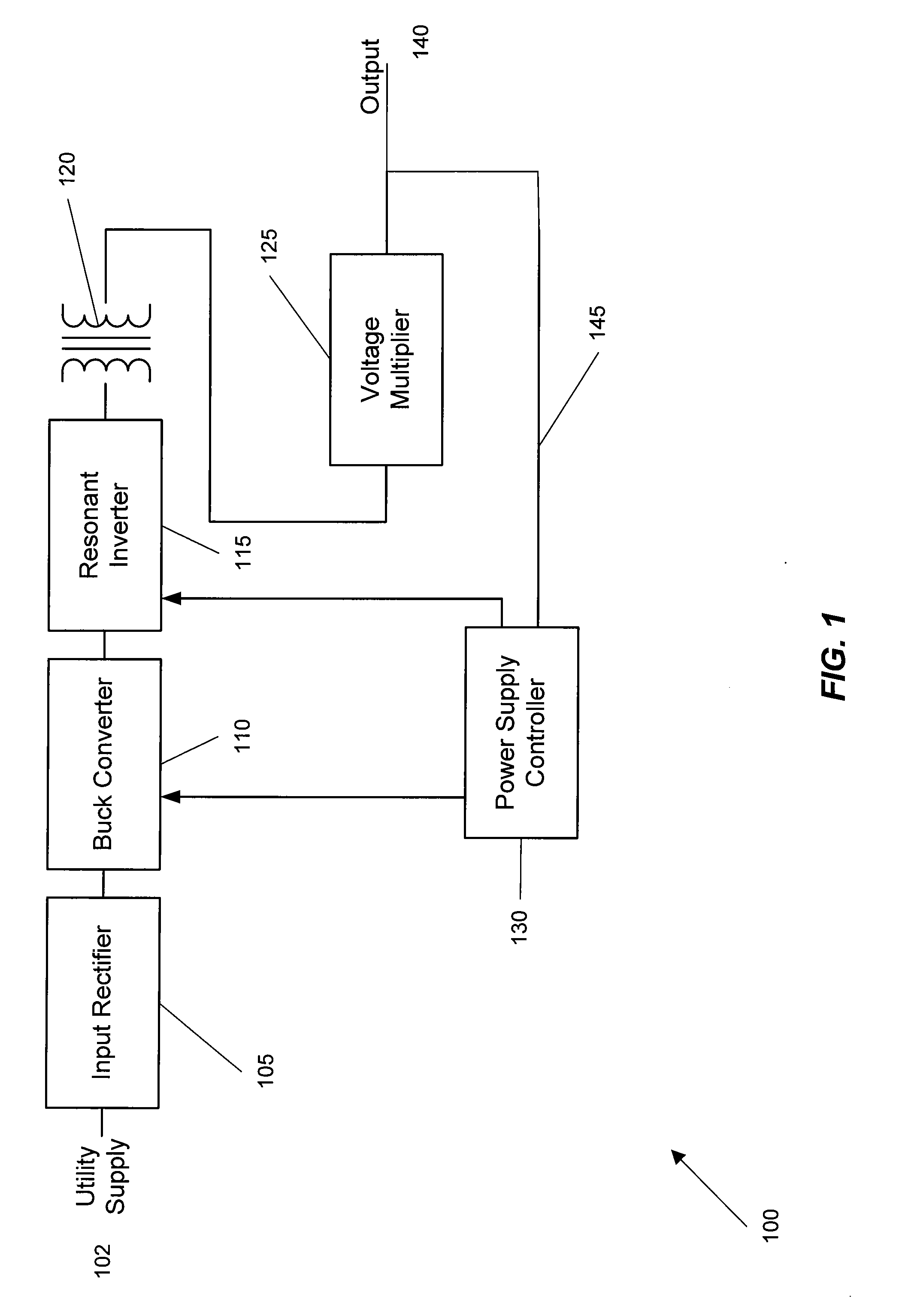

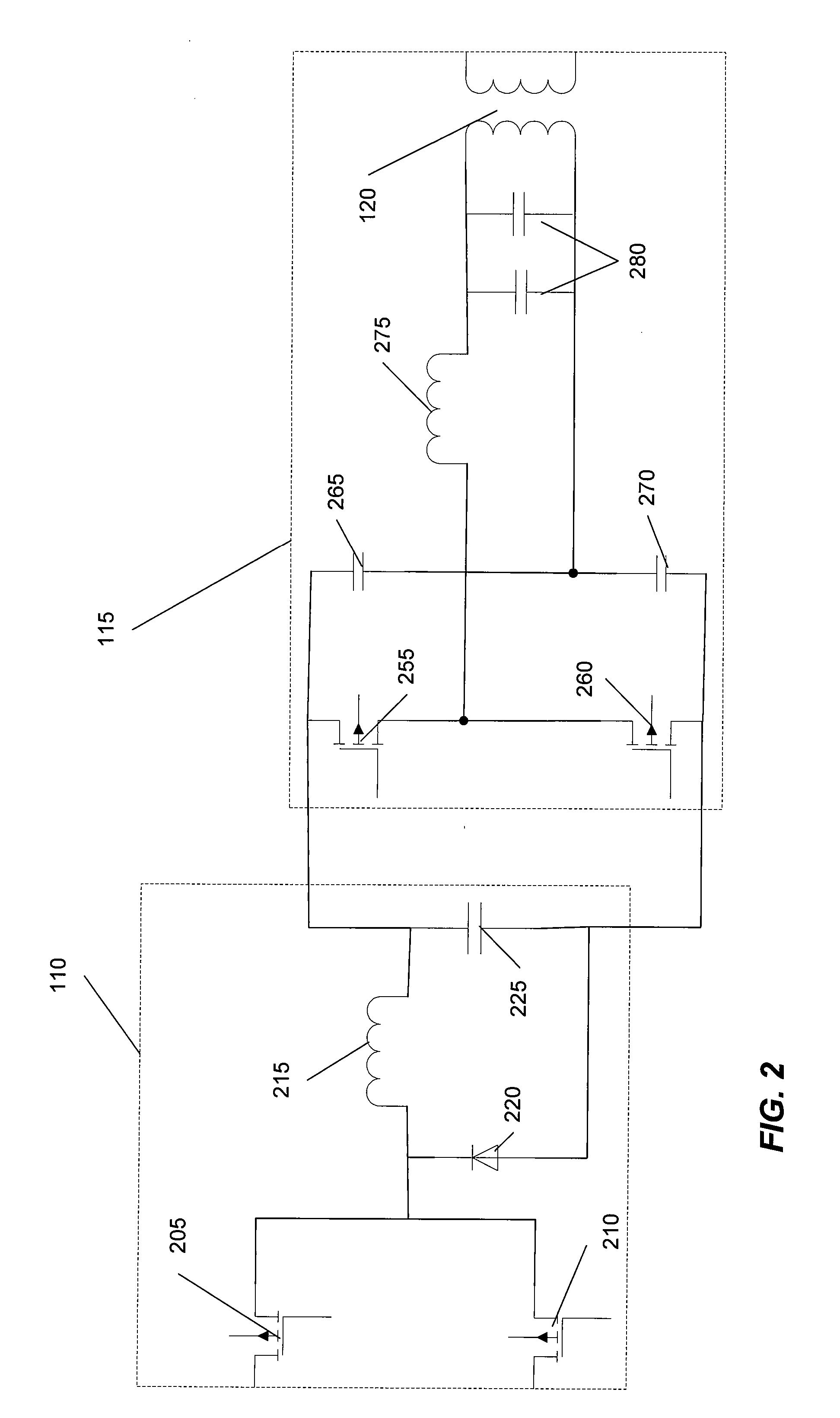

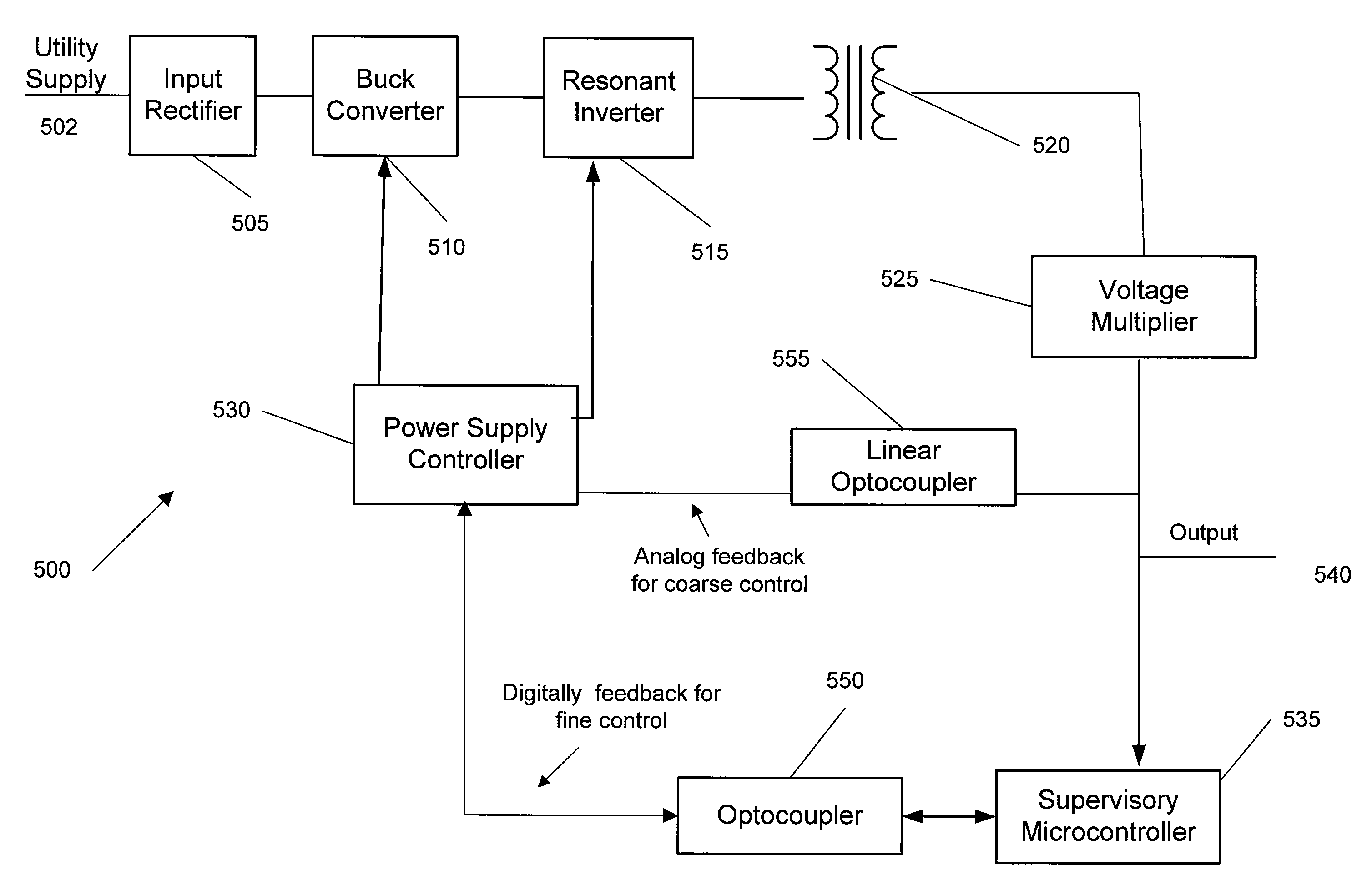

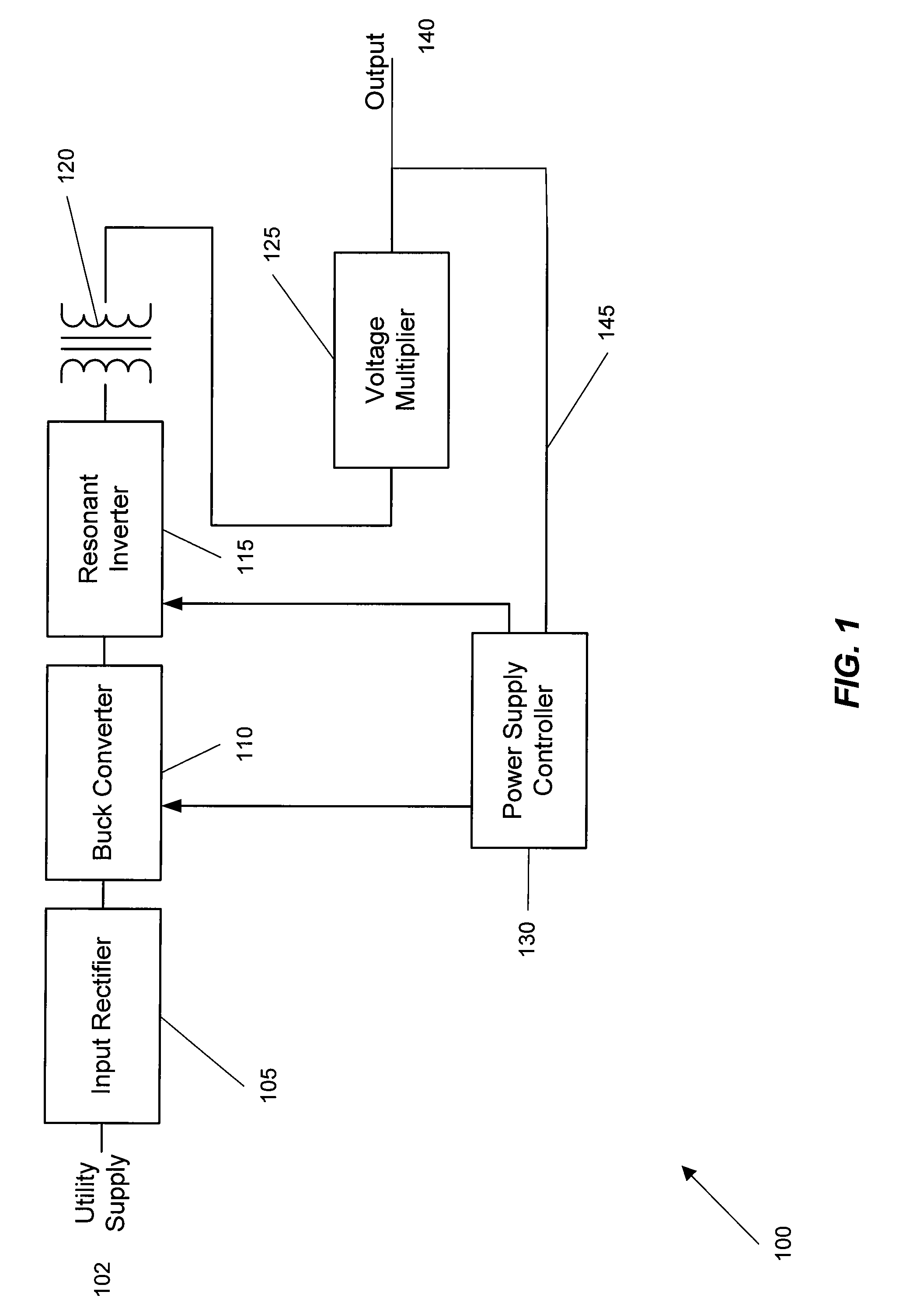

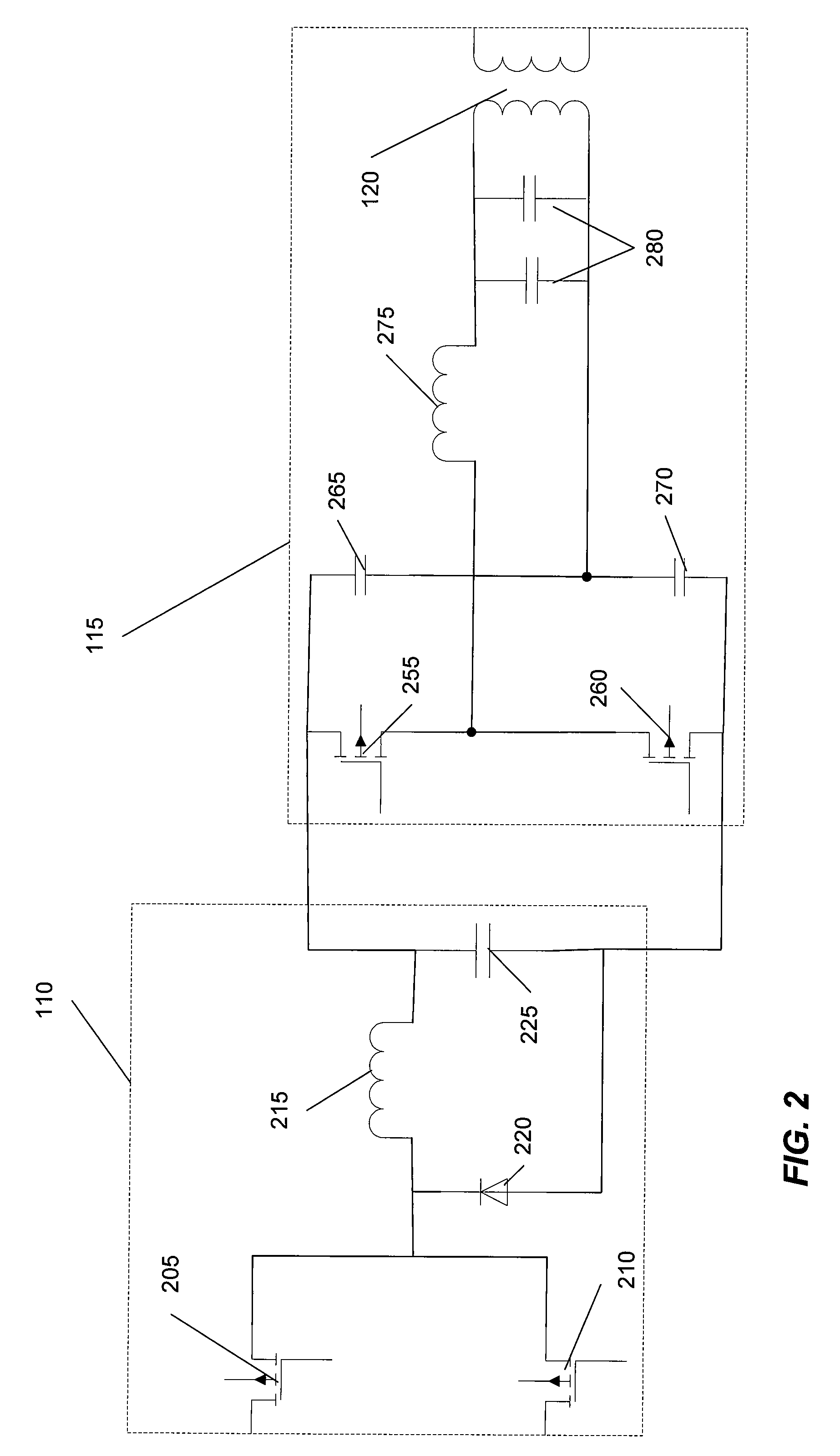

Wide range power supply

ActiveUS20070008745A1Operation efficiency is highHigh operating requirementsEfficient power electronics conversionConversion with intermediate conversion to dcResonant inverterAnalog feedback

A wide range power supply capable of delivering 20V to 5000V is provided. The power supply of the present invention uses switch mode technology to achieve high overall operating efficiency and is capable of operating from no load to full load without loss of regulation. The power supply in accordance with the embodiments of the present invention operates directly from the utility supply (e.g., 110V / 220V and 50 Hz / 60 Hz). In one embodiment, the power supply's power conversion stage includes the following stages: an input rectifier; a buck converter; a quasi-resonant inverter; and a voltage multiplier. The above indicated stages are connected in series to achieve the large output voltage range. High precision is obtained from a use of a digital feedback loop, possibly in connection with an analog feedback loop.

Owner:BIO RAD LAB INC

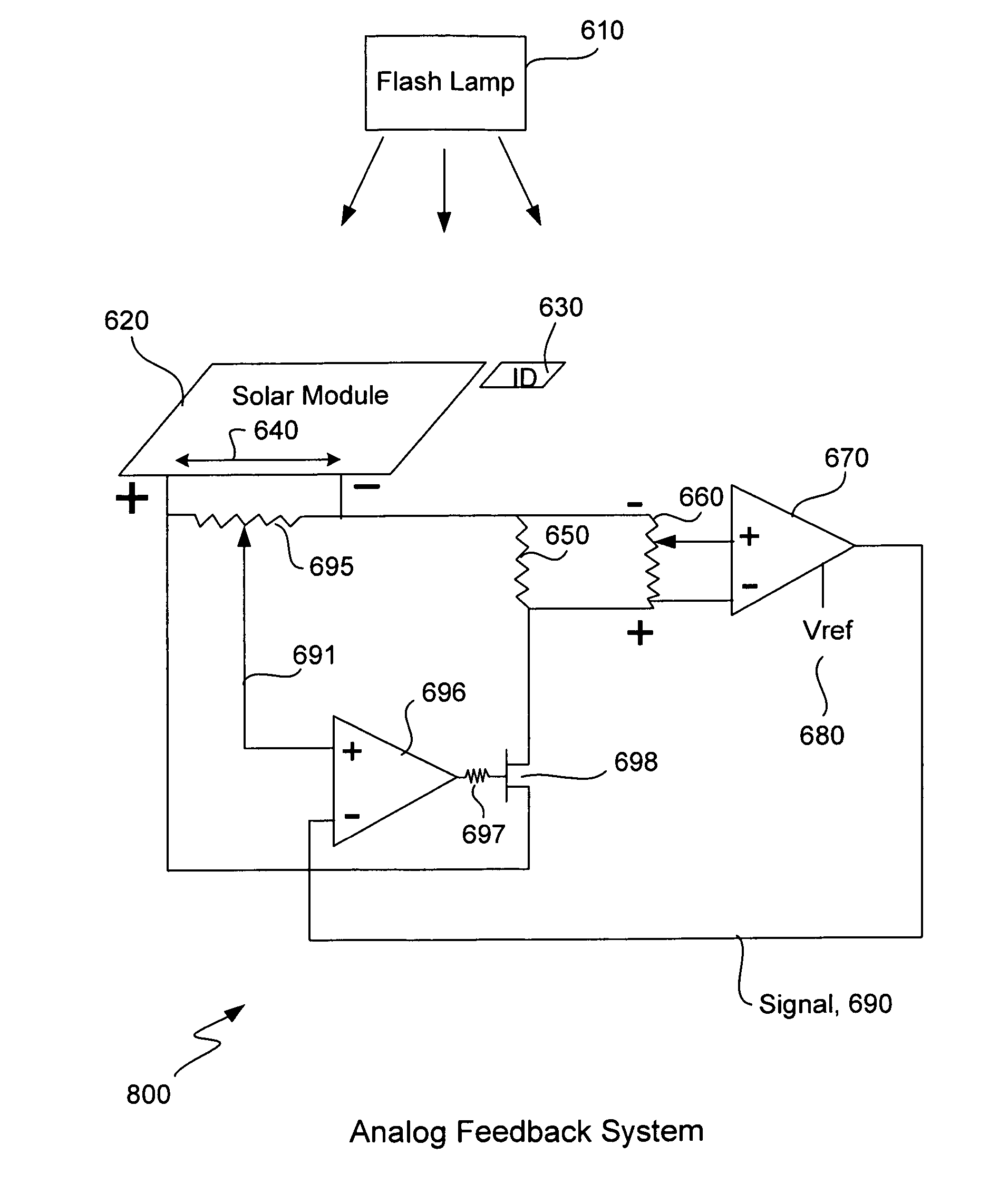

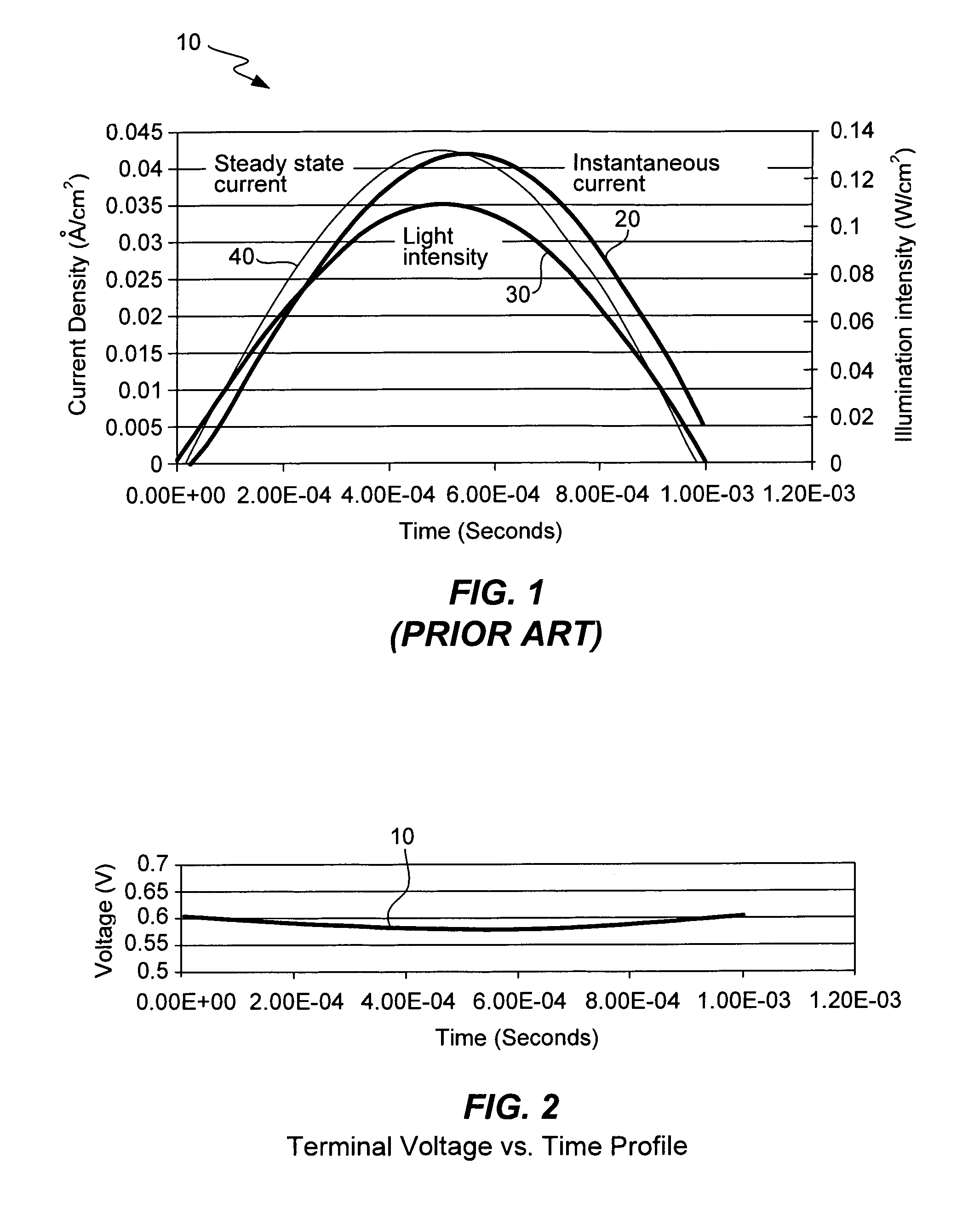

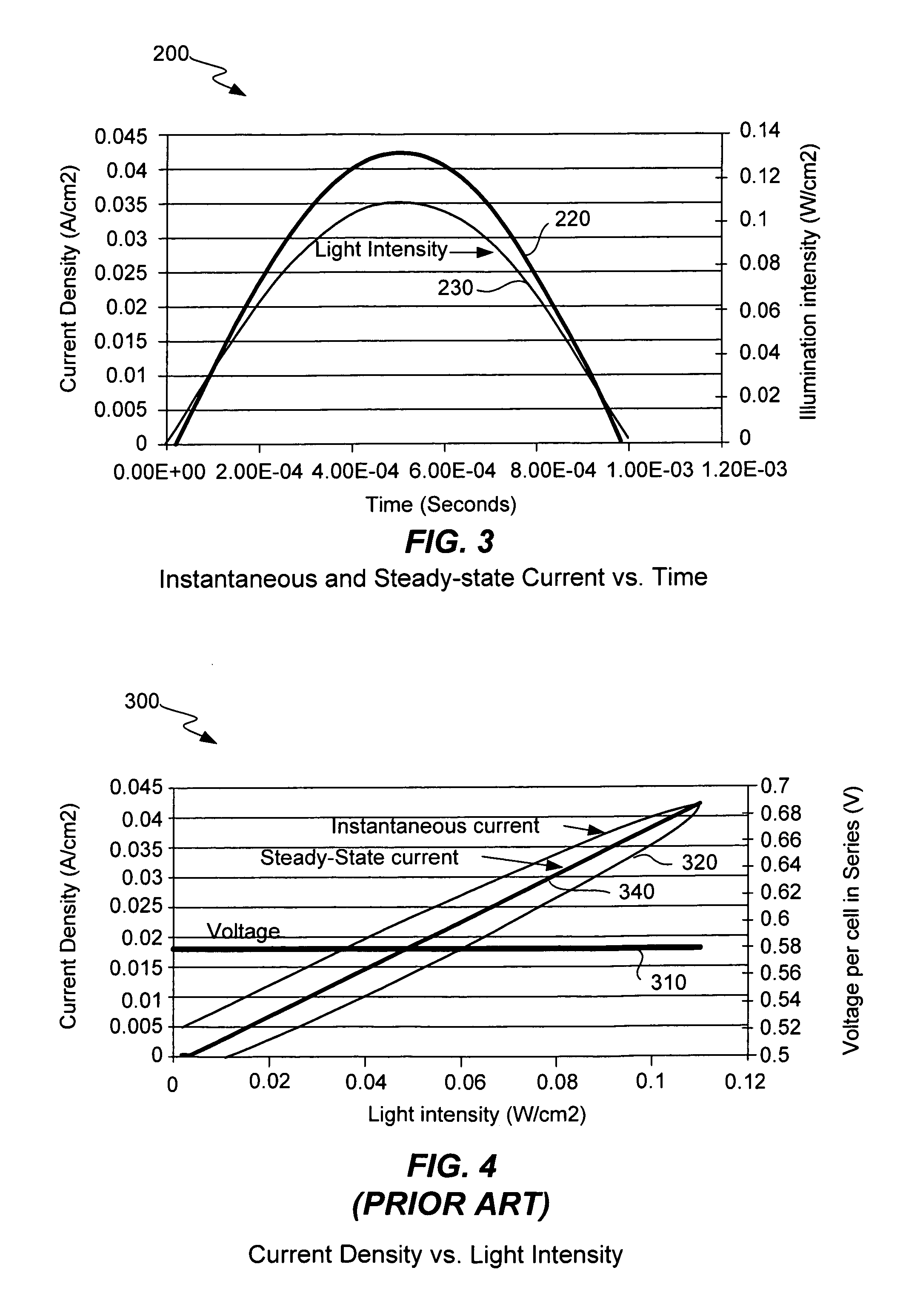

Measurement of current-voltage characteristic curves of solar cells and solar modules

ActiveUS7309850B2Accurate measurementPredictive performancePhotometry using reference valuePhotovoltaic monitoringAnalog feedbackSignal correction

A solar cell or solar module is measured during a short pulse of light in such a way that the resulting data for current and voltage at each light intensity is the same as would be measured under steady-state illumination conditions and therefore predictive of the actual performance of the solar cell or solar module in sunlight. A varying voltage is applied to the terminals of the solar cell during a light pulse so that the instantaneous current at a given voltage and light intensity during the light pulse is the same as would be measured under constant illumination at that same given intensity. A constant voltage is modified by a small signal correction that is proportional to the terminal current. Or, the small signal correction is proportional to the light intensity. An analog feedback circuit is constructed using the terminal current or light intensity for feedback in order to provide the requisite varying voltage. The varying voltage may also be supplied by digital synthesis.

Owner:SINTON CONSULTING

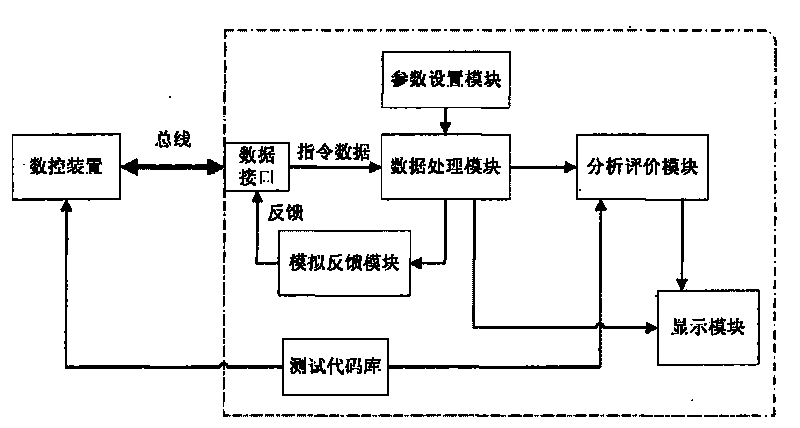

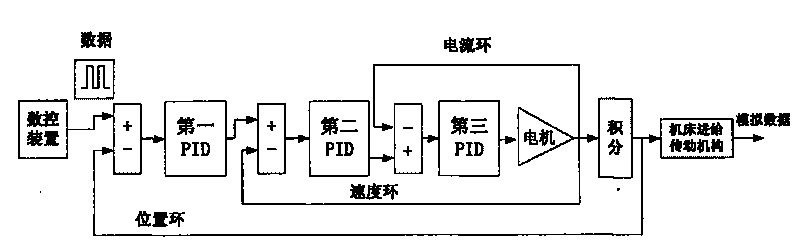

Detection analysis device for technical indexes of numerical control device

InactiveCN101758422AComprehensive detection effectComprehensive evaluationMeasurement/indication equipmentsAnalog feedbackTest fixture

The invention discloses a detection analysis device for technical indexes of a numerical control device, belongs to a test device for the numerical control device, and solves the problems that the conventional detection analysis devices for the technical indexes of the numerical control device are not universal for various numerical control devices and the detected and analyzed technical indexes are not comprehensive. The detection analysis device comprises a data interface, a parameter setting module, a data processing module, an analog feedback module, an analysis evaluation module, a display module and a test code library. The data processing module computes the indication data received by the data interface, and the test result is output to the analysis evaluation module and the display module. The parameter setting module sets parameters of the analog feedback module. The test code library provides standard test G codes for each item to be tested. The detection analysis device for the technical indexes of the numerical control device simulates characteristics of actual servo drive, motor and machine tool by using the analog feedback module, computes corresponding feedback data, removes the influence of uncertainty of an actual electromechanical system and inconsistent processing performance of the machine tool, and can accurately and objectively analyze and evaluate each important technical index of the numerical control device.

Owner:HUAZHONG UNIV OF SCI & TECH +1

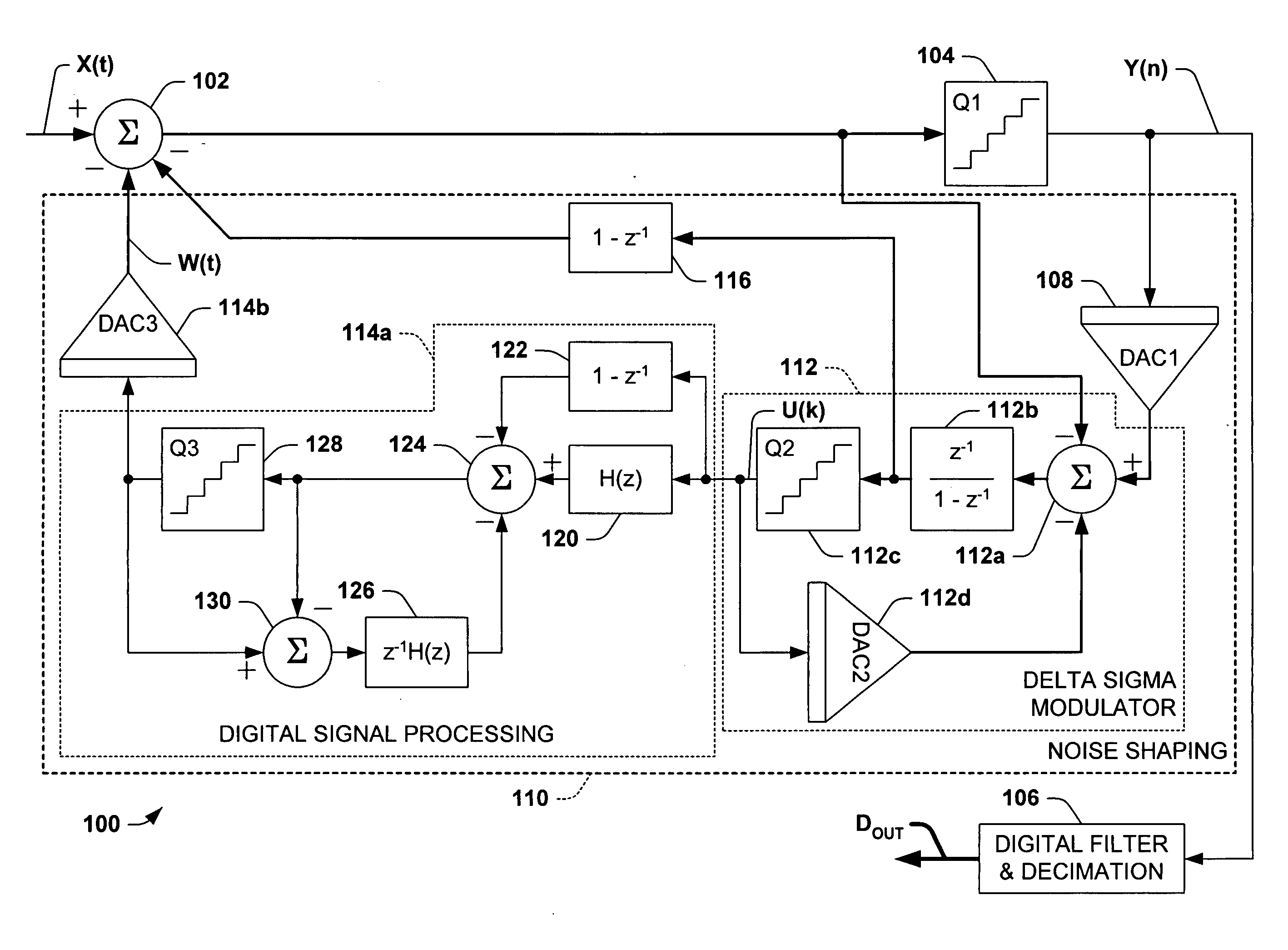

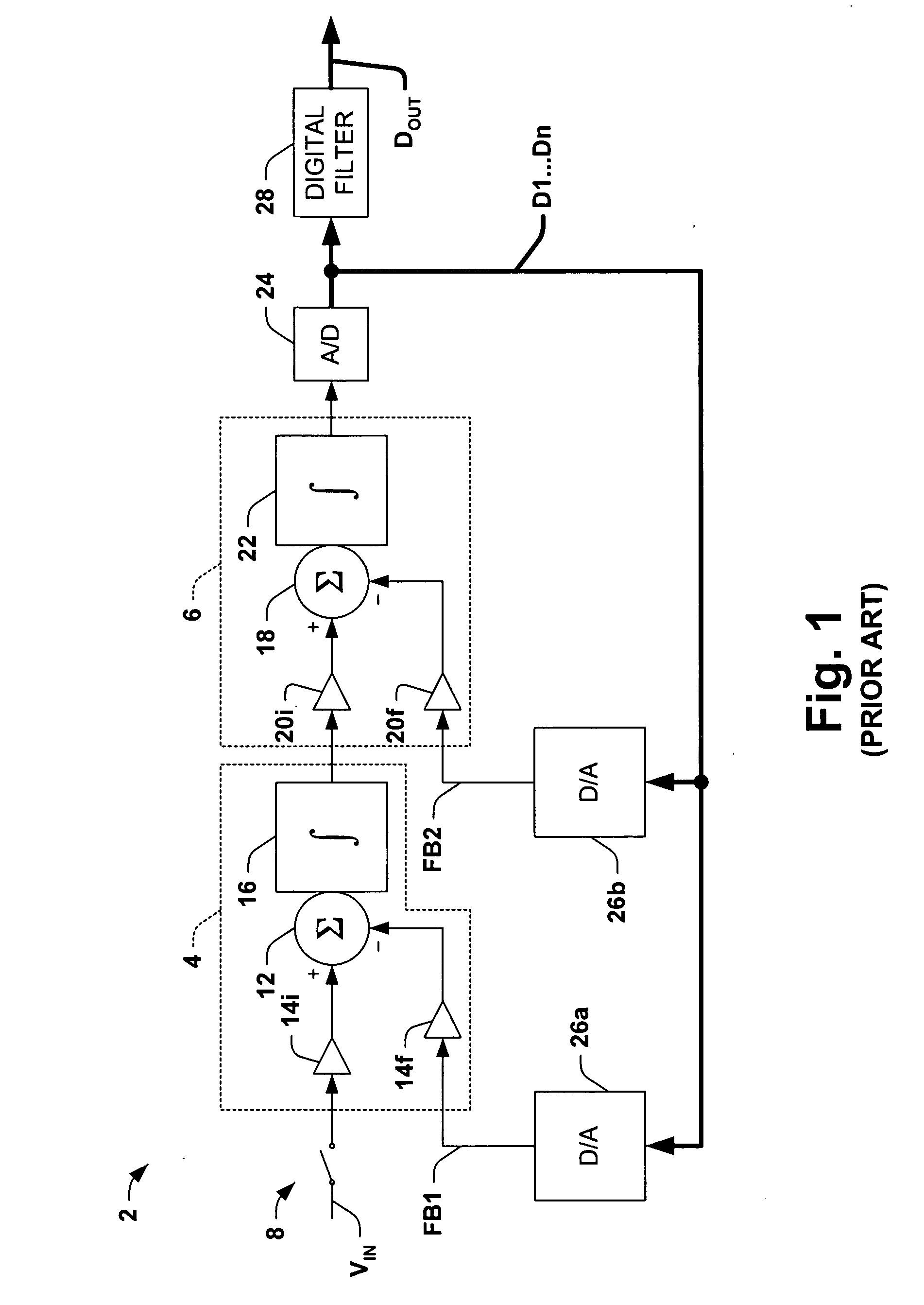

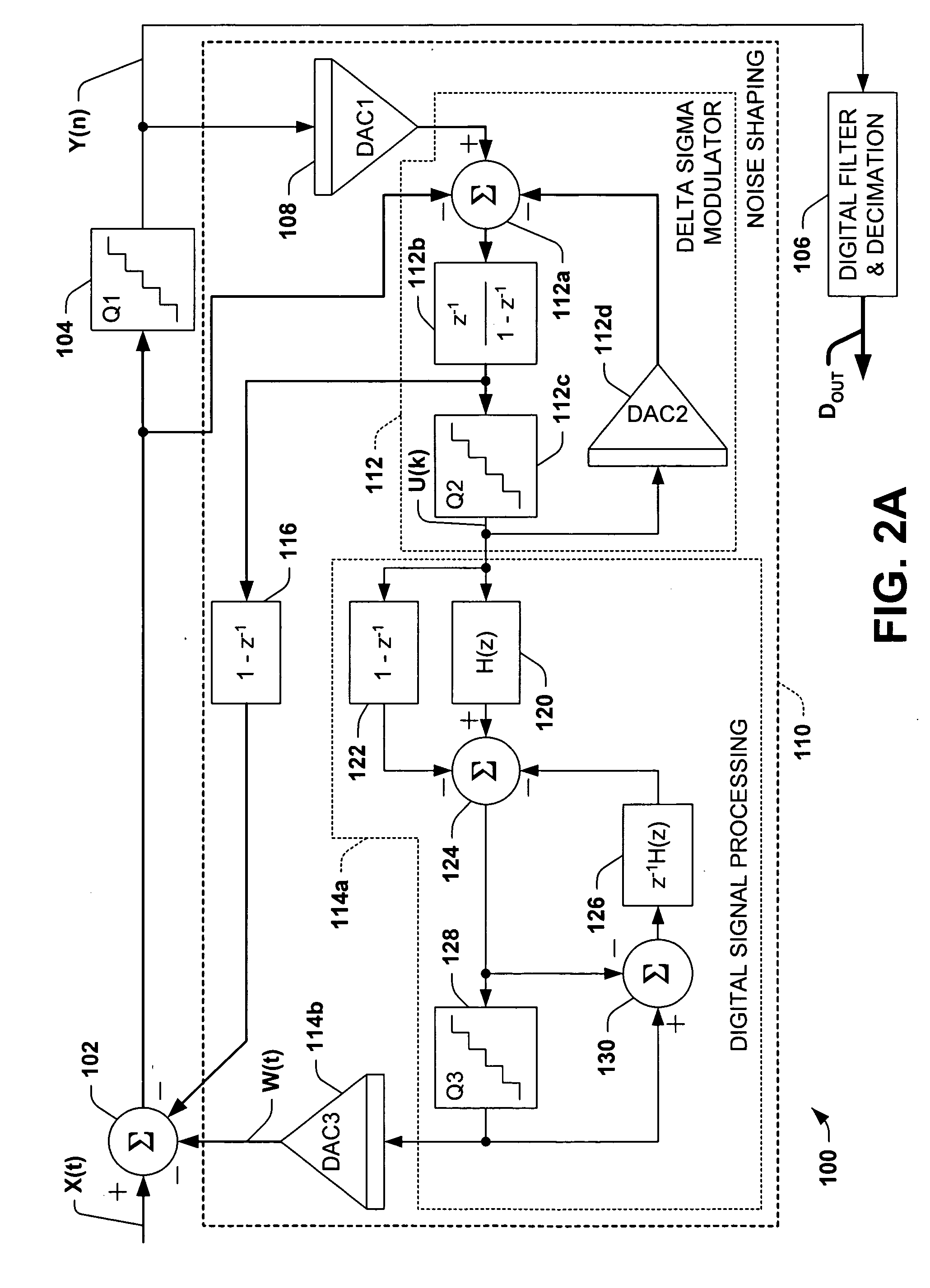

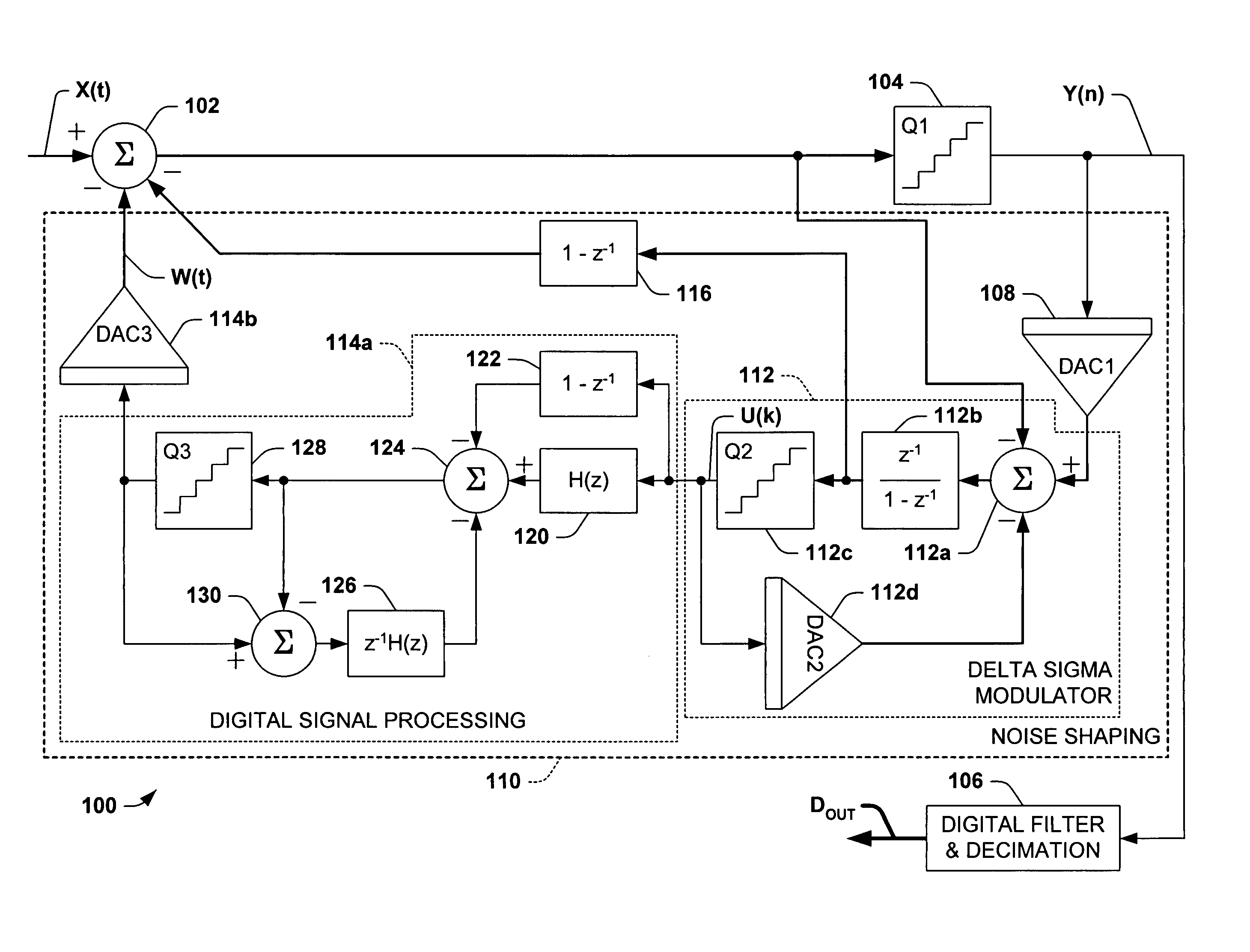

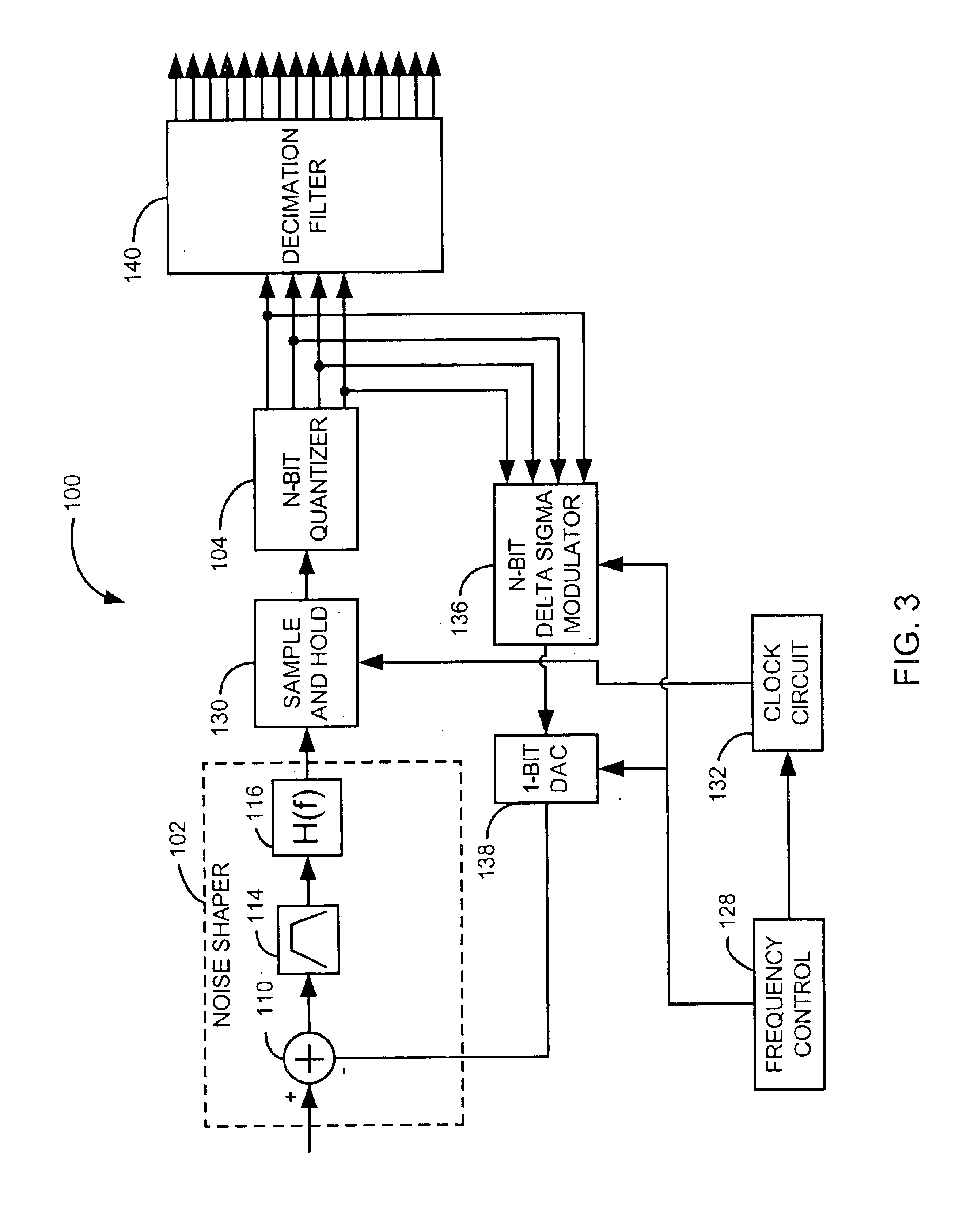

Analog-to-digital conversion system with second order noise shaping and a single amplifier

ActiveUS20050093726A1Well formedElectric signal transmission systemsDifferential modulationDigital signal processingIntegrator

A analog-to-digital converters and second order noise shaping systems are presented for providing a noise shaped analog feedback signal to a A / D converter in an analog-to-digital conversion system. The noise shaping system comprises a first order integrator having a single amplifier, and a digital error feedback system comprising a digital signal processing system, in which the digital error feedback system provides an analog feedback signal to the A / D converter with second order noise shaping with respect to a quantization error associated with the A / D converter.

Owner:TEXAS INSTR INC

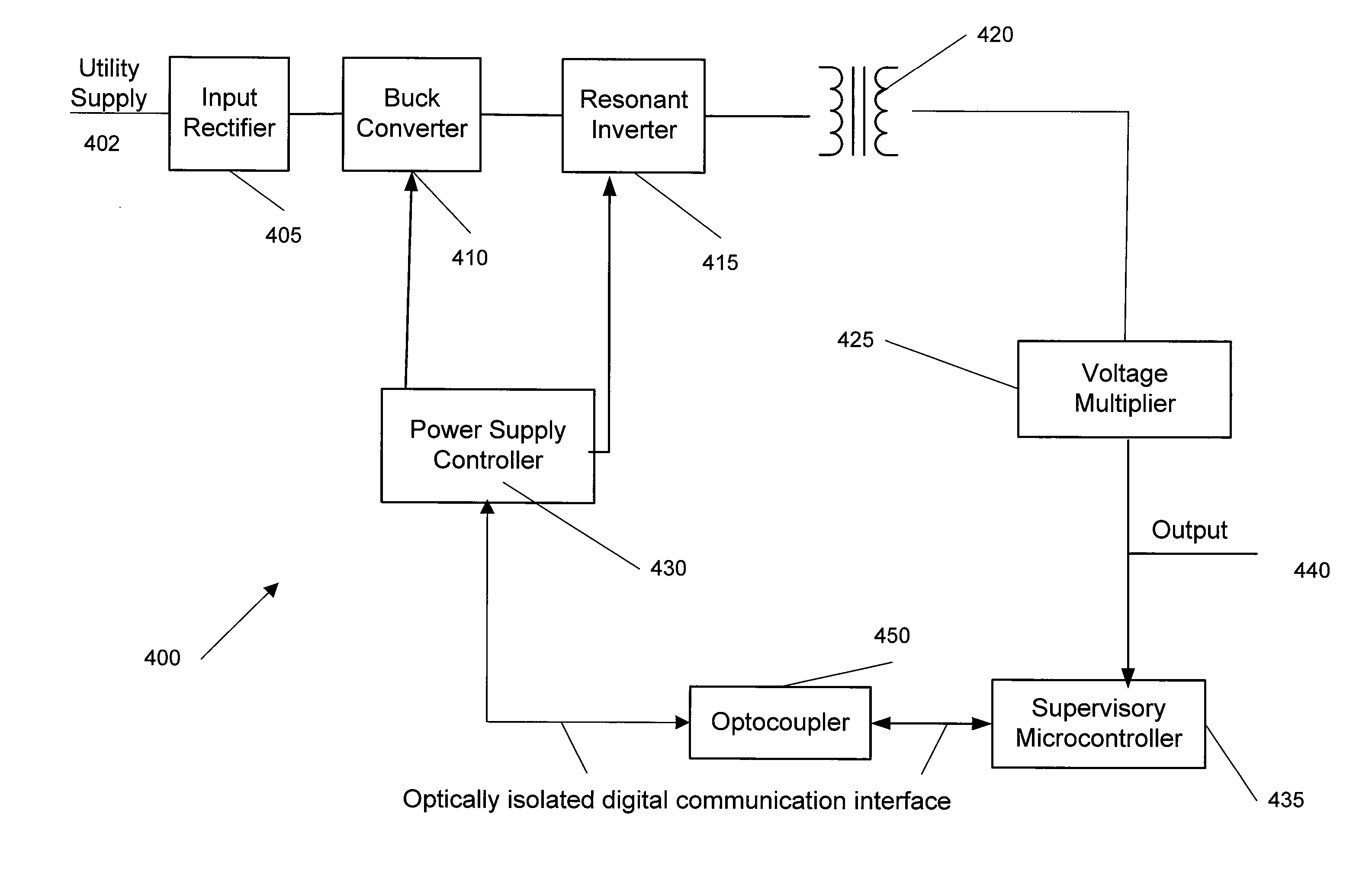

Power supply with a digital feedback loop

ActiveUS7324354B2High operating requirementsLow costEfficient power electronics conversionConversion with intermediate conversion to dcResonant inverterDigital feedback

A wide range power supply capable of delivering 20V to 5000V is provided. The power supply of the present invention uses switch mode technology to achieve high overall operating efficiency and is capable of operating from no load to full load without loss of regulation. The power supply in accordance with the embodiments of the present invention operates directly from the utility supply (e.g., 110V / 220V and 50 Hz / 60 Hz). In one embodiment, the power supply's power conversion stage includes the following stages: an input rectifier; a buck converter; a quasi-resonant inverter; and a voltage multiplier. The above indicated stages are connected in series to achieve the large output voltage range. High precision is obtained from a use of a digital feedback loop, possibly in connection with an analog feedback loop.

Owner:BIO RAD LAB INC

Analog-to-digital conversion system with second order noise shaping and a single amplifier

InactiveUS6940436B2Electric signal transmission systemsDifferential modulationDigital signal processingAudio power amplifier

Owner:TEXAS INSTR INC

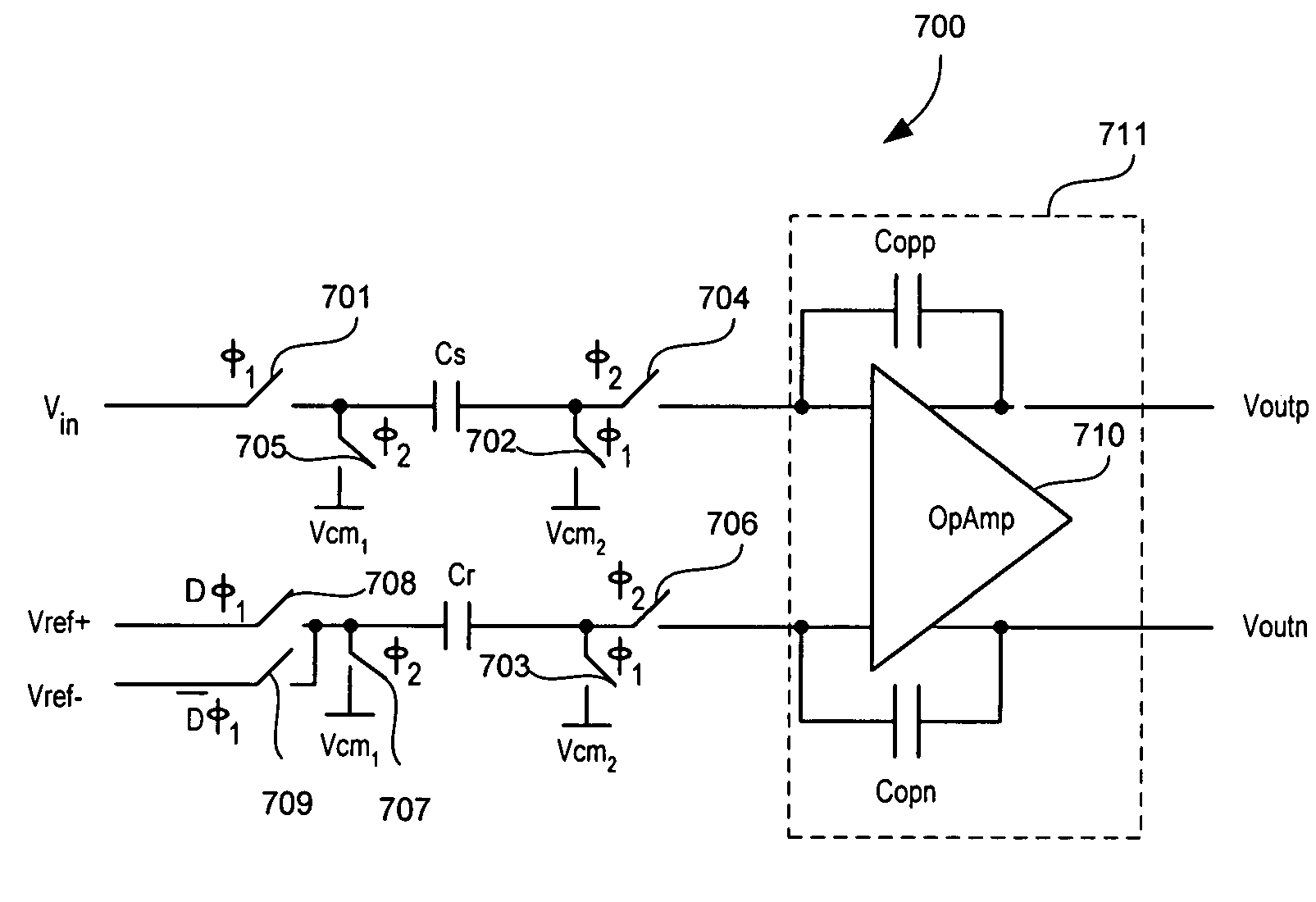

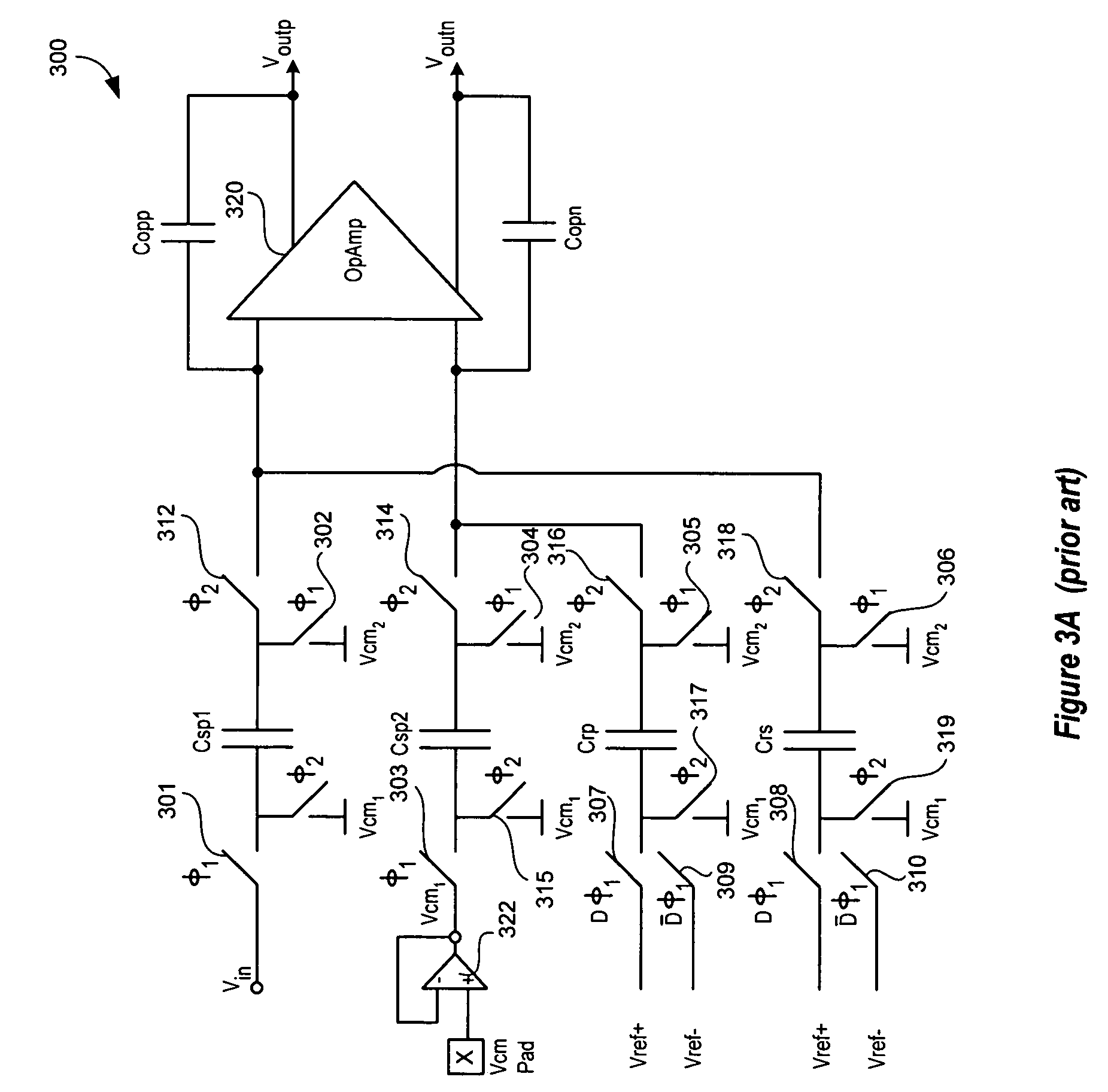

Signal processing system having an ADC delta-sigma modulator with single-ended input and feedback signal inputs

ActiveUS6972705B1Electric signal transmission systemsDifferential modulationAnalog feedbackEngineering

Signal processing systems described herein include an analog-to-digital delta sigma modulator to process a single-ended input signal using a single-ended analog feedback reference signal. The delta sigma modulator includes a switched capacitor circuit that integrates a difference between the single-ended input signal and the single-ended analog feedback signal derived from a quantization output of the delta sigma modulator. Embodiments of the switched capacitor circuit allow the delta sigma modulator to be implemented with fewer switches, less complicated reference signal generators, and smaller capacitors relative to conventional counterparts. Thus, embodiments of the delta sigma modulator described herein can cost less to build and use less power. Embodiments of the signal processing systems can be implemented in single and multi-bit delta sigma modulators and various sampling topologies, including single and double sampling topologies.

Owner:CIRRUS LOGIC INC

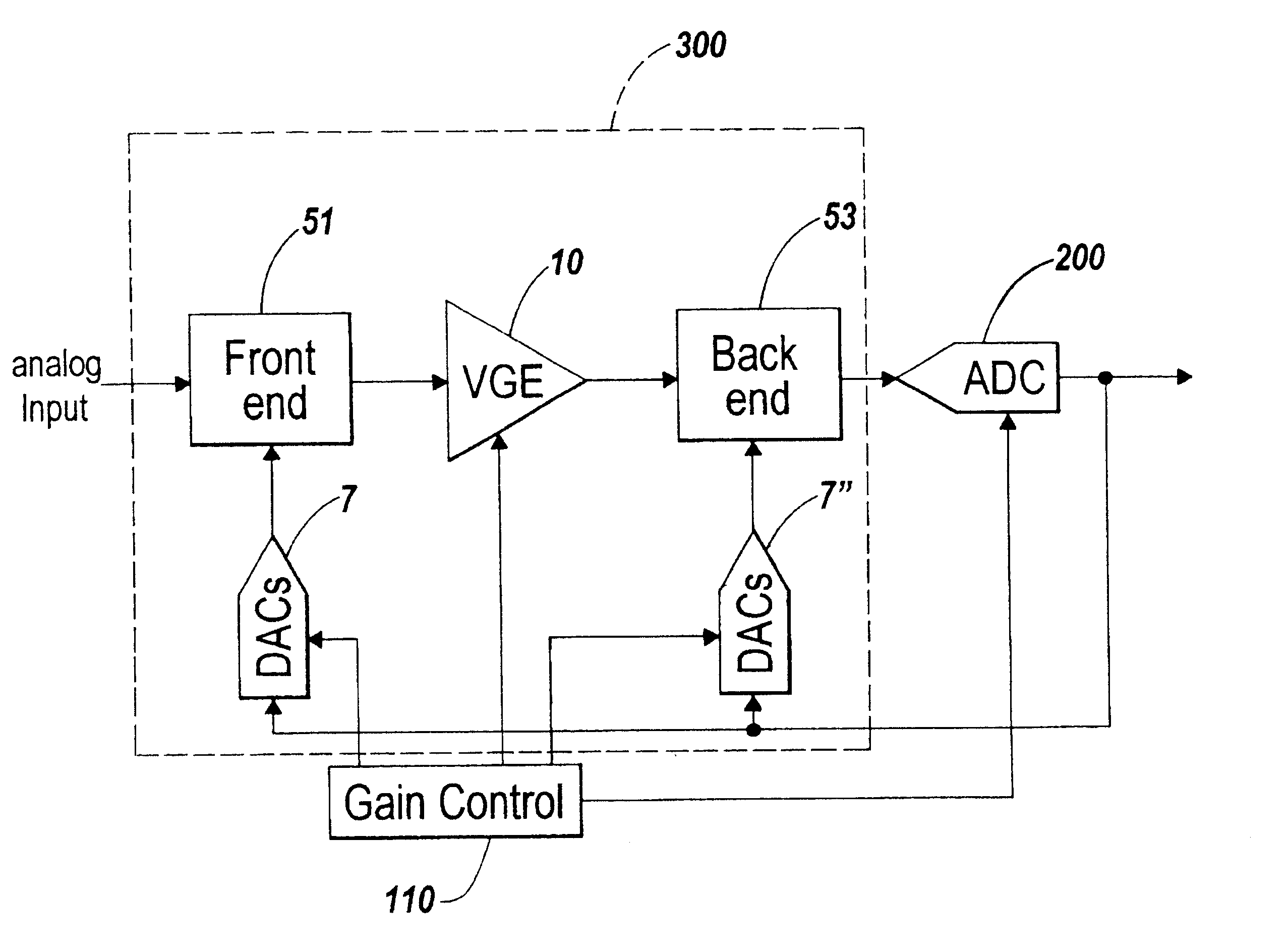

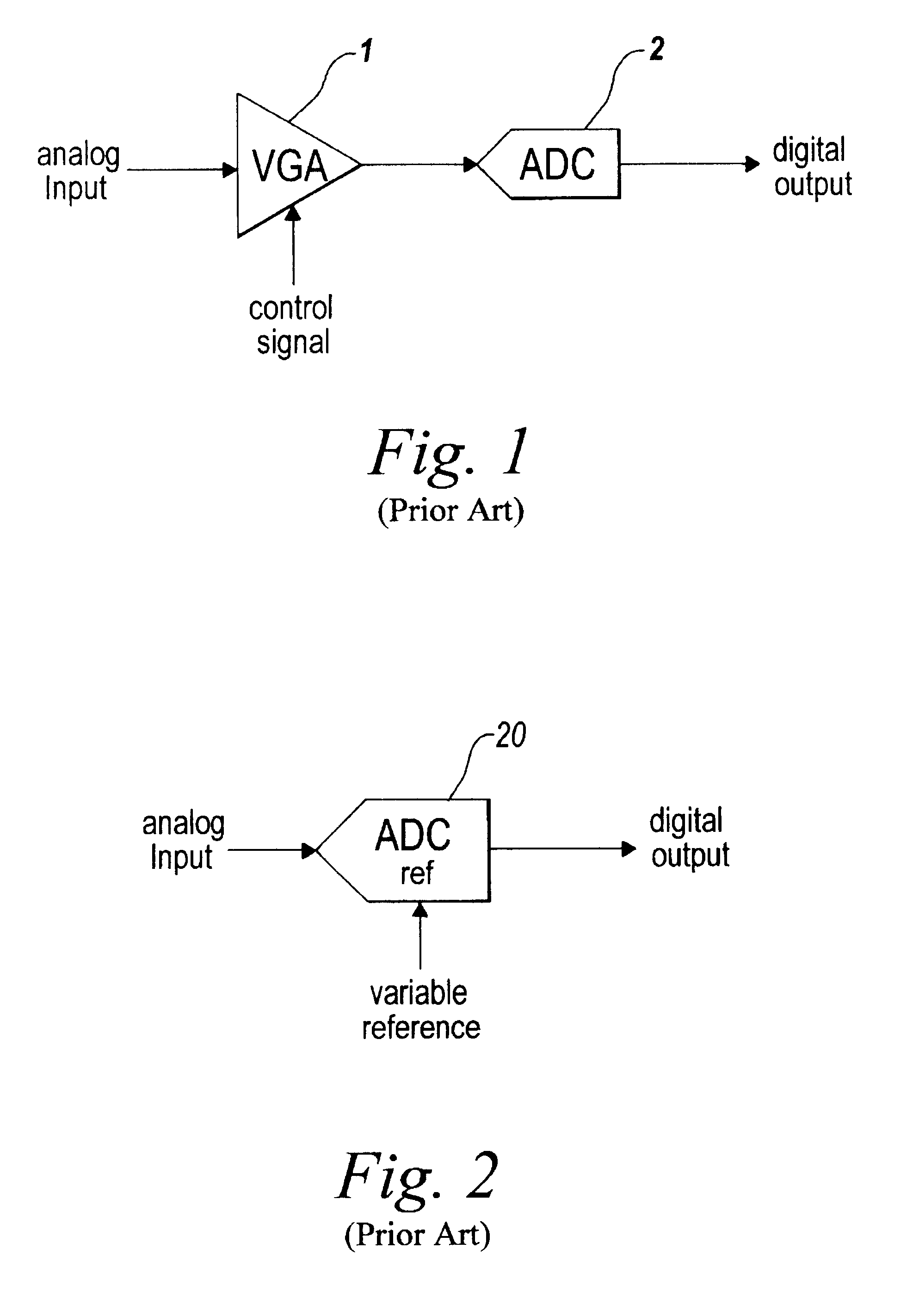

Multi-bit sigma-delta analog to digital converter with a variable full scale

InactiveUS6567025B2Analogue/digital conversionElectric signal transmission systemsLoop filterAnalog feedback

A multi-bit sigma-delta analog to digital converter has a quantizer, a loop filter circuit, and a digital to analog feedback circuit. The quantizer, loop filter, and digital to analog feedback circuit have a loop gain associated therewith. The quantizer and loop filter have a combined gain associated therewith. The full-scale of the digital to analog feedback circuit is varied. The combined gain of the quantizer and loop filter is also varied. More specifically, the combined gain of the quantizer and loop filter is varied in inverse proportion to the full-scale of the digital to analog feedback circuit to maintain the loop gain at a substantially constant level.

Owner:ANALOG DEVICES INC

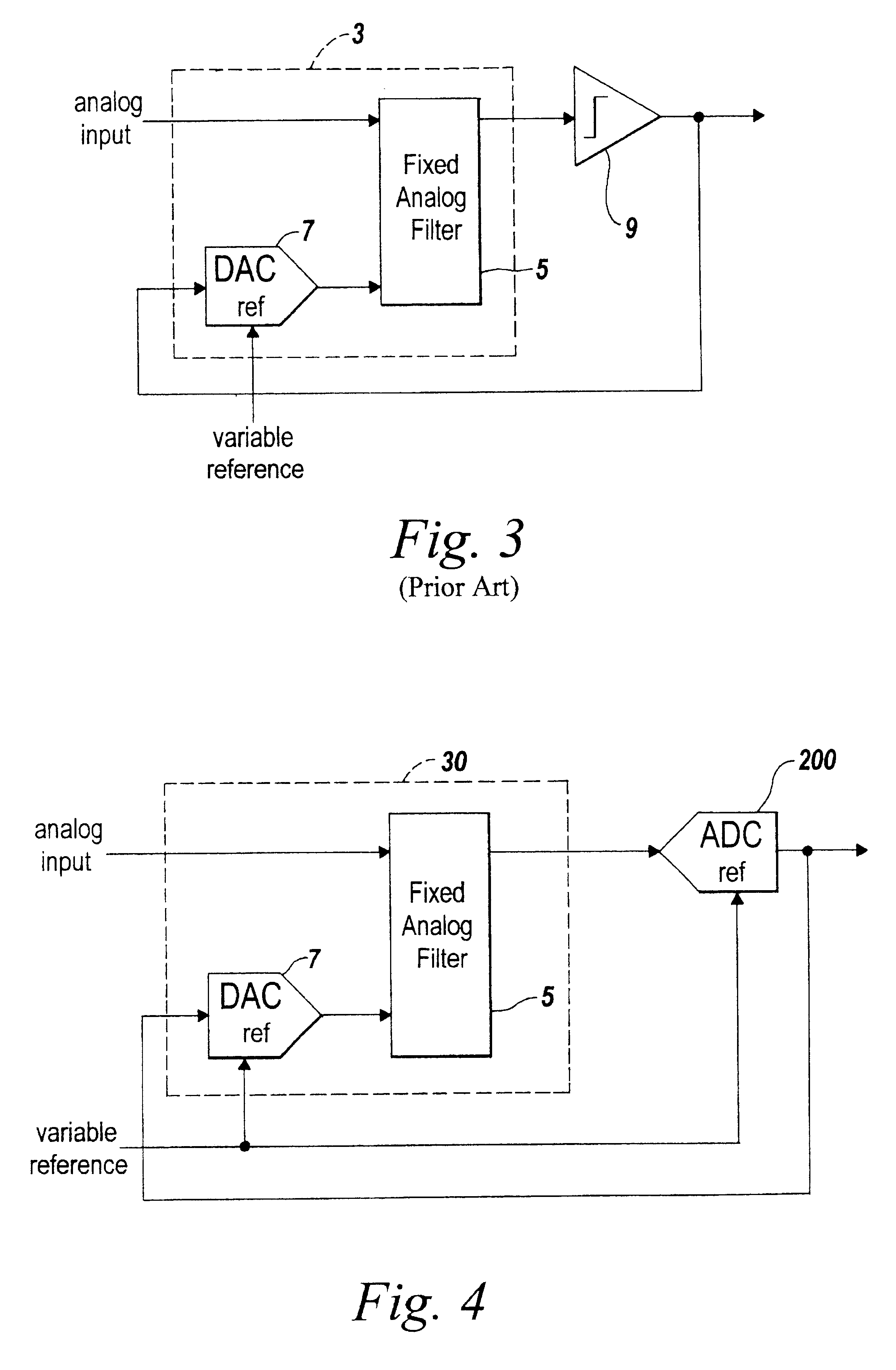

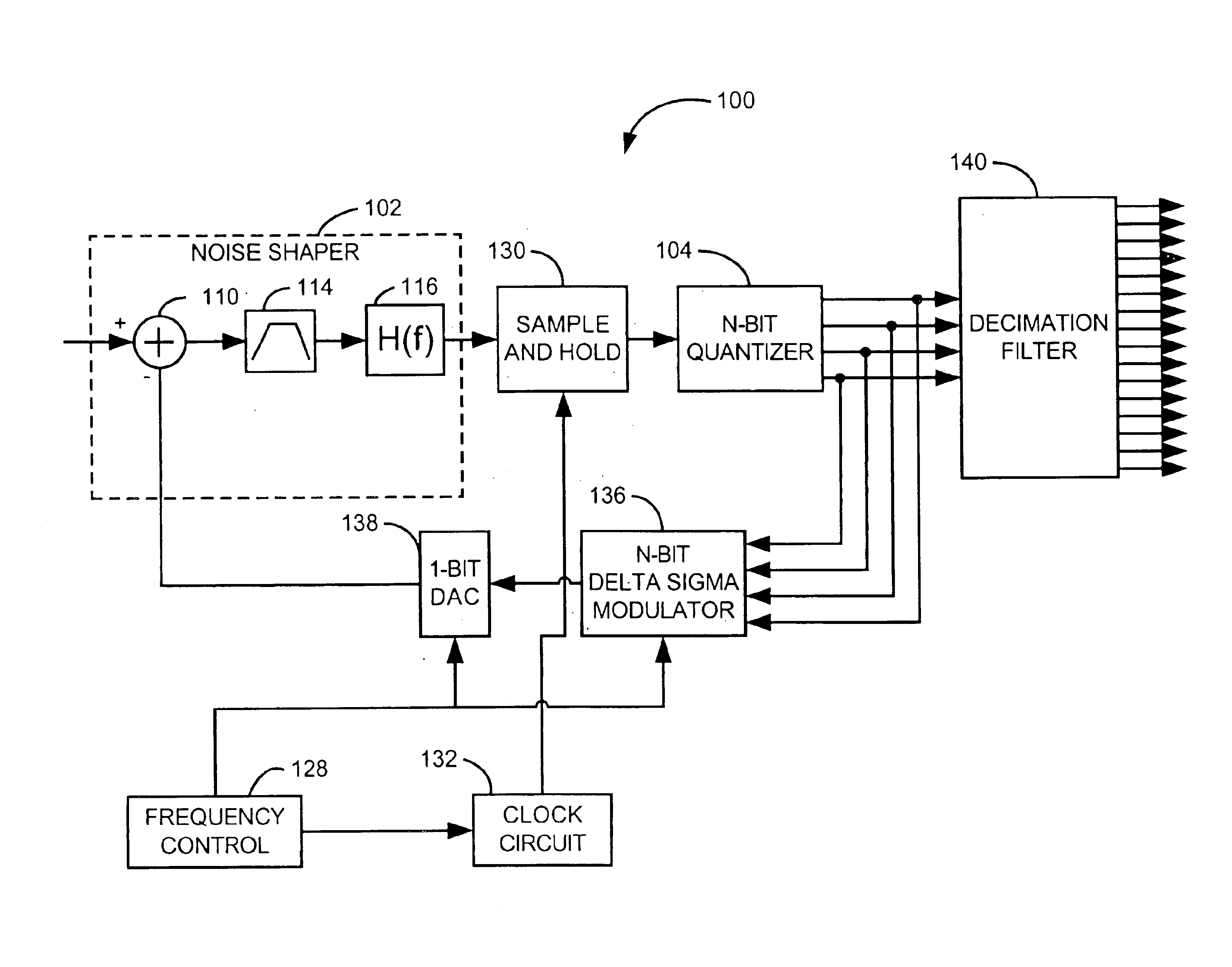

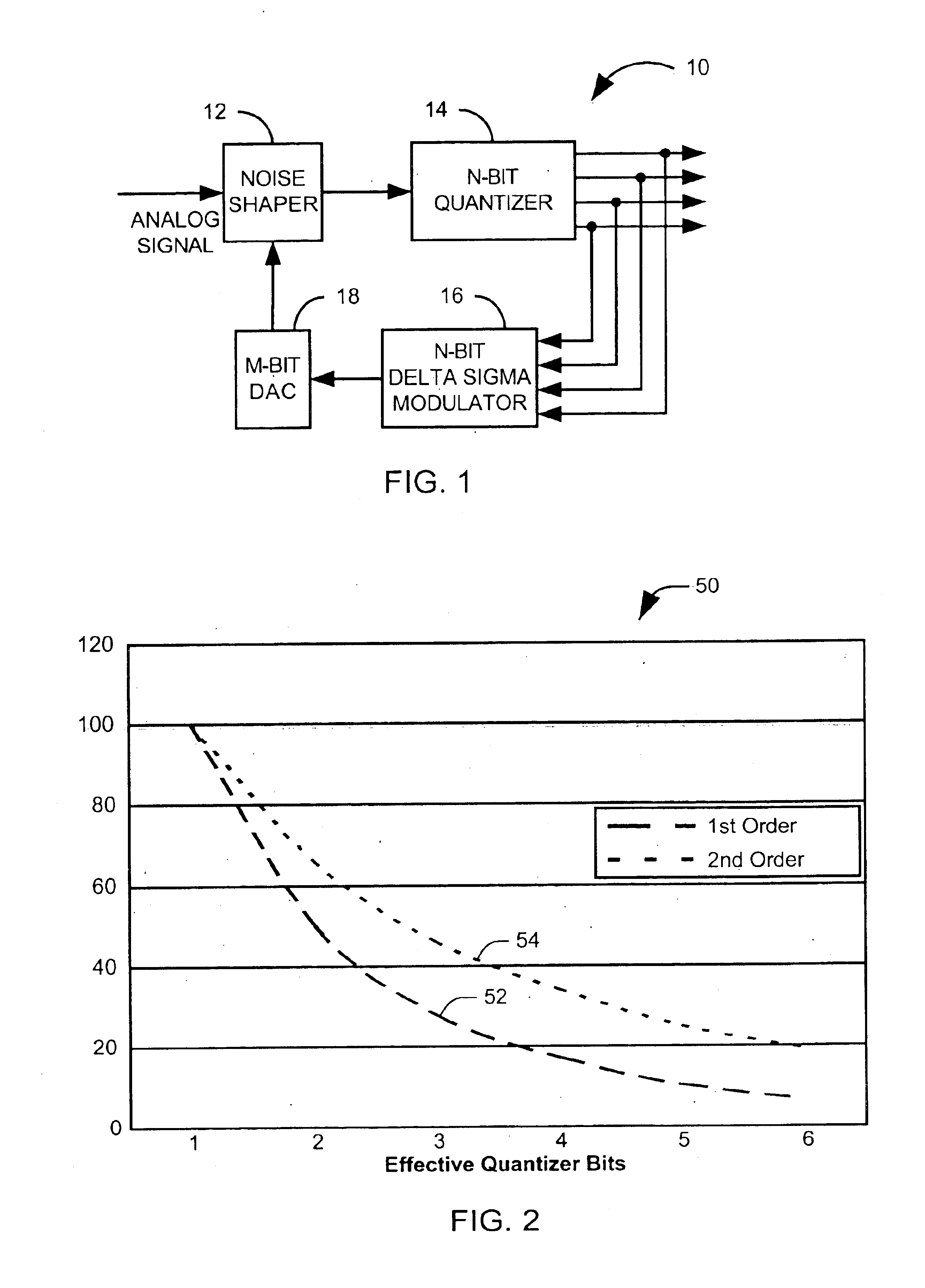

Delta-sigma analog-to-digital converter

ActiveUS6842129B1Electric signal transmission systemsDifferential modulationDigital analog converterDigital down converter

Systems and methods are provided for providing feedback to a delta-sigma analog-to-digital converter assembly. A noise shaper preprocesses an analog input signal according to an analog feedback signal and an associated transfer function. A quantizer converts the preprocessed analog input signal into a digital output signal. A delta-sigma modulator shapes noise within a sample of the digital output signal. A digital-to-analog converter converts the shaped digital signal into an analog signal to provide the analog feedback signal.

Owner:NORTHROP GRUMMAN SYST CORP

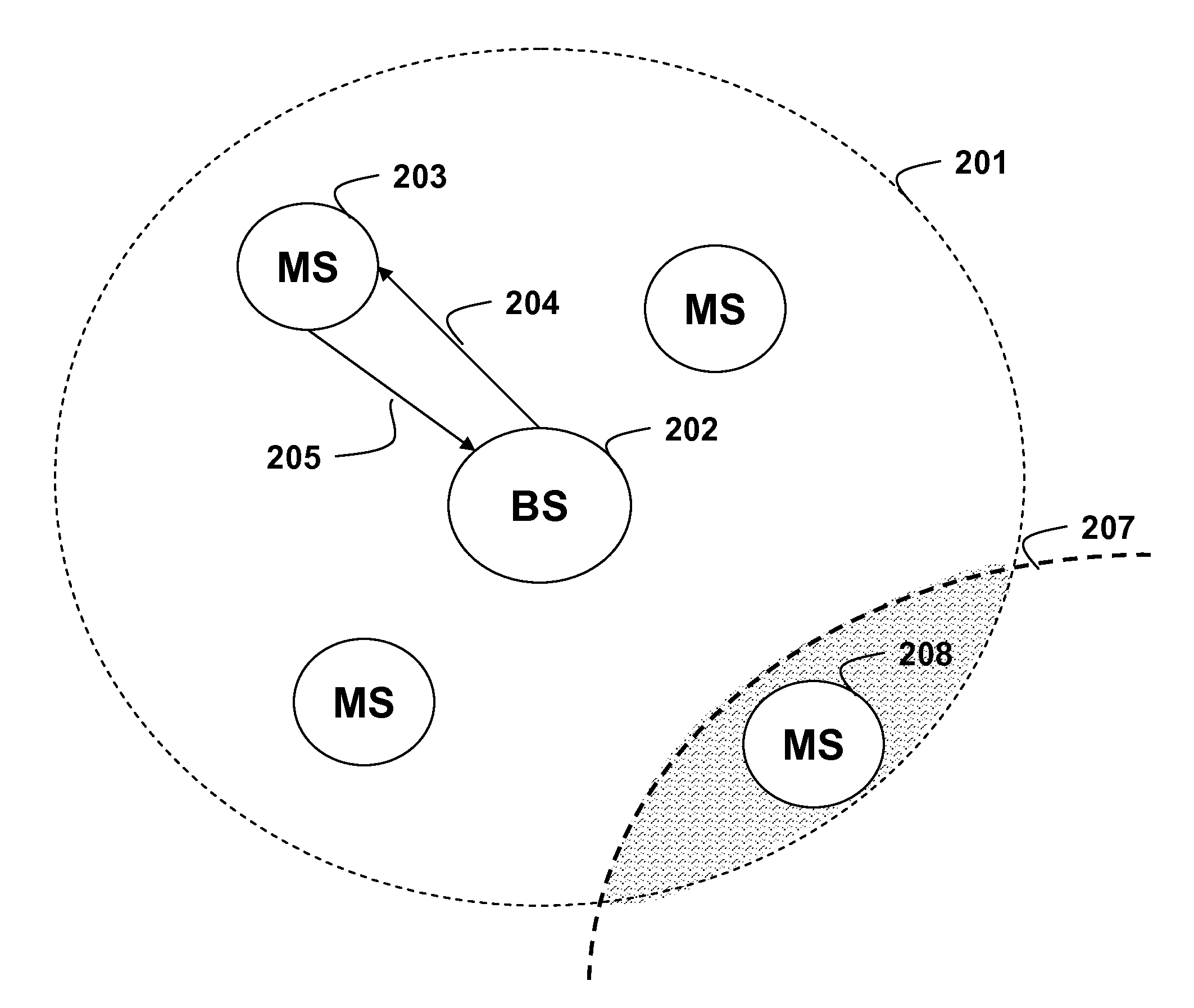

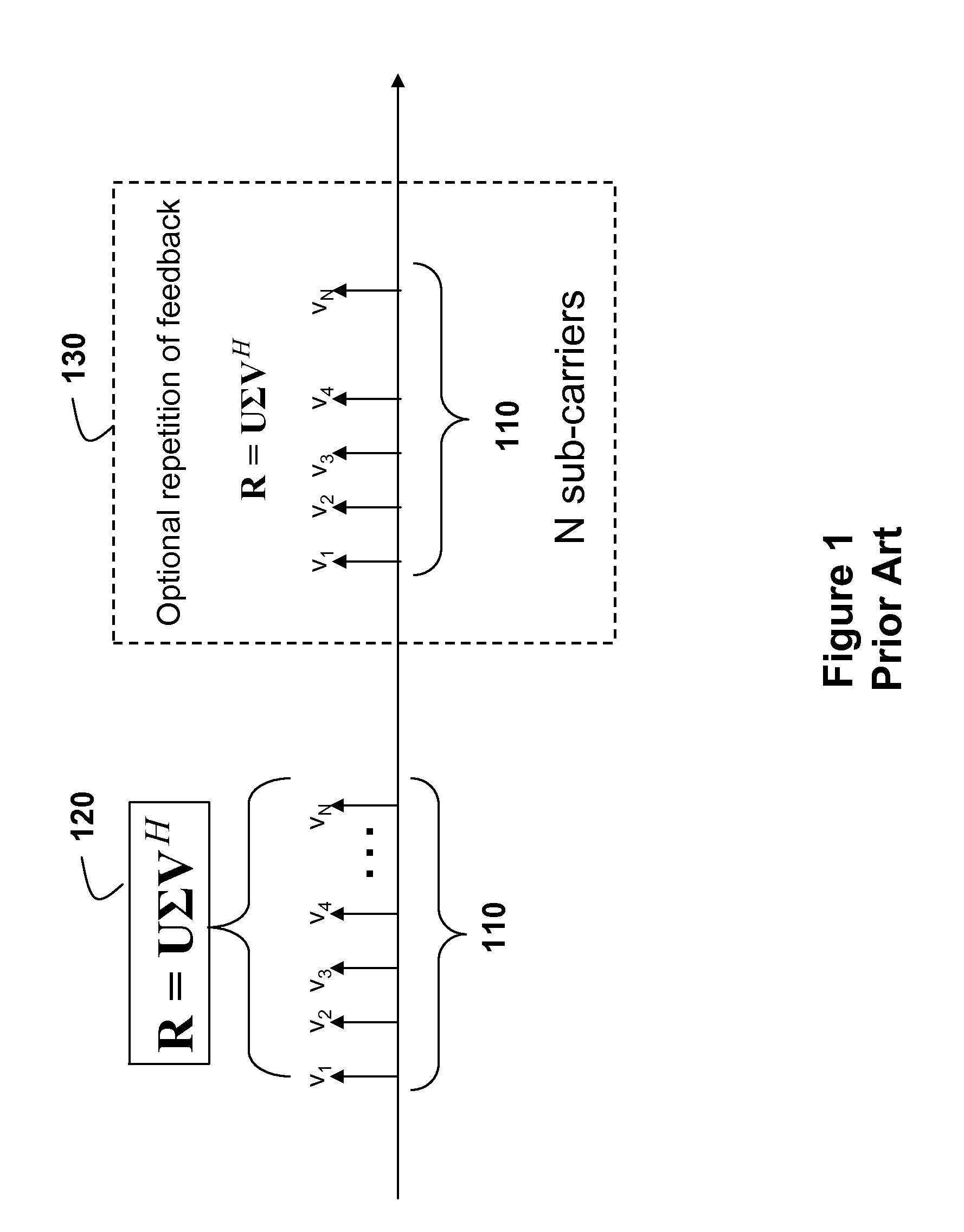

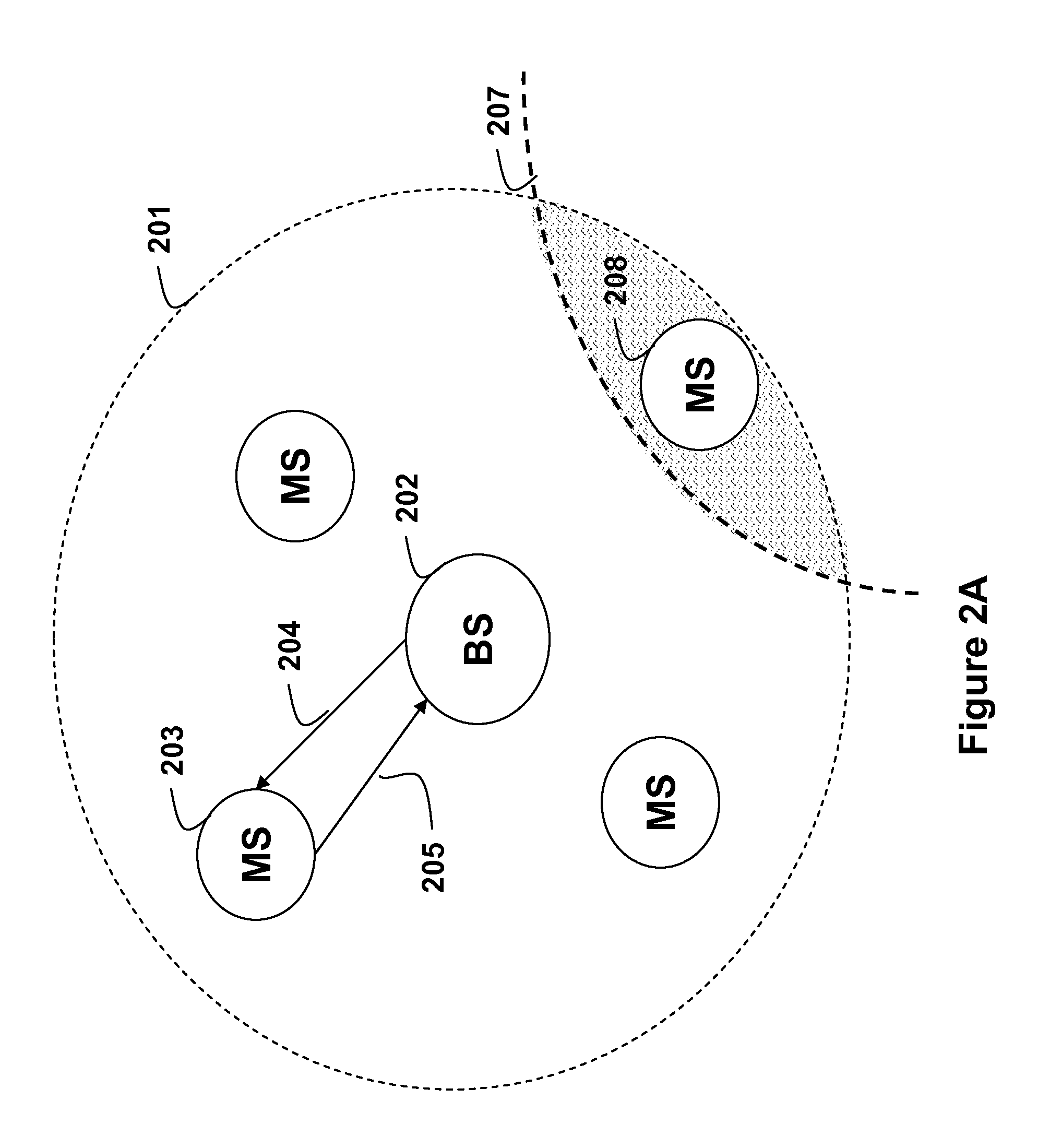

Parametric Compression of Rank-1 Analog Feedback

InactiveUS20100272014A1Radio transmissionWireless commuication servicesSingular value decompositionCarrier signal

Channel state information in a closed-loop, multiple-input, multiple-output wireless networks is fed back from each mobile station to a base station by first determining a transmit covariance matrix R, and applying a singular value decomposition (SVD) R=UΣVH, where U, V are left and right singular vector matrices, Σ is a diagonal matrix with singular values. The matrix V includes column vectors V. A beamforming vector vmax=[1 exp(jΦ)exp(j2Φ) . . . exp(jΦ)] / √{square root over (N)}] is approximated by the column vector V having a maximum magnitude, where Φ is a real number. Then, only the angle Φ is fed back using a phase modulation mapping of the components exp(jΦ) onto the associated subcarrier.

Owner:MITSUBISHI ELECTRIC RES LAB INC

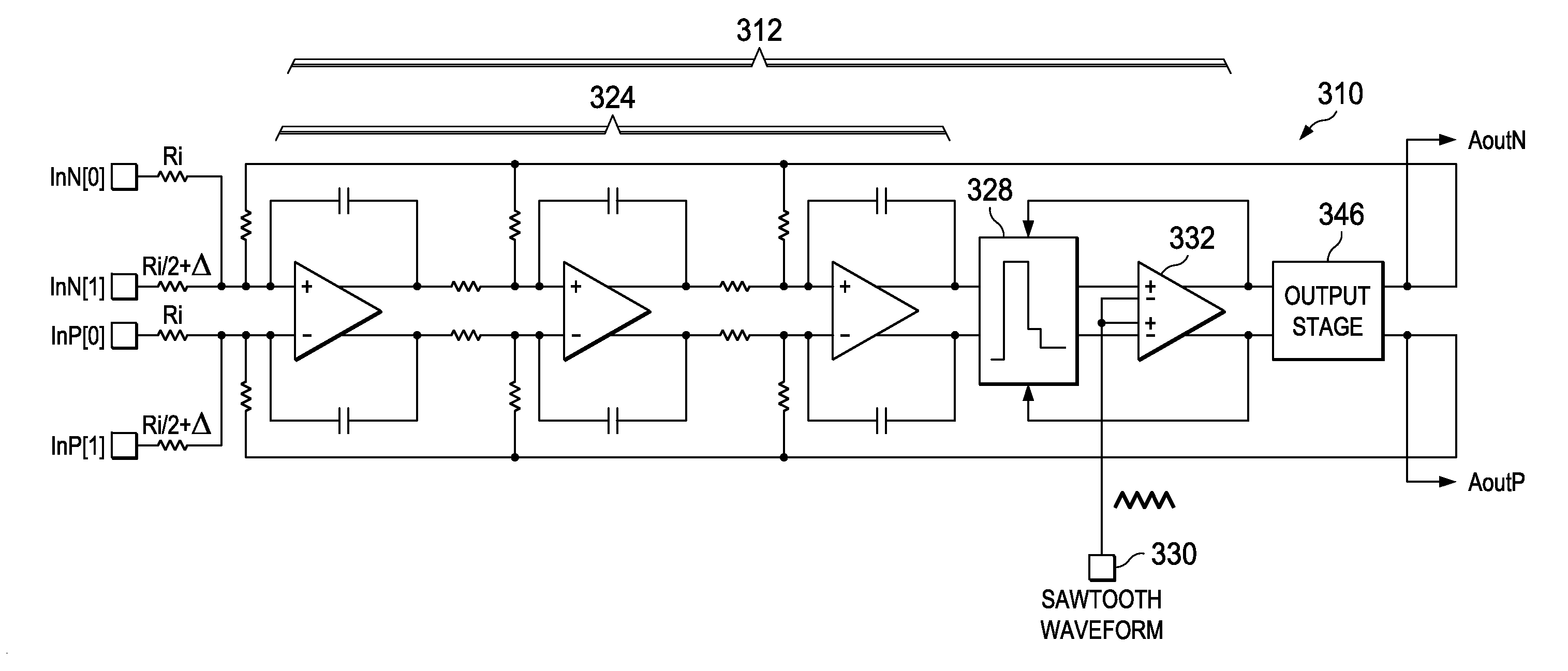

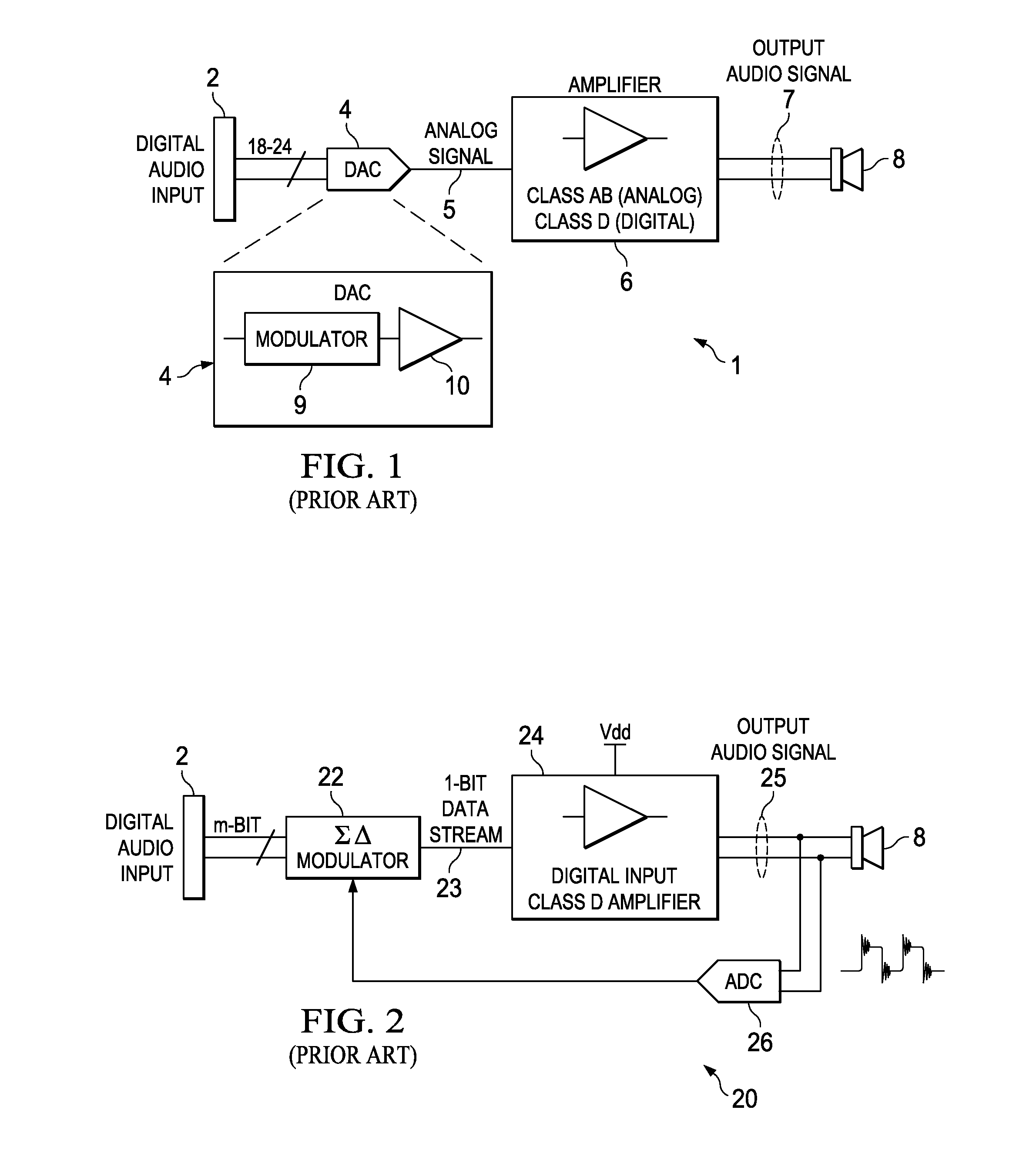

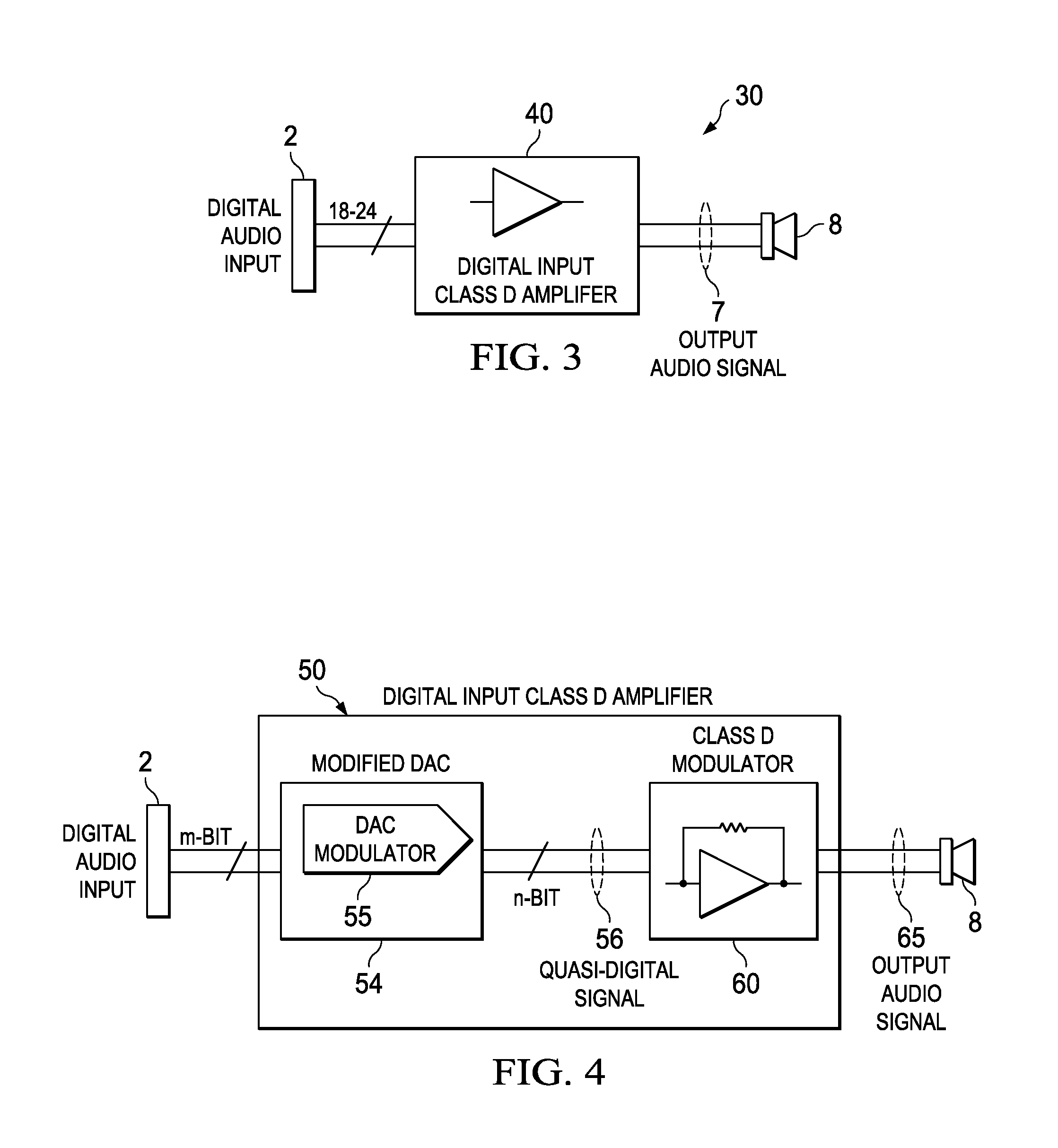

Digital Input Class-D Audio Amplifier

ActiveUS20130223652A1Amplifier modifications to reduce temperature/voltage variationLow frequency amplifiersAnalog feedbackAudio power amplifier

An audio amplifier receiving a digital input audio signal and generating an output audio signal for driving a speaker includes a digital input class D amplifier configured to receive the digital input audio signal and to generate the output audio signal. The digital input class D amplifier includes a first modulator configured to receive the digital input audio signal and to generate a quasi-digital signal in n-bit, and a class D modulator configured to receive the n-bit quasi-digital signal and to generate the output audio signal, the class D modulator implementing an analog feedback loop. In some embodiments, the class D modulator is implemented using a PWM modulator. In other embodiments, the PWM modulator incorporates enhanced features to improve the output noise characteristics.

Owner:TEXAS INSTR INC

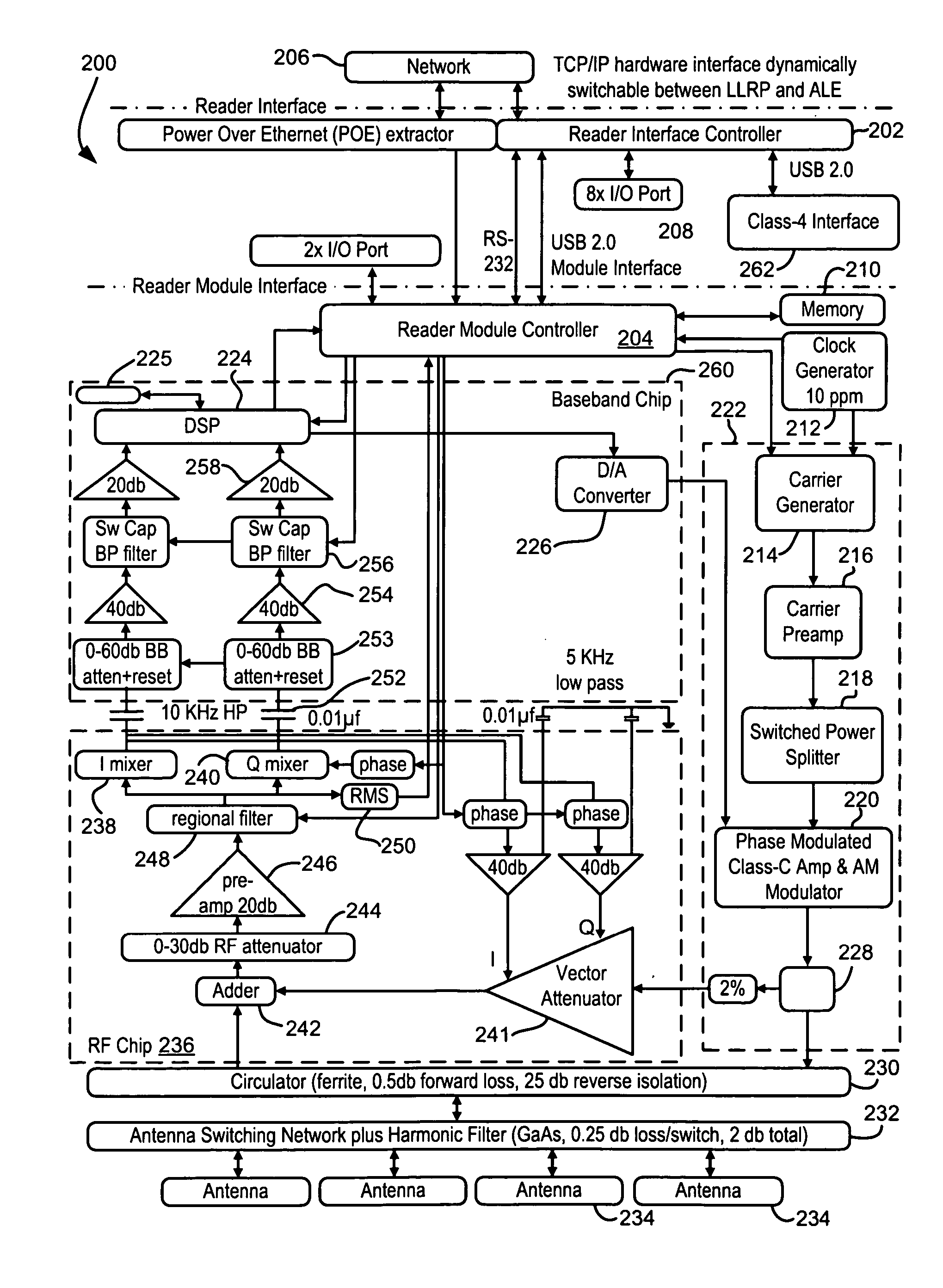

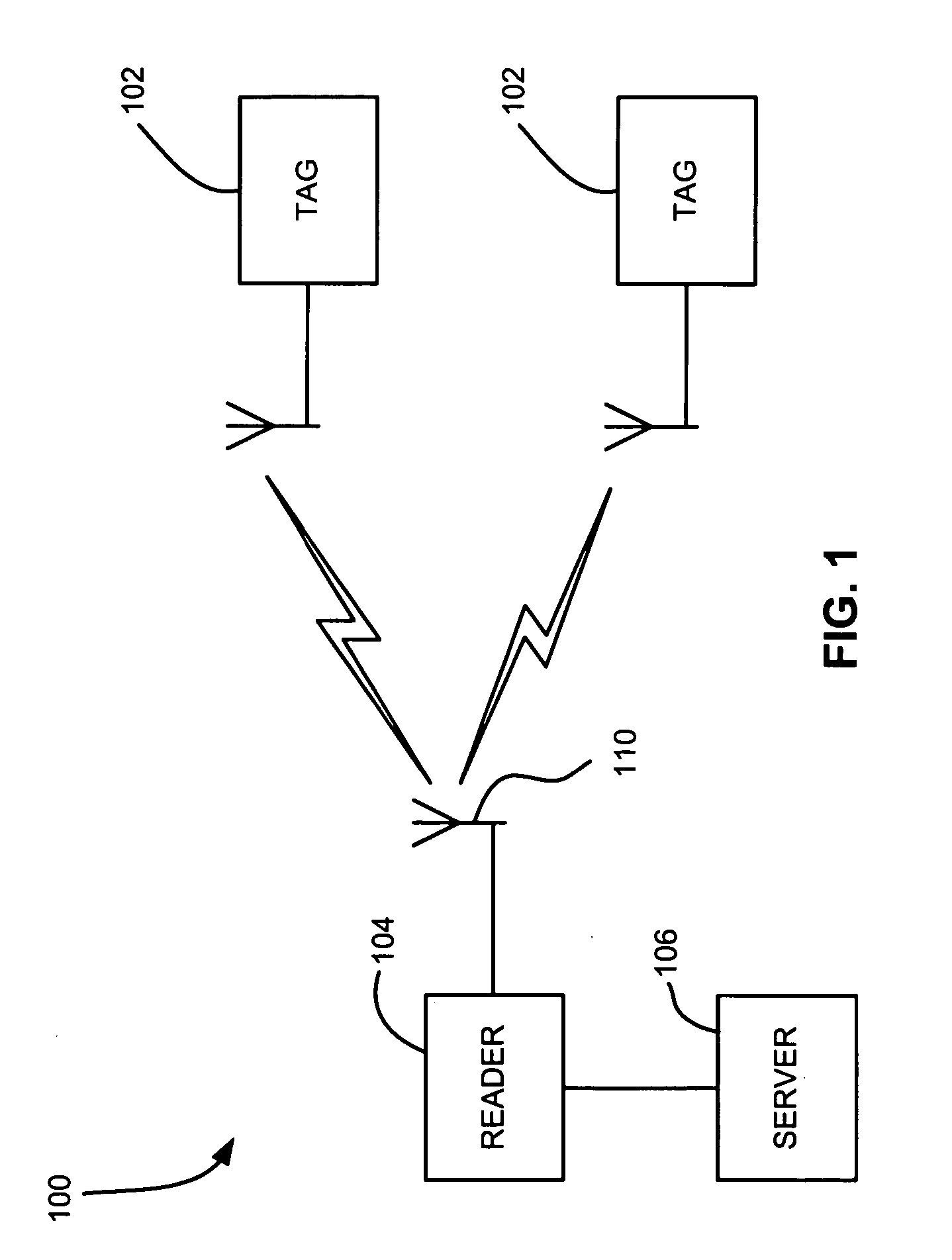

RFID reader with adaptive carrier cancellation

InactiveUS20070206704A1Modulated-carrier systemsMemory record carrier reading problemsAnalog feedbackCarrier signal

An RFID reader includes first and second mixers receiving an incoming signal, circuitry for adding a portion of an outgoing signal to an incoming signal, first and second analog feedback loops coupling outputs of the first and second mixers to the circuitry for adding the outgoing signal to the incoming signal. An amount of outgoing signal added to the incoming signal depends on signals in the feedback loops. An RFID reader in another embodiment of the present invention includes a first mixer receiving an incoming signal, a second mixer receiving the incoming signal, an AC-coupled section coupled to the mixer outputs, and a DC-coupled section coupled to the mixer outputs. An RFID reader in another embodiment of the present invention includes an analog loop for adaptive carrier signal cancellation from an incoming signal, and a digital loop for controlling a gain of the incoming signal. Methods are also presented.

Owner:APPLIED WIRELESS IDENTIFICATIONS GROUP

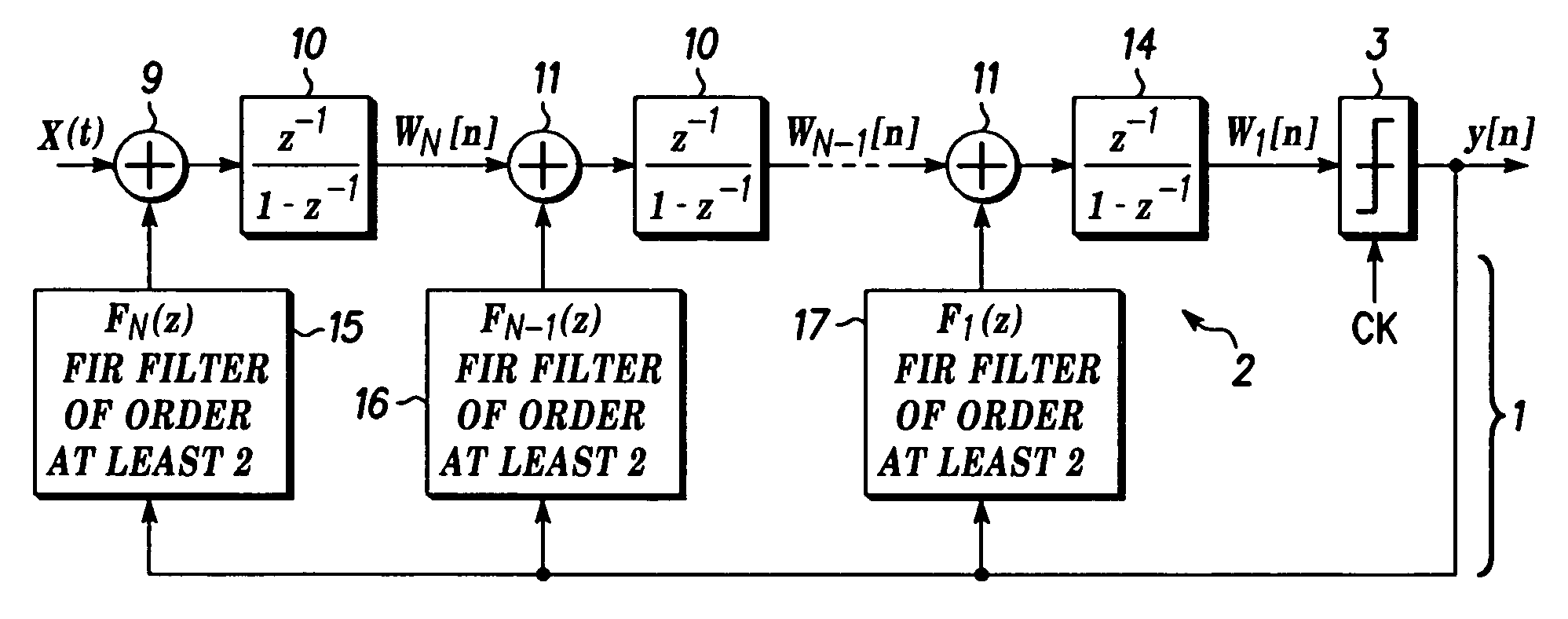

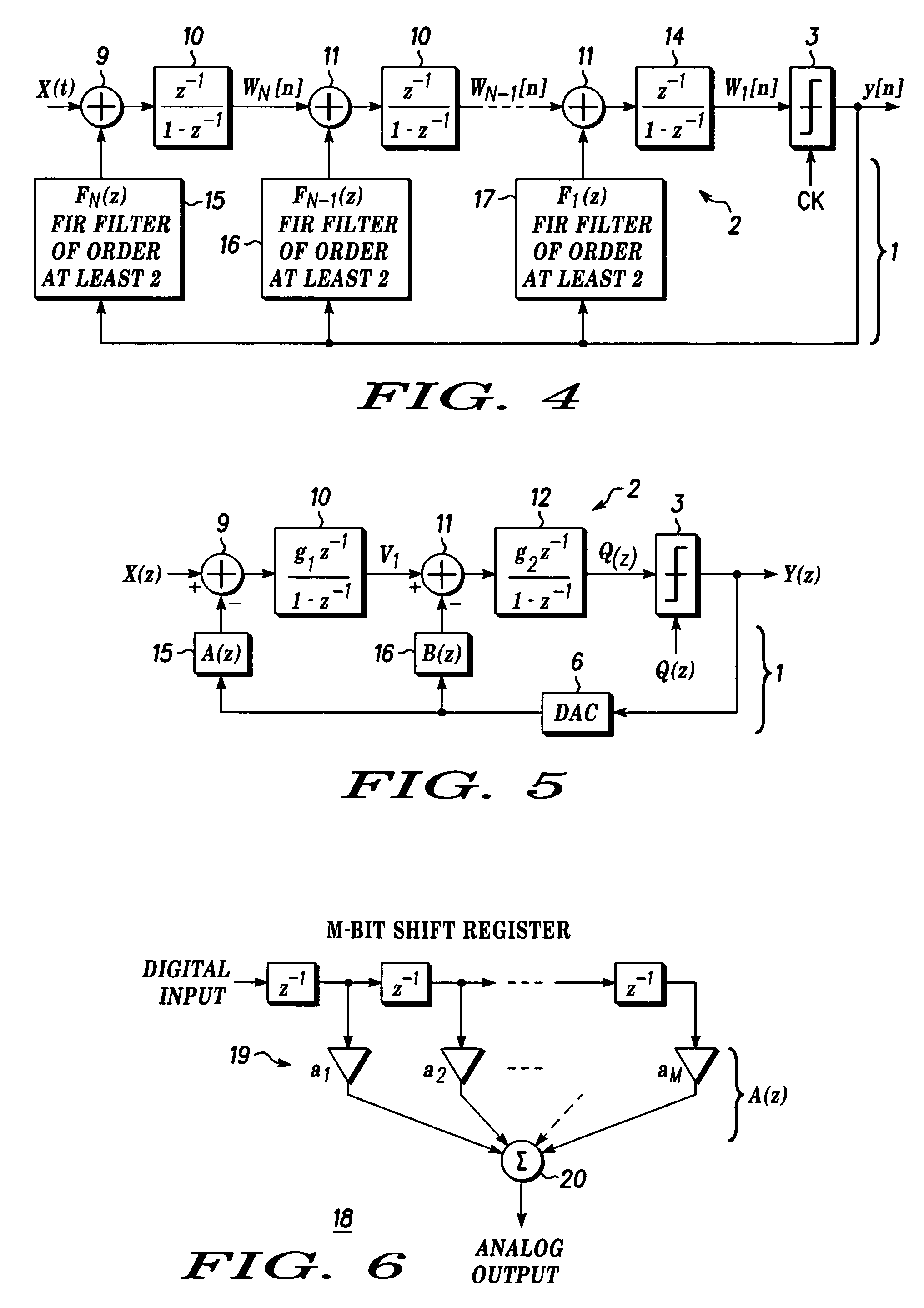

Analog-to-digital sigma-delta modulator with FIR filter feedback

InactiveUS7042377B2Electric signal transmission systemsDelta modulationFinite impulse responseIntegrator

Owner:NORTH STAR INNOVATIONS

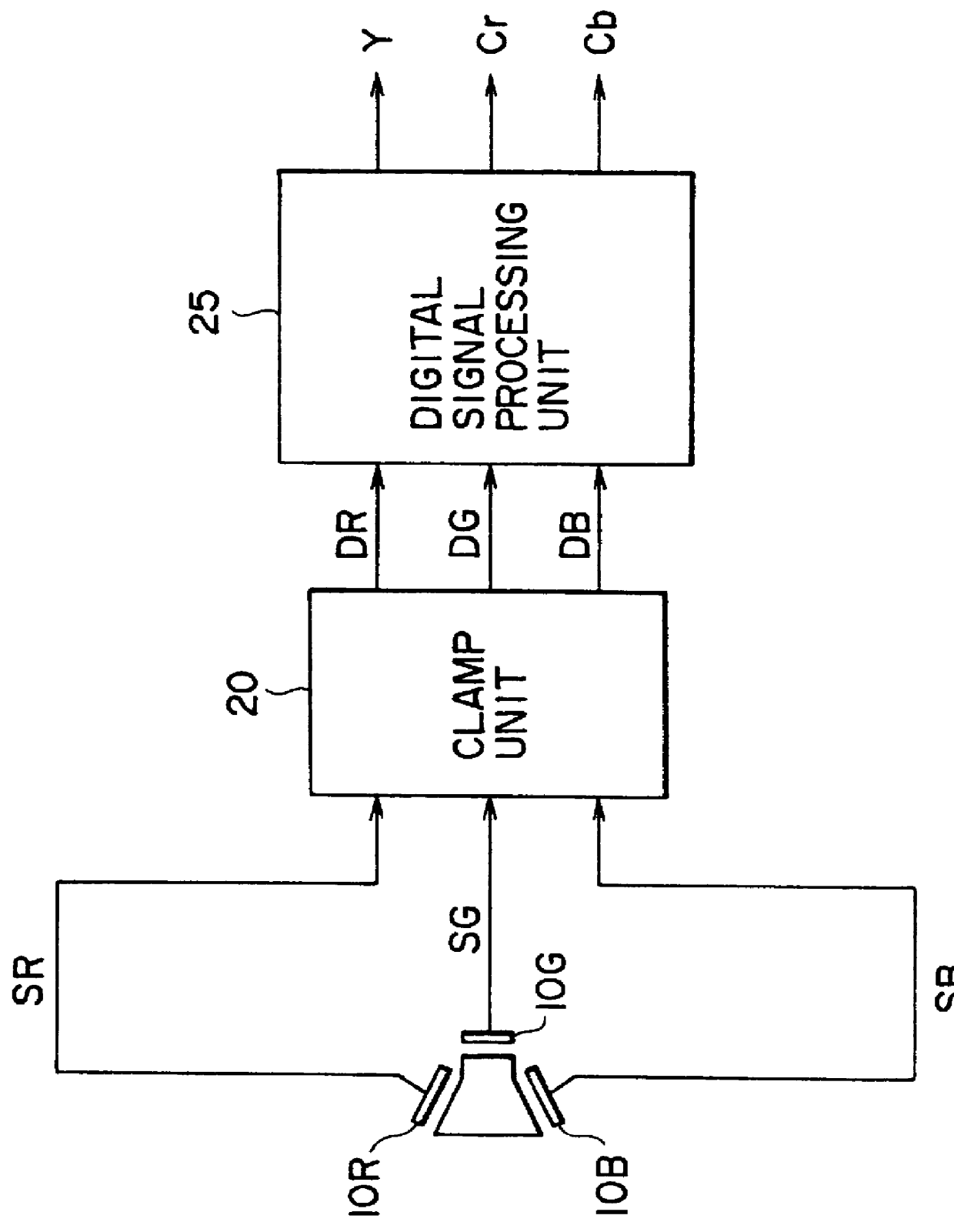

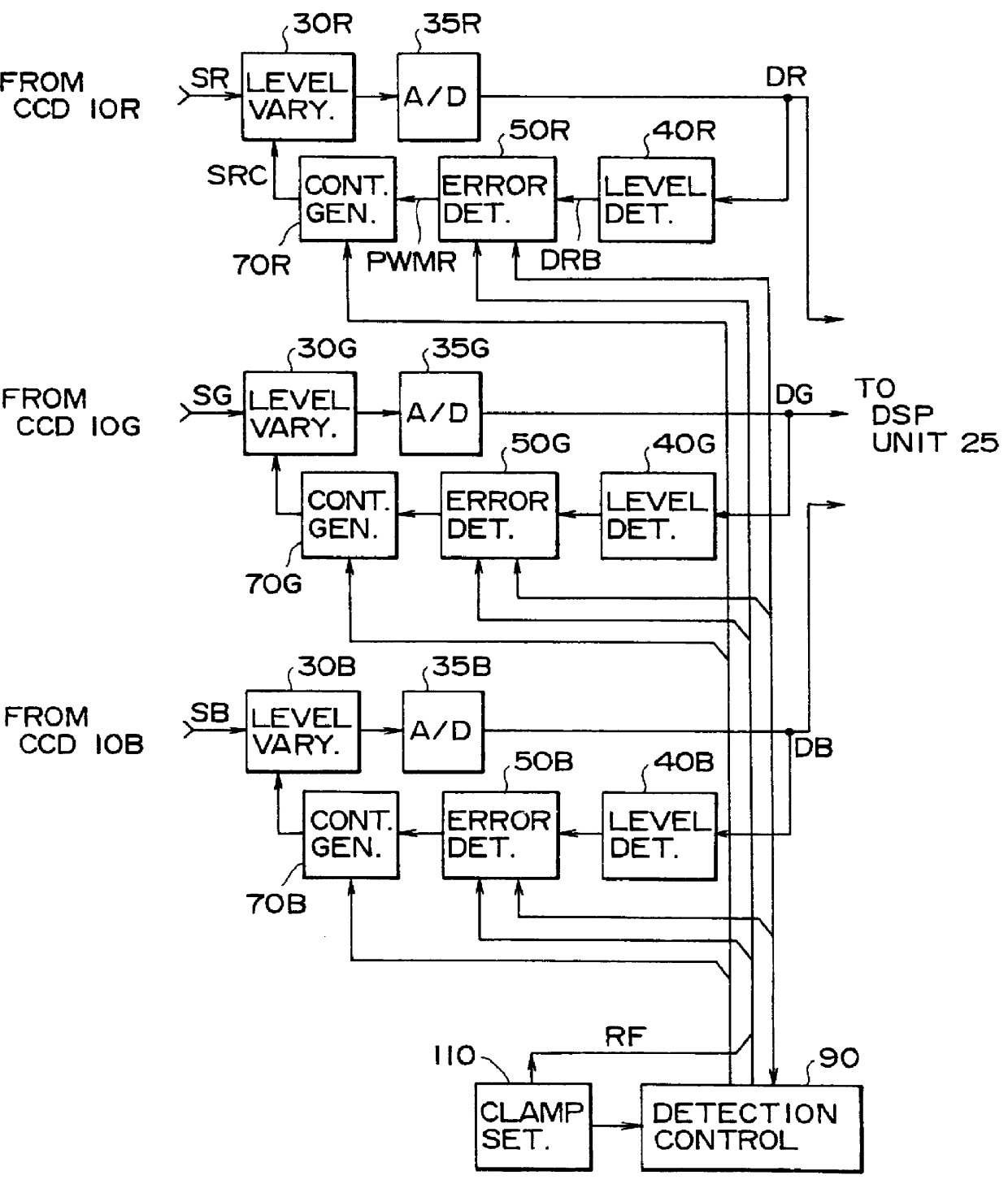

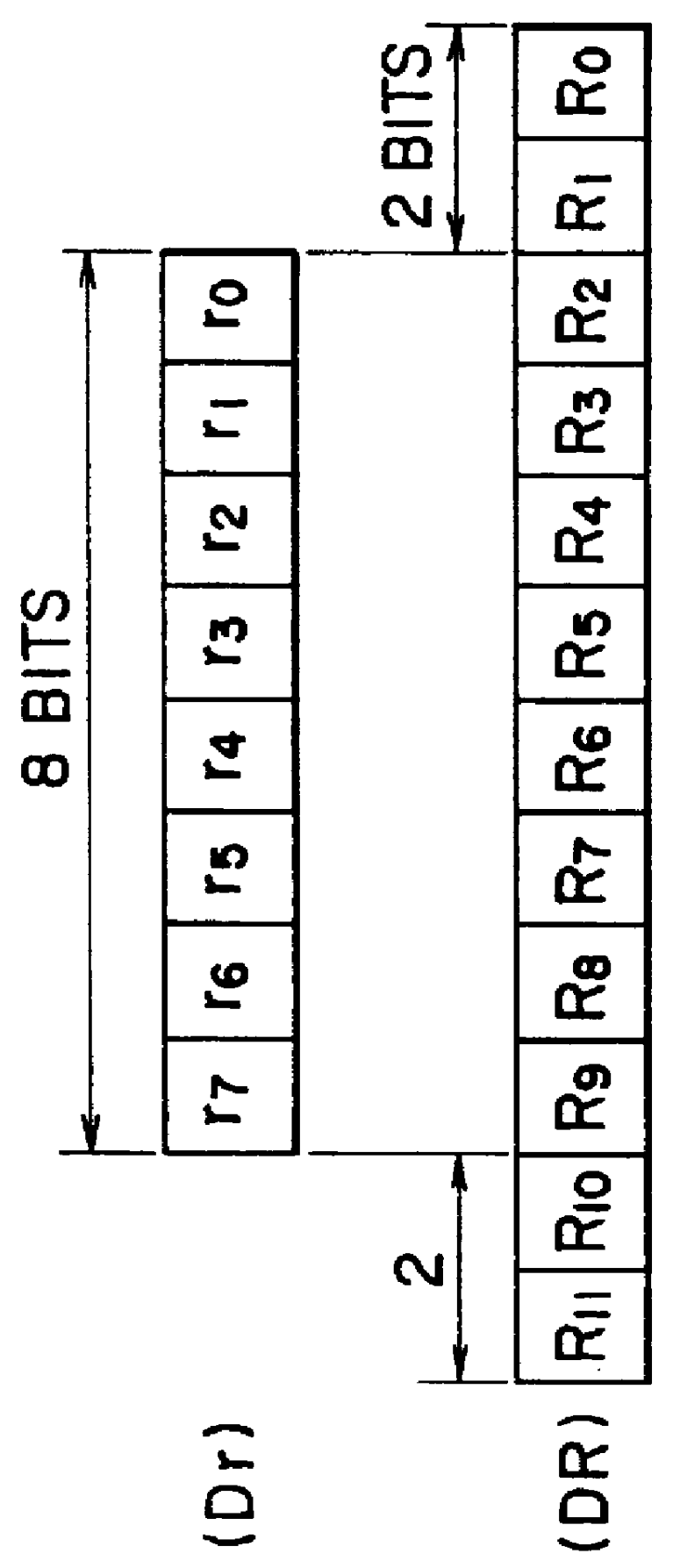

Apparatus and method for clamping an image signal

InactiveUS6049355AImprove stabilityHigh precisionTelevision system detailsTelevision system scanning detailsControl signalReference Region

A clamping circuit for use in a video camera varies a level of an image signal utilizing an analog feedback control signal, converts the varied image signal to a digital image signal, generates a digital zone value signal that corresponds to a level of a reference zone of the digital image signal, digitally detects an amount of error between the digital zone value signal and a predetermined zone value having a non-zero fractional portion, generates from the detected amount of error a digital error signal that has a predetermined number of data bits, switches between a coarse adjustment mode and a fine adjustment mode of the clamping circuit in accordance with a level of the digital error signal, generates, in the coarse adjustment mode, a pulse width modulated signal from the most significant bits of the digital error signal, generates, in the fine adjustment mode, the pulse width modulated signal from the least significant bits of the digital error signal, and generates from the generated pulse width modulated signal the analog feedback control signal.

Owner:SONY CORP

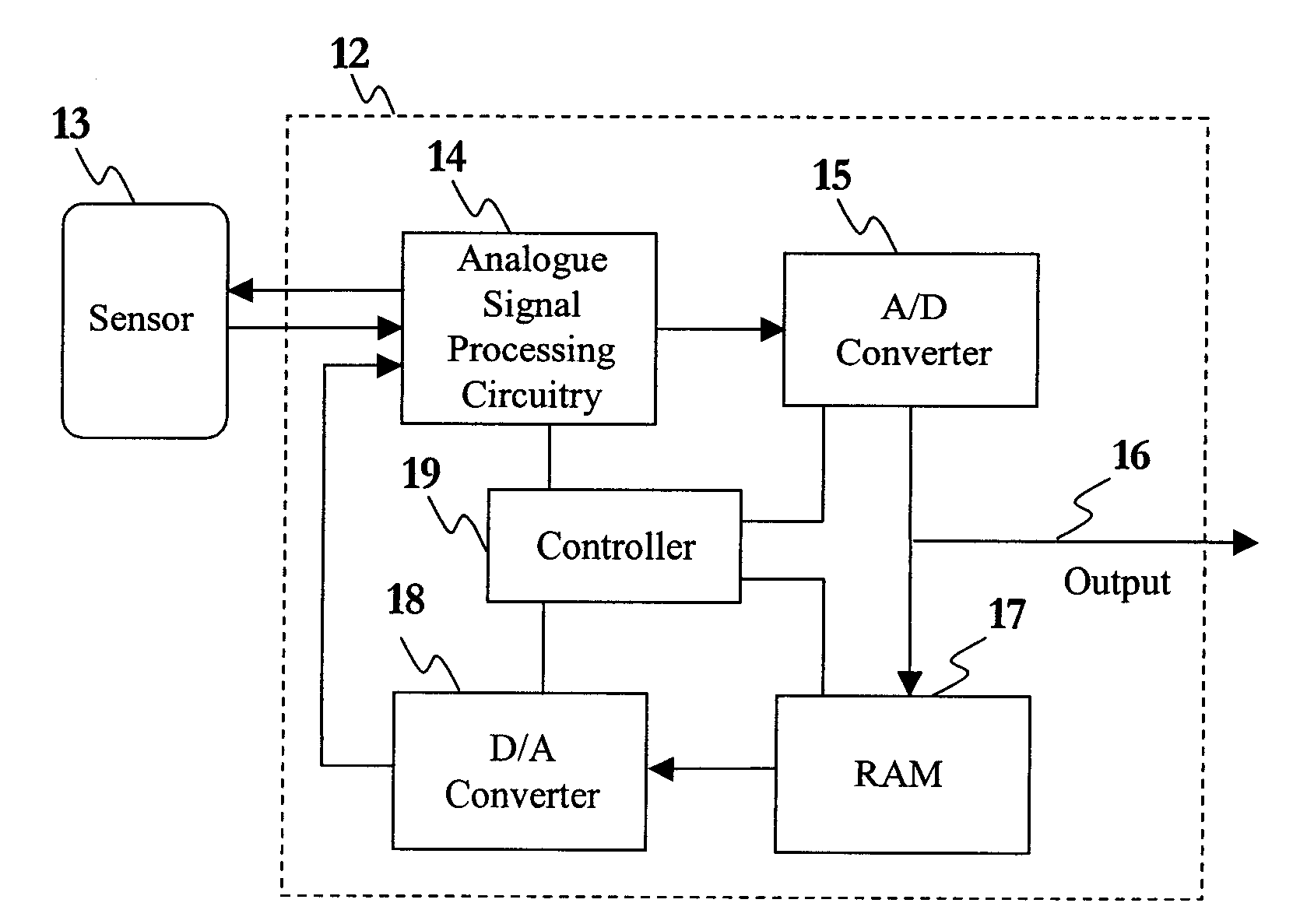

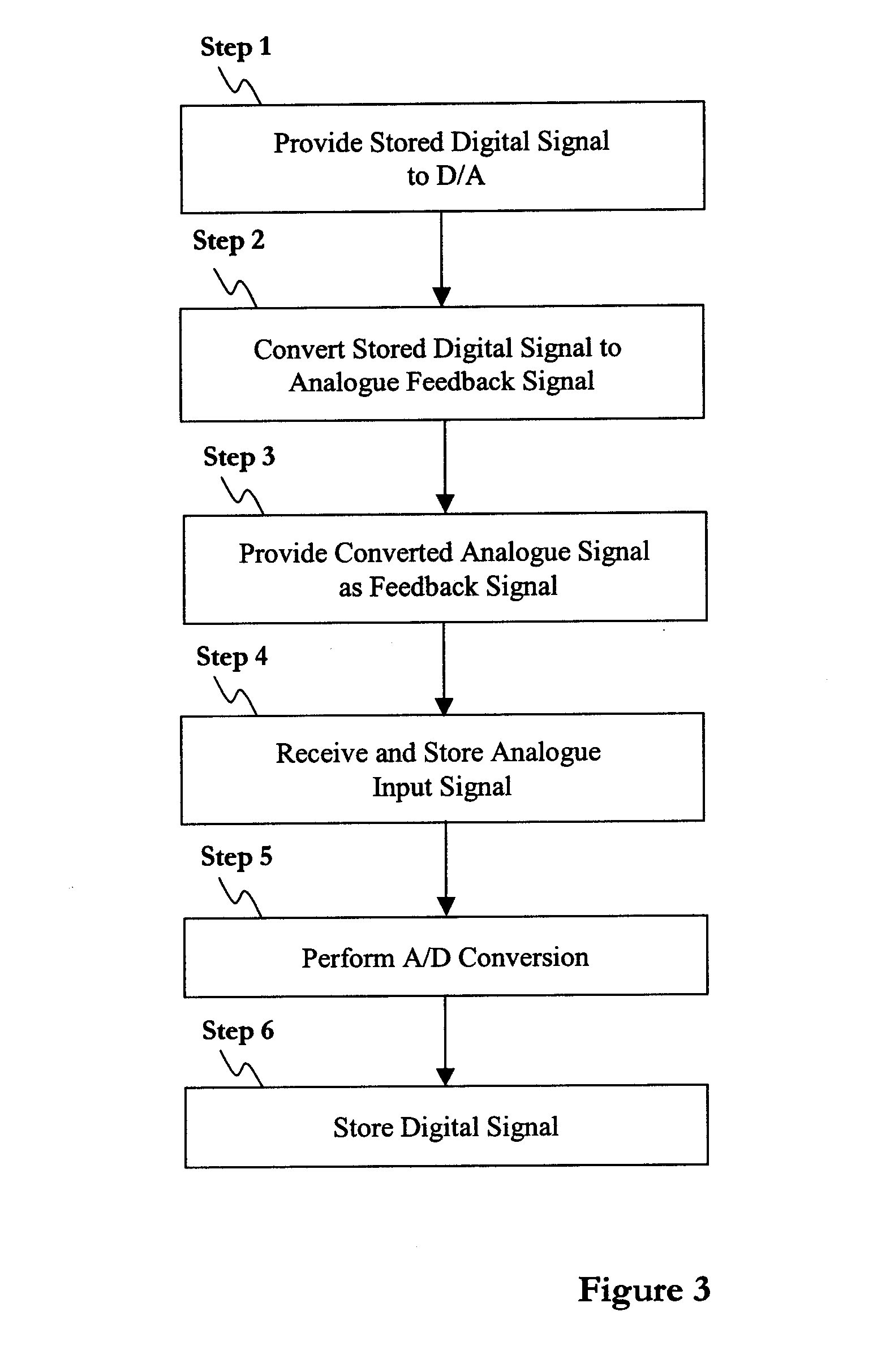

Providing feedback in an electronic circuit

InactiveUS20100259285A1Improve accuracyReduce leakage current effectAnalogue/digital conversionElectric signal transmission systemsAnalog feedbackDrain current

The invention relates to an electronic circuit and a method capable of providing feedback in the electronic circuit, such that the effect of leakage currents in the circuit are minimised. The method includes the steps of storing an analogue input signal using an analogue storage device, converting the stored analogue input signal into a digital signal and storing the digital signal, converting the stored digital signal into an analogue feedback signal, and providing feedback in the electronic circuit using the analogue feedback signal.

Owner:NOKIA CORP

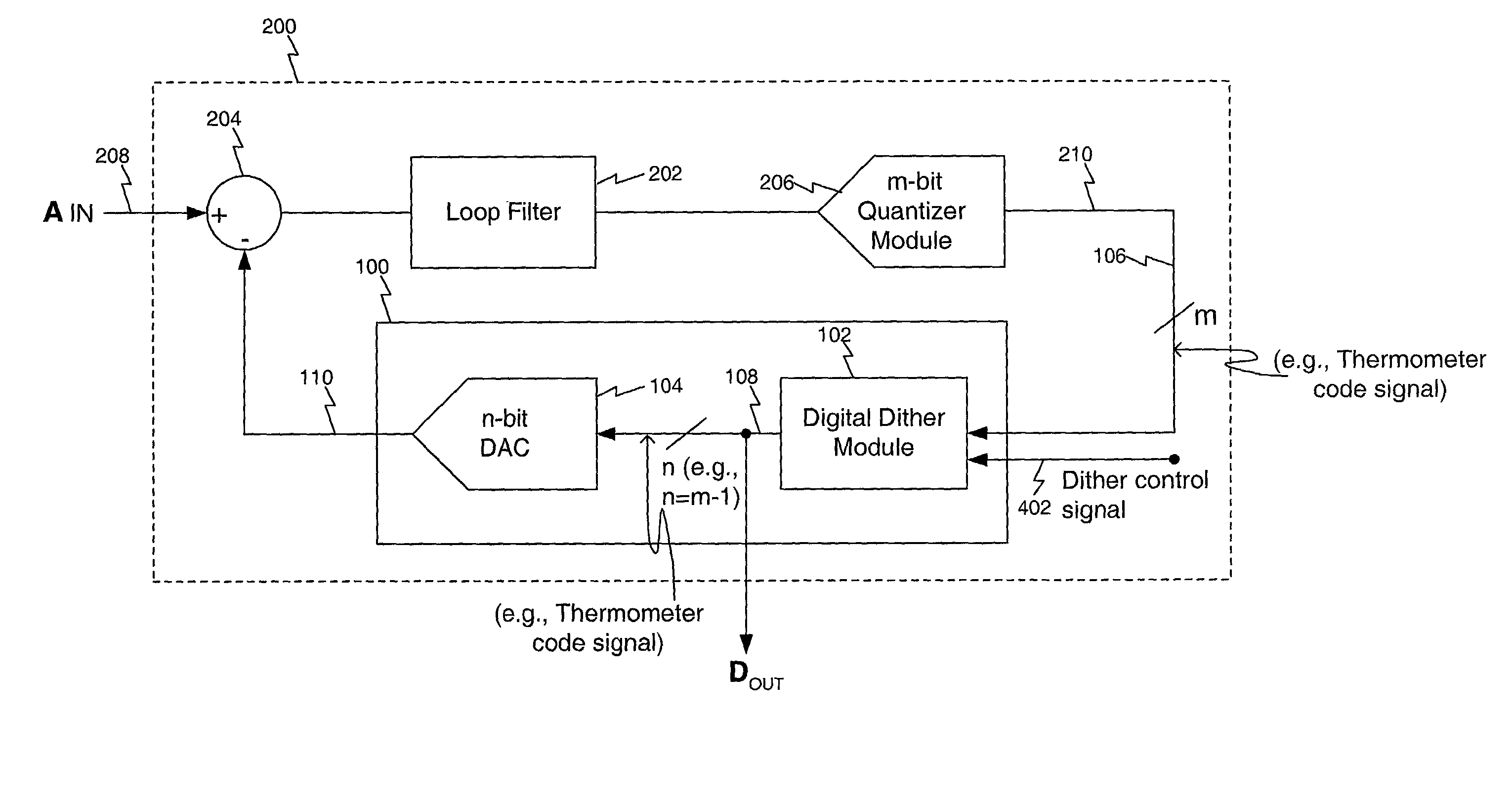

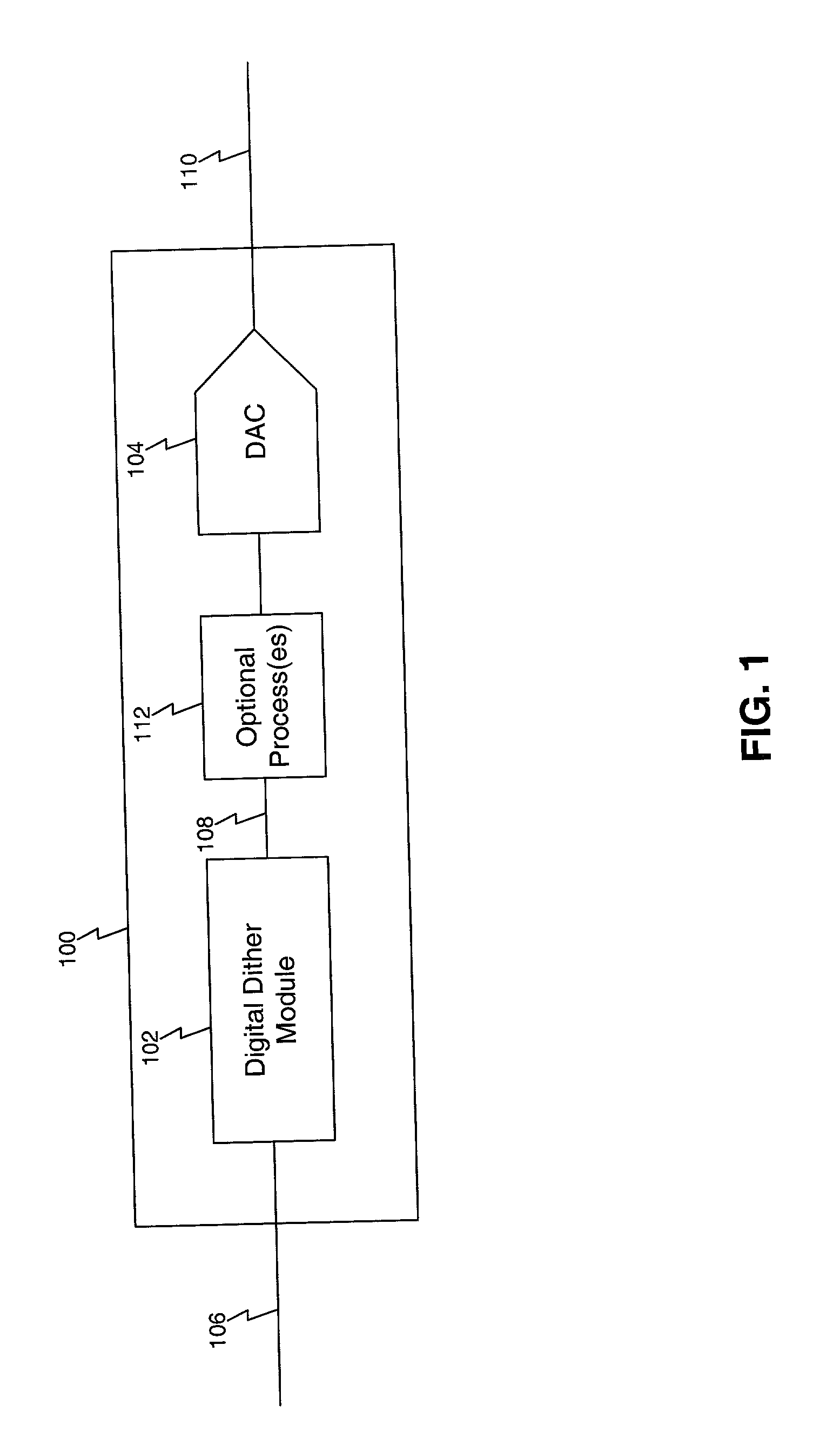

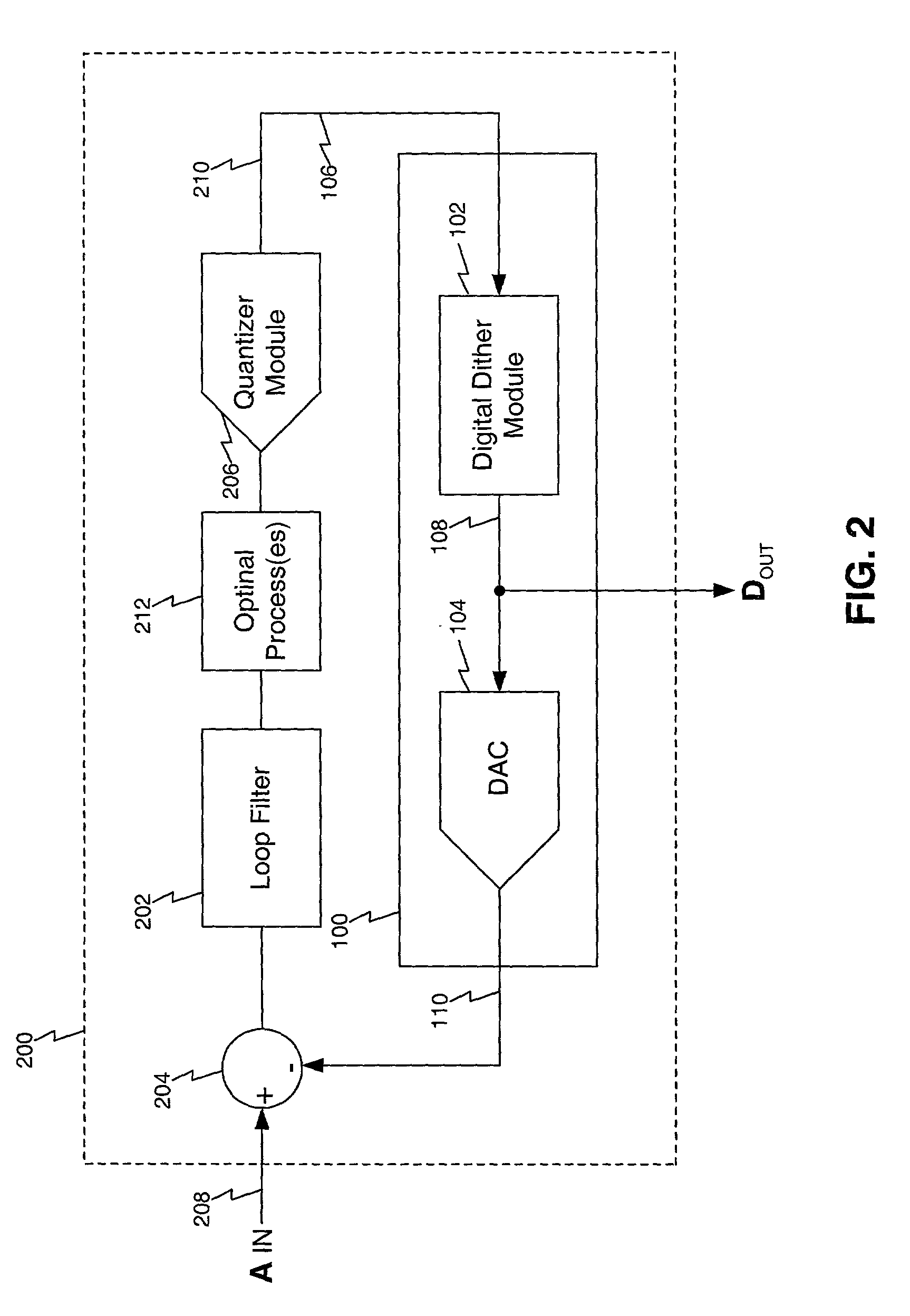

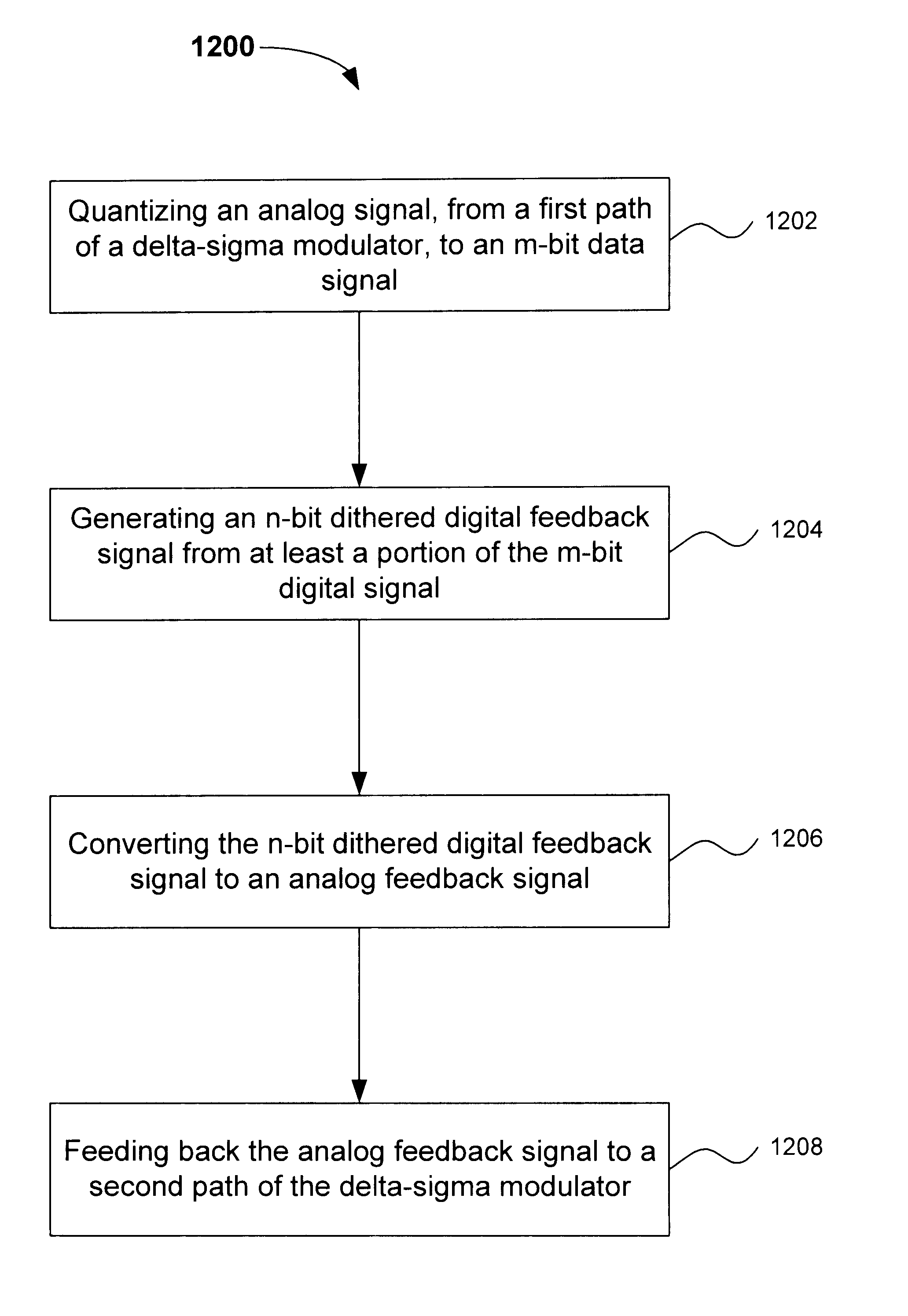

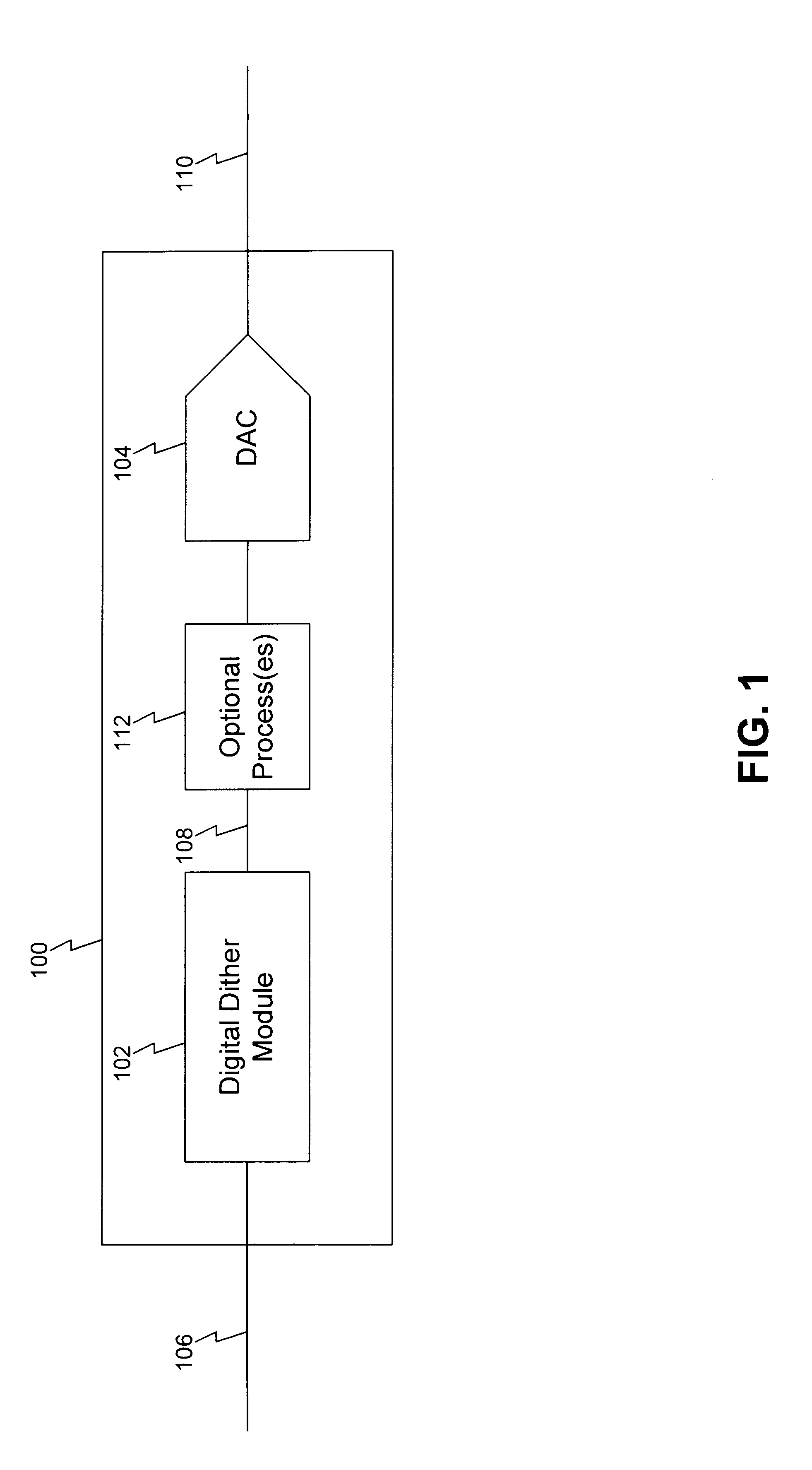

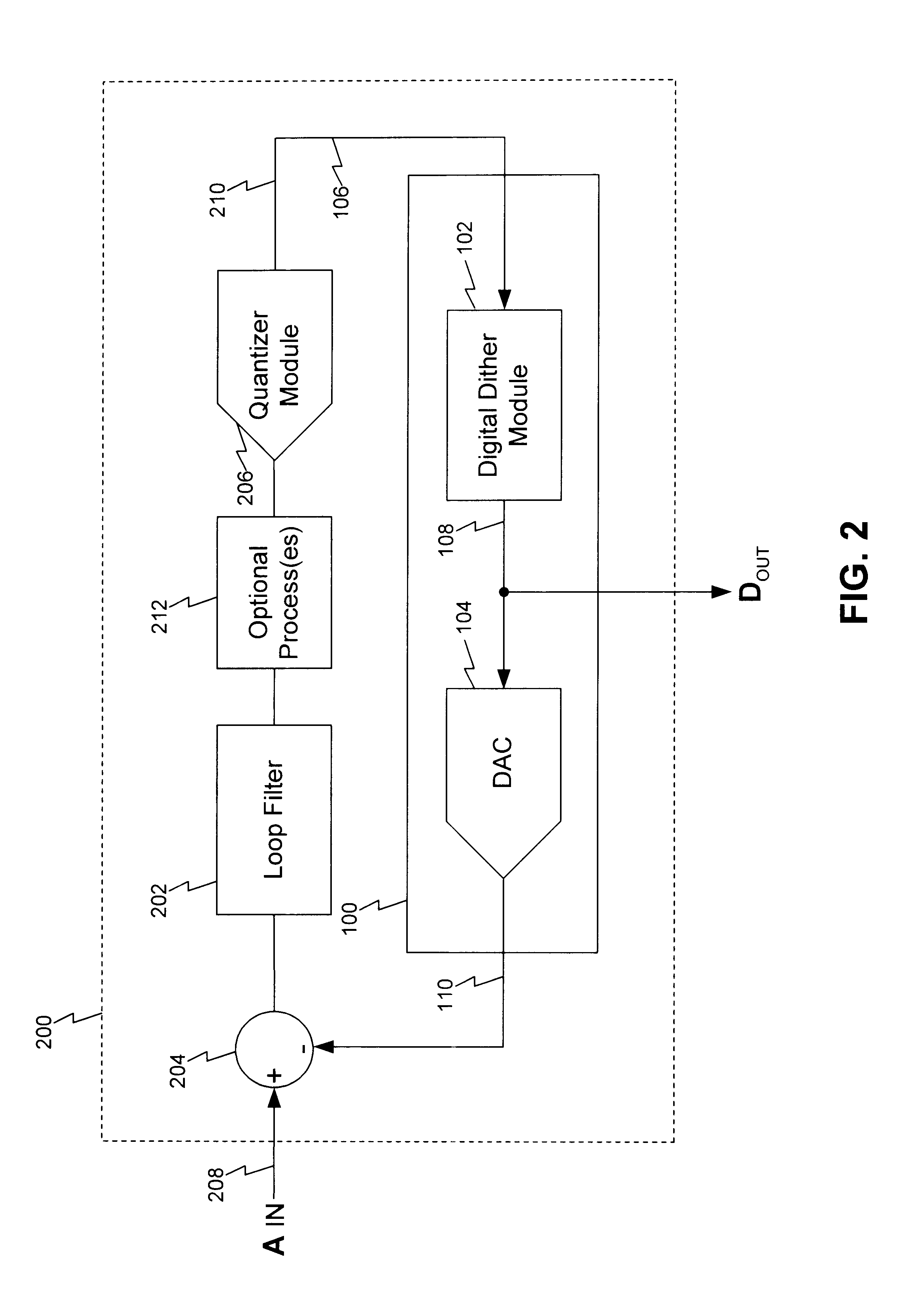

Methods and systems for digital dither

InactiveUS20020057214A1Electric signal transmission systemsDifferential modulationDigital feedbackAnalog feedback

Methods and systems for applying digital dither includes methods and systems for applying digital dither in data converters, such as, for example, delta-sigma data converters. In an embodiment, an analog signal from a first path of a delta-sigma modulator is quantized to an m-bit digital signal and an n-bit dithered digital feedback signal is generated from at least a portion of the m-bit digital signal. The n-bit dithered digital feedback signal is converted to an analog feedback signal and fed back to a second path of the delta-sigma modulator. In an embodiment, the n-bit dithered digital feedback signal is generated by selecting one of a plurality of sets of n-bits from the m-bit digital signal depending upon a state of a dither control signal. The dither control signal can alternate between a plurality of states or pseudo-randomly switch between a plurality of states. In an embodiment, the m-bit digital signal is an m-bit thermometer code signal and the n-bit dithered digital feedback signal is generated by selecting between bits 0 through m-2 and bits 1 through m-1 of the m-bit digital signal. In an alternative embodiment, the m-bit digital signal is an m-bit thermometer code signal and the n-bit dithered digital feedback signal is generated by selecting between even and odd bits of the m-bit digital signal.

Owner:AVAGO TECH INT SALES PTE LTD

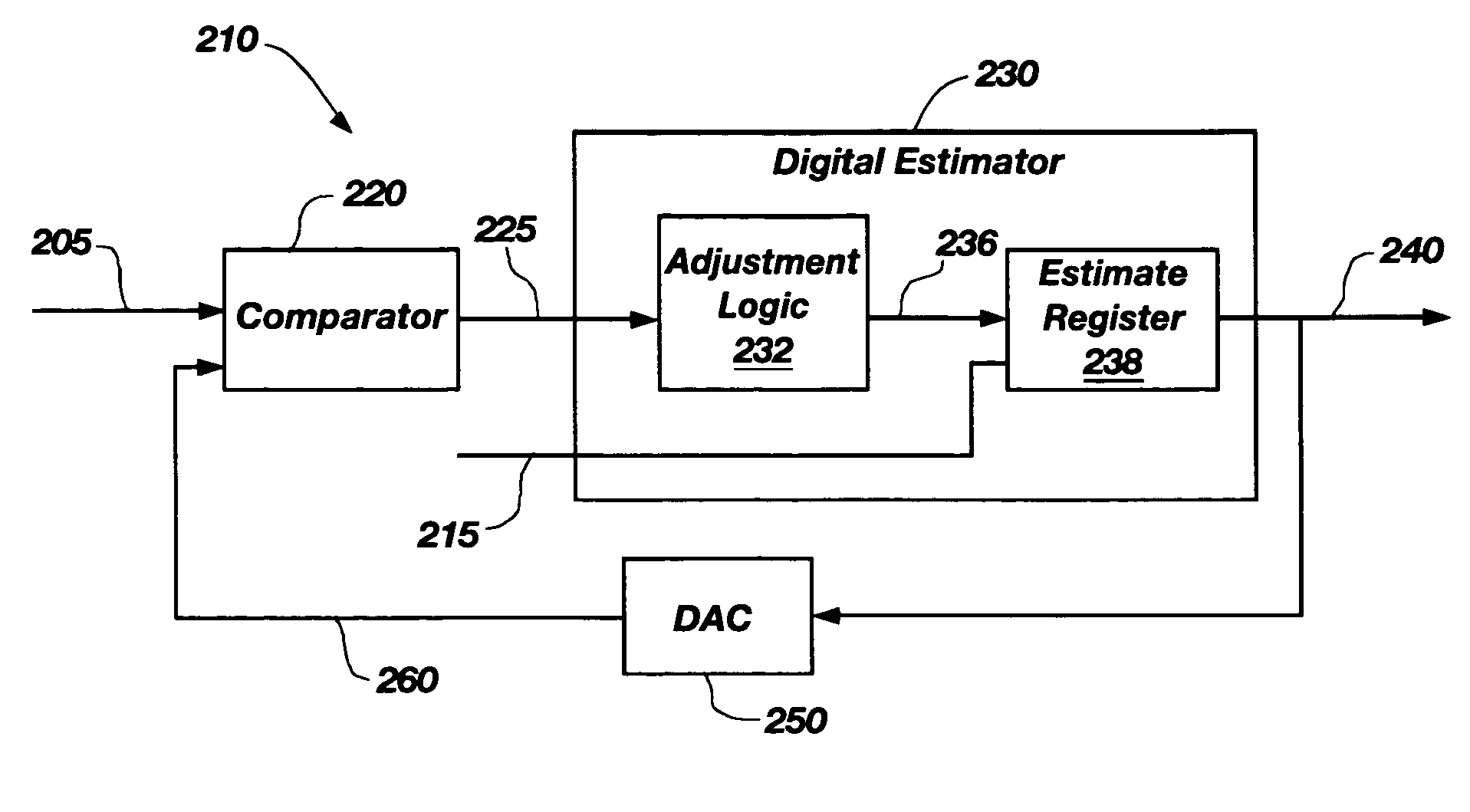

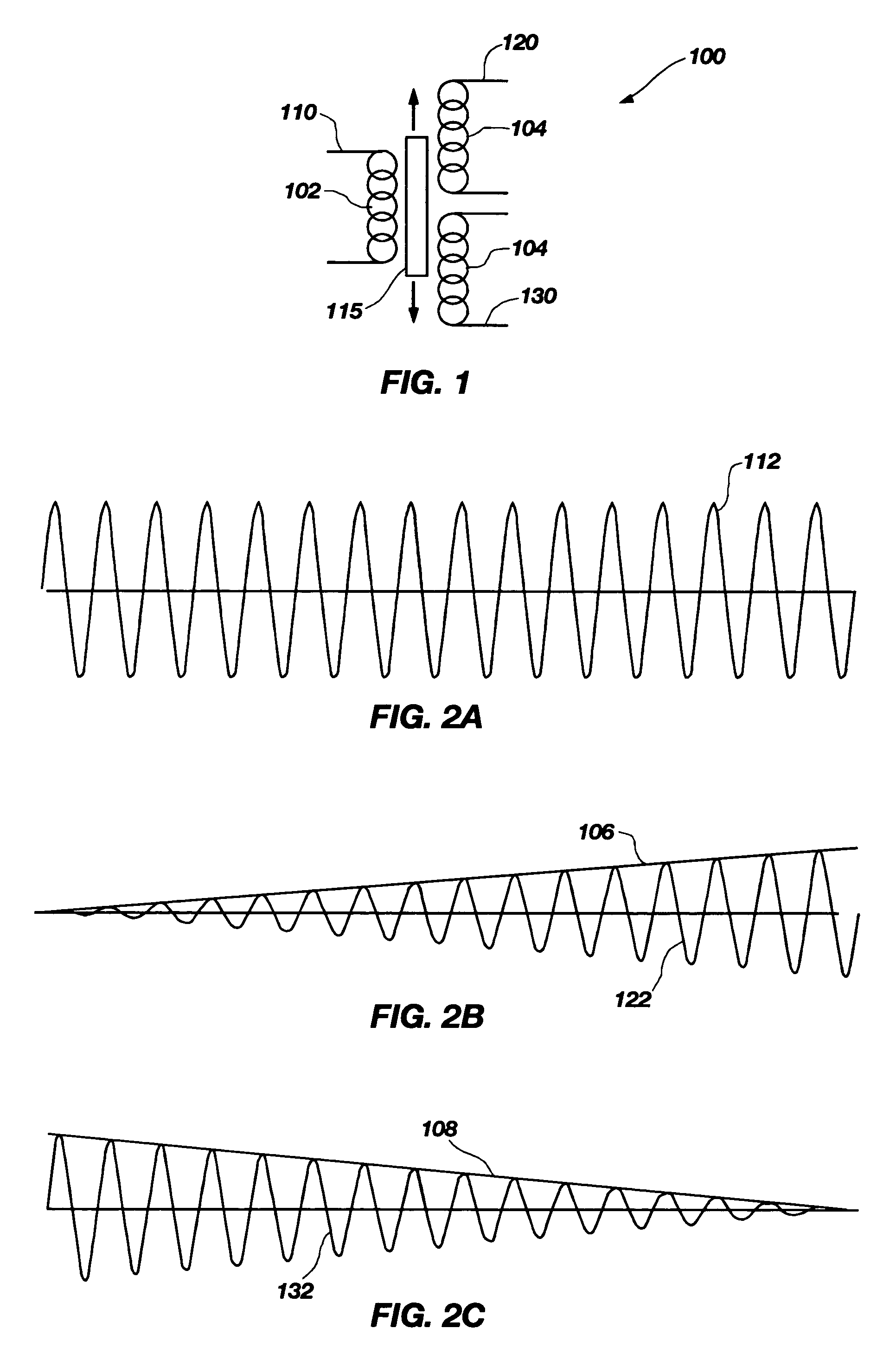

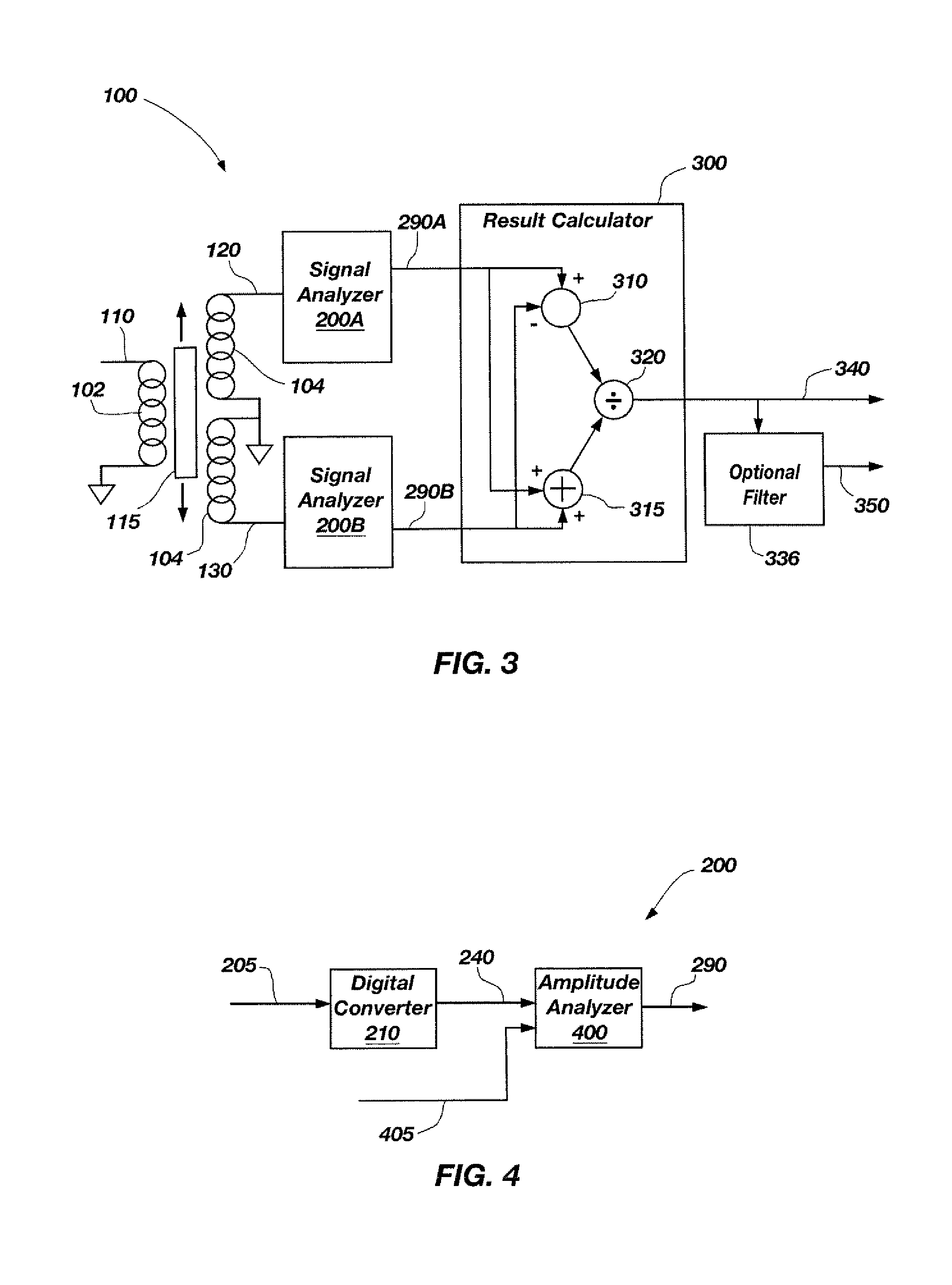

Digital method and apparatus for sensing position with a linear variable differential transformer

ActiveUS7248994B1Reduce complexityReduce the numberMagnetic measurementsIncline measurementLinear variable differential transformerAnalog feedback

An apparatus and method for determining a linear position from a linear variable differential transformer (LVDT) including a primary coil driven by an excitation signal, and two secondary coils coupled to two correlated signals. The method includes converting the correlated signals to a digital estimate, for each of the correlated signals, and evaluating an amplitude of the correlated signals to determine the linear position. The process of converting the correlated signals comprises comparing the correlated signal to an analog feedback signal to generate a comparison result and incrementally adjusting the digital estimate in response to sampling the comparison result at an estimation frequency. The converting process also includes converting the digital estimate to the analog feedback signal, collecting a digital estimate history at a sample frequency that is a binary multiple of the excitation frequency, and analyzing the digital estimate history to determine the amplitude substantially near the excitation frequency.

Owner:NORTHROP GRUMMAN SYST CORP

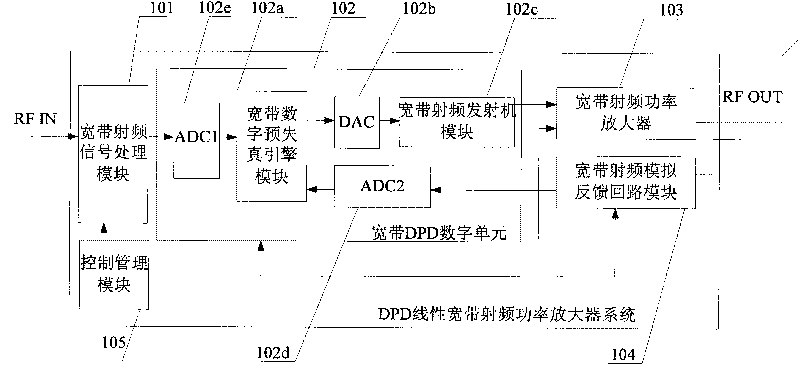

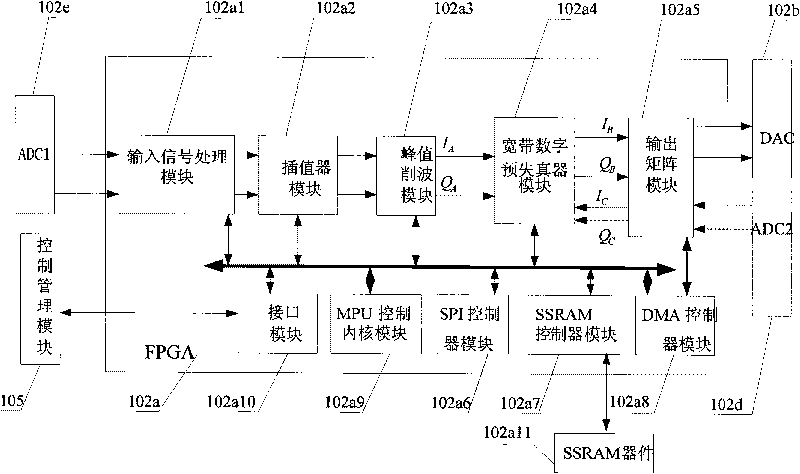

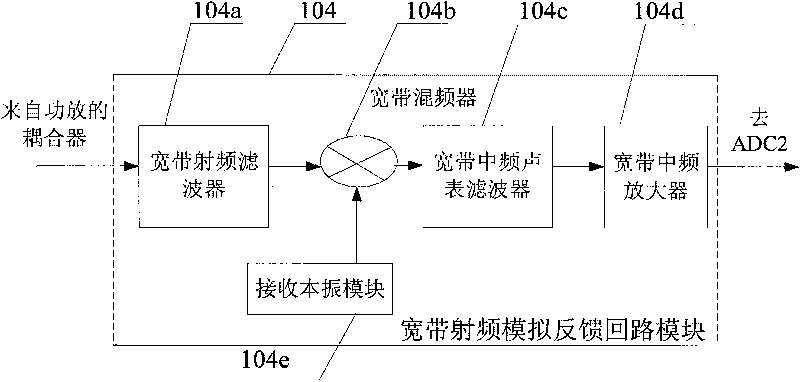

Digital predistortion linear broadband radio-frequency power amplifier device

ActiveCN101741317AIncrease flexibilityLow costEnergy efficient ICTAmplifier modifications to reduce non-linear distortionEngineeringTransmitter

The invention discloses an administrable digital predistortion linear broadband radio-frequency power amplifier (ADPDWPA) device. The device comprises a broadband radio-frequency signal processing module, a broadband digital predistortion DPD digital unit, a broadband radio-frequency power amplifier, a broadband radio-frequency analog feedback loop module and a control administration module, wherein the broadband digital predistortion DPD digital unit comprises a broadband digital predistortion engine module, a DAC, an ADC1, an ADC2 and a broadband radio-frequency transmitter module. The ADPDWPA device adopts a modularization structure concept easy to expand, has high flexibility, low cost, easy administration and openness, supports various communication system requirements, only needs to replace different modules and upgrade different algorithms, can be applied to a base station system with different communication systems, can also be applied to a mobile communication base station system of the next generation and provides a reliable application basis for the industrialization of a future high-efficiency linear broadband radio-frequency power amplifier.

Owner:WUHAN HONGXIN TELECOMM TECH CO LTD

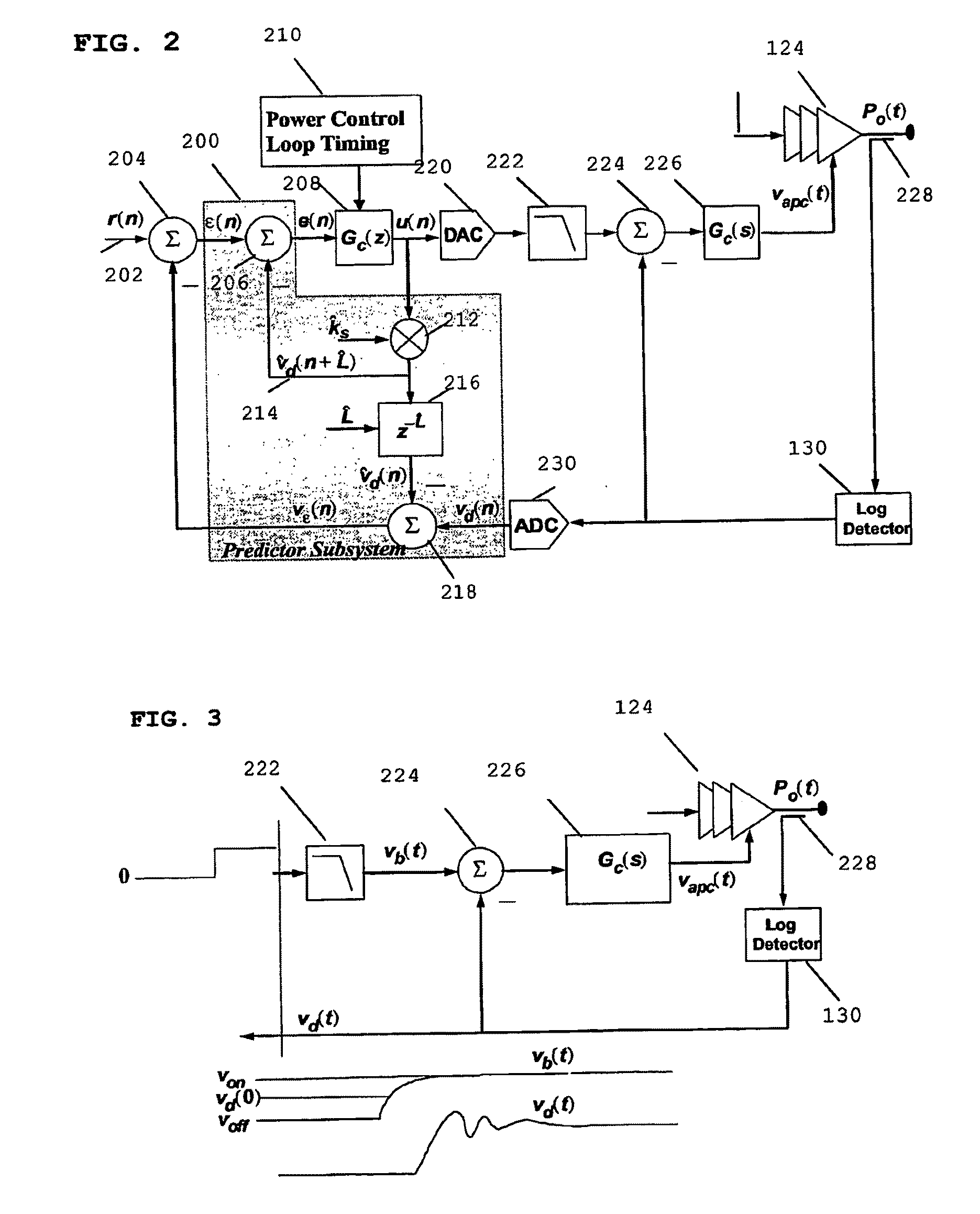

Power control system for a wireless communication unit

InactiveUS20100009642A1Amplifier modifications to reduce non-linear distortionResonant long antennasLoop controlAudio power amplifier

A wireless communication unit comprises a transmitter having an analogue feedback power control loop with an input and a power amplifier having a power amplifier output, where the analogue feedback power control loop is arranged to feedback a signal to the input to set an output power level of the transmitter. The wireless communication unit further comprises an outer digital loop operably coupled from the power amplifier output to the transmitter.In this manner, the inner analogue loop is used to linearise a response obtained from the power amplifier and an outer digital loop wherein the outer digital loop controls the inner analogue loop with regard to saturation detection and correction as well as facilitating multi-mode operation of the wireless communication unit.

Owner:NORTH STAR INNOVATIONS

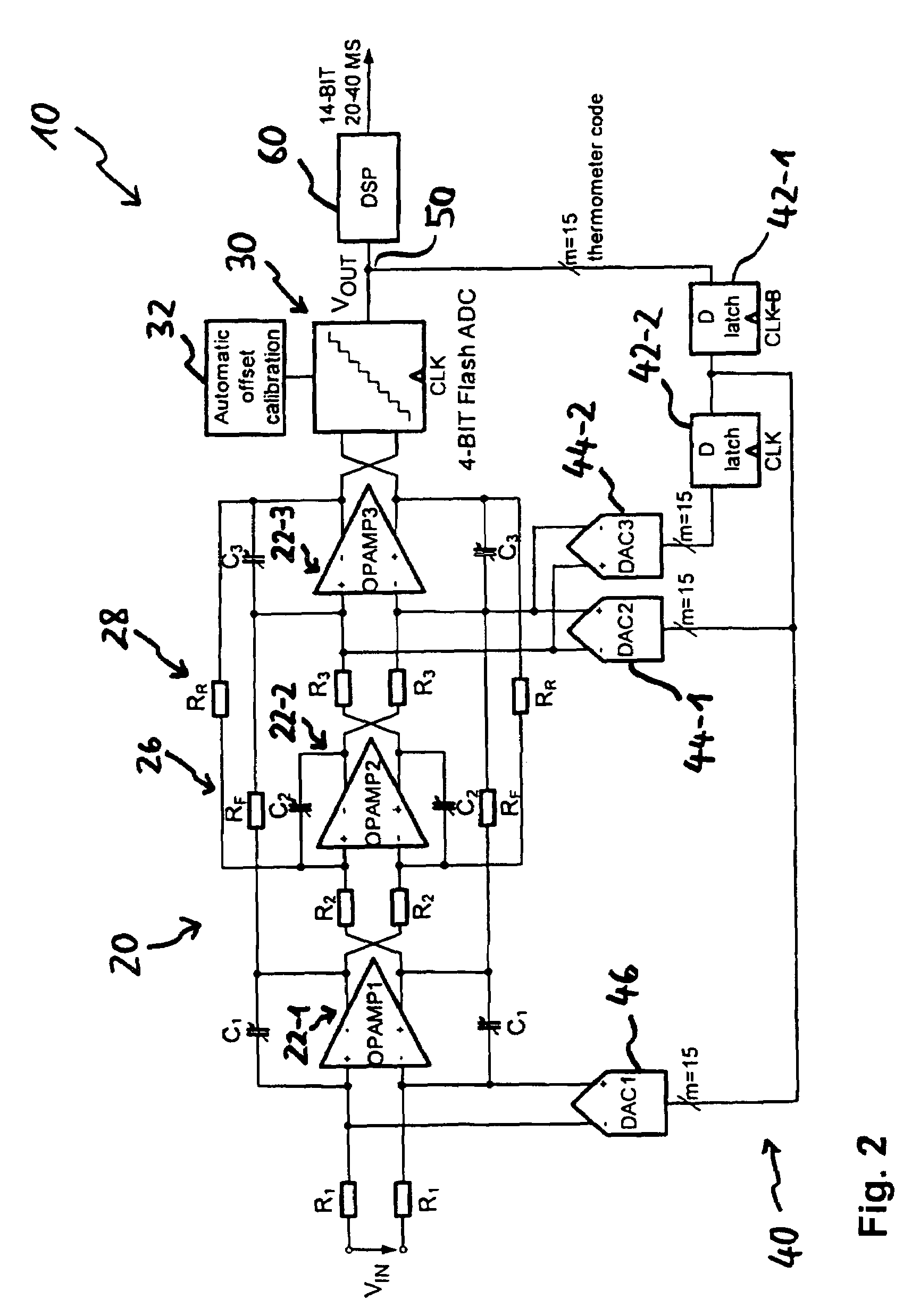

Continuous-time delta-sigma analog digital converter

ActiveUS7405687B2Rapid quantitationQuick conversionElectric signal transmission systemsAnalogue conversionAnalog feedbackAnalog signal

The invention relates to a continuous-time delta-sigma analog digital converter (10) for converting an analog input signal (IN) to a digital output signal (OUT), comprising an analog filter (20), which filters the analog input signal, a quantifier (30) cycled by a clock signal (CLK), which quantifier quantifies the filtered analog signal transmitted by the analog filter (20) to generate the digital output signal, and a feedback device (40) with at last one digital analog converter, which transmits at least one analog feedback signal based on the digital output signal (OUT) to the analog filter (20). To simplify the feedback without adversely affecting the converter stability and power consumption, provision is made, according to the invention, for the feedback device (40) for generating a feedback signal corresponding to the differentiated output signal of the quantifier, to comprise two digital analog converters (44-1, 44-2) to which the digital output signal (OUT) of the quantifier (30) is transmitted via a delay stage (42-1, 42-2) with different delays, and hose analog output signals are transmitted to an analog subtractor (24-3).

Owner:NAT SEMICON GERMANY

Methods and systems for digital dither

InactiveUS6577257B2Electric signal transmission systemsDifferential modulationDigital feedbackAnalog feedback

Owner:AVAGO TECH INT SALES PTE LTD

Multi-bit sigma-delta analog to digital converter with a variable full scale

InactiveUS20020105449A1Electric signal transmission systemsDifferential modulationLoop filterAnalog feedback

A multi-bit sigma-delta analog to digital converter has a quantizer, a loop filter circuit, and a digital to analog feedback circuit. The quantizer, loop filter, and digital to analog feedback circuit have a loop gain associated therewith. The quantizer and loop filter have a combined gain associated therewith. The full-scale of the digital to analog feedback circuit is varied. The combined gain of the quantizer and loop filter is also varied. More specifically, the combined gain of the quantizer and loop filter is varied in inverse proportion to the full-scale of the digital to analog feedback circuit to maintain the loop gain at a substantially constant level.

Owner:ANALOG DEVICES INC

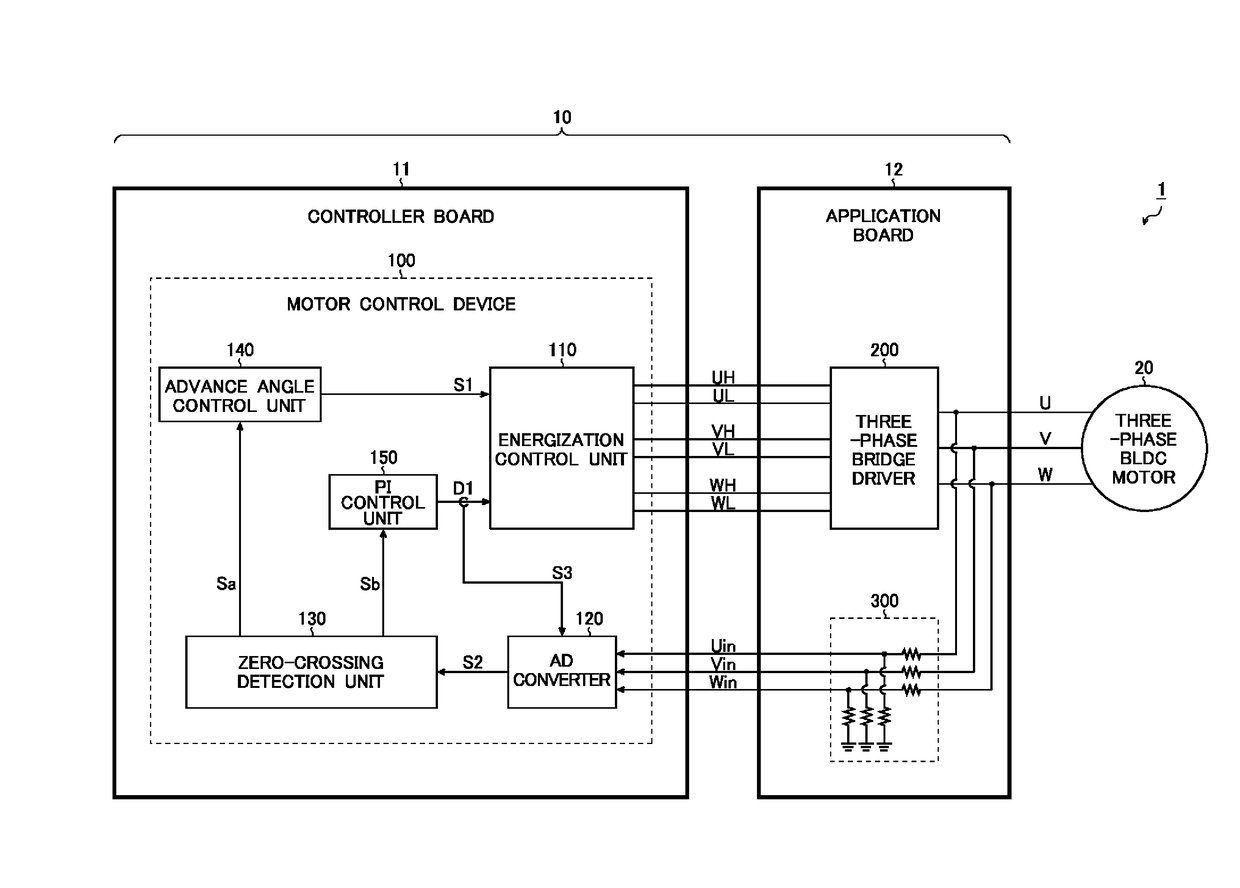

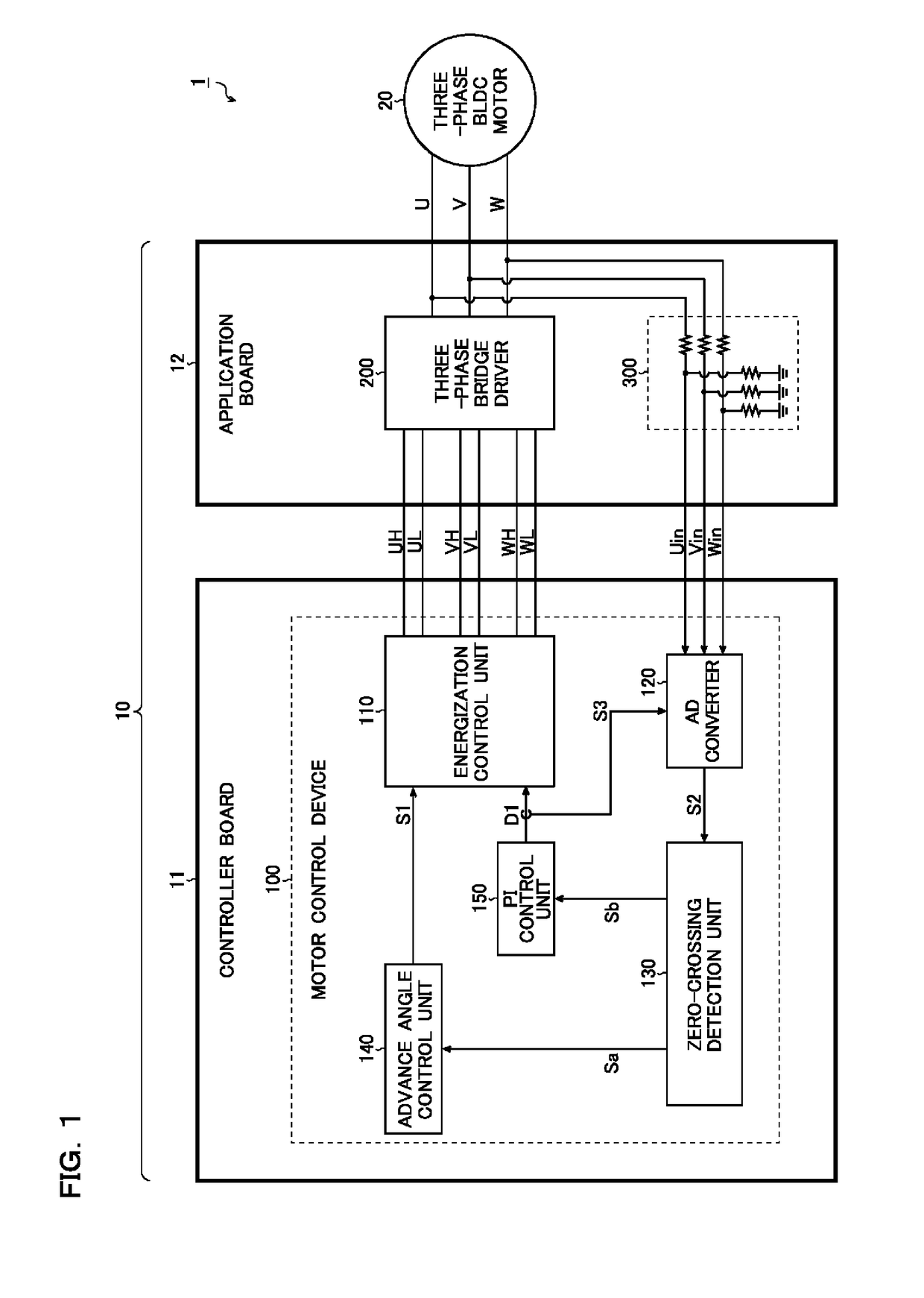

Motor control device

ActiveUS20170353131A1Ensure correct executionSingle motor speed/torque controlGeneral control strategiesDigital feedbackAnalog feedback

A motor control device includes an energization controller that generates energization control signals of a bridge driver, an ADC that samples and converts analog feedback voltages corresponding to output voltages of the bridge driver into digital feedback signals, and a zero-crossing detector that receives the feedback signals so as to perform zero-crossing detection for determining commutation timing and PWM duty of the energization control signal. Sampling timings of the ADC are switched to one of PWM on period and PWM off period according to the PWM duty. The energization controller PWM drives lower side switches of the bridge driver, and the sampling timings of the ADC are set to the PWM off period. The ADC performs an ADC process of the feedback voltage both in the PWM on period and in the PWM off period, and the zero-crossing detector adopts one of ADC results according to the PWM duty.

Owner:ROHM CO LTD

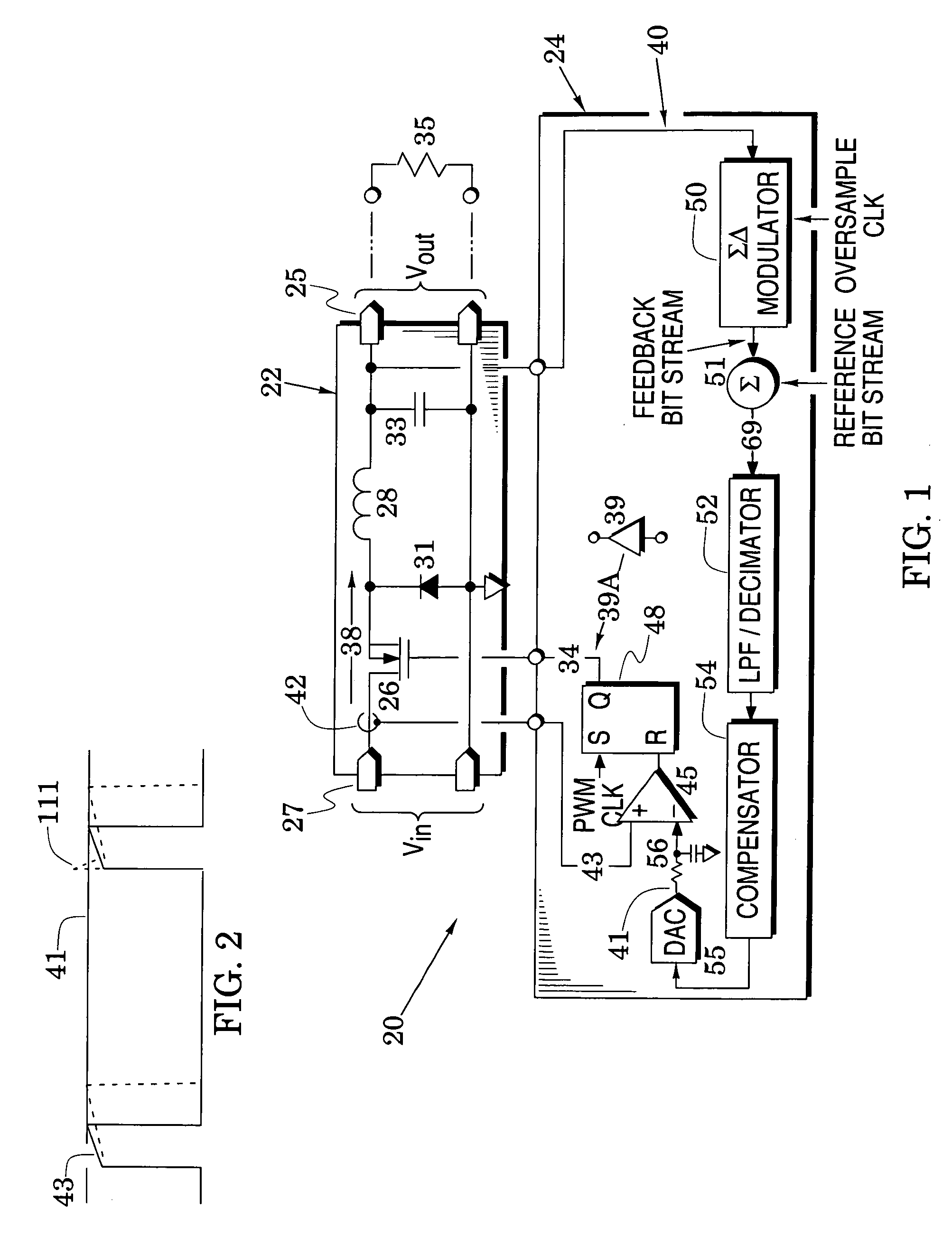

Switching converters controlled via sigma delta modulation

ActiveUS7773016B2Analogue/digital conversionElectric signal transmission systemsControl signalVoltage reference

Low-cost switching converter systems are provided which combine analog generation of a current signal with digital generation of a loop error signal that is realized with a control loop that includes a high-resolution, low-bandwidth sigma-delta modulator and a low-resolution digital-to-analog converter. The current signal and error signal are differenced to provide a control signal to the switching converter. This economical system structure facilitates quick and easy digital alteration of system parameters (e.g., loop compensation and voltage reference). System embodiments add a high-frequency analog feedback path in parallel with the control loop to supplement and enhance its control performance.

Owner:ANALOG DEVICES INC

Switching converters controlled via sigma delta modulation

ActiveUS20100079323A1Electric signal transmission systemsDc-dc conversionControl signalGreek letter sigma

Low-cost switching converter systems are provided which combine analog generation of a current signal with digital generation of a loop error signal that is realized with a control loop that includes a high-resolution, low-bandwidth sigma-delta modulator and a low-resolution digital-to-analog converter. The current signal and error signal are differenced to provide a control signal to the switching converter. This economical system structure facilitates quick and easy digital alteration of system parameters (e.g., loop compensation and voltage reference). System embodiments add a high-frequency analog feedback path in parallel with the control loop to supplement and enhance its control performance.

Owner:ANALOG DEVICES INC

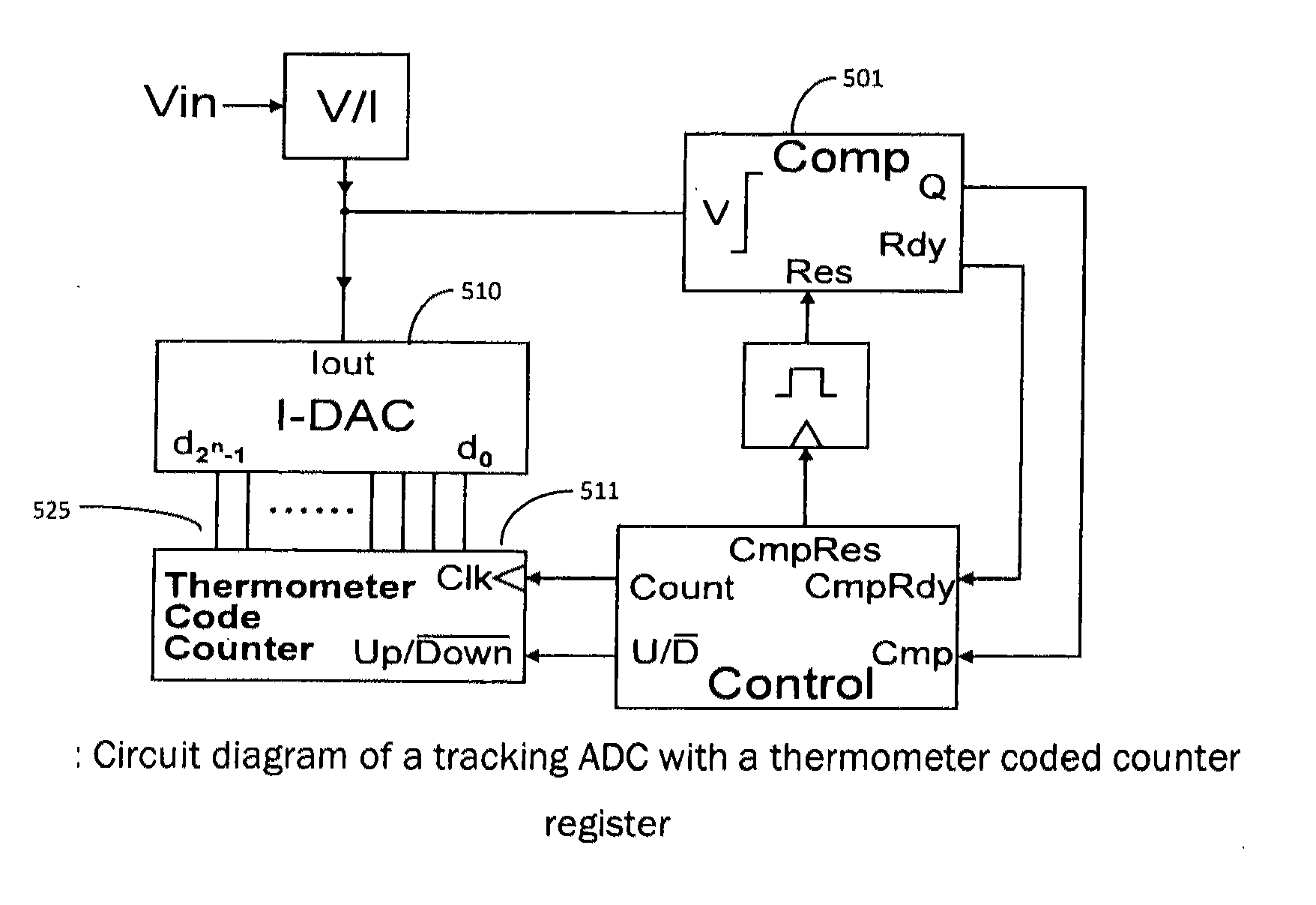

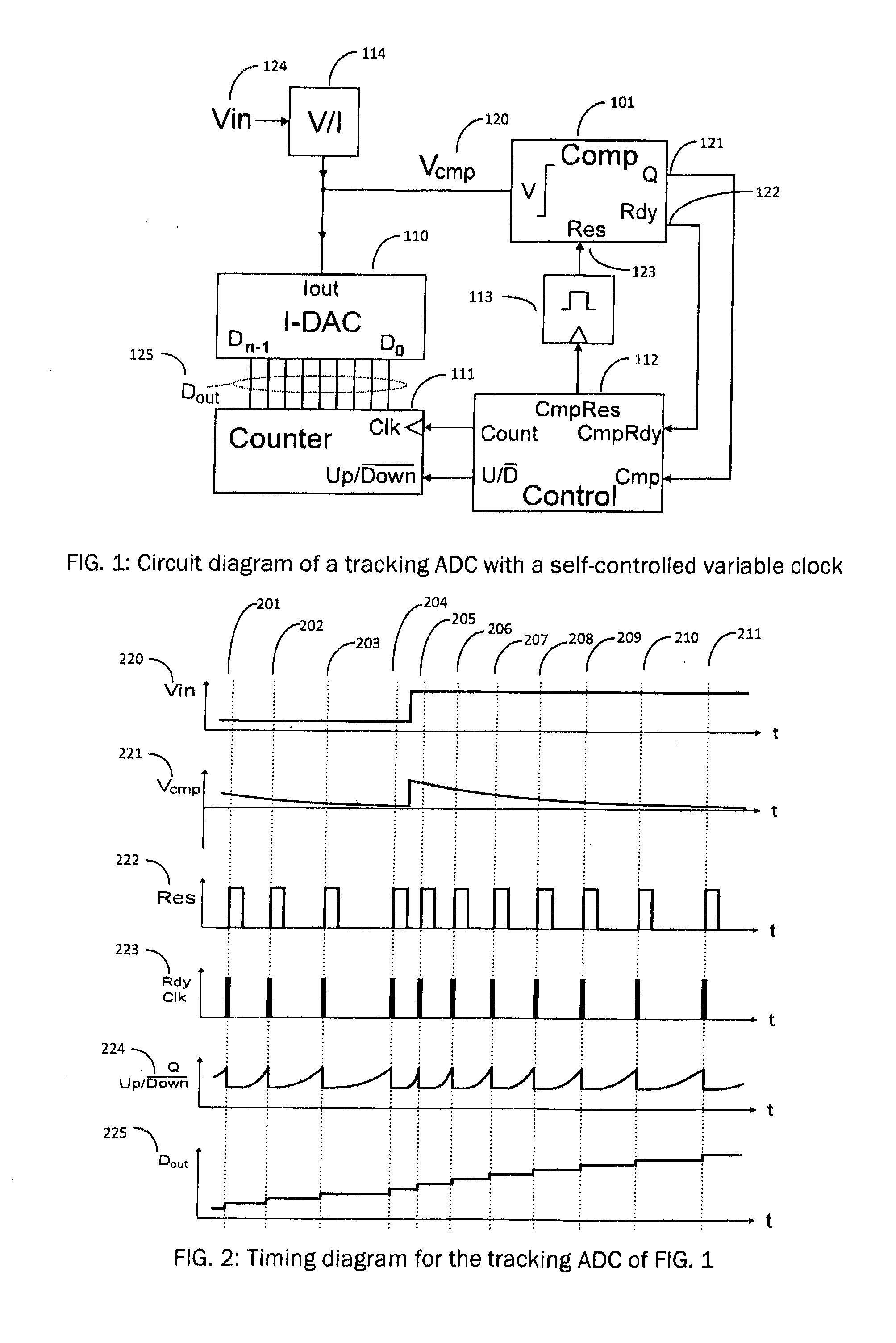

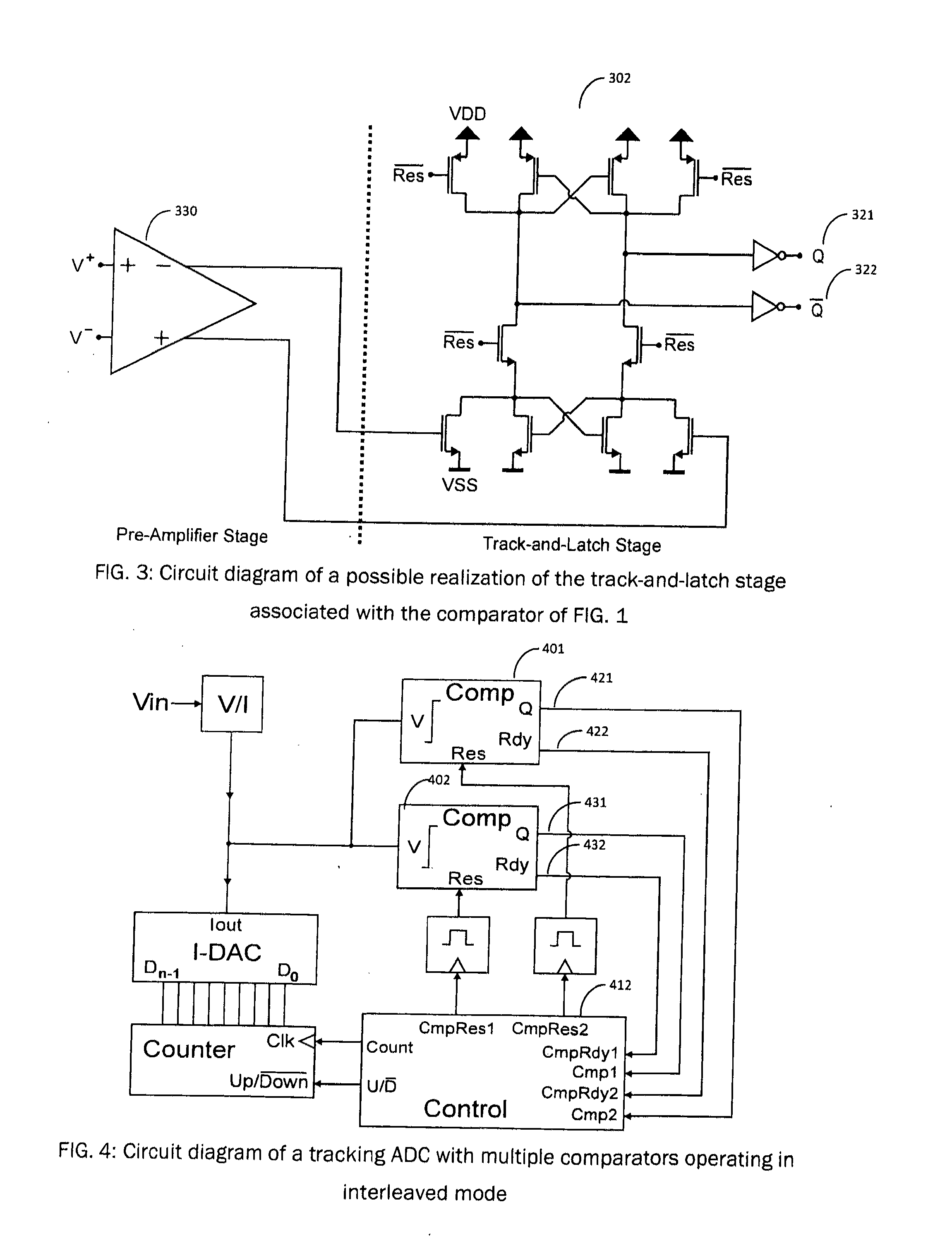

Tracking analog-to-digital converter (ADC) with a self-controlled variable clock

InactiveUS20120212356A1Increase clock frequencyReduced conversion timeElectric signal transmission systemsAnalogue-digital convertersAnalog feedbackEngineering

A tracking analog-to-digital converter “ADC” with a self-controlled variable clock comprises: a digital register; a digital-to-analog converter “DAC” coupled to said digital register providing an analog feedback signal; a comparator coupled to an analog input signal and said analog feedback signal and providing a comparison signal based on a comparison between said analog input signal and said analog feedback signal, said comparison signal being coupled to the digital register; a means for determining comparator readiness to determine if said comparator is ready, indicating that said comparison signal can be reliably read, said means for determining comparator readiness further comprising a determination of a comparison ready indicator; a means for clocking to generate a clock signal to drive said digital register in response to said means for determining comparator readiness determining that said comparator is ready; and said digital register being configured to count in response to said clock signal based on said comparison signal of the comparator.

Owner:DIALOG SEMICONDUCTOR GMBH

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com