Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

45results about How to "Reduce time jitter" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

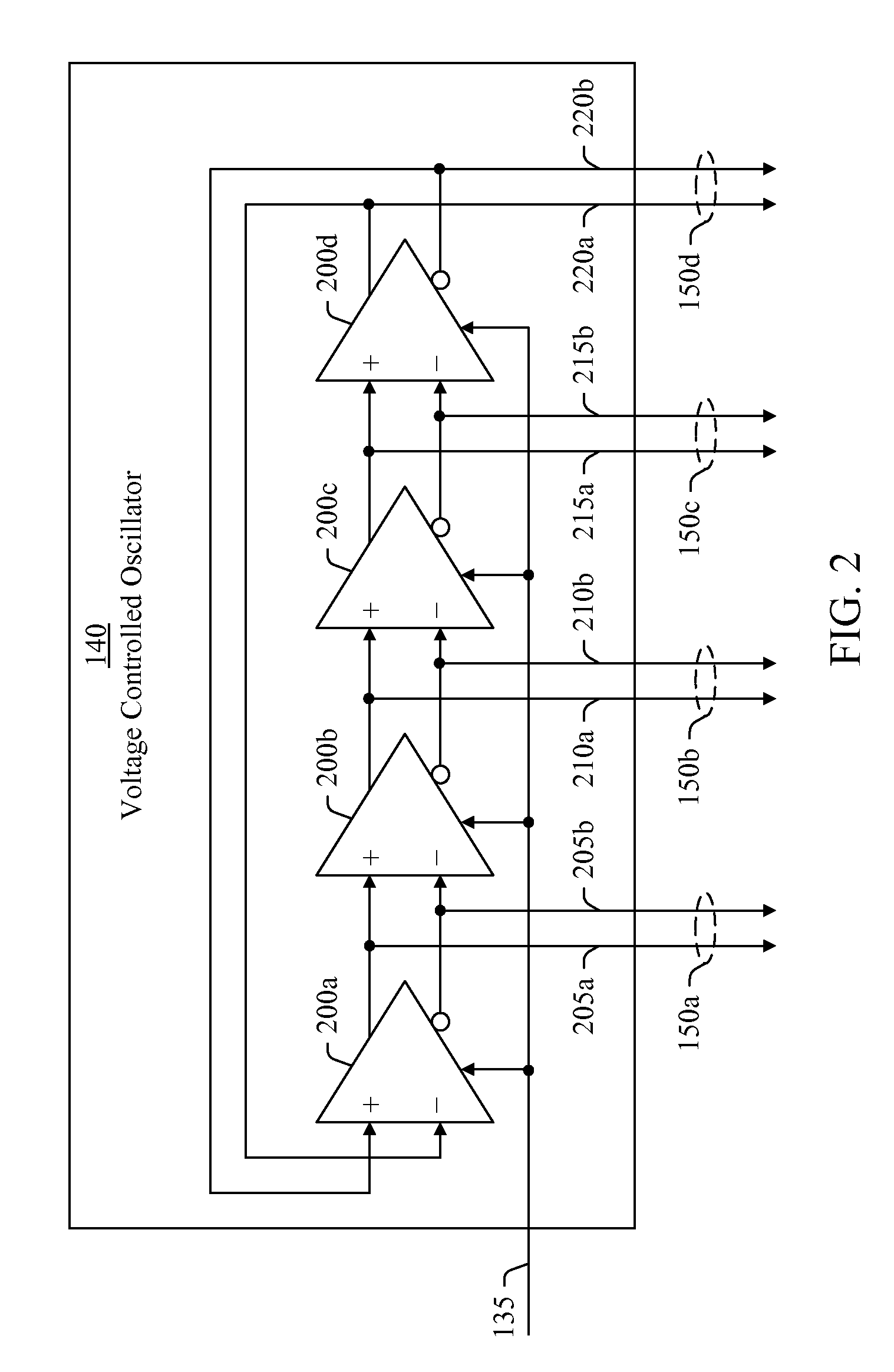

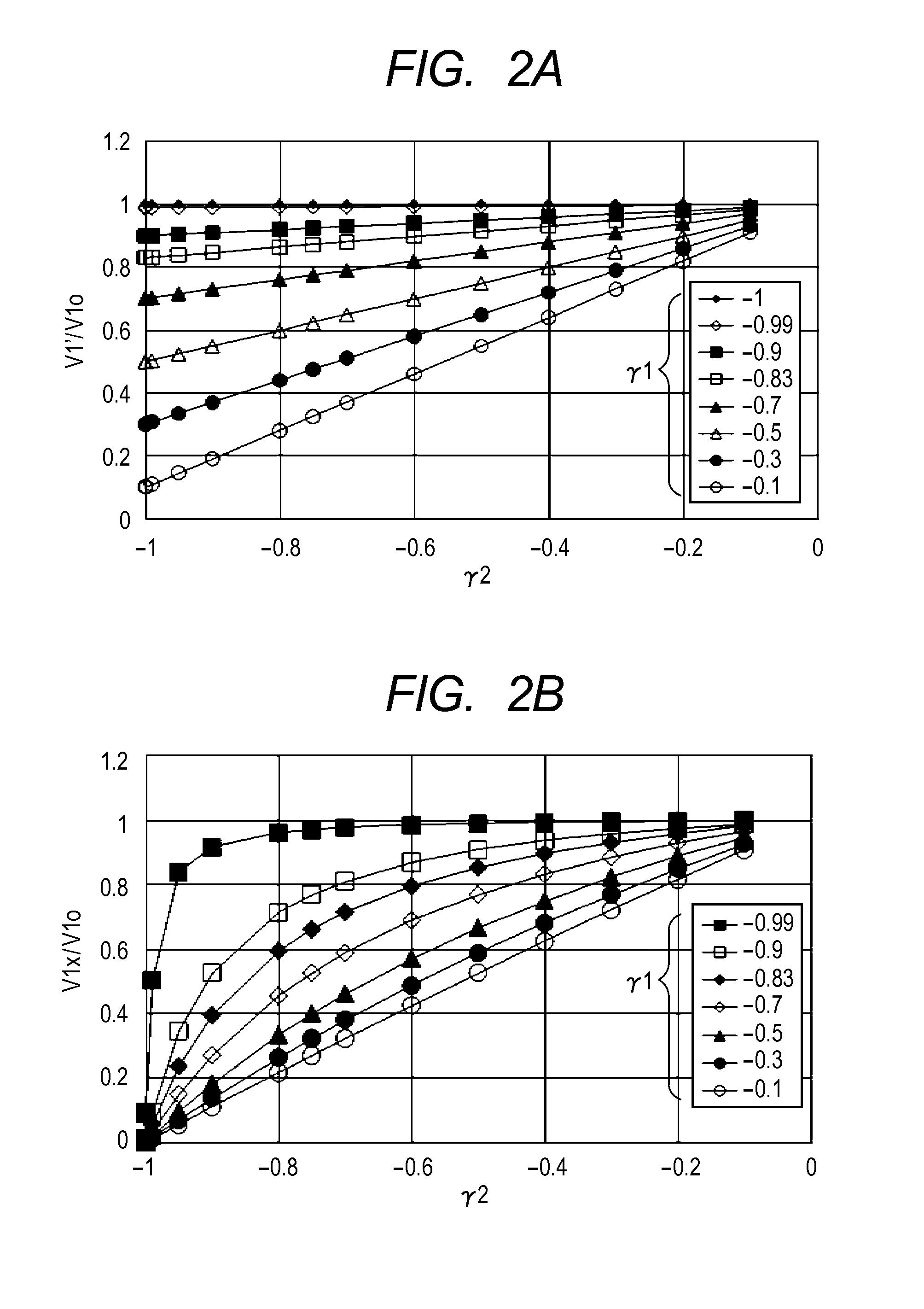

Multiphase clock generator

InactiveUS7545188B1Consumes less power and areaConsumes less power and chip areaModulation transferencePulse automatic controlPhase shiftedControl signal

A clock generator generates multiple clock signals based on an input signal and adjusts the phases of the clock signals relative to a phase of the input signal, based on a control signal. The clock generator includes a phase locked loop that includes a phase shift unit. The phase shift unit selects some of the clock signals based on the control signal and generates a feedback signal based on the selected clock signals. The feedback signal has a phase based on the phases of the selected clock signals. The phase locked loop aligns the phase of the feedback signal with the phase of the input signal. In this process, the phase locked loop shifts the phase of each of the clock signals relative to the phase of the input signal.

Owner:INTEGRATED DEVICE TECH INC

Device for generating Nyquist optical pulse based on ultra-broadband optical frequency comb

ActiveCN104330940AGood time stabilityReduce time jitterLight demodulationPhase shiftedOptical coupler

The invention discloses a device for generating Nyquist optical pulse based on an ultra-broadband optical frequency comb. The device comprises the following components: a narrow line-width laser, a first wavelength division multiplexer, a polarization controller, a Fabry-Perot electro-optic modulator, a temperature control device, an optical coupler, a circulator, a phase-shifted fiber bragg grating, an optical amplifier, a photoelectric detector, an electric amplifier, an electric phase shifter, a bias T, a direct-current bias, an optical band-pass filter, an optical spectrum analyzer, a quantum dot mode-locked laser, a second wavelength division multiplexer and a plurality of electro-optical modulators. By virtue of the device, the disadvantage of bandwidth of the conventional electronics method can be overcome; the device is used as a light source for optical fiber communication; the frequency spectrum utilization rate of an optical fiber communication system can be greatly improved.

Owner:INST OF SEMICONDUCTORS - CHINESE ACAD OF SCI

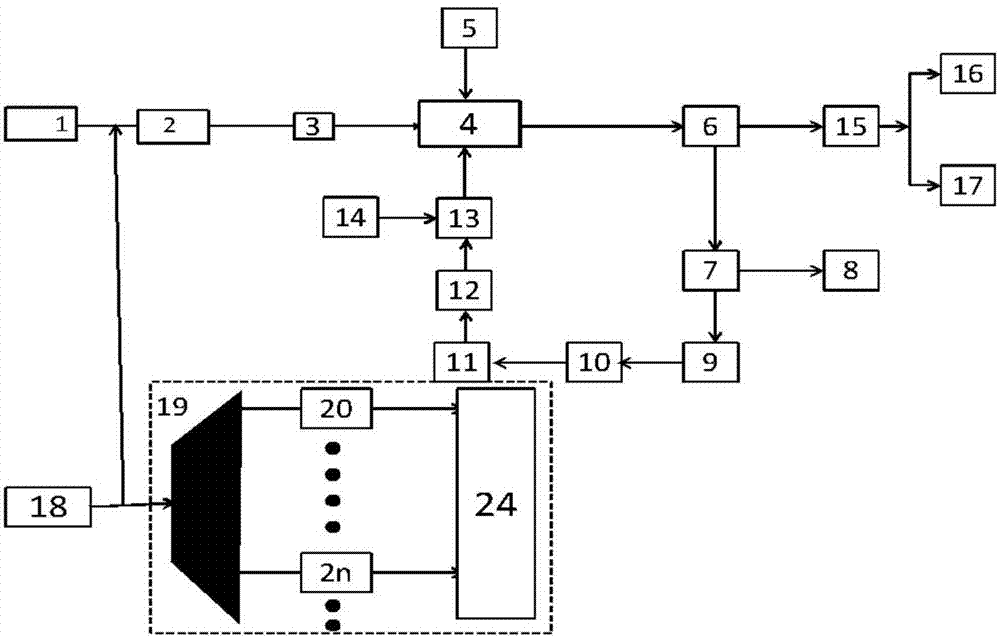

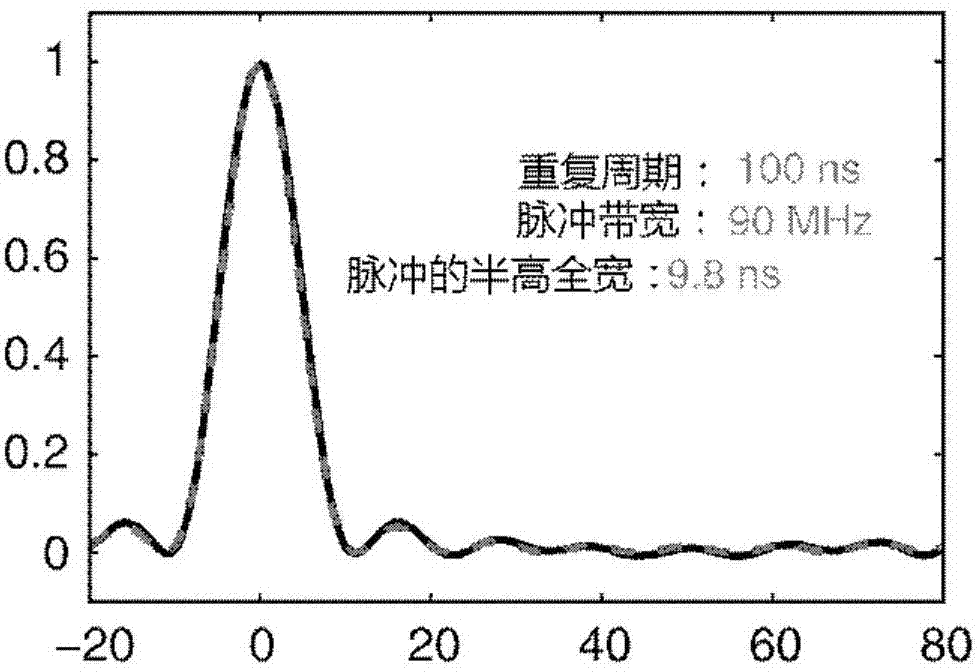

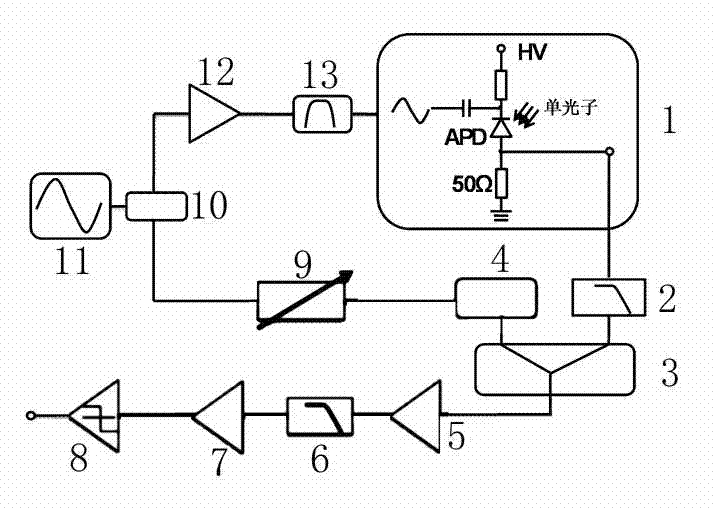

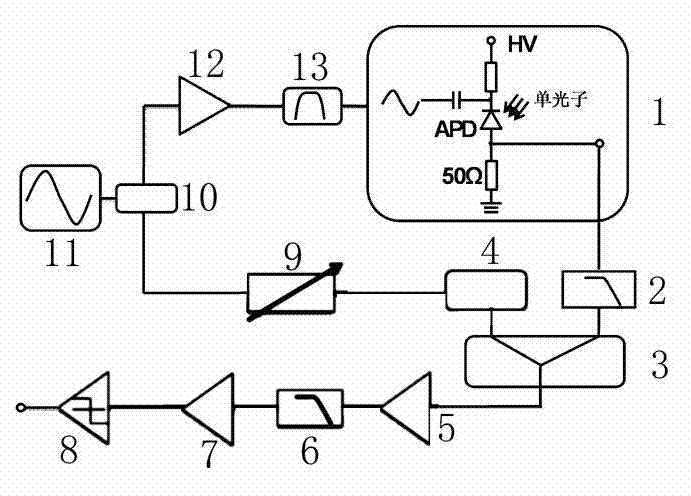

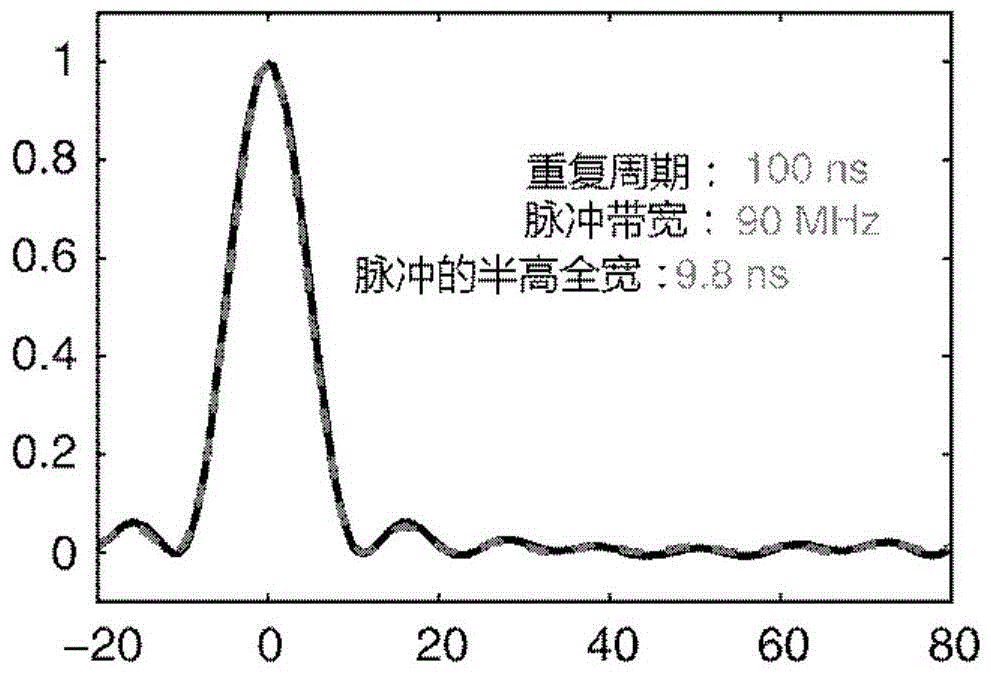

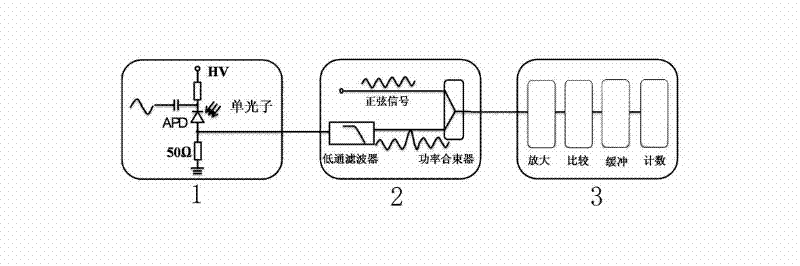

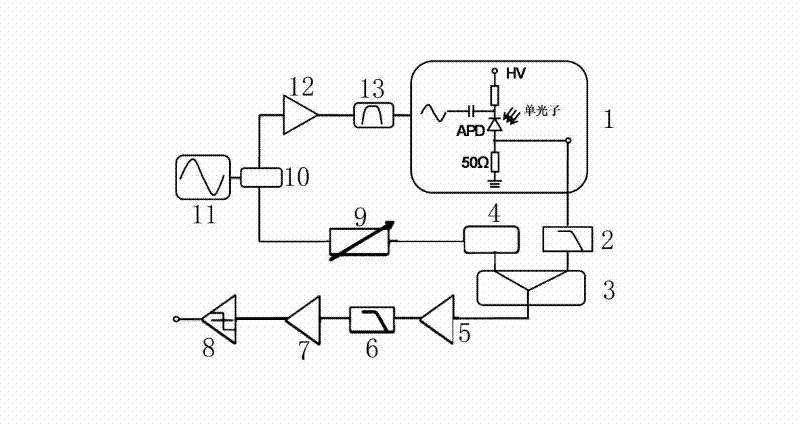

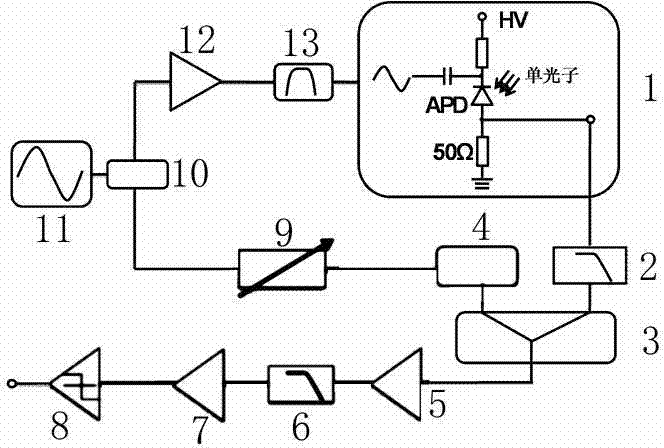

Method for detecting gigahertz single photon with low time jitter and low noise

ActiveCN102230828AImprove signal-to-noise ratioReduce time jitterInstrumentsFiber-optic communicationSignal on

The invention relates to the field of quantum secret communication and weak infrared light detection in the technical field of optical fiber communication, in particular to a method for detecting a gigahertz high-speed near infrared single photon with low time jitter and low noise. A control circuit related to the method consists of a signal detection circuit, a noise suppressing circuit and a signal processing circuit, wherein the noise suppressing circuit is used for extracting an avalanche electric signal by the following steps of: dividing a sine signal of gigahertz into two paths; loading one path serving as a gate signal on an avalanche photoelectric diode; transmitting a response output signal of the avalanche photoelectric diode to a low-pass filter; attenuating the other path of sine signal to an amplitude which is same as that of the response signal of the avalanche photoelectric diode passing through the low-pass filter; and transmitting the other path of sine signal to a balance circuit for balancing with the response signal of the avalanche photoelectric diode passing through the low-pass filter to remove spike noise and extract the avalanche electric signal. In the method, the spike noise is removed in a way of combining low-pass filtering with the balance circuit, so that the avalanche signal is extracted, higher detection efficiency is achieved, and the time jitter is controlled within dozens of picoseconds.

Owner:EAST CHINA NORMAL UNIVERSITY

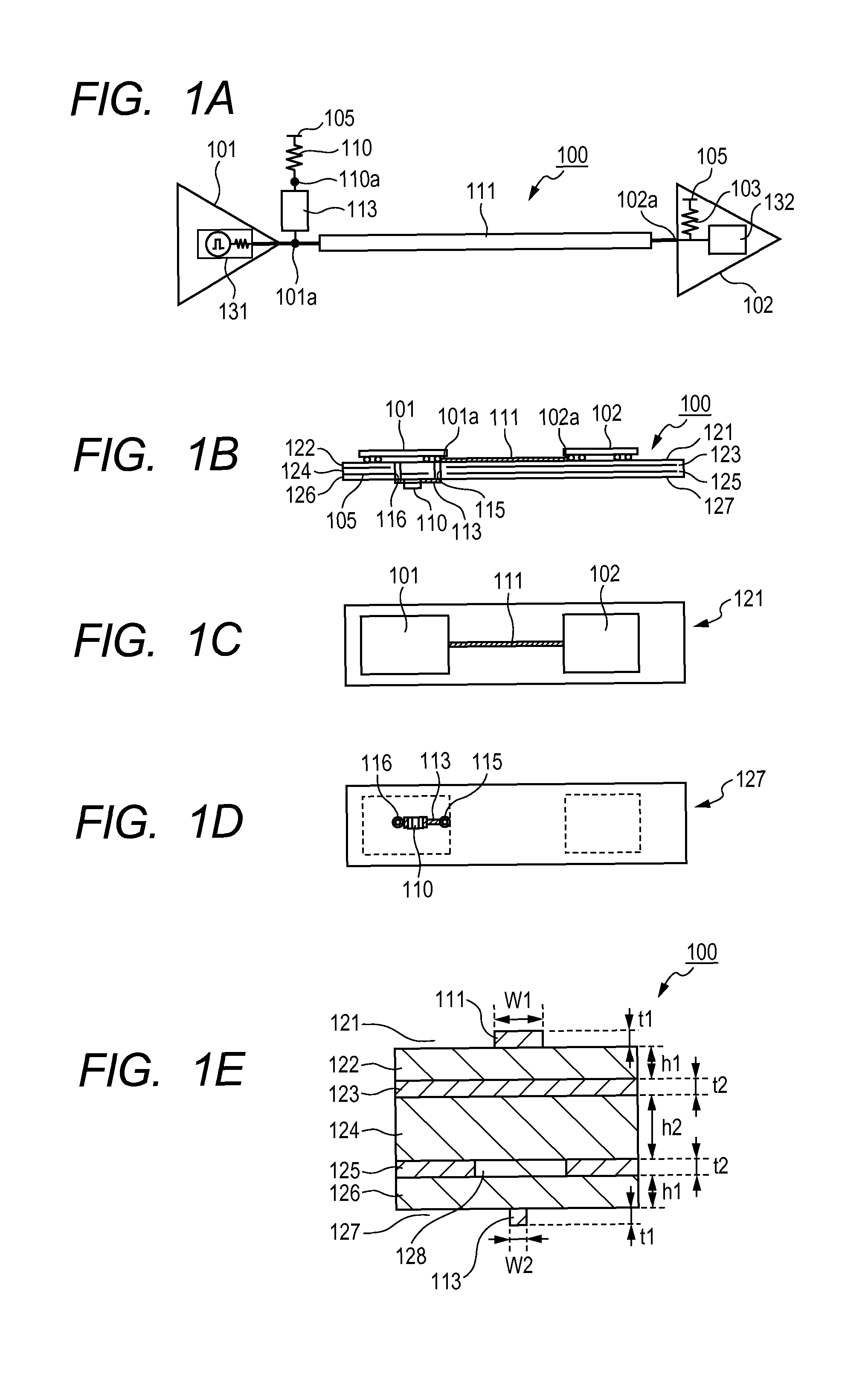

Printed circuit board

InactiveUS8428155B2Reduce time jitterBaseband system detailsPrinted circuit detailsElectrical resistance and conductancePropagation time

One end of a sub transmission line of which an impedance value is equal to or higher than a parallel impedance value of an output impedance value of a transmission circuit and an impedance value of a transmission line is connected to a connection point between the transmission circuit and the transmission line, and a correction resistor of which resistance is lower than an impedance value of the sub transmission line is connected to the other end of the sub transmission line. A length of the sub transmission line is set to satisfy a condition of 0.5×Tr (signal rise time)≦Td (signal propagation time of sub transmission line)≦0.5×Tmin (signal minimum pulse width), thereby achieving a de-emphasis function by a passive component, correcting a high-frequency component of a signal attenuated on the transmission line, and thus reducing timing jitters caused by intersymbol interference.

Owner:CANON KK

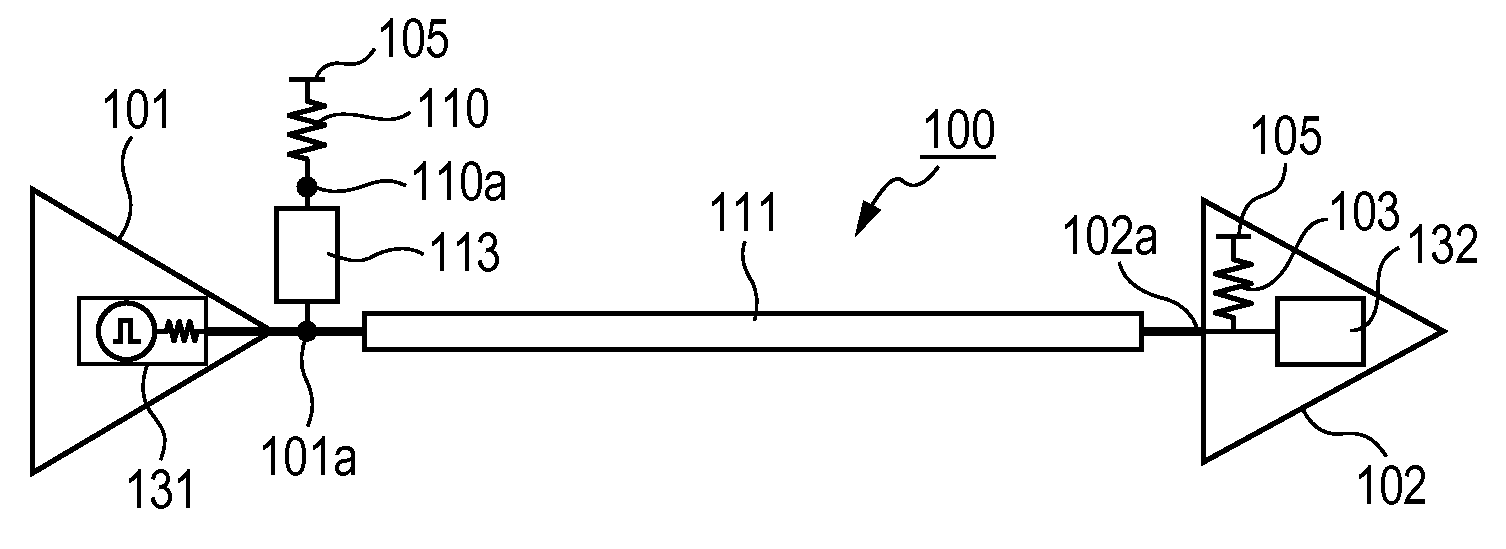

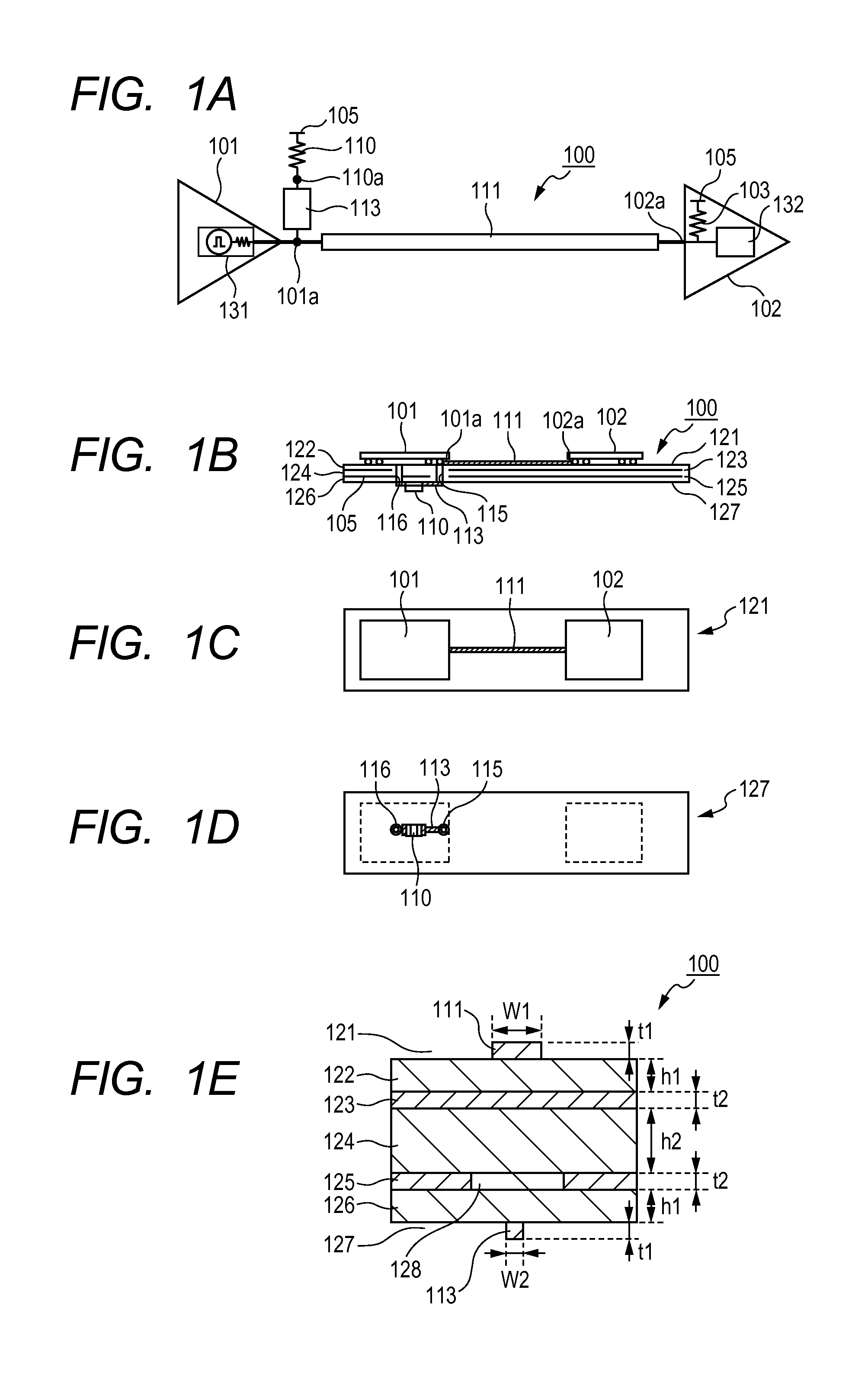

Photonically-Sampled Electronically-Quantized Analog-to-Digital Converter

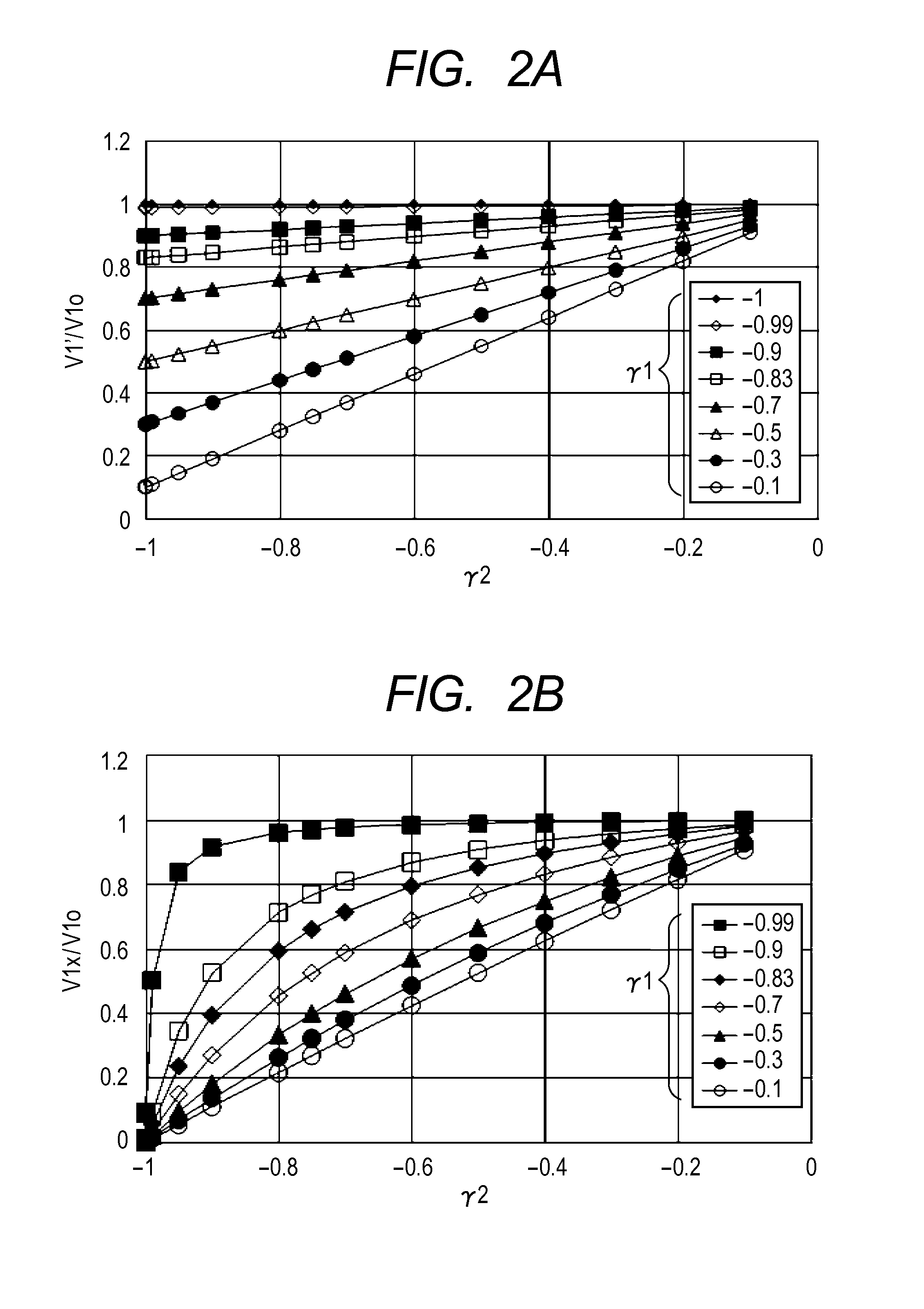

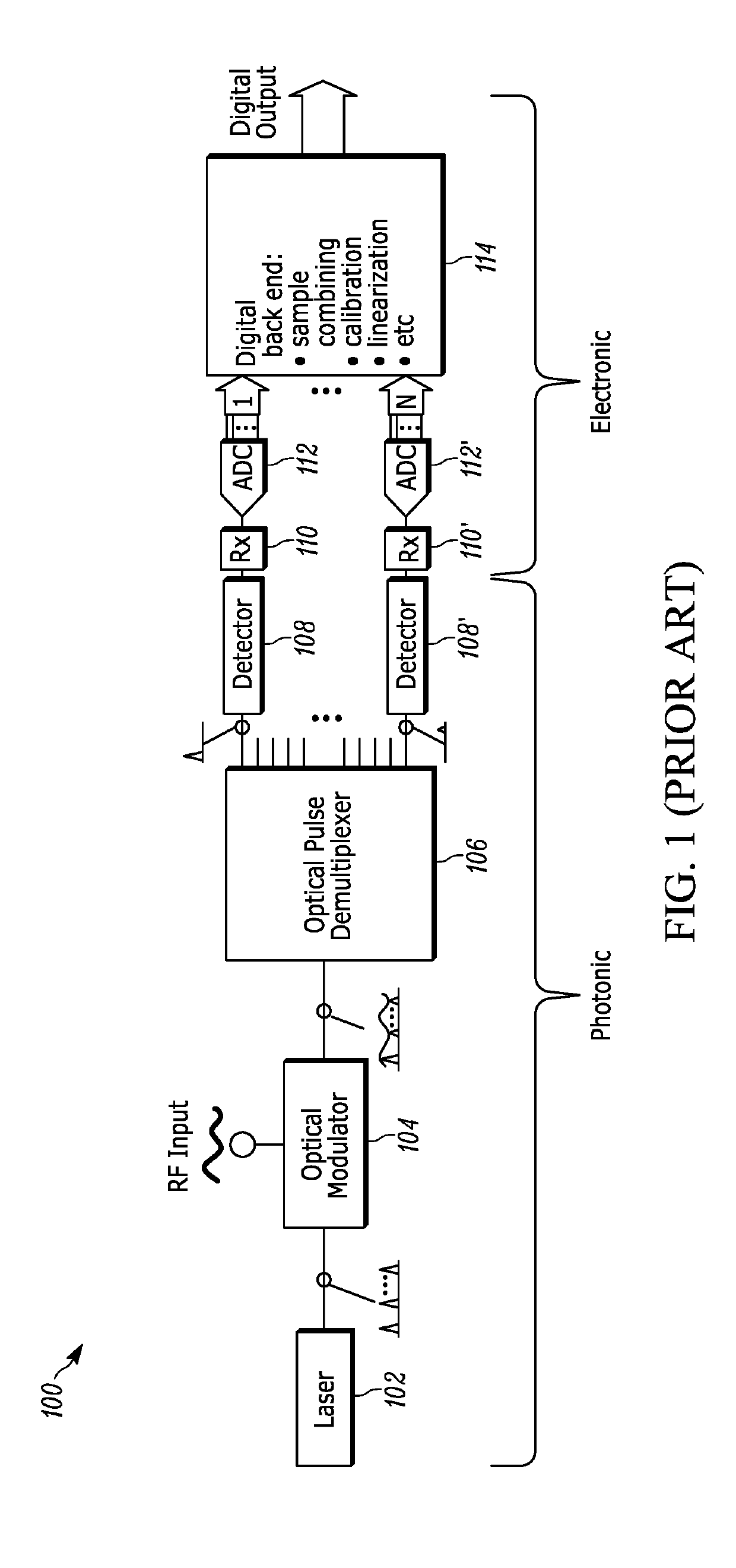

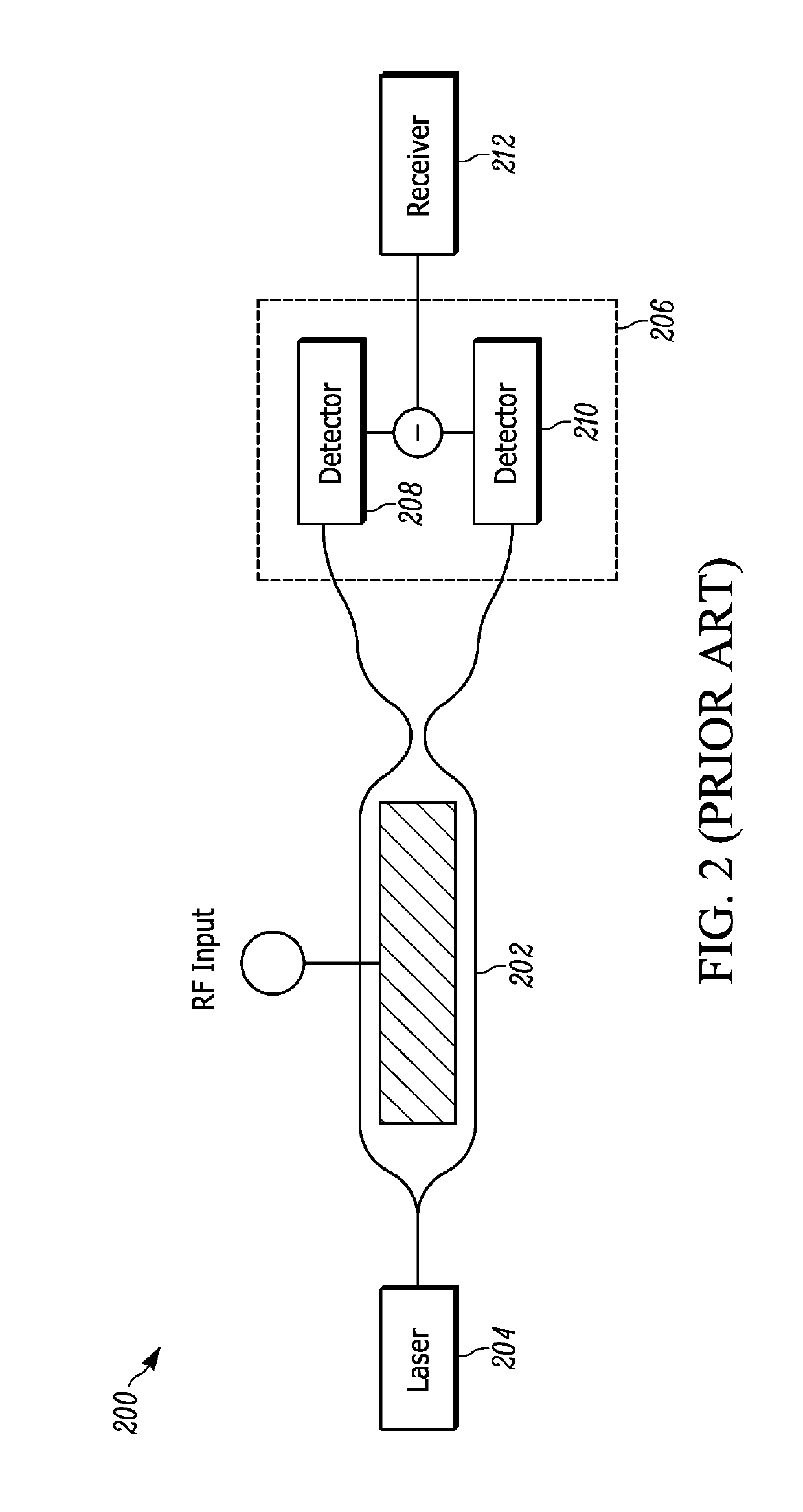

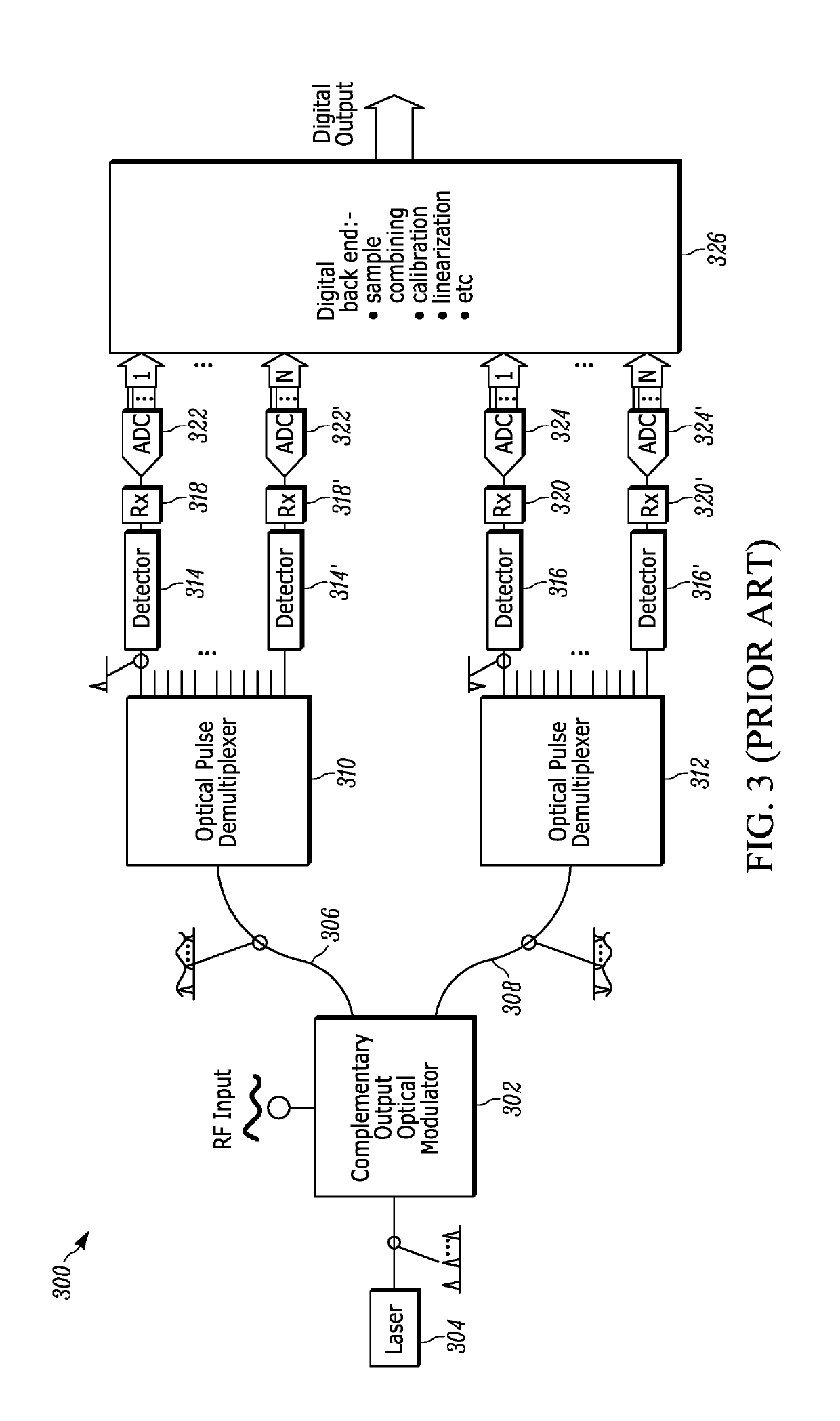

ActiveUS20190302571A1Eliminate bottlenecksReduce time jitterOptical analogue/digital convertersAnalogue-digital convertersOptical pathDigital signal processing

A photonically-sampled electronically-quantized analog-to-digital converter generates an optical signal comprising a series of optical pulses. The optical signal is split into a first and a second optical path. The split optical signal is detected in the first path and then the detected optical signal is converted to a reference digital signal. The split optical signal in the second path is modulated with an input RF signal and a plurality of demultiplexed RF-modulated optically-sampled signals is generated from the modulated optical signal. The plurality of demultiplexed RF-modulated optically-sampled signals is then pulse broadened, detected, and converted to a plurality of sampled-RF digital signals. The reference digital signal and the plurality of sampled-RF digital signals are digital signal processed to generate a digital representation of the input RF signal.

Owner:PHOTONICSYST

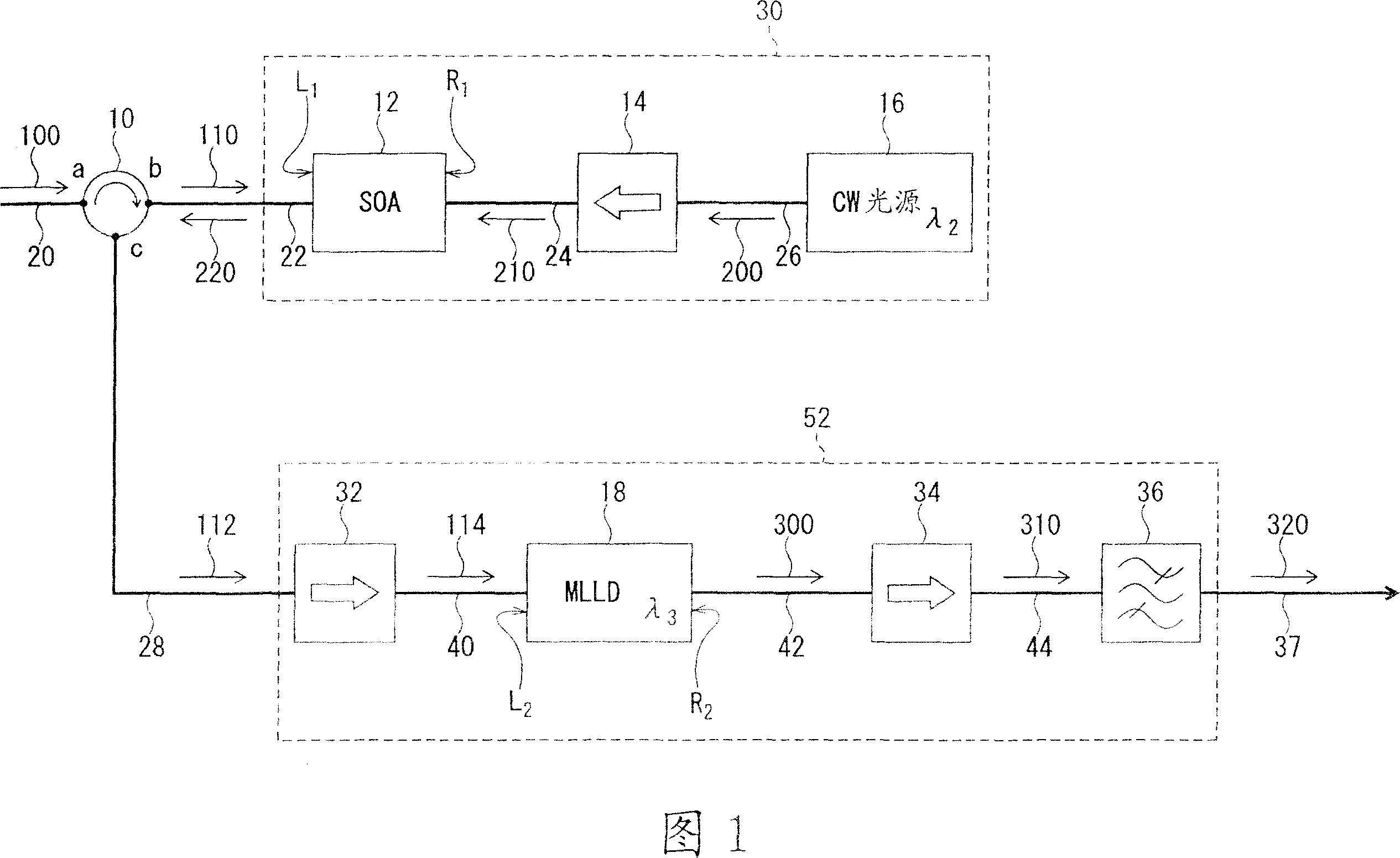

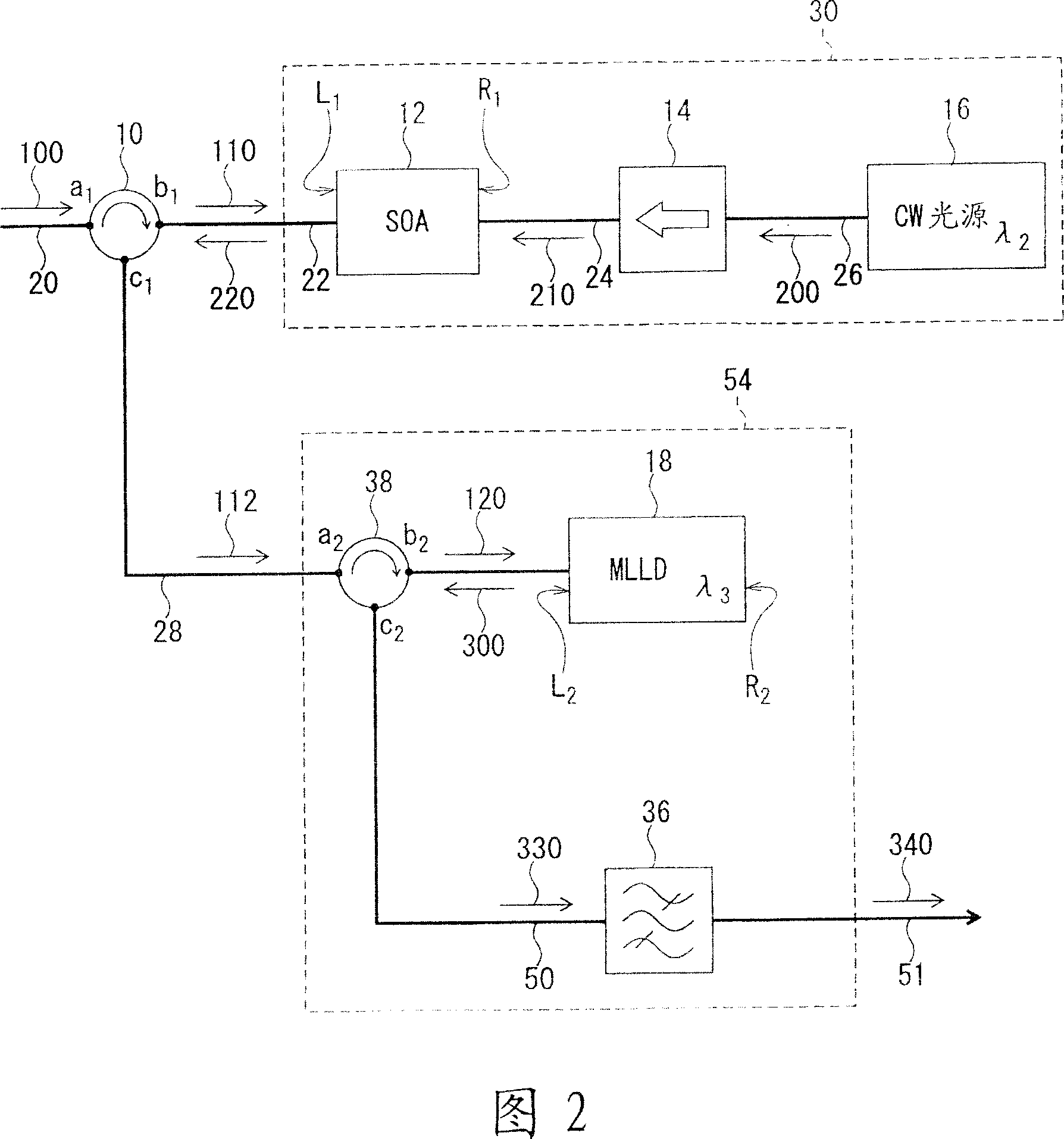

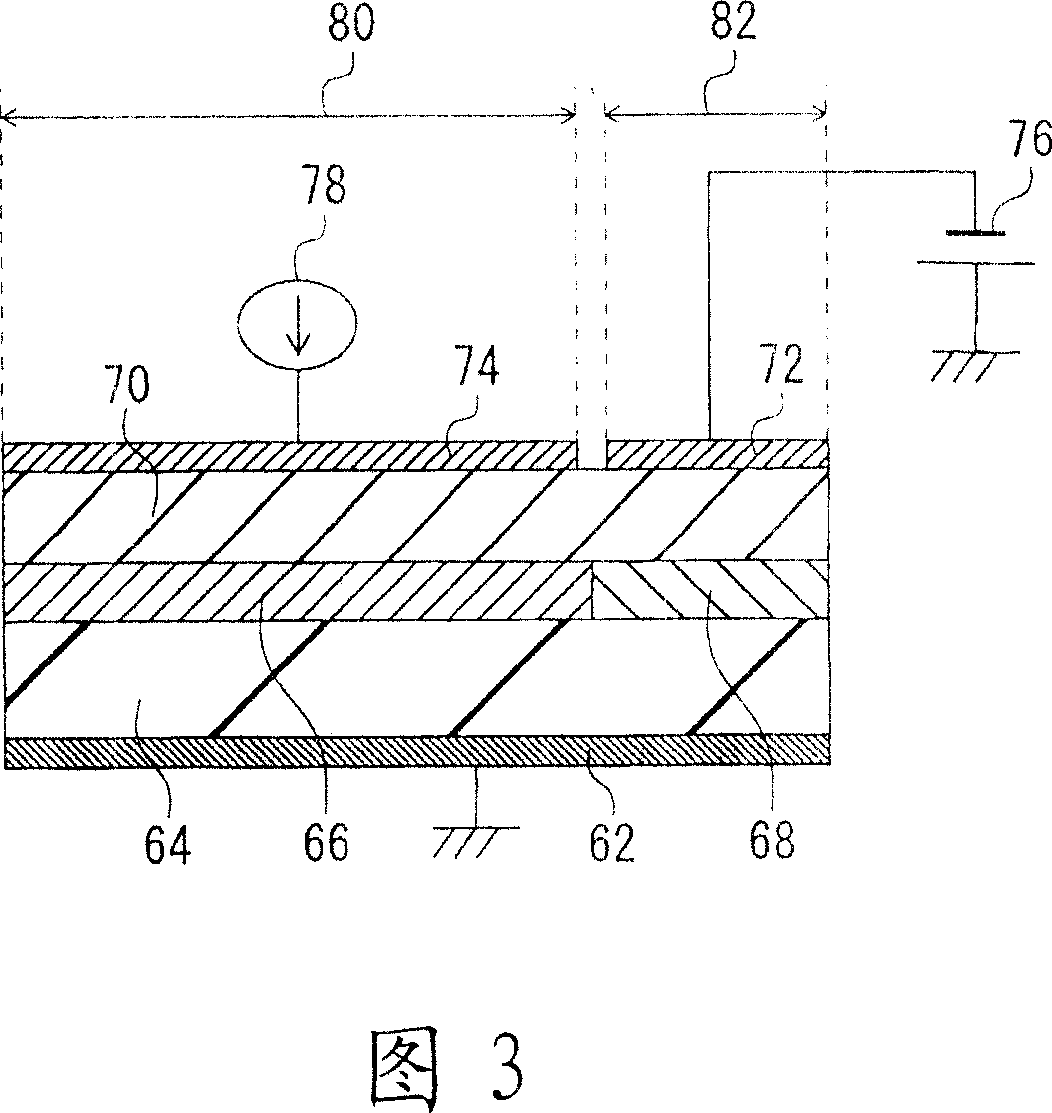

Optical clock signal extraction device and optical clock signal extraction method

InactiveCN101022313AReduce gainStable generationTime-division optical multiplex systemsTime-division multiplexMode-lockingOptical clock

Owner:OKI ELECTRIC IND CO LTD

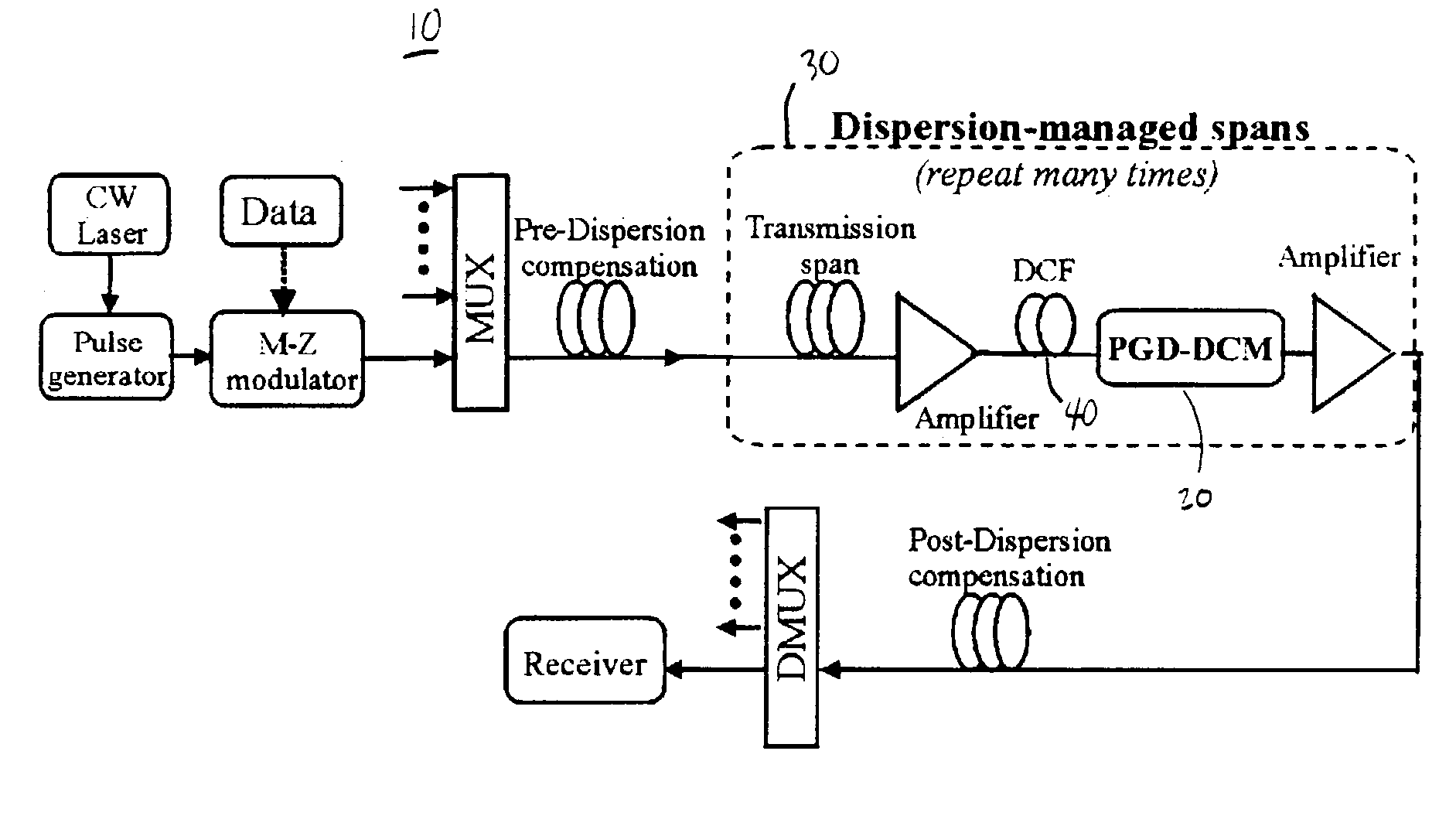

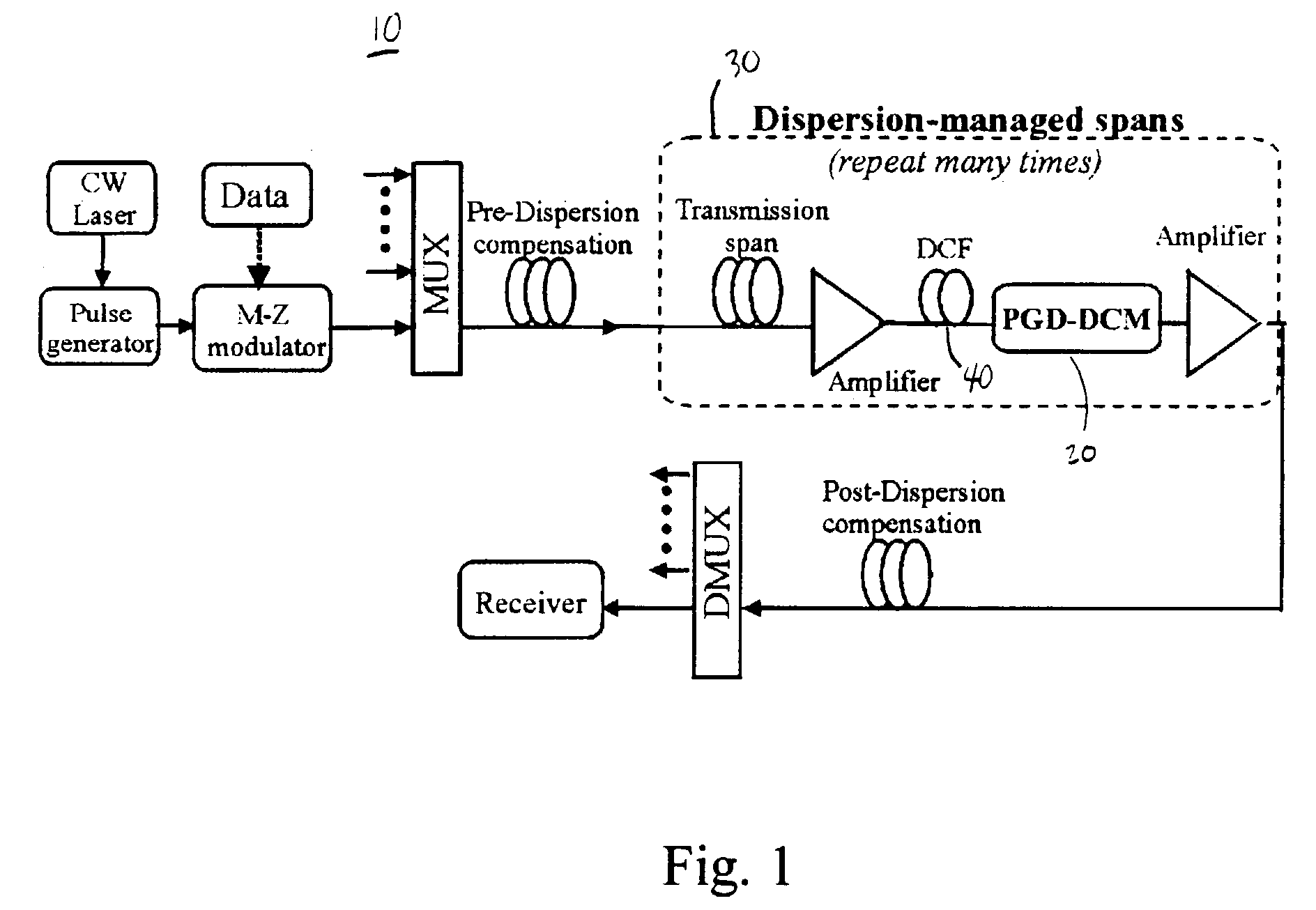

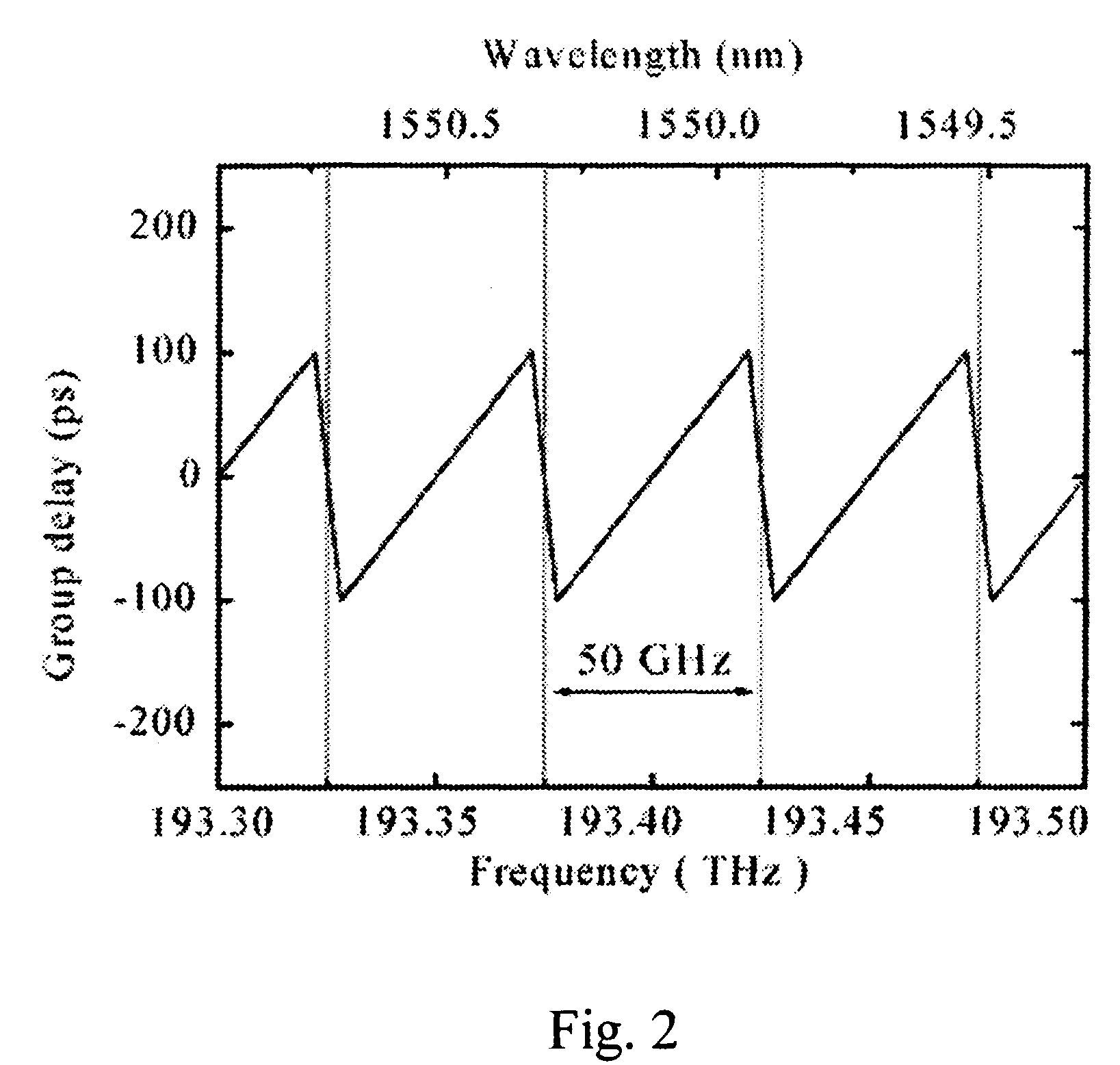

Dispersion compensation method and apparatus

InactiveUS7369778B2Reduce time jitterWavelength-division multiplex systemsElectromagnetic transmissionDispersion managedEngineering

In one embodiment of the invention a dispersion compensator is provided for use in a dense wavelength division multiplexed optical communication system. The dispersion compensator comprises a periodic-group-delay dispersion compensation module which provides a portion of the dispersion compensation for a dispersion managed span of the optical communication system. A remaining portion of the dispersion compensation for the dispersion managed span is provided by dispersion compensating fiber. The portions of the dispersion compensation provided by each of the periodic-group-delay dispersion compensation module and the dispersion compensating fiber is selected such that the collision-induced timing jitter is reduced.

Owner:LUCENT TECH INC

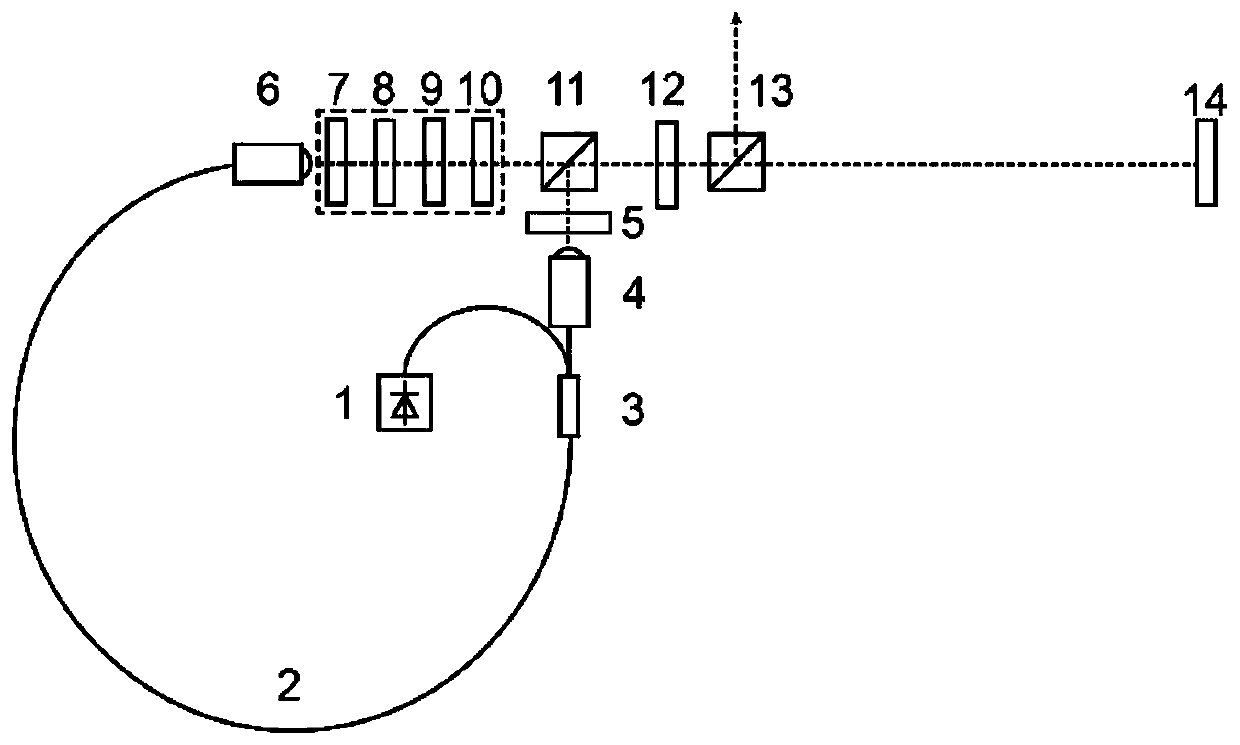

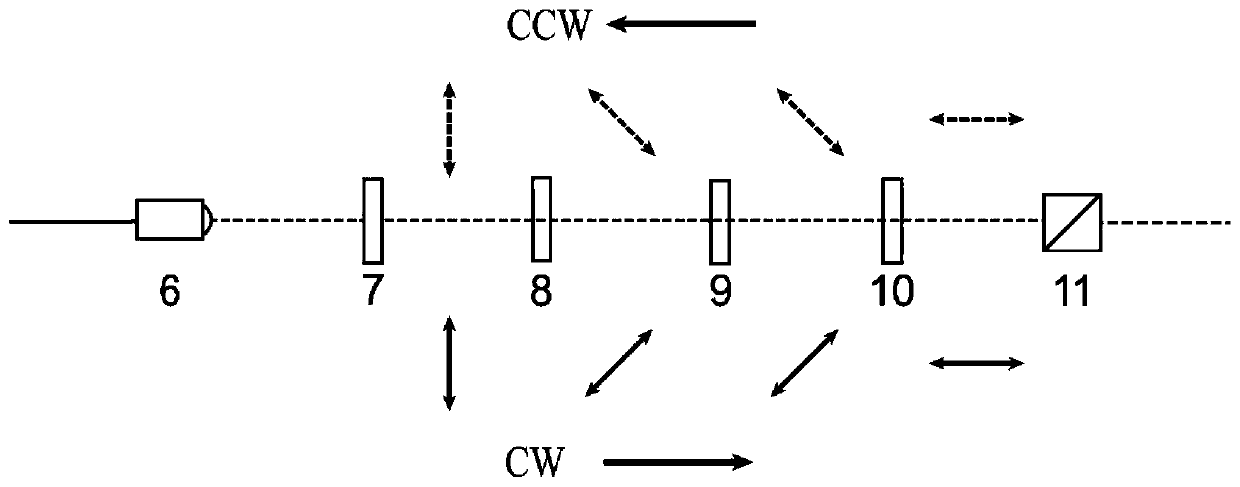

Full polarization-maintaining 9-shaped cavity mode-locked laser with high repetition frequency

InactiveCN110797742AHigh repetition rateShorten the lengthActive medium shape and constructionBeam splitterMultiplexer

The invention discloses a full polarization-maintaining word cavity mode-locked laser with high repetition frequency, which comprises a pumping source, a non-reciprocal phase shifter, a wavelength division multiplexer, a first optical fiber collimator, a second optical fiber collimator, a first polarization beam splitter, a third half-wave plate, a second polarization beam splitter, a first half-wave plate and a reflector, wherein the non-reciprocal phase shifter is composed of a second half-wave plate, a first Faraday rotator, a quarter-wave plate and a second Faraday rotator which are arranged in sequence; the wavelength division multiplexer comprises a common end, a signal optical end and a pumping end; the pumping source is connected with the pumping end of the wavelength division multiplexer; the signal optical end of the wavelength division multiplexer is connected with the first optical fiber collimator; the common end of the wavelength division multiplexer is connected with thesecond optical fiber collimator through an erbium-doped optical fiber; the output end of the second optical fiber collimator is sequentially provided with the non-reciprocal phase shifter, the firstpolarization beam splitter, the third half-wave plate, the second polarization beam splitter and the reflector; and the output light of the first optical fiber collimator passes through the first half-wave plate and then enters the first polarization beam splitter.

Owner:TIANJIN UNIV

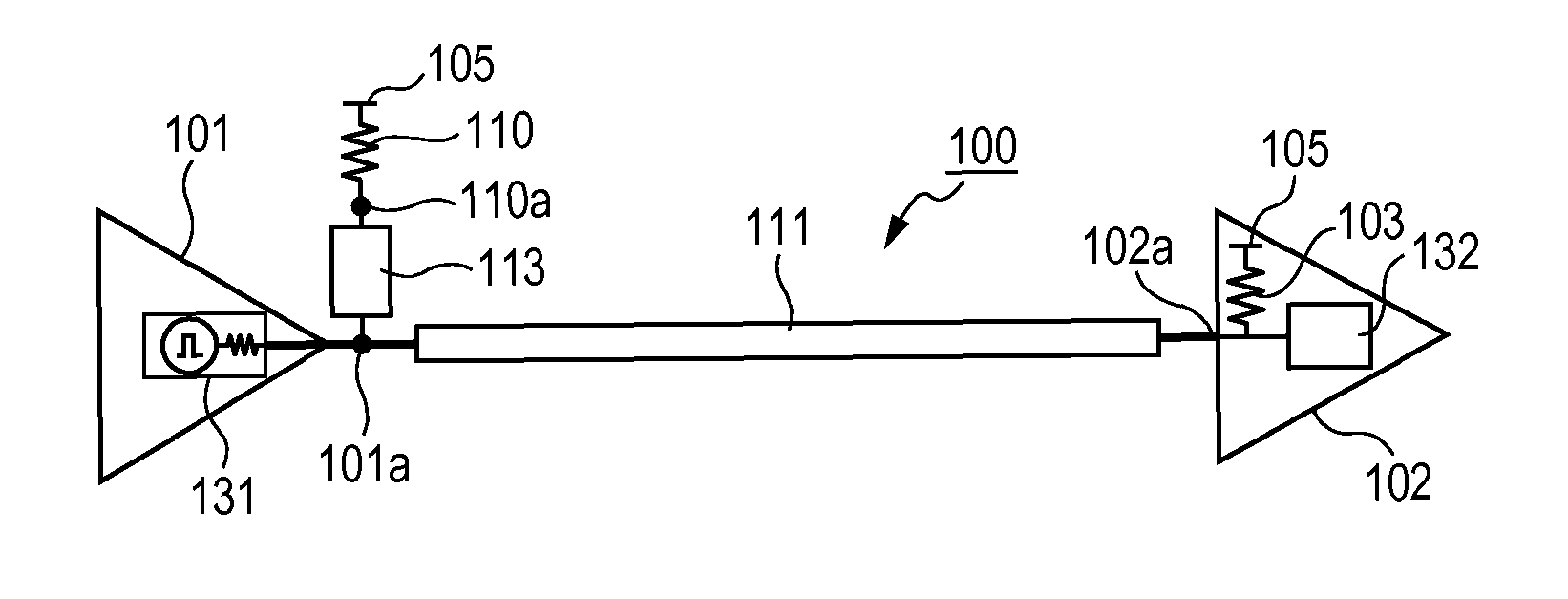

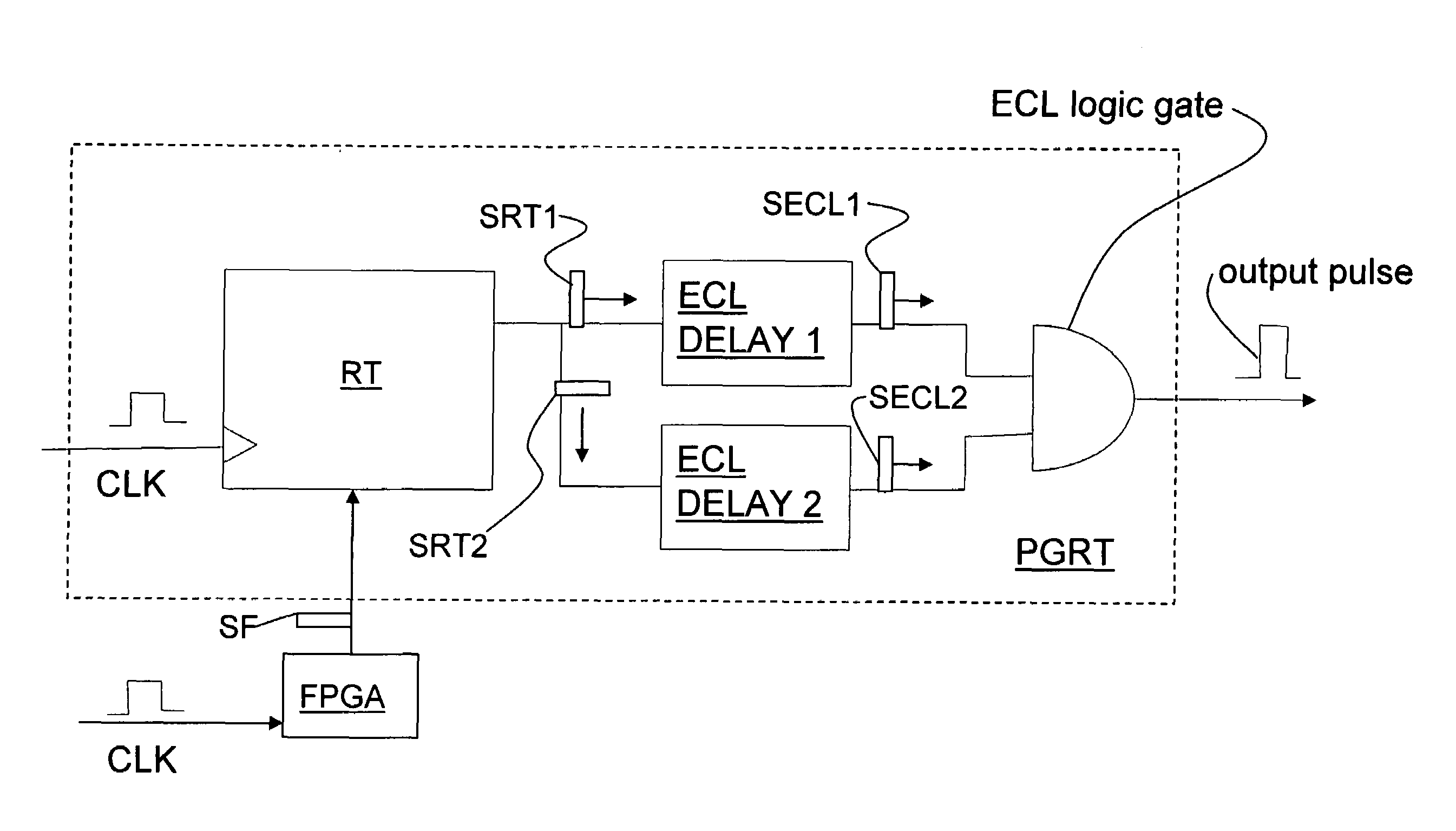

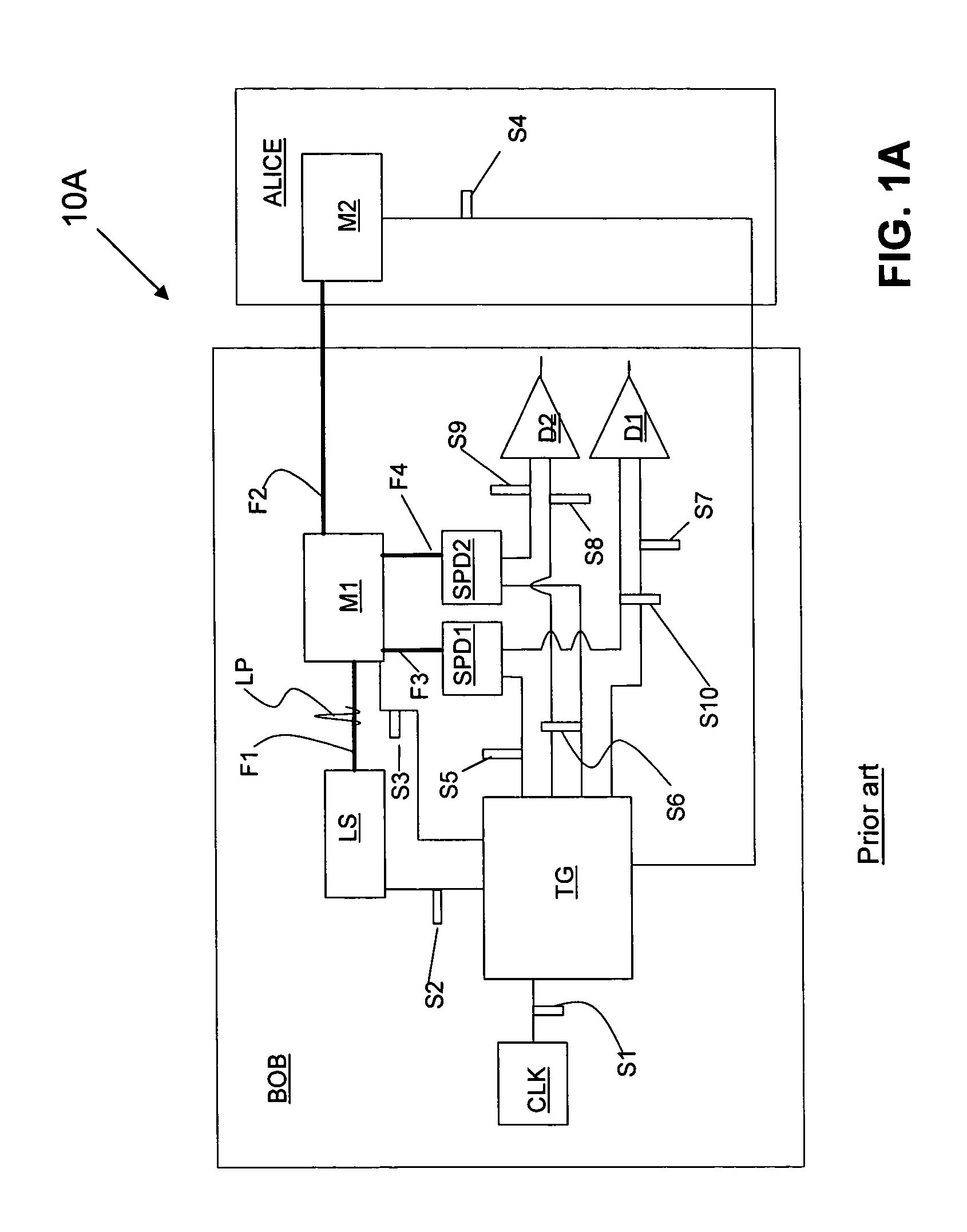

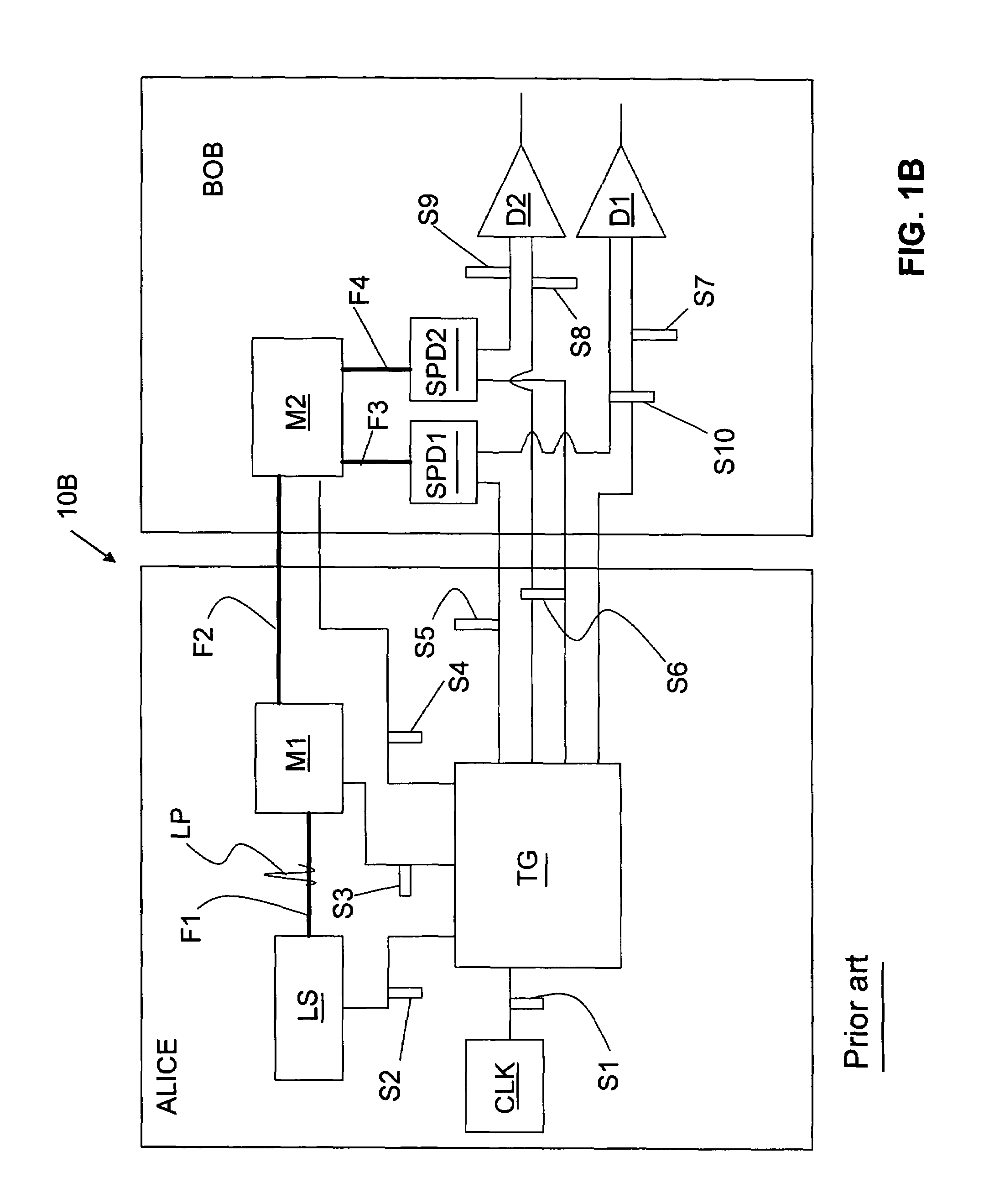

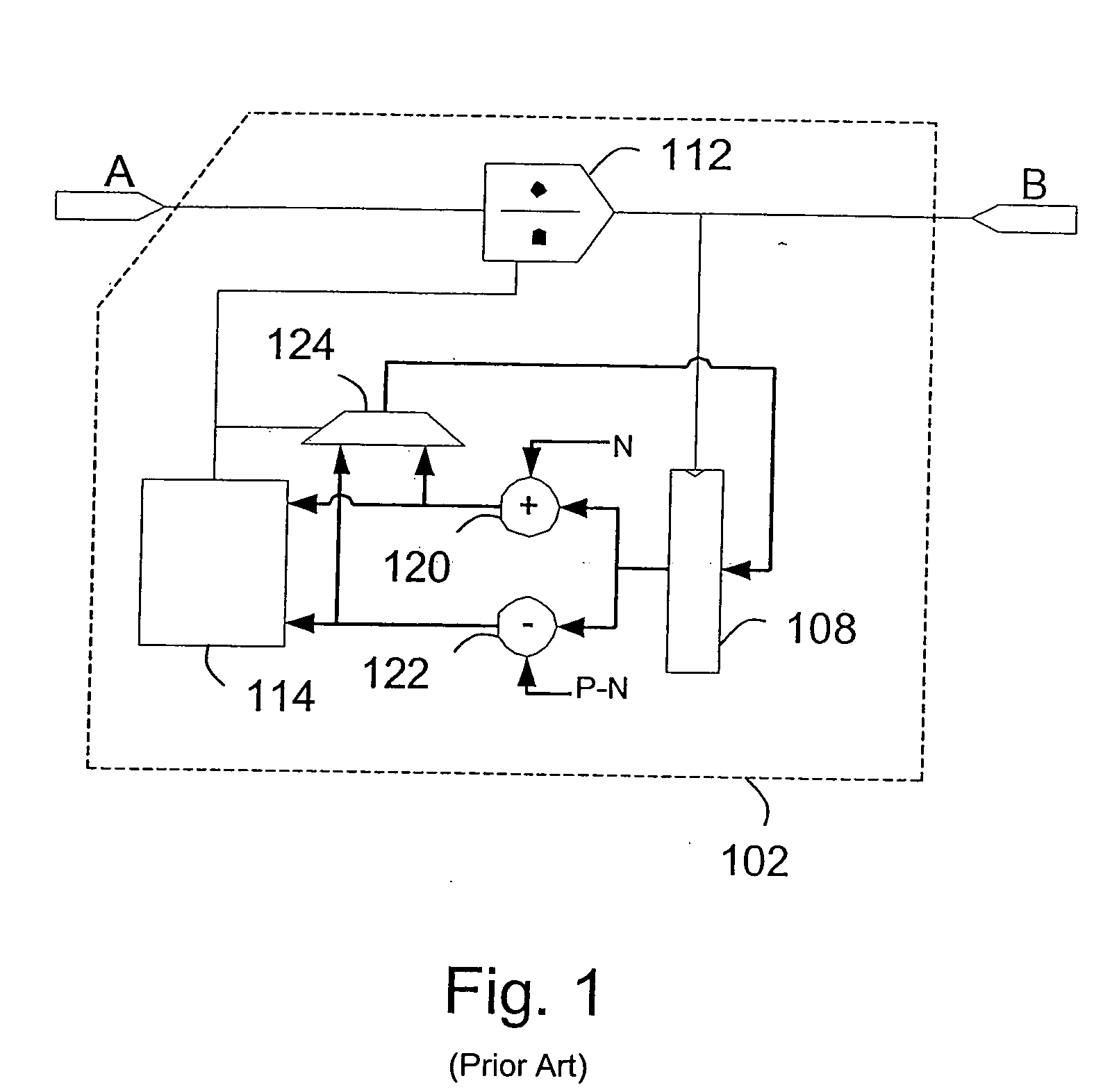

Timing error reduction in QKD systems

ActiveUS7409162B2Reducing and eliminating timing errorReduce time jitterSynchronisation information channelsSynchronisation by photonic/optical meansTiming generatorEmitter-coupled logic

Systems and methods for reducing or eliminating timing errors in a quantum key distribution (QKD) system (100) are disclosed. The QKD system has a pulse generator with retimer (PGRT) that includes a field-programmable gate array (FPGA) (or FPGA output) which is used as a timing generator (TG). While an FPGA has the desired degree of programmability for use in a QKD system, it also suffers from undue amounts of jitter in the digital output. The present invention utilizes emitter-coupled logic (ECL) to reduce the timing jitter from the FPGA by coupling two ECL delays (ECL delay 1 and ECL delay 2) to the FPGA and to retiming block, and by using an ECL logical AND gate to set the pulse width of the various synchronization signals. An embodiment of the present invention includes multiple clock domains having individual clocks (CLK), phase-lock loops (PLLs), retiming circuits (RT) and timing generators (TG) for robust jitter reduction and hence highly accurate QKD system timing.

Owner:MAGIQ TECH INC

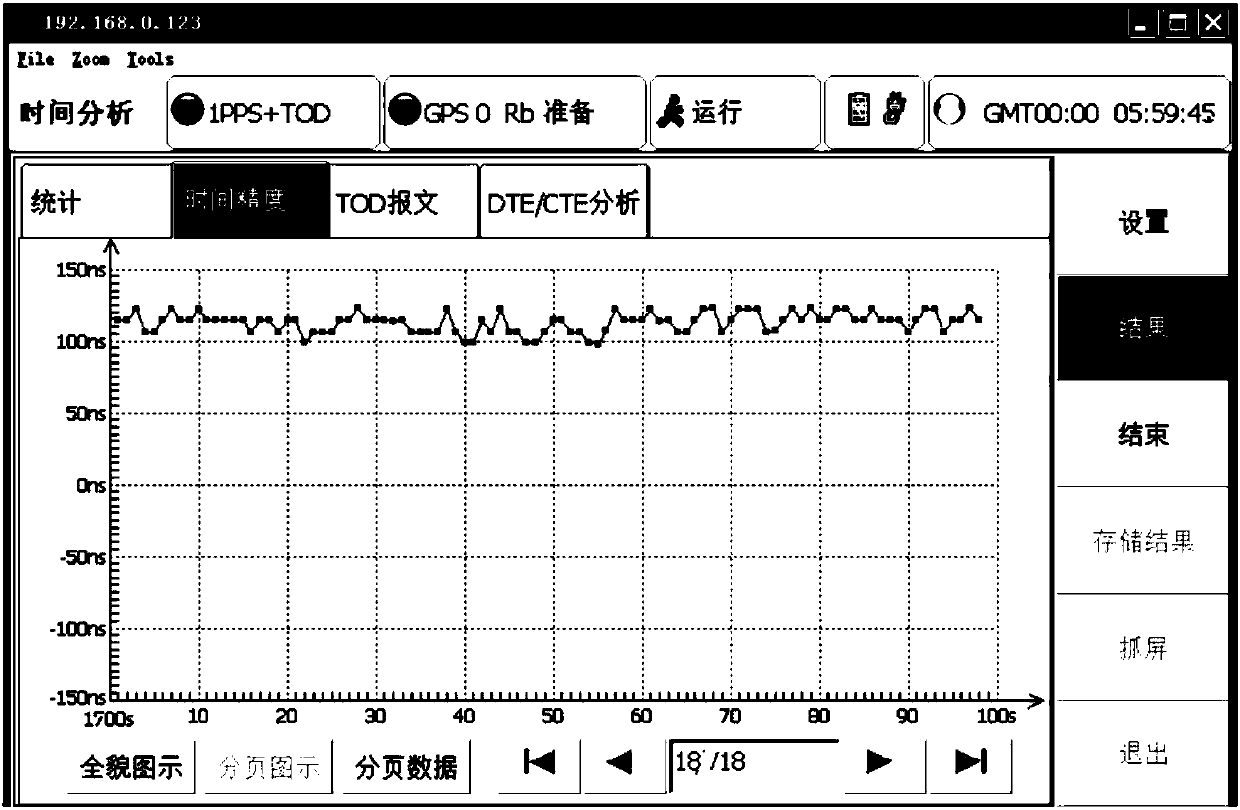

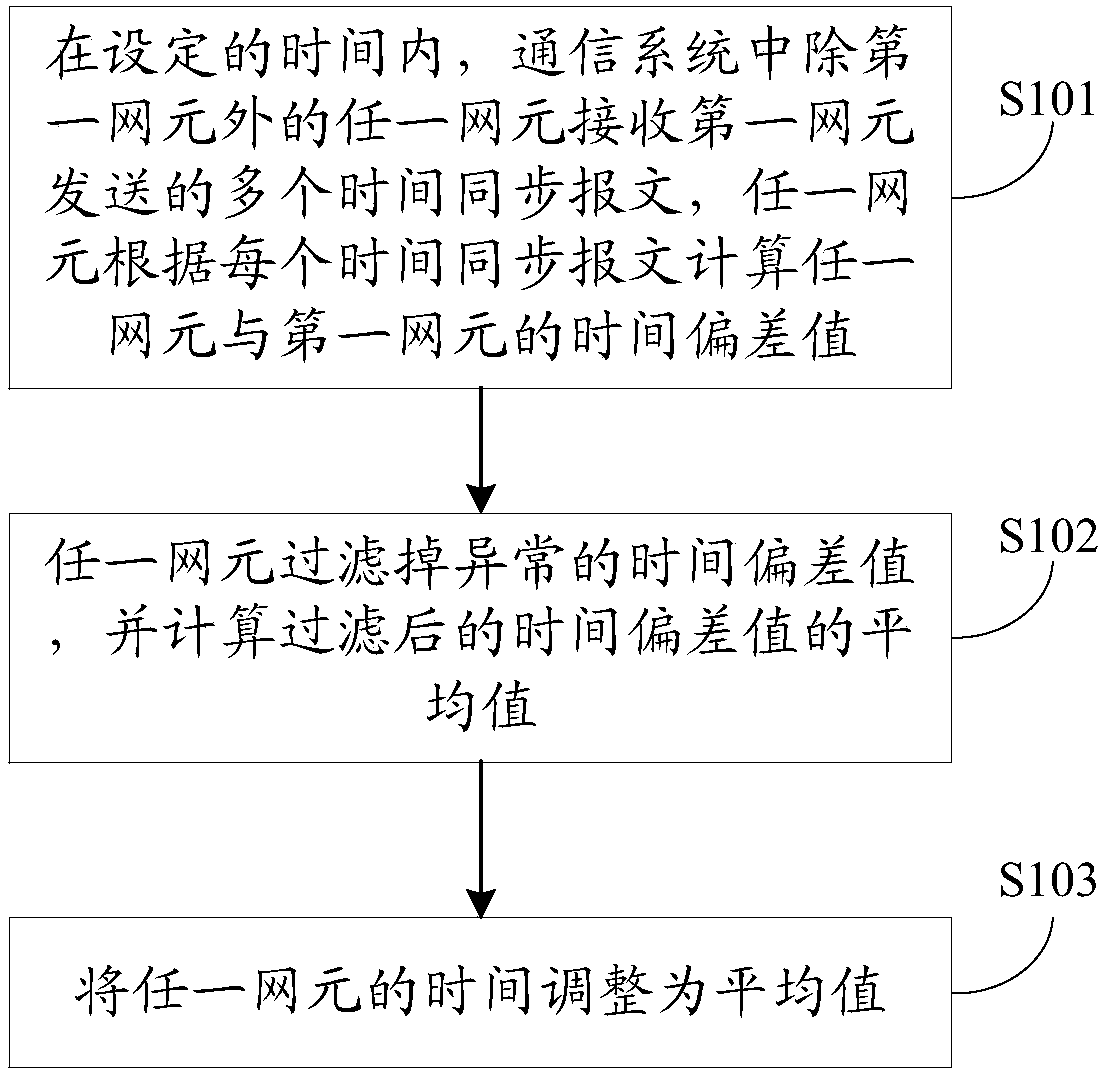

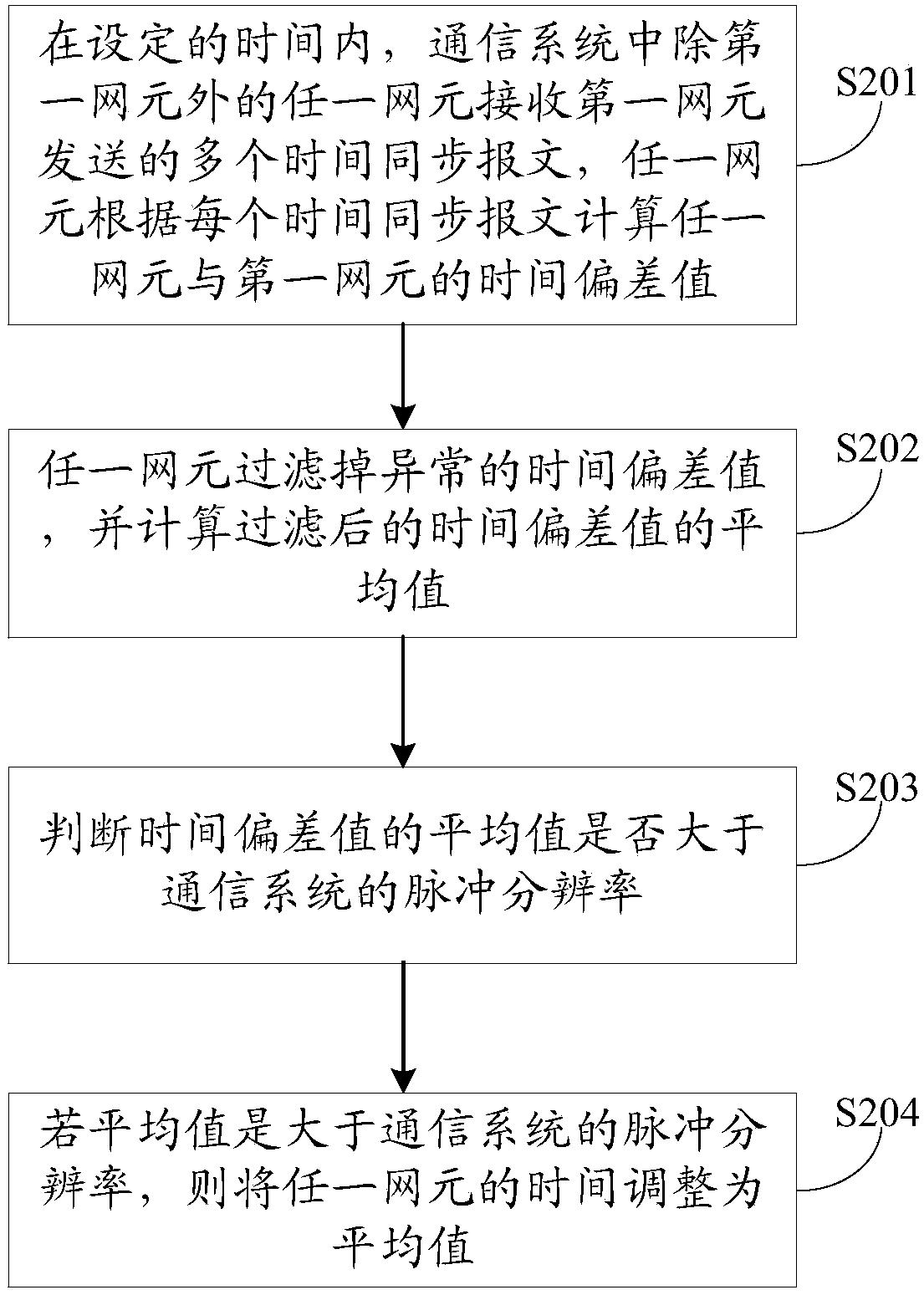

Time synchronization method and apparatus

InactiveCN107786319AImprove time synchronization stabilityReduce time jitterSynchronisation error correctionTime deviationCommunications system

The invention provides a time synchronization method and apparatus. The method comprises the following steps: receiving a plurality of time synchronization messages sent by a first network element within a set time, and calculating a time deviation value of any network element and the first network element according to each time synchronization message; filtering the abnormal time deviation values, and calculating the average value of the filtered time deviation values; and adjusting the time of any network element as the average value. By adoption of the time synchronization method and apparatus, the time synchronization stability of the network elements in the communication system can be effectively improved, and the time jitter of the network elements is reduced.

Owner:ZTE CORP

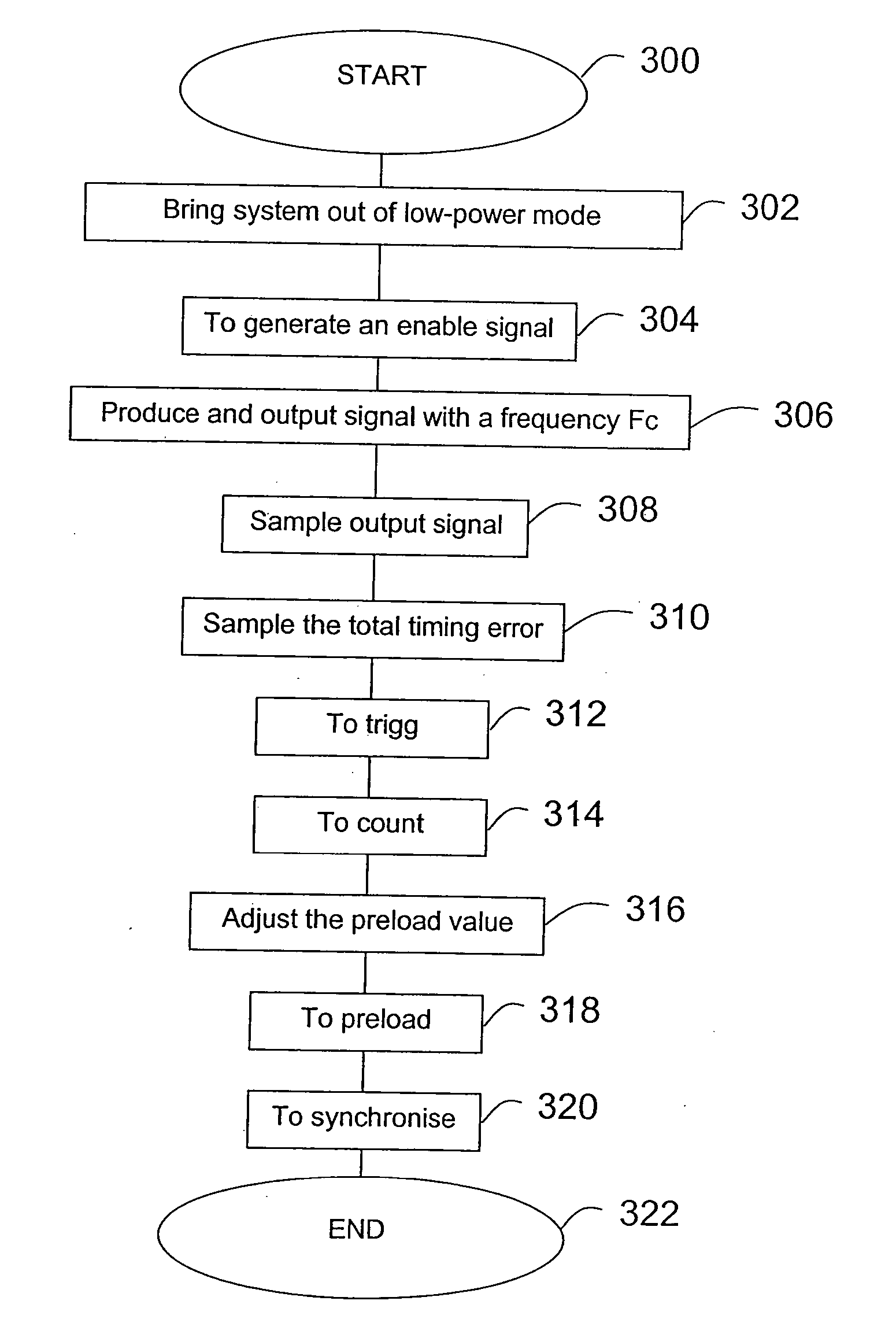

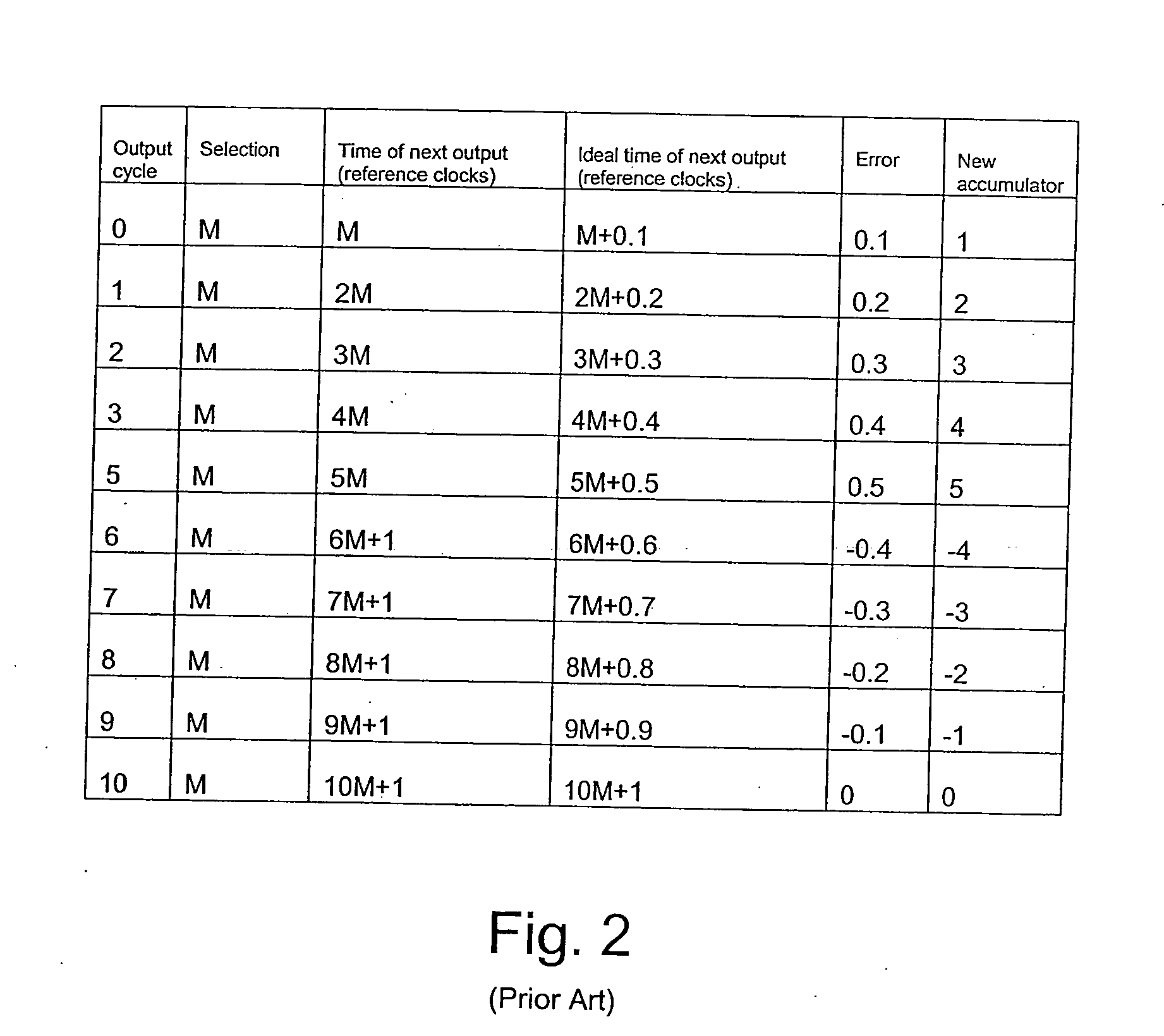

Fractional divider system and method

InactiveUS20060001498A1Shorten the timeReduce time jitterCounting chain pulse countersOscillations generatorsPower modeEngineering

The present invention relates to a fractional divider system for a low-power timer with reduced timing error at wake-up. The fractional divider system includes a fractional divider circuit operable to produce an output signal. The fractional divider system also includes a high speed crystal oscillator connected to the fractional divider circuit operable to start on wake-up from the low power mode, and a high speed clock divider circuit connected to the high speed crystal oscillator circuit. The high speed crystal oscillator circuit is configured to sample the output signal and a current state of the total timing error from the fractional divider circuit. The sampled output signal is employed to trigger the high speed clock divider circuit and the sampled current state of the total timing error preloads the high speed clock divider circuit, which is operable to synchronize a first pulse of the output signal to the ideal clock timing to an accuracy within 1.5 periods of the high speed clock.

Owner:INTEL MOBILE COMM GMBH

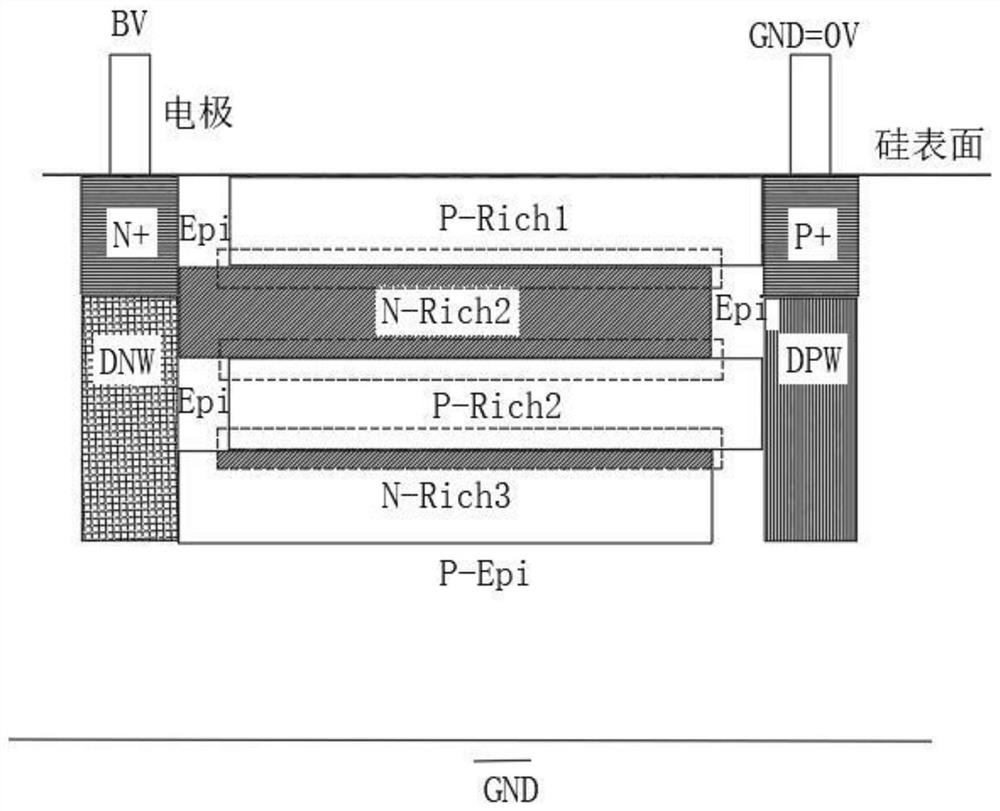

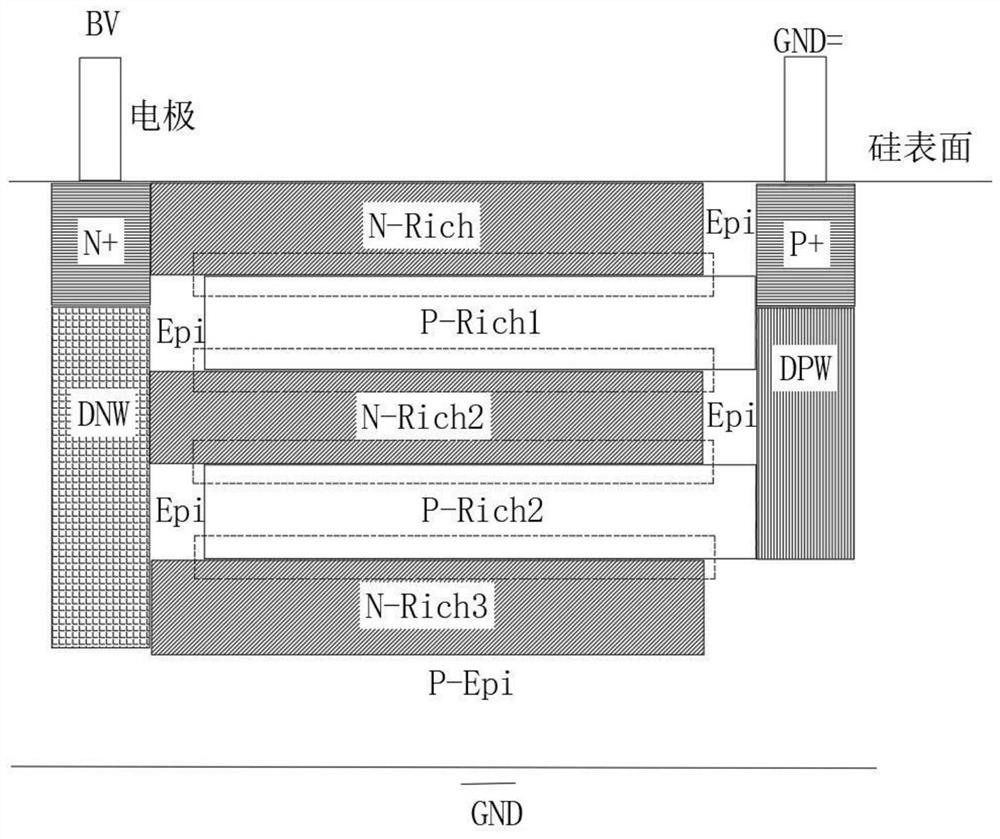

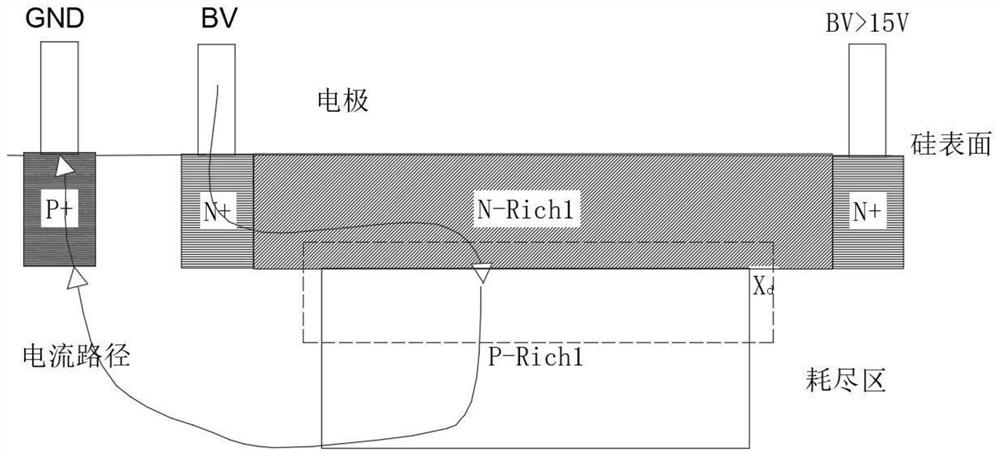

High-performance single-photon pixel spad structure

PendingCN113380912AAdd depthImprove detection efficiencySolid-state devicesDiodeIon implantationMaterials science

The invention discloses a high-performance single-photon pixel spad structure, and relates to the technical field of integrated circuits. The device comprises a silicon surface, a cathode and an anode, high voltage is applied to the cathode, and the anode is grounded; impurities with different properties are doped on the surface of silicon for multiple times, ions of N-type impurities and P-type impurities are injected with energy to form a plurality of back-to-back PN junctions, and finally the plurality of back-to-back PN junctions are connected in parallel; multiple times of doping are adopted, so that signals can be effectively led out from the deep part, and any two PN junctions are connected in parallel, so that the depth of a space depletion region is effectively increased in the longitudinal direction; the cathode and the deep N well injection are isolated from the P-type impurities by using epitaxial layer low-concentration doping; and the anode and the deep P well injection are isolated from the N-type impurities by using epitaxial layer low-concentration doping. According to the invention, the depth of the depletion region is effectively expanded, the detection efficiency is improved, and the diffusion time of photoelectrons is reduced, so that the time jitter is reduced, and the SPAD avalanche voltage can be effectively reduced.

Owner:上海矽印科技有限公司

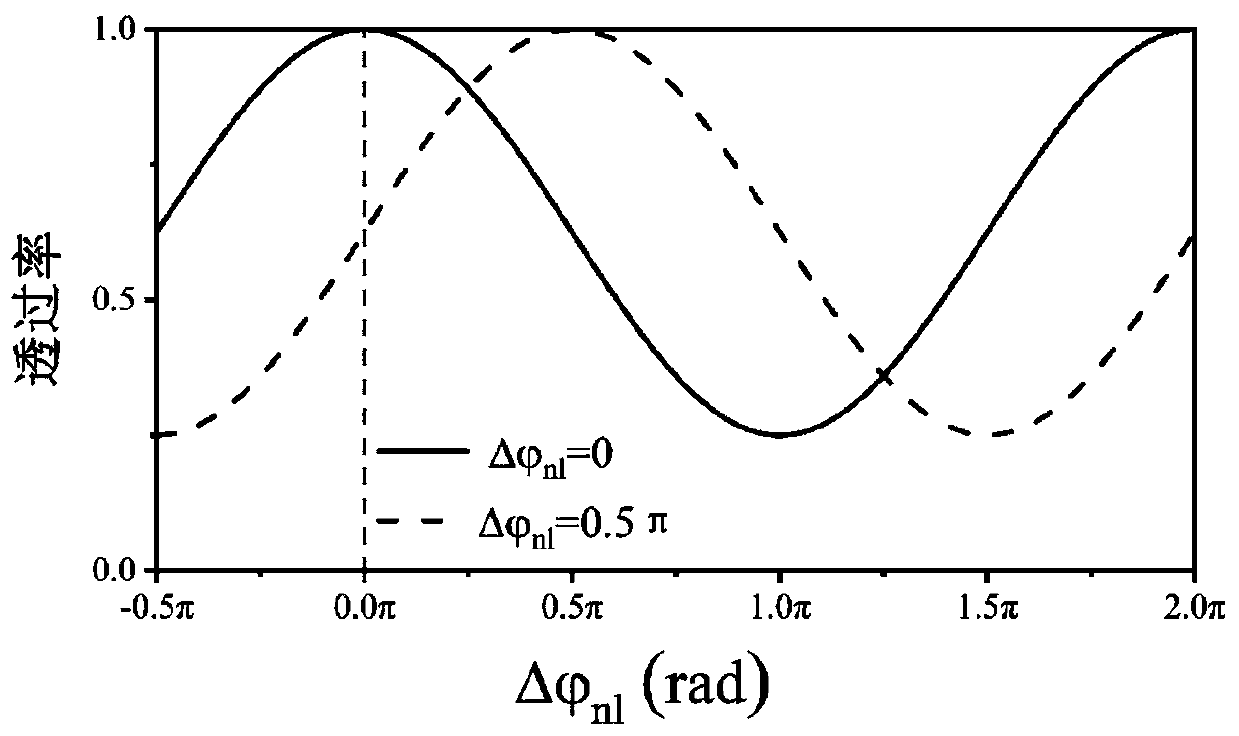

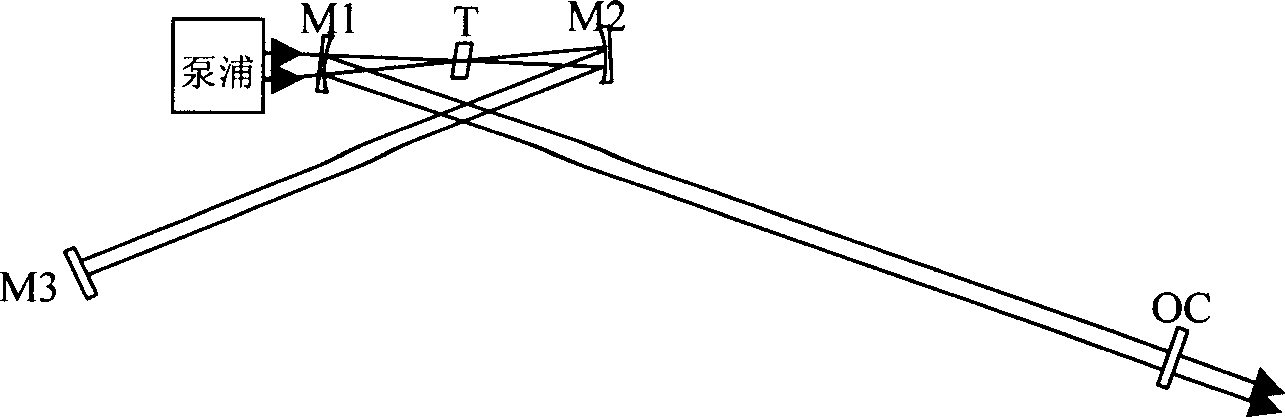

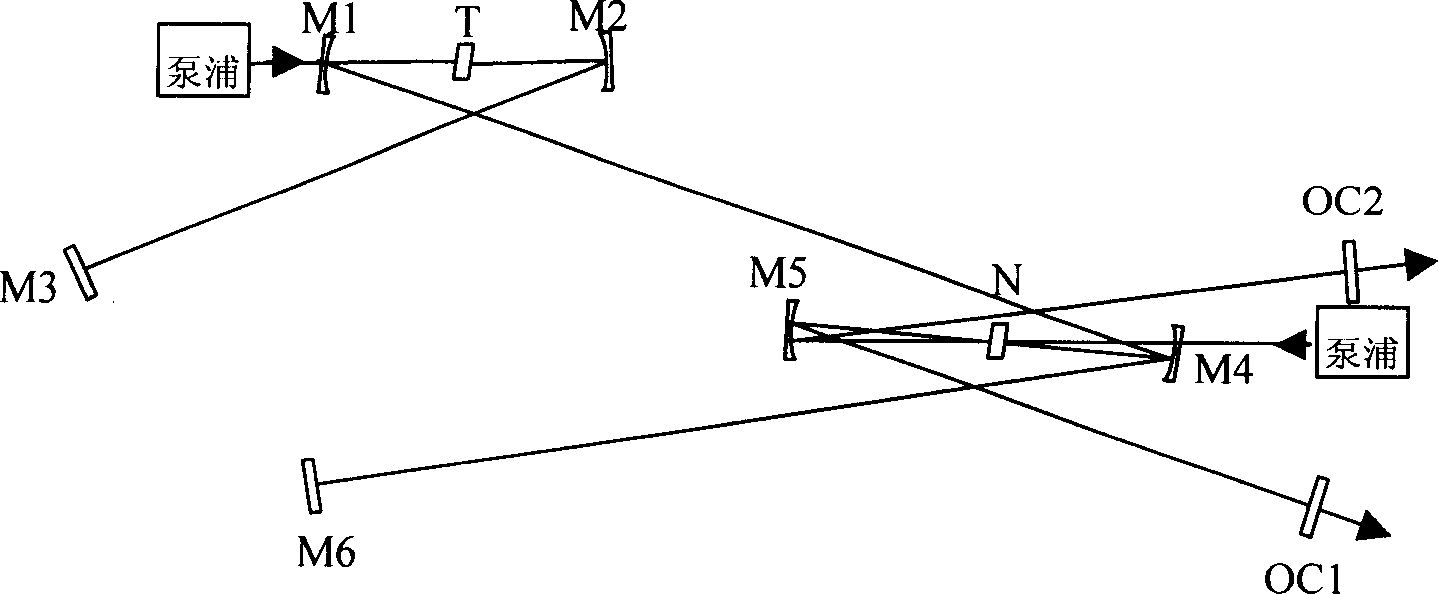

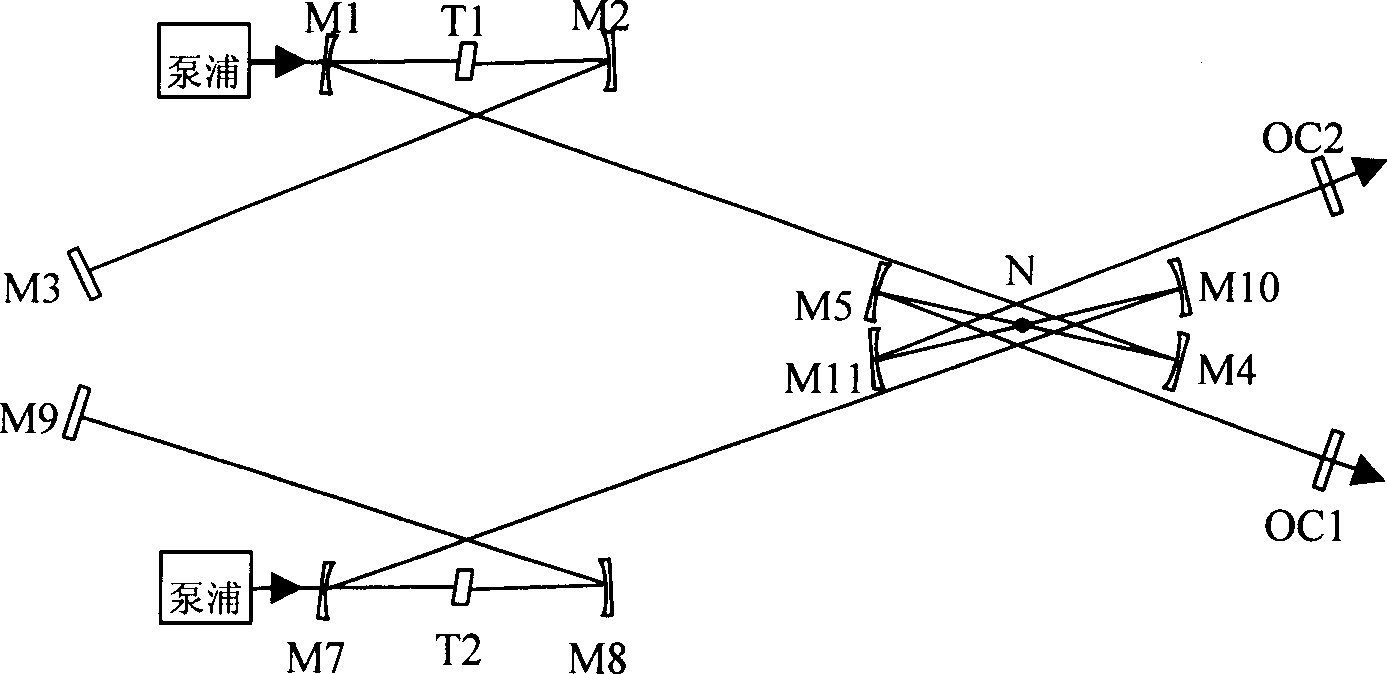

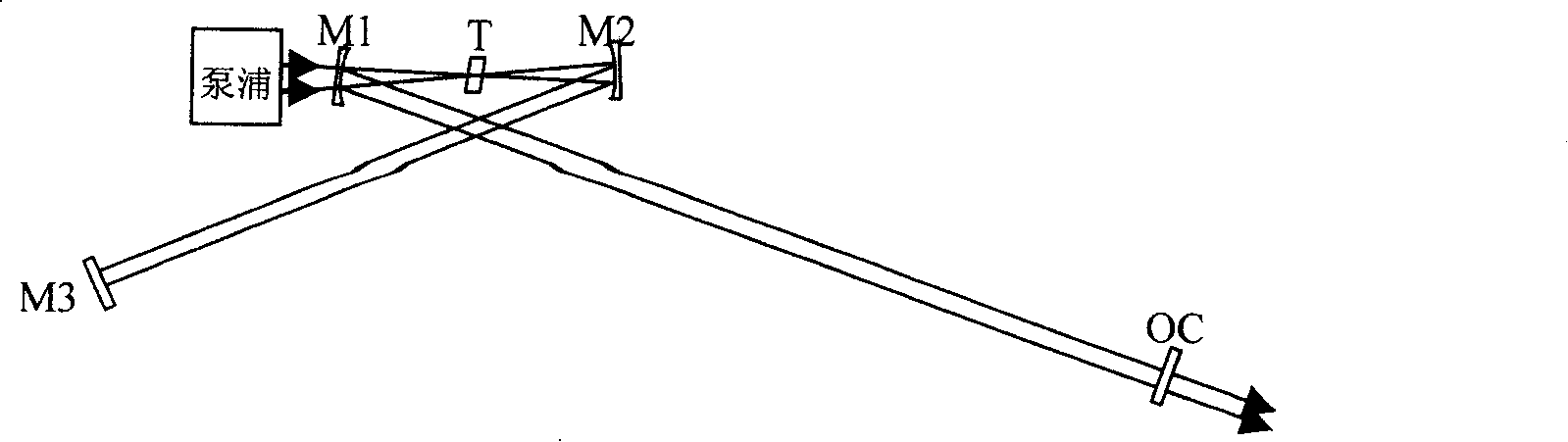

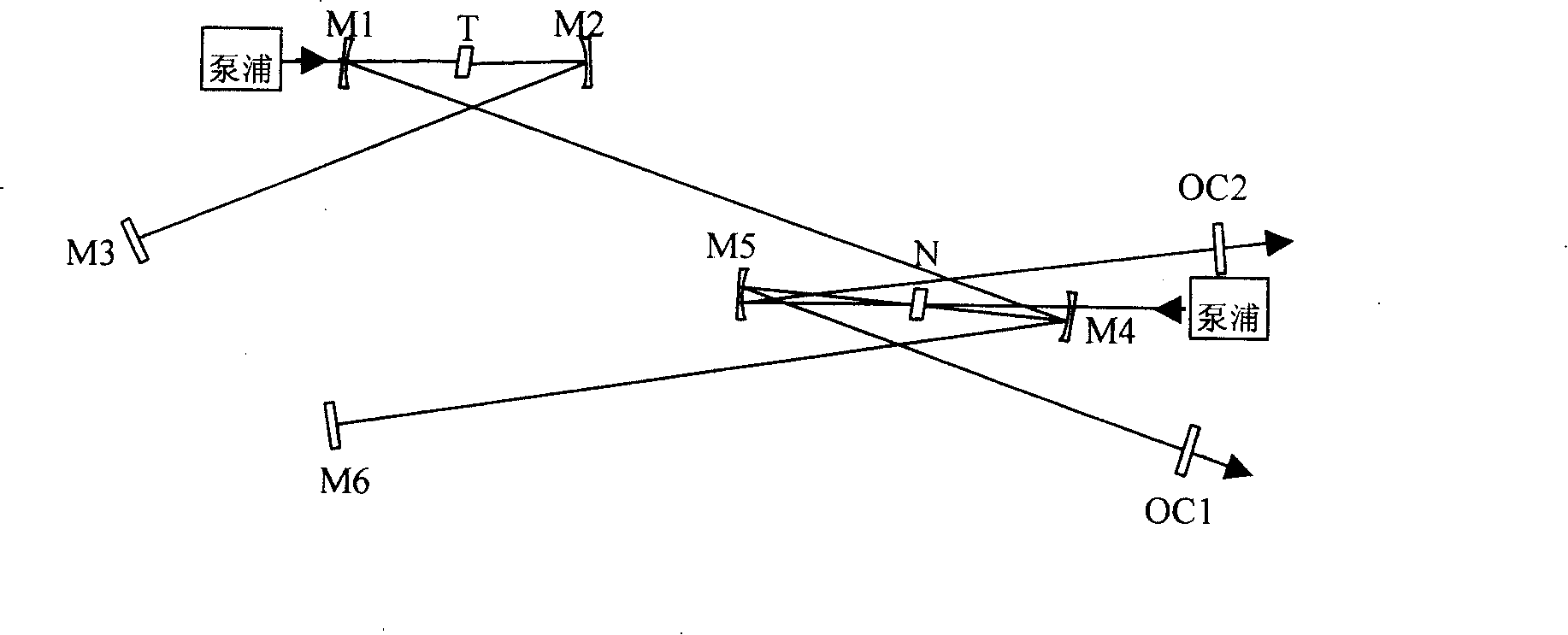

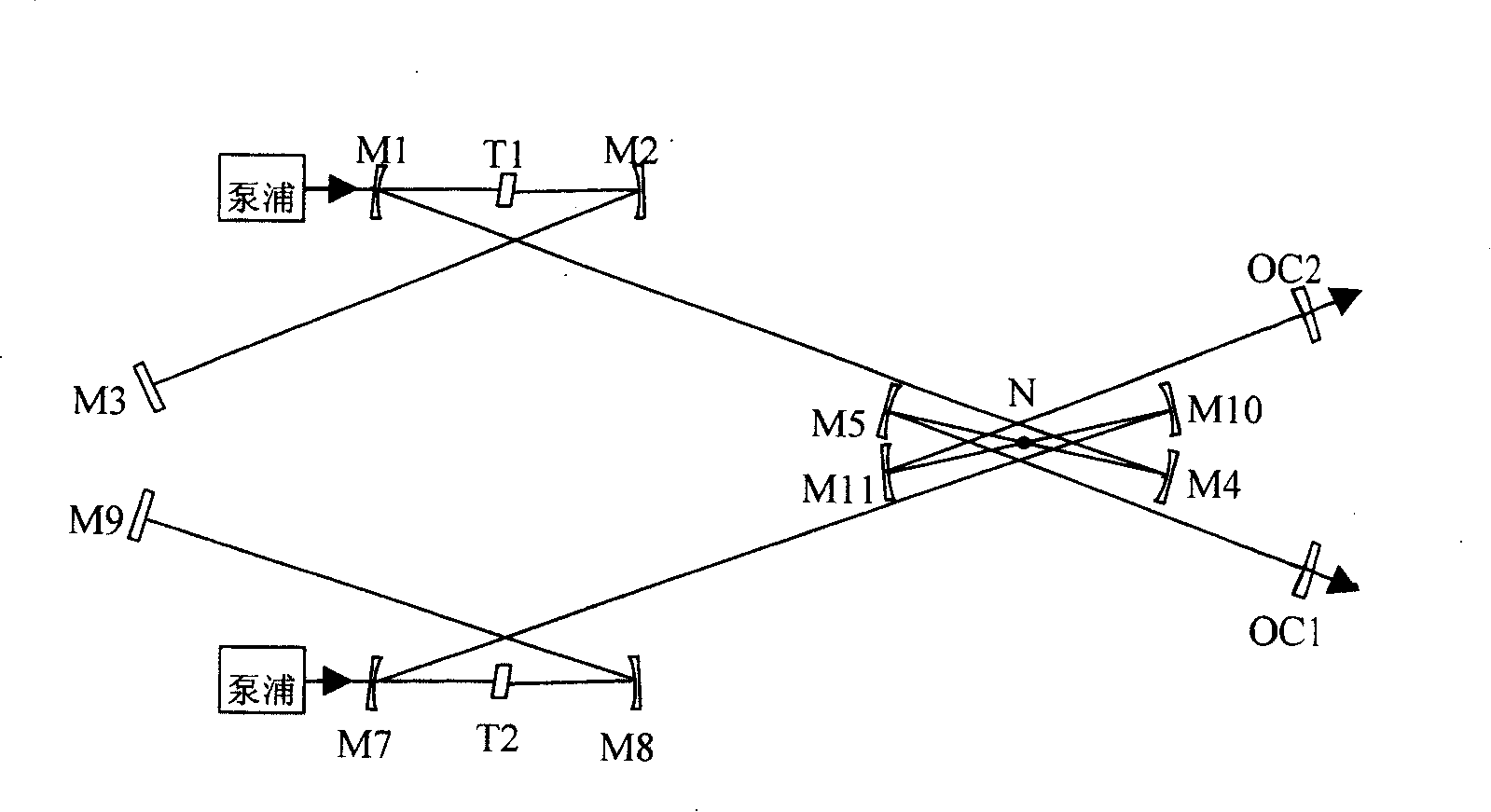

Method of full light control laser synchronization

This invention relates to a method for realizing total optical control laser synchronization in far distance, which utilizes the cross phase modulation action of multiple lasers in medium to realize synchronous control of far distance multi-beam laser. Advantage: small dithering of time, far distance multi-color total optical control laser synchronization can be realized, when the absolute phase of a far beam is locked, other beams can trace locking automatically so as to get new beams.

Owner:EAST CHINA NORMAL UNIV

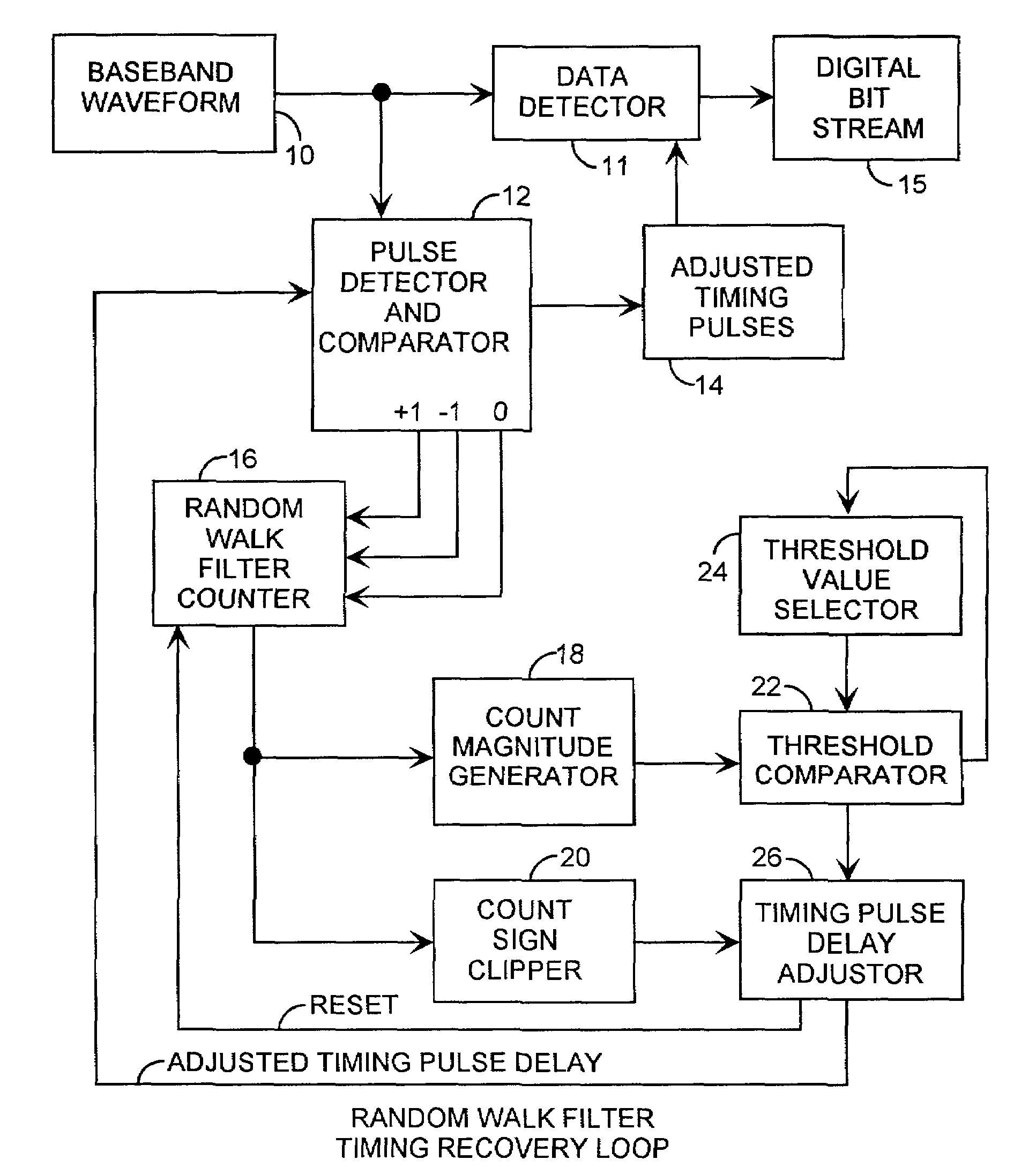

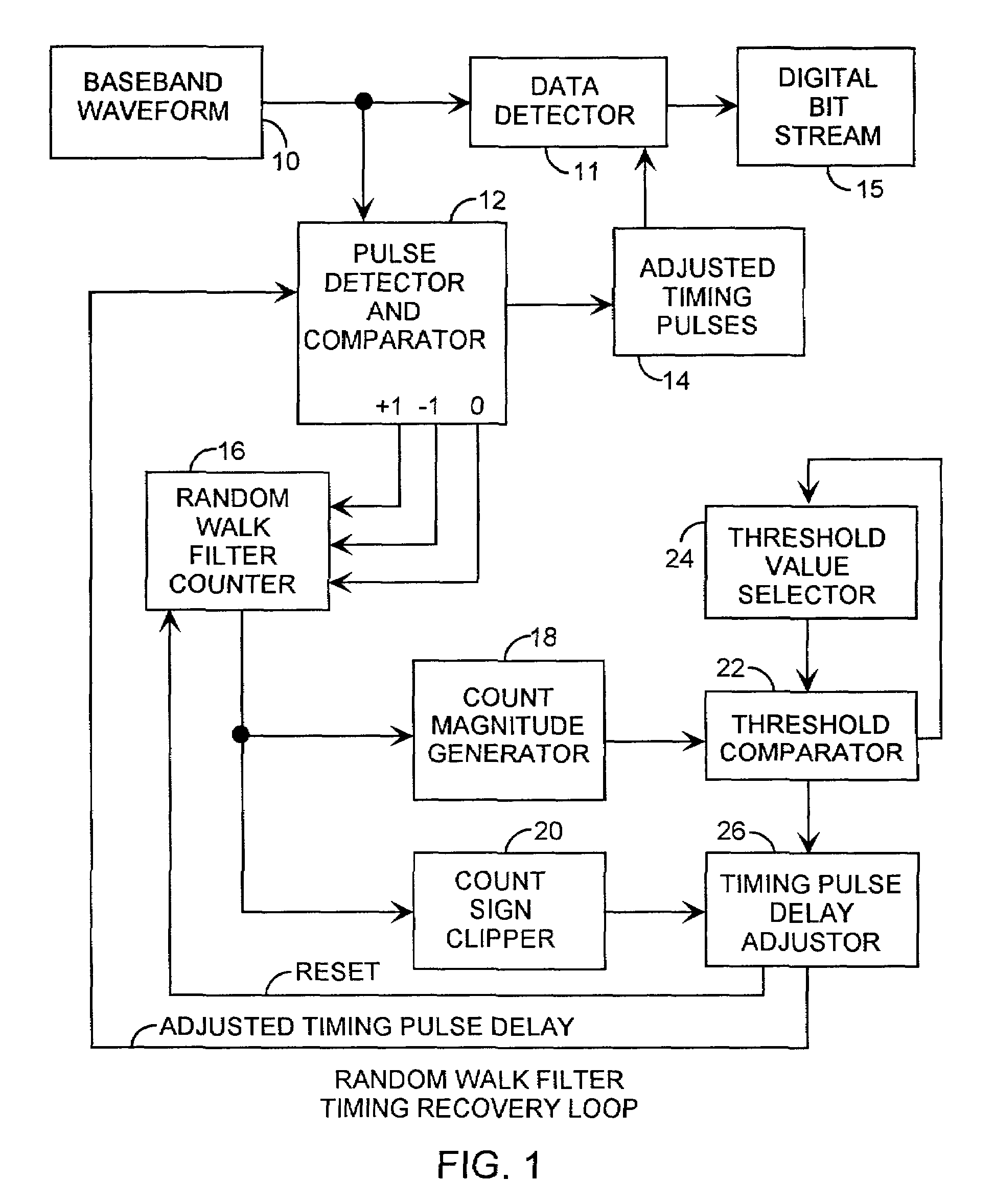

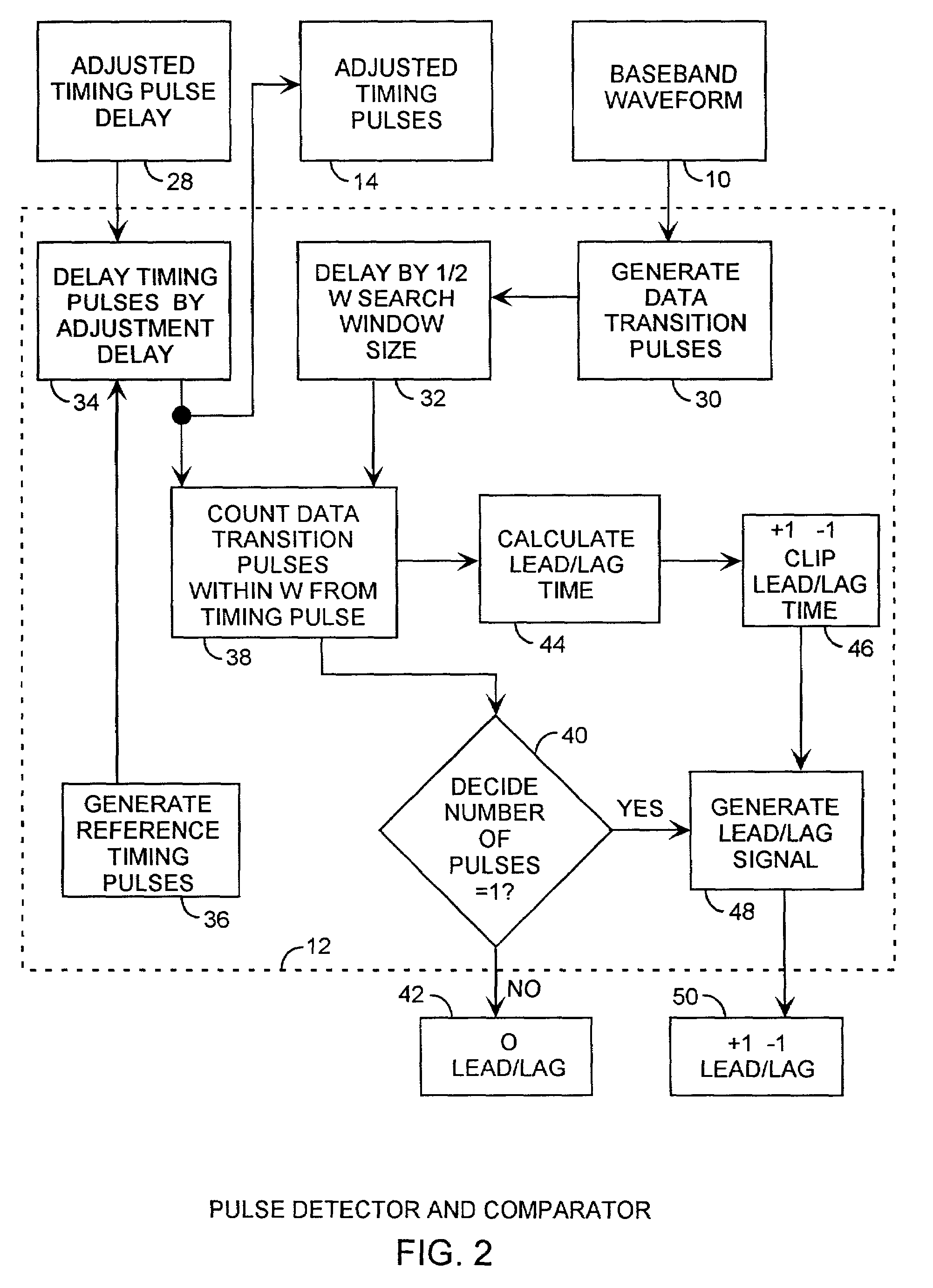

Random walk filter timing recovery loop

ActiveUS7469026B2Easy to detectReduce time jitterSynchronisation signal speed/phase controlAngle demodulation by phase difference detectionComputer scienceBit time

A timing recovery loop includes a random walk filter counter for counting early, nominal and late arrivals of data transitions pulses of an input baseband signal waveform encoding a digital bit stream, and provides magnitude counts that are compared to a threshold value that when exceeded by the magnitude counts results in a delay adjustment of the generated adjusted timing pulses then remaining synchronized with the actual bit timing for maintaining bit timing lock. The adjusted timing pulses can then be used by a data detector for reliable data detection and reconstruction of the digital bit stream. The threshold value can be adaptively adjusted for reducing drop lock rates in the presence of changing channel environments.

Owner:THE AEROSPACE CORPORATION

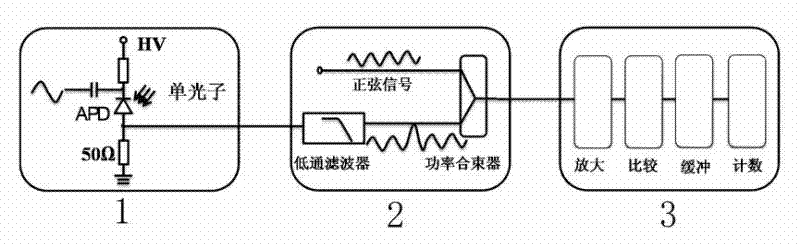

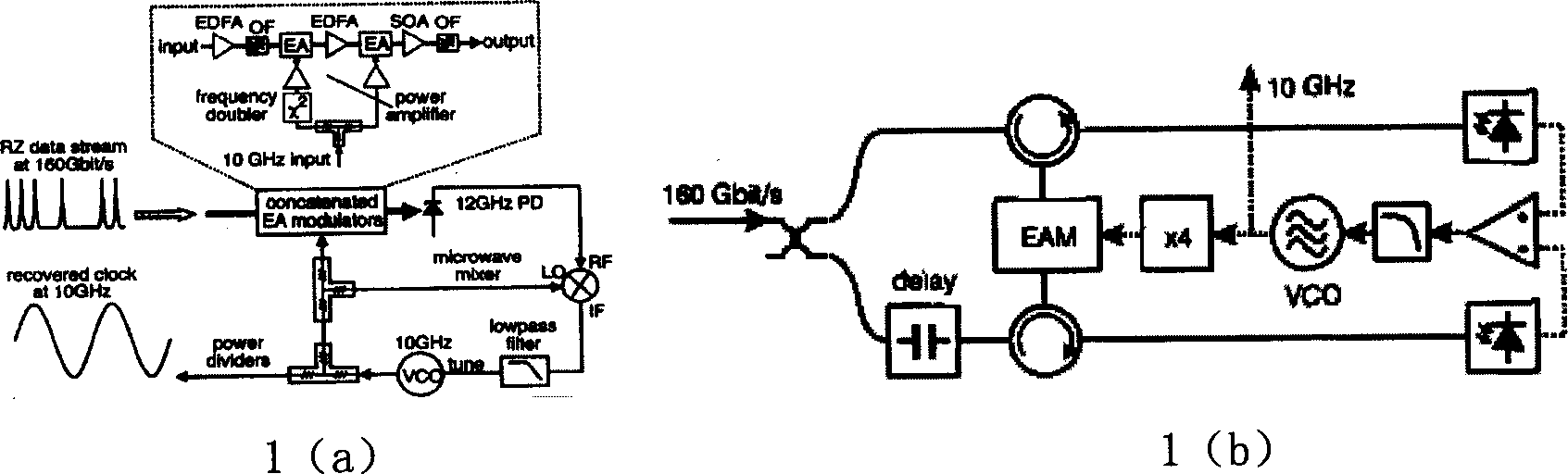

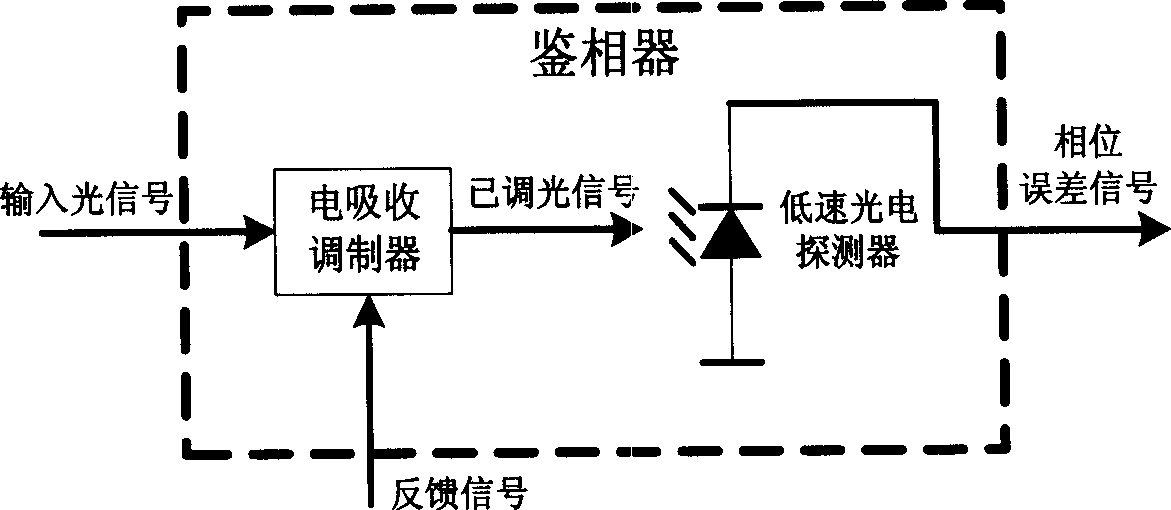

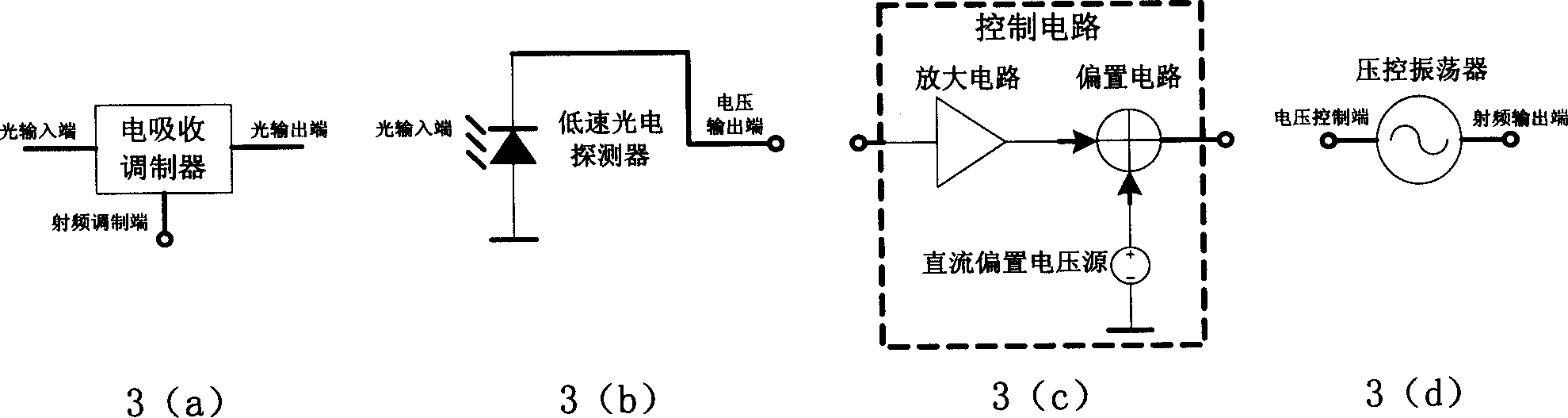

Photoelectric mixed phase-locked loop based on electric absorption regulator

A photoelectric mixed phase lock loop based on the electroabsorption modulator. It has the phase discriminator with the light signal as its input signal, which is made in the means of that the electroabsorption modulator connects with the low speed photo detector in series, the control circuit which is composed of the amplifying circuit and the bias circuit, and the voltage controlled oscillator, whose input terminal connects with the output terminal of the bias circuit and whose radio frequency output terminal connects with the feedback signal input terminal of the electroabsorption modulator. The input terminal of the abovementioned amplifying circuit connects with the phase error signal output terminal of the low speed photo detector. It has simple structure and can realize the locking of the input light signal by adjusting the central frequency of the voltage controlled oscillator.

Owner:TSINGHUA UNIV

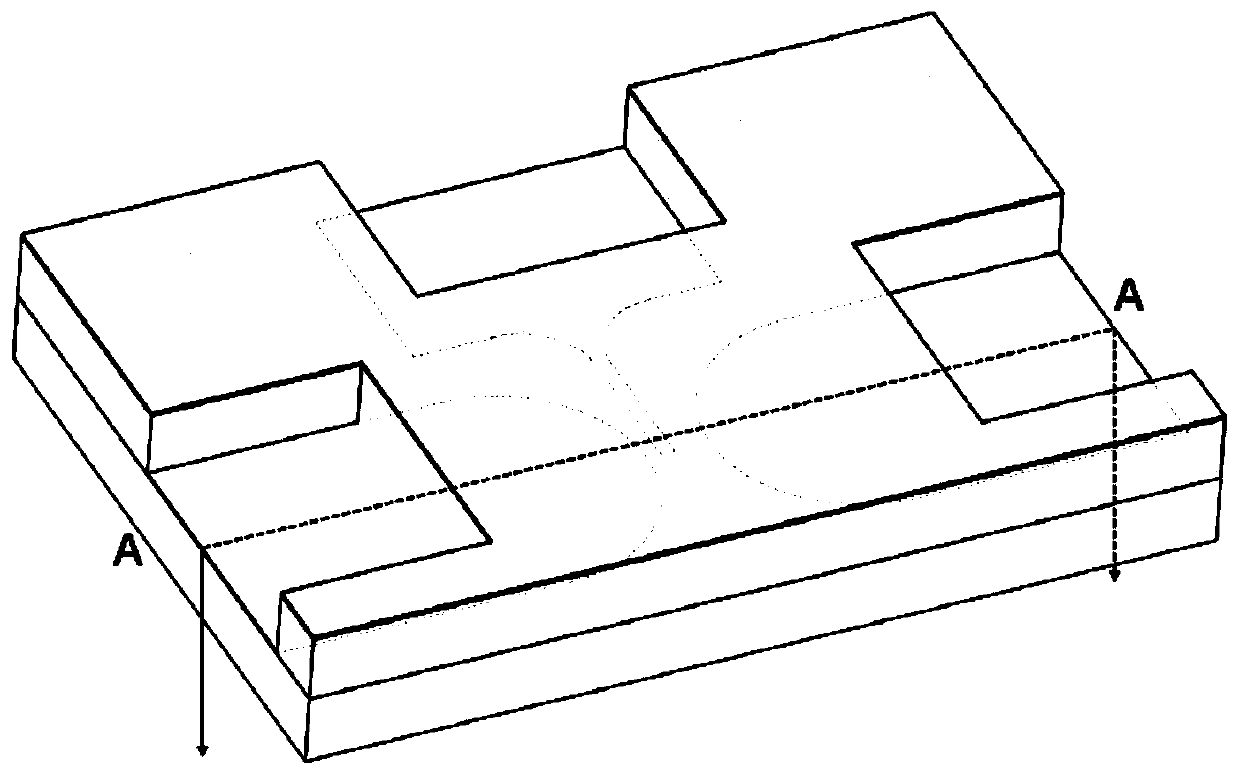

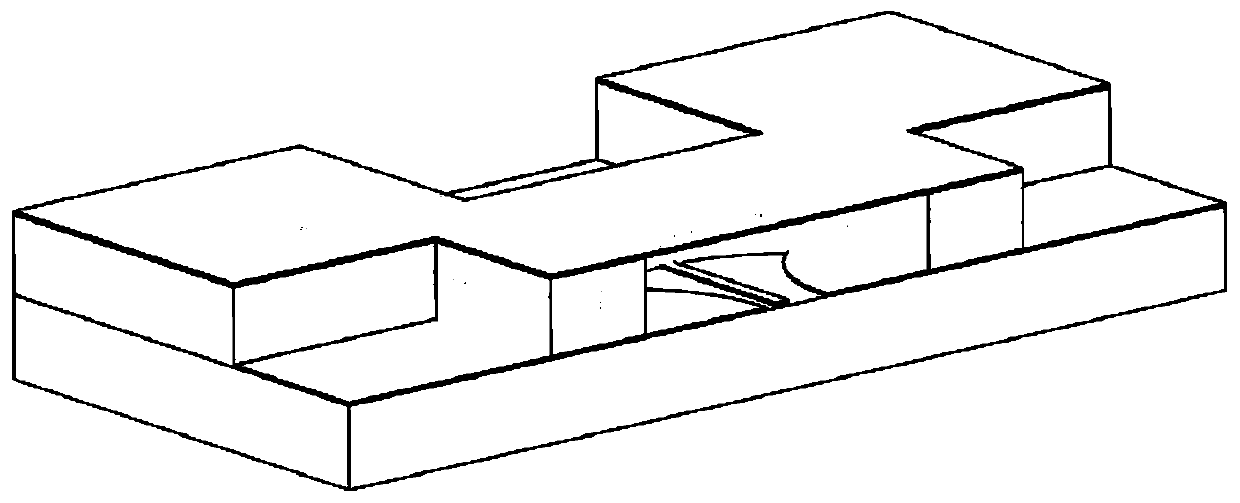

Closed planar three-electrode switch chip based on LTCC process

ActiveCN109802302ARealize integrated sintering manufacturingRealize batchSparking plugsSpark gaps with auxillary triggeringEngineeringMetal

The invention relates to the technical field of high-power pulses and in particular to a closed planar three-electrode switch chip based on an LTCC process. The three electrodes of the switch chip aresealed in a cavity. The switch chip specifically includes a substrate layer which serves as a carrier structure of the planar three-electrode switch chip; a metal layer placed on the substrate layerand including the cathode, the trigger pole and the anode of the switch chip, and bonding pads connected to the cathode, the trigger pole and the anode of the switch; a structural layer A placed overthe metal layer and including an electrode cavity and bonding pad slots exposing the bonding pads; and a structural layer B placed over the structural layer A and including an upper cover of the electrode cavity, and bonding pad slots exposing the bonding pads. The three electrodes of the switch can be sealed in the cavity by using the LTCC process, so that the switch-on capacity of the switch isenhanced and the stability of the switch is improved. Further, the LTCC process can make the switch integrally sintered and manufactured, realize mass production, and improve product consistency and reduces production cost.

Owner:NANJING UNIV OF SCI & TECH

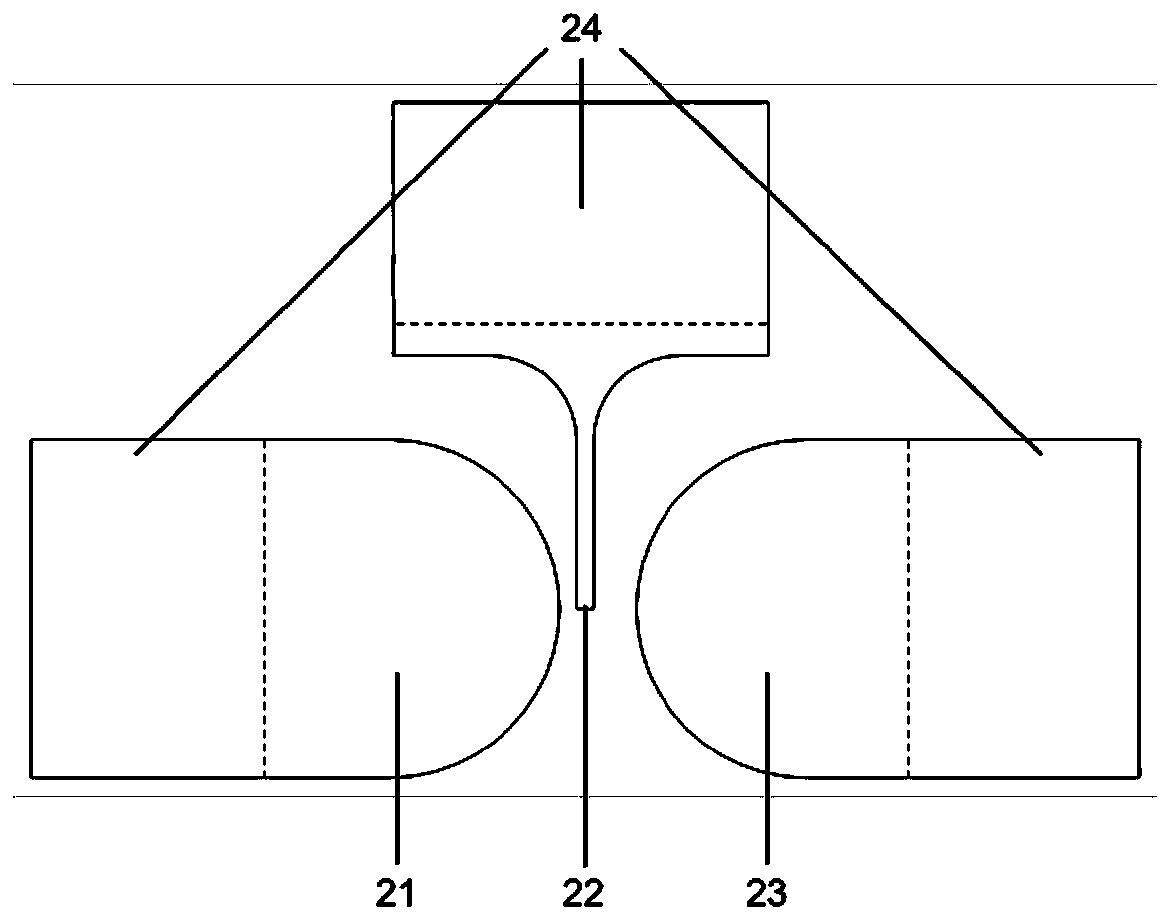

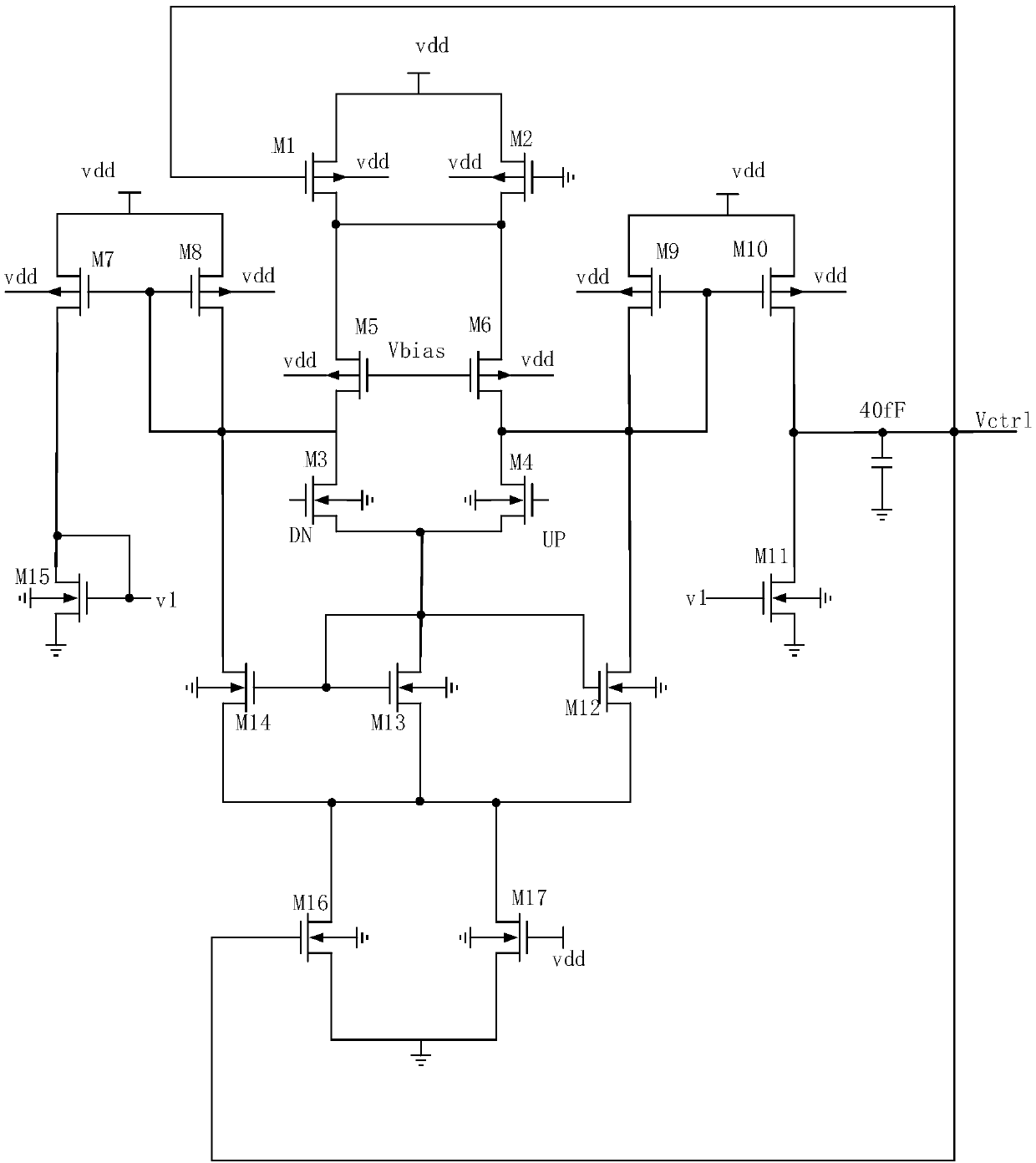

Single-ended negative feedback charge pump for delay-locked loop

ActiveCN107565961ASuppressing Current Mismatch IssuesReduce time jitterPulse automatic controlIntegrated circuitDelay-locked loop

The invention relates to the field of integrated circuits, and can suppress a current mismatch problem and enhance output stability. The technical scheme of the invention is as follows: provided is asingle-ended negative feedback charge pump for a delay-locked loop, wherein sources of two PMOS transistors M1 and M2 are connected with a drain of a power supply vdd, a grid of the M2 is earthed, anda grid of the M1 is connected with a last output Vctrl; sources of PMOS transistors M5 and M6 are connected with a drain of the M1, grids of the M5 and M6 are connected, a grid voltage Vbias is 0.8V;drains of the M5 and M6 are connected with drains of NMOS transistors M3 and M4, and DN and UP signals are input into grids of the M3 and M4; sources of the M3 and M4 are connected and further connected to grids of NMOS transistors M12, M13 and M14; a grid and a drain of the M13 are connected with each other, drains of the M14 and M12 are connected with the drains of the M3 and M4. The single-ended negative feedback charge pump for the delay-locked loop provided by the invention is mainly applied to design and manufacture occasions of the integrated circuits.

Owner:青岛展诚科技有限公司

Printed circuit board

InactiveUS20120093201A1Reduce time jitterBaseband system detailsPrinted circuit detailsElectrical resistance and conductancePropagation time

One end of a sub transmission line of which an impedance value is equal to or higher than a parallel impedance value of an output impedance value of a transmission circuit and an impedance value of a transmission line is connected to a connection point between the transmission circuit and the transmission line, and a correction resistor of which resistance is lower than an impedance value of the sub transmission line is connected to the other end of the sub transmission line. A length of the sub transmission line is set to satisfy a condition of 0.5×Tr (signal rise time)≦Td (signal propagation time of sub transmission line)≦0.5×Tmin (signal minimum pulse width), thereby achieving a de-emphasis function by a passive component, correcting a high-frequency component of a signal attenuated on the transmission line, and thus reducing timing jitters caused by intersymbol interference.

Owner:CANON KK

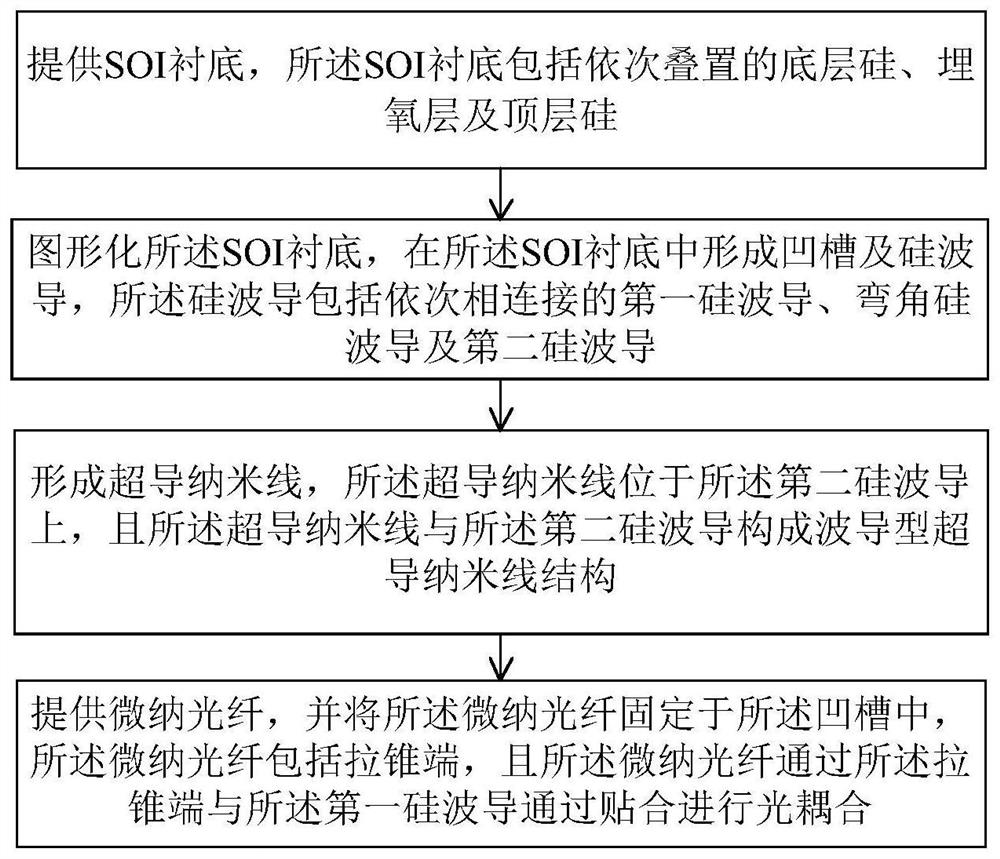

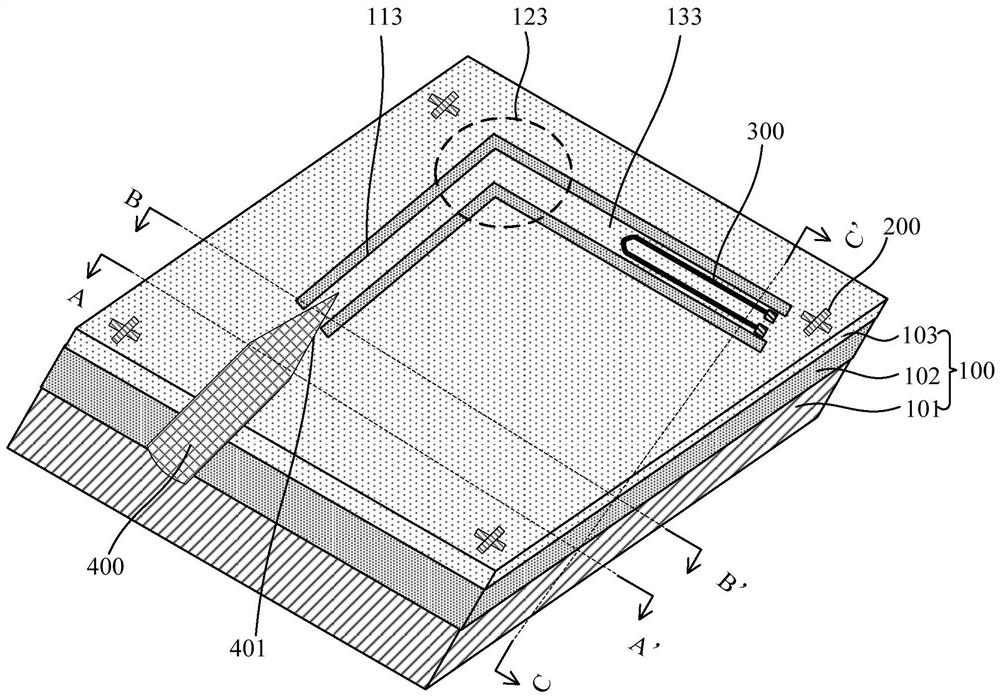

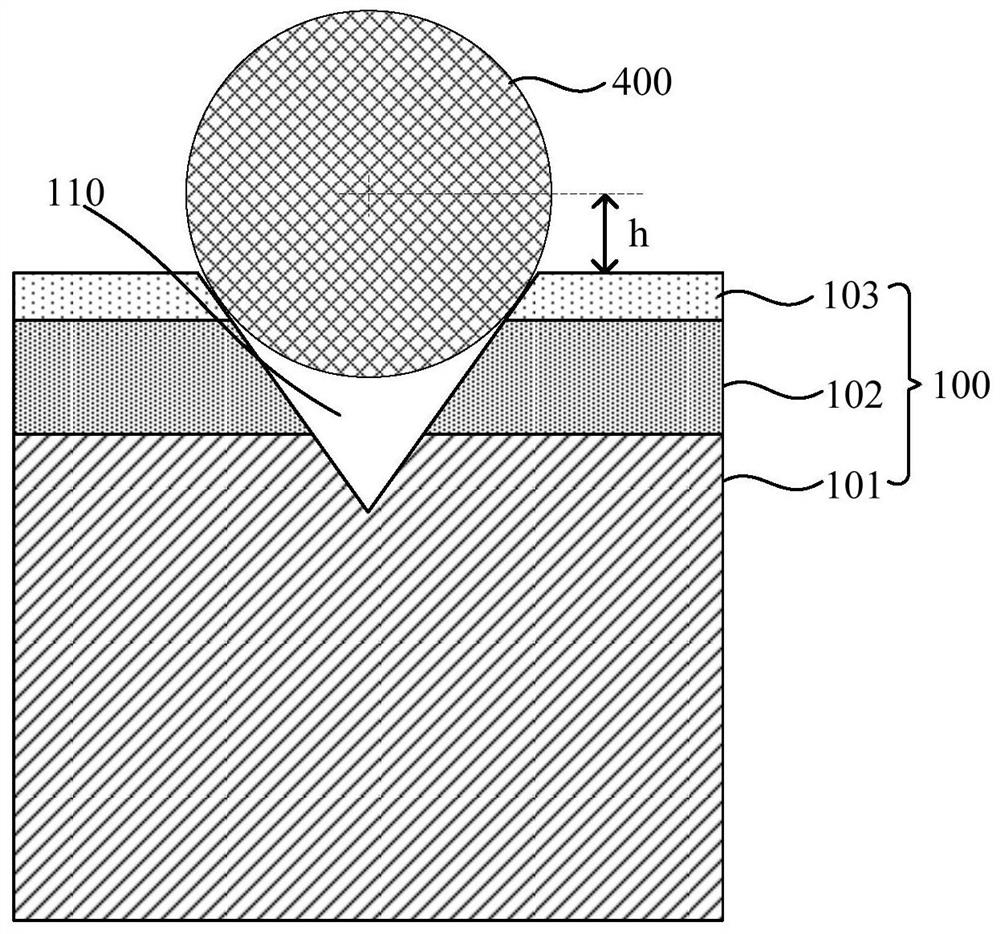

Micro-nano optical fiber-waveguide-superconducting nanowire single-photon detector and preparation method thereof

ActiveCN113204075AAchieve absorptionOptical coupling is easyNanosensorsCoupling light guidesNanowireWaveguide (optics)

The invention provides a micro-nano optical fiber-waveguide-superconducting nanowire single-photon detector and a preparation method thereof. A micro-nano optical fiber fixed in a V-shaped groove can realize high-precision optical coupling alignment with a waveguide, and the transition section, which becomes thin from thick, of the micro-nano optical fiber is suspended, so that light is prevented from leaking to a substrate, and the loss in the optical transmission process is further reduced; the waveguide type superconducting nanowire structure can completely absorb light on a chip; due to the design of the corner waveguide, an optical coupling area of the micro-nano optical fiber-waveguide can be completely separated from an optical detection area of the waveguide type superconducting nanowire structure, dark counting caused by background radiation propagating along the optical fiber can be effectively reduced, and the influence of the background dark counting on optical detection is reduced; according to the invention, a single-photon detector integrating high detection efficiency, high counting rate, low time jitter and low dark counting can be realized, and the detector is expected to play a role in the fields of light quantum information processing, quantum optics and the like.

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI

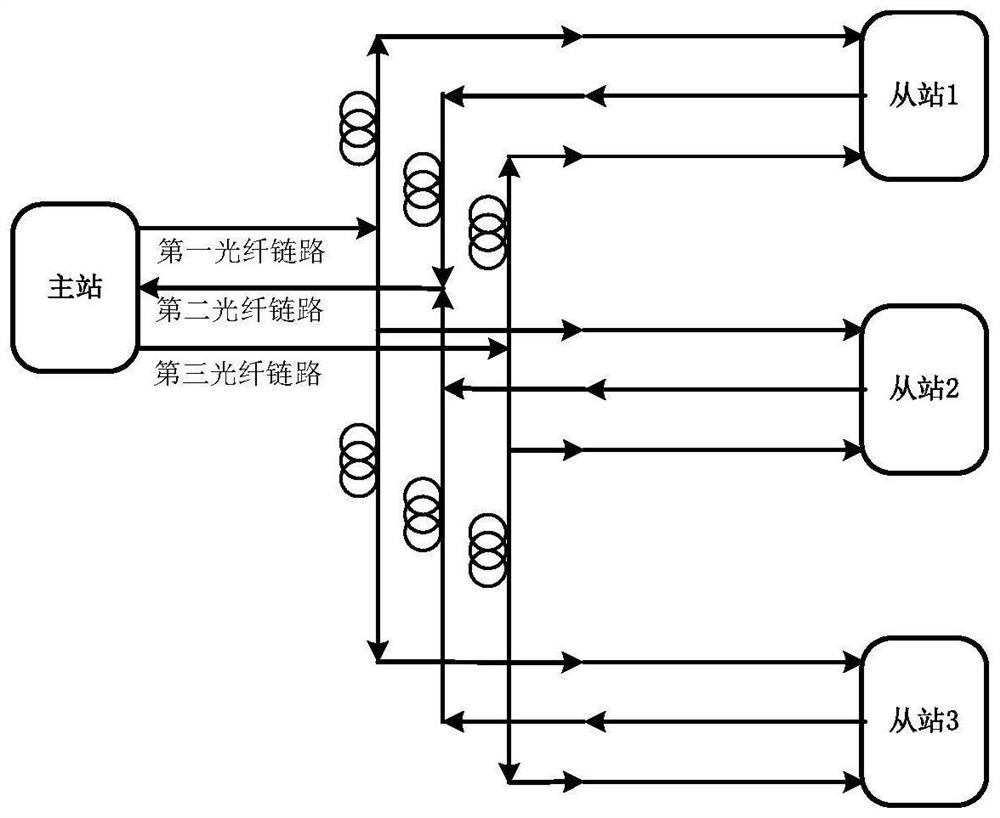

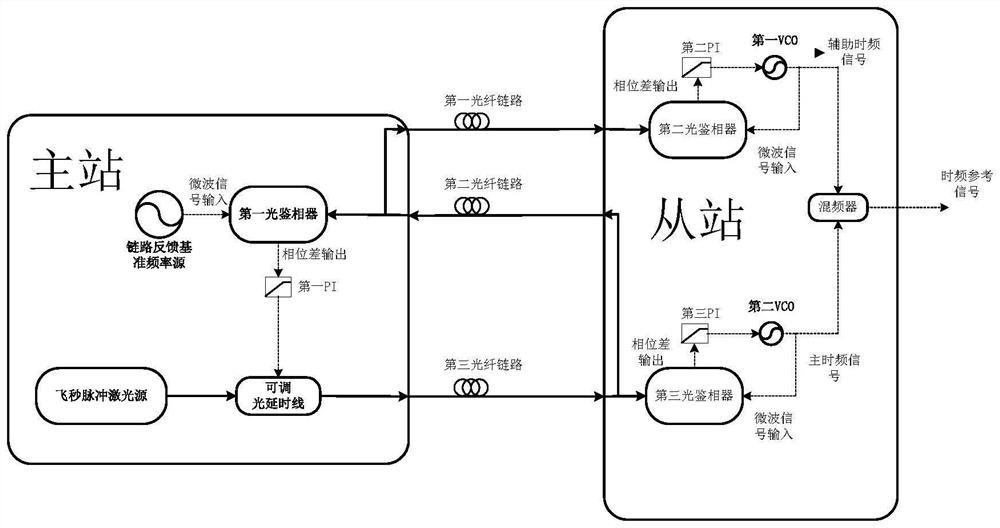

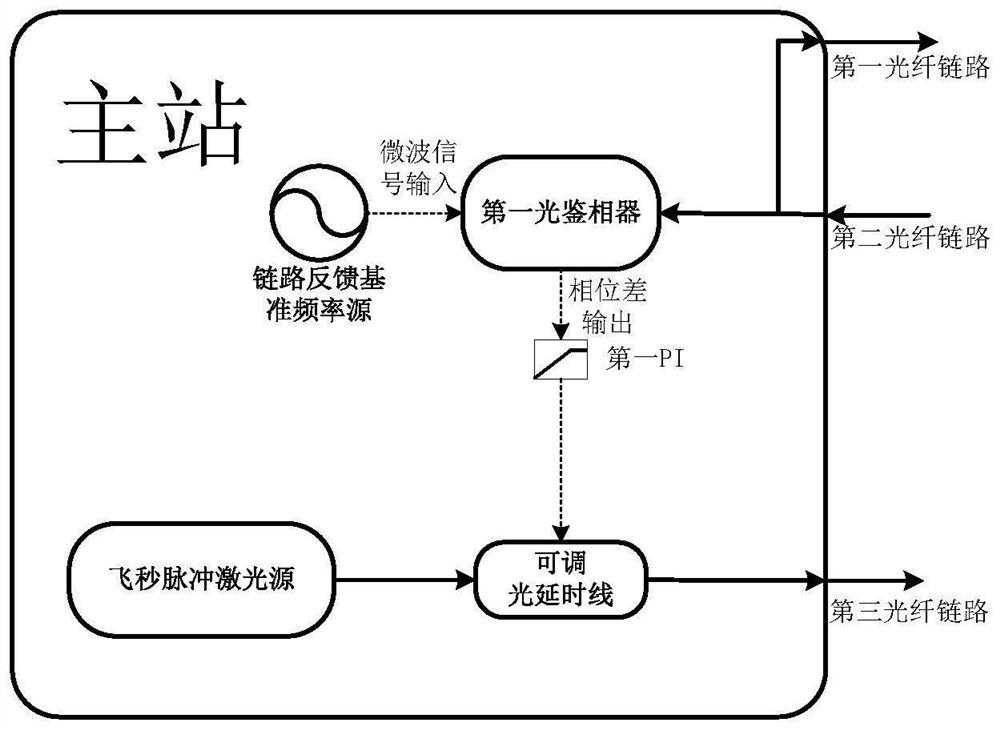

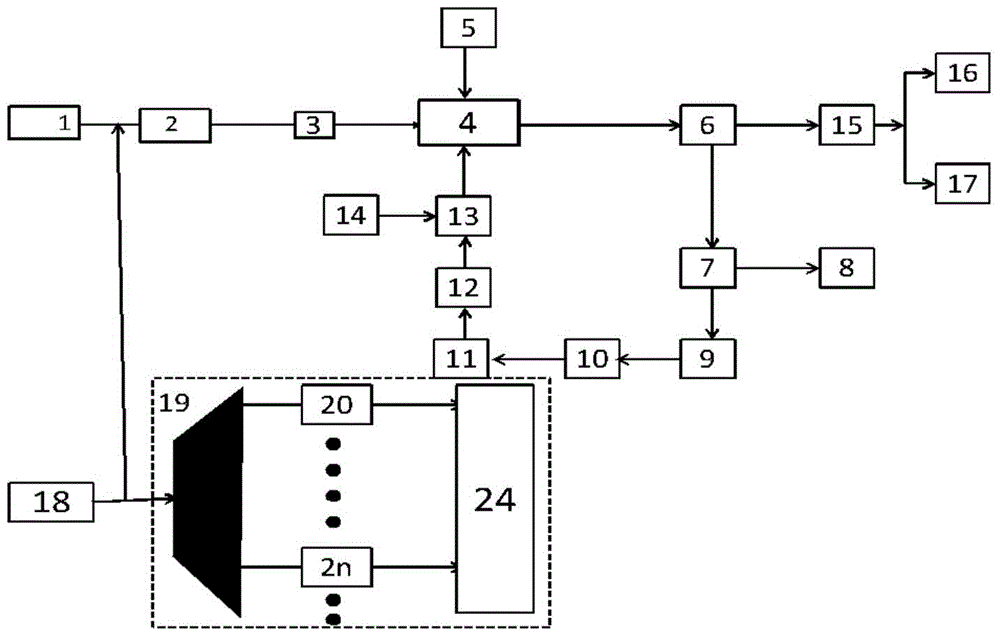

High-precision time-frequency synchronization signal distribution system and distribution method thereof

PendingCN114401066ALow phase noiseReduce time jitterTime-division multiplexDistortion/dispersion eliminationPhase noiseMaster station

The invention discloses a high-precision time-frequency synchronization signal distribution system and a distribution method thereof, which are characterized in that femtosecond optical pulses with ultra-low phase noise are used as system reference frequency sources and are distributed to all stations of a distributed system through optical fibers to serve as reference sources; extracting a picosecond-level high-precision time-frequency reference signal from the station through a time-frequency synchronization signal extraction technology based on an optical phase discriminator; in order to reduce phase noise deterioration caused by external environment interference on an optical fiber link between a master station and a slave station, an optical fiber stable-phase transmission technology based on a phase-locked loop and an optical fiber stable-phase transmission technology based on frequency mixing elimination are adopted, time jitter introduced by the link can be compensated and eliminated, ultra-low-phase-noise time-frequency reference signals are provided for all substations, and the system performance is improved. And the picosecond-level high-precision time-frequency synchronization among the stations is realized.

Owner:NO 8511 RES INST OF CASIC

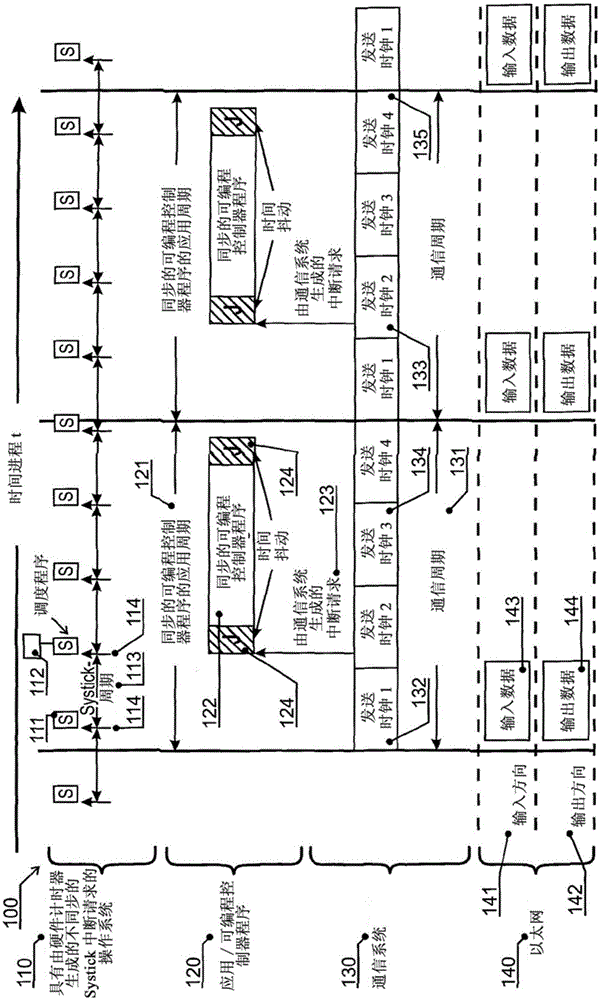

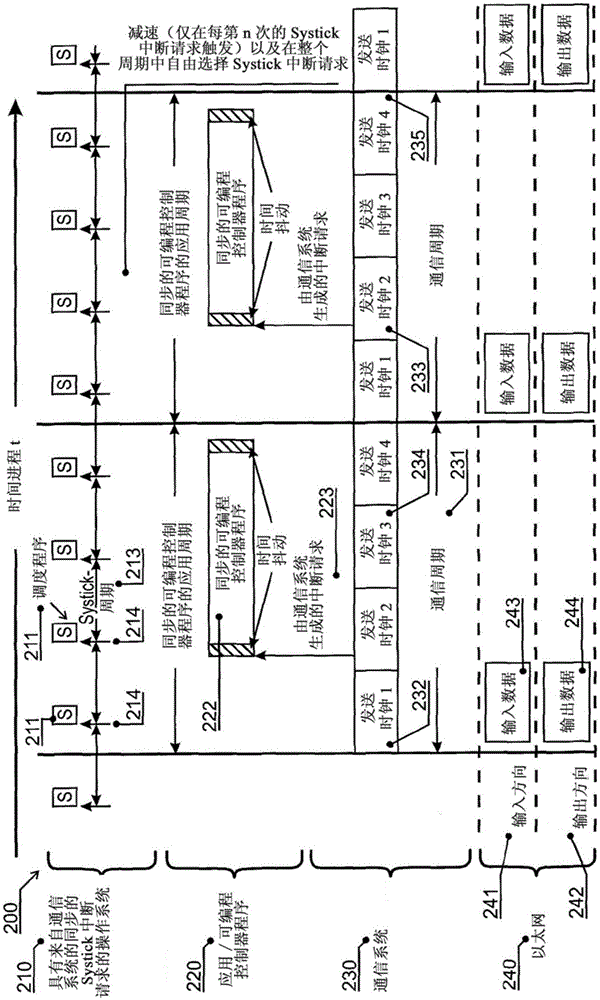

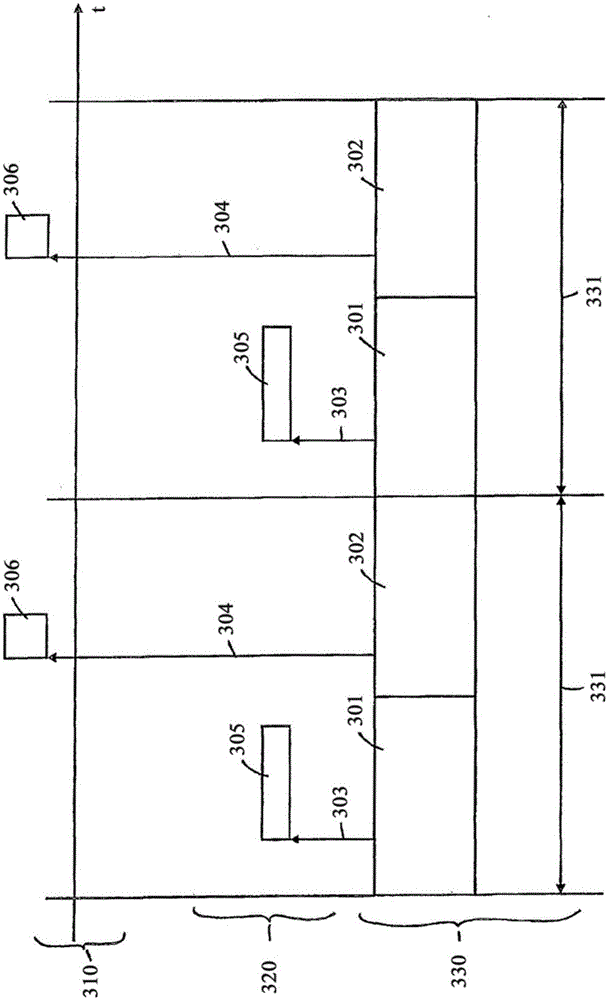

Automation device and method for reducing jitter

ActiveCN105075155AReduce time jitterSynchronisation arrangementProgram synchronisationControl communicationsEmbedded system

The invention relates to an automation device (200), which has an operating system (210) having a first system clock pulse and a communication system (230) having a second system clock pulse. The first system clock pulse is intended to control a system time cycle (213) of the operating system (210), and the second system clock pulse is intended to control a system time cycle (231) of the communication system (230). Furthermore, the first system clock pulse and the second system clock pulse are synchronized.

Owner:PHOENIX CONTACT GMBH & CO KG

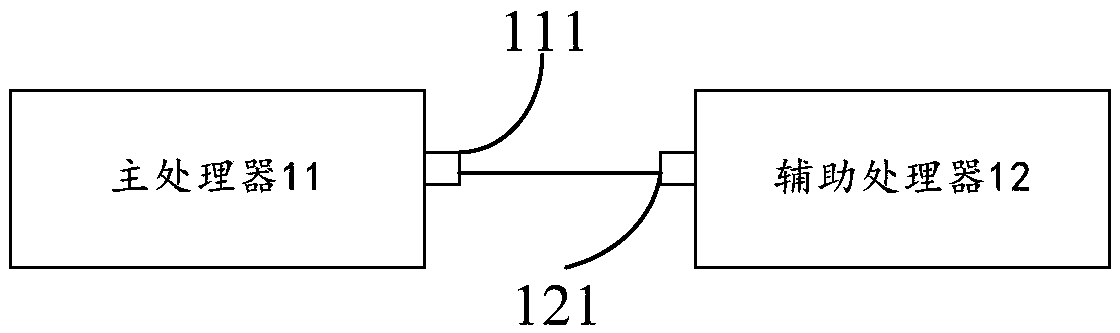

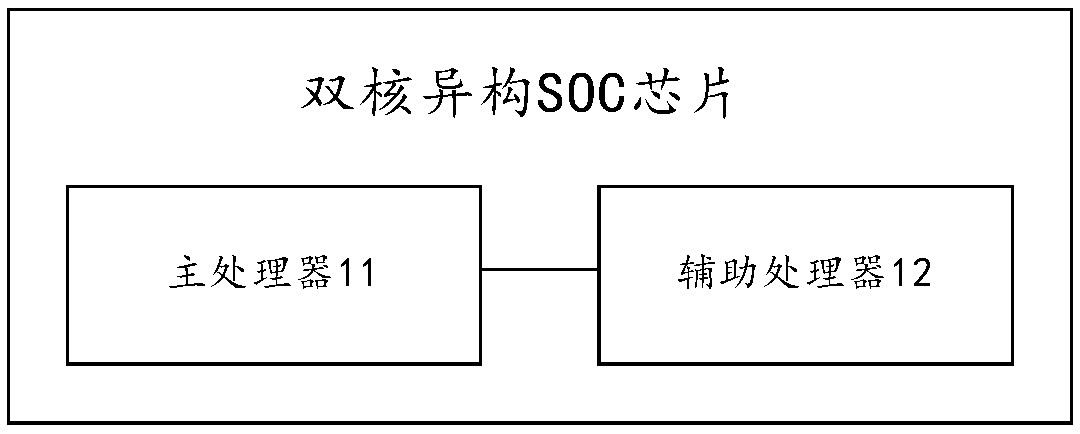

Control equipment and system

PendingCN109613873ALow resource occupancyAccurate operationProgramme controlComputer controlIndustrial EthernetCoprocessor

The embodiment of the invention relates to control equipment and system. The control equipment comprises a main processor and an auxiliary processor; the main processor is connected with the auxiliaryprocessor and is used for generating a control data set for controlling at least one object and sending the control data set to the auxiliary processor; and the auxiliary processor is used for performing parallel conversion processing on the control data set by using a real-time industrial Ethernet master station protocol to obtain at least one control instruction for controlling the object and sending the control instruction to the at least one object through an Ethernet interface. The real-time industrial Ethernet master station protocol runs on the auxiliary processor, the parallel processing mode of the auxiliary processor is compared with the serial processing mode of the main processor, the efficiency is higher, the real-time capability is higher, the time jitter caused by serial processing is reduced, and real-time accurate control over the object is further realized.

Owner:GREE ELECTRIC APPLIANCES INC

Superconducting nanowire single photon detection system provided with impedance matching transmission line

InactiveCN110793630AImprove performancePulse amplitude amplificationPhotometry electrical circuitsNanowirePhoton detection

The invention provides a superconducting nanowire single photon detection system provided with an impedance matching transmission line. The system comprises a superconducting nanowire single photon detector (SNSPD), the 1 / 4 wavelength impedance matching transmission line, a high-pass filter, a three-port device, a current source and an amplifier, wherein one end of the 1 / 4 wavelength impedance matching transmission line is connected with the SNSPD; one end of the high-pass filter is connected with the end, connected to the SNSPD, of the 1 / 4 wavelength impedance matching transmission line, andthe other end of the high-pass filter is grounded; a first port of the three-port device is connected with the end, away from the SNSPD, of the 1 / 4 wavelength impedance matching transmission line; oneend of the current source is connected with a second port of the three-port device; and the input end of the amplifier is connected with a third port of the three-port device, and the grounded end ofthe amplifier is grounded. Through the system, matching reading of a specific frequency signal can be realized, amplification of a pulse amplitude is realized; and time jitter is lowered; and low-frequency components in the signal can be shaped and removed, so that the counting rate and detection rate are increased.

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI

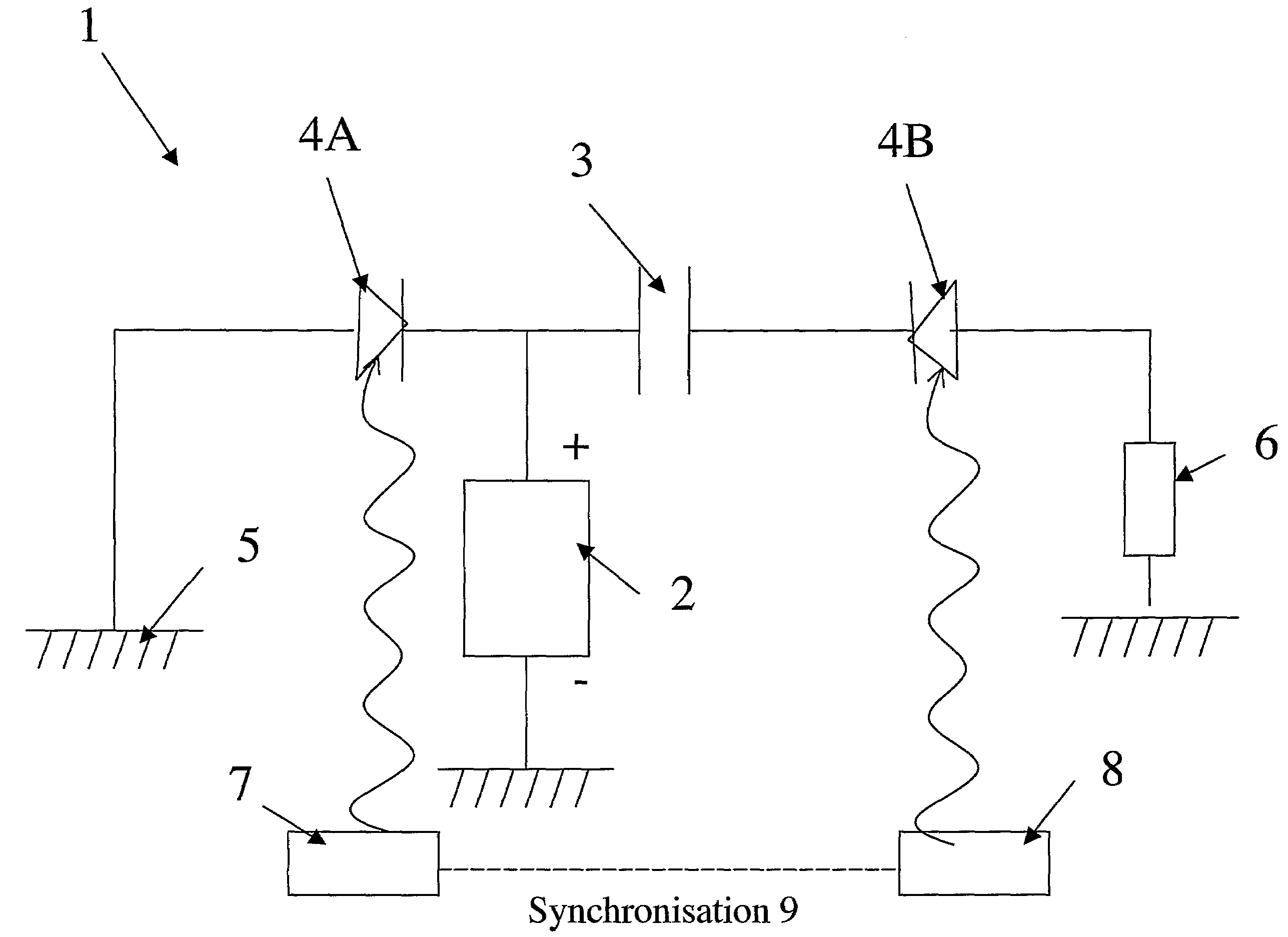

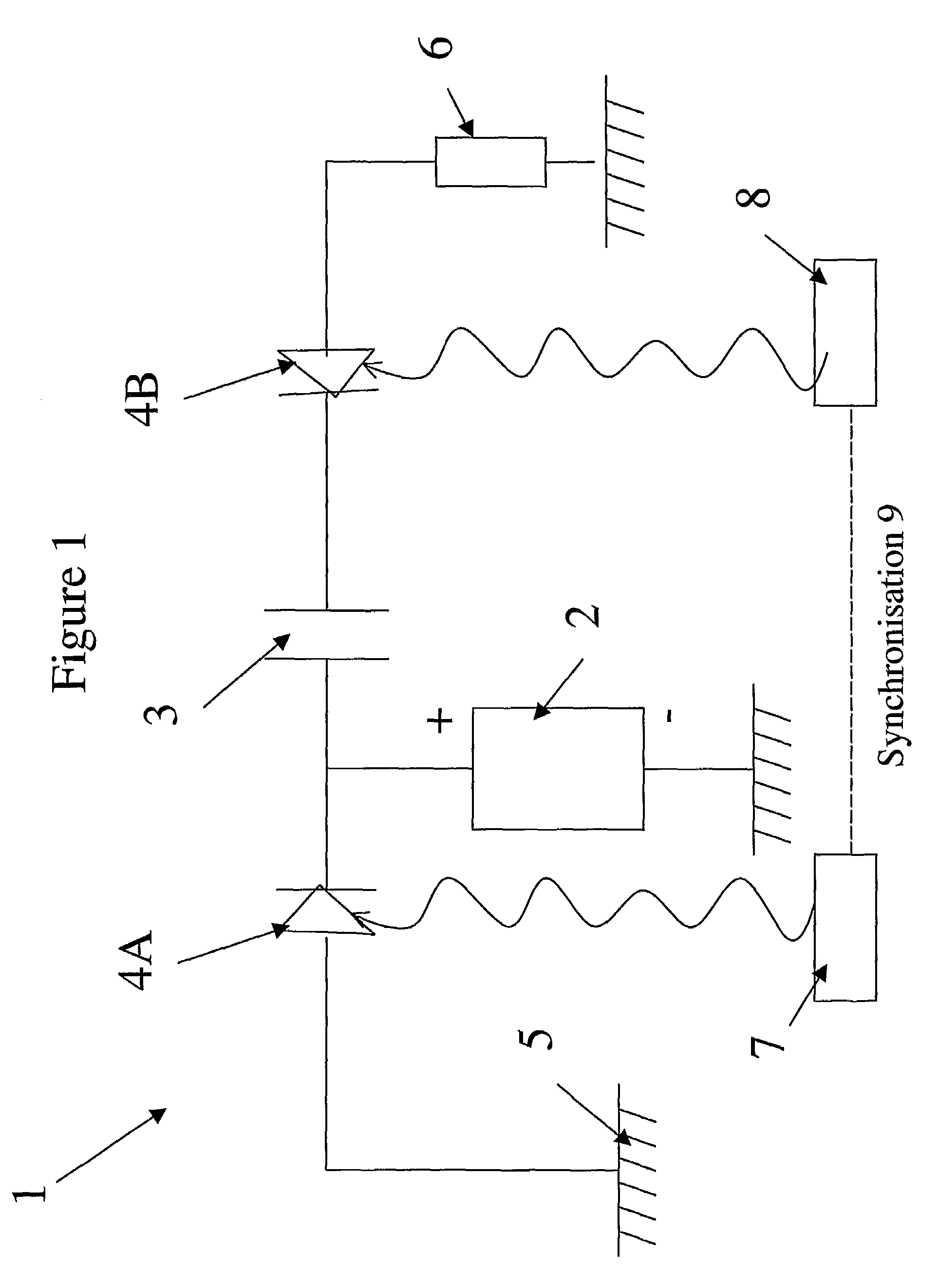

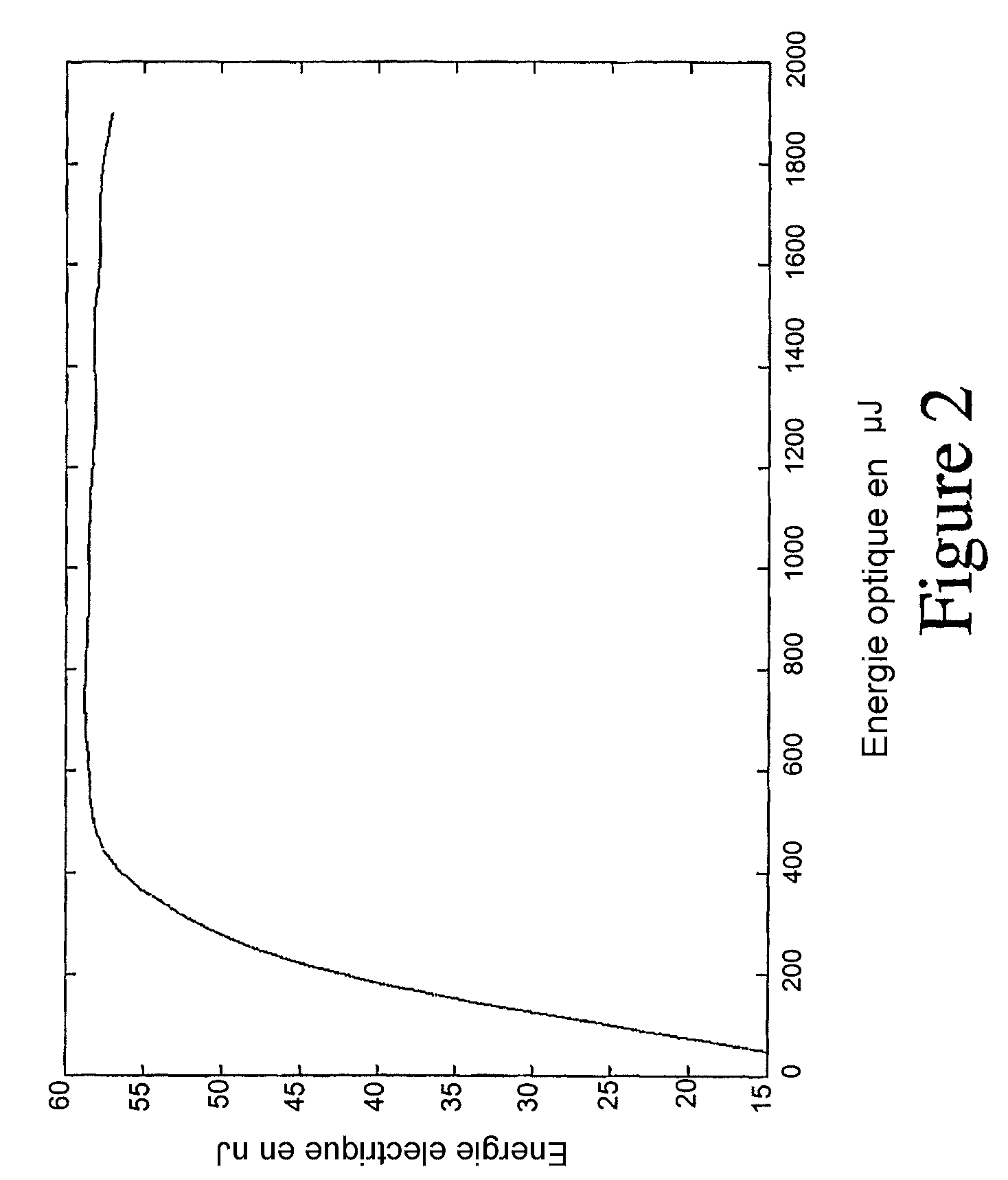

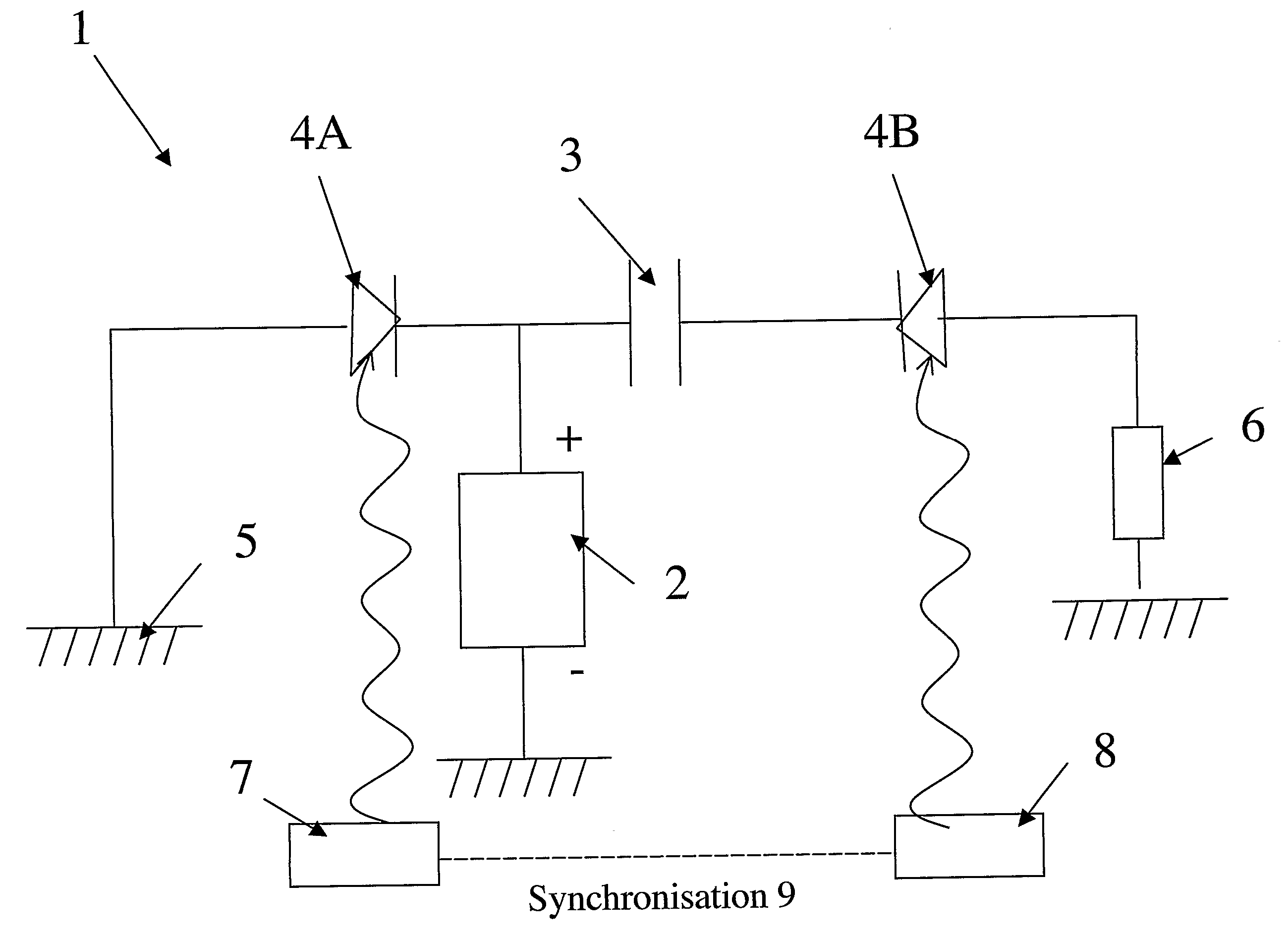

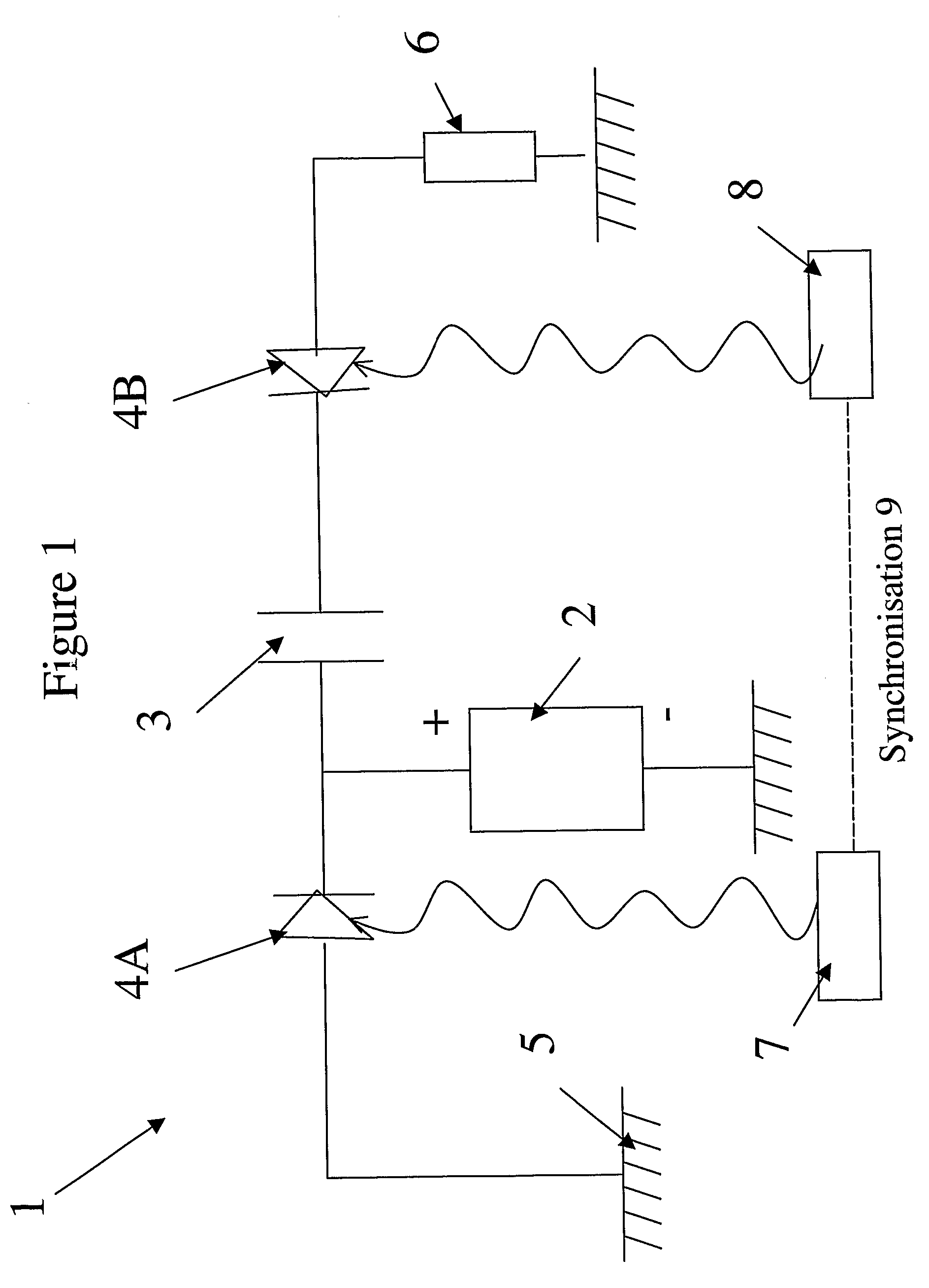

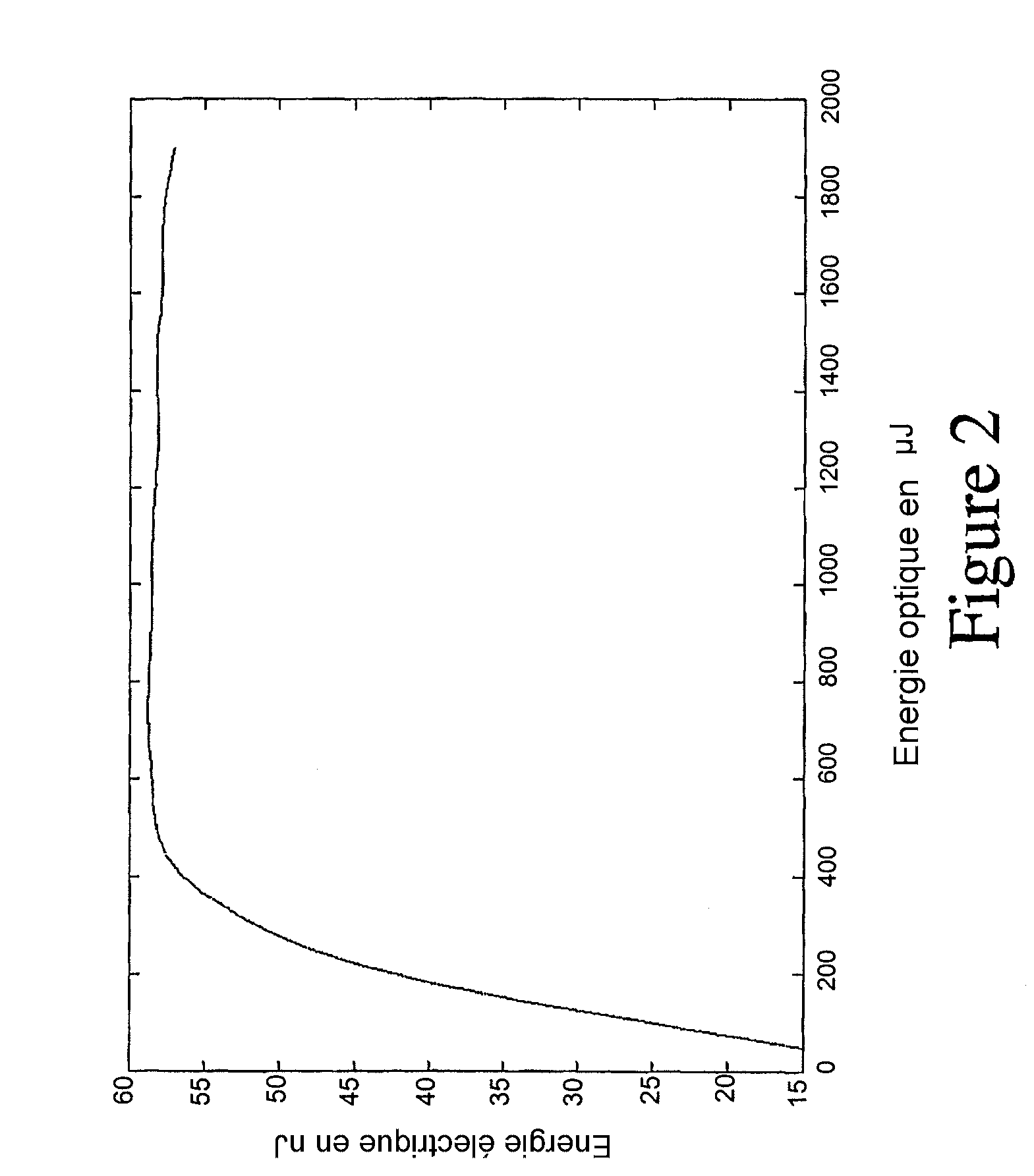

High-power electric pulse generator

InactiveUS7605632B2Good reproducibilityEasy to useLaser detailsPulse generation by energy-accumulating elementLinear regionElectrical conductor

A high power electric pulse generator includes a charge storage device, a high voltage source for charging the charge storage device, a first photoconductor element connected to the reference potential and to the storage device, a second photoconductor element connected to the storage device and to a useful load, a first light source for delivering a pulse of light to the first photoconductor, a second light source for delivering a pulse of light to the second photoconductor and a synchronization device for synchronizing the emission delay between the first light source and the second light source. The first photoconductor and the second photoconductor are passive semiconductor elements with a linear regime forming photosensitive switches, with the first and second photoconductors being doped silicon photoconductors.

Owner:CENT NAT DE LA RECHERCHE SCI +1

High-Power Electric Pulse Generator

InactiveUS20090009227A1Reduce time jitterEasy to controlLaser detailsPulse generation by energy-accumulating elementLinear regionElectrical conductor

A high power electric pulse generator includes a charge storage device, a high voltage source for charging the charge storage device, a first photoconductor element connected to the reference potential and to the storage device, a second photoconductor element connected to the storage device and to a useful load, a first light source for delivering a pulse of light to the first photoconductor, a second light source for delivering a pulse of light to the second photoconductor and a synchronization device for synchronizing the emission delay between the first light source and the second light source. The first photoconductor and the second photoconductor are passive semiconductor elements with a linear regime forming photosensitive switches, with the first and second photoconductors being doped silicon photoconductors.

Owner:CENT NAT DE LA RECHERCHE SCI +1

Method of full light control laser synchronization

This invention relates to a method for realizing total optical control laser synchronization in far distance, which utilizes the cross phase modulation action of multiple lasers in medium to realize synchronous control of far distance multi-beam laser. Advantage: small dithering of time, far distance multi-color total optical control laser synchronization can be realized, when the absolute phase of a far beam is locked, other beams can trace locking automatically so as to get new beams.

Owner:EAST CHINA NORMAL UNIV

A device for generating Nyquist optical pulses based on an ultra-broadband optical frequency comb

ActiveCN104330940BGood time stabilityOvercoming Bandwidth DisadvantagesLight demodulationFrequency spectrumBand-pass filter

The invention discloses a device for generating Nyquist optical pulse based on an ultra-broadband optical frequency comb. The device comprises the following components: a narrow line-width laser, a first wavelength division multiplexer, a polarization controller, a Fabry-Perot electro-optic modulator, a temperature control device, an optical coupler, a circulator, a phase-shifted fiber bragg grating, an optical amplifier, a photoelectric detector, an electric amplifier, an electric phase shifter, a bias T, a direct-current bias, an optical band-pass filter, an optical spectrum analyzer, a quantum dot mode-locked laser, a second wavelength division multiplexer and a plurality of electro-optical modulators. By virtue of the device, the disadvantage of bandwidth of the conventional electronics method can be overcome; the device is used as a light source for optical fiber communication; the frequency spectrum utilization rate of an optical fiber communication system can be greatly improved.

Owner:INST OF SEMICONDUCTORS - CHINESE ACAD OF SCI

Method for detecting gigahertz single photon with low time jitter and low noise

ActiveCN102230828BImprove signal-to-noise ratioMaintain integrityInstrumentsLow noiseSignal processing circuits

The invention relates to the field of quantum secret communication and weak infrared light detection in the technical field of optical fiber communication, in particular to a method for detecting a gigahertz high-speed near infrared single photon with low time jitter and low noise. A control circuit related to the method consists of a signal detection circuit, a noise suppressing circuit and a signal processing circuit, wherein the noise suppressing circuit is used for extracting an avalanche electric signal by the following steps of: dividing a sine signal of gigahertz into two paths; loading one path serving as a gate signal on an avalanche photoelectric diode; transmitting a response output signal of the avalanche photoelectric diode to a low-pass filter; attenuating the other path of sine signal to an amplitude which is same as that of the response signal of the avalanche photoelectric diode passing through the low-pass filter; and transmitting the other path of sine signal to a balance circuit for balancing with the response signal of the avalanche photoelectric diode passing through the low-pass filter to remove spike noise and extract the avalanche electric signal. In the method, the spike noise is removed in a way of combining low-pass filtering with the balance circuit, so that the avalanche signal is extracted, higher detection efficiency is achieved, and the time jitter is controlled within dozens of picoseconds.

Owner:EAST CHINA NORMAL UNIV

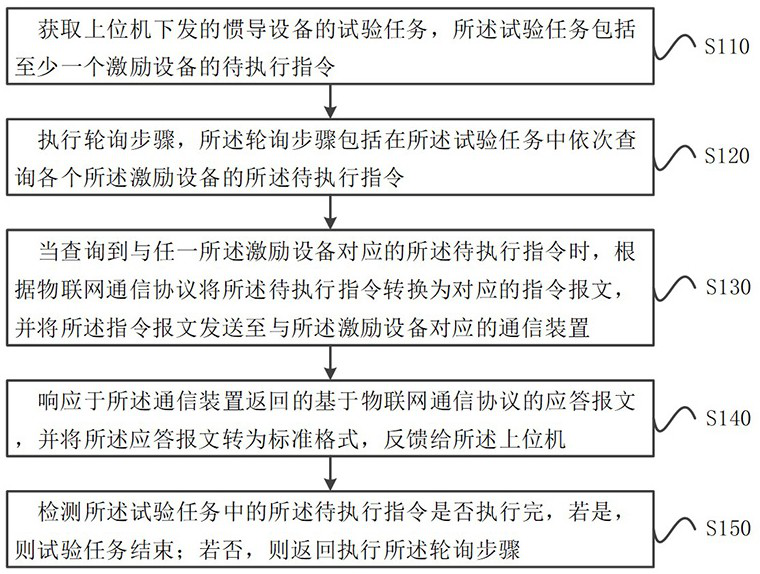

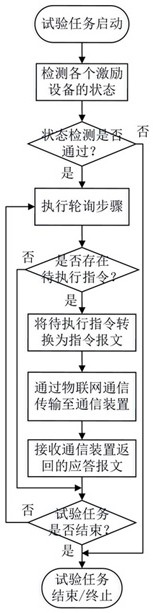

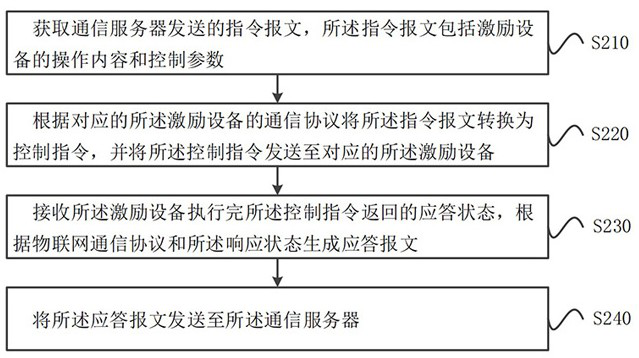

Inertial navigation equipment test method, communication server, communication device and storage medium

ActiveCN113411410BImprove real-time performanceAvoid replacementMeasurement devicesTransmissionComputer hardwareTest efficiency

The invention provides a method for testing inertial navigation equipment, a communication server, a communication device and a storage medium. The method includes: obtaining the test task of the inertial navigation equipment issued by the host computer, the test task including at least one instruction to be executed for stimulating the equipment; executing The polling step, the polling step includes sequentially inquiring about the instructions to be executed of each stimulus device in the test task; when inquiring about the instructions to be executed corresponding to any stimulus device, converting the instructions to be executed into corresponding Command message, and send the command message to the communication device corresponding to the incentive device; respond to the response message based on the Internet of Things communication protocol returned by the communication device, and convert the response message into a standard format, and feed it back to the host computer; Detect whether the instructions to be executed in the test task have been executed, if yes, the test task ends; if not, return to the polling step. The technical scheme of the invention improves the test efficiency and real-time response of the inertial navigation equipment.

Owner:北京中天星控科技开发有限公司

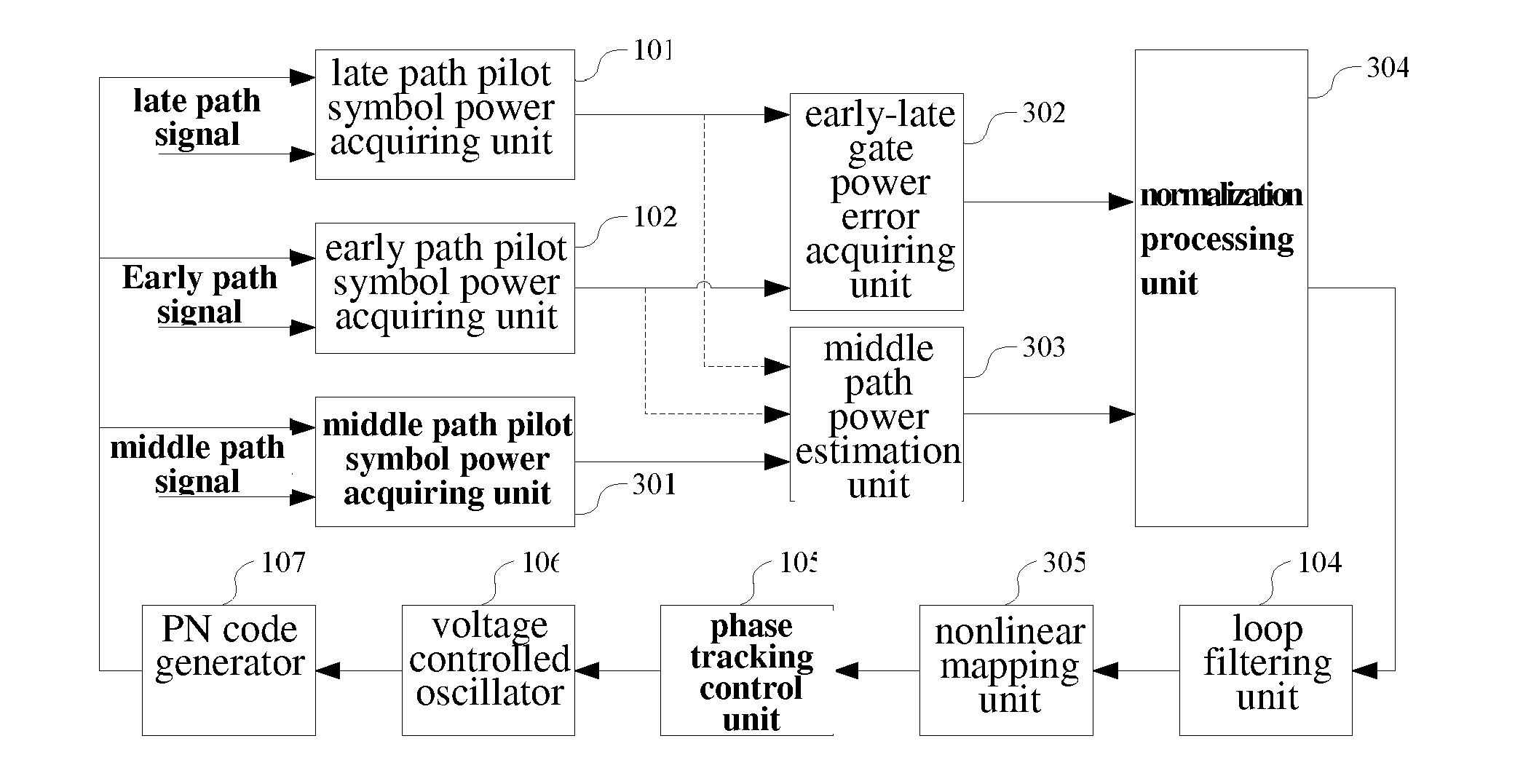

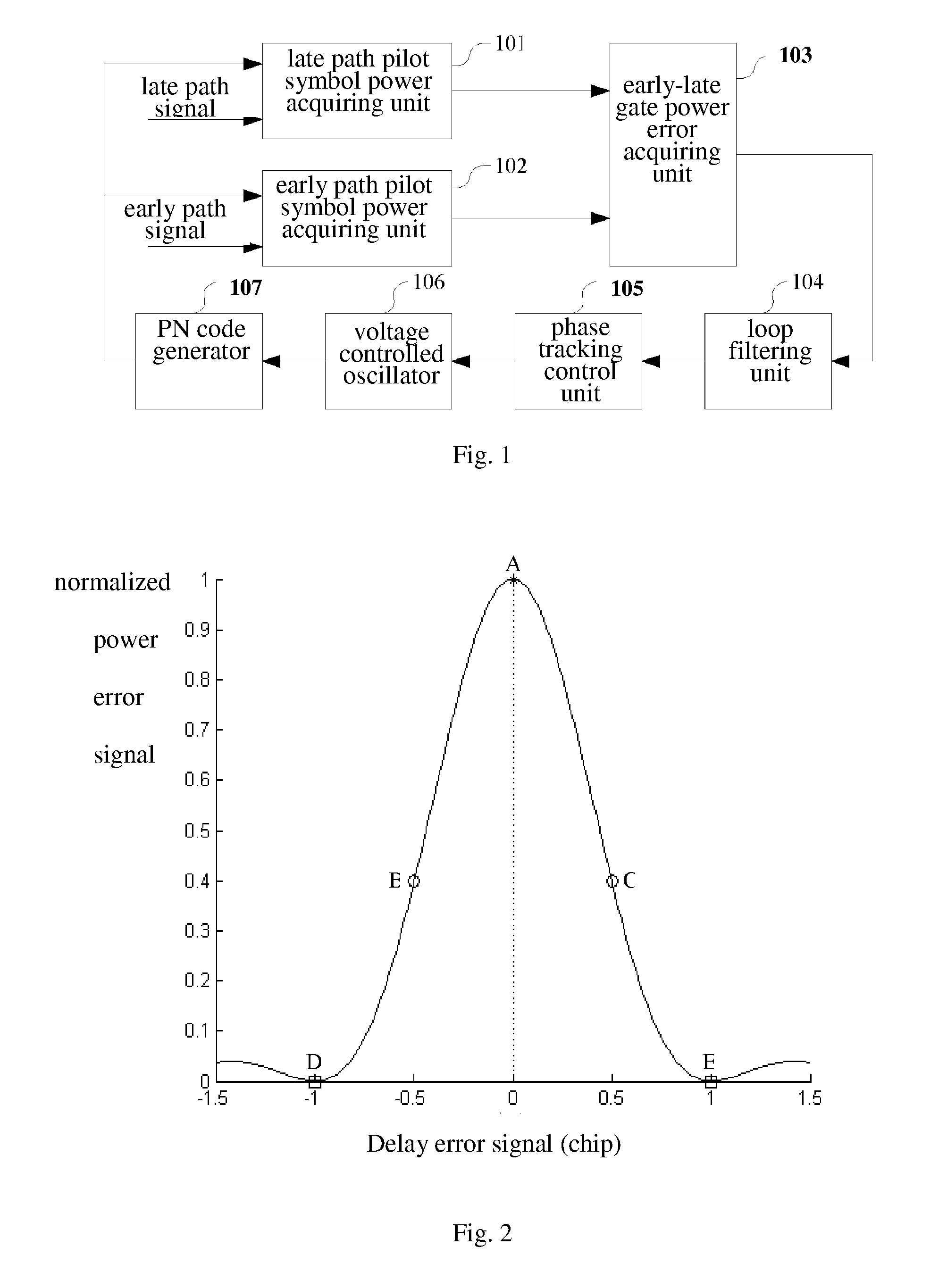

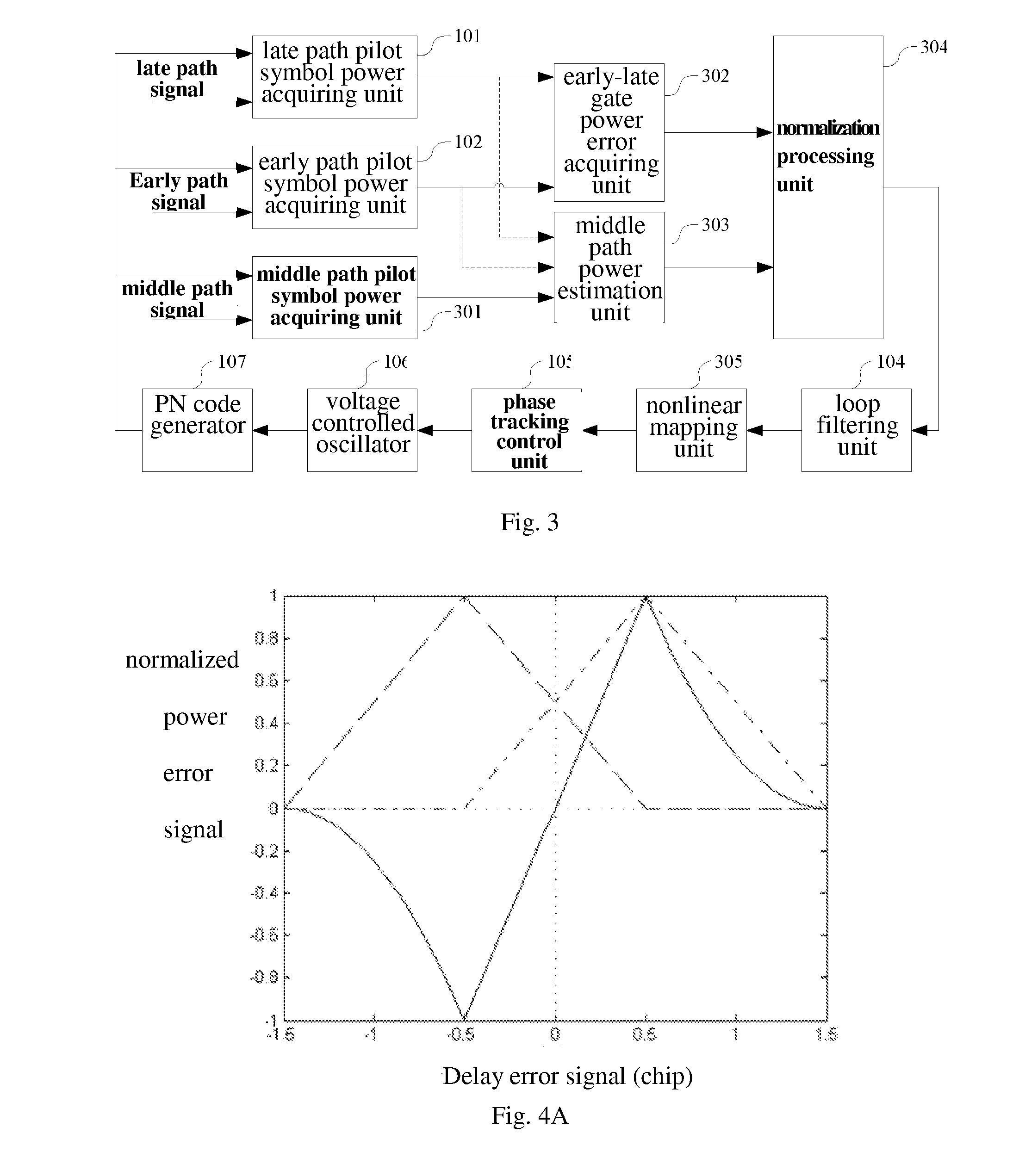

Multipath Tracking Device and Method in A CDMA Communication System

InactiveUS20100177805A1Exclude influenceSmooth and stable normalized power error signalCode division multiplexTransmissionEngineeringVoltage control

A multipath tracking device and method in a CDMA communication system adds a middle path power estimation unit, a normalization processing unit and a nonlinear mapping unit in an existing multipath tracking device. A precise current middle path signal power is acquired by the middle path power estimation unit; the normalization processing is performed for the power errors of the late, early path signals in the normalization processing unit, and thus the impact of the middle path signal power on the power error is eliminated, the active normalization for the power error is realized; after obtaining the smooth and stable normalized power error signal, the precise delay error signal is determined in the nonlinear mapping unit according to the nonlinear mapping relation between the normalized power error signal and the delay error signal, thereby the precise voltage control signal is acquired.

Owner:MASSHALL

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com