Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

61results about How to "Increase the trigger voltage" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Oscillator circuit having stable frequency

ActiveUS7129798B2Simple circuit designTemperature dependency increaseGenerator stabilizationPulse generation by logic circuitsEngineeringCapacitor

An oscillator includes first, second and third inverters (1, 2, 3) connected in series. A feedback path is connected from the output terminal of the third inverter (3) to the input terminal of the first inverter 1 through a resistor (5) while a second feedback path is connected from the output terminal of the second inverter (2) to the input terminal of the first inverter (1) through a capacitor (4). The second feedback path further includes a resistor (6) having a temperature coefficient larger than that of resistor (5) is inserted to adjust the charge / discharge trigger voltage and charge / discharge time of the capacitor (4).

Owner:DENSO CORP

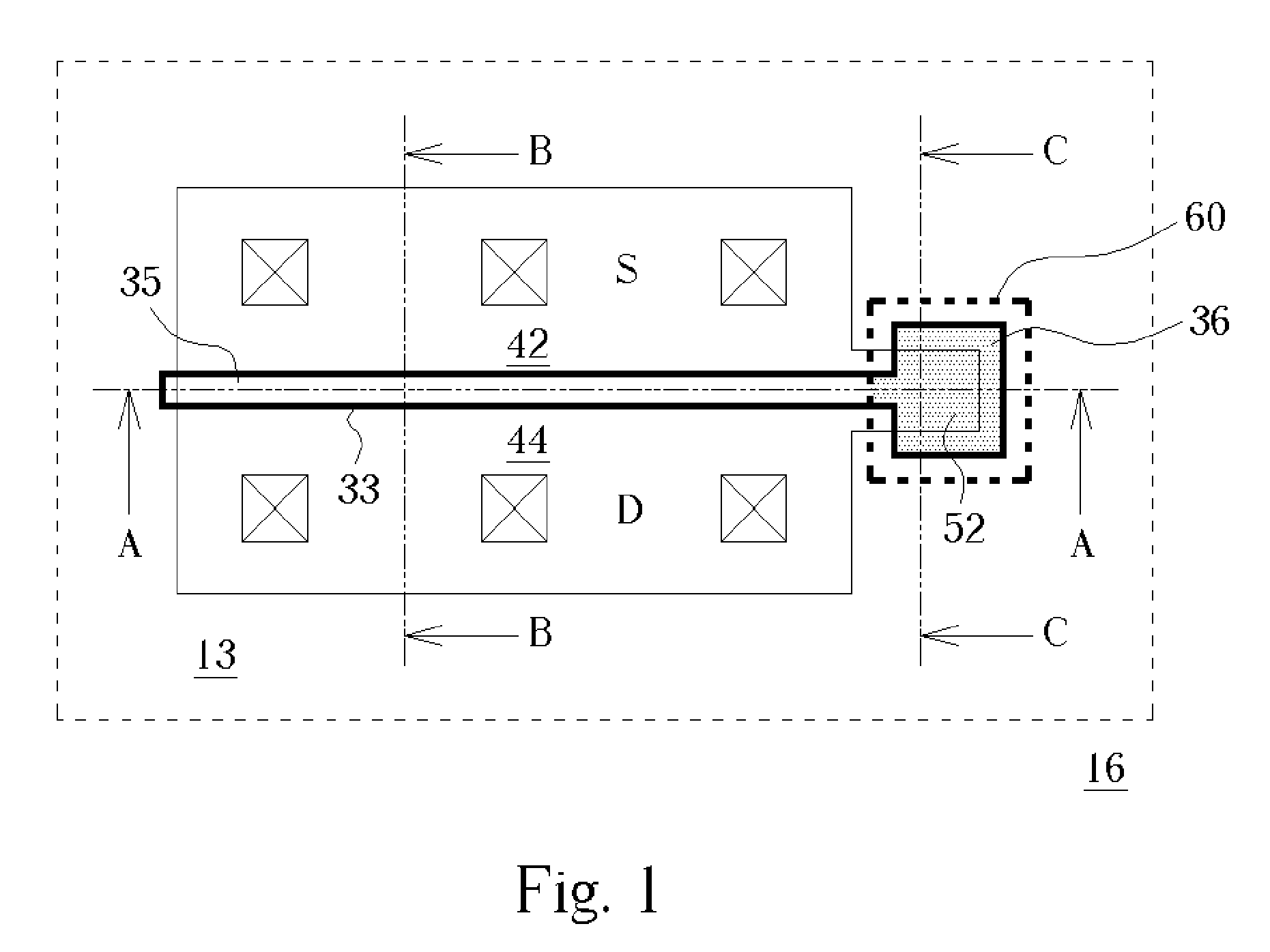

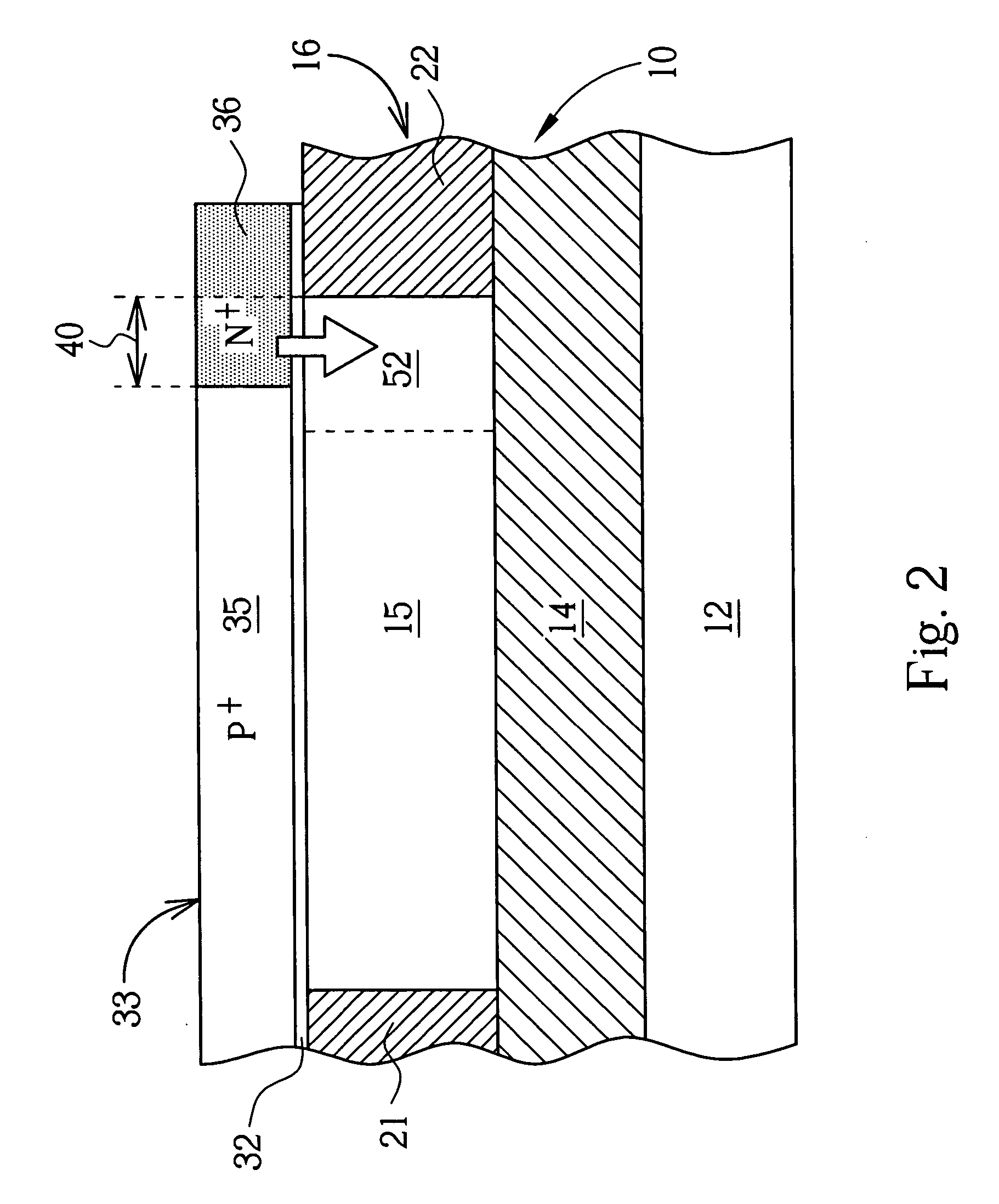

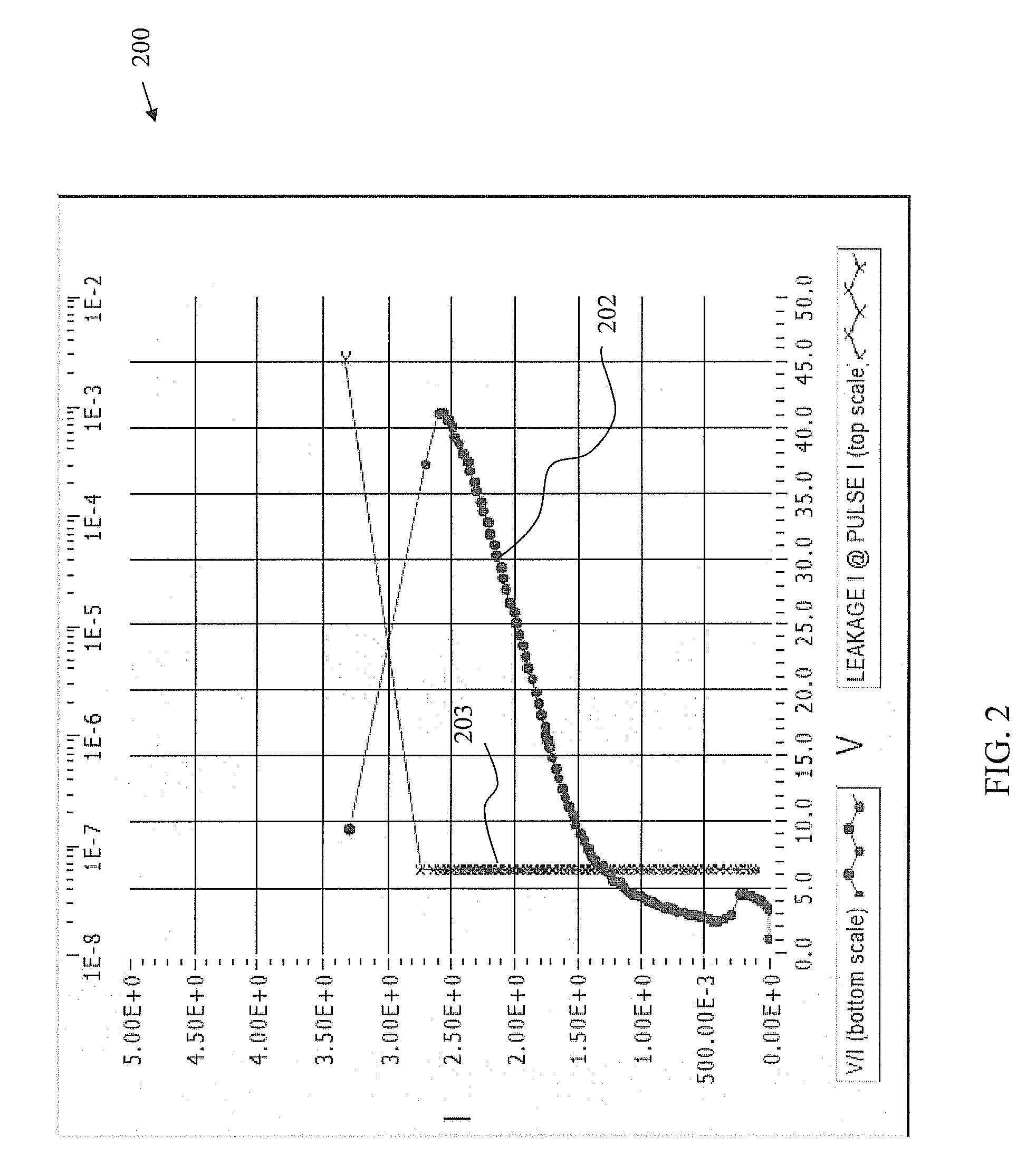

Partially depleted SOI mosfet device

A partially depleted SOI MOS device includes a well of first conductivity type isolated in a thin film body of an SOI substrate. The SOI substrate encompasses the thin film body, a support substrate, and a buried oxide layer interposed between the thin film body and the support substrate. A gate dielectric layer is disposed on a surface of the well. A polysilicon gate is patterned on the gate dielectric layer. The polysilicon gate consists of a first gate section of first conductivity type overlapping with an extended well region of the well and a second gate section of second conductivity type lying across the well, whereby a tunneling connection is formed between the first gate section and the extended well region of said well. Source and drain regions of second conductivity type are formed on opposite sides of the second gate section.

Owner:UNITED MICROELECTRONICS CORP

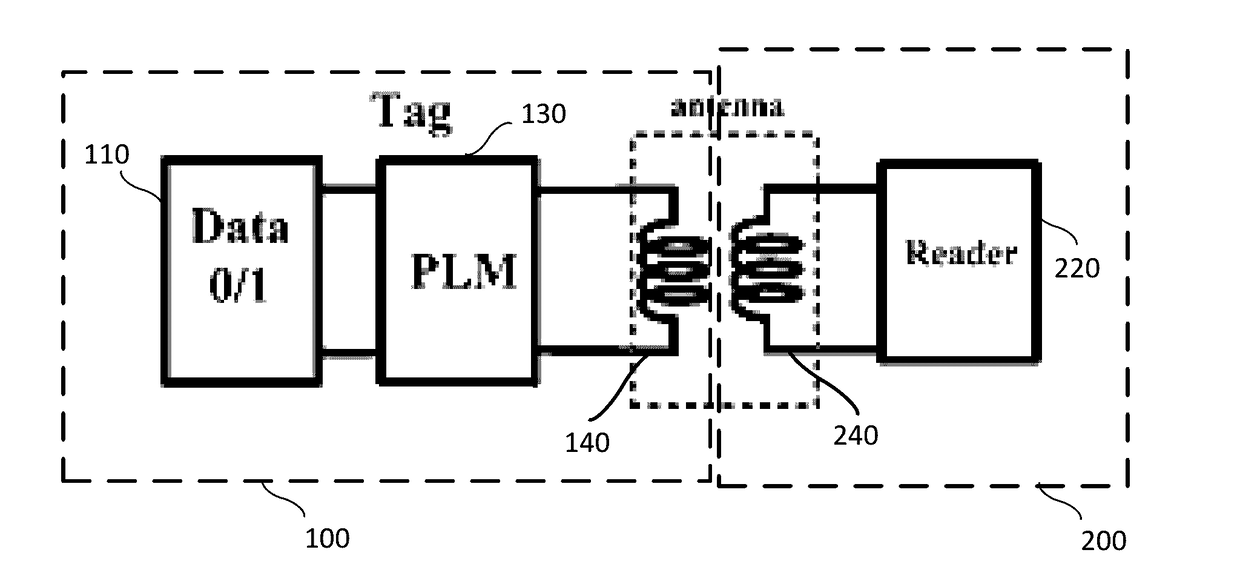

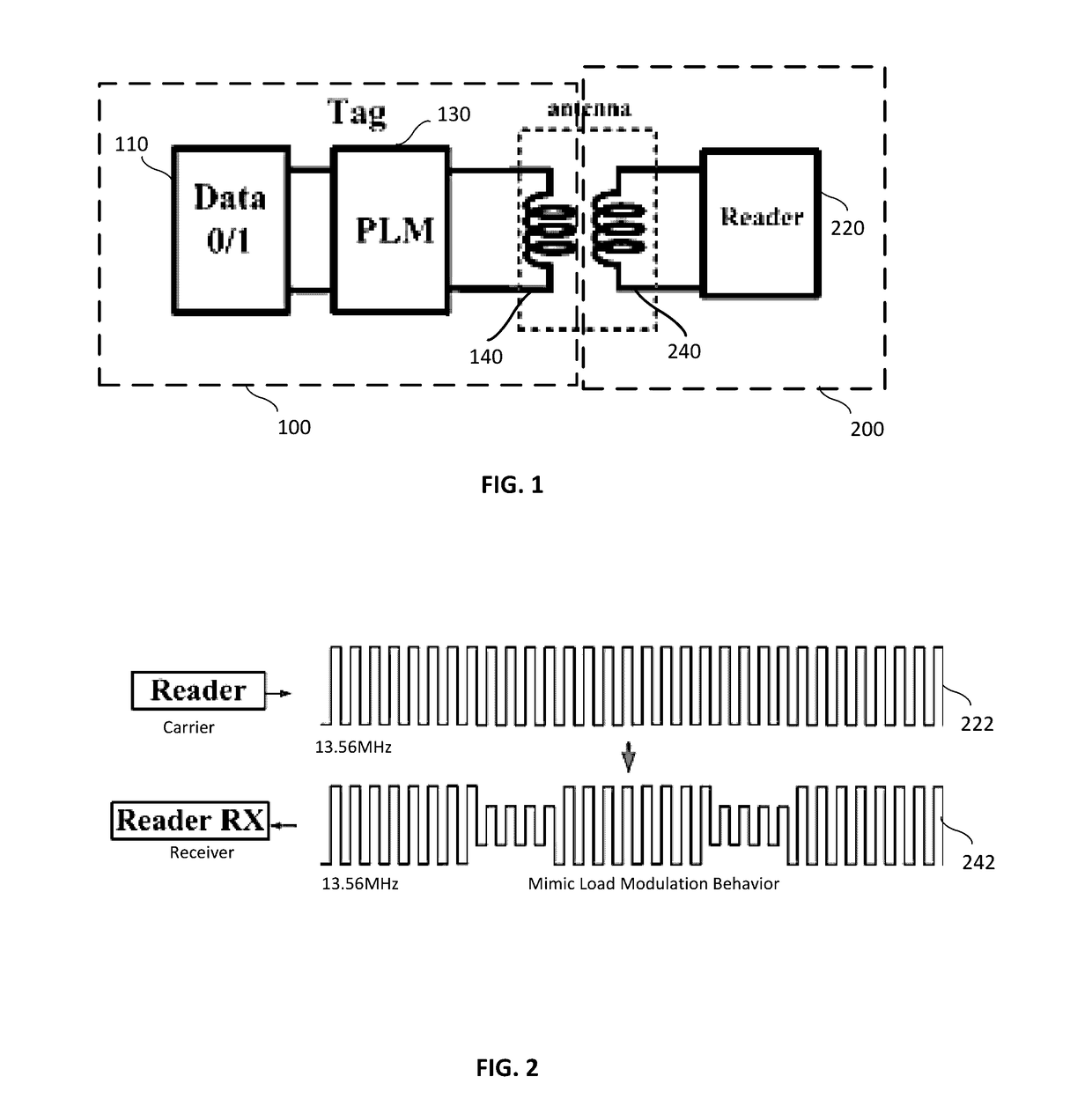

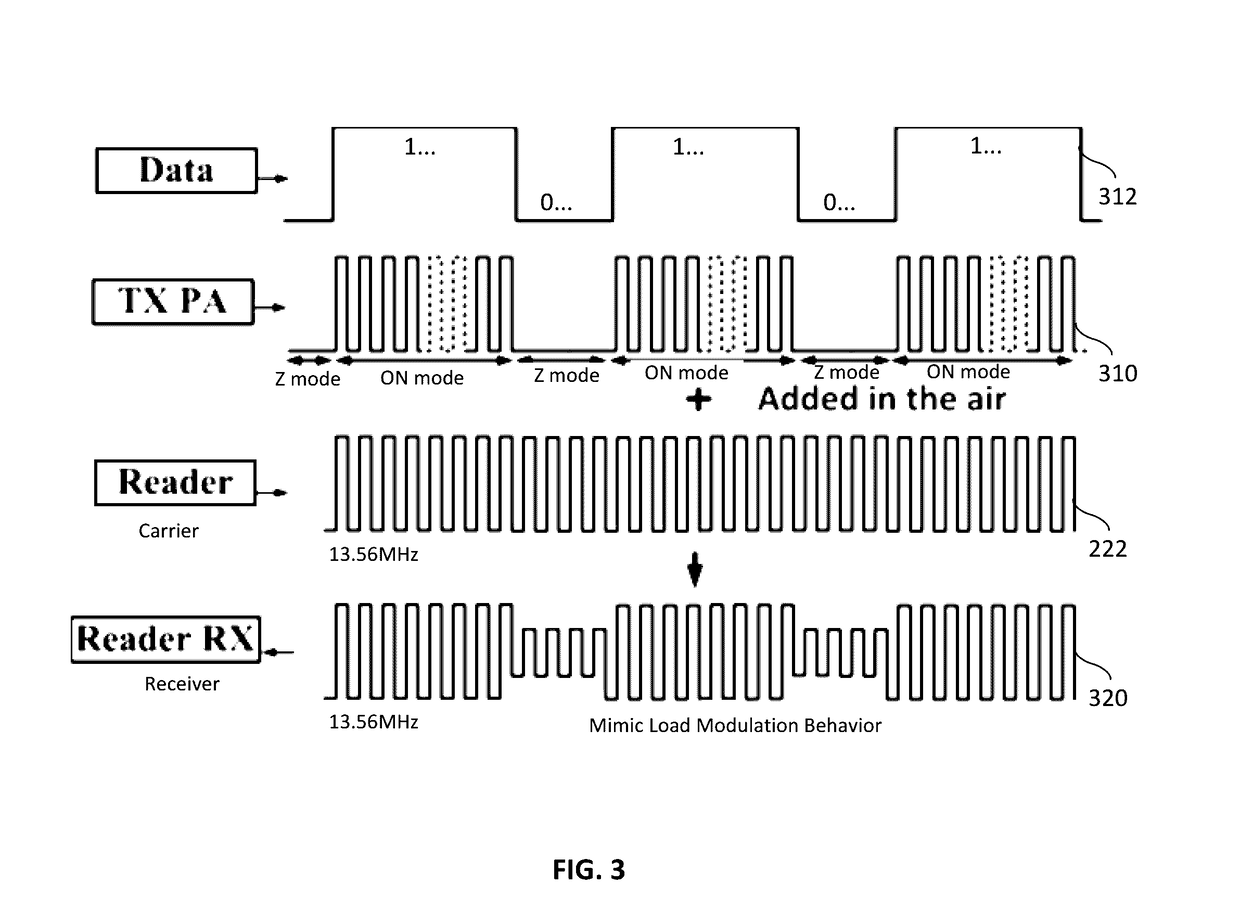

Power adaptive dual mode card emulation system for NFC and RFID application

ActiveUS20170155429A1Increase powerIncrease the trigger voltagePower managementNear-field for read/write/interrrogation/identification systemsDual modeCarrier signal

An adaptive dual mode card emulation system (in Card Emulation Mode or PICC design) within an NFC device is disclosed to solve the strong field power delivering issue and also achieve longer communication range. The NFC device may be a NFC tag or an electronic device (such as a smartphone) operated in a card emulation mode. The NFC device comprises an antenna used for wireless communication. The adaptive dual mode card emulation system comprises a passive load modulation (PLM) module, an active load modulation (ALM) module and an automatic power control (APC) module. The APC module couples to both the ALM and PLM modules and selectably enables the ALM or PLM module depending on the strength of received carrier signal sent from an NFC reader.

Owner:MAXIM INTEGRATED PROD INC

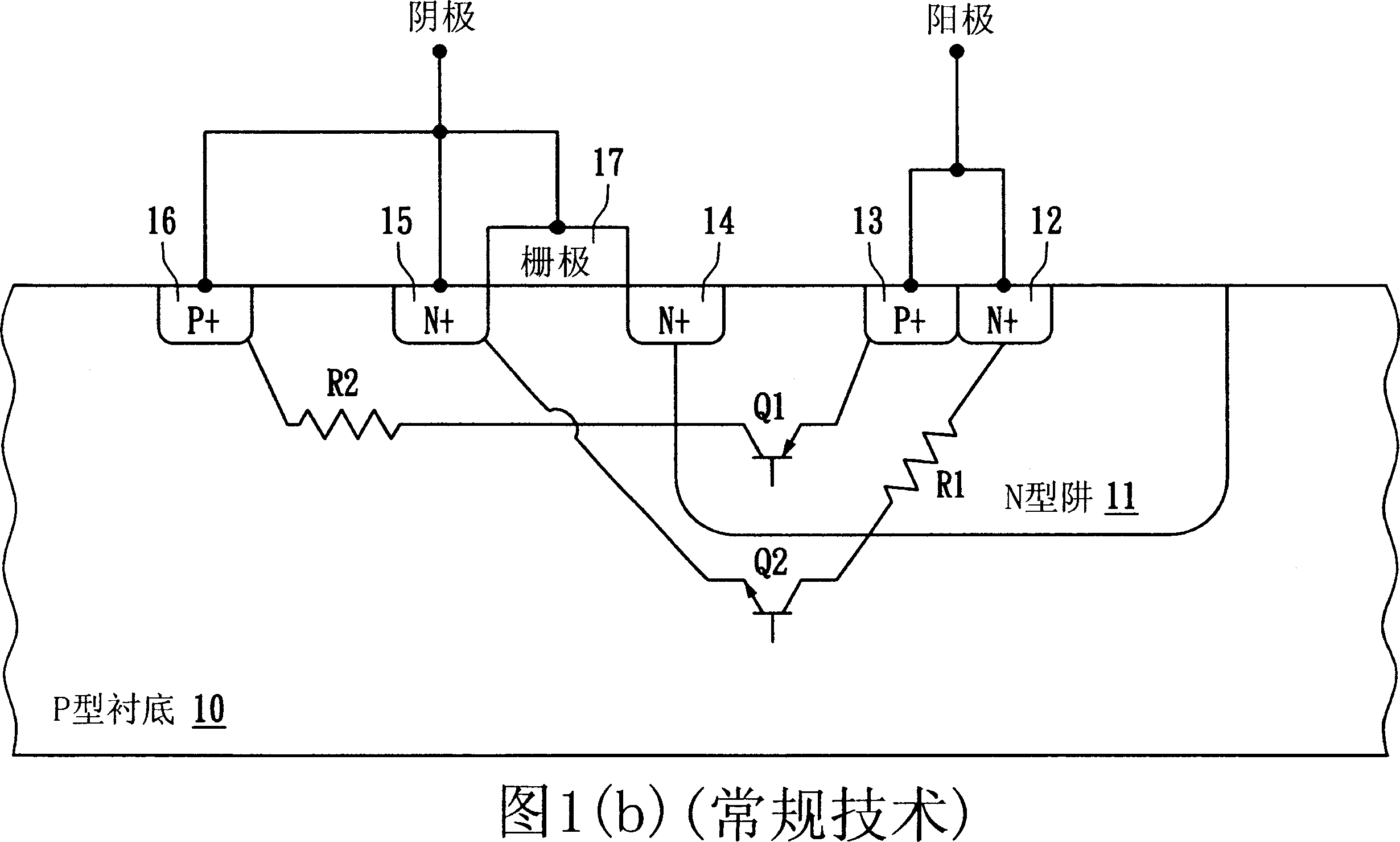

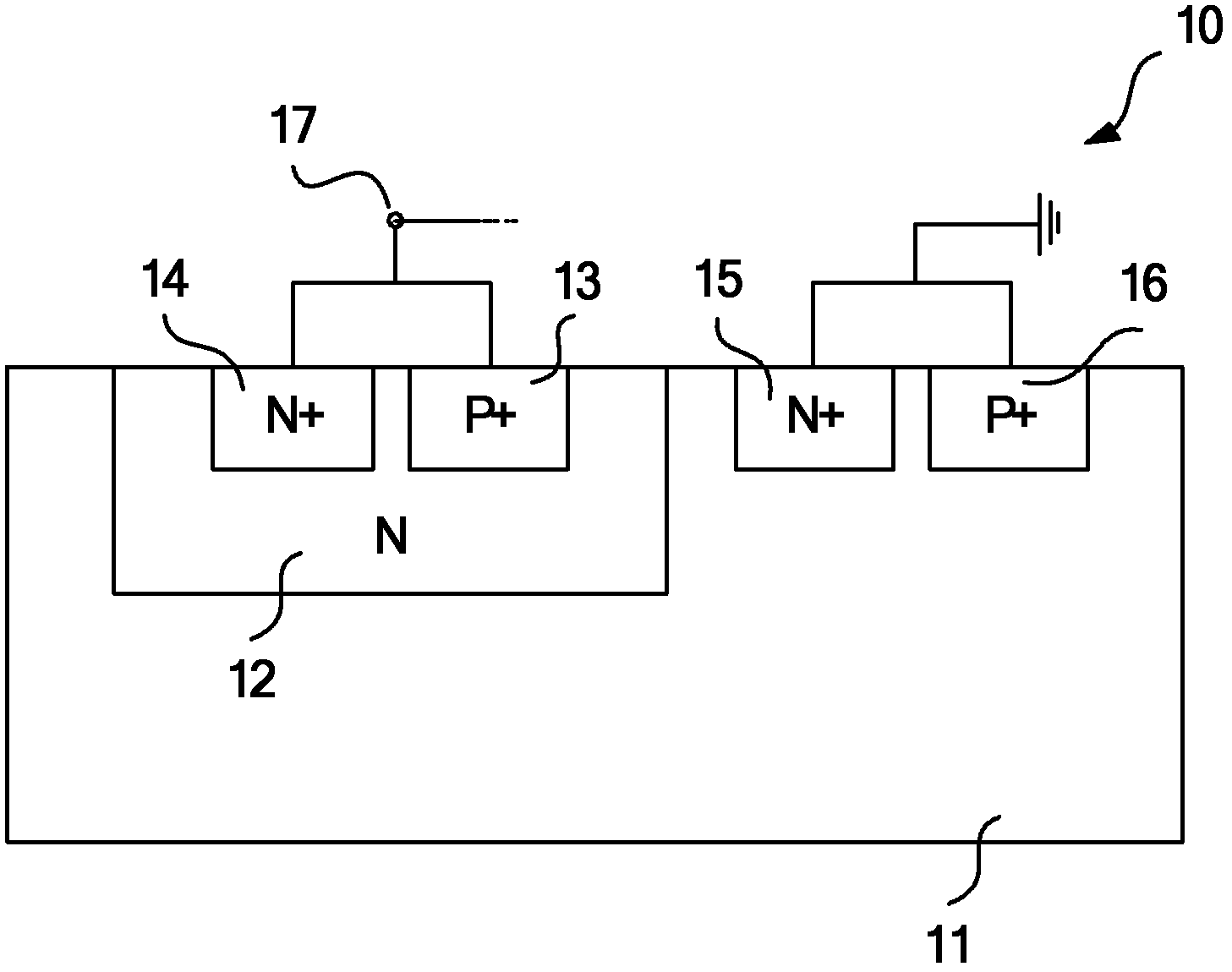

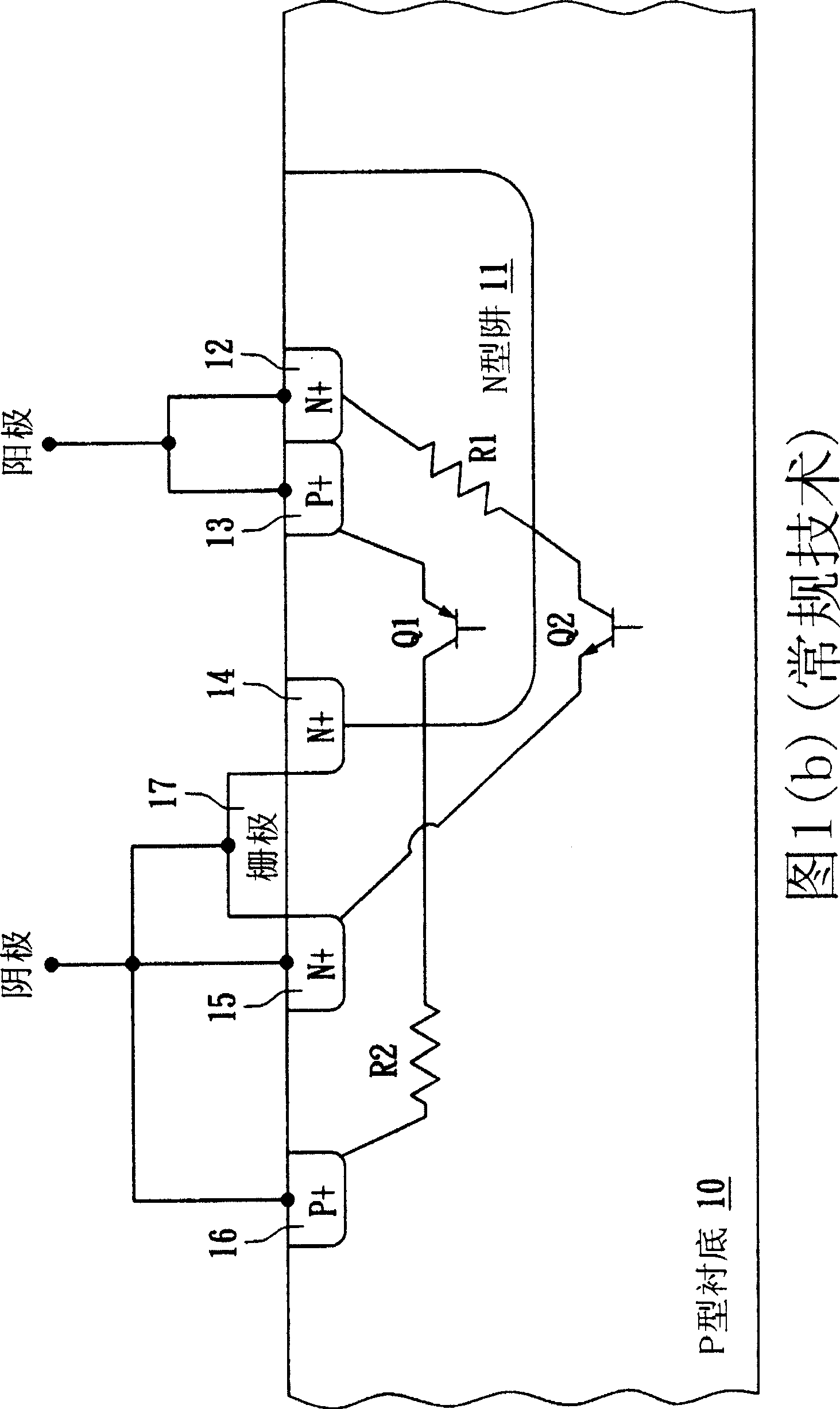

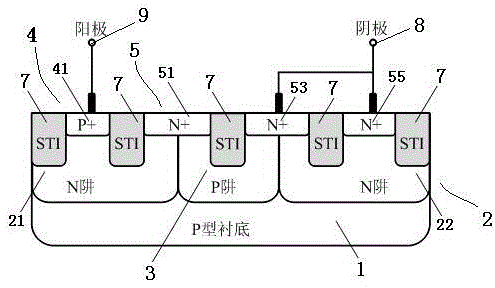

Low trigger voltage silicon control rectifier and its circuit

InactiveCN101047178AIncrease the trigger voltageLower the trigger voltageSolid-state devicesSemiconductor devicesSilicon-controlled rectifierElectrical conductor

The present invention relates to a low voltage triggering silicon controlled rectifier (SCR). It is characterized by that it utilizes addition of second doped zone which is set between the described low voltage triggering silicon controlled rectifier anode and its parasitic PNP transistor emitter to raise the holding voltage when the described low voltage triggering silicon controlled rectifier is triggered. The described low voltage triggering silicon controlled rectifier includes a semiconductor substrate with first conducting type and a grid. The described semiconductor substrate contains a first doped zone with second conducting type, a second doped zone with first conducting type, a third doped zone with second conducting type, a fourth doped zone with second conducting type and a fifth doped zone with first conducting type. The described grid is characterized by utilizing lower trigger voltage to trigger the described low voltage triggering silicon controlled rectifier.

Owner:ADVANCED ANALOG TECH INC

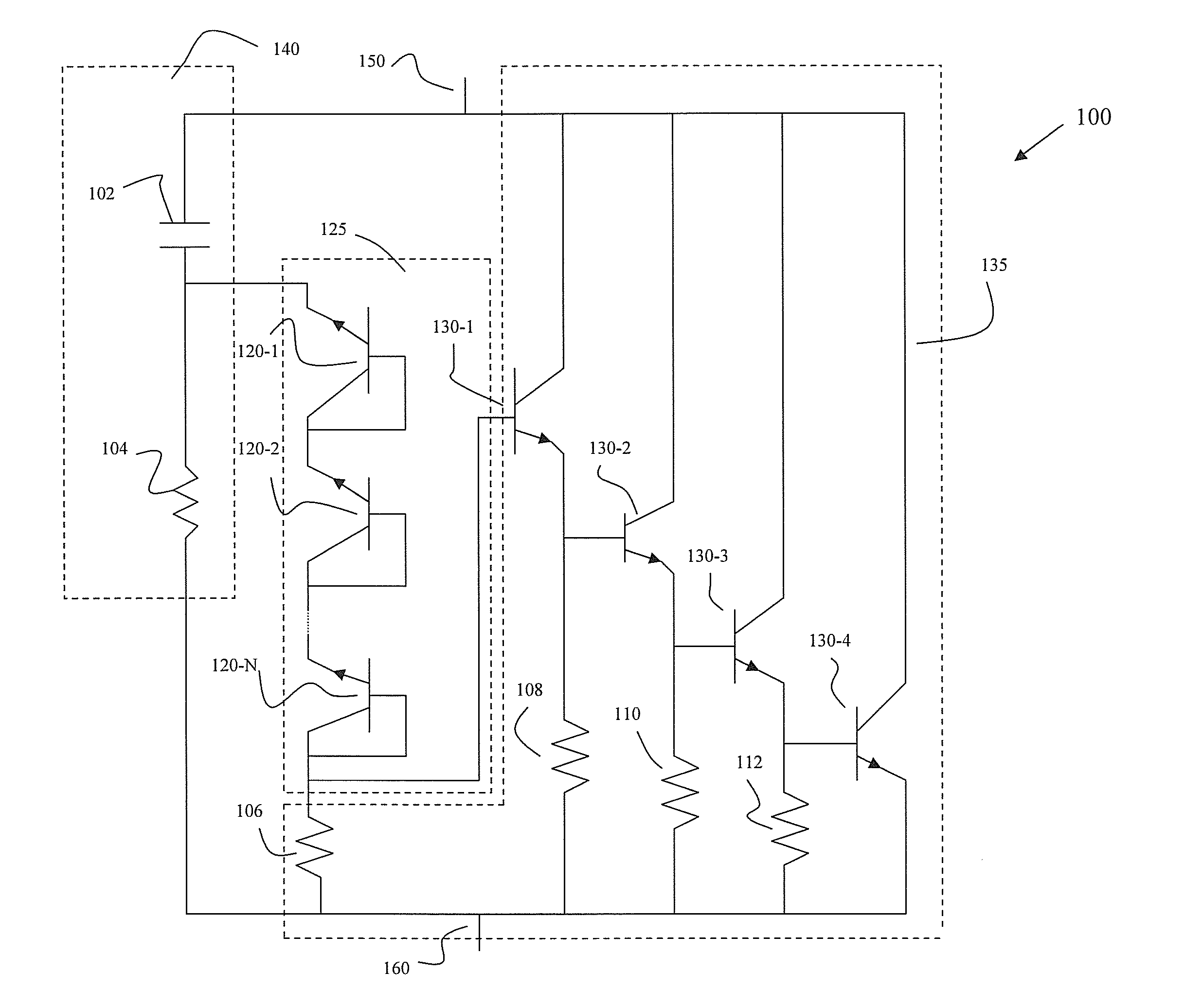

Eos robust bipolar transient clamp

InactiveUS20080247102A1Increase the trigger voltageEmergency protective arrangements for limiting excess voltage/currentArrangements responsive to excess voltageEngineeringRC circuit

A bipolar transient clamp including a RC circuit, a clamping circuit and a breakdown circuit. The RC circuit is configured to control the rate of change of clamp. Moreover, the RC circuit is coupled between a first rail and a second rail. The clamping circuit is configured to pass a current from the first rail to the second rail. In addition, the clamping circuit is coupled to be activated by the RC circuit. The breakdown circuit is coupled between the RC circuit and the clamping circuit. The breakdown circuit is configured to increase the transient trigger voltage of the clamping circuit.

Owner:INTERSIL INC

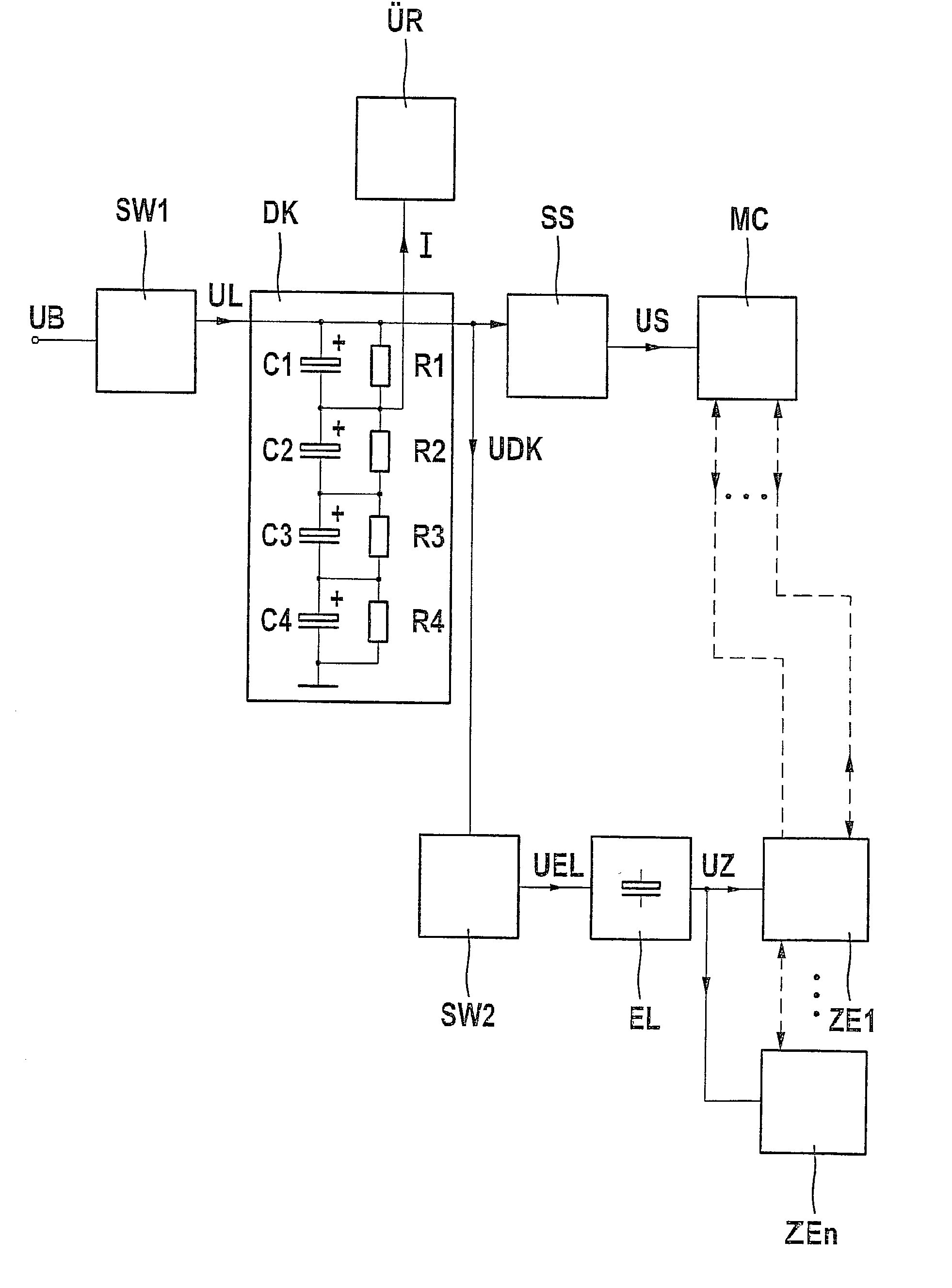

Circuit arrangement for the power supply of protective devices for the passengers of a vehicle

InactiveUS20020180268A1Increase capacitanceLong storage timeBatteries circuit arrangementsElectric devicesCapacitanceHigh availability

In order that the circuit arrangement ensures a high availability of the protective functions of all necessary passenger protection devices, it comprises multiple double-layer capacitors (C1, C2, C3, C4) connected in series and an electrolytic capacitor (EL), which obtains its charge from the double-layer capacitors (C1, C2, C3, C4), which have a higher capacitance but a lower nominal voltage than the electrolytic capacitor (EL). The electrolytic capacitor (EL) exclusively supplies the triggering voltage (UZ) necessary for the trigger power modules (ZE1, . . . , ZEn) of the protective devices.

Owner:ROBERT BOSCH GMBH

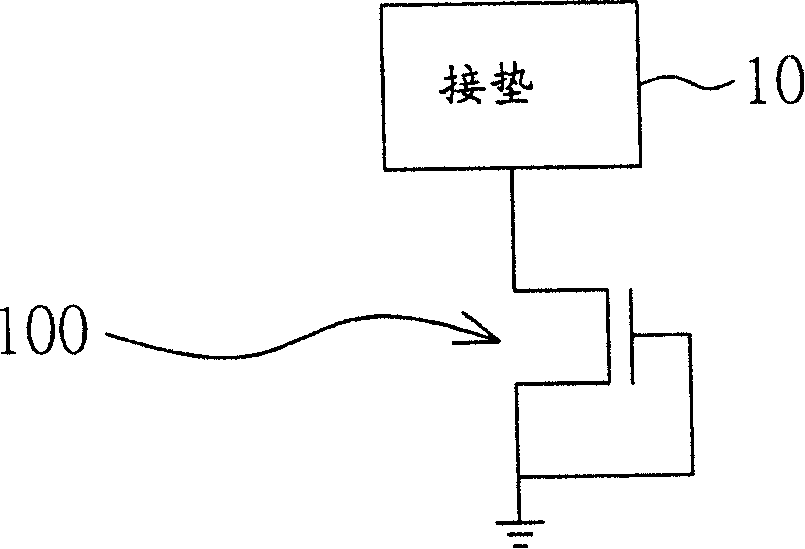

Electrostatic discharge protecting equipment of connection pad and its method and structure

ActiveCN101174622ADoes not increase the areaIncrease the trigger voltageSemiconductor/solid-state device detailsSolid-state devicesSilicon-controlled rectifierCharge carrier

An electrostatic discharge protection device for a contact pad includes a regulating circuit, a snapback component and a control circuit. The regulating circuit includes a silicon controlled rectifier coupled to the pad. The silicon controlled rectifier includes a first diode. The snapback component is coupled to the N pole of the first diode when the second diode is not used, and is coupled to the N pole of the second diode when the second diode is used. The control circuit is coupled to the N pole of the first diode. In normal operation mode, the control circuit is used to provide a first voltage to the N pole of the first diode, so that the N pole of the first diode Collect a plurality of charged carriers, and make the silicon controlled rectifier not be turned on. In the electrostatic discharge mode, the control circuit does not provide the first voltage to the N pole of the first diode, so that the N pole of the first diode Charge carriers are not collected.

Owner:MACRONIX INT CO LTD

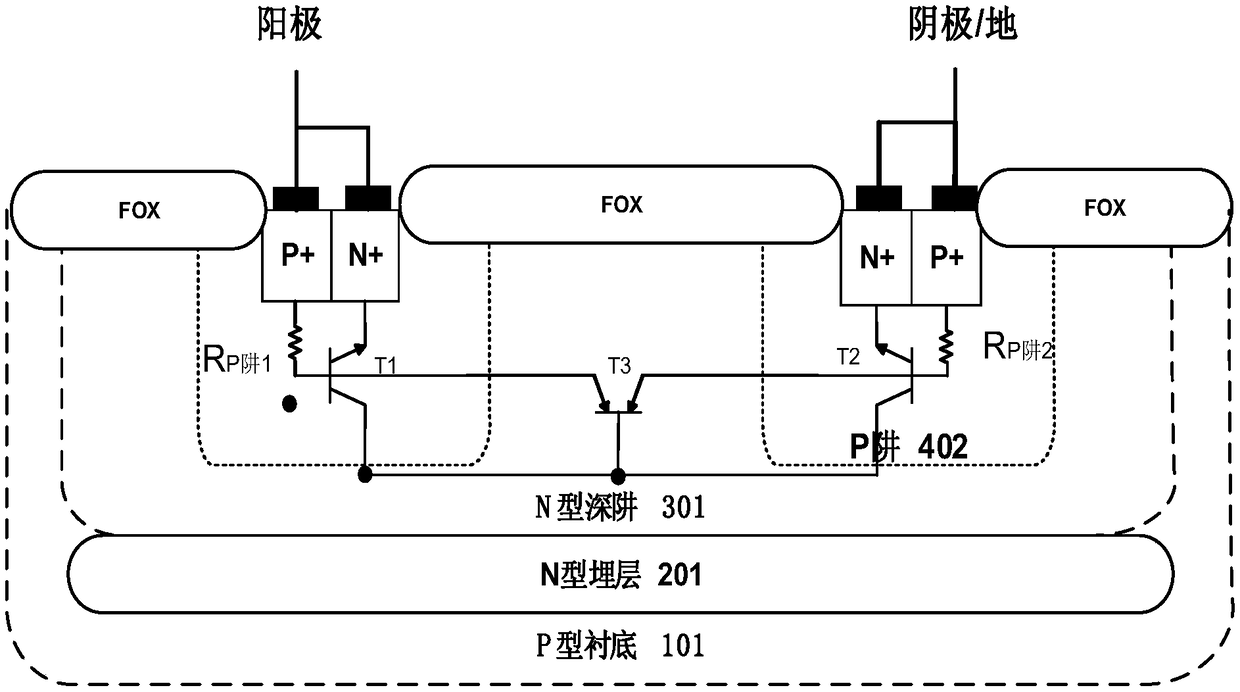

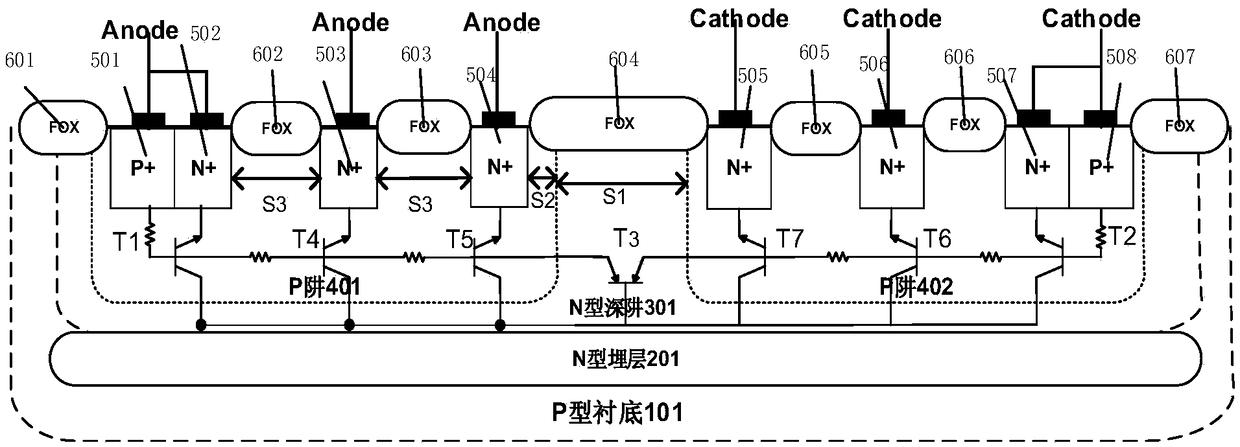

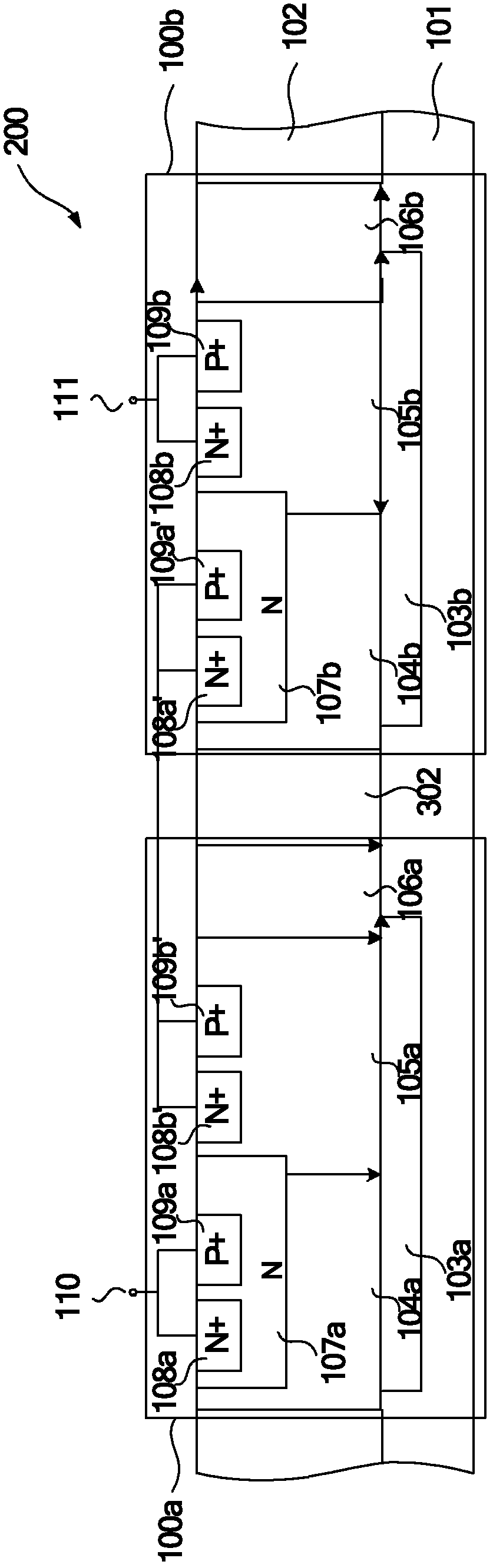

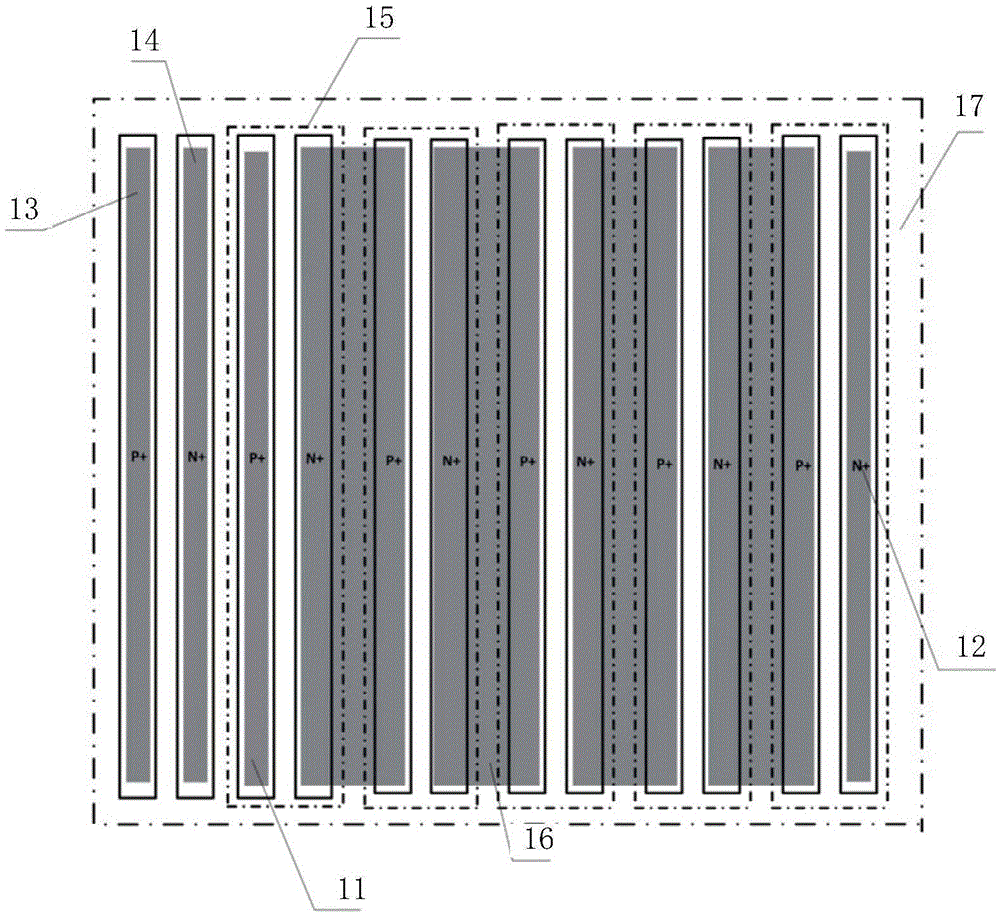

Bidirectional silicon-controlled electrostatic protection device with high protection level and fabrication method thereof

ActiveCN108807371AReduce in quantityImprove even distributionTransistorSolid-state devicesDIACCurrent distribution

The invention discloses a bidirectional silicon-controlled electrostatic protection device with high protection level. The bidirectional silicon-controlled electrostatic protection device comprises aP-type substrate, wherein an N-type buried layer is arranged in the substrate, an N-type deep well is arranged on the N-type buried layer, a first P well and a second P well are arranged in the N-typedeep well, a first P+ injection region and a plurality of N+ injection regions I are arranged in the first P well, a second P+ injection region and a plurality of N+ injection regions II are arrangedin the second P well, the first P+ injection region and all N+ injection regions I are connected and used as a positive electrode of the device, and the second P+ injection region and all N+ injection regions II are connected and used as a negative electrode of the device. The numbers of the N+ injection regions I and the N+ injection regions II can be increased or reduced according to differentprotection levels, the numbers of the N+ injection regions I and the N+ injection regions II are increased if the protection level is high, the uniform current distribution of the device is improved,and the robustness of the device is improved; and if the protection level is low, the numbers of the N+ injection regions I and the N+ injection regions II are reduced, and the layout area is reduced.

Owner:XIANGTAN UNIV

Radio frequency LDMOS (laterally diffused metal oxide semiconductor) device and manufacture method thereof

ActiveCN103050536AReduce doping concentrationDoping concentration unchangedSemiconductor/solid-state device manufacturingSemiconductor devicesLDMOSGate oxide

The invention discloses a radio frequency LDMOS (laterally diffused metal oxide semiconductor) device. The side surface of a channel doping region and the side surface of a drift region of the radio frequency LDMOS device are contacted; a gate oxide and a grid electrode are successively arranged above the channel doping region and the drift region; and the doping density of the part of the drift region, which is below the channel doping region, is smaller than the doping density of rest parts. The invention also discloses a manufacture method for the radio frequency LDMOS device. Because the doping density of the drift region is unevenly distributed, the hot carrier effect can be lowered while the low-conduction resistance is obtained.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

A method and device for changing the trigger voltage of an electrostatic protection device

InactiveCN102290340AChange the momentReduce capacitanceSolid-state devicesSemiconductor/solid-state device manufacturingCapacitanceDopant

A method for changing the trigger voltage of an electrostatic protection device is disclosed, which includes doping implantation at the drain of the electrostatic protection device; the impurity type of the drain doping implantation is the same or opposite to the impurity type of the drain. The invention also discloses a device for changing the trigger voltage of the electrostatic protection device. The method and device for changing the trigger voltage of the electrostatic protection device provided by the present invention can effectively reduce the trigger voltage, so that the electrostatic protection device can be applied to the electrostatic protection of small-sized and low-voltage circuits. The capacitance of the electrostatic protection device can also be reduced while the trigger voltage is increased, and the electrostatic protection capability of the electrostatic protection device is basically not affected.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

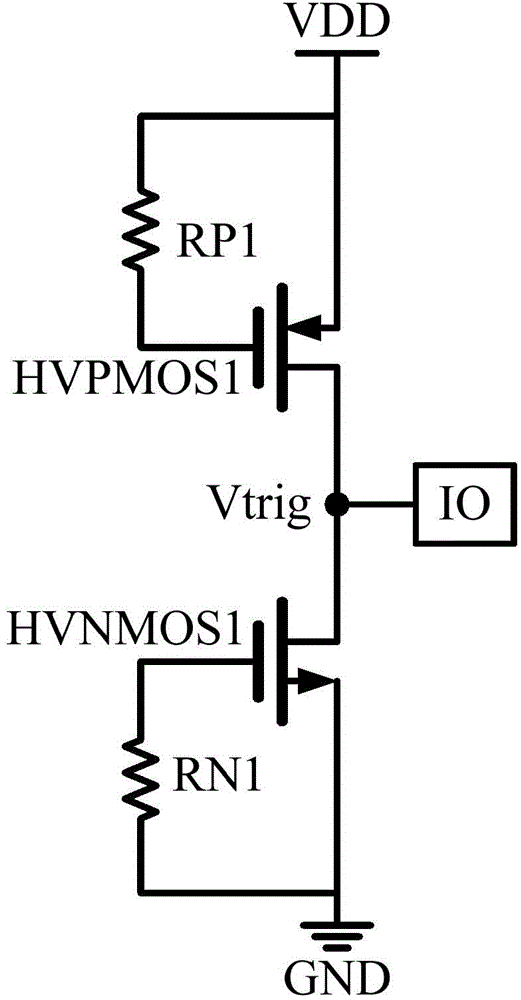

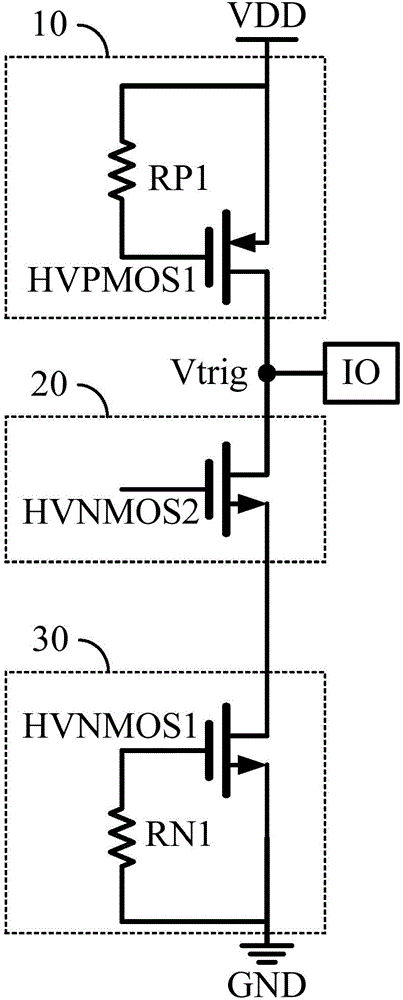

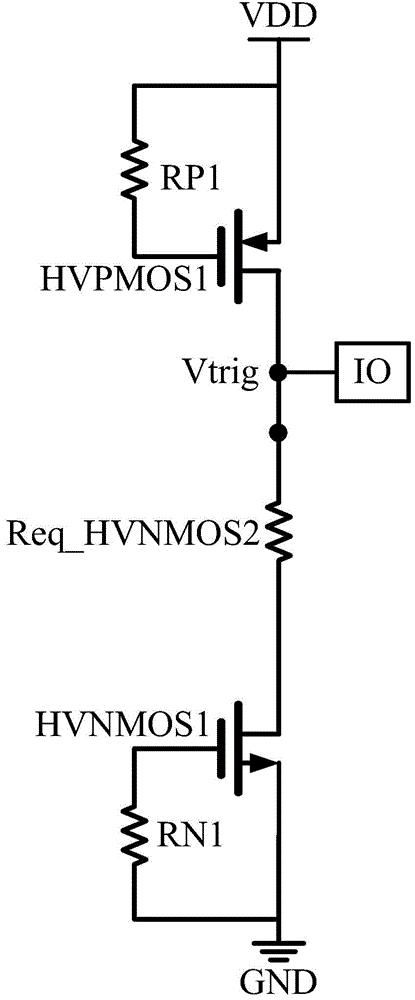

High-voltage ESD protective circuit

ActiveCN106033756ACause malfunctionIncrease the trigger voltageSolid-state devicesSemiconductor devicesGgNMOSHigh pressure

The invention provides a high-voltage ESD protective circuit which is used for discharging ESD current that flows from an IO PAD. The high-voltage ESD protective circuit at least comprises the components of a GDPMOS discharging unit which is arranged between a power supply and the IO PAD; an auxiliary discharging unit which is arranged between the IO PAD and ground and is connected with the GDPMOS discharging unit; and a GGNMOS discharging unit which is connected with the auxiliary discharging unit, wherein the auxiliary discharging unit is used for supplying an auxiliary discharging path of the GGNMOS discharging unit. The auxiliary discharging unit of the invention can supply the auxiliary discharging path of the GGNMOS discharging unit and improves ESD capability. By means of the stacked structure for aiming at high-voltage process, ESD capability of the circuit can be improved, and furthermore triggering voltage and noise resistance of the whole high-voltage ESD protective circuit can be improved, thereby preventing misoperation of the whole high-voltage ESD protective circuit caused by noise.

Owner:CHINA RESOURCES MICROELECTRONICS (CHONGQING) CO LTD

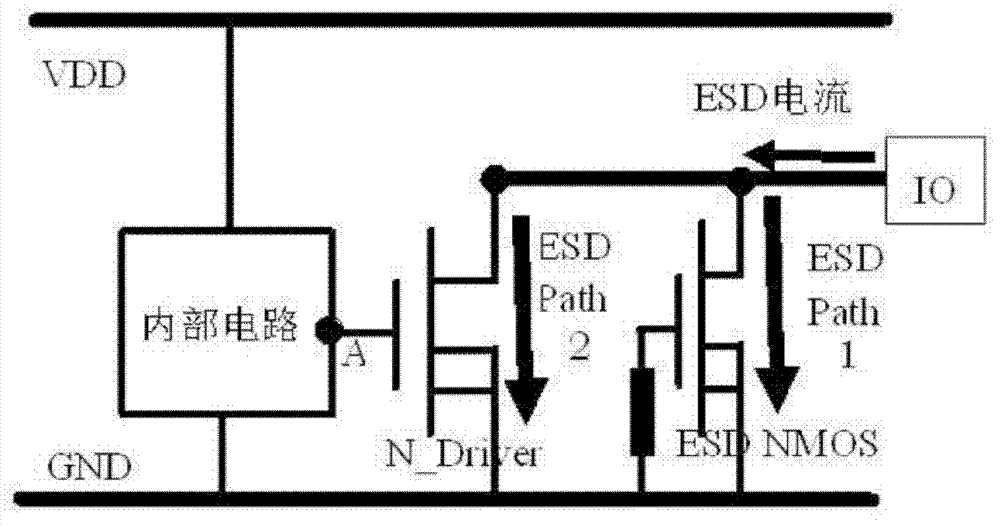

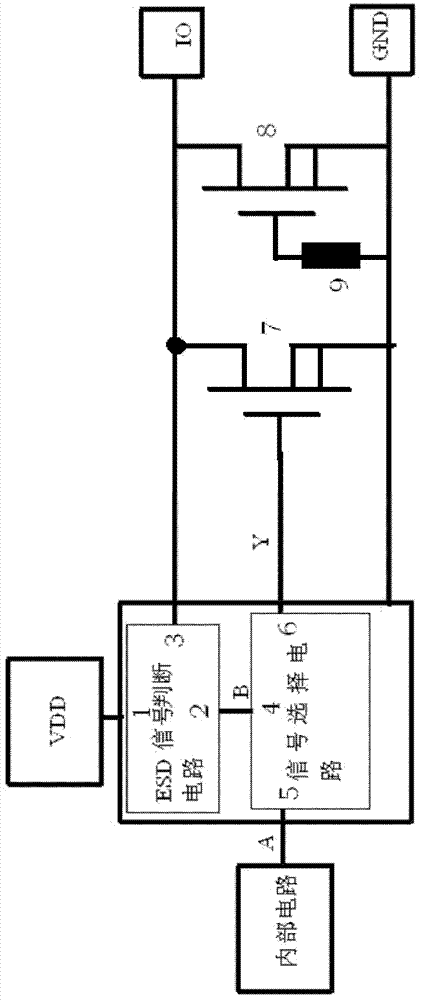

Electro spark detector (ESD) circuit protection structure

ActiveCN103036220AIncrease the trigger voltageEmergency protective arrangements for limiting excess voltage/currentControl signalEngineering

The invention discloses an electro spark detector (ESD) circuit protection structure which comprises an ESD signal judgment circuit, a signal selection circuit, a drive N-channel metal oxide semiconductor (NMOS) and an ESD NMOS. Port one of the ESD signal judgment circuit is connected with a power supply. Port two of the ESD signal judgment circuit is connected with the signal selection circuit. Port three of the ESD signal judgment circuit is connected with the input / output (IO) end and capable of detecting and judging whether the IO end has ESD accidents and sending judgment signal to the signal selection circuit. Port one and port two of the signal selection circuit are respectively connected with the port two of the ESD signal judgment circuit and control signals of an internal circuit. Port three of the signal selection circuit outputs signals to a grid electrode of the drive NMOS and is capable of selecting output signals and judging whether the IO end has the ESD accidents. The output signal of the port three of the signal selection circuit is low level. When the IO end has no ESD accidents after judgment, the output signal is the control signal of the inner circuit. A drain electrode of the drive NMOS is connected with the IO end. A source electrode of the drive NMOS is connected with the ground. A grid electrode of the ESD NMOS is connected with the ground through a resistor. A drain electrode of the ESD NMOS is connected with the IO end and a source electrode of the ESD NMOS is connected with the ground. The ESD circuit protection structure can solve the problem that an IO ESD protection circuit in the prior art can not protect the circuit under the state that the drive NMOS is communicated.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

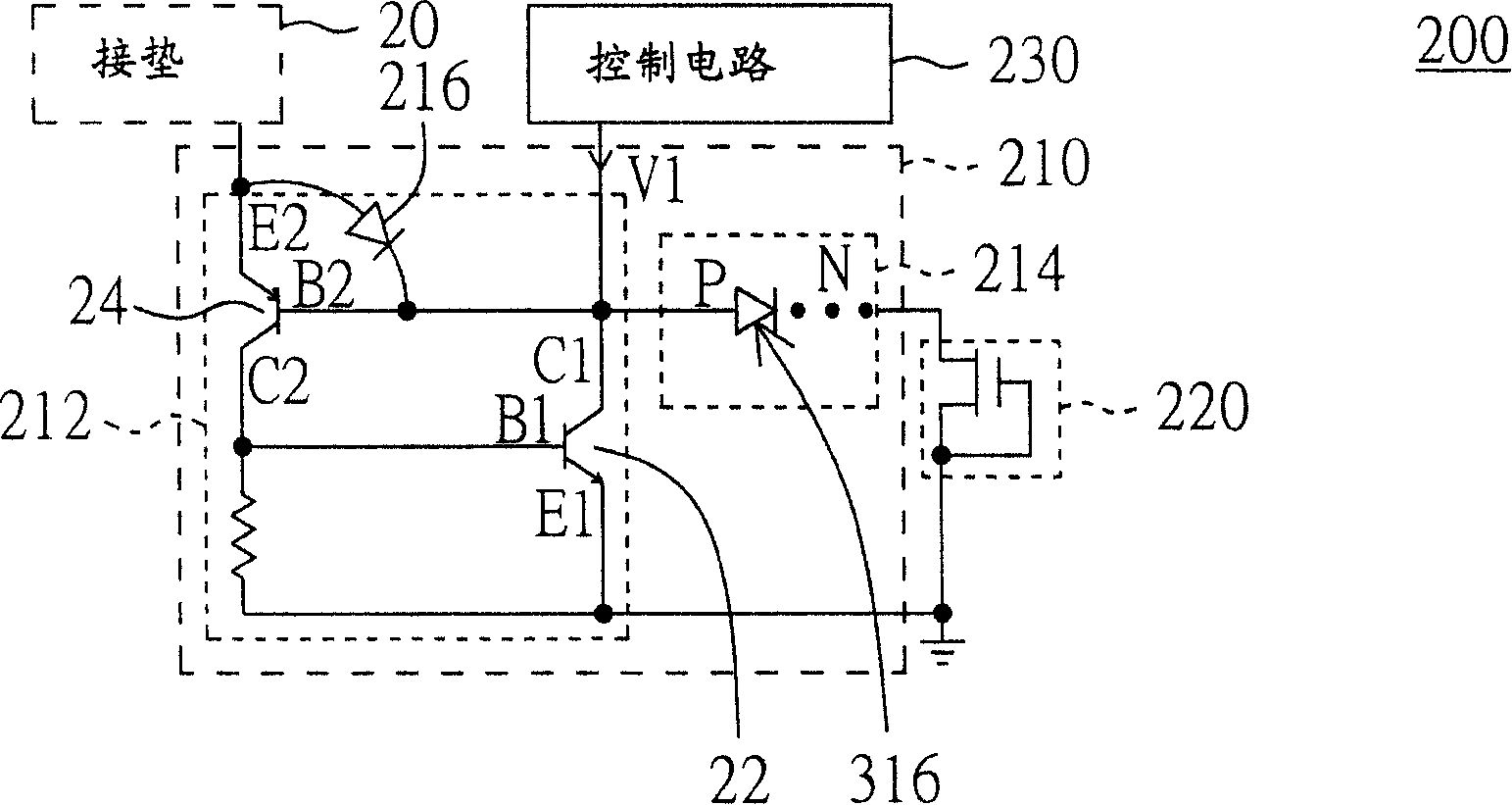

Electrostatic discharge protecting device and method thereof

ActiveCN102386620AReduced ability to eliminate static signalsImproved ability to eliminate static signalsSemiconductor/solid-state device detailsSolid-state devicesEngineeringElectrostatic discharge protection

The invention provides an electrostatic discharge protecting device and an electrostatic discharge protecting method. The electrostatic discharge protecting device is used for protecting an inner circuit which is operated under a supply voltage. The electrostatic discharge protecting device comprises a protecting unit and a controlling unit. The protecting unit is used for providing a discharge path so as to conduct an electrostatic signal from a bonding pad to an earth lead. The protecting unit is used for adjusting a holding voltage and a trigger voltage which decide whether the discharge path is conducted according to the voltage level of a control end of the protecting unit. When the supply voltage is supplied, the control unit is used for conducting an input voltage into a control end of the protecting unit, so that the holding voltage and the trigger voltage of the discharge path are improved by the protecting unit. When the supply voltage is not supplied, the control unit is used for switching a control end of the protecting unit to be a suspension joint status by the electrostatic signal, so that the holding voltage and the trigger voltage of the discharge path are reduced by the protecting unit.

Owner:MACRONIX INT CO LTD

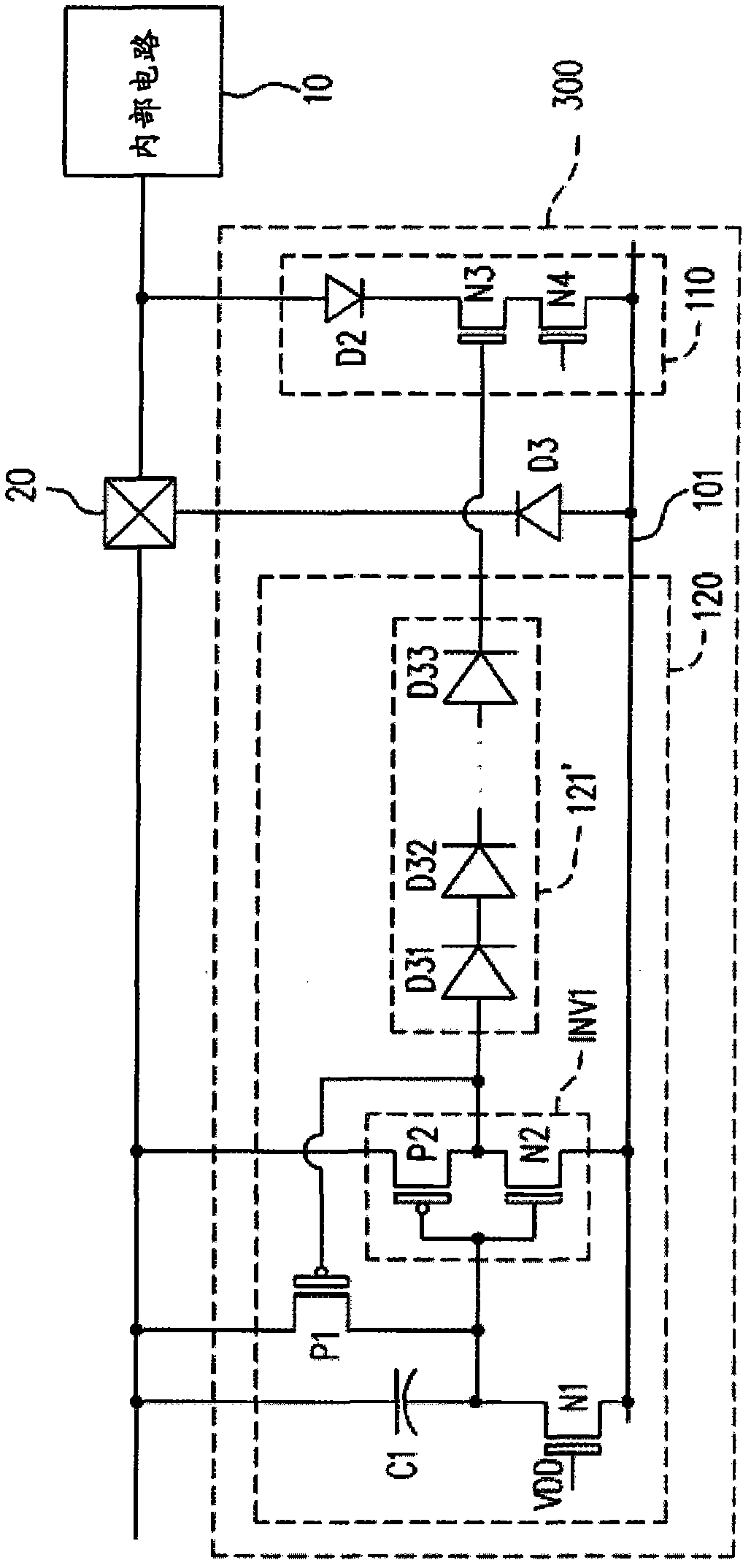

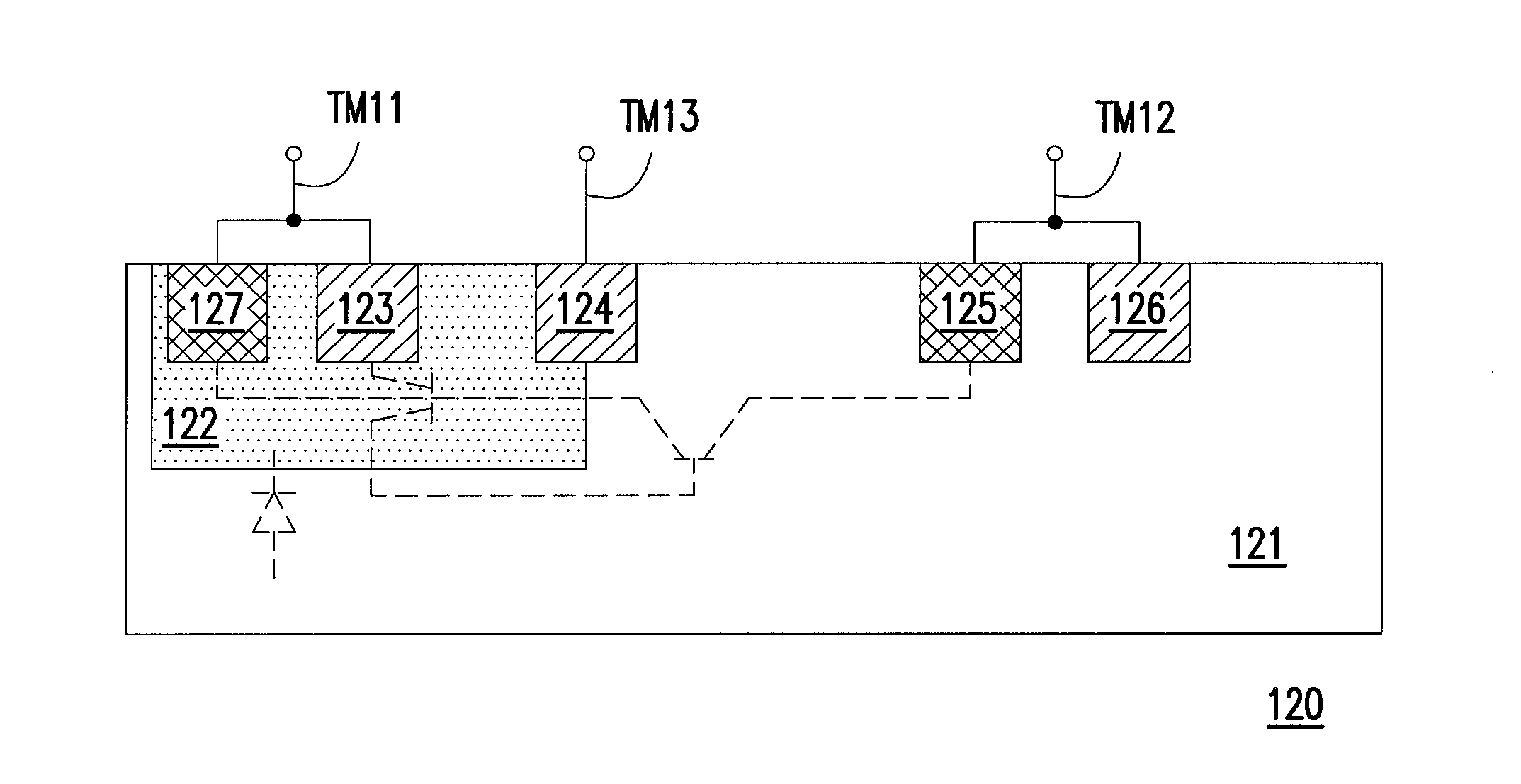

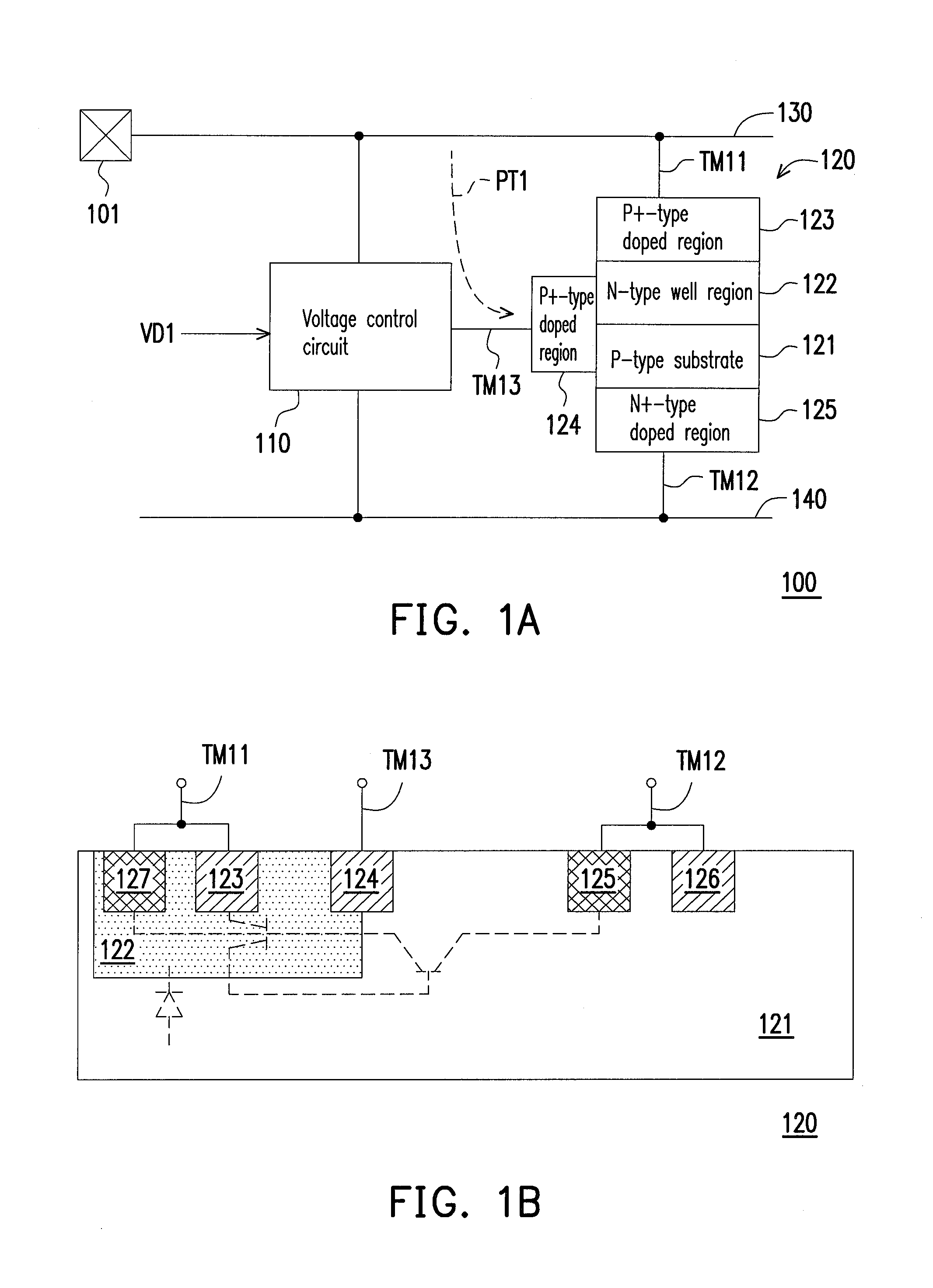

Electrostatic discharge protection device

ActiveUS20130201584A1Improve boot speedReduce voltageSolid-state devicesEmergency protective arrangements for limiting excess voltage/currentElectricitySilicon-controlled rectifier

An electrostatic discharge (ESD) protection device including a modified lateral silicon-controlled rectifier (MLSCR) and a voltage control circuit is provided. The MLSCR has a first terminal, a second terminal and a control terminal connected to a first P+-type doped region, where the first terminal and the second terminal are electrically connected to a first line and a second line, respectively. The voltage control circuit is electrically connected to the first line, the second line and the control terminal. When an electrostatic pulse is appeared on the first line, the voltage control circuit provides a current path from the first line to the control terminal. When an input signal is supplied to the first line, the voltage control circuit receives a power voltage, and stops providing the current path according to the power voltage.

Owner:MACRONIX INT CO LTD

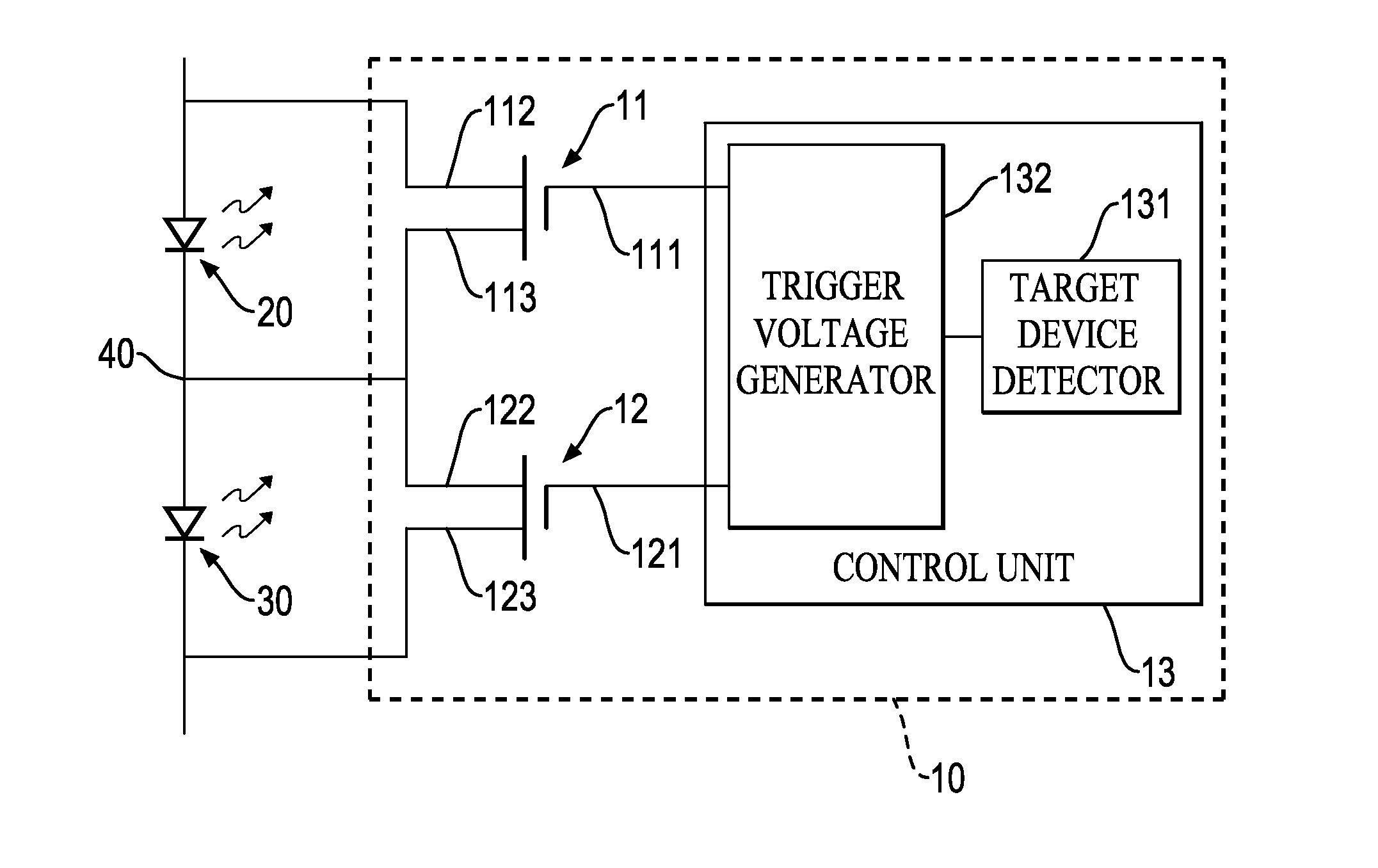

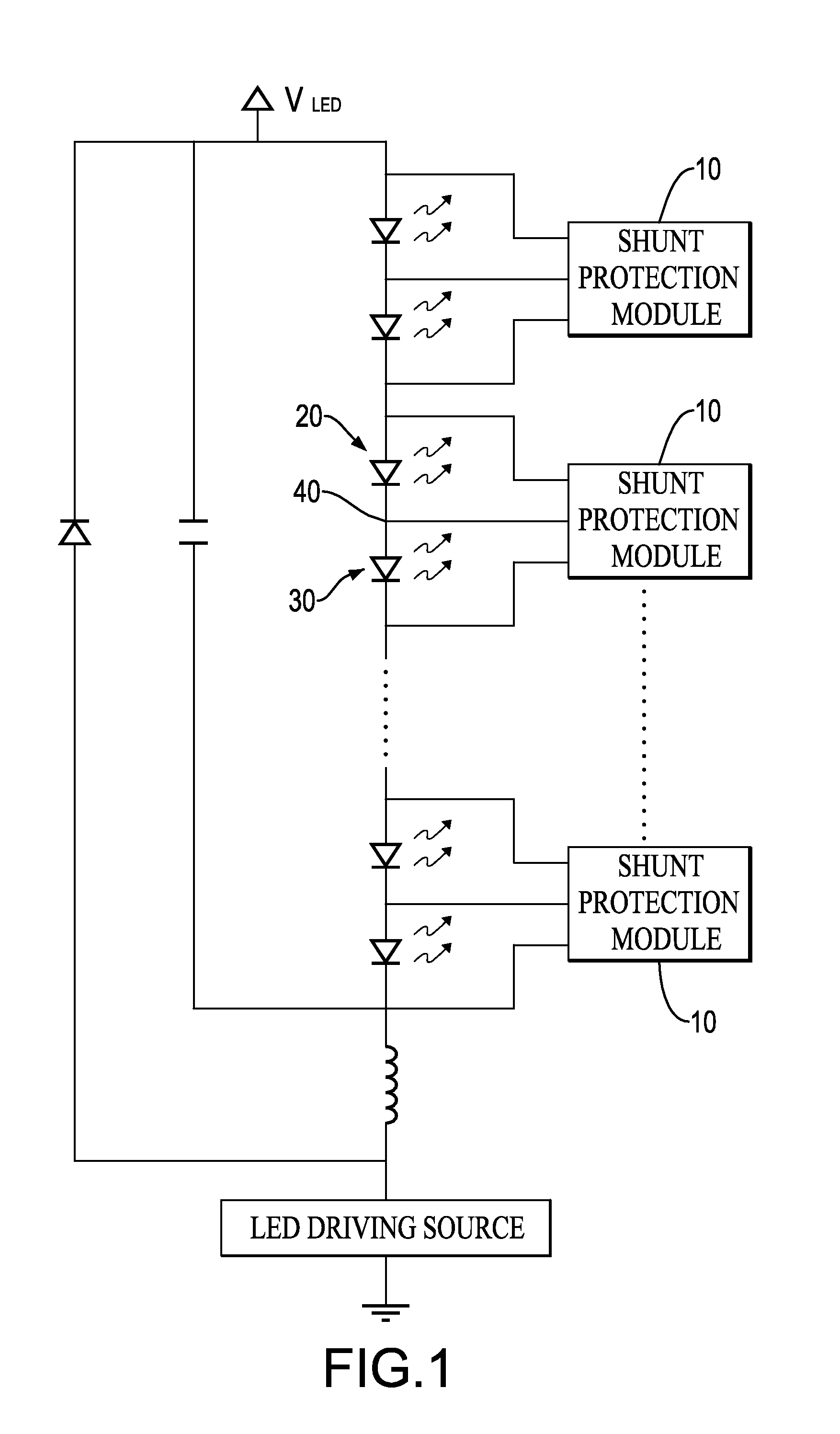

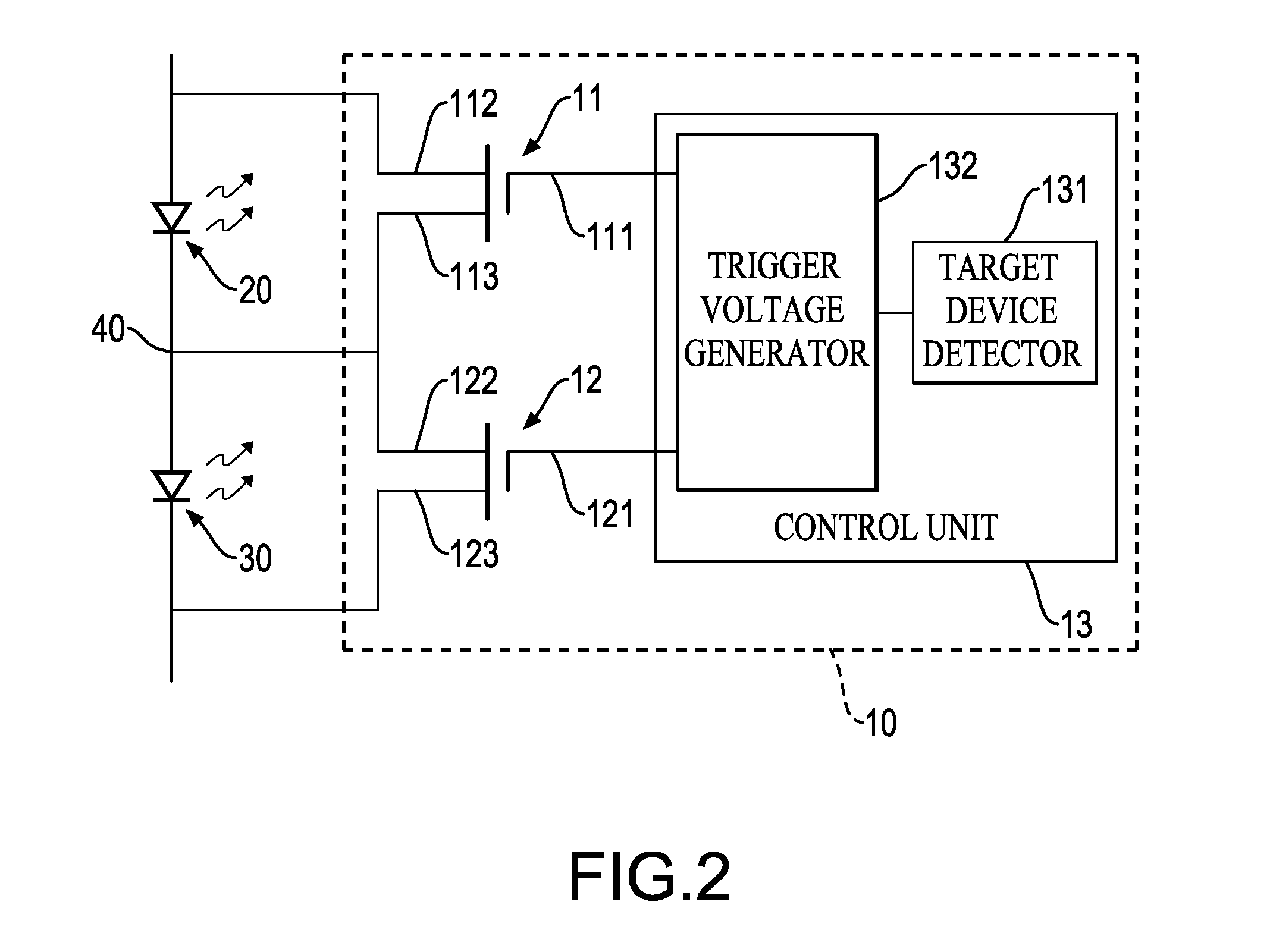

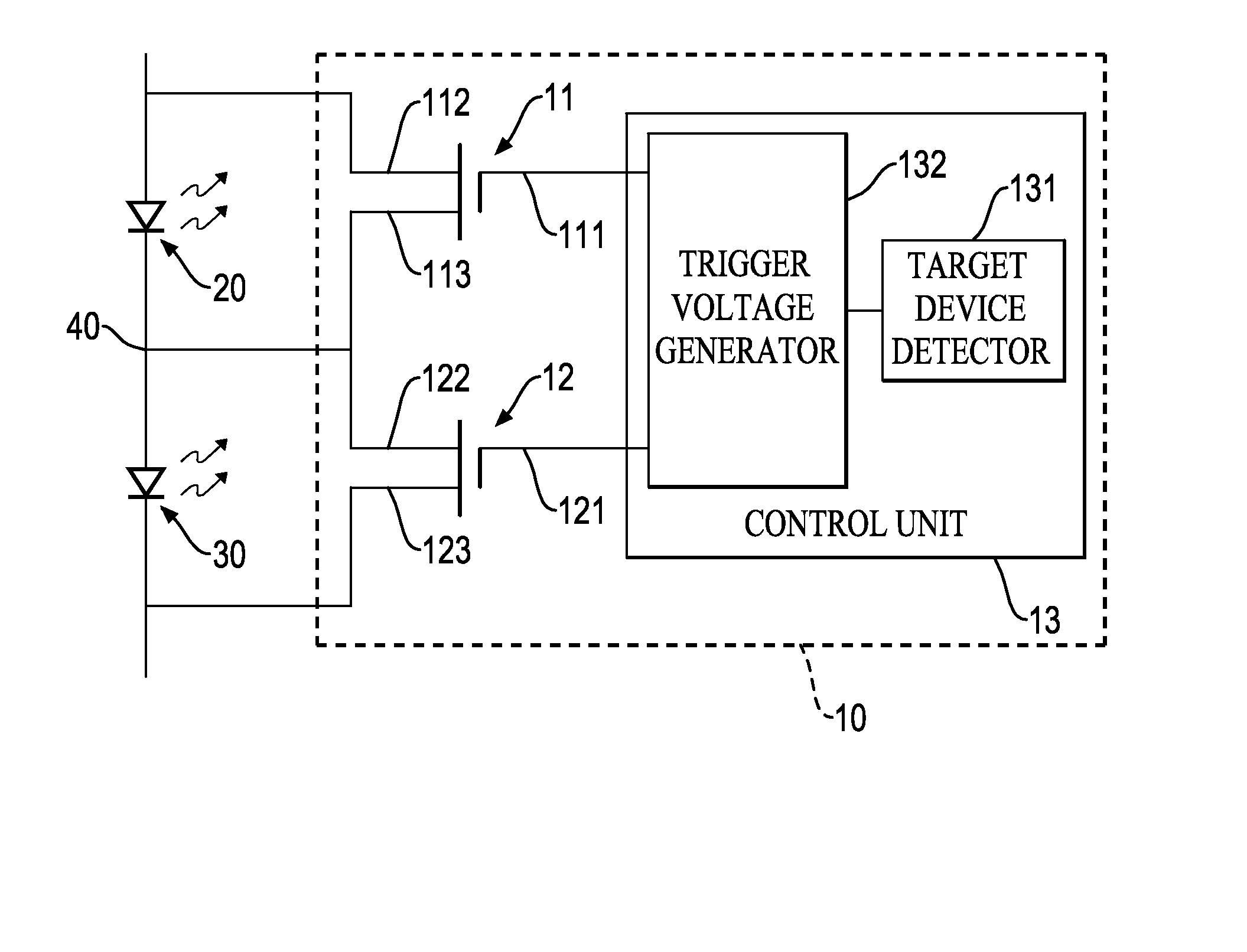

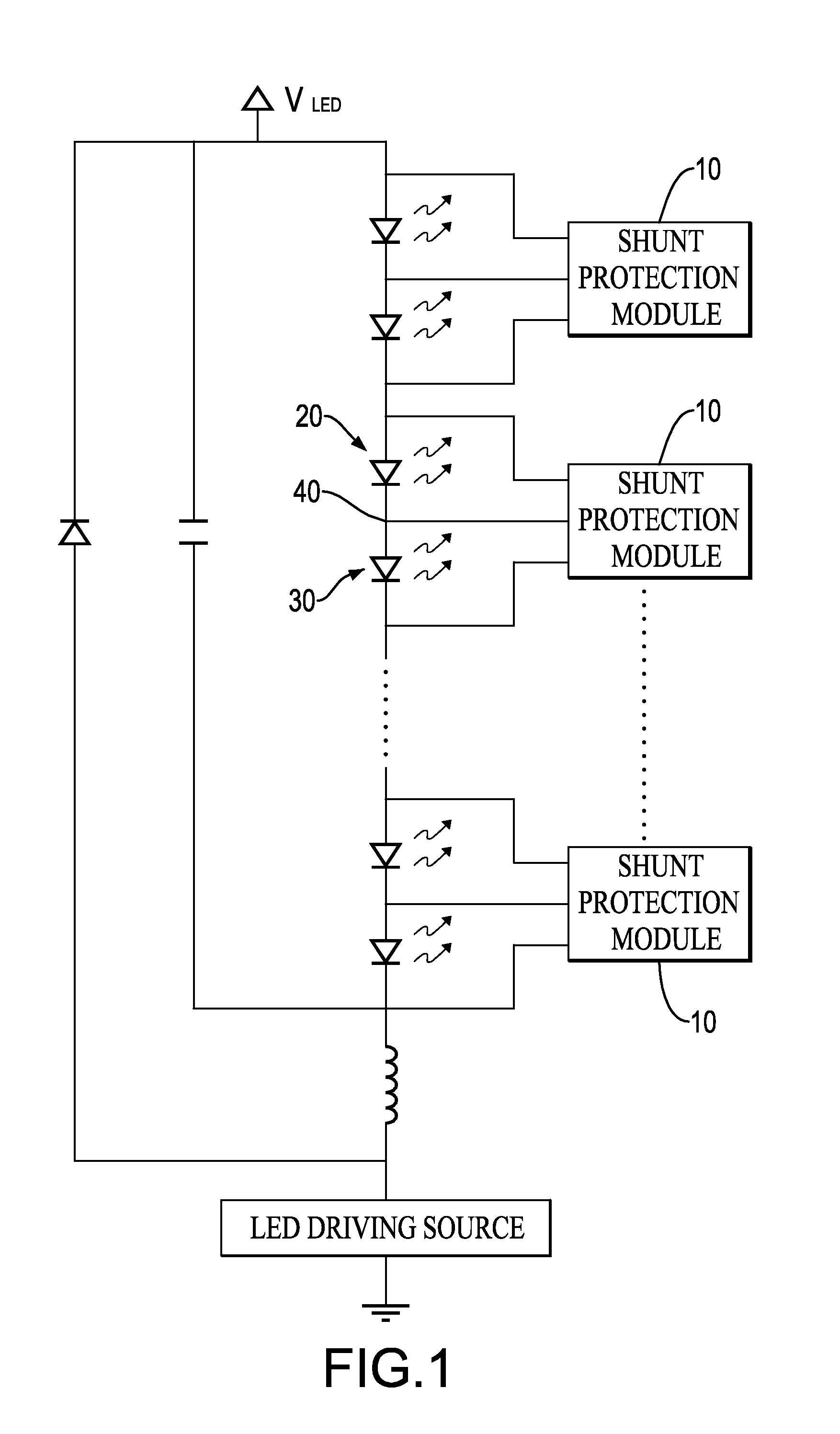

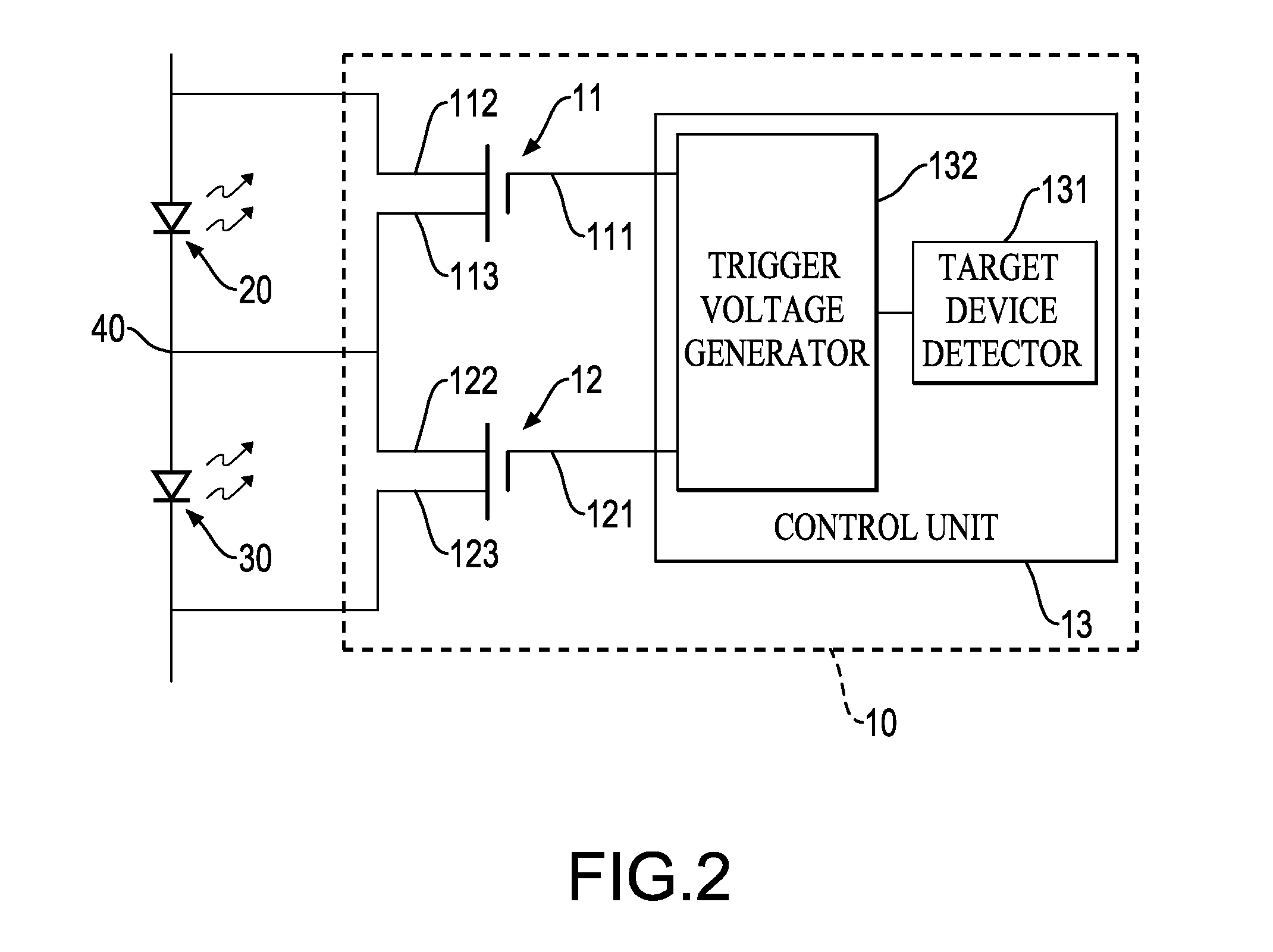

Shunt protection module and method for series connected devices

ActiveUS20130077202A1Reduce power consumptionIncrease the trigger voltageElectroluminescent light sourcesSemiconductor lamp usagePotential differenceComputer module

A shunt protection module and method for series connected devices use multiple shunt semiconductors and a control unit. The shunt semiconductors correspond respectively to multiple target devices. Each shunt semiconductor connects to a corresponding target device in parallel. The control unit connects to trigger terminals of the shunt semiconductors. Because each shunt semiconductor has a characteristic that with the higher voltage the trigger terminal is input, the lower the electrical potential difference between shunt terminals is, and the control unit outputs a trigger voltage that is equal to the electrical potential difference on at least two adjacent target devices to the shunt semiconductor corresponding to a failed target device, an electrical potential difference on the shunt semiconductor is low when it operates. The shunt protection module and method ensure providing high trigger voltage to the shunt semiconductor corresponding to the failed target device.

Owner:SILICON TOUCH TECH INC

Electrostatic discharge protection device

ActiveCN103035635AAvoid false triggersIncrease the trigger voltageSolid-state devicesEmergency protective arrangements for limiting excess voltage/currentEngineeringHigh pressure

The invention provides an electrostatic discharge protection device. An electrostatic discharge (ESD) mixture filling layer is led to a positive-negative-positive-negative (PNPN) structure, proper trigger voltage is decided through adjustment for filling energy and dosage of the ESD mixture injection layer, proper maintenance voltage is obtained through adjustment for the size of the ESD mixture filling layer, and the latch-up problem is prevented. According to the electrostatic discharge protection device, self-insulation effects are formed based on an extension wafer high voltage process or a silicon-on-insulator (SOI) wafer high voltage process, a component can be prevented from being triggered by noise, and the trigger voltage can be conveniently increased through single electrostatic discharge protection units in serial connection.

Owner:CSMC TECH FAB2 CO LTD

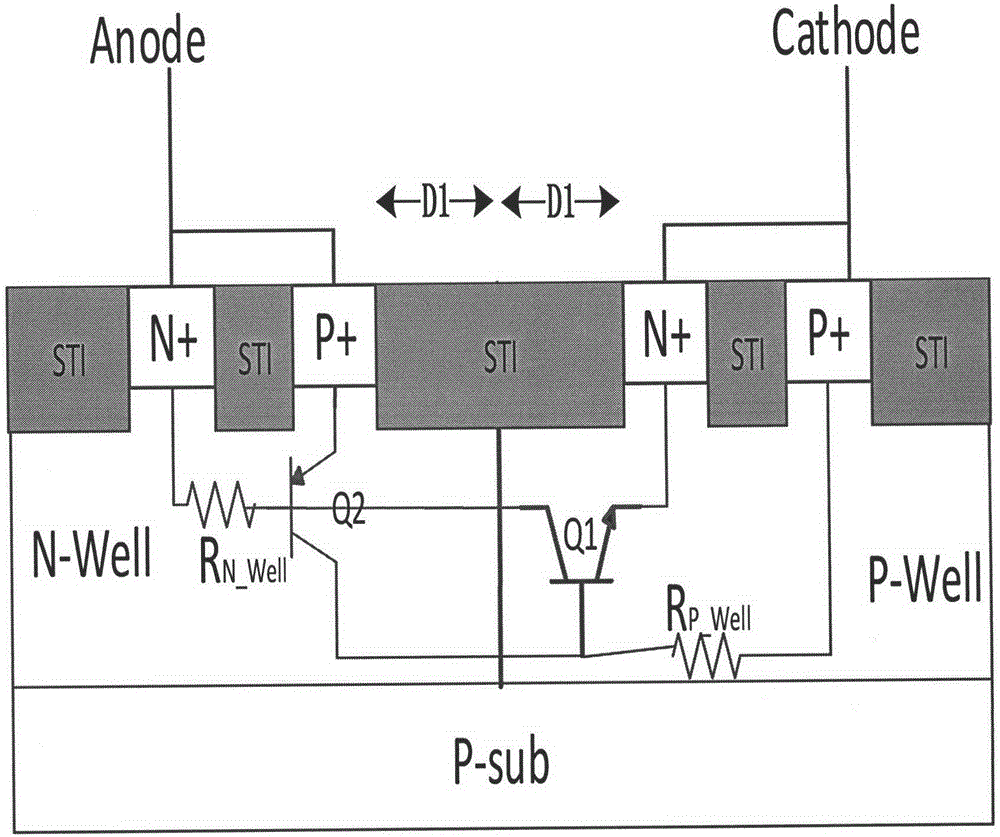

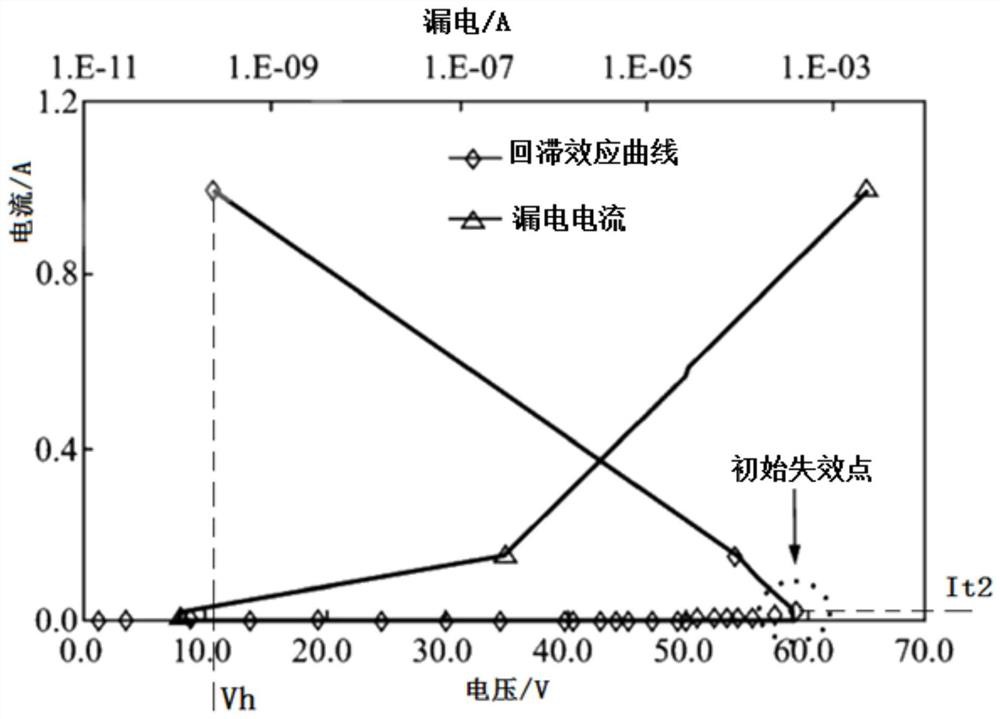

Double-gate SCR structure design for ESD protection

InactiveCN106373955ALower the trigger voltageIncrease the trigger voltageThyristorSolid-state devicesHysteresisDouble gate

The invention, which belongs to the technical field of the integrated circuit, discloses a double-gate SCR structure design for ESD protection, wherein the structure has the excellent anti-latching performance. According to the designed double-gate SCR structure, a parasitic PMOS and a parasitic diode structure are introduced into a conventional SCR device, thereby reducing a device trigger voltage and increasing a maintaining voltage. The parasitic PMOS is formed by self-aligned injection of P+ heavily doping between two gates and combination of a substrate and two gates. Because of introduction of the device, the large hysteresis characteristic of the SCR can be reduced to a certain extent, thereby improving the maintaining voltage to a certain extent. Besides, the parasitic diode is from N+, P-Well, P+, and N-Well. On the basis of the structure, the trigger voltage of the device can be reduced effectively. When the IC chip is in a non-electrified state during production, packaging, and testing processes, the SCR structure is turned on and the high electrostatic protection capability is realized.

Owner:马利峰

Reinforcing structure of radiation-resistant groove type MOS field effect transistor for satellite and preparation method

ActiveCN112510081APrecise control of concentration distributionIncrease the trigger voltageTransistorSemiconductor/solid-state device manufacturingEngineeringField effect

The invention discloses a reinforcing structure of a radiation-resistant groove type MOS field effect transistor for a satellite and a preparation method. The reinforcing structure comprises a substrate, a slowly-changing epitaxial layer, an interlayer dielectric layer and a metal layer which are stacked in sequence, a P+ body doped region and an N+ source doped region are sequentially arranged onthe surface of the slowly-changing epitaxial layer, and a gate trench is formed in the slowly-changing epitaxial layer; a first gate oxide, a floating polycrystalline gate, a second gate oxide and acontrol polycrystalline gate are sequentially stacked in the gate trench from bottom to top to form a double-layer shielding gate structure; the interlayer dielectric layer is provided with source shallow trenches, the source shallow trenches are symmetrically distributed at two sides of the gate trench, the source shallow trenches sequentially pass through the interlayer dielectric layer, the N+source doped region and the P+ body doped region, and the depth of the source shallow trenches does not exceed the longitudinal polycrystalline thickness of a control polycrystalline gate in the gatetrench; a P+ deep source is formed in each source shallow trench through ion implantation, wherein the P+ deep source is connected with the P+ body doped region; the metal layer is arranged on the interlayer dielectric layer and fills the source shallow trenches.

Owner:XIAN MICROELECTRONICS TECH INST

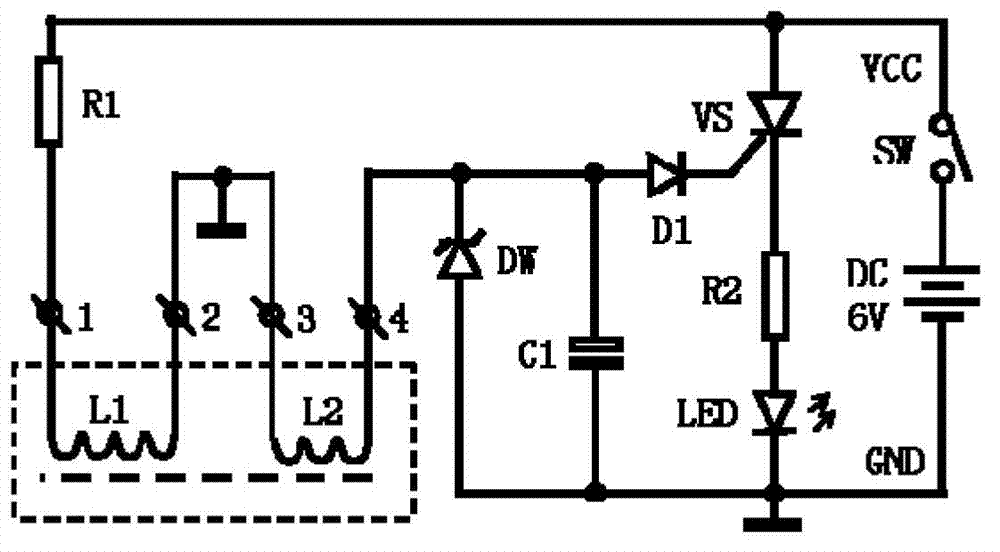

Transformer primary and secondary coil homonymous terminal and synonym terminal recognition device

InactiveCN103116110AIncrease the trigger voltageLong lastingElectrical testingTransformerEngineering

The invention discloses a transformer primary and secondary coil homonymous terminal and synonym terminal recognition device. The transformer primary and secondary coil homonymous terminal and synonym terminal recognition device is characterized by comprising a 6V direct current power supply, an electromagnetic signal input circuit, a one-way controllable silicon triggering and amplitude limiting circuit and a detecting and indication circuit. Primary and secondary homonymous terminals and synonym terminals of some transformers, coupling coils or oscillating coils need to be known clearly. Sometimes, the recognition of homonymous terminals of a plurality of windings of the transformer is troublesome during the process of electric production and transformer maintenance and replacement. A dedicated instrument for detecting the homonymous terminals of the windings of the transformer does not exist in a market so that designing and manufacturing the transformer primary and secondary coil homonymous terminal and synonym terminal recognition device is quite necessary. A recognition circuit is composed by utilizing elements of one-way controllable silicon and the like so that homonymous terminals or synonym terminals of high-frequency and low-frequency transformers can be rapidly recognized, magnitude of power of the transformer does not need to be distinguished, a boosting transformer or a step-down transformer does not need to be distinguished, and detection and recognition are achieved.

Owner:李宁杭

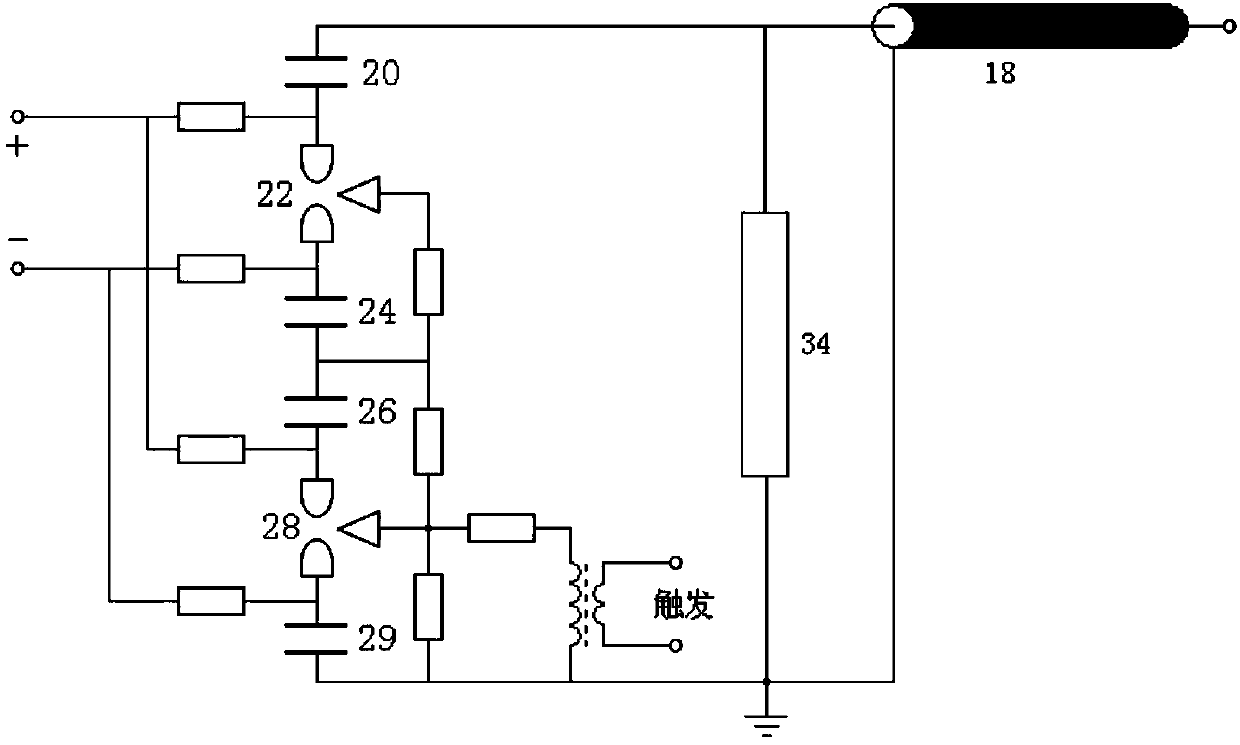

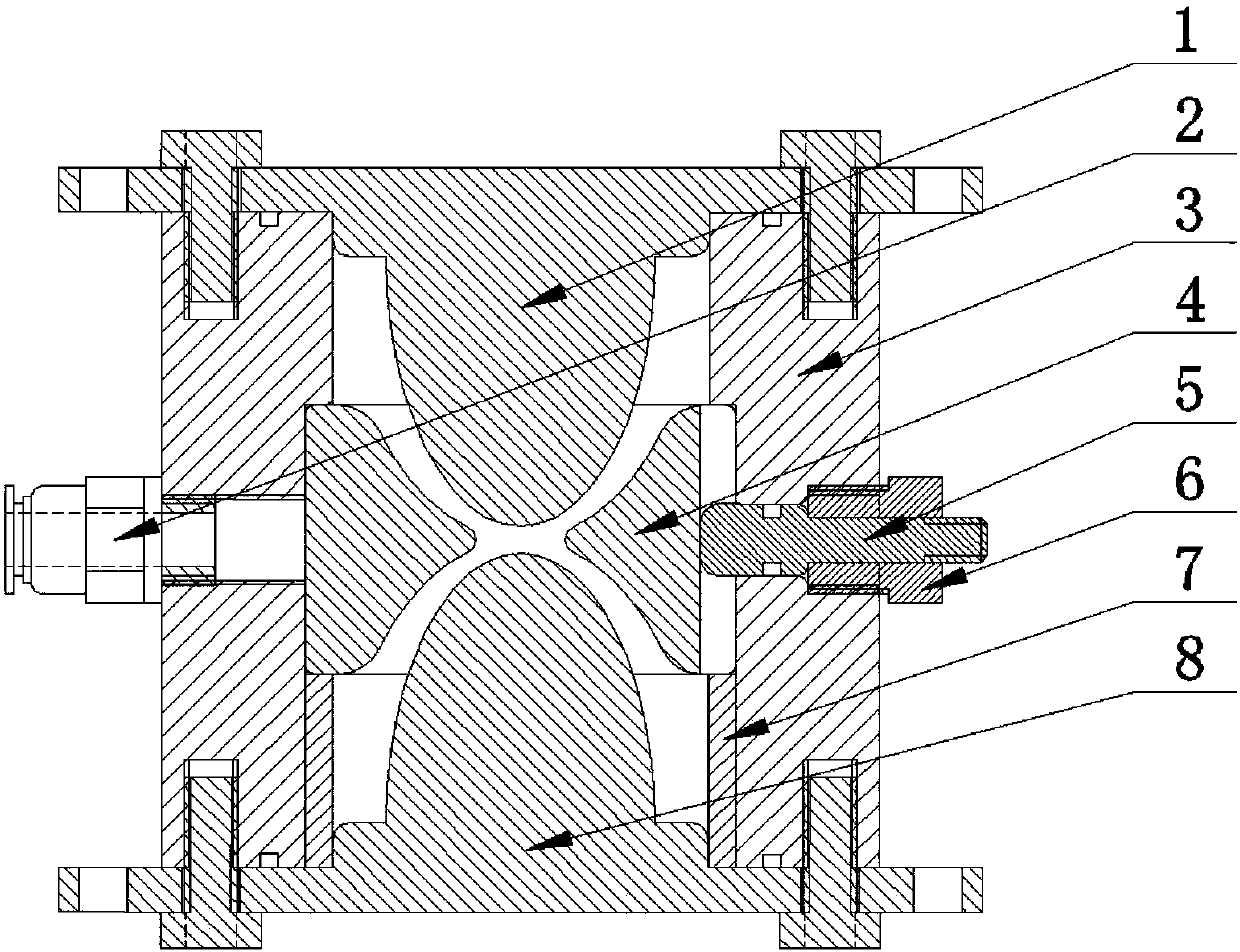

High-voltage pulse generator with low jitter

PendingCN107659291AUniform electric field distributionSmall delay jitterPulse generation by energy-accumulating elementElectric pulse generator detailsLow jitterHigh voltage pulse

The invention discloses a high-voltage pulse generator with low jitter. The high-voltage pulse generator comprises an outer barrel and a cover plate, wherein a gas switch I and a gas switch II which have the same structure, an earth plate and a center connection piece are arranged in a cavity formed by the outer barrel and the cover plate; the center connection piece is arranged between the gas switch I and the gas switch II; a trigger connecting rod of the gas switch I is connected to the center connection piece through an earth resistor A; the center connection piece is connected to a trigger connecting rod of the gas switch II through an earth resistor B; and the trigger connecting rod of the gas switch II is connected to the earth plate through an earth resistor C. The pulse generatorhas small delay jitter, small self-breakdown probability, stable work, adjustable working voltage and high anti-interference capability.

Owner:INST OF FLUID PHYSICS CHINA ACAD OF ENG PHYSICS

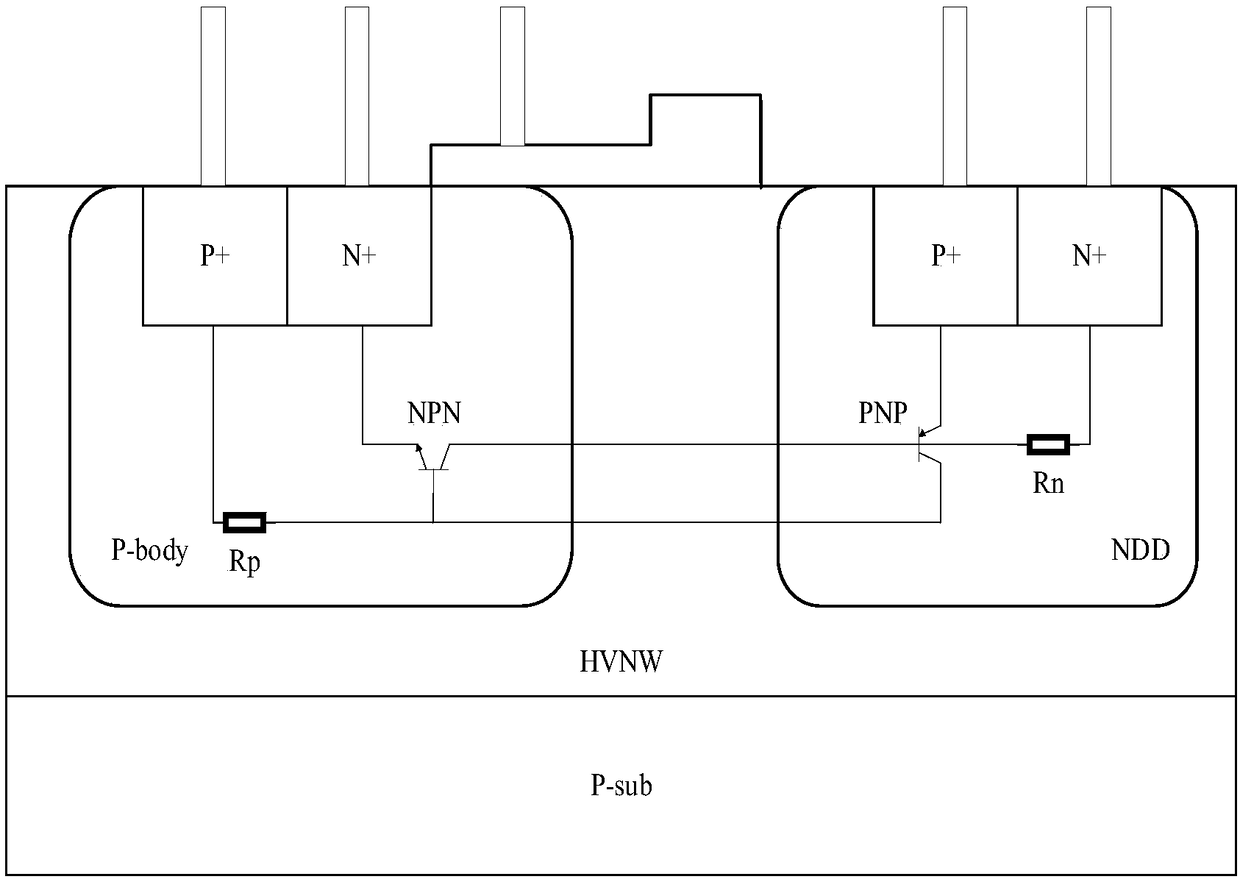

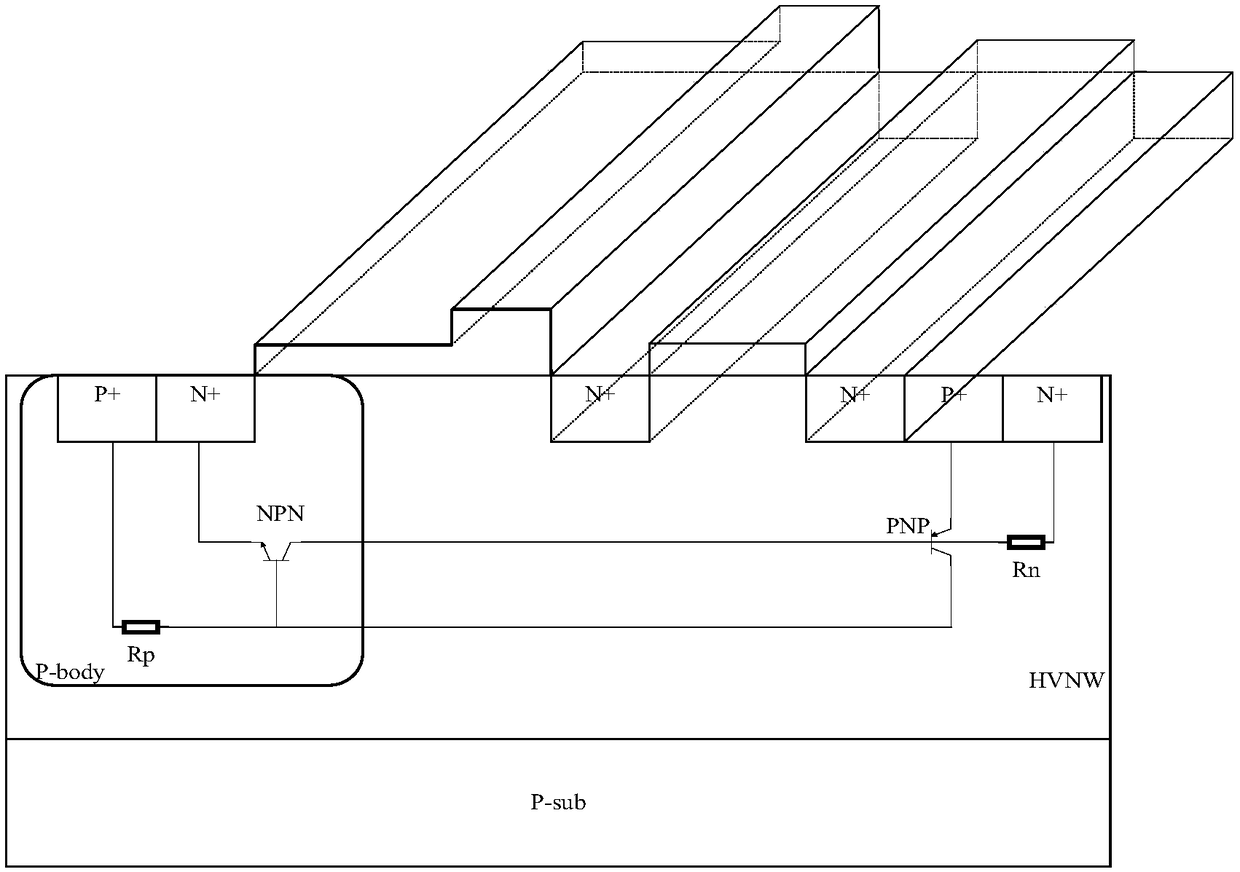

Polysilicon pseudo-gate electrostatic discharge device for improving maintaining voltage and manufacturing method thereof

ActiveCN108389857AAvoid thermal breakdownIncrease holding voltageTransistorSolid-state devicesElectrostatic dischargeEngineering

The invention discloses a polysilicon pseudo-gate electrostatic discharge device for improving a maintaining voltage. The electrostatic discharge device comprises a substrate; an HVNW region is arranged in the substrate; a P-body region is arranged in the left half part of the HVNW region; a first P+ injection region and a first N+ injection region are arranged in the P-body region; a first polysilicon gate stretches across the junction of the P-body region and the HVNW region; a second N+ injection region, a second polysilicon pseudo gate, a third N+ injection region, a second P+ injection region and a fourth N+ injection region are arranged in the right half part of the HVNW region; and the second polysilicon pseudo gate forms the polysilicon pseudo-gate structure. The device disclosed in the invention adopts the polysilicon pseudo-gate structure, so that ESD of the LDMOS-SCR device structure can be far from the surface of a channel, and the majority of ESD current stress can be released from the device structure, so that the device structure can bear high enough electrostatic discharge pulse stress, thereby preventing thermal breakdown from occurring on the surface of the device.

Owner:HUNAN NORMAL UNIVERSITY

Low trigger voltage silicon control rectifier and its circuit

InactiveCN100463177CIncrease the trigger voltageLower the trigger voltageSolid-state devicesSemiconductor devicesSilicon-controlled rectifierLow voltage

The present invention relates to a low voltage triggering silicon controlled rectifier (SCR). It is characterized by that it utilizes addition of second doped zone which is set between the described low voltage triggering silicon controlled rectifier anode and its parasitic PNP transistor emitter to raise the holding voltage when the described low voltage triggering silicon controlled rectifier is triggered. The described low voltage triggering silicon controlled rectifier includes a semiconductor substrate with first conducting type and a grid. The described semiconductor substrate contains a first doped zone with second conducting type, a second doped zone with first conducting type, a third doped zone with second conducting type, a fourth doped zone with second conducting type and a fifth doped zone with first conducting type. The described grid is characterized by utilizing lower trigger voltage to trigger the described low voltage triggering silicon controlled rectifier.

Owner:ADVANCED ANALOG TECH INC

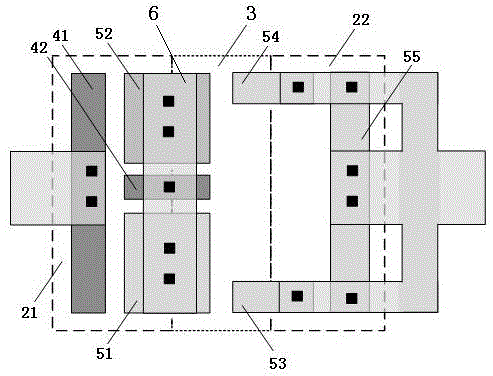

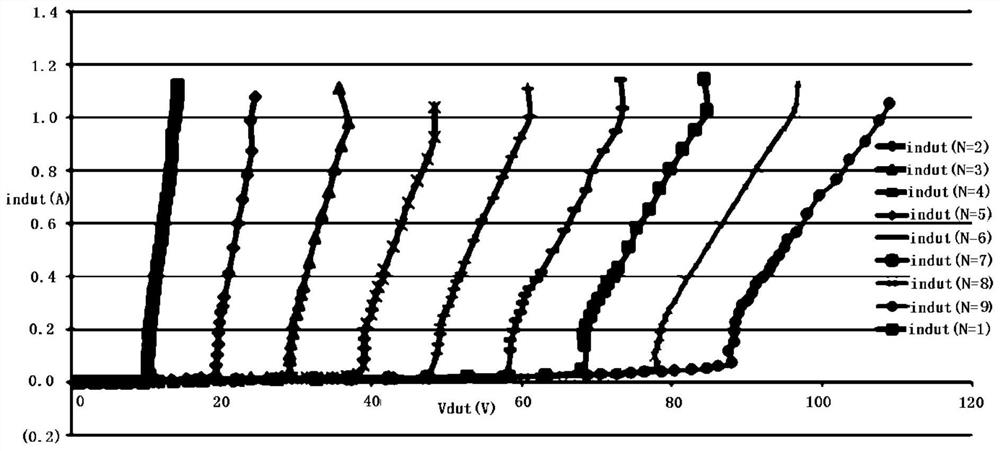

High area efficiency diode triggered controllable silicon based on two-dimension design

The invention discloses high area efficiency diode triggered controllable silicon based on two-dimension design. The high area efficiency diode triggered controllable silicon based on the two-dimension design comprises a P-type substrate, N wells, a P well, P+ injection regions, N+ injection regions, metal, a shallow-trench isolation part, a cathode and an anode, wherein the N wells comprise a first N well and a second N well, the P+ injection region comprises a first P+ injection region and a second P+ injection region, the N+ injection regions comprise a first N+ injection region, a second N+ injection region, a third N+ injection region, a fourth N+ injection region and a fifth N+ injection region, and the first N well, the P well and the second N well are arranged on the P-type substrate in sequence along the transverse direction. According to the high area efficiency diode triggered controllable silicon based on the two-dimension design, a diode is embedded into the controllable silicon at a trigger stage, electric current flows mainly along the longitudinal direction of a device, thereby, well resistance in the longitudinal direction of the device is fully utilized, and compared with conventional diode triggered controllable silicon, the high area efficiency diode triggered controllable silicon based on the two-dimension design has the advantages that only a few of series diodes of the device are required so that high trigger voltage can be achieved, and the area efficiency is increased.

Owner:HAINING BERNSTEIN BIOTECH CO LTD

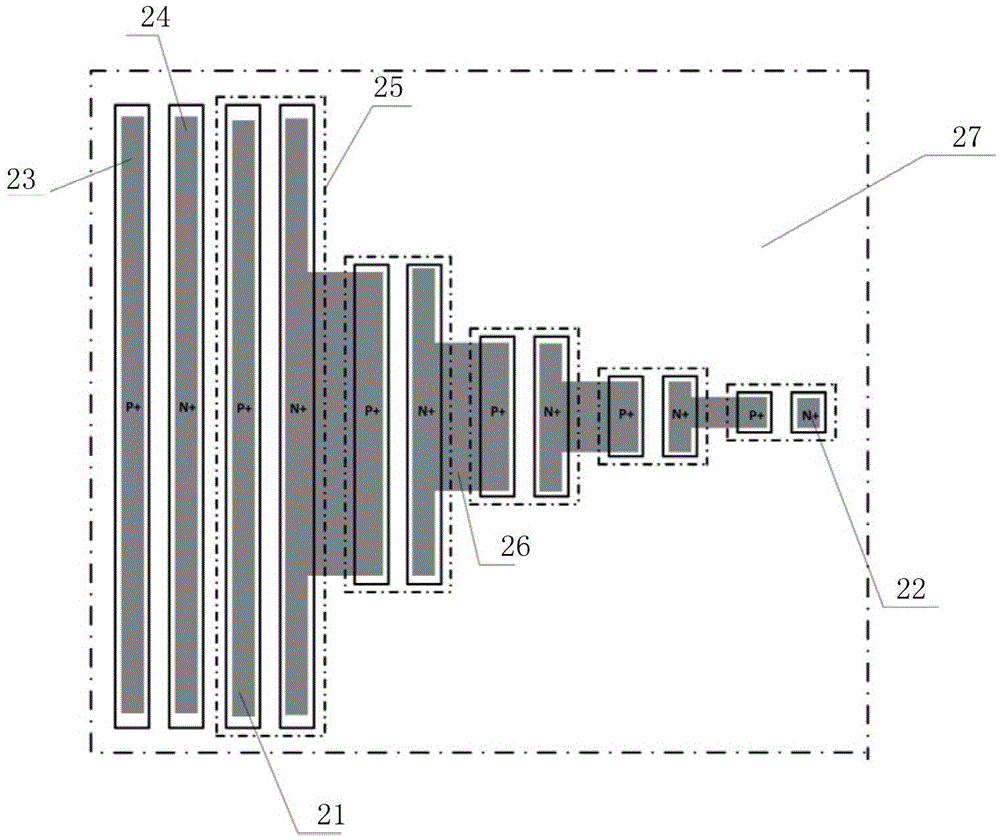

Diode assist-triggered thyristor device and manufacturing method and integrated circuit thereof

ActiveCN105552076AIncrease the trigger voltageIncrease current densitySolid-state devicesSemiconductor/solid-state device manufacturingStart timeInterconnection

The invention discloses a diode assist-triggered thyristor device, and a manufacturing method and an integrated circuit thereof. The device comprises a first P+ injection region, a first N+ injection region and at least two N well regions, which are sequentially arranged on a P-type substrate; each N well region is provided with a second P+ injection region near the first P+ injection region and a second N+ injection region far away from the first P+ injection region; the device also comprises a metal interconnection region, which is used for connecting the second N+ injection regions and the second P+ injection regions in the adjacent N well regions; the areas of patterns formed by the second P+ injection regions on the surface of the P-type substrate are not identically equal and are not greater than those of the patterns formed by the first P+ injection regions formed on the surface of the P-type substrate; and the areas of the patterns formed by the second N+ injection regions on the surface of the P-type substrate are not identically equal and are not greater than those of the patterns formed by the first N+ injection regions formed on the surface of the P-type substrate. The DTSCR device reduces the leakage current on the basis of not increasing the layout area and shortens the starting time of the DTSCR device in a VF-TLP test.

Owner:PEKING UNIV

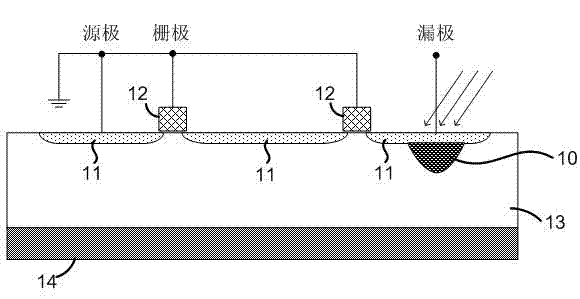

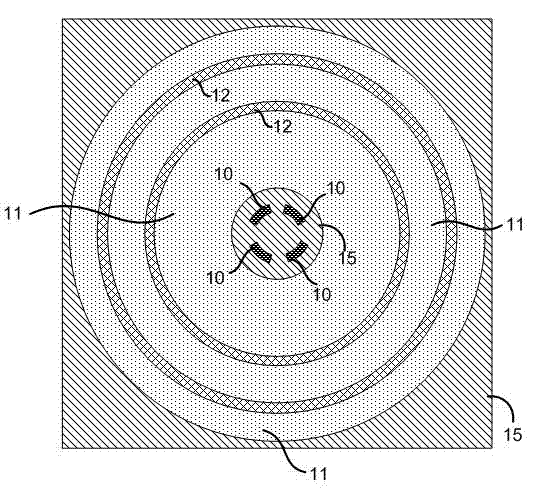

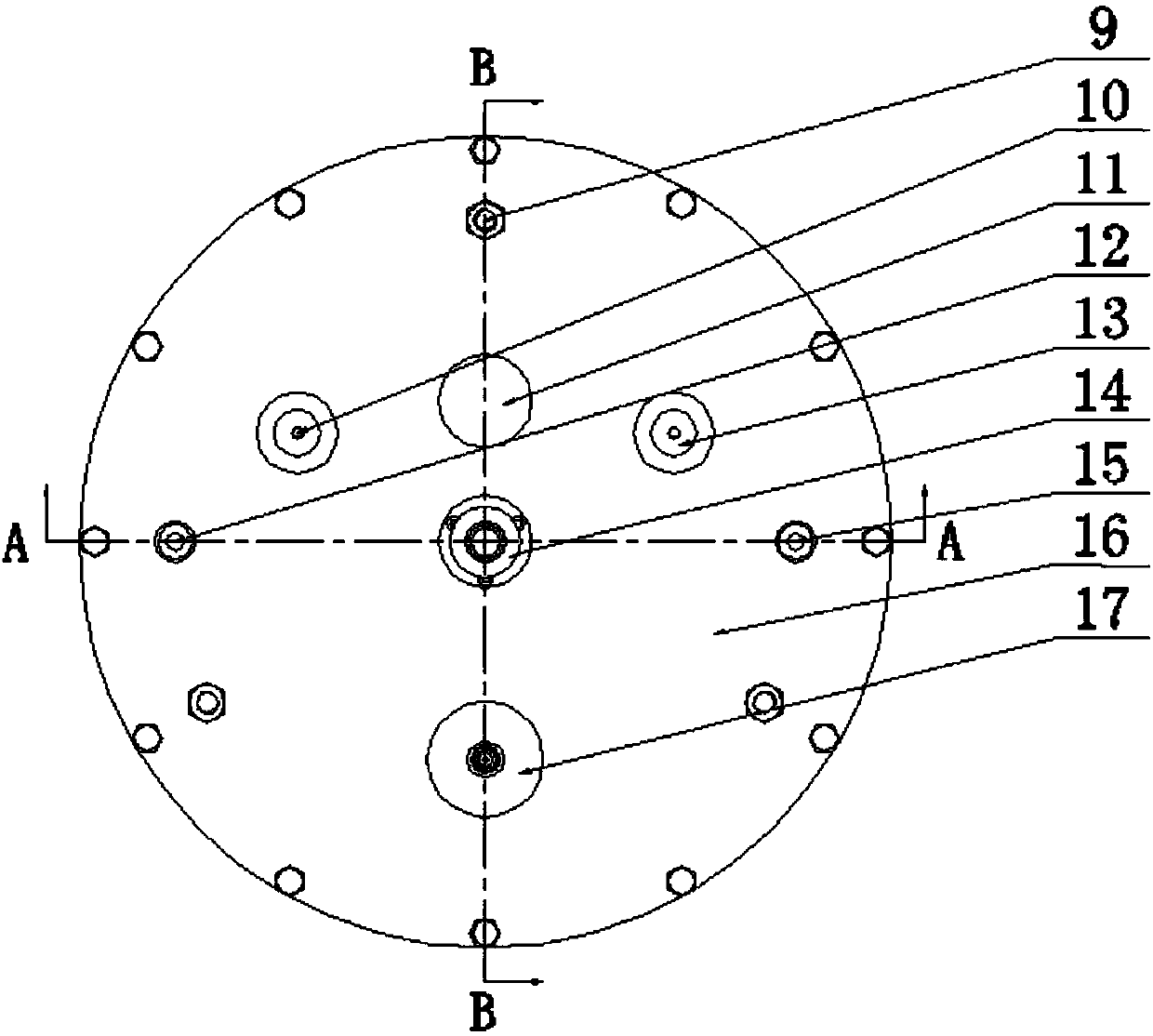

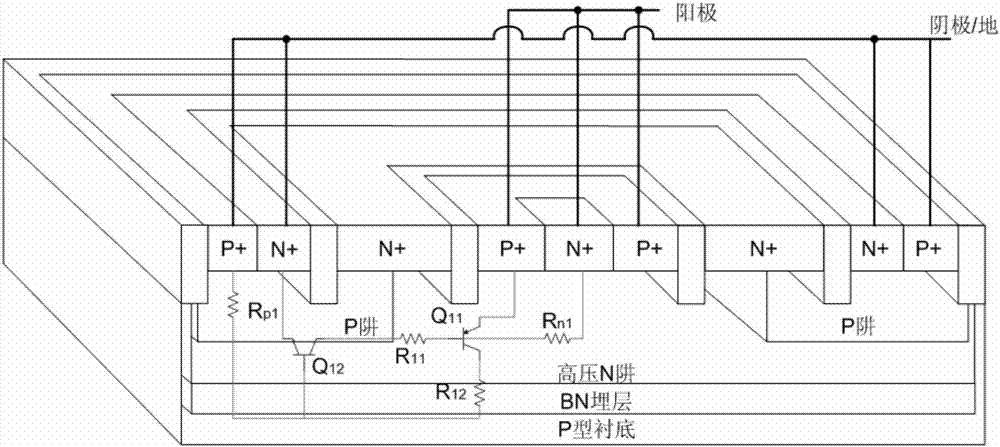

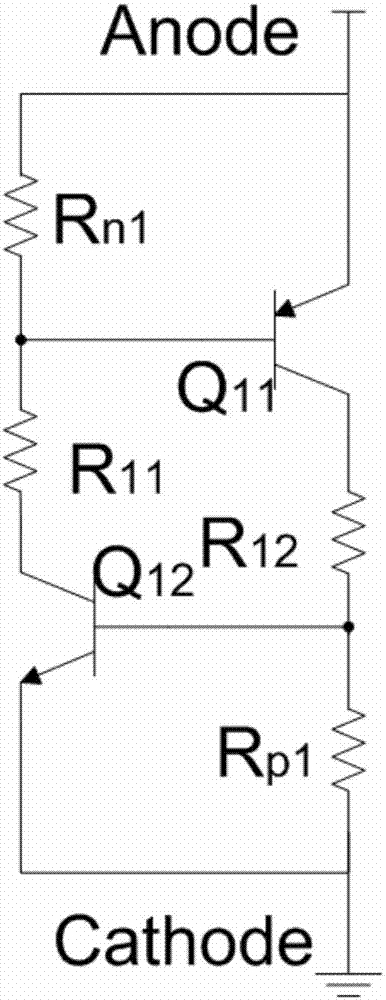

Waffle island type diode triggered silicon controlled electrostatic protection device

ActiveCN107546223AIncrease the trigger voltageAbility to discharge static pulses stronglySolid-state devicesSemiconductor devicesPhysicsElectrostatic discharge

The invention discloses a waffle island type diode triggered silicon controlled electrostatic protection device. The waffle island type diode triggered silicon controlled electrostatic protection device comprises a P type substrate and a BN buried layer inside the P type substrate, wherein a high-voltage N trap is arranged on the BN buried layer; a first P trap, a first P-base injection layer, a second P+ injection area, a third N+ injection area, a third P+ injection area, a second P-base injection layer and a second P trap are arranged on the high-voltage N trap in sequence from left to right; a first P+ injection area, a first N+ injection area and a second N+ injection area are arranged inside the first P trap in sequence from left to right; and a fourth N+ injection area, a fifth N+ injection area and a fourth P+ injection area are arranged inside the second P trap in sequence from left to right. The device is embedded in a parallel island type diode, the electrostatic discharge capacity of the device is strengthened while the trigger voltage of the device is reduced, and discharge efficiency of the device is improved by adopting a waffle type array to implement layout.

Owner:XIANGTAN UNIV

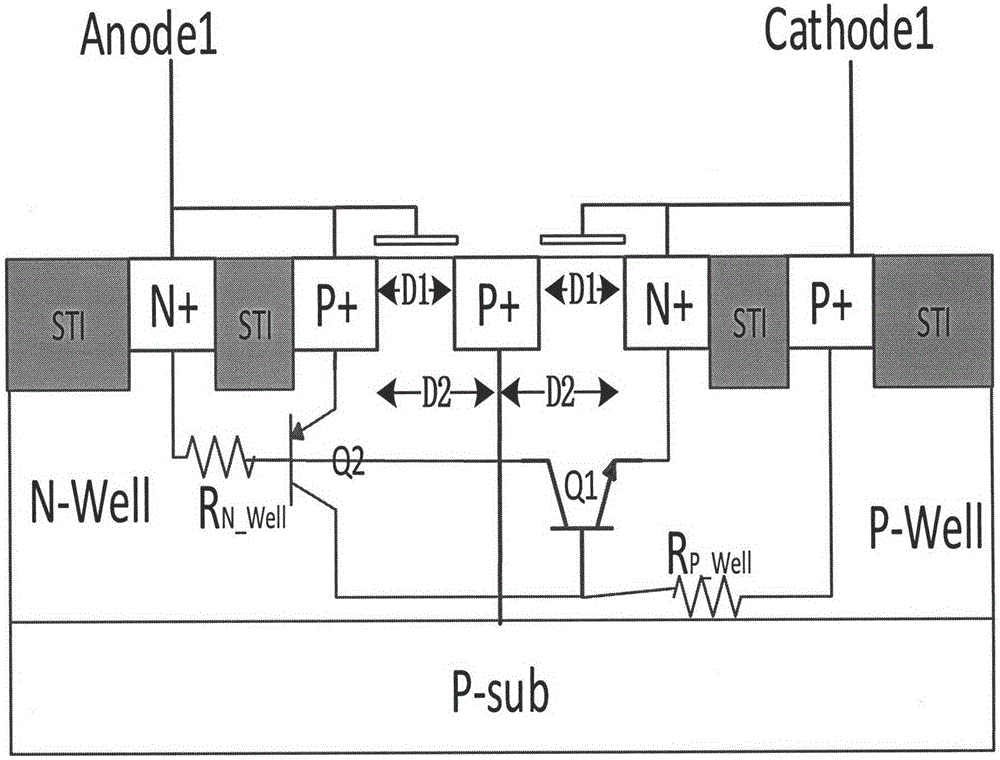

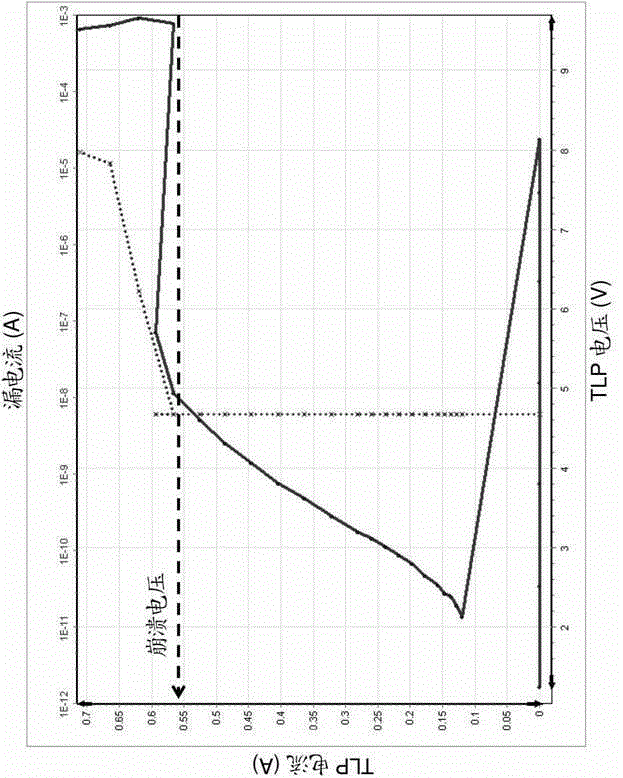

Bidirectional silicon-controlled rectifier and preparation method thereof

PendingCN111403383AIncrease the trigger voltageTransistorSolid-state devicesSilicon-controlled rectifierEngineering

The invention discloses a bidirectional silicon controlled rectifier and a preparation method thereof. Actually, the structure of the cathode of the original unidirectional silicon-controlled rectifier without the hysteresis effect is completely removed; the bidirectional silicon-controlled rectifier provided by the invention is a bidirectional device, and can be simultaneously suitable for the design of an anti-static protection circuit of positive and negative high-voltage IO ports. Besides, the trigger voltage of the hysteresis effect of the bidirectional silicon-controlled rectifier can beadjusted by adjusting the second distance, and compared with a silicon-controlled rectifier without the hysteresis effect in the prior art, the bidirectional silicon-controlled rectifier provided bythe invention has higher trigger voltage.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

Polysilicon dummy gate electrostatic discharge device with increased sustain voltage and manufacturing method thereof

ActiveCN108389857BAvoid thermal breakdownIncrease holding voltageTransistorSolid-state devicesLDMOSEngineering

Owner:HUNAN NORMAL UNIVERSITY

Shunt protection module and method for series connected devices

ActiveUS8699194B2Reduce power consumptionIncrease the trigger voltageElectroluminescent light sourcesSemiconductor lamp usagePotential differenceComputer module

A shunt protection module and method for series connected devices use multiple shunt semiconductors and a control unit. The shunt semiconductors correspond respectively to multiple target devices. Each shunt semiconductor connects to a corresponding target device in parallel. The control unit connects to trigger terminals of the shunt semiconductors. Because each shunt semiconductor has a characteristic that with the higher voltage the trigger terminal is input, the lower the electrical potential difference between shunt terminals is, and the control unit outputs a trigger voltage that is equal to the electrical potential difference on at least two adjacent target devices to the shunt semiconductor corresponding to a failed target device, an electrical potential difference on the shunt semiconductor is low when it operates. The shunt protection module and method ensure providing high trigger voltage to the shunt semiconductor corresponding to the failed target device.

Owner:SILICON TOUCH TECH INC

Anti-static protection structure and high-voltage integrated circuit

PendingCN114121937ALower resistanceIncrease the trigger voltageTransistorSolid-state devicesMaterials scienceElectrical current

The invention discloses an anti-static protection structure. The anti-static protection structure comprises an N well and a P well which are formed in a substrate, the upper parts and the middle parts of the N well and the P well are separated by STI, and the lower parts are adjacent; sTI is attached to the upper portion of the N well, P-type heavy doping is injected, and an N well P heavy doping area is formed; n-type heavy doping is injected at the upper part of the N well far away from the STI to form an N-well N heavily doped region; sTI is attached to the upper portion of the P well, P-type heavy doping is injected, and a P well P heavy doping area is formed; the N-well P heavily doped region and the N-well N heavily doped region are short-circuited to form an anode of the anti-static protection structure; and the P heavily doped region of the P well is used as a cathode of the anti-static protection structure. According to the anti-static protection structure, no hysteresis effect can be achieved, high trigger voltage and maintaining voltage can be easily obtained, high secondary breakdown current is achieved, and when the anti-static protection structure is applied to high-voltage port anti-static protection design, the series connection number needed by multi-stage series connection and the layout area of a single-stage protection unit can be saved. The invention also discloses a high-voltage integrated circuit.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

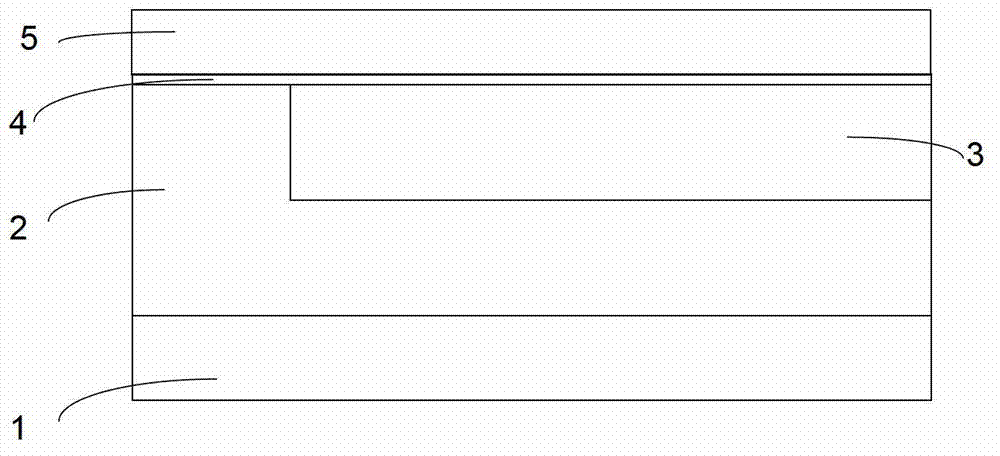

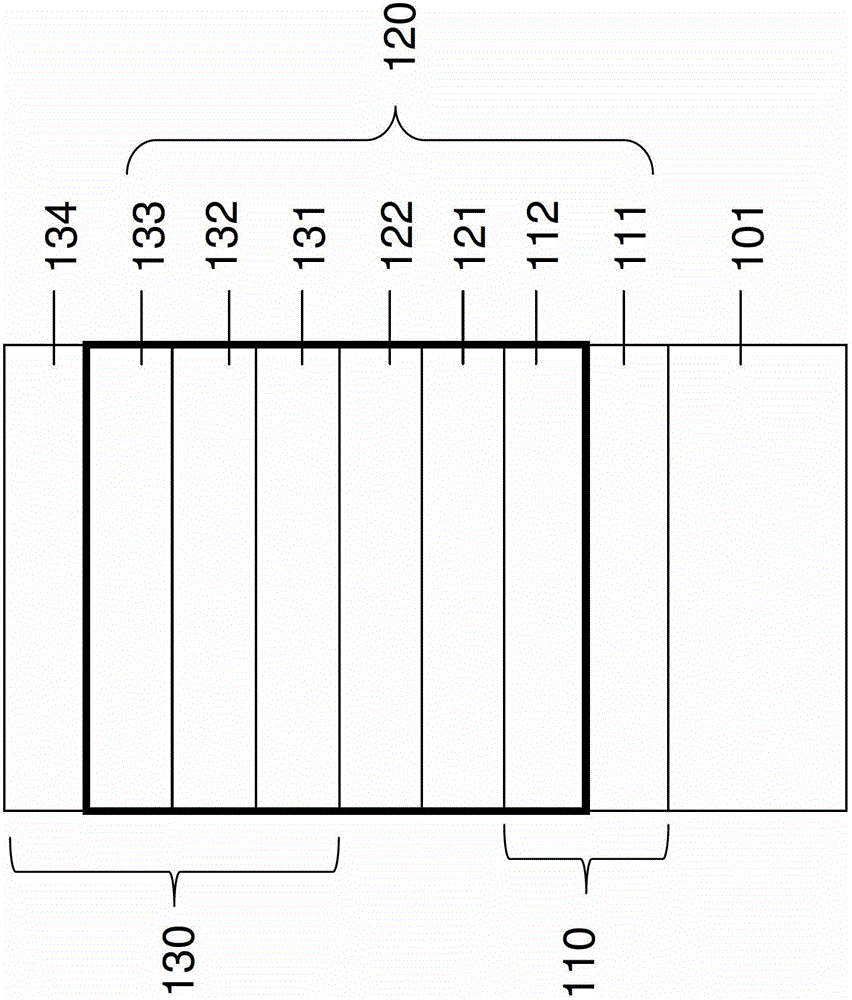

A compound semiconductor wafer structure

ActiveCN103489860BReduce the use of areaIncrease the trigger voltageSolid-state devicesSemiconductor devicesField-effect transistorHeterojunction bipolar transistor

The invention relates to a compound semiconductor wafer structure. The compound semiconductor wafer structure comprises a substrate, an n-type field effect transistor expitaxy structure, an n-type adulteration erosion stopping layer, a p-type inserting layer and an npn heterojunction bipolar transistor expitaxy structure, and can be used for manufacturing a field effect transistor or a heterojunction bipolar transistor or a thyristor.

Owner:WIN SEMICON

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com