Double-gate SCR structure design for ESD protection

A technology of structural design and metal gate, applied in electrical components, thyristors, electric solid devices, etc., can solve the problems of low sustaining voltage, high triggering voltage, ineffectively increasing the sustaining voltage, etc., and achieve the effect of reducing the triggering voltage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0012] The specific implementation manners of the present invention will be described in detail below in conjunction with the accompanying drawings.

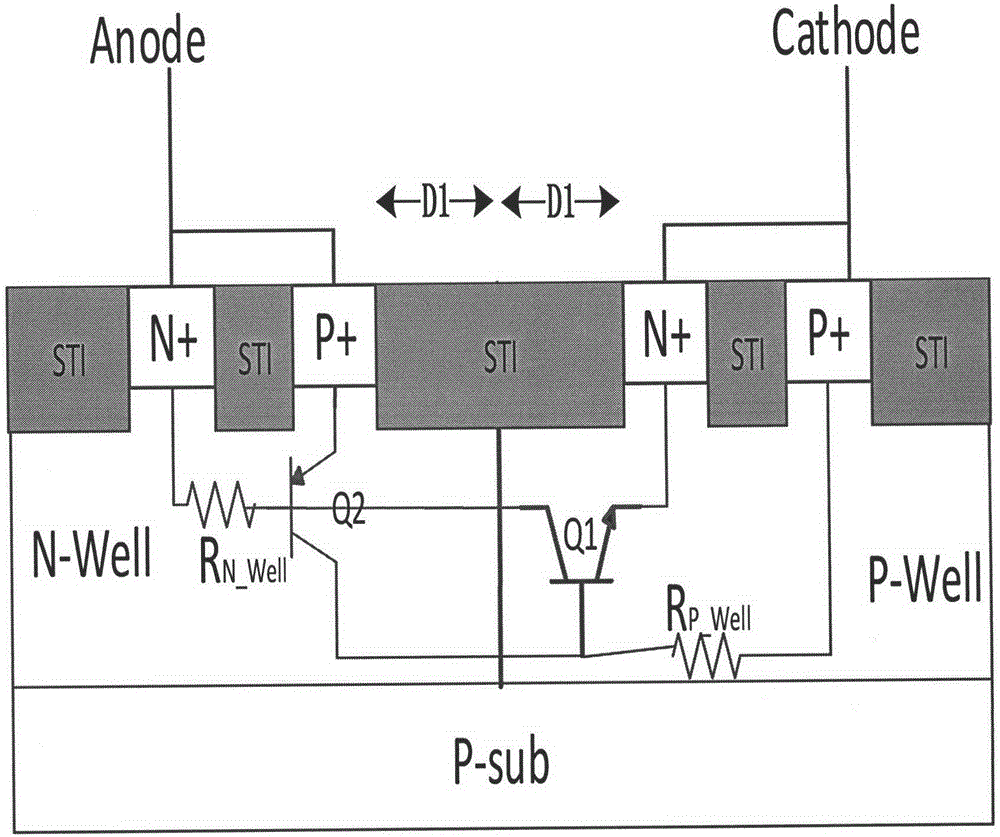

[0013] The sectional view and equivalent circuit diagram of the conventional SCR device in the prior art are as follows Figure 1 As shown, a conventional SCR is composed of two BJTs, in which P+ and N+ in N-Well are shorted and connected to Anode, and N+ and P+ in P-Well are shorted and connected to Cathode. Such a layout structure forms a PNP transistor Q2 and NPN transistor Q1 connected by positive feedback, when Cathode is grounded and a positive pulse appears on Anode, N-Well and P-Well form a reverse-biased PN junction, and when the reverse-biased voltage of the PN junction is high enough, it will occur Avalanche breakdown generates electron-hole pairs. The electrons and holes are collected by Anode and Cathode respectively, flow through the corresponding well resistance and generate a voltage drop, so that the Q1 and Q2 t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com