Polysilicon pseudo-gate electrostatic discharge device for improving maintaining voltage and manufacturing method thereof

A technology for maintaining voltage and electrostatic discharge, which is applied in the fields of electric solid-state devices, semiconductor/solid-state device manufacturing, electrical components, etc. The effect of breakdown

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0032] The present invention will be further described below in conjunction with the accompanying drawings and embodiments.

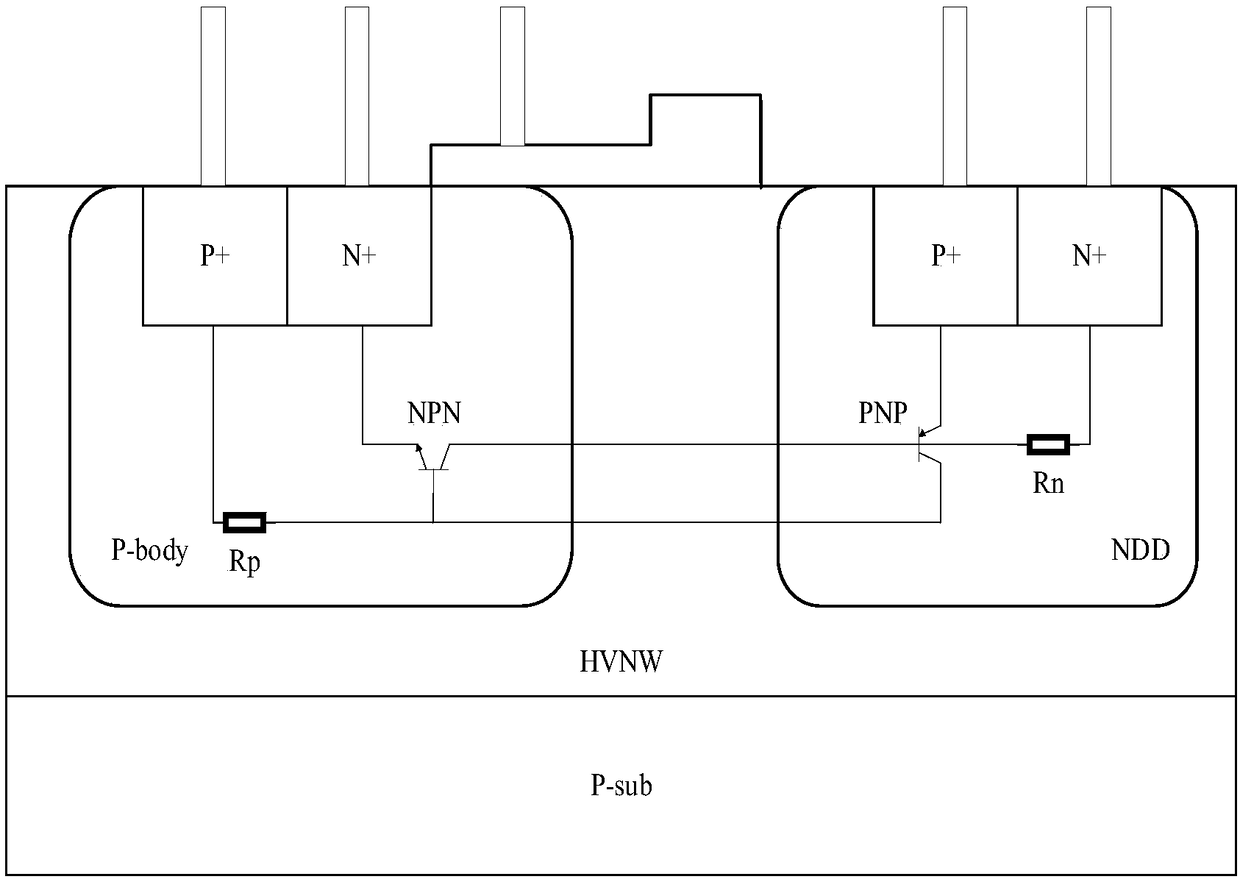

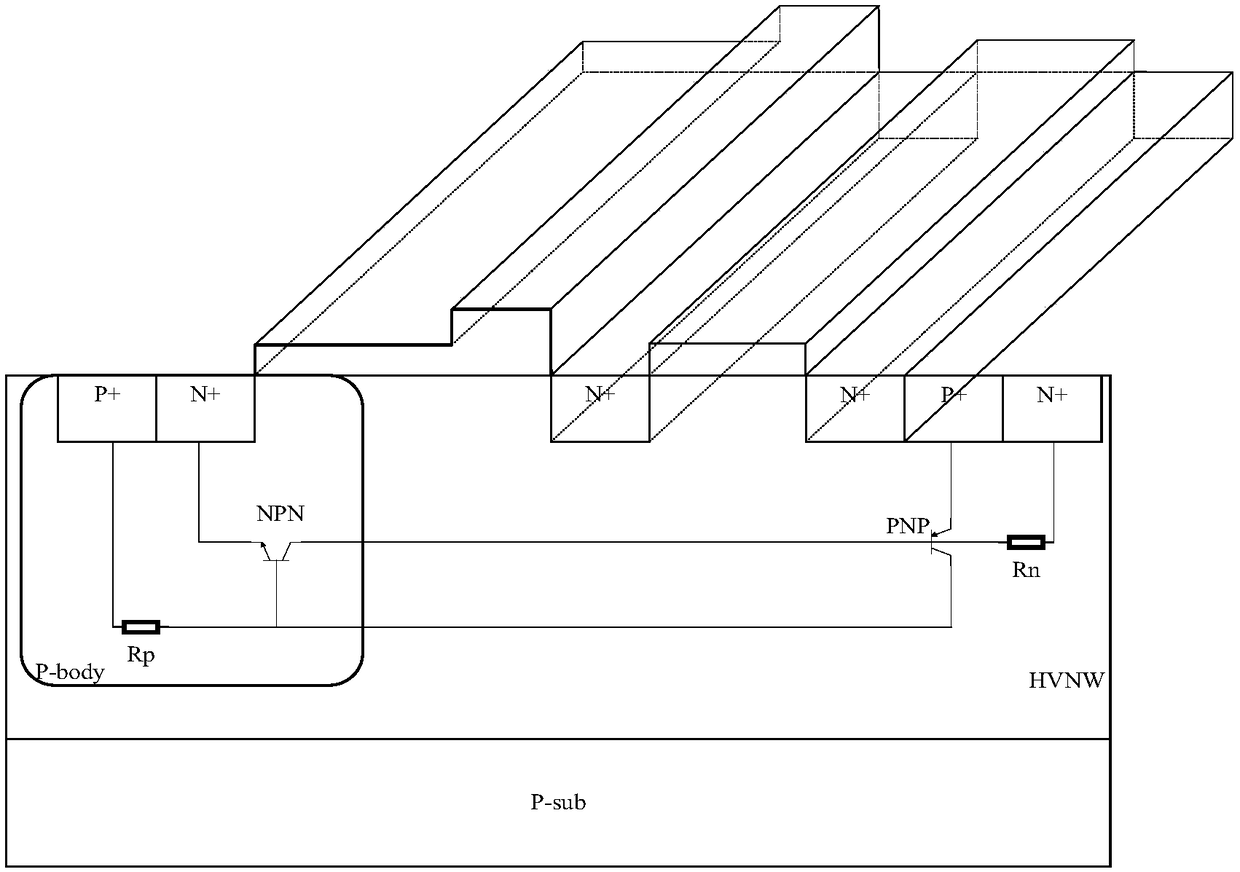

[0033] like figure 2 , image 3 As shown, a polysilicon dummy gate ESD device with increased sustain voltage includes substrate P-SUB101, P-body region 102, HVNW region 103, first P+ implantation region 104, first N+ implantation region 105, second N+ implanted region 106, third N+ implanted region 107, second P+ implanted region 108, fourth N+ implanted region 109, first polysilicon gate 201, second polysilicon dummy gate 202, the substrate P-SUB 101 A HVNW region 103 is arranged in the middle, and a P-body region 102 is arranged in the left half of the HVNW region 103. In the P-body region 102, a first P+ implantation region 104, a first N+ implantation region 105, and a A polysilicon gate 201 spans the junction of the P-body region 102 and the HVNW region 103, and the second N+ implantation region 106 and the second polysilicon dummy gate 202 are ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com