Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

72results about How to "Improve electrical quality" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

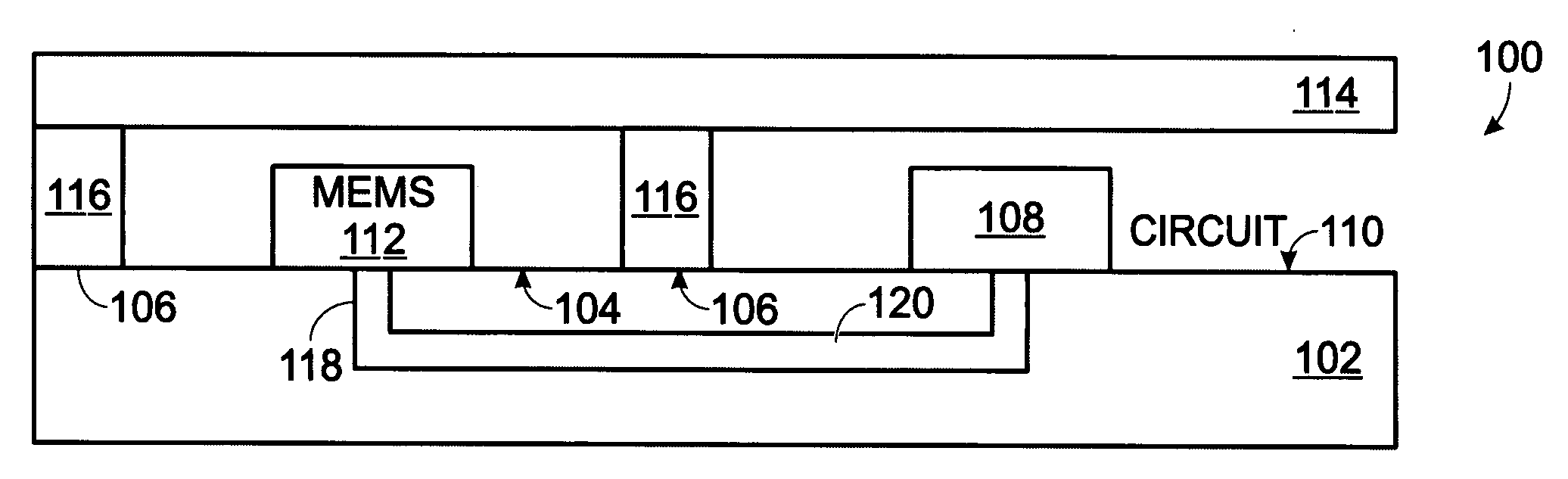

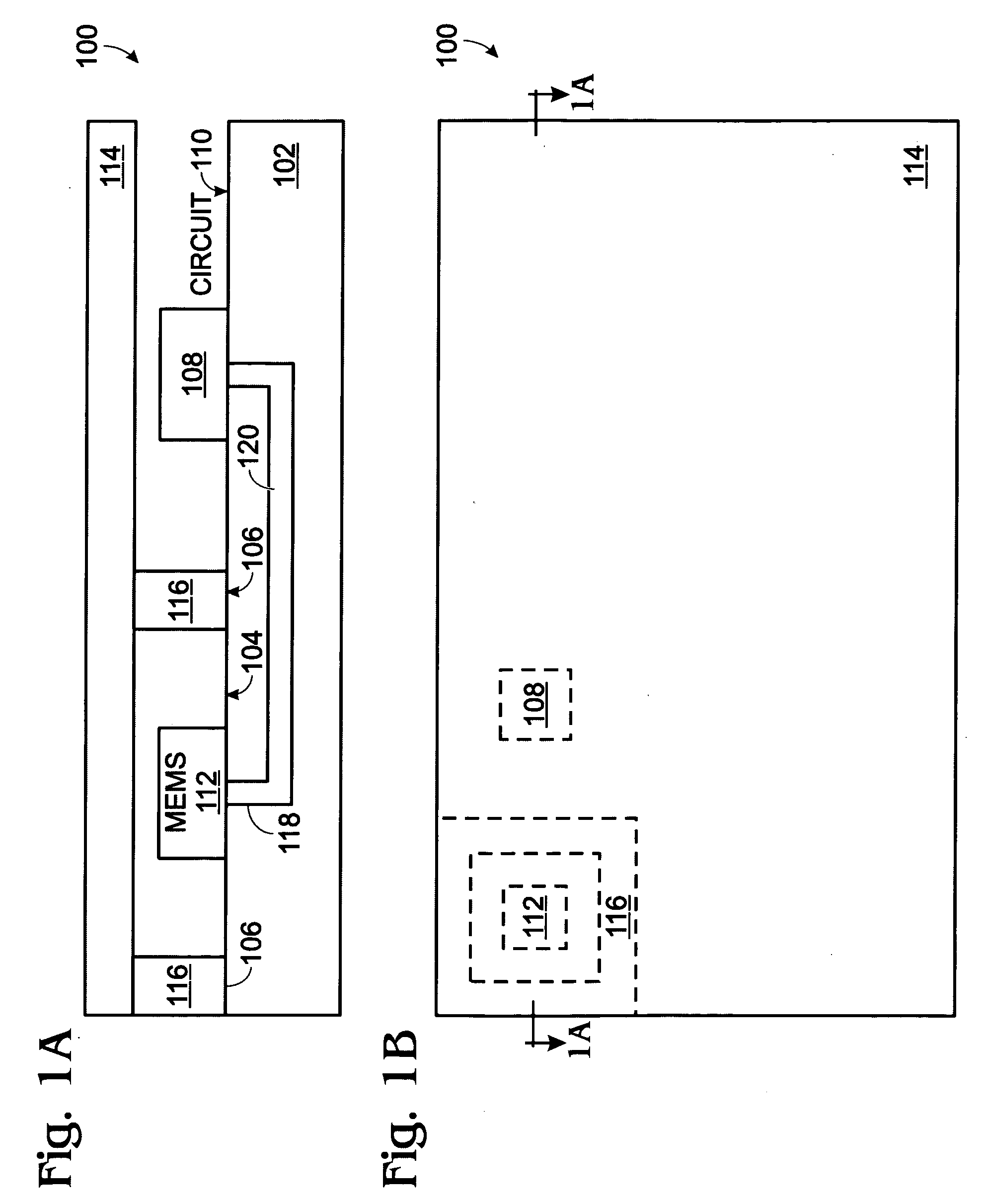

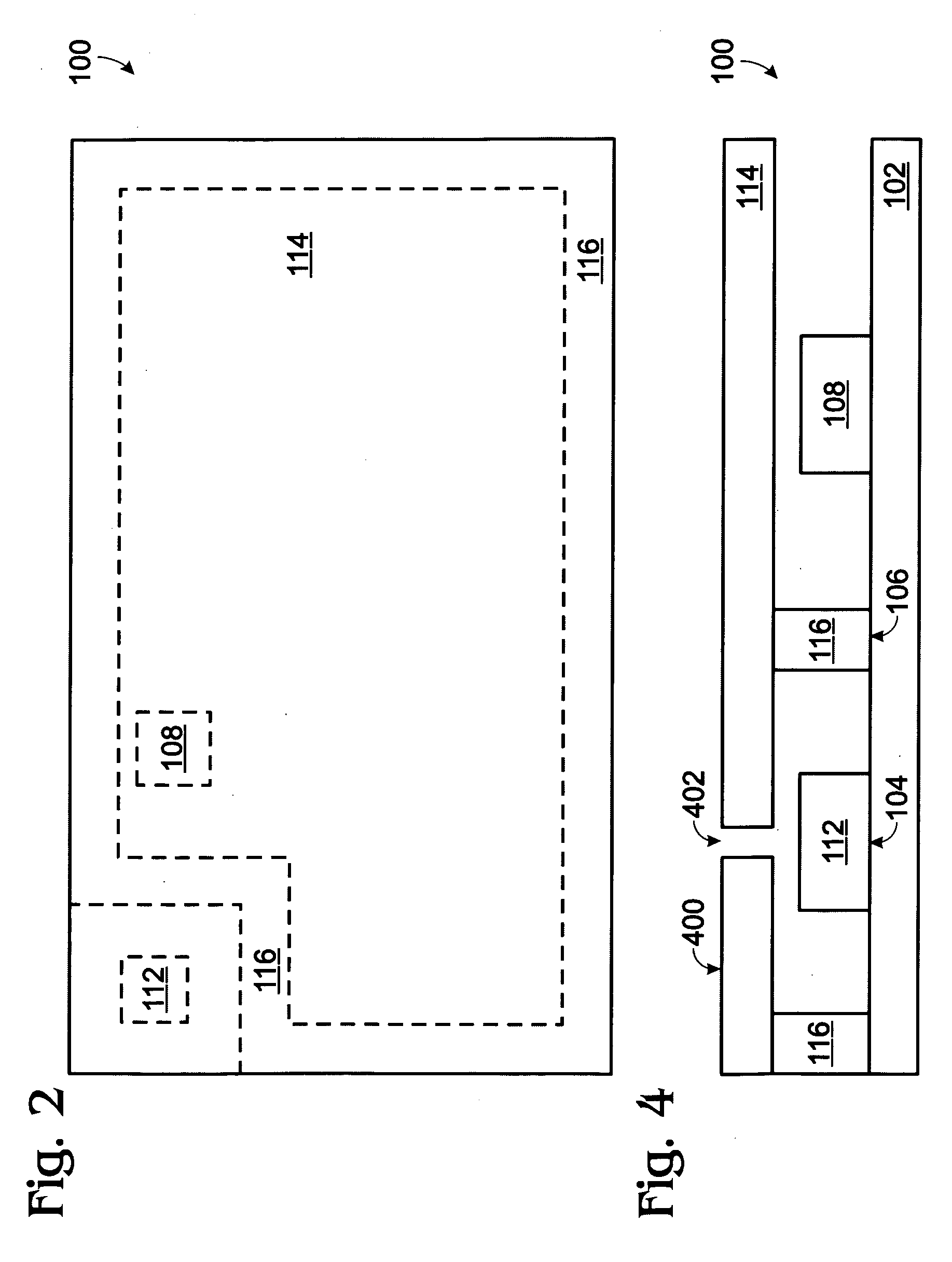

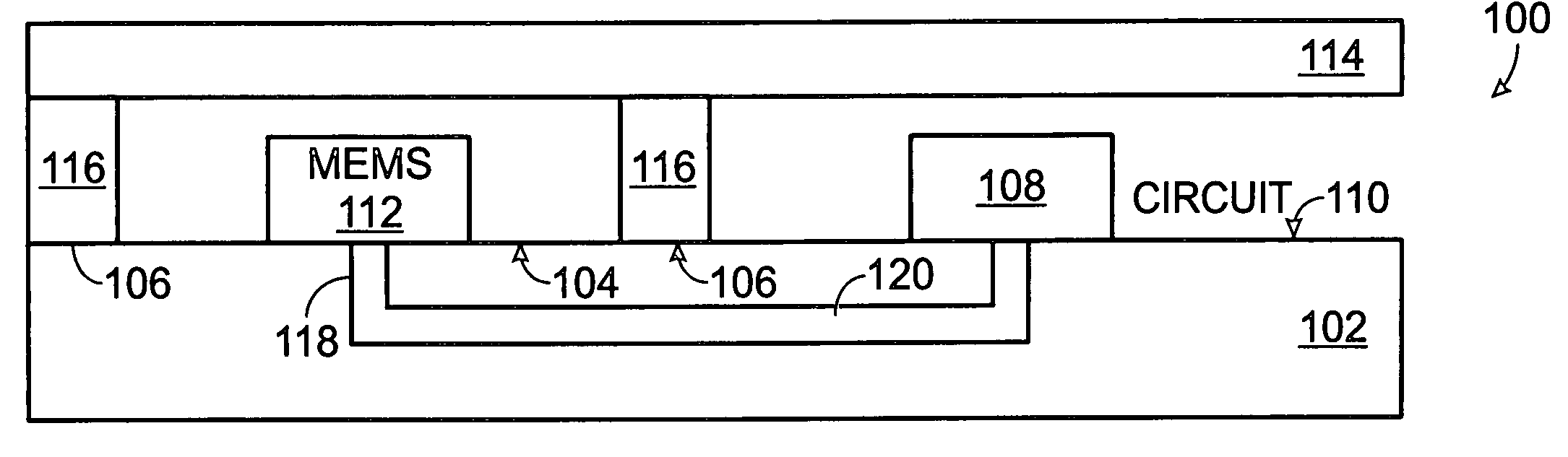

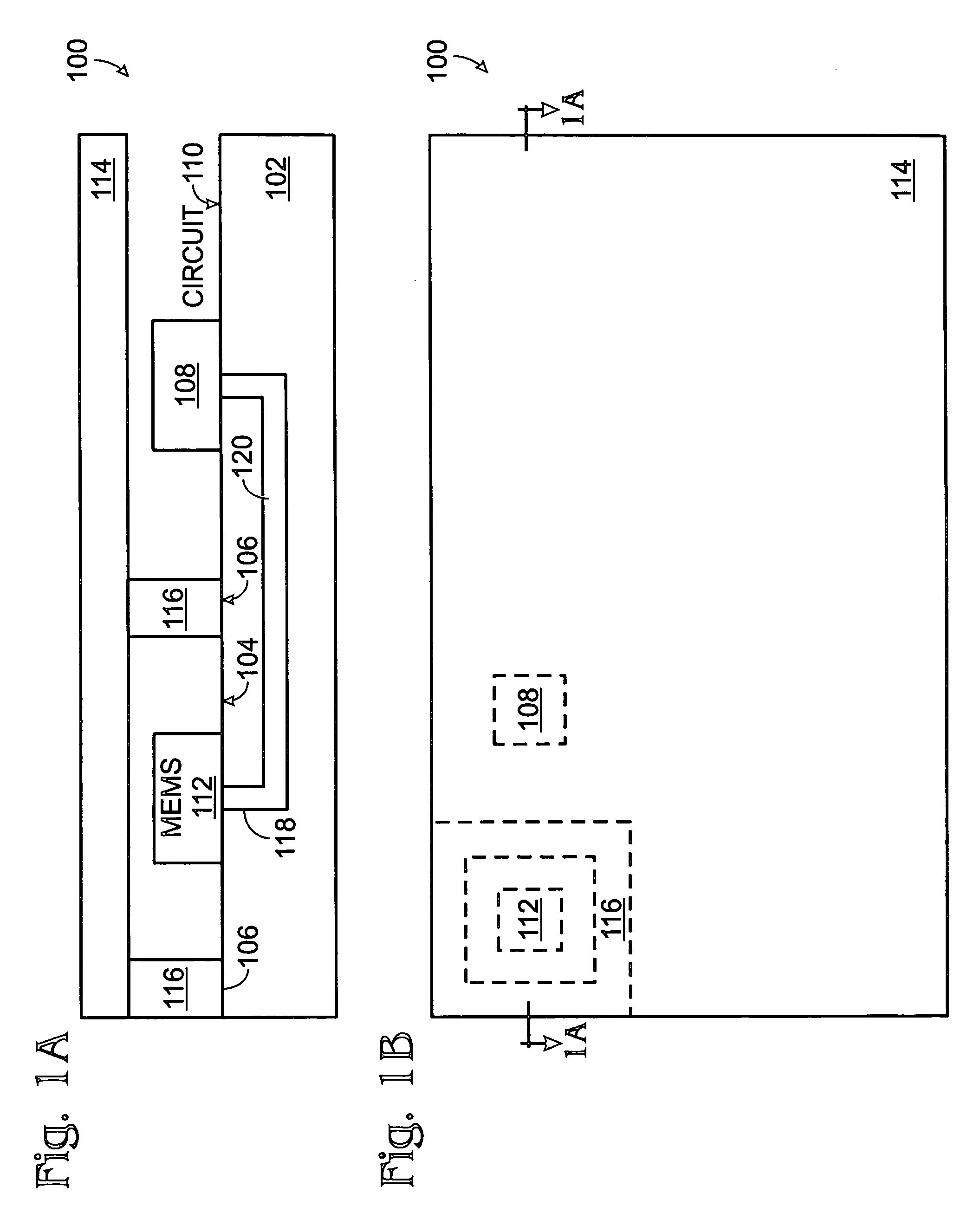

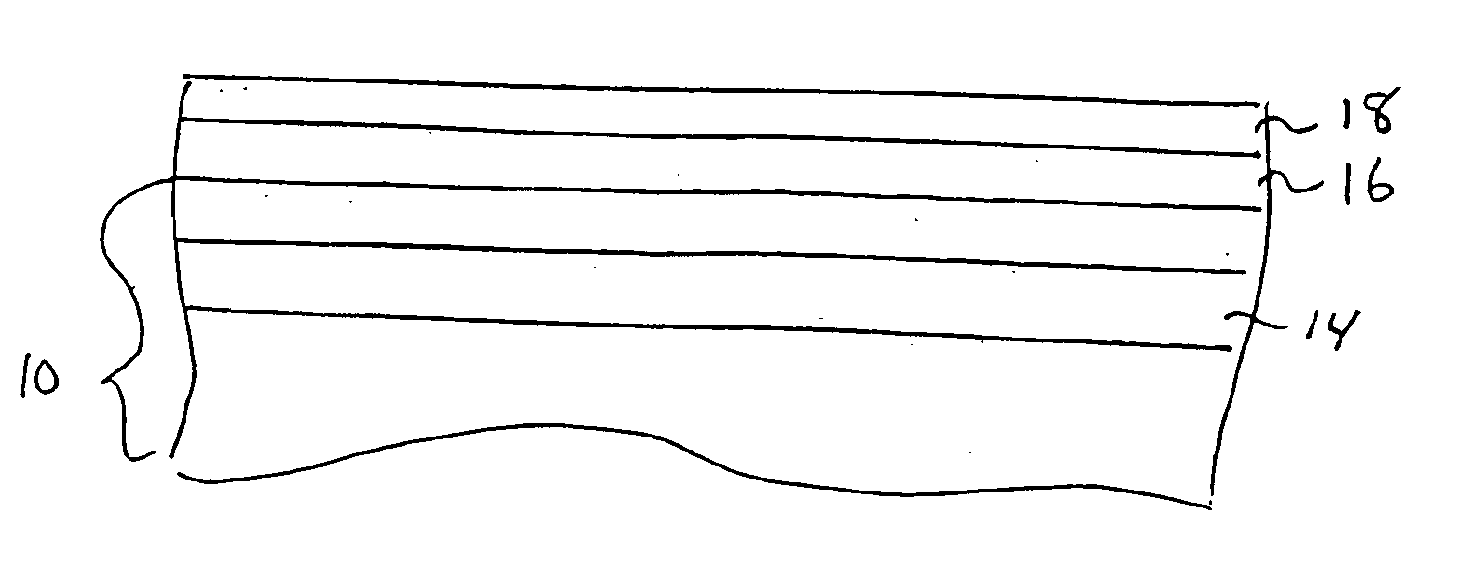

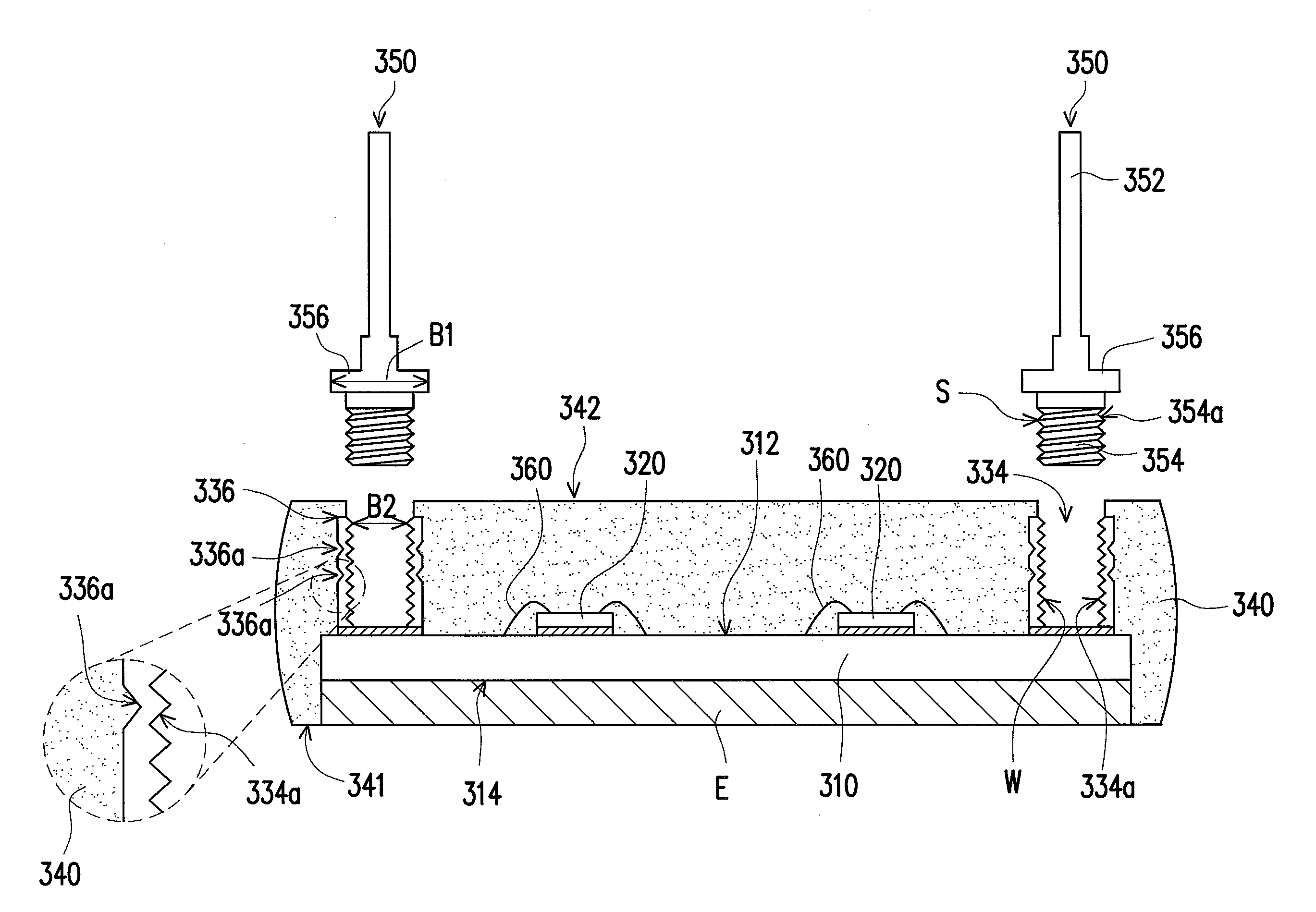

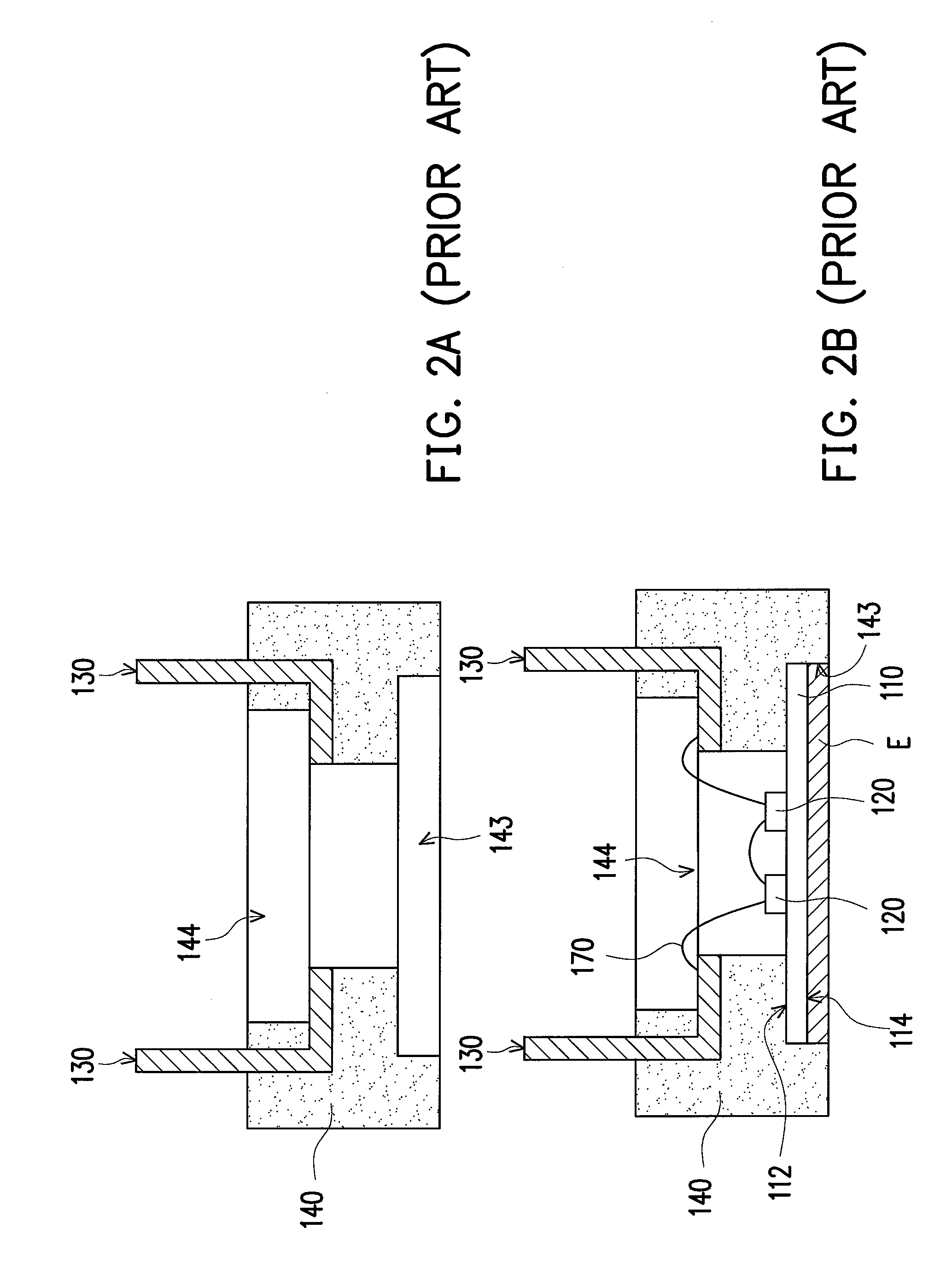

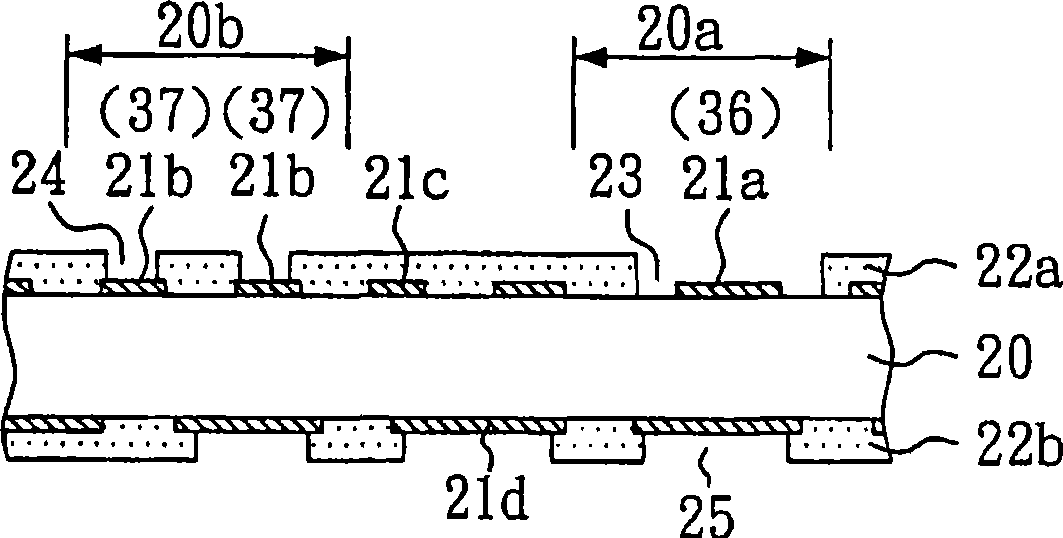

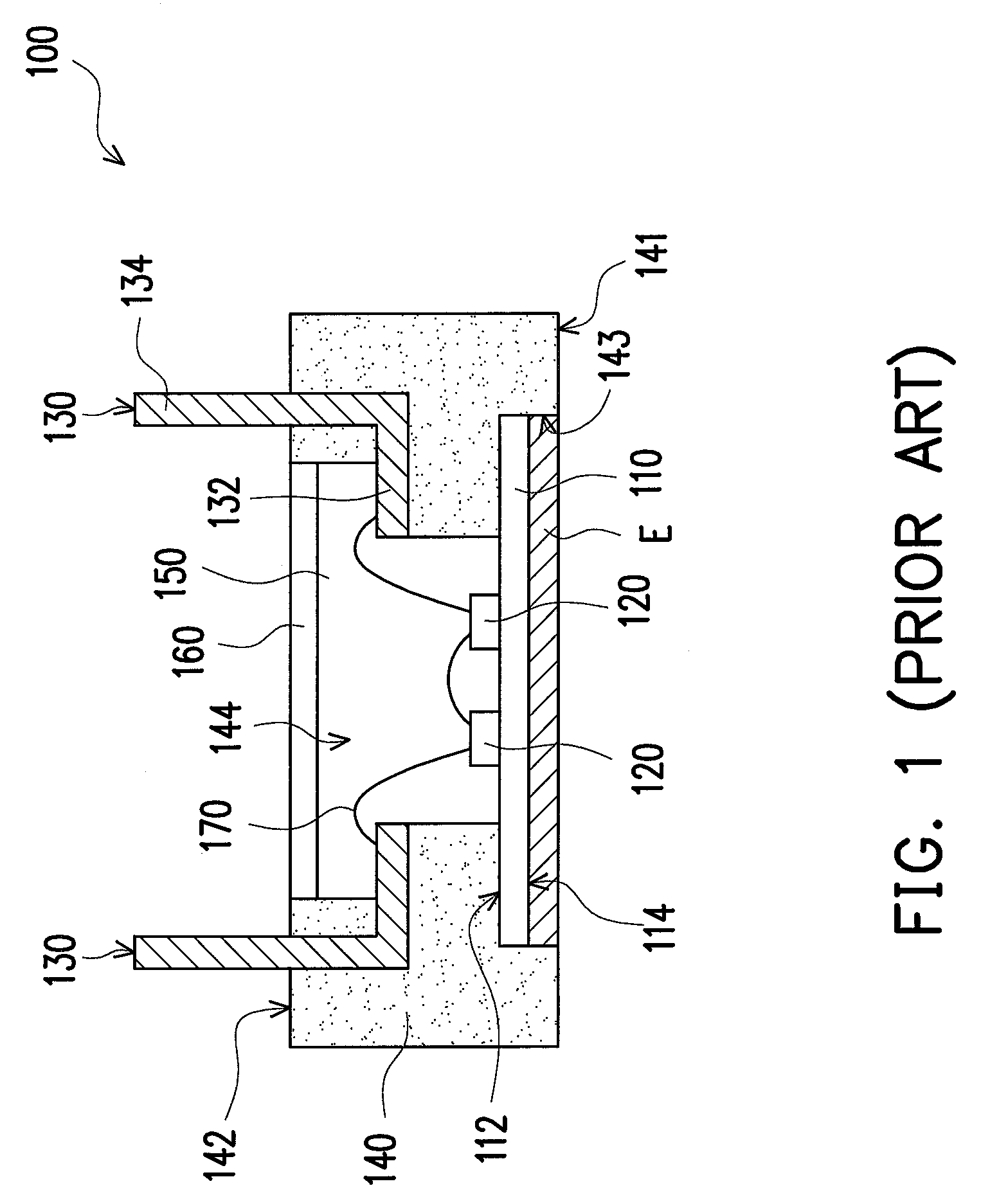

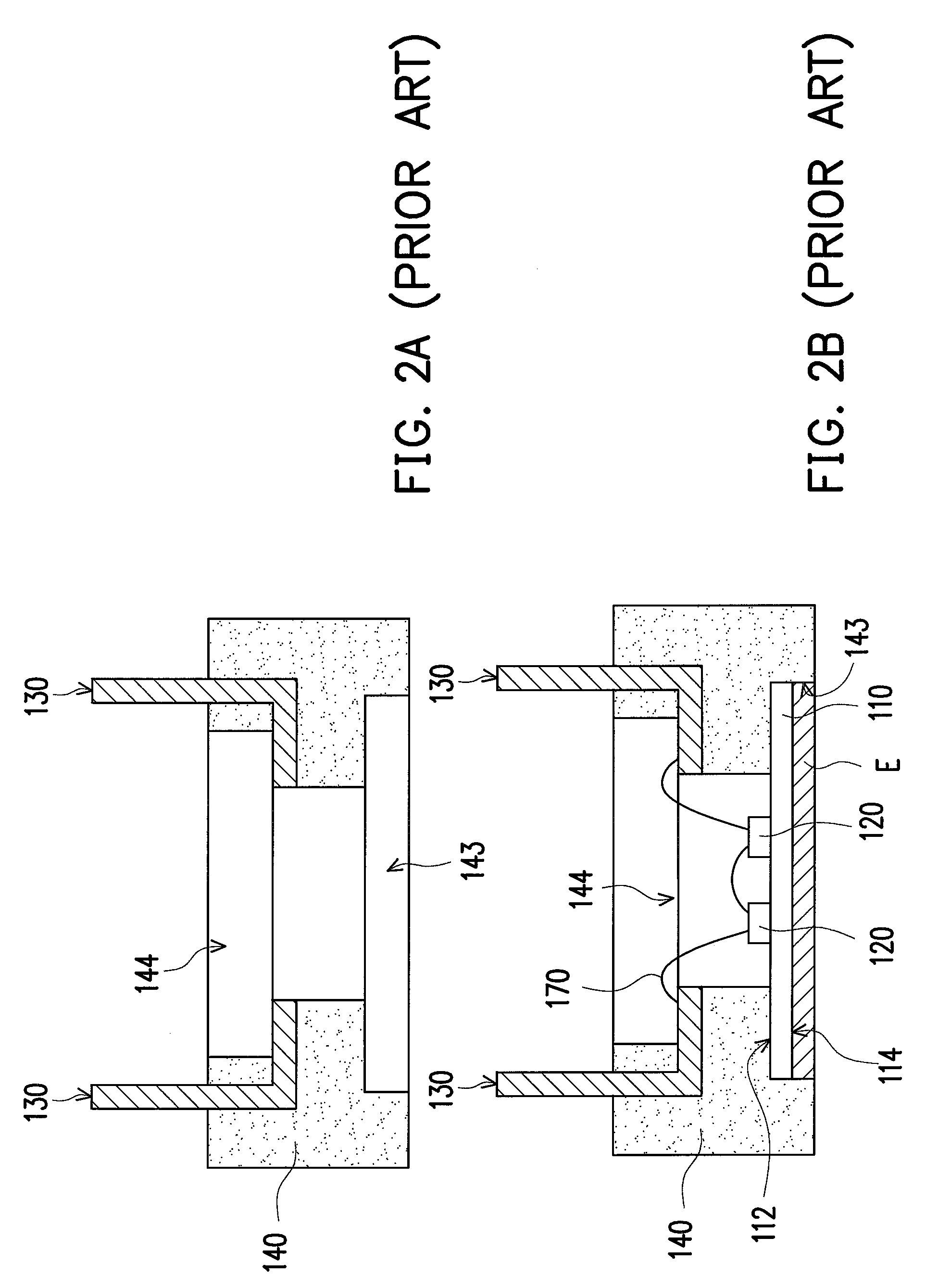

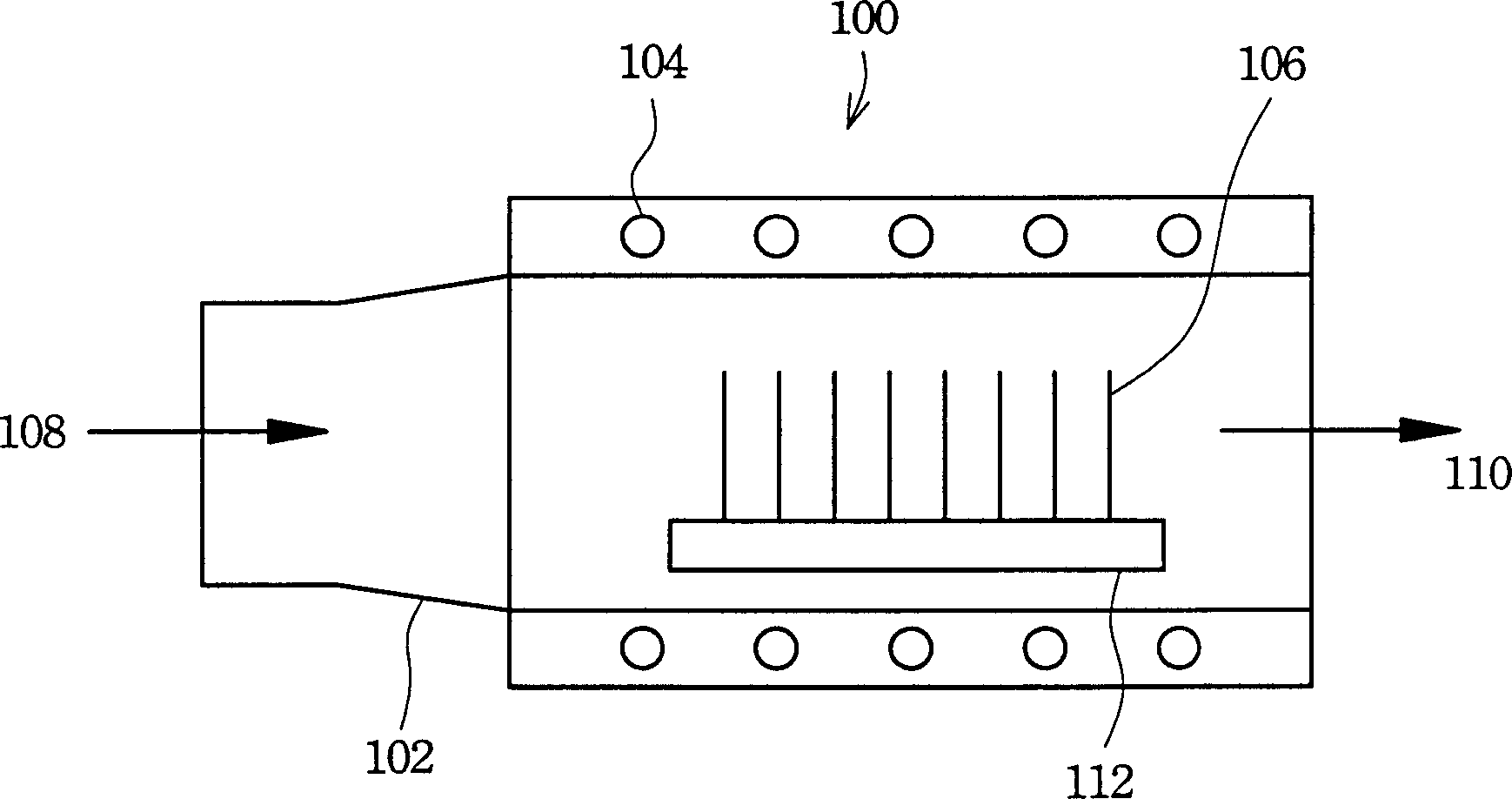

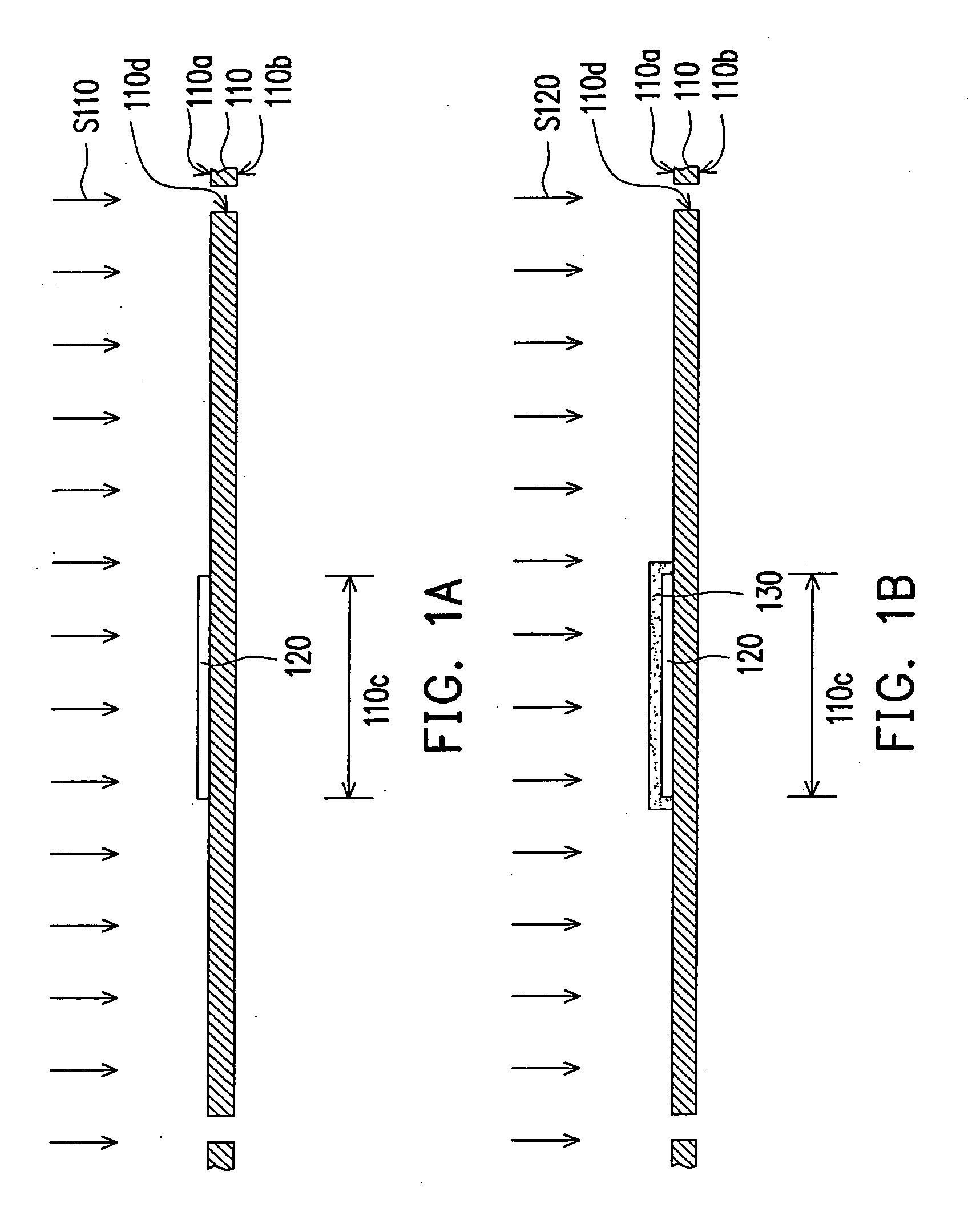

Method for integrated MEMS packaging

InactiveUS20070099327A1Improve electrical qualitySolid-state devicesSemiconductor/solid-state device manufacturingEngineeringInterconnection

An integrated MEMS package and associated packaging method are provided. The method includes: forming an electrical circuit, electrically connected to the first substrate; integrating a MEMS device on a first substrate region, electrically connected to the first substrate; providing a second substrate overlying the first substrate; and, forming a wall along the first region boundaries, between the first and second substrate. In one aspect, the electrical circuit is formed using thin-film processes; and, wherein integrating the MEMS device on the first substrate region includes forming the MEMS using thin-film processes, simultaneous with the formation of the electrical device. Alternately, the MEMS device is formed in a separate process, attached to the first substrate, and electrical interconnections are formed to the first substrate using thin-film processes.

Owner:SHARP KK

Integrated MEMS packaging

ActiveUS20060148137A1Improve electrical qualitySolid-state devicesSemiconductor/solid-state device manufacturingInterconnectionElectron

An integrated MEMS package and associated packaging method are provided. The method includes: forming an electrical circuit, electrically connected to the first substrate; integrating a MEMS device on a first substrate region, electrically connected to the first substrate; providing a second substrate overlying the first substrate; and, forming a wall along the first region boundaries, between the first and second substrate. In one aspect, the electrical circuit is formed using thin-film processes; and, wherein integrating the MEMS device on the first substrate region includes forming the MEMS using thin-film processes, simultaneous with the formation of the electrical device. Alternately, the MEMS device is formed in a separate process, attached to the first substrate, and electrical interconnections are formed to the first substrate using thin-film processes.

Owner:SHARP KK

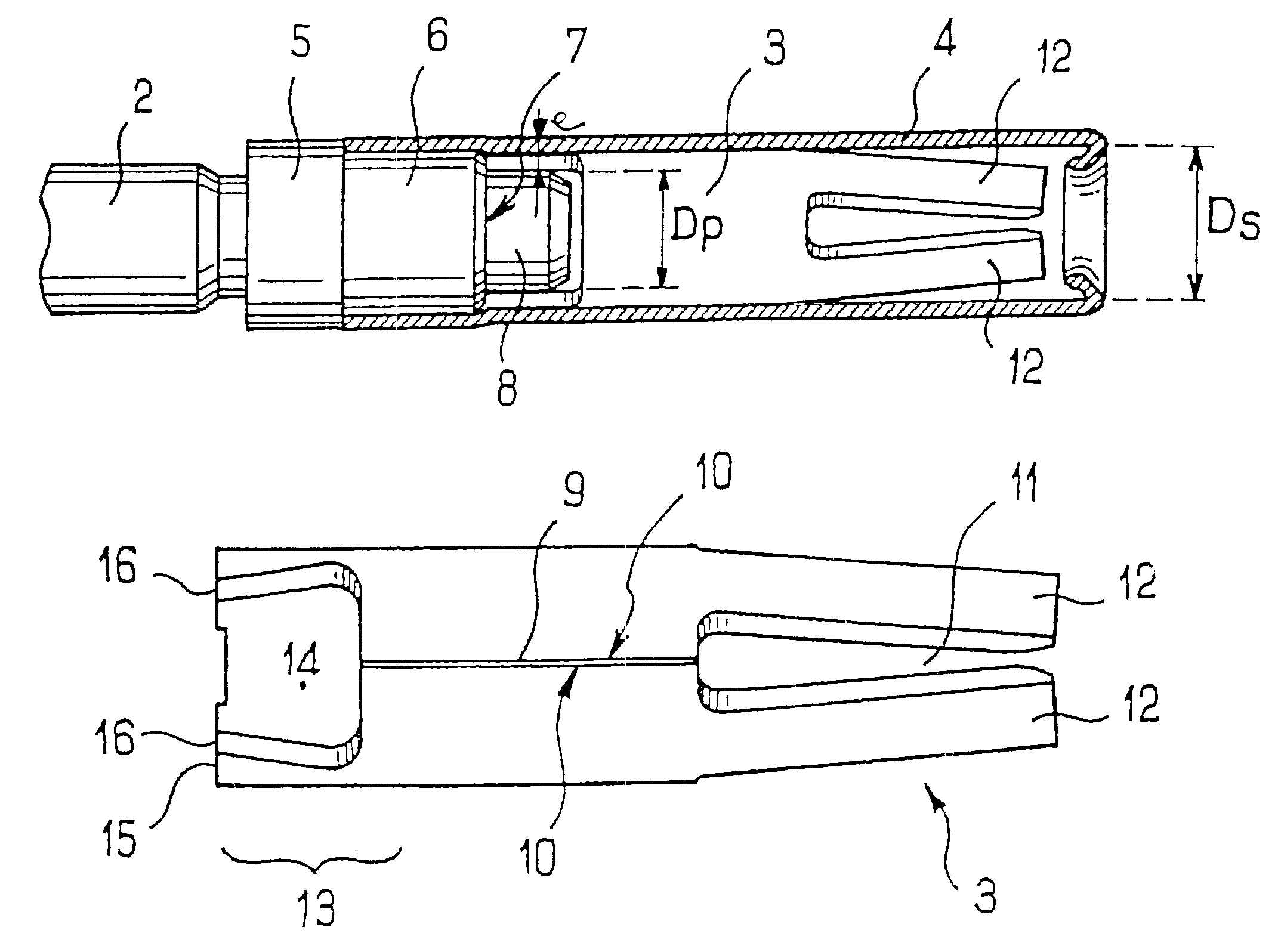

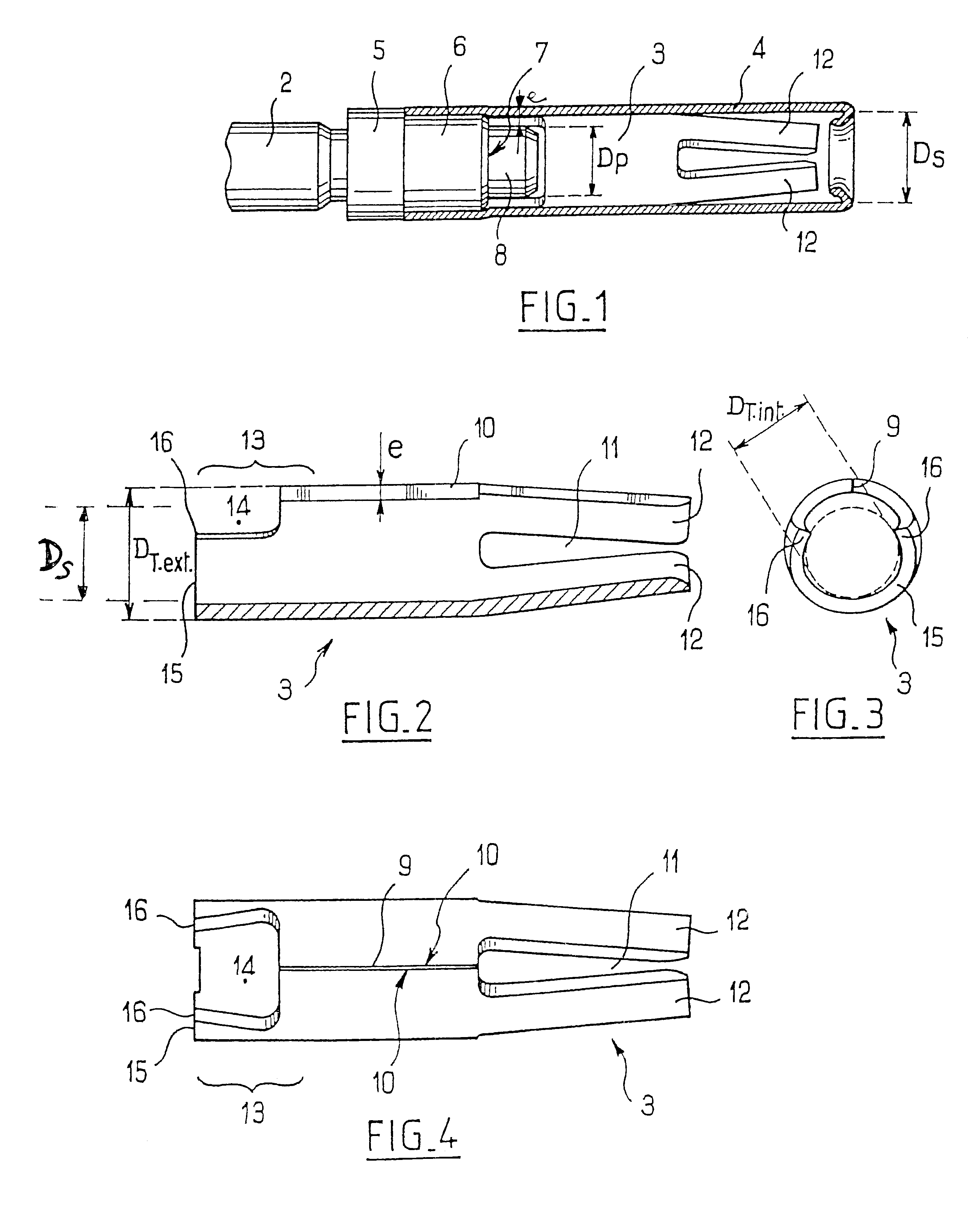

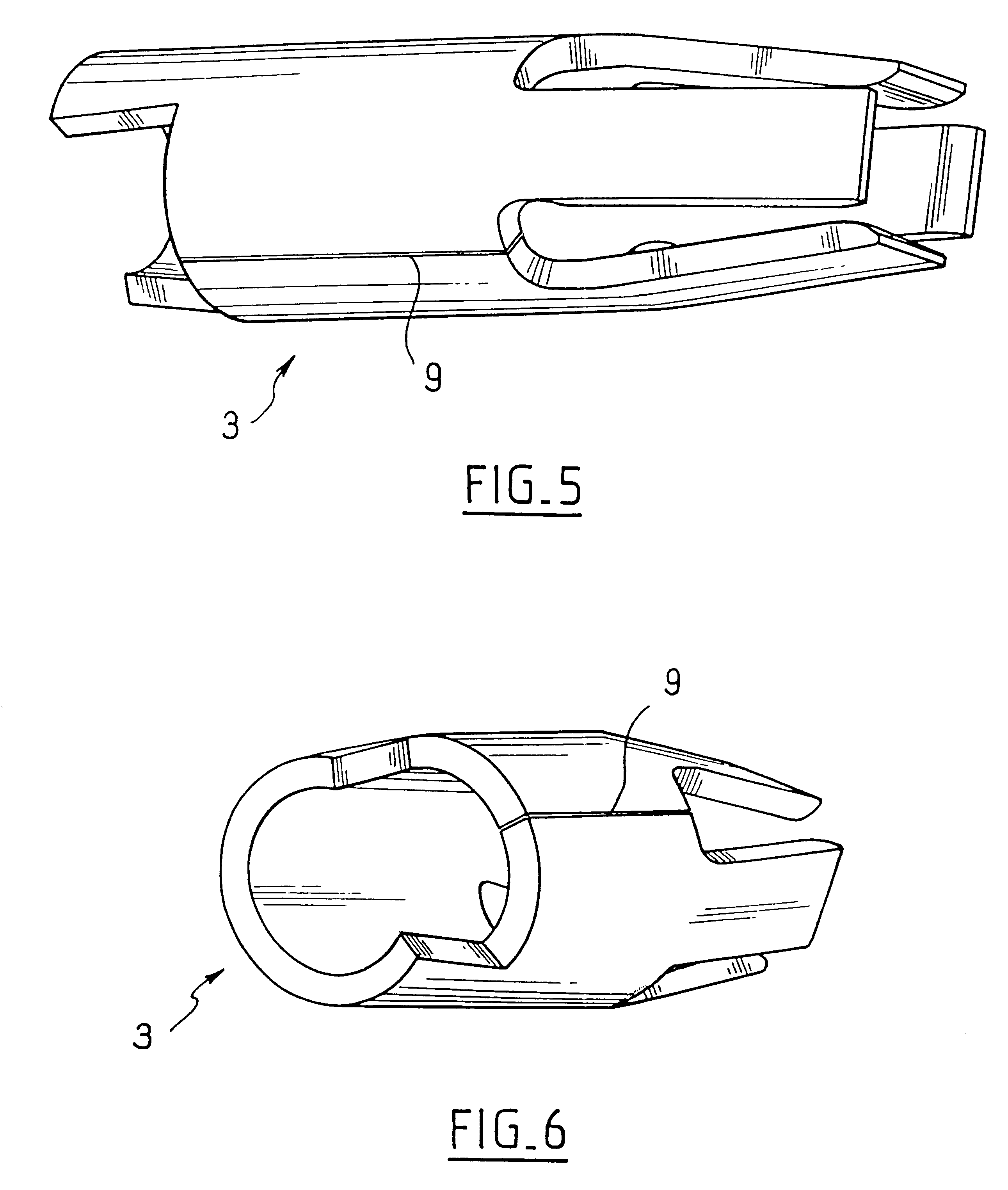

Electrical connector contact pin

InactiveUS6475039B1Little strengthImprove Manufacturing TolerancesContact member manufacturingCoupling contact membersCouplingEngineering

A contact pin for an electrical connector comprises a body, a connector element, and a sheath, the connector element being maintained in the extension of the body by being coupled with a peg projecting from the front face of the body, the sheath being disposed around the connector element and maintained on the body by clamping an annular portion of the latter. At the peg end, connector element comprises an end for coupling with said pin, conformed such that the pin cannot fit inside the cross section of said coupling end, the connector element being capable of deforming elastically to enable its coupling end to friction fit onto the pin, the thus deformed connector element being unable to fit inside the cross section of the sheath.

Owner:RADIALL SA

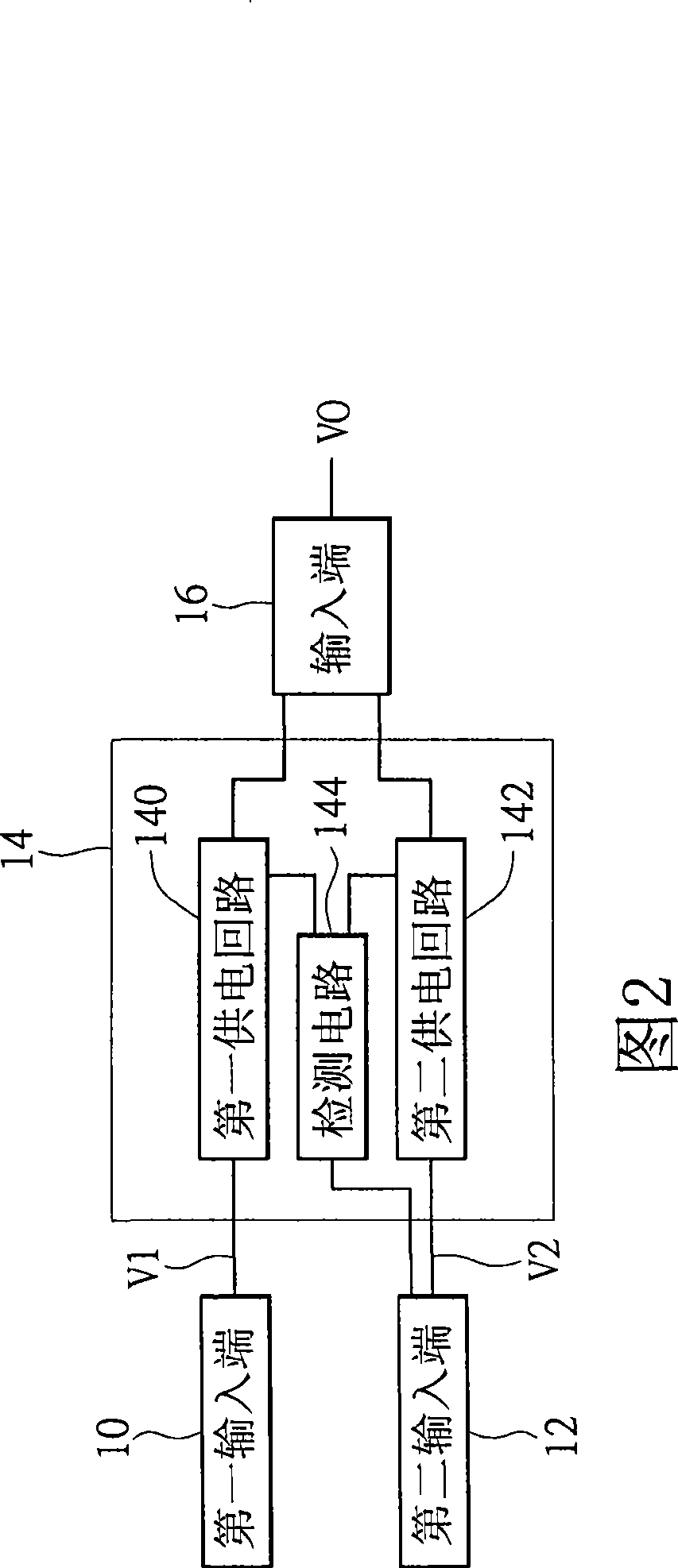

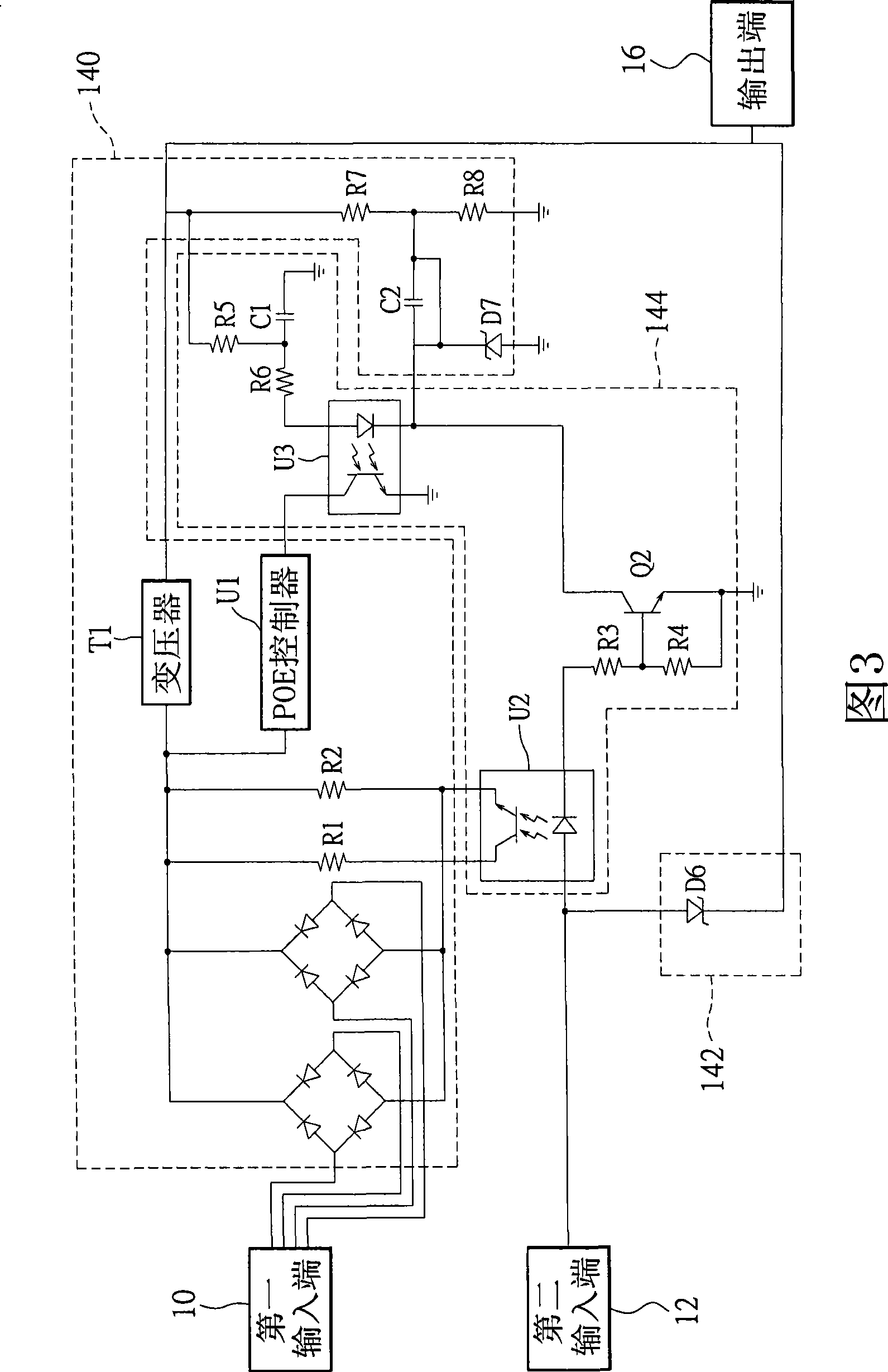

Power supply switching device and network appliance

ActiveCN101436786AImprove electrical qualityAvoid wastingData switching current supplyEmergency power supply arrangementsPower switchingEthernet

Owner:UNIVERSAL SCIENTIFIC INDUSTRIAL (SHANGHAI) CO LTD

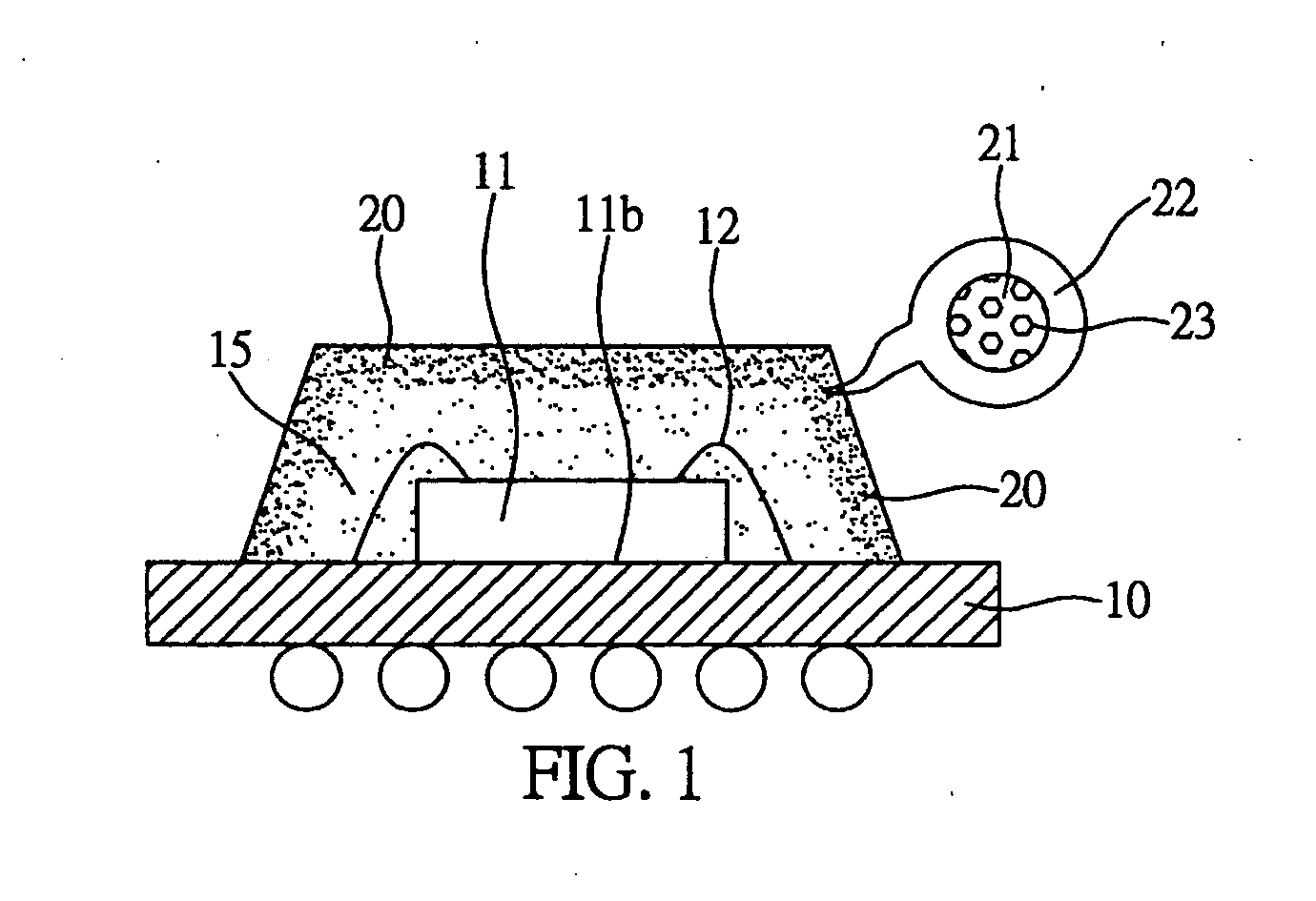

Semiconductor package for lowering electromagnetic interference and method for fabricating the same

InactiveUS20050184405A1Reduce electromagnetic interferenceImprove electricity qualitySemiconductor/solid-state device detailsSolid-state devicesElectromagnetic interferenceSemiconductor package

A semiconductor package for lowering electromagnetic interference and a method for fabricating the same are proposed. The semiconductor package includes a chip carrier, at least one chip attached and electrically connected to the chip carrier, and an encapsulation body formed on the chip carrier for encapsulating the chip. The encapsulation body includes an electromagnetic absorbing layer made of an organic material filled with a plurality of porous metal particles. The electromagnetic absorbing layer absorbs electromagnetic waves generated by the chip and converts the electromagnetic waves to heat so as to improve the heat dissipation efficiency and reduce electromagnetic interference for the semiconductor package.

Owner:STACK DEVICES CORP

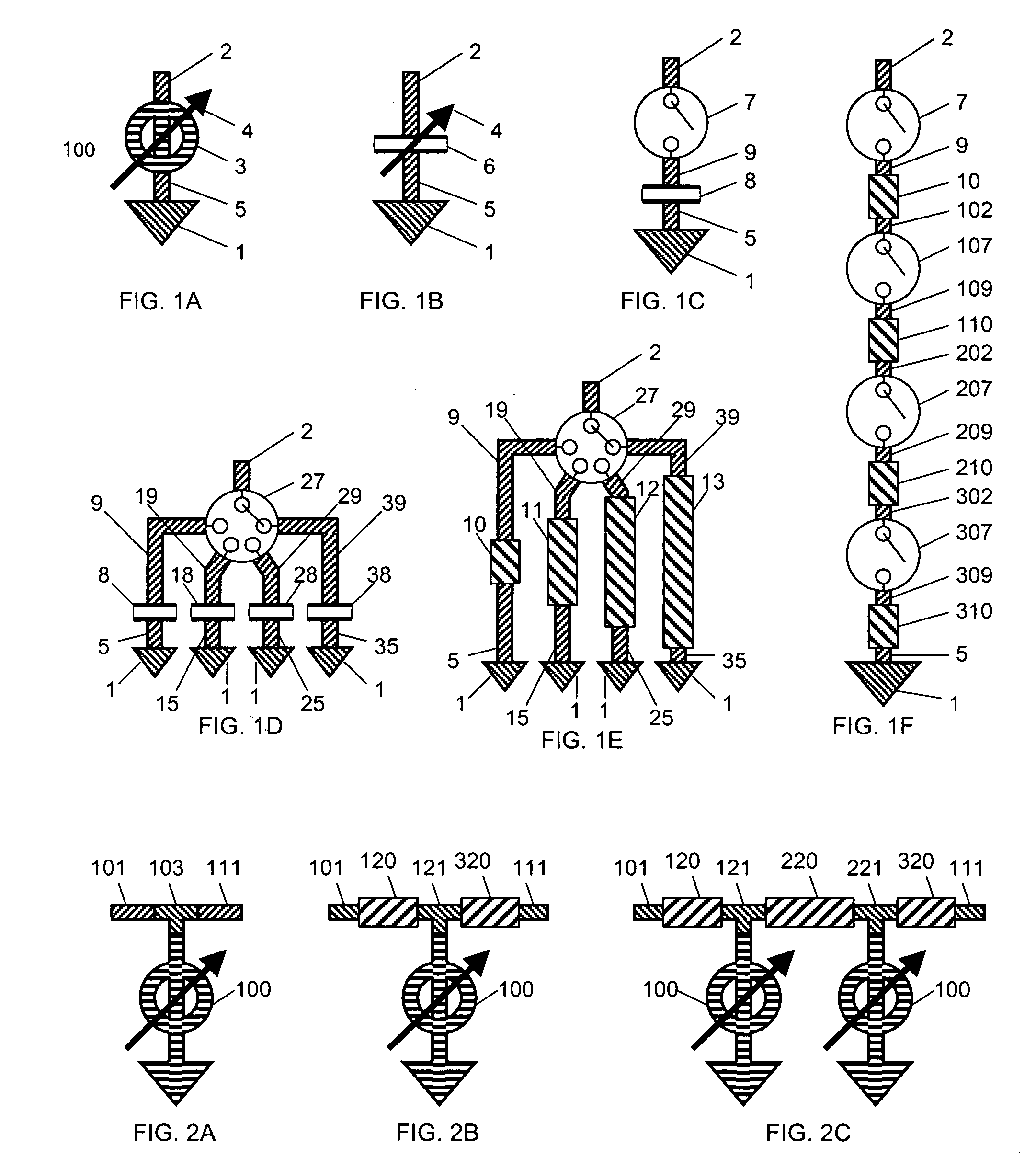

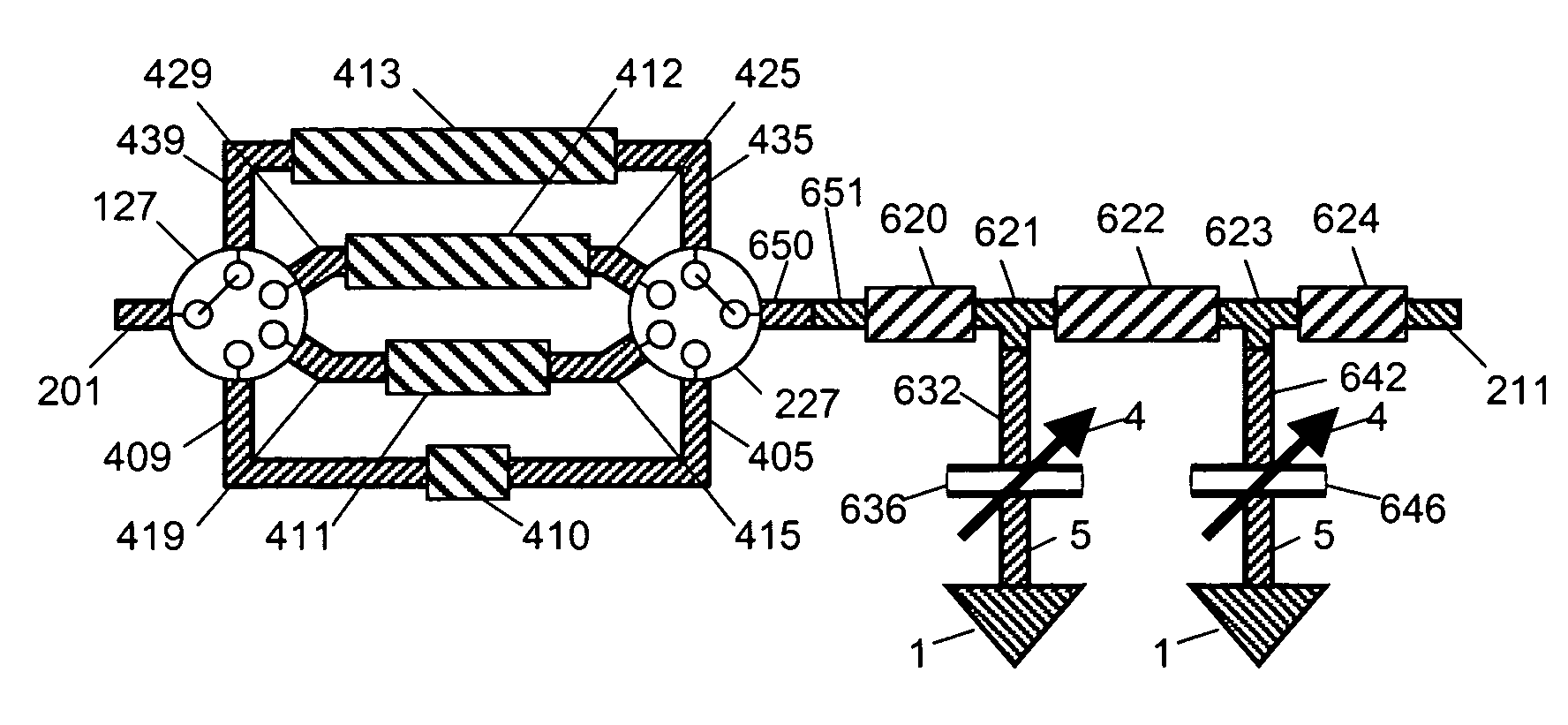

Electronically controlled hybrid digital and analog phase shifter

InactiveUS20050270122A1Wide tuning rangeCorrection errorMultiple-port networksDigital technique networkPhase shiftedImage resolution

The inventions presented herein provide a electronically controlled phase shifters that incorporate analog and digital phase shift architectures in a novel manner that realizes the best advantages of each architecture. This combination of complementary phase shift architectures provides the high-performance and low loss characteristics of switched digital phase shift architectures with the high resolution and precision of continuous analog phase shift architectures. The circuit embodiments are electronically controlled, which simplifies implementation of what is a complex circuit. The analog phase shift elements comprise electronically-tuned varactors, which provide fine resolution and enables the incorporation of active compensation for manufacturing variation before use or for environmental conditions during use.

Owner:XCOM WIRELESS

Formation of silicon-germanium-on-insulator (SGOI) by an integral high temperature SIMOX-Ge interdiffusion anneal

InactiveUS6861158B2Improve electrical qualityMinimized Ge lossSolid-state devicesSemiconductor/solid-state device manufacturingSingle crystalIon implantation

A method of forming a substantially relaxed, high-quality SiGe-on-insulator substrate material using SIMOX and Ge interdiffusion is provided. The method includes first implanting ions into a Si-containing substrate to form an implanted-ion rich region in the Si-containing substrate. The implanted-ion rich region has a sufficient ion concentration such that during a subsequent anneal at high temperatures a barrier layer that is resistant to Ge diffusion is formed. Next, a Ge-containing layer is formed on a surface of the Si-containing substrate, and thereafter a heating step is performed at a temperature which permits formation of the barrier layer and interdiffusion of Ge thereby forming a substantially relaxed, single crystal SiGe layer atop the barrier layer.

Owner:GLOBALFOUNDRIES INC

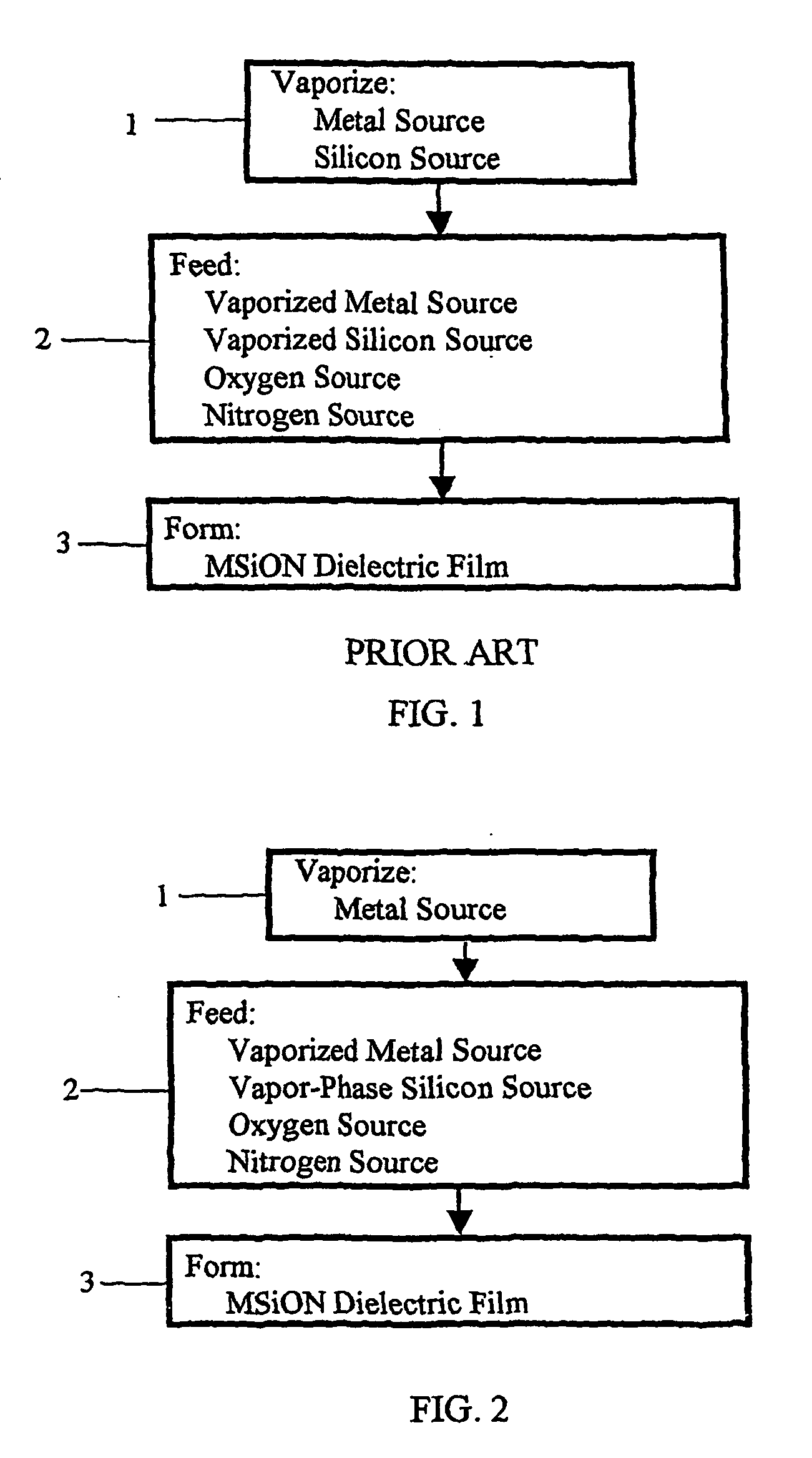

Method for forming dielectric or metallic films

InactiveUS20070190807A1Maintain good propertiesImprove conductivitySemiconductor/solid-state device manufacturingChemical vapor deposition coatingDielectricNitride

Method for producing a metal silicon (oxy)nitride by introducing a carbon-free silicon source (for example, (SiH3)3N), a metal precursor with the general formula MXn (for example, Hf(NEt2)4), and an oxidizing agent (for example, O2) into a CVD chamber and reacting same at the surface of a substrate. MsiN, MSIo and / or MSiON films may be obtained. These films are useful are useful as high k dielectrics films.

Owner:LAIR LIQUIDE SA POUR LETUDE & LEXPLOITATION DES PROCEDES GEORGES CLAUDE

Electronically controlled hybrid digital and analog phase shifter

InactiveUS7355492B2Highly precise and tunable phase shiftSmall sizeMultiple-port networksDigital technique networkPhase shiftedImage resolution

The inventions presented herein provide a electronically controlled phase shifters that incorporate analog and digital phase shift architectures in a novel manner that realizes the best advantages of each architecture. This combination of complementary phase shift architectures provides the high-performance and low loss characteristics of switched digital phase shift architectures with the high resolution and precision of continuous analog phase shift architectures. The circuit embodiments are electronically controlled, which simplifies implementation of what is a complex circuit. The analog phase shift elements comprise electronically-tuned varactors, which provide fine resolution and enables the incorporation of active compensation for manufacturing variation before use or for environmental conditions during use.

Owner:XCOM WIRELESS

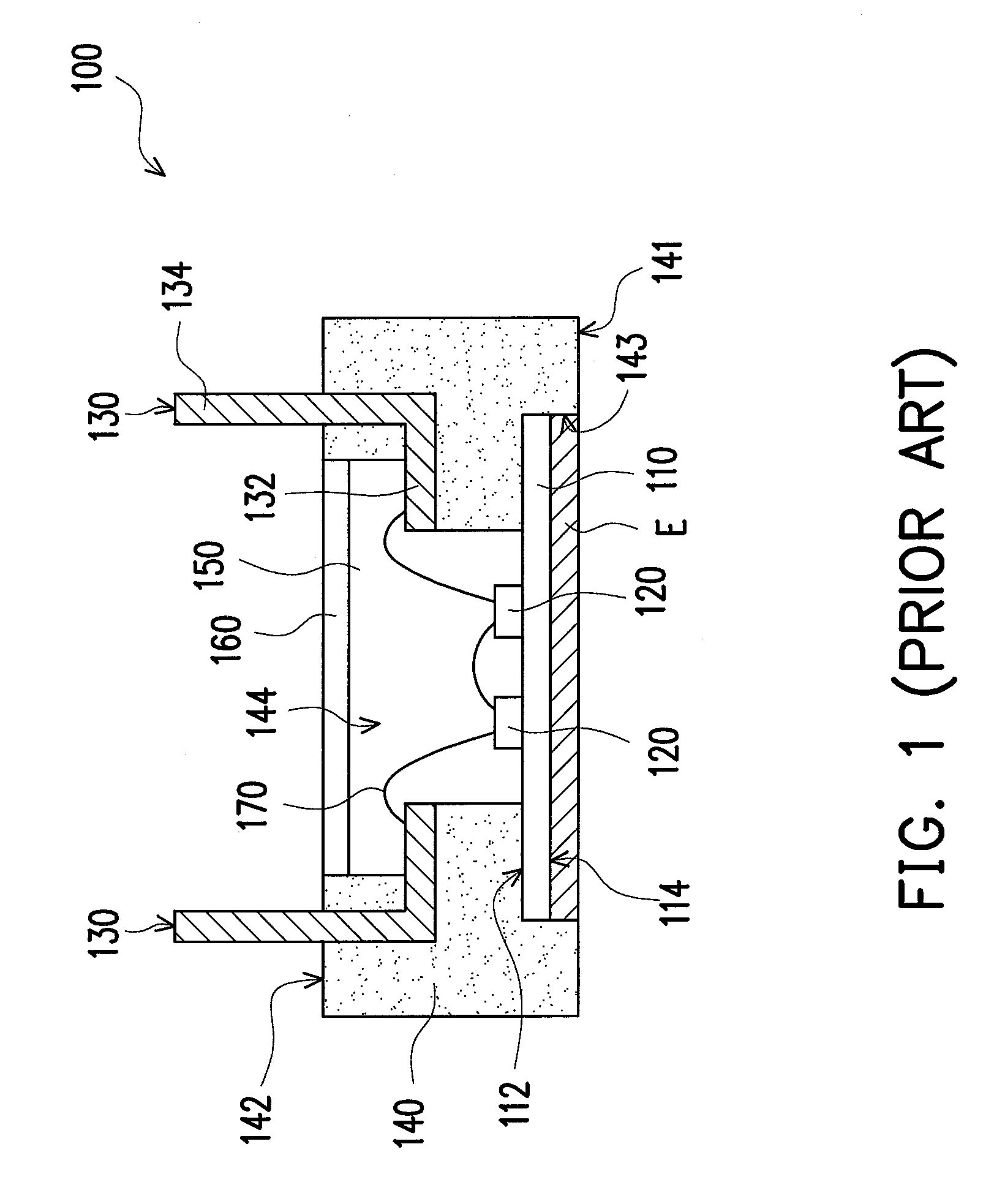

Chip package structure

ActiveUS20100117216A1Increase creepage distanceMeet the requirementsSemiconductor/solid-state device detailsSolid-state devicesElectrical and Electronics engineering

A chip package structure including a substrate, at least one chip, a heat dissipation device, at least one first conductive bar, a molding compound, and at least one second conductive bar is provided. The chip and the heat dissipation device are respectively disposed on a first and a second surface of the substrate. The first conductive bar has two opposite end surfaces, wherein one end surface is disposed on the first surface of the substrate, the other end surface is extended away from the substrate, and a fastening slot is disposed between the two end surfaces and passes through the other end surface. The molding compound encapsulates the substrate, the chip, part of the heat dissipation device, and the first conductive bar. The second conductive bar is disposed on one surface of the molding compound and has a protrusion portion fastened to the fastening slot of the first conductive bar.

Owner:CYNTEC

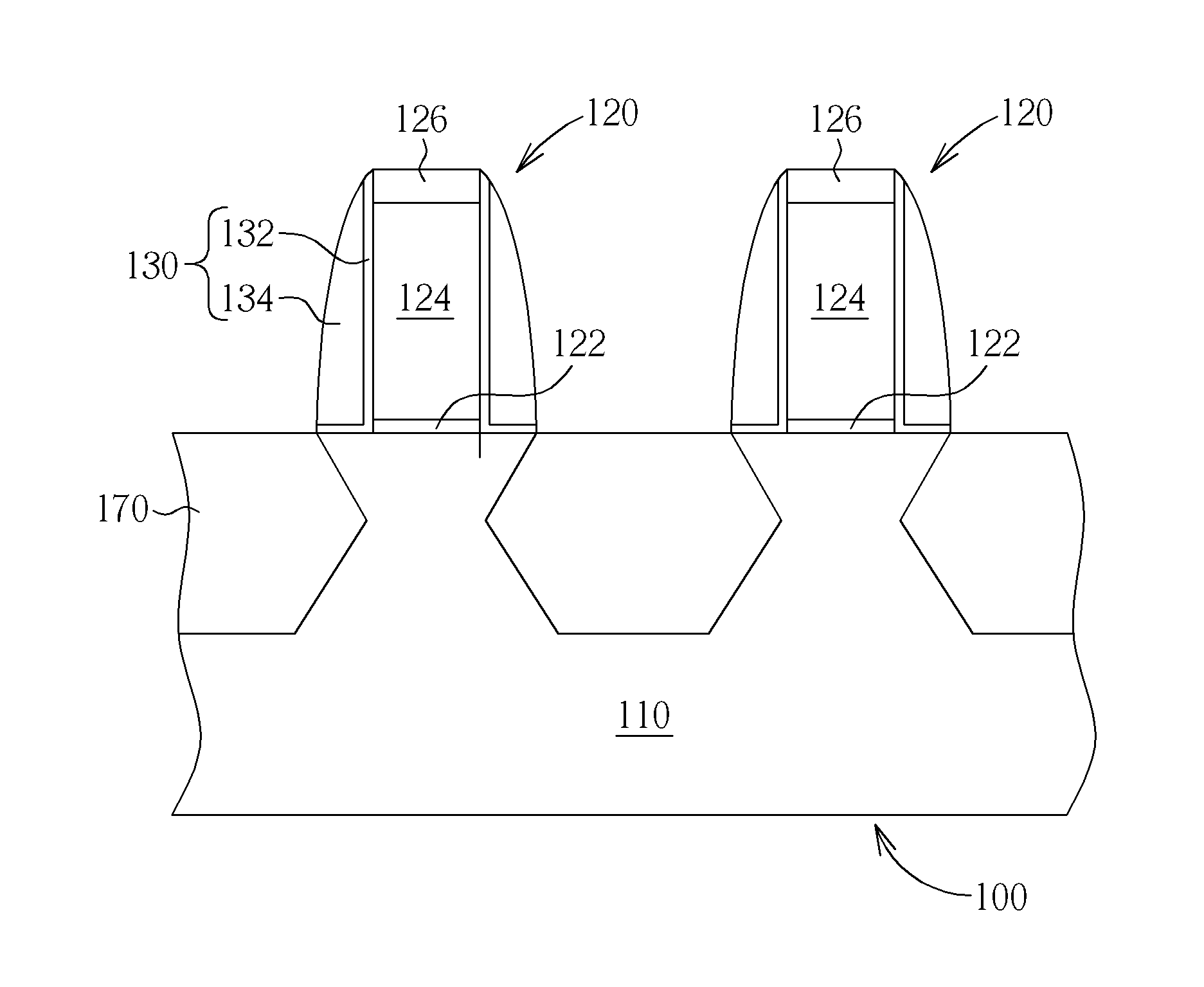

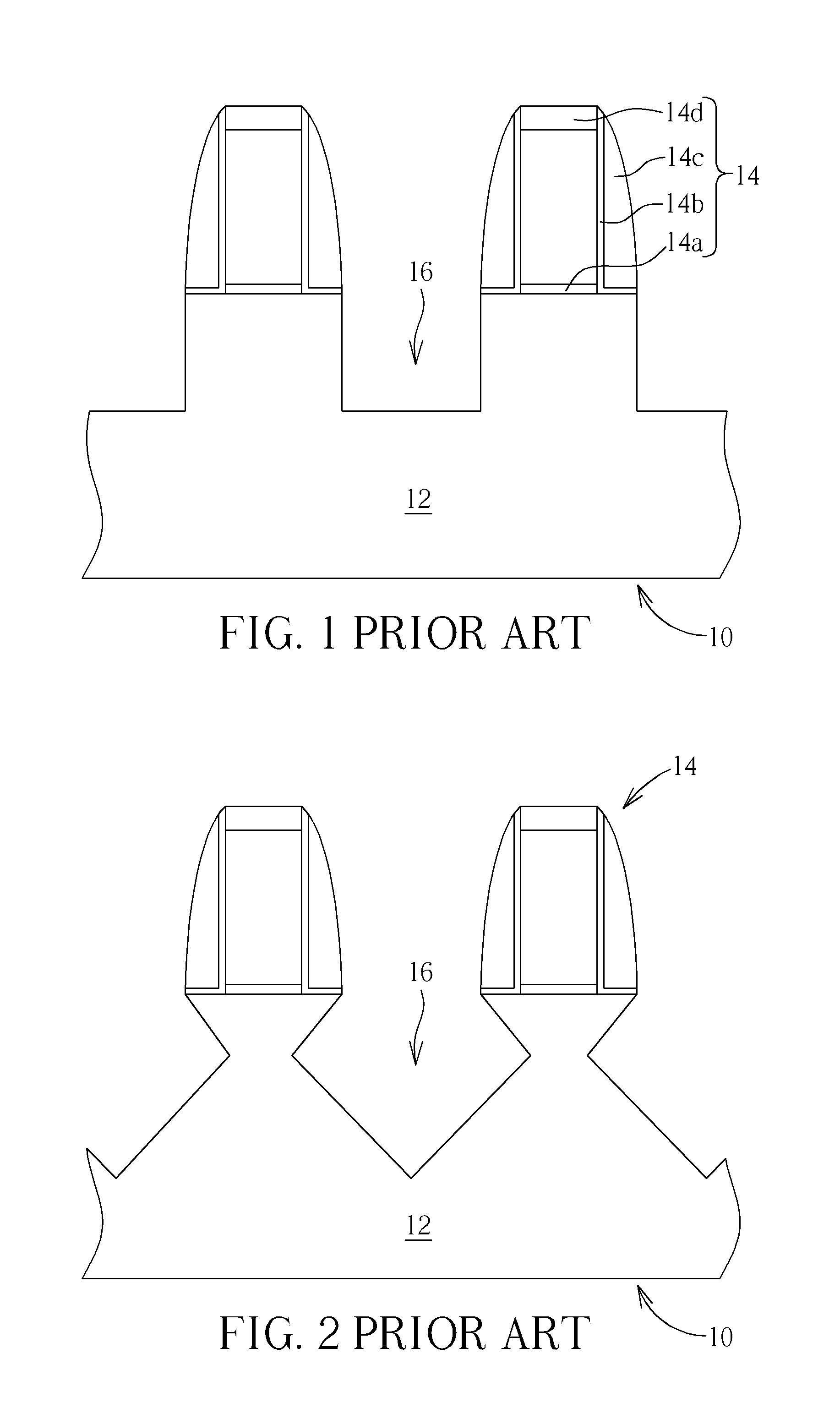

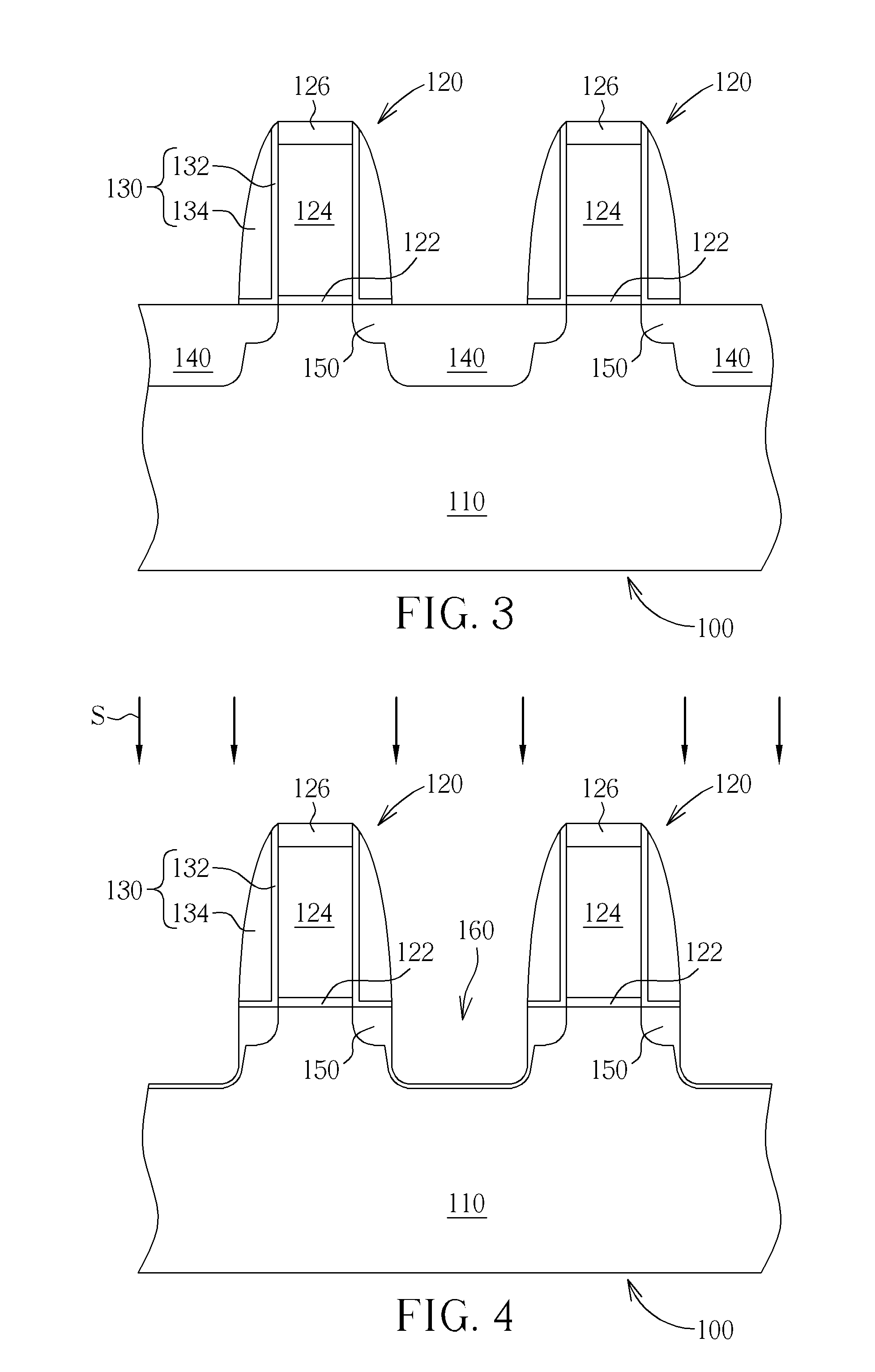

Semiconductor process

ActiveUS20120021583A1Improve electrical qualitySemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringSemiconductor

A semiconductor process is disclosed. The semiconductor process includes the steps of: providing a substrate having a specific area defined thereon; and performing an etch process by using an etchant comprising H2O2 to etch the specific area for forming a recess.

Owner:UNITED MICROELECTRONICS CORP

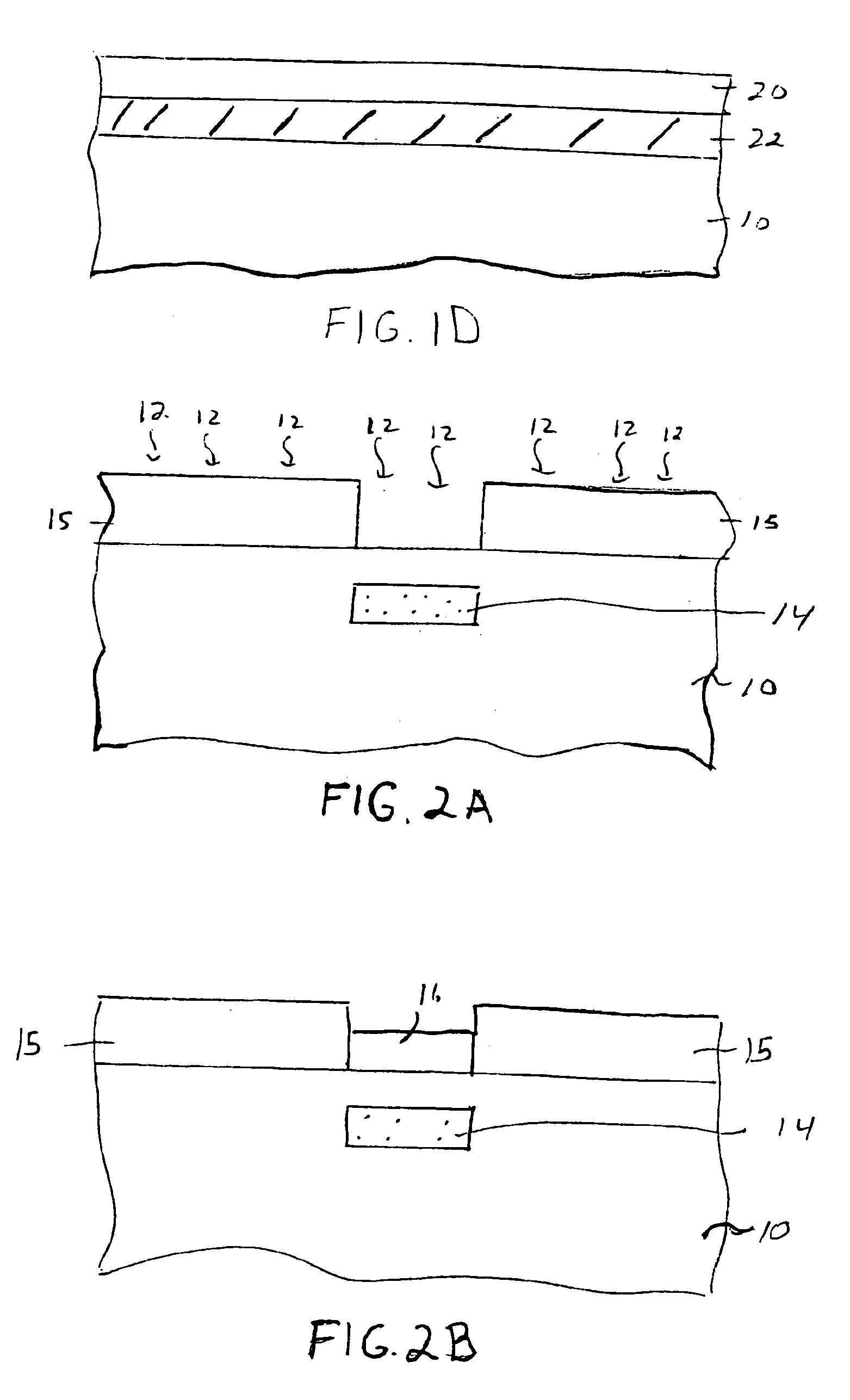

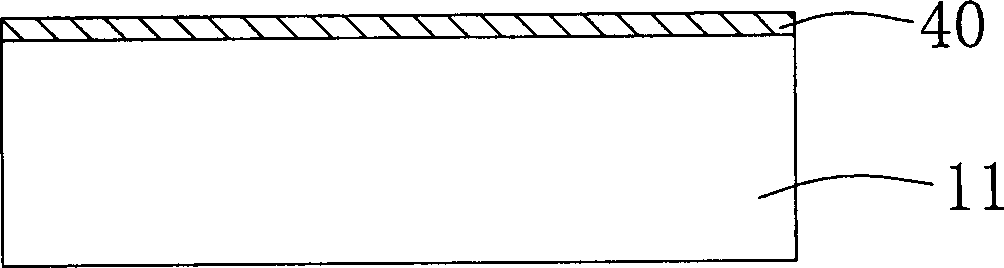

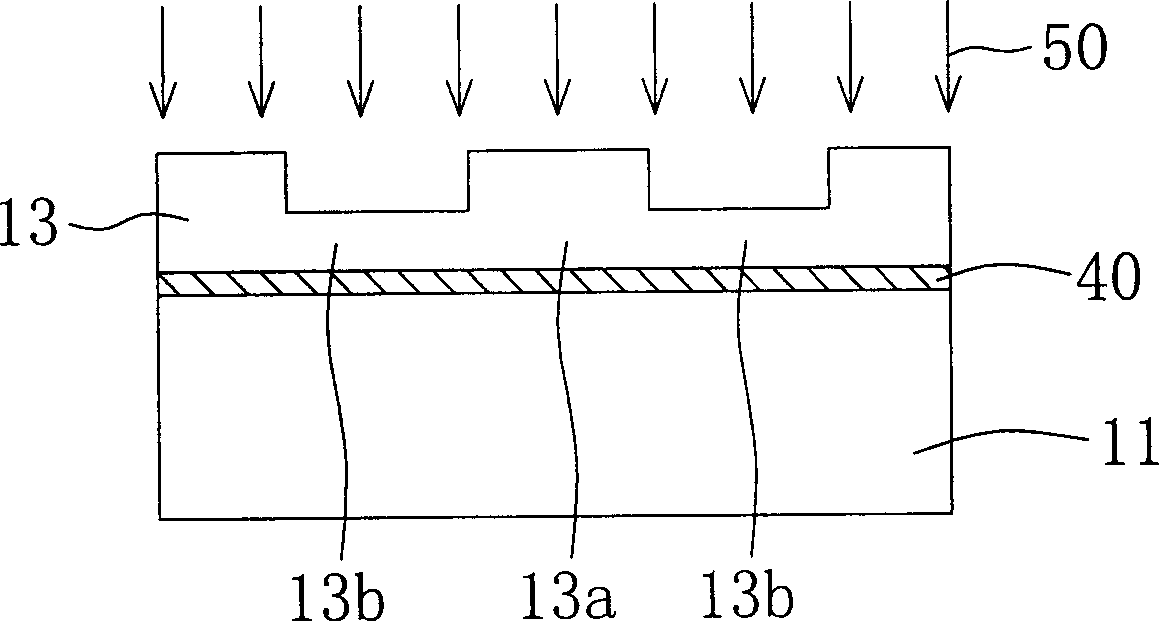

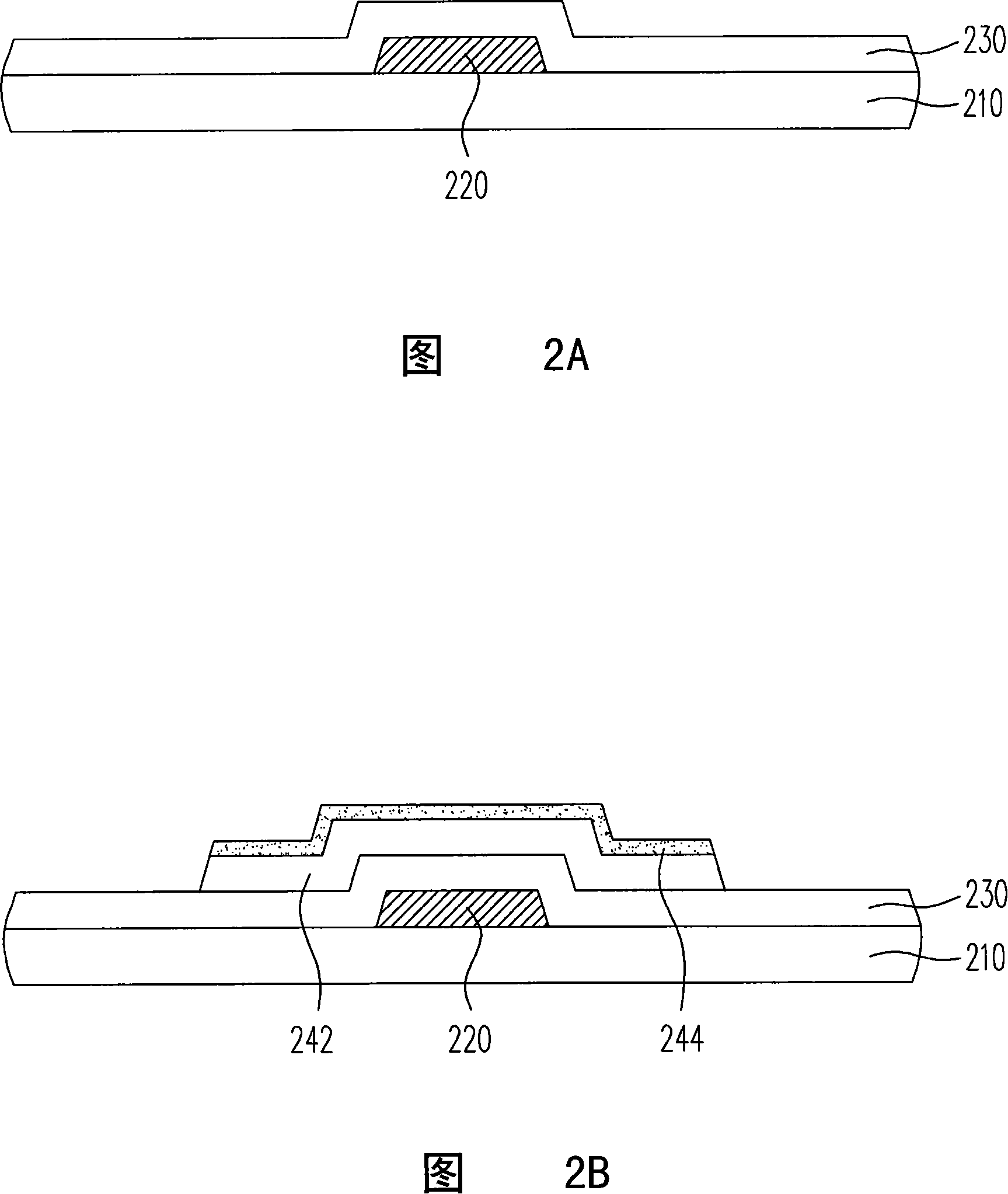

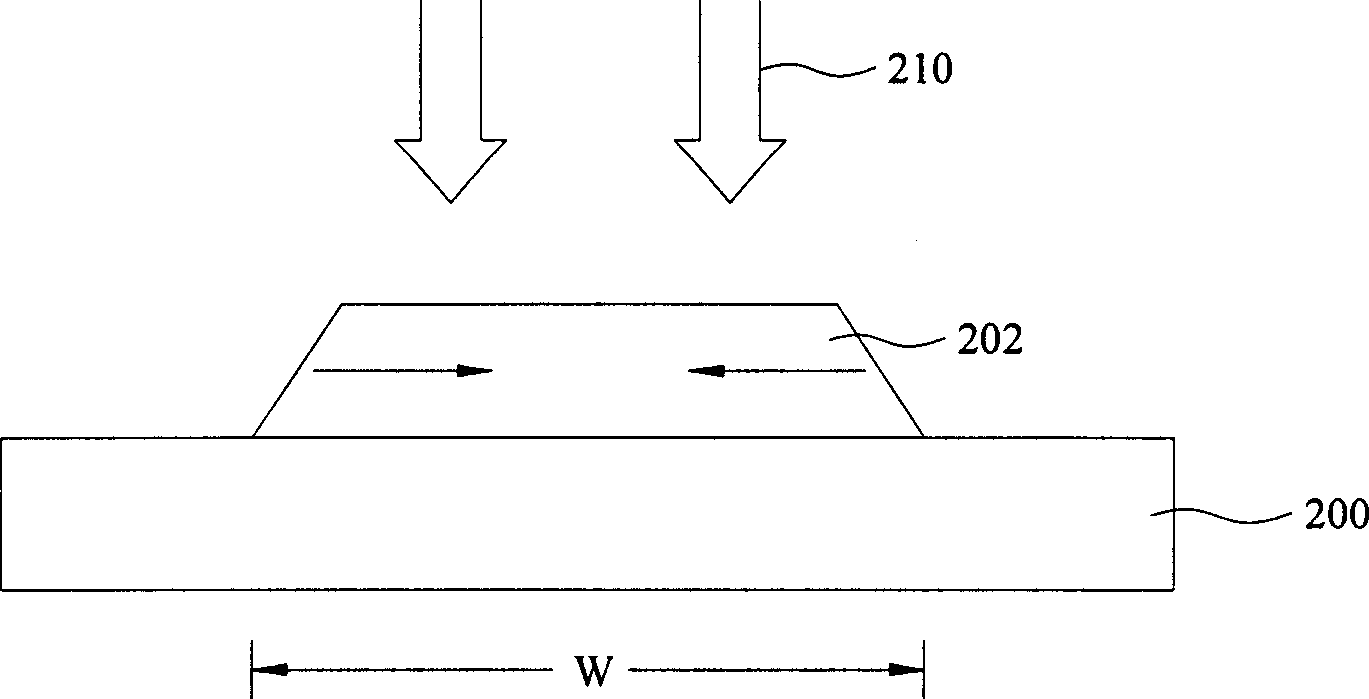

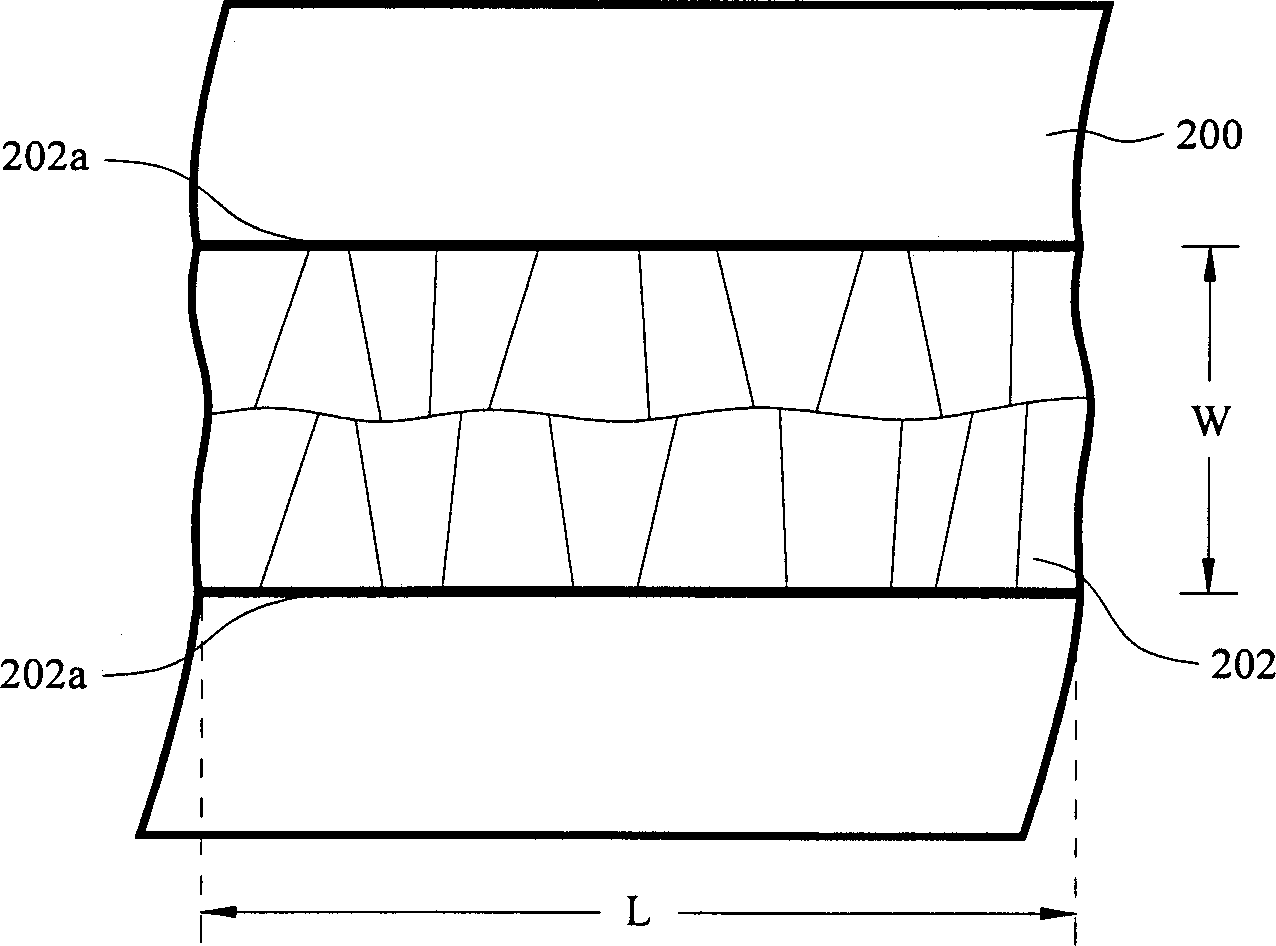

Method for producing multicrystalline silicon layer

ActiveCN1588621AAvoid it happening againImprove electrical qualitySemiconductor/solid-state device manufacturingMolten stateAmorphous silicon

The method includes the steps: 1) to from a insulating layer on a base board, 2) to form an amorphous silicon layer on the insulating, layer, the amorphous silicon layer includes a amorphous silicon thick area and a amorphous silicon thin area, 3) to fully melt the amorphous silicon layer to a first molten state amorphous silicon area that center of the bottom is corresponding to center of bottom of the amorphous silicon thick area and a second molten state amorphous silicon area that center of the bottom is corresponding to center of the amorphous silicon thin area. The temp. of first molten state amorphous silicon area is lower than the temp. of second molten state amorphous silicon area. Finally, to crystallize from first molten state amorphous silicon area to second molten state amorphous silicon area, thus to form polysilicon layer.

Owner:AU OPTRONICS CORP

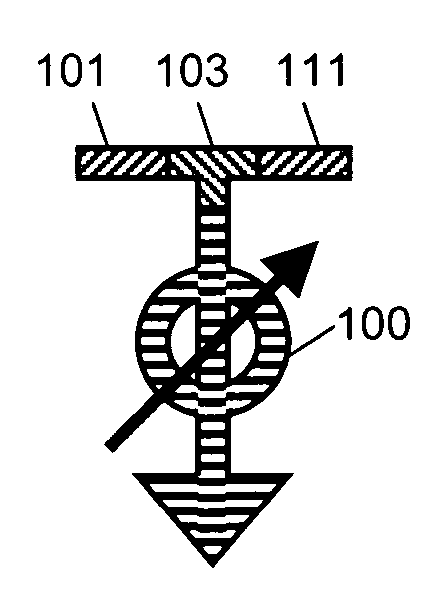

Integrated passive device wafer-level packaging three-dimensional stacked structure and manufacturing method

ActiveCN104009014AImprove reliabilitySmall sizeSemiconductor/solid-state device detailsSolid-state devicesShortest distanceInterconnection

The invention relates to an integrated passive device wafer-level packaging three-dimensional stacked structure and a manufacturing method. The integrated passive device wafer-level packaging three-dimensional stacked structure comprises a wafer-level packaging chip and an IPD chip. The IPD chip comprises a glass substrate, wherein an IPD device and a metal wiring layer are arranged on the front surface of the glass substrate, the back surface of the glass substrate is etched to form TGV holes, back surface metal wiring layers are arranged on the back surface of the glass substrate and the inner surfaces of the TGV holes, a welding ball is arranged on a welding pad of each back surface metal wiring layer, and the welding balls are connected with a PCB. The manufacturing method of the three-dimensional stacked structure comprises the following steps that (1) the wafer-level packaging chip and the IPD chip of the glass substrate are stacked; (2) the back surface of the IPD chip is etched to form the TGV holes, the back surface metal wiring layer is manufactured on the back surface of the glass substrate; (3) the back surface metal wiring layer is etched into two insulated parts; the welding pads and welding balls are manufactured on the two parts of the back surface metal wiring layer, and the welding balls are connected with the PCB. By means of the integrated passive device wafer-level packaging three-dimensional stacked structure and the manufacturing method, short-distance interconnection between the chip and the IPD device is achieved, and the electric quality is improved.

Owner:NAT CENT FOR ADVANCED PACKAGING

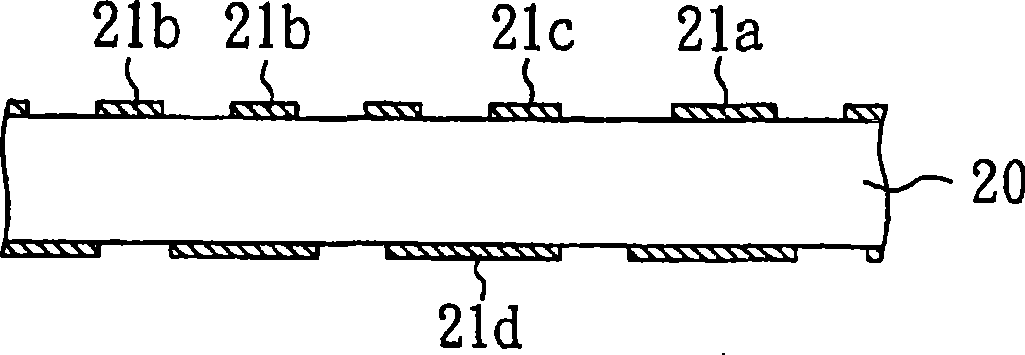

Semiconductor package substrate and fabrication method thereof

ActiveCN101383335AMaintain electrical qualityLow costSemiconductor/solid-state device detailsSolid-state devicesSemiconductor packageEngineering

The invention relates to a semiconductor packaging substrate and a fabricating method thereof. The invention is characterized in that electric connection pads on the surface of a circuit board provided with a wire bonding area and a lug area synchronously form a nickel / palladium / metal layer, so as to reduce the flow of process and the waste of time. The effect for enhancing the binding force between the substrate and the chip exists in the nickel / palladium / metal layer.

Owner:PHOENIX PRECISION TECH CORP

Electronic device, thin-film transistor, display device and conductor contact process

InactiveCN101645456ANot easily oxidizedReduce contact resistanceTransistorSemiconductor/solid-state device detailsElectrical conductorLanthanide

The invention relates to an electronic device, a thin-film transistor, a display device and conductor contact process. The electronic device is at least provided with a conductor pattern configured ona substrate. The conductor pattern comprises a substantive pure aluminum layer and an aluminum nickel lanthanide alloy layer, the substantive pure aluminum layer is configured on the substrate, and the aluminum nickel lanthanide alloy layer is configured on the substantive pure aluminum layer. The electronic device has the advantages of low manufacturing cost, good electrical property and good manufacturing yield.

Owner:INNOLUX CORP

Light-emitting diode structure, and manufacturing method thereof

The invention discloses a light-emitting diode structure, and a manufacturing method thereof. The light-emitting diode structure comprises a substrate, an epitaxy structure, a protection layer and at least one electrode. The epitaxy structure is arranged on the substrate. The protection layer covers the epitaxy structure, wherein the protection layer comprises at least one opening which is positioned on at least one part of the epitaxy structure. The at least one electrode is arranged in the at least one opening, and extends and covers the at least one part of the epitaxy structure, and the protection layer around the at least one opening.

Owner:佛山市奇明光电有限公司 +1

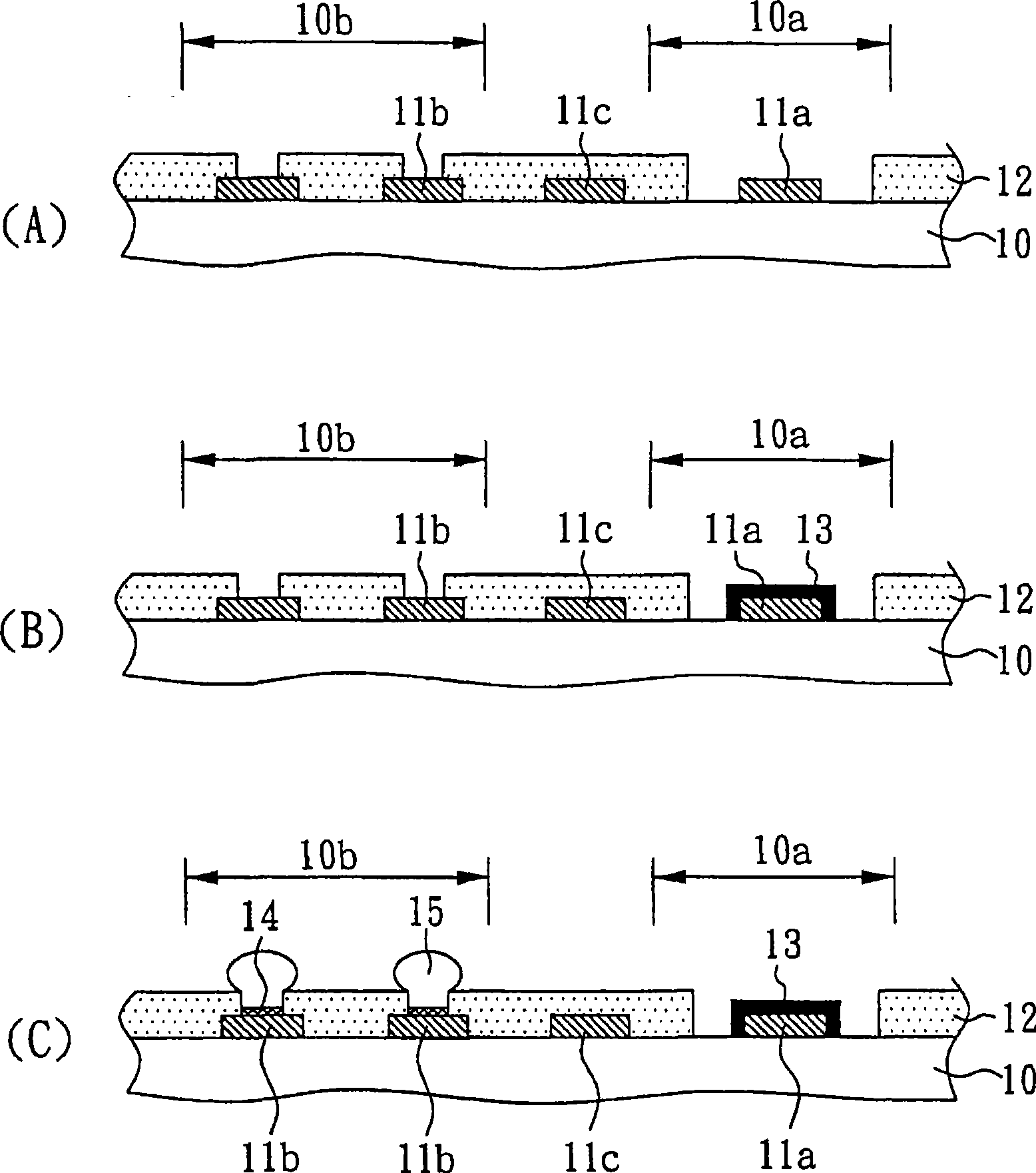

Pixel construction and manufacturing method thereof

InactiveCN101425481BImprove electrical qualityPrevent proliferationSemiconductor/solid-state device detailsSolid-state devicesOhmic contactElectric current flow

The invention relates to a pixel structure and a manufacturing method thereof for reducing leakage current. The pixel structure comprises a grid electrode, a grid insulating layer, a semiconductor layer, an ohmic contact layer, a source electrode, a drain electrode, a first patterning dielectric layer, a second patterning dielectric layer and a pixel electrode which are arranged on the base platein sequence. The grid electrode is covered by the grid insulating layer, and the semiconductor layer is positioned above the grid electrode. The ohmic contact layer is arranged on the semiconductor layer; the source electrode and the drain electrode expose out of partial semiconductor layer exposing out of the ohmic contact layer. The source electrode / the drain electrode above the grid electrode is covered by the first patterning dielectric layer and the partial semiconductor layer is exposed. The first patterning dielectric layer and the second first patterning dielectric layer are respectively provided with a first opening and a second opening to expose the partial drain electrode. The pixel electrode is electrically connected with the drain electrode by means of the first and the second openings.

Owner:CHUNGHWA PICTURE TUBES LTD

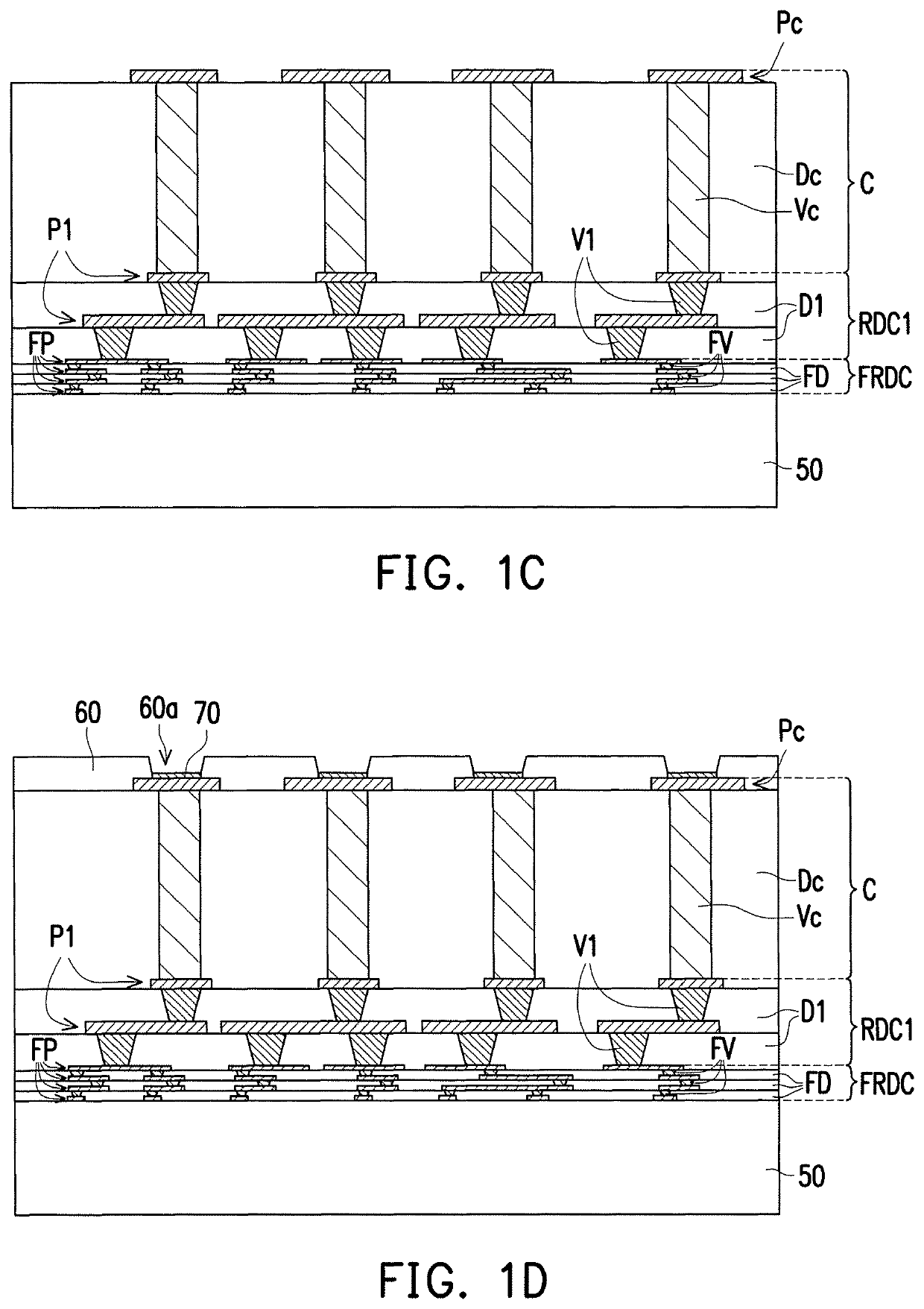

Package substrate and package structure

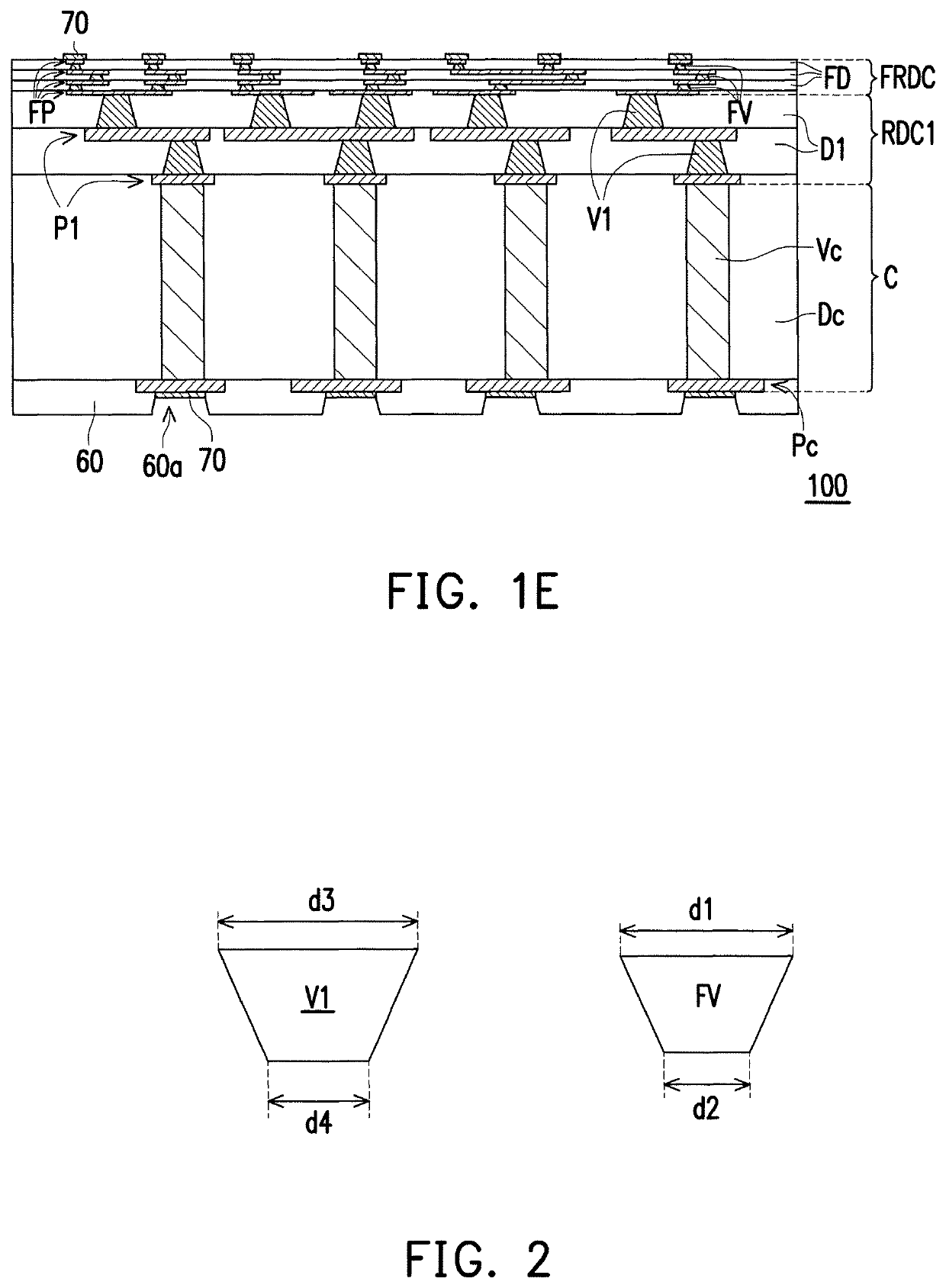

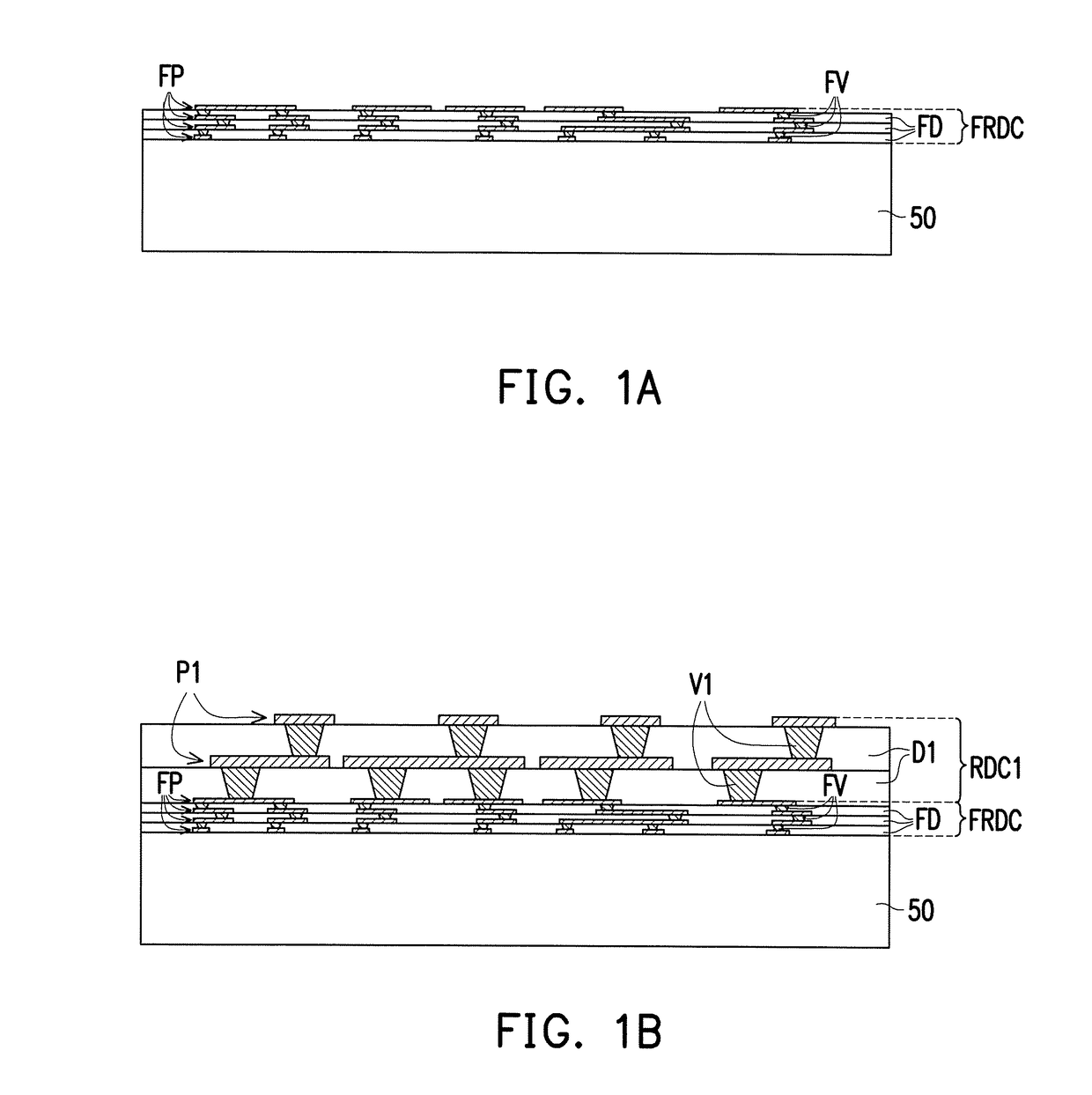

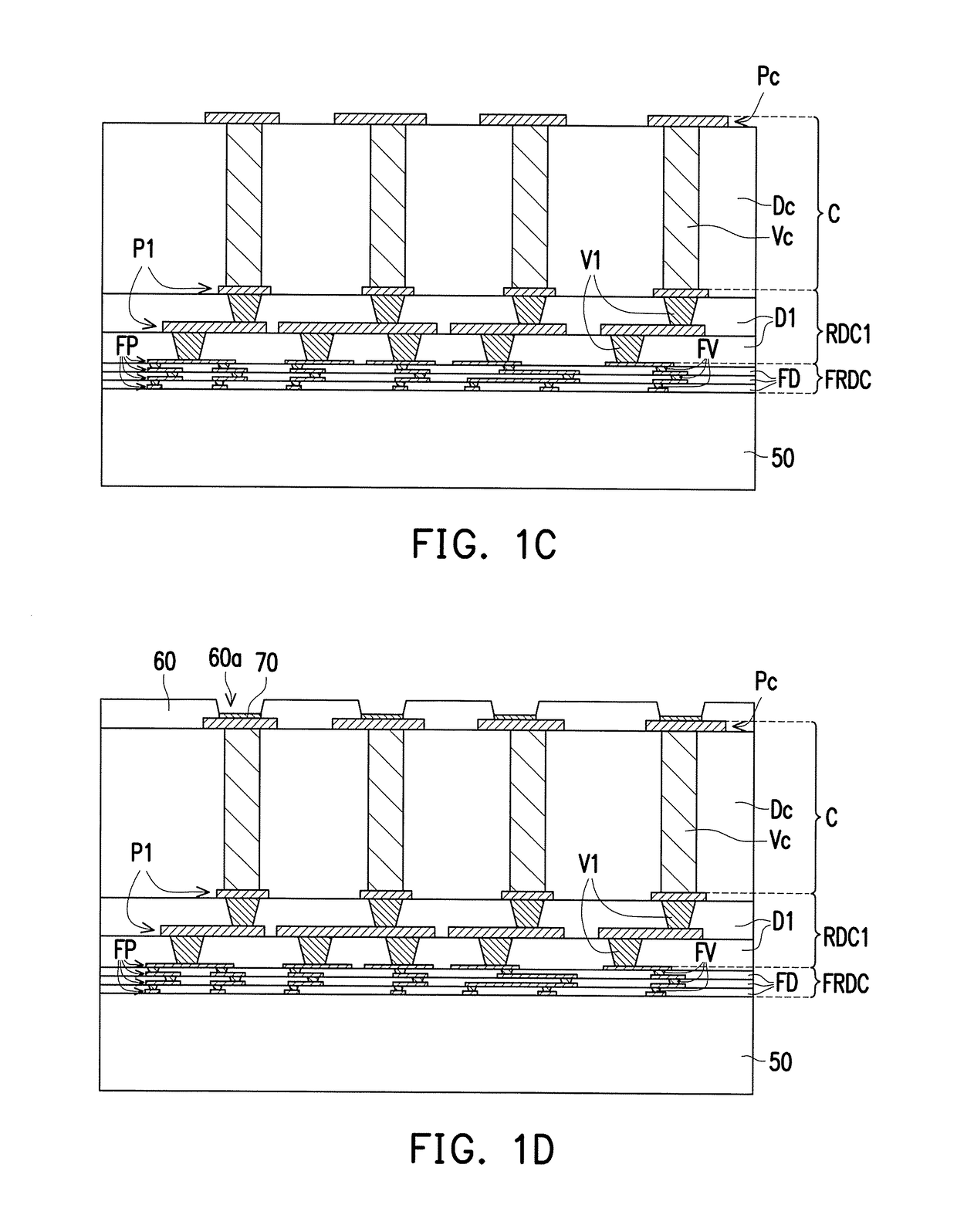

ActiveUS10643936B2Improve electrical qualityReduce warpageSemiconductor/solid-state device detailsSolid-state devicesHemt circuitsElectrical connection

A package substrate including a fine redistribution circuitry, a first redistribution circuitry disposed on the fine redistribution circuitry and a core disposed on the first redistribution circuitry opposite to the fine redistribution circuitry. The fine redistribution circuitry includes a fine conductive pattern. The first redistribution circuitry includes a first conductive pattern electrically connected to the fine conductive pattern. A thickness of the fine redistribution circuitry is less than a thickness of the first redistribution circuitry and a dimension of the fine conductive pattern is less than a dimension of the first conductive pattern. The core is electrically connected to the first conductive pattern. The Young's modulus of the core is greater than the Young's modulus of the first redistribution circuitry. A package structure is also provided.

Owner:HU DYI CHUNG

Package substrate and package structure

ActiveUS20180350731A1Reduce warpageImprove mechanical stabilitySemiconductor/solid-state device detailsSolid-state devicesYoung's modulusEngineering

A package substrate including a fine redistribution circuitry, a first redistribution circuitry disposed on the fine redistribution circuitry and a core disposed on the first redistribution circuitry opposite to the fine redistribution circuitry. The fine redistribution circuitry includes a fine conductive pattern. The first redistribution circuitry includes a first conductive pattern electrically connected to the fine conductive pattern. A thickness of the fine redistribution circuitry is less than a thickness of the first redistribution circuitry and a dimension of the fine conductive pattern is less than a dimension of the first conductive pattern. The core is electrically connected to the first conductive pattern. The Young's modulus of the core is greater than the Young's modulus of the first redistribution circuitry. A package structure is also provided.

Owner:HU DYI CHUNG

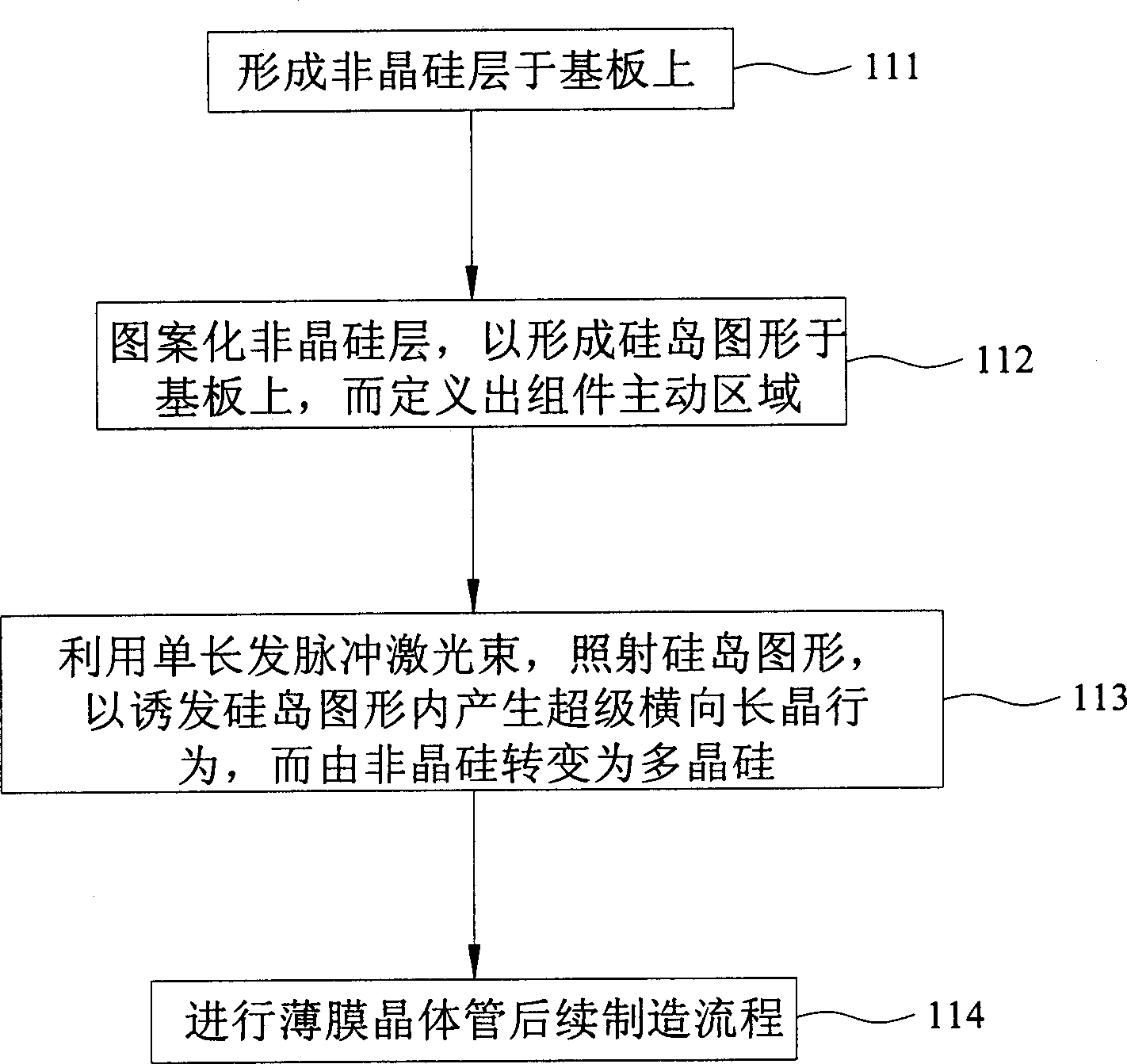

Method for producing polycrystalline thin film transistor

InactiveCN1822334AExtended growth timeImprove uniformitySemiconductor/solid-state device manufacturingSemiconductor devicesAmorphous siliconOptoelectronics

Said polysilicon thin film transistor making method makes patterning to non-crystalline silicon layer after forming non-crystalline silicon layer on substrate to form silicon island graphic, advance defining out assembly active area. Then said method utilizes single shot long pulse laser bean to radiate silicon island graphic, to induce silicon island generating super transverse direction long glittering acting, converting non-crystalline silicon to polysilicon, finally according to sequence to proceed follow-up thin film transistor making process to complete polysilicon thin film transistor manufacture.

Owner:IND TECH RES INST

Semiconductor process for etching a recess into a substrate by using an etchant that contains hydrogen peroxide

ActiveUS8329547B2Improve electrical qualitySemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringSemiconductor

A semiconductor process is disclosed. The semiconductor process includes the steps of: providing a substrate having a specific area defined thereon; and performing an etch process by using an etchant comprising H2O2 to etch the specific area for forming a recess.

Owner:UNITED MICROELECTRONICS CORP

Chip package structure

ActiveUS7982304B2Increase creepage distanceMeet the requirementsSemiconductor/solid-state device detailsSolid-state devicesEngineeringElectrical and Electronics engineering

A chip package structure including a substrate, at least one chip, a heat dissipation device, at least one first conductive bar, a molding compound, and at least one second conductive bar is provided. The chip and the heat dissipation device are respectively disposed on a first and a second surface of the substrate. The first conductive bar has two opposite end surfaces, wherein one end surface is disposed on the first surface of the substrate, the other end surface is extended away from the substrate, and a fastening slot is disposed between the two end surfaces and passes through the other end surface. The molding compound encapsulates the substrate, the chip, part of the heat dissipation device, and the first conductive bar. The second conductive bar is disposed on one surface of the molding compound and has a protrusion portion fastened to the fastening slot of the first conductive bar.

Owner:CYNTEC

Manufacture of tunnel oxide layer

InactiveCN1417846AReduce qualityImprove production efficiencySemiconductor/solid-state device manufacturingPhysical chemistrySingle crystal

In the manufacture of tunnel oxide layer, the present invention adopts rapid thermal process to replace available furnace process and grow SiO92 film as tunnel oxide layer through rapid thermal oxidation of monocrystal chip. The tunnel oxide layer is in-situ annealed in the repid thermal annealing process resulting in improved tunnel oxide layer quality. The present invention can reduce the growth time of the tunnel oxide layer, lower the required thermal budget, raise the homogenity of the tunnel oxide layer, and avoid pollution and manpower caused by replacing reactor chamber.

Owner:MACRONIX INT CO LTD

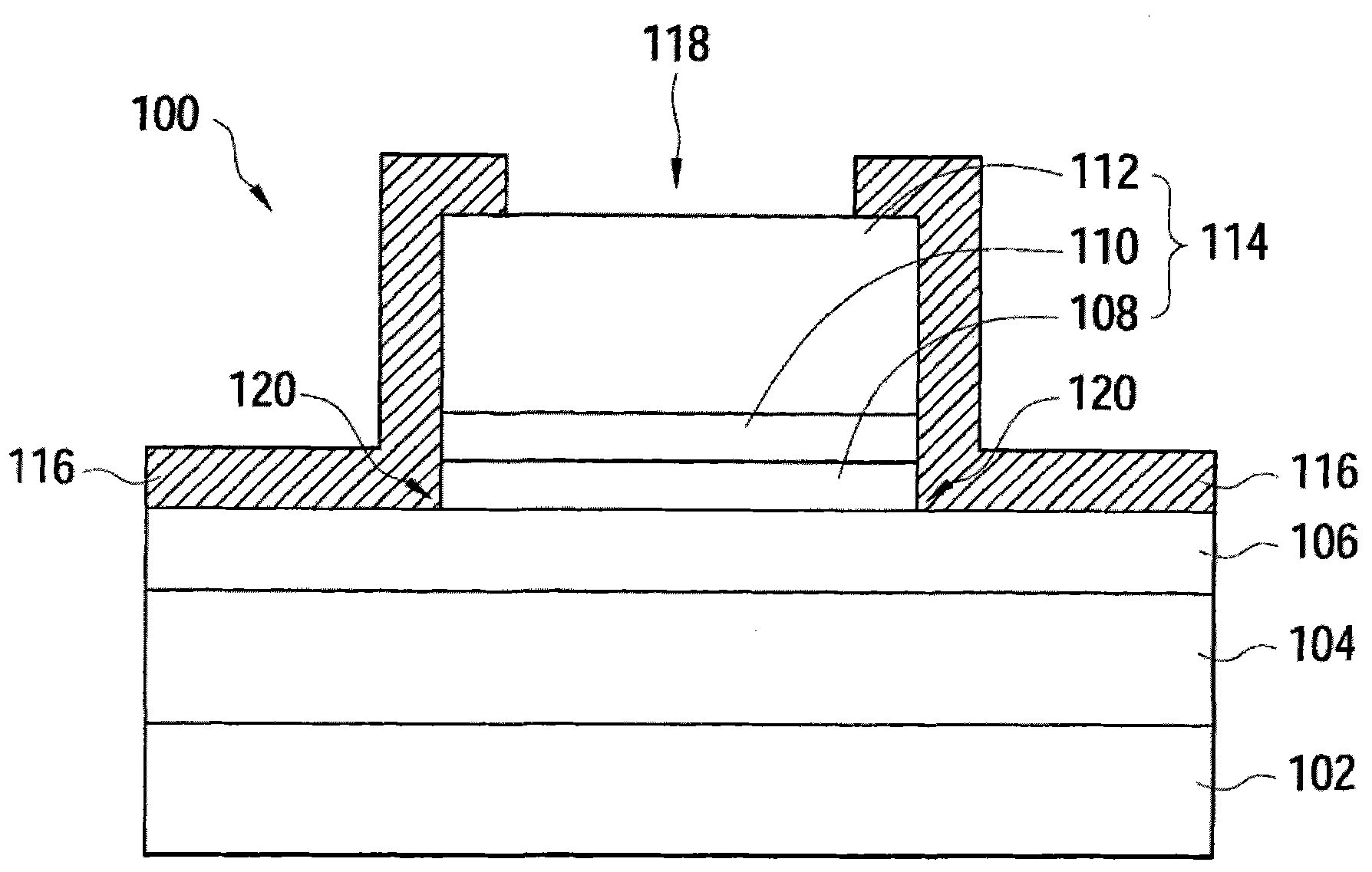

Light sensor located above an integrated circuit

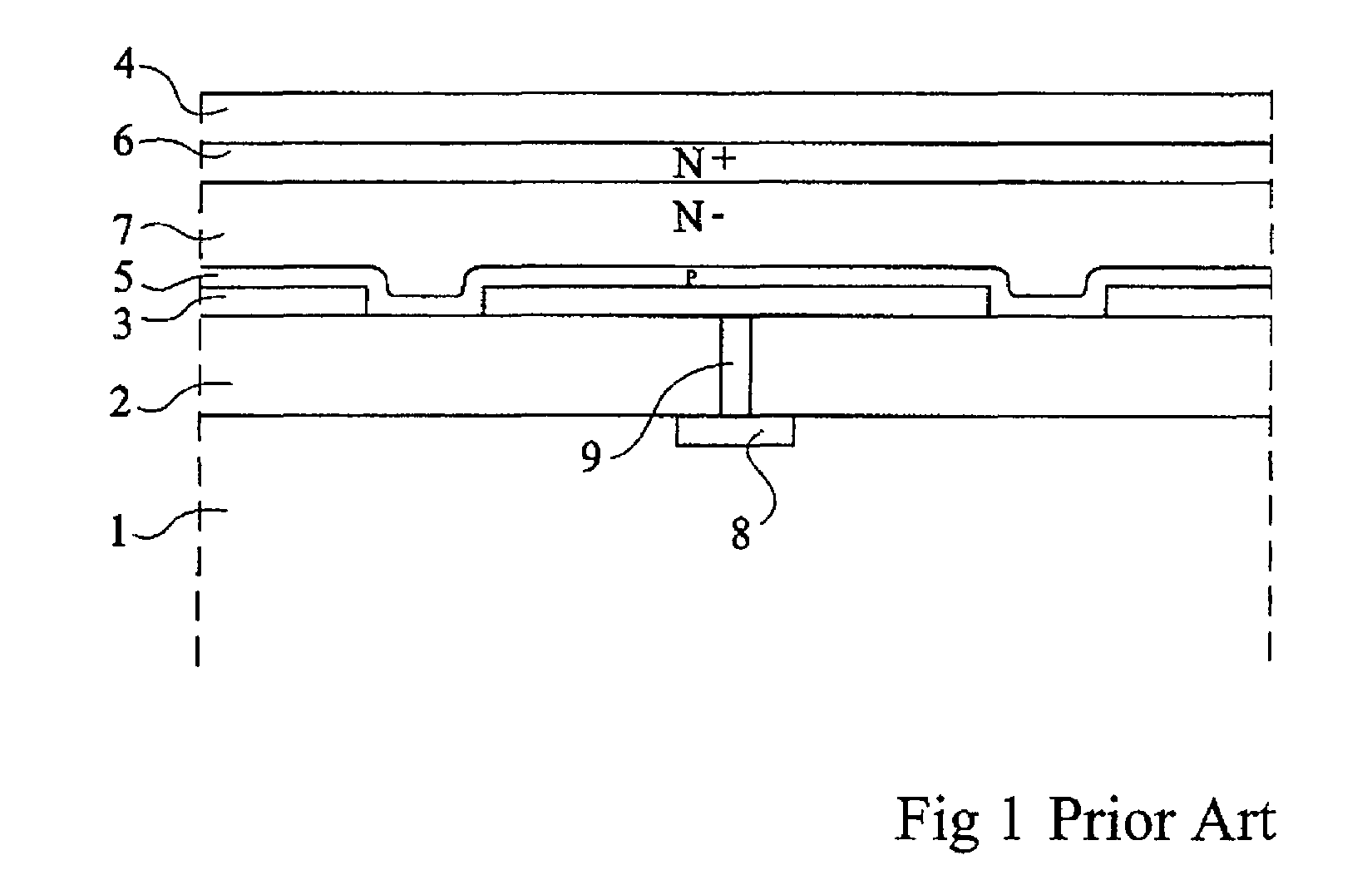

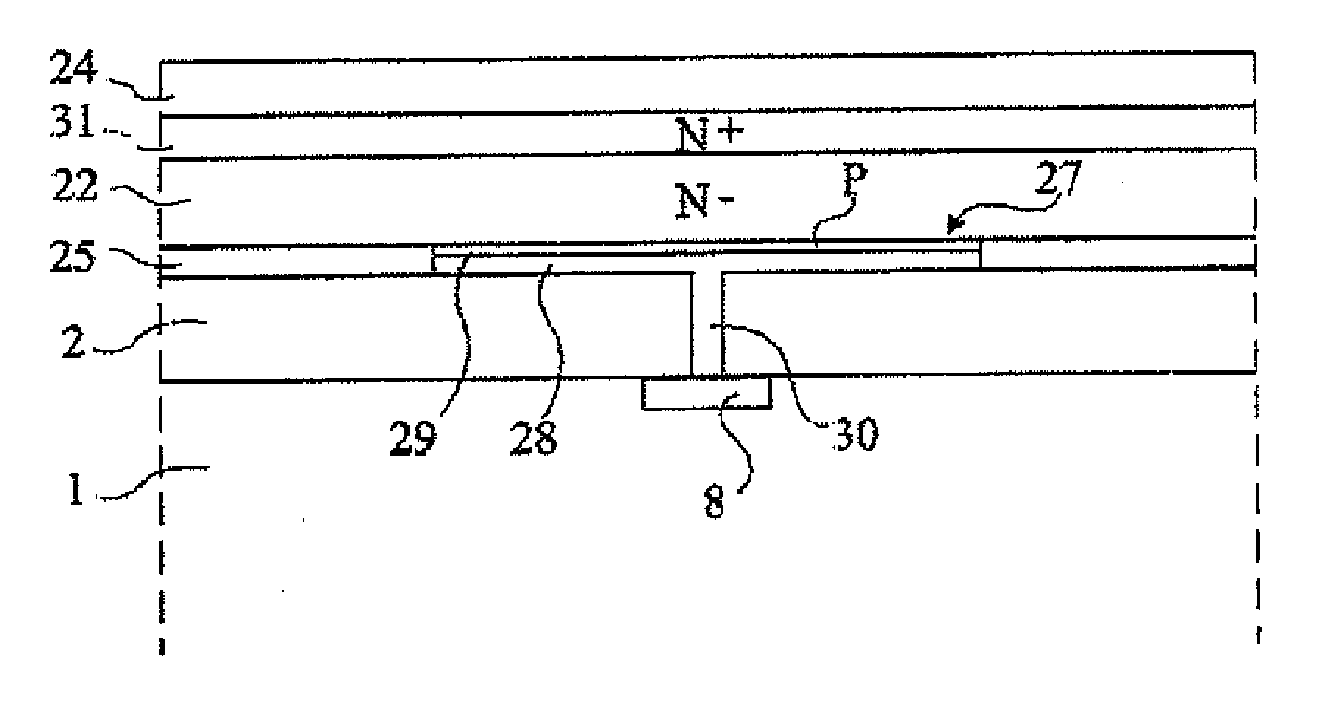

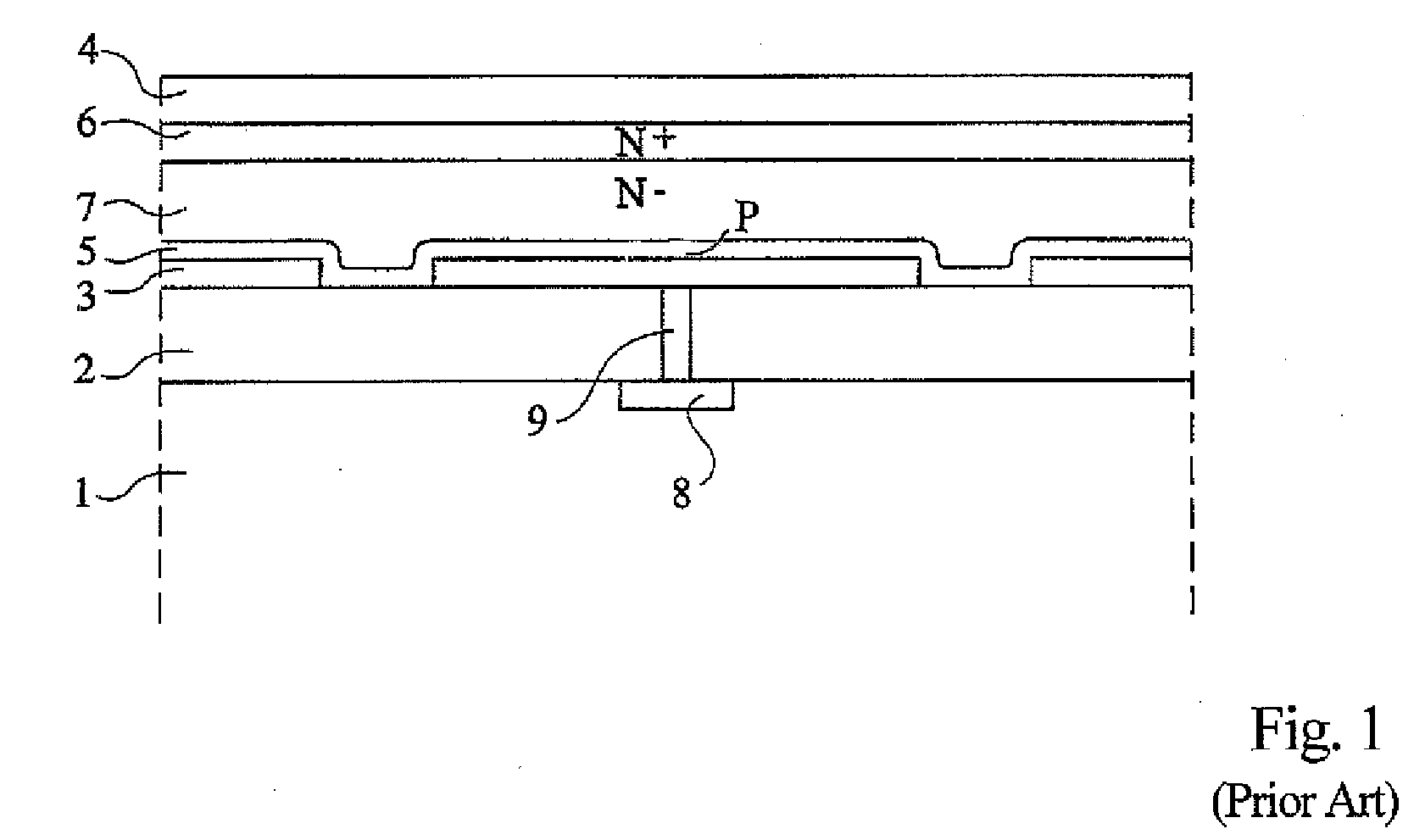

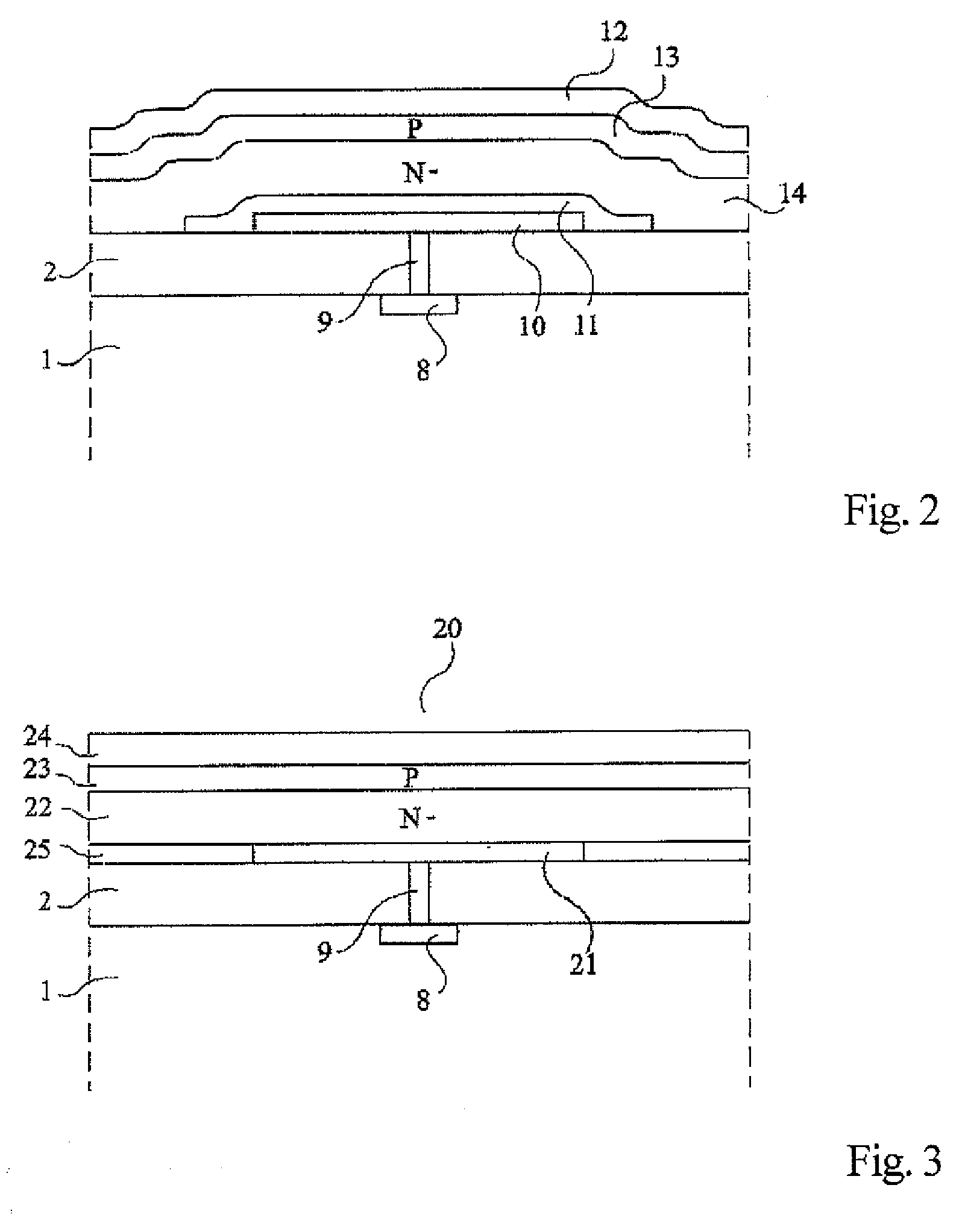

InactiveUS7492026B2Improve electrical qualityMinimum dark currentSolid-state devicesSemiconductor/solid-state device manufacturingAmorphous siliconIntegrated circuit

Owner:STMICROELECTRONICS SRL

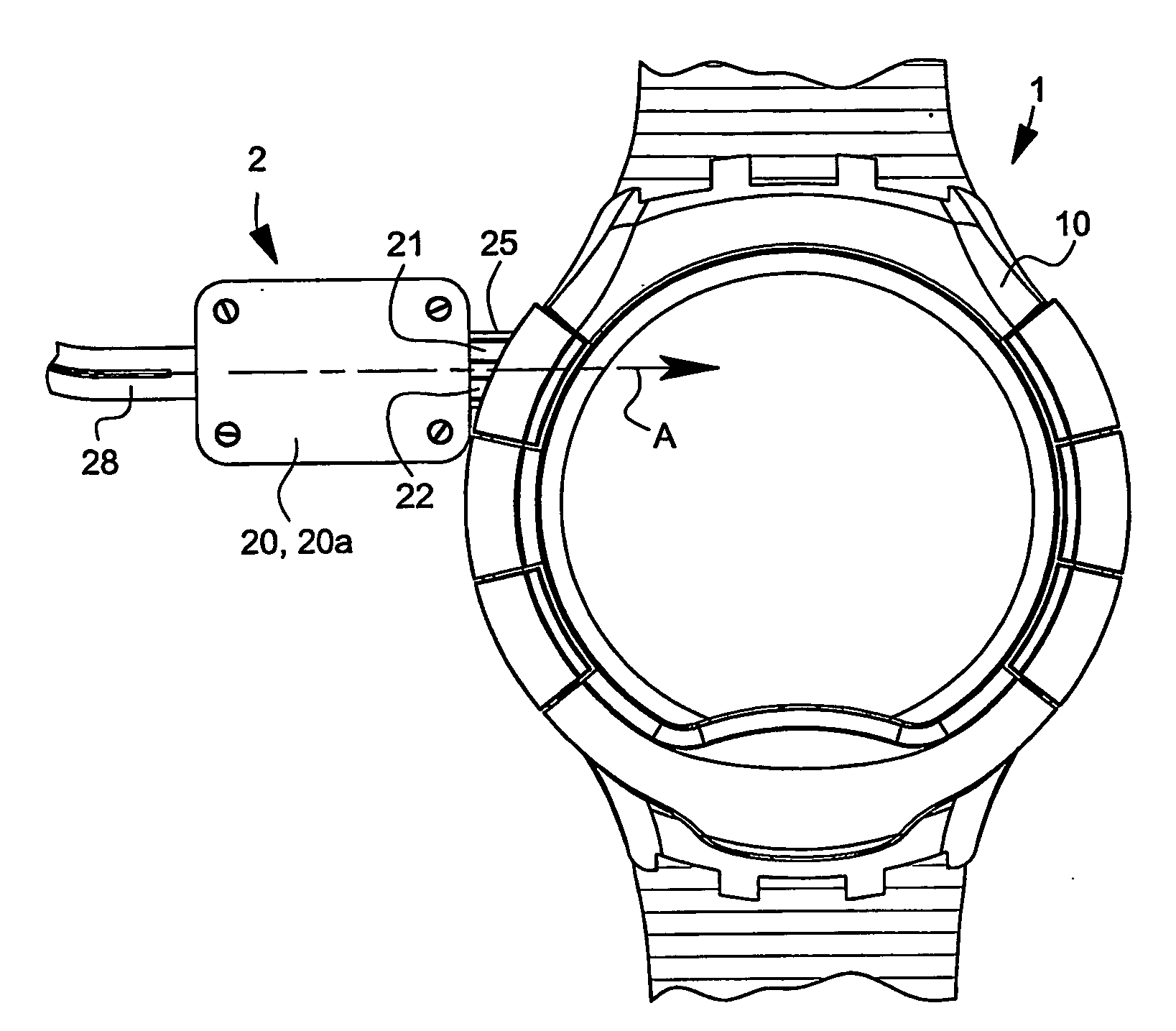

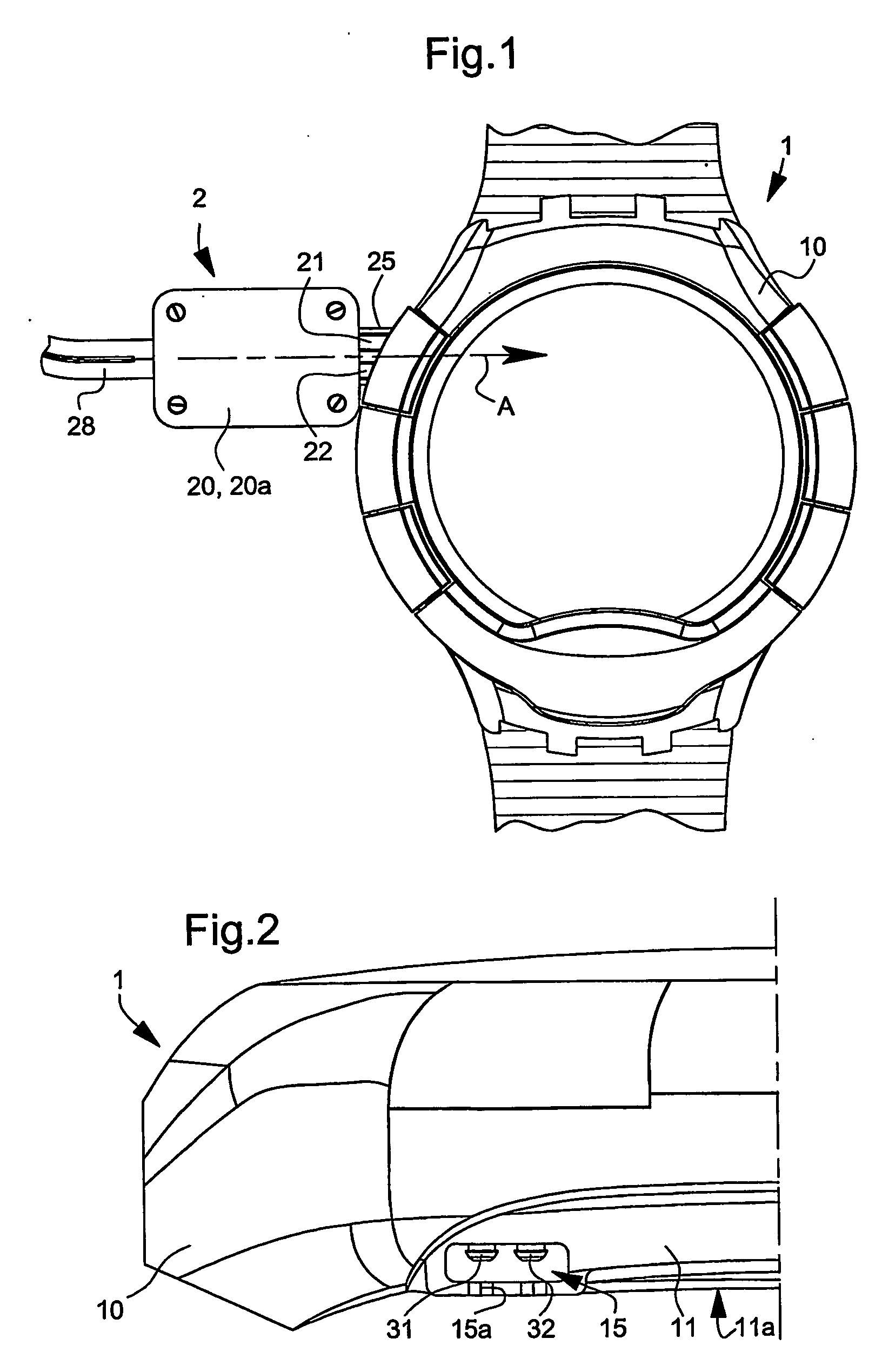

Device for establishing an electrical connection between a portable electronic instrument and an external device, in particular for performing the recharge of a battery of said instrument

InactiveUS20060178055A1Improve simplicityEasy to useElectric discharge tubesCoupling contact membersElectricityElectrical battery

A device is described for establishing an electrical connection between a portable electronic instrument and an external device, the portable electronic instrument comprising a casing provided with a socket in which a plurality of electrical contact elements is disposed, this socket being shaped to permit the insertion of a plug-in adaptor which is electrically connected to the external device and comprises a plurality of electrical contact zones, each intended to come into contact with a corresponding electrical contact element in the socket. The electrical contact elements are disposed substantially perpendicularly to the direction of insertion of the plug-in adaptor, and the electrical contact zones extend substantially parallel to the direction of insertion of the plug-in adaptor. Also described is a system for recharging a battery of a portable electronic instrument comprising such a connection device, as well as a plug-in adaptor for such a connection device.

Owner:ETA SA MFG HORLOGERE SUISSE

Light sensor located above an integrated circuit

ActiveUS20090075410A1Improve electrical qualityMinimum dark currentSolid-state devicesSemiconductor/solid-state device manufacturingAmorphous siliconIntegrated circuit

A light sensor located above an integrated circuit including a lower electrode, a heavily-doped amorphous silicon layer of a first conductivity type, and a lightly-doped amorphous silicon layer of a second conductivity type. The lightly-doped amorphous silicon layer rests on a planar surface at least above and in the vicinity of the lower electrode.

Owner:STMICROELECTRONICS FRANCE

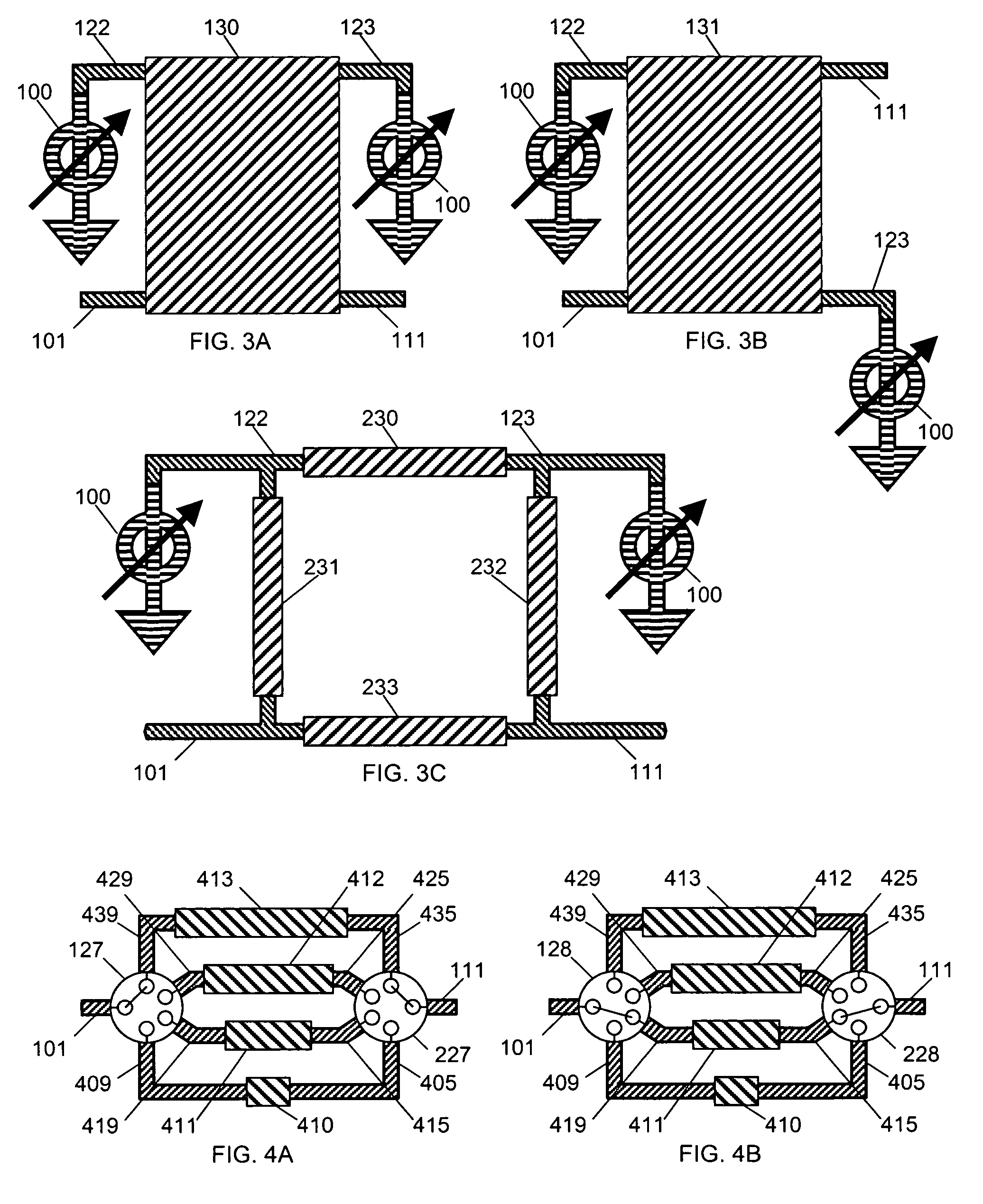

Fabricating process of circuit board with embedded passive component

InactiveUS20090139756A1Reduce the impactReduce impactPrinted circuit assemblingPrinted circuit aspectsInsulation layerEngineering

A fabricating process of a circuit board with an embedded passive component is described. First, a conductive layer including a first surface and a second surface opposite thereto is provided. The first surface has at least one component region on which at least one passive component material layer is formed. A passivation layer is formed on the first surface to cover the passive component material layer. A brown oxidation process is performed on the conductive layer. A circuit unit and an insulation layer are provided, and the insulation layer is set between the circuit unit and the conductive layer. The conductive layer, the circuit unit and the insulation layer are laminated. The passive component material layer is between the insulation layer and the conductive layer. The conductive layer is patterned to form a circuit layer.

Owner:SUBTRON TECH

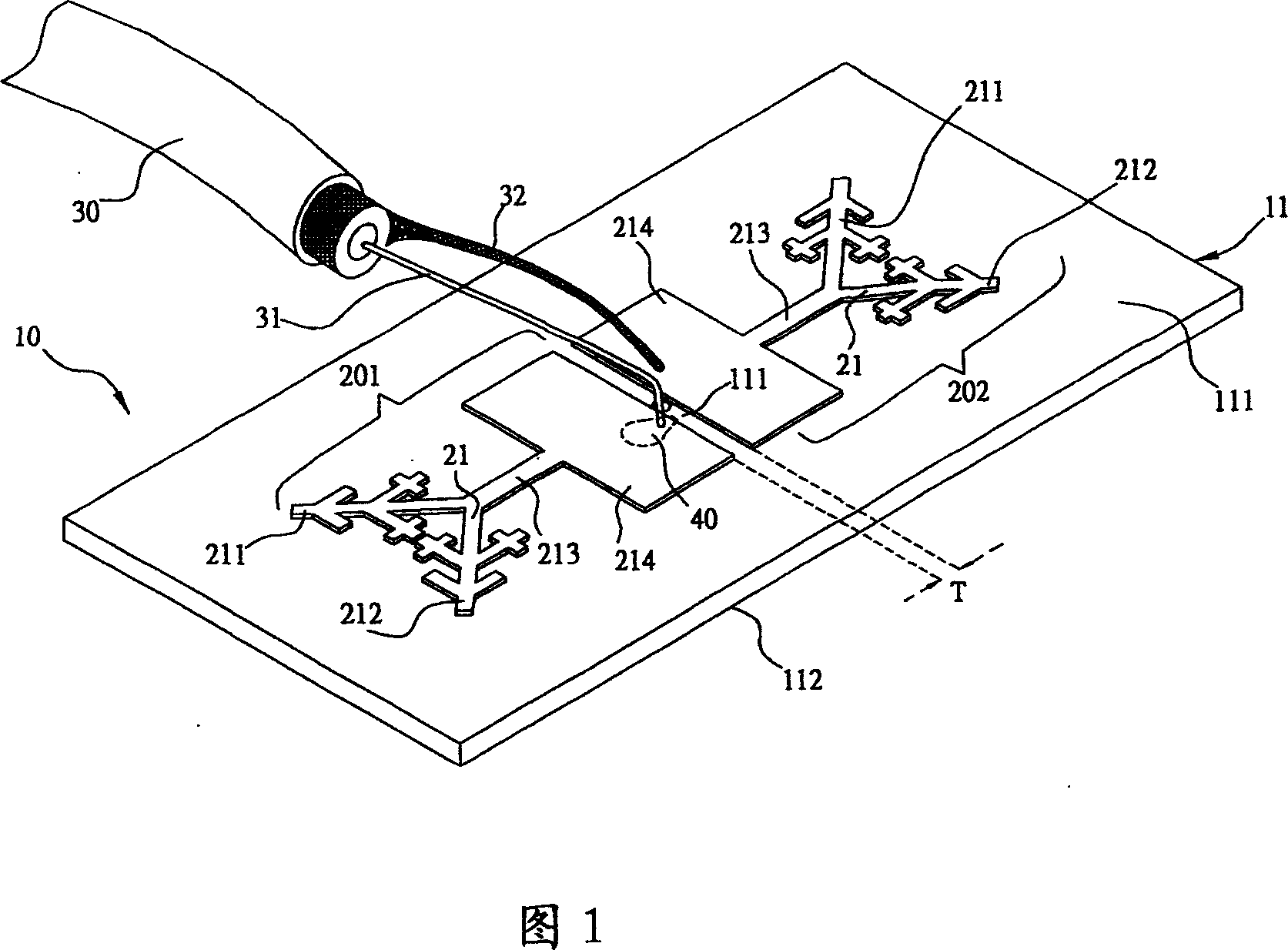

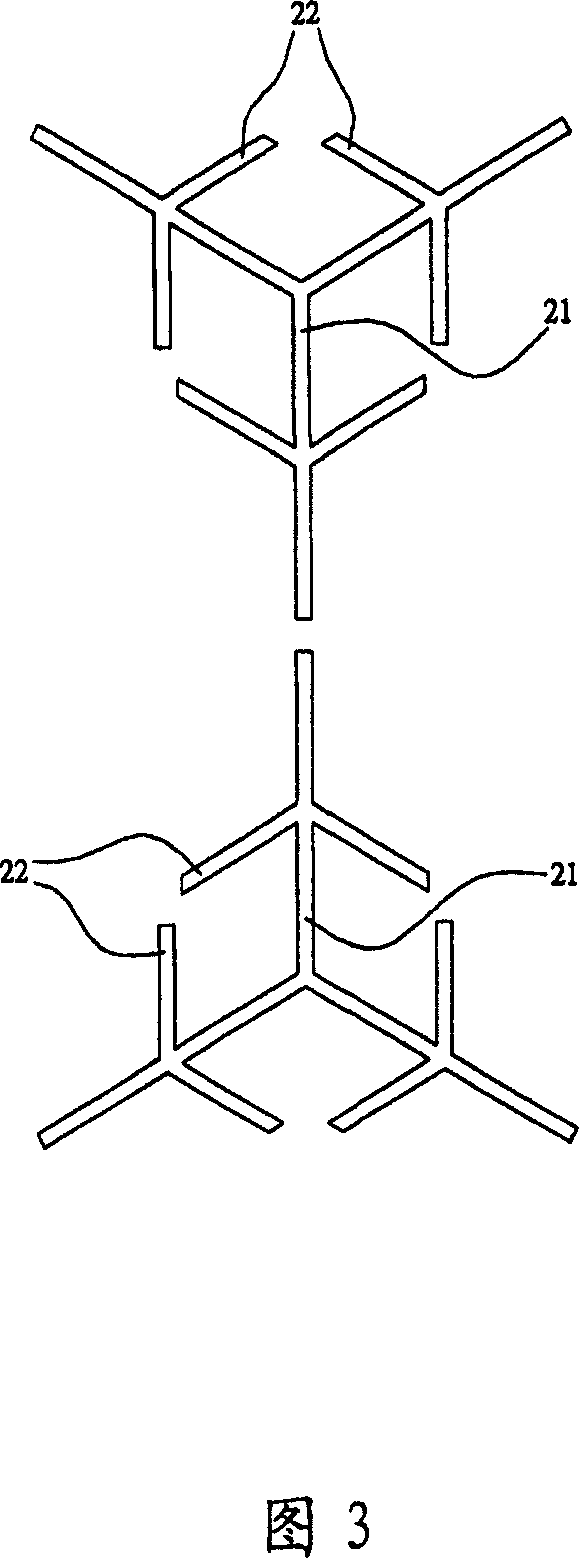

Crushed shape antenna

InactiveCN101051705AReduce assembly proceduresLow costAntenna arraysRadiating elements structural formsCapacitanceCoaxial cable

Being setup on side face of a dielectric material, fractal type antenna composed of two symmetrical arranged antenna modules forms a dipole antenna. Each antenna module is produced by iteration based on fractal algorithm for prearranged shaped metal microstrip. A matching network is respectively connected to one end of adjacent metal microstrips. There is a gap between matching networks. Being setup on the other side face of the dielectric material, a metal piece is corresponding to an antenna module and a gap. Passing through the dielectric material, central core wire of coaxial cable is connected to the metal piece in use for coupling. Shielding wire of the coaxial cable is connected to a matching network of another antenna module. Capacitance coupling type Balun interface is formed between the antenna and the coaxial cable. Thus, electric wave signal received by antenna can be transferred to the coaxial cable successfully.

Owner:黄启芳

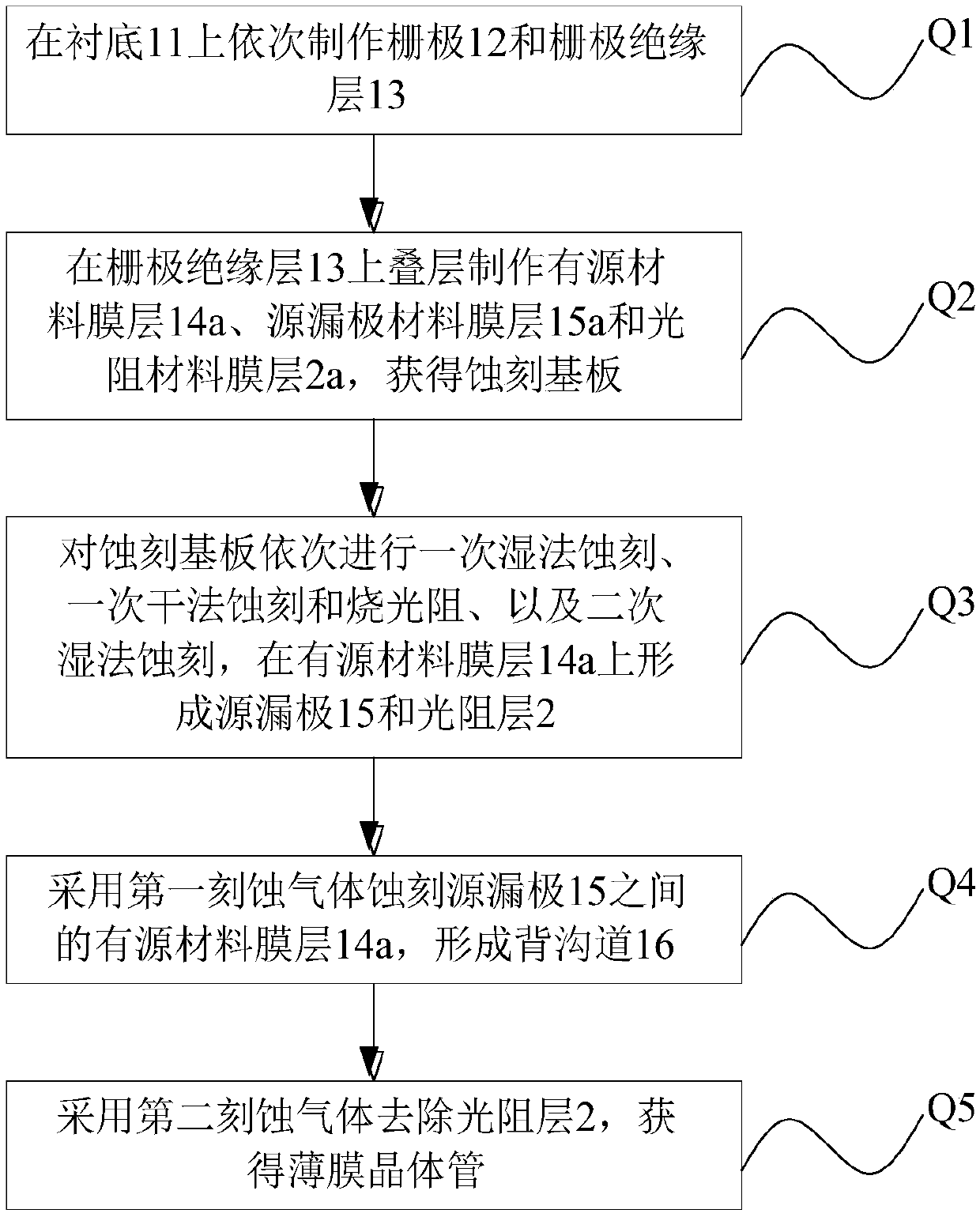

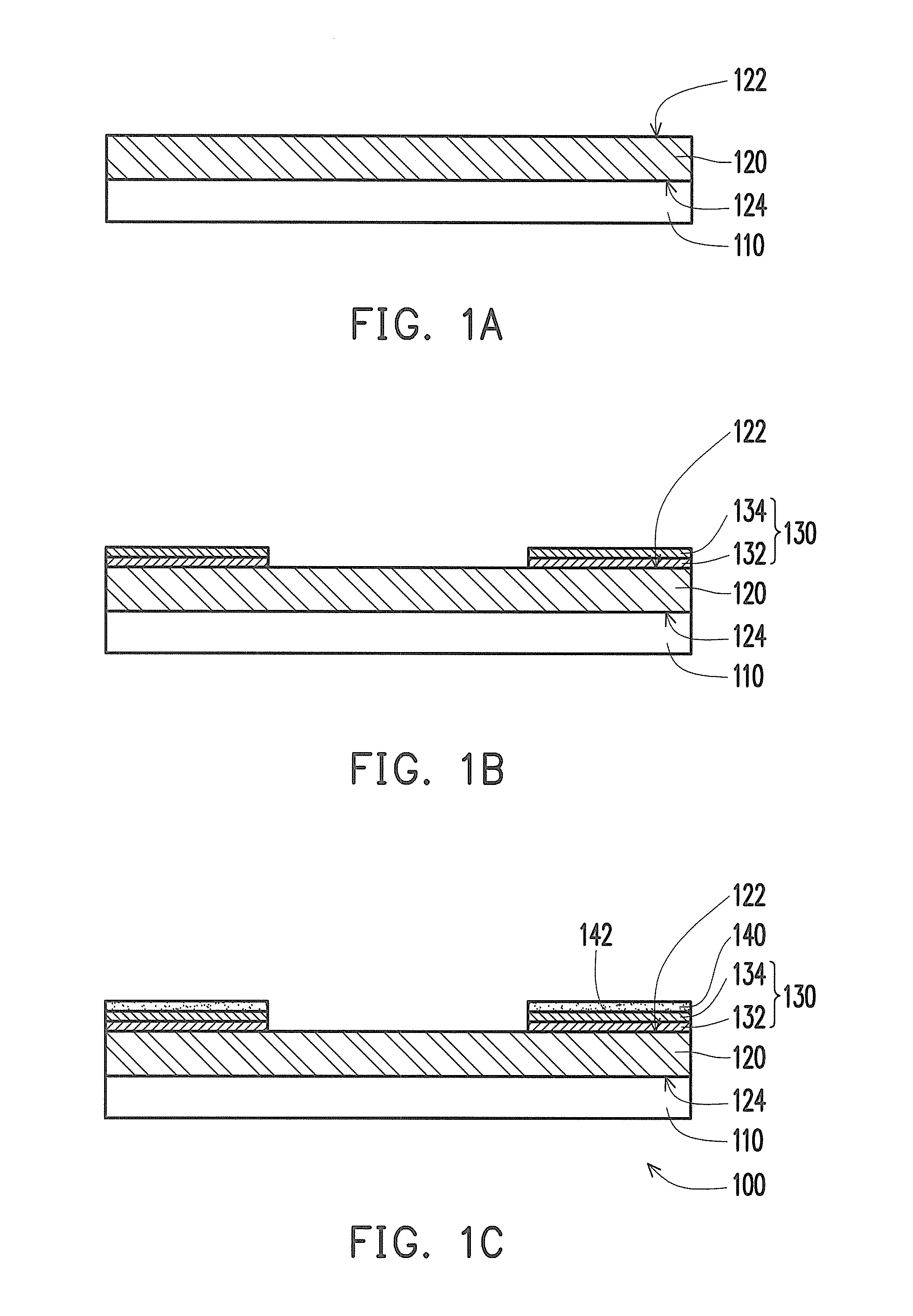

Manufacturing method of thin film transistor and manufacturing method of array substrate

ActiveCN108022875AImprove leakageImprove electrical qualitySolid-state devicesSemiconductor/solid-state device manufacturingState of artInsulation layer

The invention provides a manufacturing method of a thin film transistor. A method for forming a back channel comprises the following steps: S21, laminating and manufacturing an active material film, asource and drain electrode material film and a photoresist material film on a gate insulation layer so as to obtain an etched substrate; S22, carrying out primary wet etching, primary dry etching andphotoresist burning and secondary wet etching on the etched substrate in sequence so as to form a source electrode, a drain electrode and a photoresist layer; S23, etching the active material film byadopting a first etching gas so as to form the back channel; and S24, removing the photoresist layer by adopting a second etching gas so as to obtain the thin film transistor. According to the manufacturing method, a copper stripping solution can be avoided from being used when the back channel is etched, and the compositions and using amounts of various etching gases are reasonably matched, so that the problems of copper ion diffusion and pollution of other impurity ions in the copper stripping solution in the prior art are further avoided while back channel etching and photoresist removal are completed. The invention also provides application of the manufacturing method in an array substrate.

Owner:WUHAN CHINA STAR OPTOELECTRONICS SEMICON DISPLAY TECH CO LTD

Circuit structure and manufacturing method thereof

ActiveUS20120282738A1Preventing Galvanic effectInhibitionSemiconductor/solid-state device detailsNanoinformaticsNanoparticleMetallurgy

A manufacturing method of a circuit structure is provided. A metal layer having an upper surface is provided. A surface passivation layer is formed on the metal layer. The surface passivation layer exposes a portion of the upper surface of the metal layer, and a material of the metal layer is different from a material of the surface passivation layer. The metal layer and the surface passivation layer are dipped into a modifier, and the modifier is selectively absorbed and attached to the surface passivation layer, so as to form a covering layer. The covering layer has a plurality of nanoparticles and covers the surface passivation layer.

Owner:SUBTRON TECH

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com