Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

1164 results about "Reliability (semiconductor)" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Reliability of semiconductor devices can be summarized as follows...

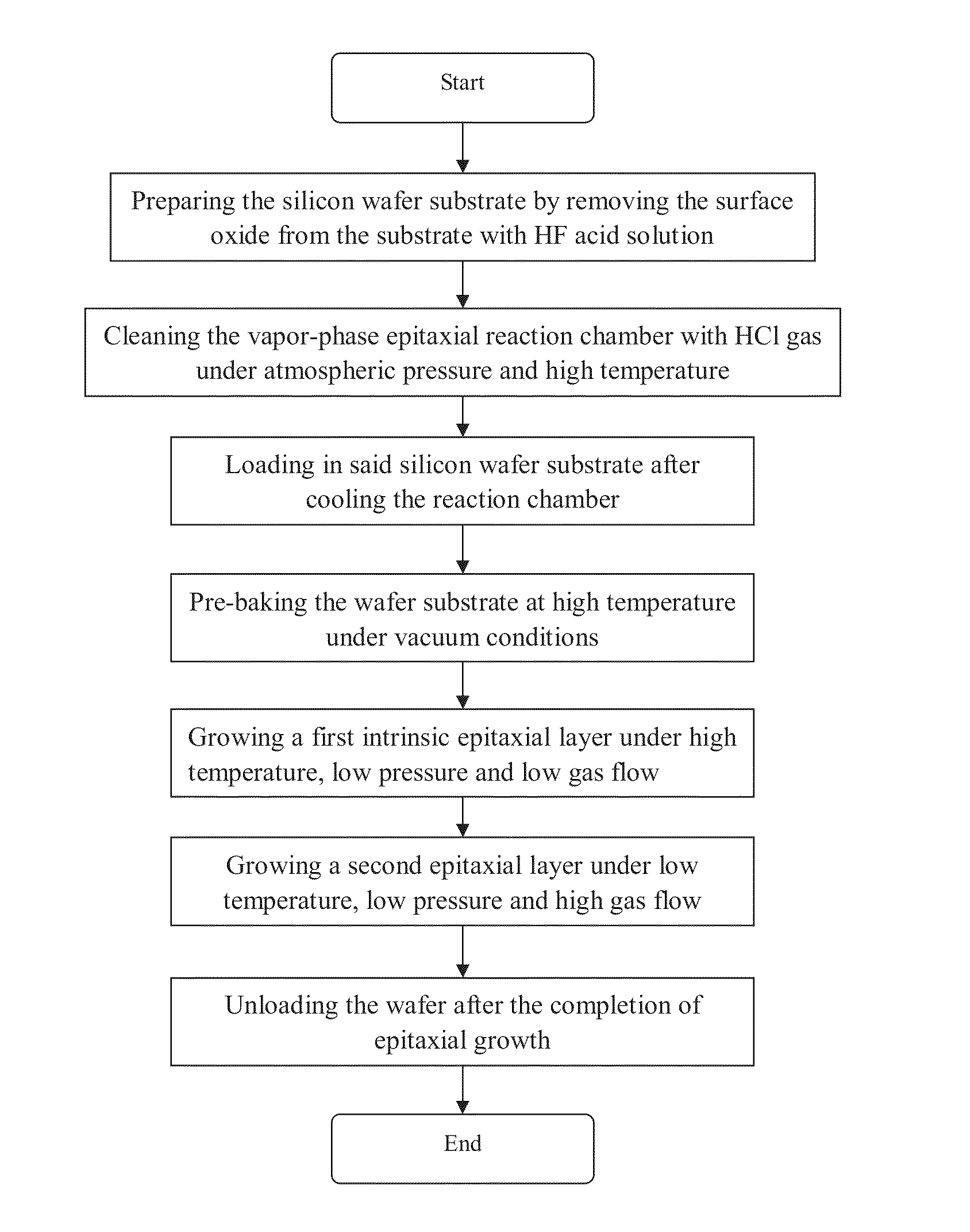

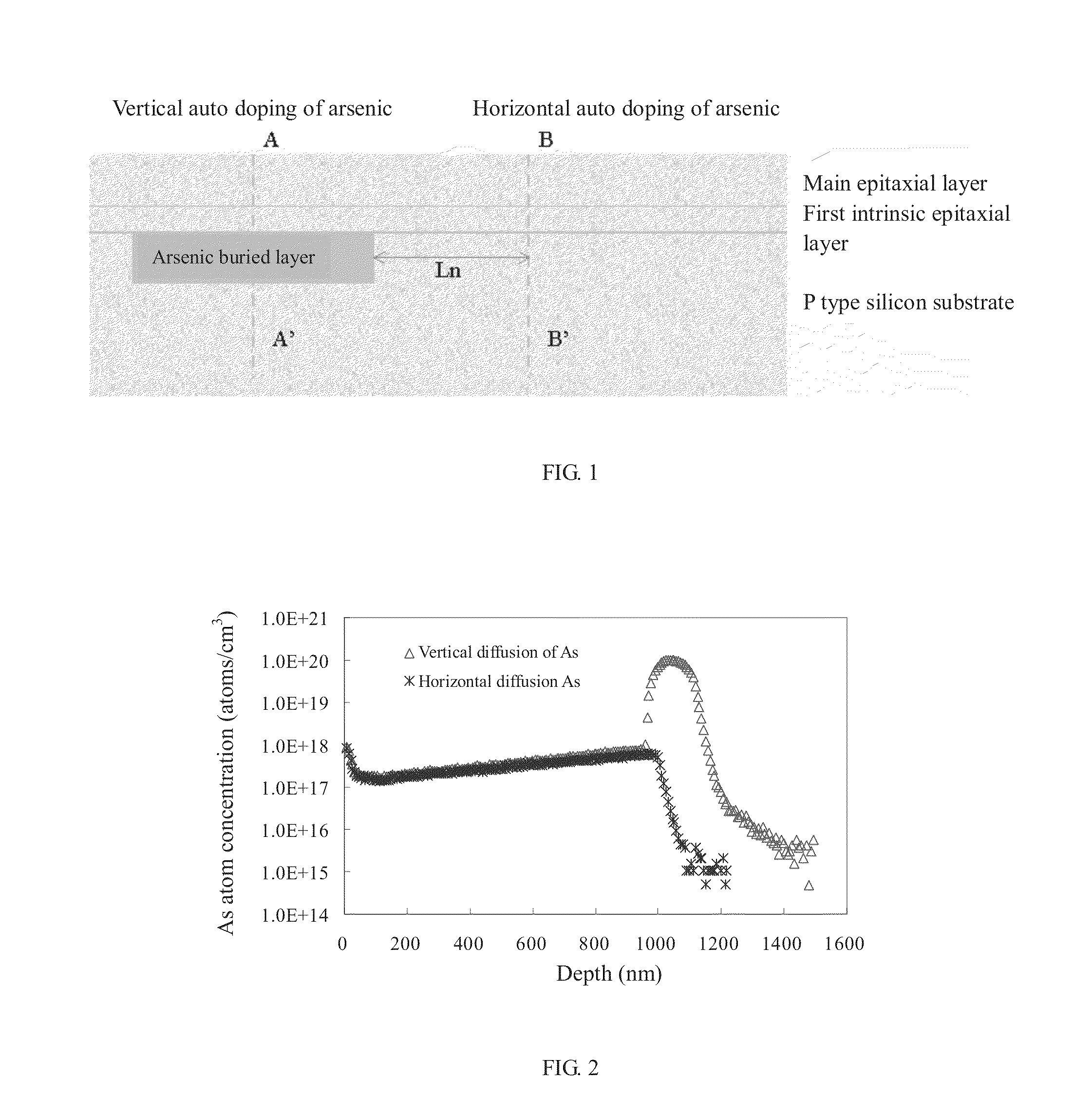

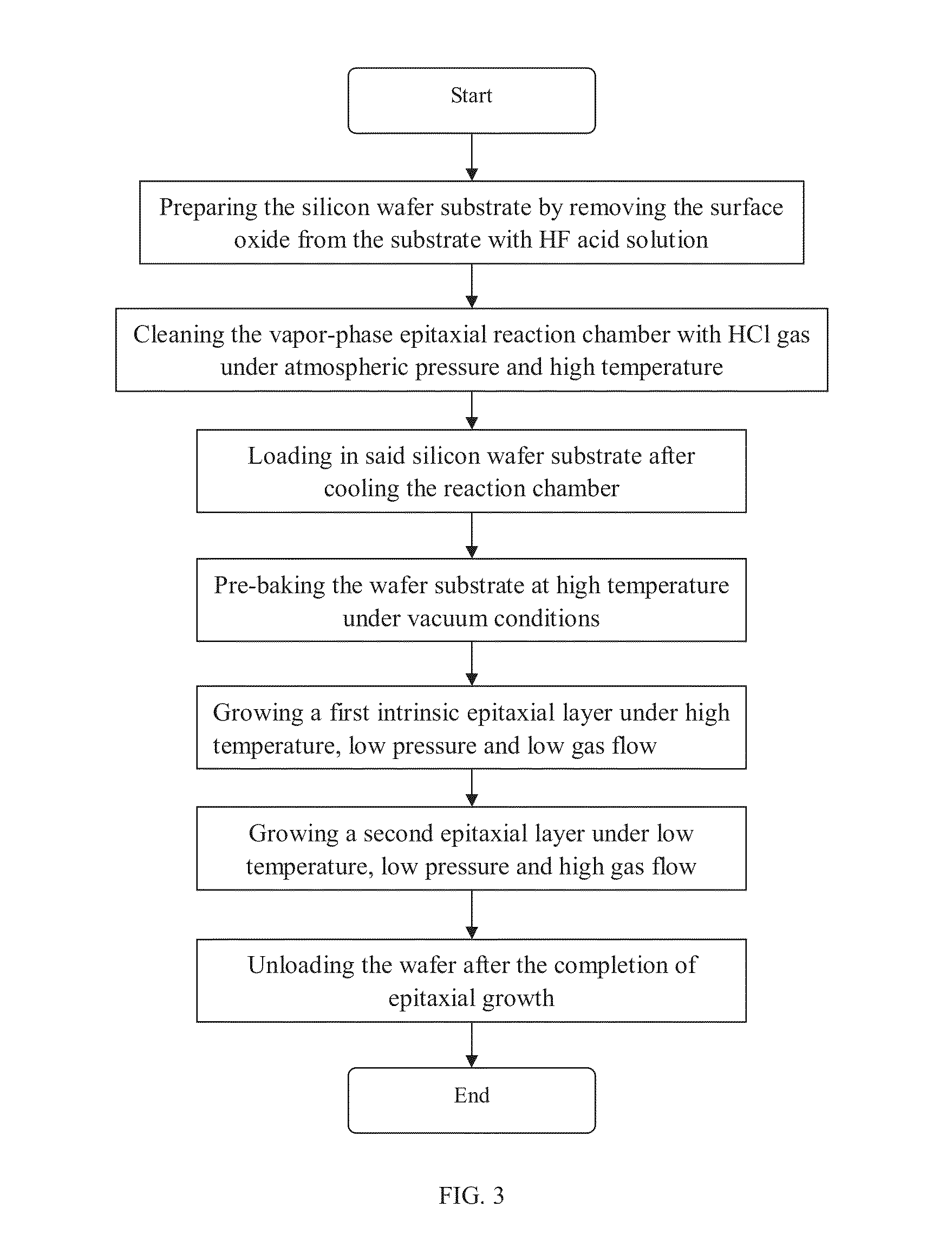

Method of epitaxial growth effectively preventing auto-doping effect

ActiveUS20130145984A1Improve equipment reliabilityInhibited DiffusionPolycrystalline material growthSemiconductor/solid-state device manufacturingDopantMoisture

This invention relates to a method of epitaxial growth effectively preventing auto-doping effect. This method starts with the removal of impurities from the semiconductor substrate having heavily-doped buried layer region and from the inner wall of reaction chamber to be used. Then the semiconductor substrate is loaded in the cleaned reaction chamber to be pre-baked under vacuum conditions so as to remove moisture and oxide from the surface of said semiconductor substrate before the extraction of the dopant atoms desorbed from the surface of the semiconductor substrate. Next, under high temperature and low gas flow conditions, a first intrinsic epitaxial layer is formed on the surface of said semiconductor substrate where the dopant atoms have been extracted out. Following this, under low temperature and high gas flow conditions, a second epitaxial layer of required thickness is formed on the structural surface of the grown intrinsic epitaxial layer. Last, silicon wafer is unloaded after cooling. This method can prevent auto-doping effect during the epitaxial growth on semiconductor substrate and thus ensure the performance and enhance the reliability of the devices in peripheral circuit region.

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI

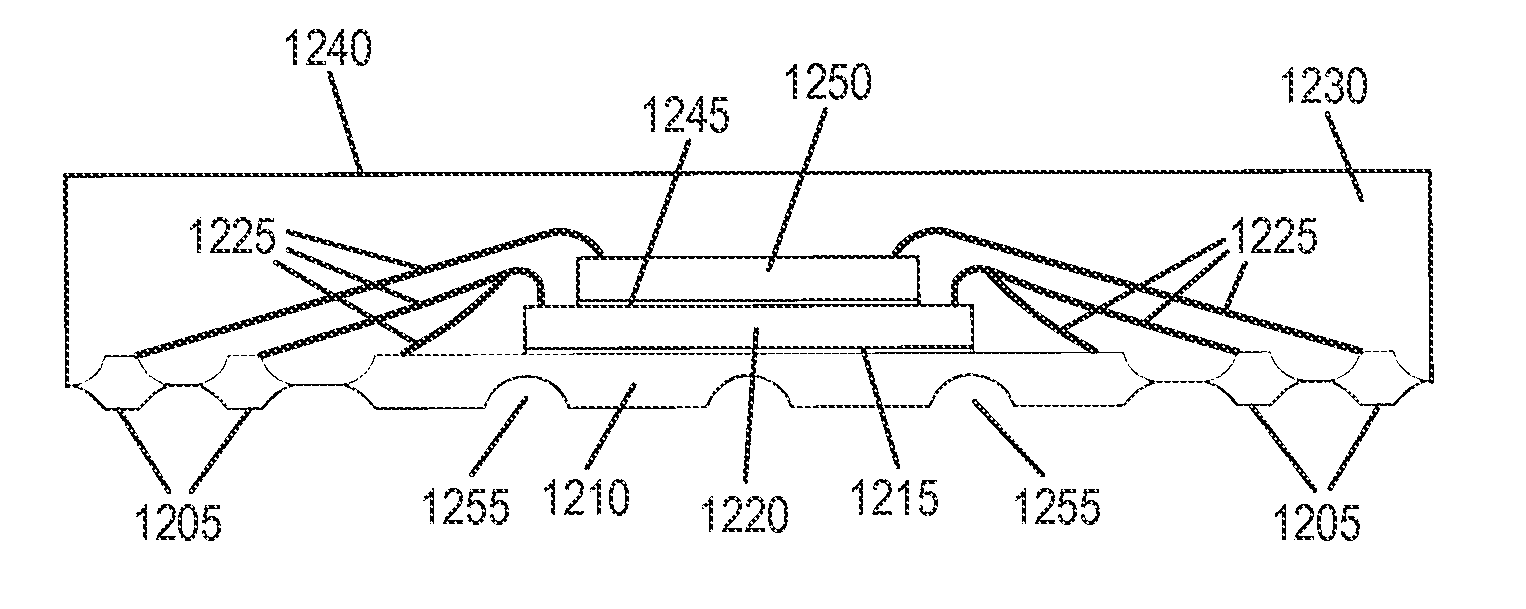

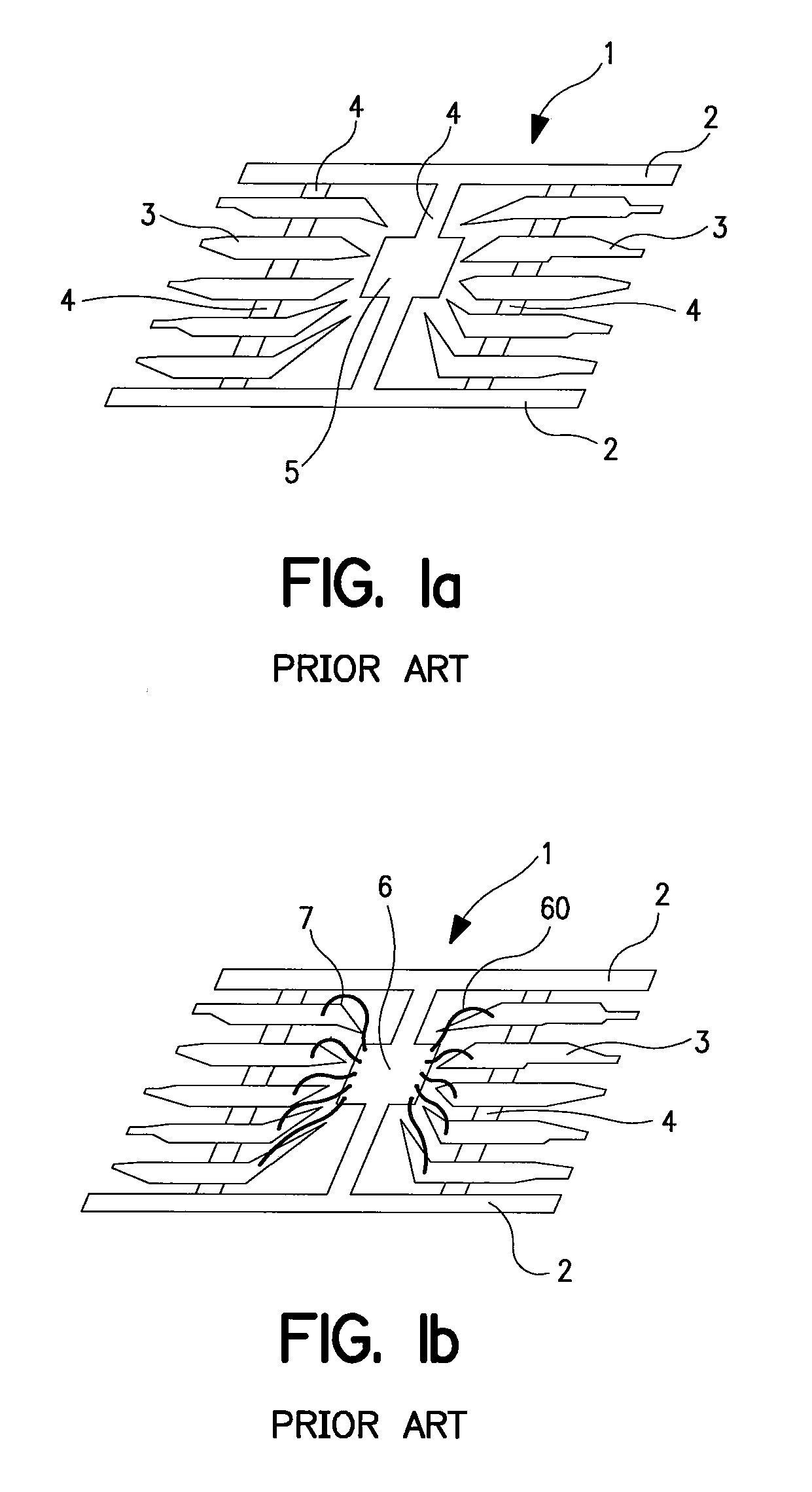

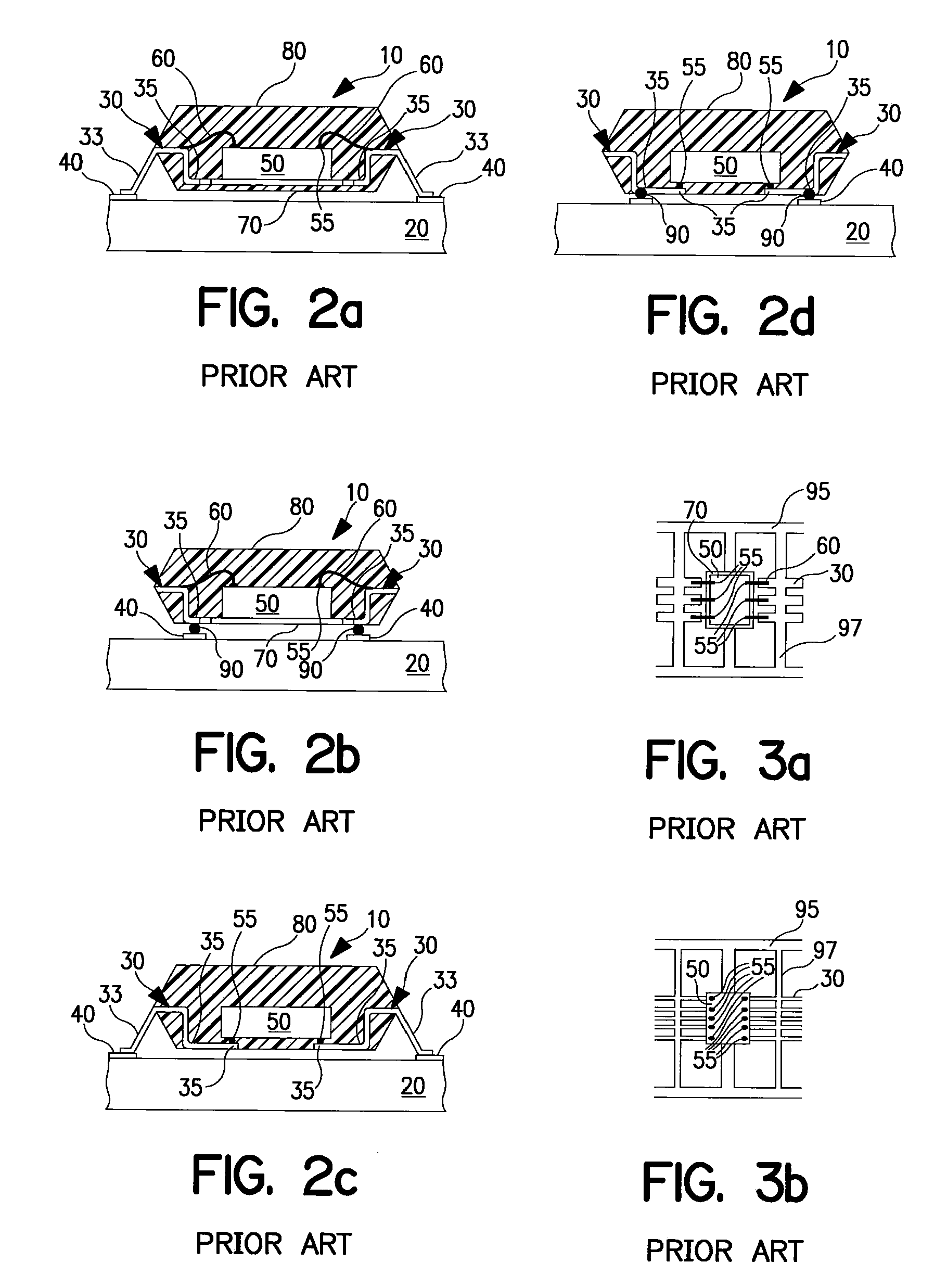

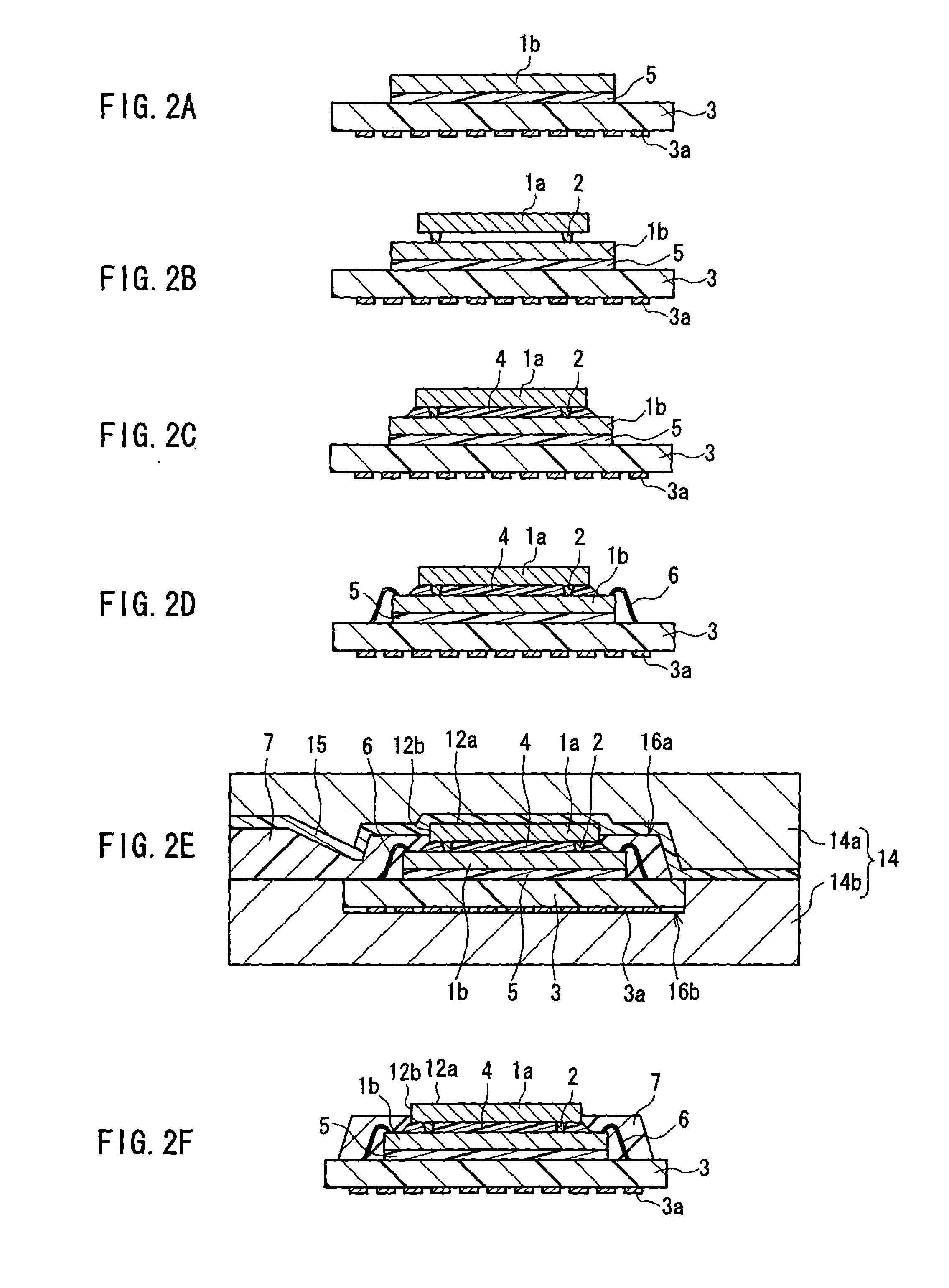

Partially patterned lead frames and methods of making and using the same in semiconductor packaging

InactiveUS20080258278A1Reduce thicknessImprove structural rigiditySemiconductor/solid-state device detailsSolid-state devicesLead bondingBonding process

A method of making a lead frame and a partially patterned lead frame package with near-chip scale packaging lead-count, wherein the method lends itself to better automation of the manufacturing line and improved quality and reliability of the packages produced therefrom. A major portion of the manufacturing process steps is performed with a partially patterned strip of metal formed into a web-like lead frame on one side so that the web-like lead frame is also rigid mechanically and robust thermally to perform without distortion or deformation during the chip-attach and wire bond processes, both at the chip level and the package level. The bottom side of the metal lead frame is patterned to isolate the chip-pad and the wire bond contacts only after the front side, including the chip and wires, is hermetically sealed with an encapsulant. The resultant package being electrically isolated enables strip testing and reliable singulation.

Owner:UNISEM M BERHAD

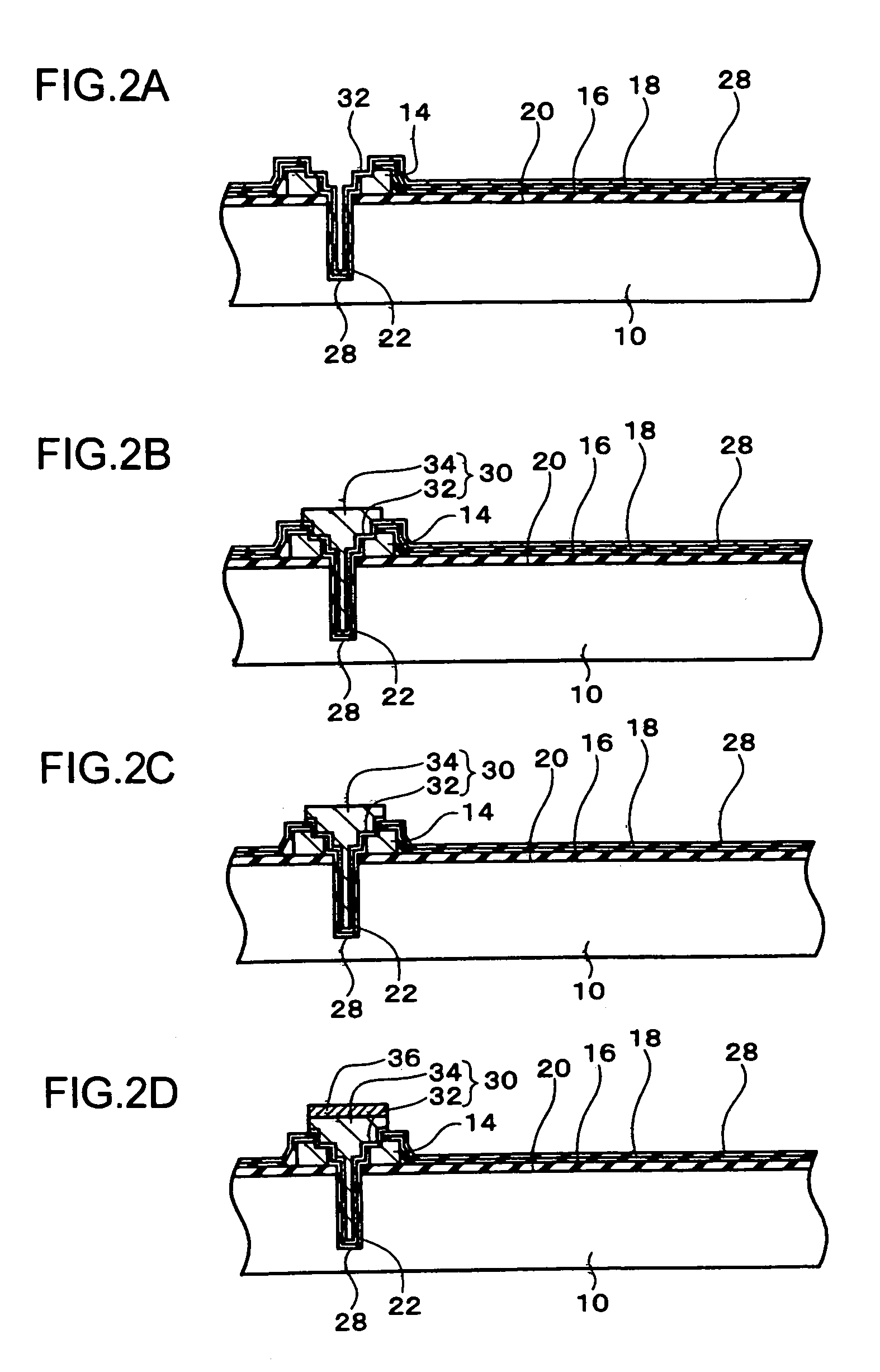

Semiconductor device and manufacturing method therefor, circuit substrate, and electronic apparatus

InactiveUS20020151171A1Stress smoothWeaken energySemiconductor/solid-state device detailsSolid-state devicesDevice materialElectrical connection

A semiconductor device and a manufacturing method therefor, a circuit substrate, and electronic apparatus are provided, in which electrical connection can be performed with high reliability and with ease. The manufacturing method for a semiconductor device includes the steps of forming a penetration hole 50 in a semiconductor chip 10 having an electrode 14, and forming a conductive layer 70 in the region including the inside of the penetration hole 50. Regarding the penetration hole 50, an intermediate portion is formed to be larger than an open end portion, and the conductive layer 70 is formed by applying a coating of a liquid containing metal fine particles by an ink-jet method.

Owner:SAMSUNG ELECTRONICS CO LTD

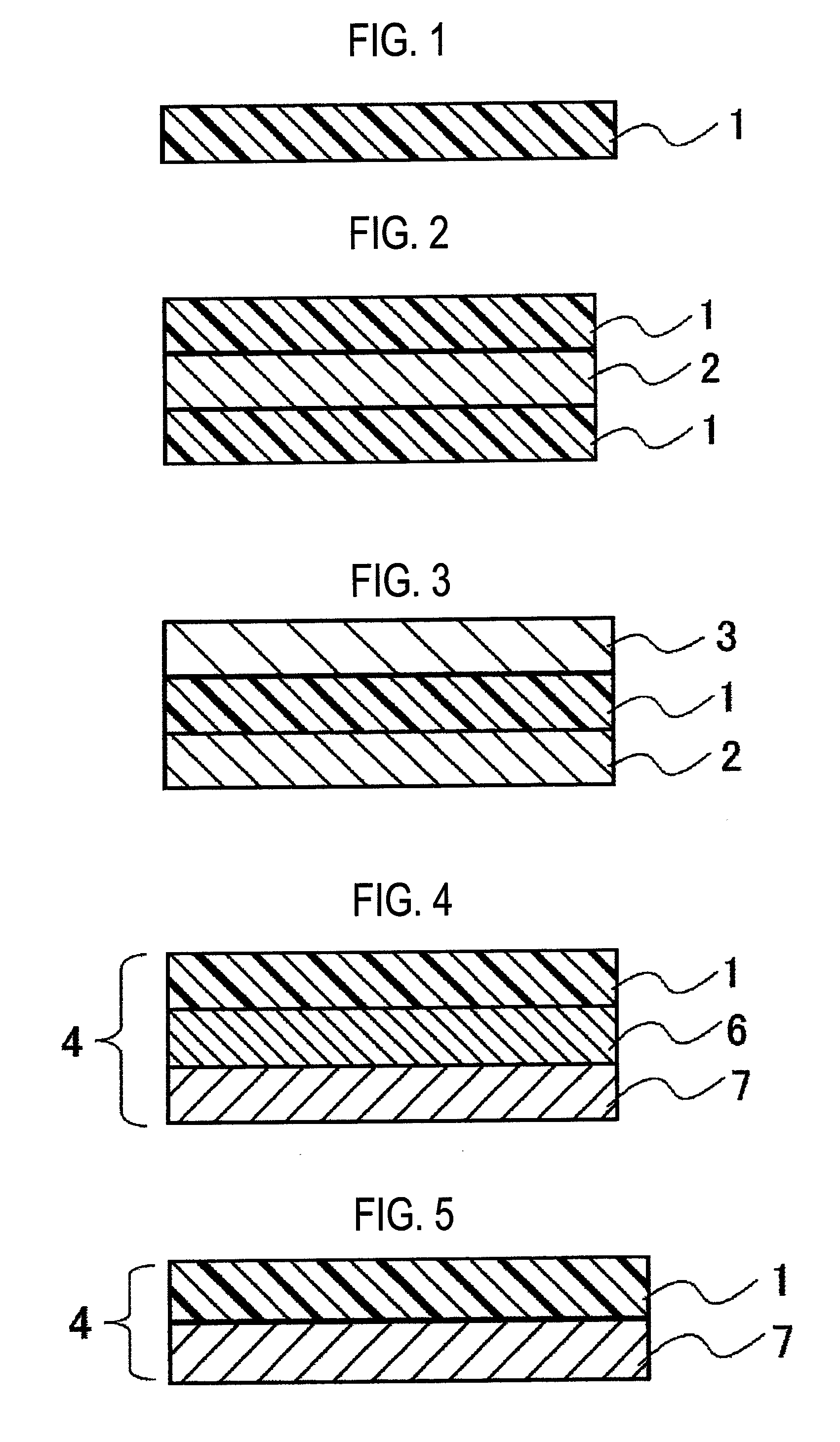

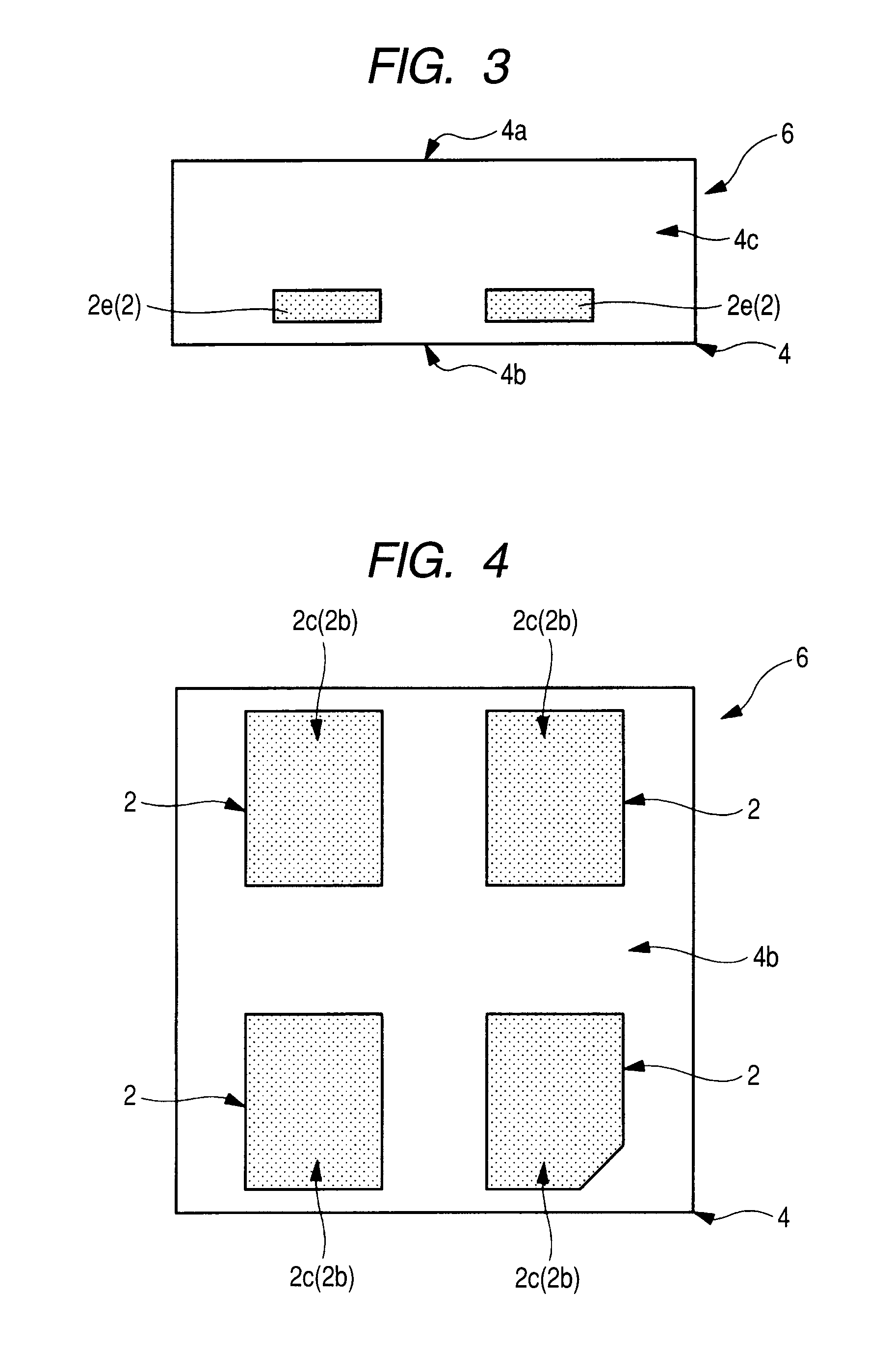

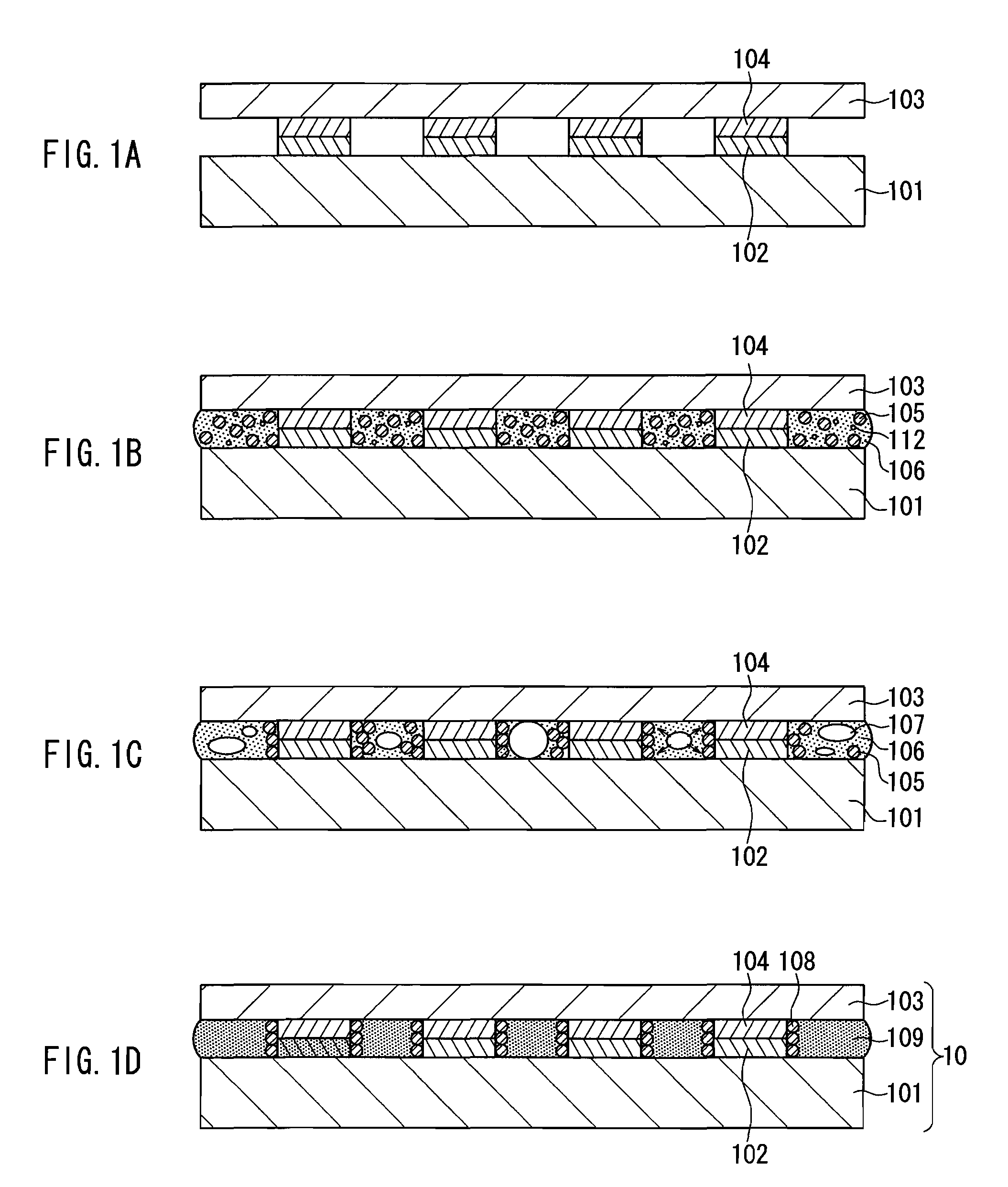

Substrate, manufacturing method of substrate, semiconductor element, and manufacturing method of semiconductor element

A semiconductor device is provided which is produced from a high-quality and large-area graphene substrate and is capable of fully exhibiting superior electronic properties that graphene inherently has. The semiconductor device is capable of realizing increased operation speed, reduced power consumption, and higher degree of integration, and thus is capable of improving the reliability and productivity. Electrical short circuit between a graphene layer (4) and a metal catalyst layer for growth of graphene is prevented by causing the metal catalyst layer to be absorbed as a compound / alloyed layer 5 at the interface between a substrate (1) and an oxide layer (2).

Owner:NEC CORP

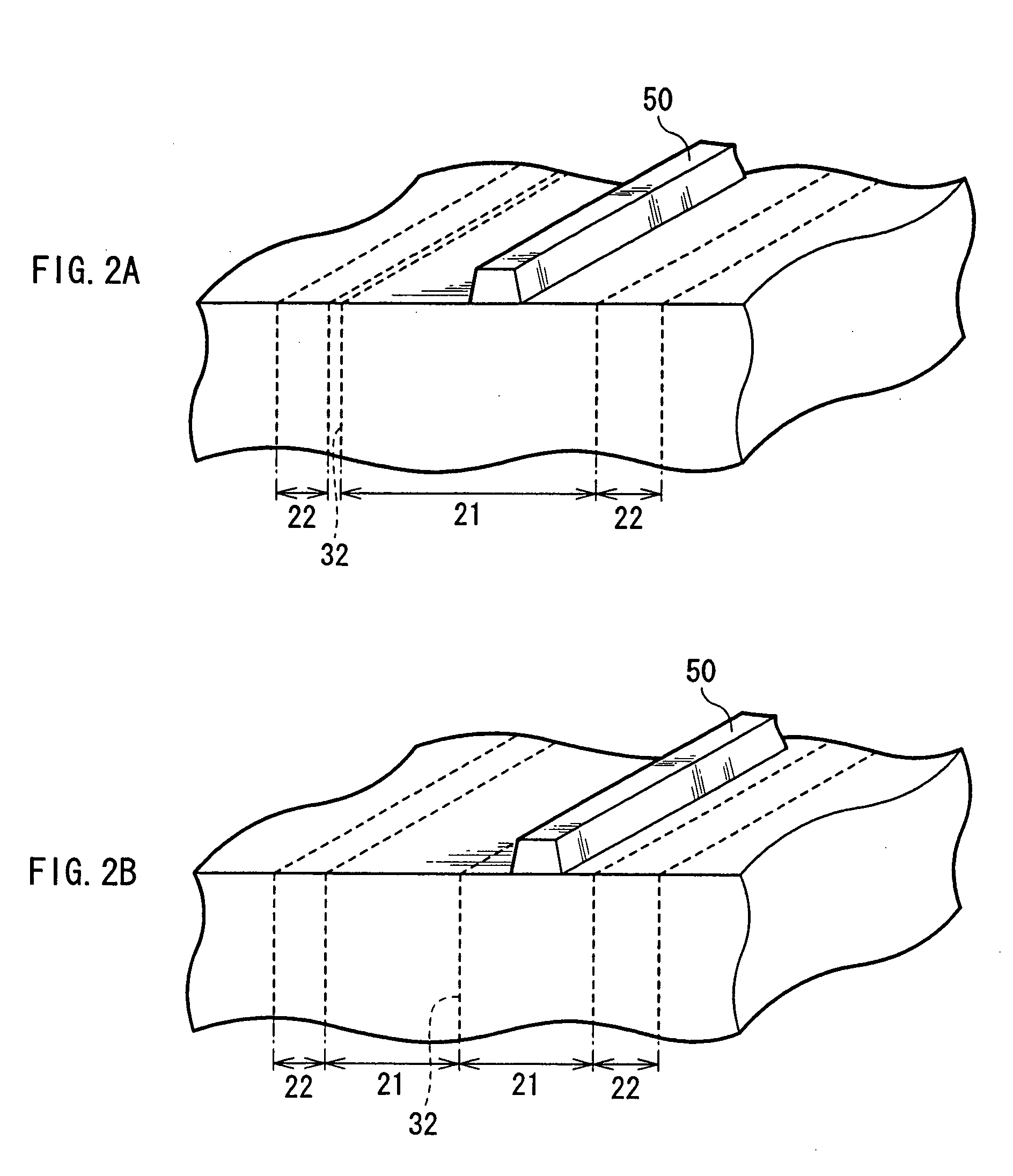

Nitride semiconductor device and method of manufacturing the same

InactiveUS20050184302A1Increase widthIncrease horizontal widthPolycrystalline material growthOrganic electrolyte cellsCrystallographyLateral overgrowth

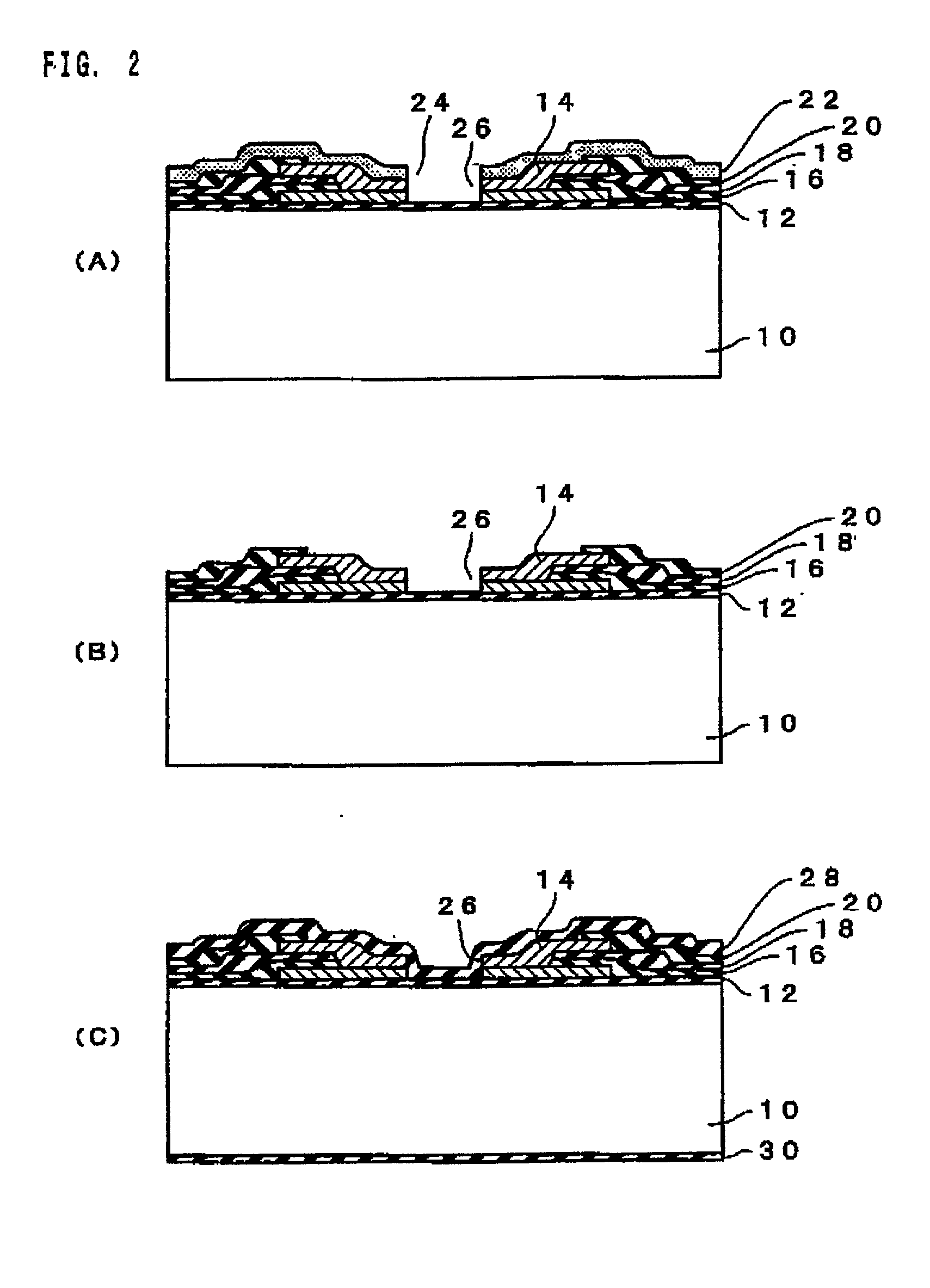

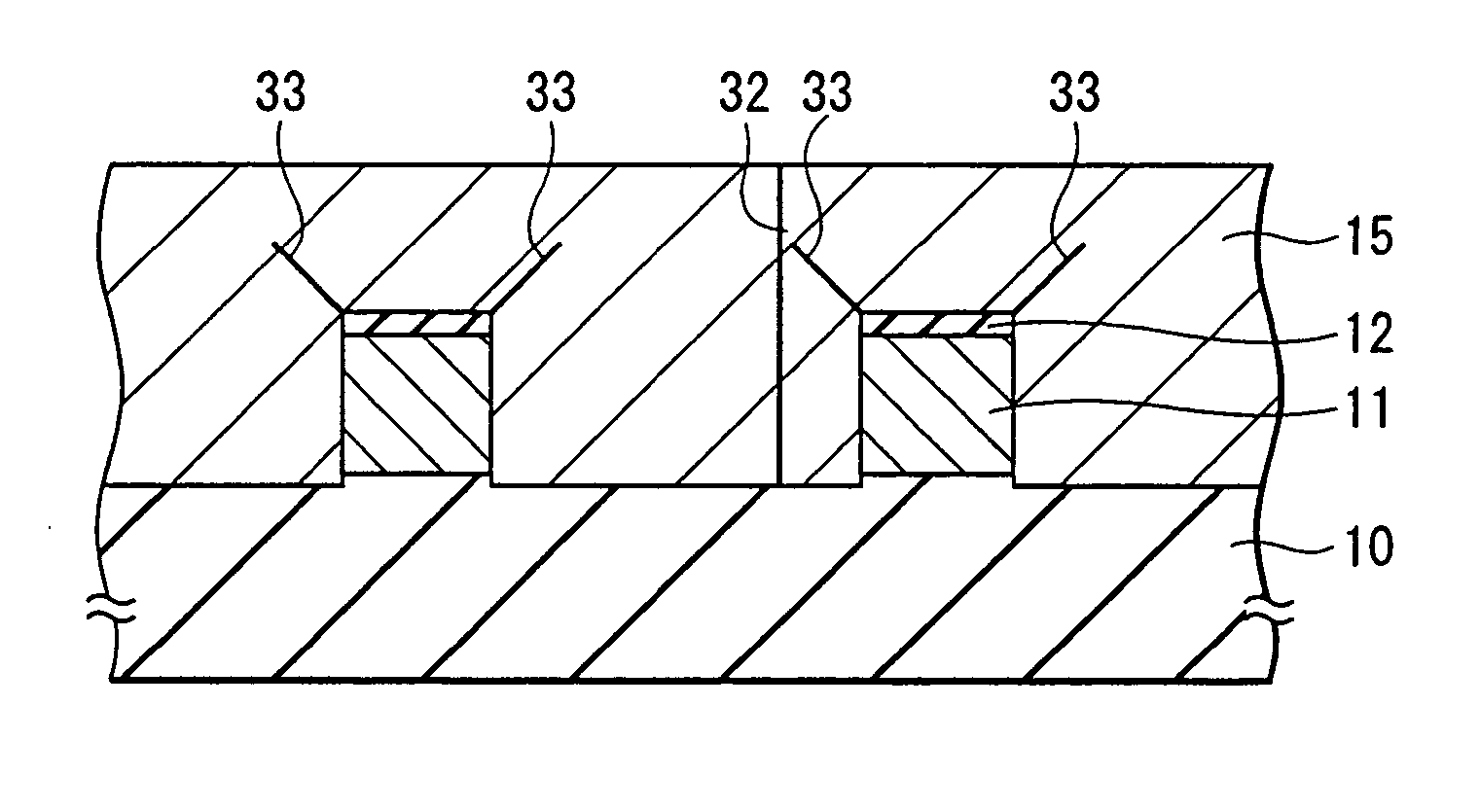

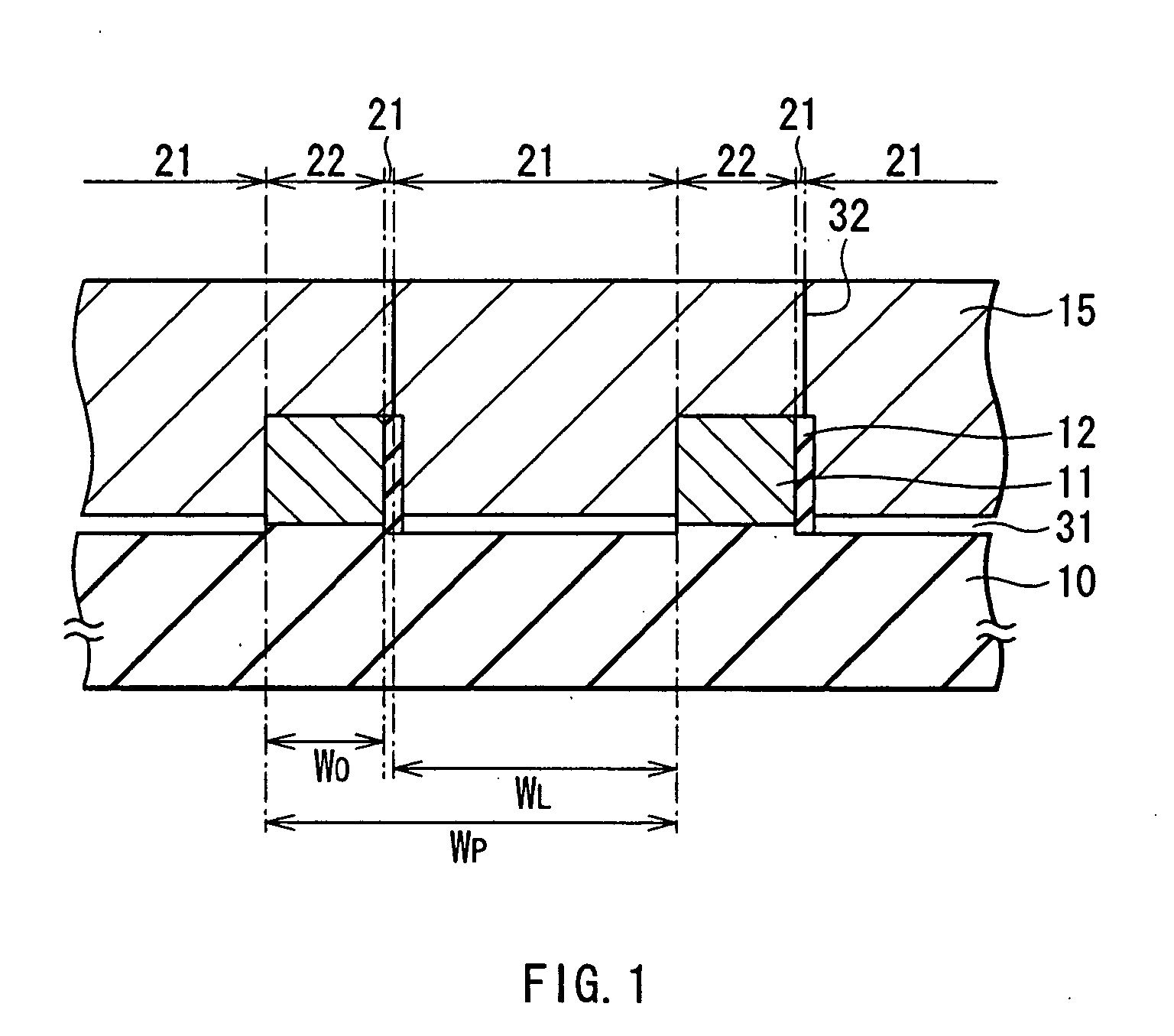

Provided is a nitride semiconductor device with high reliability and high flexibility in design and manufacture of the device. The nitride semiconductor device comprises a seed crystal portion (11) formed on a sapphire substrate (10) and having a mask (12) on one side surface thereof, and a GaN layer (15) grown on the sapphire substrate (10) and the seed crystal portion (11) through epitaxial lateral overgrowth. The GaN layer (15) is grown only from an exposed side surface of the seed crystal portion (11) which is not covered with the mask (12), so the lateral growth of the GaN layer (15) is asymmetrically carried out. Thereby, a meeting portion (32) is formed in the vicinity of a boundary between the seed crystal portion (11) and the mask (12) in a thickness direction of the GaN layer (15). Therefore, as the meeting portion (32) is formed in a position away from the center between the adjacent seed crystal portions (11) in a direction parallel to a surface of the substrate, a width WL of a lateral growth region is larger with respect to a pitch WP of the seed crystal potion (11), compared with conventional configurations.

Owner:KOBAYASHI TOSHIMASA +3

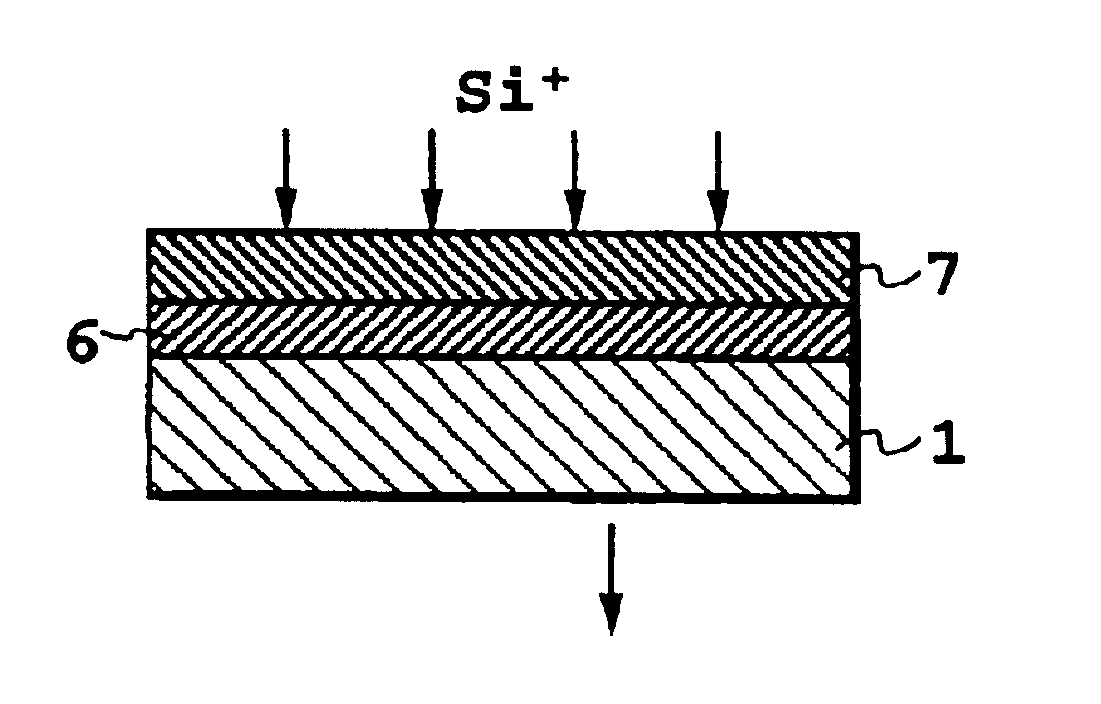

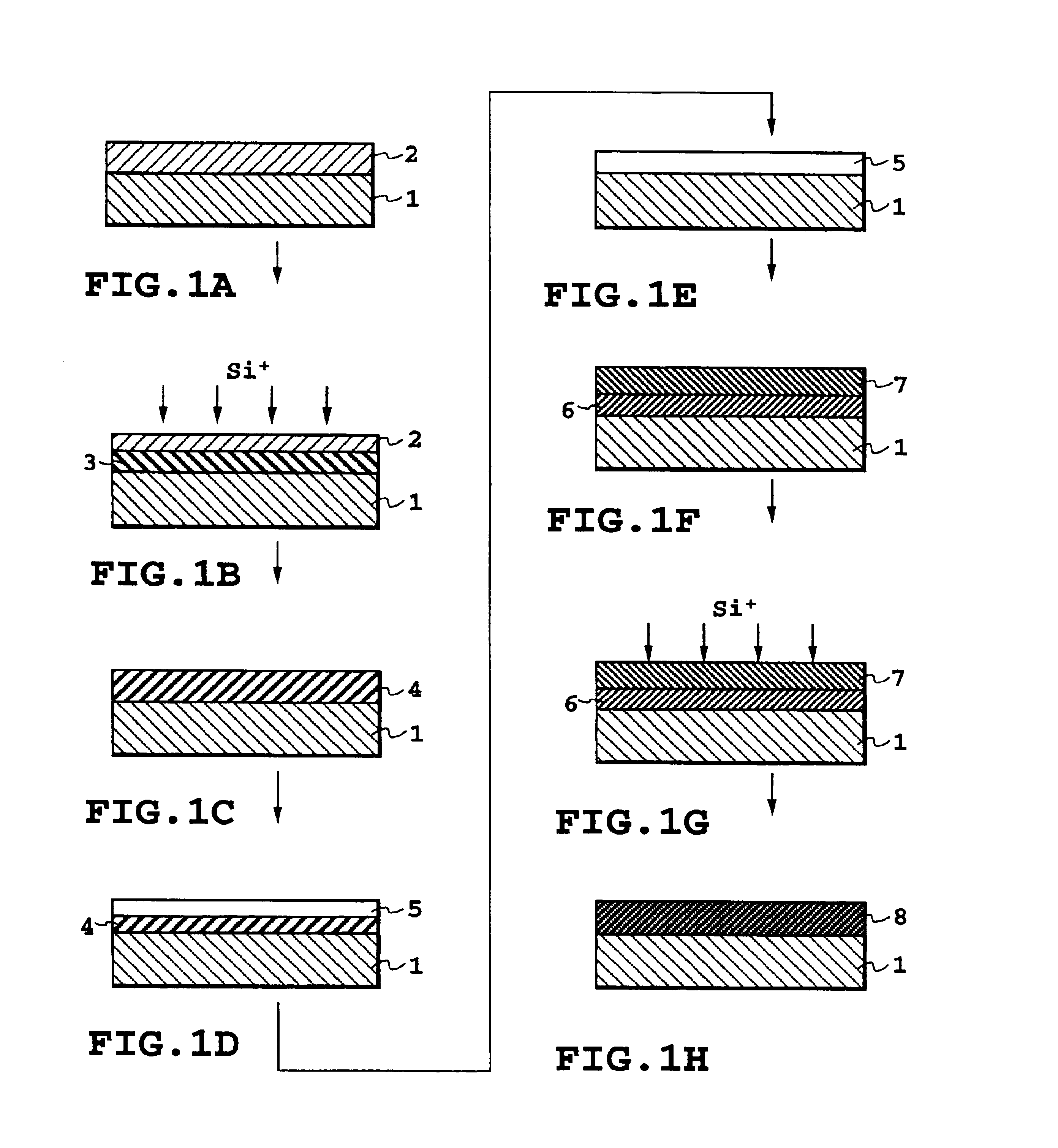

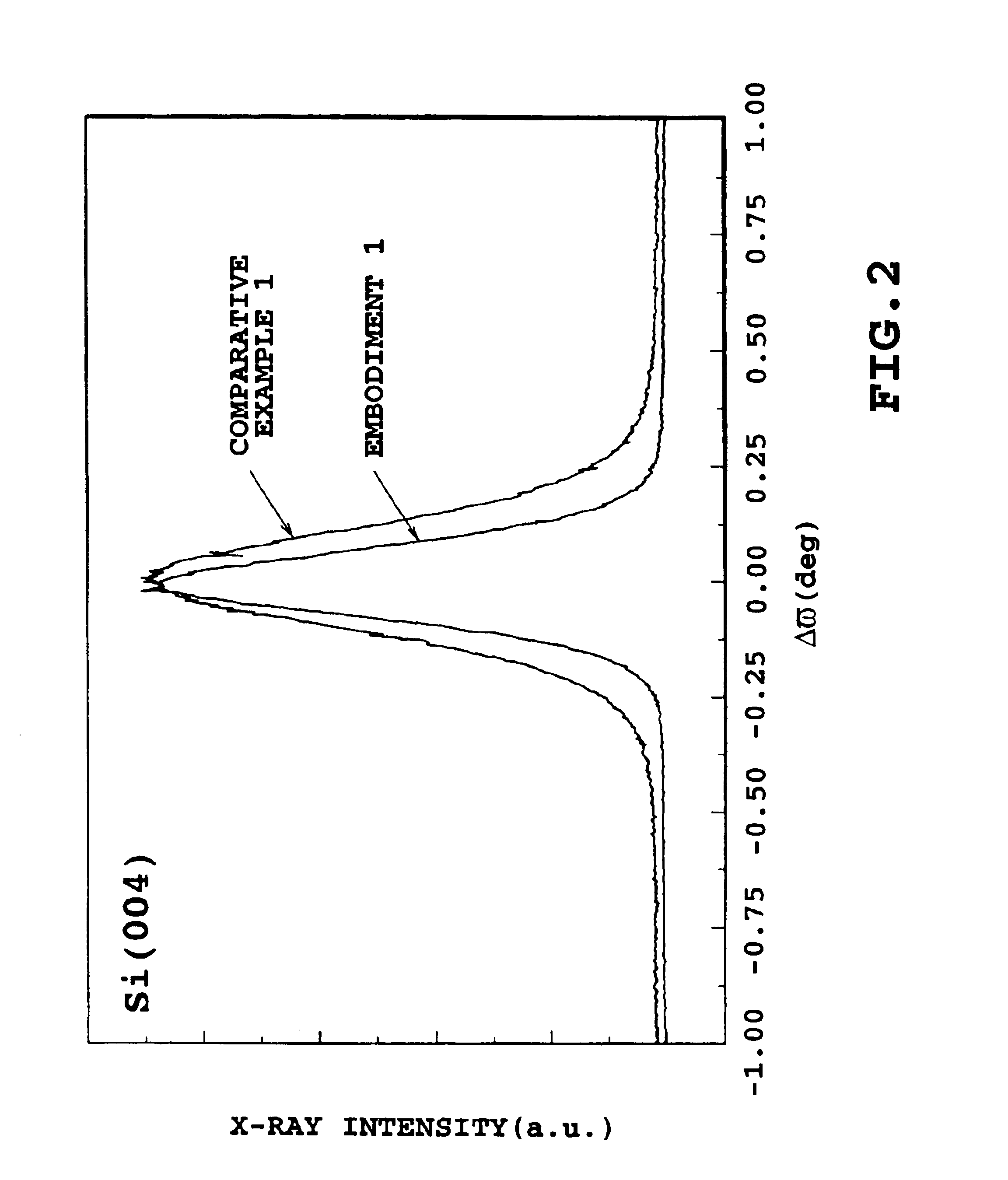

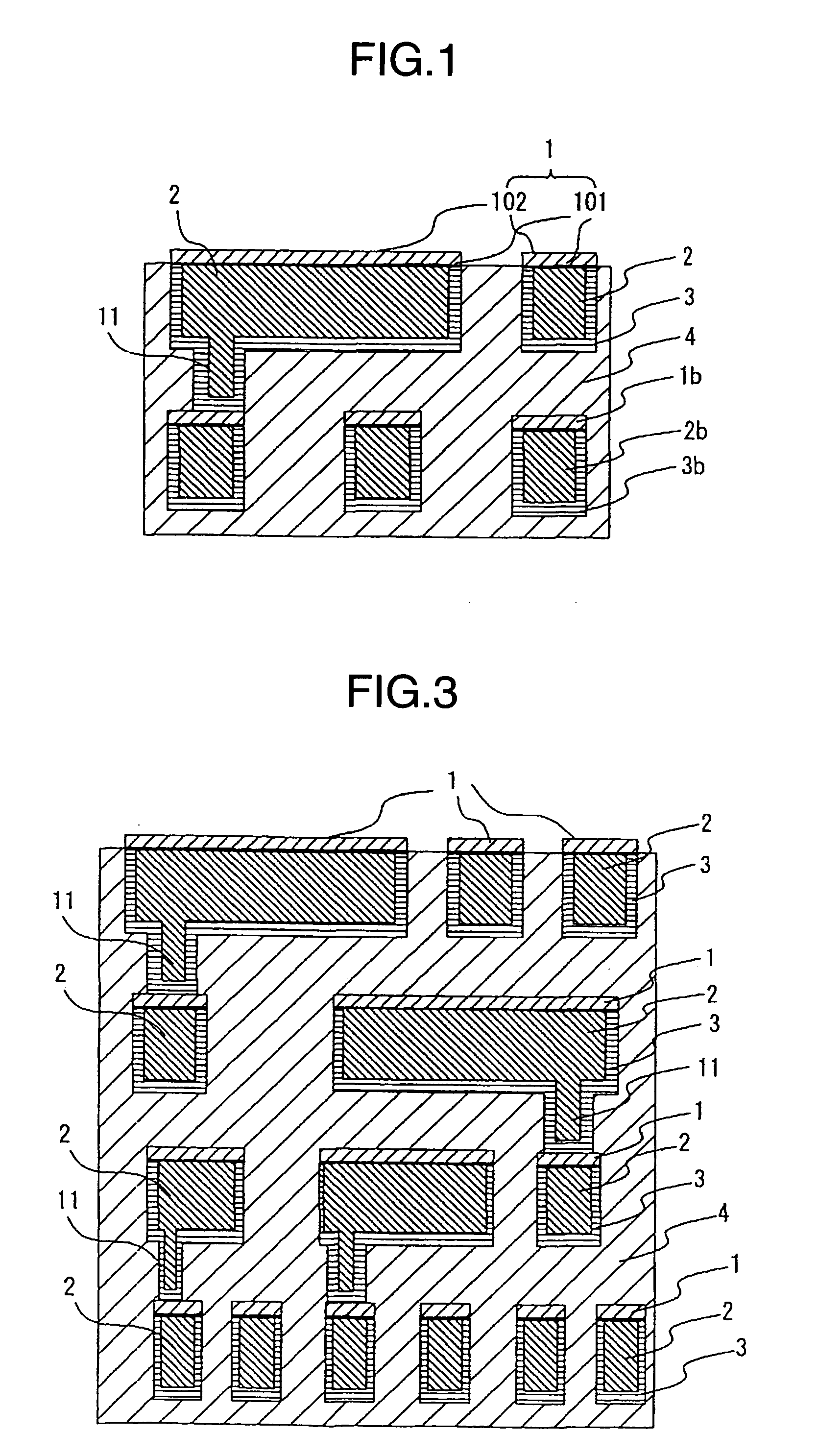

Semiconductor substrate and its production method, semiconductor device comprising the same and its production method

InactiveUS6768175B1High crystallinityFew defectSemiconductor/solid-state device testing/measurementSolid-state devicesSilicon oxideSoi substrate

When a SOI substrate is produced a first silicon layer epitaxially grown on the insulating underlay is ion implanted to make deep part of interface of the silicon layer amorphous, and then annealed to recrystallize. Next, the silicon layer is heat treated to oxidize part of the surface side, and after the silicon oxide is removed by etching, a silicon layer is epitaxially grown on the remaining first silicon layer to form a second silicon layer. Subsequently, the second silicon layer is again ion implanted to make deep part of interface amorphous, then annealing is performed to recrystallize. With this method, a SOI substrate, which is very small in crystal defect density of the silicon layer and good in surface flatness, can be produced. Therefore, on the semiconductor substrate an electronic device or optical device having high device performance and reliability can be realized.

Owner:ASAHI KASEI KK

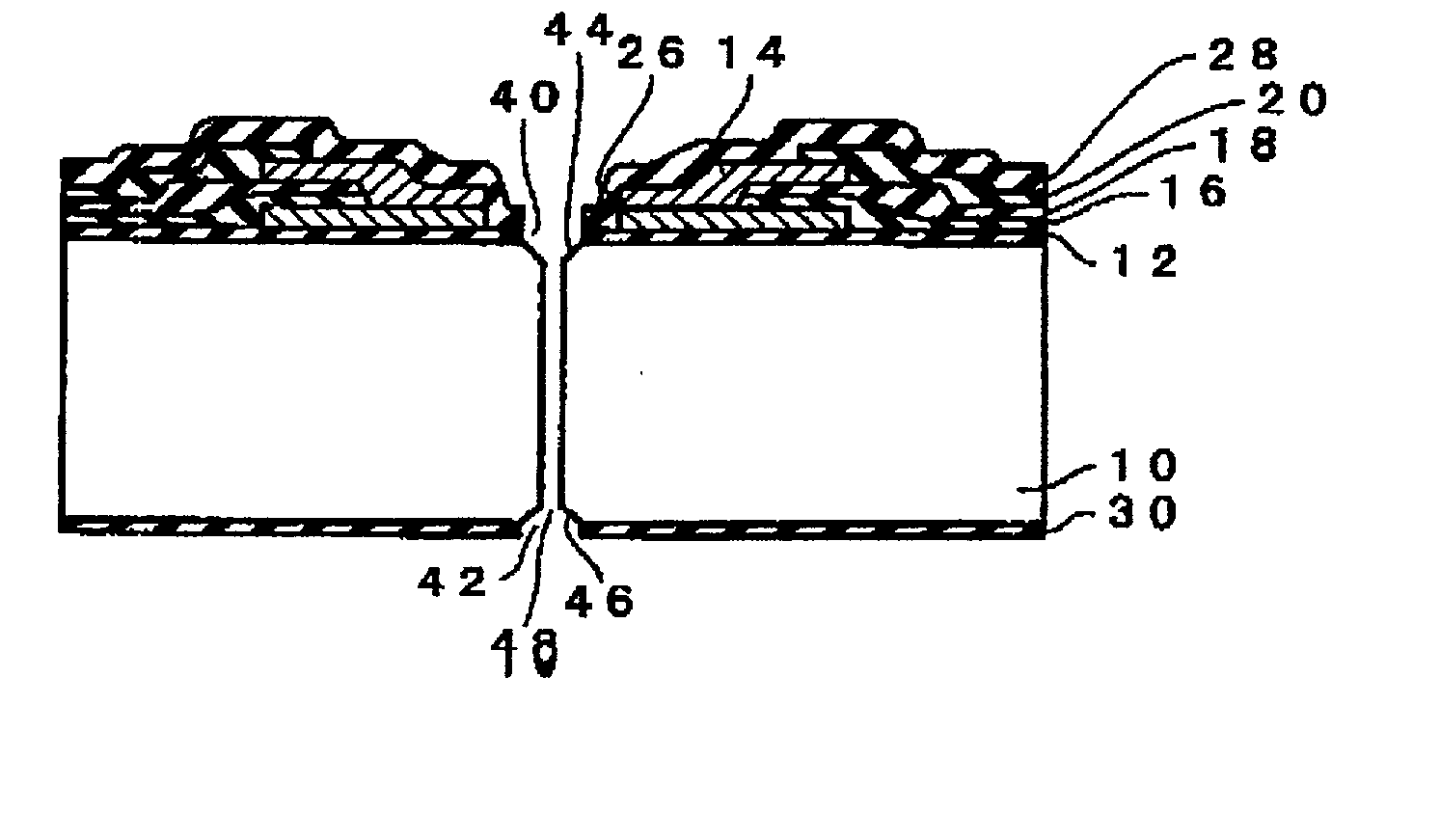

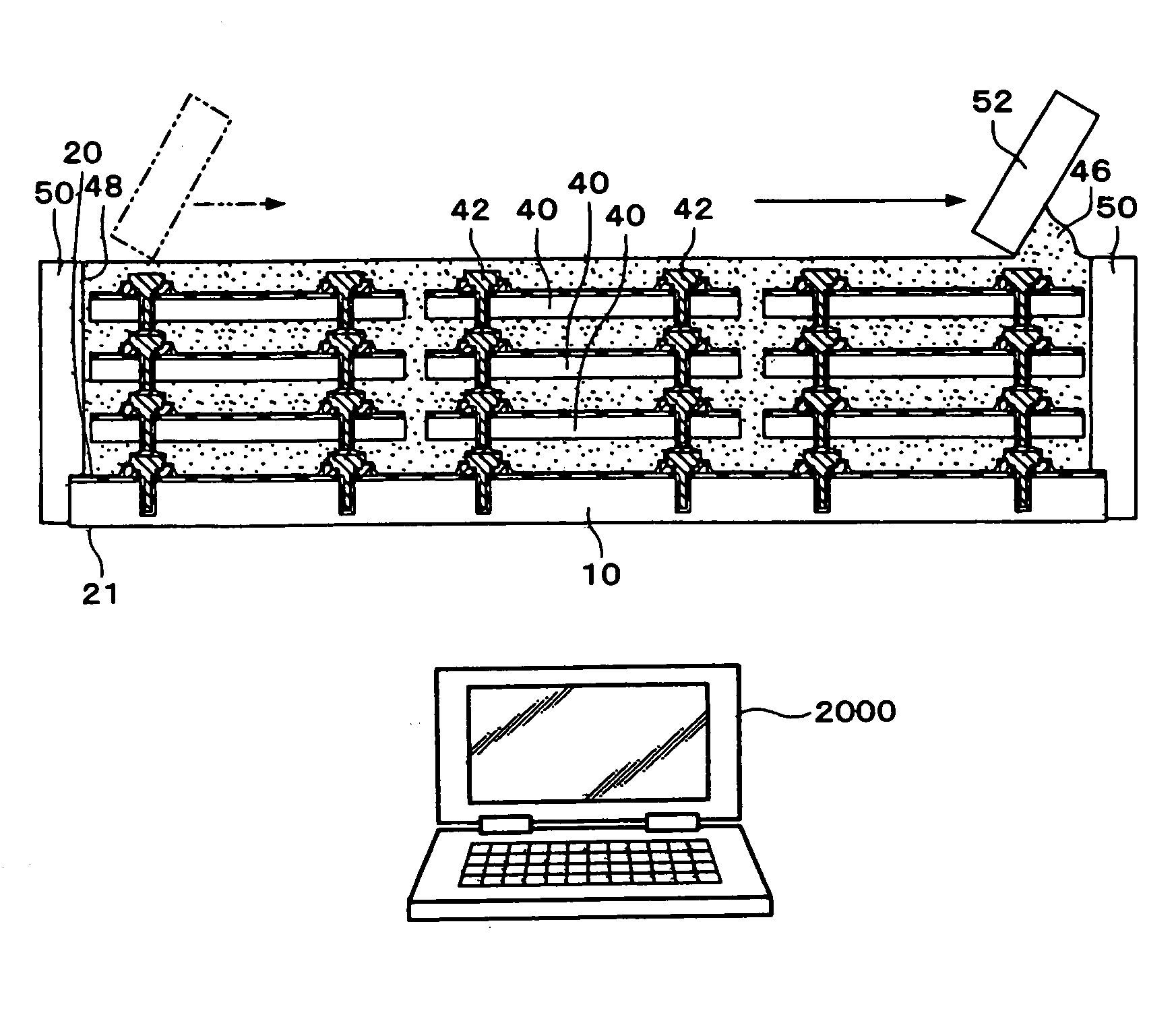

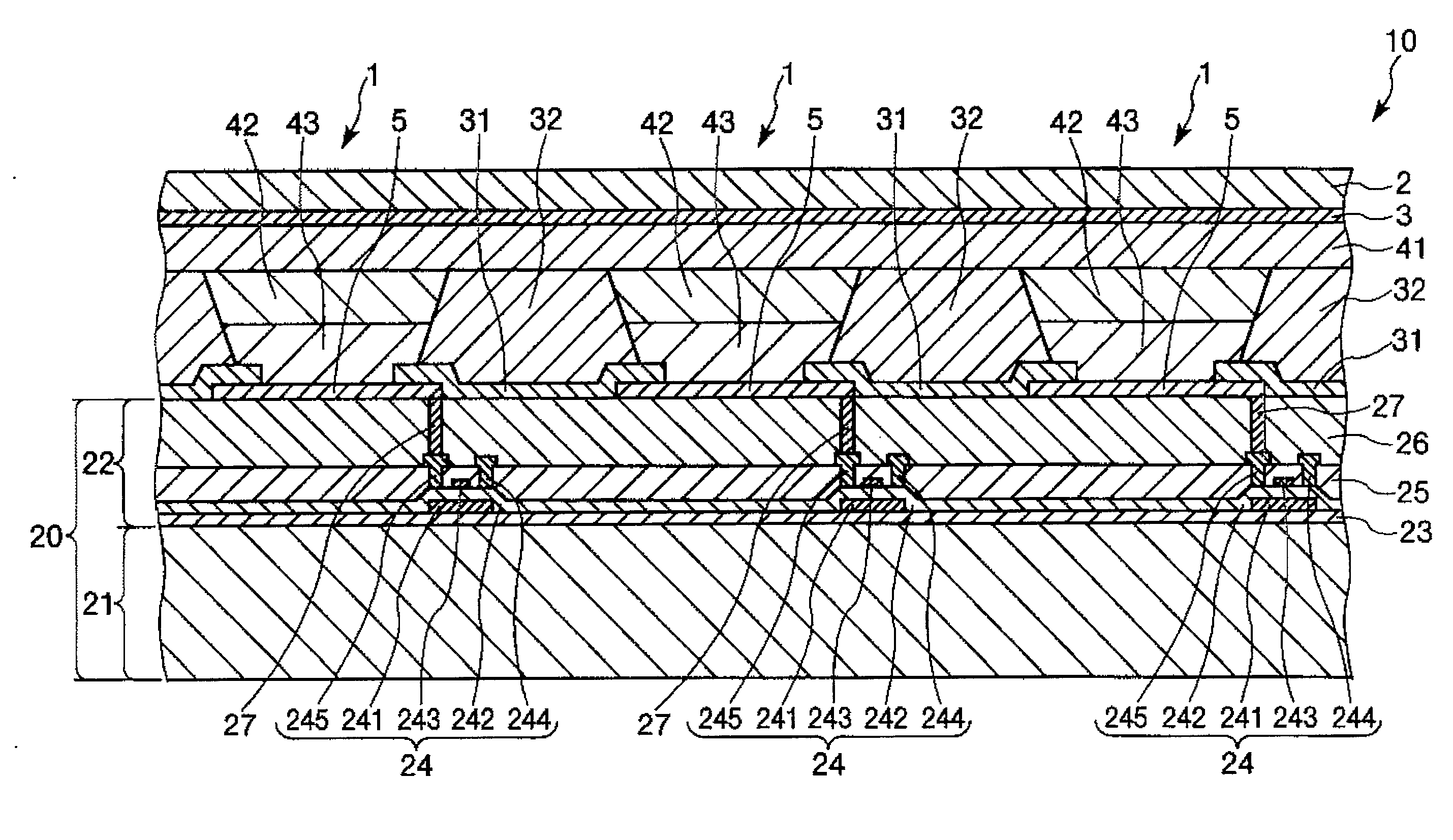

Semiconductor device, method for manufacturing the same, circuit board, and electronic apparatus

ActiveUS7223634B2Increase productivityImprove reliabilitySemiconductor/solid-state device detailsSolid-state devicesProduction rateSemiconductor chip

Exemplary embodiments of the present invention include a semiconductor device, a method for manufacturing the same, a circuit board and an electronic apparatus with increased productivity and reliability. An exemplary method for manufacturing a semiconductor device of the present invention includes forming a conductive part in a concave part on a first surface of a semiconductor substrate, the first surface having a plurality of chip mounting areas. Stacking at least one semiconductor chip in each of the chip mounting areas, providing a sealing member on the first surface of the semiconductor substrate and making part of a second surface of the semiconductor substrate thin so as to make the conductive part penetrate from the first surface to the second surface.

Owner:ADVANCED INTERCONNECT SYST LTD

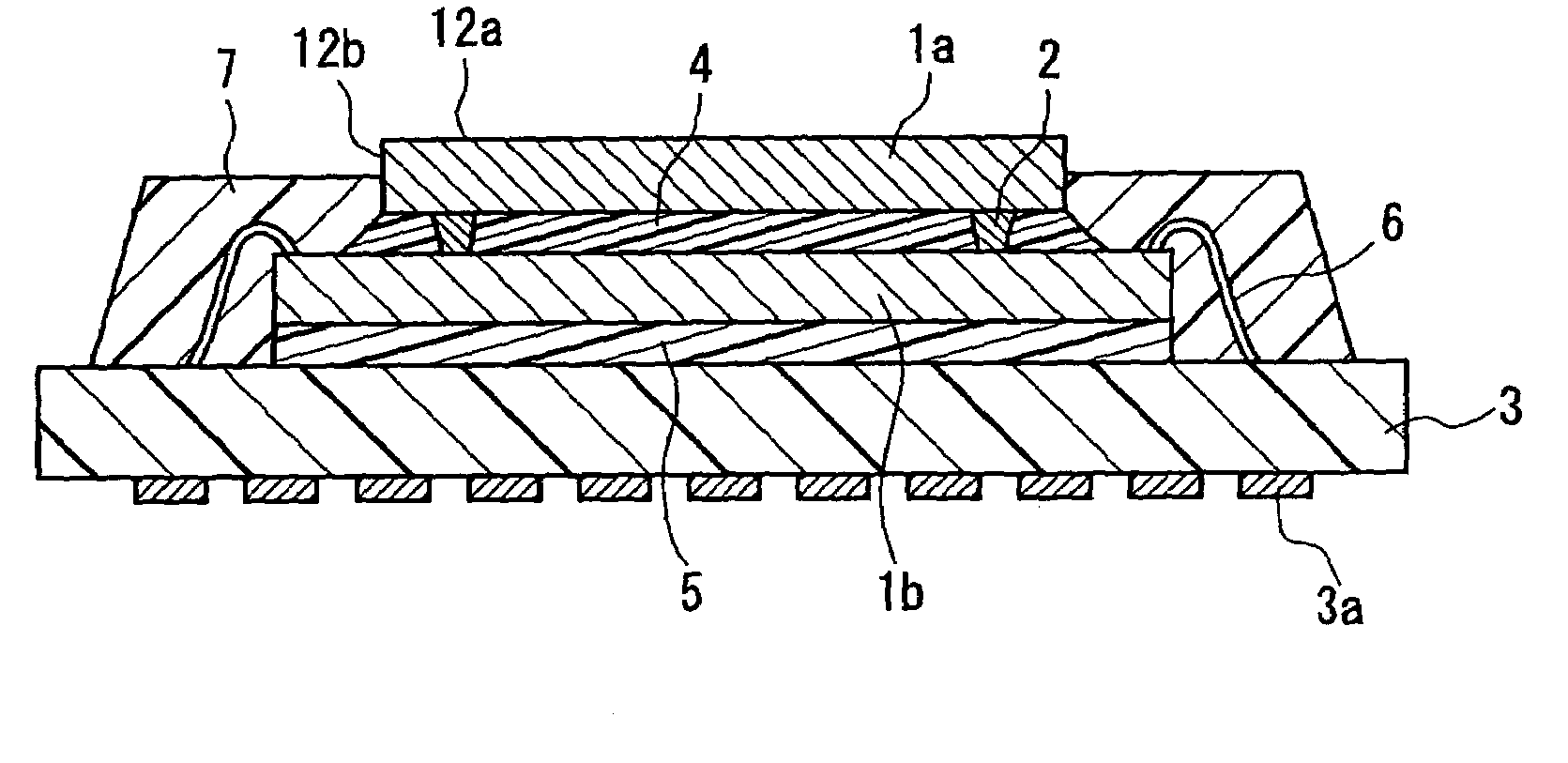

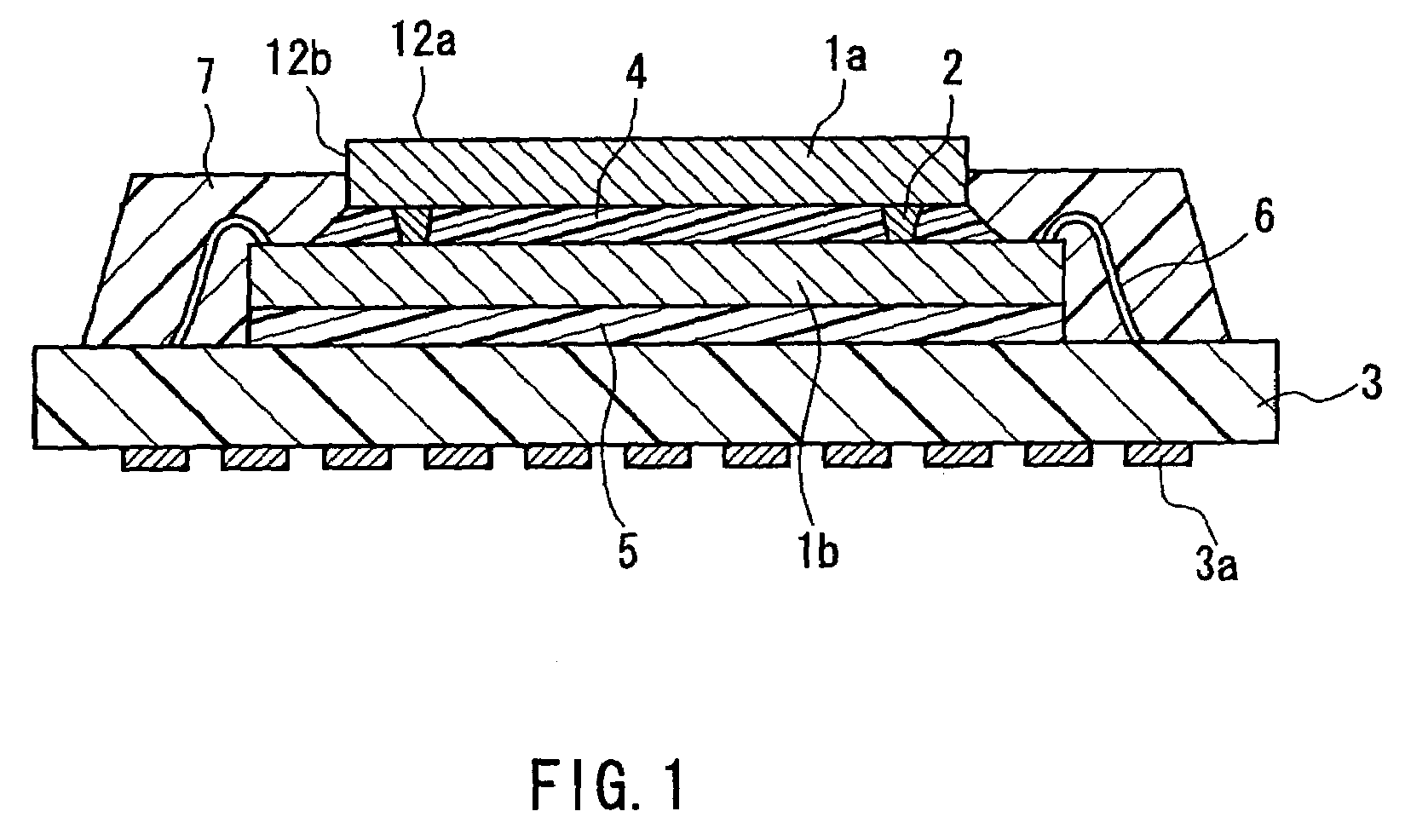

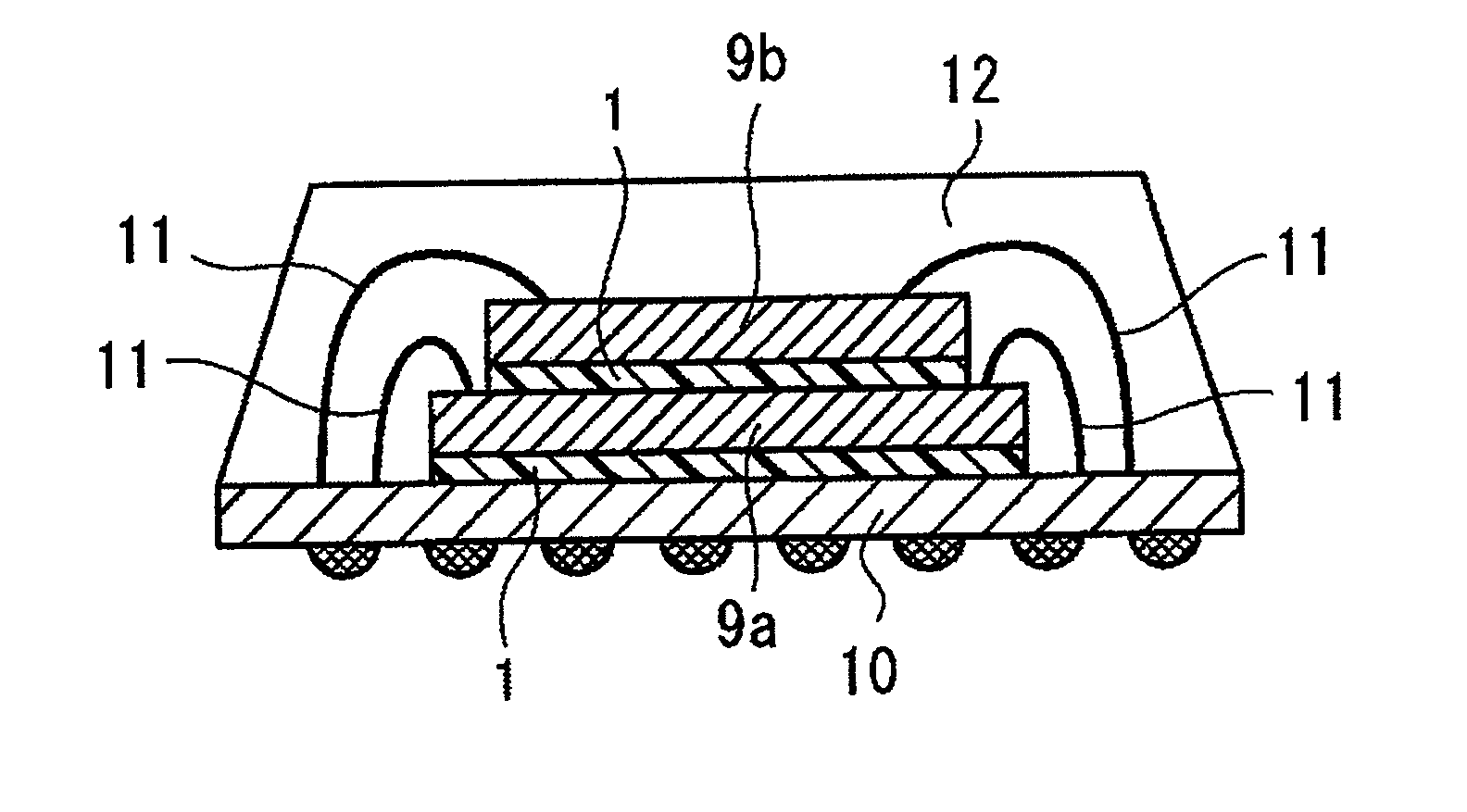

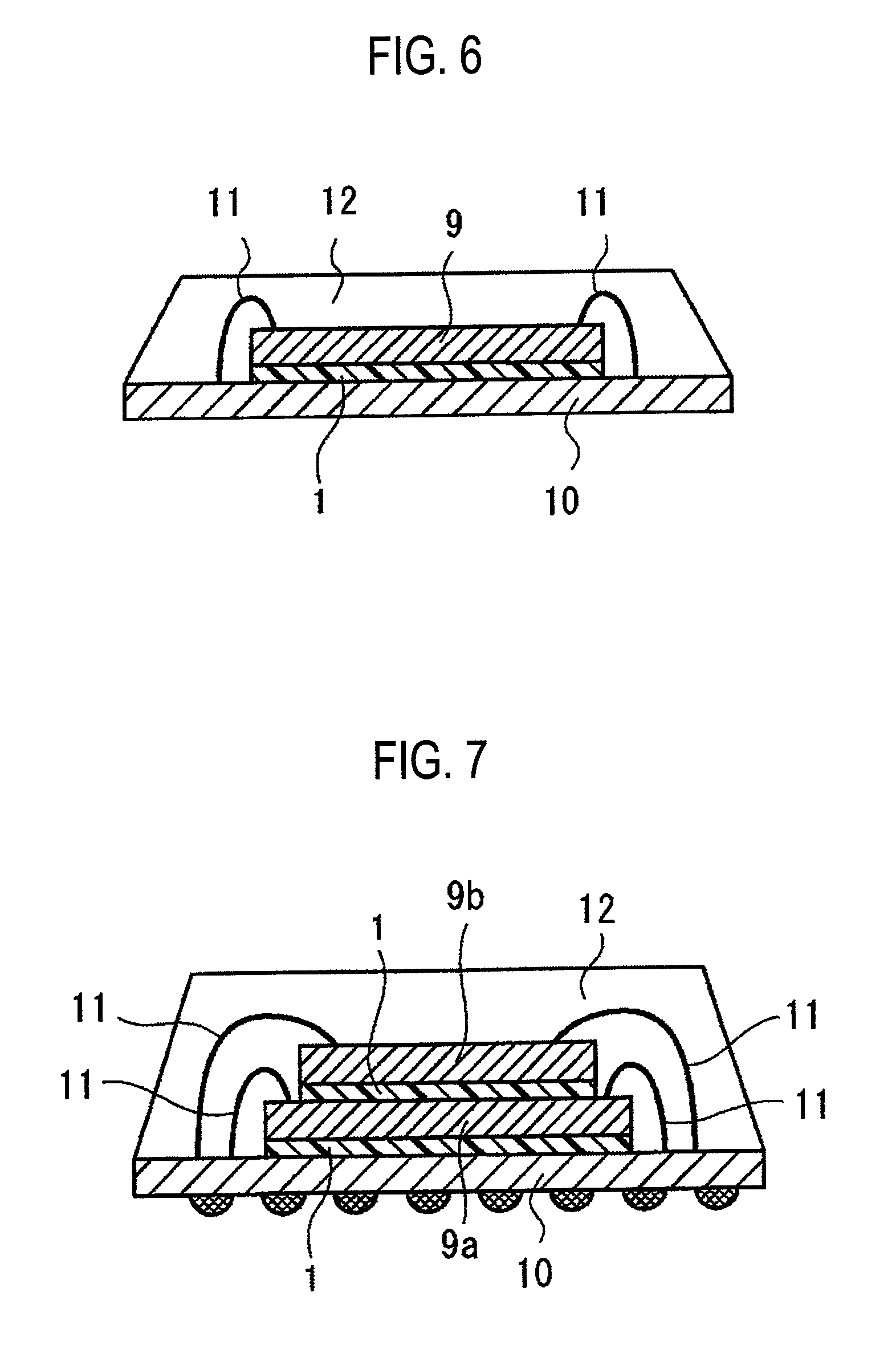

Semiconductor device and method for manufacturing the same

ActiveUS7138706B2Good heat dissipationImprove reliabilitySemiconductor/solid-state device detailsSolid-state devicesForming faceSemiconductor chip

A semiconductor device with excellent heat dissipation characteristics that can achieve a high reliability when mounted in electronic equipment such as a cellular phone or the like and a method for manufacturing the same are provided. The semiconductor device includes a substrate, a plurality of semiconductor chips mounted on the substrate by stacking one on top of another, and an encapsulation resin layer made of encapsulation resin. Among the plurality of semiconductor chips, a first semiconductor chip as an uppermost semiconductor chip is mounted with a surface thereof on which a circuit is formed facing toward the substrate, and the encapsulation resin layer is formed so that at least a surface of the first semiconductor chip opposite to the surface on which the circuit is formed and a part of side surfaces of the first semiconductor chip are exposed to the outside of the encapsulation resin layer.

Owner:TESSERA ADVANCED TECH

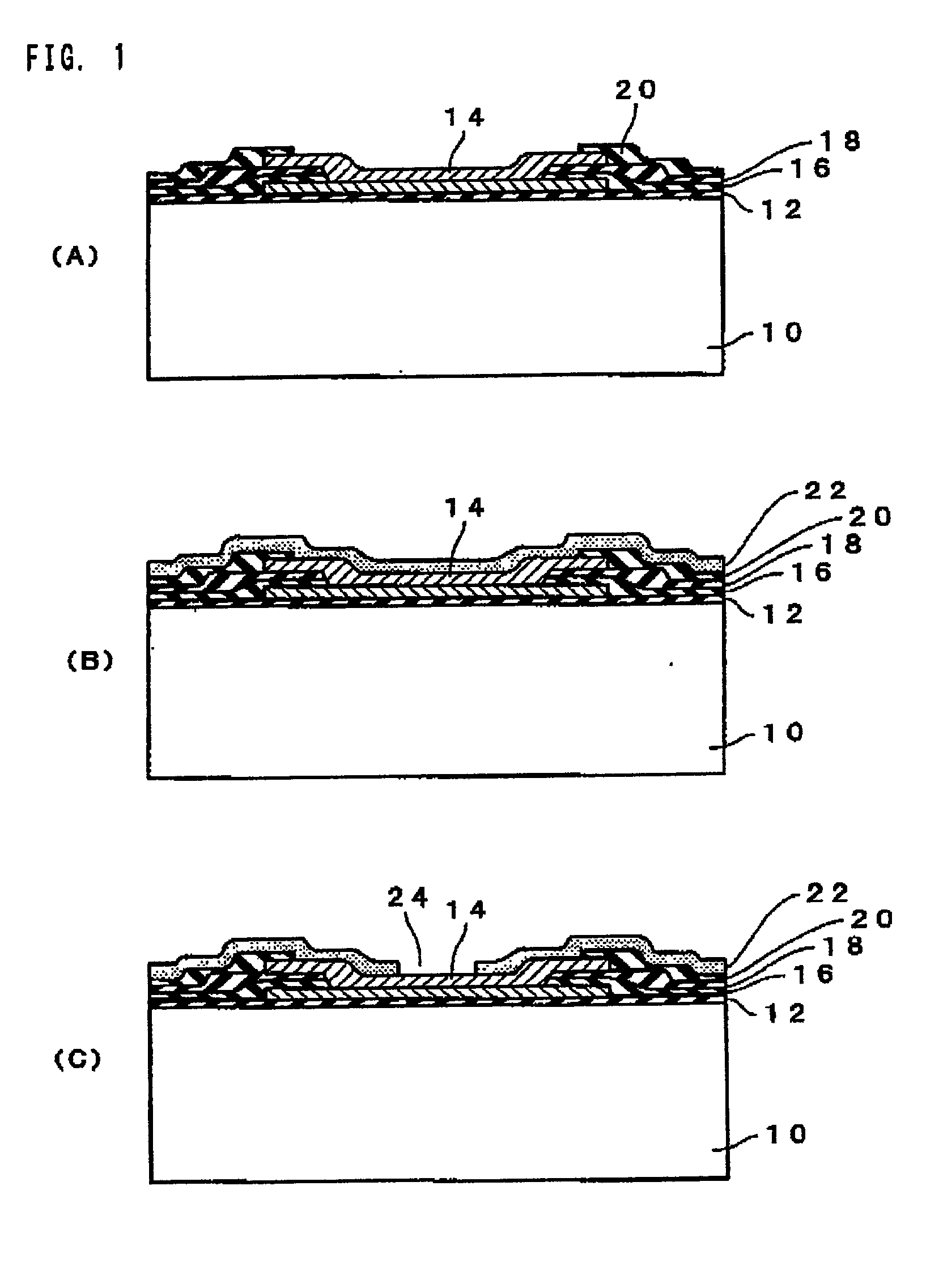

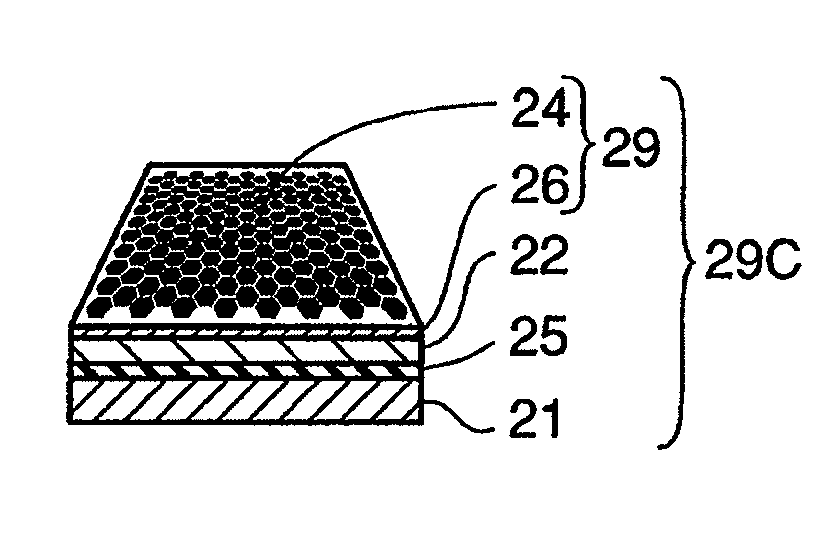

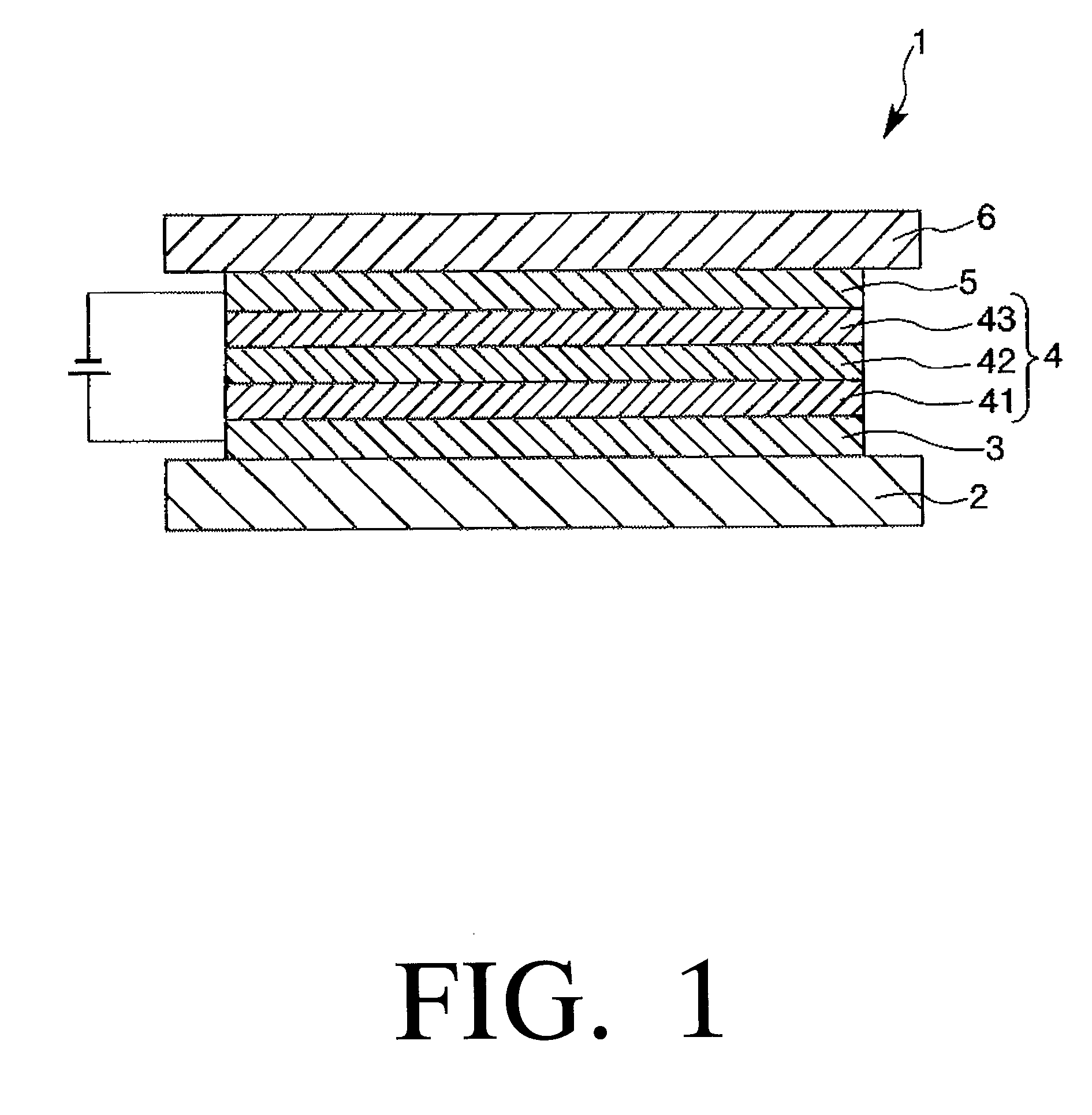

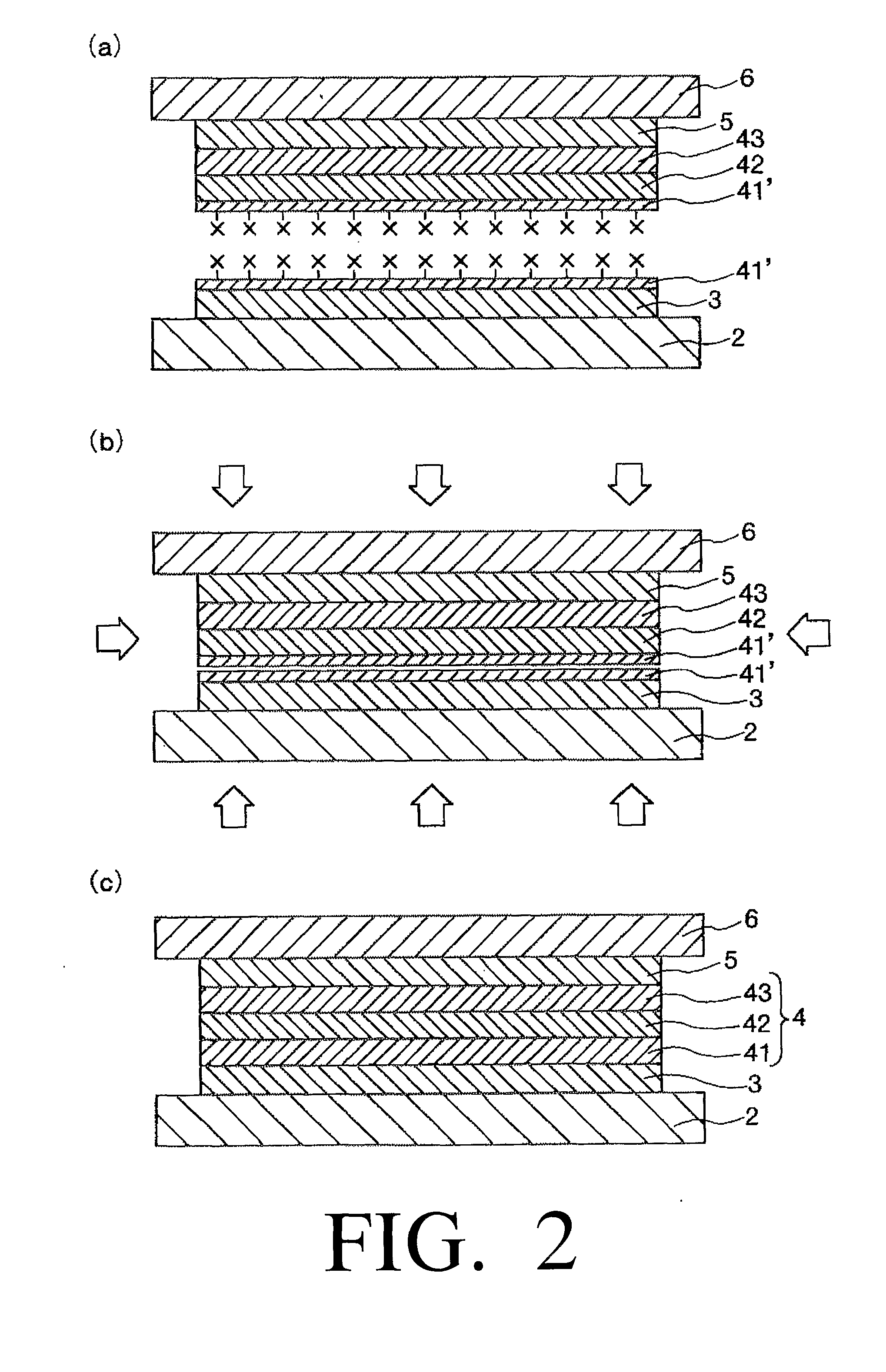

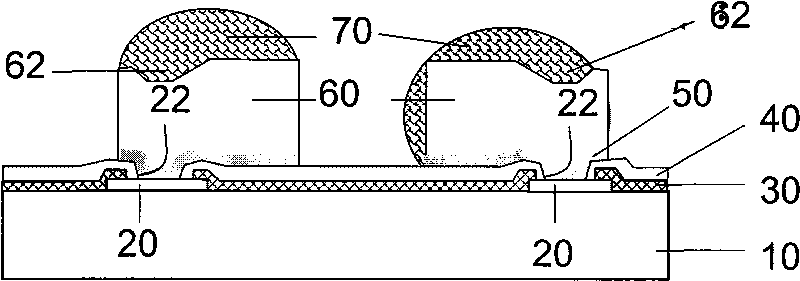

Method of Manufacturing Semiconductor Element, Semiconductor Element, Electronic Device, and Electronic Equipment

ActiveUS20090032807A1Good adhesionExcellent hole transport abilityFinal product manufactureSolid-state devicesEngineeringSemiconductor components

The object of the present invention is to provide a method of manufacturing a semiconductor element which can produce a semiconductor element provided with a semiconductor layer having a high carrier transport ability, a semiconductor element manufactured by the semiconductor element manufacturing method, an electronic device provided with the semiconductor element, and electronic equipment having a high reliability. In order to achieve the object, the present invention is directed to a method of manufacturing a semiconductor element having an anode, a cathode, and a hole transport layer provided between the anode and the cathode, the method comprising steps of: a first step for forming layers mainly comprised of a hole transport material having polymerizable groups X on the side of one surface of the anode and on the side of one surface of the cathode, respectively, and a second step for obtaining the hole transport layer by integrating the two layers together by polymerizing the hole transport materials via a polymerization reaction through their polymerizable groups in a state that the layer on the side of the anode and the layer on the side of the cathode are made contact with each other.

Owner:SEIKO EPSON CORP

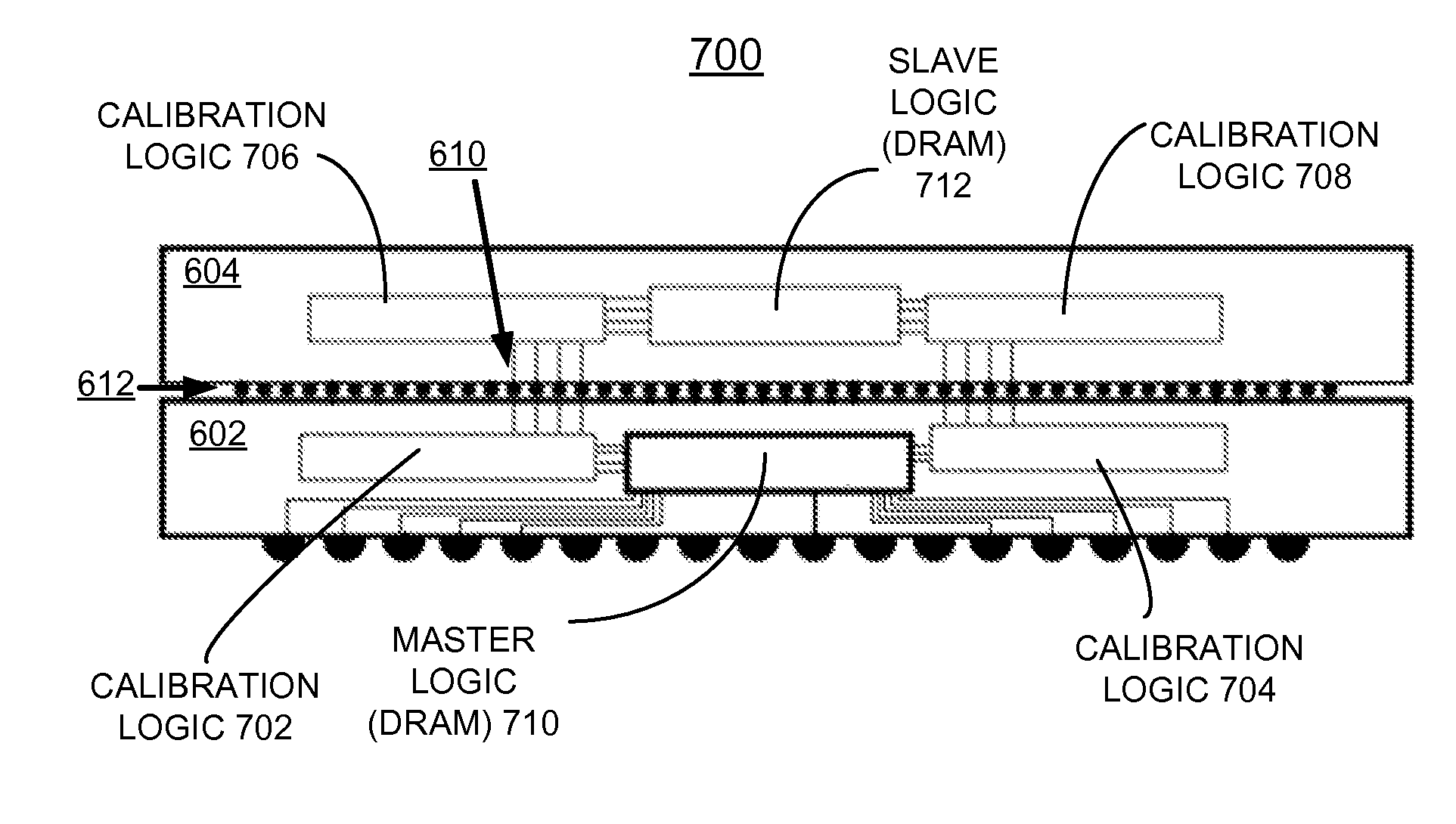

Iimplementing chip to chip calibration within a TSV stack

ActiveUS20130038380A1Overcome disadvantageOvercome disadvantagesImpedence convertorsSemiconductor/solid-state device detailsEngineeringControl circuit

A method and circuit for implementing a chip to chip calibration in a chip stack, for example, with through silicon vias (TSV) stack, and a design structure on which the subject circuit resides are provided. A first chip and a second chip are included within a semiconductor chip stack. The semiconductor chip stack includes a vertical stack optionally provided with Though Silicon Via (TSV) stacking of the chips. At least one of the first chip and the second chip includes a calibration control circuit and a performance indicator circuit coupled to the calibration control circuit to train and calibrate at least one of the first chip and the second chip to provide enhanced performance and reliability for the semiconductor chip stack.

Owner:IBM CORP

Semiconductor production method

InactiveUS20050029662A1Inhibit deteriorationImprove reliabilitySemiconductor/solid-state device detailsSolid-state devicesCopper interconnectDevice material

It is an object of the present invention to provide a semiconductor device production method in which an electroconductive capping (metal) layer is formed on a copper interconnect surface, wherein the capping (metal) layer is selectively formed to produce the semiconductor device of high reliability. In the semiconductor device production method, a capping (metal) layer is formed on a copper interconnect in a semiconductor integrated circuit, a first capping (metal) layer is formed by electroless plating with a plating solution containing a reducing agent active on a copper interconnect surface, and then a second capping (metal) layer is formed by another electroless plating.

Owner:HITACHI LTD

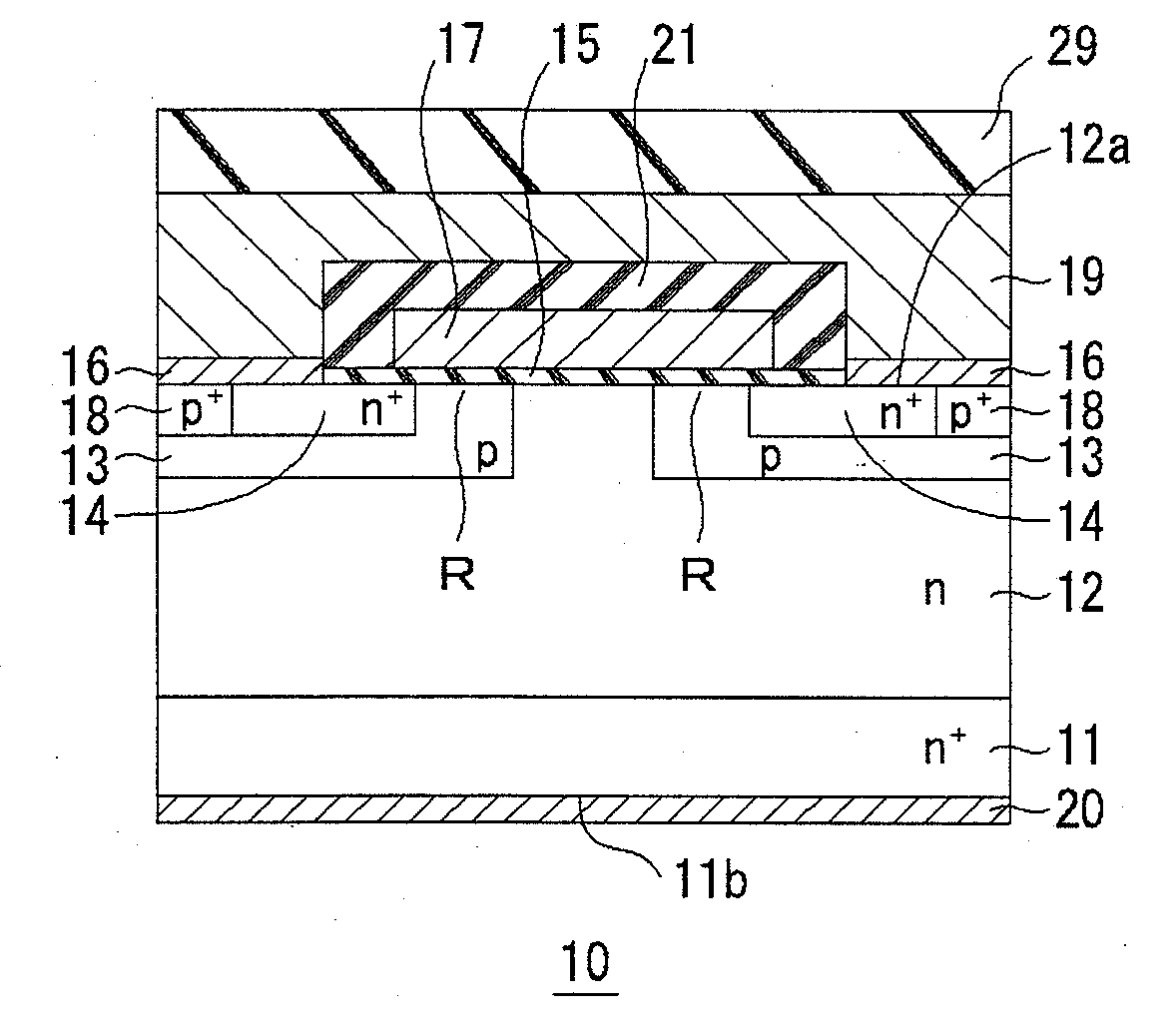

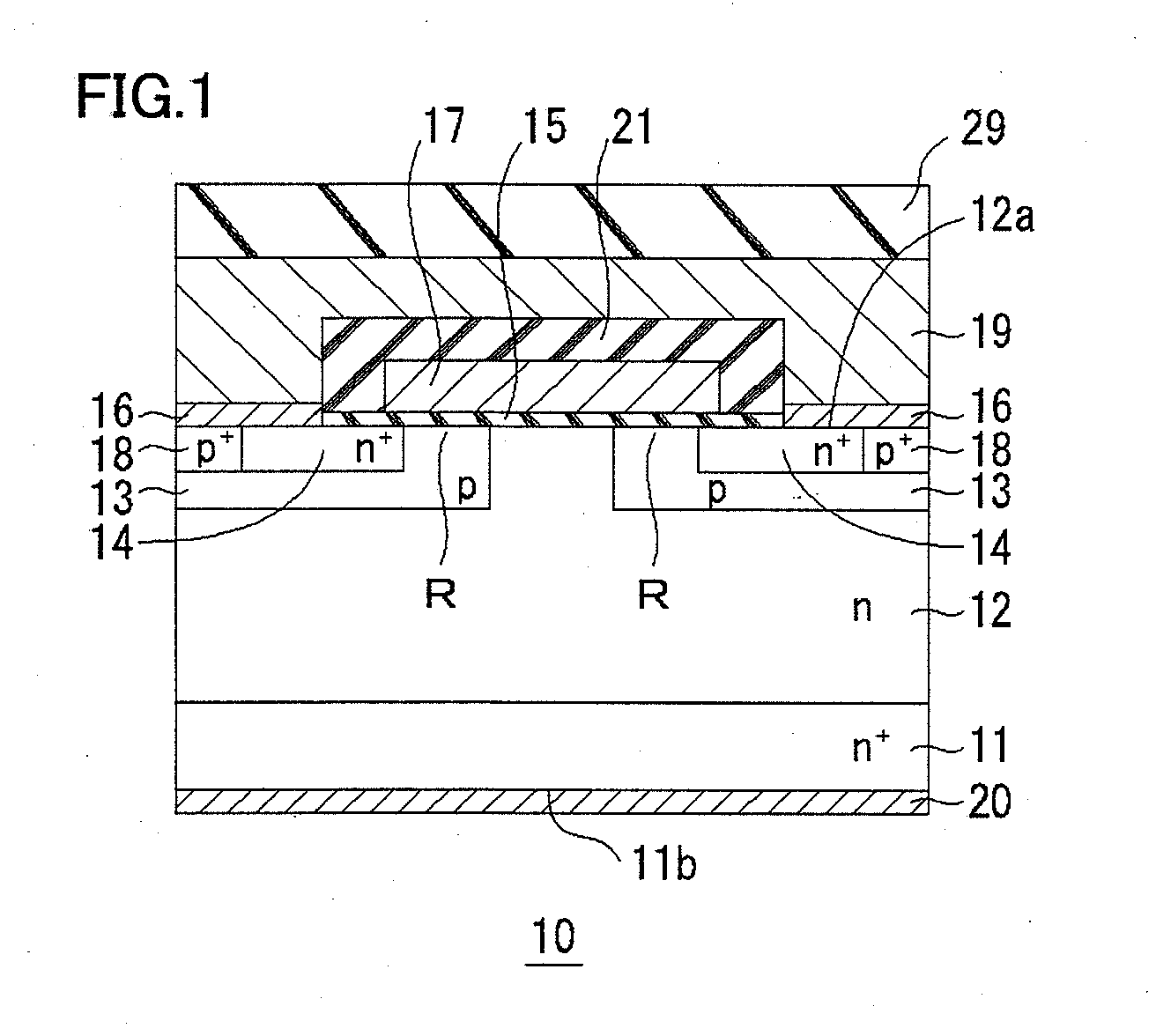

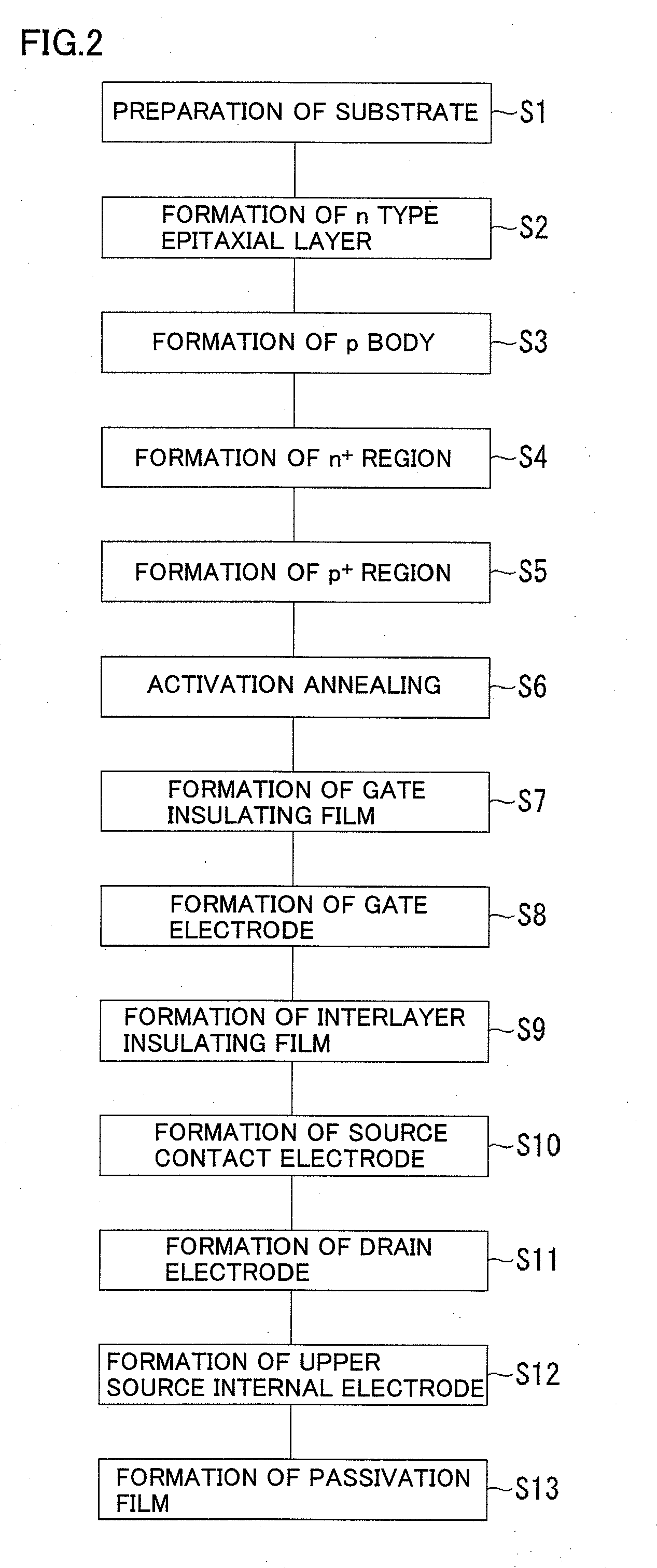

Semiconductor device and method for manufacturing same

InactiveUS20120007104A1Improve reliabilityLower resistanceTransistorSemiconductor/solid-state device manufacturingTitaniumSemiconductor

A semiconductor device employing silicon carbide, and the like are provided. In the semiconductor device, even when an electrode material and an upper electrode material are different, a problem does not take place at an interface at which these different types of metals are in contact with each other, thus obtaining high reliability in long-term use.The semiconductor device includes: a contact electrode 16 in contact with silicon carbides 14, 18; and an upper electrode 19 electrically conductive to the contact electrode. The contact electrode 16 is formed of an alloy including titanium, aluminum, and silicon, the upper electrode 19 is formed of aluminum or an aluminum alloy, and the upper electrode achieves the electric conduction to the contact electrode with the upper electrode making contact with the contact electrode.

Owner:SUMITOMO ELECTRIC IND LTD

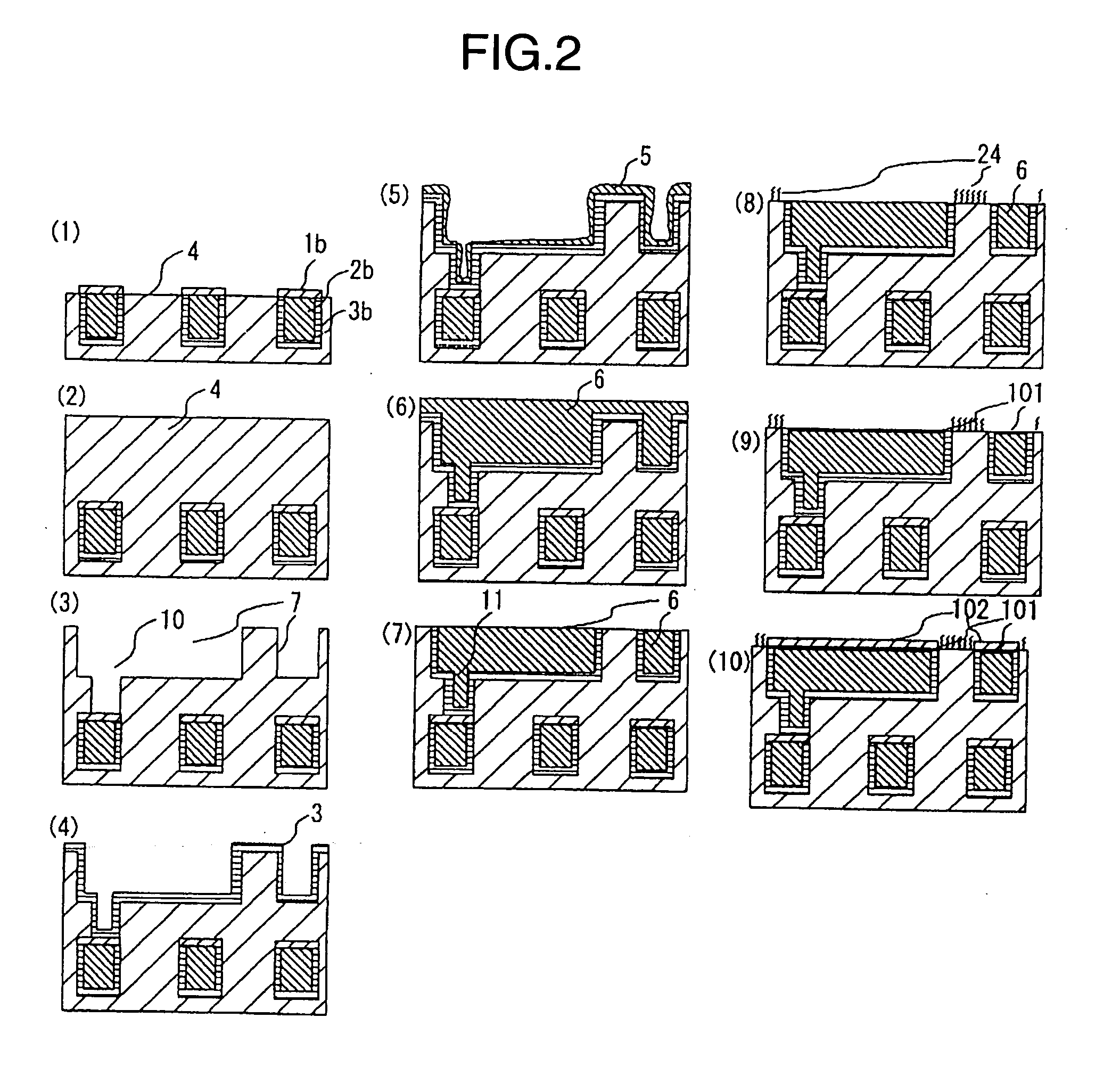

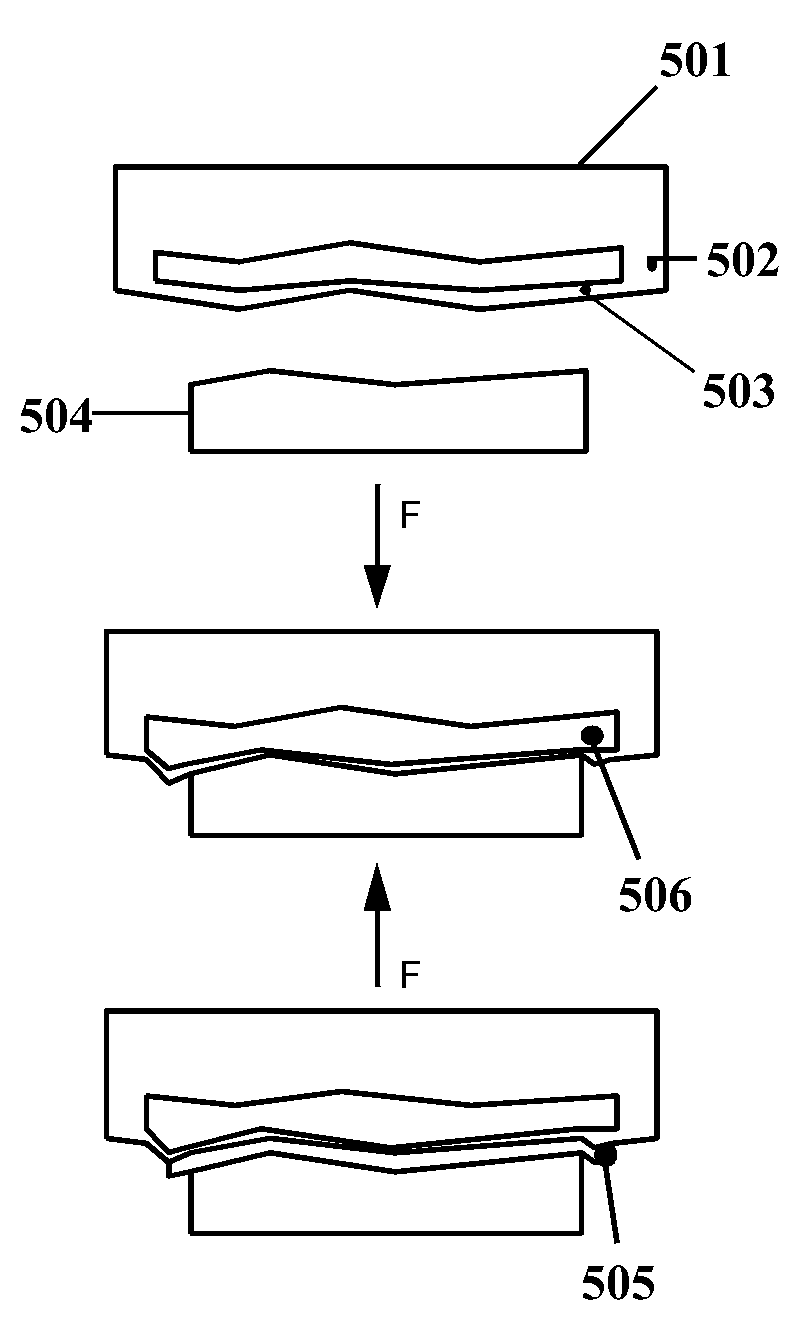

Manufacturing method for semiconductor devices

InactiveUS20110081750A1Enhance characteristicImprove reliabilitySemiconductor/solid-state device detailsSolid-state devicesPower semiconductor deviceEngineering

The reliability of a semiconductor device is enhanced. A first lead frame, a first semiconductor chip, a second lead frame, and a second semiconductor chip are stacked over an assembly jig in this order with solder in between and solder reflow processing is carried out to fabricate their assembly. Thereafter, this assembly is sandwiched between first and second molding dies to form an encapsulation resin portion. The upper surface of the second die is provided with steps. At a molding step, the second lead frame is clamped between the first and second dies at a position higher than the first lead frame; and a third lead frame is clamped between the first and second dies at a higher position. The assembly jig is provided with steps at the same positions as those of the steps in the upper surface of the second die in positions corresponding to those of the same.

Owner:RENESAS ELECTRONICS CORP

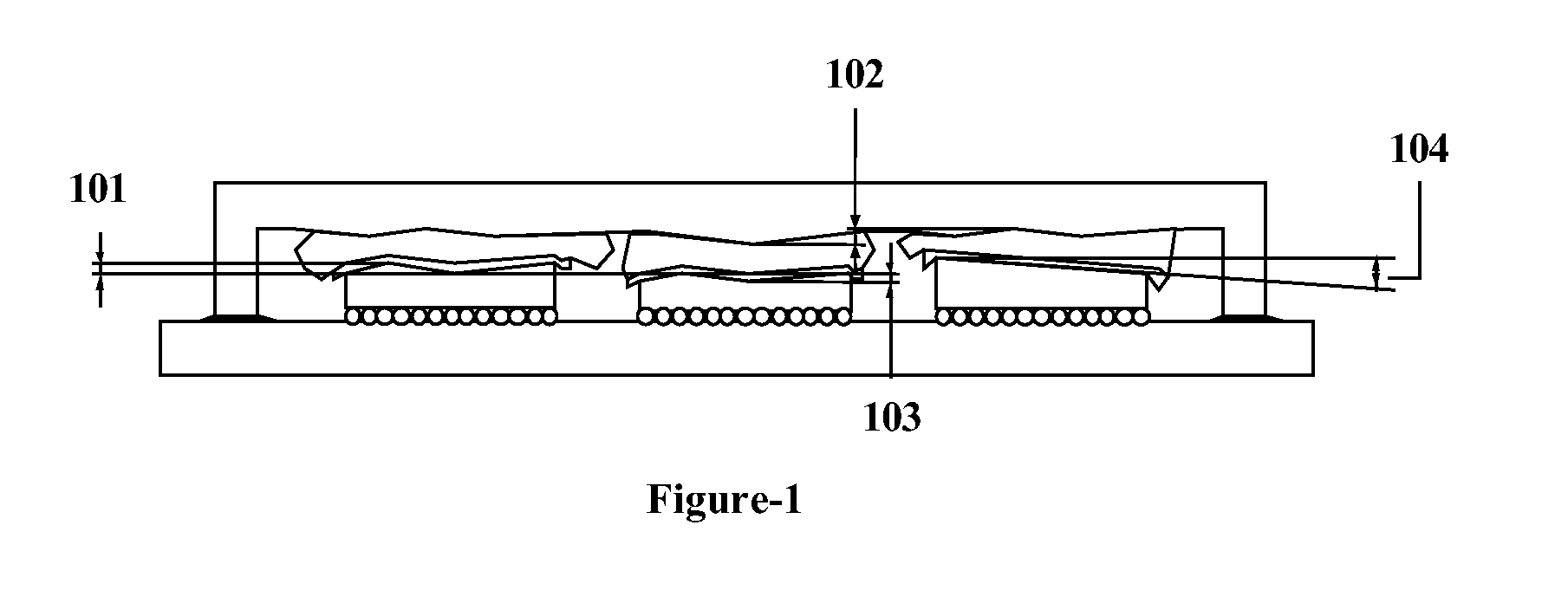

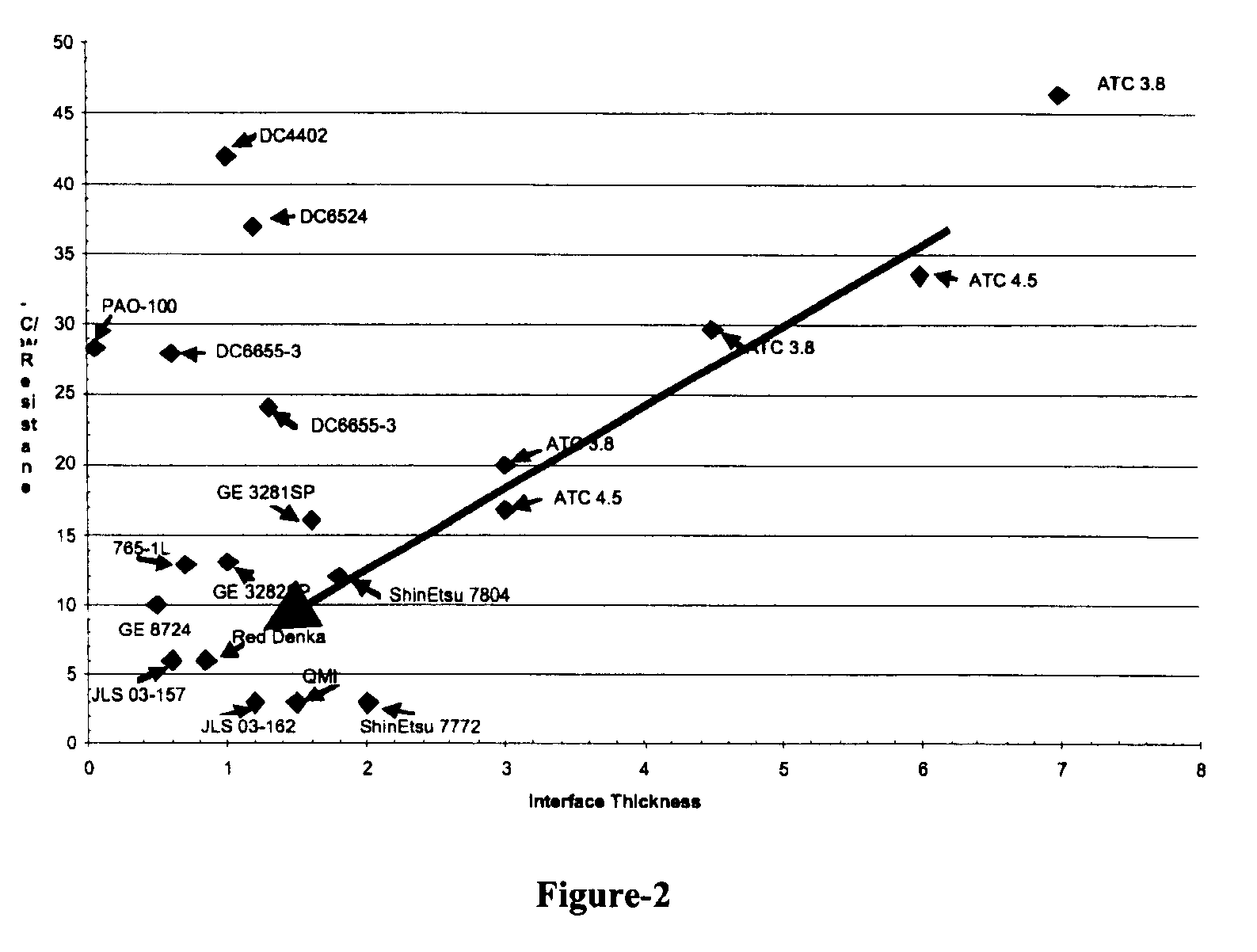

Method of fabricating a surface adapting cap with integral adapting material for single and multi chip assemblies

InactiveUS7547582B2Mitigate the aforesaid drawbacksReduce gap toleranceSemiconductor/solid-state device detailsSolid-state devicesThermodynamicsDevice material

A surface adapting cap with an integrated adapting thermally conductive material on single and multi chip module provides reduced gap tolerance and hence better thermal performance of the semiconductor device which enhances the reliability of the semiconductor device. In one of the embodiments the cap is modified with an integrated, confined, and high thermal adaptive material. The membrane on this system is highly flexible. The cap is preassembled to the chip at a temperature above liquidus below curing temperature of the adaptive material. At this state, a hydrostatic pressure in the material develops due to the compression exerted from the cap to the chip and the confined volume of the buried material. This hydrostatic pressure causes the membrane to deflect and to adapt the warping and tolerances of the chip. Due to the adaptive surface the gap on each position of the chip and from chip to chip is same.

Owner:GLOBALFOUNDRIES INC

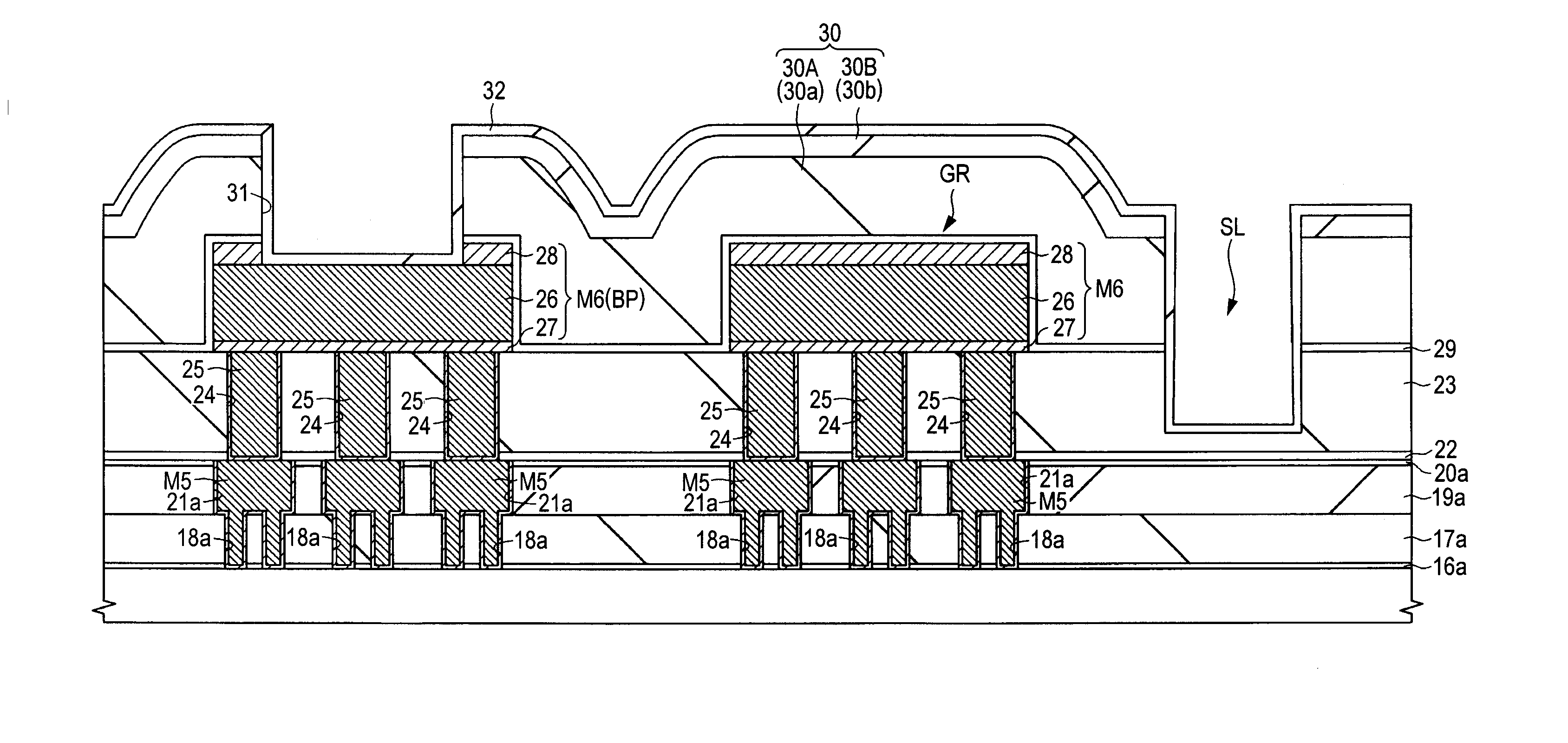

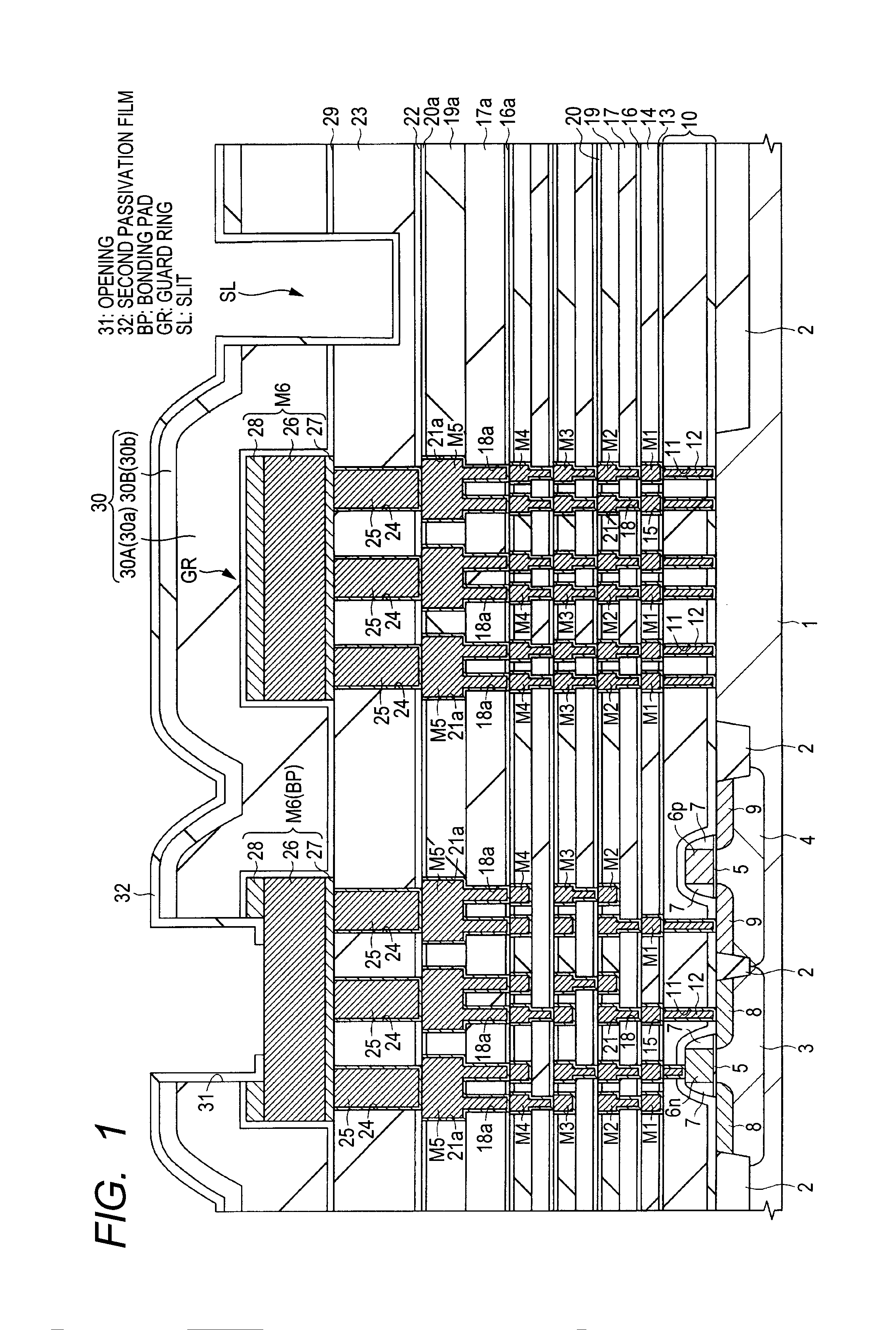

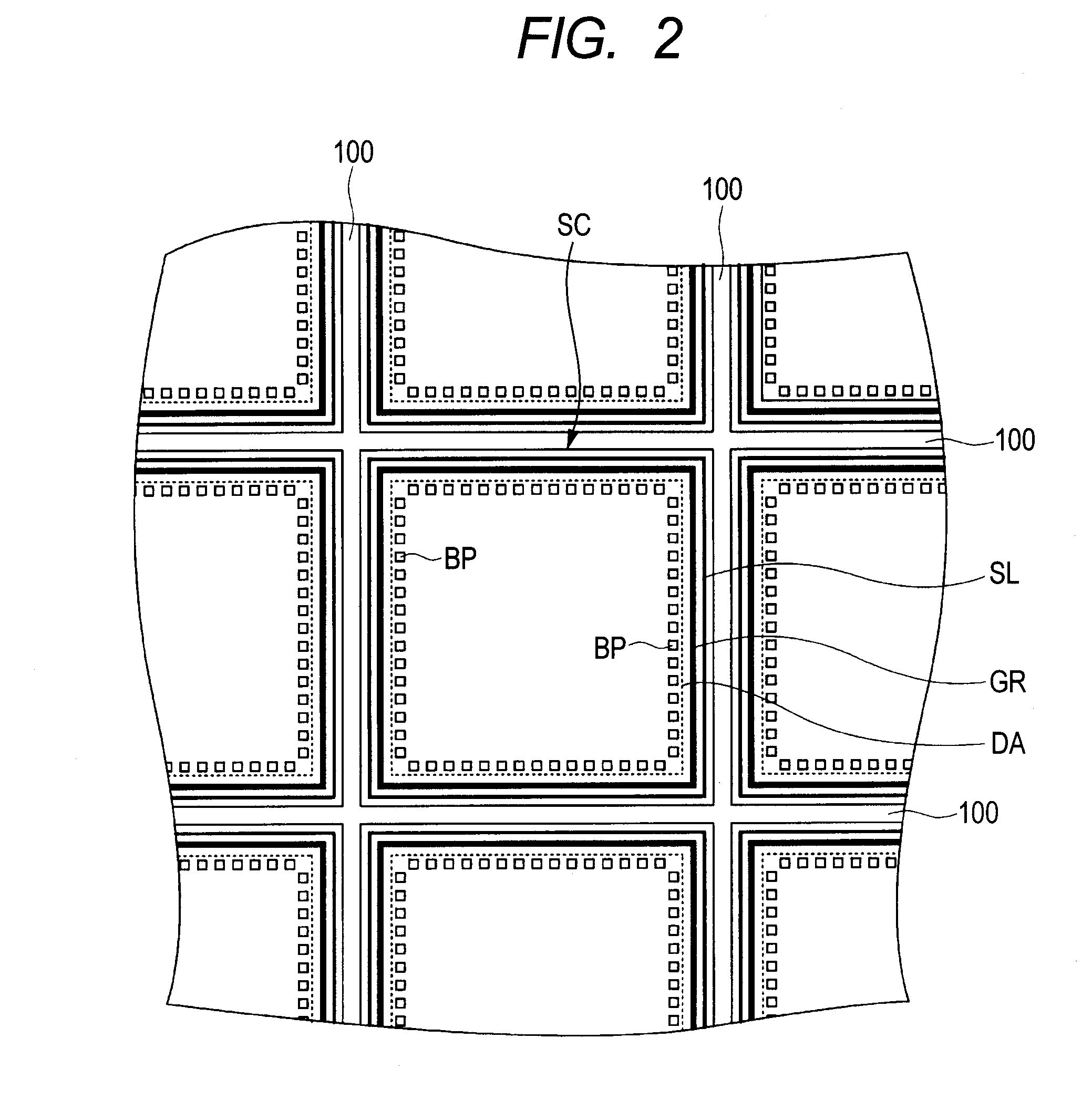

Semiconductor device, and manufacturing method of semiconductor device

ActiveUS20110266679A1Improve reliabilityTransistorSemiconductor/solid-state device detailsEngineeringSemiconductor device modeling

Provided is a technique capable of improving the reliability of a semiconductor device having a slit made over a main surface of a semiconductor substrate, so as to surround each element formation region. In the technique, a second passivation film covers the side surface of an opening made to make the upper surface of a sixth-layer interconnection M6 used for bonding pads naked, and the inner walls (the side surfaces and the bottom surface) of a slit made to surround the circumference of a guard ring and made in a first passivation film, an insulating film for bonding, and an interlayer dielectric, so as to cause the bottom thereof not to penetrate through a barrier insulating film.

Owner:RENESAS ELECTRONICS CORP

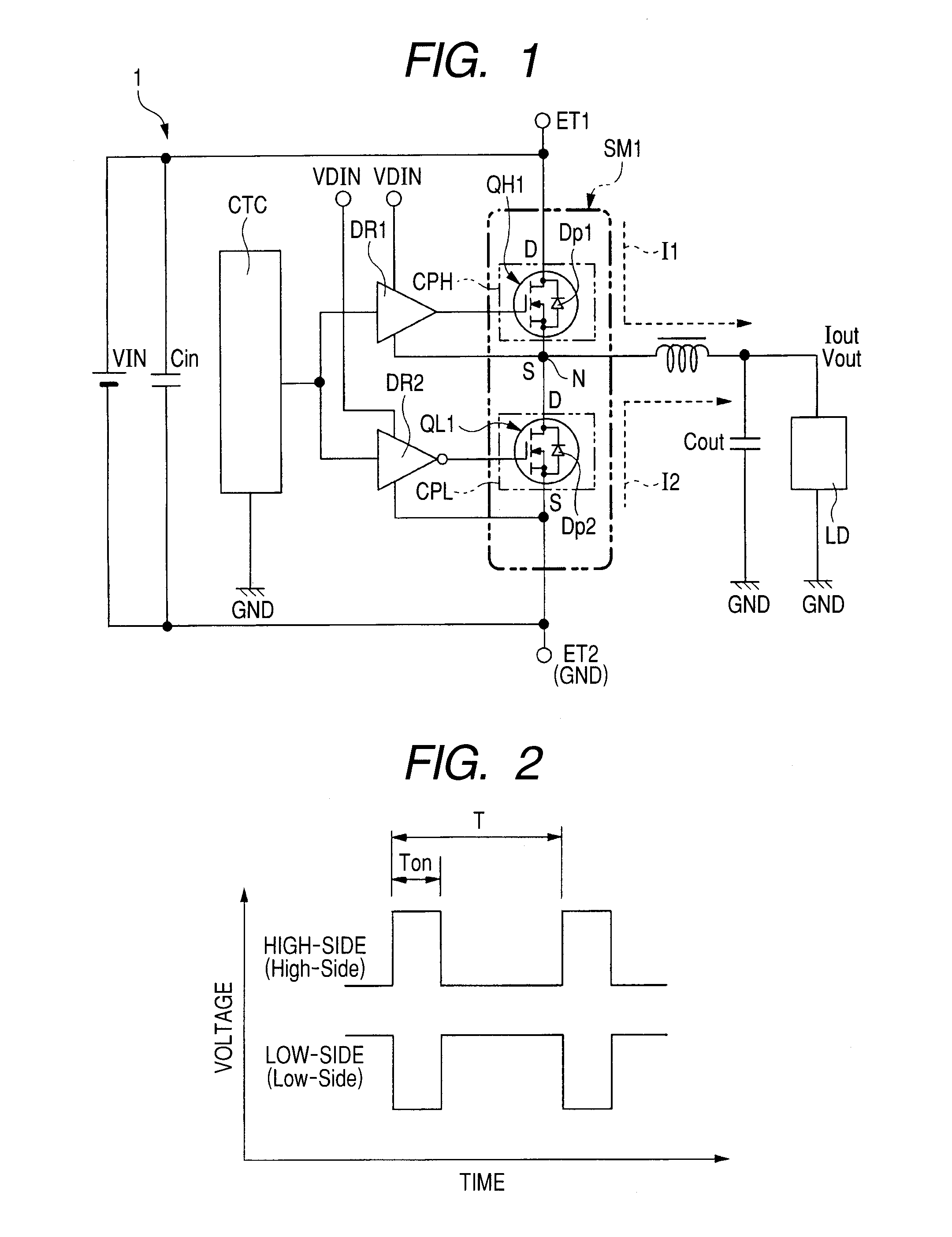

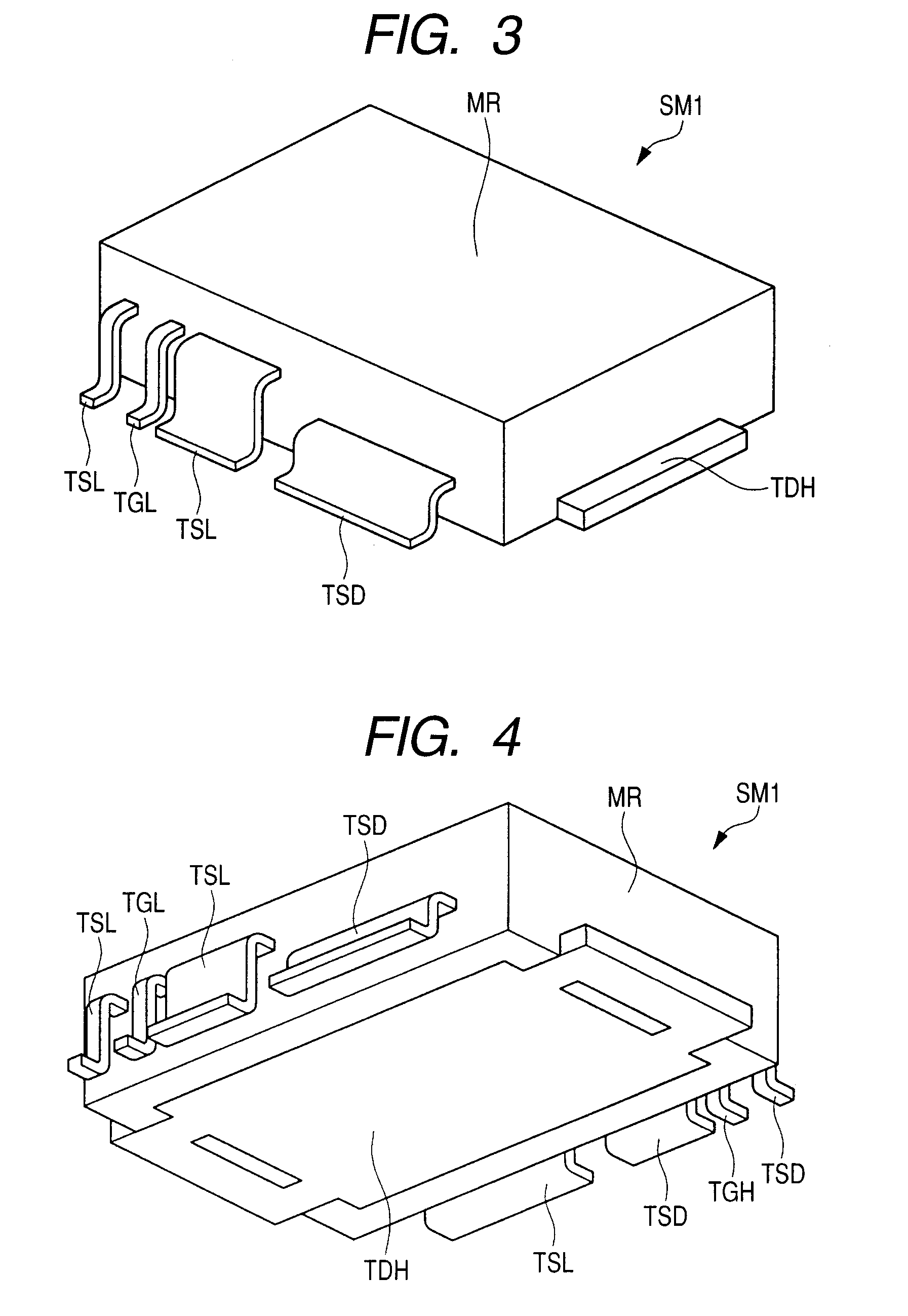

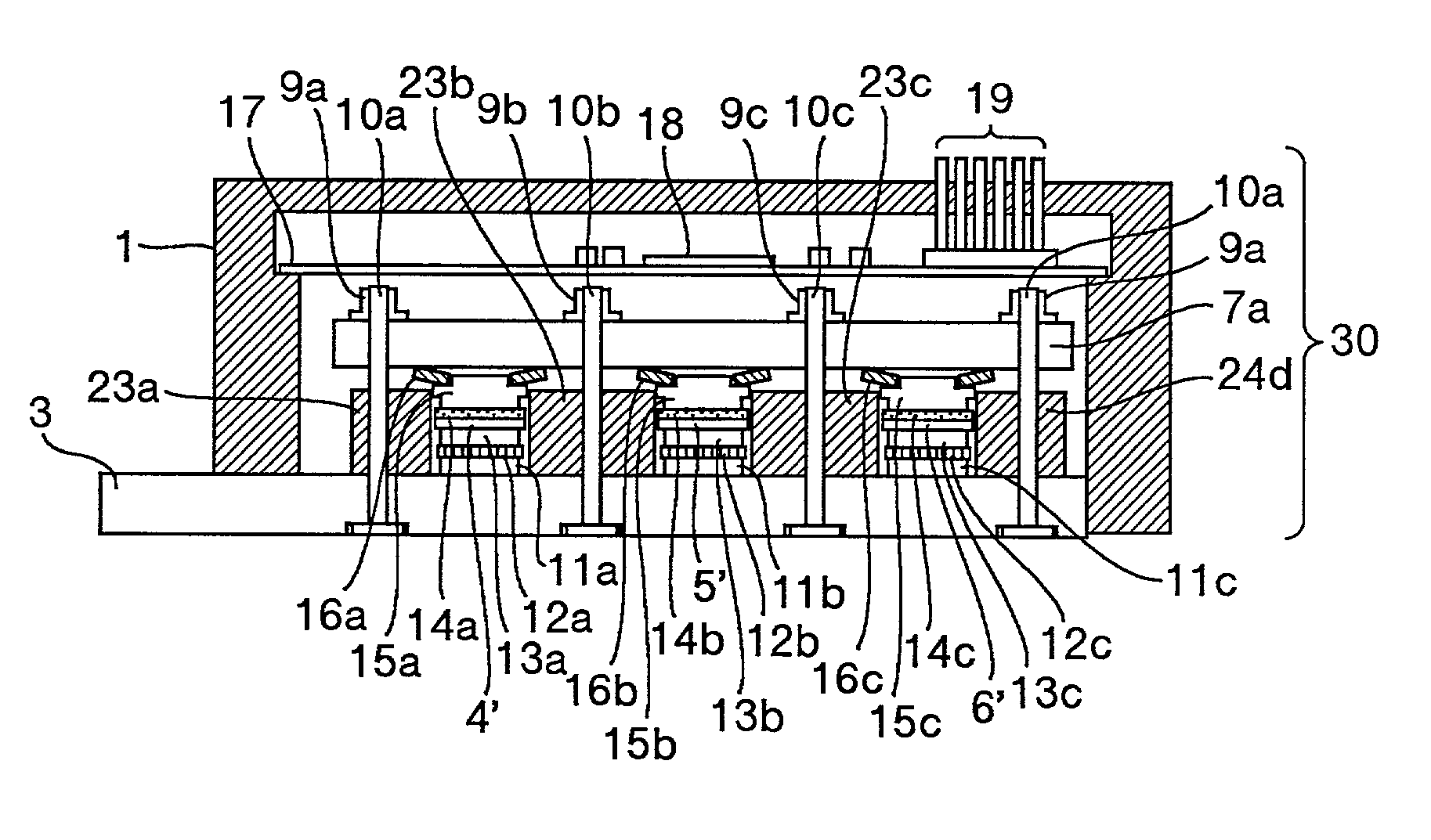

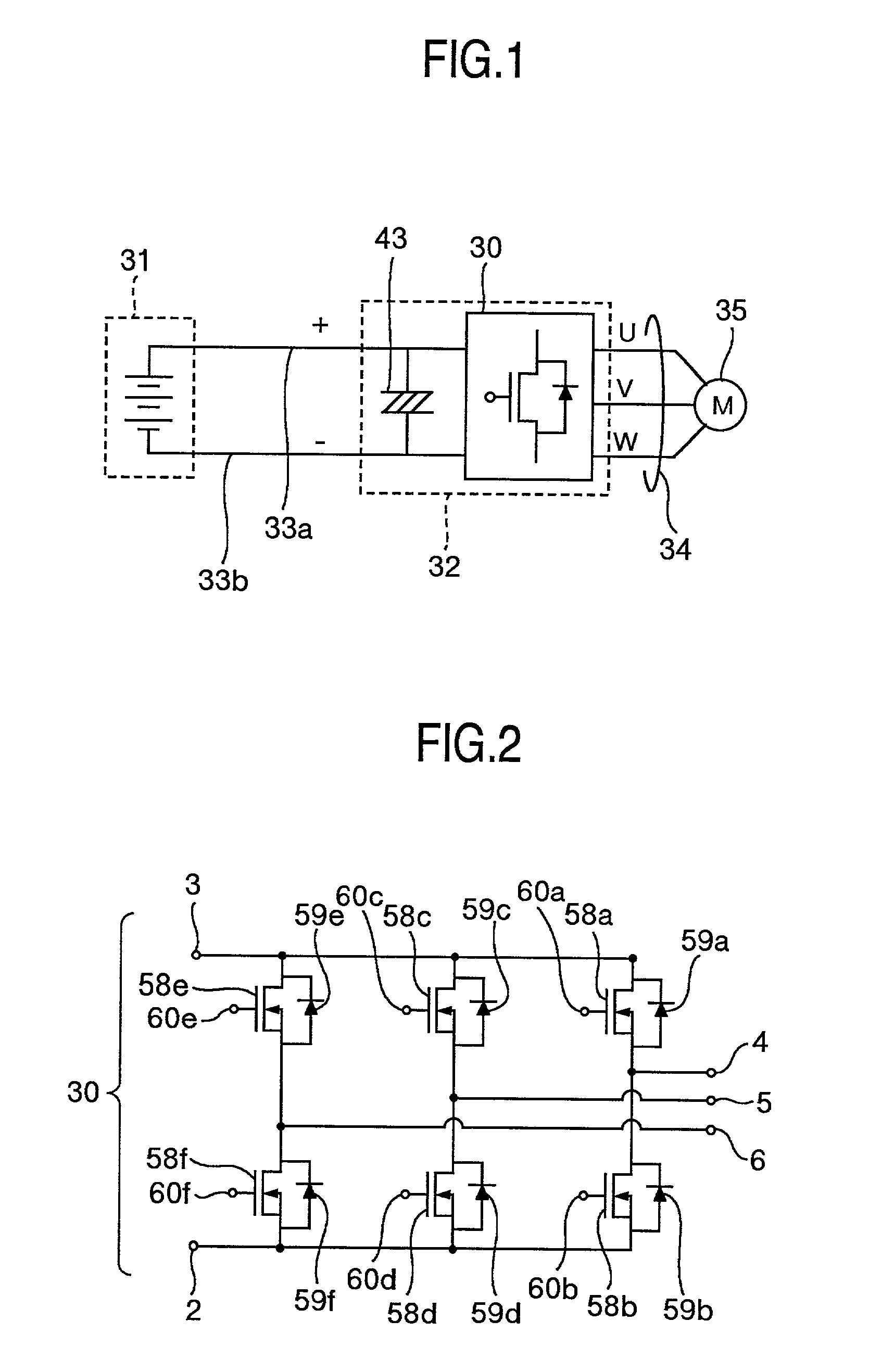

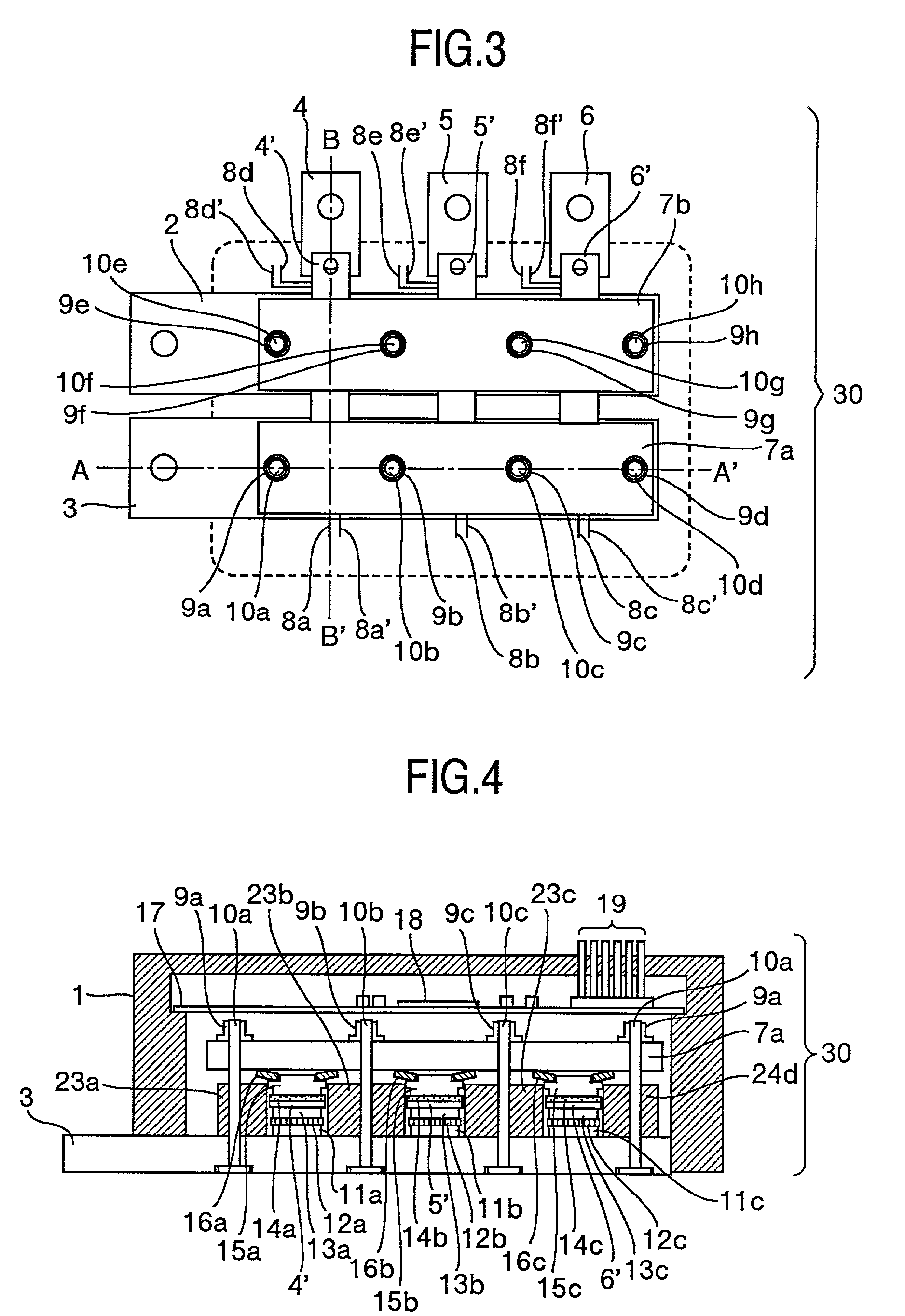

Semiconductor device

InactiveUS20020180037A1Semiconductor/solid-state device detailsSolid-state devicesEngineeringInductance

A semiconductor device including a positive polarity wiring plate, negative wiring plate, more than one output wiring plate, semiconductor switch element and conductive buffer or "cushion" member is disclosed. The semiconductor switch element and cushion member are compressively interposed between the output wiring plate and positive wiring plate and also between the output wiring plate and negative wiring plate to thereby constitute bridge circuitry. The positive wiring plate, negative wiring plate or output wiring plate is for use as one support body of a pressurization structure. With such an arrangement, it is possible to improve the heat releasability of semiconductor elements while at the same time reducing the inductance of direct current (DC) circuitry to thereby suppress heat generation of the semiconductor elements, thus increasing the reliability relative to temperature cycles.

Owner:HITACHI LTD

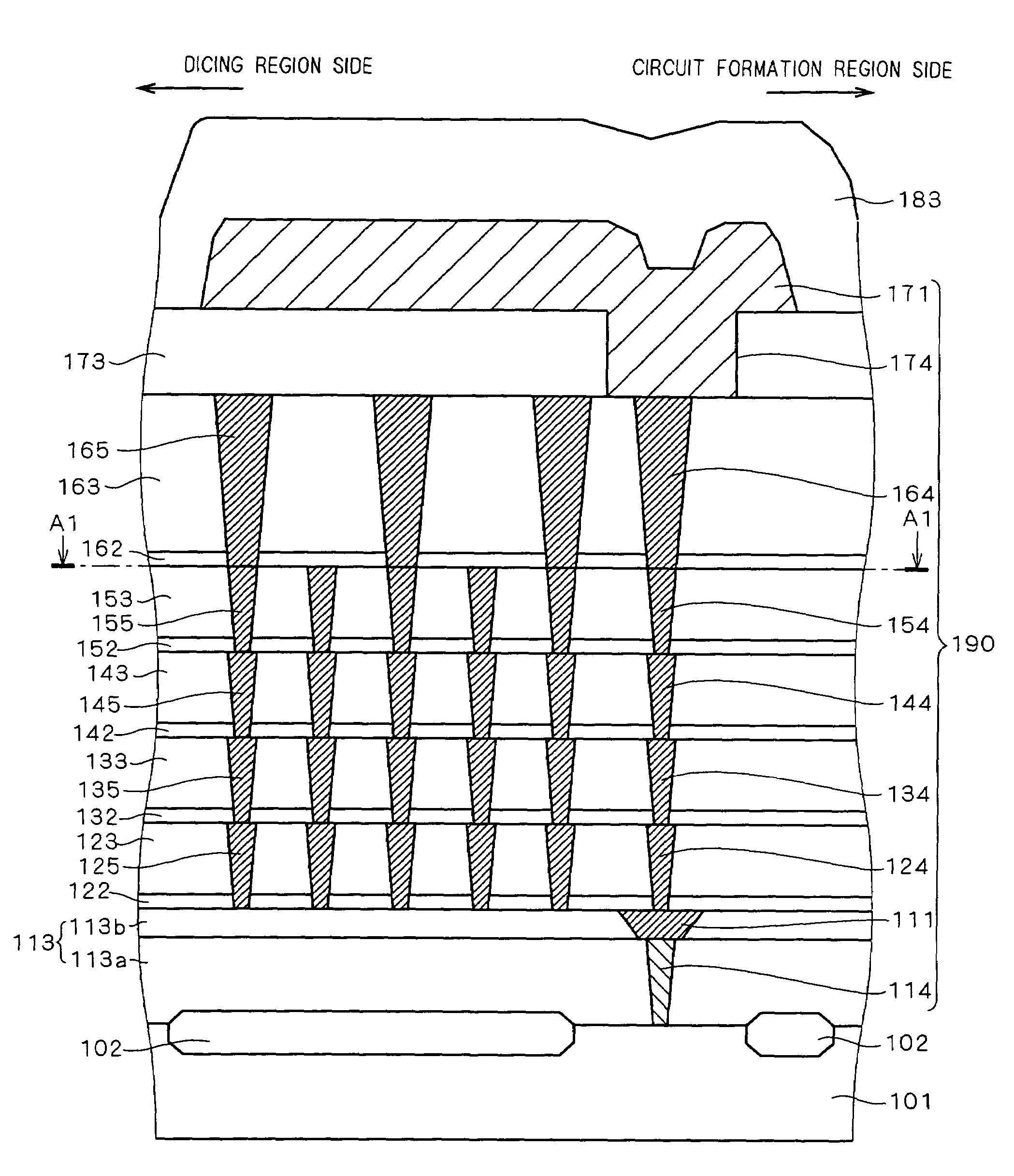

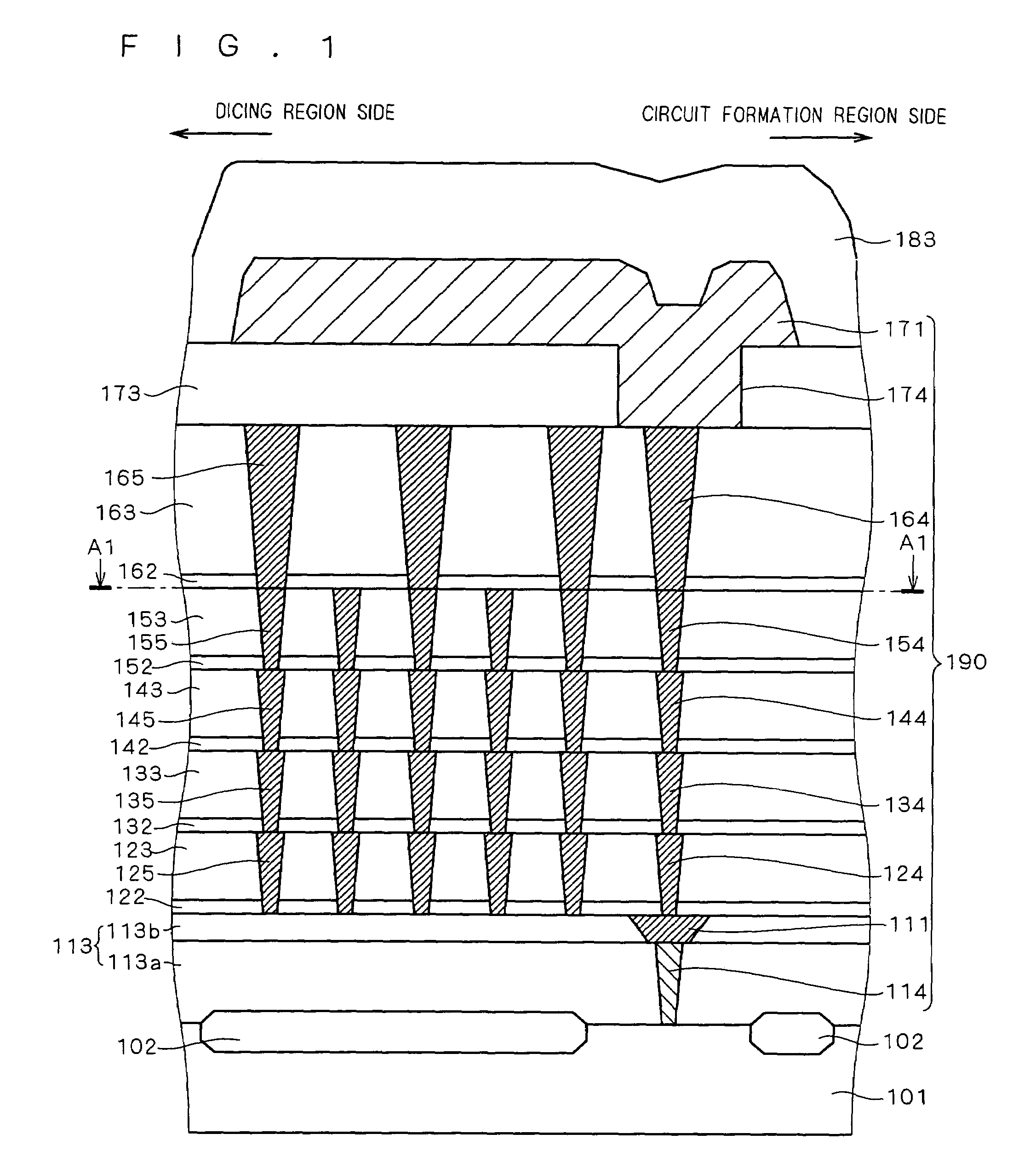

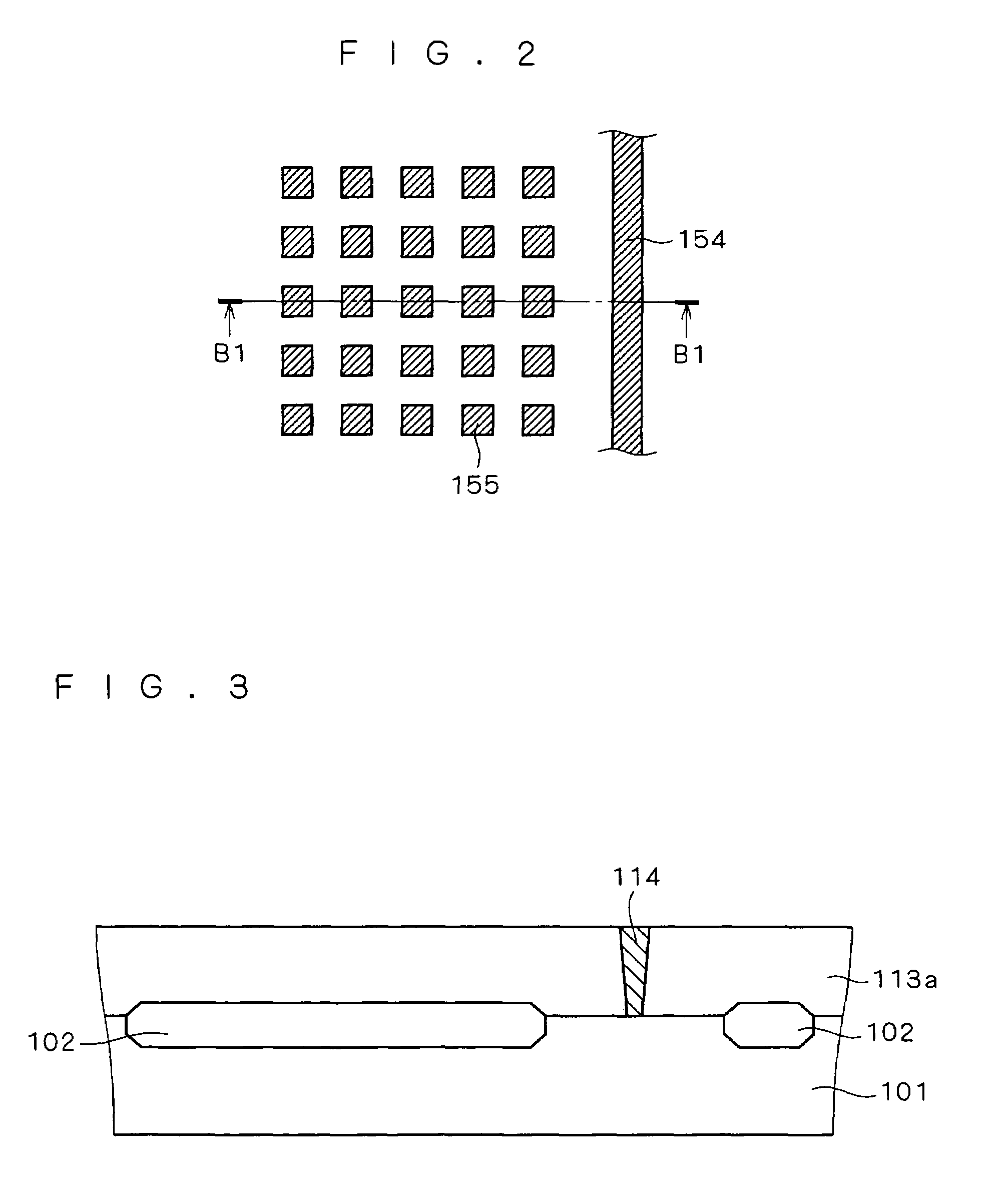

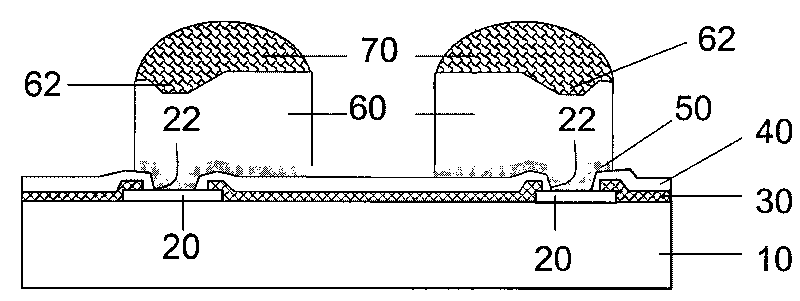

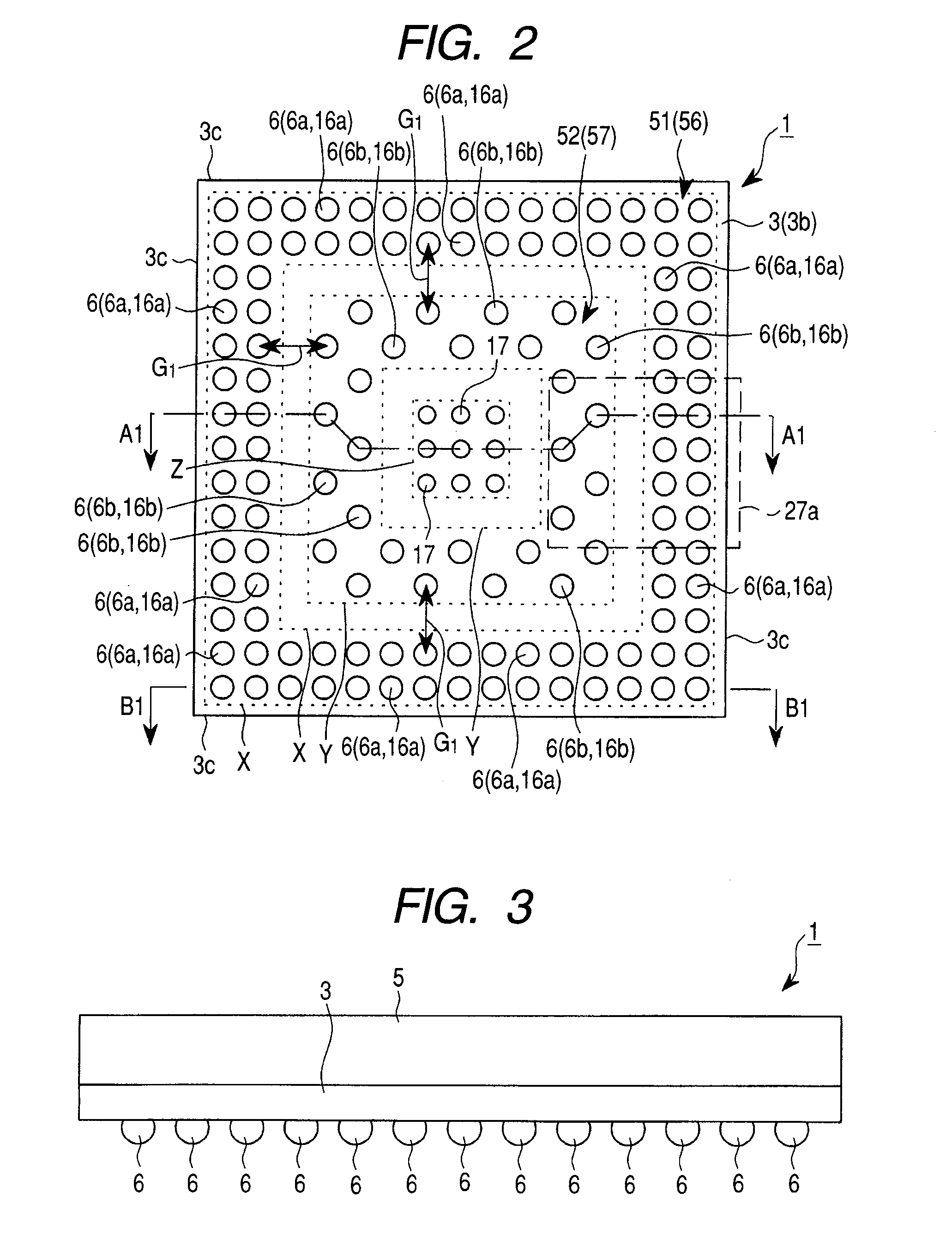

Semiconductor device

ActiveUS7400028B2Improve reliabilityAvoid crackingSemiconductor/solid-state device detailsSolid-state devicesEngineeringMoisture

The present invention provides a technique for improving the reliability of a semiconductor device where spreading of cracking that occurs at the time of dicing to a seal ring can be restricted even in a semiconductor device with a low-k film used as an interlayer insulating film. Dummy vias are formed in each layer on a dicing region side. The dummy vias are formed at the same intervals in a matrix as viewed in a top view. Even in the case where cracking occurs at the time of dicing, the cracking can be prevented from spreading to a seal ring by the dummy vias. As a result, resistance to moisture absorbed in a circuit formation region can be improved, and deterioration in reliability can be prevented.

Owner:RENESAS ELECTRONICS CORP

Package structure and manufacture method thereof

InactiveCN101728347AUniform thicknessPrevent collapseSemiconductor/solid-state device detailsSolid-state devicesEngineeringSemiconductor

The invention provides a package structure and a manufacture method thereof, belonging to the technical field of micro-electronics manufacture. The package structure comprises a semiconductor substrate, a contact welding pad, a passivation layer, a stress buffer layer and columnar lugs formed on the buffer layer, wherein the areas corresponding to any of the columnar lug structures in the stress buffer layer are provided with main openings and one or more than one auxiliary opening, the main openings and the auxiliary openings are distributed evenly in the composition plane range of the corresponding columnar lugs. The package structure provided in the invention can avoid welding flux from collapsing during reflux in the forming process of columnar lugs and has the characteristic of high reliability.

Owner:SEMICON MFG INT (SHANGHAI) CORP

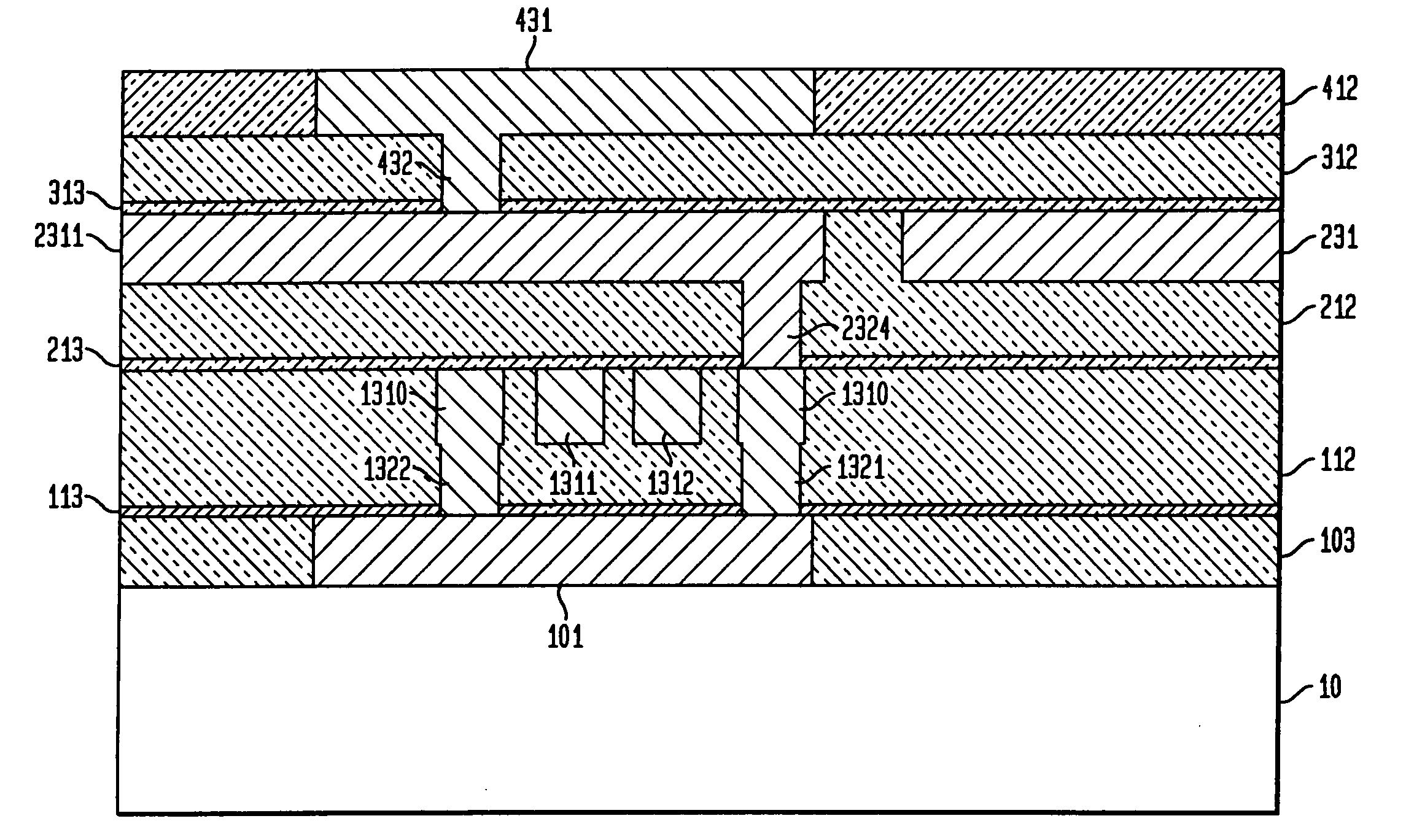

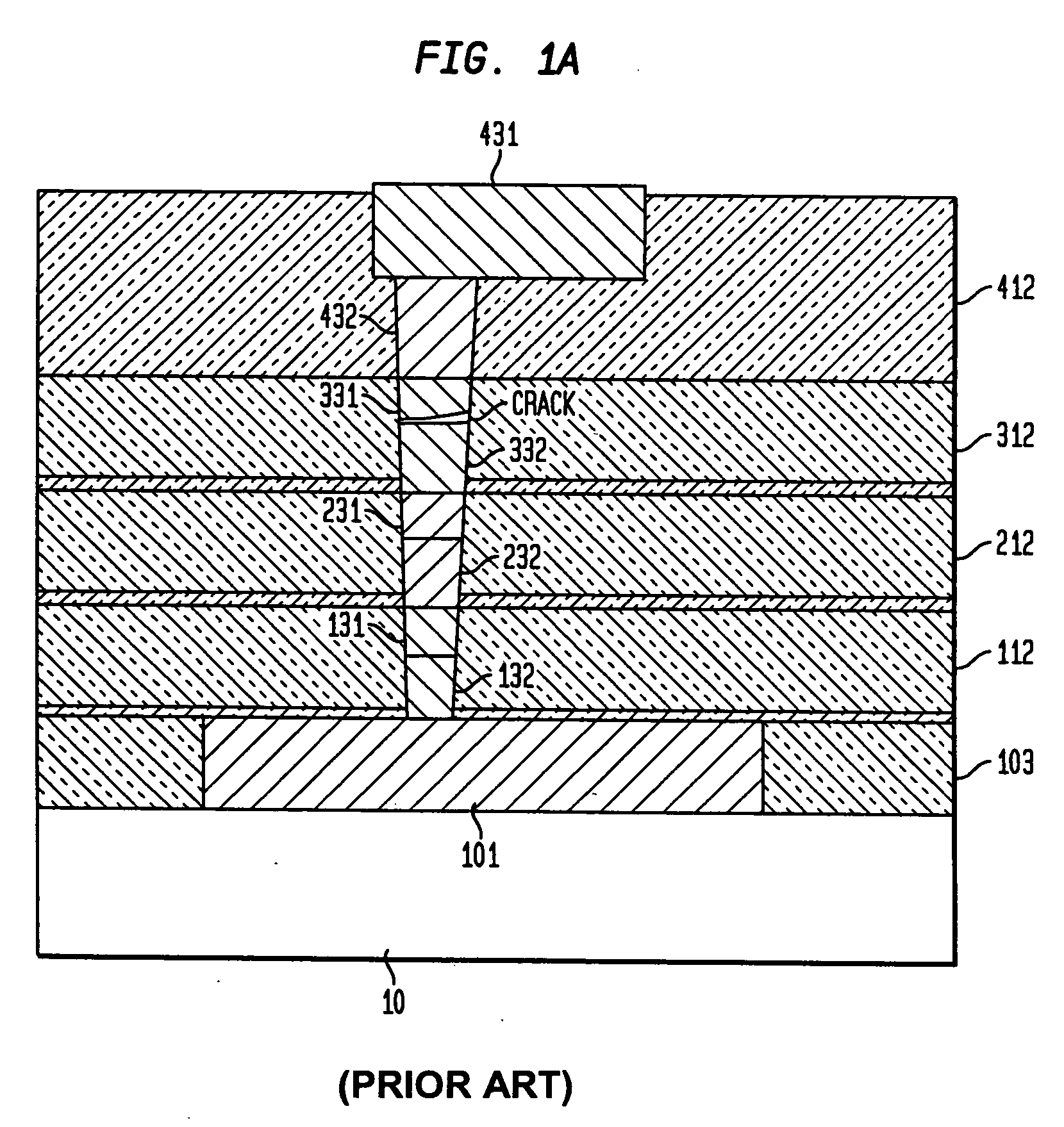

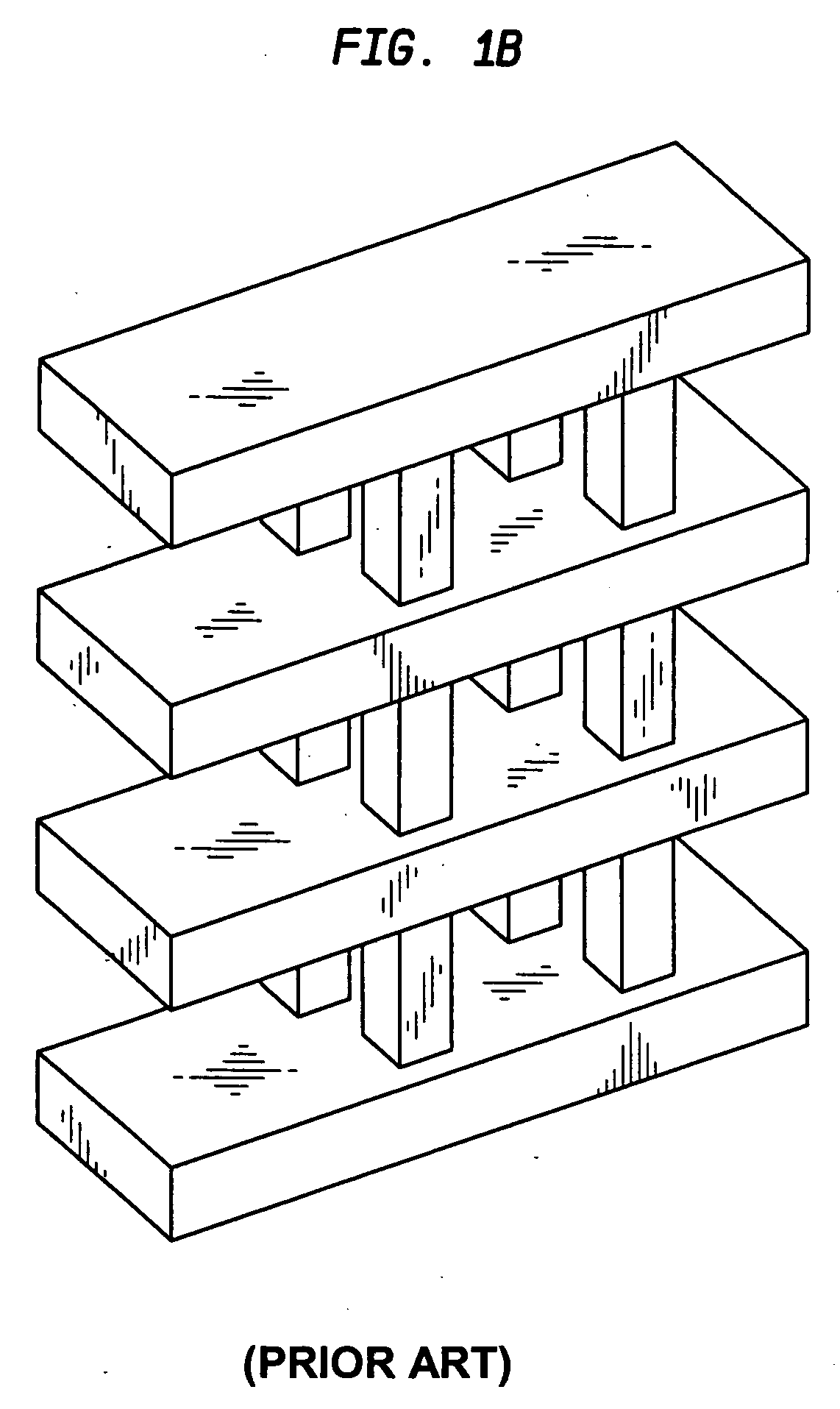

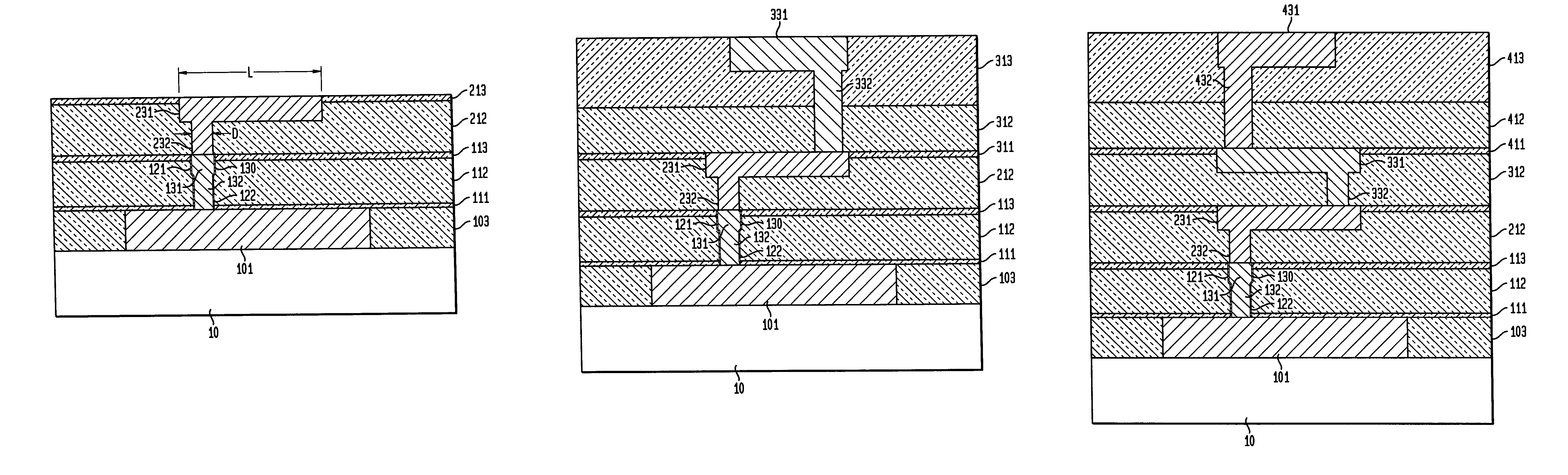

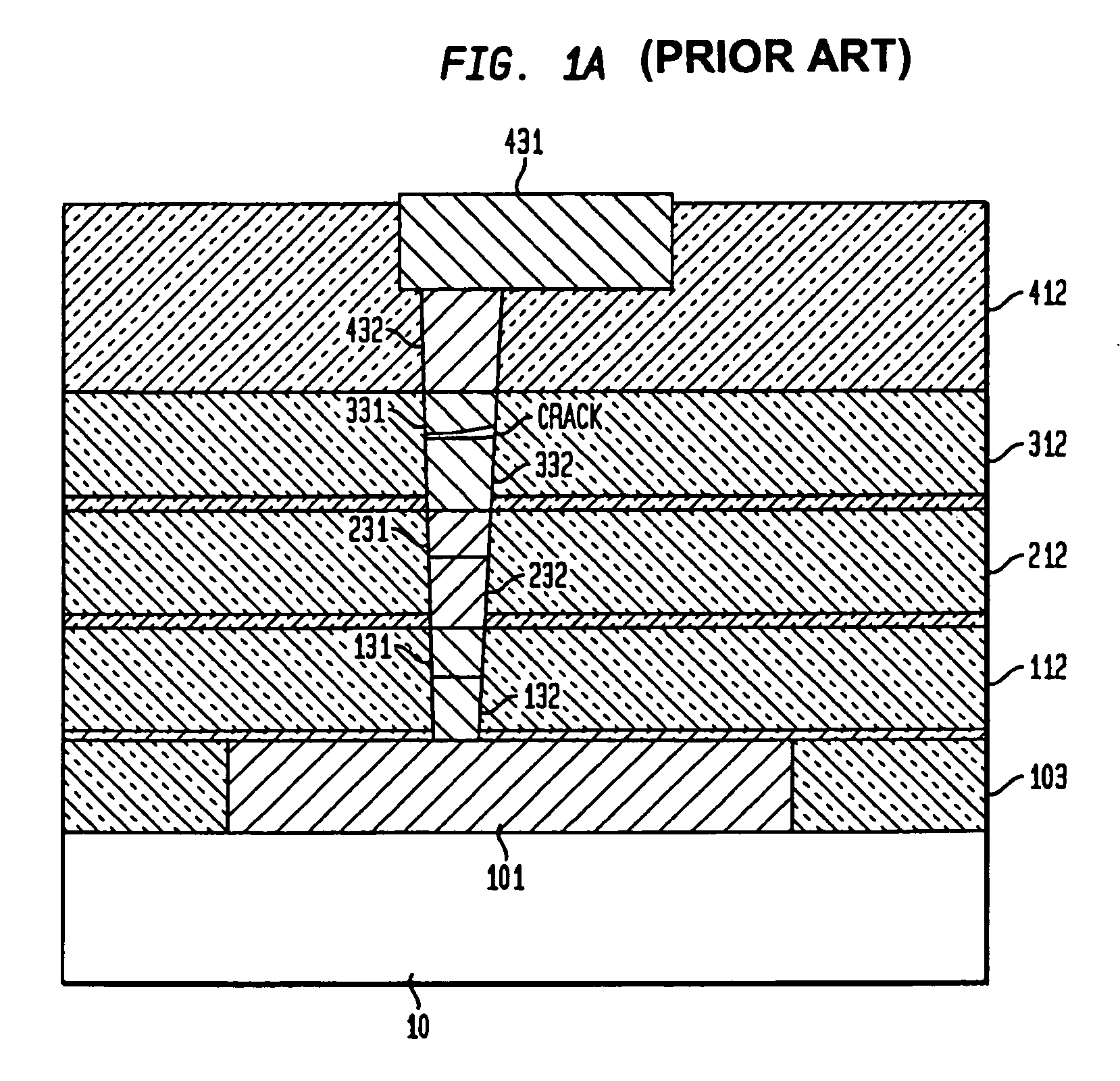

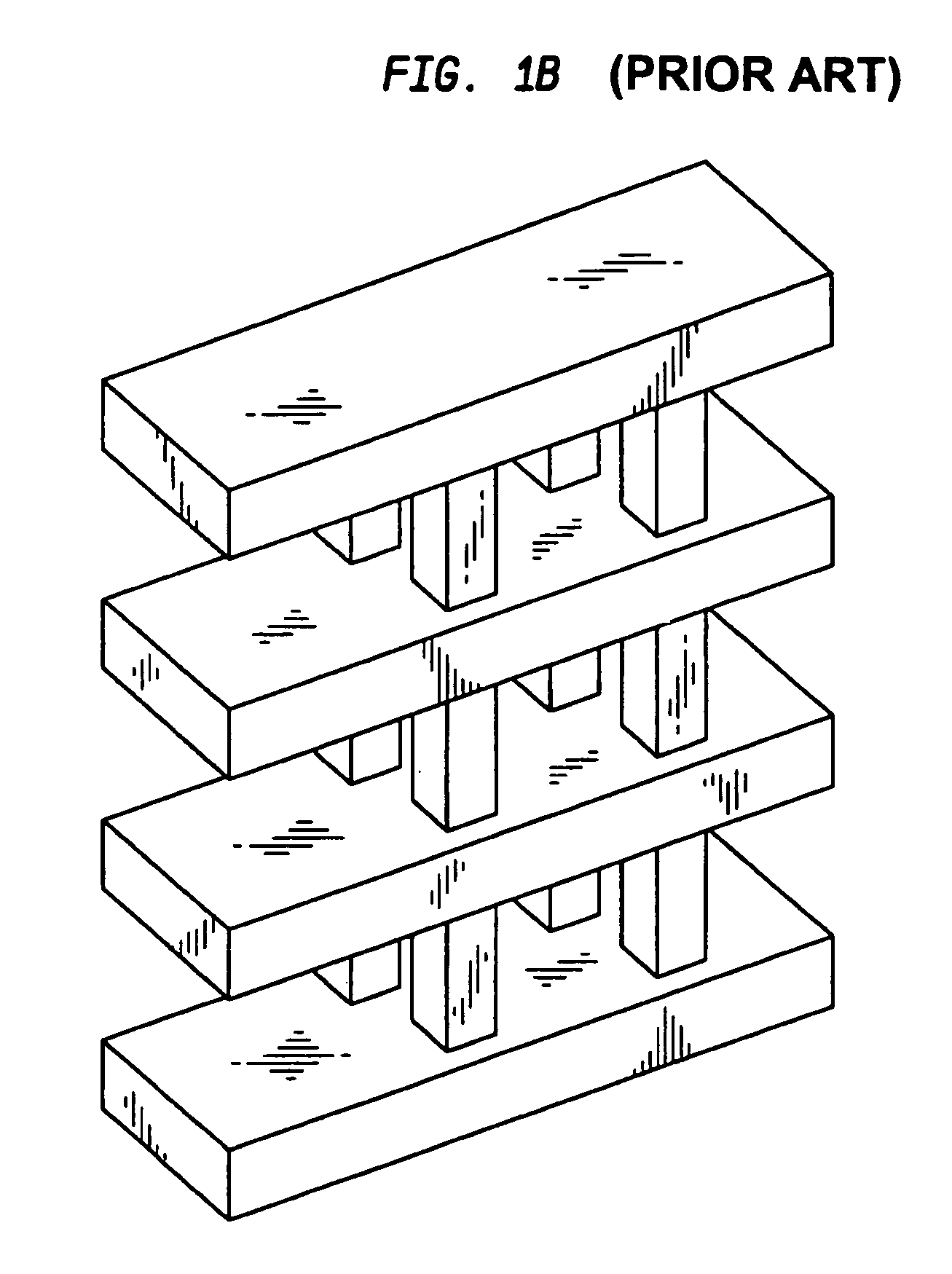

Stacked via-stud with improved reliability in copper metallurgy

InactiveUS20060014376A1Reduce intensityAllow flexibilitySemiconductor/solid-state device detailsSolid-state devicesElectrical conductorMaterials science

A multilevel semiconductor integrated circuit (IC) structure including a first interconnect level including a layer of dielectric material over a semiconductor substrate, the layer of dielectric material comprising a dense material for passivating semiconductor devices and local interconnects underneath; multiple interconnect layers of dielectric material formed above the layer of dense dielectric material, each layer of dielectric material including at least a layer of low-k dielectric material; and, a set of stacked via-studs in the low-k dielectric material layers, each of said set of stacked via studs interconnecting one or more patterned conductive structures, a conductive structure including a cantilever formed in the low-k dielectric material. The dielectric layer of each of the multiple interconnection levels includes a soft low-k dielectric material, wherein the cantilever and set of stacked via-studs are integrated within the soft low-k dielectric material to increase resistance to thermal fatigue crack formation. In one embodiment, each of the set of stacked via-studs in the low-k dielectric material layers is provided with a cantilever, such that the cantilevers are interwoven by connecting a cantilever on one level to a bulk portion of the conductor line on adjacent levels of interconnection, thereby increasing flexibility of stacked via-studs between interconnection levels.

Owner:GLOBALFOUNDRIES INC

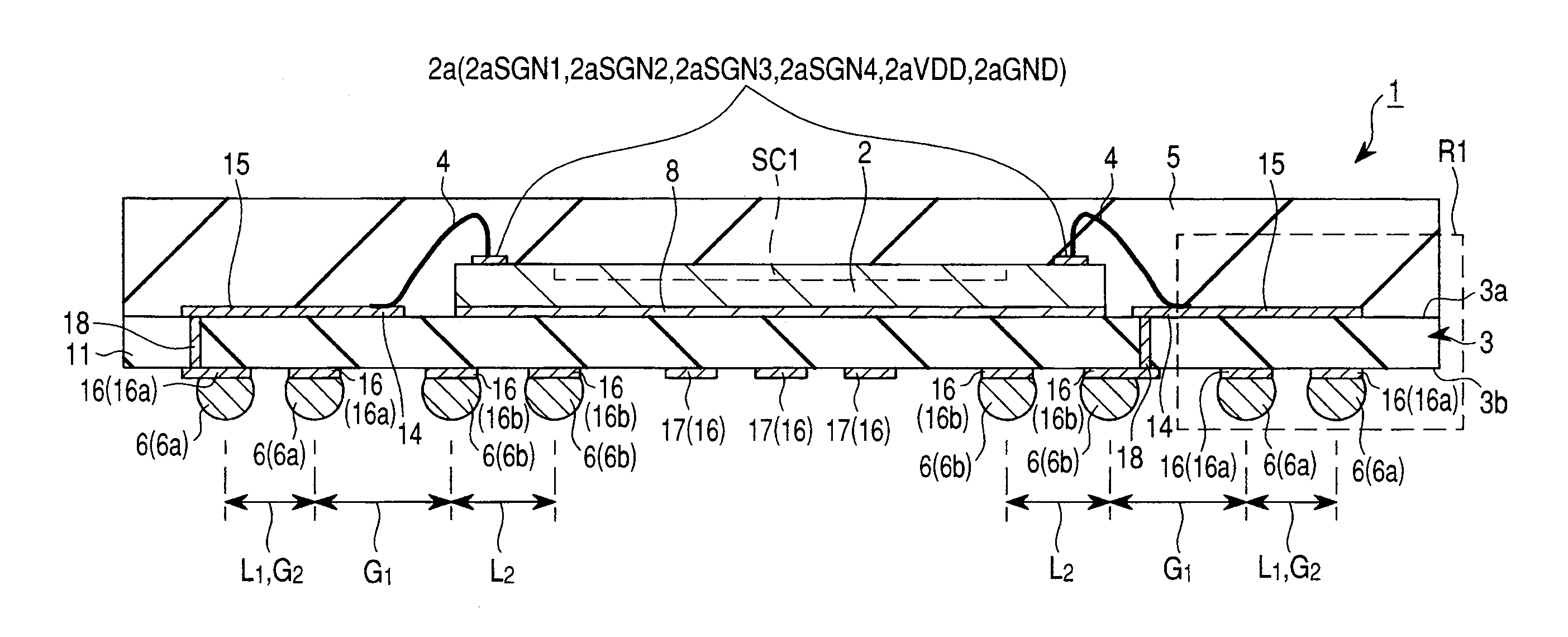

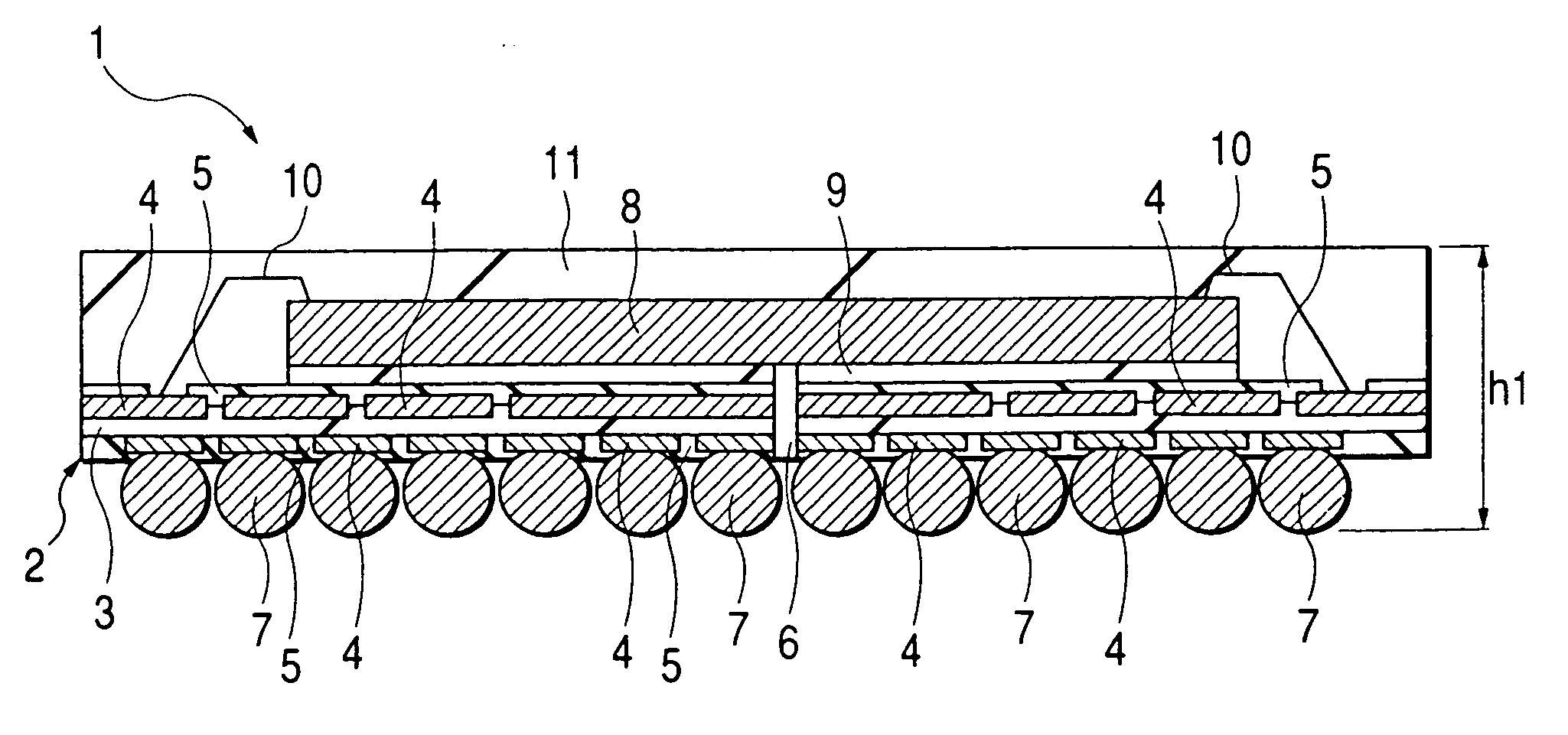

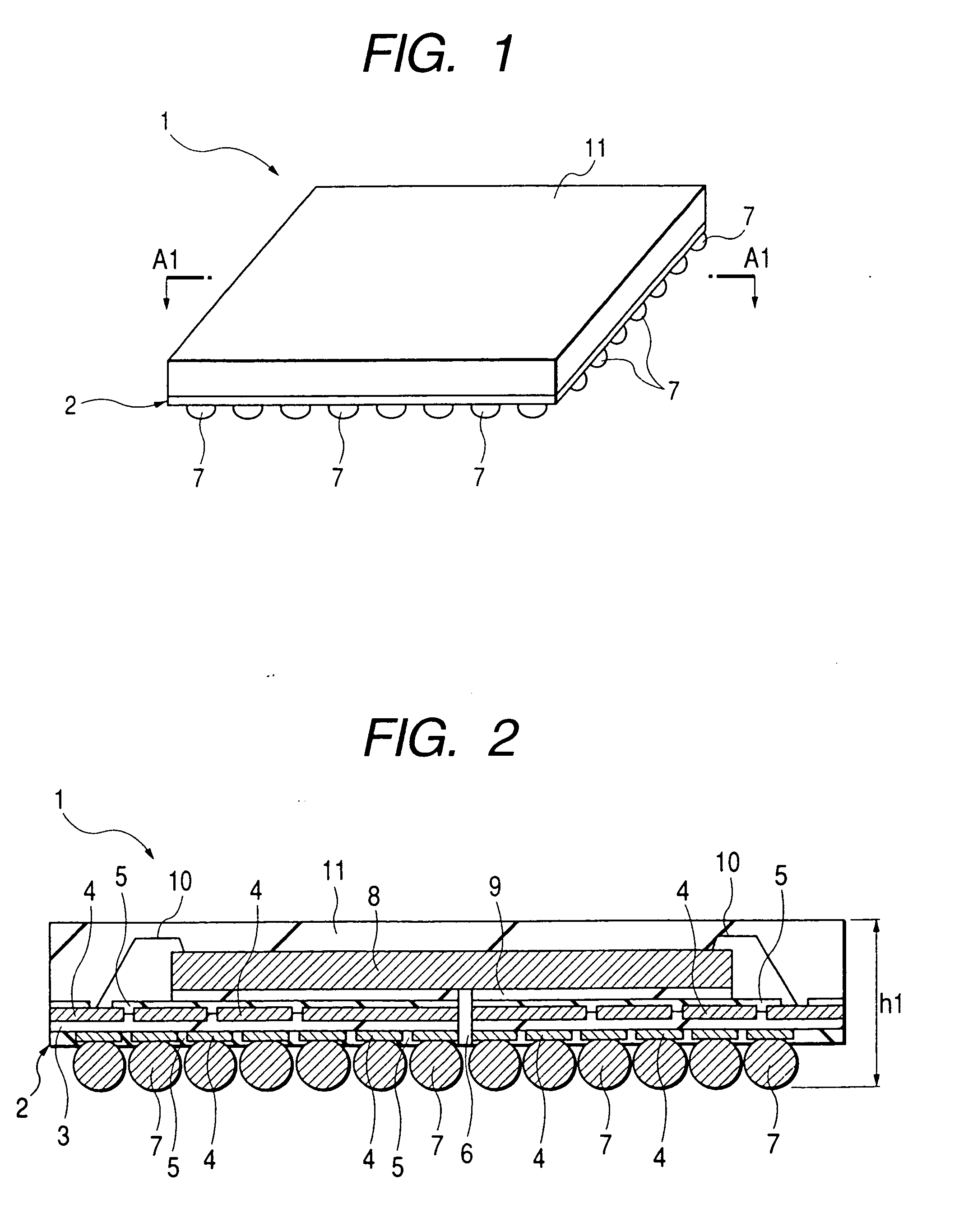

Semiconductor device, manufacturing method thereof, and manufacturing method of semiconductor module

InactiveUS20100090333A1Improve reliabilityMounting yield is increasedFinal product manufactureSemiconductor/solid-state device detailsSolder ballSemiconductor chip

An improvement is achieved in the mounting reliability of a semiconductor device. A semiconductor chip is mounted over an upper surface of a wiring substrate. A plurality of solder balls are disposed individually over a plurality of lands formed on a lower surface of the wiring substrate. The plural lands include a first land group arranged in a plurality of rows and arranged along a peripheral edge portion of the lower surface of the wiring substrate, and a second land group arranged inside the first land group in the lower surface of the wiring substrate. The lands in the first land group are arranged with a first pitch, and the lands in the second land group are arranged with a second pitch higher than the first pitch.

Owner:RENESAS ELECTRONICS CORP

Adhesive composition, film-like adhesive, adhesive sheet, and semiconductor device made with the same

InactiveUS20100178501A1Improve liquiditySolution value is not highOrganic chemistryNon-macromolecular adhesive additivesMeth-Device material

An adhesive composition that is capable of achieving a superior combination of process characteristics such as adherend fill properties (embedability) and low-temperature lamination properties, and semiconductor device reliability such as reflow resistance, as well as a film-like adhesive, an adhesive sheet that exhibits excellent process characteristics including ready releasability from dicing sheets, and a semiconductor device that exhibits excellent productivity, superior adhesive strength when heated and superior moisture resistance, all of which use the adhesive composition. The adhesive composition comprises (A) a thermoplastic resin, (B) a bisallylnadimide represented by a general formula (I) shown below, and (C) a bifunctional or higher (meth)acrylate compound.(wherein, R1 represents a bivalent organic group containing an aromatic ring and / or a straight-chain, branched or cyclic aliphatic hydrocarbon).

Owner:HITACHI CHEM CO LTD

Stacked via-stud with improved reliability in copper metallurgy

InactiveUS6972209B2Facilitate redundant pathIncrease flexibilitySemiconductor/solid-state device detailsSolid-state devicesElectrical conductorMaterials science

A multilevel semiconductor integrated circuit (IC) structure including a first interconnect level including a layer of dielectric material over a semiconductor substrate, the layer of dielectric material comprising a dense material for passivating semiconductor devices and local interconnects underneath; multiple interconnect layers of dielectric material formed above the layer of dense dielectric material, each layer of dielectric material including at least a layer of low-k dielectric material; and, a set of stacked via-studs in the low-k dielectric material layers, each of said set of stacked via studs interconnecting one or more patterned conductive structures, a conductive structure including a cantilever formed in the low-k dielectric material. The dielectric layer of each of the multiple interconnection levels includes a soft low-k dielectric material, wherein the cantilever and set of stacked via-studs are integrated within the soft low-k dielectric material to increase resistance to thermal fatigue crack formation. In one embodiment, each of the set of stacked via-studs in the low-k dielectric material layers is provided with a cantilever, such that the cantilevers are interwoven by connecting a cantilever on one level to a bulk portion of the conductor line on adjacent levels of interconnection, thereby increasing flexibility of stacked via-studs between interconnection levels.

Owner:GLOBALFOUNDRIES INC

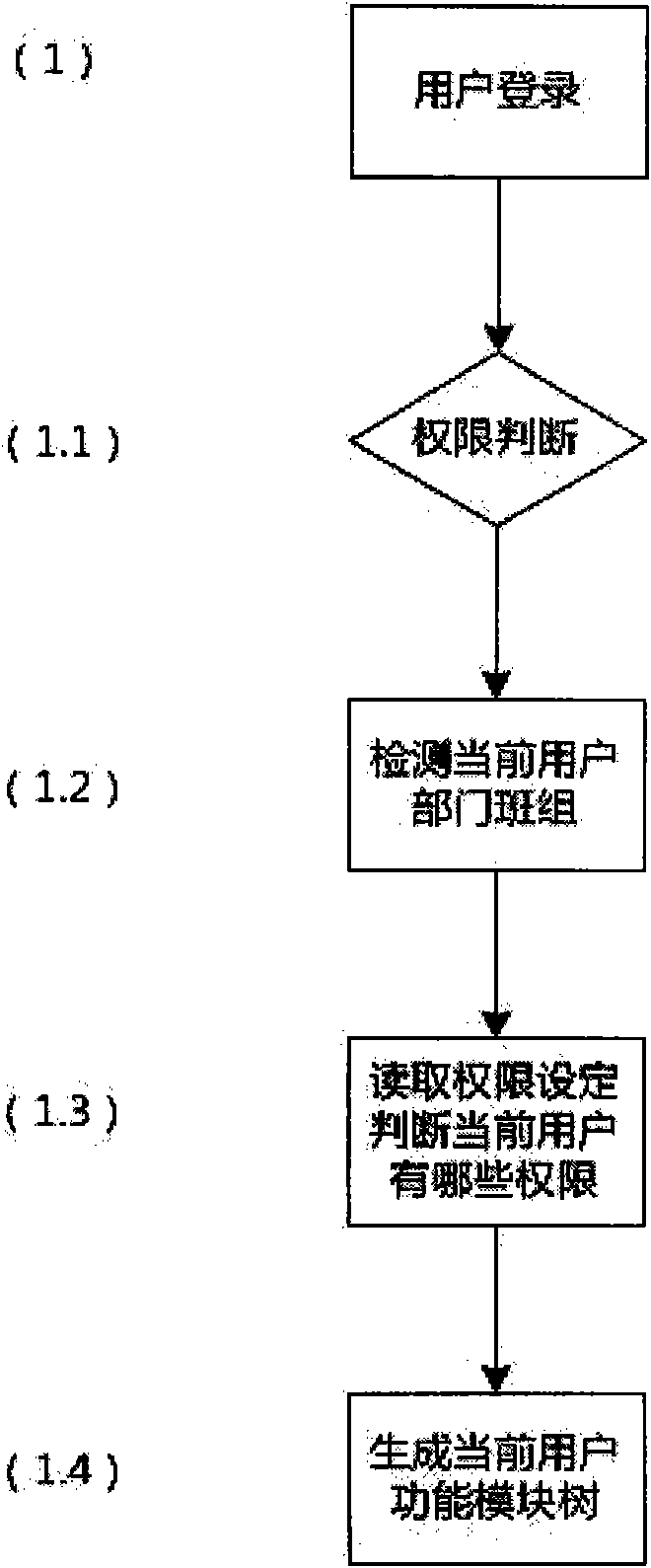

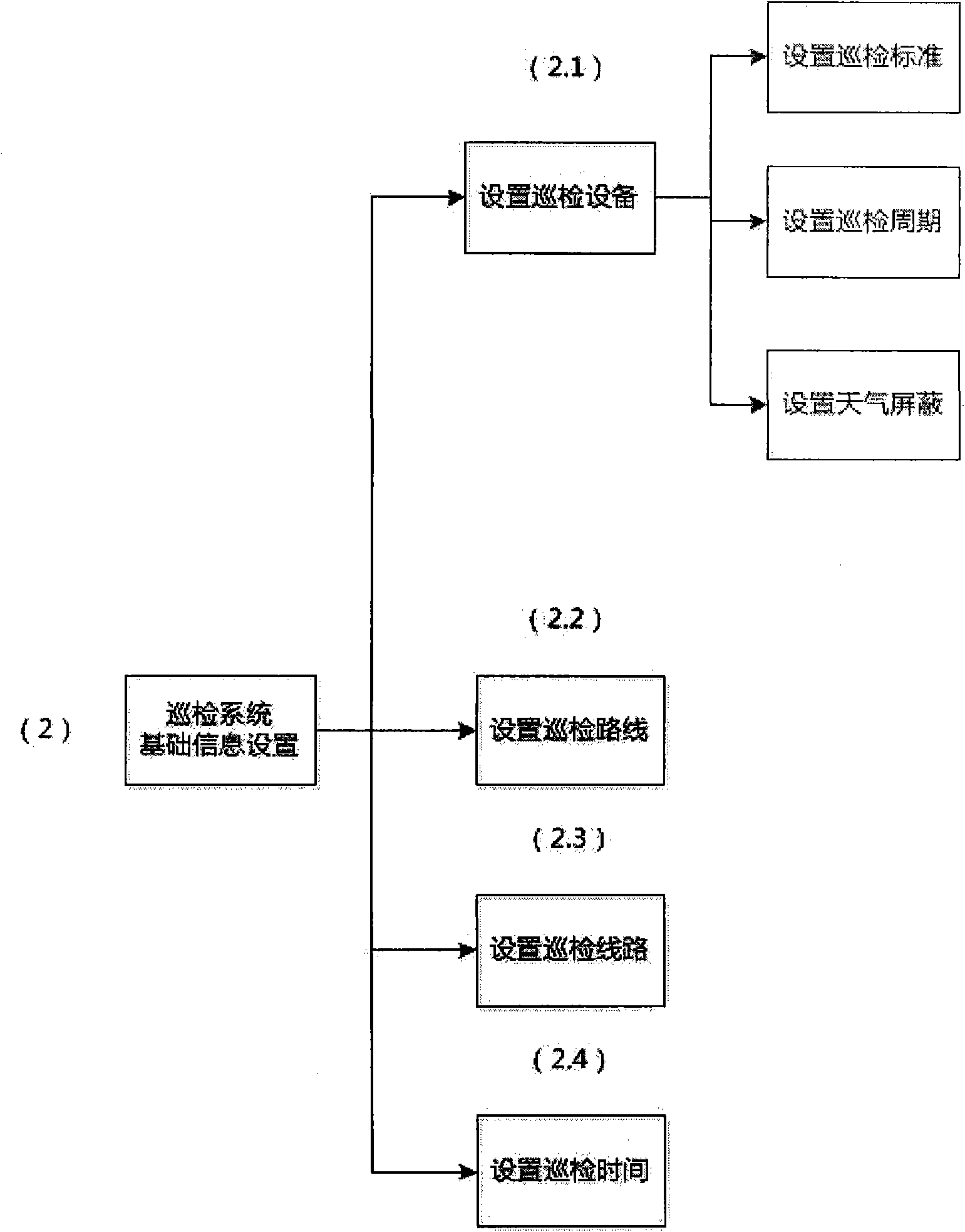

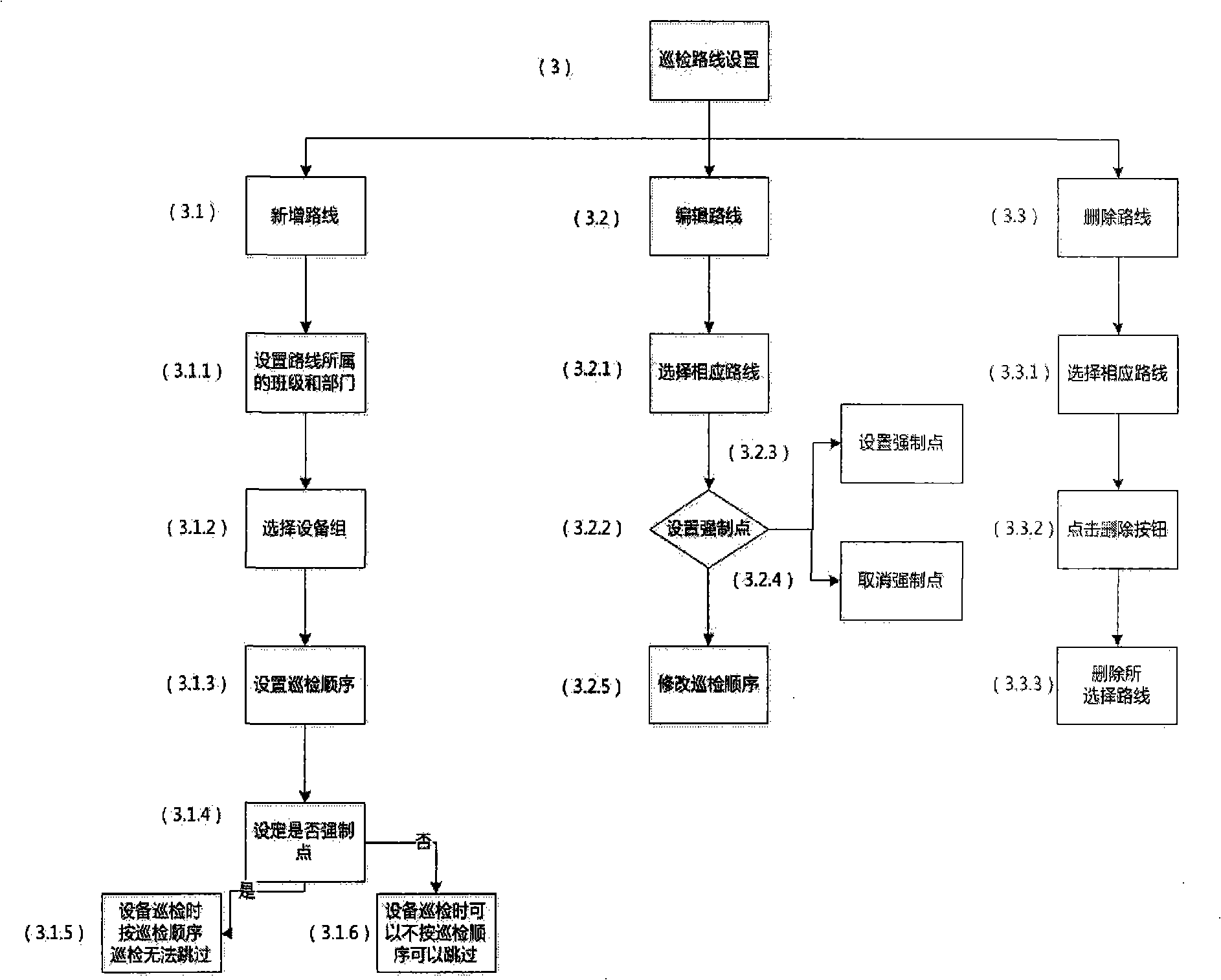

Handheld inspection device of maintenance and operation system for equipment and method thereof

ActiveCN102005065AInspection records are standardized and trueInspection records are standardized and reliableRegistering/indicating working of machinesElectric power equipmentElectric equipment

The invention discloses a handheld inspection device of a EMOS (enhanced metal oxide semiconductor) for accurately detecting the parameters of electric equipment, realizing the paperless office and guaranteeing the reality and the reliability of the data standards, and comprises a handheld data terminal, a client computer and a server computer, wherein an inspection data collecting module is arranged in the handheld data terminal and is used for user leading, user register, data entry, data transmission, conventional inspection, random inspection, equipment inspection and inspection record inquiry; a communication control module is arranged in the handheld data terminal, the client computer and the server computer and is used for the communication of the random inspection, the equipment inspection and the inspection record inquire; and an inspection data managing module is arranged in the server computer and is used for the arrangement of the inspection equipment, the arrangement of an inspection group, the arrangement of an inspection route, the arrangement of an inspection task, the inspection record, the historical record of the inspection, the abnormal record of the inspectionand the arrangement of a dictionary. The invention also provides a handheld inspection method of the EMOS.

Owner:松花江水力发电有限公司 +3

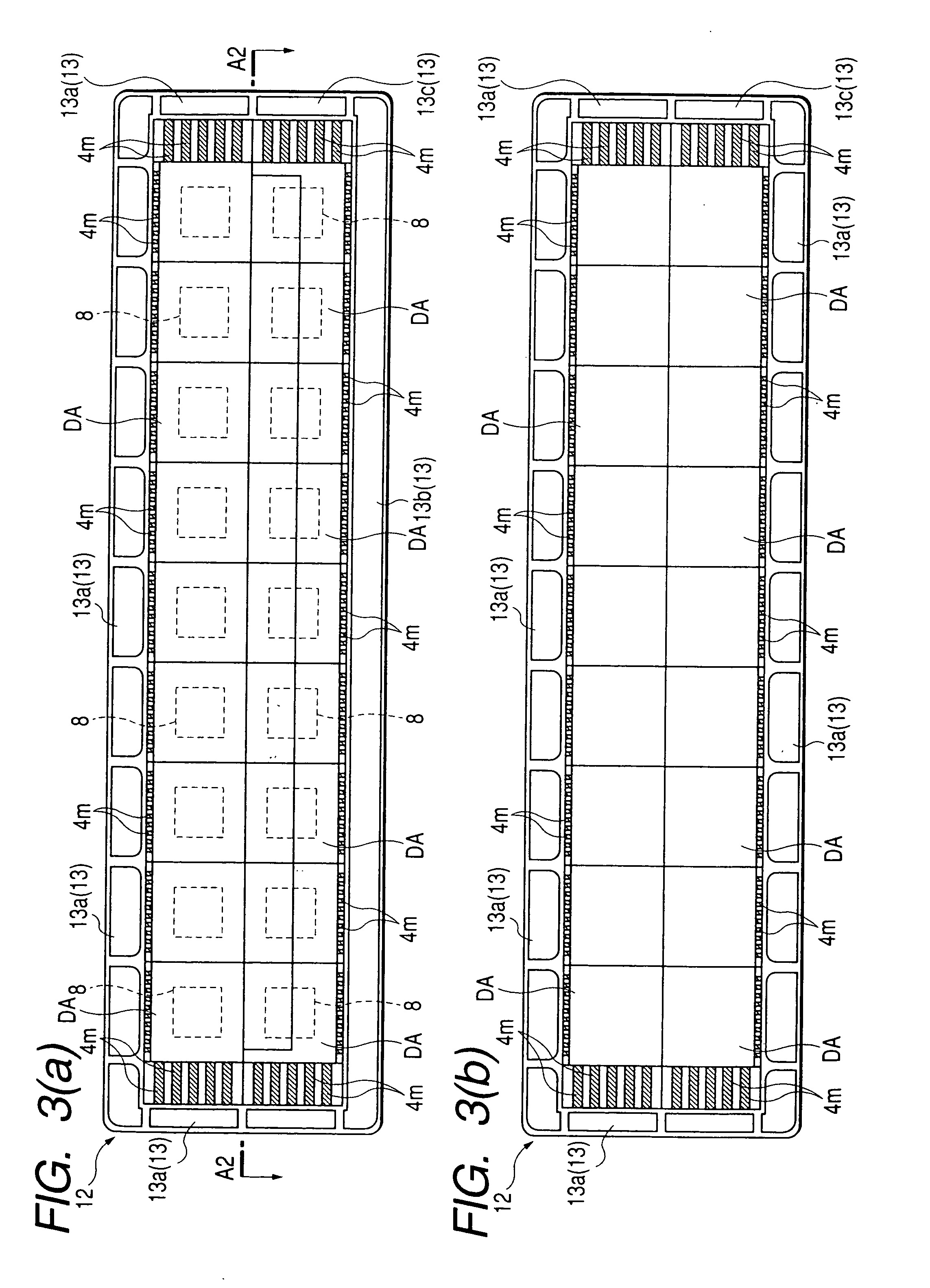

Method of manufacturing a semiconductor device and a semiconductor device

InactiveUS20050127535A1Improve reliabilityLow costSemiconductor/solid-state device detailsSolid-state devicesDevice materialSemiconductor chip

The back side of a strip substrate with plural semiconductor chips mounted thereon is vacuum-chucked to a lower mold half of a mold, and in this state the plural semiconductor chips are sealed with resin simultaneously to form a seal member. Thereafter, the strip substrate and the seal member are released from the mold and are cut into plural semiconductor devices. The semiconductor devices thus obtained are improved in their mounting reliability.

Owner:RENESAS SEMICON PACKAGE & TEST SOLUTIONS +1

Semiconductor device and manufacturing method therefor

ActiveUS20110074016A1Inhibit productionSmall sizeSemiconductor/solid-state device detailsSolid-state devicesSemiconductor chipSemiconductor package

The size and thickness of a semiconductor device are reduced. A semiconductor package with a flip chip bonding structure includes: a semiconductor chip having a main surface with multiple electrode pads formed therein and a back surface located on the opposite side thereto; four lead terminals each having an upper surface with the semiconductor chip placed thereover and a lower surface located on the opposite side thereto; and a sealing body having a main surface and a back surface located on the opposite side thereto. In this semiconductor package, the distance between adjacent first lower surfaces of the four lead terminals exposed in the back surface of the sealing body is made longer than the distance between adjacent upper surfaces thereof. This makes it possible to suppress the production of a solder bridge when the semiconductor package is solder mounted to a mounting board and to reduce the size and thickness of the semiconductor package and further enhance the reliability of the semiconductor package.

Owner:RENESAS ELECTRONICS CORP

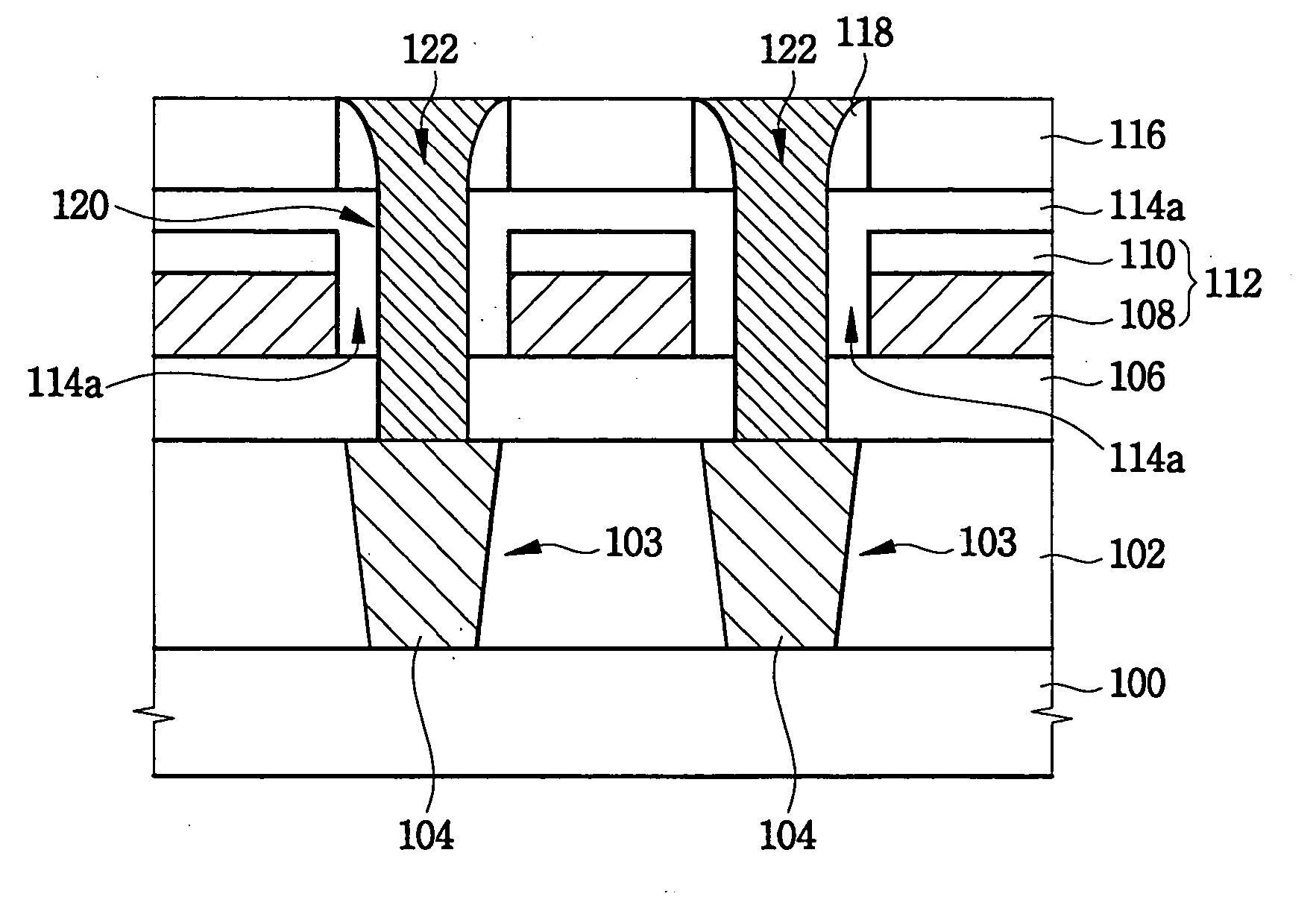

Semiconductor device and method of manufacturing the same

ActiveUS20040140486A1TransistorSemiconductor/solid-state device detailsParasitic capacitanceSilicon oxide

Disclosed herein are a semiconductor device and a method of manufacturing the same that increases the reliability of these devices as size design limitations decrease. Generally, a first insulating film, and wiring, including conductive film patterns and second insulating film patterns are formed on a substrate. Third insulating film patterns including a silicon-oxide-based material are formed on sidewalls of the wiring, and contact patterns and spacers on the sidewalls thereof for defining contact hole regions are formed on the wiring. The contact holes contact surfaces of the third insulating film patterns and pass through the first insulating film. Thus, the thickness of a second insulating film pattern used in the wiring can be minimized, thereby increasing a gap-fill margin between the wiring. A parasitic capacitance between the wiring can be reduced because silicon oxide spacers with a low dielectric constant are formed on sidewalls of the wiring.

Owner:SAMSUNG ELECTRONICS CO LTD

Packaging structure of semiconductor element and manufacture method thereof

ActiveCN101800207AAdvantages Package structureMerit methodSemiconductor/solid-state device detailsSolid-state devicesEngineeringSemiconductor

The invention discloses a packaging structure of a semiconductor element and a manufacture method thereof, wherein the packaging structure of the semiconductor element comprises a base body, a semiconductor element, a plurality of welding pads, through holes, a dielectric metal layer and a solder bump, wherein the base body comprises a front face and a back face opposite to the front face; the semiconductor element is positioned on the front face of the base body; the welding pads are positioned on the front face of the base body and are respectively distributed at the periphery of the semiconductor element; the through holes are positioned in the back face of the base body and correspond to the welding pads; the dielectric metal layer is electrically connected with the welding pads; the solder bump is electrically connected with the dielectric metal layer; and the thickness of the base body at the periphery of the through holes is smaller than that of the base body at the inner side of the through holes, which prevents insulating materials or metal from being accumulated in the openings of the through holes, improves the reliability of products, and reduces the size of the packaging structure.

Owner:CHINA WAFER LEVEL CSP

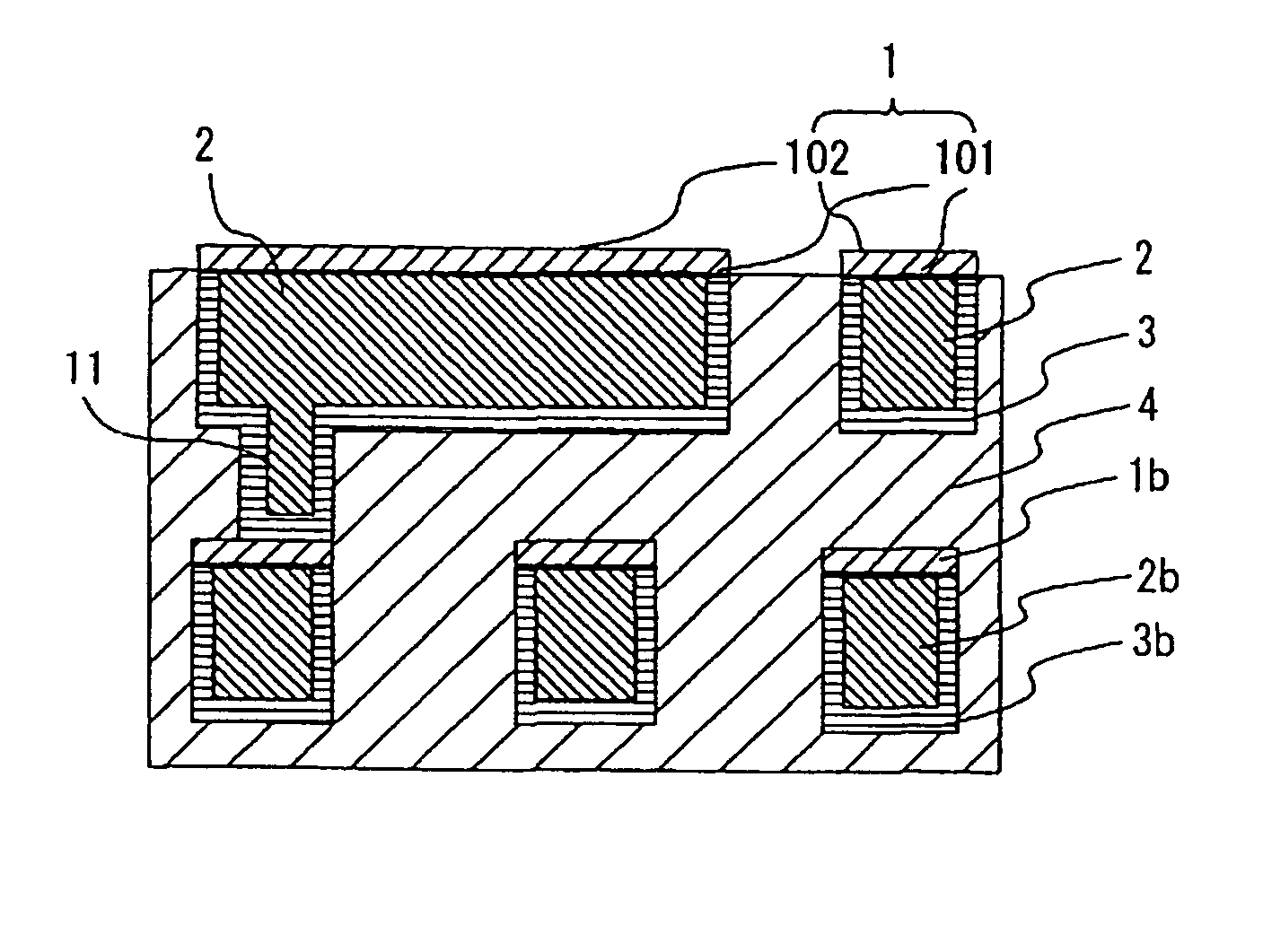

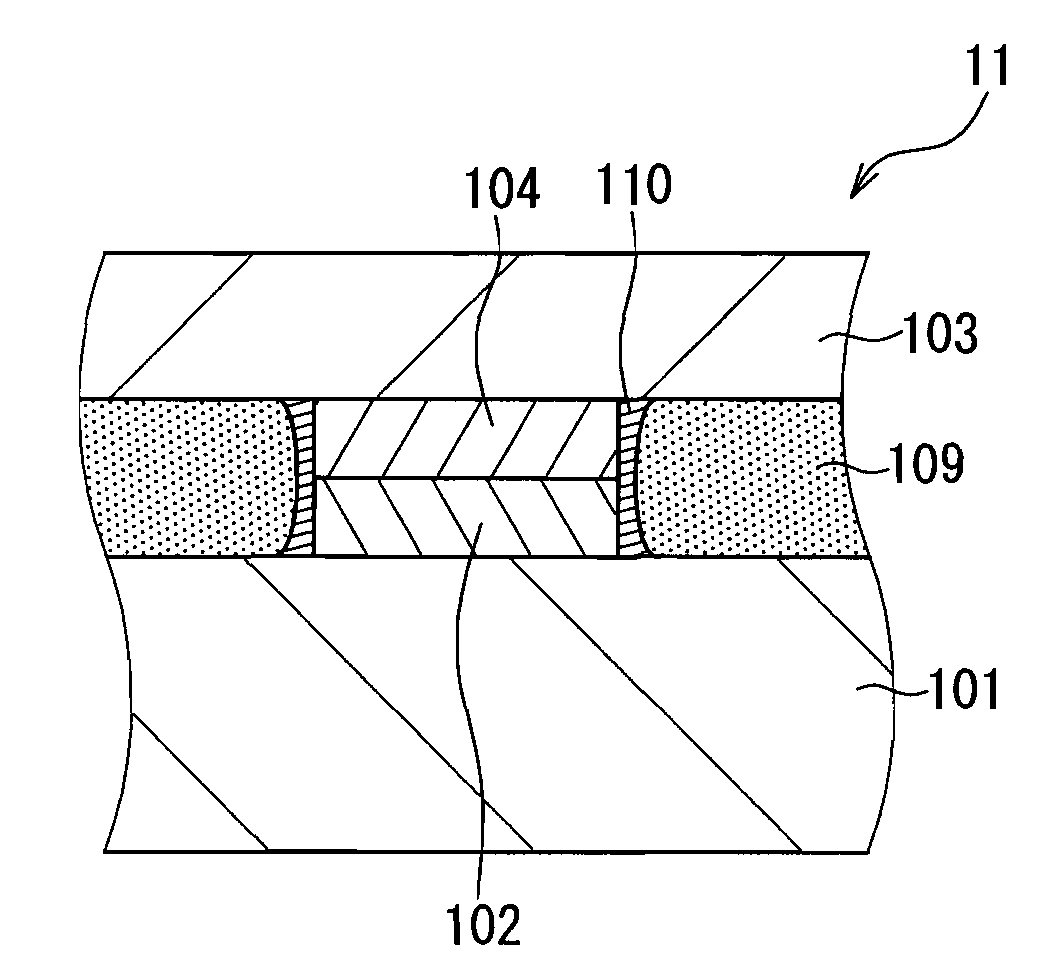

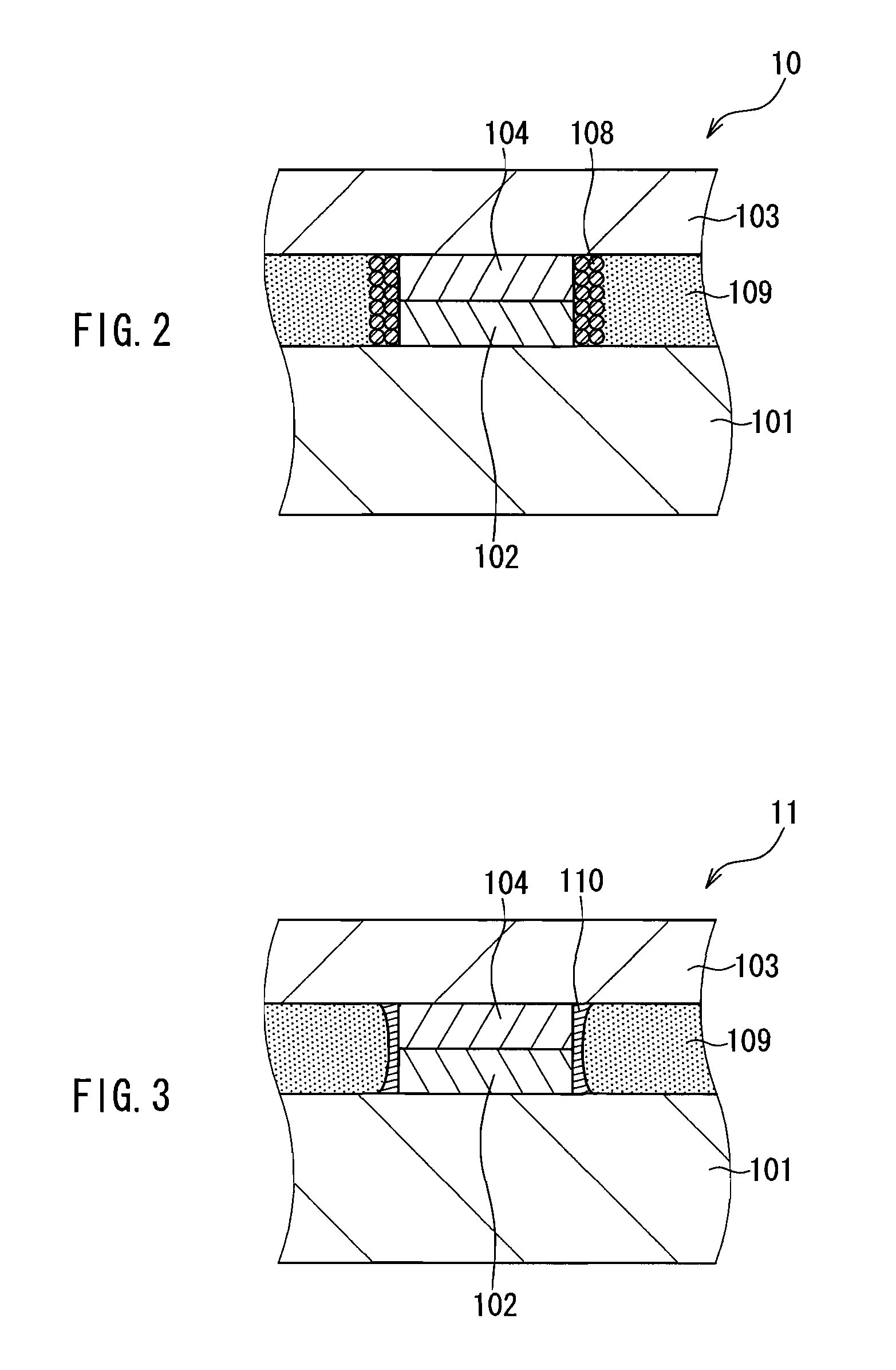

Connection structure and method of producing the same

ActiveUS20090102064A1Improve reliabilityIncrease productionFinal product manufactureSemiconductor/solid-state device detailsProduction rateSemiconductor chip

A connection structure (package 10) has a first plate body 101 and a second plate body; in the first plate body 101, a wiring pattern having a plurality of connection terminals 102 is formed, and the second plate body has at least two connection terminals (electrode terminals 104) arranged facing the connection terminals of the first plate body 101. The connection terminals of the first and second plate bodies are connection terminals formed as projections on the surfaces of the first and second plate bodies. A conductive substance 108 is accumulated to cover at least a part of each side face of the connection terminals opposed to each other of the first and second plate bodies, and the connection terminals thus opposed are connected to each other via the conductive substance. The package thus formed is ready for a high-pin-count, narrow-pitch configuration of a next-generation semiconductor chip, and exhibits excellent productivity and reliability. The present invention is advantageous for such a package, for a connection structure applicable to the production of the package, and for a method of producing the connection structure.

Owner:PANASONIC CORP

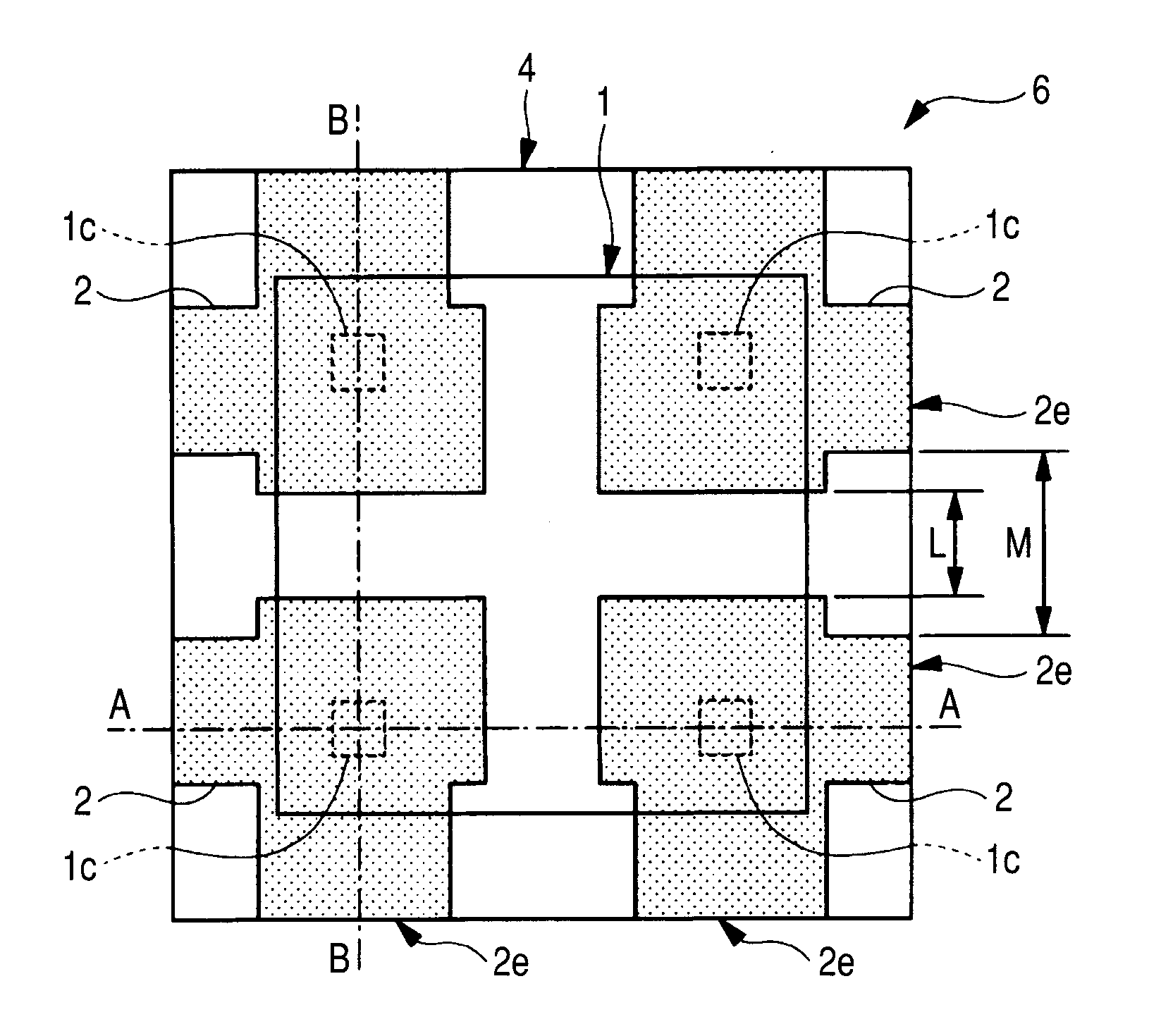

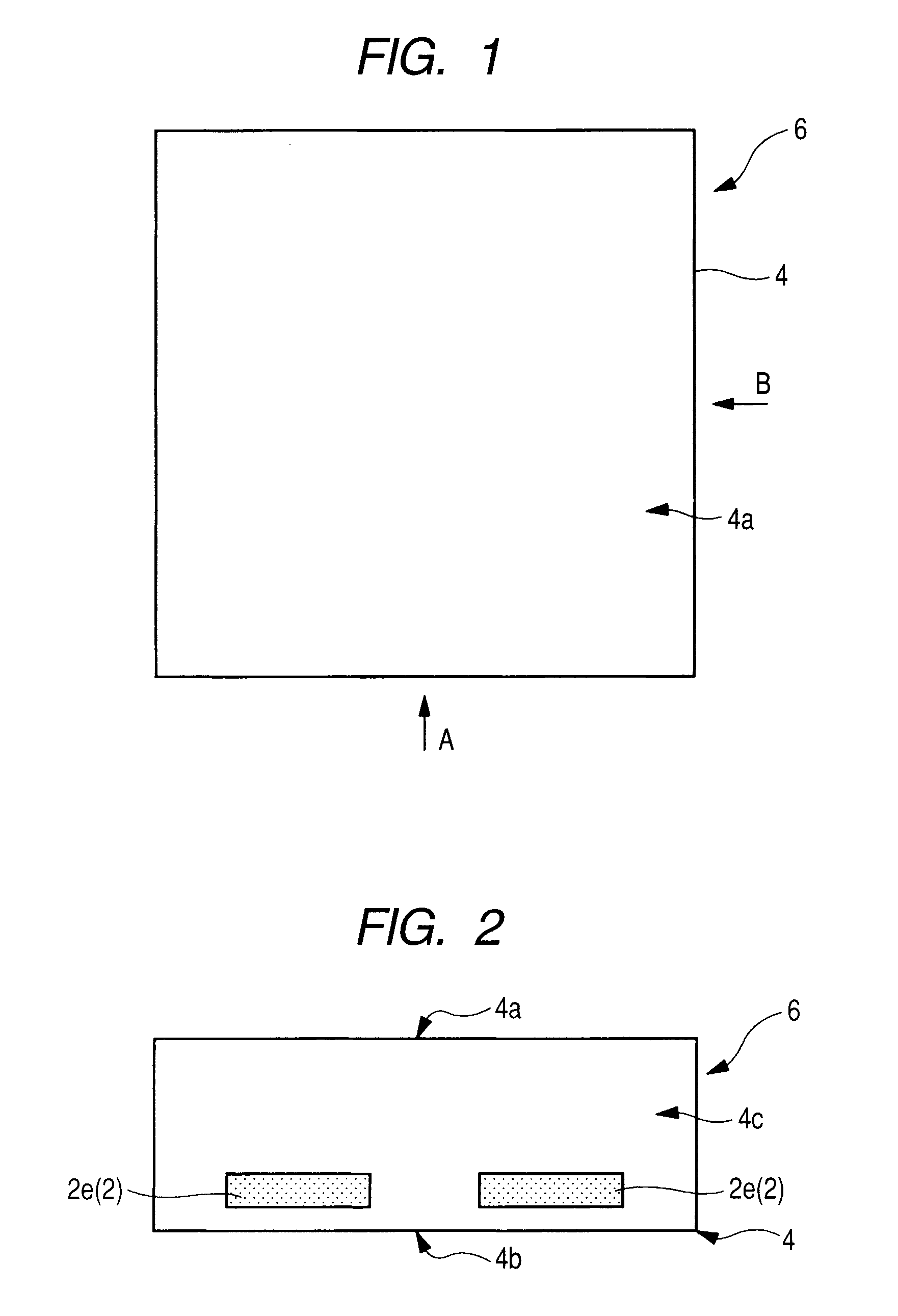

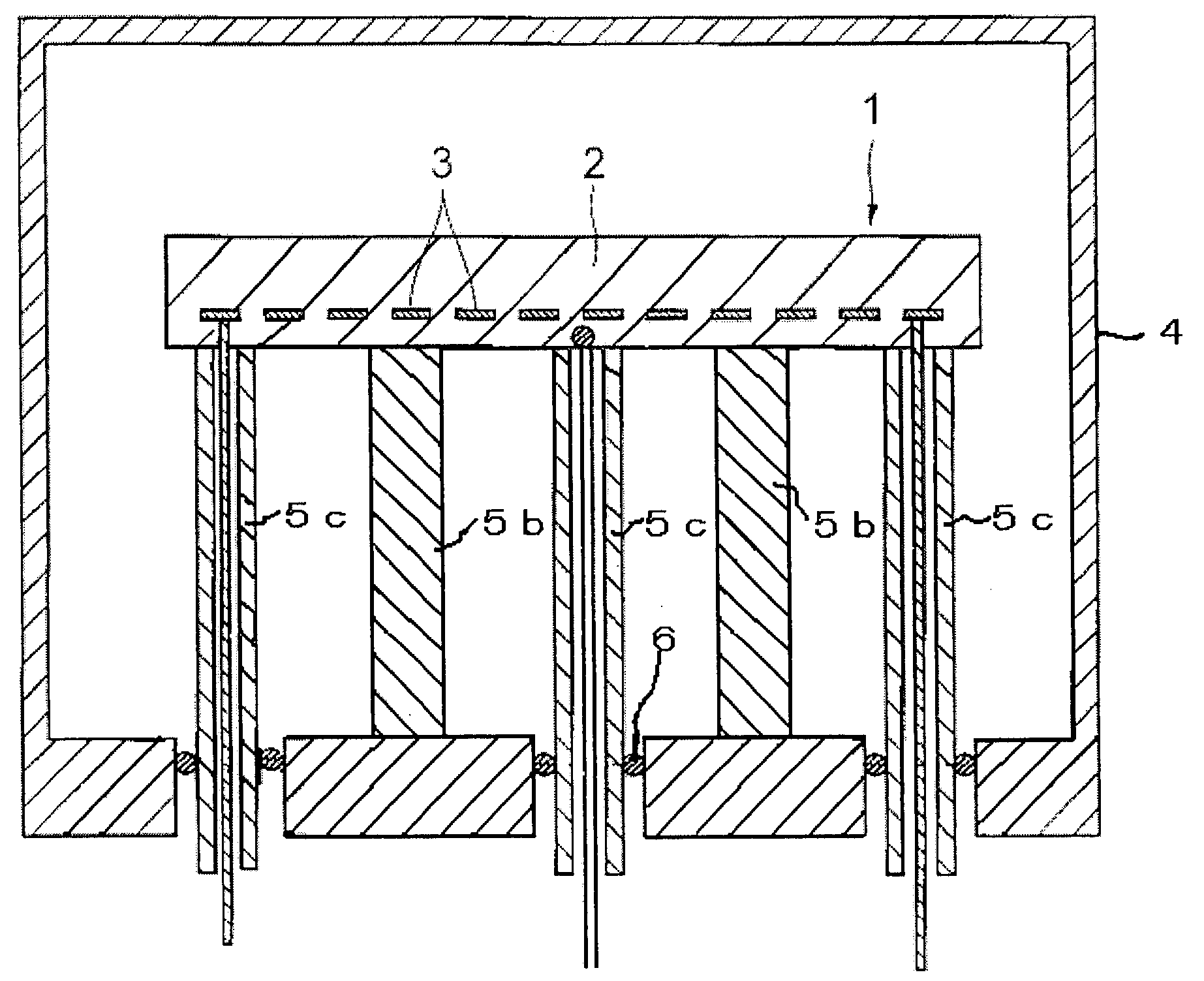

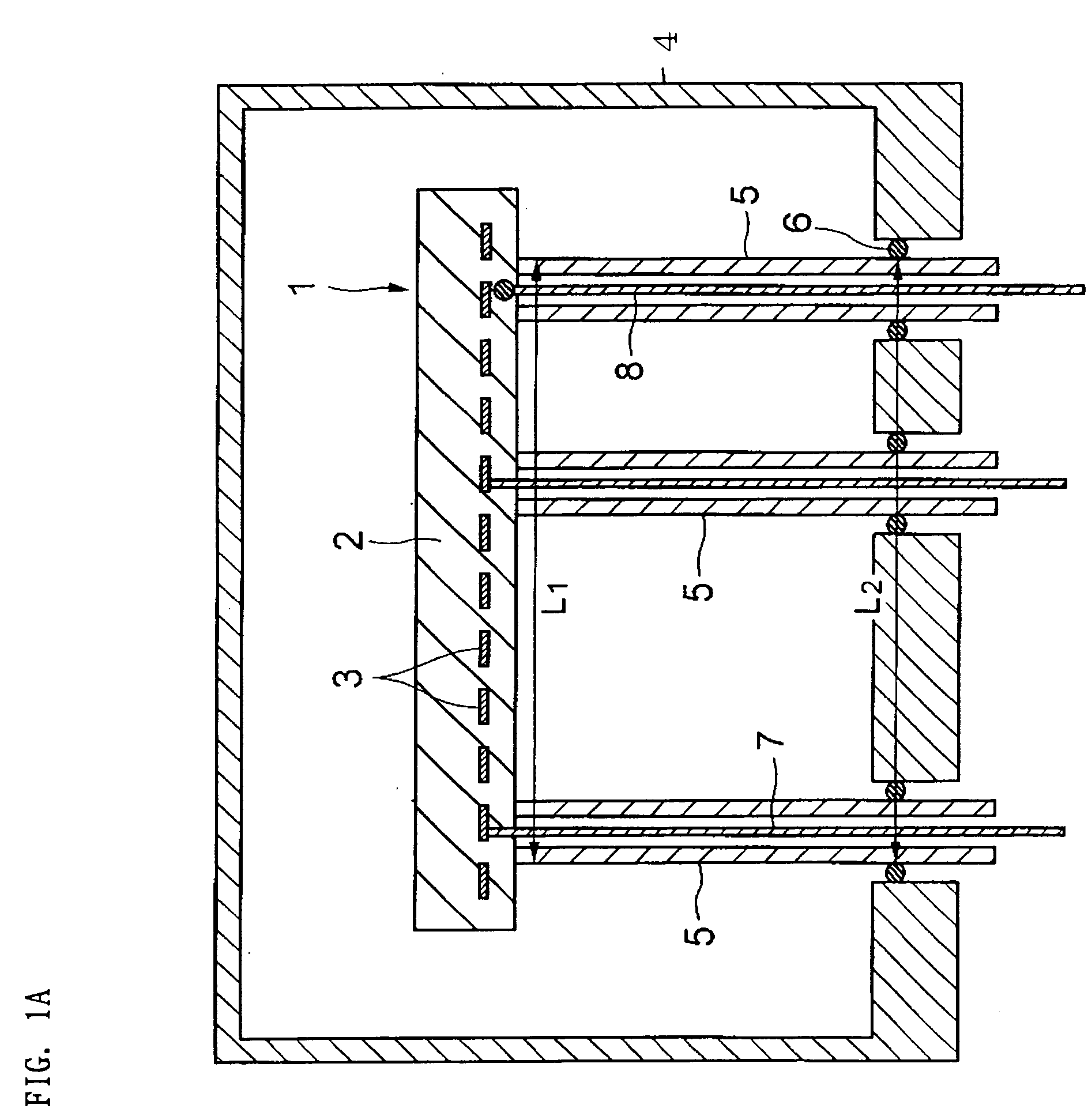

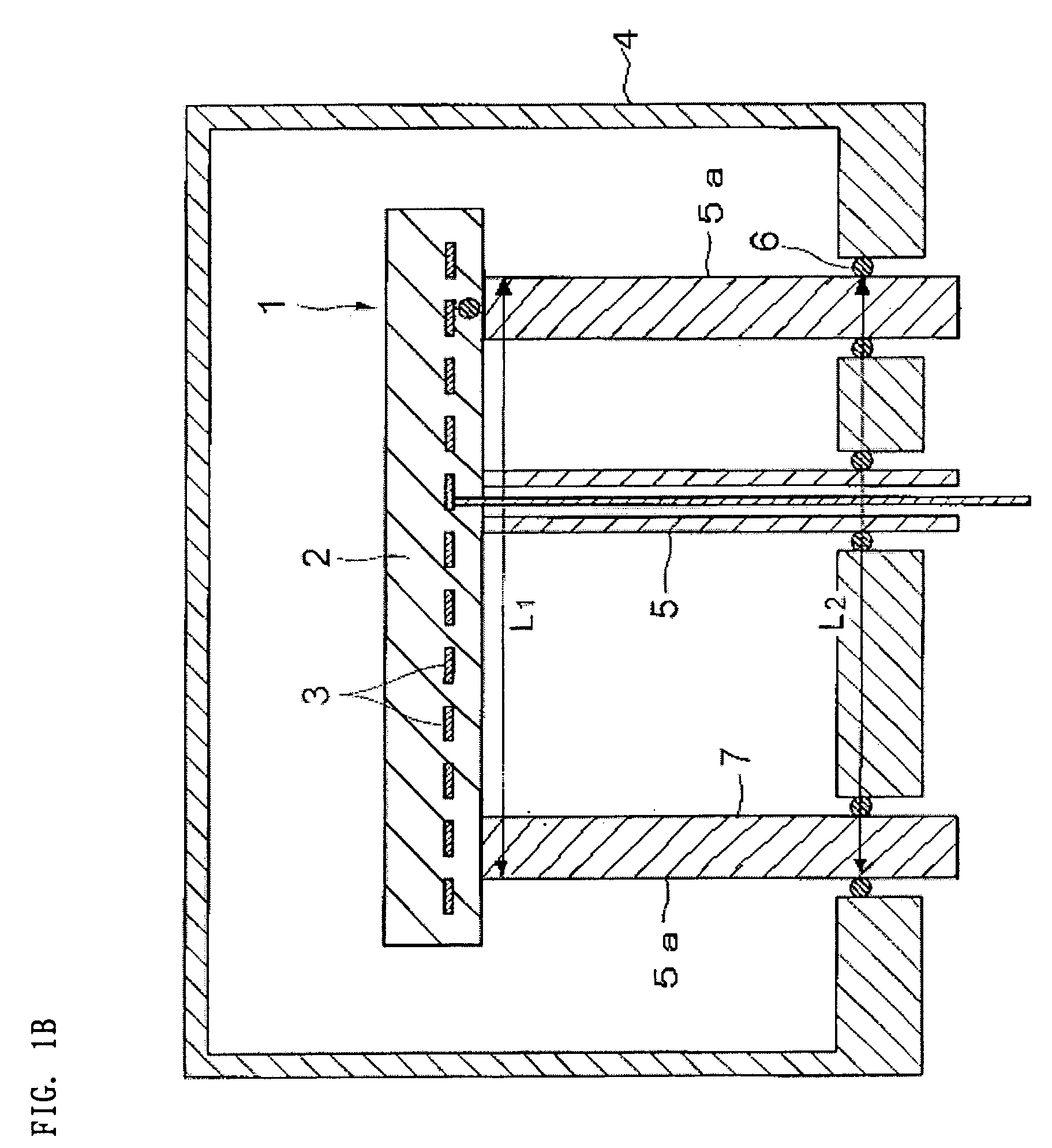

Wafer holder and semiconductor manufacturing apparatus

InactiveUS20050166848A1Prevent be damageHigh reliabilityLiquid surface applicatorsSemiconductor/solid-state device manufacturingEngineeringSemiconductor

A wafer holder furnished with a plurality of anchored tubular pieces and / or anchored support pieces affixed to the holder's ceramic susceptor and in which damage to the anchored tubular pieces due to thermal stress during heating operations is prevented, and a high-reliability semiconductor manufacturing apparatus utilizing the wafer holder are made available. One end of at least two of the anchored tubular pieces (5) and / or anchored support pieces is affixed to the ceramic susceptor (2) and the other end is fixed in the reaction chamber (4), wherein letting the highest temperature the ceramic susceptor (2) attains be T1, the thermal expansion coefficient of the ceramic susceptor (2) be α1, the highest temperature the reaction chamber (4) attains be T2, the thermal expansion coefficient of the reaction chamber (4) be α2, the longest inter-piece distance on the ceramic susceptor (2) among the plurality of anchored tubular pieces (5) and / or anchored support pieces at normal temperature be L1, and the longest inter-piece distance on the reaction chamber (4) among the plurality of anchored tubular pieces (5) and / or anchored support pieces at normal temperature be L2, then the relational formula |(T1×α1×L1)−(T2×α2×L2)|≦0.7 mm is satisfied.

Owner:SUMITOMO ELECTRIC IND LTD

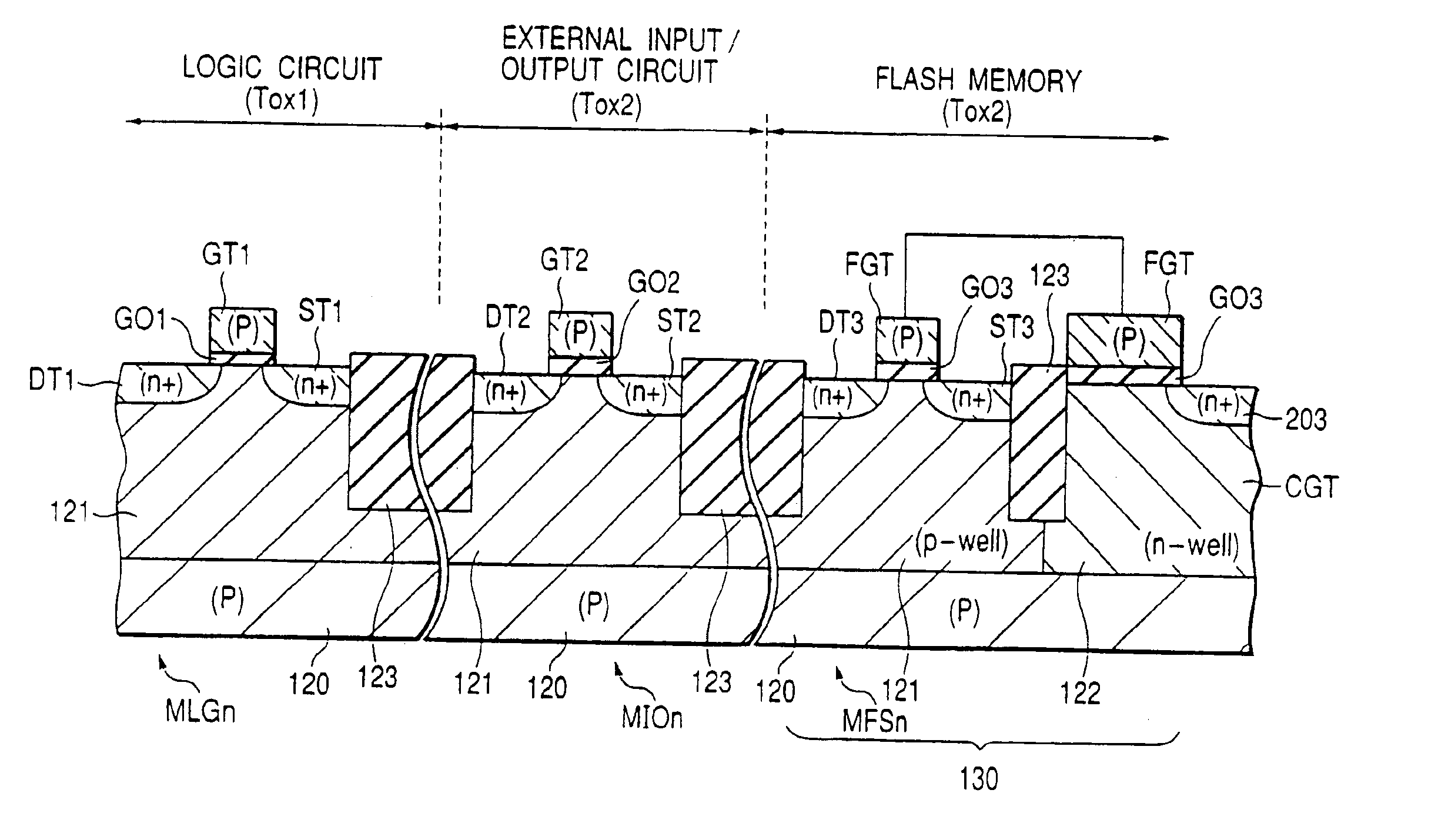

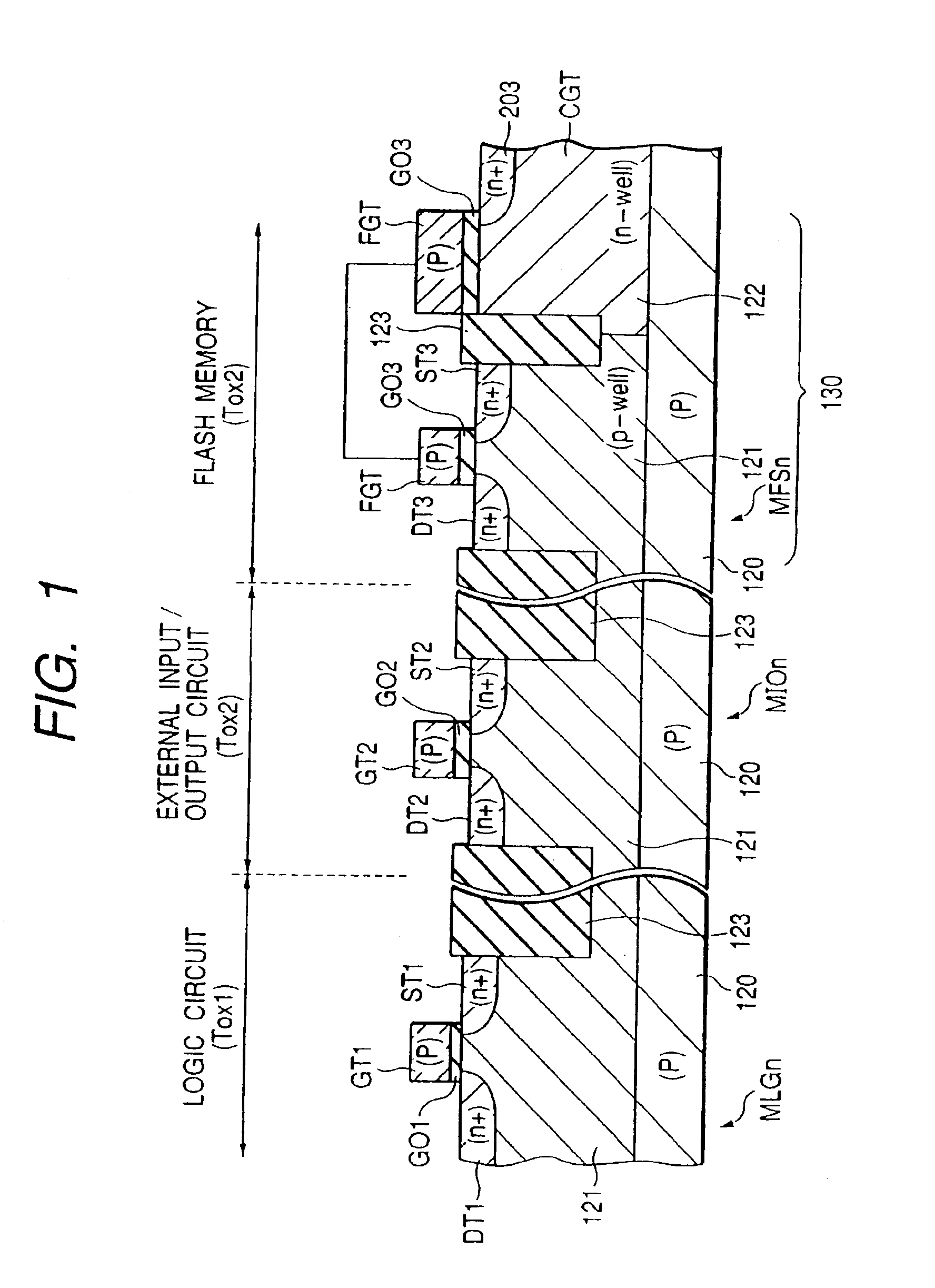

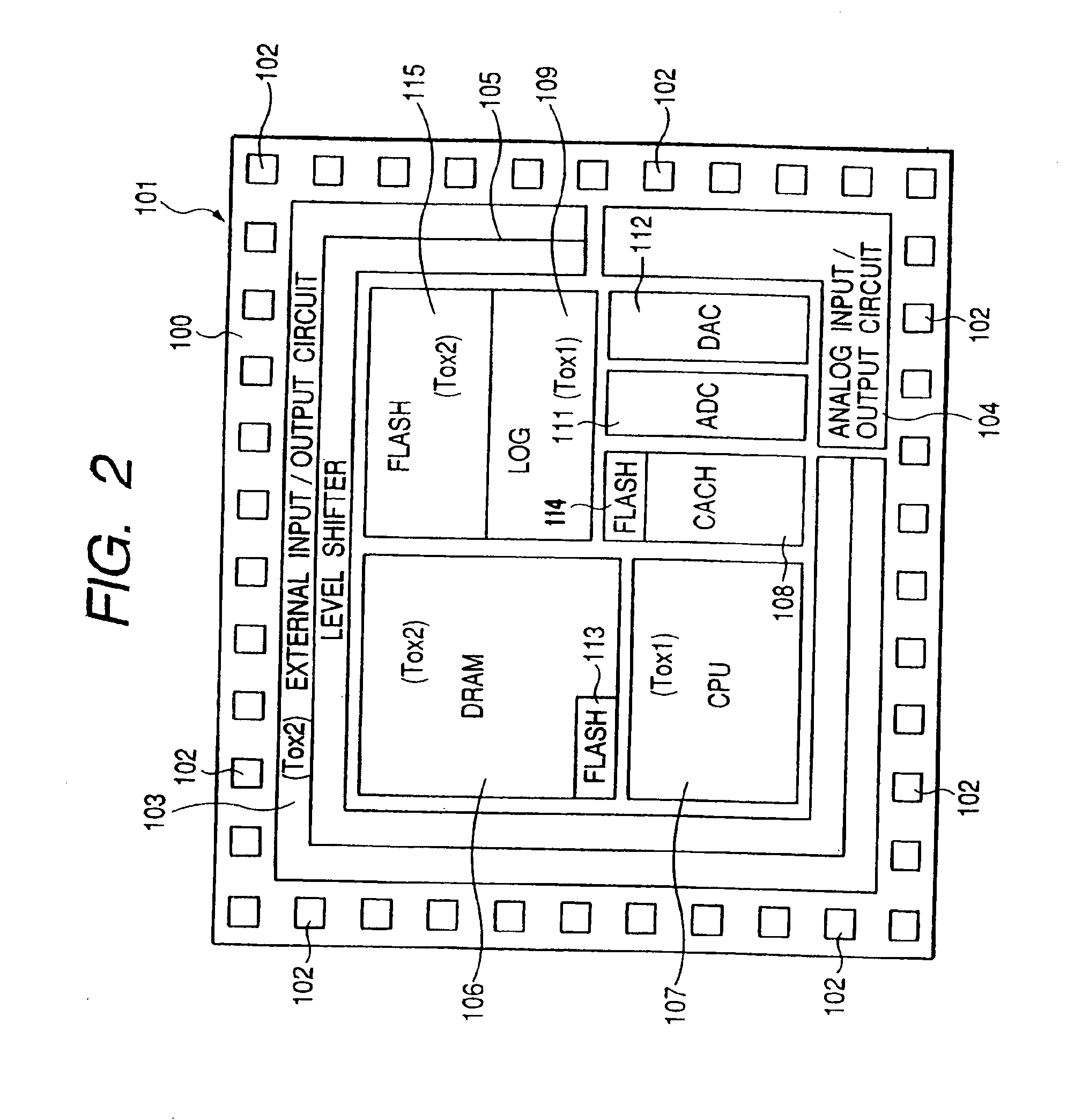

Semiconductor integrated circuit and nonvolatile memory element

InactiveUS6906954B2Enhance long-term information retention capabilityImprove rendering capabilitiesNanoinformaticsSolid-state devicesCMOSPolysilicon gate

0 Owing to the above, even with the single-layer gate process such as single-layer polysilicon gate process, it is possible to obtain a semiconductor integrated circuit such as system LSI in which a nonvolatile memory which is excellent in data retention capability is merged and packaged with a DRAM etc. Further, since the nonvolatile memory of high reliability can be formed without adding any step to a related art manufacturing process, such as a standard CMOS manufacturing process, the present invention may be readily applied to an LSI in which the nonvolatile memory and a logic LSI, or the nonvolatile memory and a DRAM are merged and packaged on an identical semiconductor substrate. Accordingly, a system LSI in which a flash memory is merged and packaged can be provided without increasing the cost of manufacture.

Owner:TESSERA ADVANCED TECH

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com