Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

269 results about "Multicore cpu" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

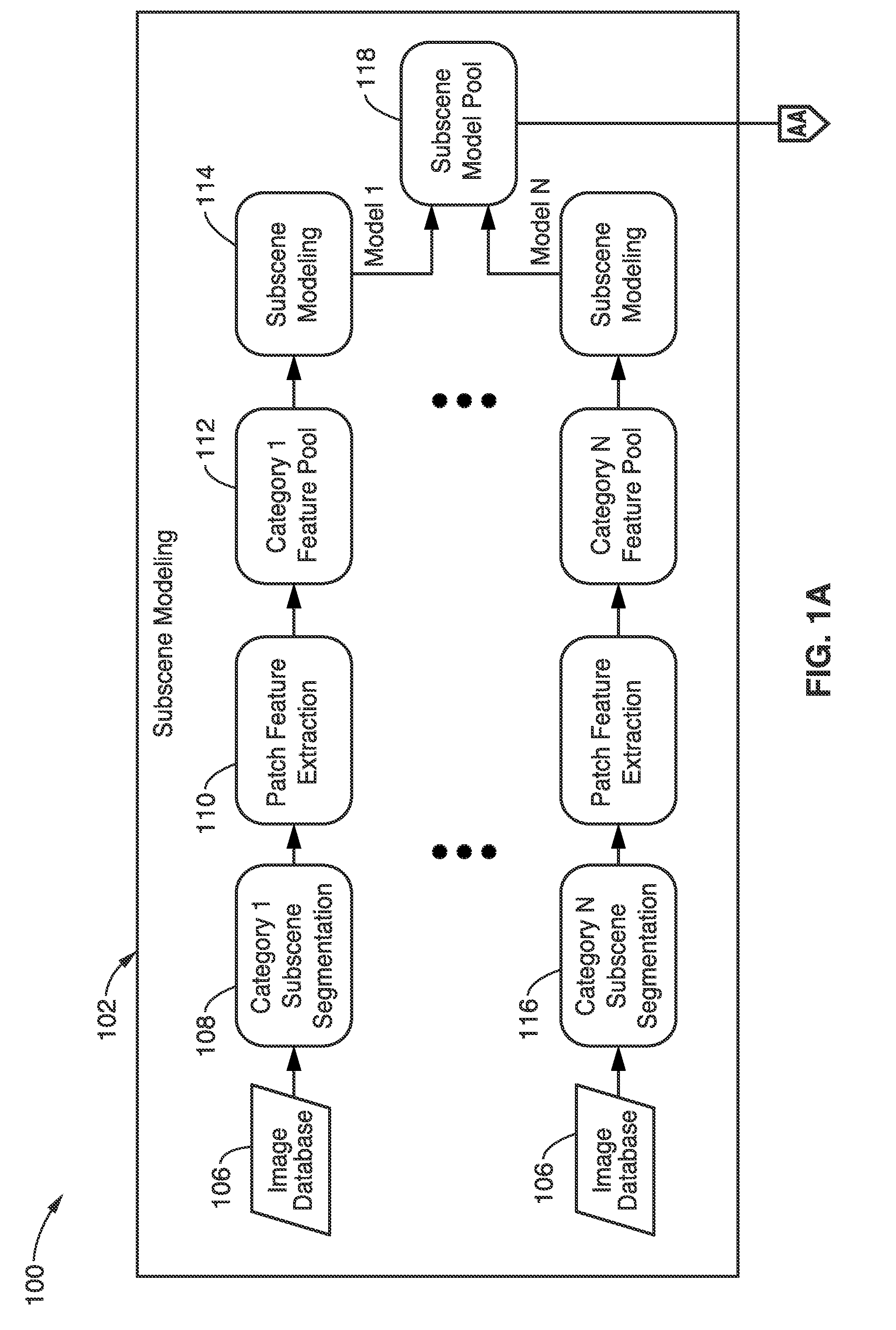

Region description and modeling for image subscene recognition

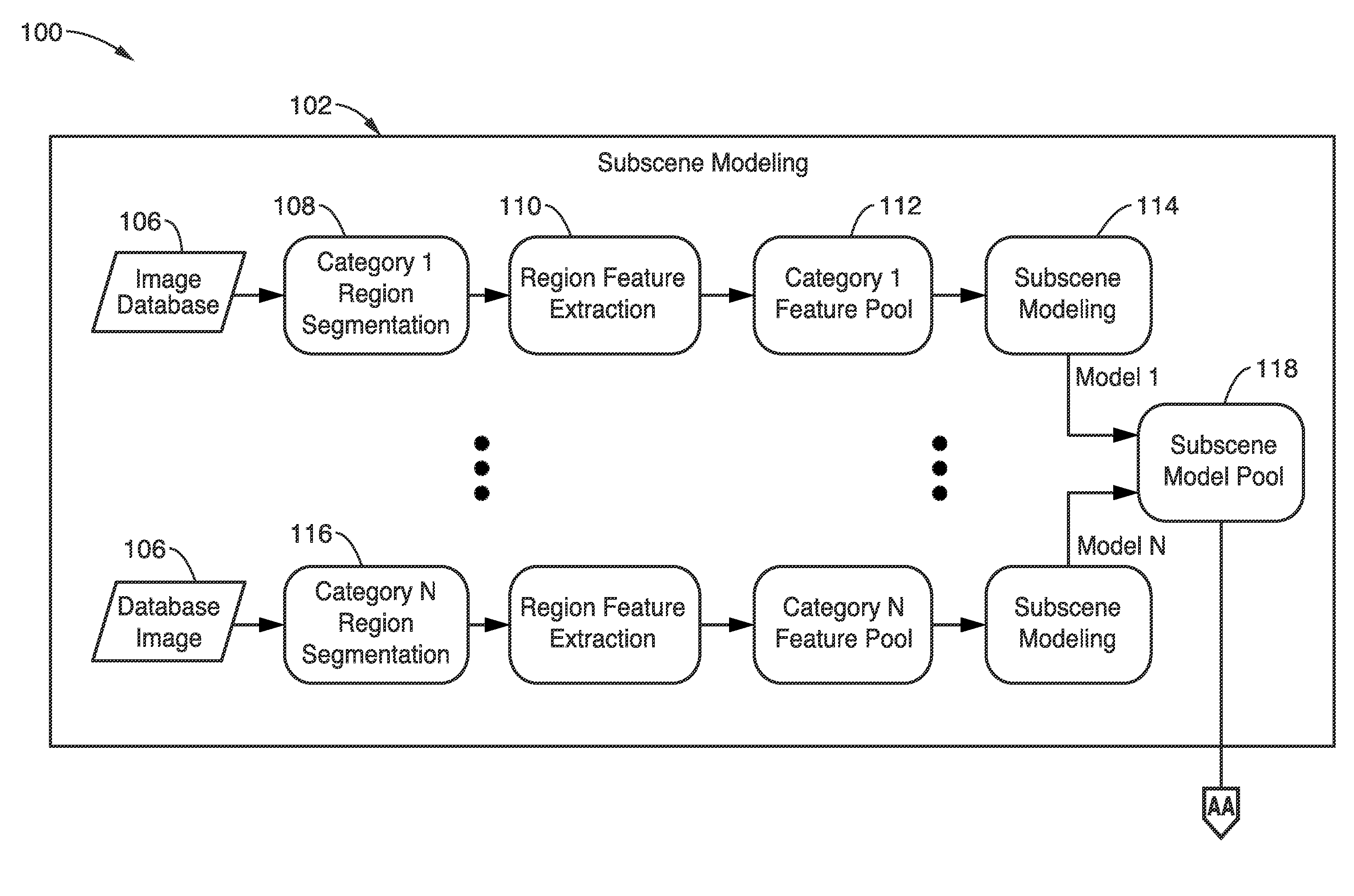

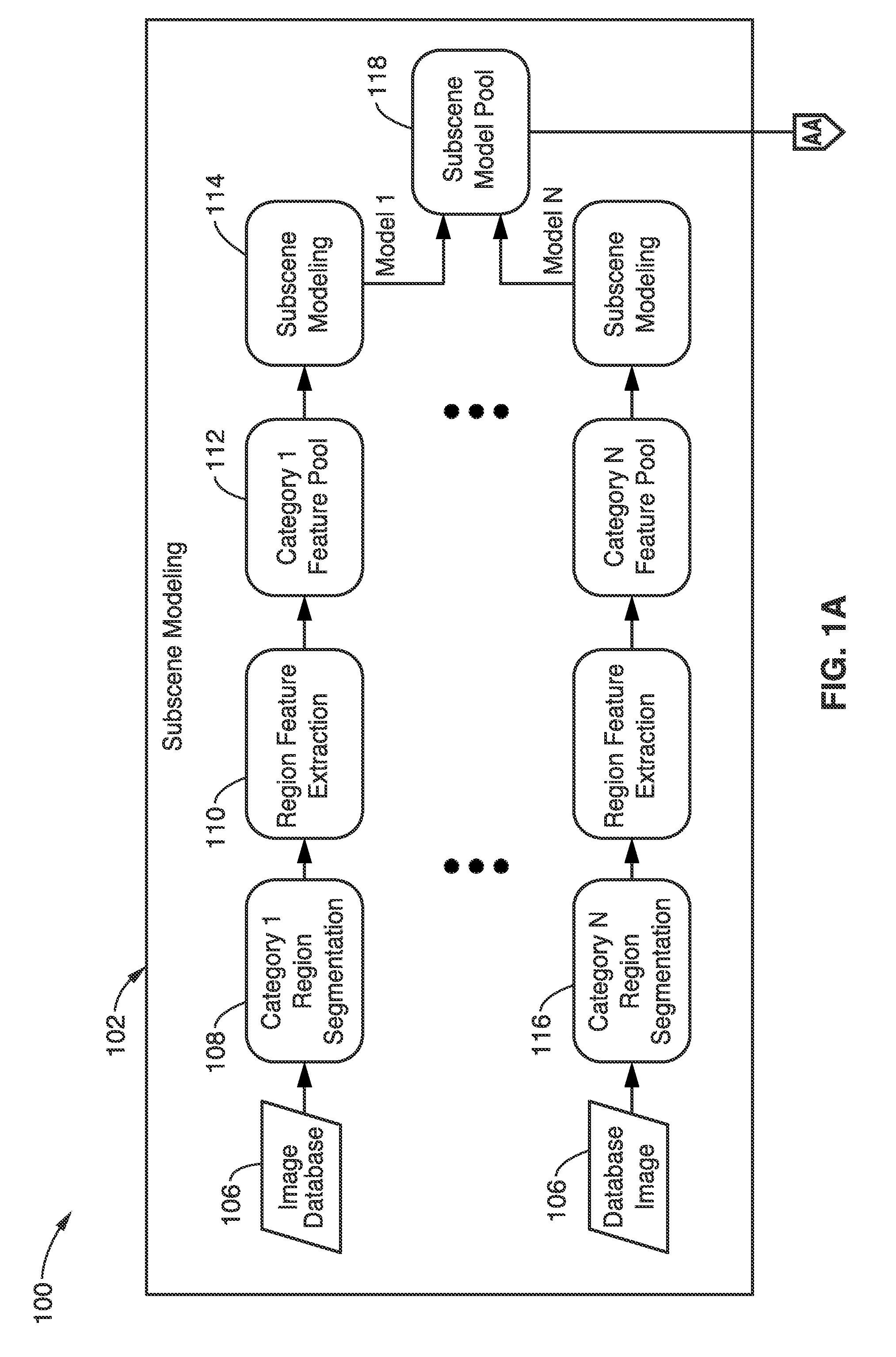

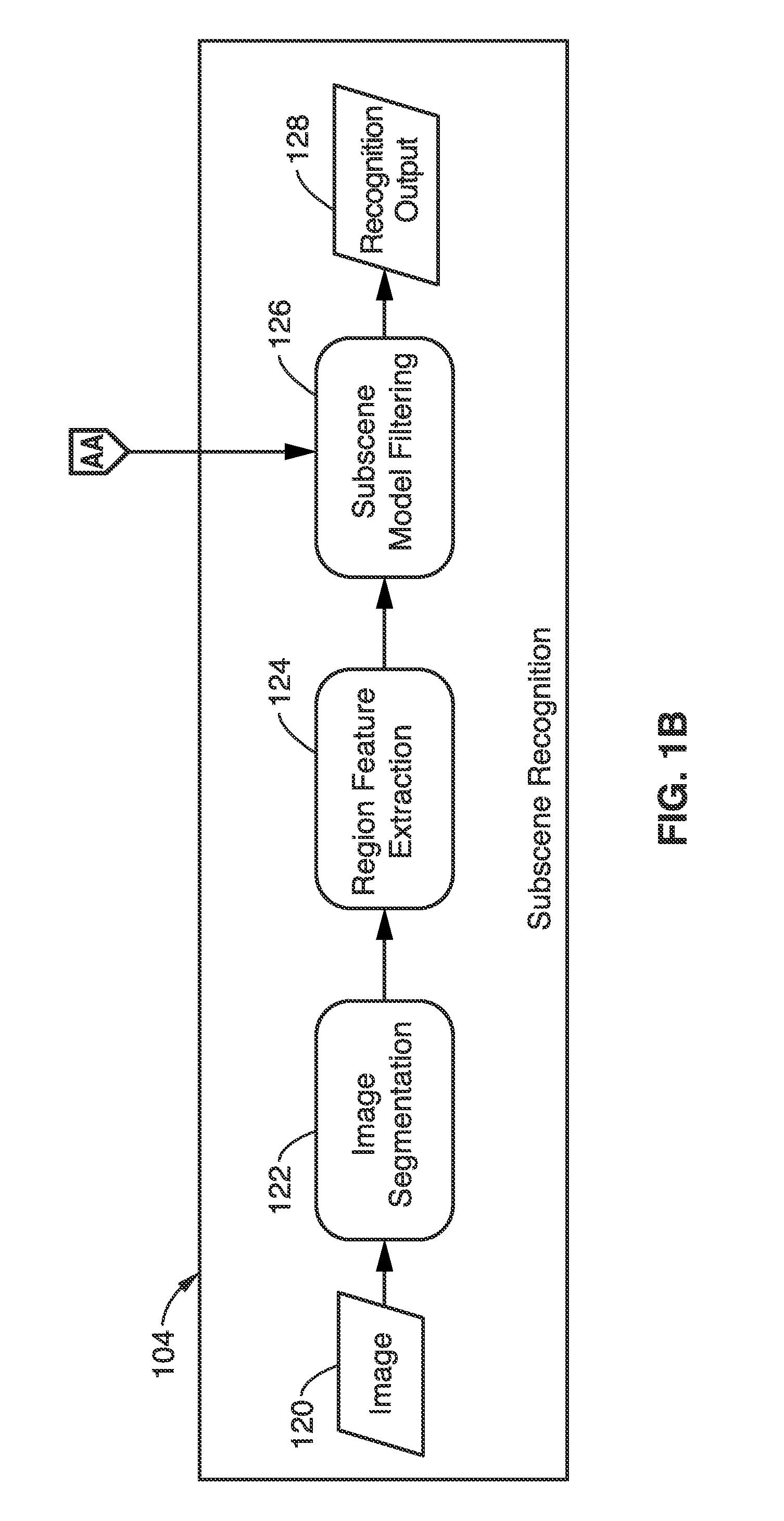

A method and apparatus is described here that categorizes images by extracting regions and describing the regions with a 16-dimensional subscene feature vector, which is a concatenation of color, texture, and spatial feature vectors. By comparing the spatial feature vectors in images with similarly-obtained feature vectors in a Gaussian mixture based model pool (obtained in a subscene modeling phase), the images may be categorized (in a subscene recognition phase) with probabilities relating to each region or subscene. Higher probabilities are likelier correlations. The device may be a single or multiple core CPU, or parallelized vector processor for characterizing many images. The images may be photographs, videos, or video stills, without restriction. When used real-time, the method may be used for visual searching or sorting.

Owner:SONY CORP

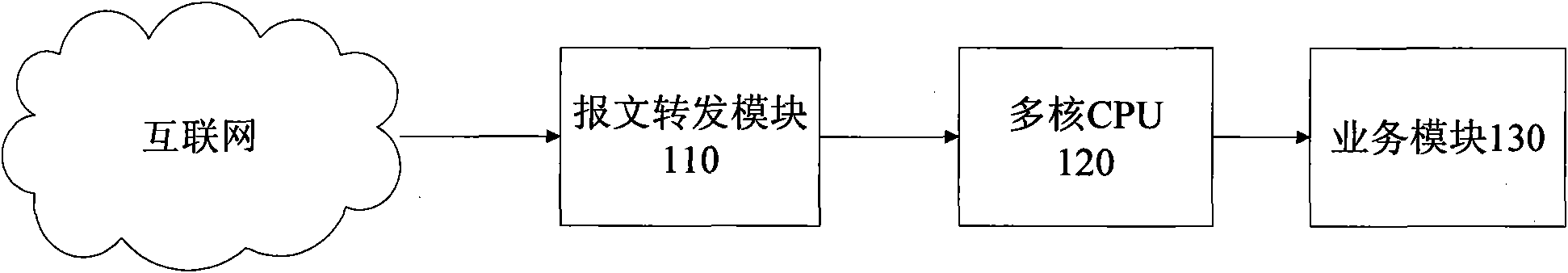

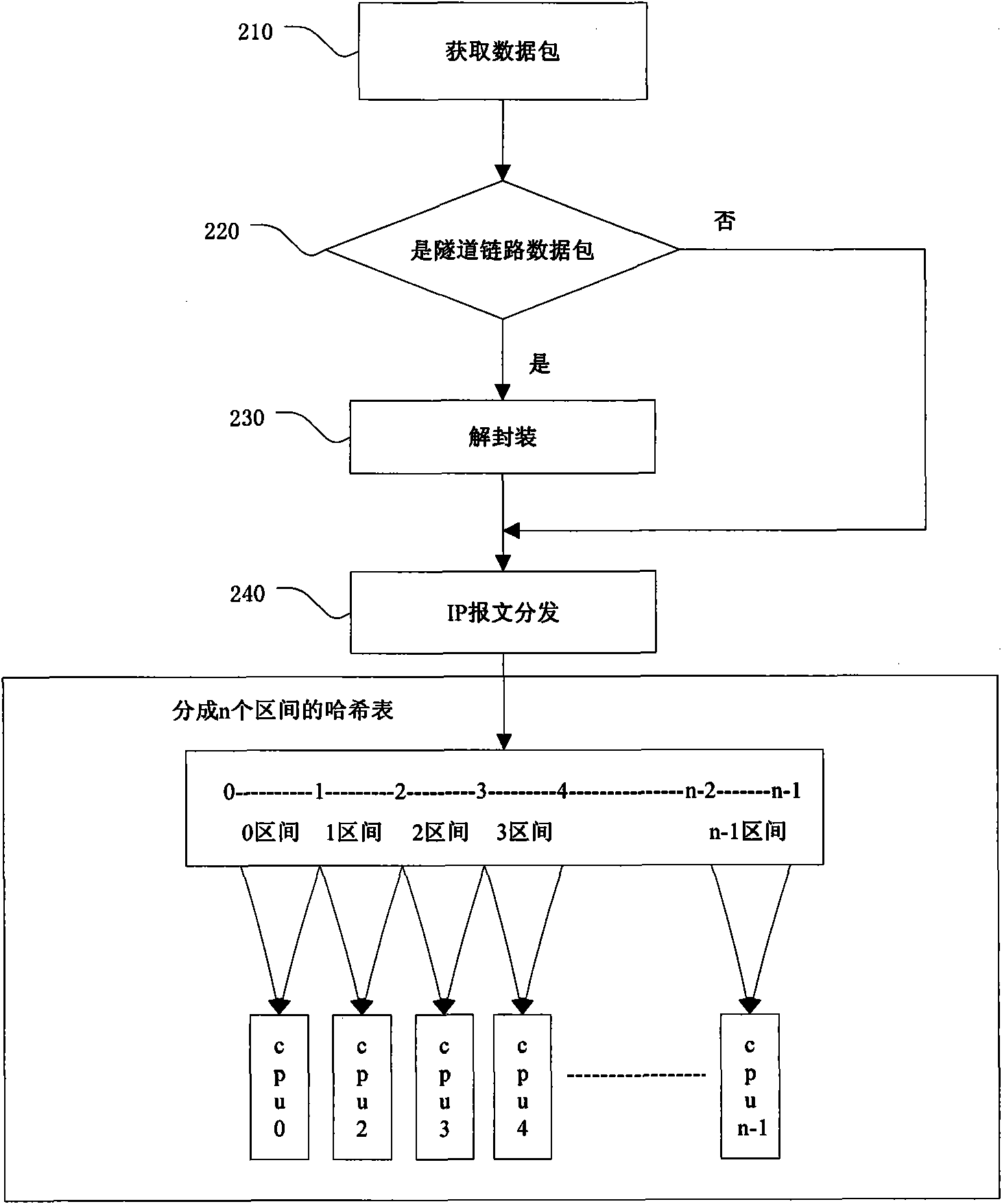

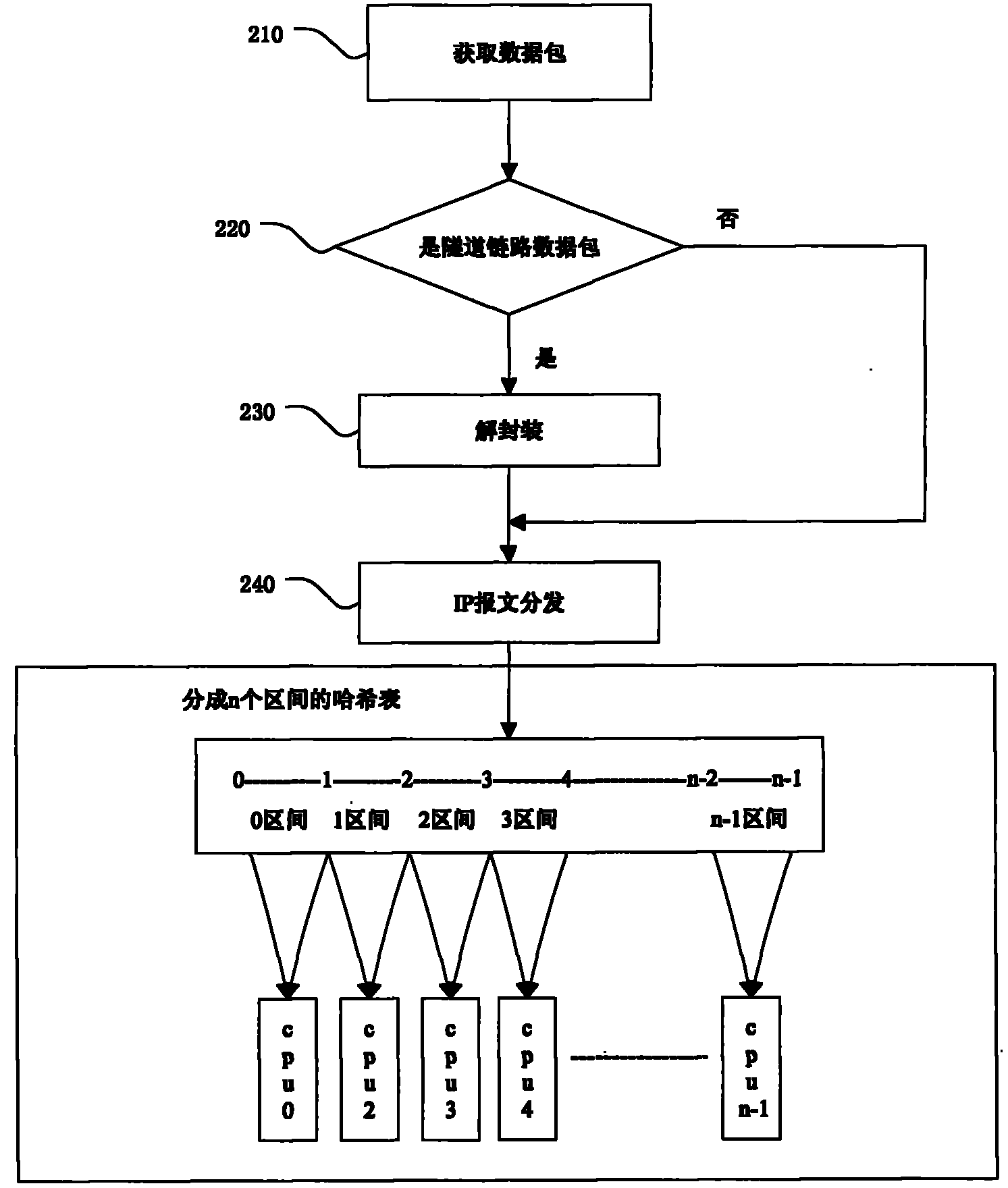

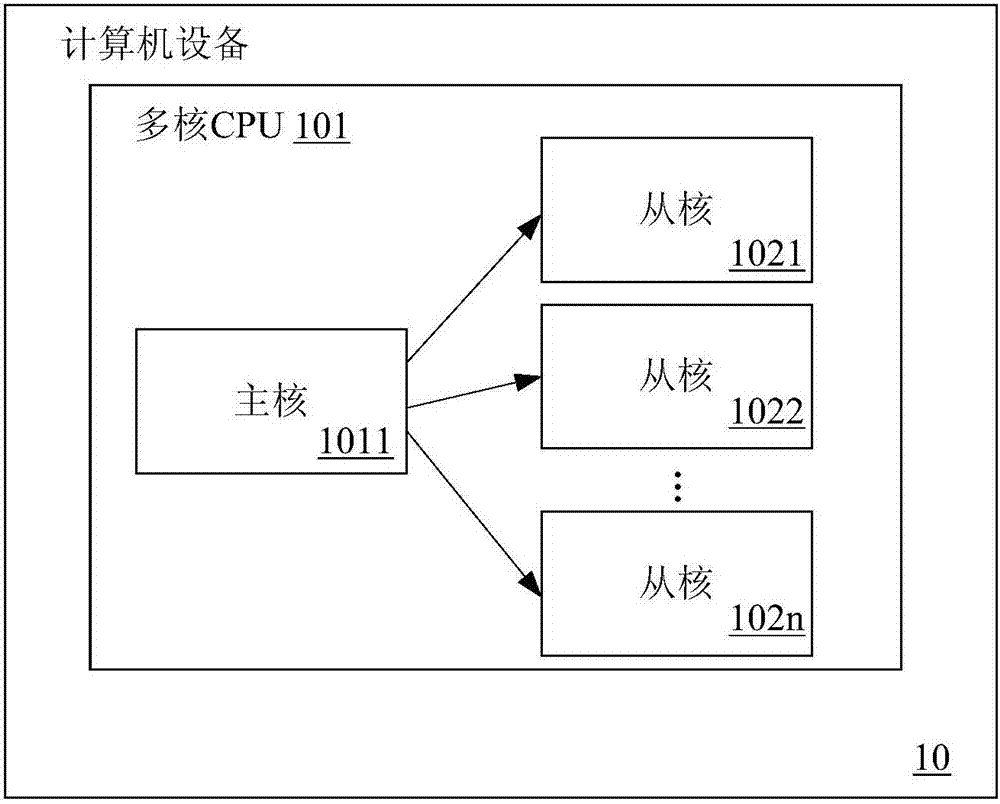

Message retransmission method and system based on multi-core architecture

InactiveCN101964749AImplement independent featuresIncrease profitData switching networksComputer hardwareNetwork packet

The invention relates to a message retransmission method and a system based on a multi-core architecture. The method comprises the following steps: acquiring a data packet in the Internet; when the data packet is a tunnel link data packet, decapsulating the data packet to obtain an IP data packet; and carrying out Hash operation on the quintuple of the IP data packet, computing according to the obtained Hash value and Hash table size thereof and the number of CPUs in the multi-core CPU to obtain the corresponding CPU, labeling the Hash value into the IP data packet, and transmitting the labeled IP data packet to the CPU. The invention increases the utilization rate of fixed network equipment in the wireless Internet, realizes lock-free design of shared resources, and is applicable to the wireless Internet.

Owner:BEIJINGNETENTSEC

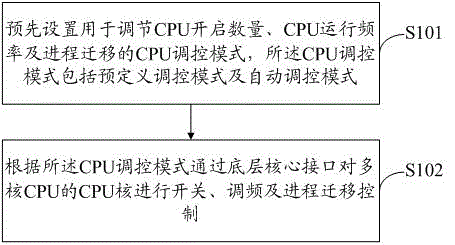

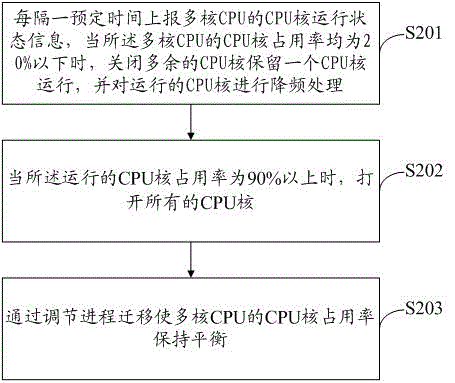

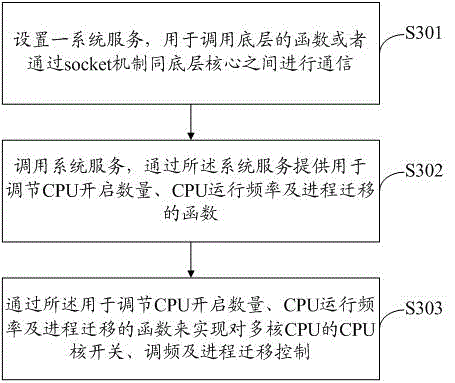

Method and system for regulating and controlling multi-core central processing unit (CPU)

ActiveCN102866921AEasy to handleTo achieve the purpose of energy savingEnergy efficient ICTResource allocationElectricityEngineering

The invention discloses a method and a system for regulating and controlling a multi-core central processing unit (CPU). The method comprises the following steps of: setting CPU regulation and control modes which are used for regulating CPU startup quantity, CPU operation frequency and process migration in advance, wherein the CPU regulation and control modes comprise a predefined regulation and control mode and an automatic regulation and control mode; and performing switching on, switching off, frequency modulation and process migration control on CPU cores of the multi-core CPU in the CPU regulation and control modes through a bottom-layer core interface. According to the method and the system, the predefined regulation and control mode and the automatic regulation and control mode of the multi-core CPU are provided, so that mobile equipment can regulate on-and-off states, the frequency and process migration of the CPU automatically or in the predefined mode according to the service condition of the CPU of the mobile equipment; and by the method and the system, a user of the mobile equipment can select to input an instruction to regulate and control the operating condition of each CPU core of the multi-core CPU in different scenes, so that the processing capability of the multi-core CPU is improved or the aims of energy conservation and electricity saving are fulfilled.

Owner:HUIZHOU TCL MOBILE COMM CO LTD

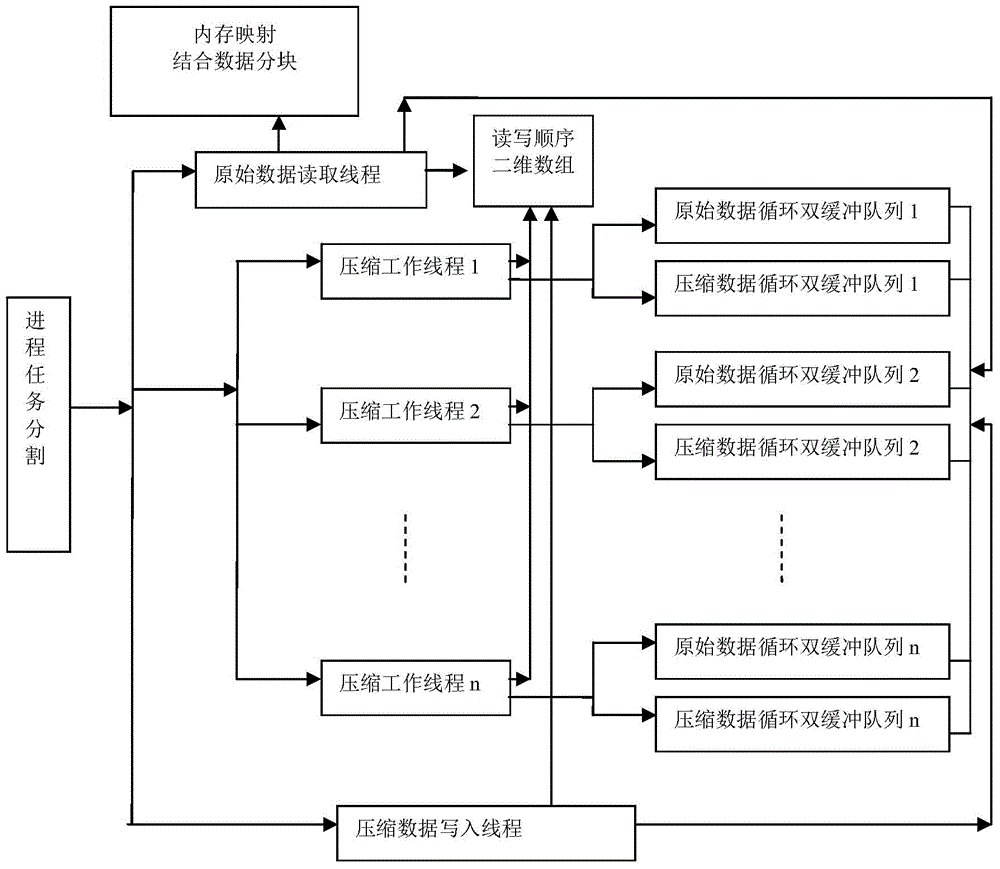

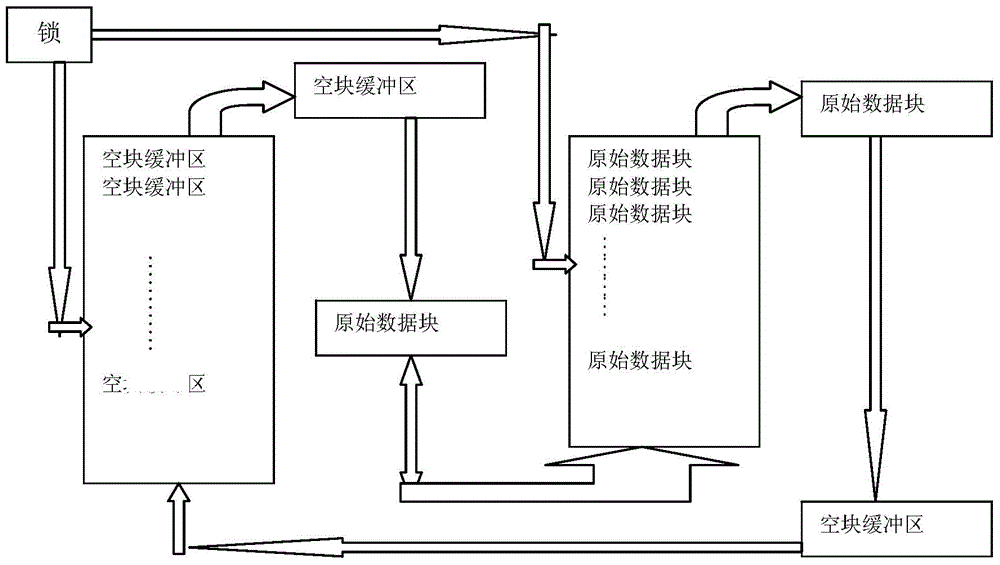

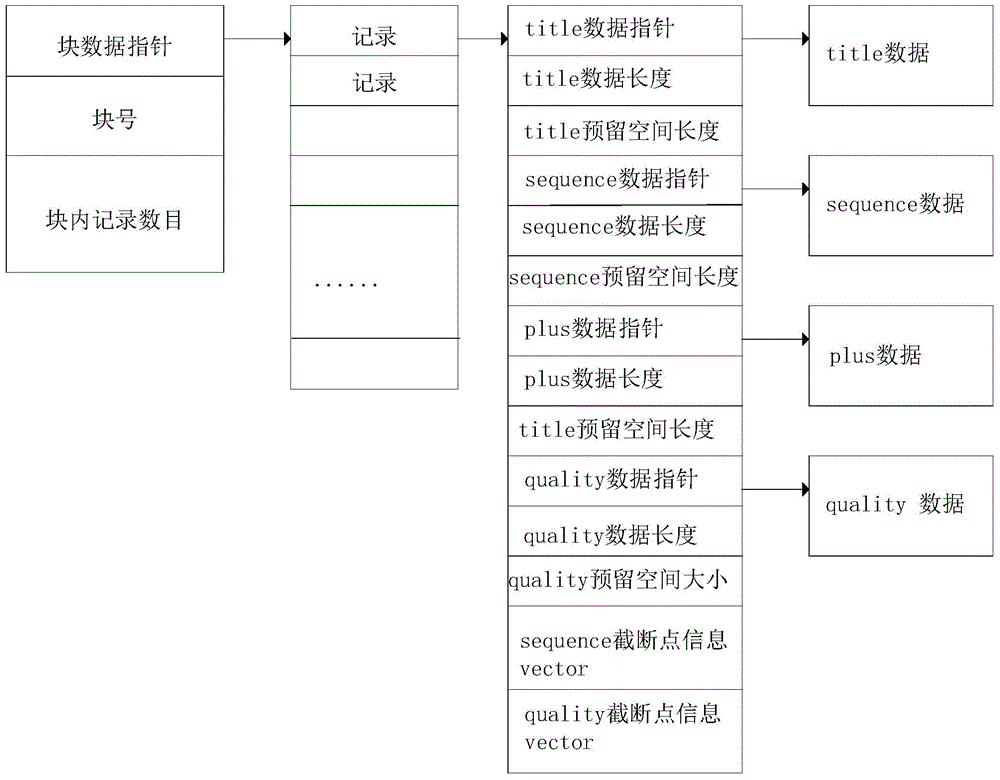

Method for realizing parallel compression and parallel decompression on FASTQ file containing DNA (deoxyribonucleic acid) sequence read data

InactiveCN103559020AAvoid restrictionsImprove flexibilityCode conversionConcurrent instruction executionParallel compressionPOSIX Threads

The invention discloses a method for realizing parallel compression and parallel decompression on an FASTQ file containing DNA (deoxyribonucleic acid) sequence read data. By aiming at the compression and the decompression of the FASTQ file containing the DNA sequence read data, by utilizing circular double buffering queues, circular double memory mapping and memory mapping and by combining the data segmentation processing technology, the multi-thread streamline parallel compression and parallel decompression technology, the read-write sequence two-dimensional array technology and the like, the parallel compression and the parallel decompression between multiple processes of the FASTQ file and between in-process multiple threads is realized. The parallel compression and parallel decompression can be realized based on MPI and OpenMP, and also can be realized based on the MPI and Pthread (POSIX thread). According to the method disclosed by the invention, by fully utilizing all computational nodes and the powerful computational capability of an intra-node multi-core CPU (central processing unit), constraints of resources, such as a processor, a memory and the like, on a serial compression and decompression program, can be released.

Owner:INST OF SOFTWARE - CHINESE ACAD OF SCI +1

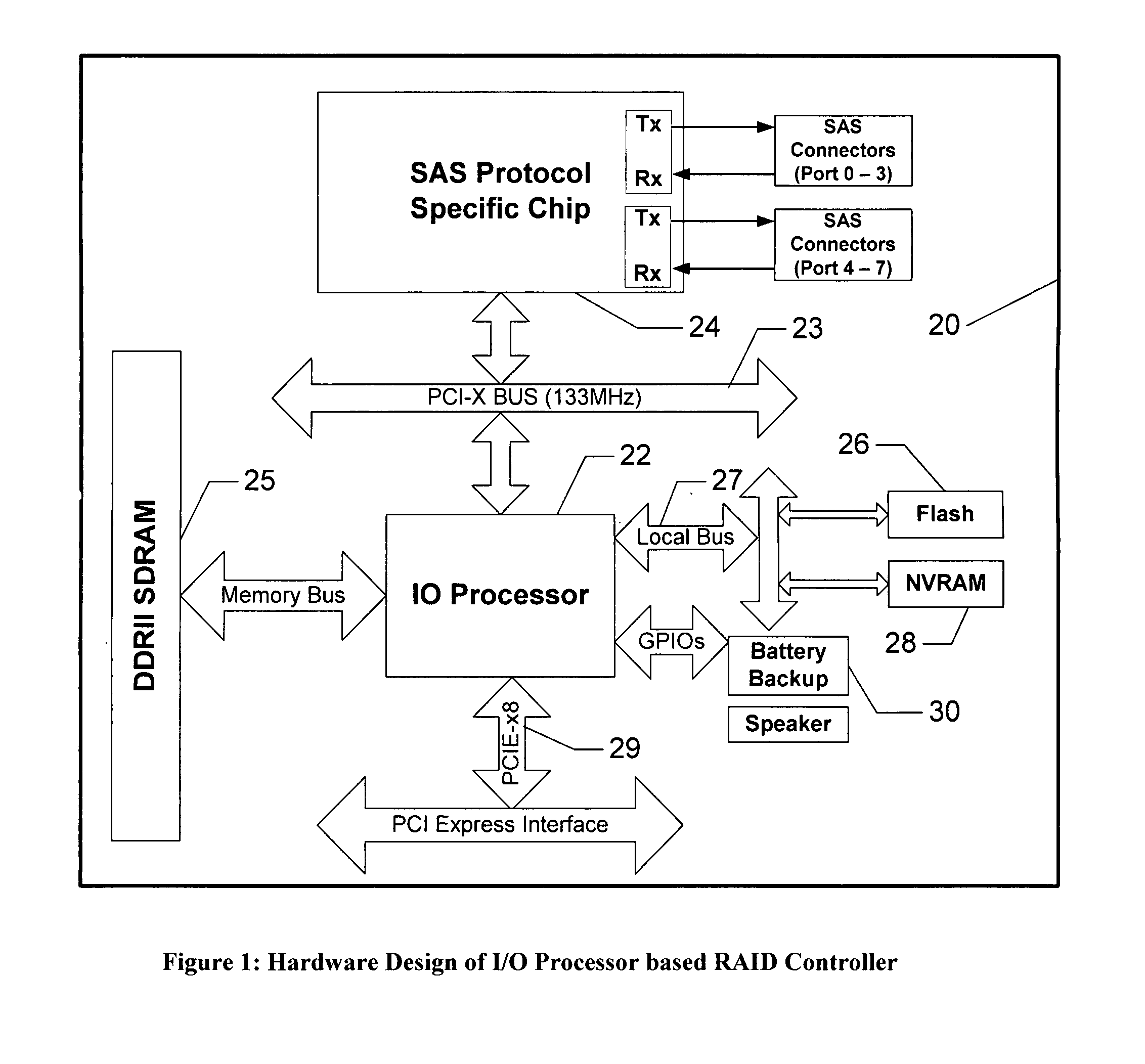

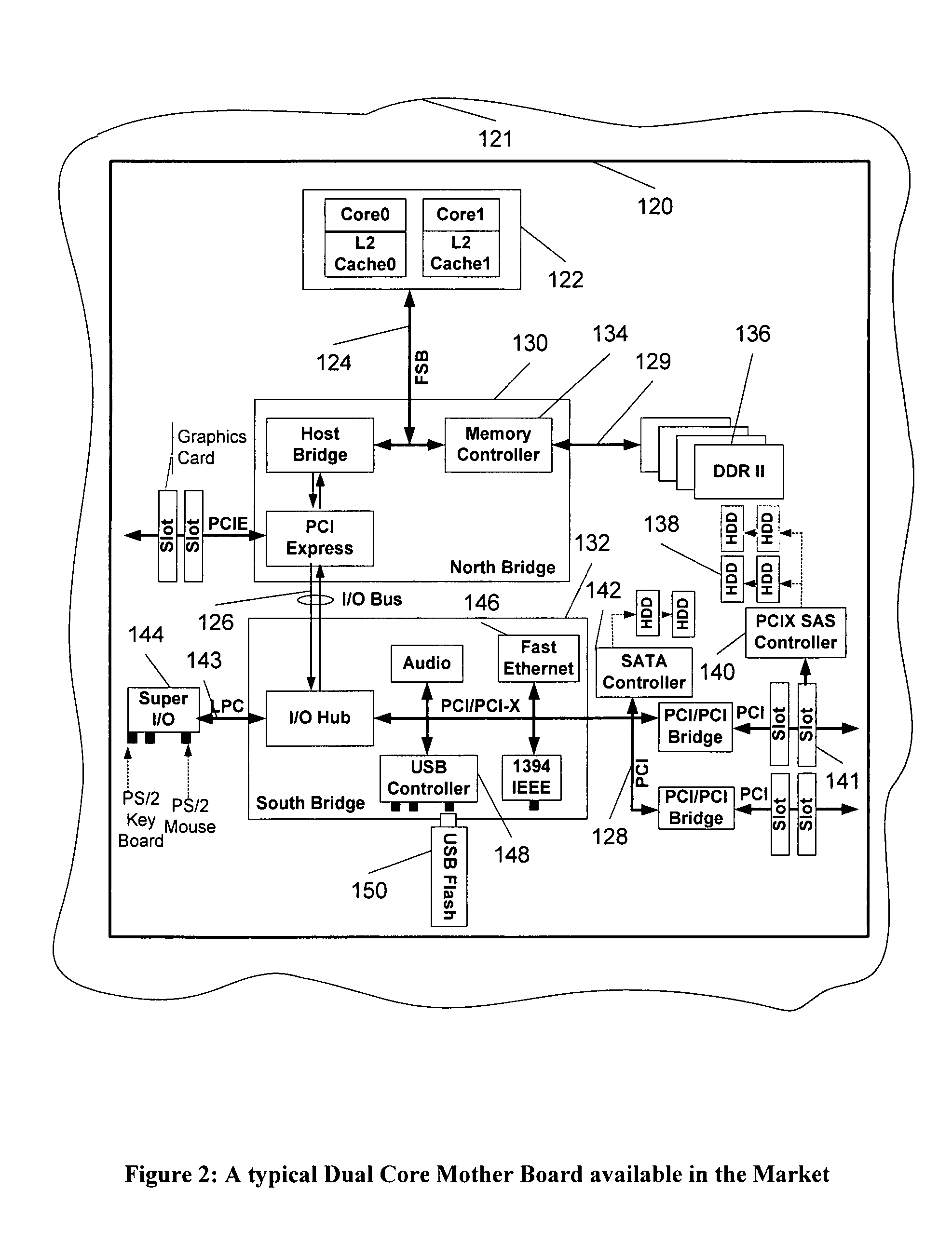

Apparatus and method for use of redundant array of independent disks on a muticore central processing unit

InactiveUS20090119449A1Simple structureEasy to processError detection/correctionMemory systemsRAIDOperational system

The invention is based on running the entire RAID stack on a dedicated core of one of the cores of the multi-core CPU. This makes it possible to eliminate the use of a conventional separate RAID controller and replace its function with a special flash memory chip that contains a program, which isolates the dedicated cores from the rest of the operating system and converts it into a powerful RAID engine. A part of the memory of the flash memory chip can also be used for storing data at power failure. This makes it possible to avoid having the battery backup module. The invention of the method of RAID on multi-core CPU may have many useful applications on an enterprise level, e.g., for increased accessibility and preserving critical data.

Owner:CHAUDHURI PUBALI RAY +2

High-speed packet filtering device and method realized based on shunting network card and multi-core CPU (Central Processing Unit)

InactiveCN102497322AImprove localityImprove performanceMultiprogramming arrangementsData switching networksTraffic capacityInternal memory

The invention provides a high-speed packet filtering device and method realized based on a shunting network card and a multi-core CPU (Central Processing Unit). The shunting network card is a specially customized hardware which can get through transmission bottleneck of network data from the network card to each CPU core. The high-speed packet filtering method comprises the steps of: homologizing and lodging the network flow; distributing the network flow into a message reception buffer region corresponding to each CPU core in a balanced load manner and reading data in a message transmission buffer region of each core into the network card in a parallel manner; sending out the data; and starting one progress (or thread) on each core of the multi-core CPU. As the message buffer region in a local internal memory of the CPU core is used for receiving and sending data, internal memory access locality is improved. Compared with the prior art, the high-speed packet filtering device and method realized based on the shunting network card and the multi-core CPU has the advantage of improving performances of the packet filtering device.

Owner:DAWNING INFORMATION IND BEIJING

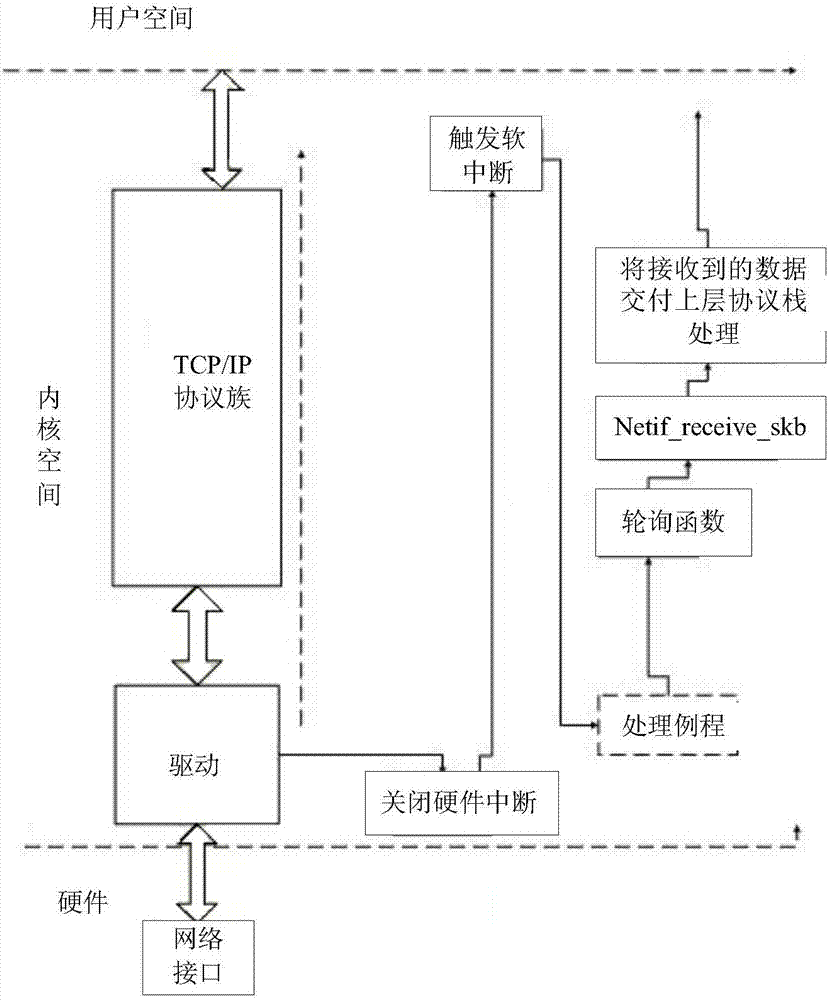

Network data packet parallel processing method based on Intel DPDK

ActiveCN105577567AEffective distributionImprove hit rateData switching networksPacket schedulingNetwork data

The invention discloses a network data packet parallel processing method based on an Intel DPDK (Data Plane Development Kit). The method comprises the following steps: step 1, establishing an Intel DPDK running environment; step 2, creating a memory pool, and creating a RX memory ring for receiving the network data packet and a TX memory ring for transmitting the network data packet; step 3, setting a network data packet scheduling strategy, and preparing to perform network data packet scheduling; step 4, creating multiple worker threads, and performing parallel processing of the network data packet. In the method provided by the invention, performance advantage of a multi-core CPU is used fully, and by lock-free data structure design, parallel network processing framework and high-efficiency network data packet distribution, parallel processing of the network data packet on multiple CPU cores is realized.

Owner:STATE GRID CORP OF CHINA +3

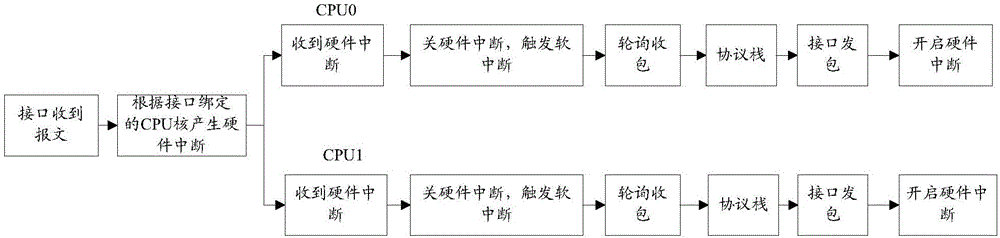

Load balancing method and apparatus of multi-core CPU

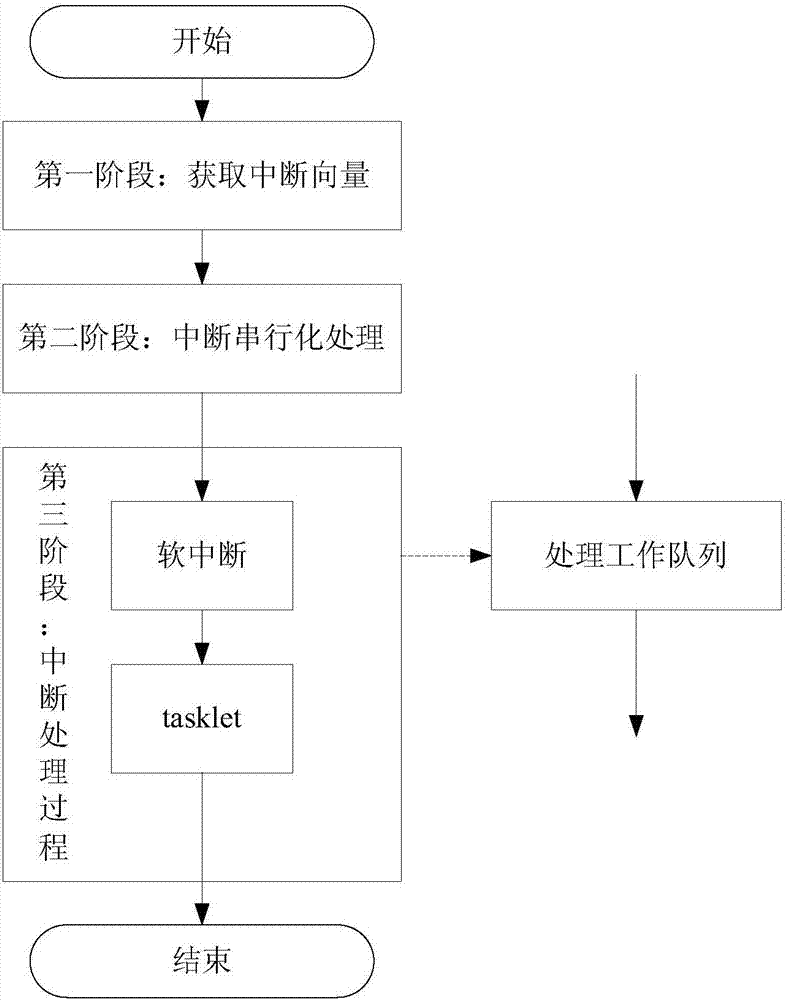

ActiveCN106713185AAvoid overheadRealize the function of data flow order preservationResource allocationData switching networksComputer moduleMessage type

The invention discloses a load balancing method and apparatus of a multi-core CPU. The load balancing method and apparatus are applied to a communication device, the communication device comprises a hardware dispatching module, receiving ports and at least two CPU cores, wherein each receiving port is configured to bind with the at least two CPU cores, the CPU cores bound with the same receiving port are configured to separately bind one or more receiving queues of the receiving port; and the load balancing method comprises the following steps: for each receiving port, the hardware dispatching module classifies messages according to a dispatching rule, and forwards the messages to the receiving queue having a distribution relationship with a belonging message type according to the distribution relationship between the receiving queue of the receiving port and the message type; the receiving port generates hardware interruption after receiving the messages, and reports the hardware interruption to all CPU cores bound with the receiving port; and each CPU core receiving the hardware interruption reads the messages from the receiving queue bound with the CPU core in a soft interruption processing procedure.

Owner:RAISECOM TECH

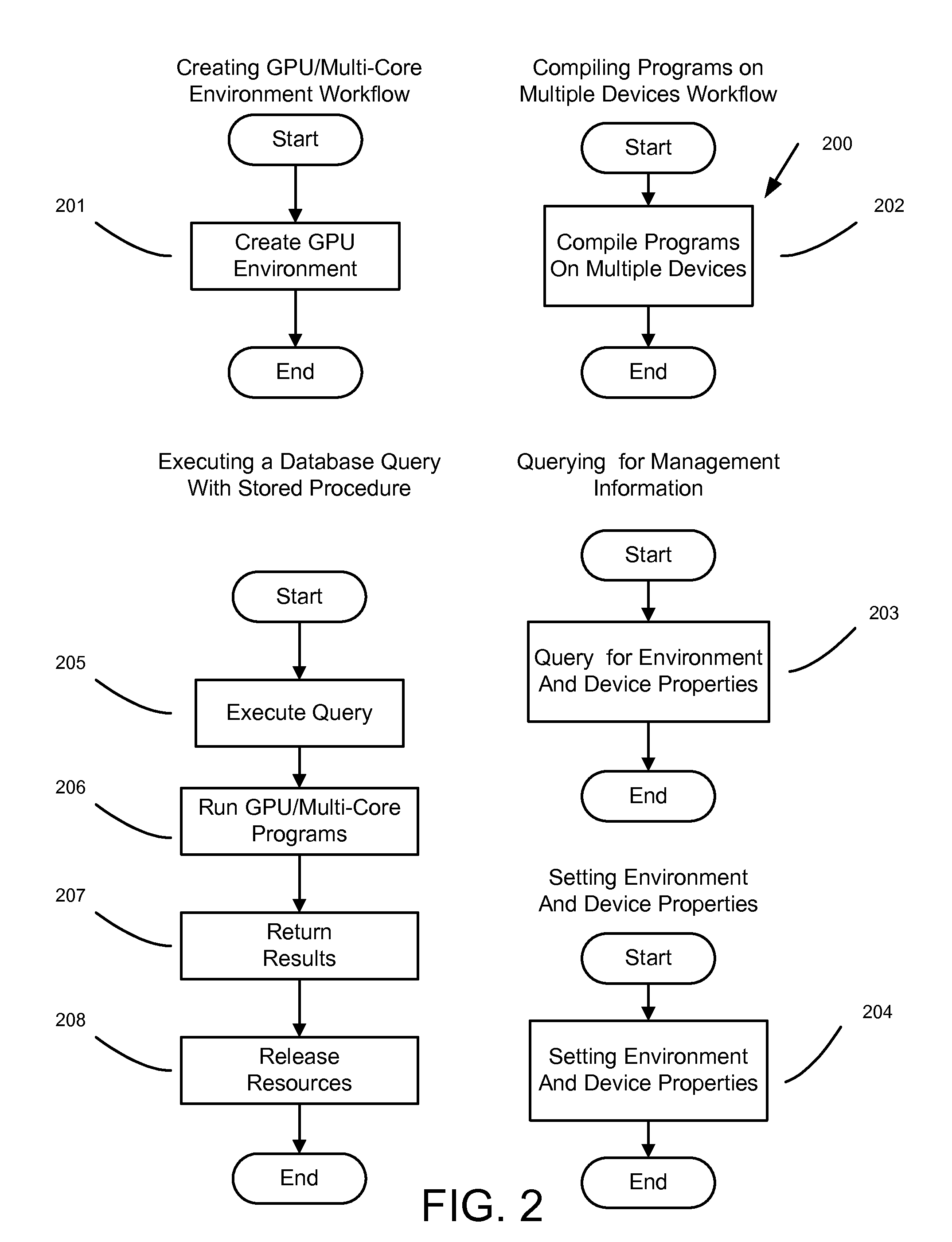

Database acceleration using GPU and multicore CPU systems and methods

InactiveUS20120259843A1Improve performanceHighly mannerDigital data information retrievalDigital data processing detailsDatabase serverMulticore cpu

A computer-implemented method for GPU acceleration of a database system, the method includes a) executing a parallelized query against a database using a database server, the parallelized query including an operation using a particular stored procedure available to the database server that includes a GPU / Many-Core Kernel executable; and b) executing the particular stored procedure on one or more GPU / Many-Core devices.

Owner:CHILD TIMOTHY

Patch description and modeling for image subscene recognition

ActiveUS20120155766A1Digital data information retrievalCharacter and pattern recognitionFeature vectorHigh probability

A method and apparatus is described that categorizes images by extracting regions and describing the regions with a set of 15-dimensional image patch feature vectors, which are concatenations of color and texture feature vectors. By comparing the image patch feature vectors in images with similarly-obtained image patch vectors in a Gaussian mixture based model pool (obtained in an image patch modeling phase), the images may be categorized (in an image patch recognition phase) with probabilities relating to each image patch. Higher probabilities are likelier correlations. The device may be a single or multiple core CPU, or parallelized vector processor for characterizing many images. The images may be photographs, videos, or video stills, without restriction. When used real-time, the method may be used for visual searching or sorting.

Owner:SONY CORP

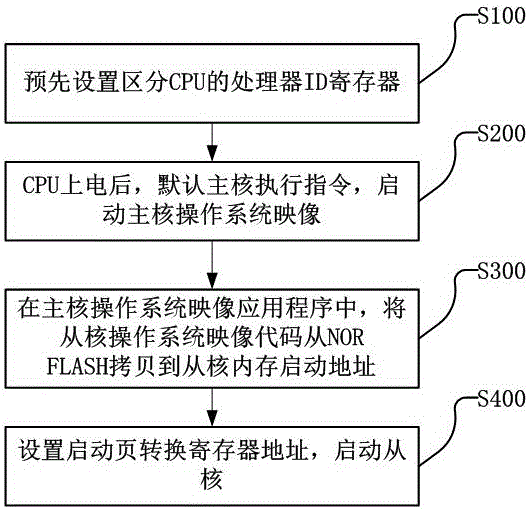

A method and a system for BOOTROM guiding multi-core CPU boot

ActiveCN106407156ASolve the problem of not being able to access NORFLASHDigital computer detailsElectric digital data processingElectricityOperational system

The invention provides a method and a system for BOOTROM guiding multi-core CPU boot. The method comprises the steps of: A, setting a processor ID register for distinguishing a CPU in advance; B, when the CPU is electrified, tacitly approving that a main core executes an instruction and starting a main core operating system image; C, in an application program of the main core operating system image, copying a slave core operating system image code from NOR FLASH to a slave core memory boot address; D, setting a boot page translation register address to start slave cores. The system comprises a presetting module, a main core boot module, a copying module and a slave core boot module. Multiple cores of a CPU can be started only by compiling one copy of a BOOTROM code, and the multiple-core CPU can be started at the same time, so that the problem of complicated burn maintenance in an AMP system is solved and the problem that NOR FLASH is non-accessible after an SMP system starts slave cores.

Owner:深圳市震有软件科技有限公司

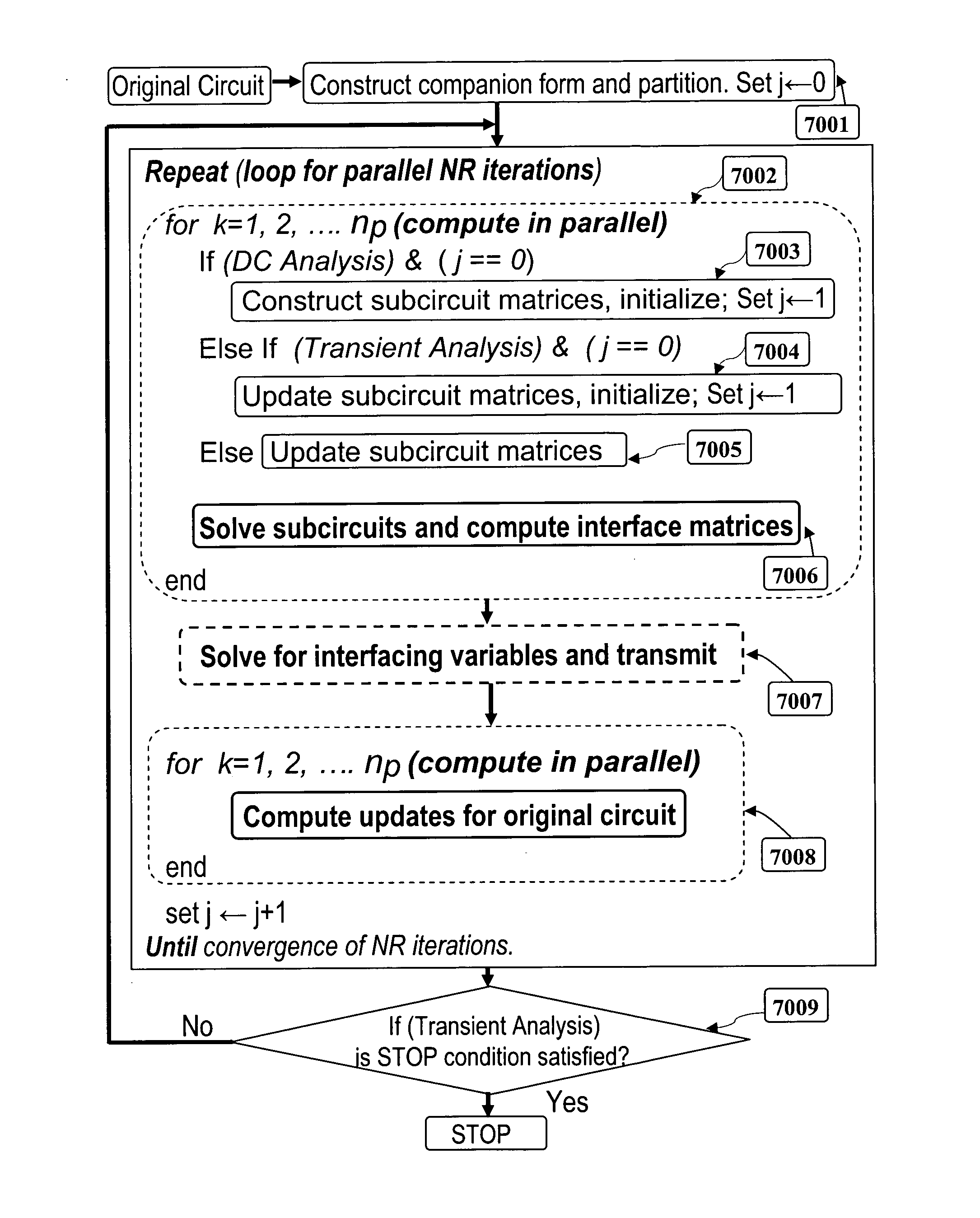

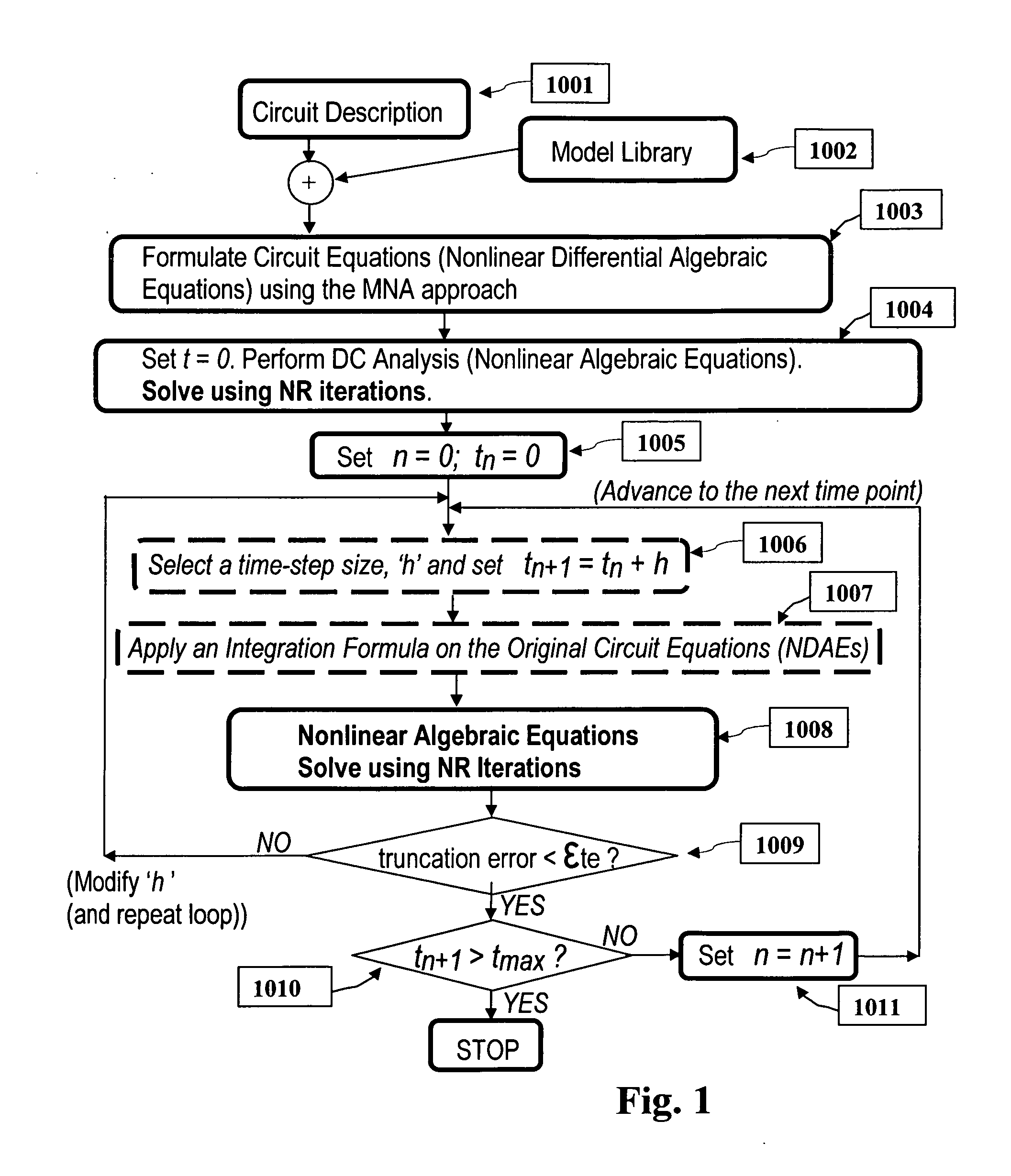

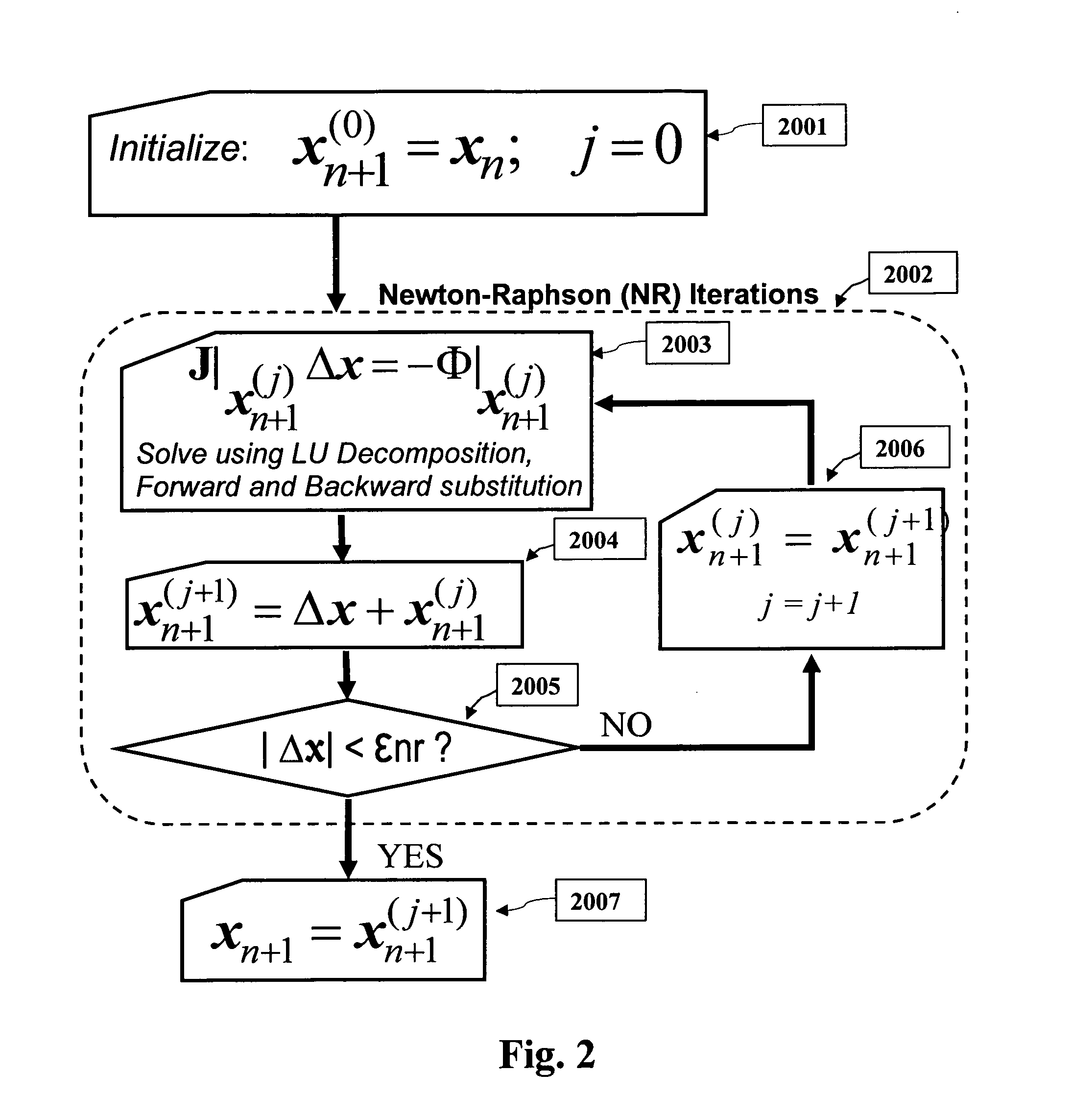

Parallel simulation of general electrical and mixed-domain circuits

InactiveUS20100332202A1Computation can be minimizedMinimize overheadComputation using non-denominational number representationComputer aided designExtensibilityTime domain

A new method for simulation of general electrical circuits on parallel computing platforms is disclosed. Parallel simulation of general time-domain circuits that are represented by nonlinear / linear differential algebraic equations is accomplished by partitioning them into smaller subcircuits via a novel combination of the companion form representation of the given circuit and an efficient form of node splitting, during Newton Raphson iterations, at any time point. The new invention formulates the interface vectors between partitions, through purely binary vectors, leading to a high degree of parallelism, scalability and reduced computational and communication costs for synchronizing the solutions between various partitions. Parallel platforms considered can be diverse such as (including but not restricted to) multicore CPUs, distributed systems of computers. The new invention also provides for scalable parallel simulation of mixed-domain formulations, such as (including but not restricted to), integrated circuits, electronic packages, PCBs, electromagnetic modules, MEMS and optical components etc.

Owner:OMNIZ DESIGN AUTOMATION CORP

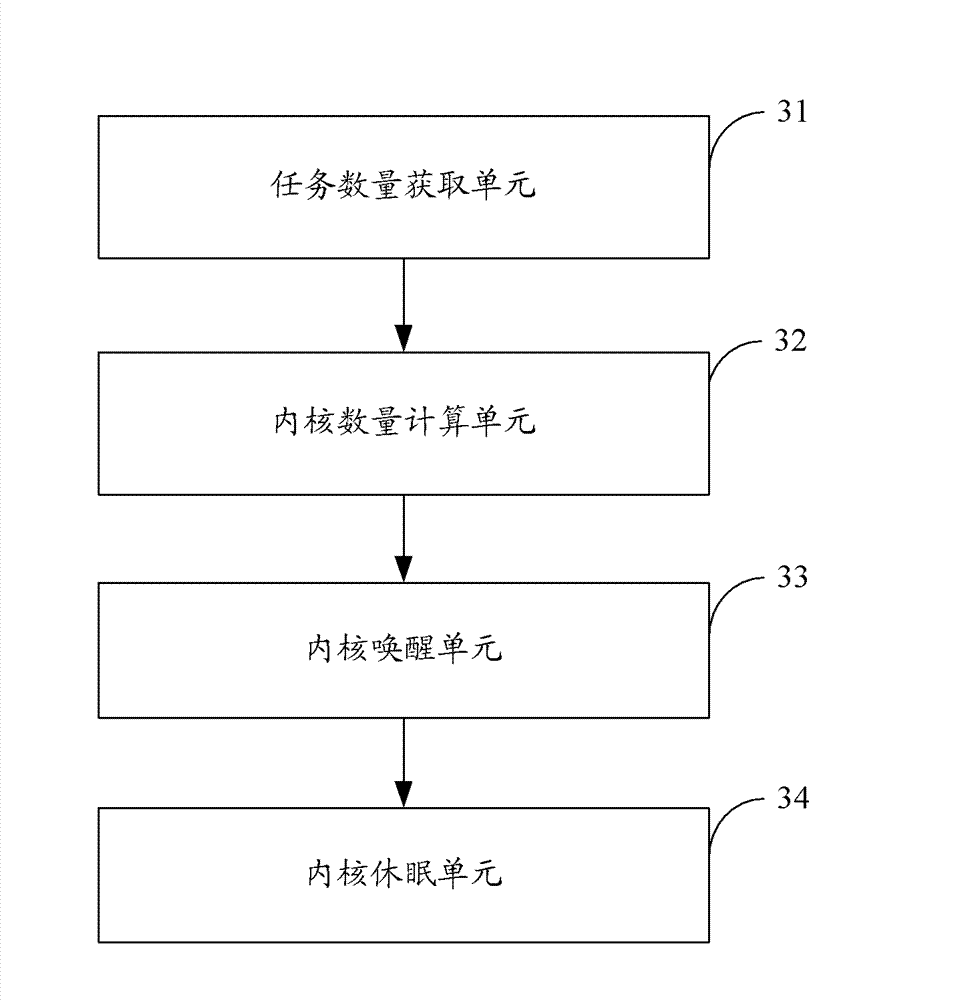

Power supply management method and power supply management system for multi-core CPU (central processing unit) and CPU

InactiveCN102955549AEfficient managementTimely processingVolume/mass flow measurementPower supply for data processingSupply managementEngineering

The invention is suitable for the technical field of computers, and provides a power supply management method and a power supply management system for a multi-core CPU (central processing unit) and the CPU. The power supply management method comprises the following steps of: in the case that a preset time cycle is achieved, obtaining the quantity of the to-be-processed tasks of a preset core group in the multi-core CPU, wherein the quantity of cores in the core group is at least greater than 1; calculating the quantity of cores needed by finishing the to-be-processed tasks in the time cycle according to the quantity of the to-be-processed tasks; in the case that the quantity of cores needed is greater than a first preset value, awakening the cores with the needed core quantity from the core group; and in the case that the quantity of cores needed is not greater than a second preset value, enabling the cores with a quantity which is a third preset value in the core group to sleep according to the needed core quantity and the quantity of the cores in a running state in the core group. According to the invention, the states of the cores are dynamically adjusted according to the tasks in the task queue of the core group of the multi-core CPU, so as to realize effective management for the power supply power consumption of the multi-core CPU, thus realizing timely processing for the tasks while reducing the power supply power consumption.

Owner:HUAWEI TECH CO LTD

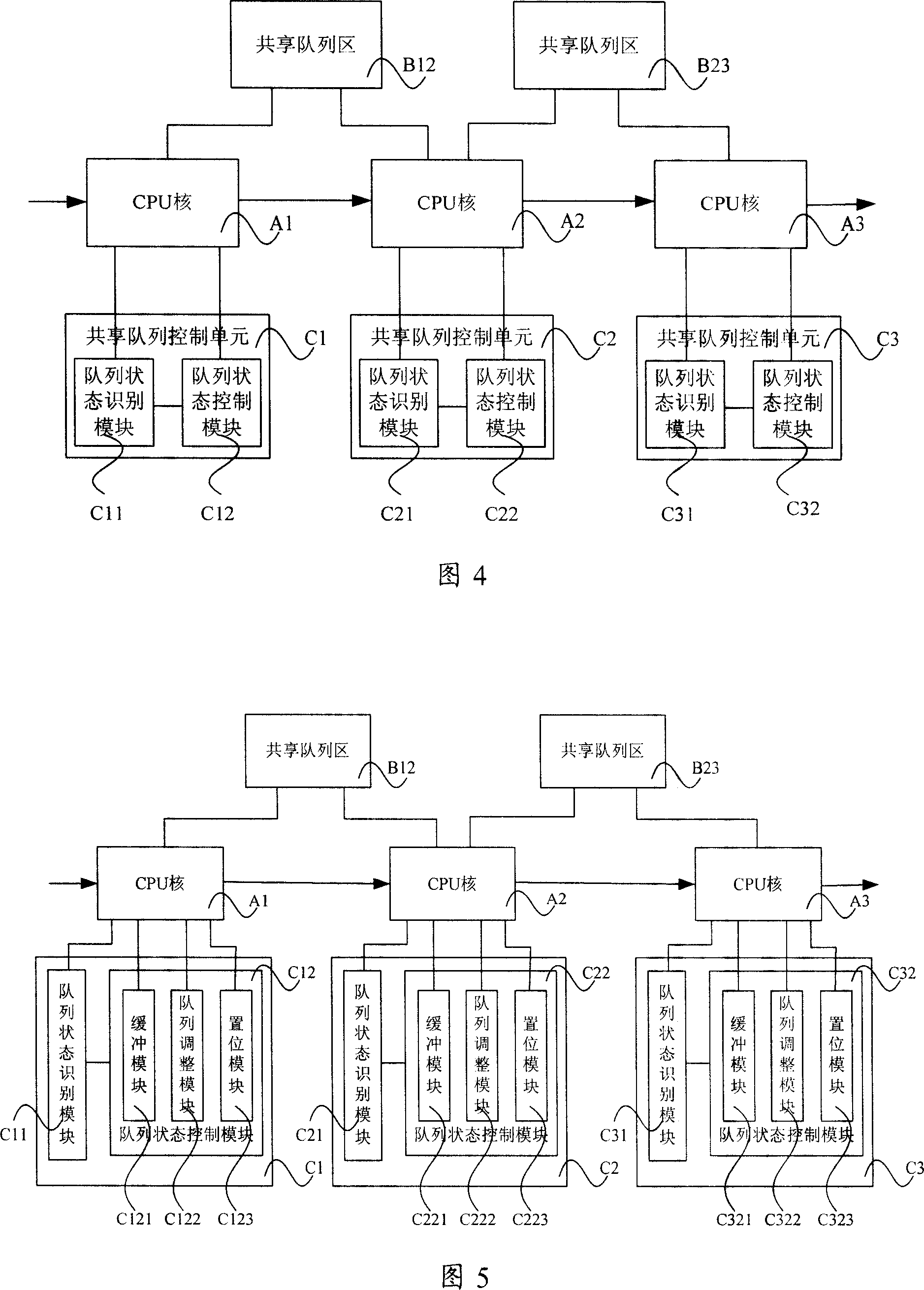

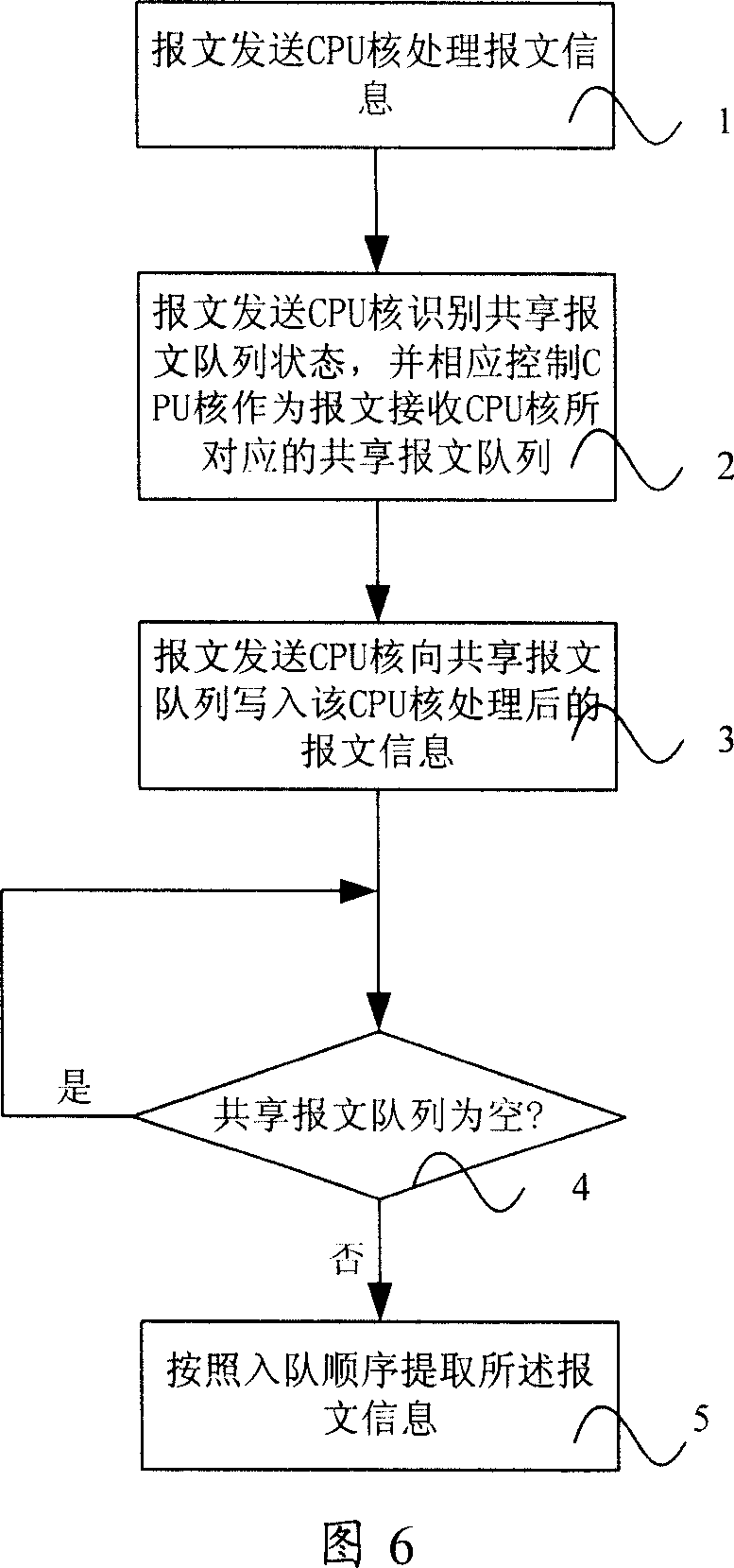

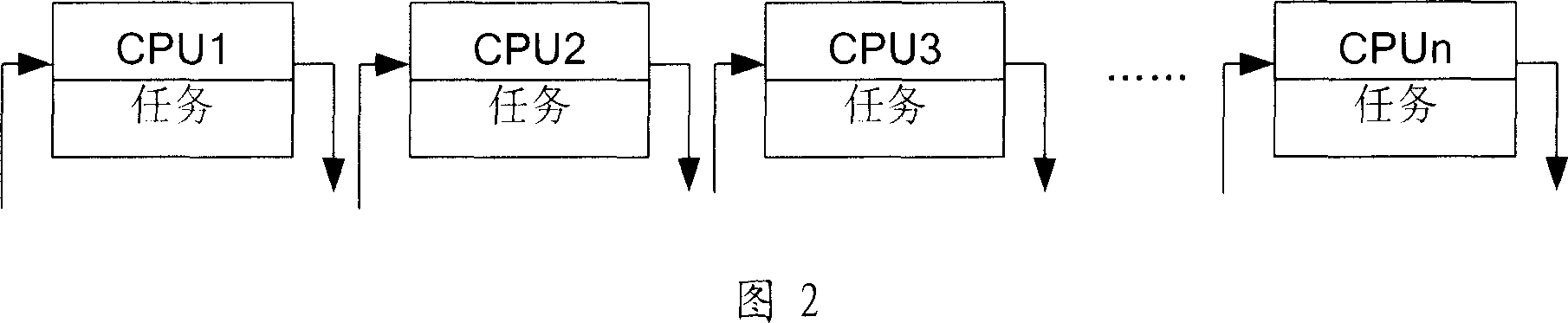

System and method for implementing packet combined treatment by multi-core CPU

ActiveCN101013383AAvoid interrupt overheadImprove throughputMultiprogramming arrangementsData switching networksMessage queueComputer hardware

The invention discloses a multi-core CPU message processing system, including multi-core CPU and a number of shared queues. Every shared queue is connected to two determined CPU cores, serving as shared message queue for the two CPU cores: the sender CPU core of the shared queue writes the message it has processed to the queue, and the receive CPU core gets the message in the same order of write to process. The invention also discloses a combined approach by multi-core CPU where the message sender CPU core write the message it has processed to the shared queues and the receive CPU core gets the message in the same order of write to process. The invention avoids the interruption expenses and it is no longer confined to the CPU hardware space constraints, increasing the flexibility of queue design and throughput.

Owner:XINHUASAN INFORMATION TECH CO LTD

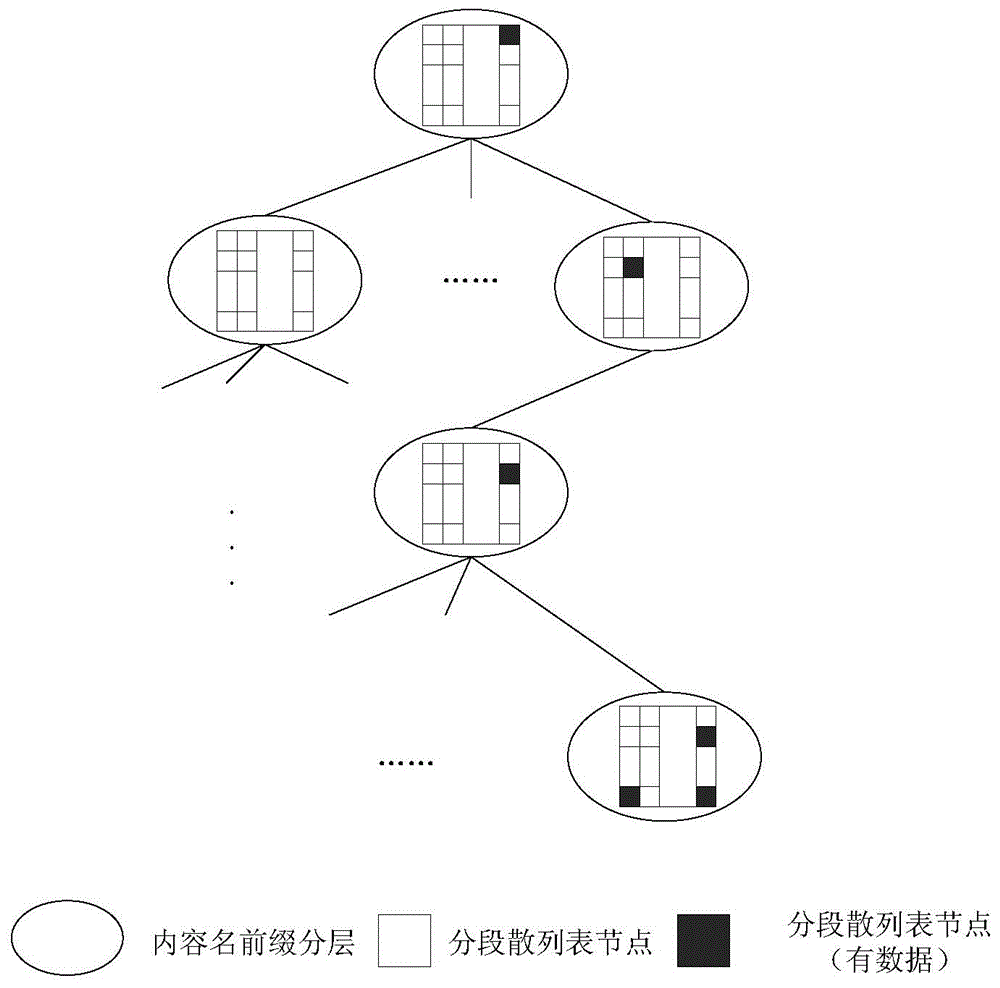

Content name storage structure oriented design method in content network

ActiveCN103559215AEasy to handleReduce overheadSpecial data processing applicationsTheoretical computer scienceBloom filter

The invention provides a content name storage structure oriented design method in a content network. Layered nested structures of nested segmented hash tables are aggregated through content names with the same prefix and accordingly the overhead of storage space is reduced; the segmented thought is introduced to segmented hash tables based on hash tables and the segmented hash tables are utilized as basic data structure units in the nested segmented hash tables, a bloom filter and a bit map are added to be utilized as index structures, pre-processing is provided for data entering into corresponding sub-table hash calculation, and accordingly the times of direct operation on storage tables are reduced and the search efficiency is improved; meanwhile a content popularity parameter based chain table method is utilized to solve the hash conflict and reduce the search time of popular content names, the parallel relationship between nodes in the same layer of sub-tables of the segmented hash tables and the nested segmented hash tables is introduced, and accordingly the computing power of a multi-core CPU (Central Processing Unit) can be effectively utilized in the implementation, data insertion, search and deletion operation in the segmented hash tables can be efficiently achieved, and the processing capacity of a content name storage structure is improved.

Owner:XI AN JIAOTONG UNIV +1

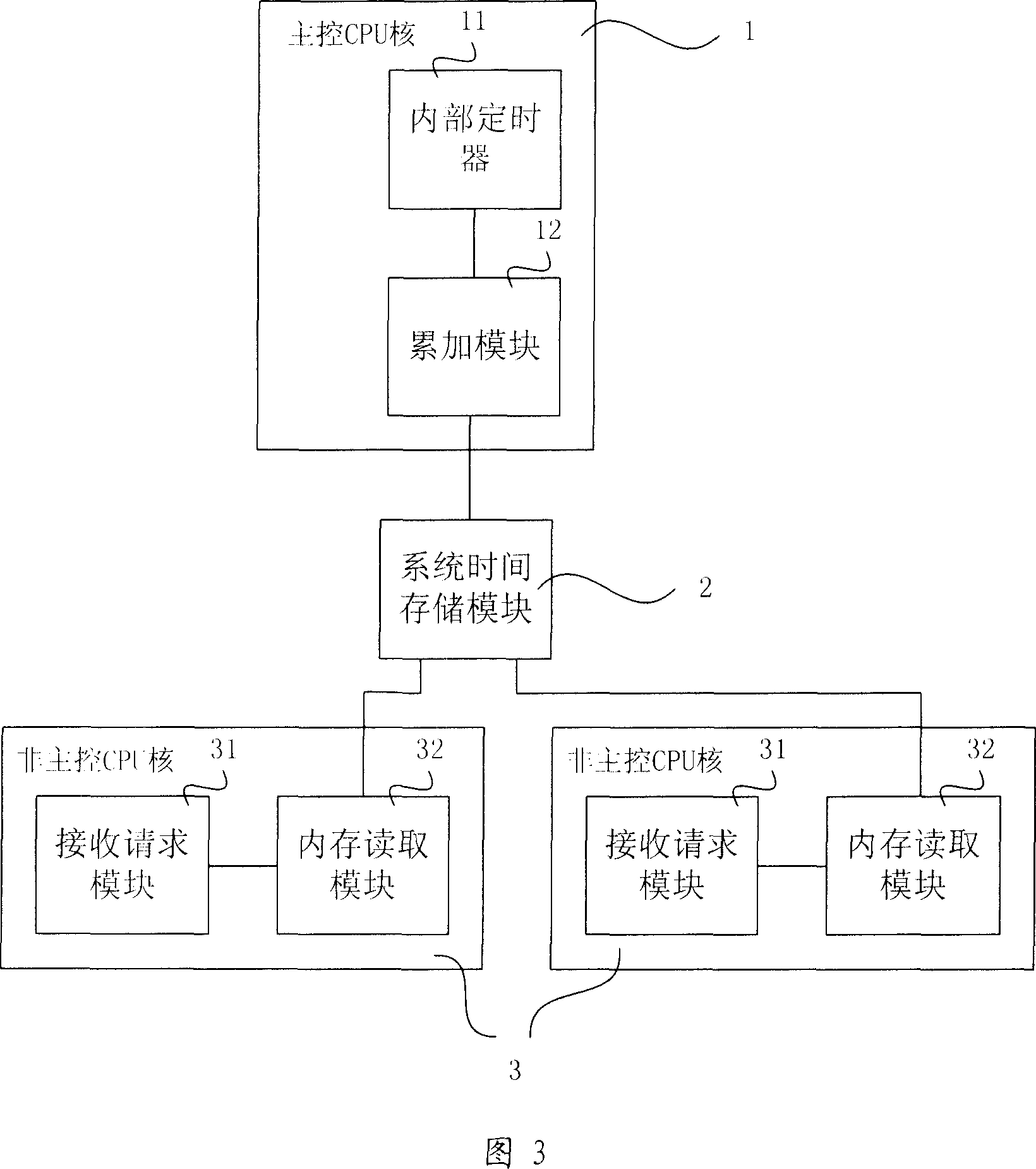

Time synchronizing method and device

The invention relates to time synchronization method. It includes the following steps: main control CPU accumulates system time according to timer interruption to gain current system time; and it writes the current system time into system time memory module; non main control CPU core acquires the system time request, reads the current system time from the system time memory module. The invention also relates to time synchronization device used in multi-core CPU system, includes main control CPU core, one or many non main control CUP cores and system time memory module. Thus it can make the non main control CPU core share the current system time, not need to interrupt timer to synchronize system time to ensure system time synchronization, but only need main control CPU to response timer interruption, reduce non main control CPU interruption spending to increase system performance.

Owner:XINHUASAN INFORMATION TECH CO LTD

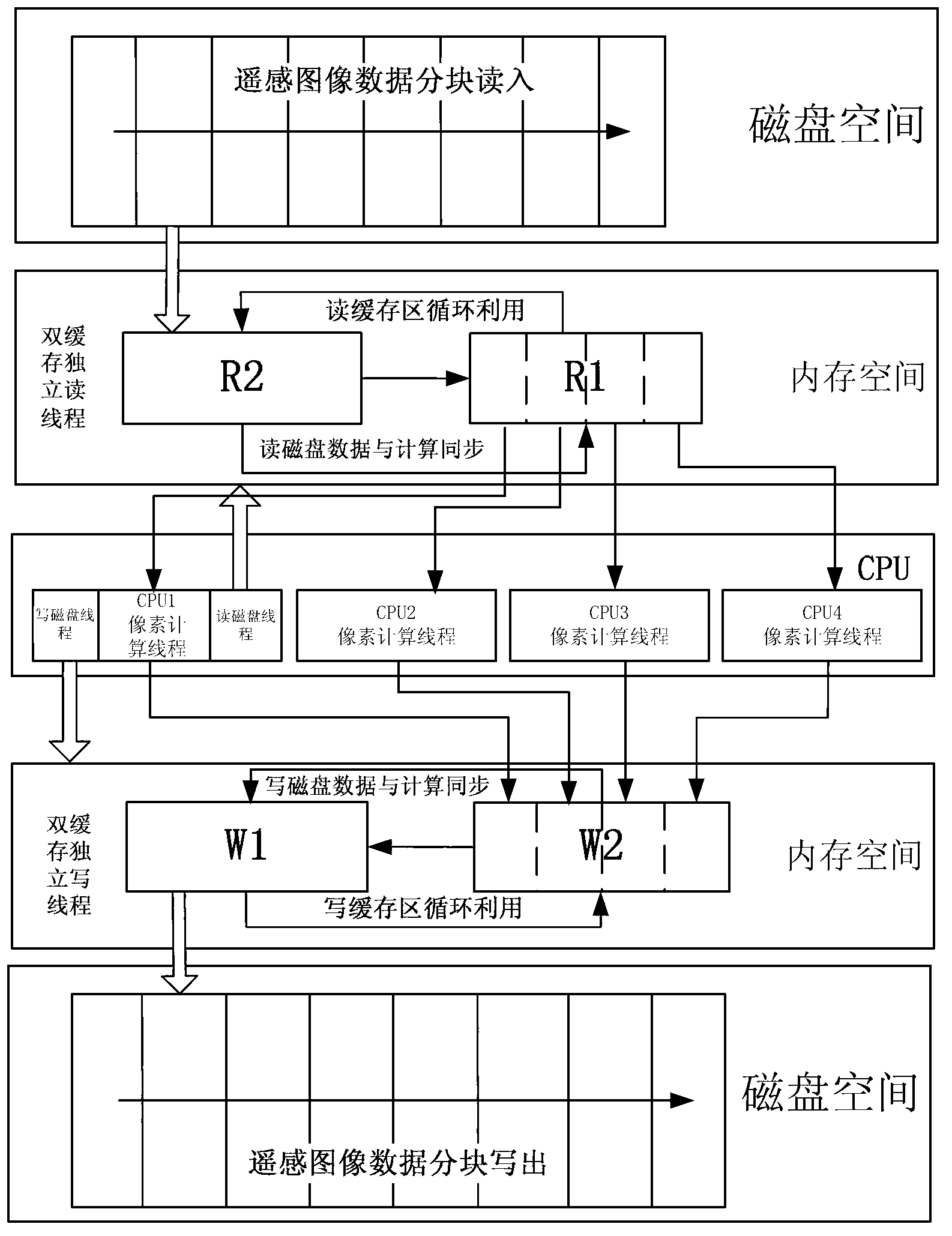

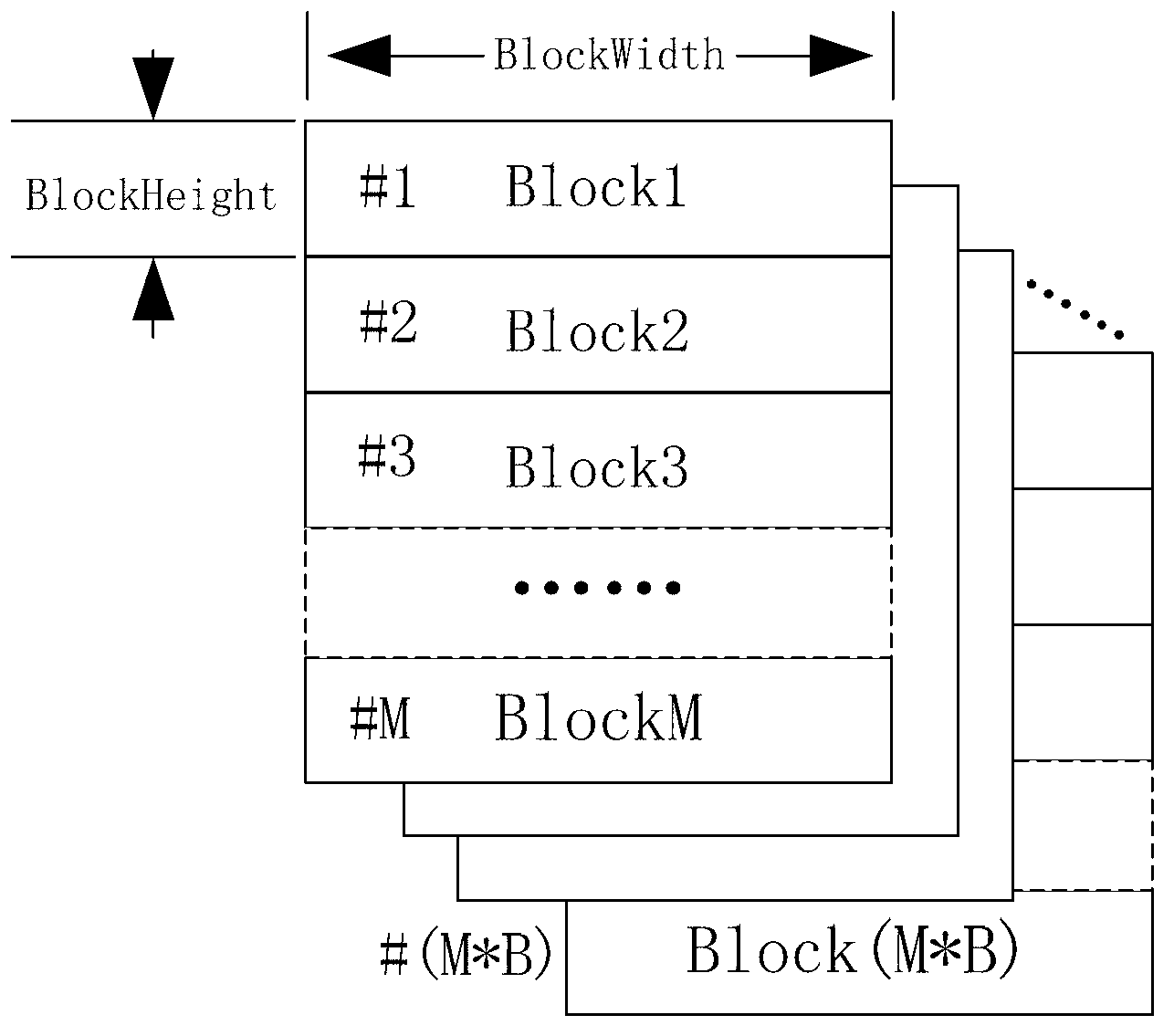

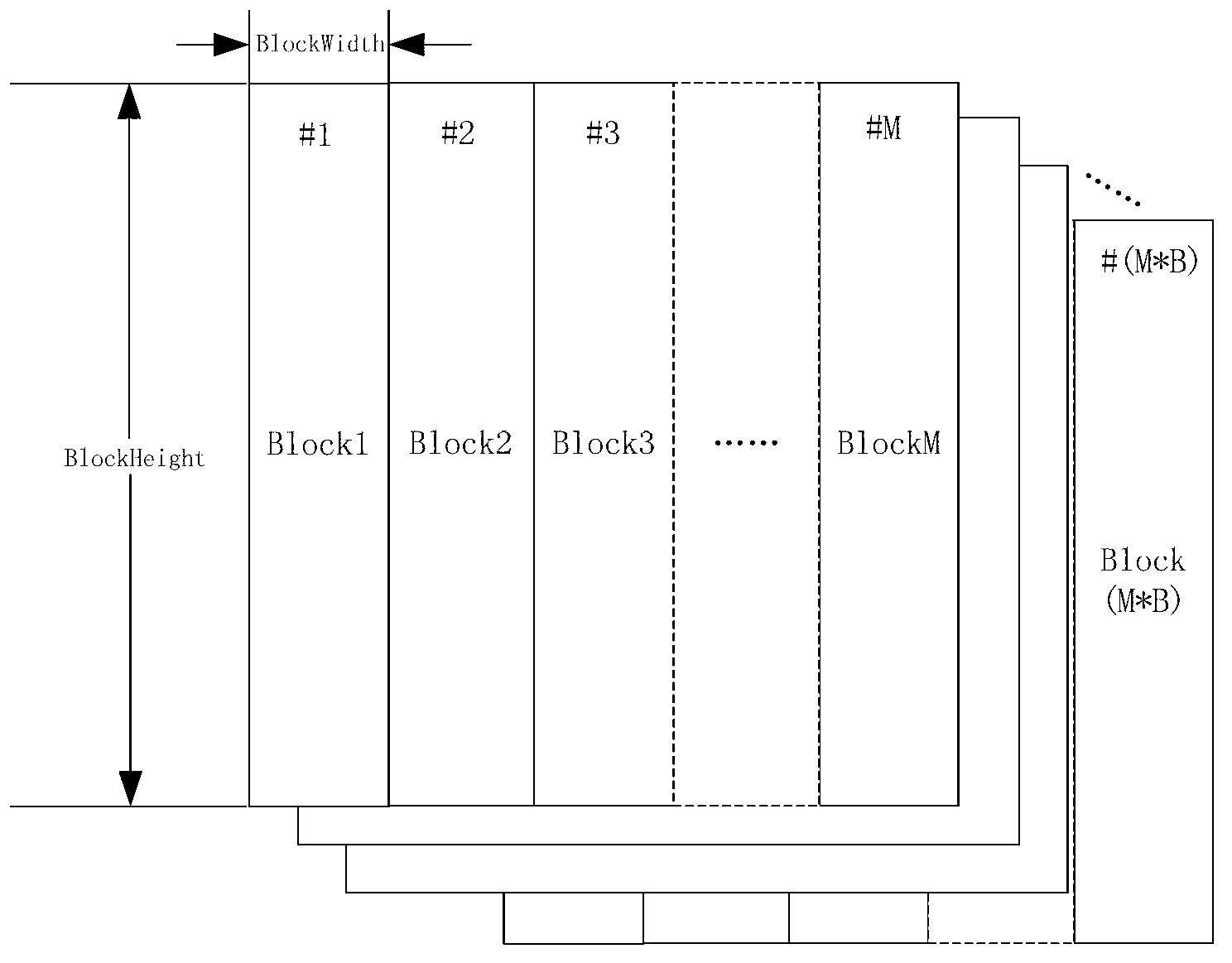

IO (Input Output) double-buffer interactive multicore processing method for remote sensing image

ActiveCN103218174AGuaranteed execution efficiencyImprove resource utilizationInput/output to record carriersConcurrent instruction executionSensing dataResource utilization

The invention discloses an IO (Input Output) double-buffer interactive multicore processing method for a remote sensing image. The method comprises the following steps of determining the quantity of multicore computing threads according to the quantity of CPU (Central Processing Unit) cores of a processing system; determining various data segmentation strategies according to various remote sensing image processing algorithms; starting each remote sensing image processing computing thread, starting to execute the remote sensing image processing algorithms and sending a data access request and an output request during the period; reading or writing in a data request according to the computing threads, starting a reading-writing data thread, reading image data into buffer memories R1 and R2 in order according to a predetermined reading segmentation strategy, and writing processed result data into writing buffers W2 and W1 in order; and destructing the reading-writing double-buffer and ending the reading-writing thread and each computing thread till the completion of the computing process according to the processing algorithms and the stopping of data reading-writing visit. With the adoption of the IO double-buffer interactive multicore processing method for the remote sensing image, the resource utilization rate of a multicore CPU and the efficiency of disk IO visit are improved, and a contradiction between limited memory space and mass remote sensing data processing is solved.

Owner:SPACE STAR TECH CO LTD

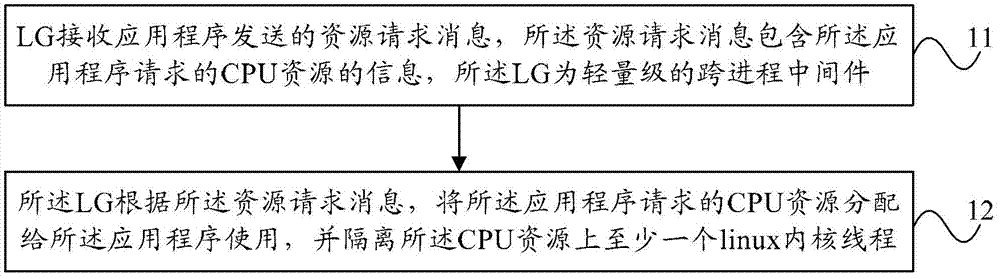

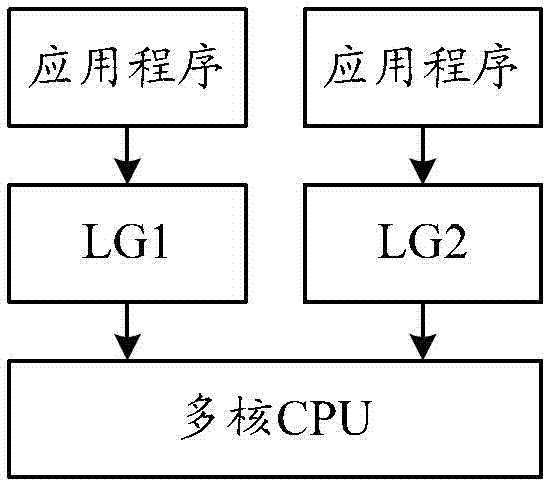

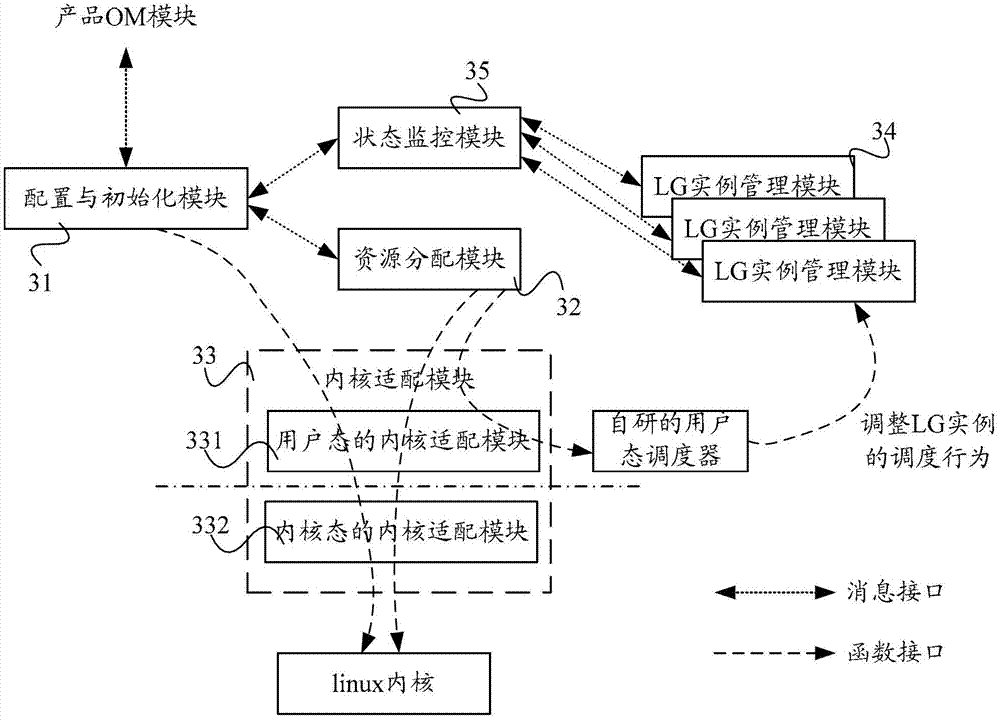

Method and equipment for scheduling multi-core processor

InactiveCN102831015AReduce overheadImprove resource utilizationResource allocationLinux kernelApplication software

The invention provides a method and equipment for scheduling a multi-core processor. The method comprises the following steps of: receiving source request information sent by an application program by an LG (Linear Generator), wherein the resource request information comprises information of CPU (Central Processing Unit) resources requested by the application program, and the LG is a lightweight-class cross-course intermediate piece; and distributing the CPU resources requested by the application program to the application program for use according to the resource request information, and isolating at least one Linux kernel thread on the CPU resources. With the adoption of the method and equipment for scheduling the multi-core processor provided by the embodiment of the invention, the cost can be reduced in a multi-core scheduling process; the multi-core displacement is simplified; and the multi-core CPU resource use ratio can be improved.

Owner:HUAWEI TECH CO LTD

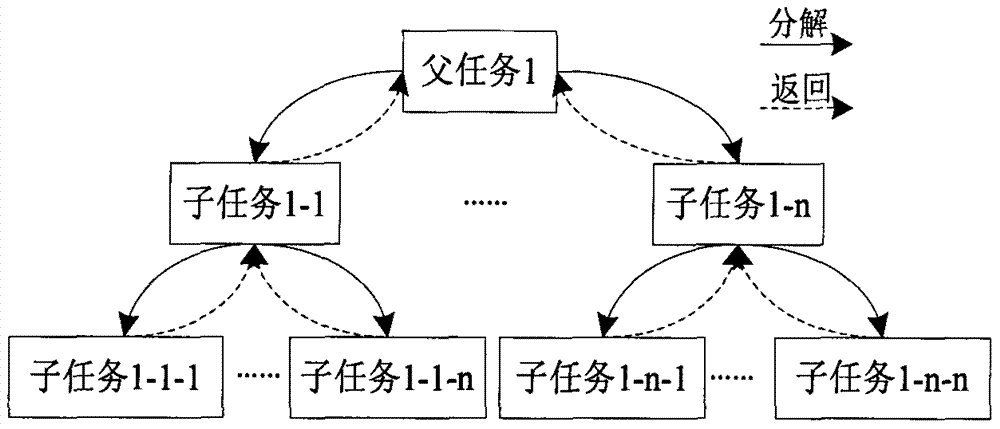

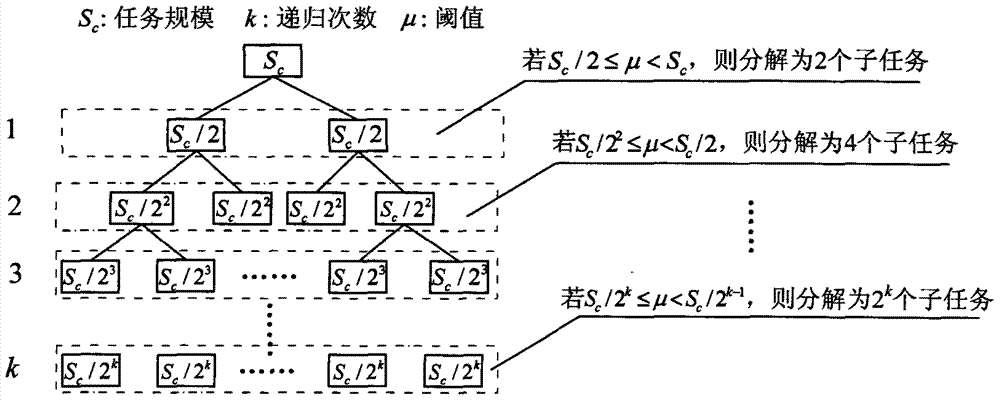

Cascade reservoir group optimized dispatching multi-core parallel computing design method based on Fork/Join framework

InactiveCN107015861AImprove computing efficiencyReduce computing timeResource allocationDesign optimisation/simulationDynamic planningParallel computing

The invention discloses a cascade reservoir group optimized dispatching multi-core parallel computing design method based on a Fork / Join framework. The method includes the following steps that 1, the Fork / Join parallel framework is established; 2, the Fork / Join parallel framework is achieved; 3, typical intelligent method parallel design in a coarse-grained mode is carried out; 4, typical dynamic planning method parallel design in a fine-grained mode is carried out. By means of PSCWAGA, PAHPSO, PDP and PDDDP method instance testing results, the Fork / Join multi-core parallel framework is adopted, the multi-core CPU parallel performance can be fully exerted, calculation time is greatly shortened, the calculation efficiency of the algorithm is remarkably improved, and the larger the calculation scale of the parallel method is, the shorter the calculation time is, and the more obvious the advantages of parallel calculation is. Along with gradual increase of the calculation scale, the speed-up ratio is gradually increased, the parallel efficiency is gradually improved, and the speed-up ratio is closer to an ideal speed-up ratio.

Owner:PEARL RIVER HYDRAULIC RES INST OF PEARL RIVER WATER RESOURCES COMMISSION

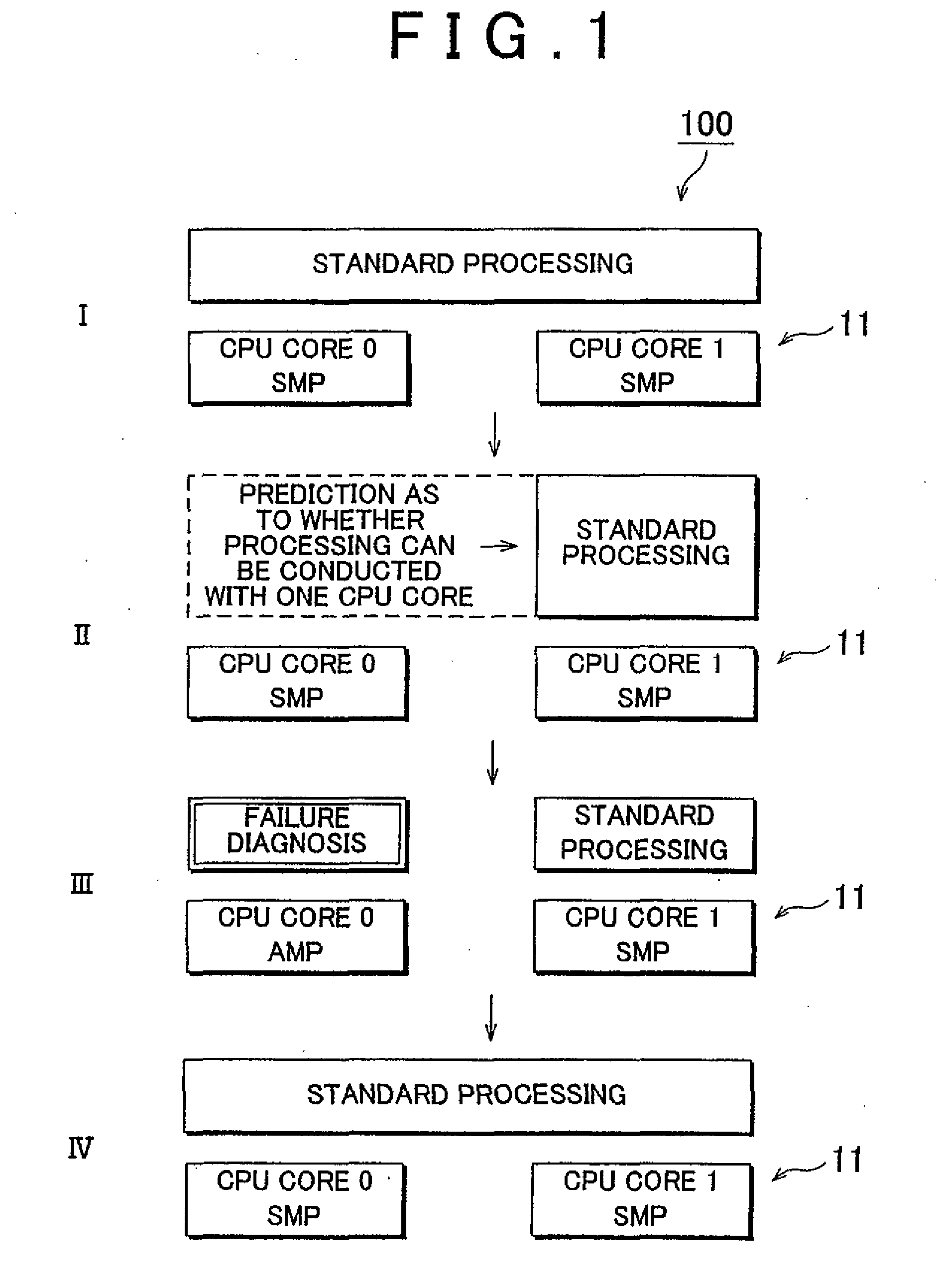

Failure diagnostic system, electronic control unit for vehicle, failure diagnostic method

A failure diagnostic system (100) for a multicore CPU having installed therein a plurality of CPU cores (11) that is configured to be switched from a SMP mode to an AMP mode includes: load prediction means for predicting a processing load of the multicore CPU; mode switching means for switching at least one of the CPU cores (11) to the AMP mode when the processing load is less than a threshold; and failure diagnostic means for performing a failure diagnosis of the CPU core that has been switched to the AMP mode.

Owner:TOYOTA JIDOSHA KK

Intelligent split screen display available mobile terminal

InactiveCN103365620ADoes not compromise portabilityLift restrictionsDigital output to display deviceIntelligent lightingLarge screen

The invention discloses an intelligent split screen display available mobile terminal which comprises a CPU (Central Processing Unit) and a GPU (Graphic Processing Unit), wherein the CPU is a single-core or multi-core CPU supporting multithreading and multitasking; an inner core of the CPU supports a multi-domain display management function; the CPU is connected with the GPU; and the GPU is a single-core or multi-core GPU supporting split screen display and full high definition graphic processing, and is connected with a multi-channel video output interface and a projection output interface. The mobile terminal utilizes the CPU with the multi-domain display management function and the GPU with a split screen display function, so that the portability is kept, and display limitation of the mobile terminal is removed; a requirement of a large screen is met; intelligent multi-domain display management is available, so that the problem that display content can only be subjected to mirror image duplication in the prior projection is solved; and mobile equipment has powerful functions of equipment such as a PC (Personal Computer) and a palmtop, and has the potentiality of replacing the equipment such as the PC and the palmtop. The intelligent split screen display available mobile terminal can be widely applied to the field of the mobile terminals.

Owner:陈飞生

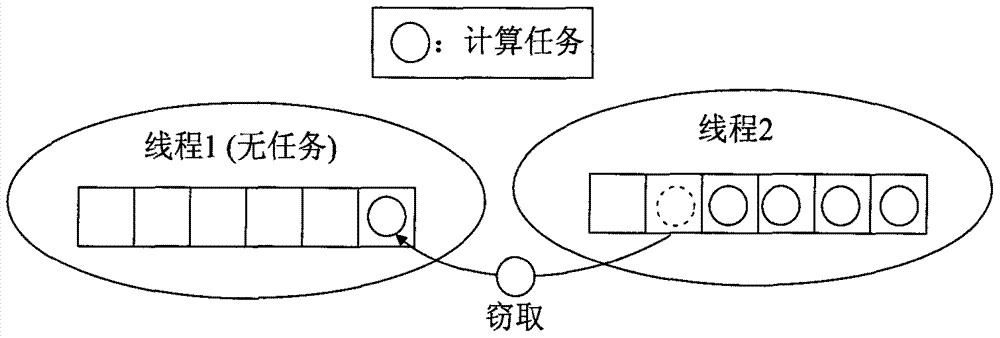

Method and device for balancing multi-core CPU load

ActiveCN104239153AReduce power consumptionResource allocationEnergy efficient computingParallel computingCpu load

The invention discloses a method and a device for balancing multi-core CPU load. The method comprises the following steps of acquiring utilization rate information and frequency information of each CPU core in the multi-core CPU; acquiring a first CPU core with the frequency satisfying the operation condition of a to-be-operated process and lowest utilization rate; configuring the to-be-operated process into the first CPU. By adopting the embodiment, after the load balance of multi-core CPU is carried out, the increment of the power consumption can be avoided.

Owner:SAMSUNG ELECTRONICS CHINA R&D CENT +1

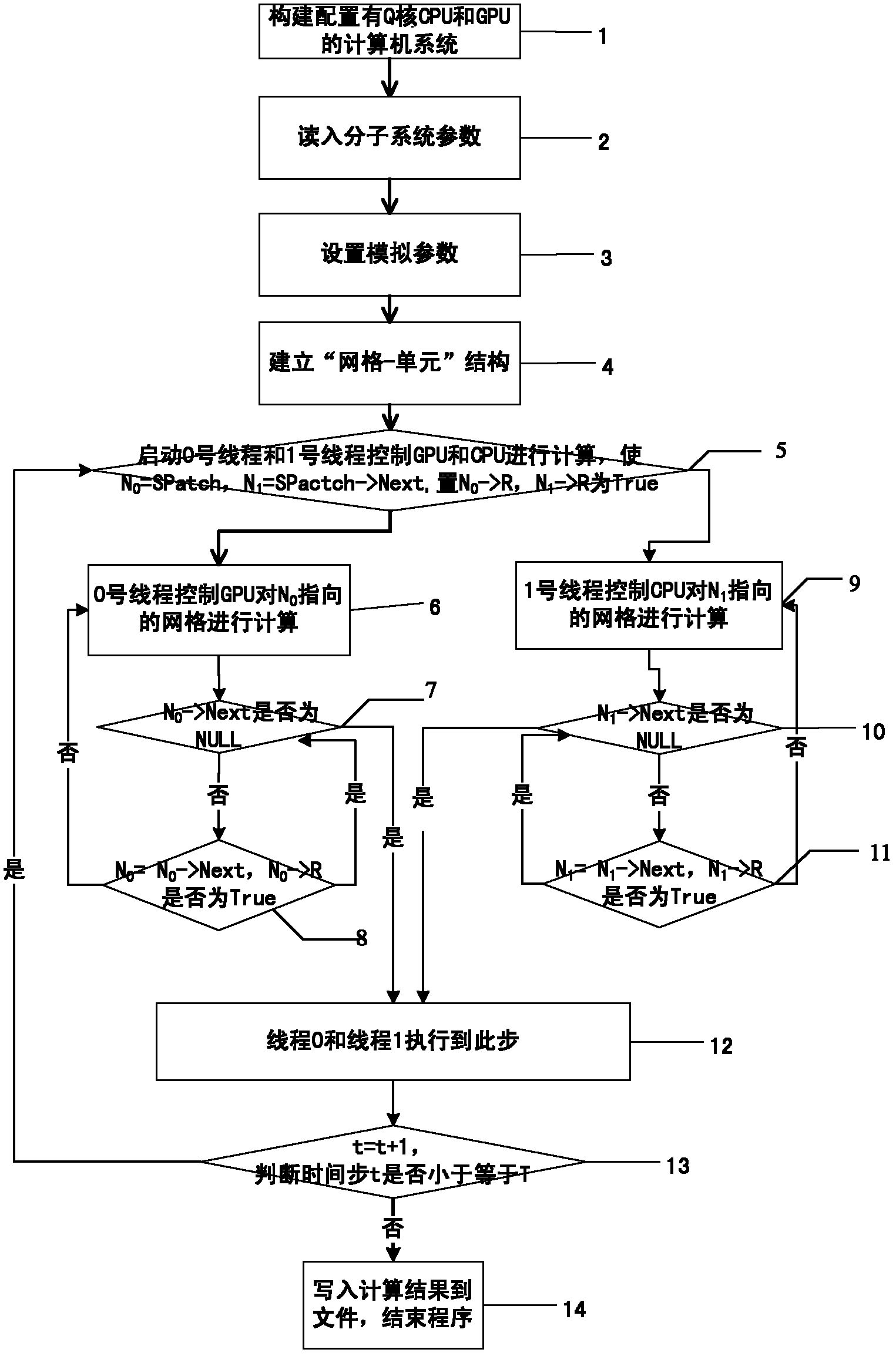

Molecular dynamics accelerating method based on CUP (Central Processing Unit) and GPU (Graphics Processing Unit) cooperation

InactiveCN102411658AAvoid idle waiting situationsIncrease profitSpecial data processing applicationsFully developedComputerized system

The invention discloses a molecular dynamics accelerating method based on CUP (Central Processing Unit) and GPU (Graphics Processing Unit) cooperation, which aims to provide a molecular dynamics accelerating method based on CUP and GPU cooperation at a lower cost. The technical scheme is executed by the following steps that: a ''grid-unit'' structure for storing molecular information is built on a to-be-simulated molecular system by a computer configured with a CPU and a GPU; the grids are dynamically applied and processed by the CPU and GPU; when the grids are processed, the CPU processes the grids by regarding cells as the unit; and the whole grid is processed by the GPU for simulating the molecular dynamics by efficient cooperation of CPU and GPU. The molecular dynamics accelerating method disclosed by the invention can balance loads among the CPU cores and avoid the phenomenon that the CPU and GPU are in idle and waiting state in statically distributing the calculating tasks. Therefore, the CPU and GPU can both fully develop the calculating properties. The use ratio of the whole computer system is improved and acceleration of molecular dynamics at lower cost is realized.

Owner:NAT UNIV OF DEFENSE TECH

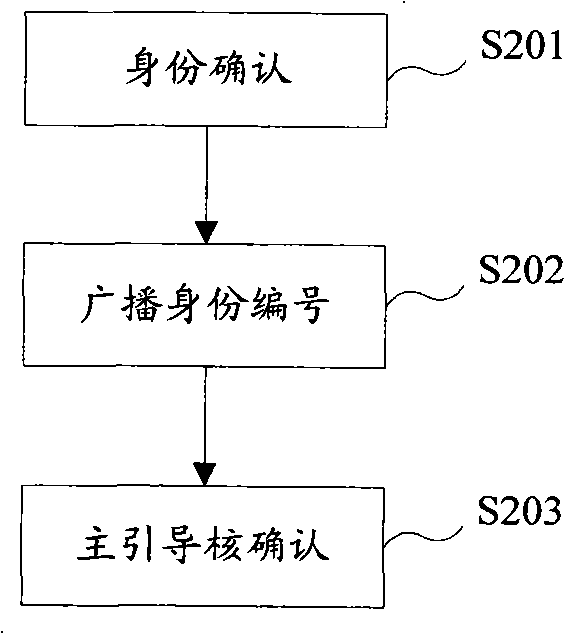

Method for automatically electing main guiding nucleus in isomerization multi-nucleus architecture

InactiveCN101256512AAvoid unbootable bugsError detection/correctionMultiprogramming arrangementsSleep stateOperational system

The invention discloses an automatic election method for a master boot kernel in heterogeneous multi-kernel system, comprising the following steps: after switched on, a multi-kernel CPU calls an election mechanism which is used for determining the master boot kernel; each kernel in the multi-kernel CPU executes the election mechanism, and judges whether itself is a master boot kernel; at the same time, all slavery kernels in normal state are recorded; the determined master boot kernel loads an operating system, and initializes peripheral hardware equipments and the operating system; the slavery kernels enter into sleep state; the master boot kernel wakes up all slavery kernels in normal state, the slavery kernels load and initialize respective operating system code segments after waken up, and then the master boot kernel and the slavery kernels enter into normal running state. The method is capable of avoiding the defect of startup failure of the whole system, which is caused by the fault occurrence of the master boot kernel.

Owner:ZTE CORP

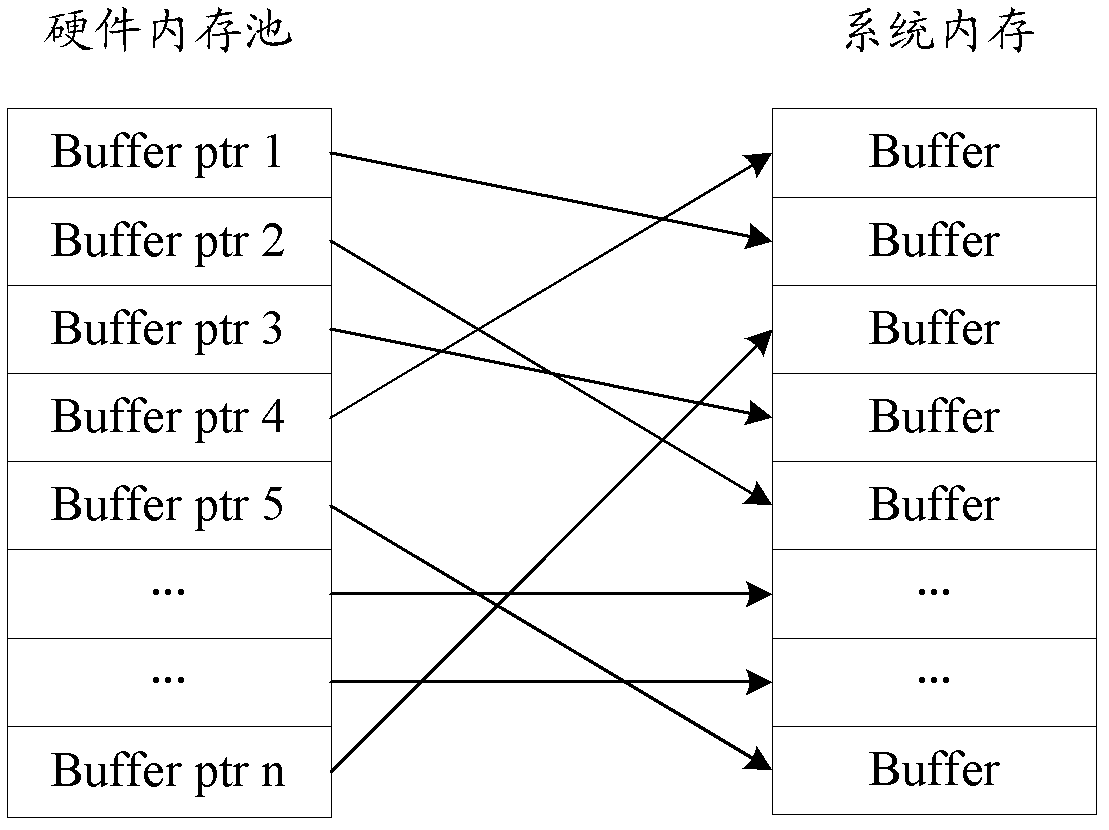

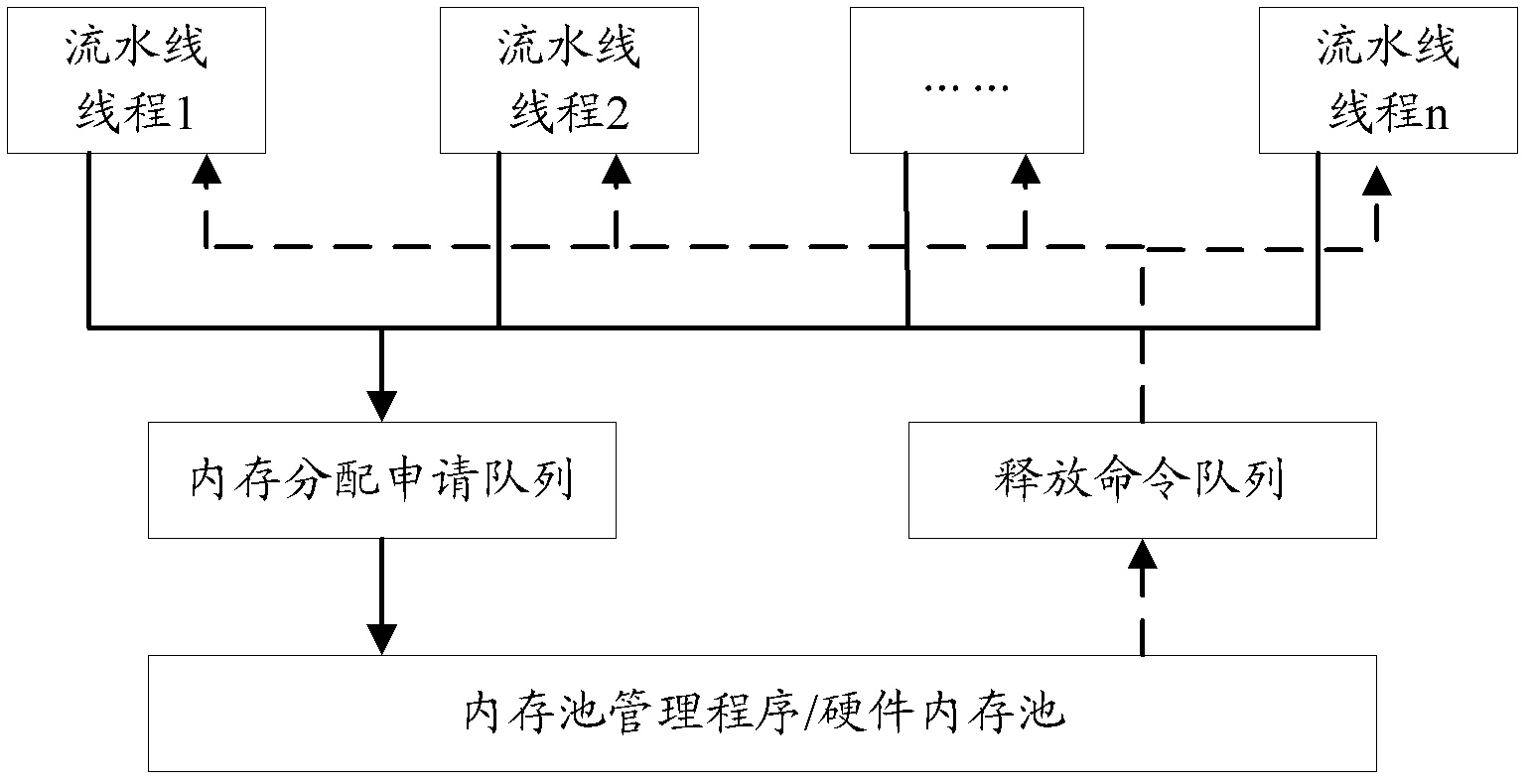

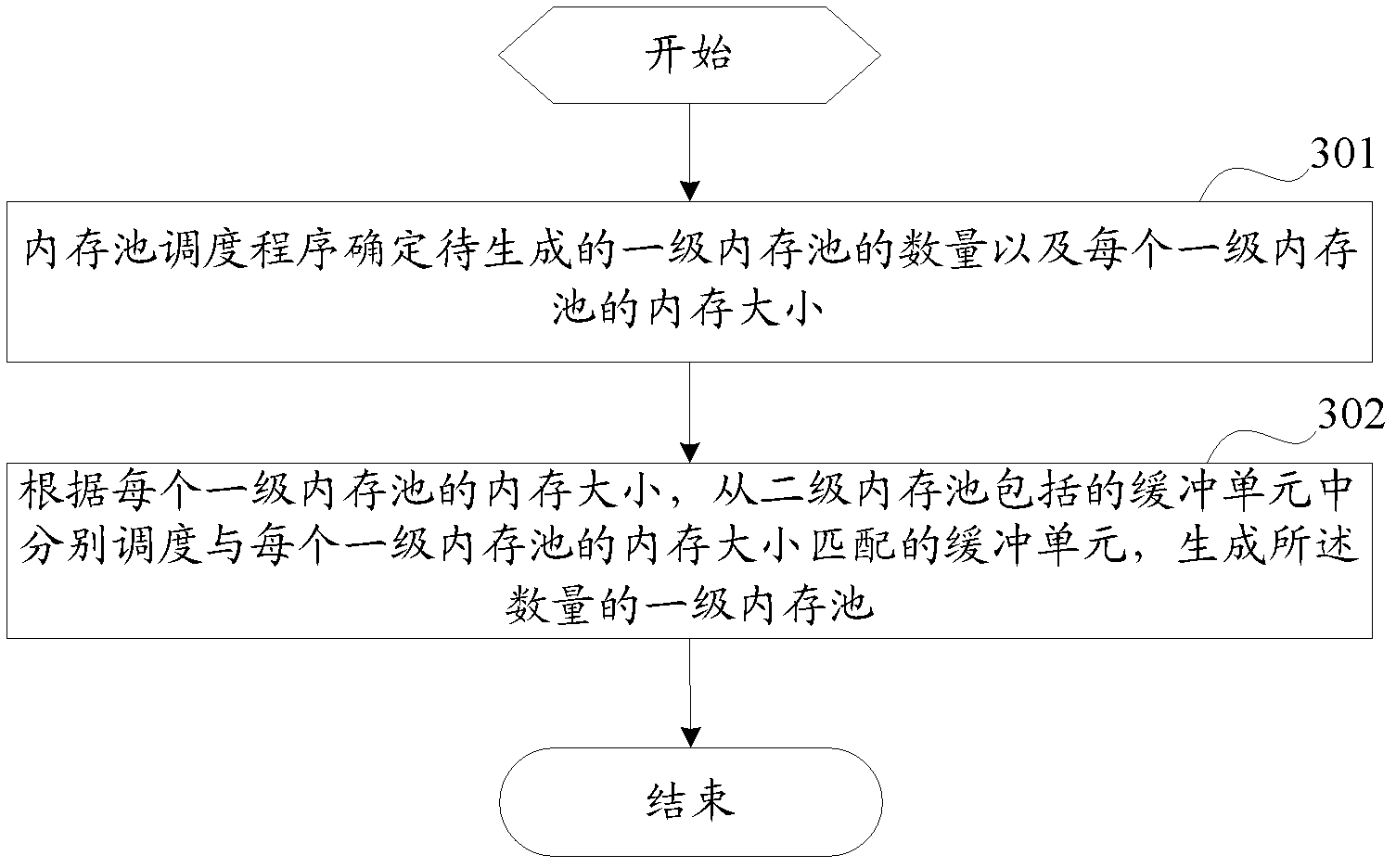

Method and device for scheduling memory pool in multi-core central processing unit system

InactiveCN102662761AImprove timelinessEasy to handleProgram initiation/switchingResource allocationProduction lineParallel computing

The invention discloses a method and a device for scheduling a memory pool in a multi-core central processing unit system. According to a technical scheme, after receiving memory allocation applications respectively sent from at least two production line threads, a memory pool scheduling program carries out memory pool allocation respectively aiming at each received memory allocation application, i.e., a primary memory pool to be pre-allocated to each production line thread sending the memory allocation application is determined from at least two pre-generated primary memory pools; and a buffer unit included in the determined primary memory pool is allocated to the production line thread to call, wherein the buffer unit included in the primary memory pool is scheduled from buffer units included in a secondary memory pool. According to the technical scheme, when multiple production line threads send applications simultaneously, corresponding memory pool resources can be respectively allocated to the multiple production line threads to schedule, so that the data processing timeliness of the multi-core CPU (central processing unit) system is improved.

Owner:RUIJIE NETWORKS CO LTD

Multi-core system single-core abnormity restoration method

ActiveCN101236515ARun in timeImprove uptimeProgram initiation/switchingError detection/correctionRecovery methodRestoration method

The present invention relates to a multi-core CPU system, in particular to a recovery method of a single-core exception for multi-core CPU systems. The technical problem to be solved by the present invention is to provide a recovery method of a single-core for multi-core CPU systems, which carries out recovery under the condition with no operation interrupt when some single core appears abnormal. In a exception processing program of the present invention, the own state is set to be abnormal first, then a single core in normal state is selected to assist recovery, and a system scheduling module is informed of the reassignment to system tasks, so as to ensure that the recovery work can be completed as soon as possible and the recovery time can be shortened. The present invention has the advantages that: the recovery method can effectively ensure that the operation of the system cannot be interrupted and the resources of the system cannot be lost before and after single-core exception and recovery; the abnormal single core can work normally after recovery, which prolongs the possible run time of the system and strengthens the reliability of the system.

Owner:MAIPU COMM TECH CO LTD

Message receiving method and network device

ActiveCN107046508AImprove receiving efficiencySave CPU resourcesData switching networksMemory addressProcessor register

The embodiment of the invention relates to a technology of message processing and particularly relates to a message receiving method and a network device. The method is applied to a multi-core CPU. The multi-core CPU comprises a master core and a plurality of slave cores. The master core is used for determining an operation state of each slave core of the plurality of slave cores and maps the operation state of each slave core through a bit map. The method comprises the steps that in the plurality of slave cores, a first slave core operating in a kernel mode determines whether an interruption signal from an interruption controller is a packet receiving interruption signal or not; and if the interruption signal is the packet receiving interruption signal, the first salve core writes a memory address of a message into a shared memory shared by a user mode and the kernel mode in an interruption process, thereby enabling the address of the message to be seen by the slave kernels in the kernel mode and the user mode, wherein the steps performed by the first slave core are performed based on a preset special register, and the preset special register is the register which is only used by the slave core in the kernel state. According to the message receiving method and the network device provided by the embodiment of the invention, the message receiving efficiency can be improved.

Owner:HUAWEI TECH CO LTD

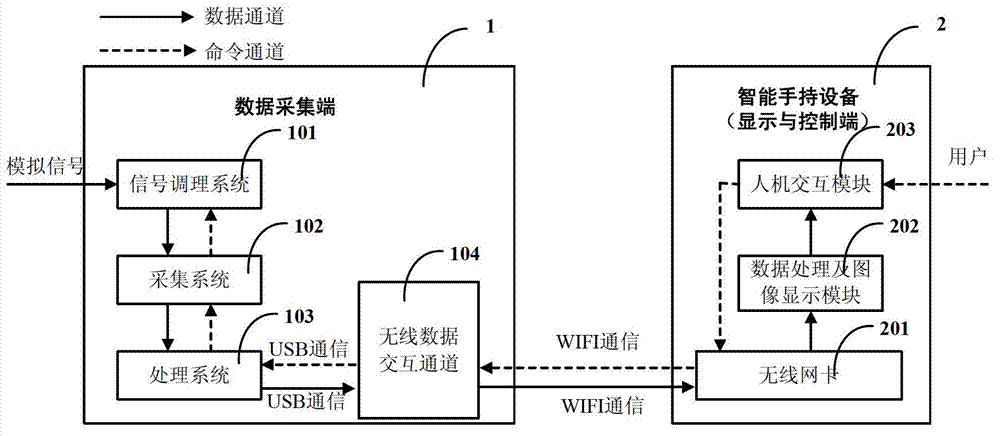

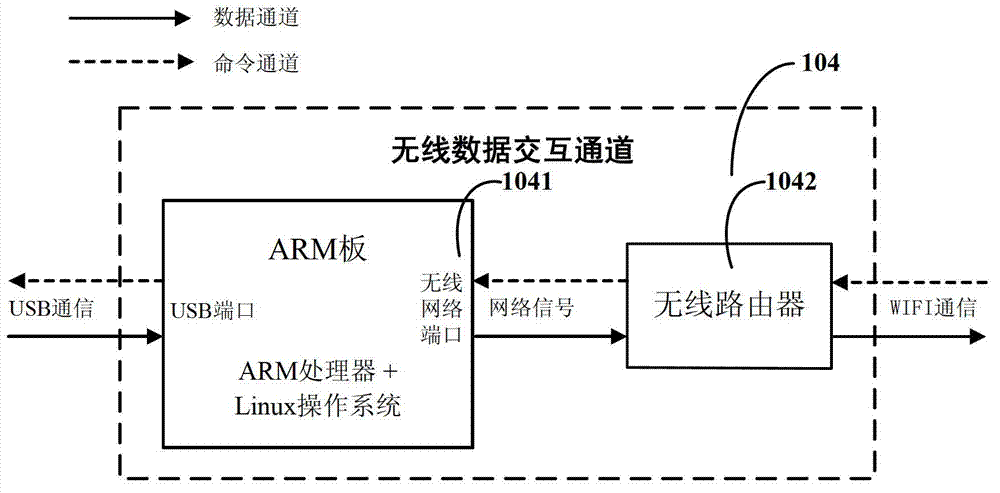

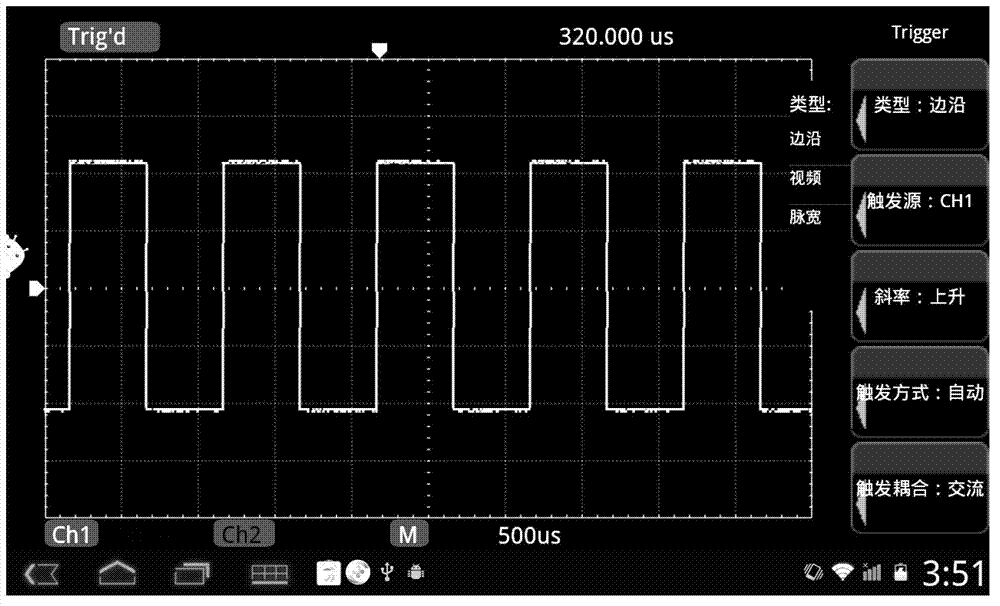

Short-distance operable digital oscilloscope

InactiveCN103048507ASampled Data Processing EnhancementsStrong computing powerDigital variable displayTransmission systemsShortest distanceWireless data

The invention discloses a short-distance operable digital oscilloscope. A wireless data interaction channel is innovatively arranged on the basis of the conventional digital oscilloscope, so that the digital oscilloscope can be wirelessly connected with any one intelligent handheld equipment, and operations such as sampled data processing, image display and operation and human-computer interaction of the conventional digital oscilloscope can be transferred to the intelligent handheld equipment. By using the strong operation capacity and good operation and portability characteristics of a high-speed multi-core CPU (Central Processing Unit), GPU (Graphic Processing Unit) and a touch liquid crystal screen of the intelligent handheld equipment, not only the sampled data processing capacity, the image display capacity and the human-computer interaction capacity of the digital oscilloscope can be obviously enhanced, but also the digital oscilloscope has the short-distance operation capacity. The short-distance operable digital oscilloscope is more suitable for field testing under hard and dangerous environments and high sensitivity requirements.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

Concurrent computation optical bar chart phase extraction method

ActiveCN103729251AProcessing speedGuaranteed accuracyResource allocationUsing optical meansConcurrent computationComputer cluster

A concurrent computation optical bar chart phase extraction method adopts a multi-node CPU computation platform consisting of a multi-core CPU or a computer cluster. A main node CPU finishes image reading and concurrent task partitioning and dispatch. A sub-node CPU processes allocated phase solution tasks and transmits results to the main node CPU. The main node CPU obtains the sub-node computation results and finishes phase unwrapping. The method improves the data processing speed while keeping the accuracy of a serial wavelet transform optical bar chart phase extraction method.

Owner:BEIJING GUOWANG OPTICAL TECH CO LTD

Router and software upgrading method thereof

ActiveCN103581008AImprove usabilityGuaranteed uptimeSoftware engineeringProgram loading/initiatingUsabilityMulticore cpu

The invention discloses a router and a software upgrading method of the router. The router comprises a multi-core CPU, a first memory area and a second memory area, wherein the first memory area and the second memory area are mutually independent. The multi-core CPU comprises a control plane CPU and a data plane CPU. The first memory area is used for storing control plane programs, and the second memory area is used for storing data plane programs. The data plane CPU is used for processing data messages by using the data plane programs in the second memory area, and the control plane CPU is used for processing protocol messages by using the control plane programs in the first memory area. When the router undergoes software upgrading, reset is performed and zero clearing is only performed on the first memory area. After reset is started, control plane programs of a new version are loaded into the first memory area, and the control plane programs of the new version in the first memory area are operated. The router and the software upgrading method of the router can improve the usability of a soft forwarding router.

Owner:NEW H3C TECH CO LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com