System and method for implementing packet combined treatment by multi-core CPU

A technology of joint processing and CPU core, applied in the field of communication, can solve the problem of hardware limitation of interrupt overhead, and achieve the effect of avoiding interrupt overhead, improving flexibility, and realizing throughput and delay.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

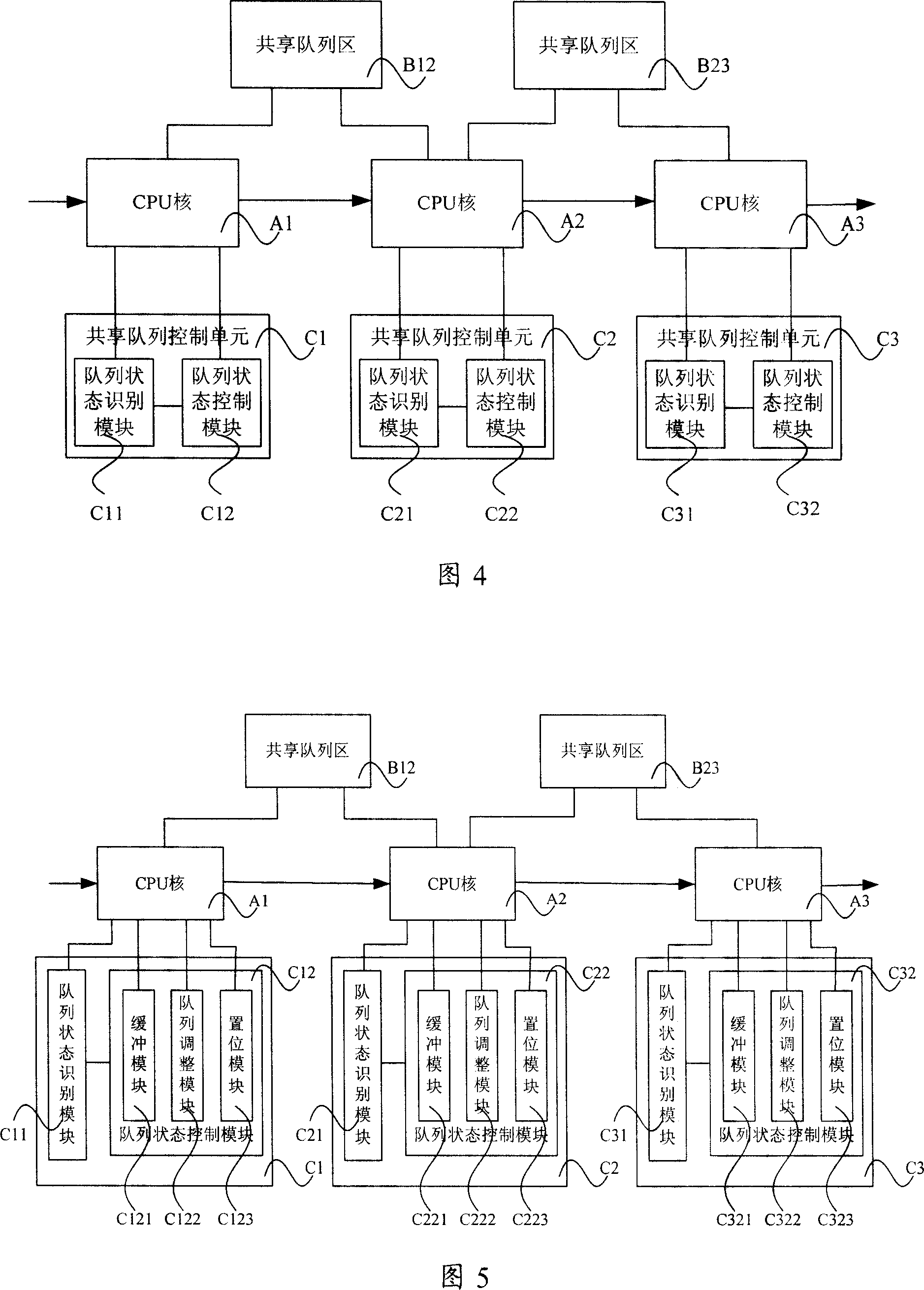

Image

Examples

Embodiment 1

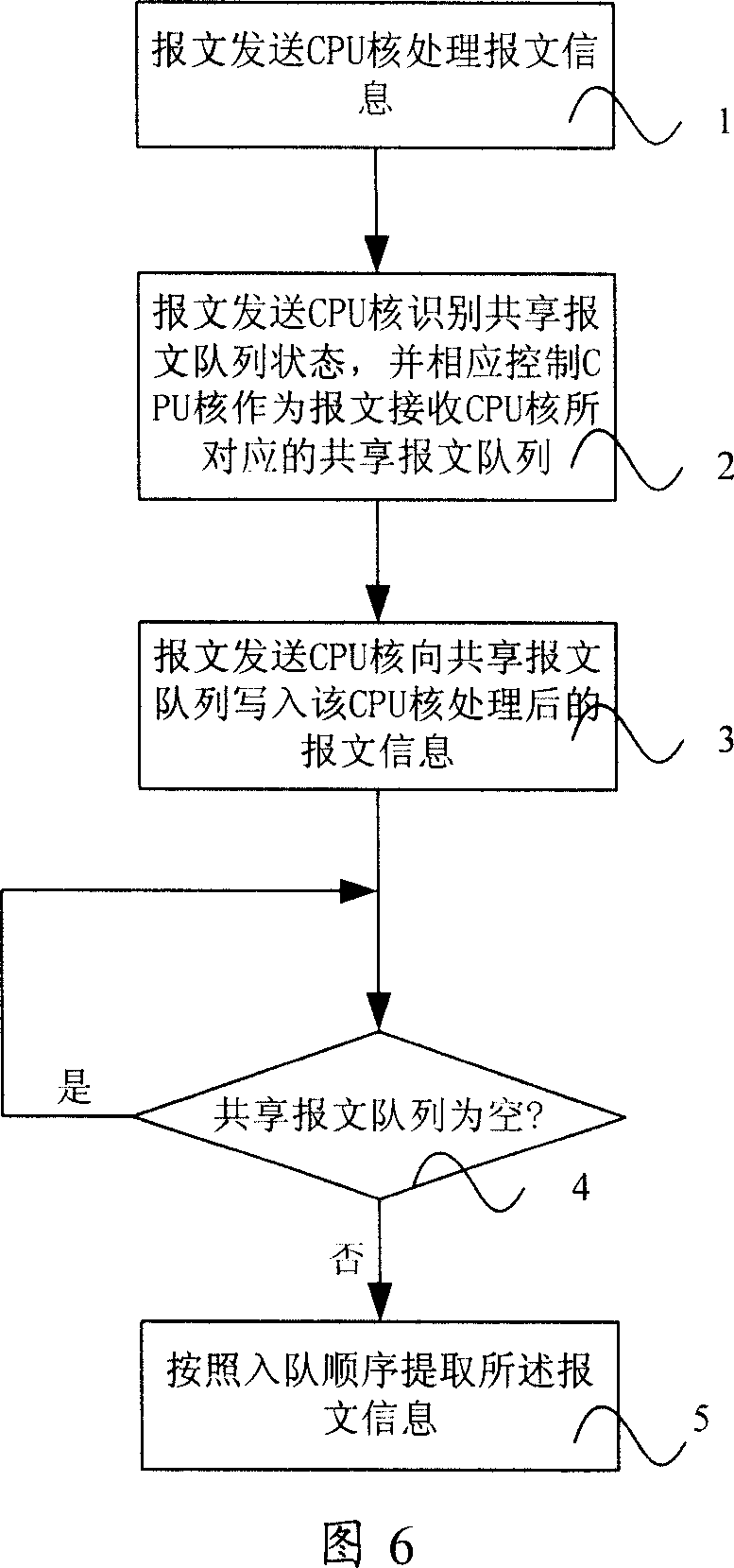

[0047] Referring to Fig. 6, embodiment 1 of the method provided by the present invention comprises the following steps:

[0048] Step 1, the message is sent and the CPU core processes the message information;

[0049] In this step, after the message sending CPU completes its own processing of the message, it encapsulates the message information into a preset message structure to ensure that the next CPU core can recognize it, for example:

[0050] struct pkt_message

[0051] {

[0052] ulong * packet;

[0053] ulong * pretreat;

[0054] ulong * parameter;

[0055]}

[0056] Step 2, the message sending CPU core identifies the state of the shared message queue, and correspondingly controls the CPU core as the shared message queue corresponding to the message receiving CPU core;

[0057] Step 3, the message sending CPU core writes the message information processed by the CPU core to the shared message queue;

[0058] Step 4, the message receiving CPU core queries w...

Embodiment 2

[0071] Referring to Fig. 9, for embodiment 2 of the method provided by the present invention, the following steps are included:

[0072] Step 21, the message is sent and the CPU core processes the message information;

[0073] Step 22. The message sending CPU core identifies the length of the shared message queue 1. If it is less than the preset minimum threshold value of 1min, it indicates that no congestion occurs, and executes step 27; it is greater than the preset minimum threshold value of 1min and less than the preset When the maximum threshold value is 1max, perform step 23, and when it is greater than the preset maximum threshold value 1max, perform step 24;

[0074] Step 23, shortening the length of the shared message queue corresponding to the CPU core as the message receiving CPU core, and performing step 27;

[0075] Step 24, indicating that the shared message queue is full, and buffering the processed message information;

[0076] Step 25, identifying the shared...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com