Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

39 results about "Global Arrays" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Global Arrays, or GA, is the library developed by scientists at Pacific Northwest National Laboratory for parallel computing. GA provides a friendly API for shared-memory programming on distributed-memory computers for multidimensional arrays. The GA library is a predecessor to the GAS (global address space) languages currently being developed for high-performance computing.

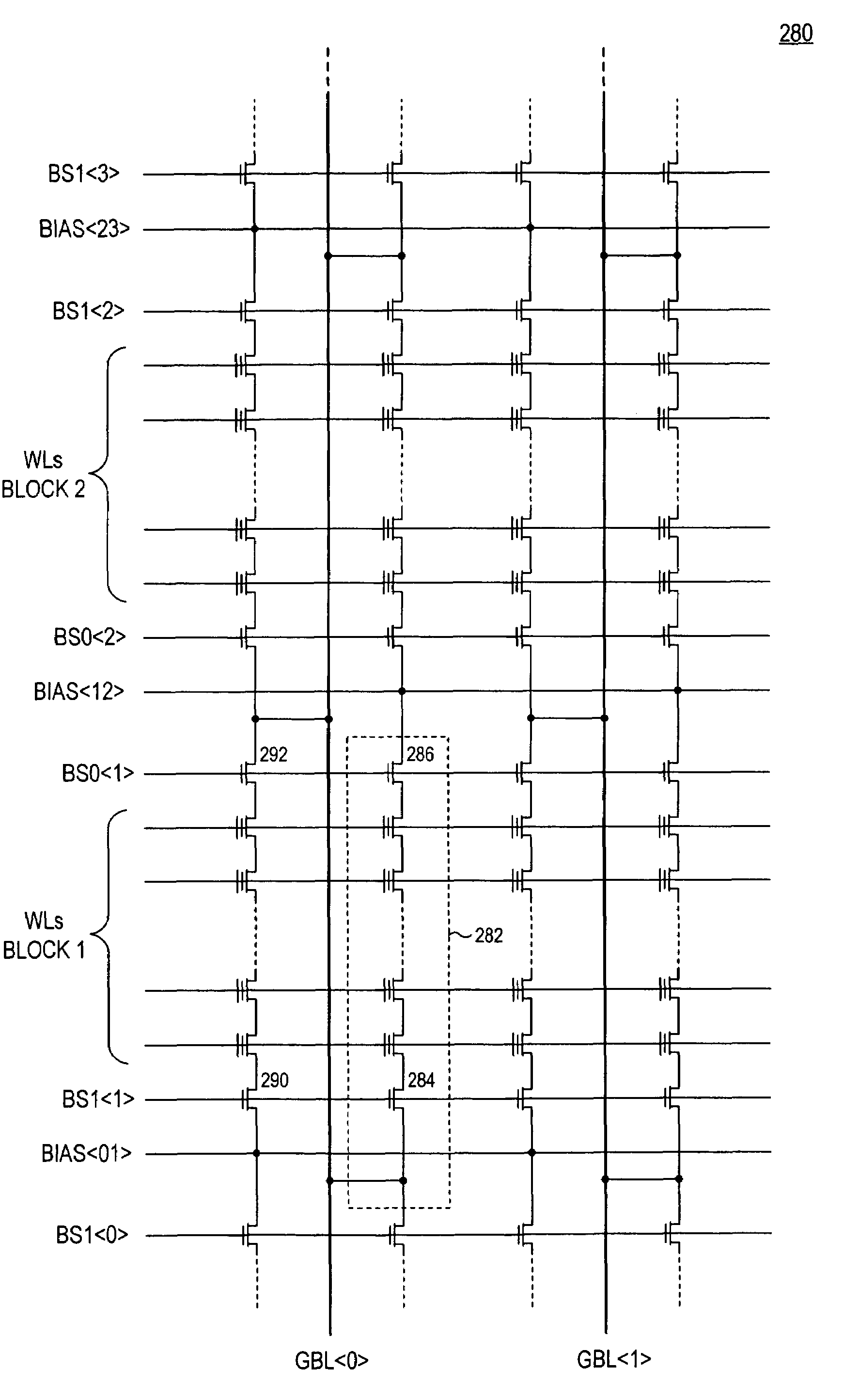

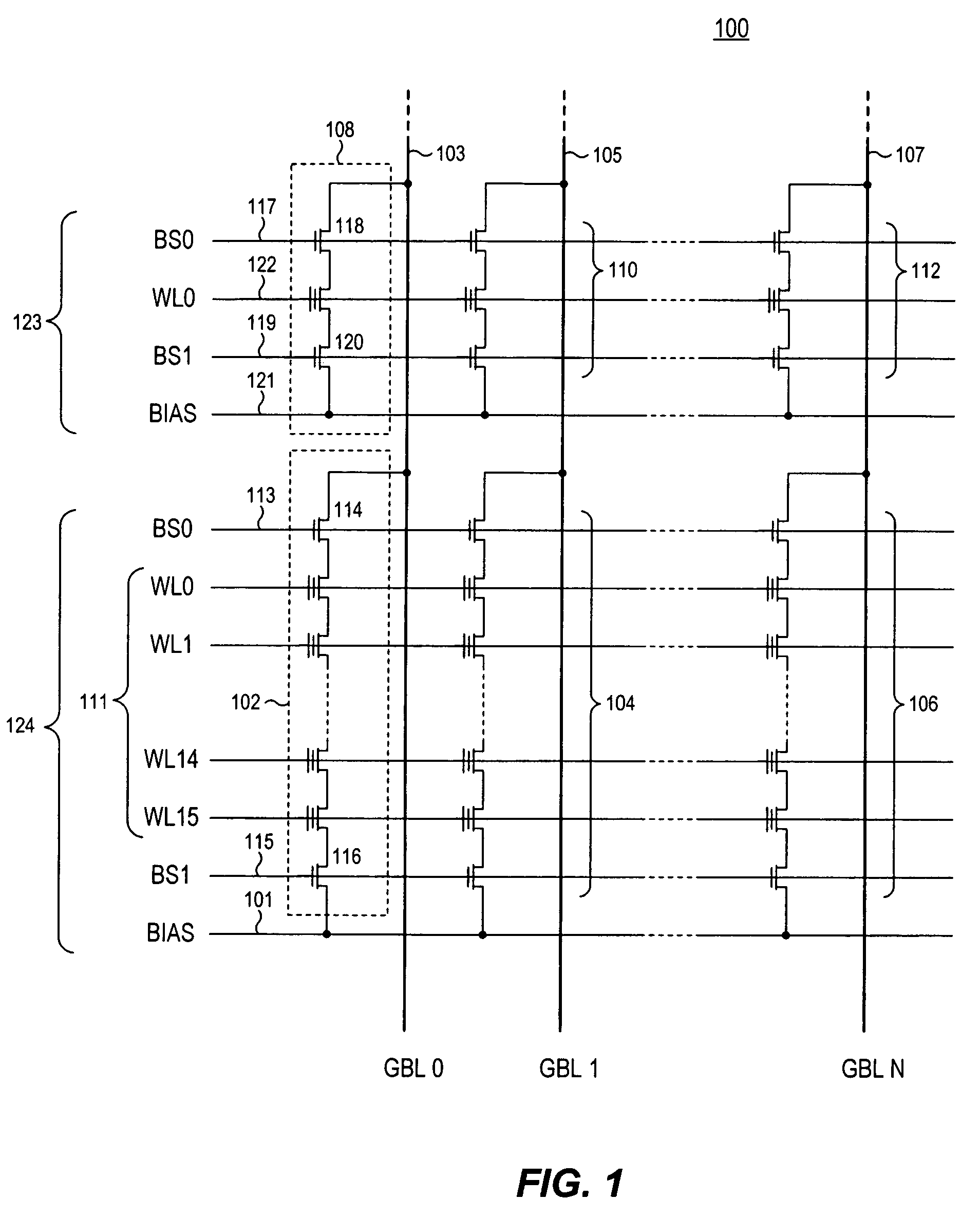

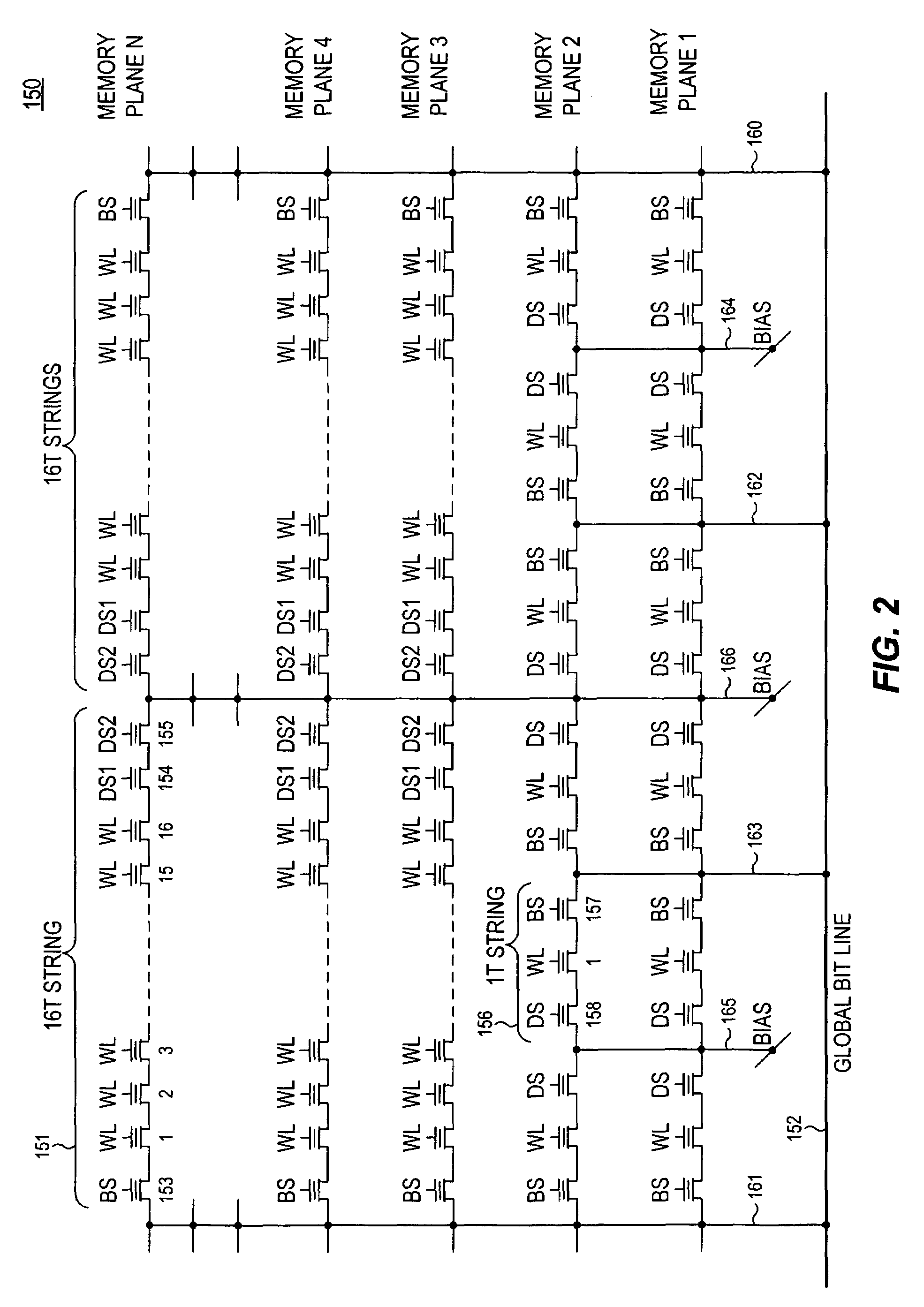

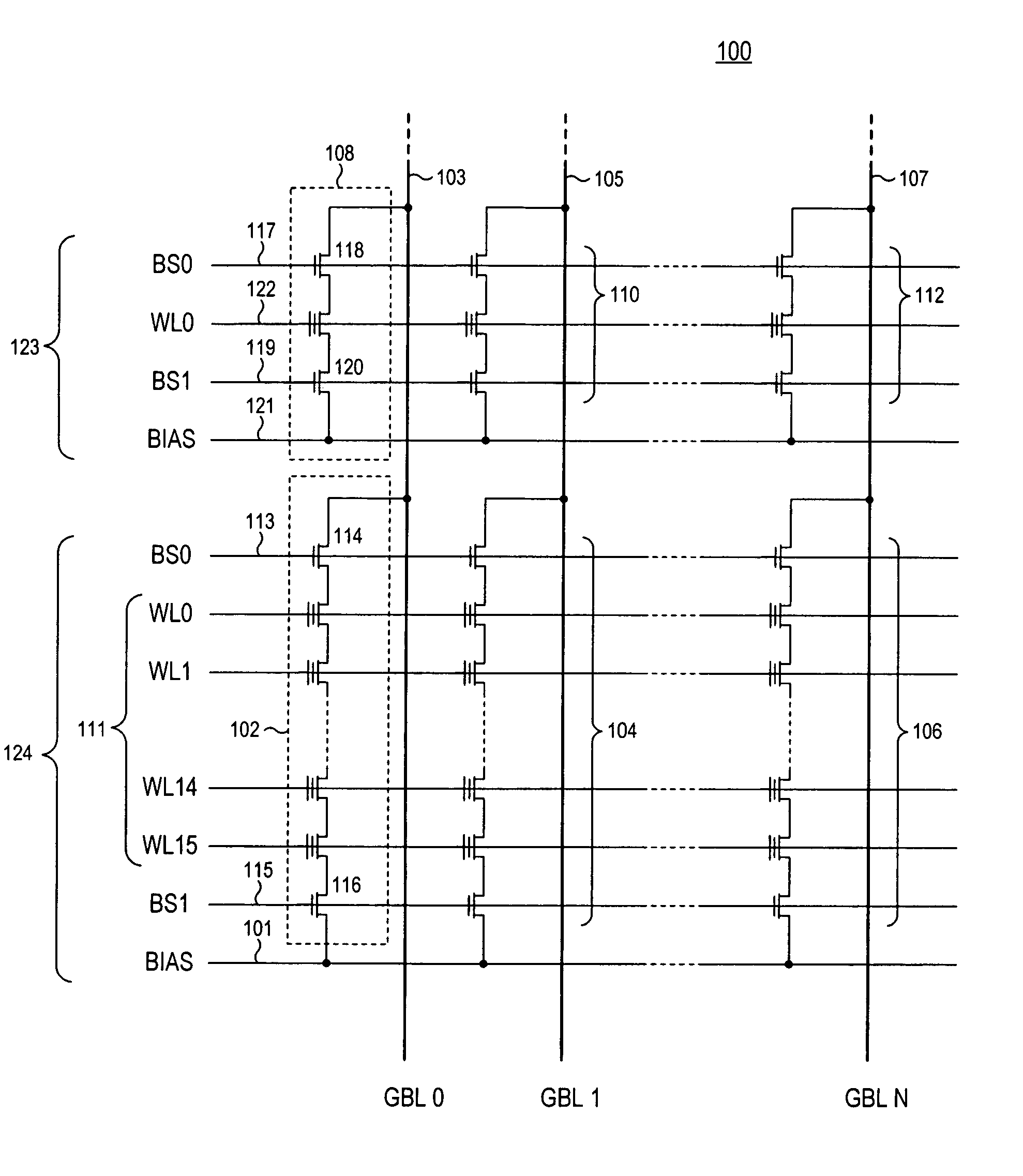

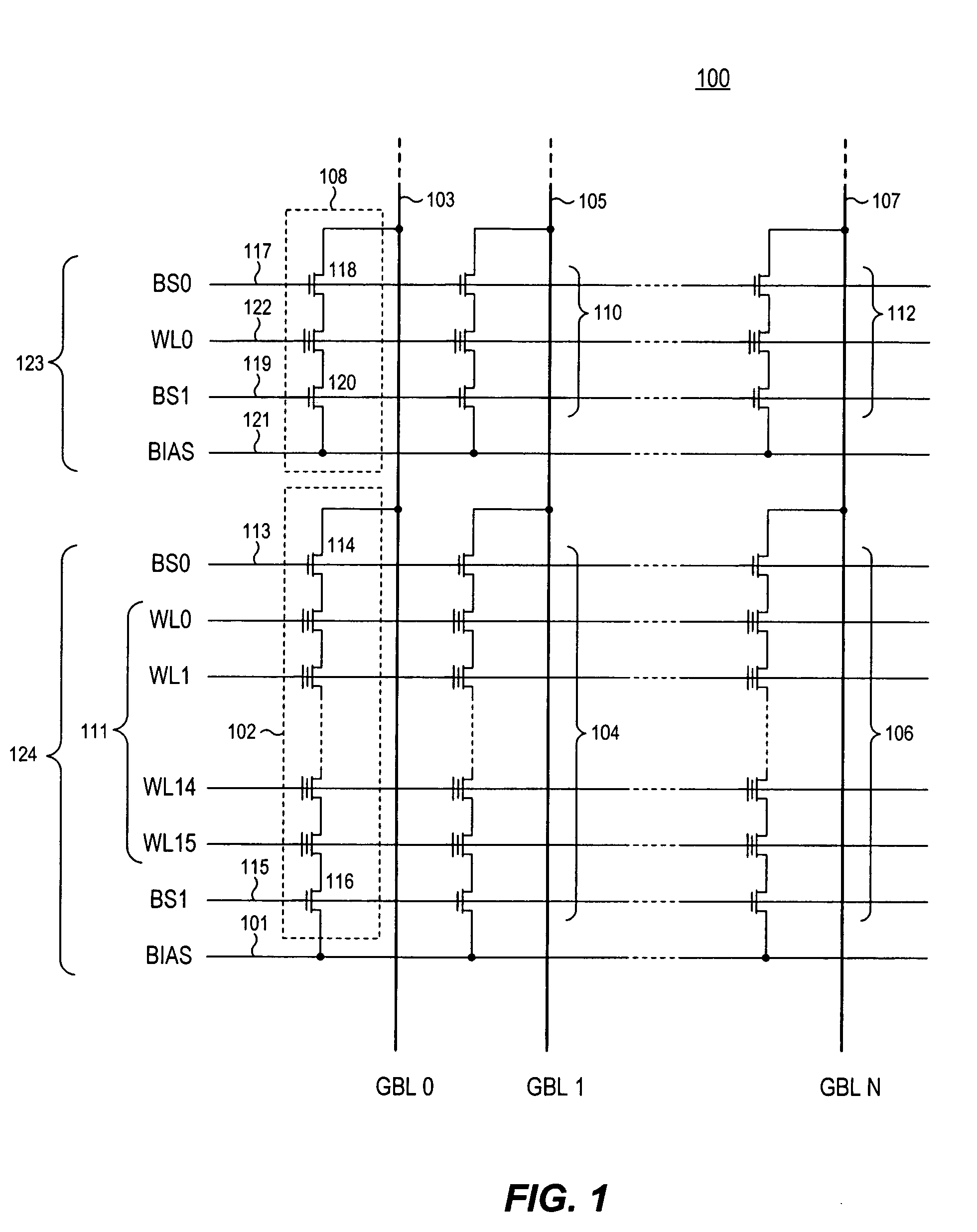

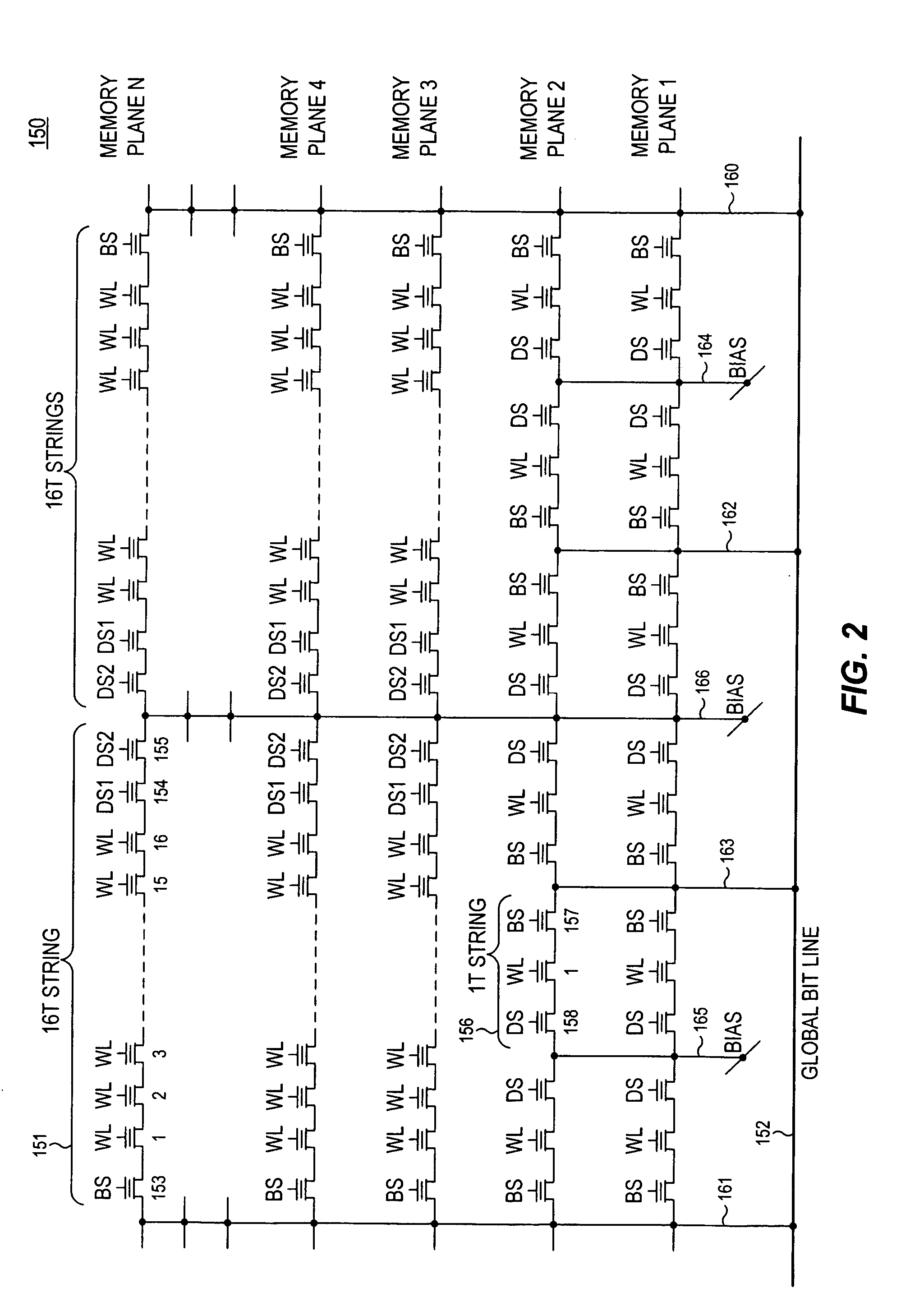

Integrated circuit including memory array incorporating multiple types of NAND string structures

ActiveUS7177191B2High densityGood flexibilitySolid-state devicesRead-only memoriesDevice formParallel computing

Owner:SANDISK TECH LLC

Integrated circuit including memory array incorporating multiple types of NAND string structures

ActiveUS20060146608A1High densityFast read-timeSolid-state devicesRead-only memoriesDevice formParallel computing

A monolithic integrated circuit includes a memory array having first and second groups of NAND strings, each NAND string comprising at least two series-connected devices and coupled at one end to an associated global array line. NAND strings of the first and second groups differ in at least one physical characteristic, such as the number of series-connected devices forming the NAND string, but both groups are disposed in a region of the memory array traversed by a plurality of global array lines. The memory array may include a three-dimensional memory array having more than one memory plane. Some of the NAND strings of the first group may be disposed on one memory plane, and some of the NAND strings of the second group may be disposed on another memory plane. In some cases, NAND strings of both groups may share global array lines.

Owner:SANDISK TECH LLC

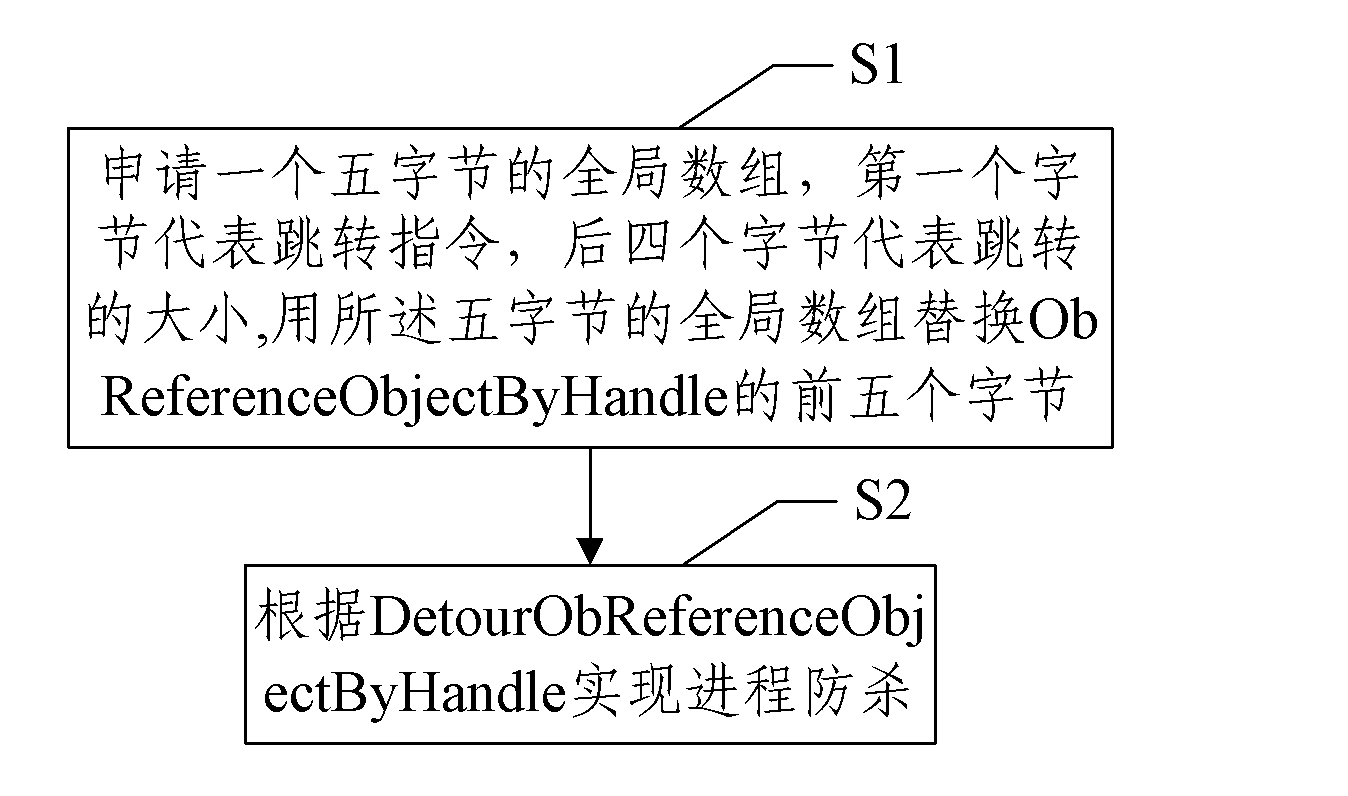

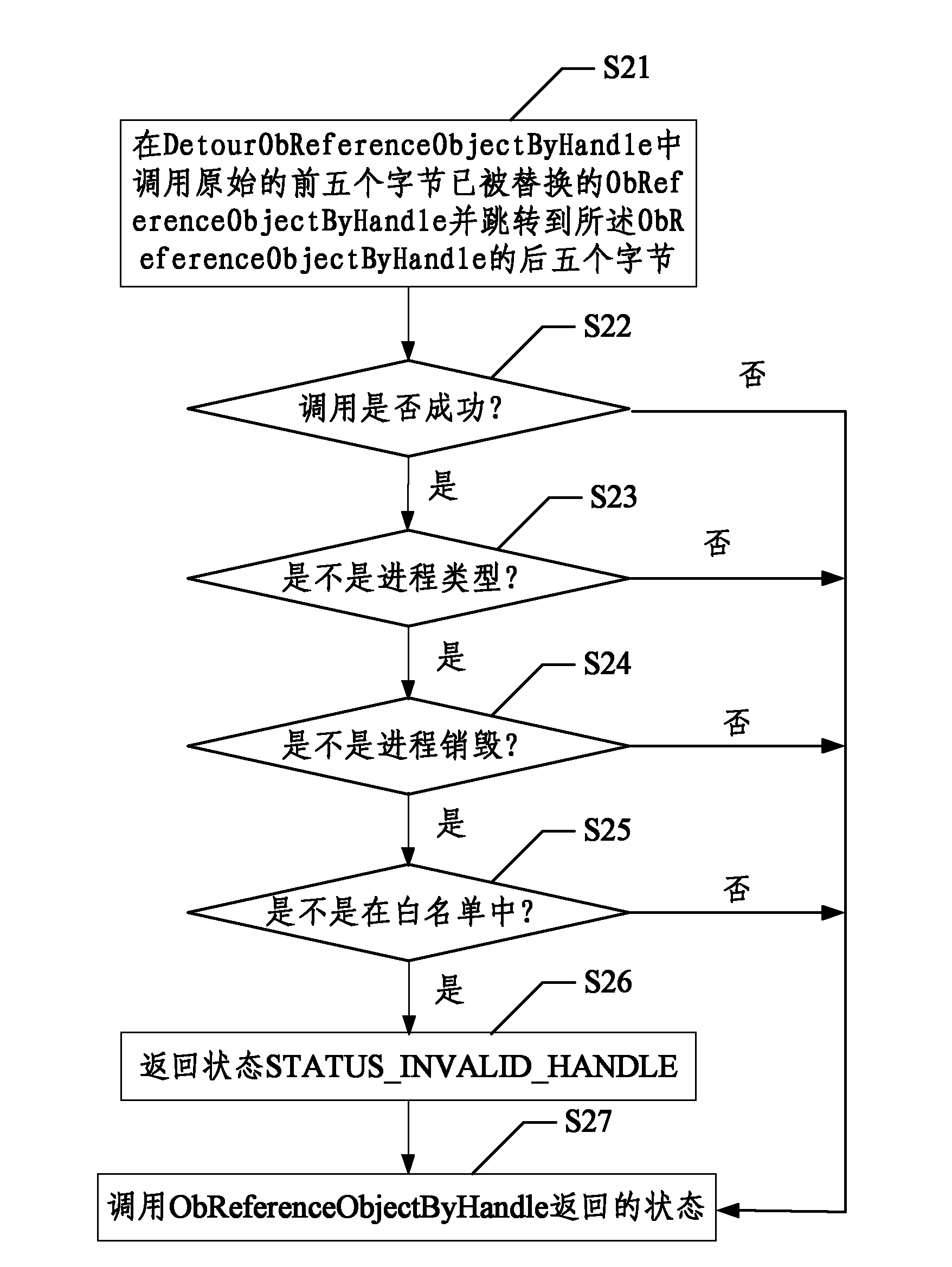

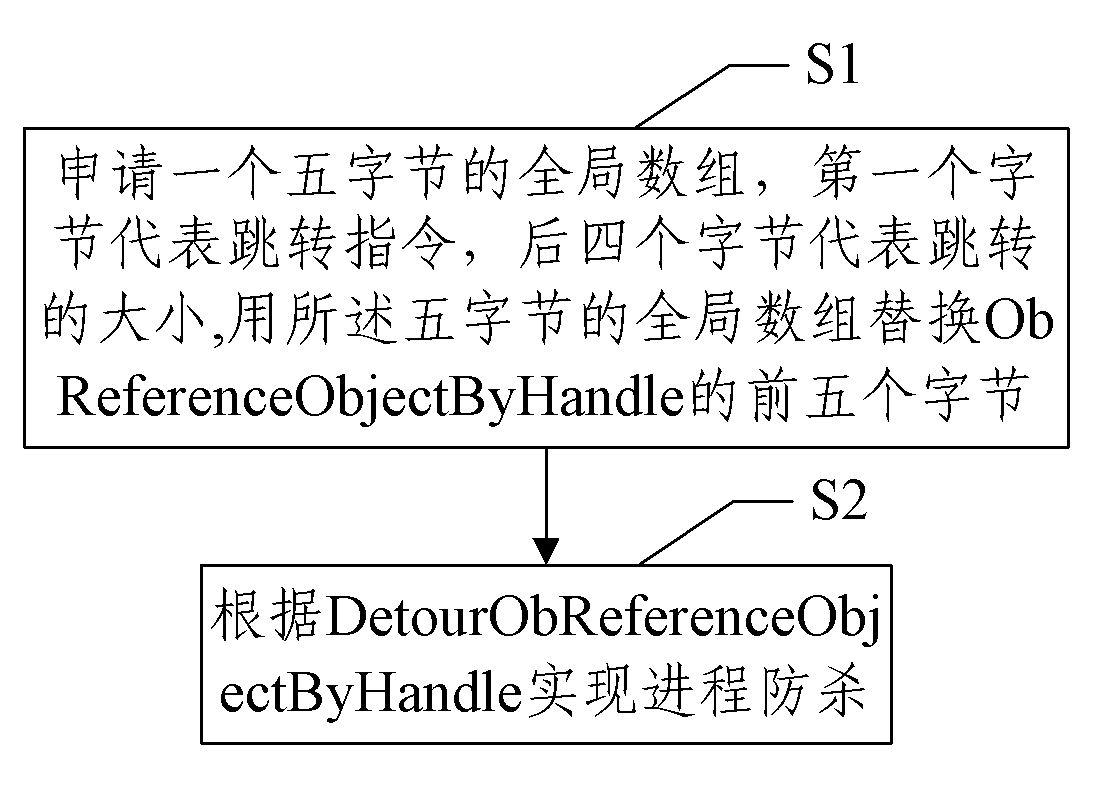

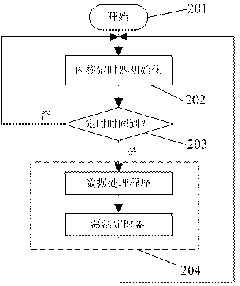

Method for realizing program killing prevention

The invention discloses a method for realizing program killing prevention, relating to the technical field of program monitoring. The method comprises the following steps of: 1, applying for a five-byte global array, and substituting the previous five bytes of ObreferenceObjectByHandle with the five-byte global array, wherein the first byte represents a jump (JMP) instruction, and the next four bytes represent size of jump; and 2, realizing program killing prevention according to DetourObreferenceObjectByHandle. By applying the method provided by the invention, since the ObreferenceObjectByHandle is opposite to a comparison bottom layer, the ObreferenceObjectByHandle is called to convert a handle into a File_Object during any illegal program closing and normal program closing and then theprogram is closed. Therefore, the program to be closed can be intercepted by hooking the ObreferenceObjectByHandle, and then whether the program is a normally closed program is judged, so that the program cannot be easily bypassed and can be protected from being illegally closed well.

Owner:北京思创银联科技股份有限公司

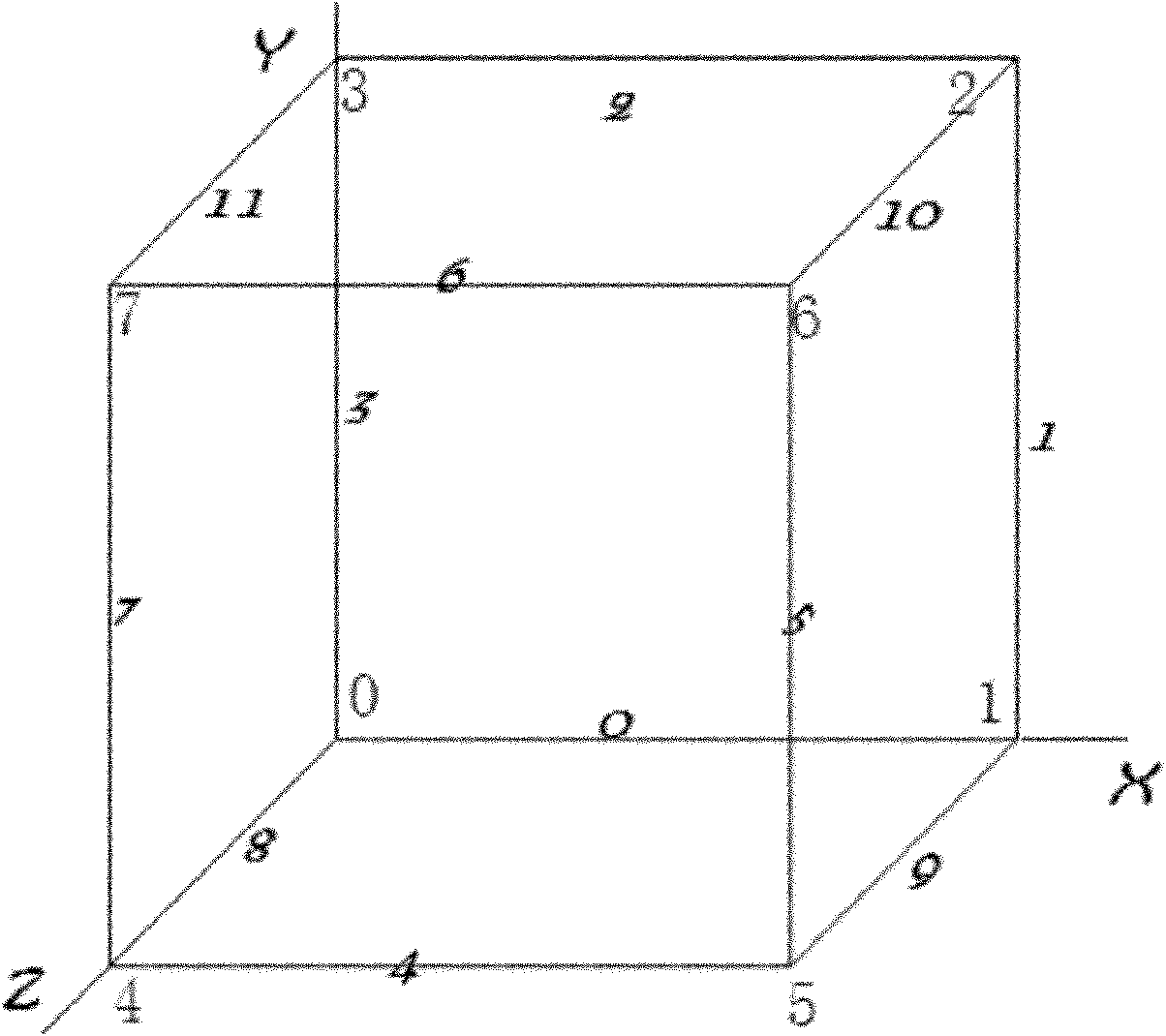

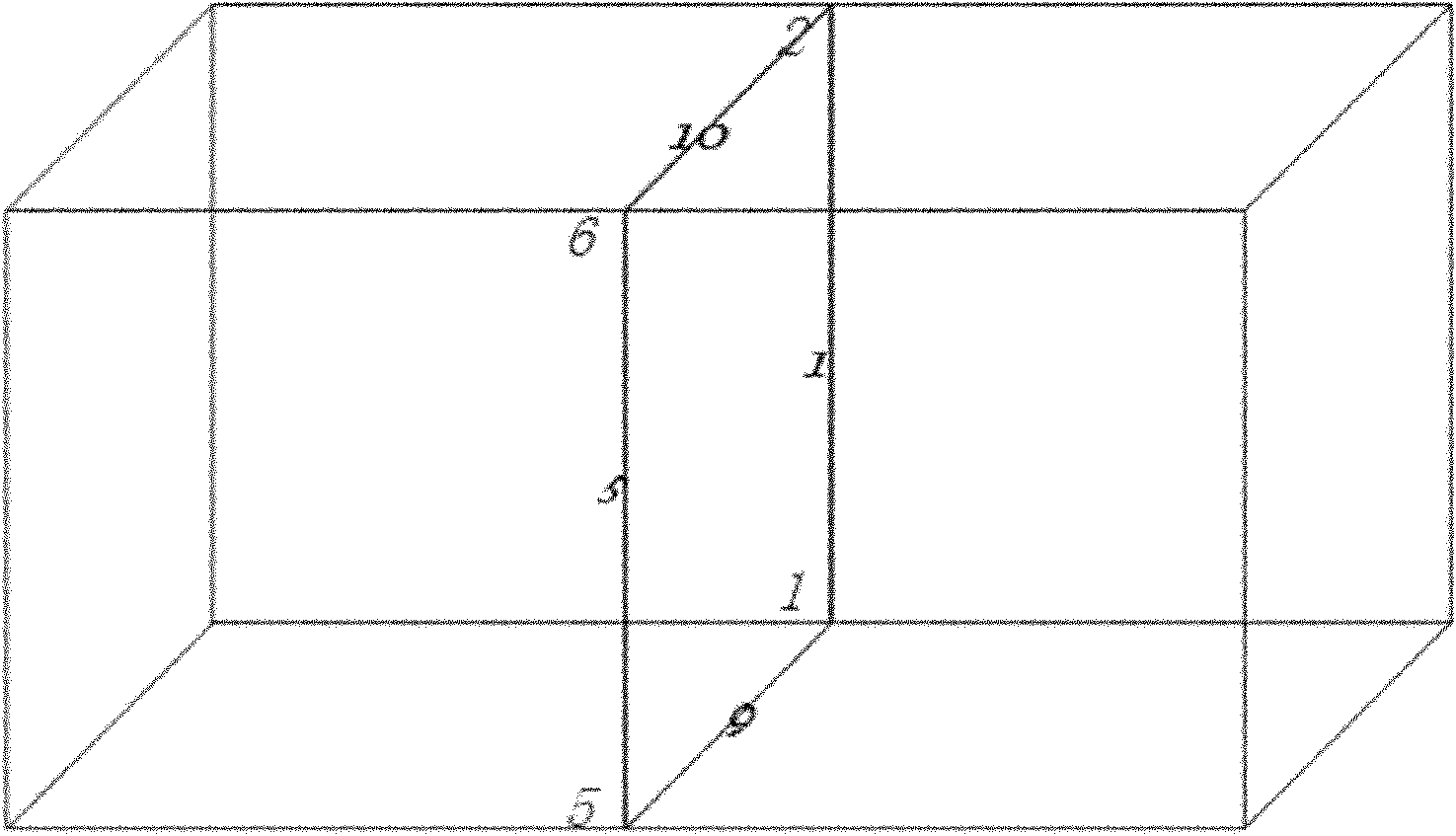

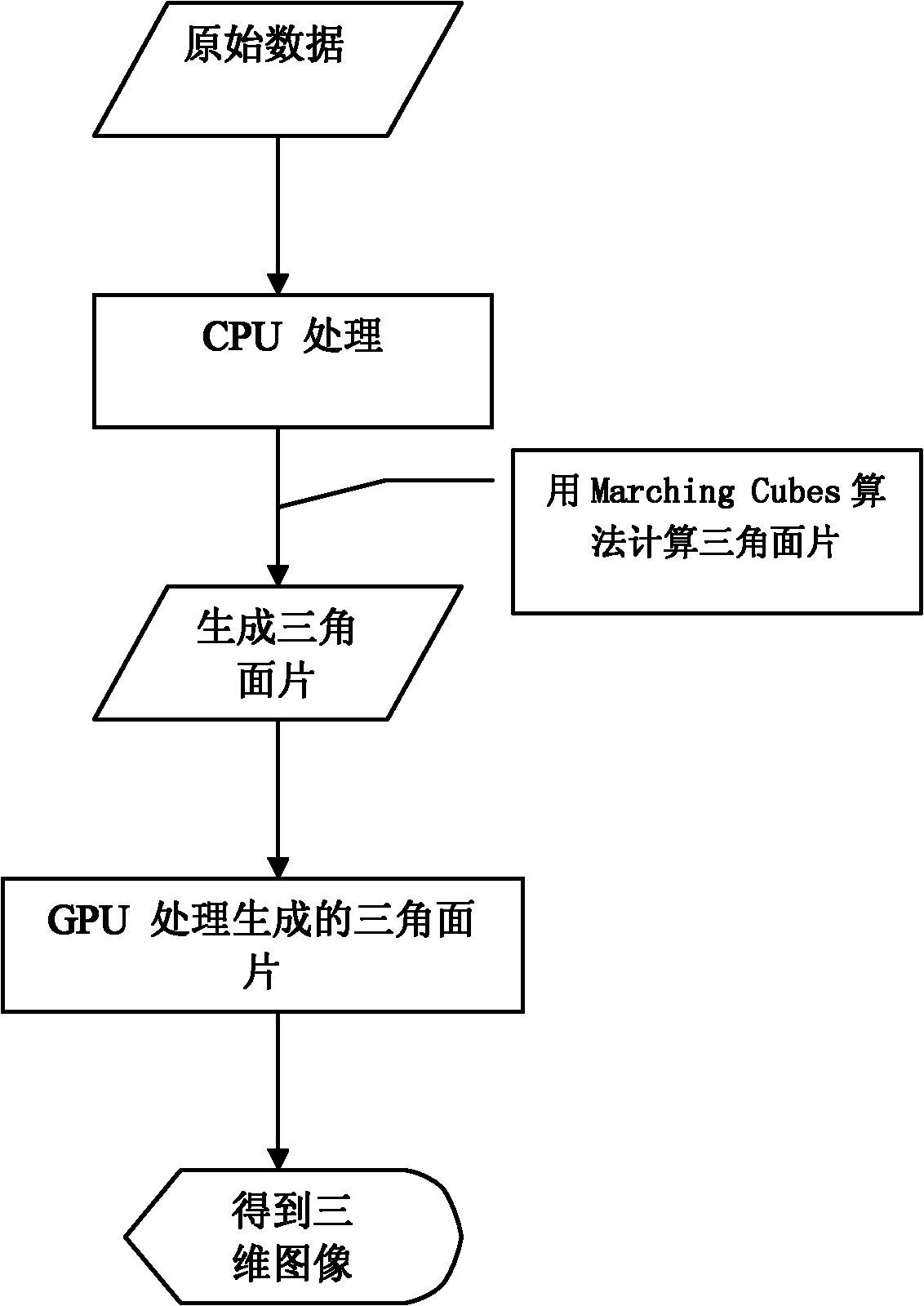

Acceleration improvement algorithm based on cube edge sharing equivalent point

The invention relates to an acceleration improvement algorithm based on cube edge sharing an equivalent point which comprises the following steps of: (1) storing related information of each edge of a cube by using a global array variable; (2) calculating equivalent point coordinates: before the equivalent point is calculated, firstly judging whether the edge is provided with the equivalent point or not , if so, extracting data stored in an array, wherein the data are used for calculating a triangular patch; if not, calculating coordinates and a normal vector of the equivalent point through linear interpolation; and recording the equivalent point of the edge of a current voxel, and giving an assignment for the equivalent point of the edge of other voxels sharing the edge; and (3) calculating the triangular patch by using a Marching Cubes algorithm, and processing the generated triangular patch through GPU (Ground Power Unit) acceleration image processing software to obtain a three-dimensional graph. By utilizing the method of the cube edges sharing the equivalent point, the algorithm efficiency can be improved and the three-dimensional reconstruction problem of medical images is effectively solved.

Owner:ZHEJIANG UNIV

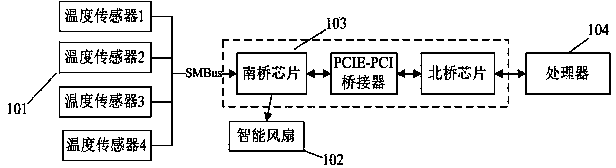

Method for detecting and controlling temperatures of processor

InactiveCN103995766AControl speedSpeed adjustmentHardware monitoringTemperature control using electric meansControl signalPwm signals

The invention provides a method for detecting and controlling the temperatures of a processor. The method includes the steps of firstly, initializing a kernel timer for initializing the structure of the timer, setting the cycle of the timer, designating the interrupt processing function of the timer and inserting the timer into a timer global array; secondly, calling the interrupt processing function of the timer when timeout of the timer occurs, reading data of a temperature sensor, and processing the read temperature data so as to determine a PWM control signal; thirdly, reactivating the kernel timer in the timer interrupt processing function so as to conduct the next time of temperature collection and so as to adjust the rotating speed of a fan. The temperature data collected by the temperature sensor connected to a south bridge chip are read periodically through the kernel timer, after software filtering is conducted on the temperature data, corresponding control information is generated according to the interval where the processed temperature data are located and is then transmitted to the south bridge chip so that the south bridge chip can be controlled to output corresponding PWM signals, and therefore the aims of adjusting the rotating speed of the fan and controlling the temperatures of the processor are achieved. According to the method, the temperatures of the processor are collected and controlled through basic elements on a main board, software filtering is conducted on the temperature data, and control accuracy is improved.

Owner:SHANDONG CHAOYUE DATA CONTROL ELECTRONICS CO LTD

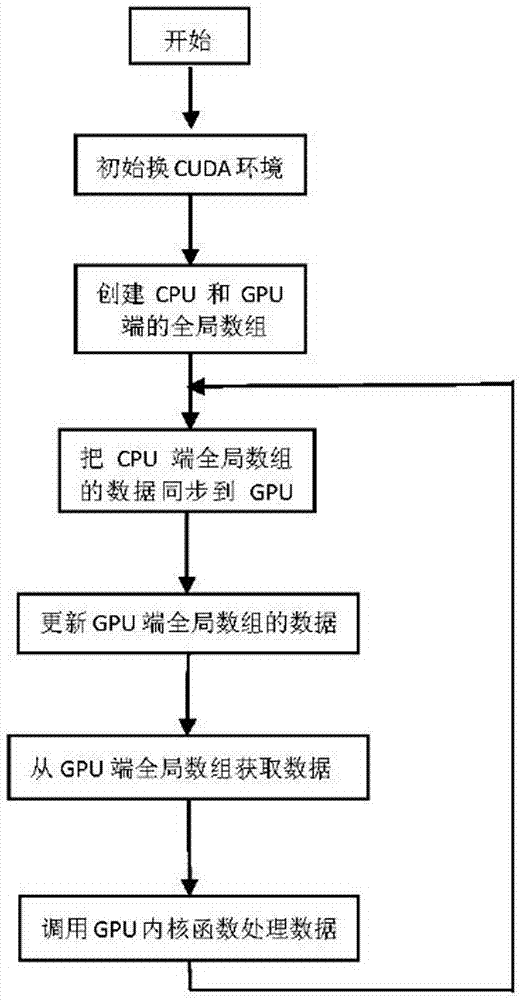

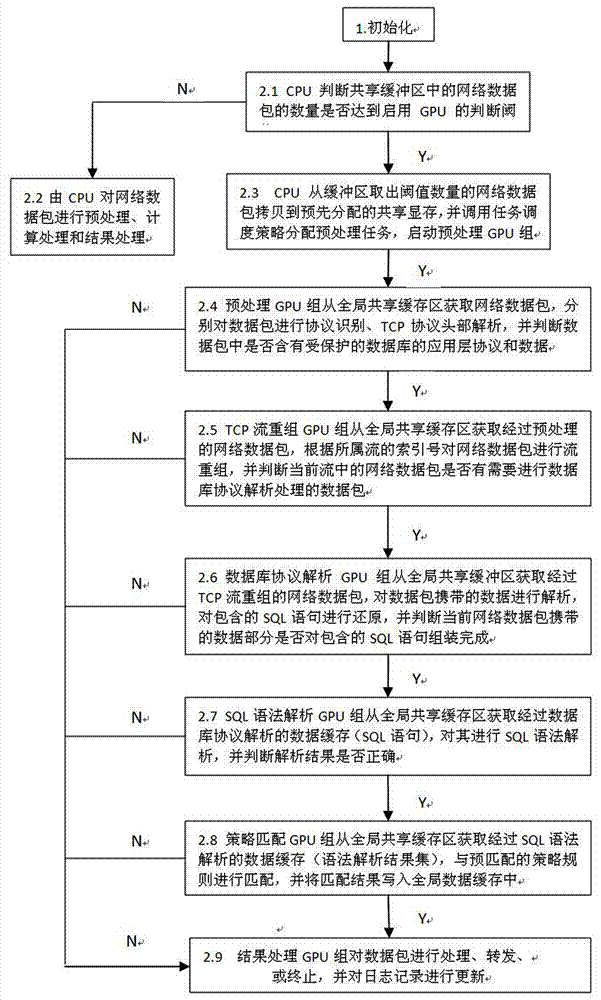

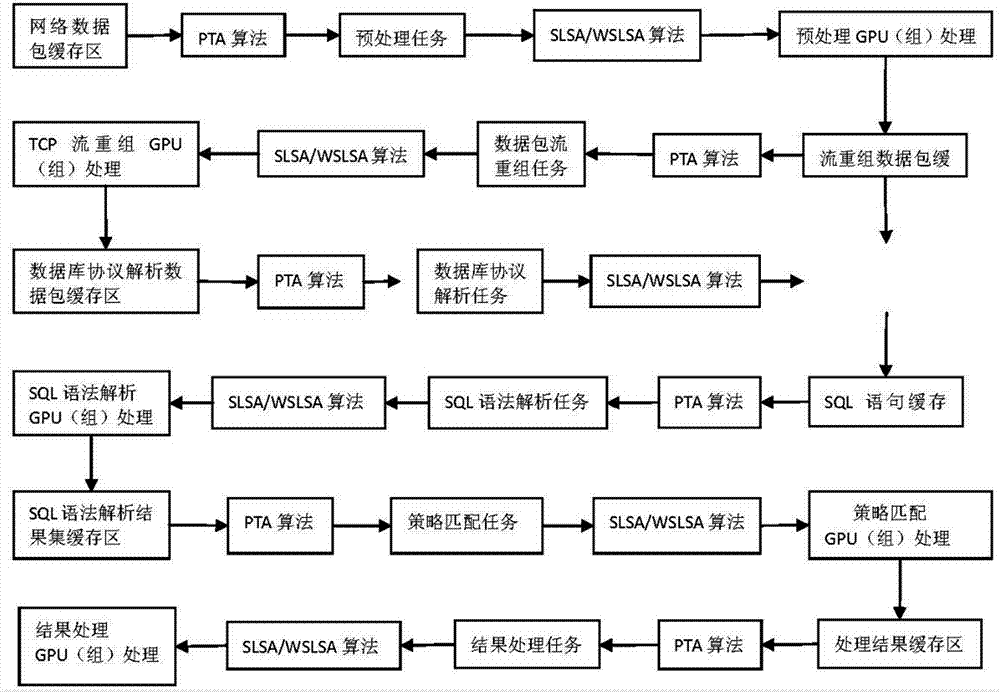

Method for active database defence for multi-GPU parallel processing

ActiveCN107102897ASolve the speed problemLower latencyResource allocationVideo memoryArray data structure

The invention discloses a method for active database defence for multi-GPU parallel processing. The method is characterized in that video memories of all the GPUs are virtualized into a shared video memory and established into a global array of a GPU side; a shared cache area is set in CPU; when a network data packet in the shared cache area reaches a judgment threshold for starting GPU processing, a data packet of the shared cache area will be synchronized to the global array of the GPU side; and then, the CPU will dispatch kernel processing functions of the multiple GPUs to process the network data packet. According to the invention, multi-GPU acceleration processing is adopted when the database active defence system faces a high parallel network flow rate, so that overall performance can be improved, and problems such as high rate and low delay faced by the CPU at the moment can be solved.

Owner:深圳市知穹科技有限公司

Ball replanting technology for global array encapsulation chip

InactiveCN101150080AIncrease success rateImprove restoration qualitySemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringSpherical form

This invention discloses a technology of re-implanting balls for spherical array package chips characteriaing that said technology takes a spherical array package chip as a PCB for assembling and applies a surface sticking technology to process it, which increases success rate and quality of modification of ball-iimplantation effectively.

Owner:伟创力电子科技(上海)有限公司

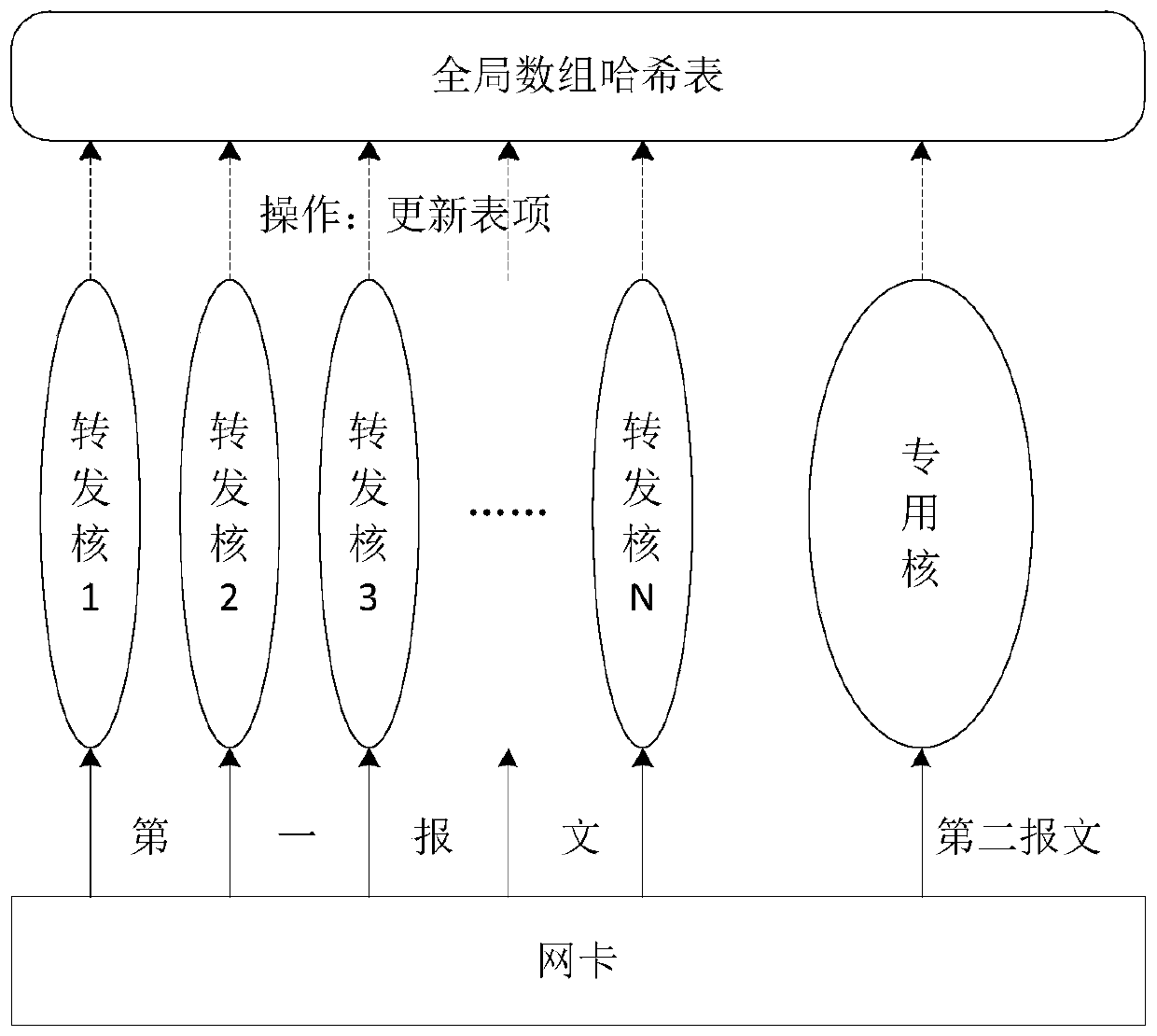

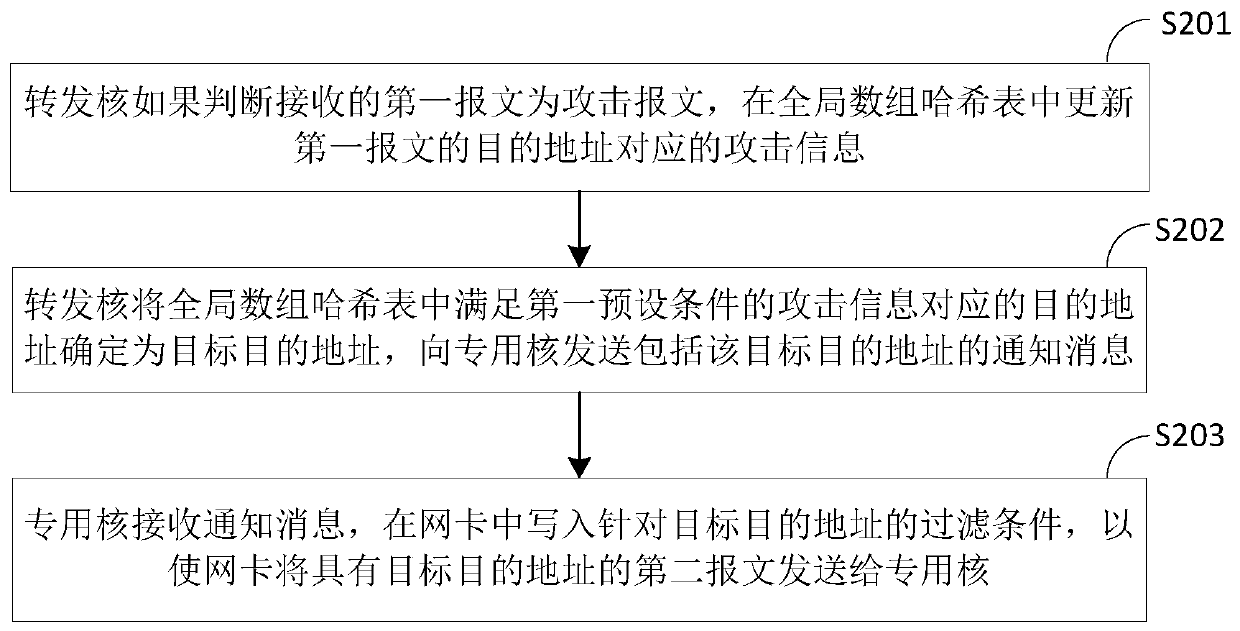

Attack message defense method, multi-core forwarding system and related products

ActiveCN110545291AForwarding performance degradationImprove forwarding performanceTransmissionArray data structureHash table

The embodiment of the invention discloses an attack message defense method, a multi-core forwarding system and related products, and the method comprises the steps: enabling a forwarding core to judgewhether a received first message is an attack message or not after the forwarding core receives the first message; and if the received first message is judged to be the attack message, updating attack information corresponding to the destination address of the first message in the global array hash table. The forwarding core determines a destination address corresponding to the attack informationmeeting a first preset condition in the global array hash table as a target destination address, and sends a notification message comprising the target destination address to the special core, so that the special core writes a filtering condition for the target destination address into the network card after receiving the notification message, and the network card sends a second message with thetarget destination address to the special core. The special core receives, analyzes and processes the massive attack messages, the normal message forwarding performance is prevented from being reduceddue to the fact that the forwarding core analyzes and processes the massive attack messages, and the overall forwarding performance of the multi-core forwarding system is improved.

Owner:NEUSOFT CORP

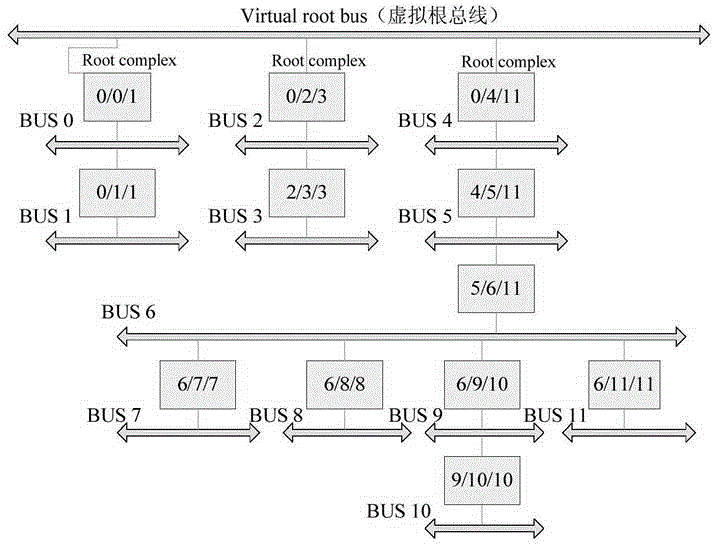

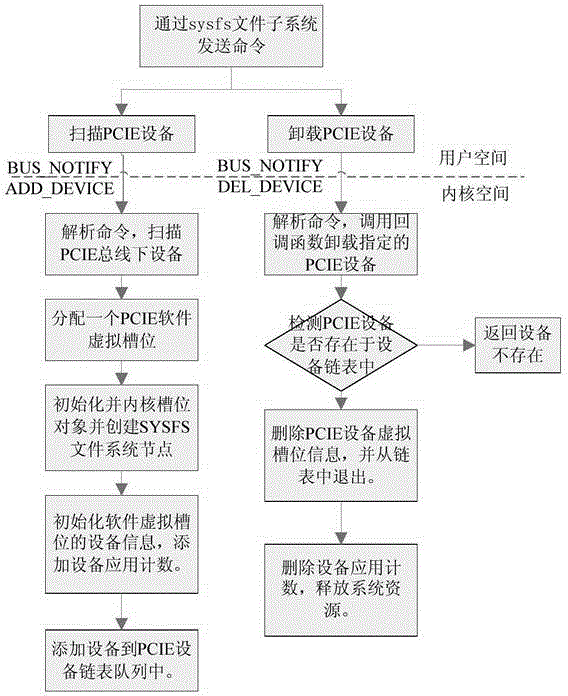

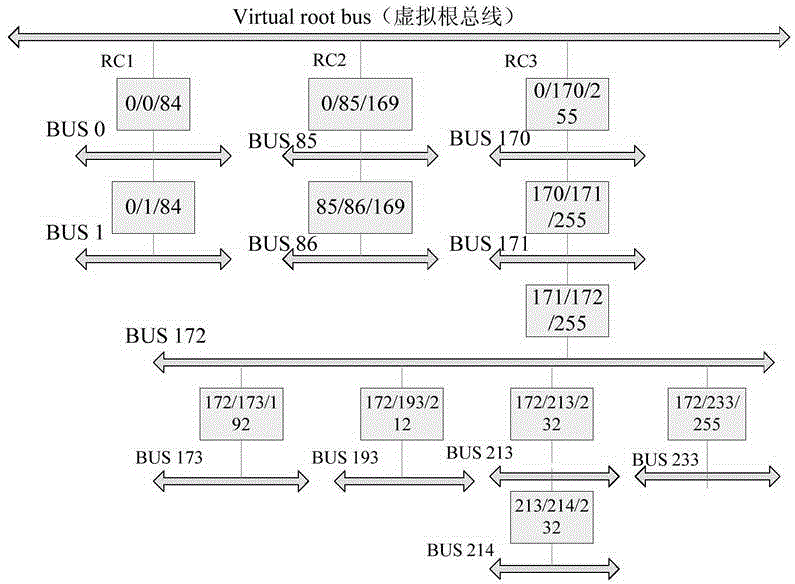

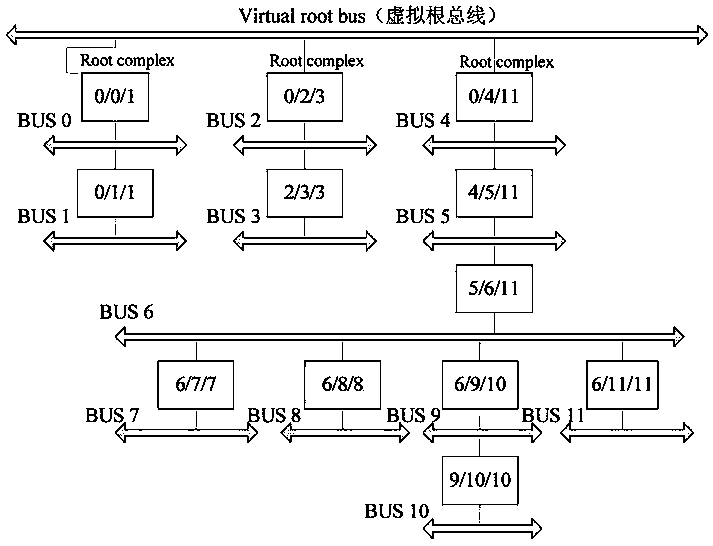

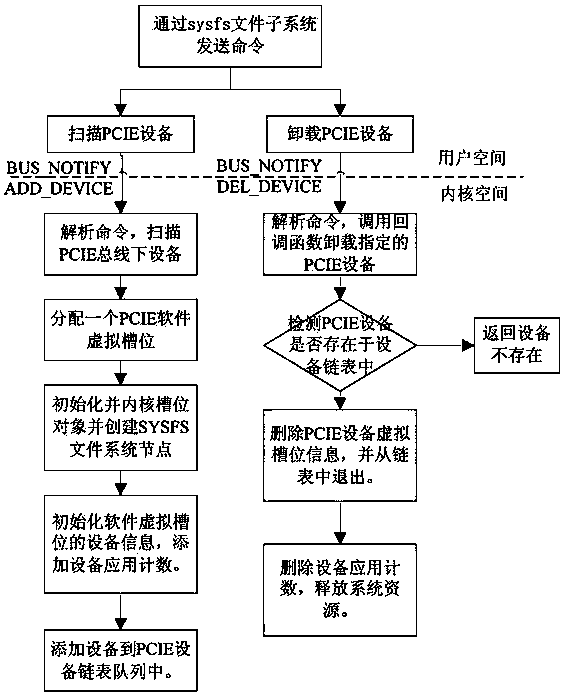

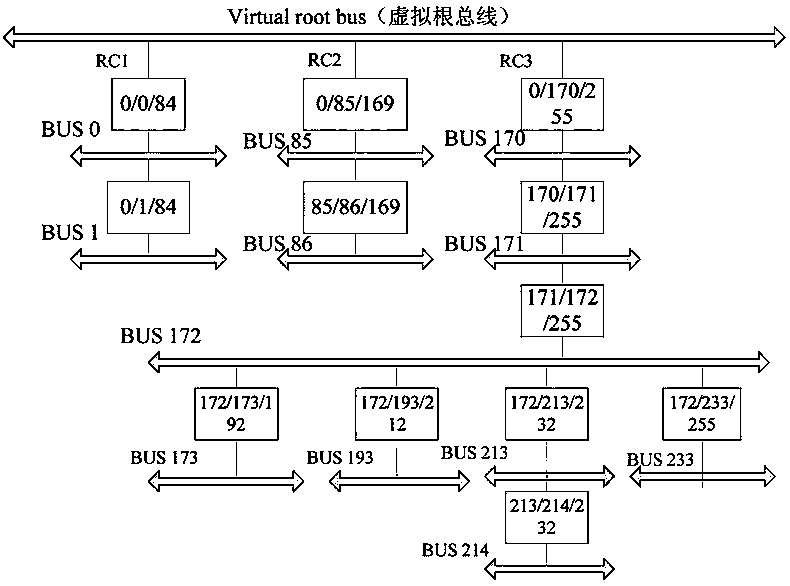

PCIE (peripheral component interface express) device dynamic scanning method supporting multi RC (remote control) in Linux system

ActiveCN104820646AResolve Dynamic ScanningSolve the uninstall problemElectric digital data processingExtensibilityArray data structure

The invention discloses a PCIE (peripheral component interface express) device dynamic scanning method supporting multi RC (remote control) in a Linux system. The PCIE device dynamic scanning method supporting the plurality of the multi RC in the Linux system includes: electrifying the Linux system, distributing continuous bus number resources to each RC controller according to the number of RC controllers of the Linux system, traversing each RC controller exists in the Linux system, recording bus number information corresponding to each RC controller to a global array, and deleting a default PCIE device or a default PCIE bridge device in each RC controller so as to release resources distributed by the Linux system in a default mode, and the RC controller root bus number as a judgement standard to scan or unload the PCIE device dynamic according to corresponding RC controller bus number information recorded in the global array. By adopting the PCIE device dynamic scanning method supporting the plurality of the multi RC in the Linux system, expandability of the Linux system is improved due to the fact that each RC controller and PCIE bridge device are newly distributed the continuous bus number resources, and safety of the Linux system is improved due to the fact that the scanning or unloading of the PCIE device under the RC controller root bus number is controlled separately, and simultaneously, stability of the Linux system is enhanced due to the fact that a linkage state is detected and controlled the scanning process.

Owner:烽火超微信息科技有限公司

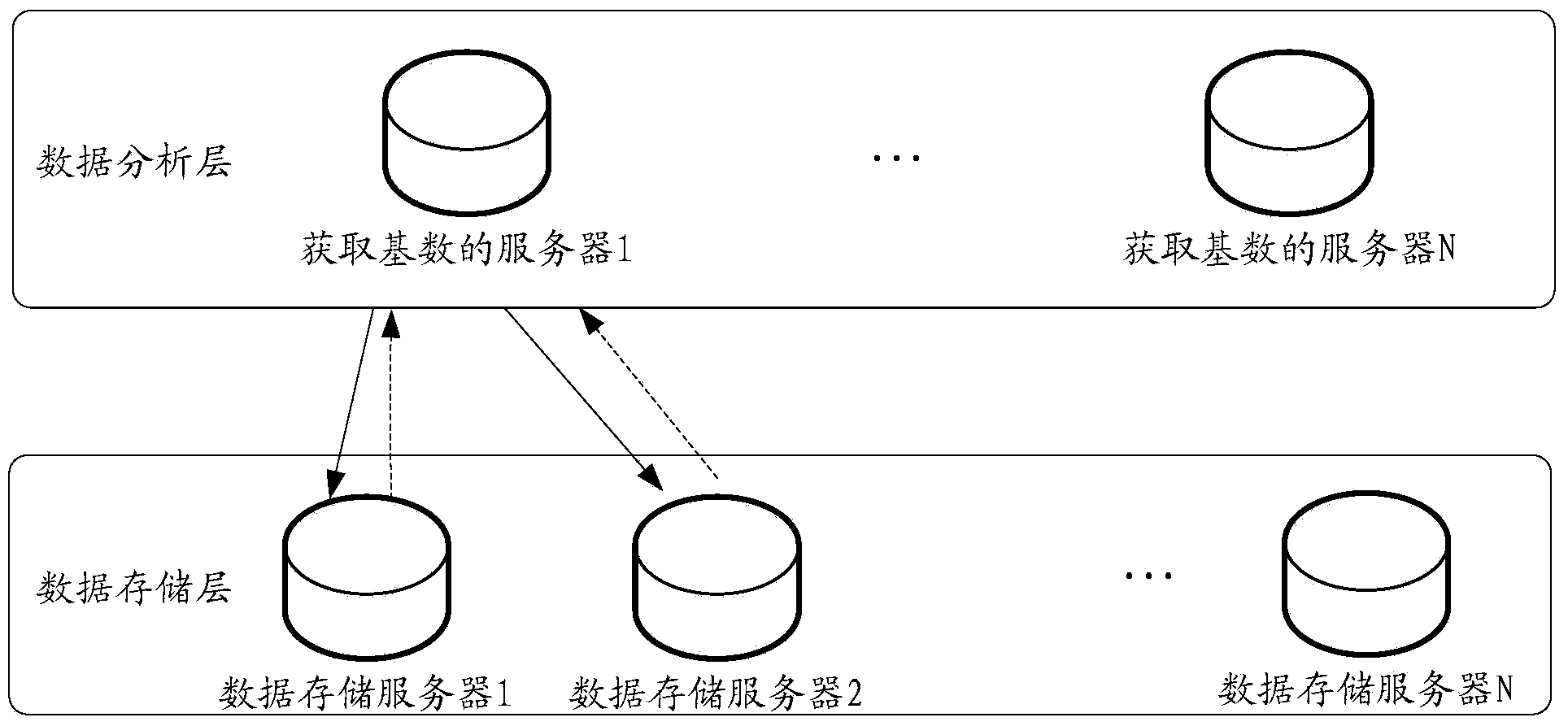

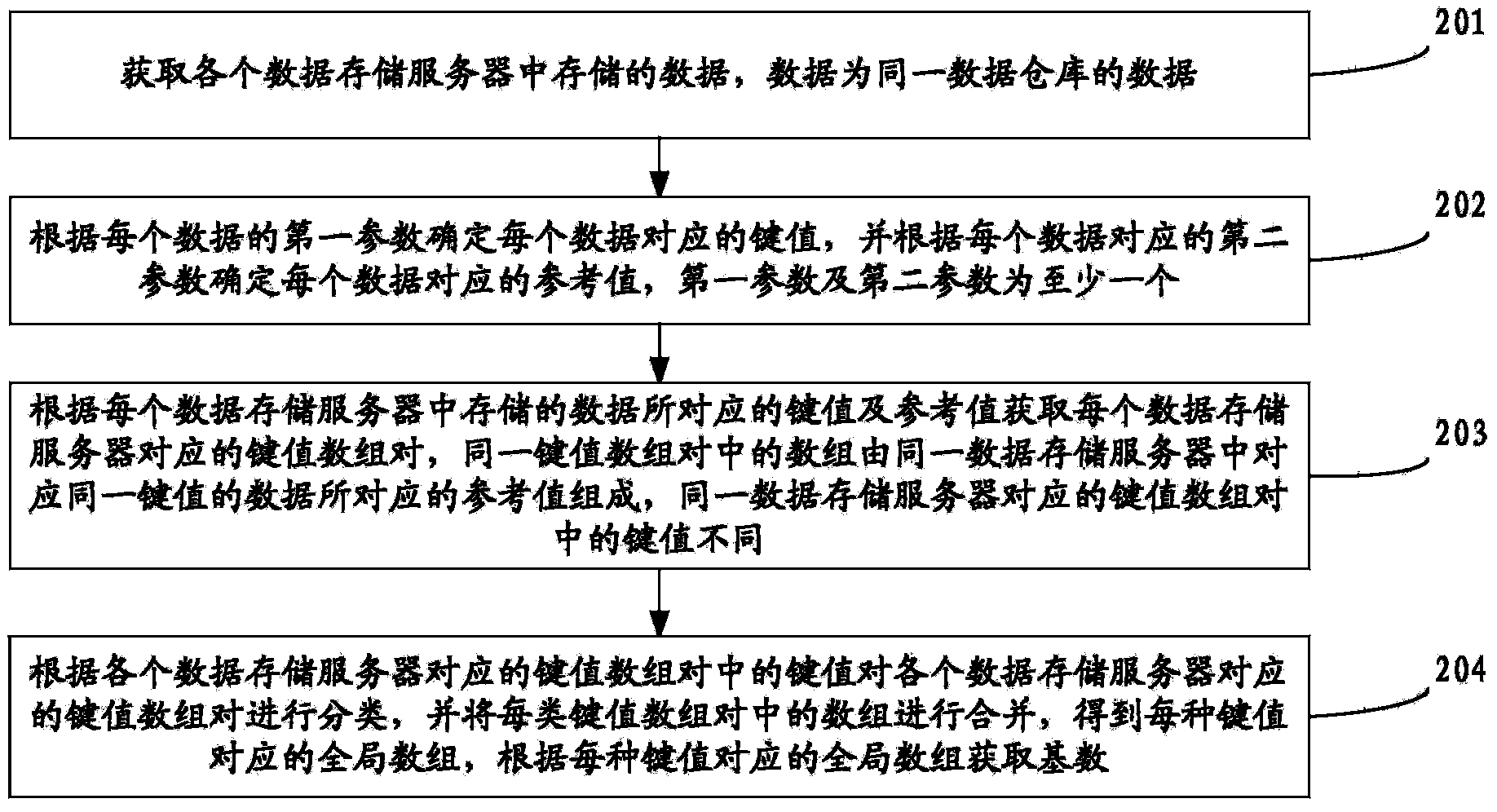

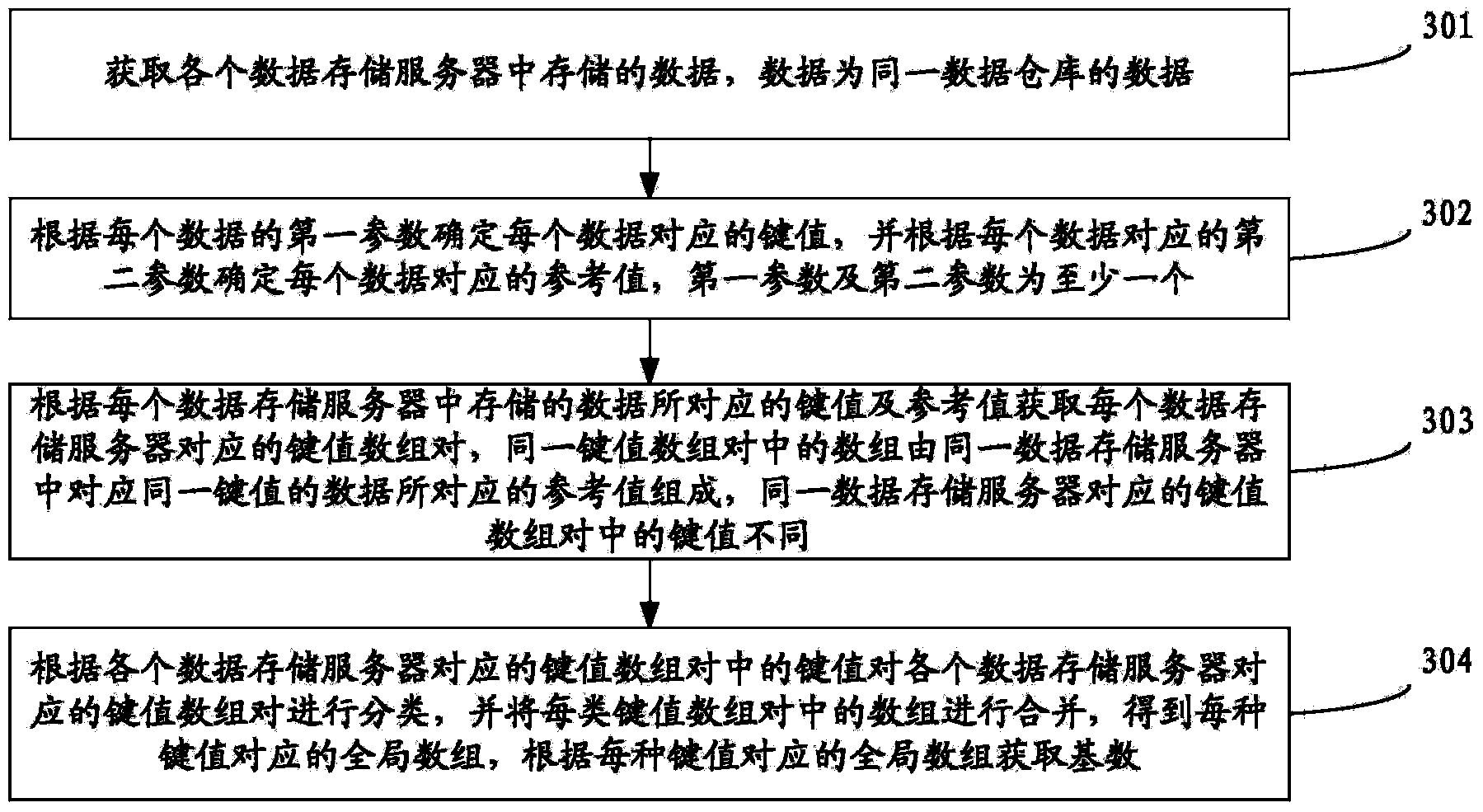

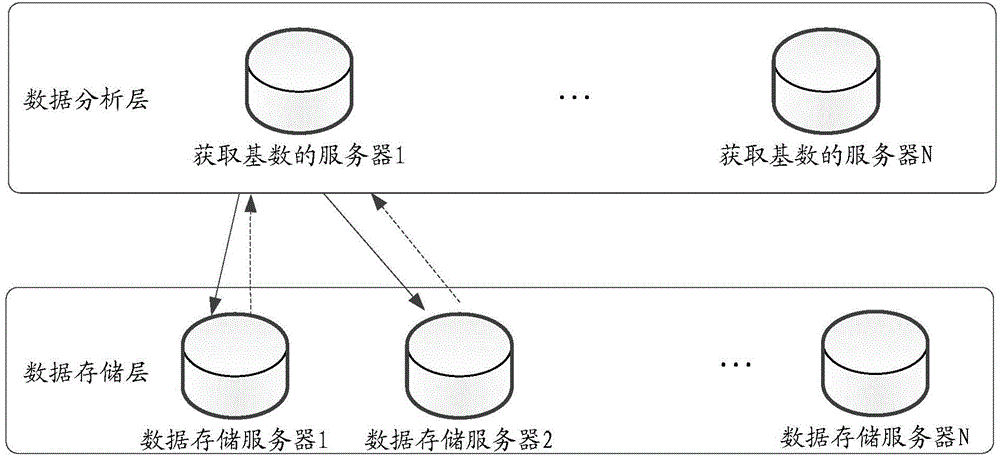

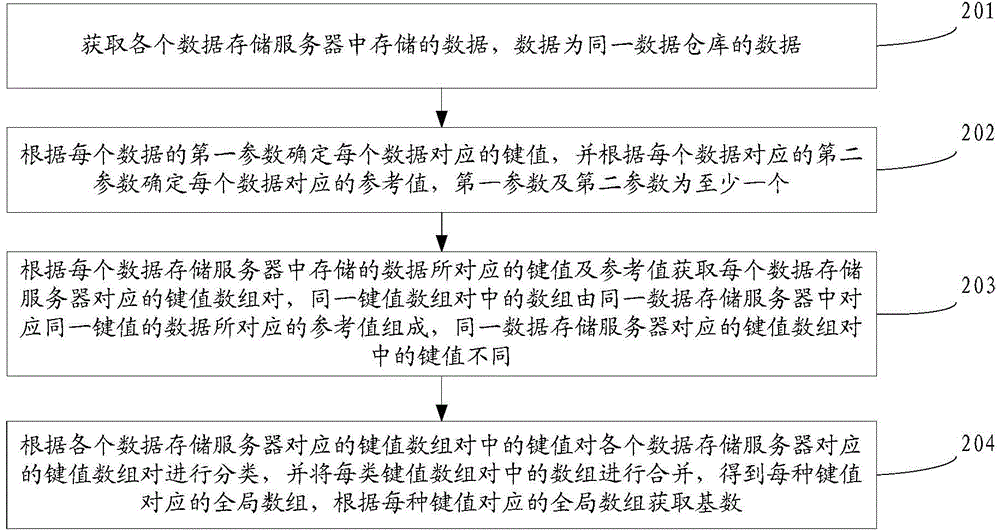

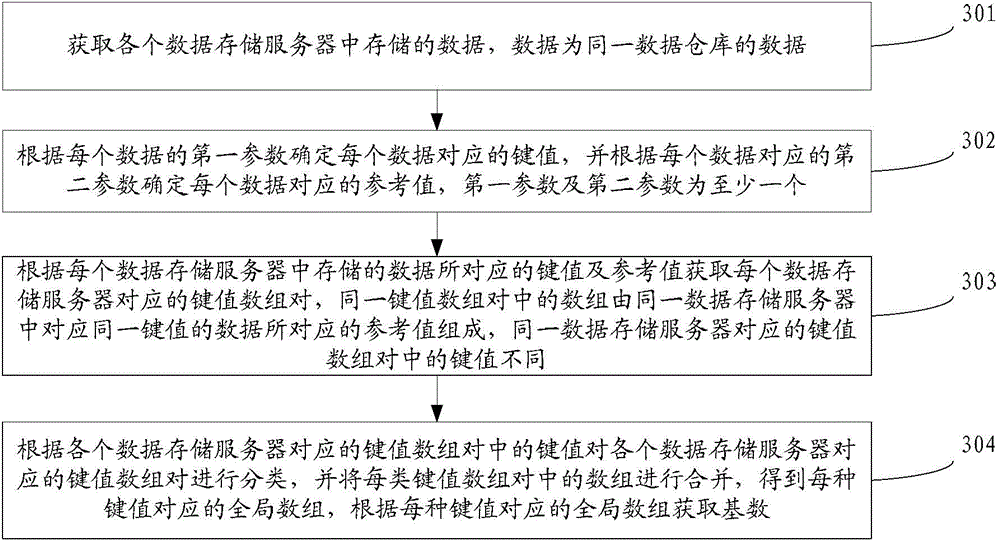

Method, device, server and system for obtaining cardinal number

ActiveCN104090895AShorten the timeReduce resource consumptionSpecial data processing applicationsArray data structureResource consumption

The invention discloses a method, device, server and system for obtaining a cardinal number, and belongs to the technical field of databases. The method comprises the following steps: obtaining data stored in each data storage server, and obtaining key value array pairs according to a key value and a reference value which correspond to each datum; classifying the key value array pairs according to the key value, merging arrays in each kind of key value array pairs to obtain a global array corresponding to each kind of key value, and obtaining the cardinal number according to the global array corresponding to each kind of the key value. In the method disclosed by the invention, after the data stored in each data storage server is obtained, the corresponding key value array pairs are obtained according to the key value and the reference value which correspond to each datum, key value arrays corresponding to each data storage server are merged to obtain the global array corresponding to each kind of key value, and the cardinal number is obtained according to the global array corresponding to each kind of key value, so that the trouble of obtaining the cardinal number by reading the data stored in each data storage server item by item is avoided, the time required for obtaining the cardinal number is shortened, and the resource consumption is reduced.

Owner:SHENZHEN TENCENT COMP SYST CO LTD

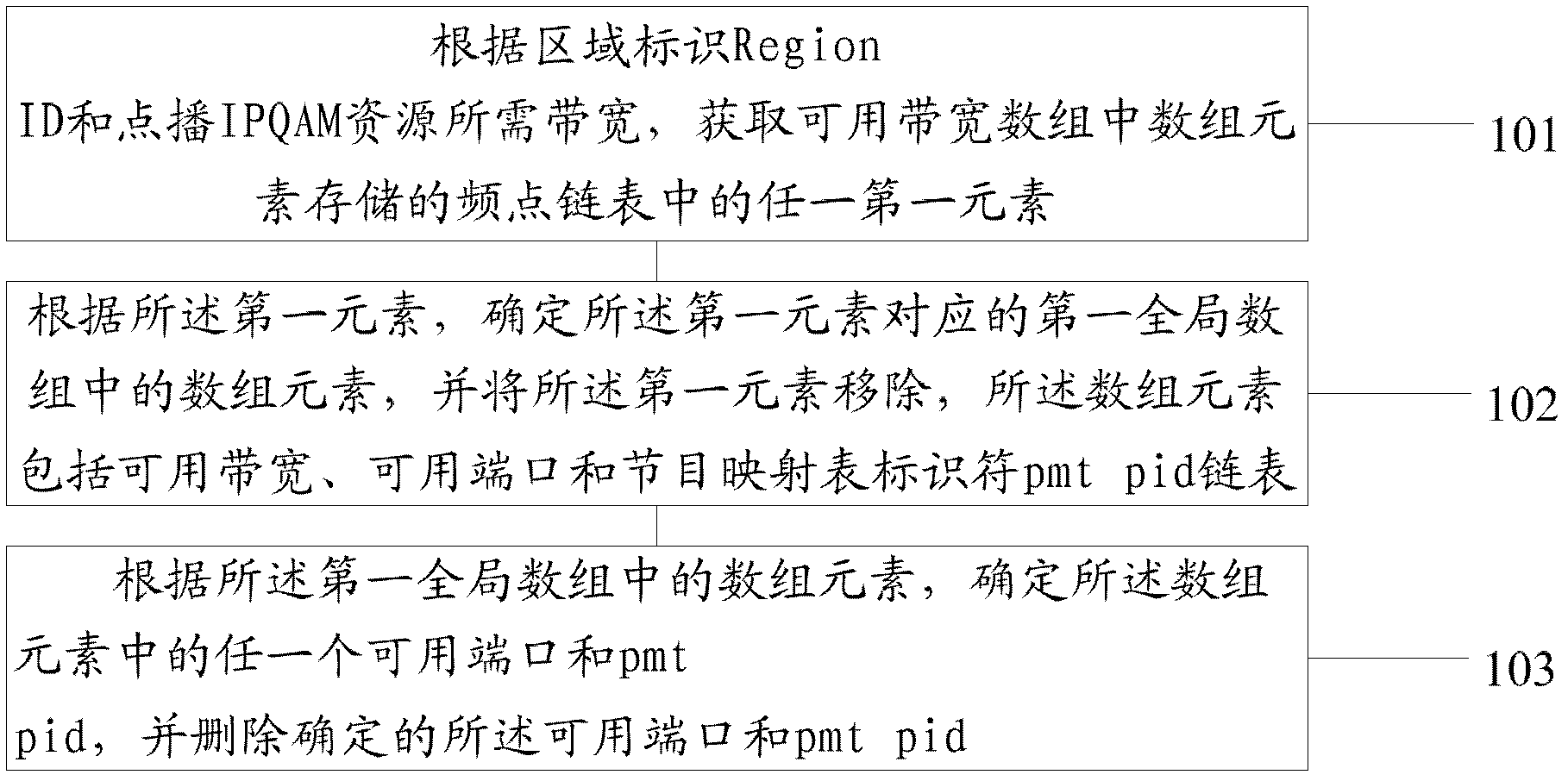

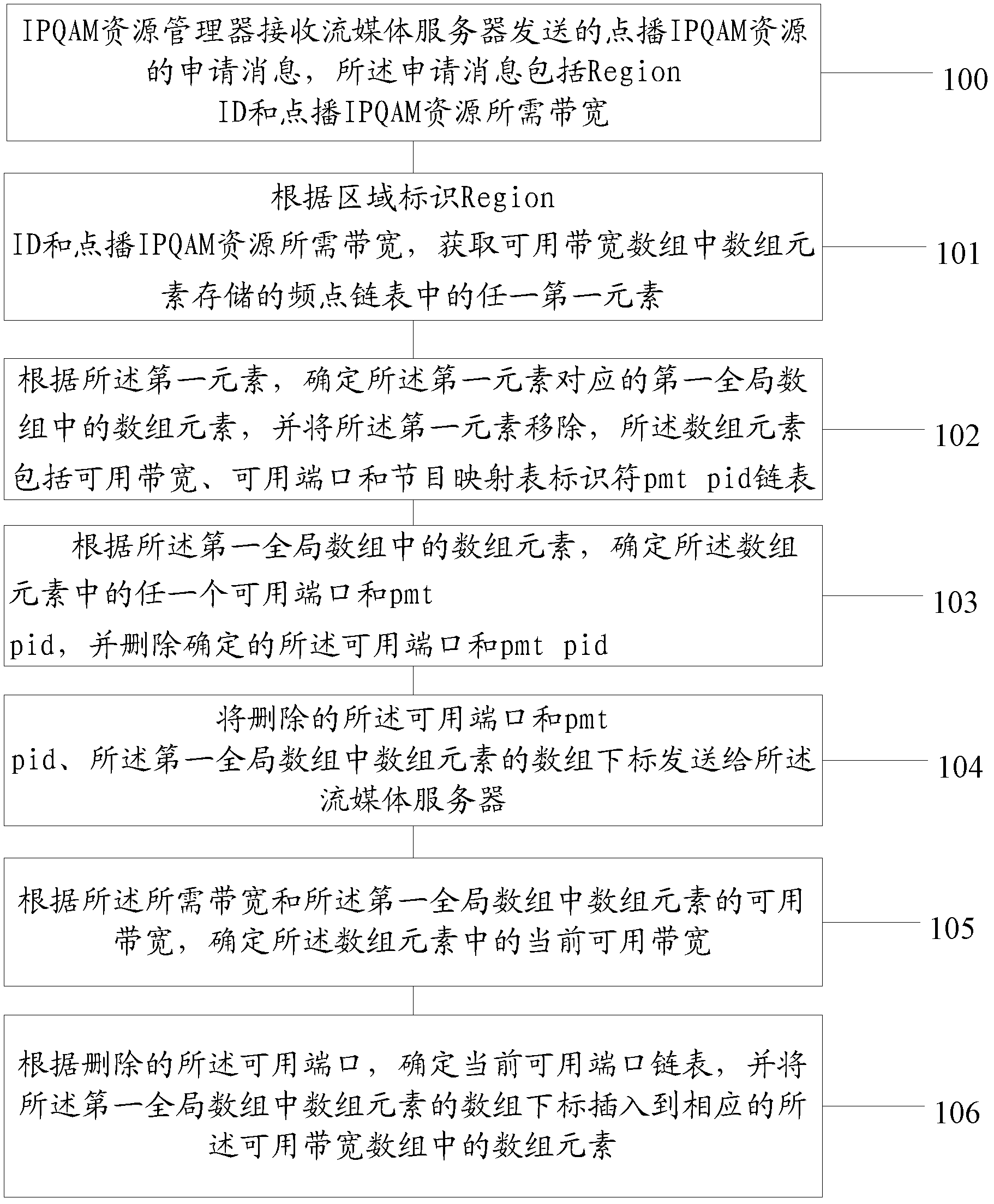

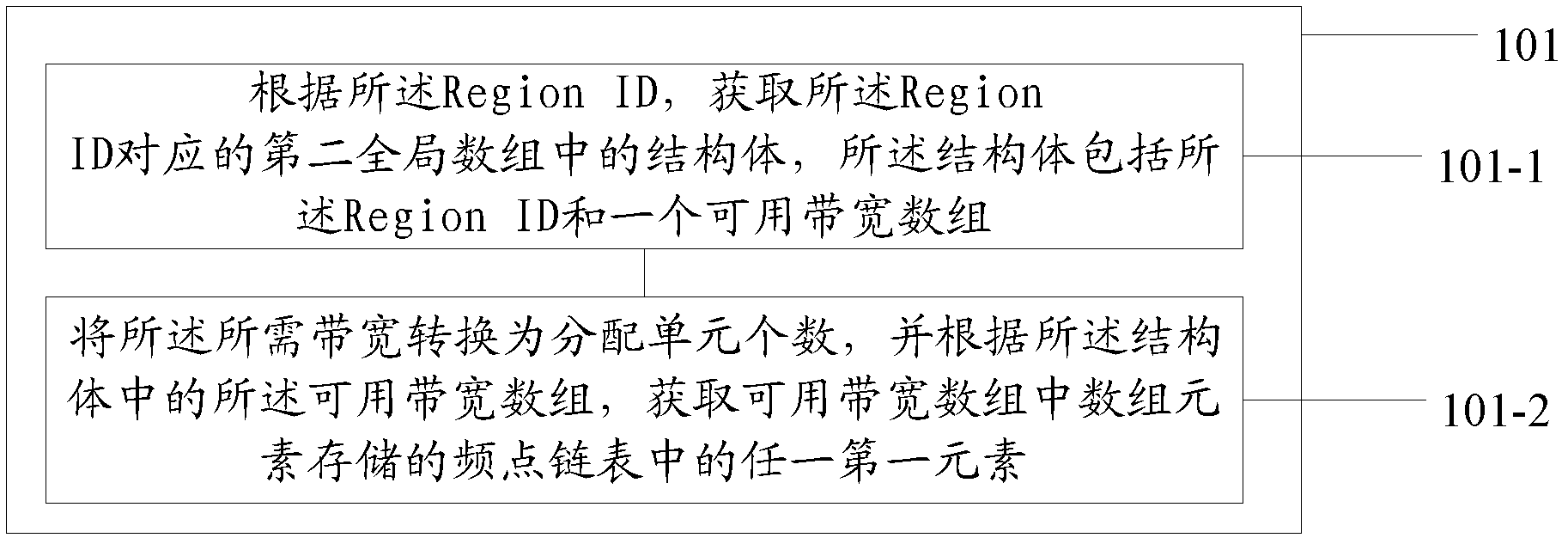

Method, device and system for allocating IPQAM (internet protocol quadrature amplitude modulation) resource

ActiveCN102387415ARapid positioningIncreased on-demand concurrencyTransmissionSelective content distributionArray data structureTechnology of television

The embodiment of the invention relates to the technical field of digital television (TV), and provides a method, a device and a system for allocating IPQAM (internet protocol quadrature amplitude modulation) resource, and can quickly determine frequency point resource matched with the needed bandwidth and improve the on-demand concurrency capability of the system. The method comprises the following steps: obtaining any one of first elements in a frequency point chain table stored with array elements in an available bandwidth array according to region identification (ID) and the needed bandwidth for the on-demand IPQAM resource; according to the first elements, determining the array elements in a first global array corresponding to the first elements, and removing the first elements; and according to the array elements in the first global array, determining any one available port and pmt (Program Map Table) pid in the array elements, and deleting the determined available port and pmt pid. The embodiment of the invention is mainly applied to management of the IPQAM resource.

Owner:JUHAOKAN TECH CO LTD

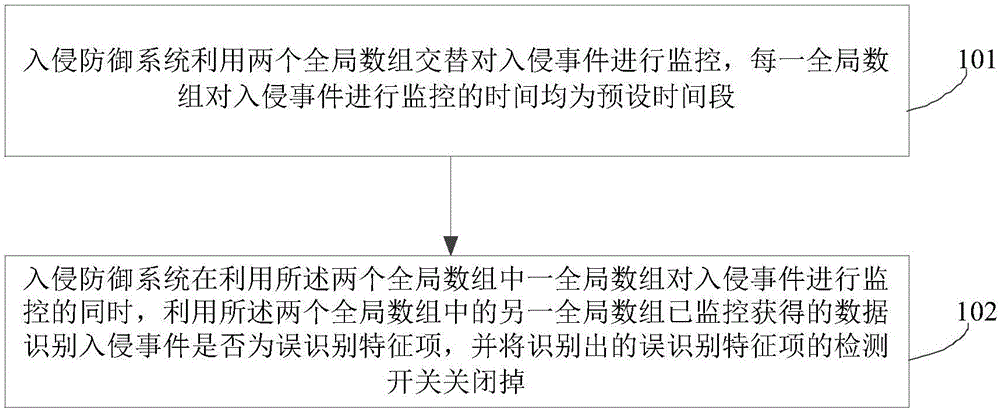

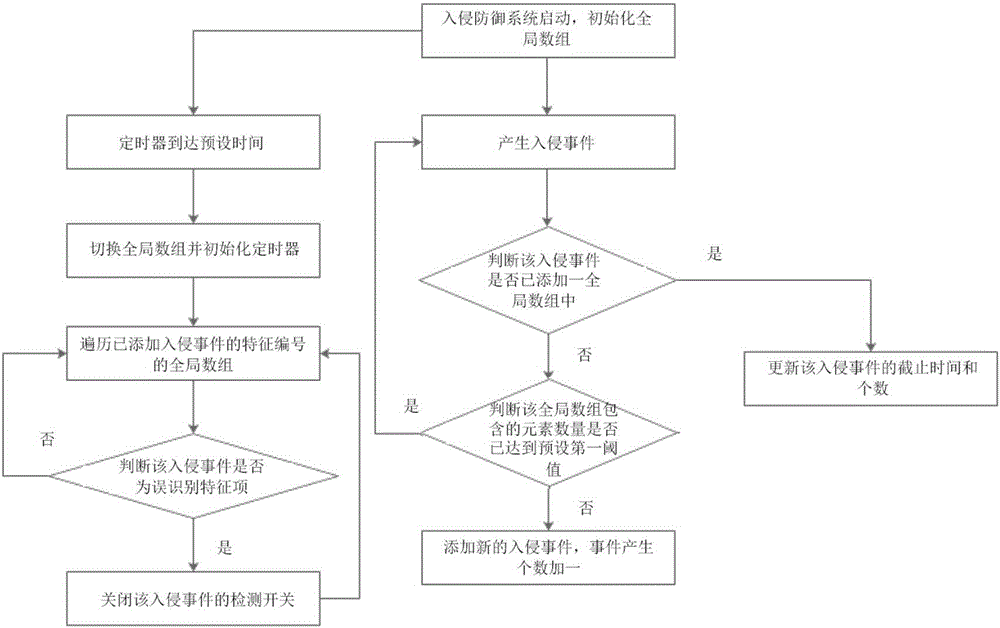

Method, device and system for IPS (Intrusion Prevention System) to actively recognize and close misrecognition feature item

PendingCN106375278AAvoid network failureAvoid lostTransmissionArray data structureIntrusion prevention system

The invention provides a method, a device and a system for an IPS (Intrusion Prevention System) to actively recognize and close a misrecognition feature item. The method comprises the following steps of the intrusion prevention system utilizes two global arrays to monitor an intrusion event alternatively, and the time for each global array to monitor the intrusion event is a preset time bucket; and when the intrusion prevention system utilizes one in the two global arrays to monitor the intrusion event, the intrusion prevention system utilizes data obtained by monitoring of the other one in the two global arrays to recognize whether the intrusion event is the misrecognition feature item and closes a detection switch of the recognized misrecognition feature item. According to the method, the device and the system, when the misrecognition feature item occurs, the misrecognition feature item can be effectively recognized and the misrecognition feature item is closed.

Owner:OPZOON TECH

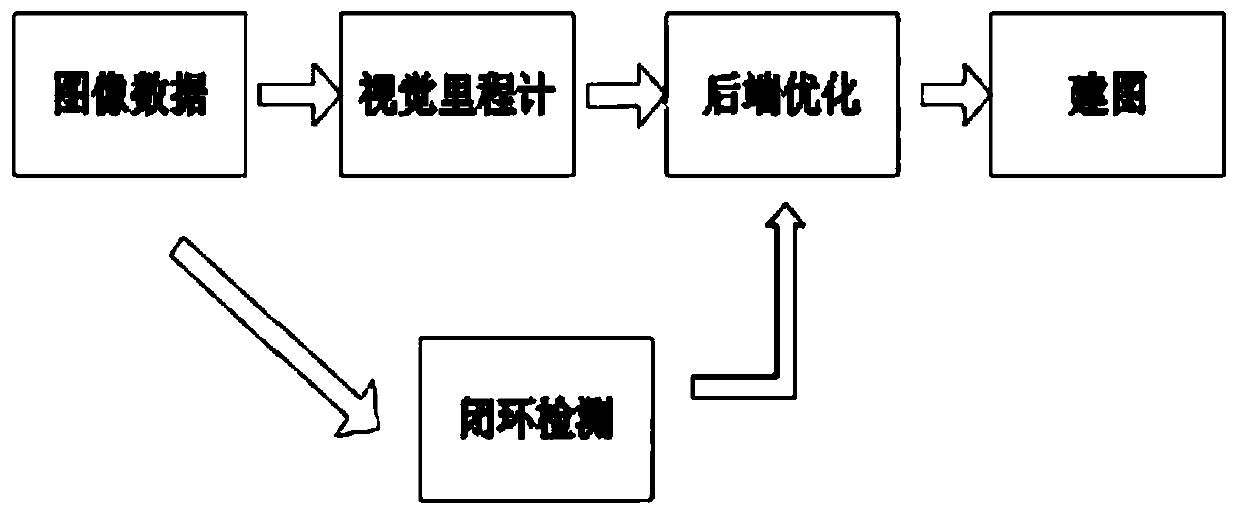

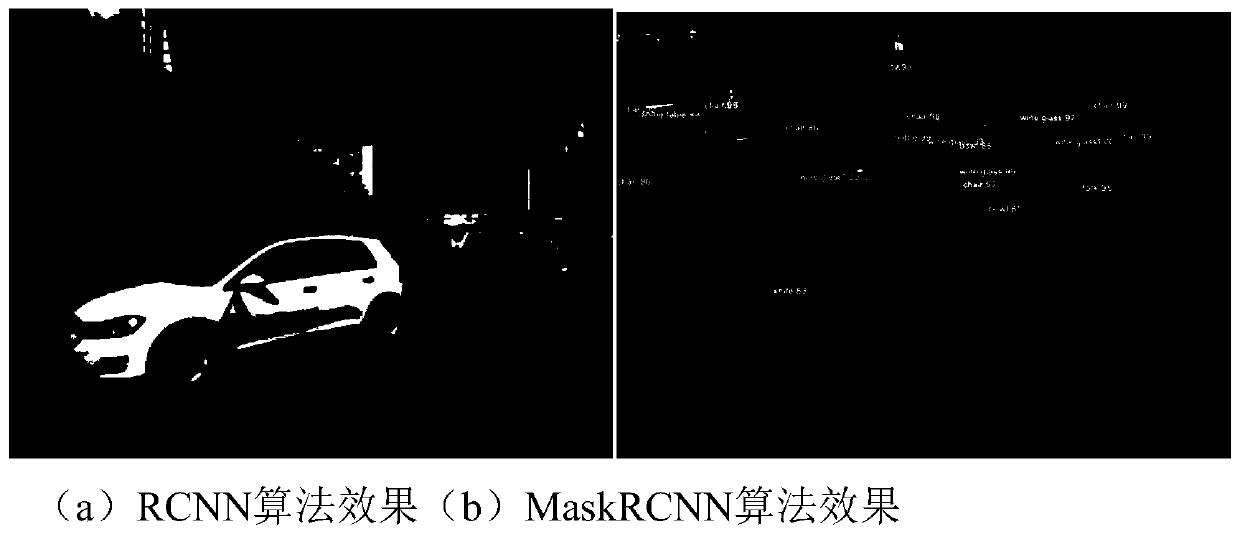

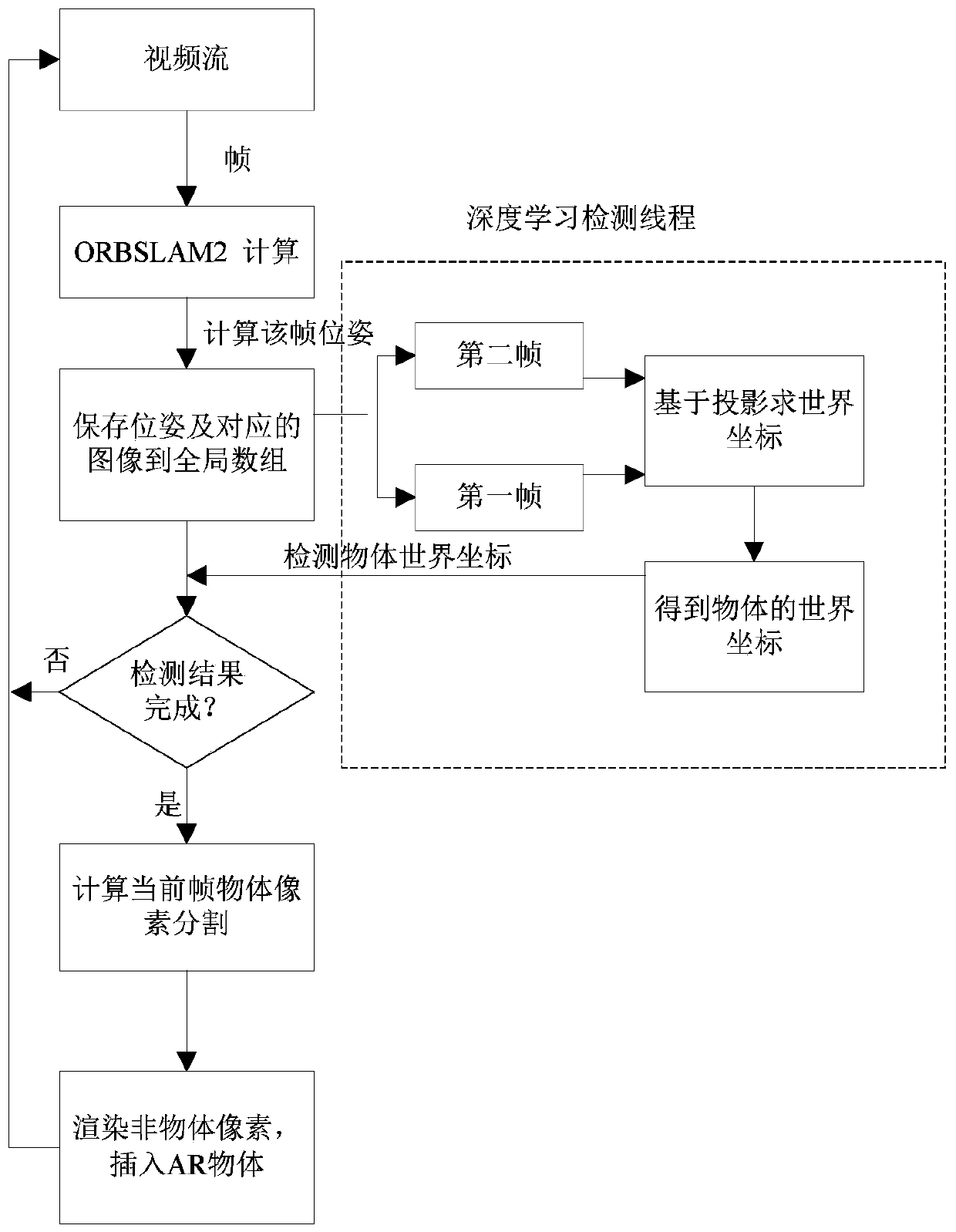

MaskRCNN-based real-time on-plane object detection method

InactiveCN110009683AHigh real-time rateImprove accuracyImage enhancementImage analysisFrame basedArray data structure

The embodiment of the invention provides a MaskRCNN-based real-time on-plane object detection method, which is characterized by comprising the following steps of: 1, acquiring each frame of image in avideo stream, calculating the pose of the frame based on ORBSLAM2, and storing the pose of the frame and the corresponding image into a global array; 2, adding a deep learning detection thread basedon ORBSLAM2, the deep learning thread extracting data from a global array; extracting two adjacent frames of images in the array; calculating projection images of two adjacent frames through poses respectively; detecting pixel points contained in an object on the second frame of projection image through a MaskRCNN; according to feature matching of the two adjacent frames of projection images, obtaining a translation relation of feature points so as to obtain pixel points of an object on the first frame of projection image, carrying out inverse transformation on the pixel points of the two frames of images according to poses, and carrying out triangularization on matching points after inverse transformation so as to calculate world coordinates of the object; and step 3, calculating the pixel coordinates of the current frame of the object according to the pose of the current frame and the world coordinates of the object, and if the pose of the camera meets a plane, not rendering the detected object, only rendering a non-detected object, and inserting an AR object into the detected object.

Owner:BEIJING JIAOTONG UNIV

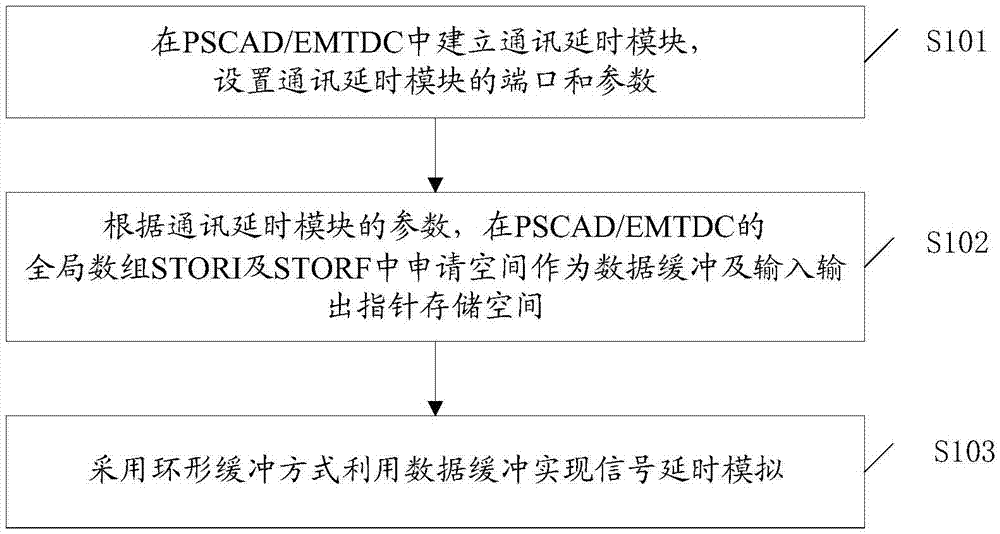

Signal communication time-delay simulation method based on PSCAD/EMTDC

InactiveCN106980271AImprove accuracyImprove the efficiency of simulation calculationsSimulator controlArray data structureTime delays

The invention discloses a signal communication time-delay simulation method based on a PSCAD / EMTDC. The method comprises steps that a communication time-delay module is established in the PSCAD / EMTDC, and ports and parameters of the communication time-delay module are set; according to the parameters of the communication time-delay module, application space is taken as data buffer and input output pointer storage space in global arrays STORI and STORF of the PSCAD / EMTDC; data buffer is utilized to realize signal time-delay simulation in an annular buffer mode. The method is advantaged in that signal communication time-delay can be simulated, and high efficiency and high accuracy are realized.

Owner:NR ELECTRIC CO LTD +2

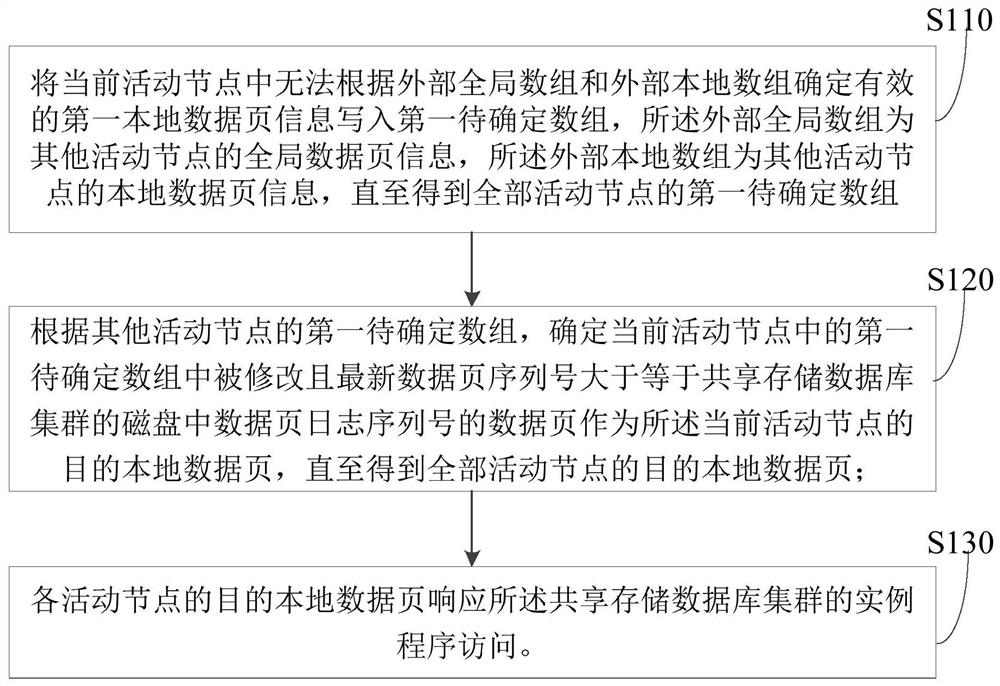

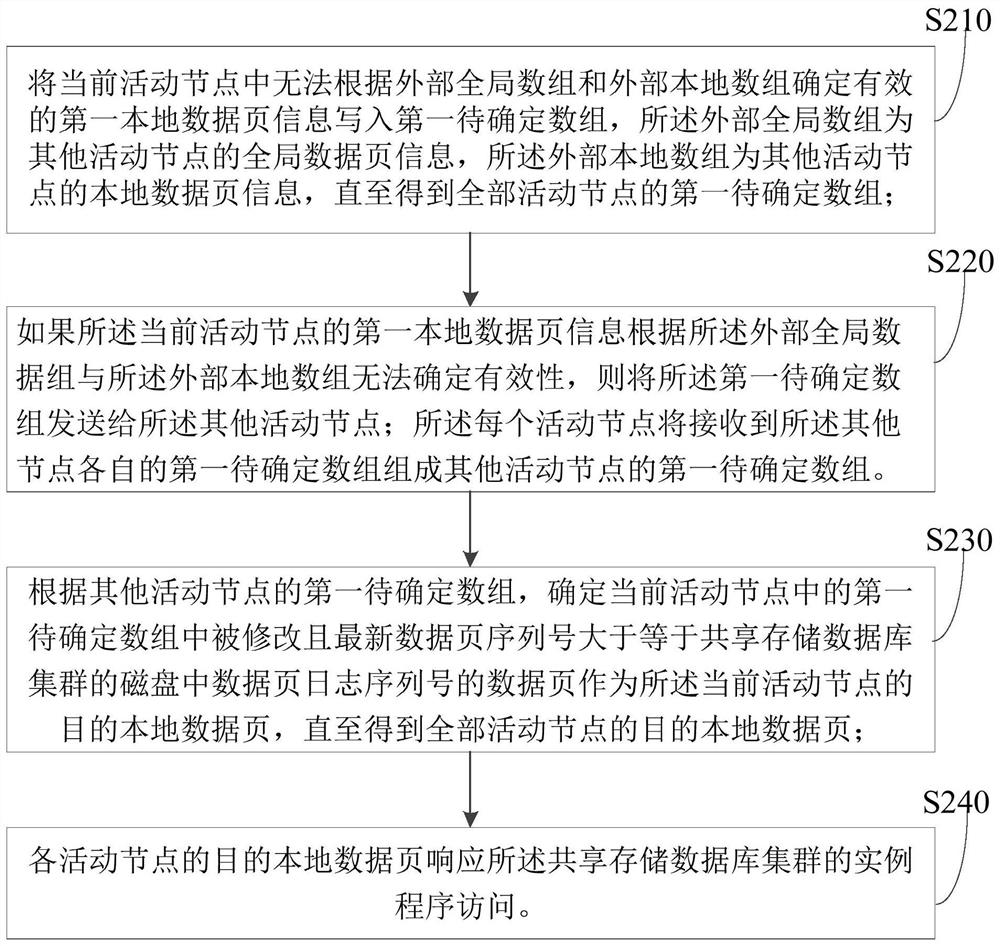

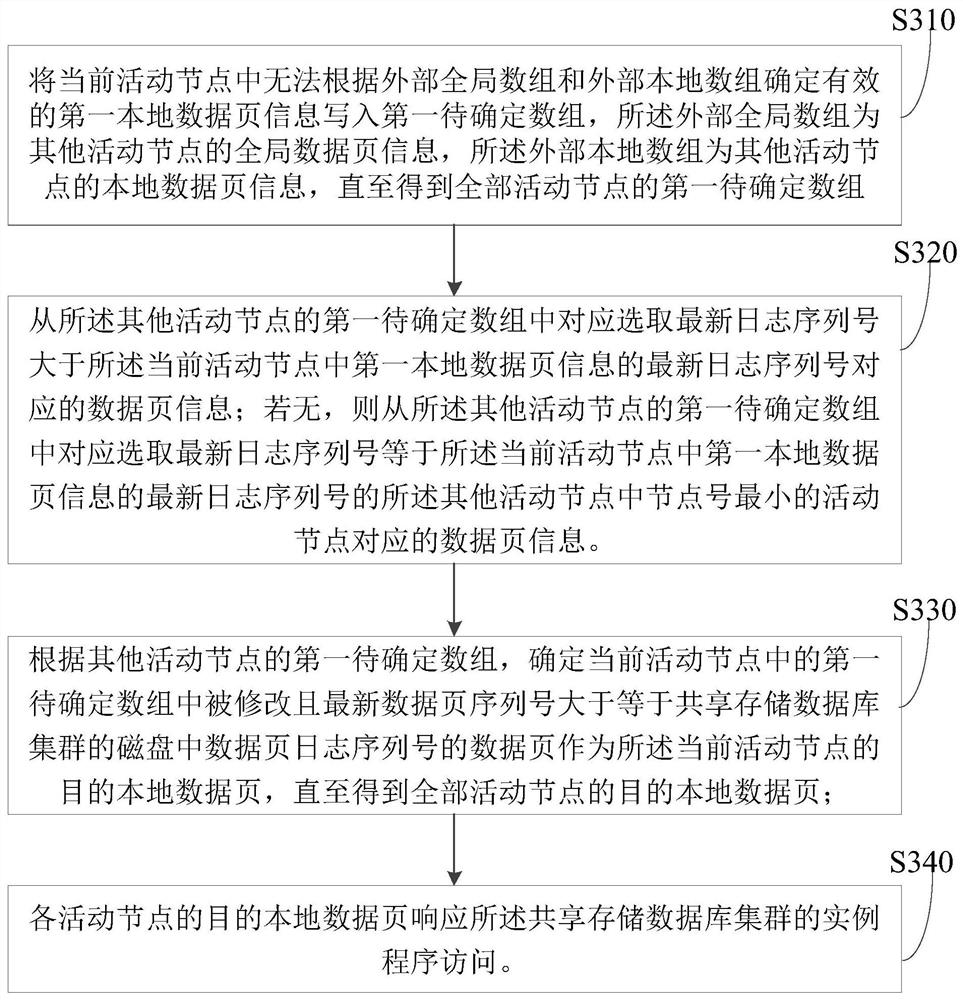

Data page management method and device, electronic equipment and storage medium

PendingCN112395141AIneffective IO reductionImprove troubleshooting efficiencyDatabase distribution/replicationSpecial data processing applicationsEngineeringDatabase

The invention discloses a data page management method and device, electronic equipment and a storage medium. The method and the device are applied to active nodes in a shared storage database cluster,and the method comprises the steps of writing first local data page information which cannot be determined to be effective according to an external global array and an external local array in currentactive nodes into a first to-be-determined array until the first to-be-determined array of all the active nodes is obtained; according to the first to-be-determined arrays of the other active nodes,determining a data page which is modified in the first to-be-determined array of the current active node and of which the latest data page serial number is greater than or equal to a data page log serial number in a disk of a shared storage database cluster as a target local data page of the current active node; and the destination local data page of each active node responding to the instance program access of the shared storage database cluster. According to the embodiment of the invention, a large number of invalid IOs in the process of determining whether the data page in the active node cache is latest are reduced, and the fault processing efficiency is improved.

Owner:SHANGHAI DAMENG DATABASE

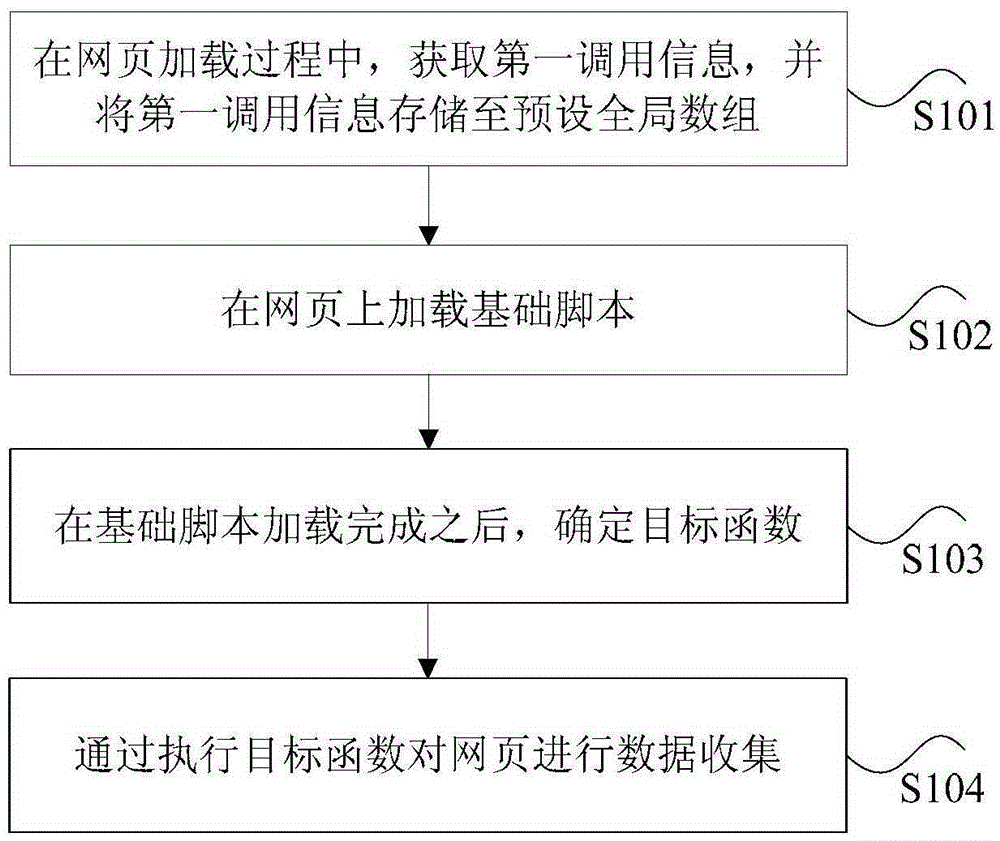

Webpage data collection method and apparatus

ActiveCN106649353ALow resolution accuracyImprove accuracyWeb data indexingSpecial data processing applicationsArray data structureData mining

Owner:BEIJING GRIDSUM TECH CO LTD

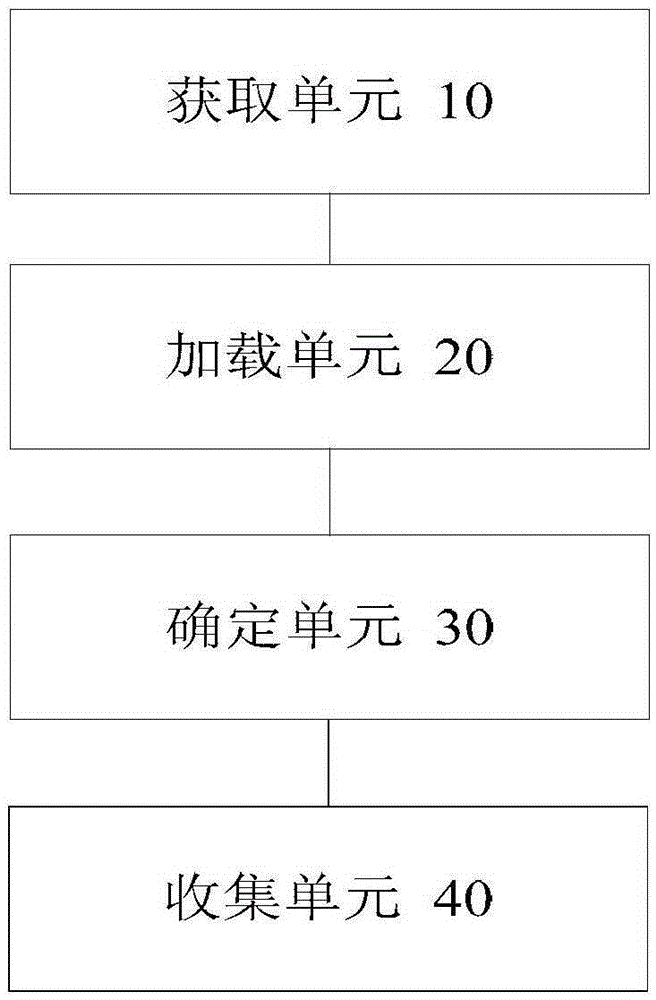

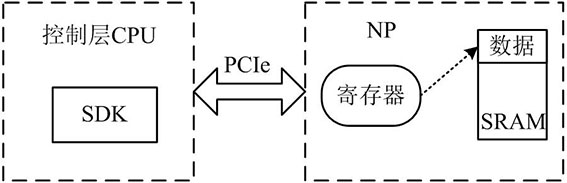

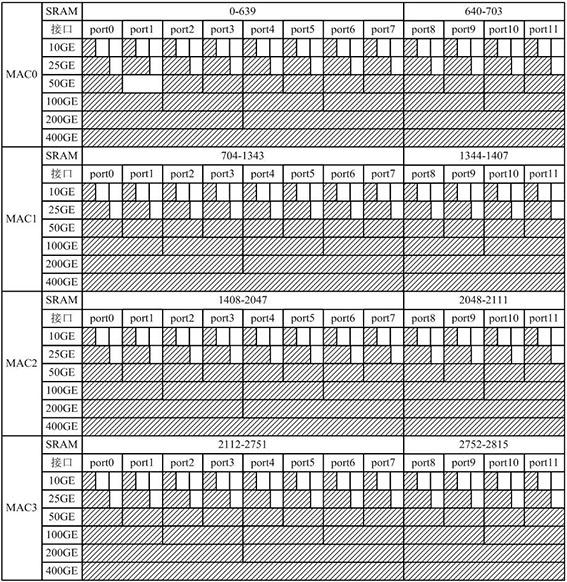

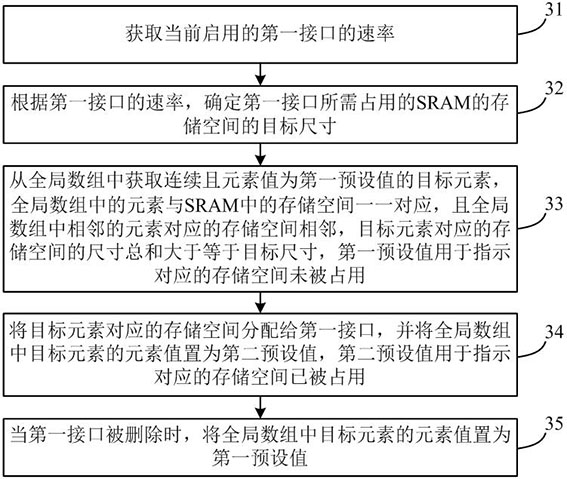

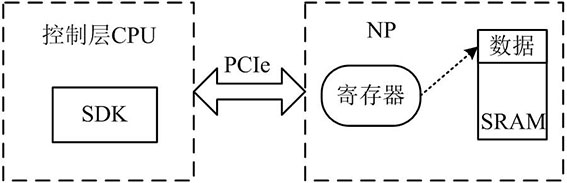

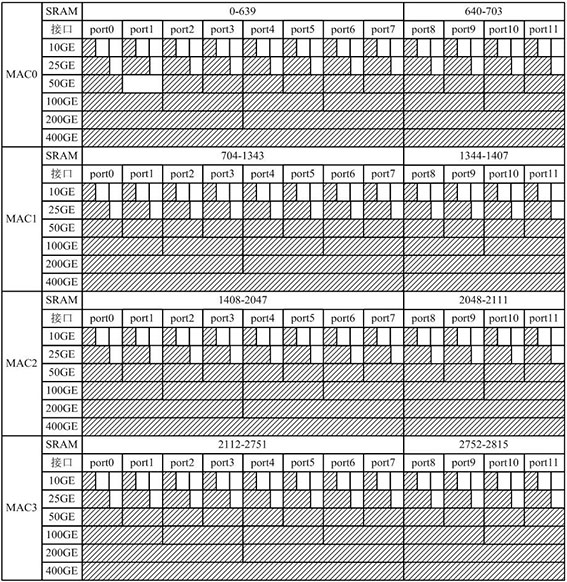

SRAM storage space allocation method and device for and chip

ActiveCN111782561AReduce areaIncrease flexibilityMemory adressing/allocation/relocationComputer hardwareEmbedded system

The embodiment of the application provides an SRAM storage space allocation method and device and a chip. The method comprises the steps: determining the target size of storage space, needing to be occupied by a first interface, of an SRAM according to the rate of a currently started first interface; acquiring continuous target elements with element values being first preset values from a global array, the size sum of the storage spaces corresponding to the target elements being larger than or equal to the target size, and the first preset values being used for indicating that the corresponding storage spaces are not occupied; allocating a storage space corresponding to the target element to the first interface, and setting an element value of the target element in the global array as a second preset value, the second preset value indicating that the storage space is occupied; and when the first interface is deleted, setting the element value of the target element in the global array as a first preset value. By applying the technical scheme provided by the embodiment of the invention, the storage space allocation flexibility of the SRAM is improved, the storage space utilization rate of the SRAM is improved, the area of the SRAM is reduced, and the wiring difficulty of back-end development is reduced.

Owner:新华三半导体技术有限公司

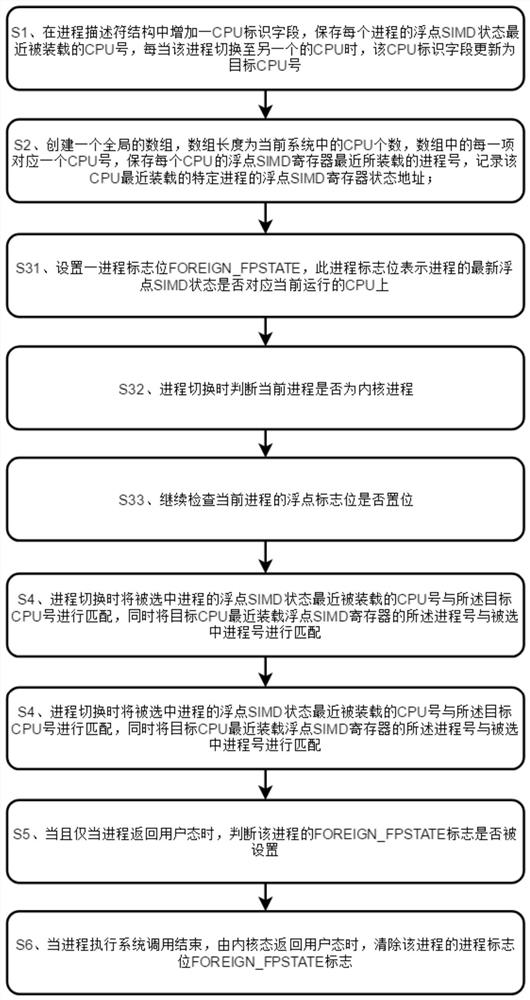

Performance optimization method for floating point SIMD context switching

ActiveCN112395005AReduce switching overheadMinor changesRegister arrangementsConcurrent instruction executionComputer architectureEngineering

The invention discloses a performance optimization method for floating point SIMD context switching, which comprises the following steps: adding a CPU identification field in a process descriptor structure, and creating a global array; when the process is switched, matching the CPU number loaded recently in the floating point SIMD state of the selected process with the target CPU number, matchingthe process number loaded recently in the floating point SIMD register of the target CPU with the selected process number, if the process number and the selected process number are equal, not recovering the floating point SIMD state of the process by the target CPU, and clearing a process flag bit FOREIGNFPSTATE flag of the process; and if not, the target CPU recovers the floating point SIMD stateof the process, and a process flag bit FOREIGNFPSTATE flag of the process is set at the moment. According to the method, the kernel process switching expenditure is reduced, the kernel is slightly changed, and the method is suitable for the retention and recovery processes of other system registers, such as a performance counter and the like.

Owner:JIANGNAN INST OF COMPUTING TECH

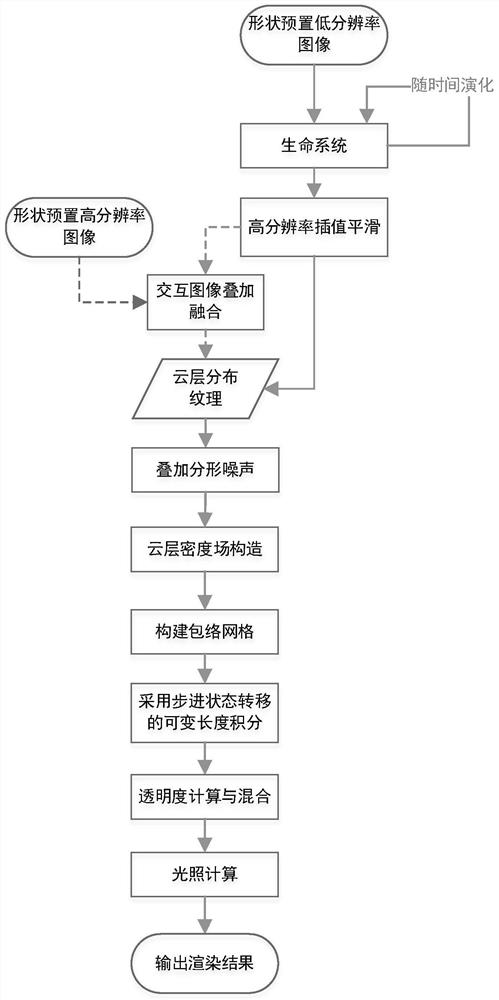

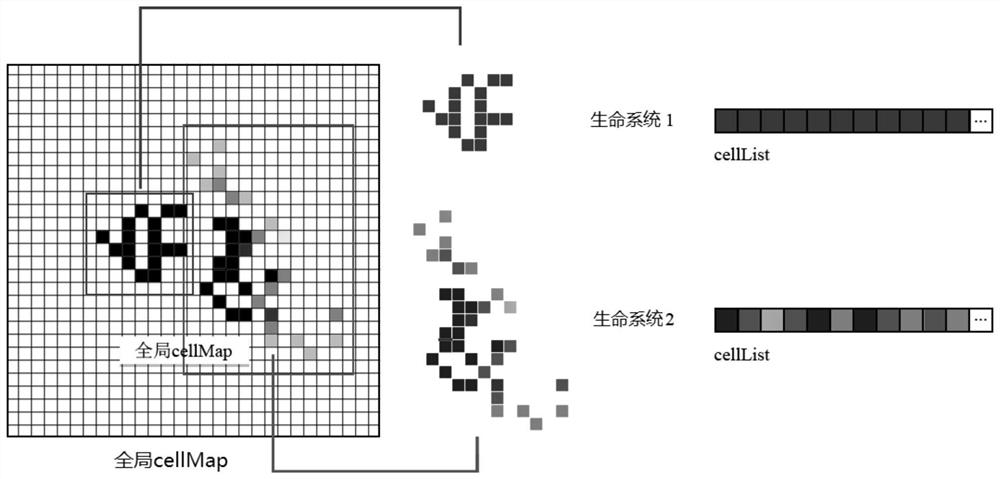

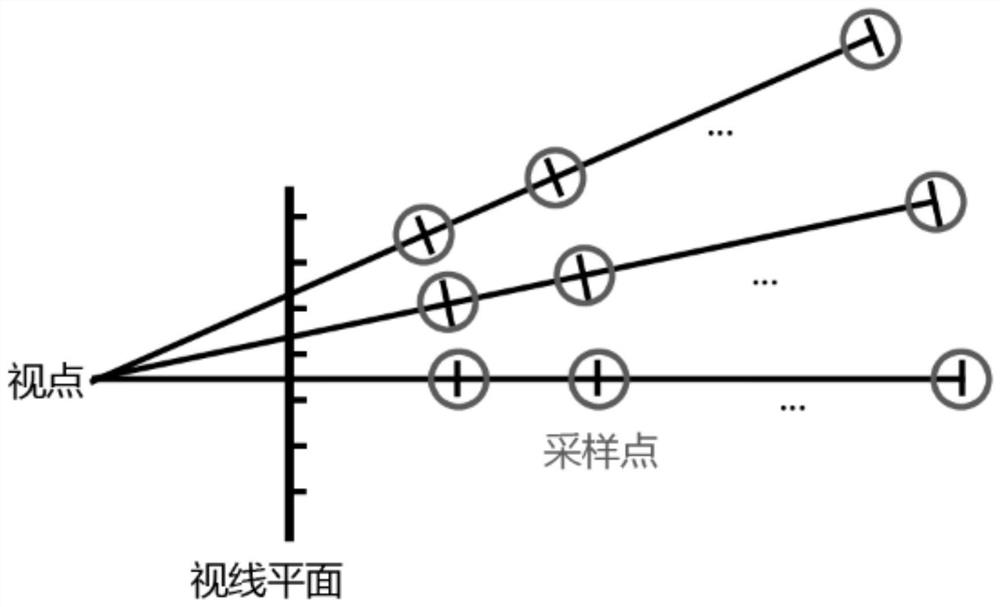

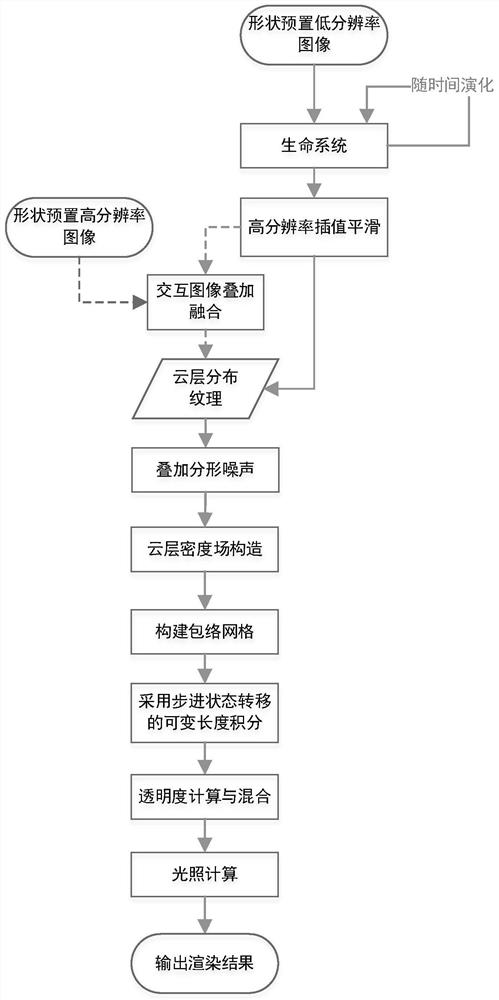

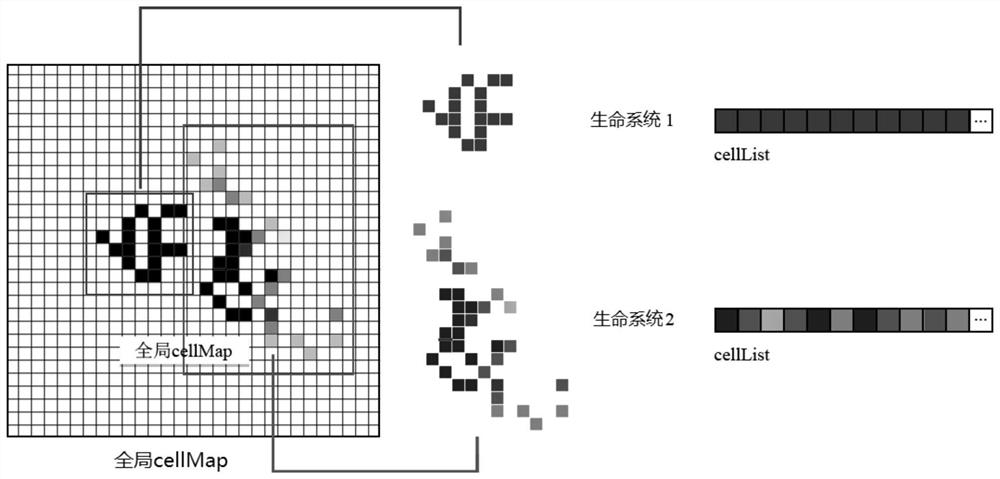

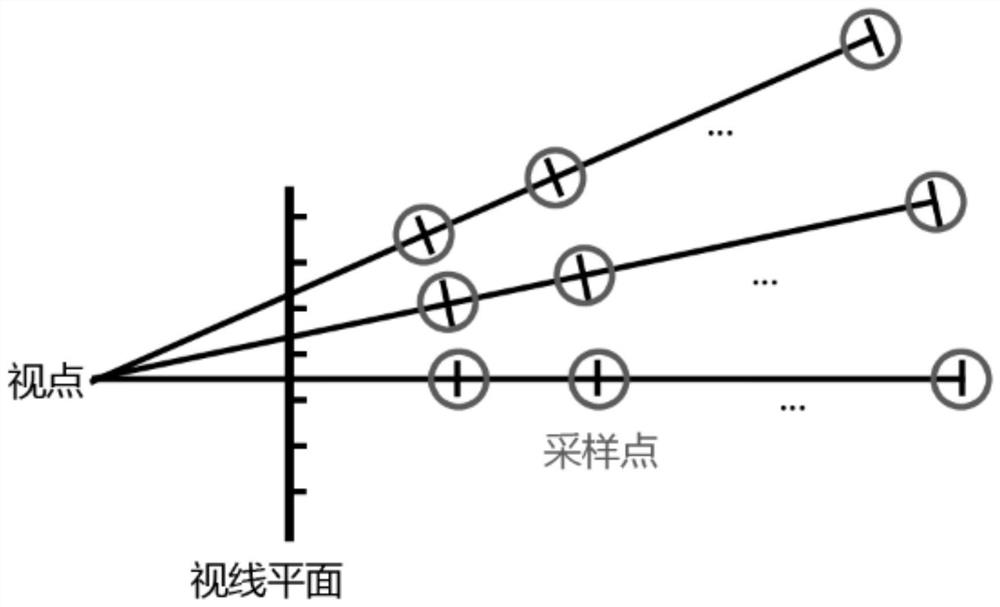

A real-time dynamic cloud layer rendering method based on cellular automata

ActiveCN113160413BIncrease variabilityImprove controllabilityImage enhancement3D-image renderingComputational sciencePoint light

The invention discloses a real-time dynamic cloud layer drawing method based on cellular automata. Judgment rule; 2) The cellular automaton establishes the data structure of the cellular automaton according to the global texture of the input initial low-resolution image, as the cell evolution texture of each frame changing with time sequence; the data structure includes the global array cellMap and each living system. 3) Smooth and interpolate the cell evolution texture of each frame to obtain the large-scale texture of the corresponding frame; 4) The large-scale texture corresponding to each frame is superimposed with fractal noise to generate cloud layer details, and the density field is calculated in each frame. The value of the point corresponding to the texture element; 5) Sampling the volume cloud formed by multiple cloud clusters; 6) Calculate the scattering effect of the point light source on the cloud layer, and finally render the realistic rendering of the cloud layer.

Owner:PEKING UNIV

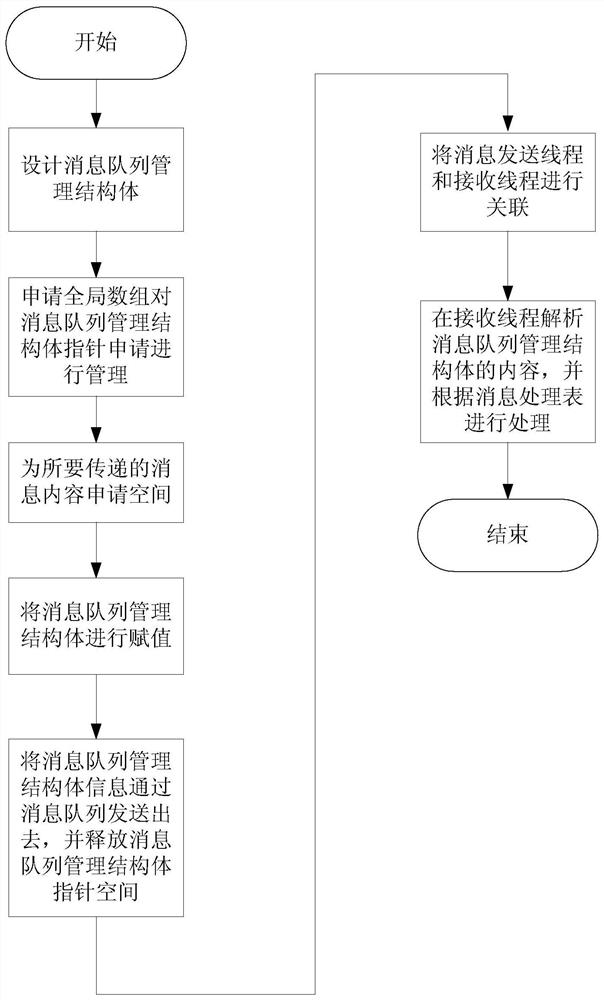

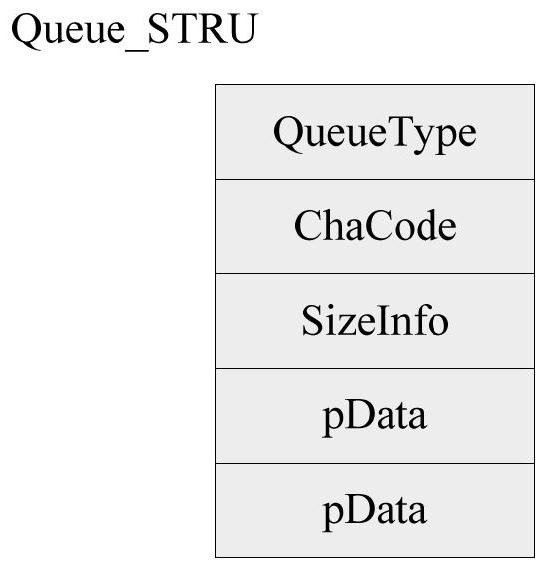

Packaging method based on VxWorks real-time operating system

PendingCN113608883AIntegrity guaranteedImprove transfer efficiencyInterprogram communicationMessage queueOperational system

The invention discloses a packaging method based on a VxWorks real-time operating system. The packaging method comprises the following steps: firstly, designing a message queue management structural body; then defining a global array management message, wherein an array element is a message queue management structural body; in a message queue sending function, applying a pointer variable for a message queue management structural body, so that a space is applied for message content to be transmitted; assigning a value to a pointer variable of the message queue management structural body; sending out the message queue management structural body through an operation system message queue sending function, and releasing the space of a pointer variable of the message queue management structural body; and associating the sending thread and the receiving thread of the message, obtaining the received message queue management structural body in the receiving thread, analyzing and processing the content of the message queue management structural body, and completing packaging. According to the method, the task and the message queue of the real-time operating system are further packaged, and the packaged framework is directly called subsequently for development, so that the efficiency is improved, and the safety of the operating system is ensured.

Owner:TIANJIN JINHANG COMP TECH RES INST

Method, device and chip for allocating storage space of SRAM

ActiveCN111782561BReduce areaIncrease flexibilityMemory adressing/allocation/relocationComputer hardwareEngineering

Embodiments of the present application provide a method, device, and chip for allocating storage space of SRAM. The method includes: determining the target size of the storage space of the SRAM required by the first interface according to the rate of the currently enabled first interface; Obtain consecutive target elements whose element values are the first preset value in the array. The sum of the sizes of the storage spaces corresponding to the target elements is greater than or equal to the target size. The first preset value is used to indicate that the corresponding storage space is not occupied; the target element corresponds to The storage space allocated to the first interface, and the element value of the target element in the global array is set to the second preset value, the second preset value indicates that the storage space has been occupied; when the first interface is deleted, the global array The element value of the target element in is set to the first preset value. Applying the technical solution provided by the embodiment of the present application improves the flexibility of SRAM storage space allocation, improves the utilization rate of SRAM storage space, reduces the area of SRAM, and reduces the wiring difficulty of back-end development.

Owner:新华三半导体技术有限公司

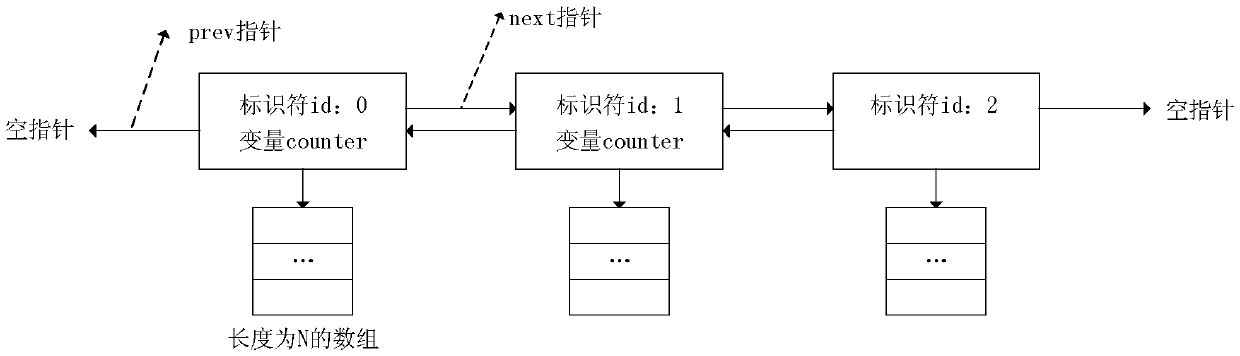

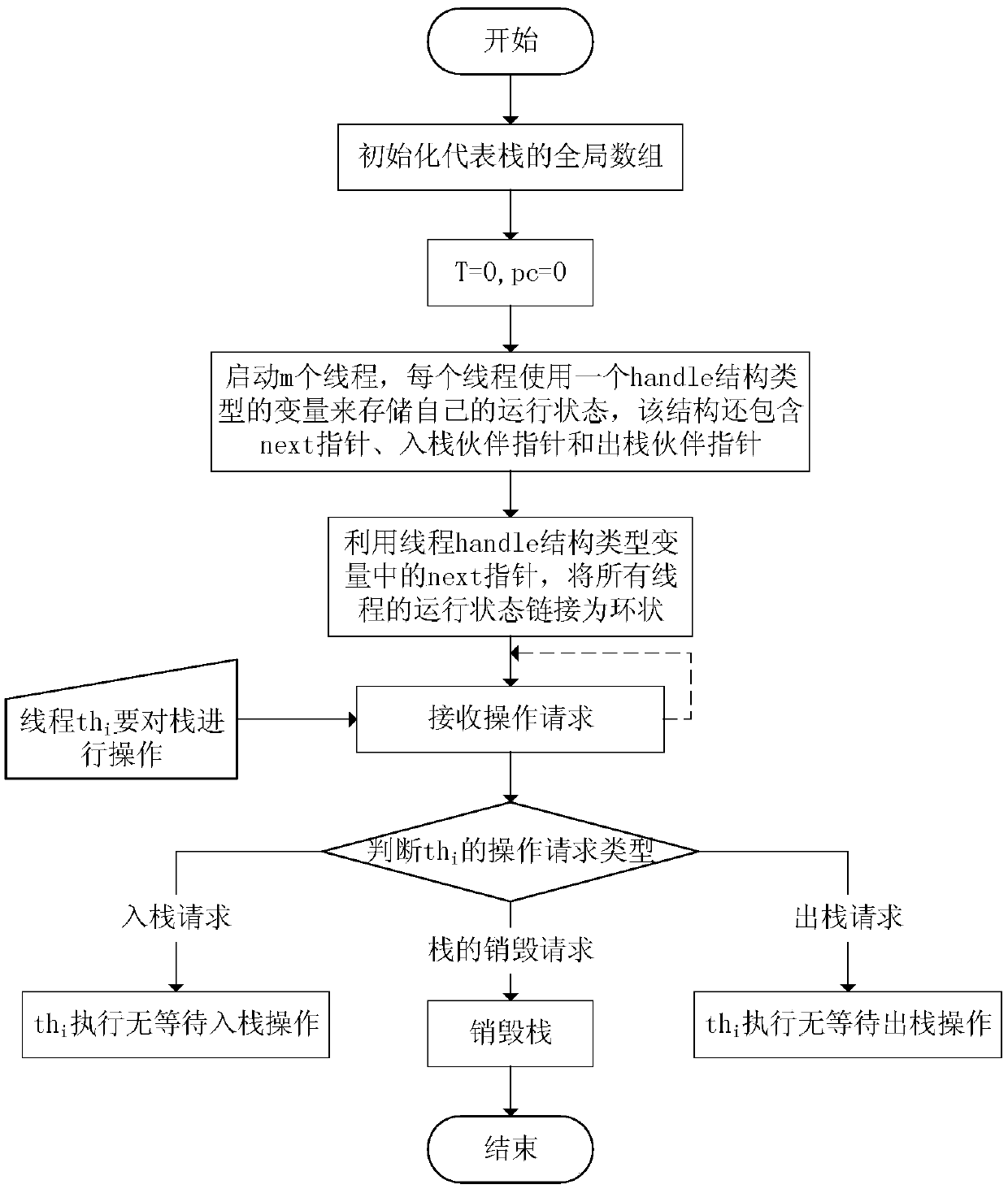

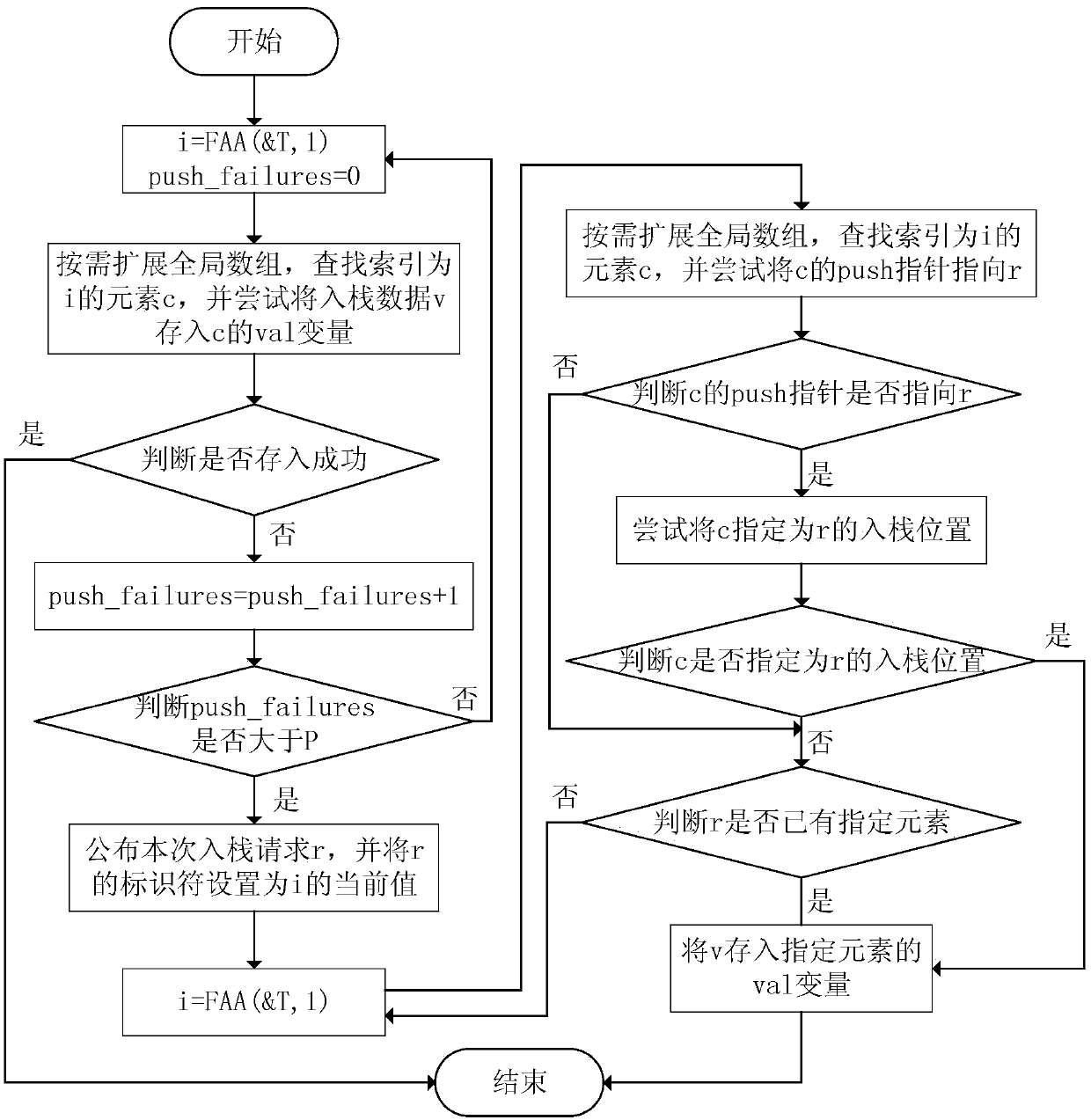

A wait-free stack operation method based on an array structure in a multi-core environment

ActiveCN106843806BImprove parallelismParallelism limitProgram synchronisationMachine execution arrangementsArray data structureStructure of Management Information

Owner:INST OF INFORMATION ENG CHINESE ACAD OF SCI

Method, device, server and system for acquiring cardinality

ActiveCN104090895BShorten the timeReduce resource consumptionSpecial data processing applicationsArray data structureResource consumption

The invention discloses a method, device, server and system for obtaining a cardinal number, and belongs to the technical field of databases. The method comprises the following steps: obtaining data stored in each data storage server, and obtaining key value array pairs according to a key value and a reference value which correspond to each datum; classifying the key value array pairs according to the key value, merging arrays in each kind of key value array pairs to obtain a global array corresponding to each kind of key value, and obtaining the cardinal number according to the global array corresponding to each kind of the key value. In the method disclosed by the invention, after the data stored in each data storage server is obtained, the corresponding key value array pairs are obtained according to the key value and the reference value which correspond to each datum, key value arrays corresponding to each data storage server are merged to obtain the global array corresponding to each kind of key value, and the cardinal number is obtained according to the global array corresponding to each kind of key value, so that the trouble of obtaining the cardinal number by reading the data stored in each data storage server item by item is avoided, the time required for obtaining the cardinal number is shortened, and the resource consumption is reduced.

Owner:SHENZHEN TENCENT COMP SYST CO LTD

Dynamic scanning method of pcie devices supporting multiple rcs under linux system

ActiveCN104820646BSituations to prevent misuseImprove scalabilityElectric digital data processingExtensibilityArray data structure

The invention discloses a PCIE (peripheral component interface express) device dynamic scanning method supporting multi RC (remote control) in a Linux system. The PCIE device dynamic scanning method supporting the plurality of the multi RC in the Linux system includes: electrifying the Linux system, distributing continuous bus number resources to each RC controller according to the number of RC controllers of the Linux system, traversing each RC controller exists in the Linux system, recording bus number information corresponding to each RC controller to a global array, and deleting a default PCIE device or a default PCIE bridge device in each RC controller so as to release resources distributed by the Linux system in a default mode, and the RC controller root bus number as a judgement standard to scan or unload the PCIE device dynamic according to corresponding RC controller bus number information recorded in the global array. By adopting the PCIE device dynamic scanning method supporting the plurality of the multi RC in the Linux system, expandability of the Linux system is improved due to the fact that each RC controller and PCIE bridge device are newly distributed the continuous bus number resources, and safety of the Linux system is improved due to the fact that the scanning or unloading of the PCIE device under the RC controller root bus number is controlled separately, and simultaneously, stability of the Linux system is enhanced due to the fact that a linkage state is detected and controlled the scanning process.

Owner:烽火超微信息科技有限公司

Method and device for operating and managing memory

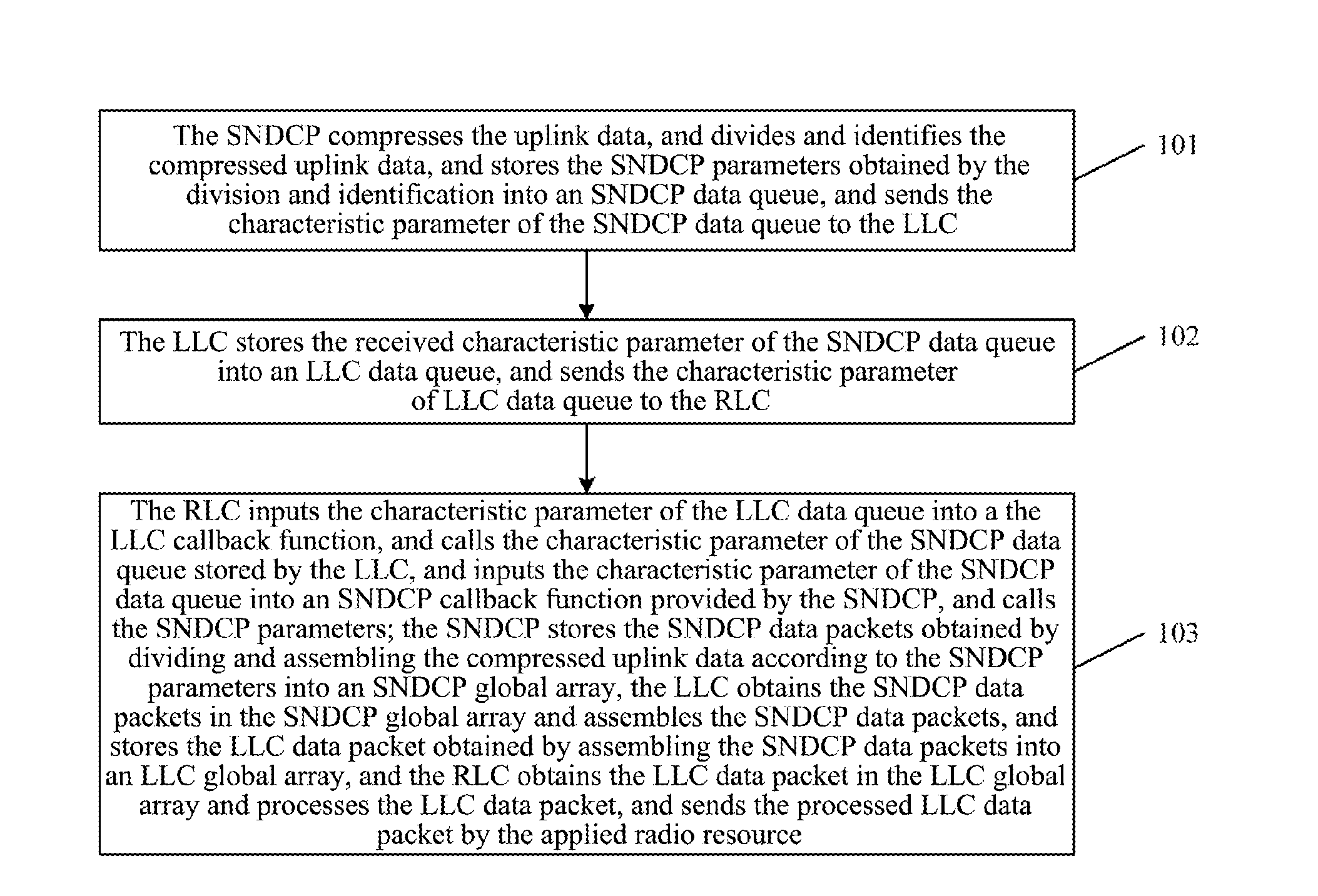

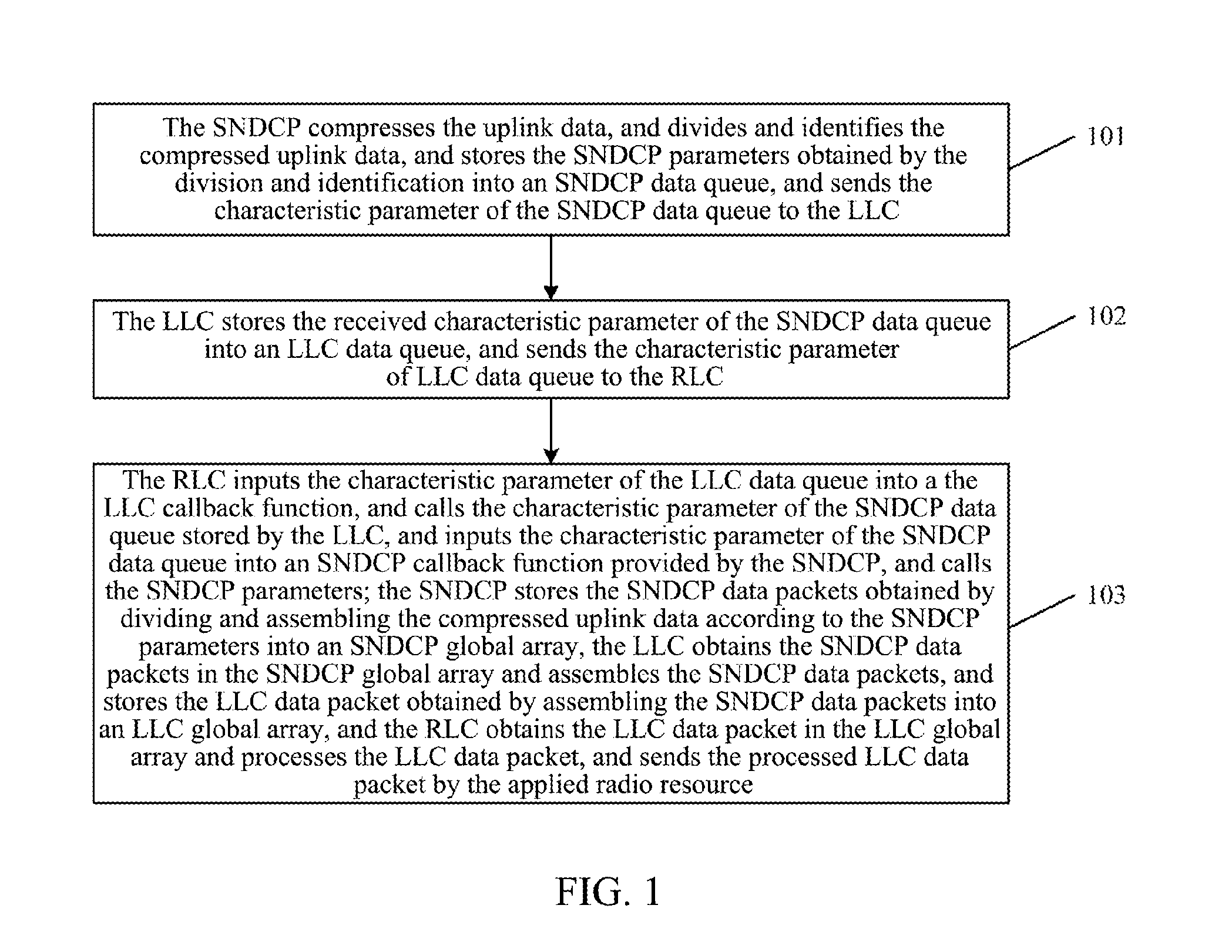

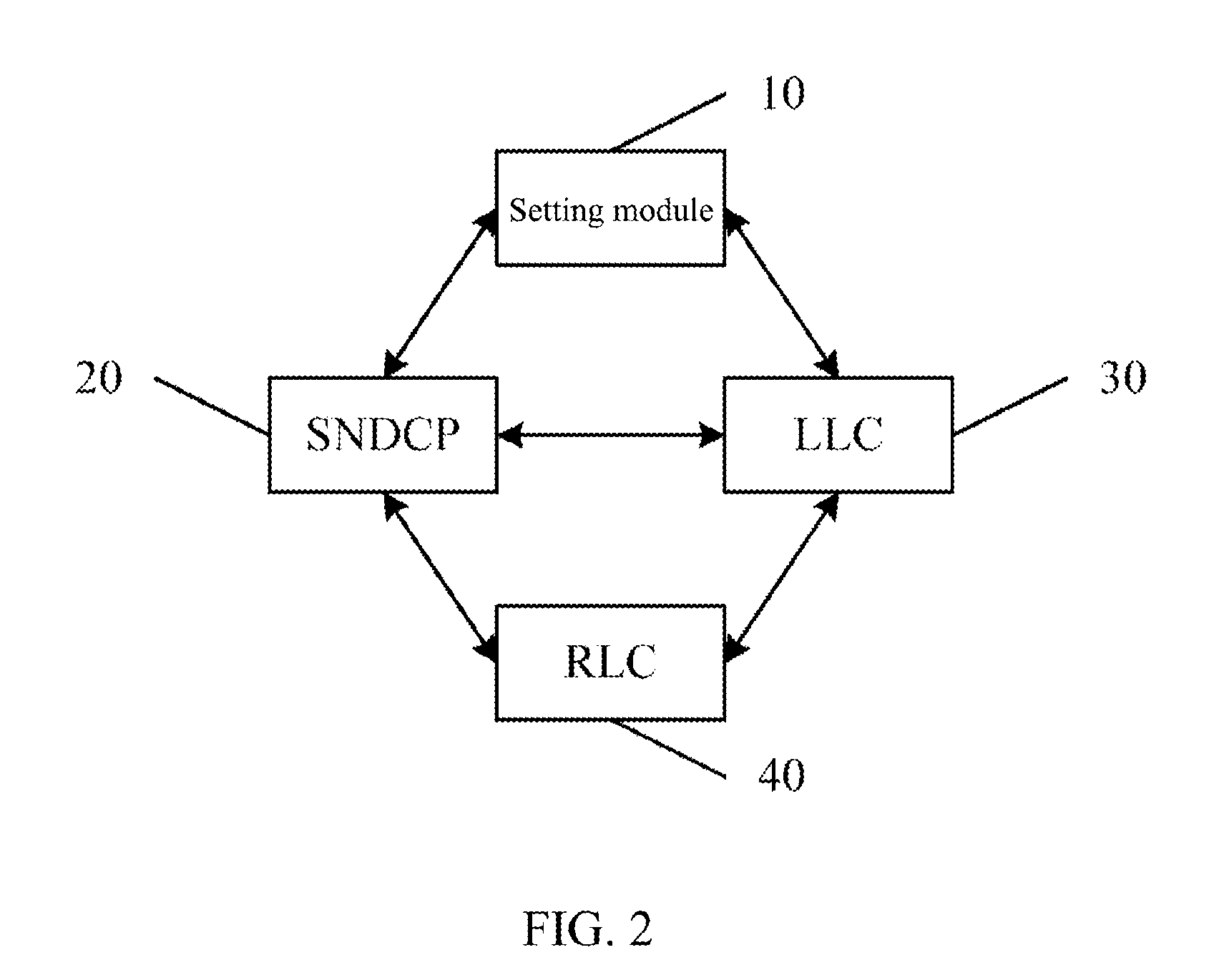

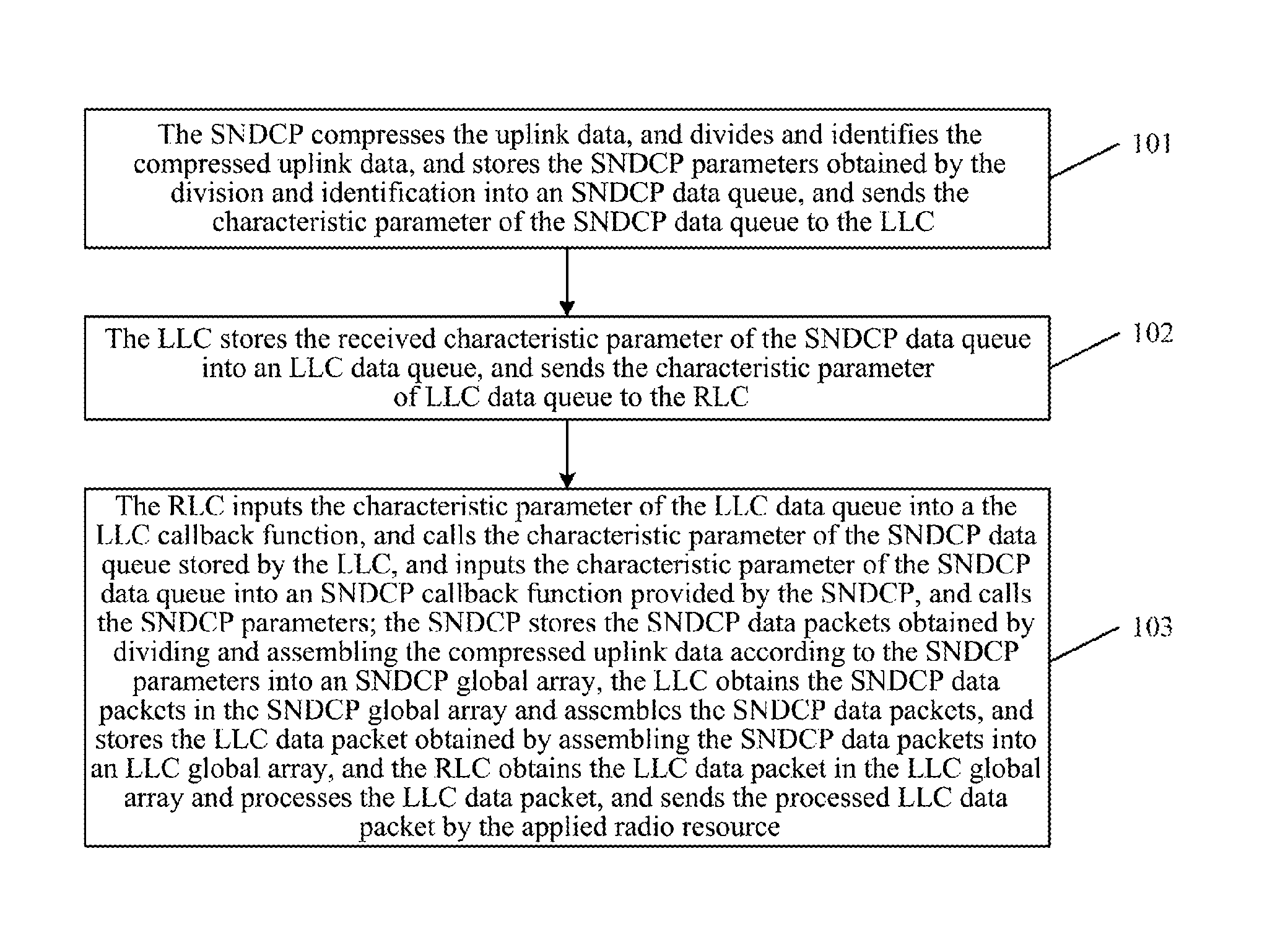

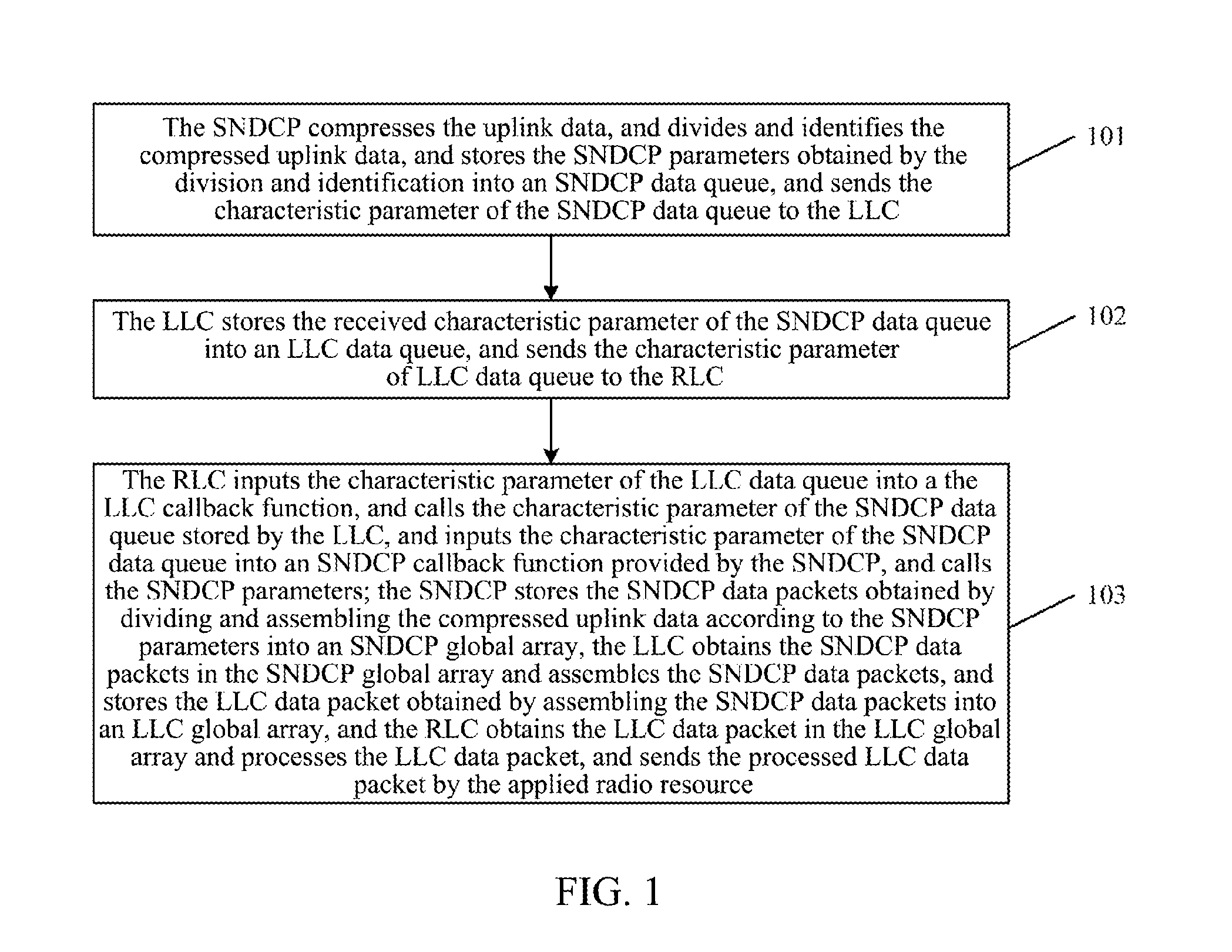

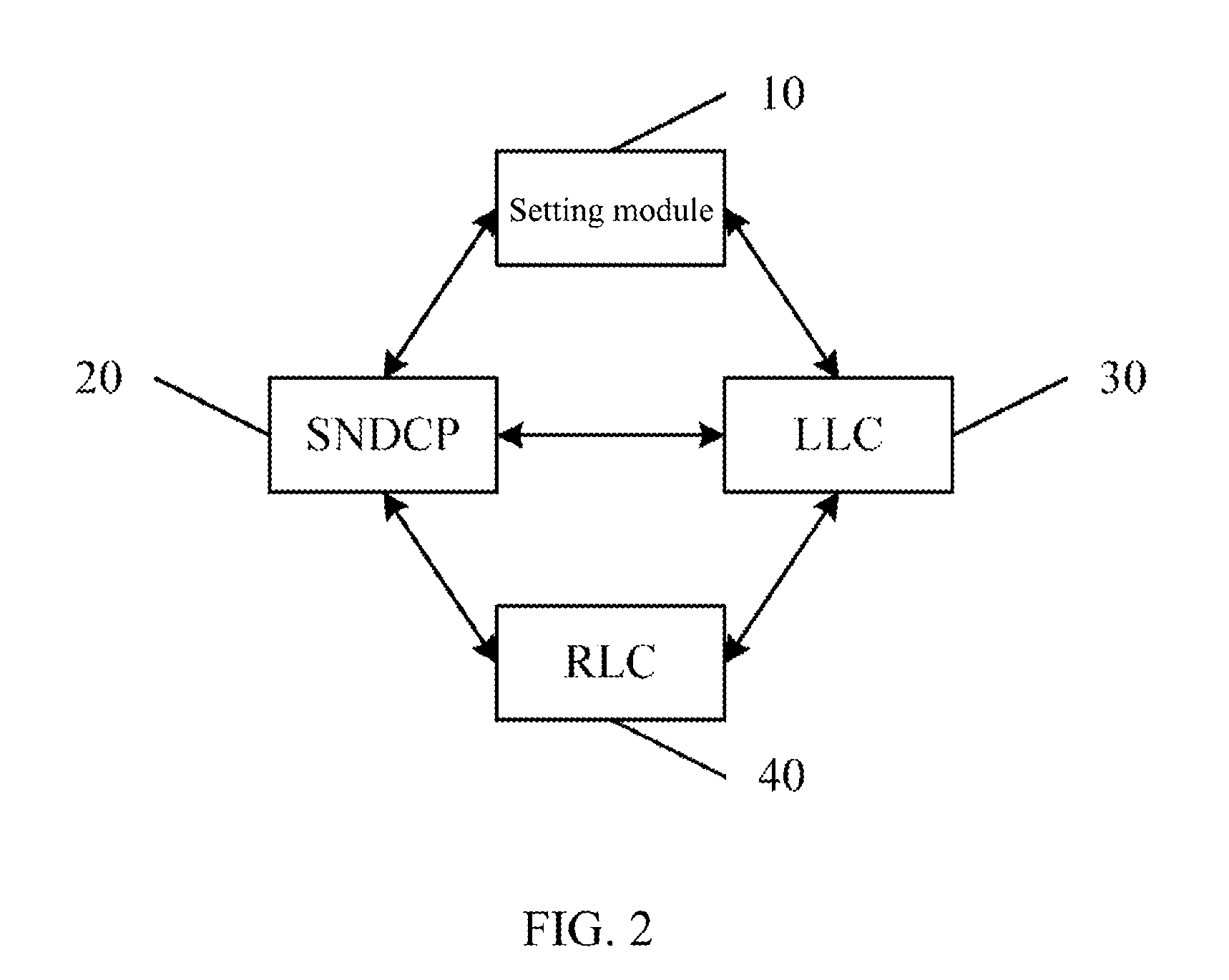

ActiveUS20120201257A1Save memory spaceAvoid useless workNetwork traffic/resource managementTime-division multiplexTransfer procedureLogical link control

A method for operating and managing memory is disclosed in present invention, during the whole transmission process of uplink data in transmission plane protocol layer of General Packet Radio Service (GPRS), only the 1520-bytes global array of Subnet Dependent Convergence Protocol (SNDCP) layer and the 1560-bytes global array of Logic Link Control (LLC) layer are used, so the memory space can be saved effectively; also, because the SNDCP global array is used to store SNDCP data packets and the LLC global array is used to store the LLC data packets, so a dynamic process of memory application releasing on the transmission plane is avoided; moreover, only the data that need to be sent by the LLC are assembled with LLC frame format, thus avoiding useless work of LLC. Moreover, according to the present invention, the memory is operated and managed by way of global array without tedious memory pool operations.

Owner:ZTE CORP

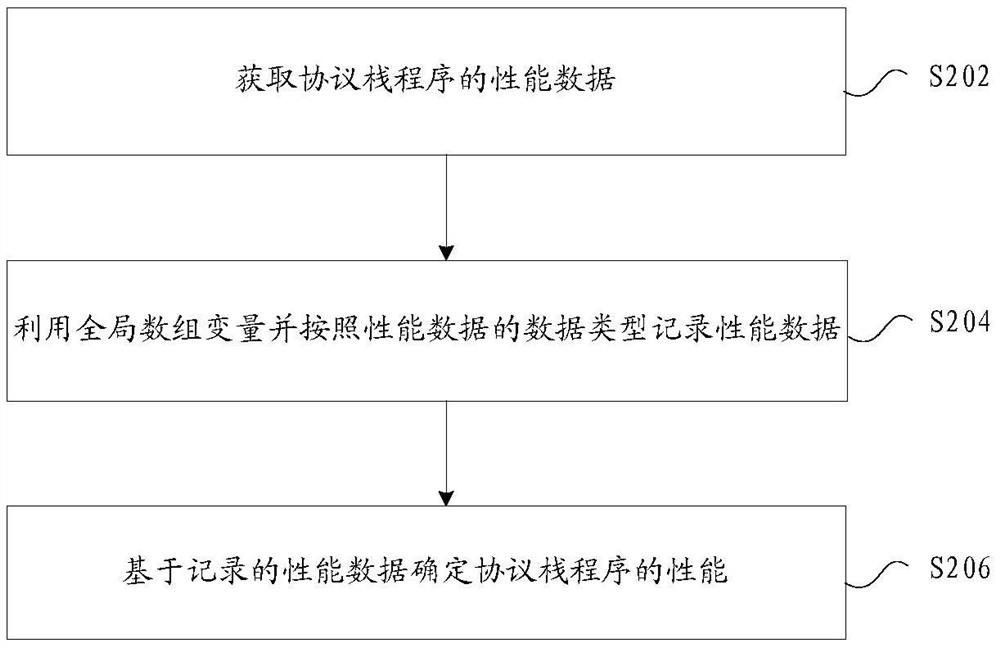

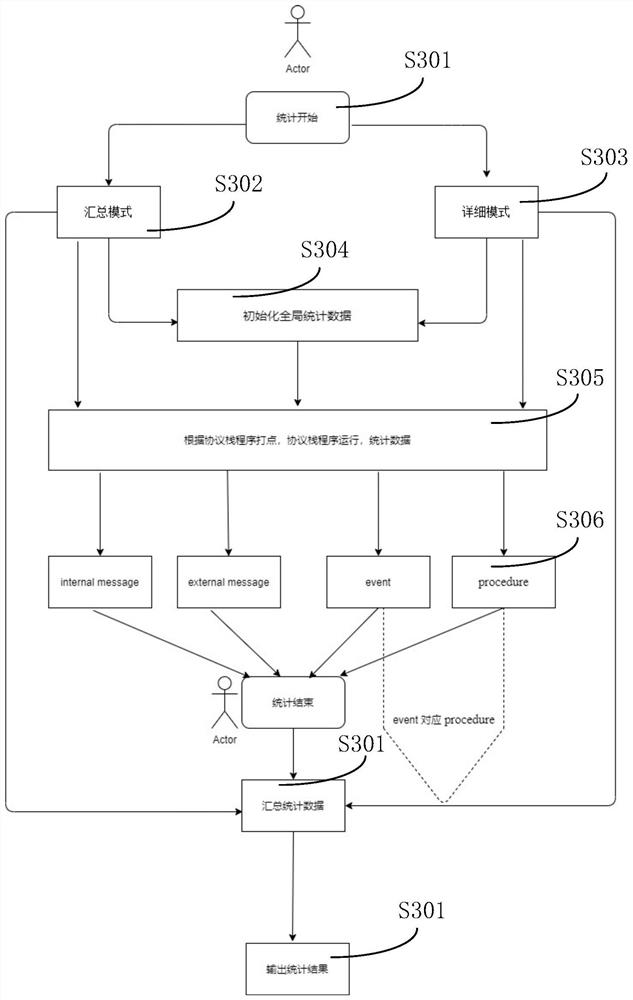

Performance determination method and device for protocol stack program of base station

PendingCN113852975ASolve the problem that the performance of the protocol stack program cannot be determinedAccurate analysisTransmissionWireless communicationComputer hardwareData class

An embodiment of the invention provides a performance determination method and device for a protocol stack program, a storage medium and an electronic device. The method comprises the steps of: acquiring performance data of a protocol stack program, wherein the performance data comprise data generated in the running process of the protocol stack program; recording the performance data by using a global array variable according to a data type of the performance data; and determining performance of the protocol stack program based on the recorded performance data. Through adopting the performance determination method and device, the problem that the performance of the protocol stack program cannot be determined in related technologies is solved, and the effect of accurately analyzing the performance of the protocol stack program is achieved.

Owner:ZHEJIANG SUNWAVE LEAPWAVE NETWORK CO LTD +1

Method and device for operating and managing memory

ActiveUS8693503B2Save memory spaceAvoid useless workNetwork traffic/resource managementTime-division multiplexTransfer procedureLogical link control

A method for operating and managing memory is disclosed in present invention, during the whole transmission process of uplink data in transmission plane protocol layer of General Packet Radio Service (GPRS), only the 1520-bytes global array of Subnet Dependent Convergence Protocol (SNDCP) layer and the 1560-bytes global array of Logic Link Control (LLC) layer are used, so the memory space can be saved effectively; also, because the SNDCP global array is used to store SNDCP data packets and the LLC global array is used to store the LLC data packets, so a dynamic process of memory application releasing on the transmission plane is avoided; moreover, only the data that need to be sent by the LLC are assembled with LLC frame format, thus avoiding useless work of LLC. Moreover, according to the present invention, the memory is operated and managed by way of global array without tedious memory pool operations.

Owner:ZTE CORP

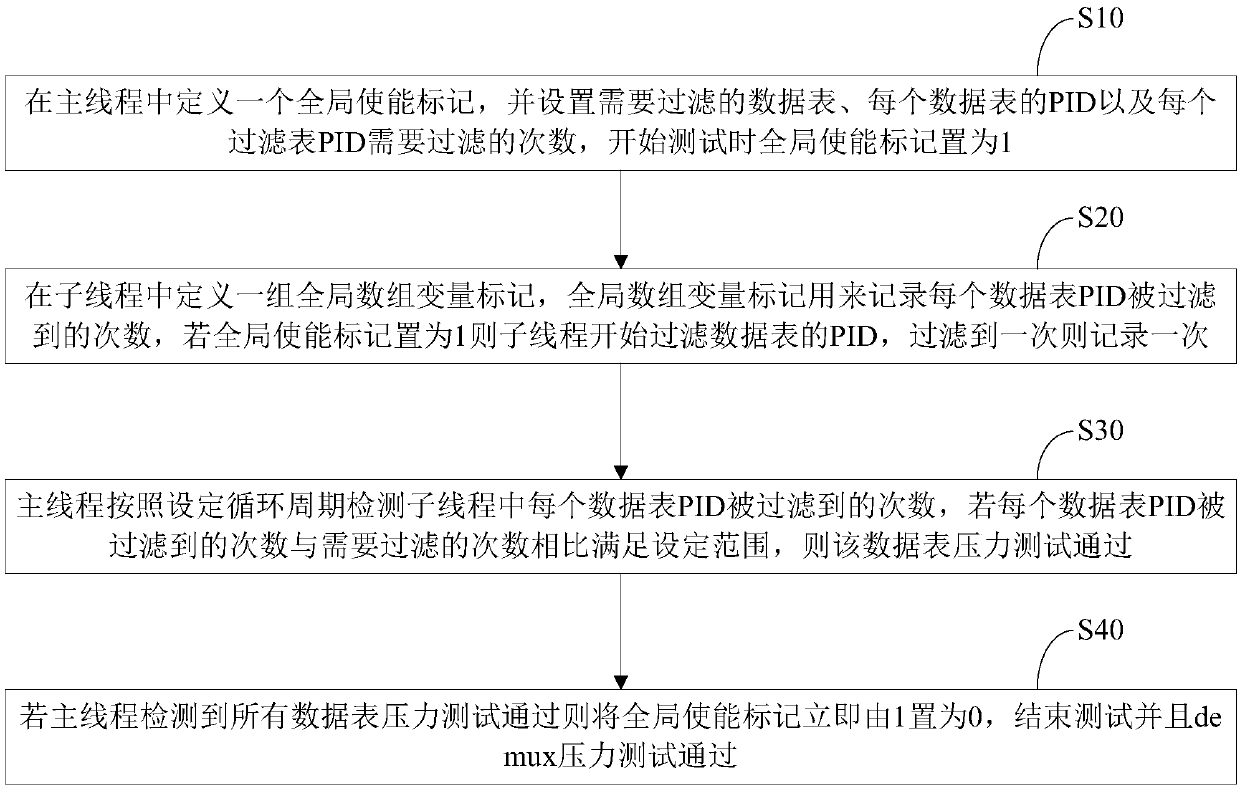

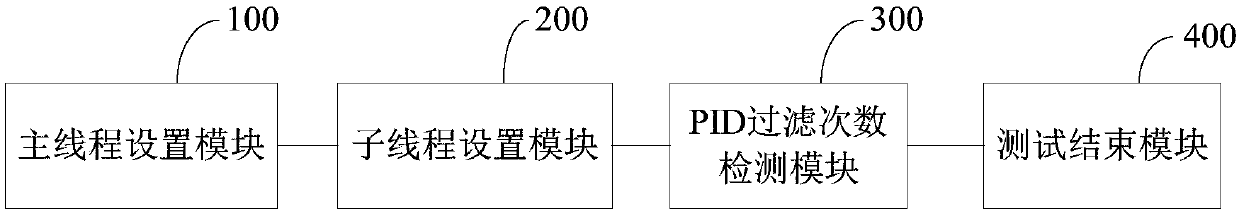

Set-top box demultiplexer stress testing method and system

InactiveCN106961600BThe test result is accurateIncrease credibilityTelevision systemsSelective content distributionArray data structureSoftware engineering

The present invention relates to a set top box demultiplexer (demux) pressure testing method, system, and testing device. The method comprises: defining a global enable flag in a main thread, and configuring data tables to be filtered, a PID of each data table, and the number of times a PID of each filter table needs to be filtered; defining a group of global array variable tags in sub-threads so as to record the number of times the PID of each data table is filtered, the data table passing a pressure test if the number of times each data table PID is filtered satisfies a set range in comparison with the number of times the filter table needs to be filtered; the main thread detecting, according to a set cycle period, the number of times each data table PID in the sub-threads is filtered; and when the main thread detects that all of the data tables pass the stress test, immediately setting the global enable flag to 0 from 1, determining that the demux stress test has been passed, and ending the test. In this way, a test can be ended after the test has been passed, without waiting a fixed length of time, and the test result is accurate and highly credible, greatly satisfying testing requirements.

Owner:SHENZHEN JIUZHOU ELECTRIC

Real-time dynamic cloud layer drawing method based on cellular automaton

ActiveCN113160413AIncrease variabilityImprove controllabilityImage enhancement3D-image renderingComputational scienceEngineering

The invention discloses a real-time dynamic cloud layer drawing method based on a cellular automaton, which comprises the following steps of: 1) generating the cellular automaton of a dynamic cloud layer, and adopting a Moore neighborhood as a death-living judgment rule of a cell neighborhood and a life game by the cellular automaton; 2) the cellular automaton establishes a data structure of the cellular automaton according to the global texture of the input initial low-resolution image, and the data structure is used as the cell evolution texture of each frame changing along with the time sequence; the data structure comprises a global array cellMap and each life system; 3) smoothing and interpolating and amplifying the cell evolution texture of each frame to obtain a large-size texture of the corresponding frame; 4) superposing the large-size texture corresponding to each frame and the fractal noise to generate cloud layer details, and calculating the value of the density field at a point corresponding to each texture element; 5) sampling a volume cloud formed by a plurality of cloud clusters; and 6) calculating the scattering effect of the point light source on the cloud layer, and finally rendering a realistic effect picture of the cloud layer.

Owner:PEKING UNIV

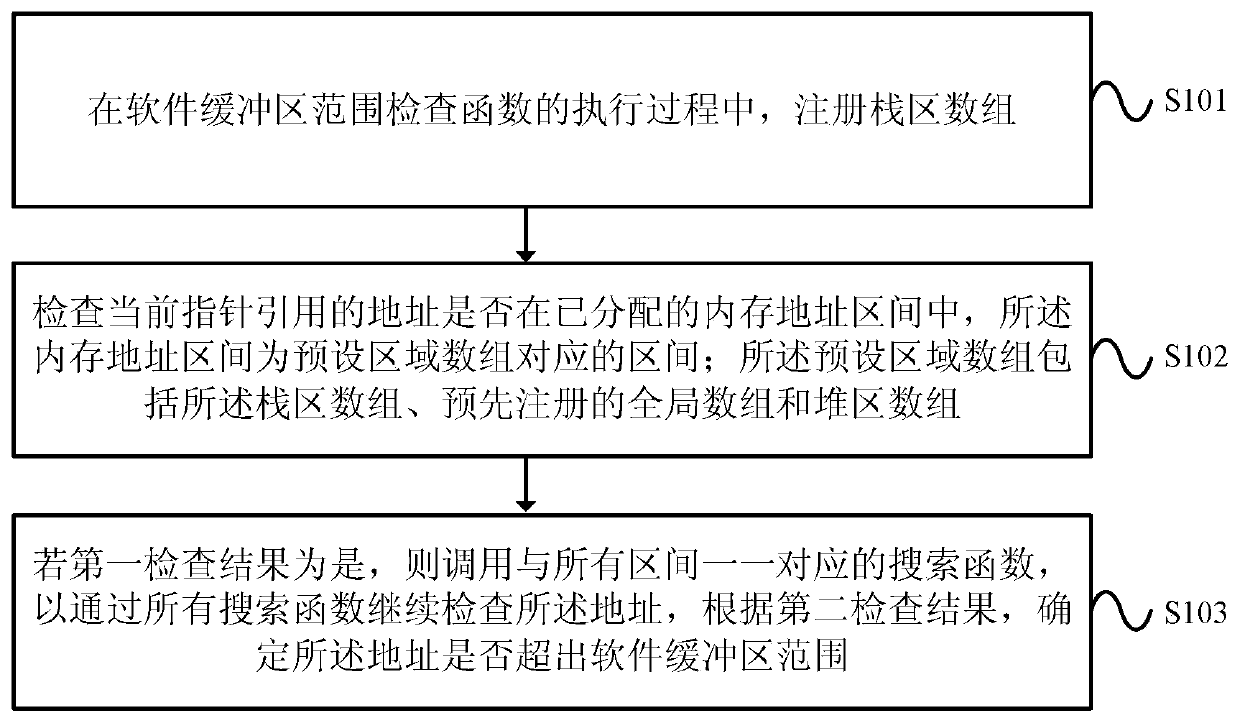

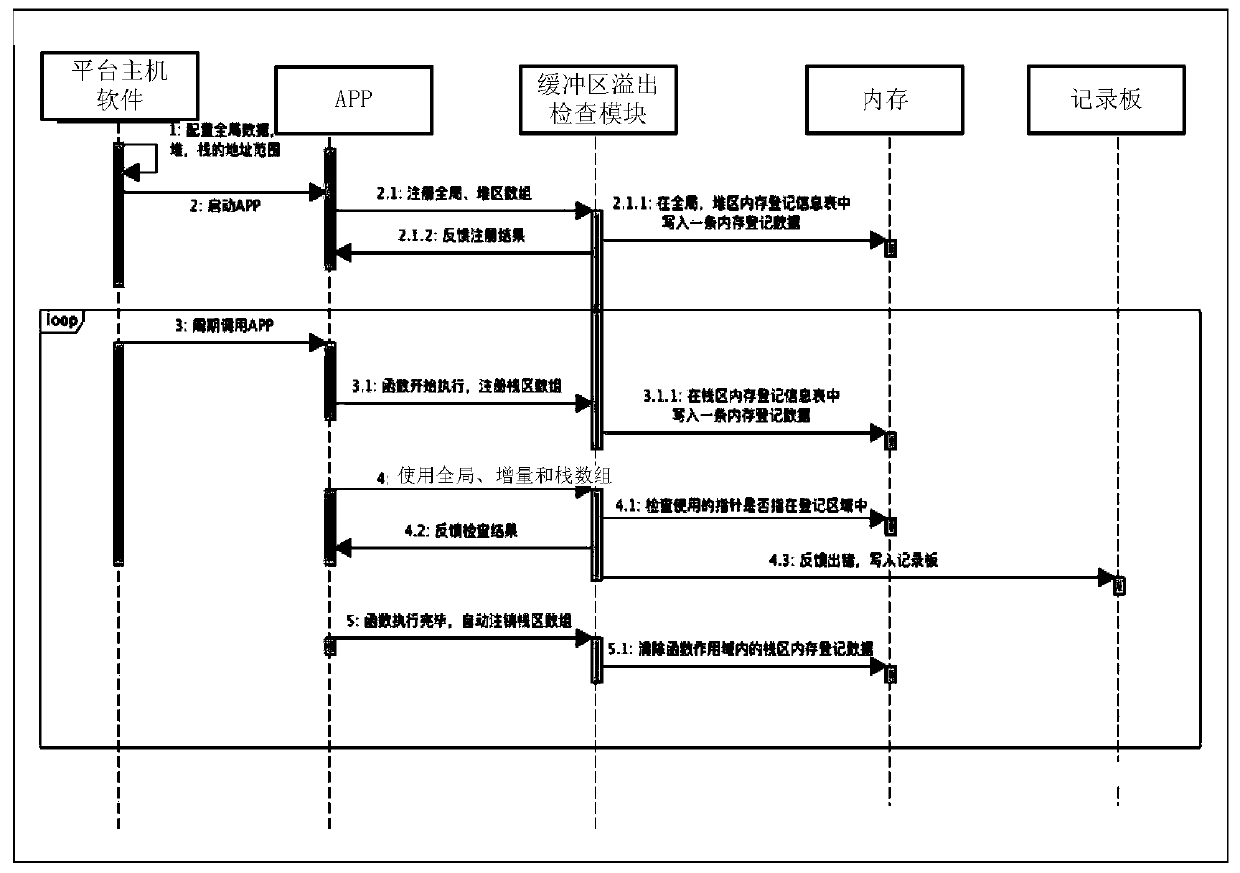

An urban rail transit signal system software buffer area checking method

The embodiment of the invention provides an urban rail transit signal system software buffer area range checking method, which comprises the following steps of: registering a stack area array in the execution process of a software buffer area range checking function; checking whether the address quoted by the current pointer is in an allocated memory address interval, wherein the memory address interval is an interval corresponding to the preset area array; wherein the preset area array comprises the stack area array, a pre-registered global array and a pre-registered stack area array; and ifthe first check result is yes, calling search functions in one-to-one correspondence with all the intervals to continue to check the address through all the search functions, and determining whether the address exceeds the range of the software buffer according to the second check result. According to the method for checking the buffer area of the urban rail transit signal system software providedby the embodiment of the invention, check of the buffer area of the urban rail transit signal system software can be realized through simplified codes.

Owner:TRAFFIC CONTROL TECH CO LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com