Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

221 results about "Free run" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Secure credit card

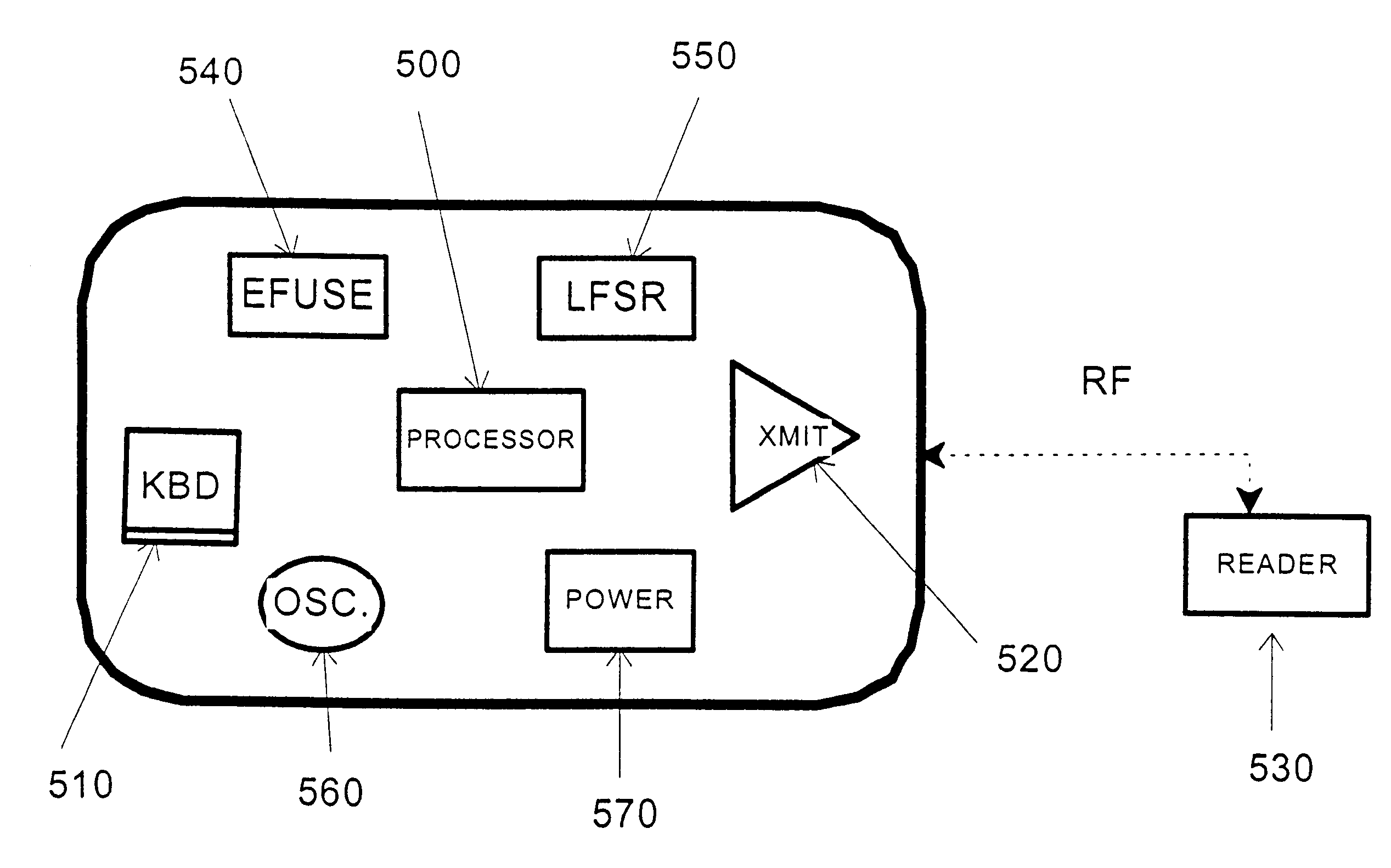

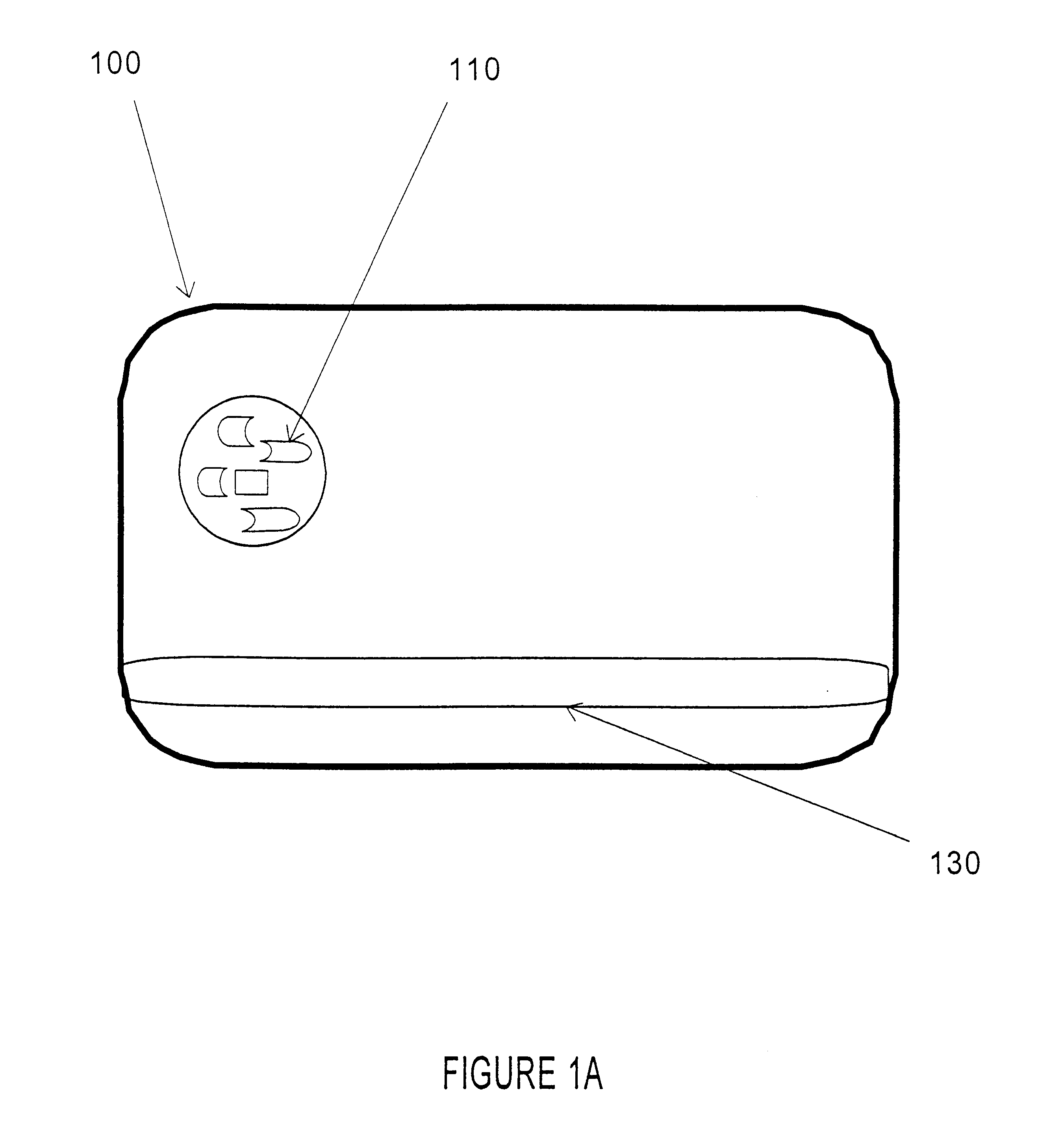

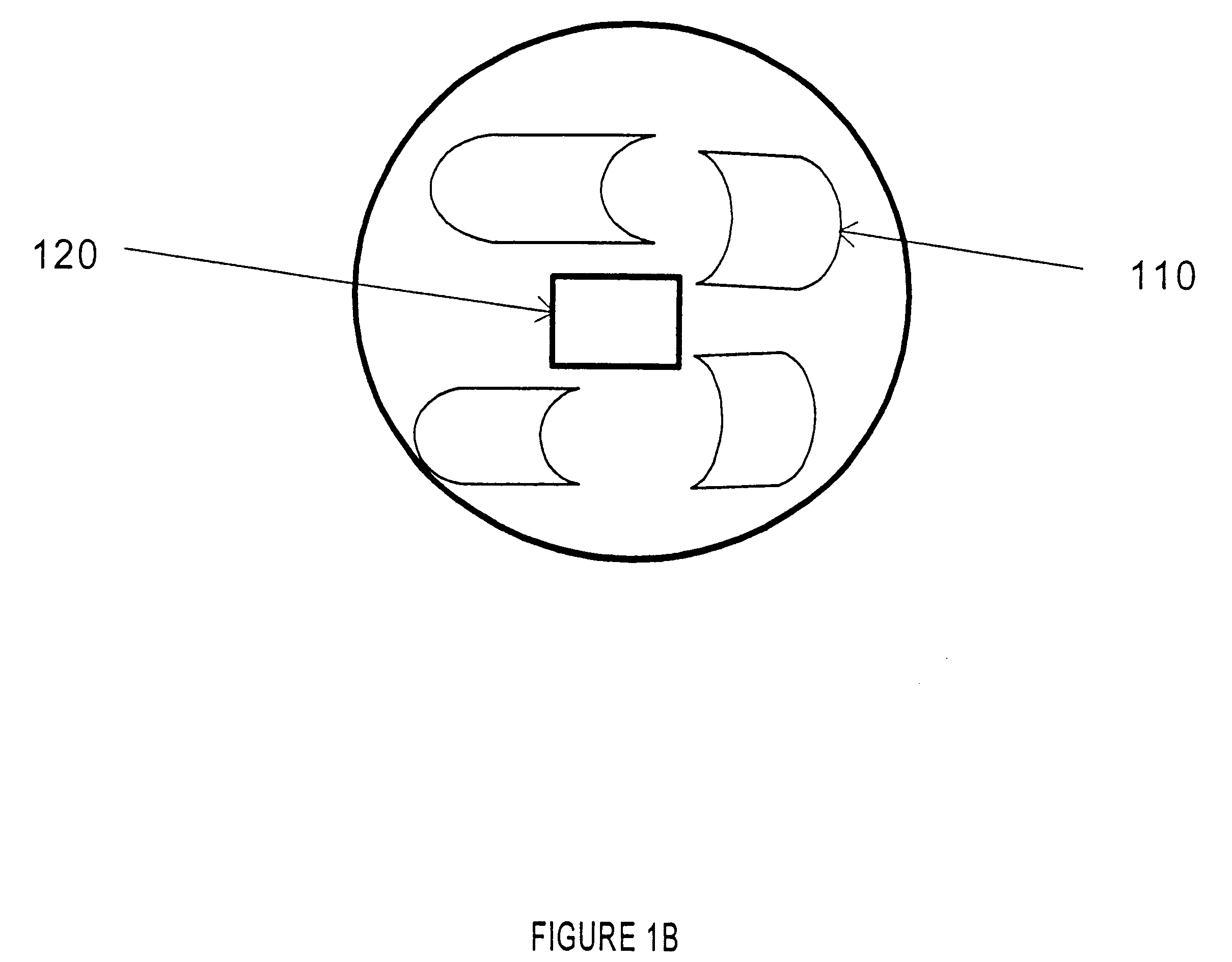

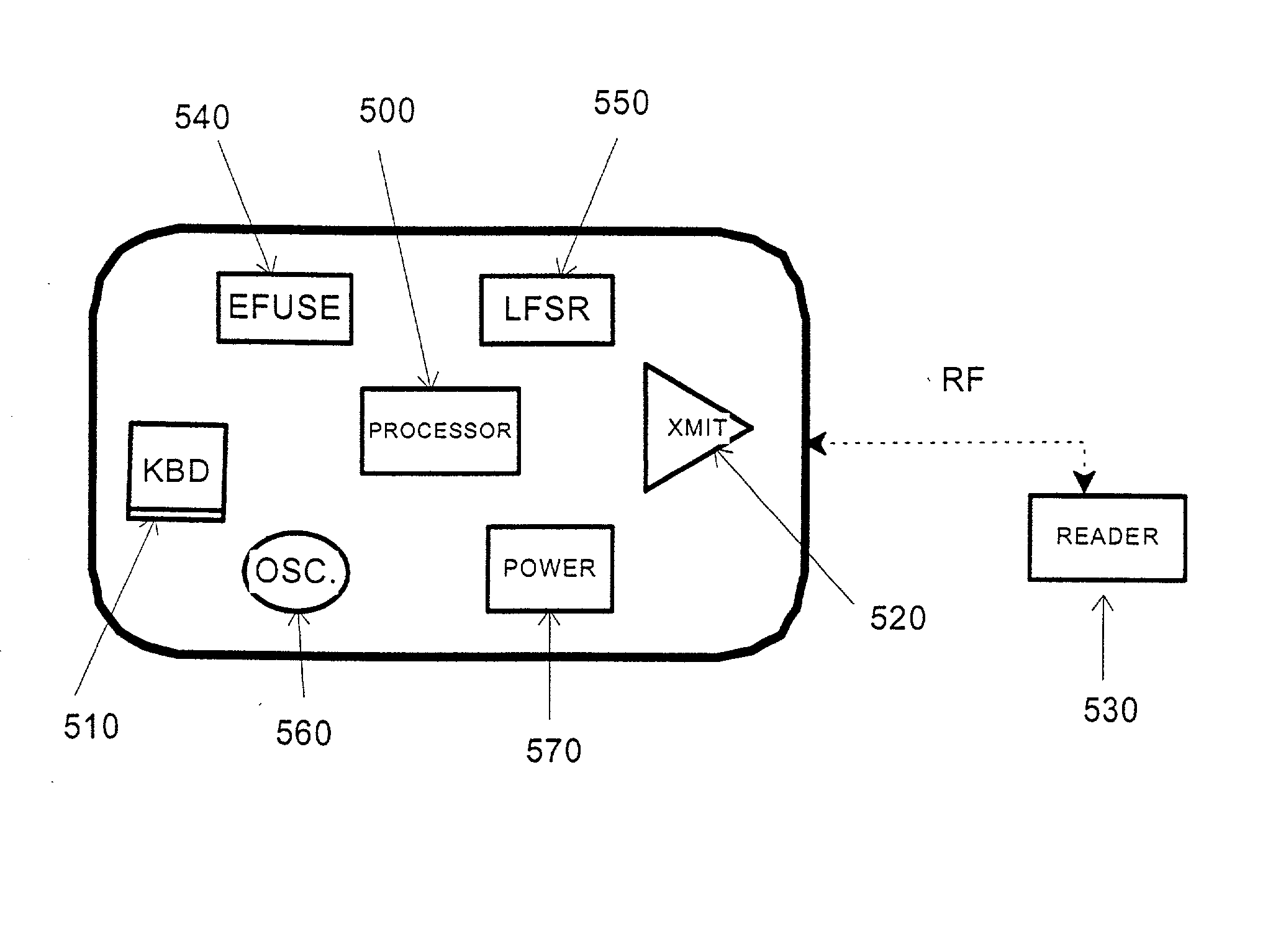

Credit card or portable identification cards containing smart card technology and electronic fuse (e-fuse) technology are combined with an LFSR pseudo random number generator to provide a secured method to prevent fraud and unauthorized use. Secure personalization via e-fuses, a pseudo-random number generator linear feedback shift register, free running clock oscillator, and power source embedded in the card provide a highly secured method to render a lost or stolen card useless. A unique card ID is permanently encoded within the card which requires a specific activation code to activate the card. A PIN number permits the card owner to activate the card for a predetermined length of time while processing a transaction. The card dynamically generates random code sequences and synchronization keys to secure a transaction.

Owner:KYNDRYL INC

Secure credit card

Credit card or portable identification cards containing smart card technology and electronic fuse (e-fuse) technology are combined with a LFSR pseudo random number generator to provide a secured method to prevent fraud and unauthorized use. Secure personalization via e-fuses, a pseudo random number generator linear feedback shift register, free running clock oscillator, and power source embedded in the card enable a highly secured method to render a lost or stolen card useless. A unique card ID is permanently encoded within the card which requires a specific activation code to activate the card. A PIN number provides a means for the card owner to activate the card for a predetermined length of time while processing a transaction. The card's security generation function dynamically generates random code sequences and synchronization keys to secure a transaction.

Owner:KYNDRYL INC

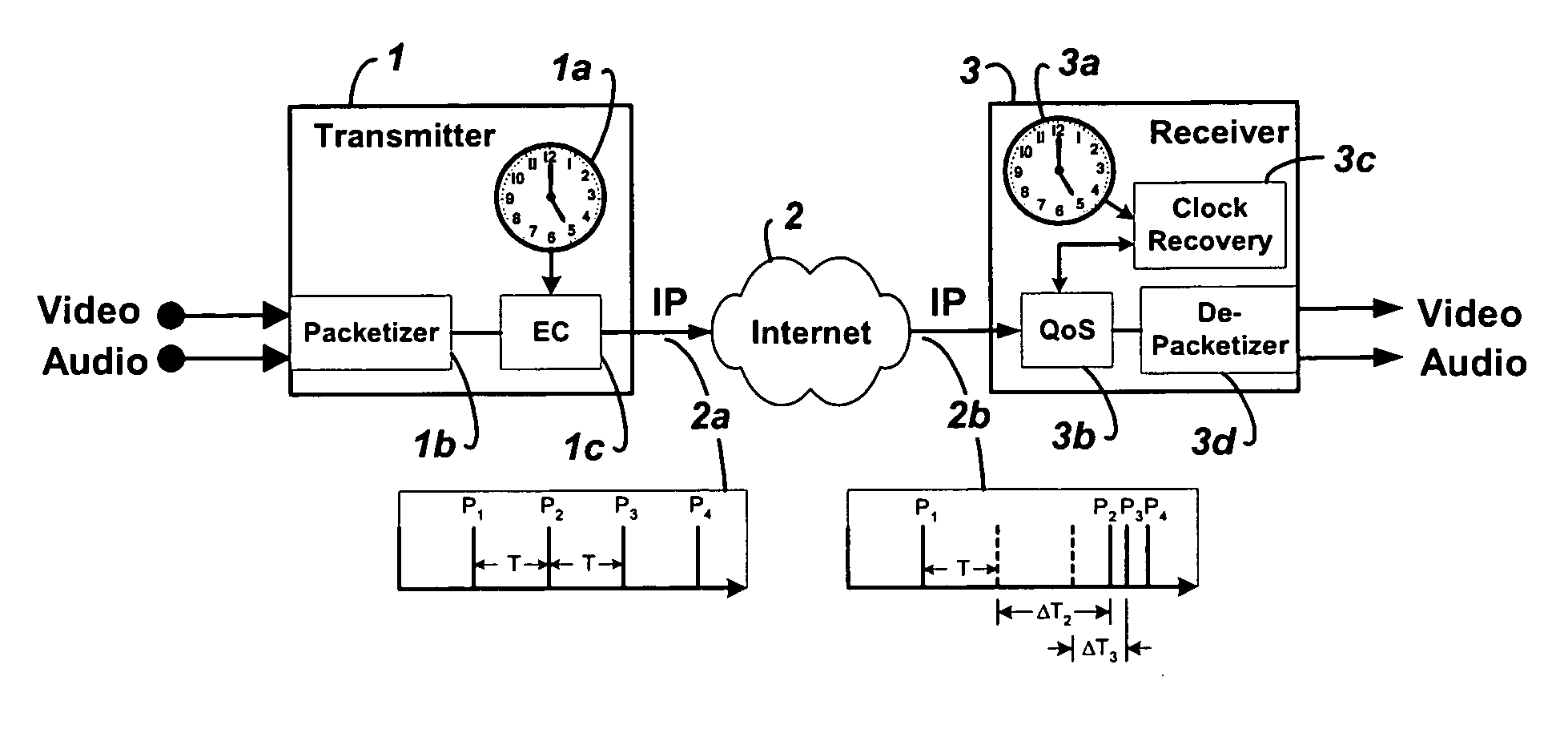

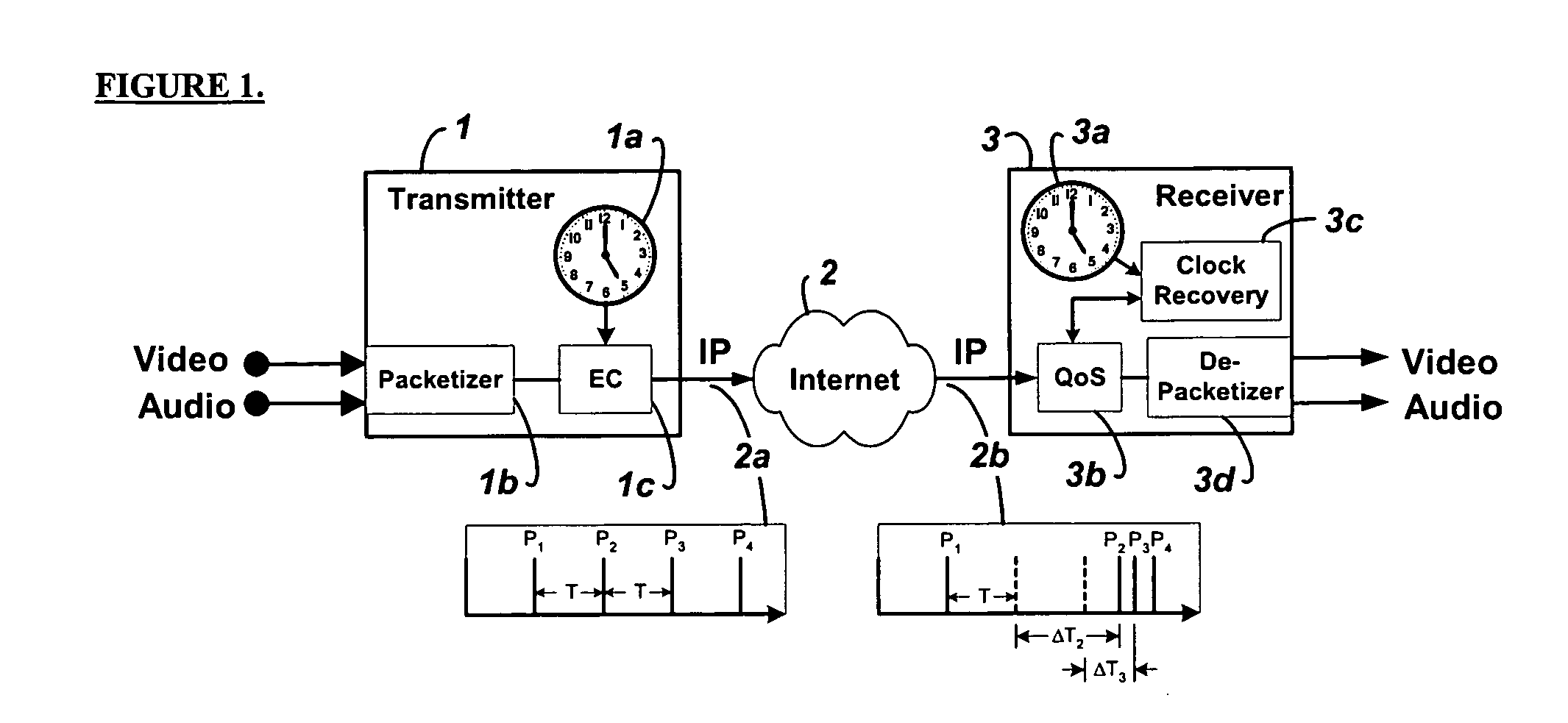

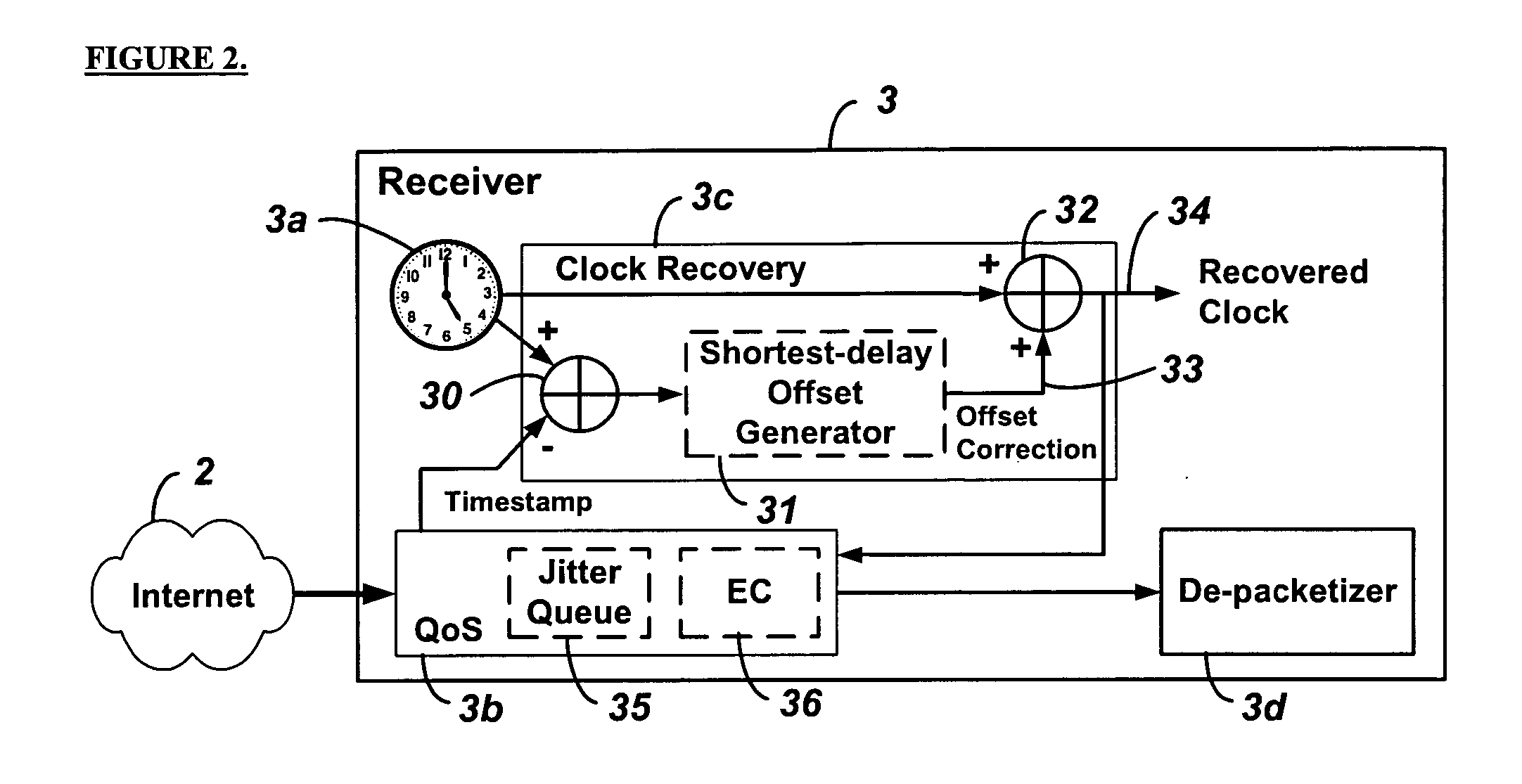

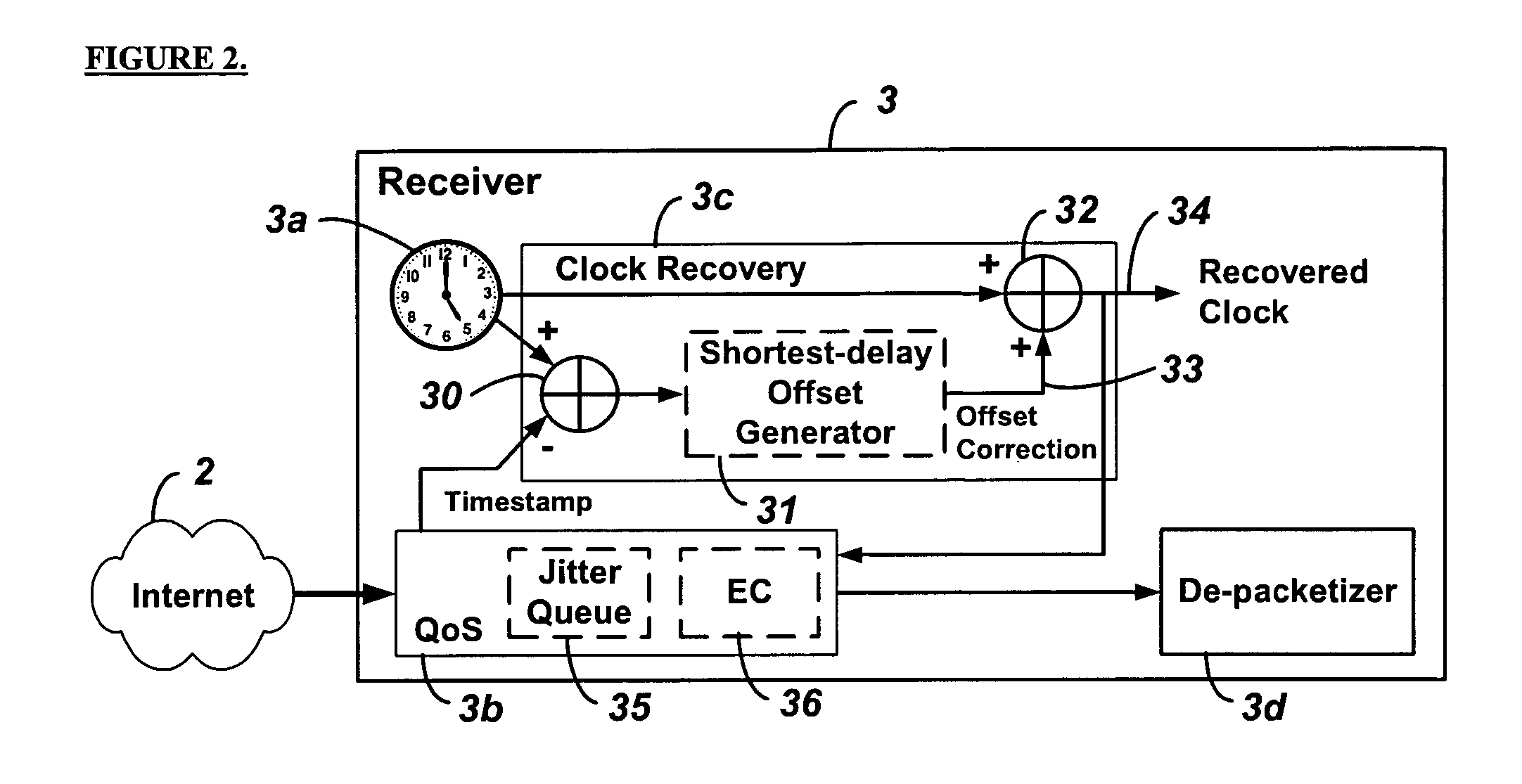

System and method for clock synchronization over packet-switched networks

ActiveUS20060013263A1Easy to replaceImprove abilitiesTime-division multiplexTransmissionQuality of serviceThe Internet

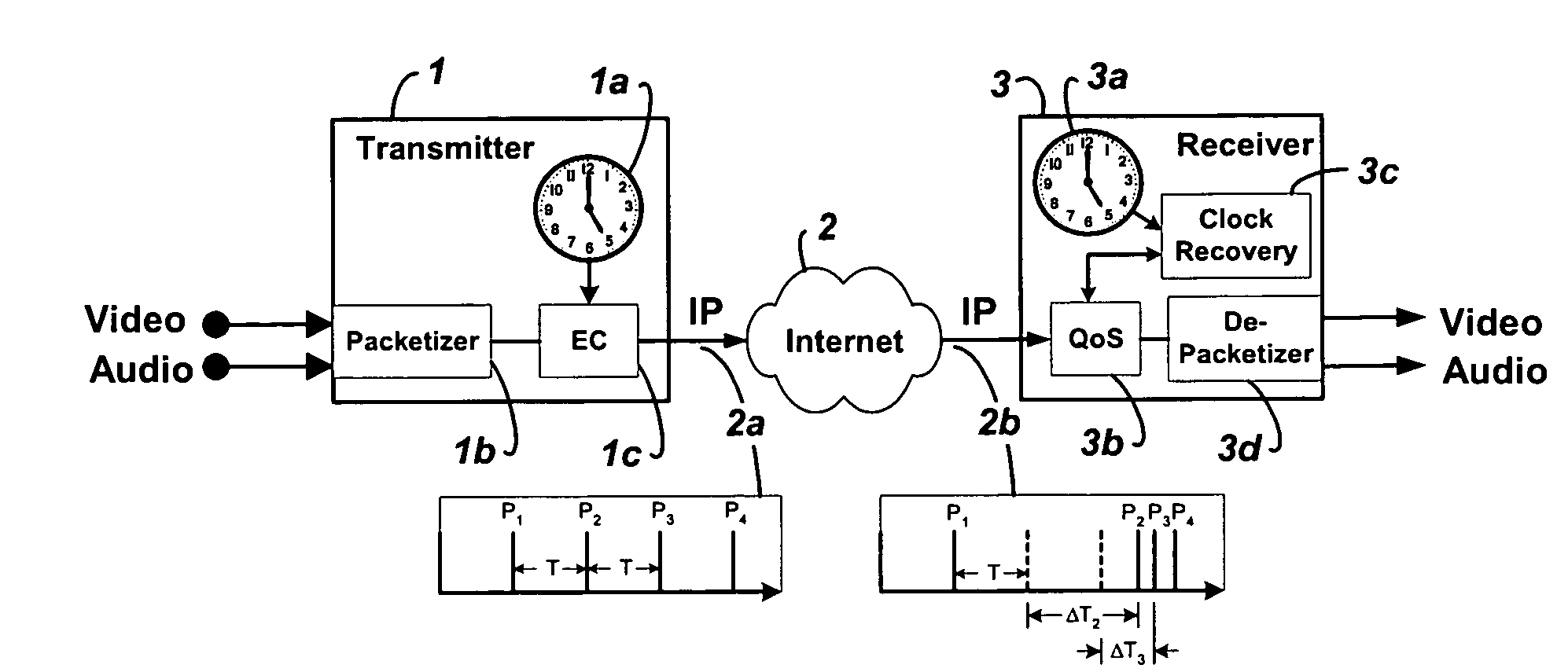

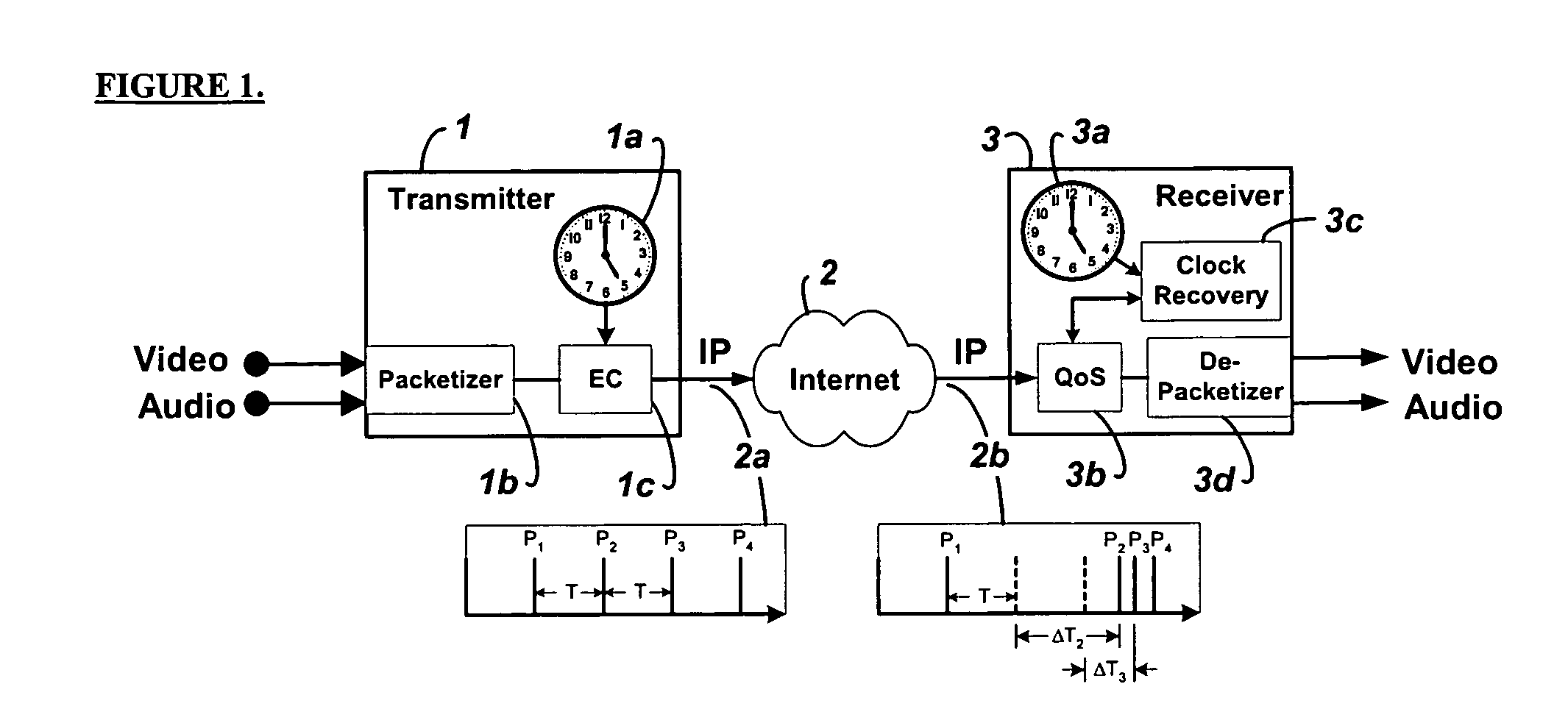

Embodiments of the invention enable the synchronization of clocks across packet switched networks, such as the Internet, sufficient to drive a jitter buffer and other quality-of-service related buffering. Packet time stamps referenced to a local clock create a phase offset signal. A shortest-delay offset generator uses a moving-window filter to select the samples of the phase offset signal having the shortest network propagation delay within the window. This shortest network propagation delay filter minimizes the effect of network jitter under the assumption that queuing delays account for most of the network jitter. The addition of this filtered phase offset signal to a free-running local clock creates a time reference that is synchronized to the remote clock at the source thus allowing for the transport of audio, video, and other time-sensitive real-time signals with minimal latency.

Owner:QVIDIUM TECH

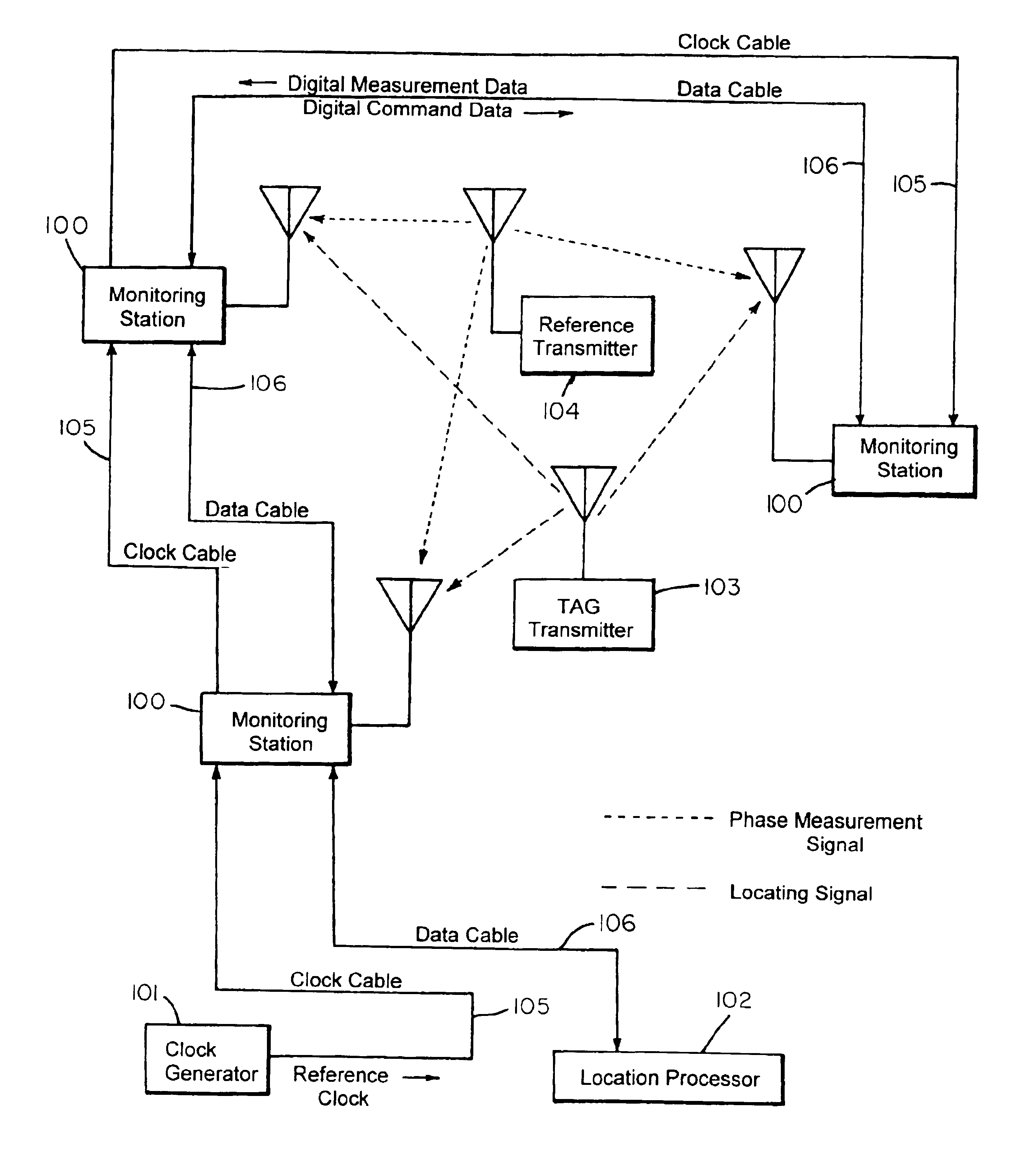

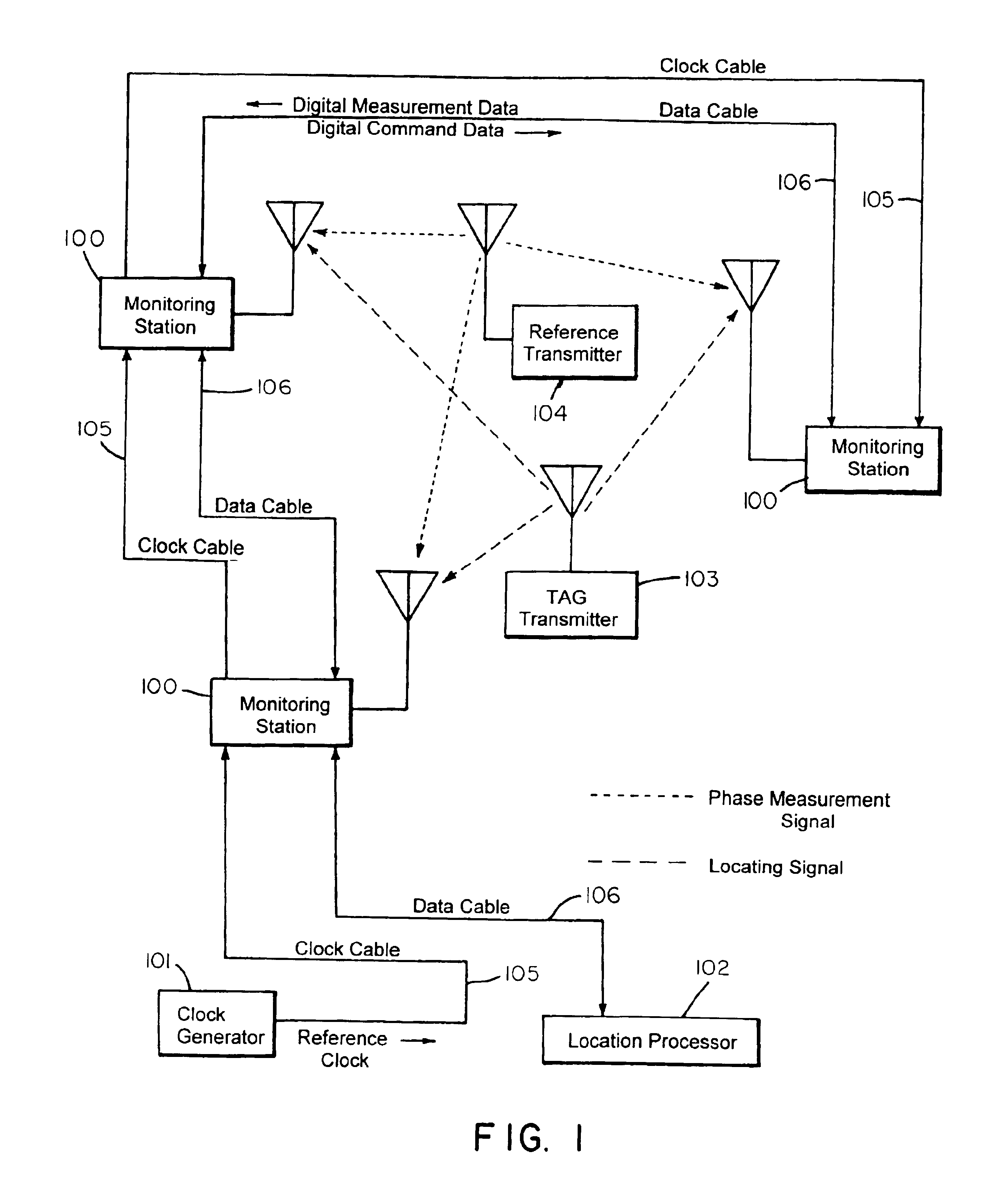

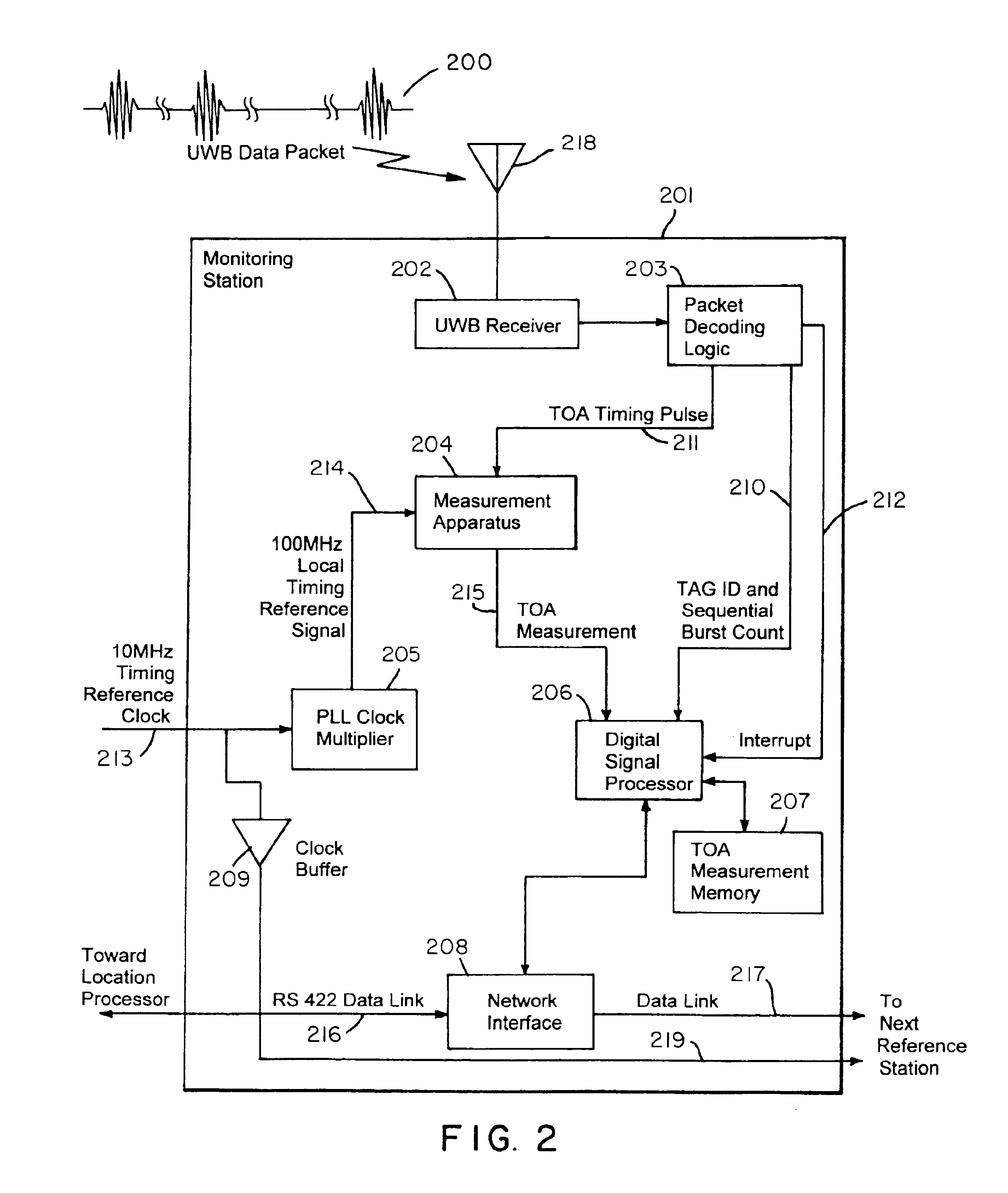

Object location system and method

InactiveUS6882315B2Highly accurate position measurementDirection finders using radio wavesPosition fixationFixed positionPositioning system

An RF object locating system and method that uses or includes a set of N (N>2) receivers (monitoring stations) located at fixed positions in and / or about a region to be monitored, one or more reference transmitters that transmit a timing reference, a location processor that determines object location based on time-of-arrival measurements, and at least one object having an untethered tag transmitter that transmits RF pulses, which may additionally include object ID or other information. Free-running counters in the monitoring stations, whose phase offsets are determined relative to a reference transmitter, are frequency-locked with a centralized reference clock. Time-of-arrival measurements made at the monitoring stations may be stored and held in a local memory until polled by the location processor. The invention permits rapid acquisition of tag transmissions thereby enabling the monitoring of large numbers of objects, and also provides a unique approach to data correlation in severe multipath environments.

Owner:ZEBRA TECH CORP

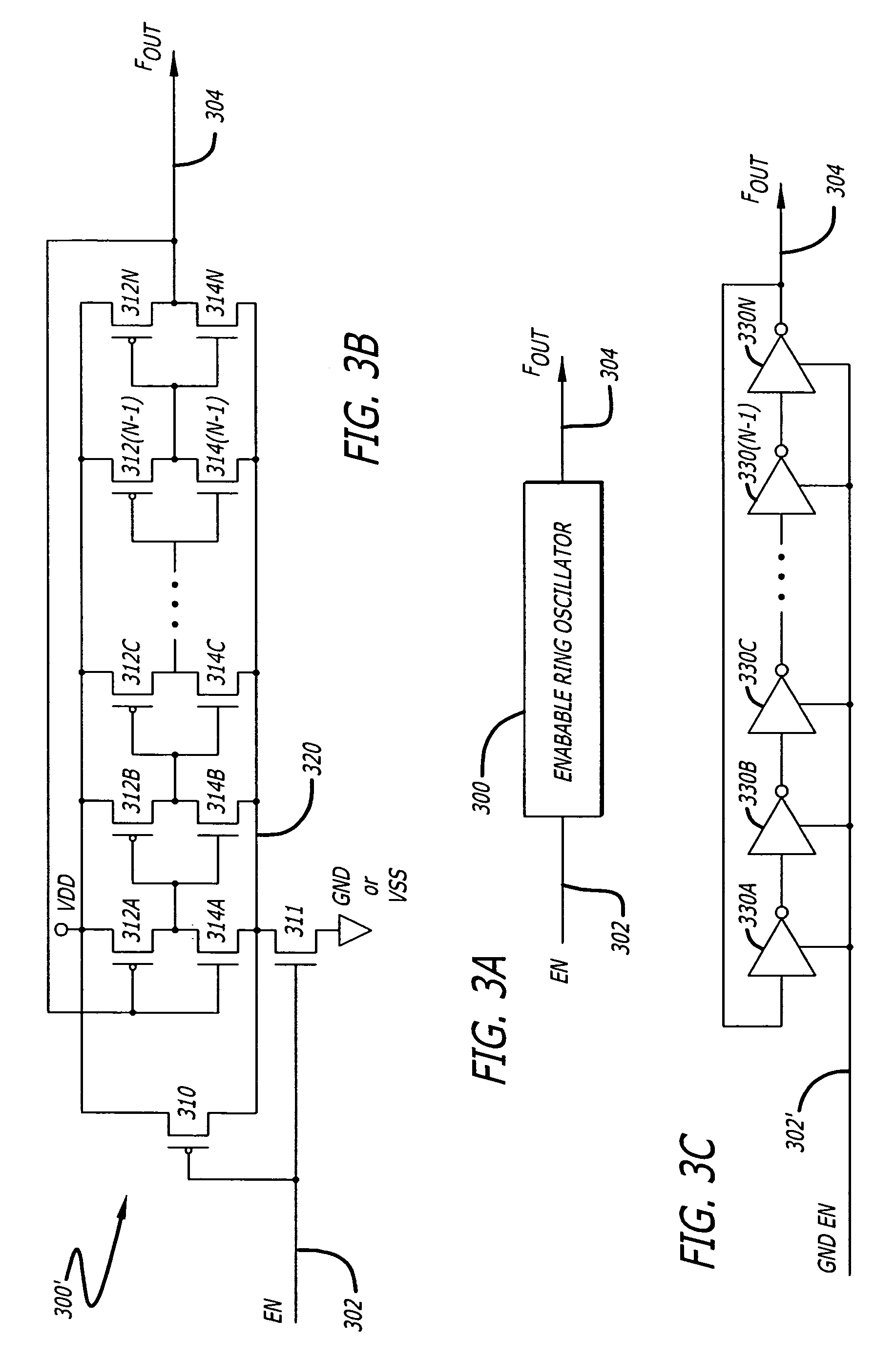

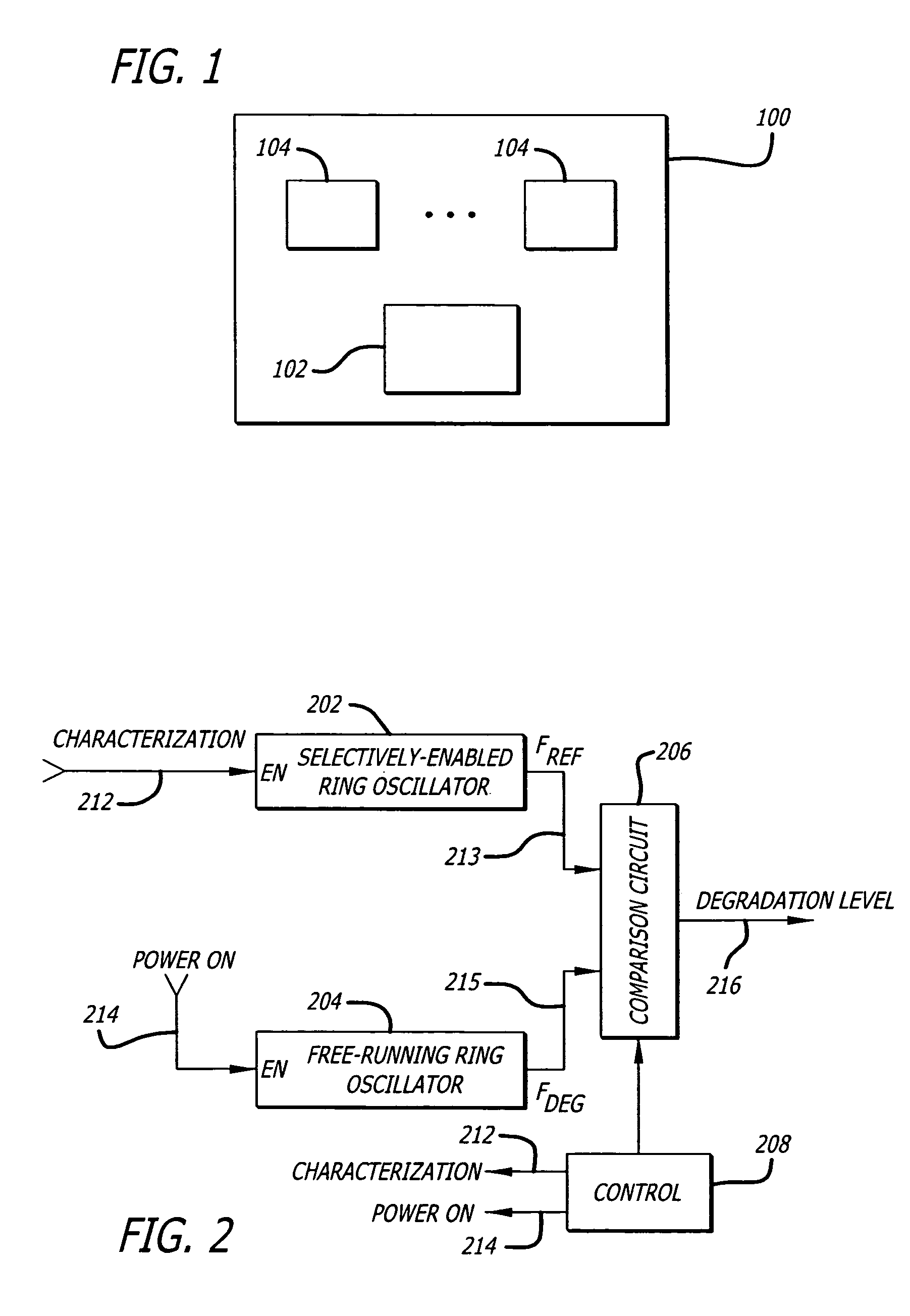

On-chip transistor degradation monitoring

InactiveUS20050134394A1Digital circuit testingPulse generation by logic circuitsEngineeringRing oscillator

Embodiments of the invention include on-chip characterization of transistor degradation. In one embodiment, includes one or more functional blocks to perform one or more functions and an integrated on-chip characterization circuit to perform on-chip characterization of transistor degradation. The integrated on-chip characterization circuit includes a selectively enabled ring oscillator to generate a reference oscillating signal, a free-running ring oscillator to generate a free-running oscillating signal, and a comparison circuit coupled to the selectively enabled ring oscillator and the free-running ring oscillator. From the reference oscillating signal and the free-running oscillating signal, the comparison circuit determine a measure of transistor degradation.

Owner:INTEL CORP

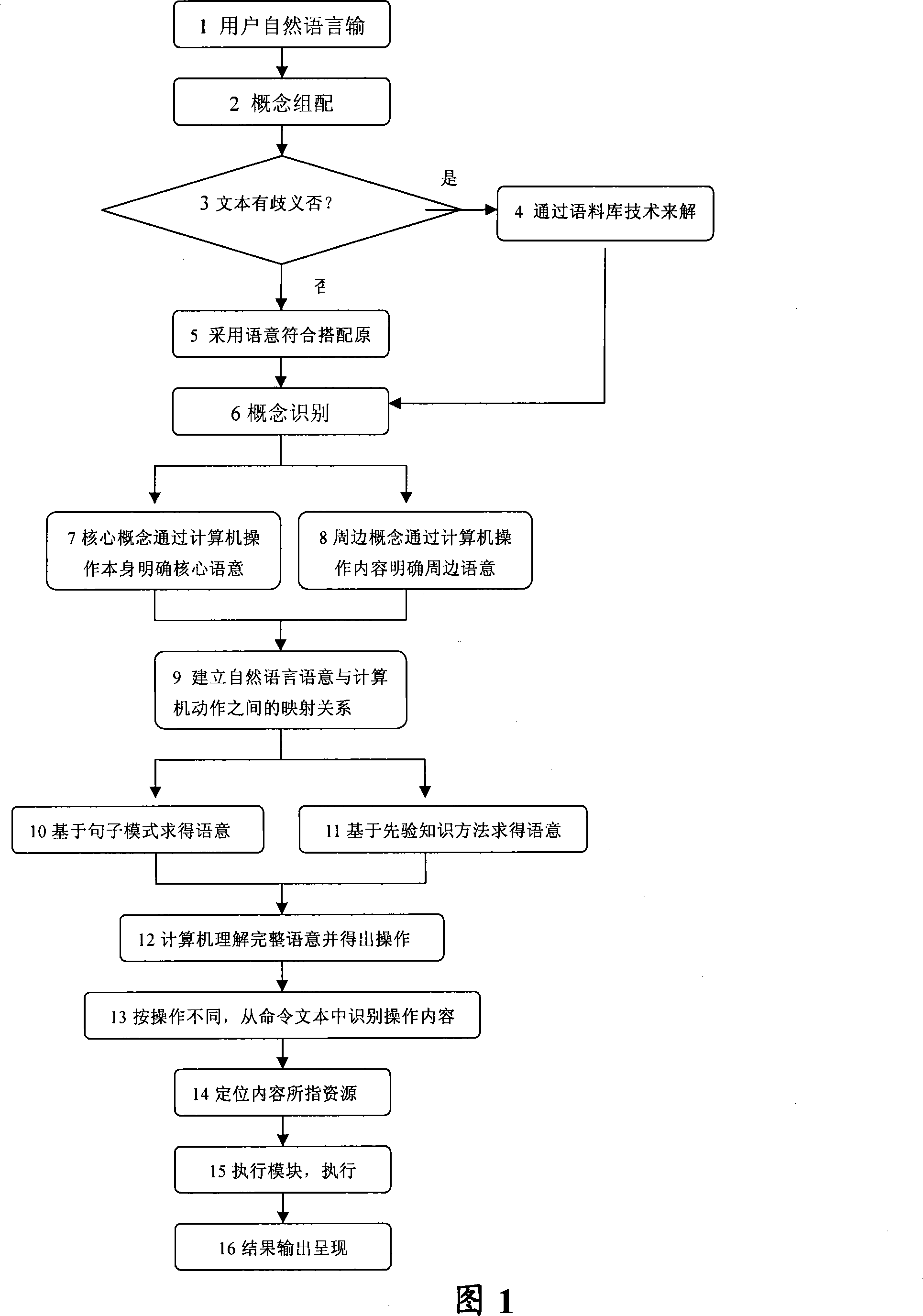

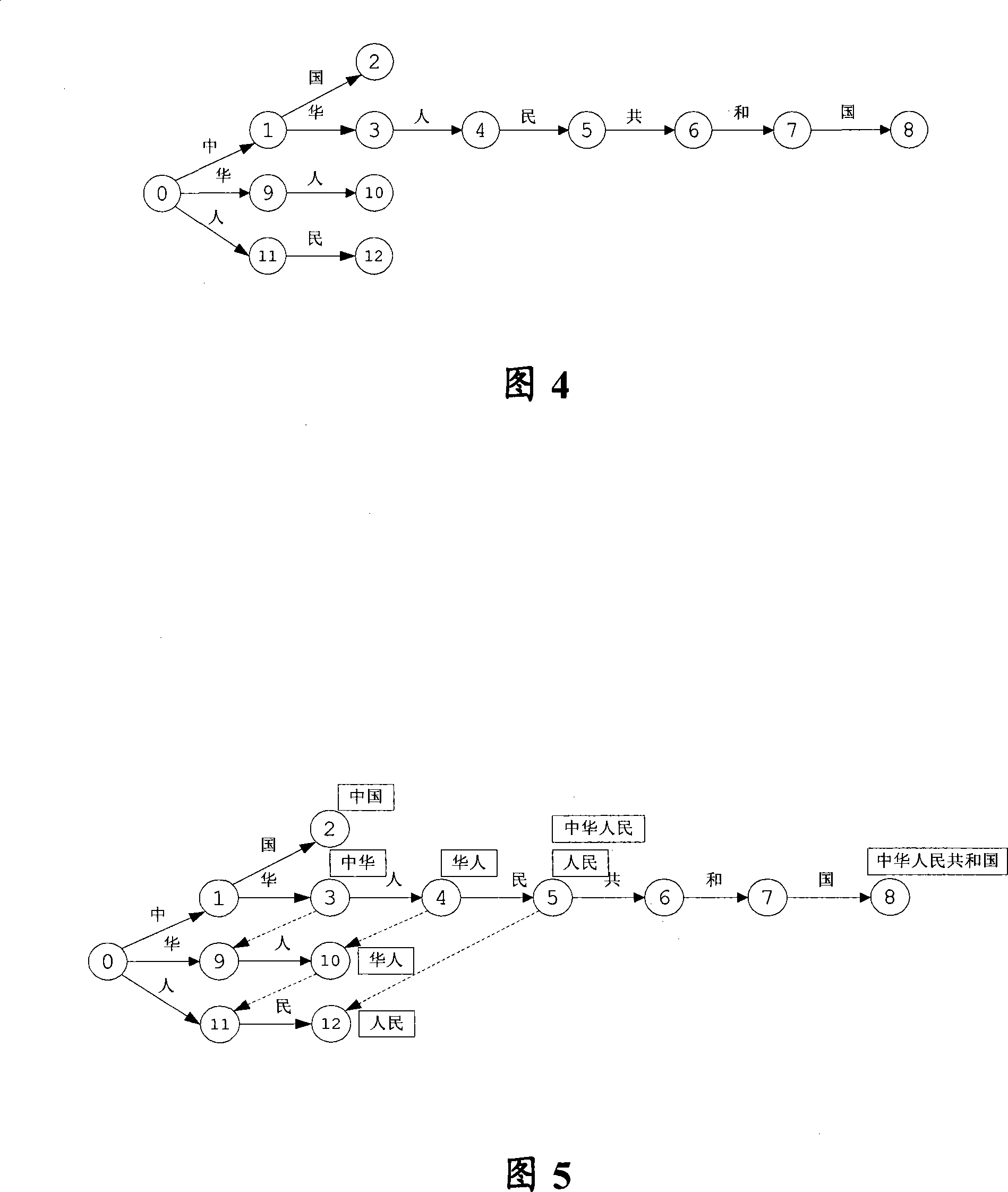

Free-running speech comprehend method and man-machine interactive intelligent system

InactiveCN101178705AEasy to understandCorrect answerSpeech recognitionSpecial data processing applicationsNatural language understandingAmbiguity

The invention discloses natural language understanding method, comprising the steps that: a natural language is matched with a conceptual language symbol after receiving the natural language input by the customer, and then a conception is associated with the conceptual language symbol; a conception which is most suitable to the current language content is selected by being compared with the preset conception dictionary, and then whether the conception is ambiguous is judged; and if the answer is YES, the conception is obtained by a language data base, entering the next step; and if the answer is NO, the conception is obtained based on the principle of language content matched, entering to the next step; a core conception and a sub conception are obtained by a conception reorganization, wherein, the core language meaning of the core conception is defined by an operation of the computer while the sub language meaning of the sub conception is defined by the operation content of the computer; and the complete language meaning is obtained by combining the core language meaning with the sub language meaning. The invention also provides a human-computer interaction intelligent system based on the method provided by the invention. The invention recognizes the natural sound input by the customer more accurately, thereby providing the customer with more intelligent and perfect services.

Owner:CHINA TELECOM CORP LTD

On-chip transistor degradation monitoring

InactiveUS7205854B2Digital circuit testingPulse generation by logic circuitsEngineeringSelf excited oscillation

Embodiments of the invention include on-chip characterization of transistor degradation. In one embodiment, includes one or more functional blocks to perform one or more functions and an integrated on-chip characterization circuit to perform on-chip characterization of transistor degradation. The integrated on-chip characterization circuit includes a selectively enabled ring oscillator to generate a reference oscillating signal, a free-running ring oscillator to generate a free-running oscillating signal, and a comparison circuit coupled to the selectively enabled ring oscillator and the free-running ring oscillator. From the reference oscillating signal and the free-running oscillating signal, the comparison circuit determine a measure of transistor degradation.

Owner:INTEL CORP

Random number generator and method for generating random numbers

InactiveUS20060069706A1AutocorrelationReduced sampling rate requirementsRandom number generatorsSecuring communicationNumber generatorComputer science

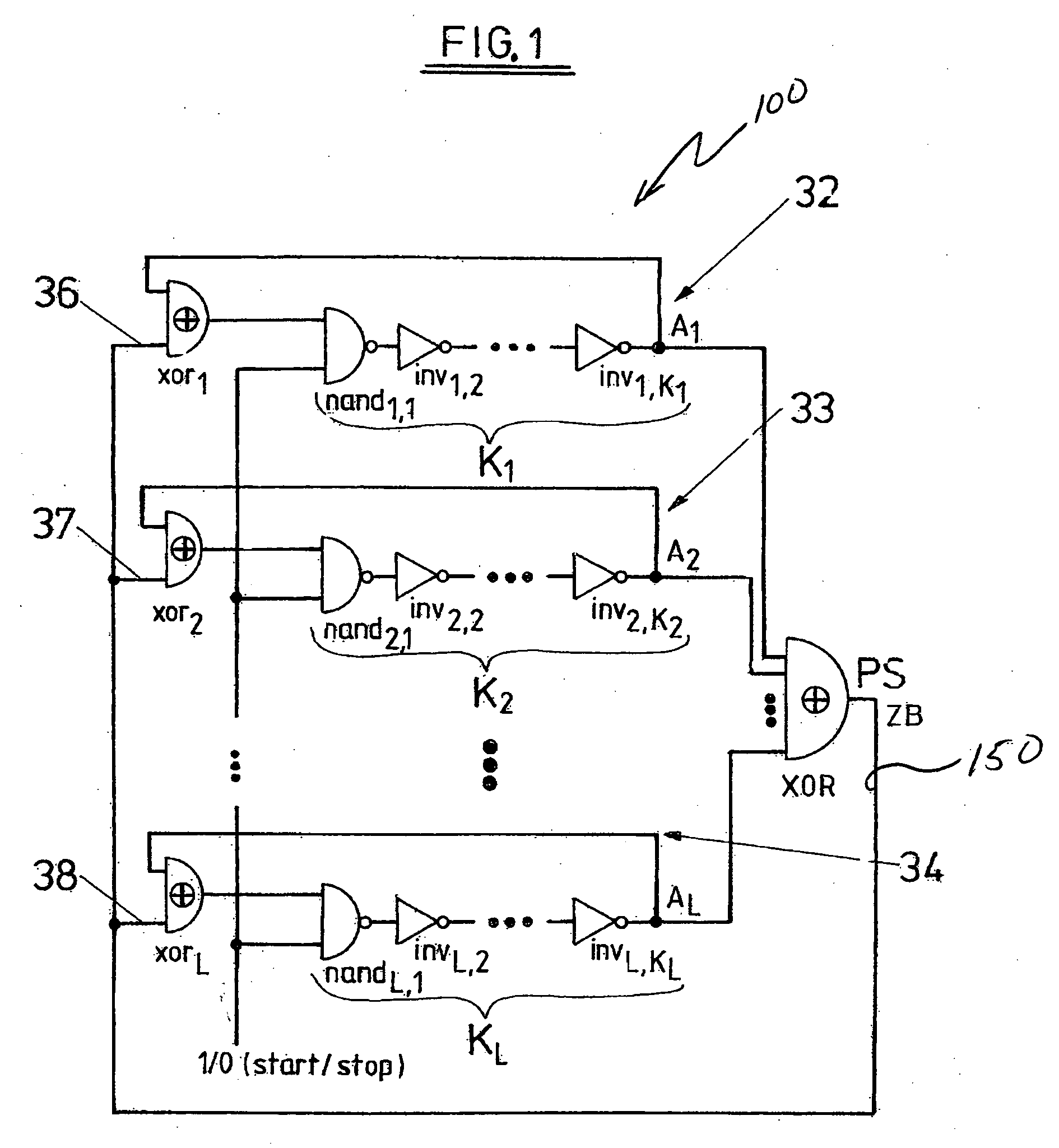

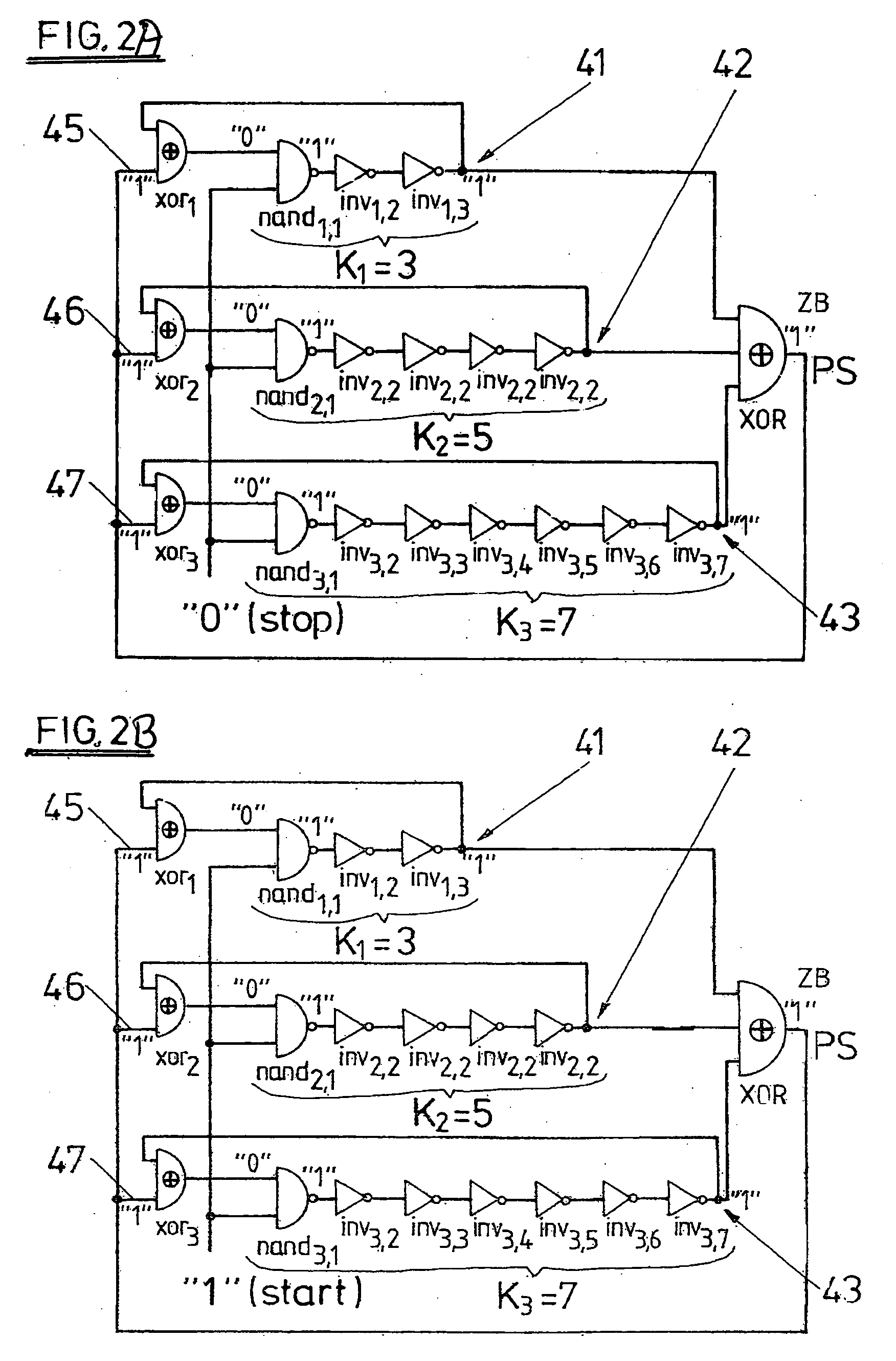

The invention relates to a method for generating random numbers in which oscillating digital output signals (A1, A2, . . . , AL) of unequal or equal periodicity are generated by at least two ring oscillators (32, 33, 34), an external parity signal (PS) representing a logical state (“0,”“1”) being generated when an odd number of the output signals (A1, A2, . . . , AL) take on a specified logical state (“1”). According to the invention, the external parity signal (PS) is fed back to an external parity input (36, 37, 38) of each of the respective ring oscillators (32, 33, 34). The invention further relates to a random number generator having at least two ring oscillators (32, 33, 34), made up in particular of independently free-running inverter chains with feedback having an odd number (K) of series-connected inverters (inv1,2, inv2,1, inv3,1, . . . , invi,j, . . . , invL,KL) that generate oscillating digital output signals (A1, A2, . . . , AL) of unequal or equal periodicity, and having first parity signal generating means (XOR) that generate an external parity signal (PS) representing a logical state (“0,”“1”) when an odd number of the output signals (A1, A2, . . . , AL) take on a specified logical state (“1”). According to the invention, there are feedback means (xor1, xor2, xor3, xor4, . . . , xorL) that feed back the external parity signal (PS) to an external parity input (36, 37, 38) of each of the respective ring oscillators (32, 33, 34). In this invention the cooperation of chaotic dynamics (feedback of the parity signal) and true randomness (jitter due to thermal noise) in digital circuits, a novel theoretical principle for generating random numbers, has been made into an efficient practical solution.

Owner:TDK MICRONAS GMBH

System and method for clock synchronization over packet-switched networks

ActiveUS7551647B2Improve abilitiesEasy to replaceTime-division multiplexData switching by path configurationQuality of serviceThe Internet

Embodiments of the invention enable the synchronization of clocks across packet switched networks, such as the Internet, sufficient to drive a jitter buffer and other quality-of-service related buffering. Packet time stamps referenced to a local clock create a phase offset signal. A shortest-delay offset generator uses a moving-window filter to select the samples of the phase offset signal having the shortest network propagation delay within the window. This shortest network propagation delay filter minimizes the effect of network jitter under the assumption that queuing delays account for most of the network jitter. The addition of this filtered phase offset signal to a free-running local clock creates a time reference that is synchronized to the remote clock at the source thus allowing for the transport of audio, video, and other time-sensitive real-time signals with minimal latency.

Owner:QVIDIUM TECH

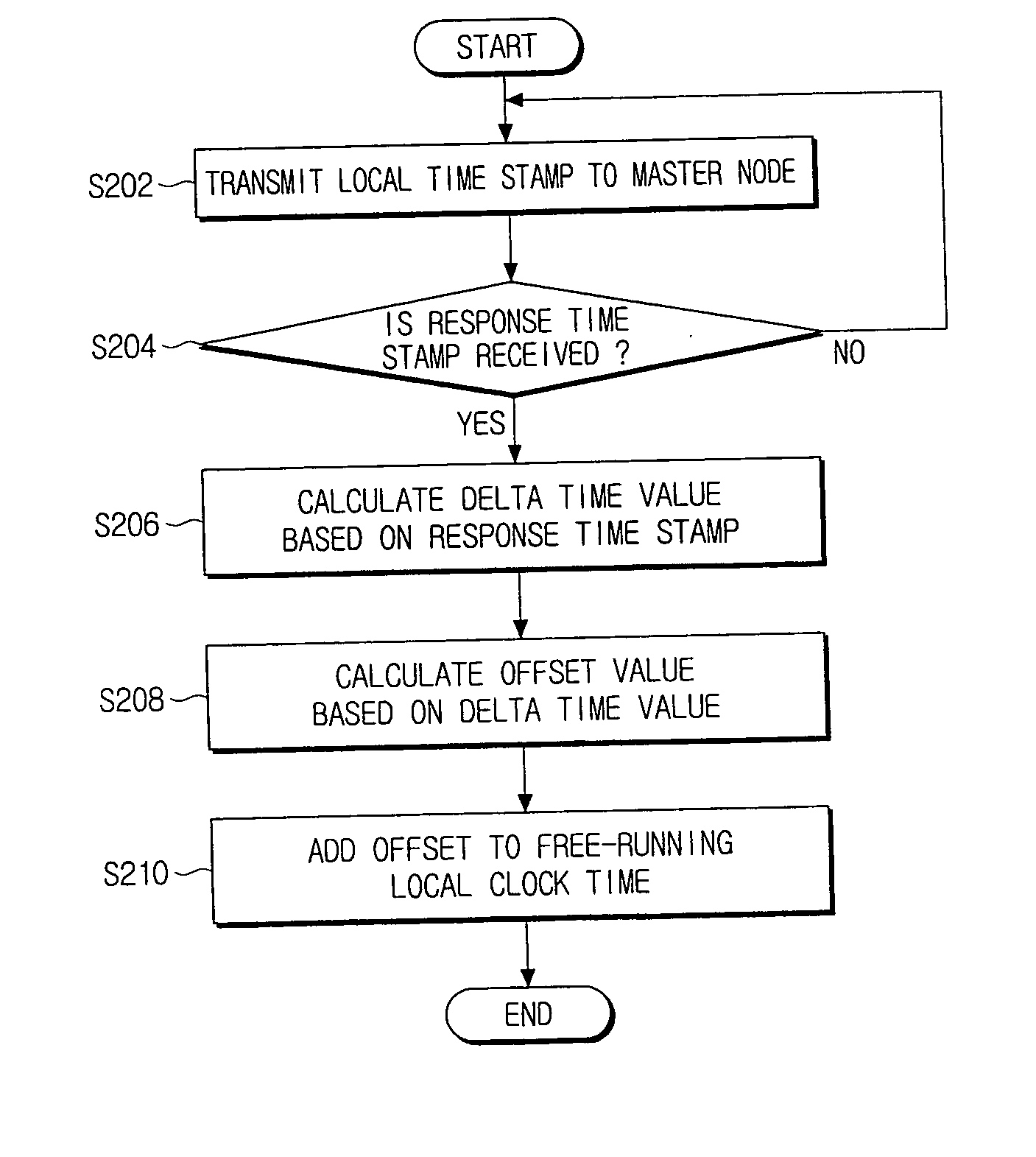

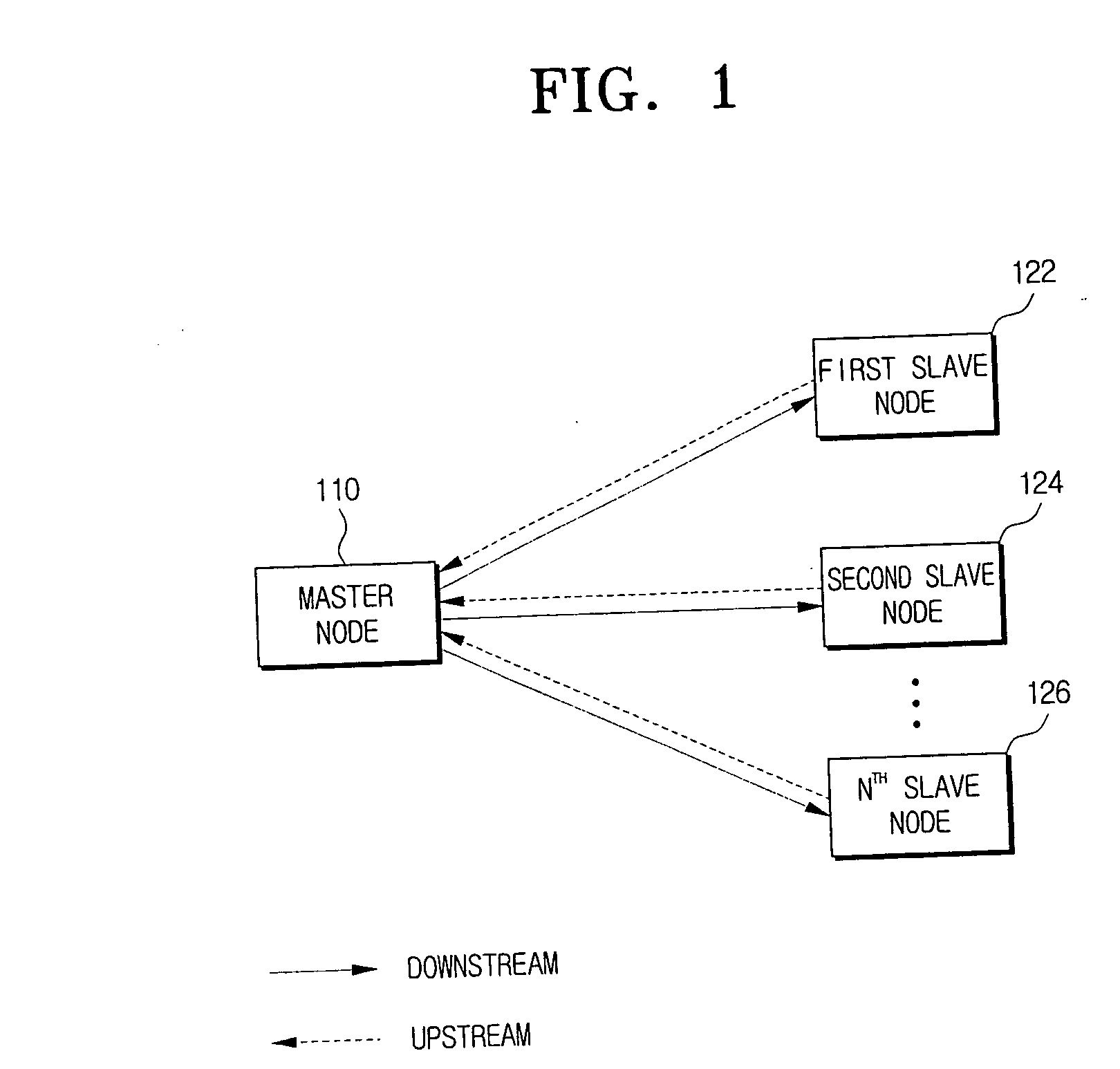

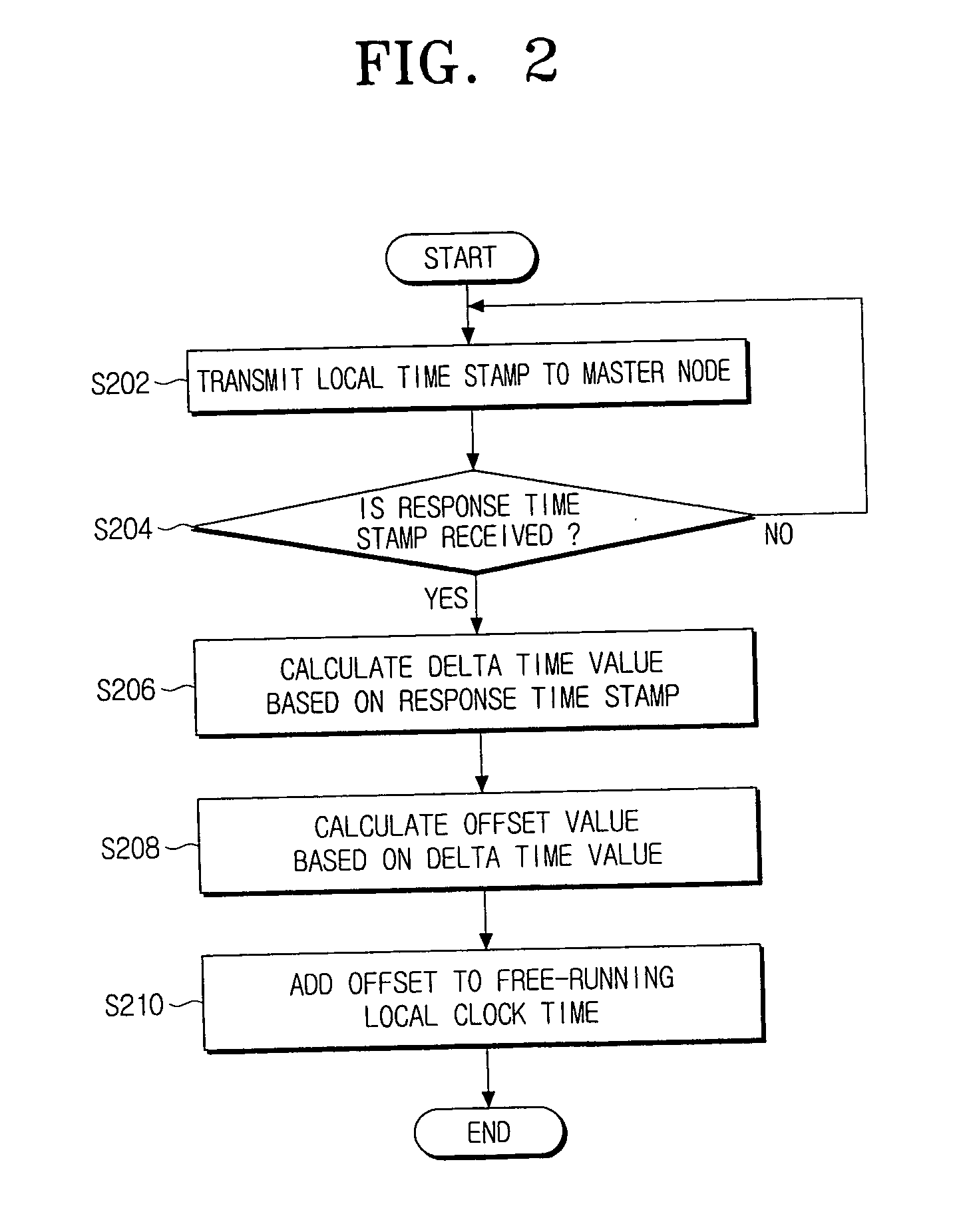

Time synchronizing method and apparatus based on time stamp

InactiveUS20070025481A1Shorten the timeIncrease blockingTime-division multiplexSynchronising arrangementClock timeClock rate

Provided are a time synchronizing method and apparatus based on a time stamp. The time synchronizing method includes: transmitting a local time stamp based on a free-running local clock to a master node; receiving a response time stamp from the master node; calculating a delta time value based on the response time stamp; filtering the delta-time using a digital low pass filter running at the free-running local clock rate; and adjusting a local clock time based on the filtered delta time value.

Owner:SAMSUNG ELECTRONICS CO LTD

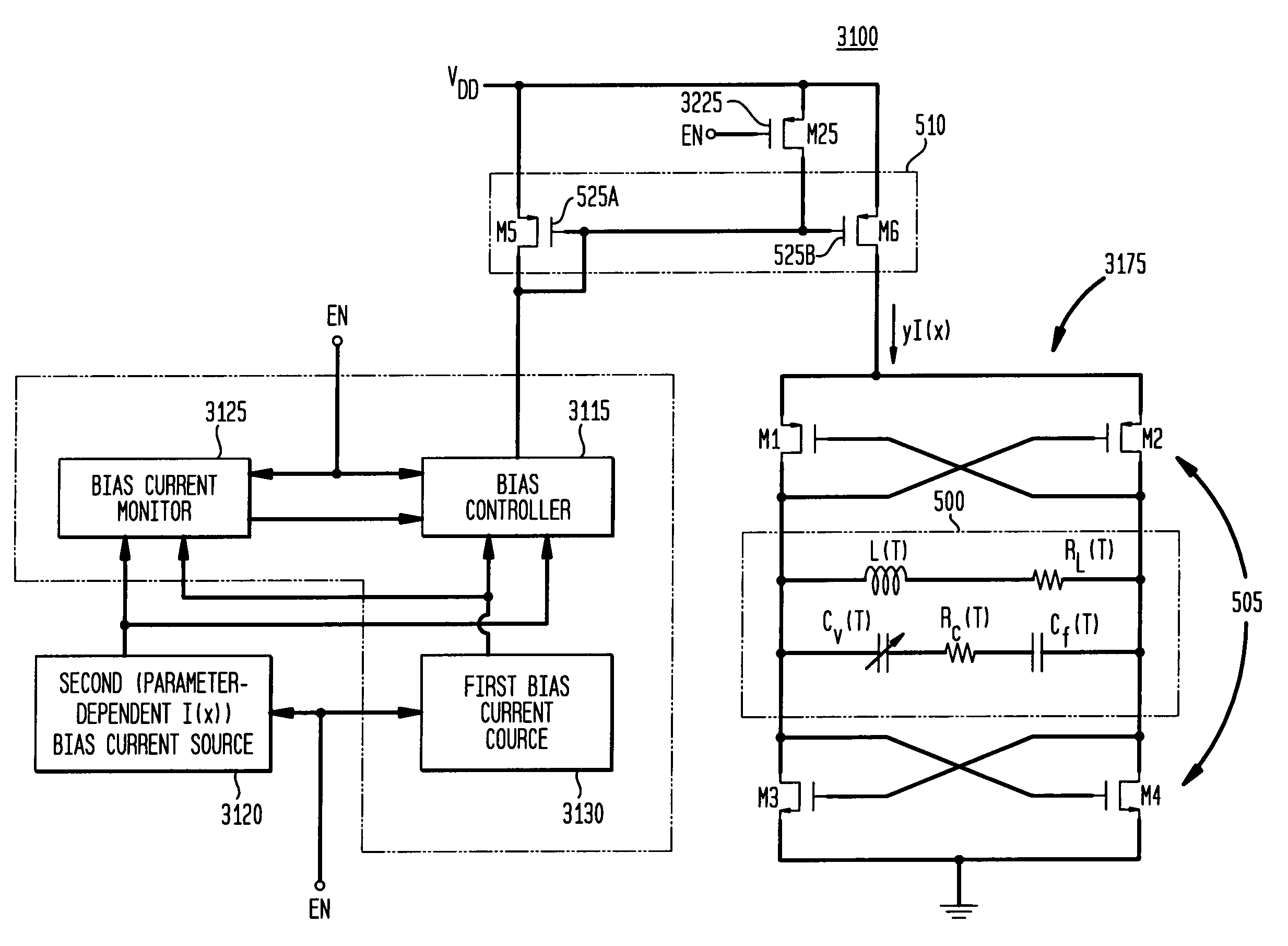

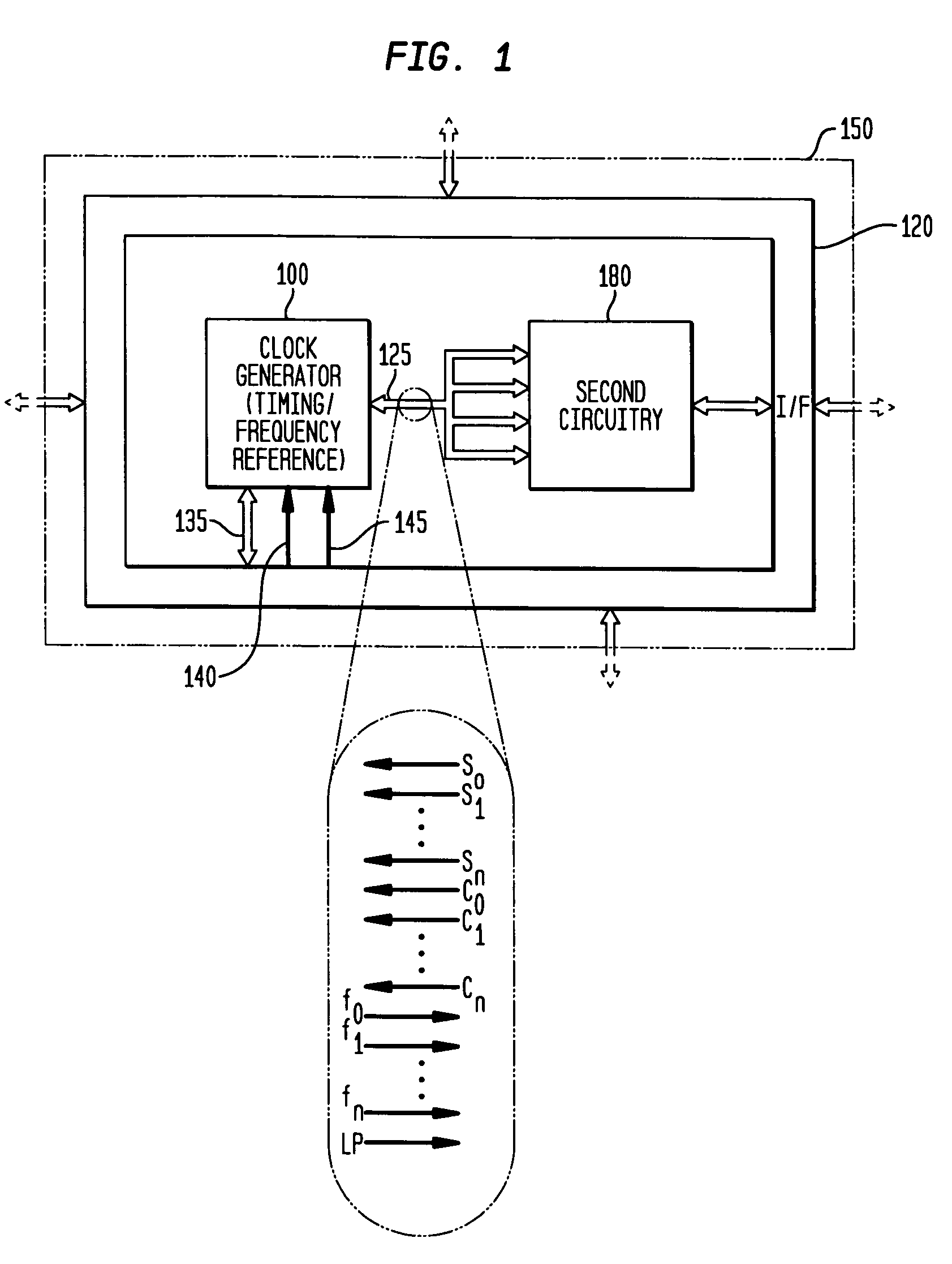

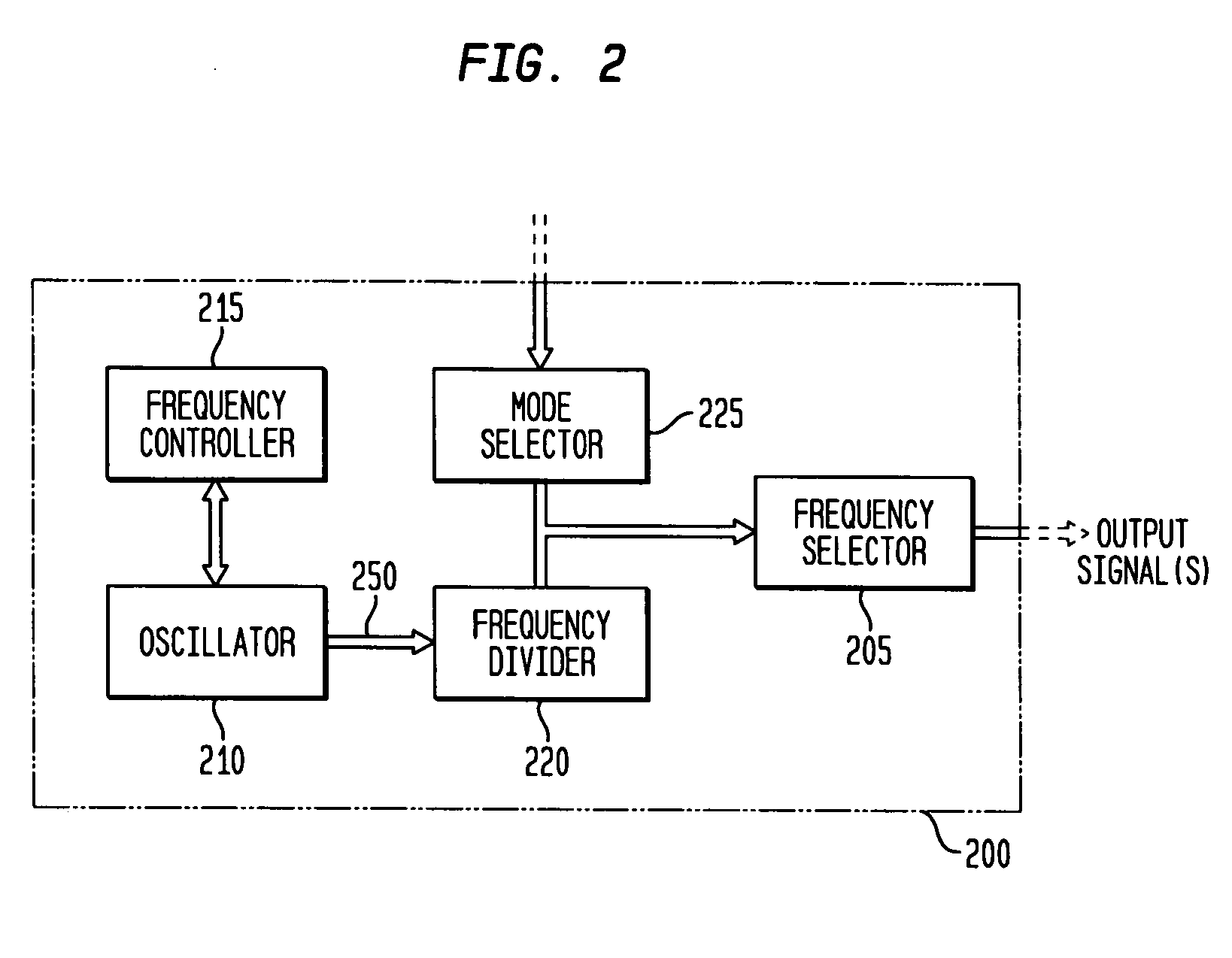

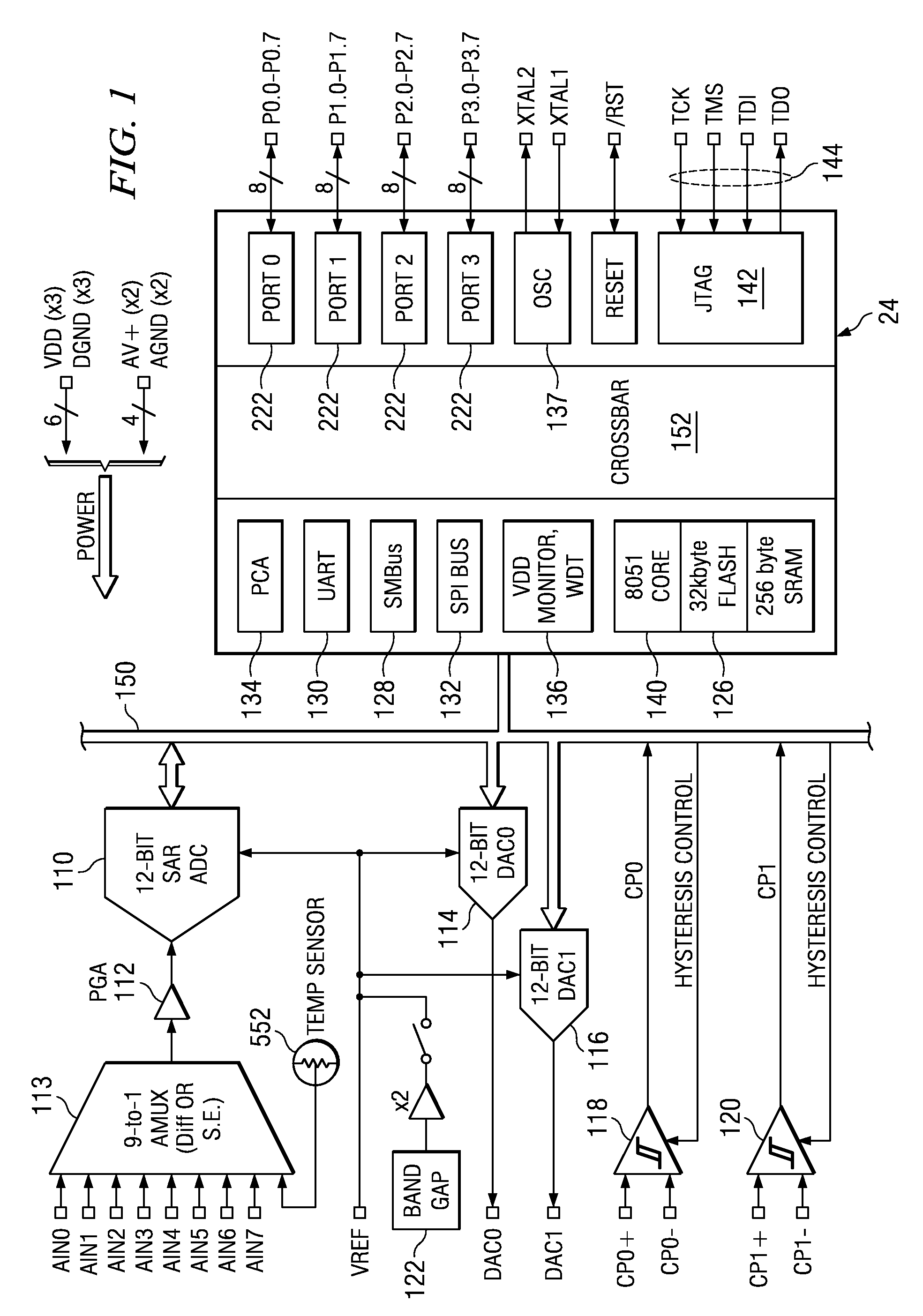

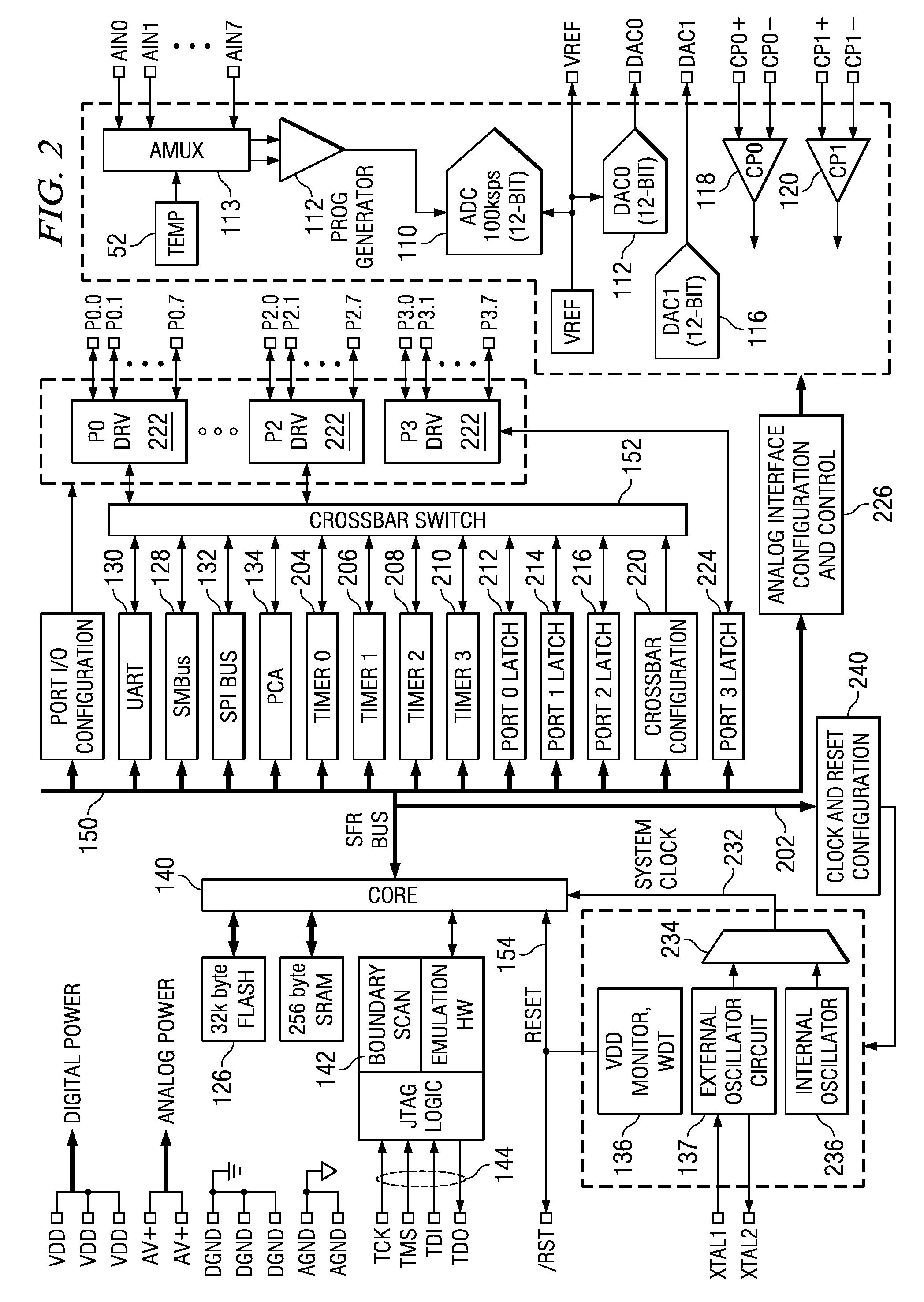

Low-latency start-up for a monolithic clock generator and timing/frequency reference

ActiveUS7307486B2High frequencyLoud noiseAngle modulation by variable impedenceResonant circuit tuningMicrocontrollerVoltage generator

An apparatus, system and method are provided for low-latency start-up of a free-running harmonic oscillator. The exemplary apparatus embodiment comprises a first and second current sources to generate first and second currents; a bias current monitor adapted to detect a magnitude of the second current and to provide a control signal when the magnitude of the second current is equal to or greater than a predetermined magnitude; and a bias controller adapted to switch the first current from the oscillator and to switch the second current to the oscillator in response to the control signal. a reference voltage generator, a comparator, and a bias controller. Exemplary embodiments include reference voltage generator, a comparator, and a bias controller.

Owner:INTEGRATED DEVICE TECH INC

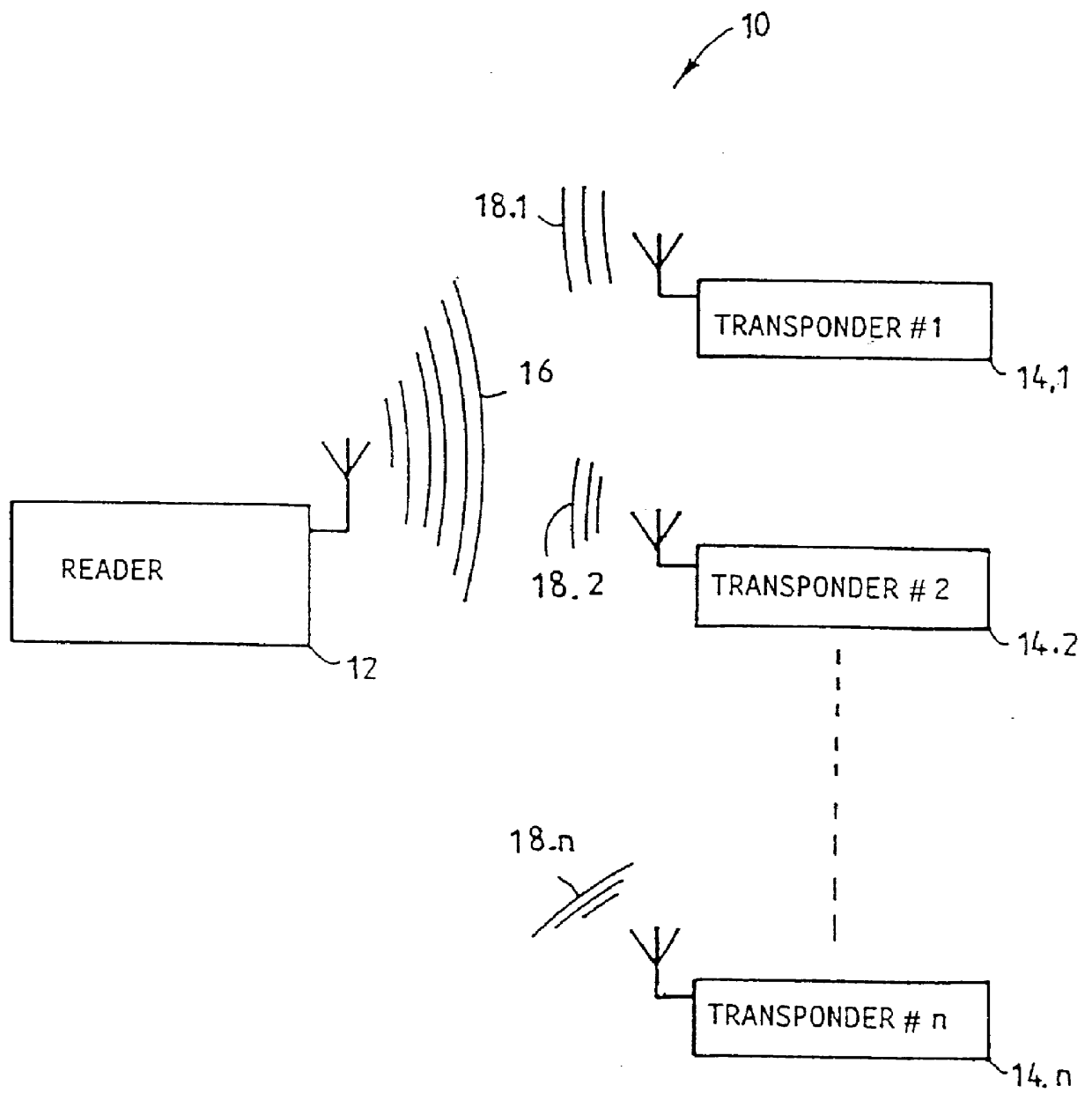

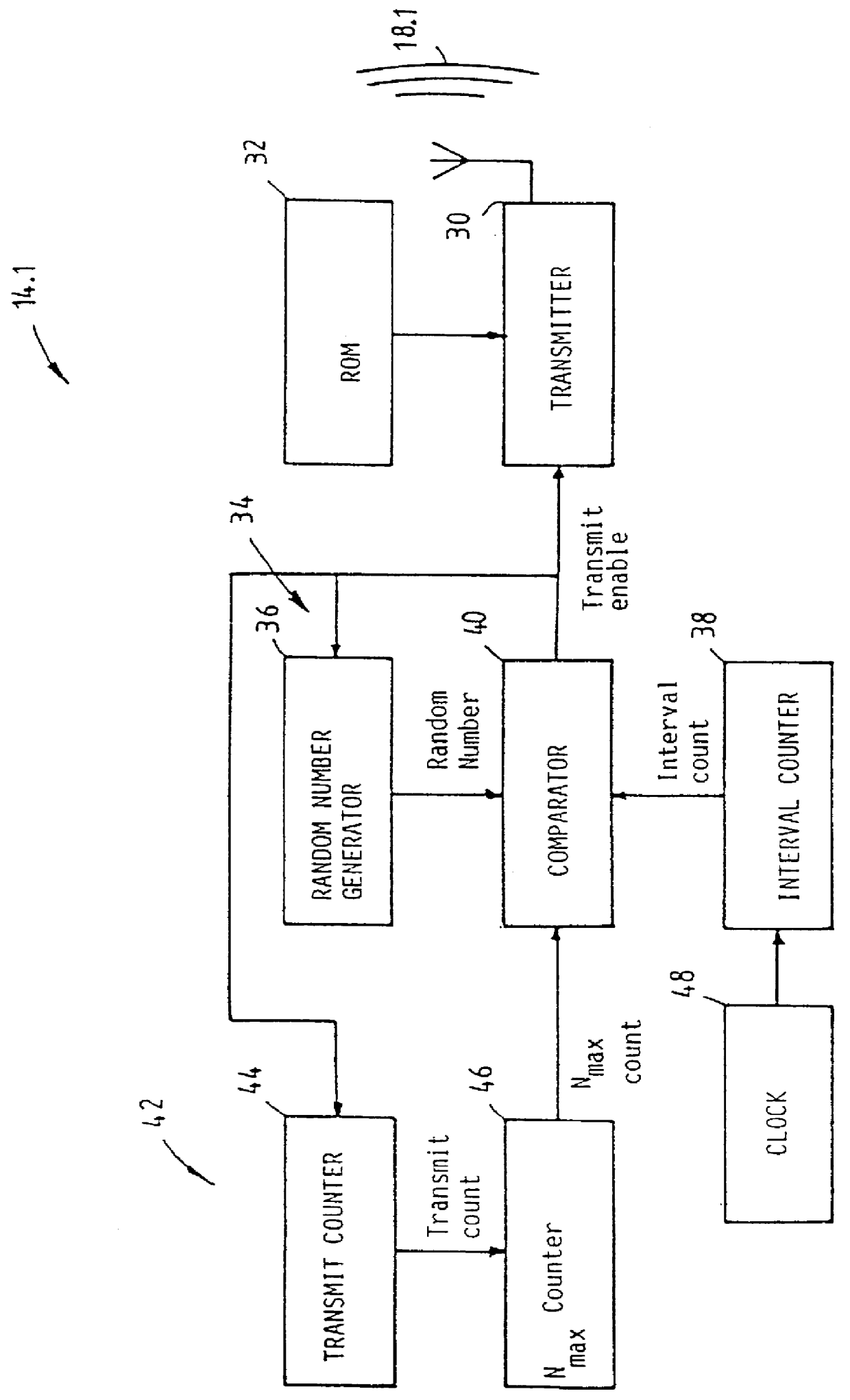

Free running RF identification system with increasing average inter transmission intervals

InactiveUS6154136ARaise countMemory record carrier reading problemsSubscribers indirect connectionElectronic identificationContinuous signal

An RF electronic identification system 10 is disclosed and claimed. The system includes a reader 12 and a plurality of transponders 14.1 to 14.n. When energized by an interrogation signal from the reader, each transponder automatically responds by repeatedly retransmitting a signal burst including identification code data associated with the relevant transponder. Each transponder includes circuitry 34 for generating random inter-transmission intervals for separating any two consecutive signal bursts and a controller 42 for the generation circuitry, to cause an average value of the inter-transmission intervals over a period of time to vary, preferably to increase. This feature enhances the probability and speed of reading a transponder population of almost any size.

Owner:ACTIVE NETWORK LLC

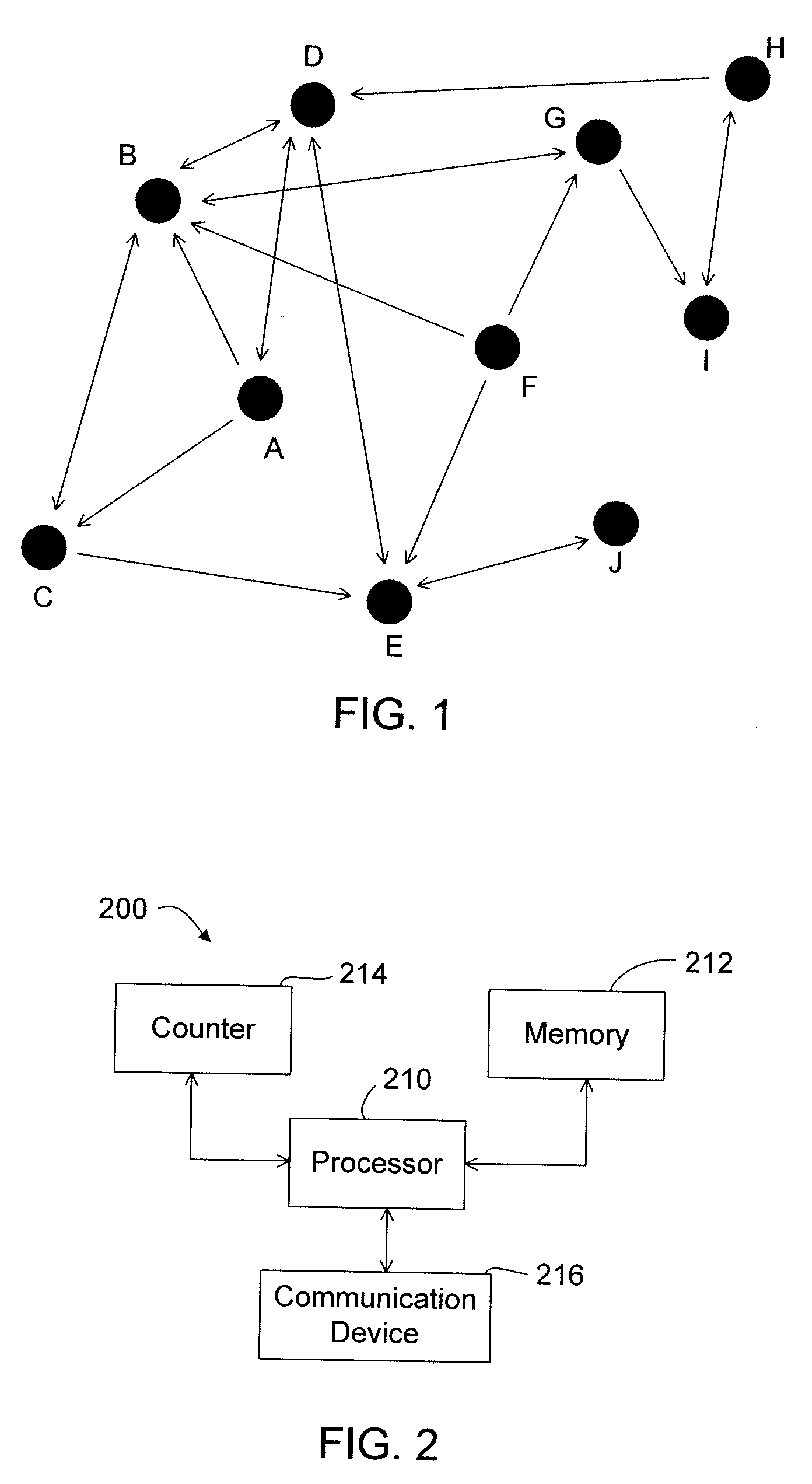

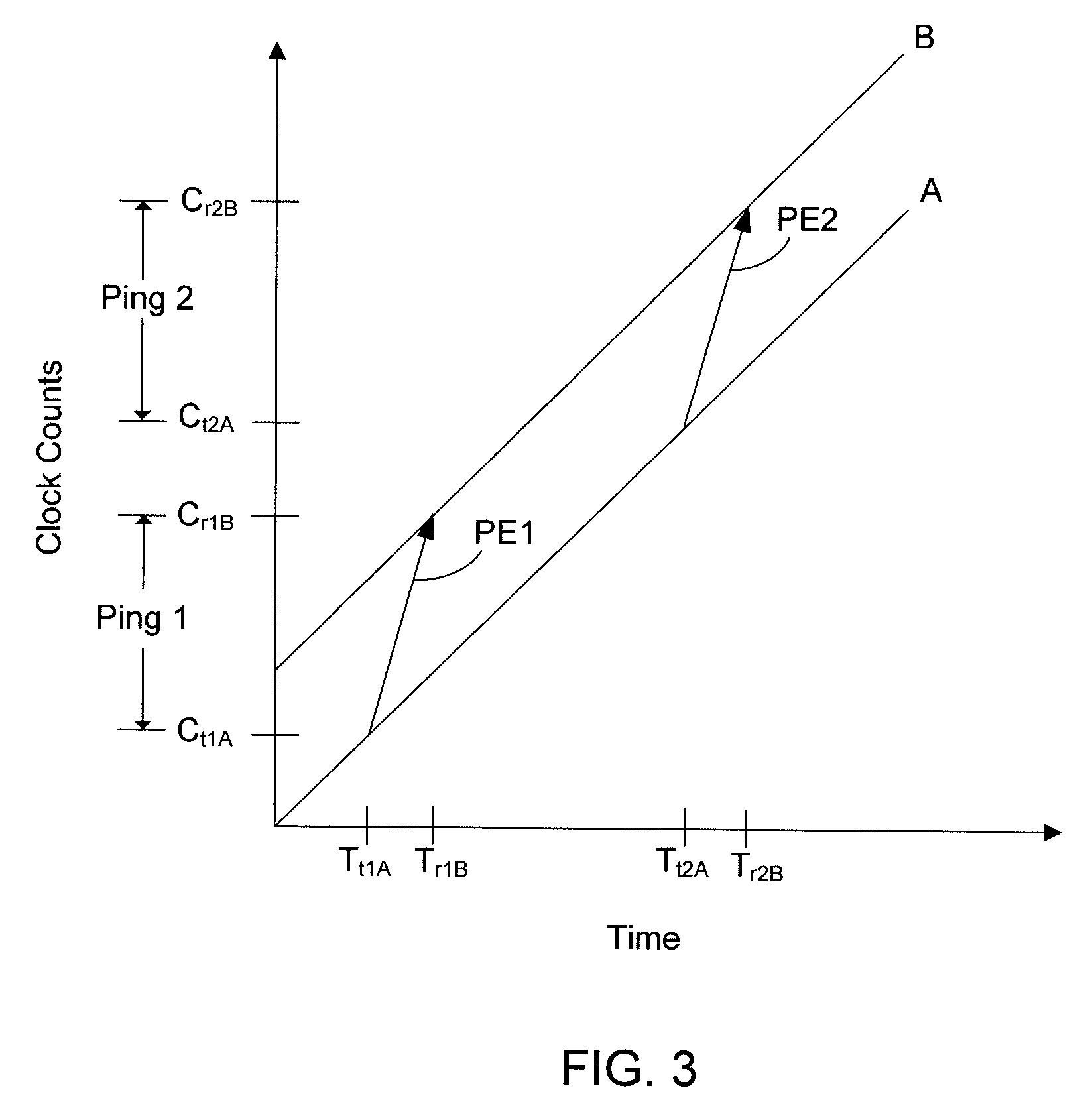

Systems and methods for space-time determinations with reduced network traffic

InactiveUS20100202300A1Direction finders using radio wavesError preventionSystem timeNavigation system

Space-time solutions are determined by exchanging pings among nodes in a network. Each ping includes a current space-time state of the transmitting node, which includes the transmitting node's currently estimated location and corrected time (as a count stamp). A particular node in the network receives pings from the other nodes in the network and uses the data in the received pings to estimate its own current position and to correct its own free-running clock relative to a common system time. As a service to the network, the particular node then transmits its corrected time (as a count stamp) and estimated position to the other nodes. In some embodiments, the space-time solutions discussed herein are used as backup to other navigation systems, such as the Automatic Dependent Surveillance-Broadcast (ADS-B) system.

Owner:DIGIMARC CORP

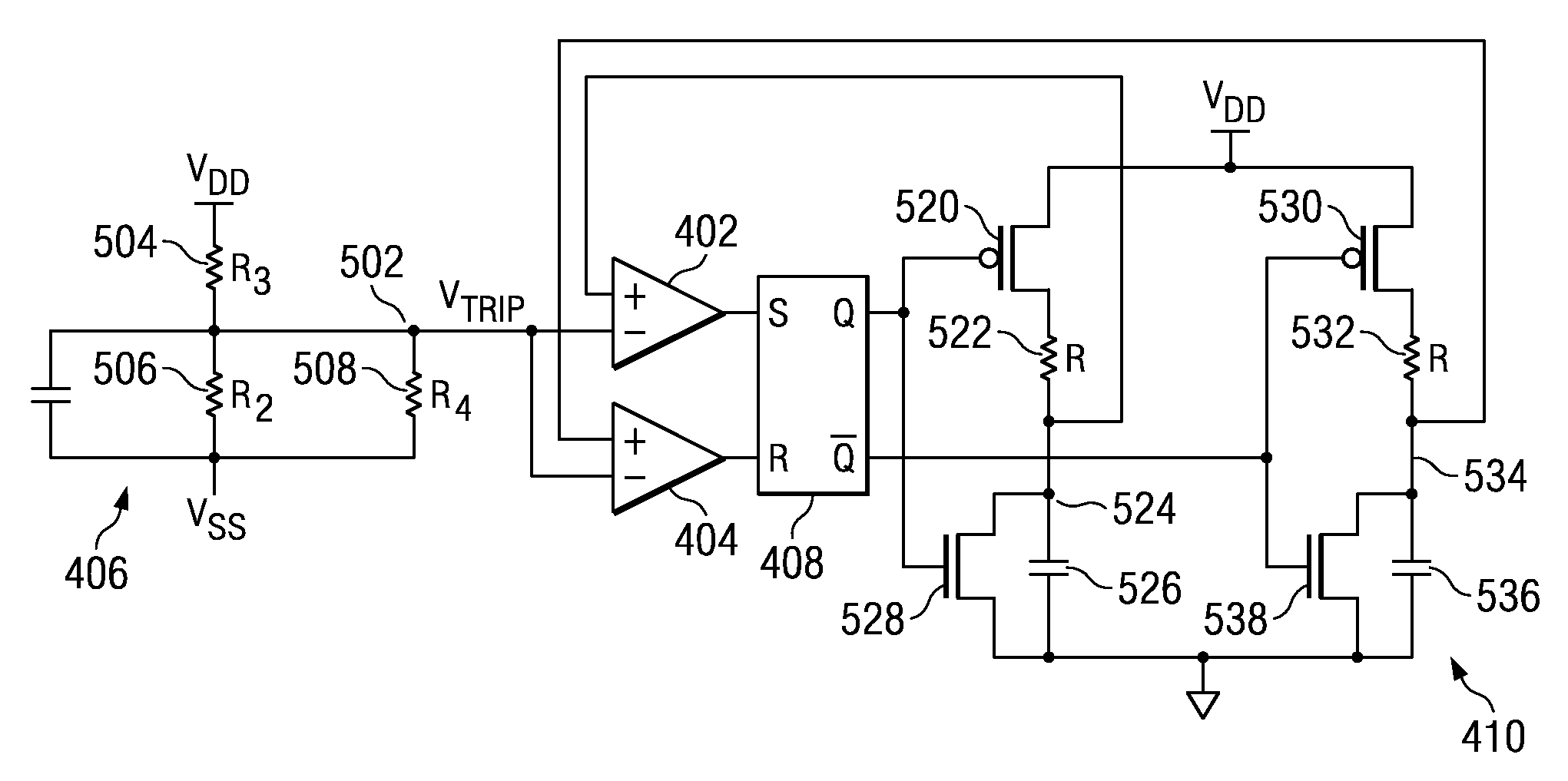

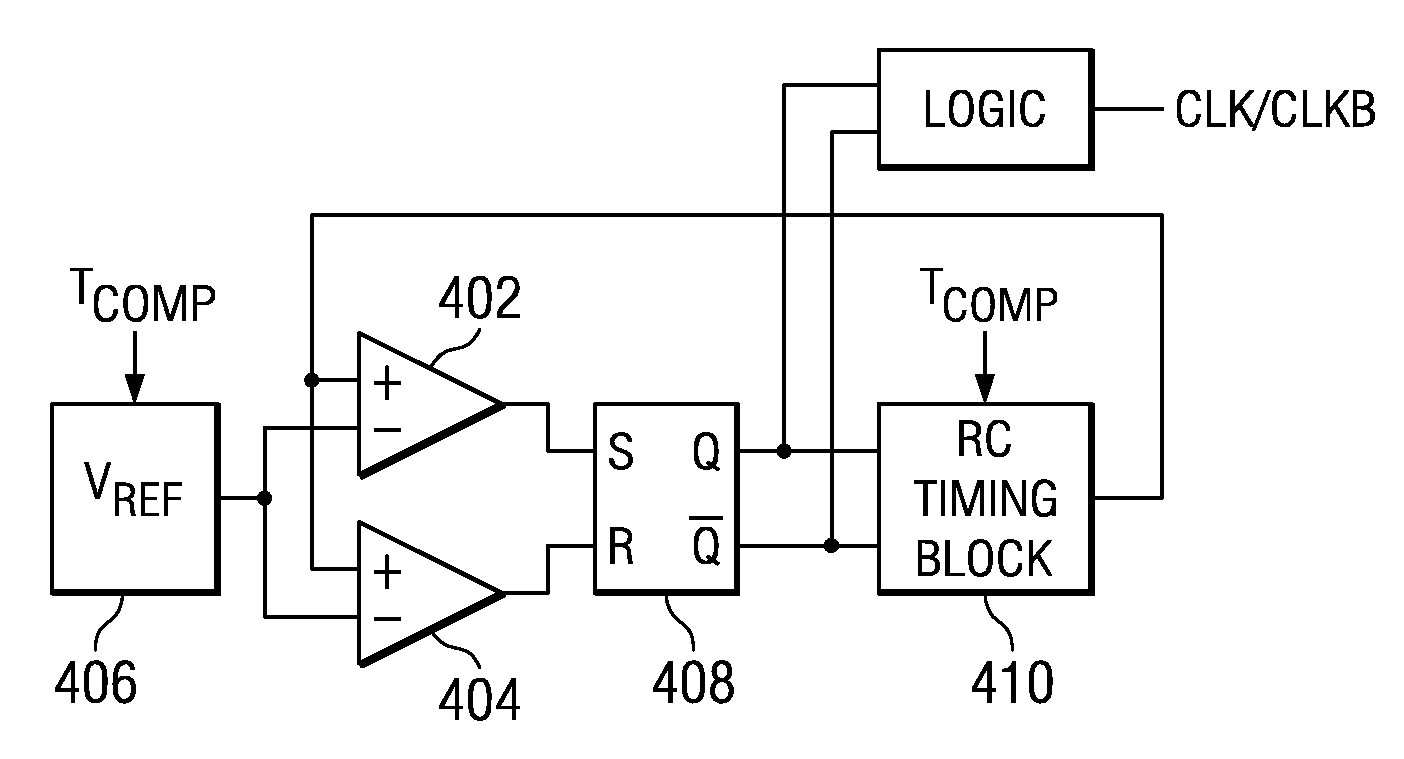

Precision oscillator having improved temperature coefficient control

InactiveUS7385453B2Angle modulation by variable impedencePulse generation by bipolar transistorsVoltage generatorTemperature curve

A free running clock circuit includes a switching circuit for switching between first and second logic states at a predetermined frequency based upon a trip voltage the switching circuit has a programmable temperature profile associated therewith. The switching circuit includes a comparator circuit that has first and second comparators. The first and second comparators have a reference input connected to receive the trip voltage, and the output of the comparators change logic states between a first logic state and a second logic state when the other input of the comparator passes the trip voltage. The first and second comparators have a programmable offset voltage enabling programming of the programmable voltage supply profile of the switching circuit. An RC timing circuit defines when the outputs of the comparators switch between the first and second logic states by providing a feedback to the other inputs of the two comparators. A temperature compensated trip voltage generator outputs a defined trip voltage that is compensated over temperature to offset the temperature profile of said switching circuit to provide an overall temperature compensated operation for said free running clock circuit.

Owner:SILICON LAB INC

Treatment of circadian rhythm disorders

Embodiments of the invention relate to the use of a melatonin agonist in the treatment of free running circadian rhythms in patients, including light perception impaired patients, e.g., blind patients, and to methods of measuring circadian rhythm.

Owner:VANDA PHARMA INC

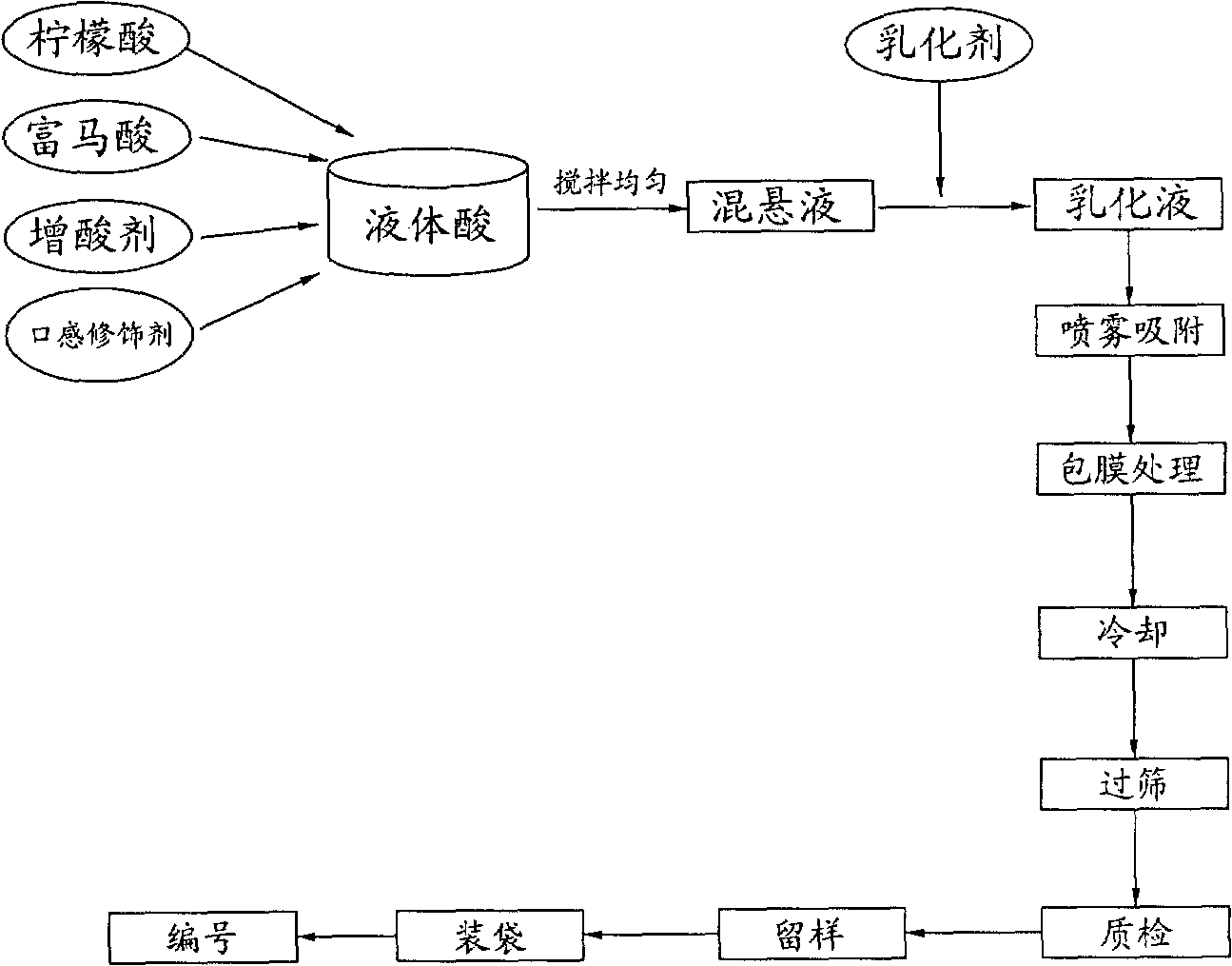

Feeding acidifier prepared by emulsifying technology and preparing method thereof

ActiveCN101513222AFully dispersedFully emulsifiedAnimal feeding stuffAccessory food factorsPhosphoric acidMoisture absorption

The present invention relates to a feeding acidifier prepared by emulsifying technology and a preparing method thereof. The invention belongs to the technical field of animal feed additive preparing. The feeding acidifier comprises the following components according to content: 8-20 parts of lemon acid; 5-20 parts of fumaric acid; 10-15 parts of phosphoric acid; 5-20 parts of malic acid; 15-25 parts of lactic acid; 6-15 parts of formic acid; 2-10 parts of acetic acid; 2-5 parts of mouthfeel modifying agent; and 3-5 parts of silicon dioxide. The invention provides a novel preparation form of acidifier and combines the physical and chemical properties of shaping material for developing the novel producing technique of acidifier according to the sustained-release control principle. The feeding acidifier prepared according to the emulsifying technique of the invention effectively settles the problem of stomach digesting of acidifier and the effect directly gets to the intestinal canal. The feeding acidifier prepared by emulsifying technology according to the invention has the advantages of reliable safety, excellent free-running property, strong moisture absorption resistance, convenient processing, growth promotion, diarrhea prevention, etc.

Owner:MYRON XIAMEN BIOTECH

Precision oscillator having improved temperature coefficient control

InactiveUS20070241833A1Pulse generation by bipolar transistorsGenerator stabilizationVoltage generatorTemperature curve

A free running clock circuit includes a switching circuit for switching between first and second logic states at a predetermined frequency based upon a trip voltage the switching circuit has a programmable temperature profile associated therewith. The switching circuit includes a comparator circuit that has first and second comparators. The first and second comparators have a reference input connected to receive the trip voltage, and the output of the comparators change logic states between a first logic state and a second logic state when the other input of the comparator passes the trip voltage. The first and second comparators have a programmable offset voltage enabling programming of the programmable voltage supply profile of the switching circuit. An RC timing circuit defines when the outputs of the comparators switch between the first and second logic states by providing a feedback to the other inputs of the two comparators. A temperature compensated trip voltage generator outputs a defined trip voltage that is compensated over temperature to offset the temperature profile of said switching circuit to provide an overall temperature compensated operation for said free running clock circuit.

Owner:SILICON LAB INC

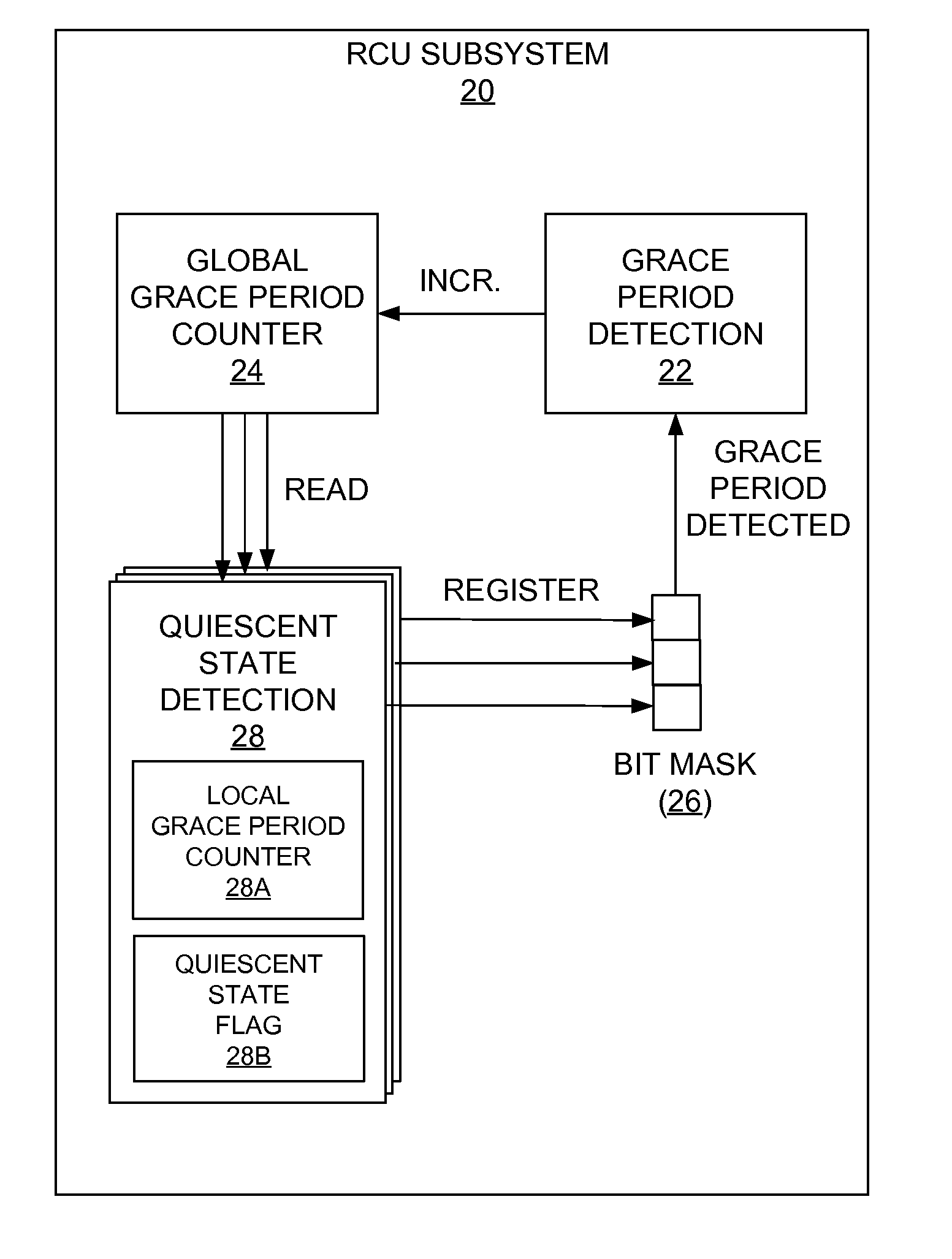

Making read-copy update free-running grace period counters safe against lengthy low power state sojourns

InactiveUS8407503B2Avoid disruptionVolume/mass flow measurementPower supply for data processingQuiescent stateRead-copy-update

A technique for making a free-running grace period counter safe against lengthy low power state processor sojourns. The grace period counter tracks grace periods that determine when processors that are capable executing read operations have passed through a quiescent state that guarantees the readers will no longer maintain references to shared data. Periodically, one or more processors may be placed in a low power state in which the processors discontinue performing grace period detection operations. Such processors may remain in the low power state for a complete cycle of the grace period counter. This scenario can potentially disrupt grace period detection operations if the processors awaken to see the same grace period counter value. To rectify this situation, processors in a low power state may be periodically awakened at a predetermined point selected prevent the low power state from extending for an entire roll over of the grace period counter.

Owner:INT BUSINESS MASCH CORP

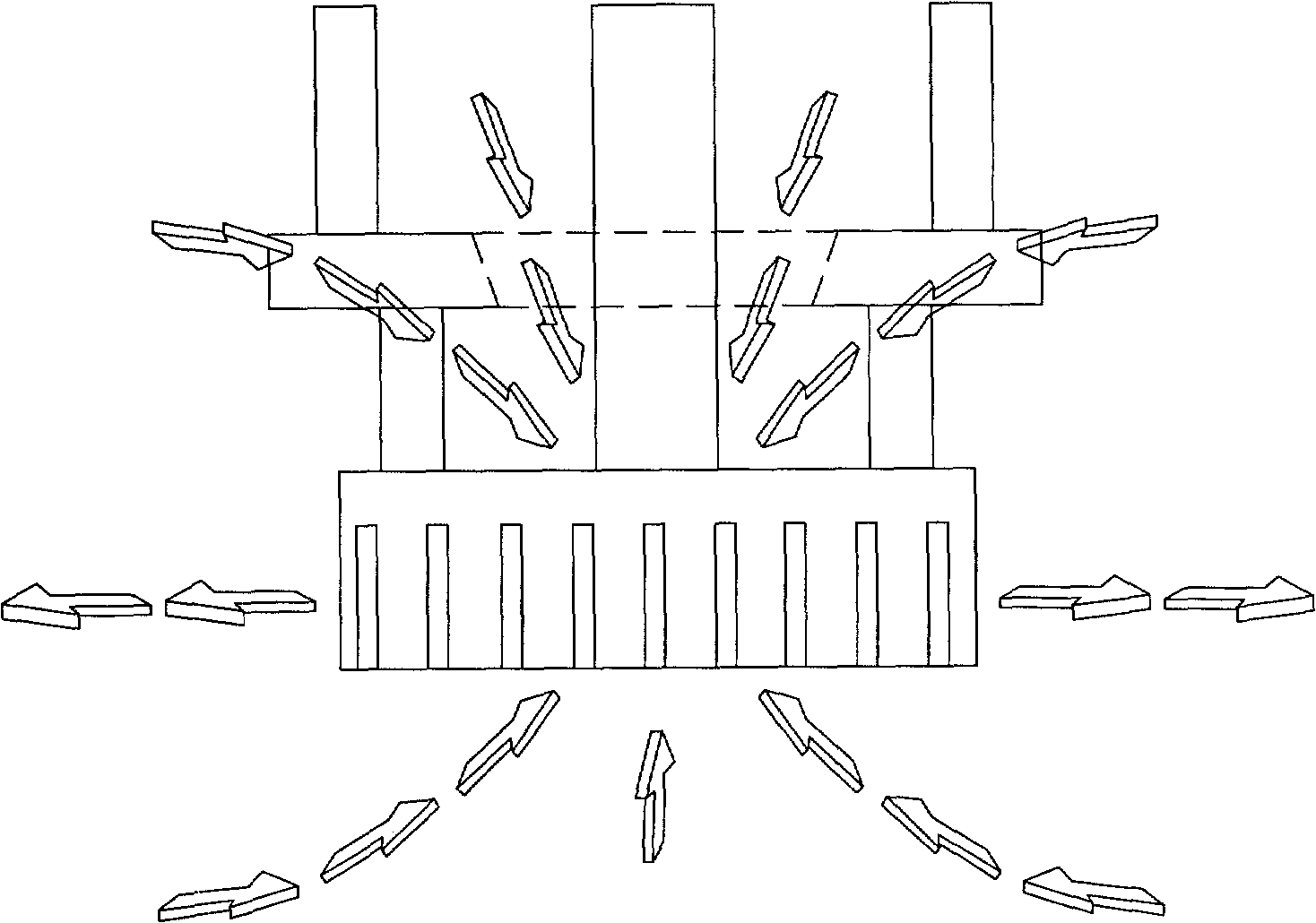

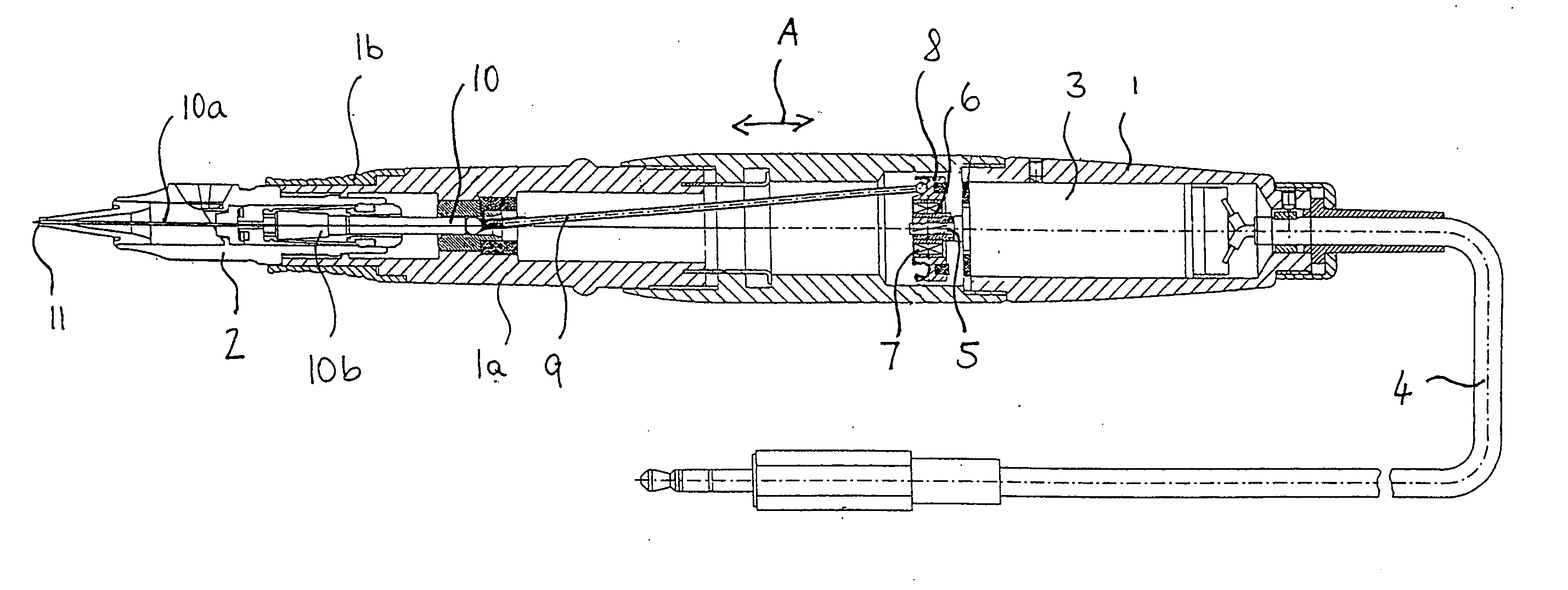

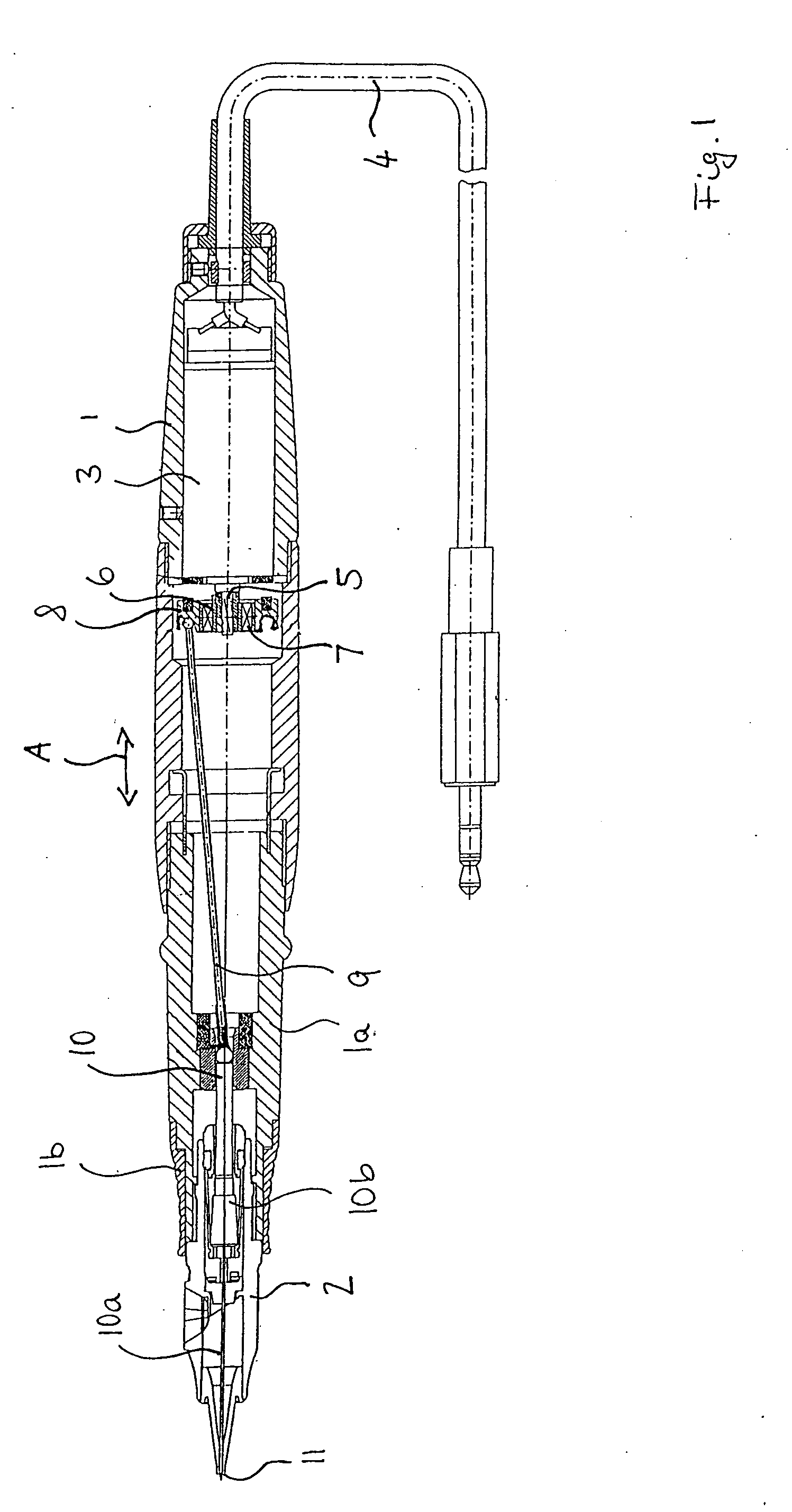

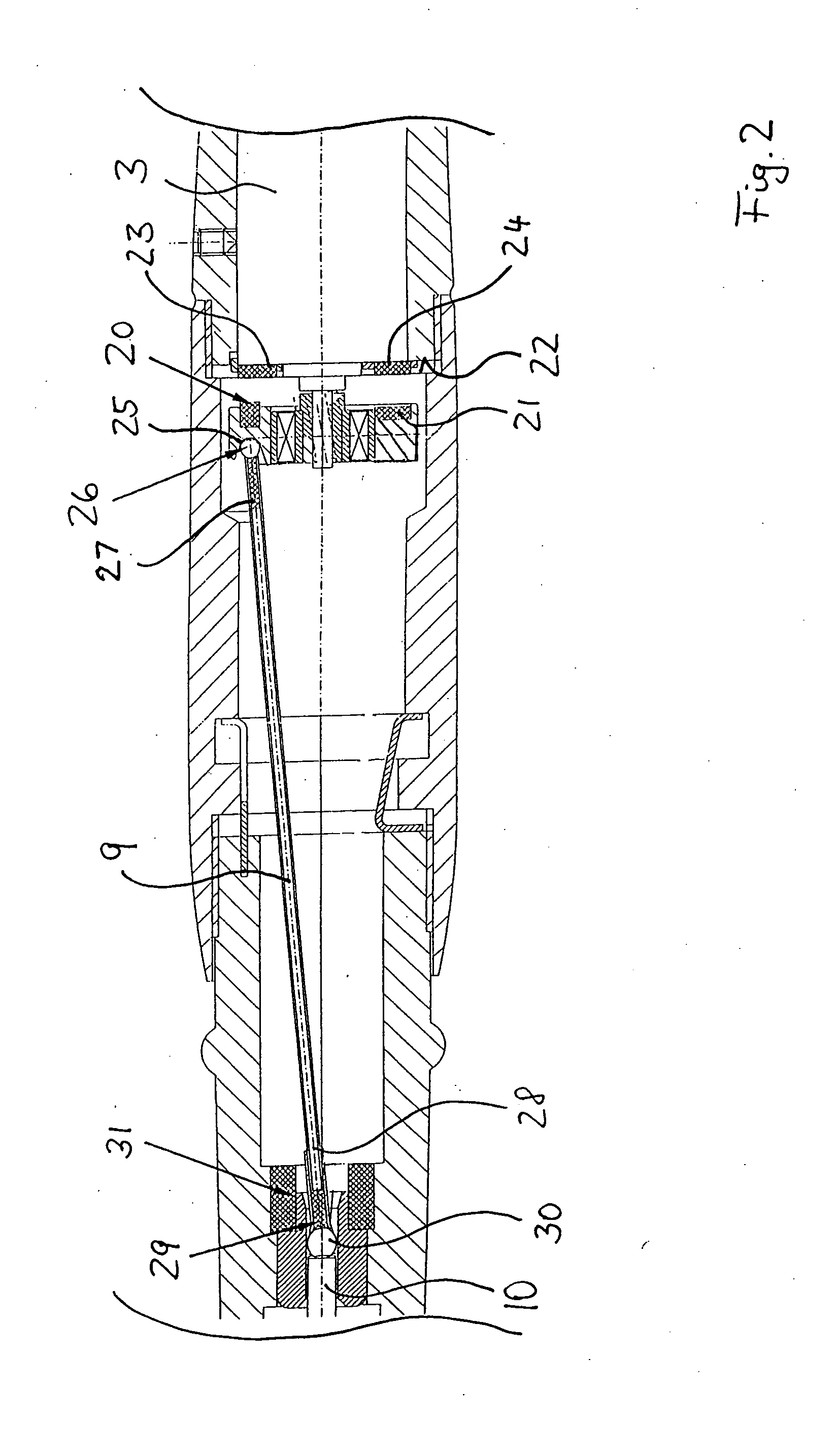

Drive module for a device for the local piercing of a human or animal skin and a handheld

InactiveUS20080306502A1Undesirable noise effect is minimized for the user during operationReduce stepsSurgical needlesMedical devicesCouplingComputer module

The invention relates to a drive module for a device for the local piercing of a human or an animal skin, with a drive apparatus which is configured for the purpose of producing a drive rotary movement and a conversion mechanism coupled to the drive apparatus which is configured for the purpose of converting the drive movement into a coupling-connectable forward / backward movement for a needle apparatus piercing the skin locally, and which comprises a free-running functional member, wherein the functional member is coupled to a magnetic anti-turn locking element allowing a wobble or tilting movement of the functional member where, with the said anti-turn locking element, a magnetic retaining force is provided which acts against a turning of the functional member. Furthermore, the invention relates to a handheld with a drive module and a processing module in which a needle apparatus having a needle is formed and which is configured for the purpose of converting the forward / backward movement provided by the drive module into a piercing movement.

Owner:MT DERM

Treatment of circadian rhythm disorders

Embodiments of the invention relate to the use of a melatonin agonist in the treatment of free running circadian rhythms in patients, including light perception impaired patients, e.g., blind patients, and to methods of measuring circadian rhythm.

Owner:VANDA PHARMA INC

Systems and methods for space-time determinations with reduced network traffic

Space-time solutions are determined by exchanging pings among nodes in a network. Each ping includes a current space-time state of the transmitting node, which includes the transmitting node's currently estimated location and corrected time (as a count stamp). A particular node in the network receives pings from the other nodes in the network and uses the data in the received pings to estimate its own current position and to correct its own free-running clock relative to a common system time. As a service to the network, the particular node then transmits its corrected time (as a count stamp) and estimated position to the other nodes. In some embodiments, the space-time solutions discussed herein are used as backup to other navigation systems, such as the Automatic Dependent Surveillance-Broadcast (ADS-B) system.

Owner:DIGIMARC CORP

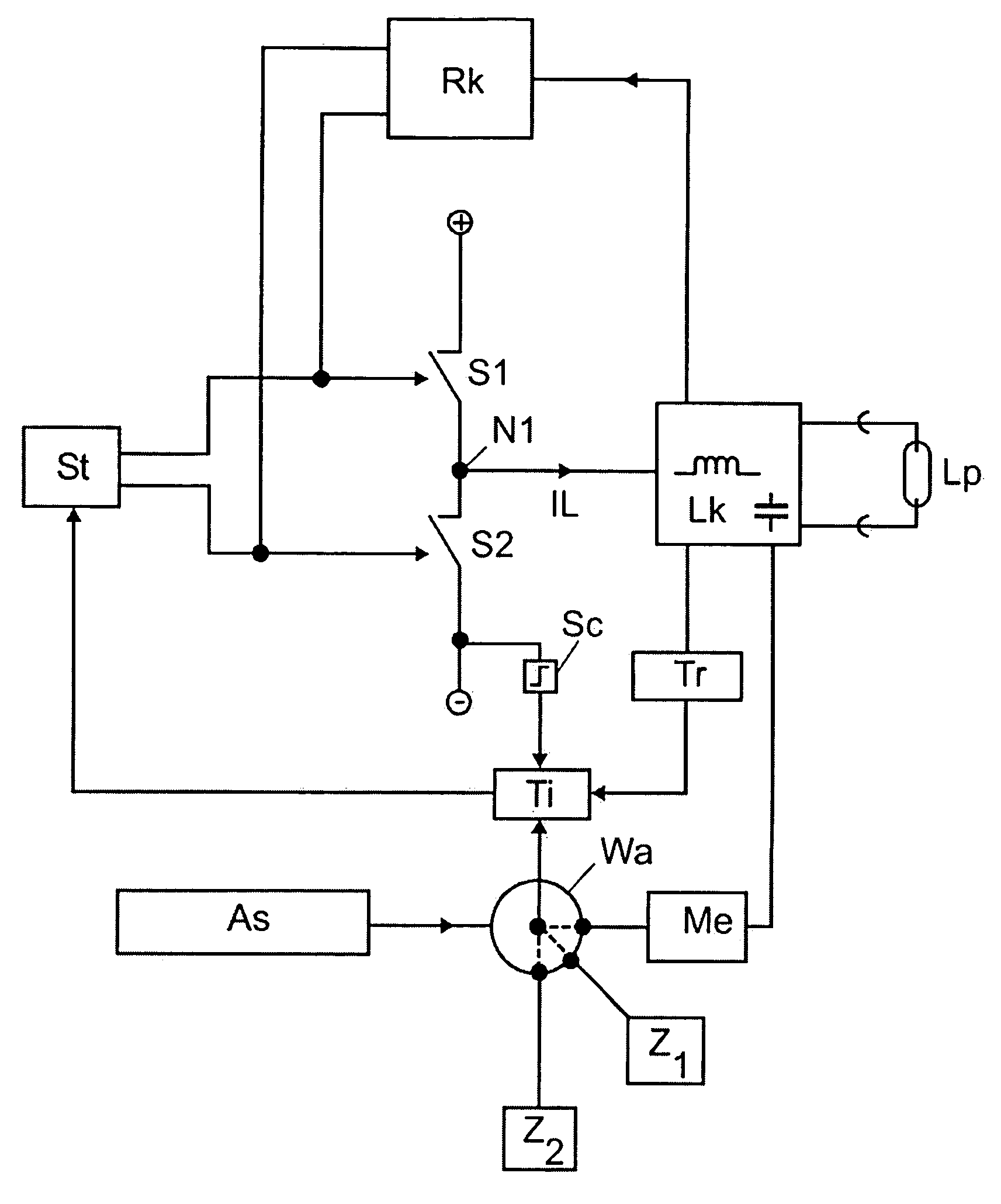

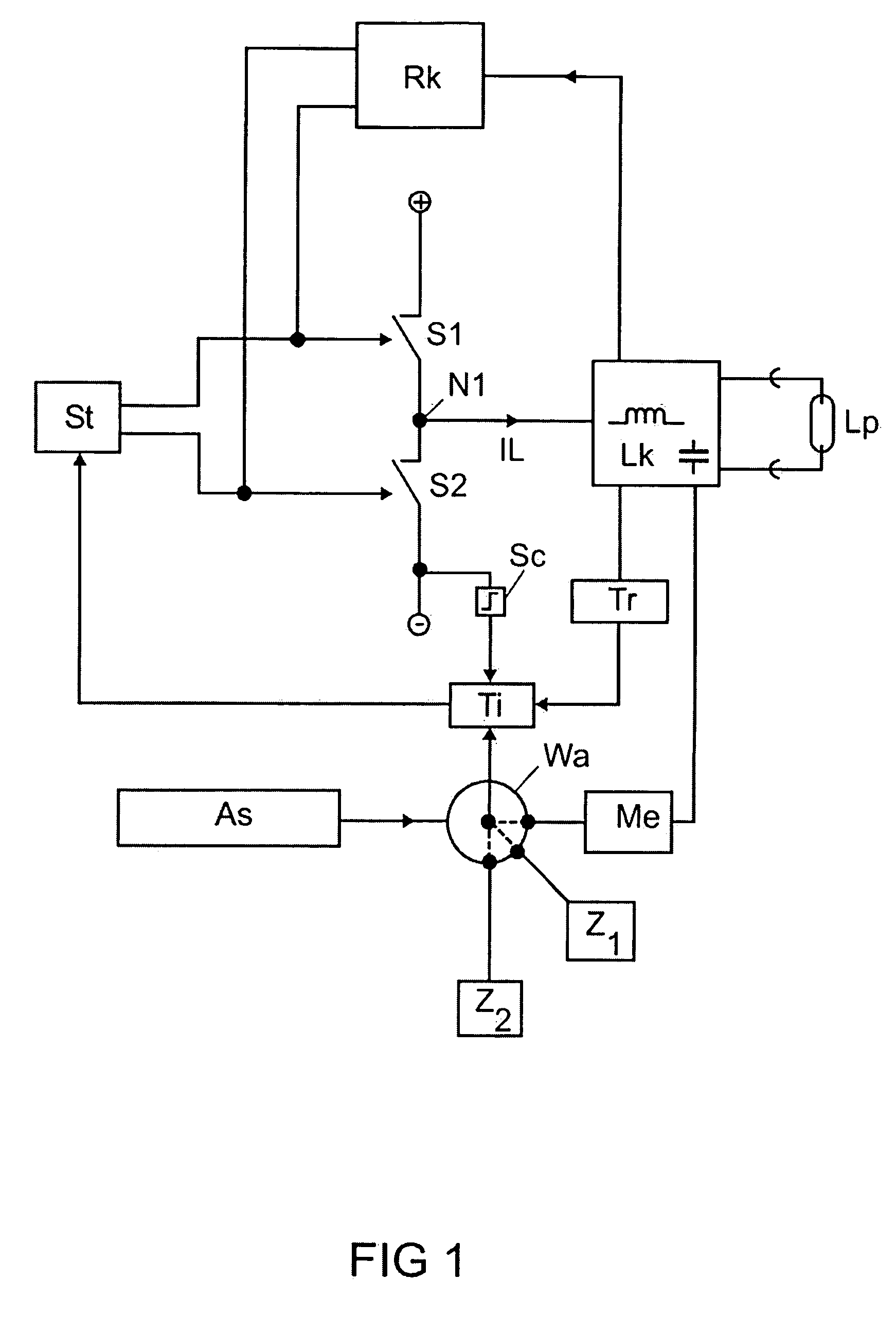

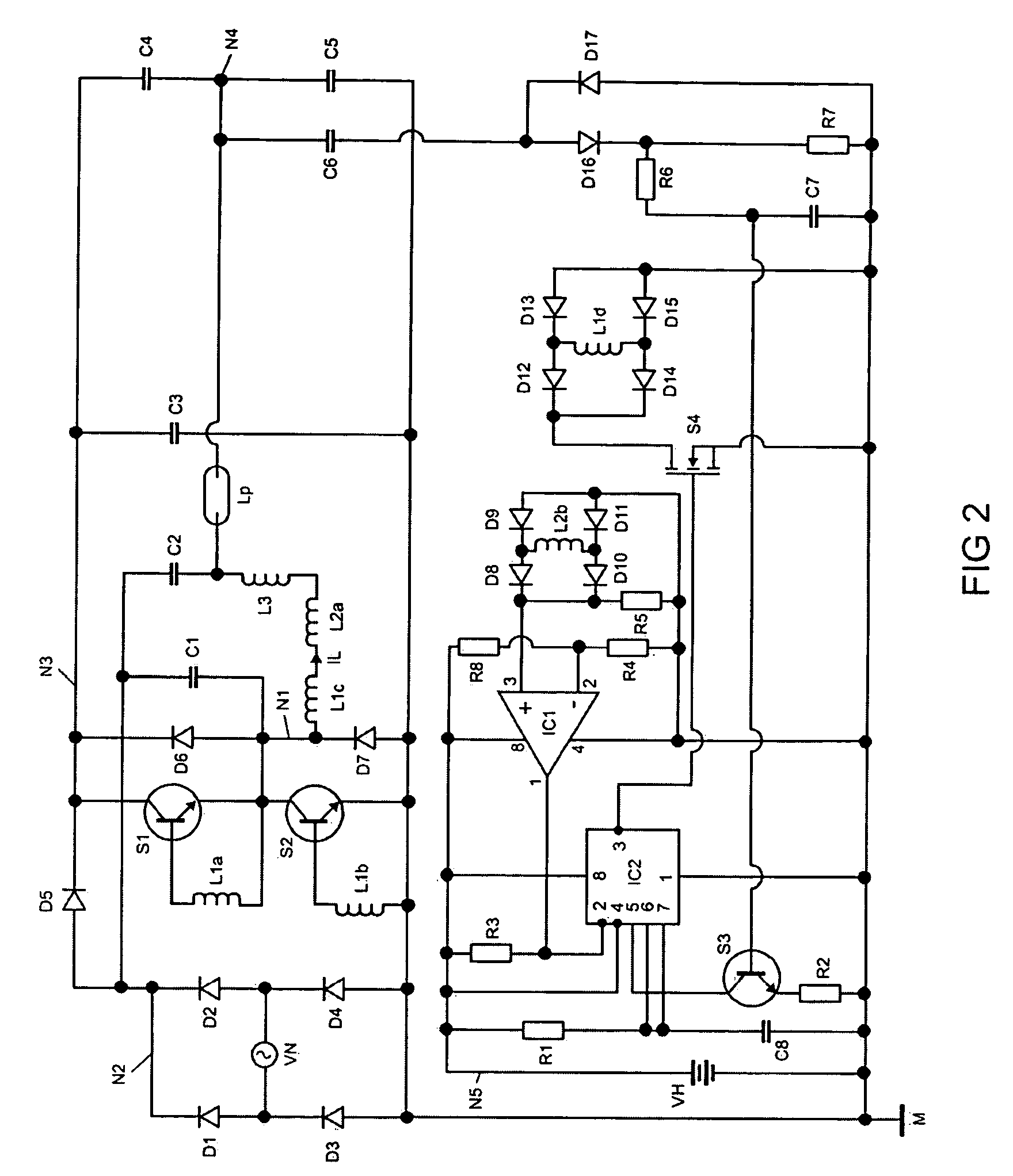

Circuit arrangement and method for operation of lamps

InactiveUS7242154B2Reliable adjustmentAvoid drivingElectrical apparatusElectroluminescent light sourcesGas-discharge lampStops device

Circuit arrangement having a free-running half-bridge inverter for operation of gas discharge lamps. A stop device is used to enable the drive to the half-bridge switches only during an on time. The oscillation frequency of the half-bridge inverter can be adjusted by the duration of the on time. This allows control of the lamp operating variables.

Owner:PATENT TREUHAND GESELLSCHAFT FUR ELECTRIC GLUEHLAMPEN MBH

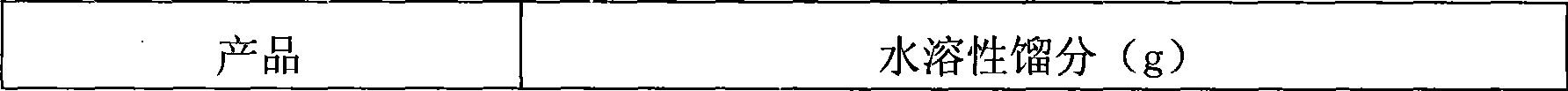

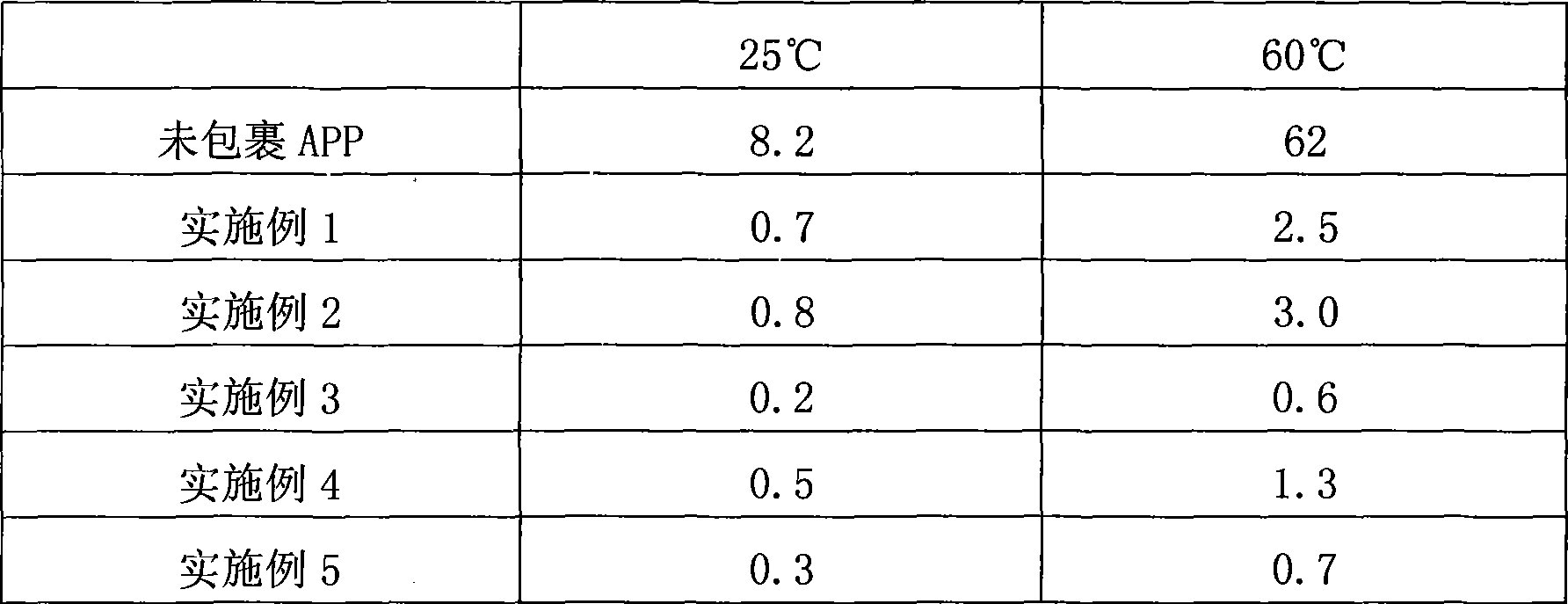

Method for preparing microencapsulated ammonium polyphosphate

ActiveCN101362836AImprove fluiditySize andMicroballoon preparationMicrocapsule preparationSolubilityPolyolefin

The invention discloses a preparation method for encapsulating ammonium polyphosphate by microcapsules; in a reaction kettle of a stirring and reflux device, the powder of the ammonium polyphosphate is suspended and dispersed in a solvent; then bisphenol A epoxy resin is added; an amine curing agent is added in a dropping mode under the situation that the solvent is a little boiled and is stirred for 2 to 10 hours to solidify the epoxy resin, then the mixture is filtered; the filter product is further solidified and dried under 90 to 120 DEG C under a nitrogen environment, thus obtaining the ammonium polyphosphate capsulated by microcapsules. Compared with the ammonium polyphosphate which is not capsulated, the free-running property of the particles of the ammonium polyphosphate prepared by the invention is good; the compatibility with a high polymer is improved; the water-solubility of the particles is greatly reduced; the electric property is obviously improved; the ammonium polyphosphate capsulated by the microcapsules can be used as the flame retardants of polymer materials such as polyolefine, and the like.

Owner:GUANGDONG JUSHI CHEM CO LTD

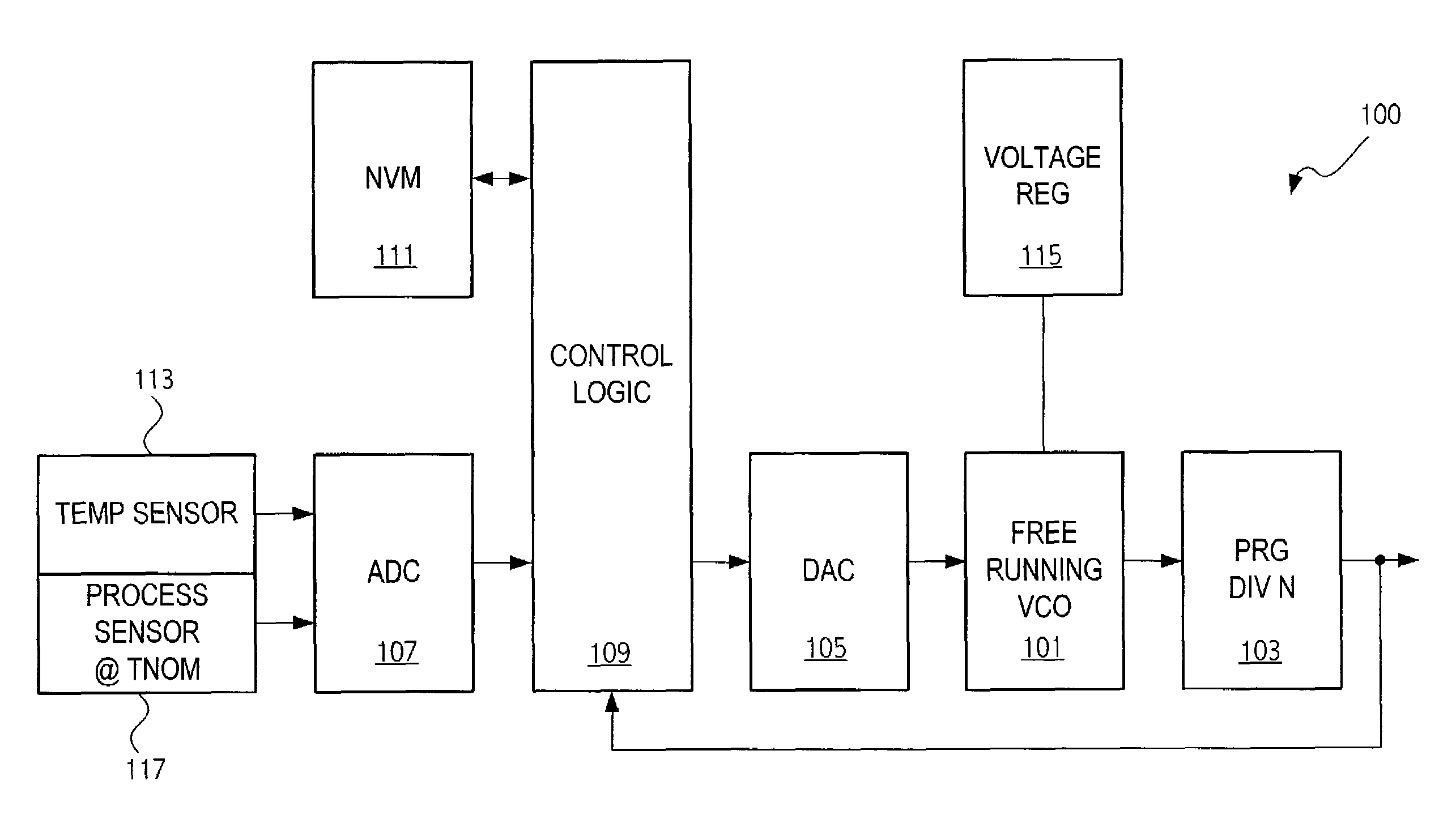

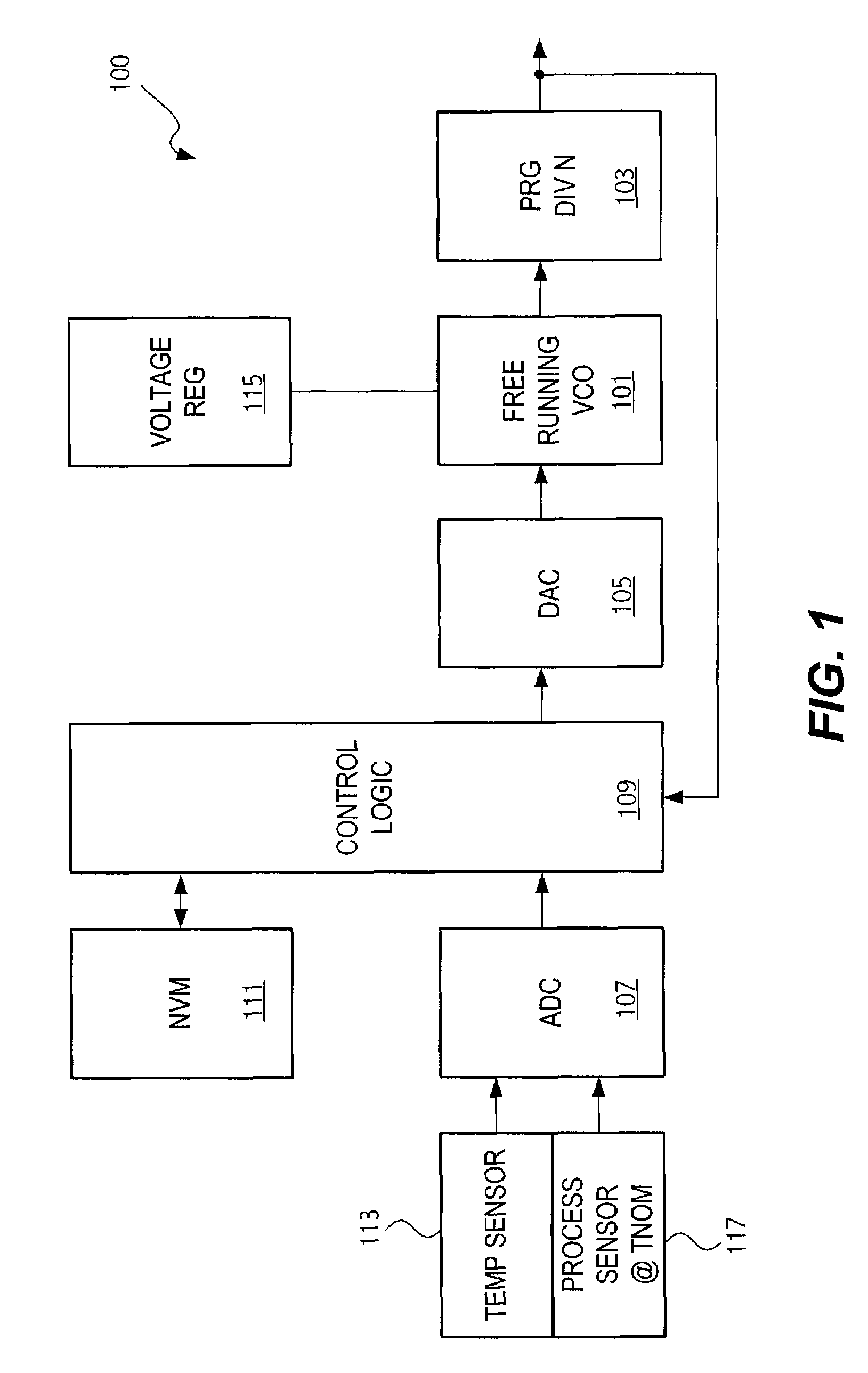

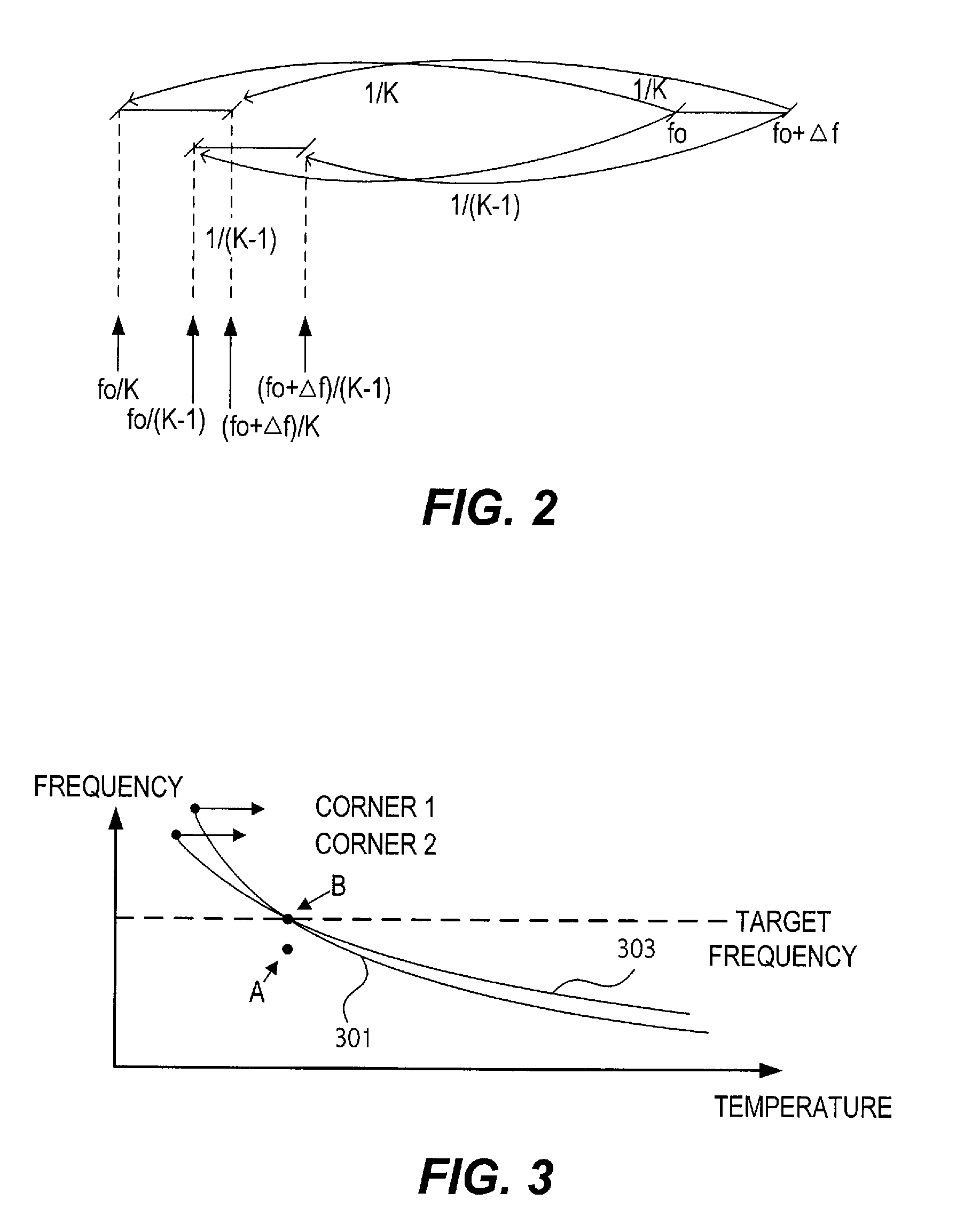

Reference-less clock circuit

A programmable reference-less oscillator provides a wide range of programmable output frequencies. The programmable reference-less oscillator is implemented on an integrated circuit that includes a free running controllable oscillator circuit such as a voltage controlled oscillator (VCO), a programmable divider circuit coupled to divide an output of the controllable oscillator circuit according to a programmable divide value. A non-volatile storage stores the programmed divide value and a control word that controls the output of the controllable oscillator circuit. The control word provides a calibration capability to achieve a desired output frequency in conjunction with the programmable divider circuit. Open loop temperature compensation is achieved by adjusting the control word according to a temperature detected by a temperature sensor on the integrated circuit. Additional clock accuracy may be achieved by adjusting the control word for process as well as temperature.

Owner:SILICON LAB INC

Treatment of circadian rhythm disorders

Embodiments of the invention relate to the use of a melatonin agonist in the treatment of free running circadian rhythms in patients, including light perception impaired patients, e.g., blind patients, and to methods of measuring circadian rhythm.

Owner:VANDA PHARMA INC

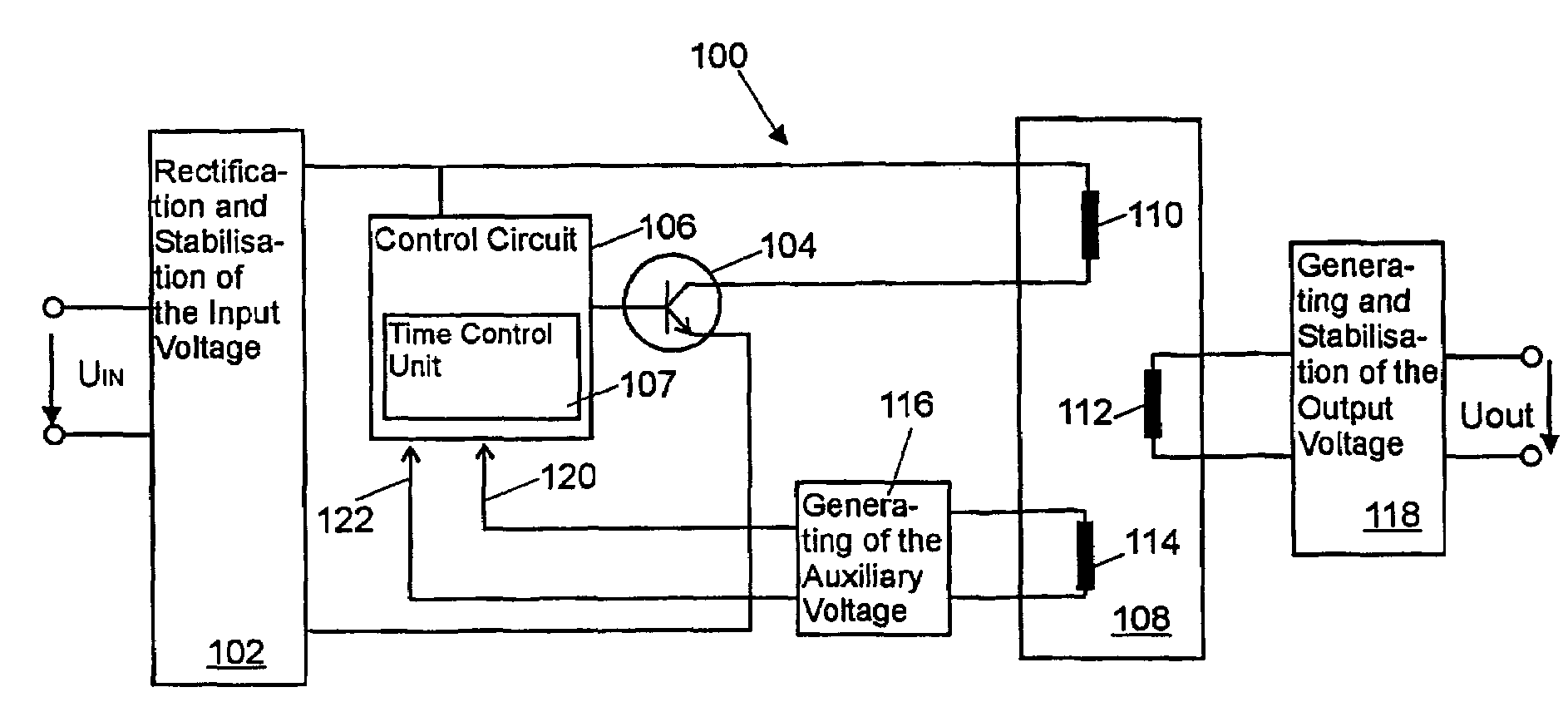

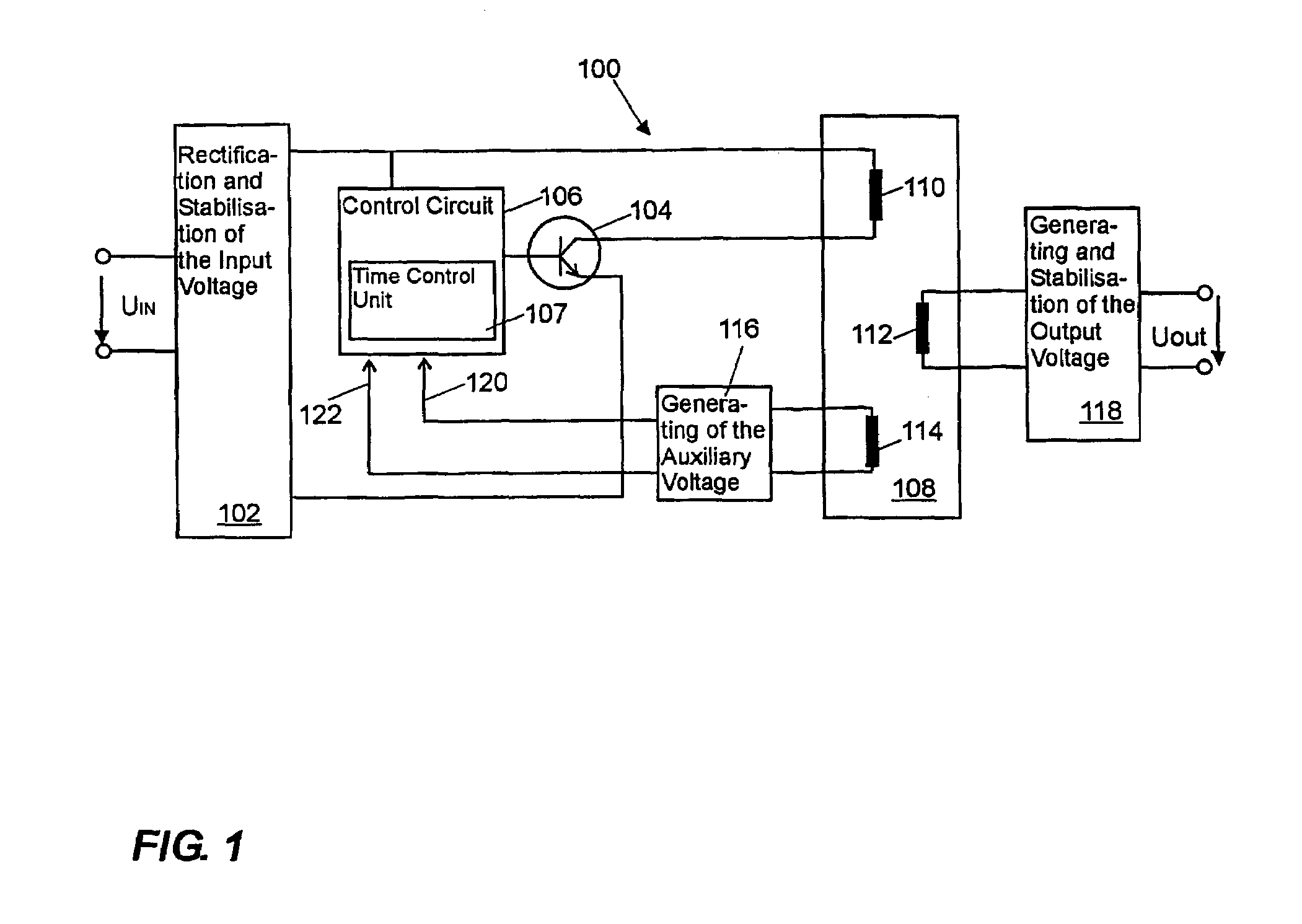

Simple switched-mode power supply with current and voltage limitation

ActiveUS7295449B2Reduce complexityImprove control characteristicsConversion with intermediate conversion to dcDc-dc conversionSwitching cycleEngineering

This invention relates to a primary-controlled switched-mode power supply of the type of a free-running flyback converter, which comprises a transformer with a primary-side winding, a secondary-side winding and at least one auxiliary winding. The switched-mode power supply comprises a primary-side switch, which is connected to the primary-side winding, in order to interrupt a current flow through the primary-side winding, a freely oscillating circuit for the generation of switching pulses, which drive the primary-side switch, and a circuit for generating an image voltage between the terminals of the auxiliary winding, in order to generate an image voltage, which on the primary side forms a voltage to be regulated on the secondary side. In order to provide a switched-mode power supply of this type, which with reduced complexity enables an improved control characteristic and an increased flexibility with regard to the operating parameters, the switched-mode power supply further comprises a time control unit, which is coupled to the primary-side switch such that the duration of a turn-off period of the primary-side switch can be adjusted within a switching cycle.

Owner:POWER SYST TECH

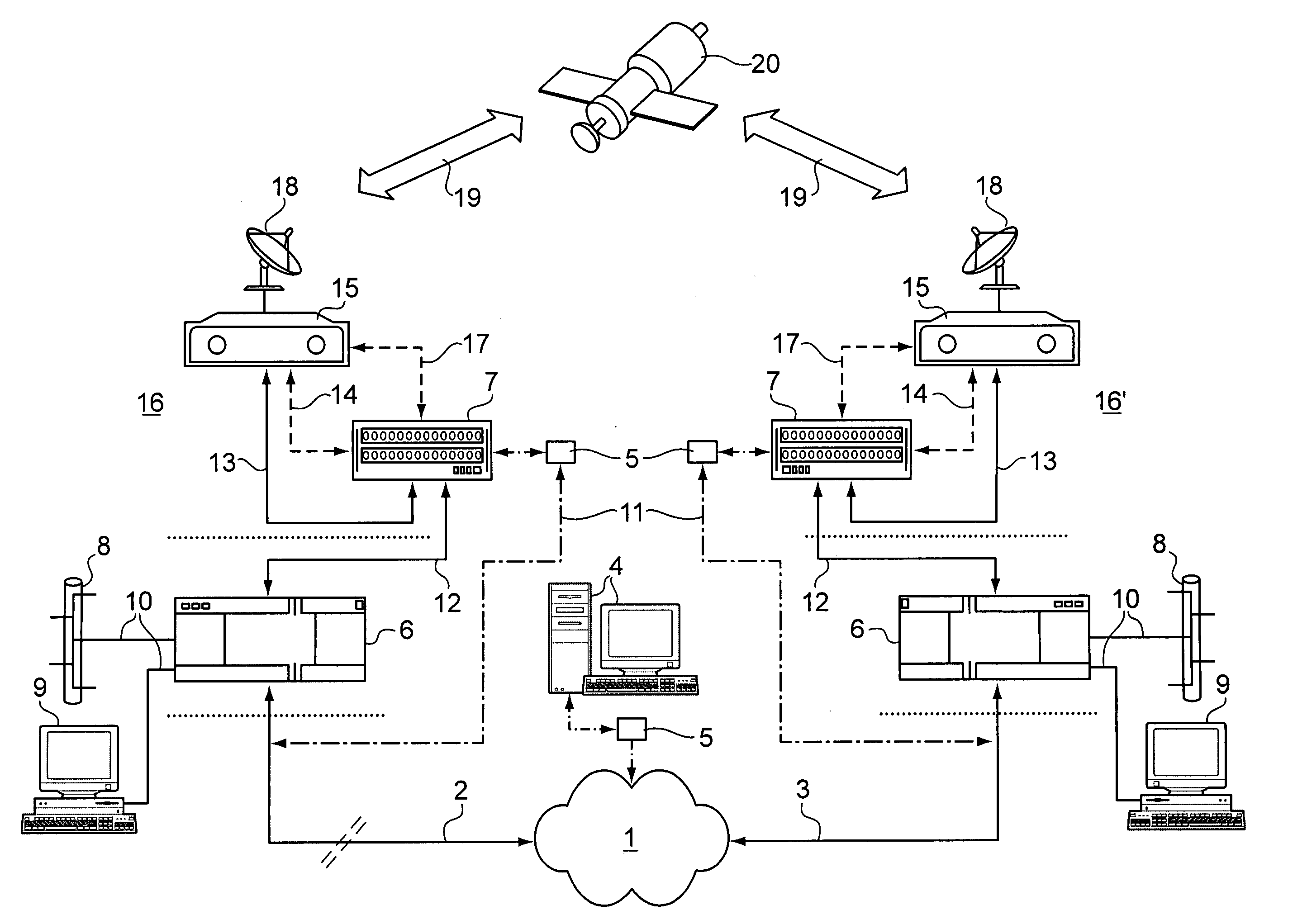

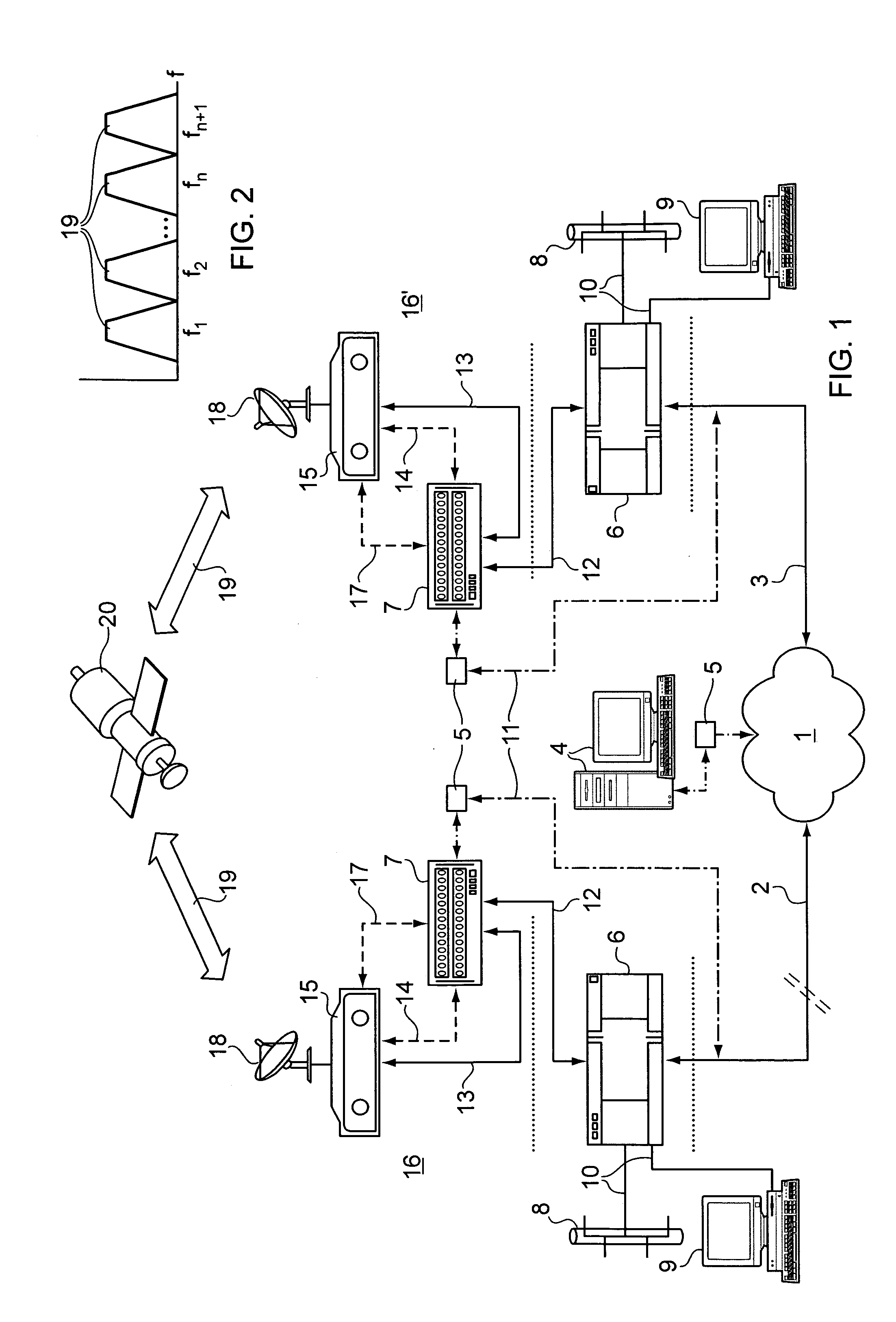

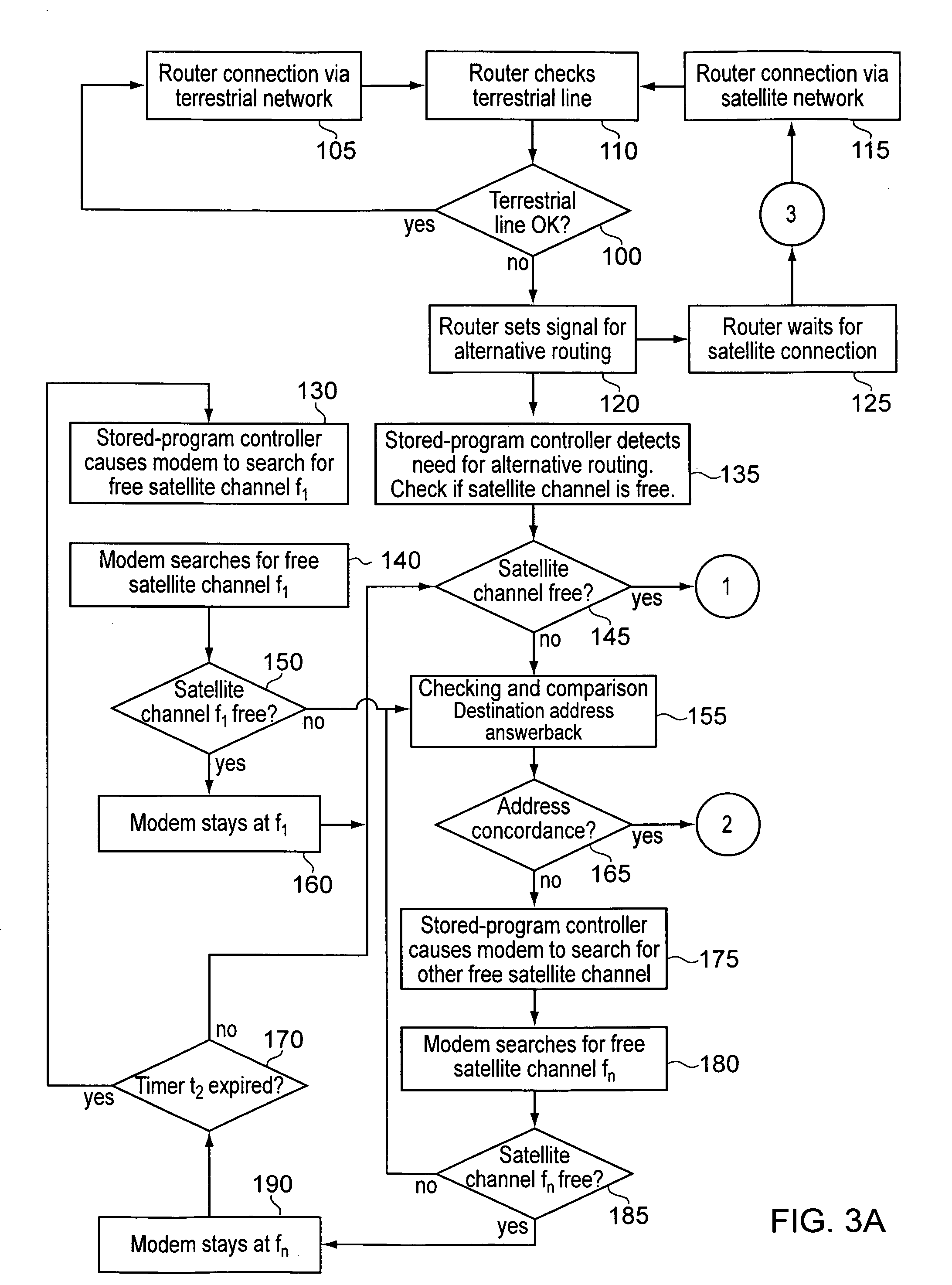

Method and system for controlling the use of satellite transmission capacity in terrestrial networks

InactiveUS7187926B1Increase the number ofReduce the numberError preventionRadio/inductive link selection arrangementsSatellite antennasModem device

A process and system for controlling the use of satellite transmission capacity in terrestrial networks for the substitution of out-of-order data lines. The circuit / process is characterized in that an independent, local control apparatus, which monitors a backup terminal with the software specially written for this application, cooperates in limited manner with the data transmission device of the user and, based on the analysis of a data control signal, detects the need for alternative routing. Via communication lines and modems, the control apparatus switches on the transmission carrier of the affected satellite modem which is connected to a satellite antenna. The satellite antennas are in communication with the satellite via the transmission carrier. All other, non-affected terminals in the network also receive the transmission carrier of the affected satellite modem. The transmission capacity of the asynchronous overhead of the satellite modem is used for the transmission of destination addresses. A hub is provided, which is connected via an interface card or a modem to the terrestrial network that, in turn, is connected via lines to routers. The line is assumed to be out of order. Customer devices or terminals are connected via lines to the routers. The system-specific software-controlled circuit permits independent, decentralized administration of the satellite transmission channels by many satellite terminals without participation of a controlling central station. Thus, even when the terrestrial transmission path is out of order, a free-running alternative routing via a different medium has been achieved.

Owner:DEUTSCHE TELEKOM AG

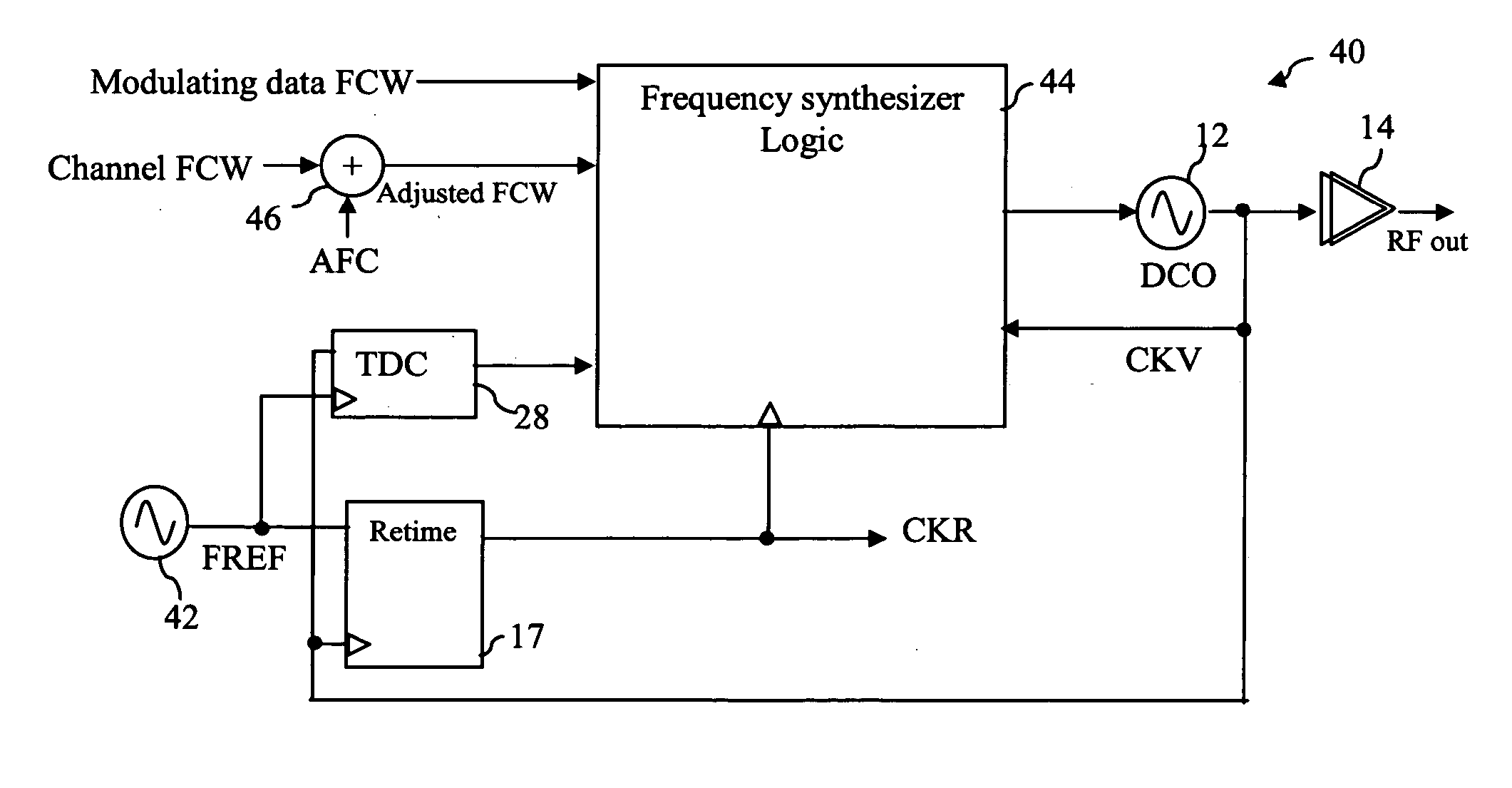

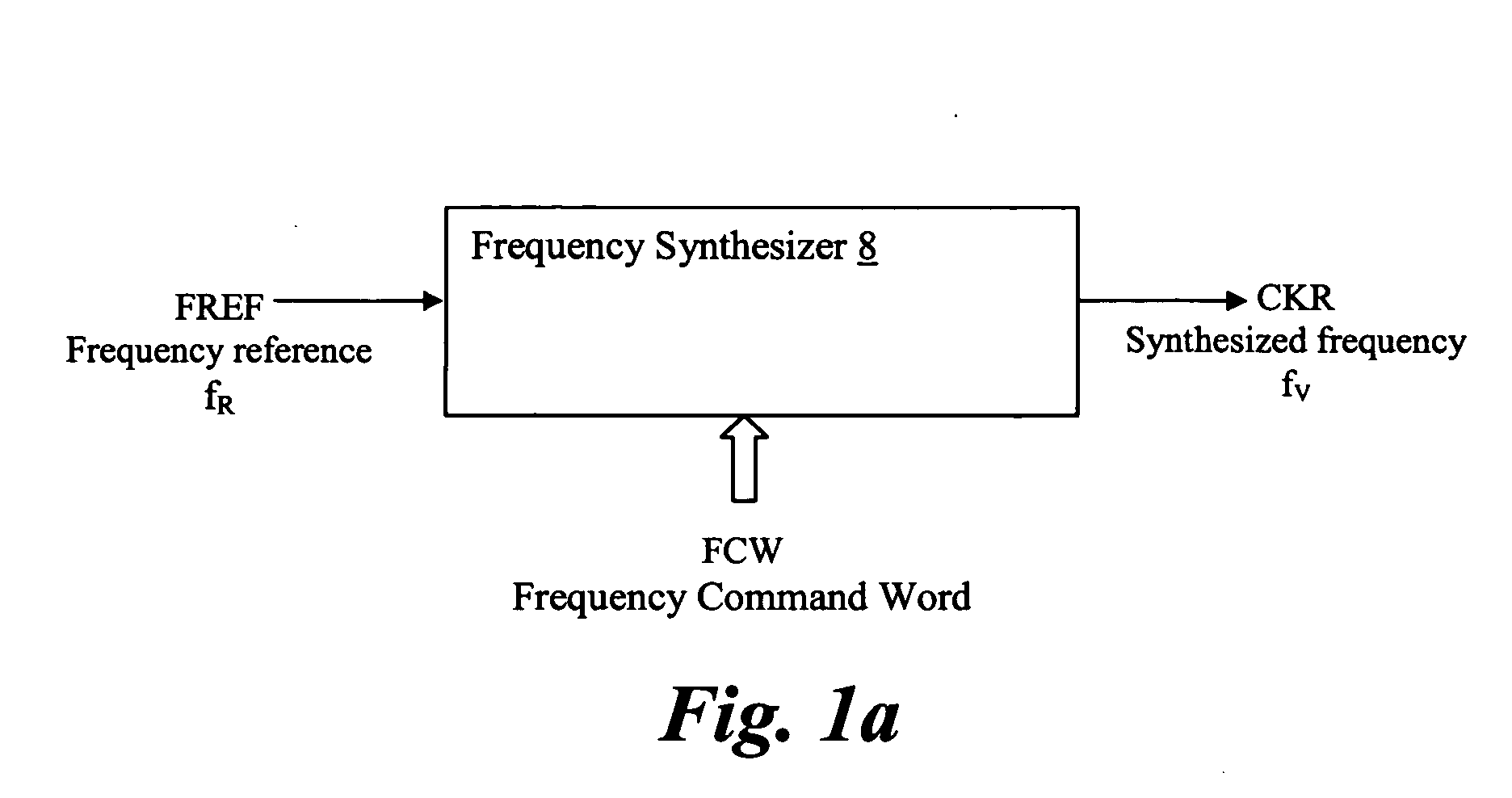

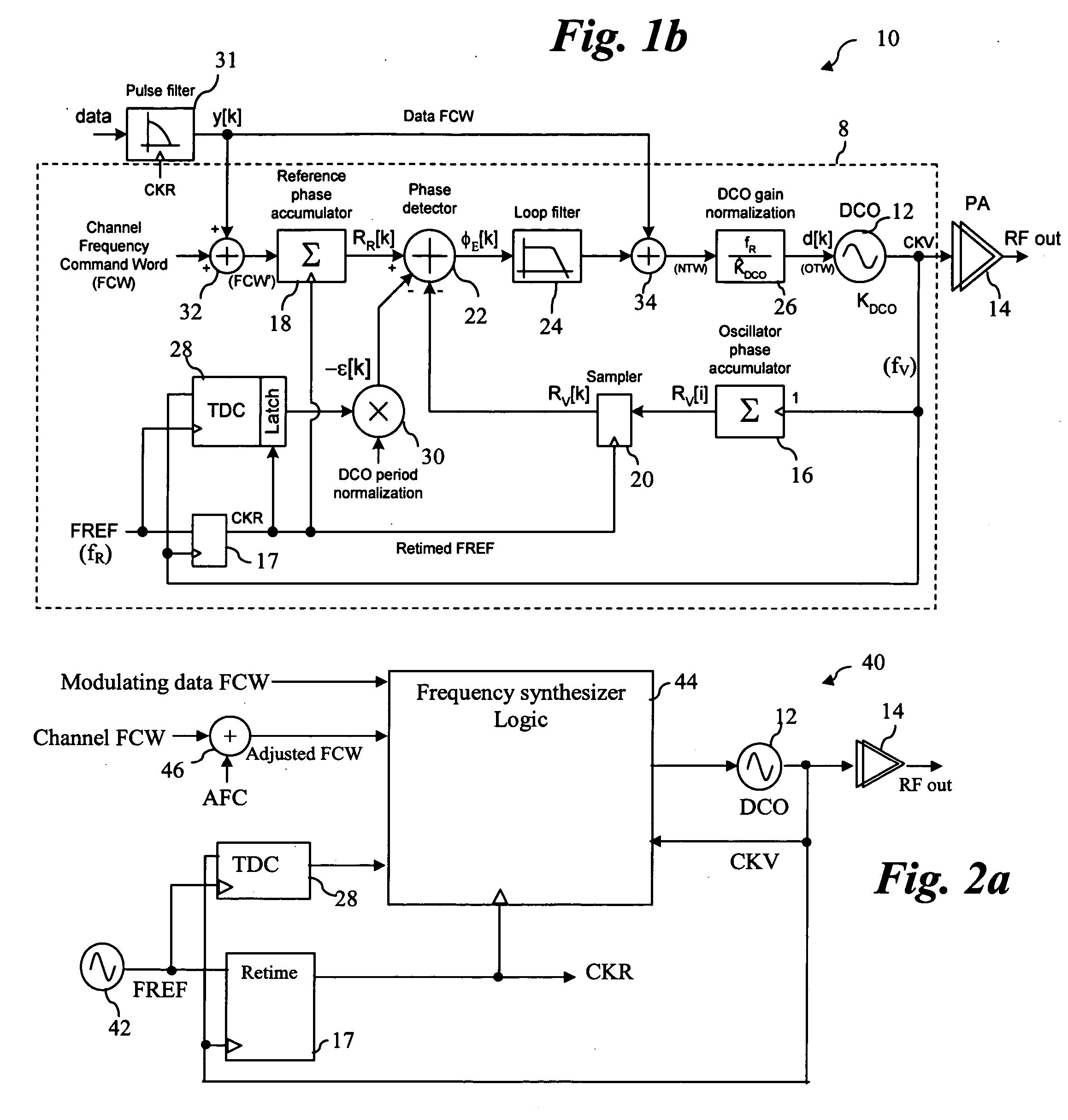

Method and apparatus for crystal drift compensation

InactiveUS20050195917A1Reduce noiseReduce circuit costPulse automatic controlGenerator stabilizationFrequency stabilizationFrequency synthesizer

A mobile device includes frequency synthesizer circuitry for generating a channel frequency at a multiple of a reference frequency. The reference frequency is generated by a free-running crystal oscillator, without frequency stabilization circuitry. Variations in the output of the crystal oscillator are compensated by adjusting the multiplication factor of the frequency synthesizer.

Owner:TEXAS INSTR INC

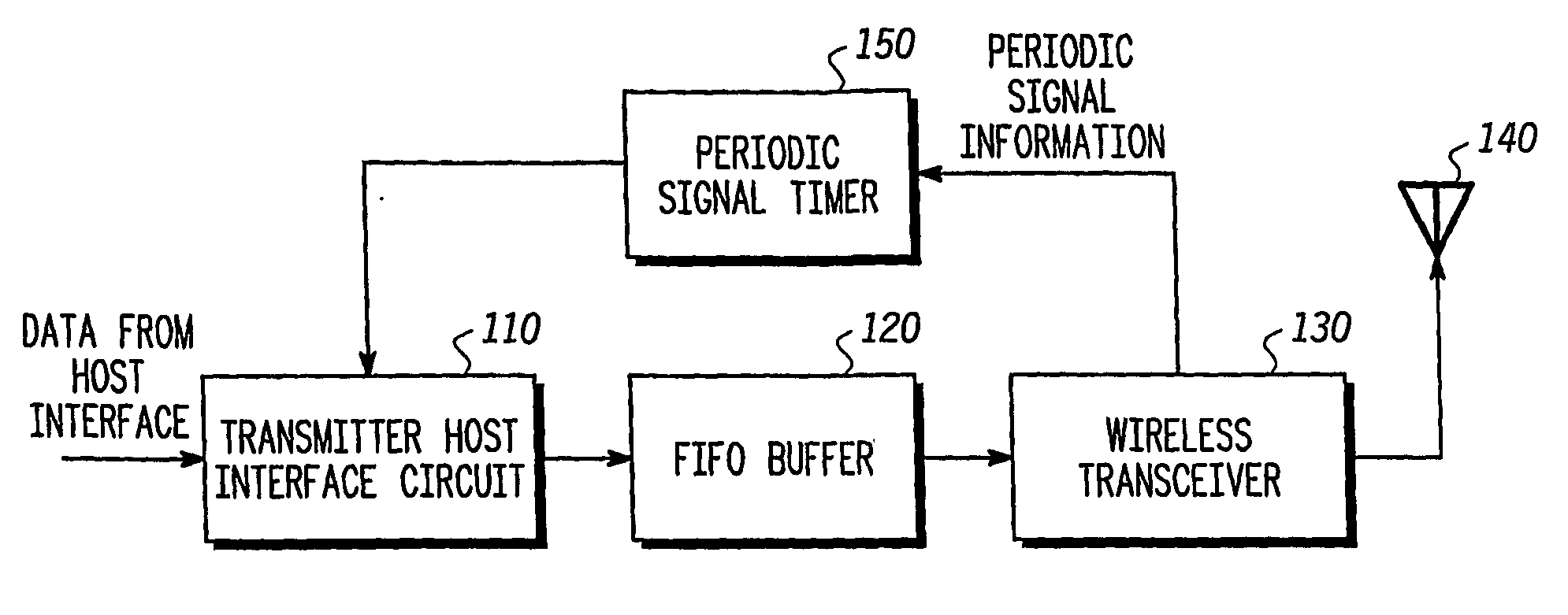

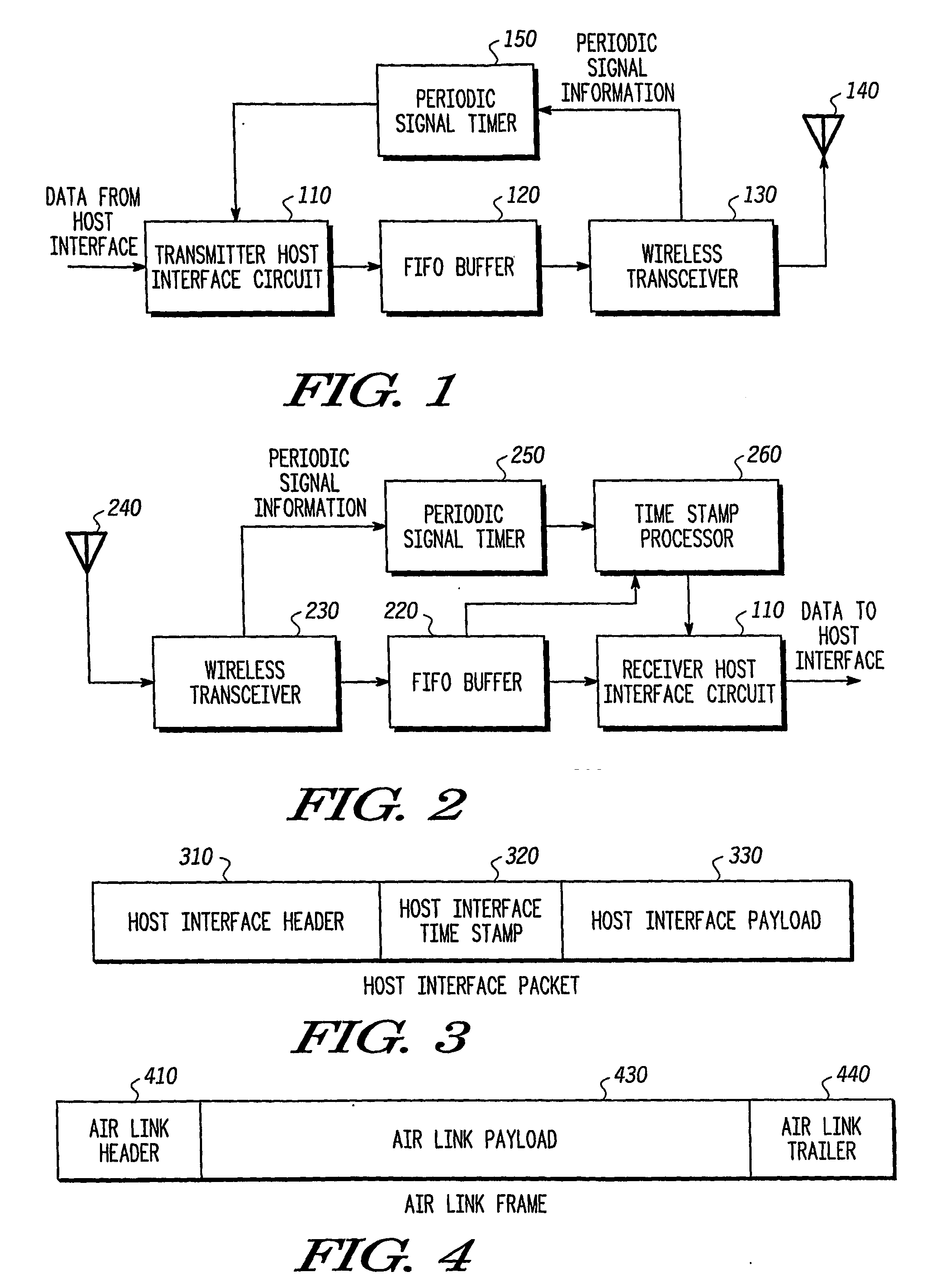

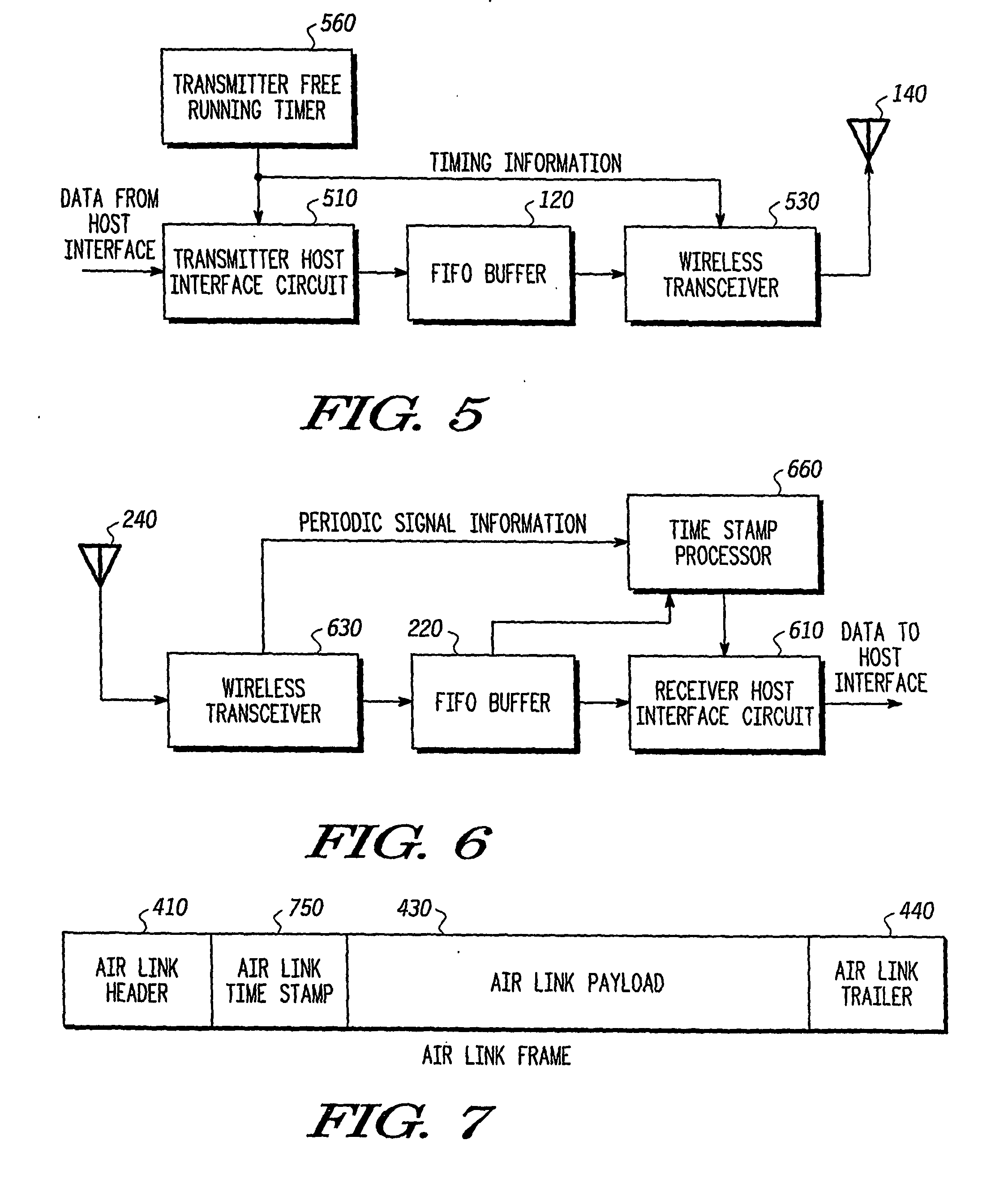

System and method for synchronization of isochronous data streams over a wireless communication link

InactiveUS20070100473A1Synchronisation arrangementPosition fixationTelecommunications linkData stream

A transmitter (500) is provided for transmitting host data over a wireless channel. The transmitter (500) includes a free-running timer (560) that provides a series of increasing free-running timing values; a host interface circuit (510) that receives host data from a local host circuit and a first free-running timing value from the series of increasing free-running timing values; a detection circuit (530) for detecting a global synchronizing event and receiving a second free-running timing value from the series of increasing free-running timing values, and for placing the host data and the first free-running timing value into a host interface packet; and a wireless transceiver (530) for adding the second free-running timing value and an identifier for the global synchronizing event to the host interface packet to form an air link frame, and transmitting the air link frame over a wireless channel to a remote wireless device.

Owner:FREESCALE SEMICON INC

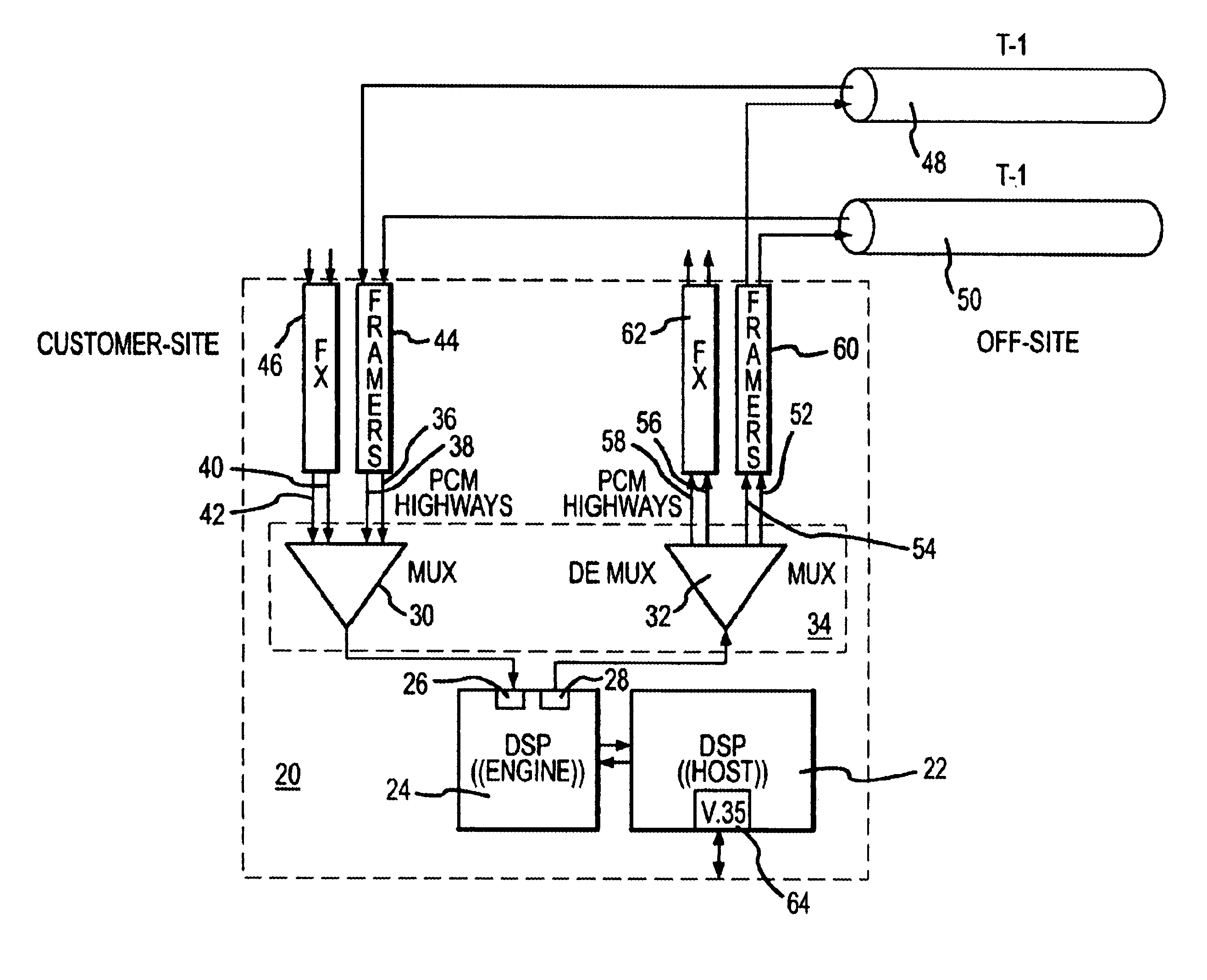

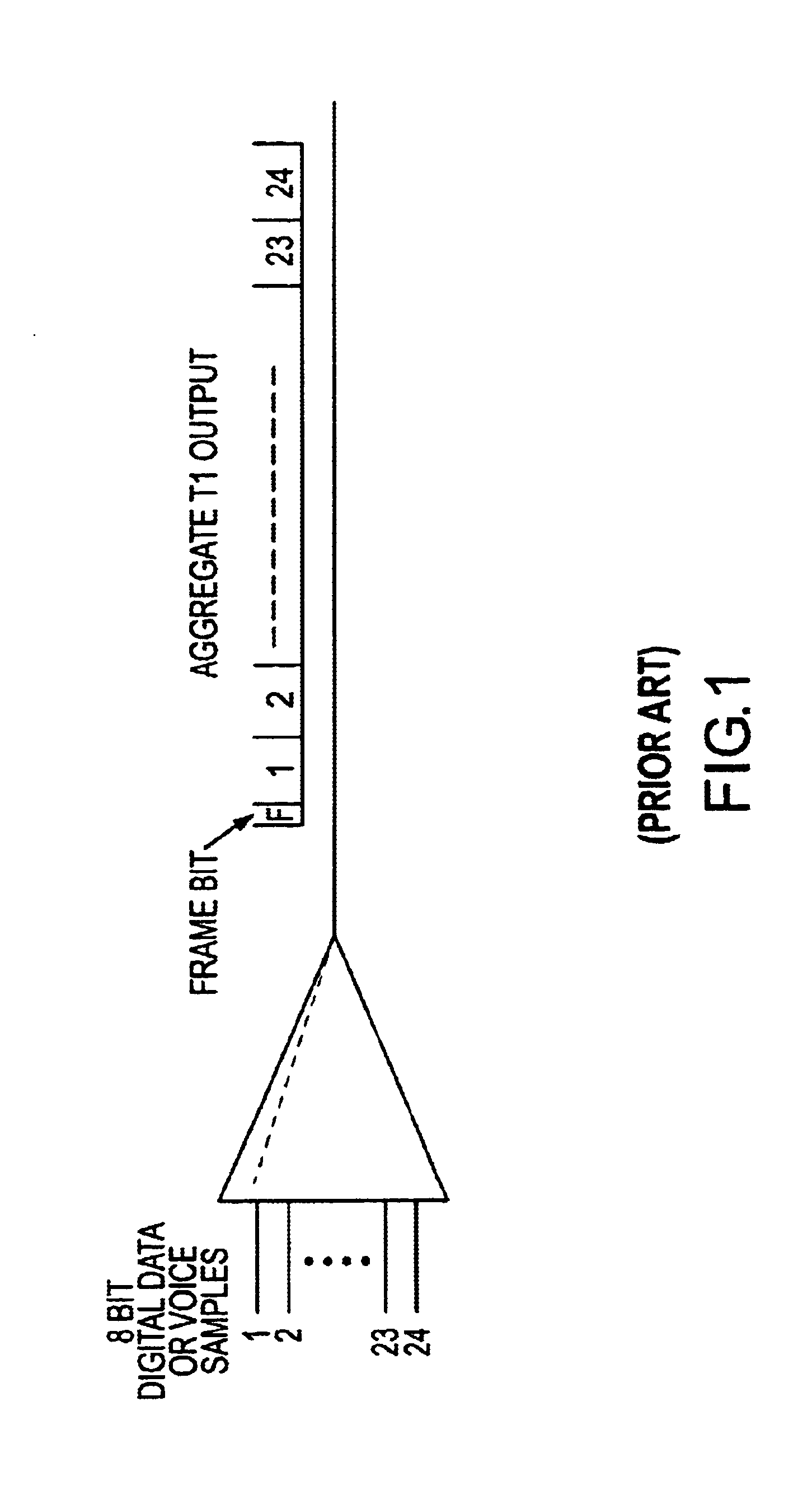

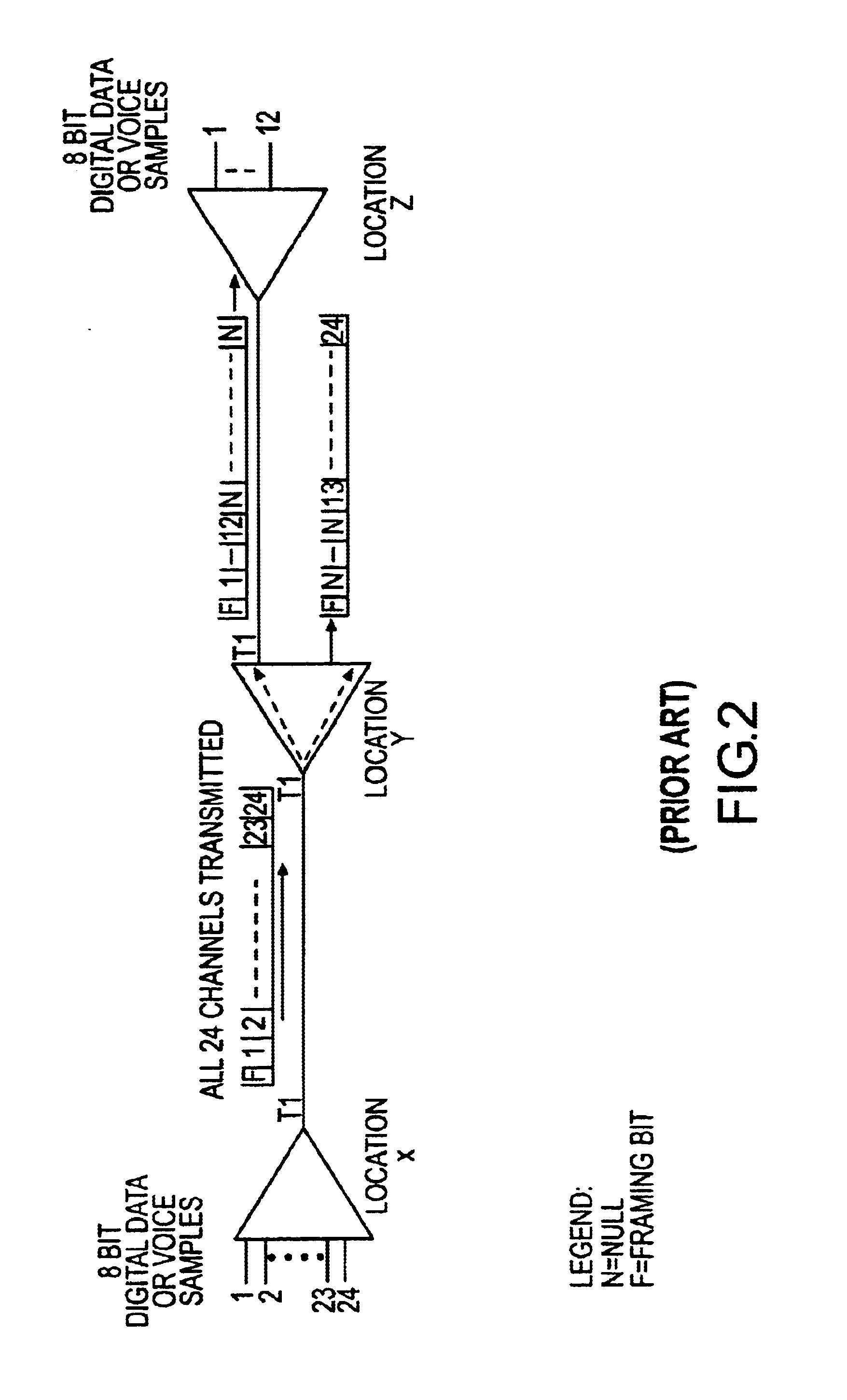

Processor-based voice and data time slot interchange system

InactiveUS6879603B1Small and less-expensiveImprove functionalityTime-division multiplexCircuit switching systemsShift registerMultiplexing

A technique for performing a time slot interchange in a processor. The TSI process is surrounded by a multiplexing / demultiplexing circuit for converting a plurality of PCM highways into a single input serial data stream. The mux / demux circuit includes elastic stores to align frames and shift resisters to mux / demux with a minimum of delay. The TSI processor includes an input and an output buffered series port, a pair of input buffers, one to receive even-numbered frames from the PCM highways and one to receive odd-numbered frames, and an output buffer. Data is read from the appropriate input buffer in a non-sequential fashion as commanded by the processor in accordance with information stored in connection arrays (address buffers). The data is then written to the output buffer sequentially. The timing of the reading and writing steps is optimized relative to free running buffered serial port pointers for each BSP to reduce the frame delay.

Owner:DELL MARKETING CORP

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com