Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

82 results about "Time-Slot Interchange" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

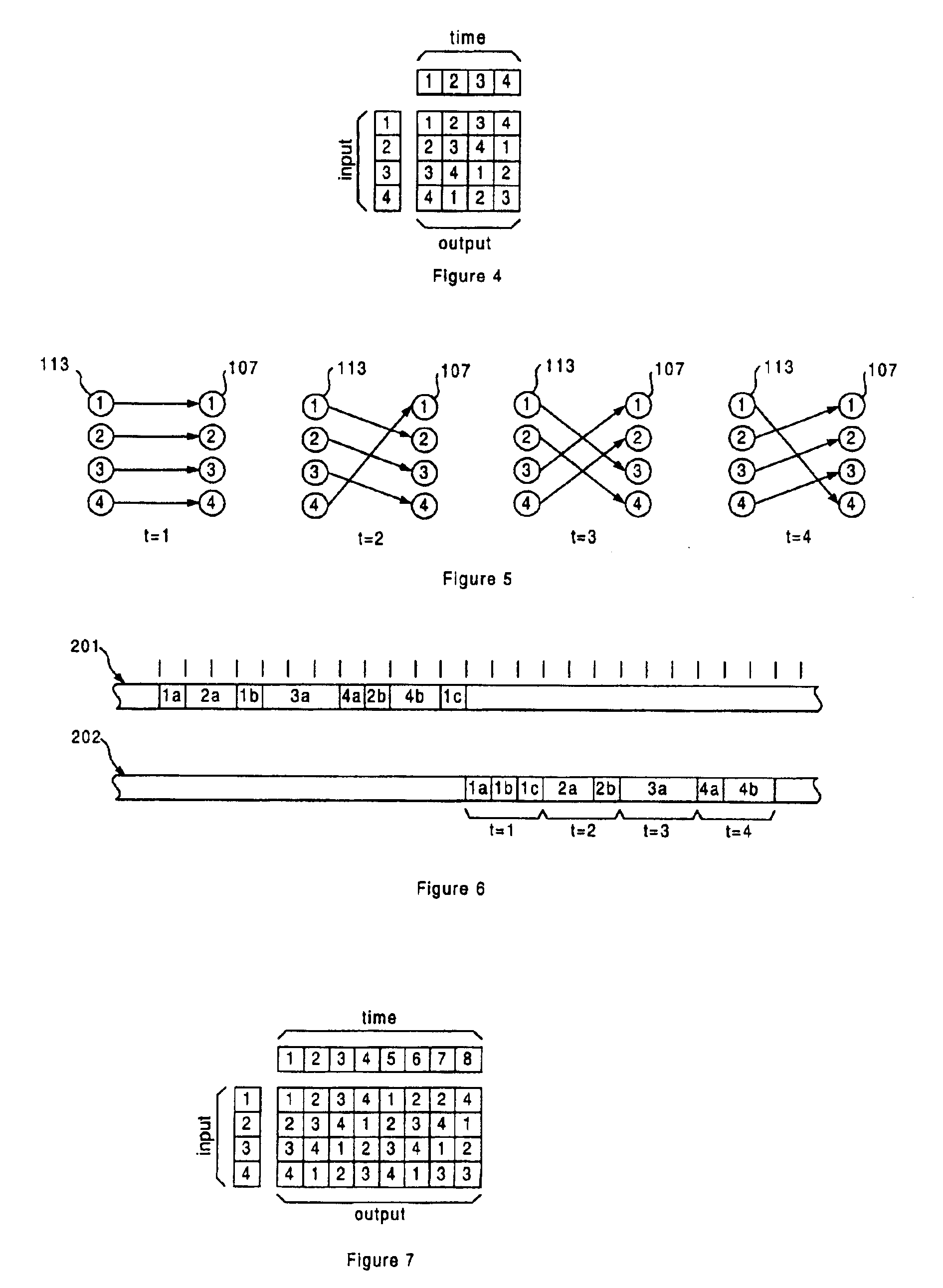

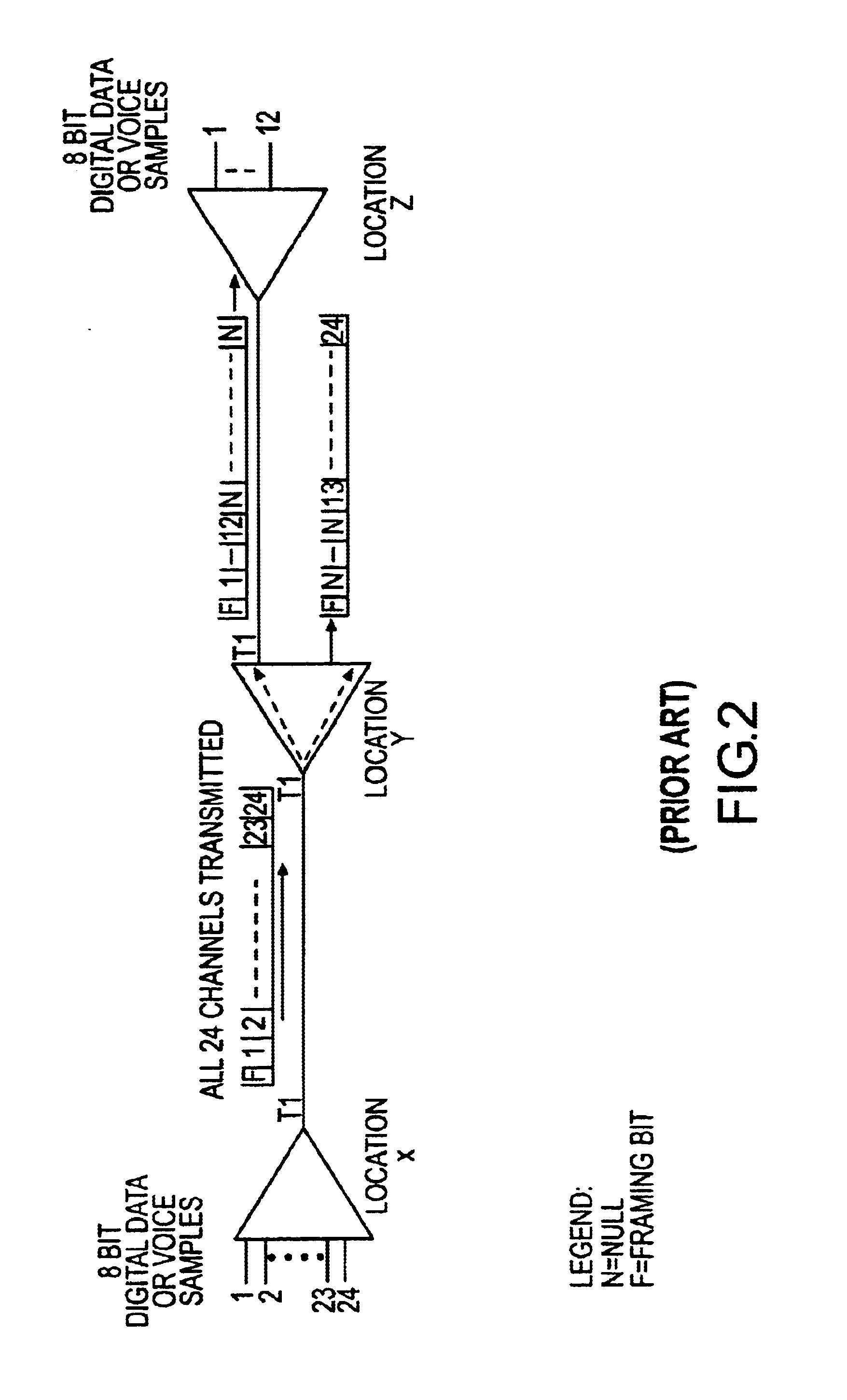

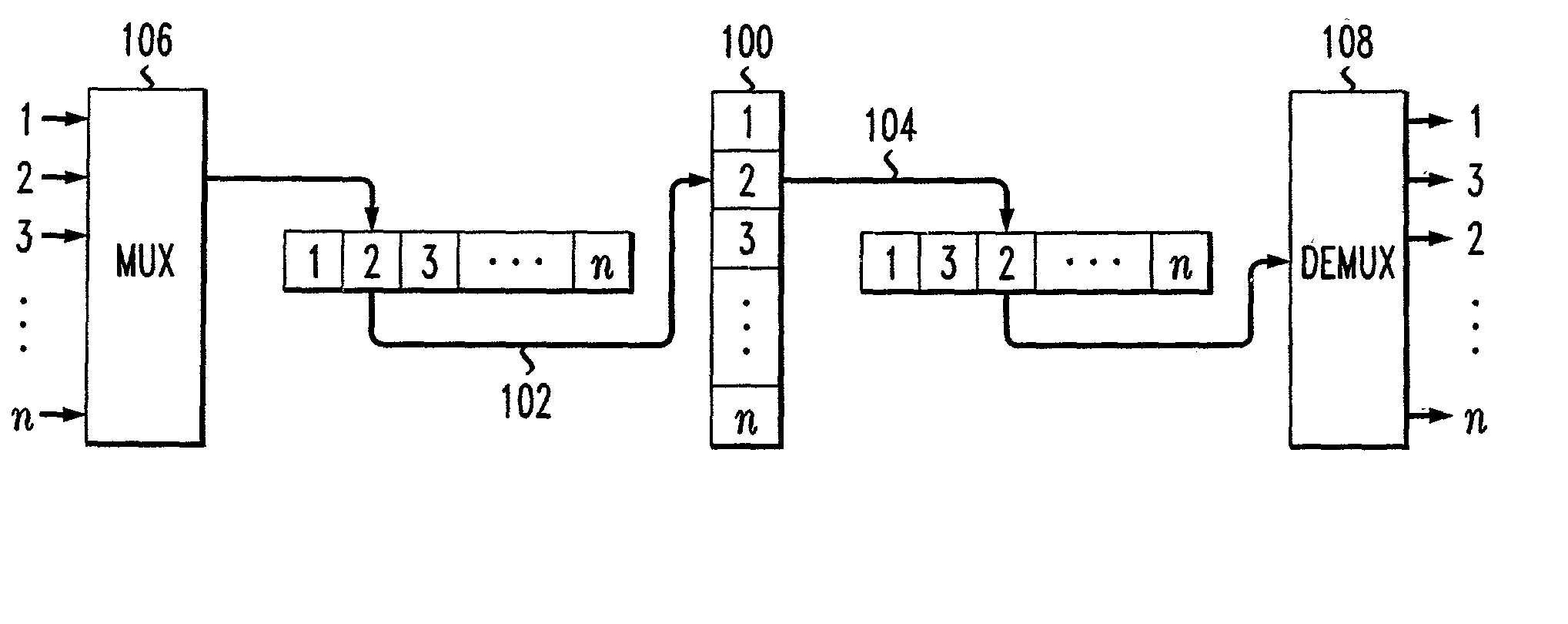

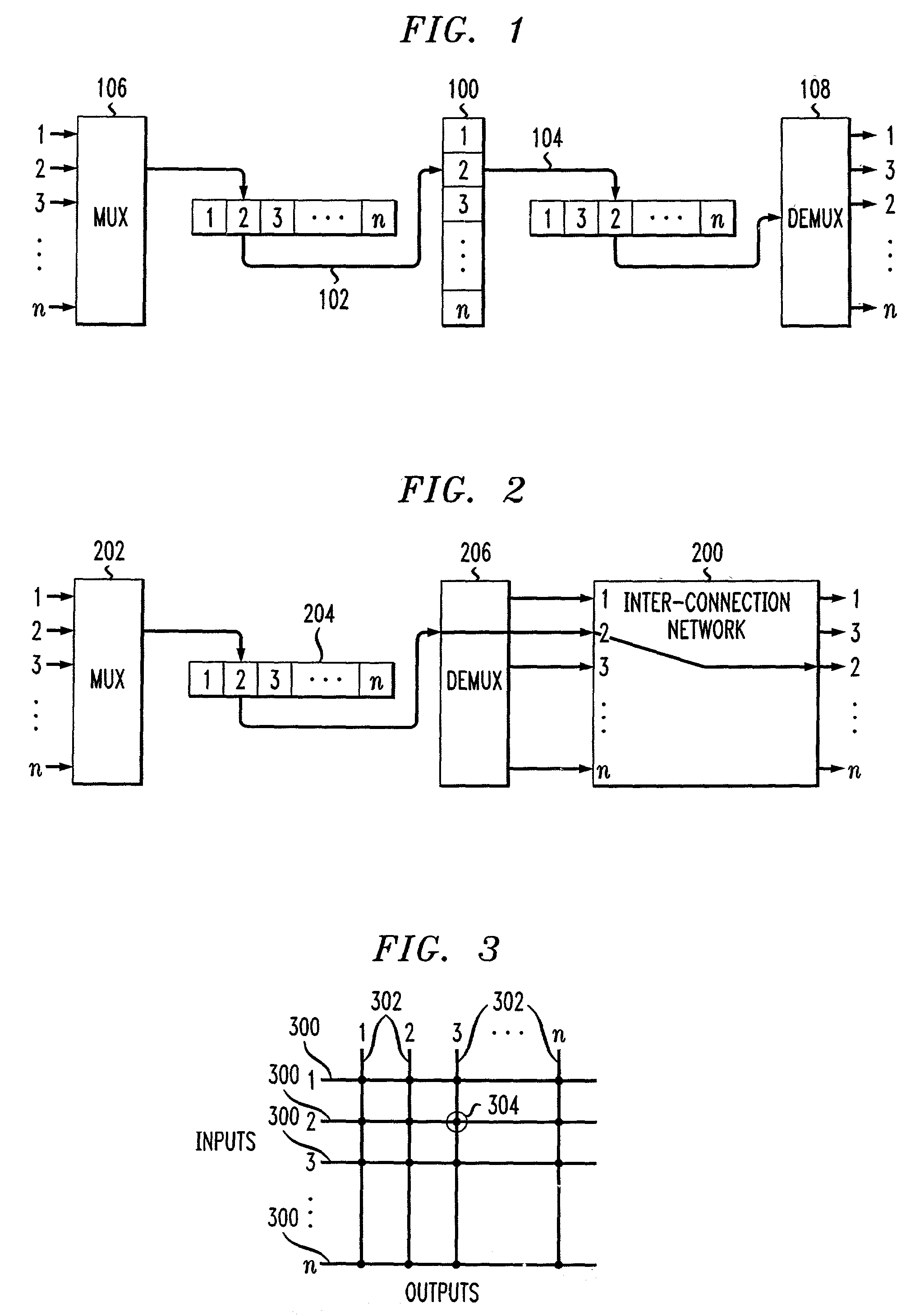

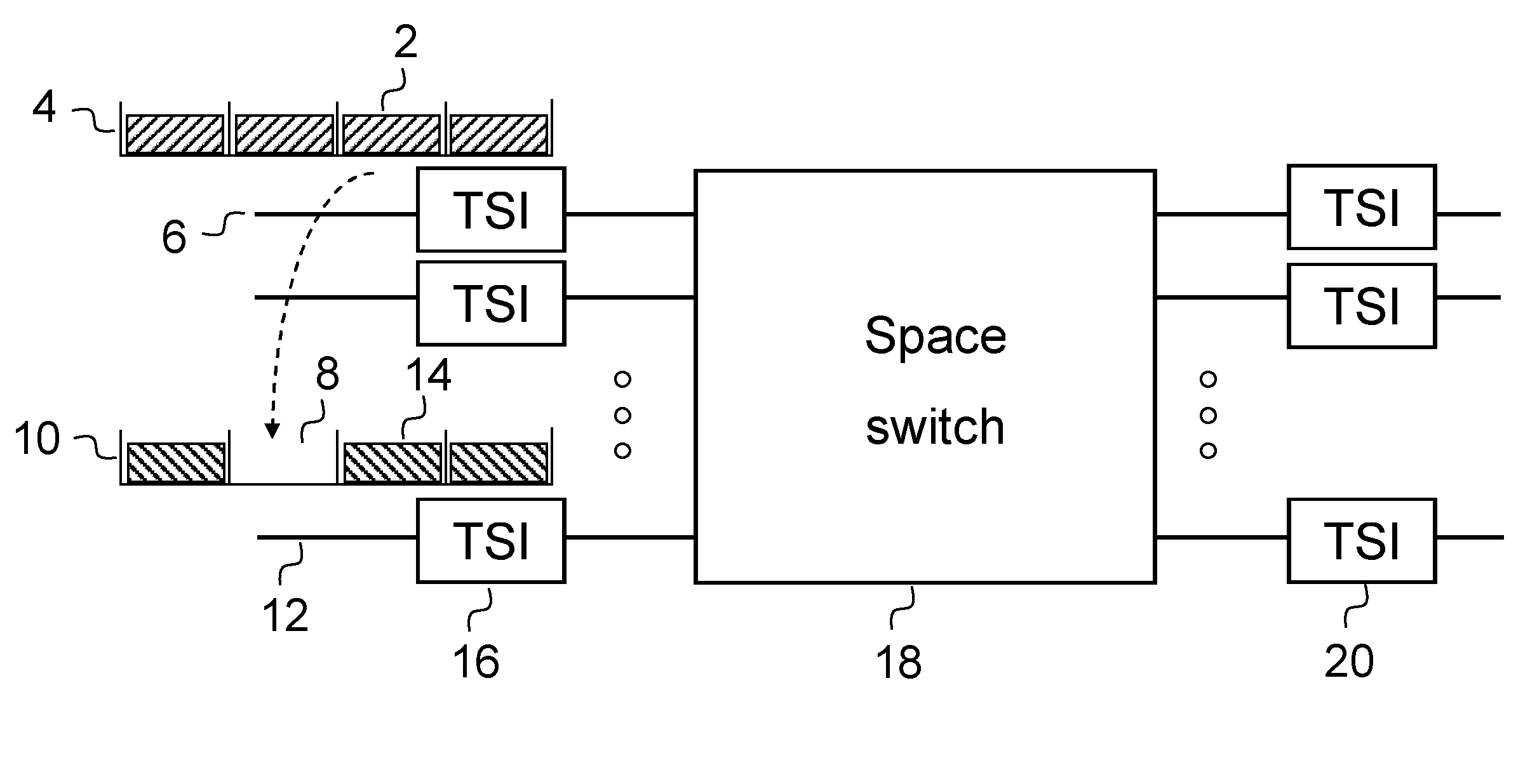

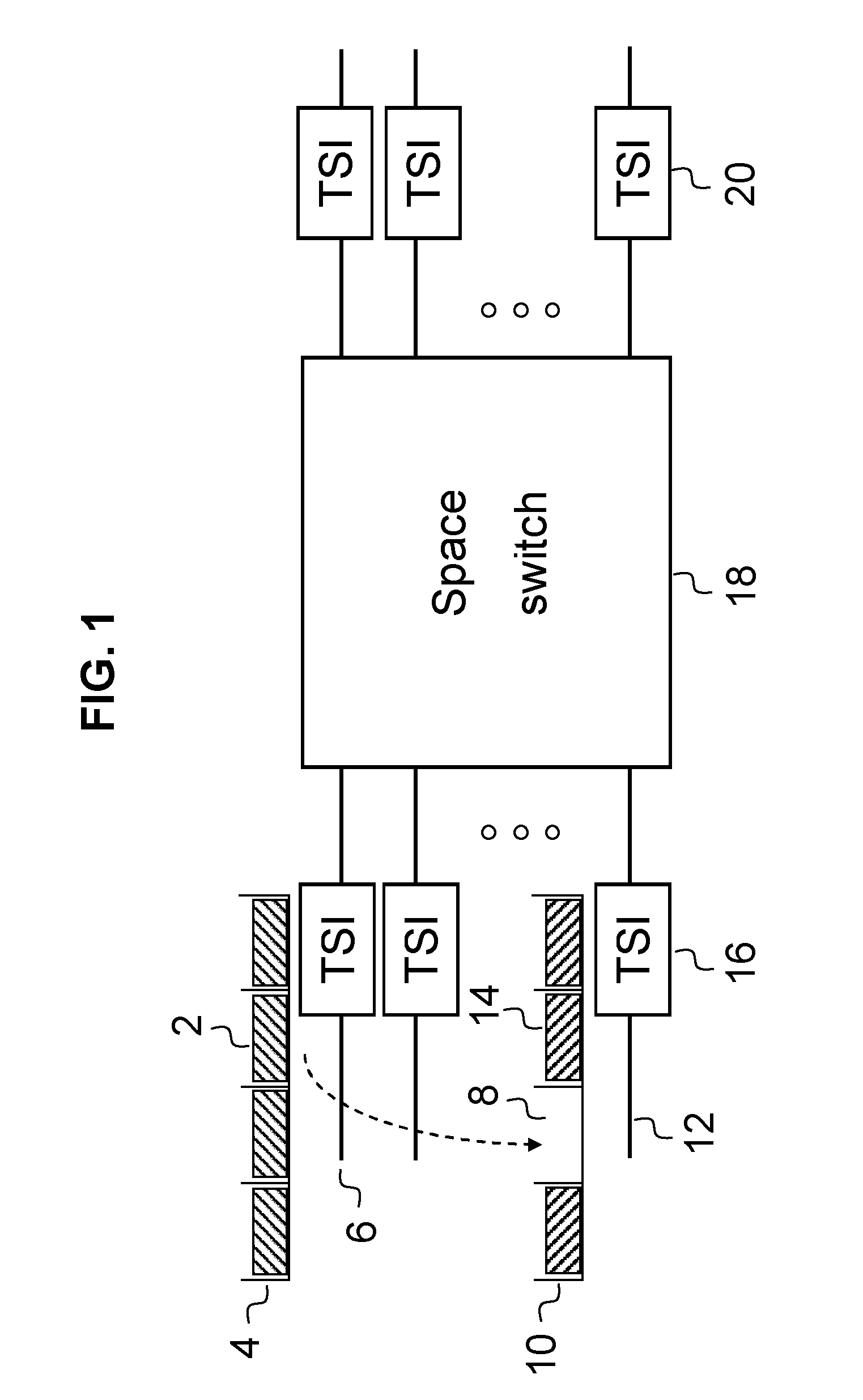

A time-slot interchange (TSI) switch is a network switch that stores data in RAM in one sequence, and reads it out in a different sequence. It uses RAM, a small routing memory and a counter. Like any switch, it has input and output ports. The RAM stores the packets or other data that arrive via its input terminal.

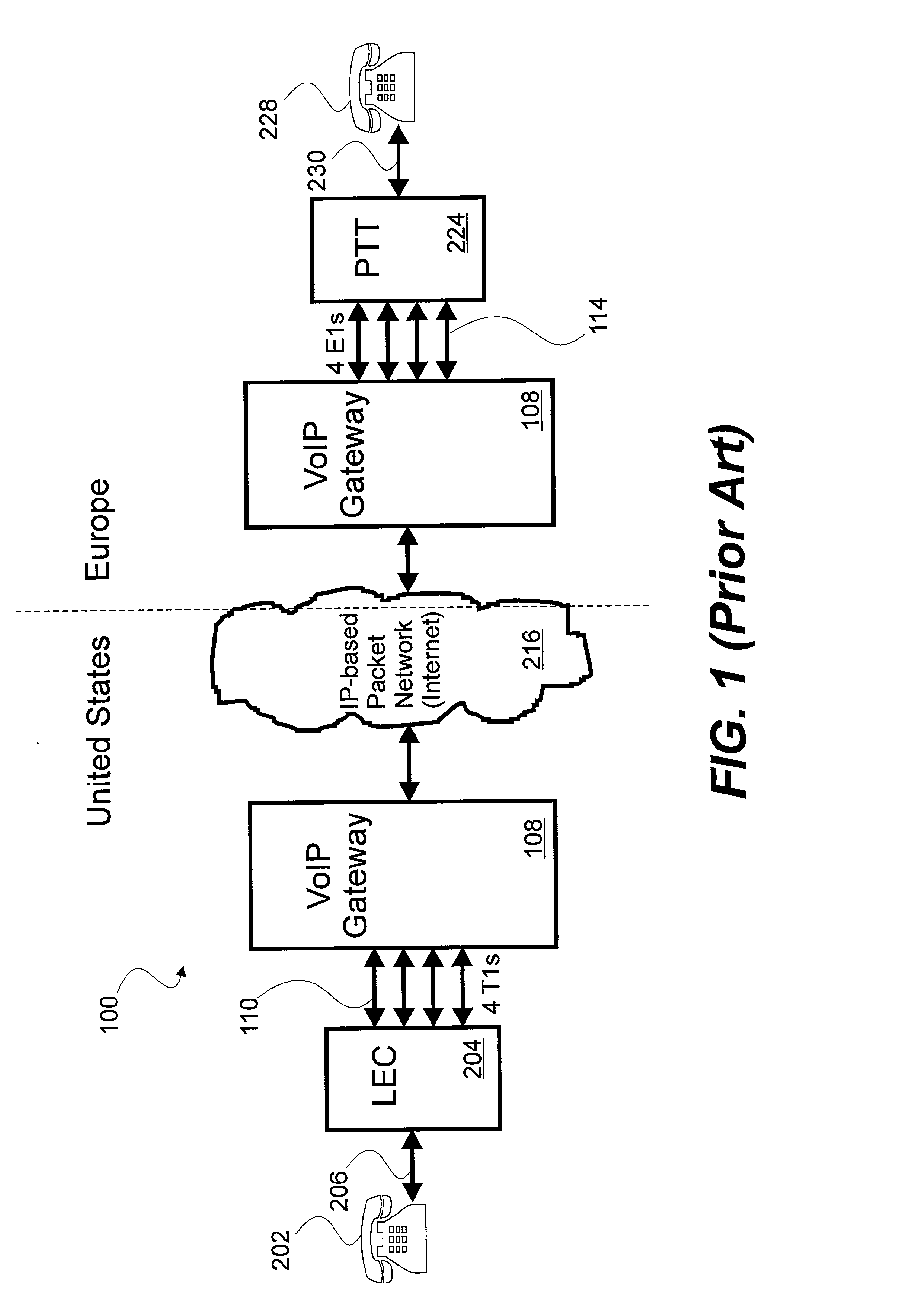

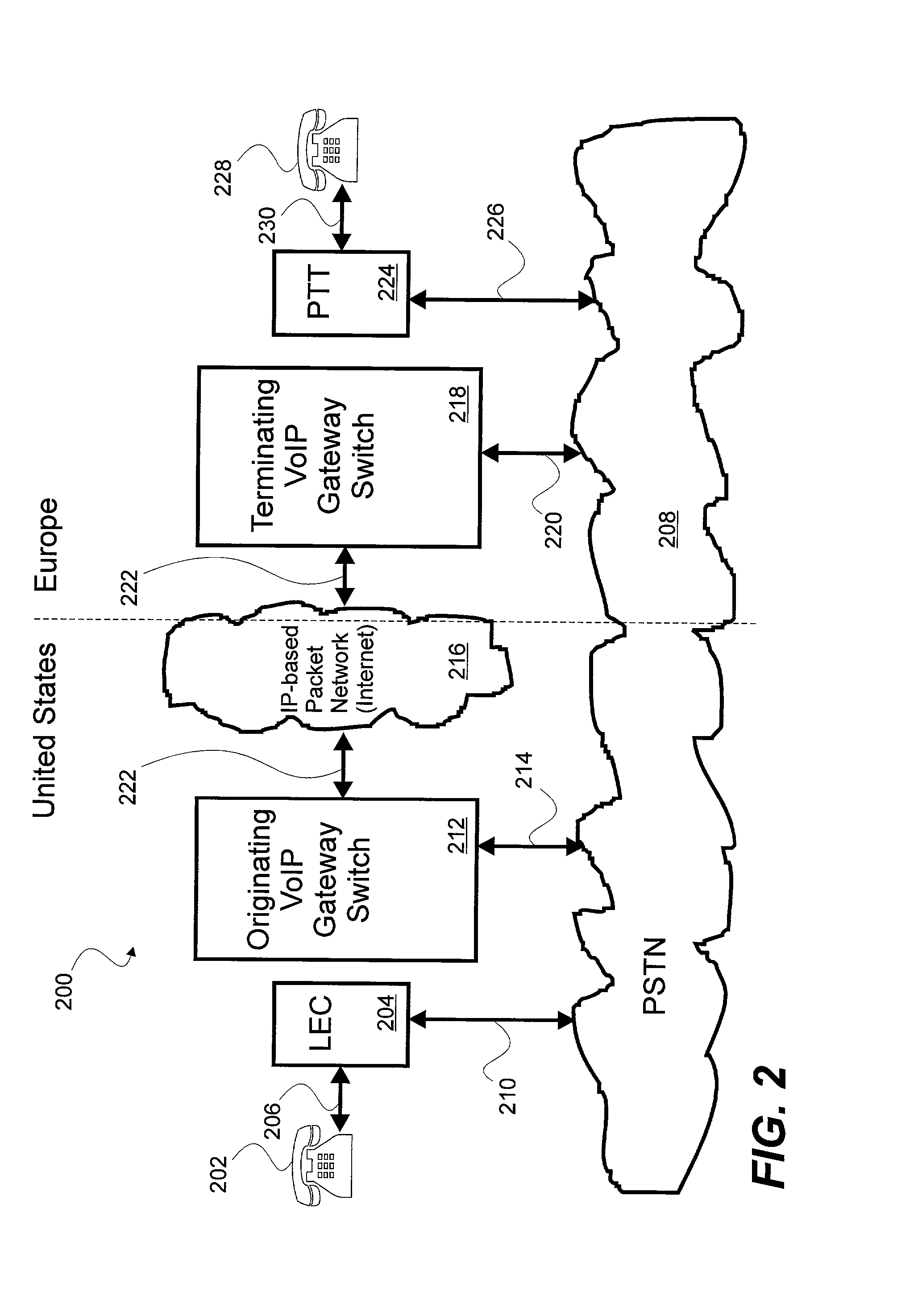

System, apparatus and method for voice over internet protocol telephone calling using enhanced signaling packets and localized time slot interchanging

InactiveUS20020141386A1Multiplex system selection arrangementsInterconnection arrangementsVoIP phoneTime-Slot Interchange

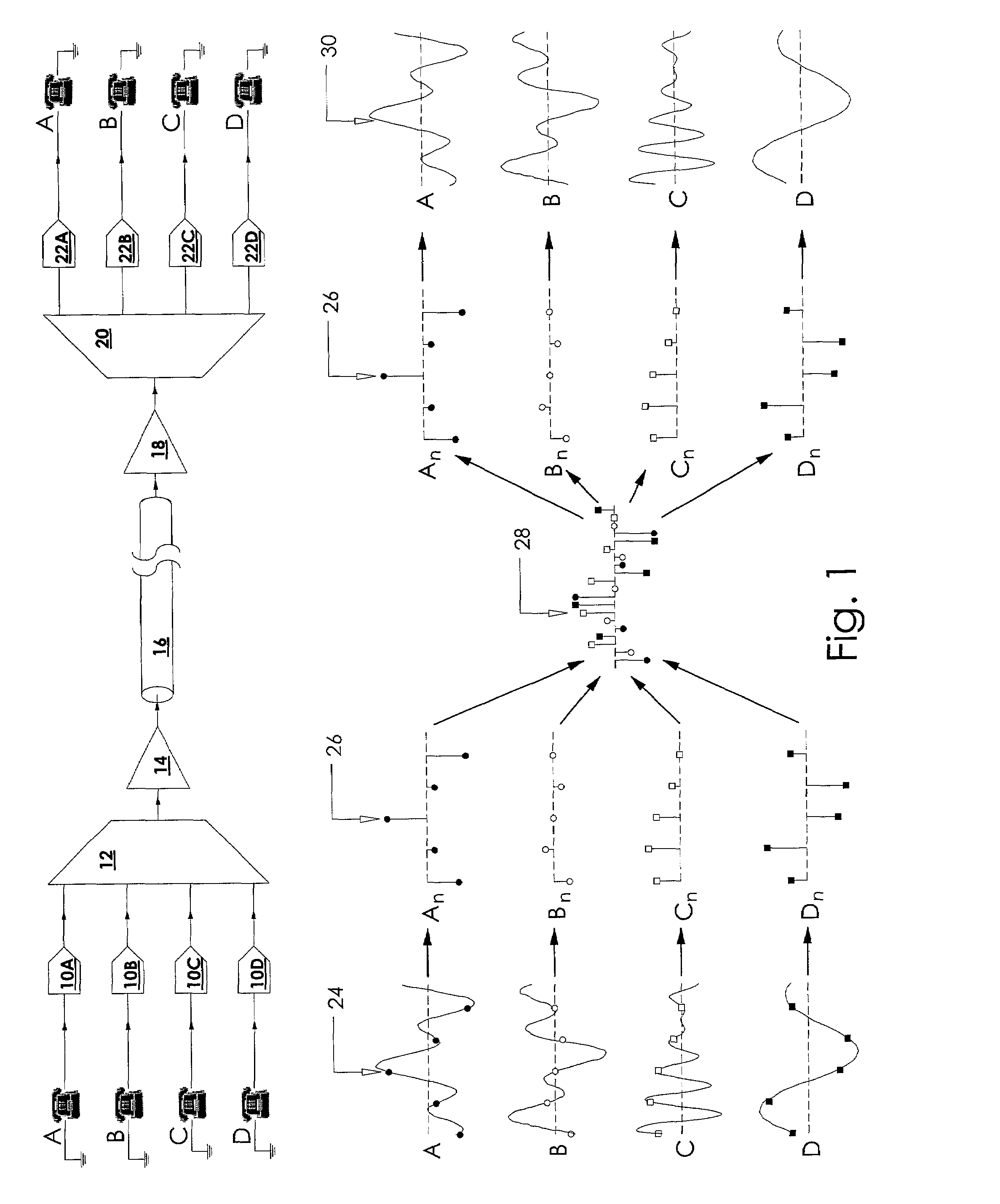

The present invention is a system, apparatus and method for voice over Internet protocol telephone (VoIP) calling using enhanced SS7 signaling packets and may include localized time slot interchanging. A system embodiment of the invention includes originating and terminating VoIP gateway switches in communication with the public switched telephone network (PSTN) and also in communication with an IP-based packet network, such as the Internet, for transmitting packets. The VoIP gateway switches are configured to exchange enhanced SS7 signaling packets over the IP-based packet network for setting up and tearing down VoIP telephone calls. A method of placing a VoIP telephone call in accordance with the present invention includes initiating a telephone call to a destination and connecting the telephone call to an originating VoIP gateway switch using enhanced SS7 signaling packets. The method also includes determining a preferred route from the originating VoIP gateway switch to the destination through an IP-based packet network and through a terminating VoIP gateway switch nearest said destination, and setting up two-way communication through the preferred route using the IP-based packet network using enhanced SS7 signaling packets.

Owner:NACT TELECOMM

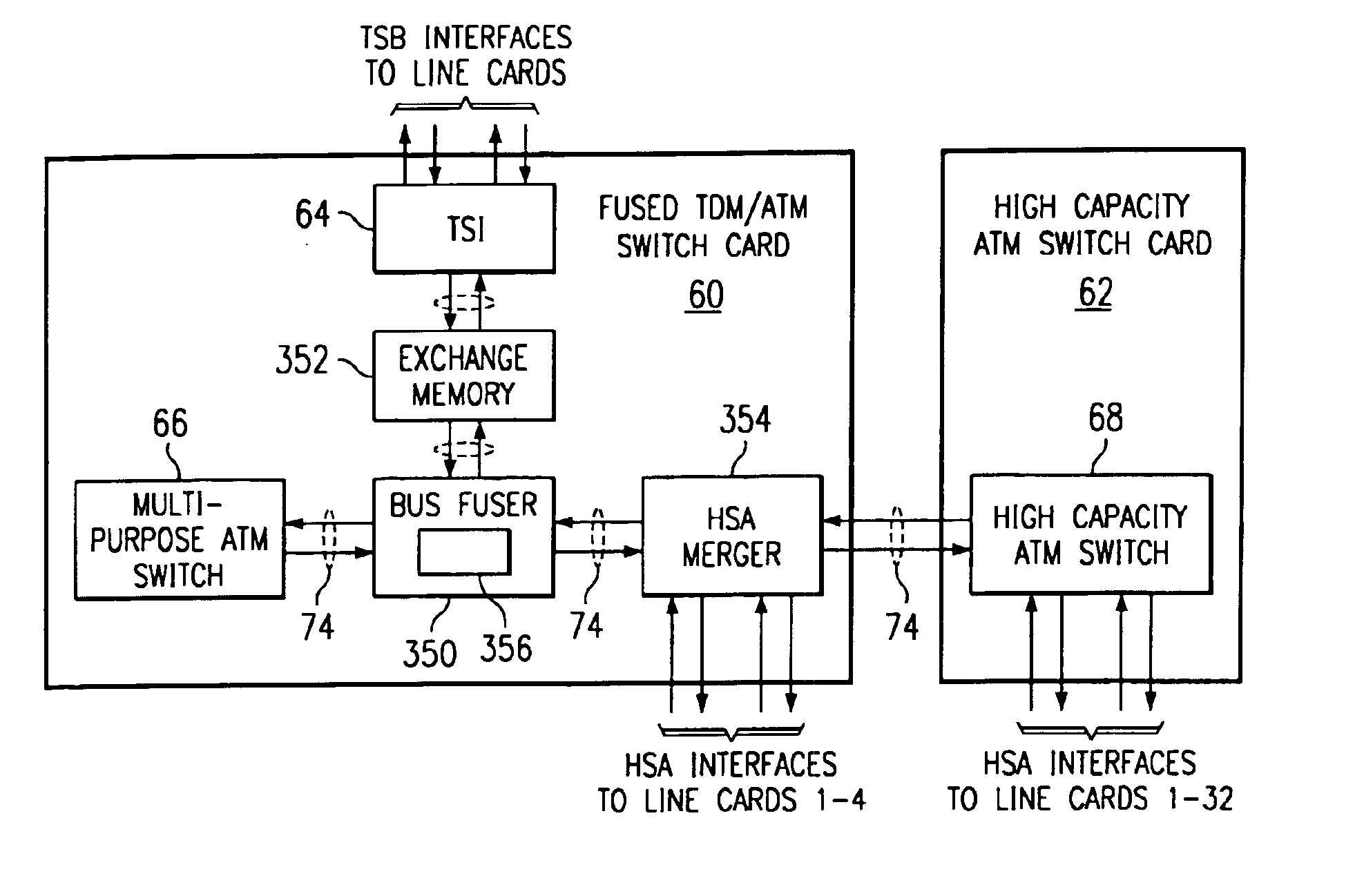

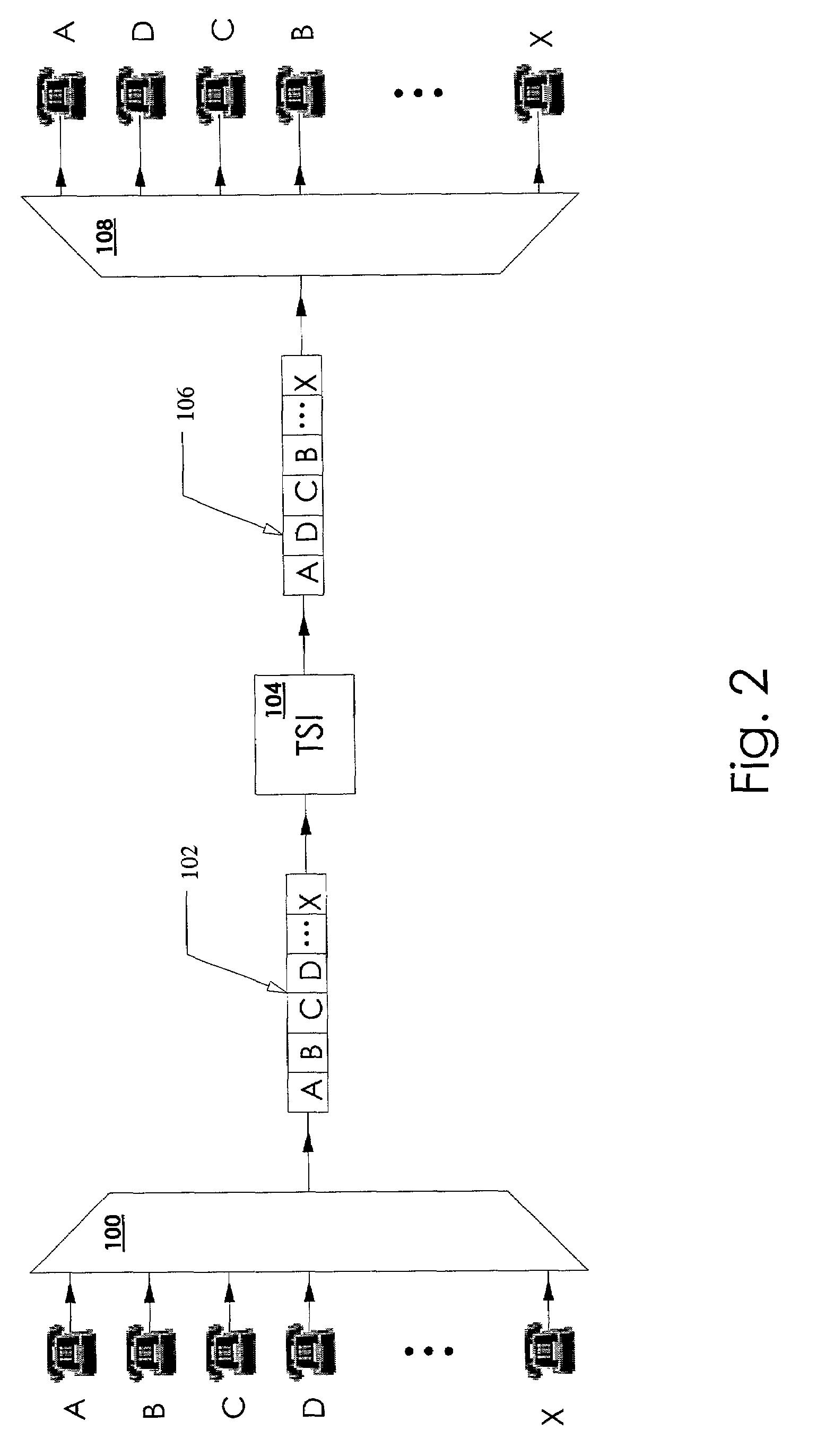

Time slot interchanger (TSI) and method for a telecommunications node

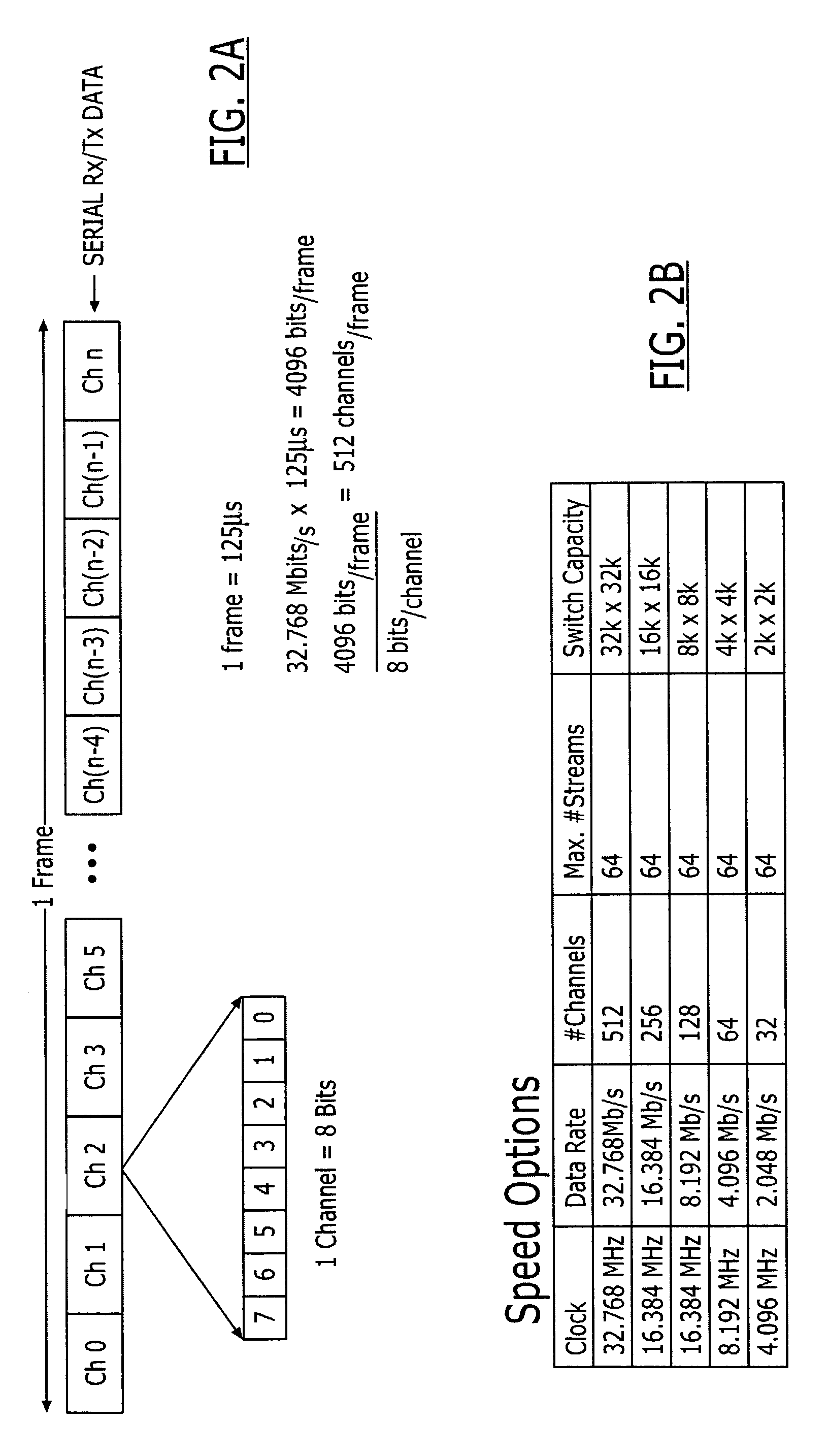

InactiveUS6944153B1Eliminate and reduce and disadvantageEliminate and reduce problemMultiplex system selection arrangementsTime-division multiplexTelecommunicationsTime-Slot Interchange

A time slot interchanger (TSI) for a telecommunications node includes an exchange memory and a controller. The exchange memory includes a plurality of exchange memory slots. Each exchange memory slot is sized to store a traffic channel and includes a plurality of discretely addressable fields sized to store a sub-channel. The controller is operable in response to predefined switching instructions to write a sub-channel received in a first traffic channel to a first field in a memory slot and to write a sub-channel received in a second traffic channel to a second field in the memory slot.

Owner:CISCO TECH INC

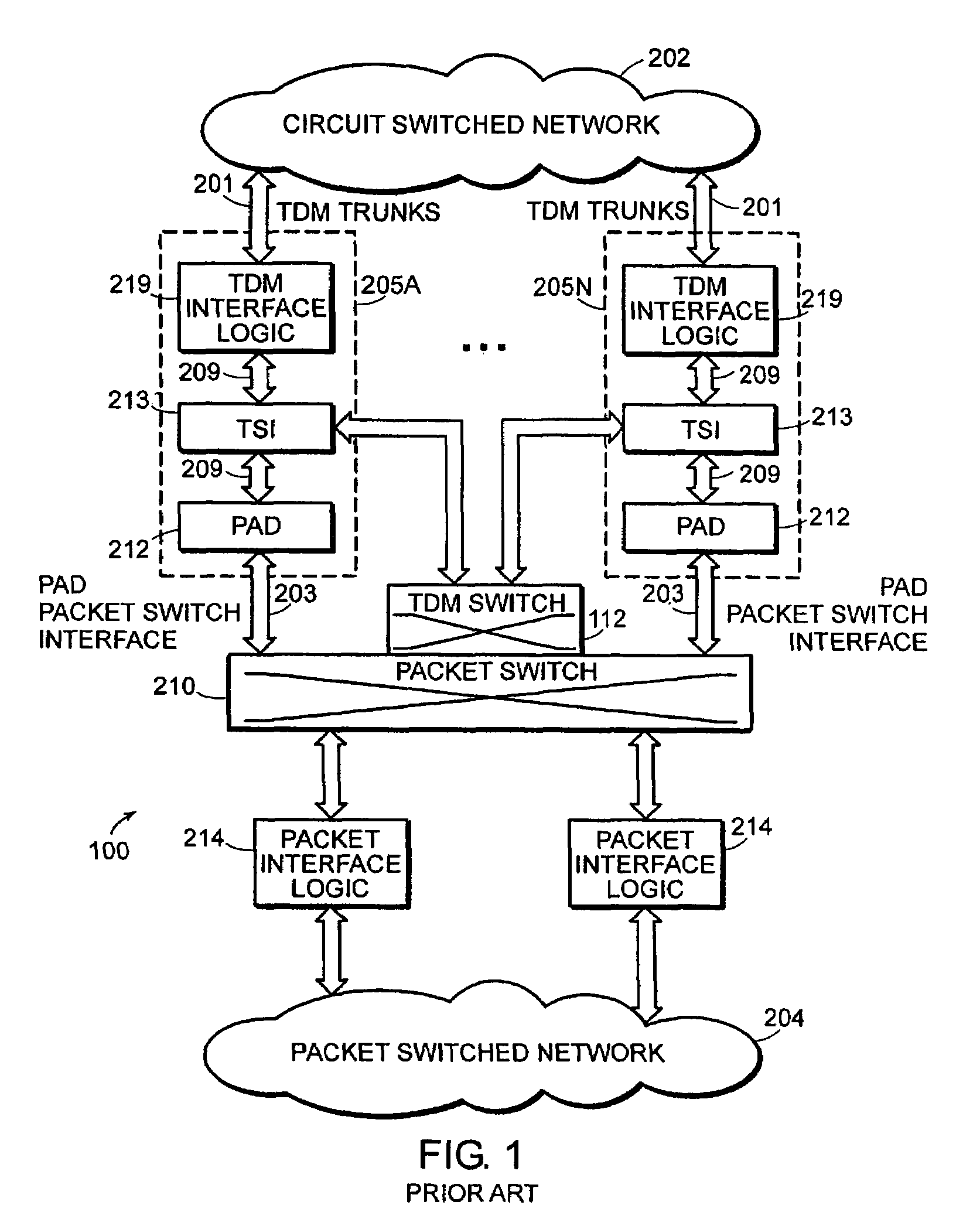

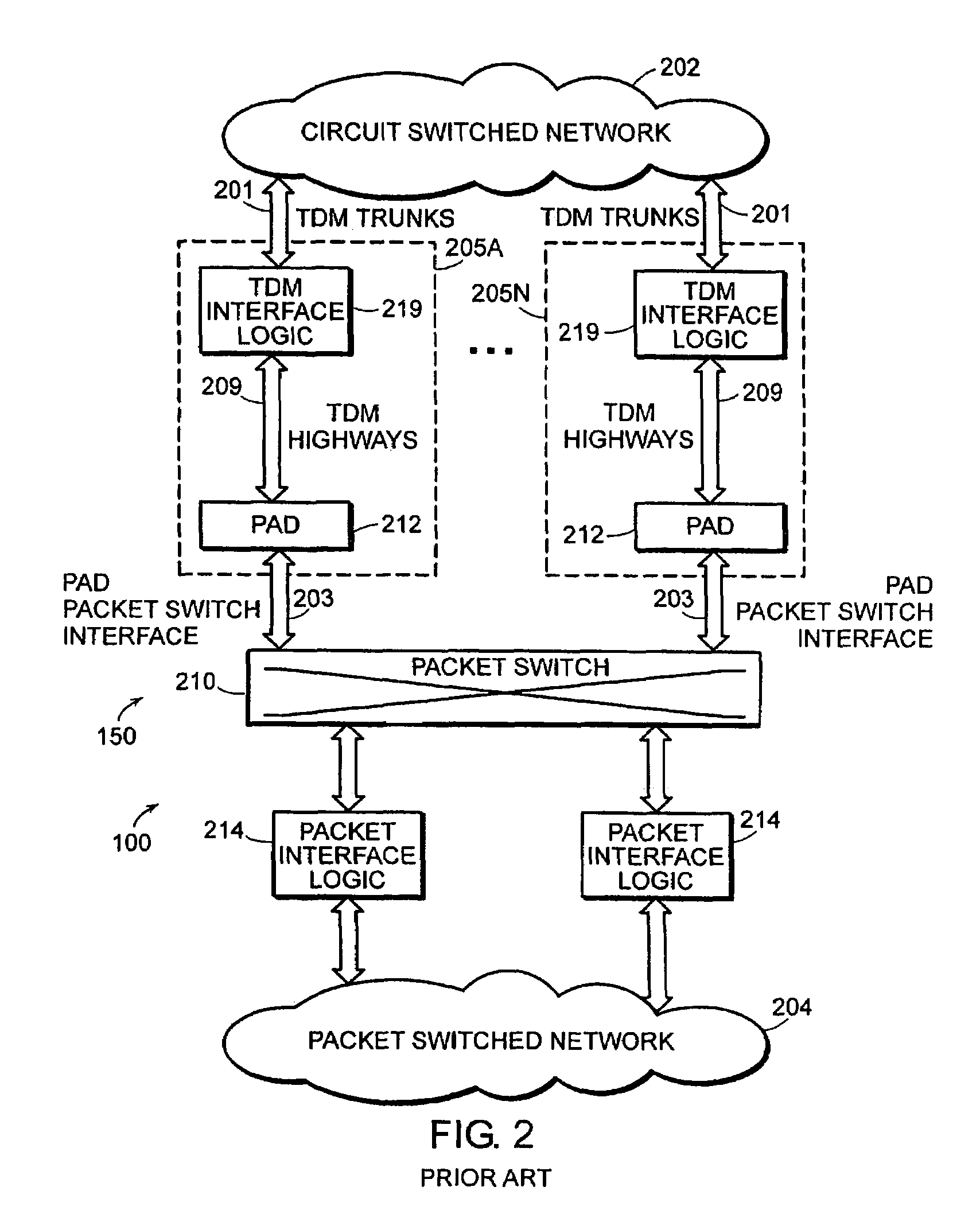

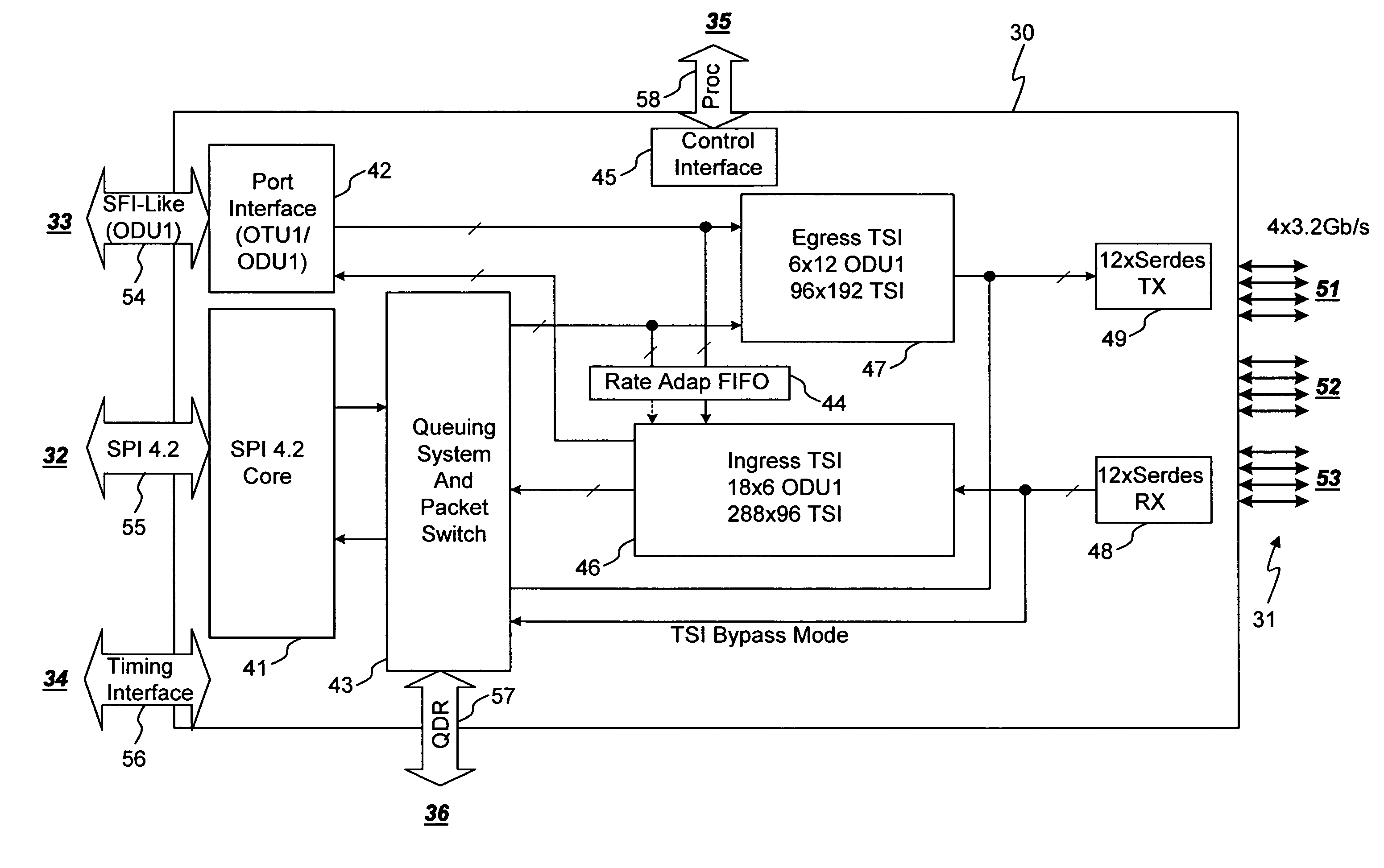

Systems and methods for combining time division multiplexed and packet connection in a meshed switching architecture

ActiveUS20080181203A1Low costAvoid complexityMultiplex system selection arrangementsTime-division multiplexComputer networkTime-Slot Interchange

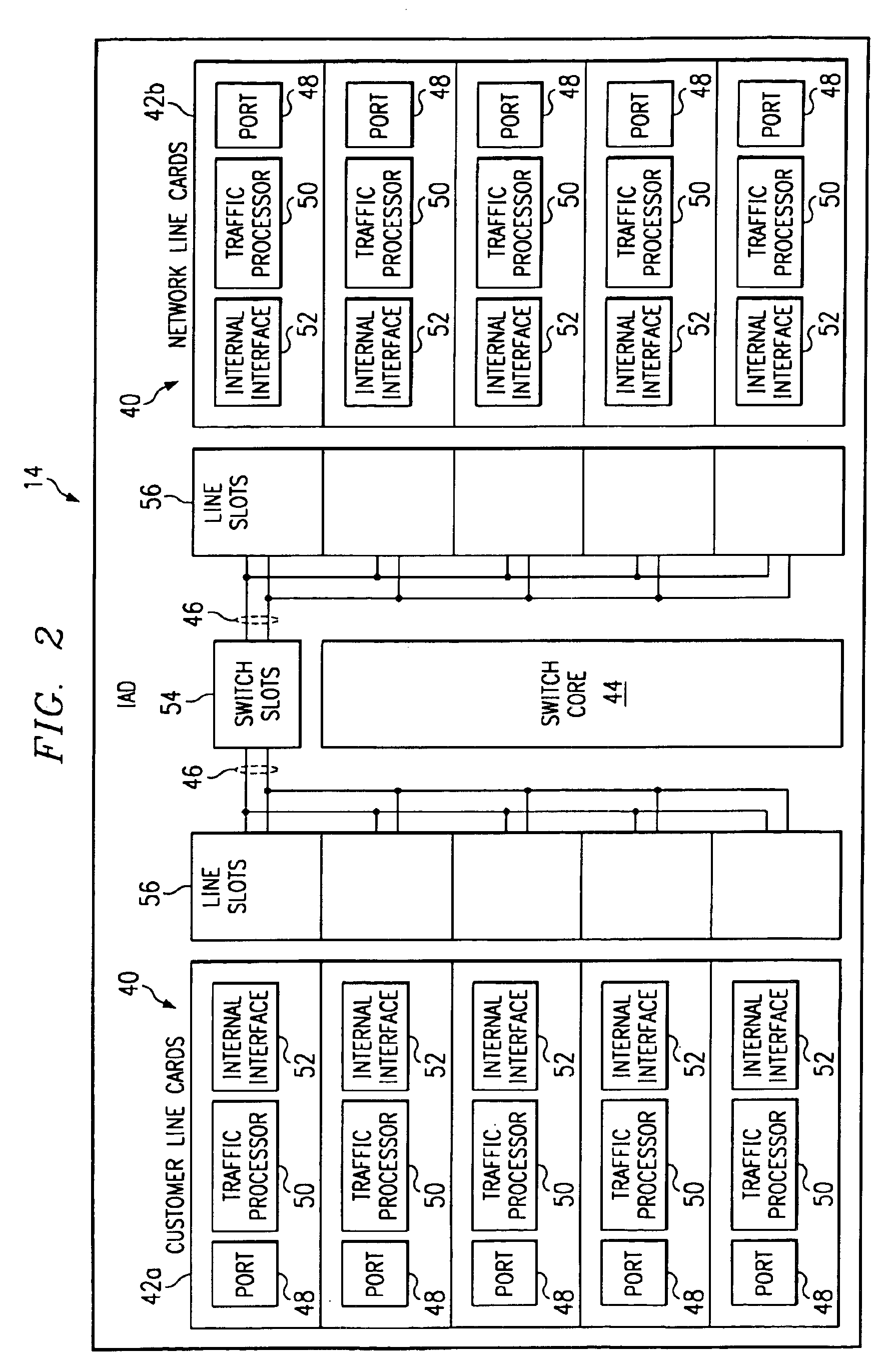

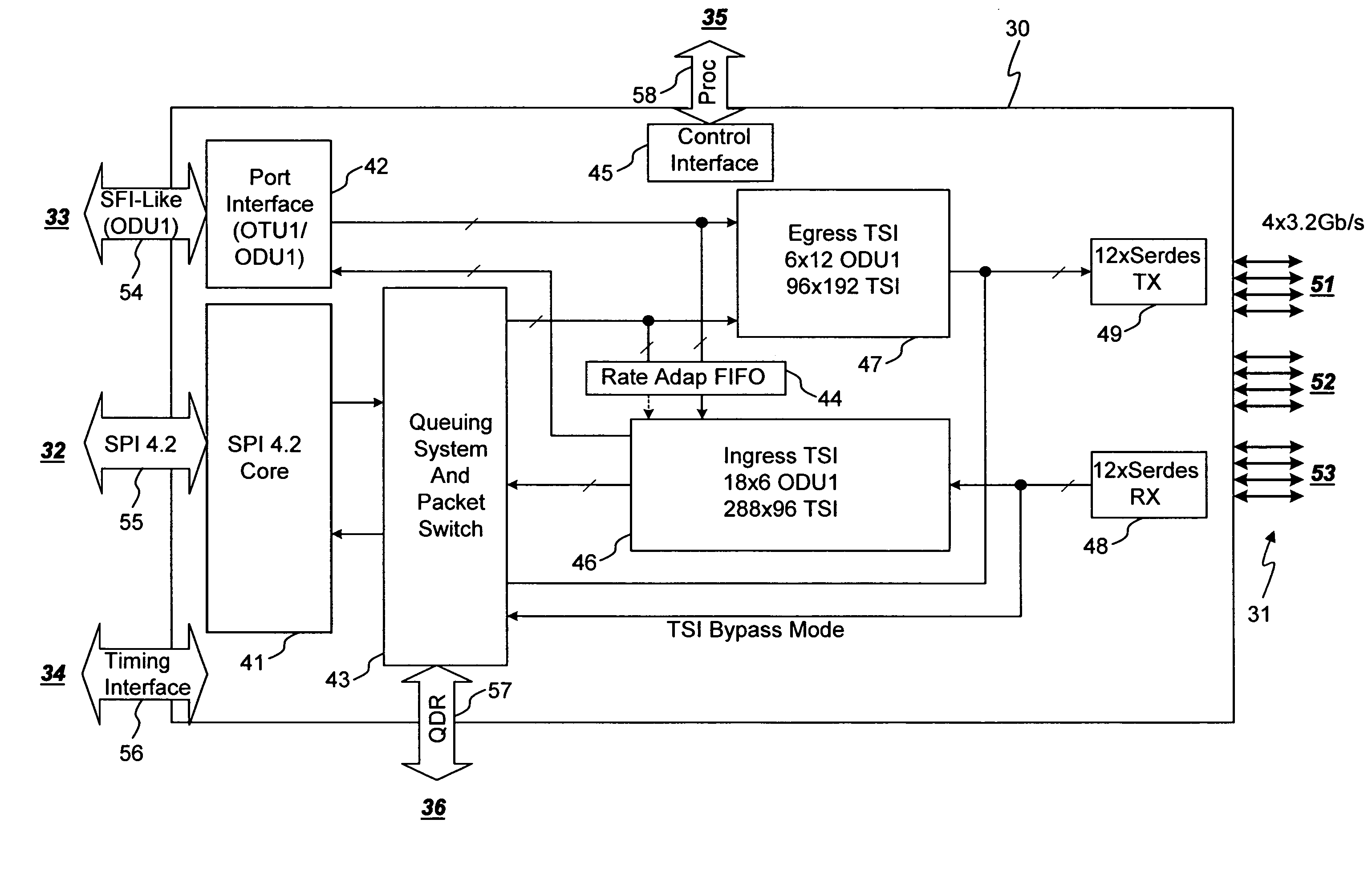

The present invention provides systems and methods for supporting native TDM and native Packet switching simultaneously in a meshed switching architecture. Specifically with the present invention, the meshed links are common to both TDM and packet traffic, and both types terminate to a common system interface without the need to separate physical resources and infrastructure; the common termination function has access to both the TDM (Time Slot Interchange (TSI)) switching and packet switching elements. Native TDM switching and packet switching operate in concurrently in the mesh over common links, with the personality of the links derived by the card type (attached to the mesh). In this, a given card or slot in a system can communicate in the native format to both packet based cards (slots) or TDM based cards (slots) simultaneously with no preconceived restrictions or limitations on slot or link definition.

Owner:CIENA

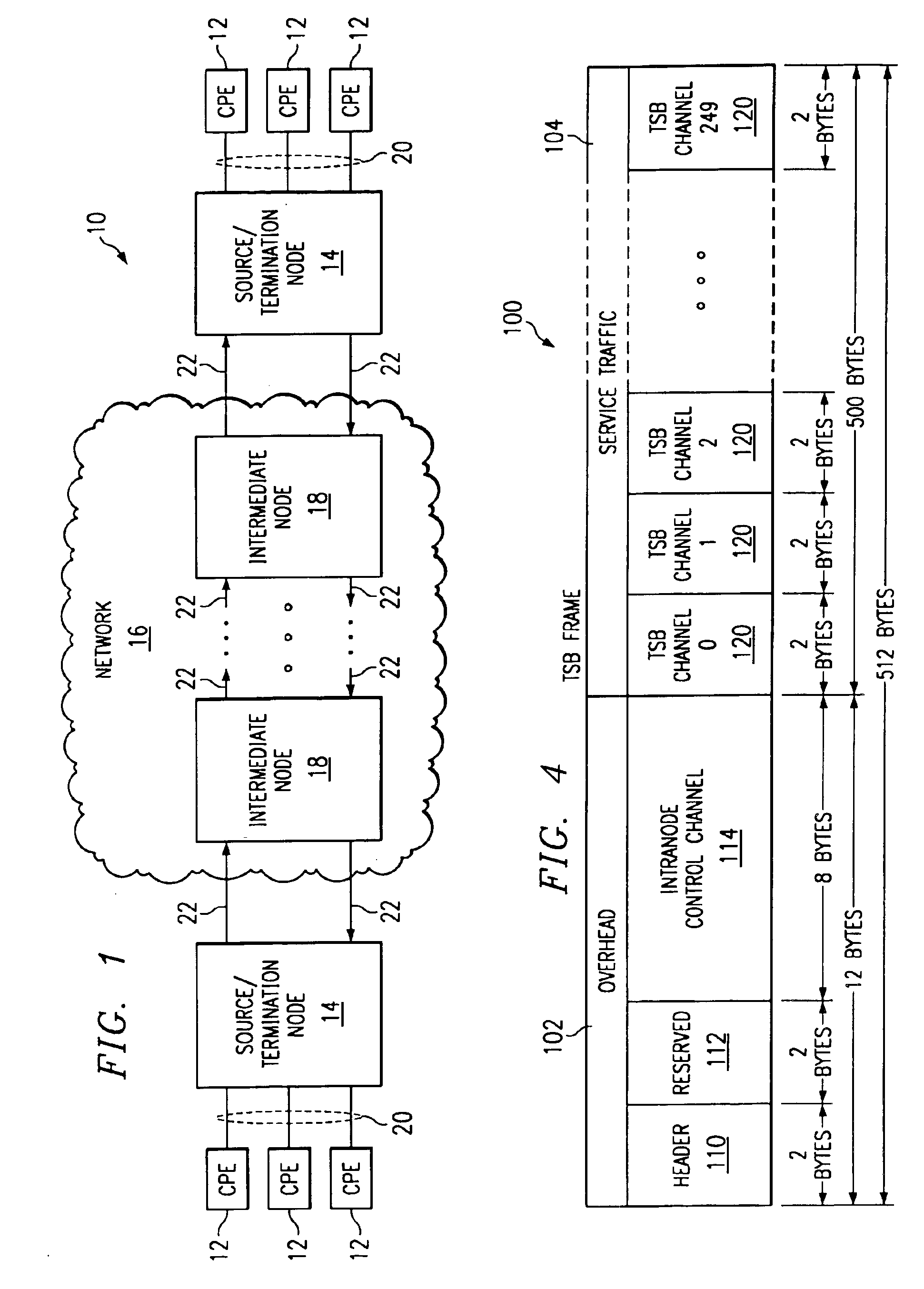

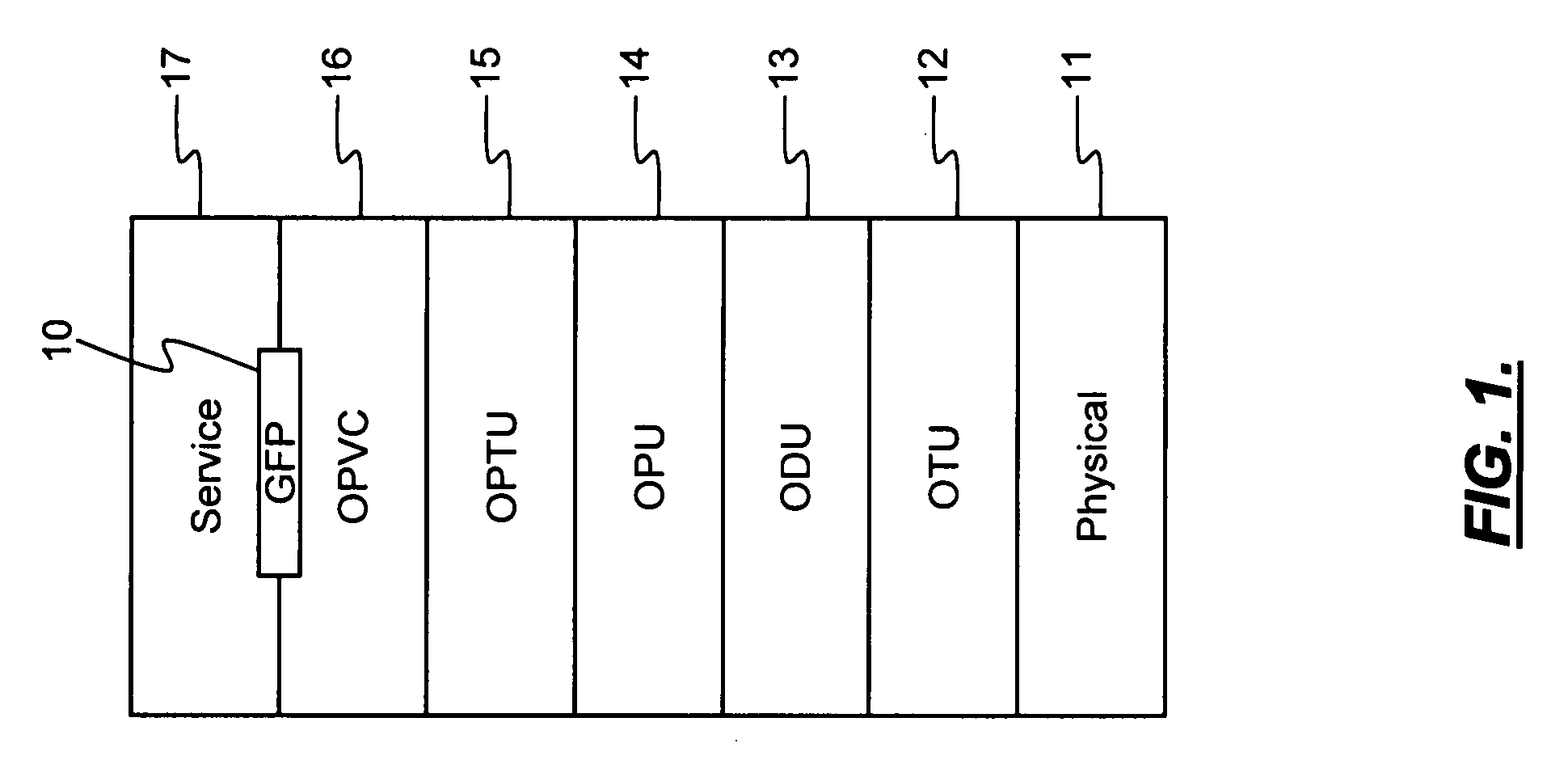

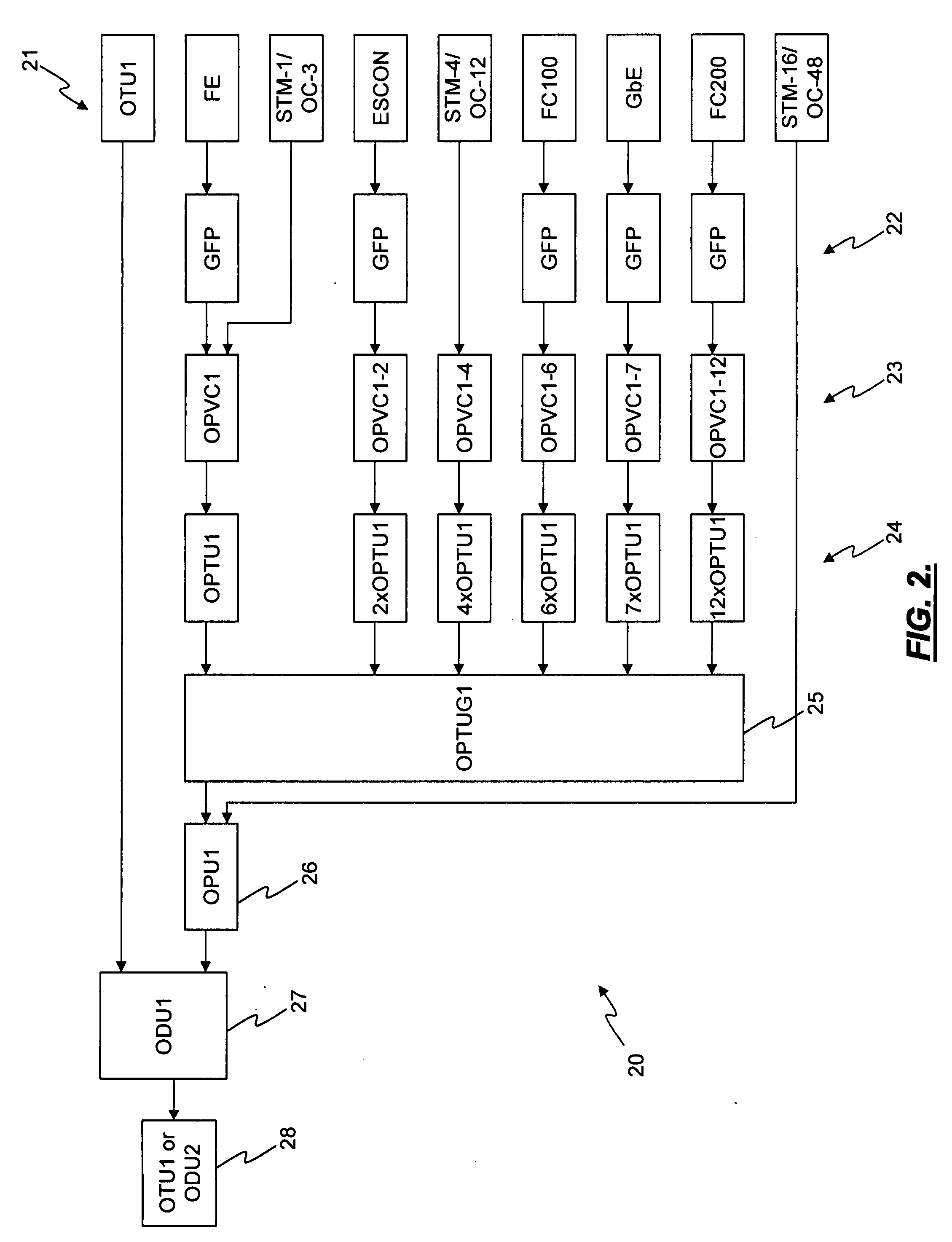

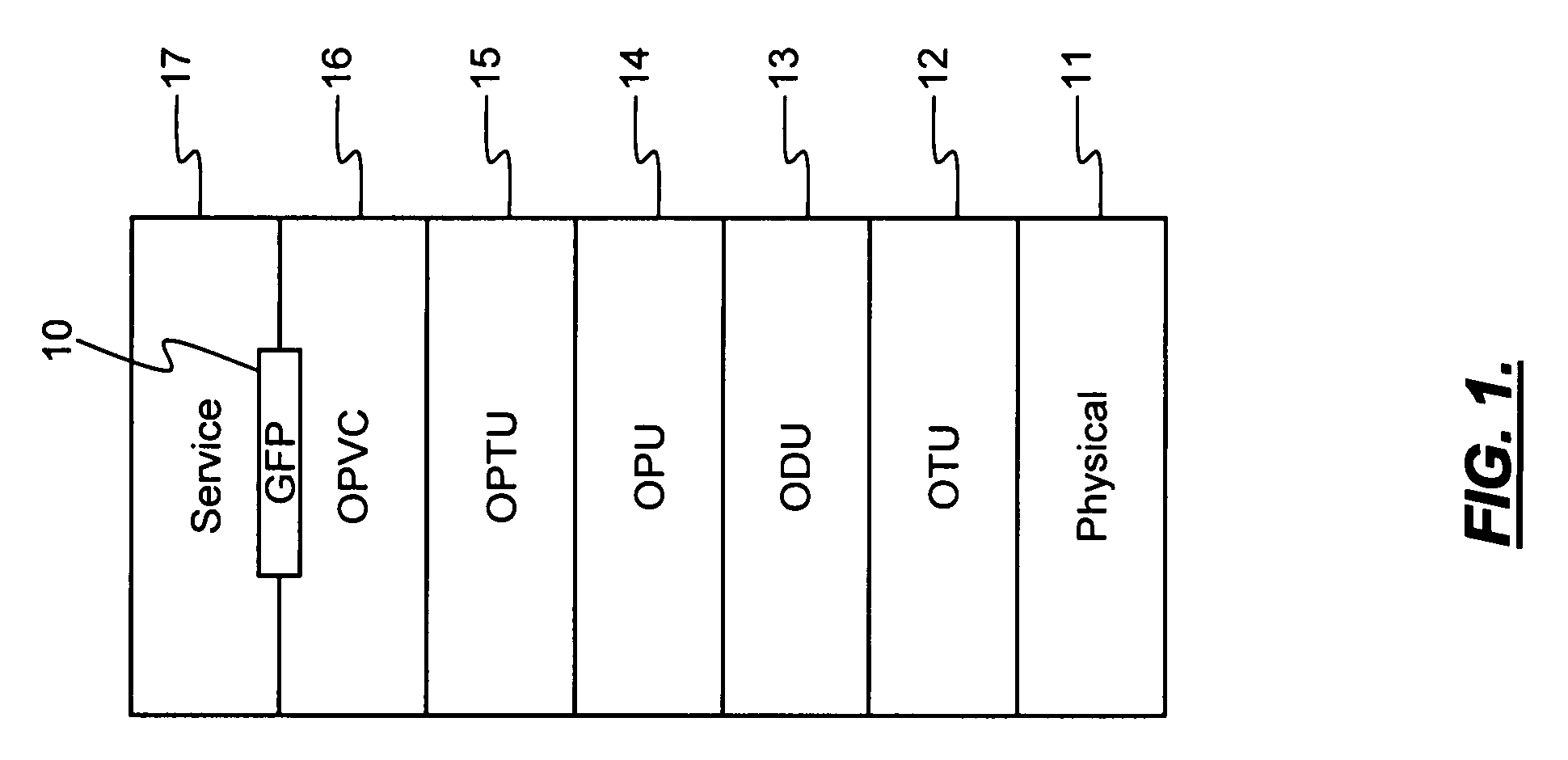

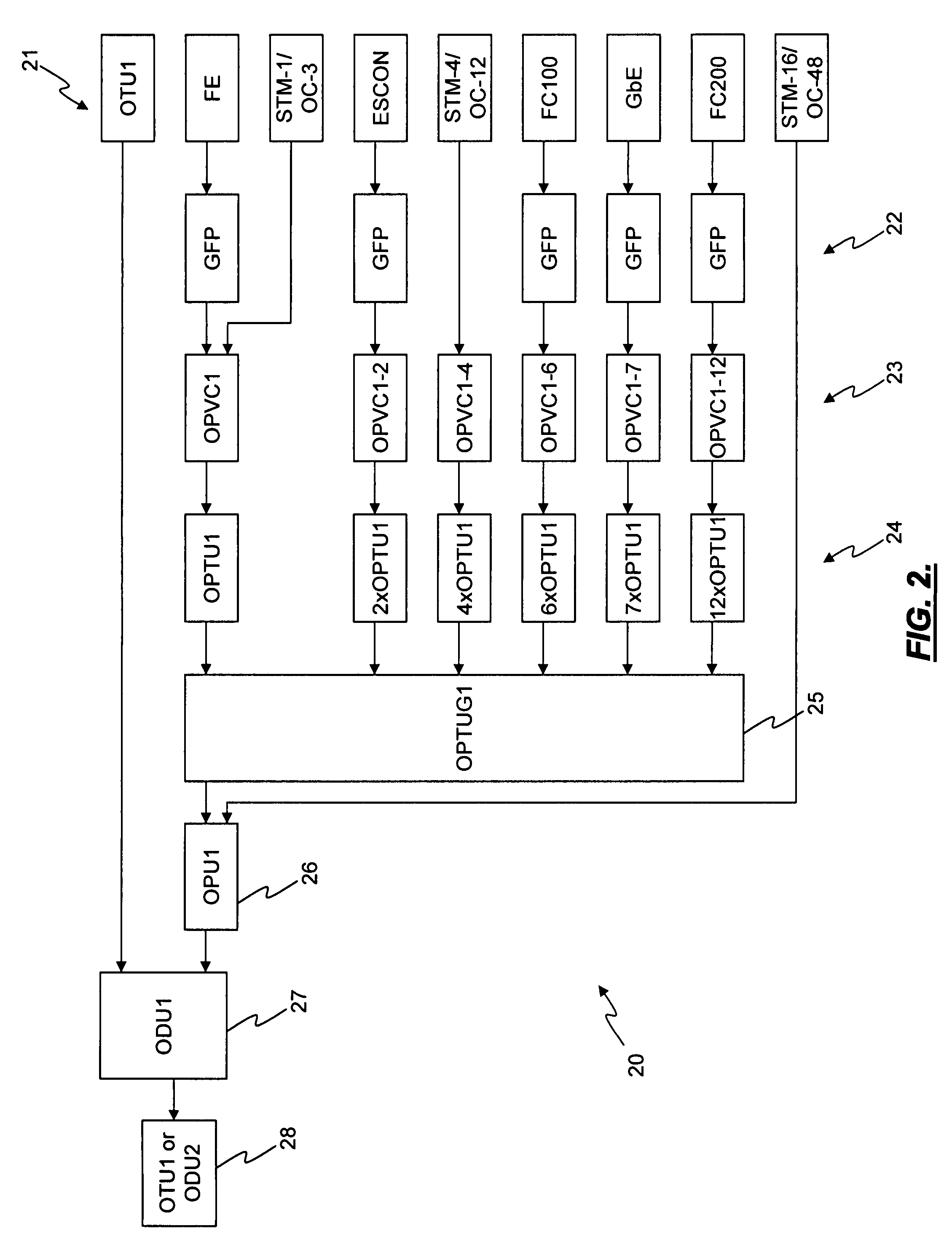

Data adaptation protocol

ActiveUS7586925B2Promote disseminationOptimize the numberTime-division multiplexData switching by path configurationNetwork packetNetwork service

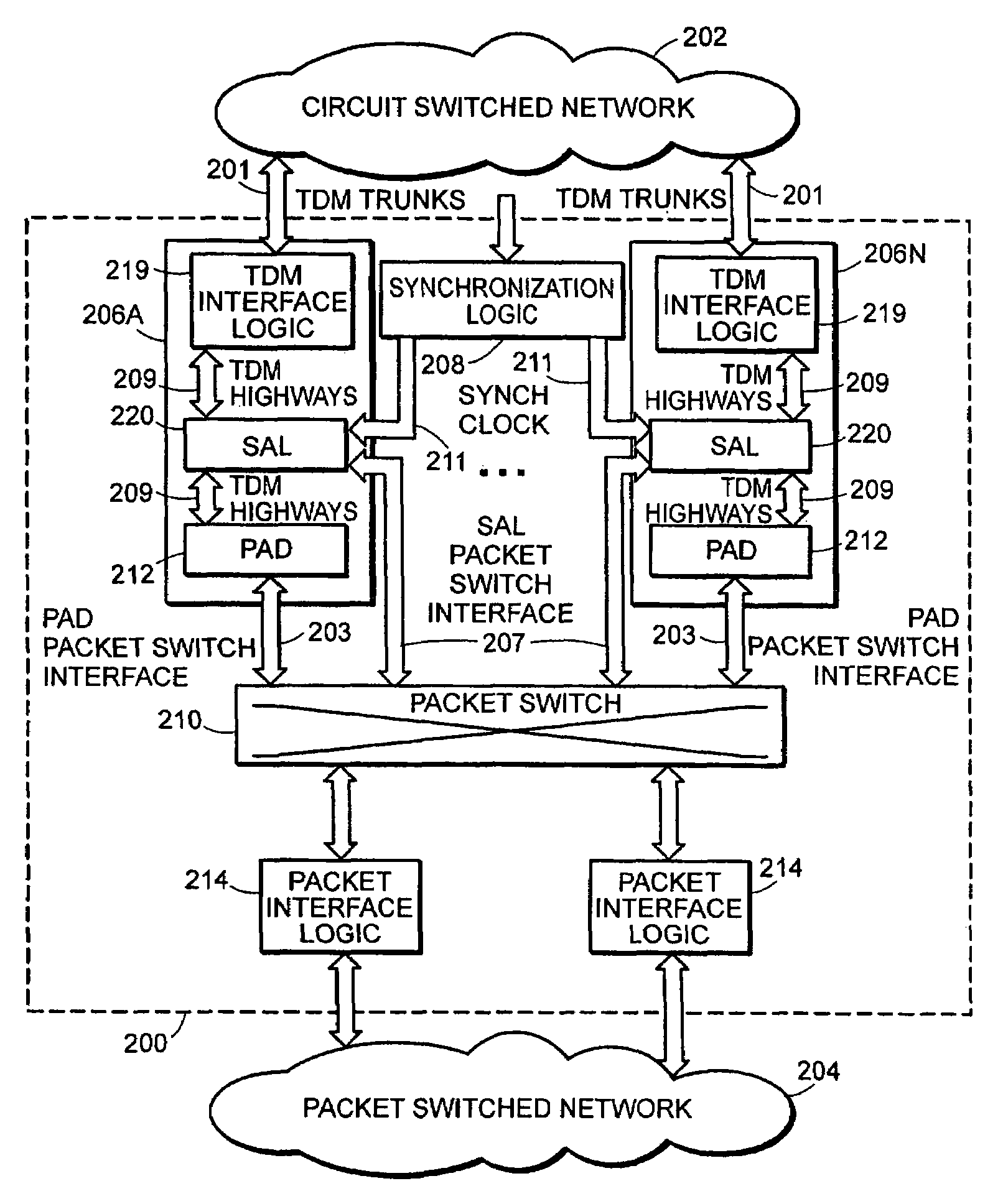

A gateway apparatus includes multiple network server cards which are synchronized with each other to allow time slot switching of synchronous data across an asynchronous medium between source and destination server cards. The gateway includes synchronization logic and a data adaptation layer which implements a protocol for formatting of synchronous serial data. The data undergoes serial to parallel conversion and is formed into per time slot subpackets which are further packetized along with context and synchronization data. The packet is transmitted through an asynchronous switch after which the packet is disassembled into its constituent subpackets and queued into play-out buffers according to each subpackets' associated context and synchronization data. The apparatus allows synchronous data to be switched from a source time slot to a destination time slot across the asynchronous switch with a known, fixed delay. The gateway apparatus requires only a single asynchronous switch to transmit data between and among both the synchronous and asynchronous domains.

Owner:RIBBON COMM OPERATING CO INC

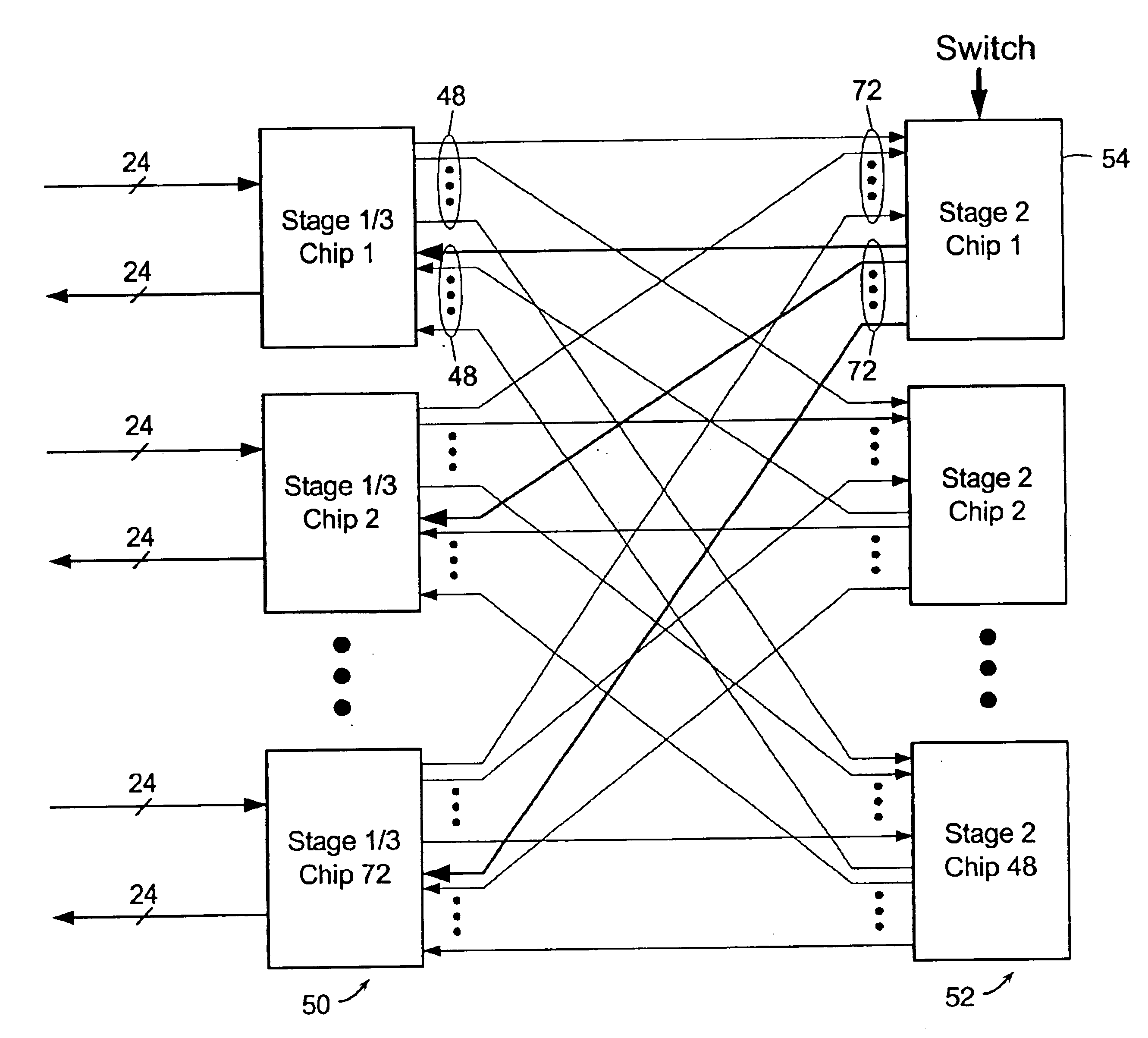

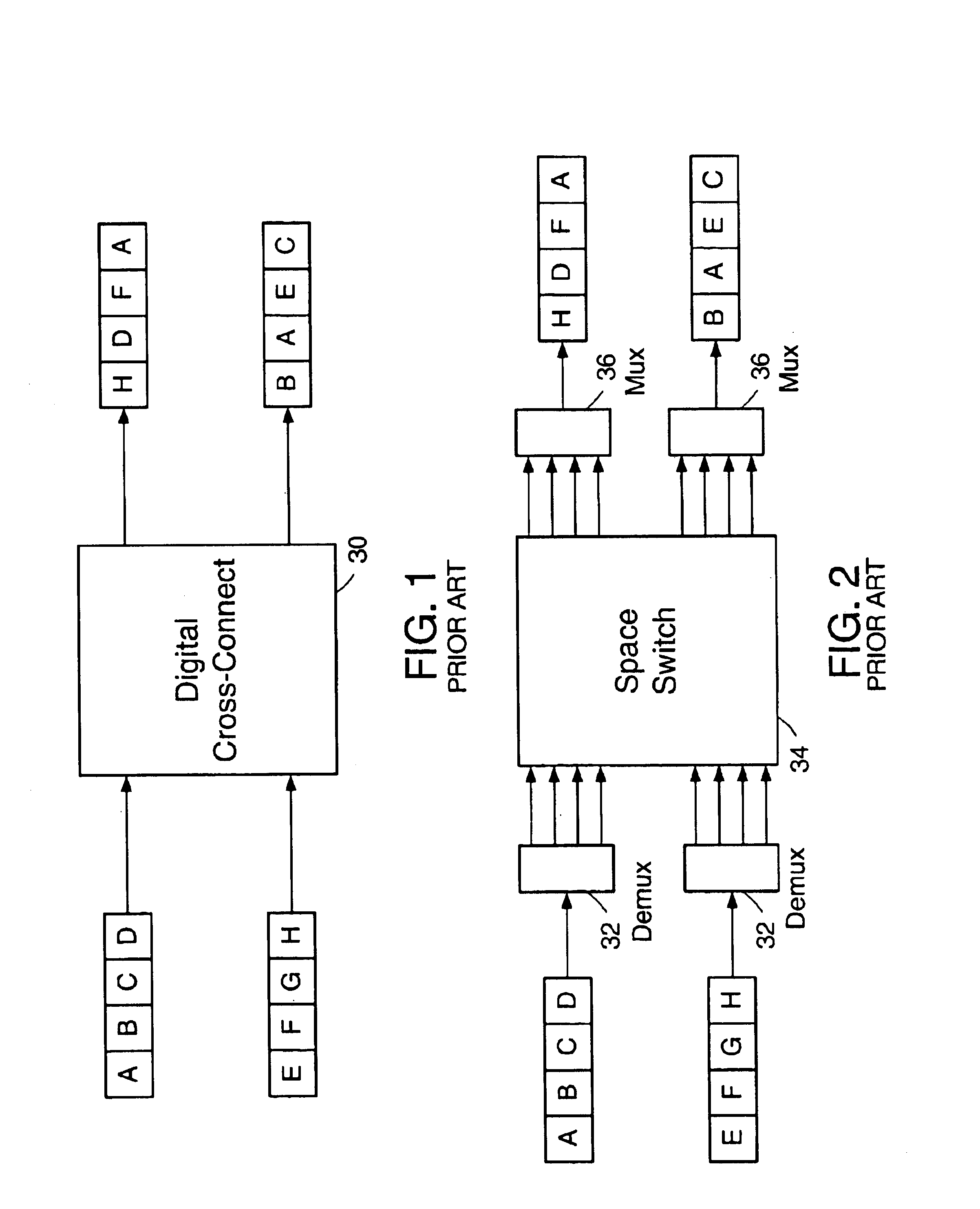

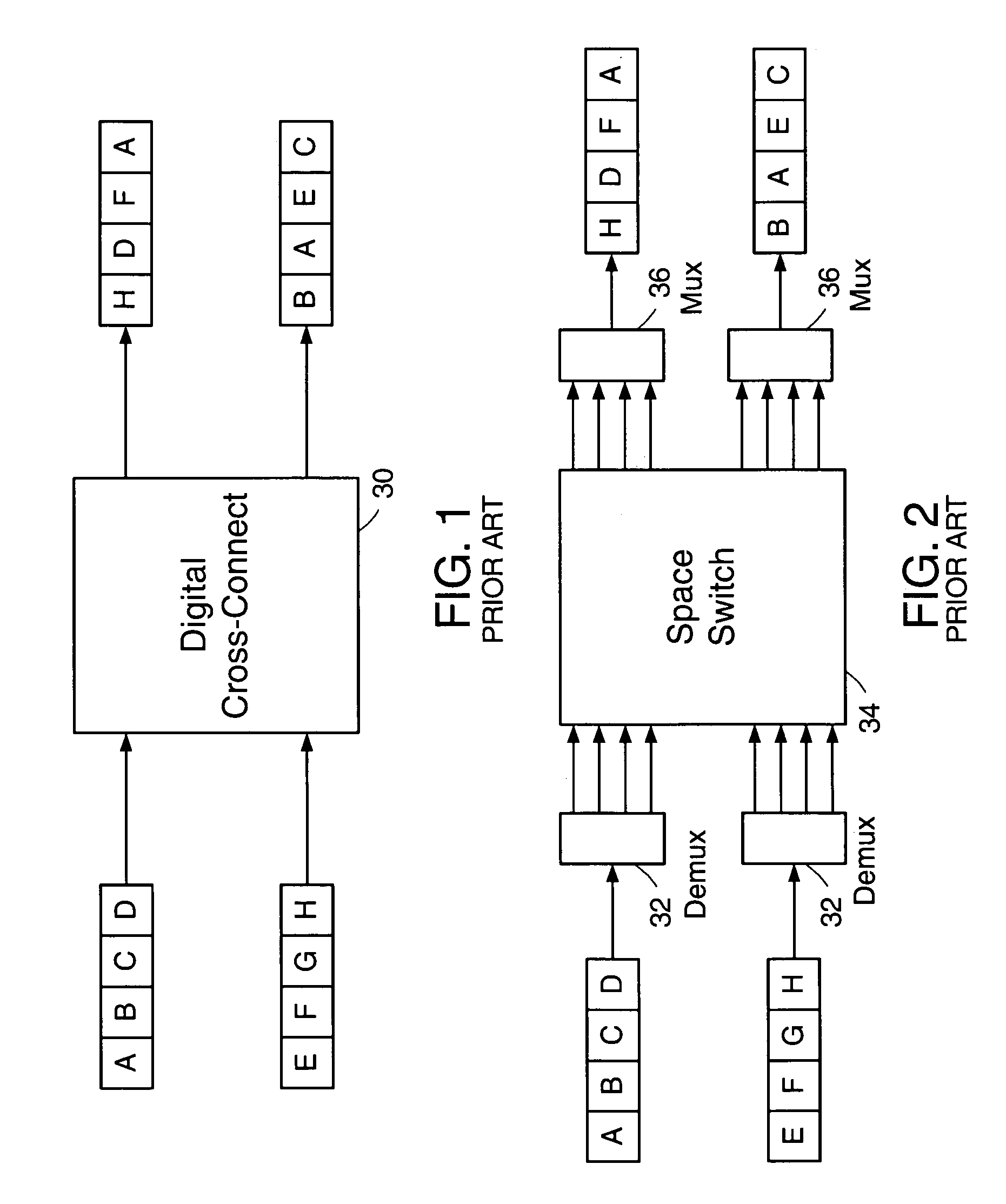

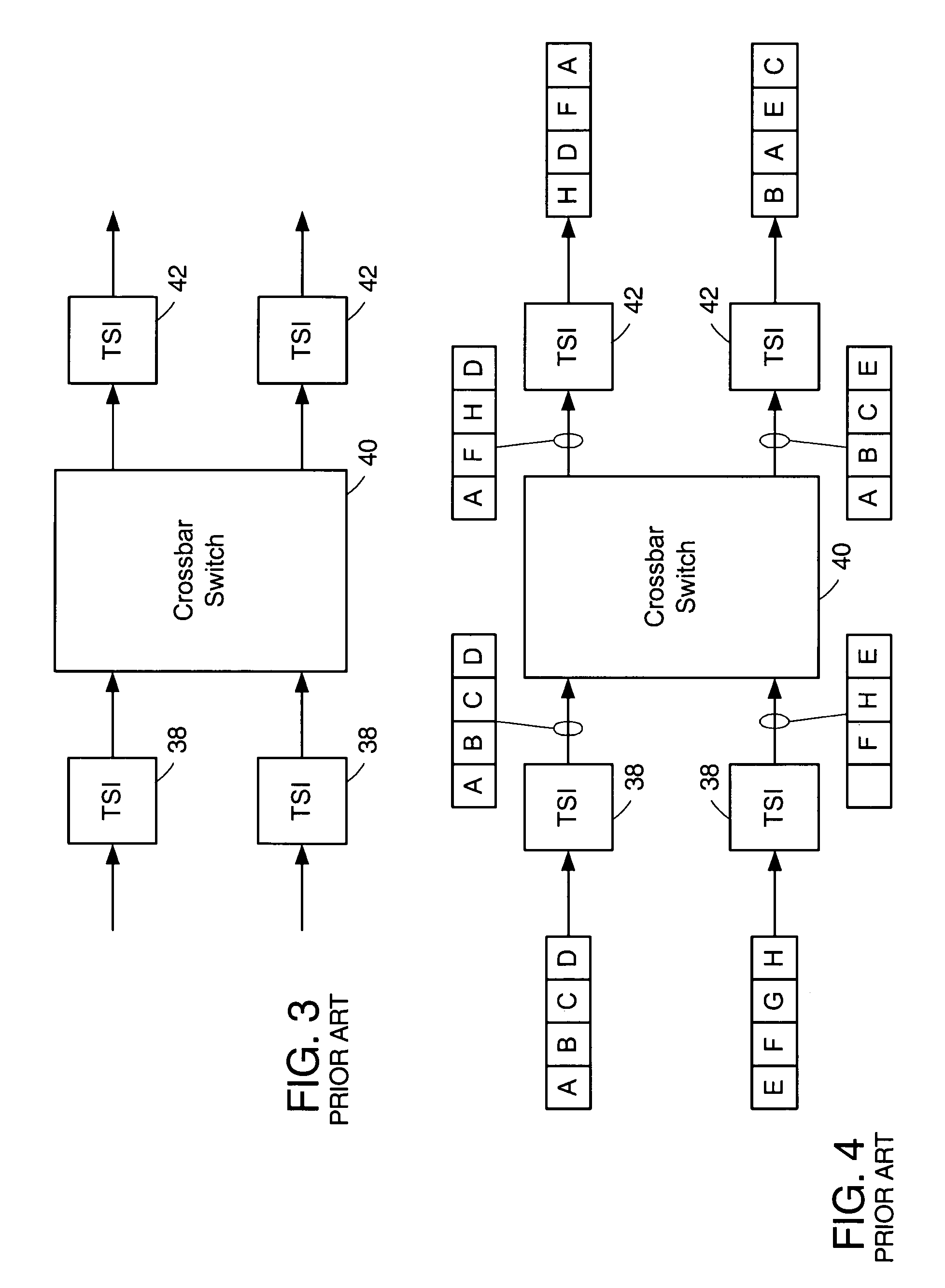

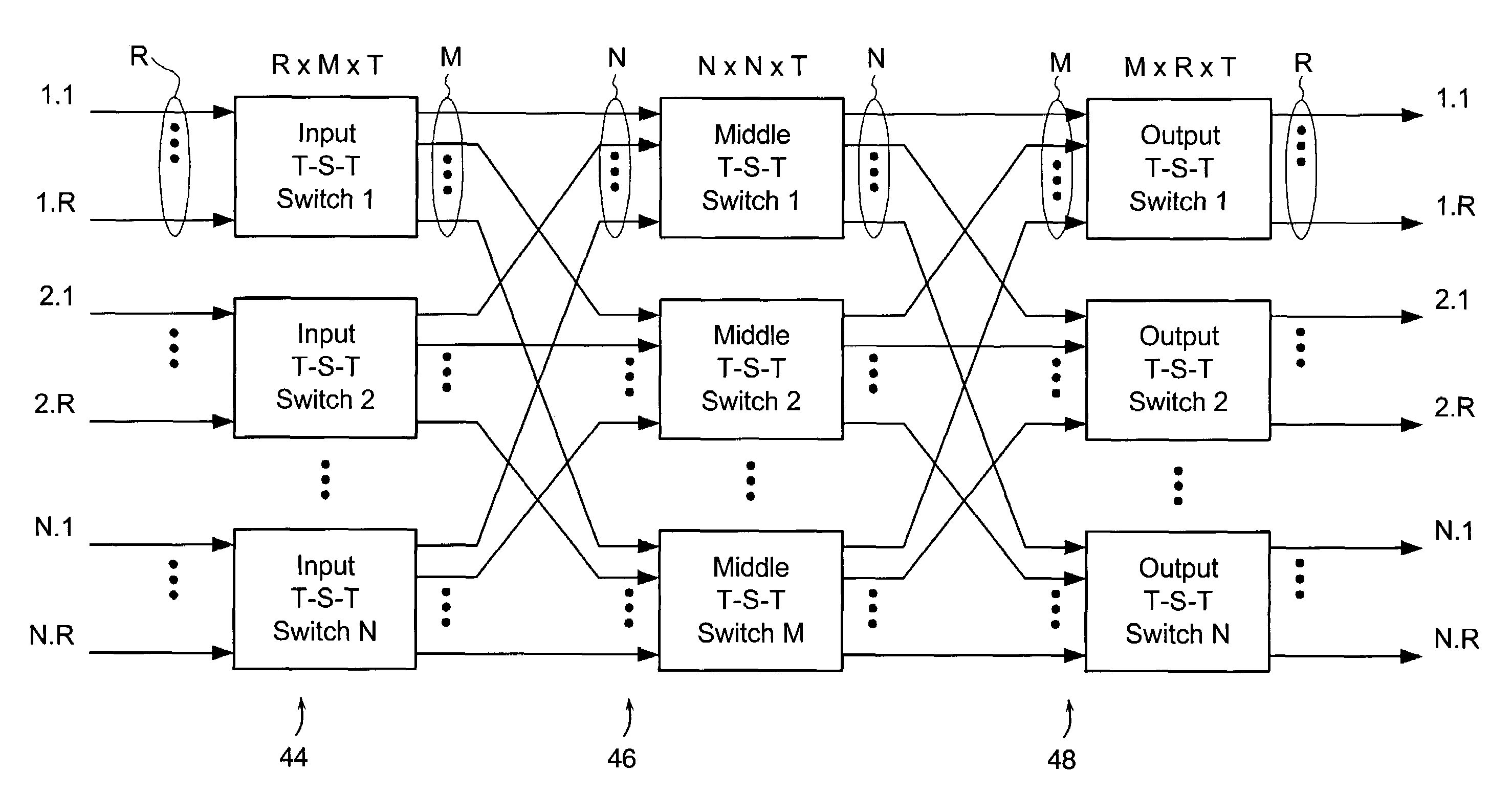

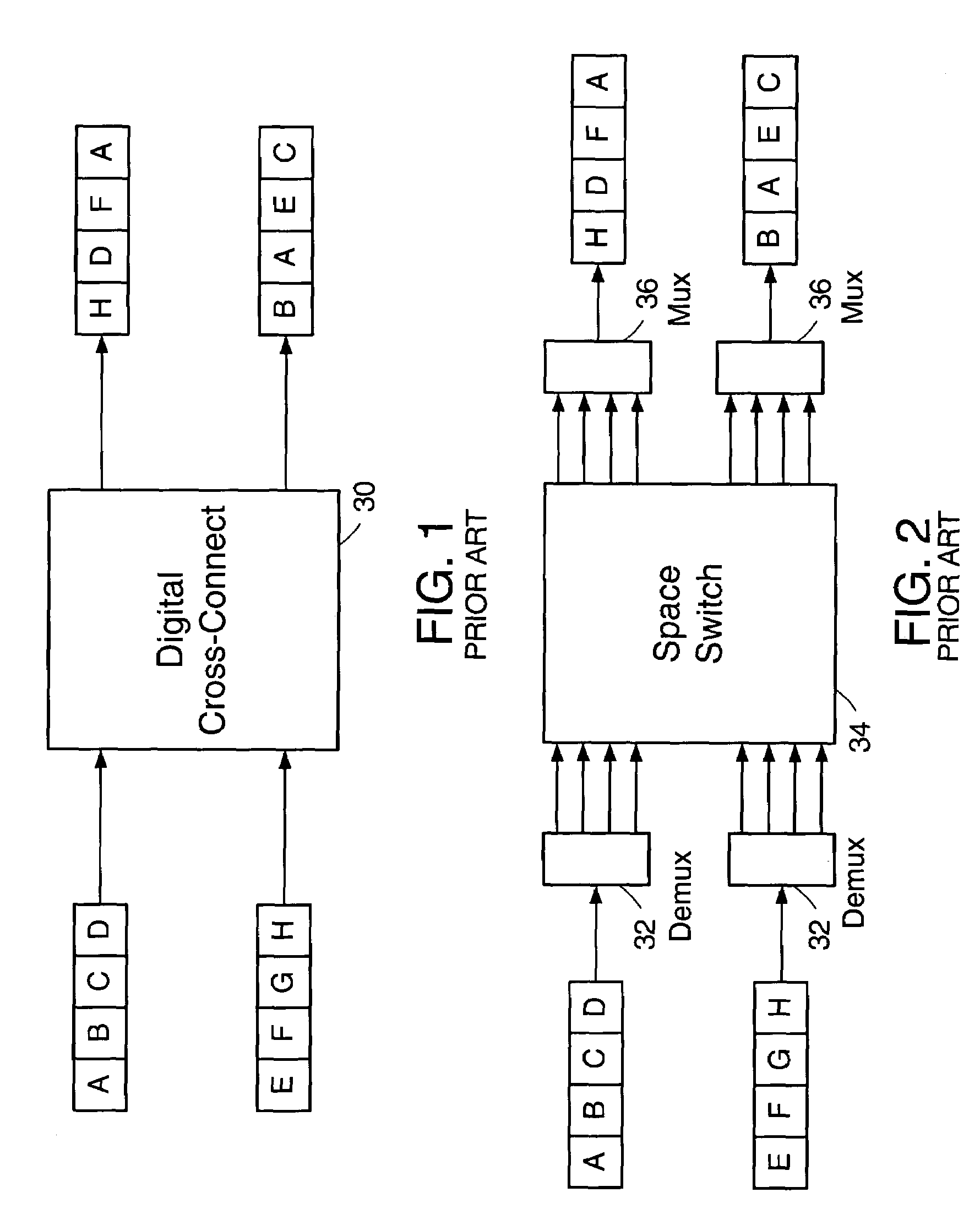

Multistage digital cross connect with integral frame timing

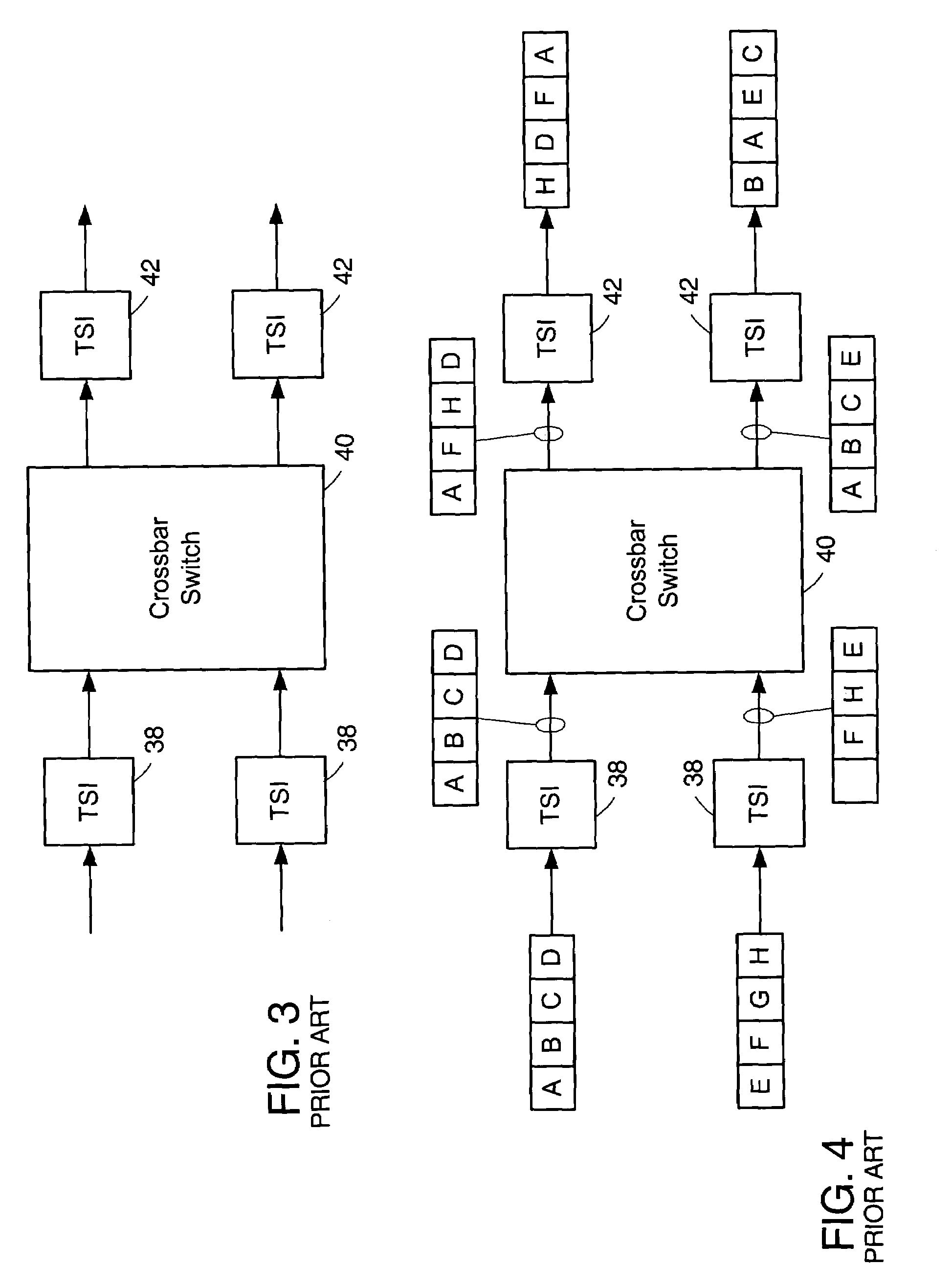

InactiveUS6870838B2Time-division multiplexCircuit switching systemsData synchronizationStatic random-access memory

A digital cross connect comprises plural switching stages. Each stage has plural switches which receive plural frames of time multiplexed input data and which switch the data in time and space. Configurations of the switches change in frame synchronization at the start of a synchronized data frame. Both the configuration data and a frame clock may be propagated through the plural stages from a master switch. First and last stages of the digital cross connect may be implemented on common chips having two framing time bases. Data may be aligned to a global frame clock and interchanged using a single random access memory in a time slot interchanger. The write address to the random access memory is generated from a local frame counter keyed to the input data frame while a read address is transformed from a global frame counter.

Owner:INTEL CORP

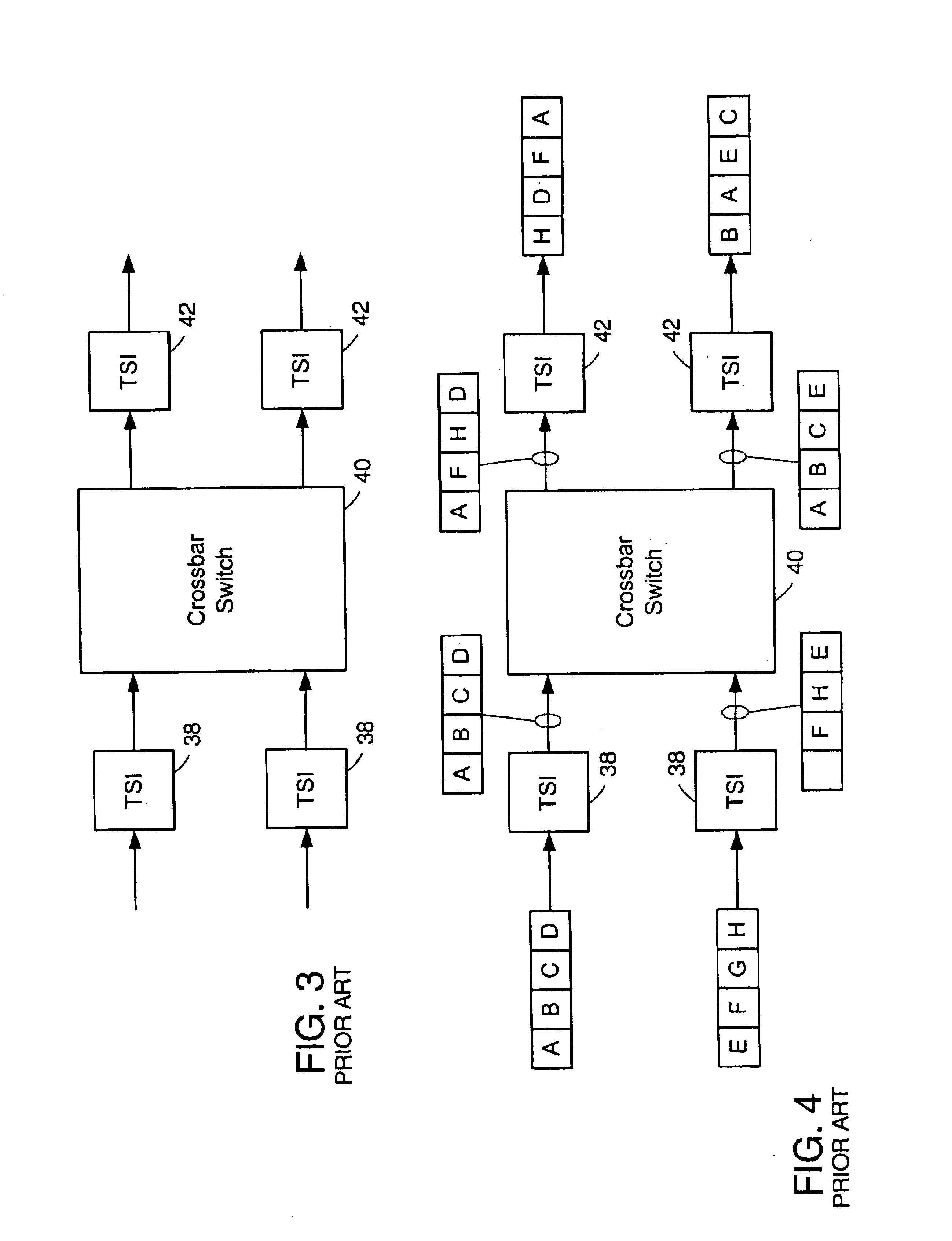

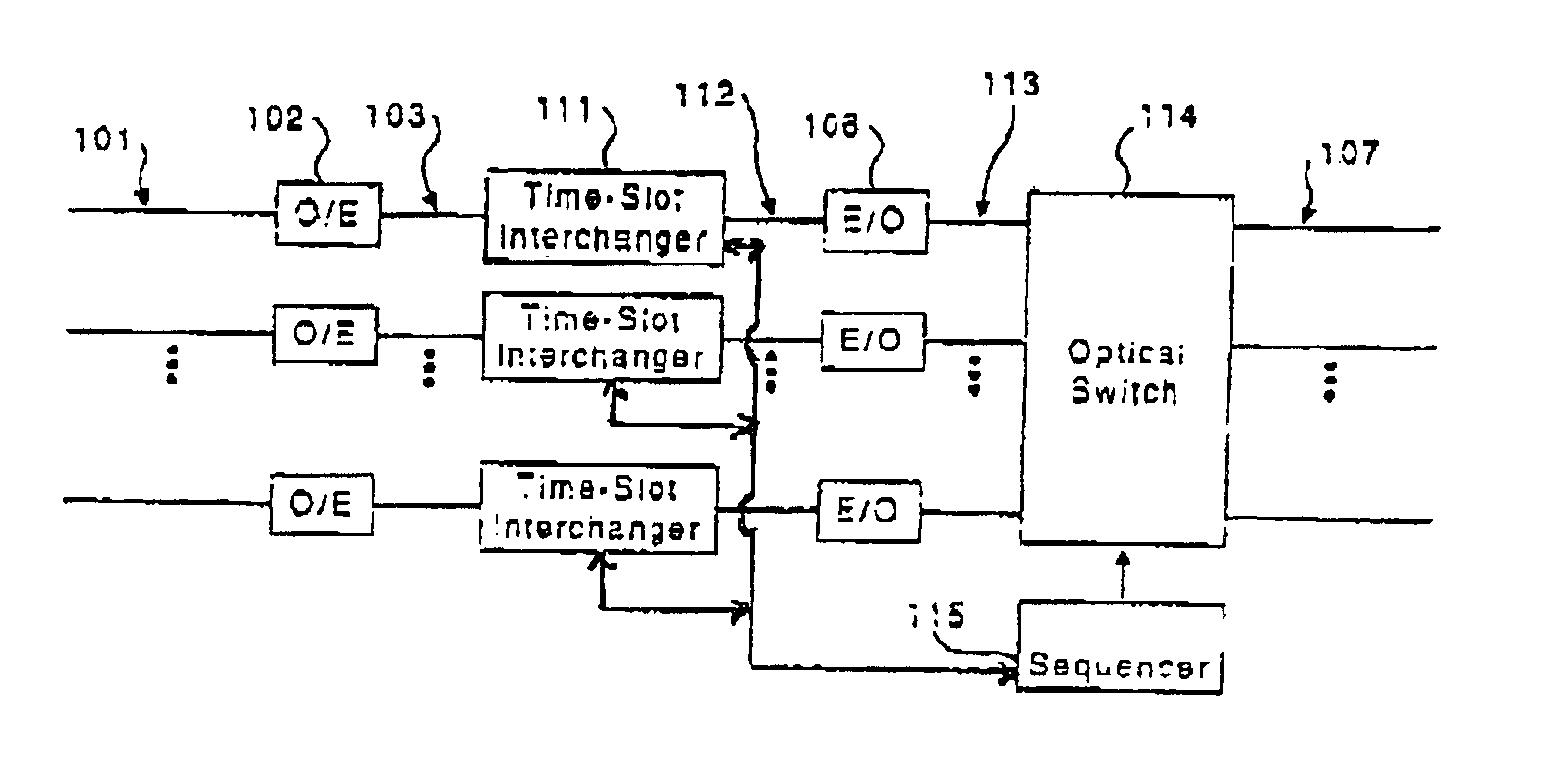

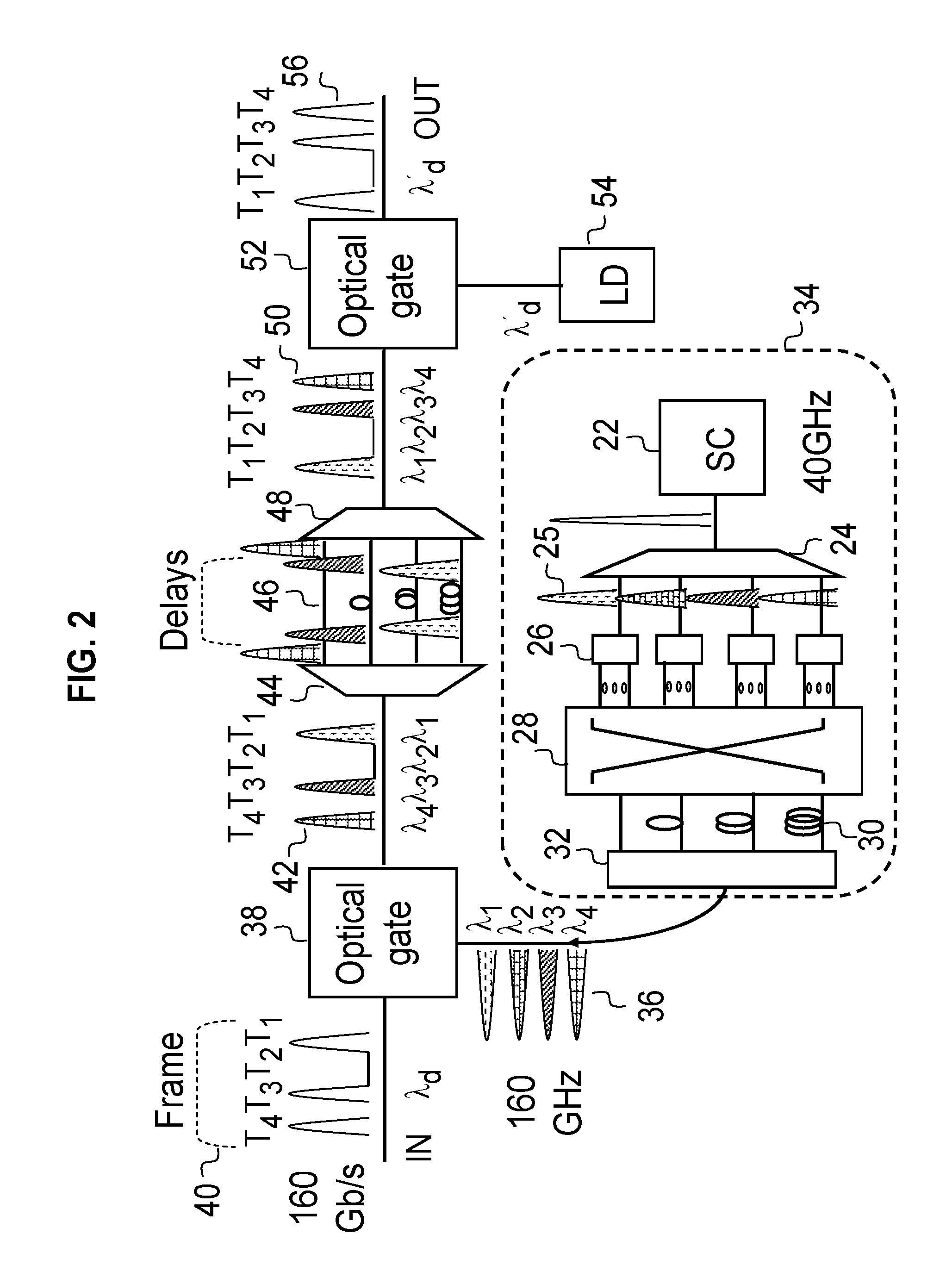

Photonic switch using time-slot interchange

An optical data stream is converted to electrical signals which are applied to a time-slot interchanger. The time-slot interchanger recorders the packets or cells of the data stream to correspond to the schedule of an optical switch. The time-slot interchanger may contain a plurality of FIFOs implemented as circular buffers in a single dual port memory. The switch schedule may be determined by the average load between inputs and outputs and may be determined by the number of packets or cells queued from each input or each output in the time-slot interchangers.

Owner:FUTUREWEI TECH INC

Processor-based voice and data time slot interchange system

InactiveUS6879603B1Small and less-expensiveImprove functionalityTime-division multiplexCircuit switching systemsShift registerMultiplexing

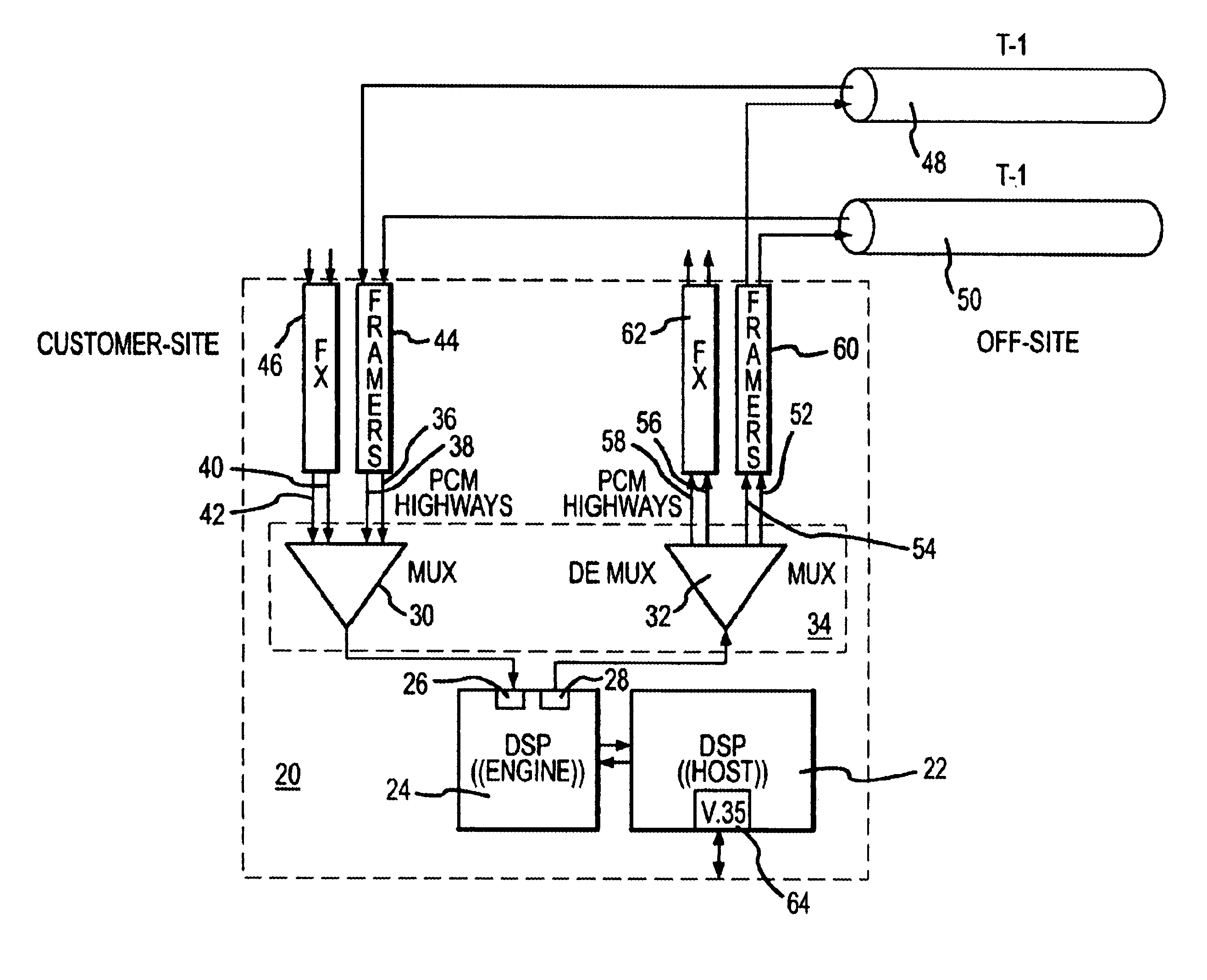

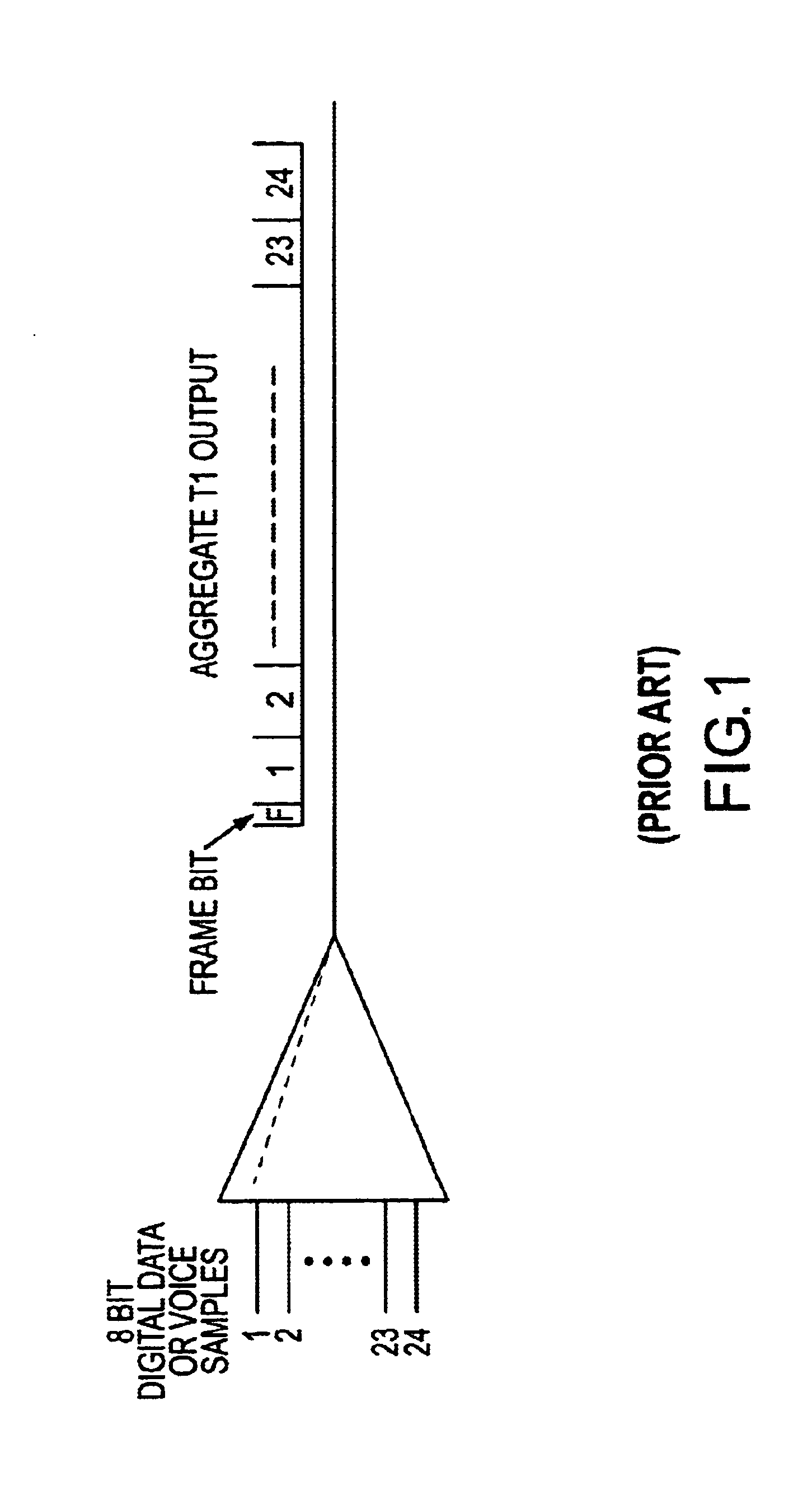

A technique for performing a time slot interchange in a processor. The TSI process is surrounded by a multiplexing / demultiplexing circuit for converting a plurality of PCM highways into a single input serial data stream. The mux / demux circuit includes elastic stores to align frames and shift resisters to mux / demux with a minimum of delay. The TSI processor includes an input and an output buffered series port, a pair of input buffers, one to receive even-numbered frames from the PCM highways and one to receive odd-numbered frames, and an output buffer. Data is read from the appropriate input buffer in a non-sequential fashion as commanded by the processor in accordance with information stored in connection arrays (address buffers). The data is then written to the output buffer sequentially. The timing of the reading and writing steps is optimized relative to free running buffered serial port pointers for each BSP to reduce the frame delay.

Owner:DELL MARKETING CORP

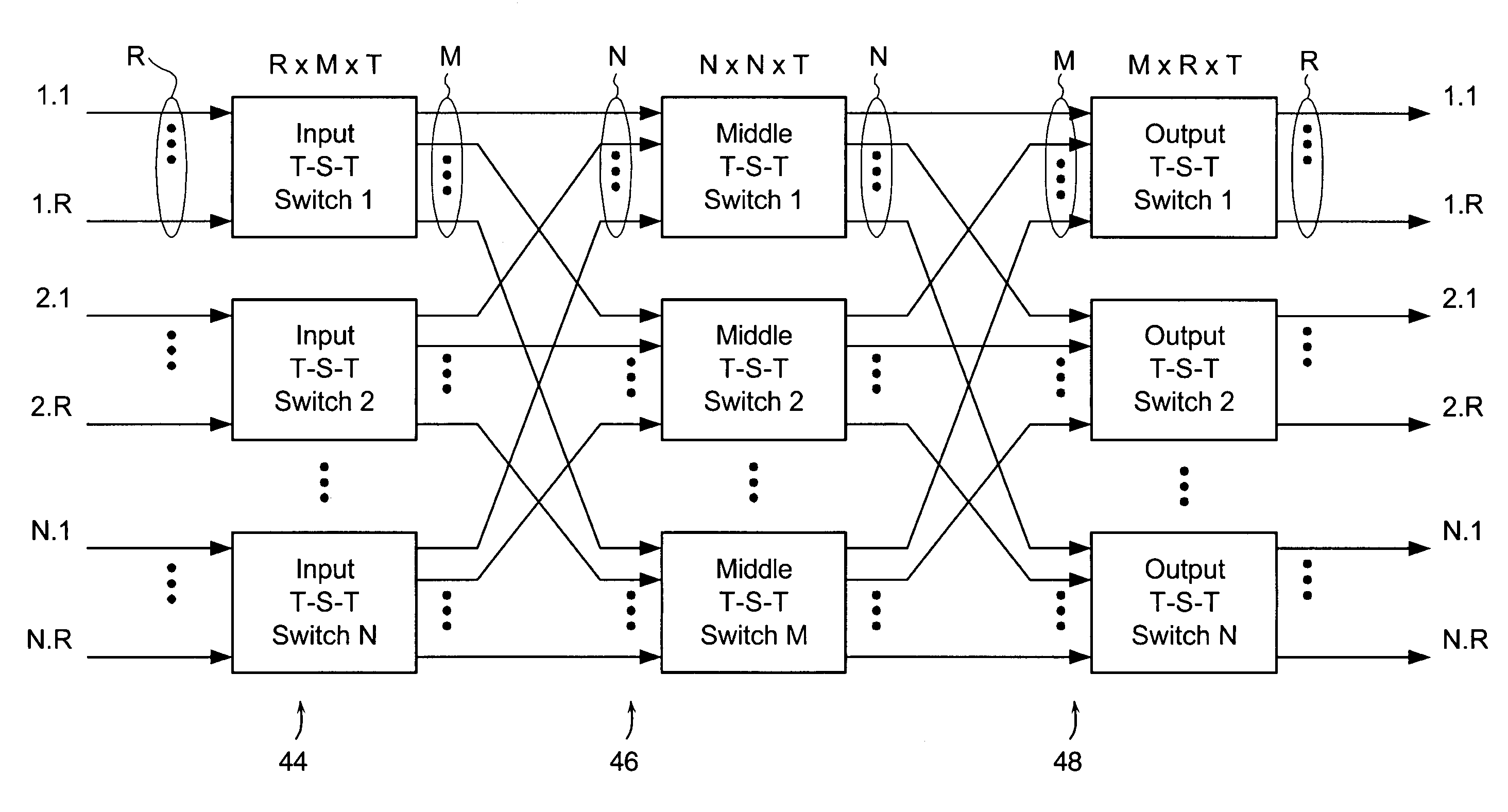

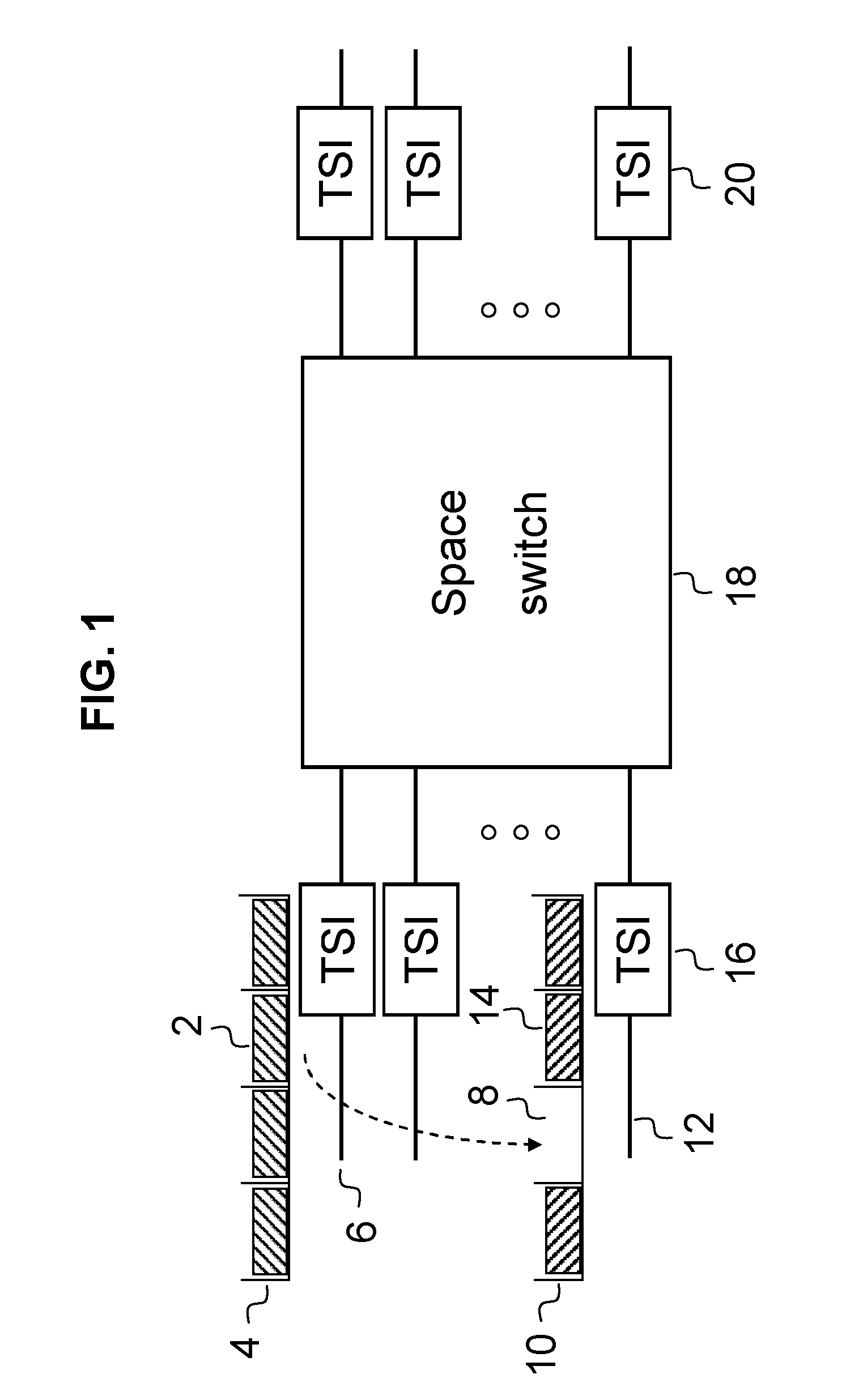

Mesh architecture for synchronous cross-connects

InactiveUS7113505B2Improve scalabilityArchitectural complexityTime-division multiplexData switching by path configurationComputer networkCross connection

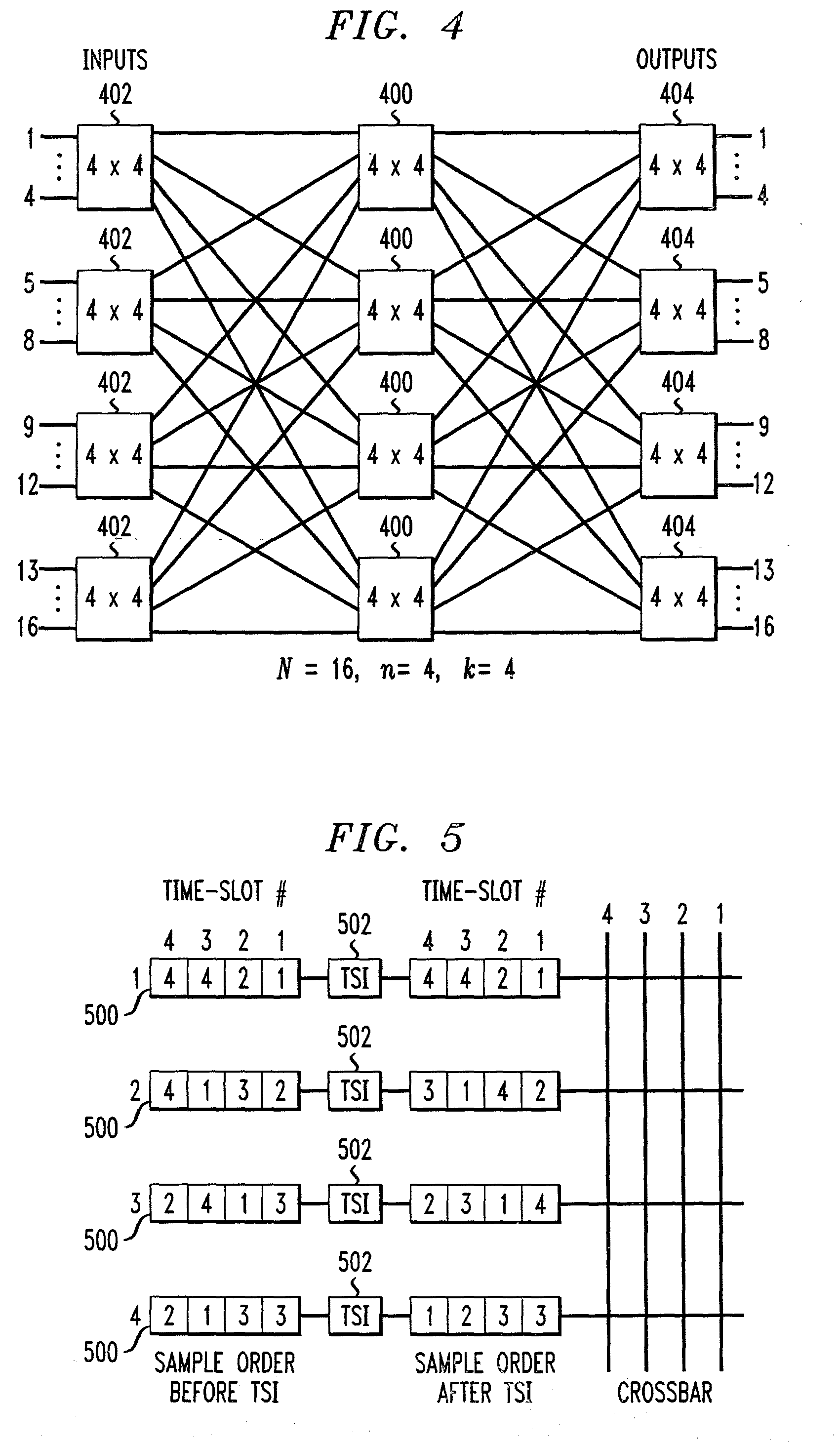

A synchronous cross-connect switch for routing data samples from a source node to a destination node comprises a mesh architecture including a plurality of inputs for receiving one or more of the data samples presented to the cross-connect switch. The mesh architecture includes a plurality of nodes operatively interconnected with one another using one or more half-duplex links. Each of the nodes further includes a receiver and a transmitter. Each node further includes an input time-slot-interchanger (TSI) operatively coupled to a first half-duplex link and to the receiver, the input TSI being configurable to selectively reorder one or more data samples received by the receiver, and an output TSI operatively coupled to a second half-duplex link and to the transmitter, the output TSI being configurable to selectively reorder one or more data samples to be transmitted by the transmitter. A controller operatively coupled to the receiver and to the transmitter is configured to selectively route a data sample to at least one of an output of the cross-connect switch and an adjacent node in the mesh architecture in a conflict-free manner.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

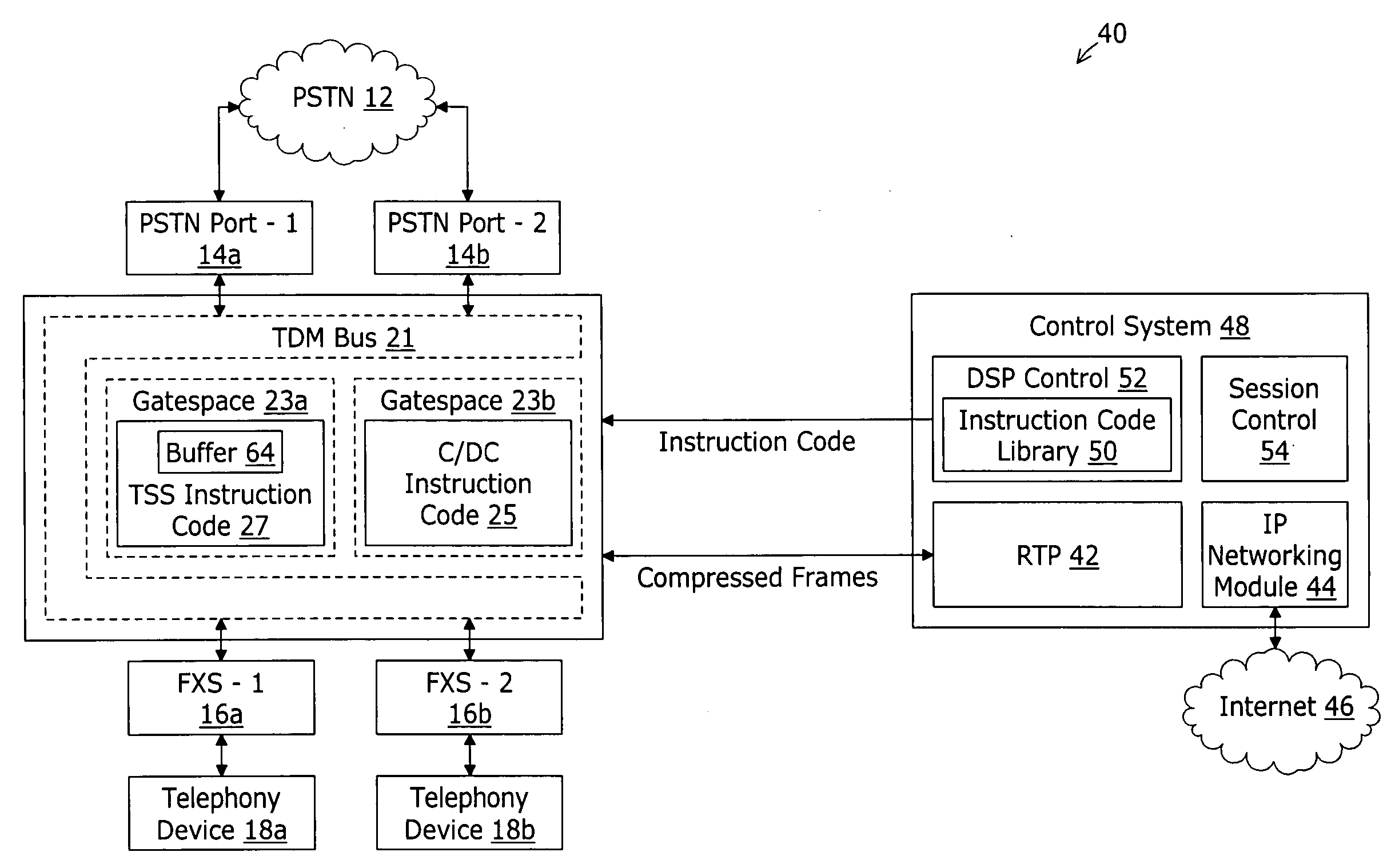

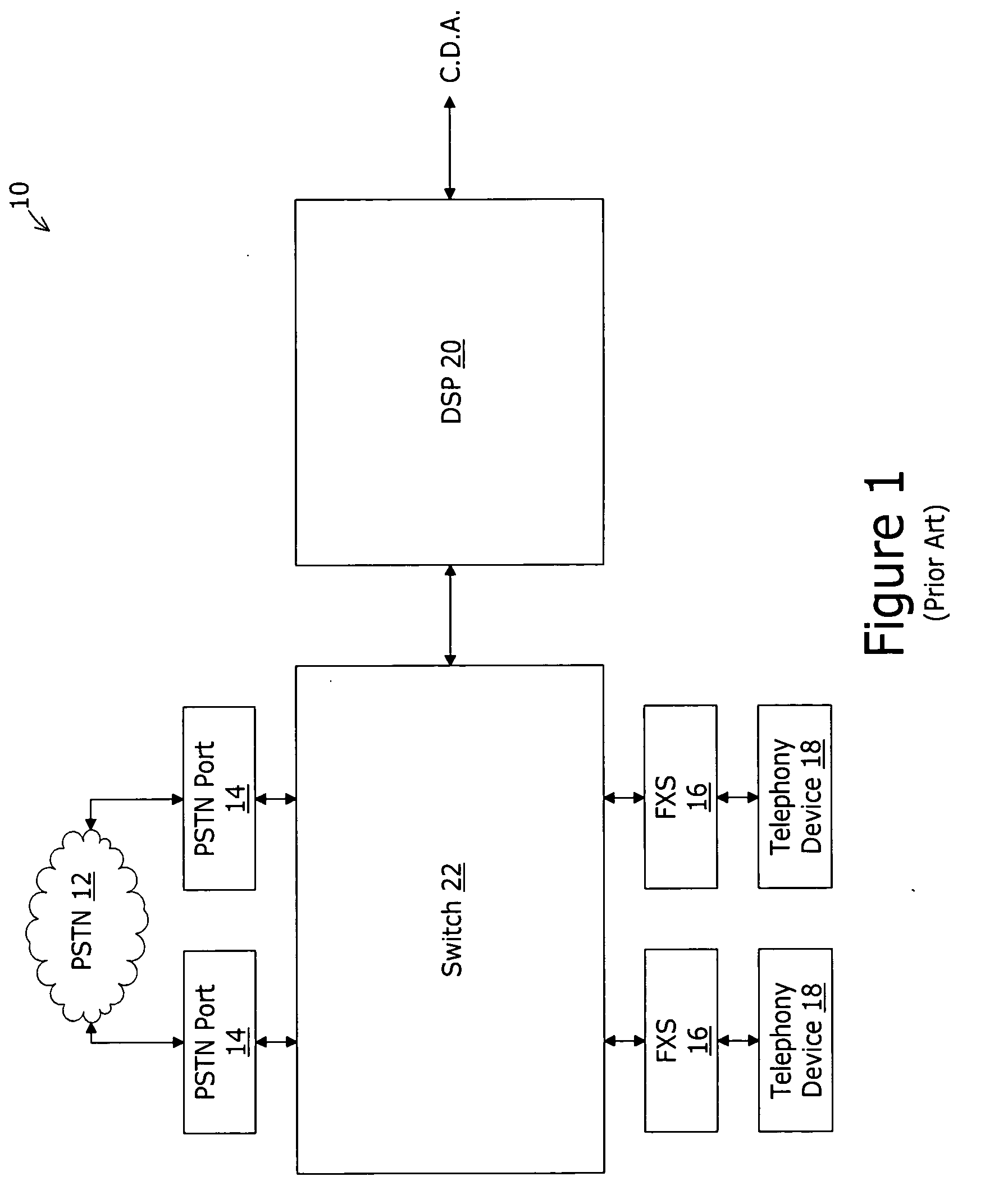

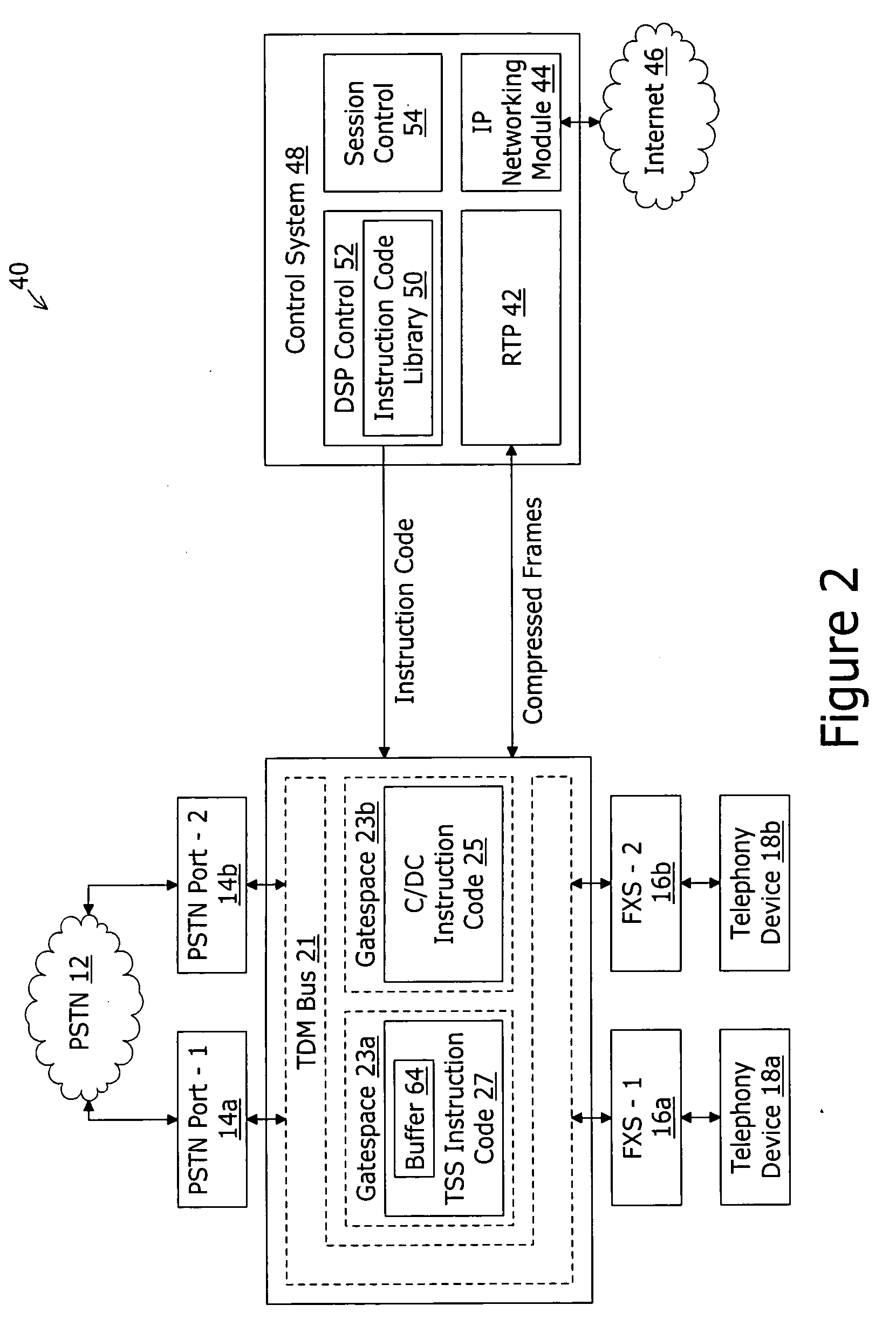

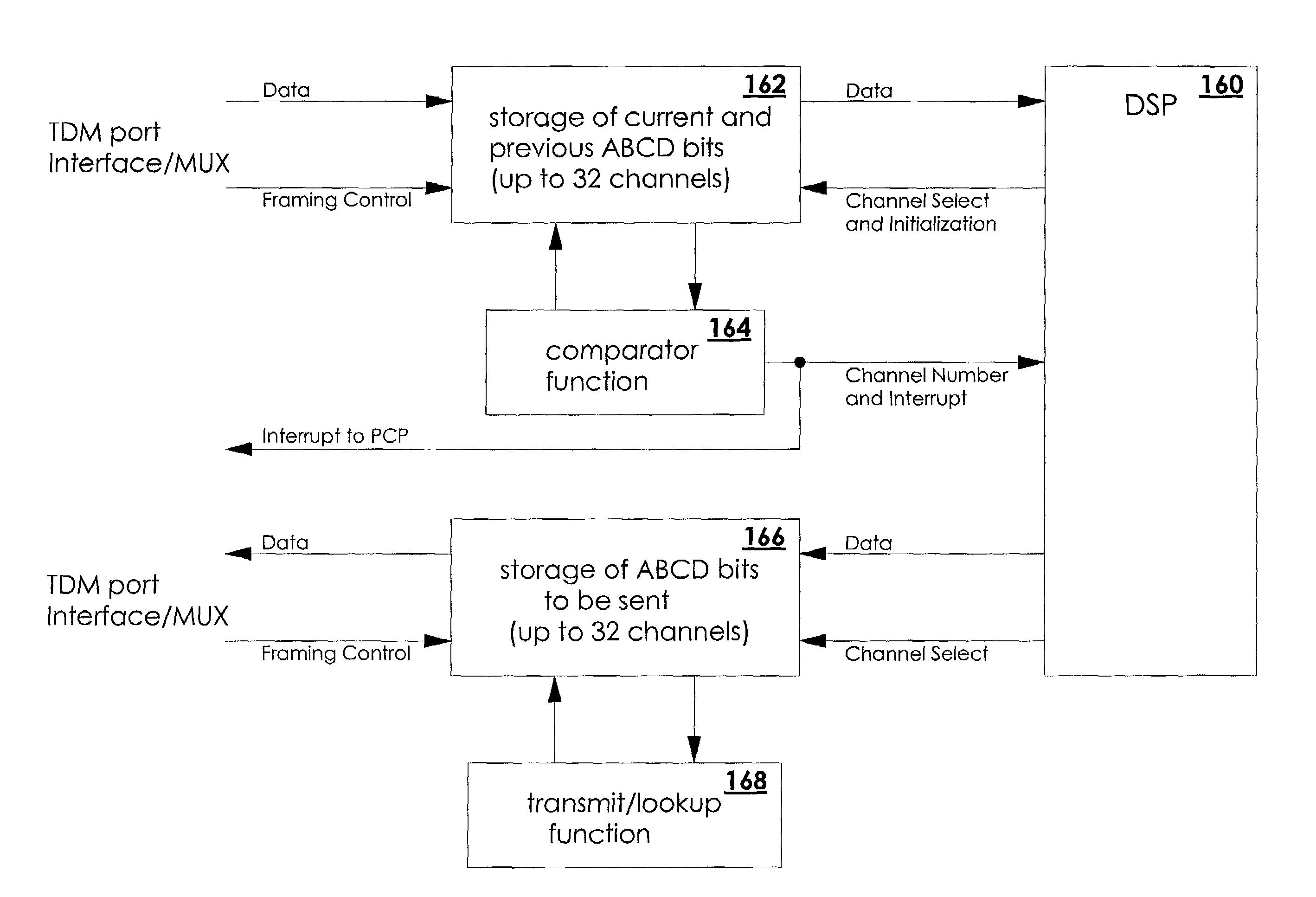

Packet media gateway with a secondary PSTN connection and method for time slot switching

InactiveUS20070064677A1Interconnection arrangementsNetwork connectionsTime-division multiplexingCircuit switching

A media gateway for coupling to both an Internet service provider frame switched network and a PSTN provider circuit switched network comprises an FXS port to which a telephony device may be coupled to initiate a connection to a destination. A programmable DSP includes a time-division multiplexing bus coupled to the FXS port and a PSTN port which couples to a subscriber loop of the circuit switched network. Compression instruction code is programmed into the digital signal processor in response to determining that the connection to the destination is to be established using a real time communication channel over the frame switched network. Time slot switching instruction code is programmed into the digital signal processor in response to determining that the connection to the destination is to be established over the circuit switched network. The time slot switching instruction code provides for: i) buffering digital audio data received from the FXS port during an occurrence of a periodic time slot assigned to the FXS port and transferring such digital audio data to the PSTN port during an occurrence of a periodic time slot assigned to the PSTN port; and ii) buffering digital audio data received from the PSTN port during an occurrence of the periodic time slot assigned to the PSTN port and transferring such digital audio data to the FXS port during an occurrence of the periodic time slot assigned to the FXS port.

Owner:INNOMEDIA PTE

Multistage digital cross connect with synchronized configuration switching

InactiveUS7301941B2Time-division multiplexCircuit switching systemsCross connectionRandom access memory

A digital cross connect comprises plural switching stages. Each stage has plural switches which receive plural frames of time multiplexed input data and which switch the data in time and space. Configurations of the switches change in frame synchronization at the start of a synchronized data frame. Both the configuration data and a frame clock may be propagated through the plural stages from a master switch. First and last stages of the digital cross connect may be implemented on common chips having two framing time bases. Data may be aligned to a global frame clock and interchanged using a single random access memory in a time slot interchanger. The write address to the random access memory is generated from a local frame counter keyed to the input data frame while a read address is transformed from a global frame counter.

Owner:INTEL CORP

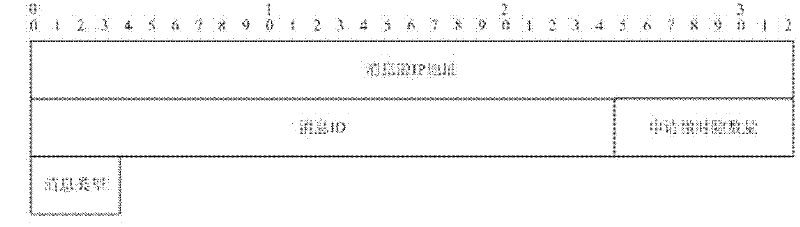

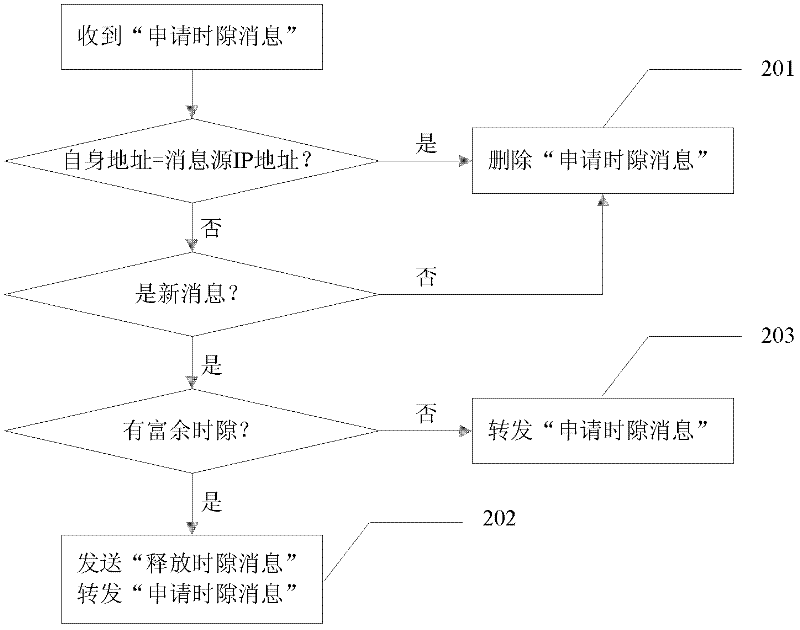

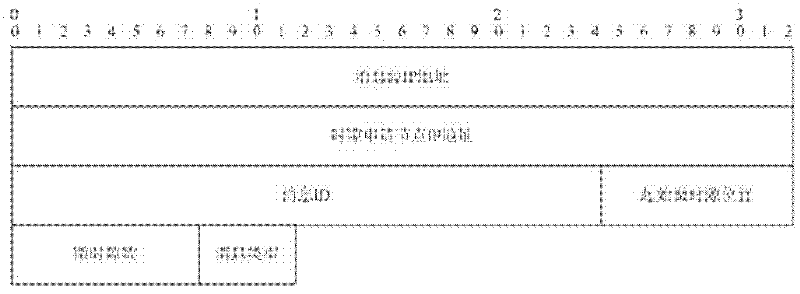

Timeslot interchange operating method for time division multiple address access system in wireless mobile self-organized network

InactiveCN102386991AIncrease profitImprove real-time performanceNetwork topologiesTime-division multiplexComputer networkTime division multiple access

The invention belongs to the wireless mobile self-organized network technical field, and specifically relates to a timeslot interchange method for achieving a time division multiple address access system in the wireless mobile self-organized network. The timeslot interchange operating method comprises the following steps: sending application timeslot information to the timeslot application node to apply required quantities of mini-slots; evaluating the network load by other nodes in the network and sending release timeslot information by the node satisfying the requirements; selecting the optimal timeslot by the timeslot application node, sending the timeslot acceptation information for confirming, releasing the node release mini-slots by the timeslot release node, and using the mini-slots by the timeslot application node. The free timeslot resource in the network is reasonably distributed by the method; the utilization rate of the network resource is improved; the real time of sending high priority message is enhanced; and the invulnerability of the system is improved.

Owner:HARBIN ENG UNIV

Unidirectional asymmetric traffic pattern systems and methods in switch matrices

ActiveUS20130230052A1Time-division multiplexData switching by path configurationTraffic capacityNon symmetric

A switch fabric system and network element based thereon include a N×M switch fabric with M Trail Termination Points (TTPs) each with N timeslots there through in a bidirectional manner, a first connection in the switch fabric, wherein the first connection includes a unidirectional asymmetric connection of X timeslots, wherein X<N, and a second connection in the switch fabric in an opposite direction as the first connection, wherein the second connection includes a unidirectional asymmetric connection of Y timeslots, wherein Y<N, and wherein at least one of the Y timeslots overlaps with one of the X timeslots on a same TTP of the M TTPs, wherein N, M, X, and Y each include an integer. A method includes establishing unidirectional asymmetric connections with overlapping portions therein as well as merging, splitting, and converting connections in-service and minimizing blocking probabilities.

Owner:CIENA

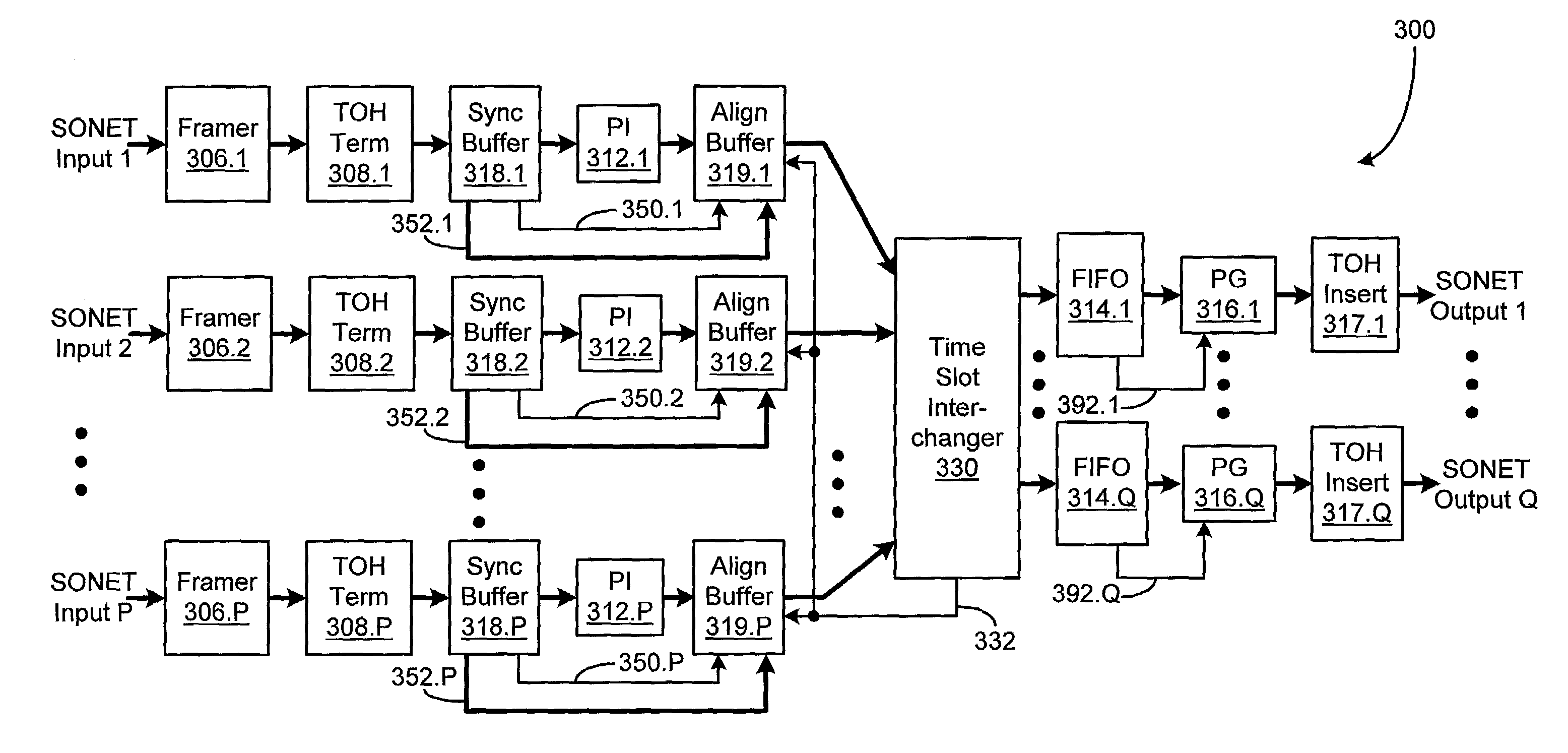

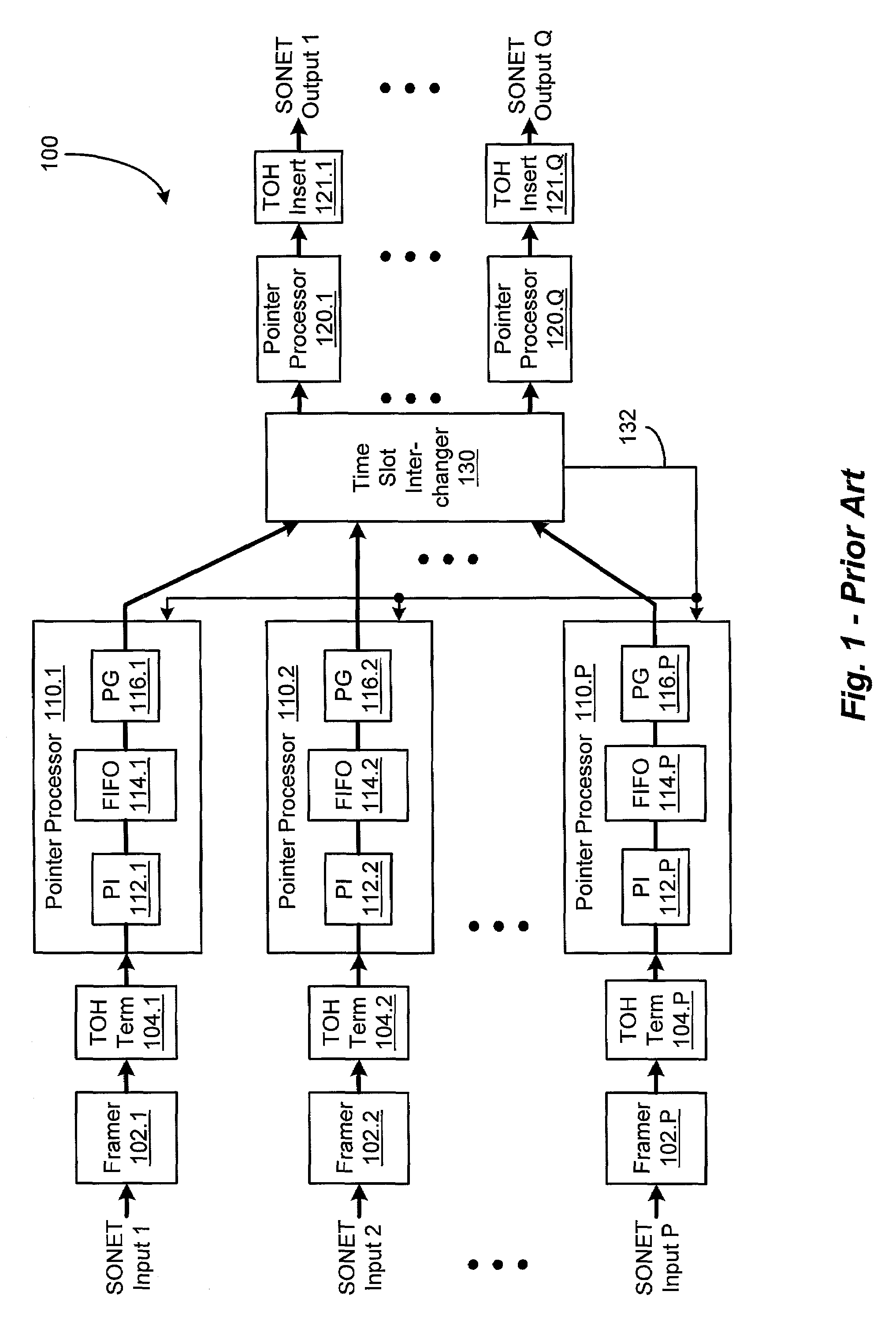

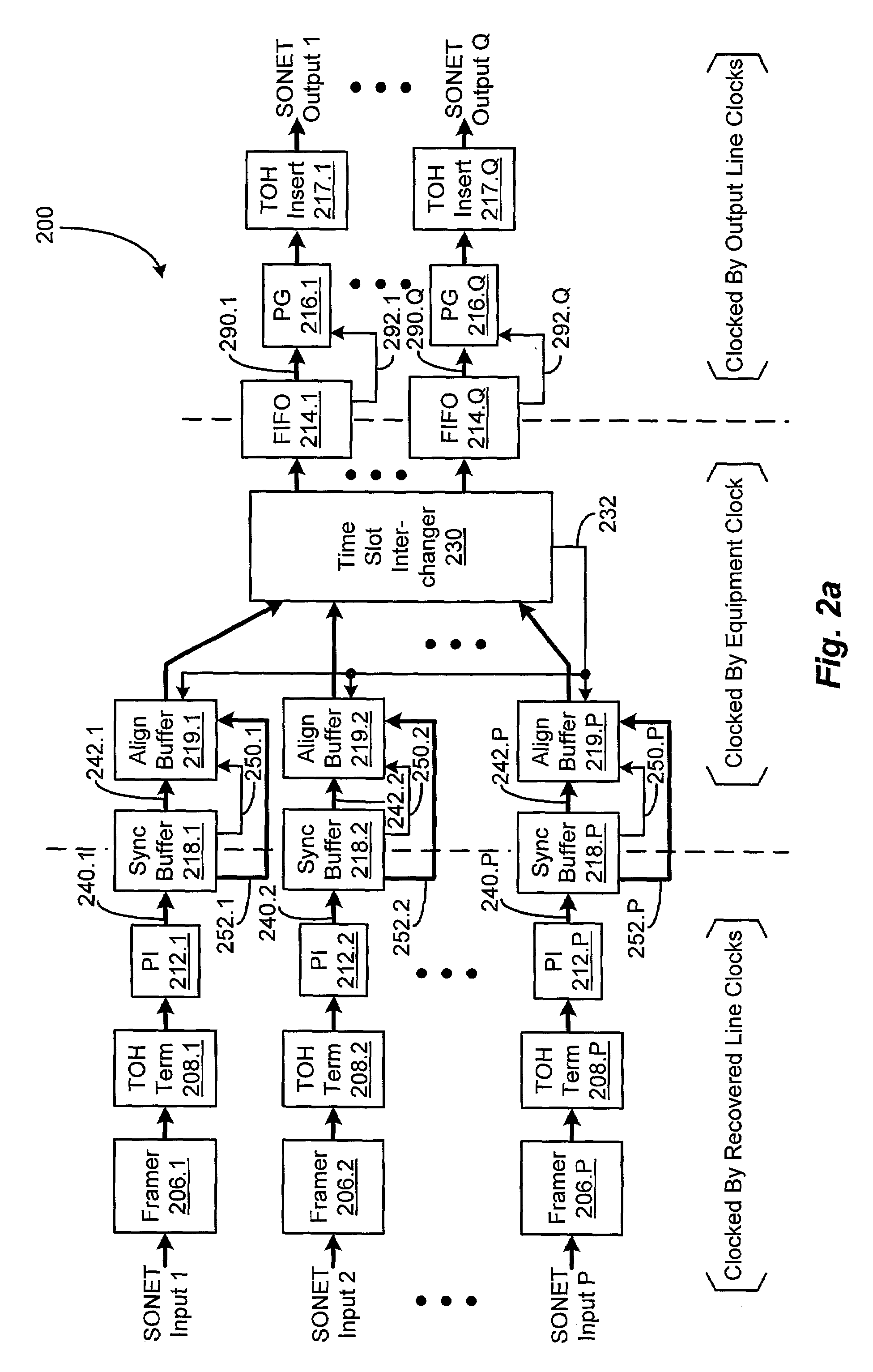

Time slot interchanging of time slots from multiple SONET signals without first passing the signals through pointer processors to synchronize them to a common clock

ActiveUS7016344B1Easy to integrateHighly integratedMultiplex system selection arrangementsPulse automatic controlClock rateComputer science

A SONET multiplexed system architecture that permits greater levels of integration. The architecture includes a time slot interchanger for routing information from at least one SONET input signal path associated with a respective first time slot to at least one SONET output signal path associated with a respective second time slot. Each input signal path includes a pointer interpreter, and each output signal path includes a FIFO buffer serially coupled to a pointer generator. The architecture further includes a synchronization buffer in each input signal path for transferring the input signal to the clock rate of the time slot interchanger. The architecture permits greater levels of integration when the time slot interchanger has more inputs than outputs, and / or the time slot interchanger provides the output signal to a pointer processor to transfer the output signal to the clock rate of the output signal path.

Owner:QUALCOMM INC

Time slot interchanger

InactiveUS7260092B2Time-division multiplexCircuit switching systemsCross connectionStatic random-access memory

A digital cross connect comprises plural switching stages. Each stage has plural switches which receive plural frames of time multiplexed input data and which switch the data in time and space. Configurations of the switches change in frame synchronization at the start of a synchronized data frame. Both the configuration data and a frame clock may be propagated through the plural stages from a master switch. First and last stages of the digital cross connect may be implemented on common chips having two framing time bases. Data may be aligned to a global frame clock and interchanged using a single random access memory in a time slot interchanger. The write address to the random access memory is generated from a local frame counter keyed to the input data frame while a read address is transformed from a global frame counter.

Owner:INTEL CORP

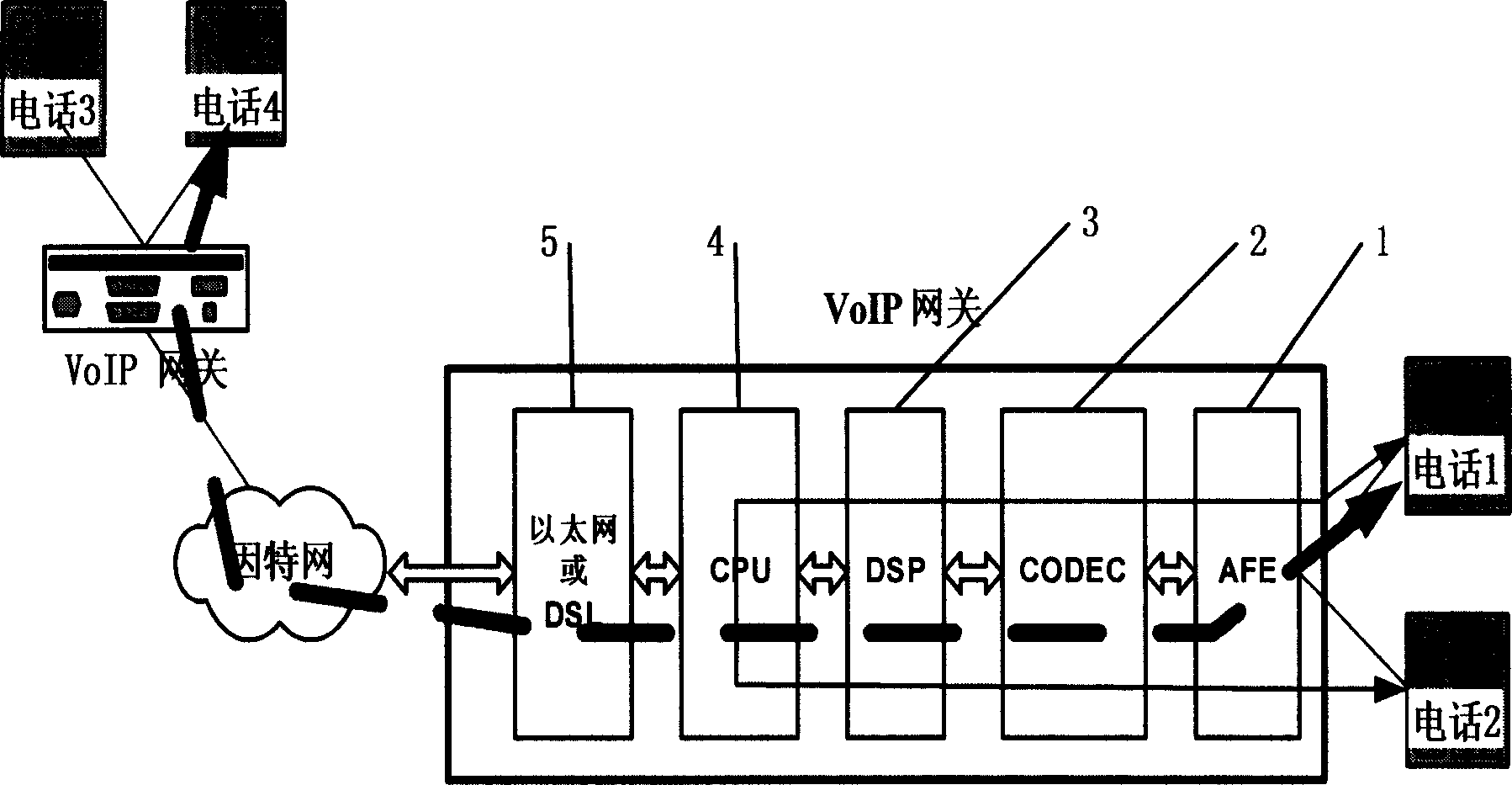

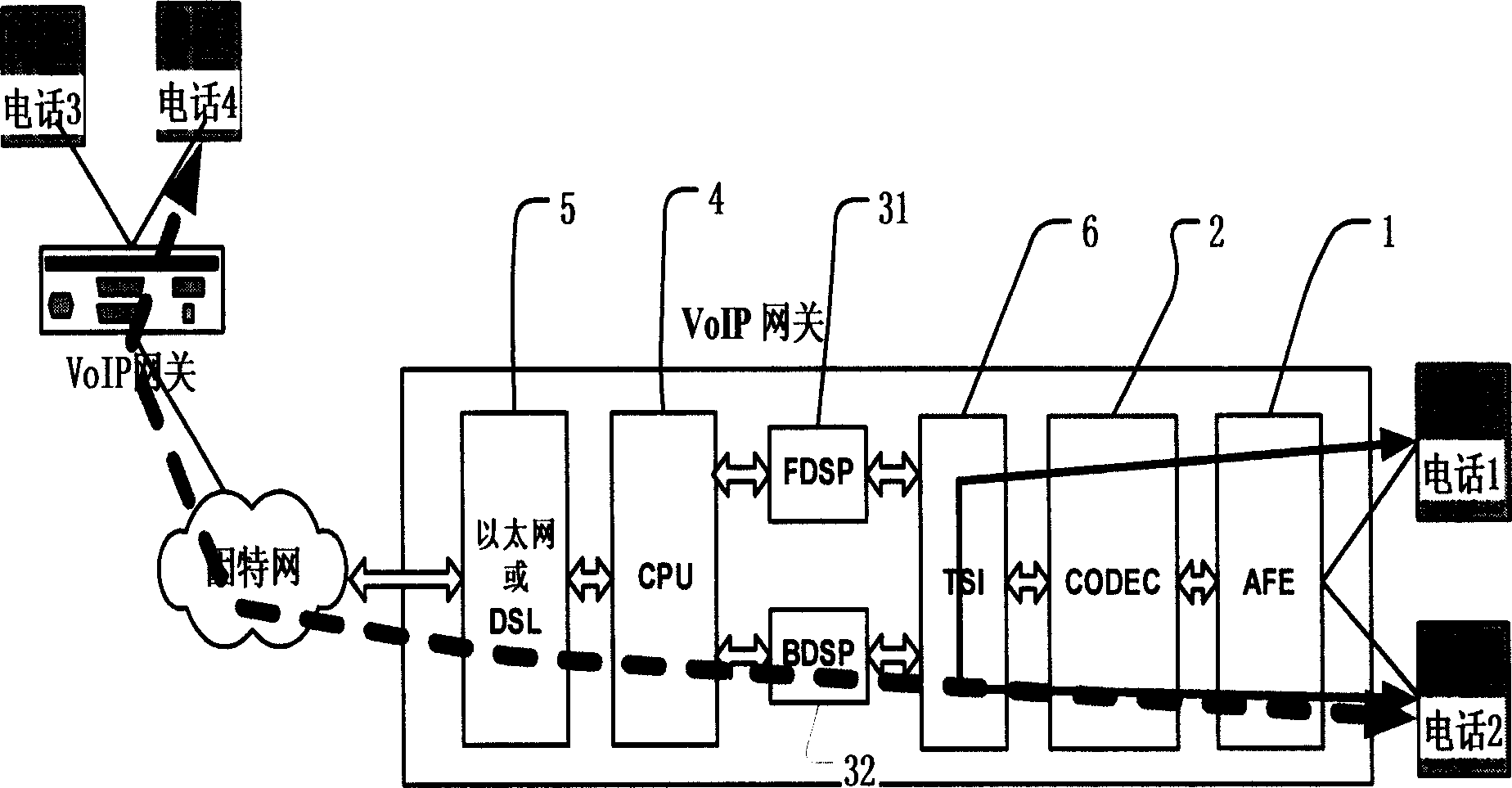

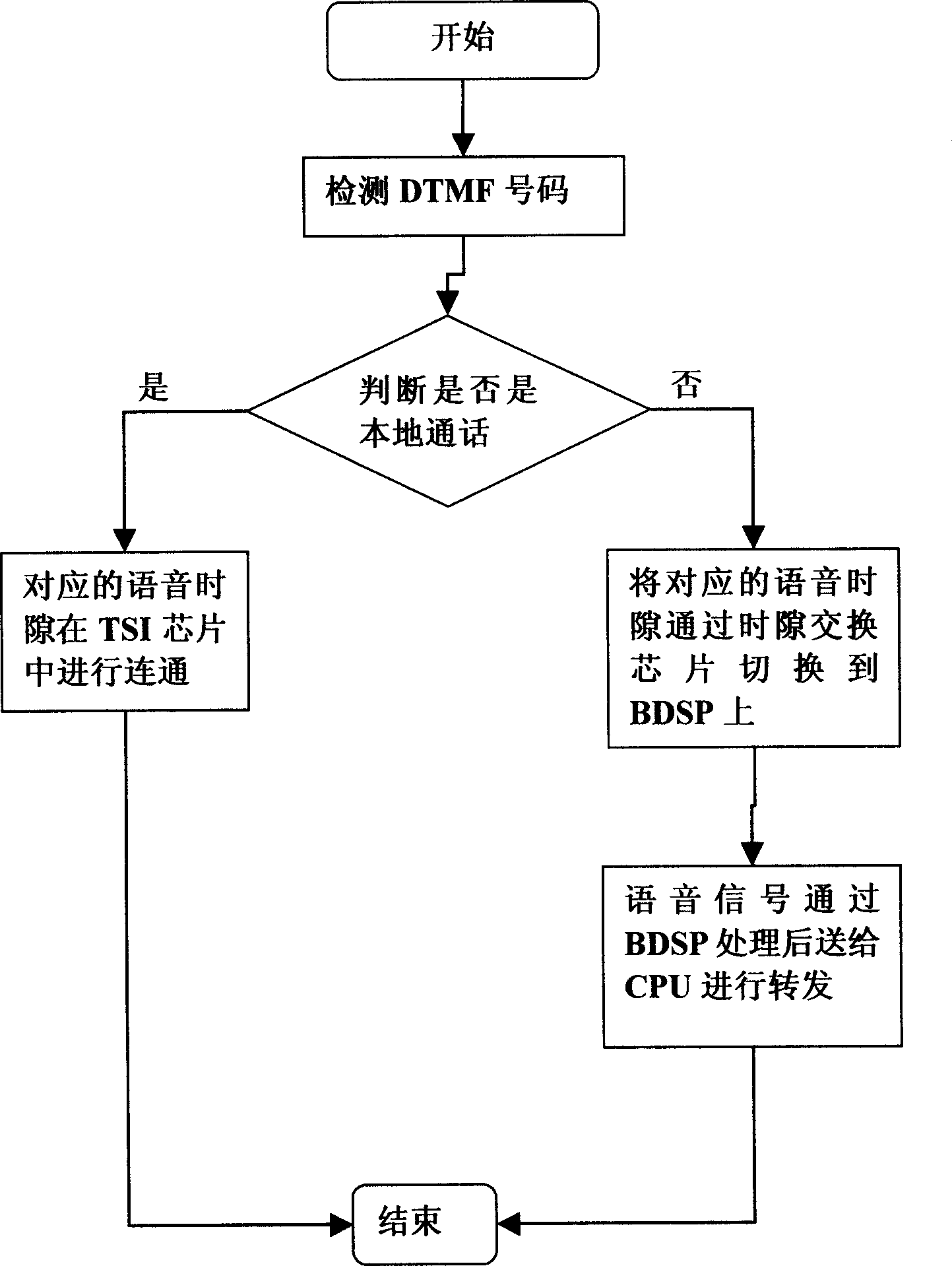

VoIP gateway and its application method

InactiveCN1885838ALower latencyImprove voice qualityInterconnection arrangementsNetwork connectionsComputer networkTime delays

The disclosed VoIP gateway comprises: based on prior art, adding a time-slot exchange chip and DSP, and using a microprocessor to distinguish local and IP dialogue. This invention reduces time delay and cost, and improves voice quality.

Owner:NEW H3C TECH CO LTD

Efficient high density voice processor

InactiveUS7346048B1Increase spacingReduce total powerMultiplex system selection arrangementsTime-division multiplexComputer hardwareDynamic range compression

A circuit and method are presented for signal processing and routing of digital voice telephony signals, using a specialized high-density integrated circuit voice processor. The voice processor performs several essential functions required for telephony processing, including echo cancellation, protocol conversion, and dynamic range compression / expansion. These functions are traditionally performed by multiple circuits or modules. By combining these capabilities in a single device, power and circuit board area requirements are reduced. The embodiment of the circuit and method disclosed herein include novel implementations of a time-slot interchange circuit and a telephony signaling circuit. Both of these circuits are designed to minimize demands on the signal processing engines incorporated within the voice processor, and account for very little of the on-chip circuitry.

Owner:INTEL CORP

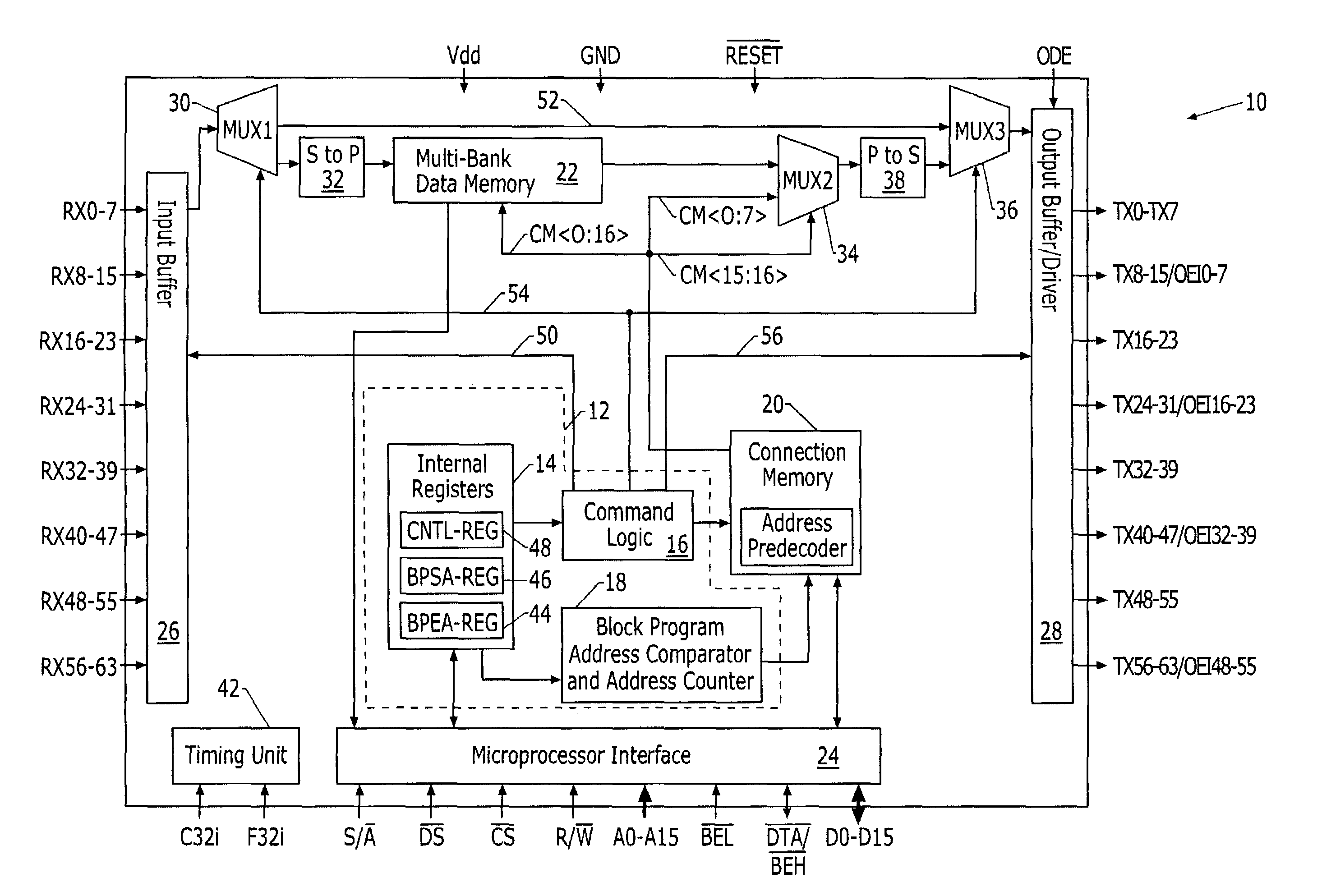

Time-slot interchange switches having efficient block programming and on-chip bypass capabilities and methods of operating same

ActiveUS7266128B1Data switching by path configurationCircuit switching systemsOperation modeData memory

Owner:INTEGRATED DEVICE TECH INC

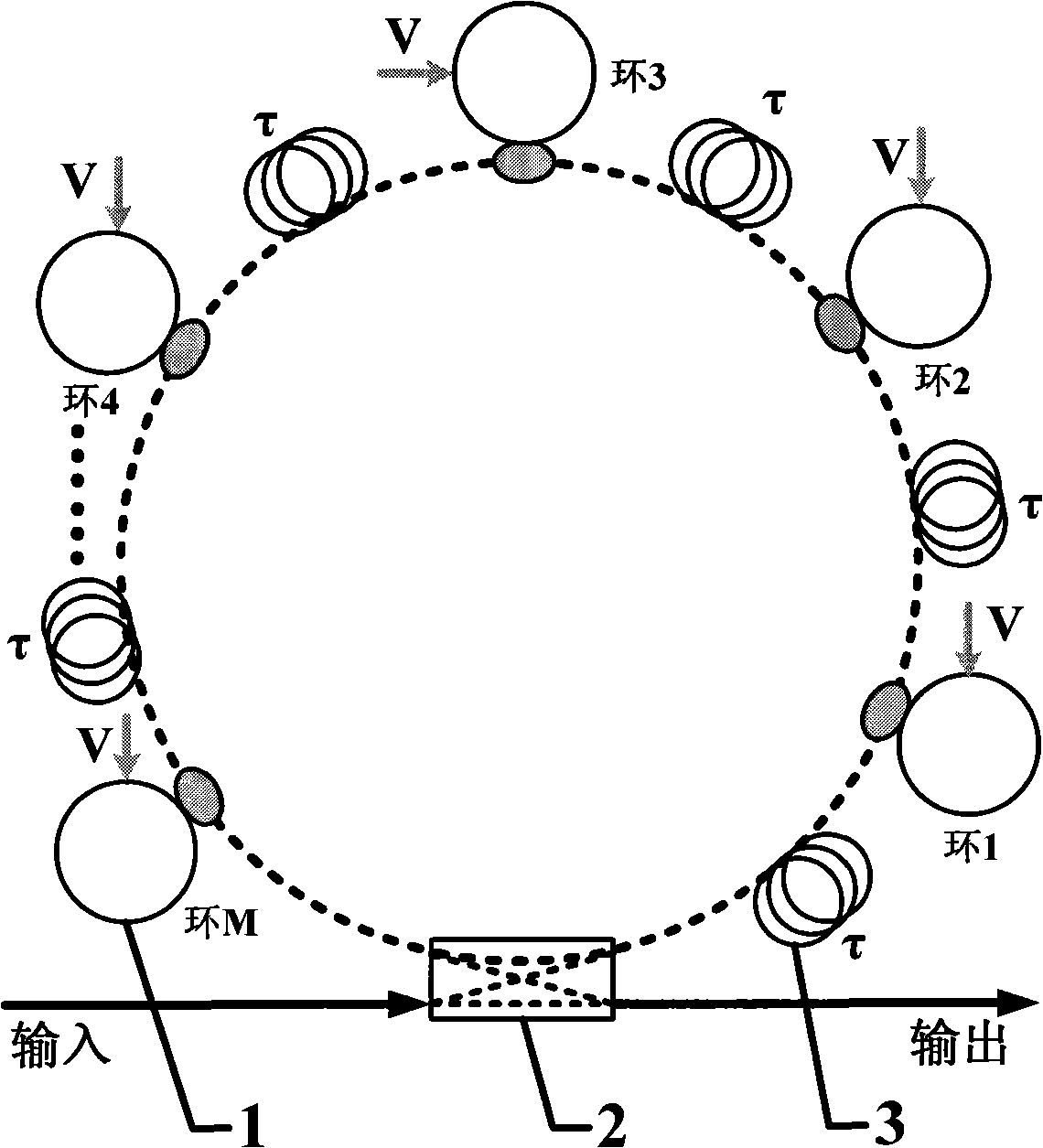

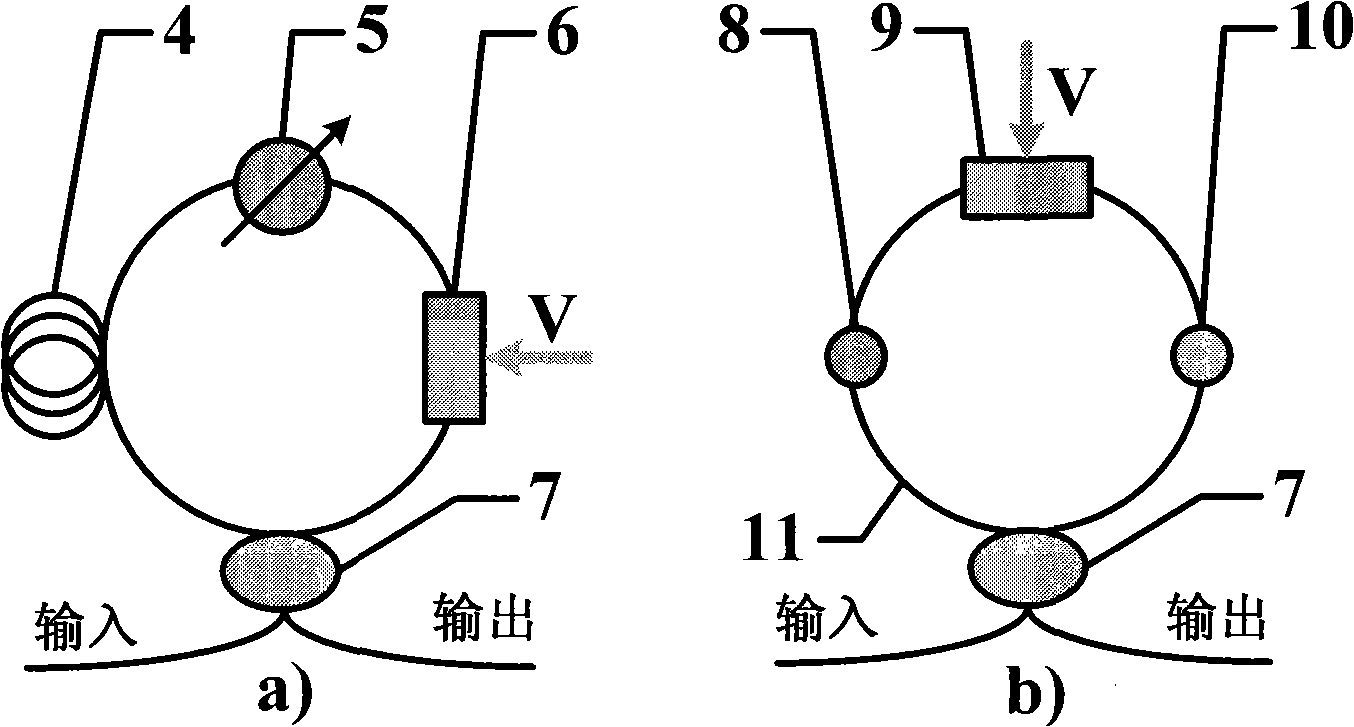

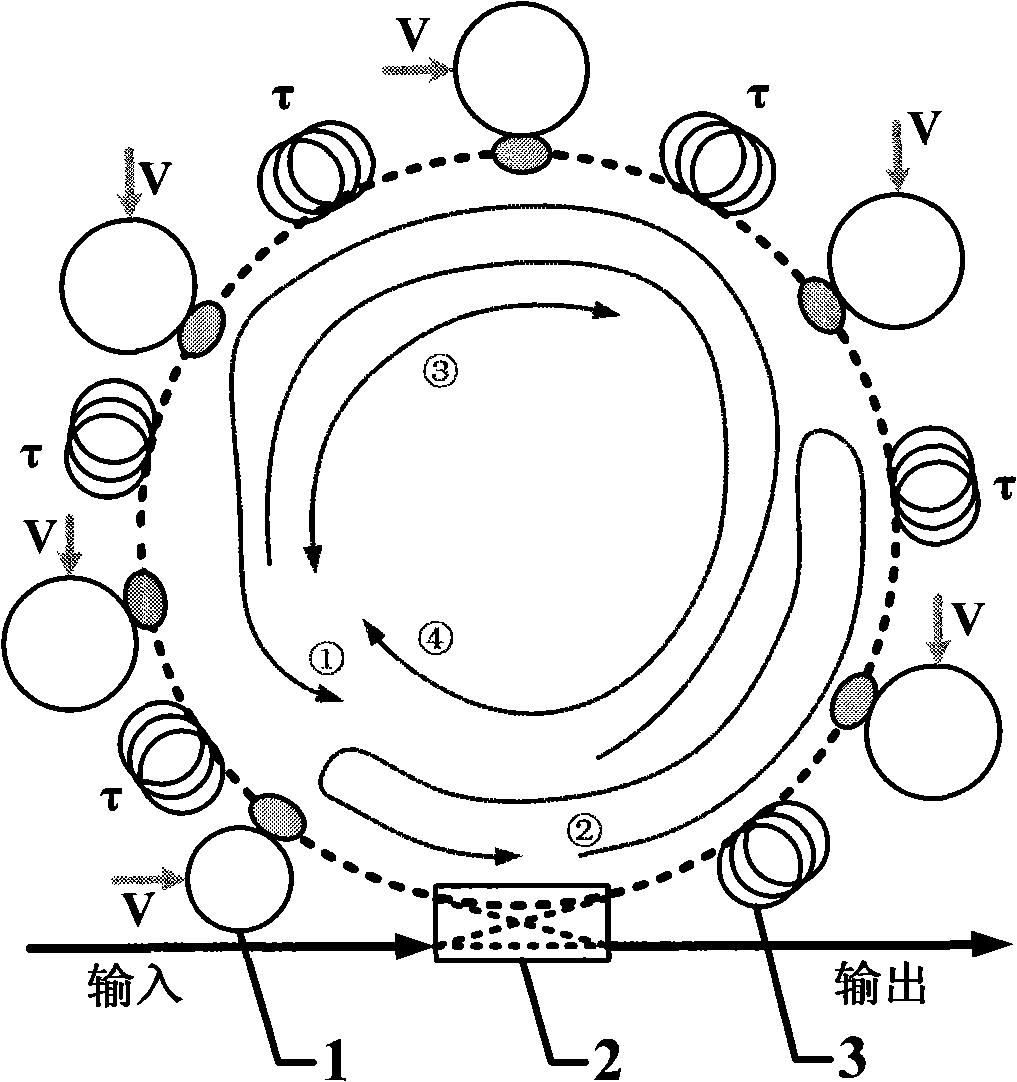

Fast dynamic configurable optical grouping caching device in full optical network

InactiveCN101344614AFunction increaseReduce physical sizeWavelength-division multiplex systemsCoupling light guidesOptical packetFiber ring

The invention relates to an all-optical network quick-dynamic configurable optical packet buffer. M Sagnac interference rings with reflex-transmission functions and M optical fiber delay lines are mutually by interval welded and connected in series; the optical fibers at the head and tail ends are welded with an input end and an output end of a 2 times 2 quick optical switch to form a buffer fiber ring. The other couple of the input end and output end of the 2 multiplied by 2 quick optical switch are adopted as the input and output ends of optical packet signals. The optical buffer of the invention enhances the re-cycle optical fiber buffering capability and provides the diverse buffer path options by embedding the Sagnac interference rings and optical fiber delay lines by interval on the basis of the existing re-cycle optical fiber ring of the traditional 2 multiplied by 2 quick optical switch so as to realize the time-slot exchanging for a plurality of optical packets and the quick-dynamic configuration of buffering time while supplying a plurality of optical packets. The invention has the advantages that the optical buffering time dynamic scope is wide; the reconfiguration time is short; the physical volume is small; the power cost is low and the potential expansibility is high, etc.

Owner:SHANGHAI JIAO TONG UNIV

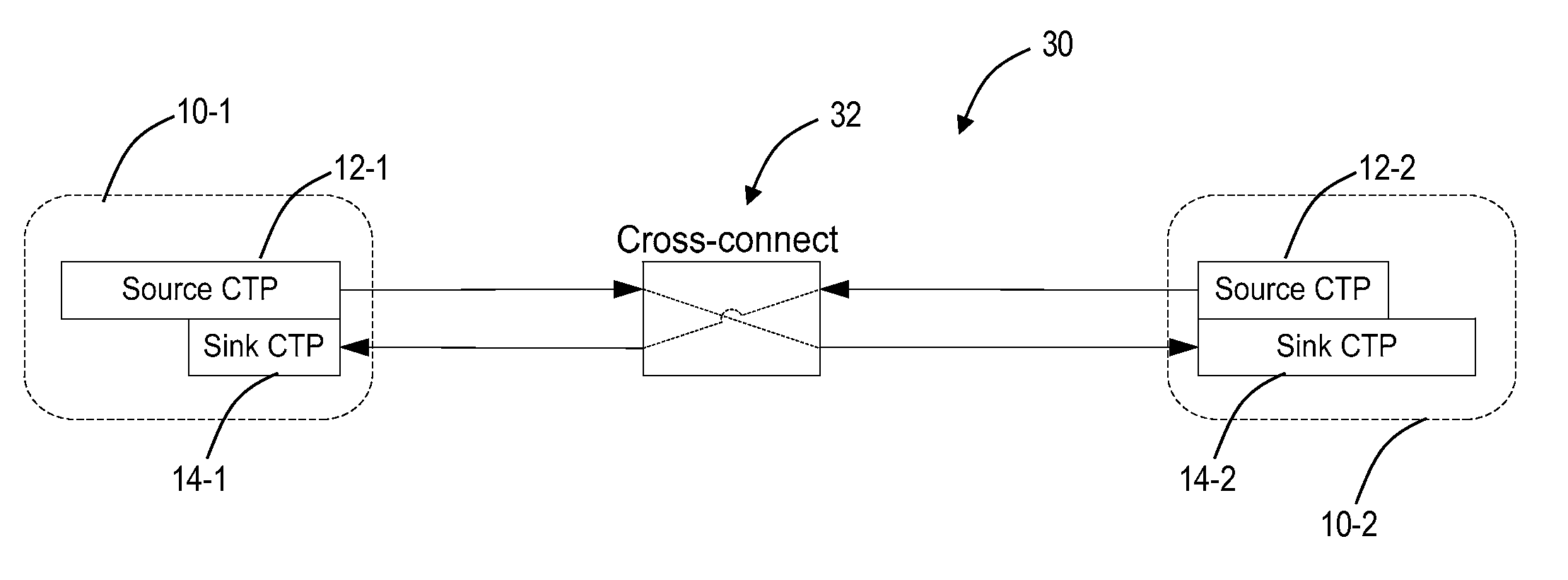

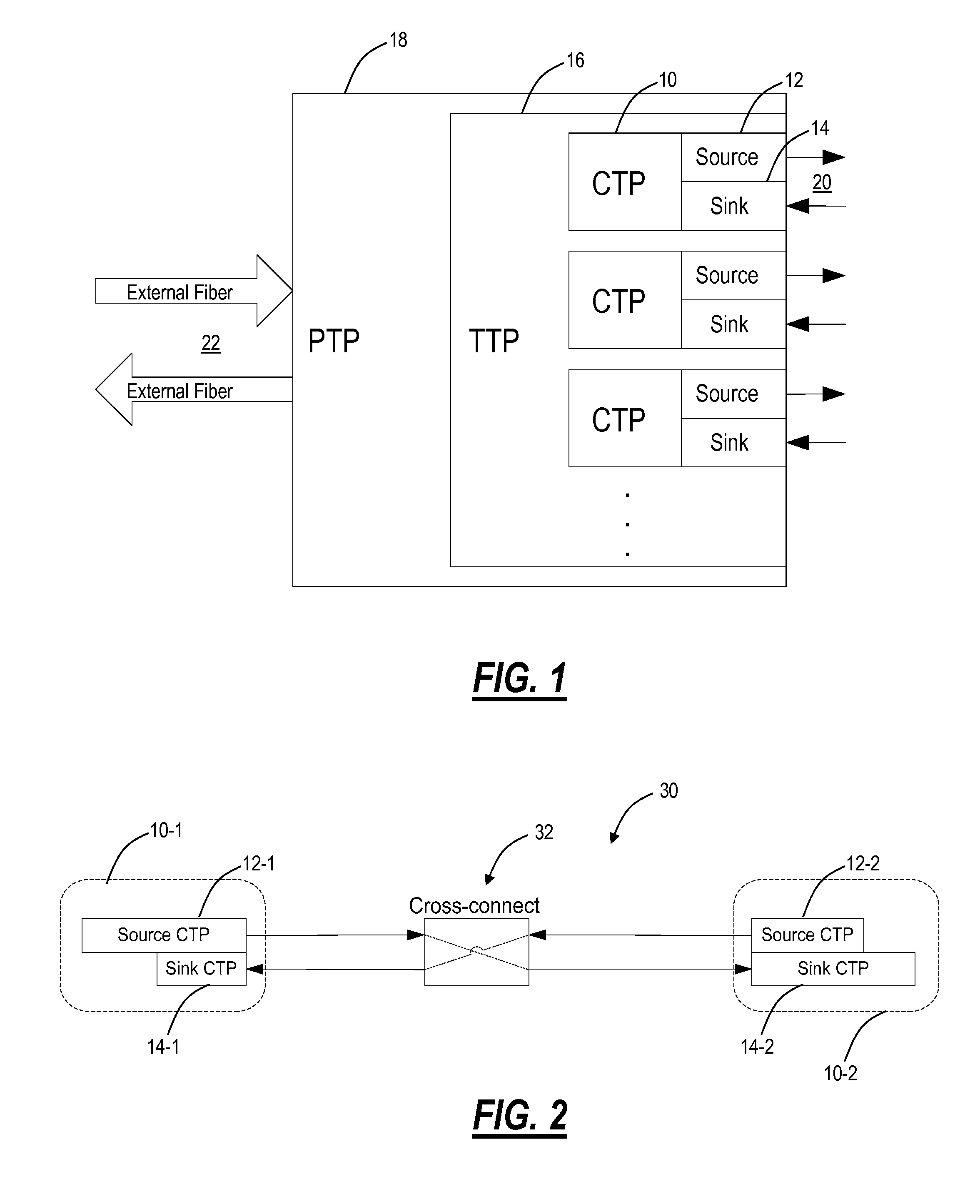

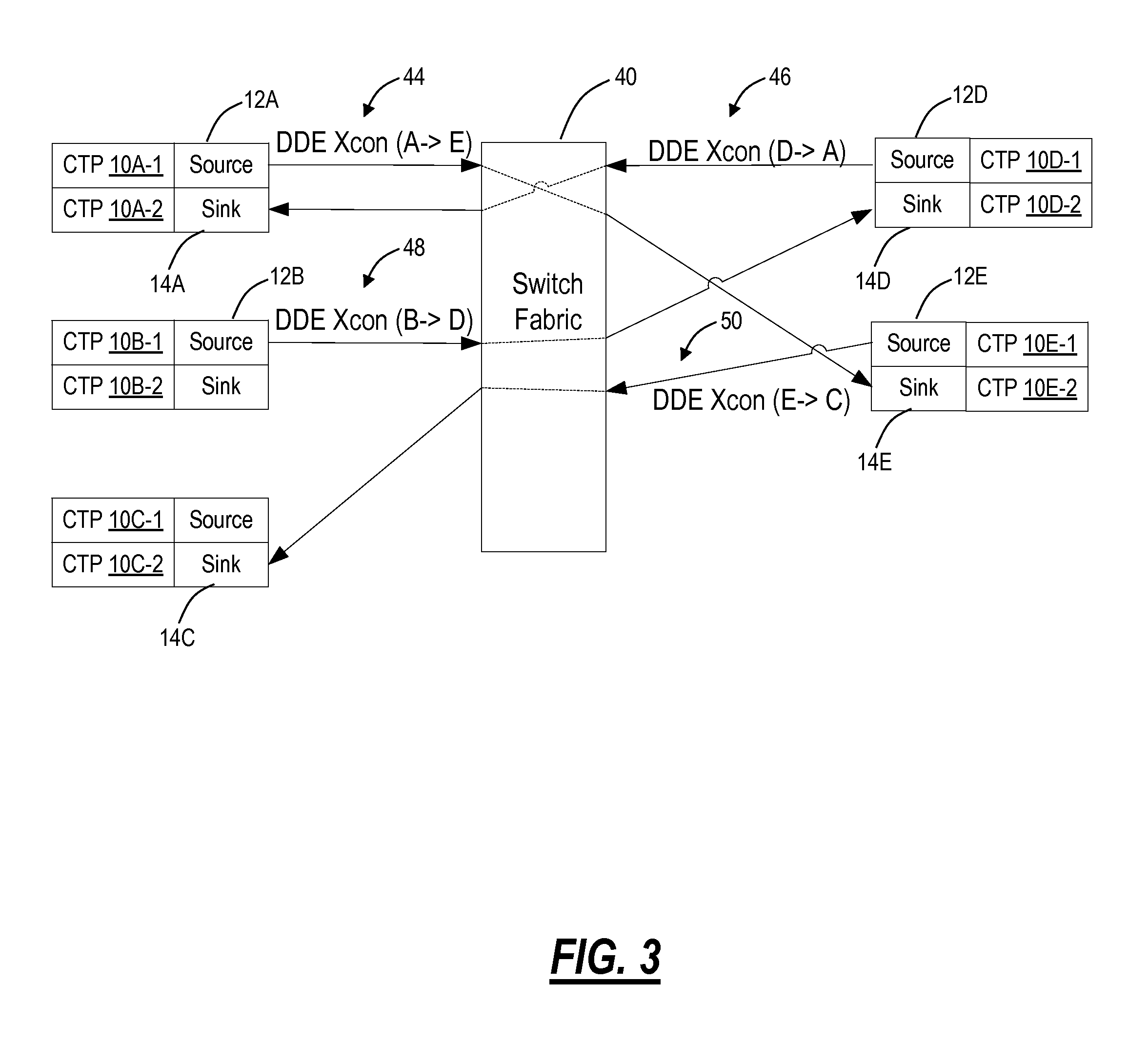

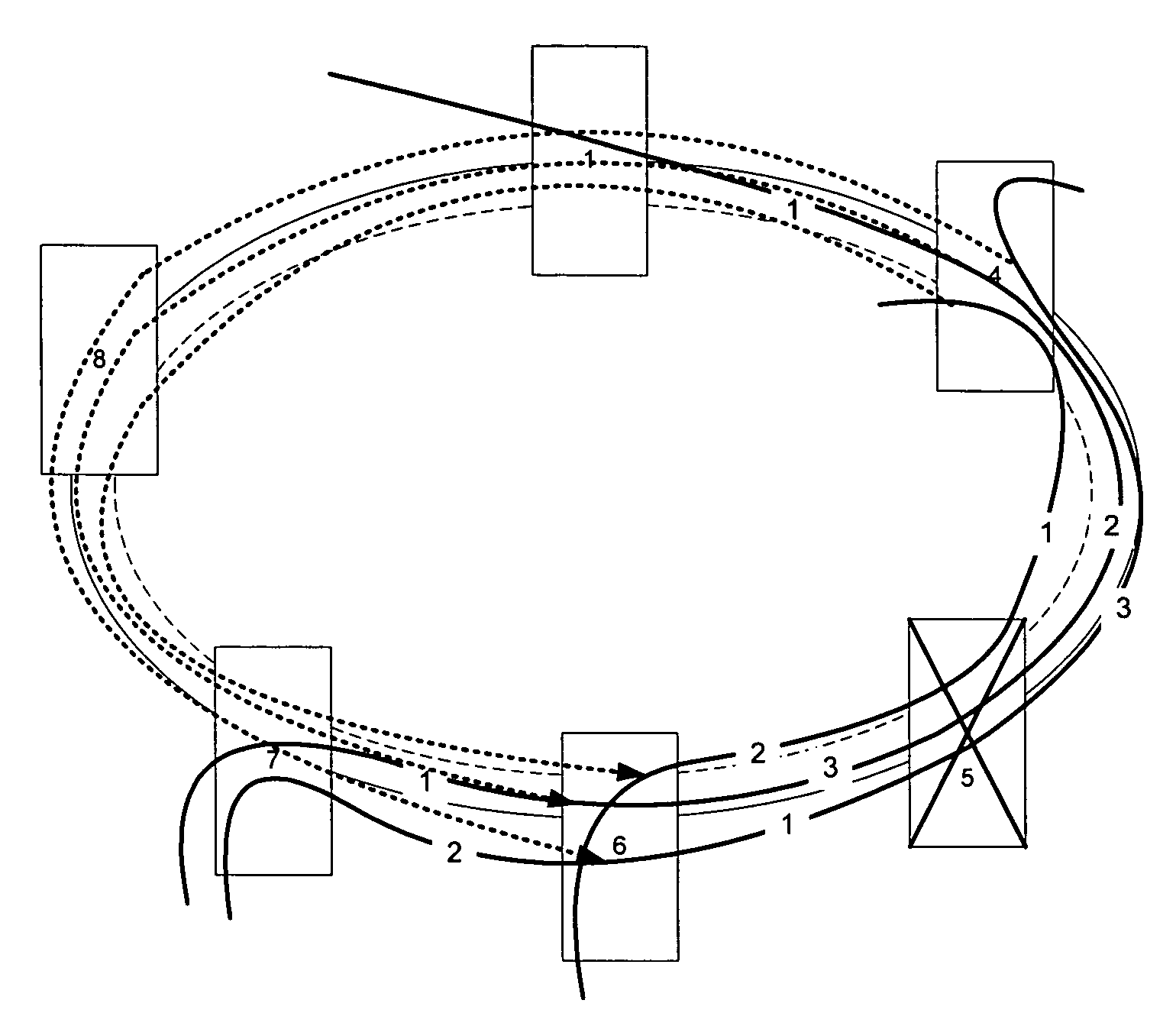

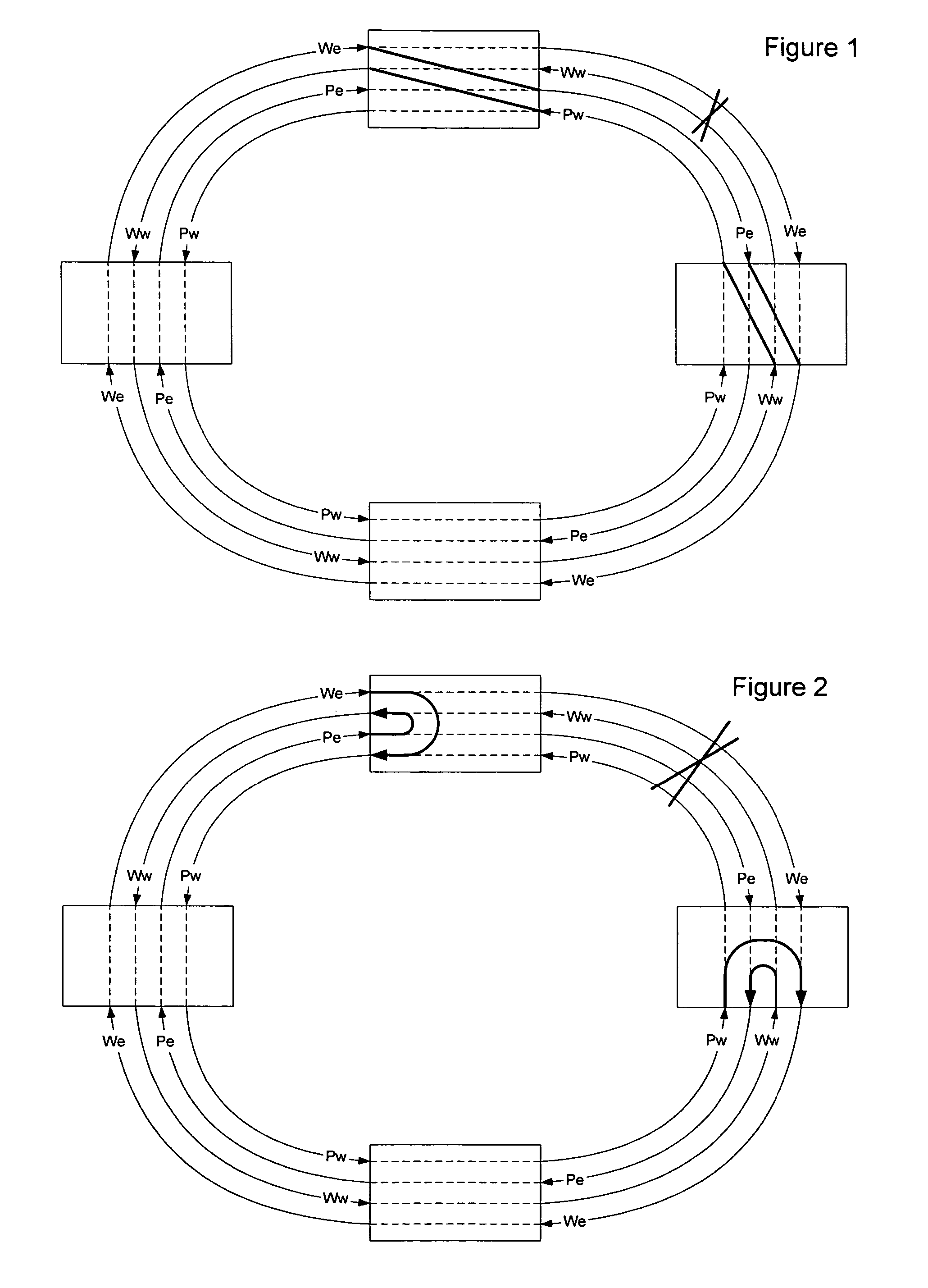

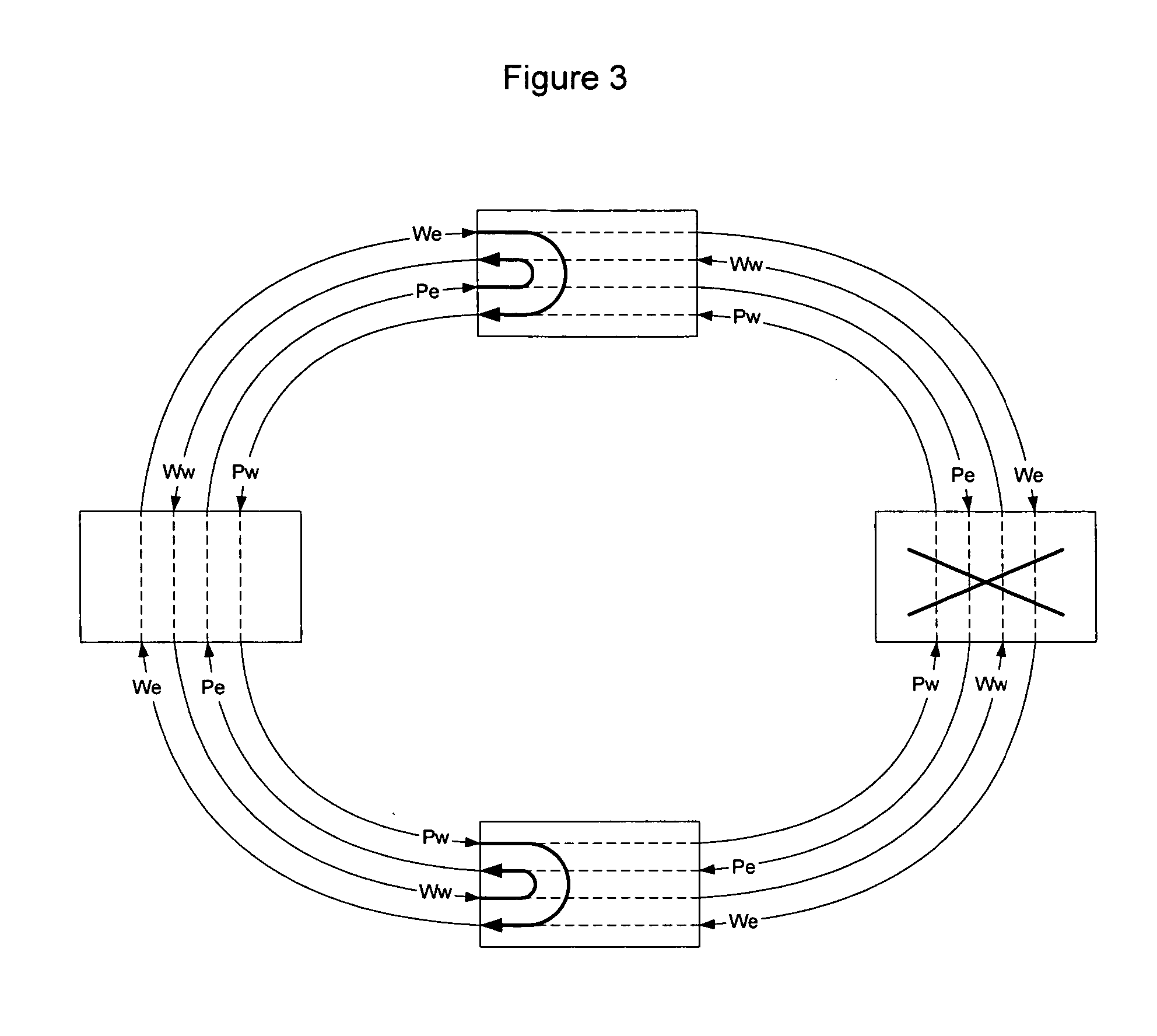

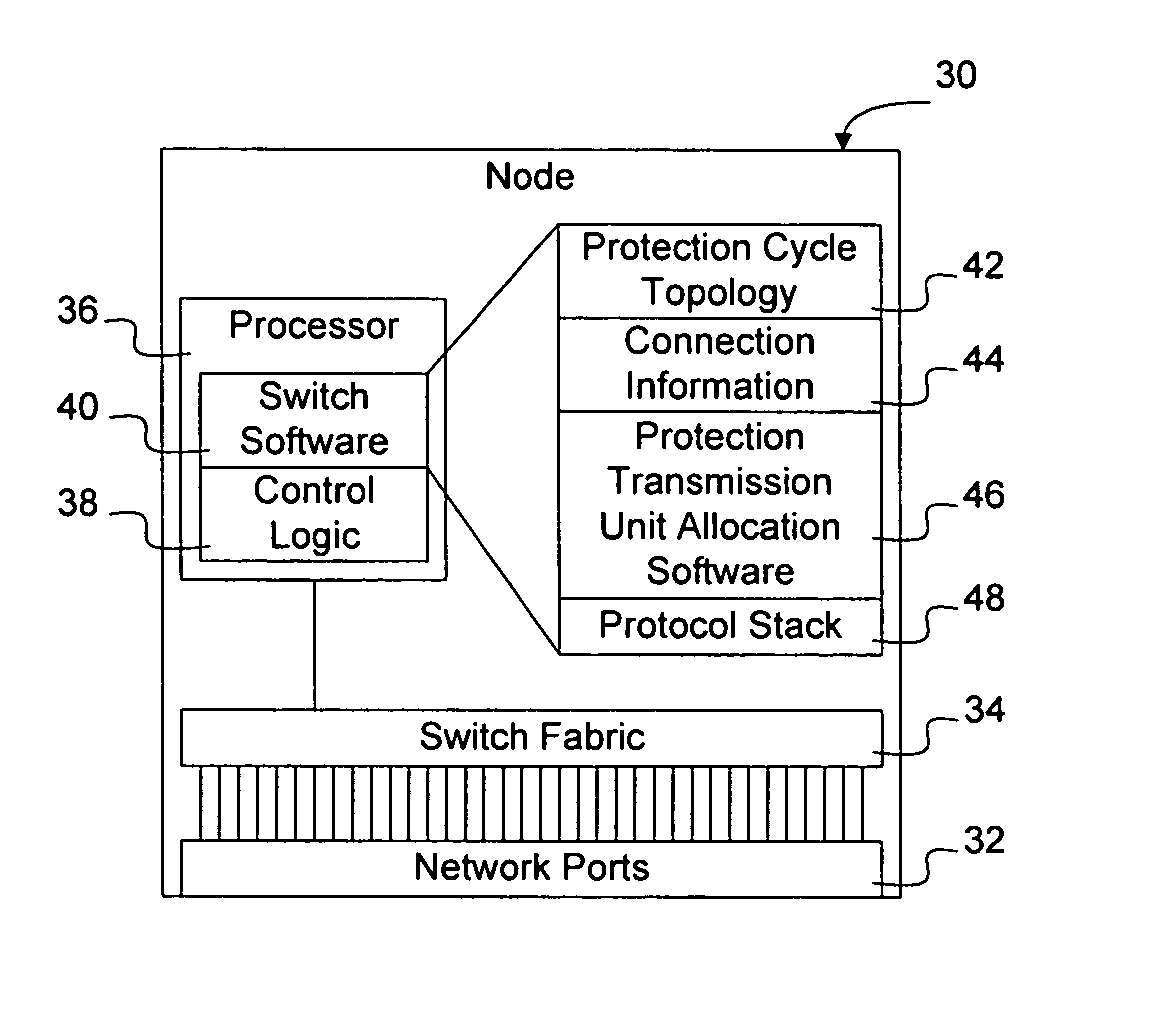

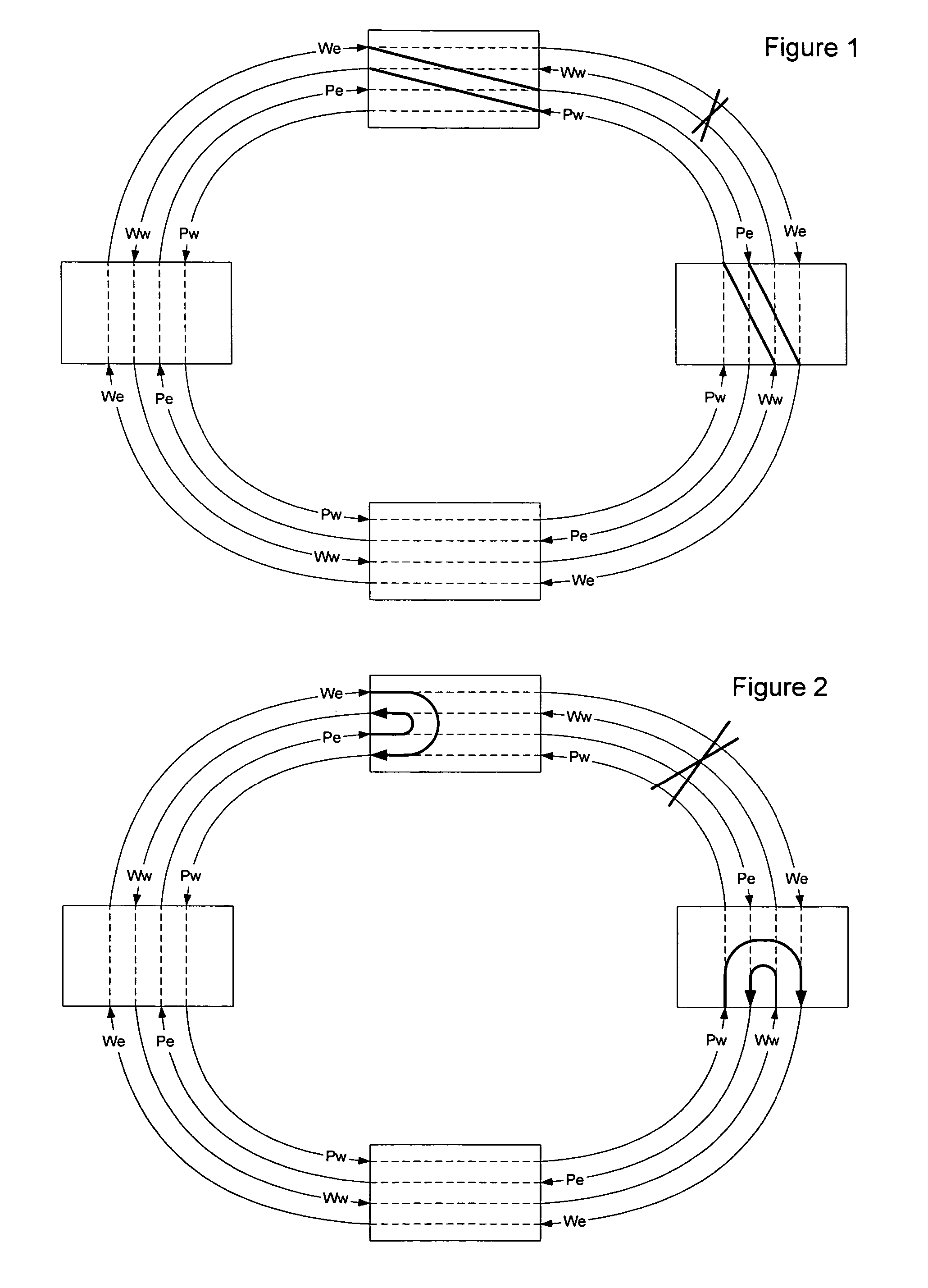

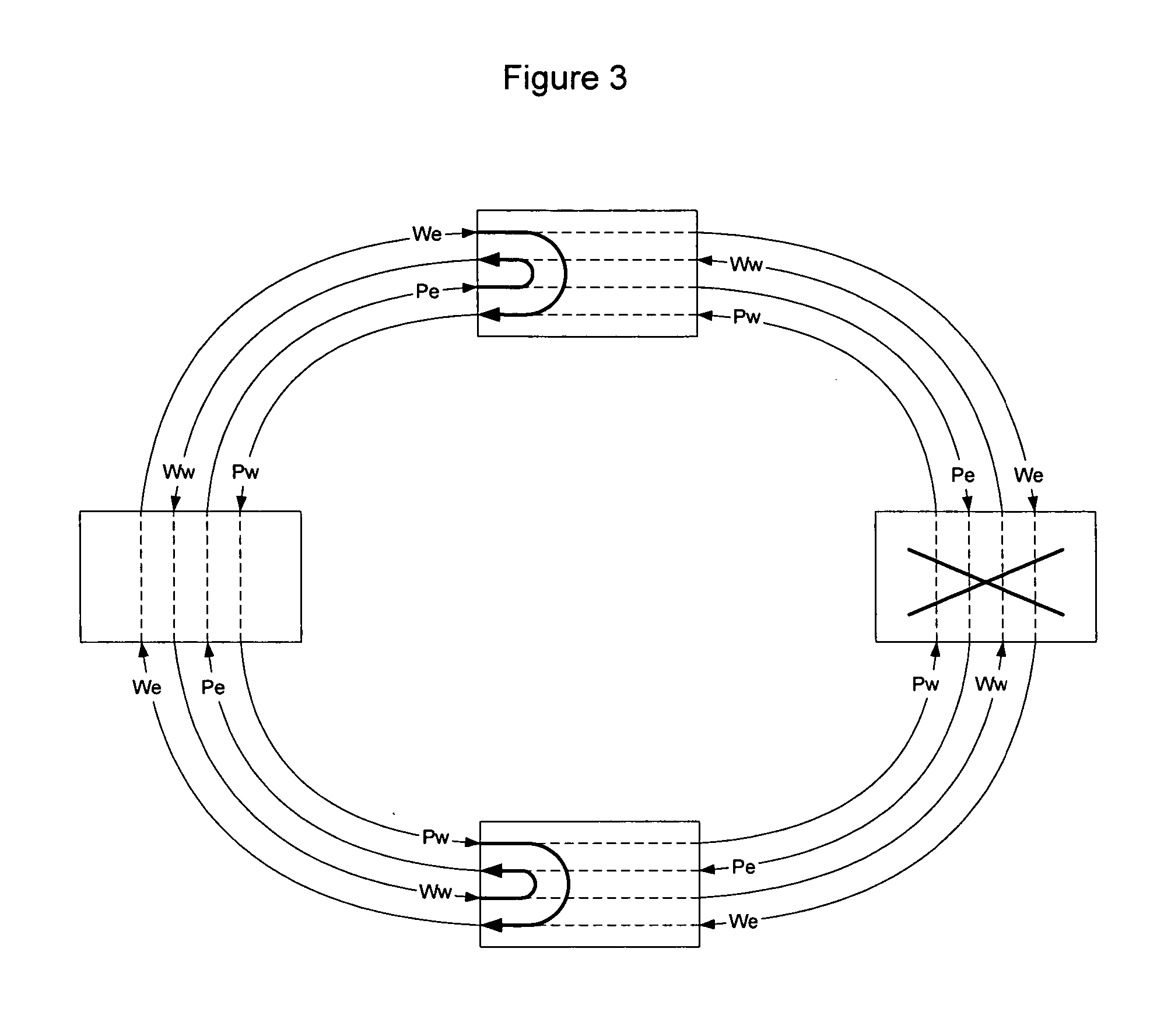

Method and apparatus for determining protection transmission unit allocation

ActiveUS7643407B2Error preventionFrequency-division multiplex detailsEngineeringTime-Slot Interchange

Protection transmission unit allocation, such as STS# in a SONET / SDH network utilizing time slot interchange on the working path, may be determined by disseminating connection information, connection identification information, and a prioritization scheme, to nodes on the network and allowing them to deterministically allocate protection transmission units to connections on the protection cycle. Network elements forming physical or logical rings may thus ascertain the location on protection for a given connection without requiring protection unit allocation to be disseminated from a central controller. Since each node is starting with the same connection information and running the same priority determination, each will end up with the same result and will know where to place and find connections on protection. Aspects of the invention may be employed for example in a SONET / SDH based network, a mesh network, or other type of network with dedicated protection paths and transmission allocation on those protection paths.

Owner:CIENA

Method and apparatus for determining protection transmission unit allocation

ActiveUS20050198524A1Error preventionFrequency-division multiplex detailsEngineeringTime-Slot Interchange

Protection transmission unit allocation, such as STS# in a SONET / SDH network utilizing time slot interchange on the working path, may be determined by disseminating connection information, connection identification information, and a prioritization scheme, to nodes on the network and allowing them to deterministically allocate protection transmission units to connections on the protection cycle. Network elements forming physical or logical rings may thus ascertain the location on protection for a given connection without requiring protection unit allocation to be disseminated from a central controller. Since each node is starting with the same connection information and running the same priority determination, each will end up with the same result and will know where to place and find connections on protection. Aspects of the invention may be employed for example in a SONET / SDH based network, a mesh network, or other type of network with dedicated protection paths and transmission allocation on those protection paths.

Owner:CIENA

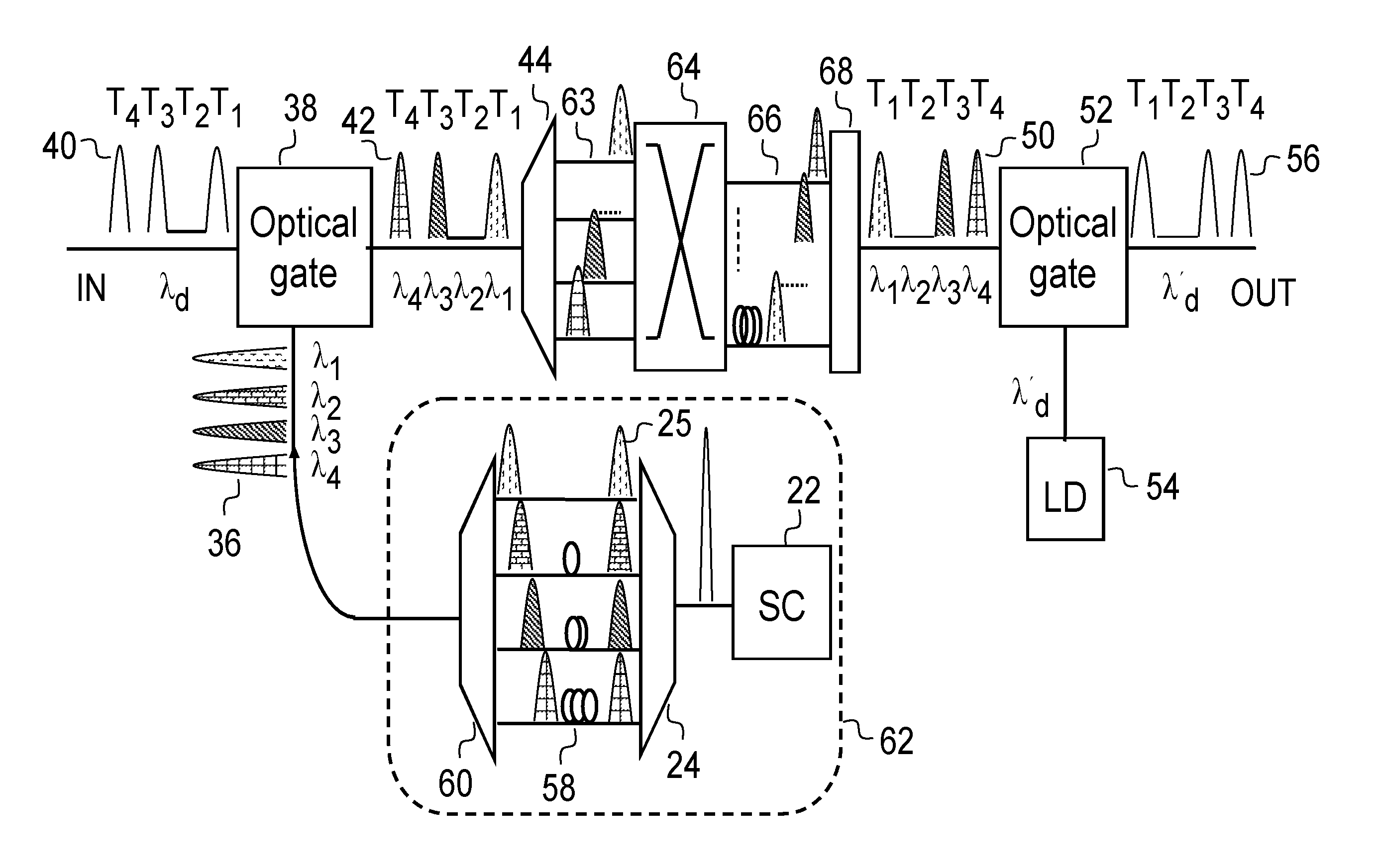

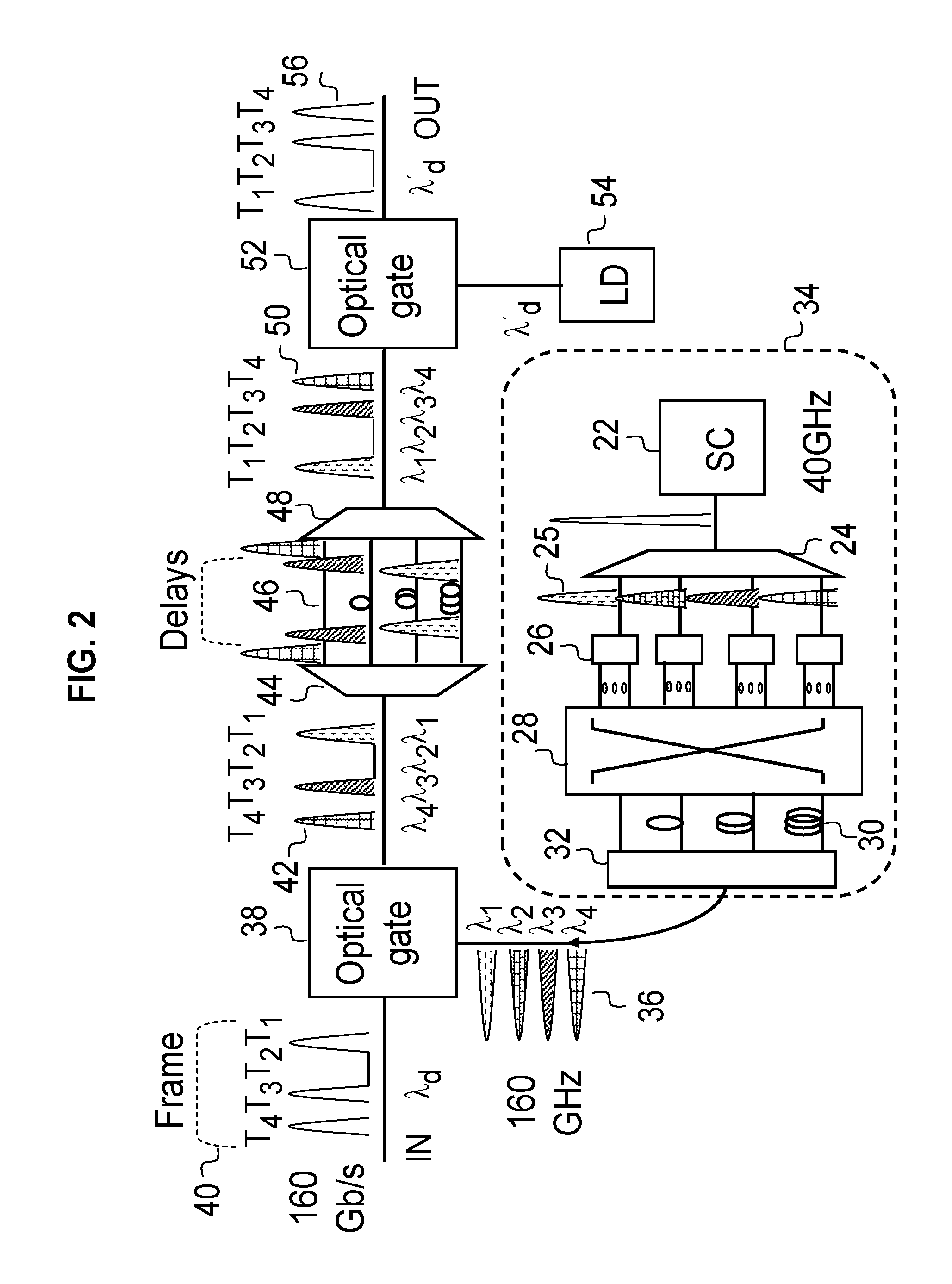

Time multiplexed space switch

InactiveUS20090080895A1Reduce in quantityQuality improvementMultiplex system selection arrangementsTime-division optical multiplex systemsLength wavePulse sequence

The present invention provides an optical time multiplexed space switch including a pulsed laser source, and means for producing from the laser source a plurality of wavelengths of pulsed radiation including means for providing permutable multi-wavelength pulse sequences from said multi-wavelength source and means for translating the input data pulses into the multi-wavelength pulse sequence. Each data pulse is subsequently guided through a wavelength selective structure, which may contain delay lines. In the case of time-slot interchange, the pulses are recombined in an interchanged sequence. In the case of tributary space switching different wavelength pulses are switched to generally different outputs and combine with pulses originating from different inputs. Alternatively, instead of or in addition to the means for providing permutable multi-wavelength pulse sequences from the pulsed source, means are provided for the permutation of the multi-wavelength data pulse sequence in reconfigurable wavelength selective structures.

Owner:ZARRIS GEORGE

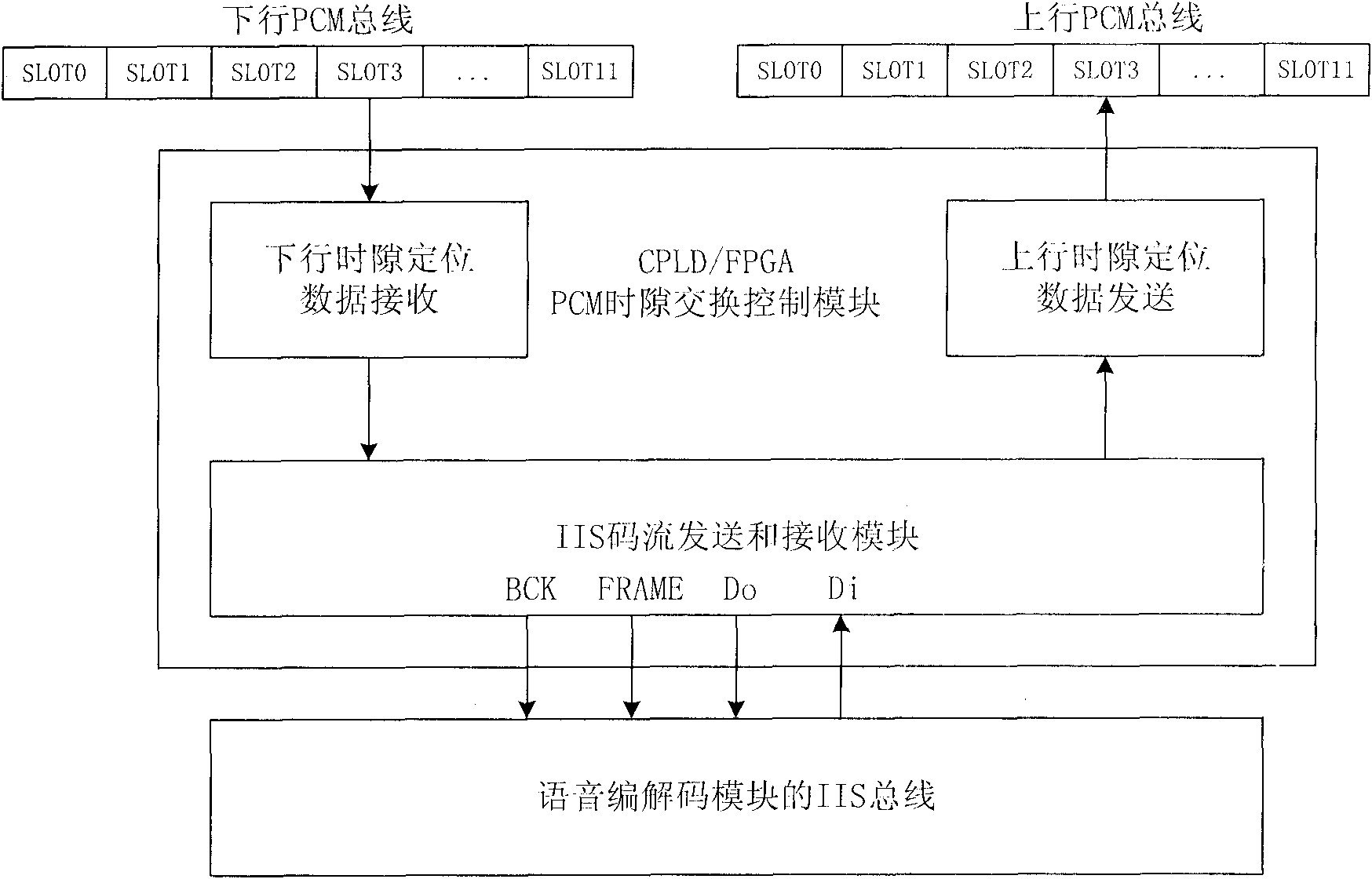

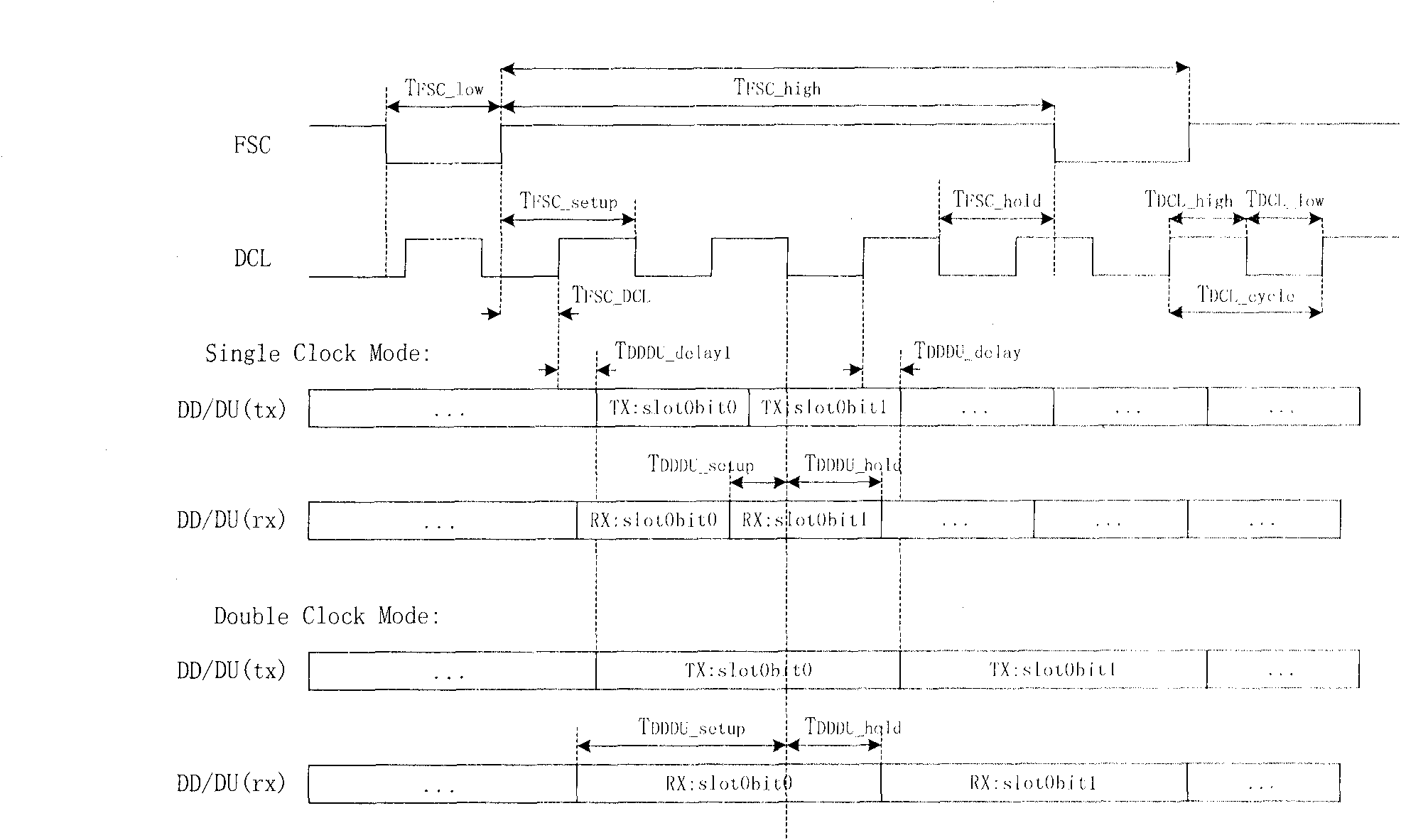

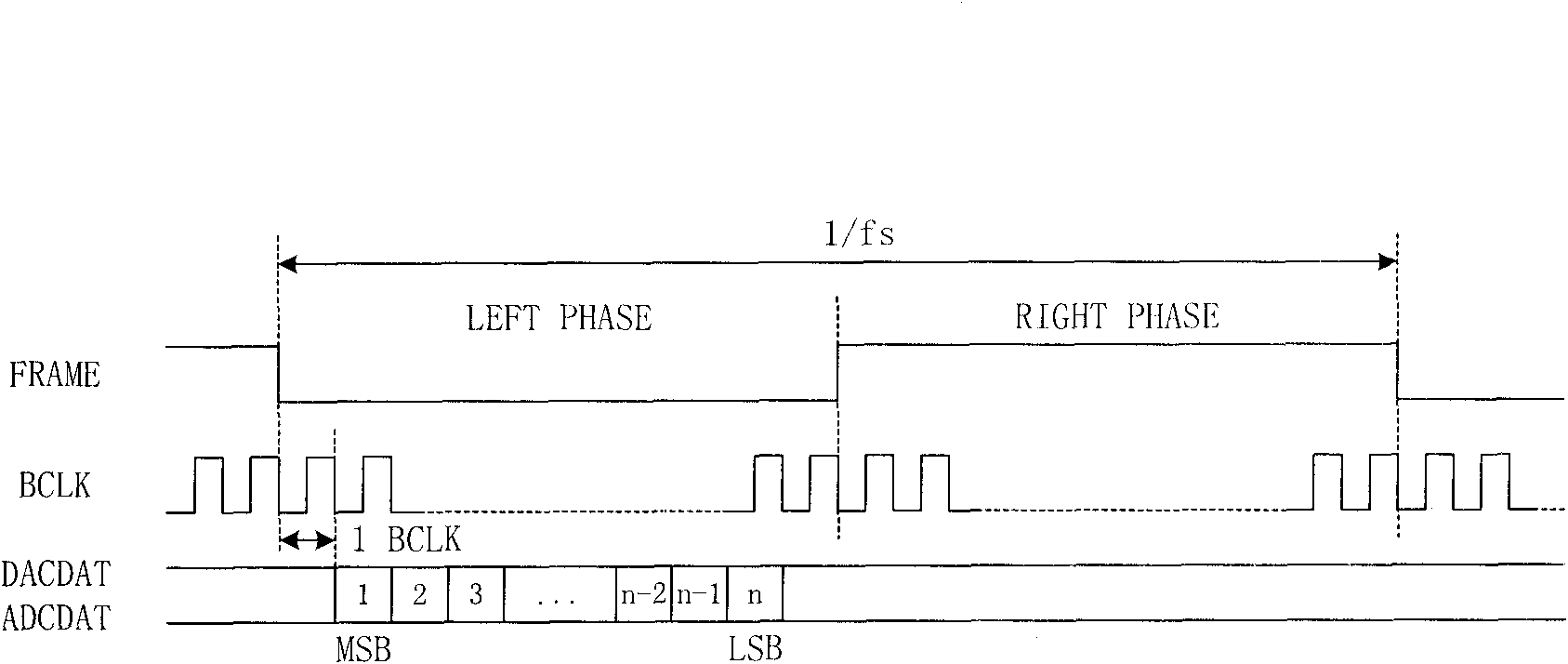

PCM time slot interchange method capable of directly carrying out voice interchange with voice codec

InactiveCN101827290ATroubleshoot real-time transmission issuesShort development timeTime-division multiplexing selectionFrequency conversionSpeech sound

The invention relates to a PCM time slot interchange method capable of directly carrying out voice interchange with a voice codec, which comprises the following steps of: taking equipment with a PCM interface as main equipment and a PCM time slot interchange controller module as the auxiliary equipment of PCM; meanwhile, taking the PCM time slot interchange controller module as an IIS main equipment interface and a voice encoder / decoder as an IIS auxiliary equipment interface; designing a time slot switch for a VHDL code, controlling concrete time slots ascending and descending from the PCM by the time slot switch, finishing the reception and the maintenance of the data of the concrete time slots of the PCM by a PCM time slot interchange controller module, forming a novel IIS bus timing and transmitting the novel IIS bus timing to the voice encoder / decoder; and meanwhile, transmitting voice data transmitted from the voice encoder / decoder to the ascending concrete time slots after carrying out frequency-conversion processing on the voice data, thereby finishing real-time interchange. The invention can solve the problem of real-time transmission of voice without the participation of a CPU and a memory and also does not need to compile an IIS driver.

Owner:FUJIAN XINO COMM TECH

Remote monitoring data transmission method and implementing device therefor

InactiveCN1543130ALow maintenanceSimplify the amount of writingTransmission monitoringData switching networksAsynchronous serial interfaceTransformation unit

This invention relates to a transmission method and its application device for remote monitor data for solving the problem of unstable monitor system resulted from software reform on the basis of using transmission channel bandwidth as much as possible. This invention applies the following technology: an asynchronous serial interface outputs the data to a serial / parallel switch unit to finish the switch then the data is put in a latch unit which outputs it to a parallel / serial switch unit for switching then to be output to a synchronous serial multiplex unit multiplexed with the data to the unit from the synchronous serial interface to occupy a time slot together which is output to a time slot exchange unit exchanging it to a definite time slot to be merged with PCM stream from the slave E1interface and output from the master E1 interface.

Owner:ZTE CORP

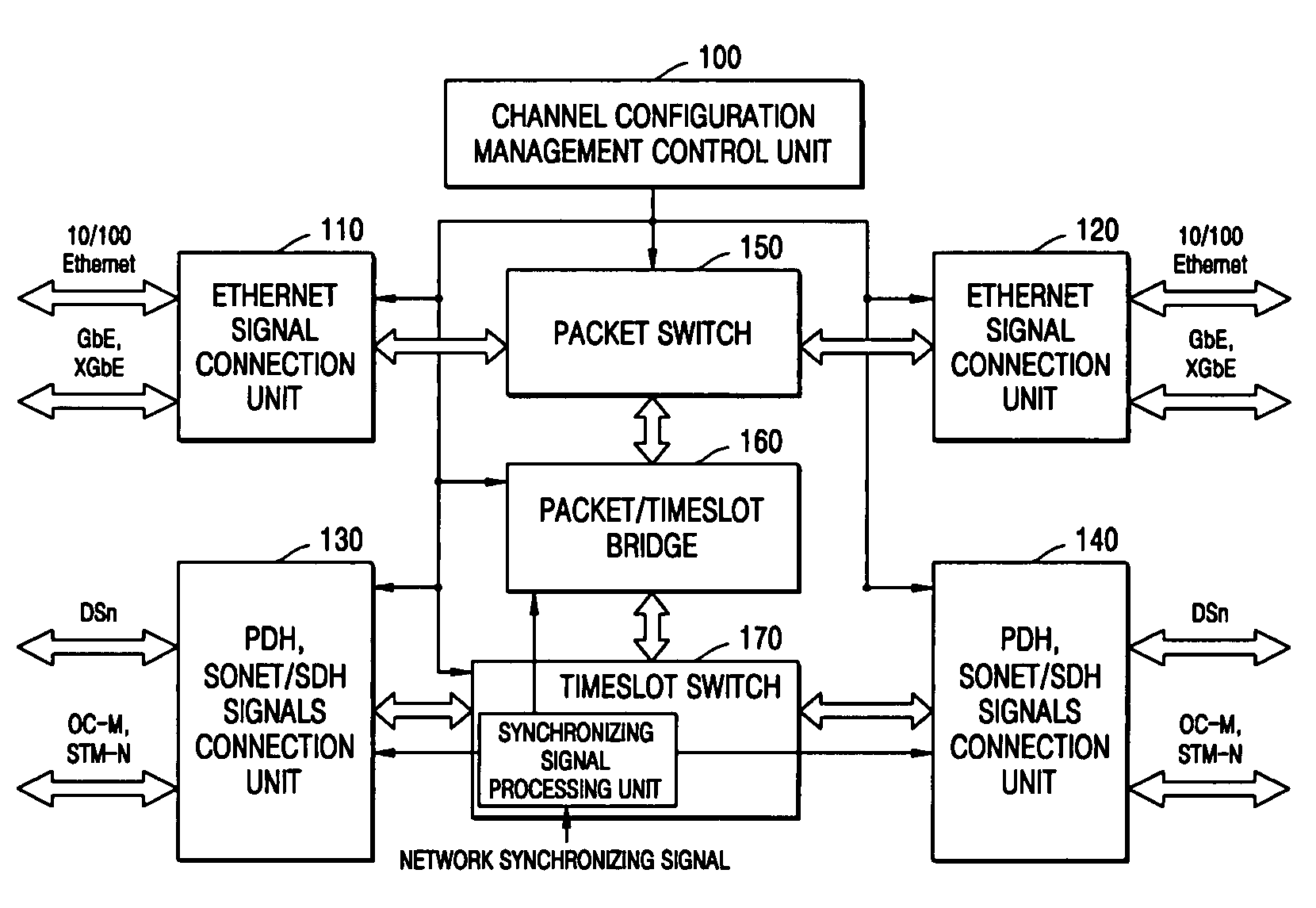

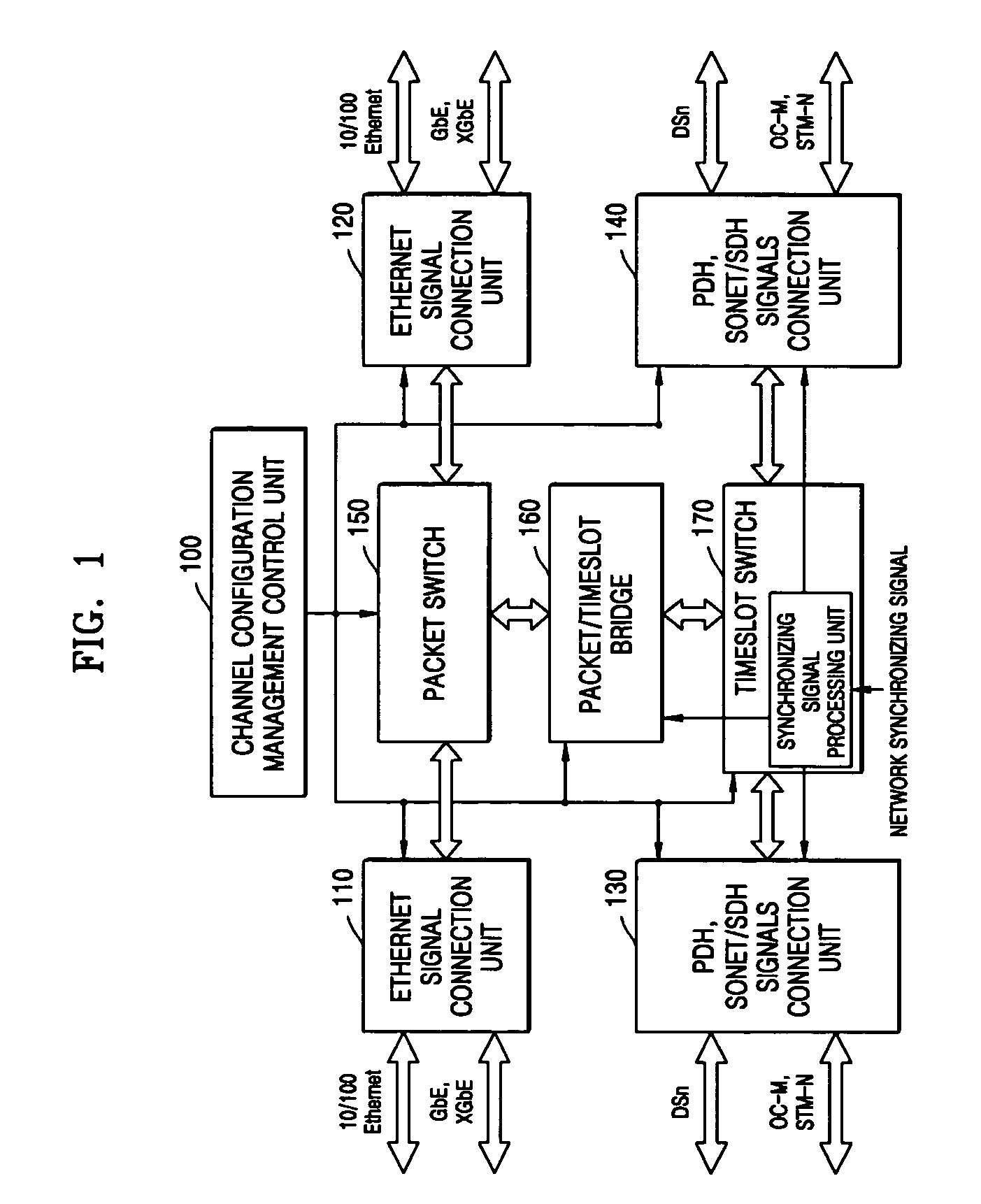

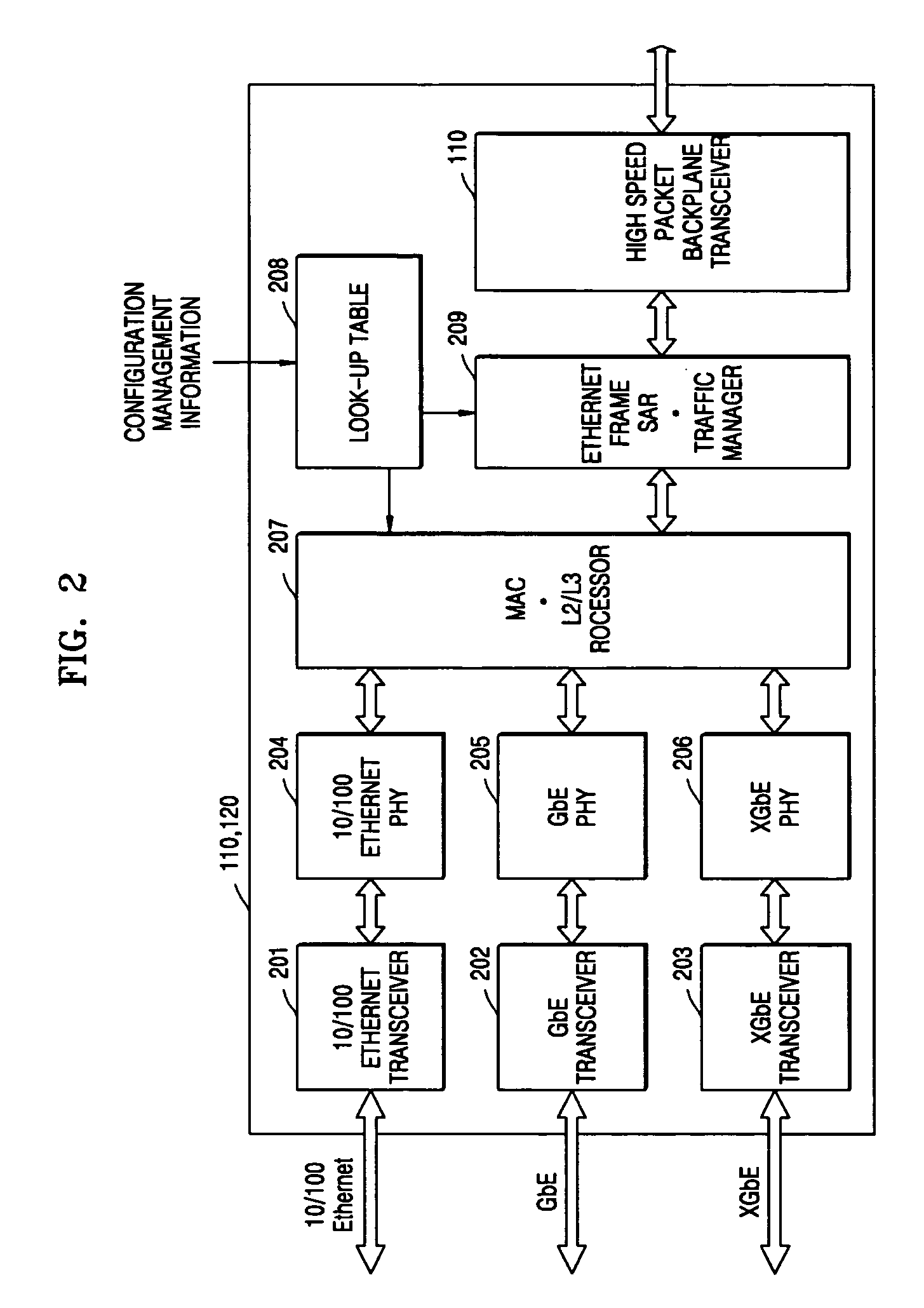

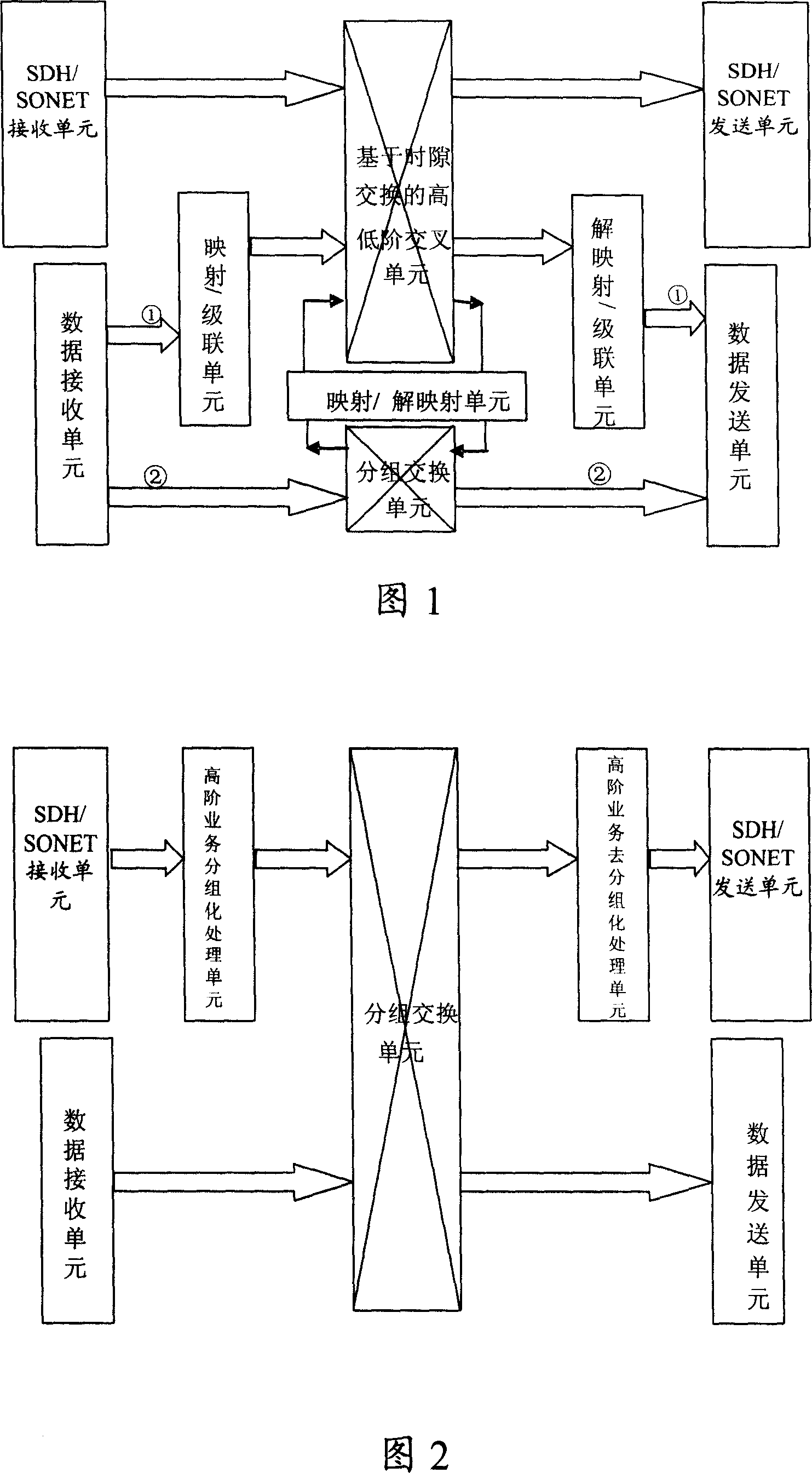

Apparatus for and method of integrating switching and transferring of SONET/SDH, PDH, and Ethernet signals

ActiveUS7599372B2Low costReduce maintenanceTime-division multiplexData switching by path configurationService provisionPlesiochronous digital hierarchy

An apparatus for and a method of integrating switching and transferring of synchronous optical network / synchronous digital hierarchy (SONET / SDH), plesiochronous digital hierarchy (PDH), and Ethernet signals, which integrate and provide connection of synchronous digital (SONET / SDH) signals, plesiochronous digital (PDH) signals, and Ethernet signals, mutually change the synchronous digital (SONET / SDH) signals, the plesiochronous digital (PDH) signals, and the Ethernet signals, packet switching, synchronous timeslot switching, and channel configuration management and control functions in one system. Thus, packet switching capacity, timeslot switching capacity, and packet / timeslot bridging capacity can be enlarged and configured according to corresponding application. Also, a distinctive service compared to a service provided by a separate Ethernet device or a SONET / SDH network device can be provided through a packet / timeslot bridge. In addition, varied and reliable communication service at a moderate price can be provided to service users, and decreased investment and maintenance fee can be provided to carrier service providers.

Owner:ELECTRONICS & TELECOMM RES INST

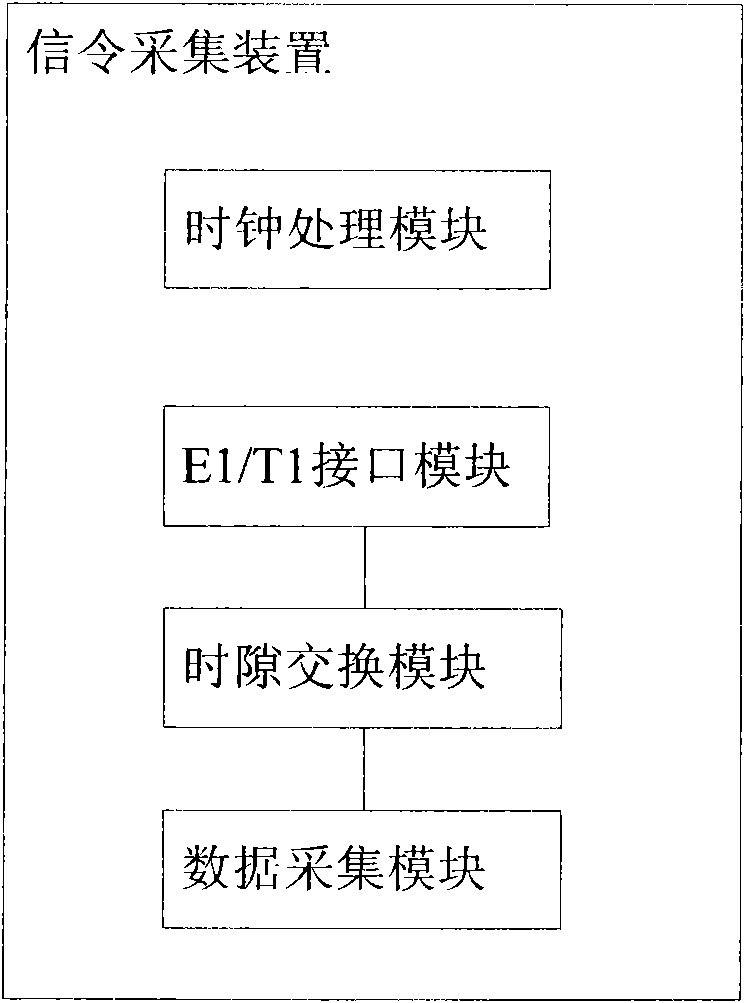

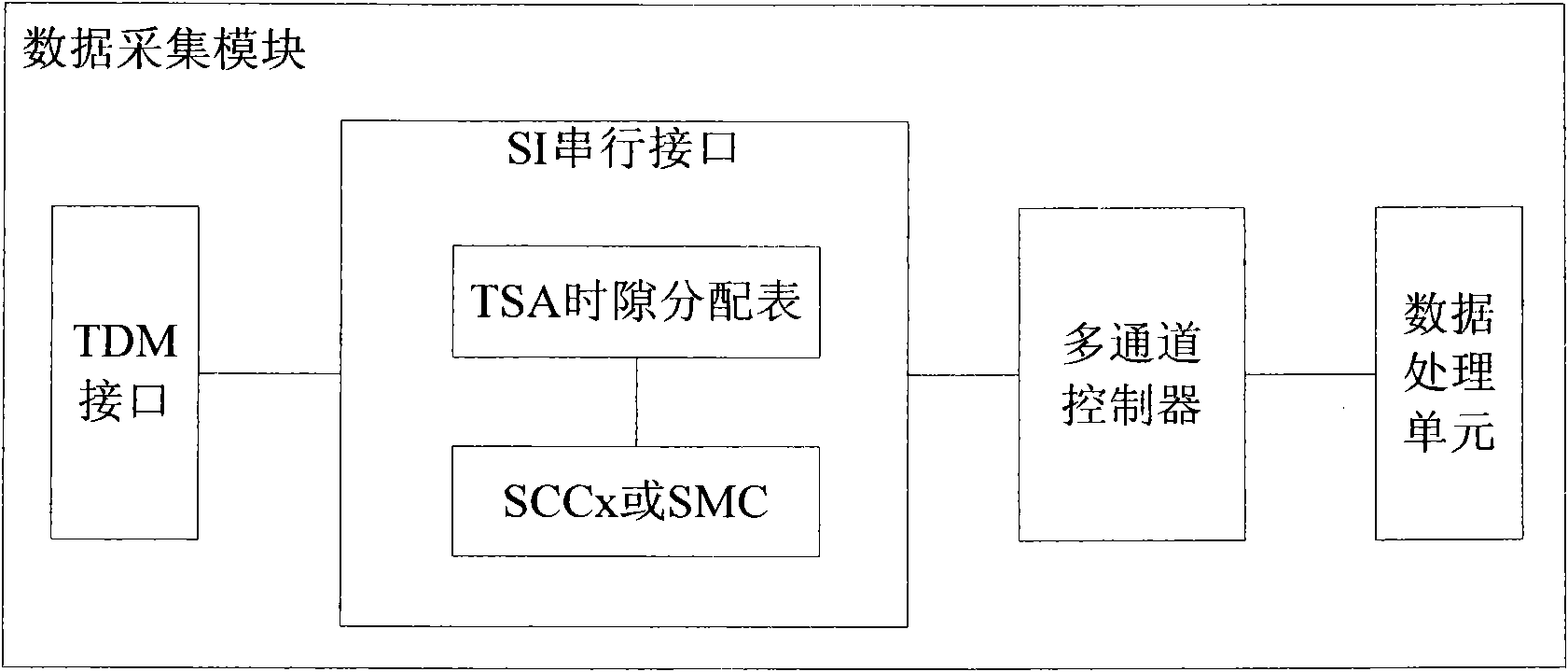

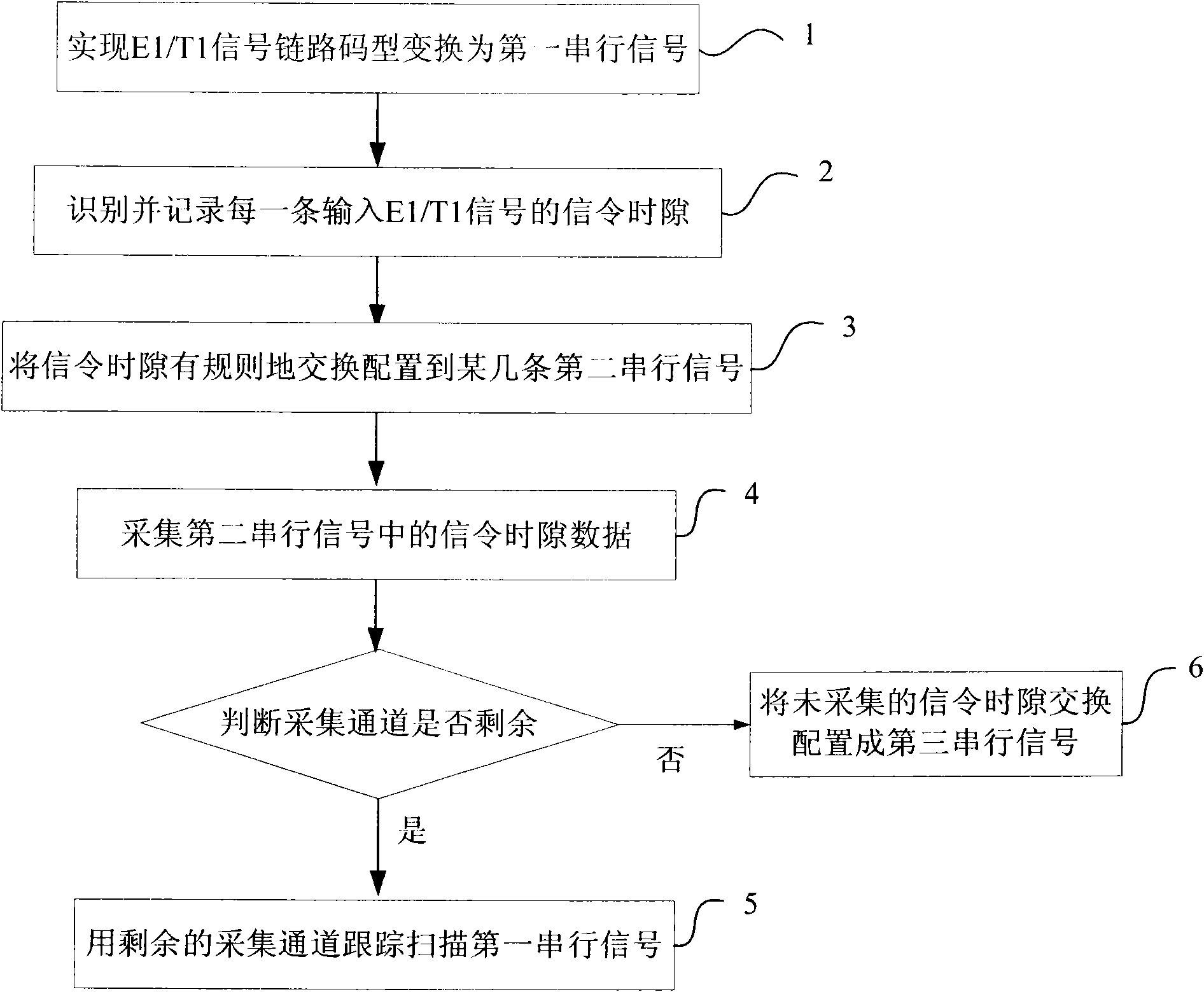

Signaling acquisition device and method

InactiveCN101651846AWith cross-convergence functionTime-division multiplexSelection arrangementsData acquisitionData acquisition module

The invention relates to signaling acquisition device and method. The signaling acquisition device comprises an E1 / T1 interface module, a time slot interchange module and a data acquisition module, wherein the E1 / T1 interface module is used for realizing the code pattern conversion of an E1 / T1 signaling link to obtain a first serial signal, and transmitting the first serial signal to the time slotinterchange module; the time slot interchange module is used for copying the first serial signal to the data acquisition module, and exchanging and configuring a signaling time slot in the received first serial signal identified by the data acquisition module to obtain a second serial data, and sending the second serial signal to the data acquisition module; and the data acquisition module is used for identifying the signaling time slot in the first serial signal copied from the time slot interchange module, feeding the signaling time slot back to the time slot interchange module, and acquiring the data of the second serial signal exchanged and configured by the time slot interchange module. The invention can identify signaling time slots, automatically configure the signaling time slotsand carry out the data acquisition of the signaling time slots according to the identification result, thereby meeting the requirement on the automation and the intellectualization of signaling acquisition.

Owner:ZTE CORP

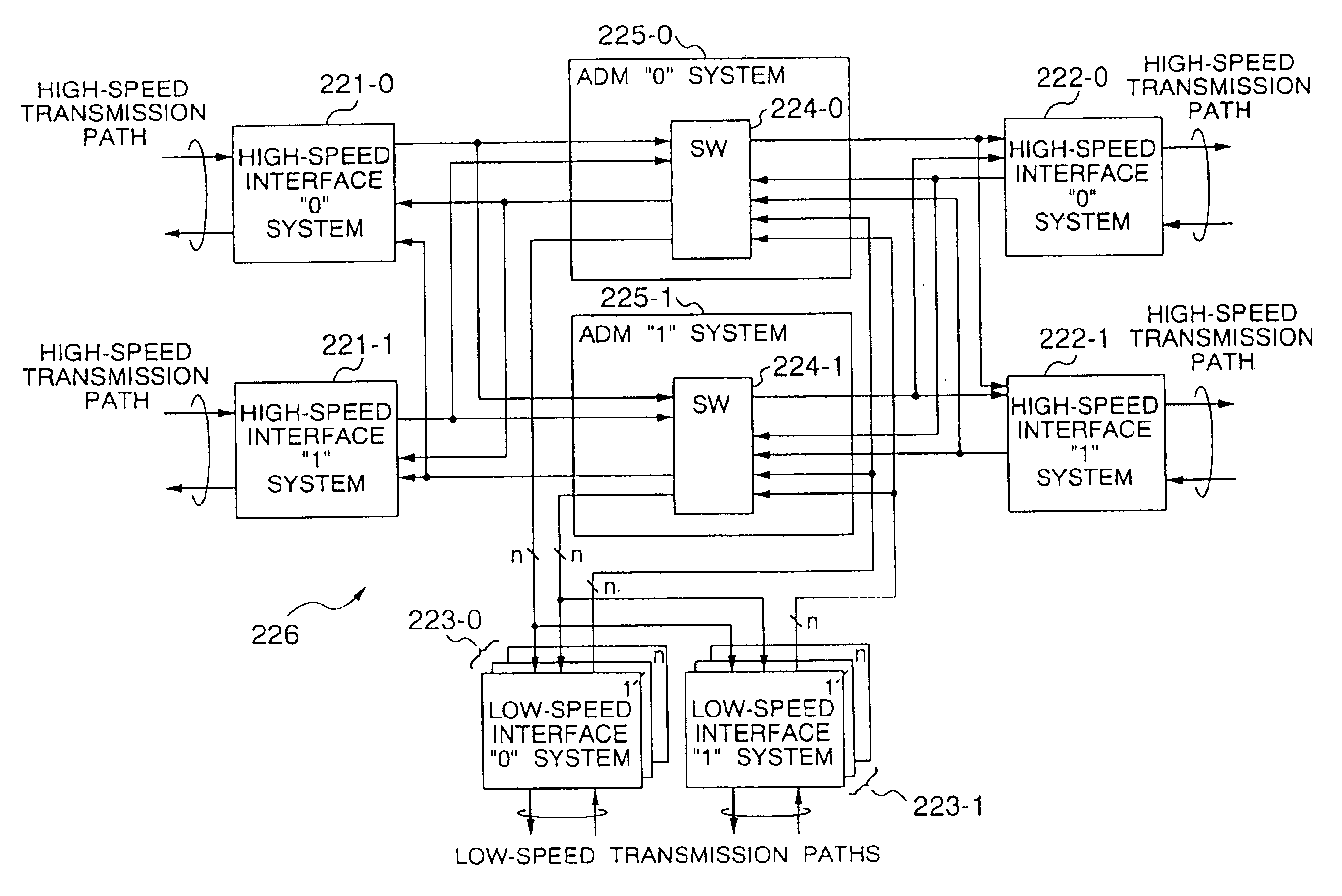

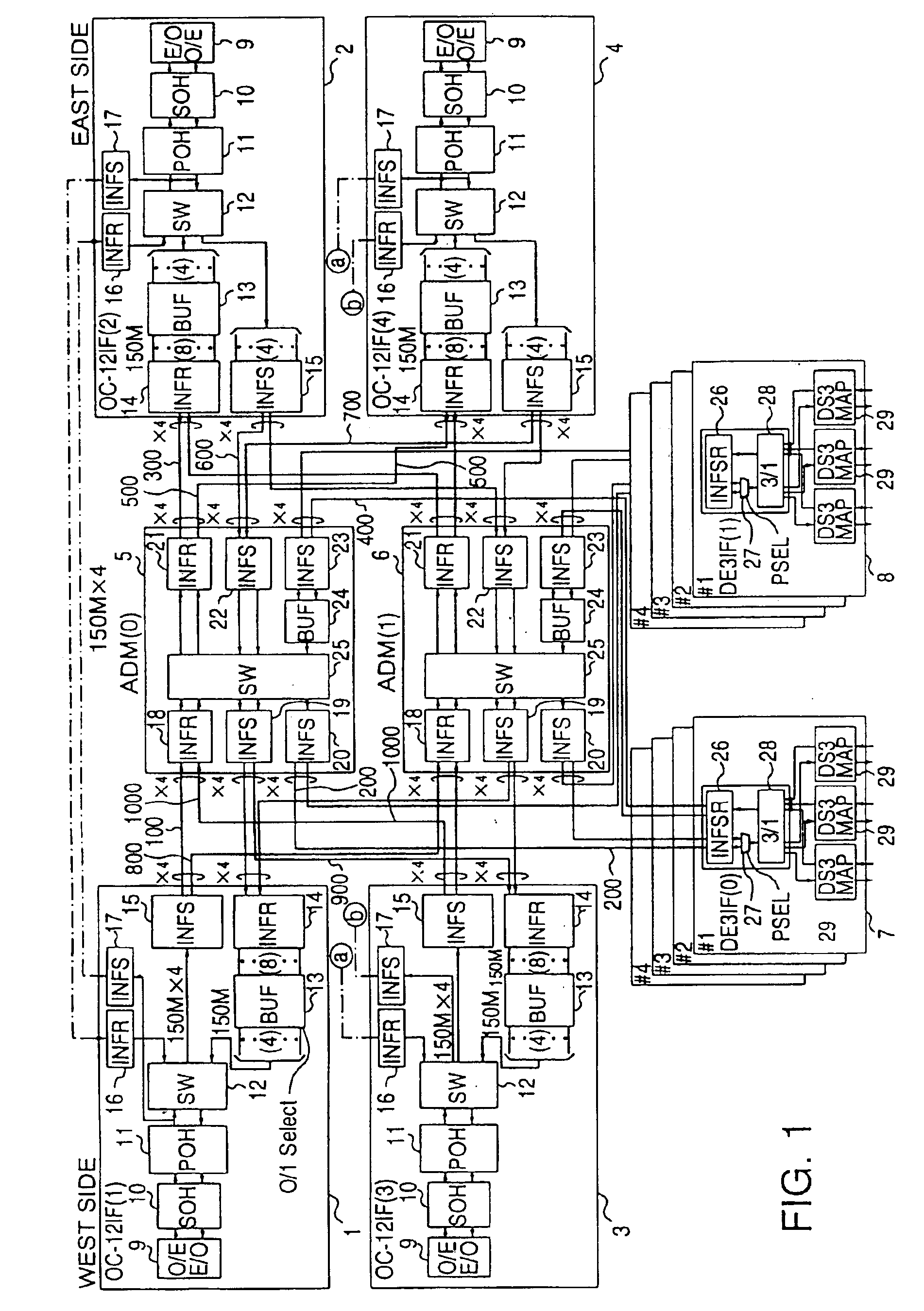

Multiplex conversion unit

InactiveUS6876624B1Low costMinimal costMultiplex system selection arrangementsError preventionMultiplexingLow speed

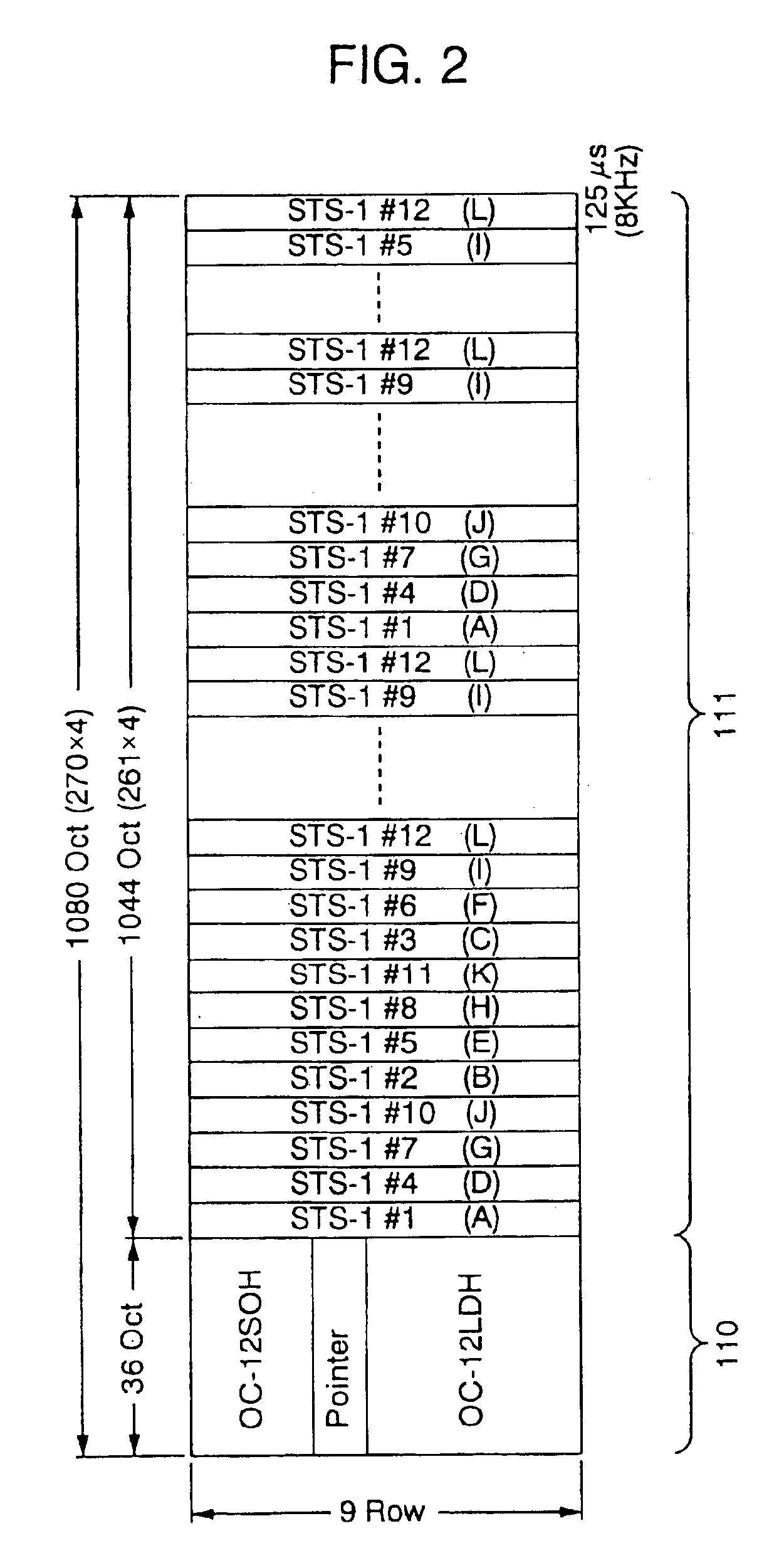

A multiplex conversion unit is configured with those functions required for a specific network to which it is more economically applicable. Each OC-12IF circuit pack includes a switch for performing time slot assignment (TSA) between a plurality of high-speed transmission lines and at least a low-speed transmission line. An ADM circuit pack includes a switch for performing time slot interchange (TSI) between the high-speed transmission lines and the low-speed transmission line. In an application to a network requiring the TSI function, the switch of the OC-12IF circuit pack performs only the add / drop multiplex (ADM) operation between the signals input / output by the high-speed transmission lines and the ADM circuit pack, and the switch on the ADM circuit pack performs the TSI operation. In an application not requiring the TSI, the TSA operation is performed using a THRU circuit pack.

Owner:HITACHI LTD

Systems and methods for combining time division multiplexed and packet connection in a meshed switching architecture

ActiveUS8054853B2Avoids cost and complexityMultiplex system selection arrangementsTime-division multiplexComputer terminalTime-Slot Interchange

The present invention provides systems and methods for supporting native TDM and native Packet switching simultaneously in a meshed switching architecture. Specifically with the present invention, the meshed links are common to both TDM and packet traffic, and both types terminate to a common system interface without the need to separate physical resources and infrastructure; the common termination function has access to both the TDM (Time Slot Interchange (TSI)) switching and packet switching elements. Native TDM switching and packet switching operate in concurrently in the mesh over common links, with the personality of the links derived by the card type (attached to the mesh). In this, a given card or slot in a system can communicate in the native format to both packet based cards (slots) or TDM based cards (slots) simultaneously with no preconceived restrictions or limitations on slot or link definition.

Owner:CIENA

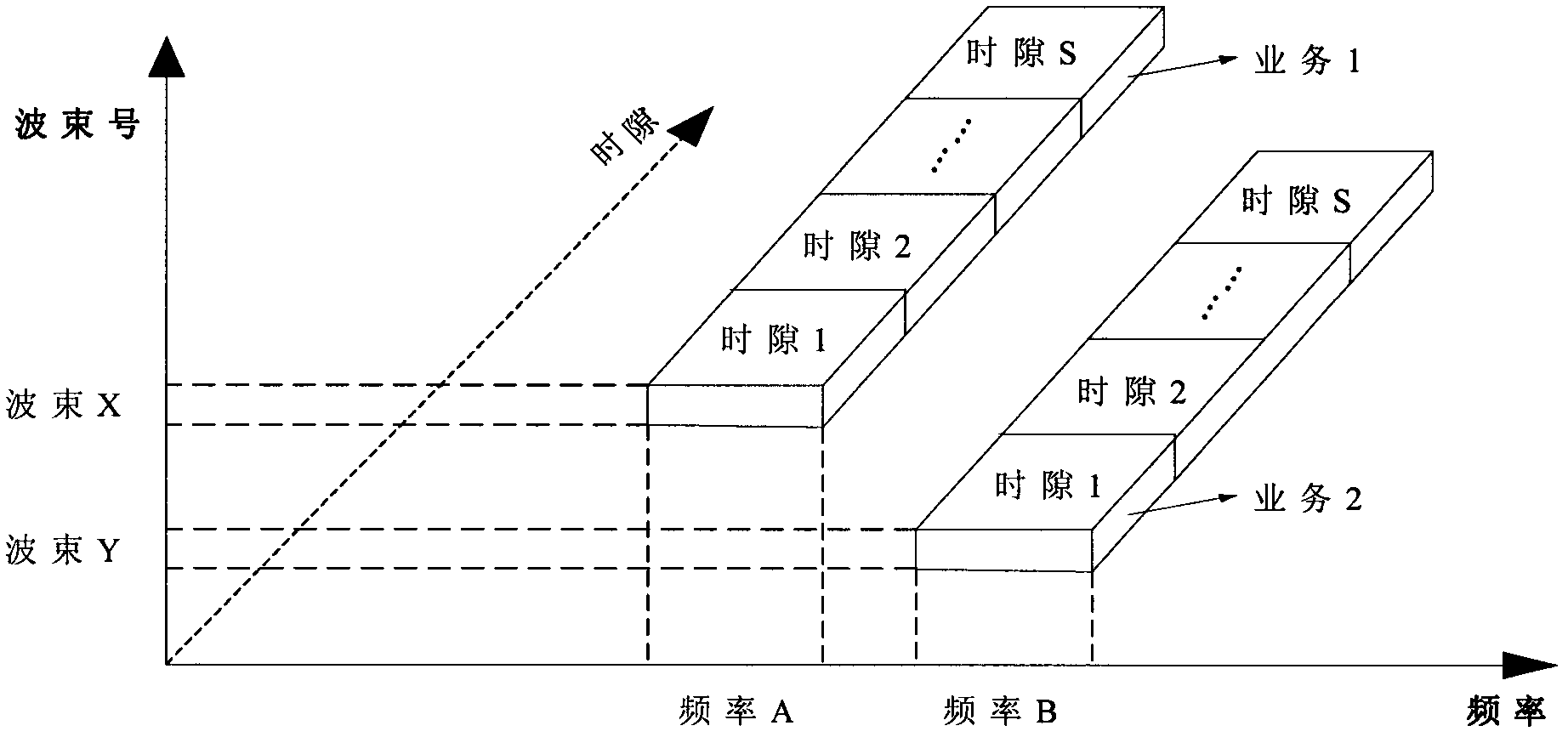

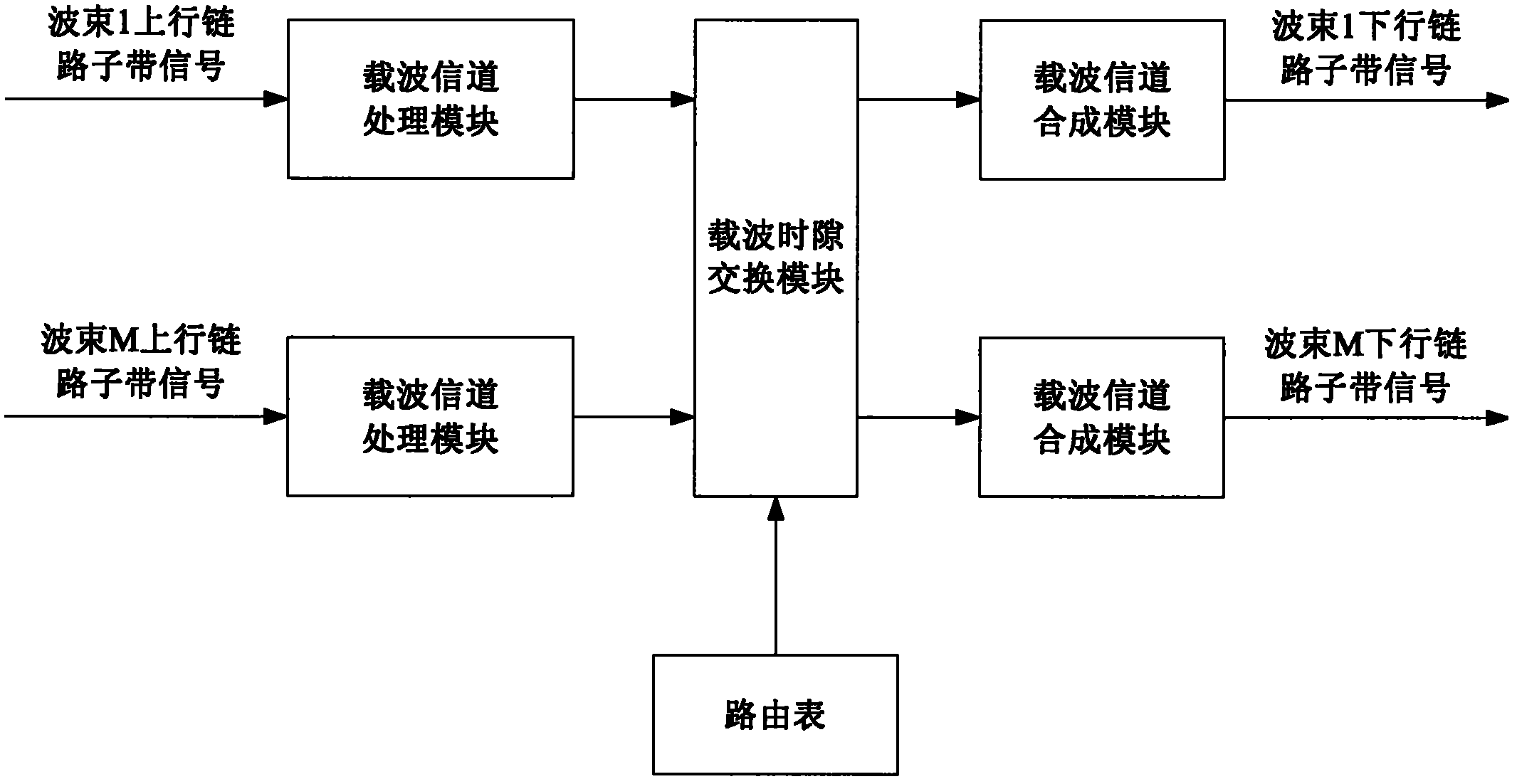

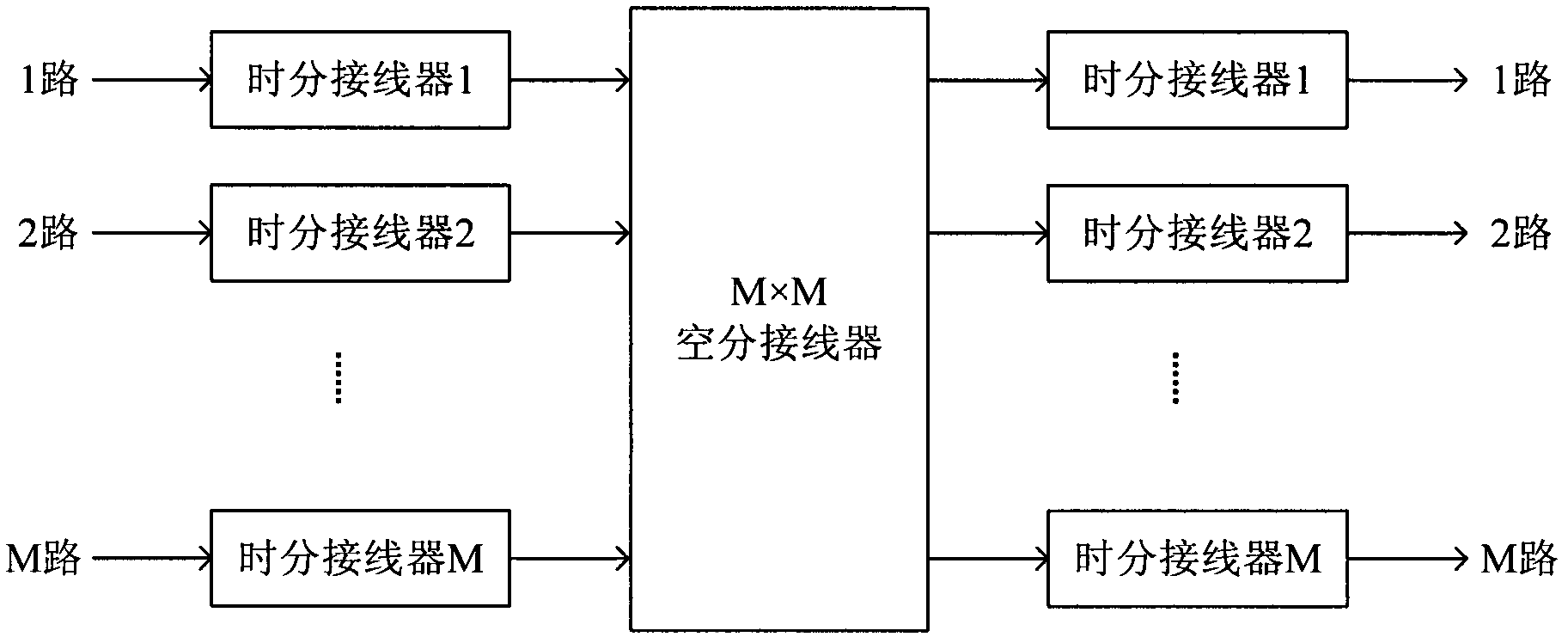

Satellite switching system based on time and frequency domains

ActiveCN102255650AImprove spectrum utilizationImprove efficiencyRadio transmissionComputer moduleCarrier signal

The invention discloses a satellite switching system based on time and frequency domains. The satellite switching system is used for realizing the switching among wave packet points on different wave packets of a mobile communication satellite, and comprises a carrier channel processing module, a carrier time slot switching module and a carrier channel synthesis module, wherein the carrier time slot switching module includes M first-stage time division wire connectors, a second-stage space division wire connector and M third-stage time division wire connectors. The first-stage time division wire connectors are used for realizing the time slot switching for service information. The second-stage space division wire connector is used for realizing the switching from the first-stage time division wire connectors to the third-stage time division wire connectors. The third-stage time division wire connectors are used for realizing the carrier switching for the service information. According to the invention, the two-dimensional switching of time and frequency domains between different sub-band signals of the mobile communication satellites can be realized.

Owner:XIAN INSTITUE OF SPACE RADIO TECH

Time multiplexed space switch

InactiveUS7953323B2Reduce in quantityQuality improvementMultiplex system selection arrangementsTime-division optical multiplex systemsPulse sequenceLength wave

The present invention provides an optical time multiplexed space switch including a pulsed laser source, and means for producing from the laser source a plurality of wavelengths of pulsed radiation including means for providing permutable multi-wavelength pulse sequences from said multi-wavelength source and means for translating the input data pulses into the multi-wavelength pulse sequence. Each data pulse is subsequently guided through a wavelength selective structure, which may contain delay lines. In the case of time-slot interchange, the pulses are recombined in an interchanged sequence. In the case of tributary space switching different wavelength pulses are switched to generally different outputs and combine with pulses originating from different inputs. Alternatively, instead of or in addition to the means for providing permutable multi-wavelength pulse sequences from the pulsed source, means are provided for the permutation of the multi-wavelength data pulse sequence in reconfigurable wavelength selective structures.

Owner:ZARRIS GEORGE

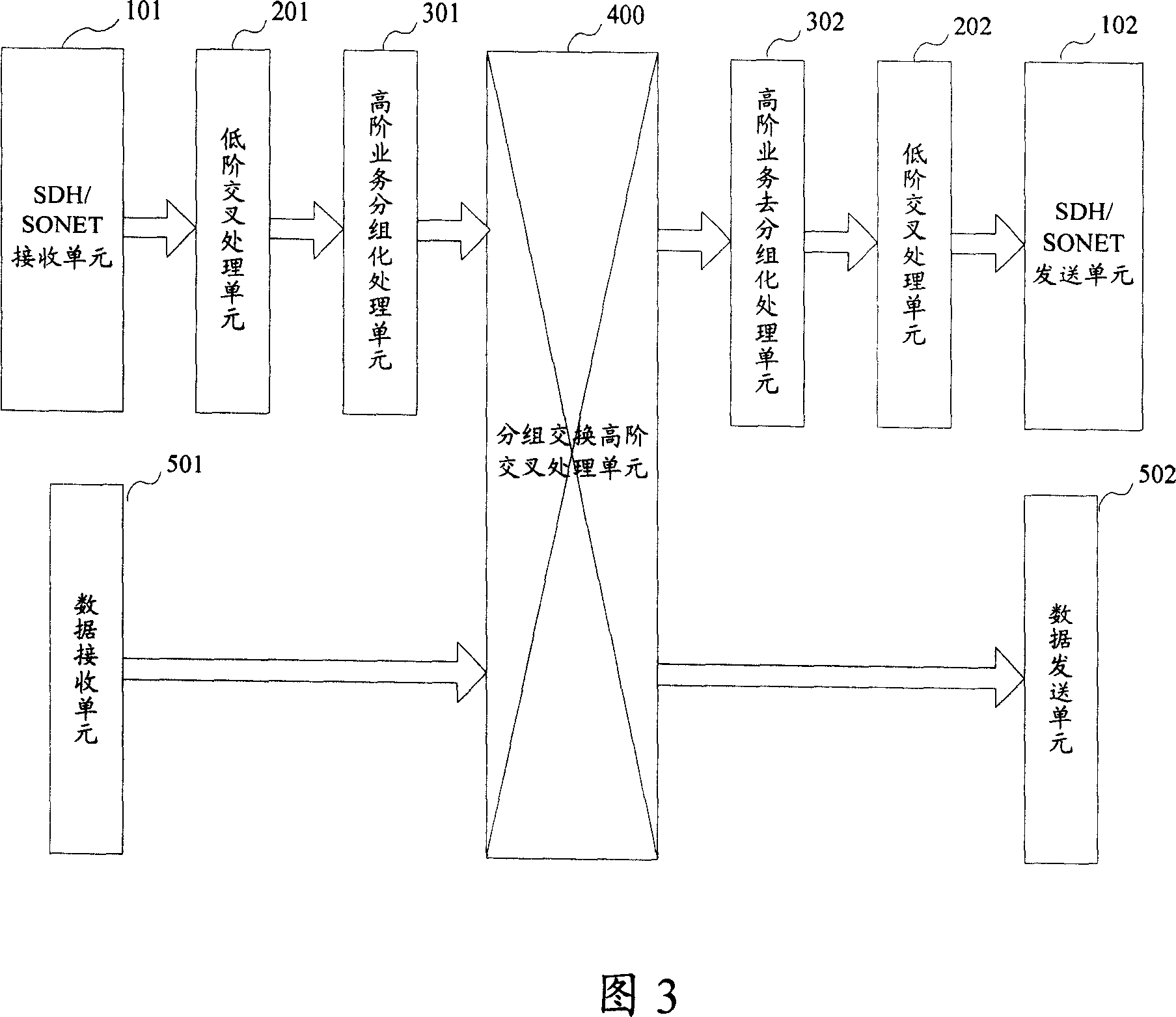

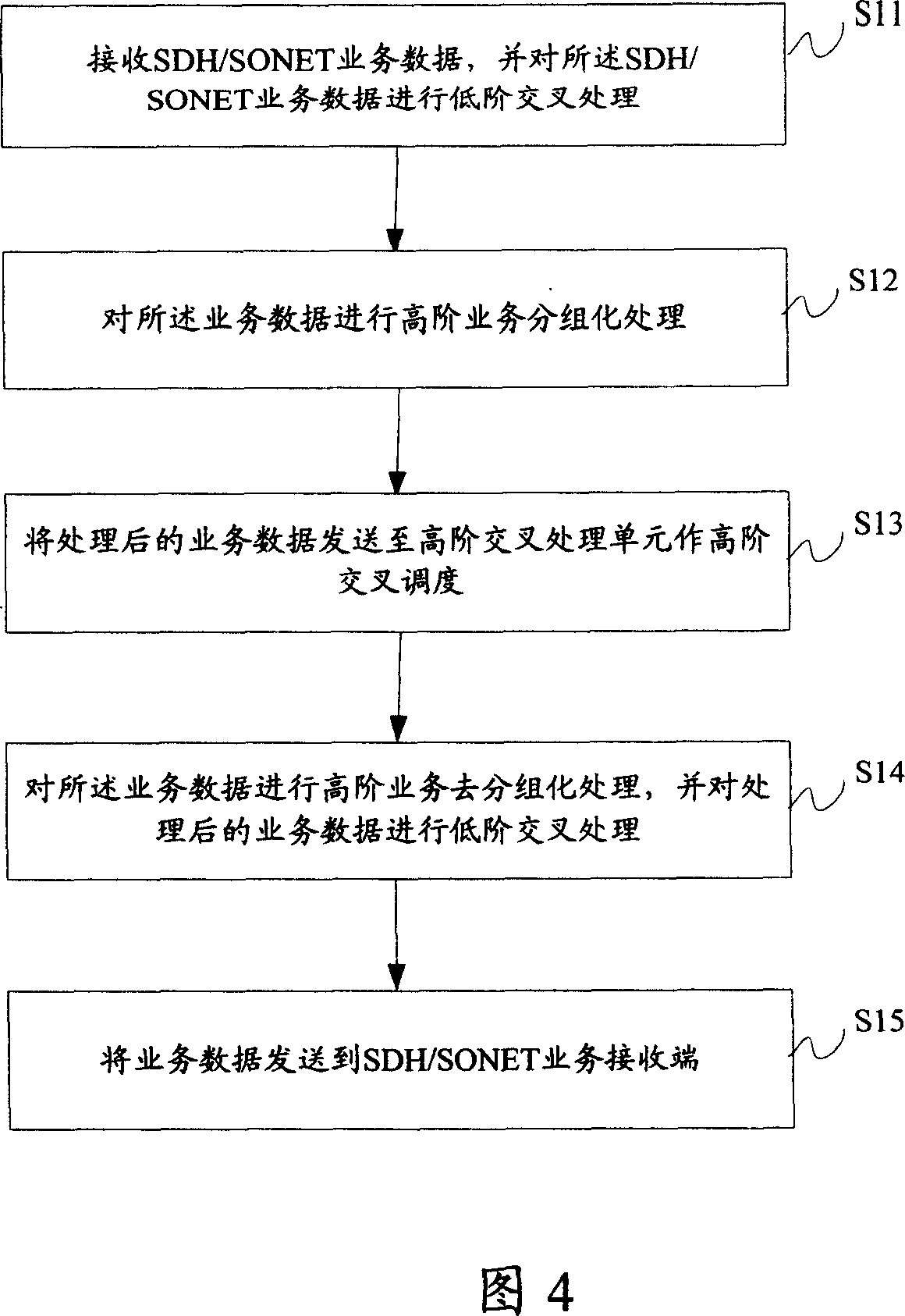

System and method for crossed scheduling

ActiveCN1984503AGuaranteed latency performanceOvercoming caching problemsTime-division multiplexing selectionScheduling functionTime delays

The system comprises: SDH / SONET receiving / transmitting unit for transmitting and receiving SDH / SONET service, data receiving / transmitting unit for receiving and transmitting data service, high level service grouping / de-grouping unit, low level cross-processing unit, and high level cross-processing unit. The invention uses the time slot exchange for low level server to ensure the time delay performance of low level service, and uses service schedule function of packet switch to ensure the support to high traffic data service.

Owner:HUAWEI TECH CO LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com