Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

72 results about "Synchronous Serial Interface" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

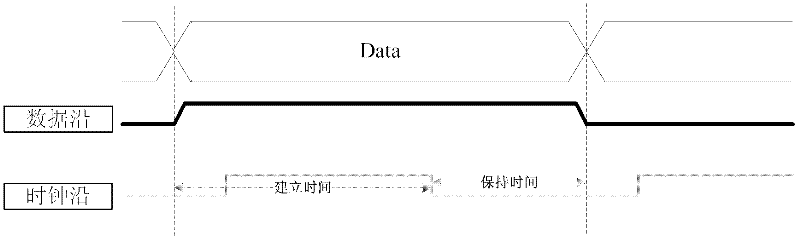

Inventor

Synchronous Serial Interface (SSI) is a widely used serial interface standard for industrial applications between a master (e.g. controller) and a slave (e.g. sensor). SSI is based on RS-422 standards and has a high protocol efficiency in addition to its implementation over various hardware platforms, making it very popular among sensor manufacturers. SSI was originally developed by Max Stegmann GmbH in 1984 for transmitting the position data of absolute encoders – for this reason, some servo/drive equipment manufacturers refer to their SSI port as a "Stegmann Interface". It was formerly covered by the German patent DE 34 45 617 which expired in 1990. It is very suitable for applications demanding reliability and robustness in measurements under varying industrial environments.

A wireless sensor network gateway device

InactiveCN101009619ALow costReduce power consumptionData switching by path configurationRadio/inductive link selection arrangementsLine sensorTransceiver

The disclosed gateway device for wireless sensor network comprises: a GPRS communication unit to communicate between the gateway and Internet or wireless communication network, a wireless RF transceiver for gateway and wireless sensor network, and a MPU to control the communication of former two units, wherein the MPU uses UART (general asynchronous serial interface) to communicate with the GPRS unit and SPI (synchronous serial interface) to communicate with the RF transceiver. This invention realizes reliable remote connection and bidirectional transmission for request in real application.

Owner:INST OF COMPUTING TECH CHINESE ACAD OF SCI

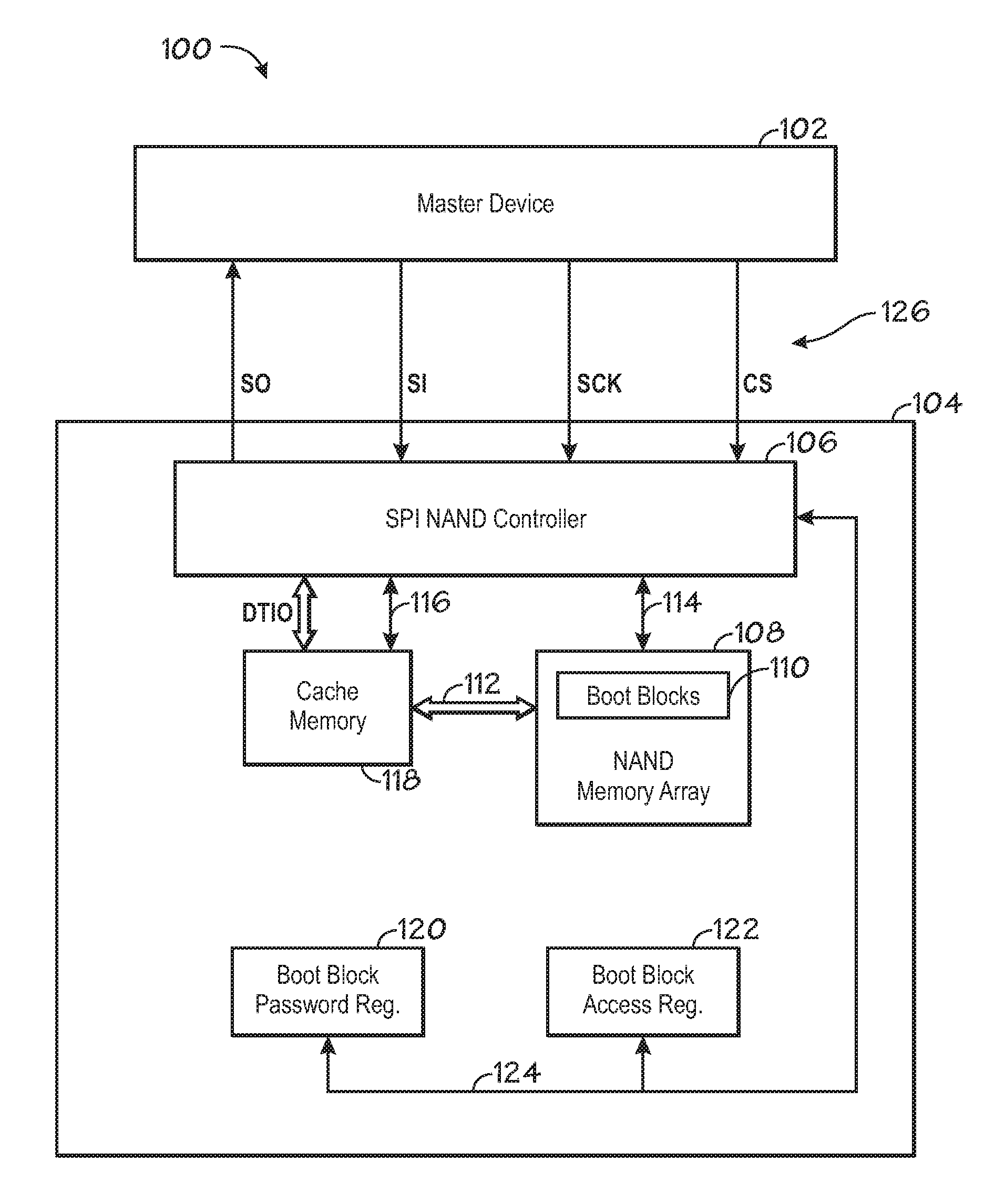

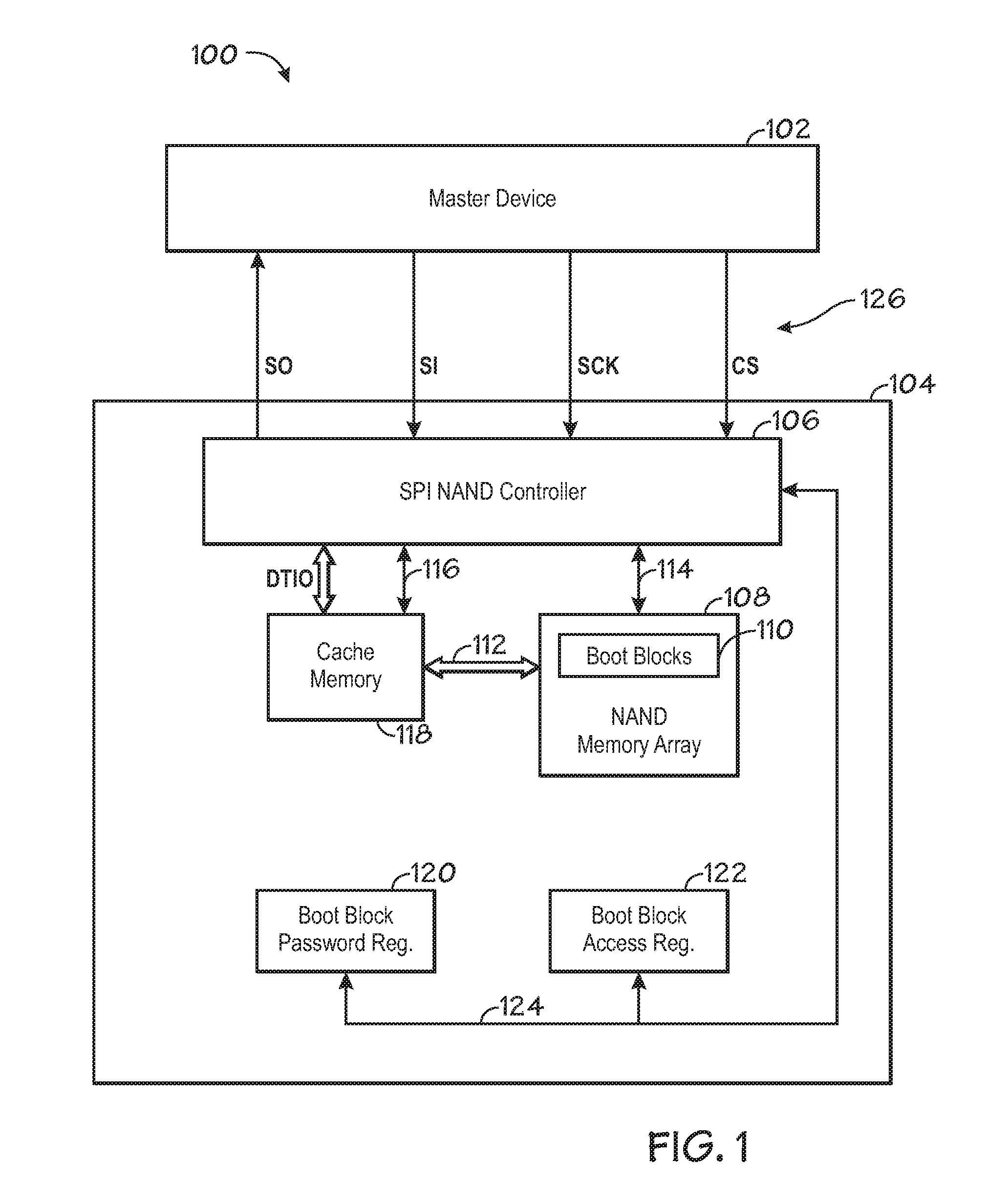

System and method for setting access and modification for synchronous serial interface NAND

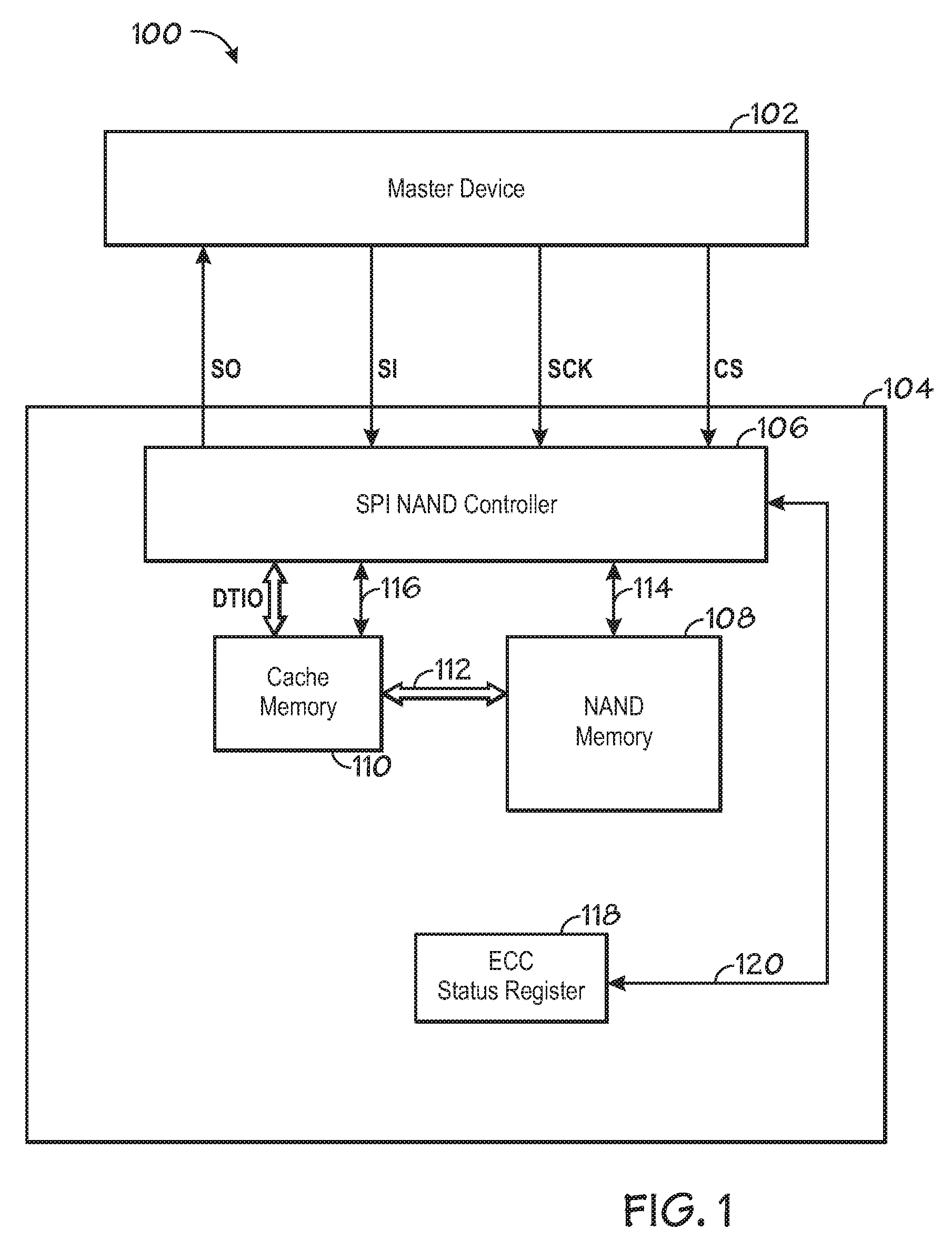

ActiveUS20090103362A1Memory architecture accessing/allocationRead-only memoriesProcessor registerMemory circuits

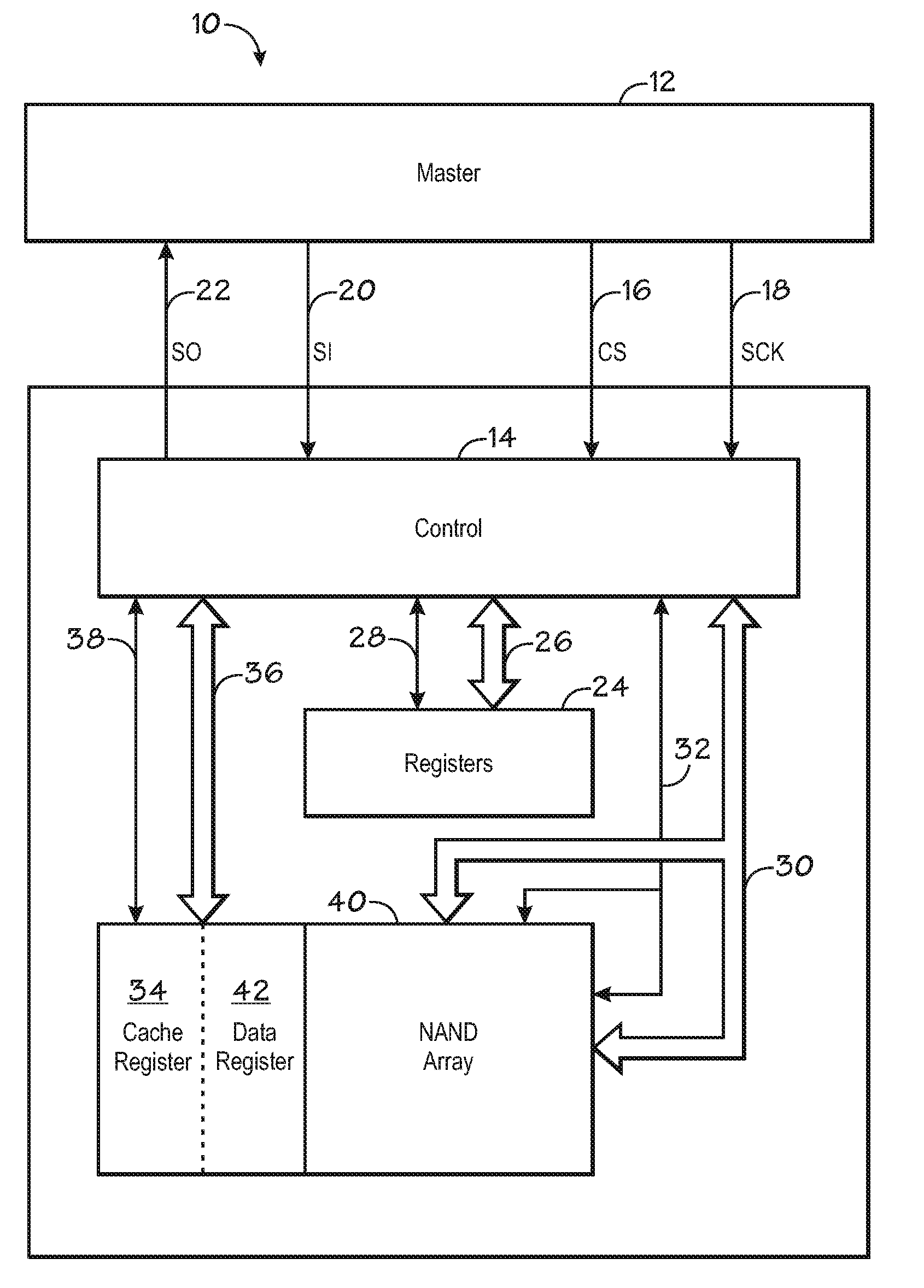

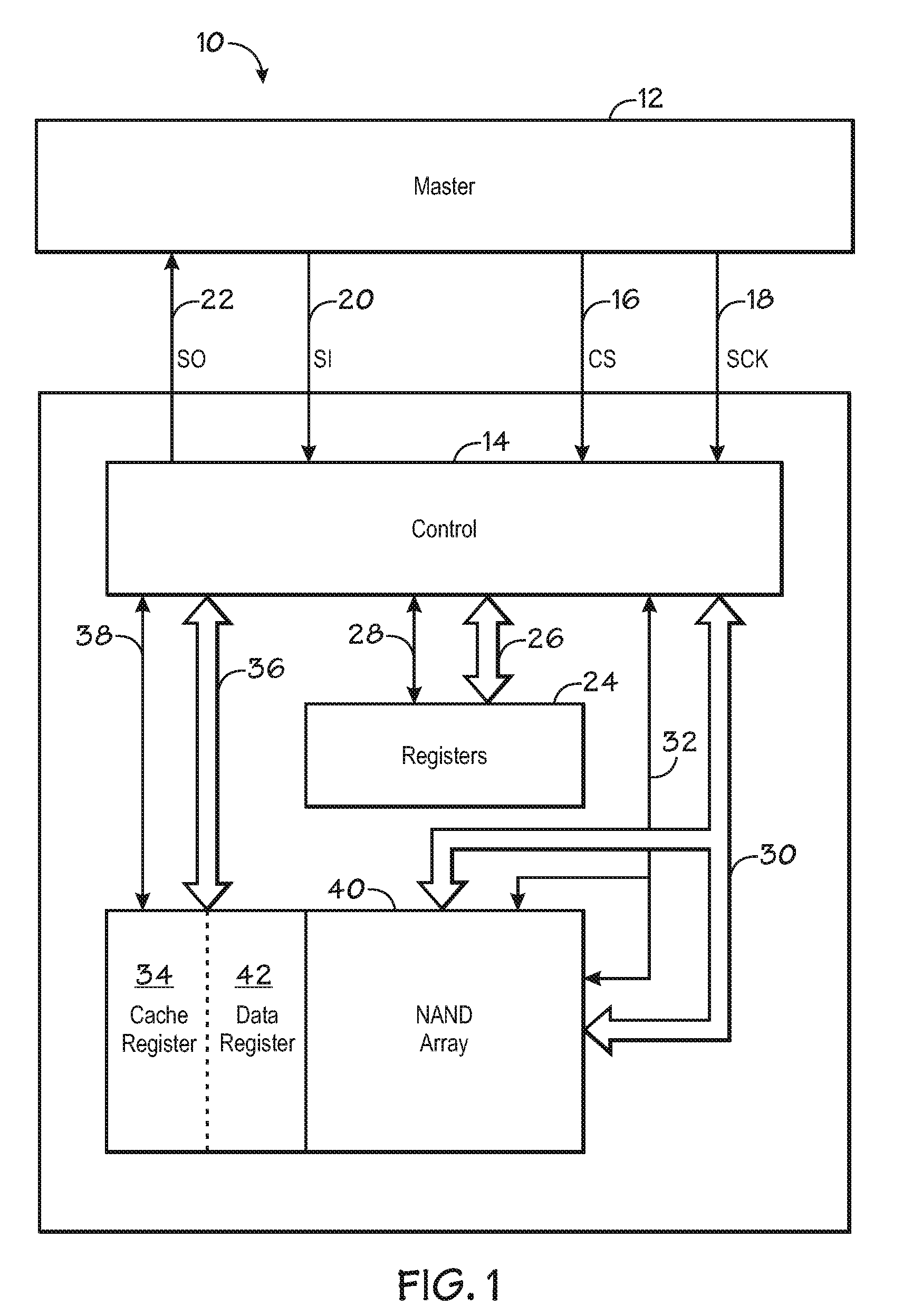

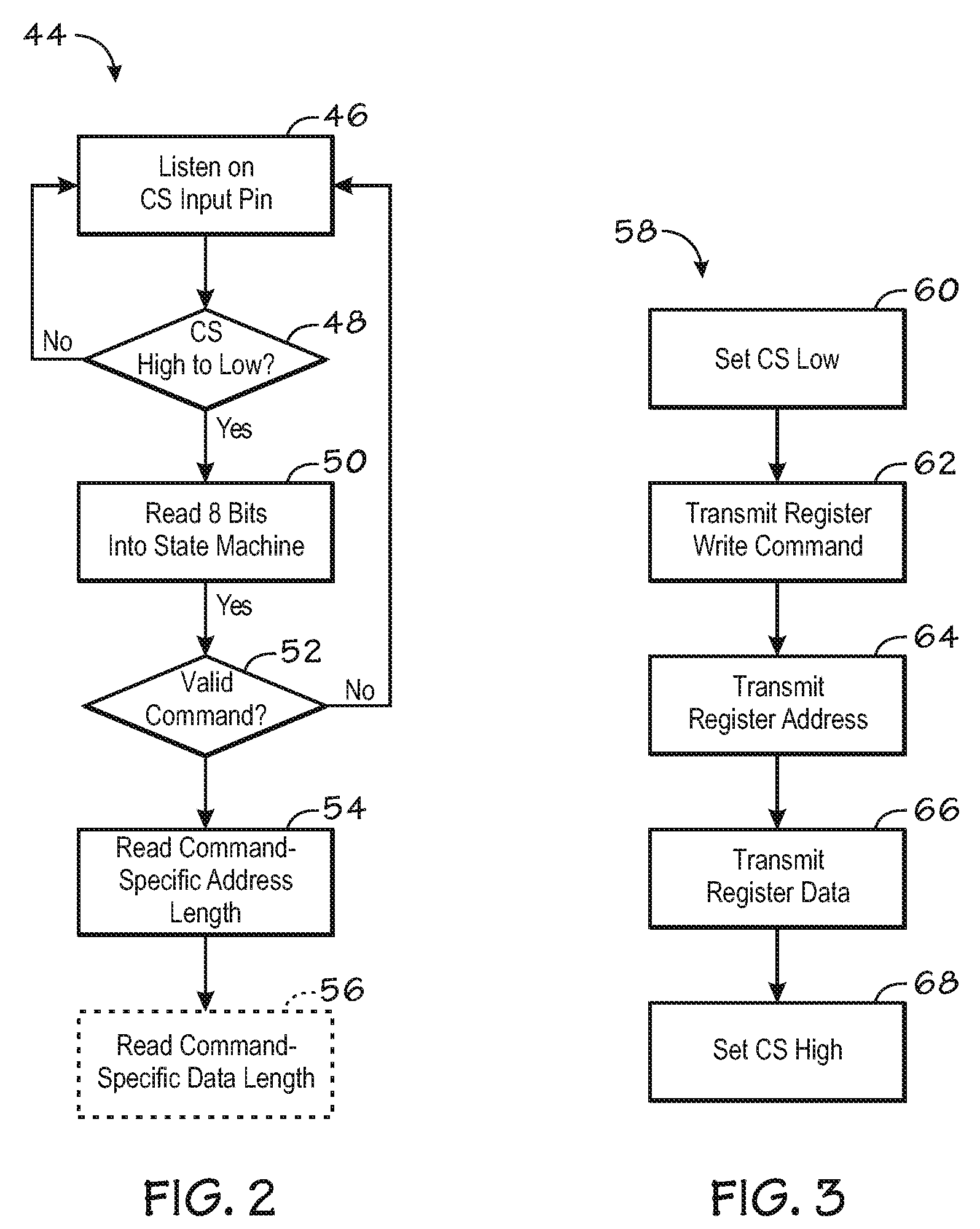

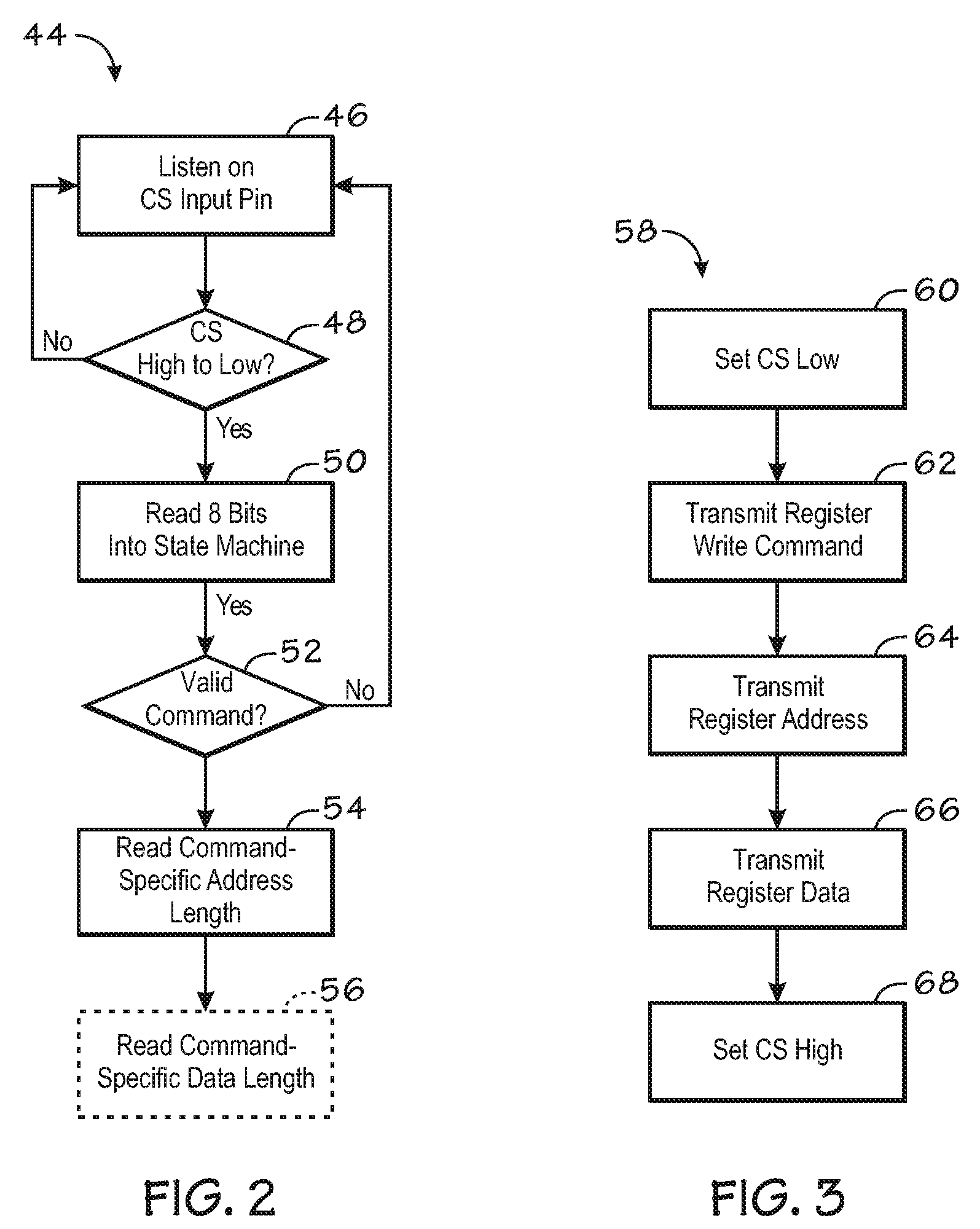

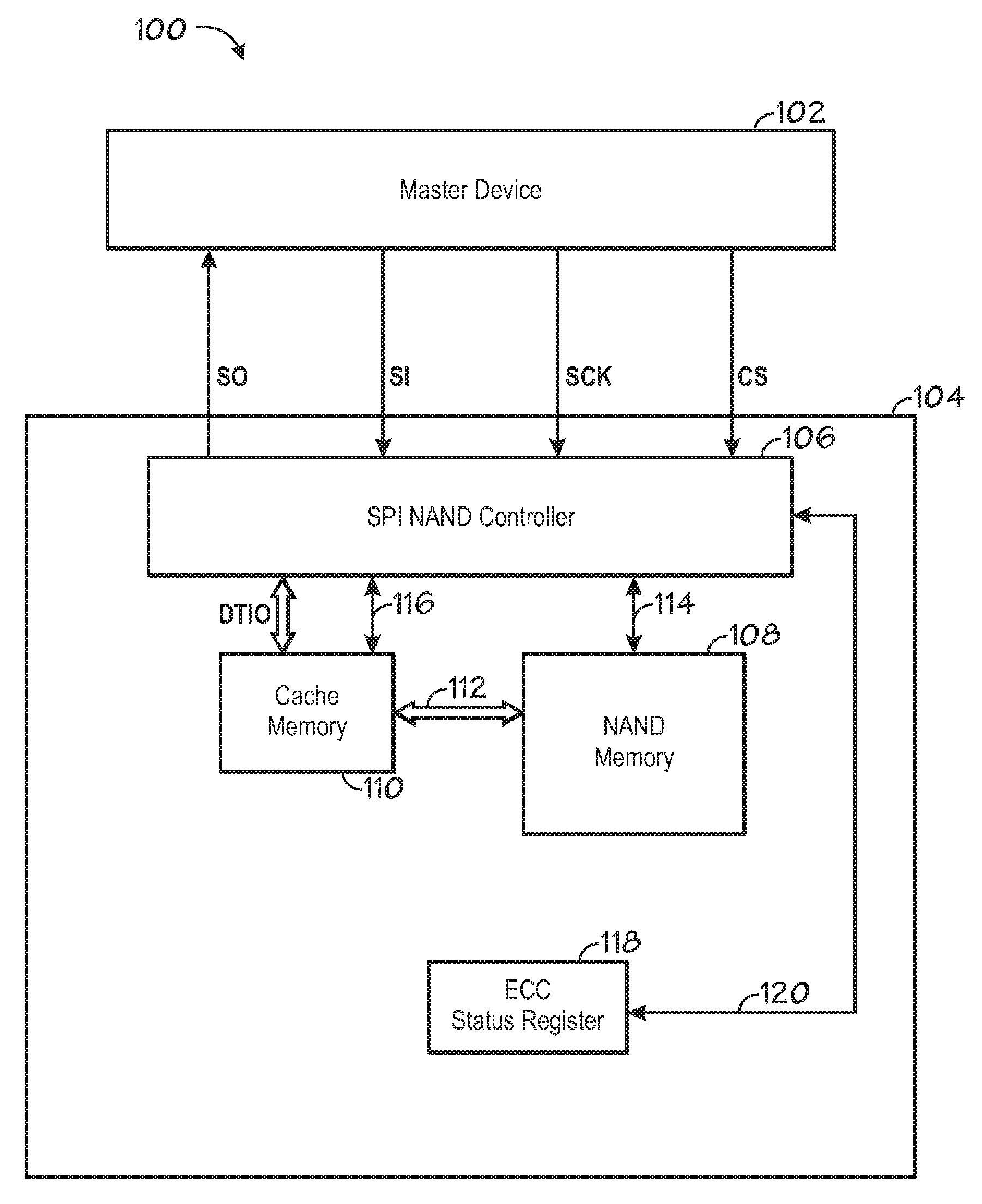

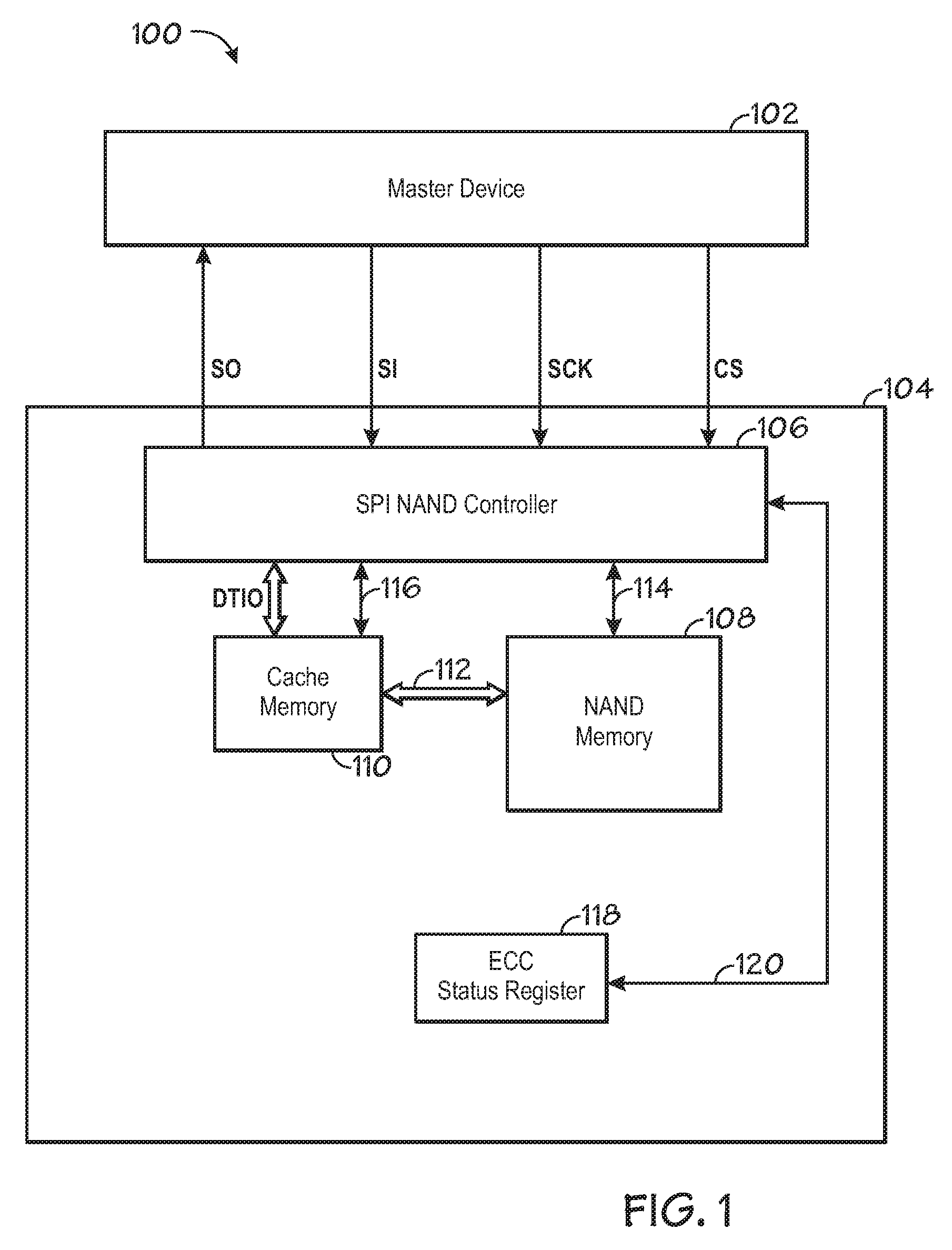

The invention includes a system and method of modifying a setting of a NAND flash memory device using serial peripheral interface (SPI) communication from a master to the NAND flash memory device. One embodiment generally includes sending an enable signal to a first memory circuit input, sending a clock signal to a second memory circuit input, sending a command signal synchronized to the clock signal to a third memory circuit input, sending a memory register address signal synchronized to the clock signal to the third memory circuit input, and sending a setting signal synchronized to the clock signal to the third memory circuit input.

Owner:MICRON TECH INC

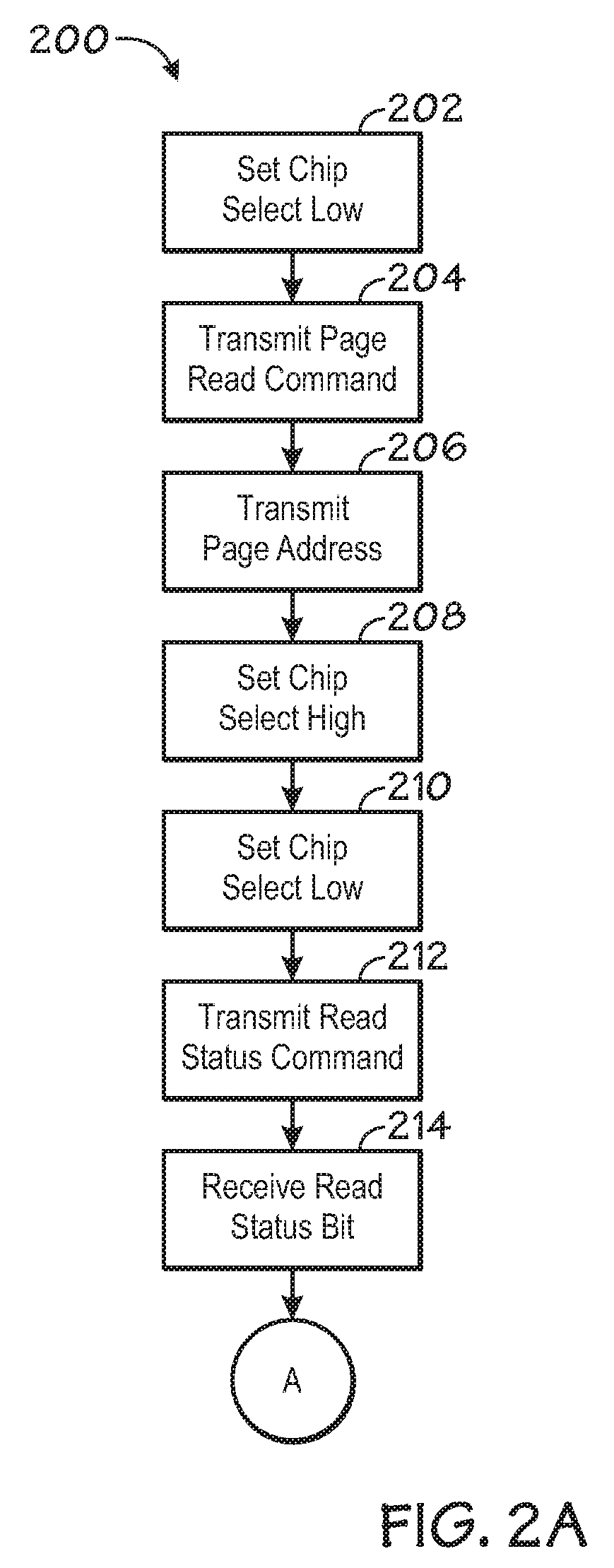

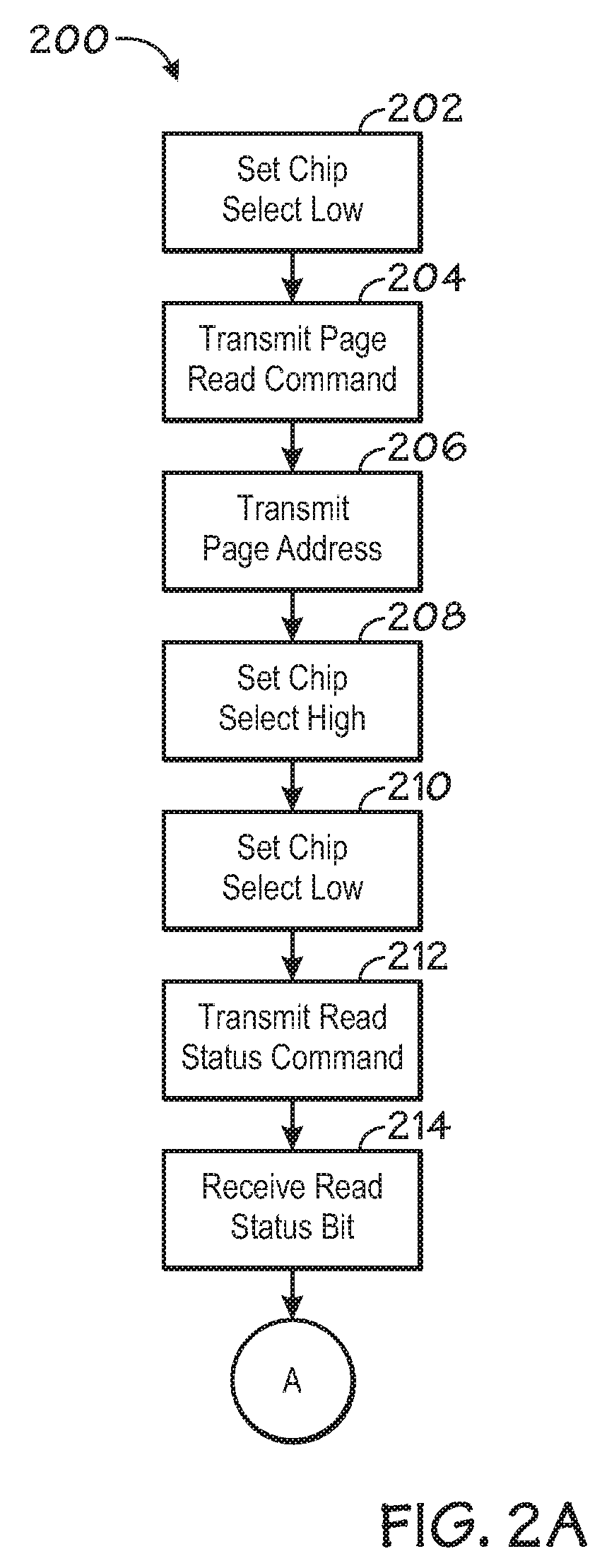

System and method for data read of a synchronous serial interface NAND

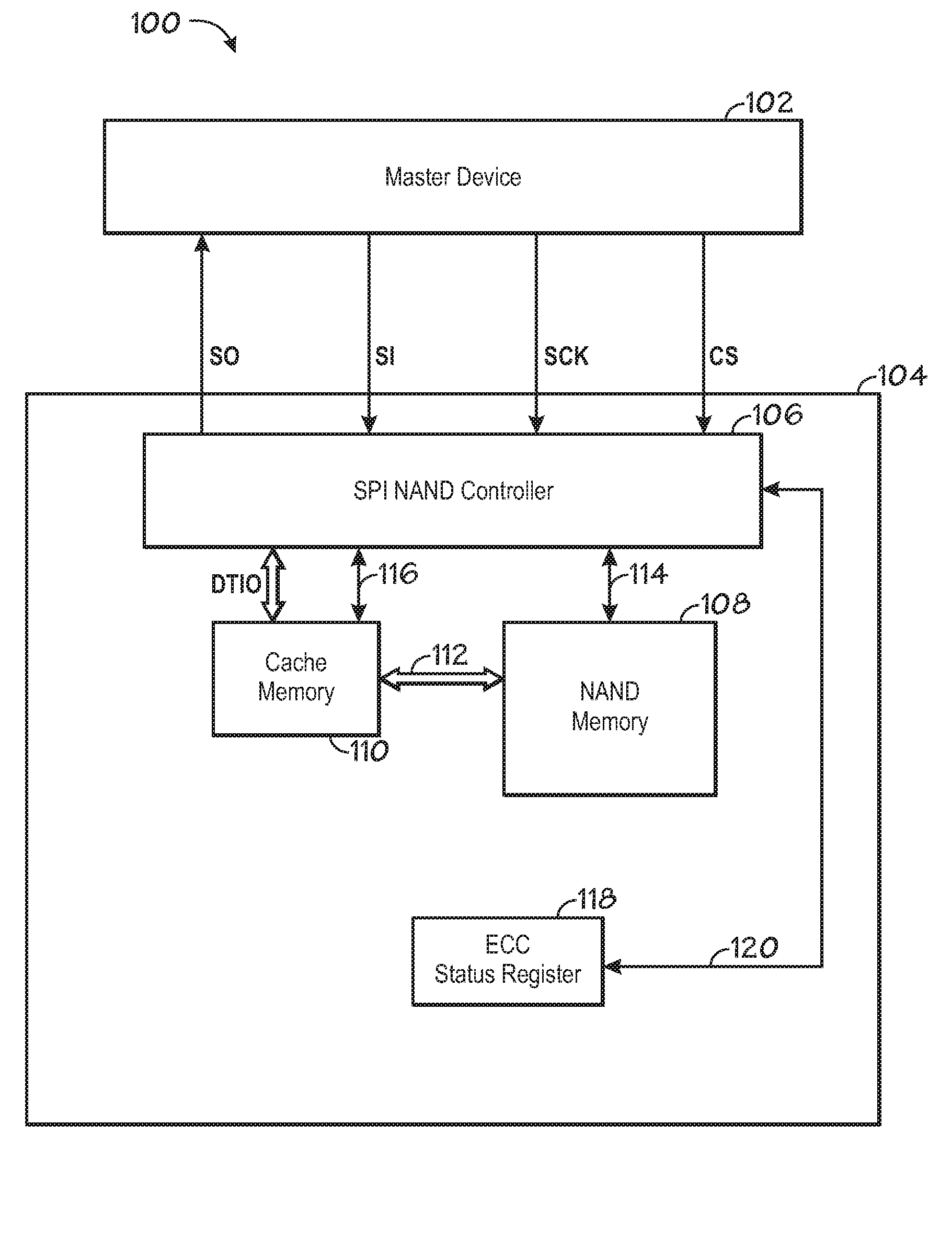

A method and system is disclosed for operating a NAND memory device. The NAND memory device is operated by transmitting serial peripheral interface signals from a host to a NAND memory device, whereby the signals are communicated to a NAND memory in the NAND memory device without modifying the signals into a standard NAND memory format. Similarly, a method and system is disclosed for receiving signals from the NAND memory device without modifying the signals from a standard NAND format into a serial format. The system also incorporates error detection and correction techniques to detect and correct errors in data stored in the NAND memory device.

Owner:MICRON TECH INC

Serial communications protocols

ActiveUS20120297233A1Identical operationIdentical performancePulse automatic controlMultiple digital computer combinationsData streamData acquisition

Systems and methods are disclosed which relate to improving synchronization of clocks between a sender and a receiver communicating via an asynchronous serial interface. In a ring topology, a master device is connected to a plurality of slaves communicating using a bi-frequency encoded bit stream. A host device communicates with the master device using a non-return-to-zero data encoding. Each slave receives data from the master and sends it to the next slave in the ring unaltered unless the master indicates a requirement for a particular data, and transmits placeholder bits with a value of 0 around the ring. A particular slave can “fill-in” the placeholder bits with the information to be sent back to the master by inverting the placeholder bit. Clock synchronization between a receiving device and a transmitting device is improved using a fractional rate multiplier to generate a data sampling clock from a system clock. By adjusting the denominator, the sampling clock can be tuned to match the baud rate of the asynchronous serial data stream received from the transmitting device. Embodiments described include power management, data acquisition (DAQ), etc.

Owner:TEXAS INSTR INC

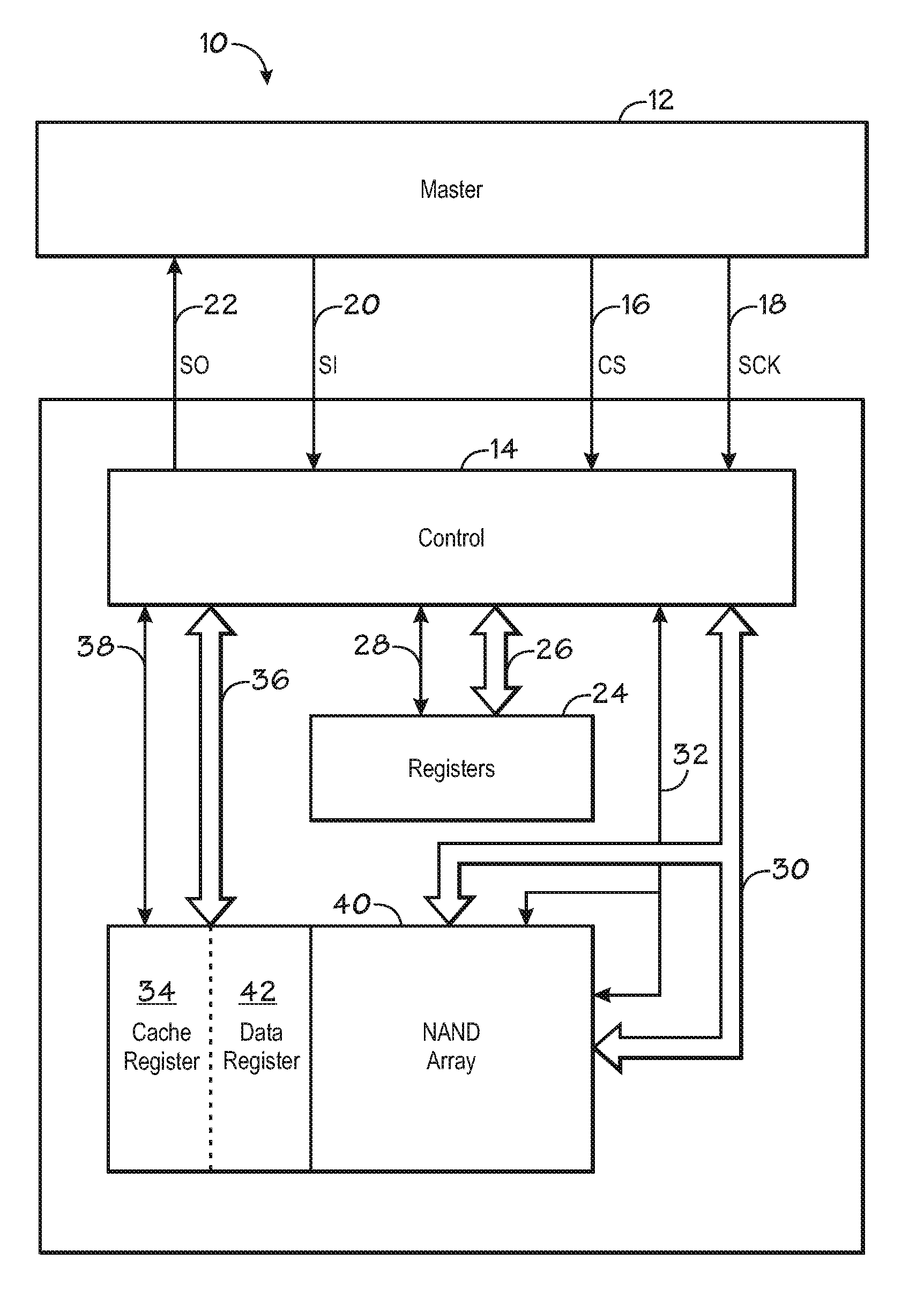

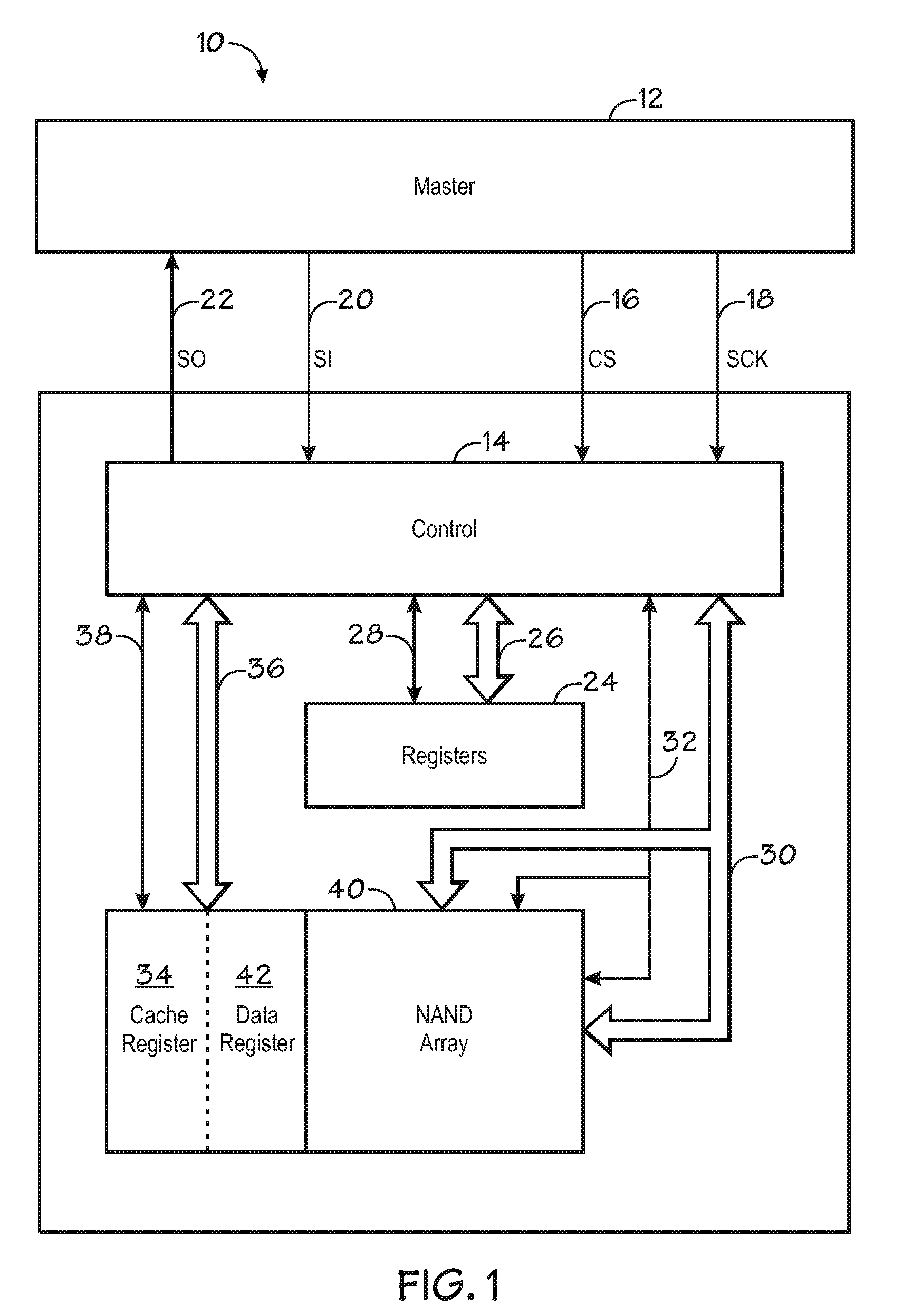

System and method for setting access and modification for synchronous serial interface NAND

ActiveUS8102710B2Memory architecture accessing/allocationRead-only memoriesProcessor registerMemory circuits

The invention includes a system and method of modifying a setting of a NAND flash memory device using serial peripheral interface (SPI) communication from a master to the NAND flash memory device. One embodiment generally includes sending an enable signal to a first memory circuit input, sending a clock signal to a second memory circuit input, sending a command signal synchronized to the clock signal to a third memory circuit input, sending a memory register address signal synchronized to the clock signal to the third memory circuit input, and sending a setting signal synchronized to the clock signal to the third memory circuit input.

Owner:MICRON TECH INC

System and method for data read of a synchronous serial interface NAND

ActiveUS20090103380A1Error detection/correctionRead-only memoriesData storingSynchronous Serial Interface

A method and system is disclosed for operating a NAND memory device. The NAND memory device is operated by transmitting serial peripheral interface signals from a host to a NAND memory device, whereby the signals are communicated to a NAND memory in the NAND memory device without modifying the signals into a standard NAND memory format. Similarly, a method and system is disclosed for receiving signals from the NAND memory device without modifying the signals from a standard NAND format into a serial format. The system also incorporates error detection and correction techniques to detect and correct errors in data stored in the NAND memory device.

Owner:MICRON TECH INC

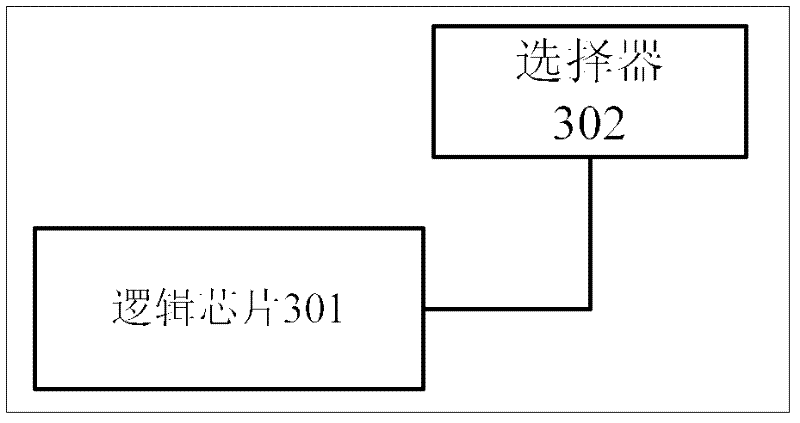

Synchronous and asynchronous switchable serial interface based on FPGA and use method

InactiveCN107451087AImprove stabilityImprove accuracyElectric digital data processingTransceiverProcessor register

An FPGA-based heterosynchronous switchable serial port and a method of use thereof, the serial port includes a universal asynchronous transceiver, a sending register, and a receiving register, and the universal asynchronous transceiver is mounted on an APB bus for realizing CPU transfer to The universal asynchronous transceiver transmits data, and the described universal asynchronous transceiver is provided with a state detection register, and the sending pin and the receiving pin of the universal asynchronous transceiver are respectively connected to the control end of the sending module FIFO and the receiving module FIFO, and the universal asynchronous transceiver The clock module of the register and the field programmable gate array is connected, and the serial port can be set to synchronous mode or asynchronous mode through the register of the asynchronous transceiver, and the input end of the receiving module FIFO and the output end of the sending module FIFO are respectively connected The receiving module and the sending module, the clock module of the field programmable gate array are respectively connected with the control ends of the receiving channel and the sending channel. The invention supports two interface forms of synchronous serial port and asynchronous serial port, and is compatible with the UART protocol. In the asynchronous serial port mode, the frequency division precision is improved, the bit error rate is reduced, and the stability and accuracy of data are obviously improved.

Owner:ZHENGZHOU YUNHAI INFORMATION TECH CO LTD

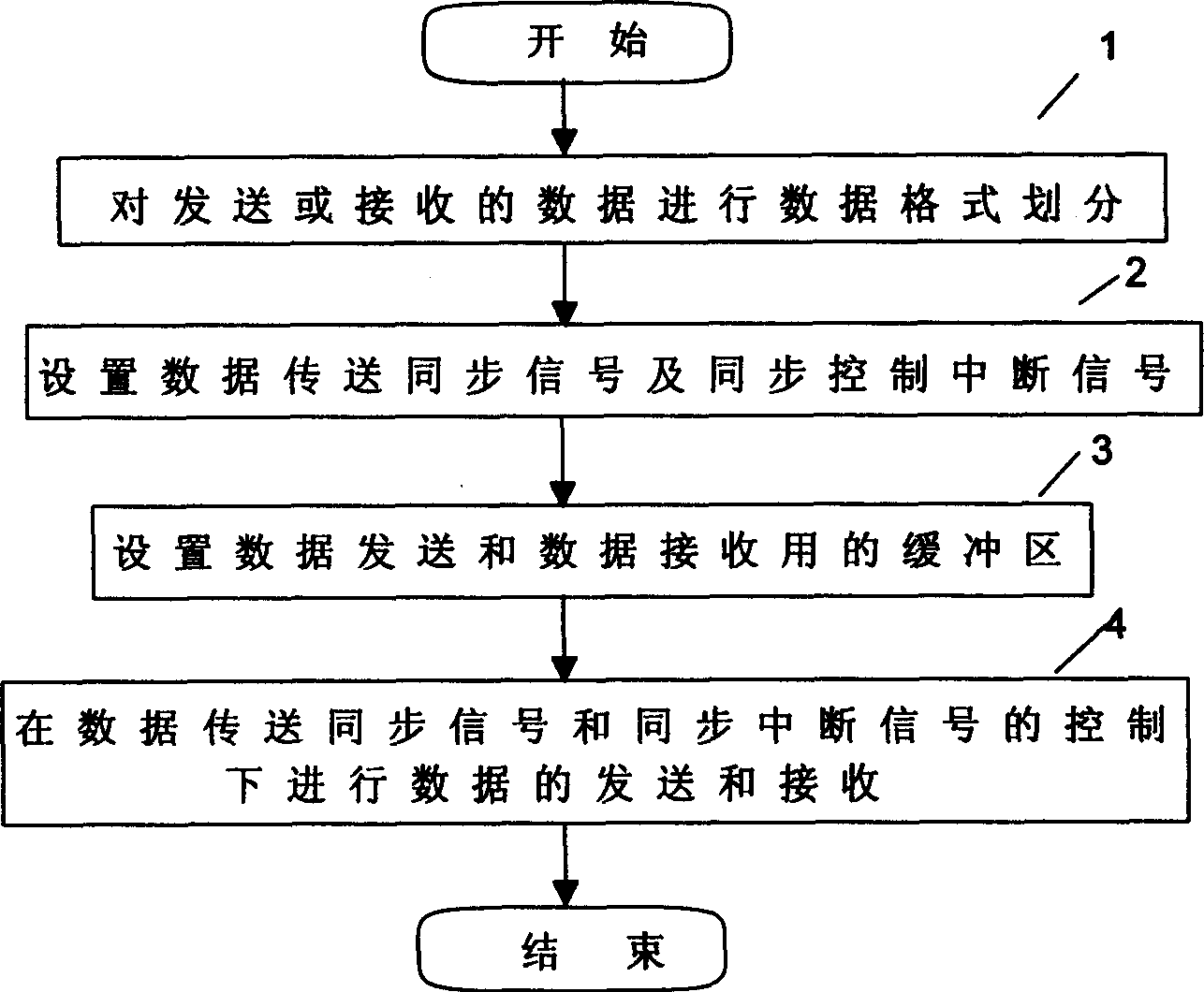

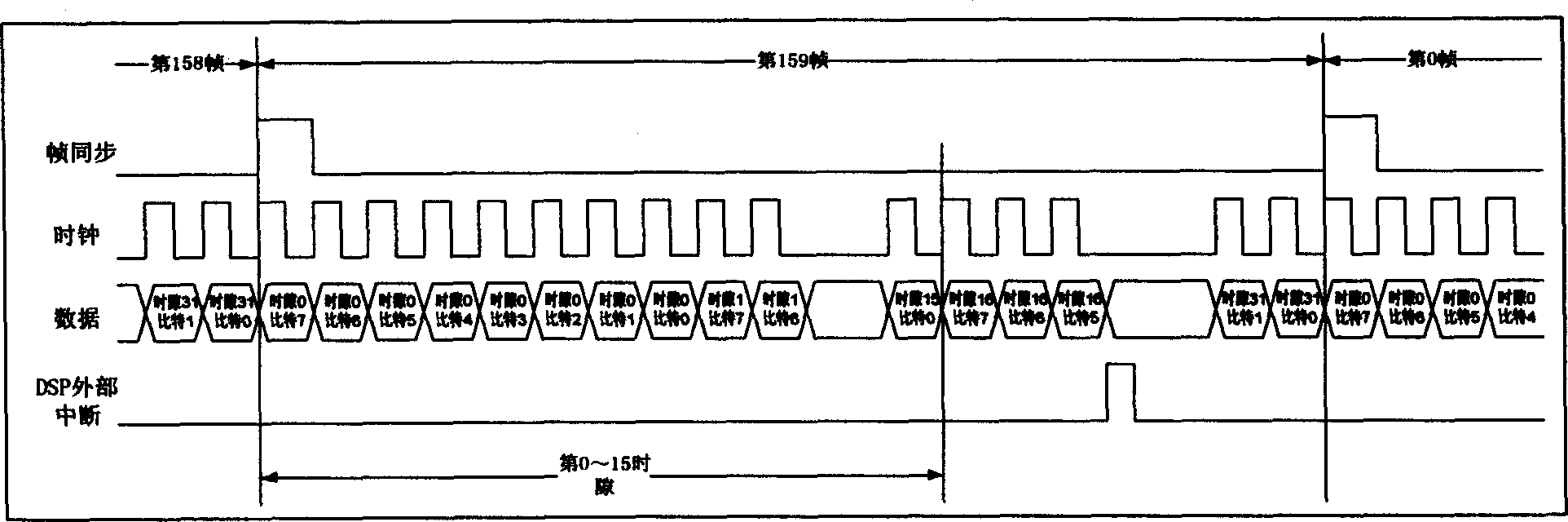

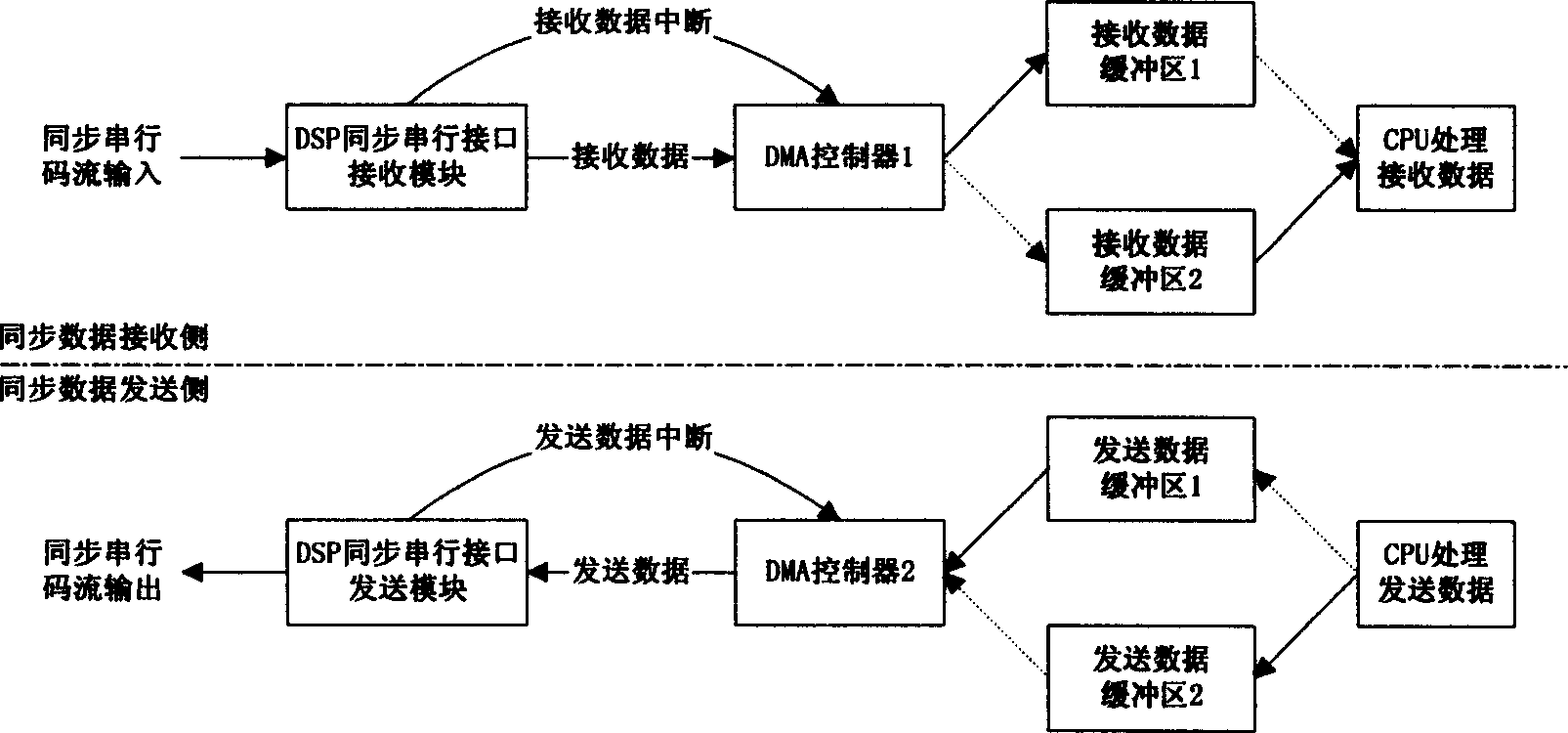

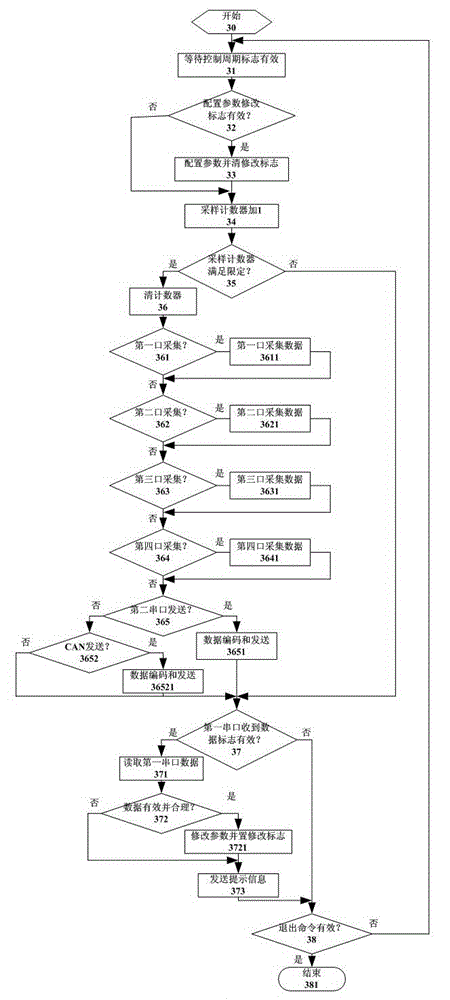

Method for sanding and receiving data based on synchronous serial interface in digital signal processor

InactiveCN1463114AReduce occupancyData Processing Capability MonitoringSynchronising arrangementDigital signal processingSynchronous control

When using synchronous serial interface of digital signal processor (DSP) sends and receives data, the data transmission signal, the synchronous control interrupt signal, the data send out buffer anddata receive buffer are setup. Under control of the transmission synchronous signal, the send module of the synchronous serial interface and the DMA send data controller sends data; the receive module of the synchronous serial interface and the DMA receive data controller receives data. The synchronous controlled interrupt signal controls the data send and data receive carried out by the DMA controller and the synchronous serial interface in DSP synchronously as well as monitors the data processing carried out by CPU in DSP. This mechanism lowers rate of occupying CPU and the data transmission can be returned to normal automatically when timing signal error or frame synchronous signal error occurs.

Owner:HUAWEI TECH CO LTD

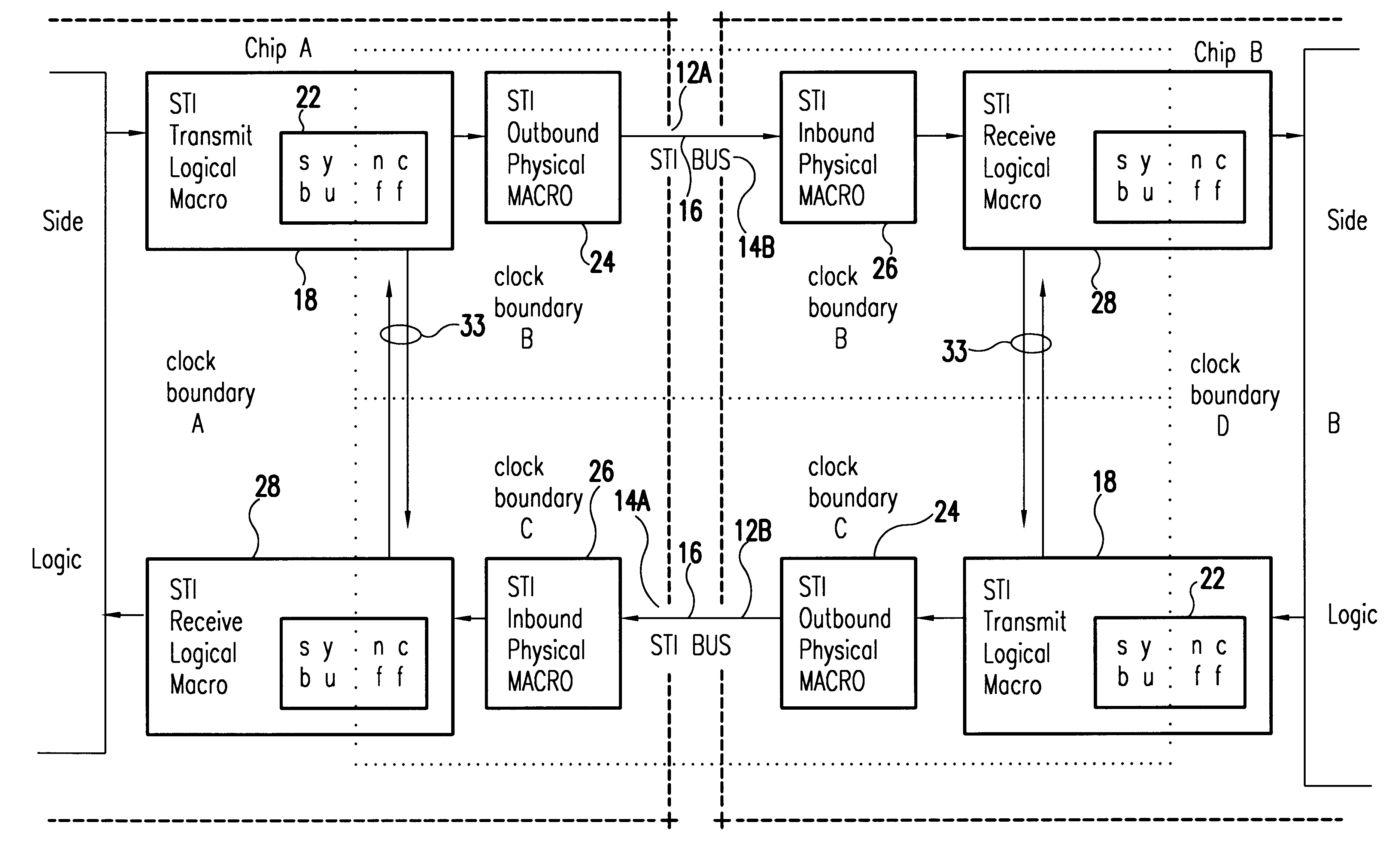

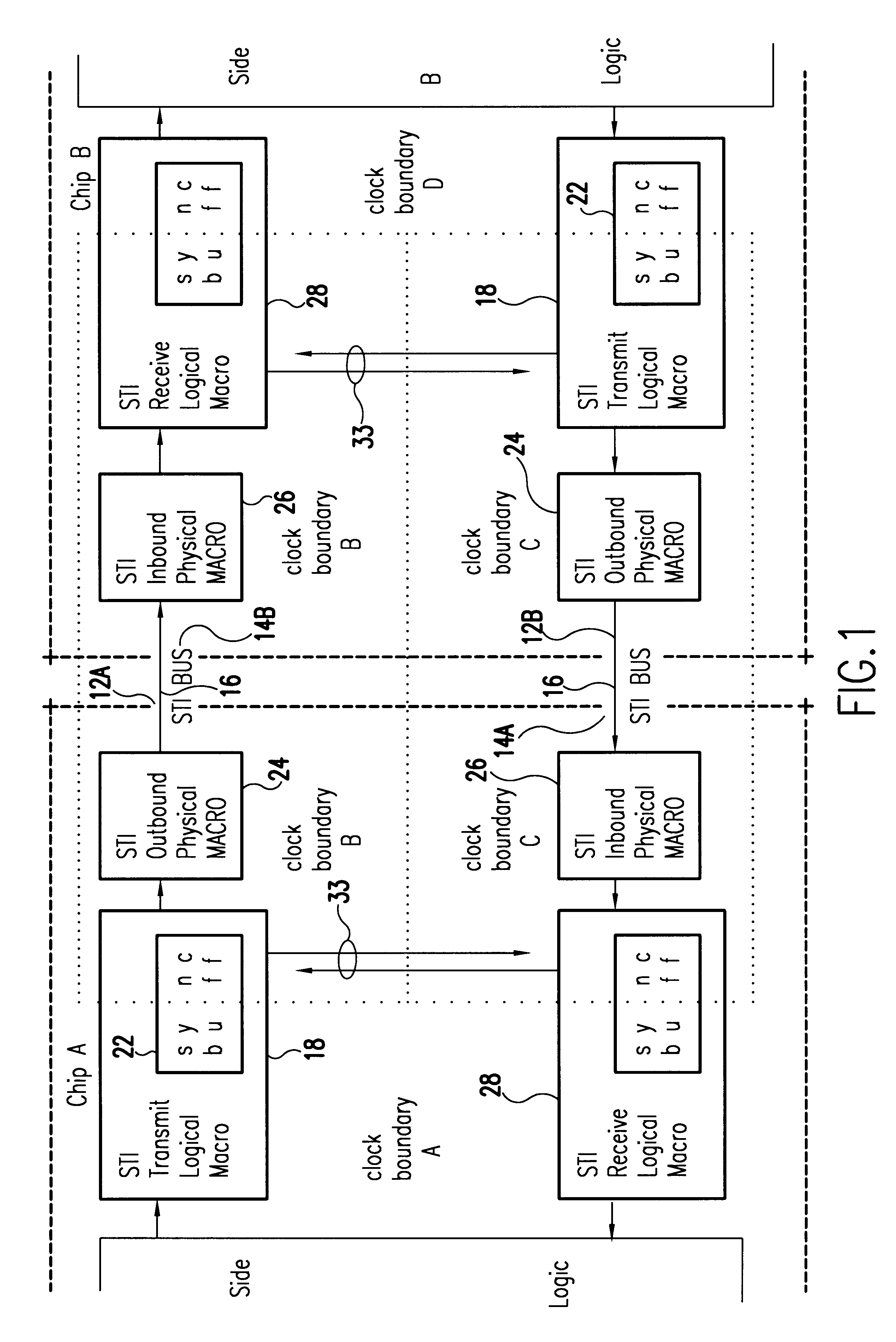

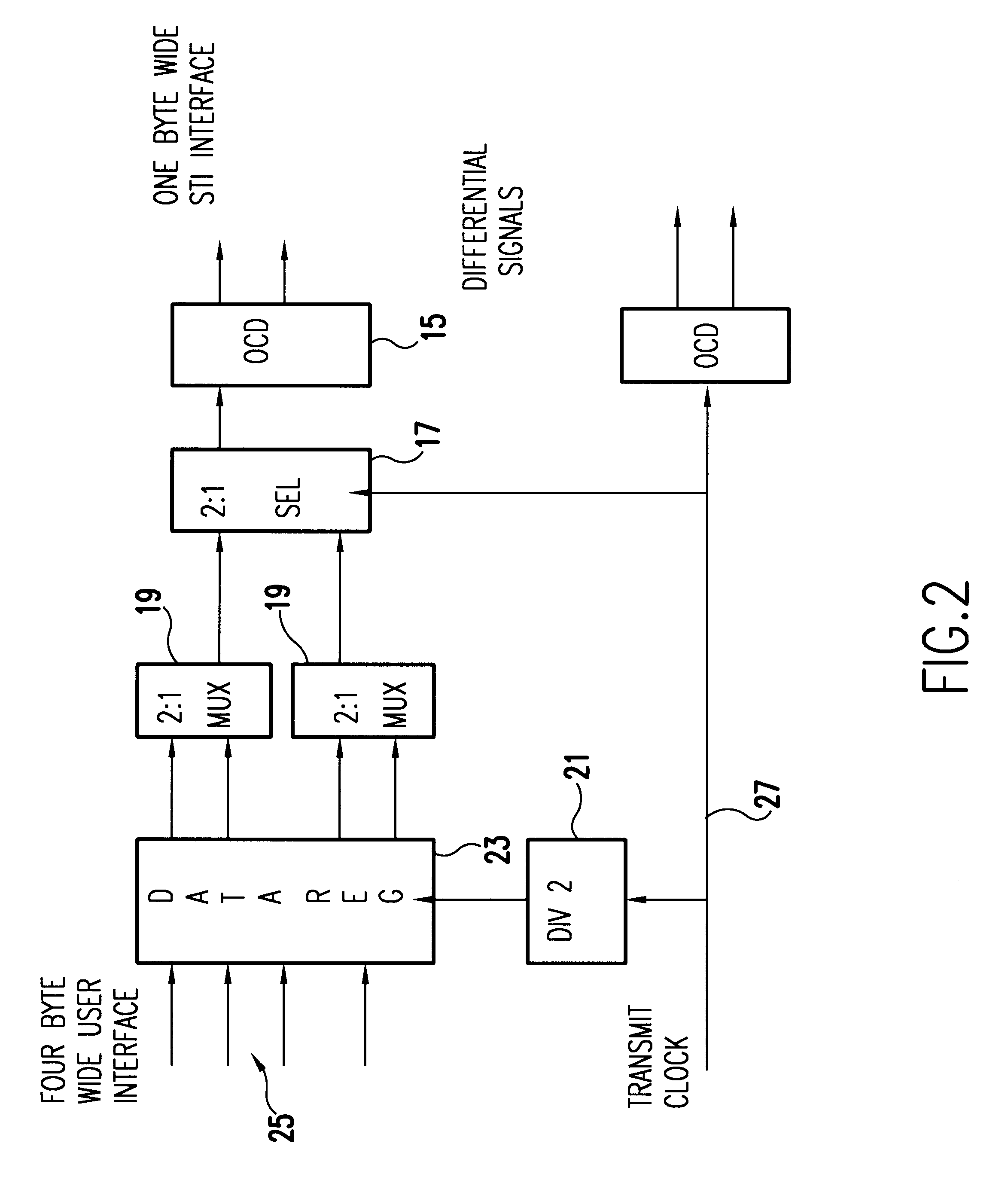

Synchronous interface for transmitting data in a system of massively parallel processors

InactiveUS6185693B1Low costImprove performanceError detection/correctionData resettingDigital dataClock rate

A massively parallel system has a self-timed interface (STI) in which a clock signal clocks bit serial data onto a parallel, electrically conductive bus and the clock signal is transmitted on a separate line of the bus. The received data on each line of the bus is individually phase aligned with the clock signal. Digital data is transmitted at high speeds via the parallel bus to provide a scalable communications network for parallel processing systems while eliminating precise bus length and system clock rates as a critical or limiting factor.

Owner:IBM CORP

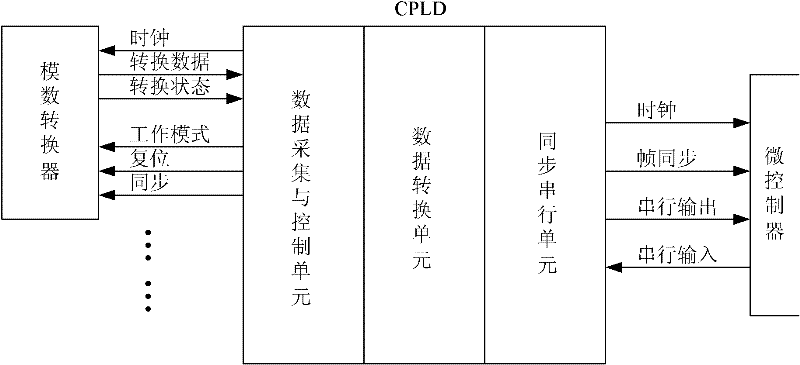

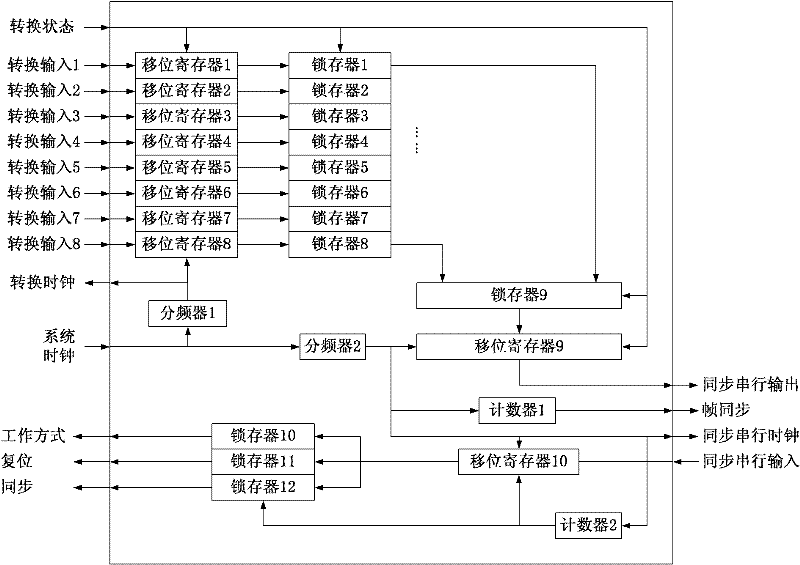

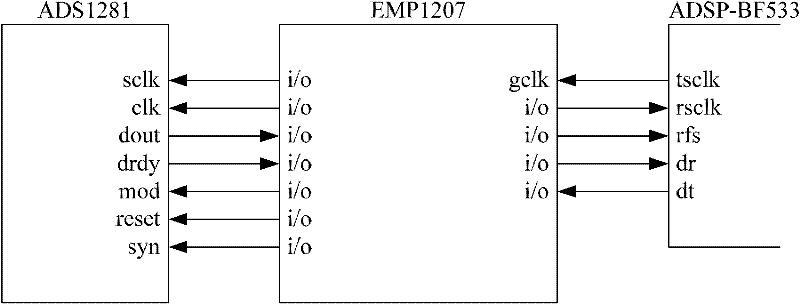

Digital strong motion seismograph and multipath data acquisition interface thereof

InactiveCN102314402AAvoid occupyingReduce processing efficiencySeismic signal receiversElectric digital data processingMicrocontrollerProgrammable logic device

Owner:CHINA EARTHQUAKE DISASTER PREVENTION CENT

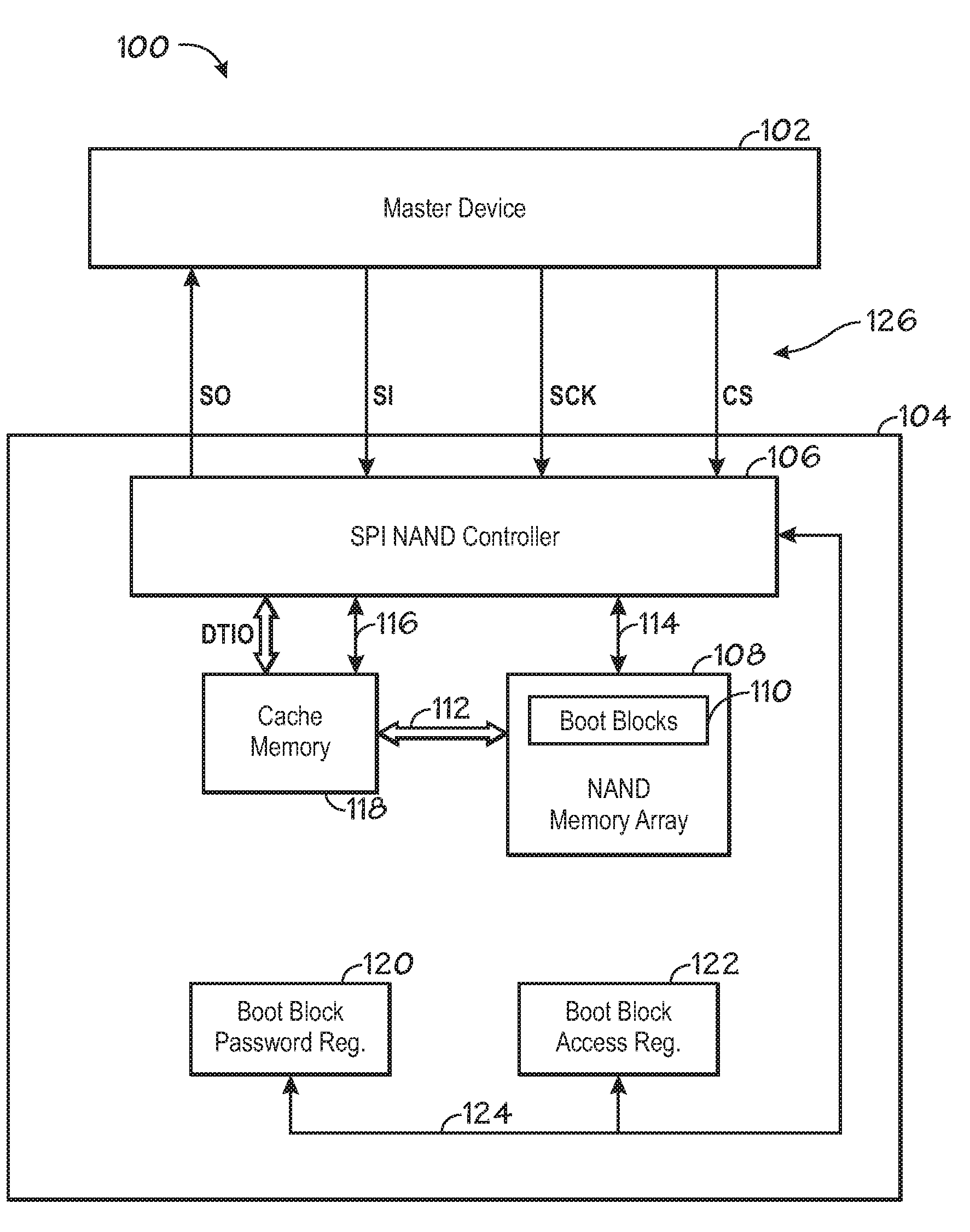

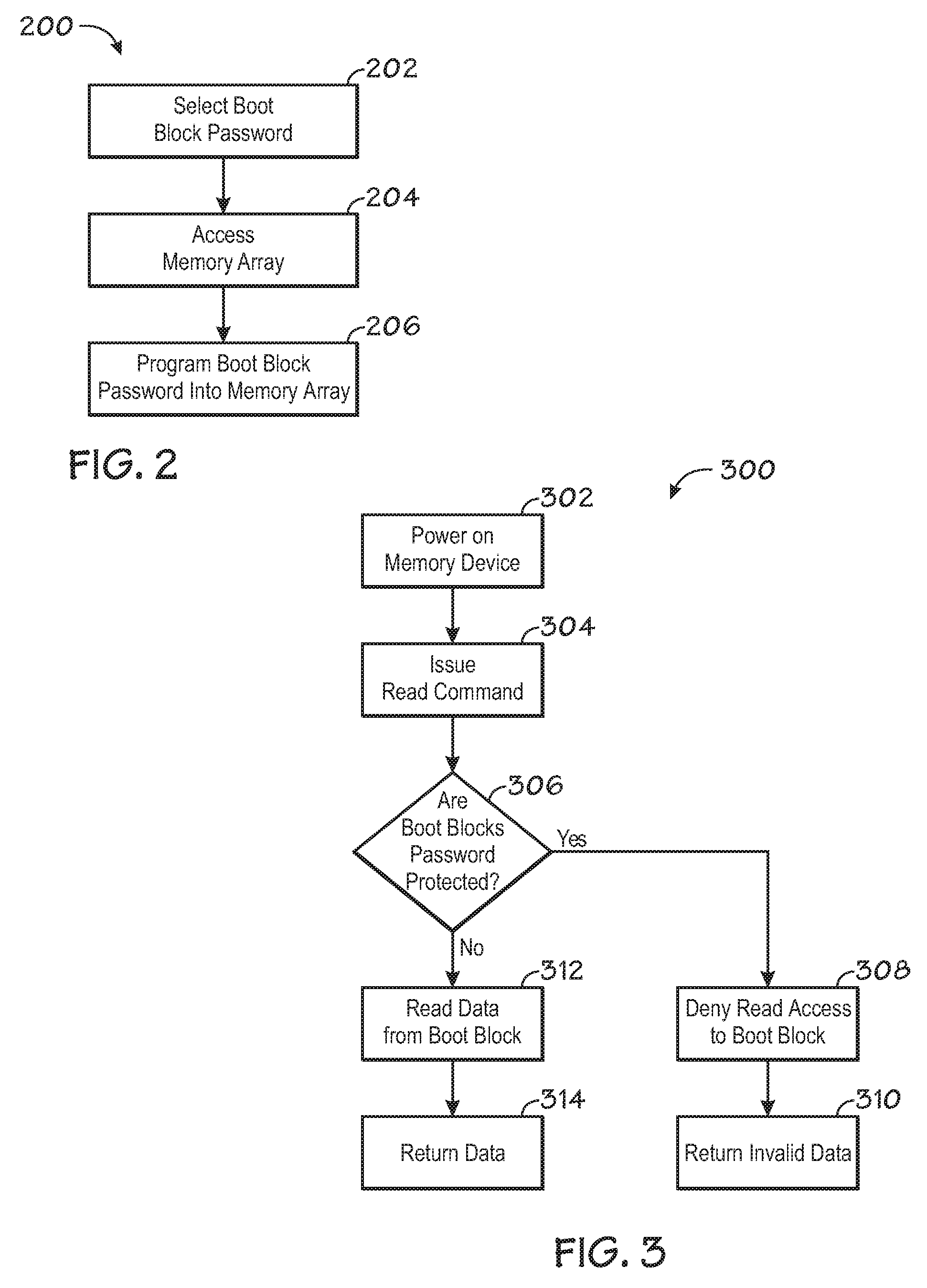

Boot block features in synchronous serial interface NAND

ActiveUS20090106543A1Memory architecture accessing/allocationDigital data processing detailsComputer hardwarePassword

Embodiments are provided for protecting boot block space in a NAND memory device connected to a host device via an SPI interface. One such method includes programming a boot block password into the NAND memory device such that the host device is required to provide the boot block password in order to access the boot block space. A counter may be provided to track the number of times the host device provides an incorrect password, permanently locking the boot block space if the counter reaches a predetermined value. A further method includes associating each of various areas of the boot block space with at least one write lock bit, setting the write lock bit to a lock enable or lock disable value, and locking or unlocking an area of the boot block space depending on the value of its associated write lock bit. Areas of the boot block space may include a single boot block page, a single boot block, or a plurality of boot blocks.

Owner:LODESTAR LICENSING GRP LLC

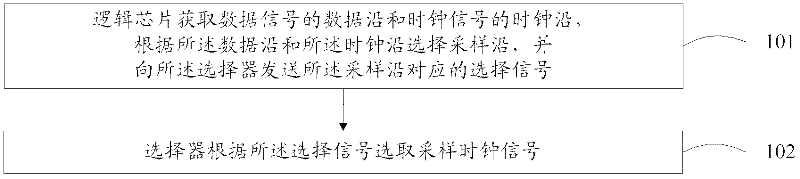

Method and equipment for selecting sampling clock signal

ActiveCN102347813ANo manual configuration requiredReduce operating and maintenance costsSynchronisation information channelsTime-division multiplexMaintainabilityData signal

Owner:HUAWEI TECH CO LTD

Boot block features in synchronous serial interface NAND

ActiveUS8090955B2Memory architecture accessing/allocationDigital data processing detailsComputer hardwarePassword

Owner:LODESTAR LICENSING GRP LLC

Electronic synchronous/asynchronous transceiver device for power line communication networks

ActiveUS20090074041A1Low costLarge spectrumTransmission/receiving by adding signal to waveImproving S/N for transmission/receivingLinear regulatorTransceiver

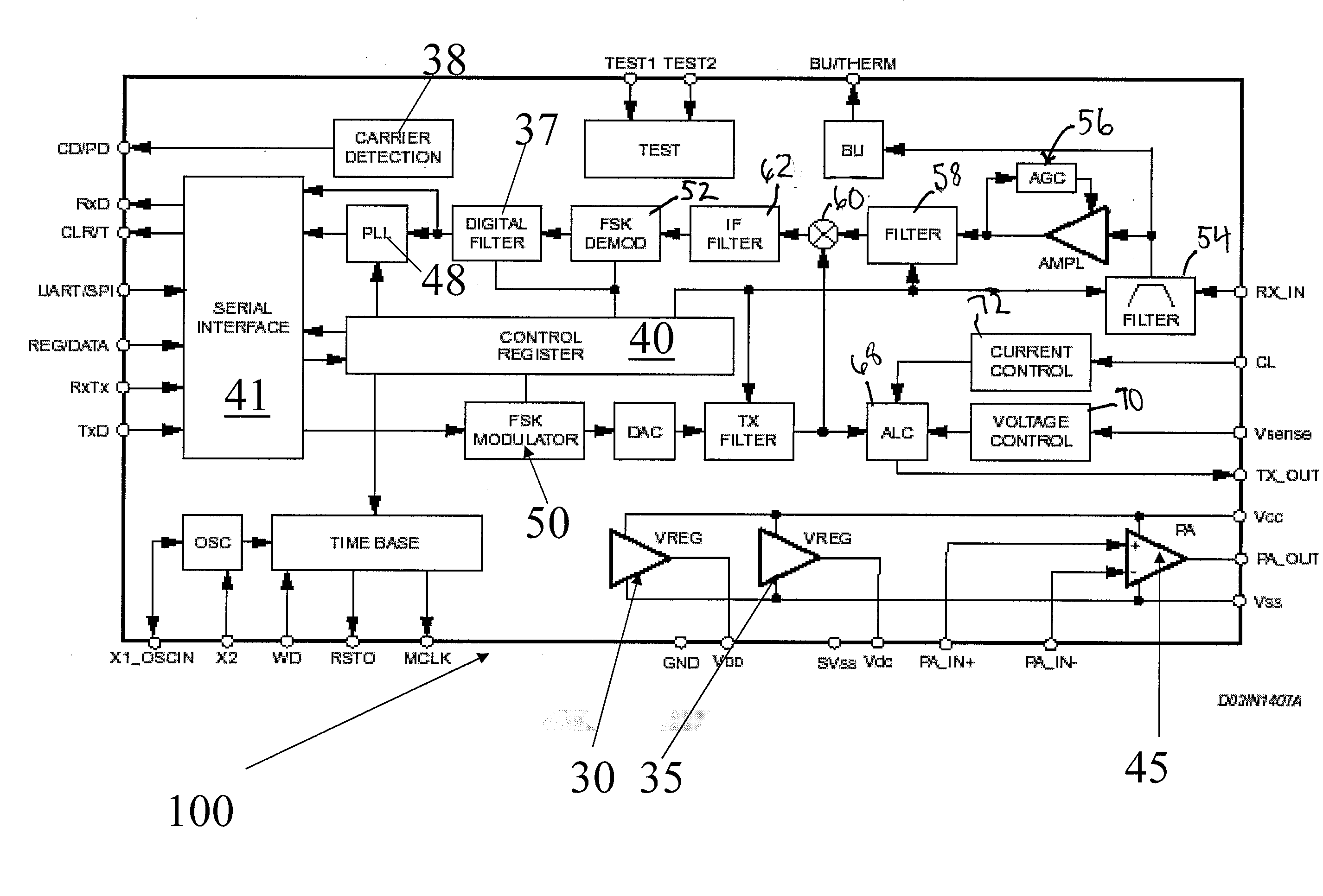

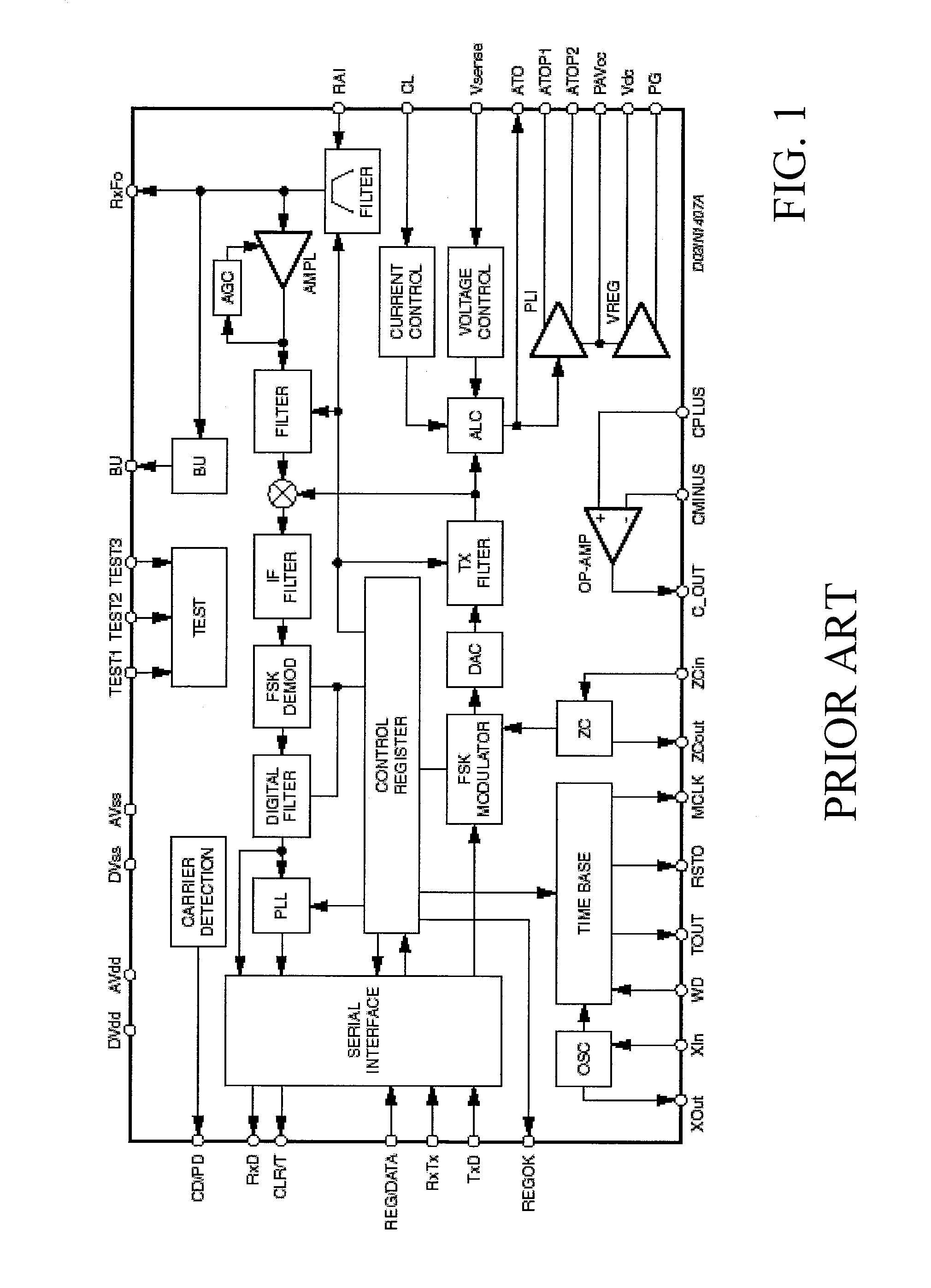

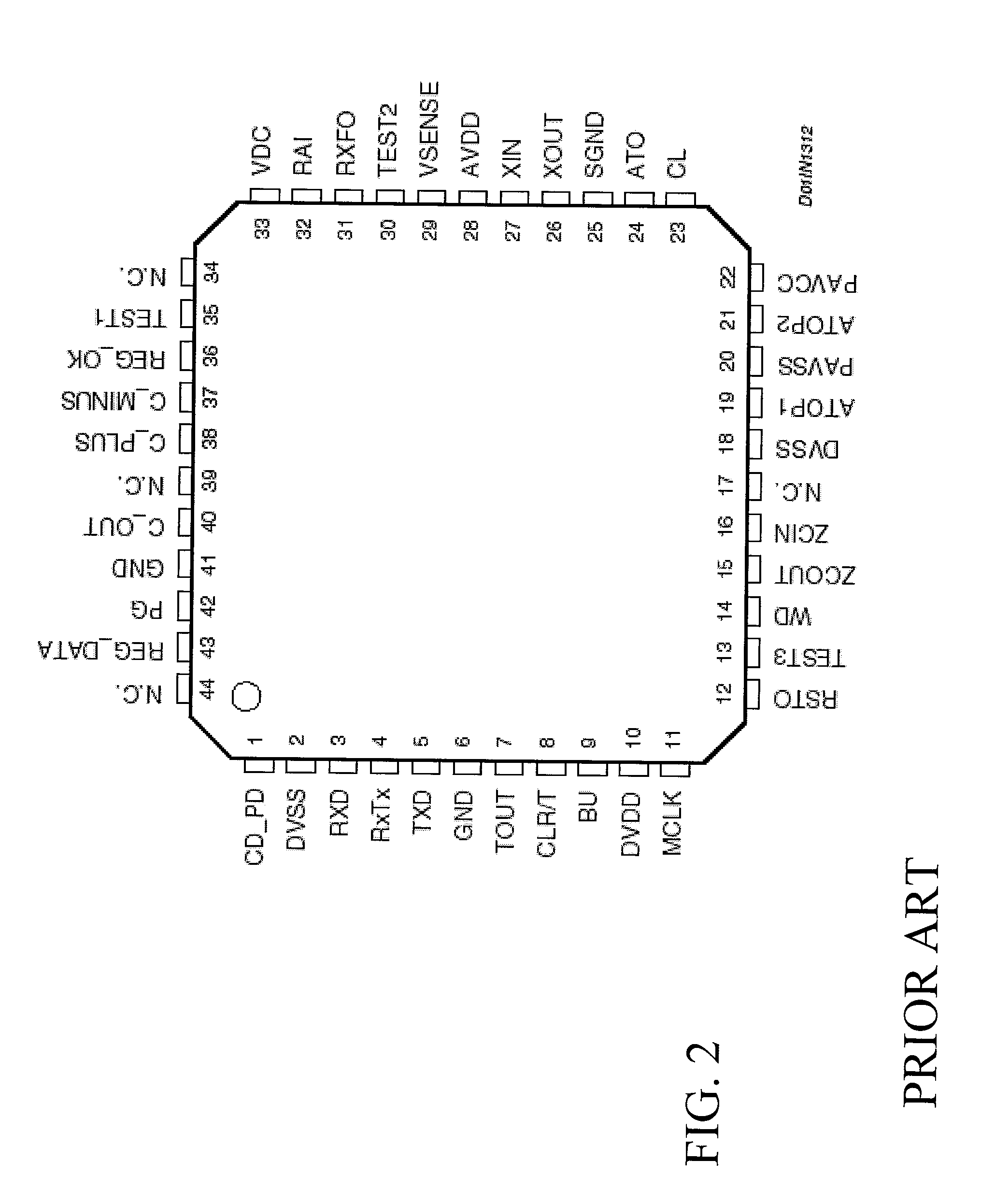

An electronic synchronous / asynchronous transceiver device for power line communication networks is integrated into a single chip and operates from a single supply voltage. The transceiver device includes: at least an internal register that is programmable through a synchronous serial interface; at least a line driver for a two-way network communication over power lines implemented by a single ended power amplifier with direct accessible input and output lines that is part of a tunable active filter for the transmission path; and at least a couple of linear regulators for powering with different voltage levels different kind of external controllers linked to the transceiver device.

Owner:STMICROELECTRONICS SRL

Methods for asynchronous serial data transmission using a synchronous serial interface

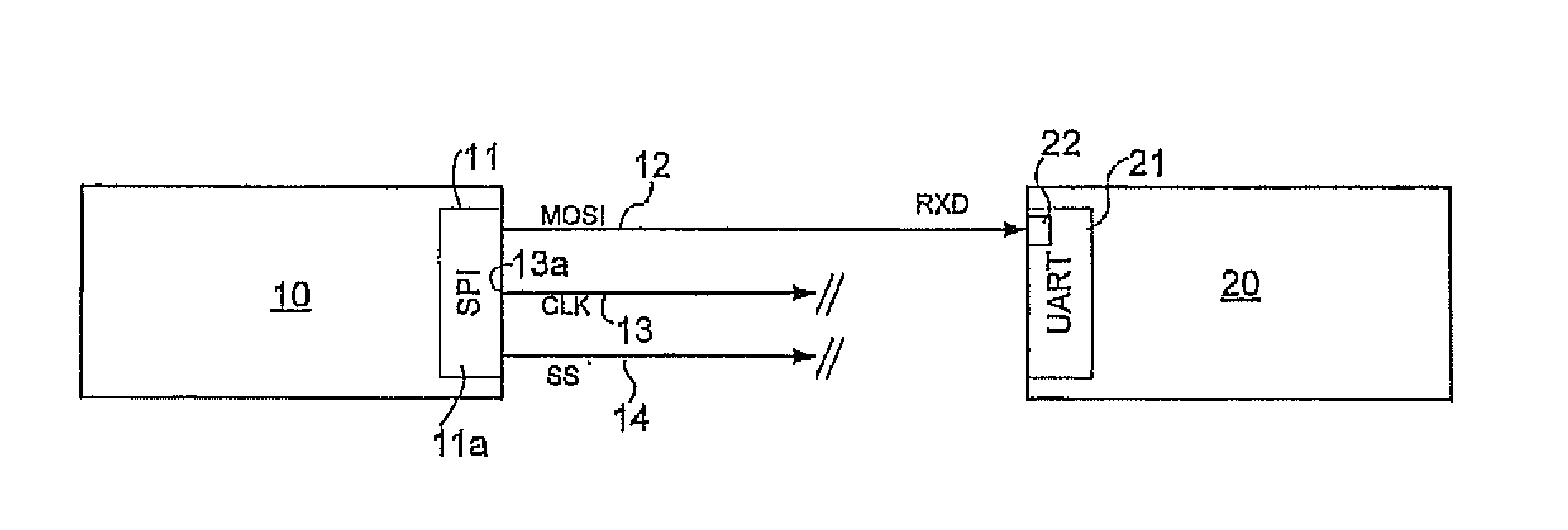

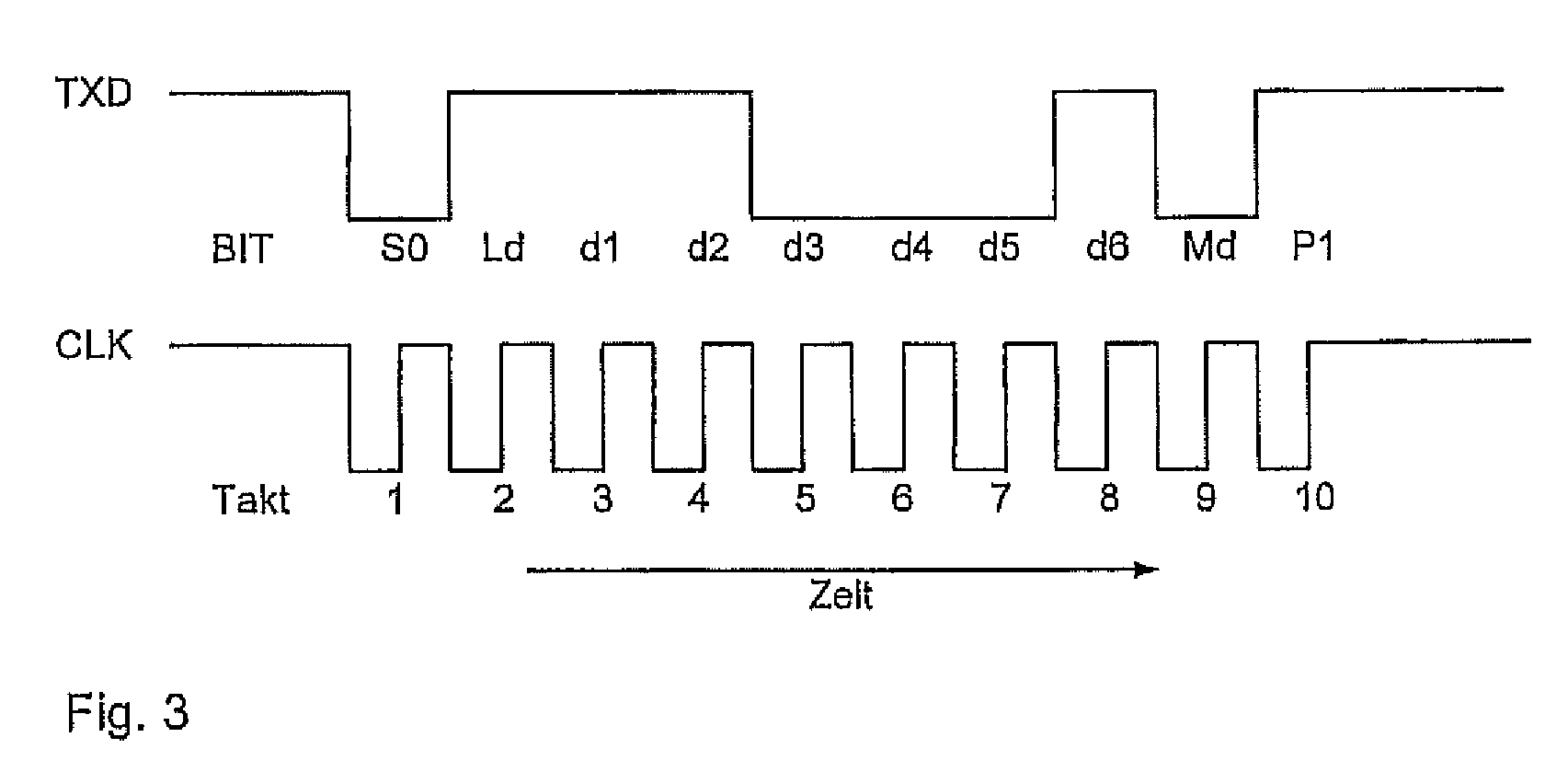

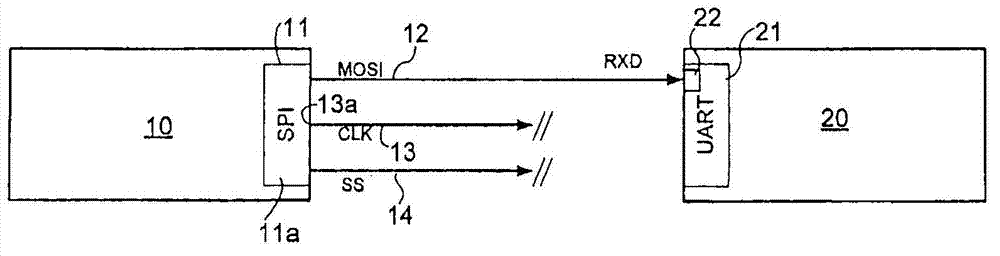

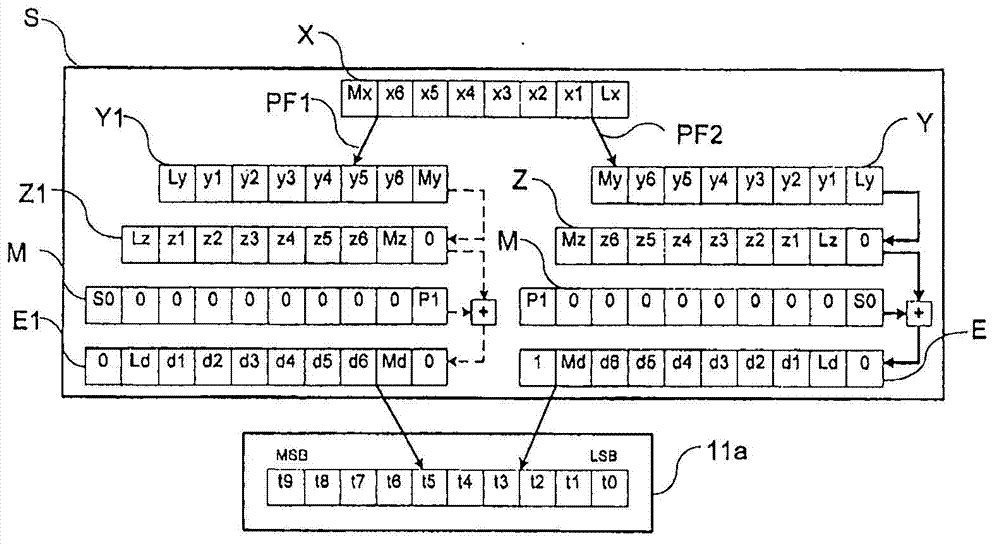

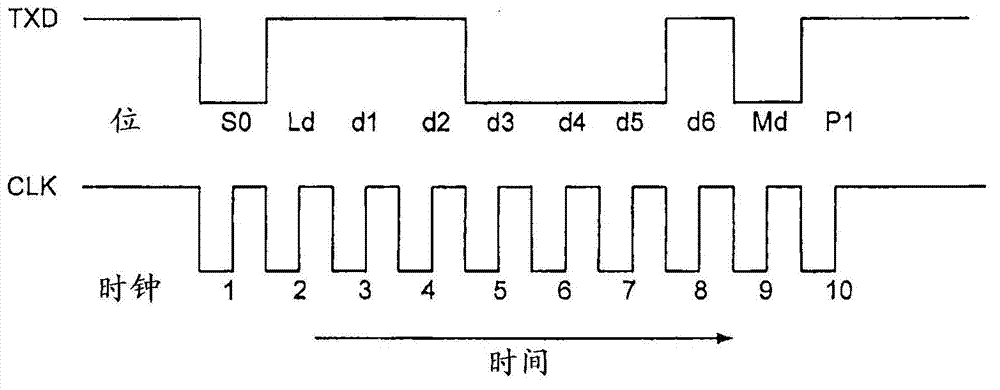

InactiveUS20130064321A1Less software expenseLess complexModulated-carrier systemsElectric digital data processingSupplementary dataData transmission

The invention relates to a method for the unidirectional, asynchronous serial data transfer with an asynchronous data format with F frame bits between a transmitting interface of a data transmitting device and between a data receiving device with a serial receiving interface comprising an asynchronous serial data input. It is provided that the transmitting interface is constructed as a synchronous serial interface with at least one data line, whereby the data line is connected to the asynchronous serial data input of the receiving interface, a data word with D data bits to be transmitted by the data transmitting device in order to generate a format with F frame bits corresponding to the asynchronous data format is supplemented. The data word supplemented with the frame bits is stored in a transmitting register for transmission to the data receiving device.

Owner:VEGA GRIESHABER GMBH & CO

Method for asynchronous-serial data transfer over a synchronous-serial interface

InactiveCN103116562AError preventionElectric digital data processingSerial digital interfaceProcessor register

The invention relates to a method used for performing one-way asynchronous serial data transmission between a transmission interface (11) of a data transmission apparatus (10) and a data receiving device (20) with a serial receive interface (21) having an asynchronous serial data input terminal in an asynchronous data format with F (F belongs to N) framing bits. According to the invention, the transmission interface (11) is configured into a synchronous serial interface (11) with at least one data line (12), wherein the data line is connected to the asynchronous serial data input terminal (22) of the receive interface (21), and is used for adding F framing bits for data word with D (D belongs to N) data bits conveyed by the data transmission apparatus (10) in order to generate a format corresponding to asynchronous data format, and storing the data word with frame bits in a transmitting register (11a) for transmission to a data receiving device (20).

Owner:VEGA GRIESHABER GMBH & CO

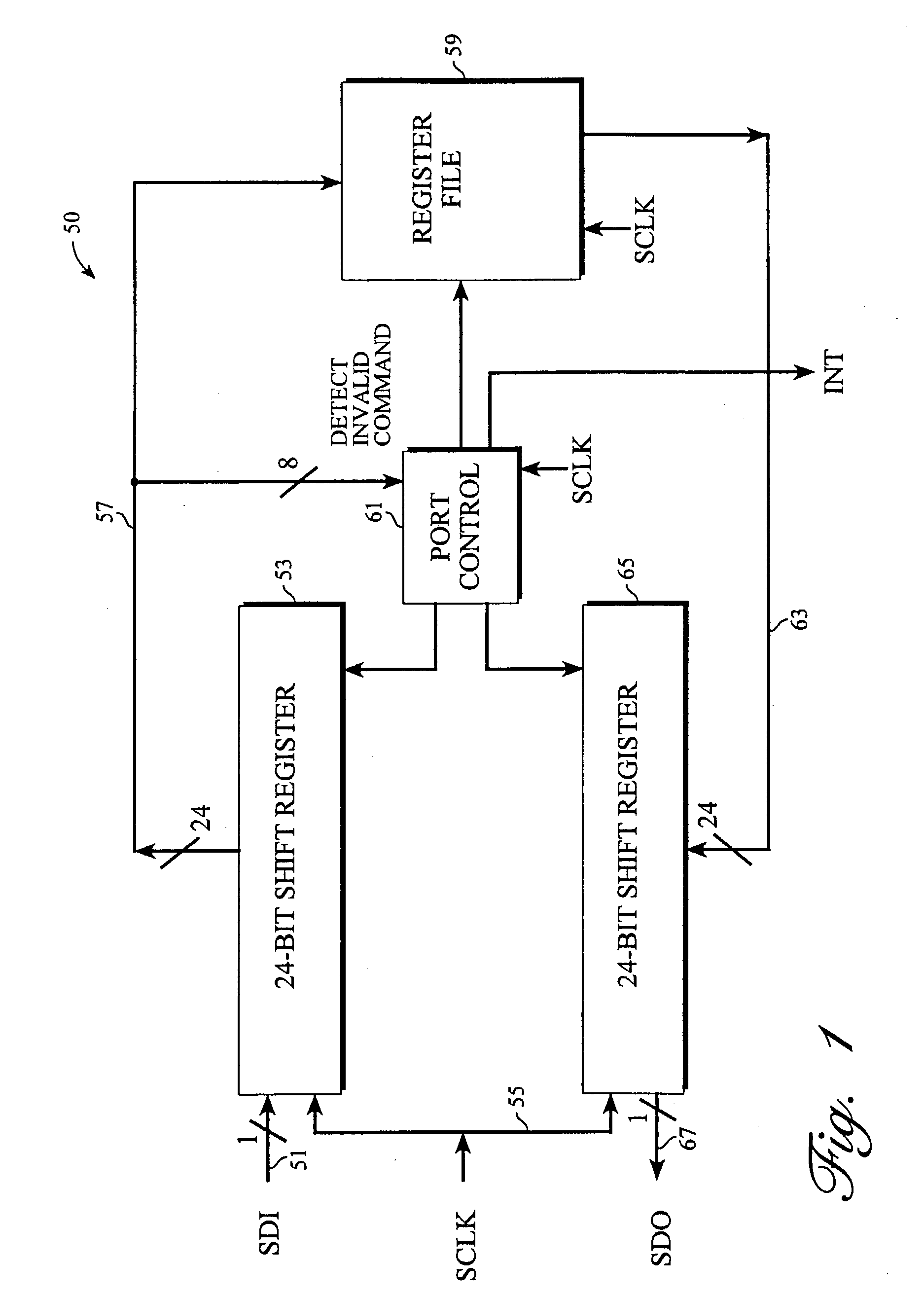

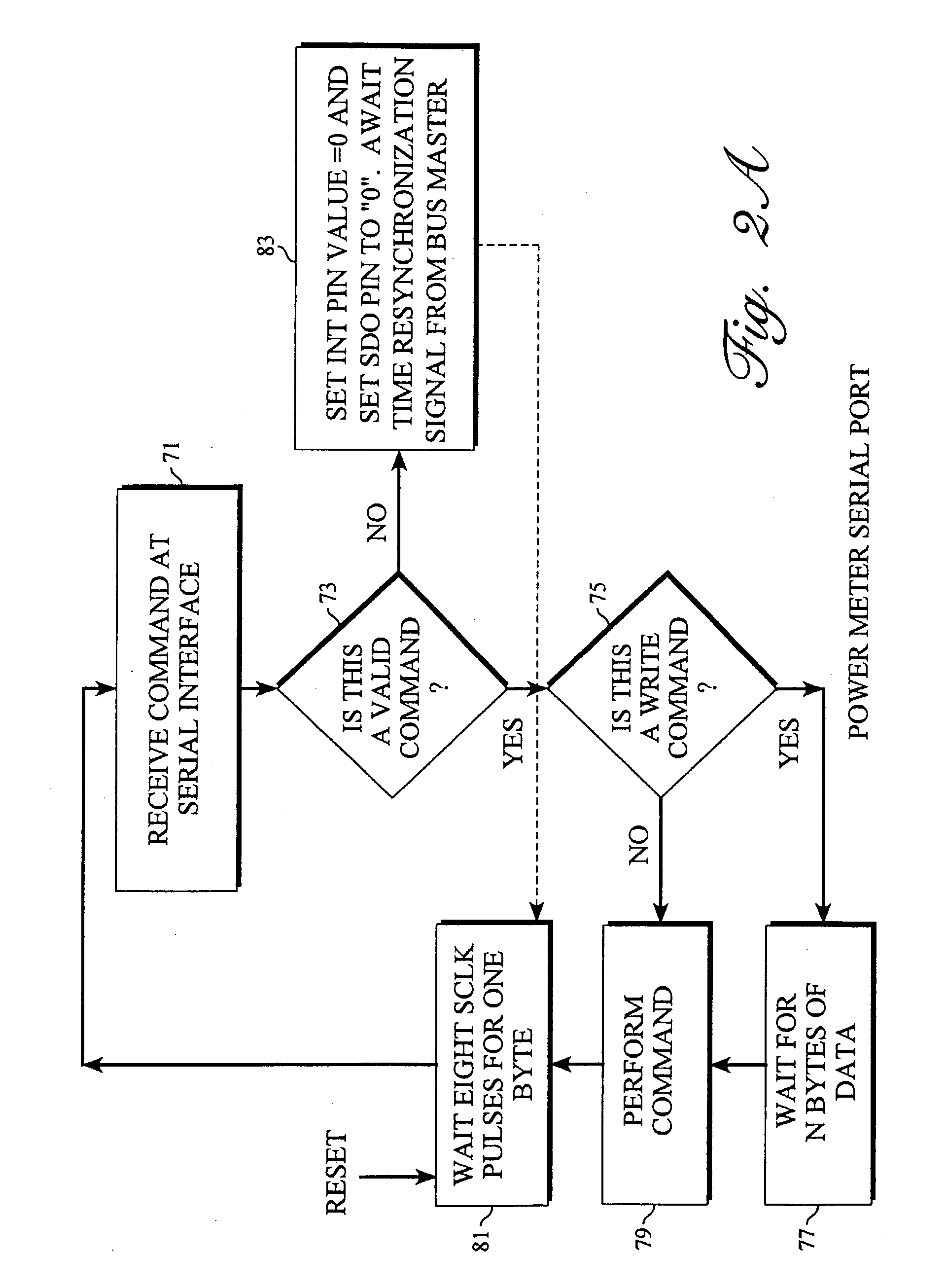

Prompt resynchronization for a serial interface

InactiveUS20030196130A1Generating/distributing signalsTransmission path multiple useByteSynchronous Serial Interface

Byte synchronization between a bus master and a serial interface or other bus slave is maintained and promptly corrected by using a unique signal, issued by the serial interface, to promptly and unambiguously notify the bus master of a loss of synchronization, followed by prompt resynchronization by the bus master. The serial interface sets a selected indicium in a status register equal to a selected value, when an invalid command is sensed at the interface. The bus master reads the status register and, when the selected indicium has the selected value, promptly resynchronizes the serial interface without further delay.

Owner:CIRRUS LOGIC INC

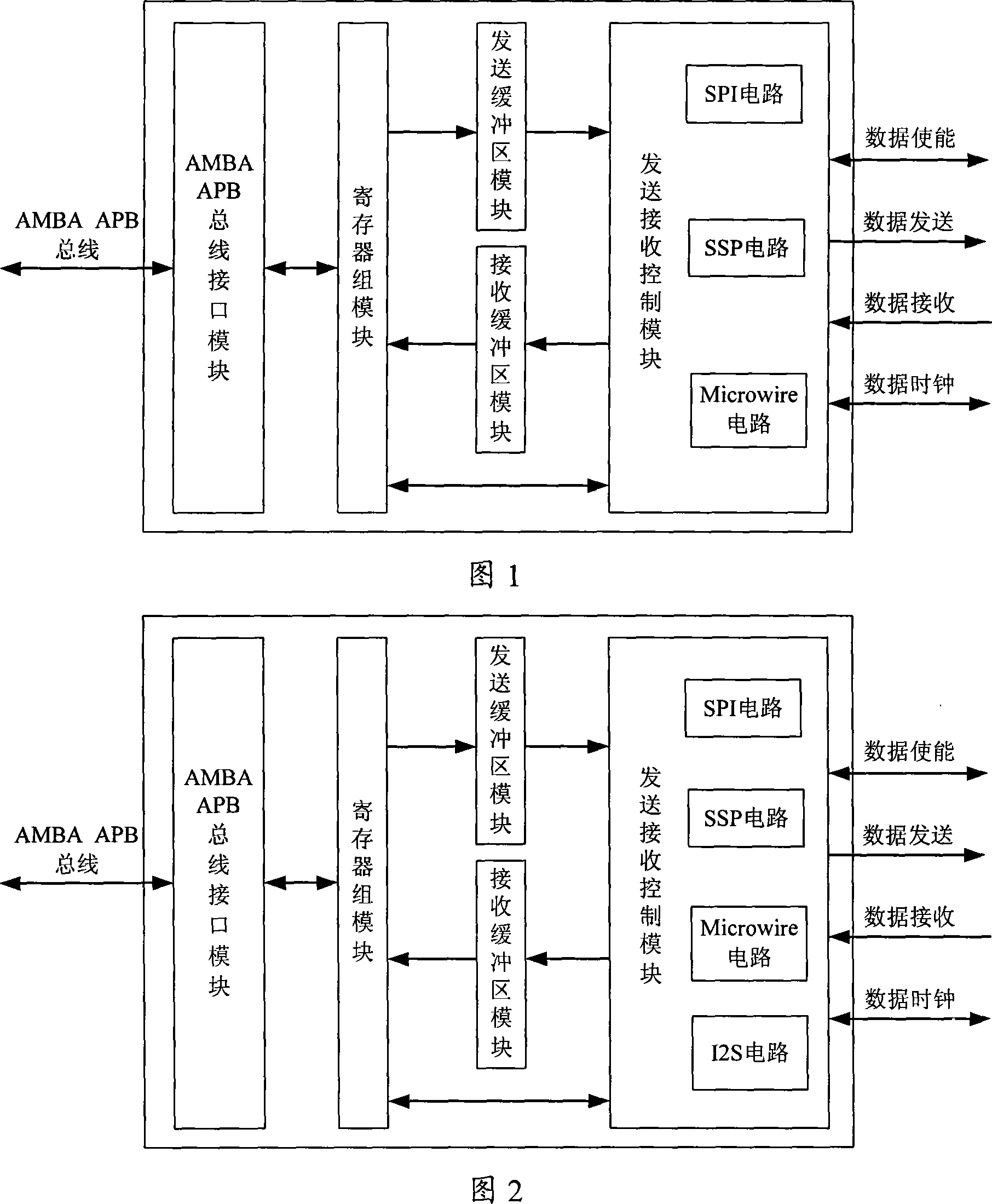

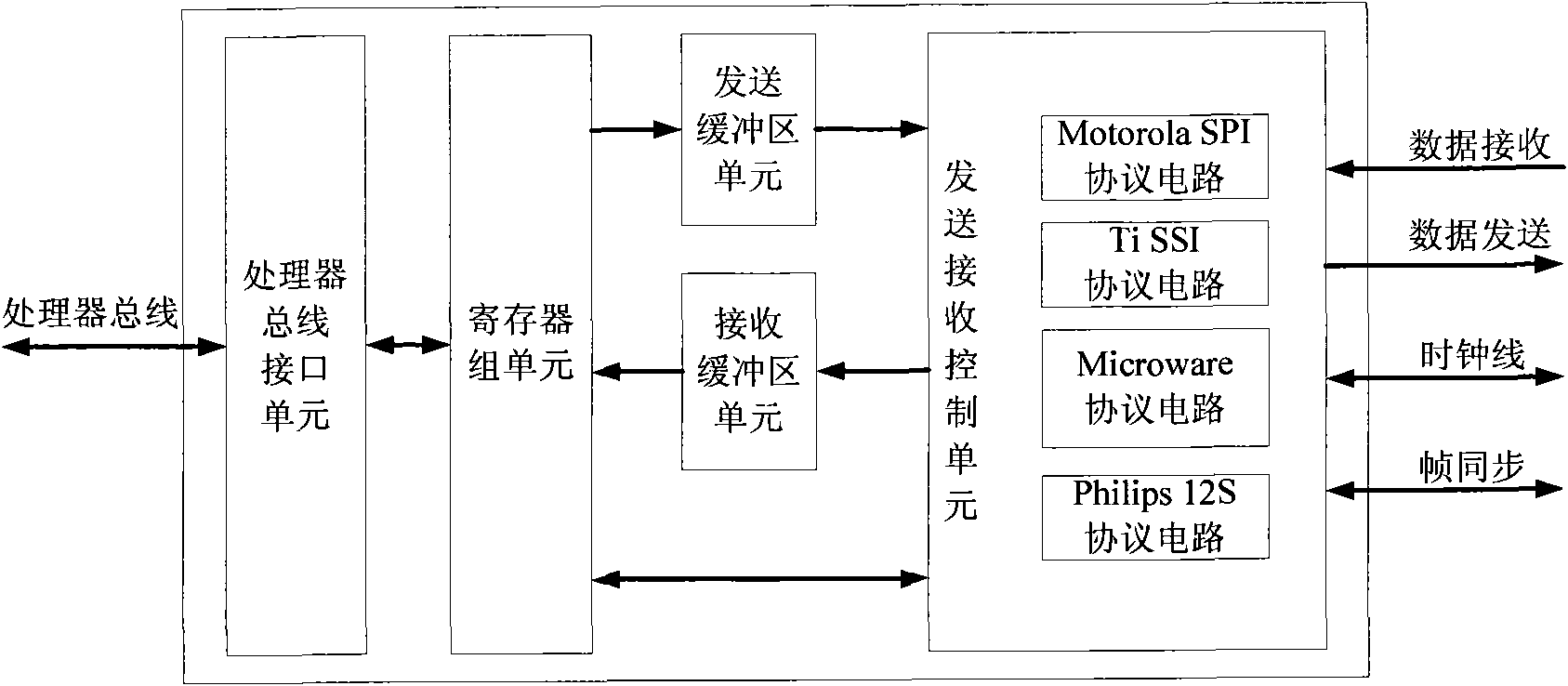

Synchronous serial interface device

ActiveCN101026528AImprove utilizationFunction increaseInput/output processes for data processingBus networksData streamProcessor register

The SYNC serial interface unit is slave unit of AMBA APB bus. The interface unit is composed of some slave module including AMBA APB bus interface module, register set module, transmitting buffer area module, receiving buffer area module, and send receive control module. Through main part configured register mode, slave unit of AMBA APB bus implements transmission of data stream according to protocols: Motorola SPI, Texas Instruments SSI, National Semiconductor Microwire, and Philips I2S. Since I2S circuit is added to the send receive control module, the multifunctional SYNC serial interface unit can be in use for transmitting and receiving audio data stream in I2S protocol. The invention raises usage of pins of chip, system performance and flexibility, and wide application range.

Owner:SANECHIPS TECH CO LTD

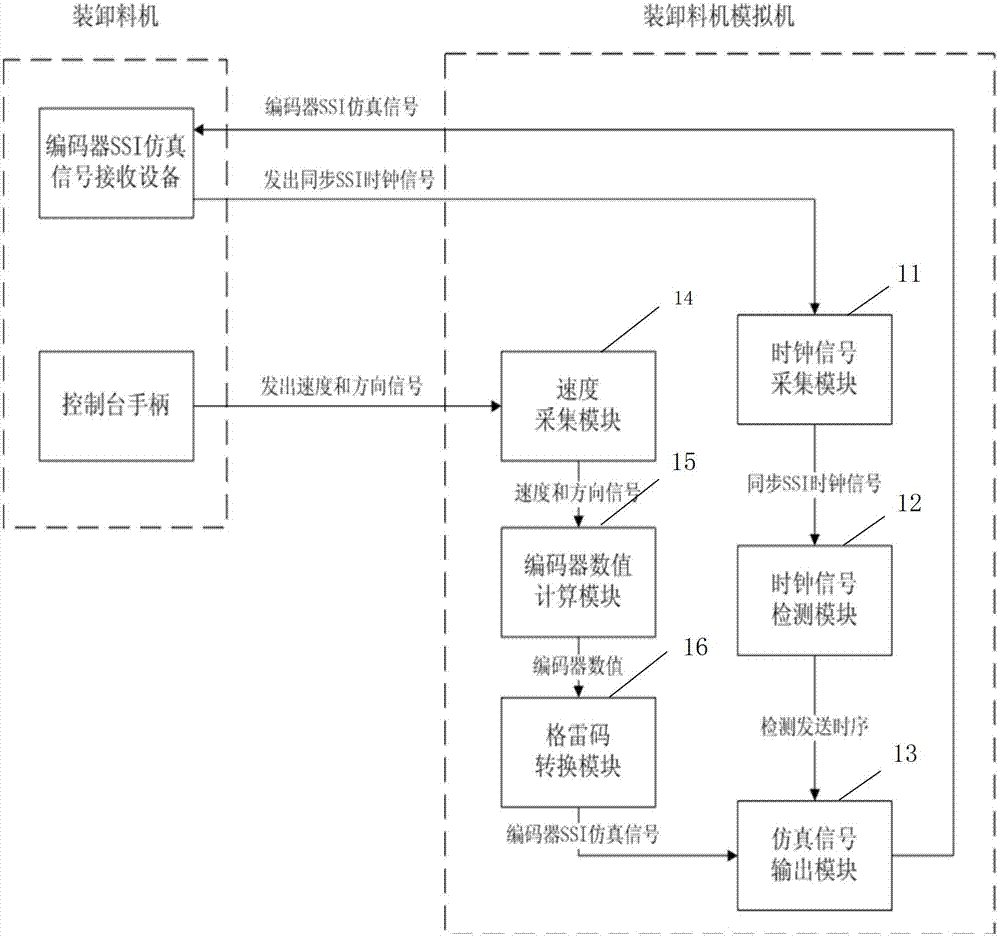

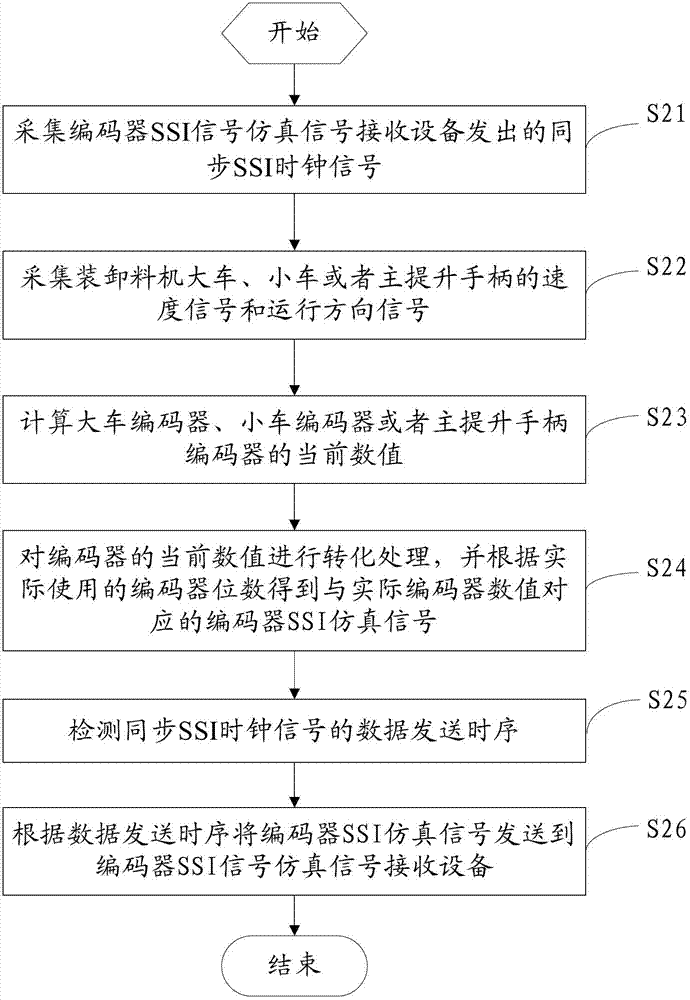

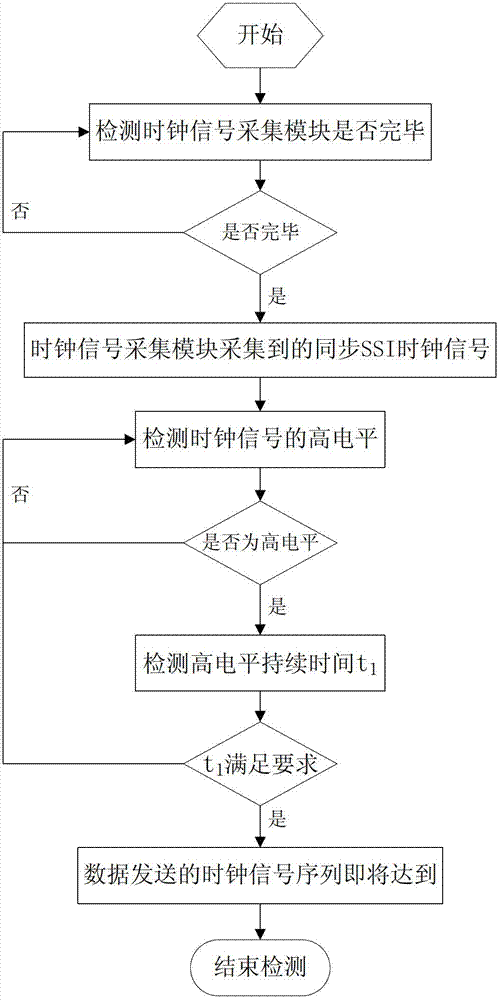

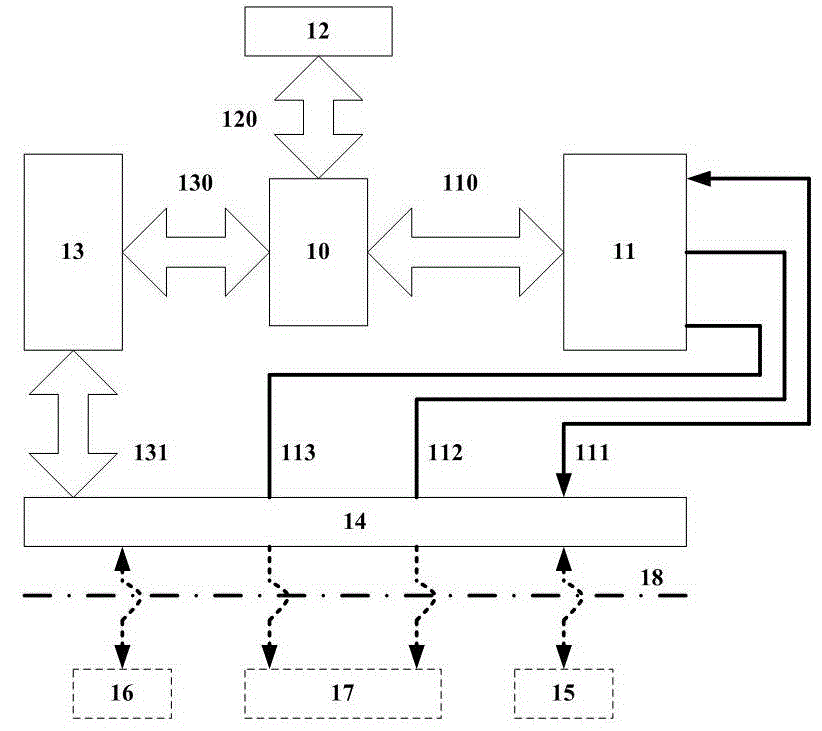

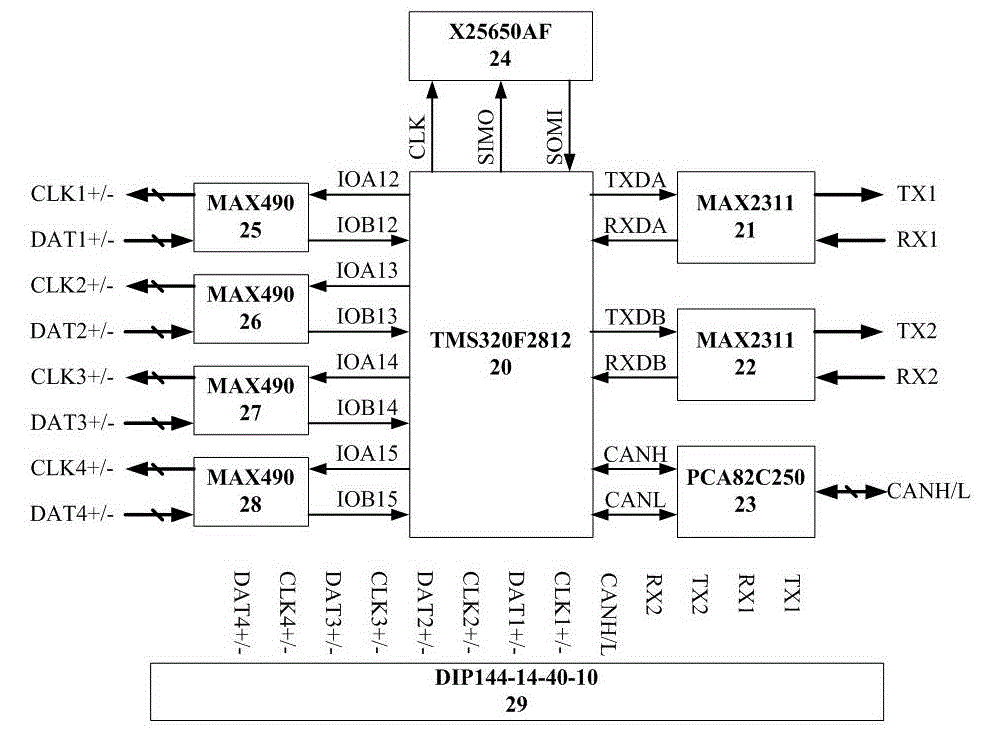

Encoder signal simulation system and method applied to simulator of loading and unloading machine

ActiveCN103207571AImprove economyEasy to operateSimulator controlNuclear powerSynchronous Serial Interface

The invention discloses an encoder signal simulation system and method applied to a simulator of a loading and unloading machine. The method includes: firstly calculating a current numerical value of the encoder according to collected speed and moving direction signals sent by a large vehicle, a small vehicle or a main lifting handle of a console of the loading and unloading machine; secondly converting the current numerical value and obtaining an encoder SSI (synchronous serial interface) simulation signal corresponding to an actual encoder value according to a real encoder hardware; and lastly, obtaining a transmission time series of the encoder SSI simulation signal according to a synchronous SSI clock signal sent by an encoder SSI simulation signal receiving device, and sending the encoder SSI simulation signal to the encoder SSI signal receiving device to finish the analogue simulation of the encoder SSI simulation signal. The simulator system and method can flexibly control the encoder simulation signal of the simulator of the loading and unloading machine and simulates different working conditions without relying on the real encoder hardware device, thereby improving the training efficiency of an operator of the loading and unloading machine of a nuclear power station.

Owner:CHINA NUCLEAR POWER ENG CO LTD

Synchronous serial interface signal sensor data acquisition device

ActiveCN102866979ASimple hardware structureElectric digital data processingProcess systemsProgrammable read-only memory

Owner:中国兵器装备集团自动化研究所有限公司

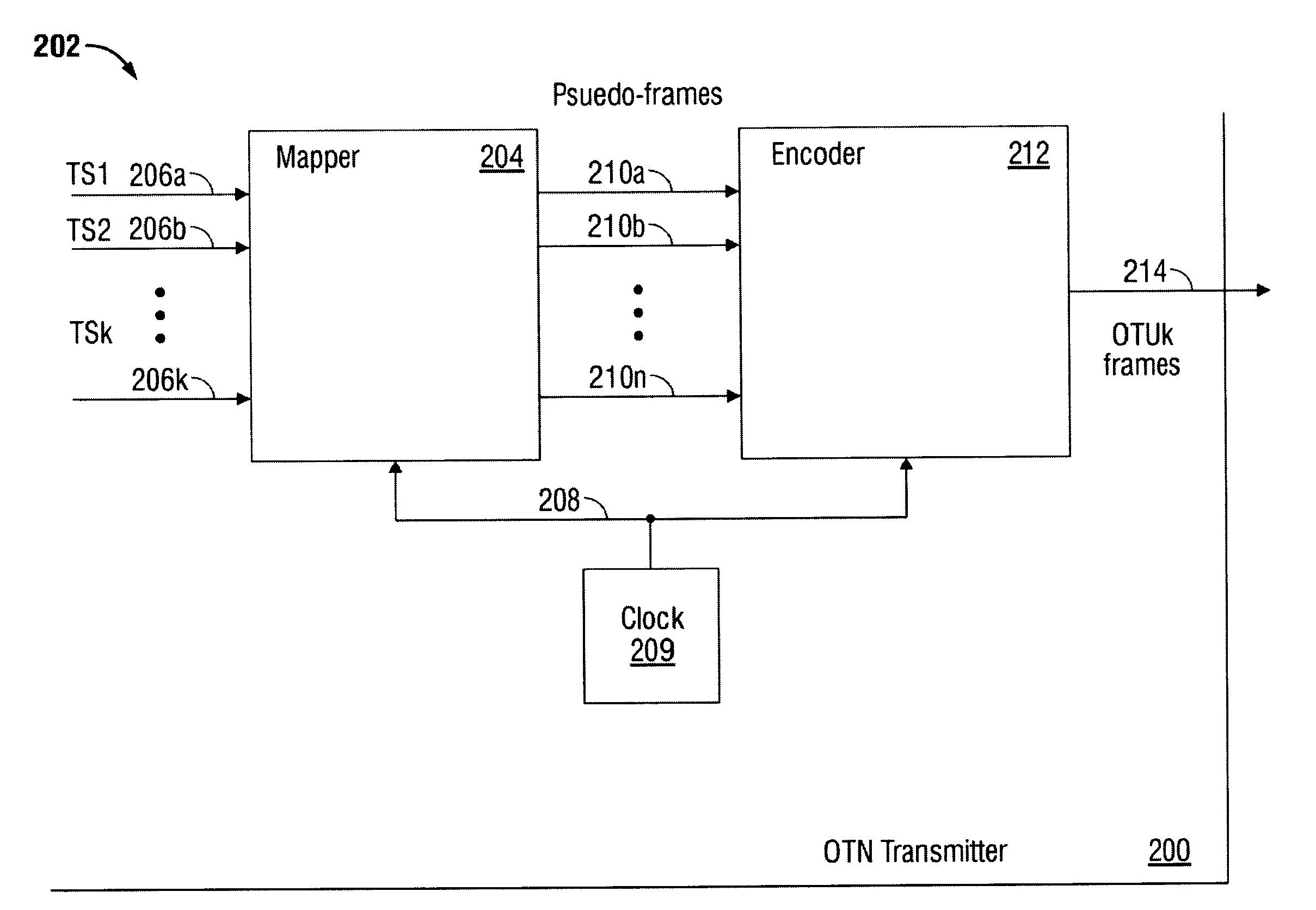

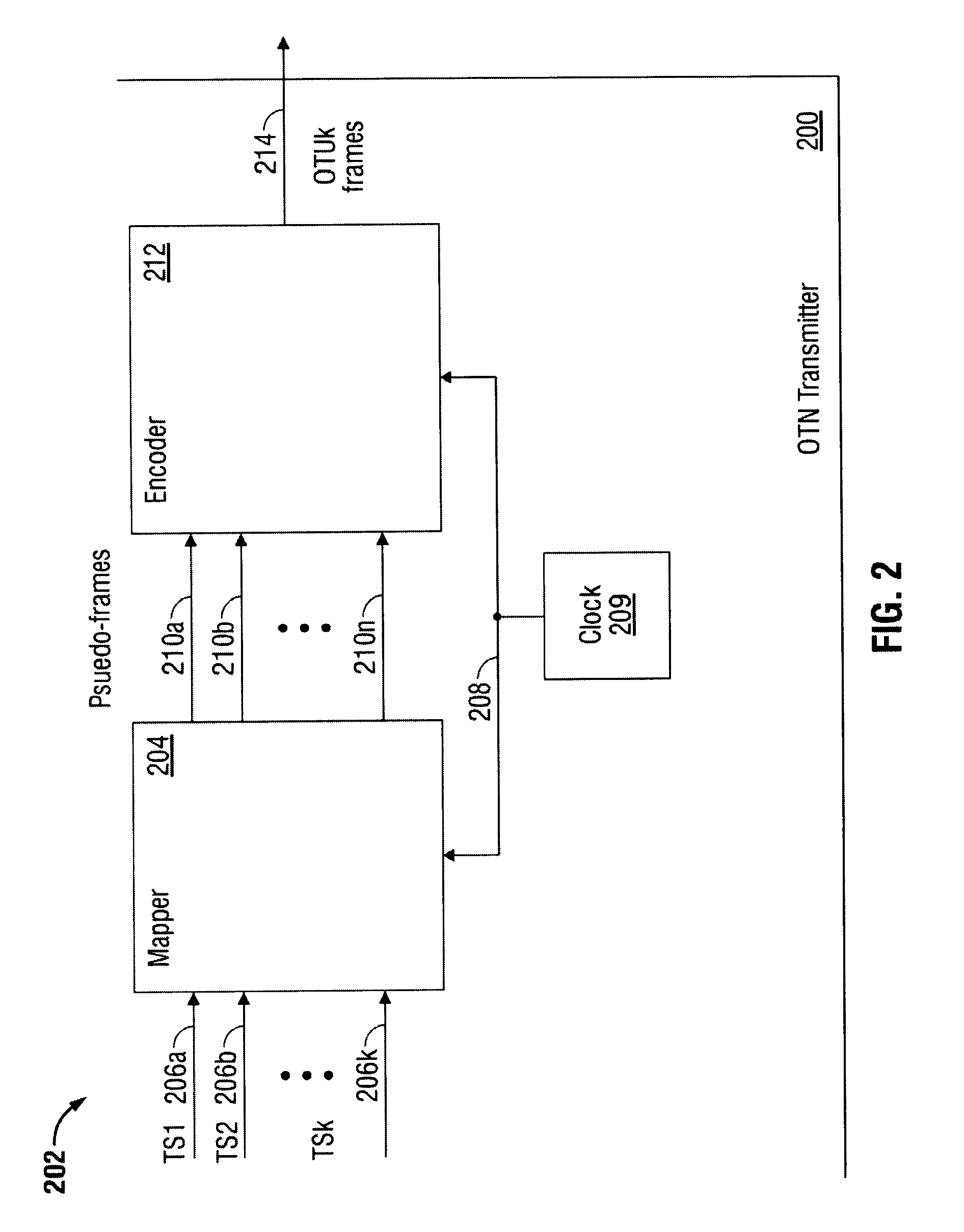

System and method for transporting asynchronous ODUk signals over a synchronous interface

ActiveUS8050567B2Minimizing buffer requirementRequires minimizationTime-division optical multiplex systemsTime-division multiplexChannel dataSynchronous Serial Interface

System and methods are provided, in an Optical Transport Network (OTN), for communicating asynchronous Tributary Slots (TSs) via a synchronous Optical Payload Transport Unit of level k (OTUk) interface. The transmission method accepts a plurality of TSs at a corresponding plurality of asynchronous data rates. The TSs are mapped, using a tangible memory medium, into pseudo-Optical channel Data Tributary Unit (ODTU) frames synchronized to a common clock. Then, the synchronized pseudo-ODTU frames can be interleaved into an OTUk frame, without the need of a phase-locked loop (PLL) or buffering.

Owner:MACOM CONNECTIVITY SOLUTIONS LLC

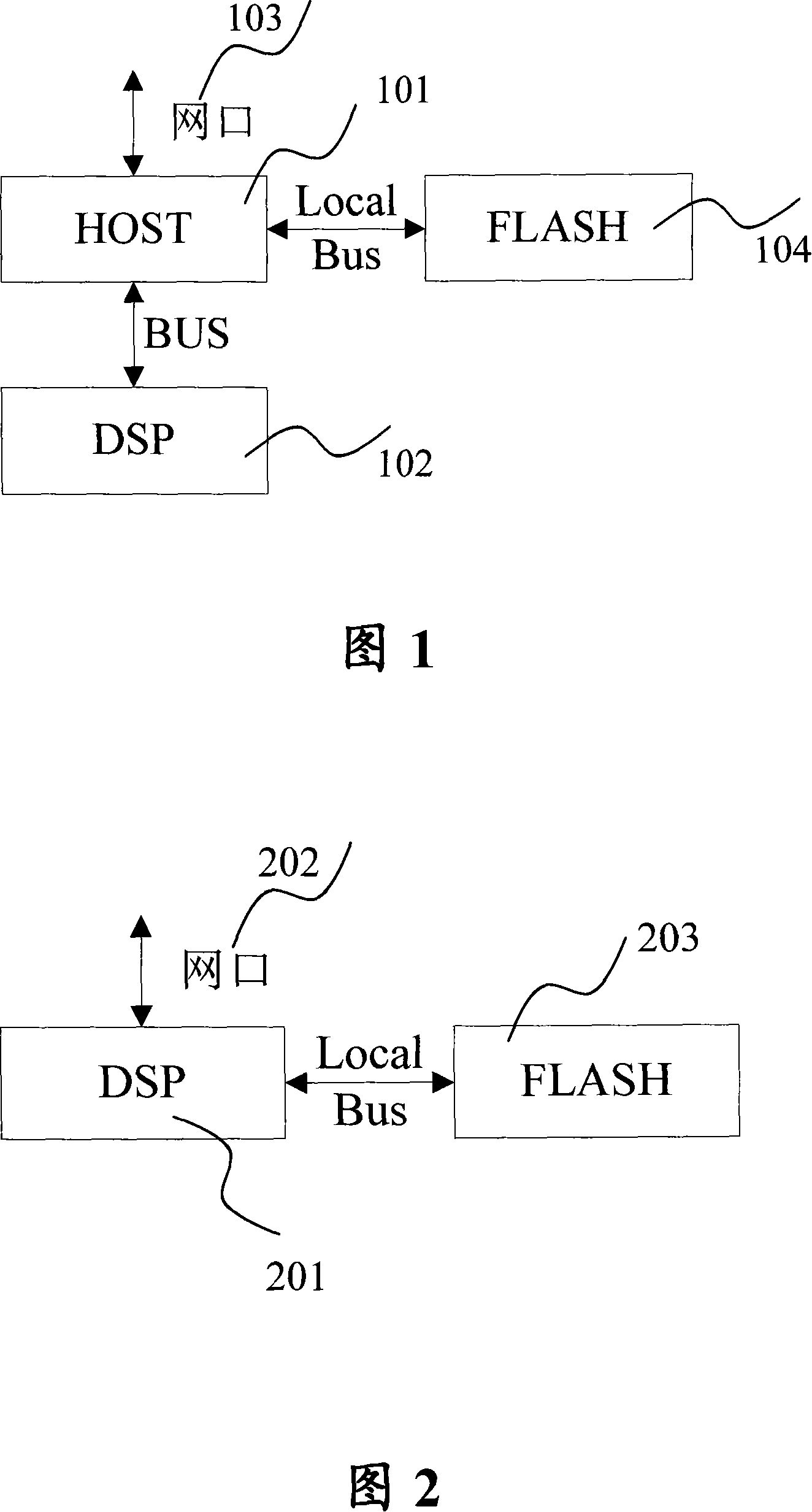

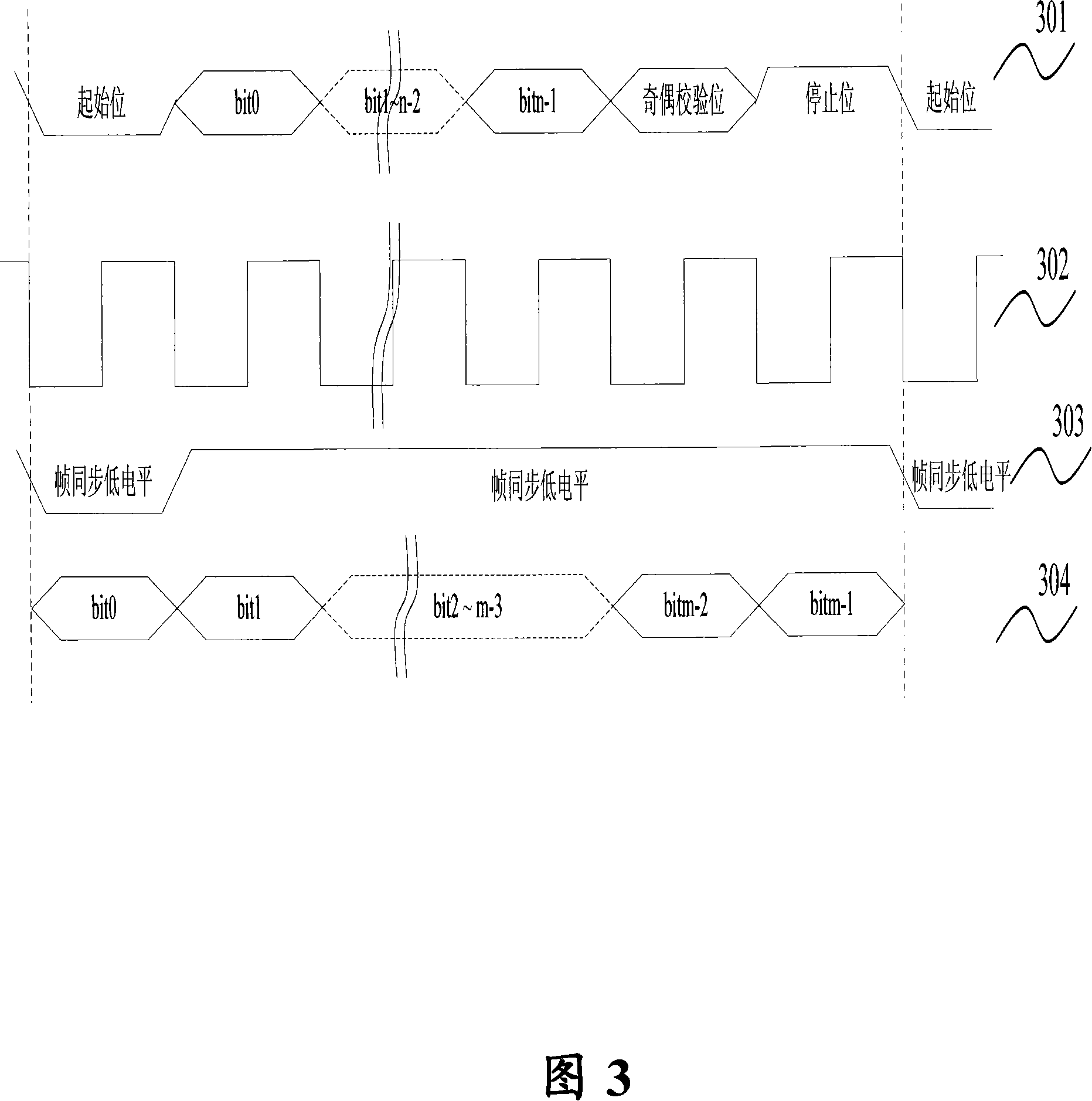

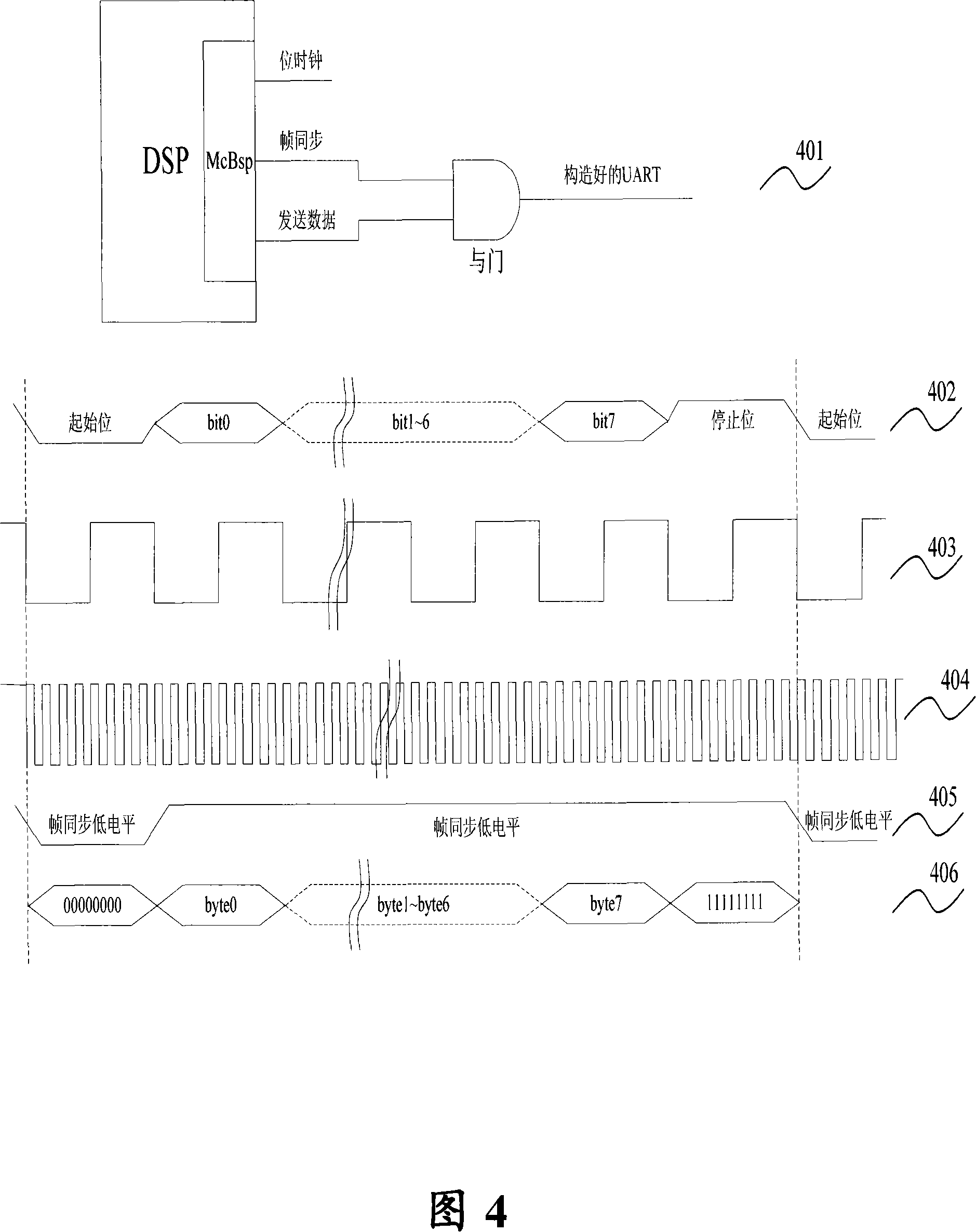

Method for using information of synchronous serial interface output and asynchronous serial port debugging on DSP

InactiveCN101131658AOvercome the disadvantages of no debug information output channelReliable debuggingSoftware testing/debuggingRedundant data error correctionSynchronous Serial InterfaceBaud

This invention provides a kind of method of using the timing serial port to output the asynchronous serial port debug information on the DSP and constructs the asynchronous serial port data frame by using the structure corresponding relationship of the synchronous serial port and the asynchronous serial port data frame and the corresponding relationship of bit clock of the synchronous serial port and the baud rate of the asynchronous serial port; at the same time synchrony the frame of synchronous serial port on the DSP and logical operate the base pin which is used to deliver the data and extend the output values making it met the time sequence of the asynchronous serial port and output the asynchronous serial port debug information. Comparing with the present technology it overcomes the defect that there is no debug information output channel during the reality process for the DSP; it has the well reality and it can capture the abnormal station for the DSP and offer the trace of the location problem; the UART baud rate can be modified and it is convenience to the user.

Owner:ZTE CORP

Remote monitoring data transmission method and implementing device therefor

InactiveCN1543130ALow maintenanceSimplify the amount of writingTransmission monitoringData switching networksAsynchronous serial interfaceTransformation unit

This invention relates to a transmission method and its application device for remote monitor data for solving the problem of unstable monitor system resulted from software reform on the basis of using transmission channel bandwidth as much as possible. This invention applies the following technology: an asynchronous serial interface outputs the data to a serial / parallel switch unit to finish the switch then the data is put in a latch unit which outputs it to a parallel / serial switch unit for switching then to be output to a synchronous serial multiplex unit multiplexed with the data to the unit from the synchronous serial interface to occupy a time slot together which is output to a time slot exchange unit exchanging it to a definite time slot to be merged with PCM stream from the slave E1interface and output from the master E1 interface.

Owner:ZTE CORP

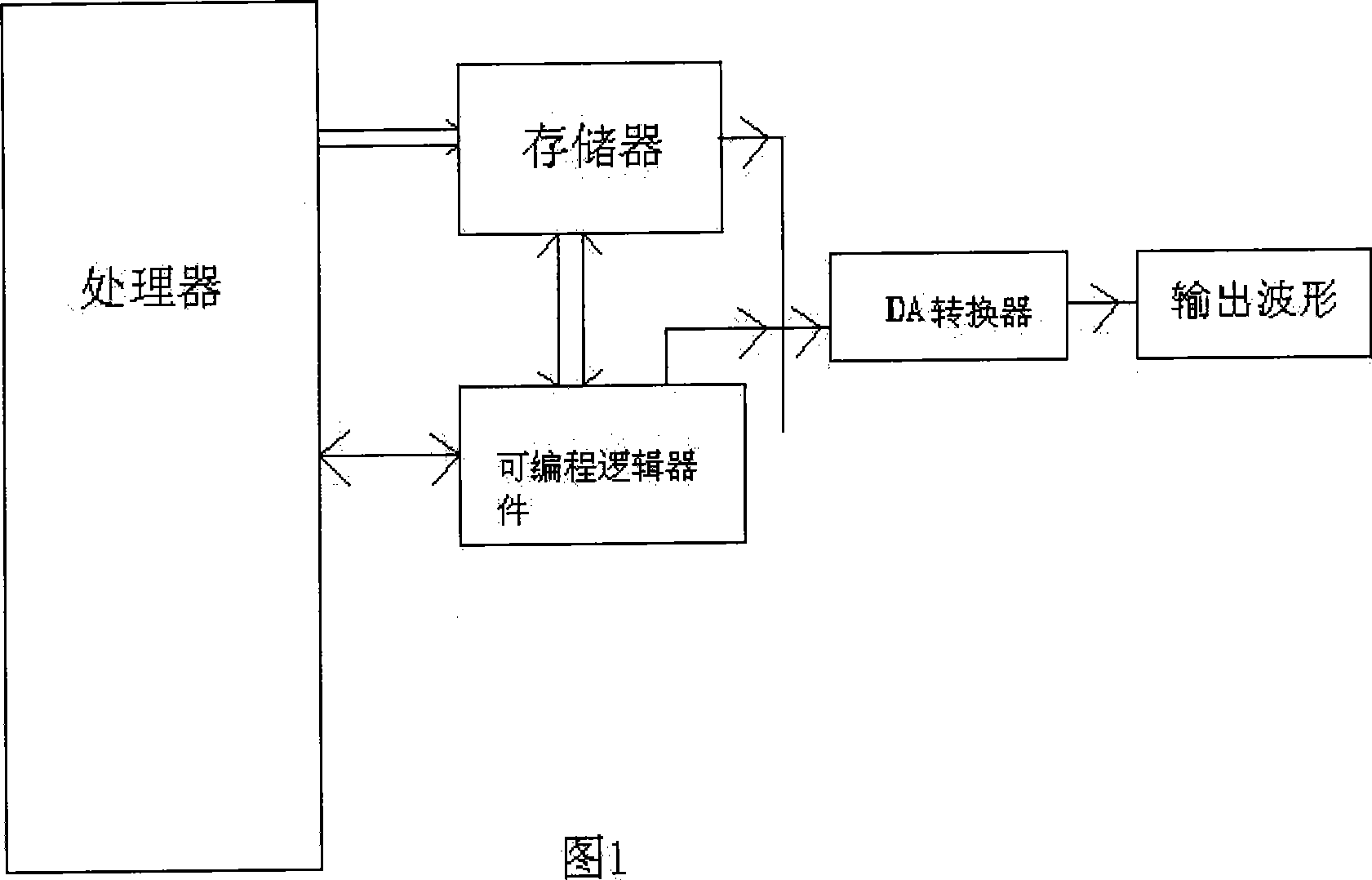

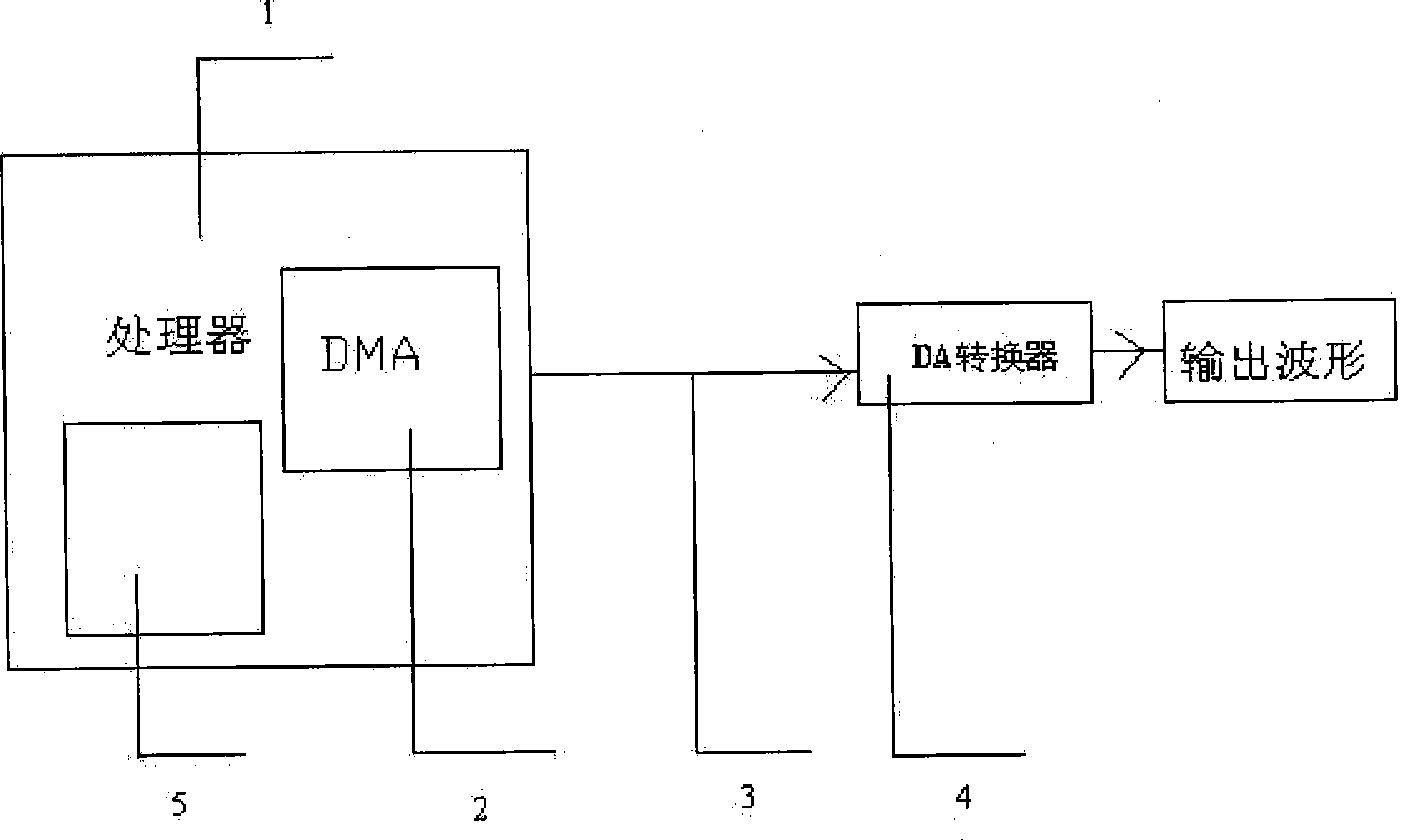

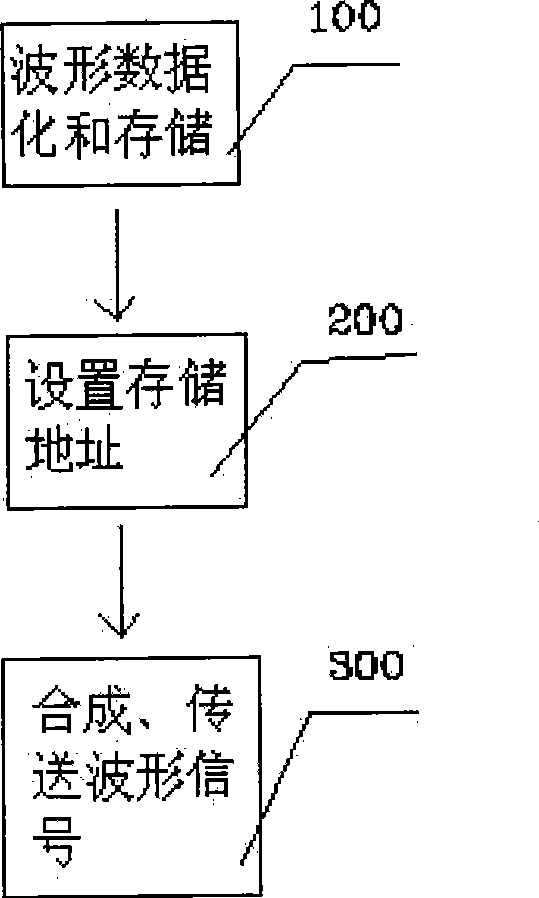

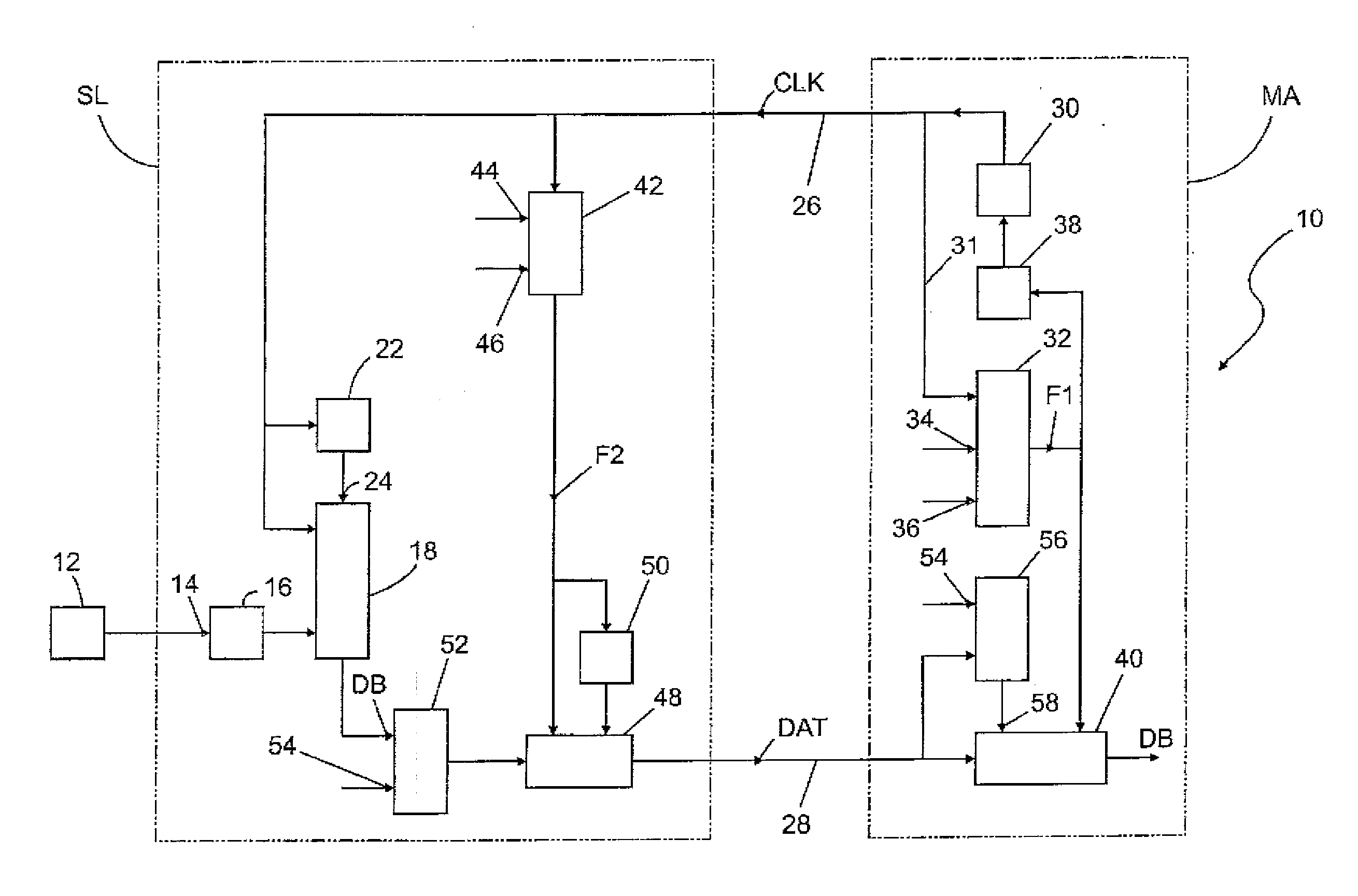

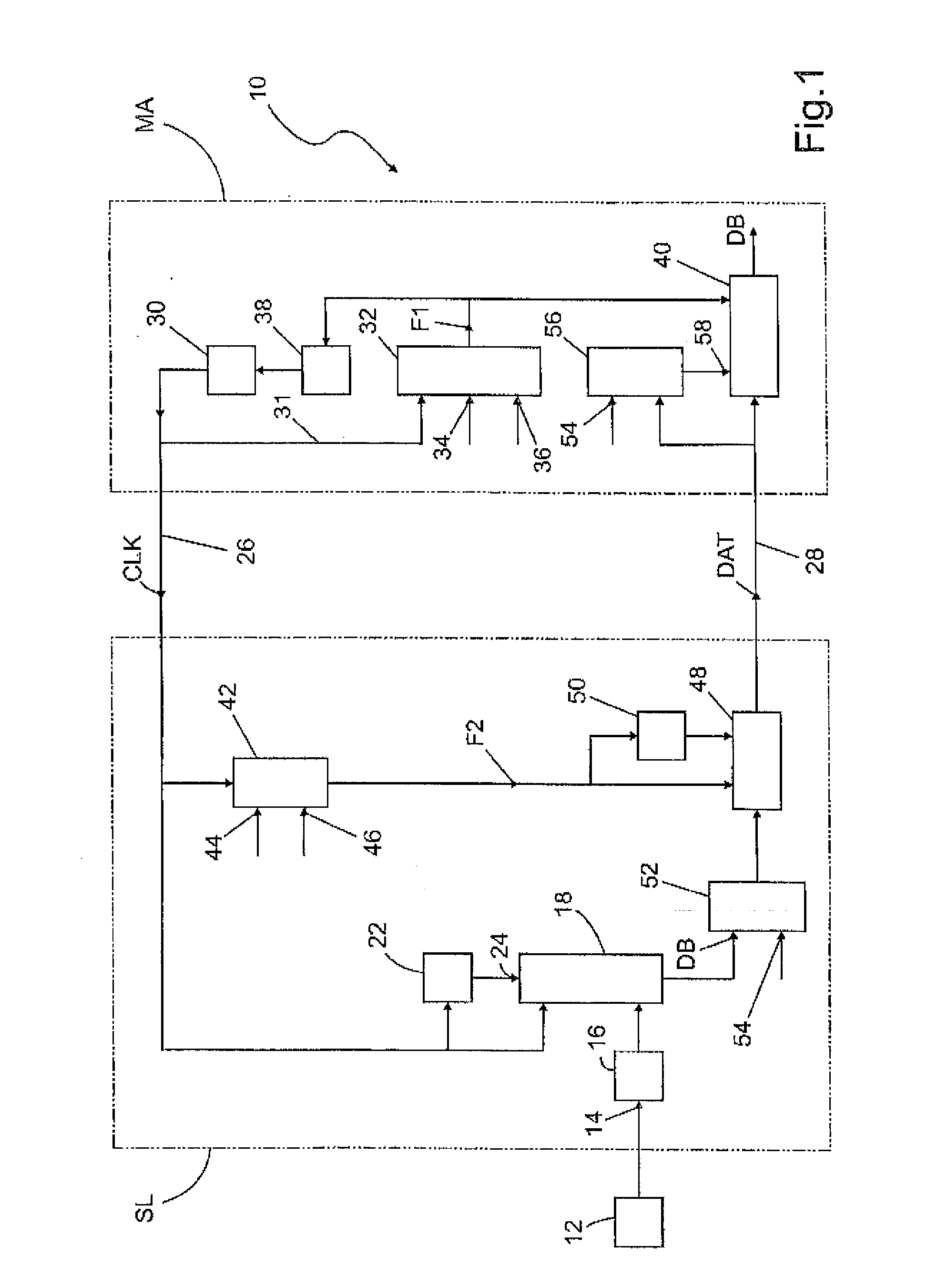

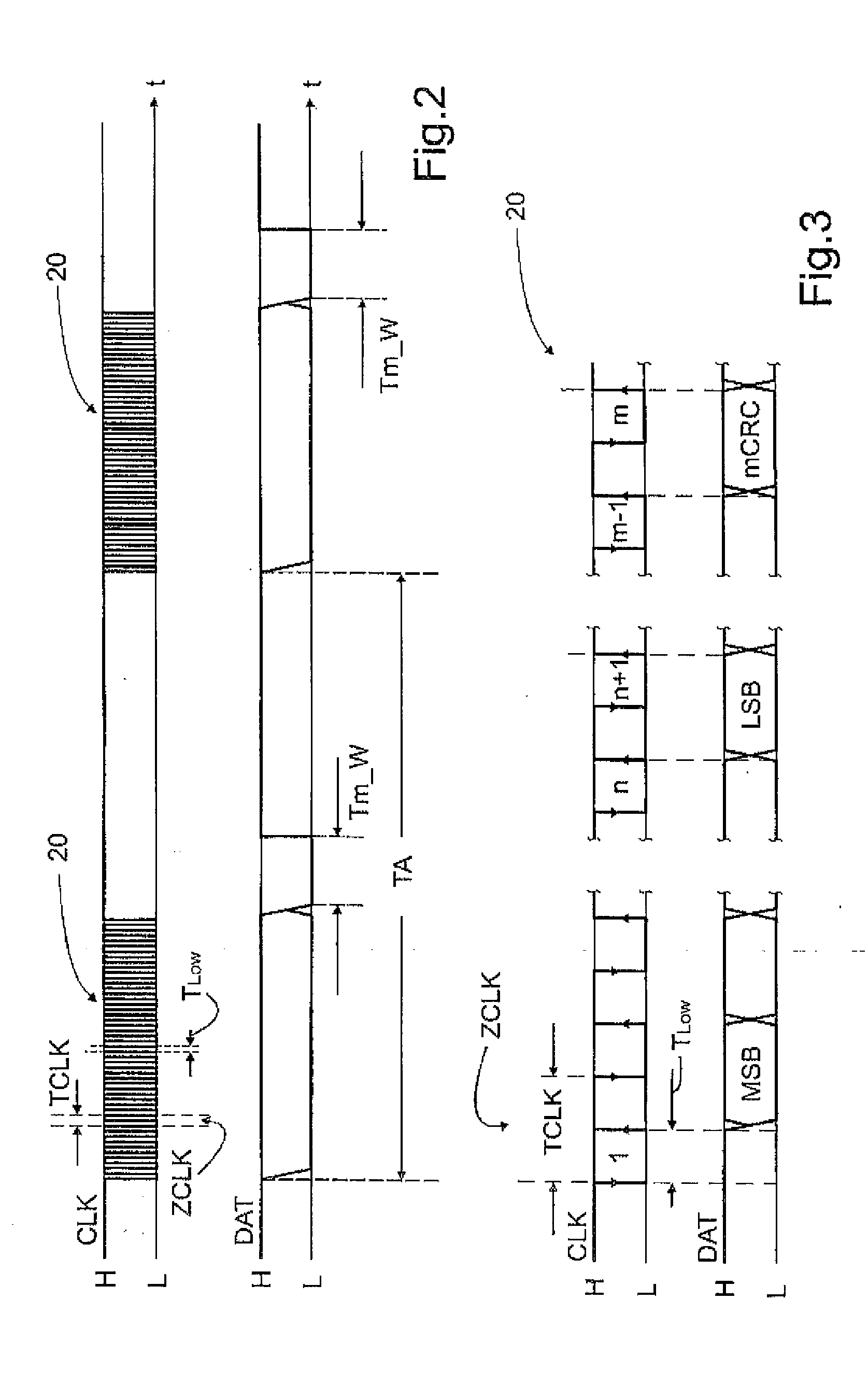

Method and device for synthesizing and transmitting waveform signal

InactiveCN101447764ALow costEasy to modifyOscillations generatorsElectric digital data processingInternal memoryDigital analog converter

The invention relates to a method and a device for synthesizing and transmitting a waveform signal. The device comprises a processor and a DA converter, wherein the processor is provided with an internal storage and a high-speed synchronous serial interface; a sinusoidal waveform signal processed by the processor is converted into waveform data and used for storing the waveform data in the internal storage of the processor; an address pointer of an access module of a direct storage points to a storage address for the waveform data; the access module of the direct storage directly controls the stored waveform data and transmits the data to the data analog converter through the synchronous serial interface; and the data analog converter synthesizes and coverts the received waveform data into an analog signal, and then outputs the signal. The invention further comprises a method for using the device. The invention has the characteristics of simple structure, saved cost and easy control.

Owner:深圳市联创知识产权服务中心

Measured value transmitting device

ActiveUS20140173391A1Improve securityAvoid excessive changesElectric signal transmission systemsSynchronisation information channelsSerial transferSynchronous Serial Interface

The invention relates to measured value transmitting devices for serially transmitting data in accordance with the SSI method, Synchronous Serial Interface. At least one slave is provided which provides the data bits of a measured value detected by at least one sensor for the purpose of a serial bit-by-bit transmission to a master. The master requests a measured value from the slave by means of a clock burst that has multiple clock cycles, the number of which matches the number of the data bits to be transmitted. A first measured value transmitting device according to the invention is characterized in that the clock cycles of the clock burst have a specified duty cycle which corresponds to the ratio of the pulse duration to the period duration of one clock cycle, and the master contains a comparator. The master reads the clock bursts outputted on the at least one clock line and checks the duty cycle in the comparator to determine whether an upper threshold and / or a lower threshold has been exceeded. A second measured value transmitting device according to the invention is characterized in that a corresponding check of the duty cycle is carried out in the slave.

Owner:BALLUFF

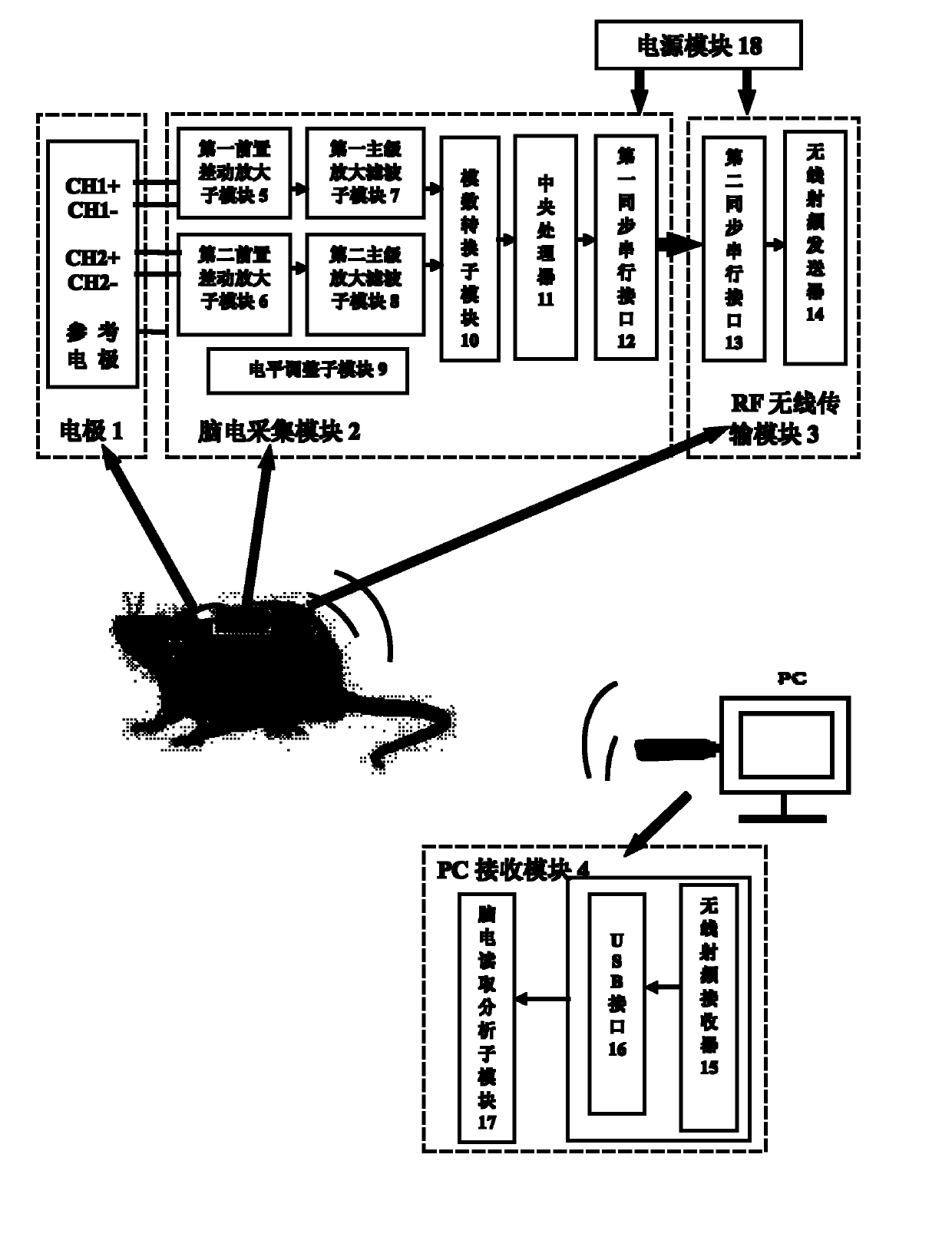

Wireless mobile real-time acquisition device for electroencephalograph of small animals

InactiveCN101766485ASimple designReduce volumeTransmission systemsWireless network protocolsSmall animalWireless transmission

The invention relates to a wireless mobile real-time acquisition device for electroencephalograph of small animals, and belongs to the technical field of wireless transmission. The device comprises an electrode, an electroencephalograph acquisition module, an RF wireless transmission module, a power supply module and a PC receiving module, wherein the electrode comprises two dual-lead channels and a reference electrode; and the RF wireless transmission module comprises a second synchronous serial interface and a wireless radio frequency transmitter. The wireless mobile real-time acquisition device has the advantages of small volume, light weight, low power consumption, convenient and accurate actual acquisition of electroencephalograph signals of the small animals, capability of performing real-time electroencephalograph acquisition on the small animals in the active state, suitability for long-term and uninterrupted electroencephalograph monitoring, low cost and high applicability.

Owner:上海交通大学中原研究院

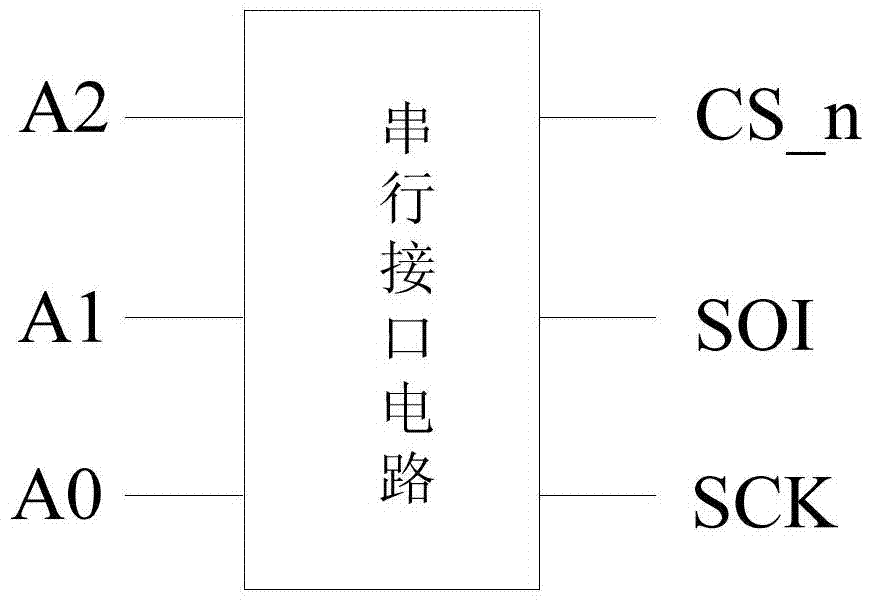

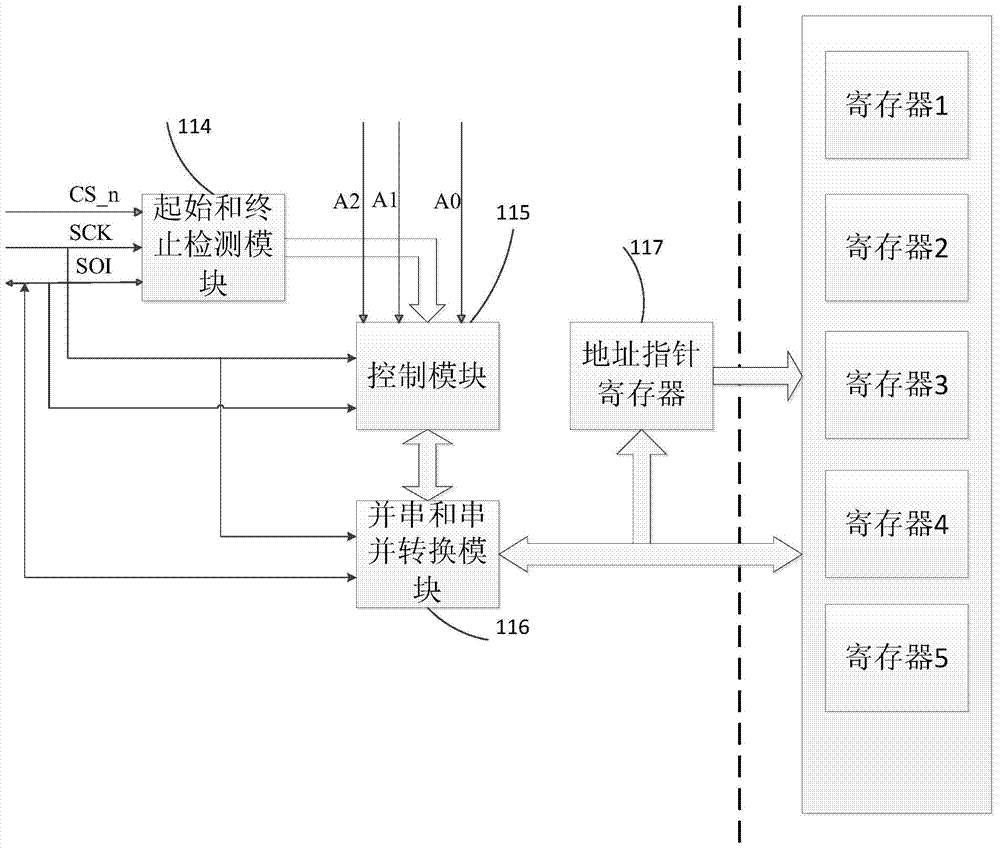

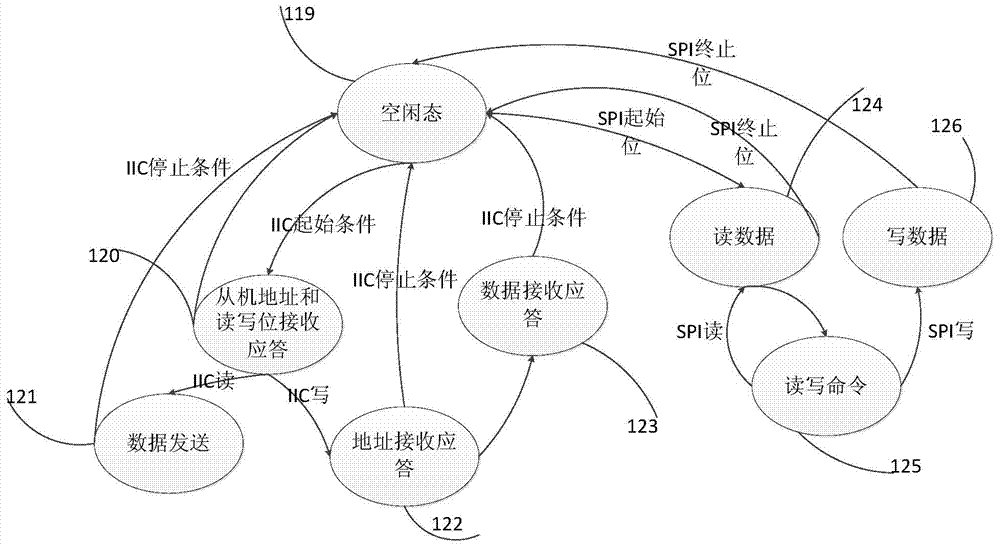

Universal auxiliary machine synchronous serial interface circuit

ActiveCN103488600ASave internal logic resourcesReduce the number of interfacesElectric digital data processingProcessor registerData transmission

The invention discloses a universal auxiliary computer synchronous serial interface circuit comprising a starting and ending detection module, a control module, a parallel-serial / serial-parallel conversion module and an address pointer register. The starting and ending detection module is used for detecting and outputting a significance bit of an SPI bus protocol, and a starting condition and an ending condition of an IIC bus protocol. The control module is used for determining a bus data transmission mode of the serial interface circuit according to an output signal of the starting and ending detection module, and controlling the parallel-serial / serial-parallel conversion module. The parallel-serial / serial-parallel conversion module is controlled by the control module, and is used for outputting data of multiple register data inside an auxiliary computer in a serial mode, and converting external serial data into the data of the registers inside the auxiliary computer. The address pointer register is used for carrying out addressing on the resisters inside the auxiliary computer. The universal auxiliary computer synchronous serial interface circuit achieves compatibility of the bus data transmission of the IIC protocol and the SPI protocol, and can meet the application requirements of different occasions.

Owner:中科芯未来微电子科技成都有限公司

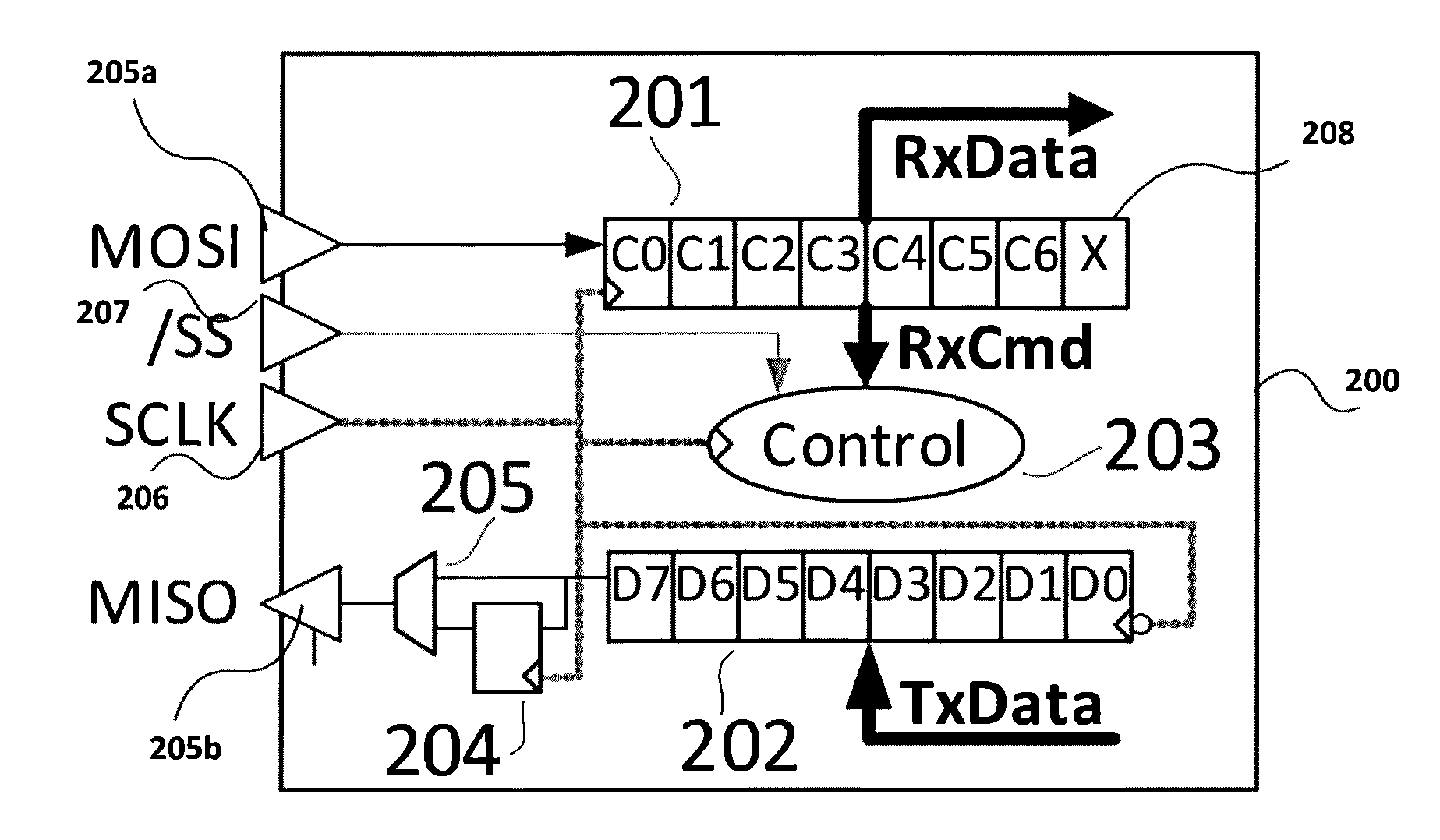

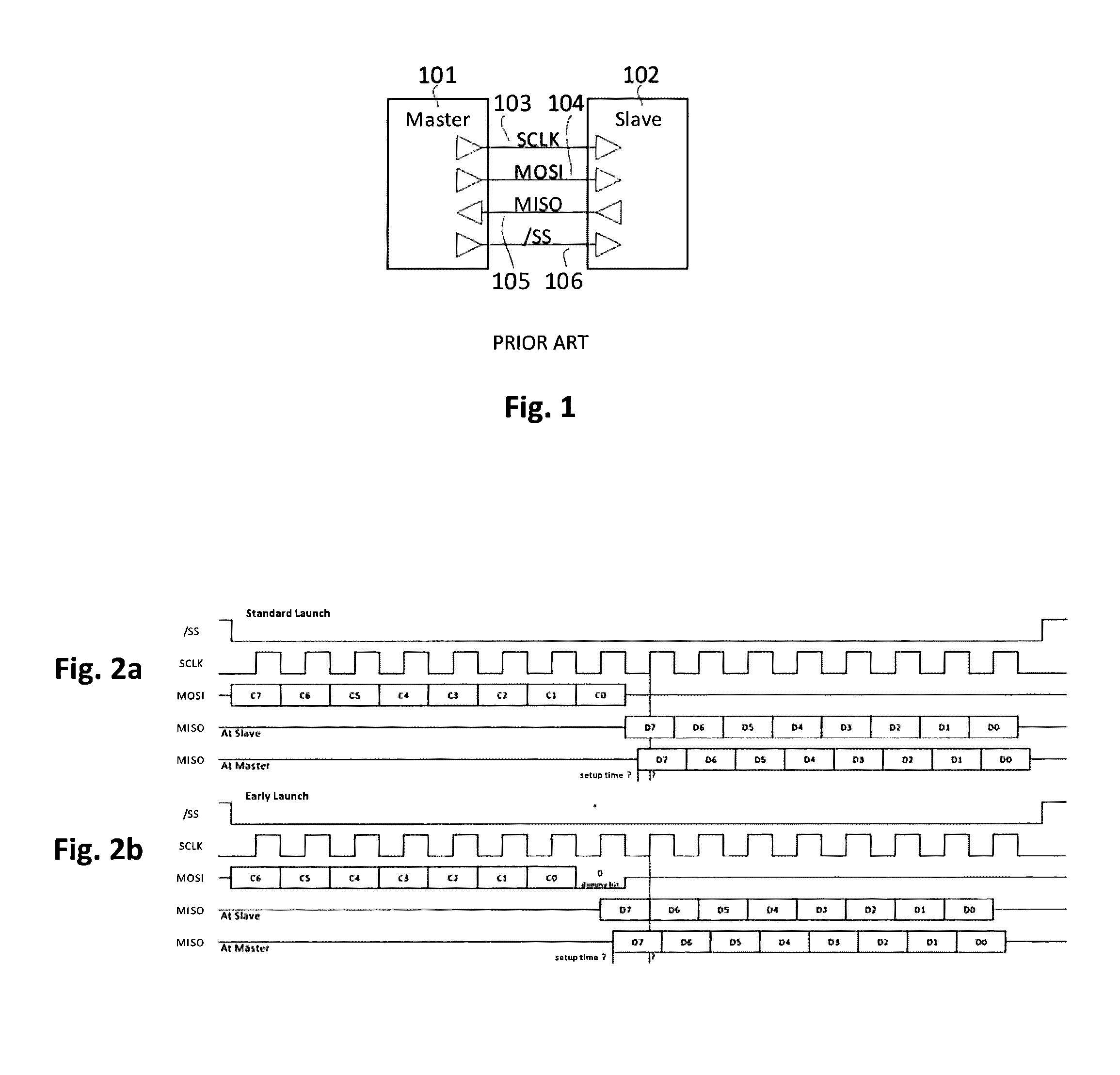

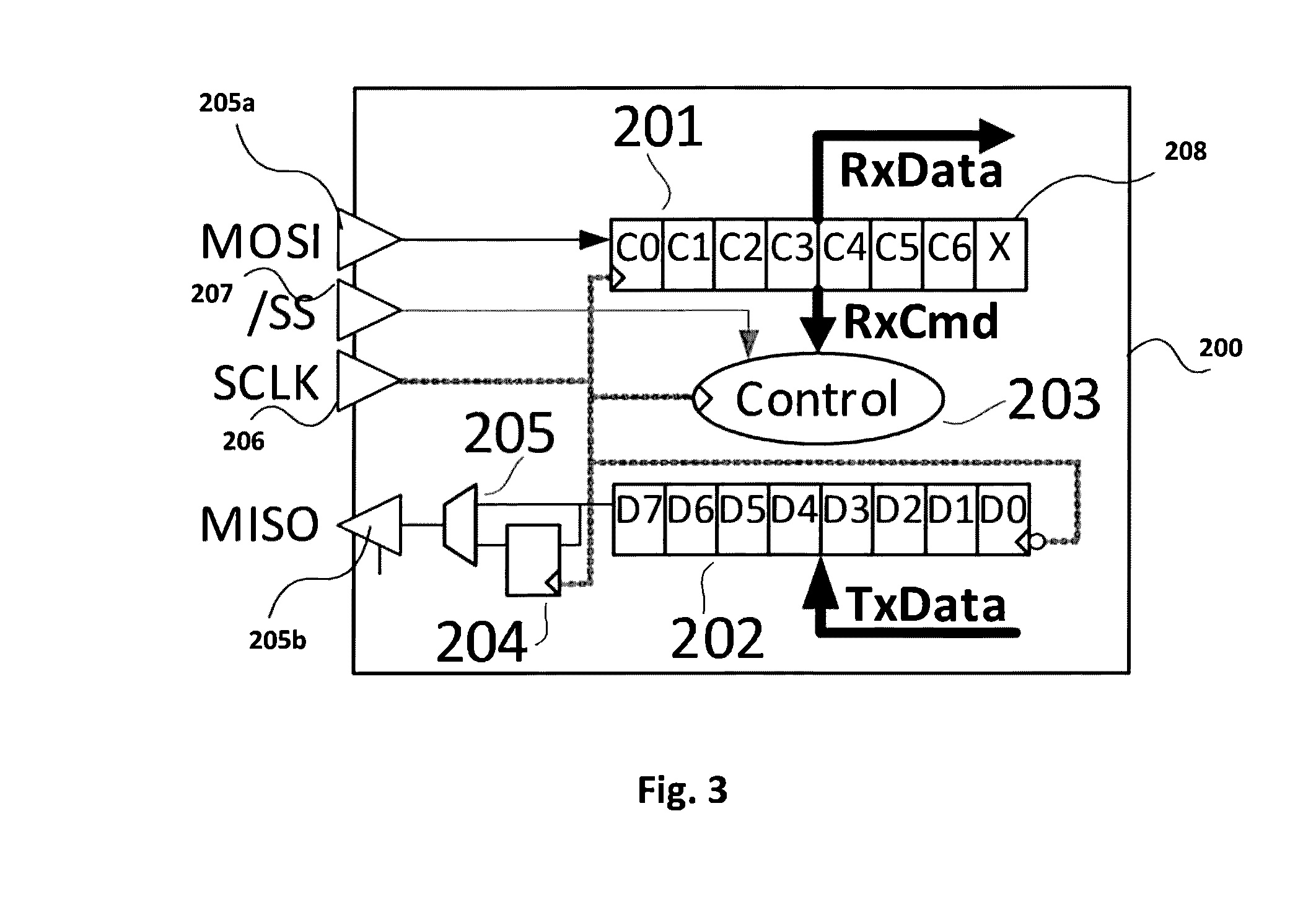

Method for improving the performance of synchronous serial interfaces

ActiveUS20160299861A1High bandwidthIncrease clock speedElectric digital data processingReceiptSynchronous Serial Interface

A slave device for exchanging data with a master device over a serial interface sends data to the master device upon receipt of a command from the master device. A controller responsive to a command byte in a receive register commences transmission of data in the transmit register under the control of a clock signal prior to reception of a complete command.

Owner:MICROSEMI SEMICON

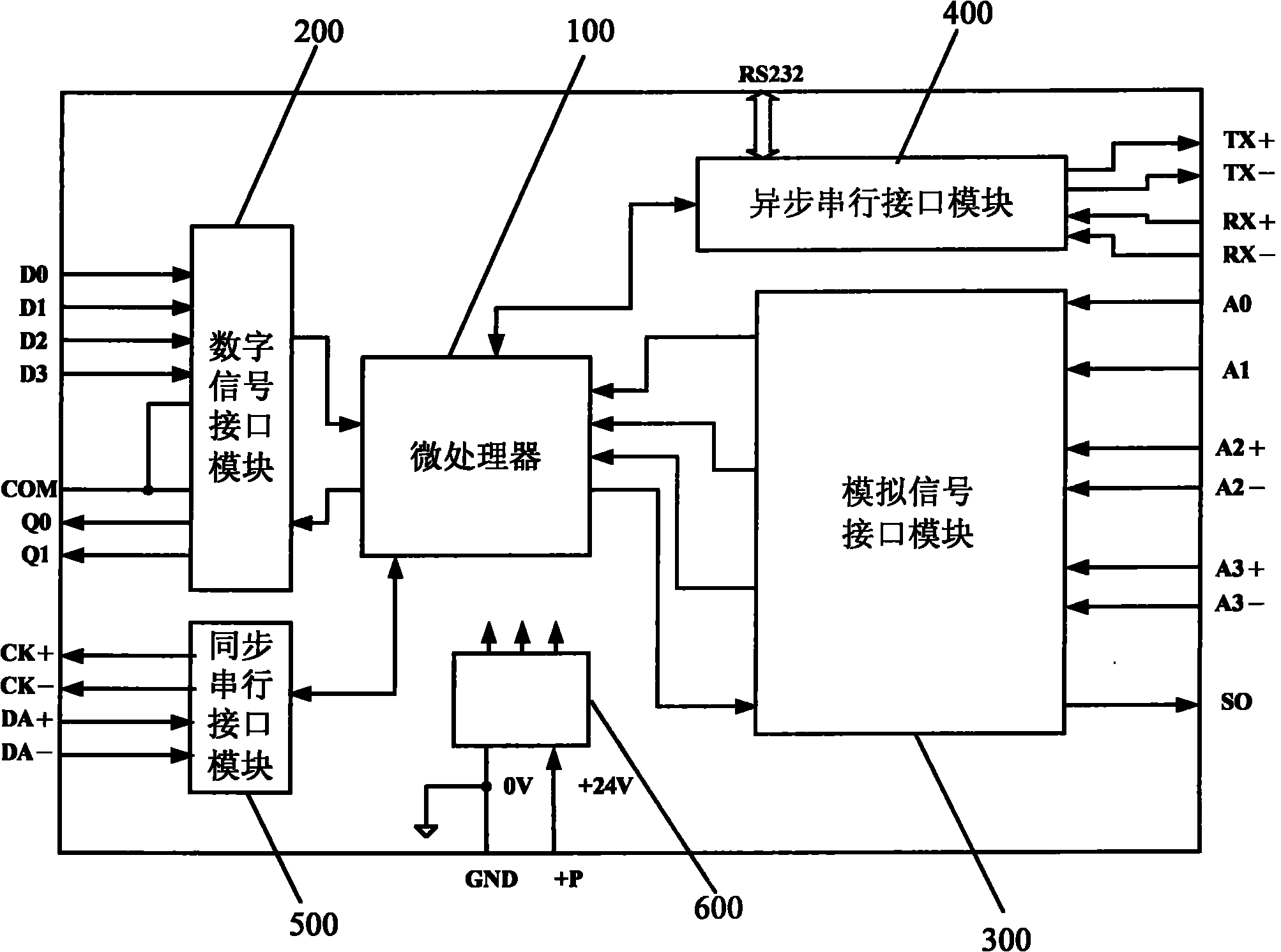

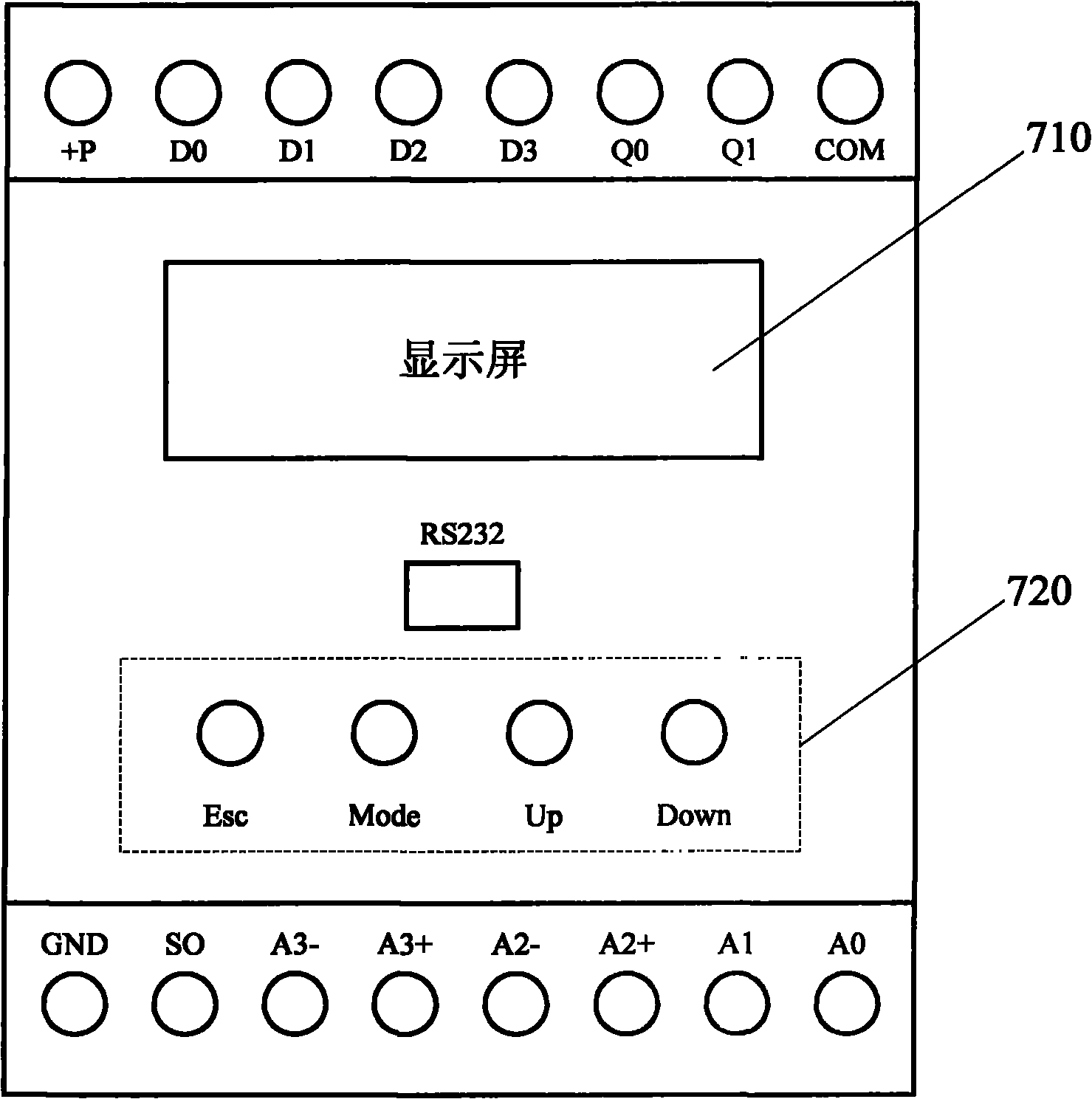

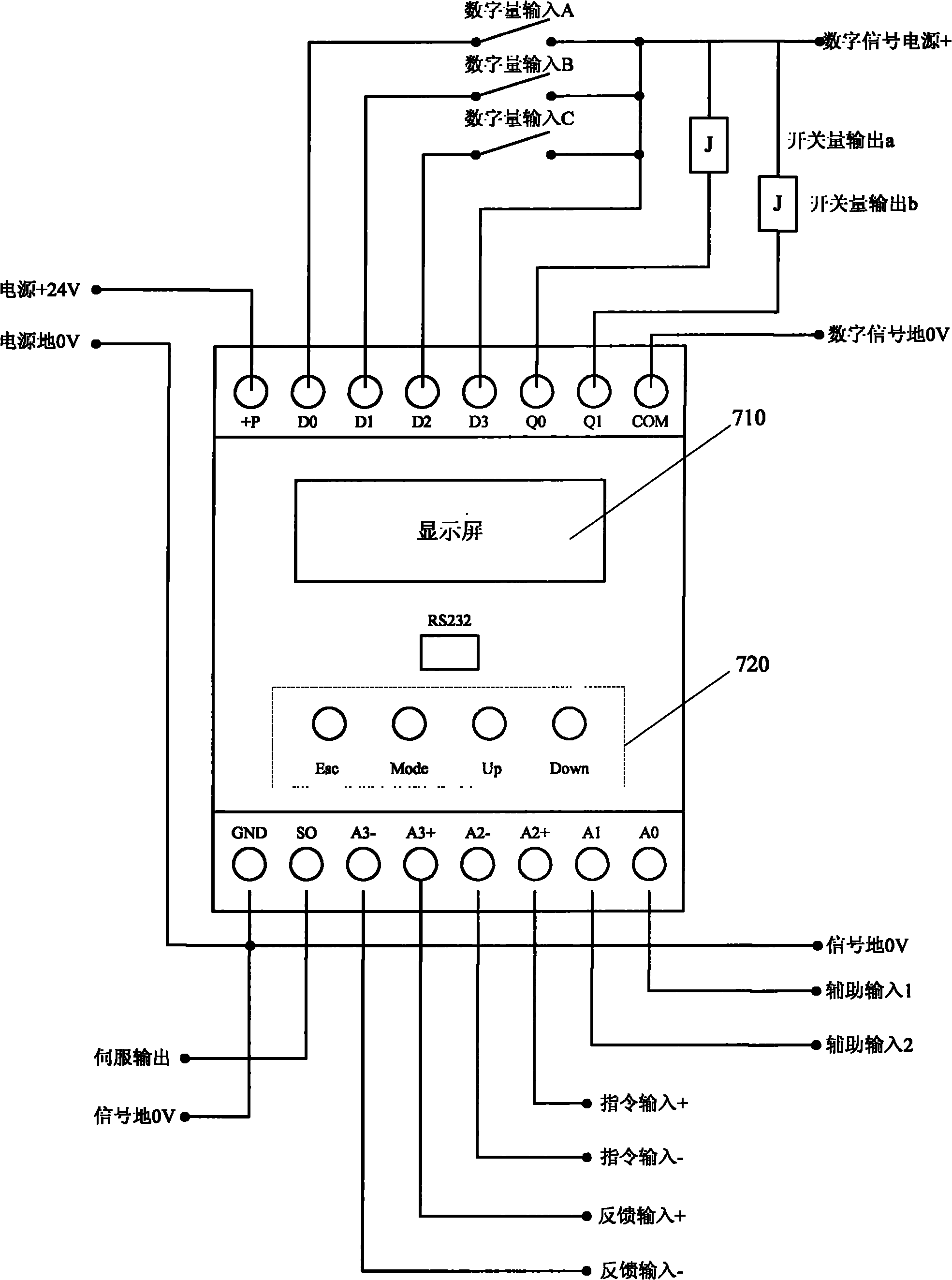

Digital servo controller and corresponding servo control system

InactiveCN102213958ASimple structureFlexible control modeTotal factory controlProgramme total factory controlSynchronous Serial InterfaceControl system

The invention discloses a digital servo controller and a corresponding servo control system. The digital servo controller comprises a power transformation circuit which is coupled to a direct-current power supply and is used for supplying power to the digital servo controller, a micro processor, and a digital signal interface module, an analog signal interface module, an asynchronous serial interface module and a synchronous serial interface module which are in signal connection with the micro processor, wherein the micro processor controls a control state of the digital servo controller according to an input signal of the digital signal interface module, acquires an instruction signal through the asynchronous serial interface module or the analog signal interface module, acquires a feedback signal through the analog signal interface module or the synchronous serial interface module, and produces a driving signal by proportion integration differential operation according to the instruction signal and the feedback signal. The digital servo controller has high reliability under a severe industrial environment; and the real-time running speed meets the requirement of high-speed and high-precision motion equipment completely.

Owner:SHANGHAI TIANXUN INTELLIGENT TECH

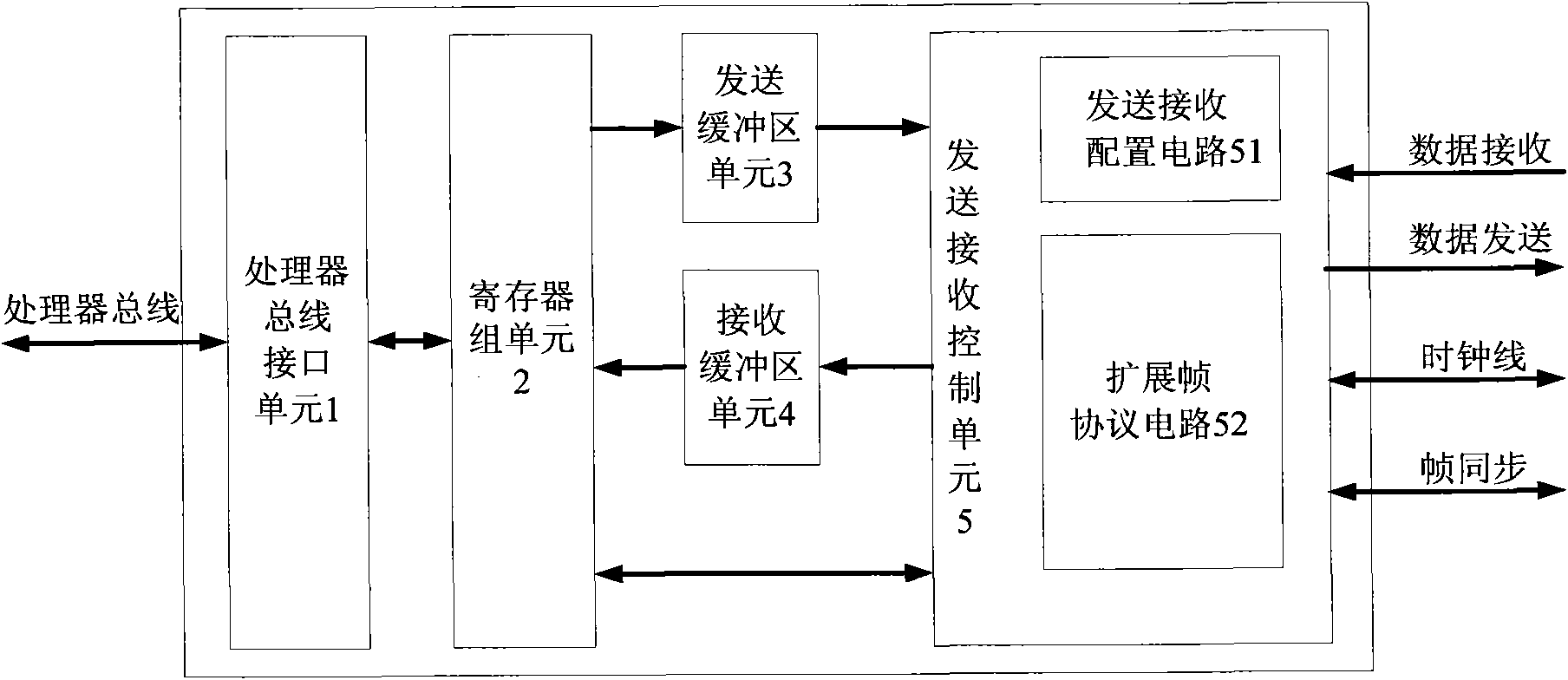

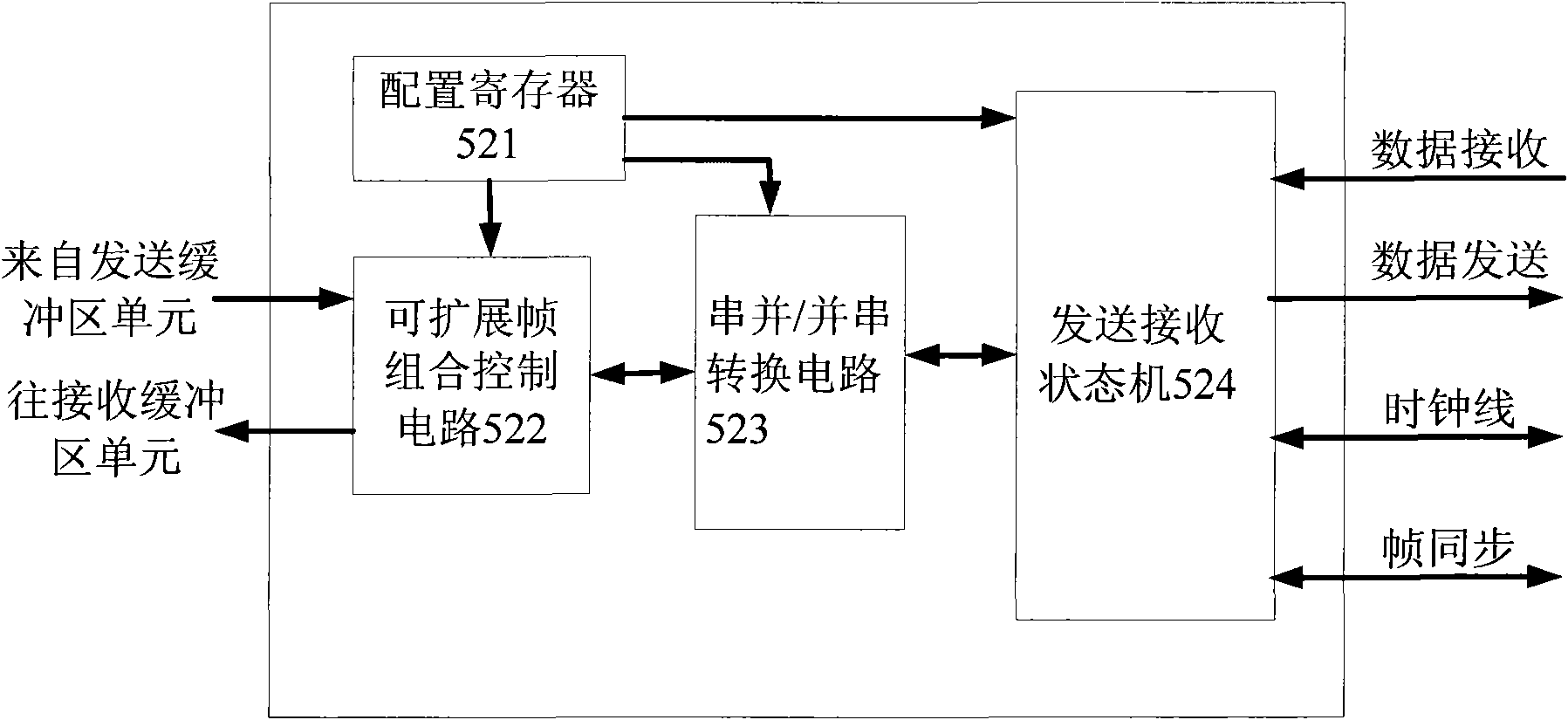

Synchronous serial interface device with expandable frame width

ActiveCN101561791ALow costQuality improvementElectric digital data processingProcessor registerBus interface

The invention discloses a synchronous serial interface device with expandable frame width, which comprises a register group unit, a processor bus interface unit , a transmitting and receiving control unit, a transmitting buffer unit, a receiving buffer unit and a receiving buffer unit, wherein the register group unit is connected with the processor bus interface unit; the processor bus interface unit is connected with a peripheral processor bus; the transmitting buffer unit is respectively connected with the register group unit and the transmitting and receiving control unit; the receiving buffer unit is respectively connected with the register group unit and the transmitting and receiving control unit; the transmitting and receiving control unit comprises a transmitting and receiving configuration circuit and an extended frame protocol circuit; the transmitting and receiving configuration circuit is used for configuring the extended frame protocol circuit; and the extended frame protocol circuit self-defines the format of an extended frame and is used for realizing the largest frame width to n bits, and n is a natural number larger than 16. The invention can provide the adjustable characteristic of larger width range of frame format to enable a SOC chip to be connected with more peripheral chips, thereby realizing a whole product with lower cost and better quality.

Owner:ZTE CORP

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com