Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

30results about How to "Reduce latch-up" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

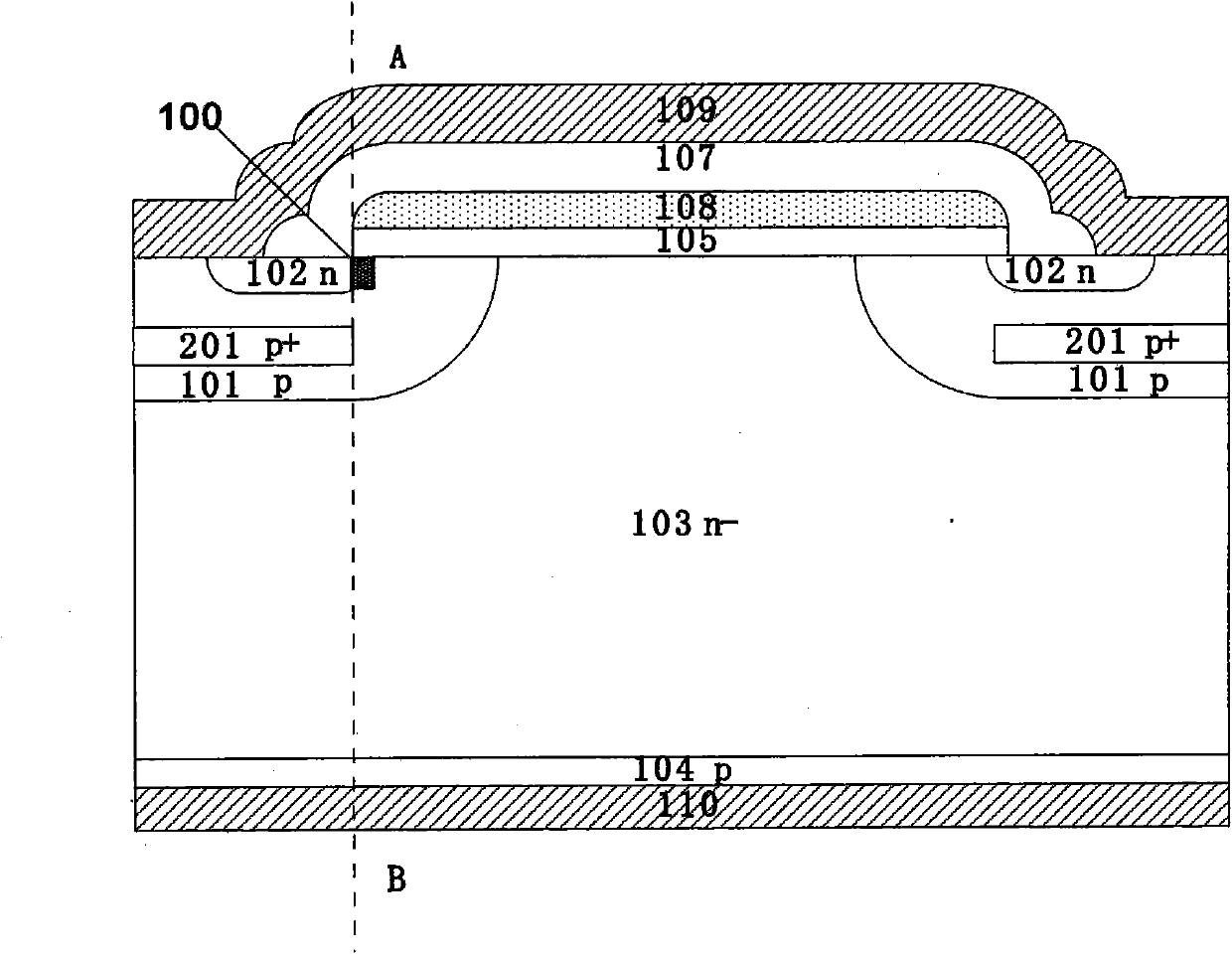

Triple-well CMOS devices with increased latch-up immunity and methods of fabricating same

Owner:INT BUSINESS MASCH CORP

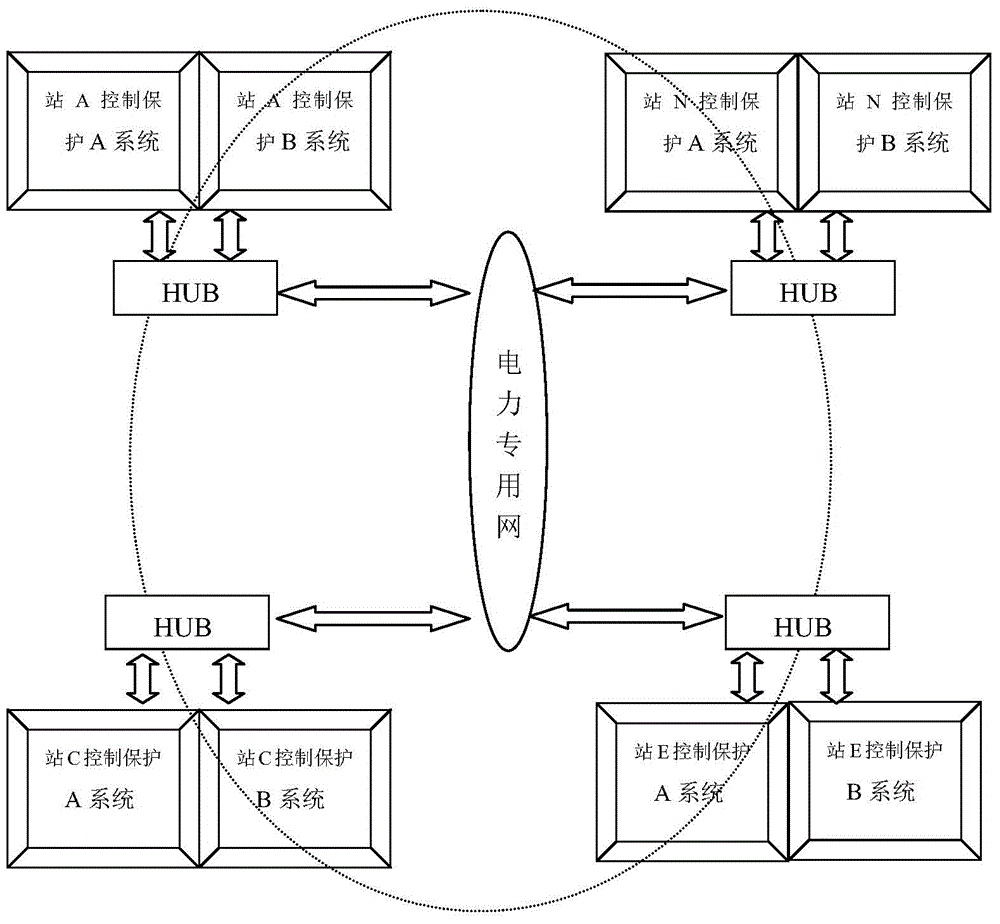

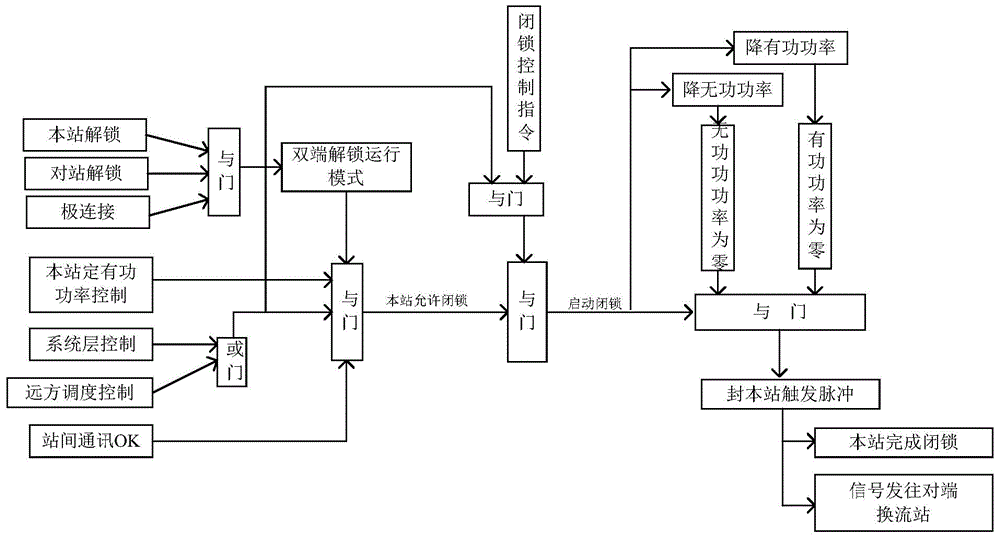

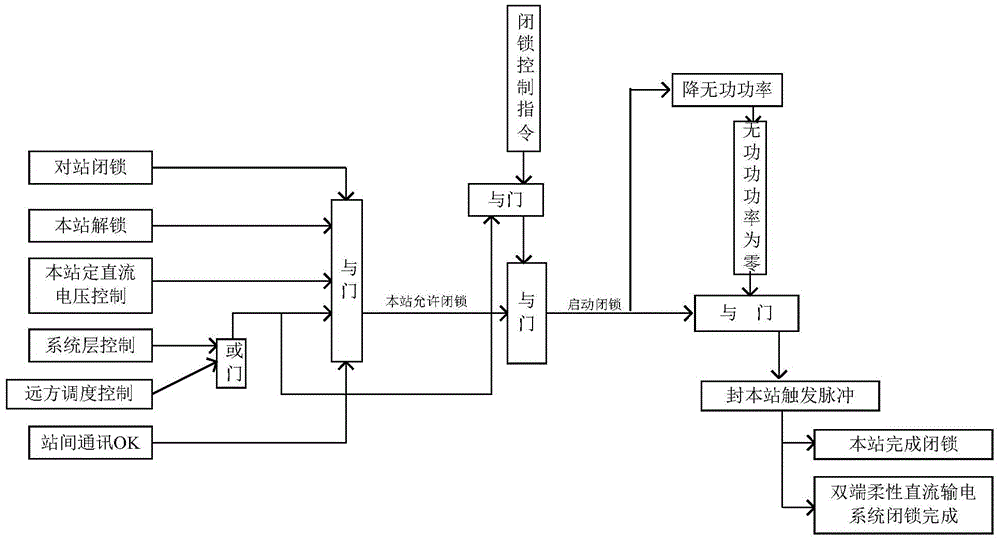

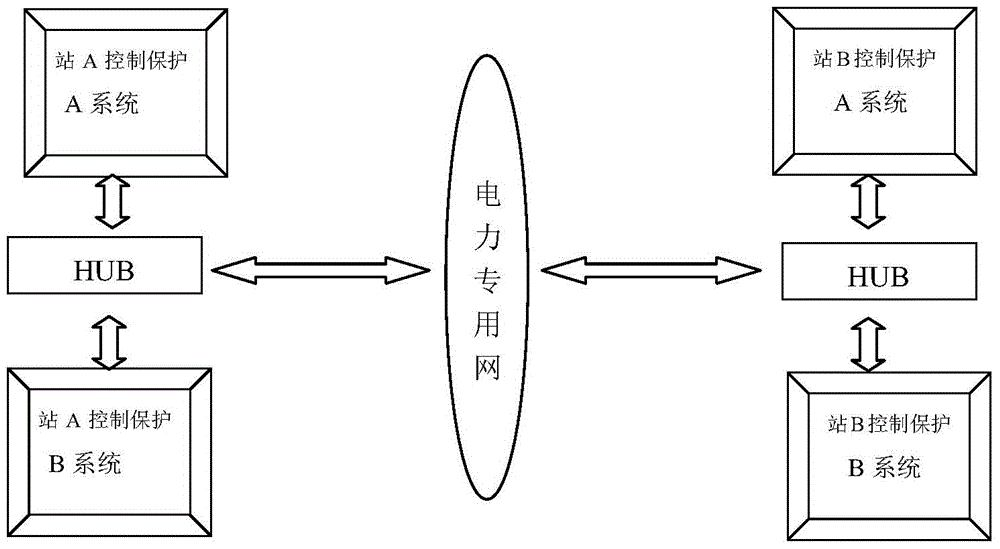

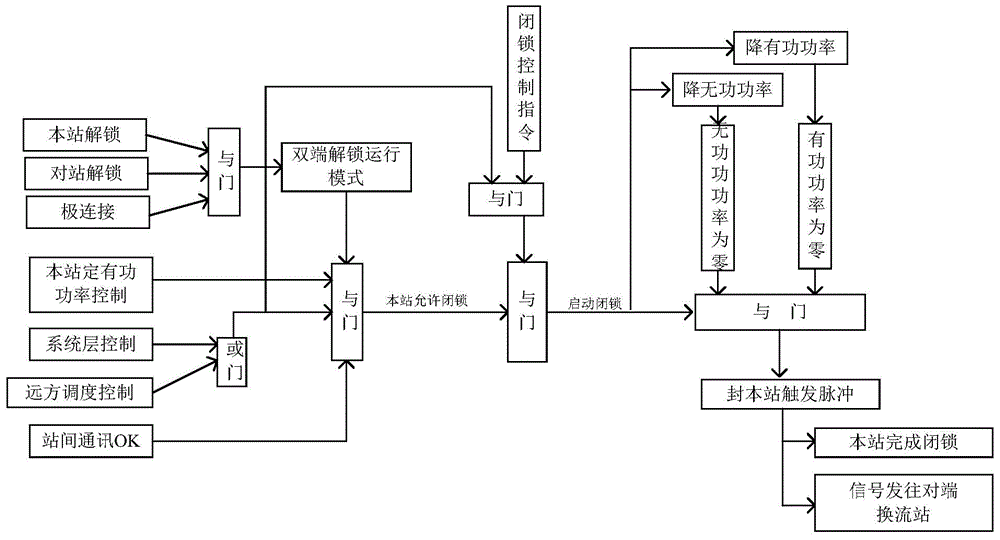

Automatic locking method for battery replacement station of flexible direct-current transmission system

ActiveCN104092232AShorten the lock-up processAvoid shockElectric power transfer ac networkTransmission systemControl pattern

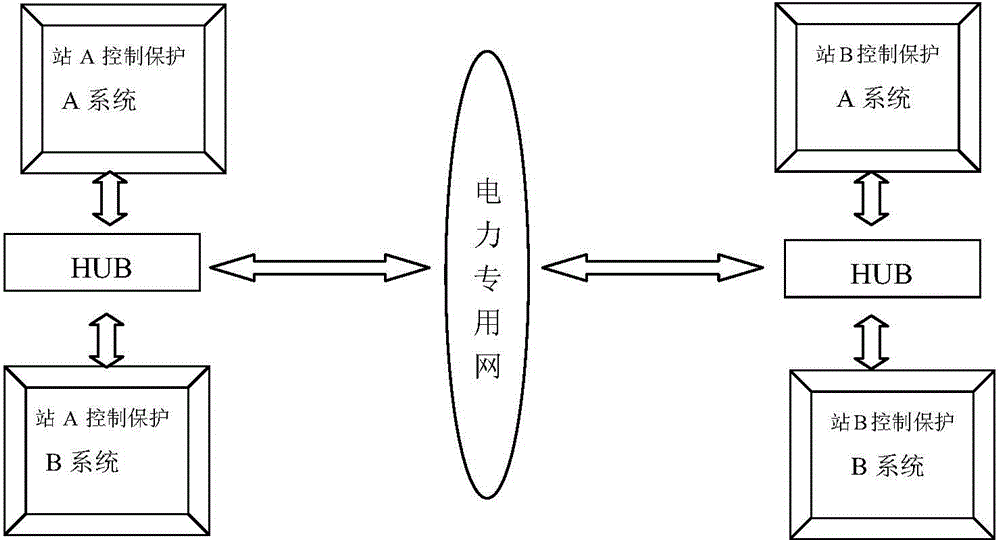

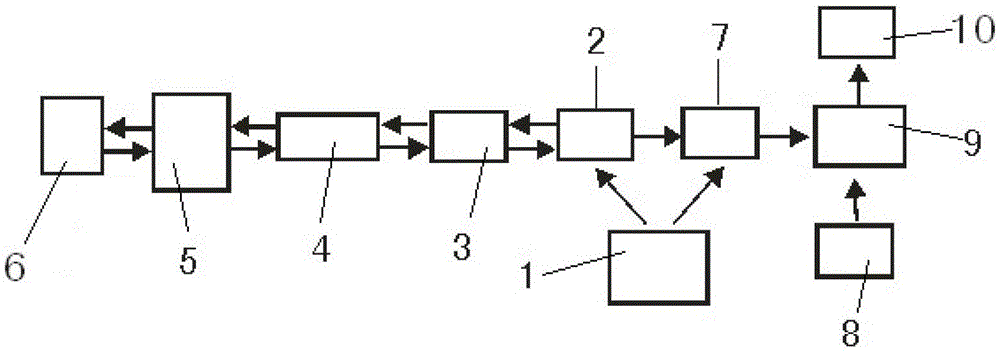

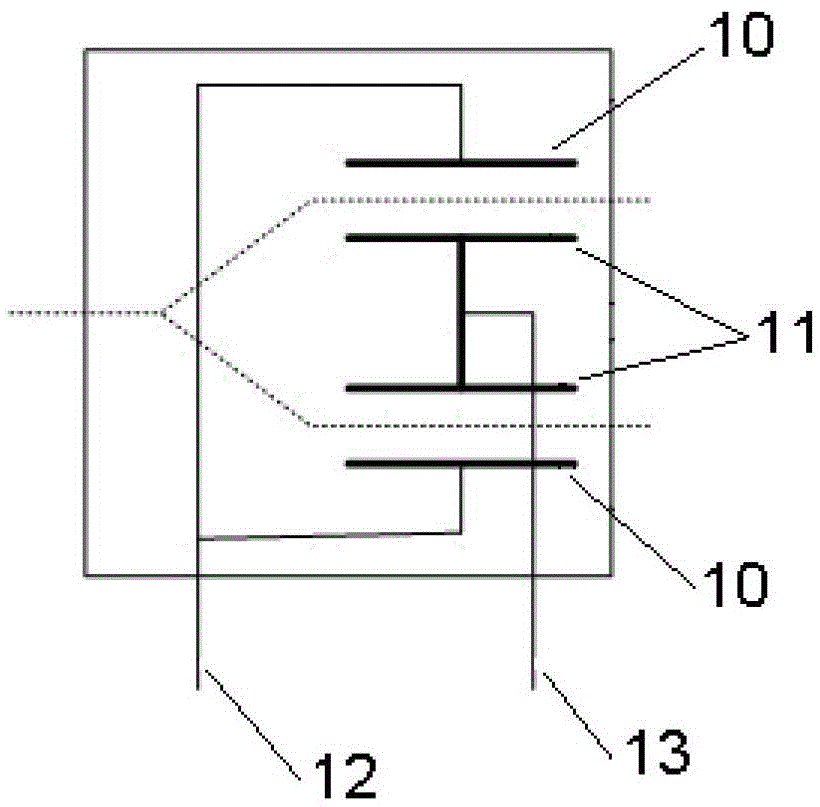

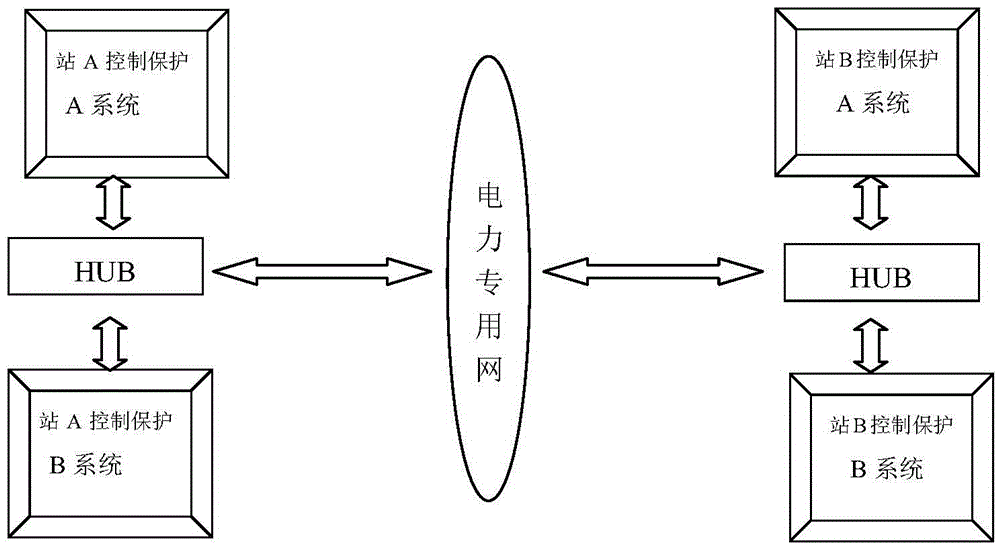

The invention discloses an automatic locking method for a battery replacement station of a flexible direct-current transmission system. The automatic locking method includes the steps of firstly, judging the control mode of the station, the running state of the station and the running states of other stations; secondly, judging the current running state when the flexible direct-current system runs if the station is judged to have the direct-current voltage control mode, the station is in the unlocked state and meanwhile other stations are all in the locked state; thirdly, starting the locking process of the station according to a received system locking control instruction if all the conditions are met, and conducting reactive power reduction control; fourthly, sending a window signal to complete the locking process if the reactive power of the convertor station is zero at present. By means of the automatic locking method, a control and protection system is automatically locked, the locking process of the flexible direct-current transmission system is shortened, impact which is caused by control and protection system incorrect operation generated due to man-made incorrect operation and the like to an alternating-current system is effectively avoided, time consumption of the whole locking process of the flexible direct-current system is lowered, and the complexity in the locking process is lowered.

Owner:STATE GRID CORP OF CHINA +2

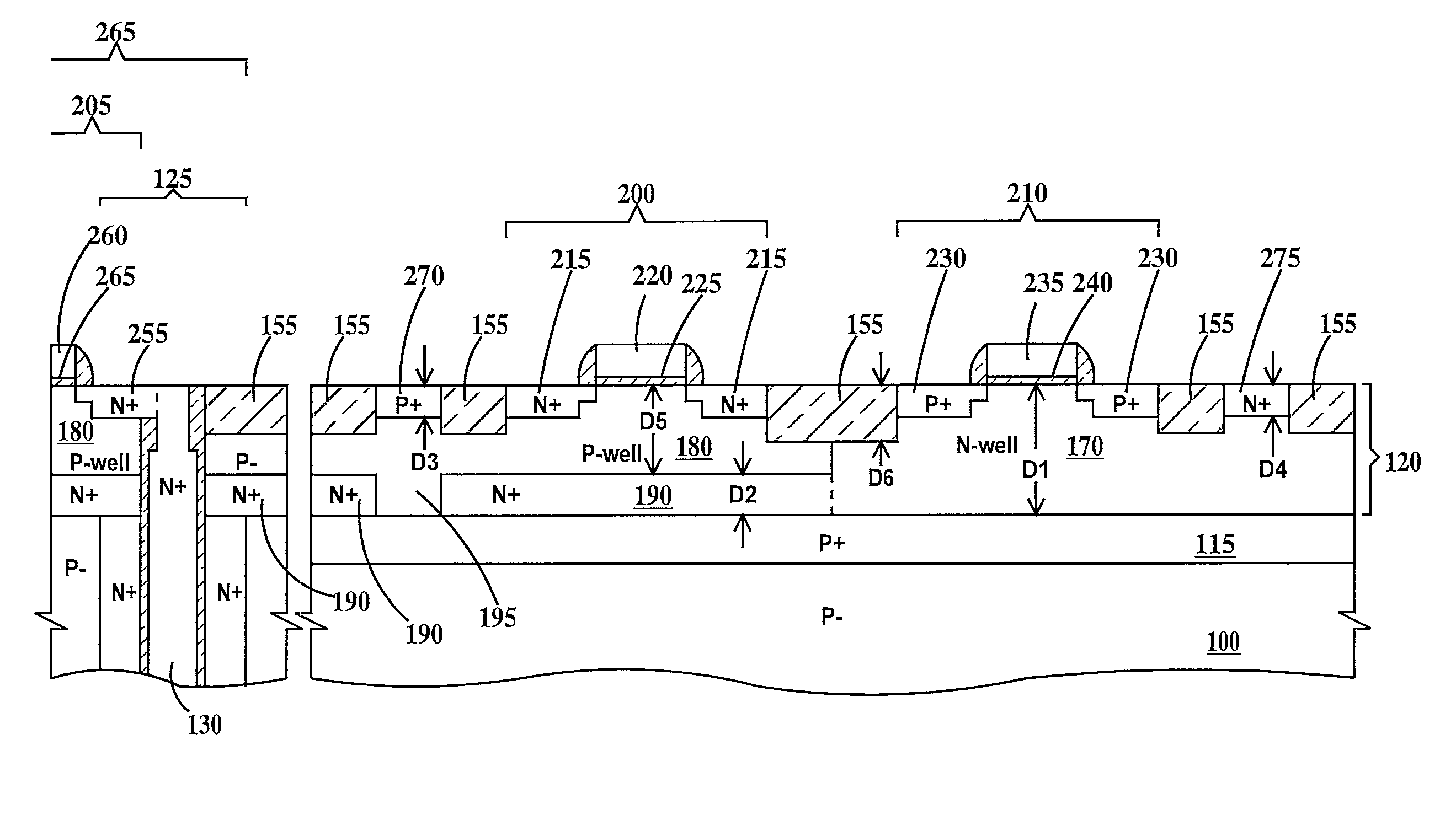

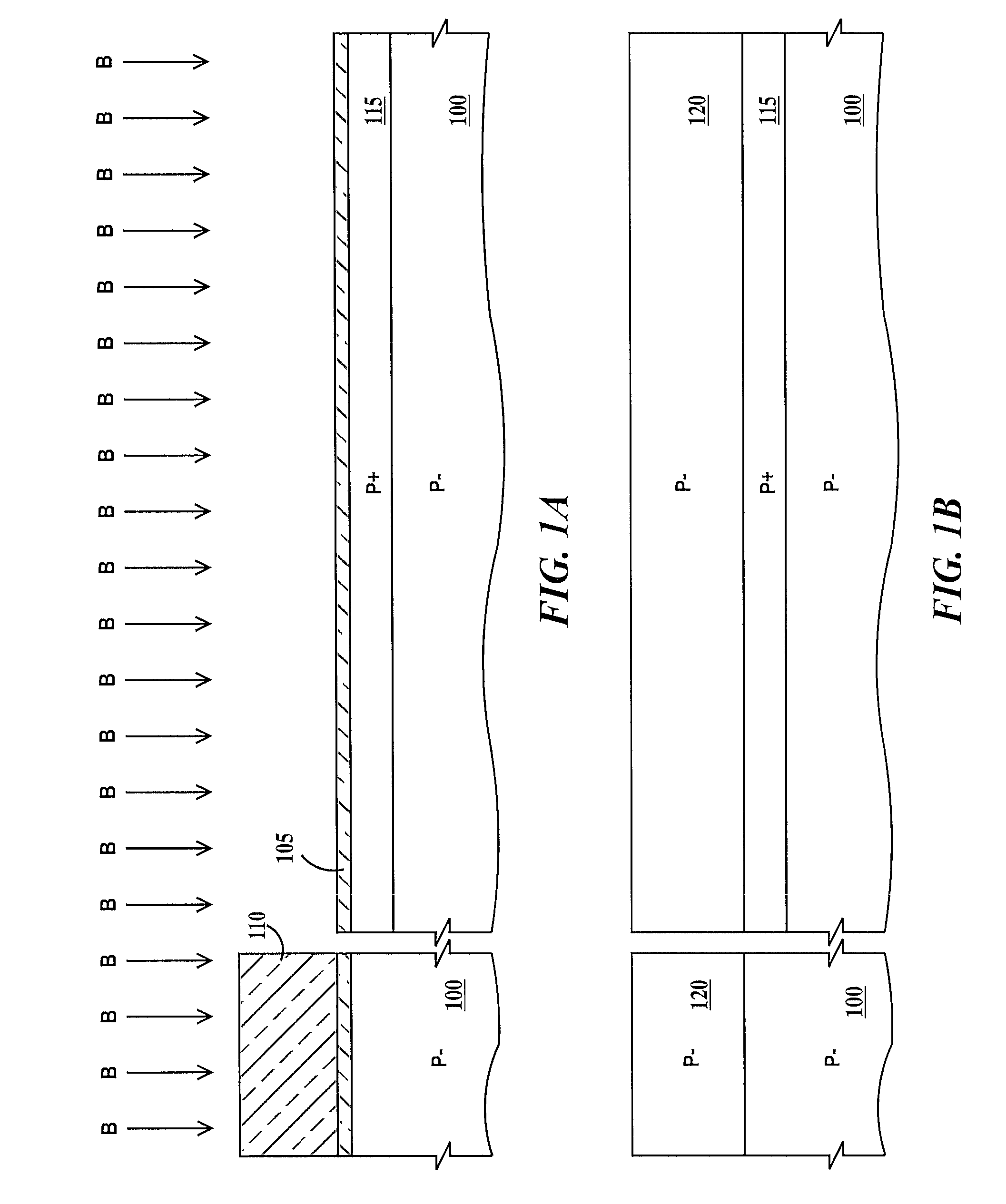

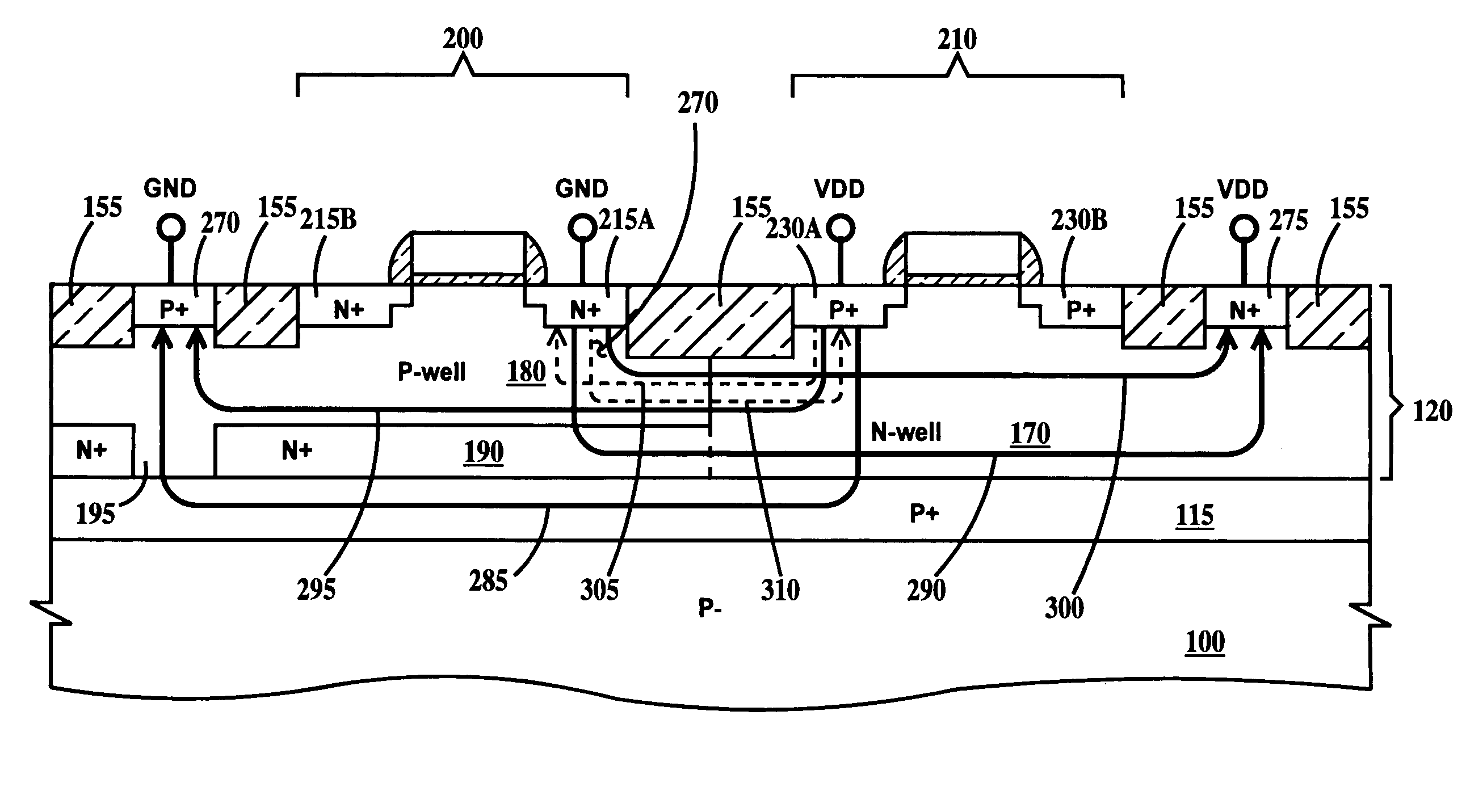

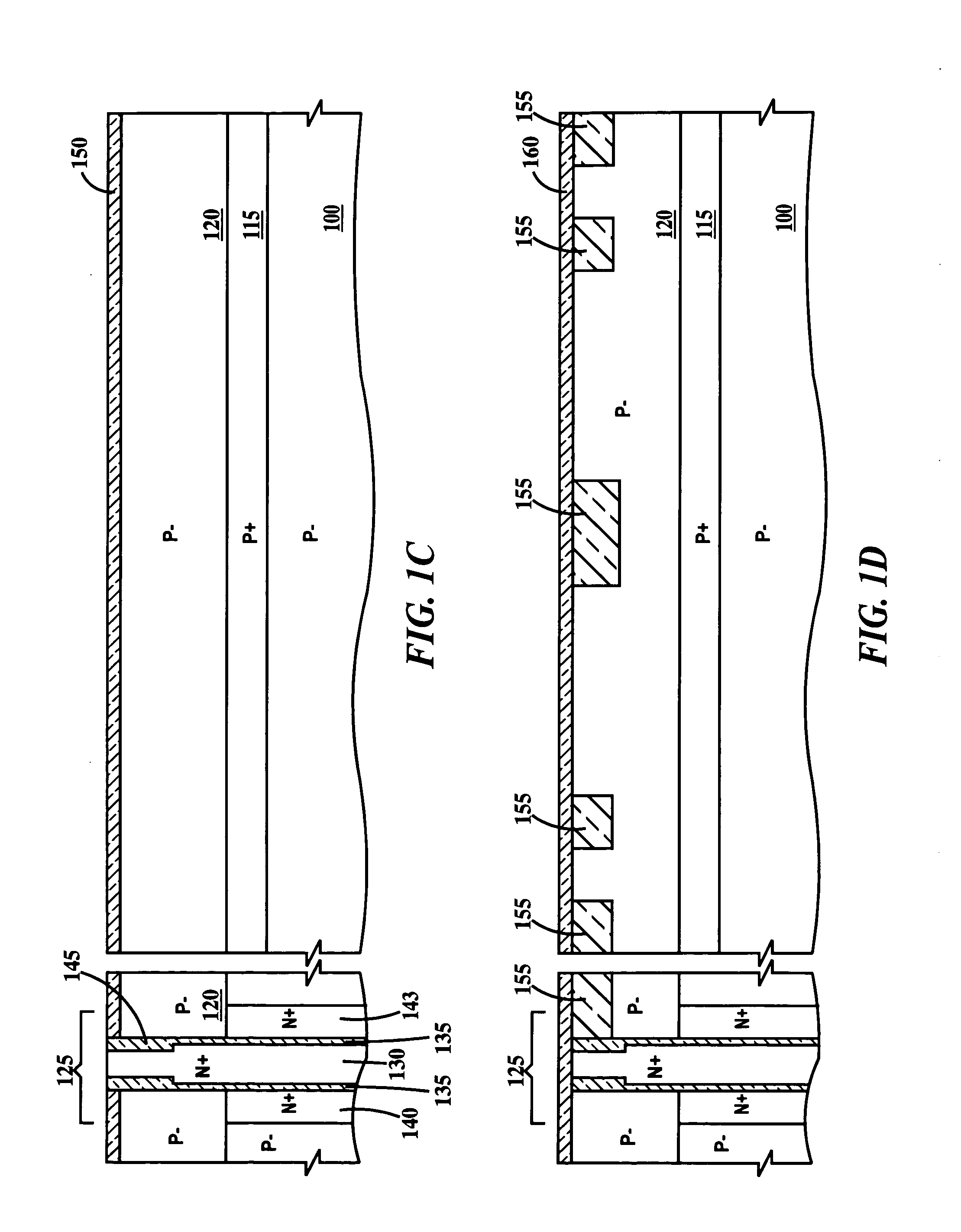

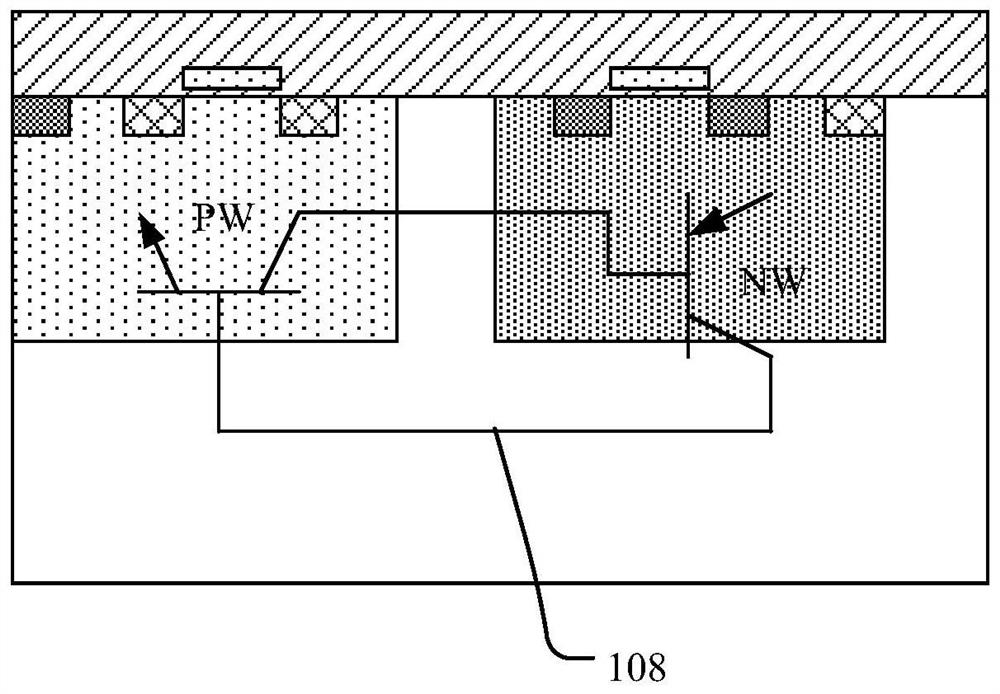

Triple-well CMOS devices with increased latch-up immunity and methods of fabricating same

A triple-well CMOS structure having reduced latch-up susceptibility and a method of fabricating the structure. The method includes forming a buried P-type doped layer having low resistance under the P-wells and N-wells in which CMOS transistors are formed and forming a gap in a buried N-type doped layer formed in the P-wells, the is gap aligned under a contact to the P-well. The buried P-type doped layer and gap in the buried N-type doped layer allow a low resistance hole current path around parasitic bipolar transistors of the CMOS transistors.

Owner:IBM CORP

Automatic locking method for flexible direct-current transmission system

ActiveCN104092299AAutomatic locking implementationReduce latch-upEmergency protective circuit arrangementsInformation technology support systemPower gridAlternating current

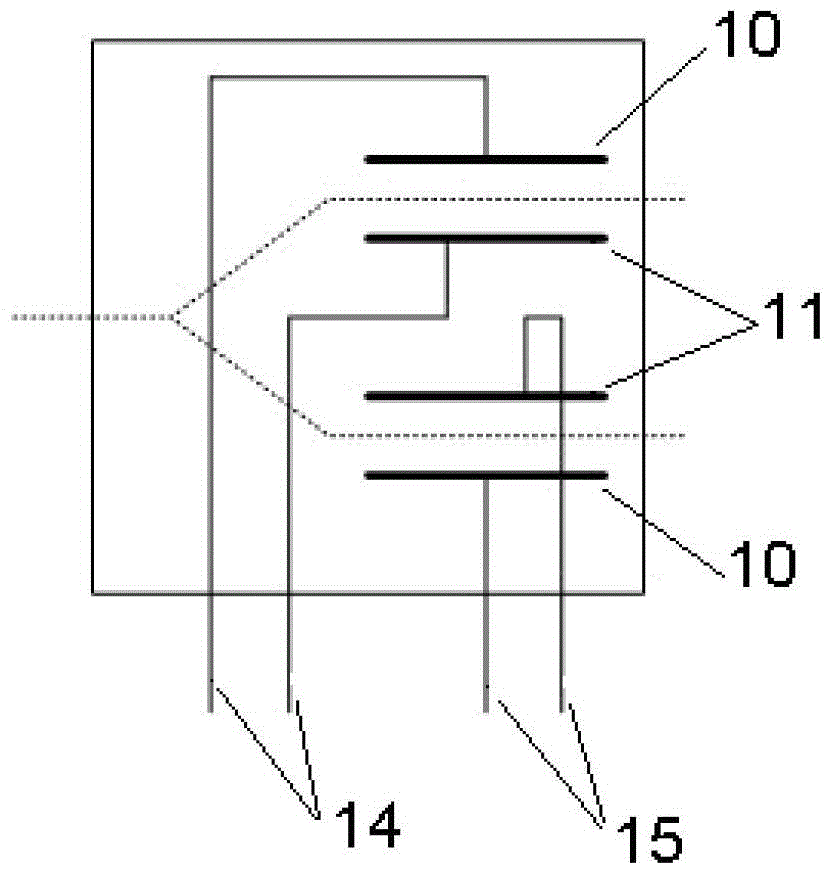

The invention discloses an automatic locking method for a flexible direct-current transmission system. The automatic locking method includes the following steps of firstly, judging the control mode of a station; secondly, judging the current running state when the flexible direct-current system runs if the station is judged to have the active power control mode; thirdly, starting the locking process of the station according to a received system locking control instruction if all the conditions are met, and conducting power reduction control; fourthly, sending a locking window signal to complete the locking process if both the active power and the reactive power of the current converter station are zero. By means of the automatic locking method for the flexible direct-current transmission system, a control and protection system in a flexible direct-current transmission project is automatically locked, the locking process of the flexible direct-current transmission system is shortened, impact which is caused by control and protection system incorrect operation generated due to man-made incorrect operation and the like to an alternating-current system is effectively avoided, time consumption of the whole locking process of the flexible direct-current system is lowered, the complexity in the locking process is lowered, and running reliability of a direct-current power grid is improved.

Owner:STATE GRID CORP OF CHINA +2

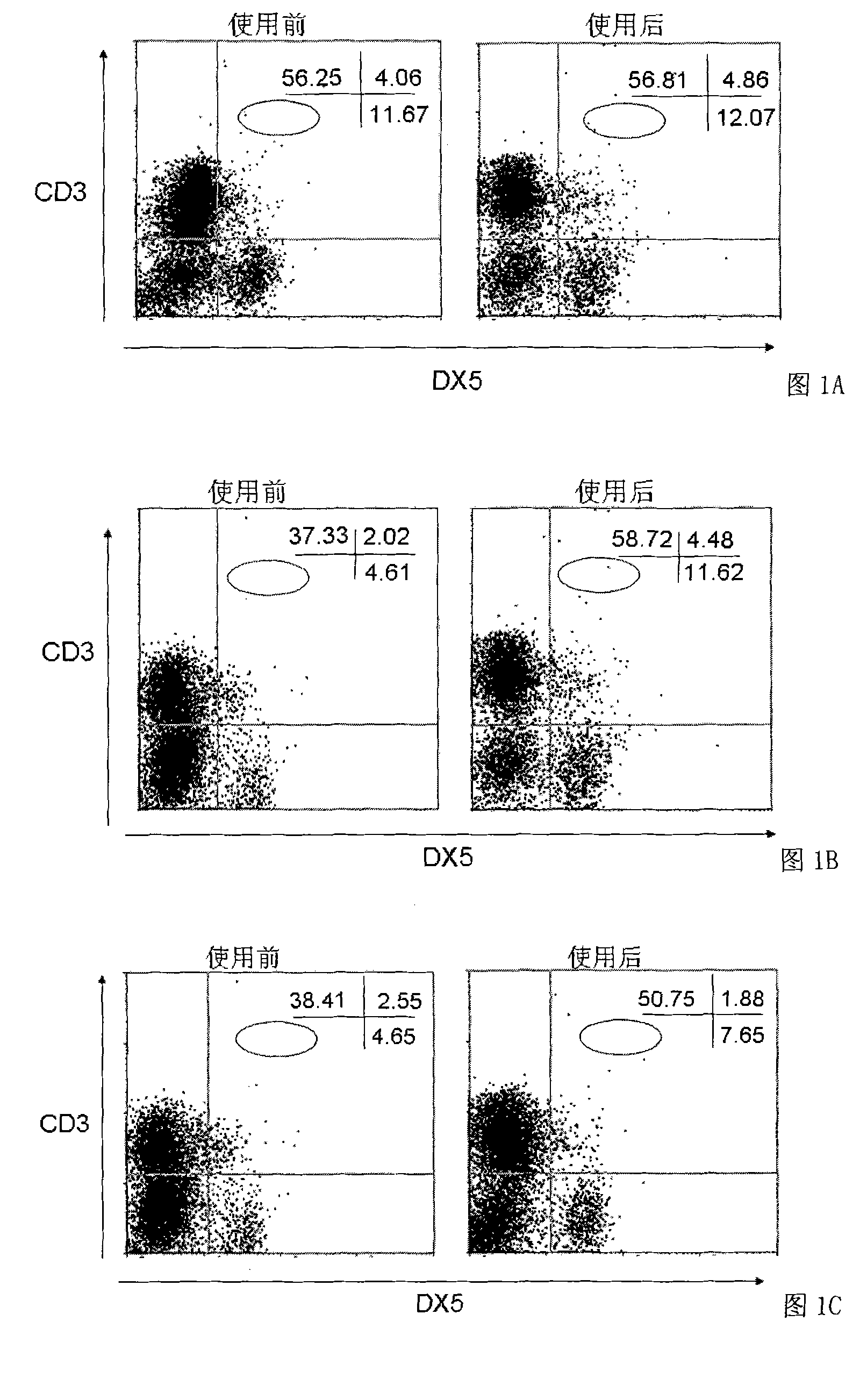

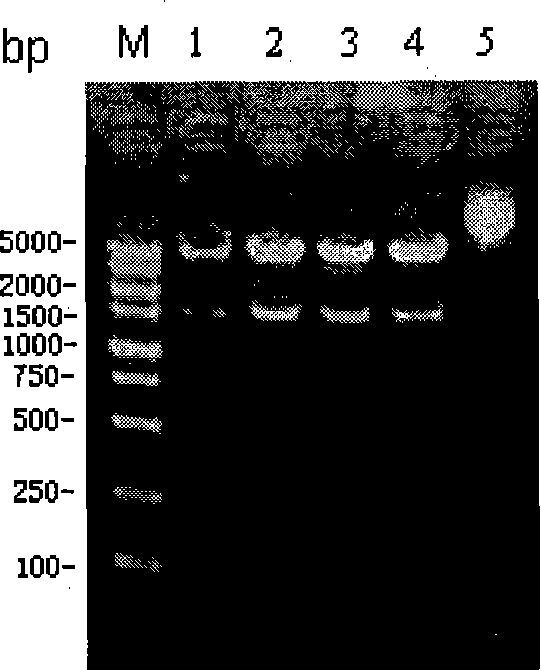

Anti-senescence product for gonad granulocyte, its preparing method and uses

InactiveCN101152215AImprove bioavailabilityConvenient sourceAerosol deliverySuppositories deliveryVaginal SuppositoryPharmaceutical preservatives

The invention provides a cellsovary granulosa cell anti-aging product, and the preparation method and the application of the product. The invention applies cellsovary granulosa cells in preparation of anti-aging products. The cellsovary granulosa cell anti-aging product of the invention is characterized in that in vitro cultivated and amplified cultivation supernatant of female mammalian animal celsovary granulose cells and / or the cell extract is contained; and one or more than one pharmaceutically acceptable medical excipient and antioxidant are contained. Via the cellsovary granulosa cells, the invention is capable of proliferating and secreting large amounts of a plurality of bioactive substances. The invention adopts granulose cells with extremely high bioavailability and similar to female physiological characteristics to cultivate supernatant and the cell extract of the supernatant. The invention can be taken orally, absorbed by skin or be prepared into vaginal suppository to achieve the purpose of anti-aging.

Owner:ANHUI PROVINCIAL HOSPITAL

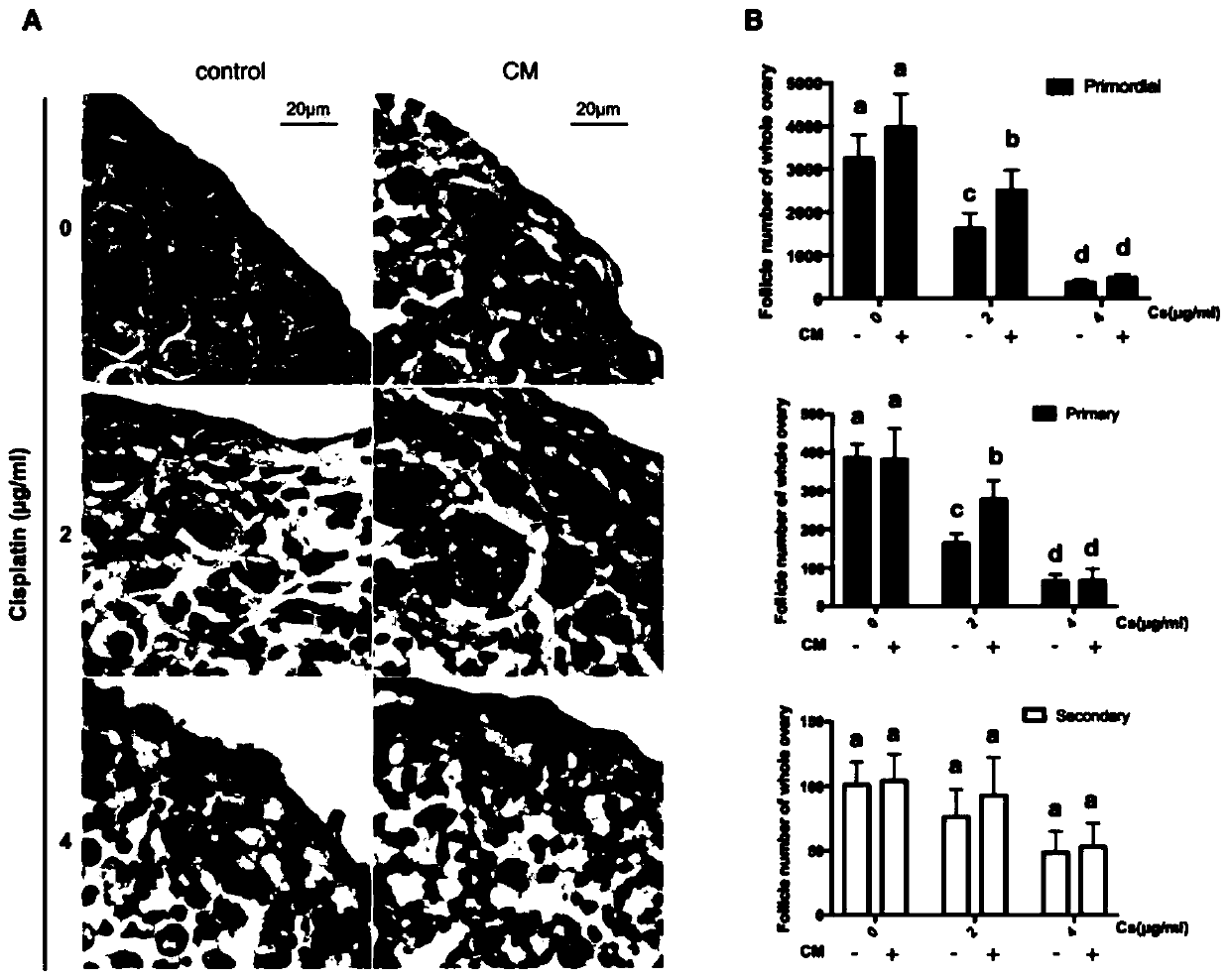

Application of umbilical cord mesenchymal stem cell conditioned medium

PendingCN110478368ASufficient sources of organizationEnvironmental factors have little influencePowder deliveryUnknown materialsMesenchymal stem cellUmbilical cord

The invention relates to an application of an umbilical cord mesenchymal stem cell conditioned medium, in particular to a protective effect of the human umbilical cord mesenchymal stem cell conditioned medium or freeze-dried powder prepared by the human umbilical cord mesenchymal stem cell conditioned medium on ovarian injury, ovarian senescence and the like.

Owner:INST OF ZOOLOGY CHINESE ACAD OF SCI

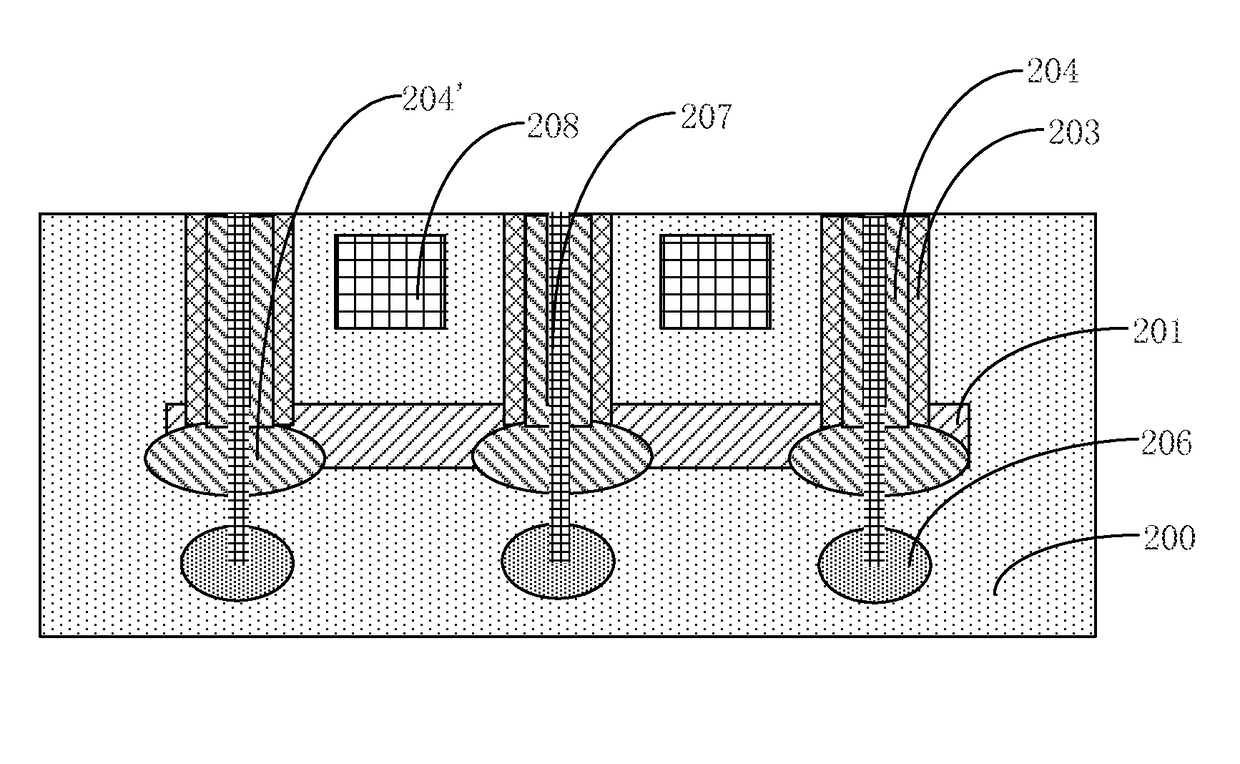

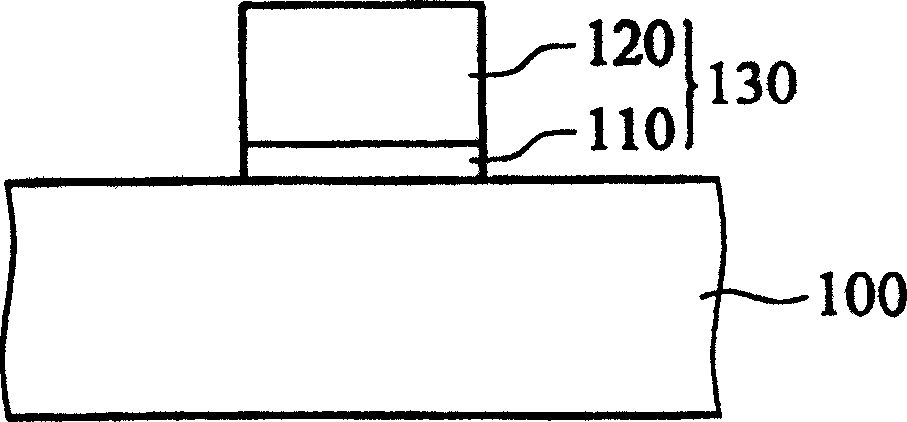

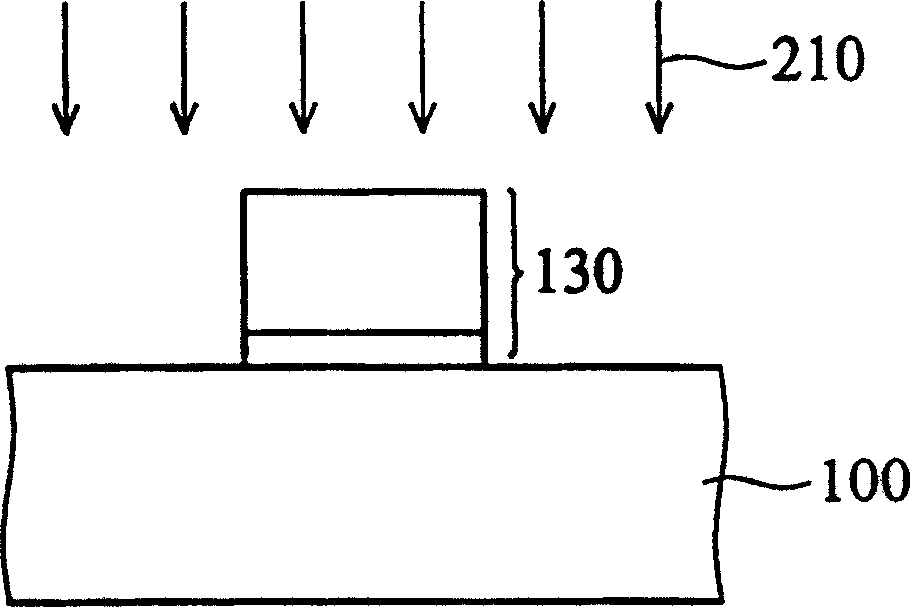

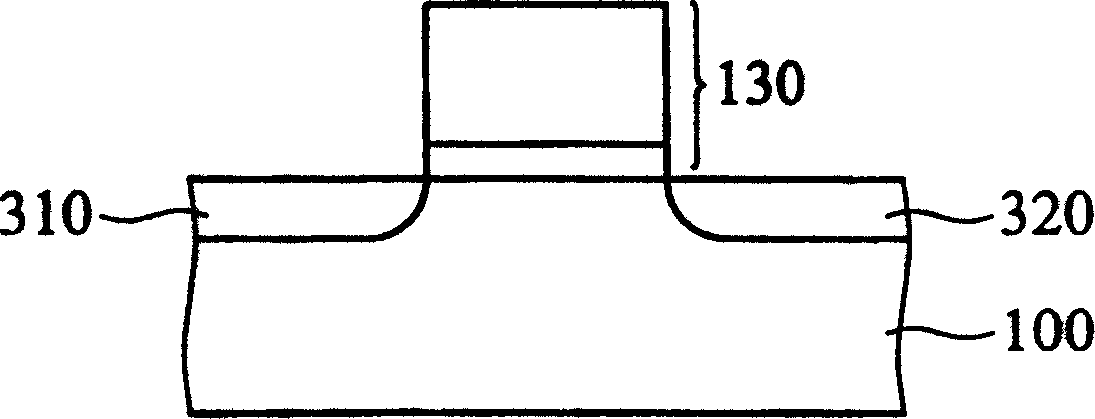

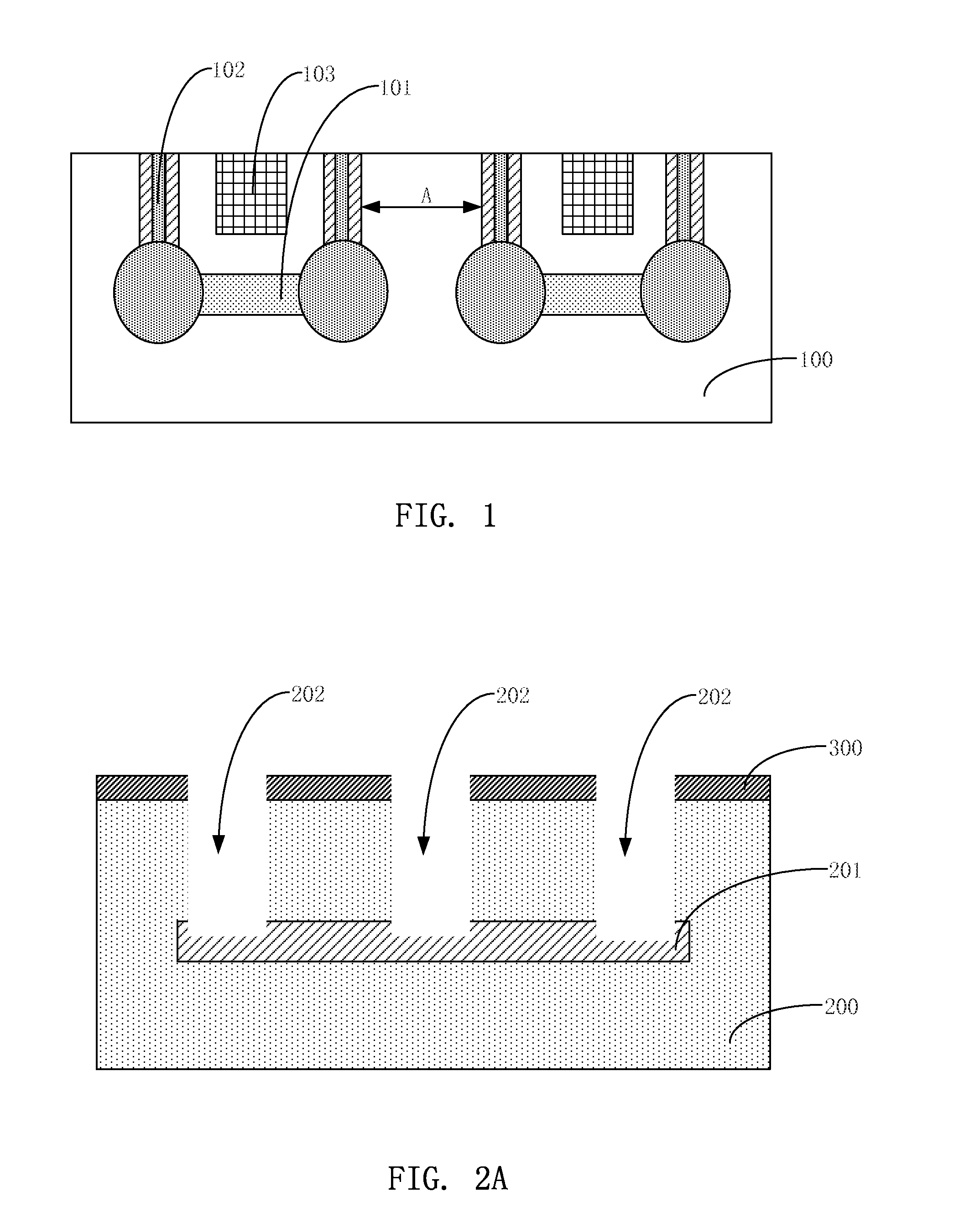

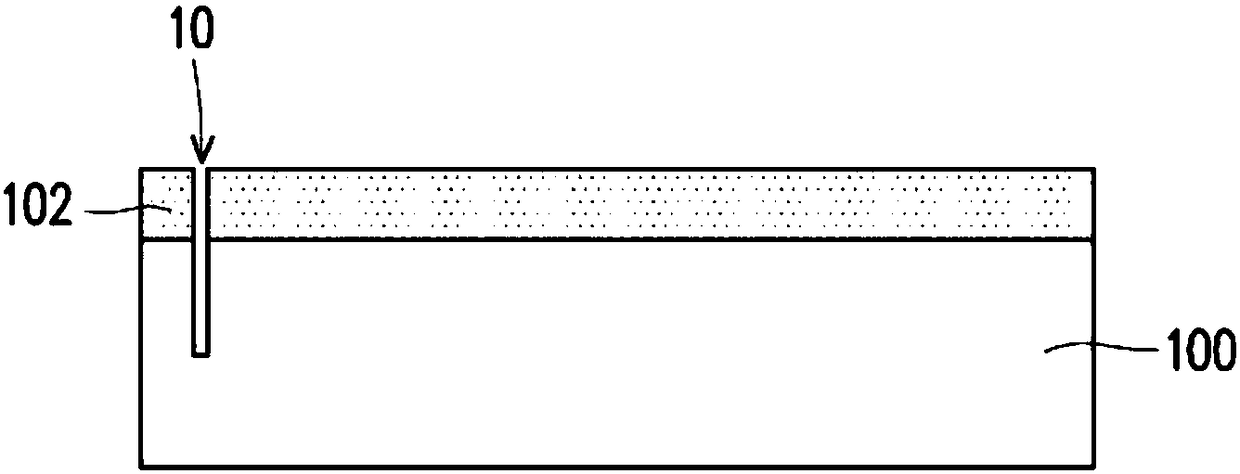

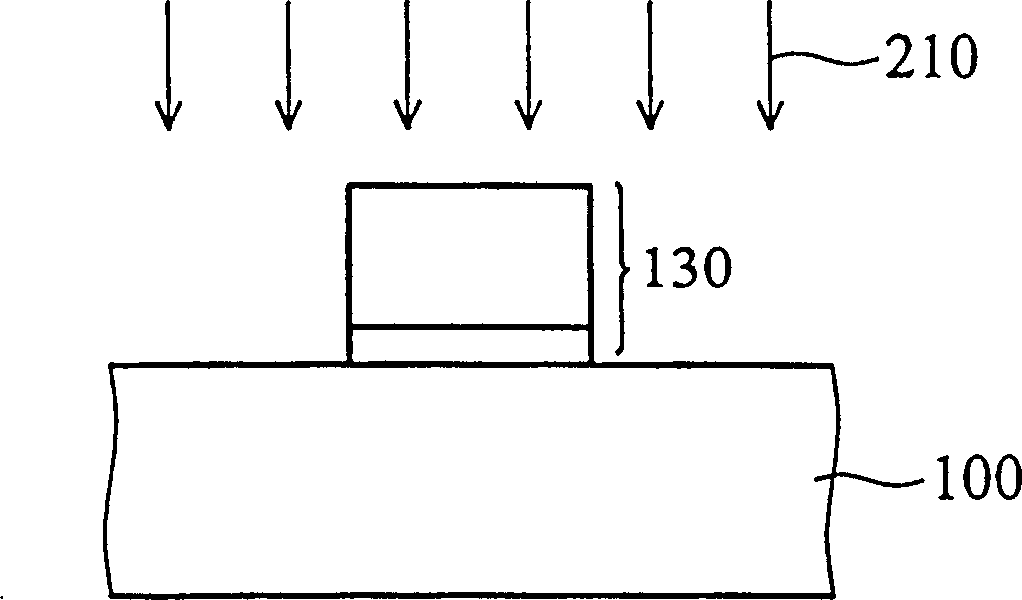

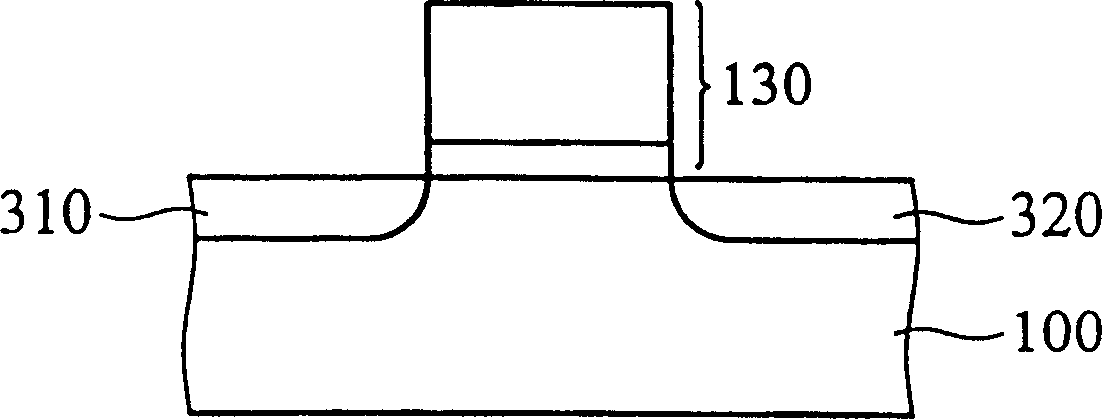

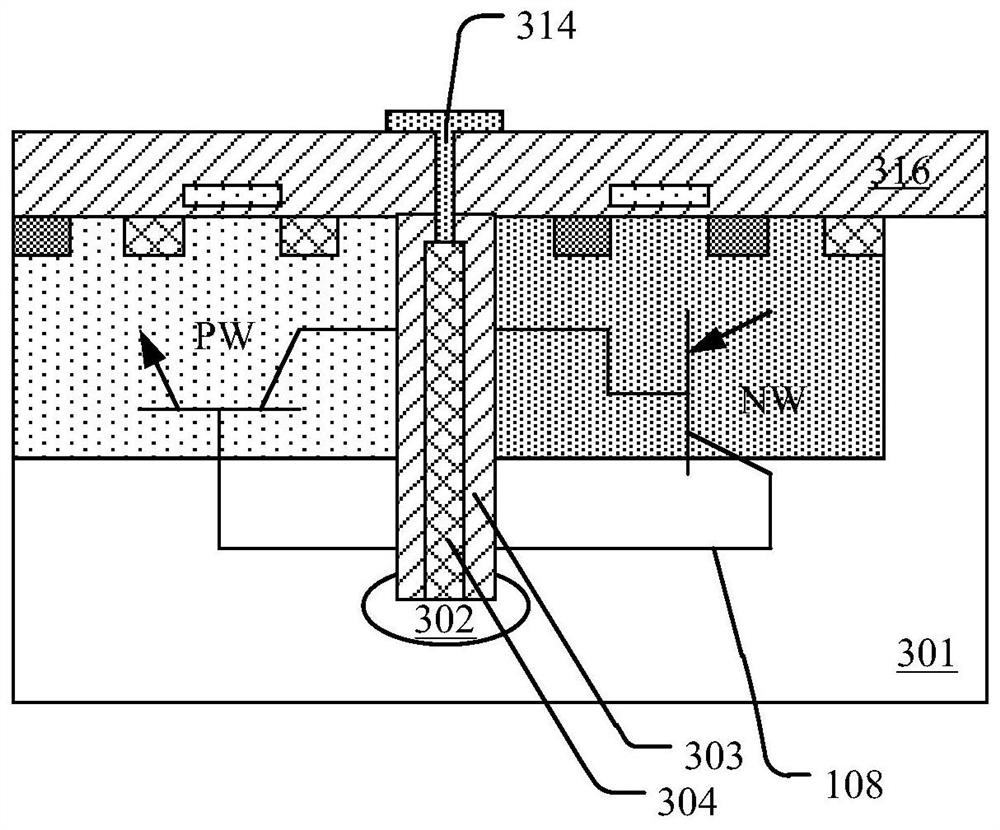

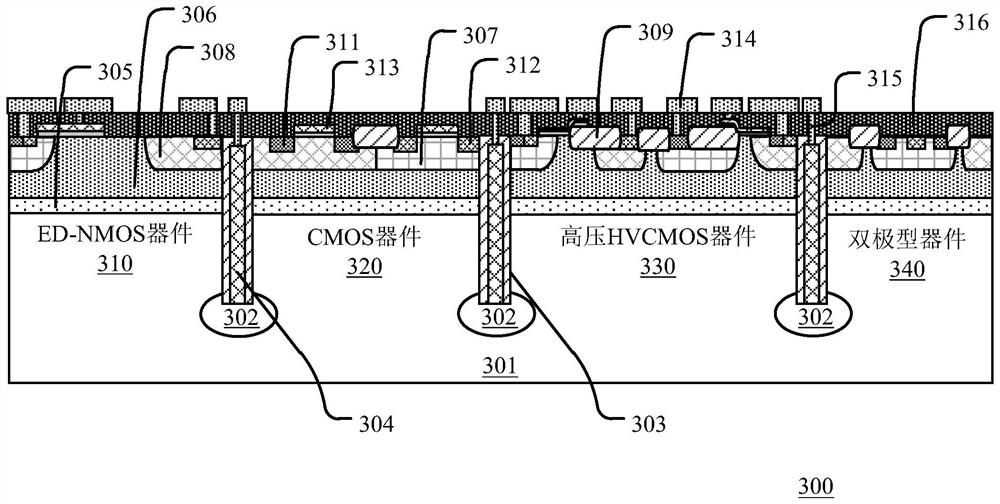

Device isolation structure and manufacture method

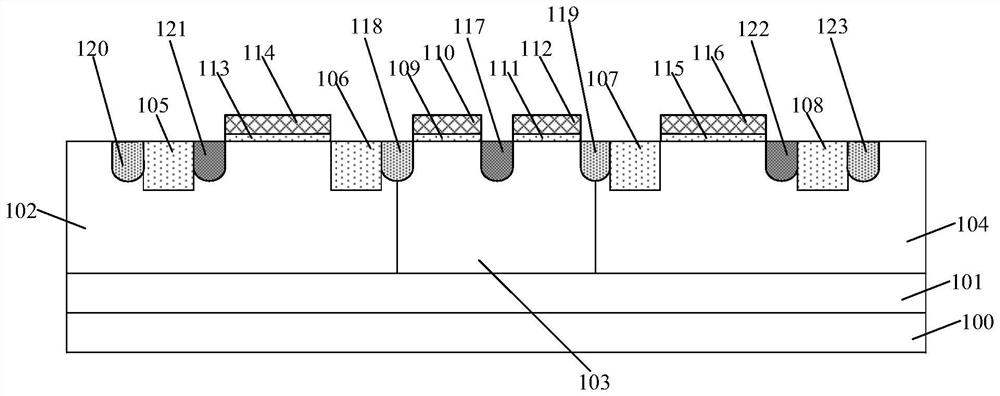

ActiveUS9653344B2Simplify manufacturing stepsImprove isolationSemiconductor/solid-state device detailsSemiconductor/solid-state device manufacturingEngineeringDielectric layer

A method for forming a semiconductor device includes forming a buried doped layer in a semiconductor substrate and forming a plurality of first trenches that expose the buried doped layer. A first dielectric layer is formed covering sidewalls of the first trenches, and a doped polysilicon layer is formed covering side surfaces of the first dielectric layer and bottom portions of the first trenches. The method also includes forming a second trench in each of the plurality of first trenches, each second trench extending through a bottom portion of the doped polysilicon layer and the buried doped layer into a lower portion of the substrate. The method also includes forming a second dielectric layer inside each second trench. An isolation pocket structure is formed that includes the doped buried layer at the bottom and sidewalls that includes the doped polysilicon layer sandwiched between the first and second dielectric layers.

Owner:SEMICON MFG INT (SHANGHAI) CORP

Method of disposing ion with high doping concentration for lowering defect on substrate

InactiveCN1499576AReduce latch-upSubstrate defect avoidanceSemiconductor/solid-state device manufacturingIon beamAtomic physics

A program of disposing ion with high doping concentration (1E14-1E16atom / cm2) is carried out for a substrate. The said program includes a low current of ion beam in range 1-7mA. In the invented method, using low current of ion beam lowers defect on substrate generated by the program of disposing ion.

Owner:MACRONIX INT CO LTD

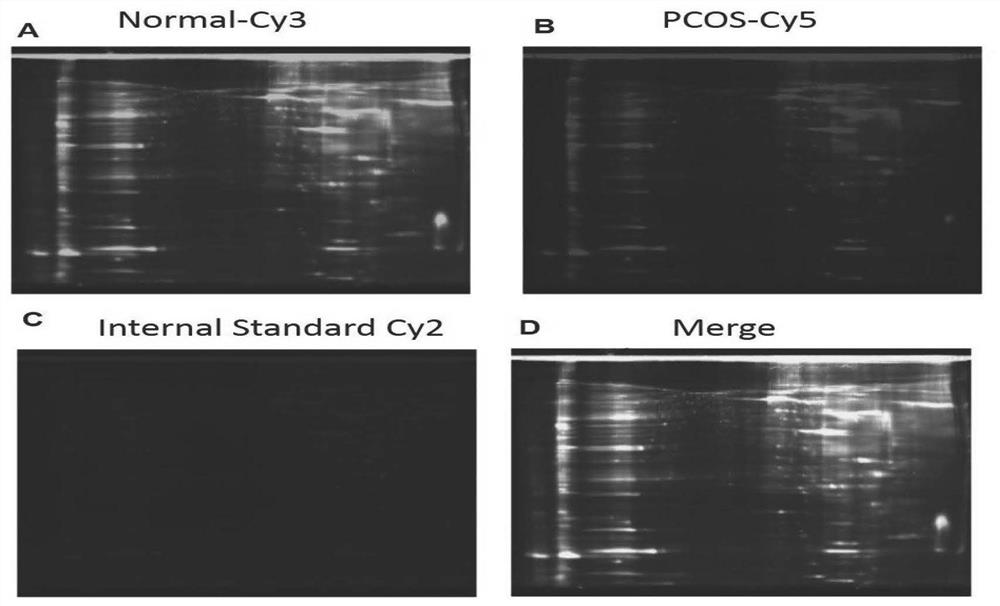

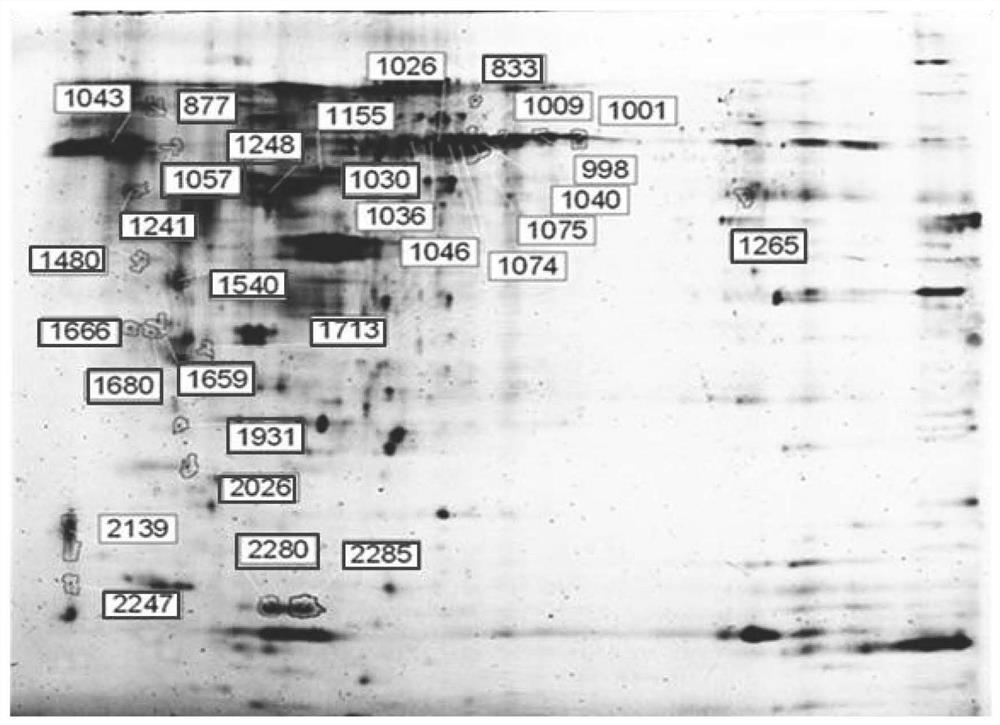

Application of preparation for regulating and controlling expression quantity of HSP90B1 in preparation of medicine for preventing or treating polycystic ovarian syndrome

PendingCN113332308APromote proliferationReduce apoptosisOrganic active ingredientsSexual disorderGranular cellGranular leucocyte

The invention discloses application of a preparation for regulating and controlling the expression quantity of HSP90B1 in preparation of a medicine for preventing or treating polycystic ovarian syndrome. Through the development of the research, HSP90B1 participates in PCOS ovarian granular cell proliferation, so that the apoptosis of granular cells in follicles is reduced, the imbalance of proliferation and apoptosis is caused, sinus follicle atresia is reduced, and polycystic change and ovulation disorder in ovaries are caused, HSP90B1 possibly participates in the pathologic mechanism of PCOS generation and development, and HSP90B1 is likely to become a drug target of PCOS (polycaprolactone).

Owner:GUANGDONG WOMEN & CHILDREN HOSPITAL

Anti-senescence product for gonad granulocyte, its preparing method and uses

InactiveCN101152215BExtend the "serving" timeReduce latch-upAerosol deliverySuppositories deliveryAntioxidantOvarian Granulosa Cell

The invention provides a cellsovary granulosa cell anti-aging product, and the preparation method and the application of the product. The invention applies cellsovary granulosa cells in preparation of anti-aging products. The cellsovary granulosa cell anti-aging product of the invention is characterized in that in vitro cultivated and amplified cultivation supernatant of female mammalian animal celsovary granulose cells and / or the cell extract is contained; and one or more than one pharmaceutically acceptable medical excipient and antioxidant are contained. Via the cellsovary granulosa cells,the invention is capable of proliferating and secreting large amounts of a plurality of bioactive substances. The invention adopts granulose cells with extremely high bioavailability and similar to female physiological characteristics to cultivate supernatant and the cell extract of the supernatant. The invention can be taken orally, absorbed by skin or be prepared into vaginal suppository to achieve the purpose of anti-aging.

Owner:ANHUI PROVINCIAL HOSPITAL

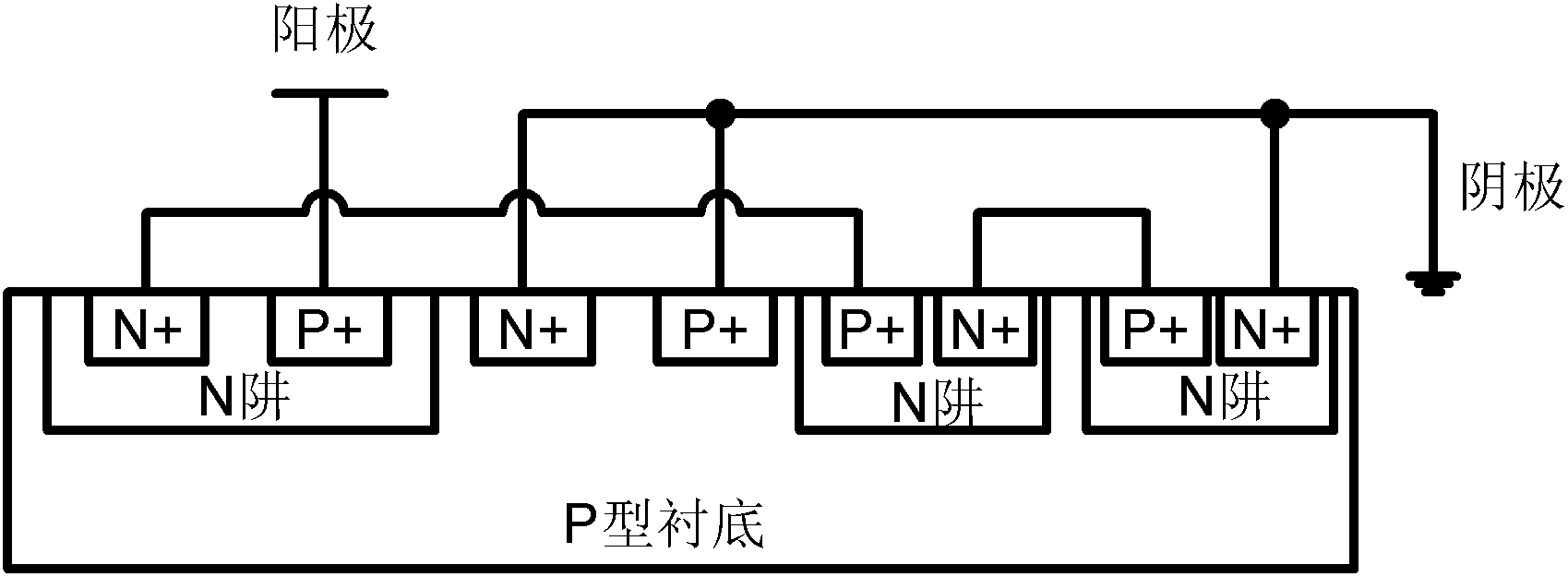

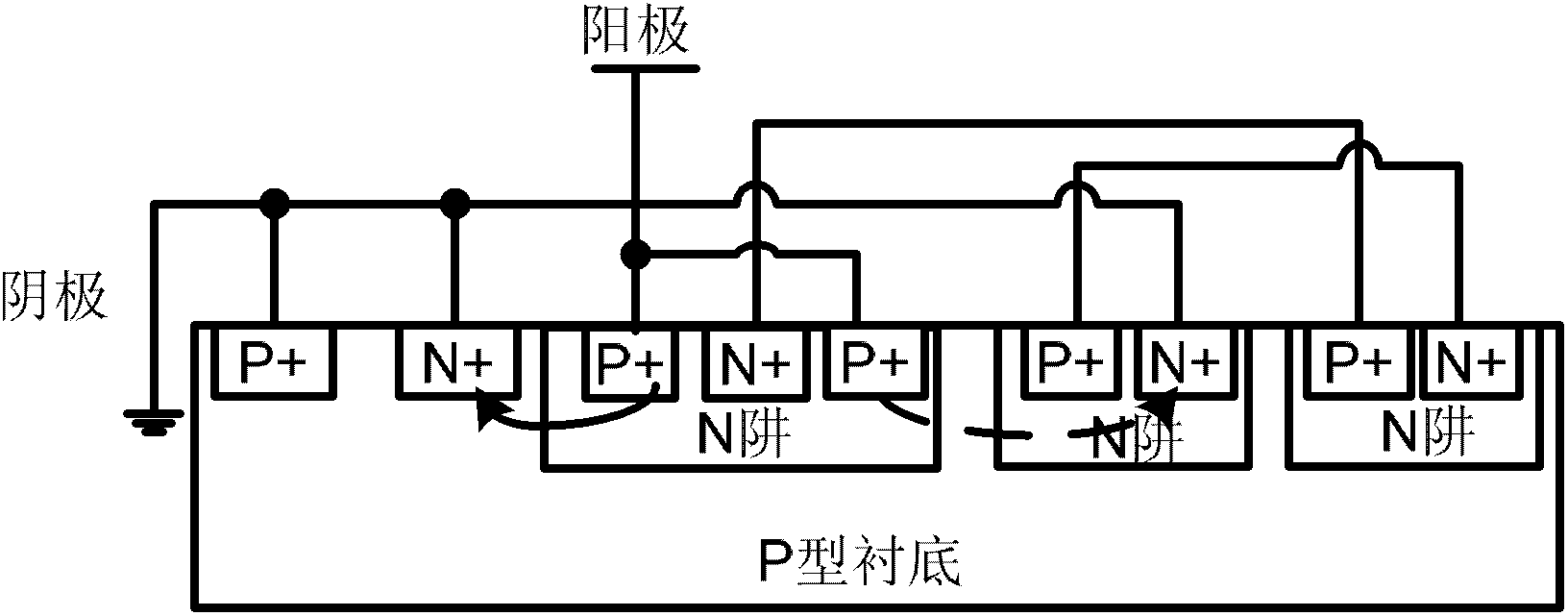

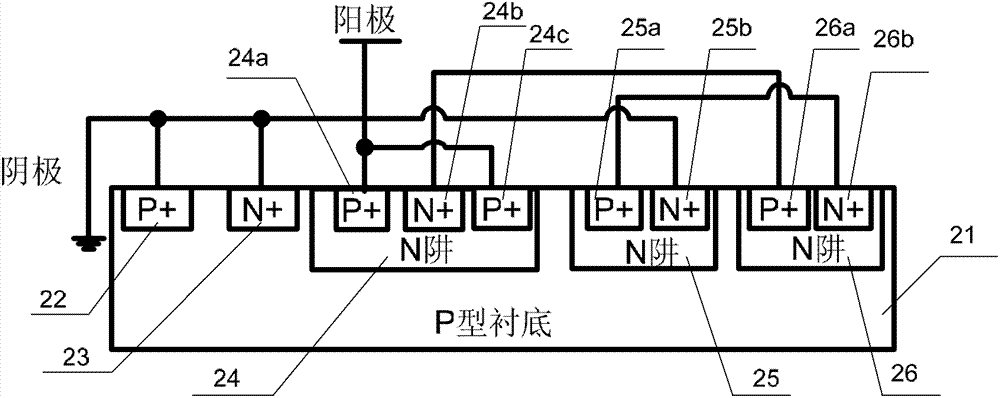

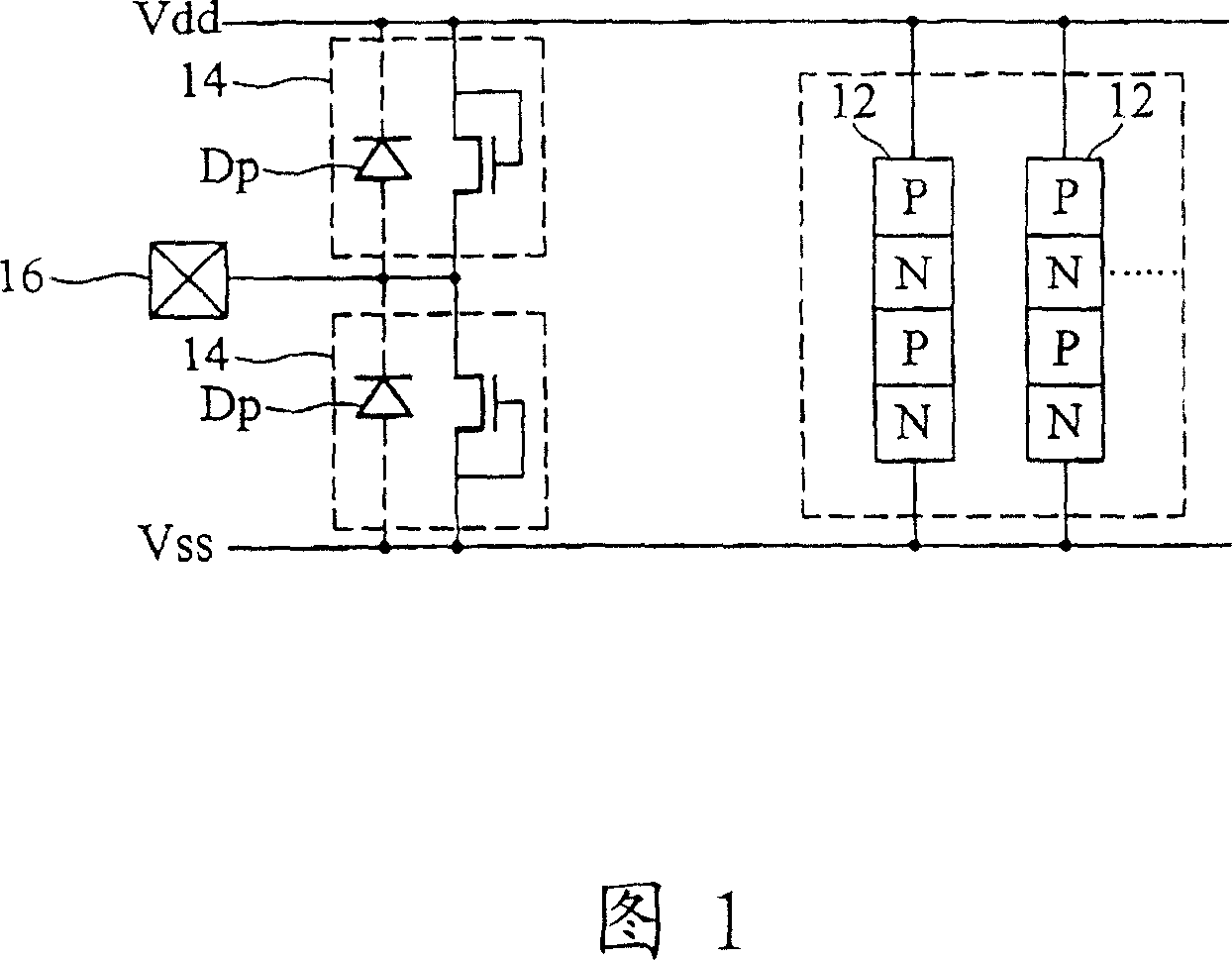

Controlled silicon device provided with secondary conductive path and triggered with help of diodes

The invention discloses a controlled silicon device provided with a secondary conductive path and triggered with the help of diodes. The connection and the layout of controlled silicon and diodes are optimized, and a parasitic controlled silicon path formed by diode strings is adopted to realize the secondary conduction of the controlled silicon which is triggered with the help of the diodes, thus improving a current value of a clamp point when the voltage of the controlled silicon is clamped so as to avoid the occurrence of the latch-up. The silicon controlled device is simple in structure, even in current and good in robustness, and is stable and reliable. Compared with a traditional ESD (electronic static discharge) protection scheme of diodes and MOS (metal oxide semiconductor) tubes,the controlled silicon device provided by the invention is superior in area efficiency; and compared with a traditional protection scheme for controlled silicon triggered with the help of diodes, thecontrolled silicon device provided by the invention has the advantage of low latch-up risk.

Owner:ZHEJIANG UNIV

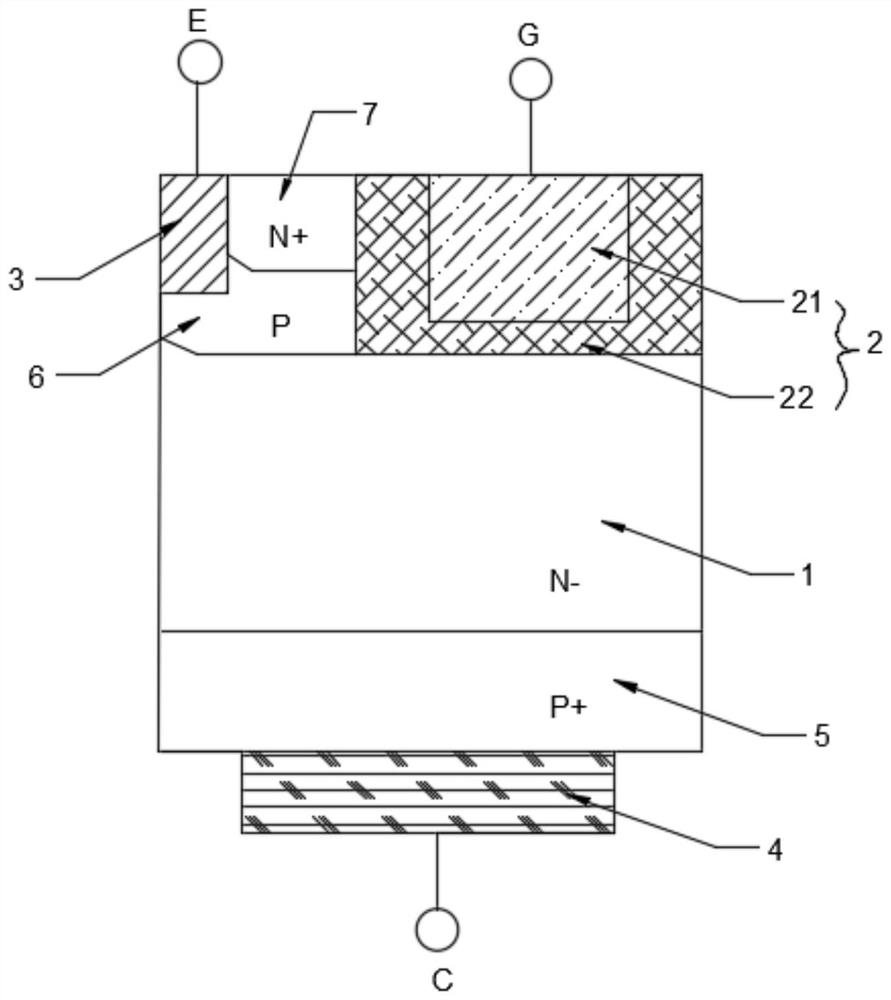

Insulated gate bipolar transistor, intelligent power device and electronic product

PendingCN112018172AEasy to collectIncrease storage capacitySemiconductor devicesVoltage dropEngineering

The invention relates to the field of semiconductors, in particular to an insulated gate bipolar transistor, an intelligent power device and an electronic product. The insulated gate bipolar transistor comprises a drift region, a gate structure, an emitter, an emitter source region and a body region in contact with the emitter source region, wherein the top layer of the drift region is provided with a first trench and a second trench along the vertical direction of the device, the gate structure is filled in the first trench, the emitter is filled in the second trench, the emitter source region is arranged between the gate structure and the emitter, and the depth of the second trench is greater than the thickness of the emitter source region. A transverse electric field is formed between the gate structure and the emitter metal, the transverse electric field acts on the junction of the emitter source region and the body region to form a carrier collection layer, and the collection andstorage effects of carriers at the junction are enhanced, so that the current between the body region and the emitter source region is reduced, the conduction voltage drop is reduced, and the latch-upeffect occurrence probability is reduced.

Owner:GUANGDONG MIDEA WHITE HOME APPLIANCE TECH INNOVATION CENT CO LTD +1

Device isolation structure and manufacture method

ActiveUS20160111321A1Simplify manufacturing stepsImprove isolationSemiconductor/solid-state device detailsSemiconductor/solid-state device manufacturingEngineeringDielectric layer

A method for forming a semiconductor device includes forming a buried doped layer in a semiconductor substrate and forming a plurality of first trenches that expose the buried doped layer. A first dielectric layer is formed covering sidewalls of the first trenches, and a doped polysilicon layer is formed covering side surfaces of the first dielectric layer and bottom portions of the first trenches. The method also includes forming a second trench in each of the plurality of first trenches, each second trench extending through a bottom portion of the doped polysilicon layer and the buried doped layer into a lower portion of the substrate. The method also includes forming a second dielectric layer inside each second trench. An isolation pocket structure is formed that includes the doped buried layer at the bottom and sidewalls that includes the doped polysilicon layer sandwiched between the first and second dielectric layers.

Owner:SEMICON MFG INT (SHANGHAI) CORP

FLIP protein and novel use of encoding gene thereof

InactiveCN101502658APromote proliferationPromote apoptosisGenetic material ingredientsSexual disorderOvulation timesGranular cell

The invention discloses an FLIP protein and new applications of encoded genes thereof. The new application of the invention refers to the application of the FLIP protein and the encoded genes thereof in blocking apoptosis induced by FADD and the application in inhibiting apoptosis of ovary granular cells and the application in promoting reproductive performance of animals. The FLIP protein and the encoded genes thereof can obviously inhibit apoptosis of the ovary granular cells induced by FADD, promote growth of oocyte, reduces follicular atresia and serve as potential medicines for improving reproductive performance of cows. The protein and the new applications of the invention provide relatively reliable and concrete experimental basis for increasing ovulation rate of dams and improving reproductive performance thereof, thus enjoying a wide application prospect in improving the reproductive performance of female animals.

Owner:INST OF ANIMAL SCI OF CHINESE ACAD OF AGRI SCI

Method of manufacturing semiconductor element

ActiveCN108461448AImprove mobilityIncrease drive currentSemiconductor/solid-state device manufacturingSemiconductor devicesHeat treatedMaterials science

The invention discloses a method of manufacturing a semiconductor element. The method comprises the following steps: respectively forming a first stress layer and a second stress layer on a substrate;forming a buffer layer on the first stress layer and the second stress layer; performing an injection manufacturing process on the substrate, to form a precut surface in the substrate on the lower part of the first stress layer and the second stress layer; performing joining treatment, to join a carrier plate on the buffer layer; performing heat treatment, to separate a part of the substrate fromthe precut surface; performing the previous manufacturing process on a precut surface on another part of the substrate.

Owner:POWERCHIP SEMICON MFG CORP

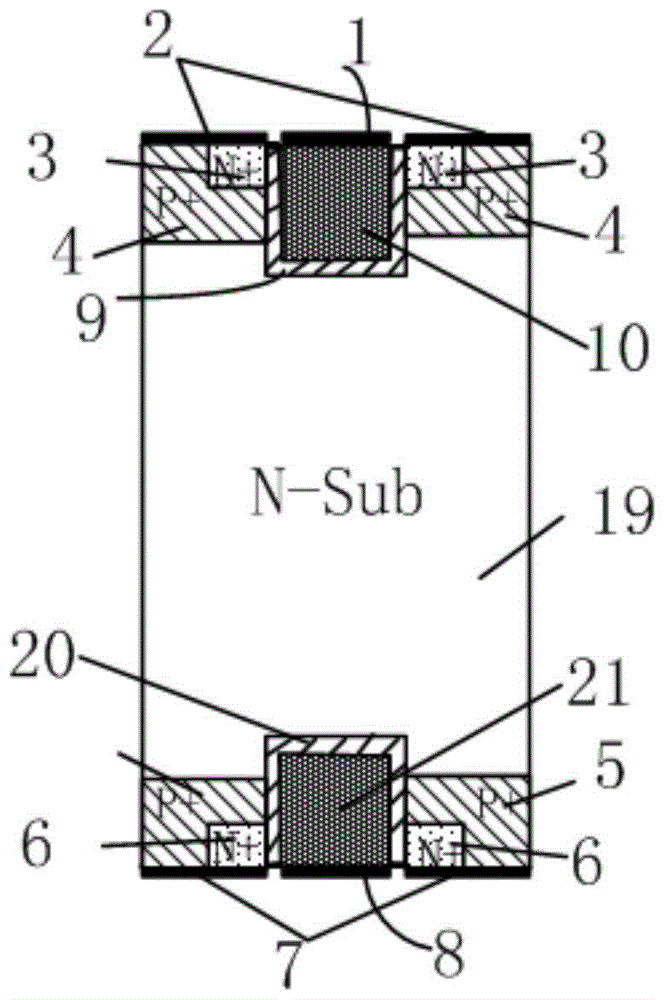

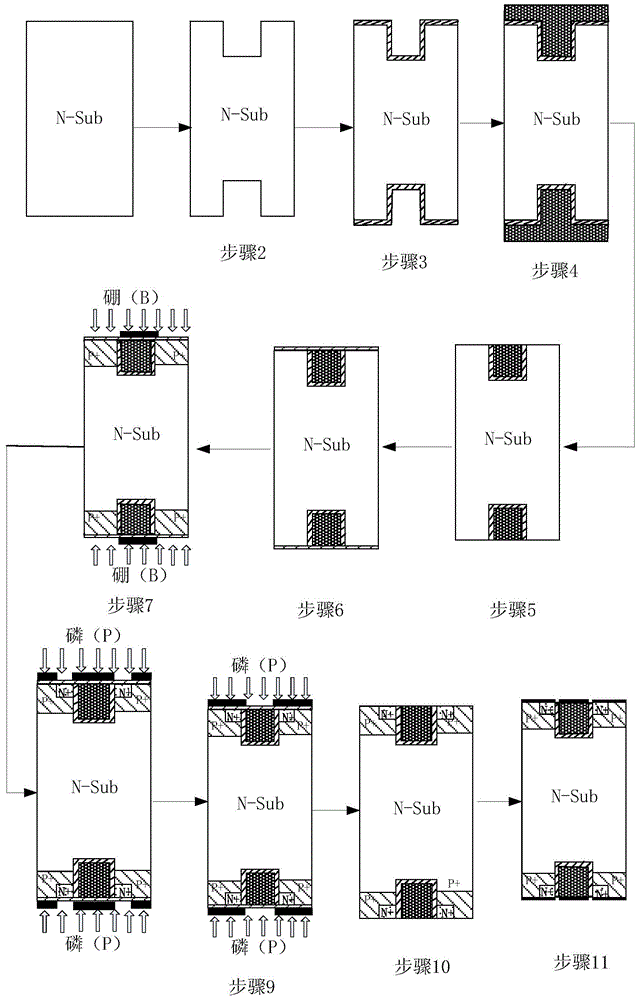

Trench type insulated gate bipolar transistor capable of double-terminal control and preparation method thereof

InactiveCN103762162BReduce latch-upReduce threatTransistorSemiconductor/solid-state device manufacturingSemiconductorTransistor

The invention discloses a double-end-controllable groove type insulated gate bipolar transistor which comprises a substrate. The two ends of the transistor are of structures with the same shape and variable parameters. The invention further discloses a preparation method of the double-end-controllable groove type insulated gate bipolar transistor. The double-end-controllable groove type insulated gate bipolar transistor effectively solves the problems that a common groove IGBT reverse blocking capability is poor and the turn-off time is long. The double-end-controllable groove type insulated gate bipolar transistor is high in applicability, and can replace a small circuit with bidirectional characteristics composed of a plurality of semiconductor devices, energy is greatly saved, the electric energy utilization rate is greatly improved, and the urgent affair that not enough power is supplied in China at present is relieved.

Owner:XIAN JIEHANG ELECTRONICS SCI & TECH CO LTD

Source/drain ion injecting method for lowering defect on substrate

InactiveCN1259696CAvoid defectsReduce latch-upSemiconductor/solid-state device manufacturingHigh concentrationIon implantation

The invention relates to a method for ion implantation of high doping concentration for reducing substrate defects. A high concentration (1E14-1E16 atom / cm 2 ) ion implantation program, wherein the ion implantation program includes a low ion beam current, the range of the low ion beam current is 1-7mA. Accordingly, the present method utilizes the low ion beam current to reduce substrate defects produced by the ion implantation process.

Owner:MACRONIX INT CO LTD

An on-site calibration device for an optical fiber current sensor and its application method

ActiveCN103616651BHigh measurement accuracyAccurate measurementMeasurement using digital techniquesWavelength filterCurrent sensor

The invention relates to an on-site verification apparatus for an optical fiber current sensor, a usage method of the on-site verification apparatus and application of the on-site verification apparatus. The on-site verification apparatus for the optical fiber current sensor includes an optical fiber current detection sensing module and an optical fiber current detection processing and display module. The optical fiber current detection sensing module is composed of a light source, a linear polariscope, a polarization separator, a modulator, a transmission optical fiber, a 1 / 4 wavelength filter, an optical fiber sensing head, a reflector and a photoelectric detector. Proceeding from installation and debugging of the optical fiber current detection sensing module, the optical fiber current sensor on-site verification apparatus has reasonable control steps, is easy to operate, and can carry out efficient, economic and accurate error detection and quantity transmission on a DC heavy current sensor working on site for a long time; the optical fiber current sensor on-site verification apparatus is suitable for detecting and verifying a current detection sensor working on site for a long time in fields of electrolytic aluminum, electrolytic copper, electric smelting, electroplate and other electrochemical engineering; the on-site verification apparatus for the optical fiber current sensor is good in safety performance, large in measuring dynamic scope, high in frequency response degree, small in size and light in weight; and by adopting the on-site verification apparatus for the optical fiber current sensor, the measuring precision of a current detection apparatus can be raised, and needs of safety and stabilization of a power supply system are met.

Owner:XUNDI SCI & TECH HUBEI PROV

A kind of automatic locking method of flexible direct current transmission system swap station

ActiveCN104092232BAutomatic locking implementationReduce latch-upElectric power transfer ac networkPower stationEngineering

The invention discloses an automatic locking method for a substation of a flexible direct current transmission system, including: (1) judging the control mode of the station and the operating status of the station and other stations; (2) if the station is in the constant DC voltage control mode, And the station is in the unlocked state while other stations are in the locked state, judge the current running state of the flexible DC system; (3) If the above conditions are met, start the blocking process of the station according to the received system (4) If the reactive power of the current converter station is zero, send a blocking trigger pulse signal to complete the blocking process. The automatic locking method of the present invention realizes the automatic locking of the control and protection system, shortens the locking process of the flexible direct current transmission system, effectively avoids the impact on the AC system caused by the misoperation of the control and protection system caused by human misoperation, and reduces the locking process of the entire flexible direct current system Time-consuming, reducing the complexity of the locking process.

Owner:STATE GRID CORP OF CHINA +2

A DC engineering AC bus split operation control method and reactive power control method, module and system

ActiveCN109038638BOvercome the defects of split operation protectionAvoid the risk of false latch-upElectric power transfer ac networkReactive power adjustment/elimination/compensationControl engineeringElectric network

A DC engineer AC bus splitting operation control method and reactive power control method, module and system are disclosed. The control logic of AC bus splitting operation is: when AC bus splitting operation is detected, the operation valve group on AC bus is not directly locked, and the reactive power control function is automatically switched from the whole reactive power control according to DCsystem of the whole station to the reactive power control according to AC bus separately. That is, according to the operating state of the valve group connected to each AC bus bar, the AC filter state and the AC bus bar state, if the reactive power of the bus bar meets the preset reactive power demand, the operating state of the valve group connected to the AC bus bar and the AC filter state aremaintained; If the reactive power of the bus bar does not meet the preset reactive power demand, the AC filter connected with the corresponding AC bus bar is automatically switched on and off according to the reactive power demand, and the power of the valve block connected with the corresponding AC bus bar or the blocking valve block is returned. The invention can effectively overcome the risk ofmislocking of the valve group existing in the busbar splitting operation protection in the current HVDC transmission project, reduce the valve group locking, effectively guarantee the safety of the electric network and bring practical economic benefits.

Owner:NR ELECTRIC CO LTD +1

Controlled silicon device provided with secondary conductive path and triggered with help of diodes

The invention discloses a controlled silicon device provided with a secondary conductive path and triggered with the help of diodes. The connection and the layout of controlled silicon and diodes are optimized, and a parasitic controlled silicon path formed by diode strings is adopted to realize the secondary conduction of the controlled silicon which is triggered with the help of the diodes, thus improving a current value of a clamp point when the voltage of the controlled silicon is clamped so as to avoid the occurrence of the latch-up. The silicon controlled device is simple in structure, even in current and good in robustness, and is stable and reliable. Compared with a traditional ESD (electronic static discharge) protection scheme of diodes and MOS (metal oxide semiconductor) tubes,the controlled silicon device provided by the invention is superior in area efficiency; and compared with a traditional protection scheme for controlled silicon triggered with the help of diodes, thecontrolled silicon device provided by the invention has the advantage of low latch-up risk.

Owner:ZHEJIANG UNIV

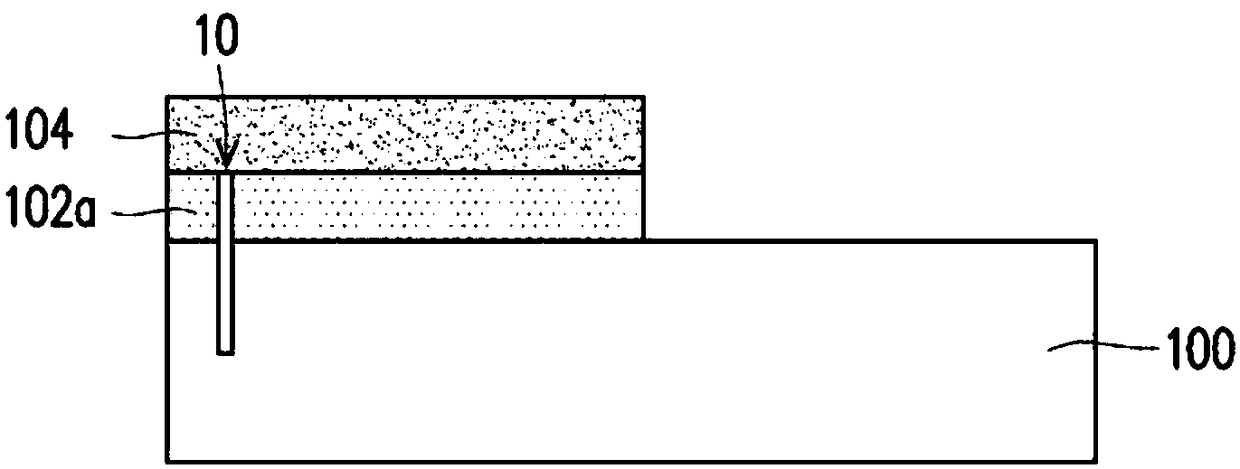

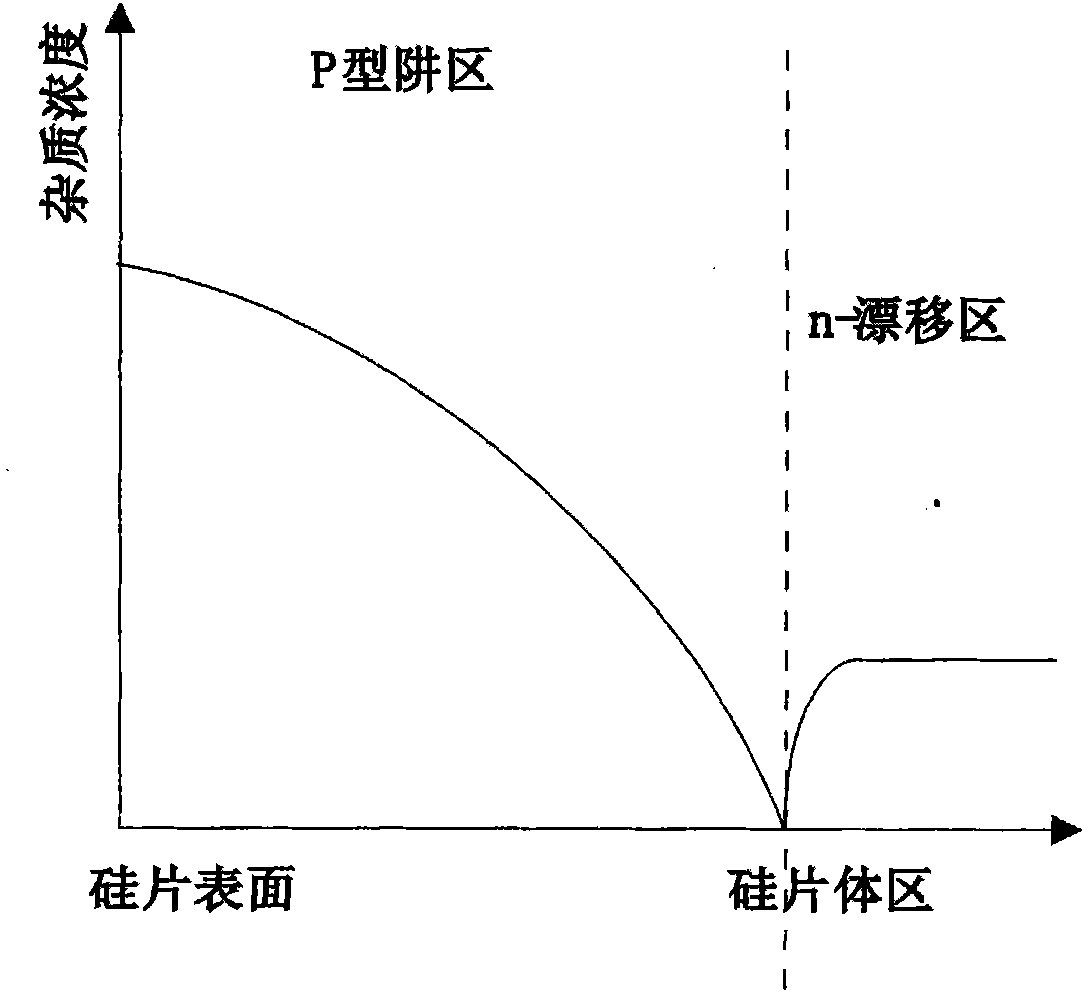

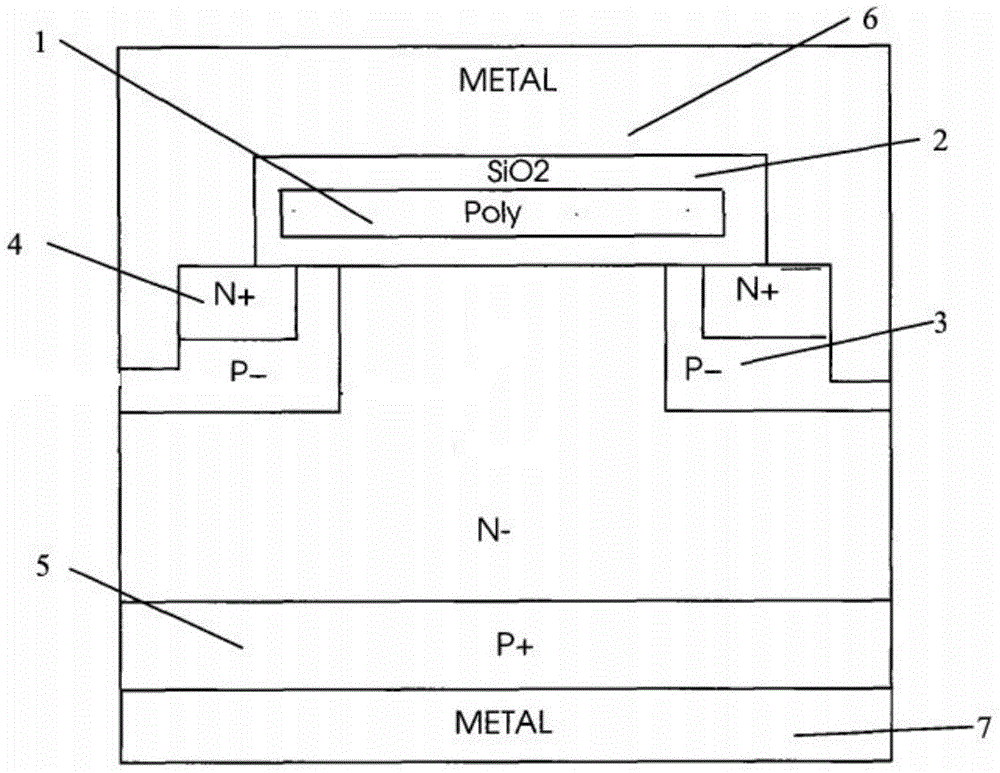

MOS (Metal Oxide Semiconductor) type power device and manufacturing method thereof

ActiveCN102263127BImprove pressure resistanceLow resistivitySemiconductor/solid-state device manufacturingSemiconductor devicesElectrical resistance and conductancePeak value

The invention relates to an MOS (Metal Oxide Semiconductor) type power device which comprises a P-type collector region, an N-type shifting region, a P well, an N-type source region, a first insulating layer, a gate pole, a second insulating layer, an emitting electrode and a collecting electrode, wherein the N-type shifting region is located on the P-type collector region; the P well is selectively formed on the N-type shifting region and has a conduction type which is opposite to the conduction type of the N-type shifting region; the N-type source region is selectively formed on a surface area of the P well; the first insulating layer is located on the N-type shifting region and partially covers the P well; the gate pole is located on the first insulating layer; the second insulating layer covers the gate pole and partially covers the N-type source region; the emitting electrode covers the second insulating layer and is electrically connected with the P well and the N-type source region partially; the collecting electrode is located on the back side of the P-type collector region and is electrically connected with the P-type collector region; a conductive impurity concentration peak area is arranged in the P well; the impurity concentration is gradually reduced from the conductive impurity concentration peak area to the edge of the P well; and a junction bending center of the P well is arranged inside the P well. The invention also provides a manufacturing method of the MOS type power device. The inside resistivity is reduced while the demand on the length of a surface trench is met, thereby reducing the bulk resistor and reducing a latch-up effect.

Owner:BYD SEMICON CO LTD

Manufacturing method of semiconductor element

ActiveCN108461448BImprove mobilityIncrease drive currentSemiconductor/solid-state device manufacturingSemiconductor devicesBonding processMechanical engineering

The invention discloses a method for manufacturing a semiconductor element, which includes the following steps. A first stress layer and a second stress layer are respectively formed on the base. A buffer layer is formed on the first stress layer and the second stress layer. Implantation process is performed on the substrate to form a pre-cut surface in the substrate below the first stress layer and the second stress layer. A bonding process is performed to bond the carrier board to the buffer layer. A heat treatment is performed such that a portion of the substrate is separated from the pre-cut facet. The front-end fabrication process is performed on the pre-cut side of another part of the substrate.

Owner:POWERCHIP SEMICON MFG CORP

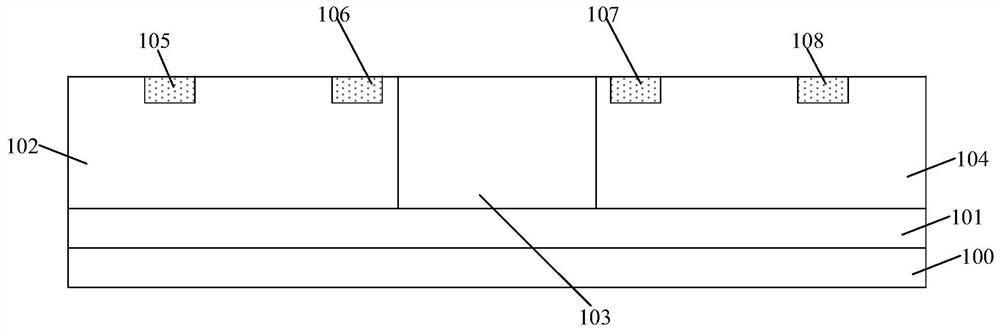

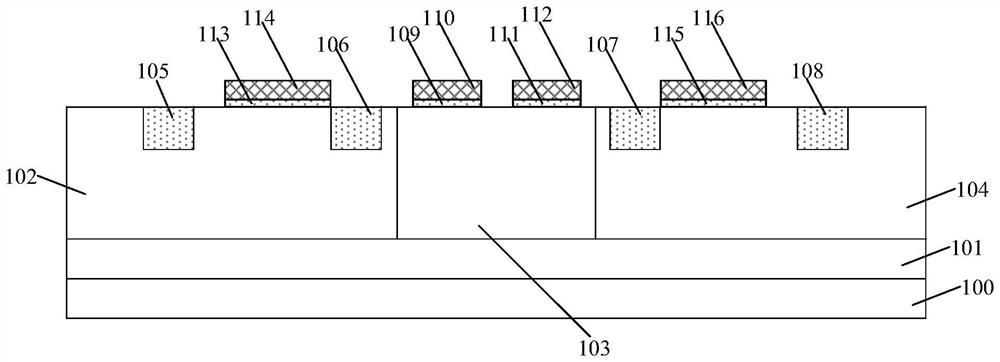

Manufacturing method of integrated circuit and integrated circuit

PendingCN114171465AImprove reliabilityReduce latch-upTransistorSolid-state devicesPhysicsIntegrated circuit

The invention discloses a manufacturing method of an integrated circuit and the integrated circuit. The manufacturing method comprises the following steps: forming an N-type buried layer on a substrate through ion implantation; forming an epitaxial layer on the N-type buried layer; forming an active region and a passive region in the epitaxial layer; forming a plurality of field oxide layers in the passive region; forming a plurality of low-voltage N-type wells and a plurality of low-voltage P-type wells in the epitaxial layer; forming a plurality of gate structures on the low-voltage N-type well, the low-voltage P-type well and the field oxide layer; and forming a plurality of deep groove isolation structures, wherein the deep groove isolation structures penetrate through the epitaxial layer and the N-type buried layer and extend into the substrate. According to the manufacturing method of the integrated circuit and the integrated circuit, the latch-up effect of the integrated circuit is reduced by adopting a process of a back-end deep groove isolation structure, so that the reliability of the integrated circuit is improved.

Owner:HANGZHOU SILAN MICROELECTRONICS

A method for automatic blocking of flexible direct current transmission system

ActiveCN104092299BAutomatic locking implementationReduce latch-upEmergency protective circuit arrangementsInformation technology support systemPower gridAlternating current

Owner:STATE GRID CORP OF CHINA +2

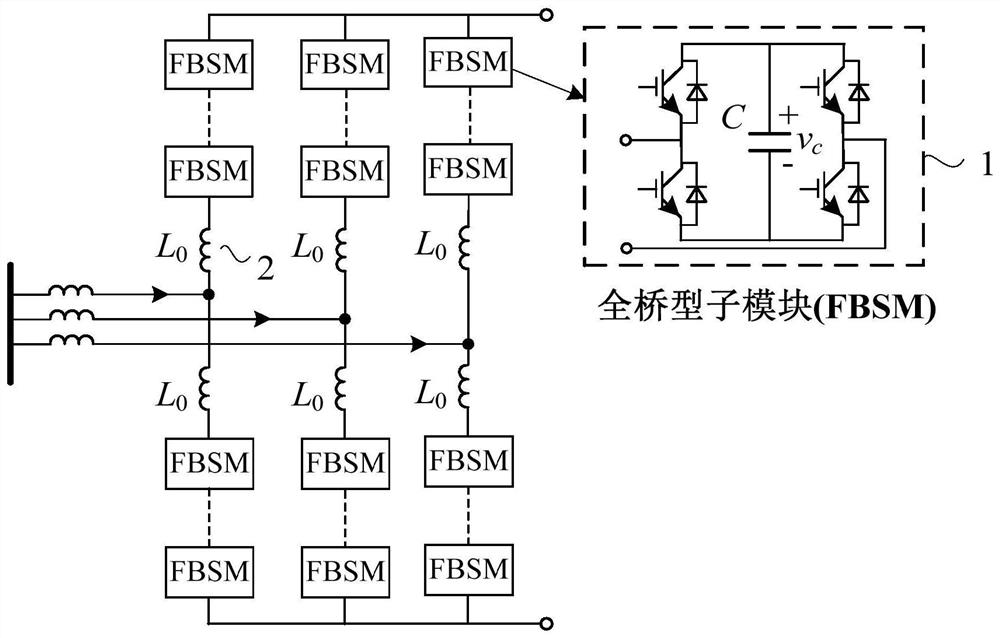

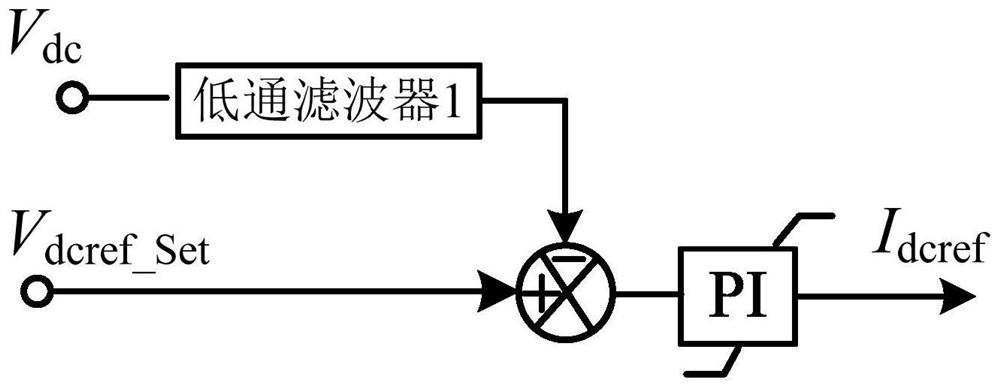

A DC voltage preset control method and application of a voltage source converter

ActiveCN109390963BReduce size requirementsReduce technical difficultyElectric power transfer ac networkVoltage sourceAlternating current

The invention discloses a DC voltage preset control method and application of a voltage source converter. At a steady-state operation stage before a DC fault, a DC voltage preset control instruction value of a DC voltage controller is a rated value set by a converter station station-stage controller. During the period of the DC fault, the converter station station-stage controller switches the DCvoltage preset control instruction value from the rated value to a newly added control reference quantity after detecting the fault, wherein the newly added control reference quantity comprises a converter station bus voltage and / or DC voltages of all DC lines connected with the DC bus. The converter station station-stage controller takes the DC bus voltage or the minimum value of the DC bus voltage and the voltages of the DC lines as a target voltage preset control instruction value during the fault. After the DC fault is eliminated, the voltage preset control instruction value is switched from the target voltage preset control instruction value to the rated value. The method can reduce the impact on the transient stability of an AC power grid from a DC grid fault.

Owner:HUAZHONG UNIV OF SCI & TECH

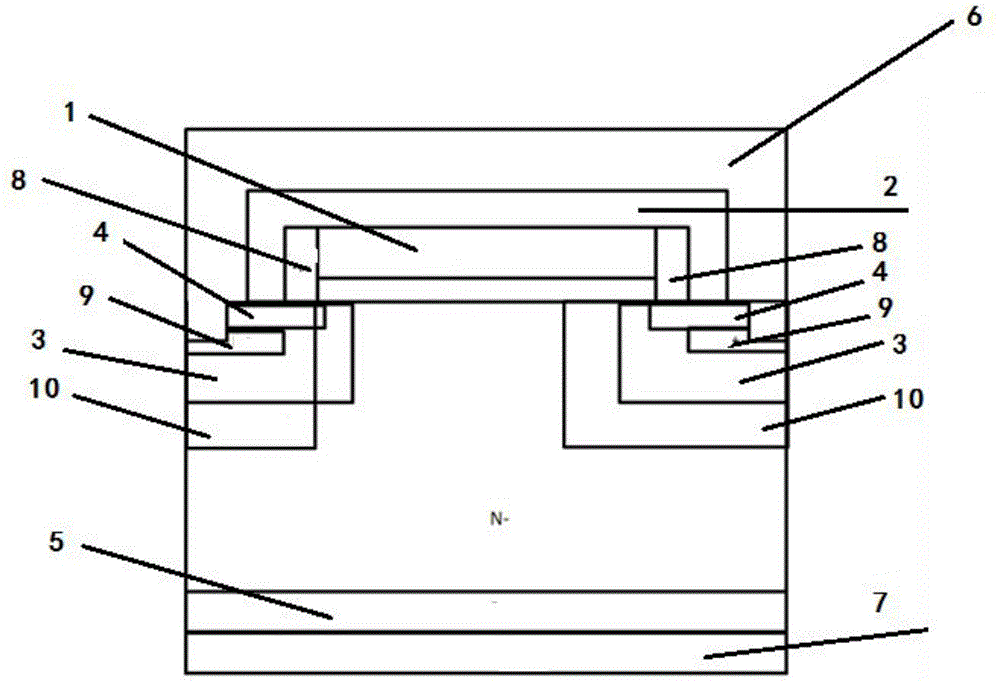

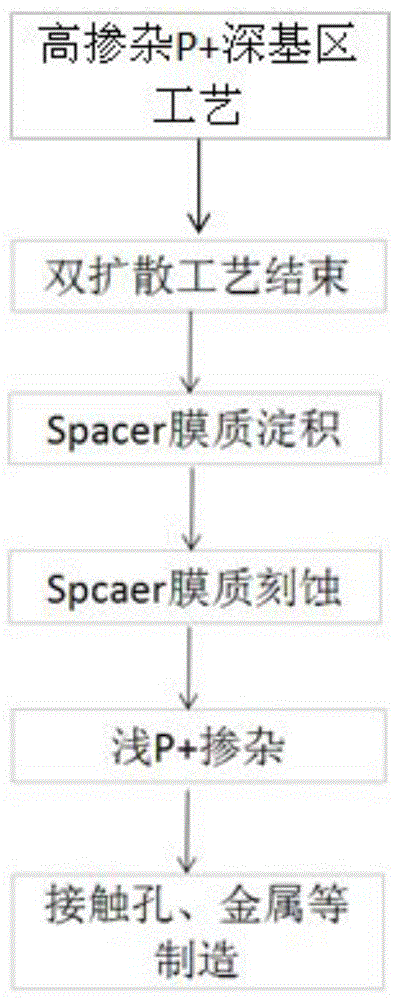

IGBT device with cavity bypass structure and manufacture method of IGBT device

InactiveCN106033773AGood effectImprove distributionSemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringElectric field

The invention relates to an IGBT device with a hole bypass structure and a manufacturing method thereof. A polycrystalline sidewall protection structure, a shallow P+ structure and a P+ deep base region are provided in the active region of the IGBT device; the polycrystalline sidewall protection The structure is located on both sides of the polysilicon gate; the shallow P+ structure is located between the N+ region and the P-base region; the P+ deep base region is set outside the P-base region and surrounds the P-base region to form a hole bypass structure. The invention introduces a highly doped P+ deep base region, improves hole flow distribution, improves electric field distribution, reduces parasitic thyristor latch, and improves IGBT reliability.

Owner:STATE GRID CORP OF CHINA +2

Electrostatic protection structure and forming method thereof

PendingCN114242718APositive Feedback Gain DecreasesReduced injection efficiencyTransistorSolid-state devicesElectrical connectionEngineering

Owner:HUA HONG SEMICON WUXI LTD

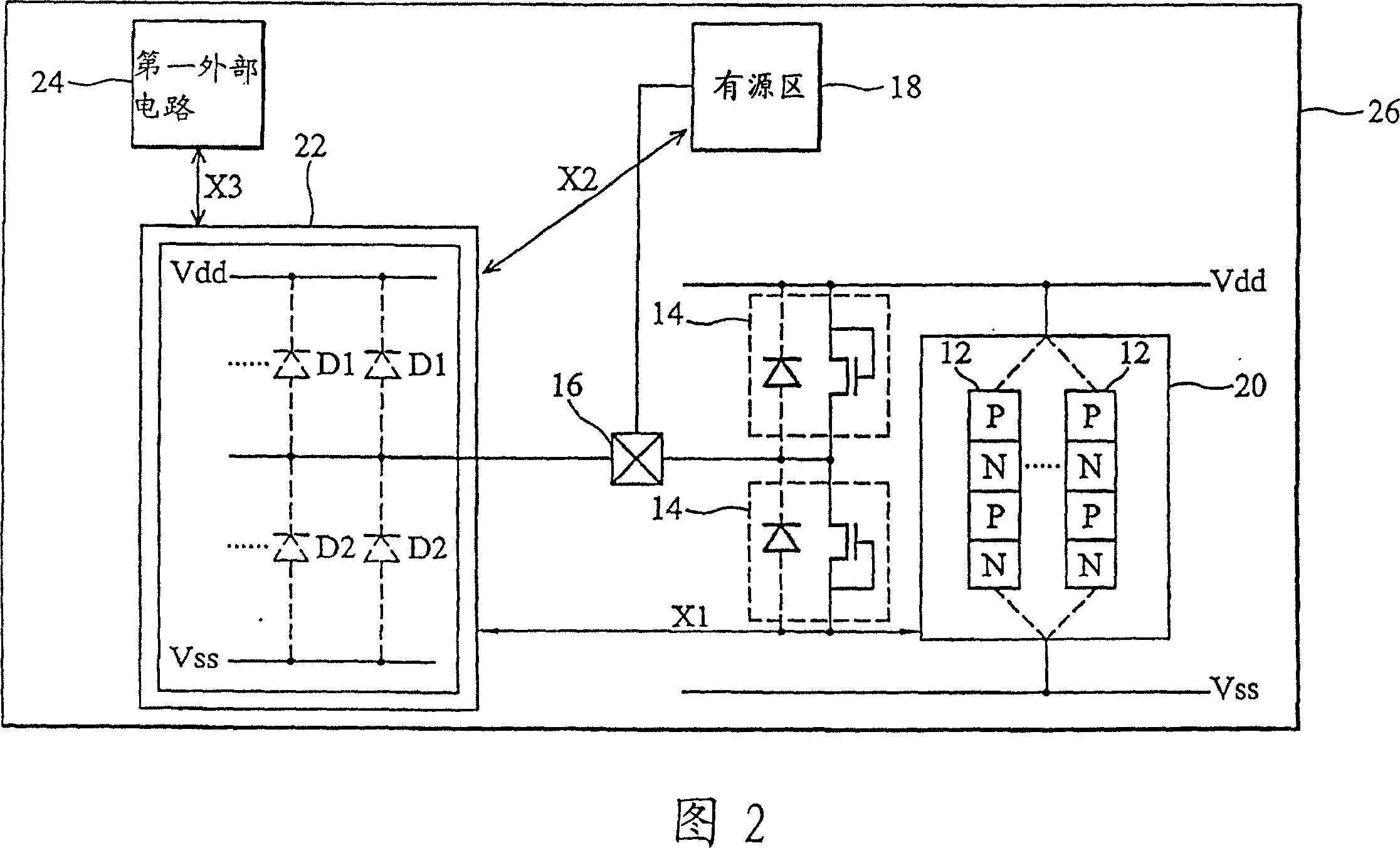

Integrated circuit capable of avoiding bolt-lock effect

ActiveCN1324705CRaise trigger levelReduced chanceTransistorSemiconductor/solid-state device detailsHemt circuitsEngineering

An integrated circuit that can avoid bolt lock effect. It includes the internal circuit on the base plate with at least one SCR structure; at least one ESD protective groupware and a driving area on the base plate and are coupled a bonding sheet; at least the first shunt diode with a positive pole coupling the bonding sheet and a negative pole coupling a first voltage source; at least a second shunt diode with a negative pole coupling the bonding sheet and a positive pole coupling a second voltage source. The distance between the first and the second shunt diodes and the internal circuit, the distance between the ESD proactive groupware and the driving area is no less than 150 micron; a protective ring to surround the first and the second shunt diodes.

Owner:WINBOND ELECTRONICS CORP

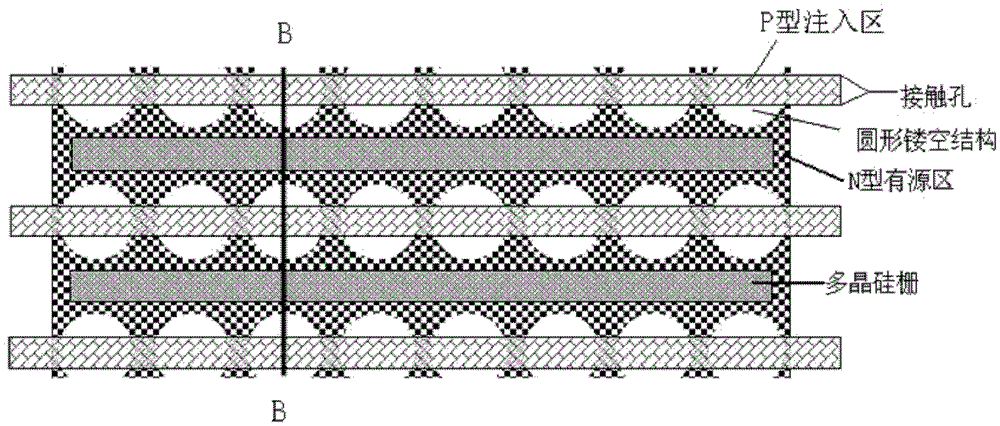

A Trench Type Insulated Gate Field Effect Transistor

ActiveCN103165673BSolve the problem that cannot be connectedReduce areaSemiconductor devicesElectrical resistance and conductanceField-effect transistor

The invention discloses a groove type insulated gate field effect tube. The groove type insulated gate field effect tube comprises an N-type epitaxial layer. A P-type injection layer is formed below the N-type epitaxial layer, a groove is formed in the upper portion of the N-type epitaxial layer, a gate oxide layer and a polysilicon gate are formed in the groove, a P-type trap and an N-type active area are formed on two sides of the groove, and the N-type active area is placed above the P-type trap. A circular hollowed-out structure is formed in the N-type active area, interlayer oxidation media are formed above the groove, the circular hollowed-out structure and the N-type active area, a P-type injection area is arranged below a contact hole, and the contact hole penetrates through the interlayer oxidation media and connects the N-type active area and the P-type injection area. The groove type insulated gate field effect tube reduces spurious base resistance (RB) of an NPN and reduces the area of an NPN emitter of a spurious thyristor at the same time, and therefore happening rates of latch-up effects of the spurious thyristor are reduced.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com