Integrated circuit capable of avoiding bolt-lock effect

A latch-up effect, integrated circuit technology, applied in circuits, electrical components, electro-solid devices, etc., can solve the problems of increasing circuit complexity and layout space, reduce the chance of latch-up effect, and improve the trigger level. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

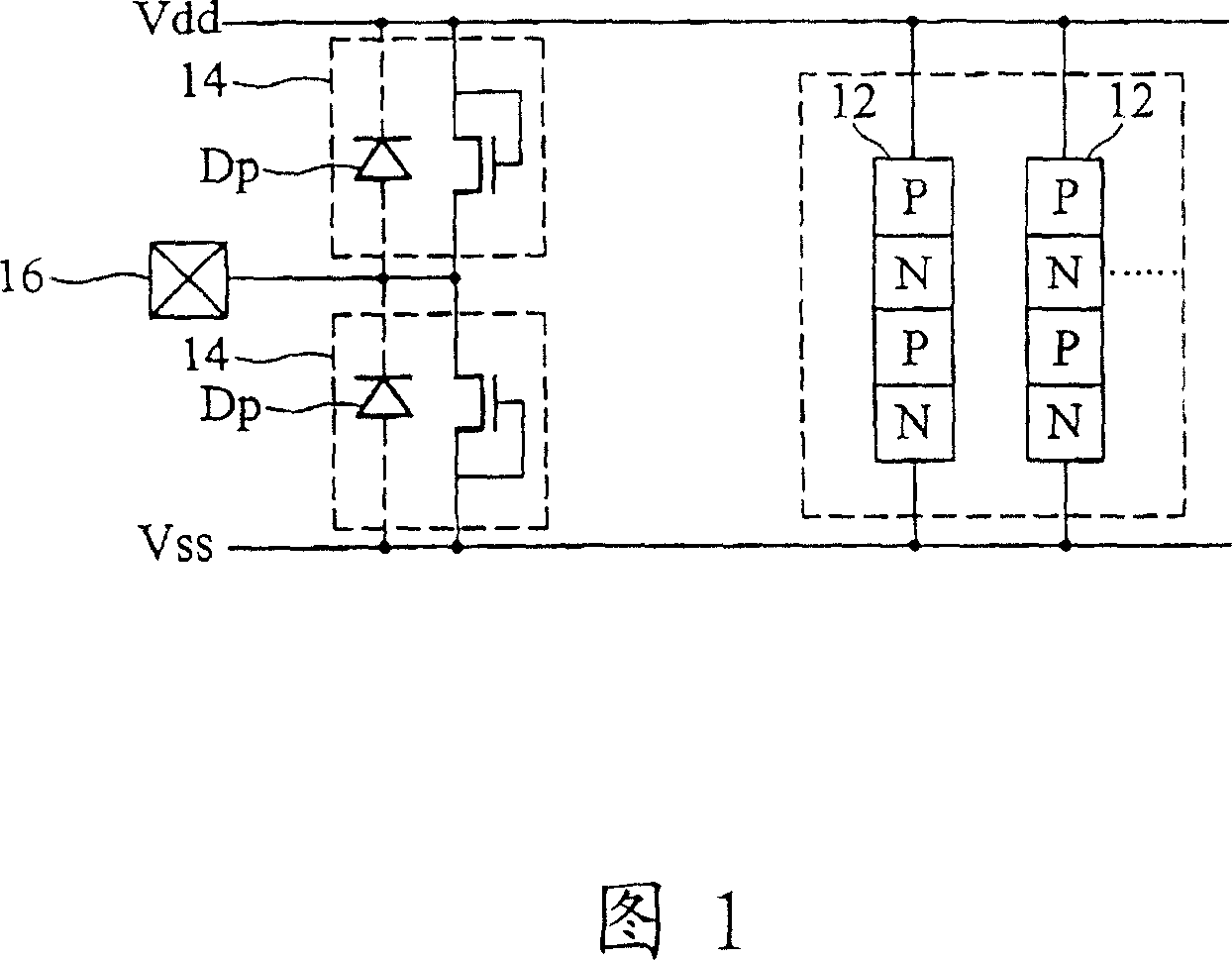

[0016] There are many factors that can cause latch-up in CMOS, however, the most obvious ones are substrate currents generated by hot carrier effects during IC operation, and / or caused by noise present on pads The forward current of the parasitic diode. And most of the substrate current generated by the latch-up effect is injected through the parasitic diode formed by the electrostatic discharge (ESD) protection circuit on the chip.

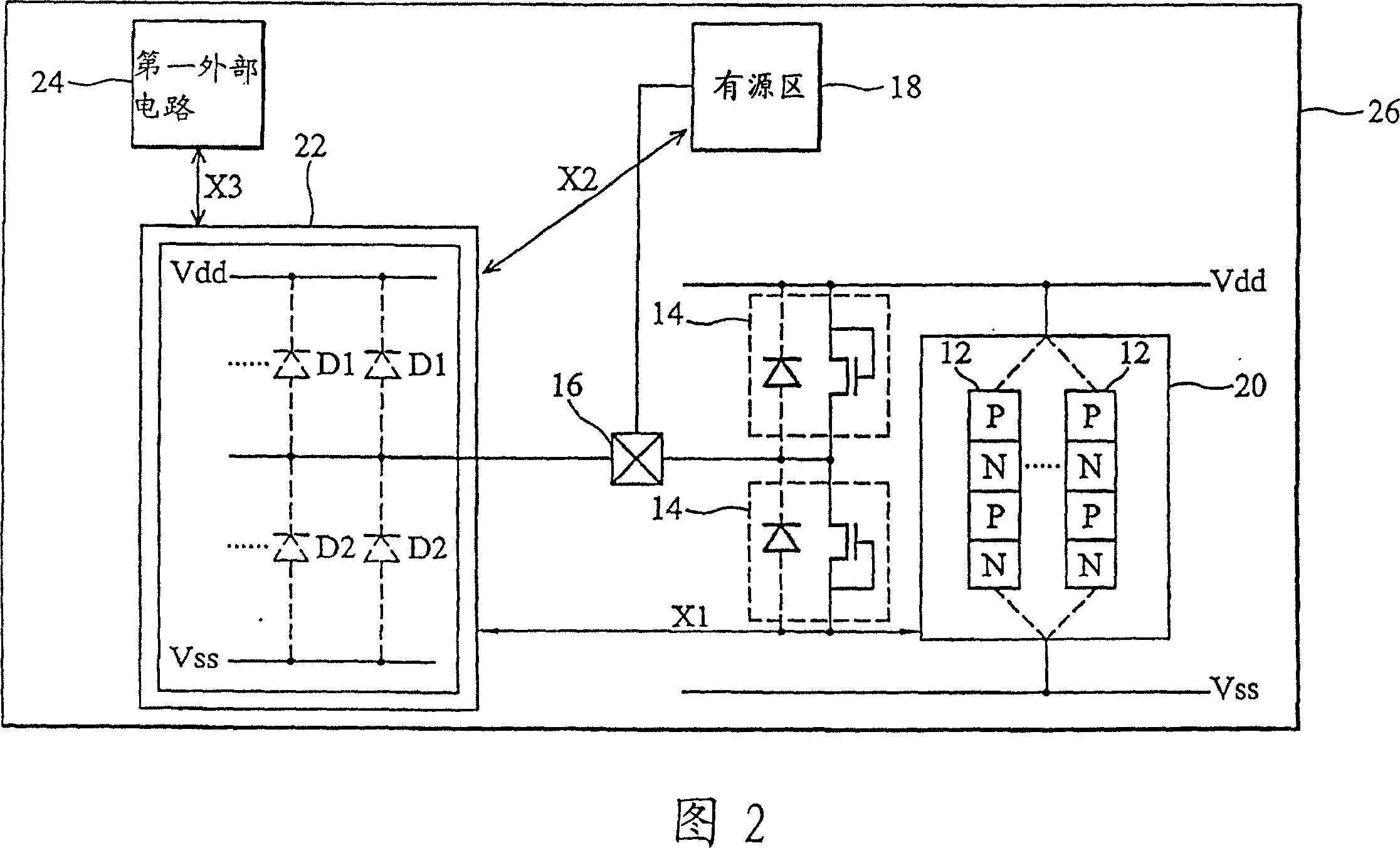

[0017] Unlike the prior art, the present invention uses a passive method of prohibiting conduction of the parasitic SCR to prevent the occurrence of latch-up effect. The spirit of the present invention is to reduce the influence of the trigger source of the latch-up effect by adding a shunt diode as the shunt path of the substrate current without changing the layout of the original internal circuit and ESD protection components, thereby reducing the chance of the latch-up effect occurring .

[0018] FIG. 2 is used to illustrate the method for a...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com