Source/drain ion injecting method for lowering defect on substrate

An ion implantation and substrate technology, which is applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., and can solve problems such as increasing manufacturing costs, affecting the performance of other components, and dislocation defects.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

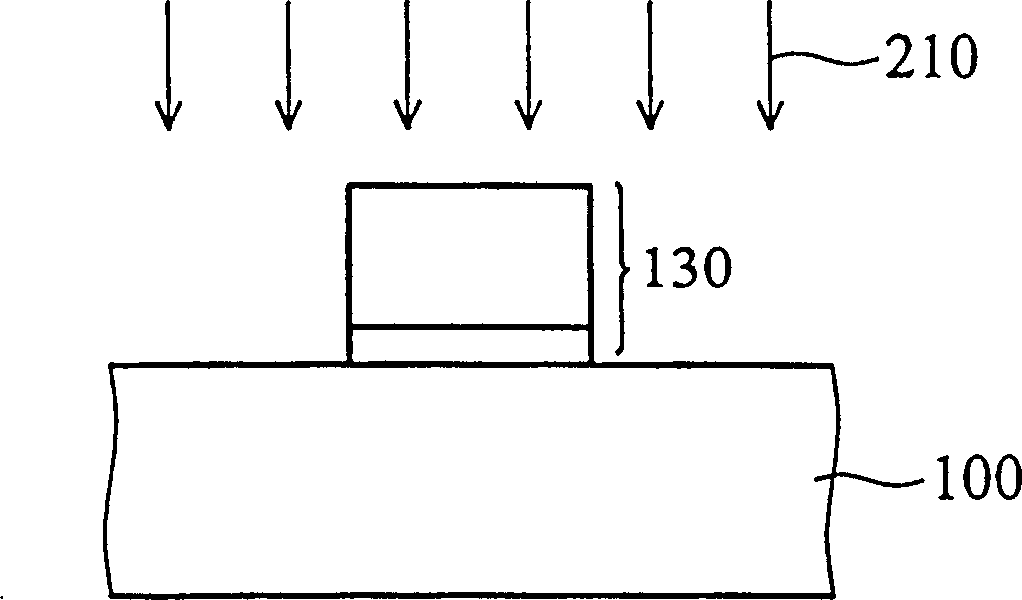

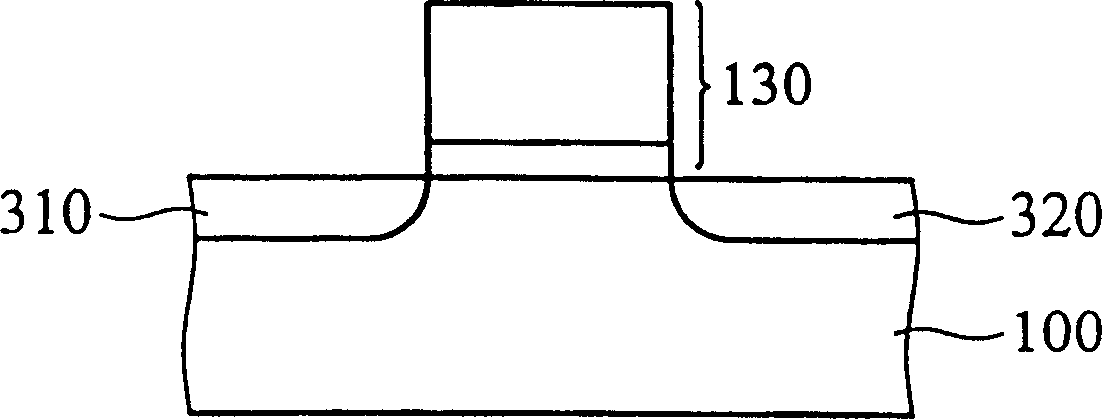

[0014] Embodiments of the present invention will be described below using the cross-sectional views of the manufacturing method shown in FIGS. 1-3. It should be noted here that although the present embodiment takes the MOS manufacturing method as an example, it does not limit the present invention. That is to say, the present invention is applicable to ion implantation manufacturing methods of any semiconductor products (such as CMOS, various memories, etc.).

[0015] First, please refer to figure 1 , providing a substrate 100 such as a silicon substrate (Si substrate). Then, using thermal oxidation, chemical vapor deposition or chemical oxidation, etc., to form a SiO 2 A gate oxide layer (not shown) of the first layer, and then a gate layer (not shown), such as a polysilicon layer, is deposited by chemical vapor deposition. Then, a patterned gate oxide layer 110 and a patterned gate layer 120 are formed through a photolithography process to form a gate structure 130 .

[...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com