Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

62results about How to "Reduce gate charge" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

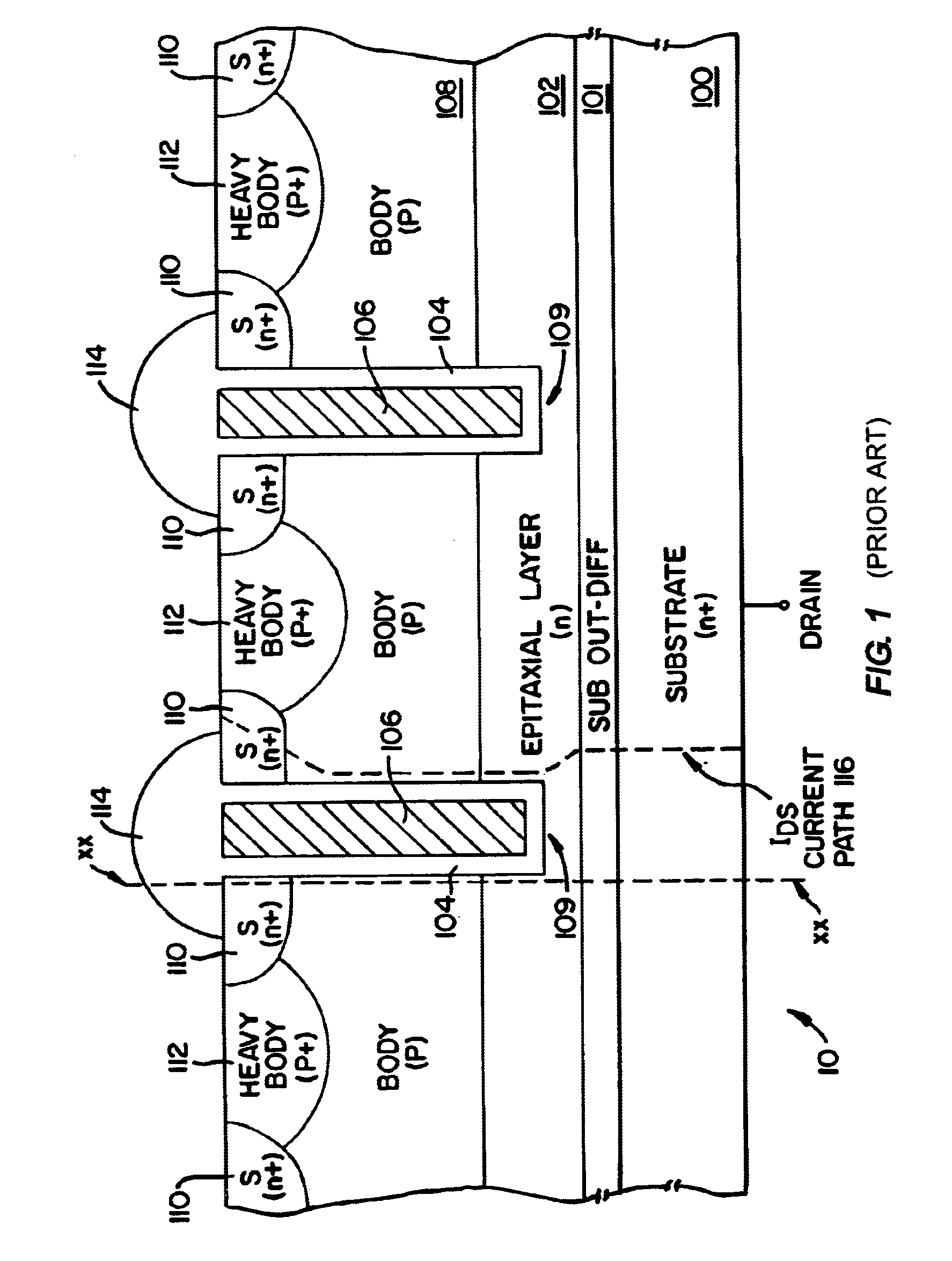

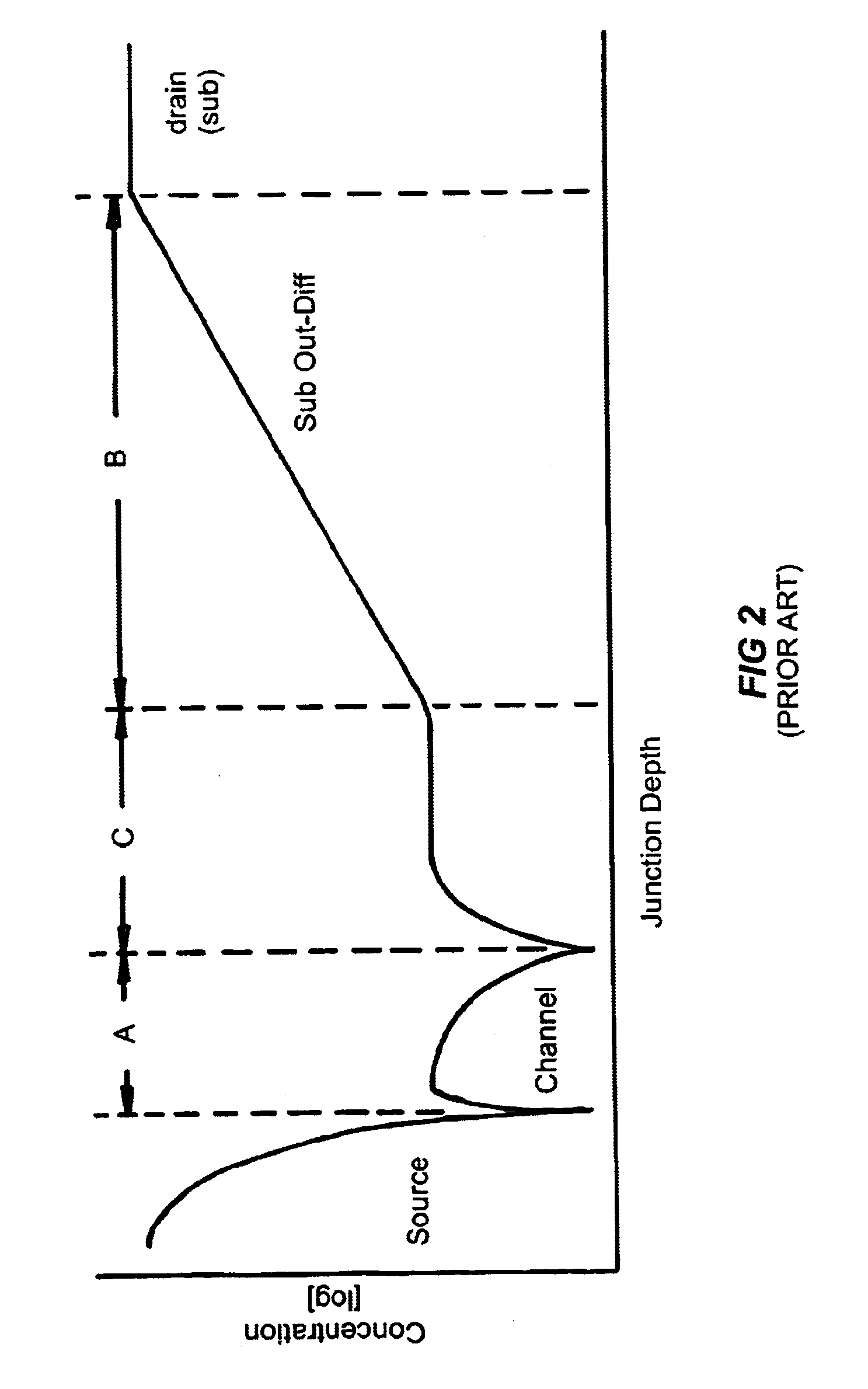

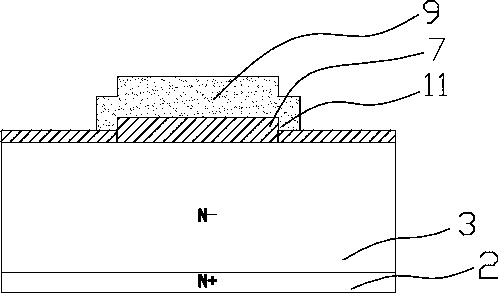

Vertical MOSFET with ultra-low resistance and low gate charge

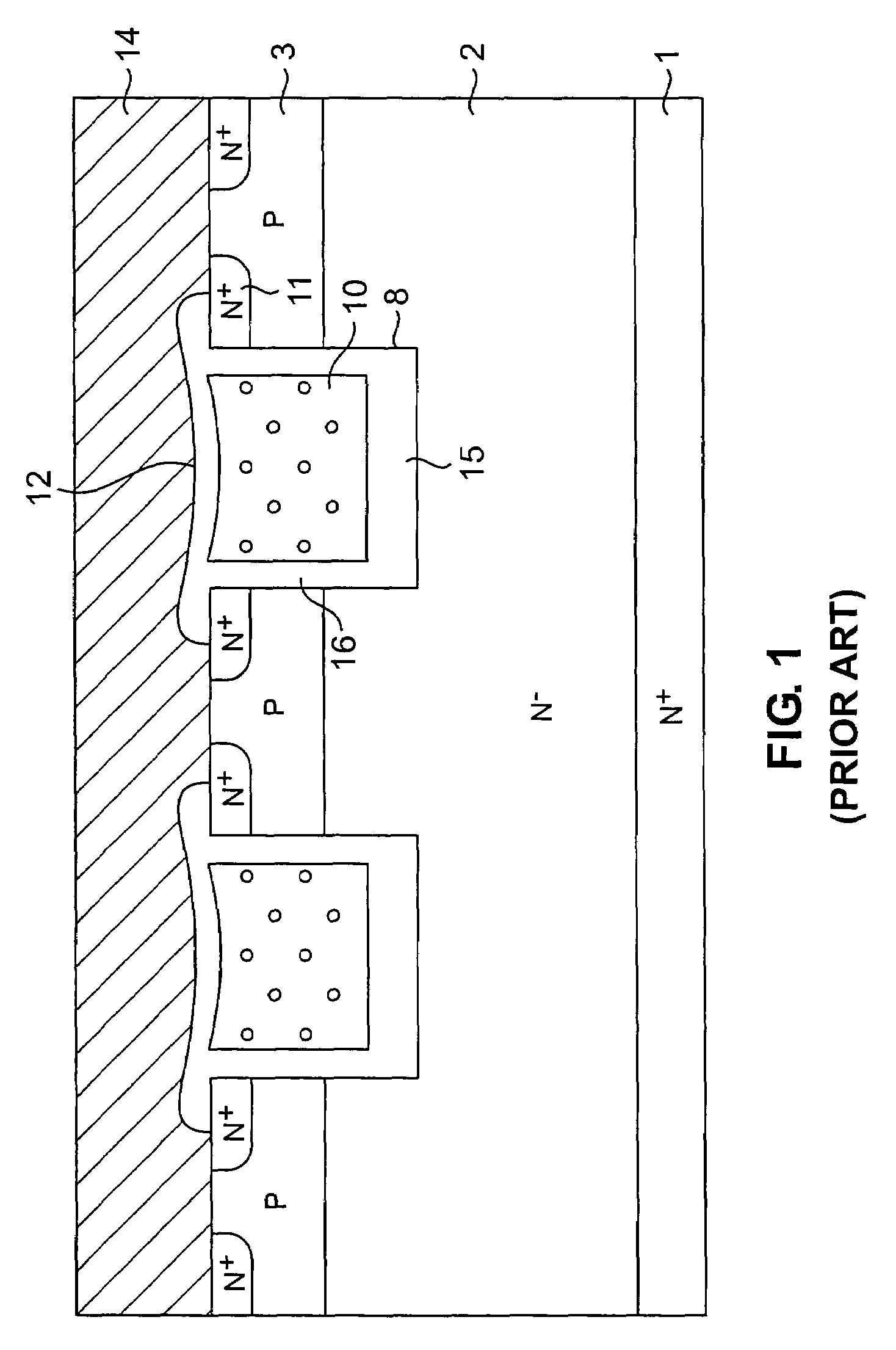

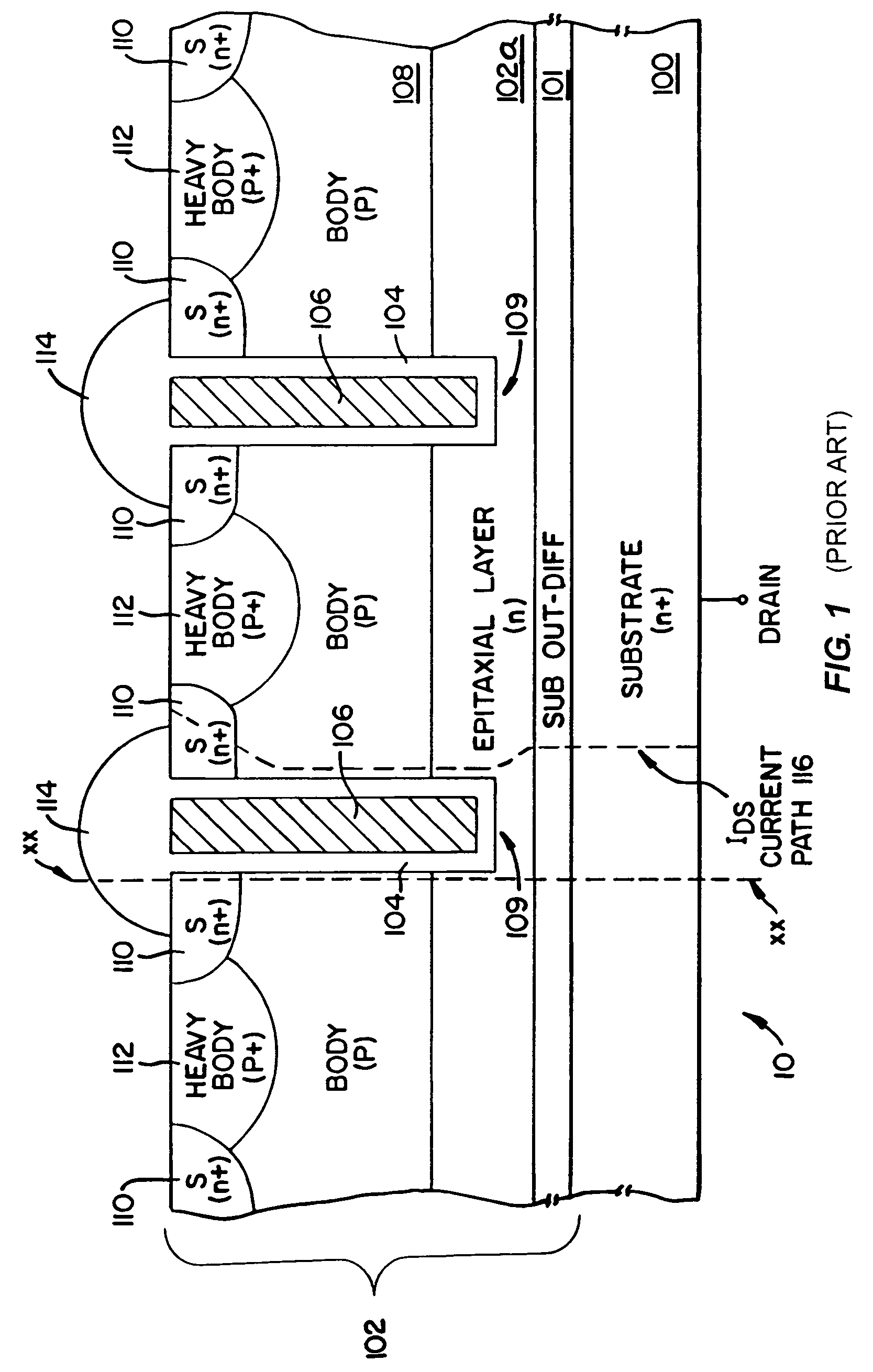

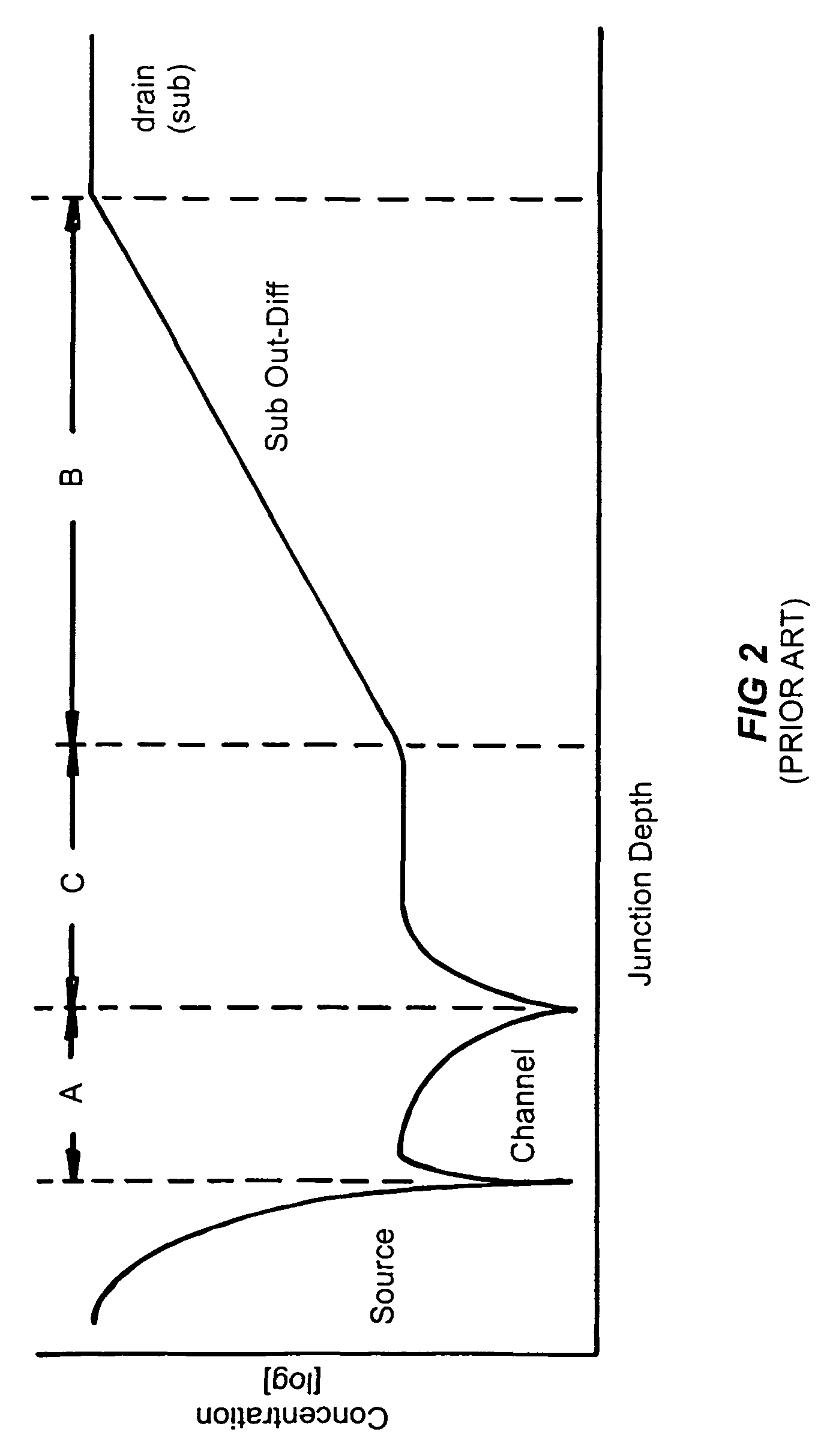

InactiveUS6696726B1Minimize changesReduce gate chargeSemiconductor/solid-state device manufacturingSemiconductor devicesMOSFETField-effect transistor

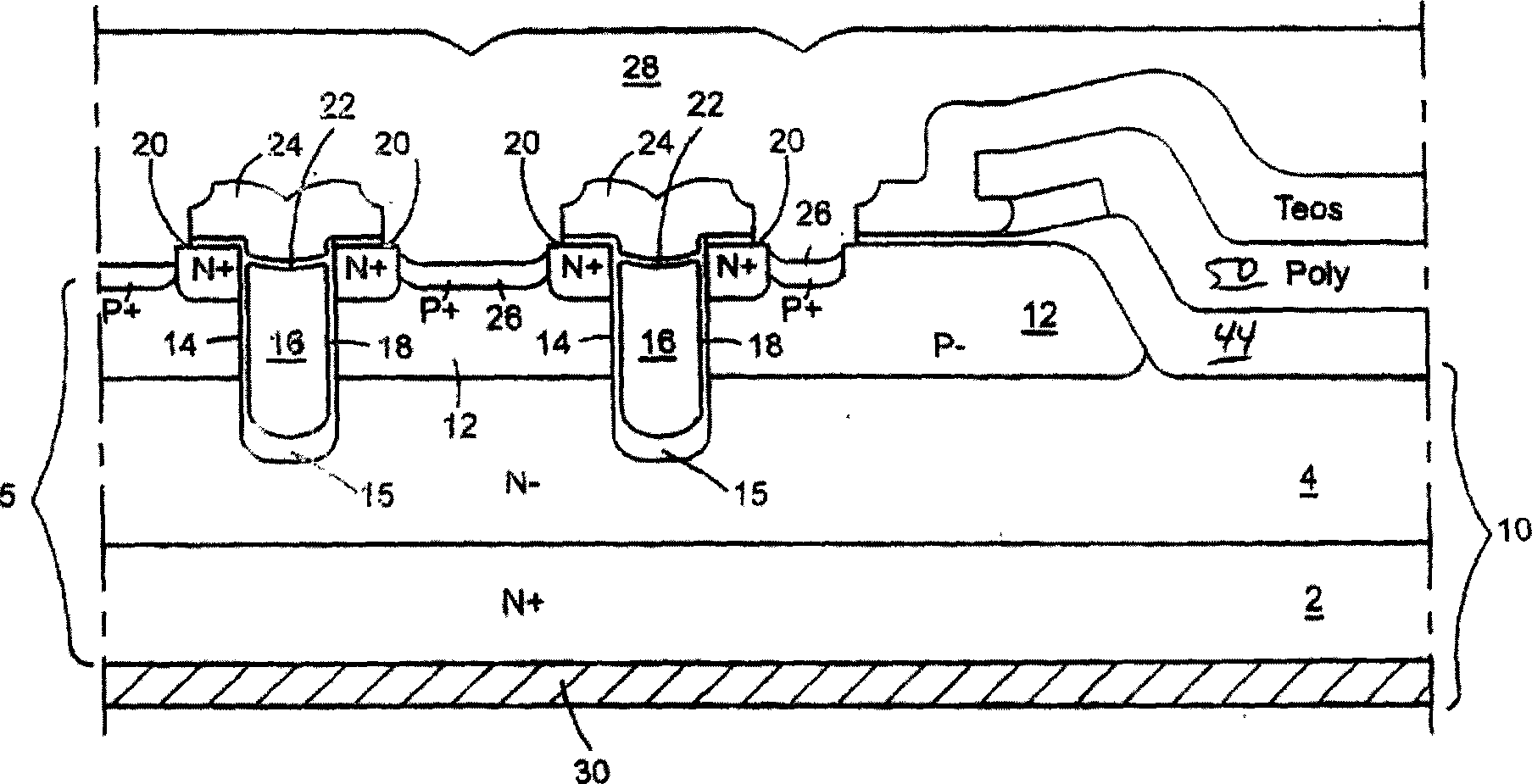

A vertical trench double-diffused metal-oxide-semiconductor (DMOS) field effect transistor characterized by a reduced drain-to-source resistance and a lower gate charge and providing a high transconductance and an enhanced frequency response.

Owner:SEMICON COMPONENTS IND LLC

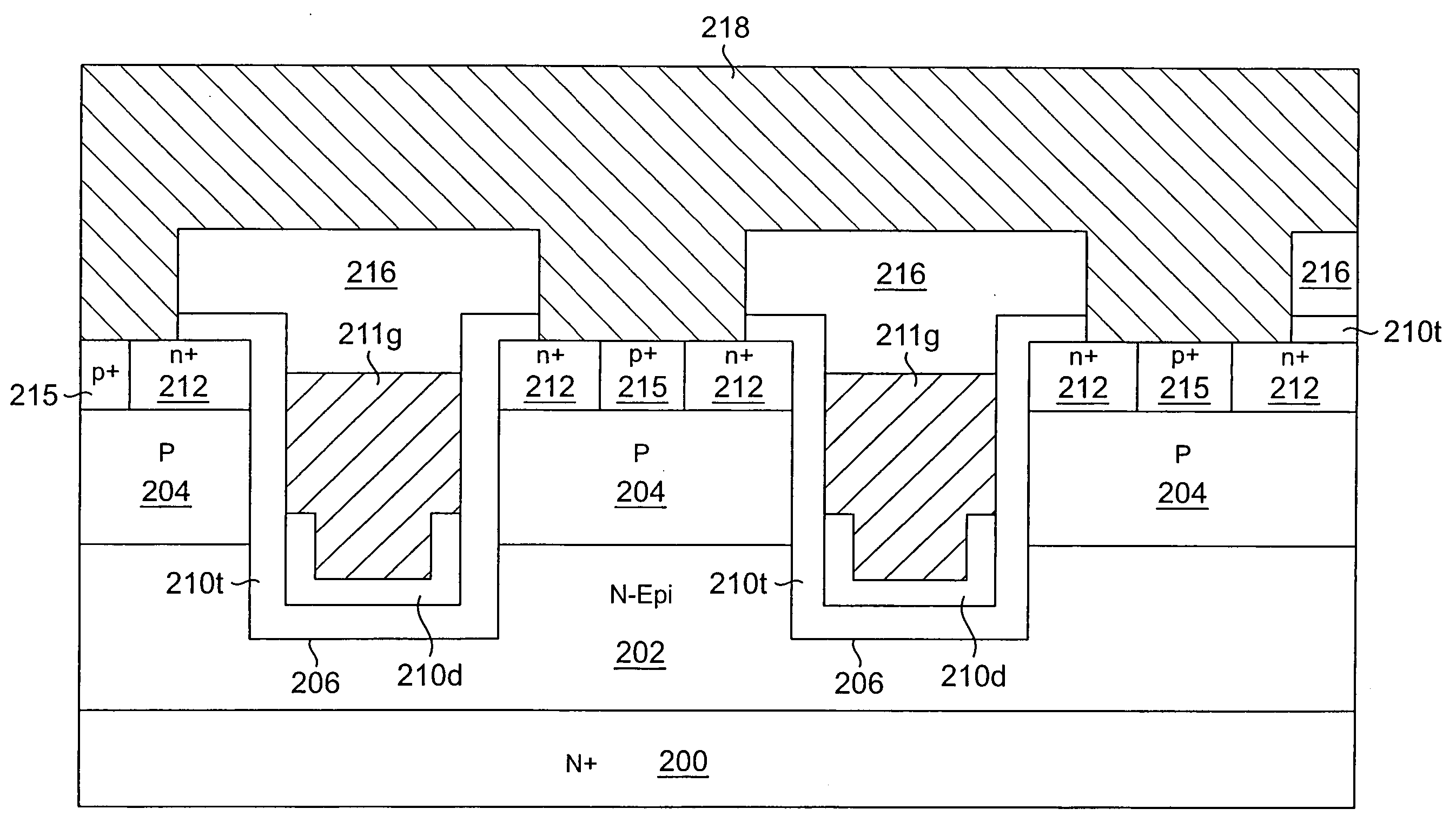

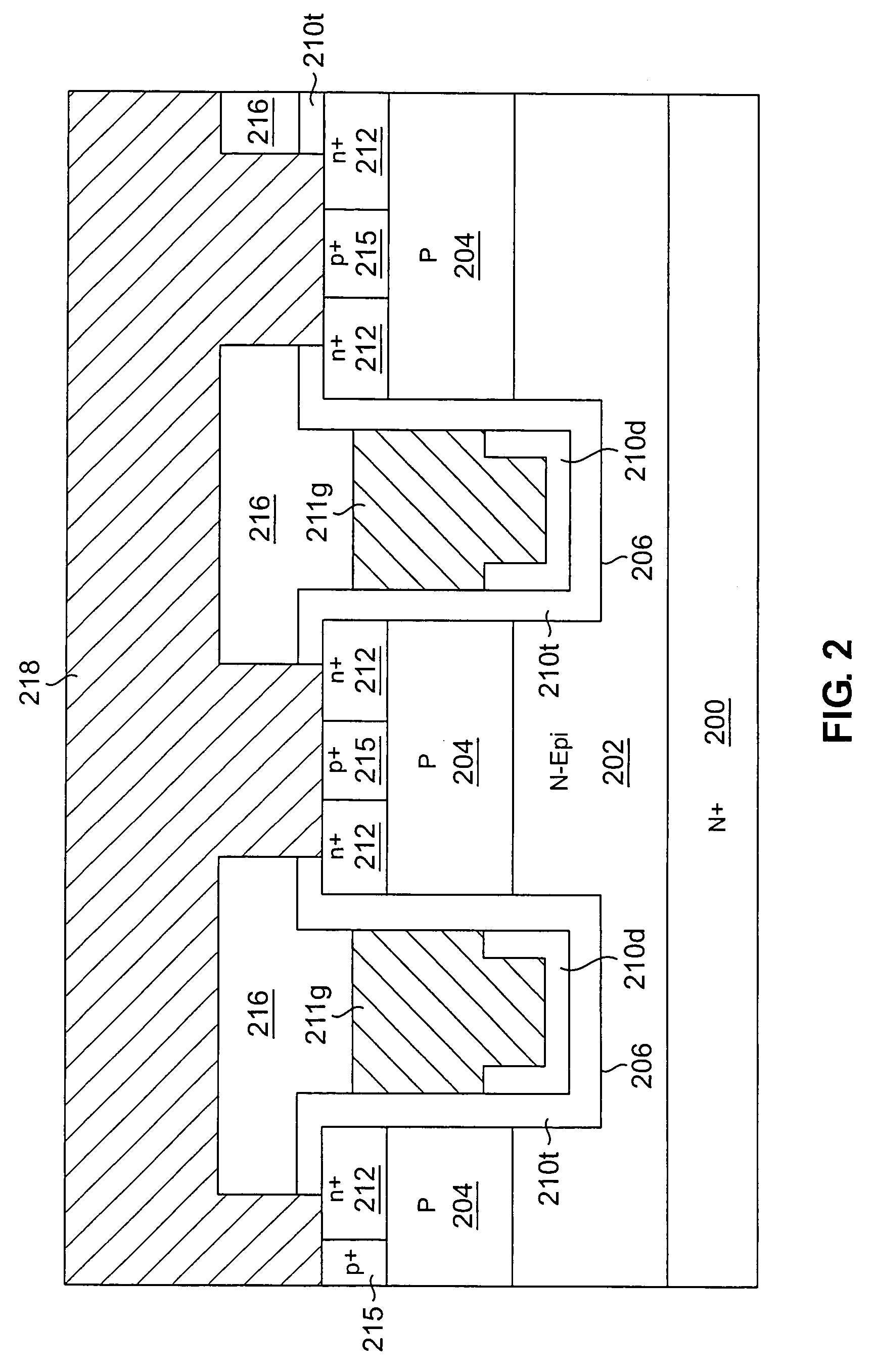

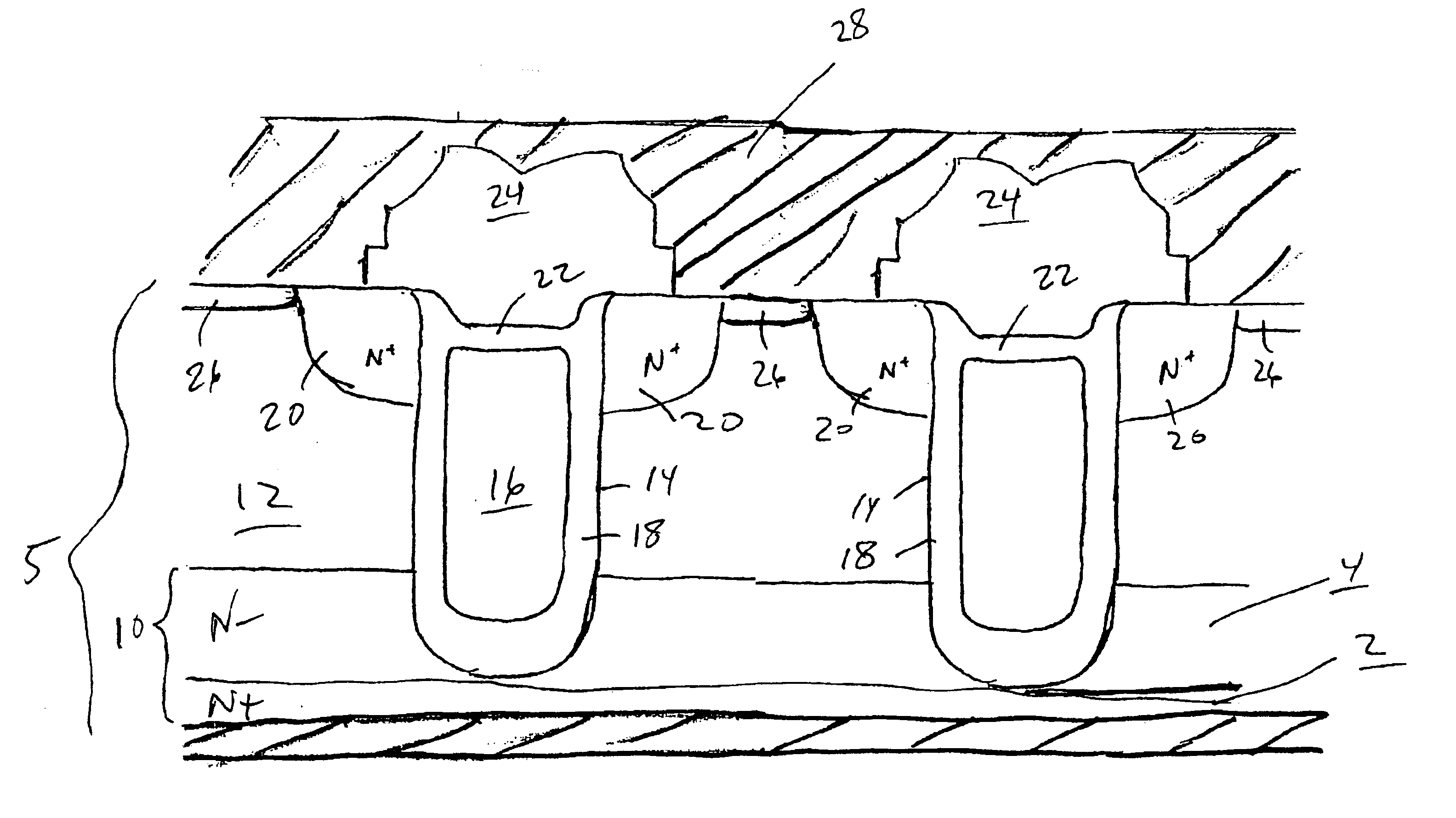

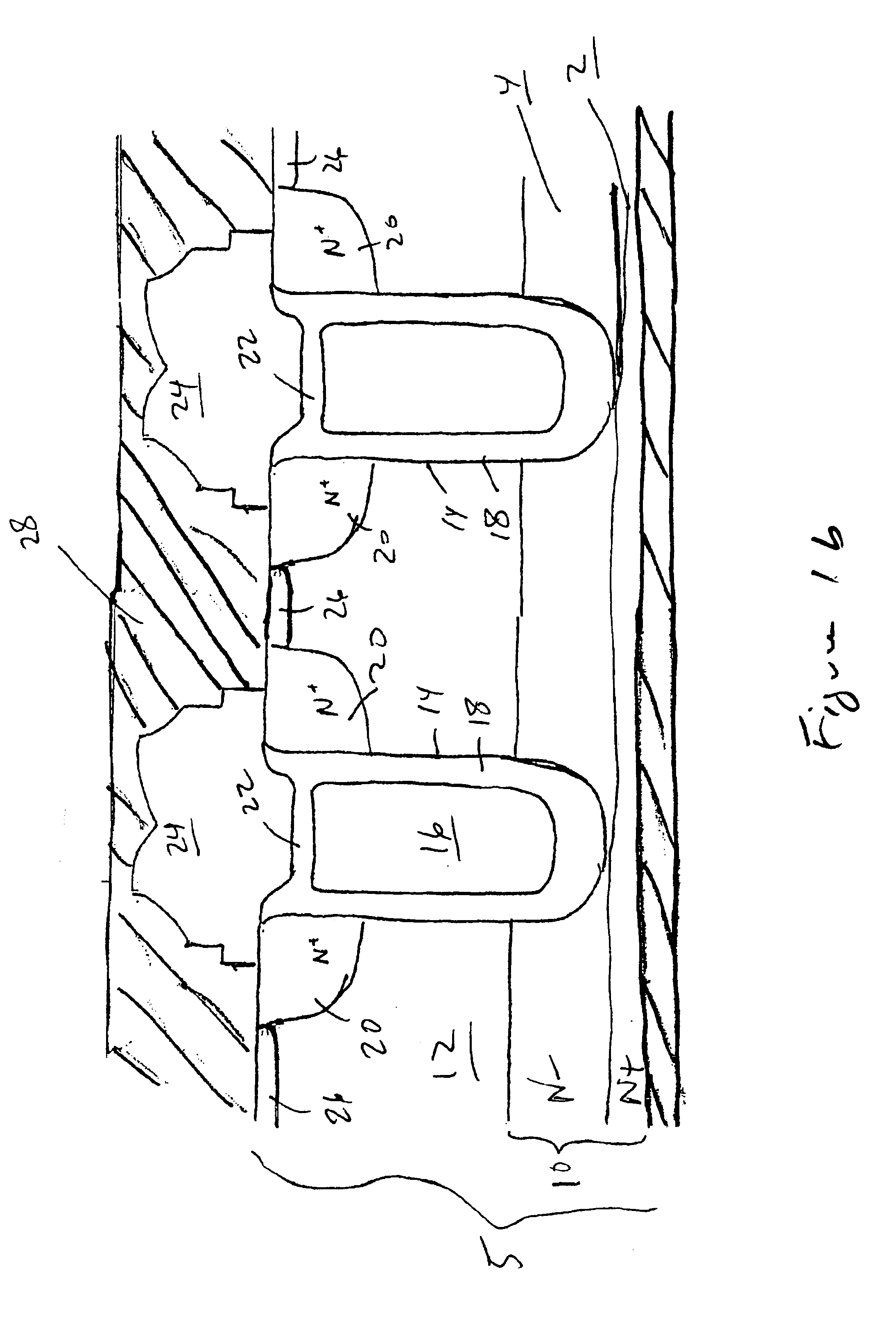

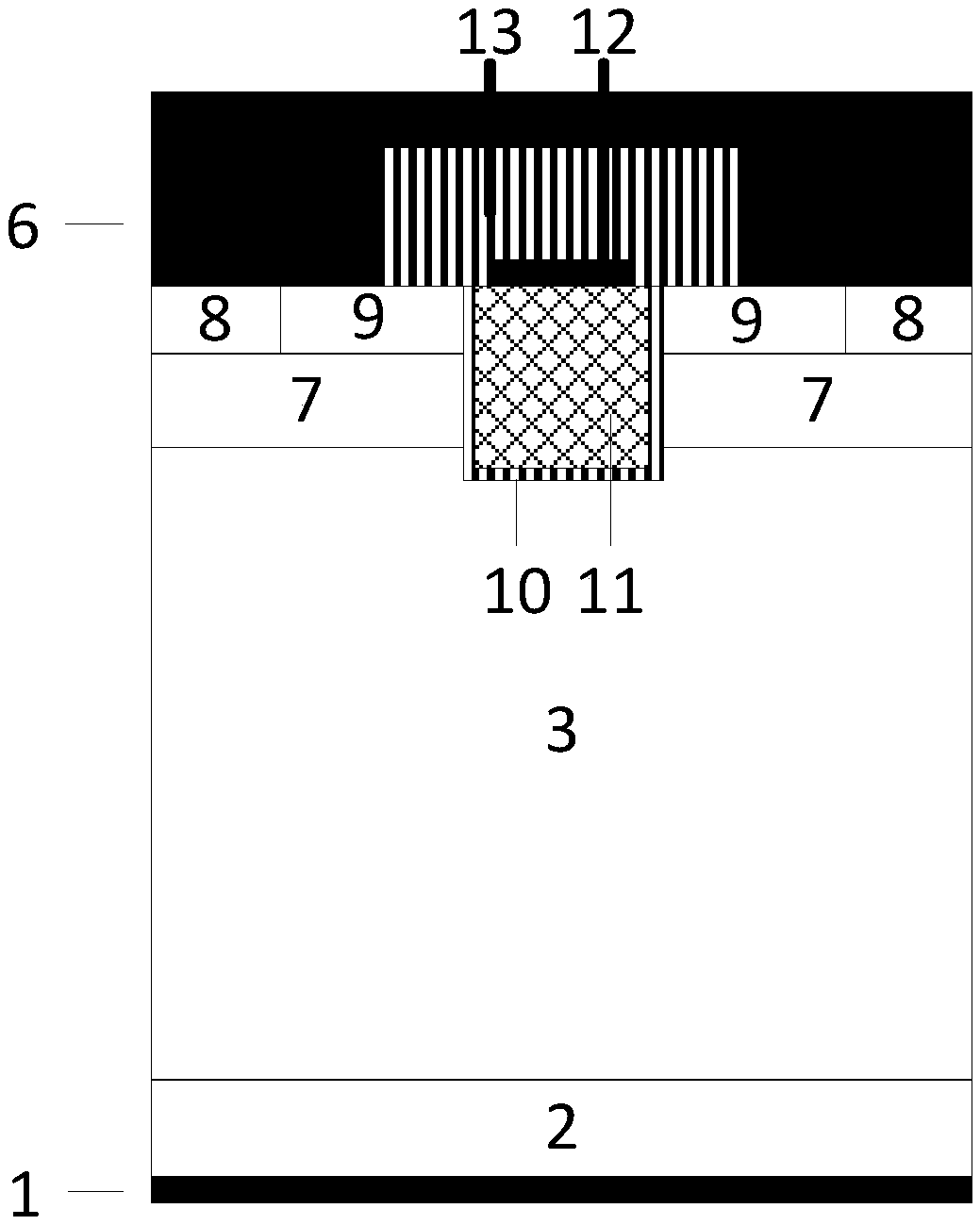

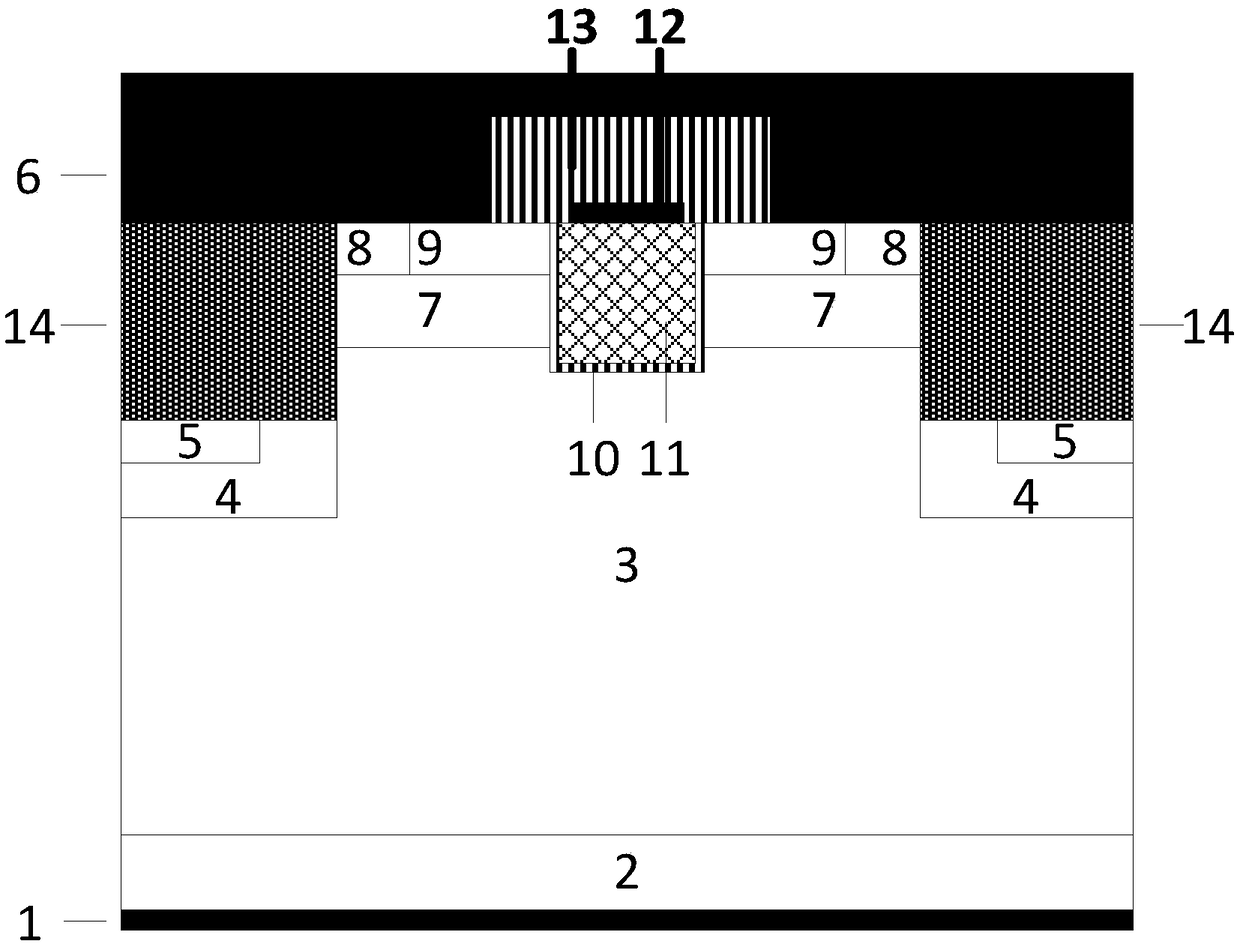

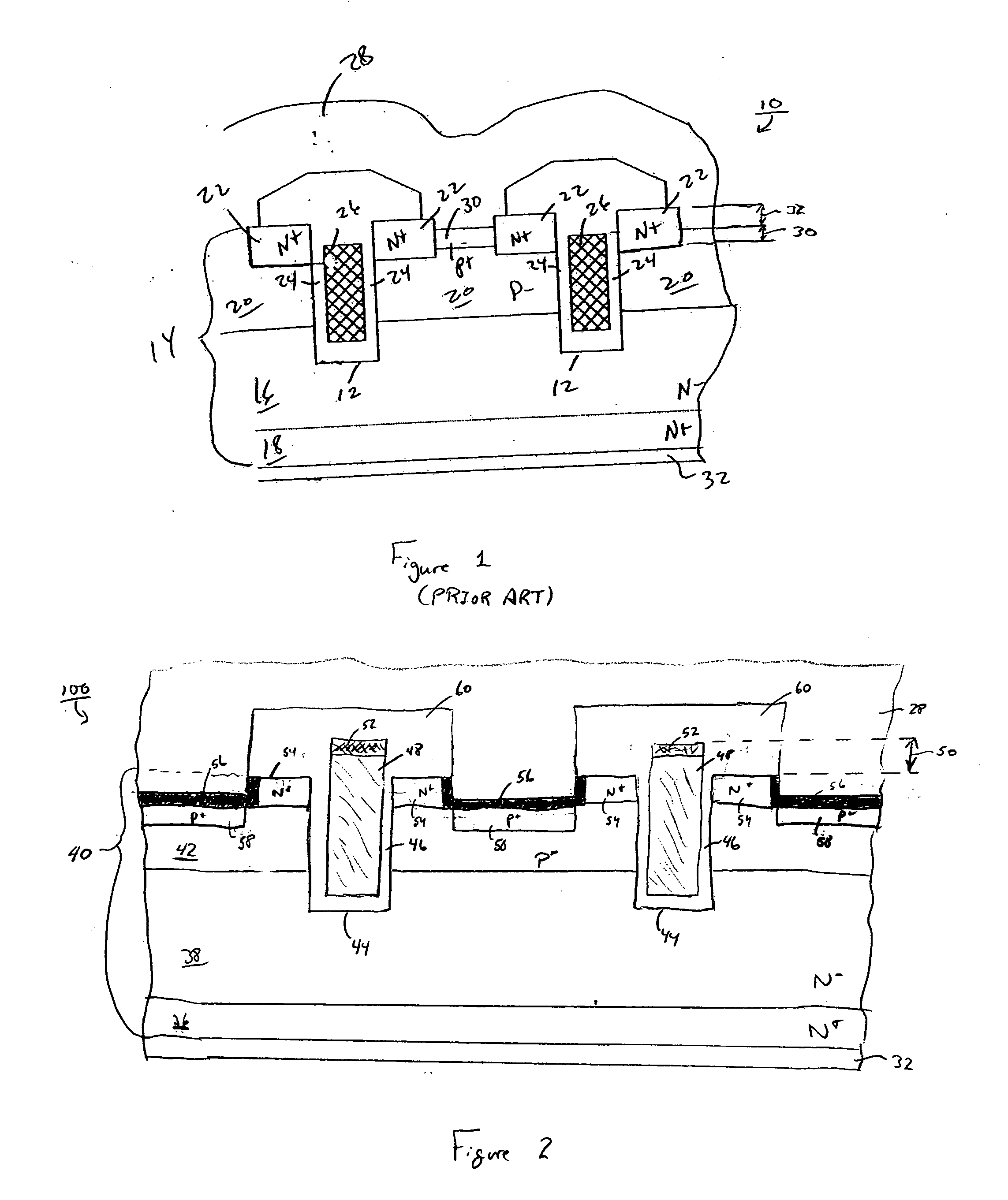

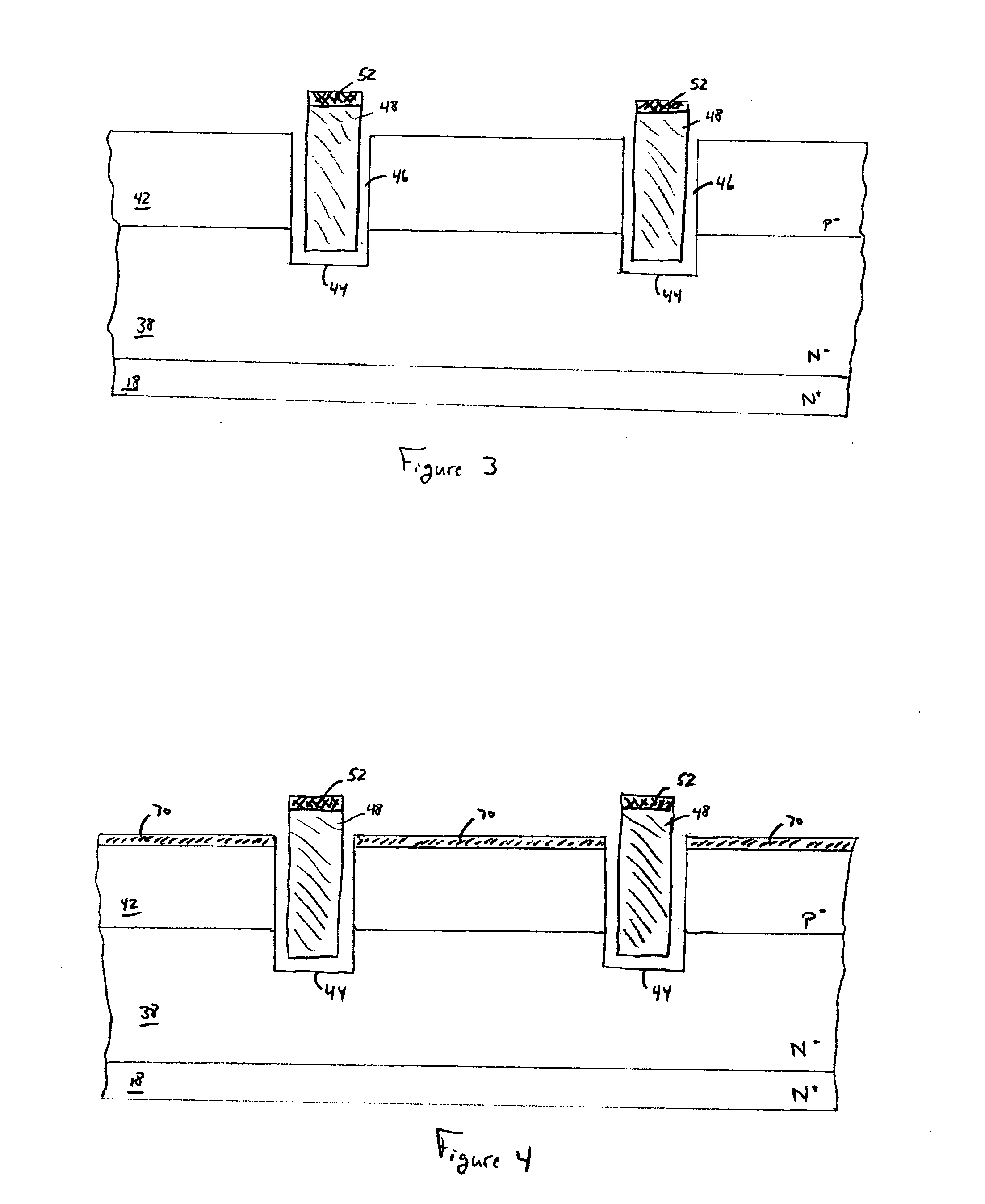

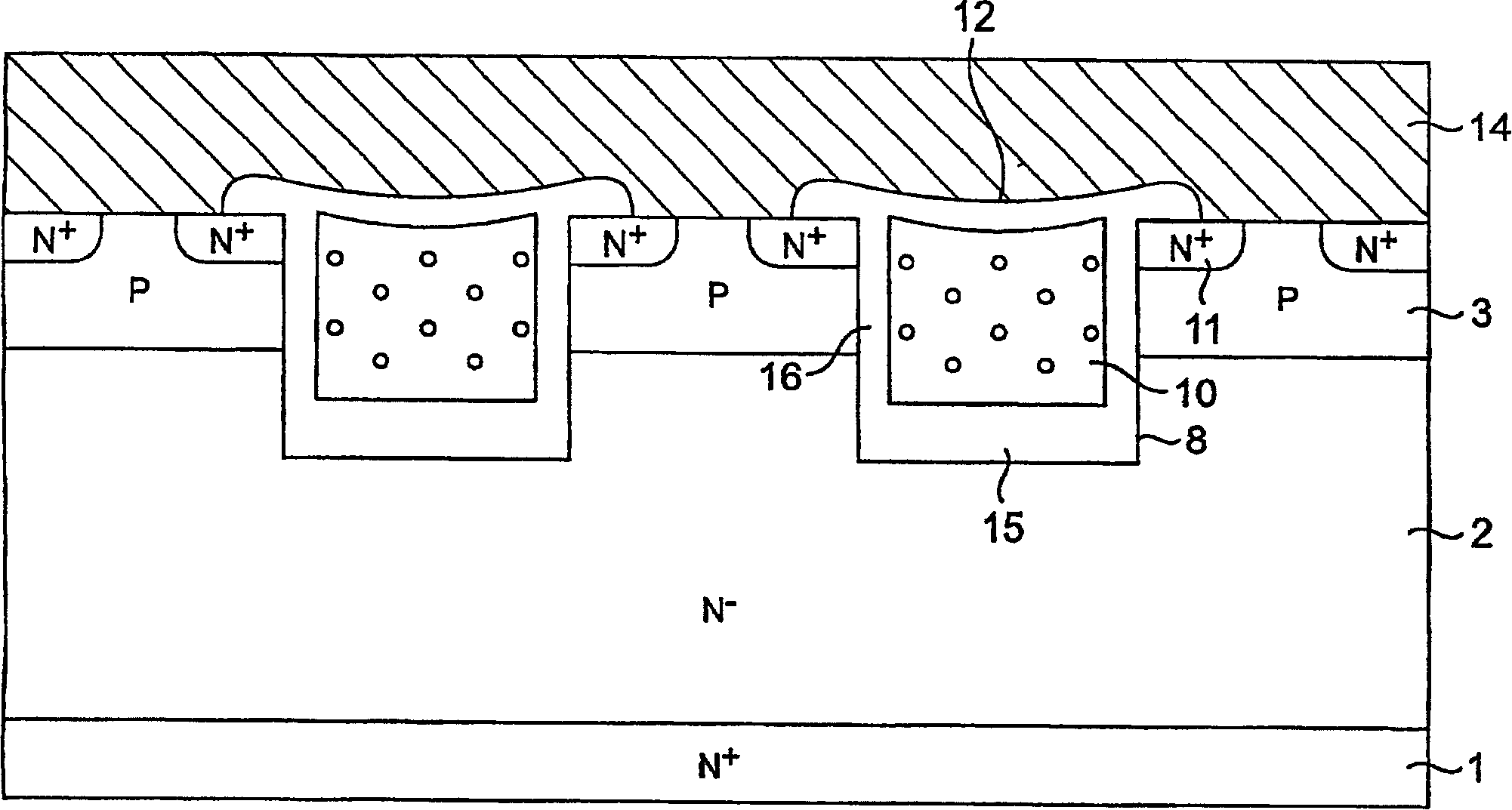

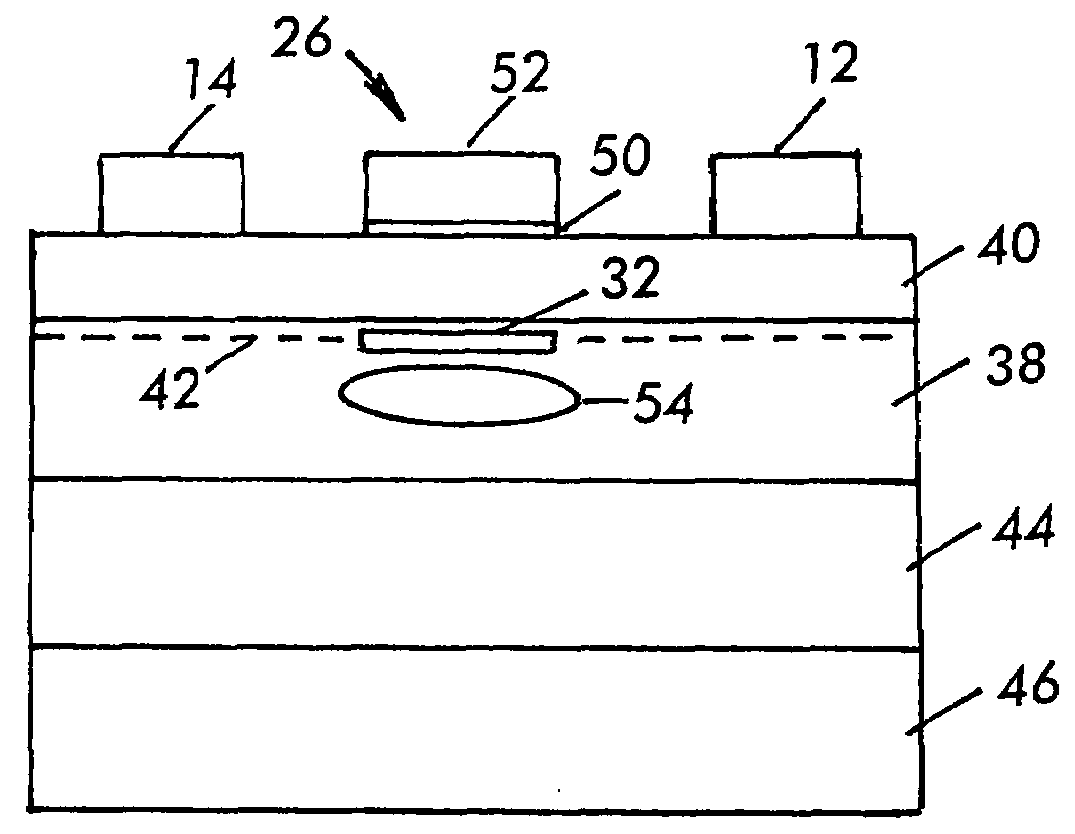

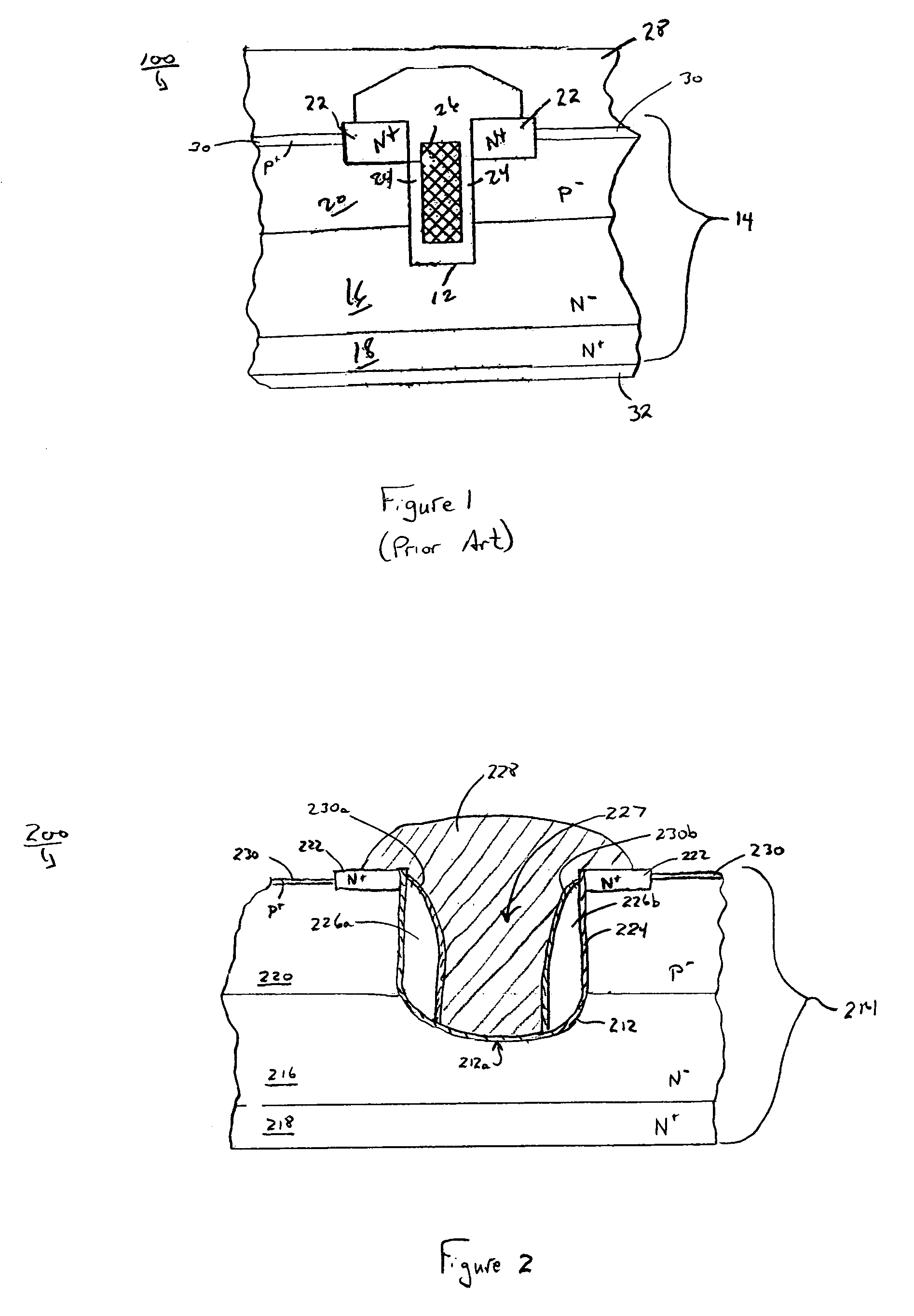

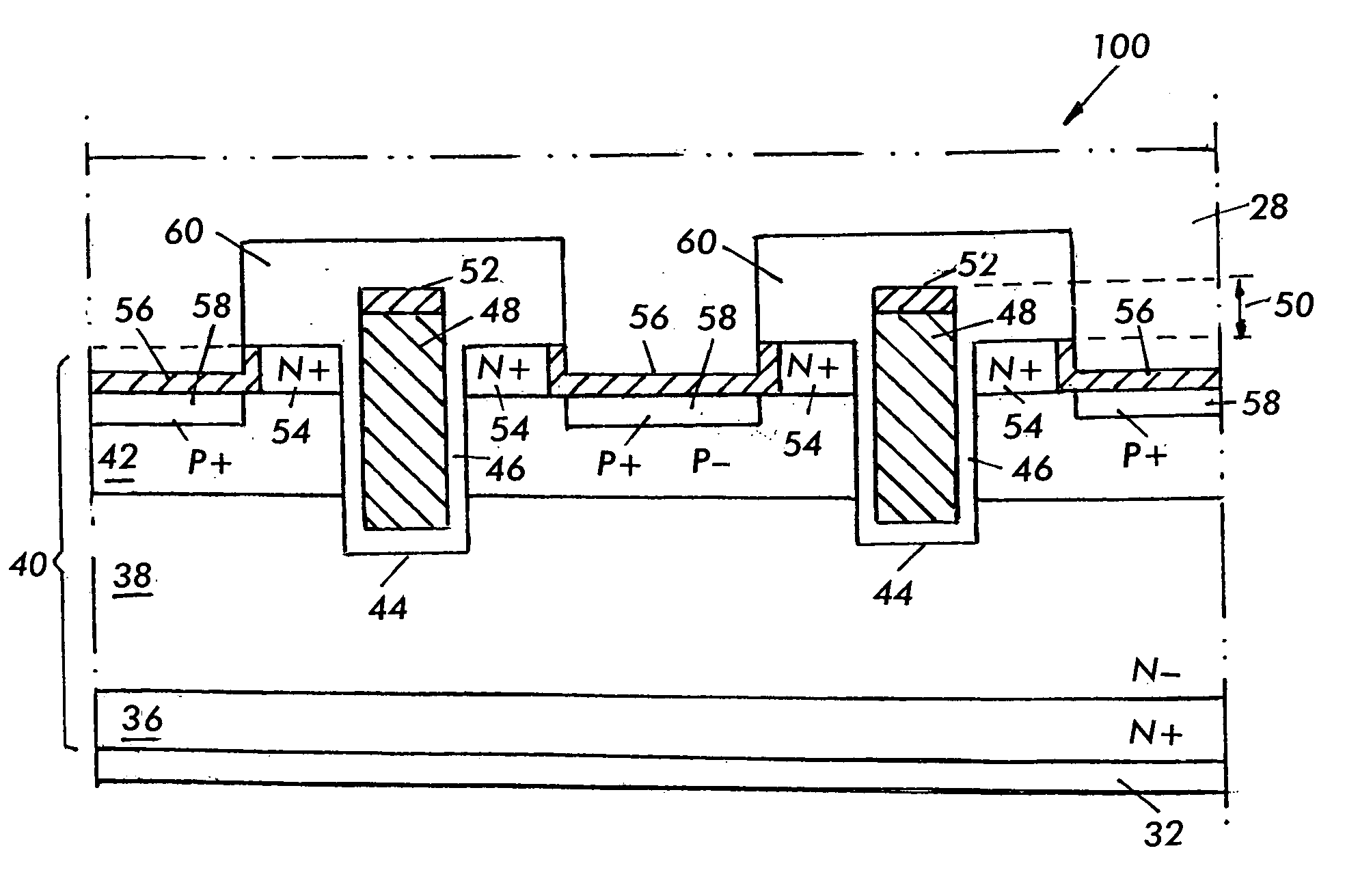

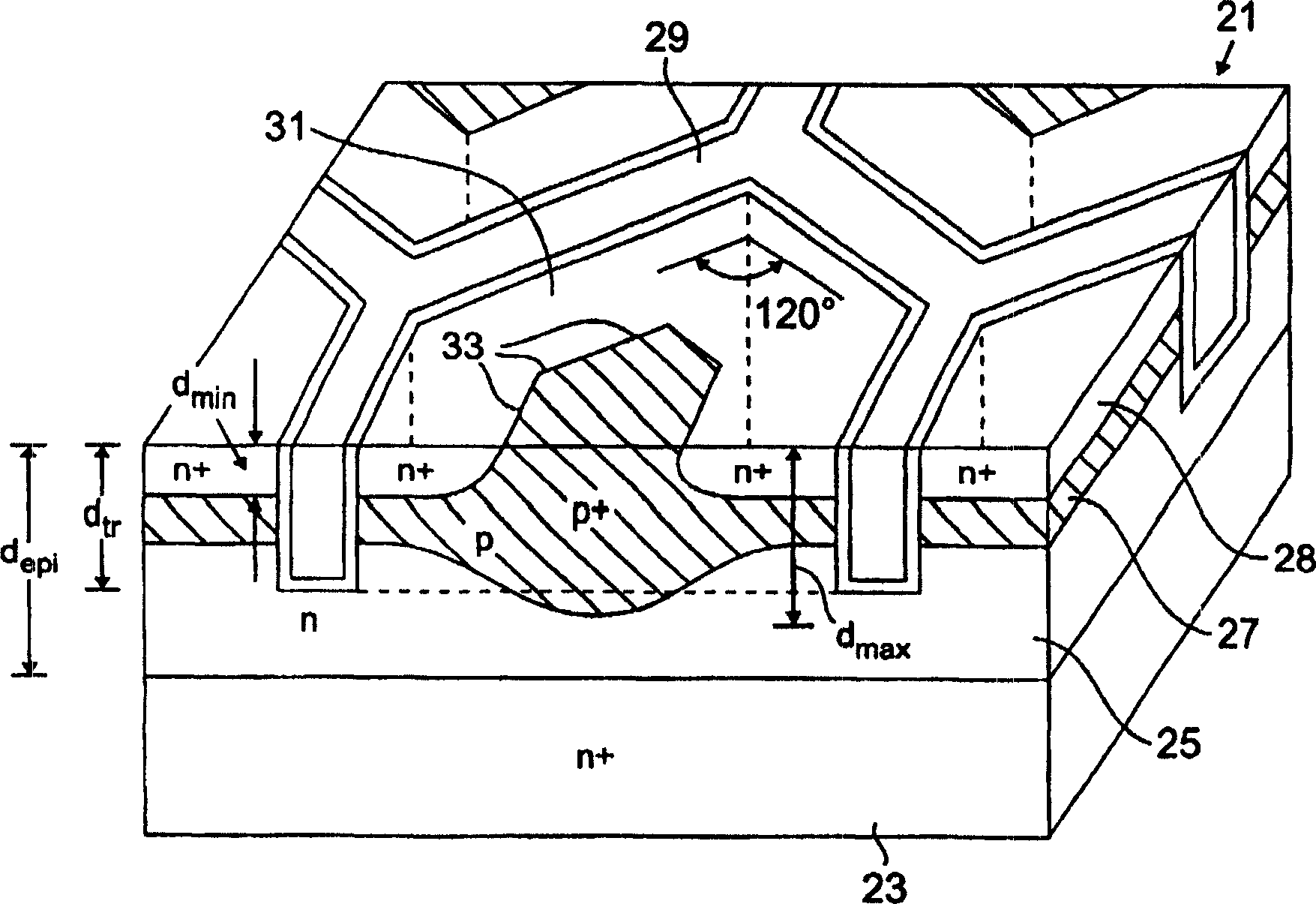

Trench MOSFET having low gate charge

InactiveUS6979621B2High cell densityLow gate chargeSolid-state devicesSemiconductor/solid-state device manufacturingBody regionTrench mosfet

A trench MOSFET device comprising: (a) a silicon substrate of a first conductivity type (preferably N-type conductivity); (b) a silicon epitaxial layer of the first conductivity type over the substrate, the epitaxial layer having a lower majority carrier concentration than the substrate; (c) a body region of a second conductivity type (preferably P-type conductivity) within an upper portion of the epitaxial layer; (d) a trench having trench sidewalls and a trench bottom, which extends into the epitaxial layer from an upper surface of the epitaxial layer and through the body region of the device; (f) an oxide region lining the trench, which comprises a lower segment covering at least the trench bottom and upper segments covering at least upper regions of the trench sidewalls; (g) a conductive region within the trench adjacent the oxide region; and (h) a source region of the first conductivity type within an upper portion of the body region and adjacent the trench. The lower segment of the oxide region is thicker than the upper segments of the oxide region in this embodiment.

Owner:GEN SEMICON

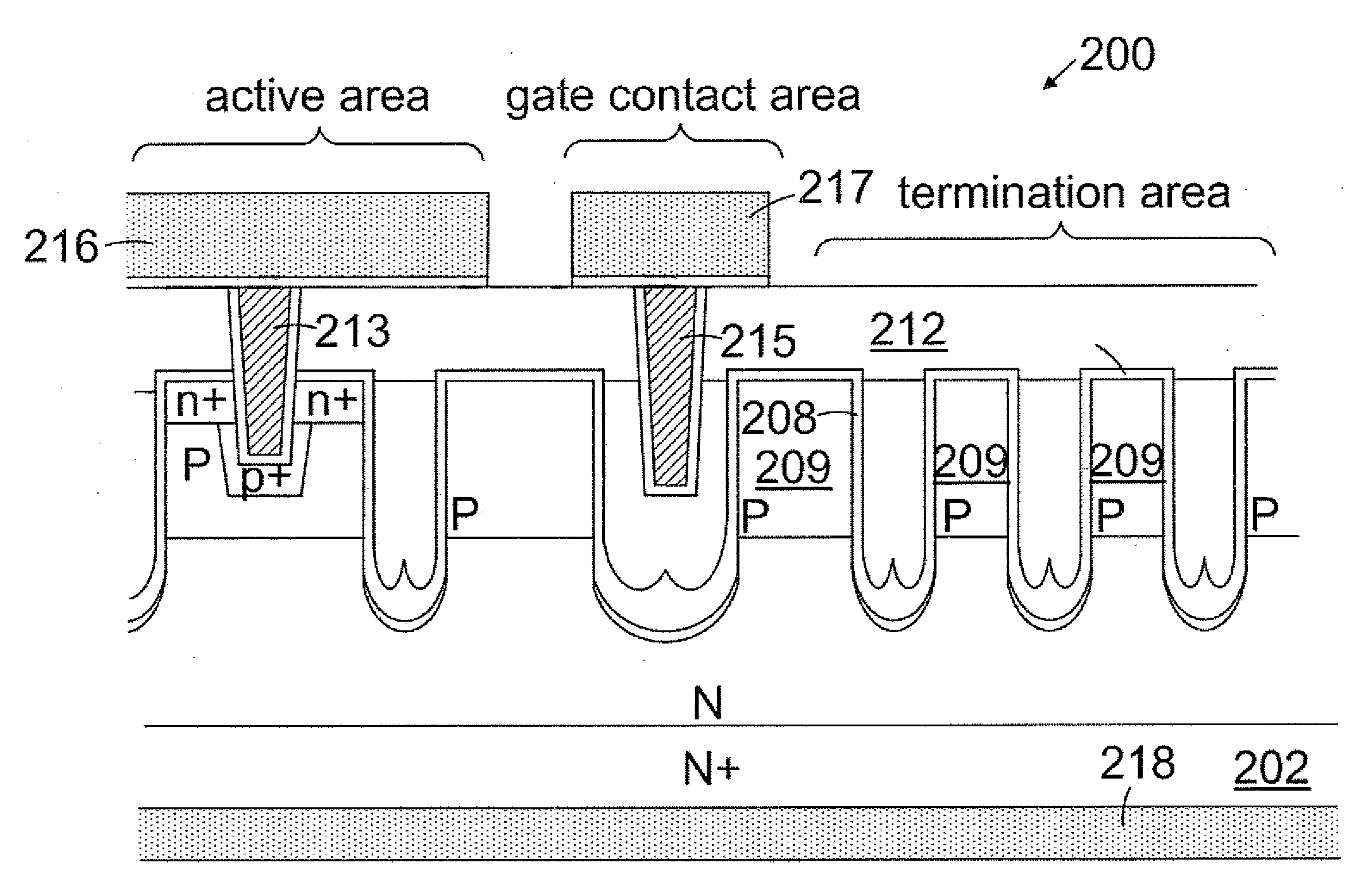

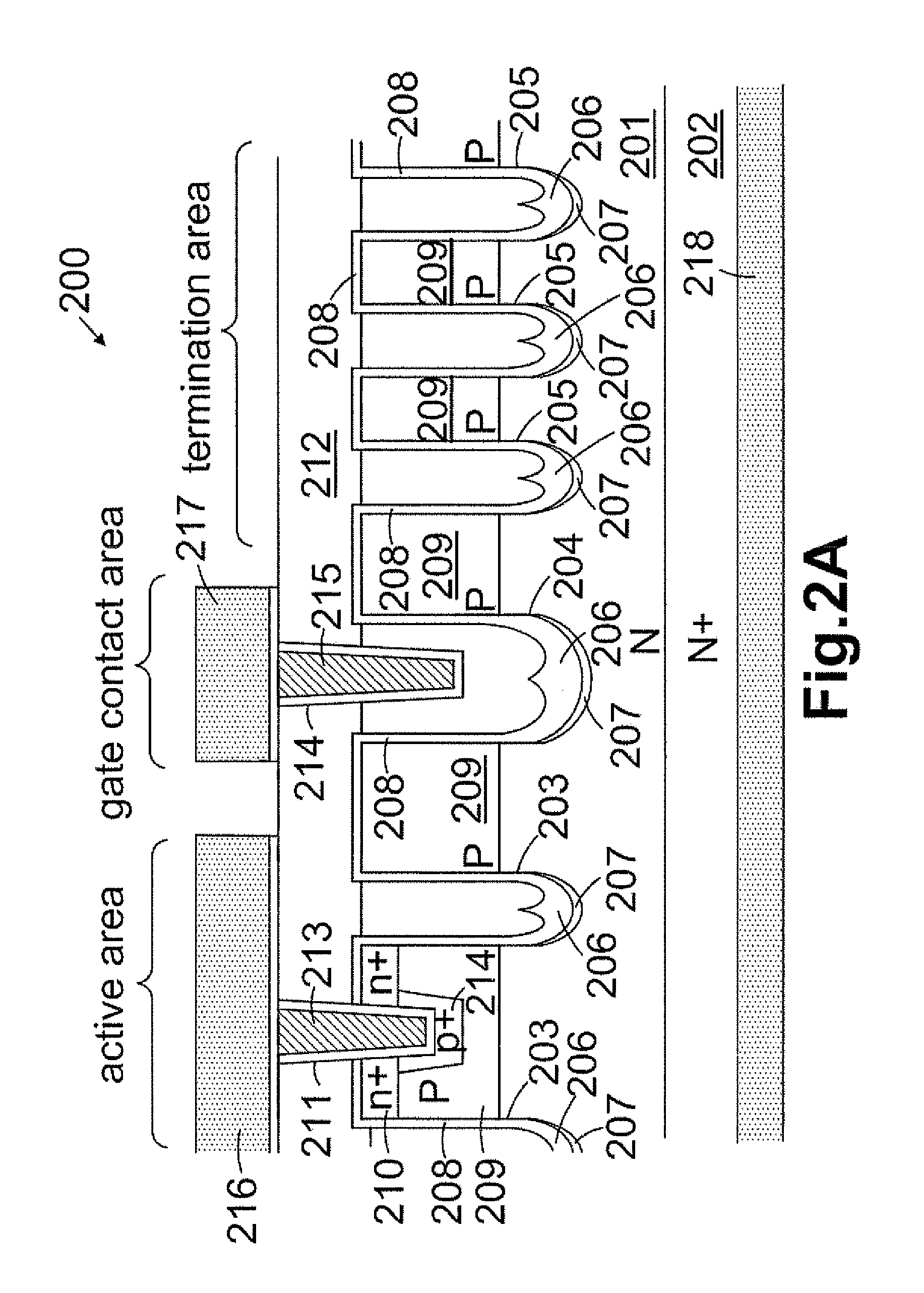

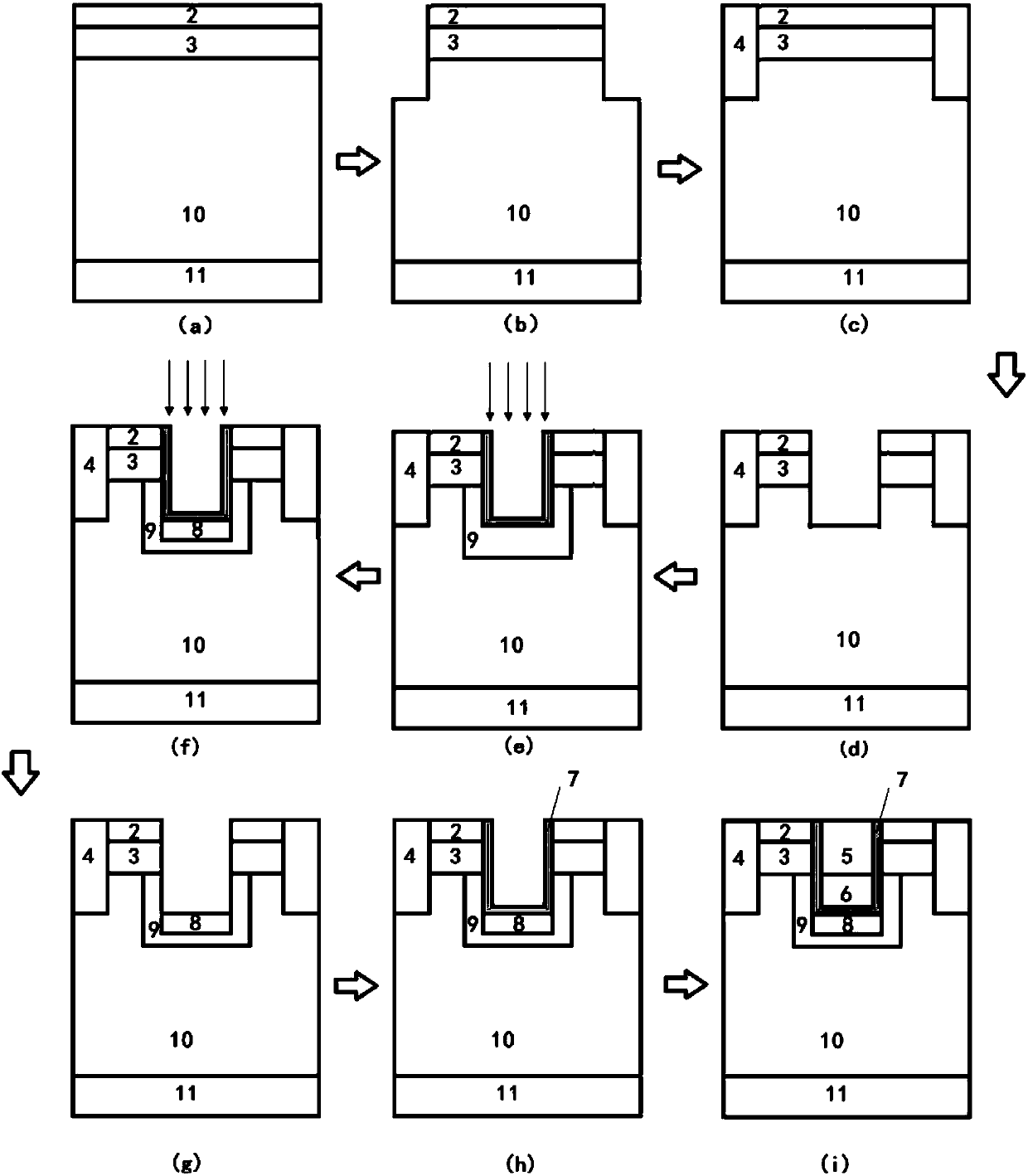

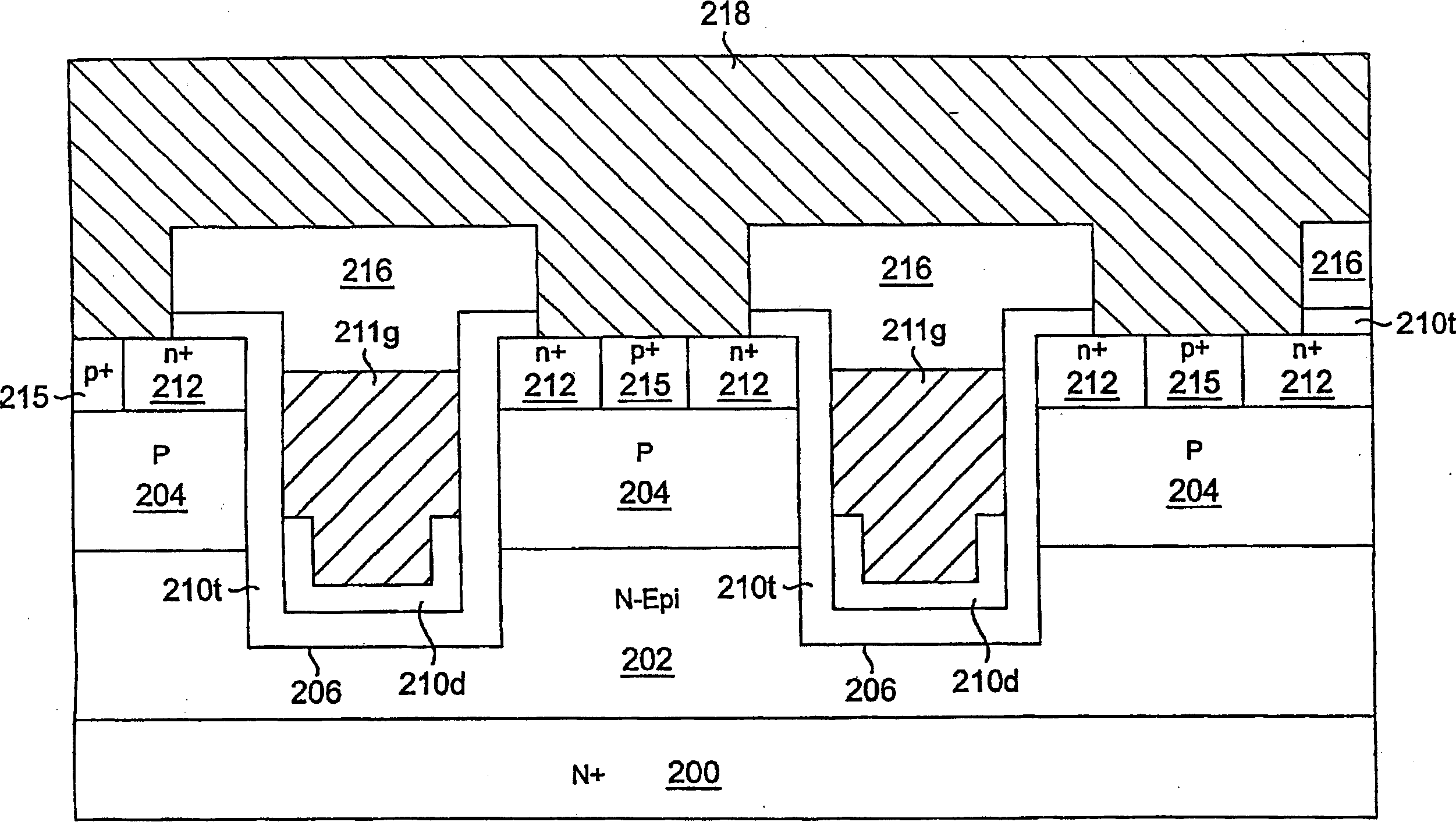

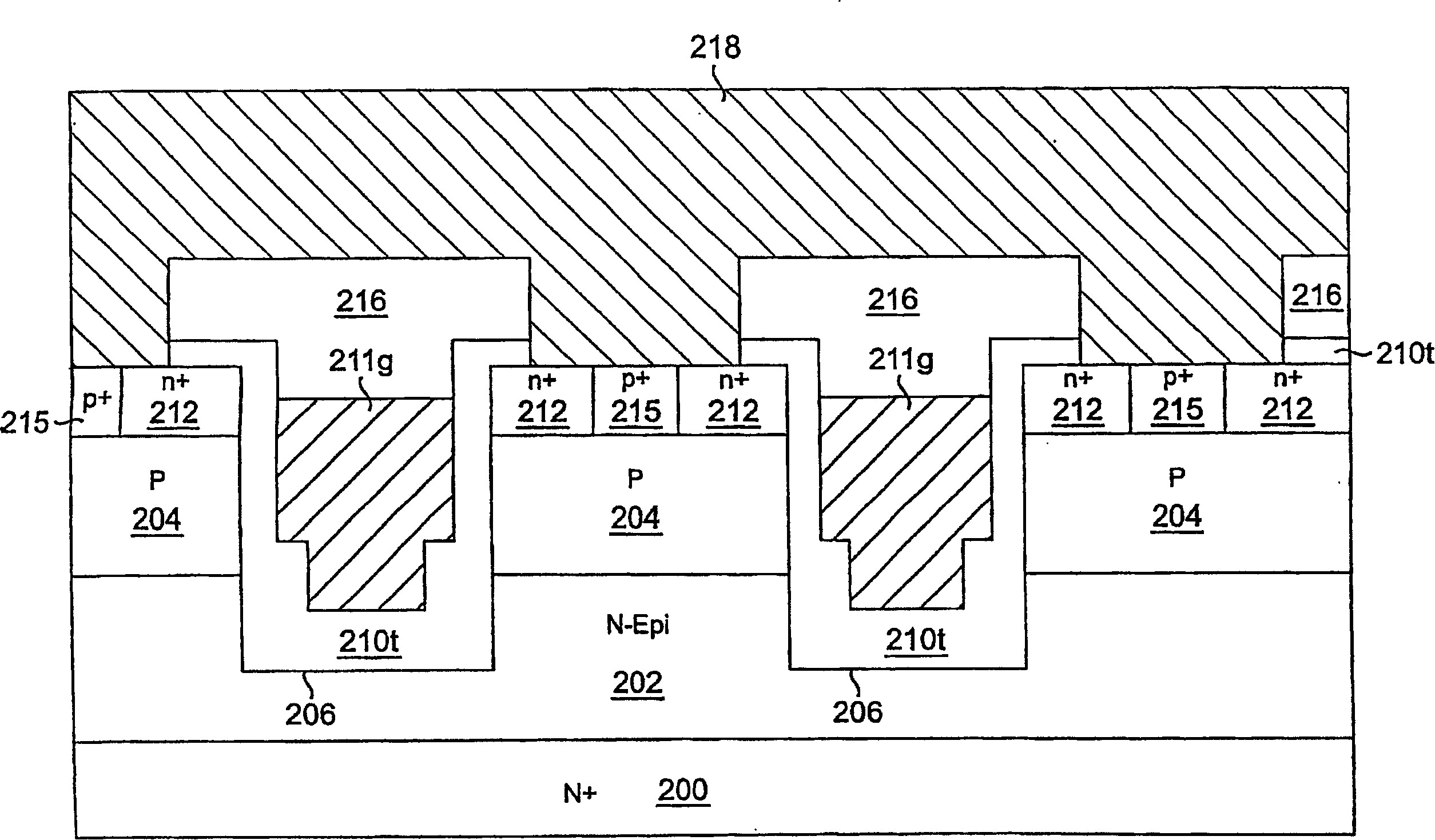

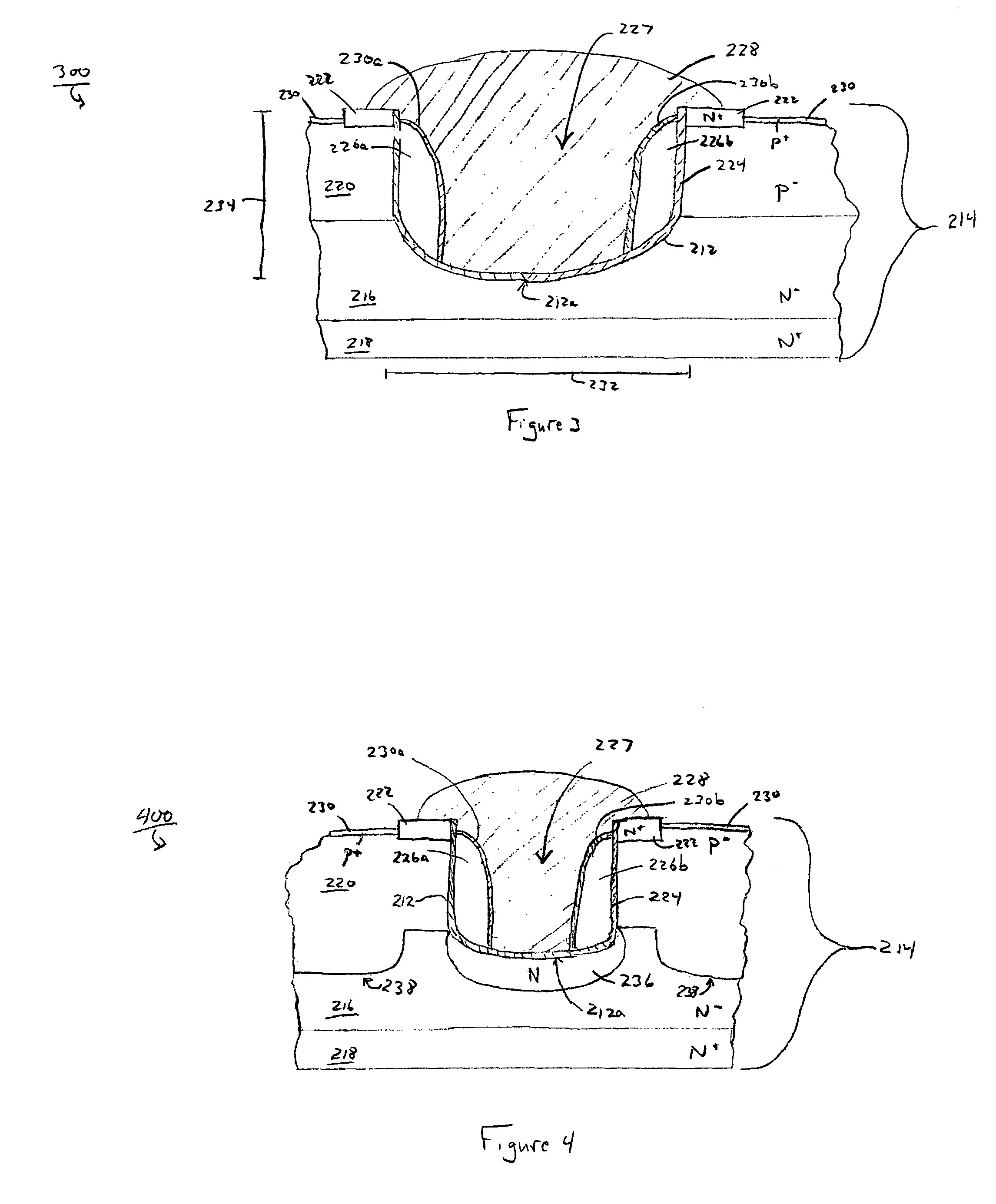

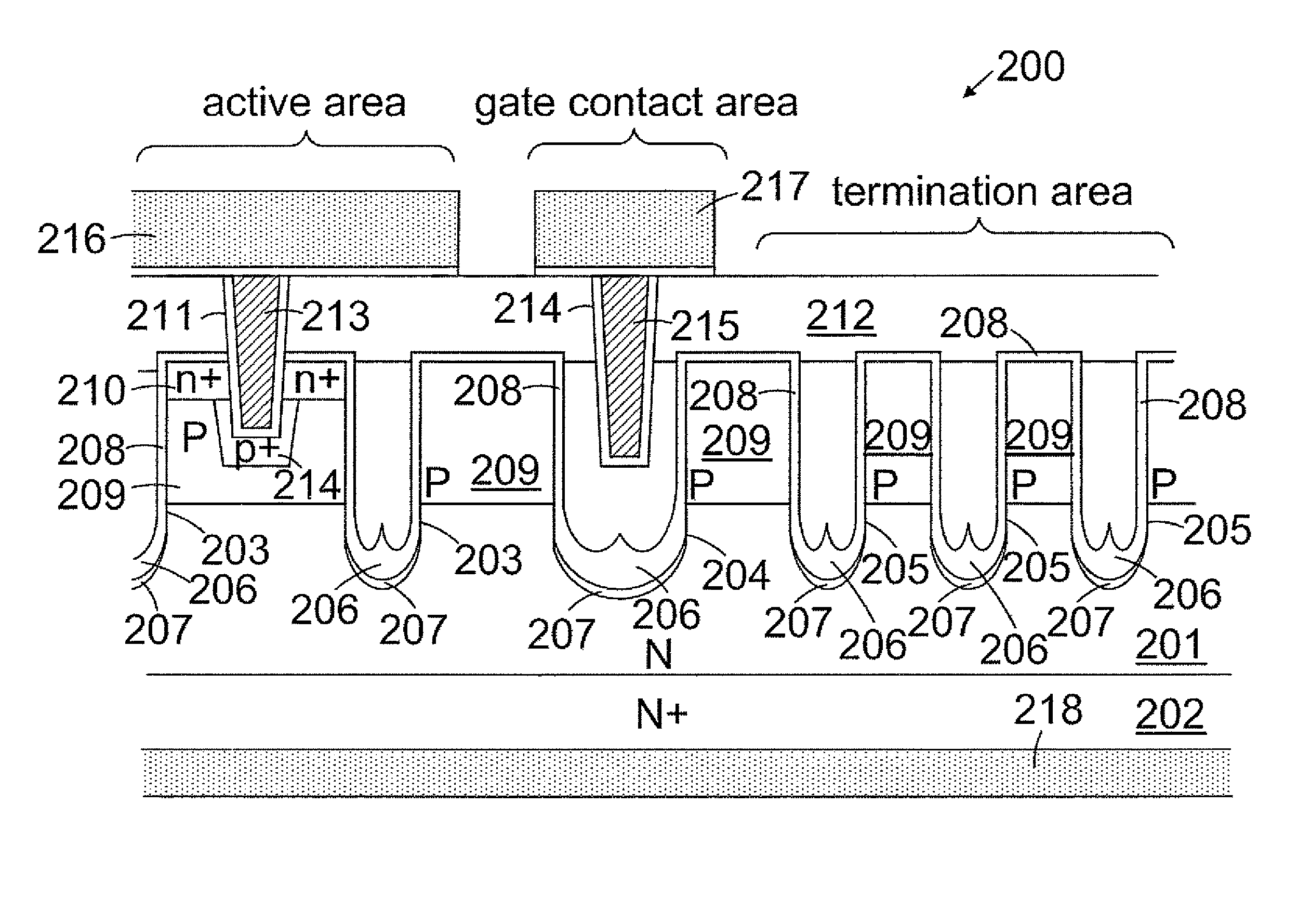

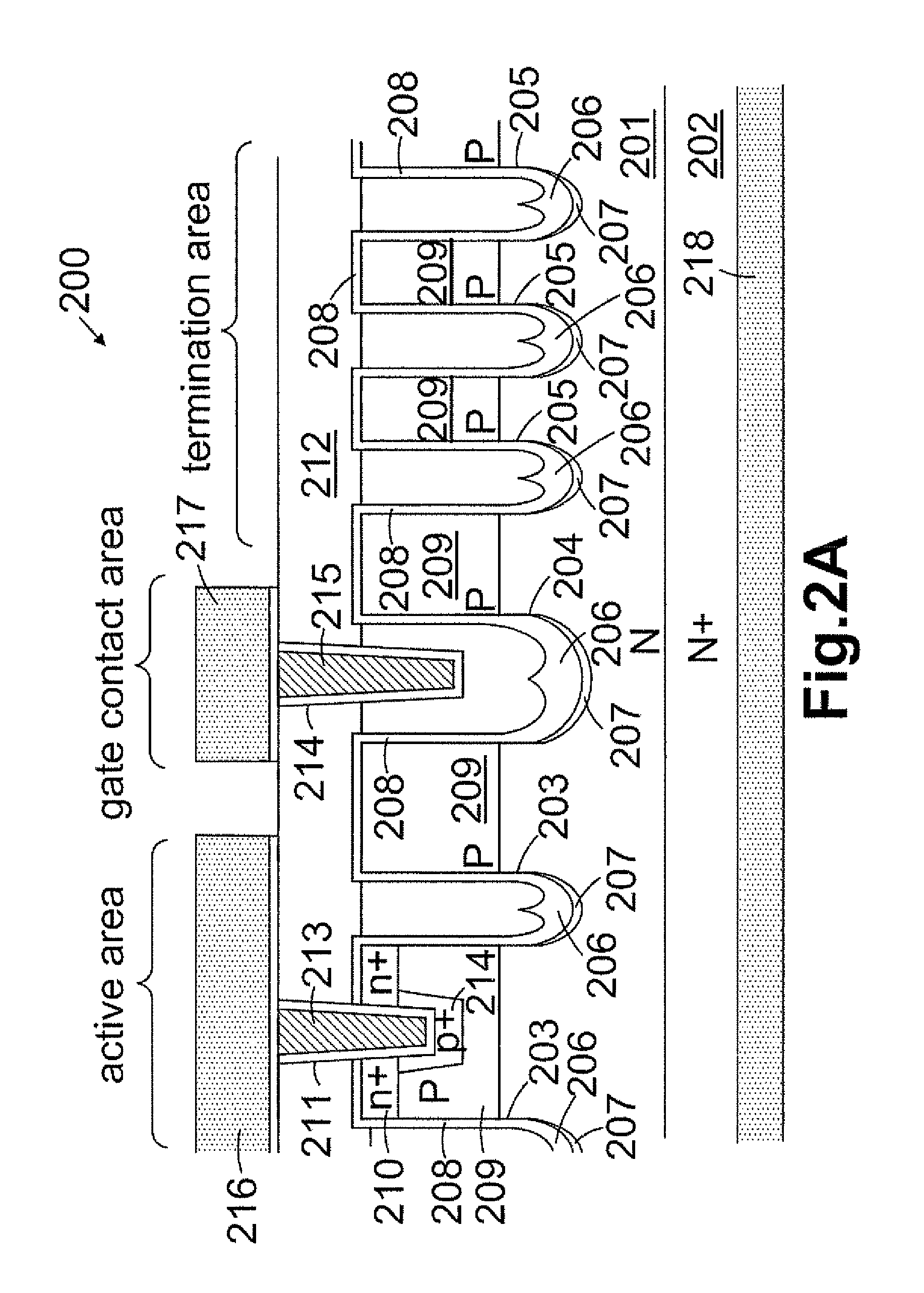

Trench mosfet with trenched floating gates having thick trench bottom oxide as termination

ActiveUS20110316075A1Good performanceImprove performanceTransistorSolid-state devicesTrench mosfetOxide

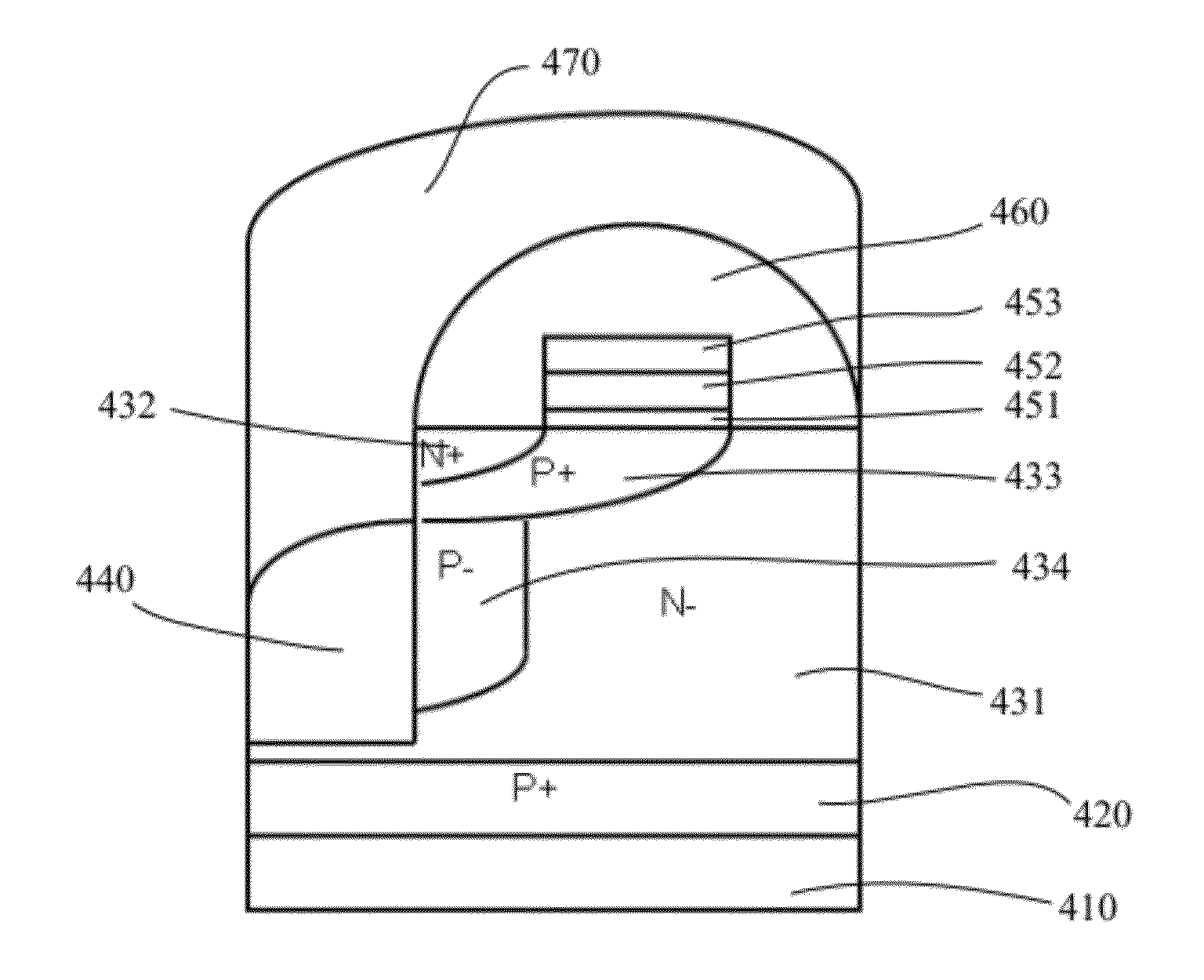

A power semiconductor power device having composite trench bottom oxide and multiple trench floating gates is disclosed. The gate charge is reduced by forming a pad oxide surrounding a HDP oxide on trench bottom. The multiple trenched floating gates are applied in termination for saving body mask.

Owner:FORCE MOS TECH CO LTD

Method for manufacturing a semiconductor device with a trench termination

ActiveUS6921699B2High current capabilityEfficient power supplySemiconductor/solid-state device manufacturingSemiconductor devicesOxideSemiconductor

A process for manufacturing a semiconductor device of the trench variety with reduced feature sizes and improved characteristics which process includes forming a termination structure having a field oxide disposed in a recess below the surface of the semiconductor die in which the active elements of the device are formed, and forming source regions after the major thermal steps have been performed.

Owner:INFINEON TECH AMERICAS

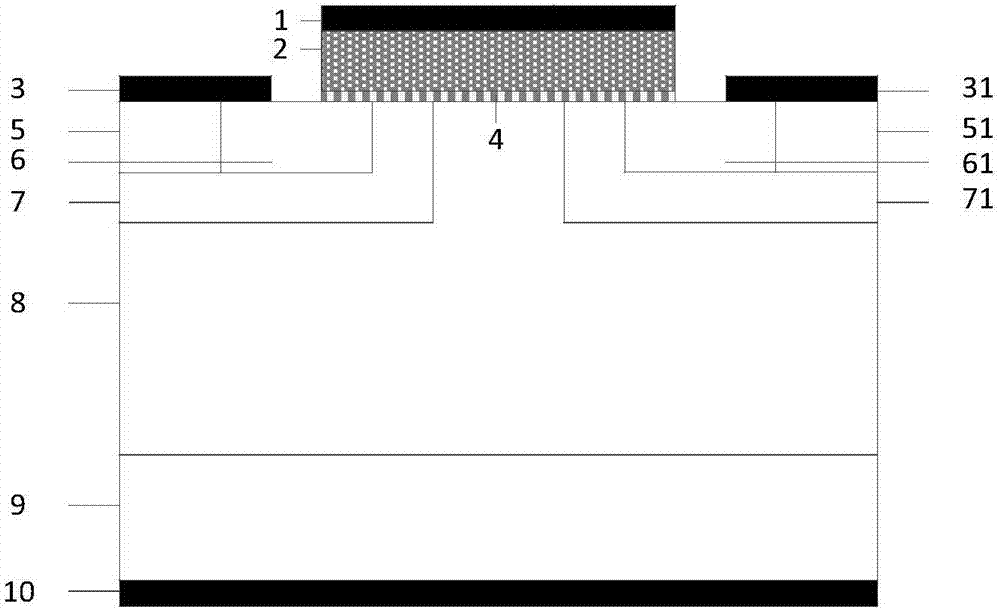

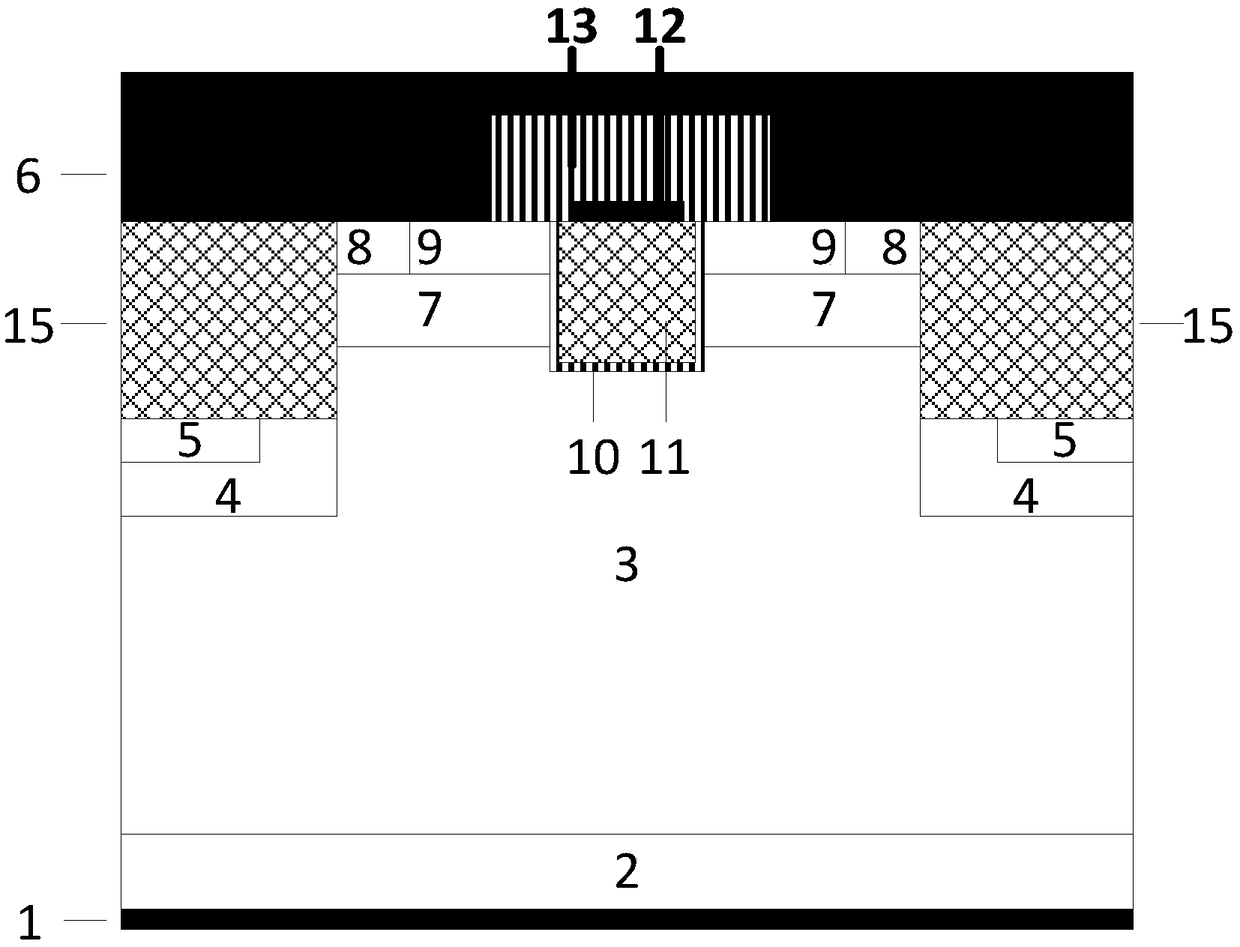

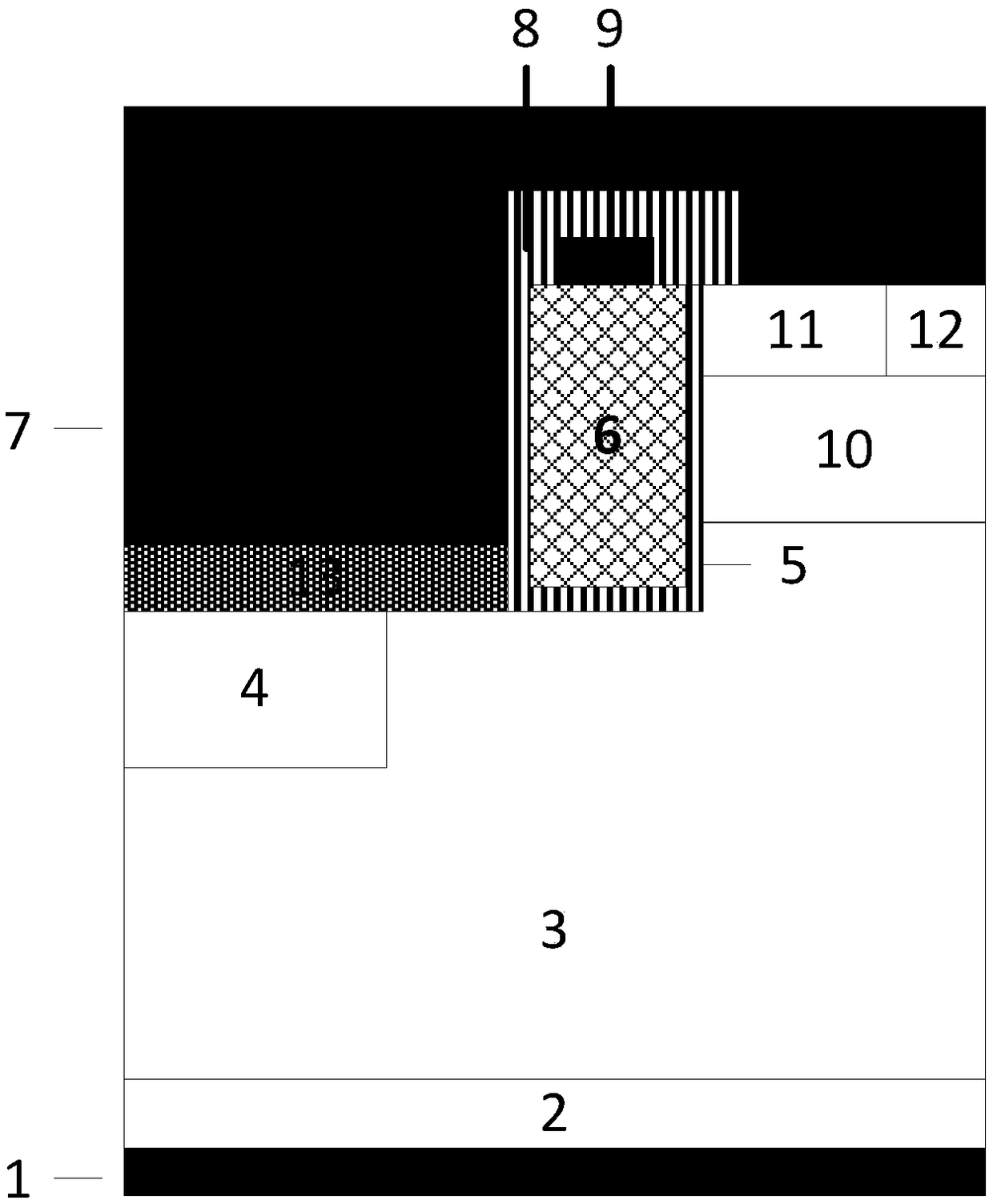

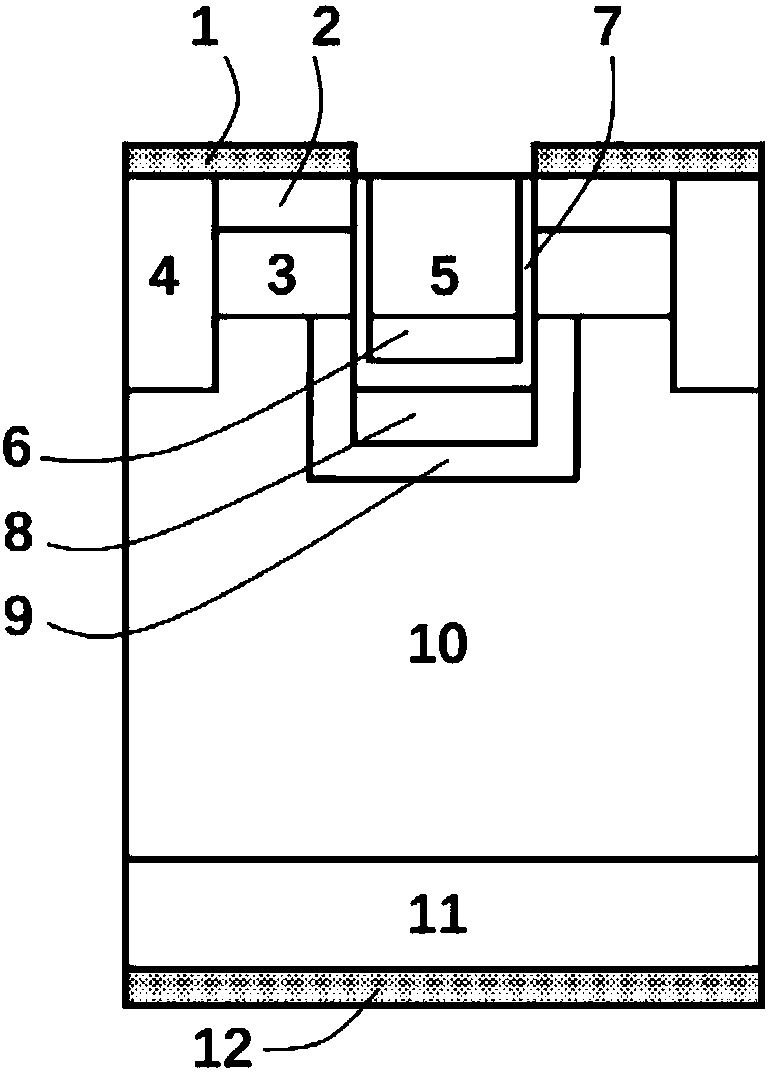

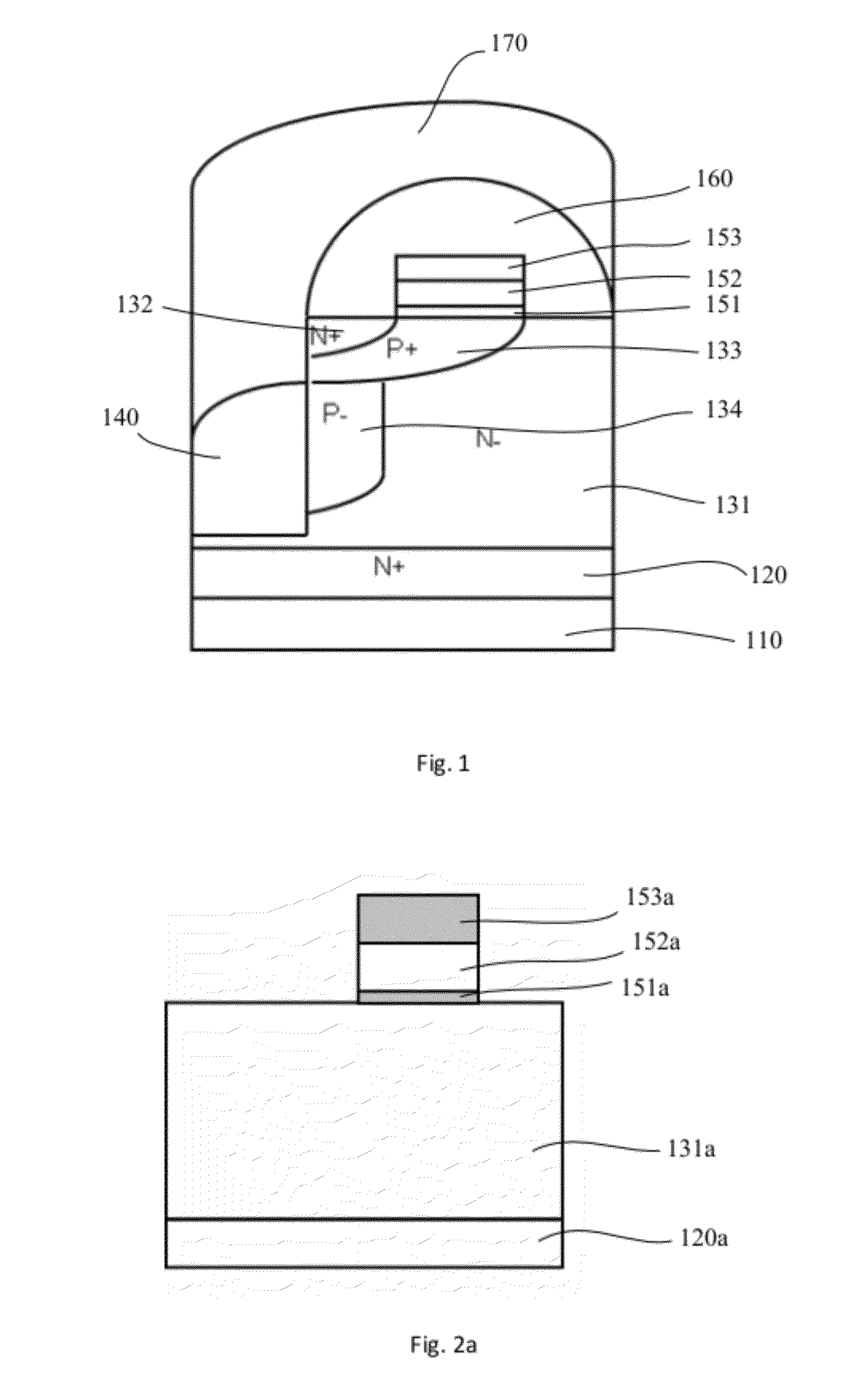

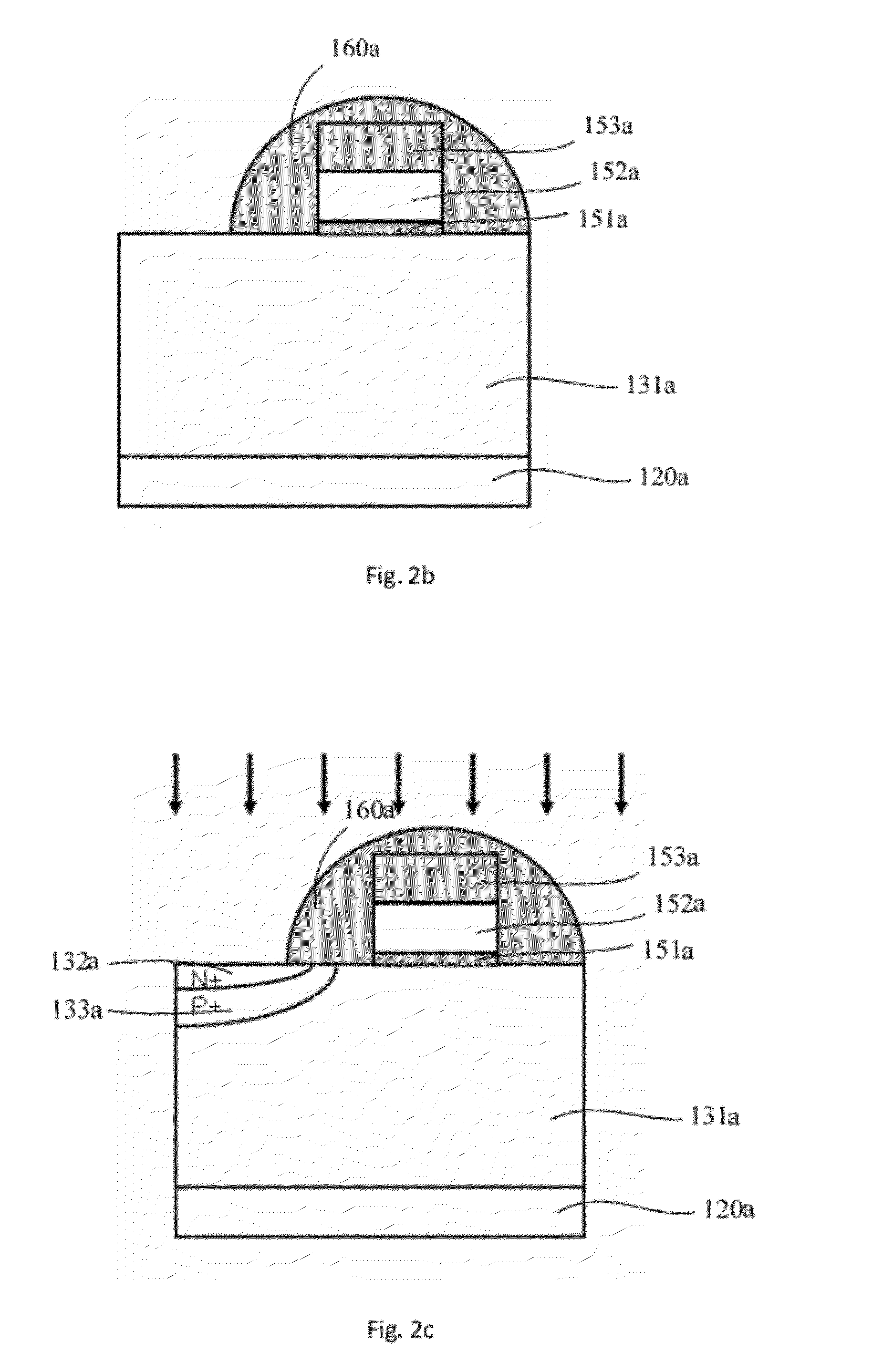

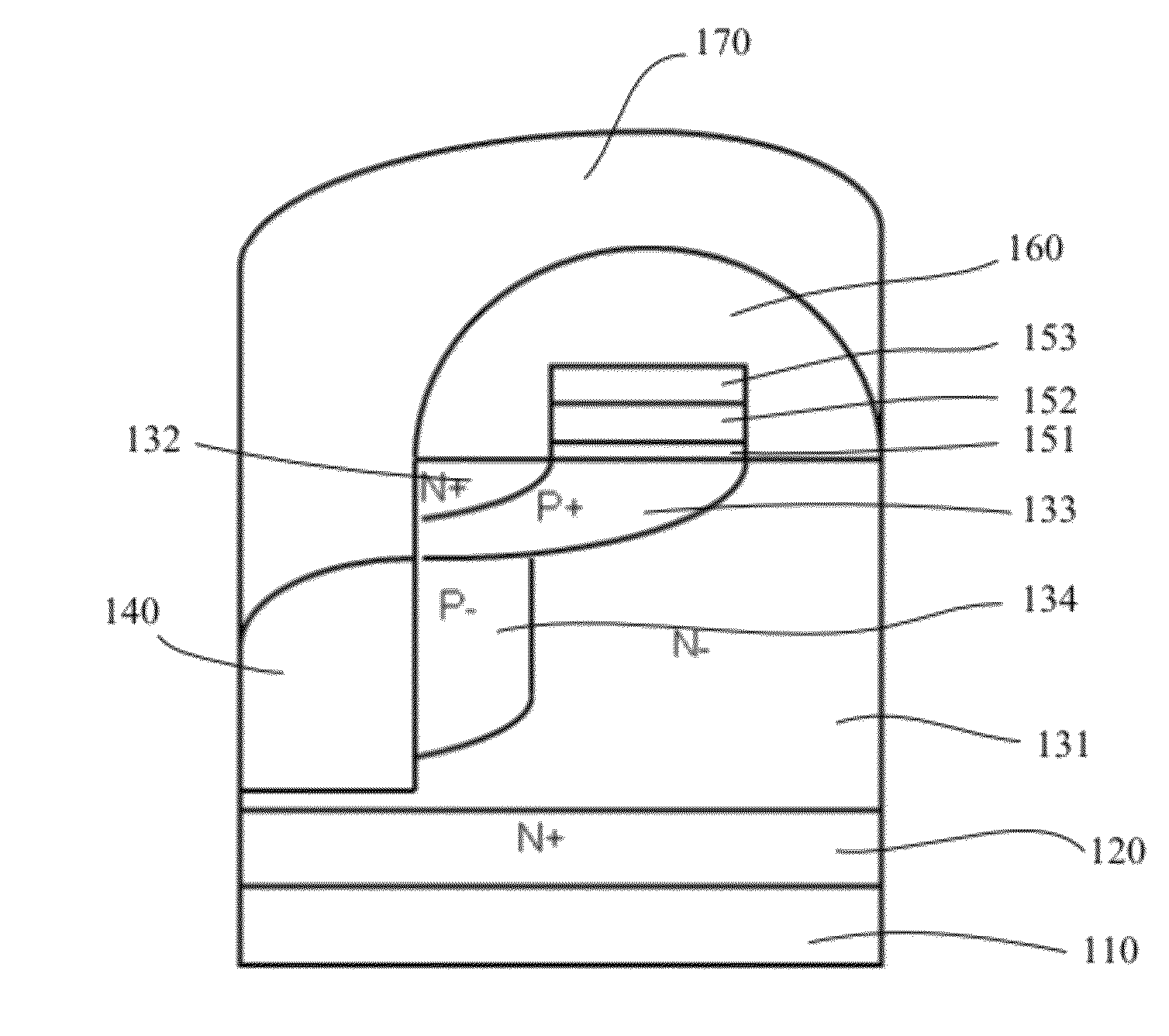

Silicon carbide VDMOS device and manufacturing method thereof

ActiveCN107275407AImprove performanceReduce power lossSemiconductor/solid-state device manufacturingDiodeCapacitanceHeterojunction

The invention discloses a silicon carbide VDMOS device and manufacturing method thereof, and belongs to the technical field of power semiconductors. A trench is etched on a JFET region surface of a traditional silicon carbide VDMOS device, P type doping is introduced into the bottom of the trench, and at the same time, a polycrystalline silicon layer is formed in the trench, so that the polycrystalline silicon layer and a side wall of the trench are in contact to form a Si / SiC heterojunction. A diode is integrated in the device, and the device has the advantages of low conduction voltage drop, fast switching speed and good reverse recovery characteristic in a diode working mode, and has the advantages of high breakdown voltage, small grid capacitance and fast switching speed in an MOS working mode. The proposed device structure optimizes application of the device in the field of inverter circuits, chopper circuits and the like, and has the advantage that the process is simple, and is compatible with a traditional silicon carbide VDMOS device process.

Owner:HANGZHOU SILICON-MAGIC SEMICON TECH CO LTD

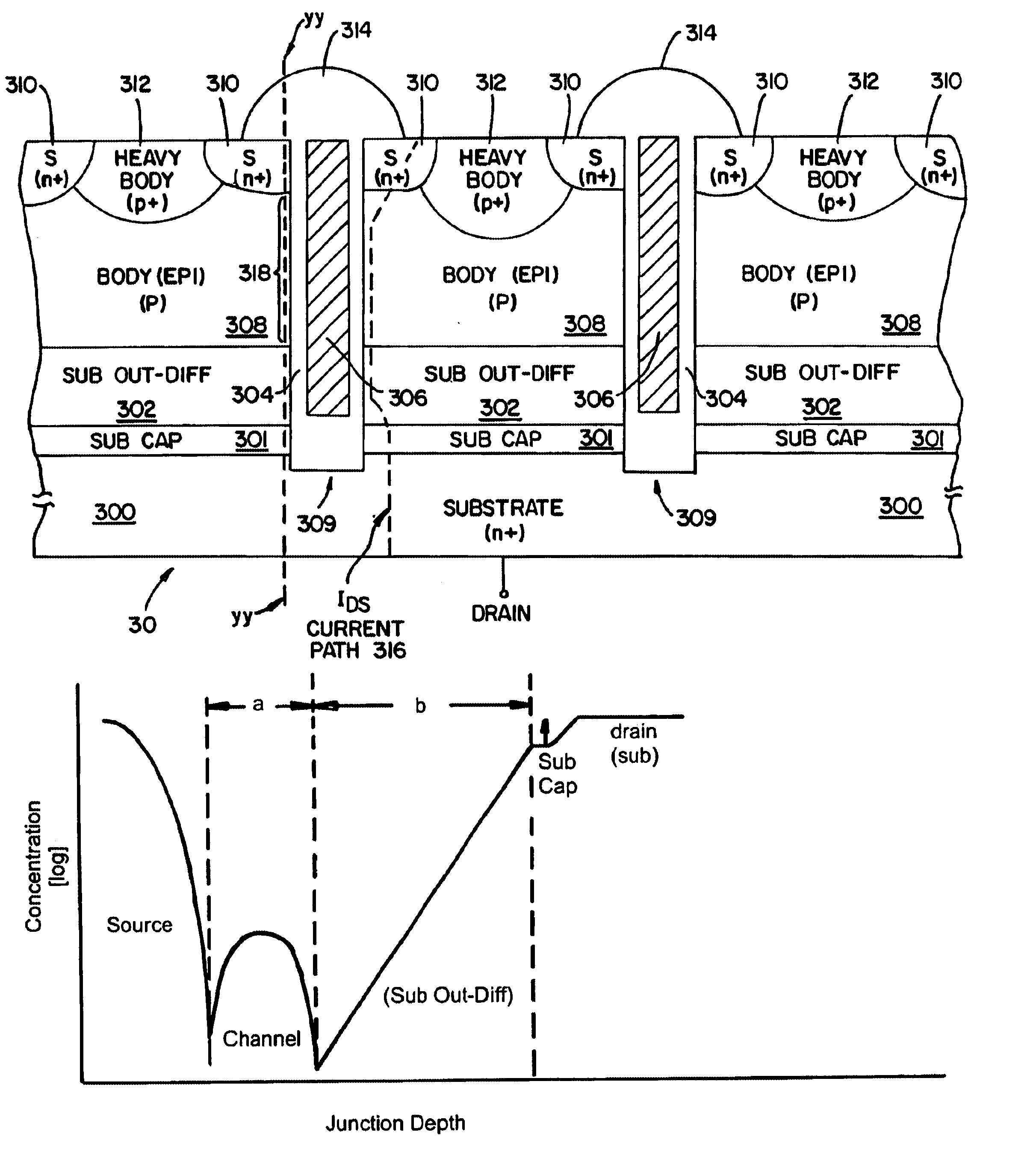

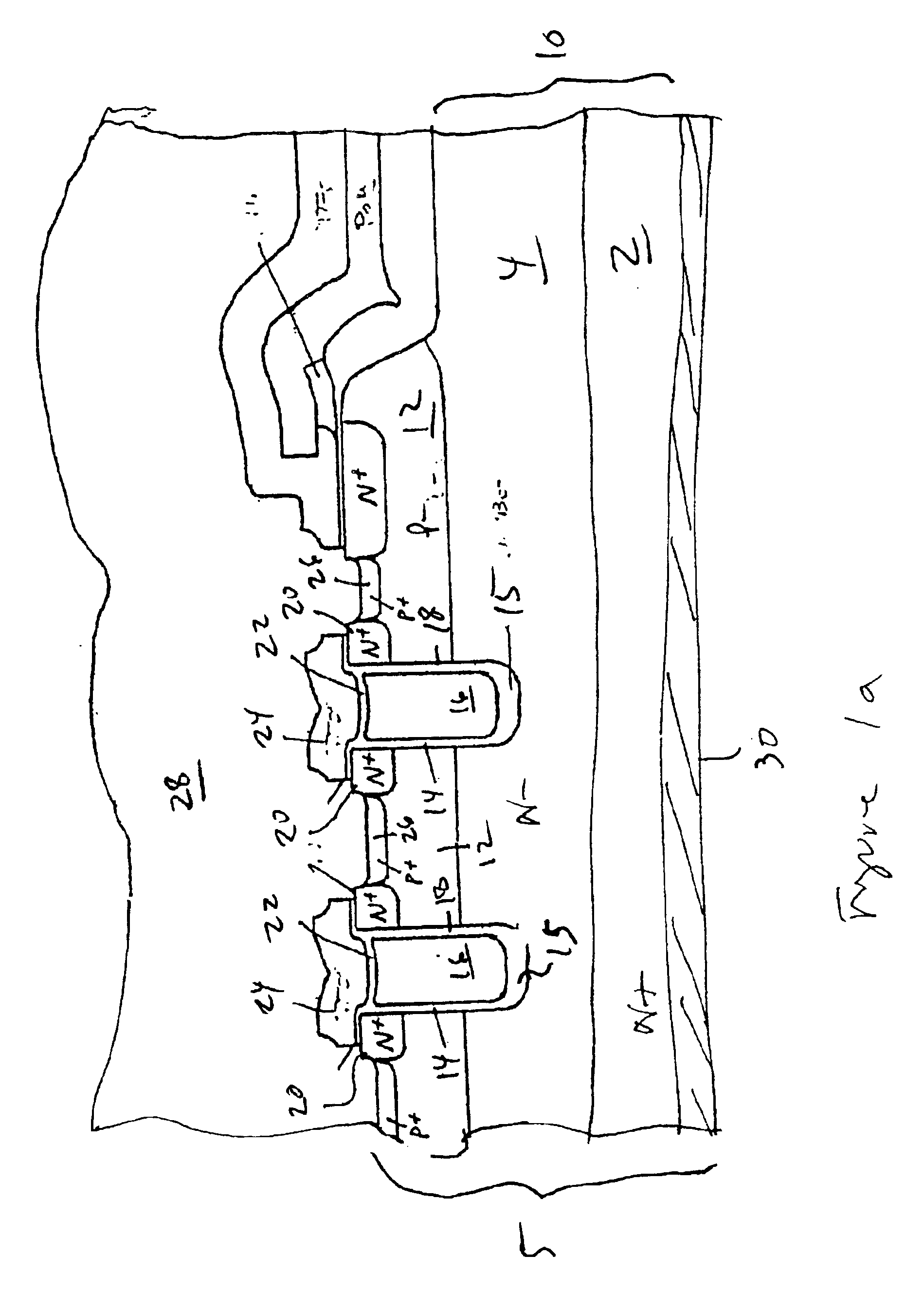

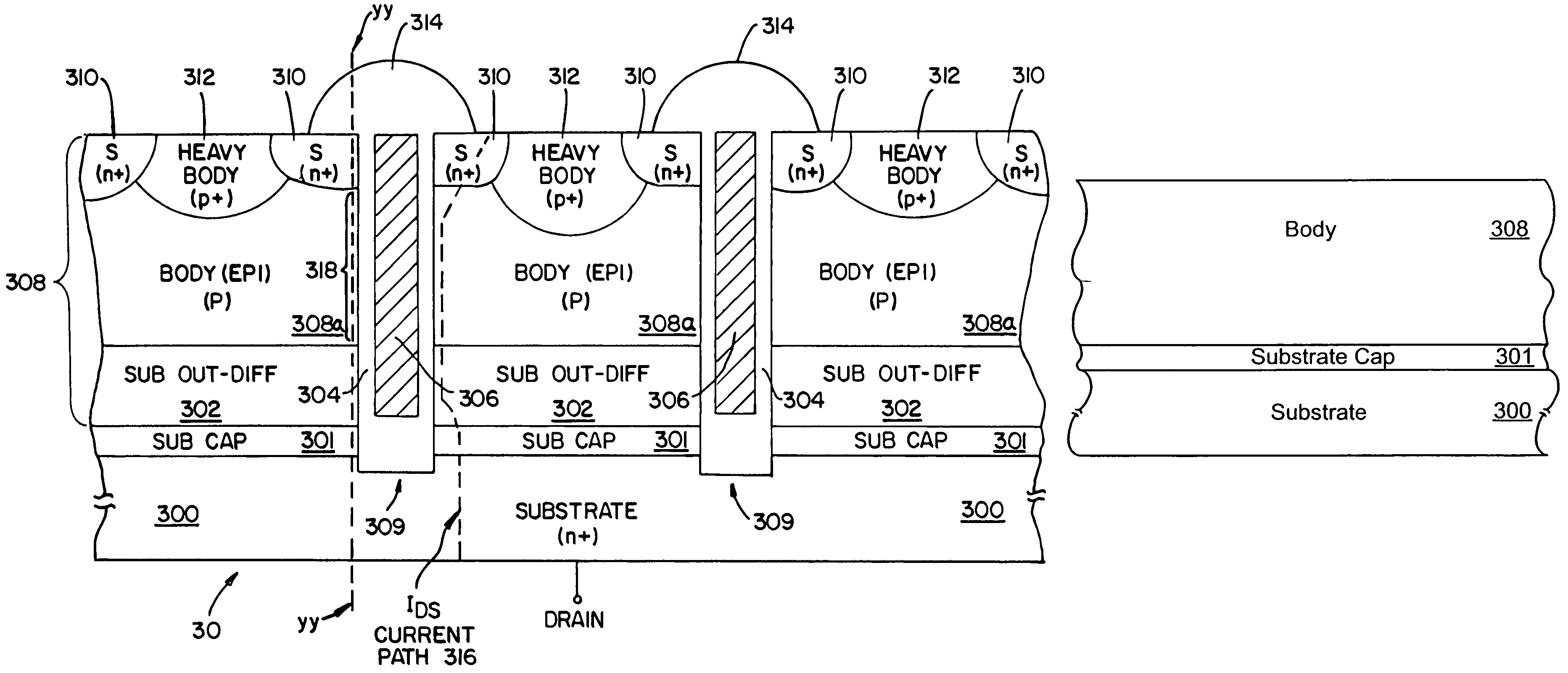

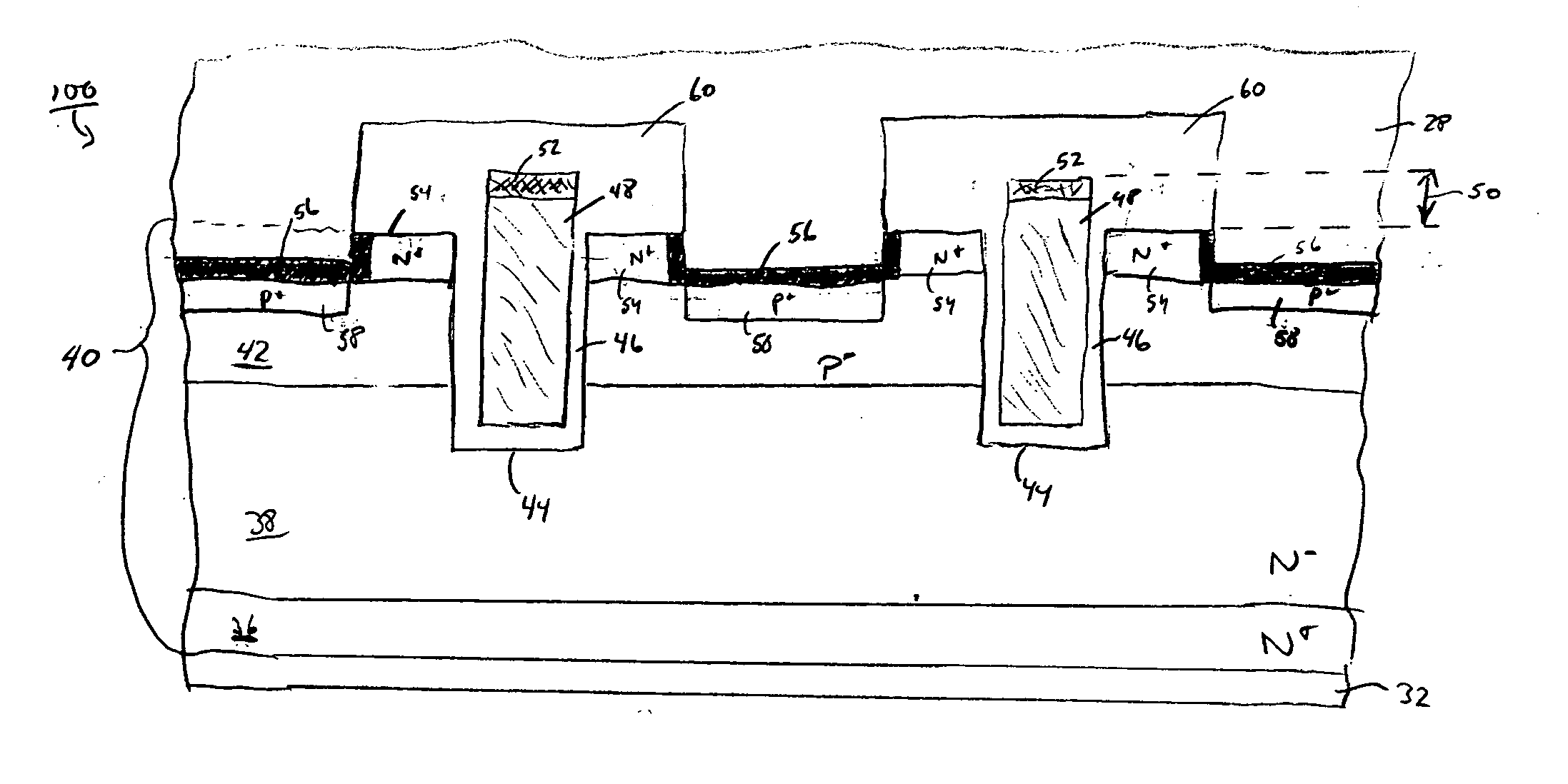

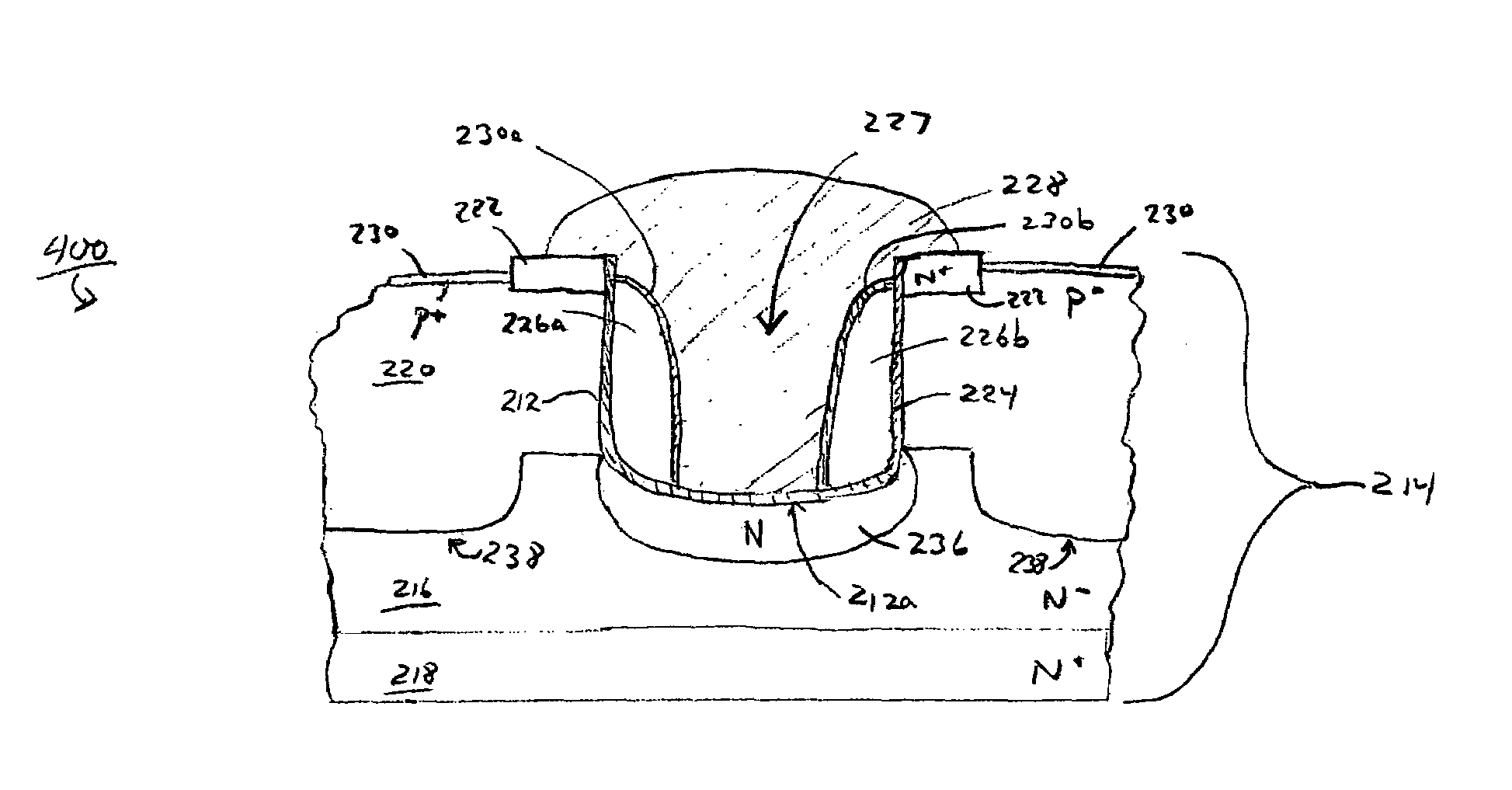

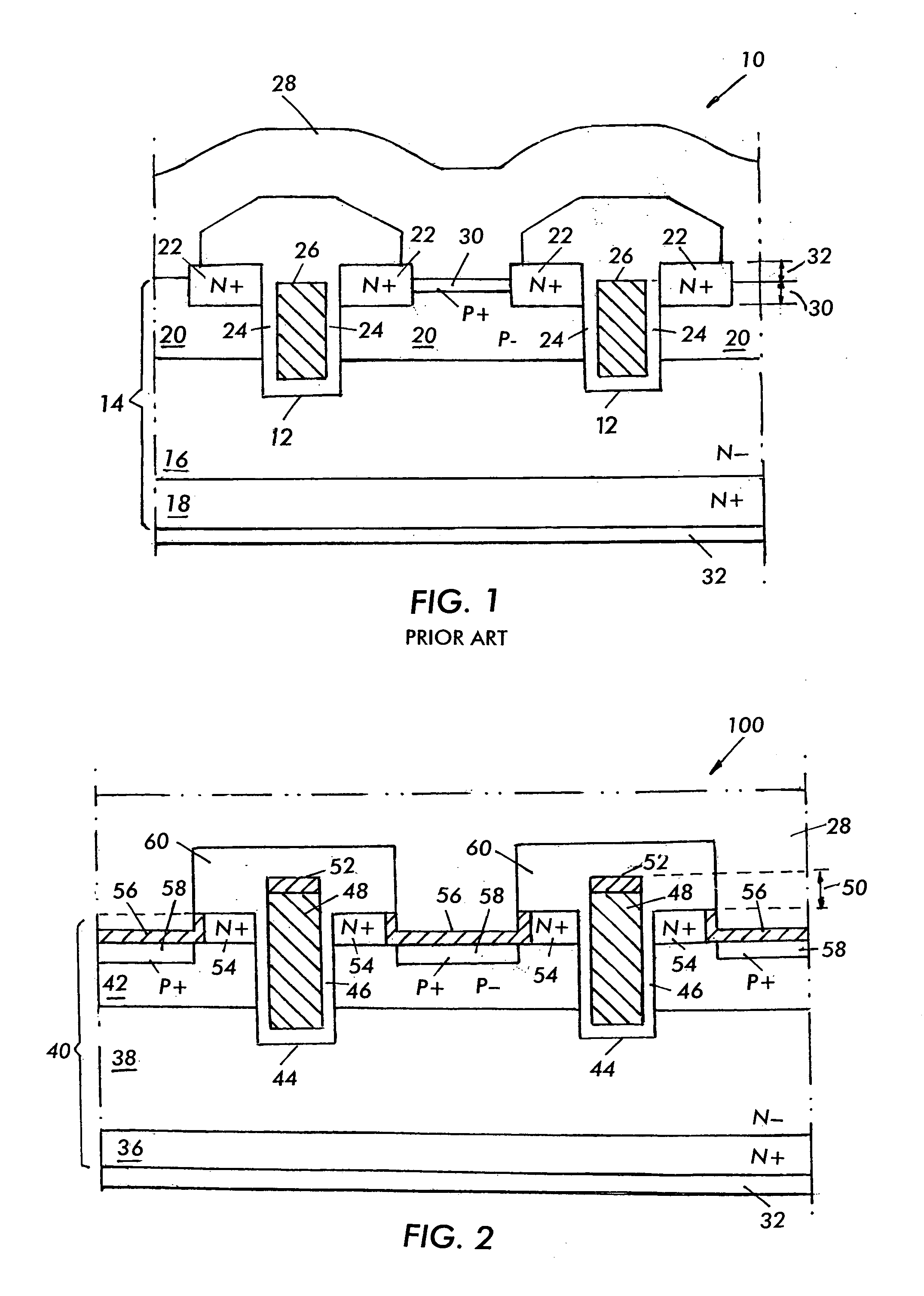

Method of forming a FET having ultra-low on-resistance and low gate charge

InactiveUS7745289B2Minimize changesUltra-low on resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesField-effect transistorBody region

In accordance with an exemplary embodiment of the invention, a substrate of a first conductivity type silicon is provided. A substrate cap region of the first conductivity type silicon is formed such that a junction is formed between the substrate cap region and the substrate. A body region of a second conductivity type silicon is formed such that a junction is formed between the body region and the substrate cap region. A trench extending through at least the body region is then formed. A source region of the first conductivity type is then formed in an upper portion of the body region. An out-diffusion region of the first conductivity type is formed in a lower portion of the body region as a result of one or more temperature cycles such that a spacing between the source region and the out-diffusion region defines a channel length of the field effect transistor.

Owner:SEMICON COMPONENTS IND LLC

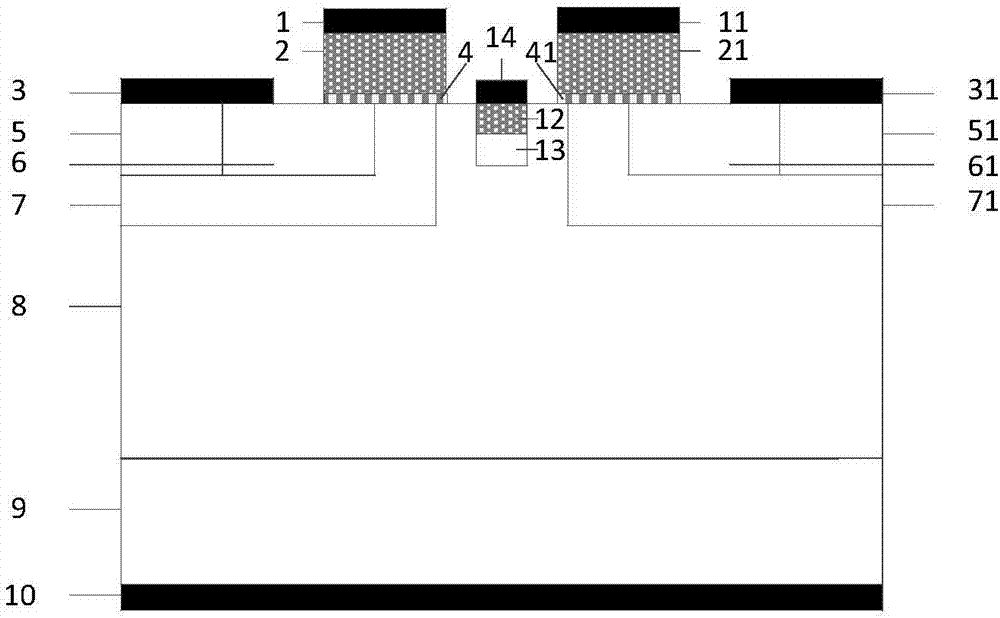

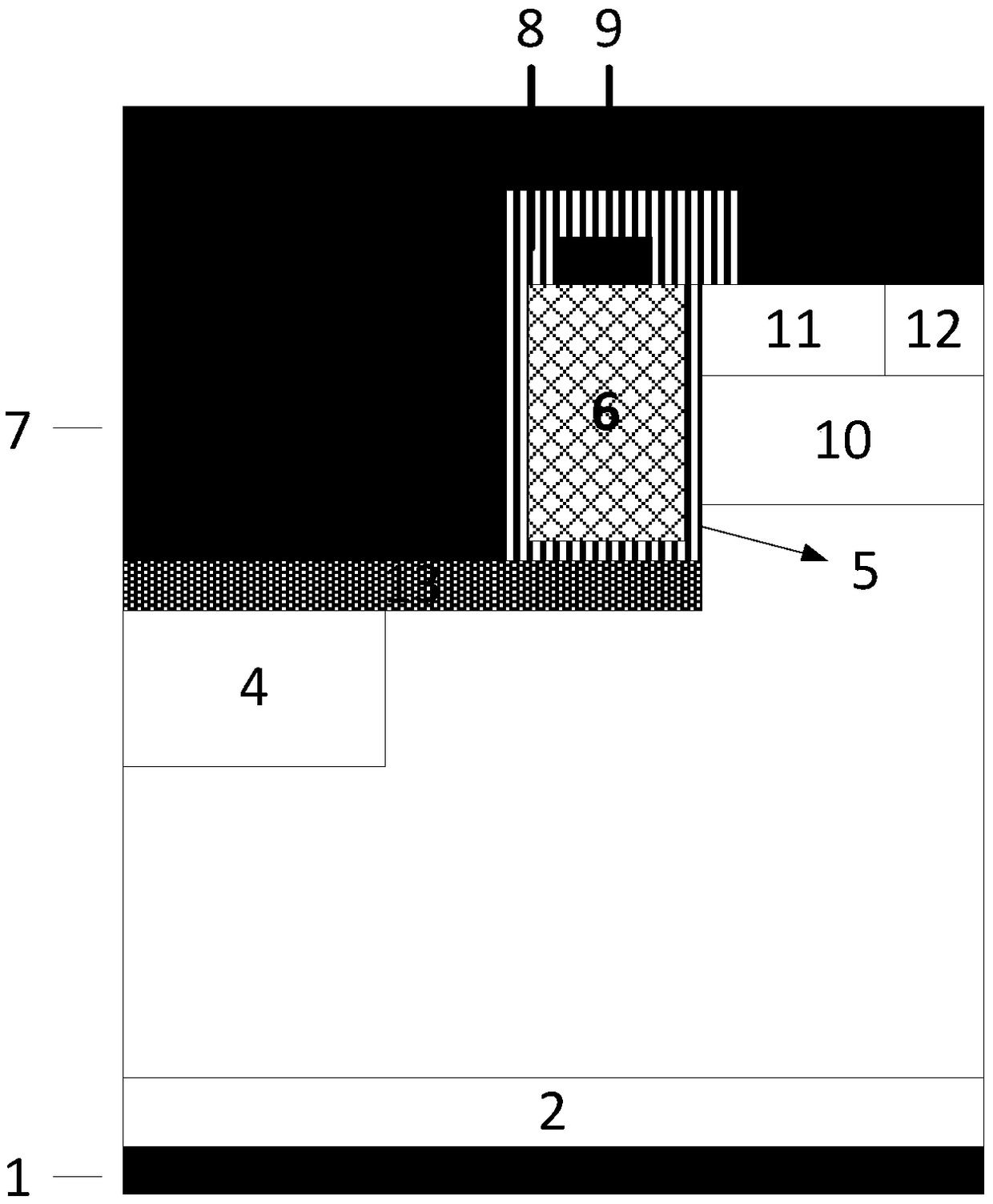

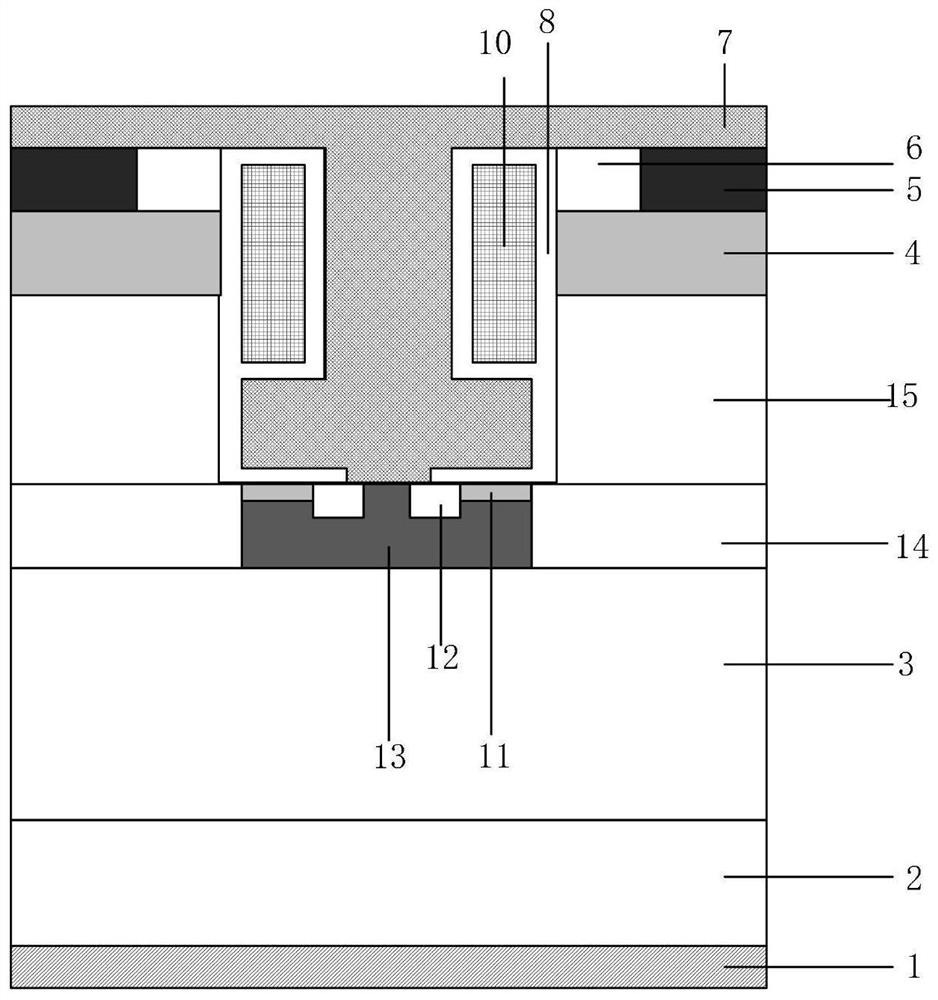

Silicon carbide MOSFET device and manufacturing method thereof

ActiveCN108807504AImprove leakageReduce leakageSemiconductor/solid-state device manufacturingSemiconductor devicesCarbide siliconMOSFET

The invention provides a silicon carbide MOSFET device and a manufacturing method thereof. Silicon carbide deep P injection is performed in a specified region, groove etching and deposition of metal or polysilicon are performed above a silicon carbide deep P doped region, and the deposited metal or polysilicon is in direct contact with the silicon carbide N-epitaxy to form a Schottky contact or aSi / SiC heterojunction contact having rectifying characteristics. Therefore, the integration of multiple sub-rectifiers is achieve while optimizing the basic performance of the conventional silicon carbide UMOSFET, the working performance of the third quadrant of the device is greatly optimized, the gate-drain capacitance of the device is reduced and the switching speed of the device is improved.

Owner:HANGZHOU SILICON-MAGIC SEMICON TECH CO LTD

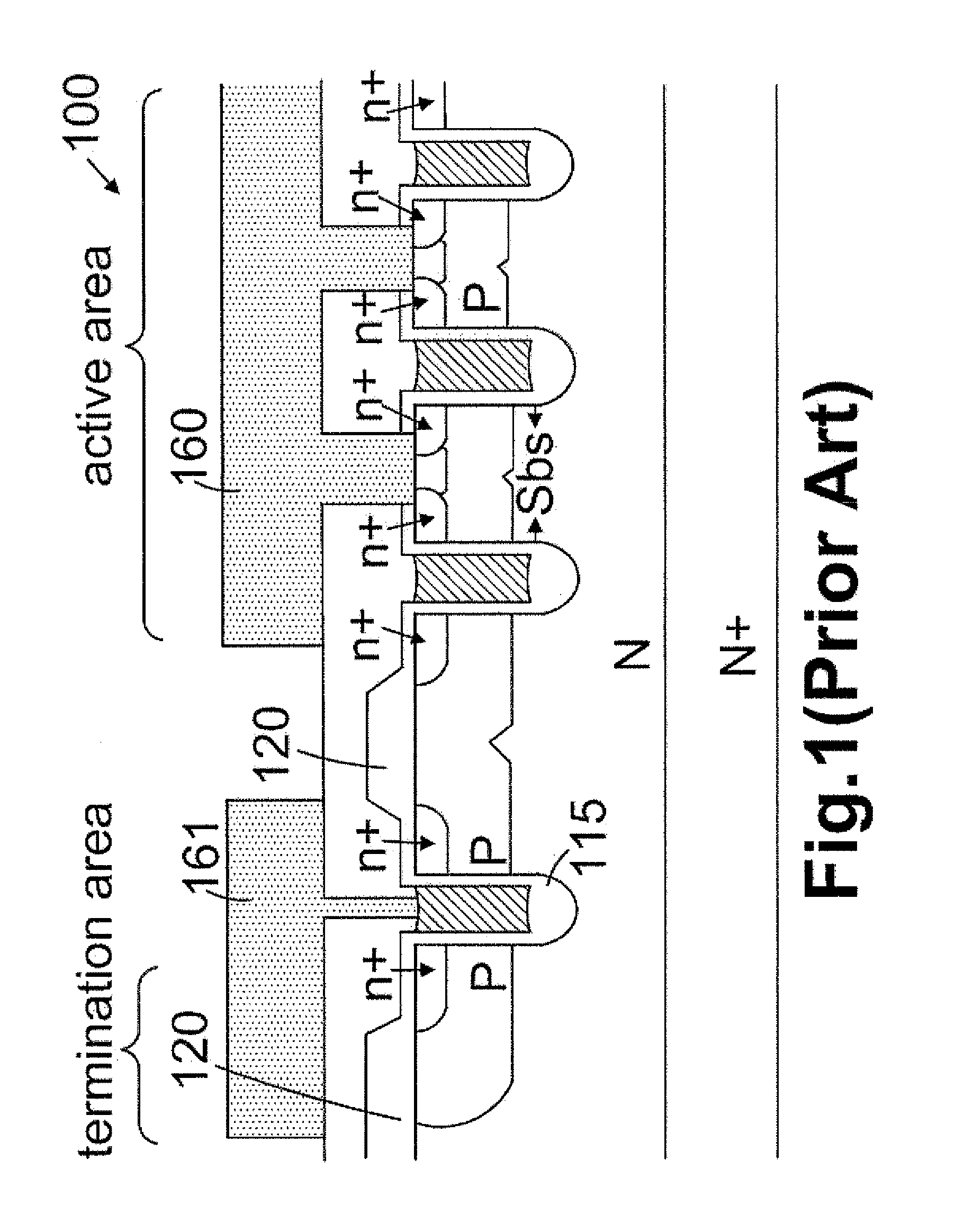

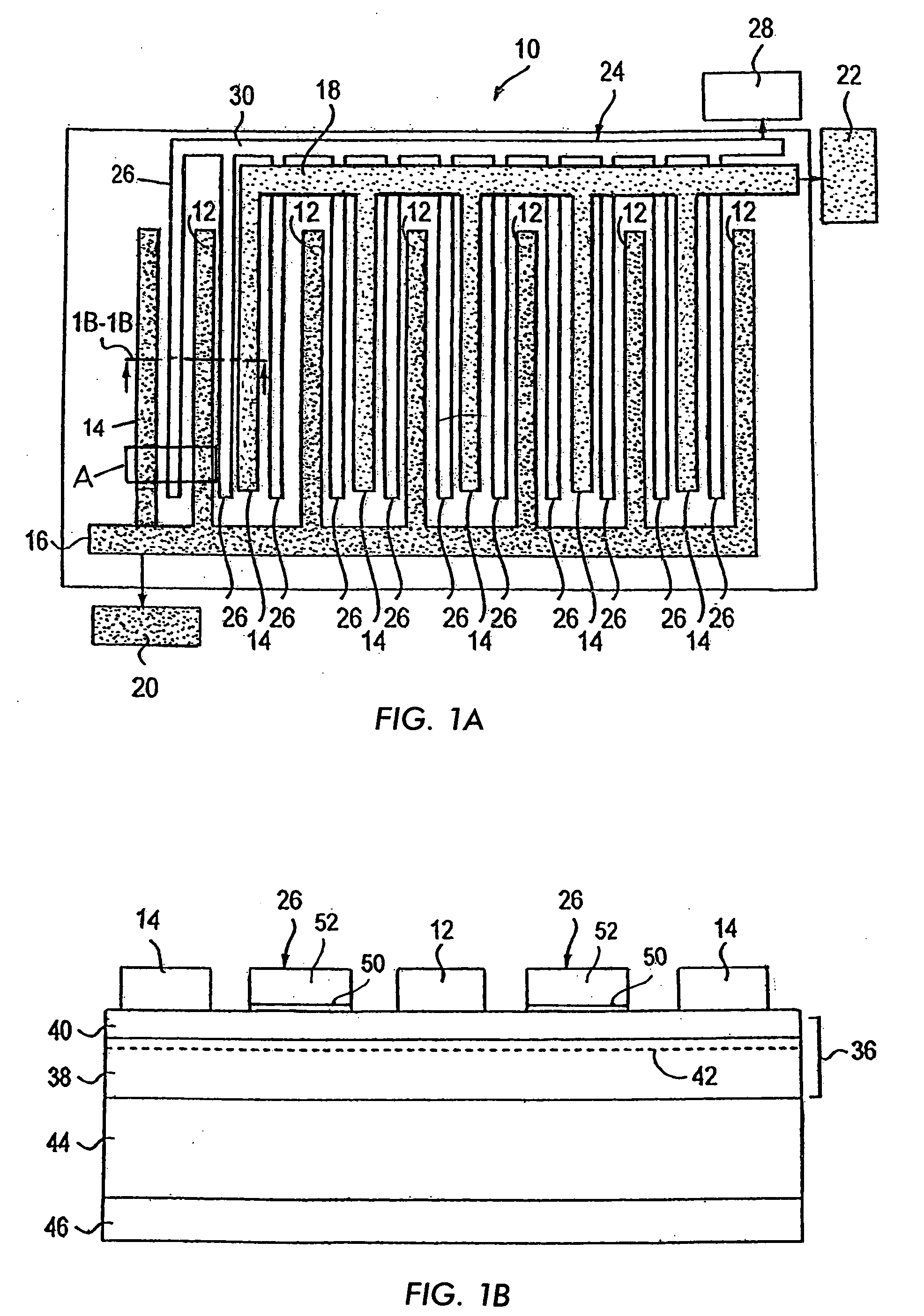

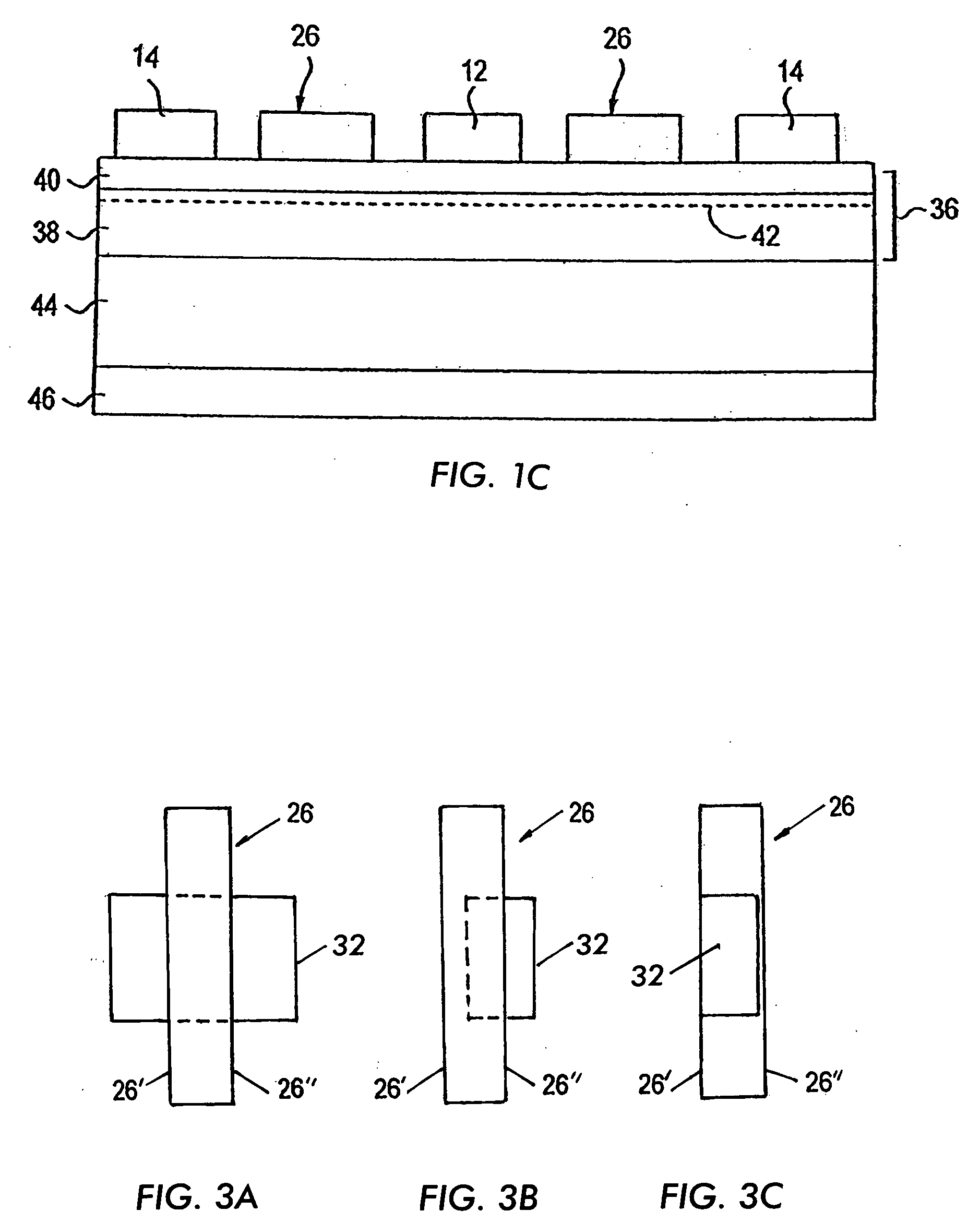

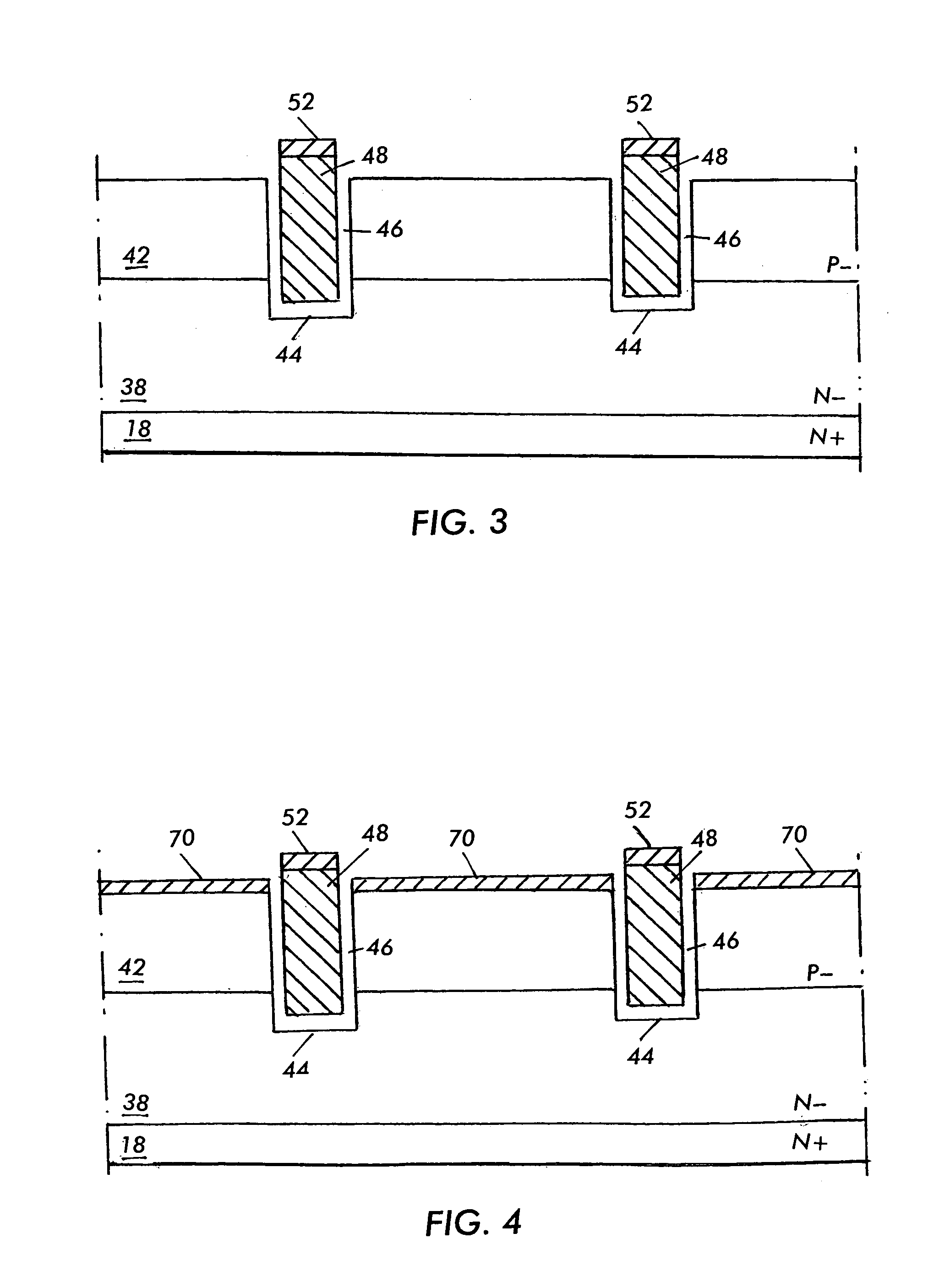

Low temperature process and structures for polycide power MOSFET with ultra-shallow source

ActiveUS20050173760A1Reduced vertical depthReduce depthTransistorSolid-state devicesPower semiconductor deviceEngineering

A trench type power semiconductor device includes proud gate electrodes that extend out of the trenches and above the surface of the semiconductor body. These proud gate electrodes allow for making ultra-shallow source regions within the semiconductor body using, for example, a low temperature source drive. In addition, a method for manufacturing the trench type power semiconductor device includes a low temperature process flow once the gate electrodes are formed.

Owner:INFINEON TECH AMERICAS CORP

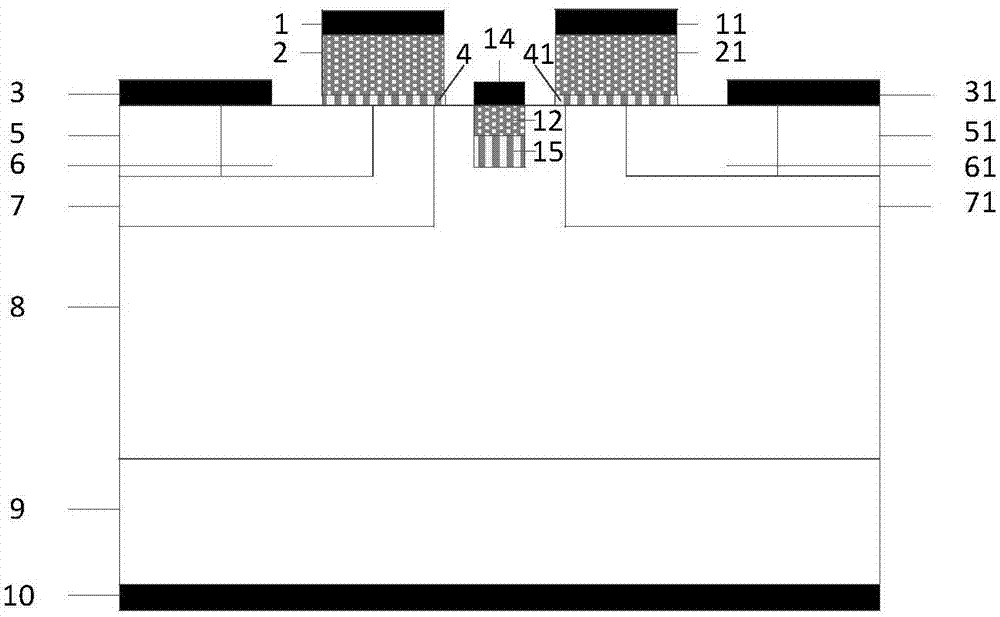

A silicon carbide MOSFET device and a manufacturing method thereof

ActiveCN109192779AGood long-term application reliabilityImprove pressure resistanceSemiconductor/solid-state device manufacturingDiodeMOSFETHeterojunction

The invention provides a silicon carbide MOSFET device and a manufacturing method thereof. The invention improves device structure design and finally integrates Schottky contact or heterojunction contact with rectifying characteristics on the basis of traditional silicon carbide UMOSFET structure. At that same time of optimize the basic characteristics of the traditional silicon carbide UMOSFET structure, the improvement realize the integration of multi-sub rectifier devices, greatly optimizes the work performance of the third quadrant of the device, and in addition, the invention also optimizes the dynamic performance of the device, and has shorter switching time; In addition, the invention also has the characteristics of simple process and easy realization.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

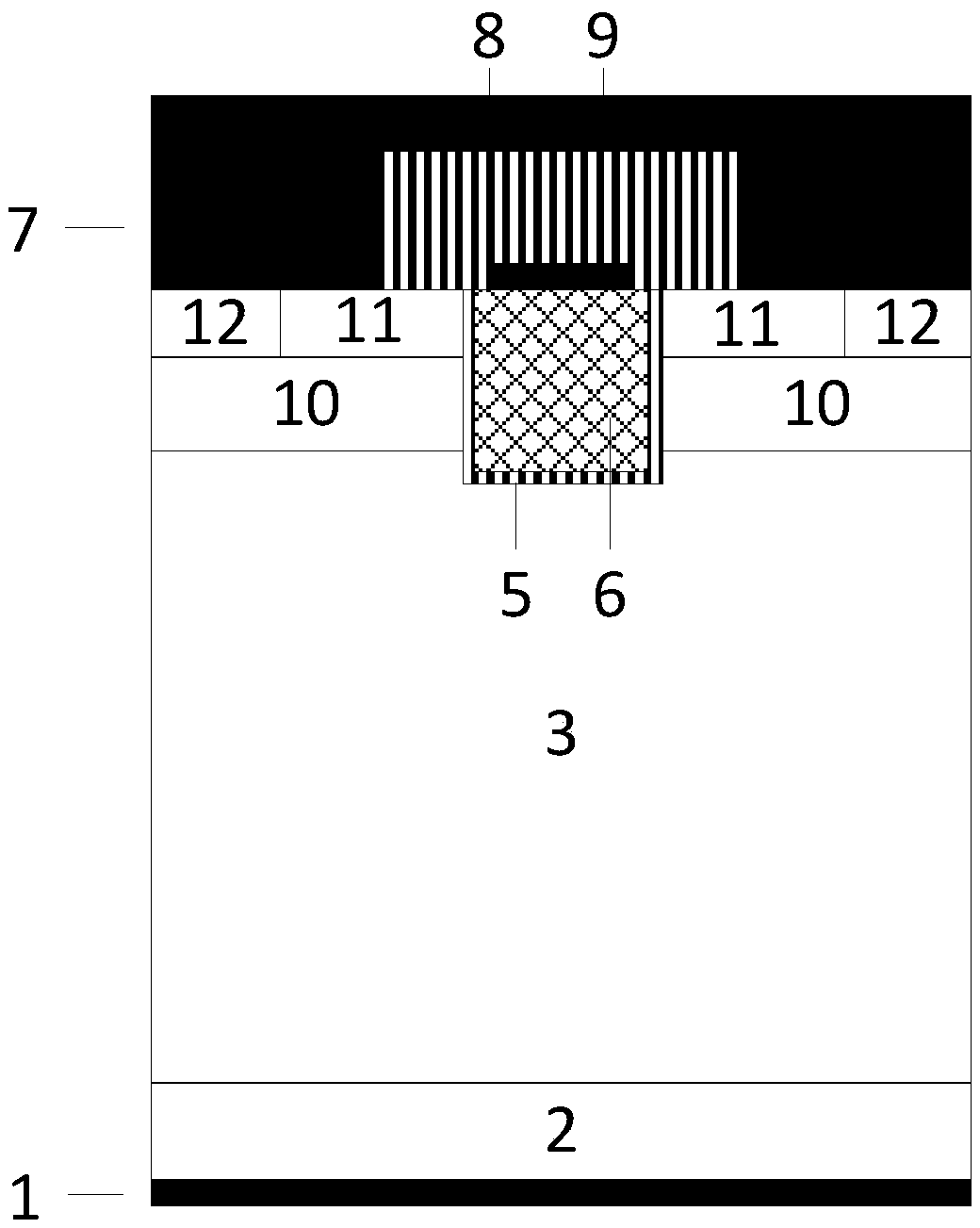

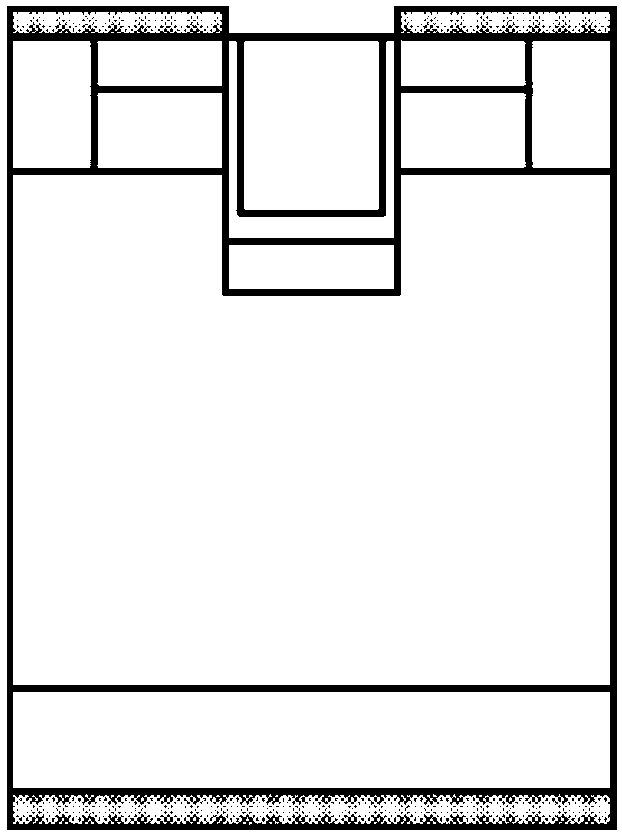

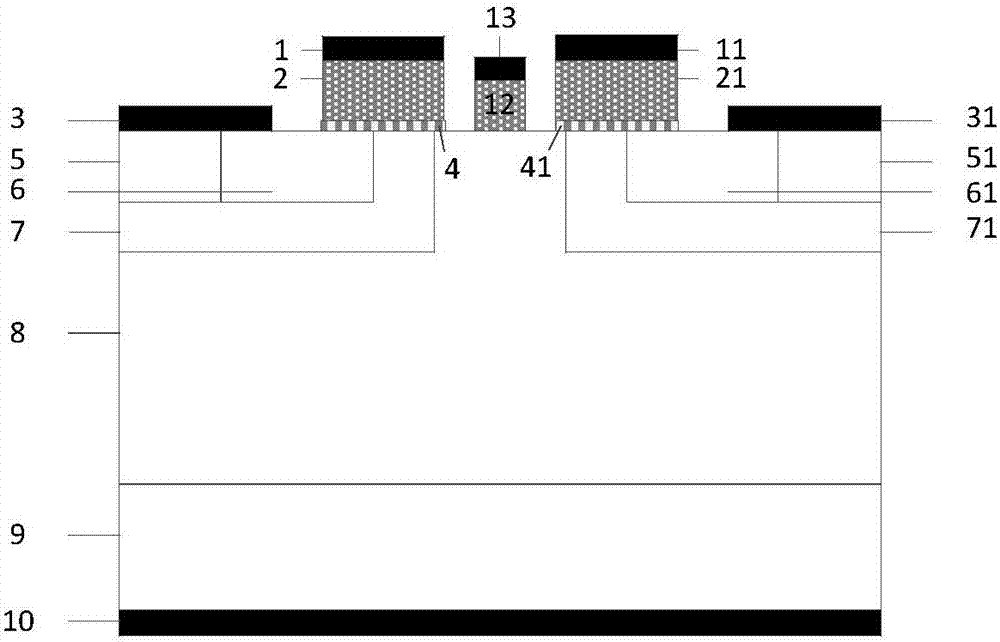

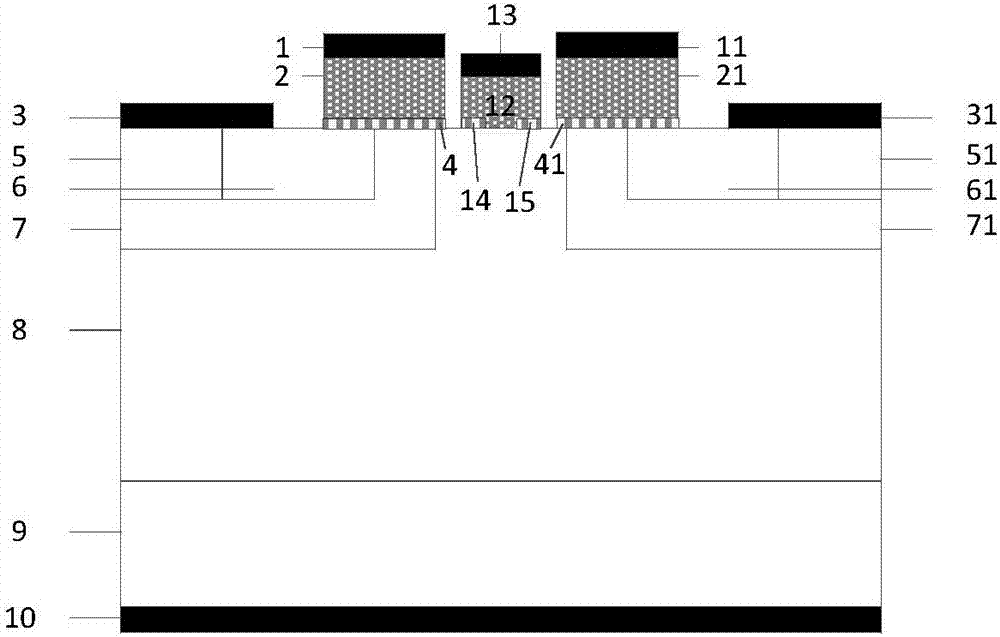

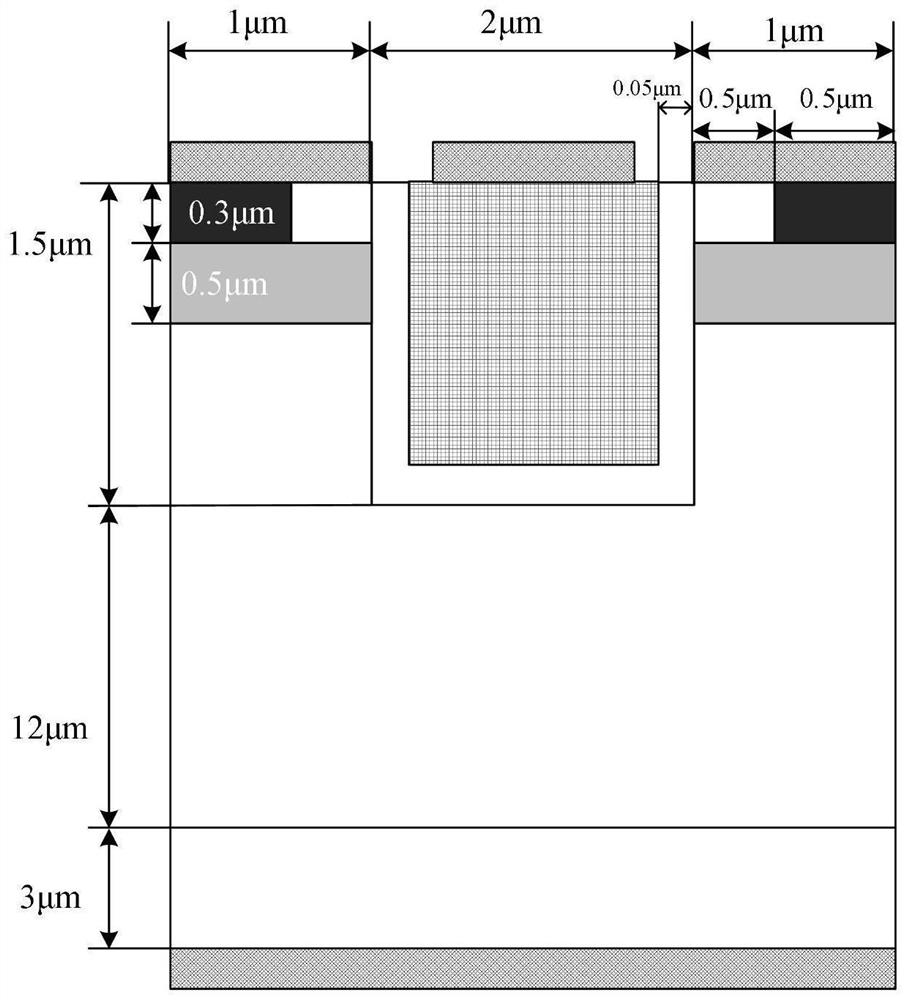

Dual-trench low-on-resistance and low-gate-charge silicon carbide MOSFET device and preparation method

ActiveCN107658340AReduce couplingLower on-resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesMOSFETGate dielectric

Disclosed are a dual-trench low-on-resistance and low-gate-charge silicon carbide MOSFET device and a preparation method. The device comprises a source, a first conductive type source region contact part, a second conductive type base region, a heavily-doped second conductive type trench region, a first conductive type polysilicon gate, a second conductive type polysilicon gate, groove gate dielectric, a second conductive type gate oxide protection region, a first conductive type packaging region, a first conductive type drift region, a first conductive type substrate and a drain. By virtue ofa space charge region formed by the first conductive type polysilicon gate and the second conductive type polysilicon gate, coupling between the gate and the drain is lowered, thereby lowering gate charge of the device; by virtue of the first conductive type packaging region, the space charge region formed by the second conductive type gate oxide protection region in the drift region can be reduced; in addition, effective current transmission can be realized, so that the on resistance of the device can be lowered; and by virtue of the heavily-doped second conductive type trench region, the gate oxide electric field can be shielded effectively, and the gate oxide can be protected.

Owner:东莞清芯半导体科技有限公司

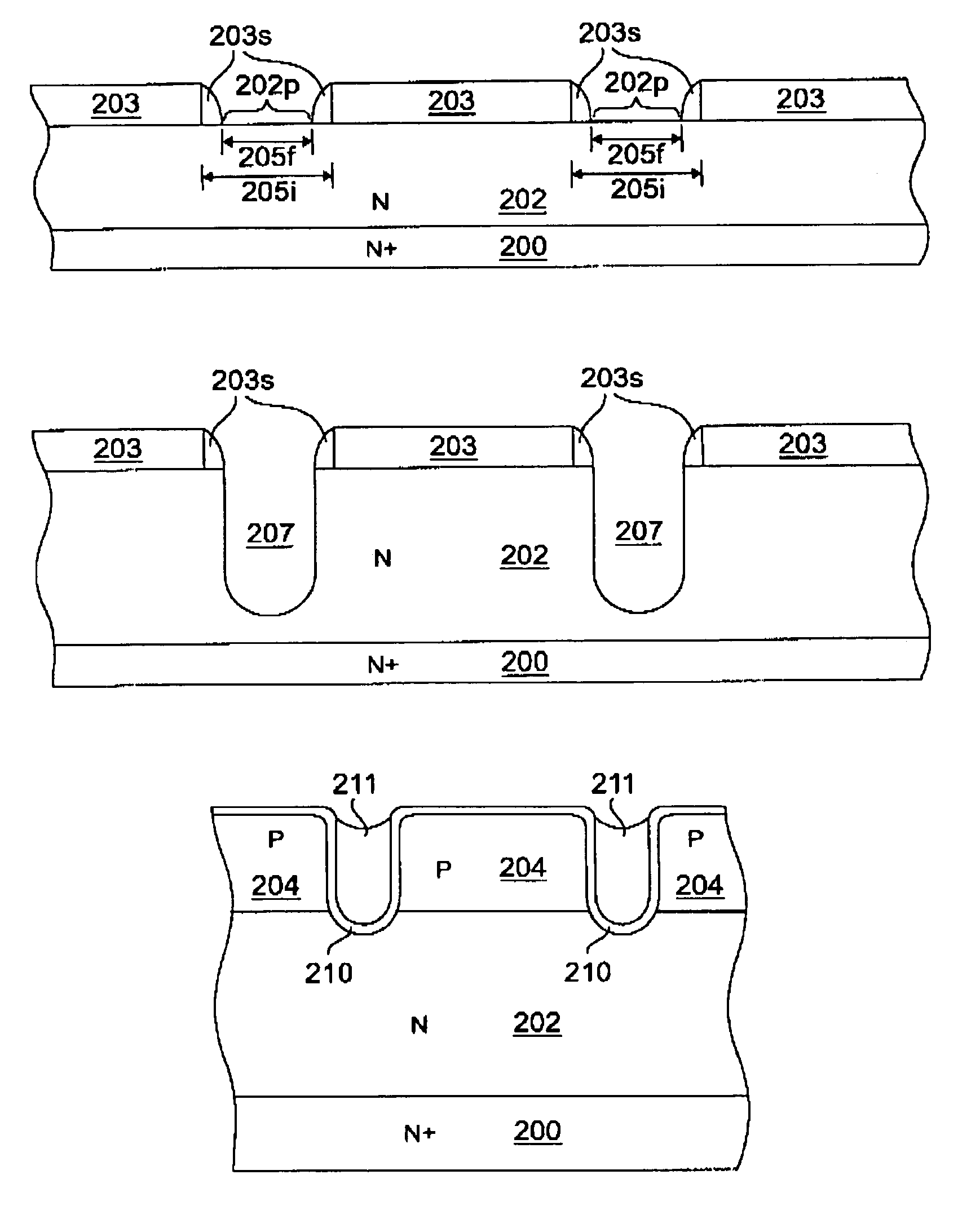

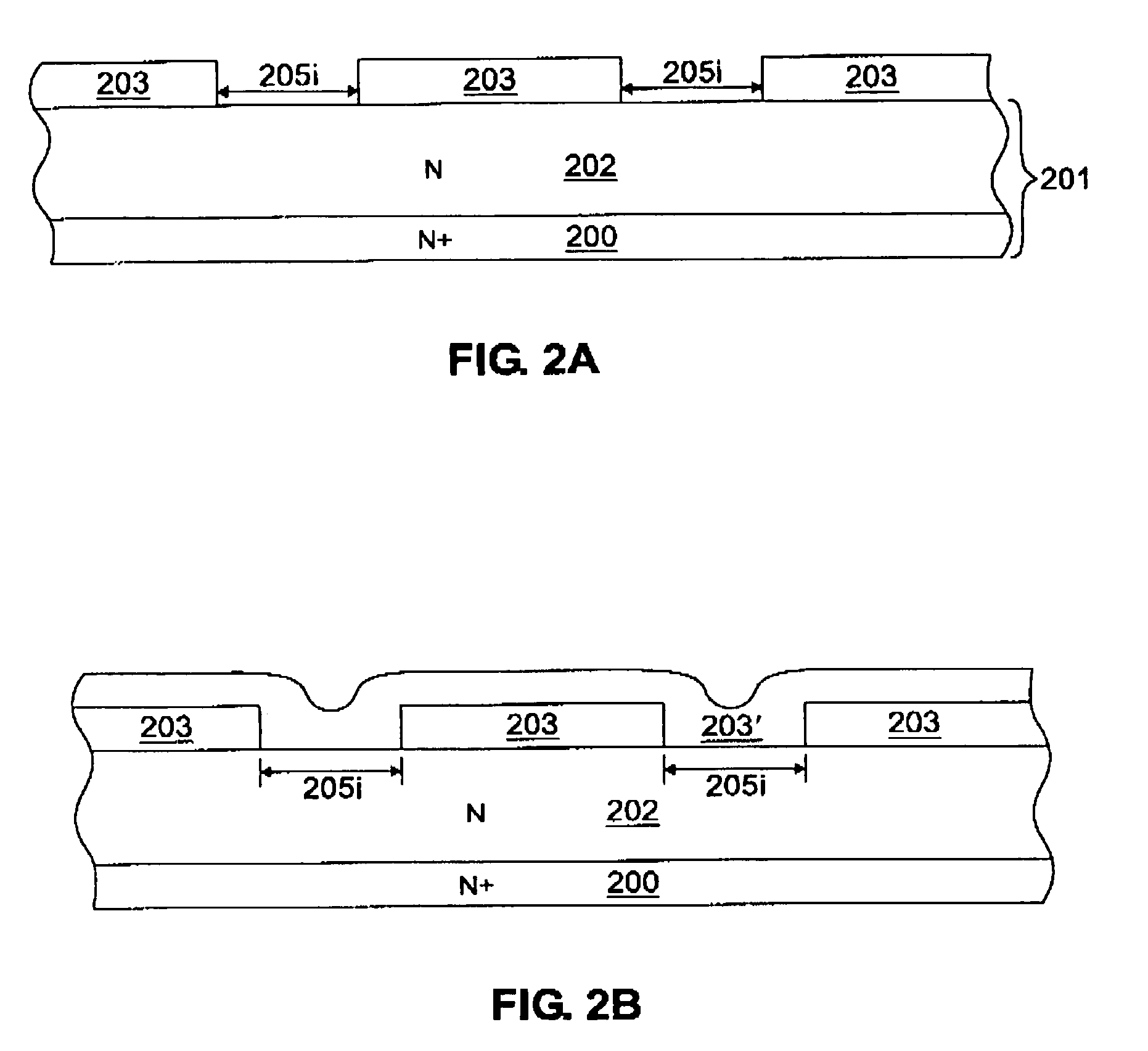

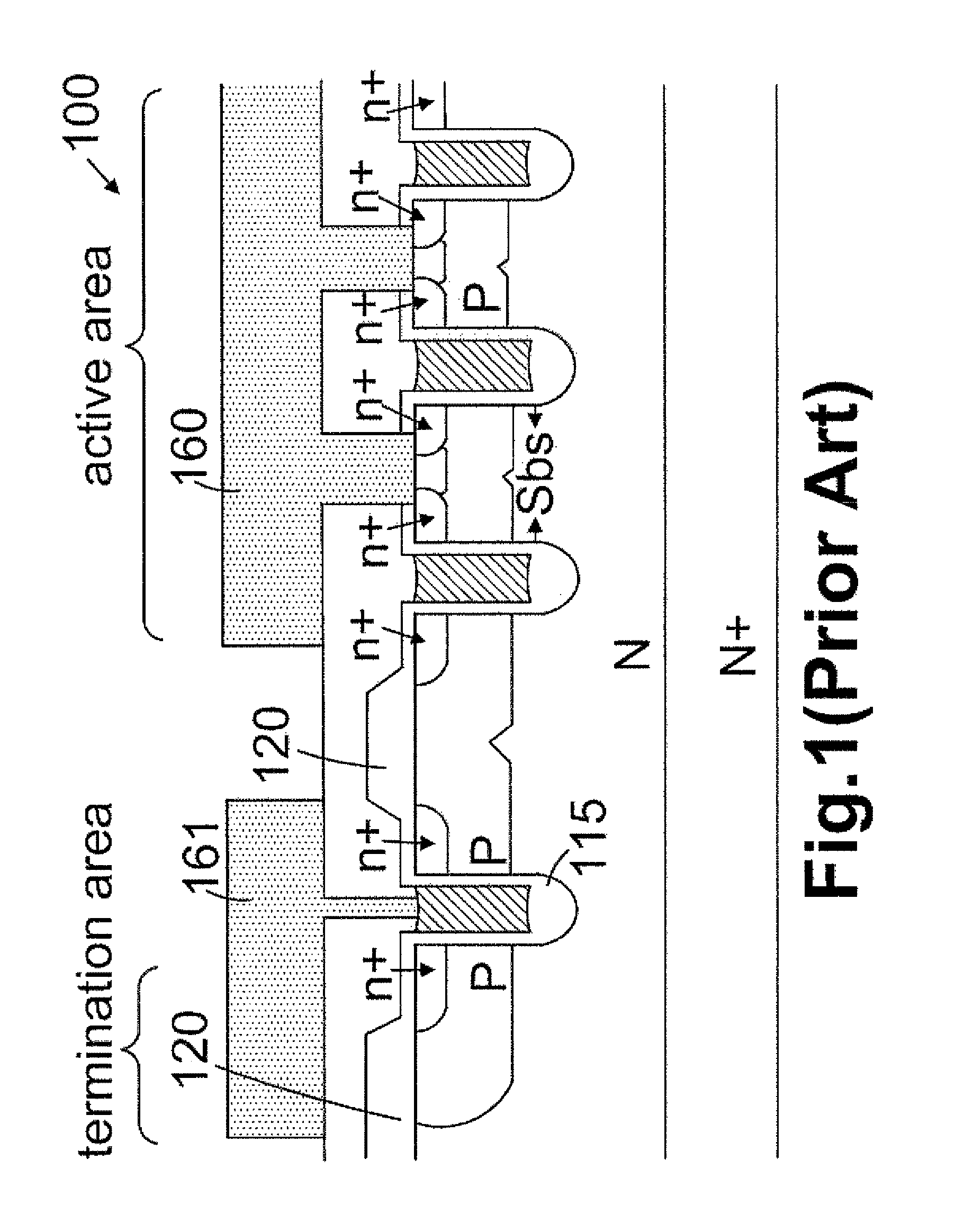

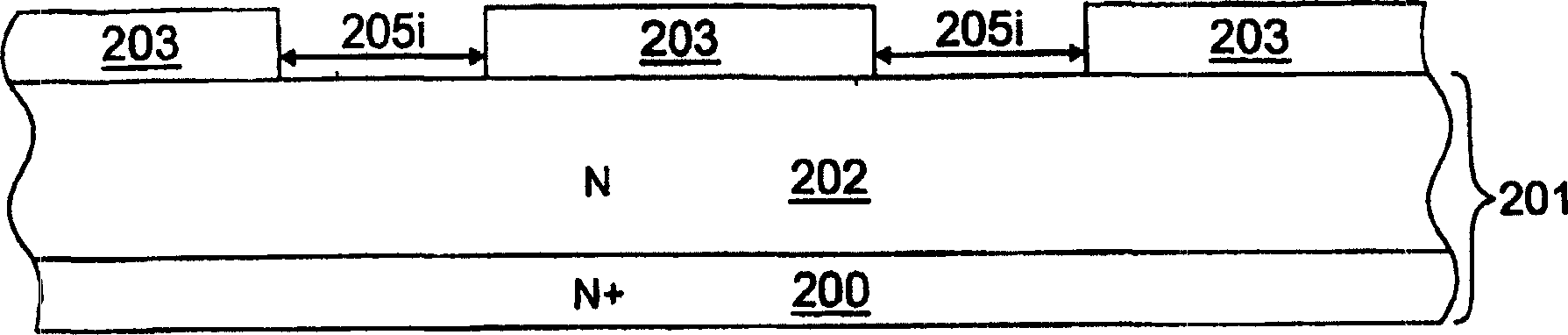

Method of forming narrow trenches in semiconductor substrates

InactiveUS6977203B2Narrow widthReduce gate chargeTransistorSemiconductor/solid-state device manufacturingTrench mosfetSemiconductor

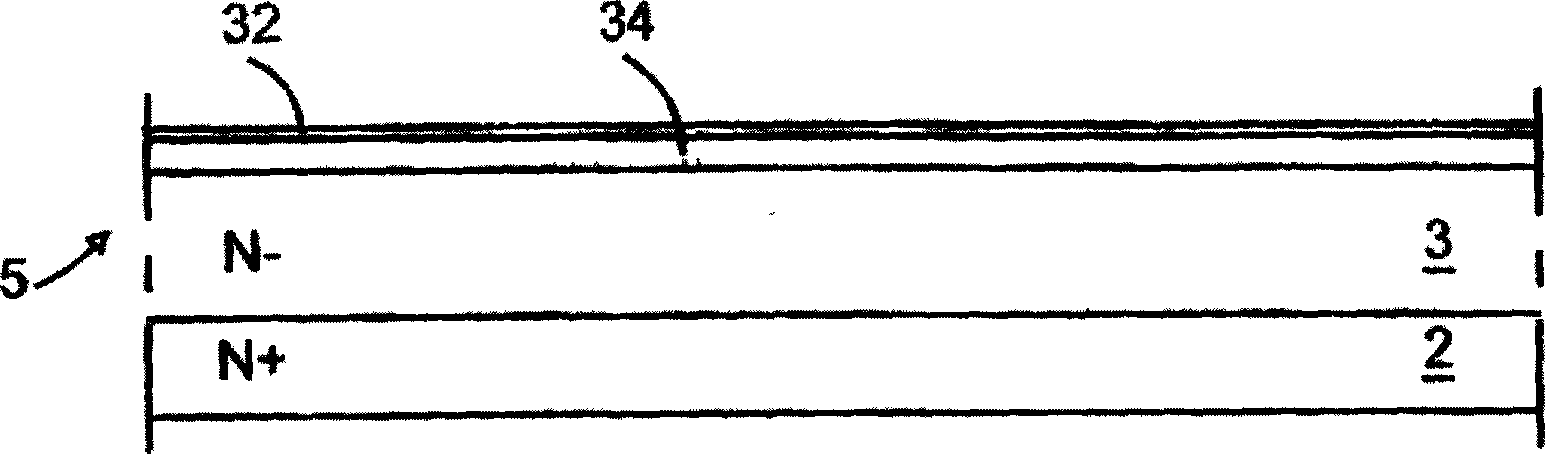

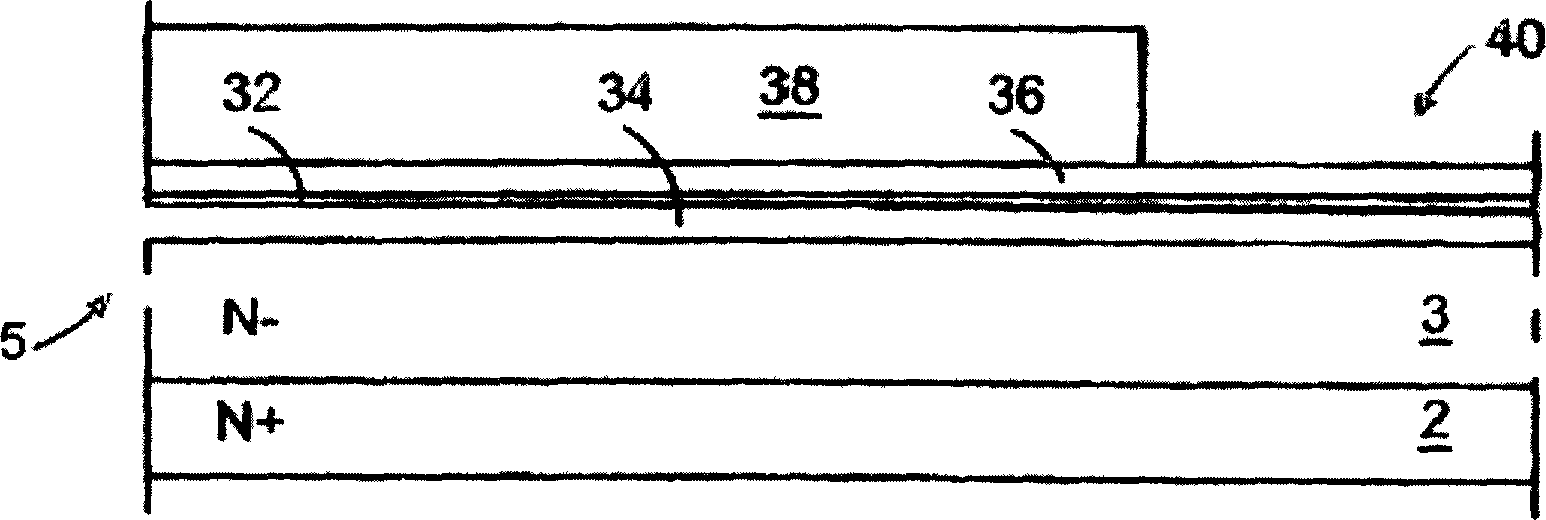

A method of forming a trench within a semiconductor substrate. The method comprises, for example, the following: (a) providing a semiconductor substrate; (b) providing a patterned first CVD-deposited masking material layer having a first aperture over the semiconductor substrate; (c) depositing a second CVD-deposited masking material layer over the first masking material layer; (d) etching the second masking material layer until a second aperture that is narrower than the first aperture is created in the second masking material within the first aperture; and (e) etching the semiconductor substrate through the second aperture such that a trench is formed in the semiconductor substrate. In preferred embodiments, the method of the present invention is used in the formation of trench MOSFET devices.

Owner:GEN SEMICON

Trench mosfet having low gate charge

InactiveCN1586012AIncrease component densityLower on-resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesTrench mosfetBody region

Owner:GEN SEMICON

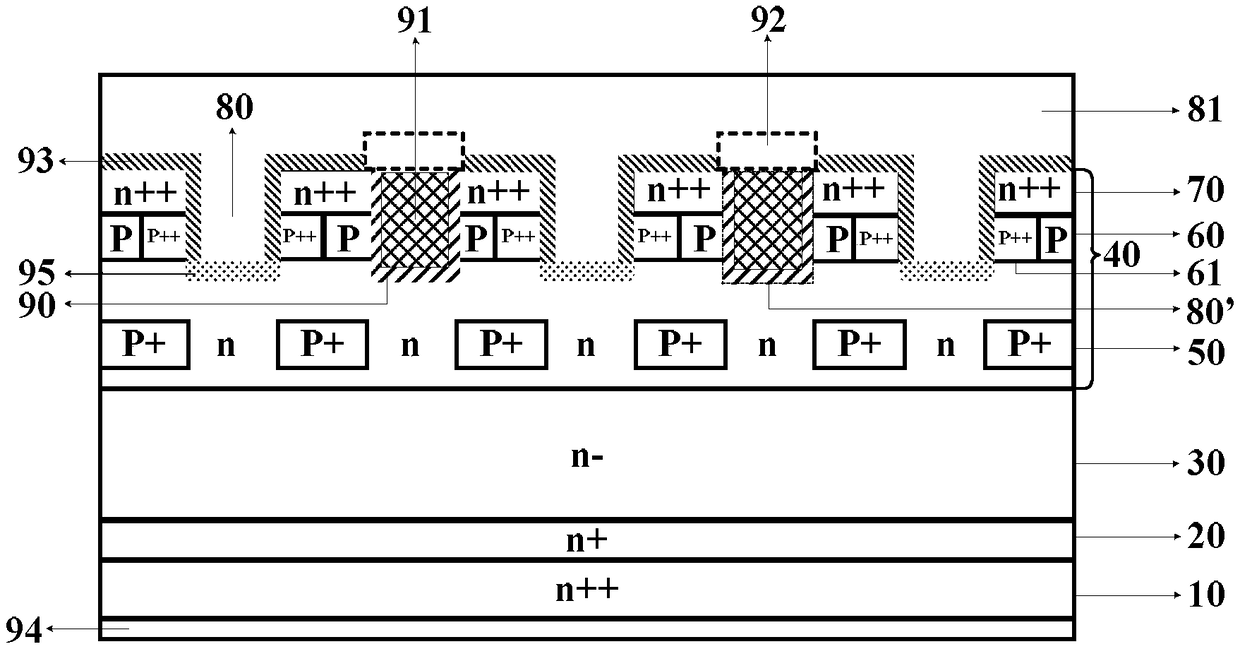

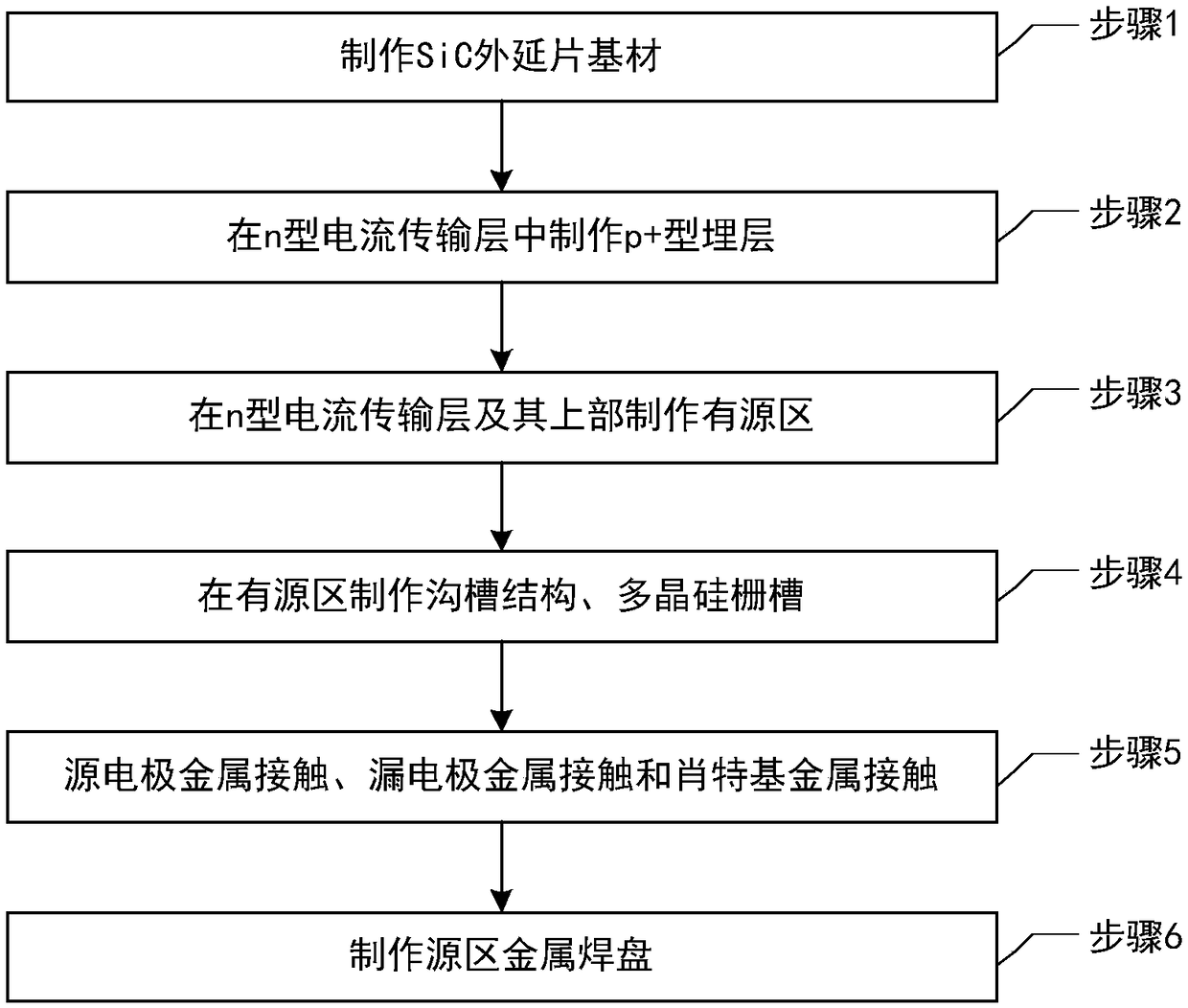

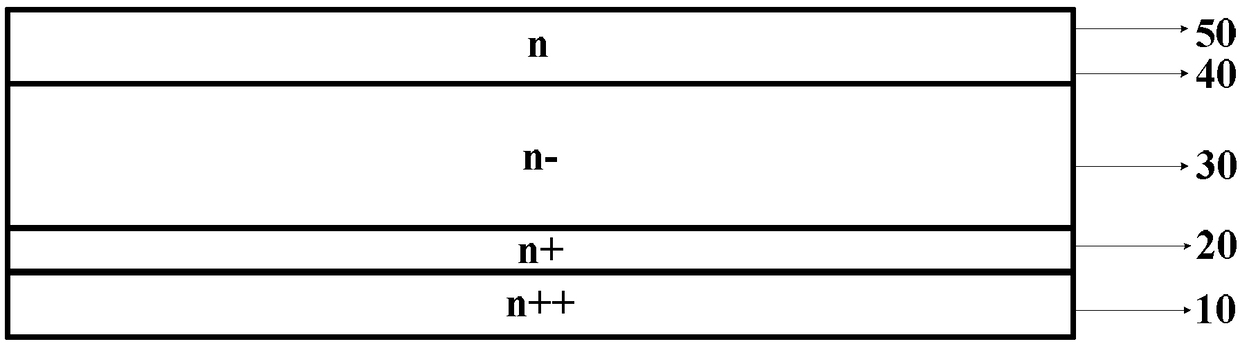

A structure of SiC UMOSFET integrated with SBD and a preparation method thereof

InactiveCN109065540AGood on-state characteristicsReduce dopingSolid-state devicesSemiconductor/solid-state device manufacturingMOSFETField-effect transistor

The invention provides a silicon carbide trench gate metal oxide with semiconductor field effect transistor (SiC UMOSFET) structure integrated Schottky diode (SBD) and a method for manufacturing the same, The structure is characterized by, a p +-type bury layer (50) is formed on the n-type current transport layer (40) by implantation, and further an n-type current transport layer (40) is epitaxially formed so that the p +-type buried layer (50) floats, and the p +-type buried layer (50) can effectively reduce the electric field in the gate trench oxide and the electric field at the Schottky contact position in the blocking mode, so that the SBD integrated SiC UMOSFET has high blocking ability, and the high temperature and high field reliability of the device are greatly improved. At that same time, the relative position of the main trench (80), the main trench (80') and the p +-type buried layer (50) and the n-type current transport layer (40) are adjusted so that when the MOSFET is operated in the first quadrant, the conduction characteristic of the MOSFET does not degrade significantly; When the MOSFET is operated in the third quadrant, the conduction of the parasitic pn diode inthe MOSFET is effectively suppressed and the Schottky diode conduction mode is obtained. SiC UMOSFETs with integrated SBD have a lower total chip area than discrete SBD and MOSFET devices.

Owner:INST OF SEMICONDUCTORS - CHINESE ACAD OF SCI

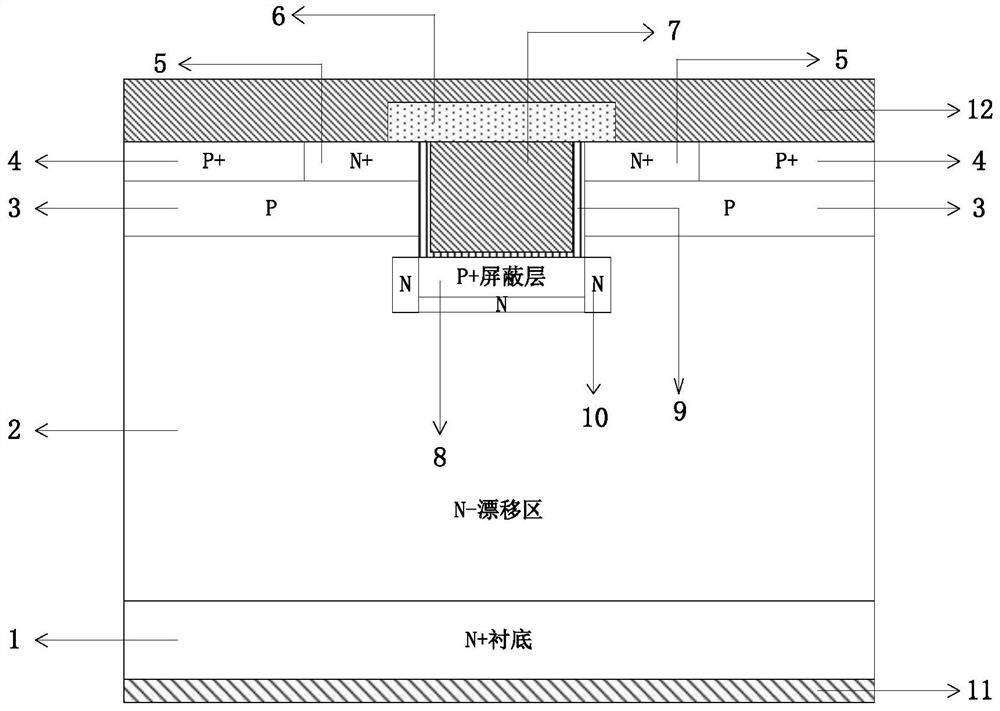

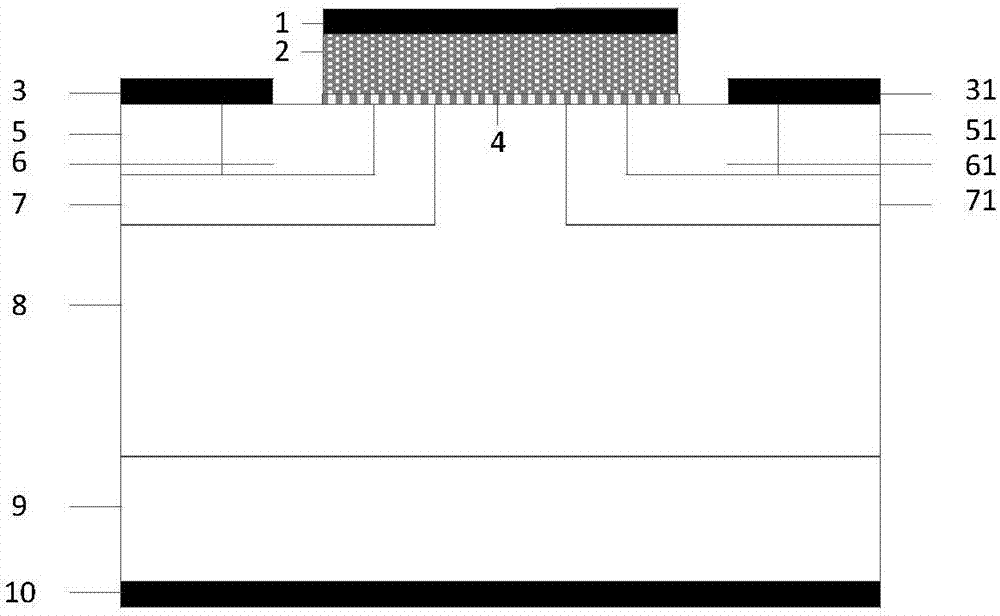

Trench silicon carbide power device with low on-resistance and manufacturing process thereof

ActiveCN111668312AImprove process precisionReduce processing difficultySemiconductor/solid-state device manufacturingSemiconductor devicesElectrical resistance and conductanceManufacturing technology

The invention provides a trench silicon carbide power device with low on-resistance and a manufacturing process thereof. The cell of the trench silicon carbide power device comprises an N-type substrate, an N-type epitaxial layer and a trench, wherein the trench is internally provided with a gate oxide layer and a polysilicon gate, a P-type body region, an N-type source region and a P+ body contact region are arranged on the two sides of the trench, a P shielding layer is arranged below the trench, and an N-type buried layer is arranged on the side of the P shielding layer. The manufacturing process of the N-type buried layer comprises the steps of epitaxially growing a first part of an N-type drift region on the N-type substrate, forming a P shielding layer and an N-type buried layer on the first part of the N-type drift region by adopting an ion implantation process, continuing to epitaxially form a second part of the N-type drift region, and carrying out a subsequent process flow. According to the invention, two sides of the P shielding layer are provided with the N-type buried layers, the electric field peak is moved downwards, the trench corner electric field is reduced, the interface state density and defects are reduced, and the reliability of the gate oxide layer is improved; and an N-type buried layer below is eliminated, the gate charge of the device is reduced, the switching characteristic is improved, and the withstand voltage of the device is further improved.

Owner:SOUTHEAST UNIV

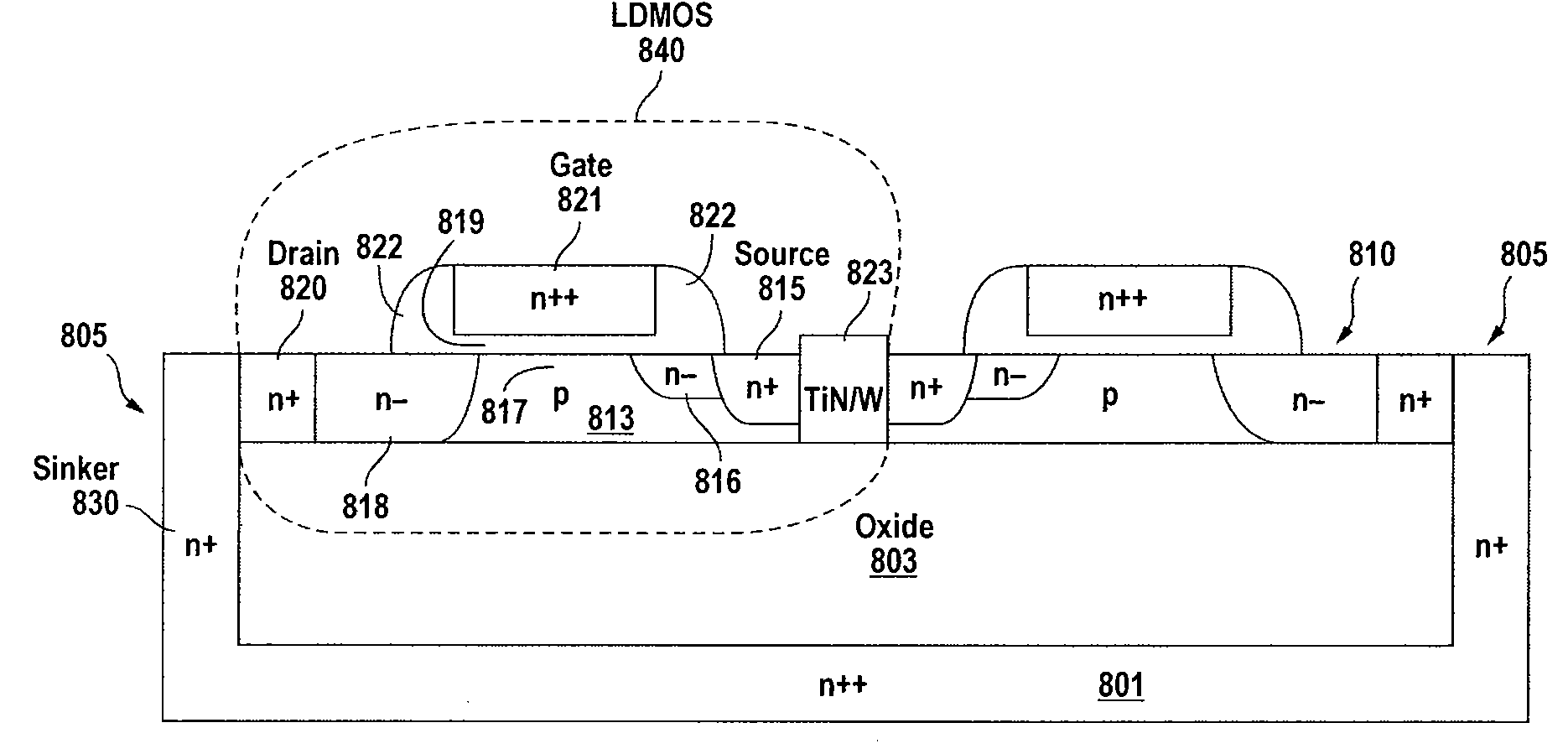

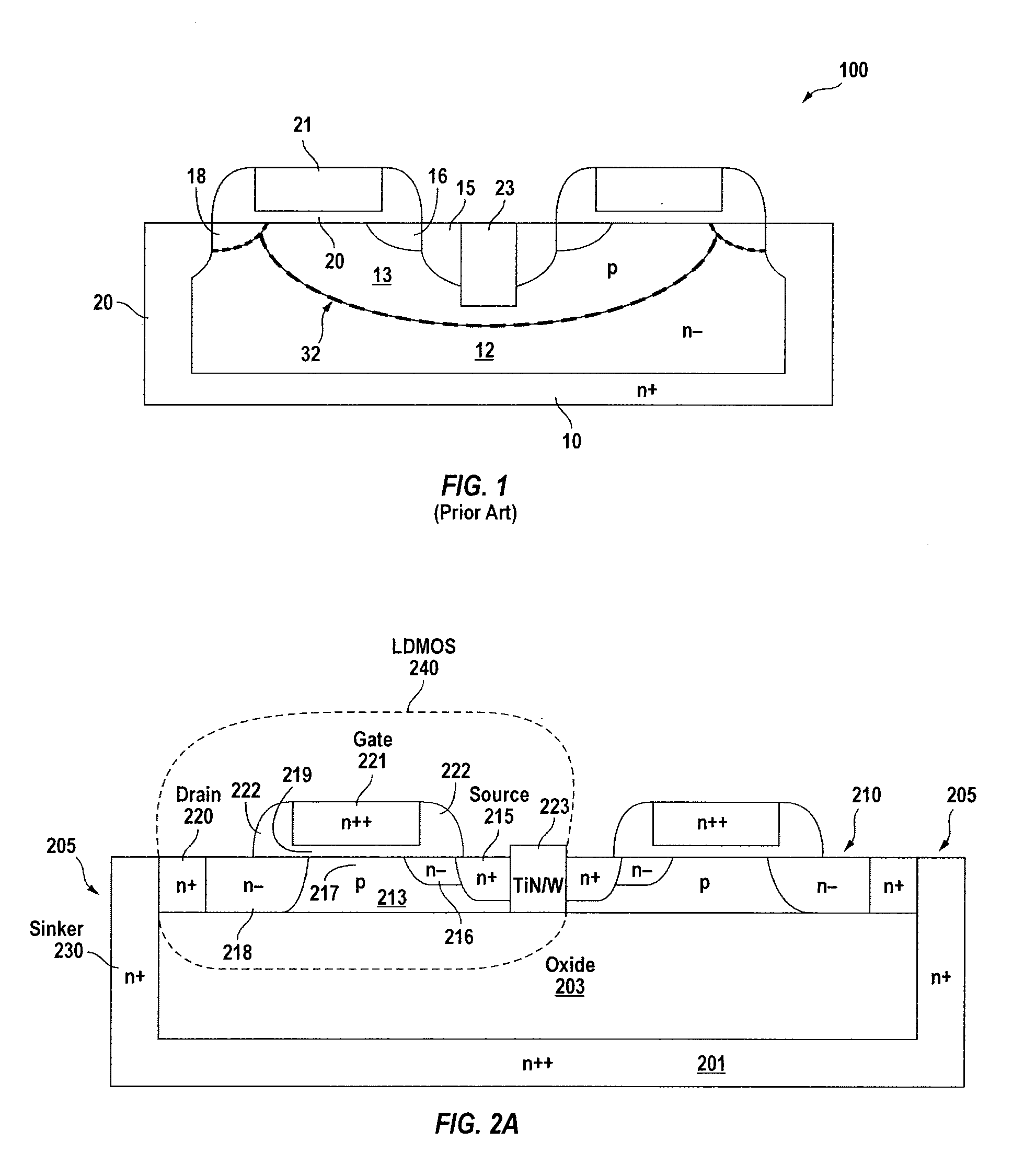

Structure and method for semiconductor power devices

ActiveUS20090267146A1Lower on-resistanceImprove breakdown voltageTransistorSolid-state devicesEngineeringBody region

A semiconductor device includes a semiconductor-on-insulator region on a substrate. The semiconductor-on-insulator region includes a first semiconductor region overlying a dielectric region. The device includes an MOS transistor and a bipolar transistor. The MOS transistor has a drain region, a body region, and a source region in the first semiconductor region. The MOS transistor also includes a gate. The device also includes a second semiconductor region overlying the substrate and adjacent to the drain region, and a third semiconductor region overlying the substrate and adjacent to the second semiconductor region. The bipolar transistor includes has the drain region of the MOS transistor as an emitter, the second semiconductor region as a base, and the third semiconductor region as a collector. Accordingly, the drain of the MOS transistor also functions as the emitter of the bipolar transistor. Additionally, the gate and the base are coupled by a resistive element.

Owner:SEMICON COMPONENTS IND LLC

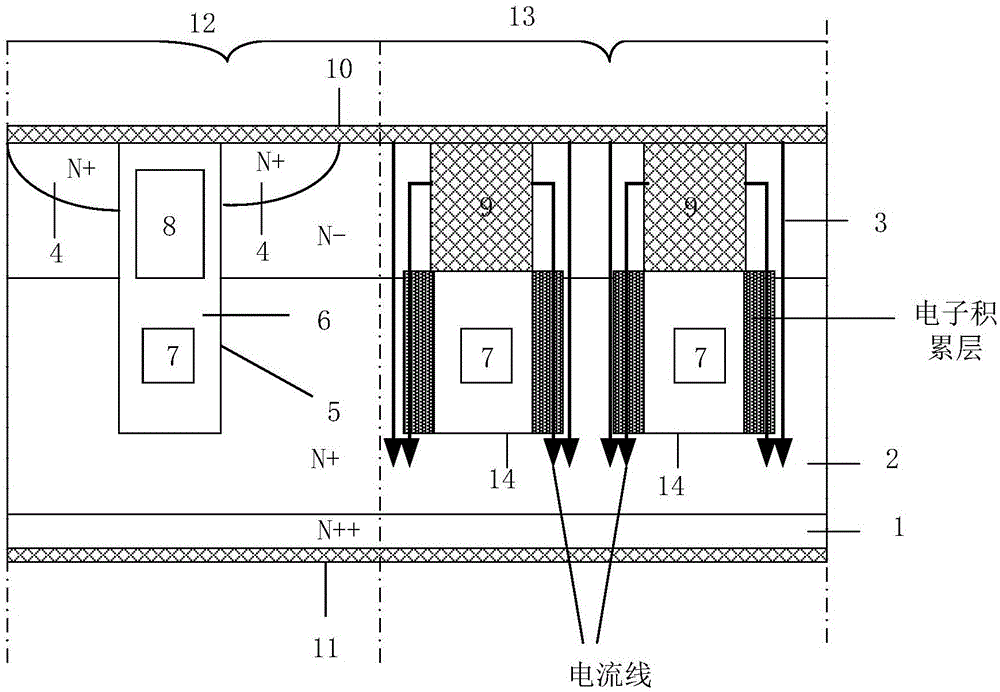

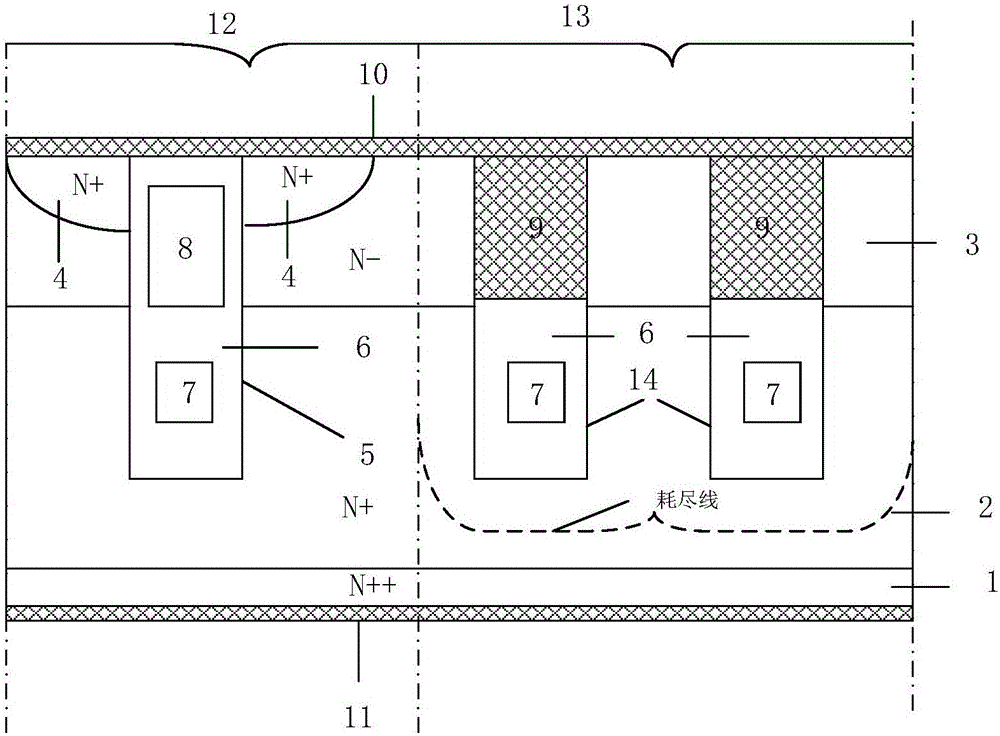

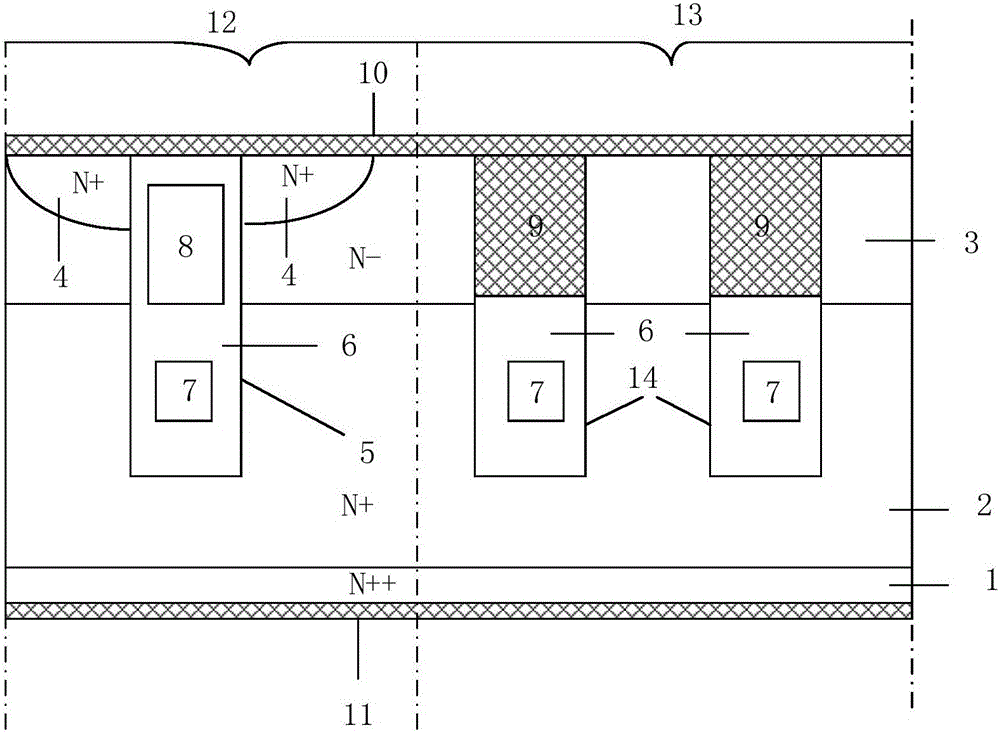

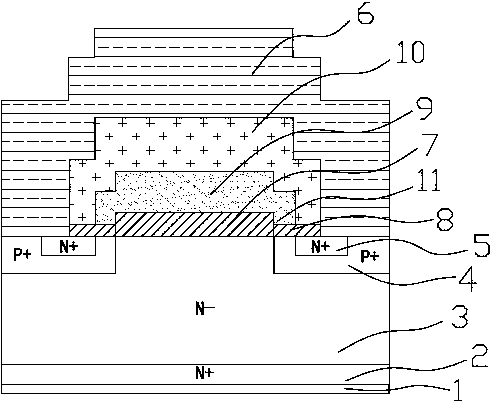

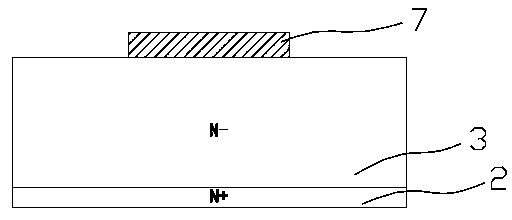

Accumulating type shield grid MOSFET integrating schottky diodes

The invention belongs to semiconductor technology, and specifically relates to an accumulating type shield grid MOSFET integrating a schottky diode. A shield grid MOSFET area formed on a silicon substrate is separated from and adjacent to a schottky diode forming area. The accumulating type shield grid MOSFET has a shield grid structure, and the schottky diode has a groove structure identical to that of the shield grid MOSFET, and the schottky diode is filled in the top of the groove through source electrode metal to form a schottky contact on the side surface of the groove to reduce a chip occupied area. The forming process of the schottky diode is compatible with the forming process of MOSFET, thereby reducing process steps. When the schottky diode is reversely biased, an electric field exists between a polysilicon 7 in the groove 14 and N+ drift region 2, the N+ drift region 2 generates depletion, and the depletion area extends to the N+ drift region 2 until complete depletion. The breakdown of schottky junctions is prevented, and reverse current leakage of schottky diode is minimized.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

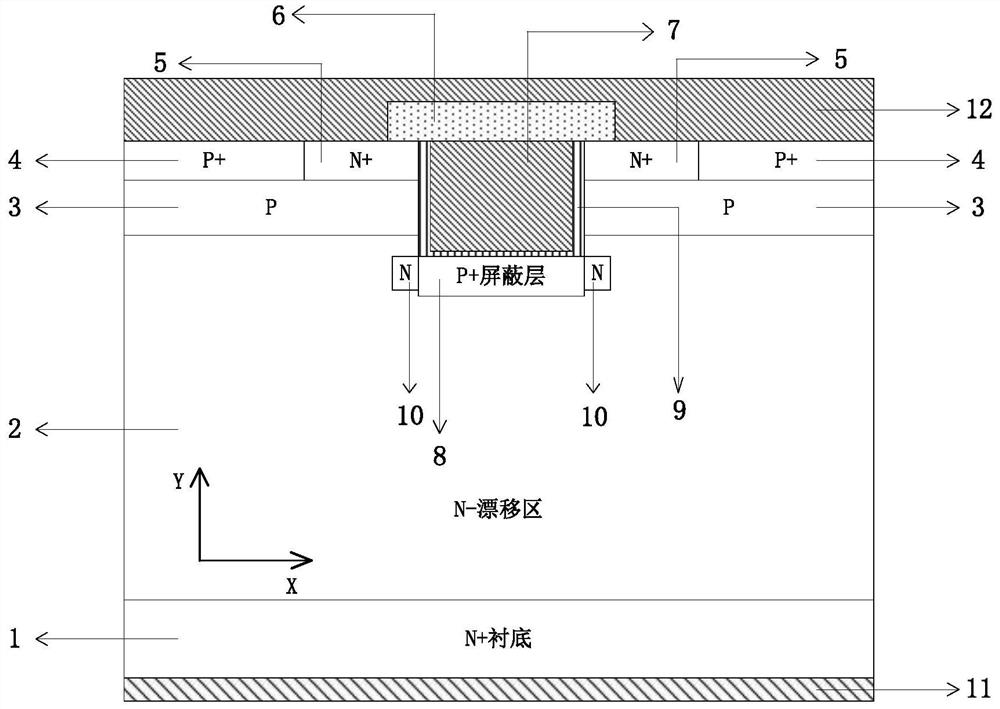

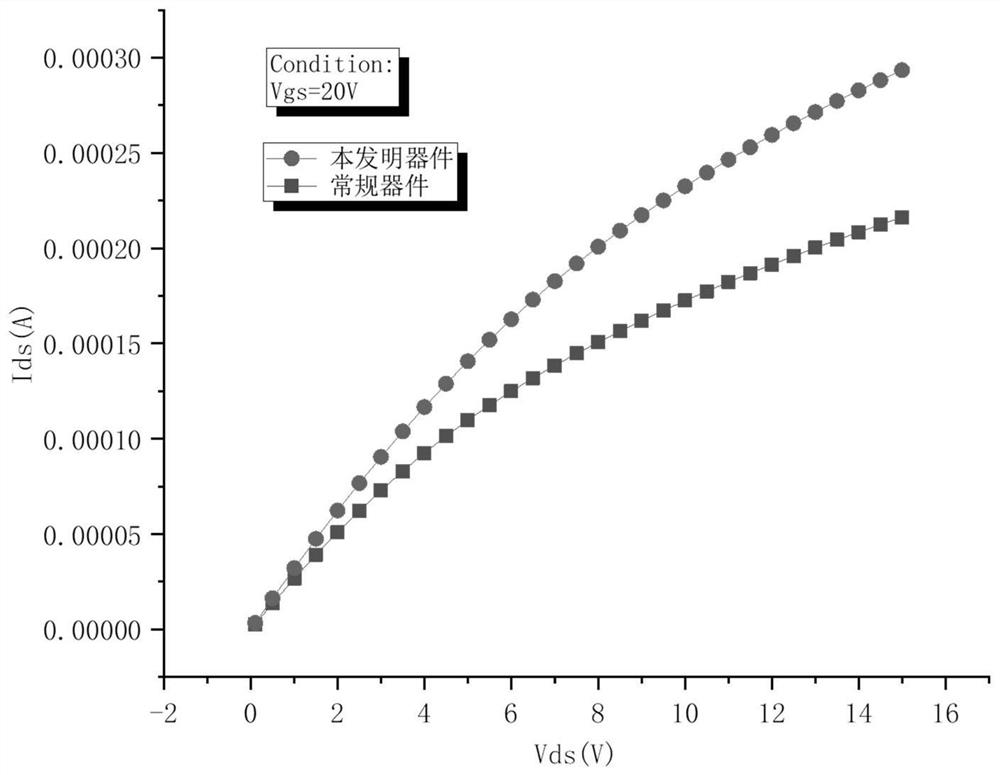

SiC vertical double diffused metal-oxide-semiconductor (VDMOS) device and fabrication method thereof

ActiveCN107248533AImprove performanceReduce power lossSemiconductor/solid-state device manufacturingSemiconductor devicesCapacitanceHeterojunction

The invention discloses a SiC vertical double diffused metal-oxide-semiconductor (VDMOS) device and a fabrication method thereof, and belongs to the technical field of a power semiconductor. A poly-silicon layer is directly deposited on a surface of a junction field-effect transistor (JFET) region of the SiC VDMOS device to form a Si / SiC heterojunction, a diode is further integrated in the device, and the application of the device in the field of an inversion circuit, a chopping circuit and the like is optimized. Compared with the prior art directly employing a VDMOS parasitic SiC diode, the SiC VDMOS device has the advantages of relatively low power loss, relatively fast working speed and relatively high working efficiency, and positive conduction is easier to achieve; compared with the prior art that a fast recovery diode (FRD) is reversely connected with the exterior of the device in parallel, the SiC VDMOS device has the advantages that the usage number of the device is reduced, connection lines between the devices are reduced, and the miniature development of the device is promoted; moreover, the grid width is reduced, the grid capacitance is reduced, and the working speed of the device is further increased; and therefore, the VDMOS device proposed by the invention has wide application prospect in the circuit field of the inversion circuit, the chopping circuit and the like.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

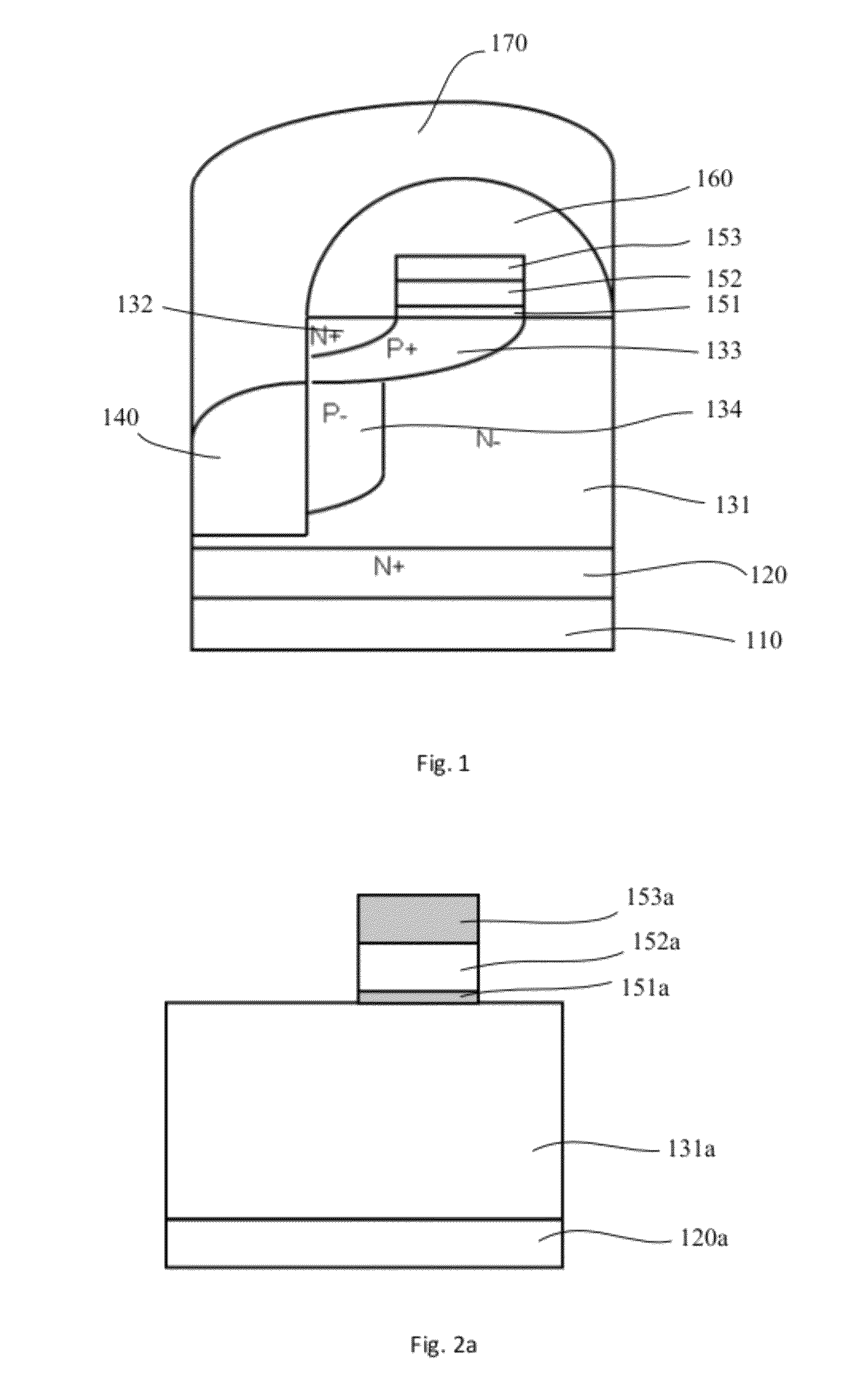

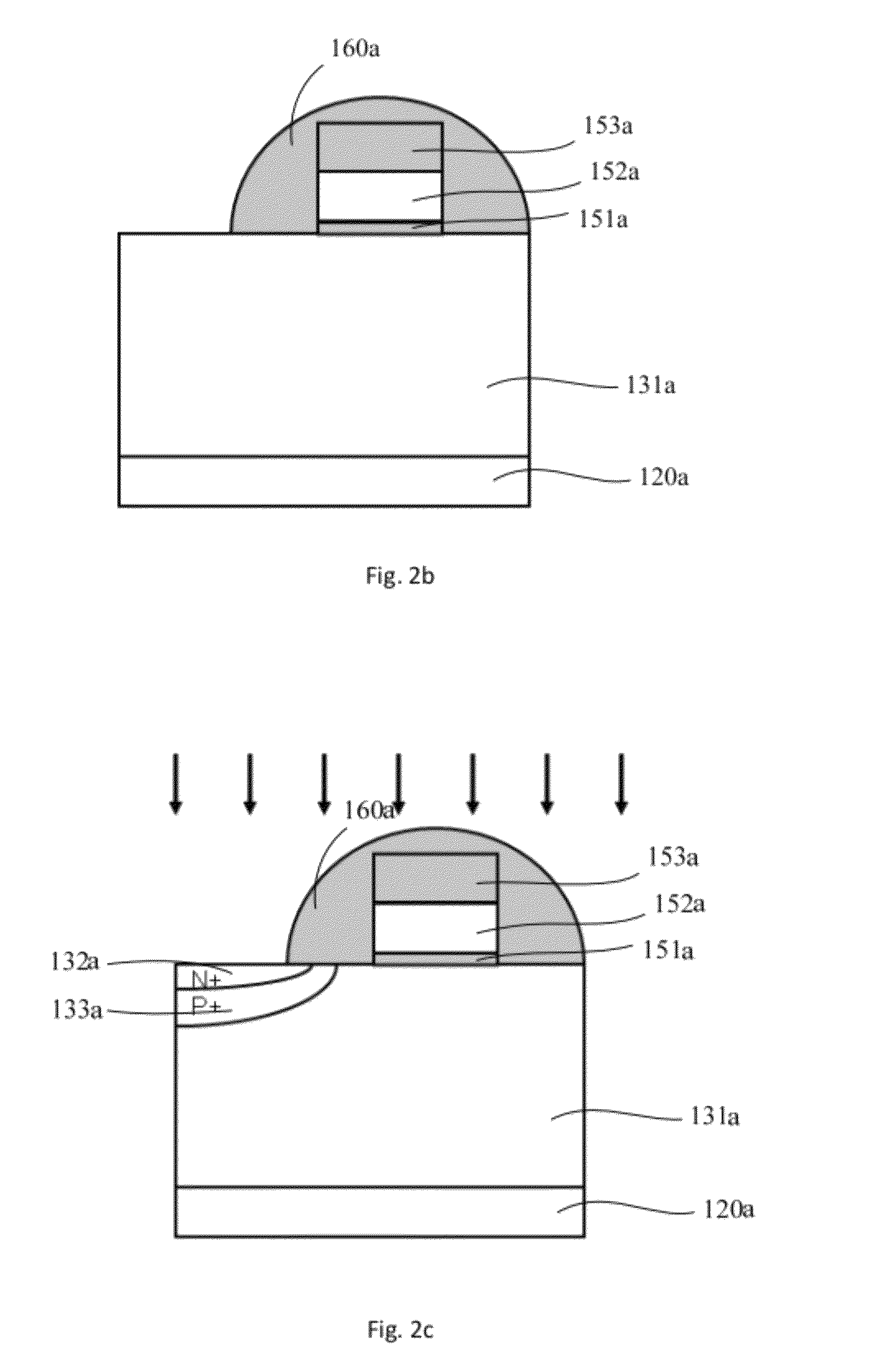

Low-grid charge power device and manufacturing method thereof

InactiveCN103730506AReduce drive power consumptionIncreasing the thicknessSemiconductor/solid-state device manufacturingSemiconductor devicesCapacitanceGate oxide

The invention discloses a low-grid charge power device. A combined type grid oxidation layer composed of a primary grid oxidation layer and a secondary grid oxidation layer is adopted in a grid oxidation layer of a grid area, a step structure is formed between the secondary grid oxidation layer and the primary grid oxidation layer, the width of the primary grid oxidation layer is smaller than or equal to the width of the top face of an N- type drift area, the thickness of the primary grid oxidation layer can be independently increased so that the overall thickness of the grid oxidation layer can be increased and the vertical thickness of the secondary grid oxidation layer in contact with a channel cannot be influenced, therefore, the capacitance between the grid area and a drain electrode is reduced under the premise of not influencing the turn-on and turn-off speed of the device, the aim of reducing grid charges is achieved, and the drive power consumption of turning on and off the device is lowered. The invention further discloses a manufacturing method of the low-grid charge power device. Under the condition of being compatible with an existing process, the primary grid oxidation layer and the secondary grid oxidation layer are formed successively by two steps to obtain the combined type grid oxidation layer, the process steps are simple, and operability is strong.

Owner:HANGZHOU LION MICROELECTRONICS CO LTD

III-nitride heterojunction device

A III-nitride heterojunction semiconductor device having a III-nitride heterojunction that includes a discontinuous two-dimensional electron gas under a gate thereof.

Owner:INFINEON TECH AMERICAS CORP

Trench MOSFET technology for DC-DC converter applications

InactiveCN1742377AImprove boot resistanceImprove featuresSemiconductor/solid-state device manufacturingSemiconductor devicesPower semiconductor deviceDc dc converter

Owner:INTERNATIONAL RECTIFIER COEP

Structure and fabrication process of super junction mosfet

InactiveUS20120256254A1Reduce resistanceImprove FOMSemiconductor/solid-state device manufacturingSemiconductor devicesMOSFETCost effectiveness

This invention discloses a specific superjunction MOSFET structure and its fabrication process. Such structure includes: a drain, a substrate, an EPI, a source, a side-wall isolation structure, a gate, a gate isolation layer and source. There is an isolation layer inside the active area underneath the source. Along the side-wall of this isolation layer, a buffer layer with same doping type as body can be introduced & source can be extended down too to form field plate. Such buffer layer & field plate can make the EPI doping much higher than convention device which results in lower Rdson, better performance, shorter gate so that to reduce both gate charge Qg and gate-to-drain charge Qgd. The process to make such structure is simpler and more cost effective.

Owner:WUXI VERSINE SEMICON CORP

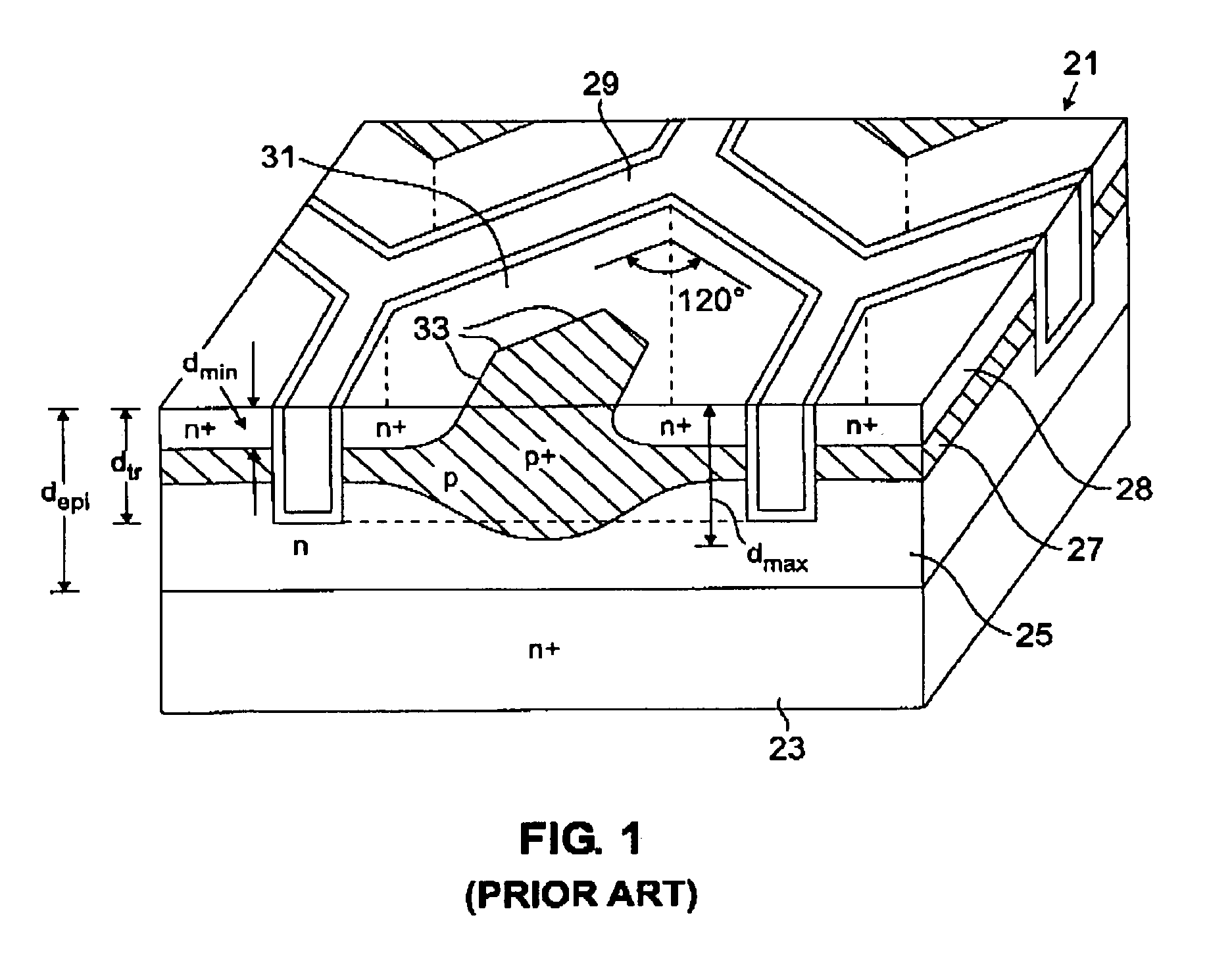

Trench MOSFET with sidewall spacer gates

ActiveUS7671441B2Lower gate resistanceReduce chargeSemiconductor/solid-state device detailsSolid-state devicesTrench mosfetEngineering

A semiconductor power device includes a semiconductor body with a plurality of gate trenches formed therein. Disposed within each gate trench is a spacer gate that extends along at least a portion of the sidewalls of the gate trench but not along at least a portion of the bottom surface of the trench. The spacer gate of each gate trench may also include a layer of silicide along outer surfaces thereof. The semiconductor body may include a channel region and each gate trench may extend through the channel region and into the semiconductor body. Formed at the bottom of each gate trench within the semiconductor body may be a tip implant of the same conductivity as the semiconductor body. In addition, a deep body implant of the same conductivity as the channel region may be formed at the base of the channel region.

Owner:INFINEON TECH AMERICAS CORP

Low temperature process and structures for polycide power MOSFET with ultra-shallow source

ActiveUS7217976B2Reduce depthReduce diffuseTransistorSolid-state devicesPower semiconductor deviceEngineering

A trench type power semiconductor device includes proud gate electrodes that extend out of the trenches and above the surface of the semiconductor body. These proud gate electrodes allow for making ultra-shallow source regions within the semiconductor body using, for example, a low temperature source drive. In addition, a method for manufacturing the trench type power semiconductor device includes a low temperature process flow once the gate electrodes are formed.

Owner:INFINEON TECH AMERICAS CORP

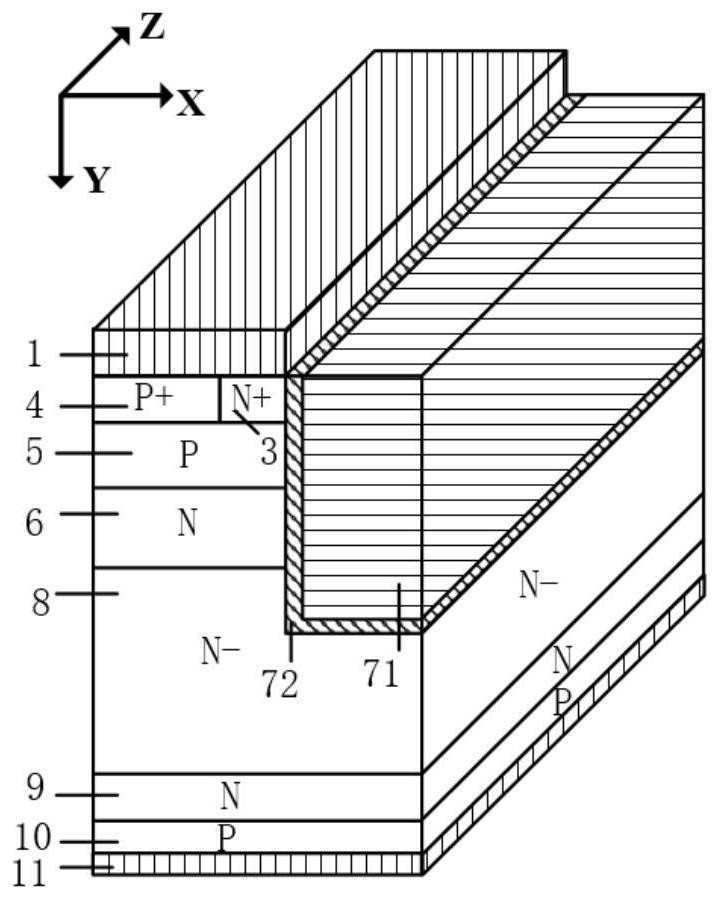

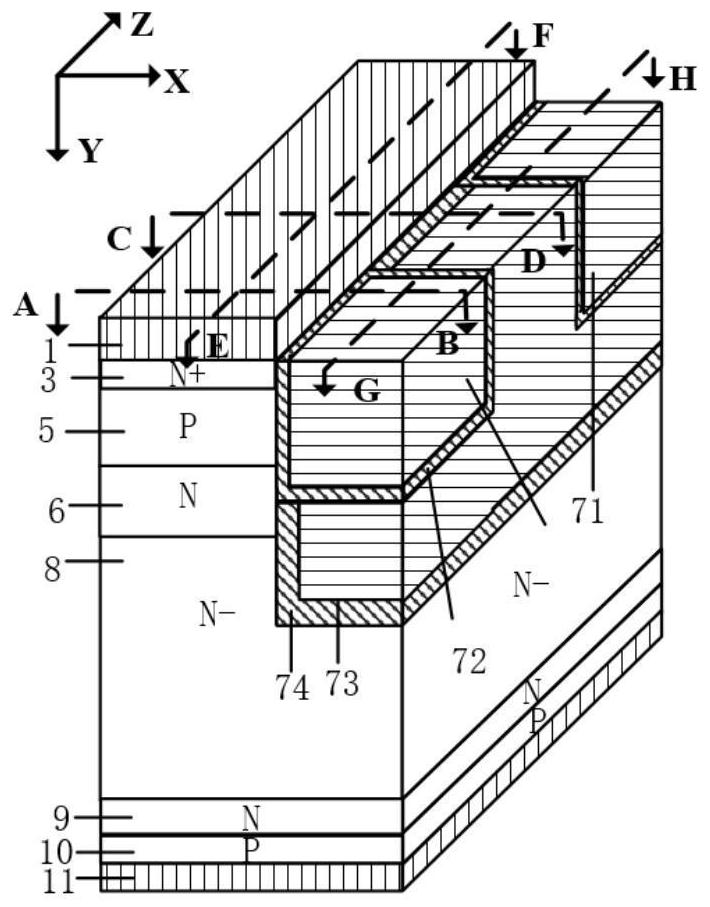

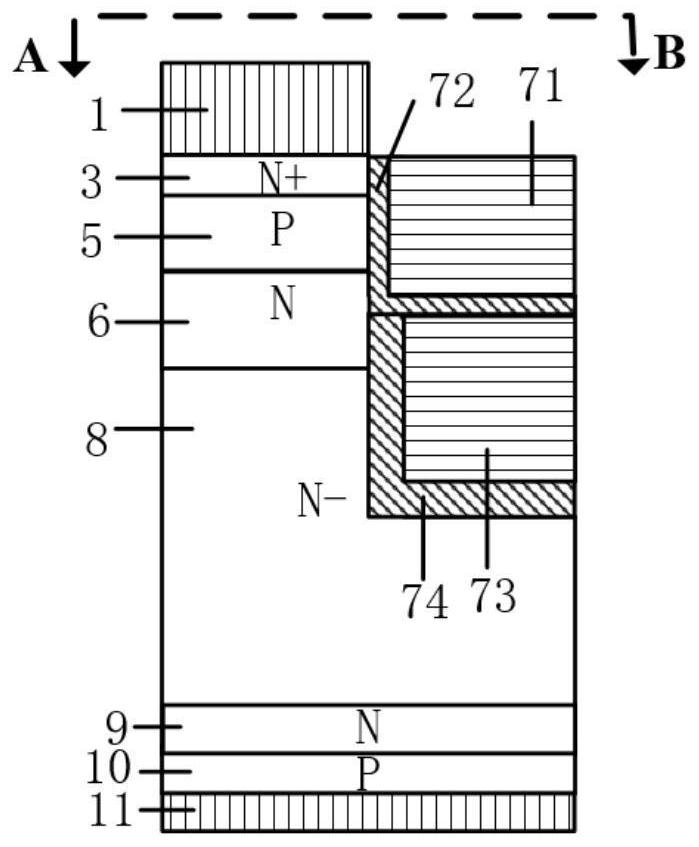

Three-dimensional separated gate trench charge storage type IGBT and manufacturing method thereof

ActiveCN113838917AEliminates the effects of breakdown characteristicsImprove breakdown voltageSemiconductor/solid-state device manufacturingSemiconductor devicesCapacitanceElectrode placement

The invention relates to a three-dimensional separated gate trench charge storage type IGBT and a manufacturing method thereof, and belongs to the technical field of power semiconductor devices. According to the present invention, a P-type buried layer and a separated gate electrode equipotential with the emitter metal are introduced on the basis of a traditional CSTBT, the influence of the doping concentration of an N-type charge storage layer on the breakdown characteristic of a device is effectively eliminated through charge compensation, and meanwhile, the conduction voltage drop can be reduced by improving the doping concentration of the N-type charge storage layer. According to the present invention, the gate electrodes and the separated gate electrodes are placed in a same groove, and the gate electrodes are arranged at intervals along the Z-axis direction, so that on one hand, the channel density can be reduced, on the other hand, a parasitic PMOS structure can be formed in a cell, the saturation current density can be reduced, and a short-circuit safe working area can be improved; and meanwhile, the gate capacitance and gate charge are reduced, the switching loss of the device is reduced, the compromise relationship between the forward conduction voltage drop Vceon and the turn-off loss Eoff is further improved; and in addition, the improvement of the current uniformity and the improvement of the reliability of the device are also facilitated.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

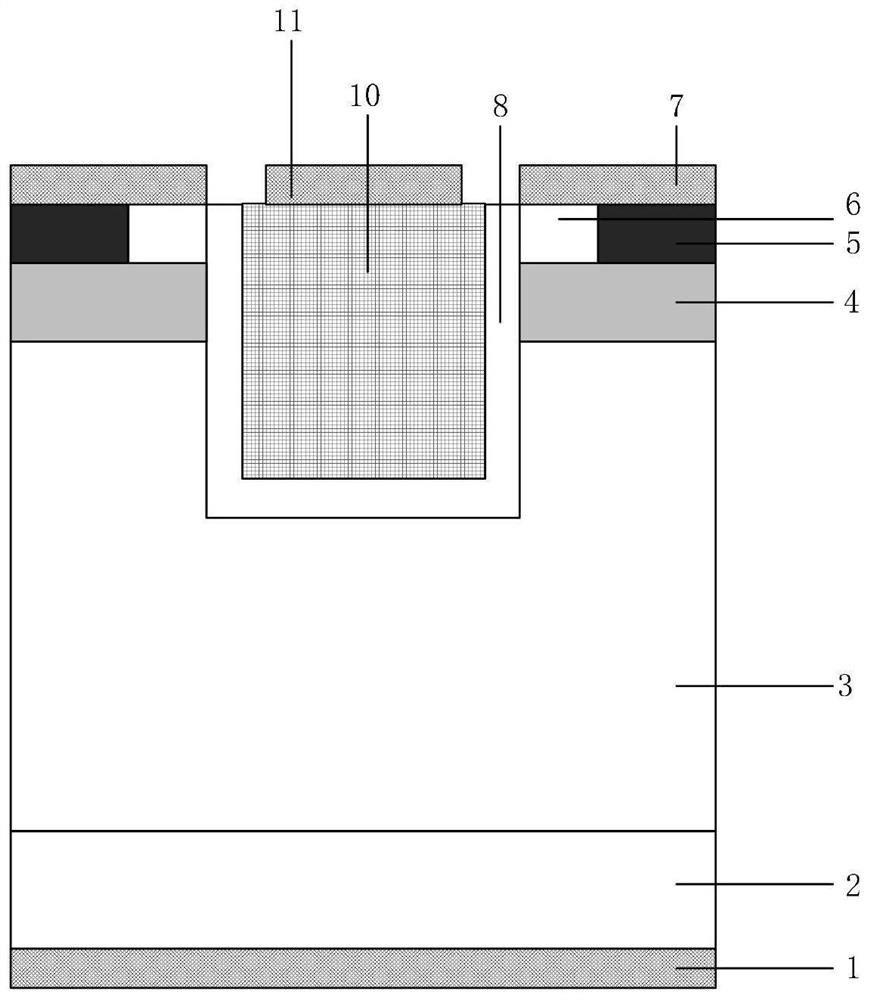

SiC MOSFET device integrating groove and body plane gate

PendingCN113629135AReduce device gate chargeImprove device switching performanceSemiconductor devicesMOSFETSemiconductor

The invention relates to a SiC MOSFET device integrated with a groove and a body plane gate, and belongs to the technical field of semiconductors. According to the MOSFET, on the basis of a traditional trench gate, a body plane gate structure is introduced into the bottom of the trench gate. The body plane gate is composed of source metal, a gate insulating dielectric layer, a gate bottom N+ source, a gate bottom P electric field shielding region and a gate bottom channel region, and the gate bottom N+ source and the gate bottom P electric field shielding region are in short circuit with the source metal. The body plane gate not only introduces a new channel, but also integrates a new PN junction diode between a P electric field shielding region and an N-drift region. Compared with a traditional groove type SiC MOSFET, the groove gate bottom peak electric field is reduced by 75.3%; the gate-drain charge is reduced by 91.5%; the starting loss is reduced by 66.6% at the frequency of 1MHZ; and the turn-off loss is reduced by 78.0%.

Owner:CHONGQING UNIV OF POSTS & TELECOMM

Trench MOSFET with trenched floating gates having thick trench bottom oxide as termination

ActiveUS8525255B2Improve performanceReduce gate chargeTransistorSolid-state devicesTrench mosfetEngineering

A power semiconductor power device having composite trench bottom oxide and multiple trench floating gates is disclosed. The gate charge is reduced by forming a pad oxide surrounding a HDP oxide on trench bottom. The multiple trenched floating gates are applied in termination for saving body mask.

Owner:FORCE MOS TECH CO LTD

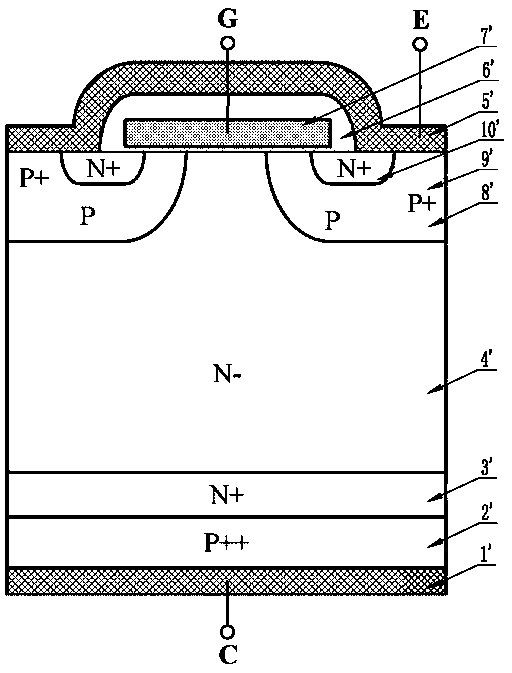

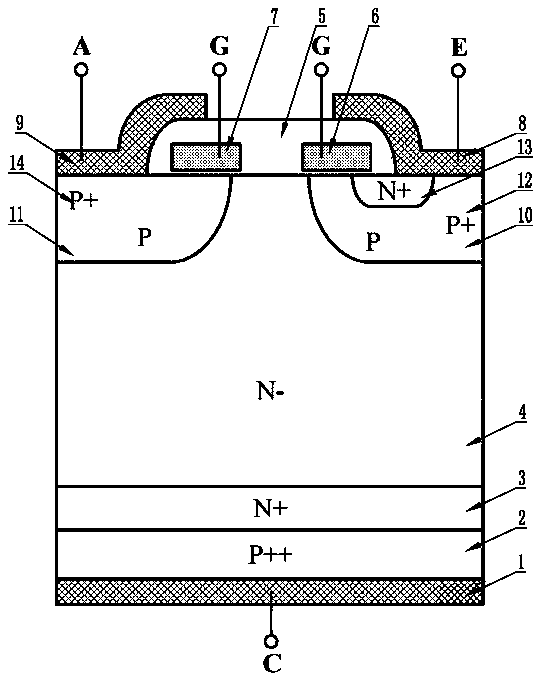

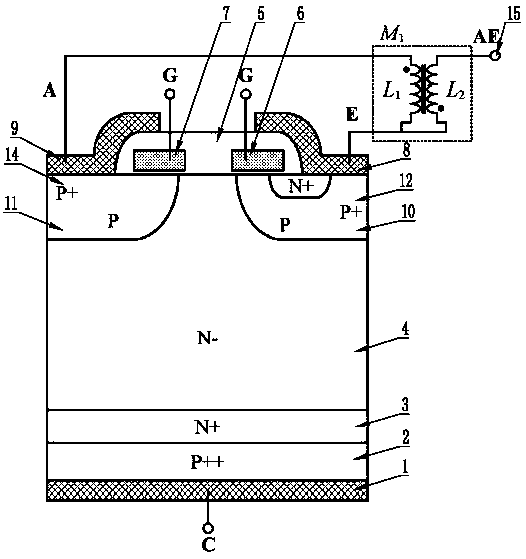

Quick switch IGBT structure

ActiveCN109817708AReduce capacitanceIncreased transient switching speedSemiconductor devicesGate dielectricAuxiliary electrode

The invention discloses a quick switch IGBT structure comprising a collector, a P++ collector region, an N+ buffer region, an N-drift region, a gate structure and a top metal layer which are laminatedfrom bottom to top, wherein the gate structure comprises a gate dielectric layer, a first gate electrode and a second gate electrode, the top metal layer comprises an emitter and an auxiliary electrode, a first P-type base region and a second P-type base region are arranged at the upper part of the N-drift region, a first P+ emitter region and an N+ emitter region are arranged at the upper part of the first P-type base region, the first P+ emitter region and the N+ emitter region are connected with the emitter, the first P-type base region and the N+ emitter region correspond to the first gate electrode, a second P+ emitter region is arranged at the upper part of the second P-type base region, the second P + emitter region is connected with the auxiliary electrode, the second P-type baseregion corresponds to the second gate electrode or the first gate electrode, an inductor L1 is connected between the auxiliary electrode and the emitter, an inductor L2 is connected between the emitter and an external terminal, and the inductor L1 and the inductor L2 form mutual inductance. The structure can greatly improve the transient switching speed of the device.

Owner:江苏矽导集成科技有限公司

Structure and fabrication process of super junction MOSFET

InactiveUS8604541B2Reduce resistanceImprove FOMSemiconductor/solid-state device manufacturingSemiconductor devicesMOSFETCost effectiveness

This invention discloses a specific superjunction MOSFET structure and its fabrication process. Such structure includes: a drain, a substrate, an EPI, a source, a side-wall isolation structure, a gate, a gate isolation layer and source. There is an isolation layer inside the active area underneath the source. Along the side-wall of this isolation layer, a buffer layer with same doping type as body can be introduced & source can be extended down too to form field plate. Such buffer layer & field plate can make the EPI doping much higher than convention device which results in lower Rdson, better performance, shorter gate so that to reduce both gate charge Qg and gate-to-drain charge Qgd. The process to make such structure is simpler and more cost effective.

Owner:WUXI VERSINE SEMICON CORP

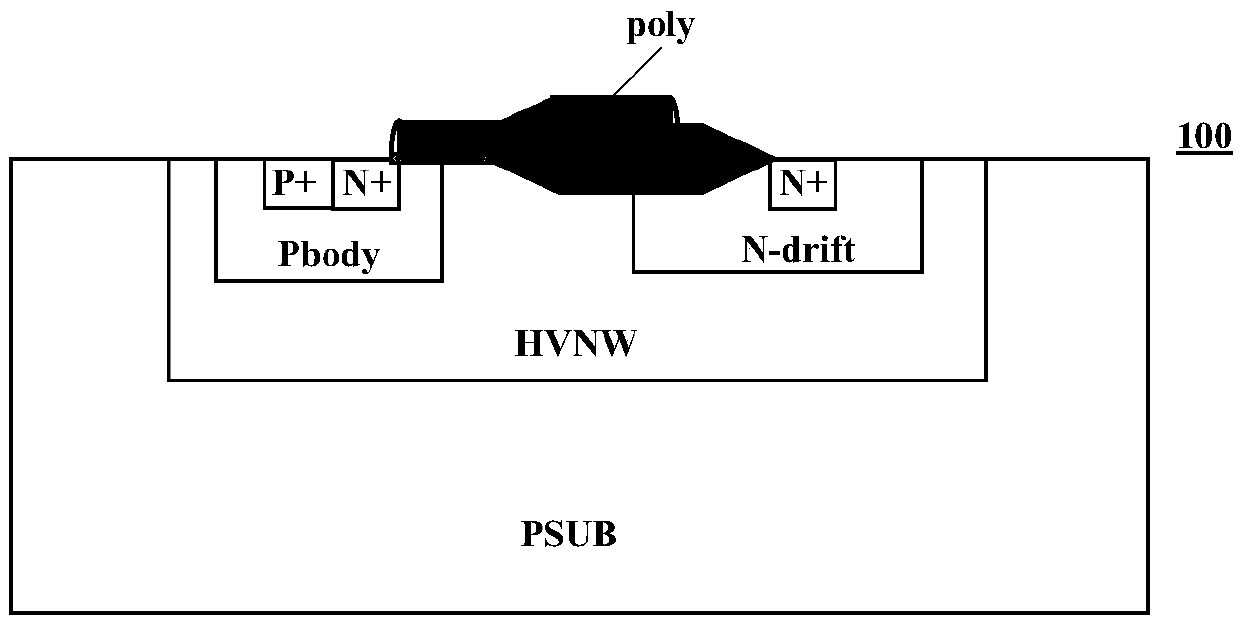

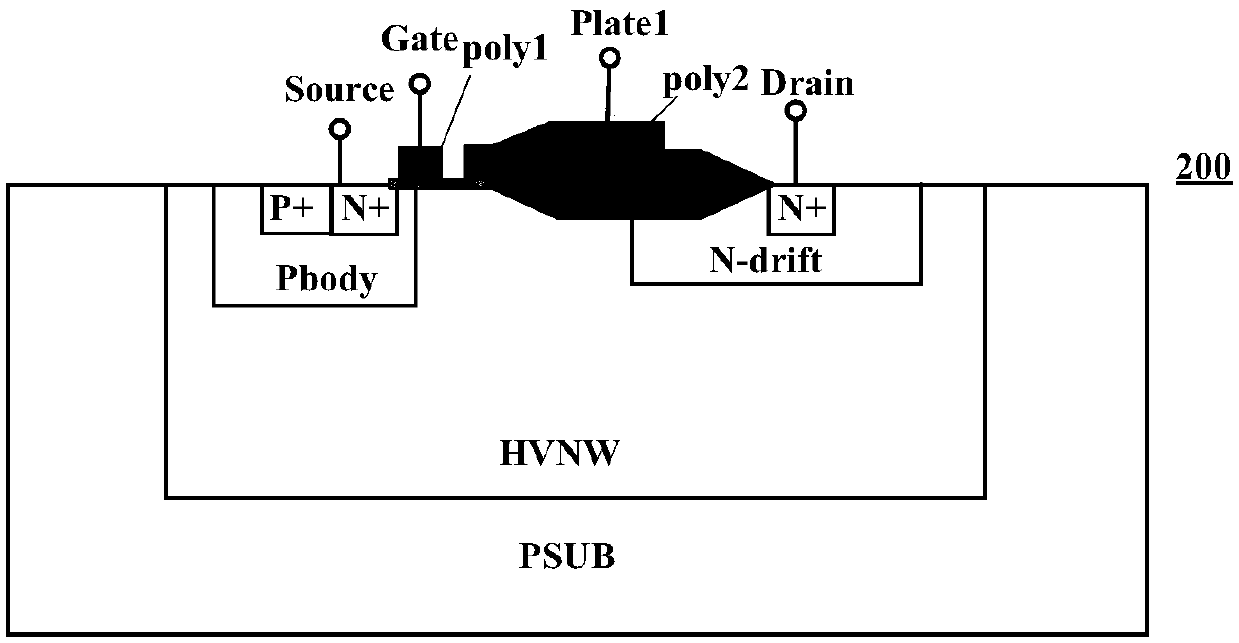

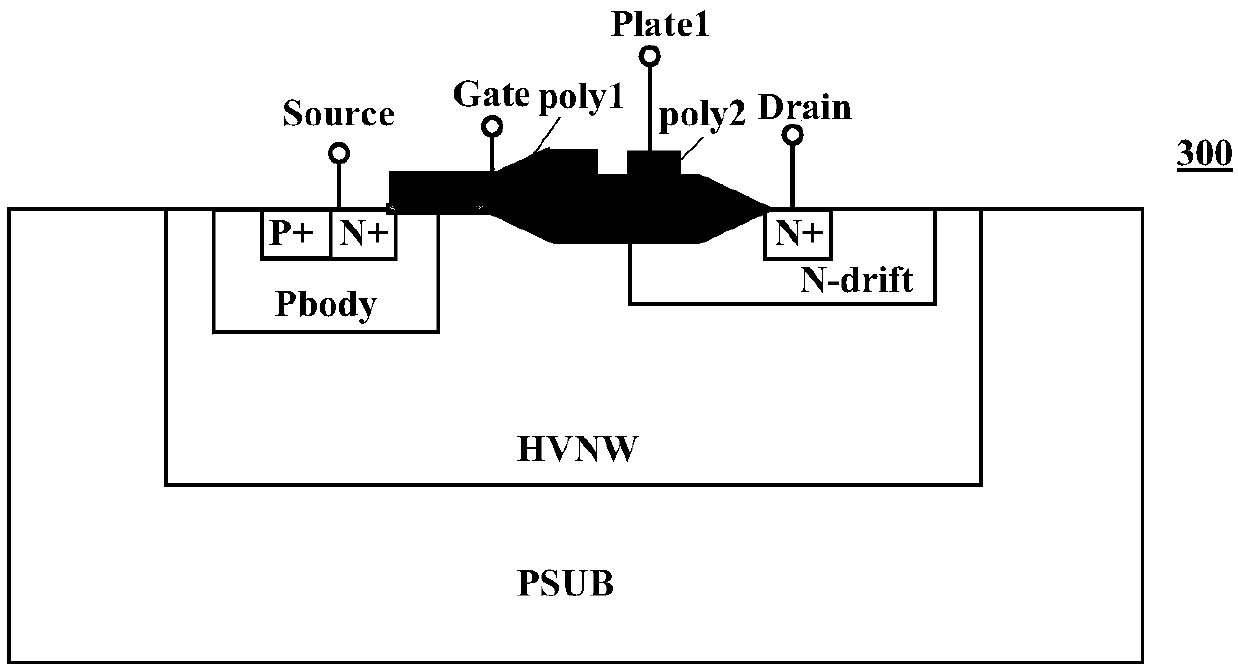

Laterally diffused metal oxide semiconductor structure and method for forming same

PendingCN108682689AImprove breakdown voltageReduce gate chargeSemiconductor/solid-state device manufacturingSemiconductor devicesLDMOSElectrical conductor

The present invention provides a laterally diffused metal oxide semiconductor structure and a method for forming the same. A conductor layer located above a first dielectric layer and a voltage-withstanding layer is divided into a first conductor which is at least partially located in the first dielectric layer and a second conductor which is at least partially located on the voltage-withstandinglayer, thus the first conductor and the second conductor are spatially isolated and can be connected to different potentials such that the semiconductor structure maintains a high breakdown voltage ina shutdown state. Furthermore, an interface between the first dielectric layer and the voltage-withstanding layer is covered by one of the first conductor and the second conductor, the gate charge ofthe semiconductor structure can be effectively reduced, and so that the semiconductor structure is adapted to high frequency applications.

Owner:SILERGY SEMICON TECH (HANGZHOU) CO LTD

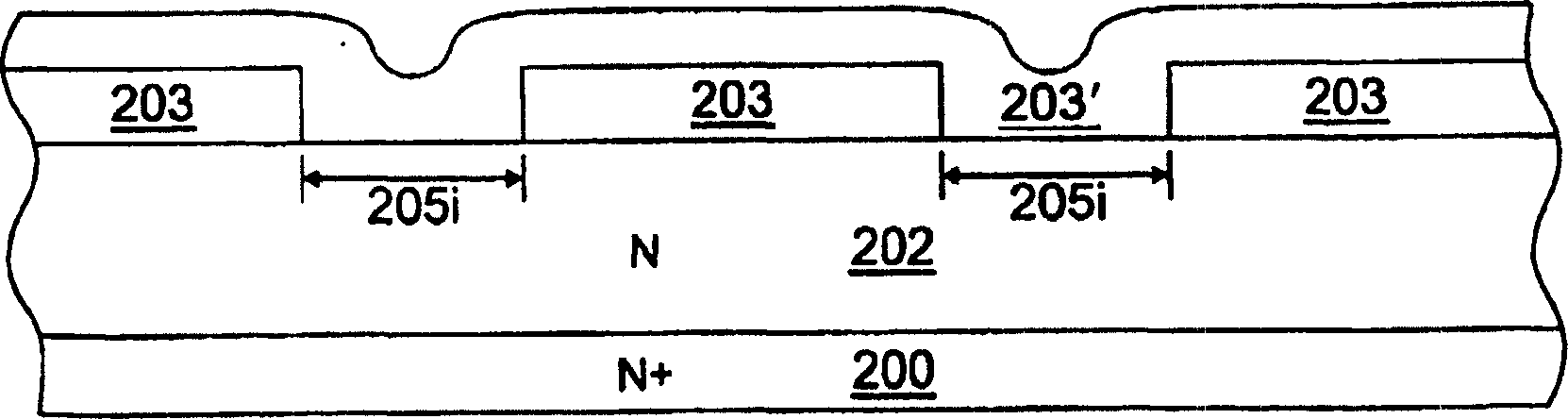

Method of forming narrow trenches in semiconductor substrates

InactiveCN1592960AReduce gate chargeTransistorSemiconductor/solid-state device manufacturingTrench mosfetSemiconductor

A method of forming a trench (207) within a semiconductor substrate (202) by providing a patterned first CVD-deposited masking material layer (203) having a first aperture over the semiconductor substrate (202). A second masking layer material is CVD-deposited and etched to form spacers (203s) in the first aperture, the spacers (203s) form a second aperture narrower than the first aperture. The semiconductor substrate (202) is etched through the second aperture such that a trench (207) is formed in the semiconductor substrate (202). In preferred embodiments, the method of the present invention is used in the formation of trench MOSFET devices.

Owner:GEN SEMICON

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com