Low-grid charge power device and manufacturing method thereof

A power device and charge technology, applied in the fields of semiconductor/solid-state device manufacturing, electrical components, semiconductor devices, etc., can solve the problems of increasing the driving power consumption of switching devices, reducing gate charge, gate charge, etc., so as to reduce the driving power. consumption, gate charge reduction, and simple process steps

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

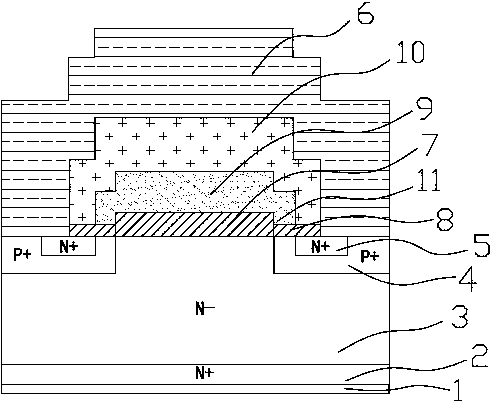

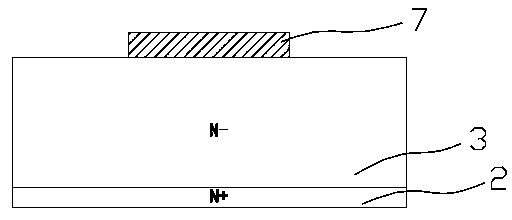

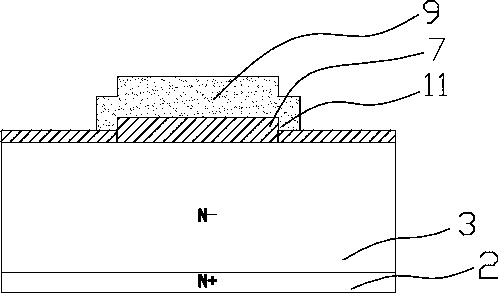

[0040] Such as figure 1 As shown, a low gate charge power device includes a drain 1 with a thickness of 5000 angstroms, an N+ type substrate 2 on the drain 1 and an N-type drift region 3 on the N+ type substrate 2, The shoulders on both sides of the N-type drift region 3 are provided with a P+ type channel region 4, the top surface of the P+ type channel region 4 is provided with an N+ type source region 5, and the N-type drift region 3 is provided with a gate region, A source 6 is provided on the gate region, and the gate region includes a gate oxide layer located on the N-type drift region 3. A polysilicon gate 9 is provided on the gate oxide layer. An ILD insulating layer 10 is provided on the polysilicon gate 9. The gate oxide layer includes The main gate oxide layer 7 with a thickness of 3000 angstroms and the sub-gate oxide layer 8 with a thickness of 800 angstroms located on both sides of the main gate oxide layer 7, the main gate oxide layer 7 is located above the N-ty...

Embodiment 2

[0052] The structure of the low gate charge power device of this embodiment is exactly the same as that of Embodiment 1, except that the drain 1 has a thickness of 12000 angstroms, the main gate oxide layer 7 has a thickness of 4000 angstroms, and the sub-gate oxide layer 8 The thickness of the gate oxide layer 7 is 900 angstroms, and the width of the main gate oxide layer 7 is smaller than the width of the top surface of the N-type drift region 3 .

[0053] The preparation method of the low gate charge power device of this embodiment is exactly the same as that of Embodiment 1, except that: an N-type epitaxial layer with a thickness of 20 μm and a resistivity of 30 Ω / □ is formed on the N+ type substrate 2, and boron The ion source of ion implantation is 11B+, the implantation energy is 100KeV, and the implantation dose is 4.0E13 ions / cm 2 , the ion source of phosphorus ion implantation is 31P+, the implantation energy is 130KeV, and the implantation dose is 3.0E15 ions / cm 2 ...

Embodiment 3

[0056] The structure of the low gate charge power device of this embodiment is exactly the same as that of Embodiment 1, except that the thickness of the drain 1 is 15,000 angstroms, the thickness of the main gate oxide layer 7 is 8,000 angstroms, and the thickness of the sub-gate oxide layer 8 The thickness is 1500 angstroms, and the width of the main gate oxide layer 7 is equal to the width of the top surface of the N-type drift region 3 .

[0057] The preparation method of the low gate charge power device of this embodiment is exactly the same as that of Embodiment 1, except that: an N-type epitaxial layer with a thickness of 60 μm and a resistivity of 40 Ω / □ is formed on the N+ type substrate 2, and boron The ion source of ion implantation is 11B+, the implantation energy is 120KeV, and the implantation dose is 6.0E13 ions / cm 2 , the ion source of phosphorus ion implantation is 31P+, the implantation energy is 160KeV, and the implantation dose is 8.0E15 ions / cm 2 .

[00...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com