Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

254results about How to "High quantitative accuracy" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Parametric stereo upmix apparatus, a parametric stereo decoder, a parametric stereo downmix apparatus, a parametric stereo encoder

ActiveUS8811621B2Quality of left and rightLeft and right signalsSpeech analysisPseudo-stereo systemsVocal tractComputer vision

A parametric stereo upmix apparatus generates left and right signals from a mono downmix signal based on spatial parameters. The parametric stereo upmix includes a predictor configured to predict a difference signal including a difference between the left and right signals based on the mono downmix signal scaled with a prediction coefficient. The prediction coefficient is derived from the spatial parameters. The parametric stereo upmix apparatus further includes an arithmetic unit configured to derive the left and right signals based on a sum and a difference of the mono downmix signal and the difference signal.

Owner:KONINKLIJKE PHILIPS ELECTRONICS NV

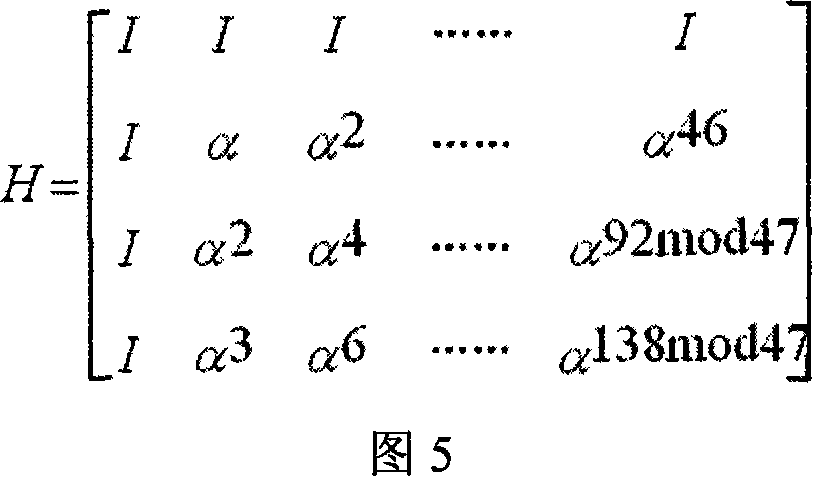

Method and equipment for generating codebook and sending and feeding back information

ActiveCN102122983AHigh quantitative accuracyMinor changesSpatial transmit diversityBaseband systemsChannel state information feedbackComputer science

The invention discloses a method and equipment for generating a codebook and sending and feeding back information. The method for sending the information comprises the following steps: after the codebook is generated, receiving signals containing codebook index information and extracting the codebook index information; according to the codebook index information, selecting corresponding precoding matrixes from the codebook or subsets of the codebook; precoding data to be sent according to the precoding matrixes; and sending the precoded signals to a receiving end. The method of feeding back channel status information comprises the following steps: receiving information sent by a sending end; estimating channel information on the basis of the received information; selecting the corresponding precoding matrixes from the codebook or the subsets of the codebook according to the channel information,; and sending signals containing codebook index information corresponding to the selected precoding matrixes. By the invention, dual-precoding matrix index feedback can be supported, the quantization accuracy of small-interval dual-polarization array channels can be improved, and the quantization accuracy of small-interval linear array channels can be enhanced.

Owner:DATANG MOBILE COMM EQUIP CO LTD

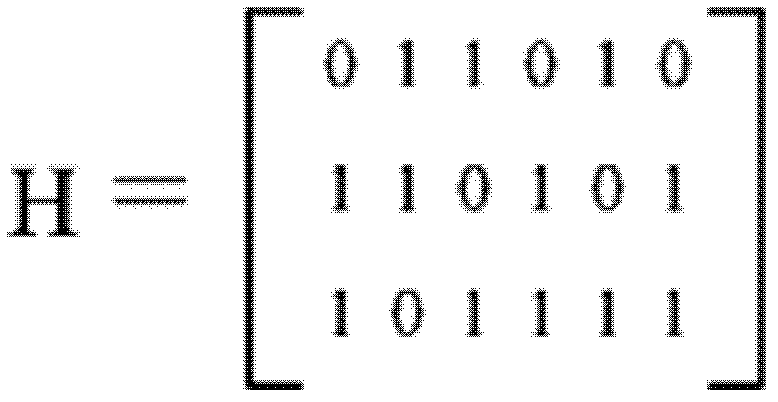

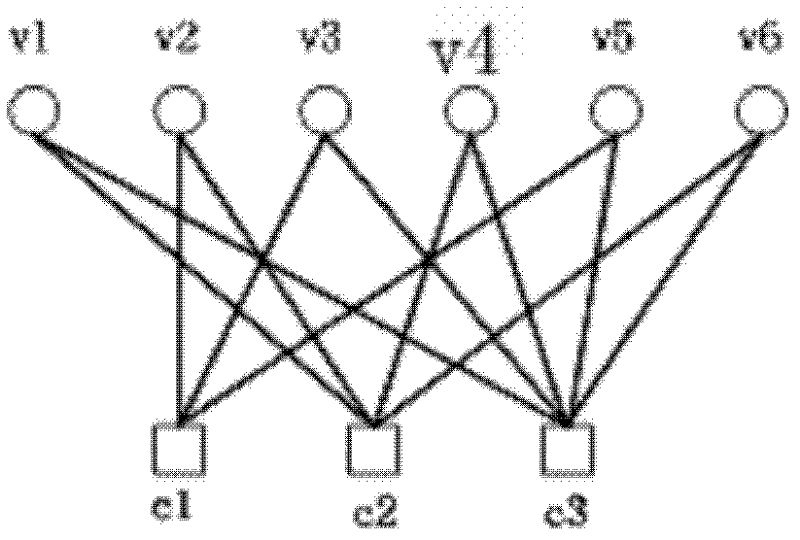

Dynamic LDPC error correction code method for flash memory

ActiveCN102394113AImprove read timeImprove reliabilityStatic storageDigital signal error detection/correctionAccess timeData error

The invention discloses a dynamic LDPC error correction code method for a flash memory, which belongs to the field of datum error correction of the non-volatile memory. According to the method, the quantification precision of soft information of LDPC codes is changed according to the page error rate of the NAND type flash memory. The method of the invention has the following beneficial effects: 1, in the initial usage phase of the NAND type flash memory, the program erasing frequency of each page in the flash memory is small, so the page error rate is small when, and the LDPC code soft information with the quantification precision of 1-bit is adopted to improve the read access time of the NAND type flash memory and reduce the power consumption of an LDPC decoder; and 2, when the flash memory is continuously used, the page error rate gradually rises, and the quantification precision of the LDPC codes is increased, so the error correction capability of the LDPC codes is improved, and the reliability of the NAND type flash memory can be improved.

Owner:TSINGHUA UNIV

Adaptive scheduling method and apparatus reducing information feedback amount

InactiveCN101291526AHigh quantitative accuracyReduce complexityDiversity/multi-antenna systemsRadio/inductive link selection arrangementsControl signalSelf adaptive

The invention discloses a self-adaptive scheduling method for a multi-user MIMO system. A transmitting terminal counts reporting times of various vectors or matrixes in a codebook first based on feedback information from a plurality of receiving terminals; then, according to the counted reporting times, the transmitting terminal determines a group of weights for the vectors or the matrixes in the codebook, and informs all transmitting terminals of the group of the weights through a downgoing common control signaling. In the process of communication, the weights are updated according to requirements. Each receiving terminal receives the informed weights, calculates channel quality information, proceses the channel quality information by the weights, and makes a choice of the recoded vectors or matrixes and feeds back according to the processed channel quality information. The self-adaptive scheduling method can simultaneously gain higher quantized precision and other benefits brought by scheduling gain and a larger codebook in the multi-user MIMO system.

Owner:PANASONIC CORP

System and Method for Adapting Codebooks

InactiveUS20110243207A1High quantitative accuracyIncrease in sizeModulated-carrier systemsTransmission monitoringTelecommunicationsCommunication device

A system and method for adapting codebooks are provided. A method for communications device operations includes receiving a pilot signal, computing a channel estimate for a channel between a controller and a communications device, the computing being based on the pilot signal, adapting a codebook based on the channel estimate and positions of codewords in the codebook, computing a representation of the channel using the adapted codebook, transmitting the representation of the channel as feedback information, and receiving a transmission beamformed based on the feedback information.

Owner:FUTUREWEI TECH INC

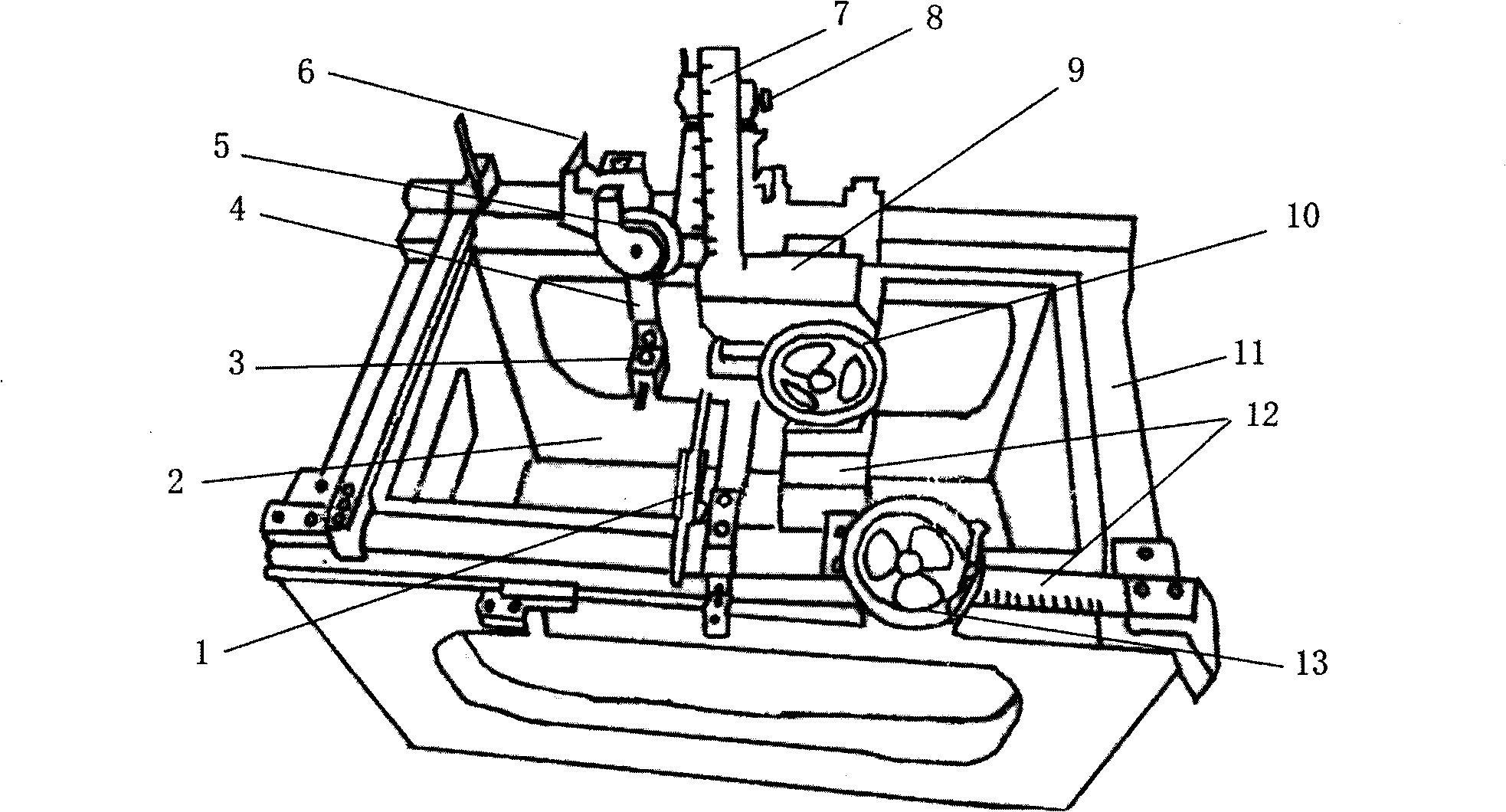

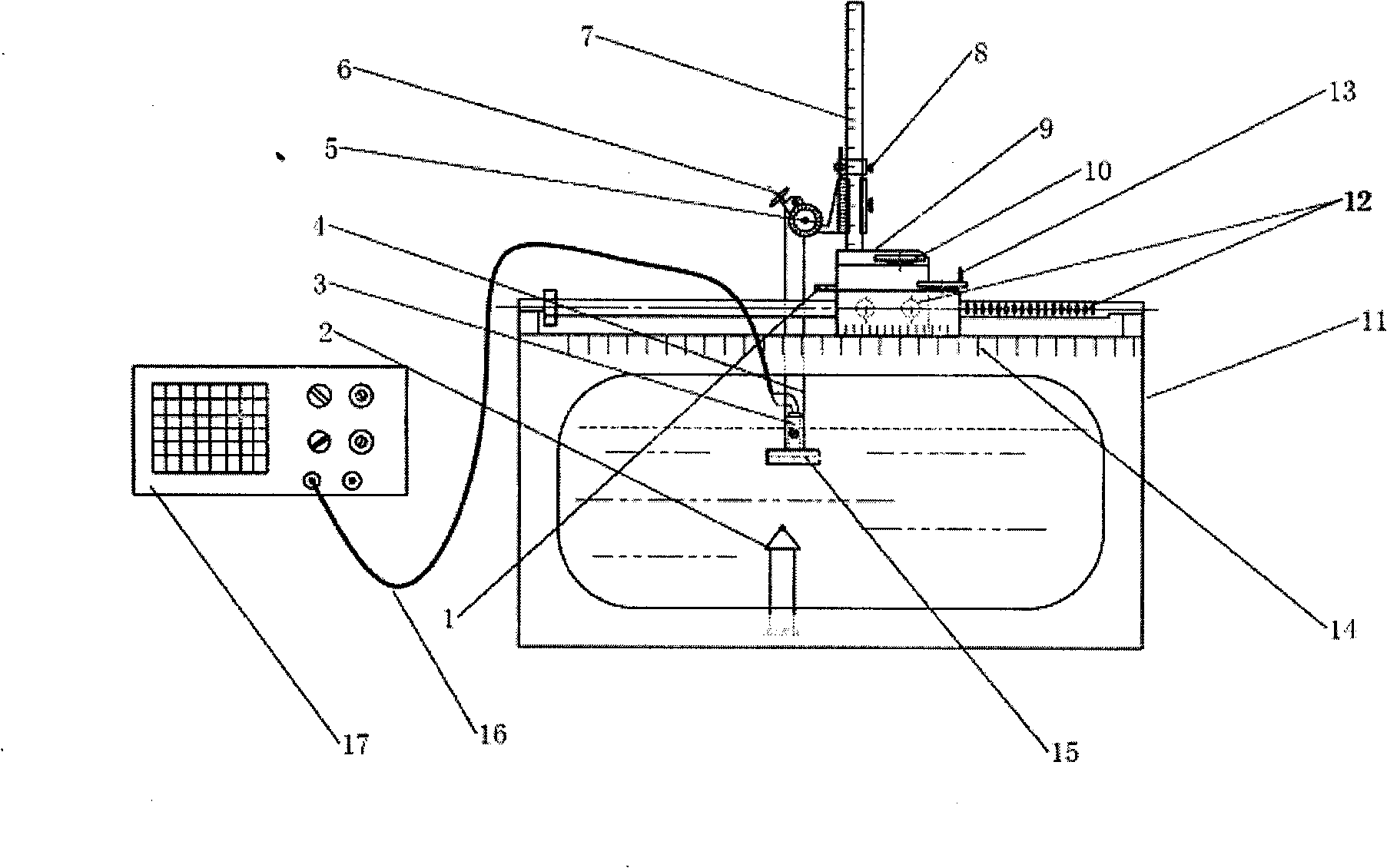

Performance test device for water immersion focusing probe and test method thereof

ActiveCN101539542AEasy to testIncreased effective beam widthMaterial analysis using sonic/ultrasonic/infrasonic wavesReflected wavesWater immersion

The invention relates to a performance test device for a water immersion focusing probe and a test method thereof. A steel ball is placed on a reference reflection seat of the performance test device placed in a water tank, the corresponding upside of the steel ball is provided and aligned with a probe to be tested, the probe to be tested generates ultrasonic signals to the steel ball through an ultrasonic gauge, and the performance difference of the probe is tested through the variation of reflection signals. A three-dimensional guide adjusting device is adjusted to test the position and variable quantity of the probe in real time so that reflection echo signals of the probe on the steel ball reaches maximum. Effective reflected wave is received by the probe and displayed on a display screen of the ultrasonic gauge in a form of wave height; scale numerical values on X axis, Y axis and Z axis of a graduated scale are recorded respectively; and various performance indexes of the probe are determined by observing the variation of the wave height. The performance test device for the water immersion focusing probe and the test method thereof are simple and practical, and can test the indexes such as focus, sound width, focus diameter, sound offset angle, sensitivity surplus, sensitivity deflection of a multi-chip probe and the like without depending on special laboratory equipment.

Owner:BAOSHAN IRON & STEEL CO LTD

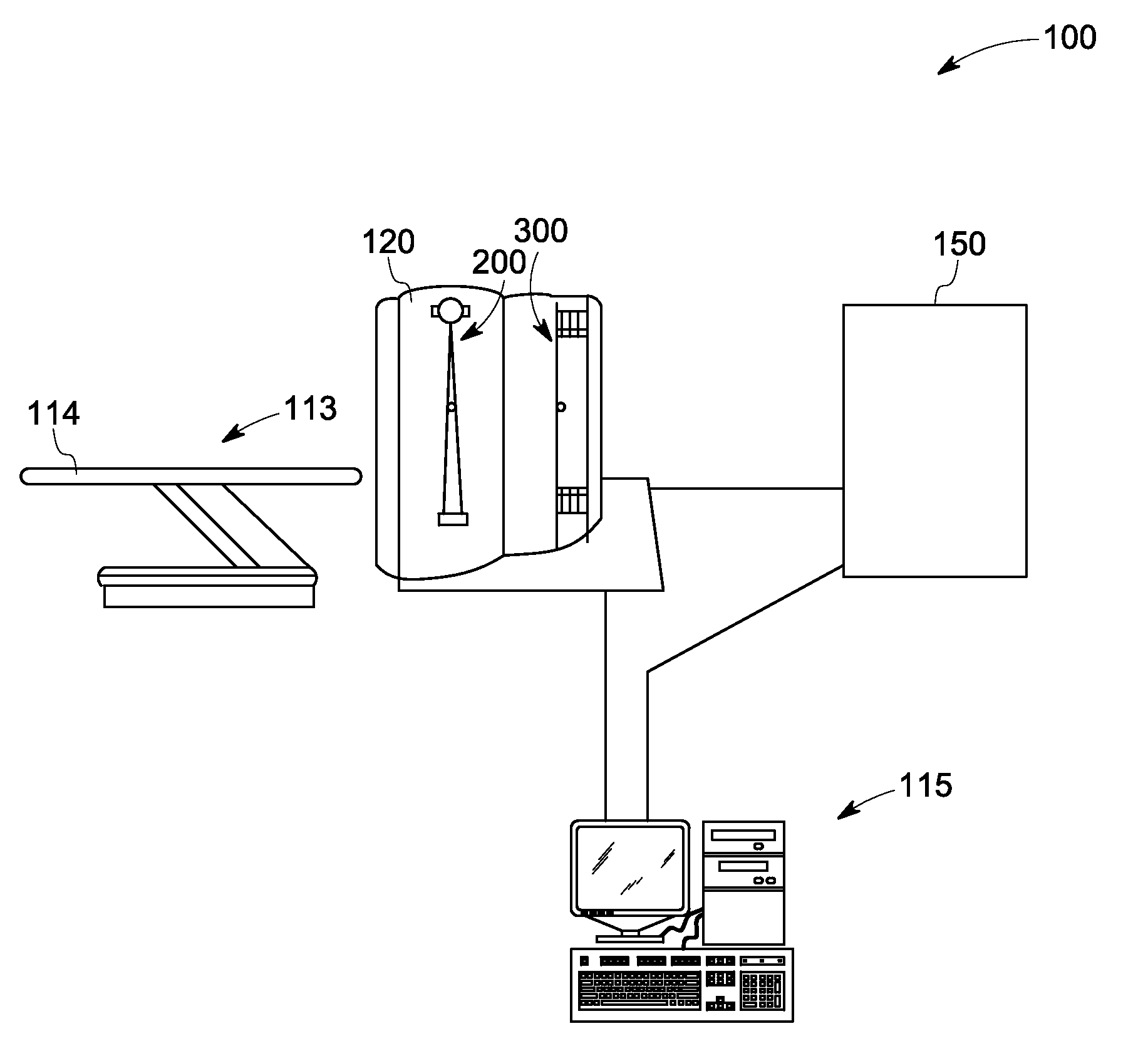

Motion correction in tomographic images

ActiveUS20100046821A1High quantitative accuracyImage enhancementReconstruction from projectionComputed tomographyTomography

An imaging method comprises reconstructing gated emission tomography images for a region of interest, adjusting a mismatch between the gated emission tomography images and a computed tomography image of the region of interest, registering the gated emission tomography images, and combining the registered gated emission tomography images to generate motion corrected images.

Owner:GENERAL ELECTRIC CO

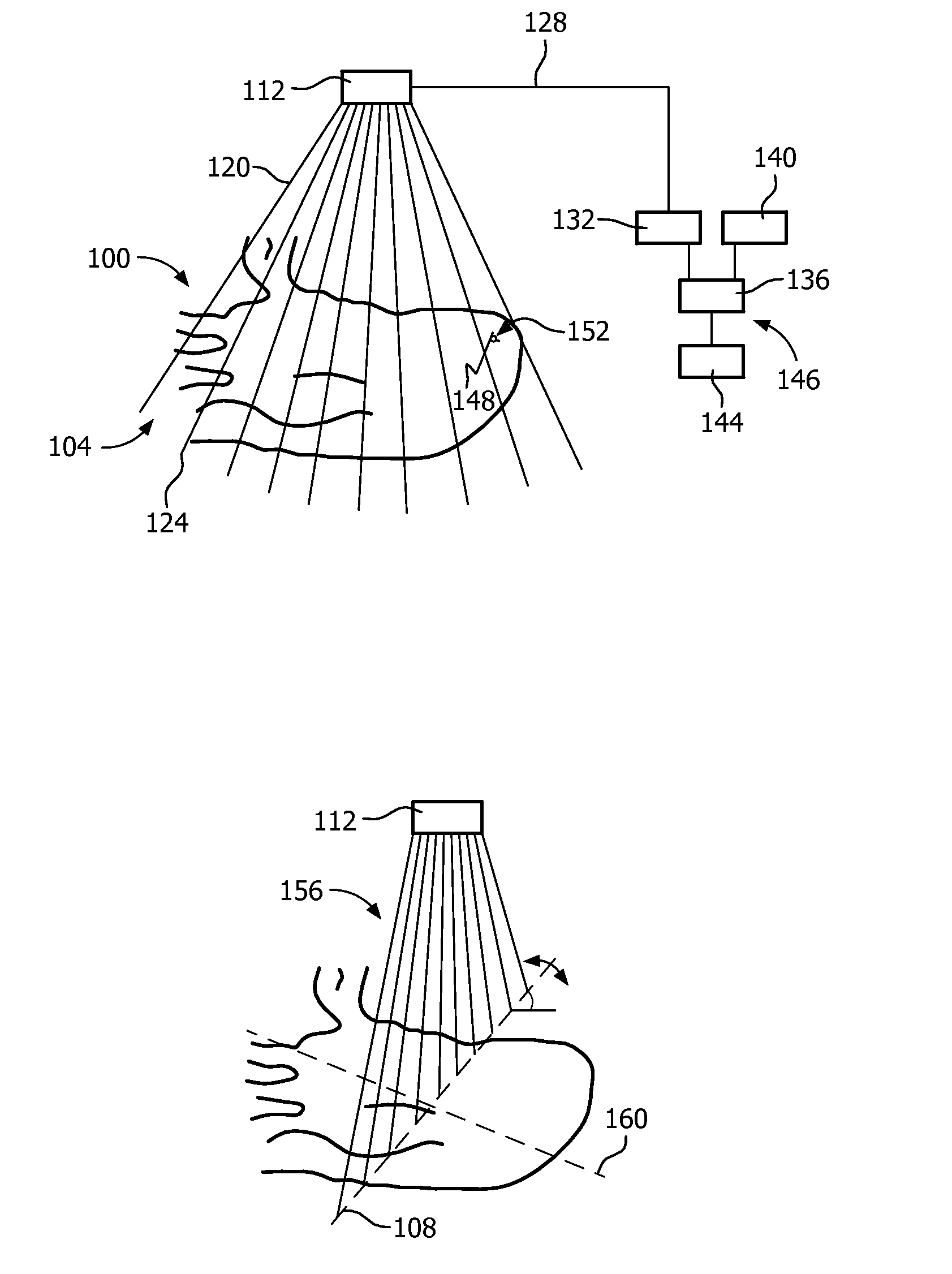

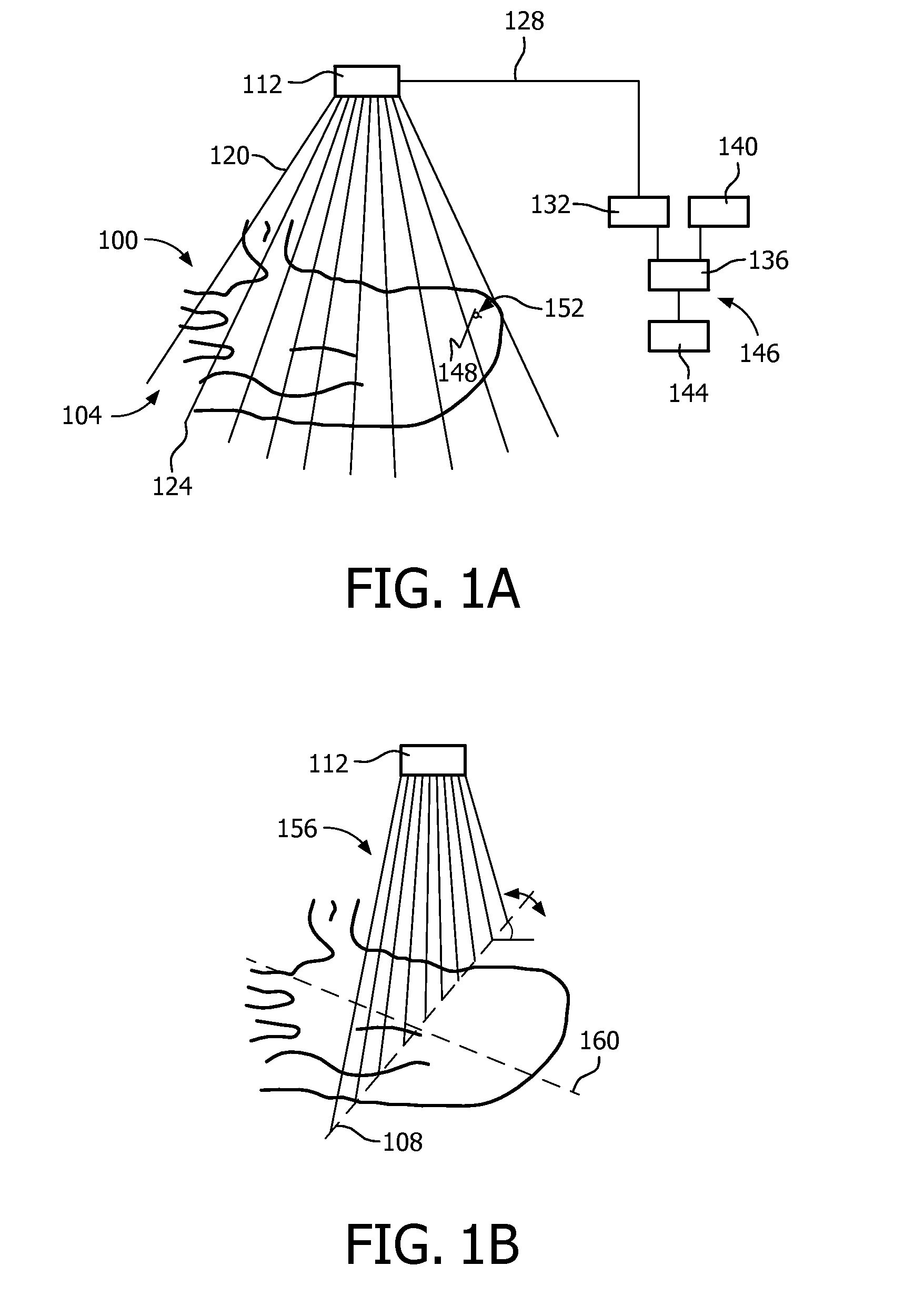

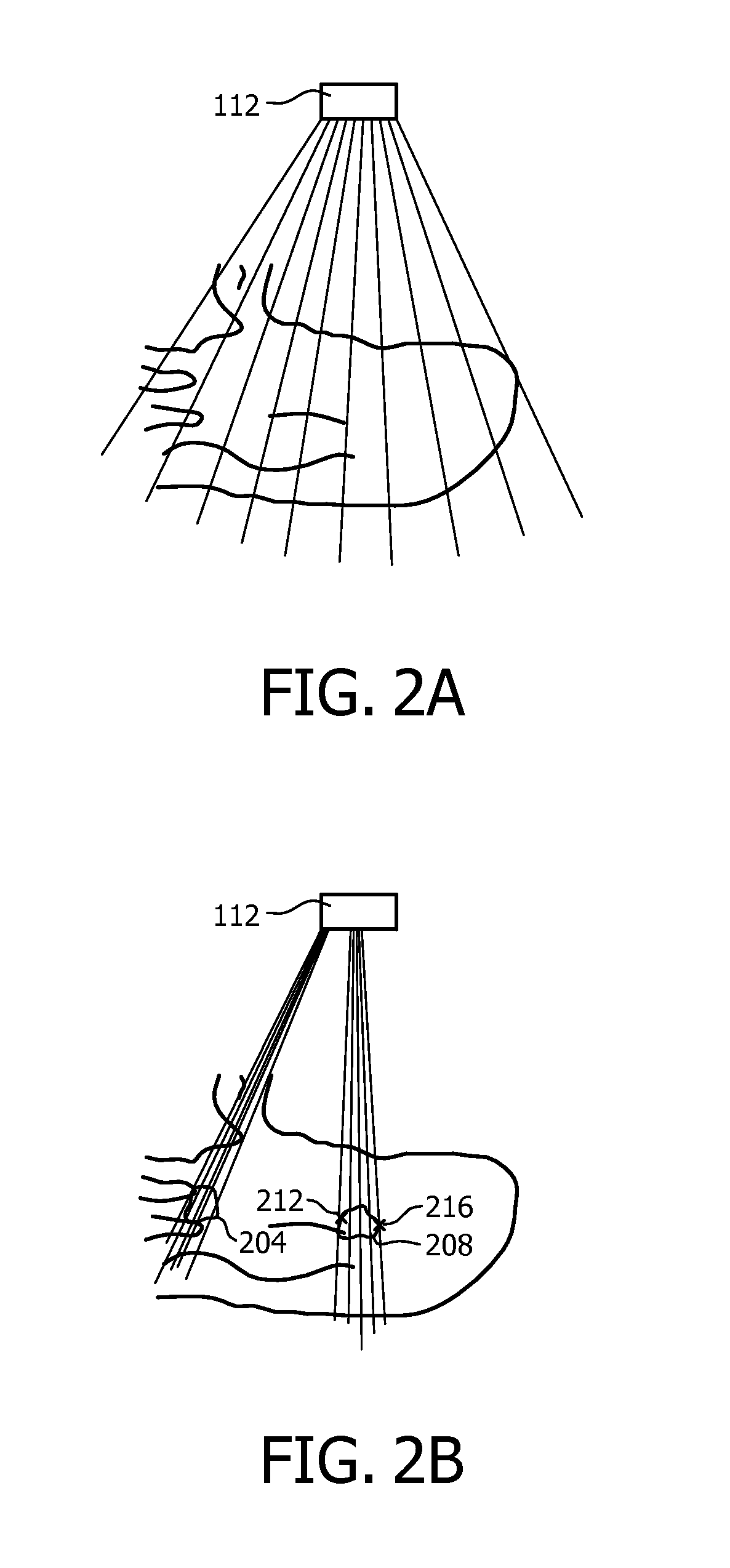

Automatic imaging plane selection for echocardiography

InactiveUS20150011886A1High resolutionRapid diagnosisWave based measurement systemsOrgan movement/changes detectionAnatomical structuresTime response

Based on anatomy recognition from three-dimensional live imaging of a volume, one or more portions (204, 208) of the volume are selected in real time. In further real time response, live imaging or the portion(s) is performed with a beam density (156) higher than that used in the volume imaging. The one or more portion may be one or more imaging plane selected for optimal orientation in making an anatomical measurement (424) or display. The recognition can be based on an anatomical model, such as a cardiac mesh model. The model may be pre-encoded with information that can be associated with image locations to provide the basis for portion selection, and for placement of indicia (416, 420, 432, 436) displayable for initiating measurement within an image provided by the live portion imaging. A single TEE or TTE imaging probe (112) may be used throughout. On request, periodically or based on detected motion of the probe with respect to the anatomy, the whole process can be re-executed, starting back from volume acquisition (S508).

Owner:KONINKLJIJKE PHILIPS NV

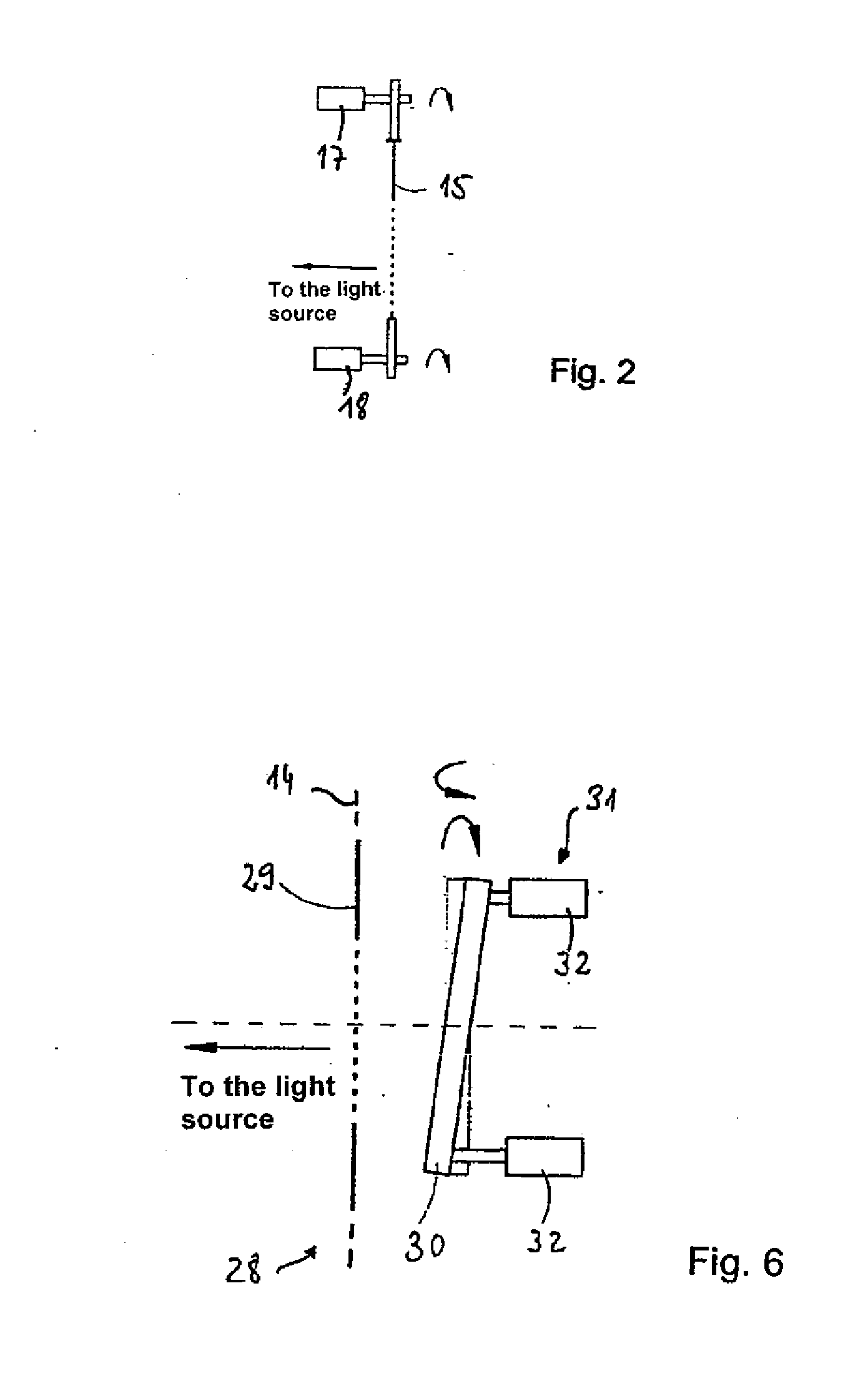

Method and device for producing an image of a thin layer of an object

InactiveUS20100066823A1Sufficient in-depth selectionHigh quantitative accuracyCharacter and pattern recognitionColor television detailsWide fieldThin layer

A method for producing an image of a layer of an object by a wide field optical element on a resolving detector. The object is illuminated in a focused manner on at least one object plane having at least two binary illuminating patterns. The corresponding images are detected. Light and / or the dark areas of the illuminating patterns completely cover the object when the illuminating pattern is superimposed. A layer image determined from the detected images, includes a partial segment that respectively reproduces a partial area of the object that is arranged inside the light area of one of the used illuminating patterns. Edges are arranged at a distance from the edges of the light area about at least one predefined minimum distance.

Owner:CARL ZEISS MEDITEC AG

Method and system for comparing image definition and automatic focusing control method

ActiveCN103473776APrecise positioningHigh quantitative accuracyImage analysisGraphicsHarmonic analysis

The invention relates to the field of high-flux gene sequencing, and provides a method and system for comparing definition of a plurality of sequencing images and an automatic focusing control method. According to the method for comparing the definition of the sequencing images, harmonic analysis processing is carried out on the sequencing images, then closed curves are fitted according to textural features of harmonic analysis processing pictures, the area ratios of the figures corresponding to the closed curves to the corresponding sequencing images are obtained according to the closed curves, and accordingly the sequencing image with the highest definition is determined by comparing the area ratios. Compared with the prior art, the method and system have the advantage of being high in quantizing precision. Besides, the invention further provides an automatic focusing control method based on the definition comparing method, and according to the method, an automatic focusing position can be accurately positioned.

Owner:SHENZHEN HYK HIGH THROUGHPUT BIOTECH INST

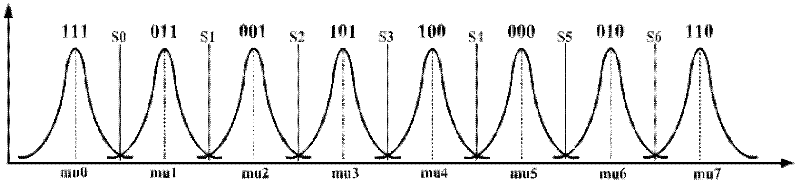

Nonuniform quantizing coding method used for decoding LDPC code and application of method in decoder

InactiveCN103957015AReduce the average quantization bitsReduce consumptionError correction/detection using multiple parity bitsAlgorithmTheoretical computer science

The invention relates to a nonuniform quantizing coding method used for decoding an LDPC code and the application of the method in a decoder. The method comprises the steps that the quantification range of messages L(rji), L(qij) and L(Qi) is determined according to information distribution of an initial message L(Pi), a coding mode is adopted for performing nonuniform quantizing on the messages L(rji), L(qij) and L(Qi), quantized intervals of positive number portions and negative number portions are respectively divided into m sections, coding is a codon composed of 1-bit polar codes, k-bit segment codes and (n-1-k)-bit in-segment codes, the polar codes mark positive numbers and negative numbers, the segment codes mark different segments, the segment internal codes show specific size of the data in the segments, each segment is divided into 2<g> small segments, and the small segments are the quantized intervals of the corresponding segments. According to the method, consumption of hardware storage resources, operation processing units and locating and wiring resources is reduced, quantization errors of small-value data are reduced, and the decoding performance is improved.

Owner:FUZHOU UNIV

System and method for photonically assisted analog to digital signal conversion

InactiveUS20130328706A1High quantitative accuracyImprove accuracyElectric signal transmission systemsOptical analogue/digital convertersBroadbandVIT signals

A photonically assisted analog to digital conversion (ADC) system is presented. The system comprises: an optical sampling signal generator configured and operable for generating an optical sampling signal comprising a predetermined sampling pulse sequence in the form of a time separated pulse train of spectral components dispersed in a periodic fashion, where each pulse is distinguishable by a central wavelength thereof different from its neighboring pulses. The generation of the pulse sampling sequence is achieved by combining broadband dispersion and compensation with a periodic dispersion compensator having a free spectral range smaller than the broad bandwidth of the ultrashort pulse. The second innovative element is the introduction of coherent detection with oversampling of the interference terms of the phase modulated pulse sampling sequence and a reference pulse. The over-sampling provides additional measurements of the beat term and by way of error minimization a more reliable phase estimation is provided, translated into a more accurate conversion to digital representation. The system further comprises an electro-optical modulator for interacting an input electric analog signal and an optical sampling signal and generating a modulated optical signal indicative of said input signal; and a detection system configured and operable for receiving said modulated optical signal and generating an output digital signal corresponding to said input electric analog signal.

Owner:YISSUM RES DEV CO OF THE HEBREW UNIV OF JERUSALEM LTD

Geographic tuple based quantitative prediction method of ore concentration areas

InactiveCN101706589ALow skill level requiredEasy to operateGeological measurementsMineral SourcesCentral asia

The invention relates to a geographic tuple based quantitative prediction method of ore concentration areas, which is characterized by establishing the quantitative prediction method of mineral resources in the Central Asia region by analyzing the time-space evolution process of the mineral resources in the region, taking GIS as a platform, applying the nonlinear theory and the artificial neural network technology, integrating multivariate information such as geology, geophysics, geochemistry, remote sensing and the like, carrying out analogy on the geological characteristics of the minerals at different levels and the metallogenetic geological setting and dividing favorable metallogenetic areas at different levels. The method solves the problem of failure of quantitative prediction in the prior art.

Owner:XINJIANG INST OF ECOLOGY & GEOGRAPHY CHINESE ACAD OF SCI

Coding and decoding device and method of ultralow-bit-rate speech

The invention provides an improved coding and decoding device and method based on the linear predictive parameter coding basic principle. Intra-frame and inter-frame correlations of parameters and the correlations among all the parameters are fully utilized, and all the parameters of a coder are compressed by the utilization of the vector quantization technology; while the compression is performed, the auditory perception characteristic of the human ears is fully utilized to perform quantization or inverse quantization on all the parameters by the utilization of different weighing distortion measurements, so that data are effectively compressed on the premise that the auditory sense quality of the human ears is not affected. On the premise that speech quality is ensured, the coding and decoding device and method of ultralow-bit-rate speech achieves coding and decoding of the ultralow-bit-rate speech with algorithm complexity as low as possible while working at the bit rate of 600bps and the bit rate of 300bps.

Owner:SHANGHAI JIAO TONG UNIV

Rail tread crack ultrasonic detection device and detecting method

ActiveCN101424664AHigh quantitative accuracyHigh precisionAnalysing solids using sonic/ultrasonic/infrasonic wavesUsing subsonic/sonic/ultrasonic vibration meansPhysicsUltrasound

The invention provides an ultrasonic detecting device and a detecting method for inclined cracks on a steel trail pedaling surface. The detecting device of the invention uses a detecting probe of the invention and a common signal processor in a whole for judging whether the inclined cracks on a steel trail pedaling surface exceeds the specific threshold value. The detecting probe of the invention comprises two independent probes encapsulated together for carrying and convenient use. The detecting method of the invention combines the detecting probe of the invention with the common signal processor to rapidly judge whether the crack depth of the surface opening is higher than the specific threshold value (for example 5 mm).

Owner:CHINA ACADEMY OF RAILWAY SCI CORP LTD +1

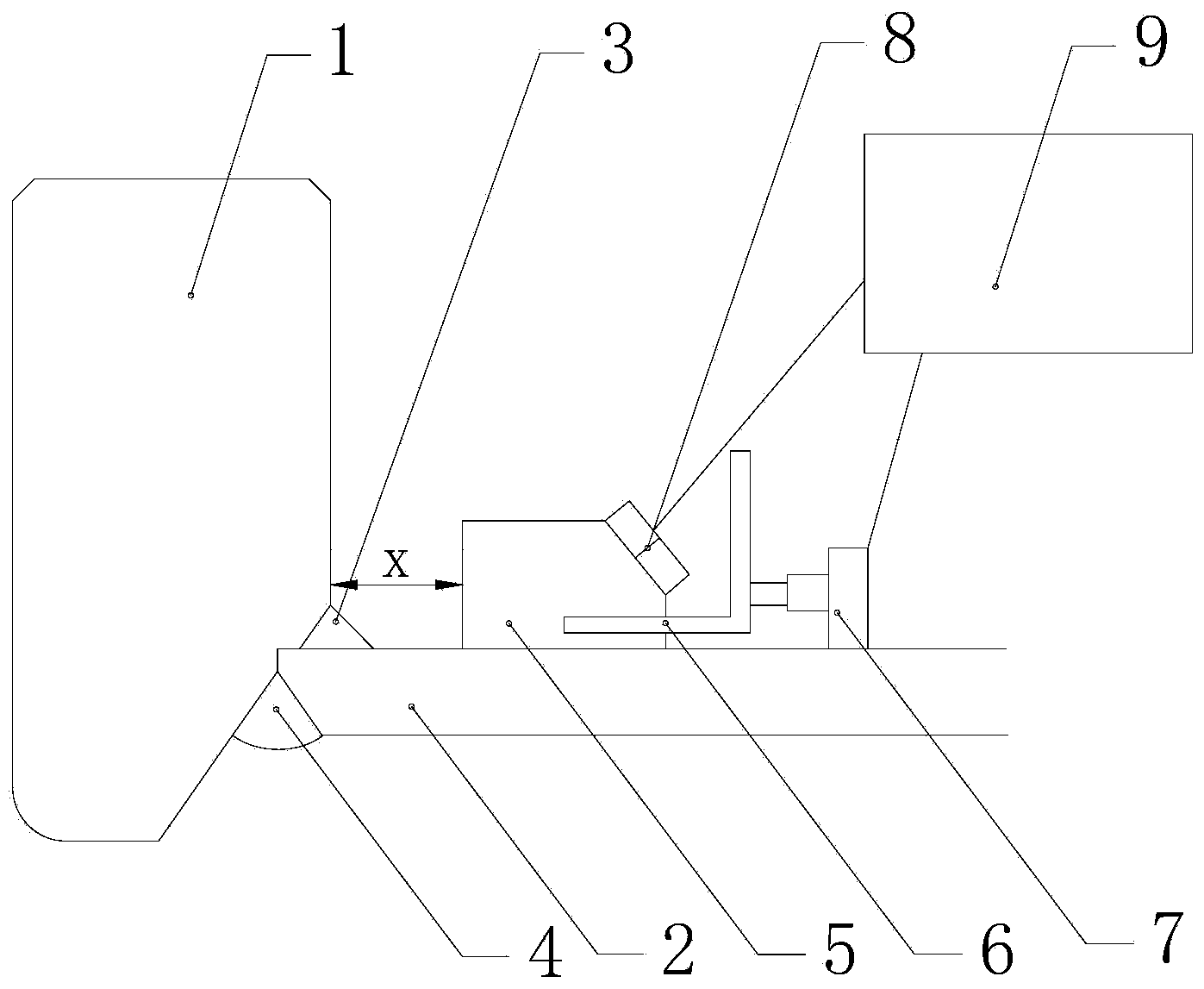

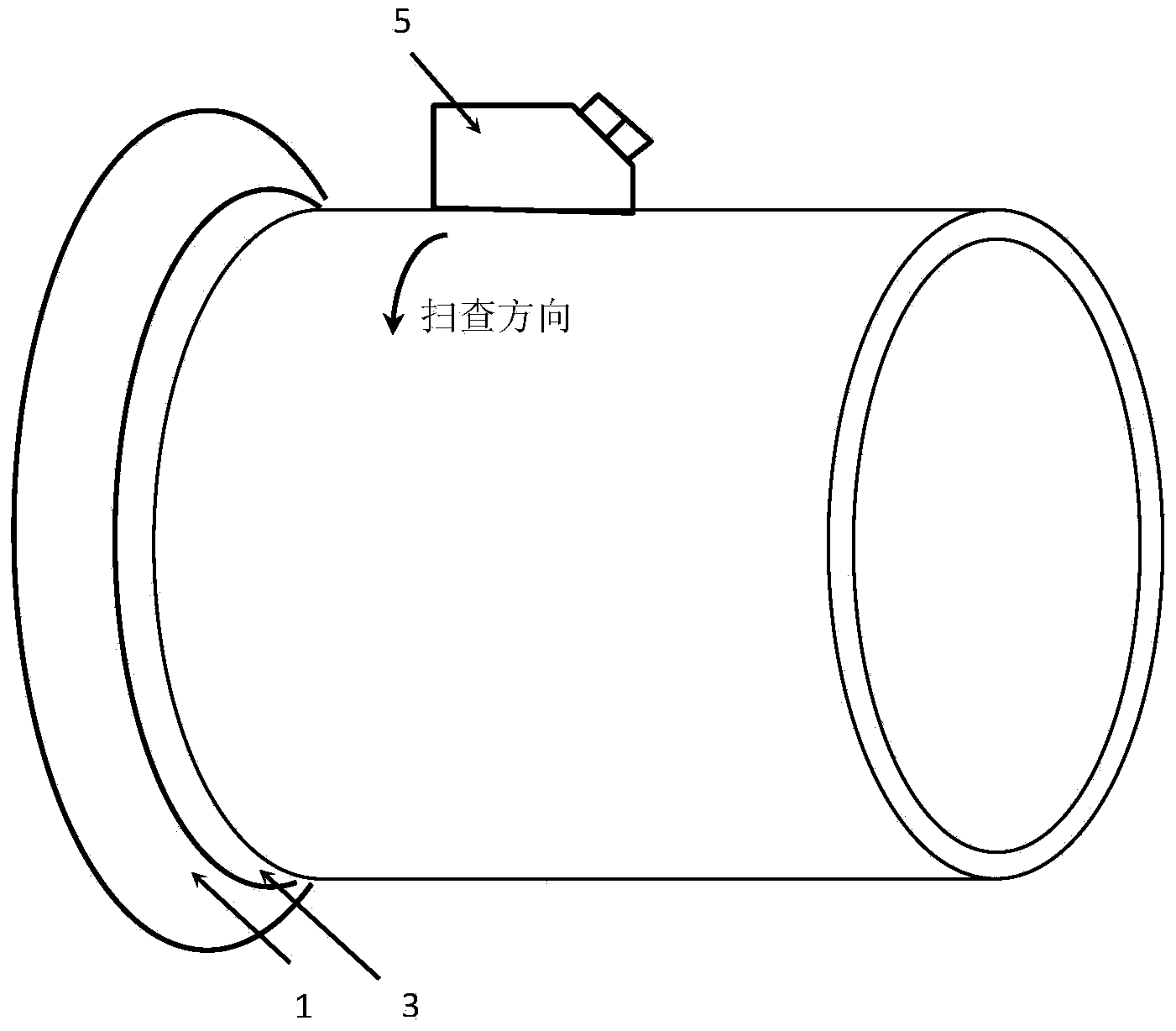

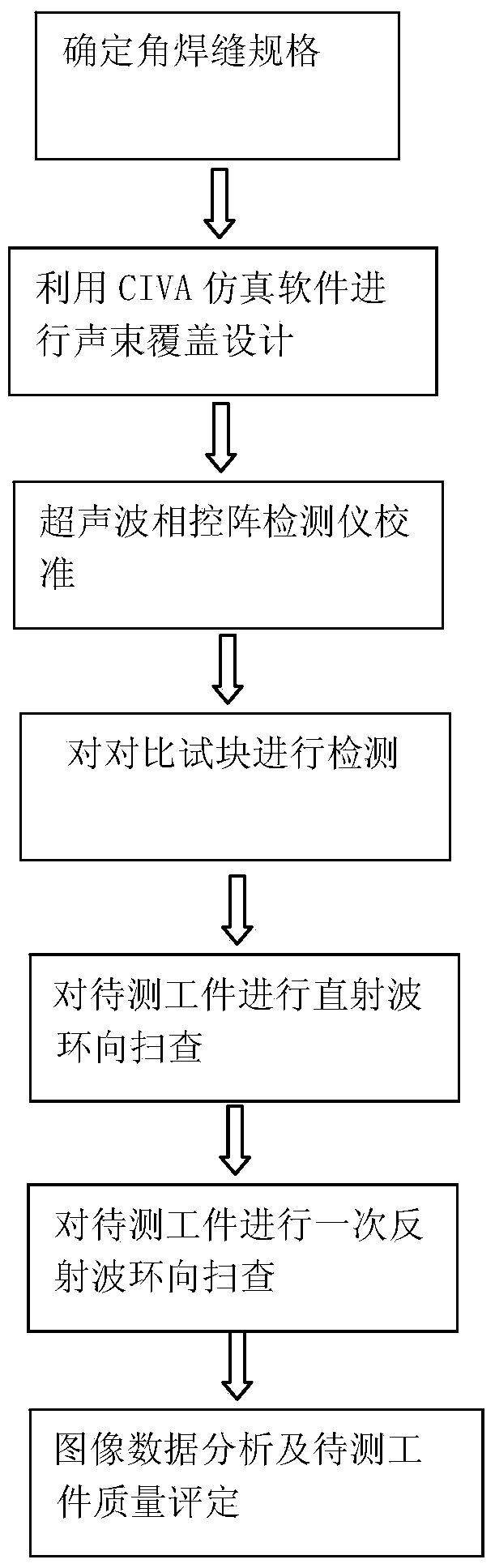

Assessment device for fillet weld of end flange of GIS (gas insulated switchgear) and barrel and lossless assessment method

ActiveCN103728375AImprove the detection effectEasy to findAnalysing solids using sonic/ultrasonic/infrasonic wavesAssessment methodsEngineering

The invention discloses an assessment device for a fillet weld of an end flange of a GIS (gas insulated switchgear) and a barrel and a lossless assessment method, aiming at solving the problem that an existing detection method cannot effectively achieve lossless assessment on the fillet weld of the end flange of the GIS and the barrel. The device is characterized in that an ultrasonic probe is installed on a wedge block, both the ultrasonic probe and a encoder are connected with a scanning rack so as to run synchronously, the encoder is connected with an ultrasonic wave phased array detector through a data line, the ultrasonic probe is connected with the ultrasonic wave phased array detector through the data line, and the surface of the ultrasonic probe is coated with a coupling agent and is connected with the wedge block through bolts. The assessment device can realize lossless assessment of total cross section of the structure, can detect both surface defect and interior defect, can detect both the outer fillet weld of the end flange of the GIS in service and the barrel and the inner fillet weld, and can comprehensively assess the quality of the structure.

Owner:STATE GRID CORP OF CHINA +1

Cursor annular time-digit converter

ActiveCN106200356AHigh quantitative accuracySmall structureTime-to-digital convertersEngineeringDigital converter

The invention provides a cursor annular time-digit converter. The cursor annular time-digit converter comprises a first pulse width generator, a quick voltage control delay chain, a second pulse width generator, a slow voltage control delay chain and a comparator array. The cursor annular time-digit converter has high quantization precision and a few structures, and the area can be effectively reduced; when a comparator in the comparator array turns over for the first time, the quick voltage control delay chain and the slow voltage control delay chain can both reset, so that signals of the quick voltage control delay chain and the slow voltage control delay chain are both at low levels, jumping never happens again, and consequently power consumption of work is lowered.

Owner:SHANGHAI ADVANCED RES INST CHINESE ACADEMY OF SCI

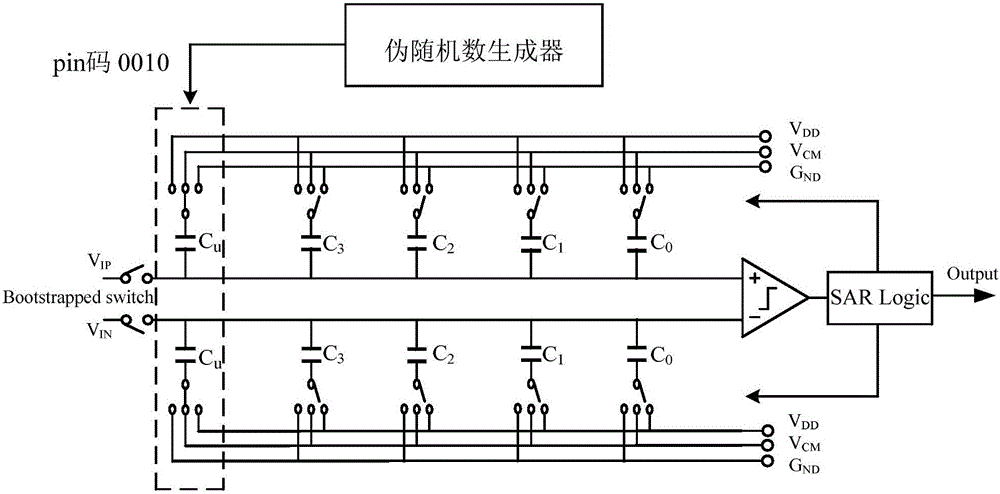

Digital weight average algorithm applied to successive approximation register analog-to-digital converter

InactiveCN106027049ARealize first-order shapingImproved scatter-free dynamic rangeAnalogue-digital convertersPhysical parameters compensation/preventionCapacitanceHarmonic

The present invention discloses a digital weight average algorithm applied to a successive approximation register analog-to-digital converter, characterized in that a pseudo-random number generator is added in a circuit of the successive approximation register analog-to-digital converter, a random pin code is generated by the pseudo-random number generator before each quantization of the successive approximation register analog-to-digital converter, and the connection of each unit capacitor is determined by the pin code through successive approximation register control logic, so that the unit capacitors form capacitors of different weights at random. In the present invention, the DWA algorithm is applied to a structure of the SAR ADC, so that the harmonic of an output signal is suppressed to the noise floor, to realize the first-order shaping of the noise of the output signal, thereby increasing the spurious-free dynamic range of the SAR ADC; and when the number of times of quantification of the SAR ADC reaches a certain number, the DWA algorithm enables capacitor mismatch to be allocated to each quantization, to average the capacitor mismatch, reduce the effect of the capacitor mismatch on the static characteristic and the dynamic characteristic of the SAR ADC, and improve the quantization accuracy of the SAR ADC.

Owner:西安电子科技大学昆山创新研究院 +1

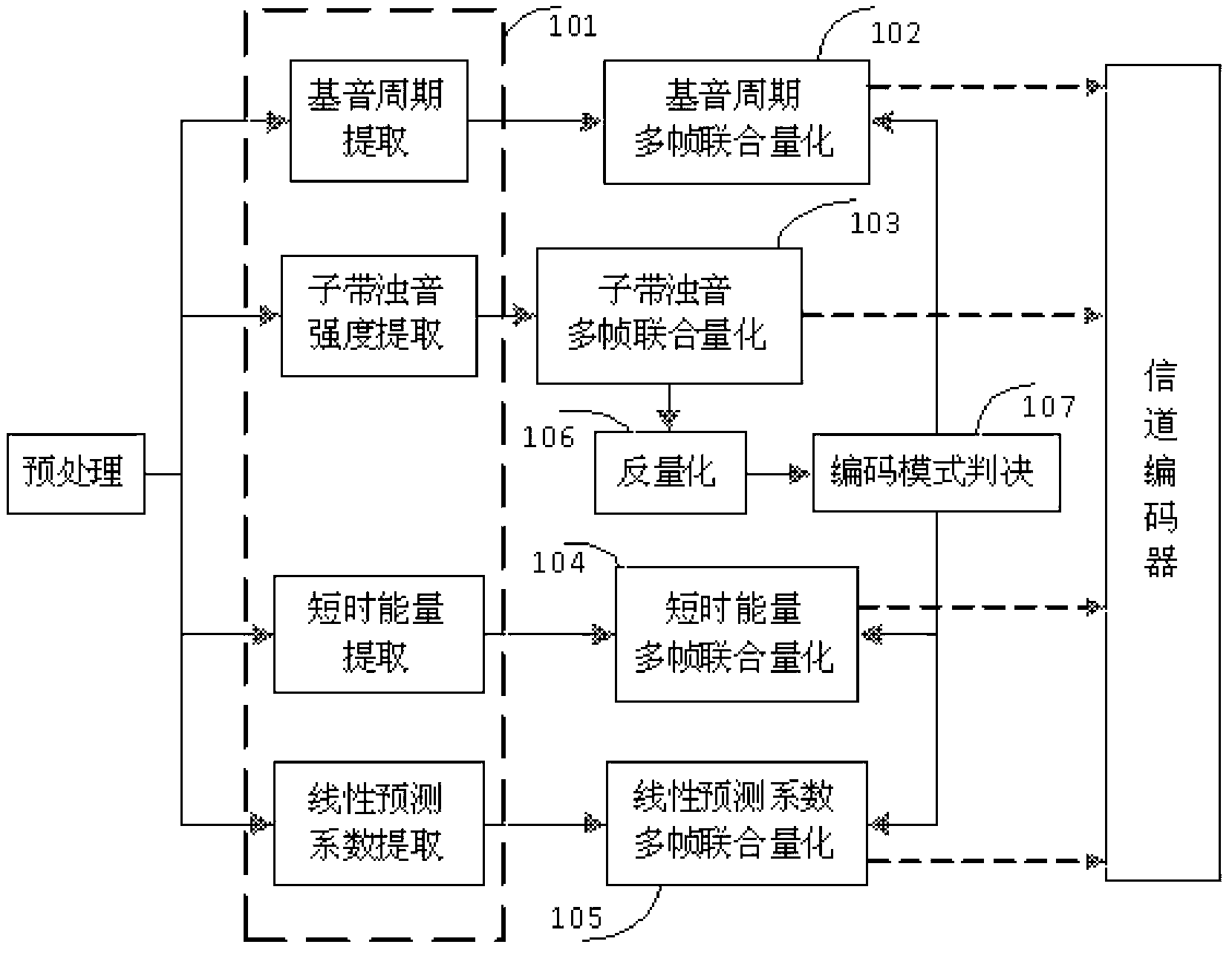

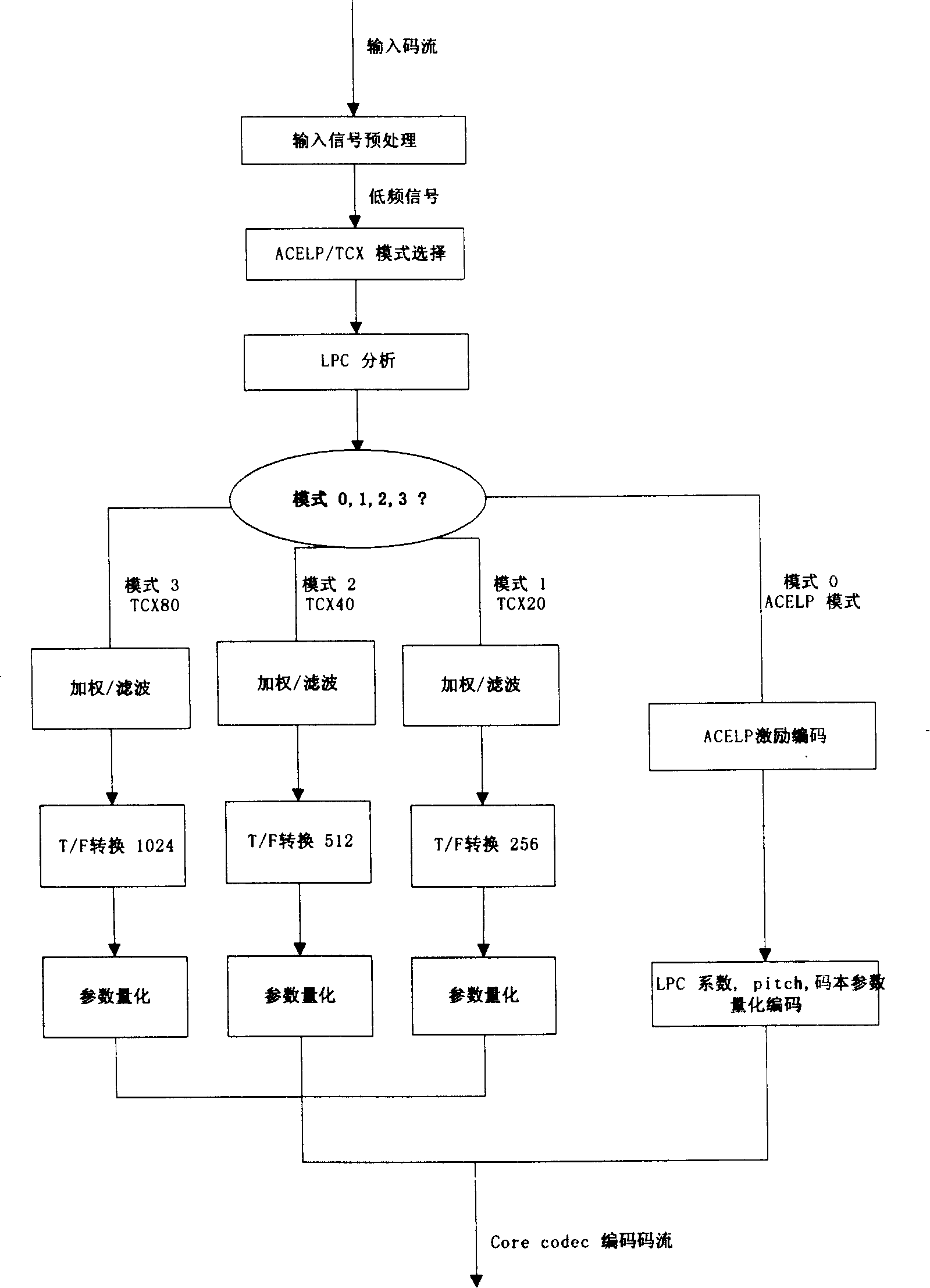

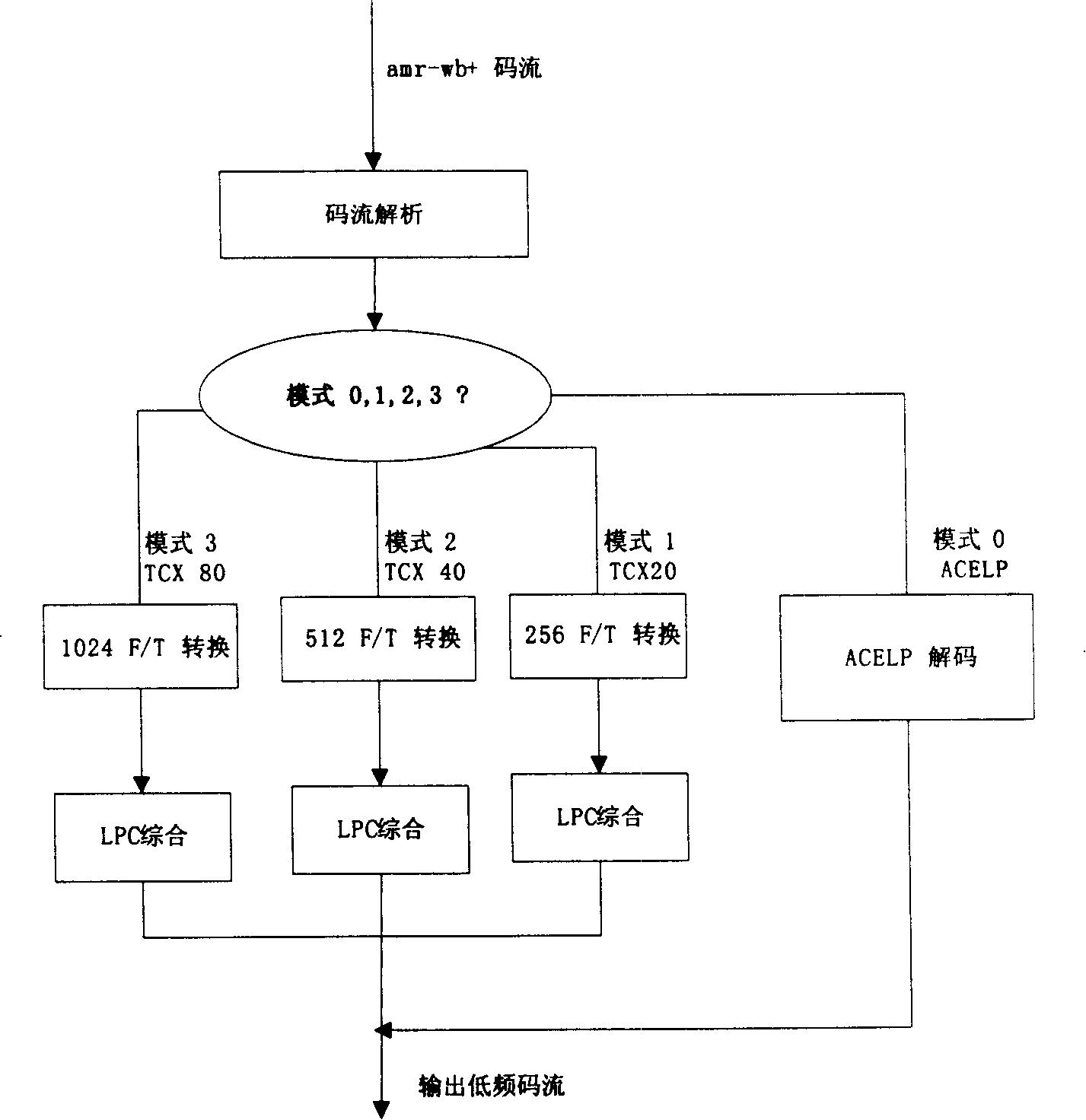

Encoding and decoding method for audio processing frame

InactiveCN101197577AHigh quantitative accuracyGuaranteed subjective qualitySpeech analysisCode conversionTime domainDecoding methods

The invention provides encoding and decoding methods for an audio processing framework, wherein, the steps of the encoding method are that: A. a low-frequency stage signal after being preprocessed is firstly selected through PCX / ACELP mode, and the signal is treated with LPC analysis; B. according to the result of selection, the signal enters into the ACELP or the PCX mode for decoding; for the PCX mode, the inputted low frequency signal is treat with LPC aggregate and perceptual weighted process to acquire an LPC residual; then the LPC residual is treated with an extraction of model parameters; finally, a LPC coefficient and the model parameters are all treated with quantization encoding. The decoding steps are that: C. an input code stream acquires an encoding mode, ACELP parameter or PCX parameter via analysis and anti-quantization; D. decoding enters into different decoding branches according to the acquired mode; for the decoding of PCX, a LPC excite signal is synthesized through the model parameters using a synthetic method of a model corresponding to the encoding end, and the signal acquires a final low frequency signal through time domain LPC filter.

Owner:SPREADTRUM COMM (SHANGHAI) CO LTD

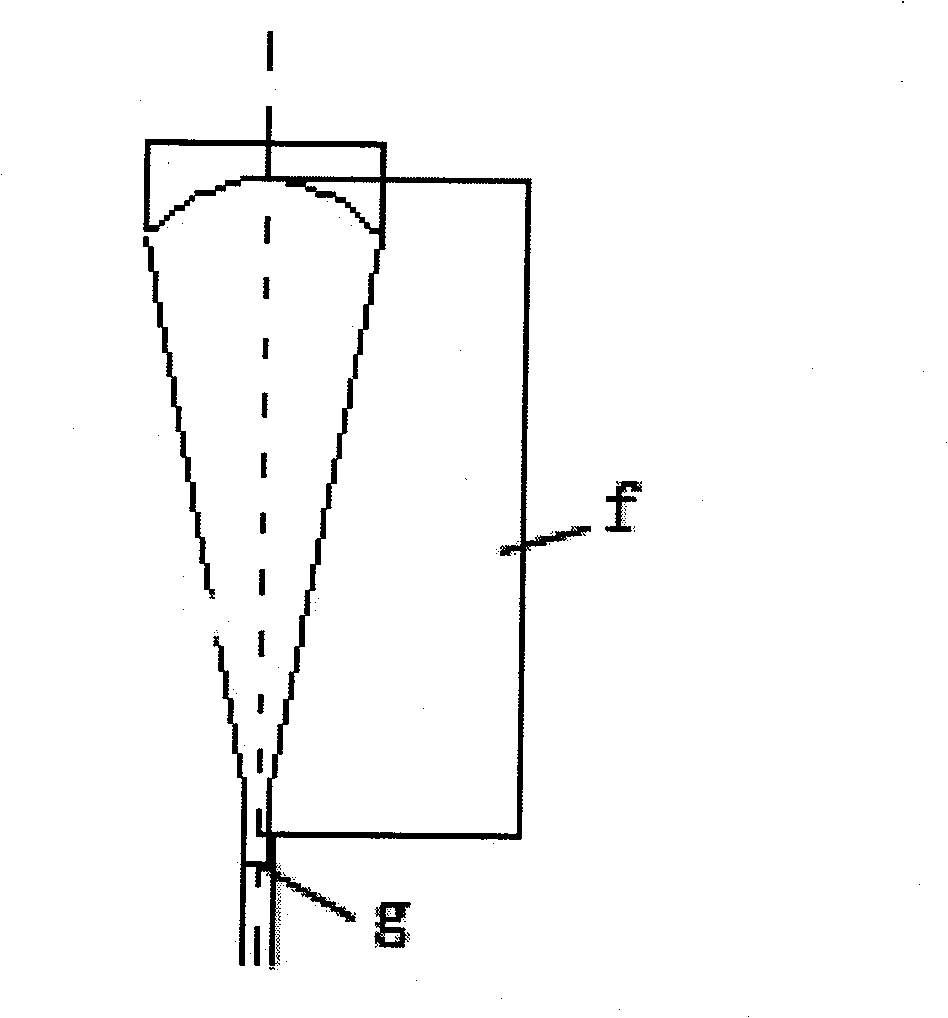

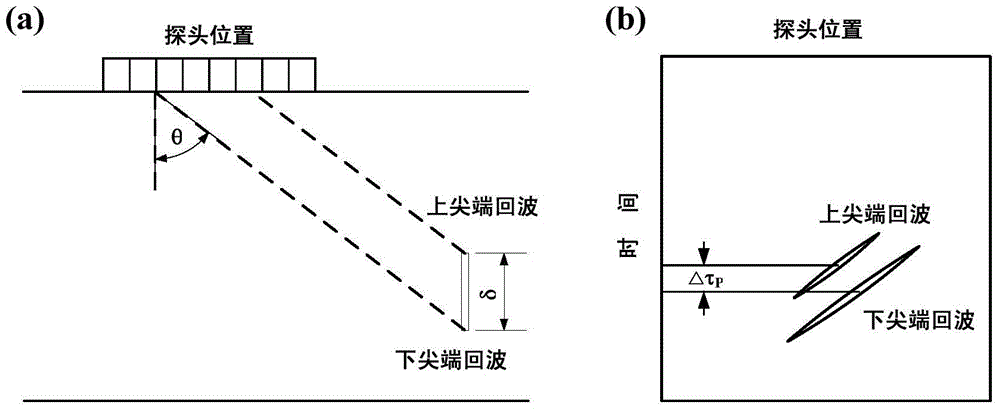

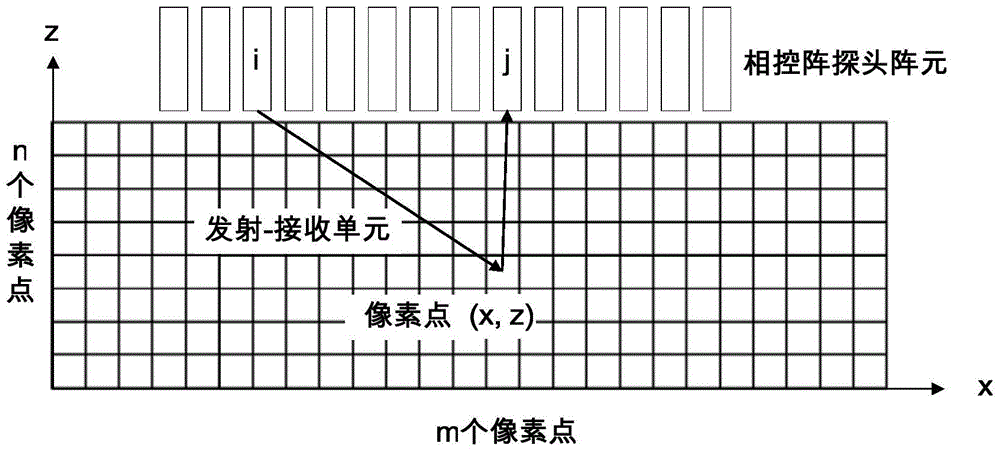

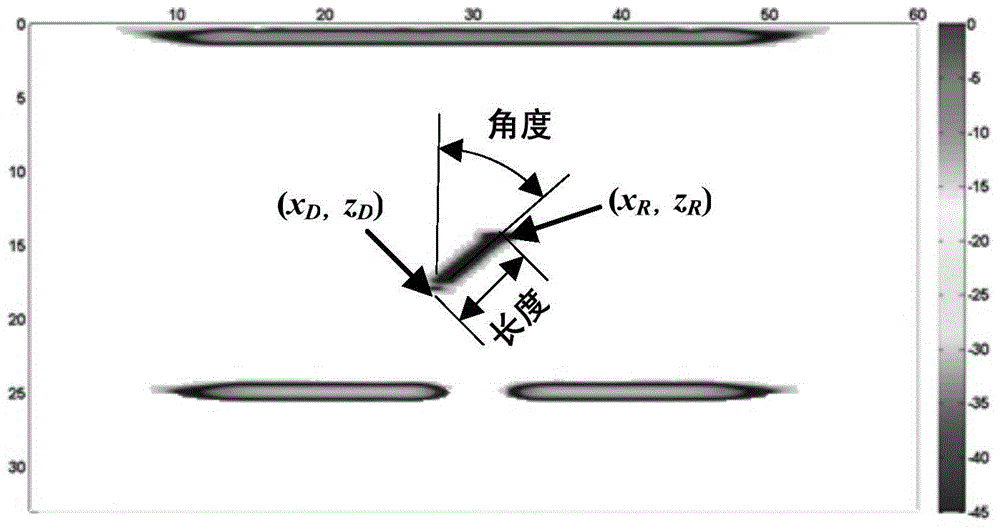

Ultrasonic relative time propagation technology suitable for inclined crack quantifying and imaging

InactiveCN104698089AQuantitatively accurateHigh quantitative accuracyAnalysing solids using sonic/ultrasonic/infrasonic wavesProcessing detected response signalSonificationQuantitative accuracy

The invention provides an ultrasonic relative time propagation technology suitable for inclined crack quantifying and imaging, and belongs to the technical field of ultrasonic nondestructive testing. According to the propagation technology, the length, the width, the inclined angle and the position of cracks are set in a two-dimensional section model, a probe with N array elementsis arranged in the model by means of signal parameters of a phased array linear array probe, N2 TXT files representing A scanning signals are formed according to phased array all-capture signal collection, the TXT files are read through software, a TFM image of the cracks is obtained, an upper tip end coordinate point (xR, zR) and a lower tip end coordinate point (xD, zD) on the cracks are found in the image through MATLAB software, and the length delta and the inclined angle gamma of the cracks are calculated. The propagation technology solves the problems that a traditional relative time propagation technology is poor in inclined crack quantifying precision and cannot be used for measuring the inclined angle of the cracks. Besides, by means of the propagation technology, the cracks can be visually imaged and accurately positioned. A solution is provided for further improving quantifying precision of the cracks in workpieces, and good application and popularization prospects are achieved.

Owner:DALIAN UNIV OF TECH +1

Sample rack for X-ray diffraction phase analysis and analysis method thereof

InactiveCN1800839AEliminate the effect of precisionInter-laboratory versatilityMaterial analysis using radiation diffractionSoft x rayQuantitative phase analysis

The invention relates to qualitative and quantitative analysis for X-ray diffraction mineral. Wherein, the X-ray diffraction phase analysis sample bracket comprises a silicon single-crystal piece in the following base frame, a base frame, and a dust-carry film stuck on said single-piece; the single-crystal piece is single diffraction peak, and is prepared by cutting into pieces along the crystal face 0-12Deg and grinding and polishing. This invention can eliminate the effect to measurement accuracy from device, time and parameter, simplifies operation, and cuts time to improve efficiency.

Owner:MAANSHAN IRON & STEEL CO LTD

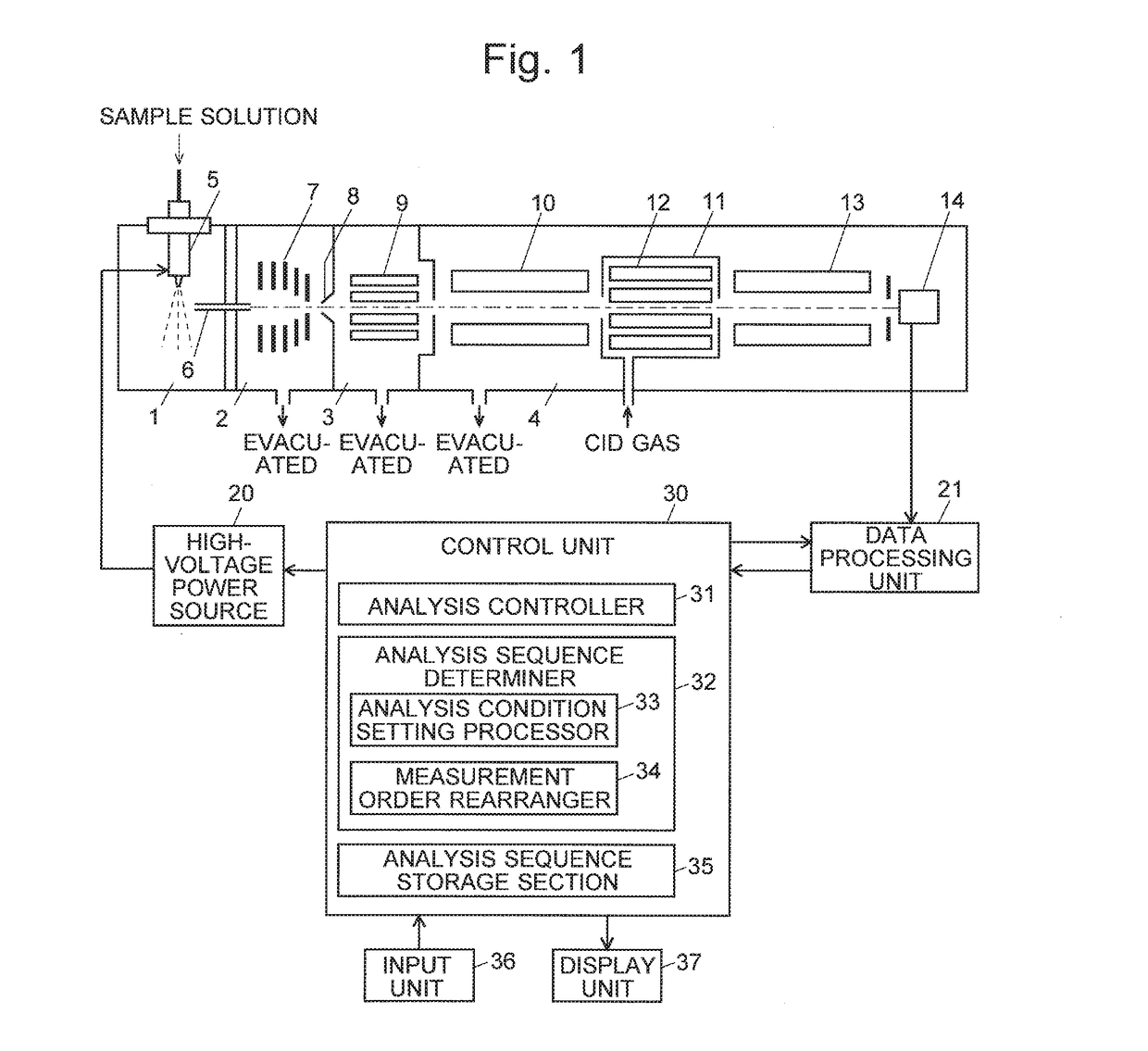

Mass spectrometer

ActiveUS20170287691A1High detection sensitivityHigh quantitative accuracyStability-of-path spectrometersPositive/negative analyte ion analysis/introduction/generationIonizationAnalytical control

In a mass spectrometer according to the present invention, when MRM measurements for a plurality of MRM transitions need to be performed within one cycle, a measurement order rearranger determines an analysis sequence by sorting the measurement in ascending order of the absolute value of an optimum application voltage (an application voltage which gives the highest ionization efficiency) to the nozzle of the ESI probe. An analysis controller performs the analysis by controlling the high-voltage power source and other relevant units according to the determined analysis sequence. Since the voltage applied to the nozzle within one cycle has no period in which the voltage is changed in the decreasing direction with the same polarity, the cycle time becomes shorter than in a conventional device.

Owner:SHIMADZU CORP

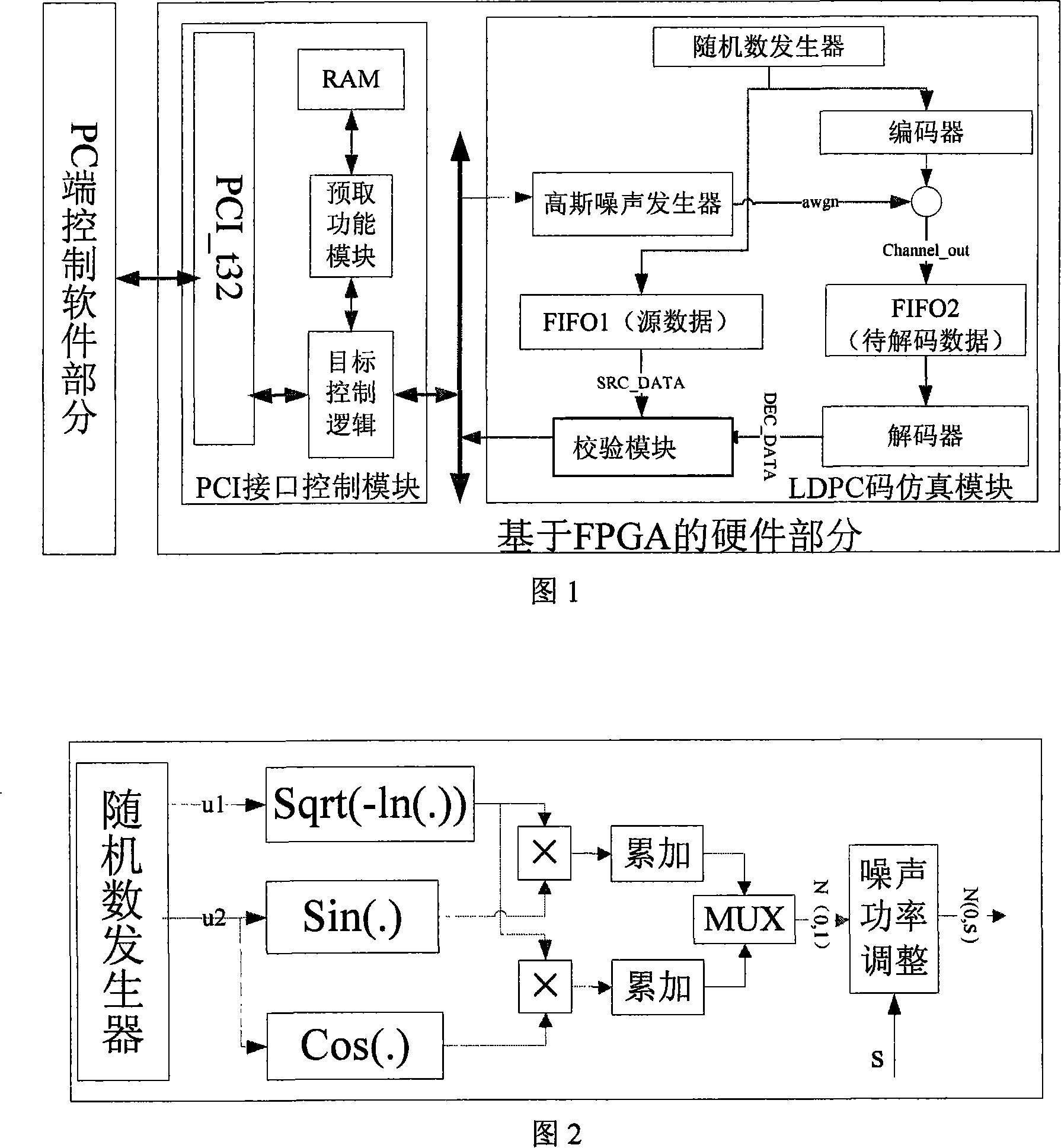

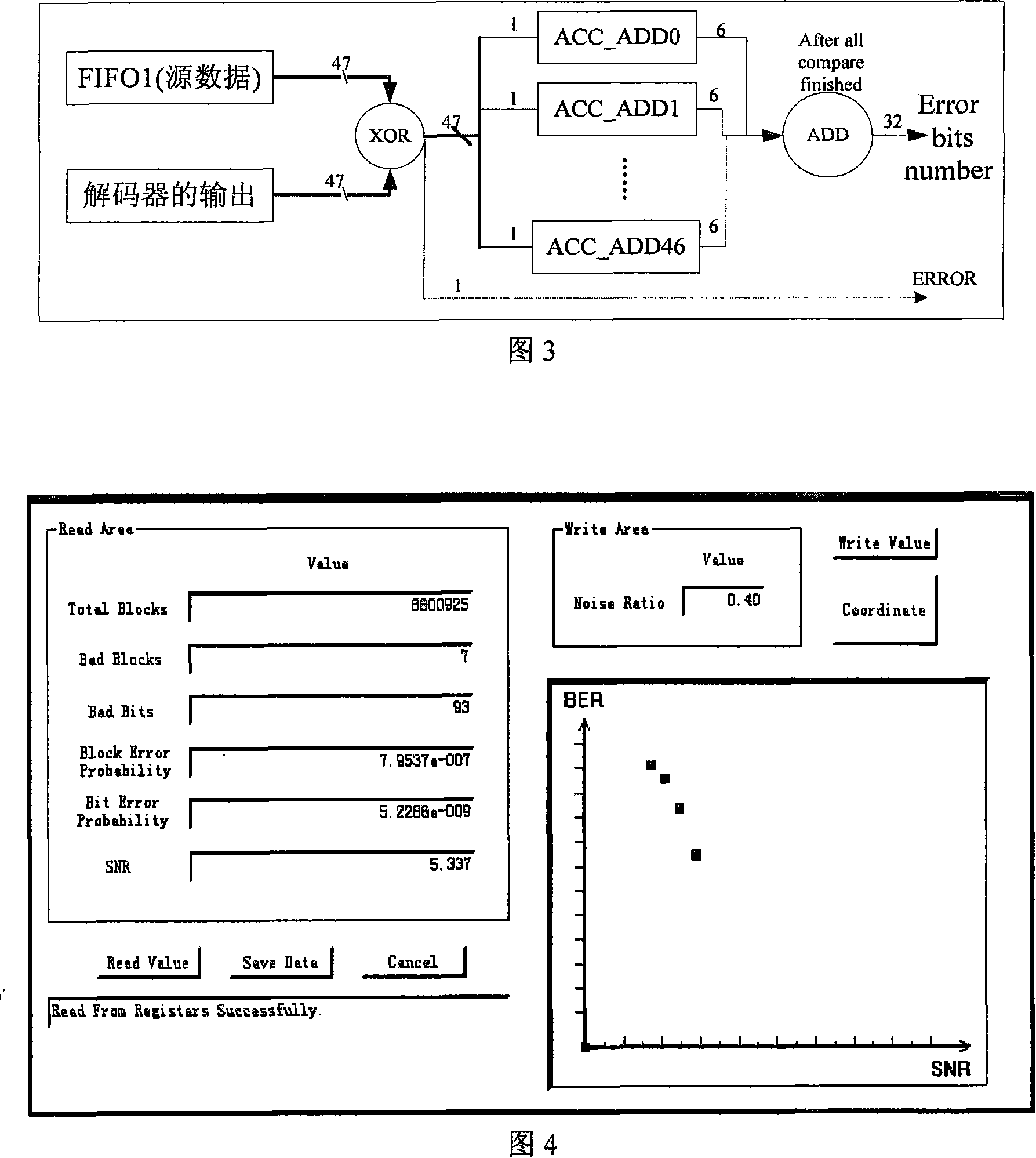

Low-density odd-even checking codec hardware simulation system based on programmable gate array

ActiveCN101131710AImplement hardware emulationImprove simulation speedError correction/detection using multiple parity bitsSpecial data processing applicationsSoftware emulationGate array

The invention discloses a kind of LDPC encode and decode hardware emulate system basing on FPGA. The system includes the control software of PC terminal and the hardware basing on DPFA which includes the control module of PCI interface, random number generator, Gaussian noise generator, LDPC encoder / decoder and so on. The invention bases on FPGA hardware and realizes simulation study of the LDPC, at the same time, the system is good at controllability, observation and reusability, and improves the pace of simulation ( is more than 300 times higher than the pace of the simulation software), offering a good lab environment for researching the same kind of error correcting codes further.

Owner:南京宁麒智能计算芯片研究院有限公司

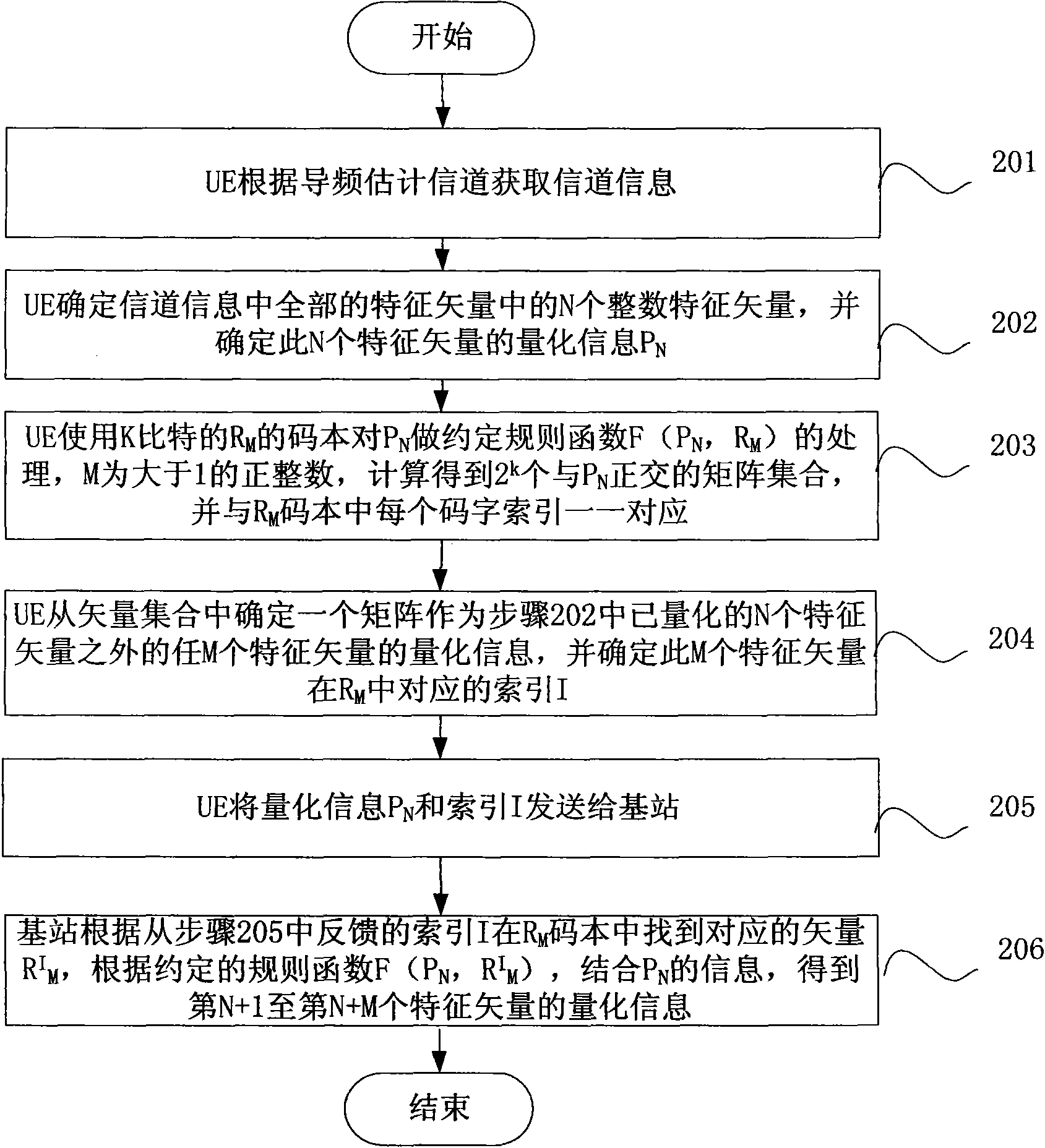

Method, system and mobile terminal for transmitting channel information

InactiveCN101777968AReduce computational complexityImprove quantization accuracyError prevention/detection by diversity receptionBase stationCodebook

The invention discloses a method, a system and a mobile terminal for transmitting channel information. The method comprises the following steps: determining the quantitative information PN of N number of channel eigenvectors by the mobile terminal, wherein N is an integer which is larger than 1; according to a codebook the sequence of which is 1, namely R1, and a function F (PN, R1), calculating to obtain a vector muster which is orthogonal with the quantitative information PN and corresponds to the codon of an R1 codebook; determining a vector and an index I which is in the R1 codebook and corresponds to the vector from the vector muster by the mobile terminal; transmitting the quantitative information PN and the index I to a base station; finding out the quantitative information of the (N+1)th eigenvector by the base station according to a vector RI1 which is in the R1 codebook and corresponds to the index I, the function F (PN, RI1) and the quantitative information PN; and obtaining a matrix muster according to a codebook RM the sequence of which is M and a function F (PN, RM). The invention can effectively reduce the complexity of codon selection and calculation, and improve the quantizing precision.

Owner:ZTE CORP

A superframe audio track parameter smoothing and extract vector quantification method

InactiveCN1632863AHigh vectorization accuracyImprove relevanceSpeech analysisCode conversionSyllableVocal tract

This invention relates to superframe track parameter quantifying method, which comprises the following steps: to frame the input voice signal sample as time sequence; to extract each frame voice track A parameter from the current superframe and then to convert it into line spectrum parameter for flatness; to extract unvoiced and voiced syllables parameters from the current super frame for vector quantifying; to minus direct current from the important frame line spectrum and to minus prediction values from the important frame off-direct current spectrum parameters; to use the importable frame line spectrum to get non-importable quantified line spectrum parameters; to convert the quantified parameters into voice track A parameters.

Owner:TSINGHUA UNIV

Method for generating codebooks under relevant channels in wireless communication system

InactiveCN101924612AHigh quantitative accuracyLower usage limitBaseband system detailsError prevention/detection by diversity receptionCommunications systemComputer compatibility

The invention relates to a method for generating codebooks under relevant channels in a wireless communication system, and belongs to the technical field of wireless communication. In the method, a base station and users use two same initial codebooks, one initial codebook is composed of conventional DFT code words, and the other initial codebook is composed of random vectors. Each user calculates the relevant matrix rank information of an own channel and feeds the matrix rank information back to the base station; and the base station and the users independently generate new two-stage target codebooks based on weighing DFT code words by the same algorithm by utilizing the initial codebooks according to the rank information. The weighing DFT code word-based codebooks designed by the method have a flexible structure of the two-stage target codebooks, improve the quantified accuracy of the channels, and can be adaptively applied to the relevant condition of different channels; and the existing rank feedback information in the conventional standard is utilized fully without causing the expense of an additional system feedback link, so the weighing DFT code word-based codebooks are compatible with the conventional system, and can be applied to the future wireless communication system conveniently.

Owner:BEIHANG UNIV +1

Time domain in-memory computing array structure based on magnetic random access memory

ActiveCN112581996AReduce power consumptionReduce memory access power consumptionDigital storagePhysical realisationTime domainComputer architecture

The invention discloses a time domain in-memory computing array structure based on a magnetic random access memory (MRAM), and belongs to the field of integrated circuit design. The circuit is characterized in that the structure comprises a dual-mode storage array, a self-adaptive pipeline decoder, a pre-charging circuit, a column selector, a sensitive amplifier, an input and output unit, a delaydifference quantization unit, a counting unit, a time sequence control circuit and a mode selection module. The method has a standard read-write mode and an in-memory calculation mode. Under the standard read-write mode, the read-write operation of the data in the storage array can be realized; the in-memory calculation mode can realize multiply-accumulate operation in binary neural network calculation. Multiply-accumulate calculation is completed during the reading of data; meanwhile, the delay quantization unit and the storage array are integrated together to reduce memory access energy consumption; compared with a conventional Von Noemann architecture neural network accelerator, the network operation energy efficiency is effectively improved.

Owner:SOUTHEAST UNIV

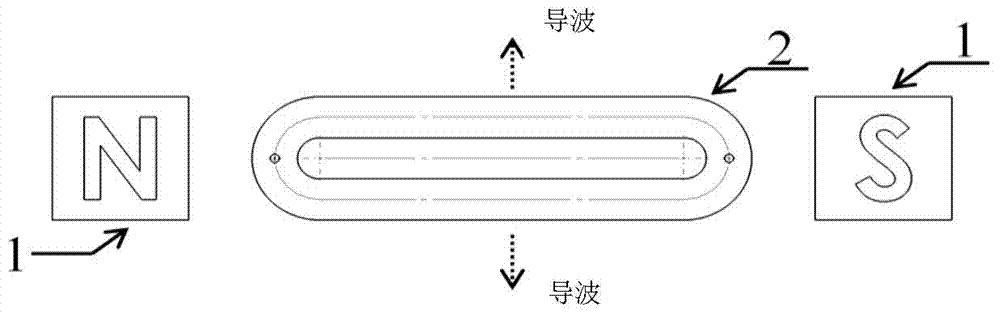

Mass spectrometry and mass spectrometer used for the same

ActiveUS20100163722A1Stable emission amountHigh quantitative accuracyMaterial analysis by optical meansIsotope separationMass Spectrometry-Mass SpectrometryVaporization

The present invention maintains a stable emission amount from an emitter. In an embodiment of the present invention, a solid sample or a liquid sample is heated to gasify an object to be measured contained in the solid sample or the liquid sample, thereby forming a neutral gaseous molecule, and a metal ion emitted from an emitter having an oxidized surface is attached to the neutral gaseous molecule to ionize the neutral gaseous molecule, which is subjected to mass spectrometry. The solid sample or the liquid sample is a sample that emits a reducing gas by heating. The heating for gasifying the object to be measured is performed at a temperature lower than the vaporization temperature of the solid sample or the liquid sample and not less than the vaporization temperature of the object to be measured, and an oxidizing gas is provided to the emitter.

Owner:CANON ANELVA CORP

Equipment for discharging a fixed amount of a particulate body

ActiveUS8534452B2High quantitative accuracyLow costLoading/unloadingConveyor partsParticulatesBelt conveyor

Fixed amount discharging equipment for simultaneously discharging a particulate body from a plurality of containers containing the particulate body, comprising a casing to the interior of which is provided a belt conveyor and having a particulate body discharge hole below the carrying direction end of the belt conveyor, and a plurality of supply arranged in the carrying direction of the belt conveyor and passing through the casing, lower ends thereof penetrating into the casing and being arranged above the belt of the belt conveyor, the lower ends of the supply pipes being such that the downstream sides thereof in the belt carrying direction have notches of a predetermined length from the end faces upward.

Owner:J POWER ENTECH

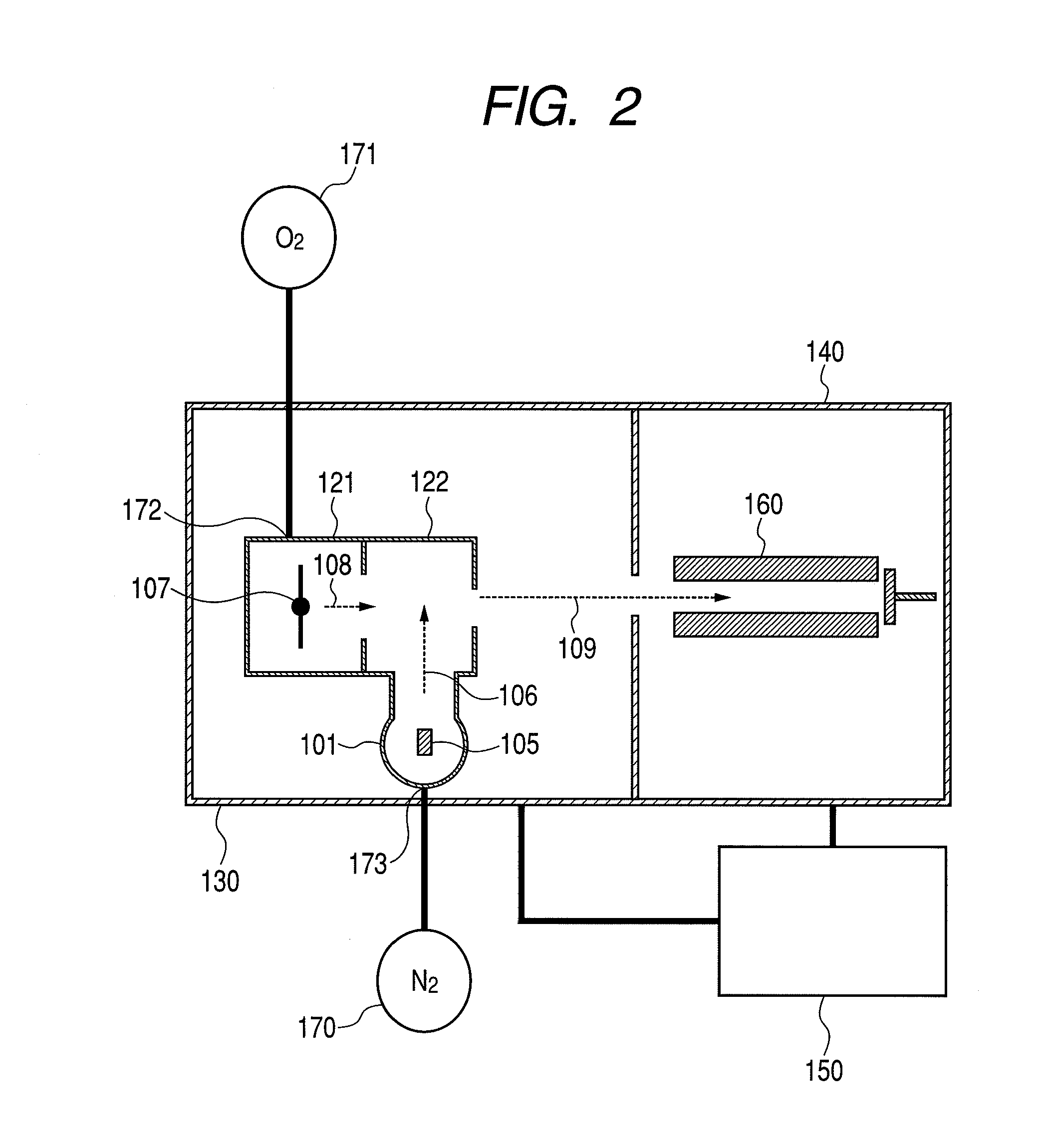

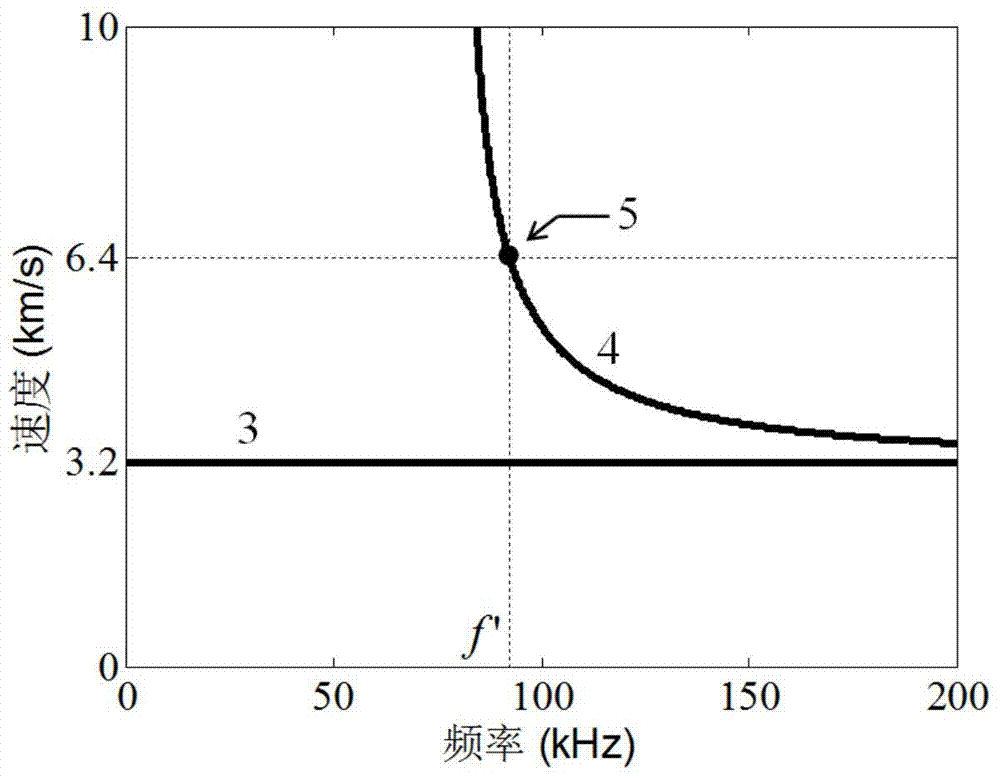

Electromagnetic ultrasonic excitation probe design method

ActiveCN104330476ASimplifyImprove signal-to-noise ratioUltrasonic/sonic/infrasonic wave generationSignal-to-noise ratio (imaging)Guided wave propagation

The invention discloses an electromagnetic ultrasonic excitation probe design method, according to the sound propagation principle, namely SH type guided wave propagation rule, in a solid plate, optimum excitation frequency is determined, and according to the frequency, an electromagnetic ultrasonic excitation probe is designed; enhancement of SH type 0 order mode guided wave and inhibition of 1 order mode guided wave in the plate can be realized, simplification of the mode of a guided wave excited in a particular frequency can be realized, the signal-to-noise ratio is improved, and defect detection probability and quantization accuracy can be effectively improved.

Owner:BC P INC CHINA NAT PETROLEUM CORP +2

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com